### (19) **日本国特許庁(JP)**

# (12) 公開特許公報(A)

(11)特許出願公開番号

特開2018-23165 (P2018-23165A)

(43) 公開日 平成30年2月8日(2018.2.8)

(51) Int. Cl. F I テーマコード (参考)

**HO4R** 19/00 (2006.01) HO4R 19/00 330 4C6O1 **A61B** 8/14 (2006.01) A61B 8/14 5DO19

## 審査請求 有 請求項の数 18 OL 外国語出願 (全 56 頁)

(21) 出願番号 特願2017-203056 (P2017-203056) (22) 出願日 平成29年10月20日 (2017.10.20) (62) 分割の表示 特願2016-501996 (P2016-501996)

の分割

原出願日 平成26年3月13日(2014.3.13)

(31) 優先権主張番号 61/794,744

(32) 優先日 平成25年3月15日 (2013.3.15)

(33) 優先権主張国 米国(US)

(71) 出願人 515244151

バタフライ ネットワーク, インコーポレ

イテッド

アメリカ合衆国, コネチカット州 O64 37 ギルフォード, オールド ウィット

フィールド ストリート 530

|(74)代理人 100079108

弁理士 稲葉 良幸

(74)代理人 100109346

弁理士 大貫 敏史

(74)代理人 100117189

弁理士 江口 昭彦

(74)代理人 100134120

弁理士 内藤 和彦

最終頁に続く

(54) 【発明の名称】相補型金属酸化膜半導体 (СМОS) 超音波振動子およびその形成方法

## (57)【要約】

【課題】 労力と時間をより少なくすることによってデバイスの製作を容易にすること。

【解決手段】 相補型金属酸化膜半導体(CMOS)超音波振動子(CUT)とCUTを形成するための方法が記載される。CUTはモノリシックに統合された超音波振動子および振動子に関連して動作するための集積回路を含んでよい。CUTは、超音波撮像デバイスおよび/または高強度焦点式超音波(HIFU)デバイスなどの超音波デバイスで使用されてよい。

【選択図】 図26

#### 【特許請求の範囲】

### 【請求項1】

超音波振動子と、

前記超音波振動子に結合された集積回路であって、СМОSウェハ内に形成された集積回路と、を備え、

前記超音波振動子が、

前記CMOSウェハ内に形成されたキャビティと、

前記キャビティの上を覆う、単結晶シリコン以外の材料で形成されたメンブレンと、 前記メンブレンと前記集積回路との間の電気的接続性を提供する電気接点と、を備える装置。

【請求項2】

CMOSウェハ内にキャビティを形成することと、

単結晶シリコンを含まない材料で形成された前面を有する転写ウェハを前記CMOSウェハに接合することと、を含み、

前記転写ウェハを前記CMOSウェハに接合することが450 未満で行われる、超音波振動子を形成する方法。

### 【請求項3】

内部に形成された集積回路(IC)を有する相補型金属酸化膜半導体(CMOS)ウェ ハと、

前記 C M O S ウェハ内のキャビティ上方に設けられるメンブレンであって、前記 C M O S ウェハと統合され、かつ前記キャビティに近い第 1 の側と前記キャビティから遠い第 2 の側を有するメンブレンと、

前記キャビティに近い前記メンブレンの前記第1の側に接触し、かつ前記メンブレンを前記ICに電気的に接続する導電性電気経路と、を備える装置。

#### 【請求項4】

前記キャビティが導電材料で形成された導電性側壁により少なくとも部分的に画定され、前記導電性電気経路が前記導電性側壁の少なくとも一部を備える、請求項3に記載の装置。

### 【請求項5】

前記導電性側壁が金属を含み、前記メンブレンの前記第1の側が前記金属の層を含む、請求項4またはその他の前記請求項のいずれかに記載の装置。

【請求項6】

前記金属が窒化チタン(TiN)を含む、請求項5またはその他の前記請求項のいずれかに記載の装置。

### 【請求項7】

前記キャビティが非導電性側壁により少なくとも部分的に画定され、前記導電性電気経路が前記非導電性側壁内に埋め込みビアを備える、請求項3またはその他の前記請求項のいずれかに記載の装置。

### 【請求項8】

前記メンブレンがポリシリコンを含む、請求項3またはその他の前記請求項のいずれかに記載の装置。

【請求項9】

前記メンブレンがアモルファスシリコンを含む、請求項3またはその他の前記請求項の いずれかに記載の装置。

#### 【請求項10】

前記メンブレンが縮退ドープシリコンを含む、請求項3またはその他の前記請求項のいずれかに記載の装置。

## 【請求項11】

前記メンブレンが、第1の厚さを有する中央部分と第2の厚さを有する外側部分とを含む不均一な厚さを有する、請求項3またはその他の前記請求項のいずれかに記載の装置。

10

20

30

00

40

#### 【請求項12】

前記第2の厚さが前記第1の厚さよりも小さい、請求項11またはその他の前記請求項のいずれかに記載の装置。

# 【請求項13】

前記第1の厚さが前記第2の厚さよりも小さい、請求項11またはその他の前記請求項のいずれかに記載の装置。

#### 【請求項14】

前記メンブレンがピストンとして構成される、請求項11またはその他の前記請求項の いずれかに記載の装置。

## 【請求項15】

10

20

30

40

前記第2の厚さがおよそ1ミクロンとおよそ5ミクロンとの間である、請求項11またはその他の前記請求項のいずれかに記載の装置。

### 【請求項16】

前記第2の厚さがおよそ0.1ミクロンとおよそ2ミクロンとの間である、請求項11 またはその他の前記請求項のいずれかに記載の装置。

#### 【 請 求 項 1 7 】

前記第1の厚さがおよそ1ミクロンとおよそ50ミクロンとの間である、請求項16またはその他の前記請求項のいずれかに記載の装置。

#### 【請求項18】

前記CMOSウェハが、複数のキャビティと、複数の超音波振動子を画定する前記複数のキャビティのそれぞれのキャビティ上方の複数のメンブレンとを含む、請求項3またはその他の前記請求項のいずれかに記載の装置。

#### 【請求項19】

前記複数の超音波振動子が超音波撮像デバイスの少なくとも一部として構成される、請求項18に記載の装置。

#### 【請求項20】

前記複数の超音波振動子が高強度焦点式超音波(HIFU)デバイスの少なくとも一部として構成される、請求項18またはその他の前記請求項のいずれかに記載の装置。

### 【請求項21】

前記複数の超音波振動子が超音波撮像デバイスおよび / または高強度焦点式超音波 ( H I F U ) デバイスとして動作可能なデバイスを形成するように構成される、請求項 1 8 またはその他の前記請求項のいずれかに記載の装置。

#### 【請求項22】

前記複数の超音波振動子が画像誘導 H I F U を行うように撮像デバイスおよび H I F U デバイスとして動作可能なデバイスを形成するように構成される、請求項 2 1 またはその他の前記請求項のいずれかに記載の装置。

#### 【請求項23】

前記 C M O S ウェハ内の前記キャビティ下方の電極をさらに備え、前記キャビティが第1の幅を有し、前記電極が第2の幅を有する、請求項3またはその他の前記請求項のいずれかに記載の装置。

## 【請求項24】

前記第1の幅が前記第2の幅よりも大きい、請求項23またはその他の前記請求項のいずれかに記載の装置。

## 【請求項25】

前記第1の幅が前記第2の幅にほぼ等しい、請求項23またはその他の前記請求項のいずれかに記載の装置。

#### 【請求項26】

前記第1の幅が前記第2の幅よりも小さい、請求項23またはその他の前記請求項のいずれかに記載の装置。

### 【請求項27】

前記電極がTiNを含む、請求項23またはその他の前記請求項のいずれかに記載の装置。

## 【請求項28】

内部に形成されたキャビティを有する基板と、

前記基板と統合され、かつ前記キャビティの上を覆うメンブレンであって、およそ0. 05ミクロンとおよそ1ミクロンとの間の厚さを有するメンブレンと、を備える超音波振動子。

### 【請求項29】

前記基板が、内部に形成された集積回路(IC)を有する相補型金属酸化膜半導体(CMOS)ウェハであり、かつ前記メンブレンが前記基板とモノリシックに統合される、請求項28に記載の超音波振動子。

【請求項30】

前記メンブレンがおよそ0.1ミクロンとおよそ0.5ミクロンとの間の厚さを有する、請求項28に記載の超音波振動子。

#### 【請求項31】

前記メンブレンがポリシリコンを含む、請求項28またはその他の前記請求項のいずれかに記載の超音波振動子。

#### 【請求項32】

前記メンブレンがアモルファスシリコンを含む、請求項28またはその他の前記請求項のいずれかに記載の超音波振動子。

【請求項33】

前記メンブレンが前記キャビティを封止する、請求項28またはその他の前記請求項のいずれかに記載の超音波振動子。

## 【請求項34】

前記メンブレンが、第1の厚さを有する中央部分と第2の厚さを有する外側部分とを含む不均一な厚さを有する、請求項28またはその他の前記請求項のいずれかに記載の超音波振動子。

### 【請求項35】

前記第1の厚さが前記第2の厚さよりも小さい、請求項34またはその他の前記請求項のいずれかに記載の超音波振動子。

【請求項36】

前記第2の厚さが前記第1の厚さよりも小さい、請求項34またはその他の前記請求項のいずれかに記載の超音波振動子。

【請求項37】

前記メンブレンがピストンとして構成される、請求項34またはその他の前記請求項のいずれかに記載の超音波振動子。

【請求項38】

前記第2の厚さがおよそ1ミクロンとおよそ5ミクロンとの間である、請求項34またはその他の前記請求項のいずれかに記載の超音波振動子。

【請求項39】

前記第2の厚さがおよそ0.1ミクロンとおよそ2ミクロンとの間である、請求項34またはその他の前記請求項のいずれかに記載の超音波振動子。

【請求項40】

前記第1の厚さがおよそ1ミクロンとおよそ50ミクロンとの間である、請求項34またはその他の前記請求項のいずれかに記載の超音波振動子。

## 【請求項41】

前記中央部分が、前記メンブレンのための質量として構成される、請求項34またはその他の前記請求項のいずれかに記載の超音波振動子。

### 【請求項42】

相補型金属酸化膜半導体(CMOS)ウェハ内の集積回路(IC)を前記CMOSウェ

10

20

30

40

ハ内のキャビティを覆うメンブレンの第1の側であって、前記キャビティに近い前記メンブレンの第1の側に接続する導電性電気経路を形成し、前記メンブレンが前記キャビティから遠い第2の側をさらに有することにより、

超音波振動子を形成すること、を含む方法。

### 【請求項43】

相補型金属酸化膜半導体(CMOS)ウェハ内の集積回路(IC)を前記CMOSウェハ内のキャビティを覆うメンブレンの第1の側であって、前記キャビティに近い前記メンブレンの第1の側に接続する導電性電気経路を形成することを含み、前記メンブレンが前記キャビティから遠い第2の側をさらに有する、超音波振動子を形成する方法。

#### 【請求項44】

前記メンブレンが前記キャビティを封止する、請求項43に記載の方法。

#### 【請求項45】

前記 C M O S ウェハ内の前記 I C を前記メンブレンの前記第 1 の側に接続する前記導電性電気経路を形成することが、前記 C M O S ウェハ内に前記導電性電気経路を形成することと、続いて前記メンブレンを前記 C M O S ウェハとモノリシックに統合することとを含む、請求項 4 3 に記載の方法。

### 【請求項46】

前記メンブレンを前記CMOSウェハとモノリシックに統合することが、転写ウェハを前記CMOSウェハと接合するためにウェハボンディングプロセスを行うことを含み、前記ウェハボンディングプロセスが450 未満で行われる、請求項45に記載の方法。

#### 【請求項47】

前記転写ウェハを前記CMOSウェハと接合することに続いて前記転写ウェハから前記 メンブレンを形成することをさらに含む、請求項46に記載の方法。

#### 【請求項48】

前記メンブレンが、第1の厚さを有する中央部分と前記第1の厚さよりも小さい第2の厚さを有する外側部分とを含む不均一な厚さを有し、前記メンブレンを前記CMOSウェハとモノリシックに統合することが、前記メンブレンの前記外側部分と前記キャビティの側壁の上側との間に封止を形成することを含む、請求項45またはその他の前記請求項のいずれかに記載の方法。

### 【請求項49】

前記キャビティの導電性側壁を形成することにより少なくとも部分的に、前記 C M O S ウェハ内に前記キャビティを形成することをさらに含む、請求項 4 3 またはその他の前記請求項のいずれかに記載の方法。

#### 【請求項50】

前記導電性電気経路が前記導電性側壁の少なくとも一部を備える、請求項49またはその他の前記請求項のいずれかに記載の方法。

#### 【請求項51】

前記導電性側壁が金属を含み、前記メンブレンの前記第1の側が前記金属の層を含む、請求項49またはその他の前記請求項のいずれかに記載の方法。

#### 【請求項52】

前記金属が窒化チタン(TiN)を含む、請求項51またはその他の前記請求項のいずれかに記載の方法。

### 【請求項53】

前記キャビティの非導電性側壁を形成することにより少なくとも部分的に、前記 C M O S ウェハ内に前記キャビティを形成することをさらに含む、請求項 4 3 またはその他の前記請求項のいずれかに記載の方法。

#### 【請求項54】

前記導電性電気経路を形成することが、前記キャビティの前記非導電性側壁内に埋め込みビアを形成することを含む、請求項53またはその他の前記請求項のいずれかに記載の方法。

10

20

30

40

#### 【請求項55】

前記メンブレンをポリシリコンで形成することをさらに含む、請求項43またはその他 の前記請求項のいずれかに記載の方法。

### 【請求項56】

前記メンブレンをアモルファスシリコンで形成することをさらに含む、請求項43また はその他の前記請求項のいずれかに記載の方法。

#### 【請求項57】

前記メンブレンが、第1の厚さを有する中央部分と前記第1の厚さよりも小さい第2の 厚さを有する外側部分とを含む不均一な厚さを有する、請求項43またはその他の前記請 求項のいずれかに記載の方法。

【請求項58】

前記メンブレンがピストンとして構成される、請求項57またはその他の前記請求項の いずれかに記載の方法。

## 【請求項59】

前記第2の厚さがおよそ1ミクロンとおよそ5ミクロンとの間である、請求項57また はその他の前記請求項のいずれかに記載の方法。

### 【請求項60】

前記第2の厚さがおよそ0.1ミクロンとおよそ2ミクロンとの間である、請求項57 またはその他の前記請求項のいずれかに記載の方法。

### 【請求項61】

前記第1の厚さがおよそ1ミクロンとおよそ50ミクロンとの間である、請求項60ま たはその他の前記請求項のいずれかに記載の方法。

#### 【請求項62】

キャビティをポリシリコンまたはアモルファスシリコンメンブレンで封止することによ り、 相 補 型 金 属 酸 化 膜 半 導 体 ( C M O S ) ウ ェ 八 内 に 有 蓋 キャ ビ ティ を 形 成 す る こ と を 含 む、超音波振動子を作製する方法。

## 【請求項63】

前記封止キャビティを形成することが、前記CMOSウェハ内に前記キャビティを形成 することと、前記CMOSウェハをポリシリコンまたはアモルファスシリコンの層を備え る転写ウェハと接合することと、前記転写ウェハの前記ポリシリコンまたはアモルファス シリコンの層から前記メンブレンを形成することとを含む、請求項62に記載の方法。

【請求項64】

前記CMOSウェハを前記転写ウェハと接合することが、前記接合を450 未満で行 うことを含む、請求項63に記載の方法。

### 【請求項65】

前 記 転 写 ウ ェ ハ の 前 記 ポ リ シ リ コ ン ま た は ア モ ル フ ァ ス シ リ コ ン の 層 か ら 前 記 メ ン ブ レ ン を 形 成 す る こ と が 、 前 記 ポ リ シ リ コ ン ま た は ア モ ル フ ァ ス シ リ コ ン の 層 を 薄 膜 化 す る こ とを含む、請求項63またはその他の前記請求項のいずれかに記載の方法。

## 【請求項66】

前記転写ウェハが、ベースシリコン層と、絶縁層と、前記ポリシリコンまたはアモルフ ァスシリコンの層とを含む多層ウェハである、請求項65またはその他の前記請求項のい ずれかに記載の方法。

【請求項67】

前 記 ポ リ シ リ コ ン ま た は ア モ ル フ ァ ス シ リ コ ン の 層 が ポ リ シ リ コ ン の 層 で あ る 、 請 求 項 6 6 またはその他の前記請求項のいずれかに記載の方法。

## 【請求項68】

前 記 ポ リ シ リ コ ン ま た は ア モ ル フ ァ ス シ リ コ ン の 層 が ア モ ル フ ァ ス シ リ コ ン の 層 で あ る 、請求項66またはその他の前記請求項のいずれかに記載の方法。

#### 【請求項69】

前記転写ウェハの前記ポリシリコンまたはアモルファスシリコンの層から前記メンブレ

10

20

30

40

ンを形成することが、前記ベースシリコン層と前記絶縁層とを除去することを含む、請求項 6 6 またはその他の前記請求項のいずれかに記載の方法。

## 【請求項70】

前記 C M O S ウェハ内に前記封止キャビティを形成することが、前記キャビティをポリシリコンメンブレンで封止することを含む、請求項 6 2 またはその他の前記請求項のいずれかに記載の方法。

#### 【請求項71】

前記 C M O S ウェハ内に前記封止キャビティを形成することが、前記キャビティをアモルファスシリコンメンブレンで封止することを含む、請求項 6 2 またはその他の前記請求項のいずれかに記載の方法。

## 【請求項72】

前記メンブレンが、第1の厚さを有する中央部分と前記第1の厚さよりも小さい第2の厚さを有する外側部分とを含む不均一な厚さを有する、請求項62またはその他の前記請求項のいずれかに記載の方法。

#### 【請求項73】

前記メンブレンの外側部分が第1の厚さを有し、前記方法が、前記キャビティを前記ポリシリコンまたはアモルファスシリコンメンブレンで封止することに続いて、前記第1の厚さよりも大きい第2の厚さを有する前記メンブレンの中央部分を形成することをさらに含む、請求項62またはその他の前記請求項のいずれかに記載の方法。

# 【請求項74】

前記第2の厚さを有する前記メンブレンの前記中央部分を形成することが、前記メンブレン上に第1の材料を堆積させてパターニングすることを含む、請求項73またはその他の前記請求項のいずれかに記載の方法。

## 【請求項75】

前記第1の材料を堆積させてパターニングすることが450 未満で行われる、請求項74またはその他の前記請求項のいずれかに記載の方法。

#### 【請求項76】

前記第1の材料がポリシリコンやアモルファスシリコンではない、請求項74またはその他の前記請求項のいずれかに記載の方法。

## 【請求項77】

前記ポリシリコンまたはアモルファスシリコンメンブレンが縮退ドープされる、請求項62またはその他の前記請求項のいずれかに記載の方法。

#### 【請求項78】

前記有蓋キャビティを形成することが前記キャビティを封止することを含む、請求項 6 2 またはその他の前記請求項のいずれかに記載の方法。

【発明の詳細な説明】

#### 【技術分野】

## [0001]

### 関連出願の相互参照

[0001] 本出願は、整理番号 B 1 3 4 8 . 7 0 0 0 7 U S 0 0 のもとに 2 0 1 3 年 3 月 1 5 日に出願された、「C O M P L E M E N T A R Y M E T A L O X I D E S E M I C O N D U C T O R ( C M O S ) U L T R A S O N I C T R A N S D U C E R S A N D M E T H O D S F O R F O R M I N G T H E S A M E 」という名称の米国仮特許出願第 6 1 / 7 9 4 , 7 4 4 号の米国特許法第 1 1 9条(e)のもとでの利益を主張し、その全体が参照により本明細書に組み込まれる。

#### [00002]

[0002] 本明細書に記載の技術は、相補型金属酸化膜半導体(CMOS)振動子およびその形成方法に関する。

### 【背景技術】

## [0003]

20

10

30

40

[0003] 容量型微細加工超音波振動子(CMUT)は微細加工キャビティ上方のメンブレンを含む公知のデバイスである。メンブレンは音響信号を電気信号に、またはその逆に変換するために使用されてよい。したがって、CMUTは超音波振動子として動作できる。

#### [0004]

[0004] CMUTを製作するために2種類のプロセスが使用され得る。犠牲層プロセスは、CMUTのメンブレンを犠牲層上方の第1の基板上に形成する。犠牲層の除去でキャビティ上方のメンブレンが残る。ウェハボンディングプロセスは、メンブレンと共にキャビティを形成させるために2つのウェハを互いに接合する。

#### 【発明の概要】

## 【課題を解決するための手段】

### [0005]

[0005] 本技術の態様によれば、超音波振動子と、超音波振動子に結合された集積回路であって、CMOSウェハ内に形成された集積回路とを備える装置が提供される。少なくともいくつかの実施形態において、そのような構成は小型で完全に統合された超音波デバイスが作製されることを可能にする。超音波振動子は、CMOSウェハ内に形成されたキャビティと、キャビティの上を覆う、単結晶シリコン以外の材料で形成されたメンブレンと、メンブレンと集積回路との間の電気的接続性を提供する電気接点とを備える。少なくともいくつかの実施形態において、メンブレンとしての単結晶シリコン以外の材料の使用は、単結晶材料を含まないことによりデバイスの製作を容易にする。少なくともいくつかの実施形態において、単結晶材料の使用は、単結晶ではない材料の使用と比較して、費やされるべき製作労力と時間をより多く必要とする。

#### [0006]

[0006] 本技術の態様によれば、CMOSウェハ内にキャビティを形成することと、単結晶シリコンを含まない材料で形成された前面を有する転写ウェハをCMOSウェハに接合することとを含む、超音波振動子を形成する方法が提供される。前面は、CMOSウェハに接触するように配置された転写ウェハの面であってよい。いくつかの実施形態において、転写ウェハは1つまたは複数のハンドル層を含んでよく、前面はハンドル層の反対側であってよい。転写ウェハをCMOSウェハに接合することは、いくつかの実施形態において、450 未満で行われ、これは、接合前にCMOSウェハ上に形成済みの集積回路および/または金属層に損傷を与えることなく超音波振動子の製作を容易にする。前述のように、転写ウェハのために単結晶シリコン以外の材料を使用することは、単結晶材料が使用される場合と比較して、必要とする費やされるべき労力と時間をより少なくすることにより製作を容易にすることができる。

## [0007]

[0007] 本技術の態様によれば、内部に形成された集積回路(IC)を有する相補型金属酸化膜半導体(CMOS)ウェハと、CMOSウェハ内のキャビティ上方に設けられるメンブレンであって、CMOSウェハと統合され、かつキャビティに近い第1の側とキャビティから遠い第2の側を有するメンブレンと、キャビティに近いメンブレンの第1の側に接触し、かつメンブレンをICに電気的に接続する導電性電気経路とを備える装置が提供される。いくつかの実施形態において、そのような構成は、統合された超音波振動子および集積回路を含むデバイスの基礎であるか、またはそれ自体を表す。したがって小型の超音波デバイスが、単一のCMOSウェハ上でデバイスコンポーネントの形成を可能にすることにより作製され得る。

# [ 0 0 0 8 ]

[0008] 少なくともいくつかの実施形態において、キャビティに近いメンブレンの第1の側に接触し、かつメンブレンをICに電気的に接続する導電性電気経路を備えることは、キャビティとは反対のメンブレンの側に電気接点を有する必要を排除することにより、超音波振動子とICの統合を容易にする。

### [0009]

[0009] いくつかの実施形態において、キャビティは導電材料で形成された導電性側壁に

10

20

30

40

20

30

40

50

より少なくとも部分的に画定され、導電性電気経路は導電性側壁の少なくとも一部分を備える。いくつかのそのような実施形態において、導電性電気経路の形成は、キャビティの境界を画定する側壁を活用することにより容易にされる。いくつかの実施形態において、導電性側壁は金属を含み、メンブレンの第1の側は金属の層を含み、この構成が、少なくともいくつかの実施形態において、をとえば接合により、導電性側壁とのメンブレンの統合を容易にする。いくつかの実施形態において、窒化チタン(TiN)が導電性側壁および/またはメンブレンの第1の側上の層のために使用される。いくつかの実施形態において、キャビティは非導電性側壁により少なくとも部分的に画定され、導電性電気経路をキャビティの境界として露出させておかないことにより有益な電気絶縁性を提供する。

[0010]

[0010] いくつかの実施形態において、メンブレンはポリシリコンを、またいくつかの実施形態において、アモルファスシリコンを含む。そのような材料の使用は、単結晶材料の使用を回避することにより製作を緩和してよい。前述のように、そのような材料の使用は、少なくともいくつかの実施形態において、単結晶材料を用いる製作よりも必要とする労力と時間が少ない。いくつかの実施形態において、メンブレンは縮退ドープシリコンを含み、これがいくつかの実施形態において、メンブレンが導電性であることに寄与する。

[0011]

[0011] いくつかの実施形態において、メンブレンは、第1の厚さを有する中央部分と第2の厚さを有する外側部分とを含む不均一な厚さを有する。いくつかの実施形態において、第2の厚さは第1の厚さよりも小さいので、メンブレンはピストンとして構成されてよい。いくつかの実施形態において、第1の厚さは第2の厚さよりも小さい。いくつかの実施形態において、第2の厚さはおよそ1ミクロンとおよそ5ミクロンとの間であり、またいくつかの実施形態において、およそ0.1ミクロンとおよそ2ミクロンとの間である。いくつかの実施形態において、第1の厚さはおよそ1ミクロンとおよそ50ミクロンとの間である。

[ 0 0 1 2 ]

[0012] 不均一な厚さのメンブレンを備えることは、所望の周波数および/または電力特性などのメンブレンの所望の動作を実現することを容易にする。

[0013]

[0013] いくつかの実施形態において、CMOSウェハは、複数のキャビティと、複数の超音波振動子を画定する複数のキャビティのそれぞれのキャビティと大方の複数のレンとを含む。いくつかの実施形態において、メンブレンはそれでれのキャビティを音波において、メンブレンはそれでれのキャはティを音波である。いくつかの実施形態において、複数の超音波振動子は、超音が振動音を形成するのに適切な超音波である。いくつかの実施形態において、複数の超音波撮像音波の少なくとも一部として構成される。いくつかの実施形態において、高強度において、対象患者にHIFUエネルギーを印加するように機能してよい、高強度において、は、対象患者にHIFUでは、対象度において、おいて、たとえば超音波撮像デバイスおよびノまたは高強度に対して動作の表がでいて、たとえば超音波振動子の少なくともいくつかにより収集される超音波において、たとえば超音波振動子の少なくともいくっかにより収集される超音ががあいて、たとえば超音波振動子の少なくともいくっかにより収集される超音がが高いて、たとえば超音波振動子の少なくともいくっかにより収集される超音がが高いて、たとえば超音な際に考慮されてよい超音波であるに使用する際に対象がイスおよびHIFUデバイスとして動作可能なデバイスを形成するように構成される。

[0014]

[0014] いくつかの実施形態において、装置は、たとえばメンブレンが位置される端の反対側のキャビティの端の近くに位置決めされる、СМОSウェハ内のキャビティ下方の電極をさらに備える。いくつかの実施形態において、キャビティは第1の幅を有し、電極は第2の幅を有する。いくつかの実施形態において、第1の幅は第2の幅よりも大きく、これが、キャビティを備える超音波振動子が有益な容量特性を示すことを可能にしてよい。

20

30

40

50

いくつかの実施形態において、第1の幅は第2の幅にほぼ等しく、またいくつかの実施形態において、第1の幅は第2の幅よりも小さく、これがいくつかの実施形態において、電極とキャビティの側壁との間の距離を増加させることにより、望ましくない容量挙動を最小化する。いくつかの実施形態において、電極はTiNを含む。

### [0015]

[0015] 本技術の態様によれば、内部に形成されたキャビティを有する基板と、基板と統合され、かつキャビティの上を覆うメンプレンとを備える超音波振動子が提供される。いくつかの実施形態において、メンプレンはキャビティを封止するように構成される。いくつかの実施形態において、メンプレンはおよそ 0 . 0 5 ミクロンとおよそ 1 ミクロンとの間の厚さを有し、これは、たとえば所望の周波数または範囲の周波数に関して、超音波振動子の有益な動作を容易にする。

#### [0016]

[0016] いくつかの実施形態において、基板は内部に形成された集積回路(IC)を有する相補型金属酸化膜半導体(CMOS)ウェハであり、メンブレンは基板とモノリシックに統合される。少なくともいくつかの実施形態において、そのような構成は、コンポーネントが同じ基板に統合されることを可能にすることにより、小型の超音波変換デバイスが作製されることを可能にする。

#### [0017]

[0017] いくつかの実施形態において、メンブレンはおよそ 0 . 1 ミクロンとおよそ 0 . 5 ミクロンとの間の厚さを有する。いくつかの実施形態において、メンブレンはポリシリコンを含み、またいくつかの実施形態において、メンブレンはアモルファスシリコンを含む。そのような材料の使用は、少なくともいくつかの実施形態において、単結晶材料を用いる製作よりも必要とする労力と時間が少ない。

## [ 0 0 1 8 ]

[0018] いくつかの実施形態において、メンブレンは、第1の厚さを有する中央部分と第2の厚さを有する外側部分とを含む不均一な厚さを有する。いくつかの実施形態において、第2の厚さは第1の厚さは第2の厚さよりも小さい。いくつかの実施形態において、第2の厚さは第1の厚さよりも小さいので、メンブレンはピストンとして構成されてよい。いくつかの実施形態において、第2の厚さはおよそ1ミクロンとおよそ5ミクロンとの間であり、またいくつかの実施形態において、およそ0.1ミクロンとおよそ2ミクロンとの間である。いくつかの実施形態において、第1の厚さはおよそ1ミクロンとおよそ50ミクロンとの間である。いくつかの実施形態において、中央部分は、たとえばメンブレンの周囲の厚さよりも大きい厚さを有するメンブレンのための質量として構成される。不均一な厚さのメンブレンを備えることは、所望の周波数および/または電力特性などのメンブレンの所望の動作を実現することを容易にする。

### [0019]

[0019] 本技術の態様によれば、相補型金属酸化膜半導体(CMOS)ウェハ内の集積回路(IC)をCMOSウェハ内のキャビティを覆うメンブレンの第1の側であって、キャビティに近いメンブレンの第1の側に接続する導電性電気経路を形成し、メンブレンがキャビティから遠い第2の側をさらに有することにより、超音波振動子を形成することを含む方法が提供される。記載されるような導電性電気経路を備えることは、キャビティとは反対のメンブレンの側に電気接点を有する必要を排除することにより、超音波振動子とICの統合を容易にすることができる。

# [0020]

[0020] いくつかの実施形態において、СМОSウェハ内のICをメンブレンの第1の側に接続する導電性電気経路を形成することは、СМОSウェハ内に導電性電気経路を形成することと、続いてメンブレンをСМОSウェハとモノリシックに統合することとを含む。したがっていくつかの実施形態において、メンブレンへの電気的接続はメンブレンがСМОSウェハと統合されるときに完了されてよい。

# [ 0 0 2 1 ]

20

30

40

50

[0021] いくつかの実施形態において、メンブレンをCMOSウェハとモノリシックに統合することは、転写ウェハをCMOSウェハと接合するためにウェハボンディングプロセスを行うことを含む。ウェハボンディングプロセスは450 未満で行われ、これは集積回路および / または金属層に損傷を与えない点から前述の利益を提供することができる。いくつかの実施形態において、方法は、転写ウェハをCMOSウェハと接合することに続いて転写ウェハからメンブレンを形成することをさらに含む。少なくともいくつかの実施形態において、接合後に転写ウェハからメンブレンを形成することは、ウェハボンディングを容易にする、より厚い転写ウェハの使用を可能にする。

### [0022]

[0022] いくつかの実施形態において、メンブレンは、第1の厚さを有する中央部分と第1の厚さよりも小さい第2の厚さを有する外側部分とを含む不均一な厚さを有し、メンブレンをCMOSウェハとモノリシックに統合することは、メンブレンの外側部分とキャビティの側壁の上側との間に封止を形成することを含む。キャビティの側壁の上側は側壁の露出側であってよく、またいくつかの実施形態において、キャビティの深さを少なくとも部分的に画定してよい。いくつかの実施形態において、上側は接合面を表してよい。

#### [0023]

[0023] いくつかの実施形態において、方法は、キャビティの導電性側壁を形成することにより少なくとも部分的に、СМОSウェハ内にキャビティを形成することをさらに含む。いくつかの実施形態において、導電性電気経路は導電性側壁の少なくとも一部分を備える。いくつかのそのような実施形態において、導電性電気経路の形成は、キャビティの境界を画定する側壁を活用することにより容易にされる。いくつかの実施形態において、導電性側壁は金属を含み、メンブレンの第1の側は金属の層を含み、この構成が、少なくともいくつかの実施形態において、たとえば接合により、導電性側壁とのメンブレンの統合を容易にする。いくつかの実施形態において、導電性側壁および / またはメンブレンの層は窒化チタン(TiN)を含む。

### [0024]

[0024] いくつかの実施形態において、方法は、キャビティの非導電性側壁を形成することにより少なくとも部分的に、СМОSウェハ内にキャビティを形成することをさらに含む。いくつかの実施形態において、導電性電気経路を形成することは、キャビティの非導電性側壁内に埋め込みビアを形成することを含む。いくつかの実施形態において、そのような構成は、導電性電気経路をキャビティの境界として露出させておかないことにより有益な電気絶縁性を提供する。いくつかの実施形態において、方法は、メンブレンをポリシリコンで形成することをさらに含み、またいくつかの実施形態において、メンブレンをアモルファスシリコンで形成することをさらに含み、これは少なくともいくつかの実施形態において、単結晶材料を用いるよりも必要とする製作労力と時間が少ない。

### [0025]

[0025] いくつかの実施形態において、メンブレンは、第1の厚さを有する中央部分と第1の厚さよりも小さい第2の厚さを有する外側部分とを含む不均一な厚さを有する。いくつかの実施形態において、第2の厚さはおよそ1ミクロンとおよそ5ミクロンとの間であり、またいくつかの実施形態において、第2の厚さはおよそ0.1ミクロンとおよそ2ミクロンとの間である。いくつかの実施形態において、第1の厚さはおよそ1ミクロンとおよそ50ミクロンとの間である。いくつかの実施形態において、メンブレンはピストンとして構成される。不均一な厚さのメンブレンを備えることは、所望の周波数および/または電力特性などのメンブレンの所望の動作を実現することを容易にする。

### [0026]

[0026] 本技術の態様によれば、キャビティをポリシリコンまたはアモルファスシリコンメンブレンで封止することにより、相補型金属酸化膜半導体(CMOS)ウェハ内に有蓋キャビティを形成することを含む、超音波振動子を作製する方法が提供される。少なくともいくつかの実施形態において、そのような構成は、単結晶材料を使用する必要に迫られた場合よりも少ない製作労力と時間での超音波振動子の製作を可能にする。

#### [0027]

[0027] いくつかの実施形態において、封止キャビティを形成することは、CMOSウェ 八内にキャビティを形成することと、CMOSウェハをポリシリコンまたはアモルファス シリコンの層を備える転写ウェハと接合することと、転写ウェハのポリシリコンまたはア モルファスシリコンの層からメンブレンを形成することとを含む。いくつかの実施形態に おいて、CMOSウェハを転写ウェハと接合することは、接合を450 未満で行うこと を 含 み 、 こ れ は 集 積 回 路 お よ び / ま た は 金 属 層 に 損 傷 を 与 え な い 点 か ら 前 述 の 利 益 を 提 供 することができる。いくつかの実施形態において、転写ウェハのポリシリコンまたはアモ ルファスシリコンの層からメンブレンを形成することは、ポリシリコンまたはアモルファ スシリコンの層を薄膜化することを含み、この技法はいくつかの実施形態において、ウェ ハボンディングでより厚い転写ウェハの使用を可能にする。いくつかの実施形態において 、転写ウェハは、ベースシリコン層と、絶縁層と、ポリシリコンまたはアモルファスシリ コンの層とを含む多層ウェハである。いくつかの実施形態において、ポリシリコンまたは アモルファスシリコンの層はポリシリコンの層であり、またいくつかの実施形態において . ア モル ファ ス シ リ コ ン の 層 で あ り 、 こ れ ら の 実 施 形 態 は 、 単 結 晶 材 料 を 使 用 す る 必 要 に 迫られた場合よりも必要とする製作労力と時間が少ないことにより製作を容易にすること ができる。いくつかの実施形態において、転写ウェハのポリシリコンまたはアモルファス シリコンの層からメンプレンを形成することは、ベースシリコン層と絶縁層とを除去する ことを含む。

## [0028]

[0028] いくつかの実施形態において、СМОSウェハ内に封止キャビティを形成することは、キャビティをポリシリコンメンブレンで封止することを含み、またいくつかの実施形態において、キャビティをアモルファスシリコンメンブレンで封止することを含む。少なくともいくつかの実施形態において、そのような技法は、単結晶材料を使用する必要に迫られた場合よりも少ない製作労力と時間での超音波振動子の製作を可能にする。

#### [0029]

[0029] いくつかの実施形態において、メンブレンは、第1の厚さを有する中央部分と第1の厚さよりも小さい第2の厚さを有する外側部分とを含む不均一な厚さを有する。いくっかの実施形態において、メンブレンの外側部分は第1の厚さを有することに続いて、オンブレンの中央部分を形成することを言いて、第1の厚さよりも大きい第2の厚さを有するメンブレンの中央部分を形成することを形成することを形成った。いくつかの実施形態において、第2の厚さを有するメンブレンの中央部分を形成った。ことは、メンブレン上に第1の材料を堆積させてパターニングすることを含む。いくっかの実施形態において、第1の材料はポリシリコンやアモルファスシリコンではない。いくつかの実施形態において、第1の材料はポリシリコンやアモルファスシリコンではない。いくつかの実施形態において、ポリシリコンとはアモルファシリコンメンブレンは縮退ドープされ、これが少なくともいくつかの実施形態において、メンブレンに電気的に接触させることを容易にする。

### [0030]

[0030] メンブレンがキャビティ上方に設けられるすべてのそのような実施形態において、メンブレンは任意選択によりキャビティを封止するように構成されてよい。

### [0031]

[0031] 本出願の様々な態様と実施形態が以下の図を参照しつつ記載される。図は必ずしも一定の縮尺で描かれてはいないことが認識されるべきである。複数の図に現れる部材は、それらが現れるすべての図において同じ参照番号で示される。

### 【図面の簡単な説明】

## [0032]

【図1A】[0032]本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプ

10

20

30

40

ロセスシーケンスを例示する図である。

【図1B】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図1C】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図1D】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図1E】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図1F】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図1G】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図1H】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図1Ⅰ】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図1J】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図1K】本出願の非限定的な実施形態に係る、CMOSウェハ内のキャビティ上方に形成されたメンブレンを有するCMOS超音波振動子(CUT)を製作するためのプロセスシーケンスを例示する図である。

【図2A】[0033]本出願の非限定的な実施形態に係る、ピストンメンブレンが転写ウェハから転写される、ピストンメンブレンを有するCUTを製作するためのプロセスシーケンスを例示する図である。

【図2B】本出願の非限定的な実施形態に係る、ピストンメンブレンが転写ウェハから転写される、ピストンメンブレンを有するCUTを製作するためのプロセスシーケンスを例示する図である。

【図2C】本出願の非限定的な実施形態に係る、ピストンメンブレンが転写ウェハから転写される、ピストンメンブレンを有するCUTを製作するためのプロセスシーケンスを例示する図である。

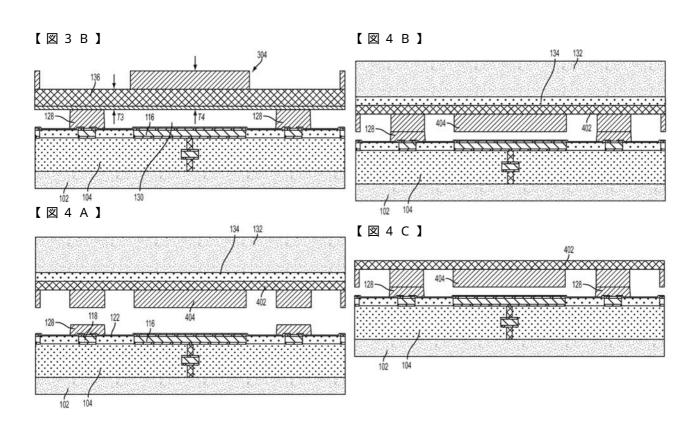

【図3A】[0034]本出願の非限定的な実施形態に係る、ピストンメンブレンがウェハボンディング後に形成される、ピストンメンブレンを有する代替のCUTを形成するためのプロセスシーケンスを例示する図である。

【図3B】本出願の非限定的な実施形態に係る、ピストンメンブレンがウェハボンディング後に形成される、ピストンメンブレンを有する代替のCUTを形成するためのプロセスシーケンスを例示する図である。

【図4A】[0035]本出願の非限定的な実施形態に係る、ピストンメンブレンが転写ウェハから転写される、ピストンメンブレンを有するCUTを形成するための代替のプロセスシーケンスを例示する図である。

【図4B】本出願の非限定的な実施形態に係る、ピストンメンブレンが転写ウェハから転

10

20

30

40

写される、ピストンメンブレンを有する C U T を形成するための代替のプロセスシーケン スを例示する図である。

【図4C】本出願の非限定的な実施形態に係る、ピストンメンブレンが転写ウェハから転写される、ピストンメンブレンを有するCUTを形成するための代替のプロセスシーケンスを例示する図である。

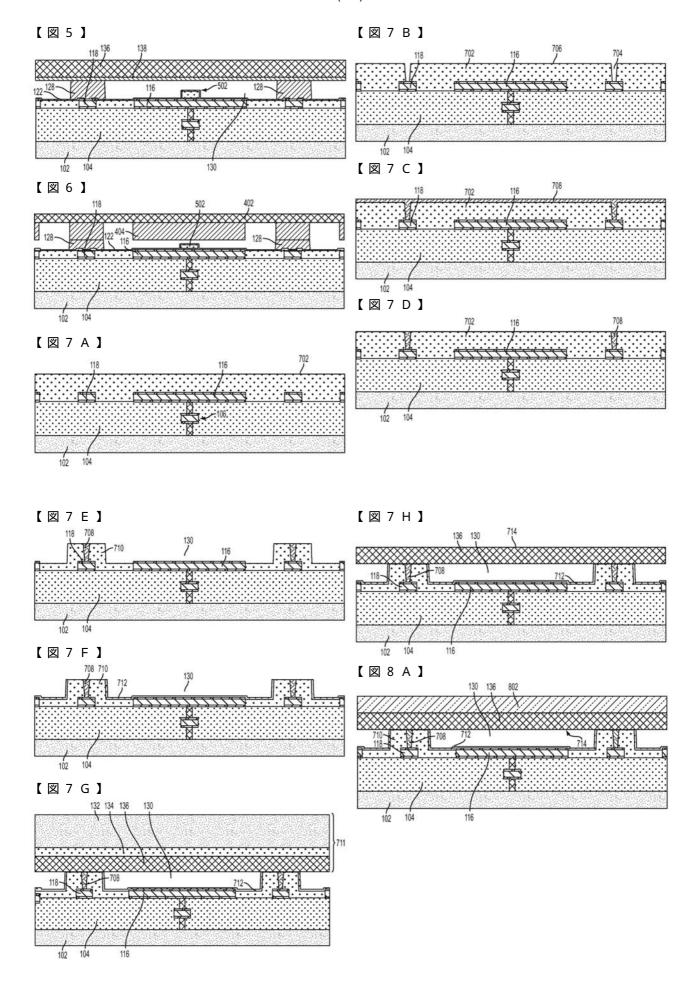

【図5】[0036]本出願の非限定的な実施形態に係る、CUTのキャビティの底面に設けられるメンブレンストッパを有するCUTを例示する図である。

【図 6 】[0037]本出願の非限定的な実施形態に係る、ピストンメンブレンとCUTのキャビティの底部分に設けられるメンブレンストッパとを有するCUTを例示する図である。

【図7A】[0038]本出願の非限定的な実施形態に係る、CUTのメンブレンの底側に電気的に接触するためにCMOSウェハ内に埋め込まれるビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図7B】本出願の非限定的な実施形態に係る、CUTのメンブレンの底側に電気的に接触させるためにCMOSウェハ内に埋め込まれるビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図7C】本出願の非限定的な実施形態に係る、CUTのメンブレンの底側に電気的に接触させるためにCMOSウェハ内に埋め込まれるビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図7D】本出願の非限定的な実施形態に係る、CUTのメンブレンの底側に電気的に接触させるためにCMOSウェハ内に埋め込まれるビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図7E】本出願の非限定的な実施形態に係る、CUTのメンブレンの底側に電気的に接触させるためにCMOSウェハ内に埋め込まれるビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図7F】本出願の非限定的な実施形態に係る、CUTのメンブレンの底側に電気的に接触させるためにCMOSウェハ内に埋め込まれるビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図7G】本出願の非限定的な実施形態に係る、CUTのメンブレンの底側に電気的に接触させるためにCMOSウェハ内に埋め込まれるビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図7H】本出願の非限定的な実施形態に係る、CUTのメンブレンの底側に電気的に接触させるためにCMOSウェハ内に埋め込まれるビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図8A】[0039]本出願の非限定的な実施形態に係る、図7A~7Hのプロセスから得られるデバイスからピストンメンブレンを形成するためのプロセスシーケンスを例示する図である。

【図8B】本出願の非限定的な実施形態に係る、図7A~7Hのプロセスから得られるデバイスからピストンメンブレンを形成するためのプロセスシーケンスを例示する図である

【図9A】[0040]本出願の非限定的な実施形態に係る、転写ウェハから転写されるピストンメンブレンを有し、かつメンブレンの底側に電気的に接触させるためにCMOSウェハ内に埋め込みビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図9B】本出願の非限定的な実施形態に係る、転写ウェハから転写されるピストンメンブレンを有し、かつメンブレンの底側に電気的に接触させるためにCMOSウェハ内に埋め込みビアを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図10A】[0041]本出願の非限定的な実施形態に係る、CMOSウェハに電気的に接触させるためにピストンメンブレンとメンブレンを貫通する埋め込みビアとを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図10B】本出願の非限定的な実施形態に係る、CMOSウェハに電気的に接触させる

10

20

30

40

ためにピストンメンブレンとメンブレンを貫通する埋め込みビアとを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図10C】本出願の非限定的な実施形態に係る、CMOSウェハに電気的に接触させるためにピストンメンブレンとメンブレンを貫通する埋め込みビアとを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図10D】本出願の非限定的な実施形態に係る、CMOSウェハに電気的に接触させるためにピストンメンブレンとメンブレンを貫通する埋め込みビアとを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図10F】本出願の非限定的な実施形態に係る、CMOSウェハに電気的に接触させるためにピストンメンブレンとメンブレンを貫通する埋め込みビアとを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図10F】本出願の非限定的な実施形態に係る、CMOSウェハに電気的に接触させるためにピストンメンブレンとメンブレンを貫通する埋め込みビアとを有するCUTを形成するためのプロセスシーケンスを例示する図である。

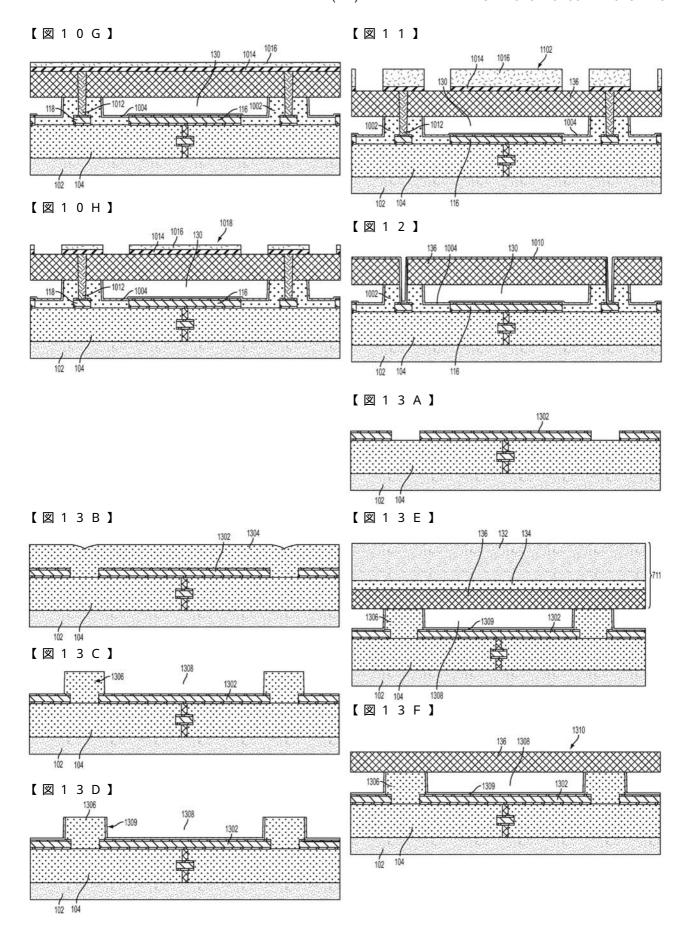

【図10G】本出願の非限定的な実施形態に係る、CMOSウェハに電気的に接触させるためにピストンメンブレンとメンブレンを貫通する埋め込みビアとを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図10H】本出願の非限定的な実施形態に係る、CMOSウェハに電気的に接触させるためにピストンメンブレンとメンブレンを貫通する埋め込みビアとを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図11】[0042]図10HのCUTのものよりも厚い中央部分を有するピストンメンブレンを含む、図10A~10Hのプロセスから得られるものの代替のCUTを例示する図である。

【図12】[0043]本出願の非限定的な実施形態に係る、CMOSウェハとCUTのメンブレンの上側との間を電気的に接触させるためにライニングビアを有するCUTを例示する図である。

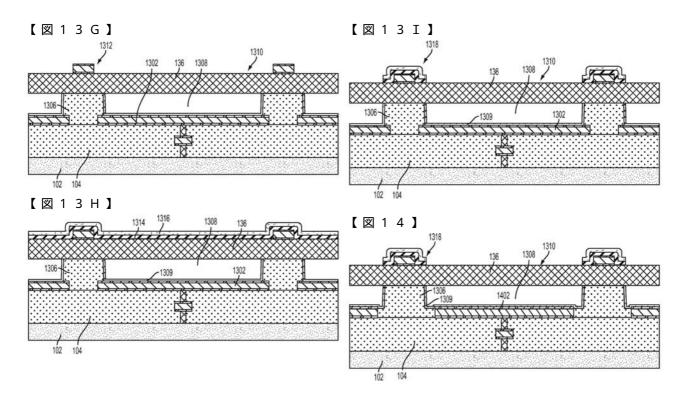

【図13A】[0044]本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図13B】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図13C】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図13D】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図13E】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図13F】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図13G】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図13H】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図13Ⅰ】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図14】[0045]本出願の非限定的な実施形態に係る、キャビティの幅よりも狭いCUTのキャビティ下方の電極を含む、図13A~13Iのプロセスから得られるものの代替のCUTを例示する図である。

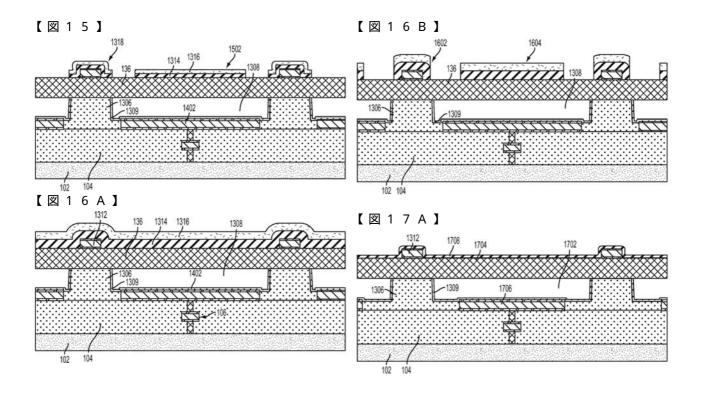

【 図 1 5 】 [0046] 本出願の非限定的な実施形態に係る、 C U T がピストンメンブレンを含む、図 1 4 のものの代替の C U T を例示する図である。

【図 1 6 A】[0047]本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレ

10

20

30

40

ンへの上側電気接点とを有する代替のCUTを形成するためのプロセスシーケンスを例示する図である。

【図16B】本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有する代替のCUTを形成するためのプロセスシーケンスを例示する図である。

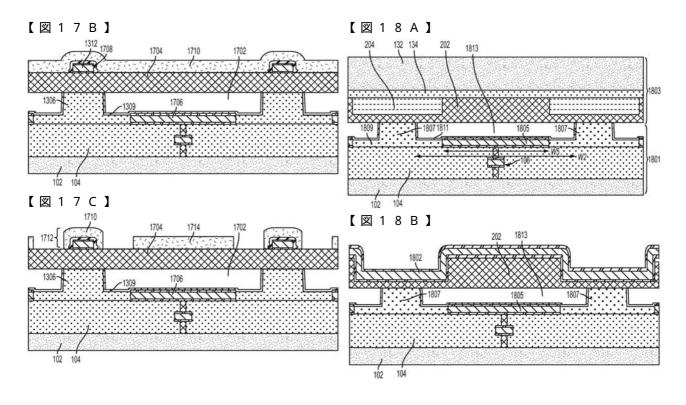

【図17A】[0048]本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図17B】本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有するCUTを形成するためのプロセスシーケンスを例示する図である

【 図 1 7 C 】本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有する C U T を形成するためのプロセスシーケンスを例示する図である

【図18A】[0049]本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有するCUTを形成するための代替のプロセスシーケンスを例示する図である。

【図18B】本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有するCUTを形成するための代替のプロセスシーケンスを例示する図である。

【図18C】本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有するCUTを形成するための代替のプロセスシーケンスを例示する図である。

【図18D】本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有するCUTを形成するための代替のプロセスシーケンスを例示する図である。

【 図 1 8 E 】本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有する C U T を形成するための代替のプロセスシーケンスを例示する図である。

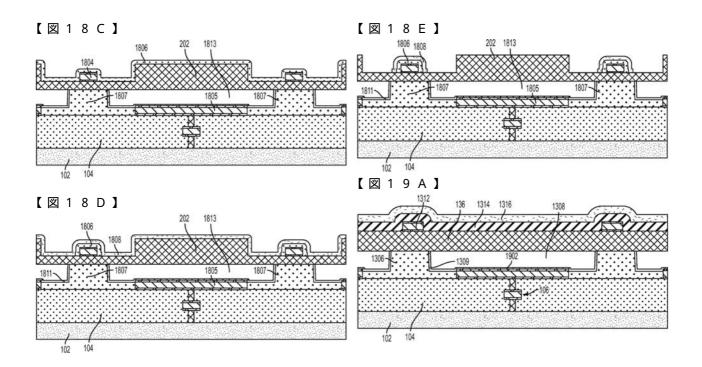

【図19A】[0050]本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有するCUTを形成するためのさらなる代替のプロセスシーケンスを例示する図である。

【図19B】本出願の非限定的な実施形態に係る、ピストンメンブレンとメンブレンへの上側電気接点とを有するCUTを形成するためのさらなる代替のプロセスシーケンスを例示する図である。

【図 2 0 A 】[0051]本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつCUTのキャビティの底面にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図20B】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつCUTのキャビティの底面にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図20C】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつCUTのキャビティの底面にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図20D】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつCUTのキャビティの底面にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図20E】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつCUTのキャビティの底面にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

10

20

30

40

. .

【図20F】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつCUTのキャビティの底面にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図20G】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつCUTのキャビティの底面にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図20H】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつCUTのキャビティの底面にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図20Ⅰ】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつCUTのキャビティの底面にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

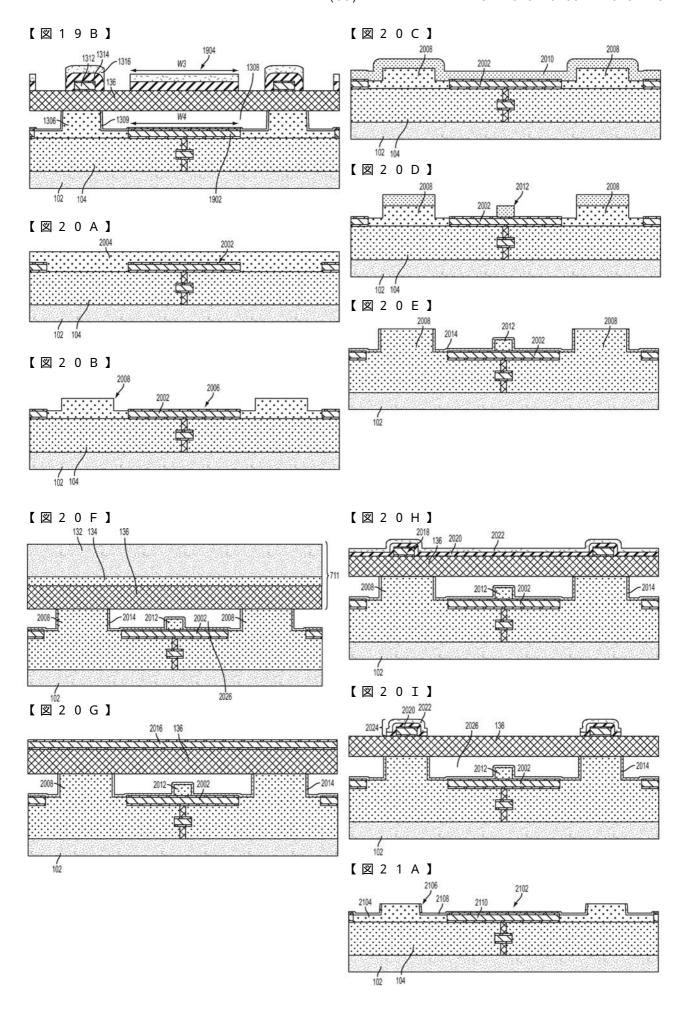

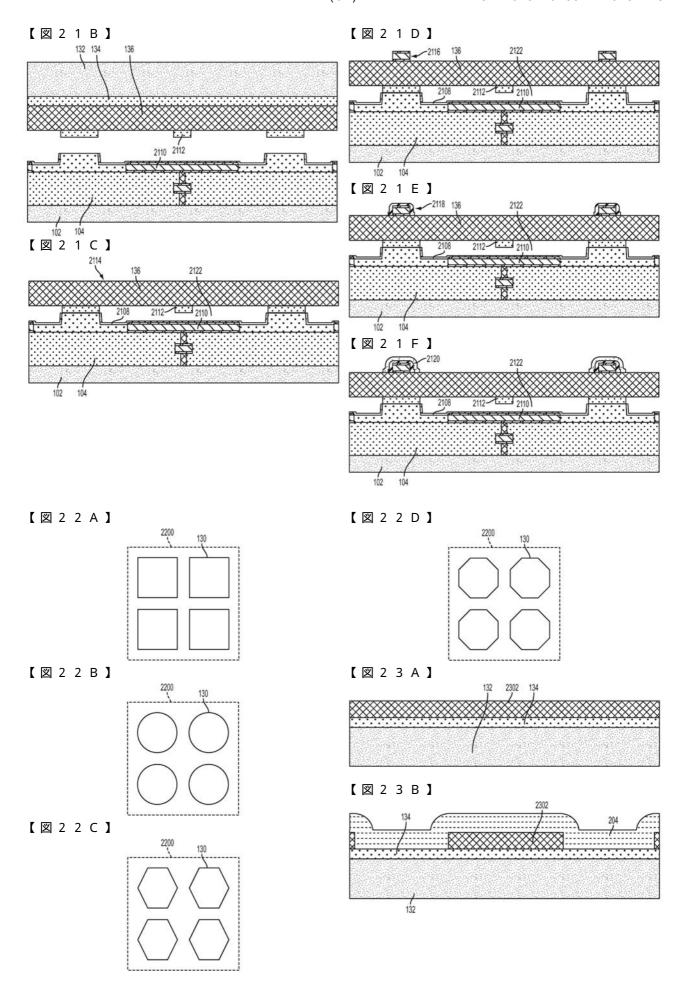

【図 2 1 A 】[0052]本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつメンブレンの底側にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図21B】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつメンブレンの底側にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図21C】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつメンブレンの底側にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図21D】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつメンブレンの底側にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図21E】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつメンブレンの底側にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図21F】本出願の非限定的な実施形態に係る、CUTのメンブレンの上側に電気接点を有し、かつメンブレンの底側にメンブレンストッパを有するCUTを形成するためのプロセスシーケンスを例示する図である。

【図22A】[0053]本出願の非限定的な実施形態に係る、CUTのキャビティのための様々な形状を例示する図である。

【図22B】本出願の非限定的な実施形態に係る、CUTのキャビティのための様々な形状を例示する図である。

【図22C】本出願の非限定的な実施形態に係る、CUTのキャビティのための様々な形状を例示する図である。

【図22D】本出願の非限定的な実施形態に係る、CUTのキャビティのための様々な形状を例示する図である。

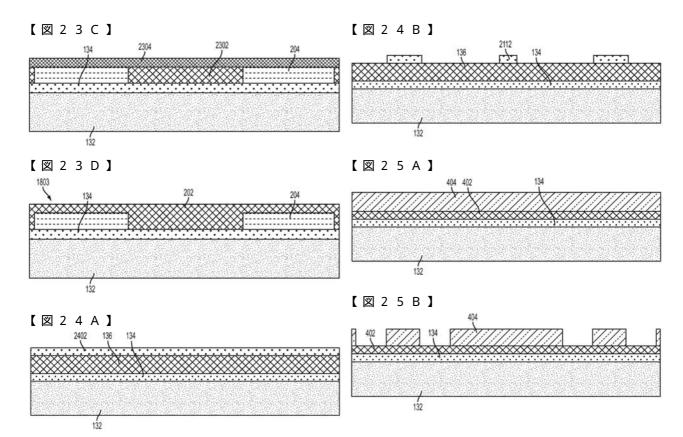

【図23A】[0054]本出願の非限定的な実施形態に係る、内部に形成されたピストンを有する転写ウェハを製作するためのプロセスシーケンスを例示する図である。

【図23B】本出願の非限定的な実施形態に係る、内部に形成されたピストンを有する転写ウェハを製作するためのプロセスシーケンスを例示する図である。

【図23C】本出願の非限定的な実施形態に係る、内部に形成されたピストンを有する転写ウェハを製作するためのプロセスシーケンスを例示する図である。

【図23D】本出願の非限定的な実施形態に係る、内部に形成されたピストンを有する転写ウェハを製作するためのプロセスシーケンスを例示する図である。

【図24A】[0055]本出願の非限定的な実施形態に係る、メンブレンストッパを有する転写ウェハを製作するためのプロセスシーケンスを例示する図である。

【図24B】本出願の非限定的な実施形態に係る、メンブレンストッパを有する転写ウェ ハを製作するためのプロセスシーケンスを例示する図である。 10

20

30

40

20

30

40

50

【図 2 5 A 】[0056]本出願の非限定的な実施形態に係る、内部に形成されたピストンを有する転写ウェハを製作するための代替のプロセスシーケンスを例示する図である。

【図25B】本出願の非限定的な実施形態に係る、内部に形成されたピストンを有する転写ウェハを製作するための代替のプロセスシーケンスを例示する図である。

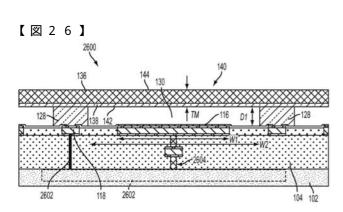

【図26】[0057] CMOSウェハ内の集積回路に接続された図1 Kの超音波振動子を、集積回路が超音波振動子下方に設けられる状態で例示する図である。

【発明を実施するための形態】

### [0033]

## [0034]

[0059] したがって本出願の態様は、CMOSウェハと統合された超音波振動子や、いくつかの実施形態において、CMOSウェハ上に形成されたCMOS ICを製作するスケーラブルな、比較的低コストの方法を提供する。そのような方法は、本明細書でCMOS超音波振動子(CUT:CMOS Ultrasonic Transducer)と呼ぶ、モノリシックに統合された超音波振動子およびCMOS ICを含む新しい部類のデバイスの形成を可能にする。CUTは、超音波撮像および/もしくは高強度焦点式超音波(HIFU)用途ならびに/または他の超音波用途のための超音波デバイスを形成するために使用されてよい。

## [0035]

[0060] C U T の ス ケ ー ラ ブ ル な 大 規 模 生 産 に 適 す る 手 法 で C M O S 処 理 技 法 と の 超 音 波 振動子技術の統合を容易にするため、製造プロセスが様々な特性のうちの1つまたは複数 を発揮することが望ましい場合がある。たとえばプロセスは、CMOSウェハとその上に 形成された任意の回路(たとえば、IC)に損傷を与えることなく超音波振動子を形成す るのに適したものにすることができる。したがってプロセスは、CMOSウェハとCMO ICに損傷をもたらすのに十分なだけ高い温度を必要とする処理工程を回避してよい 。むしろ、低温プロセスが利用されてよい。プロセスは、単一結晶(単結晶)形よりもむ しる多結晶および / または非晶形の材料など、CMOSプロセスラインに一般的であり、 また製作および/または堆積のために莫大な労力または時間を必要としない材料を活用し て よ い 。 プ ロ セ ス は 、 個 別 の 超 音 波 振 動 子 セ ル に 直 接 的 ま た は 間 接 的 に 電 気 的 に 接 続 す る 適切な手法を提供してよい。プロセスはまた、低電圧動作(たとえば、70V未満、50 V未満、30V未満、または振動子動作のための他の適切な低電圧)を可能にするのに適 したサイズの超音波振動子を作製するのに適したものにすることができ、それらが低電圧 CMOS ICとより互換的となる。たとえばプロセスは、所望の振動子挙動(たとえば 、所望の動作周波数、帯域幅、電力、または他の特性)を依然果たしながら、低電圧デバ イスとしての動作のための十分なサイズ(たとえば、十分に小さい厚さ)と形状のメンブ レンを作製するのに適したものにすることができる。製造プロセスのその他の特性も、C MOSウェハとの超音波振動子の統合を容易にするためにいくつかの実施形態において望 ましいものにすることができる。

### [0036]

[0061] したがって本出願の態様は、CMOSウェハ上に超音波振動子メンブレンを形成するために低温(たとえば、450 未満)ウェハボンディングを実装する。この状況下での低温は、いくつかの実施形態において、450 未満、400 未満、350 未満

、200 と450 との間、その範囲内の任意の温度、またはCMOSウェハ上の構造を保持するのに適切な任意の温度であってよい)。したがって、いくつかの実施形態に係るCUTを形成するためのボンディングプロセスだけでなく他の製作工程も450 超の任意のアニールを回避してよい。いくつかの実施形態において、メンブレンは、多結晶シリコンやアモルファスシリコン、二酸化ケイ素、窒化ケイ素(SiN)、窒化チタン(TiN)など、比較的単純かつ安価な材料で形成されてよい。メンブレンはまた薄くてよく、また少なくともいくつかの実施形態において、CMUTでこれまでに達成可能なものよりも薄くてよい。そのような薄いメンブレンの使用は、CMOS技術に準拠するのに十分なだけ低い電圧で動作可能な超音波振動子の形成を容易にすることができる。

[0037]

[0062] 本出願の態様は、CMOS集積回路との超音波振動子の統合を容易にする手法で超音波振動子のメンブレンに電気的に接続するための様々な設計とプロセスを提供する。いくつかの実施形態において、接続はメンブレンのキャビティ側(たとえば、底側)から行われてよい。そのような接続は、埋め込みビアや導電性スタンドオフもしくはキャビティ壁経由で、または任意の他の適切な手法で行われてよい。そのような電気的相互接続は、全体的接続よりはむしろメンブレンへの局所的接続を提供してよく、それにより個別のメンブレンへの接続は、関連する回路から大きく離れかつ複数メンブレンへの局所的接続の機能は、たとえばメンブレンの個別的な制御の機能のため、全体的相互接続によりもたらされるものよりも広い範囲の動作体系を可能にしてよい。

[0038]

[0063] 本出願の態様は、メンブレンが1つまたは複数の比較的厚い中央部分と比較的薄い周辺(または外側)部分とを含む、ピストン構成を有するCUTを提供する。そのような構造は本明細書でピストンメンブレンと呼ばれてよい。いくつかの実施形態において、ピストンメンブレンはウェハボンディング前に転写ウェハ上に完全に形成されてよい。転写ウェハは次いで低温処理方法でCMOSウェハに接合されてよく、ピストンメンブレンが転写ウェハの残りから除去されてよい。この手法で、一体の本体を画定する単一の材料で形成されたピストンメンブレンが形成されてよく、そのようなピストンメンブレンは、ウェハボンディング後にそのような処理が行われたならばCMOS ICに損傷を与えるのに十分なだけ高い温度で処理された材料で形成されてよい。

[0039]

[0064] 上述の態様と実施形態だけでなく追加の態様と実施形態も以下にさらに記載される。これらの態様および / または実施形態は、個別に、すべて一緒に、または 2 つ以上の任意の組み合わせで使用されてよく、本出願はこの点では限定されない。

[0040]

[0065] CMOSウェハ内のキャビティ上方にメンプレンを有する超音波振動子を形成するための第1のプロセスがここで記載される。図1Aを参照すると、プロセスは、基板102、誘電または絶縁層104、第1の金属化層106および、いくつかの実施形態においてCMOSウェハ100の最上部金属化層であってよい第2の金属化層108を含むCMOSウェハ100で開始してよい。

[0041]

[0066] 基板 1 0 2 はシリコンまたは任意の他の適切な C M O S 基板であってよい。いくつかの実施形態において、 C M O S ウェハ 1 0 0 は C M O S 集積回路 ( I C ) を含んでよく、したがって基板 1 0 2 はそのような回路を支持するのに適した基板であってよい。

[0042]

[0067] 絶縁層 1 0 4 は S i O  $_2$  または任意の他の適切な誘電絶縁材料で形成されてよい。いくつかの実施形態において、絶縁層 1 0 4 はオルトケイ酸テトラエチル(TEOS)を介して形成されてよいが、代替のプロセスが使用されてもよい。

[0043]

10

20

30

20

30

40

50

[0068] CMOSウェハ100は2つの金属化層106および108を含むものとして示されるが、本出願の様々な態様に係るCMOSウェハは2つの金属化層を有することに限定されず、むしろいくつかの実施形態においての3つ以上を含み、任意の適切な数の金属化層を有してよいことが認識されるべきである。そのような金属化層はいくつかの実施形態において配線のために(たとえば、配線層として)使用されてよいが、すべての実施形態がこの点で限定されるわけではない。

#### [0044]

[0069] 第1および第2の金属化層106および108は任意の適切な構造を有してよい。例示の実施形態において、少なくとも第2の金属化層108は、中間導電層112(たとえば、アルミニウムまたは他の適切な導電材料で形成される)と上ライナ層110および下ライナ層114とを含む多層構造を有してよい。ライナ層110および114は至少(TiN)または他の適切な導電材料(たとえば、タンタル、または他のランので形成されてよい。いくつかの金属など、TiN以外の金属)で形成されてよい。いくっかの形形態において、上ライナ層110は、たとえば超音波振動子のためのキャビティを形態において、上ライナ層110は、たとえば超音波振動子のためのキャビティを形態において、上ライナ層110は、たとえば超音波振動子のためのキャビティを形態において、カーコングストッパとして使用される10または複数のエッチングストッパとして使用するのに適した材料で形成されてよい。形態においてエッチングストッパとして作用するのに適した材料で形成されてよい。形態においてエッチングストッパとして作用するのに適した材料で形成されてよいの上、図示しないが、第1および第2の金属化層106および108だけでなく本明に記載の任意の他の金属化層も任意選択により、リソグラフィ段階の間に反射防止コーティングとして役立つように酸窒化ケイ素(SiON)を上層として(たとえば、ライナ層10の上に)含んでよい。

#### [0045]

[0070] いくつかの実施形態において、超音波振動子の電極として働く第2の金属化層108から電極を形成することが望ましい場合がある。また第2の金属化層108は、CMOSウェハ上に形成されるべきCUTのメンブレンに電気的に接触させるために使用されてよい。したがって図1Bに示すように、第2の金属化層108は、電極116と1つまたは複数の接点118とを形成するように適切にパターニングされてよい。

#### [0046]

[0071] 図1Bは、電極と電気接点とがCMOSウェハ上に金属化層から形成された構成を例示するが、電極(たとえば、電極116)および/または電気接点(たとえば、電気接点118)を形成する他の手法が実装されてもよいことが認識されるべきである。たとえば、金属以外であるが電極および/または電気接点として作用するのに適する導電材料が、例示の電極および/または電気接点を形成するためにCMOSウェハ上で適切に処理されてよい。

## [0047]

[0072] 絶縁層120が次いで図1Cに示すように堆積されてよい。絶縁層120はSiO₂または任意の他の適切な絶縁体であってよく、また任意の適切な手法で形成されてよい。いくつかの実施形態において、絶縁層120は高密度プラズマ(HDP)堆積により形成されてよい。絶縁層120は次いで、たとえば化学機械研磨(CMP)または他の適切な平坦化技法を用いて平坦化されてよい(図示せず)。

## [ 0 0 4 8 ]

[0073] 図1Dでは、絶縁層120は、電極116と電気接点118との上面を露出するように図示のようにエッチングされてよい。いくつかの実施形態において、上ライナ層110は、絶縁層120をエッチングするために使用される選択エッチングのためのエッチングストッパとして使用されてよい。例として、ライナ層110はTiNで形成されてよく、またエッチングストッパとして使用されてよいが、すべての実施形態がこの点で限定されるのではない。

## [0049]

[0074] さらなる絶縁層122が、図1Eに示すように、電極116と電気接点118との上面を覆うように堆積されてよく、また次いで図1Fに示すように、電気接点118の

20

30

40

50

ためのコンタクトホール 1 2 4 を開放するようにパターニングされてよい。絶縁層 1 2 2 は S i O っまたは任意の他の適切な絶縁体であってよい。

## [0050]

[0075] 図1Gに示すように、導電層126が堆積されてよい。導電層は、図1Jに関連して後に示すように、超音波振動子のメンブレンへの電気接点を形成するために使用されてよい。また導電層126は、CUTために内部にキャビティを形成するようにパターニングされてよく、導電層126の残りの部分は、キャビティの1つまたは複数の側壁を画定する。いくつかの実施形態において、次いで導電層126は、メンブレンが導電層126の高さだけCMOSウェハ100の面から分離されてよいという点でスペーサを表してもよい。したがって導電層126は、複数の可能な機能のうちの1つまたは複数を果たしてよい。

#### [0051]

[0076] 導電層 1 2 6 は任意の適切な導電材料で形成されてよい。いくつかの実施形態において、導電層 1 2 6 は金属で形成されてよい。たとえば導電層 1 2 6 は、いくつかの実施形態において TiNであってよい。

### [0052]

[0077] 導電層126はCMPまたは他の適切な平坦化技法を用いて平坦化されてよく(図示せず)、また次いで図1Hに示すように、接点128を形成するようにパターニングされてよい。この段階ではキャビティ130は、接点128がキャビティを少なくとも部分的に画定する役目となり、CMOSウェハ内に形成されていることが見られ得る。すなわち接点128(いくつかの実施形態において、閉輪郭を形成する単一の接点を表してよい)は、例示の実施形態においてキャビティ130の側壁として機能し、また図1Kの考慮から後にさらに認識されるように、電極116とキャビティ130の上を覆うメンブレンとの間のスタンドオフを作製する。

### [ 0 0 5 3 ]

[0078] 図1I~1Jに示すように、第2のウェハ131がCMOSウェハに接合されてよい。一般に第2のウェハは、バルクシリコンウェハ、シリコン・オン・インシュレータ (SOI)ウェハ、またはポリシリコンまたはアモルファスシリコン層を含み、単結晶シリコン層とポリシリコンまたはアモルファスシリコン層との間に絶縁層を持つエンジニアド基板など、任意の適切な種類のウェハであってよい。例示の実施形態において、第2のウェハ131は、ベース層またはハンドル層132、絶縁層134、層136、および層138を含む4つの層を含んでよい。第2のウェハ131は、キャビティ130上方にメンブレンを形成するように層136および138をCMOSウェハに転写するために使用されてよく、したがって本明細書で転写ウェハと呼ばれてよい。

# [ 0 0 5 4 ]

[0079] 第2のウェハ131を構成する適切な材料の非限定的な例として、ベース層13 2 はシリコン層(たとえば、単結晶シリコン)であってよく、絶縁層134はSiO₂であってよく、また埋め込み酸化物(BOX)層を表してよく、かつ層136はシリコンであってよい。いくつかの実施形態において、層136はポリシリコンまたはアモルファスシリコンであってよいが、他の実施形態は単結晶シリコンを活用してよい。層138はCMOSウェハ上の接点128への接合に適する材料で形成されてよい。たとえば、接点128と層138は同じ材料で形成されてよい。いくつかの実施形態において、接点128と層138はTiNで形成されてよい。

### [0055]

[0080] CMOSウェハ100に第2のウェハ131を接合するために使用されるプロセスは、たとえば450 を超えない低温接合プロセスであってよい。いくつかの実施形態において、接合プロセスの温度はおよそ200 と450 との間、およそ300 とおよそ400 との間、それらの範囲内の任意の温度、低温接合に関して本明細書に記載した任意の他の温度、または任意の他の適切な温度であってよい。したがって、CMOSウ

ェハ上の金属化層やCMOSウェハ上の任意のICへの損傷が回避され得る。

#### [0056]

[0081] ウェハボンディングプロセスは様々な種類のうちの1つであってよい。いくつかの実施形態において、ウェハボンディングは直接接合(すなわち、融着)であってよい。したがってウェハボンディングは、СМОSおよび第2のウェハのそれぞれの面に通電することと、次いで接合を生成するのに適切な圧力でウェハを押し合わせることとを必要とする場合がある。低温アニールが行われてよい。融着は適切な接合技法の一例を表すものの、たとえば1つまたは複数の中間層(たとえば、接着剤)の使用を通して2つのウェハを接合することを含め、他の接合技法が代替で使用されてよい。いくつかの実施形態において、陽極またはプラズマ支援接合が使用されてよい。

[0057]

[0082] 図1I~1Jに例示する接合は、第2のウェハ131がCMOSウェハ100とモノリシックに統合されるという結果になってよい。したがって、両者はいくつかの状況では一体の本体を形成してよい。

#### [0058]

[0083] メンブレンが次いで第2のウェハ131から形成されてよい。第2のウェハ131は裏側から薄膜化されてよい。そのような薄膜化は段階的に行われてよい。たとえば、粗い厚さ制御(たとえば、10ミクロン制御)を提供する機械研削が、比較的多量のバルクウェハを除去するために最初に実施されてよい。いくつかの実施形態において、機械研削の厚さ制御は、薄膜化プロセスが進行するにつれて粗い状態から細かい状態へ変化してよい。次いで、たとえば層136に近い点に達するために、CMPが裏面に行われてよい。次に、選択化学エッチングなどの選択エッチングが層136上で停止するように行われてよい。他の薄膜化の手法も可能である。

[0059]

[0084] したがって図1Kに示すように、ベース層またはハンドル層132と絶縁層134とが除去されてよい。層136と層138とで形成されたメンブレン140が残ってよい。メンブレンは任意の適切な厚さTMであってよく、その非限定的な例は以下に記載される。いくつかの実施形態において、層136は、所望のメンブレン厚を提供するようにエッチングまたは他の方法で薄膜化されてよい。

[0060]

[0085] 図1Kに例示する構造の様々な特徴に言及する。最初に、構造はメンブレン140により封止された封止キャビティ130を含む。また、キャビティの側壁は導電性であり、すなわち、接点128が導電性であり、封止キャビティの側壁を形成する。この点で接点128は、CMOSウェハの面からメンブレン140のための導電性スタンドオフを表す。接点128は比較的大面積の電気接点であり、メンブレンの比較的大面積に接触してもよく、したがってメンブレンに又はメンブレンから低抵抗の電気経路を提供する。たとえば接点は、メンブレンと、電気信号を提供又は受信するためにメンブレンと相互作用し、したがっていくつかの実施形態においてメンブレンの動作を制御してよい、CMOSウェハ上のIC(たとえば、キャビティ下方に設けられる)との間の電気的制御を提供してよい。

[0061]

[0086] その上、メンブレン140はキャビティ130に近い第1の側142とキャビティから遠い第2の側144とを有すること、および第1の側142に接点128を介して直接電気的に接触させることが留意される。第1の側142はメンブレンの底側と呼ばれてよく、第2の側144はメンブレンの上側と呼ばれてよい。メンブレン140への局所的接続はこの手法で行われてよく、またメンブレン140はこの接続を介して(たとえば、接点118を介して)CMOSウェハ内の集積回路に接続されてよい。いくつかの実施形態において、ICはキャビティ130下方に位置決めされてよく、例示の導電性経路構成はキャビティ下方の集積回路とメンブレン140との間を接続することを容易にしてよい。図1Kの構成は、電気的接触が第2の側144上で行われる接触よりもむしろCMO

10

20

30

40

20

30

40

50

Sウェハ内の導電性経路(たとえば、接点118へ)を経由して提供されるという点で、 メンブレンへの埋め込み接点の非限定的な例を提供する。第2の側144上の接触はメン プレン140の振動に(悪)影響を与えかねないので、上記のような構成は第2の側14 4上で電気的に接触させることよりも好ましくてよい。

### [0062]

[0087] また図1Kの実施形態において、電極116はキャビティ130よりも狭いことが留意される。すなわち、電極116はキャビティ130の幅W2よりも小さい幅W1を有する。そのような構成は、少なくとも、キャビティが導電性側壁(たとえば、接点128)を有するような実施形態において、側壁と電極との間を電気的に分離するために望ましい場合がある。

[0063]

[0088] その上、図1Kの構造は実施形態において層138を含まないことにより変更されてよいことが留意される。したがって実施形態において、直接接合が接点128(たとえば、TiNで形成される)と層136(たとえば、シリコン)との間に形成されてよい

[0064]

[0089] 図1Kに例示の構造は任意の適切な寸法を有してよい。メンブレン140とキャビティ130の寸法の非限定的な例が以下にさらに記載される。

[0065]

[0090] 非限定的な例として、キャビティ130の幅W2はおよそ5ミクロンとおよそ500ミクロンとの間、およそ20ミクロンとおよそ100ミクロンとの間であってよく、またおよそ30ミクロン、およそ40ミクロン、およそ50ミクロン、その間の任意の幅もしくは幅の範囲、または任意の他の適切な幅であってよい。いくつかの実施形態において、幅は、間隙率、すなわち、周囲の構造により占有される領域の量と比較したキャビティにより占有される領域の量を最大化するように選択されてよい。幅寸法はまた、キャビティの開口サイズを識別するために使用されてよく、したがってキャビティは上述の値のうちのいずれか、または任意の他の適切な値の開口を有してよい。

[0066]

[0091] 深さ D 1 はおよそ 0 . 0 5 ミクロンとおよそ 1 0 ミクロンとの間、およそ 0 . 1 ミクロンとおよそ 5 ミクロンとの間、およそ 0 . 5 ミクロンとおよそ 1 . 5 ミクロンとの 間、その間の任意の深さもしくは深さの範囲、または任意の他の適切な深さであってよい 。接点128がTiNで形成される場合、TiNは一般に薄膜として形成されるので、D 1が5ミクロンよりも小さいことが、そのような実施形態において好ましい場合がある。 いくつかの実施形態において、キャビティ寸法および/またはキャビティの上を覆う任意 のメンブレンのメンブレン厚はメンブレンの周波数挙動に影響を与えかねず、したがって 所望の周波数挙動(たとえば、メンブレンの所望の共振周波数)を提供するように選択さ れてよい。たとえば、およそ20kHzとおよそ200MHzとの間、およそ1MHzと およそ10MHzとの間、およそ2MHzとおよそ5MHzとの間、およそ50kHzと およそ200kHzとの間、およそ2.5MHz、およそ4MHz、その間の任意の周波 数 も し く は 周 波 数 の 範 囲 、 ま た は 任 意 の 他 の 適 切 な 周 波 数 の 中 心 共 振 周 波 数 を 持 つ 超 音 波 振動子を有することがいくつかの実施形態において望まれる場合がある。たとえば、例と し て 医 用 撮 像 や 材 料 分 析 の た め 、 ま た は 様 々 な 動 作 周 波 数 が 望 ま れ る 場 合 が あ る 他 の 理 由 で、空気、ガス、水、または他の環境でデバイスを使用することが望まれる場合がある。 キャビティおよび/またはメンブレンの寸法は適宜選択されてよい。

[0067]

[0092] メンブレン厚TM(たとえば、深さD1に略平行な方向に測定されるような)は 1 0 0 ミクロンよりも小さく、 5 0 ミクロンよりも小さく、 4 0 ミクロンよりも小さく、 3 0 ミクロンよりも小さく、 2 0 ミクロンよりも小さく、 1 0 ミクロンよりも小さく、 5 ミクロンよりも小さく、 1 ミクロンよりも小さく、 6 . 1 ミクロンよりも小さく、 その間の任意の厚さの範囲、または任意の他の適切な厚さであってよい。厚さは、メンブレンの

所望の共振周波数などのメンブレンの所望の音響挙動に基づいて、いくつかの実施形態に おいて選択されてよい。

## [0068]

[0093] また、キャビティ130、およびより一般的に本明細書に記載の任意の実施形態のキャビティは様々な形状を有してよいこと、および複数のキャビティが形成されるとき、すべてのキャビティが同じ形状またはサイズを有する必要はないことが認識されるべきである。たとえば図22A~22Dは、キャビティ130および本明細書に記載のその他のキャビティのための様々な可能な形状を例示する。具体的には、図22A~22Dは、様々な形状の内部に形成されたキャビティ130を有するCMOSウェハの部分2200の上面図を例示する。図22Aは、キャビティ130が正方形の開口を有してよいことを例示する。図22Dは、キャビティ130が円形の開口を有してよいことを例示する。図22Dは、キャビティ130が八角形の開口を有してよいことを例示する。他の形状も可能である。

### [0069]

[0094] 部分2200は4つのキャビティを含むとして示されるが、本出願の態様はCMOSウェハ内に形成された1つまたは複数のそのようなキャビティを提供することが認識されるべきである。いくつかの実施形態において、単一の基板(たとえば、単一のCMOSウェハ)は数十、数百、数千、数万、数十万、または数百万のCUT(および対応するキャビティ)が内部に形成されてよい。

## [ 0 0 7 0 ]

[0095] 図1Kは、キャビティ130の上を覆うメンブレン140を有する超音波振動子を例示し、メンブレンは実質的に均一な厚さを有する。いくつかの実施形態において、メンブレンが不均一な厚さを有することが望ましい場合がある。たとえば、メンブレンがピストンとして構成され、中央部分がメンブレンの外側部分よりも大きい厚さを有することが望ましい場合があり、その非限定的な例は以下に記載される。

### [0071]

[0096] 図1Kに例示するもののような超音波振動子は、音響信号を送信および / または受信するために使用されてよい。発生電力、動作周波数(たとえば、帯域幅)、およびメンブレンの振動を制御するために必要とされる電圧の点からの振動子の動作はメンブレンの形状およびサイズに依存してよい。より薄い周辺部分によりCMOSウェハに接続される、中央質量状部分を持つピストン形状のメンブレンは様々な有益な動作特性を提供してよい。

#### [0072]

[0097] したがって、本出願の態様はピストンメンブレンを有する超音波振動子を提供する。そのような振動子は、本出願のいくつかの実施形態に係るウェハボンディングプロセスにより形成されてよい。一般に、そのようなメンブレンのより厚い中央部分はメンブレンの上側または底側に形成されてよく、またウェハボンディング前または後に形成されてよい。適切な製作プロセスの非限定的な例がここで記載される。

## [0073]

[0098] 本出願の実施形態によれば、メンブレンの上側により厚い中央部分を有し、転写ウェハから形成されたピストンメンブレンを作製する方法が提供される。方法は、図1Hの構造に到達するために、図1A~1Hに関連して前述した同じ処理工程を含んでよい。その点から、図2A~2Bに示すように、転写ウェハ201がたとえば前述のような低温(450 未満)直接接合技法を用いて、CMOSウェハと接合されてよい。

### [0074]

[0099] 図2A~2Bの転写ウェハ201はベース層132、絶縁層134、および層138を含む。転写ウェハはまたピストン202、およびいくつかの実施形態においてSiO2(たとえば、オルトケイ酸テトラエチル(TEOS)または他の適切なプロセスを介して形成される)などの絶縁層であってよいが、任意の特定の種類の材料で形成されることに限定されない層204を含む。ピストン202はいくつかの実施形態においてシリコ

10

20

30

40

ンで形成されてよく、またいくつかの実施形態においてポリシリコンまたはアモルファスシリコンで形成されるが、他の実施形態は単結晶シリコンを使用してよい。ポリシリコンまたはアモルファスシリコンの使用は、いくつかの場合では、他の可能な利益の中で、製造プロセスを簡略化および/またはコストを低減することができる。いくつかの実施形態において、ピストン202は縮退ドープされてよい。いくつかの実施形態において、ピストン202はSiP+で形成される。

#### [0075]

[00100] 図2Bに示すように、転写ウェハ201は接合プロセスの結果として、CMOSウェハとモノリシックに統合されてよい。続いて図2Cに示すように、ベース層132、絶縁層134および層204がウェハ研削、次いでエッチング、そして埋め込み酸化物の除去、または任意の他の適切な手法で除去されてよい。結果はしたがって、キャビティ130の上を覆うピストン202を含んでよい。ピストン202と層138とは図示のようなメンブレンを形成してよく、したがってピストンメンブレンとみなされてよい。ピストンメンブレンは厚さT1の周辺(または外側)部分と厚さT2の中央部分を有してよい、いくつかの実施形態において、T1は可能な限り薄くされてよく、かつたとえばおよそ1ミクロンとおよそ10ミクロンとの間であってよい。ピストン202は幅WPを有してよい。いくつかの実施形態において、幅WPは電極116の幅W1と実質的に同じであってよい。しかしながら、すべての実施形態がこの点で限定されるとは限らず、幅WPはいくつかの実施形態においてW1よりも大きくてよくまたはいくつかの実施形態においてW1よりも大きくてよくまたはいくつかの実施形態においてW1よりも大きくてよくまたはいくつかの実施形態においてW1より小さくてよい。

#### [0076]

[00101] 寸法の非限定的な例として、図2Cに例示するキャビティ130は、本明細書で前述したキャビティ寸法のうちのいずれか、または任意の他の適切な寸法を有してよい。たとえば、D1およびW2は、それらの寸法に関して前述したいくつかのうちのいずれかを有してよい。

## [0077]

[00102] 厚さT1は、T1に関して前述した値のうちのいずれかまたはTMに関して記載した値のうちのいずれかであってよい。同様に厚さT2は、TMに関連して前述した値のうちのいずれか、または任意の他の適切な値を有してよい。いくつかの実施形態において、厚さT1は可能な限り小さくされてよく、厚さT2はTMに関連して前述した値のうちのいずれかをとってよい。たとえば、厚さT2は1ミクロンとおよそ100ミクロンとの間、およそ10ミクロンとおよそ50ミクロンとの間、そのような範囲内の任意の値、または任意の他の適切な値であってよい。

## [0078]

[00103] キャビティの上を覆うピストンメンブレンを形成するための非限定的な代替のプロセスが図 3 A ~ 3 Bに例示され、ピストンのより厚い中央部分がメンブレンの上側にある。プロセスは図 1 K の構造で開始し、そこから図 3 A に示すようにパッシベーション層 3 0 2 を追加してよい。パッシベーション層は窒化ケイ素(Si₃ N 4 )またはС M O S ウェハへの損傷を防止するのに十分なだけ低い温度で形成されてよい他の適切なパッシベーション材料であってよい。

# [0079]

[00104] パッシベーション層 3 0 2 は次いで、ピストンメンブレンのための中央部分 3 0 4 を作製するために図 3 B に示すように適切にエッチングされてよい。本実施形態において、中央部分 3 0 4 が層 1 3 6 のものとは異なる材料で形成されることが留意されるべきである。

## [0800]

[00105] 図 3 B のピストンメンブレンは厚さT 3 を持つ外側部分を有してよく、中央部分は厚さT 4 を有してよい。厚さT 3 はT 1 に関連して前述した値のうちのいずれかであってよい一方、T 4 はT 2 に関連して前述した値のうちのいずれかであってよい。

## [ 0 0 8 1 ]

30

10

20

40

20

30

40

50

[00106] ピストンメンブレンを形成するためのさらなる代替のプロセスが図4A~4Cに例示される。プロセスは図1Hのものと類似の、実質的に同じ、または同一の構造いるしかしながら接点128は、図4A~4Cの実施形態においてより小小さを有してよい。たとえば、図1Hでの接点128が図1Hにより表される実施形態においてキャビティ130の深さD1と同じ高さであってよく、したがってD1に関して出まいでまであってよく、したがってD1に関して出まに前述した値(たとえば、1ミクロンと10ミクロンとの間や、5ミクロンよりよいさくてよい(たとえば、1ミクロンと10ミクロンとの間や、5ミクロンよりもよび、リ小さくてよい(たとえば、前述のD1の2分の1の高さや、D1の4分の1の高さなでリ小さくてよい(たとえば、前述のD1の2分の1の高さや、D1の4分の1の高さなで、単結晶シリコンや、ポリシリコン、アモルファスシリコン、SiP+)およびパターン化層404はおよそ1ミクロンとおよそ10ミクロンとの間、およそ3ミクロンとの間、それらの範囲内の任意の値、5ミクロンよりも小さい、または任意の他の適切な値の厚さを有してよい。

### [0082]

[00107] パターン化層 4 0 4 は接点 1 2 8 への接合に適する材料で形成されてよく、またいくつかの実施形態において接点 1 2 8 と同じ材料で形成されてよい。実施形態においてパターン化層 4 0 4 は T i N で形成されてよい。

#### [0083]

[00108] 図4Cに示すように、ベース層132と絶縁層134とが、CMOSウェハとの転写ウェハの接合に続いて除去されてよい。そのような除去は、研削、エッチングおよび/もしくは埋め込み酸化物の除去、または他の適切な技法を用いて行われてよい。いくつかの実施形態において、層402は所望のメンブレン厚に薄膜化されてよい。図示のように、得られる構造は、より厚い中央部分がメンブレンの下側に形成されたピストンを含んでよい。この構成では、電気的接続性がパターン化層404から層402を通じてキャビティ側壁に提供されてよいが、これはこれらのコンポーネントを構成する材料が導電性であってよいからである。

### [ 0 0 8 4 ]

[00109] 図4A~4Cの考察から、例示のCUTは2つのウェハと単一のウェハボンディングプロセスのみで形成されてよいことが認識されるべきである。層402はいくつかの実施形態においてエッチングストッパとして機能してよく、これがピストンメンブレン(402と404の組み合わせ)の形成物が単一の転写ウェハから形成されることを可能にしてよい。したがってプロセスは、ピストンメンブレンを形成するために3つ以上のウェハと複数のウェハボンディング工程が使用される場合と比べて、比較的単純であって比較的少数の処理工程を含んでよい。

### [0085]

[00110] 本出願の態様に係る超音波振動子の一部として形成されてよい別の構造はメンブレンストッパであり、これはいくつかの実施形態において分離柱として機能してよれてよれなの実施形態において分離柱として機能を表して機能を表して機能を表して機能を表してよりにキャビティの深さを効果的に変更更してよれると、メンブレンはキャビティの底に接触する。そのような動作は定ってよれると、メンブレンをキャビティの底に衝突または接触させることが特定の共振である。しかしながら「電荷が最大により振動子の電極上に堆積してよい、それにステリの関連を表である。しかしない。メンブレンをキャビティの底に衝突を広げるからである。しかしながら「電荷が最大になった」が増加しまたによりまままでの動作特性が変更され(たとえば、必要なバイアス電圧が増加しまたによりの動作特性が変更され(たとえば、必要なバイアスである。と、メンブレンストッパを持つ超音波振動子は、そのようなメンブレンストッパはメンブレンストッパを持つ超音波振動子は、そのようなメンブレンストッパはメンブレストッパを持つ超音波振動子は、その上、メンブレンストッパはメンブレカーがである。その上、メンブレンストッパはメンブレカーが表によりました。その上、メンブレンストッパはメンストッパであり、メンブレンストッパはメンブレンストッパであります。

レンがキャビティの最底部に接触することを防止することができるので、すべての実施形態においてキャビティの底面に絶縁体が形成される必要はなくなり、したがって、超音波振動子を製作する際の処理工程および時間を低減できる。しかしながら、メンブレンとキャビティの底との間に予期せぬ接触がある(いかなるメンブレンストッパがあってとしても)場合、および/またはキャビティにわたる放電を防止するためには、キャビティの底面上の絶縁体が使用されてよい。

### [0086]

[00111] メンブレンストッパは超音波振動子の異なる位置に形成されてよい。たとえば、メンブレンストッパは超音波振動子のキャビティの底に形成されてよい。いくつかの実施形態において、メンブレンストッパは超音波振動子のメンブレンの底に(たとえば、転写ウェハから転写されたメンブレンの底側に)形成されてよい。他の実施形態において、メンブレンストッパは超音波振動子のキャビティの底とメンブレンの底との両方に形成されてよい。非限定的な例がここで記載される。

## [0087]

[00112] 図 5 は図 1 K のものの代替の超音波振動子を例示する。図示のように、超音波振動子は図 1 K の構造に加えて、キャビティ 1 3 0 の底に形成されたメンブレンストッパ 5 0 2 を含む。

#### [0088]

[00113] メンブレンストッパ 5 0 2 は、図 1 D および図 1 E の段階間で形成されてよい。すなわち工程 1 D に続いて、メンブレンストッパが電極 1 1 6 上に堆積されてパターニングされてよい。図 5 の構造に到達するために、図 1 E ~ 1 K の処理工程が次いで行われてよい。

### [0089]

[00114] 本出願の態様によれば、超音波振動子はピストンメンブレンと1つまたは複数のメンブレンストッパとを有してよい。非限定的な例が図6に関連して例示され、これは前述した図4Cおよび図5の特徴の組み合わせである。

## [0090]

[00115] 図1A~1Kは、超音波振動子のメンブレンの底側に接続する埋め込み電気接点の非限定的な一例を例示する。その非限定的な例では、導電性接点は超音波振動子のキャビティの側壁でもあり、超音波振動子が導電性側壁を有したことを意味する。CMOSウェハから超音波振動子のメンブレンの下側に直接電気的に接触させるための代替の構成は埋め込みビアを使用することである。図7A~7Hは非限定的な例を例示する。

#### [0091]

[00116] 図 1 A ~ 1 C の処理段階が行われてよい。次いで図 7 A に示すように、絶縁層 7 0 2 が、たとえば高密度プラズマ堆積を用いて堆積されてよい。絶縁層 7 0 2 は S i O  $_2$  または任意の他の適切な絶縁体であってよい。絶縁層は、たとえば C M P により平坦化されてよい。

### [0092]

[00117] 図 7 B に示すように、 1 つまたは複数のビア 7 0 4 が、たとえばエッチングストッパとして機能してよい第 2 の金属化層 1 0 8 上に行き着くようにエッチングされてよい。任意選択により、ライナ材料(たとえば、 T i N ) の比較的薄い層 7 0 6 が共形に堆積され、したがってビア 7 0 4 と C M O S ウェハの上面を覆ってよい。

### [0093]

[00118] 図7Cに示すように、ビアは次いで、たとえばタングステン(W)などの導電材料の層を堆積させることにより、導電性プラグ708で充填されてよい。図7Dに示すように、導電層はエッチバックされてよい。

#### [0094]

[00119] 図 7 E では、キャビティ 1 3 0 が次いで絶縁層 7 0 2 からエッチングされてよく、内部に埋め込まれる導電性プラグ(すなわち、導電性プラグ 7 0 8 )を有する側壁 7 1 0 が残る。

10

20

30

#### [0095]

[00120] 図 7 F では、 C M O S ウェハの上面が絶縁層 7 1 2 で覆われていてよく、これは続いてウェハボンディングの準備のために側壁 7 1 0 の頂部から除去されてよい。

#### [0.096]

[00121] 図7Gでは、図1Iの転写ウェハと類似または同じであるが、層138を欠いてよい転写ウェハ711が、CMOSウェハとウェハ接合されてよい。図7Hに示すように、ベース層132と絶縁層134とが次いで適切な技法により除去されてよく、したがってメンプレン714が残る。

## [ 0 0 9 7 ]

[00122] 図7Gに例示の接合はプラグ708をプラグの頂部上の層136と直接接触させ、すなわち交点でのプラグ708と層136との間にライナは形成されなくてよいことが認識されるべきである。いくつかの実施形態において、層136はシリコン(たとえば、単結晶、多結晶、またはアモルファス)であってよい。従来の処理技法は、たとえばタングステンで形成されるプラグのそのような直接接続を回避しようと努めるが、本出願人らはそのような直接接続は、直接接続がプラグと高品質集積回路を支持するためには使用されていない層(たとえば、層136)との間であるシナリオでは、許容可能であってよいことを認識した。むしろ、層136はメンブレンを形成するために使用されているので、層136へのプラグ708からの材料の拡散は、いくつかの実施形態において許容可能であってよい。

## [0098]

[00123] 図 8 A ~ 8 B は、図 7 H の構造からピストンを形成するための方法を例示する。すなわち、S i  $_3$  N  $_4$  または任意の他の適切なパッシベーション材料のパッシベーション層 8 0 2 がメンブレン 7 1 4 上に堆積されてよい。次いで図 8 B に示すように、パッシベーション層 8 0 2 は適切にパターニングされてよい。

#### [0099]

[00124] 図 9 A ~ 9 B は、キャビティが内部に埋め込みビアを有する非導電性側壁により囲まれる、 C M O S ウェハ内のキャビティ上方にピストンメンブレンを形成する代替の手法を例示する。図 9 A に示すように、図 7 F の構造が、図 2 B に関連して前述した種類から層 1 3 8 を除いたものと類似の転写ウェハ 1 8 0 3 と接合されてよい。図 2 C に関連して前述のように、ベース層 1 3 2 、絶縁層 1 3 4 および層 2 0 4 は除去されてよい。

### [0100]

[00125] 本出願のいくつかの実施形態は、CMOSウェハ内のキャビティ上方にあり、 メンブレンの上側への接触を行う埋め込みビアを有するメンブレンを製作するための実用 的な方法を提供する。図10A~10Hは例を例示する。

# [0101]

[00126] 図 7 A の構造で開始すると、絶縁層 7 0 2 は、図 1 0 A に示すように、キャビティ 1 3 0 を少なくとも部分的に画定する側壁 1 0 0 2 を形成するようにパターニングされてよい。図 1 0 B では、絶縁体(たとえば、 S i O  $_2$  ) 1 0 0 4 が堆積され、次いで側壁 1 0 0 2 の上側を別のウェハとの接合のために調整するように C M P が行われてよい。 【 0 1 0 2 】

[00127] 図10Cに示すように、次いでウェハボンディングがCMOSウェハと第2のウェハ(たとえば、転写ウェハ)を用いて行われてよい。転写ウェハは、図7Gに関連して前述したものと同じ種類であってよいが、他の種類の転写ウェハも可能である。接合プロセスは、CMOSウェハ上の任意のシリコン回路(たとえば、IC)を保持してよい低温(たとえば、450 未満)直接接合プロセスであってよい。

# [0103]

[00128] 図10Dに示すように、ベース層132と絶縁層134とが、たとえばそのような除去に関して前述した技法のうちのいずれかを用いて除去されてよい。したがって、メンブレン1006はCMOSウェハとモノリシックに統合され、キャビティ130の上を覆ってよい。

10

20

30

#### [0104]

[00129] 図10Eに示すように、ビア1008がメンブレン1006と側壁1002とを通して形成されてよく、接点118上で行き止まる。エッチングは選択エッチングであってよく、また深堀り反応性イオンエッチング(DRIE)のように指向性であり、または任意の他の適切なエッチングであってよい。ライナ1010が次いでビア内およびメンブレン1006の上側に形成されてよい。ライナは導電性であってよく、金属であってよく、またいくつかの実施形態においてTiNであるが、他の材料が代替で使用されてもよい。

## [ 0 1 0 5 ]

[00130] 図10Fに示すように、プラグ1012が次いで、適当な堆積およびエッチバックによりビア1008内に形成されてよい。たとえば、プラグ1012はタングステンで形成されよく、またビア1008を充填するためにタングステンを堆積させ、次いでライナ1010(たとえば、TiN)をエッチングストッパとして使用してタングステンをエッチバックすることにより形成されてよい。

#### [0106]

[00131] 続いて図 1 0 G では、層 1 0 1 4 および 1 0 1 6 がメンブレン 1 0 0 6 の上側に堆積されてよい。層はパッシベーション層を含んでよい。たとえば、層 1 0 1 4 は S i O  $_2$  または任意の他の適切なパッシベーション層であってよい。層 1 0 1 6 もパッシベーション層であってよく、いくつかの実施形態において S i  $_3$  N  $_4$  であってよい。

## [ 0 1 0 7 ]

[00132] したがって図10Gは、CMOSウェハとモノリシックに統合されたメンブレン(したがってメンブレンの上側)を通じて電気接点を提供する超音波振動子の構成を例示し、ここで接点は、CMOSウェハのキャビティの側壁内に埋め込まれるビアにより少なくとも部分的に形成された導電性経路を含む。任意選択により、図10Hに示すように、層1014および1016はピストンメンブレン1018を画定するようにパターニングされてよい。

#### [0108]

[00133] 図 1 0 Hのピストンメンブレン 1 0 1 8 は、図 1 0 A  $\sim$  1 0 Gの処理工程を用いて形成されてよいピストンメンブレンの非限定的な例である。ピストンメンブレンは、 T 1 に関して本明細書に前述した値のうちのいずれかをとる厚さを持つ外側部分(メンブレンが側壁 1 0 0 2 に接触する箇所に近い)と、 T 2 に関して本明細書に前述した値のうちのいずれかをとる厚さを有する中央部分とを有してよい。例として、中央部分は 5 0 ミクロンよりも小さい厚さを有してよい。代替として、いくつかの実施形態において、ピストンが図 1 0 Hに示すものよりも厚いことが望ましい場合がある。図 1 1 は非限定的な例を例示する。

## [0109]

[00134] 図示のように、図11のピストンメンブレン1102は、図10Hのピストンメンブレン1018よりも厚くてよい(たとえば、1.5倍の厚さ、2倍の厚さ、3倍の厚さ、または任意の他の適切な厚さ)が、超音波振動子の残りは図10Hに例示のものと実質的に同じであってよい。そのような構成は、層1016を図11の実施形態で図10Gの実施形態でよりも大きい厚さに形成することにより達成されてよい。

#### [0110]

[00135] CMOSウェハの金属化層からメンブレンの上側に電気的に接触させるためのさらなる代替の構成として、図12は図10Eの構造に実質的に対応する実施形態を例示する。しかしながら図12の実施形態において、ライナ1010は図10Eの実施形態のものよりも厚くてよい。たとえばライナ1010は、図10Eの実施形態においては1ミクロンよりも小さくてよいが、図12の実施形態においてはおよそ2ミクロンと3ミクロンとの間であってよい。図12でのライナ1010はそこで、ビア内に形成される導電性プラグなしに、一次電気接点として働いてよい。そのような構成は、ビア内にプラグを形成することに関連するさらなる処理工程を回避することにより、超音波振動子の処理を簡

10

20

30

40

略化してよい。

## [0111]

[00136] いくつかの実施形態において、上側電気接点を有するが、埋め込み電気接点を有しないCUTが提供される。本出願の態様は、そのようなCUTのいくつかの異なる設計を製作する実用的で、費用効果の高い手法を提供する。いくつかの非限定的な例がここで記述される。

### [0112]

[00137] 図 1 3 A ~ 1 3 I は、上側電気接点を有する C U T を製作するためのプロセスの第 1 の非限定的な実施形態を例示する。図 1 A の構造から開始すると、第 2 の金属化層 1 0 8 が、電極 1 3 0 2 を形成するように、図 1 3 A に示すようにパターニングされてよい。

#### [0113]

[00138] 図13Bに示すように、絶縁層1304が次いで堆積されてよい。絶縁層はいくつかの実施形態において、たとえばTEOSまたは他の適切な堆積技法により形成されたSiOっであってよい。

### [0114]

[00139] 図13Cに示すように、絶縁層1304は、キャビティを少なくとも部分的に画定する側壁またはスペーサ1306を有するキャビティ1308を形成するようにエッチングされてよい。絶縁層の任意の適切なエッチングが行われてよい。いくつかの実施形態において、エッチングは選択エッチングであってよく、第2の金属化層108はエッチングストッパとして機能してよい。たとえば第2の金属化層108は、エッチングストッパとして機能してよいTiN(たとえば、上面のTiNライナ)を含んでよい。

### [0115]

[00140] 図 1 3 D に示すように、絶縁層 1 3 0 9 (たとえば、  $SiO_2$ ) が次いで堆積されてよい。 CMOS ウェハは、表面処理を行うことにより、ウェハボンディングのために平坦化され(たとえば、 CMP を用いて)調製されてよい。 したがって絶縁層 1 3 0 9 は、側壁 1 3 0 6 の頂部から除去されてよい。

#### [0116]

[00141] ウェハボンディングは次いで、図10Cに前述した種類の転写ウェハ、または任意の他の適切なウェハを用いて、図13Eで行われてよい。転写ウェハのベース層132と絶縁層134とが次いで、図13Fに示すように前述の手法で除去されてよく、キャビティ1308を封止するメンブレン1310が残る。本実施形態において、電極1302がキャビティ1308よりも広いことが認識されるべきである。たとえば、キャビティはW2に関して本明細書に前述した値のうちのいずれかをとる幅を有してよく、電極1302はその幅よりも2ミクロン大きく、その幅よりも5ミクロン大きく、その幅よりも10ミクロン大きく、その幅よりも15ラロンとの間大きく、または任意の他の適切な値であってよい。

### [0117]

[00142] 図13Gに示すように、接点1312がメンブレン1310の上側に形成されてよい。接点は任意の適切な構造を有してよい。いくつかの実施形態において、接点は、メンブレンの上側に金属化層を形成し、次いで例示の構造に到達するために金属化層をパターニングすることにより形成されてよい。金属化層は、たとえば、第2の金属化層108に関連して前述した3層構造または任意の他の適切な構造を有する、多層構造を含んでよい。したがって非限定的な例として、接点1312は上下のTiN層の間に挟まれるアルミニウムの層を含んでよいが、他の構成も可能である。

# [0118]

[00143] 図 1 3 H に示すように、パッシベーション工程が次いで、たとえば層 1 3 1 4 および 1 3 1 6 を堆積させることにより行われてよい。層 1 3 1 4 はたとえば S i O  $_2$  で形成された絶縁層であってよい。層 1 3 1 6 は S i  $_3$  N  $_4$  または任意の他の適切な材料で形成されてよい。

10

20

30

40

20

30

40

50

#### [0119]

[00144] 図13Iに示すように、層1314および1316は次いでメンブレン131 0の上側にパッシベーション接点1318を形成するようにパターニングされてよい。

#### [0120]

[00145] 図14は、図13Iのものの代替のCUTを例示する。図13IのCUTに類似するものの、図14のCUTはキャビティ1308ほど広くない底電極1402を有し、これがキャビティ側壁との静電容量を低減してよい。たとえば、キャビティ1308は、W2に関して本明細書に前述した値のうちのいずれかをとる幅を有してよく、電極1402は4分の3の大きさ、2分の1の大きさ、3分の1の大きさ、または任意の他の適切な値の幅を有してよい。図14のCUTを製作するために使用される処理工程は、図13IのCUTを製作するために使用されるものと実質的に同じであってよいが、電極がより狭いがゆえに、図13Dで堆積された絶縁層は、図13Cの間に起こり得るオーバーエッチングを補償するために、図14のCUTを製作する状況ではより厚くてよい。たとえば図13Dで堆積された絶縁層は、図13IのCUTを製作するために使用されるものの2倍の厚さ、3倍の厚さ、または任意の他の適切な厚さであってよい。

#### [0121]

[00146] 前述のように、いくつかの実施形態においてCUTはピストンを含んでよく、そのようなピストンを製作するためのプロセスは本明細書に記載される。さらなる非限定的な例として、図15のCUTがピストン1502を含むように製作されてよい。例示のCUTは図14に示すものと類似する。しかしながら、層1314および1316をパターニングする際に、これらの層の一部が、ピストン構造を形成するようにメンブレン1310の中心上の適所に残されてよい。

## [0122]

[00147] 他の可能な要件の中で、周波数応答、電力処理能力、および堅牢性の点で様々な超音波振動子挙動を提供するために様々な厚さのピストンが望ましい場合がある。図 15 のものの代替であり厚いピストンを有する CUT構造が図 16 Aおよび図 16 Bに関連して記載される。

### [0123]

[00148] 図16Aの構造は前述の図13Hのものと類似する。しかしながら、図15で提供されるものよりも厚いピストンを形成することを見越して、層1314および1316は図16Aの実施形態においてより大きい厚さに形成されてよい。たとえば、層1314および1316は各々およそ2ミクロンと20ミクロンとの間、およそ3ミクロンと10ミクロンとの間、これらの範囲内の任意の値、または任意の他の適切な値であってよい

# [0124]

[00149] 図16Bでは、層1314および1316は、パッシベーション接点1602 およびピストン1604を形成するために適切なエッチング技術を用いてパターニングされてよい。

## [0125]

[00150] 図16BのCUTは、前述のようにキャビティの幅よりも小さい幅を有する電極1402を有することが留意される。しかしながら、図16Bのピストン構成は代替で、CUTのキャビティと同じ幅またはそれよりも大きい幅を有する電極を有するCUTの一部として形成されてよい。

### [0126]

[00151] 図17A~17Cは、キャビティの下にある電極の幅に一致した幅を有するピストンメンブレンを含む、図15および図16Bのものの代替のCUT設計を製作する非限定的な手法を例示する。

## [0127]

[00152] 図17Aに示すように、プロセスは(たとえば、本明細書に記載の任意の適切な処理工程を用いて)CMOSウェハとモノリシックに統合されたメンブレン1704で

20

30

40

50

封止された封止キャビティ 1 7 0 2 を有する構造で開始してよい。電極 1 7 0 6 がキャビティの下に設けられてよい。接点 1 3 1 2 が前述の手法で形成されてよい。絶縁層 1 7 0 8 がメンブレン 1 7 0 4 と接点 1 3 1 2 との上部上側に堆積されてよい。絶縁層 1 7 0 8 は S i O っまたは他の適切な絶縁材料であってよい。

### [ 0 1 2 8 ]

[00153] 図17Bに示すように、絶縁層1708はパターニングされてよく、次いで層1710がメンブレン1704の上側に堆積されてよい。層1710はいくつかの実施形態においてパッシベーション層として機能してよく、またSi<sub>3</sub>N<sub>4</sub>または他の適切なパッシベーション材料で形成されてよい。

## [0129]

[00154] 図17Cに示すように、層1710は次いで、パッシベーション接点1712とピストン1714とを形成するために適切にパターニングされてよい。層1710はそれがパッシベーション接点1712の絶縁層1708を完全に覆う、すなわち層1710がメンブレン1704の上面まで延下するように、パターニングされてよいことが見られ得る。この手法で、層1710は湿気が絶縁層1708を通過して接点1312を害する(たとえば、腐食させる)のを防止することができる。

## [0130]

[00155] 前述のように、いくつかの実施形態において、プロセスは、ピストンメンブレンが最初に転写ウェハ上に形成され、低温ウェハボンディングにより CMOSウェハとモノリシックに統合される、ピストンメンブレンを有する CUTを製作するために提供される。この手法で形成され、かつメンブレンへの上側電気接点を有する CUTの非限定的な例が図 18A~18Eに関連して記載される。

### [0131]

[00156] 図18Aに示すように、そのようなCUTを製作するためのプロセスは、CMOSウェハ1801を図2Aの転写ウェハ201に関して前述したようなものと同じ層のいくつかを有する(すなわち、層132、134、202、および204を有するが、138を欠く)転写ウェハ1803とウェハ接合することにより開始してよい。CMOSウェハは電極1805と側壁1807とを含んでよく、その後者は例示の非限定的な実施形態において、絶縁層1809および1811により形成されてよい。ウェハボンディングは、CMOSウェハ上のシリコン回路などの構造を保持するのに適した低温接合プロセスであってよく、また封止キャビティ1813を作製してよい。図示のように、本実施形態において、電極1805の幅W5はキャビティ1813の幅W2よりも小さくてよい。

#### [0132]

[00157] ベース層132、絶縁層134、および層204は、そのような除去に関して前述した手法のうちのいずれかで転写ウェハ1803から除去されてよい。次いで図18 Bに示すように、たとえば第2の金属化層108に関連して前述した構造を有する金属層1802が堆積されてよい。

### [0133]

[00158] 図 1 8 C に示すように、金属層 1 8 0 2 は接点 1 8 0 4 を形成するようにパターニングされてよく、絶縁層(たとえば、 S i O 2 ) 1 8 0 6 が堆積されてよい。

## [0134]

[00159] 図 1 8 D に示すように、絶縁層 1 8 0 6 はパターニングされてよく、次いで層 1 8 0 8 がパッシベーション層として堆積されてよい。いくつかの実施形態において、層 1 8 0 8 は S i  $_3$  N  $_4$  であってよいが、他の材料が使用されてもよい。図 1 8 E に示すように、層 1 8 0 8 はそれがピストン 2 0 2 に接触し、それにより層 1 8 0 6 の残りの部分を完全に覆うような手法でパターニングされてよい。この手法で、層 1 8 0 8 は湿気が絶縁層 1 8 0 6 を通過して接点 1 8 0 4 を害する(たとえば、腐食させる)のを防止することができる。

#### [ 0 1 3 5 ]

[00160] 図19A~19Bは、ピストン幅がCUTのキャビティ下の電極の幅と一致し

たピストンメンブレンを有するCUTを製作するためのプロセスを例示する。図19Aに示すように、プロセスは、キャビティ下方の電極1902がより狭くてよいことを除き図16Aに関連して前述したものと類似の構造で開始してよい。

## [0136]

[00161] 図 1 9 B に示すように、層 1 3 1 4 および 1 3 1 6 は、電極 1 9 0 2 の幅 W 4 と同じまたは実質的に同じ幅 W 3 を有するピストン 1 9 0 4 を形成するようにパターニングされてよい。

## [0137]

[00162] 前述のように、いくつかの実施形態においてCUTはメンブレンストッパを含んでよい。メンブレンストッパはいくつかの実施形態においてCUTのキャビティの底に位置決めされてよい。CUTのメンブレンの上側の電気接点を持つようなCUTの非限定的な例が図20A~20Iと関連して示される。

## [0138]

[00163] 図20Aに示すように、プロセスは、絶縁層2004により覆われる電極2002を含むCMOSウェハで開始してよい。エッチングが次いで図20Bに示すように、側壁またはスペーサ2008を有するキャビティ2006を形成するように行われてよい

## [0139]

[00164] 続いて図 2 0 C では、絶縁層 2 0 1 0 が堆積されてよい。絶縁層 2 0 1 0 は S i O  $_2$  または任意の他の適切な絶縁材料であってよい。絶縁層 2 0 1 0 は図 2 0 D に示すように、キャビティ 2 0 0 6 内にメンプレンストッパ 2 0 1 2 を形成するようにパターニングされてよい。

## [0140]

[00165] 図 2 0 E に示すように、絶縁層(たとえば、 S i O  $_2$  ) 2 0 1 4 が堆積されてよい。絶縁層 2 0 1 4 は、 C U T (図 2 0 I に示す)のメンブレンが底付く場合に、電気的短絡を防止するように作用してよい。しかしながら、メンブレンストッパ 2 0 1 2 自体が絶縁材料で形成されてよいので、絶縁層 2 0 1 4 はいくつかの実施形態において省略されてよい。

## [0141]

[00166] 絶縁層 2 0 1 4 の堆積後、 C M O S ウェハは平坦化されてよく(たとえば、 C M P を用いて)、表面はウェハボンディングのために調製されてよい。したがって、絶縁層 2 0 1 4 は側壁 2 0 0 8 の頂部から除去されてよい。

#### [0142]

[00167] 図20Fに示すように、ウェハボンディングが次いで、CMOSウェハを図7Gに関連して前述した種類の転写ウェハ711(たとえば、ベースシリコン基板と、埋め込み酸化物層と、いくつかの実施形態において単結晶シリコン、ポリシリコンまたはアモルファスシリコンで形成されたシリコンメンブレン層とを有する多層ウェハ)と接合するように行われてよい。ウェハボンディングプロセスは、CMOSウェハ上のCMOS構造(たとえば、IC)を保持するために低温プロセス(たとえば、450 未満)であってよい。ウェハボンディングプロセスは封止キャビティ2026という結果になってよい。

## [0143]

[00168] 図 2 0 G に示すように、ベース層 1 3 2 と絶縁層 1 3 4 とが除去されてよく(本明細書で前述した、そのような層を除去するための技法のうちのいずれかを用いて)、金属化層 2 0 1 6 はいくつかの実施形態において第2 の金属化層 1 0 8 と同じ構造を有してよいが、代替の構成が可能である。

# [0144]

[00169] 図 2 0 H に示すように、金属化層 2 0 1 6 は接点 2 0 1 8 を形成するようにパターニングされてよく、層 2 0 2 0 および 2 0 2 2 が堆積されてよい。いくつかの実施形態において、層 2 0 2 0 および 2 0 2 2 はパッシベーション層として働いてよく、またそれぞれ S i O  $_2$  および S i  $_3$  N  $_4$  で形成されてよい。

10

20

30

40

#### [0145]

[00170] 図 2 0 I に示すように、層 2 0 2 0 および 2 0 2 2 は、 C U T のメンブレンの上側にパッシベーション接点 2 0 2 4 を生成するようにパターニングされてよい。パッシベーション接点 2 0 2 4 はメンブレンに電気信号を印加するおよび / またはそこから電気信号を受信するために使用されてよい。動作に際して、メンブレンは振動時にメンブレンストッパ 2 0 1 2 はメンブレンストッパに関して前述した手法で C U T の周波数挙動を変更してよい。

### [0146]

[00171] 図 2 1 A ~ 2 1 F は、メンブレンストッパとCUTのメンブレンへの上側電気接点とを有するCUTを製作するための代替のプロセスを例示する。本実施形態において、メンプレンストッパはCUTのキャビティの底によりもむしろCUTのメンブレンの下側にあってよい。

## [0147]

[00172] プロセスは図 2 1 A に示すように、ウェハボンディングのために調製された C M O S ウェハで開始してよい。 C M O S ウェハは、側壁またはスペーサ 2 1 0 6 を画定するようにパターニングされた絶縁層 2 1 0 4 に形成されたキャビティ 2 1 0 2 を有してよい。第 2 の絶縁層 2 1 0 8 が電極 2 1 1 0 を覆ってよい。

#### [0148]

[00173] 図 2 1 B に示すように C M O S ウェハは、メンブレンストッパ 2 1 1 2 を形成するパターニングされた絶縁層を有する転写ウェハに接合されてよい。接合は図 2 1 C に示すように封止キャビティ 2 1 2 2 という結果になってよい。

#### [0149]

[00174] 図 2 1 C に示すように、ベース層 1 3 2 と絶縁層 1 3 4 とが除去されてよく、メンブレン 2 1 1 4 が残る。

### [ 0 1 5 0 ]

[00175] 次いで電気接点 2 1 1 6 が、たとえば金属化層を堆積させてパターニングすることにより、図 2 1 D に示すようにメンブレン 2 1 1 4 の上側に形成されてよい。続いて図 2 1 E では、電気接点 2 1 1 6 をパッシベートするためにパッシベーション層 2 1 1 8 はいくつかの実施形態において S i O 2 で形成されてよい。

### [0151]

[00176] 図 2 1 F では、たとえば S i  $_3$  N  $_4$  で形成された第 2 のパッシベーション層が電気接点 2 1 1 6 上に堆積されてパターニングされてよい。

## [0152]

[00177] したがって図21FのCUTは、メンブレンへの上側電気接点を持つメンブレンの底側のメンブレンストッパを含んでよい。CUTを形成するためのプロセスは低温処理のみを含んでよく、したがってICなど、CMOSウェハ上に形成された構造を保持する。

## [0153]

[00178] 本明細書に記載の構造は、たとえば超音波撮像用途および / またはHIFU用途における超音波振動子としての使用に適する様々な寸法を有してよい。たとえば、キャビティサイズ(たとえば、幅、またはより一般的には開口サイズ、および深さ)は所望の周波数特性を提供する任意の適切な値をとってよい。メンブレンおよびピストンメンブレンは同様に任意の適切な値をとってよい。いくつかの実施形態において、寸法は、CUTを低電圧動作に適合させるように選択されてよく、したがって低電圧CMOS ICとのそれらの統合を容易にするが、すべての実施形態がこの点で限定されるのではない。たとえば高電圧設計も、たとえばCUTがHIFUを提供するために動作する状況では、使用されてよい。低電圧動作用に設計されると、CUTはたとえば、70Vよりも低く、50Vよりも低く、30Vよりも低く、10Vよりも低く、2Vと60Vの間で、10Vと30Vの間で、15Vと25Vとの間で、それらの範囲内の任意の電圧

10

20

30

40

20

30

40

50

で、または任意の他の適切な電圧で動作するのに適切な寸法を有してよい。これらのより低電圧での動作は、少なくとも部分的にはメンブレンをこれらのより低電圧で適切に撓むように十分に薄くすることにより、可能にされてよい。本出願の実施形態で達成可能なメンブレン厚の非限定的な例がさらに以下に記述される。

### [0154]

[00179] 非限定的な例として、本明細書に記載のようなCUTのキャビティが有してよい幅、またはより一般的には開口は、およそ5ミクロンとおよそ500ミクロンとの間、およそ20ミクロンとおよそ100ミクロンとの間、およそ30ミクロン、およそ40ミクロン、およそ50ミクロン、その間の任意の幅もしくは幅の範囲、または任意の他の適切な幅である。いくつかの実施形態において、幅は、間隙率、すなわち、周囲の構造により占有される領域の量と比較したキャビティにより占有される領域の量を最大化するように選択されてよい。

### [0155]

[00180] 本明細書に記載のCUTのキャビティは任意の適切な深さを有してよく、たとえば、およそ0.05ミクロンとおよそ10ミクロンとの間、およそ0.1ミクロンとの間、およそ0.1ミクロンとの間、およそ0.1ミクロンとの間、およそ0.1ミクロンとの間、その間の任意の深さもしくは深さの範囲、または任意の他の適切な深さである。いくつかの実施形態において、キャビティ寸法および/またはキャビティの上を覆う任意のメンブレンの周波数挙動に影響を与えかねず、したがって所望の周波数学動に影響を与えかねず、したがって所望の周波数学動(たとえば、メンブレンの所望の共振周波数)を提供するように選択されてよい。たHzとの間、およそ20kHzとおよそ200MHzとおよそ1 MHzとおよそ10MHzとの間、およそ20kHzとおよそ5 MHzとの間、およそ50kHzとおよそ200kHzとの間、およそ2.5 MHzとおよそ5 MHzとの間の任意の周波数もしくは周波の範囲、または任意の他の適切な周波数の中心共振周波数を持つ超音波振動子を有像や材料分析のため、または様々な動作周波数が望まれる場合がある。キャビティおよび/またはメンブレンの寸法は適宜選択されてよい。

### [0156]

[00181] 本明細書に記載のようなCUTは任意の適切なメンブレン厚を有してよい。たとえば、本明細書に記載のメンブレンが有してよい厚さ(たとえば、対応するキャビティの深さに略平行な方向に測定されるような)は、100ミクロンよりも小さく、50ミクロンよりも小さく、40ミクロンよりも小さく、30ミクロンよりも小さく、20ミクロンよりも小さく、10ミクロンよりも小さく、5ミクロンよりも小さく、1ミクロンよりも小さく、0.1ミクロンよりも小さく、その間の任意の厚さの範囲、または任意の他の適切な厚さである。厚さは、メンブレンの所望の共振周波数などのメンブレンの所望の音響挙動に基づいて、いくつかの実施形態において選択されてよい。

### [0157]

[00182] ピストンメンブレンが形成される場合、ピストンメンブレンの中央および外側部分は任意の適切な厚さと任意の適切な厚さ比を有してよい。いくつかの実施形態において、メンブレンの外側部分(メンブレンをCMOSウェハに接続する)は可能な限り薄くされてよい(たとえば、非限定的な例としておよそ50nmとおよそ100nmとの間)。ピストンメンブレンの中央部分は、メンブレンに関して前述したものに応じて任意の厚さを有してよい。いくつかの実施形態において、ピストンメンブレンの外側および中央部分の両方は、およそ1ミクロンとおよそ100ミクロンとの間、およそ10ミクロンとおよそ50ミクロンとの間、そのような範囲での任意の値、または任意の他の適切な値の厚さを有してよい。

## [0158]

[00183] 前述のように、本出願の態様は、回路が振動子下方に設けられる、CMOS回路と統合された超音波振動子セルを提供する。図26は、図1Kの超音波振動子を用いて

、そのようなデバイスの非限定的な例を例示する。

### [0159]

[00184] 図示のように、デバイス 2 6 0 0 は、図 1 Kの超音波振動子に加えて、集積回路 2 6 0 2 を含んでよい。集積回路は C M O S ウェハのベース層 1 0 2 に形成されてよい。たとえば、ベース層はバルクシリコン層であってよく、集積回路は 1 つまたは複数の能動シリコン回路素子(たとえば、シリコン内にドープされたソースおよびドレイン領域を有する M O S トランジスタ)、コンデンサ、抵抗器、または他の回路部品を含んでよい。集積回路 2 6 0 2 は、送信および / または受信モードで超音波振動子を動作させるのに適したものにすることができる。

#### [0160]

[00185] 図示のように、電極116と接点118の両方が集積回路2602に接続されてよい。電極116は、たとえばベース層102内のMOSトランジスタのドープされたソース / ドレイン端子に直接接触してよい例示のビア2604により接続されてよい。接点118は、いくつかの実施形態においてビアであってよい導電性ライン2606により集積回路2602に接続されてよい。電極116と接点118から集積回路2602に接続する他の手法も可能である。

### [0161]

[00186] 前述のように、かつ図26に示すように、いくつかの実施形態において、CUTのメンプレンに対して全体的接続よりもむしる局所的接続が行われてよい。たとえば接点118は、例示のCUTのメンプレンへの局所的接続を提供する。そのような局所的接続は、局所的接続により提供される他の潜在的な利益の中で、メンプレンにバイアスを印加する際の不要な電気的挙動(たとえば、長い信号線で発生し得る不要な静電容量)を軽減する点で有益であってよい。

### [0162]

[00187] いくつかの態様において、CUTのメンブレンはバイアスを印加されてよく、いくつかのそのような実施形態において、接点118はバイアス信号を供給するために使用されてよい。そのような状況では、接点118は所望のバイアスレベルを提供または維持するためのコンデンサ(図示せず)を介して集積回路2602に接続されてよい。他のバイアス構成も可能である。

## [ 0 1 6 3 ]

[00188] いくつかの実施形態において、電極 1 1 6 は駆動されてよく、したがって集積 回路 2 6 0 2 は電極を駆動するために適切に接続されてよい。いくつかの実施形態におい て、メンブレンよりもむしろ、電極 1 1 6 がバイアスを印加されてよい。

## [0164]

[00189] したがって、超音波振動子に関して様々な動作シナリオが可能であることが認識されるべきである。集積回路 2 6 0 2 は、メンブレンの駆動、電極 1 1 6 の駆動、または他の動作モードを含む様々な動作モードを可能にするために、適切な回路(たとえば、スイッチング回路、コンデンサなど)を含んでよい。

# [ 0 1 6 5 ]

[00190] 転写ウェハの様々な例が、様々な実施形態と共に用いるために本明細書に記載されてきた。いくつかの実施形態において、従来のSOIウェハが使用されてよく、これはハンドル層、埋め込み酸化物層、および単結晶シリコン層としてシリコンバルクウェハを有する。しかしながら前述のように、いくつかの実施形態は、ポリシリコンまたはアモルファスシリコン層を有する転写ウェハを含む、代替の種類の転写ウェハを実装する。転写ウェハは、高品質回路を支持するためのシリコン層を提供するために使用されるよりもむしろ、メンブレン、ピストン、および/またはメンブレンストッパを形成するために使用されてよいので、本出願人らは、高品質単結晶シリコン層はすべての実施形態において使用される必要はないことを認識した。むしろ前述のように、メンブレン、ピストン、およびメンブレンストッパはポリシリコン、アモルファスシリコン、酸化物、TiN、または他の適切な材料で形成されてよい。したがって出願人らは、そのような材料を有する転

10

20

30

40

写ウェハがいくつかの実施形態において従来のSOIウェハの代わりに実装されてよいこと、およびそのような代替の種類の転写ウェハが、従来のSOIウェハを形成するために必要とされるよりも有意に少ない労力とコストで製作され得ることを認識した。したがって、そのような比較的単純な多層転写ウェハの使用がCUTの生産を有意に単純化することができ、またCUTの費用効果的な大規模生産を可能にすることができる。

### [0166]

[00191] 本明細書に記載の転写ウェハの一部の製作の仕方の非限定的な例がここで記載される。たとえば、転写ウェハ131が層136としてポリシリコン(たとえば、ドープされたポリシリコン)またはアモルファスシリコンを有する実施形態において、転写ウェハは、ベース層132としてシリコンバルクウェハから始めて、次いで絶縁層134としてSiO₂の層を堆積させ、次いでポリシリコンまたはアモルファスシリコンを堆積させて製作してよい。次に、層138(たとえば、TiN)が堆積されてよい。これらの工程を行うことは、従来のSOIウェハを形成するために使用されるものよりも必要とする精度が有意に低くてよく、したがってこの手法で転写ウェハ131を製作することは、CUTを形成するための全体的なプロセスを単純化し、そのコストを低減し得る。

#### [0167]

[00192] 図 2 3 A ~ 2 3 D は、本出願の非限定的な実施形態に係る、内部に形成された ピストンを有する、図 9 A および図 1 8 A の転写ウェハ 1 8 0 3 を製作するためのプロセ スシーケンスを例示する。

## [0168]

[00193] ベース層 1 3 2 (たとえば、シリコン)から始まり、図 2 3 A に示すように、絶縁層 1 3 4 (たとえば、5 i O  $_2$ ) が堆積されてよく、続いて層 2 3 0 2 の堆積となる。層 2 3 0 2 は前述のピストン 2 0 2 の一部を形成してよく、したがってピストンのために望まれる材料で作製されてよい。たとえば、層 2 3 0 2 はいくつかの実施形態においてドープされたポリシリコンであってよく、またはいくつかの実施形態においてアモルファスシリコンであってよい。

### [0169]

[00194] 図 2 3 B に示すように、層 2 3 0 2 がパターニングされてよく、前述の層 2 0 4 が堆積されてよい。層 2 0 4 は、TEOSまたは他の適切な絶縁材料により形成されたSiO  $_2$  などの絶縁材料であってよい。CMPが行われてよく、ウェハが平坦化されてよい。

# [0170]

[00195] 次いで図23Cに示すように、層2304が堆積されてよい。層2304はピストン202の一部を形成してよく、したがってピストンのために望まれる材料で形成されてよい。たとえば、層2302はいくつかの実施形態においてドープされたポリシリコンであってよく、またはいくつかの実施形態においてアモルファスシリコンであってよい。次いでCMPが行われてよい。

## [ 0 1 7 1 ]

[00196] 図23 Cに例示する処理の段階で、ピストン202を構成する層2302および2304は適所にある。しかしながら、二層間の水平線により反映されるように、それらは別工程で堆積されているので、それらは一体の本体を画定はしない。したがって、ピストン202が一体の本体を表す転写ウェハ1803を実現するために、アニールが行われてよく、したがって図23Dに示すような最終転写ウェハ1803が生成される。アニールは低温アニールである必要はないが、そうであってもよく、というのも、転写ウェハは本明細書に記載のCMOSウェハとは別に製作され、したがって転写ウェハの製作は、CMOSウェハ上で行われたならばCMOS回路に損傷を与えるであろう温度での処理工程を含んでよいためである。その上、転写ウェハ1803を形成するための記載の工程は、従来のSOIウェハを形成するために必要とされるものと比較して比較的に単純であることが認識されるべきである。

## [0172]

50

10

20

30

[00197] 任意選択により、図 2 3 D に示す転写ウェハ 1 8 0 3 は前述の層 1 3 8 (たとえば、T i N) を堆積させることによりさらに処理されて、図 2 A の転写ウェハ 2 0 1 を生成してよい。

### [0173]

[00198] 図 2 4 A ~ 2 4 B は、本出願の非限定的な実施形態に係る、メンプレンストッパを有する、図 2 1 B に示す種類の転写ウェハを製作するためのプロセスシーケンスを例示する。ベース層 1 3 2 (たとえば、シリコン)から始まり、絶縁層 1 3 4 (たとえば、  $SiO_2$ )が堆積されてよい。次いで前述の層 1 3 6 が堆積されてよい。絶縁層 2 4 0 2 が次いで図 2 4 A の構造を生成するように堆積されてよい。絶縁層 2 4 0 2 は  $SiO_2$ であってよく、また T E O S または他の適切な堆積方法により形成されてよい。

[0174]

[00199] 図 2 4 B に示すように、絶縁層 2 4 0 2 はメンブレンストッパ 2 1 1 2 を形成するようにパターニングされてよい。したがって、図 2 4 B に示す種類の転写ウェハの製作は、層 1 3 6 が単結晶シリコンではない実施形態において、従来の S O I ウェハの製作と比較して比較的に単純であってよいことが認識されるべきである。

#### [0175]

[00200] 図 2 5 A ~ 2 5 B は、本出願の非限定的な実施形態に係る、内部に形成された ピストンを有する転写ウェハを製作するための代替のプロセスシーケンスを例示する。転 写ウェハは図 4 A に関連して前述した種類であってよい。

## [0176]

[00201] ベース層 1 3 2 はバルクシリコンであってよい。絶縁層 1 3 4 (たとえば、 S i O 2 ) がシリコン上に堆積されてよい。次いで層 4 0 2 が絶縁層 1 3 4 上に堆積されてよい。いくつかの実施形態において、層 4 0 2 はポリシリコンまたはアモルファスシリコンであってよいが、単結晶シリコンがいくつかの実施形態において使用されてよい。次に、層 4 0 4 が図 2 5 A に示す構造を提供するように堆積されてよい。

### [0177]

[00202] 続いて図 2 5 Bに示すように、層 4 0 4 はピストン構成を提供するようにパターニングされてよい。したがって、例示の転写ウェハは比較的単純な堆積およびエッチング工程により製作されてよく、また層 4 0 2 が単結晶シリコンではない実施形態において、従来のSOIウェハの製作と比較して製作が比較的単純であってよいことが認識されるべきである。

# [0178]

[00203] 上記の説明は、単純化の目的で、単一のCUTとその形成に焦点を当ててきた。しかしながら、本出願の様々な態様は単一のCUTに限定されないことが認識されるべきである。むしろ、本明細書に開示の方法はウェハレベルで行われてよく、したがって本明細書に記載の種類のCUTを複数製作するために使用されてよく、すなわち本出願の態様はCUTのウェハレベルの処理を提供する。たとえば、単一の基板(たとえば、単一のCMOSウェハ)は数十、数百、数千、数万、数十万、または数百万のCUTが内部に形成されてよい。

## [0179]

[00204] 本出願の態様によれば、本明細書に記載のCUTは完全なレチクルを用いて製作されてよい。そのような能力は、単一チップ上の多数のCUTの製作を容易にし得る。 【 0 1 8 0 】

[00205] その上、本出願の態様は、これまでに達成可能であったよりも多数の所与チップ面積当たりの超音波振動子を提供し得る。ここまで記載のように、本出願の態様は、従来可能であったよりも小さい超音波振動子の形成を提供する。本出願の態様に係るメンブレンのために使用されてよい多種多様な種類の材料のため、および本明細書に記載の転写ウェハからメンブレンが形成されてよい手法のため、メンブレンは従来の超音波振動子のものよりも(たとえば、従来のCMUTよりも)薄くされてよい。振動子挙動はメンブレン厚とキャビティサイズ(たとえば、振動子開口)との間の関係に少なくとも部分的に依

10

20

30

40

10

20

30

40

50

存してよいので、より薄いメンブレンを作製することは、これまでに可能であったよりも 小さな振動子を作製可能にし得る。したがって、これまでに可能であったよりも多くの振 動子が単一のチップ上に作成され得る。

## [ 0 1 8 1 ]

[00206] 複数のCUTが形成される場合、それらは所望のデバイスを形成するために様々な手法で電気的に相互接続されてよい。単一のCUTは本明細書でセルと呼ばれてよい。いくつかの実施形態において、複数のCUTセルを含んでよい。セルおよび/または要素は、すなわち要素は1つまたは複数のCUTセルを含んでよい。セルおよび/または要素は、たとえば、超音波撮像および/またはHIFUのために動作可能な超音波振動子配置を形成するように適切に配置されて電気的に接続されてよい。したがって、たとえばセルおよび/または要素は、超音波撮像および/またはHIFUデバイスに所望の周波数挙動(たとえば、帯域幅、中心周波数など)を提供するように適切に配置されて電気的に接続されてよい。マルチセル要素へのCUTセルのグルーピングまたは接続は、いくつかの実施形態において、CMOSウェハのICへのCUTの適切な接続を通じて達成されてよい

### [0182]

[00207] 様々な態様と実施形態が、内部に形成されたICを有する、モノリシックに統合された超音波振動子およびCMOSウェハを提供するものであると記載されてきたが、すべての態様と実施形態がこの点で限定されるのではない。たとえば本出願のいくつかの態様は、フリップチップ接合およびマルチチップ構成にも適用されてよい。たとえば、メンブレンの底側に電気的に接触させることは、フリップチップ接合構成で行われてよい。他の態様も非モノリシックデバイスに適用されてよい。

### [0183]

[00208] 本出願の態様は1つまたは複数の利益を提供してよく、そのうちのいくつかが前述されている。ここで記述されるのはそのような利益のいくつかの非限定的な例である。すべての態様と実施形態が必ずしもここで記述される利益のうちのすべてを提供するわけではないことが認識されるべきである。さらには、本出願の態様はここで記述されるものへの付加の利益を提供してよいことが認識されるべきである。

### [0184]

[00209] 本出願の態様は、モノリシックに統合された超音波振動子とCMOS構造(たとえば、CMOS IC)の形成に適した製造プロセスを提供する。少なくともいくつかの実施形態において、プロセスは実行が比較的安価であってよく、また多量の超音波振動子に拡張可能であってよい。本出願の態様は、低電圧CMOS ICに関連して動作するための適切なサイズの超音波振動子を製造するためのプロセスを提供する。本出願の態様は、様々な構成の超音波振動子を作製するための堅牢なプロセスを提供する。他の利益も本出願の1つまたは複数の態様に従って提供され得る。

# [0185]

[00210] このように本出願の技術のいくつかの態様と実施形態を記述してきたが、当業者には様々な変更、修正、および改良が容易に想起されることが認識されるべきである。そのような変更、修正、および改良は、本出願に記載の技術の精神および範囲内であると意図される。たとえば当業者は、機能を行うためかつ/または結果および/もしくは本明細書に記載の利点のうちの1つまたは複数を得るための種々の他の手段および/または修正の各々は本明細書に記載の実施形態に記載の実施形態に記載の等価物を認識する、または通常程度の実験のみを用いて確認することができるである。の等価物を認識する、または通常程度の実験のみを用いて確認することができるができるができるがである。したがって、上記の実施形態は単に例として提示されること、および添付の特許請求の範囲およびその均等物の範囲内で、発明の実施形態は具体的に記載した以外の方法での範囲およびその均等物の範囲内で、発明の実施形態は具体的に記載の2つ以上の特許で、かるよびとが理解されるべきである。加えて、本明細書に記載の2つ以上の特徴、システム、物品、材料、キット、および/または方法が互いに矛盾しない限り、本

開示の範囲内に含まれる。

#### [0186]

[00211] 上述の実施形態は多数の方法のうちのいずれかで実装できる。プロセスまたは方法の性能に関係する本出願の1つまたは複数の態様と実施形態は、そのプロセスままたは方法を行う、またはその性能を制御するためにデバイス(たとえば、コンピュータ、こので、様々な発明の概念は、1つまたは複数のコンピュータまたは他のプロセッサ上されると、上述の様々な実施形態のうちの1つまたは複数を実装する方法を実施のこと、上述の様々な実施形態のうちの1つまたは複数を実装する方法を実施のこと、上述の様々な実施形態のうちの1つまたは複数を実装する方法を実施のことには複数のプログラムで符号化されたコンピュータ可読記憶媒体(または複数のッピーイスク、カープラインでイスク、光ディスク、磁気テープ、フラッシュメモリ、オスク・プログラマブル・ゲート・アレイもしくは他の半導体デバイスの回路構成、またはであるでは、1つまたは複数のの出いでありまたは複数のプログラムが、上述の態様のは、または複数ののよいとして具現化されてよい。1つまたは複数の影様のおりに、1つまたは複数のの実施形態において、コンピュータでありに、可搬型であり得る。いくつかの実施形態において、コンピュータで読媒体は、非一時的な媒体であってよい。

### [0187]

[00212] 用語「プログラム」または「ソフトウェア」は、コンピュータまたは他のプロセッサを上述のような様々な態様を実装するようにプログラムするために利用され得る、任意の種類のコンピュータコードまたはコンピュータ実行可能命令のセットを指すために本明細書中で一般的な意味で使用される。加えて、一態様によれば、実行されると本出願の方法を実施する1つまたは複数のコンピュータプログラムは、単一のコンピュータまたはプロセッサ上に常駐する必要はなく、本出願の様々な態様を実装するために多数の異なるコンピュータまたはプロセッサ間でモジュール方式で分散されてよいことが認識されるべきである。

#### [0188]

[00213] コンピュータ実行可能命令は、1つまたは複数のコンピュータまたは他のデバイスにより実行されるプログラムモジュールなどの多くの形態であってよい。一般にプログラムモジュールは、特定のタスクを実施するかまたは特定の抽象データ型を実装するルーチン、プログラム、オブジェクト、コンポーネント、データ構造などを含む。プログラムモジュールの機能は典型的に、様々な実施形態において望まれるように組み合わされるかまたは分散されてよい。

### [0189]

[00214] またデータ構造は、任意の適切な形態のコンピュータ可読媒体に記憶されてよい。例証を簡単にするため、データ構造は、データ構造内の位置を介して関連するフィールドを有することが示されてよい。そのような関係は同様に、フィールド間の関係を伝えるコンピュータ可読媒体内の位置をフィールドのための記憶領域に割り当てることにより達成されてよい。しかしながら、任意の適切な機構が、ポインタ、タグ、またはデータ要素間の関係を確立する他の機構の使用を含め、データ構造のフィールドの情報間の関係を確立するために使用されてよい。

#### [0190]

[00215] ソフトウェアで実装される場合、ソフトウェアコードは、単一のコンピュータに設けられようと複数のコンピュータ間で分散されようと、任意の適切なプロセッサまたはプロセッサの集合上で実行され得る。

# [0191]

[00216] さらには、コンピュータは、非限定的な例としては、ラックマウントコンピュータ、デスクトップコンピュータ、ラップトップコンピュータ、またはタブレットコンピュータのような多数の形態のうちのいずれかで具現化されてよいことが認識されるべきである。加えて、コンピュータは、携帯情報端末(PDA)、スマートフォンまたは任意の他

10

20

30

40

10

20

30

40

50

の適切な携帯用または固定型電子デバイスを含め、一般にはコンピュータとみなされない ものの適切な処理能力を持つデバイスに埋め込まれてよい。

## [0192]

[00217] また、コンピュータは1つまたは複数の入出力デバイスを有してよい。これらのデバイスは、とりわけユーザインタフェースを提示するために使用され得る。ユーザインタフェースを提供するために使用され得る出力デバイスの例は、出力の視覚提示のためのプリンタまたはディスプレイスクリーン、および出力の可聴提示のためのスピーカまたは他の音声発生デバイスを含む。ユーザインタフェースのために使用され得る入力デバイスの例は、キーボード、ならびにマウス、タッチパッド、およびデジタル化タブレットなどのポインティングデバイスを含む。別の例として、コンピュータは音声認識を介してまたは他の可聴フォーマットで入力情報を受信してよい。

#### [0193]

[00218] そのようなコンピュータは、ローカルエリアネットワークまたは企業ネットワークなどのワイドエリアネットワーク、およびインテリジェントネットワーク(IN)またはインターネットを含む、任意の好適な形態の1つまたは複数のネットワークにより相互接続されてよい。そのようなネットワークは任意の適切な技術に基づいてよく、任意の適切なプロトコルに従って動作してよく、また無線ネットワークまたは有線ネットワークを含んでよい。

### [0194]

[00219] また記載のように、いくつかの態様は1つまたは複数の方法として具現化されてよい。方法の一部として行われる行為は、任意の適切な様式で順序付けされてよい。したがって実施形態は、例示的な実施形態では一連の行為として示されるとしても、いくつかの行為を同時に行うことを含め、行為が例示とは異なる順序で行われるように構成されてよい。

### [0195]

[00220] すべての定義は、本明細書で定義されて使用される場合、辞書の定義、参照により組み込まれる文書における定義、および / または定義された用語の通常の意味を支配すると理解されるべきである。

### [0196]

[00221] 不定冠詞「a(ある1つ)」および「an(ある1つ)」は、本明細書および特許請求の範囲において使用される場合、明確にそうではないと示されない限り、「少なくとも1つ」を意味すると理解されるべきである。

#### [0197]

[00222] 句「and/or(および/または)」は、本明細書および特許請求の範囲において使用される場合、そのように結合される要素、すなわち、いくつかの場合に接続的に存在し、他の場合に離接的に存在する要素の「either or both(いずれか一方または両方)」を意味すると理解されるべきである。「および/または」で列記される複数の要素は同様に、すなわち、そのように結合される要素の「one or more(1つまたは複数)」と解釈されるべきである。「および/または」節により具体的に識別されるもの以外の要素は、具体的に識別される要素に関連するかまたは関連しないかを問わず、任意選択により存在してよい。したがって非限定的な例として、「Aおよび/またはB」への言及は、「comprising(備える)」などのオープンエンド言語と併用される場合、一実施形態において、Aのみ(任意選択によりB以外の要素を含む)、などを表し得る。実施形態において、AとBの両方(任意選択により他の要素を含む)、などを表し得る。

## [0198]

[00223] 本明細書および特許請求の範囲において使用される場合、1つまたは複数の要素の列記に関する句「atleastone(少なくとも1つ)」は、要素の列記内の要素のうちの任意の1つまたは複数から選択される少なくとも1つの要素を意味するが、必ずしも要素の列記内に具体的に列記されるあらゆる要素のうちの少なくとも1つを含

むわけではなく、かつ要素の列記内の要素の任意の組み合わせを除外するわけでもないと理解されるべきである。この定義はまた、句「少なくとも1つ」の対象となる要素の列記内に具体的に識別される要素以外の要素が、具体的に識別される要素に関連するかまたは関連しないかを問わず、任意選択により存在してよいことを認める。したがって非限定的な例として、「at least one of A or B (A および B の少なくとも1つ)」(または同等に、「at least one of A or B (A および / または B の少なくとも1つ)」)は、一実施形態において、少なくとも1つの、任意選択により2つ以上のAでありBは存在しない(さらに任意選択によりB以外の要素を含む)、別の実施形態において、少なくとも1つの、任意選択により2つ以上のBでありAは存在しない(さらに用意選択によりA以外の要素を含む)、などを表し得る。

## [0199]

[00224] また、本明細書で使用される語法および術語は説明のためであり、限定的とみなされるべきではない。本明細書での「including(含む)」、「comprising(備える)」、「having(有する)」、「containing(含有する)」、「involving(伴う)」、およびその変形の使用は、その後に列記される項目およびその均等物、ならびに追加の項目を包含することを意味する。

## [0200]

[00225] 特許請求の範囲、および上記明細書において、「comprising(備える)」、「including(含む)」、「carrying(運ぶ)」、「having(有する)」、「containing(含有する)」、「involving(伴う)」、「holding(保持する)」、「composed of(構成される)」などのすべての移行句はオープンエンドである、すなわち、含むがこれらに限定されないことを意味すると理解されるべきである。移行句「consisting of(から成る)」と「consisting essentially of(から本質的に成る)」のみがそれぞれクローズド、セミクローズドの移行句であるべきである。

10

#### 【手続補正書】

【提出日】平成29年11月8日(2017.11.8)

#### 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

### 【請求項1】

相補型金属酸化膜半導体(CMOS)集積回路を有する半導体ウェハと、

少なくとも部分的にキャビティが形成された絶縁材料と、

前記絶縁材料に接触し、前記キャビティを封止し、前記キャビティに近い第1の側と前記キャビティから遠い第2の側とを有する導電メンブレンであって、前記電極と前記導電メンブレンとの間に前記キャビティを挟んだ状態で、前記電極と、前記キャビティと、前記導電メンブレンとが合わせて超音波振動子を少なくとも部分的に画定する、導電メンブレンと、

前記電極を前記CMOS集積回路に結合する導電性接点と、

前記絶縁材料に埋め込まれた導電性プラグであって、前記導電メンブレンを貫通することなく前記キャビティに近い前記導電メンブレンの前記第1の側を終端とすることで、前記導電性プラグの表面が前記導電メンブレンの前記第1の側と前記絶縁材料との間の接合界面の少なくとも一部を形成し、前記導電性プラグは前記導電メンブレンを前記CMOS集積回路に電気的に接続する、導電性プラグと、を備え、

前記電極と前記導電性プラグとは互いに電気的に絶縁され、

前記装置は、前記導電メンブレンの前記第2の側にあり前記キャビティの上を覆う電極を欠いている、装置。

#### 【請求項2】

前記絶縁材料、前記電極、および前記導電性プラグが前記半導体ウェハ上にある、請求項1に記載の装置。

### 【請求項3】

前記導電メンブレンがドープシリコンを含む、請求項2に記載の装置。

## 【請求項4】

前 記 ド ー プ シ リ コ ン が 単 結 晶 シ リ コ ン で あ る 、 請 求 項 3 に 記 載 の 装 置 。

#### 【請求項5】

前記ドープシリコンがポリシリコンである、請求項3に記載の装置。

### 【請求項6】

前記ドープシリコンがアモルファスシリコンである、請求項3に記載の装置。

### 【請求項7】

前記導電性プラグがタングステンを含む、請求項3に記載の装置。

#### 【請求項8】

前記絶縁材料が前記キャビティの側壁を画定する、請求項2に記載の装置。

#### 【請求項9】

前記電極が少なくとも部分的に前記絶縁材料の内部にある、請求項8に記載の装置。

### 【請求項10】

前記キャビティが 0 . 1 ミクロンと 1 0 ミクロンとの間の深さおよび 2 0 ミクロンと 1 0 0 ミクロンとの間の幅を有し、前記導電メンブレンが 3 0 ミクロン未満の厚さを有する、請求項 2 に記載の装置。

### 【請求項11】

前記導電メンブレンがドープシリコンを含む、請求項1に記載の装置

### 【請求項12】

前記ドープシリコンが単結晶シリコンである、請求項11に記載の装置。

## 【請求項13】

前記ドープシリコンがポリシリコンである、請求項11に記載の装置。

## 【請求項14】

前記ドープシリコンがアモルファスシリコンである、請求項11に記載の装置。

### 【請求項15】

前記導電性プラグがタングステンを含む、請求項11に記載の装置。

## 【請求項16】

前記絶縁材料が前記キャビティの側壁を画定する、請求項1に記載の装置。

### 【請求項17】

前記電極の幅が前記キャビティの幅よりも小さい、請求項1に記載の装置。

#### 【請求項18】

前記キャビティが 0 . 1 ミクロンと 1 0 ミクロンとの間の深さおよび 2 0 ミクロンと 1 0 0 ミクロンとの間の幅を有し、前記導電メンブレンが 3 0 ミクロン未満の厚さを有する、請求項 1 に記載の装置。

### フロントページの続き

- (72)発明者 ロスバーグ,ジョナサン,エム.アメリカ合衆国,コネチカット州 06437,ギルフォード,アンカス ポイント ロード 215

- (72)発明者ファイフ,キース,ジー.アメリカ合衆国,カリフォルニア州94306,パロアルト,マタデロアベニュー635

- (72)発明者ラルストン,タイラー,エス.アメリカ合衆国,コネチカット州06413,クリントン,ビーチパークロード56

- (72)発明者 ハルヴァート,グレゴリー,エル.アメリカ合衆国,コネチカット州 06498,ウェストブルック,オールド クリントン ロード 630

- (72)発明者サンチェス,ネバダ,ジェイ.アメリカ合衆国,コネチカット州06405,ブランフォード,イーストウッドドライブ14

- F ターム(参考) 4C601 EE14 GB41 5D019 DD01 EE06

【外国語明細書】 2018023165000001.pdf

| 专利名称(译)        | 互补金属氧化物半导体(CMOS)超声换能器及其形成方法                                                                                                                               |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | JP2018023165A                                                                                                                                             | 公开(公告)日 | 2018-02-08 |

| 申请号            | JP2017203056                                                                                                                                              | 申请日     | 2017-10-20 |

| [标]申请(专利权)人(译) | 蝴蝶网络有限公司                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 蝴蝶网络公司                                                                                                                                                    |         |            |

| [标]发明人         | ロスバーグジョナサンエム<br>ファイフキースジー<br>ラルストンタイラーエス<br>ハルヴァートグレゴリーエル<br>サンチェスネバダジェイ                                                                                  |         |            |

| 发明人            | ロスバーグ,ジョナサン,エム.<br>ファイフ,キース,ジー.<br>ラルストン,タイラー,エス.<br>ハルヴァート,グレゴリー,エル.<br>サンチェス,ネバダ,ジェイ.                                                                   |         |            |

| IPC分类号         | H04R19/00 A61B8/14                                                                                                                                        |         |            |

| CPC分类号         | B06B1/0292 B81C1/00158 B81C1/00246 B81C2201/0195 B81C2203/0735 B81C2203/0771 G01N29 /2406 B06B1/02 B81B7/007 B81C1/00134 B81C1/00301 H01L29/84 H04R19/005 |         |            |

| FI分类号          | H04R19/00.330 A61B8/14                                                                                                                                    |         |            |

| F-TERM分类号      | 4C601/EE14 4C601/GB41 5D019/DD01 5D019/EE06                                                                                                               |         |            |

| 代理人(译)         | 江口明彦<br>内藤一彦                                                                                                                                              |         |            |

| 优先权            | 61/794744 2013-03-15 US                                                                                                                                   |         |            |

| 其他公开文献         | JP6553695B2                                                                                                                                               |         |            |

| 外部链接           | <u>Espacenet</u>                                                                                                                                          |         |            |

# 摘要(译)