#### [19] 中华人民共和国国家知识产权局

[51] Int. Cl.

G01S 7/521 (2006. 01)

A61B 8/00 (2006. 01)

# [12] 发明专利申请公布说明书

「21] 申请号 200810136157.1

[43] 公开日 2009年1月14日

[11] 公开号 CN 101344588A

[22] 申请日 2008.7.10

[21] 申请号 200810136157.1

[30] 优先权

[32] 2007. 7.10 [33] US [31] 11/827179

[71] 申请人 美国西门子医疗解决公司

地址 美国宾夕法尼亚州

[72] 发明人 D·A·彼得森 S·C·恩隆德

[74] 专利代理机构 中国专利代理(香港)有限公司 代理人 卢 江 刘春元

权利要求书 3 页 说明书 12 页 附图 17 页

#### [54] 发明名称

超声换能器上的嵌入式电路以及制造方法

#### [57] 摘要

本发明涉及超声换能器上的嵌入式电路以及制造方法。在背衬块(54)内嵌入一个或多个芯片、集成电路(44)、或半导体(44)。 形成背衬材料(54)的平面薄片(32),其中集成电路(44)位于薄片(32)中的孔(34)内。 轨道(46)把集成电路(44)连接到电极或所暴露的传导表面(52)。 多个平面薄片(32)可以利用晶片处理来制造,比如在背衬材料(54)的晶片中对芯片的拾取和放置(16)以及 IC 重新分配用于形成轨道(46)。 从晶片切割不同的薄片(32),并彼此相邻地堆叠(22)。 换能器与所暴露的电极或背衬(54)的传导表面(52)相连接。

1. 在具有形成多个元件(58)的换能器材料(56)、每个元件(58) 上的电极、以及声衰减背衬材料(54)的超声换能器中,一种改进包括:

嵌入在声衰减背衬材料 (54) 中的集成电路 (44).

- 2. 根据权利要求 1 所述的改进,其中在声衰减背衬材料 (54) 中的多个轨道 (46) 把集成电路 (44) 连接到电极。

- 3. 根据权利要求1所述的改进,其中集成电路(44)包括专用集成电路(44)。

- 4. 根据权利要求 3 所述的改进,其中专用集成电路 (44)包括发射波束形成器、接收波束形成器、发射器、子阵列波束形成器、多路 复用器、混合器或其组合中的至少一部分。

- 5. 根据权利要求 1 所述的改进,其中集成电路 (44)包括可配置的集成电路 (44),其可利用不同的元件间距和成像系统运行。

- 6. 根据权利要求 1 所述的改进,其中声衰减背衬材料 (54) 位于集成电路 (44) 的第一侧与换能器材料 (56) 之间,并至少邻近集成电路 (44) 的第二和第三侧。

- 7. 根据权利要求 6 所述的改进,其中声衰减背衬材料 (54) 邻近集成电路 (44) 的第四侧,所述第四侧与所述第一侧相对,所述第二侧与所述第三侧相对。

- 8. 根据权利要求 1 所述的改进,其中声衰减背衬材料 (54)包括 多个切片 (50),所述切片 (50)中的第一个具有所述集成电路 (44)、 以及其他切片 (50)具有其他集成电路 (44)。

- 9. 根据权利要求 8 所述的改进,其中元件 (58)包含有在仰角和方位上的多维布置;

其中每个切片(50)对准在方位或仰角维度上的一行元件(58),切片(50)的导体从所述行中的元件间距连接为集成电路输入端间距,元件间距不同于集成电路间距。

- 10. 根据权利要求 1 所述的改进,其中声衰减背衬材料 (54) 包含加载的环氧树脂。

- 11. 一种用于对来自换能器背侧的能量进行声衰减的背衬,所述背衬包括:

具有用于与换能器的背侧相接触的第一表面(72)的背衬材料(54);以及

具有有源电路的半导体(44),所述半导体(44)位于背衬材料(54)内。

12. 根据权利要求 11 所述的背衬还包括:

第一多个导体(46),所述第一多个导体从半导体(44)通过背 衬材料(54)或在其之上延伸到第一多个传导表面(52),其中所述 第一多个传导表面(52)与第一表面(72)平行并暴露在第一表面(72) 上;以及

第二多个导体(46),所述第二多个导体从半导体(44)通过背 衬材料(54)或在其之上延伸到与第一表面相对的第二表面,其中第 二多个导体少于第一多个导体。

- 13. 根据权利要求 11 所述的背衬,其中半导体 (44)包括发射波束形成器、接收波束形成器、发射器、子阵列波束形成器、多路复用器、混合器或其组合中的至少一部分,其中可针对不同的元件间距和成像系统配置有源电路。

- 14. 根据权利要求 11 所述的背衬,其中背衬材料 (54)位于半导体 (44)的第一侧与第一表面 (72)之间并至少邻近半导体 (44)的 第二和第三侧。

- 15. 根据权利要求 11 所述的背衬,其中背衬材料 (54)包括多个切片 (50),所述切片 (50)中的第一个具有所述半导体 (44),并且其他切片 (50)具有其他半导体 (44),多个切片 (50)中的每一个都具有在第一表面上以行的方式暴露的导体,所述导体以多行的多维图样分布,其中多个轨道 (46)把每一行的导体 (46)连接到相应的半导体 (44),每一行中的导体 (46)的间距大于、等于或小于在相应半导体 (44)处轨道 (46)的间距。

- 16. 根据权利要求 11 所述的背衬,其中背衬材料 (54)包含加载的环氧树脂。

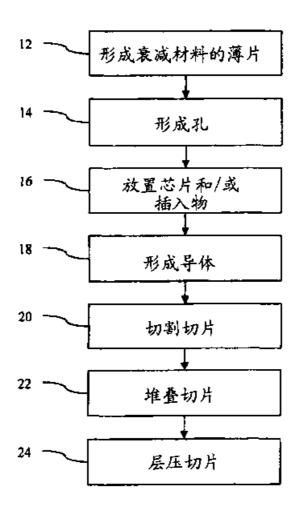

- 17. 一种用于制造超声换能器阵列用的背衬的方法,所述方法包括:

形成(12)声衰减材料的薄片; 在薄片内放置(16)芯片;以及 从芯片到薄片的线形成(18)导体。

18. 根据权利要求 17 所述的方法,其中形成(12)薄片包括形成晶片,

还包括在晶片中形成(14)孔;

其中放置(16)包括在晶片的孔中对芯片和其他芯片进行拾取与 放置处理:以及

还包括:

从晶片切割(20)多个切片(50),每个切片(50)包括所述芯片中的一个;以及

彼此相邻地对切片(50)堆叠(22).

- 19. 根据权利要求 17 所述的方法,其中形成(18)导体包括把导体沉积到芯片上、沉积到薄片的一部分上方、以及沉积到在线处延伸到薄片中的电极上,导体在电极处的间距大于、等于、或小于在芯片处导体的间距。

- 20. 根据权利要求 17 所述的方法,其中薄片的高度约是在超声换能器阵列的一个维度上的元件间距。

- 21. 根据权利要求 17 所述的方法,还包括:

将薄片与其他薄片层压(24)。

- 22. 根据权利要求 17 所述的方法,其中形成 (18) 导体包括平面 IC 重新分配处理。

- 23. 根据权利要求 17 所述的方法,其中形成(12)薄片包括从加载的环氧树脂的晶锭上对晶片切片。

- 24. 根据权利要求 17 所述的方法, 还包括:

在薄片中形成(14)第一孔,所述第一孔针对芯片被定尺寸,所述芯片所具有的高度小于薄片的高度;

在薄片中形成(14)至少一个第二孔,所述第二孔沿着线;以及在第二孔内放置(16)具有多个电极的插入物;其中放置(16)包括在第二孔内放置芯片。

## 超声换能器上的嵌入式电路以及制造方法

#### 技术领域

本发明实施例涉及超声换能器。尤其是提供背衬的制造方法。

#### 背景技术

换能器的一维阵列通过柔性材料与系统通道相连接。这种柔性材料(flex material)与阵列的元件相对准。在这些元件和柔性材料后面是声背衬材料。声背衬材料衰减声能,对不是来自正被扫描的组织的信号反射进行限制。柔性材料足够薄以便避免反射。

对于二维阵列,柔性材料不能提供足够的导体密度。已提出替代方案,比如 z 轴导体。声背衬利用沿着距离维度 (range dimension)穿过背衬材料延伸的导体构成。然而在形成背衬材料期间这些导体的对准和保持可能是困难的。在背衬材料的背面上导线的密度仍很大,从而导致连接困难。

另一问题是至超声成像系统的电缆的数目.为了限制电缆的数目, 电路被安置在超声探头外壳中.所述电路与元件、比如与背衬中的 2 轴导体相连接。所述电路比如通过部分波束形成或多路复用来组合来 自多个元件的信号。这种组合减少对成像系统所需的电缆的数目。然 而,元件的电极至电路的互连可能是困难的。

阵列的每个元件都与两个传导路径相连接。传导路径可以包括至探头内的电路的连接、从电路至电缆的连接、以及从电缆至成像系统中的波束形成器的连接。可能存在电路中的数千个互连、数千多个用于元件至柔性材料的互连、数千多个用于柔性材料至电路的互连、以及更多从电路至电缆的互连。连接的数目可能是巨大的,从而导致增加的寄生效应、增加的短路可能性和所需的昂贵制造。

## 发明内容

通过介绍,下文中所述的优选实施例包括用于声衰减超声能量的 方法、背衬、换能器以及系统。在背衬内嵌入一个或多个芯片、集成 电路或半导体。

在一个实施例中,背衬材料的平面薄片被形成,其中集成电路位于薄片中的孔内。轨道 (Trace) 将集成电路连接到电极或所暴露的传

导表面. 多个平面薄片可以利用晶片处理来制造,比如芯片在背衬材料的晶片中的拾取和放置和 IC 重新分配用于形成轨道. 从晶片切割不同的薄片并彼此堆叠. 换能器与所暴露的电极或者背衬的传导表面相连接.

在第一方面中,超声换能器具有形成多个元件的换能器材料、每个元件上的电极、以及声衰减背衬材料。集成电路被嵌入到声衰减背 衬材料中。

在第二方面中,提供一种背衬用于对来自换能器背侧的能量声衰减。背衬材料具有第一表面用以与换能器的背侧相连接。半导体具有有源电路,并位于背衬材料中。

在第三方面中,提供一种用于构造超声换能器阵列用的背衬的方法。形成声衰减材料的薄片。把芯片放置在薄片中。从芯片至薄片的 线形成导体。

本发明通过后面的权利要求来限定,本部分不应被认为是对这些 权利要求的限制。本发明的其他方面和优点在下文中结合优选实施例 来予以讨论、并可以随后独立地或组合地要求保护。

#### 附图说明

组件和附图不必按比例绘制,而重点在于阐述本发明的原理。而且,在附图中,同样的附图标记贯穿不同的视图表示相应的部分。

图 1 示出用于制造超声换能器阵列用的背衬的方法的一个实施例的流程图:

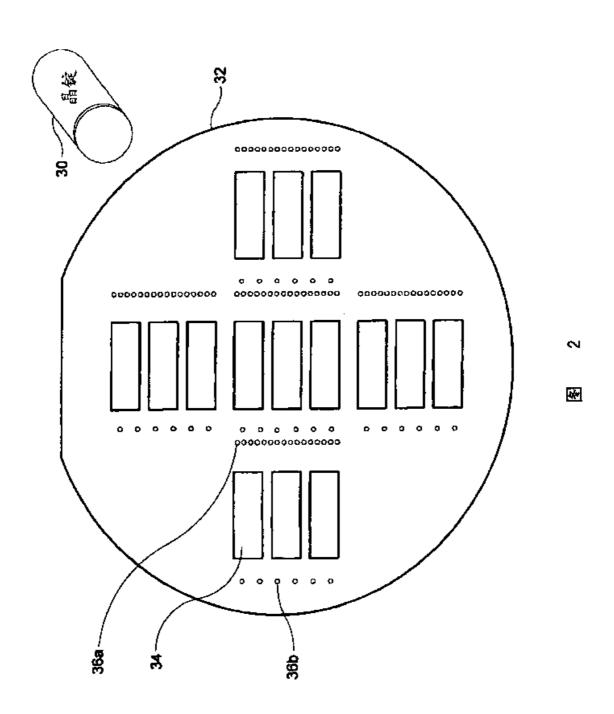

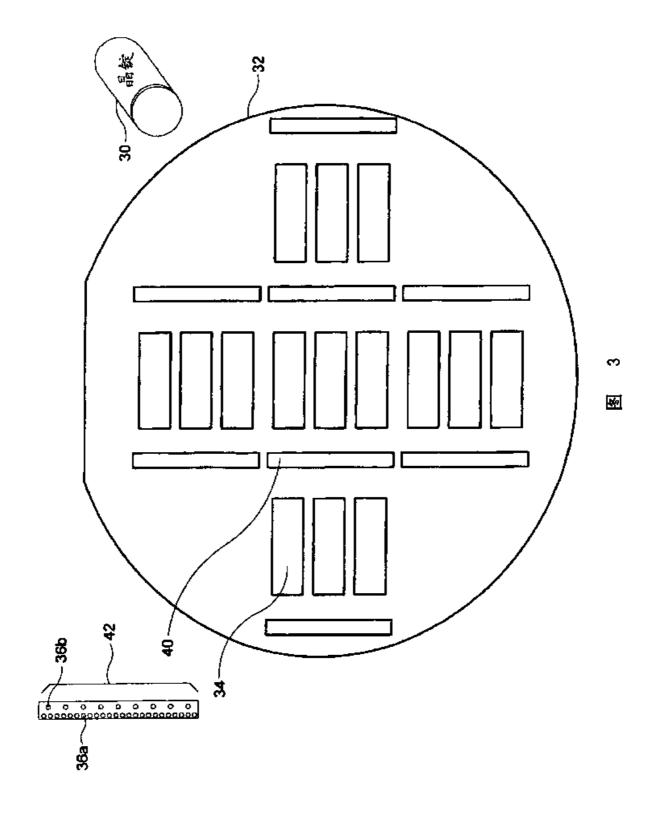

- 图 2 和 3 示出用于在晶片实施例中形成薄片的替代途径;以及

- 图 4-8 示出用于晶片实施例的处理步骤和结构;

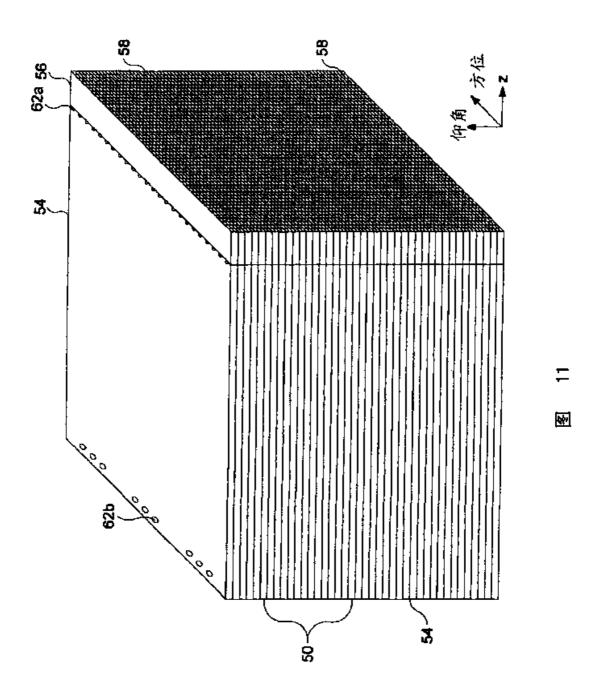

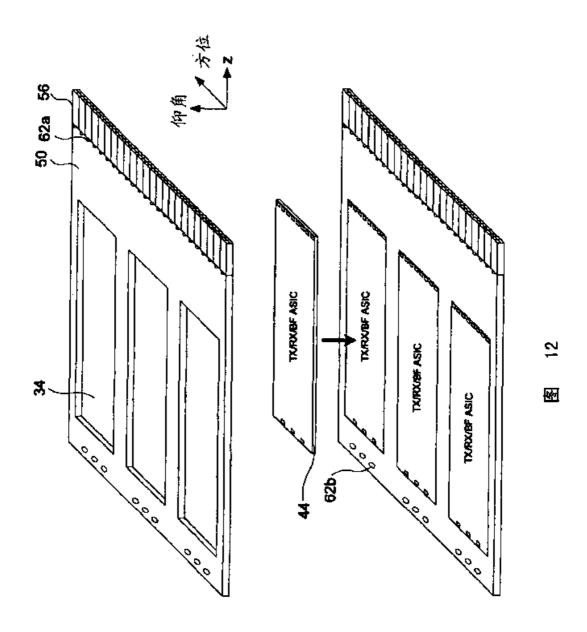

- 图 9-12 示出用于可替代的块实施例的处理步骤和结构;

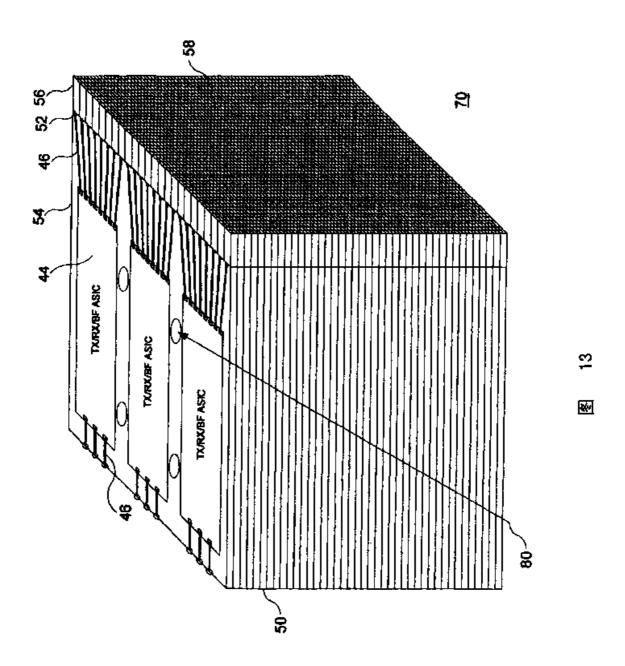

- 图 13 示出在背衬中具有冷却通道的换能器阵列的一个实施例;

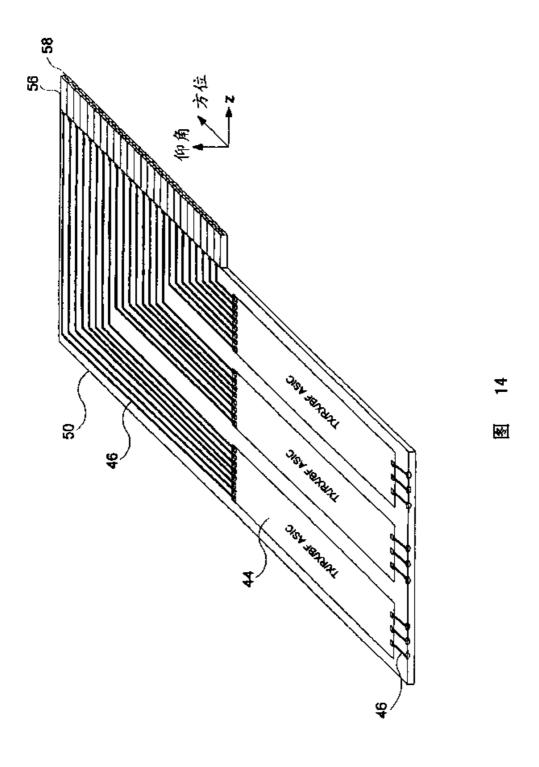

- 图 14 示出在经食道探头阵列中所使用的切片的一个实施例;

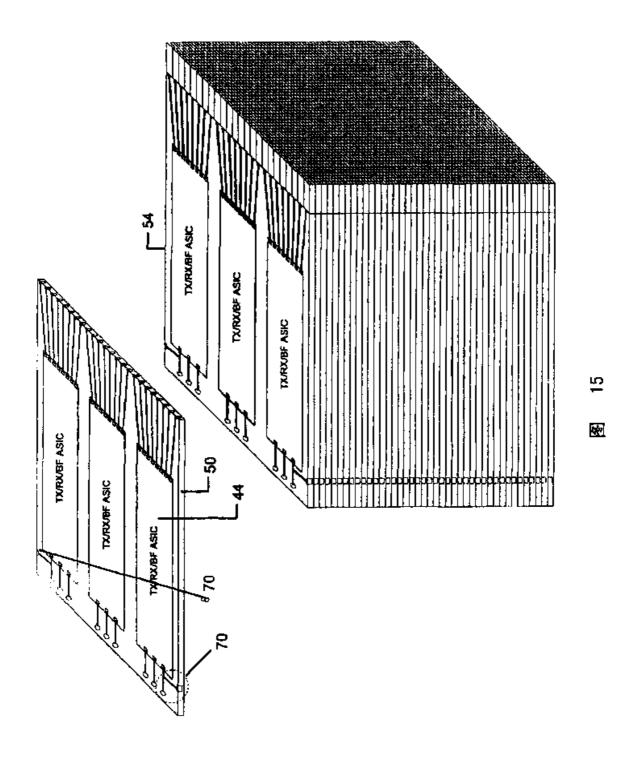

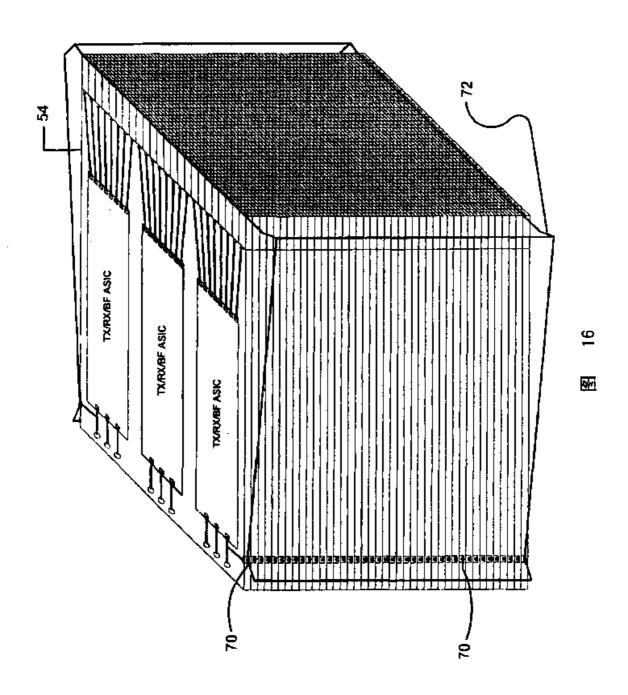

- 图 15 和 16 示出在换能器阵列中路由的导体的替代实施例;以及

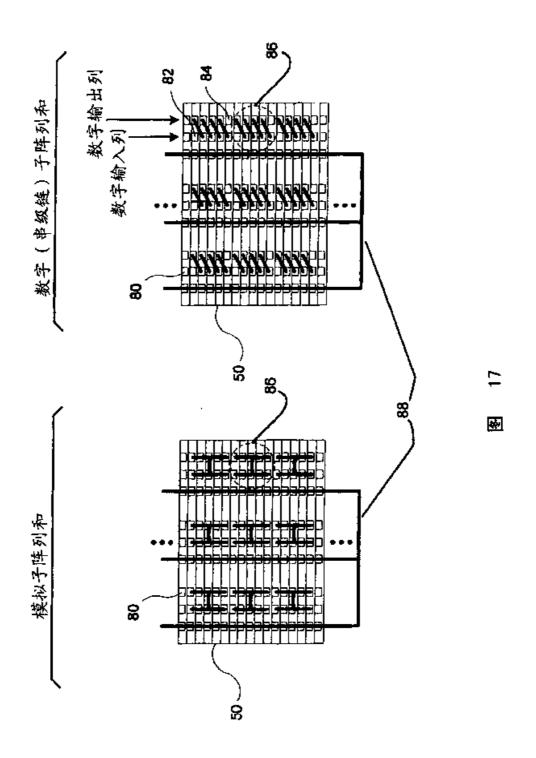

- 图 17 示出换能器阵列的背衬切片之间的互连的替代实施例。

## 具体实施方式

对于给定的元件沿传导路径的连接的数目可以通过在背衬材料中使用半导体类型构造或嵌入式电路而被减少。锯切、切成小方块以及层压与半导体集成电路重新分配技术相组合。半导体类型构造可以允

许更廉价和更密集的互连,支持高元件数。

在一个实施例中,处理为多维阵列产生单元件仰角宽度、多元件方位长度模块。利用光刻或其他集成电路技术形成嵌入式电路的导体,从而提供从电路输入端间距(pitch)至元件间距的密度重新分配。这些模块可以被层压用以产生全背衬或具有背衬的换能器。

图 1 示出一种用于制造超声换能器阵列用的背衬的方法。可以与换能器材料一起使用背衬来形成超声换能器。背衬用于与多维换能器阵列一起运行,但也可以与一维阵列一起运行。

该方法以所示的顺序被实施。可替代地,还提供不同的顺序。比如,切割切片动作 20 在动作 12 的形成薄片之前或作为其一部分来实施。可以提供附加的、不同的、或较少的动作。比如,在芯片或插入物周围形成薄片 (sheet)而不需比如通过铸造或塑造在薄片中形成孔。

很多实施例都是可行的。图 2-8 示出晶片工艺类型实施例。图 9-12 示出块工艺实施例。两种实施例都包括图 1 的动作中一些或全部。可以使用其他的实施例,比如在一个或多个芯片的多个侧面周围或附近塑造或铸造背衬材料。

在动作12中,形成声衰减材料的薄片32. 可以使用铸造、塑造、沉积或其他工艺。在图 2 所示的一个实施例中,使用背衬材料的晶锭(Boule)30 或圆柱体。晶锭通过塑造加载的环氧树脂(loaded epoxy)、比如栽钨环氧树脂来形成。可以使用其他背衬材料,包括固体、聚合物、半固体或环氧树脂。可以不使用填料或使用不同的填料。填料或基础背衬材料的密度可以变化,比如从晶锭30的一侧到另一侧改变声衰减。

薄片 32 被形成为晶片。晶片从晶锭 30 被切片。这种切片利用晶片锯、划片机、ID 锯、或其他晶片形成工艺来实施。晶片的厚度或高度大致是元件间距。比如,背衬用于在仰角上具有 400 微米元件间距的多维阵列。晶片被切片为约 400 微米,比如 360-420 微米。可以使用其他厚度,包括在仰角(elevation)或方位(azimuth)上大于一个、两个或多个元件间距的高度。晶片可以被切割为大于所需的厚度,并在从晶锭 30 上切割之后被磨削成规格。薄片 32 被安置在晶片带上或其他的晶片支持物上。

在图 2 所示的实施例中, 晶锭 30 被形成, 其中多个导线 36 从顶

端到底端或在晶锭 30 内延伸. 导线 36 是金、铜、具有轨道的柔性材料或其他导体。导线 36 以多个图样来分布。每个图样对应于为元件 58 (未示出)的行要使用的一个切片 50. 图 2 示出了具有五个背衬切片 50 的薄片 32。每个切片的一组导线 36a 处于元件间距,比如仰角或方位间距。为要使用切片 50 的该行的每个元件提供一个导线 36a. 每个切片 50 的另一组导线 36b 处于用于连接到电缆或比如系统互连 PC 板 60 (未示出)的其他电子系统的间距。

当作为晶片来形成薄片 32 时,对晶锭 30 的切片还对导线 36 切片. 导线 36 延伸穿过薄片 32.

在图 3 所示的替代实施例中, 晶锭 30 不包括导线 36. 代替地, 晶锭 32 不具有附加的组件。可以提供不同于导线的附加物。代替在晶锭 30 中的导线 36, 可以使用插入物 42. 插入物由背衬材料形成, 比如与用于晶锭 30 的相同的或不同的背衬材料。可以提供其他的材料, 比如塑料、半导体或环氧树脂。插入物 42 包括导体, 比如导线 36a、36b、补块、球或电极。所述导体伸入但不贯通插入物 42. 可替代地, 所述导体贯穿插入物 42. 插入物 42 具有与薄片 32 相同的或相似的厚度, 比如稍小一些。

所述导体具有针对导线 36 以上所讨论的间隔。在给定插入物 42上的导体用于不同的切片 50。当对薄片 32 切片时,切割穿过插入物 42,分离并暴露出不同的导体。可替代地,为不同的切片 50 提供不同的插入物 42. 多个插入物 42 可以用在示出一个的情况下。一个插入物 42 可以用在示出两个或多个的情况下,比如插入物 42 沿着薄片 32 的三个切片部分延伸。

在动作 14 中,在薄片 32 中形成孔 34、40。孔 34、40 被模具冲孔。可以使用用于形成孔的其他技术。比如,通过塑造、切割、铸造或蚀刻来形成孔。在一个实施例中,所述孔 34、40 位于晶锭 30 中。在其他实施例中,所述孔 34、40 在薄片 32 中被形成。

孔 34 针对芯片 44 (未示出)被定尺寸。孔 34 延伸穿过薄片 32,但具有与芯片 44 相同或稍微大些的形状和尺度。孔 40 针对插入物 42被定尺寸。在使用不同尺寸的插入物 42 的情况下,使用不同尺寸的孔42。根据由薄片 32 要形成的切片 50 来确定孔的位置和方向。可以使用与所示不同的相关位置和方向。

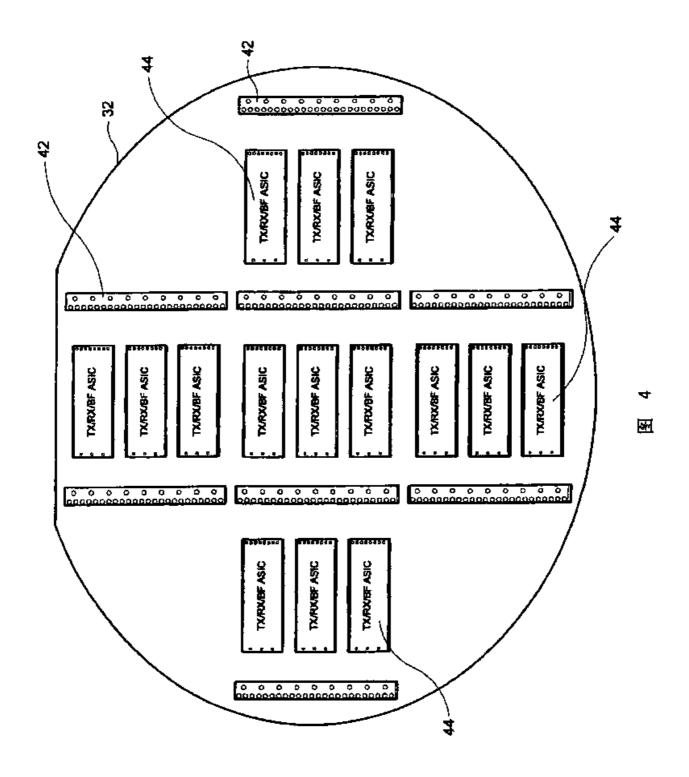

在动作 16 中,在薄片 32 中放置一个或多个芯片 44. 图 4 示出了一个例子,其中在与切片 50 相关的每个区域中安置三个芯片 44. 每切片 50 或每薄片 32 可使用更少的或更多的芯片 44. 插入物 42 也被放置在薄片 32 中. 每切片 50 或每薄片可使用更少的或更多的插入物 42.

芯片 44 和插入物 42(如果有的话)通过拾取和放置处理(pick and place processing)而被放置、芯片 44 与有源组件一起被向下安置,用以插入到晶片带或支持物上或由其保护。在与薄片 32 的底面相同的平面中提供有源表面。芯片有源表面可选地也可以被涂敷有保护层,其中所述保护层稍后被去除或者在重新分配工艺期间被蚀刻。可以使用其他现在已知的或今后开发的用于在孔 34、40 中放置芯片 44 和插入物 42 的工艺。可以使用自动的或手动的放置。

芯片 44 和/或插入物 42 所具有的厚度大于、等于、或小于薄片 32 的厚度. 比如, 芯片 44 和插入物 42 的厚度大致相同,但小 5-10%。 芯片 44 和插入物 42 不伸出孔 34、40。孔 34、40 的剩余部分被填充有环氧树脂用以回填。使用涂刷或其他工艺来跨薄片 32 的顶端提供平坦表面。由于芯片 44 的有源表面朝下安置,所以环氧树脂很可能不接触有源表面。可替代地,芯片 44 和/或插入物 42 伸出孔 34、40,并被研磨、磨削、或蚀刻掉用以与薄片 32 一起形成平坦表面。可以提供回填用以填充任何缝隙。

回填材料整治、形成复合薄片 32. 一旦被整治,薄片 32 就可以从框架、带、或其他支持物移除。在其他实施例中,在移除之前还进行其他工艺。

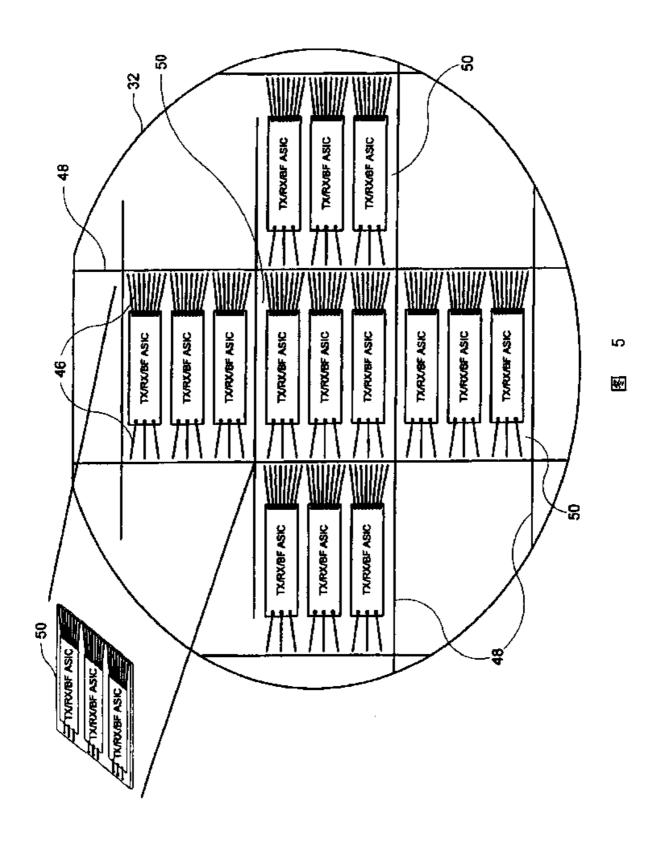

在动作 18 中,从芯片 44 到薄片 32 的线 48 构成导体 46(见图 5). 线 48 对应于要从薄片 32 上切割的切片的边缘。线 48 对准插入物 42 或者导线 36a、36b,以便在进行切割时暴露导线 36a、36b 或者传导表面。导体 46 把芯片 44 上的焊盘、焊球、或其他导体与元件的导线 36 以及输出传导表面相连接。导体 46 从芯片、经由任何填充物、经由声 背衬材料延伸并延伸到导线 36 或传导表面。

导体 46 通过沉积、光刻、蚀刻、电镀、和/或其他半导体工艺来形成。 比如使用平面 IC 重新分配处理 (planar IC redistribution processing)。 导体 46 针对薄片 32 的不同切片 50 被图样化。虽然示出在薄片 32 上,但导体 46 可以位于分层的薄片 32 内。

由于不同的阵列和/或芯片 44 可能具有不同的连接配置或间距,所以导体 46 被图样化用以匹配差异。比如芯片 44 的输入端的间距小于要被连接到芯片 44 的元件 58 的间距,因此导体 46 呈扇状分散开。可以使用其他的重新分配。这种重新分配允许使用具有不同阵列的模块芯片。

为了电气或机械保护,薄片 32 可以被涂敷有绝缘体。比如,整个薄片 32 被旋转涂敷。这种涂敷在朝上的表面、朝下的表面、或两者上。 在替代实施例中,不提供涂敷。

在动作 20 中,从薄片 32 切割一个或多个切片 50。这种切割是比如利用金刚石锯或其他半导体切割技术的切成小方块(dice)。切割沿着线 48. 这种切割暴露出沿着线 48 的导体,比如插入物 42 的导线 36. 所暴露的导体具有用于与换能器的电极、其他导体、或元件相连接的面积。在替代实施例中,所述切割不暴露导线 36, 导线 36 稍后通过磨削而被暴露。

每个切片都包括一个或多个芯片 44、重新分配导体 46、以及所暴露的边缘表面导体 52。在图 5 所示的例子中,每个切片都包括三个芯片 44. 导体 46 把所暴露的边缘表面导体 52 连接到芯片 44 的输入端,并把芯片 44 的输出端连接到其他所暴露的边缘表面导体 52.

切片 50 被定尺寸用以相邻于阵列来安装。比如,每个切片 50 被定尺寸用以覆盖元件的整个方位行,而仅覆盖仰角元件的一列。芯片 44 与切片 50 的元件侧相距足够的距离,用以提供所期望的声衰减,比如约为 5-10 毫米。从芯片 44 到其他边缘可以设置任何的距离,包括没有被薄片 32 的背衬材料所覆盖的芯片 44 的一个或多个边缘。

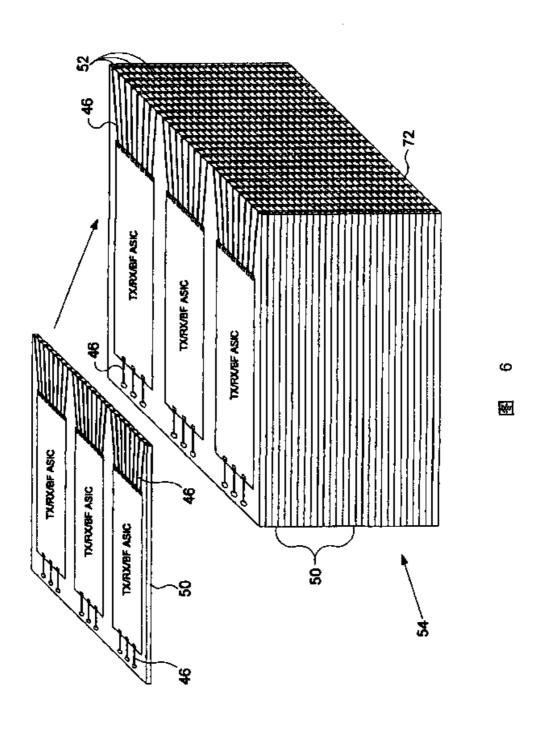

在动作 22 中,多个切片 50 被堆叠在一起。图 6 示出了形成背衬块 54 的堆叠. 基准 (fiducial)、框架、或其他结构使切片 50 对准. 绝缘涂层、环氧树脂、或背衬材料将一个切片 50 的导体与其他切片 50 相绝缘.

背衬块 54 提供所暴露的元件接触 52 的表面,例如所暴露的导线 36a 的表面。可替代地,背衬块 54 被磨削以便暴露元件接触 52. 元件接触 52 通过背衬材料和/或绝缘材料而彼此电绝缘。元件接触 52 在表面上以与换能器的元件分布相一致的方式被分配。每个元件接触 52 都可以被用作阵列的电极,或者用于与元件电极连接。在每个切片 50 在

一个维度中对应于元件 58 的单个行的情况下,在另一维度中为多个元件 58 提供足够数目的切片 50。可以使用具有两行或多行用的所暴露的元件接触 52 的切片 50。可以使用小于阵列的整个宽度伸展的切片 50。

在动作 24 中所堆叠的切片 50 被层压在一起。可以使用加热或其他催化剂来用于层压。可以使用环氧树脂或其他粘合物。在替代实施例中,在使用期间,刚性结构或夹具将堆叠 54 保持在一起。

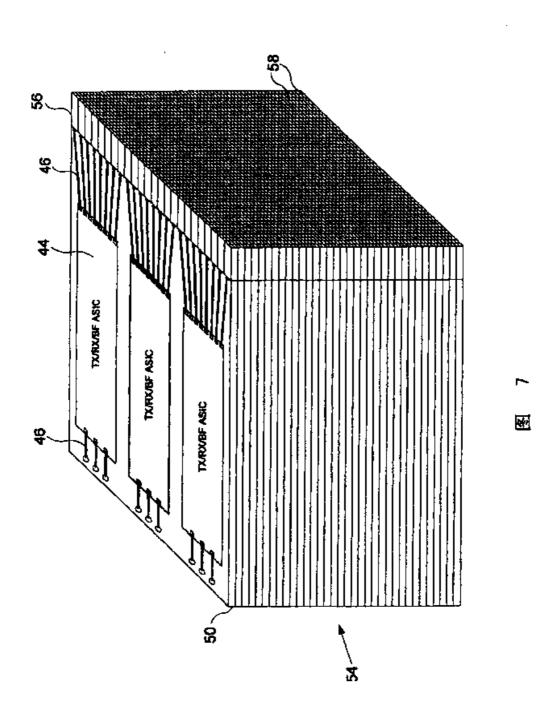

图 7 示出添加换能器材料 56 的层。换能器材料 56 的层是固态压电陶瓷、合成物、或其他换能材料。该层可以包括电极和/或匹配层。在一个实施例中,该层被结合到背衬块 54 上,并然后通过切成小方块来形成元件 58。也可以形成子元件。在其他实施例中,元件 58 在结合到背衬材料 54 之前被形成。元件 58 和相应的切口对准元件接触 52。在任何匹配层之上或之下可以包括接地平面,用以将元件 58 的顶面接地。

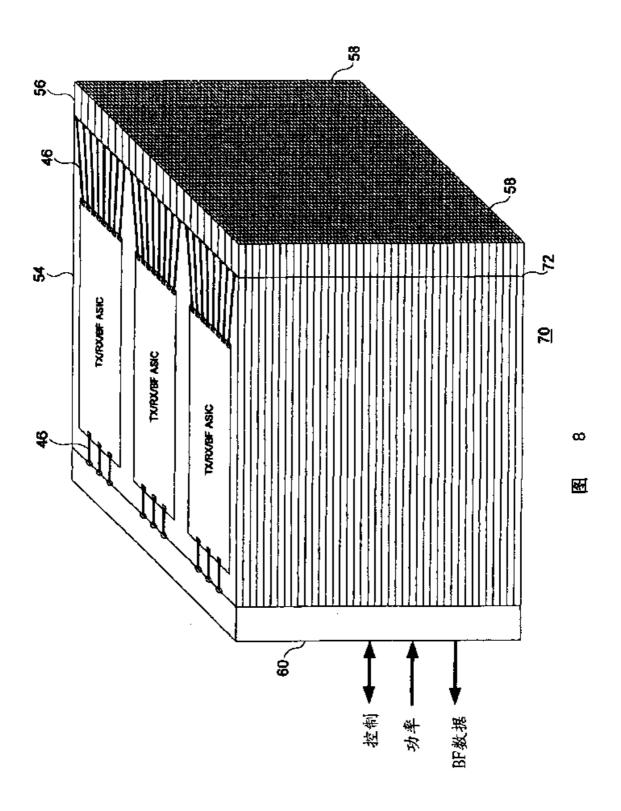

图 8 示出了系统互连板 60 的连接。背衬块 54 被磨削以便在背衬块 54 的背面上暴露系统侧传导表面 52. 可替代地,动作 20 的切片暴露传导表面 52. 表面 52 布置在背衬块 54 上用以与板 60 中的导体紧密配合,比如使用倒装芯片 (flip chip) 型焊接。互连板 60 被结合、挤压、或者另外与背衬块 54 相连接。通过对准,板 60 的导体与由芯片44 输出的背衬块 54 的导体连接。

图 17 示出了用于互连板 60 的连接的不同实施例。一个实施例用于模拟连接,另一个用于数字信号连接。可以使用其他模拟的、数字的、或两种连接。从与至互连板 60 的连接相关联的背侧以堆叠的方式示出切片 50。接触 80 把板 60 连接到芯片 44. 对于数字实施,来自不同切片 50 的接触 80 对以串级链或其他格式连接在一起。一行代表由芯片 44 所处理的切片 50 部分的输入,另一行代表由芯片 44 所处理的用于切片 50 部分的输出。每个输出都是部分或子阵列和(比如在方位上而不是在仰角上相加)。另一切片的输入可以与输出相加,来提供在方位上以及在仰角上的子阵列和。给定子阵列的接触 82 悬浮或被接地。另一接触 82 是至系统的输出。对于模拟实施例,每个接触 80 是部分子阵列(比如在方位上而不是在仰角上相加)。接触 80 的组连接在一起用以形成子阵列(比如由"H"形来表示)。全部子阵列信号被接线到系统。其他接触 88 用于电源、接地、和/或控制信号。这些接触

88 被示出为每芯片 44 仅一个,但也可以提供多个。互连板 60 提供用于串级链、"H"连接、和/或电源/接地/控制连接的导线。可以使用其他配置。

芯片 44 降低了用于每个给定切片 50 的通道数。可以使用多路复用、子阵列混合、部分波束形成、其组合、或用于减少通道的其他技术。输入元件数据被组合到较少的输出。输出数据是模拟的或数字的。输出数据被提供给互连板 60。互连板 60 是具有信号轨道(trace)和/或通孔(via)的绝缘材料的 PC 板。在互连板 60 上可以提供或不提供有源或无源电路。比如,提供电容器用于功率存储或 DC 退耦。

互连板 60 把芯片 44 的输出端连接到电缆,诸如连接至互连板 60 的同轴电缆。控制信号、功率、和/或发射波形可以利用一个或多个导体 46 通过或者由互连板 60 被提供给芯片 44. 互连板 60 可以从一个切片 50 向另一切片 50 的芯片 44 提供信号,比如用于进行进一步的通道减少。比如,通过将来自元件的不同仰角行的信号相组合来提供部分波束形成。

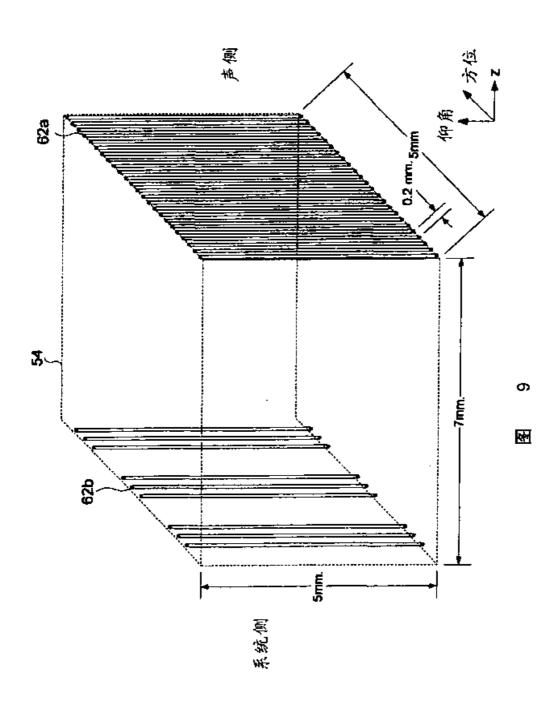

图 9-12 示出了用于实现图 1 的方法的替代实施例。在动作 12 中由块形成背衬材料薄片。图 9 示出了背衬材料块 54, 其被定尺寸和形状用于与多维换能器阵列一起运行。可以使用与图示不同的尺寸,比如由于下述的切割而沿着高度具有较大的尺度。块 54 是加载的环氧树脂,但也可以使用其他的声衰减材料。

块 54 包括多个导线 62. 导线 62a 在声侧或换能器侧。导线 62b 在系统侧。作为导线 62 的替代方案,可以使用在柔性材料上的轨道或其他导体。导线 62a 沿着块 54 的整个高度延伸,并且以元件间距相间隔、比如 0.2mm。系统侧的导线 62b 沿着整个高度延伸,并且适当地相间隔用于在互连板 60 与背衬中的芯片 44 (未示出)之间的系统侧连接。在芯片 44 (未示出)减少通道数的情况下,可需要较少的导线 62b. 导线 62 在外部边缘上,但也可以嵌入到块 54 内,用以稍后通过磨削暴露。

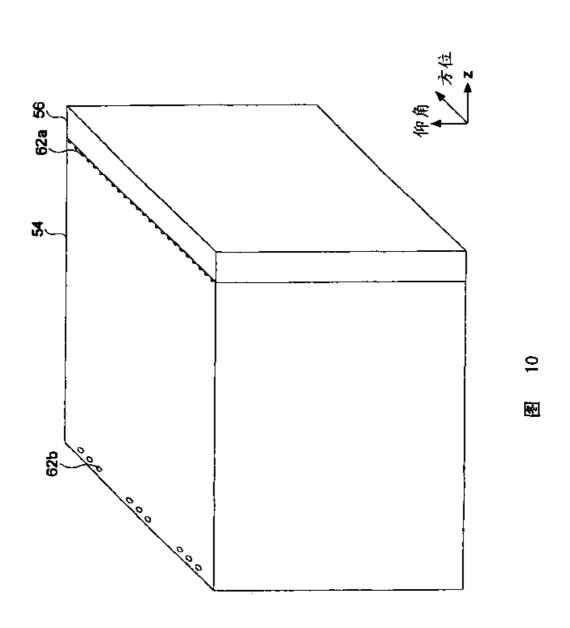

图 10 示出了给块 54 添加换能器材料层 56. 块 54 的声侧被磨削用以在导线 62a 上提供平坦表面. 换能器材料 56 被结合到或者否则被连接到块 54.

换能器材料 56 被切成小方块用以形成元件和/或子元件。切口 64

中的一些穿过换能器材料 56 以及块 54 延伸,形成切片 50。这种切成小方块利用金刚石磨粒 ID 锯来进行,但也可以使用其他的切割装置。这种切割用于在仰角上的导线 62,而维持导线 62a 与通过切成小方块所形成的元件 58 的接触。图 12 示出了所形成的切片 50。与图 2-8 的实施例不同,切片 50 在堆叠之前可以在每个切片 50 上包含换能器材料 56。这种构造方法不需要把换能器材料 56 施加到每个切片 50。无论块 54 如何被构造,换能器材料 56 的阵列可以作为一个整体被附在端部。

在图 1 的动作 14 和 16 中,在切片 50 中形成孔 34,并把芯片 44 放置到孔 34 中。在动作 18 中形成导体。动作 20 与动作 12 一起发生。在动作 22 和 24 中,切片 50 被堆叠并被层压。

可以提供其他实施例用于形成切片 50。比如,单独地形成切片而不是从块或晶片上切割。

图 8 示出了超声换能器 70. 在堆叠和层压之后,提供具有嵌入芯片 44 的衰减材料的背衬块 54. 背衬块 54 与换能器材料 56 一起被使用来提供超声换能器 70. 超声换能器 70 包括换能器材料 56、元件 58 上的电极、背衬块 54、以及互连板 60. 也可以提供额外的、不同的、或更少的组件。比如,包含匹配层、接地平面柔性材料、透镜、外壳、同轴电缆、和/或无线收发器。作为另一例子,具有轨道的柔性材料或电缆连接器在没有互连板 60 的情况下与背衬块 54 相连接。

换能器材料 56 被切成小方块或被形成为多个元件 58. 元件 58 以 元件 58 的一维、二维、或其他多维阵列的形式相间隔。对于元件 58 的多维阵列,元件 58 在方位和仰角上以矩形栅格的方式相间隔。也可以使用其他栅格。元件 58 是具有或不具有子方块 (sub-dicing) 的单层或多层压电元件 58. 其他类型的换能器材料 (比如非压电的) 也是可能的。在构建块 54 之后,可以附上任何类型的换能器。比如,具有背侧接触通孔的 CMUT 被附到块 54 上。

每个元件 58 在元件 58 的相对面上包括电极。在换能器材料 56 与背衬块 54 之间布置一个电极。另一电极位于元件 58 的、发射和从患者接收声信号的侧。所述电极被沉积到元件上,通过在柔性材料上的导体形成(比如在用于发射和接收的元件侧的接地平面),通过导线62、传导表面 52、或背衬块 54 的其他导体或其他技术来形成。邻近背

衬块 54 的电极比如通过切成与元件图样相匹配的图样而彼此电绝缘。

背衬块 54 用于来自换能器 70 背侧的能量的声衰减。穿过换能器 材料 56 或者从远离患者的换能器材料 56 传播的声能被衰减。这种衰 减限制或避免了大得足以在由换能所生成的电信号中产生不期望的干 扰的声能反射,背衬块 54 防止或限制不是来自患者的回波的信号份额。

背衬块 54 是任何现在已知的或今后开发的用于以所期望的声频率、比如 1-20Hz 衰减的材料。背衬块 54 包括用于衰减的固态或合成材料。材料可以是可塑造的、可铸造的、和/或可加工的。在一个实施例中,使用环氧树脂的合成材料和一种或多种填充物,比如钨。

背衬块 54 包含用于与换能器材料 54 的背侧相接触的表面 72. 表面 72 包括多个间隔开的或电绝缘的、所暴露的导体 52, 用于与电极和/或元件 58 连接。可替代地,通过切成小方块来提供电绝缘。

背衬块 54 包括一个或多个半导体,比如芯片 44. 所述半导体包含有源电路,比如晶体管。在一个实施例中,半导体是专用集成电路,但也可以使用其他的集成电路(比如通用处理器). 半导体减少了要被通信至成像系统的信息的通道的数目。可以使用任何的减少技术。比如,半导体使用时间和/或频率多路复用来复用。作为另一例子,半导体包含脉冲发生器,比如开关,用以生成波形。可以包含发射和/或接收波束形成组件,比如延迟、相位旋转器、放大器、加法器、或用于使发射和接收孔径相对延迟和变迹(apodizing)的其他组件。对于接收波束形成,可以使用相加来为元件 58 的阵列的子孔径部分地波束形成。在其他例子中,半导体包含混合器或具有放大器的开关,用于把来自不同元件 58 的信号混合到较少的通道上。半导体可以包含有不同于用于通道减少的其他电路,比如模拟数字转换器、控制器、发射/接收开关、和/或过滤装置。

半导体可操作用于特定的阵列和/或成像系统。比如,半导体针对给定的带宽和运行频率为元件 58 的阵列以特定的间距实施部分或子阵列波束形成。可替代地,半导体可被配置用以利用不同的元件间距、成像系统、频率、和/或带宽运行。通过配置,相同的半导体可以利用不同的阵列运行。在提供多个阵列的情况下,由于相同的芯片 44 可以供任何阵列使用,所以可以降低制造集成电路的成本。

半导体位于背衬材料内,比如嵌入在声衰减背衬材料中的集成电

路.背衬块 54 的背衬材料位于半导体与表面 72 或换能器材料 54 之间。比如,提供约 5-10mm 或其他的空隙。芯片 44 的一侧邻近于背衬材料或与之连接。背衬材料也可以邻近一个或两个其他侧,比如与所述的一侧相连的侧。在一个实施例中,背衬材料邻近或环绕芯片 44 的四侧。对于切片 50,背衬材料邻近两组相对侧。另外两侧邻近其他芯片,但通过环氧树脂或一个或多个绝缘层相分隔。在其他实施例中,背衬材料围绕六个侧或整个芯片 44. 背衬材料可以完全地沿着所述侧延伸,或者仅仅邻近一个或多个侧的一部分。处于芯片 44 "内"可以包括芯片 44 的至少一部分处于背衬块 54 之外或者暴露在其边缘上。

可以在整个背衬块 54 中提供一个芯片 44. 在其他实施例中,在背衬块 54 中嵌入多于一个的芯片 44. 比如,多个切片 50 组成背衬块 54. 每个切片 50 都包括一个或多个芯片 44. 在背衬块 54 中为与每个切片相关联的元件 58 提供集成电路。比如,每个切片 50 在方位或仰角维度上对准一行元件 58。每个切片 50 的嵌入式集成电路为元件 58 的相应行进行通道减少。

在声衰减背衬材料内,背衬块 54 也包括多个轨道或导体 46. 导体 46 是所沉积的轨道,比如与切片 50 相关联的.可替代地,导体 46 是导线、柔性材料、或者在背衬块 54 中通过塑造或其他工艺所形成的其他装置。导体 46 可以包括不同的部分,比如焊接到或与焊盘、导线、电极、或其他导体相连接的轨道。导体 46 可以包括用于暴露在背衬块54 的表面上的部分以及用于接触芯片 44 的输入/输出焊盘的部分。

导体 46 把元件 58 或相应的电极连接到芯片 44 或集成电路的输入端。导体 46 从半导体通过背衬材料或在其之上延伸到元件 58。在一个实施例中,导体 46 在背衬块 54 的表面 72 上延伸到传导表面 52。

导体 46 从传导表面 52 的元件间距至芯片 44 的集成电路的输入端间距重新分配。这些间距是不同的,但也可以是相同的。比如在采用具有切片 50 的实施例的情况下,传导表面 52 在表面 72 上成行地暴露。导体 46 把每一行的传导表面连接到相应的半导体芯片 44。导体 46 可以朝向芯片 44 扇入 (fan in) 或扇出 (fan out)。在每切片一个芯片的解决方案中,导体 46 可以扇出用以适合较大的芯片。由于可以使用导体 46 的不同图样,所以可以以不同的元件间距来使用相同的芯片 44。可以以相同的元件间距来使用不同的芯片 44。

其他的导体46从半导体通过背衬材料或在其之上延伸到背衬块54的背面,但也可以延伸到侧面。四个表面可以用于至切片的接触。换能器阵列侧以及系统互连侧是主要表面,但块54的与切片垂直的所有四个表面可以具有接触。比如,图15和16示出在切片50的侧面上的接地接触70,其可以用于阵列的接地或其他目的。作为另一例子,用于至芯片44的功率、芯片44的控制信号、或来自芯片44的输出的导体46延伸到与换能器材料56相对的表面。由于通过集成电路所实施的通道组合,所以可以提供较少数目的导体46。

图 15 和 16 示出了侧接触 70. 接触 70 连接到其他的导体 46 和/或芯片 44。在一个实施例中,接触 70 用于接地。图 16 示出了环绕的传导薄膜 72 用于将阵列 56 的前面接地。传导薄膜 72 通过压力、传导胶、焊料肿块、或其他工艺而连接到接触 70。接触 70 可以在一侧或两侧。在其他实施例中,一侧或多侧接触 70 用于把块 54 电接地到外部屏蔽。在侧面上可以不使用或使用多个接触 70.

图 13 示出了具有冷却的换能器 70 的另一实施例。换能器 70 在背衬块 54 中包含一个或多个管子 80。这些管子 80 通过背衬块 54 延伸或仅仅部分地延伸到背衬块 54 中。管子 80 在堆叠和层压之后形成,或者通过在每个切片 50 中单独制造的孔来形成。管子 80 是垂直的,但也互连或成角度的。管子 80 是中空的。强制气体或液体流经管子 80 用以主动冷却。可替代地,提供被动冷却。管子 80 可以是有衬里的(lined),也可以是没有衬里的。在替代实施例或附加实施例中,管子 80 被填充有热传导材料,比如金属。填充物把热量从芯片 44 传导到热排放口或泵。

图 14 示出了切片 50 的另一实施例。在换能器材料 56 和元件 58 后面的空间受限的情况下,比如在经食道探头中,芯片 44 可以布置在背衬材料的其他地方。导体 46 允许对来自元件 58 的信号路由。切片50 如所示在具有换能器材料 56 的情况下被形成。可替代地,切片 50 在无换能器材料 56 的情况下被形成,并在堆叠之后添加材料 56.

虽然在上文中通过参照不同实施例对本发明进行了描述,但是应理解的是:可以在不脱离本发明范畴的情况下进行很多的改变和修改。因此,前文的详述应认为是解释性的而不是限定的,并且应理解的是,后面的权利要求、包括所有的等效用来限定本发明的精神和范畴。

图 1

| 专利名称(译)        | 超声换能器上的嵌入式电路以及制造方法                                                                                                                                       |       |     |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------------|

| 公开(公告)号        | CN101344588A                                                                                                                                             | 公开(公台 | 壹)日 | 2009-01-14 |

| 申请号            | CN200810136157.1                                                                                                                                         | 申     | 清日  | 2008-07-10 |

| [标]申请(专利权)人(译) | 美国西门子医疗解决公司                                                                                                                                              |       |     |            |

| 申请(专利权)人(译)    | 美国西门子医疗解决公司                                                                                                                                              |       |     |            |

| 当前申请(专利权)人(译)  | 美国西门子医疗解决公司                                                                                                                                              |       |     |            |

| [标]发明人         | DA彼得森<br>SC恩隆德                                                                                                                                           |       |     |            |

| 发明人            | D·A·彼得森<br>S·C·恩隆德                                                                                                                                       |       |     |            |

| IPC分类号         | G01S7/521 A61B8/00                                                                                                                                       |       |     |            |

| CPC分类号         | H01L2924/0002 G01S7/5208 H01L2225/06589 G01S15/8909 G01S15/8927 B06B1/0622 G10K11/002 H01L25/0657 H01L2225/06551 H01L2225/06527 Y10T29/49005 H01L2924/00 |       |     |            |

| 代理人(译)         | 卢江<br>刘春元                                                                                                                                                |       |     |            |

| 优先权            | 11/827179 2007-07-10 US                                                                                                                                  | }     |     |            |

| 其他公开文献         | CN101344588B                                                                                                                                             |       |     |            |

| 外部链接           | Espacenet SIPO                                                                                                                                           |       |     |            |

|                |                                                                                                                                                          |       |     |            |

#### 摘要(译)

本发明涉及超声换能器上的嵌入式电路以及制造方法。在背衬块(54)内嵌入一个或多个芯片、集成电路(44)、或半导体(44)。形成背衬材料(54)的 14 平面薄片(32),其中集成电路(44)位于薄片(32)中的孔(34)内。轨道(46) 把集成电路(44)连接到电极或所暴露的传导表面(52)。多个平面薄片(32) 15 可以利用晶片处理来制造,比如在背衬材料(54)的晶片中对芯片的拾取和放置(16)以及IC重新分配用于形成轨道(46)。从晶片切割不同的薄片 (32),并彼此相邻地堆叠(22)。换能器与所暴露的电极或背衬(54)的传导表面(52)相连接。