(12) 实用新型专利

(10) 授权公告号 CN 204906507 U

(45) 授权公告日 2015. 12. 23

(21) 申请号 201520474499. X

A61B 1/05(2006. 01)

(22) 申请日 2015. 06. 30

(ESM) 同样的发明创造已同日申请发明专利

(73) 专利权人 广东实联医疗器械有限公司

地址 510440 广东省广州市白云区白云大道

北友谊路嘉禾生产基地八一科技园 E

栋四楼

(72) 发明人 陈锦棋

(74) 专利代理机构 广州新诺专利商标事务所有

限公司 44100

代理人 华辉 张奇洲

(51) Int. Cl.

H04N 5/225(2006. 01)

H04N 7/18(2006. 01)

A61B 1/045(2006. 01)

权利要求书5页 说明书16页 附图34页

(54) 实用新型名称

一种医用内窥镜的视频采集处理、视频录制

及显示电路

(57) 摘要

本实用新型涉及一种医用内窥镜的视频采集

处理、视频录制及显示电路，包括视频采集芯片、

图像处理芯片、信号转换芯片、图像增强芯片、视

频录制芯片和显示驱动芯片；所述视频采集芯片

将采集后的视频数据发送至图像处理芯片进行处

理；所述信号转换芯片包括第一信号转换芯片和

第二信号转换芯片；所述图像处理芯片将处理后

的图像信号发送至第一信号转换芯片，并由该第一

信号转换芯片发送至第二信号转换芯片；所述第

二信号转换芯片将信号转换后发送至图像增强

芯片；所述图像增强芯片将接收的视频图像进行

增强处理，并同时发送至视频录制芯片和显示驱

动芯片，由该视频录制芯片进行录制，由该显示驱

动芯片进行实时播放。

1. 一种医用内窥镜的视频采集处理、视频录制及显示电路,其特征在于:包括视频采集芯片、图像处理芯片、信号转换芯片、图像增强芯片、视频录制芯片和显示驱动芯片;

所述视频采集芯片将采集后的视频数据发送至图像处理芯片进行处理;

所述信号转换芯片包括第一信号转换芯片和第二信号转换芯片;所述第一信号转换芯片用于将bt1120信号转换为1vds信号;所述第二信号转换芯片用于将1vds信号转换为bt1120信号;

所述图像处理芯片将处理后的图像信号发送至第一信号转换芯片,并由该第一信号转换芯片发送至第二信号转换芯片;所述第二信号转换芯片将信号转换后发送至图像增强芯片;

所述图像增强芯片将接收的视频图像进行增强处理,并同时发送至视频录制芯片和显示驱动芯片,由该视频录制芯片进行录制,由该显示驱动芯片进行实时播放;

所述视频录制芯片完成视频录制后,发送至显示驱动芯片,进行视频回放。

2. 根据权利要求1所述医用内窥镜的视频采集处理、视频录制及显示电路,其特征在于:

所述视频采集芯片内部包括:控制器、驱动器、感光器、取样器和输出器;

—所述控制器,其用于接收外部的触发信号,发送触发信号至驱动器;

—所述驱动器,其用于接收控制器的触发信号,并驱动感光器工作;

—所述感光器,其用于接收外界的光信号,并将该光信号转换为电信号;

—所述取样器,其用于对感光器的电信号进行取样处理,并将处理完的电信号发送至输出器;

—所述输出器,其用于将该电信号转换为数字信号,并进行输出图像处理芯片;

所述图像处理芯片包括:数据接收器、中心控制器、图像处理器、数据输出器;

—所述数据接收器,其用于接收外部的图像数据;

—所述中心控制器,其用于接收外部的触发信号,并相应控制所述数据接收器、图像处理器和数据输出器的工作状态;

—所述图像处理器,其用于对图像进行处理;所述图像处理器包括一白平衡固定电路,其用于根据预设的参数,进行白平衡的固定调整;

—所述数据输出器,其用于将处理后的图像数据进行输出;

所述第一信号转换芯片包括:控制器、数据读取器、信号格式转换器、串行器、数据输出器;

—所述控制器,其用于接收外部的触发信号,并控制数据读取器、信号格式转换器、串行器和数据输出器的工作;

—所述数据读取器,其用于接收外部的bt1120传输信号,并发送至信号格式转换器;

—所述信号格式转换器,其用于将bt1120视频信号转换为1vds的视频信号,并发送至串行器;

—所述串行器,其用于将并行数据转换为串行数据,并发送至数据输出器;

—所述数据输出器,用于将1vds信号数据输出至第二信号转换芯片;

所述第二信号转换芯片包括:控制器、数据读取器、信号格式转换器、并行器、数据输出

器；

——所述控制器，其用于接收外部的触发信号，并控制数据读取器、信号格式转换器、并行器和数据输出器的工作；

——所述数据读取器，其用于第一信号转换芯片的 lvd 视频传输信号，并发送至信号格式转换器；

——所述信号格式转换器，其用于将 lvd 视频信号转换为 bt1120 的视频信号，并发送至并行器；

——所述并行器，其用于将串行数据转换为并行数据，并发送至数据输出器；

——所述数据输出器，用于将 bt1120 视频信号数据输出；

所述图像增强芯片包括：数据接收器、控制器、静态存储器、图像增强器、数据输出器和时钟发生器；

——所述数据接收器，其用于接收图像数据信号，并发送至该图像增强器；

——所述控制器，其用于接收外部触发信号，并相应控制数据接收器、图像增强器和数据输出器的工作状态；

——所述静态存储器，其用于存储图像增强器的驱动数据，以驱动该图像增强器的工作；

——所述图像增强器，其包括一图像边缘增强电路；所述图像边缘增强电路用于增强图像边缘的清晰度；

——所述数据输出器，其用于接收图像增强器处理后的图像数据，并进行数据输出；

——所述时钟发生器，其用于为图像增强芯片产生时钟信号；

所述视频录制芯片包括：数据接收器、视频编码器、视频解码器、数据输出器和处理器；

——所述数据接收器，用于接收外部的视频信号，并发送至视频编码器；

——所述视频编码器，用于对视频信号进行编码录制；

——所述视频解码器，用于对视频信号进行解码回放；

——所述数据输出器，用于对视频信号进行输出；

——所述处理器，用于控制数据接收器、视频编码器、视频解码器和数据输出器的工作；

所述显示驱动芯片包括：模拟信号接收器、数字信号接收器、模数转换器、复用器、输出格式转换器、数据输出器和控制器；

——所述模拟信号接收器，用于接收模拟信号，并发送至模数转换器；

——所述模数转换器，用于将模拟信号转换为数据信号，并发送至复用器；

——所述数据信号接收器，用于接收数据信号，并发送至复用器；

——所述复用器，用于将两路信号进行整合，并进行输出至输出格式转换器；

——所述输出格式转换器，用于将信号格式进行转换，并输出至数据输出器；

——所述数据输出器，将信号输出，并进行显示；

——所述控制器，用于控制模拟信号接收器、数字信号接收器、模数转换器、复用器、输出格式转换器和数据输出器的工作。

3. 根据权利要求 1 所述医用内窥镜的视频采集处理、视频录制及显示电路，其特征在

于：

所述视频采集芯片还包括一倍频器，其用于将外部输入的触发信号的频率进行增倍处理，再发送至控制器；

所述图像处理芯片还包括一倍频器，其用于将外部输入的触发信号的频率进行增倍处理，再发送至中心控制器；

所述第一信号转换芯片还包括一锁相回路，分别与信号格式转换器和串行器连接，用于统一整合时脉信号；

所述第二信号转换芯片还包括一锁相回路，分别与信号格式转换器和串行器连接，用于统一整合时脉信号；

所述图像增强芯片还包括一降噪处理器；所述数据接收器接收到的图像数据信号，发送至降噪处理器进行降噪处理，再转发至图像增强器；

所述视频录制芯片还包括一图像处理器，用于对数据接收器所接收的视频进行处理，并将处理后的图像发送至视频编码器；

所述显示驱动芯片还包括一视频解码器、场逆程数据处理器和存储器；

所述视频解码器，用于将模拟信号接收器接收的模拟信号进行解码，并发送至场逆程数据处理器；

所述场逆程数据处理器，用于将解码后的模拟信号插入数据行，并发送至所述存储器进行存储；

所述存储器，用于存储经场逆程数据处理器处理后的数据，并发送至输出格式转换器。

4. 根据权利要求 3 所述医用内窥镜的视频采集处理、视频录制及显示电路，其特征在于：

所述图像处理芯片中的图像处理器还包括一曝光增益电路，用于增加曝光增益大小；

所述第一信号转换芯片还包括一时钟数据恢复器，其与数据读取器连接，用于从传输信道的失真和噪声中恢复数据；

所述第二信号转换芯片还包括一时钟数据恢复器，其与数据读取器连接，用于从传输信道的失真和噪声中恢复数据；

所述图像增强芯片还包括一动态存储器；所述降噪处理器处理后的图像数据，先发送至动态存储器进行存储，再转发至图像增强器；

所述视频录制芯片的图像处理器包括边缘增强电路和消除噪音干扰电路；

所述显示驱动芯片还包括一图像边缘平滑处理器，用于接收复位器的信号，并对视频图像的边缘进行平滑处理，再发送至格式转换器。

5. 根据权利要求 3 所述医用内窥镜的视频采集处理、视频录制及显示电路，其特征在于：

所述图像处理器还包括一光学探测电路和闪烁探测电路，其用于探测图像的亮度和闪烁情况，并将探测结果发送至曝光增益电路；

所述图像增强芯片还包括一像素自适应校对器；所述图像增强器先将处理后的图像数据发送至所述像素自适应校对器，由该像素自适应校对器进行像素适应校对，再发送至数据输出器。

6. 根据权利要求 1 所述医用内窥镜的视频采集处理、视频录制及显示电路，其特征在

于：

所述视频采集芯片外部设有：用于接收供电电压的电源端口、用于输出视频信号的视频信号端口、用于输出行场信号的行场信号端口、用于接收参考电压电频的参考信号端口和一用于接收外部时钟信号的时钟信号端口；

所述图像处理芯片外部设有：用于接收供电电压的电源端口、用于接收图像信号的信号接收端口、用于输出视频信号的视频信号端口、用于输出行场信号的行场信号端口、用于接收外部时钟信号的时钟信号端口、用于接收存储数据的数据接收端口和一用于接收外部通讯命令的通讯端口；

所述第一信号转换芯片外部设有：用于接收供电电压的电源端口、用于接收 bt1120 视频信号的信号接收端口、用于输出 1vds 视频信号的视频信号端口和用于输出行场信号的行场信号端口；

所述所述第二信号转换芯片外部设有：用于接收供电电压的电源端口、用于接收 1vds 视频信号的信号接收端口和用于输出 bt1120 视频信号的视频信号端口；

所述图像增强芯片外部设有：用于接收供电电压的电源端口、用于接收图像信号的信号接收端口、用于输出视频信号的视频信号端口、用于输出行场信号的行场信号端口、用于接收外部时钟信号的时钟信号端口和用于接收存储数据的数据接收端口；

所述视频录制芯片外部设有：电源端口、视频输入端口、视频输出端口和通讯端口；所述视频输入端口与该视频录制芯片内部的数据接收器连接，用于接收外部的视频数据；所述视频输出端口，与所述数据输出器连接，用于输出视频数据；所述通讯端口，与所述处理器连接，用于接收外部的串口命令；

所述显示驱动芯片外部设有：电源端口、视频输入端口、视频输出端口和通讯端口；所述视频输入端口与该视频录制芯片内部的数据接收器连接，用于接收外部的视频数据；所述视频输出端口，与所述数据输出器连接，用于输出视频数据；所述通讯端口，与所述处理器连接，用于接收外部的串口命令。

7. 根据权利要求 6 所述医用内窥镜的视频采集处理、视频录制及显示电路，其特征在于：所述视频采集芯片的电源端口外接有一用于稳压的滤波电路；所述滤波电路包括一个电感和至少一个电容；所述电感一端与外部电源连接，另一端分别与每个电容连接，所述每个电容的另一端与接地；所述电感与电容连接的一端接入电源端口；

所述图像处理芯片的电源端口外接有一用于稳压的滤波电路；所述滤波电路包括一个电感和至少一个电容；所述电感一端与外部电源连接，另一端分别与每个电容连接，所述每个电容的另一端与接地；所述电感与电容连接的一端接入电源端口；

所述视频录制芯片的电源端口外接有一滤波电路；所述滤波电路包括一磁珠和至少一个电容；所述磁珠与电容的一端连接，且该电容的另一端接地；所述电源端口连接于磁珠和电容之间；

所述显示驱动芯片电源端口外接有一滤波电路；所述滤波电路包括一磁珠和至少一个电容；所述磁珠与电容的一端连接，且该电容的另一端接地；所述电源端口连接于磁珠和电容之间。

8. 根据权利要求 6 所述医用内窥镜的视频采集处理、视频录制及显示电路，其特征在于：所述视频采集芯片的行场信号端口外接有一用于提供信号强度的电阻。

9. 根据权利要求 6 所述医用内窥镜的视频采集处理、视频录制及显示电路, 其特征在于: 所述视频采集芯片的参考信号端口外接有作为电压电频参考基准的电容。

10. 根据权利要求 6 所述医用内窥镜的视频采集处理、视频录制及显示电路, 其特征在于: 所述视频采集芯片的时钟信号端口外接一时钟电路, 其包括一钟振芯片; 所述钟振芯片的电源端通过一滤波电路与电源连接, 该钟振芯片的输出端通过一调试电路与所述时钟信号端口连接; 所述滤波电路包括由一电感和电容串联组成, 所述电感的一端与电源连接, 另一端与电容连接, 且该电容的另一端接地; 所述钟振芯片的电源端与连接与电感和电容之间; 所述调试电路由电阻和电容组成; 该调试电路的电阻的一端与钟振的输出端连接, 另一端与电容连接, 且该电容的另一端接地; 所述时钟信号端口连接于该电阻与电容之间;

所述图像处理芯片时钟信号端口外接一时钟电路, 其包括一钟振芯片; 所述钟振芯片的电源端通过一滤波电路与电源连接, 该钟振芯片的输出端通过一调试电路与所述时钟信号端口连接; 所述滤波电路包括由一电感和电容串联组成, 所述电感的一端与电源连接, 另一端与电容连接, 且该电容的另一端接地; 所述钟振芯片的电源端与连接与电感和电容之间; 所述调试电路由电阻和电容组成; 该调试电路的电阻的一端与钟振的输出端连接, 另一端与电容连接, 且该电容的另一端接地; 所述时钟信号端口连接于该电阻与电容之间;

所述图像增强芯片的时钟信号端口外接一时钟电路, 其包括一钟振芯片; 所述钟振芯片的电源端通过一滤波电路与电源连接, 该钟振芯片的输出端与所述时钟信号端口连接; 所述滤波电路包括由一电感和电容串联组成, 所述电感的一端与电源连接, 另一端与电容连接, 且该电容的另一端接地。

## 一种医用内窥镜的视频采集处理、视频录制及显示电路

### 技术领域

[0001] 本实用新型涉及一种视频采集电路,特别是一种用于医用内窥镜的视频采集处理、视频录制及显示电路。

### 背景技术

[0002] 内窥镜是一种常用的医疗器械,由可弯曲部分、光源及一组镜头组成。经人体的天然孔道,或者是经手术做的小切口进入人体内,使用时将内窥镜导入预检查的器官,可直接窥视有关部位的变化。

[0003] 其中,图像质量的好坏直接影响着内窥镜的使用效果。现有的一般使用电子内窥镜进行观察。通常的电子内窥镜采用尺寸极小的电子成像元件—CCD(电荷耦合器件),将所要观察的腔内物体通过微小的物镜光学系统成像到CCD上,然后通过导像纤维束将接收到的图像信号送到图像处理系统上,最后在监视器上输出处理后的图像,供医生观察和诊断。然而,现有的CCD芯片仍然存在功耗过高、画质不够清的缺陷。

[0004] 同时,现有的一般使用电子内窥镜进行观察,并将观察后的图像发送至外部连接的处理系统进行图像处理。然而,由于在人体内进行图像采集时,会由于人体内部的各种原因,而导致出现噪音干扰、亮度无法自动调节或由于灯光的颜色而导致图像出现色差,如此导致在后期的图像处理中,难以还原真实的图像,使医生在观察时难以辨认。

### 实用新型内容

[0005] 本实用新型在于克服现有技术的缺点与不足,提供一种高清、低功耗、低照度的医用内窥镜的视频采集处理、视频录制及显示电路。

[0006] 本实用新型通过以下技术方案实现:一种医用内窥镜的视频采集处理、视频录制及显示电路,包括视频采集芯片、图像处理芯片、信号转换芯片、图像增强芯片、视频录制芯片和显示驱动芯片;

[0007] 所述视频采集芯片将采集后的视频数据发送至图像处理芯片进行处理;

[0008] 所述信号转换芯片包括第一信号转换芯片和第二信号转换芯片;所述第一信号转换芯片用于将bt1120信号转换为1vds信号;所述第二信号转换芯片用于将1vds信号转换为bt1120信号;

[0009] 所述图像处理芯片将处理后的图像信号发送至第一信号转换芯片,并由该第一信号转换芯片发送至第二信号转换芯片;所述第二信号转换芯片将信号转换后发送至图像增强芯片;

[0010] 所述图像增强芯片将接收的视频图像进行增强处理,并同时发送至视频录制芯片和显示驱动芯片,由该视频录制芯片进行录制,由该显示驱动芯片进行实时播放;

[0011] 所述视频录制芯片完成视频录制后,发送至显示驱动芯片,进行视频回放。

[0012] 相比于现有技术,本实用新型通过在镜头部分增加一图像处理芯片,对采集的图像进行处理,在主机后台上增加一图像增强芯片,进行二级图像增强,使最后输出的图像更

加清晰。

[0013] 首先,在图像处理芯片中划分为多个功能模块,分别并由各个功能模块独立协调工作,能够实现低功耗、低照度,以及可以是输出的画面更加高清。同时,进一步在该图像处理器中设置一白平衡固定电路,用于将该白平衡参数进行固定,无需在工作时进行白平衡的调节,从而防止出现色差干扰的现象。

[0014] 然后,在图像增强芯片中也划分为多个功能模块,分别并由各个功能模块独立协调工作,能够实现对图像的增强处理。同时,进一步在该图像增强器中设置一图像边缘增强电路,用以增强图像边缘的清晰度。

[0015] 另外,为了提高信号传输的稳定性,本实用新型通过先将 bt1120 信号转换为 lvds 信号,从而稳定的传输,并具有低噪声能力。然后,在将 lvds 信号还原为 bt1120 信号,从而保证了后续播放的画面的质量。

[0016] 作为本实用新型的进一步改进,所述视频采集芯片内部包括:控制器、驱动器、感光器、取样器和输出器;

[0017] ——所述控制器,其用于接收外部的触发信号,发送触发信号至驱动器;

[0018] ——所述驱动器,其用于接收控制器的触发信号,并驱动感光器工作;

[0019] ——所述感光器,其用于接收外界的光信号,并将该光信号转换为电信号;

[0020] ——所述取样器,其用于对感光器的电信号进行取样处理,并将处理完的电信号发送至输出器;

[0021] ——所述输出器,其用于将该电信号转换为数字信号,并进行输出图像处理芯片;

[0022] 所述图像处理芯片包括:数据接收器、中心控制器、图像处理器、数据输出器;

[0023] ——所述数据接收器,其用于接收外部的图像数据;

[0024] ——所述中心控制器,其用于接收外部的触发信号,并相应控制所述数据接收器、图像处理器和数据输出器的工作状态;

[0025] ——所述图像处理器,其用于对图像进行处理;所述图像处理器包括一白平衡固定电路,其用于根据预设的参数,进行白平衡的固定调整;

[0026] ——所述数据输出器,其用于将处理后的图像数据进行输出;

[0027] 所述第一信号转换芯片包括:控制器、数据读取器、信号格式转换器、串行器、数据输出器;

[0028] ——所述控制器,其用于接收外部的触发信号,并控制数据读取器、信号格式转换器、串行器和数据输出器的工作;

[0029] ——所述数据读取器,其用于接收外部的 bt1120 传输信号,并发送至信号格式转换器;

[0030] ——所述信号格式转换器,其用于将 bt1120 视频信号转换为 lvds 的视频信号,并发送至串行器;

[0031] ——所述串行器,其用于将并行数据转换为串行数据,并发送至数据输出器;

[0032] ——所述数据输出器,用于将 lvds 信号数据输出至第二信号转换芯片;

[0033] 所述第二信号转换芯片包括:控制器、数据读取器、信号格式转换器、并行器、数据输出器;

[0034] ——所述控制器,其用于接收外部的触发信号,并控制数据读取器、信号格式转换

器、并行器和数据输出器的工作；

[0035] ——所述数据读取器，其用于第一信号转换芯片的 lvds 视频传输信号，并发送至信号格式转换器；

[0036] ——所述信号格式转换器，其用于将 lvds 视频信号转换为 bt1120 的视频信号，并发送至并行器；

[0037] ——所述并行器，其用于将串行数据转换为并行数据，并发送至数据输出器；

[0038] ——所述数据输出器，用于将 bt1120 视频信号数据输出；

[0039] 所述图像增强芯片包括：数据接收器、控制器、静态存储器、图像增强器、数据输出器和时钟发生器；

[0040] ——所述数据接收器，其用于接收图像数据信号，并发送至该图像增强器；

[0041] ——所述控制器，其用于接收外部触发信号，并相应控制数据接收器、图像增强器和数据输出器的工作状态；

[0042] ——所述静态存储器，其用于存储图像增强器的驱动数据，以驱动该图像增强器的工作；

[0043] ——所述图像增强器，其包括一图像边缘增强电路；所述图像边缘增强电路用于增强图像边缘的清晰度；

[0044] ——所述数据输出器，其用于接收图像增强器处理后的图像数据，并进行数据输出；

[0045] ——所述时钟发生器，其用于为图像增强芯片产生时钟信号；

[0046] 所述视频录制芯片包括：数据接收器、视频编码器、视频解码器、数据输出器和处理器；

[0047] ——所述数据接收器，用于接收外部的视频信号，并发送至视频编码器；

[0048] ——所述视频编码器，用于对视频信号进行编码录制；

[0049] ——所述视频解码器，用于对视频信号进行解码回放；

[0050] ——所述数据输出器，用于对视频信号进行输出；

[0051] ——所述处理器，用于控制数据接收器、视频编码器、视频解码器和数据输出器的工作；

[0052] 所述显示驱动芯片包括：模拟信号接收器、数字信号接收器、模数转换器、复用器、输出格式转换器、数据输出器和控制器；

[0053] ——所述模拟信号接收器，用于接收模拟信号，并发送至模数转换器；

[0054] ——所述模数转换器，用于将模拟信号转换为数据信号，并发送至复用器；

[0055] ——所述数据信号接收器，用于接收数据信号，并发送至复用器；

[0056] ——所述复用器，用于将两路信号进行整合，并进行输出至输出格式转换器；

[0057] ——所述输出格式转换器，用于将信号格式进行转换，并输出至数据输出器；

[0058] ——所述数据输出器，将信号输出，并进行显示；

[0059] ——所述控制器，用于控制模拟信号接收器、数字信号接收器、模数转换器、复用器、输出格式转换器和数据输出器的工作。

[0060] 作为本实用新型的进一步改进，所述视频采集芯片还包括一倍频器，其用于将外部输入的触发信号的频率进行增倍处理，再发送至控制器；

[0061] 所述图像处理芯片还包括一倍频器,其用于将外部输入的触发信号的频率进行增倍处理,再发送至中心控制器;

[0062] 所述第一信号转换芯片还包括一锁相回路,分别与信号格式转换器和串行器连接,用于统一整合时脉信号;

[0063] 所述第二信号转换芯片还包括一锁相回路,分别与信号格式转换器和串行器连接,用于统一整合时脉信号;

[0064] 所述图像增强芯片还包括一降噪处理器;所述数据接收器接收到的图像数据信号,发送至降噪处理器进行降噪处理,再转发至图像增强器;

[0065] 所述视频录制芯片还包括一图像处理器,用于对数据接收器所接收的视频进行处理,并将处理后的图像发送至视频编码器;

[0066] 所述显示驱动芯片还包括一视频解码器、场逆程数据处理器和存储器;

[0067] 所述视频解码器,用于将模拟信号接收器接收的模拟信号进行解码,并发送至场逆程数据处理器;

[0068] 所述场逆程数据处理器,用于将解码后的模拟信号插入数据行,并发送至所述存储器进行存储;

[0069] 所述存储器,用于存储经场逆程数据处理器处理后的数据,并发送至输出格式转换器。

[0070] 作为本实用新型的进一步改进,所述图像处理芯片中的图像处理器还包括一曝光增益电路,用于增加曝光增益大小;

[0071] 所述第一信号转换芯片还包括一时钟数据恢复器,其与数据读取器连接,用于从传输信道的失真和噪声中恢复数据;

[0072] 所述第二信号转换芯片还包括一时钟数据恢复器,其与数据读取器连接,用于从传输信道的失真和噪声中恢复数据;

[0073] 所述图像增强芯片还包括一动态存储器;所述降噪处理器处理后的图像数据,先发送至动态存储器进行存储,再转发至图像增强器;

[0074] 所述视频录制芯片的图像处理器包括边缘增强电路和消除噪音干扰电路;

[0075] 所述显示驱动芯片还包括一图像边缘平滑处理器,用于接收复位器的信号,并对视频图像的边缘进行平滑处理,再发送至格式转换器。

[0076] 作为本实用新型的进一步改进,所述图像处理器还包括一光学探测电路和闪烁探测电路,其用于探测图像的亮度和闪烁情况,并将探测结果发送至曝光增益电路;

[0077] 所述图像增强芯片还包括一像素自适应校对器;所述图像增强器先将处理后的图像数据发送至所述像素自适应校对器,由该像素自适应校对器进行像素适应校对,再发送至数据输出器。

[0078] 作为本实用新型的进一步改进,所述视频采集芯片外部设有:用于接收供电电压的电源端口、用于输出视频信号的视频信号端口、用于输出行场信号的行场信号端口、用于接收参考电压电频的参考信号端口和一用于接收外部时钟信号的时钟信号端口;

[0079] 所述图像处理芯片外部设有:用于接收供电电压的电源端口、用于接收图像信号的信号接收端口、用于输出视频信号的视频信号端口、用于输出行场信号的行场信号端口、用于接收外部时钟信号的时钟信号端口、用于接收存储数据的数据接收端口和一用于接收

外部通讯命令的通讯端口；

[0080] 所述第一信号转换芯片外部设有：用于接收供电电压的电源端口、用于接收bt1120 视频信号的信号接收端口、用于输出 1vds 视频信号的视频信号端口和用于输出行场信号的行场信号端口；

[0081] 所述所述第二信号转换芯片外部设有：用于接收供电电压的电源端口、用于接收 1vds 视频信号的信号接收端口和用于输出 bt1120 视频信号的视频信号端口；

[0082] 所述图像增强芯片外部设有：用于接收供电电压的电源端口、用于接收图像信号的信号接收端口、用于输出视频信号的视频信号端口、用于输出行场信号的行场信号端口、用于接收外部时钟信号的时钟信号端口和用于接收存储数据的数据接收端口；

[0083] 所述视频录制芯片外部设有：电源端口、视频输入端口、视频输出端口和通讯端口；所述视频输入端口与该视频录制芯片内部的数据接收器连接，用于接收外部的视频数据；所述 视频输出端口，与所述数据输出器连接，用于输出视频数据；所述通讯端口，与所述处理器连接，用于接收外部的串口命令；

[0084] 所述显示驱动芯片外部设有：电源端口、视频输入端口、视频输出端口和通讯端口；所述视频输入端口与该视频录制芯片内部的数据接收器连接，用于接收外部的视频数据；所述视频输出端口，与所述数据输出器连接，用于输出视频数据；所述通讯端口，与所述处理器连接，用于接收外部的串口命令。

[0085] 作为本实用新型的进一步改进，所述视频采集芯片的电源端口外接有一用于稳压的滤波电路；所述滤波电路包括一个电感和至少一个电容；所述电感一端与外部电源连接，另一端分别与每个电容连接，所述每个电容的另一端与接地；所述电感与电容连接的一端接入电源端口；

[0086] 所述图像处理芯片的电源端口外接有一用于稳压的滤波电路；所述滤波电路包括一个电感和至少一个电容；所述电感一端与外部电源连接，另一端分别与每个电容连接，所述每个电容的另一端与接地；所述电感与电容连接的一端接入电源端口；

[0087] 所述视频录制芯片的电源端口外接有一滤波电路；所述滤波电路包括一磁珠和至少一个电容；所述磁珠与电容的一端连接，且该电容的另一端接地；所述电源端口连接于磁珠和电容之间；

[0088] 所述显示驱动芯片电源端口外接有一滤波电路；所述滤波电路包括一磁珠和至少一个电容；所述磁珠与电容的一端连接，且该电容的另一端接地；所述电源端口连接于磁珠和电容之间。

[0089] 作为本实用新型的进一步改进，所述视频采集芯片的行场信号端口外接有一用于提供信号强度的电阻。

[0090] 作为本实用新型的进一步改进，所述视频采集芯片的参考信号端口外接有作为电压电频参考基准的电容。

[0091] 作为本实用新型的进一步改进，所述视频采集芯片的时钟信号端口外接一时钟电路，其包括一钟振芯片；所述钟振芯片的电源端通过一滤波电路与电源连接，该钟振芯片的输出端通过一调试电路与所述时钟信号端口连接；所述滤波电路包括由一电感和电容串联组成，所述电感的一端与电源连接，另一端与电容连接，且该电容的另一端接地；所述钟振芯片的电源端与连接与电感和电容之间；所述调试电路由电阻和电容组成；该调试电路的

电阻的一端与钟振的输出端连接,另一端与电容连接,且该电容的另一端接地;所述时钟信号端口连接于该电阻与电容之间;

[0092] 所述图像处理芯片时钟信号端口外接一时钟电路,其包括一钟振芯片;所述钟振芯片的电源端通过一滤波电路与电源连接,该钟振芯片的输出端通过一调试电路与所述时钟信号端口连接;所述滤波电路包括由一电感和电容串联组成,所述电感的一端与电源连接,另一端与电容连接,且该电容的另一端接地;所述钟振芯片的电源端与连接与电感和电容之间;所述调试电路由电阻和电容组成;该调试电路的电阻的一端与钟振的输出端连接,另一端与电容连接,且该电容的另一端接地;所述时钟信号端口连接于该电阻与电容之间;

[0093] 所述图像增强芯片的时钟信号端口外接一时钟电路,其包括一钟振芯片;所述钟振芯片的电源端通过一滤波电路与电源连接,该钟振芯片的输出端与所述时钟信号端口连接;所述滤波电路包括由一电感和电容串联组成,所述电感的一端与电源连接,另一端与电容连接,且该电容的另一端接地。

[0094] 为了更好地理解和实施,下面结合附图详细说明本实用新型。

## 附图说明

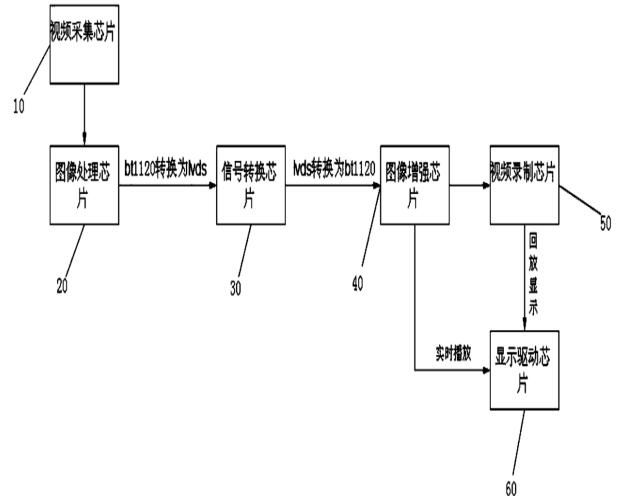

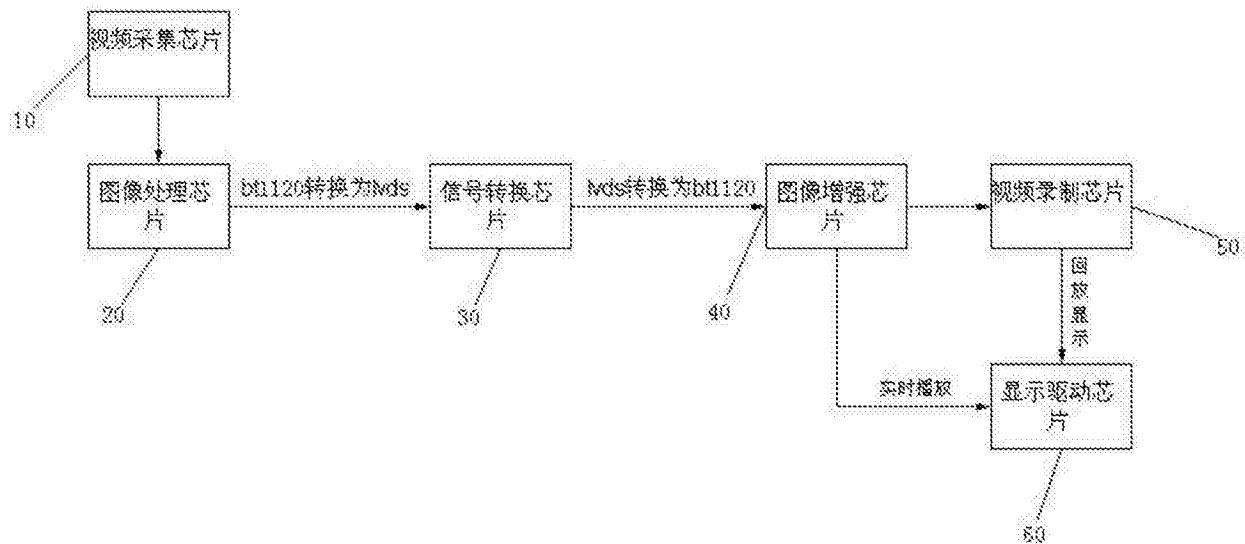

- [0095] 图 1 是本实用新型的芯片连接示意图。

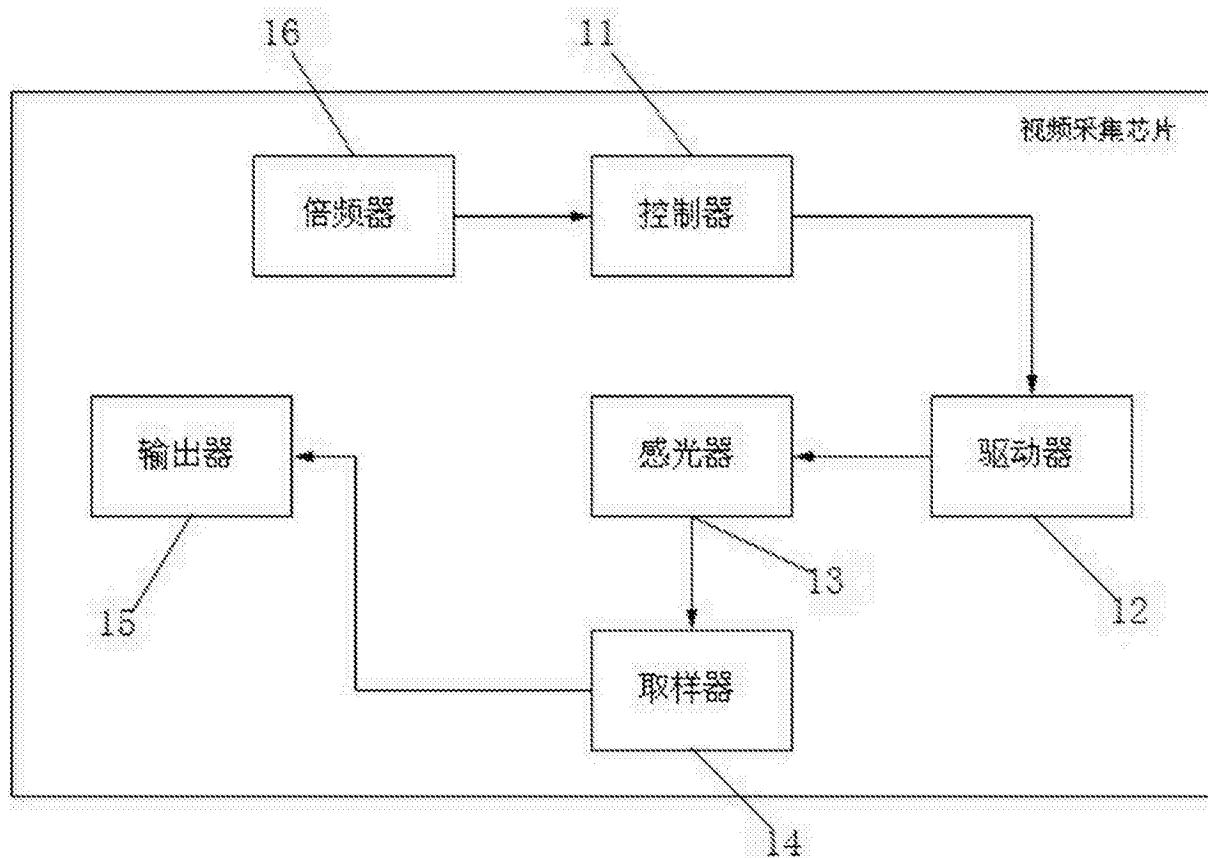

- [0096] 图 2 是视频采集芯片的内部模块连接示意图。

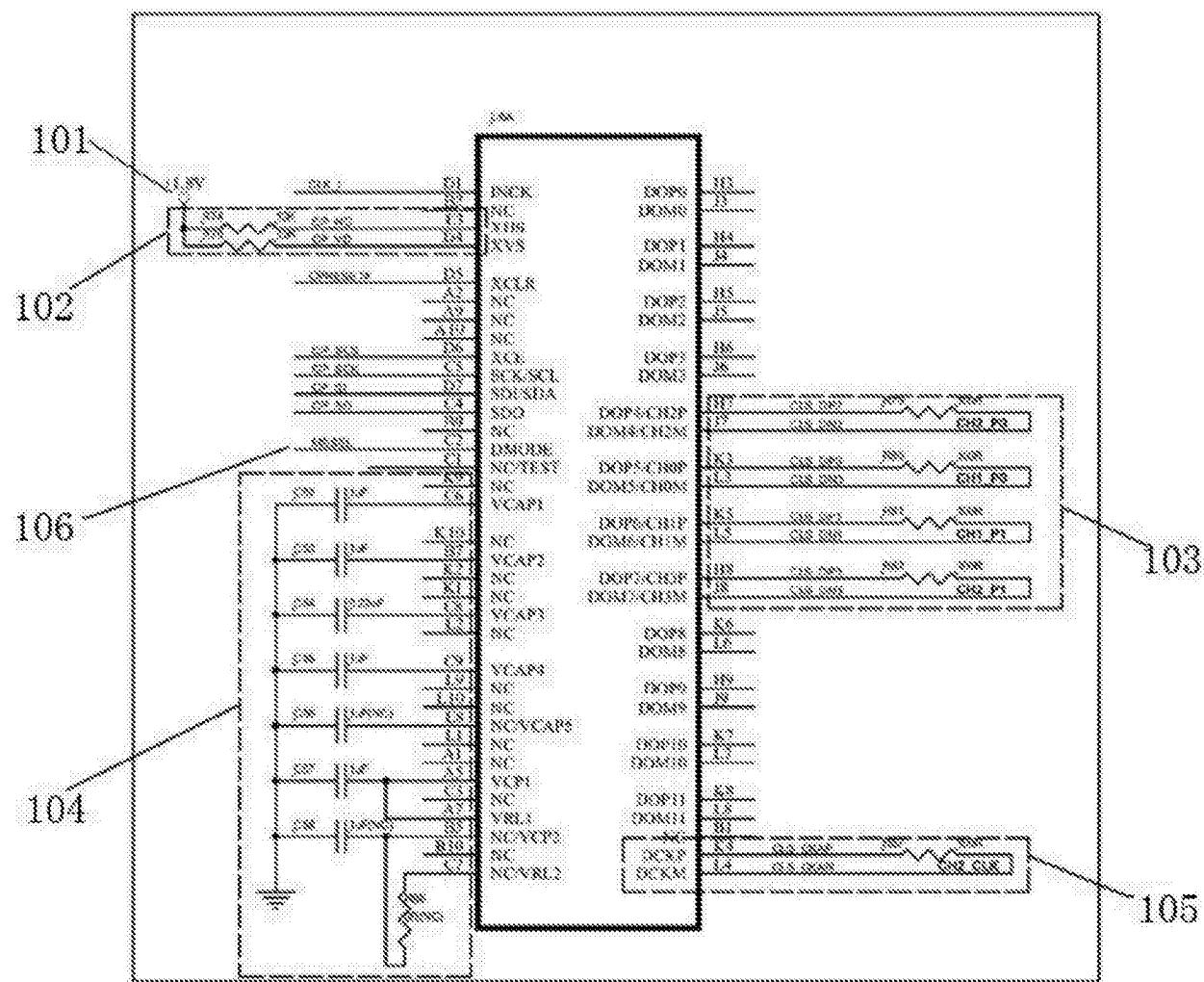

- [0097] 图 3 是视频采集芯片的外部端口连接电路图。

- [0098] 图 4 是视频采集芯片的电源部分连接的电路图。

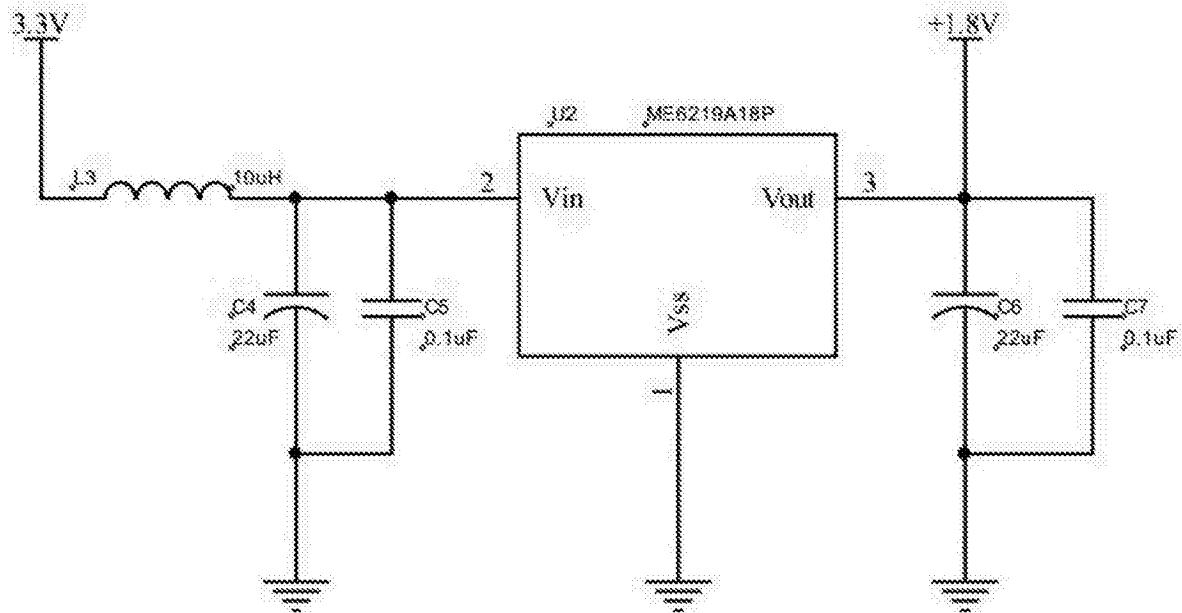

- [0099] 图 5 视频采集芯片的 2.7V 的电压接入电路图。

- [0100] 图 6 是视频采集芯片的 1.8V 的电压接入电路图。

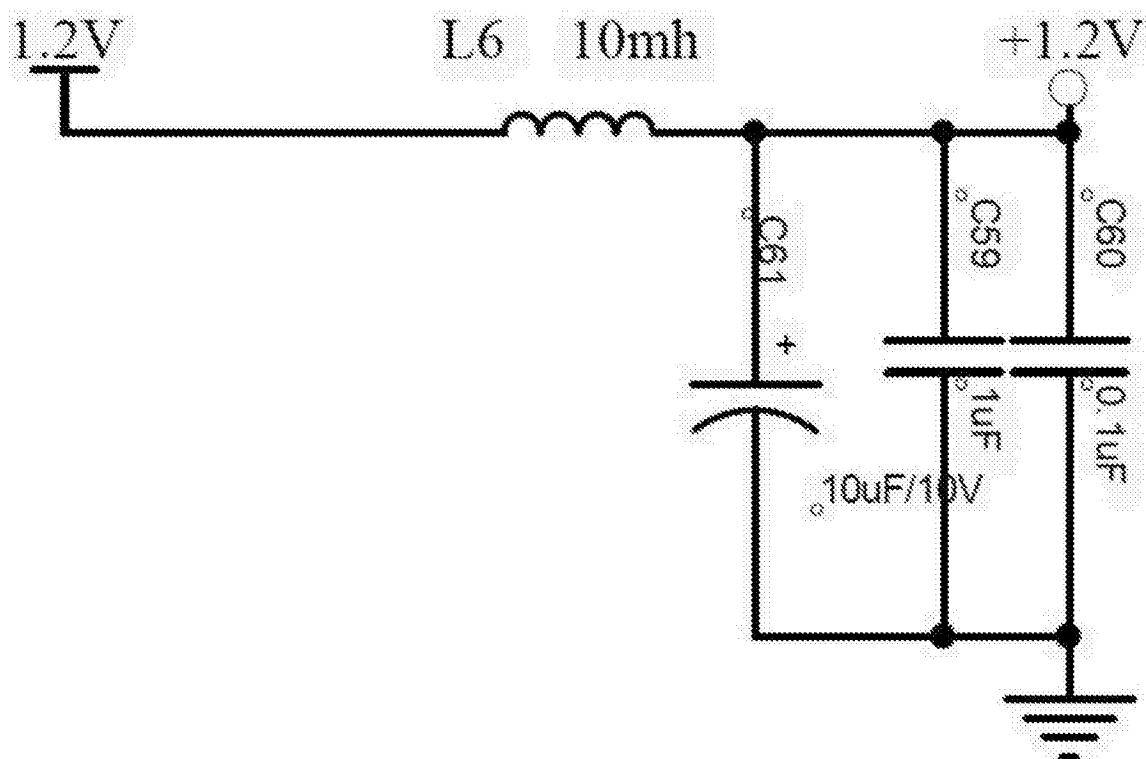

- [0101] 图 7 是视频采集芯片的 1.2V 的电压接入电路图。

- [0102] 图 8 是视频采集芯片的行场信号的局部放大图。

- [0103] 图 9 是视频采集芯片的参考信号端口的局部放大图。

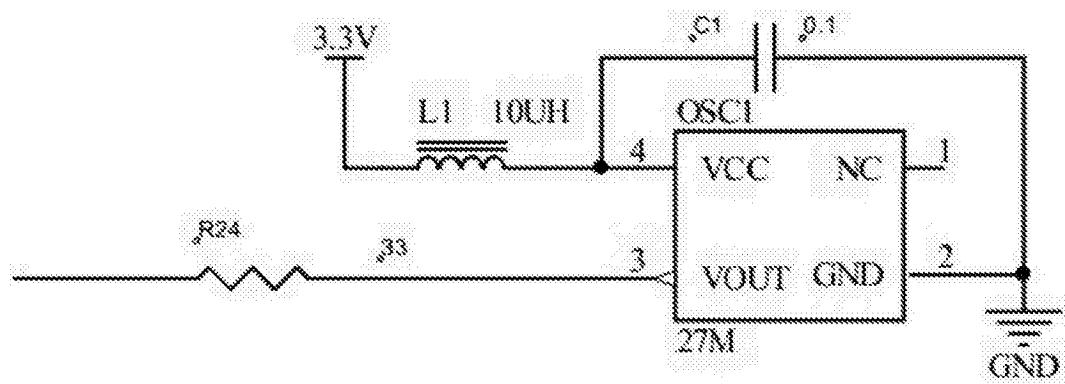

- [0104] 图 10 是视频采集芯片的时钟电路的电路图。

- [0105] 图 11 是视频采集芯片的配置电路的电路图。

- [0106] 图 12 是图像处理芯片的内部模块连接示意图。

- [0107] 图 13 是图像处理芯片的图像处理器的电路模块示意图。

- [0108] 图 14 是图像处理芯片的电压部分电路图。

- [0109] 图 15 是图像处理芯片的外部端口电路图。

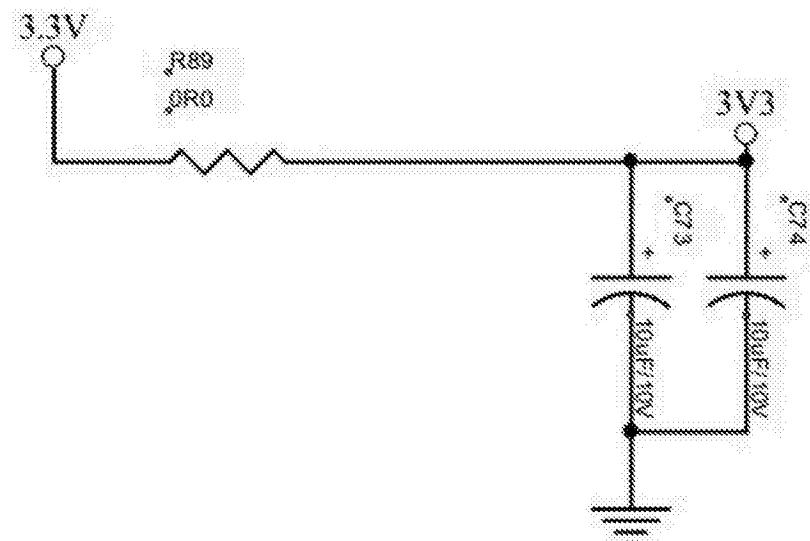

- [0110] 图 16 是图像处理芯片的 3.3V 电压的滤波电路的电路图。

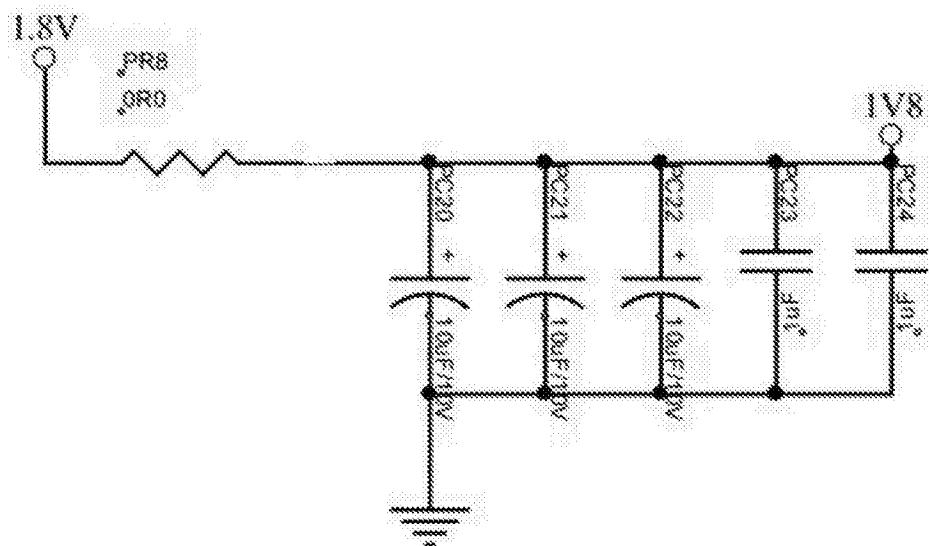

- [0111] 图 17 是图像处理芯片的 1.8V 电压的滤波电路的电路图。

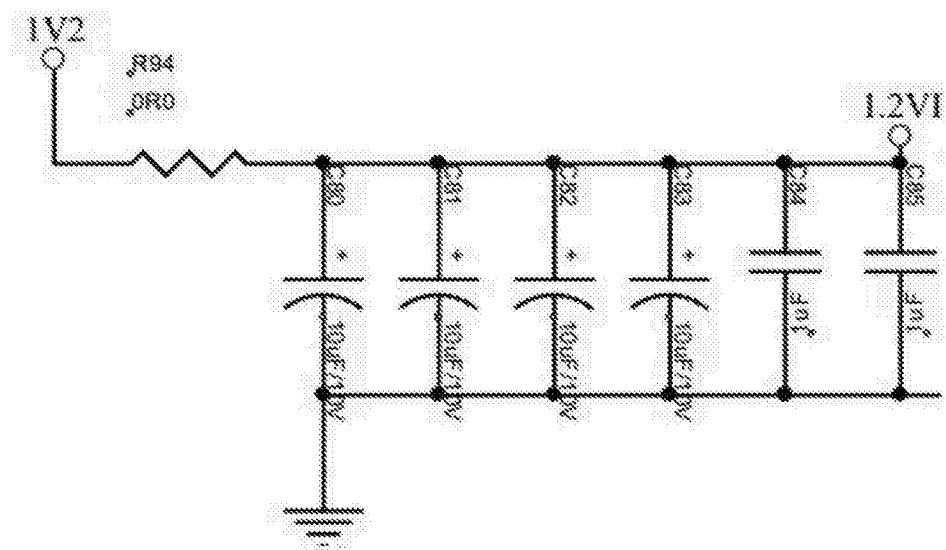

- [0112] 图 18 是图像处理芯片的 1.2V 电压的滤波电路的电路图。

- [0113] 图 19 是图像处理芯片的信号接收端口的局部放大图。

- [0114] 图 20 是图像处理芯片的视频信号端口的局部放大图。

- [0115] 图 21 是图像处理芯片的行场信号端口的局部放大图。

- [0116] 图 22 是图像处理芯片的时钟电路的示意图。

- [0117] 图 23 是图像处理芯片的存储电路的示意图。

- [0118] 图 24 是图像处理芯片的通讯端口的局部放大图。

- [0119] 图 25 是第一信号转换芯片的内部器件连接示意图。

- [0120] 图 26 是第二信号转换芯片的内部模块连接示意图。

- [0121] 图 27 是第一信号转换芯片的外部端口连接示意图。

- [0122] 图 28 是第一信号转换芯片的电源端口的局部放大示意图。

- [0123] 图 29 是第一信号转换芯片的信号接收端口的局部放大图。

- [0124] 图 30 是第一信号转换芯片的视频信号端口的局部放大图。

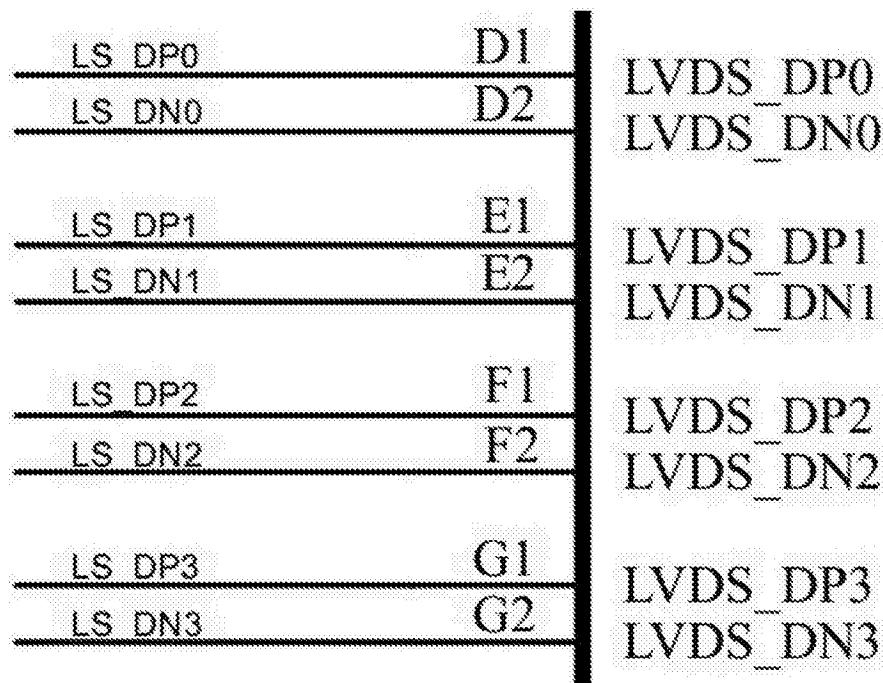

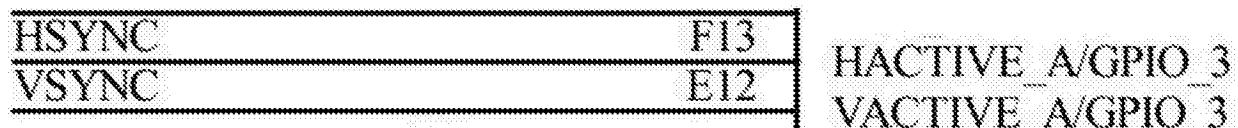

- [0125] 图 31 是第一信号转换芯片的行场信号端口的局部放大图。

- [0126] 图 32 是第二信号转换芯片的外部连接电路图。

- [0127] 图 33 是第二信号转换芯片的信号接收端口的局部放大图。

- [0128] 图 34 是第二信号转换芯片的视频信号端口的局部放大图。

- [0129] 图 35 是第二信号转换芯片的行场信号端口的局部放大图。

- [0130] 图 36 是图像增强芯片的内部模块连接示意图。

- [0131] 图 37 是图像增强芯片的第一部分外部连接电路图。

- [0132] 图 38 是图像增强芯片的第二部分外部连接电路图。

- [0133] 图 39 是图像增强芯片的 3.3V 电压的稳压滤波电路的电路图。

- [0134] 图 40 是图像增强芯片的 3.3V 转换为 1.8V 的电源转换电路图。

- [0135] 图 41 是图像增强芯片的 3.3V 转换为 1.2V 的电源转换电路图。

- [0136] 图 42 是图像增强芯片的信号接收端口的局部放大图。

- [0137] 图 43a 是图像增强芯片的视频信号端口第一部分的局部放大图。

- [0138] 图 43b 是图像增强芯片的视频信号端口第二部分的局部放大图。

- [0139] 图 44 是图像增强芯片的时钟电路的电路图。

- [0140] 图 45 是图像增强芯片的行场信号端口的局部放大图。

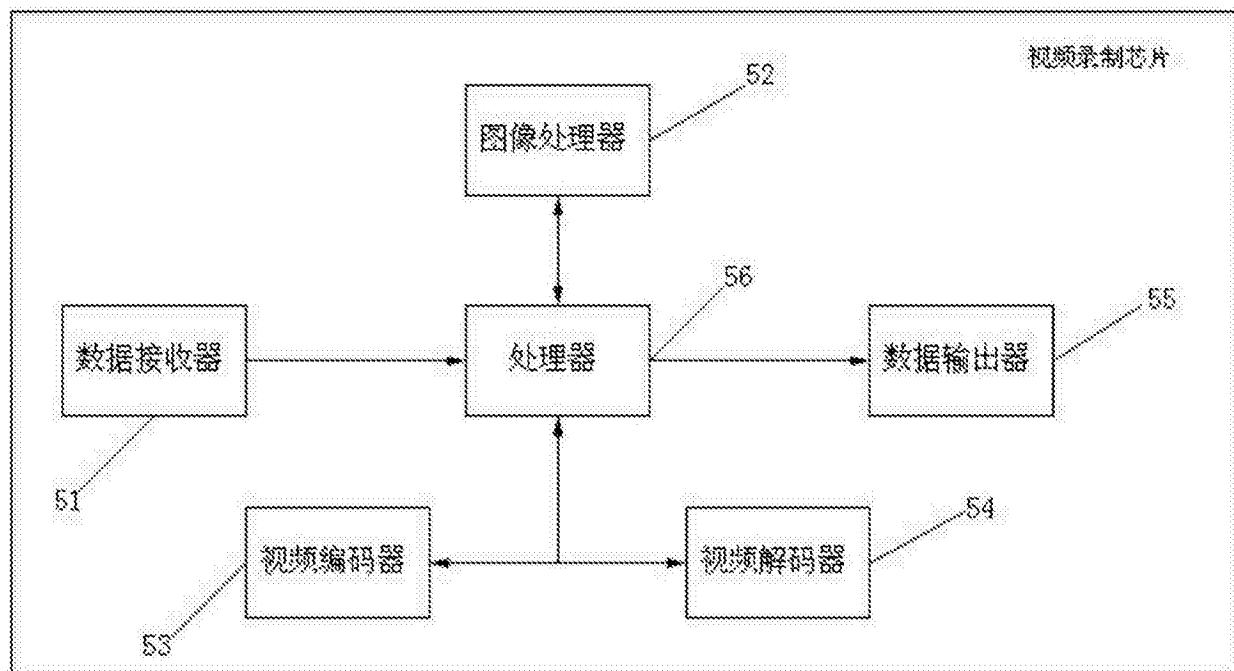

- [0141] 图 46 是视频录制芯片的内部器件连接示意图。

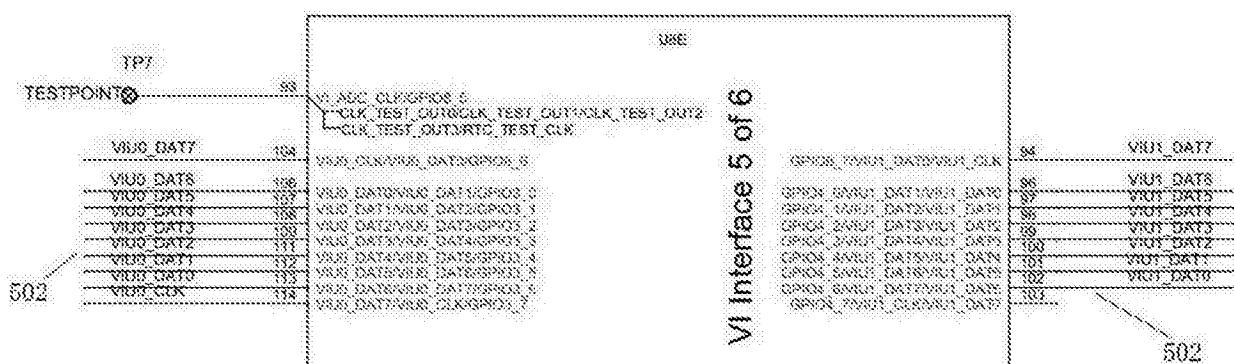

- [0142] 图 47 是视频录制芯片的视频输入电路图。

- [0143] 图 48 是视频录制芯片的视频输出电路图。

- [0144] 图 49 是视频录制芯片的和通讯输入电路图。

- [0145] 图 50 是视频录制芯片的电源端口的局部放大图。

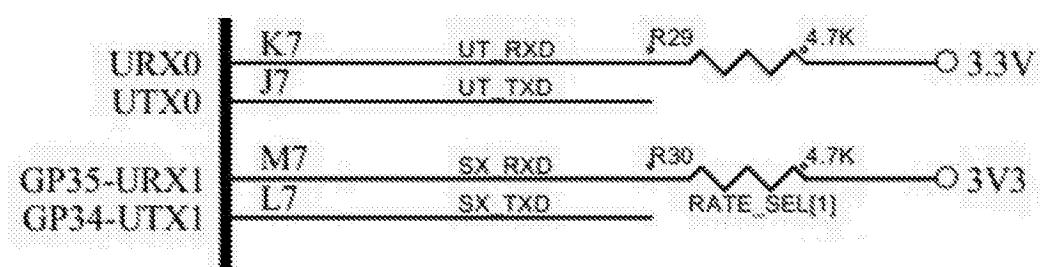

- [0146] 图 51 是视频录制芯片的通讯端口的局部放大图。

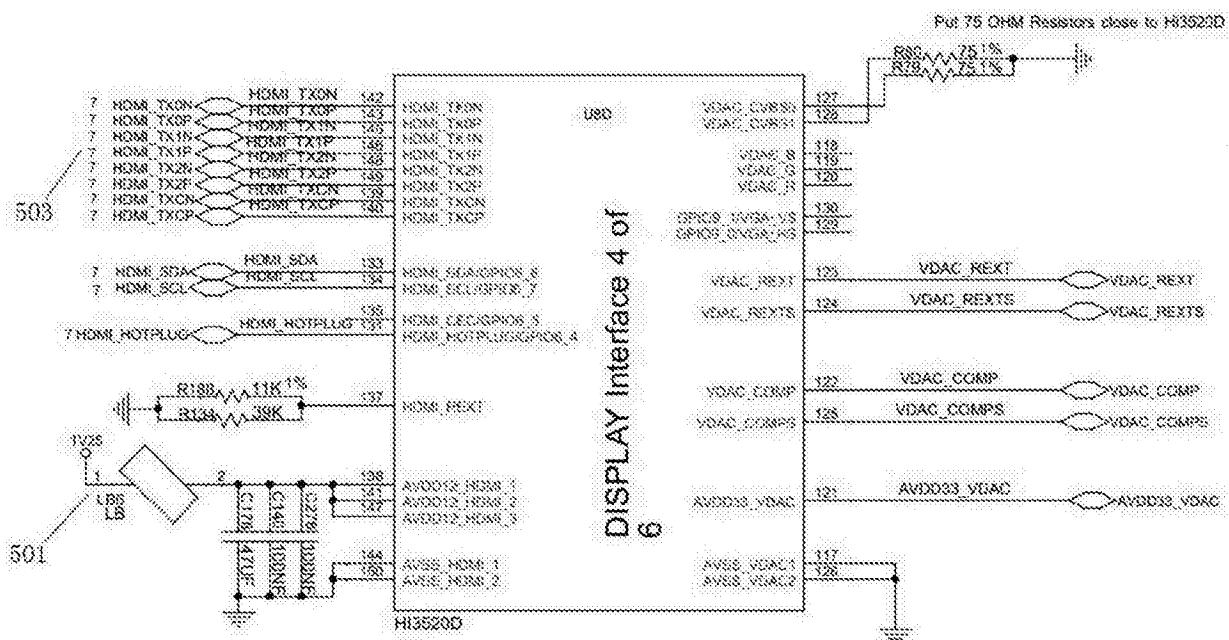

- [0147] 图 52 是显示驱动芯片的内部器件连接示意图。

- [0148] 图 53 是显示驱动芯片的外部信号输入电路图。

- [0149] 图 54 是显示驱动芯片的外部信号输出电路图。

- [0150] 图 55 是显示驱动芯片的电源端口的局部放大图。

- [0151] 图 56 是显示驱动芯片的视频输入端口的局部放大图。

- [0152] 图 57 是显示驱动芯片的视频输出端口的局部放大图。

## 具体实施方式

- [0153] 请参阅图 1, 其为实用新型的芯片连接示意图。本实用新型提供了一种医用内窥镜的视频采集处理、视频录制及显示电路, 包括视频采集芯片 10、图像处理芯片 20、信号转换

芯片 30 和图像增强芯片 40。

[0154] 所述视频采集芯片 10 将采集后的视频数据发送至图像处理芯片 20 进行处理 ; 所述信号转换芯片 30 包括第一信号转换芯片 31 和第二信号转换芯片 32 ;

[0155] 所述第一信号转换芯片 31 用于将 bt1120 信号转换为 lvds 信号 ; 所述第二信号转换芯片 32 用于将 lvds 信号转换为 bt1120 信号 ;

[0156] 所述图像处理芯片 20 将处理后的图像信号发送至第一信号转换芯片 31 , 并由该第一信号转换芯片 31 发送至第二信号转换芯片 32 ; 所述第二信号转换芯片 32 将信号转换后发送至图像增强芯片 40 。

[0157] 请参阅图 2, 其为视频采集芯片的内部模块连接示意图。所述视频采集芯片 10 内部包括 : 控制器 11 、驱动器 12 、感光器 13 、取样器 14 、输出器 15 和倍频器 16 ;

[0158] 所述控制器 11 , 其用于接收外部的触发信号, 发送触发信号至驱动器 ;

[0159] 所述驱动器 12 , 其用于接收控制器的触发信号, 并驱动感光器工作 ;

[0160] 所述感光器 13 , 其用于接收外界的光信号, 并将该光信号转换为电信号 ;

[0161] 所述取样器 14 , 其用于对感光器的电信号进行取样处理, 并将处理完的电信号发送至输出器 ;

[0162] 所述输出器 15 , 其用于将该电信号转换为数字信号, 并进行输出。

[0163] 所述倍频器 16 , 其用于将外部输入的触发信号的频率进行增倍处理, 再发送至控制器。进一步, 为了方便于视频采集芯片的使用频率的要求, 通过倍频器实现频率的调节放大。

[0164] 请同时参阅图 3, 其为视频采集芯片的外部端口电路图。另外为了适应该视频采集芯片的应用, 在所述视频采集芯片外部设有 : 用于接收电压的电源端口 101 、用于输出视频信号的视频信号端口 102 、用于输出行场信号的行场信号端口 103 、用于接收参考电压电频的参考信号端口 104 、用于接收外部时钟信号的时钟信号端口 105 和用于接收外部工作模式命令的通讯命令端口 106 。

[0165] 请同时参阅图 4, 其为视频采集芯片的电源部分的电路图。具体的, 视频采集芯片中的电源部分同时采用三种电压, 分别为 2.7V 、 1.8V , 和 1.2V 。

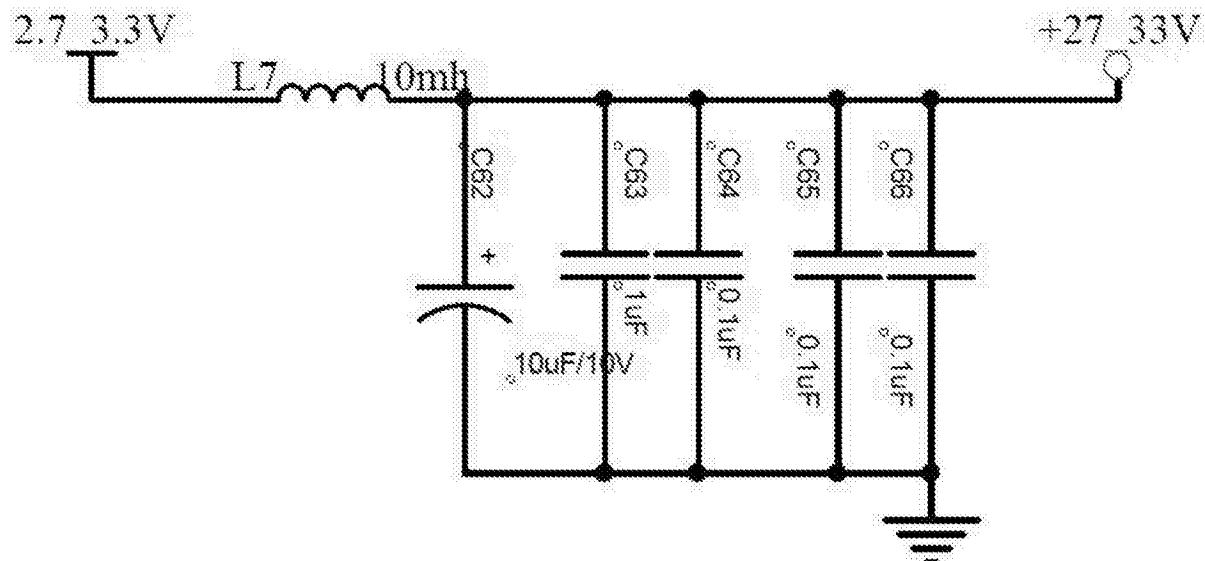

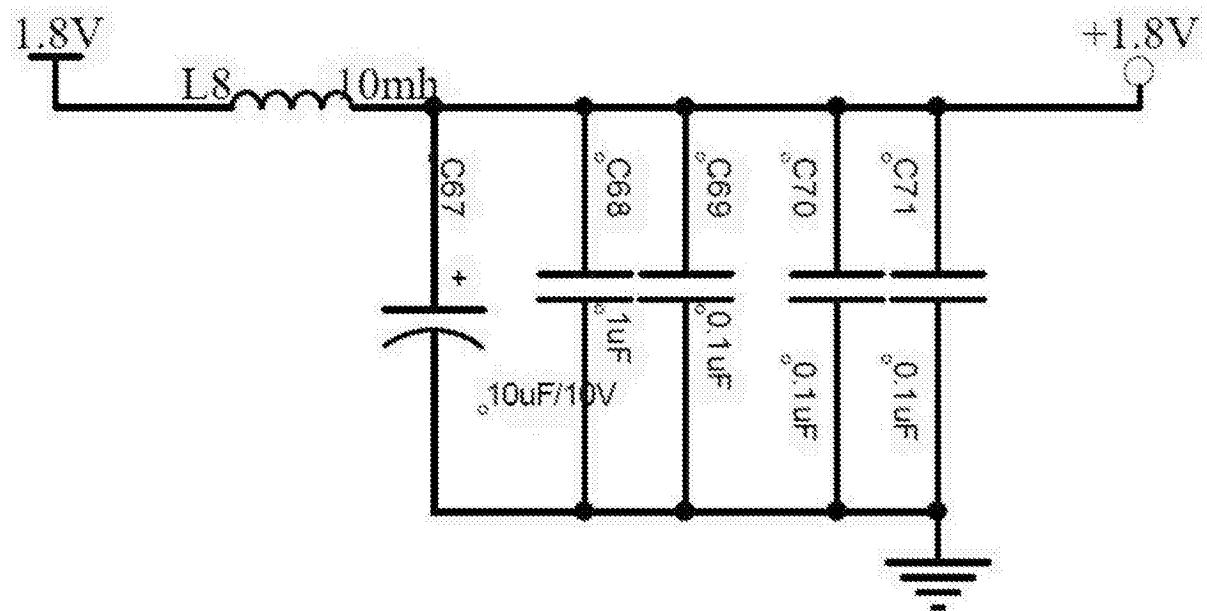

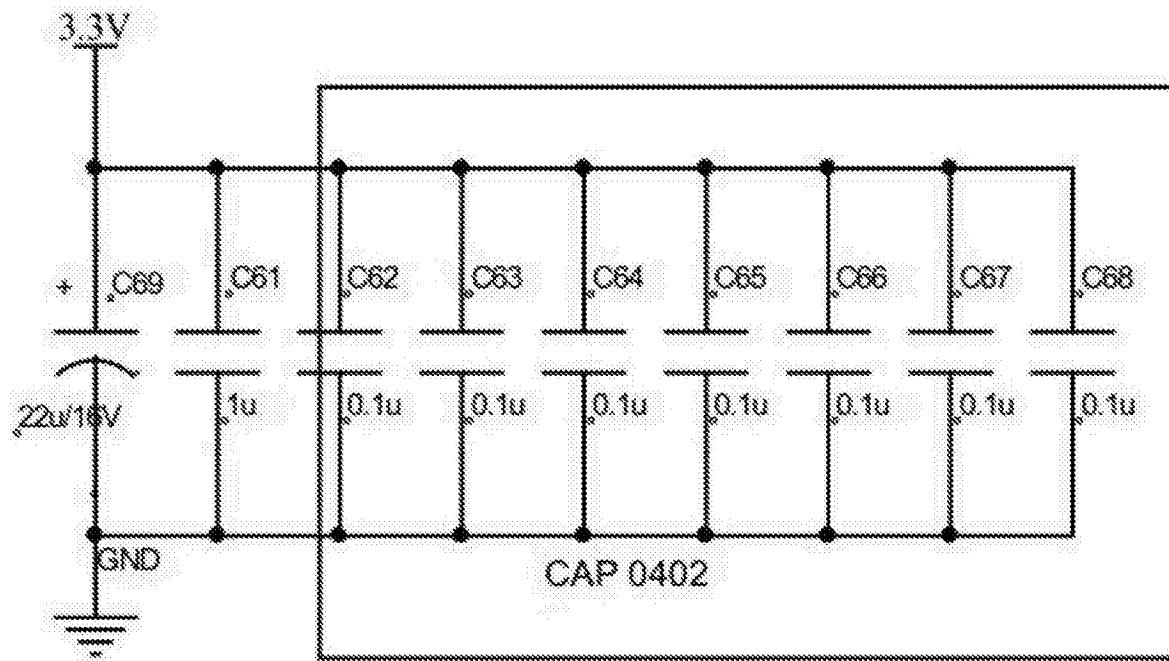

[0166] 请同时参阅图 5-7, 其分别为视频采集芯片的 2.7V 、 1.8V 和 1.2V 的电路图。具体的, 视频采集芯片的三种电压的输入端口 101 都外接有一用于稳压的滤波电路 ; 所述滤波电路包括一个电感和至少一个电容 ; 所述电感一端与外部电源连接, 另一端分别与每个电容连接, 所述每个电容的另一端与接地 ; 所述电感与电容连接的一端接入电源端口。其中, 2.7V 和 1.8V 的电压接入电路包括四个电容, 1.2V 的电压接入电路包括三个电容, 以滤掉不同频率的干扰信号。

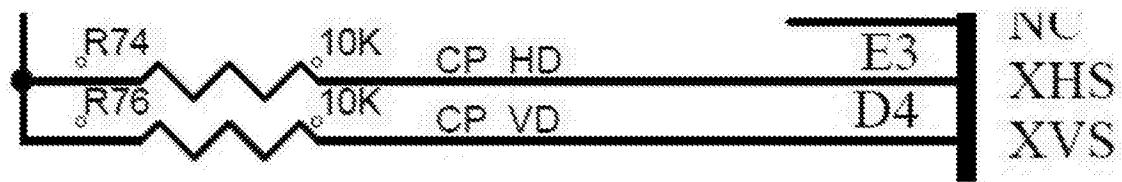

[0167] 请参阅图 8, 其为行场信号的接口放大图。进一步, 所述行场信号端口 103 外接有一用于提供信号强度的电阻。通过该行场信号, 用于控制视频输出的频率和顺序。比如 : 可以控制视频信号在屏幕上的显示频率和显示顺序, 可以是从上之下每行输出, 也可以是从左至右输出。

[0168] 请参阅图 9, 其为视频采集芯片的参考信号端口的局部放大图。进一步, 所述参考信号端口 104 外接有作为电压电频参考基准的电容。在本实施例中, 所述参考信号端口有 7 个, 每个端口都外接一个 1uF 的电容。

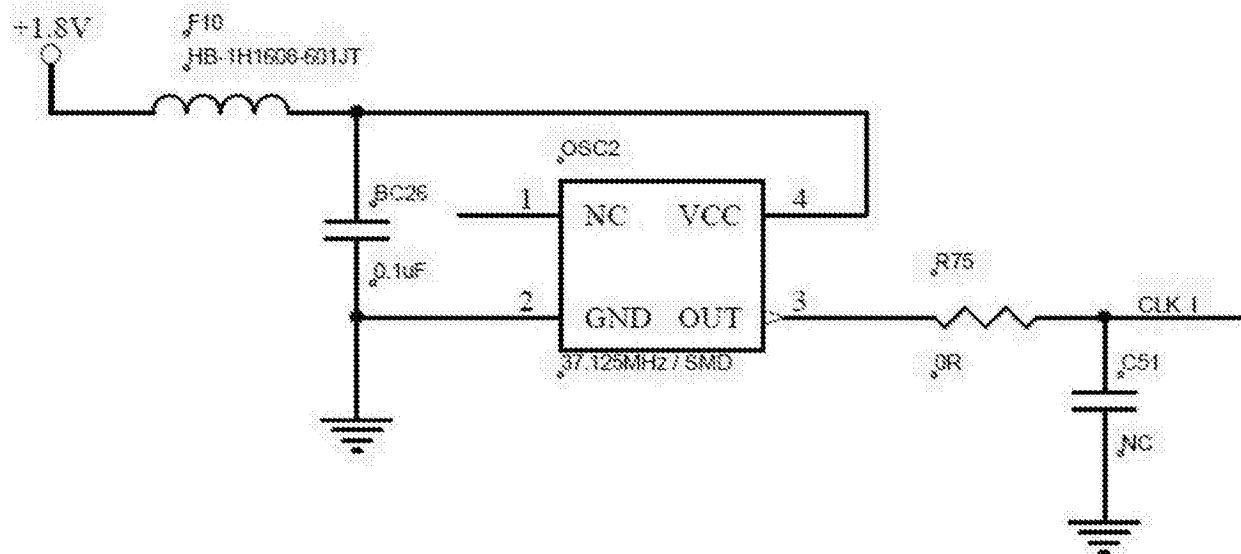

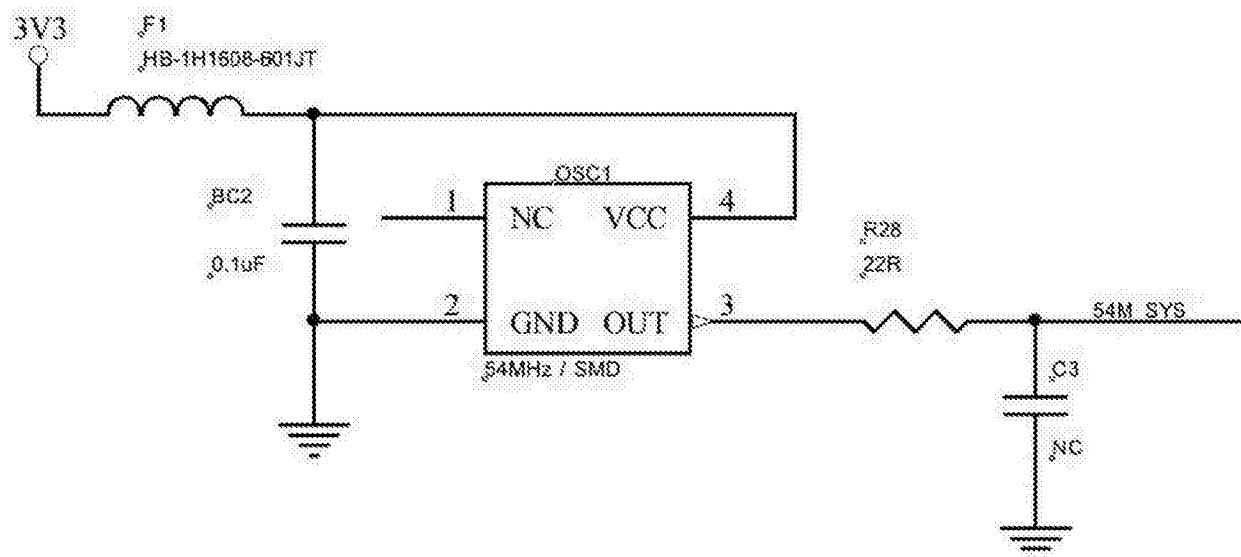

[0169] 请参阅图 10, 其为视频采集芯片的时钟电路的电路图。所述时钟信号端口 105 外接一时钟电路, 其包括一钟振芯片; 所述钟振芯片的电源端通过一滤波电路与电源连接, 该钟振芯片的输出端通过一调试电路与所述时钟信号端口连接; 所述滤波电路包括由一电感和电容串联组成, 所述电感的一端与电源连接, 另一端与电容连接, 且该电容的另一端接地; 所述钟振芯片的电源端与连接与电感和电容之间; 所述调试电路由电阻和电容组成; 该调试电路的电阻的一端与钟振的输出端连接, 另一端与电容连接, 且该电容的另一端接地; 所述时钟信号端口连接于该电阻与电容之间。

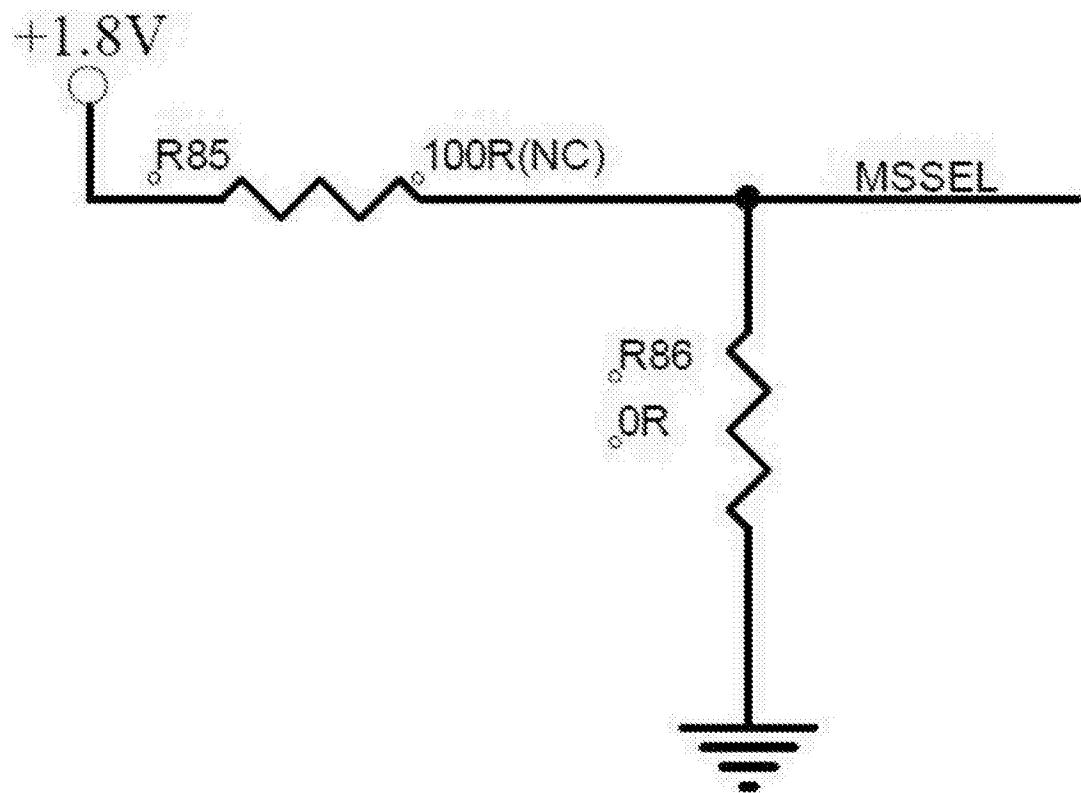

[0170] 请参阅图 11, 其为视频采集芯片的配置电路的电路图。进一步, 所述通讯命令端口 106, 其外接有一工作模式配置电路; 所述配置电路由两个电阻串联组成, 所述通讯命令端口连接于两电阻之间。

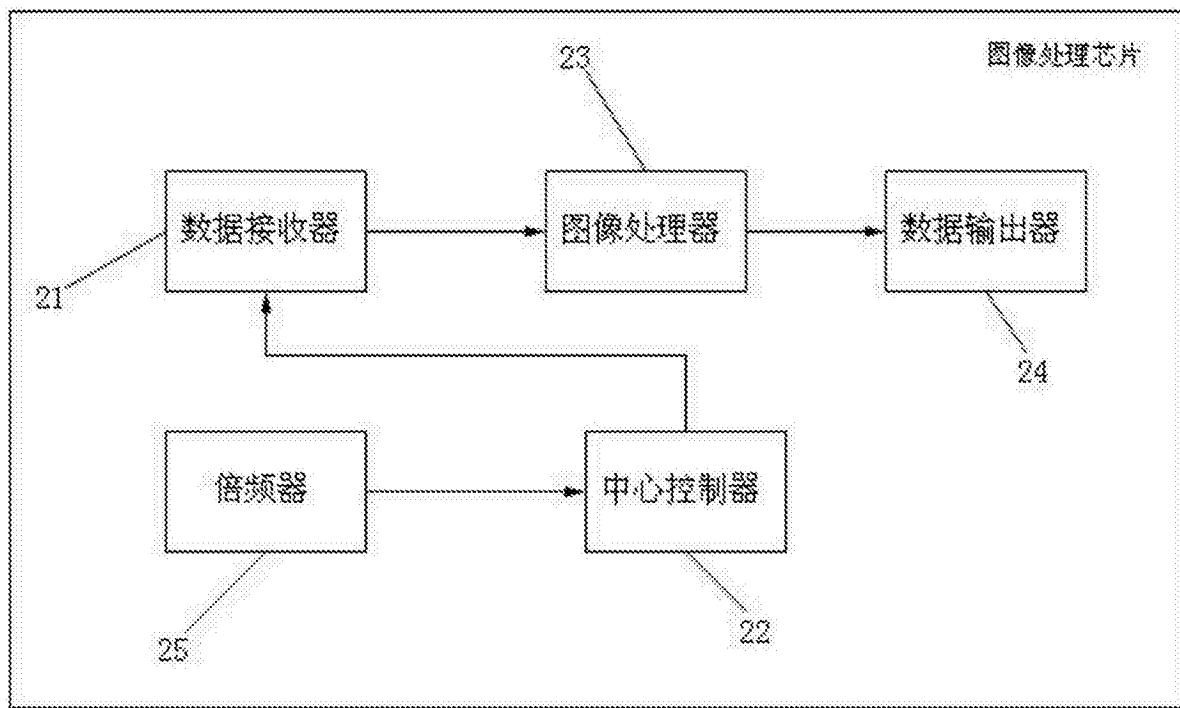

[0171] 请参阅图 12, 其为图像处理芯片的内部模块连接示意图。所述图像处理芯片 20 包括: 数据接收器 21、中心控制器 22、图像处理器 23、数据输出器 24。

[0172] 所述数据接收器 21, 其用于接收外部的图像数据;

[0173] 所述中心控制器 22, 其用于接收外部的触发信号, 并相应控制所述数据接收器、图像处理器和数据输出器的工作状态;

[0174] 所述图像处理器 23, 其用于对图像进行处理。

[0175] 所述数据输出器 24, 其用于将处理后的图像数据进行输出。

[0176] 进一步, 所述视频采集芯片还包括一倍频器 25, 其用于将外部输入的触发信号的频率进行增倍处理, 再发送至中心控制器 22。

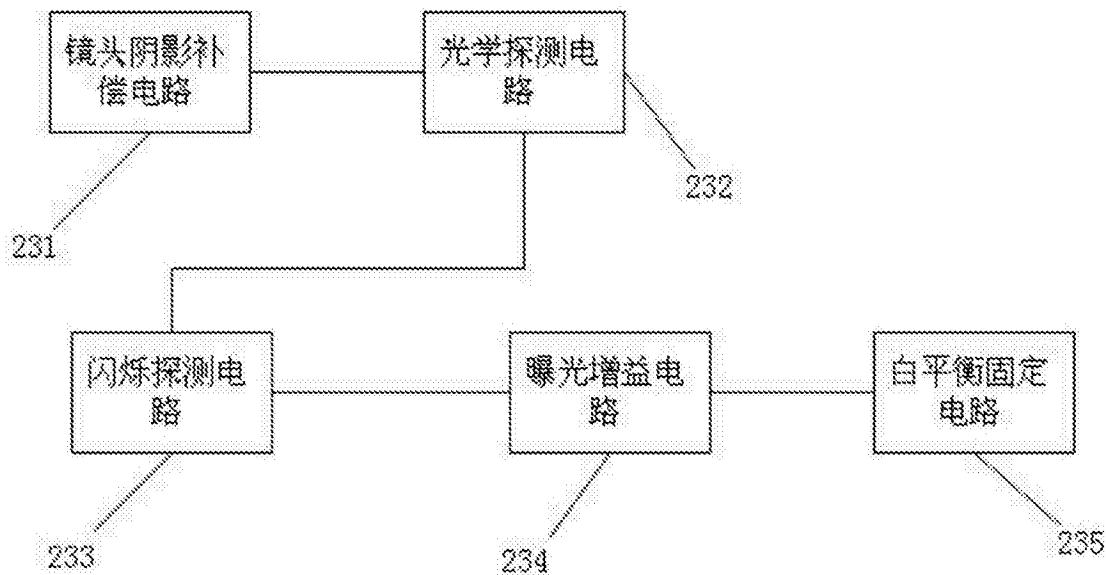

[0177] 请参阅图 13, 其为图像处理芯片的图像处理器的电路模块示意图。具体的, 所述图像处理器 23 包括一镜头阴影补偿电路 231、光学探测电路 232、闪烁探测电路 233、曝光增益电路 234 和白平衡固定电路 235。

[0178] 所述镜头阴影补偿电路 231, 其用于将镜头产生的阴影进行补偿处理。

[0179] 所述光学探测电路 232 和闪烁探测电路 233, 其用于探测图像的亮度和闪烁情况, 并将探测结果发送至曝光增益电路。

[0180] 所述曝光增益电路 234, 用于增加曝光增益大小。

[0181] 所述白平衡固定电路 235, 其用于根据预设的参数, 进行白平衡的固定调整。

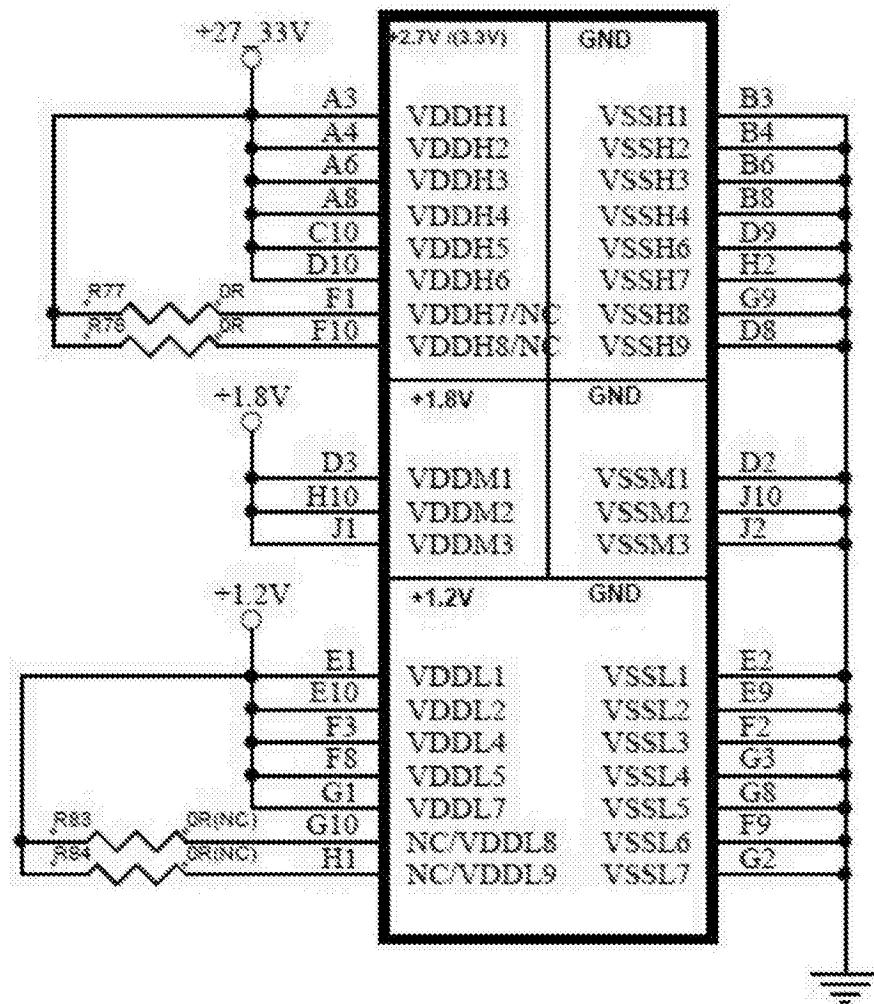

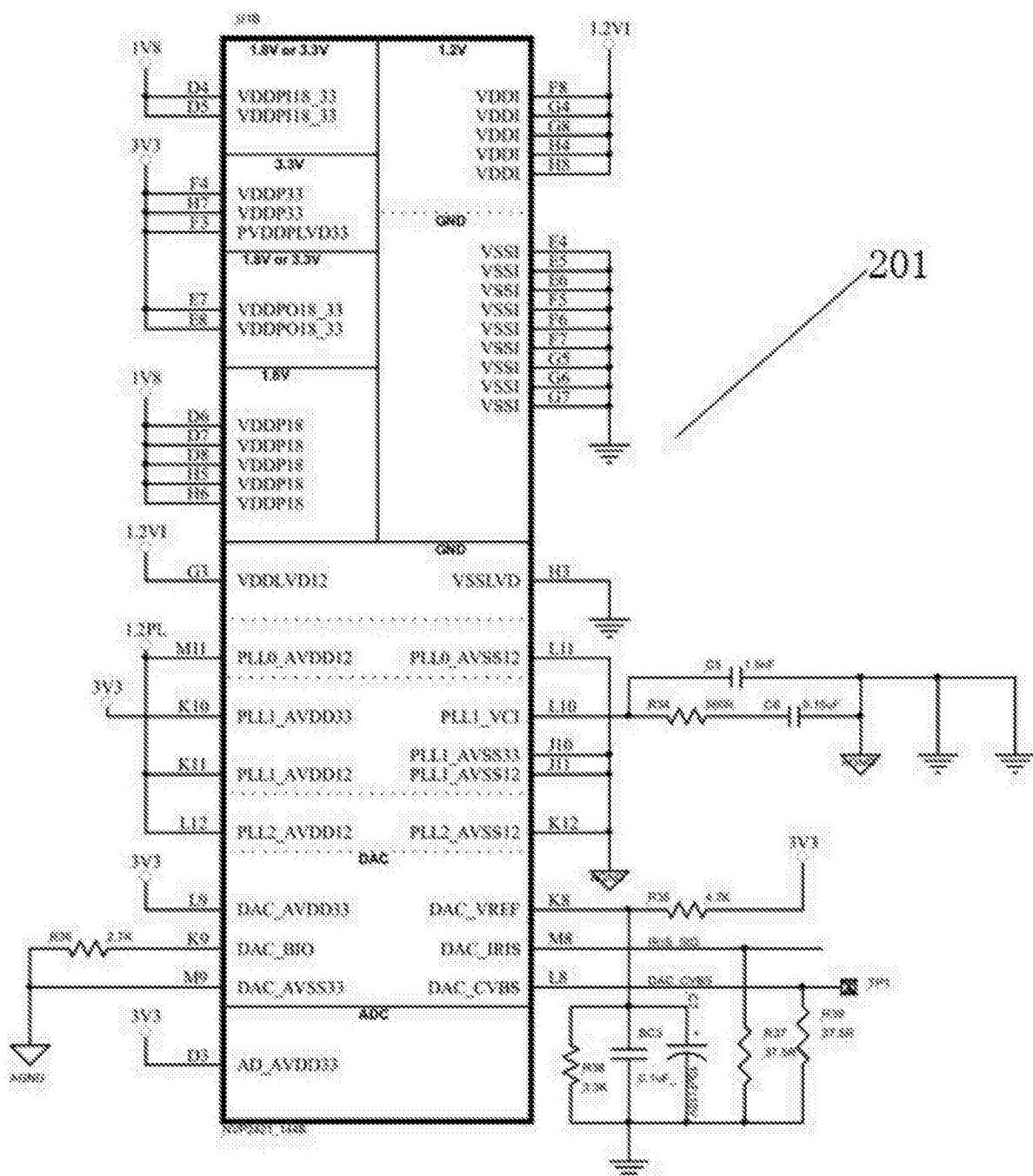

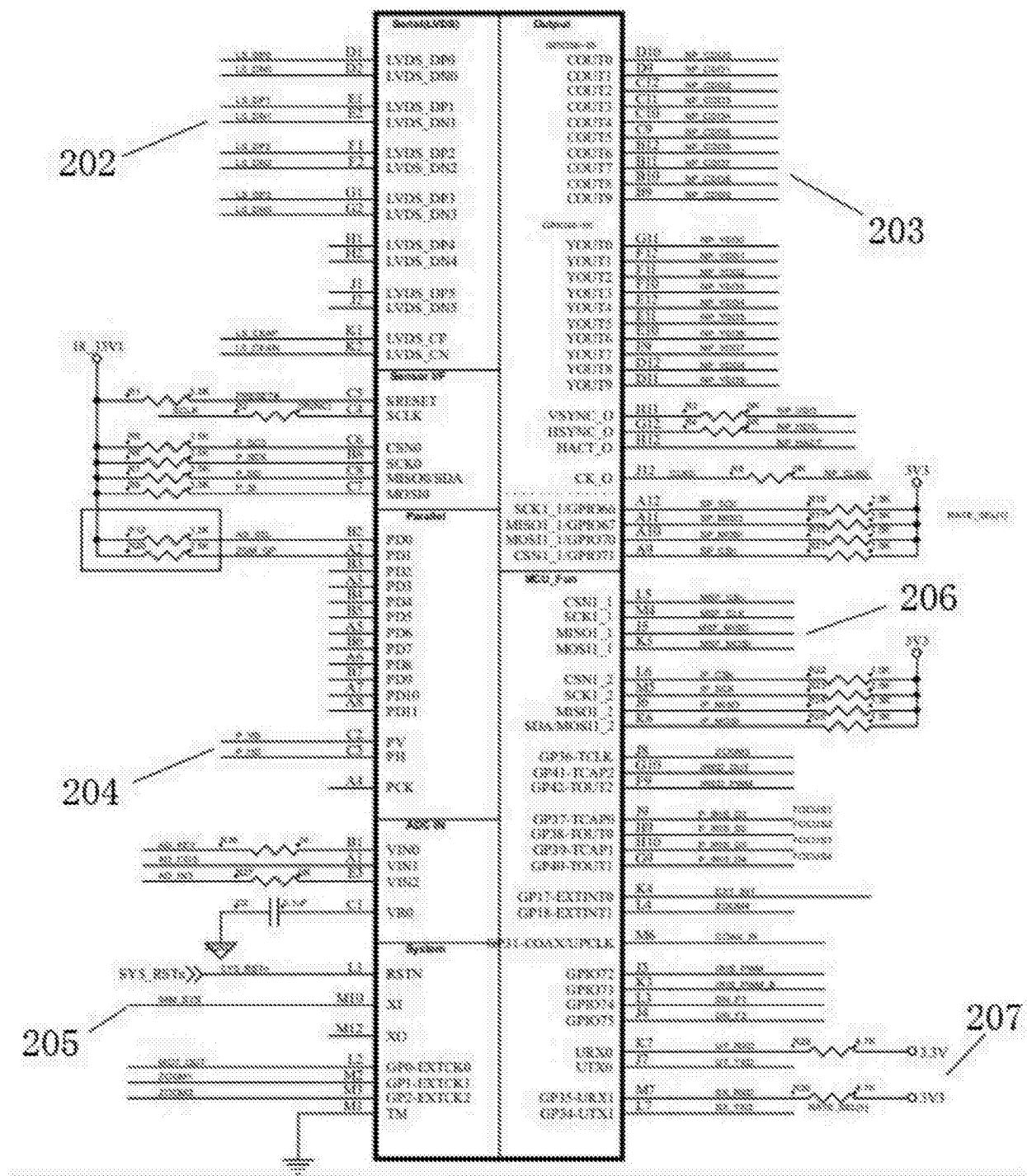

[0182] 请同时参阅图 14 和图 15, 其分别为图像处理芯片的视频采集芯片的电压部分和其他外部端口电路图。另外, 为了适应该视频采集芯片的应用, 进一步在所述视频采集芯片外部设有: 用于接收供电电压的电源端口 201、用于接收图像信号的信号接收端口 202、用于输出视频信号的视频信号端口 203、用于输出行场信号的行场信号端口 204、用于接收外部时钟信号的时钟信号端口 205、用于接收存储数据的数据接收端口 206 和一用于接收外部通讯命令的通讯端口 207。

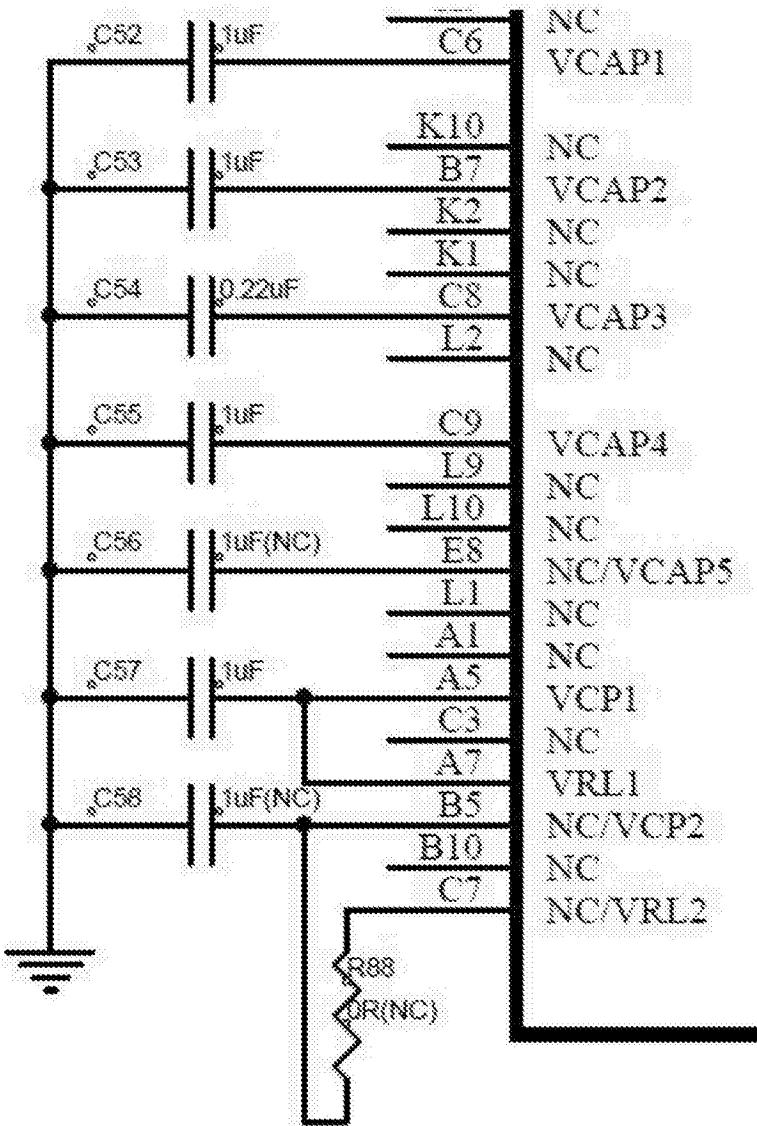

[0183] 请参阅图 16-18, 其分别为图像处理芯片的电源为 3.3V、1.8V 和 1.2V 的电路图。进一步, 所述电源端口 201 外接有一用于稳压的滤波电路; 所述滤波电路包括一个电感和至少一个电容; 所述电感一端与外部电源连接, 另一端分别与每个电容连接, 所述每个电容的另一端与接地; 所述电感与电容连接的一端接入电源端口。具体的, 本实用新型的视频采集芯片的外接电压包括: 3.3V、1.8V 和 1.2V 三种。其中, 3.3V 电压接入电路包括 2 个电容, 1.8V 电压接入电路包括 5 个电容, 1.2V 的电压接入电路包括 6 个电容, 以分别滤掉不同频

率的干扰信号。

[0184] 请参阅图 19, 其为图像处理芯片的信号接收端口的局部放大图。所述信号接收端口 202 包括 8 个引脚, 用于接收外部的视频图像信号。

[0185] 请参阅图 20, 其为图像处理芯片的视频信号端口的局部放大图。所述视频信号端口 203 包括两组不同格式的视频信号, 进行双路输出, 以方便分别进行实时播放和录制。

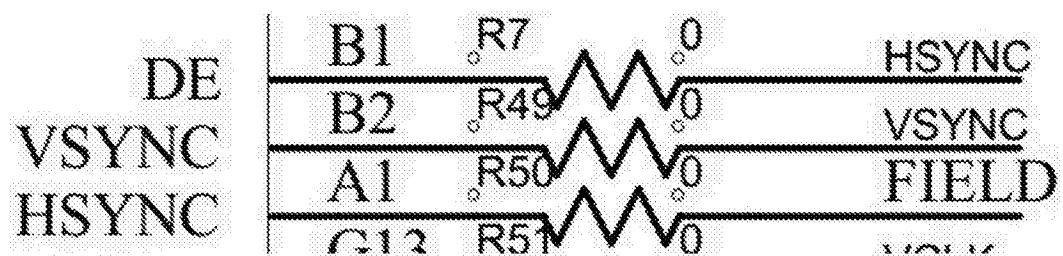

[0186] 请参阅图 21, 其为图像处理芯片的行场信号端口的局部放大图。所述行场信号端口 204 用于控制视频输出的频率和顺序。比如: 可以控制视频信号在屏幕上的显示频率和显示顺序, 可以是从上之下每行输出, 也可以是从左至右输出。

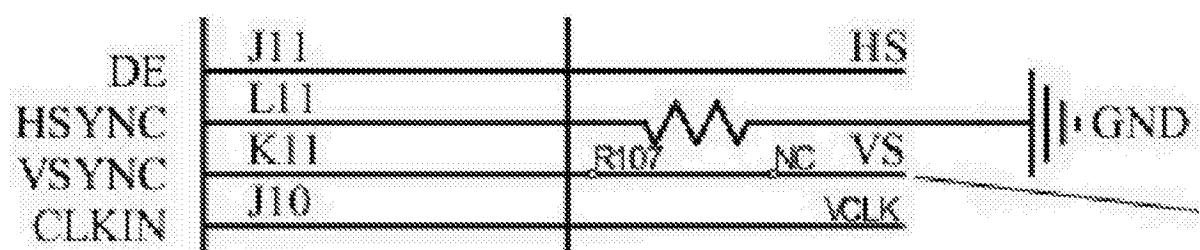

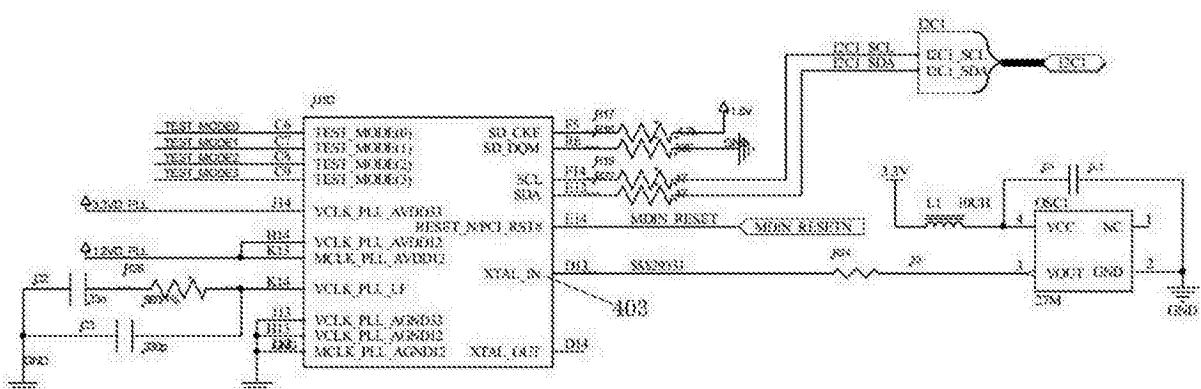

[0187] 请参阅图 22, 其为图像处理芯片的时钟电路的示意图。所述时钟信号端口 205 外接一时钟电路, 其包括一钟振芯片; 所述钟振芯片的电源端通过一滤波电路与电源连接, 该钟振芯片的输出端通过一调试电路与所述时钟信号端口连接; 所述滤波电路包括由一电感和电容串联组成, 所述电感的一端与电源连接, 另一端与电容连接, 且该电容的另一端接地; 所述钟振芯片的电源端与连接与电感和电容之间; 所述调试电路由电阻和电容组成; 该调试电路的电阻的一端与钟振的输出端连接, 另一端与电容连接, 且该电容的另一端接地; 所述时钟信号端口连接于该电阻与电容之间。

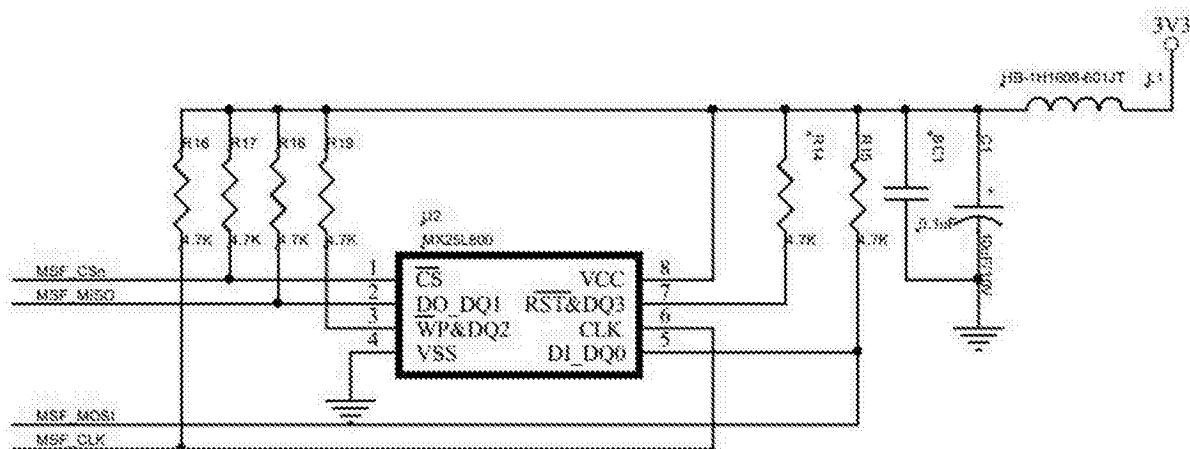

[0188] 请参阅图 23, 其为图像处理芯片的存储电路的示意图。进一步, 所述数据接收端口 206 外接有一存储器电路, 其包括一存储器、连接在该存储器的电压端口的滤波电路, 以及连接在该存储器的输出端口的电阻。

[0189] 请参阅图 24, 其为图像处理芯片的通讯端口的局部放大图。所述通讯端口 207 用于接收外部传输的触发命令, 以触发该图像处理芯片的进行工作。

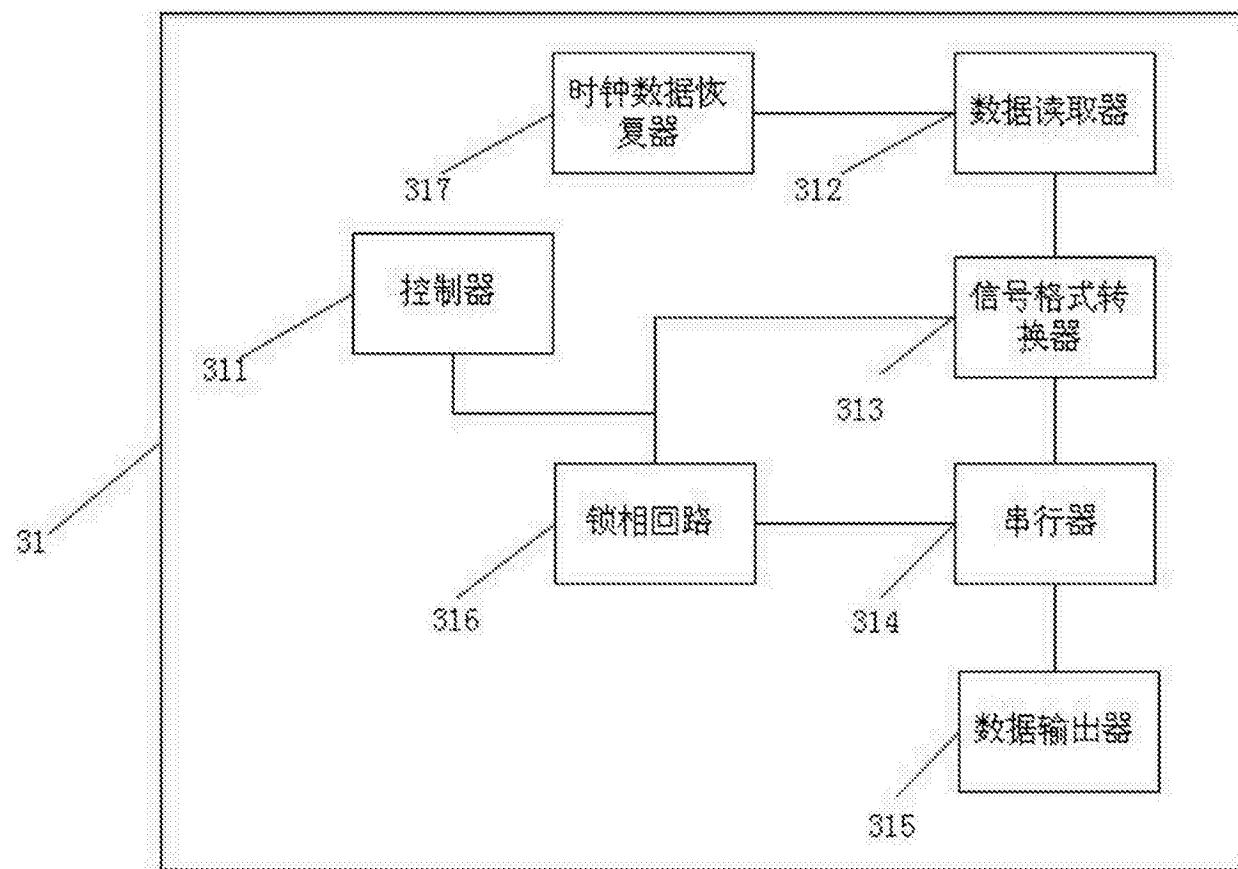

[0190] 请参阅图 25, 其为第一信号转换芯片的内部器件连接示意图。所述第一信号转换芯片 31 包括: 控制器 311、数据读取器 312、信号格式转换器 313、串行器 314、数据输出器 315、锁相回路 316 和时钟数据恢复器 317;

[0191] 所述控制器 311, 其用于接收外部的触发信号, 并控制数据读取器 312、信号格式转换器 313、串行器 314 和数据输出器 315 的工作;

[0192] 所述数据读取器 312, 其用于接收外部的 bt1120 传输信号, 并发送至信号格式转换器;

[0193] 所述信号格式转换器 313, 其用于将 bt1120 视频信号转换为 lvds 的视频信号, 并发送至串行器;

[0194] 所述串行器 314, 其用于将并行数据转换为串行数据, 并发送至数据输出器;

[0195] 所述数据输出器 315, 用于将 lvds 信号数据输出至第二信号转换芯片。

[0196] 所述锁相回路 316, 分别与信号格式转换器和串行器连接, 用于统一整合时脉信号。

[0197] 所述时钟数据恢复器 317, 其与数据读取器连接, 用于从传输信道的失真和噪声中恢复数据。

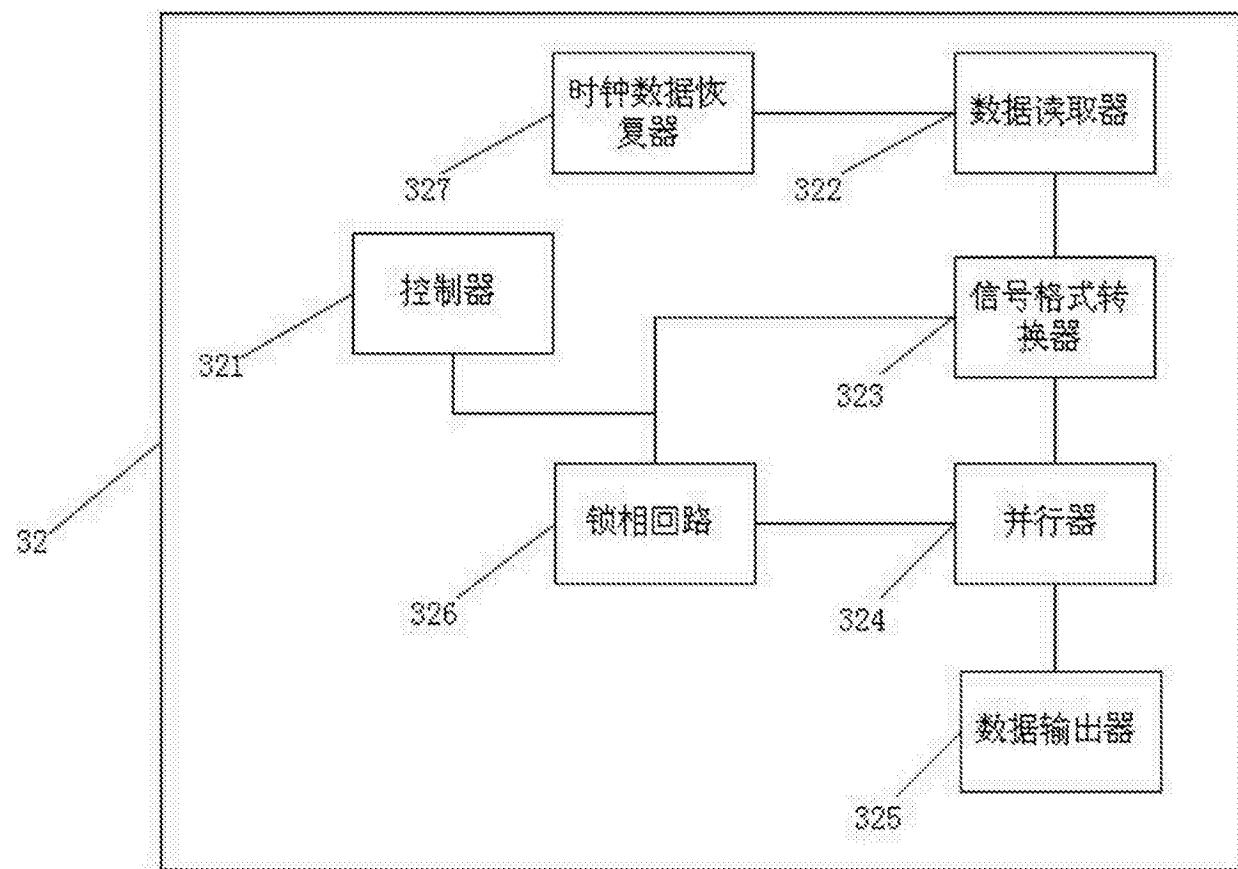

[0198] 请参阅图 26, 其为第二信号转换芯片的内部模块连接示意图。所述第二信号转换芯片 32 包括: 控制器 321、数据读取器 322、信号格式转换器 323、并行器 324、数据输出器 325、锁相回路 326 和时钟数据恢复器 327;

[0199] 所述控制器 321, 其用于接收外部的触发信号, 并控制数据读取器 322、信号格式

转换器 323、并行器 324 和数据输出器 325 的工作；

[0200] 所述数据读取器 322，其用于第一信号转换芯片的 lvds 视频传输信号，并发送至信号格式转换器；

[0201] 所述信号格式转换器 323，其用于将 lvds 视频信号转换为 bt1120 的视频信号，并发送至并行器 324；

[0202] 所述并行器 324，其用于将串行数据转换为并行数据，并发送至数据输出器；

[0203] 所述数据输出器 325，用于将 bt1120 视频信号数据输出。

[0204] 所述锁相回路 326，分别与信号格式转换器和并行器连接，用于统一整合时脉信号。

[0205] 所述时钟数据恢复器 327，其与数据读取器 222 连接，用于从传输信道的失真和噪声中恢复数据。

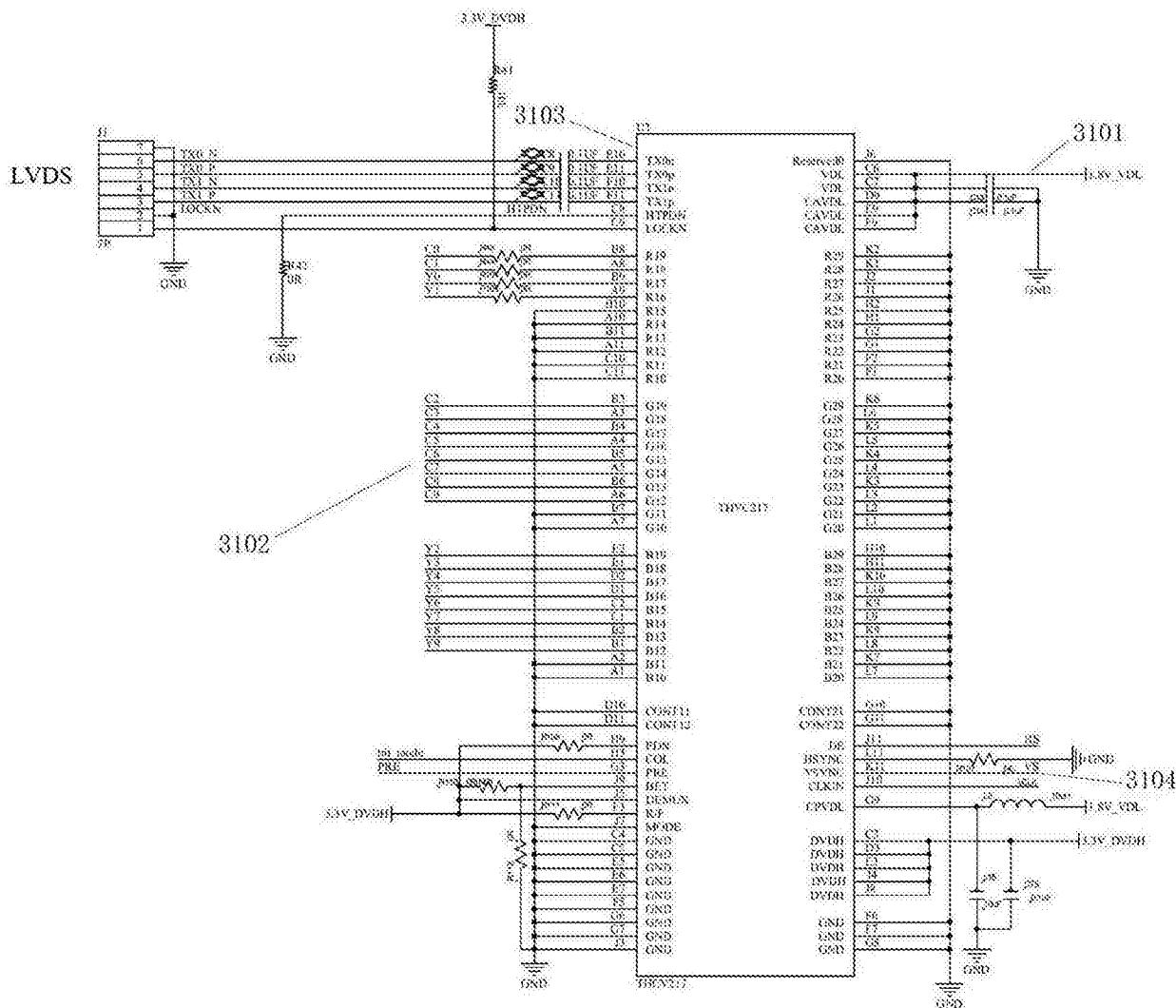

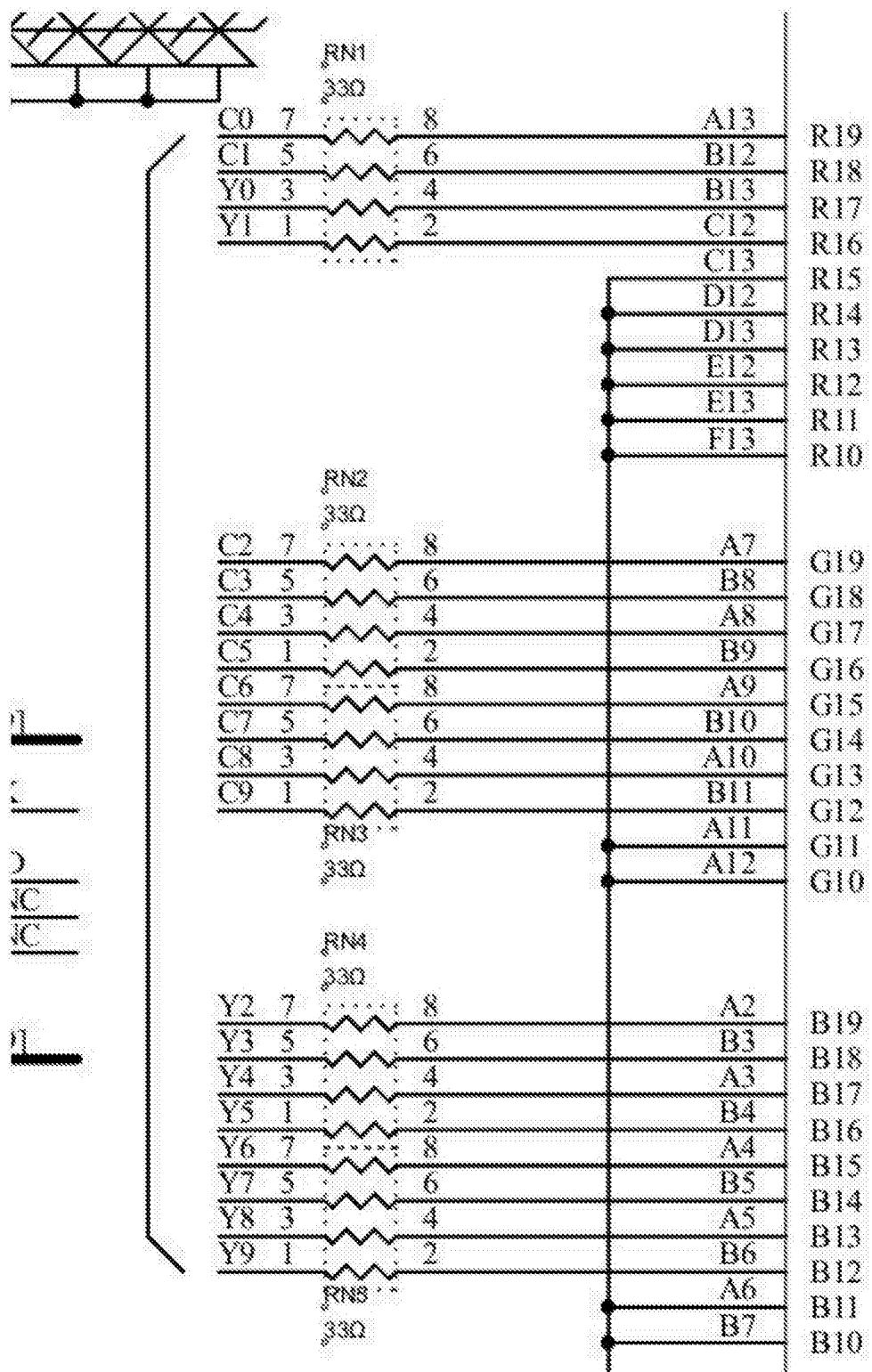

[0206] 请参阅图 27，其为第一信号转换芯片的外部端口连接示意图。所述第一信号转换芯片外部设有：用于接收供电电压的电源端口 3101、用于接收 bt1120 视频信号的信号接收端口 3102、用于输出 lvds 视频信号的视频信号端口 3103 和用于输出行场信号的行场信号端口 3104。

[0207] 请同时参阅图 28，其为第一信号转换芯片的电源端口的局部放大示意图。所述电源端口 3101 处外接有用于过滤交流电的电容。

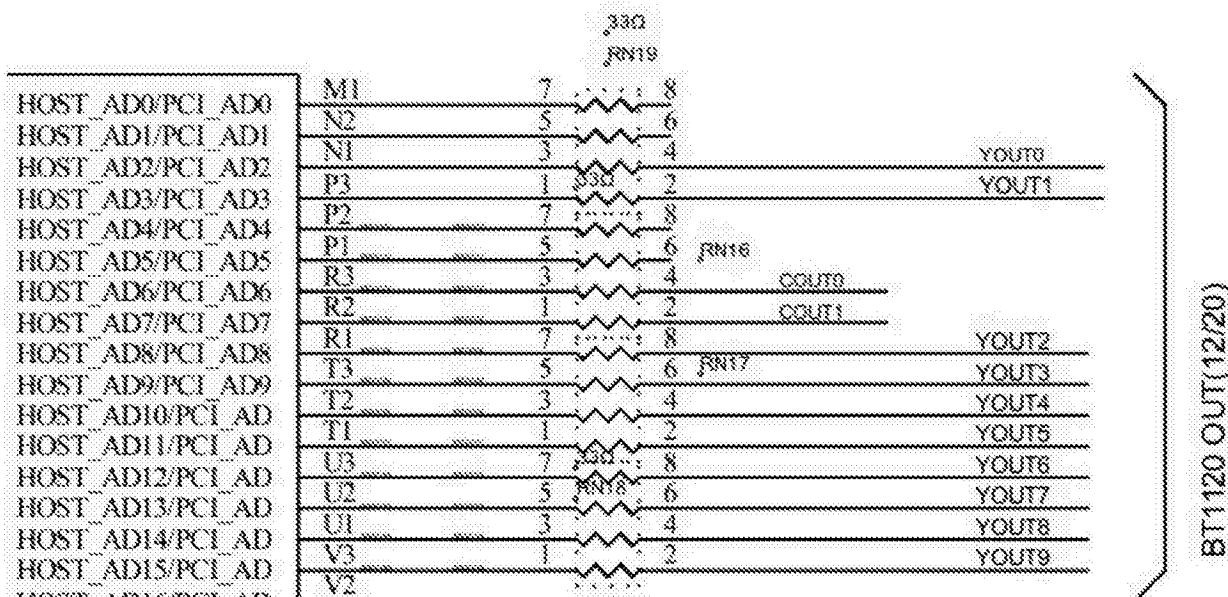

[0208] 请参阅图 29，其为第一信号转换芯片的信号接收端口的局部放大图。所述信号接收端口 3102，其与所述数据读取器 31 连接；具体的，该信号接收端口包括了 20 个引脚，用于接收外部 bt1120 的视频信号。

[0209] 请参阅图 30，其为第一信号转换芯片的视频信号端口的局部放大图。所述视频信号端口 3103 包括了 4 个输出引脚，用于输出 lvds 视频信号，且该视频信号端口与该数据输出器连接。

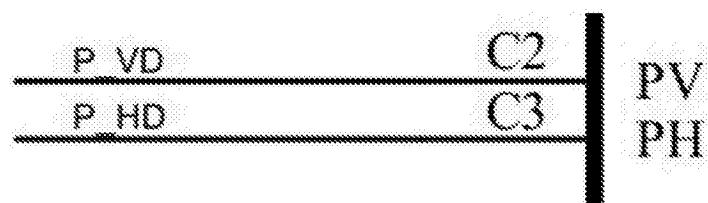

[0210] 请参阅图 31，其为第一信号转换芯片的行场信号端口的局部放大图。所述行场信号端口 3104 包括了一行信号输出引脚和一场信号输出引脚；所述行场信号端口 3104 用于控制视频输出的频率和顺序。比如：可以控制视频信号在屏幕上的显示频率和显示顺序，可以是从上之下每行输出，也可以是从左至右输出。

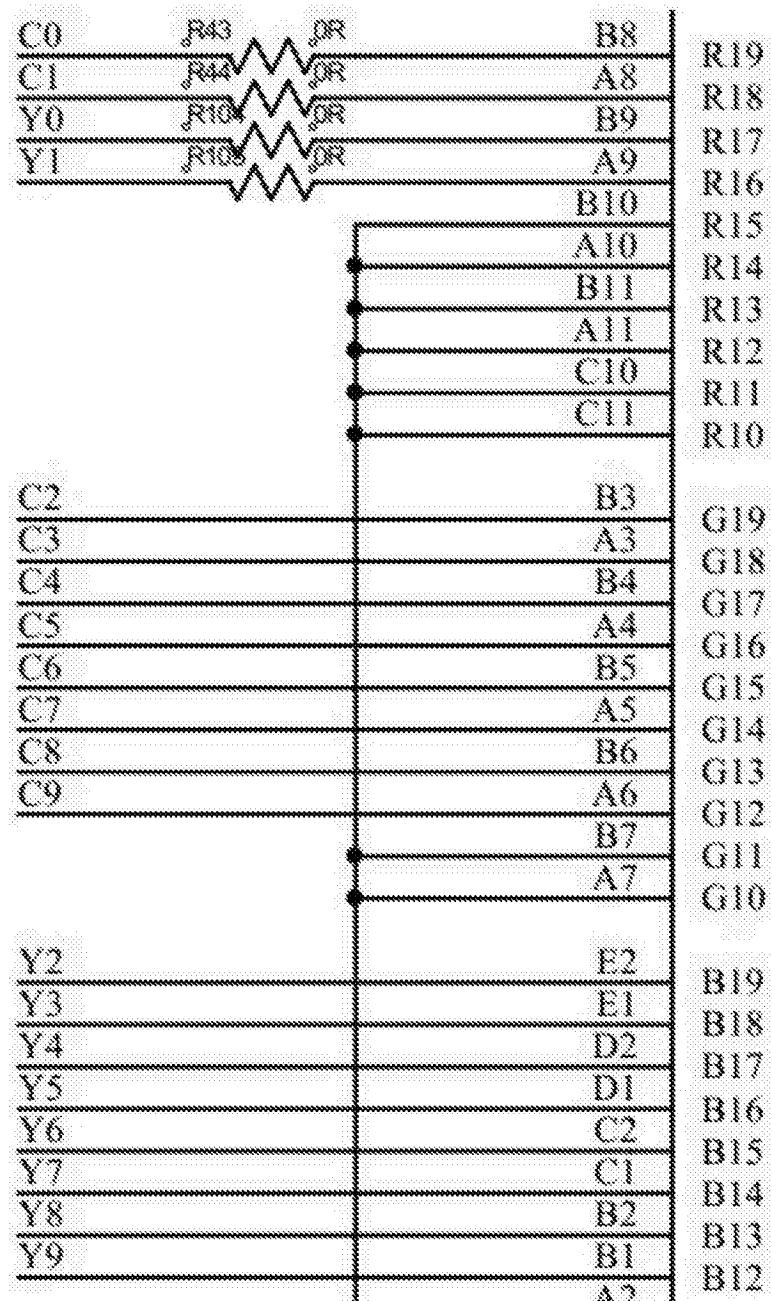

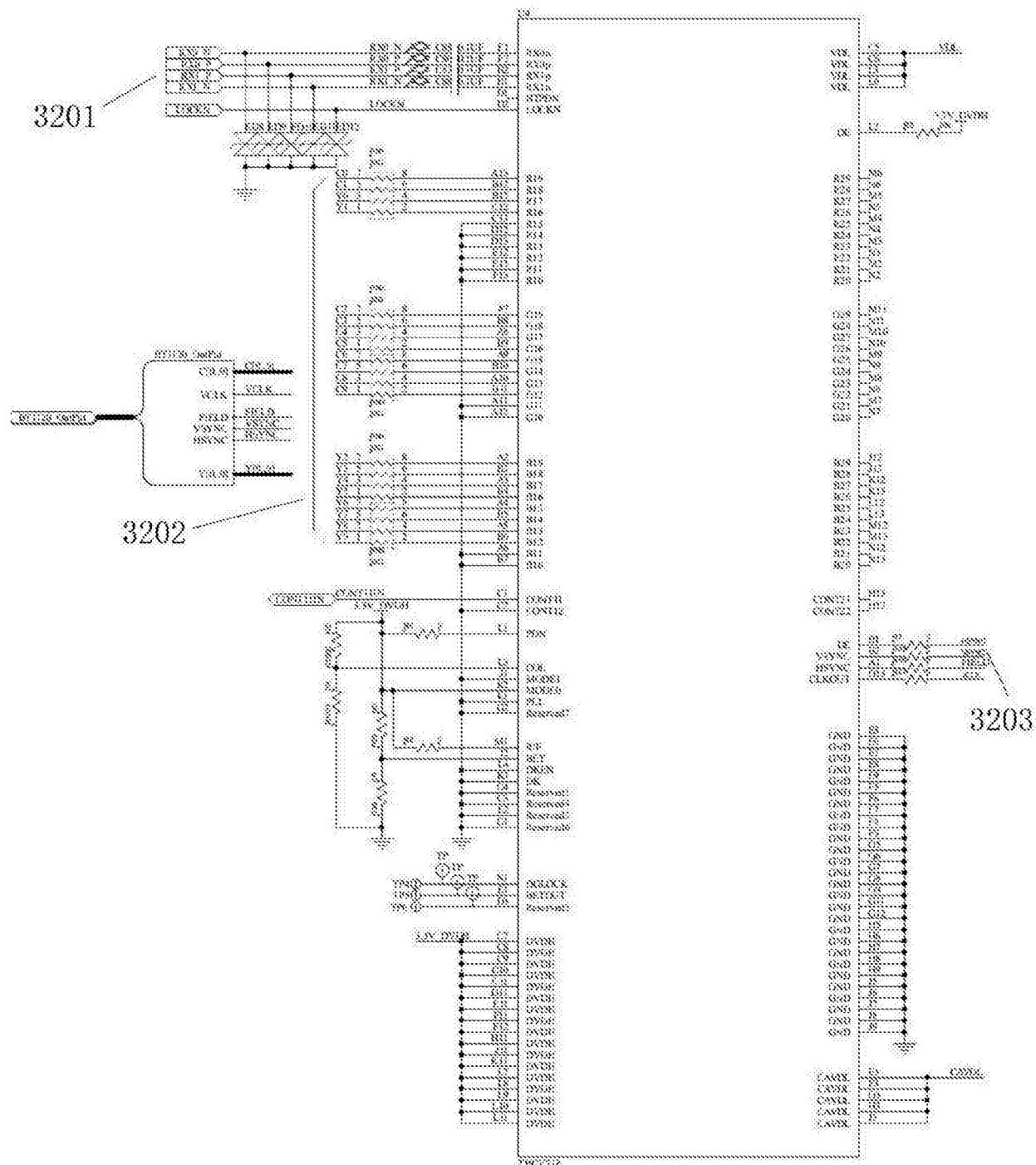

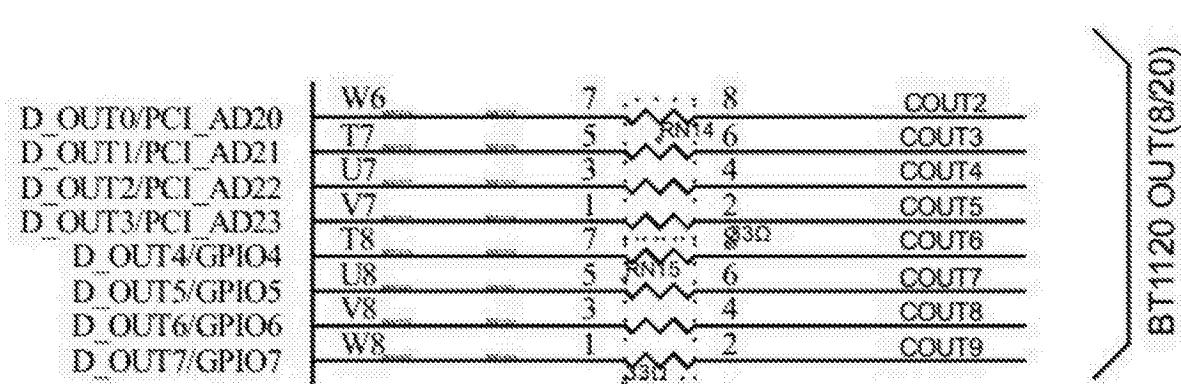

[0211] 请参阅图 32，其为第二信号转换芯片的外部连接电路图。所述所述第二信号转换芯片外部设有：用于接收 lvds 视频信号的信号接收端口 3201、用于输出 bt1120 视频信号的视频信号端口 3202 和行场信号端口 3203。

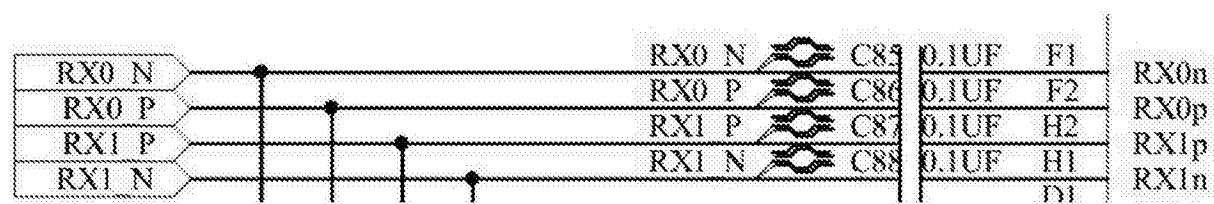

[0212] 请参阅图 33，其为第二信号转换芯片的信号接收端口的局部放大图。所述信号接收端口 3201，其与所述数据读取器 321 连接；具体的，该信号接收端口包括了 4 个引脚，用于接收第一信号转换芯片输出的 lvds 视频信号。

[0213] 请参阅图 34，其为第二信号转换芯片的视频信号端口的局部放大图。所述视频信号端口 3202 包括了 20 个输出引脚，用于输出 bt1120 视频信号，且该视频信号端口与该数据输出器连接。

[0214] 请参阅图 35，其为第二信号转换芯片的行场信号端口的局部放大图。所述行场信号端口 3203 包括了一行信号输出引脚和一场信号输出引脚；所述行场信号端口 3104 用于控制视频输出的频率和顺序。比如：可以控制视频信号在屏幕上的显示频率和显示顺序，可

以是从上之下每行输出,也可以是从左至右输出。

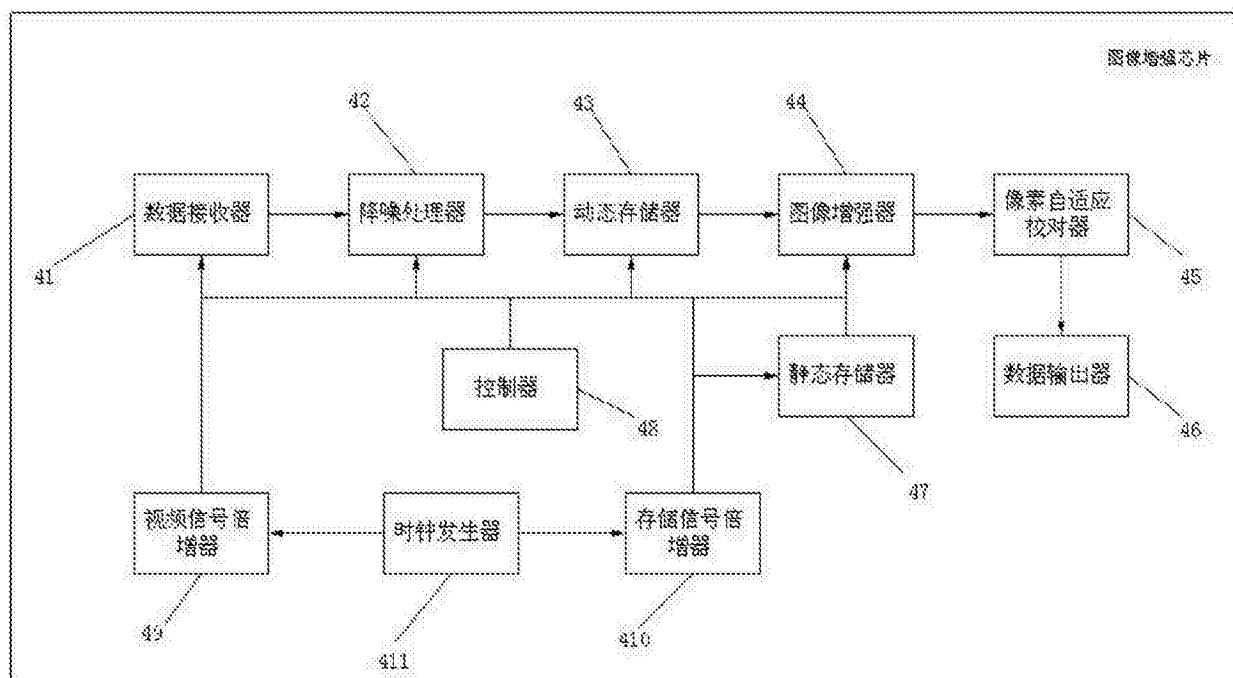

[0215] 请参阅图36,其为图像增强芯片的内部模块连接示意图。所述图像增强芯片40包括:数据接收器41、降噪处理器42、动态存储器43、图像增强器44、像素自适应校对器45、数据输出器46、静态存储器47、控制器48、视频信号倍增器49、存储信号倍增器410、时钟发生器411。

[0216] 所述数据接收器41,其用于接收图像数据信号,并发送至降噪处理器42;

[0217] 所述数据接收器41接收到的图像数据信号,发送至降噪处理器42进行降噪处理,再转发至动态存储器43。

[0218] 所述动态存储器43在接收到降噪处理器22处理后的图像数据后,再转发至图像增强器44。

[0219] 所述图像增强器44,其包括一图像边缘增强电路;所述图像边缘增强电路用于增强图像边缘的清晰度。进一步,所述图像增强器先将处理后的图像数据发送至所述像素自适应校对器45,由该像素自适应校对器45进行像素适应校对,再发送至数据输出器46。

[0220] 所述数据输出器46,其用于接收图像增强器处理后的图像数据,并进行数据输出;

[0221] 所述静态存储器47,其用于存储图像增强器的驱动数据,以驱动该图像增强器的工作;

[0222] 所述控制器48,其用于接收外部触发信号,并相应控制数据接收器、图像增强器和数据输出器的工作状态;

[0223] 所述时钟发生器411,其用于为图像增强芯片产生时钟信号。进一步,所述时钟发生器,将产生的时钟信号分别发送至视频信号倍增器49和存储信号倍增器410,并由该视频信号倍增器49将时钟信号发送至数据接收器,由该存储信号倍增器410将时钟信号发送至动态存储器和静态存储器。

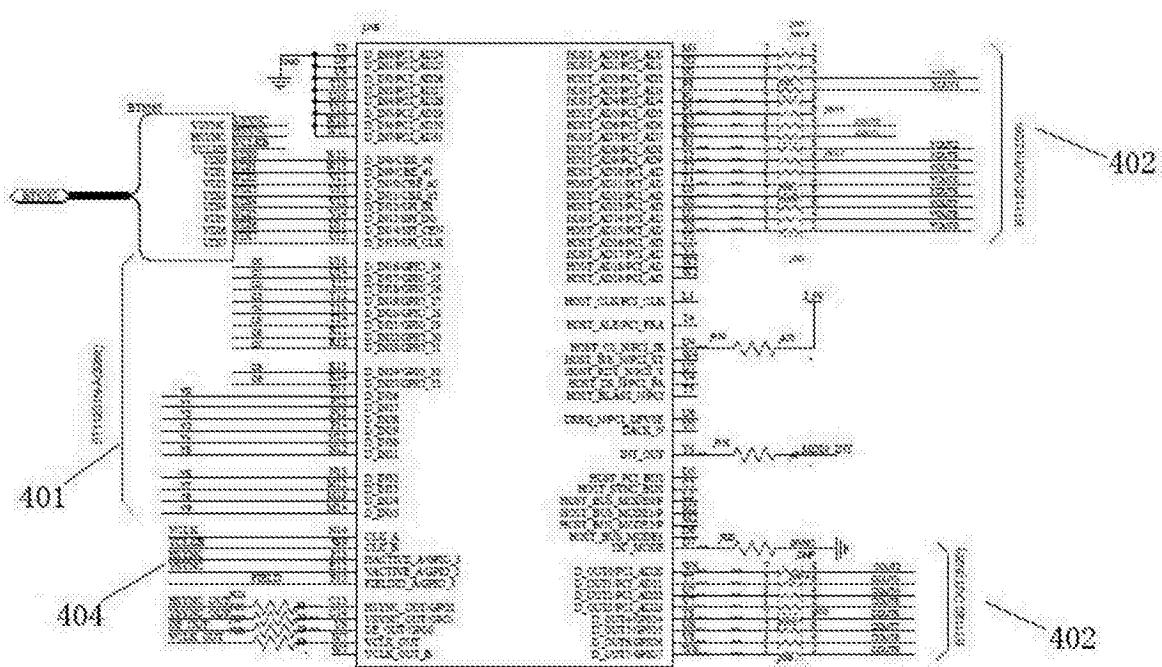

[0224] 请同时参阅图37和图38,其分别为图像增强芯片的外部连接电路图。

[0225] 进一步,所述图像增强芯片外部设有:用于接收供电电压的电源端口、用于接收图像信号的信号接收端口401、用于输出视频信号的视频信号端口402、用于接收外部时钟信号的时钟信号端口403、用于输出行场信号的行场信号端口404。

[0226] 具体的,在本实施例中,所述电源端口外接的电压包含3.3V、1.8V和1.2V三种电压。请参阅图39,其为3.3V电压的稳压滤波电路的电路图。所述滤波电路包括一个电感和至少一个电容;所述电感一端与外部电源连接,另一端分别与每个电容连接,所述每个电容的另一端与接地;所述电感与电容连接的一端接入电源端口。

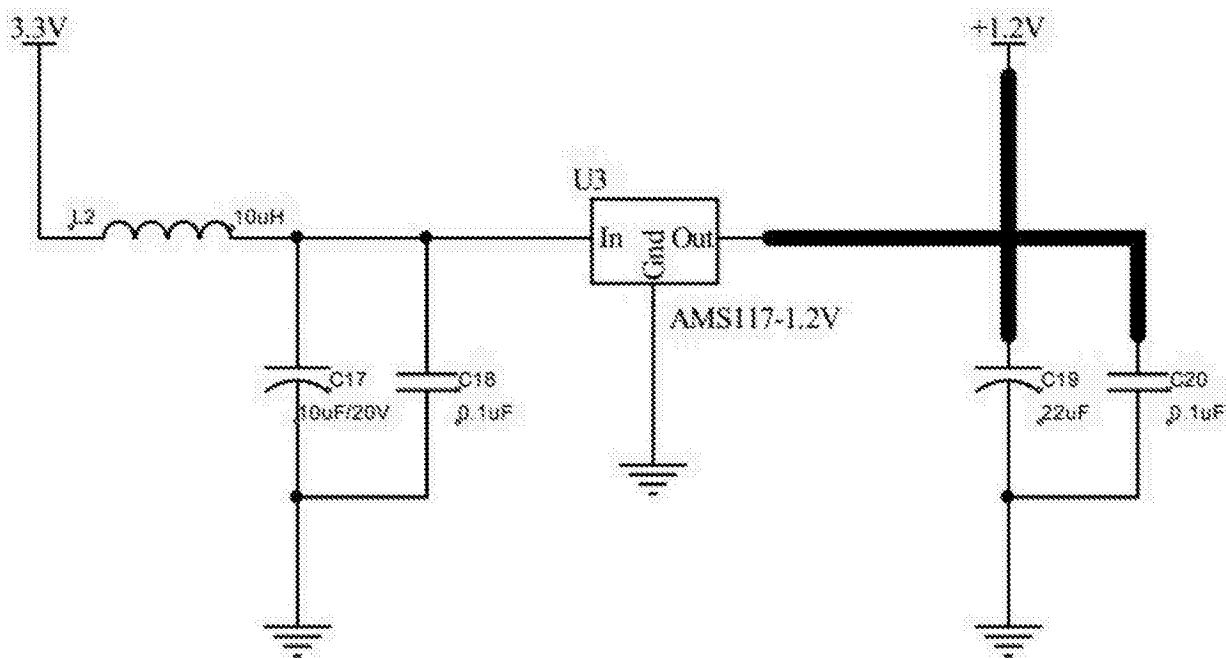

[0227] 请参阅图40-41,其分别为3.3V转换为1.8V的电源转换电路图和3.3V转换为1.2V的转换电路图。在本实施例中,通过一电源转换电路,将3.3V的电压分别转换为1.8V和1.2V的电压。具体的,所述电源转换电路包括一电源转换芯片;所述电源转换芯片的输入端接入3.3V的电压,输出端分别输出1.8V和1.2V的电压,以对图像增强芯片进行供电。

[0228] 请参阅图42,其为图像增强芯片的信号接收端口的局部放大图。所述信号接收端口401包括20个信号引脚,与内部的数据接收器41连接,用于接收输入的图像信号。

[0229] 请参阅图43a和43b,其分别为图像增强芯片的视频信号端口的第一部分和第二部分的局部放大图。所述视频信号端口402包括20个信号引脚,其与内部的数据输出器46

连接,用于输出图像信号。

[0230] 请参阅图 44,其为图像增强芯片的时钟电路的电路图。进一步,所述时钟信号端口 403 外接一时钟电路,其包括一钟振芯片;所述钟振芯片的电源端通过一滤波电路与电源连接,该钟振芯片的输出端与所述时钟信号端口连接;所述滤波电路包括由一电感和电容串联组成,所述电感的一端与电源连接,另一端与电容连接,且该电容的另一端接地。

[0231] 请参阅图 45,其为图像增强芯片的行场信号端口的局部放大图。所述行场信号端口 404 包括一个行信号引脚和一个场信号引脚。所述行场信号端口 404 用于控制视频输出的频率和顺序。比如:可以控制视频信号在屏幕上的显示频率和显示顺序,可以是从上之下每行输出,也可以是从左至右输出。

[0232] 请参阅图 46,其为视频录制芯片的内部器件连接示意图。所述视频录制芯片包括:数据接收器 51、图像处理器 52、视频编码器 53、视频解码器 54、数据输出器 55 和处理器 56;

[0233] 所述数据接收器 51,用于接收外部的视频信号,并发送至图像处理器;

[0234] 所述图像处理器 52,用于接收数据接收器发送的视频进行,并对视频图像进行处理,再发送至视频编码器;其中,所述图像处理器包括用于增强图像边缘的清晰度的边缘增强电路和用于消除信号干扰的消除噪音干扰电路。

[0235] 所述视频编码器 53,用于对视频信号进行编码录制;

[0236] 所述视频解码器 54,用于对视频信号进行解码回放;

[0237] 所述数据输出器 55,用于对视频信号进行输出;

[0238] 所述处理器 56,用于控制数据接收器 51、图像处理器 52、视频编码器 53、视频解码器 54 和数据输出器 55 的工作。

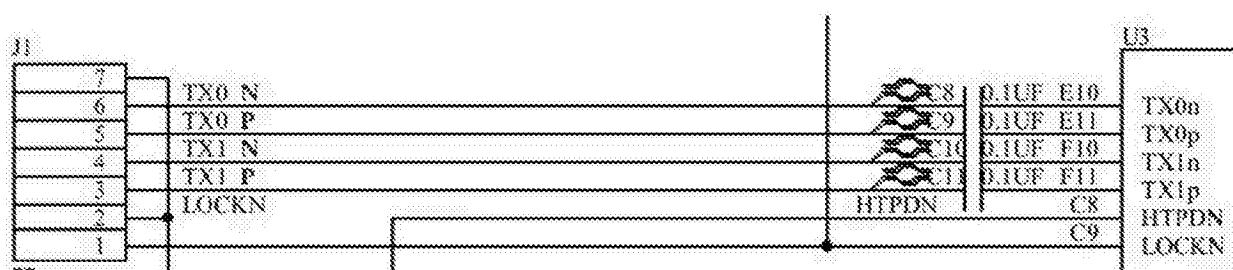

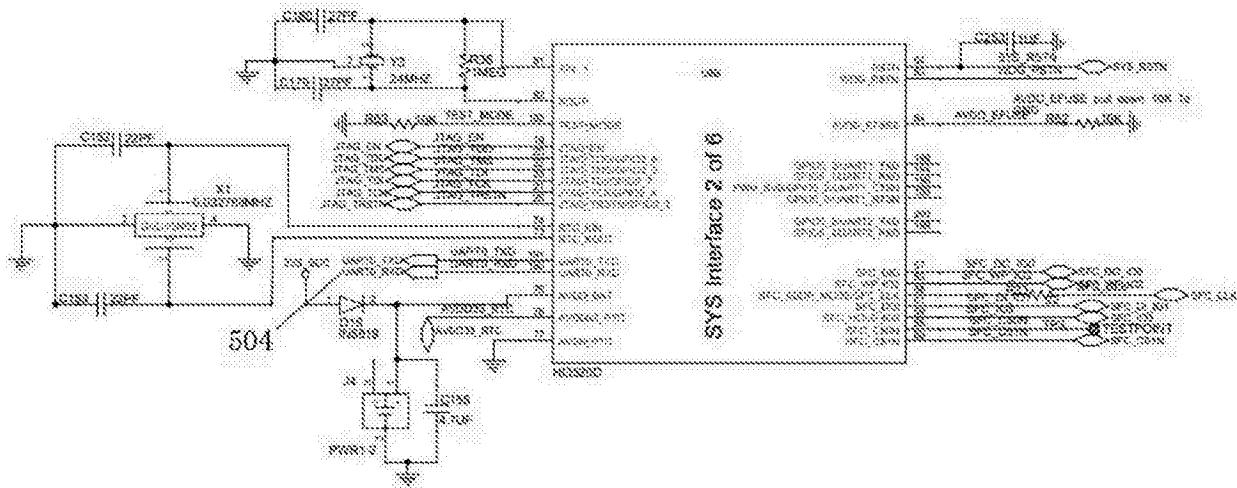

[0239] 请参阅图 47-49,其为视频录制芯片的视频输入、视频输出和通讯输入电路图。进一步,所述视频录制芯片外部设有:电源端口 501、视频输入端口 502、视频输出端口 503 和通讯端口 504。所述视频输入端口与该视频录制芯片内部的数据接收器连接,用于接收外部的视频数据;所述视频输出端口,与所述数据输出器连接,用于输出视频数据;所述通讯端口,与所述处理器连接,用于接收外部的串口命令。

[0240] 请参阅图 50,其为视频录制芯片的电源端口的局部放大图。所述电源端口 501 外接有一滤波电路;所述滤波电路包括一磁珠和至少一个电容;所述磁珠与电容的一端连接,且该电容的另一端接地;所述电源端口连接于磁珠和电容之间。

[0241] 请参阅图 51,其为视频录制芯片的通讯端口的局部放大图。所述通讯端口 504 包括了两个引脚,作为串口与外部命令进行通讯。通过串口通讯的方式,使用的数据线少,可以节约通信成本。

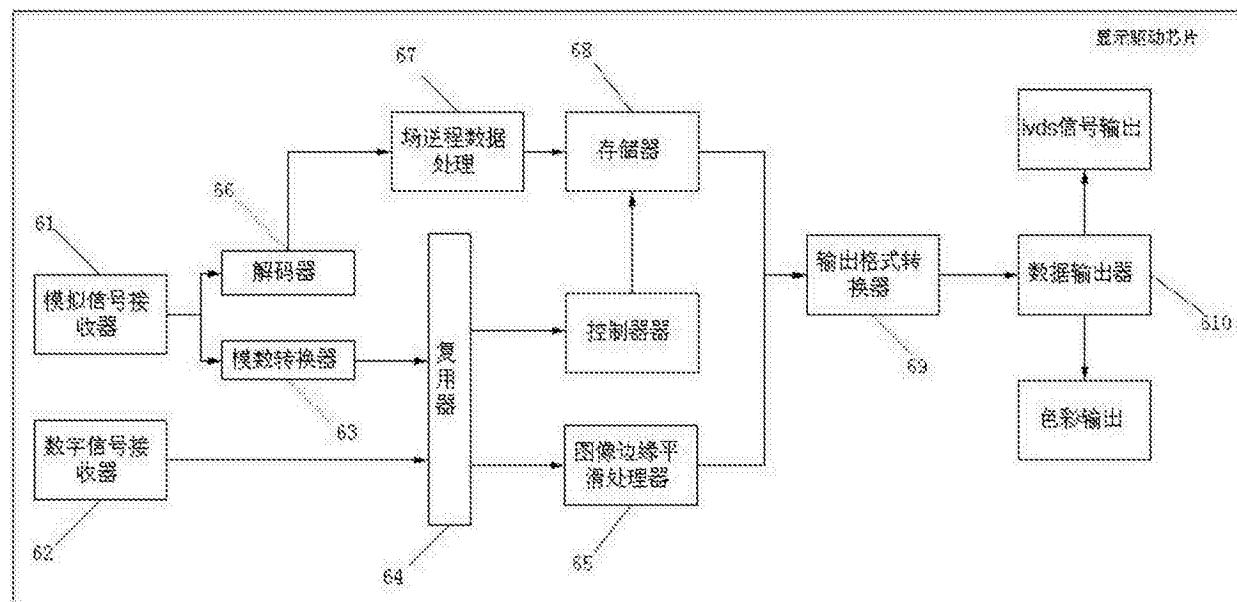

[0242] 请参阅图 52,其为显示驱动芯片的内部器件连接示意图。所述显示驱动芯片 60 包括:模拟信号接收器 61、数字信号接收器 62、模数转换器 63、复用器 64、图像边缘平滑处理器 65、视频解码器 66、场逆程数据处理器 67、存储器 68、输出格式转换器 69、数据输出器 610 和控制器 611。

[0243] 所述模拟信号接收器 61,用于接收模拟信号,并发送至模数转换器 63;

[0244] 所述数据信号接收器 62,用于接收数据信号,并发送至复用器 64;

[0245] 所述模数转换器 63,用于将模拟信号转换为数据信号,并发送至复用器 64;

[0246] 所述复用器 64,用于将两路信号进行整合,并进行输出至输出图像边缘平滑处理

器 65 ；

[0247] 所述图像边缘平滑处理器 65, 用于接收复位器的信号, 并对视频图像的边缘进行平滑处理, 再发送至格式转换器 69。

[0248] 所述视频解码器 66, 用于将模拟信号接收器接收的模拟信号进行解码, 并发送至场逆程数据处理器 67 ；

[0249] 所述场逆程数据处理器 67, 用于将解码后的模拟信号插入数据行, 并发送至所述存储器 68 进行存储；

[0250] 所述存储器 68, 用于存储经场逆程数据处理器处理后的数据, 并发送至输出格式转换器 69。

[0251] 所述输出格式转换器 69, 用于将信号格式进行转换, 并输出至数据输出器 610 ；

[0252] 所述数据输出器 610 同时进行色彩输出和 1vds 视频信号输出。

[0253] 所述控制器 611, 用于控制模拟信号接收器 61、数字信号接收器 62、模数转换器 63、复用器 64、图像边缘平滑处理器 65、视频解码器 66、场逆程数据处理器 67、存储器 68、输出 格式转换器 69 和数据输出器 610 的工作。

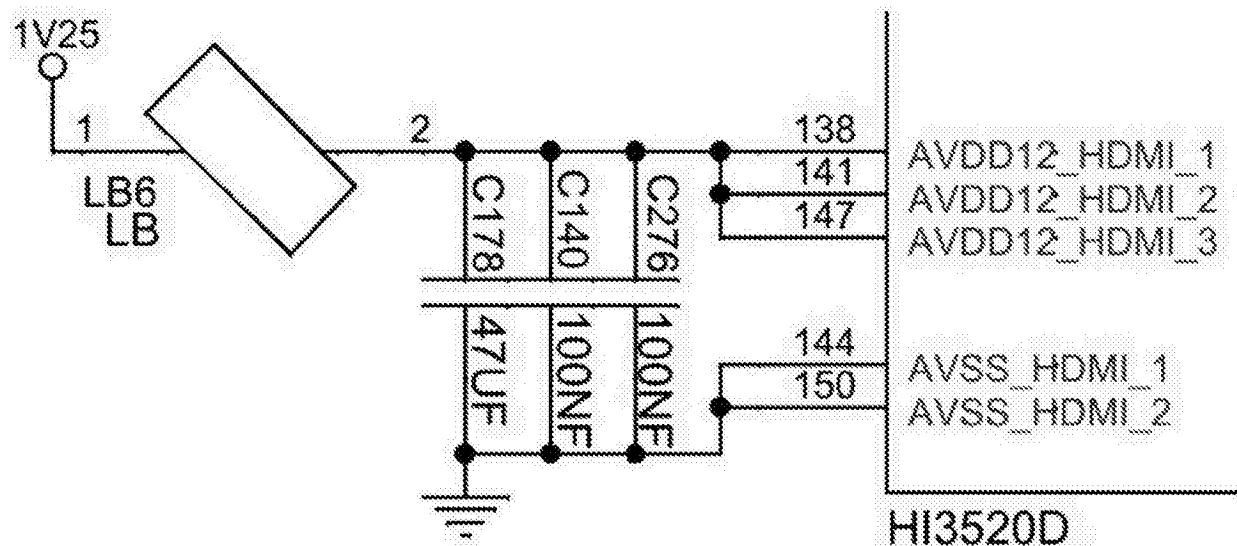

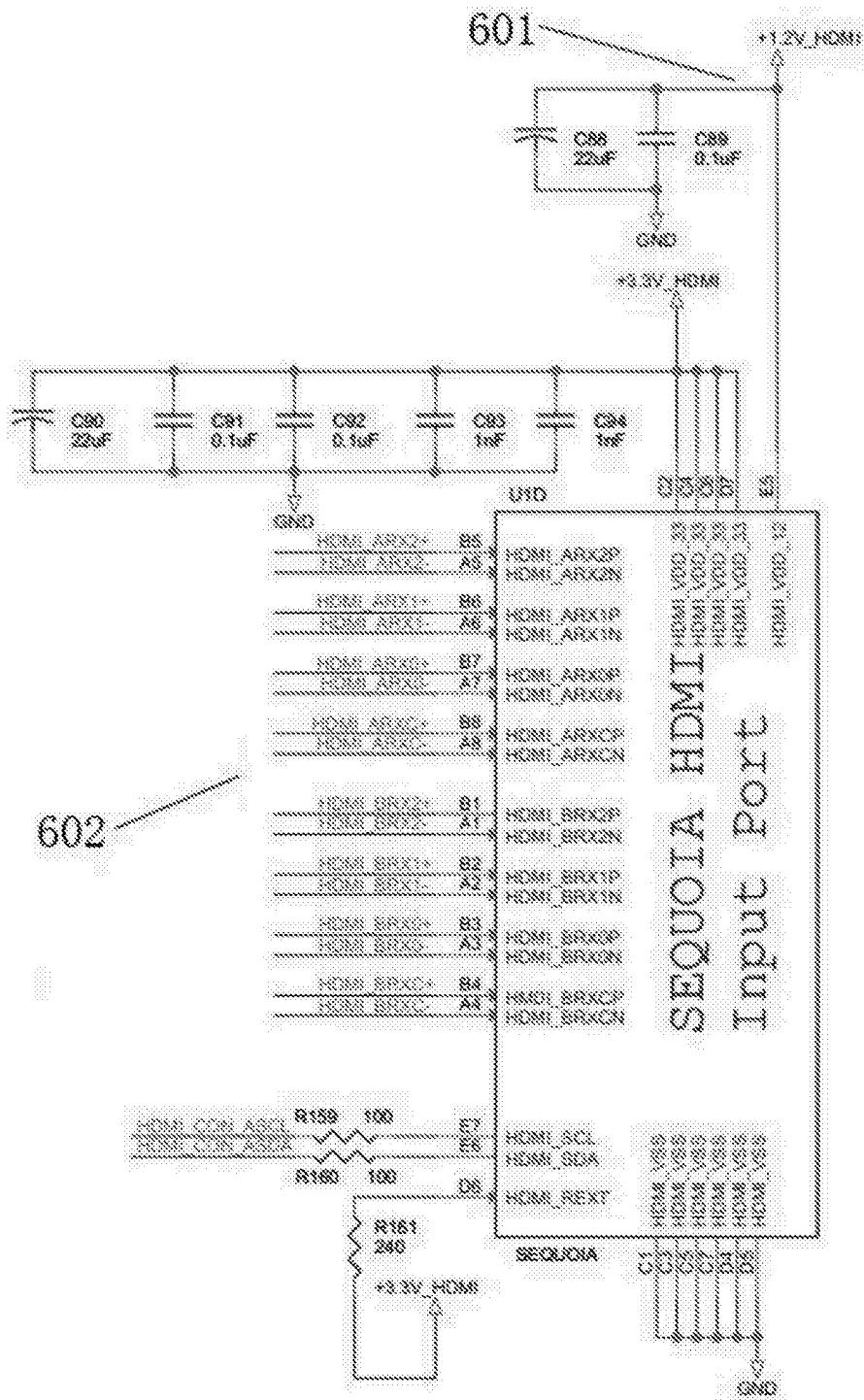

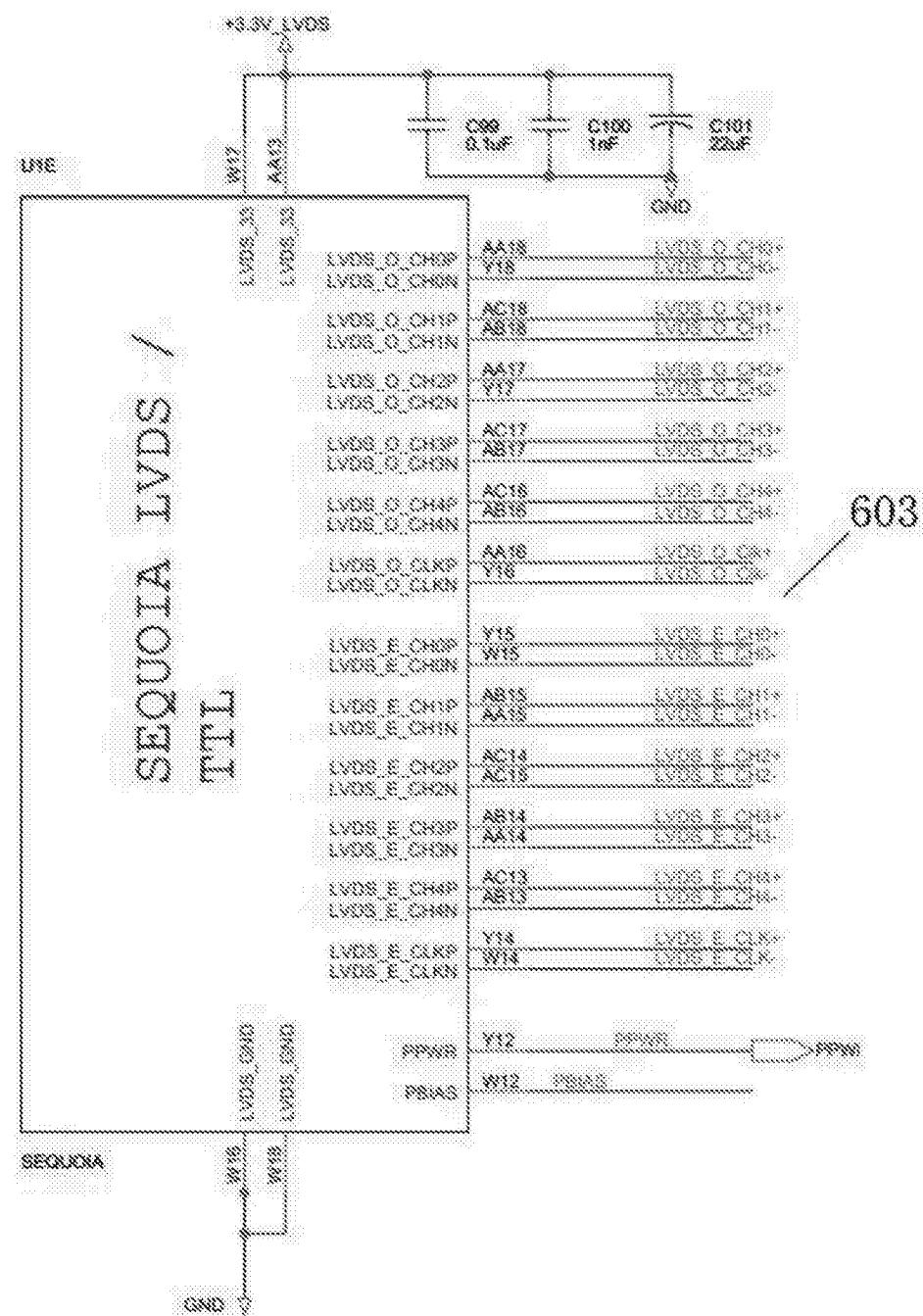

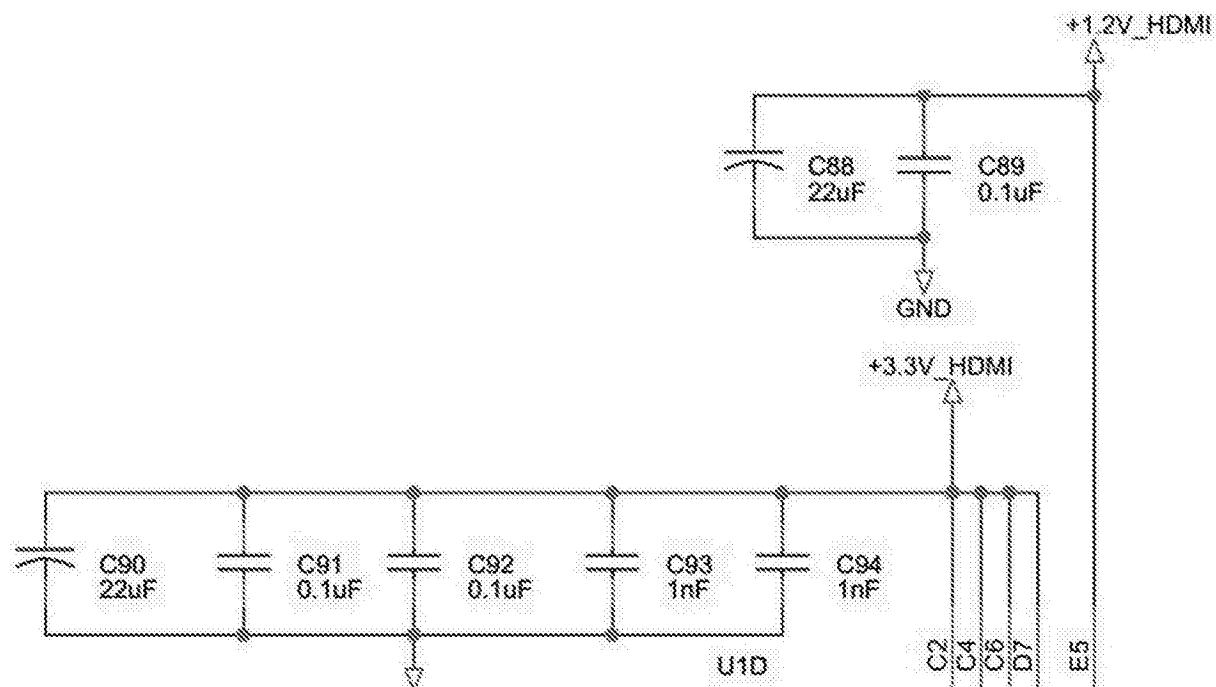

[0254] 请参阅图 53 和图 54, 其分别为显示驱动芯片的外部信号输入电路图和信号输出电路图。进一步, 所述显示驱动芯片的外部设有: 电源端口 601、视频信号接收端口 602 和视频信号输出端口 603 ; 所述视频信号接收端口 602 与显示驱动芯片内部的模拟信号接收器 61 和数据信号接收器 62 连接 ; 所述视频输出端口 603 与显示驱动芯片内部的数据输出器 610 连接。

[0255] 请参阅图 55, 其为显示驱动芯片的电源端口的局部放大图。所述电源端口 601 包括一个 1. 2V 的电源引脚和 3. 3V 的电源引脚 ; 所述 1. 2V 引脚外接有两个并联的电容, 用于过滤交流信号 ; 所述 3. 3V 外接有 5 个并联电容, 用于过滤不同频率的交流信号。

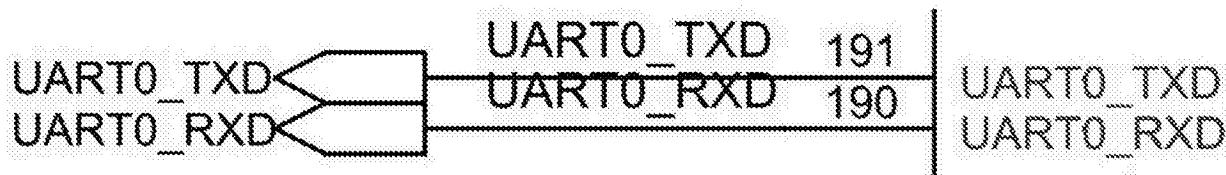

[0256] 请参阅图 56, 其为显示驱动芯片的视频输入端口的局部放大图。所述视频输入端口 602 包括两组引脚, 一组用于接收录制电路的录制信号, 另一组用于接收实时播放的视频信号。其中, 引脚 B5 ~ B8、A5 ~ A8 用于接收录制电路的录制信号, 引脚 B1 ~ B4、A1 ~ A4 用于接收实时播放的视频信号。

[0257] 请参阅图 57, 其为显示驱动芯片的视频输出端口的局部放大图。所述视频输出端口 603 包括 12 组引脚, 分别与数据输出器连接, 用于输出回放视频信号和实时视频信号。

[0258] 以下对本实用新型的视频采集处理电路的工作过程进行描述 :

[0259] S11 : 将对该视频采集芯片、图像处理芯片、信号转换芯片和图像增强芯片的外部端口依照上述的要求进行电路接入 ;

[0260] S12 : 当视频采集芯片通电时, 先通过该倍频器将输入电压频率进行倍增调节, 以适应当前的工作频率 ;

[0261] S13 : 所述控制器 11 发送触发信号至驱动器 12, 由驱动器 12 驱动感光器 13 工作 ;

[0262] S14 : 当光线照射到感光器 13 上时, 由该感光器 13 将光信号转换为电信号, 并传输至取样器 14 ;

[0263] S15 : 当取样器 14 接收来自感光器 13 的电信号时, 对该电信号进行取样处理, 并将处理完的电信号发送至输出器 15 ;

[0264] S16 : 最后通过所述输出器 15 将该电信号转换为数字信号, 并进行输出至图像处

理芯片 30。

[0265] S17 :所述数据接收器 21 接收外部的图像数据；

[0266] S8 :所述图像处理器 23 对图像进行处理。具体分别通过所述镜头阴影补偿电路 231 将镜头产生的阴影进行补偿处理；通过所述光学探测电路 232 和闪烁探测电路 233 探测图像的亮度和闪烁情况，并将探测结果发送至曝光增益电路；接着由所述曝光增益电路 234 增加曝光增益大小。最后再通过所述白平衡固定电路 35 根据预设的参数，进行白平衡的固定调整。

[0267] S19 :所述数据输出器 24 将处理后的图像数据进行输出至第一信号转换芯片 31。

[0268] S20 :所述第一信号转换芯片的数据读取器 312 接收图像处理芯片输出的 bt1120 传输信号，并发送至信号格式转换器；

[0269] S21 :所述信号格式转换器 313 将 bt1120 视频信号转换为 lvds 的视频信号，并发送至串行器 314；

[0270] S22 :所述串行器 314 将并行数据转换为串行数据，并发送至数据输出器；

[0271] S23 :所述数据输出器 315，用于将 lvds 信号数据输出至第二信号转换芯片。

[0272] S24 :由第二信号转换芯片内的数据读取器 322 将第一信号转换芯片的 lvds 视频传输信号，并发送至信号格式转换器；

[0273] S25 :所述信号格式转换器 323 将 lvds 视频信号转换为 bt1120 的视频信号，并发送至并行器；

[0274] S26 :所述并行器 324 将串行数据转换为并行数据，并发送至数据输出器；

[0275] S27 :所述数据输出器 325 将 bt1120 视频信号数据输出至图像增强芯片 40。

[0276] S28 :由图像增强芯片 40 的数据接收器 41 接收外部的图像数据；

[0277] S29 :所述数据接收器 41，接收图像数据信号，并发送至降噪处理器 42；

[0278] S30 :所述降噪处理器 42 进行降噪处理，再转发至动态存储器 43。

[0279] S31 :所述动态存储器 43 在接收到降噪处理器 42 处理后的图像数据后，再转发至图像增强器 44。

[0280] S32 :所述图像增强器 44，其包括一图像边缘增强电路；所述图像边缘增强电路增强图像边缘的清晰度。所述图像增强器先将处理后的图像数据发送至所述像素自适应校对器 45。

[0281] S33 :所述像素自适应校对器 45 进行像素适应校对，再发送至数据输出器 46。

[0282] S34 :所述数据输出器 46 将处理后的图像数据分别输出至视频录制芯片 50 和显示驱动芯片 60。

[0283] S35 :由视频录制芯片 50 的所述数据接收器 51 于接收外部的视频信号，并发送至图像处理器 52；

[0284] S36 :所述图像处理器 52 接收数据接收器发送的视频进行，并对视频图像进行处理，再发送至视频编码器 53；其中，所述图像处理器包括用于增强图像边缘的清晰度的边缘增强电路和用于消除信号干扰的消除噪音干扰电路。

[0285] S37 :所述视频编码器 53 对视频信号进行编码录制；

[0286] S38 :当接收到外部通讯命令时，所述视频解码器 54 对视频信号进行解码回放，并发送至数据输出器 55；

- [0287] S39 :所述数据输出器 55 对视频信号进行输出至显示驱动芯片 60。

- [0288] S40 :所述显示驱动芯片的模拟信号接收器 61 接收模拟信号,并发送至模数转换器 63 ;

- [0289] S41 :所述数据信号接收器 62 接收数据信号,并发送至复用器 64 ;

- [0290] S42 :所述模数转换器 63 将模拟信号转换为数据信号,并发送至复用器 64 ;

- [0291] S43 :所述复用器 64 将两路信号进行整合,并进行输出至输出图像边缘平滑处理器 65 ;

- [0292] S44 :所述图像边缘平滑处理器 65 接收复位器的信号,并对视频图像的边缘进行平滑处理,再发送至格式转换器 69。

- [0293] S45 :所述视频解码器 66 将模拟信号接收器接收的模拟信号进行解码,并发送至场逆程数据处理器 67 ;

- [0294] S46 :所述场逆程数据处理器 67,用于将解码后的模拟信号插入数据行,并发送至所述存储器 68 进行存储 ;

- [0295] S47 :所述存储器 68 存储经场逆程数据处理器处理后的数据,并发送至输出格式转换器 69。

- [0296] S48 :所述输出格式转换器 69,用于将信号格式进行转换,并输出至数据输出器 610 ;

- [0297] S49 :所述数据输出器 610 同时进行色彩输出和 1vds 视频信号输出。

- [0298] 相比于现有技术,本实用新型通过在镜头部分增加一图像处理芯片,对采集的图像进行处理,在主机后台上增加一图像增强芯片,进行二级图像增强,使最后输出的图像更加清晰。

- [0299] 首先,在图像处理芯片中划分为多个功能模块,分别并由各个功能模块独立协调工作,能够实现低功耗、低照度,以及可以是输出的画面更加高清。同时,进一步在该图像处理器中设置一白平衡固定电路,用于将该白平衡参数进行固定,无需在工作时进行白平衡的调节,从而防止出现色差干扰的现象。

- [0300] 然后,在图像增强芯片中也划分为多个功能模块,分别并由各个功能模块独立协调工作,能够实现对图像的增强处理。同时,进一步在该图像增强器中设置一图像边缘增强电路,用以增强图像边缘的清晰度。

- [0301] 另外,为了提高信号传输的稳定性,本实用新型通过先将 bt1120 信号转换为 1vds 信号,从而稳定的传输,并具有低噪声能力。然后,在将 1vds 信号还原为 bt1120 信号,从而保证了后续播放的画面的质量。

- [0302] 本实用新型并不局限于上述实施方式,如果对本实用新型的各种改动或变形不脱离本实用新型的精神和范围,倘若这些改动和变形属于本实用新型的权利要求和等同技术范围之内,则本实用新型也意图包含这些改动和变形。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13

图 14

图 15

图 16

图 17

图 18

图 19

|           |                 |

|-----------|-----------------|

| GPIO56~65 |                 |

| COUT0     | D10 NP_CD00     |

| COUT1     | D9 NP_CD01      |

| COUT2     | C12 NP_CD02     |

| COUT3     | C11 NP_CD03     |

| COUT4     | C10 NP_CD04     |

| COUT5     | C9 NP_CD05      |

| COUT6     | B12 NP_CD06     |

| COUT7     | B11 NP_CD07     |

| COUT8     | B10 NP_CD08     |

| COUT9     | B9 NP_CD09      |

| GPIO46~55 |                 |

| YOUT0     | G11 NP_YD00     |

| YOUT1     | F12 NP_YD01     |

| YOUT2     | F11 NP_YD02     |

| YOUT3     | F10 NP_YD03     |

| YOUT4     | E12 NP_YD04     |

| YOUT5     | E11 NP_YD05     |

| YOUT6     | E10 NP_YD06     |

| YOUT7     | E9 NP_YD07      |

| YOUT8     | D12 NP_YD08     |

| YOUT9     | D11 NP_YD09     |

| VSYNC_O   | H11 R3 OR NP_VD |

| HSYNC_O   | G12 R4 OR NP_HD |

| ACT_O     | H12 NP_HACT     |

图 20

图 21

图 22

图 23

图 24

图 25

图 26

图 27

图 28

图 29

图 30

图 31

图 32

图 33

图 34

图 35

图 36

图 37

图 38

图 39

图 40

图 41

|    |     |                |

|----|-----|----------------|

| C0 | UI3 | D_IN16/GPIO_24 |

| C1 | UI4 | D_IN17/GPIO_25 |

| C2 | T11 | D_IN18/GPIO_26 |

| C3 | T12 | D_IN19/GPIO_27 |

| C4 | T13 | D_IN20/GPIO_28 |

| C5 | T14 | D_IN21/GPIO_29 |

| C6 | R11 | D_IN22/GPIO_30 |

| C7 | R12 | D_IN23/GPIO_31 |

| C8 | R13 | D_IN24/GPIO_32 |

| C9 | R14 | D_IN25/GPIO_33 |

| Y0 | PI1 | D_IN26         |

| Y1 | PI2 | D_IN27         |

| Y2 | PI3 | D_IN28         |

| Y3 | PI4 | D_IN29         |

| Y4 | NI1 | D_IN30         |

| Y5 | NI2 | D_IN31         |

| Y6 | NI3 | D_IN32         |

| Y7 | MI2 | D_IN33         |

| Y8 | MI3 | D_IN34         |

| Y9 | MI4 | D_IN35         |

图 42

图 43a

图 43b

图 44

图 45

图 46

图 47

图 48

图 49

图 50

图 51

图 52

图 53

图 54

图 55

|            |    |                          |

|------------|----|--------------------------|

| HDMI_ARX2+ | B5 |                          |

| HDMI_ARX2- | A6 | HDMI_ARX2P<br>HDMI_ARX2N |

| HDMI_ARX1+ | B6 |                          |

| HDMI_ARX1- | A6 | HDMI_ARX1P<br>HDMI_ARX1N |

| HDMI_ARX0+ | B7 |                          |

| HDMI_ARX0- | A7 | HDMI_ARX0P<br>HDMI_ARX0N |

| HDMI_ARXC+ | B8 |                          |

| HDMI_ARXC- | A8 | HDMI_ARXCP<br>HDMI_ARXCN |

| HDMI_BRX2+ | B1 |                          |

| HDMI_BRX2- | A1 | HDMI_BRX2P<br>HDMI_BRX2N |

| HDMI_BRX1+ | B2 |                          |

| HDMI_BRX1- | A2 | HDMI_BRX1P<br>HDMI_BRX1N |

| HDMI_BRX0+ | B3 |                          |

| HDMI_BRX0- | A3 | HDMI_BRX0P<br>HDMI_BRX0N |

| HDMI_BRXC+ | B4 |                          |

| HDMI_BRXC- | A4 | HDMI_BRXCP<br>HDMI_BRXCN |

图 56

|             |      |             |

|-------------|------|-------------|

| LVDS_O_CH0P | AA18 | LVDS_O_CH0+ |

| LVDS_O_CH0N | Y18  | LVDS_O_CH0- |

| LVDS_O_CH1P | AC18 | LVDS_O_CH1+ |

| LVDS_O_CH1N | AB18 | LVDS_O_CH1- |

| LVDS_O_CH2P | AA17 | LVDS_O_CH2+ |

| LVDS_O_CH2N | Y17  | LVDS_O_CH2- |

| LVDS_O_CH3P | AC17 | LVDS_O_CH3+ |

| LVDS_O_CH3N | AB17 | LVDS_O_CH3- |

| LVDS_O_CH4P | AC16 | LVDS_O_CH4+ |

| LVDS_O_CH4N | AB16 | LVDS_O_CH4- |

| LVDS_O_CLKP | AA16 | LVDS_O_CLK+ |

| LVDS_O_CLKN | Y16  | LVDS_O_CLK- |

| LVDS_E_CH0P | Y15  | LVDS_E_CH0+ |

| LVDS_E_CH0N | W15  | LVDS_E_CH0- |

| LVDS_E_CH1P | AB15 | LVDS_E_CH1+ |

| LVDS_E_CH1N | AA15 | LVDS_E_CH1- |

| LVDS_E_CH2P | AC14 | LVDS_E_CH2+ |

| LVDS_E_CH2N | AC15 | LVDS_E_CH2- |

| LVDS_E_CH3P | AB14 | LVDS_E_CH3+ |

| LVDS_E_CH3N | AA14 | LVDS_E_CH3- |

| LVDS_E_CH4P | AC13 | LVDS_E_CH4+ |

| LVDS_E_CH4N | AB13 | LVDS_E_CH4- |

| LVDS_E_CLKP | Y14  | LVDS_E_CLK+ |

| LVDS_E_CLKN | W14  | LVDS_E_CLK- |

图 57

|                |                                       |                      |            |

|----------------|---------------------------------------|----------------------|------------|

| 专利名称(译)        | 一种医用内窥镜的视频采集处理、视频录制及显示电路              |                      |            |

| 公开(公告)号        | <a href="#">CN204906507U</a>          | 公开(公告)日              | 2015-12-23 |

| 申请号            | CN201520474499.X                      | 申请日                  | 2015-06-30 |

| [标]申请(专利权)人(译) | 广东实联医疗器械有限公司                          |                      |            |

| 申请(专利权)人(译)    | 广东实联医疗器械有限公司                          |                      |            |

| 当前申请(专利权)人(译)  | 广东实联医疗器械有限公司                          |                      |            |

| [标]发明人         | 陈锦棋                                   |                      |            |

| 发明人            | 陈锦棋                                   |                      |            |

| IPC分类号         | H04N5/225 H04N7/18 A61B1/045 A61B1/05 |                      |            |

| 代理人(译)         | 华辉<br>张奇洲                             |                      |            |

| 外部链接           | <a href="#">Espacenet</a>             | <a href="#">Sipo</a> |            |

### 摘要(译)

本实用新型涉及一种医用内窥镜的视频采集处理、视频录制及显示电路，包括视频采集芯片、图像处理芯片、信号转换芯片、图像增强芯片、视频录制芯片和显示驱动芯片；所述视频采集芯片将采集后的视频数据发送至图像处理芯片进行处理；所述信号转换芯片包括第一信号转换芯片和第二信号转换芯片；所述图像处理芯片将处理后的图像信号发送至第一信号转换芯片，并由该第一信号转换芯片发送至第二信号转换芯片；所述第二信号转换芯片将信号转换后发送至图像增强芯片；所述图像增强芯片将接收的视频图像进行增强处理，并同时发送至视频录制芯片和显示驱动芯片，由该视频录制芯片进行录制，由该显示驱动芯片进行实时播放。