US008469893B2

# (12) United States Patent Chiang et al.

#### 54) PORTABLE ULTRASOUND IMAGING SYSTEM

(75) Inventors: Alice Chiang, Weston, MA (US); Steven R. Broadstone, Woburn, MA (US)

(73) Assignee: Teratech Corp., Burlington, MA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 1026 days.

(21) Appl. No.: 12/008,098

(22) Filed: Jan. 8, 2008

(65) **Prior Publication Data**

US 2008/0300490 A1 Dec. 4, 2008

#### Related U.S. Application Data

(60) Division of application No. 09/619,123, filed on Jul. 19, 2000, now Pat. No. 7,500,952, which is a continuation-in-part of application No. 09/123,991, filed on Jul. 28, 1998, now Pat. No. 6,106,472, which is a continuation of application No. 08/971,938, filed on Nov. 17, 1997, now Pat. No. 5,957,846, which is a continuation of application No. PCT/US96/11166, filed on Jun. 28, 1996, now Pat. No. 5,964,709, which is a continuation-in-part of application No. 08/599,816, filed on Feb. 12, 1996, now Pat. No. 5,690,114, which is a continuation-in-part of application No. 08/496,804, filed on Jun. 29, 1995, now Pat. No. 5,590,658.

(51) Int. Cl. *A61B 8/14*

(2006.01)

(52) U.S. Cl.

(58) Field of Classification Search

USPC ...... 600/459, 437, 440, 441, 444, 446,

#### (10) Patent No.: U

US 8,469,893 B2

(45) Date of Patent:

Jun. 25, 2013

600/447, 453, 457; 348/77, 163, 198, 442, 348/572, 726

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 3,626,417 A | 12/1971 | Gilbert         |

|-------------|---------|-----------------|

| 3,742,947 A | 7/1973  | Hashem          |

| 3,964,296 A | 6/1976  | Matzuk          |

| 3,965,296 A | 6/1976  | Miller          |

| 4,058,003 A | 11/1977 | Macovski        |

| 4,080,838 A | 3/1978  | Kuroda et al.   |

| 4,110,835 A | 8/1978  | Dubil et al.    |

| 4,127,034 A | 11/1978 | Lederman et al. |

|             |         |                 |

(Continued)

#### FOREIGN PATENT DOCUMENTS

DE 42 41 712 6/1993 DE 43 02 538 4/1994

(Continued)

#### OTHER PUBLICATIONS

Mustafa Karaman; "A VLSI Receive Beamformer for Digital Ultrasound Imaging"; IEEE; (1992); V-657-V-660.

#### (Continued)

Primary Examiner — Unsu Jung

Assistant Examiner — Daniel Huntley

(74) Attorney, Agent, or Firm — McCarter & English, LLP

#### (57) ABSTRACT

A portable ultrasound imaging system includes a scan head coupled by a cable to a portable battery-powered data processor and display unit. The scan head enclosure houses an array of ultrasonic transducers and the circuitry associated therewith, including pulse synchronizer circuitry used in the transmit mode for transmission of ultrasonic pulses and beam forming circuitry used in the receive mode to dynamically focus reflected ultrasonic signals returning from the region of interest being imaged.

#### 47 Claims, 36 Drawing Sheets

### US 8,469,893 B2

Page 2

| II C DATENT                                | DOCLD CENTER                                 | 5 412 105              |                         | F                                 |

|--------------------------------------------|----------------------------------------------|------------------------|-------------------------|-----------------------------------|

| U.S. PATENT                                | DOCUMENTS                                    | 5,413,105<br>5,414,803 |                         | Forestieri<br>Malzbender          |

|                                            | Maslak                                       | 5,417,217              |                         | Morita et al.                     |

|                                            | Shott et al.                                 | 5,419,330              |                         | Nishigaki et al.                  |

|                                            | Engeler<br>Pridham et al.                    | 5,423,086              | A 6/1995                | Cannon et al.                     |

|                                            | McKeighen et al.                             | 5,435,313              |                         | Noda et al.                       |

|                                            | Thomas                                       | 5,437,281<br>5,438,994 |                         | Lin et al.<br>Starosta et al.     |

|                                            | Thomenius et al.                             | 5,450,851              |                         | Hancock                           |

|                                            | Pridham                                      | 5,456,257              |                         |                                   |

| 4,227,417 A 10/1980<br>4,267,584 A 5/1981  | McKeighen et al.                             | 5,460,180              |                         | Klepper et al.                    |

|                                            | Gilmour                                      | 5,462,057              |                         | Hunt et al.                       |

| 4,288,764 A 9/1981                         |                                              | 5,465,011              |                         |                                   |

| 4,386,528 A 6/1983                         | Engle                                        | 5,465,720<br>5,483,963 |                         | Kurzynski et al.<br>Butler et al. |

| 4,386,529 A 6/1983                         |                                              | 5,515,341              |                         |                                   |

|                                            | Brandestini<br>McKeighen et al.              | 5,517,994              |                         | Burke et al.                      |

|                                            | Durley, III                                  | 5,520,187              |                         | Snyder                            |

|                                            | Burke et al.                                 | 5,522,391              |                         | Beaudin et al.                    |

|                                            | Chiang                                       | 5,528,302<br>5,538,004 |                         | Basoglu et al.<br>Bamber          |

|                                            | Wilson et al.                                | 5,544,128              |                         | Kim et al.                        |

|                                            | Cimilluca                                    | 5,544,654              |                         | Murphy et al.                     |

| 4,542,653 A 9/1985                         | Liu<br>Lizzi et al.                          | 5,546,807              | A 8/1996                | Oxaal et al.                      |

| 4,561,019 A 12/1985<br>4,561,308 A 12/1985 |                                              | 5,549,111              |                         | Wright et al.                     |

| -,,                                        | Riley et al.                                 | 5,551,433              |                         | Wright et al.                     |

|                                            | Hiller et al.                                | 5,551,434              |                         | Iinuma<br>Maslak et al.           |

| 4,663,973 A 5/1987                         |                                              | 5,555,534<br>5,588,435 |                         | Weng et al.                       |

|                                            | Maslak et al.                                | 5,590,658              |                         | Chiang et al.                     |

|                                            | Moeller et al.                               | 5,603,323              |                         | Pflugrath et al.                  |

|                                            | Saugeon<br>O'Donnell et al.                  | 5,617,864              |                         |                                   |

|                                            | Ikeda et al.                                 | 5,623,930              |                         | Wright et al.                     |

|                                            | Chiang                                       | 5,628,321<br>5,634,465 |                         | Scheib et al.                     |

| 5,063,541 A 11/1991                        | Kondo et al.                                 | 5,640,960              |                         | Schmiesing et al.<br>Jones et al. |

|                                            | Chiang                                       | 5,642,732              |                         |                                   |

|                                            | Uchiumi et al.                               | 5,655,535              |                         | Friemel et al.                    |

|                                            | Harrison, Jr. et al.<br>Harrison, Jr. et al. | 5,655,536              |                         | Takamizawa                        |

|                                            | Daigle                                       | 5,690,114              |                         | Chiang et al.                     |

|                                            | Chiang                                       | 5,697,372<br>5,709,209 | A 12/1997               | Hughes<br>Friemel et al.          |

|                                            | Daigle                                       | 5,722,412              |                         | Pflugrath et al.                  |

|                                            | Hirama                                       | 5,724,974              |                         | Goodsell, Jr. et al.              |

|                                            | O'Donnell<br>Ishizuka                        | 5,732,705              |                         | Yokoyama et al.                   |

|                                            | Yamazaki et al.                              | 5,763,785              |                         | Chiang                            |

|                                            | Kumazawa                                     | 5,782,769<br>5,785,655 |                         | Hwang et al.                      |

| 5,173,837 A 12/1992                        | Blackwell et al.                             | 5,785,035              |                         | Goodsell, Jr. et al.<br>Daigle    |

|                                            | Mallart                                      | 5,817,024              |                         | Ogle et al.                       |

|                                            | Peterson et al.                              | 5,839,442              | A 11/1998               | Chiang et al.                     |

|                                            | Langberg<br>Noujaim et al.                   | 5,893,363              |                         | Little et al.                     |

|                                            | Larson, III                                  | 5,921,932<br>5,957,846 |                         | Wright et al.                     |

|                                            | Rhyne                                        | 5,964,709              |                         | Chiang et al.<br>Chiang et al.    |

|                                            | O'Donnell                                    | 6,106,472              | A 8/2000                | Chiang et al.                     |

|                                            | Iida et al.                                  | 6,135,961              | A 10/2000               | Pflugrath et al.                  |

|                                            | Karp et al.<br>Kitney et al.                 | 6,416,475              | B1 7/2002               | Hwang et al.                      |

|                                            | Fife et al.                                  | 7,500,952              |                         | Chiang et al.                     |

| 5,287,753 A 2/1994                         | Routh et al.                                 | 8,241,217              |                         | Chiang et al.                     |

|                                            | Noponen                                      | 2008/0294046           |                         | Chiang et al.                     |

| 5,295,485 A 3/1994                         |                                              | 2009/0112091           | A1 4/2009               | Chiang et al.                     |

| 5,322,068 A 6/1994<br>5,343,864 A 9/1994   | Thiele et al.                                | FC                     | REIGN PATE              | NT DOCUMENTS                      |

|                                            | Sugiyama<br>Lipschutz                        | EP                     | 0430450 A2              | 6/1991                            |

|                                            | Engeler et al.                               | EP                     | 0 585 070               | 3/1994                            |

| 5,357,962 A 10/1994                        |                                              | EP                     | 0 627 635               | 12/1994                           |

| 5,360,005 A 11/1994                        |                                              | EP                     | 1 016 875               | 5/2000                            |

|                                            | Peterson                                     | GB                     | 2 219 089               | 11/1989                           |

|                                            | Eberle et al.<br>Fukukita et al.             | JP<br>JP               | 55-158706<br>55151952 A | 11/1980<br>11/1980                |

| 5,373,317 A 12/1994                        |                                              | JP<br>JP               | 57-175352 A             | 10/1982                           |

|                                            | Nordgren et al.                              | JP                     | 62227326 A              | 10/1987                           |

| 5,386,830 A 2/1995                         | Powers et al.                                | JP                     | 63-309246               | 12/1988                           |

|                                            | Kim et al.                                   | JP                     | 3-206986                | 9/1991                            |

|                                            | Robinson et al.                              | JP                     | 3234246 A               | 10/1991                           |

|                                            | Lewis et al.<br>Hedberg et al.               | JP<br>JP               | 4-314437<br>5-103397    | 11/1992<br>4/1993                 |

|                                            | Gruner et al.                                | JP<br>JP               | 05228141 A              | 9/1993                            |

| 5,102,755 71 7/1995                        | Cranor et ai.                                | **                     | JUDEOLII II             | J. 1220                           |

| 7051270 A    | 2/1995                                                                                 |

|--------------|----------------------------------------------------------------------------------------|

| 7079981 A    | 3/1995                                                                                 |

| 07116163 A   | 5/1995                                                                                 |

| 7124160 A    | 5/1995                                                                                 |

| 7222744 A    | 8/1995                                                                                 |

| 8038473 A    | 2/1996                                                                                 |

| 8112279 A    | 5/1996                                                                                 |

| 8117227 A    | 5/1996                                                                                 |

| 8505556      | 6/1996                                                                                 |

| 8173431 A    | 7/1996                                                                                 |

| 8224237 A    | 9/1996                                                                                 |

| WO-9624053 A | 1 8/1996                                                                               |

|              | 07116163 A<br>7124160 A<br>7222744 A<br>8038473 A<br>8112279 A<br>8117227 A<br>8505556 |

#### OTHER PUBLICATIONS

O'Donnell, M.; "Real-Time Phased Array Imaging Using Digital Beam Forming and Autonomous Channel Control"; IEEE Ultrasonic Symposium; (1990); 1499-1502.

Hatfield, J.V.; "Transmit and Receive ASICs for an Ultrasound Imaging Multi-Element Array Transducer"; The Institution of Electrical Engineers; (1994); Jun. 1-Jun. 5; IEE Savoy Place, London.

Schwarz, et al.; "Experience rounding with a hand-held two-dimensional cardiac ultrasound device"; The American Journal of Cardiology; (1988); 157-159.

Smith, et al.; "Two-dimensional arrays for medical ultrasound"; Ultrasonic Imaging 14; (1992); 213-233.

Roelandt, et al.; "The ultrasound cardioscope: A hand-held scanner for real-time cardiac imaging"; Clin. Ultrasound; (1980); 8(3): 221-225

Shattuck, et al.; "Explososcan: A parallel processing technique for high speed ultrasound imaging with linear phrased arrays"; J. Acoust. Soc. Am.; (1984); 75(4).

Von Ramm, et al.; "High-speed ultrasound volumetric imaging sys-

Von Ramm, et al.; "High-speed ultrasound volumetric imaging system—Part II: Parallel processing and image display"; IEEE Transactions on ultrasonics, ferroelectrics and frequency control; (1991); 38(2).

Sasaki, K., et al.; "A 7-ns 140 mW 1-Mb CMOS SRAM with Current Sense Amplifer"; IEEE Journal of Solid State Circuits; (1992); 27(11): 1511-1518.

Scales, N.R., et al.; "A programmable Multi-Channel CMOS Pulser Chip to Drive Ultrasonic array Transducers"; IEEE Journal of Solid State Circuits; (1994); 29(8): 992-994.

Kerr, S., et al. "Session VI: Integrated signal-Processing Subsystems: A Mixed Analog-Digital Chip for a Phased-Array Signal Processor"; (1988); IEEE International Solid-State Circuits Conference, Feb. 17-19, 1988, Digest of Technical Papers, pp. 58-59 & 296.

O'Donnell, M. "Applications of VLSI Circuits to Medial Imaging"; Proceedings of the IEEE; (1988); 76(9): 1106-1114.

Karaman, M. and O'Donnell, M.; "Synthetic Aperture Imaging for Small Scale systems"; IEEE Transactions on Ultrasonics, Ferroelectrics and Frequency Control; (1995); 42(3): 429-442.

Minivisor Service Manual; Organon Teknika (Sep. 1979).

Daft, C.M.W. and Engeler, W.E.; "Windowing of Wide-Band Ultrasound Transducers"; IEEE Ultrasonic Symposium; (1996); 1541-1544.

ARPA/ONR Medical Ultrasonic Imaging Technology Workshop, Presentation Abstracts, Office of Naval Research, Lansdown, Virginia, Jan. 24-26, 1995.

FIG. 27

FIG. 29A

FIG. 29B

FIG. 31

FIG. 34

FIG. 35

FIG. 36

FIG. 38

1

## PORTABLE ULTRASOUND IMAGING SYSTEM

### CROSS REFERENCE TO RELATED APPLICATIONS

This application is a divisional of U.S. application Ser. No. 09/619,123 filed Jul. 19, 2000, now U.S. Pat. No. 7,500,952, which is a continuation-in-part of U.S. application Ser. No. 09/123,991 filed Jul. 28, 1998, now U.S. Pat. No. 6,106,472, which is a continuation of U.S. application Ser. No. 08/971, 938 filed Nov. 17, 1997, now U.S. Pat. No. 5,957,846, which is a continuation of PCT/US96/11166 filed Jun. 28, 1996, now U.S. Pat. No. 5,964,709, which is a continuation-in-part of U.S. application Ser. No. 08/599,816 filed Feb. 12, 1996, 15 now U.S. Pat. No. 5,690,114, which is a continuation-in-part of U.S. application No. 08/496,804 filed Jun. 29, 1995, now U.S. Pat. No. 5,590,658. The entire content of the above applications are being incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

Typical conventional ultrasound systems can have transducer arrays which consist of 128 ultrasonic transducers. Each of the transducers is associated with its own processing circuitry located in the console processing unit. The processing circuitry typically includes driver circuits which, in the transmit mode, send precisely timed drive pulses to the transducer to initiate transmission of the ultrasonic signal. These transmit timing pulses are forwarded from the console processing unit along the cable to the scan head. In the receive mode, beam forming circuits of the processing circuitry introduce the appropriate delay into each low-level electrical signal from the transducers to dynamically focus the signals such that an accurate image can subsequently be generated.

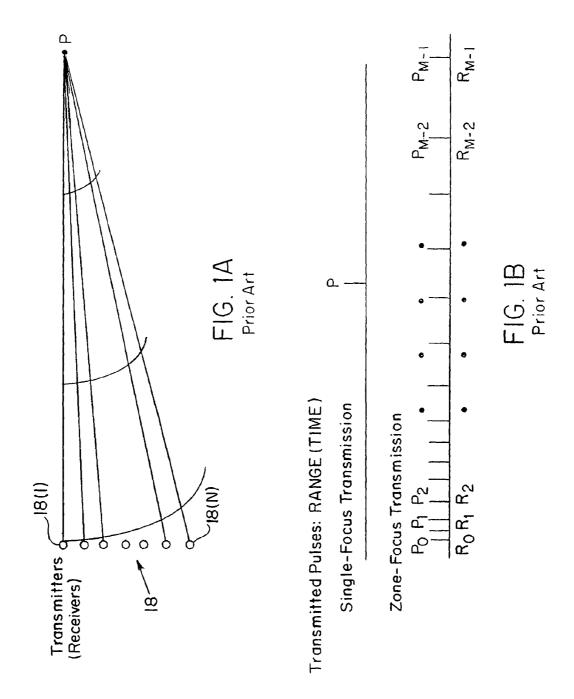

A schematic block diagram of an imaging array 18 of N piezoelectric ultrasonic transducers 18(1)-18(N) as used in an ultrasound imaging system is shown in FIG. 1A. The array of piezoelectric transducer elements 18(1)-18(N) generate acoustic pulses which propagate into the image target (typically a region of human tissue) or transmitting media with a narrow beam. The pulses propagate as a spherical wave with a constant velocity. Acoustic echoes in the form of returning signals from image points P or reflectors are detected by the same array 18 of transducer elements or another receiving 45 array and can be displayed in a fashion to indicate the location of the reflecting structure P.

The acoustic echo from the point P in the transmitting media reaches each transducer element **18(1)-18(N)** of the receiving array after various propagation times. The propagation time for each transducer element is different and depends on the distance between each transducer element and the point P. This holds true for typical ultrasound transmitting media, i.e. soft bodily tissue, where the velocity of sound is assumed (or relatively) constant. Thereafter, the received 55 information is displayed in a manner to indicate the location of the reflecting structure.

In two-dimensional B-mode scanning, the pulses can be transmitted along a number of lines-of-sight as shown in FIG. 1A. If the echoes are sampled and their amplitudes are coded 60 as brightness, a grey scale image can be displayed on a CRT. An image typically contains 128 such scanned lines at  $0.75^{\circ}$  angular spacing, forming a 900 sector image. Since the velocity of sound in water is  $1.54 \times 10^{5}$  cm/sec, the round-trip time to a depth of 16 cm will be  $208/\mu s$ . Thus, the total time 65 required to acquire data along 128 lines of sight (for one image) is 26.6 ms. If other signal processors in the system are

2

fast enough to keep up with this data acquisition rate, twodimensional images can be produced at rates corresponding to standard television video. For example, if the ultrasound imager is used to view reflected or back scattered sound waves through the chest wall between a pair of ribs, the heart pumping can be imaged in real time.

The ultrasonic transmitter is typically a linear array of piezoelectric transducers 18(1)-18(N) (typically spaced half-wavelength apart) for steered arrays whose elevation pattern is fixed and whose azimuth pattern is controlled primarily by delay steering. The radiating (azimuth) beam pattern of a conventional array is controlled primarily by applying delayed transmitting pulses to each transducer element 18(1)-18(N) in such a manner that the energy from all the transmitters summed together at the image point P produce a desired beam shape. Therefore, a time delay circuit is needed in association with each transducer element 18(1)-18(N) for producing the desired transmitted radiation pattern along the predetermined direction.

For a given azimuth angle, as can be seen in FIG. 1B, there can be two different transmitting patterns: a "single-focus" and a "zone-focus" pattern. The single-focus method employs a single pulse focused at mid-range of the image line along a particular line of sight. In a single pulse mode, the azimuth focus depth can be electronically varied, but remains constant for any predetermined direction. In zone-focus operation, multiple pulses, each focused at a different depth (zone), are transmitted along each line of sight or direction. For multiple pulse operation, the array of transmitters is focused at M focal zones along each scan direction, i.e., a series of M pulses is generated  $P_0, P_1, \ldots, P_{M-1}$ , each pulse being focused at its corresponding range  $R_0, R_1, \ldots, R_{M-1}$ , respectively.

The pulses are generated in a repeated sequence so that, after start up, every Mth pulse either begins a look down a new direction or corresponds to the initial pulse  $P_o$  to repeat the series of looks down the present direction. For the zone-focused mode, a programmable time-delay circuit is needed in association with each transducer element to produce beam patterns focused at different focal zones.

As previously described, the same array 18 of transducer elements 18(1)-18(N) can be used for receiving the return signals. The reflected or echoed beam energy waveform originating at the image point reaches each transducer element after a time delay equal to the distance from the image point to the transducer element divided by the assumed constant speed of the waveform of signals in the media. Similar to the transmitting mode, this time delay is different for each transducer element. At each receiving transducer element, these differences in path length should be compensated for by focusing the reflected energy at each receiver from the particular image point for any given depth. The delay at each receiving element is a function of the distance measured from the element to the center of the array and the viewing angular direction measured normal to the array. It should be noted that in ultrasound, acoustic pulses generated by each transducer are not wideband signals and should be represented in terms of both magnitude and phase.

The beam forming and focusing operations involve forming a sum of the scattered waveforms as observed by all the transducers, but in this sum, the waveforms must be differentially delayed so that they will all arrive in phase and in amplitude in the summation. Hence, a beam forming circuit is required which can apply a different delay on each channel, and vary that delay with time. Along a given direction, as

echoes return from deeper tissue, the receiving array varies its focus continually with depth. This process is known as dynamic focusing.

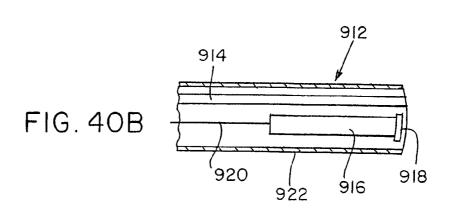

FIGS. 2A-2C show schematic block diagrams of three different conventional imaging or beam focusing techniques. 5 A non-programmable physical lens acoustic system 50 using an acoustic lens 51 is shown in FIG. 2A. In turn, dynamic focusing systems where associated signal processing electronics are employed to perform real-time time delay and phase delay focusing functions are respectively shown in FIGS. 2B and 2C. FIG. 2B shows a time delay system 52 using time delay elements 53, and FIG. 2C shows a phase delay system 54 using phase delay elements 55.

In the lensless systems of FIGS. 2B and 2C, the signal processing elements 53, 55 are needed in association with each receiving transducer element, thus defining processing channels, to provide time delay and focus incident energy from a field point to form an image. Accordingly, a beam forming circuit is required which can provide a different 20 delay on each processing channel, and to further vary that delay with time. Along a predetermined direction, as echoes return from distances further away from the array of transducer elements, the receiving array varies its focus continually with depth to perform dynamic focusing.

After the received beam is formed, it is digitized in a conventional manner. The digital representation of each received pulse is a time sequence corresponding to a scattering cross section of ultrasonic energy returning from a field point as a function of range at the azimuth formed by the beam. Successive pulses are pointed in different directions, covering a field of view from -45° to +45°. In some systems, time averaging of data from successive observations of the same point (referred to as persistence weighting) is used to improve image quality.

For example, in an ultrasound imaging system operating at a 2-5 MHz frequency range, an electronic circuit capable of providing up to 10 to 20 j·1s delay with sub-microsecond time resolution is needed for the desired exact path compensation. As shown in FIG. 2B, a delay line is inherently matched to the 40 time-delay function needed for dynamic focusing in a lensless ultrasound system.

More specifically, in an exemplary ultrasound imaging system with a 5 MHz operating frequency and an array of 128 transducer elements on half-wavelength centers, a straight-forward delay implementation requires each processing channel/transducer element to include either a 480-stage delay line with a clock period programmable with a 25 ns resolution or a 480-stage tapped delay line clocked at 40 MHz in conjunction with a programmable 480-to-one time-select switch to set the appropriate delay. There are two problems associated with these conventional techniques. First, a simple variable-speed clock generator has not been developed to date. Secondly, for an N-stage tapped delay line, the area associated with the tap select circuit is proportional to N<sup>2</sup>, 55 thus such a circuit would require a large amount of microchip area to realize an integrated tap architecture.

Due to the difficulty and complexity associated with the generation of the control circuits of the conventional approach, only a few time-delay structures could be integrated on one microchip, and therefore a large number of chips would be needed to perform a multi-element dynamic beam forming function. For these reasons, none of the prior art ultrasound imaging systems utilize the straightforward time-delay implementation. Instead, a plane-wave mixer 65 approximation is used. In this approximation process, the total delay is separated into two parts: an analog plane-wave

4

mixer technique is used to approximate the required fine delay time and a true coarsely spaced delay line is used to achieve the coarse delay time.

In accordance with the plane-wave approximation, the fine delay can be achieved by modifying the phase of AC waves received by each receiving processing channel and implemented by heterodyning the received waves from each receiving transducer element with different phases of a local oscillator, i.e., creating analog phase shifting at each processing channel. Specifically, by selecting a local oscillator with a proper phase angle of the form  $\cos(\omega_o t + \Omega_n(t))$ , where  $\Omega_n$  is chosen to satisfy the expression  $\Omega_n(t) = \omega_o(T_n(t) - T_n(t))$ ,  $T_n(t)$  is the ideal compensating delay and  $T_n(t)$  is a coarsely quantized approximation of  $T_n$ . It will be appreciated that when the mixer output is delayed by  $T_n$  the phase of one of its intermediate frequency (IF) sidebands provides phase coherence among all the processing channels.

In the conventional implementation of the aforementioned technique, a tap select is used which connects any received down-conversion mixer output to any tap on a coarsely spaced, serially connected delay line. The tap select is essentially a multiposition switch that connects its input to one of a number of output leads. One output lead is provided for each tap on the delay line. Therefore, each mixer output can be connected to a few coarsely spaced taps on a delay line, and all the tap outputs can be summed together coherently. However, for an exemplary 5 MHz operation, if a single mixer arrangement as described above is used, a delay line with delay resolution less than one microsecond is needed.

In summary, the conventional technique described heretofore involves heterodyning the received signals with an oscillator output by selecting a local oscillator frequency so as to down convert the output to an IF frequency. This down converted signal is then applied to another mixer. By selecting the proper phase angle of the second oscillator, the phase of the intermediate frequency waves produced by the second heterodyning is controlled. The output of the second mixer is then connected through a tap select to only one, or at most a few, coarsely spaced taps on a delay line during the focal scanning along each direction.

The aforementioned approximation technique is used due to the fact that given an image that is somewhat out of focus, the image can be focused in an economically feasible manner by utilizing readily available techniques such as analog mixers and RC networks. Unfortunately, the mixer approximation method suffers from image misregistration errors as well as signal loss relative to the ideally-focused (perfect delay) case.

Modem ultrasound systems require extensive complex signal processing circuitry in order to function. For example, hundreds of delay-and-sum circuits are needed for dynamic beam forming. Also, pulsed or continuous Doppler processors are needed for providing two-dimensional depth and Doppler information in color flow images, and adaptive filters are needed for clutter cancellation. Each of these applications requires more than 10,000 MOPS (million operations per second) to be implemented. Even state-of-the-art CMOS chips only offer several hundred MOPS per chip, and each chip requires a few watts of electric power. Thus, an ultrasound machine with a conventional implementation requires hundreds of chips and dissipates hundreds of watts of power. As a result, conventional systems are implemented in the standard large rack-mounted cabinets.

Another drawback in conventional ultrasound systems is that the cable connecting the scan head to the processing and display unit is required to be extremely sophisticated and, hence, expensive. Since all the beam forming circuitry is

located in the console, all of the low-level electrical signals from the ultrasonic transducers must be coupled from the scan head to the processing circuitry. Because the signals are of such a low level, they are extremely susceptible to noise, crosstalk and loss. With a typical transducer array of 128 transducers, the cable between the scan head and the processing and display console is required to contain 128 low-noise, low-crosstalk and low-loss coaxial cables. Such a cable requires expensive materials and extensive assembly time and is therefore very expensive.

## SUMMARY OF THE INVENTION

The present invention is directed to a portable ultrasound imaging system and method. The imaging system of the 15 invention includes a hand-held scan head coupled to portable processing circuitry by a cable. The scan head includes a housing which houses the array of ultrasonic transducers which transmit the ultrasonic signals into the region of interest being imaged and which receive reflected ultrasonic sig- 20 nals from the region of interest and which convert the received ultrasonic signals into electrical signals. The housing of the scan head also contains the beam forming circuitry used in the imaging system of the invention to combine the electrical signals from the ultrasonic transducers into an electronic 25 representation of the region of interest. The electronic representation of the region of interest is forwarded over an interface via the system cable to data processing and display circuitry which uses the representation to generate an image of the region of interest.

In one embodiment, the portable processing circuitry is implemented in the form of a lap-top computer which can include an integrated keyboard, a PCMCIA standard modem card for transferring image data and a flip-top flat panel display, such as an active matrix LCD. The lap-top computer, and, therefore the entire system, can be powered by a small lightweight battery. The entire system, including scan head, cable and computer is therefore very lightweight and portable. The total weight of the system preferably does not exceed ten pounds. The interior of the scan head can also 40 include a Faraday shield to shield the electronics of the scan head from interference from extraneous RF sources.

In one embodiment, the system also includes an interface unit between the scan head and the lap-top computer. Instead of being connected directly to the computer, the system cable 45 is connected to the interface unit. Another cable couples the interface unit to the computer. The interface unit performs control and signal/data processing functions not performed by the computer. This reduces the overall processing load on the computer.

In another embodiment, higher quality images are displayed on a cathode ray tube (CRT) display. In that embodiment, signals from the scan head are transferred over the cable to a processor such as a personal computer or lap-top which is in turn interfaced to the CRT display. Signals received from 55 the scan head are received by the processor, which processes the signals and generates appropriate display signals and forwards them to the CRT.

To allow implementation of the functions of the ultrasound imaging system of the invention in the scan head, much of the 60 signal processing circuitry associated with the ultrasonic transducers is integrated on small CMOS chips. For example, the beam forming circuitry used to introduce individual delays into the received ultrasonic signals can be implemented on a single chip for a 64-element array. Thus, two 65 chips are used for 128-element systems. The pulse synchronizing circuitry used to generate transducer driving pulses can

also be implemented on a chip. In addition, high voltage driver circuits used in the transmit mode to drive the transducers and preamplifying circuits and gain control circuits used in a receive mode to condition the electrical signals from the transducers can also be integrated on single chips. Also, control circuits such as multiplexer circuits for selecting signals from the transducers and other such control circuits can be formed on single chips.

In one preferred embodiment of the invention, the signal 10 processing circuitry in the scan head is implemented in lowpower, high-speed CMOS technology. The integrated circuitry can also be adapted to be operated at lower voltages than conventional circuitry. As a result, the power dissipated in the integrated circuitry and, consequently, the thermal effects caused thereby, are substantially lower than those of conventional circuits. In one embodiment, the total power dissipated in the scan head is less than two watts. This allows the temperature of the scan head to be maintained below 41° C. With such low power dissipation and temperature, the circuits can be implemented in the relatively small volume of the scan head housing without suffering any degradation in performance due to thermal effects. The patient being examined also suffers no harmful thermal effects. Also, because the system requires comparatively little power, it can be powered by a battery located in the data processor and display unit.

As discussed above, in ultrasound systems, individual delays are typically introduced into each individual transmitted ultrasonic pulse and into each signal from each transducer indicative of received reflected ultrasonic energy. These individual delays are used to ensure that the image of the region of interest is properly focused.

The form or pattern of delays introduced into each transducer element are affected by the shape of the array and the desired region scan pattern. For example, in phased arrays, different individual beam steering delays are introduced into each pulse and/or each returning signal for every scan line to produce a properly focused image of a curved region.

Linear and curve linear arrays are typically flat or curved. The arrays can be used to perform linear scanning in which a uniform pattern of delays is introduced to all the transducers. The delays are the same for each scan line. Curved arrays have different delay patterns for each scan line. The present invention is also capable of performing trapezoidal region scans.

In one embodiment, a linear array is used in a sub-aperture scanning process. For example, in this embodiment, the transducer array can include 192 adjacent transducers arranged in a line. During the sub-aperture scanning, only a small portion of the transducers, e.g., 64, are used to generate and receive signals. The transducers at opposite ends of the linear array are used to perform the phased-array scanning process to produce a curved image region at opposite ends of the overall trapezoidal-shaped scan region. Since the phased-array approach is used at the ends of the array, different delay patterns must be introduced for each individual scan line. Between the phased array portions, linear scanning is used. Consequently, during the linear scanning portion of the process, one set of delays can be used for all scan lines. Hence, the trapezoidal scanning embodiment of the invention involves a combination of phased array scanning at both ends of the region and linear scanning in the middle of the region.

In a typical ultrasound imaging system, electronic circuitry capable of providing up to 10-20-s delay with sub-microsecond time resolution is needed to provide precise signal path compensation. In one preferred embodiment of the present invention, this wide range of delays with fine resolution is provided by a dual-stage programmable tapped delay line

using CCD technology. The first stage introduces a fine delay and the second stage introduces a coarse delay. The delays are controlled by tapping clock frequencies, the fine delay being controlled by a higher clock frequency than the coarse delay. In one embodiment, the fine delay clock frequency is set at eight times the ultrasound signal frequency, and the coarse delay clock frequency is set at one-tenth the fine delay clock frequency. The clock frequencies are separately controllable to facilitate varying the ultrasound signal frequency to vary imaging depth.

Such devices are described in copending U.S. patent application Ser. No. 08/496,915, entitled, "Integrated Beam Forming and Focusing Processing Circuit for Use in an Ultrasound System," by Alice M. Chiang and copending U.S. patent application Ser. No. 08/496,463, entitled, "Integrated 15 Delay Processing Circuit," by Alice M. Chiang, both of which were filed on Jun. 29, 1995. Both patent applications are incorporated herein by reference.

In one embodiment, the frequency of the ultrasound signals is variable to allow for imaging at varying depths. This can be 20 accomplished by internal or external adjustment of transducer signal driving frequency. Alternatively, for wider variations in frequency, the system of the invention accommodates different scan heads having arrays which operate at different frequencies. Also, the scan head of the invention can be provided with a facility for changing arrays based on the desired operating frequency.

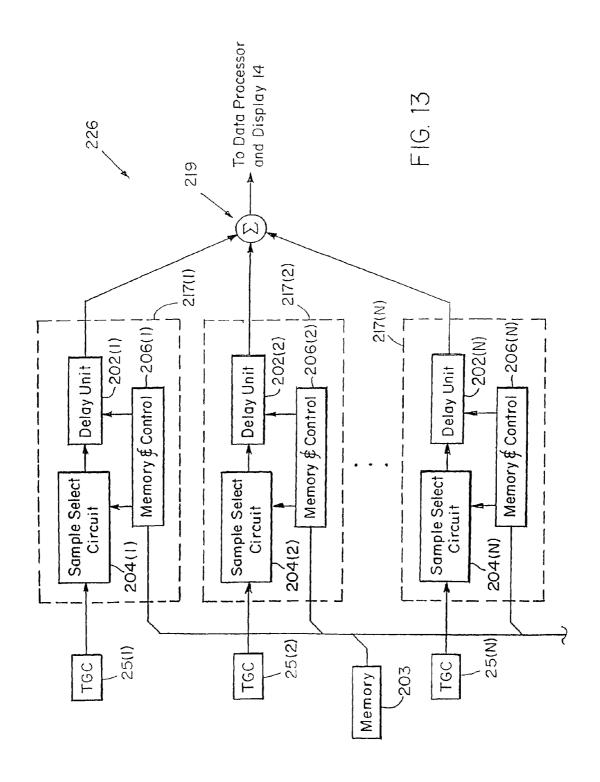

In an alternative preferred embodiment of the present invention, the delay processing circuits utilize a single charge-coupled device delay line with a programmable input 30 sampling selection circuit. The programmable input sampling selection circuit allows nonuniformly sampled imaging signals to be loaded into the programmable delay line to provide the required variable delay.

In this embodiment, each delay processing circuit includes a programmable input sampling circuit and a programmable delay unit. According to a user specified selection pattern, the programmable sampling circuit converts a continuous-time input waveform into a sequence of discrete-time analog sample data, which can be uniformly or nonuniformly 40 spaced, and which are loaded into the programmable delay unit. A control circuit is included to provide programmable delay to each selected sampled data. A summation circuit is incorporated for summing the sampled, delayed data from each of the delay units to produce a focused image.

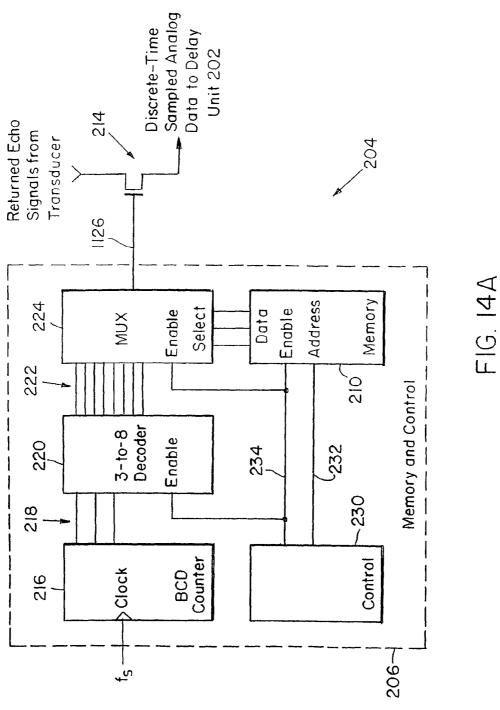

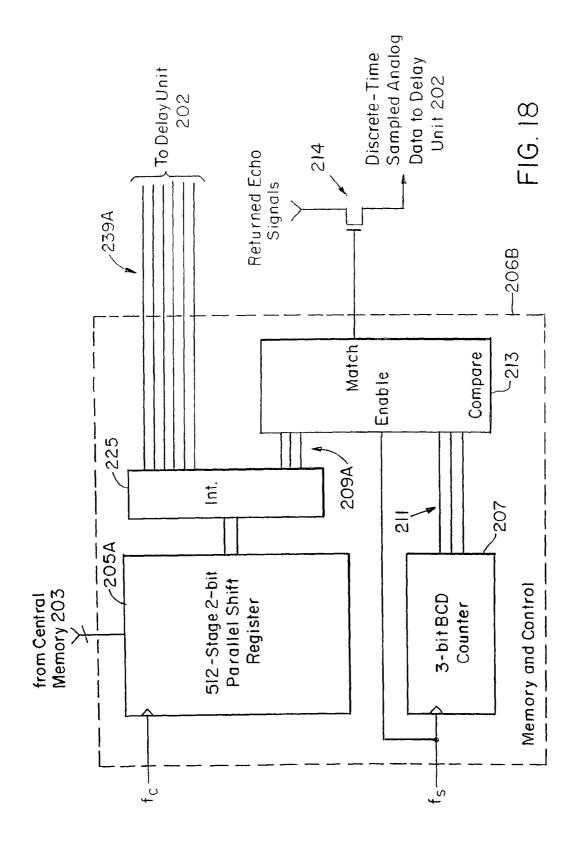

In one embodiment, the control circuit used to control the delay of each sample includes a counter and a storage circuit, which can be a shift register or a memory circuit. The shift register can be formed using CCD technology or other logic circuit technology. Before each scan line is generated, the storage circuit is loaded with a series of data values which define the delays used for each focus point along a scan line. Under control of a sampling clock, counter outputs are compared one at a time to values stored in the shift register. A matched value results in a sample being taken of the signal. 55 Hence, by storing appropriate values in the memory circuit (shift register), sample delay can be controlled.

In one embodiment, the shift register also stores a value that addresses the appropriate stage of the programmable delay line depending upon the predetermined delay for the 60 sample. Preferably, this delay tap value is stored as a series of data bits with the corresponding value used to provide sampling delay as described above. In one embodiment, the two values are combined into a single data word comprising nine data bits, three for the sample delay selection and six for the 65 delay tap selection in the delay line. In one embodiment of the invention, each scan line includes 512 focus points. Thus, the

shift register is a 512-stage 9-bit shift register. Alternatively, four bits can be used for sample delay selection and seven for the delay top selection, resulting in a 512-stage II-bit shift register being used.

In another embodiment, the 9-bit data words are compressed to permit more efficient storage of the data. In this embodiment, instead of storing each individual delay, only the differences in delay between adjacent focus points are stored. Each first difference requires fewer bits to store than does the actual absolute delay value. In another embodiment, second differences, Le., the difference between adjacent first differences, is stored at each register location. This requires even fewer bits. To process each delay, a processor of the invention reads each difference and integrates it to generate an actual delay value which is used to control both the sampling and tapping of the delay line. In the first difference embodiment, a single summing stage is used to perform the integration. In the case of second difference storage, a two-stage adder is used.

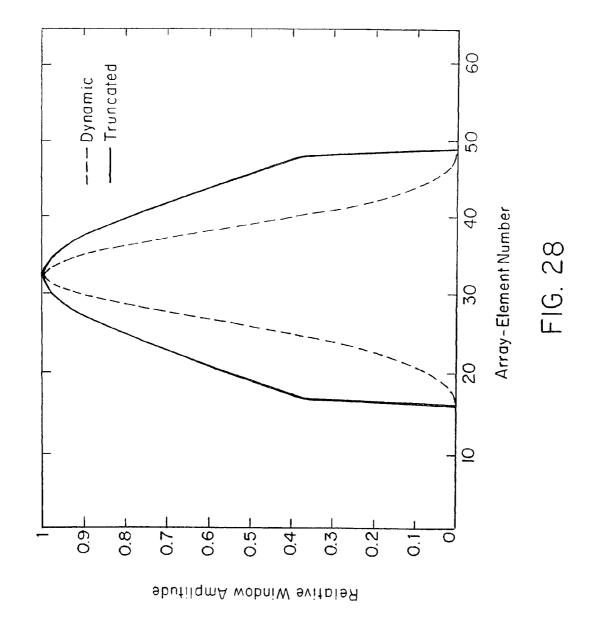

In one embodiment of the invention, a process referred to as sub-aperture scanning can be implemented. Under this process, processing circuits are shared by the transducers such that the total number of processing circuits is fewer than the number of transducer elements. For example, the array can include 128 transducer elements but only 64 processing channels. In this embodiment, a multiplexing process is used whereby only a portion of the 128 transducers, i.e., a "subaperture," is used at one time. A multiplexing circuit is used to route signals from the active transducers to the processing circuitry. In one embodiment, 64 transducers are used at once, and they are serviced by the 64 channels of processing circuitry. After image data is obtained for a first group of 64 transducers, a next group of transducers is activated to collect more data. Typically, a sliding scanning process is used in which each successive group of 64 elements slides over one element, resulting in overlapping sub-aperture scanning regions. During sub-aperture scanning, a spatial windowing process is used to reduce image clutter, i.e., energy in the image obtained through the side lobes rather than the main lobe of the array response. Either a dynamically varying spatial window or a truncated non-varying spatial window can be used. However, it has been found that the truncated window is easier to implement.

In this embodiment, to set the delays for each group of active elements, in the linear scanning mode, the same set of delays is downloaded to memory for the sets of elements. As the sub-aperture moves to successive groups, the digital words representing the individual delays are effectively rotated through the memory and control circuits of each processing channel. That is, for the first, group of elements, delay sets numbered 1-64 are loaded into processing channels 1-64, respectively. For the next set, delay sets 1-64 are loaded into processing channels 2-64, 1, respectively. For the next set, delays 1-64 are loaded into channels 3-64, 1-2, respectively, and so forth. This rotational multiplexing of delay data values substantially enhances the efficiency of the invention since the amount of memory required to store all the delays is substantially reduced. The amount of hardware required is also reduced

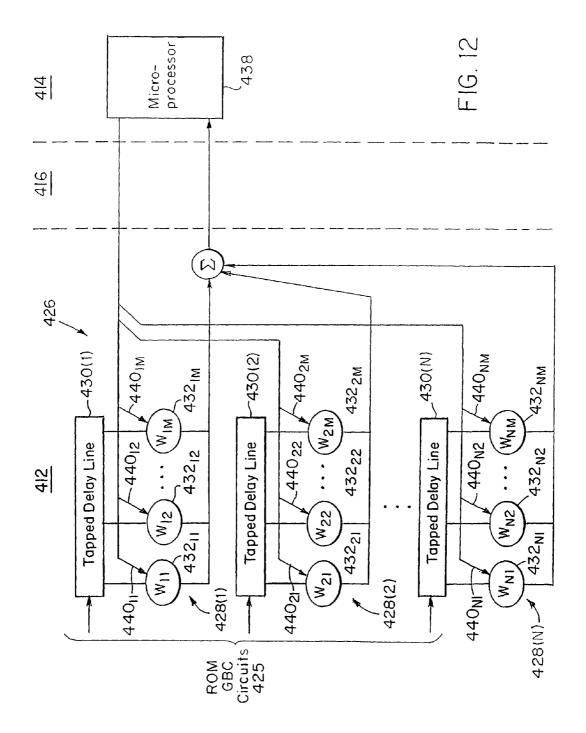

In another, alternative preferred embodiment, an adaptive beam forming circuit is used instead of the dual-stage delay line to provide the required delays at the required resolution. In the adaptive beam forming technique, a feedback circuit senses summed received signals from a tapped delay line and generates correction signals. The correction signals control individual multiplier weights in the beam forming circuitry to

adjust the summed signal and eliminate the effects of clutter and interference from the Image.

As described above, after the beam forming circuits dynamically focus and sum the signals from the ultrasonic transducers, the summed signal is forwarded over the system 5 cable to the data processing and display subsystem of the imaging system. The data processing subsystem includes, among other things, demodulation, log compression and scan conversion circuitry for converting the polar coordinates of received ultrasonic signals to rectangular coordinates suitable for further processing such as display. The scan conversion process of the present invention provides a higher quality image and requires far less complex circuitry than that of prior systems.

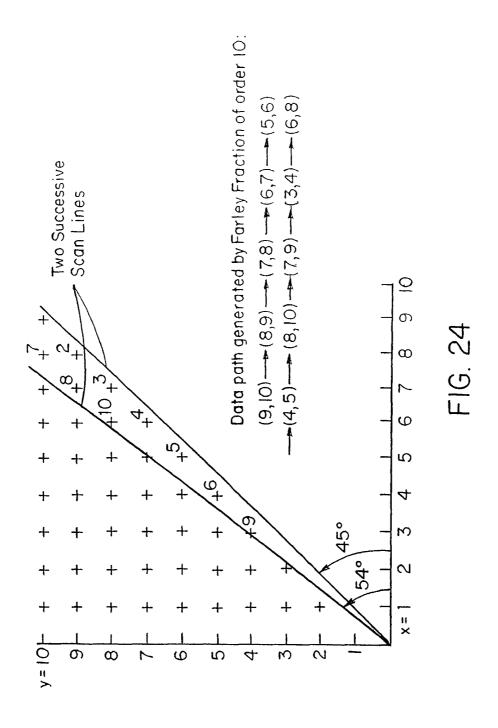

In the scan conversion of conventional systems, the value of each point on the (x,y) coordinate system is computed from the values of the four nearest neighbors on the polar (r,8) array by simple linear interpolation. This is accomplished by use of a finite state machine to generate the (x,y) traversal pattern, a 20 bi-directional shift register to hold the (r,8) data samples and a large number of digital logic and memory units to control the process and ensure that the correct samples of (r,8) data arrive for interpolation at the right time for each (x,y) point since the (x,y) data points are received asynchronously.

In the present invention, hardware complexity and cost are reduced by using a number-theoretic scheme for reliably generating the (x,y) grid traversal path in natural order, i.e., using the (r,8) samples as they are acquired. This provides greater flexibility and better fidelity to the actual medical data since it permits the array traversals to be designed so that they do not impose an unnatural image reconstruction scheme. The approach taken in the present invention provides greater flexibility in that multiple effective paths through the (x,y) array are possible. As a result, full advantage is taken of 35 different ultrasound scan frequencies and, hence, imaging depth.

After the image data is scan converted, it is post processed in accordance with its eventual intended presentation format. For example, the data can be digitized and formatted for 40 presentation on a display. Alternatively, the (x,y) data values can be presented to a video compression subsystem which compresses the data to allow for data transmission to remote sites by modem or other known communication means.

The ultrasound imaging system of the invention also 45 allows for imaging of moving objects by including a pulsed Doppler processing subsystem. Data from the beam forming circuitry is forwarded to the pulsed Doppler processor to generate data used to image the moving object. For example, the pulsed Doppler processor can be used to produce color 50 flow map images of blood flowing through tissue.

In another preferred embodiment, the data processing and display unit can be a single small battery-operated unit. It can be hand-held or worn clipped to the user or in the user's pocket. This, in conjunction with the hand-held scan head of 55 the invention, makes the ultrasound system of the invention completely portable.

The ultrasound imaging system of the invention has several advantages over prior conventional systems. Because much of the signal processing circuitry is integrated on small chips, 60 the signal processing can be carried out in the scan head. Because of the proximity of the transducers to the processing circuitry, signal loss is substantially reduced. This results in greatly improved system performance in the form of high-resolution high-quality images. Also, since the signal summing is also performed in the scan head, only a single or very few cable conductor lines are required to transmit image

10

signals to the data processing circuitry. The required cable is far less complex and expensive than that used in conventional systems.

The portability of the imaging system of the invention is also a very important asset. As described above, the system includes a small hand-held scan head, a small cable and a portable data processing and display unit such as a lap-top computer or hand-held computer with integrated liquid crystal or other flat panel display and keypad. It can be battery powered and hence can easily be carried to persons needing immediate attention at remote locations to perform quick diagnostic evaluation. By using the video data compression of the invention, the image data gathered at a remote site can be transferred by modem or wireless cellular link or other known means to a hospital for evaluation. Treatment instructions can then be relayed back to the operator where the patient can be administered treatment immediately.

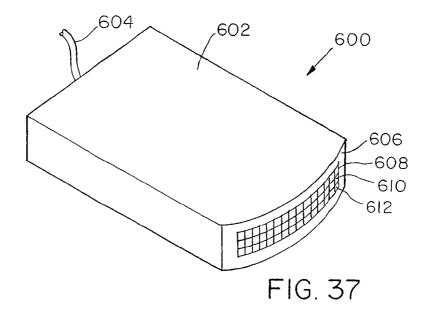

Another preferred embodiment of the invention involves the above described circuits and methods for a two-dimensional transducer array device. The transducer device provides focusing in a second dimension and can employ a coarser spacing between the rows of a multi-linear array, for example.

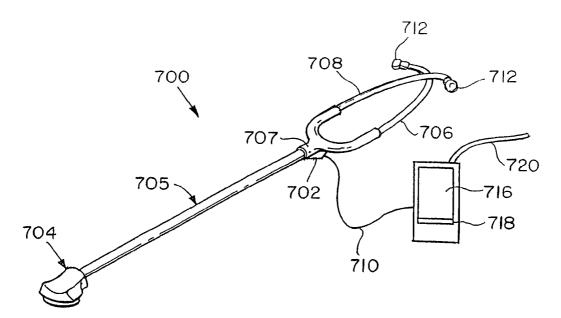

Another preferred embodiment of the invention involves 25 the use of an ultrasound transducer device in an electronic stethoscope. This system provides both audio information to the user as well as an ultrasound imaging capability.

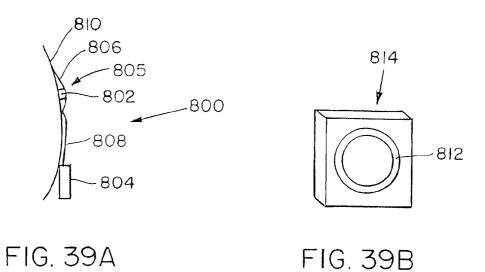

Another preferred embodiment of the invention involves the use of an ultrasound transducer device in a skinpatch. This can be used for cardiac monitoring by positioning the transducer device to transmit and receive between the ribs of a patient.

Another preferred embodiment of the invention incorporates the processing and control circuitry described herein in a distal end of an ultrasound internal probe or imaging catheter. This provides a more flexible and less expensive imaging probe that is useful for both diagnosis and treatment.

## BRIEF DESCRIPTION OF THE DRAWINGS

The foregoing and other objects, features and advantages of the invention will be apparent from the following more particular description of preferred embodiments of the invention, as illustrated in the accompanying drawings in which like reference characters refer to the same parts throughout the different views. The drawings are not necessarily to scale, emphasis instead being placed upon illustrating the principles of the invention.

FIGS. 1A and 1B respectively show a block diagram of a conventional imaging array as used in an ultrasound imaging system and associated transmitting pulse patterns of a single pulse and multiple pulses in a zone-focused mode.

FIGS. 2A-2C respectively show block diagrams of three different conventional imaging or beam focusing techniques involving optical lens, time delay and phase delay operations.

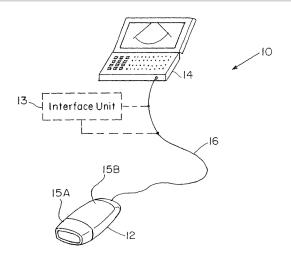

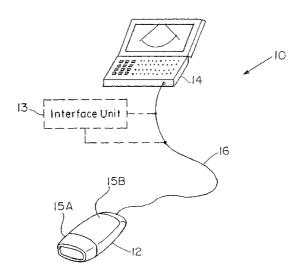

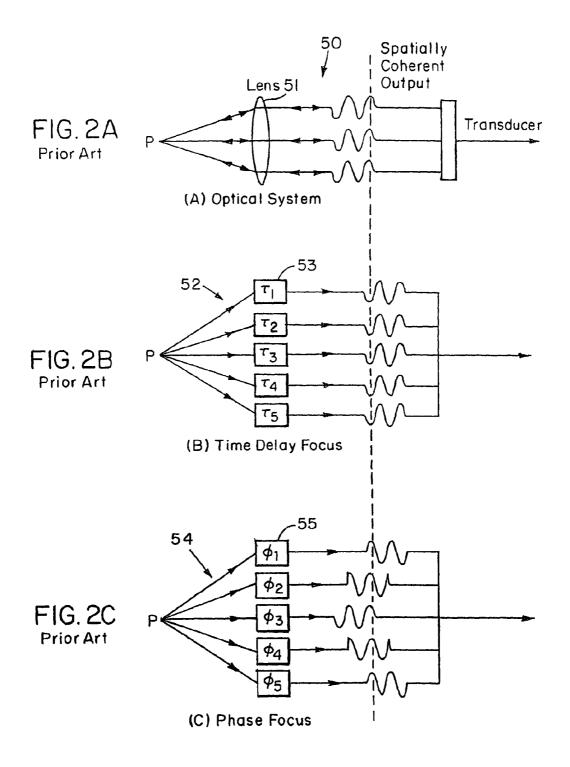

FIG. 3 is a schematic pictorial view of a preferred embodiment of the ultrasound imaging system of the present invention.

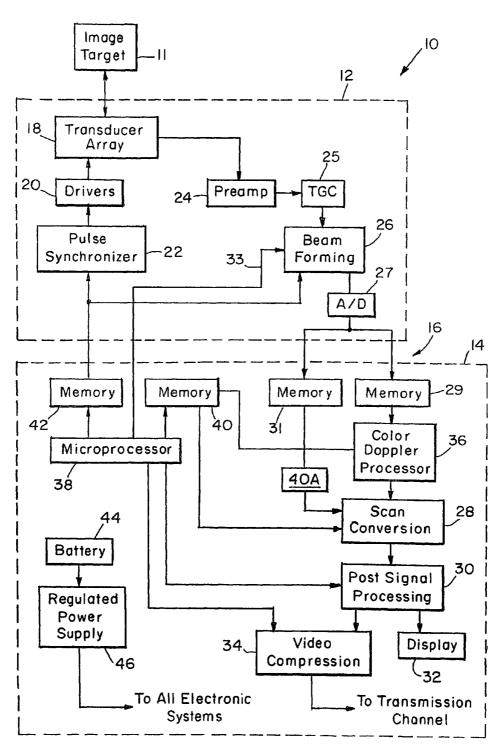

FIG. **4** is a schematic functional block diagram of a preferred embodiment of the ultrasound imaging system of the invention.

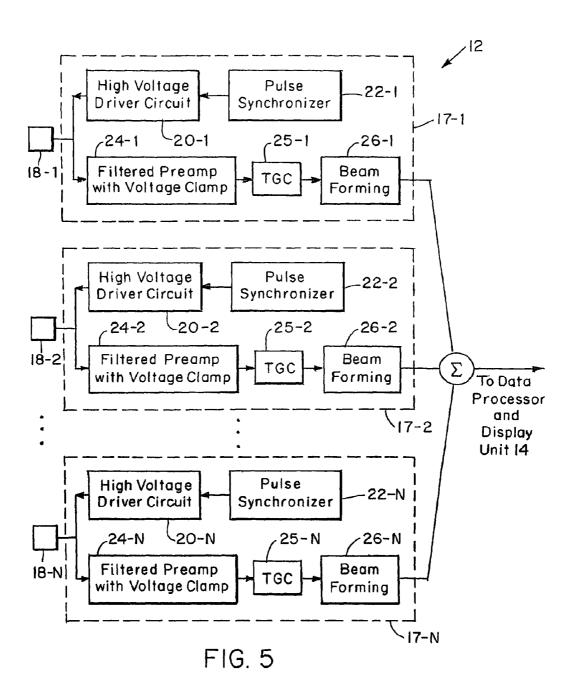

FIG. **5** is a schematic functional block diagram of a preferred embodiment of the ultrasound scan head of the present invention.

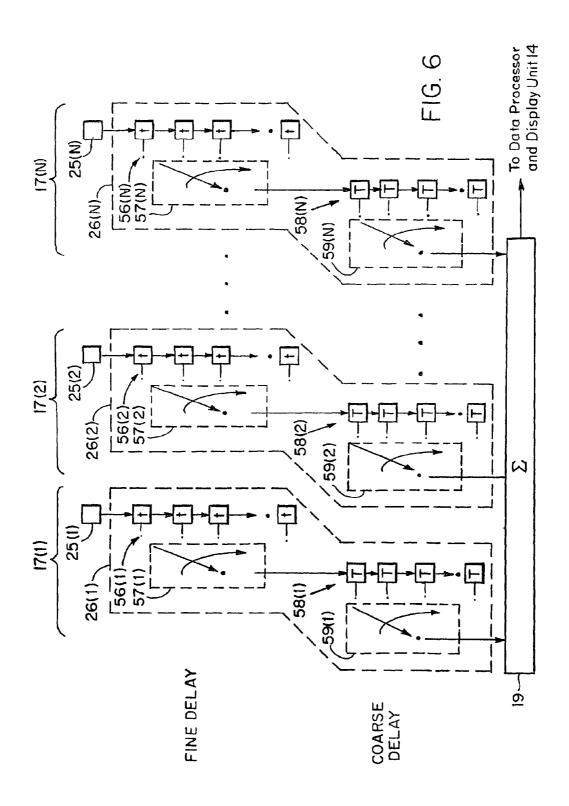

FIG. 6 shows an operational block diagram of an array of the beam forming and focusing circuits in accordance with the present invention.

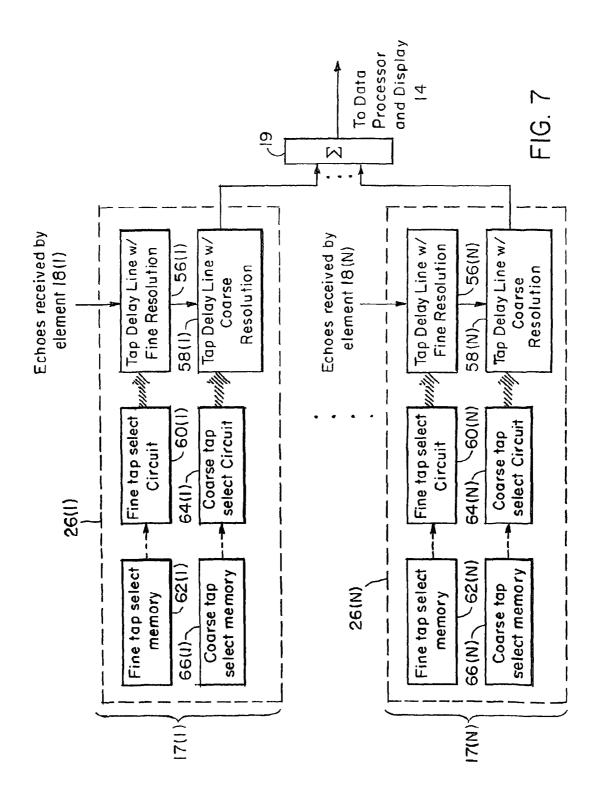

FIG. 7 shows a more detailed operational block diagram of an array of the beam forming and focusing circuits in accordance with the present invention.

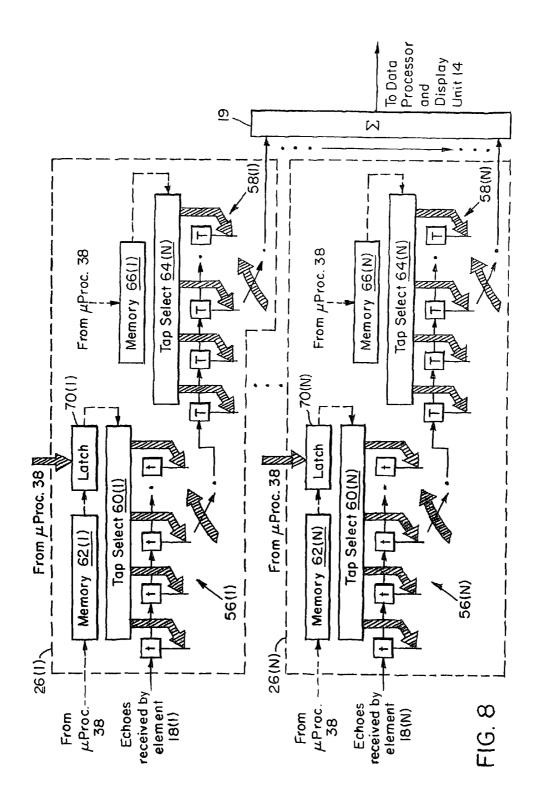

FIG. **8** shows an operational block diagram of an alternative embodiment of the present invention in which each of the beam forming and focusing circuits incorporates a latching circuit.

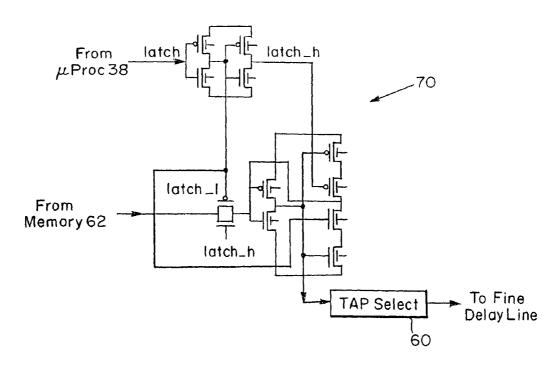

FIG. 9 shows a schematic block diagram of an exemplary embodiment of the latching circuit used in accordance with the present invention.

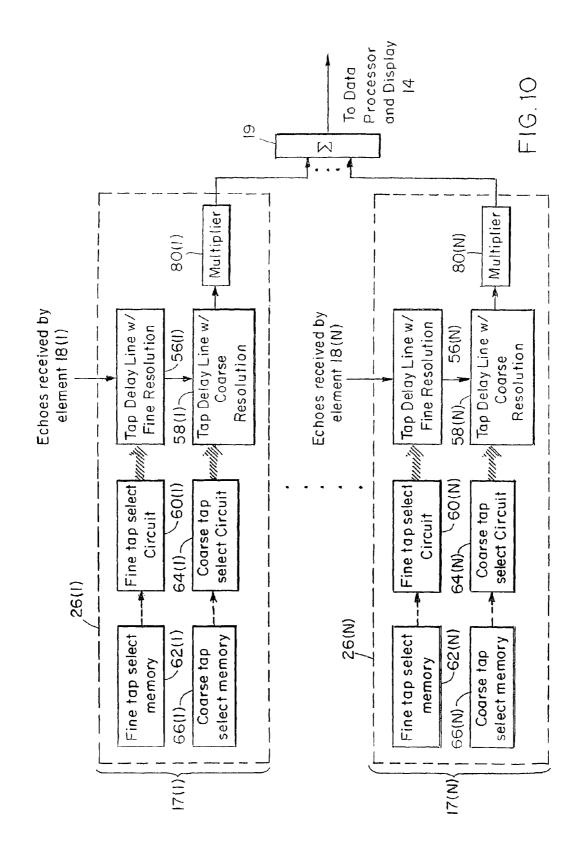

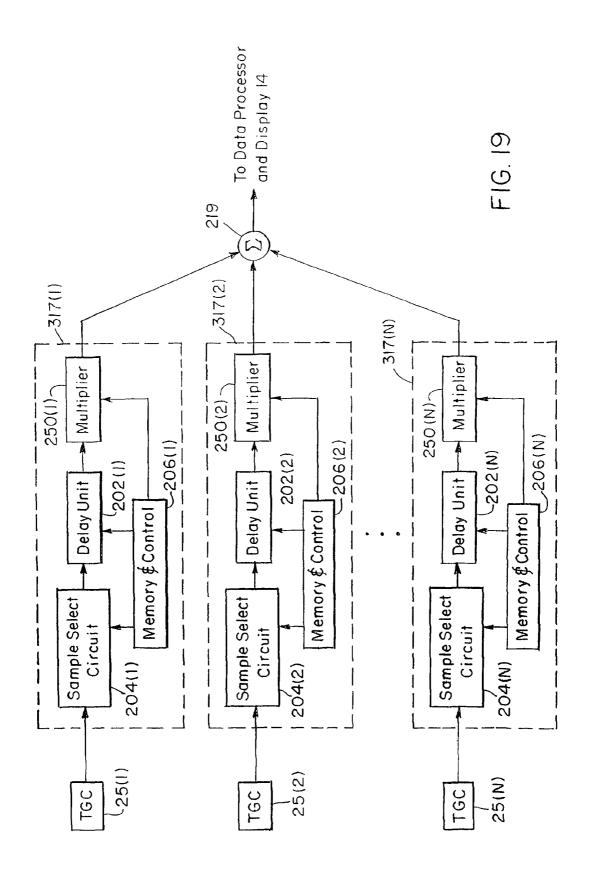

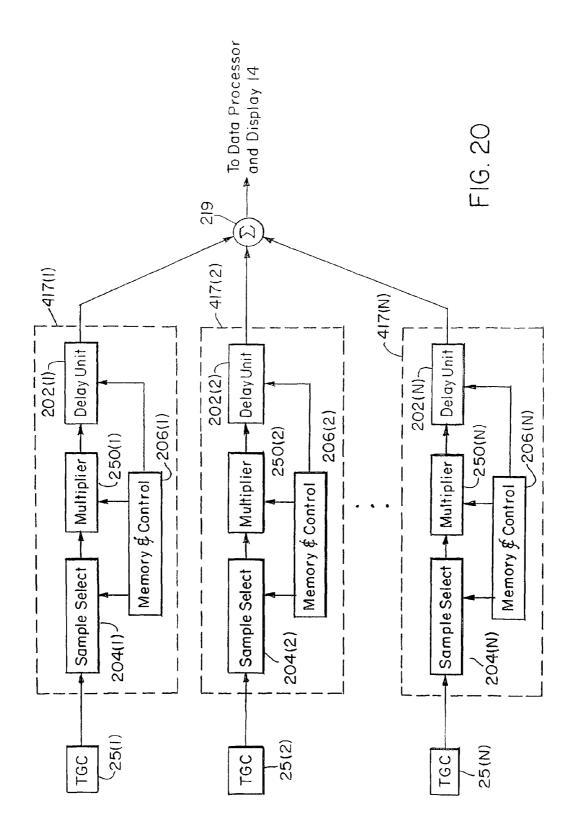

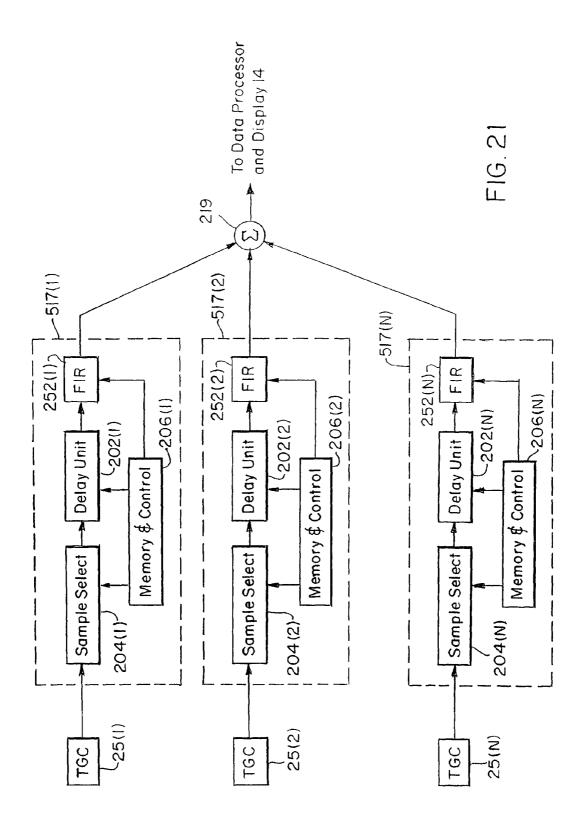

FIG. 10 shows an operational block diagram of an alternative embodiment of the present invention in which the selected outputs of each beam forming and focusing circuit are applied to respective multiplier circuits.

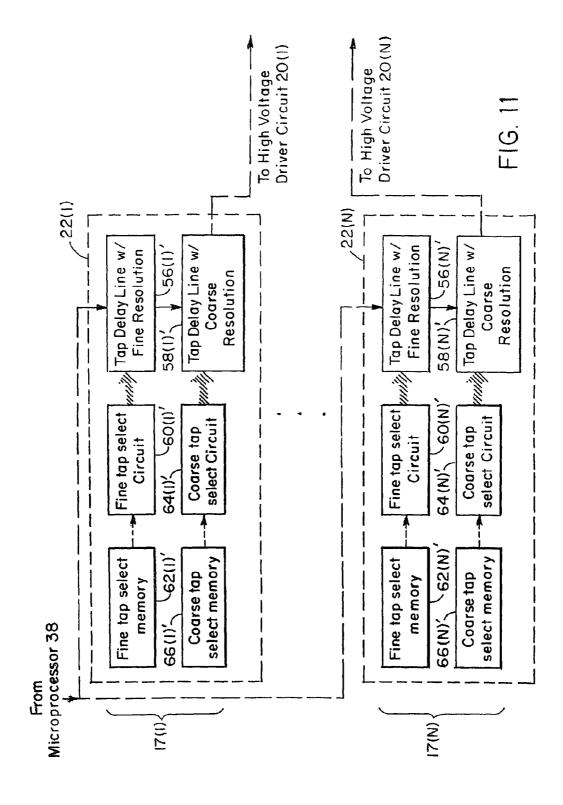

FIG. 11 shows an operational block diagram of an alternative embodiment of the present invention in which a plurality of beam forming and focusing circuits of the present invention are arranged for operation in a transmission mode.

FIG. 12 is a schematic functional block diagram of one 20 preferred embodiment of adaptive beam forming circuitry in accordance with the present invention.

FIG. 13 shows a schematic block diagram of an alternative embodiment of an array of beam forming and focusing circuits in accordance with the present invention using a programmable sample selection circuit and a programmable delay unit.

FIG. **14**A shows a schematic diagram of an exemplary embodiment of a memory controlled programmable sample selection circuit used in accordance with the present invention

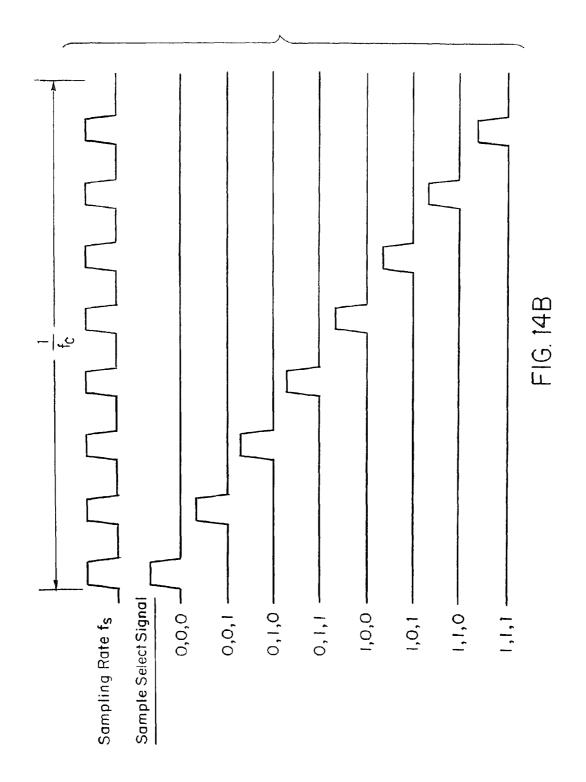

FIG. 14B contains timing diagrams for the sample selection circuit of FIG. 14A.

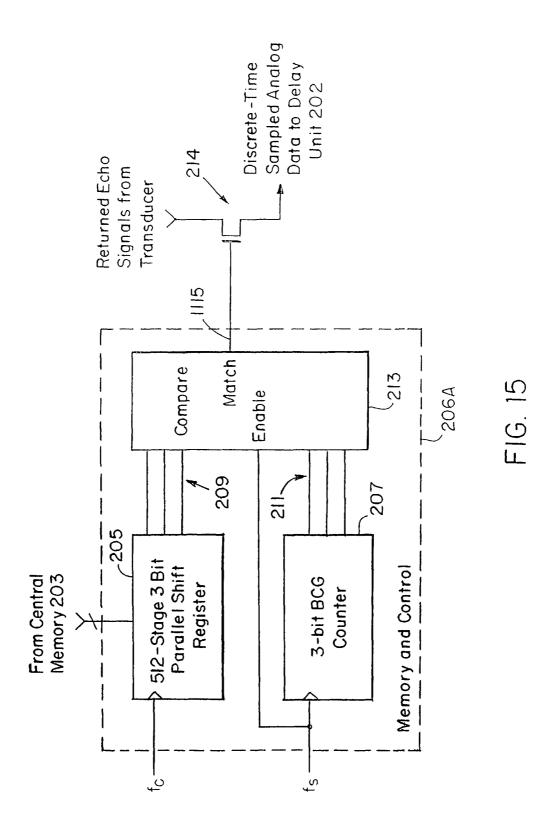

FIG. **15** is a schematic detailed block diagram of an alternative preferred embodiment of memory and control circuitry 35 in accordance with the invention.

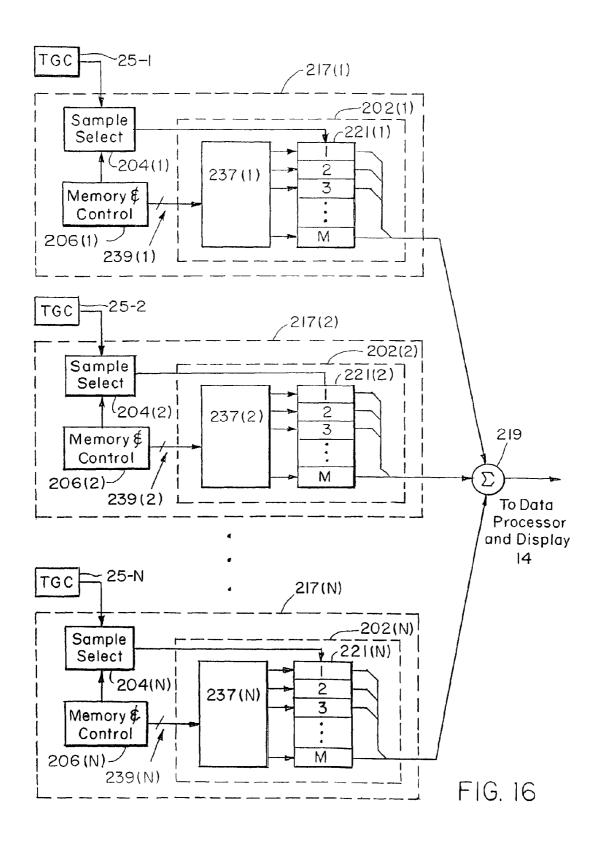

FIG. 16 shows a schematic block diagram of an embodiment of the beam forming circuits of FIG. 13, in which CCD programmable delay lines are employed.

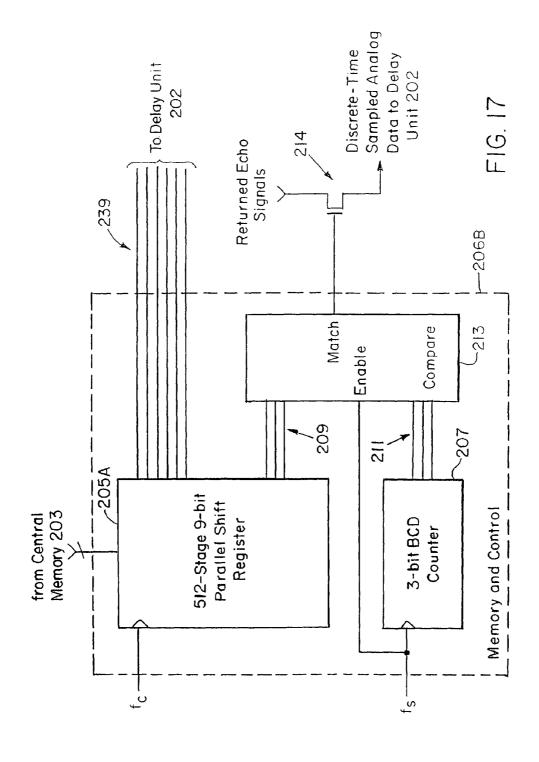

FIG. 17 is a schematic detailed block diagram of another 40 alternative preferred embodiment of memory and control circuitry in accordance with the invention.

FIG. **18** is a schematic detailed block diagram of another alternative preferred embodiment of memory and control circuitry in accordance with the invention.

FIG. 19 shows a block diagram of an alternative embodiment of the present invention in which the selected outputs of each of the beam forming and focusing circuits are applied to respective multiplier weighting circuits.

FIG. **20** shows a block diagram of an alternative embodiment of the present invention in which the multiplier weighting circuit is placed to the input of the delay unit.

FIG. 21 shows a block diagram of an alternative implementation of the present invention, in which a finite-impulse response (FIR) filter for time-domain interpolation is placed 55 following the delay units.

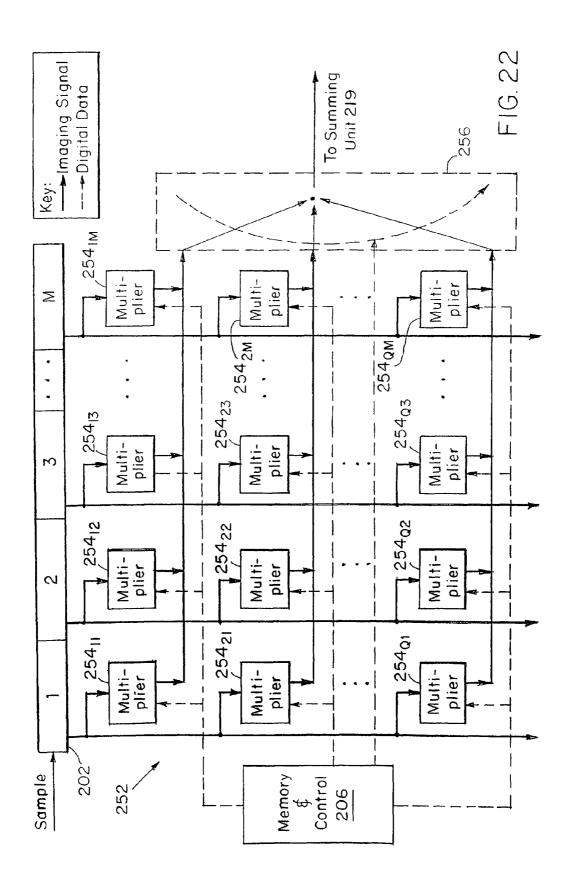

FIG. 22 shows a block diagram of a FIR filter implementation in which fixed weight multipliers are used for input sample interpolation.

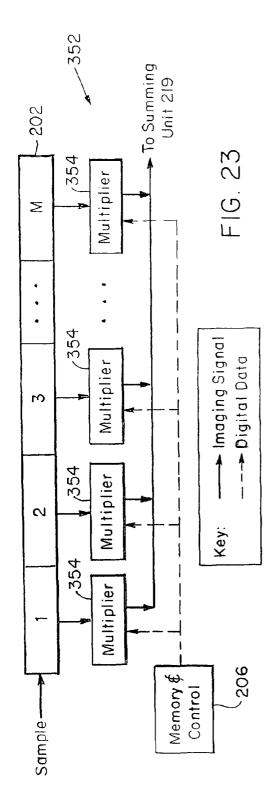

FIG. 23 shows a block diagram of an alternative FIR filter 60 implementation in which programmable multipliers are used for input sample interpolation.

FIG. **24** is a schematic diagram showing the scan conversion process of the invention.

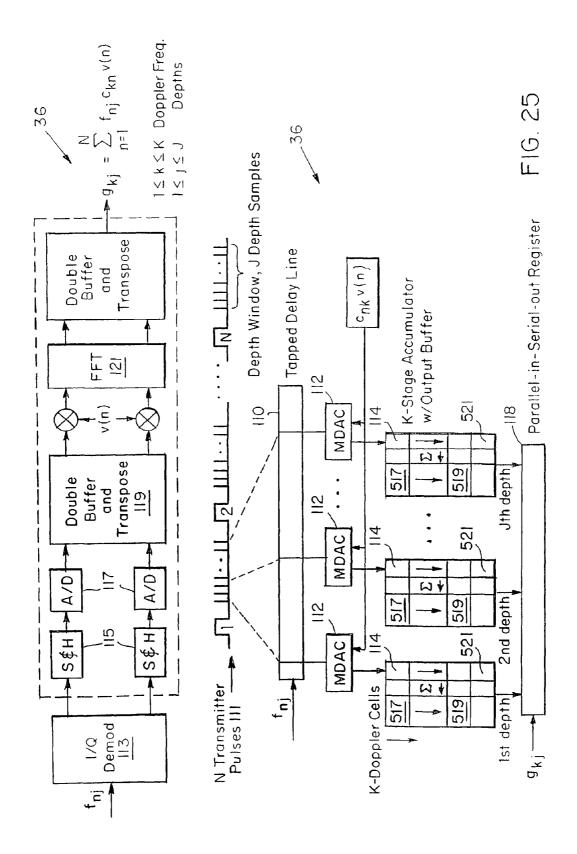

FIG. **25** is a schematic functional block diagram of a pulsed 65 Doppler processing unit in accordance with the present invention.

12

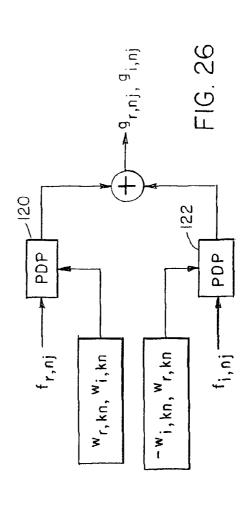

FIG. **26** is a schematic block diagram of a color flow map chip implementation using dual pulsed Doppler processors in accordance with the present invention.

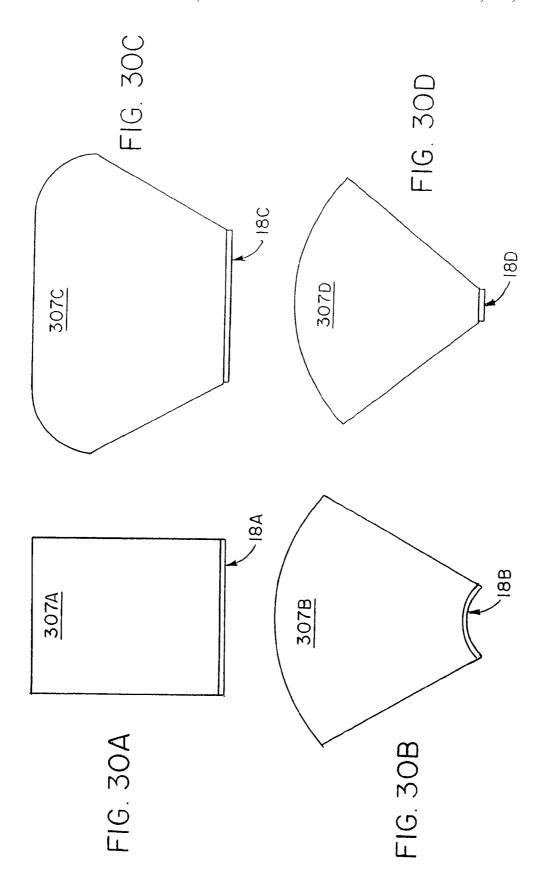

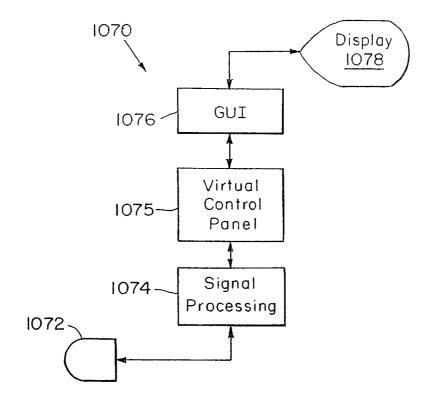

FIG. 27 is a schematic functional block diagram of an alternative preferred embodiment of the ultrasound imaging system of the invention.

FIG. 28 is a plot comparing truncated non-varying spatial windows and dynamic spatial windows used during sub-aperture scanning in accordance with the present invention.

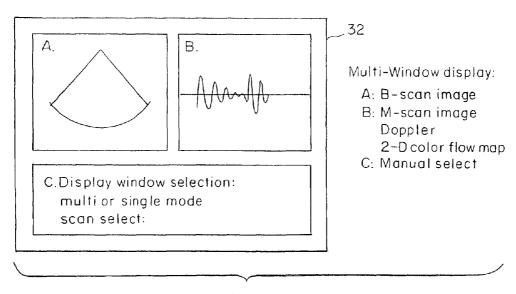

FIGS. **29**A and **29**B are schematic pictorial views of two user-selectable display presentation formats used in the ultrasound imaging system of the invention.

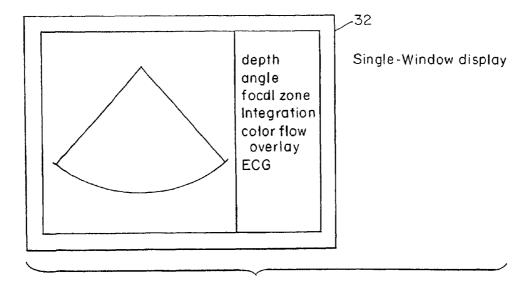

FIG. 30A is a schematic illustration of the relationship between a linear ultrasound transducer array and a rectangular scan region in accordance with the present invention.

FIG. **30**B is a schematic illustration of the relationship between a curved ultrasound transducer array and a curved scan region in accordance with the present invention.

FIG. **30**C is a schematic illustration of the relationship between a linear ultrasound transducer array and a trapezoidal scan region in accordance with the present invention.

FIG.  $30\bar{\mathrm{D}}$  is a schematic illustration of a phased array scan region.

FIG. **31** is a schematic functional block diagram of a circuit board in accordance with the present invention.

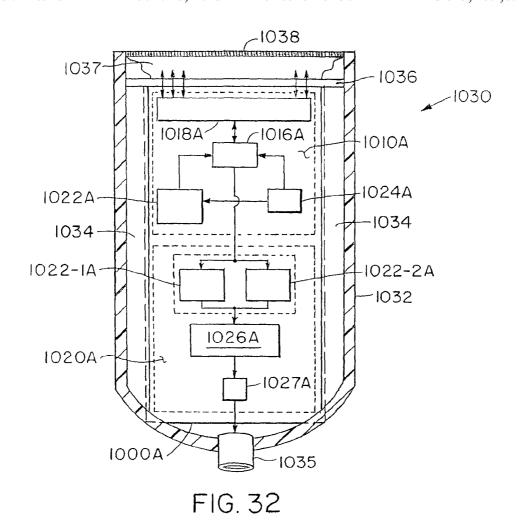

FIG. 32 is a schematic partial cross-sectional diagram of one embodiment of a linear scan head in accordance with the present invention.

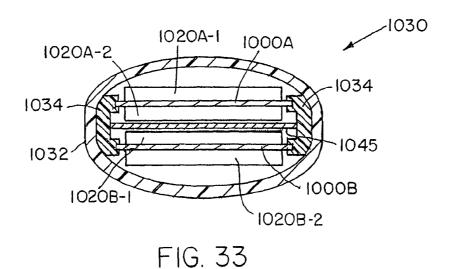

FIG. 33 is a schematic side cross-sectional view of the scan head of FIG. 31.

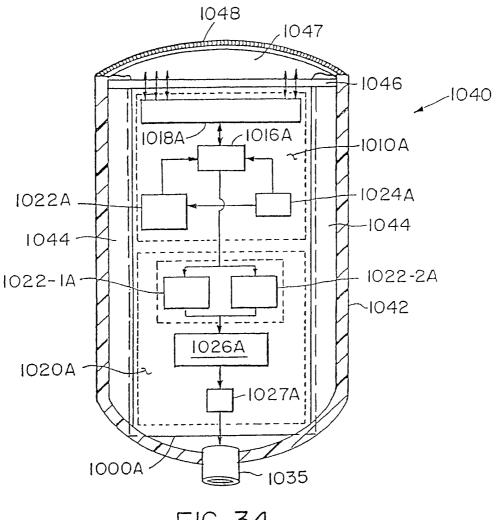

FIG. 34 is a schematic partial cross-sectional view of a scan head using a curve transducer array in accordance with the present invention.

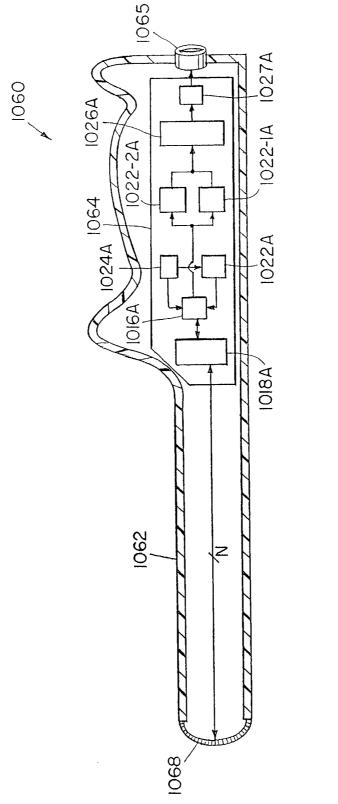

FIG. **35** is a schematic cross-sectional diagram of an internal ultrasonic probe in accordance with the present invention.

FIG. 36 is a top-level flow diagram illustrating the logical flow of the software used to control the operation of the present invention.

FIG. **37** is a perspective view of a two dimensional transducer array in accordance with the invention.

FIG. **38** is a schematic illustration of an electronic ultrasound stethoscope in accordance with the invention.

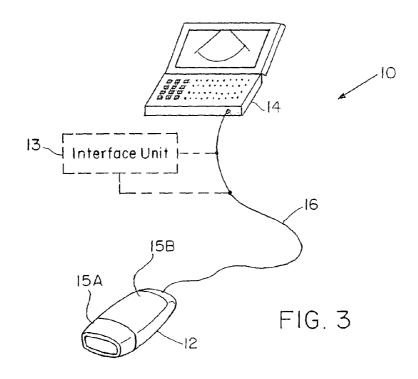

FIGS. **39**A and **39**B illustrate an ultrasound transducer patch system in accordance with the invention.

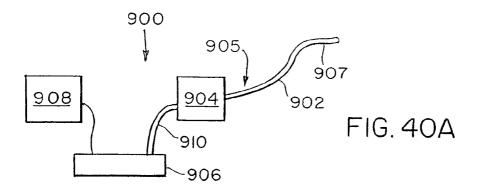

FIGS. **40**A and **40**B illustrate an ultrasound probe or catheter in accordance with the invention.

The foregoing and other objects, features and advantages of the invention will be apparent from the following more particular description of preferred embodiments of the invention, as illustrated in the accompanying drawings in which like reference characters refer to the same parts throughout the different views. The drawings are not necessarily to scale, emphasis instead being placed upon illustrating the principles of the invention.

## DETAILED DESCRIPTION OF THE INVENTION

A description of preferred embodiments of the invention follows.

FIG. 3 is a schematic pictorial view of the ultrasound imaging system 10 of the present invention. The system includes a hand-held scan head 12 coupled to a portable data processing and display unit 14 which can be a lap-top computer. Alternatively, the data processing and display unit 14 can include a personal computer or other computer interfaced to a cathode ray tube (CRT) for providing display of ultrasound images. The data processor display unit 14 can also be

------

a small, lightweight, single-piece unit small enough to be hand-held or worm or carried by the user. The hand-held display is less than 1000 cm<sup>3</sup> in volume and preferably less than 500 cm<sup>3</sup>. Although FIG. 3 shows an external scan head, the scan head of the invention can also be an internal scan head adapted to be inserted through a lumen into the body for internal imaging. For example, the head can be a transesophogeal probe used for cardiac imaging.

The scan head 12 is connected to the data processor 14 by a cable 16. In an alternative embodiment, the system 10 10 includes an interface unit 13 (shown in phantom) coupled between the scan head 12 and the data processing and display unit 14. The interface unit 13 preferably contains controller and processing circuitry including a digital signal processor (DSP). The interface unit 13 performs required signal processing tasks and provides signal outputs to the data processing unit 14 and/or scan head 12.

The hand-held housing 12 includes a transducer section 15A and a handle section 15B. The transducer section 15A is maintained at a temperature below 41° C. so that the portion 20 of the housing that is in contact with the skin of the patient does not exceed this temperature. The handle section 15B does not exceed a second higher temperature preferably 50° C. The hand-held scan-head occupies a volume of less than 1000 cm³ and preferably less than 500 cm³, and is less than 25 twenty centimeters in length along it's major axis.

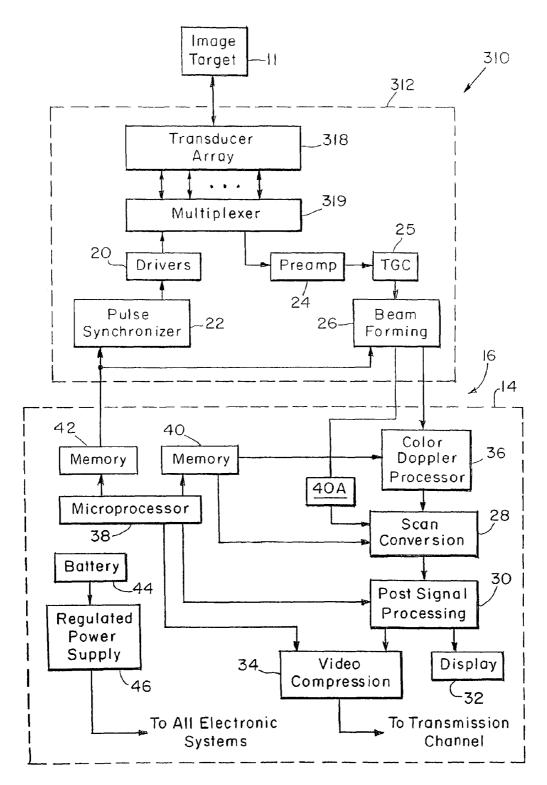

FIG. 4 is a schematic functional block diagram of one embodiment of the ultrasound imaging system 10 of the invention. As shown in FIG. 4, the scan head 12 includes an ultrasonic transducer array 18 which transmits ultrasonic signals into a region of interest or image target 11, such as a region of human tissue, and receives reflected ultrasonic signals returning from the image target. The scan head 12 also includes transducer driver circuitry 20 and pulse synchronization circuitry 22. The pulse synchronizer 22 forwards a series of precisely timed and delayed pulses to high voltage driver circuits in the drivers 20. As each pulse is received by the drivers 20, the high-voltage driver circuits are activated to forward a high-voltage drive signal to each transducer in the transducer array 18 to activate the transducer to transmit an 40 ultrasonic signal into the image target 11.

Ultrasonic echoes reflected by the image target 11 are detected by the ultrasonic transducers in the array 18. Each transducer converts the received ultrasonic signal into a representative electrical signal which is forwarded to preampli- 45 fication circuits 24 and time-varying gain control (TGC) circuitry 25. The preamp circuitry 24 sets the level of the electrical signals from the transducer array 18 at a level suitable for subsequent processing, and the TGC circuitry 25 is used to compensate for attenuation of the sound pulse as it 50 penetrates through human tissue and also drives the beam forming circuits 26 (described below) to produce a line image. The conditioned electrical signals are forwarded to the beam forming circuitry 26 which introduces appropriate differential delay into each of the received signals to dynami- 55 cally focus the signals such that an accurate image can be created. The signals delayed by the beam forming circuitry 26 are summed to generate a single signal which is forwarded over the cable 16 to the data processor and display unit 14. The details of the beam forming circuitry 26 and the delay 60 circuits used to introduce differential delay into received signals and the pulses generated by the pulse synchronizer 22 will be described below in detail.

In one preferred embodiment, the dynamically focused and summed signal is forwarded to an A/D converter 27 which 65 digitizes the summed signal. Digital signal data is then forwarded from the A/D 27 over the cable 16 to buffer memories

29 and 31. It should be noted that the A/D converter 27 is not used in an alternative embodiment in which the analog summed signal is sent directly over the system cable 16. The

AID converter 27 is omitted from further illustrations for simplicity.

Data from buffer memory 31 is forwarded through demodulation and log compression circuitry 40A to scan conversion circuitry 28 in the data processing unit 14. The scan conversion circuitry 28 converts the digitized signal data from the beam forming circuitry 26 from polar coordinates (r,8) to rectangular coordinates (x,y). After the conversion, the rectangular coordinate data is forwarded to post signal processing stage 30 where it is formatted for display on the display 32 and/or for compression in the video compression circuitry 34. The video compression circuitry 34 will be described below in detail.

Digital signal data is forwarded from buffer memory 29 to a pulsed or continuous Doppler processor 36 in the data processor unit 14. The pulsed or continuous Doppler processor 36 generates data used to image moving target tissue 11 such as flowing blood. In the preferred embodiment, with pulsed Doppler processing, a color flow map is generated. The pulsed Doppler processor 36 forwards its processed data to the scan conversion circuitry 28 where the polar coordinates of the data are translated to rectangular coordinates suitable for display or video compression.

A control circuit preferably in the form of a microprocessor 38 controls the operation of the ultrasound imaging system 10. The control circuit 38 controls the differential delays introduced in both the pulsed synchronizer 22 and the beam forming circuitry 26 via a memory 42 and a control line 33. In one embodiment, the differential delays are introduced by programmable tapped CCD delay lines to be described below in detail. The delay lines are tapped as dictated by data stored in the memory 42. The microprocessor 38 controls downloading the coarse and fine delay line tap data from memory 42 to on-chip memories in both the pulsed synchronizer 22 and the beam forming circuitry 26. In another embodiment, the delays are controlled by delay processing circuitry which includes programmable input sampling circuits coupled to programmable delay units as described in detail below.

The microprocessor 38 also controls a memory 40 which stores data used by the pulsed Doppler processor 36 and the scan conversion circuitry 28. It will be understood that memories 40 and 42 can be a single memory or can be multiple memory circuits. The microprocessor 38 also interfaces with the post signal processing circuitry 30 and the video compression circuitry 34 to control their individual functions. The video compression circuitry 34 as described below in detail compresses data to permit transmission of the image data to remote stations for display and analysis via a transmission channel. The transmission channel can be a modem or wireless cellular communication channel or other known communication means.

The portable ultrasound imaging system 10 of the invention can preferably be powered by a battery 44. The raw battery voltage out of the battery 44 drives a regulated power supply 46 which provides regulated power to all of the subsystems in the imaging system 10 including those subsystems located in the scan head 12. Thus, power to the scan head is provided from the data processing and display unit 14 over the cable 16.

FIG. 5 is a detailed schematic functional block diagram of one embodiment of the scan head 12 used in the ultrasound imaging system 10 of the invention. As described above, the scan head 12 includes an array of ultrasonic transducers labeled in FIG. 3 as 18-(1), 18-(2), ..., 18-(N), where N is the

total number of transducers in the array, typically 128. Each transducer **18**(1)-**18**(N) is coupled to a respective processing channel **17**(1)-**17**(N).

Each processing channel 17(1)-17(N) includes a respective pulse synchronizer 22(1)-22(N) which provides timed activation pulses to a respective high voltage driver circuit 20(1)-20(N) which in turn provides a driving signal to a respective transducer 18(1)-18(N) in the transmit mode. Each processing channel 17(1)-17(N) also includes respective filtered preamplification circuits 24(1)-24(N) which include voltage 10 clamping circuits which, in the receive mode, amplify and clamp signals from the transducers 18(1)-18(N) at an appropriate voltage level. The time varying gain control circuitry (TGC) 25(1)-25(N) controls the level of the signals, and the beam forming circuitry 26(1)-26(N) performs dynamic 15 focusing of the signals by introducing differential delays into each of the signals as described below in detail. The outputs from beam forming circuits 26(1)-26(N) are summed at a summing node 19 to generate the final focused signal which is transmitted over the cable 16 to the data processor and 20 display unit 14 for subsequent processing.

In the present invention, one embodiment of the beam forming and focusing circuit 26 can be integrated on a single microchip and utilizes cascaded charge-coupled device (CCD) tapped delay lines to provide individual coarse and 25 fine delays resulting in a wide range of delays with fine time resolution. This embodiment of the beam forming system of the invention, referred to herein as charge domain processing (CDP) circuitry, includes a plurality of processing circuits which, in a receiving mode, differentially delay signals rep- 30 resentative of image waveforms received as reflected ultrasonic energy from the target object in order to generate a focused image. In a transmitting mode, the processing circuits differentially delay signals, which are to be transmitted as ultrasonic energy to a target object by the array 18 of 35 transducers 18(1)18(N), in order to generate a focused directional beam.

Each of the processing circuits includes a first delay line having a plurality of delay units operable in the receiving mode for receiving an image waveform and converting same 40 into sampled data such as charge packets. In the transmitting mode, the first delay line receives the imaging signals and converts them into sampled data such as charge packets. A selection control circuit is operable for reading the sampled data from a selected first delay unit of the first delay line so as 45 to correspond to a selected first time delay to accommodate fine delay resolution of the image waveform or imaging signals. A second delay line having a plurality of delay units is operable for sensing the sampled data from the selected first delay unit. The control circuit is further operable for reading 50 the sampled data from a selected second delay unit of said second delay line so as to correspond to a selected second delay time to accommodate coarse delay resolution of the image waveform or imaging signals.

In the receiving mode, a summation circuit is provided for 55 summing the sampled data from each of the selected second delay units in each of the processing circuits in order to produce a focused image. In the transmitting mode, an output circuit is provided for converting the sampled data from each of the selected second delay units in each of the processing 60 circuits into signals representative of the focused directional beam.

The beam forming and focusing operations involve forming a summation of the waveforms as observed by all of the transducer elements. However, in this summation, the waveforms must be differentially delayed so that they all arrive in phase at a summation circuit 19 (see FIG. 5). Accordingly,

each beam forming circuit 26 in accordance with the present invention provides a different time delay on each processing channel, and further varies that delay with time. The signals which are added in phase to produce a focused signal are then forwarded to the data processor and display unit 14.

For each nominal scanning direction, the differential delay required for information received by a transducer element  $\mathbf{18}(k)$  in the array, relative to the first element  $\mathbf{18}(1)$ , varies predominantly with k, with a small correction as a function of time to correct focus for depth. The overall control of delay can involve very fine time resolution as well as a large range of delays. However, for a selected beam forming direction, this set of delays is achieved by a combination of a coarse delay in each channel to approximately compensate for direction, and a fine delay for each channel which combines the functions of focusing and refining the original coarse correction.

According to one preferred embodiment of the beam forming circuitry 26 shown in operational block diagram form in FIG. 6, each of the beam forming circuits 26 is respectively arranged in a predetermined one of the N-parallel processing channels 17(1)-17(N), one for each of the array of transducer elements 18(1)-18(N). Each beam forming circuit 26 includes two cascading tapped delay lines 56(1)-56(N), 58(1)-58(N). Each circuit 26 receives as an input a signal from a TGC circuit 25 (see FIG. 3). The first delay line 56 in each channel provides a fine time delay for its received signal, while the cascaded second delay line 58 provides a coarse time delay. Each fine delay line has an associated programmable tap-select circuit 57(1)-57(N), and each coarse delay line has a programmable tap-select circuit 59(1)-59(N), both of which will be described in more detail hereinafter. The tap-select circuits are operable for effecting a variable delay time as a function of tap location.