(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3939652号

(P3939652)

(45) 発行日 平成19年7月4日(2007.7.4)

(24) 登録日 平成19年4月6日(2007.4.6)

(51) Int.CI.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>HO4R 17/00</b> | <b>(2006.01)</b> | HO4R 17/00 | 330H |

| <b>A61B 8/00</b>  | <b>(2006.01)</b> | HO4R 17/00 | 330J |

| <b>GO1N 29/24</b> | <b>(2006.01)</b> | HO4R 17/00 | 332Y |

|                   |                  | A61B 8/00  |      |

|                   |                  | GO1N 29/24 | 502  |

請求項の数 14 (全 10 頁)

(21) 出願番号 特願2002-542543 (P2002-542543)

(86) (22) 出願日 平成13年11月13日 (2001.11.13)

(65) 公表番号 特表2004-514340 (P2004-514340A)

(43) 公表日 平成16年5月13日 (2004.5.13)

(86) 國際出願番号 PCT/EP2001/013182

(87) 國際公開番号 WO2002/040184

(87) 國際公開日 平成14年5月23日 (2002.5.23)

審査請求日 平成16年11月10日 (2004.11.10)

(31) 優先権主張番号 09/714,030

(32) 優先日 平成12年11月15日 (2000.11.15)

(33) 優先権主張国 米国(US)

(73) 特許権者 590000248

コーニングレッカ フィリップス エレクトロニクス エヌ ヴィ

オランダ国 5621 ベーアー アインドーフェン フルーネヴアウツウェッハ

1

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100120167

弁理士 木田 博

最終頁に続く

(54) 【発明の名称】多次元超音波トランステューサアレイ

## (57) 【特許請求の範囲】

## 【請求項 1】

望ましくない超音波エネルギーを発する底面を有する超音波トランステューサ素子の2次元アレイと、

上記2次元アレイの底面に対向して取り付けられた、音響的なバッキング材料の離隔プレート及び伝導性のトレースの回路のセットを交互に結合してなる伝導性のバッキングブロックアセンブリとを含み、

上記回路の伝導性のトレースは、上記2次元アレイに対向する上記伝導性のバッキングブロックアセンブリの表面で終端し、

上記伝導性のトレースが終端する上記伝導性のバッキングブロックアセンブリの上記表面は伝導性のメッキを施され、上記伝導性のメッキは、上記伝導性のトレースに電気的に接続し、

上記伝導性のメッキを施された表面は、上記トランステューサアレイが切断されるときにアレイトランステューサの素子の着座領域に対応する別々の領域に電気的に分割される2次元超音波トランステューサプローブ。

## 【請求項 2】

上記伝導性のトレースの回路のセットは、伝導性のトレースを備えたプリント回路基板であり、上記離隔プレート及び上記プリント回路基板は、上記プレートの結合面と上記プリント回路基板との間に位置する接着剤により共に結合される、請求項1記載の2次元超音波トランステューサプローブ。

**【請求項 3】**

上記プリント回路基板は、フレックス回路を構成する、請求項 2 記載の 2 次元超音波トランスデューサプローブ。

**【請求項 4】**

上記フレックス回路は、上記伝導性のバッキングブロックアセンブリの、上記 2 次元アレイに対向しない一端で上記プレートの端部を越えて延在する、請求項 3 記載の 2 次元超音波トランスデューサプローブ。

**【請求項 5】**

上記伝導性のトレースの回路のセットは、共に接着結合される上記離隔プレート上に形成される、請求項 1 記載の 2 次元超音波トランスデューサプローブ。 10

**【請求項 6】**

上記プレートは、上記伝導性のトレースへのアクセスを提供するよう異なる長さを有する、請求項 5 記載の 2 次元超音波トランスデューサプローブ。

**【請求項 7】**

上記伝導性のトレースは、上記伝導性のバッキングブロックの表面上の電極端子のグリッドアレイで終端し、そのグリッドアレイで上記アセンブリへの接続がなされる、請求項 1 乃至 6 のうちのいずれか記載の 2 次元超音波トランスデューサプローブ。

**【請求項 8】**

上記 2 次元アレイは、望ましくない超音波エネルギーを発する底面を有する微細加工された超音波トランスデューサ素子の 2 次元アレイである、請求項 1 乃至 7 のうちのいずれか記載の 2 次元超音波トランスデューサプローブ。 20

**【請求項 9】**

上記微細加工された超音波トランスデューサ素子は、容量性の微細加工された超音波トランスデューサ素子を含む、請求項 8 記載の 2 次元超音波トランスデューサプローブ。

**【請求項 10】**

上記微細加工された超音波トランスデューサ素子は、圧電性の微細加工された超音波トランスデューサ素子を含む、請求項 9 記載の 2 次元超音波トランスデューサプローブ。

**【請求項 11】**

上記音響的なバッキング材料からなるプレートは、上記伝導性のトレースの回路間のエレベーション方向の所定間隔を確立するように選択された厚さを有する、請求項 1 乃至 10 のうちのいずれか記載の 2 次元超音波トランスデューサプローブ。 30

**【請求項 12】**

上記音響的なバッキング材料のプレートは、音響的な吸収材料及び音響的な散乱体を含有する、請求項 1 乃至 16 のうちのいずれか記載の 2 次元超音波トランスデューサプローブ。

**【請求項 13】**

上記接着剤は、エポキシ接着剤である、請求項 1 乃至 11 のうちのいずれか記載の 2 次元超音波トランスデューサプローブ。

**【請求項 14】**

2 次元超音波トランスデューサアレイのための伝導性バッキングブロックアセンブリであって、 40

音響的なバッキング材料のプレートと、

伝導性のトレースの回路とを含み、上記プレート及び伝導性のトレースの回路は、請求項 1 乃至 13 のうちのいずれか記載の伝導性のバッキングブロックアセンブリと同様に配列される、伝導性バッキングブロックアセンブリ。

**【発明の詳細な説明】****【0001】**

本発明は、超音波診断撮像システムのためのトランスデューサプローブに係り、より詳細には、2 若しくはそれ以上の次元に延在する素子を有するプローブに関する。

**【0002】**

超音波撮像に使用される音響素子アレイ内の素子は、素子の反対側の面に接続する電極により素子両端に電位を印加することによって励起する。印加される電位により、圧電素子が振動して超音波が発せられる。受信中、素子は、電気的信号に変換される音波により振動し、電気的信号は、素子を励起させるために使用された同一の電極により画像システムに送出される。圧電素子は2次元超音波撮像に使用されるようなトランスデューサアレイにおける単一の素子の列のひとつであり、電極を素子の反対側の面に接続させる選択肢は多数存在する。特に、アレイの裏側の望ましくない音響エネルギーを減衰させる音響的なバッキングブロックから隔たって、アレイの側部からの接続をなすことは通常的である。

#### 【0003】

しかしながら、トランスデューサアレイが2次元アレイを構成するとき、アレイの側部から素子へのすべての接続をなすことは困難になる。これは、3若しくはそれ以上の列の素子のアレイの場合、1若しくはそれ以上の列が、アレイの内部に位置し、アクセスがアレイの外側の列により阻止されるからである。かかる場合、一般的には、トランスデューサスタッカの音響的なバッキングを通した接続をなすことが必要となる。

#### 【0004】

2次元アレイへの接続をなす1つの先行技術のアプローチは、米国特許第4825115号に開示される。この特許では、フレキシブルプリント回路（フレックス回路）が、圧電素子プレートの裏側に取り付けられ、取付け位置からプレートに垂直に延在するよう上方に曲げられる。音響的なバッキングは、フレックス回路周辺に鋳造され、その組立体は裏返しされ、圧電プレートは個々の素子へとダイシングされる。米国特許第5757727号は、同様のアプローチを開示するが、フレックス回路を完全なアレイ領域に取り付けし、一体的なアセンブリにバッキングを鋳造し、バッキング及びフレックス回路の個々のサブアセンブリは、予備成形され、次いで共に組み立てられ、列並びのアセンブリが完成する。このアプローチは、一定の性能及び導線間隔を保証する為、列から列への厳密に調整された均一性を必要とする。更に、これら双方の技術は、導線をトランスデューサ素子への取付け位置で90度曲げることを必要とし、これは、導線に応力を発生させ、インピーダンスの変動や接続の不具合を招いてしまう。

#### 【0005】

米国特許第6043590号及び第6044533号は、導線を曲げる必要を回避するアプローチを開示する。その代わりに、導線は、鉛直に素子の裏側に当接し曲げられない。更に、導線及びバッキング材料は、一体的なアセンブリとして予備成形され、圧電阻止材料への取り付け前に、必要な素子間のアラインメントのために検査できる。後者の場合、剥き出しの導線の窓部を備えた誘電体基板が積層され、導線間の空間は減衰材料で充填される。材料が硬化したとき、固定された積層は材料を通過する切断がなされて、切断面で終了する導線を備えたバッキングブロックが作製される。しかしながら、このプロセスは、剥き出しの導線のアラインメントを維持することや、空隙を残すことなくそれら周辺の空間を完全に充填することが困難となりがちである。それ故に、簡易で高精度且つ高い反復性の方法で上述のような伝導性のバッキングアセンブリを作製できることが望ましいだろう。

#### 【0006】

本発明の原理によれば、超音波トランスデューサプローブは、音響的な素子の2次元アレイを含み、この音響的な素子に、導線が伝導性のバッキングブロックアセンブリにより取り付けられる。アセンブリは、交互する複数のフレックス回路及びバッキング材料のプレートを含み、それらが接着結合されて一体のアセンブリを形成する。或いは、伝導性のトレースは、共に結合される各プレートに直接形成することもできる。アセンブリは、導線を曲げることがなく、従来的なトランスデューサ組立て処理を用いて、容易且つ高精度に製造可能である。

#### 【0007】

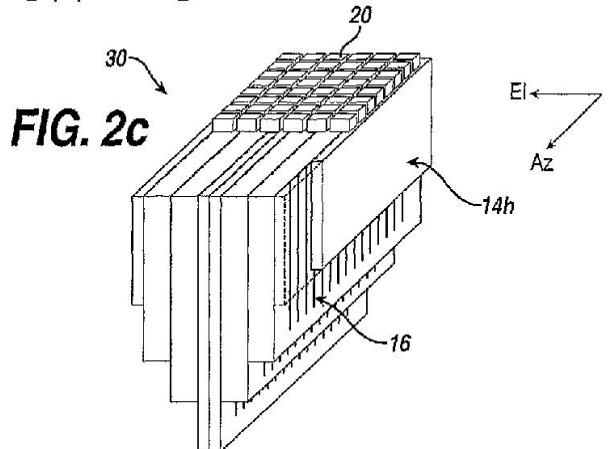

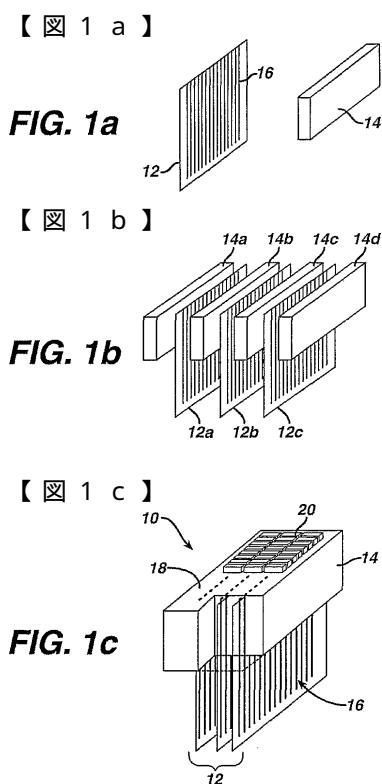

図1a-1cを参照するに、2次元(2D)超音波アレイトランスデューサスタッカのための伝導性バッキングブロックをアセンブルするためのステップが斜視方向から示される

10

20

30

40

50

。バッキングブロックアセンブリは、2つの主要な構成要素、即ちフレックス回路12とバッキングブロックプレート14とを有する。フレックス回路は、カプトン（Kapton）のシートのような分離された基板を含み、その上に、一般的にはフォットエッティングにより、複数の導電性のトレース（配線パターン）が形成される。典型的にはカプトンシートは、1 - 3ミルス（25 μm - 75 μm）の厚さを有する。図1aには、トレース16はカプトン基板の上部で終了するよう示されているが、構成された実施例では、以下で議論するマイクロ写真に示すように、基板の上側のエッジをわずかに越えて延在するトレースを有することが望ましいことがある。トレースの延長部は、トレースとトランステューサ素子の接点から基板をオフセットし、当該接合部でのカプトンの熱膨張による不具合を減らす。トランステューサ素子の最も背後の音響インピーダンスが良好に制御され、カプトン粒子は、研削及びダイシングから低減若しくは完全に除去される。トレース16の下側の終端は、通常的に伝導性の電極端子（図示せず）で終了し、トレースが他のプリント回路や構成要素に接続するようとする。

#### 【0008】

バッキングブロックプレート14は、所定厚さを有するバッキング材料のシートから形成される。バッキングブロックは、通常的に、マイクロバルーン及び小さな粒子のような超音波吸収体及び散乱体が混合されたエポキシから鋳造される。これらの材料の混合物は、知られているように、バッキングブロックに所定の音響インピーダンス及び減衰を付与するように調整される。バッキングブロックプレート14は、制御された研削処理により得られる所定厚さを有する。

#### 【0009】

本発明の原理によると、伝導性のバッキングブロックアセンブリは、図1bの分解図に示すように、フレックス回路12a - 12cとバッキング材料のプレート14a - 14dの交互の層から構成され、これらは、エポキシのような接着剤により共に積層される。プレート14a - 14dは、好ましくは、すべてのプレートが同一の成分を有しそれ故に同一の音響特性を示すようにバッキング材料の同一シートから切断され、同一の調整された厚さまで研削される。構成された実施例では、アセンブリは熱プレスでの圧力下で硬化する。圧搾は、過剰なエポキシを搾り出して、交互のフレックス回路がエレベーション次元に均等に離間するようにし、また、層間から気泡を追い出すようにする。アセンブリが硬化したとき、トランステューサ素子20への接続がなされる上面は、滑らかな仕上げに研削され、好ましくはトランステューサ素子の下側への取り付けのために金メッキされ、トランステューサ素子も好ましくは金メッキされる。伝導性のバッキングブロックアセンブリのトランステューサ素子への接続のための好ましい方法は、エポキシのような低粘度の接着剤を用いた接着取り付けによる。低粘度は、伝導性のバッキングブロックアセンブリの金メッキとトランステューサ素子との間の直接的オーム接触を生むと同時に、2つの表面間の確実な接着結合を形成する。アセンブルされたトランステューサスタック10は、図1cに示され、図中右の矢印は、アジマス（Az）及びエレベーション（El）次元を示す。各フレックス回路12のトレースの列は、一般的には、アレイのアジマス次元を構成し、フレックス回路間の間隔は、エレベーション次元を構成するが、その逆でもよい。通常的な使用は、一般的には、単一のアジマス面で配向及び合焦されるがエレベーション面では合焦のみされる1.5Dアレイに対するケースである。配向及び合焦はアレイの前部の容積で実現される、3次元撮像のための2Dアレイは、定義可能なアジマス及びエレベーション次元を有していないことから、一般的には、極座標で表わされる。しかしながら、この用語は、本出願においては明瞭性のために使用され、図面に対する参照の整合性を維持するために使用される。

#### 【0010】

本発明のアセンブリが、代替的にフレキシブルプリント回路の代わってリジット（例えば、FR4）プリント回路を使用して構成されることは認識されるだろう。フレックス回路は、その薄い形状及び基板を越えて延在するトレースを形成する製造の容易性から好ましい。

10

20

30

40

50

## 【0011】

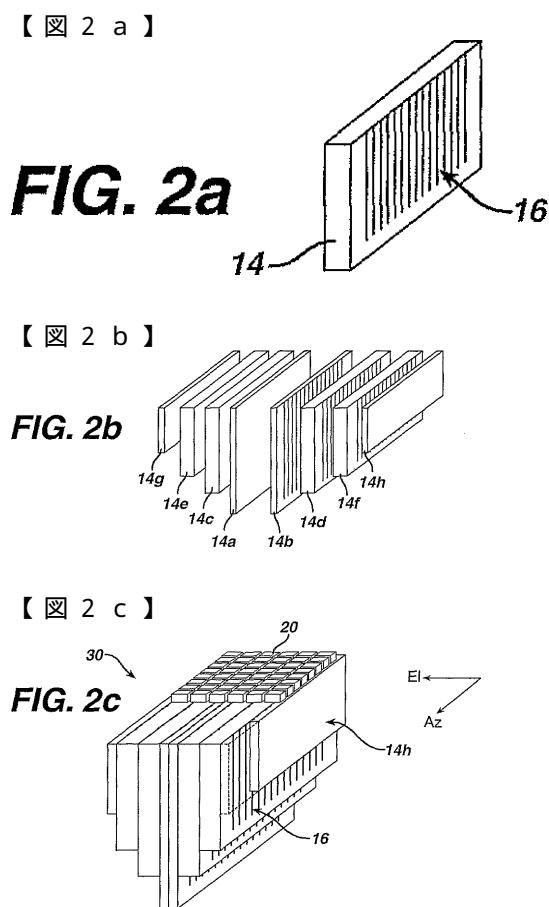

図2a-2cは、本発明の第2実施例を示す。本実施例では、フレックス回路が存在しない。代わりに、伝導性のトレース16は、バッキングブロックプレート14に直接に形成されており、これは、フォットエッチング処理によりなされてよい。従って、トランステューサ素子のエレベーション方向の間隔(ピッチ)は、本実施例のフレックス回路基板の厚さを含まないだろう。上述の如く、トレース16は、底部にて相互接続する電極端子で終了してよいが、プレート4の上部エッジを越えて延在する必要はないだろう。伝導性のバッキングブロックアセンブリは、図2bの分解図に示されるように形成される。この特定の実施例では、バッキングブロックプレート14a-14hは、積極的に異なる長さを有して、トレース(本実施例では、プレートの底部を越えて延在しない)のすべての終端が接続されやすくしてよい。或いは、バッキングブロックプレートは、同一の長さを有して、トレースがバッキングブロックアセンブリの下面で、上面で終了するのと同様に終了するようとする。かかる場合、トレースは、コネクタによる接続のために下面上の電極端子グリッドアレイで終了してよく、コネクタは、アセンブリの下面及びそのトレースと接続する。図示した例の2つの中央のプレート14a, 14bは、それらを囲むプレートに比して半分の厚さとし、これらプレート上の対向する側と逆側にあるトレースが、同一の数の列のトランステューサ素子の2つの中央の列を基準に中心化されるようにする。エンドキャッププレート14g, 14hには、素子が形成されておらず、それらは、最も外側の素子の列を支持しつつ、アセンブリの残り部分を取り囲むためにだけ用いられる。伝導性のバッキングアセンブリの最終処理及びトランステューサの取付は、上述の如く実行される。完成したトランステューサスタック30は、図2cにおいて、伝導性のバッキングアセンブリの上面内を横断するトレースアラインメントを明らかにするために部分的に分離した視点で部分的なアセンブリとして示される。

## 【0012】

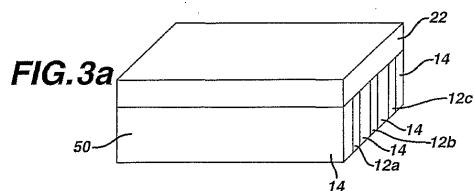

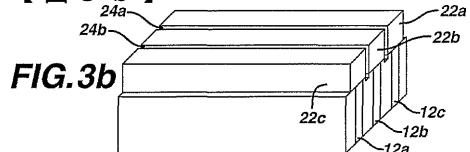

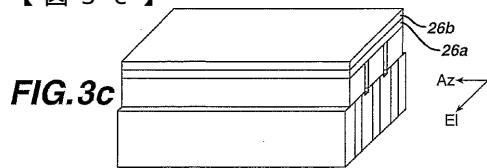

図3a-3cは、伝導性のバッキングブロックアセンブリを備えた本発明のトランステューサスタックの構成を詳細に示す。これらの図面では、伝導性のバッキングブロックアセンブリ50は、交互にあるフレックス回路12及びバッキングプレート14の層を含むが、当該アセンブリは、上述の如く、伝導性のトレースを備えたバッキングプレートから形成されうる。図3aにおいて、伝導性のバッキングブロックアセンブリは、上部に金メッキされ、上部及び底部に金メッキされた圧電素子プレート22に接着により取り付けられている。圧電素子プレート下方のこのアセンブリ50には、例えばアジマス次元に延在する、3つのフレックス回路12a, 12b, 12cが存在する。図3bにおいて、圧電素子プレート22は、2つの切断部24a, 24bによりアジマス次元でダイシングされ、これにより、各々のフレックス回路12a, 12b, 12cの上部にそれぞれ位置する、3つの列の圧電素子22a, 22b, 22cが形成される。切断部は、アセンブリ50と圧電素子22との間の金メッキの接続部を貫通して延在し、これにより、圧電素子の各列の下側のフレックス回路の電気的接続を電気的に分離する。

## 【0013】

2つのマッチング層26a, 26bは、図3cに示すように、圧電素子の上に位置する。マッチング層は、トランステューサの音響インピーダンスを、音響信号を送受する身体に適合させる。マッチング層を積層する前に、伝導性のシート(図示せず)が、上述の如く金メッキされている圧電素子の上面に配設されてよい。好ましくは、圧電素子に接続するマッチング層26aの表面は、トランステューサ素子の上面への接続のために金属被覆される。図3dでは、圧電素子列は、符合30で示すように、アセンブリ50と圧電素子22との間の金メッキの接続部を完全に通過してエレベーション次元でダイシングされて、個々のトランステューサ素子を形成するとともに、各トランステューサ素子の下側の金メッキされたコンタクト部を電気的に分離する。符合28で示すように、これらの切断部は、下側のマッチング層26aを完全に貫通することなく延在し、これにより、エレベーション次元で素子の各ラインを横切る伝導性のシートの連続的なストリップが残される。従って、アレイの内部の素子を含むすべての素子の上側の電極への電気的接続は、アレイの

エレベーション側から実行できる。

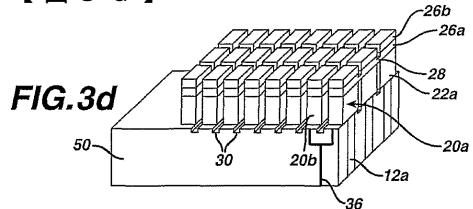

**【0014】**

この特定の例では、サブダイシングされた素子が形成されており、これによりサブダイシングされた素子のアジマス方向で隣接する各対は、より良好な高周波数性能のために一体的な素子として動作する。一のかかる対は、サブ素子20a, 20bからなり、アセンブリ50の側面のフレックス回路12aのY字型の導線36の投影図により指示されるように、下方にあるフレックス回路12aの単一のトレースに接続する。各サブ素子に導線を分配する導線の上部でのY字型により、フレックス回路の導線のビットによるダイシング鋸の巻き込みが生ずることなく、切断部30をアセンブリ50内に作成することができる。アジマス方向にサブダイシングされることに加えて、サブダイシングは、音響性能を改善するために素子のエレベーション方向で実行されてもよい。10

**【0015】**

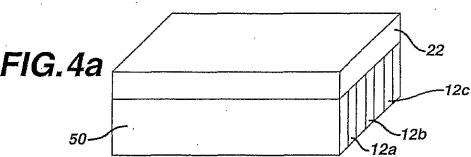

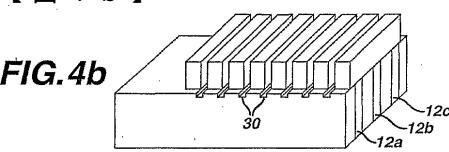

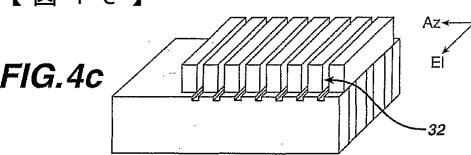

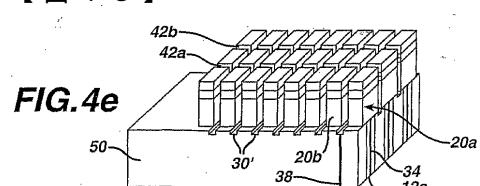

図4a-4eは、例えば米国特許[1999年11月3日に出願された出願シリアル番号09/457, 196]に開示されるようなk<sub>31</sub>モードで動作することになる本発明のトランスデューサスタックの構成を示す。素子の上部(患者に対向する側)と底部との間の縦方向の従来的な励振ではなく、k<sub>31</sub>モードでは、トランスデューサ素子は、横方向に偏極及び励振される。これにより、素子の電極が上部及び底部ではなく素子の側部に位置することが可能となる。図4aの例では、圧電素子プレート22は、埋設されたフレックス回路12a, 12b, 12cを含む伝導性のバッキングブロックアセンブリ50に接着結合されるが、上述の如くエッチングされた導線を備えたバッキングプレートを含みうる。図3の例とは異なり、本実施例では、圧電素子プレートとアセンブリ50との間に金メッキされた電極が存在せず、圧電素子は、単にアセンブリ50の仕上げ面に取り付けられる。図4bでは、圧電素子プレート22は、エレベーション次元でダイシングされて、バッキングブロック及びフレックス回路12a, 12b, 12cの列を横断する圧電素子材料の行を形成する。これらのダイシング切断部30は、下方にあるフレックス回路上の伝導性のトレースに合わせて作製されて、トレースの端部が切断部30の底部に位置するようとする。図4cでは、切断部30内の横方向の対向する壁体32には、電極材料がメッキされ、これは、ウエットメッキ、蒸着やスパッタリング処理により被覆されてよい。この電極は、ダイシング切断部30の横方向の圧電素子の壁体32の双方にだけでなく、伝導性のトレースが終了する切断部の底部にも付着される。従って、この電極は、各切断部の両側で、切断部の底部の伝導性のトレースを圧電素子の横方向の側部に電気的に接続する。2030

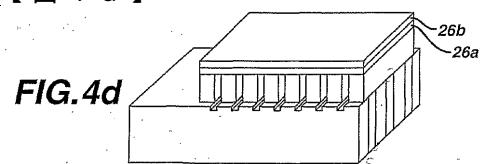

**【0016】**

図4dでは、マッチング層26a, 26bが被覆されている。本実施例では、すべての接続はフレックス回路の導線を介して底部からなされるので、圧電素子の上部に、メッキされた電極若しくはシートを必要としない。2Dアレイは、図4eに示すように、先の切断部30に合わせてエレベーション次元でマッチング層をダイシングすると共に、アジマス次元に延在する個々のトランスデューサ素子の異なる列を形成するために42a, 42bに示すようにアジマス次元で圧電素子の行をダイシングすることにより完成される。ダイシング切断部42a, 42bは、伝導性のバッキングブロック50の上面内部まで作製され、切断部30の交差する底部の伝導性の材料を貫通して、素子の各々の列を電気的に分離するようとする。サブ素子のサブダイシングされた対は、フレックス回路からの接続によりk<sub>31</sub>モードで作動され、列で連続する切断部の導線が、下方にあるフレックス回路のトレースを介して信号(ホット)及びリターン(グランド)経路を交互に提供する。例えば、サブ素子20a, 20bにより形成されるトランスデューサ素子は、図4e中の投影図で示すような、当該素子の列の下方にあるフレックス回路12a上の導線38に、接続する横方向の対向する電極表面を有する。サブ素子の反対側の側面は、フレックス回路12a上の導線34に接続し、また、サブ素子の他の電極側面にて共通の電位若しくはグランド電位を供給する、ダイシング切断部30'(図示せず)の底部で終了する導線に接続する。従って、トランスデューサ素子へのすべての電気的接続は、伝導性のバッキング4050

ブロック 50 の伝導性のトレースを介して実現できる。

#### 【0017】

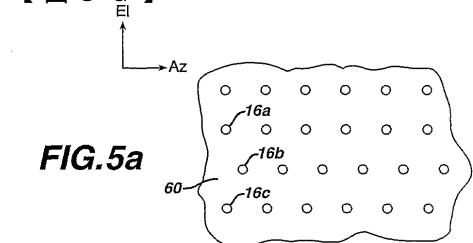

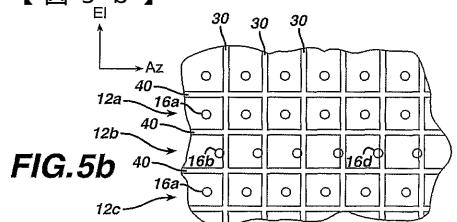

トランステューサ素子が底部で伝導性のバックングブロックのメッキ面と接続する場合には、完全な導線のアラインメントが必要とされないで、伝導性のトレース及び表面上のメッキの組み合わせにより、製造プロセスからのトランステューサスタックの高い生産性が可能となる。例えば、図 5 a は、伝導性のバックングブロックを貫通する伝導性のトレース 16 a, 16 b, 16 c の端部により交差される、バックングブロックの金メッキ表面 60 の平面図である。4 つの水平に配列されたフレックス回路若しくはバックングプレート表面から延在する、伝導性のトレースの 4 つの水平方向の列が示されている。これから、上部、第 2 及び底部の列が本例では鉛直なアラインメントにあるが、伝導性のトレース 16 b を含む第 3 の列は、その他の列と鉛直なアラインメントがないことがわかる。圧電素子プレートがメッキ表面 60 に取り付けられ、整列された伝導性のトレースを基準に中心合わせされて別個のトランステューサ素子にダイシングされるとき、メッキ面は、図 5 b に示すように、素子の底部の着座領域（フットプリント）に適合するメッキ領域に分割される。メッキ領域は、ダイシング切断部 30, 40 により分割される。列 12 a, 12 c の伝導性のトレースは、意図したとおり、各々の素子の着座領域のメッキ領域の中心に良好にアラインされていることがわかる。不整列の伝導性のトレースの列 16 b は、メッキ領域の中心でアラインされていないが、それぞれは意図したメッキ領域に依然として交差しているので、依然として所望の機能を実現するだろう。劇的に中心ずれする 16 d のようなトレースでさえ、メッキ領域との満足できる電気的接続を依然として供給するだろう。特定の実施例では、メッキ領域は、約 0.5 μm の厚さを有してよく、外形寸法は、200 μm × 200 μm のオーダであり、伝導性のトレース 16 の幅は、50 μm のオーダであってよく、各直交方向で 4 : 1 の配置許容公差をトレースに付与する。エレベーション方向の精度は、バックングブロックプレートの厚さを、所望厚さまで研削される際に調整することにより維持される。サブダイシングされた素子は、125 μm × 250 μm の寸法の 2 つのサブ素子を有してよく、比較的広い許容誤差を依然として可能とする。トランステューサ素子及びメッキ領域の着座領域が小さくなり、50 μm × 50 μm に近づくにつれて、伝導性のトレースは、対応してより小さくなることが予測される。

#### 【0018】

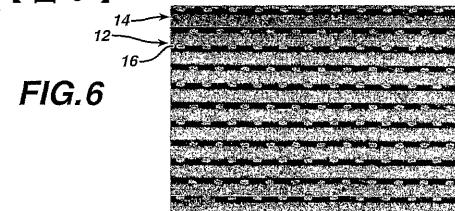

図 6 は、本発明の伝導性のバックングブロックの上面のメッキされる前のマイクロ写真である。このマイクロ写真は、フレックス回路 12 及びバックングブロックプレート 14 の交互に水平の列を明瞭に示している。フレックス回路から延在する伝導性のトレース 16 の端部が明らかにマイクロ写真で確認される。各列におけるこれらの伝導性のトレース 16 の間の黒の領域は、アセンブリと共に結合するエポキシ接着剤が充填されていた空孔である。この図では、伝導性のトレースの端部は、伝導性のバックインプアセンブリの表面でのその終端部までカプトン基板の上で延在する。

#### 【0019】

また、このマイクロ写真は、フレックス回路の列が、列から列へと千鳥配列で交互に整列されていることを示す。これは、この特定の伝導性のバックインプアセンブリが、トランステューサ素子が六角形の集合を形成するような相互に三角形関係を繰り返す、六角形の 2D アレイトランステューサのために設計されているからである。かかる 2D 六角形アレイは、例えば米国特許 [2000 年 1 月 21 日に出願された出願シリアル番号 09/488,583] に開示される。従って、本発明は、かかる六角形アレイのような構成及び他の形状と共に直線 2D アレイに適用可能である。

#### 【0020】

例示された実施例は、圧電素子トランステューサを使用して示されているが、本発明は、伝導性のバックングブロックアセンブリを介して電気的に接続されてよい、容量性及び圧電性の微細加工された変換器（micromachined transducer）（Cmut s 及び Pmut s）のような他のトランステューサ技術にも同等に適用可能である。Cmut 型トランステューサは、例えば米国特許第 5619476 号に開示されている。

10

20

30

40

50

## 【図面の簡単な説明】

【図 1】 図 1 a - 1 c は、本発明の原理により構成された伝導性のバッキングブロックを備えた超音波トランスデューサスタックの第 1 実施例を示す。

【図 2】 図 2 a - 2 c は、本発明の原理により構成された伝導性のバッキングブロックを備えた超音波トランスデューサスタックの第 2 実施例を示す。

【図 3】 図 3 a - 3 d は、本発明の原理により構成された細切断されたトランスデューサ素子を備えた超音波トランスデューサスタックを示す。

【図 4】 図 4 a - 4 e は、本発明の原理により構成され  $k_{3,1}$  モードで動作するトランスデューサ素子を備えた超音波トランスデューサスタックを示す。

【図 5】 図 5 a 及び 5 b は、トランスデューサ素子の着座領域を基準とした本発明のバッキングブロック内の導線のアラインメントを示す。

【図 6】 2 次元六角形アレイに対する本発明の伝導性のバッキングブロックのマイクロ写真である。

【図 3 a】

【図 3 b】

【図 3 c】

【図 3 d】

【図 4 a】

【図 4 b】

【図 4 c】

【図 4 d】

【図 4 e】

【図 6】

【図 5 a】

【図 5 b】

---

フロントページの続き

(72)発明者 ダヴィッドセン, リチャード

オランダ国, 5656 アーアー アインドーフェン, プロフ・ホルストラーン 6

審査官 志摩 兆一郎

(56)参考文献 特開2000-214144(JP, A)

特開平06-335091(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04R 17/00

|                |                                                                        |         |            |

|----------------|------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 多维超声换能器阵列                                                              |         |            |

| 公开(公告)号        | <a href="#">JP3939652B2</a>                                            | 公开(公告)日 | 2007-07-04 |

| 申请号            | JP2002542543                                                           | 申请日     | 2001-11-13 |

| [标]申请(专利权)人(译) | 皇家飞利浦电子股份有限公司                                                          |         |            |

| 申请(专利权)人(译)    | 皇家飞利浦电子股份有限公司的Vie                                                      |         |            |

| 当前申请(专利权)人(译)  | 皇家飞利浦电子股份有限公司的Vie                                                      |         |            |

| [标]发明人         | ダヴィッドセンリチャード                                                           |         |            |

| 发明人            | ダヴィッドセン,リチャード                                                          |         |            |

| IPC分类号         | H04R17/00 A61B8/00 G01N29/24 B06B1/06                                  |         |            |

| CPC分类号         | B06B1/0622 B06B1/0607                                                  |         |            |

| FI分类号          | H04R17/00.330.H H04R17/00.330.J H04R17/00.332.Y A61B8/00 G01N29/24.502 |         |            |

| 代理人(译)         | 伊藤忠彦<br>木田 博                                                           |         |            |

| 优先权            | 09/714030 2000-11-15 US                                                |         |            |

| 其他公开文献         | JP2004514340A                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                              |         |            |

## 摘要(译)

公开了二维超声波换能器阵列堆叠包括板和交替的声吸收材料，其被粘结在一起的柔性电路。板的厚度限定柔性电路之间的高度尺寸并且对应于二维阵列的仰角方向上的间距。可以通过将导电迹线直接光刻蚀到背衬材料板上来形成背衬块，将背衬块胶合在一起以形成背衬块组件。

【図 2c】