(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-188423

(P2008-188423A)

(43) 公開日 平成20年8月21日(2008.8.21)

(51) Int.Cl.

A61B 8/00 (2006.01)

F 1

A 61 B 8/00

### テーマコード（参考）

4C601

審査請求 未請求 請求項の数 5 O.L. (全 17 頁)

|              |                            |

|--------------|----------------------------|

| (21) 出願番号    | 特願2008-14688 (P2008-14688) |

| (22) 出願日     | 平成20年1月25日 (2008. 1. 25)   |

| (31) 優先権主張番号 | 11/669, 235                |

| (32) 優先日     | 平成19年1月31日 (2007. 1. 31)   |

| (33) 優先権主張国  | 米国 (US)                    |

(71) 出願人 390041542

ゼネラル・エレクトリック・カンパニー

GENERAL ELECTRIC COMPANY

アメリカ合衆国、ニューヨーク州、スケネクタディ、リバーロード、1番

(74) 代理人 100093908

弁理士 松本 研一

(74) 代理人 100105588

弁理士 小倉 博

(74) 代理人 100129779

弁理士 黒川 俊久

(74) 代理人 100137545

弁理士 荒川 聰志

最終頁に続く

(54) 【発明の名称】 超音波撮像システム

(57) 【要約】

【課題】サイズ及び重量の低減した超音波撮像システムを提供する。

【解決手段】超音波撮像システム(100)は、サブアレイ(140)内に形成した複数のトランシージューサ素子(136)と、複数のサブアレイ回路ユニット(160')とを含む。各ユニット(160')内の回路は、第1の集積回路(340)が第2の集積回路(330)を覆うように積み重ね型構成で形成される複数の集積回路(330、340、350)を備える。一例では、第1の集積回路(340)はその表面(342)に沿った第1の複数の第1結合パッド(345)を含み、また第2の集積回路(330)はその表面(331)に沿った第2の複数の第2結合パッド(335)を含んでおり、第1及び第2の結合パッドの対の間にこれらの間に入力/出力信号接続を提供するために結合ワイヤ(344)が伸びている。

### 【選択図】図 3

**【特許請求の範囲】****【請求項 1】**

探触子ユニット(130)と該探触子ユニット(130)とケーブル(132)を介して接続させたシステムコンソール(110)とを有するタイプの超音波撮像システム(100)であって、

隣り合わせたサブアレイ(140)の形に形成される横列と縦列の形に配列させた複数のトランスジューサ素子と、

その各々が前記トランスジューサ素子の1つのサブアレイ(140)に接続されている複数のサブアレイ回路ユニット(160)であって、各ユニット内の回路は少なくともその第1の集積回路(240)がその第2の集積回路(230)を覆うように積み重ね型構成で形成されるような複数の集積回路(230、240、250)を備えている複数のサブアレイ回路ユニット(160)と、

前記トランスジューサ素子(136)と前記サブアレイ回路ユニット(160)の間に電気接続を提供する複数の配線構造と、を備えている、

前記回路ユニットのうちの少なくとも1つについて、その第1の集積回路(240)はその表面(342)に沿って第1の複数の第1結合パッド(345)を含みかつその第2の集積回路(230)はその表面に沿って第2の複数の第2結合パッド(335)を含んでおり、第1と第2の結合パッドの対(335、345)の間をこれらの間に入力/出力信号接続を提供するための結合ワイヤが延びている、超音波撮像システム(100)。

**【請求項 2】**

各回路ユニットは、そのうちの1つが音響信号を生成するための送信回路を備え、そのうちの1つが反射された信号の処理のための受信器回路を備え、かつそのうちの1つがパルスタイミング調整のための制御回路を備えるような少なくとも3つの集積回路を含む、請求項1に記載の超音波撮像システム。

**【請求項 3】**

前記複数のサブアレイ回路ユニット及び前記複数の配線構造は前記探触子ユニット内に位置決めされた回路基板構造である、請求項1に記載の超音波撮像システム。

**【請求項 4】**

前記複数のサブアレイの各々は、複数のトランデューサ素子の全アレイが複数のトランデューサ素子の行及び列に配された二次元アレイであり、前記複数のサブアレイ回路ユニットのうちの少なくとも幾つかは前記システムコンソール内に位置決めされている、請求項1に記載の超音波撮像システム。

**【請求項 5】**

第3の集積回路と、前記第2の集積回路と該第3の集積回路の間の接続を実現する前に前記第1の集積回路上の結合パッドから延び出ている追加的な結合ワイヤと、を含む請求項3に記載の超音波撮像システム。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は超音波撮像システムに関し、さらに詳細にはビーム形成用電子回路を有するシステムに関する。

**【背景技術】****【0002】**

医学的用途のためのリアルタイム3D超音波撮像はハンドヘルド型探触子ユニット内に恐らくは数千個のトランスジューサ素子及び付属の信号処理電子回路からなるアレイを収容することが必要である。これより小さいシステム(例えば、有するアレイ素子がわずか数百個など)では、画像作成のための処理回路の本質的にすべてを包含するようにマルチワイヤケーブルを介してトランスジューサ信号をシステムコンソールに伝達することが通常であった。しかし数千個や数万個あるいはこれ以上の数のトランスジューサ素子を包含するより大型のアレイでは、遠隔ユニットでその信号処理のすべてを実行することは困難

でありかつ非現実的である。これをすると、トランジューサ素子とコンソール内に配置された処理回路との間にそれぞれが別々の接続を形成するような専用のリードが必要となる。この問題に対処するために、処理回路の限られた部分が探触子内に配置されてきた。例えば、トランジューサ素子の大きなアレイを、例えば各サブアレイごとにビーム形成及び処理回路からなる専用のユニット（本明細書において、サブアレイ回路ユニットと呼ぶ）を備えるトランジューサ素子の数を10～40個の範囲とした均一なサイズのサブアレイに分割することがある。各サブアレイ回路ユニットは、そのサブアレイ内のトランジューサ素子のすべてによって生成された信号を単一のチャンネルまたはワイヤ内で合成とすることが可能である（例えば、アナログビーム形成による）。この構成や別の構成では、より低減した数のケーブルリードを介してアレイ内の素子のすべてから受け取った信号をコンソール内の処理回路に転送することができる。この方法では、管理可能なケーブルサイズを維持しながら数千個の信号を転送することが可能である。

10

#### 【0003】

探触子の回路機能を実現するために、各サブアレイ回路ユニットは通常、高電圧送信器回路、低電圧受信器回路及びディジタル制御回路を含む。これらの異なる回路機能を実現するには、これら異なる回路機能が異なる半導体製造プロセスを必要とするため、複数の集積回路（例えば、特定用途向け集積回路（ASIC））が必要となる。サブアレイ回路のすべてに関して必要な複数のASIC構成要素は、探触子ユニットの利用可能なスペースのうちの比較的大きな体積を消費する。3つの機能のすべてを1つのモノリシックなダイ内に製作することは非現実的であるため、これらのサブアレイ回路ユニットの収容に要する体積はハンドヘルド型探触子ユニット内に収容されるトランジューサアレイの実用的サイズを制限する1つの要因となることがある。サイズ及び重量の問題は、検査手技の間にハンドヘルド型探触子ユニットを操縦し得る容易さに影響を及ぼす。

20

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0004】

探触子ユニット及びコンソールのサイズ及び重量の低減に対する要求は、ノートブック型コンピュータシステムを用いて構成されることがある可搬型超音波撮像システムに特に関連性が高い。一般にサイズ及び重量は、可搬型のハンドヘルド探触子ユニットを用いるシステムに関する達成可能な画質を制限する可能性がある制約要因である。このために、多くのハンドヘルド型探触子ユニットは、配線及び回路の量を最小限にしこれによりこれらの基準を満たすために比較的少ない数のトランジューサ素子を利用する。しかしながら、画質が向上すればこれらのシステムの診断上の有用性を増大させ得ることが分かっている。

30

#### 【課題を解決するための手段】

#### 【0005】

一実施形態では、超音波撮像システムは、その各々がトランジューサ素子を複数包含したサブアレイのマトリックスの形で形成したアレイ状のトランジューサ素子を含む。回路ユニットに接続されたトランジューサ素子の各サブアレイは、各ユニットの回路が2個以上の集積回路を積み重ね型構成で含んでおり、各ユニットは音響信号を発生させるための送信回路、反射された信号を処理するための受信器回路及び制御回路を含んでいる。回路ユニットから画像情報を受け取るためにシステムコンソールが結合されており、このシステムコンソールは画像を表示するための画像処理回路を含んでいる。このサブアレイはすべて第1の面に沿って位置決めされており、その集積回路のうちの第1の集積回路は第1の面と平行な第2の面内に位置決めされており、かつその集積回路のうちの第2の集積回路は第1の面と平行な第3の面内に位置決めされている。

40

#### 【0006】

別の実施形態では、超音波撮像システムは、隣り合わせたサブアレイの形に形成されたトランジューサ素子と、その各々が該トランジューサ素子の1つのサブアレイに接続されたサブアレイ回路ユニットと、を含む。各ユニット内の回路は、少なくともその集積

50

回路のうちの第1の集積回路がその集積回路のうちの第2の集積回路を覆うように積み重ね型構成で形成された複数の集積回路を含む。複数の回路基板構造によって、トランジスタ素子とサブアレイ回路ユニットの間に電気接続が提供される。回路ユニットの少なくとも1つに関して、その第1の集積回路はその表面に沿って第1の複数の第1結合パッドを含みかつその第2の集積回路はその表面に沿って第2の複数の第2結合パッドを含み、また第1及び第2の結合パッドからなる対の間にはこれらの間に入力／出力信号接続を提供するために結合ワイヤが延びている。

【0007】

さらに別の実施形態では、超音波撮像システムは、トランジスタ素子ユニットと、画像データを処理し表示するためのシステムコンソールと、を含む。この探触子ユニットは、その各々がトランジスタ素子を複数包含したサブアレイのマトリックスの形で配列させたアレイ状のトランジスタ素子を含む。複数のサブアレイ回路ユニットの各々は、互いを覆うように積み重ね型構成で形成させた複数の集積回路を含む。各回路ユニットは、トランジスタ素子のサブアレイのうちの1つに接続されている。マルチ配線ユニットによって、トランジスタ素子のサブアレイと回路ユニットのサブアレイとの間に電気接続が提供され、また少なくとも1つのサブアレイ回路ユニットとシステムコンソールの間に入力／出力信号接続が提供される。複数の取外し可能クランプによって1つまたは複数のフレキシブル回路と回路基板の間に接続が提供される。その集積回路のうちの第1の集積回路は第1の面内に位置決めされており、またその集積回路のうちの第2の集積回路は第1の面と平行な第2の面内に位置決めされており、ここでこの第1の集積回路はその表面に沿って形成した複数の結合パッドを含んでおり、この回路ユニットはこれら第1及び第2の集積回路の間に接続を提供するために第1の集積回路上の結合パッドのうちの幾つかから第2の回路まで延びる結合ワイヤを含んでいる。

10

20

30

40

50

【発明を実施するための最良の形態】

【0008】

以下の説明を添付の図面と合わせて読むことによって本発明をより明瞭に理解できよう。

【0009】

図面全体を通じて同じ参照番号は同じ特徴要素を示すために使用している。図面内の個々の特徴要素は縮尺どおりでない場合がある。

【0010】

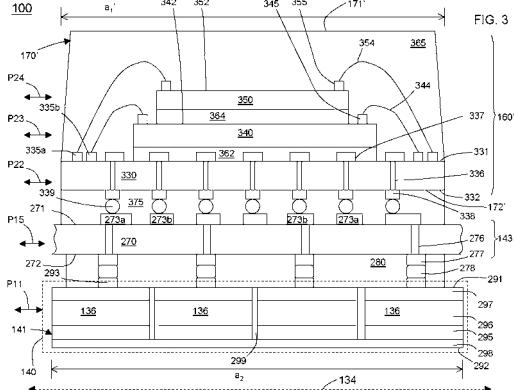

図1は、システムコンソール110、ディスプレイ120及び大面積トランジスタ素子ユニット130を含む例示的な超音波撮像システム100の部分像を示している。探触子ユニットは、順に160-1から160-128までの参照番号を付けた128個のサブアレイ回路ユニット160を収容している。探触子ユニット130はハンドヘルド型とすることがある。探触子ユニット130とシステムコンソール110の間で128本の信号線133を備えたマルチワイヤケーブル132を介して情報が転送される。各信号線133は、システムコンソール110内のラインコネクター115と探触子ユニット130内のラインコネクター135との間を結合している。コンソール110は、主ビーム形成回路114及び走査変換器116と結合させたシステム制御器112を含む電子回路により処理するために信号線133を介してサブアレイ回路ユニット160から画像情報を受け取る。制御器112はさらに、探触子130内のサブアレイ回路ユニット160と結合され、これによりシステム100に対する全体的制御を提供する。主ビーム形成回路114は個々のサブアレイ回路ユニット160から受け取った電気信号を処理し、セクタ走査信号を生成する。画像処理回路を有する走査変換器116はこのセクタ走査信号を、ディスプレイ120上への画像提示に適したラスタ信号に変換する。

【0011】

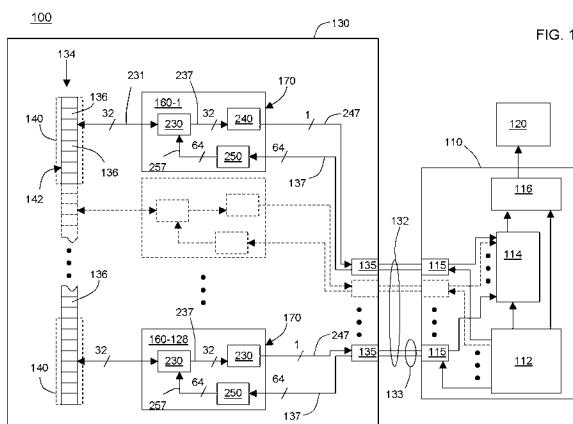

さらに図2を見ると、探触子ユニット130は、マルチ配線ユニット143により形成されたインターフェースを介してサブアレイ回路ユニット160に接続されたトランジスタ素子13からなる2次元線形アレイ134を含む。例示的なトランジスタ素子

134は、128個のサブアレイ140からなるマトリックスの形に配列させた4096個のトランスジューサ素子136を含む。各サブアレイ140は、4横列141と8縦列142に沿って配列させた32個のトランスジューサ素子136を有する。図1では、素子136の例示的な縦列142をサブアレイ140内の8つの縦列からなる群を示す破線によって表している。あるサブアレイ140の横列に対応するような4つの隣接する横列141の素子136を図2に表している。この例では、面P11に沿った直交する方向に横列141と縦列142が形成されている。

#### 【0012】

動作時においてサブアレイ140内の各トランスジューサ素子136は超音波信号を送信し、対象物（例えば、検査を受けている患者）から反射された超音波信号を受信する。各サブアレイ回路ユニット160は、パルス信号を発生させてトランスジューサ素子サブアレイ140に送るための回路を有する送信器ASIC230と、トランスジューサ素子136から受け取った反射信号を処理するための回路を有する受信器ASIC240と、パルスタイミング調整のための送信制御回路を有する制御器ASIC250と、を備える。各回路ユニット160において、制御器ASIC250は受信器ASIC240を覆うように形成され、受信器ASIC240は送信器ASIC230を覆うように形成される積み重ね型構成170となっており、本明細書ではこれをマルチチップモジュール170とも呼ぶ。ASICを積み重ねる具体的な順序は様々とすることができる、図示した例示的実施形態は可能な複数の構成のうちの1つである。さらに、ASIC230、240及び250の間で機能を分担している例示的なシステムは単に一例であって、様々なASIC設計及びマルチチップモジュールの様々な層の中で送信器、受信器及び制御回路に関する可能な多くのグループ分けが存在する。マルチチップモジュール170の構成によって、同じ面内にサブストレートと接続する（例えば、ボールグリッドアレイを用いる）ために位置決めされた複数の集積回路のそれぞれを有するシステムと比べてサブアレイ回路ユニット160のサイズが大幅に低減される。

10

20

30

40

#### 【0013】

マルチチップモジュール170では、ユニット160内部のASICデバイス間の電気接続に関する寄生キャパシタンスが大幅に低減される。というのは結合ワイヤのうちの多くが、回路基板内に形成された比較的長い電気的トレースを用いて製作されることになるのが一般的であるような接続が比較的短い距離で実現されることに由来する。

#### 【0014】

図1に示すように、各制御器ASIC250は、ライン137に沿ってシステム制御器112から64個の信号を受け取り、マルチチップモジュール170内のライン257に沿って64個の送信信号を送信器ASIC230に送出する。送信信号に応答して、送信器ASIC230は32個のパルス信号を生成してトランスジューササブアレイ140に送出する。各パルス信号は32本の個別ライン231のうちの1つに沿って伝播し、これにより各トランスジューサ素子136は異なるパルス信号を受け取ることができ、また一体となってアレイ内の素子が検査中の対象物に伝播させた所望の特性をもつ音響信号を同期させている。次いで各サブアレイ140内の素子は対象物から反射された信号のエネルギーを吸収しており、また送信器ASIC230はこれを示す電気信号を32本の個別ライン231のうちの1つに沿ったサブアレイ140から受け取っている。この信号情報は、32本のライン上の情報が单一チャンネルサブアレイ信号線247の上に組み合わせられるように32本の個別ライン237に沿ってASIC230から受信器ASIC240に転送される。この方式により、ケーブル132内の信号線の本数を大幅に低減することができる。

30

#### 【0015】

図2は、サブアレイ回路ユニット160内におけるASIC230、240及び250の接続、及び上側表面291及び下側表面292を有する対応するサブアレイ140内のトランスジューサ素子136へのマルチ配線ユニット143を介した接続を表している。この例では、マルチ配線ユニット143は、上側表面271に沿って形成した複数の上側

50

F C B トレース 273 (例えば、273a、273b、その他) 及び下側表面 272 に沿って形成した複数の下側 F C B 接触パッド 277 を有するフレキシブル回路基板 (F C B) 270 である。下側 F C B 接触パッド 277 の各々の上には、はんだバンプ 278 が形成される。トランジスタ素子 136 の隣接するトランジスタササブアレイ 140 は、向き設定を目的としたその水平方向を規定する面 P11 に沿って延びており、これにより垂直方向が面 P11 と直交すると共に、上側と下側位置は水平方向を基準とすることになる。

【0016】

上側表面 171 及び下側表面 172 を有するマルチチップモジュール 170 では、制御器 A S I C 250 はその上側表面 252 に沿って複数の制御器 A S I C 結合パッド 255 を有しており、また受信器 A S I C 240 はその上側表面 242 に沿って複数の受信器 A S I C 結合パッド 245 を有しており、さらにまた送信器 A S I C 230 はその上側表面 232 に沿って複数の送信器 A S I C 結合パッド 235 を有している。A S I C 230 は、上側表面 227、下側表面 228、複数のサブストレート結合パッド 225 (例えば、225a、225b 及び 225c) 並びに複数のサブストレートビア 226 を有するルート設定用サブストレート 220 上に形成される。サブストレート 220 は、上側及び下側表面 227 及び 228 に沿って銅またはアルミニウムから形成した導電層と積層させた絶縁材料 (例えば、ポリイミド樹脂薄膜) の層 221 を備えており、これを上側導電性トレース 222 及び下側導電性トレース 224 を形成するようにパターン形成しあつエッティングしている。

10

【0017】

複数の制御器 A S I C 結合用ワイヤ 254、受信器 A S I C 結合ワイヤ 244 並びに送信器 A S I C 結合ワイヤ 234 によって、各マルチチップモジュール 170 内部の A S I C 間の電気接続が提供される。別の実施形態では、マルチチップモジュール 170 の上側表面 171 に沿ってパッケージからの熱除去を強化するために熱拡散器を設けることがある。

20

【0018】

制御器 A S I C 結合用ワイヤ 254 は、ルート設定用サブストレート 220 上で制御器 A S I C 結合用パッド 255 を第 1 群 225a のサブストレート結合用パッド 225 と電気的に接続させている。受信器 A S I C 結合用ワイヤ 244 は受信器 A S I C 結合用パッド 245 を第 2 群 225b のサブストレート結合用パッド 225 と電気的に接続させており、また送信器 A S I C 結合用ワイヤ 234 は送信器 A S I C 結合用パッド 235 を第 3 群 225c のサブストレート結合用パッド 225 と電気的に接続させている。サブストレート結合用パッド 225 は、ルート設定のためにパターン形成された上側トレース 222 に接続されている。ルート設定用サブストレート 220 内の貫通ビア 226 (すなわち、めっき貫通穴) は、上側トレース 222 を下側トレース 224 と電気的に接続させている。下側トレース 224 上に形成した入力 / 出力 (I / O) はんだボール 229 によって、マルチチップモジュール 170 とマルチ配線ユニット 143 の F C B 270 の間の電気接続が実現される。送信器 A S I C 230 は、第 1 の接着剤層 260 によりサブストレート 220 の上側表面 227 に取り付けるために面 P11 と平行で上方にある第 2 の面 P12 内に位置決めされている。受信器 A S I C 240 は、第 2 の接着剤層 262 により送信器 A S I C 230 に取り付けるために第 2 の面 P12 と平行で上方にある第 3 の面 P13 内に位置決めされている。制御器 A S I C 250 は、第 3 の接着剤層 264 により受信器 A S I C に取り付けるために面 P13 と平行で上方にある第 4 の面 P14 内に位置決めされている。絶縁プラスチックモールドキャップ 265 が、A S I C 230、240 及び 250、結合パッド 235、245 及び 255、結合用ワイヤ 234、244 及び 254、並びにサブストレート 220 の上側表面 227 を封入保護している。

30

【0019】

個々のトランジスタ素子 136 のそれぞれは、圧電材料層 296 に押し当てて形成した整合層 295 を備える。整合層 295 によって検査対象に音響エネルギーを送信し検

40

50

査対象から音響信号を受信するのに適した音響特性が提供される。圧電材料層 296 は、トランスジューサ接触パッド 293 及びはんだバンプ 278 を介してマルチ配線ユニット 143 に接続させた下側または後側電極 297 を覆うように形成されている。各トランスジューサ素子内の後側電極 297、整合層 295 及び圧電材料層 296 は、トランスジューサ構成要素 296 及び後側電極 297 のそれぞれを生成するように平行鋸引きによって作成され得る一連のスペースまたは切溝 299 によって、別のトランスジューサ素子の同種の構成要素から電気的に隔離させている。比較的薄い導体材料から形成するのが典型的である前側電極 298 は、トランスジューサ素子のサブアレイ 140 全体内の素子 136 の整合層 295 を覆うように被着させ、これによりサブアレイ 140 に対する共通接地を提供している。

10

## 【0020】

トランスジューサ素子 136 はさらに、検査中の対象物から離れる方向に送信された音響エネルギーを吸収または散乱させるのに適した音響特性を有する脱整合層（図示せず）または裏当て層を含むことがある。これによって、トランスジューサ素子の後ろ側にある構造または界面から音響エネルギーが反射されて圧電材料に戻るのが防止される。この音響裏当て材料は、ゴム、エポキシ、プラスチックなどの減衰用の軟材料内に金属粒子（例えば、タングステン）を複合させたものからなることがある。別の音響裏当て材料組成を用いることもある。トランスジューサ素子は例えば、ジルコン酸チタン酸鉛トランスジューサ（PZT）、容量性マイクロマシン加工超音波トランスジューサ（cMUT）、圧電マイクロマシン加工超音波トランスジューサ（pMUT）、あるいはポリフッ化ビニリデン（PVDF）トランスジューサとすることがある。

20

## 【0021】

各はんだバンプ 278 を下側 FCB 接触パッド 277 上に形成した状態で、複数の導電性フレックス貫通ビア 276 が、FCB 270 の上側表面 271 から下側表面 272 まで延びてあり、第 1 群 273a の上側 FCB トレース 273 によってサブアレイ 140 内の各トランスジューサ素子 136 と対応する上側導電性トレース 222 との間に電気接続が提供される。上側トレース 222 は、サブストレート結合パッド 225c と送信器 ASIC 結合パッド 235 に接続した送信器 ASIC 結合ワイヤ 234 とを介して送信器 ASIC 230 に接続されている。第 2 群 273b の上側 FCB トレース 273 によって、マルチチップモジュール 170 とシステムコンソール内の電子回路の間に I/O 接続（図示せず）が提供される。マルチチップモジュール 170 は、誘電体接着剤 275 によって FCB 270 の上側表面 271 に取り付けられている。第 1 の面 P11 と平行な第 5 の面 P15 に沿って位置決めされた FCB 270 は、誘電体接着剤 280 によって各トランスジューササブアレイ 140 の上側表面 291 に沿って取り付けられている。FCB 270 はさらに脱整合層の役割をすることがある。別の実施形態では、複数のフレキシブル回路基板によって I/O 接続用のマルチ配線ユニット 143 を形成することがあり、またマルチチップモジュール 170 と FCB 270 の間に、あるいは FCB 270 とトランスジューササブアレイ 140 の間に追加的な脱整合層が設けられることがある。

30

## 【0022】

図 2 の像を得た面に沿った方向において、マルチチップモジュール 170 の下側表面 172 に沿って計測した横方向寸法  $a_1$  は、トランスジューササブアレイ 140 の下側表面 292 に沿って計測した横方向寸法  $a_2$  より小さいかこれに等しい。これによって、隣接するサブアレイ 140 間に大きなギャップを有することなくサブアレイ 140 の大きなマトリックスの形成が可能となる。

40

## 【0023】

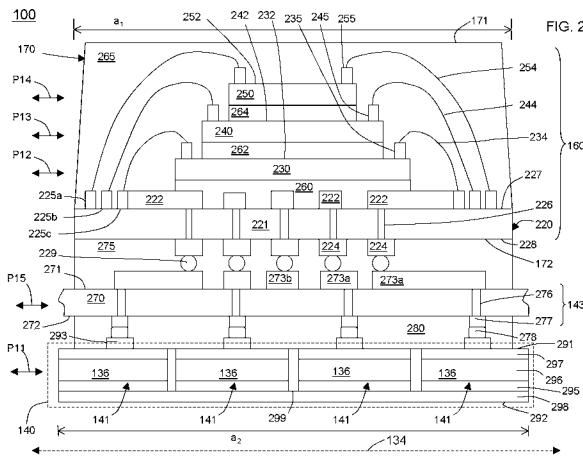

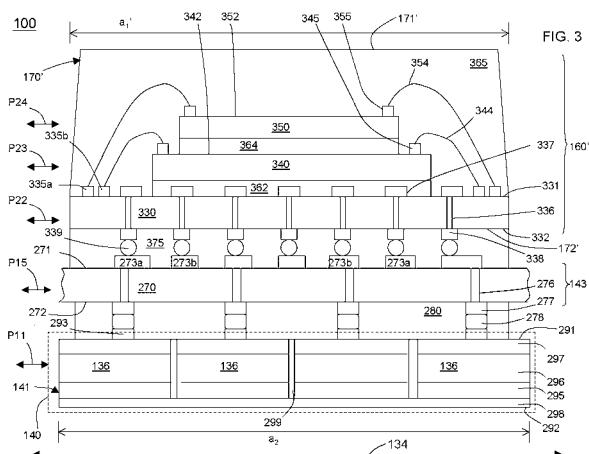

図 3 は、トランスジューサ素子 136 の隣接するトランスジューササブアレイ 140 を面 P11 に沿って延びるようにした図 2 に関連して記載したようなマルチ配線ユニット 143 を介してトランスジューサ素子サブアレイ 140 に対して、回路ユニット 160 の代わりに複数のサブアレイ回路ユニット 160' が各々接続されているような第 2 のマルチチップモジュール 170' を表している。

50

## 【0024】

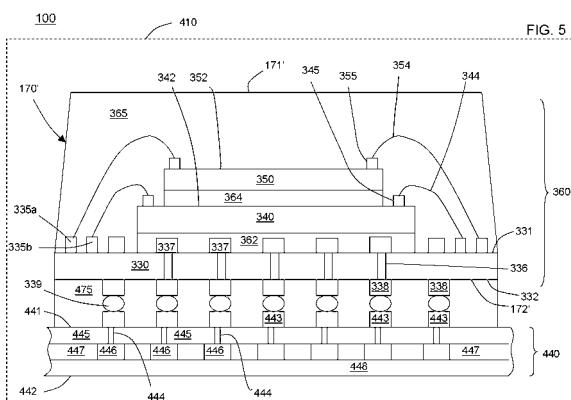

上側及び下側表面 171'、172'を有する各マルチチップモジュール 170'は積み重ね型構成となった一連のASICを含む。その上側表面 352に沿って形成した複数の結合パッド 355を有する制御器ASIC 350は、その上側表面 342に沿って形成した複数の結合パッド 345を有する受信器ASIC 340を覆うように形成されており、また受信器ASIC 340はその上側表面 331に沿って形成した複数の結合パッド 335を有する送信器ASIC 330を覆うように形成されている。送信器ASIC 330はさらに、複数のダイ貫通ビア 336と、下側表面 332に沿って形成した複数の接触パッド 338と、を含む。この例では、マルチチップモジュール 170'内の3つのASICダイのうちの最下側にあるASIC 330は、制御器ASIC 350及び受信器ASIC 340上の回路のためのルート設定用サブストレートの役割をする。マルチチップモジュール 170'内の3つのASIC間に電気接続を提供するために、ASIC 330から複数の制御器ASIC 結合用ワイヤ 354及び複数の受信器ASIC 結合用ワイヤ 344が伸びている。10

## 【0025】

制御器ASIC 結合用ワイヤ 354は、制御器ASIC 結合用パッド 355を第1群 335aの送信器ASIC 結合用パッド 335に電気的に接続させている。受信器ASIC 結合用ワイヤ 344は、受信器ASIC 結合用パッド 345を第2群 335bの送信器ASIC 結合用パッド 335に電気的に接続させている。送信器ASIC ダイ 330内部の金属化構造(図示せず)を介してASIC間のルート設定が提供される。送信器ASIC 結合用パッド 335は、上側表面 331に沿って形成した上側トレース 337を介して、銅やアルミニウムなどの導体材料で満たすことがあるダイ貫通ビア 336に接続されている。ダイ貫通ビア 336は、結合パッド 335を下側表面 172'に沿って形成した接触パッド 338に電気的に接続させている。接触パッド 338上にはI/O接続のために入力/出力(I/O)はんだボール 339が形成されている。したがってASIC 330、340及び350をはんだボール 339と電気的に接続させている。配線パターンまたはトレース 337を有する送信器ASIC 330が面P11と平行な第2の面P22内に位置決めされると共に、誘電体接着剤層 375によってFCB270の上側表面に取り付けられている。受信器ASIC 340は第2の面P22と平行な第3の面P23に沿って位置決めされると共に、接着剤層 362によって送信器ASIC 330に対してこれから垂直方向に離間させて取り付けられている。制御器ASIC 350は同じく第2の面P22と平行な第4の面P24に沿って位置決めされると共に、別の接着剤層 364によって受信器ASIC 340に取り付けられている。絶縁プラスチックモールドキャップ 365はASIC 340及び350、結合用ワイヤ 344及び354、結合パッド 335、345及び355、並びに送信器ASIC 330の上側表面 331を封入保護している。20

## 【0026】

図3の像を得た面内において、下側表面 172'に沿って得られるマルチチップモジュール 170'の横方向寸法 a<sub>1</sub>'は、下側表面 292'に沿って得られるトランジューササブアレイ 140の横方向寸法 a<sub>2</sub>より小さいかこれに等しい。これによって、隣接するサブアレイ 140間に大きなギャップを有することなく、サブアレイ 140の大きなマトリックスの形成が可能となる。30

## 【0027】

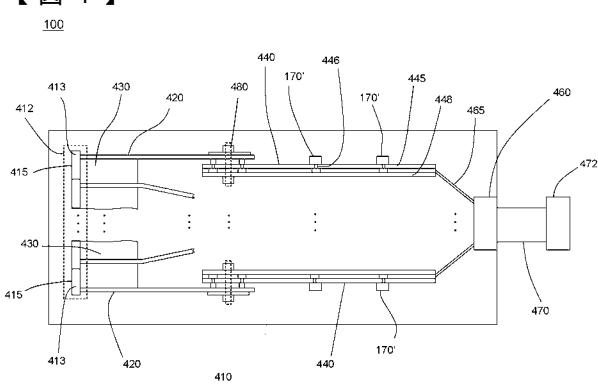

別の実施形態では図4は、図3を参照しながら記載した複数のマルチチップモジュール 170'を備えるシステム 100に関する探触子ユニット 410の部分断面図を示している。探触子 410は、トランジューサ素子 413の2次元アレイ 412と、電気的トレース(図示せず)を有する複数のフレキシブル回路 420またはフレックスと、その各々が1つまたは複数のマルチチップモジュール 170'を有する複数のプリント回路基板(PCB) 440と、を備える。トランジューサ素子 413は、その各々が1横列のトランジューサ素子 413を備える複数のサブアレイ 415の形に配列させている。各サブアレイ 415は、対応するマルチチップモジュール 170'との接続のためにフレックス40

回路 420 と結合させている。フレックス 420 は、エポキシなどの材料から形成した非導電性スペーサ 430 によって互いから隔離させている。各フレックス 420 は、1つまたは複数の取外し可能クランプ 480 によって対応する PCB 440 と結合させている。複数のフレキシブルコネクター 465 は PCB 440 を探触子ラインコネクター 460 と連絡している。探触子ラインコネクター 460 は、マルチチップモジュール 170' と図 1 に示した主ビーム形成器 114 などの電子構成要素との間で信号を転送するためにケーブルバンドル 470 によってシステムライン 472 と結合させている。

#### 【0028】

クランプ 480 により PCB 440 にフレックス 420 を接続することによって構成要素を別々に製作して組み上げることが可能となる。したがって、トランジスタアレイ 412 を従来どおり低温度条件下で製作し、PCB 440 を形成する構成要素の比較的高温での組み上げとは別に分離された処理においてフレックス 420 と組み上げができる。マルチチップモジュール 170' は、トランジスタアレイ 415 を高温条件に曝すことなくリフロー炉内で 250°C を超える温度で PCB 440 上に装着することができる。さらに、別の分離した処理であるため、PCB 440 内の敏感な構成要素を汚染物質に曝露させることなくトランジスタアレイ 412 に鋸引き処理や研磨処理などの物理的処理を受けさせることができる。これがなければ、研磨処理中に発生する導電性粒子によって PCB 構成要素内に短絡が生じる可能性がある。クランプ接続によって、PCB 構成要素の製作及び組み上げに関連する工程から分離させてトランジスタアレイ 412 を製作した後にフレックス 420 と PCB 440 の組み上げが実現される。したがって、別の構成要素が劣化することを懸念することなく各構成要素ごとに製作工程を最適化することが可能である。各フレックス 420 は係合用コネクター、異方性導電薄膜、バンプ結合またはホットバー (hot bar) 結合によって対応する PCB と結合させることができる。クランプ接続または係合用コネクターを利用する場合、フレックス 420 と PCB 440 は容易かつ反復して結合及び脱結合させることができる。これによって、トランジスタアレイ 412 と PCB 440 のいずれに障害が生じた際にも探触子ユニット 410 の修復が容易になり、これにより損傷した構成要素をそれ以外の構成要素を廃棄することなく交換することができる。

#### 【0029】

図 5 は、システム 100 に関して、マルチチップモジュール 170' (図 3 に図示) と図 4 に示した PCB 440 のうちの 1 つとの間の例示的な電気接続を表している。各マルチチップモジュール 170' が送信器 ASIC 330 を覆うように位置決めされた受信器 ASIC 340 を覆うように位置決めされた制御器 ASIC 350 を含む場合、複数の接触パッド 338 は送信器 ASIC の下側表面 332 に沿って形成される。接触パッド 338 上には I/O 接続のために入力 / 出力 (I/O) はんだボール 339 が形成される。送信器 ASIC 結合用パッド 335 は上側トレース 337 によってダイ貫通ビア 336 に接続される。上側表面 441 及び下側表面 442 を有する PCB 440 は 3 つの隣接する誘電体層 445、447 及び 448 を備える。I/O はんだボール 339 と上側レベル誘電体層 445 内に形成された上側レベルビア 444 との間に接続を提供するように、PCB 接触パッド 443 が上側表面 441 に沿って形成される。ビア 444 は、中間レベル誘電体 447 内に形成したアンダーレイ内側導体 446 と接触している。送信器 ASIC 330 は誘電体接着剤層 475 によって PCB 440 の上側表面 441 に取り付けられている。PCB 440 は、トランジスタアレイ 415 とマルチチップモジュール 170' の間に電気接続を提供し、さらにマルチチップモジュール 170' と図 1 に示したシステムコンソール 110 内の電子回路との間に電気接続を提供している。

#### 【0030】

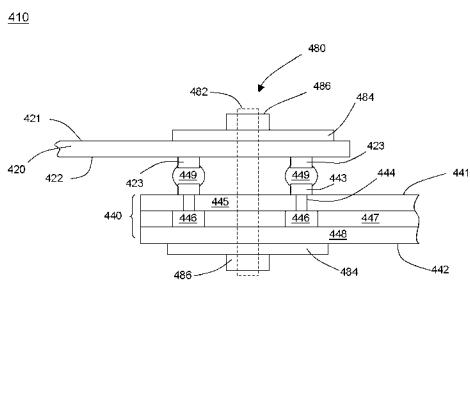

1 つまたは複数のクランプ 480 による PCB 440 とフレックス 420 の間の例示的な電気接続を図 6 の部分断面図に表している。図 6 に関連して記載する PCB 440 は、上側表面 441 と、下側表面 442 と、3 つの隣接する誘電体層 (上側層 445、中間レベル層 447 及び下側層 448) と、を含む。1 つまたは複数の接触パッド 443 が上側

10

20

30

40

50

表面441に沿って形成されており、また上側レベルビア444が上側レベル誘電体層445内に形成されている。アンダーレイ内側導体446が中間レベル誘電体447内に形成されている。複数の金バンプ449はPCB接触パッド443上に形成される。上側表面421及び下側表面422を有するフレックス420は、下側表面422に沿って形成したフレックス接触パッド423を含む。図示を簡略とするために図6では、2つのPCB接触パッド443と2つのフレックス接触パッド423のみを示している。フレックス420内及びPCB440内にはクランプ用に1つまたは複数の穴が設けられている。各クランプ480は、接続用ボルト482、1対のワッシャー484及び1対のナット486を備える。フレックス420のクランプ用穴をPCB440のクランプ用穴と整列させた後、クランプボルト482を挿入してワッシャー484及びナット486で固定させる。クランプ圧によって、金バンプ449、フレックス接触パッド423及びPCB接触パッド443の間の電気的接触が実現される。代替として、フレックス接触パッド423とPCB接触パッド443を圧縮によって一体に結合させることがある。この結合は圧縮の前に接触パッド423及び443に金めっきを施すことによって実現されることがある。

10

## 【0031】

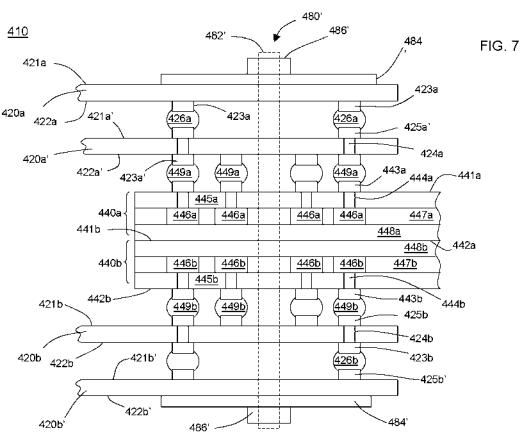

図7の部分断面図で示した一実施形態では、フレックス420とPCB440間の電気接続はさらにクランプ処理によって実現される。2つのPCB440a及び440bと4つのフレックス420a、420a'、420b及び420b'が1つまたは複数のクランプ480'によって接合される。第1のPCB440aは第1及び第2のフレックス420a及び420a'に結合されており、また第2のPCB440bは第3及び第4のフレックス420b及び420b'に結合されている。別の実施形態では、PCB440に對して3つ以上のフレックス420を結合させることがある。

20

## 【0032】

上側表面421a及び下側表面422aを有する第1のフレックス420aは下側表面422aに沿って形成した2つのフレックス接触パッド423a（本明細書ではこれを第1のフレックス下側接触パッド423aと呼ぶ）を有する。上側表面421a'及び下側表面422a'を有する第2のフレックス420a'は上側表面421a'に沿って形成した2つのフレックス接触パッド425a'（本明細書ではこれを第2のフレックス上側接触パッド425a'と呼ぶ）を有する。下側表面422a'に沿って4つのフレックス接触パッド423a'が形成されている。第2のフレックス420a'はさらに、第2のフレックス上側接触パッド425a'と第2のフレックス下側接触パッド423a'の間に接続を提供する2つのフレックス貫通ビア424aを含む。第1のフレックス420aの下側接触パッド423aの各々は、第1のフレックス420aの対応するフレックストレース（図示せず）と結合されており、また第2のフレックス420a'の下側接触パッド423a'の各々は、第2のフレックス420a'の対応するフレックストレース（図示せず）と結合されている。上側表面421b及び下側表面422bを有する第3のフレックス420bは上側表面421bに沿って形成した4つの上側フレックス接触パッド425bと、下側表面422bに沿って形成した2つの下側フレックス接触パッド423bと、を有する。第3のフレックス420bはさらに、第3のフレックス上側接触パッド425bと第3のフレックス下側接触パッド423bの間に接続を提供する2つのフレックス貫通ビア424bを含む。上側表面421b'及び下側表面422b'を有する第4のフレックス420b'は、上側表面421b'に沿って形成した2つの上側フレックス接触パッド425b'を有する。第3のフレックス420bの各上側接触パッド425bは、第3のフレックス420bの対応するフレックストレース（図示せず）と結合されており、また第4のフレックス420b'の各上側接触パッド425b'は第4のフレックス420b'の対応するフレックストレース（図示せず）と結合されている。フレックス420内にはクランプ用に1つまたは複数の穴（図示せず）が設けられている。

30

## 【0033】

上側表面441a及び下側表面442aを有する第1のPCB440aは、上側表面441aに沿って形成したPCB第1接触パッド443aと、上側レベル誘電体層445a

40

50

内に形成した上側レベルピア 444a と、中間レベル誘電体 447a 内に形成したアンダーレイ内側導体 446a と、誘電体層 448a と、を含む。上側表面 441b 及び下側表面 442b を有する第 2 の PCB440b は、下側表面 442b に沿って形成した第 2 の PCB 接触パッド 443b と、下側レベル誘電体層 445b 内に形成した下側レベルピア 444b と、中間レベル誘電体 447b 内に形成したアンダーレイ内側導体 446b と、オーバーレイ誘電体層 448b と、を含む。PCB440 内にはクランプ用に 1 つまたは複数の穴（図示せず）が設けられている。各クランプ 480' は、接続用ボルト 482'、1 対のワッシャー 484' 及び 1 対のナット 486' を備える。複数の金バンプ 426（例えば、426a、426b）は、第 2 のフレックス上側接触パッド 425a' 上及び第 4 のフレックス上側接触パッド 425b' 上に形成されている。複数の金バンプ 449（例えば、449a、449b）は、第 1 の PCB 接触パッド 443a 上及び第 2 の PCB 接触パッド 443b 上に形成されている。フレックス 420 と PCB440 のクランプ用穴を整列させた後、クランプボルト 482' を挿入してワッシャー 484' 及びナット 486' で固定させる。クランプ圧によって金バンプ 426、449 とフレックス接触パッド 423 の間の電気的接触が実現される。別の実施形態では、フレックス 420 が 1 つまたは複数のマルチチップモジュールを有する半剛性フレキシブル回路基板（FCB）に取り付けられることがある。さらに別の実施形態では、マルチチップモジュール 440 がフレックス回路 420 上に直接装着されることがある。

10

## 【0034】

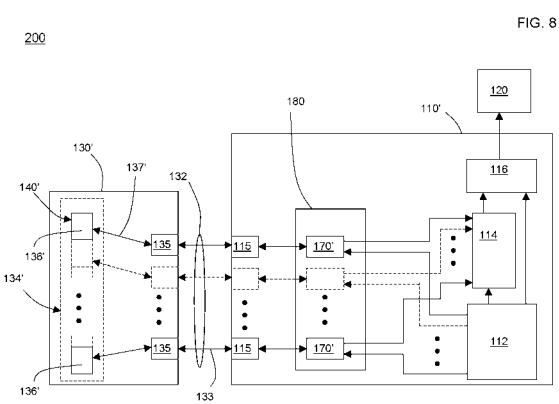

図 8 は、超音波撮像システム 200 内にマルチチップモジュール 170' を備える別の実施形態を表している。例示的な超音波撮像システム 200 は、システムコンソール 110'、ディスプレイ 120 及びトランスジューサアレイ探触子 130' を含む。図 8 のマルチチップモジュール 170' はシステムコンソール 110' 内に配置されている。探触子 130' は、トランスジューサ素子 136' のアレイ 134' を備える。トランスジューサ素子 136' は、その各々が 1 横列のトランスジューサ素子 136' を備えた複数のサブアレイ 140' の形に配列させている。探触子 130' とシステムコンソール 110' の間でマルチワイヤケーブル 132 を介して情報が転送される。ケーブル 132 内の各ワイヤ 133 は、システムラインコネクター 115 と探触子ラインコネクター 135 のそれぞれによってシステムコンソール 110' と探触子 130' に結合されている。フレキシブル回路 137' はトランスジューサ素子 136' のサブアレイ 140' を対応する探触子ラインコネクター 135 に接続している。コンソール 110' は、主ビーム形成回路 114、走査変換器 116、並びに送信器回路、受信器回路及び制御器回路を有する複数のマルチチップモジュール 170' と結合されたシステム制御器 112 を含む。マルチチップモジュール 170' は PCB180 上に装着されている。システム制御器 112 は、マルチチップモジュール 170' 内の制御器回路を不要としてマルチチップモジュール 170' 内の送信回路にタイミング信号を直接提供することができる。主ビーム形成器 114 は、個々のマルチチップモジュール 170' から電気信号を受け取り、この信号を処理してセクタ走査信号を発生させる。走査変換器 116 はこのセクタ走査信号をディスプレイ 120 上での提示に適したラスタ表示信号に変換する。

20

30

## 【0035】

超音波撮像システムのマルチチップモジュール 170 の実施形態を説明してきた。マルチチップモジュール 170 は、トランスジューサ 142 のサブアレイ 140 と直接結合されることがある。モジュール 170 は図 4 に示すように探触子 410 内のフレキシブル回路 420 及び PCB440 を介して結合せざることがある。モジュール 170 は図 8 に示すようにシステムコンソール 110 内の PCB 上に装着されることがある。各マルチチップモジュールは積み重ねた一連の集積回路ダイを備えること（例えば、制御器 ASIC、受信器 ASIC 及び送信器 ASIC を積み重ねることによって形成すること）ができる。マルチチップモジュールはさらにビーム形成器回路を備えることがある。マルチチップモジュール構成によってサブアレイ回路ユニット 160 の 3 次元空間要件に関する大幅な軽減が提供される。これによって、ハンドヘルド型探触子内に高密度で比較的大面積のト

40

50

ンスジューサアレイを形成するように比較的稠密なサブアレイ 140 をタイル配置することが可能となる。マルチチップモジュール構成によって、サイズの低減及び性能の向上（例えば、寄生キャパシタンスの低下）が提供される。

【0036】

本発明の幾つかの実施形態について図示し説明してきたが、本発明はこれに限定されるものではない。当業者によって本特許請求の範囲に記載した本発明の精神及び趣旨を逸脱することなく多くの修正形態、変形形態、代替形態及び等価形態が実施されよう。また、図面の符号に対応する特許請求の範囲中の符号は、単に本願発明の理解をより容易にするために用いられているものであり、本願発明の範囲を狭める意図で用いられたものではない。そして、本願の特許請求の範囲に記載した事項は、明細書に組み込まれ、明細書の記載事項の一部となる。

10

【図面の簡単な説明】

【0037】

【図1】超音波撮像システムの簡略概要図である。

【図2】図1のシステム内に形成し得る例示的なトランジューサ及びマルチチップモジュール回路の断面図である。

【図3】図1のシステム内に形成し得るトランジューサ及びマルチチップモジュール回路の別の例の断面図である。

【図4】図1のシステム内への組み込みに適した例示的な探触子ユニットの断面図である。

20

【図5】図4の探触子ユニット内のマルチチップモジュールを表した断面図である。

【図6】図4に示した探触子ユニットの特徴要素を表した別の断面図である。

【図7】図4に示した探触子ユニットの特徴要素を表した別の断面図である。

【図8】本発明の一実施形態による超音波撮像システムを表した図である。

【符号の説明】

【0038】

P 1 1 面

30

P 1 2 第2の面

P 1 3 第3の面

P 1 4 第4の面

P 1 5 第5の面

P 2 2 第2の面

P 2 3 第3の面

P 2 4 第4の面

1 0 0 超音波撮像システム

40

1 1 0 システムコンソール

1 1 2 システム制御器

1 1 4 主ビーム形成回路

1 1 5 ラインコネクター

1 1 6 走査変換器

1 2 0 ディスプレイ

1 3 0 大面積トランジューサアレイ探触子ユニット

1 3 2 マルチワイヤケーブル

1 3 3 1 2 8 本の信号線

1 3 4 2次元線形アレイ

1 3 5 ラインコネクター

1 3 6 トランジューサ素子

1 3 7 ライン

1 4 0 1 2 8 個のサブアレイ

1 4 1 4つの横列

50

|       |                           |    |

|-------|---------------------------|----|

| 1 4 2 | 8 つ の 縦 列                 |    |

| 1 4 3 | マルチ配線ユニット                 |    |

| 1 6 0 | 1 2 8 個 の サブアレイ回路ユニット     |    |

| 1 7 0 | マルチチップモジュール               |    |

| 1 7 1 | 上 側 表 面                   |    |

| 1 7 2 | 下 側 表 面                   |    |

| 2 2 0 | ルート 設 定 用 サブストレート         |    |

| 2 2 1 | 層                         |    |

| 2 2 2 | 上 側 導 電 性 ト レース           | 10 |

| 2 2 4 | 下 側 導 電 性 ト レース           |    |

| 2 2 5 | サブストレート 結合 パッド            |    |

| 2 2 6 | サブストレート ビア                |    |

| 2 2 7 | 上 側 表 面                   |    |

| 2 2 8 | 下 側 表 面                   |    |

| 2 2 9 | 入力 / 出力 ( I / O ) はんだ ボール |    |

| 2 3 0 | 送信器 A S I C               |    |

| 2 3 1 | 個 別 の ライン                 |    |

| 2 3 2 | 上 側 表 面                   |    |

| 2 3 4 | 送信器 A S I C 結合 ワイヤ        | 20 |

| 2 3 5 | 送信器 A S I C 結合 パッド        |    |

| 2 3 7 | 個 別 の ライン                 |    |

| 2 4 0 | 受信器 A S I C               |    |

| 2 4 2 | 上 側 表 面                   |    |

| 2 4 4 | 受信器 A S I C 結合 ワイヤ        |    |

| 2 4 5 | 受信器 A S I C 結合 パッド        |    |

| 2 4 7 | 単一 チャンネル サブアレイ 信号線        |    |

| 2 5 0 | 制御器 A S I C               |    |

| 2 5 2 | 上 側 表 面                   |    |

| 2 5 4 | 制御器 A S I C 結合 用 ワイヤ      | 30 |

| 2 5 5 | 制御器 A S I C 結合 パッド        |    |

| 2 5 7 | ライン                       |    |

| 2 6 0 | 第 1 の 接 着 剂 層             |    |

| 2 6 2 | 第 2 の 接 着 剂 层             |    |

| 2 6 4 | 第 3 の 接 着 剂 层             |    |

| 2 6 5 | 融 蝕 性 プラスチック モールド キャップ    |    |

| 2 7 0 | フレキシブル 回路 基板 ( F C B )    |    |

| 2 7 1 | 上 側 表 面                   |    |

| 2 7 2 | 下 側 表 面                   |    |

| 2 7 3 | F C B ト レース               | 40 |

| 2 7 5 | 誘 電 体 接 着 剂               |    |

| 2 7 6 | ビア                        |    |

| 2 7 7 | 下 側 F C B 接 触 パッド         |    |

| 2 7 8 | はんだ バンプ                   |    |

| 2 8 0 | 誘 電 体 接 着 剂               |    |

| 2 9 1 | 上 側 表 面                   |    |

| 2 9 2 | 下 側 表 面                   |    |

| 2 9 3 | トランスジュー サ 接 触 パッド         |    |

| 2 9 5 | 整 合 層                     |    |

| 2 9 6 | 圧 電 材 料 层                 |    |

| 2 9 7 | 下 側 ま た は 後 側 電 極         | 50 |

|       |                          |    |

|-------|--------------------------|----|

| 2 9 8 | 前側電極                     |    |

| 2 9 9 | 切溝                       |    |

| 3 3 0 | 送信器 A S I C              |    |

| 3 3 1 | 上側表面                     |    |

| 3 3 2 | 下側表面                     |    |

| 3 3 5 | 送信器 A S I C 結合用パッド       |    |

| 3 3 6 | ダイ貫通ビア                   |    |

| 3 3 7 | トレース                     |    |

| 3 3 8 | 接触パッド                    |    |

| 3 3 9 | 入力 / 出力 ( I / O ) はんだボール | 10 |

| 3 4 0 | 受信器 A S I C              |    |

| 3 4 2 | 上側表面                     |    |

| 3 4 4 | 受信器 A S I C 結合用ワイヤ       |    |

| 3 4 5 | 受信器 A S I C 結合用パッド       |    |

| 3 5 0 | 制御器 A S I C              |    |

| 3 5 2 | 上側表面                     |    |

| 3 5 4 | 制御器 A S I C 結合用ワイヤ       |    |

| 3 5 5 | 結合用パッド                   |    |

| 3 6 2 | 接着剤層                     |    |

| 3 6 4 | 接着剤層                     | 20 |

| 3 6 5 | 絶縁プラスチックモールドキャップ         |    |

| 3 7 5 | 誘電体接着剤層                  |    |

| 4 1 0 | 探触子ユニット                  |    |

| 4 1 2 | 2次元アレイ                   |    |

| 4 1 3 | トランジスチューサ素子              |    |

| 4 1 5 | サブアレイ                    |    |

| 4 2 0 | フレキシブル回路                 |    |

| 4 2 1 | 上側表面                     |    |

| 4 2 2 | 下側表面                     |    |

| 4 2 3 | フレックス接触パッド               | 30 |

| 4 2 6 | 金パンプ                     |    |

| 4 3 0 | 非導電性スペーサ                 |    |

| 4 4 0 | プリント回路基板 ( P C B )       |    |

| 4 4 1 | 上側表面                     |    |

| 4 4 2 | 下側表面                     |    |

| 4 4 3 | P C B 接触パッド              |    |

| 4 4 4 | レベルビア                    |    |

| 4 4 5 | 隣接する誘電体層                 |    |

| 4 4 7 | 隣接する誘電体層                 |    |

| 4 4 8 | 隣接する誘電体層                 | 40 |

| 4 4 6 | 内側導体                     |    |

| 4 4 9 | 金パンプ                     |    |

| 4 6 0 | 探触子ラインコネクター              |    |

| 4 6 5 | フレキシブルコネクター              |    |

| 4 7 0 | ケーブルバンドル                 |    |

| 4 7 2 | システムライン                  |    |

| 4 7 5 | 誘電体接着剤層                  |    |

| 4 8 0 | 取外し可能クランプ                |    |

| 4 8 2 | 接続用ボルト                   |    |

| 4 8 4 | 1対のワッシャー                 | 50 |

4 8 6 1 対のナット

( 义 1 )

FIG. 1

【 図 2 】

【 义 3 】

【图4】

【圖 5】

【図6】

【 四 7 】

〔 8 〕

---

フロントページの続き

- (72)発明者 ブルーノ・ハンス・ハイダー

アメリカ合衆国、ニューヨーク州、ボールストン・レイク、ウエストサイド・ドライブ、64番

- (72)発明者 キール・クリストファーソン

ノルウェイ、オスロ、モンテベロヴェイエン・7番

- (72)発明者 レイエット・アン・フィッシャー

アメリカ合衆国、ニューヨーク州、ニスカユナ、バークレー・アベニュー、2305番

- (72)発明者 トーマス・ハリヴォースロッド

ノルウェイ、ヴェストフォード、トルヴスロッド、バーベリスヴェイエン・5番

- (72)発明者 ロバート・ウッドニッキ

アメリカ合衆国、ニューヨーク州、ニスカユナ、ドアウォルツ・ブルヴァード、1509番

F ターム(参考) 4C601 BB03 EE13 GA02 GA03 GB06 GB18 GB41 LL26

|                |                                                                                         |         |            |

|----------------|-----------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | <无法获取翻译>                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2008188423A5</a>                                                          | 公开(公告)日 | 2012-11-22 |

| 申请号            | JP2008014688                                                                            | 申请日     | 2008-01-25 |

| [标]申请(专利权)人(译) | 通用电气公司                                                                                  |         |            |

| 申请(专利权)人(译)    | 通用电气公司                                                                                  |         |            |

| [标]发明人         | ブルーノ・ハンス・ハイダー<br>キール・クリストファーソン<br>レイエット・アン・フィッシャー<br>トーマス・ハルヴォースロッド<br>ロバート・ウッドニッキ      |         |            |

| 发明人            | ブルーノ・ハンス・ハイダー<br>キール・クリストファーソン<br>レイエット・アン・フィッシャー<br>トーマス・ハルヴォースロッド<br>ロバート・ウッドニッキ      |         |            |

| IPC分类号         | A61B8/00                                                                                |         |            |

| CPC分类号         | A61B8/00 A61B1/0005 B06B1/0622 G01S7/5208 G01S15/8925 G01S15/8927 G03B42/06             |         |            |

| FI分类号          | A61B8/00                                                                                |         |            |

| F-TERM分类号      | 4C601/BB03 4C601/EE13 4C601/GA02 4C601/GA03 4C601/GB06 4C601/GB18 4C601/GB41 4C601/LL26 |         |            |

| 代理人(译)         | 松本健一<br>小仓 博                                                                            |         |            |

| 优先权            | 11/669235 2007-01-31 US                                                                 |         |            |

| 其他公开文献         | <a href="#">JP5530597B2</a><br><a href="#">JP2008188423A</a>                            |         |            |

### 摘要(译)

要解决的问题：提供尺寸和重量减小的超声成像系统。超声成像系统包括形成在子阵列中的多个换能器元件和多个子阵列电路单元。每个单元(160')中的电路包括以堆叠配置形成的多个集成电路(330,340,350)，使得第一集成电路(340)覆盖第二集成电路(330)。配备了。在一个示例中，第一集成电路(340)包括沿其表面(342)的第一多个第一接合焊盘(345)和第二集成电路(330)。沿着第一和第二键合焊盘沿着第一多个键合焊盘(335)的第二多个第二键合焊盘(335)，在第一和第二键合焊盘对之间提供耦合线(305)以提供输入/344)延伸。点域