(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2008-517736

(P2008-517736A)

(43) 公表日 平成20年5月29日(2008.5.29)

(51) Int.Cl.

A 6 1 B 8/00 (2006.01)

F 1

A 6 1 B 8/00

テーマコード(参考)

4 C 6 0 1

審査請求 未請求 予備審査請求 未請求 (全 41 頁)

(21) 出願番号 特願2007-556129 (P2007-556129)

(86) (22) 出願日 平成17年8月25日 (2005.8.25)

(85) 翻訳文提出日 平成19年6月19日 (2007.6.19)

(86) 國際出願番号 PCT/US2005/030237

(87) 國際公開番号 WO2007/086817

(87) 國際公開日 平成19年8月2日 (2007.8.2)

(31) 優先権主張番号 10/978,175

(32) 優先日 平成16年10月29日 (2004.10.29)

(33) 優先権主張国 米国(US)

(71) 出願人 390041542

ゼネラル・エレクトリック・カンパニー

GENERAL ELECTRIC COMPANY

アメリカ合衆国、ニューヨーク州、スケネクタディ、リバーロード、1番

(74) 代理人 100093908

弁理士 松本 研一

(74) 代理人 100105588

弁理士 小倉 博

(74) 代理人 100129779

弁理士 黒川 俊久

(74) 代理人 100137545

弁理士 荒川 聰志

最終頁に続く

(54) 【発明の名称】センサ素子の再構成可能なアレイのための最適化スイッチング構成

## (57) 【要約】

【課題】再構成可能な超音波アレイを提供する。

【解決手段】超音波アレイは、結果として得られる素子の形状を波頭の形状に合致するように作ることができるよう、複数群の部分素子を動的に接続することができる。これにより、性能を改善し、及び/又はチャンネル数を減らすことができる。このような再構成可能性はスイッチング回路網を使用して達成することができる。このスイッチング回路網の性能を改善するためにスイッチング回路網の構成を適切に選ぶための方法及びアルゴリズムを開示する。

【選択図】図1 2

**【特許請求の範囲】****【請求項 1】**

再構成可能なセンサ素子アレイの制御中にスイッチ回路網によって導入されるエラーを最小にするスイッチング構成を具現化するための方法であって、

( a ) 初期スイッチング構成を生成する段階と、

( b ) ( i ) スイッチング回路網のエラー、開始時に入力される前記初期スイッチング構成、及びその後に相次いで入力される相次いで導き出された修正スイッチング構成の全てを考慮に入れてシステムの応答を算出するシステム・モデルに、スイッチ構成を入力する段階、

( i i ) 前記入力されたスイッチ構成と共に前記モデルを使用して画像又は放射パターンを生成する段階、

( i i i ) 生成されたパターンを表すデータに少なくとも部分的に基づいてコスト関数についての値を算出する段階、

( i v ) 算出した値が前記コスト関数についての最小値を実質的に表しているかどうか決定する段階、及び

( v ) 算出した値が前記コスト関数についての最小値でない場合、前記値算出の結果の関数として現在のスイッチング構成を修正して、修正スイッチング構成に達する段階を含み、

これらの段階( i )乃至( v )を各スイッチング構成について繰り返す反復アルゴリズムを遂行する段階と、

( c ) 算出した値が前記コスト関数についての最小値である場合、コスト関数の値を最小にした修正スイッチング構成により前記スイッチング回路網を構成する段階と、を有する方法。

**【請求項 2】**

前記の構成する段階は、前記スイッチの状態を制御するための制御回路をプログラムする段階を含んでいる、請求項 1 記載の方法。

**【請求項 3】**

前記の算出した値が前記コスト関数についての最小値を実質的に表しているかどうか決定する段階は、模擬アニーリング型のアルゴリズムを使用して遂行される、請求項 1 記載の方法。

**【請求項 4】**

使用される前記コスト関数は、所定の閾値よりも大きいスイッチ距離を持つセンサ素子の数である、請求項 1 記載の方法。

**【請求項 5】**

使用される前記コスト関数は用途により変わる、請求項 1 記載の方法。

**【請求項 6】**

第1のコスト関数が、前記センサ素子アレイが送信モードで動作しているときに使用するための第1のスイッチング構成を最適化するために使用され、また第2のコスト関数が、前記センサ素子アレイが受信モードで動作しているときに使用するための第2のスイッチング構成を最適化するために使用される、請求項 5 記載の方法。

**【請求項 7】**

第1のコスト関数が、前記センサ素子アレイが第1組のシステム・パラメータに従って動作しているときに使用するための第1のスイッチング構成を最適化するために使用され、また第2のコスト関数が、前記センサ素子アレイが第2組のシステム・パラメータに従って動作しているときに使用するための第2のスイッチング構成を最適化するために使用される、請求項 5 記載の方法。

**【請求項 8】**

前記方法は、前記センサ素子アレイの構成が変わったときに常に遂行される、請求項 1 記載の方法。

**【請求項 9】**

10

20

30

40

50

前記方法は、前記センサ素子アレイの動作環境内の所定の温度変化が検出されたときに常に遂行される、請求項1記載の方法。

【請求項10】

前記センサ素子アレイは撮像システムに結合され、前記方法は前記撮像システムがターンオンされたときに常に遂行される、請求項1記載の方法。

【請求項11】

前記センサ素子アレイは、撮像システムに結合することのできるプローブ内に組み込まれており、またコスト関数の値を最小にした前記修正スイッチング構成を表すデータが前記プローブ内のメモリに記憶される、請求項1記載の方法。

【請求項12】

前記センサ素子アレイは、撮像システムに結合することのできるプローブ内に組み込まれており、またコスト関数の値を最小にした前記修正スイッチング構成を表すデータが前記撮像システム内のメモリに記憶され且つ後で前記プローブ内の局部的メモリへダウンロードされる、請求項1記載の方法。

【請求項13】

コスト関数の値を最小にした前記修正スイッチング構成を表すデータが走査中にプローブ内の局部的メモリから読み出される、請求項1記載の方法。

【請求項14】

前記方法は、前記スイッチングについて理想的な抵抗値を仮定して設計段階中に遂行される、請求項1記載の方法。

【請求項15】

各センサ素子はそれぞれの超音波トランステューサ素子であり、前記方法は、前記超音波トランステューサ素子について理想的な容量値を仮定して設計段階中に遂行される、請求項13記載の方法。

【請求項16】

再構成可能なセンサ素子アレイの制御中にスイッチ回路網によって導入されるエラーを最小にするスイッチング構成を具現化するための方法であって、

(a) 初期スイッチング構成を生成する段階と、

(b) (i) システムにスイッチ構成を入力する段階であって、前記初期スイッチング構成が開始時に入力され、またその後に相次いで導き出された修正スイッチング構成が相次いで入力される段階、

(ii) 入力されたスイッチ構成によるシステムの性能を決定する段階、

(iii) システムの決定された性能に少なくとも部分的に基づいてコスト関数についての値を算出する段階、

(iv) 算出した値が前記コスト関数についての最小値を実質的に表しているかどうか決定する段階、及び

(v) 算出した値が前記コスト関数についての最小値でない場合、前記値算出の結果の関数として現在のスイッチング構成を修正して、修正スイッチング構成に達する段階を含み、

これらの段階(i)乃至(v)を各スイッチング構成について繰り返す反復アルゴリズムを遂行する段階と、

(c) 算出した値が前記コスト関数についての最小値である場合、コスト関数の値を最小にした修正スイッチング構成により前記スイッチング回路網を構成する段階と、を有する方法。

【請求項17】

前記の構成する段階は、前記スイッチの状態を制御するための制御回路をプログラムする段階を含んでいる、請求項16記載の方法。

【請求項18】

前記の算出した値が前記コスト関数についての最小値を実質的に表しているかどうか決定する段階は、模擬アニメーリング型のアルゴリズムを使用して遂行される、請求項16記載

10

20

30

40

50

の方法。

【請求項 19】

使用される前記コスト関数は、所定の閾値よりも大きいスイッチ距離を持つセンサ素子の数である、請求項 16 記載の方法。

【請求項 20】

前記段階 (b) (i i) は、前記システムの放射パターンを算出する段階を含んでいる、請求項 16 記載の方法。

【請求項 21】

前記段階 (b) (i i) は、前記システムによって生成された画像を評価する段階を含んでいる、請求項 16 記載の方法。

10 【請求項 22】

前記段階 (b) (i i) は、前記システムの電気的測定を行う段階を含んでいる、請求項 16 記載の方法。

【請求項 23】

各センサ素子はそれぞれの超音波トランスデューサ素子であり、前記段階 (b) (i i) は、スイッチのオン時抵抗を測定する段階、及び超音波トランスデューサ素子の容量を測定する段階を含んでいる、請求項 16 記載の方法。

【請求項 24】

使用される前記コスト関数は用途により変わる、請求項 16 記載の方法。

【請求項 25】

第 1 のコスト関数が、前記センサ素子アレイが送信モードで動作しているときに使用するための第 1 のスイッチング構成を最適化するために使用され、また第 2 のコスト関数が、前記センサ素子アレイが受信モードで動作しているときに使用するための第 2 のスイッチング構成を最適化するために使用される、請求項 24 記載の方法。

【請求項 26】

第 1 のコスト関数が、前記センサ素子アレイが第 1 組のシステム・パラメータに従って動作しているときに使用するための第 1 のスイッチング構成を最適化するために使用され、また第 2 のコスト関数が、前記センサ素子アレイが第 2 組のシステム・パラメータに従って動作しているときに使用するための第 2 のスイッチング構成を最適化するために使用される、請求項 24 記載の方法。

30 【請求項 27】

前記方法は、前記センサ素子アレイの構成が変わったときに常に遂行される、請求項 16 記載の方法。

【請求項 28】

前記方法は、前記センサ素子アレイの動作環境内の所定の温度変化が検出されたときに常に遂行される、請求項 16 記載の方法。

【請求項 29】

前記センサ素子アレイは撮像システムに結合され、前記方法は前記撮像システムがターンオンされたときに常に遂行される、請求項 16 記載の方法。

【請求項 30】

前記センサ素子アレイは、撮像システムに結合することのできるプローブ内に組み込まれてあり、またコスト関数の値を最小にした前記修正スイッチング構成を表すデータが前記プローブ内のメモリに記憶される、請求項 16 記載の方法。

【請求項 31】

前記センサ素子アレイは、撮像システムに結合することのできるプローブ内に組み込まれてあり、またコスト関数の値を最小にした前記修正スイッチング構成を表すデータが前記撮像システム内のメモリに記憶され且つ後で前記プローブ内の局部的メモリへダウンロードされる、請求項 16 記載の方法。

【請求項 32】

コスト関数の値を最小にした前記修正スイッチング構成を表すデータが走査中にプローブ

10

20

30

40

50

内の局部的メモリから読み出される、請求項 1 6 記載の方法。

【請求項 3 3】

各センサ素子はそれぞれの超音波トランステューサ素子であり、前記方法は、受信モード中に複数の焦点区域で再構成するための多数の開口構成の各々について遂行される、請求項 1 6 記載の方法。

【請求項 3 4】

スイッチ回路網のスイッチのそれぞれの状態を制御することによって再構成可能である超音波トランステューサ素子のアレイを持つ超音波撮像システムを動作させる方法であって、

（a）超音波撮像システムの第 1 の動作状態で使用するための第 1 のスイッチング構成を最適化する段階と、

（b）超音波撮像システムの第 2 の動作状態で使用するための第 2 のスイッチング構成を最適化する段階とを有し、

これら最適化する段階が、反復アルゴリズムを使用してコスト関数を最小にすることを含んでいる、方法。

【請求項 3 5】

前記超音波トランステューサ素子のアレイは、前記第 1 の動作状態で第 1 の開口構成を持ち且つ前記第 2 の動作状態で前記第 1 の開口構成とは異なる第 2 の開口構成を持つ、請求項 3 4 記載の方法。

【請求項 3 6】

前記超音波トランステューサ素子のアレイは、前記第 1 の動作状態では送信モードで動作し且つ前記第 2 の動作状態では受信モードで動作する、請求項 3 4 記載の方法。

【請求項 3 7】

使用される前記コスト関数は、所定の閾値よりも大きいスイッチ距離を持つセンサ素子の数である、請求項 3 4 記載の方法。

【請求項 3 8】

スイッチ回路網のスイッチのそれぞれの状態を制御することによって再構成可能である超音波トランステューサ素子のアレイを持つ超音波撮像システムを動作させる方法であって、

（a）第 1 の反復アルゴリズムを使用して第 1 のコスト関数を最小にすることによって超音波撮像システムの第 1 の動作状態で使用するための第 1 のスイッチング構成を最適化する段階と、

（b）第 2 の反復アルゴリズムを使用して、前記第 1 のコスト関数とは異なる第 2 のコスト関数を最小にすることによって超音波撮像システムの第 2 の動作状態で使用するための第 2 のスイッチング構成を最適化する段階と、

を有する方法。

【請求項 3 9】

前記モデルは、部分素子が完全なマルチプレクサを介してシステム・チャンネルに接続されると仮定している、請求項 1 記載の方法。

【請求項 4 0】

前記モデルは、部分素子がまばらなマルチプレクサを介してシステム・チャンネルに接続されると仮定している、請求項 1 記載の方法。

【請求項 4 1】

スイッチ回路網のスイッチのそれぞれの状態を制御することによって再構成可能である超音波トランステューサ素子のアレイを持つ超音波撮像システムを動作させる方法であって、

（a）第 1 組の選択された超音波トランステューサ素子を有する第 1 の開口を設定する第 1 のスイッチング構成を最適化する段階と、

（b）第 2 組の選択された超音波トランステューサ素子を有する第 2 の開口を設定する第 2 のスイッチング構成を最適化する段階とを含み、

10

20

30

40

50

前記第2の開口のビーム中心を、前記第1の開口のビーム中心に対して相対的に超音波トランスデューサ素子1個の分数の増分で歩進させるようにした、方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的に云えば、(例えば、光学、熱、圧力、超音波)センサの再構成可能な(reconfigurable)アレイに関するものである。より具体的には、本発明は、再構成可能な微小加工(micromachined)超音波トランスデューサ(MUT)アレイに関するものである。MUTについての1つの特定の用途は、医学的診断用超音波撮像システムにある。別の特定の例は、鋳造品、鍛造品又はパイプラインのような部材の非破壊評価(NDE)のためである。

10

【背景技術】

【0002】

従来の超音波撮像システムは、超音波ビームを送出し且つ検査している対象物からの反射ビームを受け取るために使用される超音波トランスデューサのアレイ(配列体)を有する。このような走査は一連の測定を含み、これらの測定では、集束超音波が送出され、システムは短い時間間隔後に受信モードに切り換えて、反射超音波を受け取り、ビーム形成し、表示のために処理する。典型的には、音響ビーム又は走査線に沿った一連の点からデータを取得するために各測定中に送信及び受信は同じ方向に集束される。受信器は、反射超音波を受信するとき走査線に沿って連続的に再集束を行う。

20

【0003】

超音波撮像のため、アレイは、典型的には、一列又は複数列に配列された多数のトランスデューサを持ち、これらは送信の際に別々の電圧で駆動される。印加電圧の時間遅延(又は位相)及び振幅を選択することによって、個々のトランスデューサはそれぞれ超音波を発生するように制御することができ、それらの超音波は組み合わさって、好ましいベクトル方向に沿って進行し且つビームに沿った選択された区域に集束される正味の超音波を形成する。

【0004】

トランスデューサ・プローブが受信モードで反射音波を受けるように用いられるとき、同じ原理が適用される。受信用トランスデューサで発生された電圧は、正味の信号が対象物内の単一の焦点区域から反射された超音波を表すように、加算される。送信モードの場合と同様に、超音波エネルギーのこの集束した受信は、各々の受信用トランスデューサからの信号に別々の時間遅延(及び/又は位相シフト)及び利得を与えることによって達成される。時間遅延は、受信時の動的集束を行うために反射信号の深さの増大につれて調節される。

30

【0005】

形成される画像の品質又は分解能は、一部は、トランスデューサ・アレイの送信及び受信開口をそれぞれ構成するトランスデューサの数の関数である。従って、高画像品質を得るためにには、2次元及び3次元撮像用途の両方にとって多数のトランスデューサを設けることが望ましい。典型的には、超音波トランスデューサは手持ち式トランスデューサ・プローブ内に配置され、該プローブは可撓性ケーブルによって電子装置ユニットに接続され、該電子装置ユニットはトランスデューサ信号を処理して超音波画像を生成する。超音波プローブは超音波送信回路及び超音波受信回路の両方を担持することができる。

40

【0006】

再構成可能な超音波アレイは、結果として得られる素子の形状を波頭の形状に合致するように作ることができるように、複数群の部分素子(subelement)を動的に接続することができる。これにより、性能を改善し、及び/又はチャンネル数を減らすことができる。このような再構成可能性(reconfigurability)は、スイッチング回路網を使用して達成することができる。

【0007】

50

ビーム形成のために必要なスイッチング回路網の性能を改善するための研究がアルゴリズムに向けられたことは殆どなかった。しかしながら、再構成可能性が大幅に制限されている幾つかの状況でスイッチング又は多重化(multiplexing)が用いられている。この例としては、開口の大きさを増大させるための合成開口についての多重化、多列アレイ、及び線形アレイでの走査のために使用される多重化が挙げられる。これらの全ての場合において、再構成可能性は極端に制限されており、スイッチング回路網を最適化するための必要性が回避されている。

#### 【0008】

近年、半導体処理技術を使用することにより、微小加工超音波トランスデューサ(MUT)として知られている種類の超音波トランスデューサが製造されており、これらは容量型(cMUT)又は圧電型(pMUT)であってよい。MUTは、受け取った超音波信号の音響振動を変調された容量(キャパシタンス)に変換する電極を持つ小さい隔膜状の装置である。送信の場合、容量性電荷が変調されて、装置の隔膜を振動させ、これにより音波を送出する。MUTの1つの利点は、それらが、「微小加工(micromachining)」の項目の下にグループ分けされる微小製造(microfabrication)プロセスのような半導体製造プロセスを使用して作ることができることである。このような微小加工プロセスの結果得られるシステムは、典型的には、微小加工電気機械システム(MEMS)と呼ばれている。

10

#### 【0009】

cMUTは通常、六角形の構造であり、それを横切って広がる隔膜を有する。この隔膜は、印加されたバイアス電圧によって基板表面に近接して保持される。この既にバイアスを加えているcMUTに振動信号を印加することによって、隔膜は振動させることができ、これにより音響エネルギーを放射させることができる。同様に、音響波が隔膜に入射したとき、その結果生じる振動はcMUT上の電圧変化として検出することができる。「cMUTセル」は、上記のような六角形「ドラム」構造の1つを表す用語である。cMUTセルは非常に小さい構造とすることができます。典型的なセルの寸法は、六角形の平坦な縁相互間の距離が25~50ミクロンである。セルの寸法は、設計された音響応答によって様々に指示される。所望の周波数応答及び感度に関して良好に動作するような一層大きいセルを作ることは可能である。

20

#### 【0010】

残念なことに、上記のような小さいセルについて個別の制御を行えるような電子装置を作ることは困難である。アレイ全体としての音響性能に関して、小さい寸法のセルは優れていって、また融通性が大きいが、制御はより大きい構造に限られている。複数のセルと一緒にグループ化して、それらを電気的に接続すれば、より大きな部分素子を生成することができますが可能になり、それは所望の音響応答を維持しながら個々に制御することができます。従つて、部分素子は一群の電気接続されたセルであり、再構成することはできない。本書の開示の目的のために、部分素子(subelement)は、最小の独立に制御される音響ユニットである。これにより、スイッチング回路網を使用して複数の部分素子と一緒に接続することによってリング又は素子を形成することができる。そこで、素子(element)は、スイッチング回路網の状態を変えることによって再構成することが可能である。しかしながら、部分素子は、スイッチにより切り離すことのできない接続されたセルで構成されており、従つて、再構成することができない。もしアレイがPZT又はその他の何らかのより普通の又は将来のトランスデューサ技術で製造されているなら、以下の分析の全てもまた有効である。

30

#### 【0011】

シリコンをベースとした超音波トランスデューサ部分素子を使用した場合の再構成可能性が米国特許出願第10/383990号に記載されている。再構成可能性の一形態はモザイク環状アレイであり、これも該特許に記載されている。モザイク環状アレイの概念は、再構成可能な電子的スイッチング回路網を使用して複数の部分素子と一緒にグループ化することによって環状の素子を構築することを含む。その目標は、画像品質を維持し且つスライス厚さを改善しながら、ビーム形成チャンネルの数を減らすことである。システム

40

50

・チャンネルを減らすため、モザイク環状アレイは、ビームをステアリングしない場合、基礎をなす2次元トランステューサ・アレイの表面での遅延の輪郭が円形であると云う事実を利用する。換言すれば、等遅延曲線がビームの中心の周りの輪になる。遅延のこの円対称性により、共通の遅延を持つ部分素子を明確にグループ化でき、また環状アレイの概念が得られる。再構成可能性は、走査又は画像を形成するためにより大形の基礎をなす2次元トランステューサ・アレイに沿ってビームを歩進(stepping)させるように利用することができる。再構成可能性はまた、近距離場においてより小さい活性開口により多数のチャンネルを割り当てることによって多重送信用途の場合の性能を改善するように利用することもできる。多数の他の用途でも、再構成可能性の有用性を証明することができる。

【特許文献1】米国特許第6733454号

10

【特許文献2】WO2004/079654

【発明の開示】

【発明が解決しようとする課題】

【0012】

再構成可能な超音波アレイは、現在利用可能な電子装置により具現化することが困難であるか又は不可能であるような複雑なスイッチング回路網を必要としている。そこで、スイッチング構成(configuration)を慎重に選ぶことによって最適な性能を維持するような簡単化したスイッチング回路網が要望される。

【課題を解決するための手段】

20

【0013】

本発明は、再構成可能なセンサ・アレイ、及びこののようなアレイについてのスイッチング構成を最適化する(すなわち、こののようなアレイの性能を最大化する)ための方法を対象とする。センサは、光学センサ、熱センサ、圧力センサ又は超音波トランステューサであってよい。本書で開示する実施形態では、より大形の素子を構成するための基礎となるグリッドとして容量型微小加工超音波トランステューサ(cMUT)の2次元アレイを使用する。しかしながら、本発明はcMUT構造に制限されず、その他の従来の又は将来のトランステューサ技術にも等しく適用できる。

【0014】

30

本発明の一面は、再構成可能なセンサ素子アレイの制御中にスイッチ回路網によって導入されるエラーを最小にするスイッチング構成を具現化するための方法である。該方法は、(a)初期スイッチング構成を生成する段階と、(b)(i)スイッチング回路網のエラー、開始時に入力される初期スイッチング構成、及びその後に相次いで入力される相次いで導き出された修正スイッチング構成の全てを考慮に入れてシステムの応答を算出するシステム・モデルに、スイッチ構成を入力する段階、(ii)入力されたスイッチ構成と共に前記モデルを使用して画像又は放射パターンを生成する段階、(iii)生成されたパターンを表すデータに少なくとも部分的に基づいてコスト関数についての値を算出する段階、(iv)算出した値がコスト関数についての最小値を実質的に表しているかどうか決定する段階、及び(v)算出した値がコスト関数についての最小値でない場合、値算出の結果の関数として現在のスイッチング構成を修正して、修正スイッチング構成に達する段階を含み、これらの段階(i)乃至(v)を各スイッチング構成について繰り返す反復アルゴリズムを遂行する段階と、(c)算出した値がコスト関数についての最小値である場合、コスト関数の値を最小にした修正スイッチング構成によりスイッチング回路網を構成する段階とを有する。

40

【0015】

50

本発明の別の面は、再構成可能なセンサ素子アレイの制御中にスイッチ回路網によって導入されるエラーを最小にするスイッチング構成を具現化するための方法である。該方法は、(a)初期スイッチング構成を生成する段階と、(b)(i)システムにスイッチ構成を入力する段階であって、初期スイッチング構成が開始時に入力され、またその後に相次いで導き出された修正スイッチング構成が相次いで入力される段階、(ii)入力されたスイッチ構成によるシステムの性能を決定する段階、(iii)システムの決定された

性能に少なくとも部分的に基づいてコスト関数についての値を算出する段階、(i) 算出した値がコスト関数についての最小値を実質的に表しているかどうか決定する段階、及び(v) 算出した値がコスト関数についての最小値でない場合、値算出の結果の関数として現在のスイッチング構成を修正して、修正スイッチング構成に達する段階を含み、これらの段階(i)乃至(v)を各スイッチング構成について繰り返す反復アルゴリズムを遂行する段階と、(c) 算出した値がコスト関数についての最小値である場合、コスト関数の値を最小にした修正スイッチング構成によりスイッチング回路網を構成する段階とを有する。

【0016】

本発明の更に別の面は、スイッチ回路網のスイッチのそれぞれの状態を制御することによって再構成可能である超音波トランステューサ素子のアレイを持つ超音波撮像システムを動作させる方法であり、該方法は、(a) 超音波撮像システムの第1の動作状態で使用するための第1のスイッチング構成を最適化する段階と、(b) 超音波撮像システムの第2の動作状態で使用するための第2のスイッチング構成を最適化する段階とを有し、これら最適化する段階は、反復アルゴリズムを使用してコスト関数を最小にすることを含んでいる。

10

【0017】

本発明のまた更に別の面は、スイッチ回路網のスイッチのそれぞれの状態を制御することによって再構成可能である超音波トランステューサ素子のアレイを持つ超音波撮像システムを動作させる方法であり、該方法は、(a) 第1の反復アルゴリズムを使用して第1のコスト関数を最小にすることによって超音波撮像システムの第1の動作状態で使用するための第1のスイッチング構成を最適化する段階と、(b) 第2の反復アルゴリズムを使用して第2のコスト関数を最小にすることによって超音波撮像システムの第2の動作状態で使用するための第2のスイッチング構成を最適化する段階とを有し、第2のコスト関数は前記第1のコスト関数とは異なる。

20

【0018】

本発明の更に別の面は、スイッチ回路網のスイッチのそれぞれの状態を制御することによって再構成可能である超音波トランステューサ素子のアレイを持つ超音波撮像システムを動作させる方法であり、該方法は、(a) 第1組の選択された超音波トランステューサ素子を有する第1の開口を設定する第1のスイッチング構成を最適化する段階と、(b) 第2組の選択された超音波トランステューサ素子を有する第2の開口を設定する第2のスイッチング構成を最適化する段階とを含み、第2の開口のビーム中心は、第1の開口のビーム中心に対して相対的に超音波トランステューサ素子1個の分数(fraction)の増分で歩進させる。

30

【0019】

本発明の他の面は以下に開示し且つ請求する。

【0020】

以下の説明で参照する図面では、様々な図面における同様な素子には同じ参照数字を付している。

40

【発明を実施するための最良の形態】

【0021】

本発明は、再構成可能なスイッチング・マトリクスと、このようなマトリクス及びその関連したセンサ素子アレイについてのスイッチング構成を最適化するための方法とを対象とする。例示の目的で、再構成可能なアレイ及び最適化方法を容量型微小加工超音波トランステューサ(cMUT)に関して説明する。しかしながら、本書に開示する本発明の様々な面がそれらの用途においてcMUTを用いるプローブに制限されず、むしろpMUT又はさいの目に切った圧電セラミック・アレイさえも用いるプローブにも適用することができることを理解されたい。その場合、さいの目に切った部分素子の各々は下側に位置するスイッチング層に相互接続手段によって接続される。本発明の同じ面はまた、光学、熱又は圧力センサの再構成可能なアレイにも適用される。

50

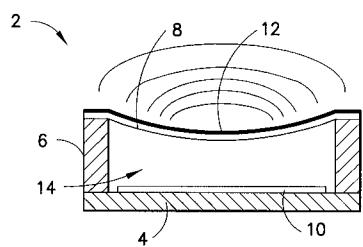

## 【0022】

図1について説明すると、典型的なcMUTトランスデューサ・セル2を断面で示している。このようなcMUTトランスデューサ・セルのアレイは、典型的には、高濃度にドープしたシリコン（従って、半導体）ウェーハのような基板4上に製造される。各々のcMUTトランスデューサ・セルでは、窒化シリコンで作ることのできる薄い膜又は隔膜8が基板4の上方に懸架される。膜8はその周縁部が絶縁支持体6によって支持され、絶縁支持体6は酸化シリコン又は窒化シリコンで作ることができる。膜8と基板4との間の空洞14は空気又はガスを充填するか、或いは完全に又は部分的に真空にすることができる。典型的には、cMUTは処理が許す限り完全に真空にする。アルミニウム合金又は他の適当な導電材料のような導電材料の膜又は層により膜8上に電極12を形成し、また導電材料で作られた膜又は層により基板4上に電極10を形成することができる。この代わりに、底部の電極は半導体基板4に適切なドーピングを行うことによって形成することができる。

## 【0023】

空洞14によって隔てられた2つの電極10及び12は容量を形成する。入射する音響信号により膜8が振動するとき、関連した電極を使用して容量の変動を検出することができる（図1に図示せず）、これにより音響信号が電気信号に変換される。逆に、AC信号が一方の電極に印加されると、電極上の電荷を変調し、これにより電極間の静電気力が変調され、静電気力は隔膜を動かして音響信号を送出させる。

## 【0024】

個々のセルは丸形、矩形、六角形又はその周辺形状を持つことができる。六角形はトランスデューサ部分素子のcMUTセルの密な詰め込みを可能にする。トランスデューサ部分素子が異なるセル寸法の複合特性を持ち、これによりトランスデューサを広帯域特性にするように、cMUTセルは異なる寸法を持つことができる。

## 【0025】

残念なことに、このような小さいセルについて個別の制御を行えるような電子装置を作ることは困難である。アレイ全体としての音響性能に関して、小さい寸法のセルは優れてい、また融通性が大きいが、制御はより大きい構造に限られている。複数のセルを一緒にグループ化して、それらを電気的に接続すれば、より大きな部分素子を生成することができ、それは所望の音響応答を維持しながら個々に制御することができる。スイッチング回路網を使用して複数の部分素子と一緒に接続することによってリング又は素子を形成することができる。そこで、素子は、スイッチング回路網の状態を変えることによって再構成することができる。しかしながら、個々の部分素子は、異なる部分素子を形成するように再構成することができない。

## 【0026】

MUTセルは微小加工プロセスにおいて（介在するスイッチ無しに）複数個一緒に接続して、部分素子を形成することができる。以下の説明で、用語「音響部分素子」とはこのような一集団を記述するために使用される。これらの音響部分素子は超小型電子スイッチによって相互接続されて、このようなスイッチを、シリコン層内に又はトランスデューサ・アレイに直ぐ隣接して設けられた異なる基板上に配置することによって、より大きい素子を形成する。

## 【0027】

本書で用いられるとき、用語「音響部分素子」は单一のセル、又は再構成することのできない一群の電気接続されたセルである。すなわち、部分素子は最小の独立に制御される音響ユニットである。また用語「部分素子」とは、音響部分素子と、その関連した集積電子装置とを意味する。また「素子」は、スイッチング回路網を使用して複数の部分素子と一緒に接続することによって形成される。素子はスイッチング回路網の状態を変えることによって再構成することができる。スイッチング回路網内に含まれるスイッチの少なくとも幾分かは、以下により詳しく説明するように、「関連した集積電子装置」の一部である。

10

20

30

40

50

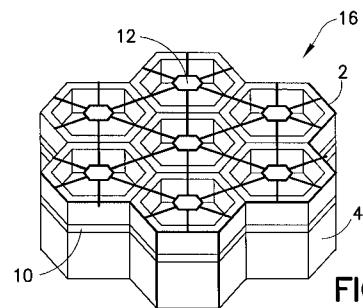

## 【0028】

例示の目的で、図2は7つの六角形のcMUTセル2より成る「ヒナギク形」トランスデューサ部分素子16を示しており、中央のセルは6つのセルのリングによって取り囲まれ、またリング内の各セルは中央のセルのそれぞれの辺とリング内の隣り合うセルとに隣接している。各cMUTセル2の頂部電極12が、スイッチによる切断ができない接続部によって一緒に電気結合されている。六角形のアレイの場合、6つの導体が頂部電極12から放射状に延出して、隣のcMUTセルの頂部電極にそれぞれ接続されている（但し、周縁にあるセルでは、（6つではなく）3つの他のセルに接続される）。同様に、各セル2の底部電極10が、スイッチによる切断ができない接続部によって一緒に電気結合されていて、7倍大きい容量型トランスデューサ部分素子16を形成する。

10

## 【0029】

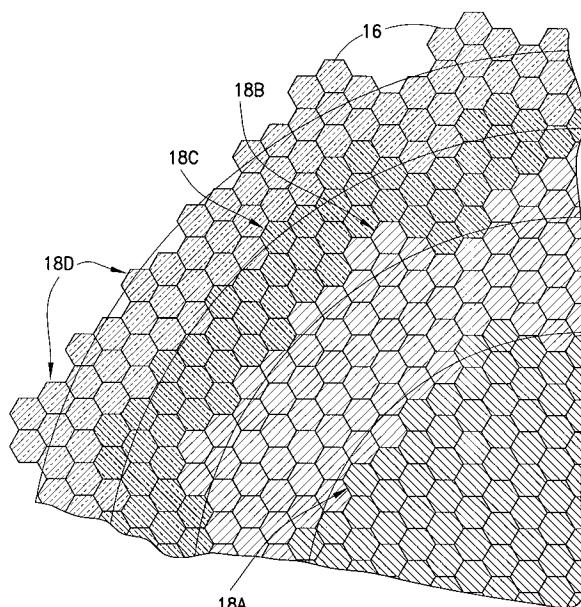

図2に見られる種類の部分素子は、半導体（例えば、シリコン）基板上に2次元アレイを形成するように配列することができる。これらの部分素子は、スイッチング回路網を使用して、環状のリングのような素子を形成するように再構成することができる。シリコンをベースとした超音波トランスデューサ部分素子を使用した場合の再構成可能性が米国特許出願第10/383990号に記載されている。再構成可能性の一形態はモザイク環状アレイであり、これも該特許に記載されている。モザイク環状アレイの概念は、再構成可能な電子的スイッチング回路網を使用して複数の部分素子と一緒にグループ化することによって環状の素子を構築することを含む。その目標は、画像品質を維持し且つスライス厚さを改善しながら、ビーム形成チャンネルの数を減らすことである。システム・チャンネルを減らすため、モザイク環状アレイは、ビームをステアリングしない場合、基礎をなす2次元トランスデューサ・アレイの表面での遅延の輪郭が円形であると云う事実を利用する。換言すれば、等遅延曲線がビームの中心の周りの輪になる。遅延のこの円対称性により、共通の遅延を持つ部分素子を明確にグループ化できる。再構成可能性は、走査又は画像を形成するためにより大形の基礎をなす2次元トランスデューサ・アレイに沿ってビームを歩進させるように利用することができる。

20

## 【0030】

MUTセル及び音響部分素子を使用してトランスデューサ・アレイを形成することができる多数の方法がある。図3は、モザイク・アレイを形成する音響部分素子のモザイク細工の一例を示す。図3に示されている実施形態では、4つのほぼ環状の素子（それぞれ参照符号18A～18Dによって表す）が1素子あたりほぼ等しい面積を持つように構成されており、各素子は「ヒナギク」形音響部分素子のモザイク細工を有する（各部分素子は7つの一緒に接続されたMUTセルより成る）。各場合におけるモザイク細工は複数の種類の部分素子から作ることができる。アレイ・パターンはモザイク細工である必要はなく、音響部分素子のない区域を持つことができる。例えば、音響部分素子又はセルの頂部電極接続部をアレイの下へ持ってくるためのバイア（貫通接続路）を設けてもよい。

30

## 【0031】

本発明の構成は、ビーム幅、サイド・ロープのレベル、又は焦点深度のような様々な音響パラメータを最適にするように変更することができる。この代わりに、音響部分素子は送信動作のための1つの開口を形成するようにグループ化し、直ちに受信動作のための別の開口へ切り換えるようにしてもよい。図3は複数のほぼ環状の素子のそれぞれの一部を示しているが、他の形状、例えば、不連続のリング、八角形のリング、円弧形に構成することができる。パターンの選択は用途の要求に依存する。

40

## 【0032】

殆どの開口は、図3に示される環状素子のような単一のより大きい素子を形成するように相互接続された連続したグループ化された部分素子で構成される。この場合、全ての部分素子の各々をそのそれぞれのバス・ラインに直接接続することは必要ではない。所与のグループ内の限られた数の部分素子を接続し、次いで残りの部分素子を互いに接続すれば充分である。このようにして、送信信号はシステムからバス・ラインに沿って伝播して、限られた数のアクセス点に沿った素子に入る。そこから、信号は局部的な接続部を介して

50

素子内に広がる。

【0033】

特定の幾何学的形状が与えられると、再構成可能なアレイは音響部分素子をシステム・チャンネルにマッピングする。このマッピングは、性能を改良するように設計される。マッピングはスイッチング回路網を介して行われ、スイッチング回路網は、cMUTセルが作成される基板の中に直接配置するのが理想的であるが、トランステューサ基板に隣接して集積された異なる基板に設けることができる。cMUTアレイはシリコン基板上に直接構築されるので、スイッチング電子装置はその基板に組み込むことができる。PZT又はより伝統的な実装の場合、スイッチ回路網は別個のシリコン基板内に製造してPZTアレイに取り付けるのが簡単であると考えられる。

10

【0034】

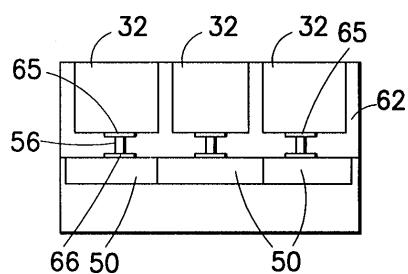

図4に、ASICからcMUTへの接続を行う方法を例示するために共同集積化(co-integrate)されたcMUT及びASICアレイの断面図を示している。図示のように、各cMUT部分素子32をその対応するCMOS部分素子(又は、セル)50に接続するためにそれぞれ1つのバイア(via)56が使用される。これらのバイア56は、信号電極65をスイッチのASIC上に形成されたそれぞれの導電パッド66に接続するものであり、音響裏当て層62の中に埋め込むことができる。

【0035】

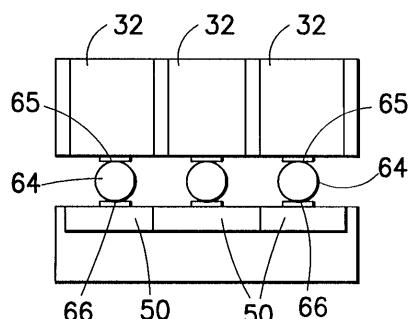

また、図5に示すように、cMUTを別個のウェーハ上に形成して、それらをASICスイッチ・マトリクスに別々に接続することもできる。この場合、例えば、個々のcMUT部分素子32をそれらの対応するスイッチ電子装置50に接続するためにハンダ・バンプ64及び導電パッド66が使用される。また、異方性導電フィルム(ACF)又は可撓性相互接続手段のような他の実装手法を用いてもよい。

20

【0036】

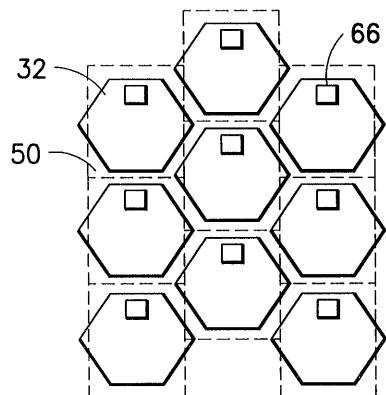

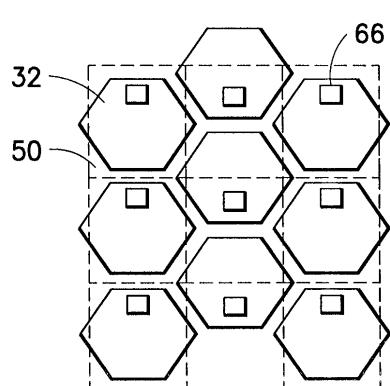

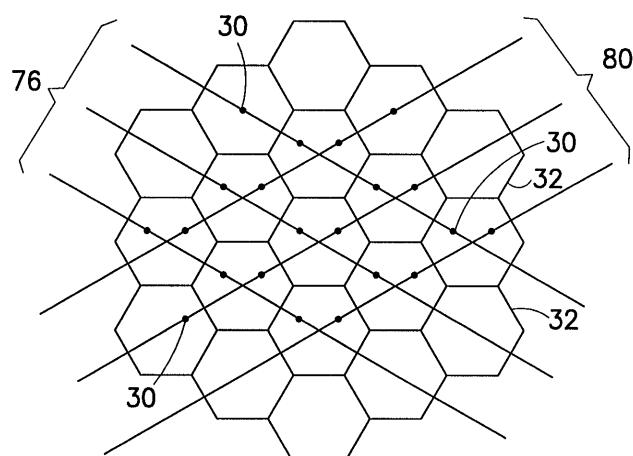

最適な詰込み密度にするため、図6(これは、ASICスイッチ・マトリクスの上面図を示す)に例示されているように、cMUT部分素子32及び六角形のグリッド上の関連した電子装置をタイル張りすることが有用である。この場合、CMOS単位スイッチ・セル50が縦列に配置され、1つ置きの縦列がセル半分の高さだけずらして配置されている。これにより、セル寸法を適正に選択すると、図示のようにパッド66の完全な六角形のアレイが得られる。次いで、バイア56(これらも六角形のアレイに配置されている)が、部分素子の六角形のアレイを有する上方のトランステューサ層への接続の基礎を形成するそれぞれのパッド(図4に示されていない)に接続される。より直接的なASICの具現例が図7に例示されている。この場合、CMOS単位スイッチ・セル50は水平な横列及び垂直な縦列に配列されて矩形のグリッドを形成し、それらの上方の六角形の部分素子32は六角形のグリッドを形成する。図7に示されているように、単位スイッチ・セル・パッド66は縦横に配列されて矩形のアレイを形成していて、単位スイッチ・セル50がそれぞれの六角形の部分素子32に電気接続されるような接続部を生成するように依然として正しく整列している。いずれの場合も、部分素子の六角形のグリッド・パターンは、図3に示されているようなモザイク環状アレイ・ビーム・パターンの実現を可能にする。

30

【0037】

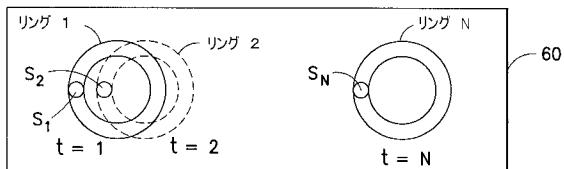

典型的な動作では、再構成可能なアレイは、図3に示されているものと同様な初期開口パターンを持つようにプログラムされる。このパターンにより、ビームフォーマがアレイの前側にビームを生成することが可能になる。撮像中、図8に例示されているように、開口がアレイ60にわたって走査され、図8では、リングが、 $t = 1$ におけるリング1から $t = 2$ におけるリング2へ、そして最終的には $t = N$ におけるリングNまで移動する。ここで、 $t$ は時間であり、 $N$ は2よりも大きい正の整数である。このようにして、ビームはアレイの前の空間内で掃引され、ビーム形成されたエコーが画像の相次ぐ線を作り上げるために使用される。再構成可能なアレイの目的は、任意の複雑なアレイ・パターンのために図8に例示された撮像動作を電子的に達成できることである。以前の超音波スキャナは電子的スキャナを行うことができるが、仰角方向におけるセンサ部分素子のきめ細かい分

40

50

布の欠如及び固定した幾何学的形状のために開口の複雑さに制限がある。

【0038】

図8に例示されているような完全に再構成可能なアレイは、具現化における多数の重要な課題を表している。センサ・アレイは何万もの部分素子に細分割される。ビーム・パターンは、部分素子をグループ化して、それらを有限数のシステム送信／受信及びビーム形成チャンネルに接続することによって、構築される。再構成可能なアレイは、モザイク環状アレイ概念を具現化するために使用されるとき、アレイを横切って電子的に平行移動させる複数のリングを形成する。平行移動における各々の新しい段階で、リング・パターン全体がアレイに再プログラムされて、新しい構成を生成する。また、形成されたときのビームの歪みを低減して、画像品質を改善するように、送信と受信との間に及び受信中に複数の間隔でリング・パターンを更新する能力を与えることが可能である。

10

【0039】

典型的なシステムでは、128個以上のチャンネルが使用される。現在の超音波システムは、128個のシステム・チャンネルから固定数のトランスデューサ素子への経路を定めることのできる多重化アーキテクチャを使用する。このようにマルチプレクサ回路網の慎重な設計を使用して、限られた量の電子装置により標準的な走査パターンを生成することが可能である。しかしながら、殆どの場合、走査パターンは固定されていて、回路網の制約により再構成可能ではない。完全に再構成可能なアレイはこのような制約に影響されないが、それを具現化するためには非常に密度の高いスイッチング・マトリクスを必要とする。

20

【0040】

図8に例示されているように、再構成可能なアレイの基本的な性質は、任意の部分素子を任意のシステム・チャンネルに任意に接続できることを必要とする。例えば、開口が第1の場所から次の場所へ走査されるとき、部分素子S2が最初は内部リング（図示せず）の一部になければならず、次いでリング2の一部でなければならぬ。これは、部分素子を、第1のシステム・チャンネルに接続されている状態から異なるシステム・チャンネルに接続される状態へ短い期間内に切り換えなければならぬことを意味する。このことは、一般に、走査動作中のアレイ内の多数の部分素子に当てはまる。

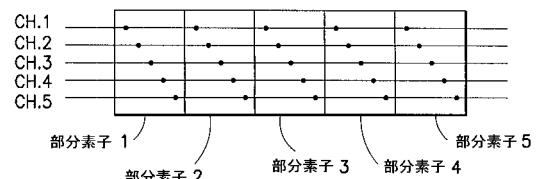

【0041】

この要件を具現化する最も簡単な方法は、各部分素子が全てのシステム・チャンネルの各々にアクセスできるように全てのシステム・チャンネルをアレイ全体にわたって分布させることであると考えられる。このアーキテクチャを図9に例示する。この場合、例示のために5つのシステム・チャンネルのみを示している。各システム・チャンネルは、どの部分素子によってどのシステム・チャンネルを捕捉するかを選択する局部スイッチにより全ての部分素子に接続される。

30

【0042】

マトリクス電子装置がトランスデューサ・アレイの背後に直接設けられているシステムでは、各部分素子のスイッチング電子装置のためのスペース（収容場所）が部分素子の大きさ（サイズ）まで狭められる。典型的な超音波システムでは、この大きさは数百ミクロン程度であるが、それより小さいこともある。スイッチの大きさはそのオン時抵抗に反比例するので、スイッチを多くするとオン時抵抗が高くなり、或いはスイッチを少なくするとオン時抵抗が小さくなると云う、二律背反に直面する。しかしながら、スイッチを可能な限り小さくした極端な場合でも、現在の半導体技術では、16個よりも多数のスイッチを割り当てられたスペース内に容易に嵌め込むことができないことは直ぐに明らかである。図9の完全装填のアーキテクチャは、実際のアレイではさらに多数のスイッチが含まれているので、現在の技術状態では解決困難であると思われる。

40

【0043】

将来の技術の進歩により同じスペース内により多くのスイッチを集積することが完全に実現できるかもしれないが、超音波の進歩が画像品質の改善のために短くする必要のあるイメージヤの波長に関係しているので、割り当てられるセルの大きさが小さくされる傾向

50

がある。更に、デジタル制御及び送信／受信回路のような更に多くの構成部品がこの同じ限られた区域内に入れられようとしている。従って、上記の完全装填のアーキテクチャは、その単純さのために魅力があるが、直ちに支持できる又は実施できるものではない。

#### 【0044】

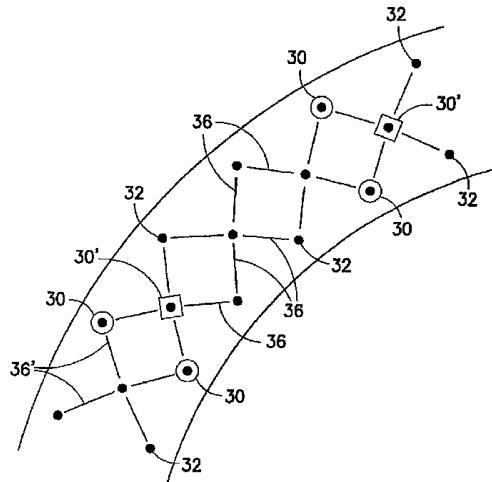

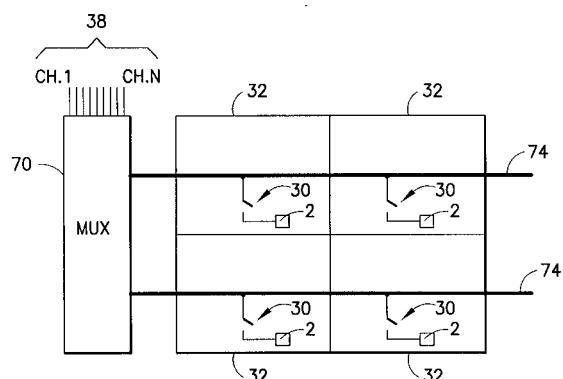

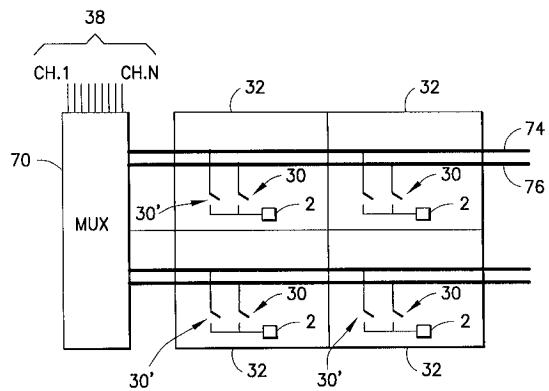

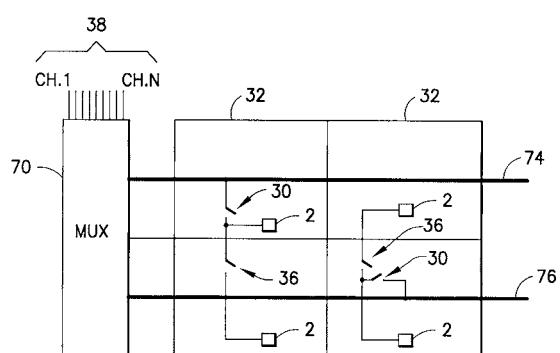

上述の相互接続の問題に対するより良い解決策は、各部分素子内のスイッチの数を制限し、同時に再構成可能なアレイに必要とされる融通性を提供することである。これは、図10に例示されているように、限られた数のバス・ラインを使用すると共に、これらを再構成可能にすることによって達成することができる。この場合、マルチブレクサ70がどのシステム・チャンネル38(CH.1～CH.N)にどのバス・ライン74を接続すべきかを任意に選択し、その際、各列(横列)の部分素子32には単一のバス・ラインのみが作用する。各部分素子のcMUTセル2(図には、各部分素子に1つのcMUTセルしか示していない)がそれぞれのアクセス・スイッチ30によってバス・ラインに接続される。このアーキテクチャの重要な特徴は、多くのスイッチがアレイの外側に配置され、従ってトランステューサの幾何学的形状によって制約されないことである。このアーキテクチャを使用して、どの部分素子列をどのシステム・チャンネルに接続するのか相次いで選択することによって、アレイにわたって1次元パターンを走査することができる。このアーキテクチャに対する更なる改善を図11に例示する。この場合、部分素子32の各列に複数のバス・ライン74, 76が通される。各部分素子32のcMUTセル2はアクセス・スイッチ30'を介してバス・ライン74に、又はアクセス・スイッチ30を介してバス・ライン76に接続することができる。このアーキテクチャは、同じ列内の異なるシステム・チャンネル上の素子をグループ化することが可能であるので、水平方向に融通性を与える。

10

20

30

40

50

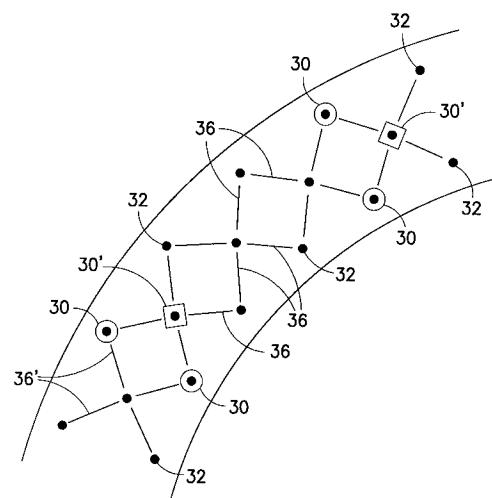

#### 【0045】

上記アーキテクチャに対する更なる改善は、殆どの開口が、単一のより大きい素子を形成するように相互接続された連続したグループ化された部分素子で構成されること、に気が付くことによって行うことができる。この場合、全ての部分素子の各々をそのそれぞれのバス・ラインに直接接続することは必要ではない。所与のグループ内の限られた数の部分素子を接続し、次いで残りの部分素子を互いに接続すれば充分である。このようにして、送信信号はシステムからバス・ラインに沿って伝播して、限られた数のアクセス点に沿って素子に入る。そこから、信号は局部的な接続部を介して素子内に広がる。このアーキテクチャは図12に例示されている。この場合、部分素子32は、それら部分素子の列に関連したバス・ラインにアクセス・スイッチ30を介して接続することができ、また隣接した列に関連したバス・ラインにマトリクス・スイッチ36を介して接続することができる。マトリクス・スイッチ36は1つの部分素子を隣接の部分素子に接続する。

#### 【0046】

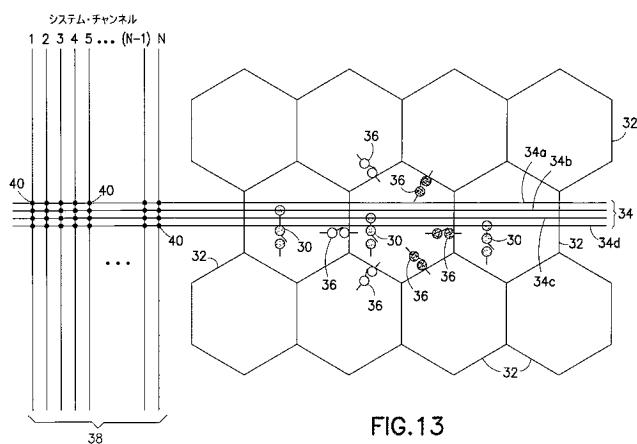

図13に示す本発明の一実施形態では、上述の改善の全てを取り入れる。この場合、アクセス・スイッチ30は所与の部分素子32をバス34の内の列バス・ラインに接続するために使用される。このアーキテクチャはモザイク環状アレイに直接に適用可能である。このような装置では、本アーキテクチャを使用して複数のリングを形成することができる。その場合、各リングは1つ以上のアクセス・スイッチを使用して1つのシステム・チャンネルに接続され、各アクセス・スイッチは1つのバス・ラインに接続され、該バス・ラインは1つのシステム・チャンネルに接続される。

#### 【0047】

アクセス・スイッチは、所与の数のバス・ラインについて必要とされる数を減らすために、図13に示されているように食違い配置(stagger)される(これについては、以下に更に説明する)。また、バス・ラインに対するアクセス・スイッチの順序をランダムにして(図示せず)、繰返しパターンに起因するアーティファクトを低減することができる。各部分素子内に2つ以上のアクセス・スイッチを使用することにより、アレイの融通性を改善することができる。このようなアーキテクチャでは、融通性と1つの部分素子あたりのアクセス・スイッチの数との間で、その数がバス・ライン及びシステム・チャンネルの

数よりも未だかなり少ない場合に、妥協点が見いだされる。また、各素子内に1つのバス・ラインあたり2つ以上のアクセス・スイッチを使用することも可能である。これは、機能していないアクセス・スイッチを冗長なアクセス・スイッチにより側路することが可能であるので、装置の歩留まりを改善すると考えられる。

【0048】

列バス・ラインは、図13に示されるように交点スイッチング・マトリクスを使用してシステム・チャンネルに接続される。まばらな交点スイッチを使用することも可能であり、その場合、必要とされるマルチプレクサの数が少なくなる。このようなアーキテクチャはスペースを使用する効率をよくするが、全てのバス・ラインを適切に接続することが確実にできるようにスイッチ構成の慎重な選択が必要となろう。図12示されているように、1つの列あたり複数のバス・ラインを使用することができる。バス・ラインの数を多くすると、マルチプレクサの数が増え且つアレイ内の経路形成区域が増大するが、アレイの融通性が改善される。列をスキップすること、又は異なる列に異なる数のバス・ラインを使用することが可能である。例えば、区域(面積)を節約するために、全ての各対の隣り合う部分素子列の間で一群のバス・ラインを共用することは有利であることがある。

10

【0049】

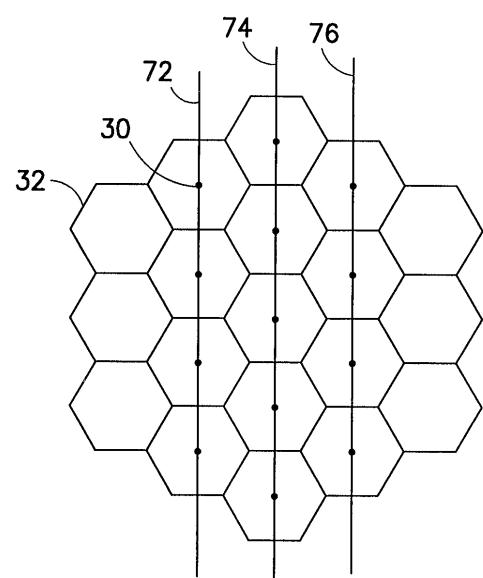

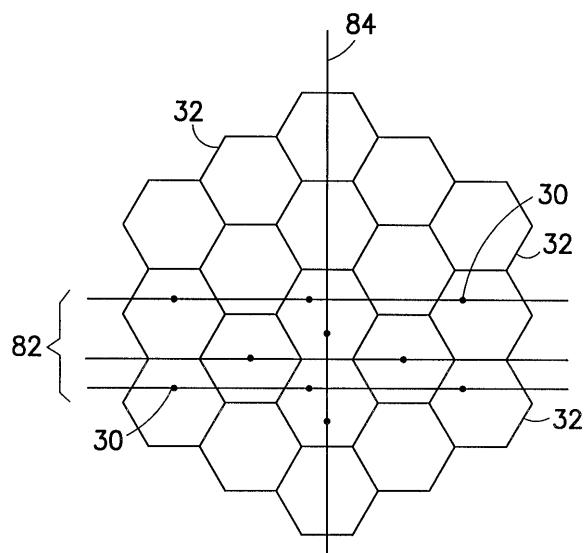

これまで水平のバス・ラインのみについて説明してきたが、アレイ内に垂直及び水平に延在するバス・ラインの両方を配置することも可能である。バス・ラインは、図14に例示されるように垂直に配置できる(バス・ライン72, 74, 76参照)。図15に見られるように、一組のバス・ライン82を水平に配置することができ、また別の一組のバス・ライン84を垂直に配置することができる。この場合、各部分素子又は一群の部分素子は、1つのアクセス・スイッチを介して垂直のバス・ラインに接続可能であり、更に異なるアクセス・スイッチを介して水平のバス・ラインに接続可能である。しかしながら、バス・ラインが両方向に延在している場合、バス・ラインのために利用可能な電子的地域が乏しく且つより多くのバス・ラインが必要であると共に、1つの部分素子内に唯一つのアクセス・スイッチがあるので、各部分素子のアクセス・スイッチは水平なバス・ライン又は垂直なバス・ラインのいずれかに接続することができ、両方には接続できない。最後に、バス・ラインは図16に例示されているように斜めに配置することができる。これらライン76, 80は、六角形のアレイの2つの自然軸に沿ってそれぞれ延在し、従って、部分素子のアドレス指定を簡単化する。

20

【0050】

アクセス・スイッチ及び列バス・ラインの数は、大きさの制約及び用途によって決定される。単なる開示の目的で模範的な一具体的例(図13に示す)について説明すると、各部分素子32について単一のアクセス・スイッチ30、アレイの各列について4本の列バス・ライン34a～34dを設けている。別の種類のスイッチはマトリクス・スイッチ36であり、これは1つの部分素子の接続点42(図17参照)を近隣の部分素子の接続点に接続するために使用される。これにより、一音響部分素子を、近隣の音響部分素子に関連した集積電子装置を介してシステム・チャンネルに接続することが可能になる。これはまた、音響部分素子がアクセス・スイッチを介して直接にシステム・チャンネルに接続されない場合でも、該音響部分素子がシステム・チャンネルに接続できることを意味する。図13は1つの部分素子あたり3つのマトリクス・スイッチを示しているが、面積を節約するためにそれより少ない数にすることも可能であり、或いはオン時抵抗の低い、従って面積のより大きいスイッチを設けることも可能である。更に、マトリクス・スイッチは所与のアレイについて既知の不良の部分素子を迂回するために使用することができる。最後に、六角形の部分素子を図示しているが、矩形の部分素子もまた可能である。

30

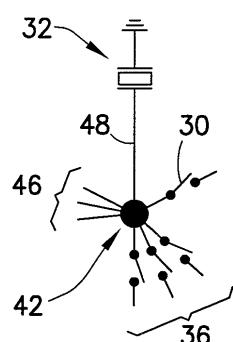

【0051】

図17に関して説明すると、各々の部分素子はその音響部分素子32に関連した電子装置内の共通接続点42に接続される。この共通接続点42は各部分素子内の8つの構成部品に電気接続される。共通接続点42は音響部分素子又はトランステューサ32を、その部分素子のためのアクセス・スイッチ30に、またその部分素子に関連した3つのマトリ

40

50

クス・スイッチ36に、また接続線46を介して3つの近隣の部分素子に関連した3つのマトリクス・スイッチに接続する。マトリクス・スイッチを通った信号は、近隣の部分素子の共通接続点に接続される。

#### 【0052】

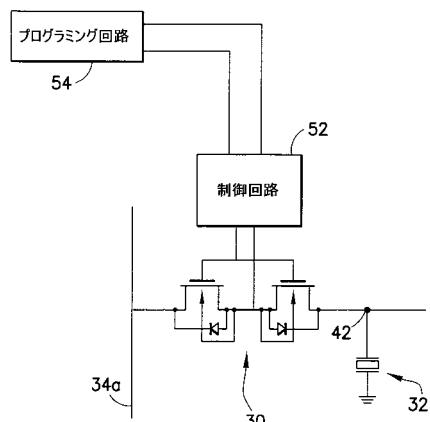

図13は、特定の部分素子についてスイッチング回路網がどのように働くことができるのかを表している。これは単なる模範的な構成である。バス34は、4本の列バス・ライン34a～34dを含んでいて、部分素子32の列の下に延在する。図13は、この列において3つの部分素子のみを示しているが、この列内の他の部分素子が示されていないことを理解されたい。バス34の列バス・ラインは、列の端部において多重化スイッチ40によってシステム・チャンネル・バス38のシステム・チャンネル・バス・ラインに多重化される。これらの多重化スイッチ40は交点スイッチング・マトリクスを形成する。図3に見られるように、各々の列バス・ライン34a～34dはバス38のシステム・チャンネル・バス・ラインの任意の1つに接続することができ、そのためには、適切な多重化スイッチ40をターンオンすると共に、特定の列バス・ラインを他のシステム・チャンネル・バス・ラインに接続する多重化スイッチをターンオフする。これらの多重化電子装置は側部へ離して置くことができ、従って、大きさによって制約を受けることはない。図13は完全装填の交点スイッチを示している。しかしながら、全てのバス・ラインを全てのシステム・チャンネルに接続できるようにスイッチを設ける必要がない場合には、所与のバス・ラインに一部のシステム・チャンネルのみを接続できるようにまばらな交点スイッチを使用することができ、この場合、図13に示したスイッチ40の内の幾つかのみが存在することになる。

10

20

30

40

#### 【0053】

アクセス・スイッチは、部分素子をバス・ラインに直接アクセスさせるものであるので、この名称が付けられている。図13に示した模範的な具現例では、各々の部分素子について6つの他のスイッチ接続部がある。これらの接続部はマトリクス・スイッチ36の形態を取っている。マトリクス・スイッチは部分素子を近隣の部分素子に接続することを可能にする。この六角形のパターンでは各々の部分素子について近隣の部分素子への6つの接続部があるが、各部分素子内には3つのスイッチのみがあり、他の3つの接続部は近隣の部分素子内のスイッチによって制御される。従って、各部分素子内には全部で4つのスイッチ及び関連したディジタル論理装置が存在する。これは単なる1つの模範的な具現例である。バス・ラインの数、アクセス・スイッチの数、並びにマトリクス・スイッチの数及びトポロジイは全て異なることができるが、全体の概念は変わらない。

#### 【0054】

アクセス・スイッチ及びマトリクス・スイッチは別々のパッケージにした構成部品とすることができるが、これらのスイッチは、MUTアレイを製造すべき同じ半導体基板内に製造することができる。これらのスイッチは、米国特許出願第10/248968号（発明の名称「超音波トランスデューサ・アレイ用の集積高電圧スイッチング回路」）に開示されている種類の高電圧スイッチング回路を含むことができる。各スイッチは、バイポーラ動作可能である背中合わせに接続された（ソ・ス電極が一緒に接続されている）2つのDMOS-FETを有する。両方のFETがターンオンされたときは常に電流がスイッチ端子を通って流れる。スイッチの状態はそれぞれのスイッチ制御回路によって制御される。スイッチ制御回路の状態はプログラミング回路からの出力によって規定される。プログラミング回路は、本書に開示したアルゴリズムを使用して導き出された最適化したスイッチング構成に従ってスイッチ制御回路をプログラムする。走査制御装置が、最適化したスイッチング構成をプログラミング回路にロード(load)する。CMOS高電圧スイッチの使用は好ましい一実施形態であるが、本発明は、低電圧スイッチ、MEMSスイッチ、開発中の他の将来のスイッチ技術のような他のスイッチング技術に直接に適用可能である。

#### 【0055】

図18は、音響部分素子32が共通接続点42を介してアクセス・スイッチ30に接続

50

されることを示している。接続点 4 2 に接続する他の 6 本の線は図示していない。この例では、アクセス・スイッチ 3 0 は、前述の一対の背中合わせの D M O S - F E T を有する。制御回路 5 2 が、プログラミング回路 5 4 から送られた制御信号の関数としてスイッチ 3 0 をターンオン又はターンオフする。アクセス・スイッチ 3 0 がターンオンされたとき、音響部分素子 3 2 ( すなわち、相互接続された c M U T セルの部分アレイ ) が列バス・ライン 3 4 a に接続される。この構成では、各音響部分素子に関連した電子装置は、1 つのアクセス・スイッチ、3 つのマトリクス・スイッチ、これらの 4 つのスイッチの各々についてのそれぞれの制御回路、及び 3 つの近隣の部分素子 ( 図示せず ) のマトリクス・スイッチに共通接続点を接続するそれぞれの導体を有する。

## 【 0 0 5 6 】

10

部分素子から列バス・ラインへ進む信号は電気的受信信号である。この場合、受信信号は、音波がトランステューサと相互作用する時に音響部分素子によって発生される電気応答信号である。超音波システムによって発生される電気パルスである送信信号は、列バス・ラインからマトリクス・スイッチへ進む。所与のチャンネルでは、この電気的励起パルスはシステム・チャンネル・バス・ラインを通じて列バス・ラインへ進む。そして、該信号は列バス・ラインからアクセス・スイッチを介して音響部分素子へ進み、またマトリクス・スイッチを介して他の部分素子へ進む。

## 【 0 0 5 7 】

20

音響部分素子の背後に収まるスイッチの数は限られている。スイッチの大きさがそのスイッチのオン時抵抗を決定し、スイッチが小さくなればなるほど、オン時抵抗は益々大きくなる。スイッチングによって惹起される遅延及び歪みは、スイッチのオン時抵抗が増大するにつれて増大する。これは、音響部分素子の背後のスイッチの数とそれらのスイッチによって導入される遅延との間に二律背反があることを意味する。その二律背反に対する 1 つの解決策は、出来る限り融通性を保ちながら、スイッチの数を或る小さい数まで低減することである。この低減を達成するには、マトリクス・スイッチを使用して、音響部分素子が他の部分素子を介してシステム・チャンネルに接続されるようにし、且つアクセス・スイッチの数を或る小さい数に制限する。

## 【 0 0 5 8 】

30

アクセス・スイッチをシステム・チャンネルに接続するバス・ラインもまた電子装置の層の中にスペースを取るので、バス・ラインの数を最小限にすることも有益である。同じ列内の音響部分素子に直接に接続することのできる独自のチャンネルの数は、バス・ラインの数によって決定される。しかしながら、マトリクス・スイッチが 1 つの列内の部分素子を他の列内の部分素子に接続できるようにするので、1 つの列内のチャンネルの数はマトリクス・スイッチによって増大する。これにより、多数のチャンネルを使用可能に維持しながら、バス・ラインの数を小さく保つことができる。勿論、バス・ラインの数をより多くすると融通性が増大するが、より大きいスペースが必要になる。

## 【 0 0 5 9 】

40

マトリクス・スイッチを使用することは、各部分素子の背後のアクセス・スイッチの数を減少させ得ることを意味する。極端な場合には、各部分素子についてアクセス・スイッチは 1 つのみである。しかしながら、2 本以上のバス・ラインがある場合、どのバス・ラインに各アクセス・スイッチを接続すべきか決定しなければならない。1 つの解決策は、接続部を食い違い配置にして、バス・ラインが一列内の N 個の部分素子毎に繰り返して接続されることである。ここで、N は、以下に説明するように最小信号歪みの要件によって決定される数である。図 1 3 を参照すると、列内の各部分素子 3 2 が列バス 3 4 内の 1 つの列バス・ラインにそれぞれのアクセス・スイッチ 3 0 を介して接続されている。この食違い配置にした接続部のパターンは、4 つの部分素子毎に繰り返される。食違い配置はより少ないアクセス・スイッチでバス・ラインをより多くすることを可能にし、またマトリクス・スイッチを組み合わせると、各部分素子にどのシステム・チャンネルを接続できるかに関して融通性を大きくすることができる。勿論、1 つのセルあたり 2 つ以上のアクセス・スイッチを設けると、接続部の融通性は増大するが、スイッチをより小

50

形にする必要があり、それに伴ってオン時抵抗がより高くなる。

【0060】

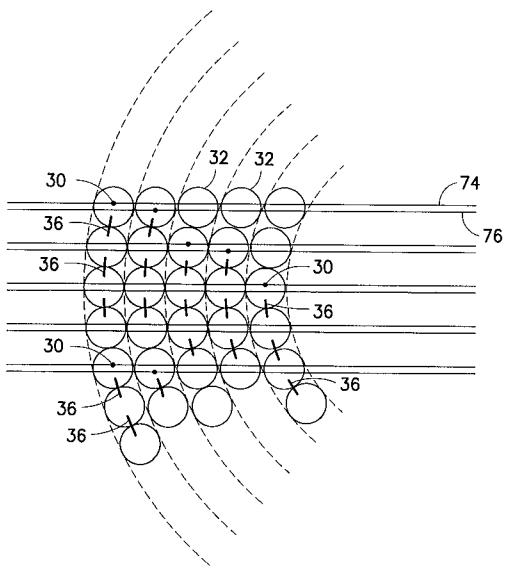

一般的に云えば、パターンを繰り返すための列の数Nは、適切な信号保全性を維持しながら、一緒に接続できるマトリクス・スイッチの最大数によって決定される。この数は、マトリクス・スイッチの抵抗とCMUTの容量とがRC遅延線を形成し、遅延の時定数が直列のタップの数Nにつれて指数関数的に変化することの理解から生じる。この概念について以下に更に検討する。複数の列バス・ライン上のアクセス・スイッチの食い違い配置は、遅延線の制約内で、支持することのできる素子の数を増大させることを可能にする。図19に例示されているように、それぞれ1個の部分素子の幅を持つ複数のリング（その一部を点線の円弧で表す）が密に詰め込まれている場合に、設計についての最悪の場合が生じる。最悪の場合は、この設計におけるバス・ライン74, 76が水平に延在しているので、リングの垂直な部分により生じる。リングの水平な部分では、バス・ラインがリングに平行に延在しているとき全て同じになることから、各部分素子に1つずつアクセス・スイッチを使用することが可能である。しかしながら、垂直な部分では、部分素子32の各列が、異なるシステム・チャンネルに接続されている異なるバス・ラインに関連している。従って、この区域において垂直に隔たって配置された部分素子を、マトリクス・スイッチ36（太い短い線で表してある）を使用して支持することができるだけである。図19では、1つの列あたり2本のバス・ラインがあり、アクセス・スイッチ30（黒い点で表してある）のパターンは4列ごとに繰り返す。各列では、2つのリングが、2つのアクセス・スイッチと、マトリクス・スイッチによりグループ化されたそれらの関連した一連の部分素子とによって支持されている。パターンは4列ごとに繰り返すので、この特定のアーキテクチャは最大で $2 \times 4 = 8$ 個のリングを支持する。一般的に、各列にM本のバス・ライン、及び各一連の部分素子についてN個のタップを持つアレイの場合、最大で $K = M \times N$ 個のシステム・チャンネルを支持することができる。勿論、リングの殆どの部分は完全に水平でも完全に垂直でもない。従って、システム設計者の課題は、アーキテクチャの制約の下で開口内の全ての点でアレイ構成を最適化することである。

10

20

30

40

【0061】

部分素子とシステム・チャンネルとの間の特定の所望のマッピングが与えられている場合、目標はそのマッピングを提供する又はほぼ提供する最適なスイッチング回路網構成を決定することである。所望のマッピングに正確に合致する構成はあり得ない。これは所与の設計の融通性に依存し、融通性はバス・ラインの数及びアクセス・スイッチの数によって制御される。所望のマッピングを生成することができない場合、密接した近似を選択しなければならない。モザイク環状アレイに再構成可能性について、より可能性の高い状況は、所望の部分素子・チャンネル間のマッピングを提供する複数の構成が存在することである。また、所望のマッピングを正確に生成することができない場合には、複数の近似構成もあり得る。これらの場合において、複数の構成が同じ部分素子・システム・チャンネル間マッピングを提供する場合、1つの構成が遅延及び振幅性能に関して別の構成よりも望ましいことがある。ここで提示する本発明の一面は、より優れた性能を持つ構成を選択することによって撮像システムの性能を改善するための最適化手順を使用することを含む。

【0062】

システム・チャンネルと所与の部分素子との間の接続が複雑になることがある。スイッチング回路網構成は部分素子とシステム・チャンネルとの間の複雑な接続網を規定する。その結果は、部分素子からシステム・チャンネルへの簡単な接続は無く、むしろ複雑な遅延線構造を形成するような一連のスイッチ（アクセス及びマトリクス・スイッチの両方）を介しての接続があることである。送信時に、同じシステム・チャンネルに接続された複数の信号は同じ送信パルスを同期して見るはずである。しかしながら、現実には、スイッチの回路網が信号を遅延させ、またシステム送信器に対して異なる経路を見る各部分素子においてパルスの振幅及び形状を変化させる。

【0063】

50

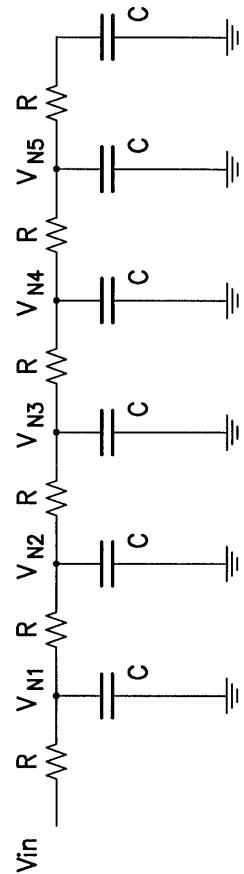

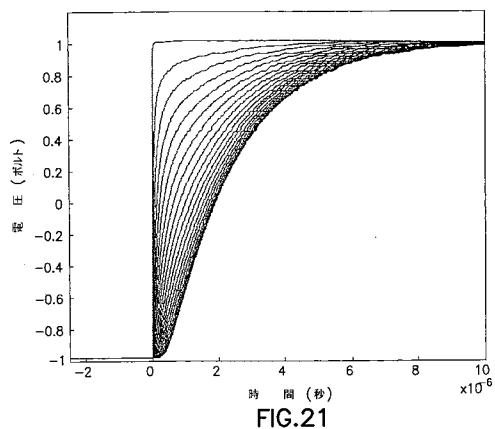

遅延線の簡単なシミュレーションを用いることにより、どれほどの遅延が存在するか及びパルスがどのように歪むのかについての知識を得ることができる。トランスデューサ・アレイ及びその関連したスイッチ・マトリクスは抵抗及び容量の分布回路網としてモデル化することができる。信号はこの回路網を伝播し、その際の遅延時間は回路網の単位抵抗及び容量に関係する。このような回路網の簡単な例は、図20に示されているような1次元RC遅延線である。この回路網では、入力から伝播する信号は、図示のように抵抗Rと容量Cの関数である遅延を受ける。回路網内の各ノード又はタップにおける波形は、入力信号に対して異なる量の遅延を受けているので異なる形状を持つ。有限RC遅延線における最悪の遅延は、 $R C N^2 / 2$ に従って変化するものとして示すことができる。ここでのNは遅延線内のタップの数である。図21は、図20に示した回路網と同様な20タップのRC遅延線について測定したデータを示す。グラフは、遅延線の各タップで測定した一群の曲線を示し、左から右へタップ番号が大きくなる。このグラフは、回路網を伝播するにつれて生じる電圧波形の歪みを明瞭に示している。（ステップ入力から出力の中間点までの時間として規定した）最悪の遅延は $R C N^2 / 2$ によって近似されることが判る。それは、この実験では約25マイクロ秒である。従って、再構成可能な超音波アレイの設計のための良好な経験則は、 $R C N^2 / 2$ がシステムによって許容することのできる最悪の遅延よりも常に小さくなるように、トランスデューサの容量及びスイッチのオン時抵抗を設計することである。この場合、任意の所与の経路において許容されるタップ（又は、スイッチ）の数Nは、システムの撮像要件と回路網のRC時定数とによって制限される。

10

20

30

40

50

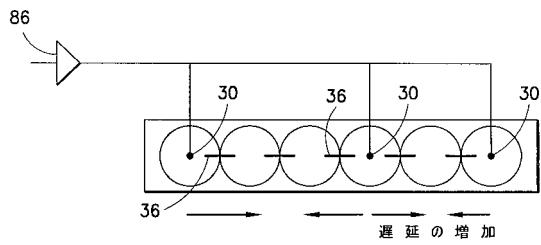

#### 【0064】

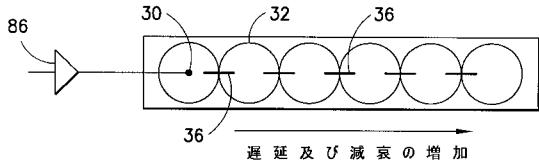

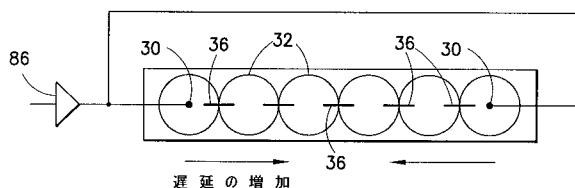

上述の考察の結果は、特定の部分素子における遅延は、信号が通過しなければならないスイッチの数と、信号が通らなければならない経路の数と、複数の接続部が分布している様態とに依存することを表している。特定の開口に依存して異なる遅延パターンがあると予想することができる。更に、シミュレーション及び逐次近似法により、遅延を低減するためにアクセス・スイッチの配置を改善することができる。図22は、素子のトポロジイにより遅延が変化する様態を例示する。この例において、符号86は駆動装置を表し、図の残りの部分は、それぞれのマトリクス・スイッチ36によって直列に接続された（線形素子を形成する）一列の部分素子32を示す。列内の第1の部分素子が駆動装置86に接続される。始めに、遅延線における信号の伝播は、点熱源からの熱の拡散と同じと見なすことができる。この類似性に留意して、図22は、強制ノードすなわちアクセス・スイッチ30からの距離が増大するにつれて遅延及び減衰量が2つの次元で増大することを示している。

#### 【0065】

開口内の各部分素子毎の信号歪みを低減するためには、アクセス・スイッチを出来る限り一様に且つ出来る限り密に分布させることは最良であることは明らかである。詳しく述べると、スイッチは、図23に示されているようにマトリクス・スイッチ接続部の長い列の両端にそれぞれの異なるアクセス・スイッチ30が確実に接続されているように、構成することができる。線形素子の場合、特に全ての部分素子が線形素子に沿ってマトリクス・スイッチによって接続されて、線形素子の一端から他端まで連続した経路が存在するようになっている場合、線形素子の両端にアクセス・スイッチ30を配置することによってかなりの改善を行うことができる。連続的に接続された線形素子の両端を接続することにより得られる改善は、同じ素子を2つの短い素子に分割して、その各々がそれ自身のアクセス・スイッチ接続部を持つようにした場合よりも、改善の程度が大きい。また、図24に示されているように、素子の内部にアクセス・スイッチ30を分布させたときには更なる改善が得られる。

#### 【0066】

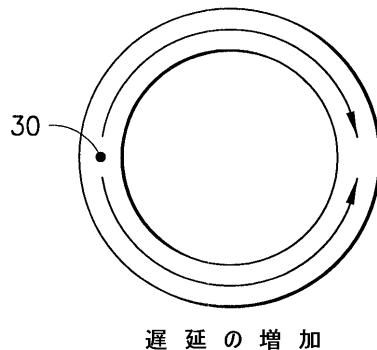

環状アレイの場合、最も簡単なアーキテクチャは図25に示されている通りである。この場合、単一のアクセス・スイッチ30が部分素子より成る1つの完全なリング（個々の部分素子は図示していない）に接続され、各部分素子はマトリクス・スイッチ（図示せず

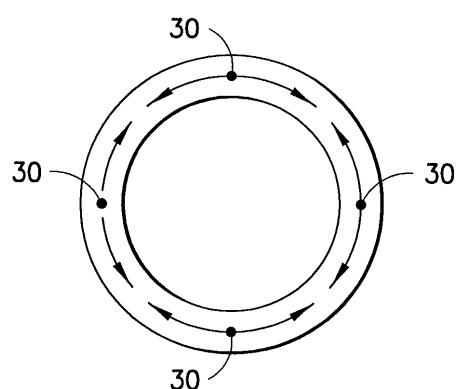

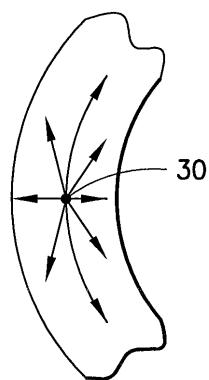

)によって一緒に接続されている。ただ一つのアクセス・スイッチを必要としているので具現化するのは簡単であるが、このアーキテクチャはマトリクス・スイッチの大きさに依存してかなりの遅延を生じさせる。従って、図26に示されているように複数のアクセス・スイッチを完全なリングに接続することができ、部分素子(図示せず)の間のマトリクス・スイッチはリングのそれぞれの一部分を形成するようにアクセス・スイッチ30を持つ。これらのアクセス・スイッチは、スイッチ相互の間の部分素子についての信号遅延を低減するためにリングに沿って等距離の間隔をおいて分布させる。このように、複数の冗長なマトリクス・スイッチ接続を用いて單一のリングを形成することにより、直列抵抗を減少させて、遅延を小さくすることができる。図27に示されているように、アクセス・スイッチは、リングの両方の縁から等距離に配置して、もしただ1つのアクセス・スイッチが用いられた場合にリング内部の遅延が最小になるように選択することができる。リングの縁は、リングの内周縁及び外周縁に近い部分素子を表す。このようにして、リング内の遅延パターンが改善される。リングの幅にわたって複数のアクセス・スイッチが使用される場合、それらは、2次元スイッチ距離を最小にすることによって遅延パターンを改善するように内周縁及び外周縁上に配置すべきである。図28はこのような事例を示す。丸点30はアクセス・スイッチを表し、これらは部分素子の各リング(個々の部分素子は図示していない)の内周縁及び外周縁の近くに対にして配列されている。アクセス・スイッチ30がリングの縁に配置されている場合、信号が両方向から駆動されて、全体のエラーが減少する。図28はまた、四角の中のアクセス・スイッチ30'を示しており、これらはリングの中央(すなわち、リングの内周縁及び外周縁の間の中間)に配置される。これは、アクセス・スイッチが両方の縁からリングを駆動しないので、リングの縁で大きなエラーを招く。

10

20

30

40

50

#### 【0067】

本アーキテクチャはモザイク環状アレイの概念を目標としているが、当業者には明白なように、遅延を最小にするようにアクセス・スイッチの配置を選択しながら、リング以外のパターンを形成することが可能である。従って、ここで説明する発明は、位相調整アレイ、線形アレイ及び2次元アレイを含む他の種類の撮像手段に適用可能である。

#### 【0068】

本発明の方法は、複雑なスイッチング回路網によって導入されたエラーを最小にするスイッチング構成を選ぶために使用することができる。その目標は、ビーム形成が損なわれることのないような方法でエラーを低減することである。これを達成できる多数の方法がある。この目的を達成しようとするアルゴリズムの幾分特定の具現例を以下に示す。これら具現例は本発明を制限するものと見るべきではなく、むしろこのようなアルゴリズムの潜在能力を表すために使用される例として見るべきである。

#### 【0069】

例えば、システムの完全なモデルが利用できる場合、このモデルを使用して、スイッチ回路網のための最良の構成を決定することができる。これを達成できるようにするには、何らかのランダム又は準ランダム処理によりスイッチング構成を生成する。次いで、このスイッチ構成をモデルに入力する。モデルは、スイッチング回路網の全てのエラーを考慮してシステムの応答を算出する。モデルを使用して或る形態の画像又は放射パターンを生成することができ、このデータに基づいて特定の判定基準又はコスト関数を算出する。コスト関数の結果を使用することにより、構成を修正する。次いで、反復アルゴリズムを生成し、模擬アニーリング(simulated annealing)又は或る他の演算方法を使用してコスト関数を試し且つ最小にする。

#### 【0070】

算出されるパラメータは、選ばれたモデルの複雑さ及び最小にすべく選ばれた特定のコスト関数に依存する。完全なモデルは、特定のスイッチング構成及び入力励起が与えられている場合、トランスデューサの面における音響出力(空間及び時間の関数としての圧力)を算出することができる。このようなモデルは、スイッチング回路網の効果及び個々のトランスデューサ・セルの応答を含む必要があると考えられる。音響出力が与えられると

、多数のコスト関数を評価することができる。例えば、結果として得られた放射パターンのビーム幅を最小にし、同時にパターンのサイドロープのレベルを最小にすことができる。この場合、モデルはビーム幅及びサイドロープ・レベルを算出する必要があると考えられる。

【0071】

代替態様では、ハードウェアが利用可能である場合、実際のハードウェアを使用してこの最適化プロセスを行うことが可能である。この場合、構成を生成して、システム制御装置に印加する。画像を作り、又は簡単化したデータを取得する。再び、コスト関数をこのデータに基づいて定めて、構成を修正するために使用する。しかしながら、この場合、何らモデル化は関連しない。また、スイッチング・アレイに整合するように設計されたプローブ・アレイを使用して、下側に位置するCMOS電子装置上で直接に電圧を測定することによって性能を評価することが可能である。この場合、スイッチング回路網をプログラムすることのできる速度と、データを収集し処理することのできる速度とが、検討することが可能である構成の数を制限する。しかしながら、この数は恐らく極めて多く、これは画像を形成することなく実際の応答を決定する良い方法であるかもしれない。

10

【0072】

場合によっては、スイッチング・トポロジイの全てのエラーを含む、システムの音響応答の完全なモデル化は、困難であり且つ演算経費が高い。実用的なハードウェア・プロトタイプは、構成についてのデータの収集に使用するために入手可能でないことがある。たとえハードウェアが入手可能であった場合でも、多数の構成についてデータを収集し処理するのに必要な時間が長くなる。そこで、この種類のアルゴリズムを使用する有効性を決定するために、回路網が音響応答にどのように影響を及ぼすことがあるかについての洞察及び理解に基づいて、多数の構成を非常に素早く評価できるようにするより簡単なモデルを採用することができる。例えば、信号が通過しなければならないスイッチの数が多くなるほど、導入される遅延及び歪みが益々大きくなることが知られている。

20

【0073】

初めに、スイッチング回路網を試して配置するための良い方法は、接続部と部分素子との間の距離が出来るだけ小さくなるようにする方法であることが判る。ここで、接続部は、オンになっているアクセス・スイッチと定義され、従って、該スイッチを備えた部分素子を特定のチャンネルについての列バス・ラインに直接に接続する。また、距離は、音響部分素子から列バス・ラインに到達するまで信号が通過しなければならないスイッチの数を表す。更に、接続されるアクセス・スイッチは、局部的な距離を短くすることにより一部の部分素子の連続した非常に長い列を生じないようにするために、出来るだけ多く分散させて配置したほうがよい。そこで、簡単化したモデルは、構成の性能についてのメトリック(metric)として、信号が通過しなければならないマトリクス・スイッチの数を使用する。これは完全に正確では無いけれど、この簡単なモデルはシミュレーションでスイッチング回路網の性能を改善することが判った。このことは、2次元減少を1次元メトリックでモデル化しようとしているにも拘わらず当てはまる。

30

【0074】

本書で開示した再構成可能性の特定の具現化では、電子装置によって課せられる制約がある。システムについてのスイッチング構成を規制する一組の規則がある。この厳しい規則に加えて、音響部分素子と接続点との間の距離を短くすることのような指導原理がある。規則は従わなくてはならず、指導原理は性能を改善するために用いることができる。規則は以下の通りである。

40

【0075】

[1] 各列はn本の列バス・ラインを持つ。本書で開示した例では、n = 4である。これは、列全体で、アクセス・スイッチが接続できる4本のみのシステム・チャンネル・バス・ラインがあることを意味する。

【0076】

[2] 列内の各部分素子はn本の列バス・ラインの内の1本のみに接続する。これは、

50

部分素子内に1つのアクセス・スイッチのみがあるということから生じる。これはまた、所与の部分素子が单一のシステム・チャンネルにのみ直接に接続できることを意味し、そのチャンネルはシステム・チャンネル・バス・ラインと列バス・ラインとの間のマルチプレクサによって決定される。

【0077】

[3] 各列バス・ラインは单一のシステム・チャンネル・バス・ラインに接続される。システム・チャンネル・バス・ラインは列バス・ラインに対して多重化されるが、この接続は所与の構成について変更できない。

【0078】

[4] 列バス・ラインが所与のアクセス・スイッチに接続されるパターンが、その列について繰り返えされる。本書で述べた事例では、パターンは4つの部分素子毎に繰り返えされる。

【0079】

[5] 所与の回路具現化のため、同じ列バス・ラインに接続されるアクセス・スイッチの合計数は小さい有限数である。後で説明する特定の場合では、限界値は4である。これは、列バス・ラインの限られた大きさによって課せられた電流引き込み限界から生じる。限界値はシミュレーションに基づくものであり、列バス・ラインの大きさを増大させることによって大きくすることができ、従って、電流引き込みをより大きくすることが可能であるが、これは部分素子をより大きくする必要があるかもしれない。

【0080】

指導原理について前に述べたが、より具体的に以下に説明する。本発明の一実施形態によれば、目標はスイッチング回路網によって導入された遅延エラーを最小にすることである。これは、接続点から部分素子までの距離を出来るだけ小さく保つことによって達成することができる。これに関連して、接続点は、そこにあるアクセス・スイッチがオンである部分素子である。更に、接続点は均等に分布させるのがより好ましい。

【0081】

スイッチング回路網構成を決定するには、どのアクセス・スイッチがオンであるか決定し、及び列バス・ラインとシステム・チャンネル・バス・ラインとの間のマルチプレクサ（図13に部分的に示されている一群のマルチプレクサ・スイッチ40を意味する）がどのように設定されるかを決定することを必要とする。一旦所望のパターンが判ると、マトリクス・スイッチの状態は決定するのが容易である。マトリクス・スイッチは、そのスイッチが接続される近隣の部分素子が同じシステム・チャンネル上にあるべきか否かを単に決定することによって設定される。そこで作業は、システム・チャンネルを多重化された列バス・ラインに接続するための方法を決定することである。一旦これが判ると、アクセス・スイッチはまた割り当てるのが容易になる。

【0082】

最適なスイッチ構成を決定することは困難である。初めに、スイッチを割り当てるための簡単なアルゴリズム的方策を開発した。アルゴリズムは幾つかの規則及び指導原則を考慮して設計したが、決して最適な解決策ではなく、むしろベンチマークに対する解決策である。探した解決策は特定の所望の構成に基づくものである。一例では、所望の構成は20個のリングを持つ、等幅の環状アレイであった。そのアルゴリズムは以下の通りである。

【0083】

アレイの一方の縁から始めて、アレイにわたって列毎に作業する。各列について、且つその列の各バス・ラインについて：

[1] どのリング（すなわち、どのシステム・チャンネル）が所与の列バス・ラインについて可能であるが決定する。例えば、アレイの頂部近くでは、外側の素子のみが存在することができる。その場合、単一のリングが可能である。中心へ向かうにつれて、全てのリングが存在するが、所与の列バス・ラインについては幾つかのリングのみ可能である。

【0084】

10

20

30

40

50

[ 2 ] 各リングについて、マルチプレクサがそのリングに対応するシステム・チャンネルに所与の列バス・ラインを設定した場合に、所与の列バス・ラインについてターンオンすることのできるアクセス・スイッチの数を決定する。

【 0 0 8 5 】

[ 3 ] 殆どのアクセス・スイッチをオンにすることのできるリングに列バス・ラインを割り当てる。しかしながら、これは以下の制約の下で行うべきである。それは、

[ a ] 同じリングを 1 つの列内の 2 本以上のバス・ラインに割り当てるることはできないこと、及び

[ b ] 同じリングが既に前の 4 つの列において割り当てられていた場合、その同じリングを列バス・ラインに割り当てるることはできないことである。

10

【 0 0 8 6 】

場合によっては、条件 [ b ] を満たし且つリングを特定の列バス・ラインに割り当てることができないことがある。例えば、特定の列バス・ラインに割り当てられる候補のリングが 3 つしかなく、それらの 3 つのリングが前の 3 本の列バス・ラインに割り当てられていた場合、この特定の列バス・ラインに割り当てる事のできるリングはない。この場合、及び条件 [ b ] により列バス・ラインを任意のリングに接続することが妨げられる全ての場合において、制約条件を取り除かなければならない。このアルゴリズムでは、アルゴリズムの意図を殆ど妨げないやり方で制約を除くことができる。そこで条件 [ b ] を満足できない場合、最も遠い列から始めて、1 つずつ、列についての制約を除く。そこで条件 [ b ] を満足できない場合、列バス・ラインの割り当てが、第 4 の前の列バス・ラインに割り当てられた同じリングになるようにする。これでも未だ割り当てる事ができない場合、列バス・ラインの割り当てが、第 3 の前の列バス・ラインに割り当てる事ができるようになると云う風に、列バス・ラインを割り当てる事ができるまで繰り返す。

20

【 0 0 8 7 】

上記のアルゴリズムは特定の所望のリング形状のためにマルチプレクサ及びアクセス・スイッチの設定を割り当てるように使用することができる。それはアクティブなアクセス・スイッチの数を最大にしようとするので、接続点と部分素子との間の距離を短くするのに役立つ。このアルゴリズムは有用なベンチマークである。

30

【 0 0 8 8 】

スイッチング回路網構成に関して、その構成が撮像状況で如何に効果的であるかを決定することは重要である。1 つの構成が別の構成よりも良好であるかどうか決定するために使用すべき最終的な判断基準は、このような構成が生成する画像の品質である。しかしながら、実用的なプロトタイプが無い場合、これは実行するのがほぼ不可能である。また、画像品質を決定することは困難なメトリックであり、実用的なプロトタイプによる場合でも、これは、必要とされるかもしれない時間と労力のせいで全ての可能な構成の各々を選別するために使用することができなかった。特定の構成に関して、電子装置の完全なコンピュータ・モデルを使用してビーム分布をシミュレートすることが可能である。しかしながら、このシミュレーションは非常に時間が掛かり、従って大量の選別処理のためではなく 2 つ乃至 3 つの構成のみに限定すべきである。また、簡略した電気モデルを使用して遅延及び振幅変化のみをシミュレートして、これらをより簡単なビームフォーマ・モデルにに対する入力として使用する事が可能であるが、しかしこれはまた必要とされる多数の入力を選別するために望ましい時間よりも余分な時間が掛かる。僅かに速くする方法は、遅延を推定するための簡略化した方程式を使用することであるが、これは多数の可能な構成を有意に選別できるほどに非常に速いシミュレーションではない。

40

【 0 0 8 9 】

多数の構成についての非常に素早い評価を可能にする方法は、遅延についての主要な効果が部分素子から接続点までの距離から生じると仮定することである。各部分素子から最も近い接続点までの距離を算出することは、ルックアップ・テーブルを使用して非常に素早く行うことができる。これにより、多数の構成を探索する事のできる反復アルゴリズムを設計することが可能になる。本発明はこの具現例に制限されないが、この評価速度は

50

、最適化を実際に使用可能にする重要な利点である。

【0090】

既に述べたスイッチ構成を決定するための簡単な方法に対して遅延エラーを大幅に改善する反復アルゴリズムが開発された。このアルゴリズムは下記の通りである。

【0091】

[1] 初期構成が与えられる。一例では、簡単なアルゴリズムの出力が使用された。これはまたランダムな構成であってよい。

【0092】

[2] 特定の幾何学的形状について、ルックアップ・テーブル (LUT) が作成される。このLUTは、リング内の任意の部分素子から該リング内の他の任意の部分素子までのスイッチにおける距離を与える。LUTの算出速度を改善するために、或る最大距離を使用して、その最大値より大きい距離は単に閾値よりも大きいとするラベルを付けて、計算は行わない。

10 【0093】

[3] 現在の構成について、アルゴリズムは下記のことを行う。

【0094】

[a] LUTを使用して、各部分素子から最も近い接続点までの距離 (スイッチの数) を算出する。

【0095】

[b] 距離を分類して、M個の最悪の (すなわち、最も大きい) 距離を持つ部分素子を保持する。一例では、M = 10 であり、そこで10個の最悪の距離を保持した。

20 【0096】

[c] M個の最悪の距離の内の1つを持つ部分素子の内の1つをランダムに選択する。この場合、部分素子を選択するために1と10との間の整数をランダムに作成する。

【0097】

[d] ランダムに選択した部分素子のためのアクセス・スイッチをターンオンする。殆どの場合、これに関連して、他のアクセス・スイッチがターンオフされ、且つシステム・チャンネル・バス・ラインと該部分素子の列の列バス・ラインとの間のマルチプレクサが変更される。

30 【0098】

[e] この新しく生成した構成についてグローバル・コスト関数を評価する。用いられた特定のコスト関数は、閾値よりも大きいスイッチ距離を持つ部分素子の数であった。使用された閾値は、単一列のスイッチによる幾つかのシミュレーションに基づいて、4とした。

【0099】

[f] コスト関数が変更前の構成のコスト関数よりも小さい場合、この新しい構成は現在最良のものとして採用される。

【0100】

[g] コスト関数がスイッチの変更でより大きい場合、それはそのまま維持することができる。これは模擬アニーリング型のアルゴリズムである。温度関数が規定され、そして多数の反復につれてゆっくりと温度が減少する。最初は温度関数は高く、従って、そのコスト関数がより大きいにも拘わらず構成を維持する可能性が一層大きい。反復の数が多くなるにつれて、温度が低下し、且つ劣った構成を保持する確率が低下する。この種のアルゴリズムは、システムが局部的な最小値から飛び出すことを可能にし、従って、より良い最小値 (多分、グローバルではない) を見付ける機会をシステムに与える。

40 【0101】

[h] このプロセスは、或る所定の反復回数まで、又は全ての距離が閾値よりも小さくなるまで繰り返す。

【0102】

模擬アニーリングは、可能な設定値の全数検索が実行可能でないときにパラメータの選

50

択を最適化するための周知の演算方法である。アニーリングは、金属が冷却するときに結晶化する物理的プロセスを表す。この冷却プロセスの最終状態は物が冷却される速度に左右される。冷却が非常にゆっくりと行われる場合、システムは最小エネルギー状態に達することができる。また物が非常に急速に冷却される場合は、エネルギーは局部的に最小になるだけである。模擬アニーリングは、冷却プロセスを模倣する数学的アルゴリズムである。コスト関数は検討しようとしているプロセスについて定義され、また模擬アニーリング・アルゴリズムはこのコスト関数を最小にしようとする。この場合、コスト関数はアニーリングの物理的プロセスにおけるエネルギーに類似する。模擬アニーリング・アルゴリズムは特定の構成で開始する。構成に対してランダムな変更を行う（すなわち、最適化しているパラメータにランダムな変更がなされる）。これらの変更は、ある特定の法則又は規則に従うことを必要とすることがある。構成に変更を行った後、コスト関数が再び評価される。コスト関数が減少した場合、構成は新しい構成に変更される。コスト関数が高くなったり、構成はランダム変数の値に依存して変更しても変更しなくてもよい。アルゴリズムが進行するにつれて、コストの高い方の構成が維持される尤度が低減される。しかし、コストの高い方の構成を生じさせることによって、アルゴリズムは局部的な最小値を防止し且つより絶対的な最小値に近づけることができる。コストの高い方の構成が維持される確率は最初は高く、アルゴリズムが進行するにつれて減少する。この確率は物理的アニーリングにおける温度に類似する。確率が低下する速度（レート）がアルゴリズムの速度（スピード）を決定する。もしレートが高い場合、答えは素早く得られるが、真の最小値に近くないことがある。レートが低い場合、答えを得るのにより長い時間が掛かるが、答えは最小値になる可能性が高い。

10

20

30

#### 【0103】

モザイク環状アレイについて簡単なアルゴリズムを使用してスイッチング構成が決定された。簡単なアルゴリズムのために、7015個の部分素子の内の172個が5スイッチ以上の距離を持っていた。これは、部分素子の97.5%以上が閾値以下であったことを意味する。この構成を反復アルゴリズムに対する入力として使用して、新しいスイッチング構成を決定した。この場合、7015個の部分素子の内の12のみが接続点へ進むために5個以上のスイッチを持っていた、すなわち、素子の内の99.8%以上が閾値以下であった。閾値判定基準を満たさなかった12個の部分素子は、全ての5スイッチの距離にあった。これは、閾値判定基準を満たさない部分素子を172から12へ減らすことによって簡単なアルゴリズムに対する改善を行ったことを示す。しかしながら、反復アルゴリズムは、システムを1つの列バス・ラインあたり4つのアクティブなアクセス・スイッチに制限すると云う規則を考慮していない。余分なスイッチを除くために追加の処理ステップを使用した。このプロセスは、平均距離の増加を最小にしようとするやり方でスイッチを除去する。これらの余分なスイッチを除去した結果、簡単なアルゴリズムについて大幅な改善がなされた。余分なスイッチの殆どは、頂部及び底部の付近にあった。そこでは接続部の密度が大きく、従って、失われるものは少ない。

30

#### 【0104】

上記の距離を、電子装置のシミュレーションから導き出された実際の遅延と比較した。反復アルゴリズムを使用してスイッチング構成を生成した場合、簡単化したモデル及び電子シミュレーション・ソフトウェア（例えば、H S P I C E）を使用して遅延をシミュレート（模擬）することが可能である。これは遅延問題の2次元性質を正確に反映しており、これは演算速度のために単一のスカラーに変換される。市販の電子シミュレーション・パッケージを使用して同じスイッチ構成についての遅延のシミュレーションを行った結果は、実際の遅延のピークが常に（最適化するために使用された）距離メトリックにおけるピークで生じたことであった。これは、距離メトリックが最適化のために使用するための良好なメトリックであると云う事実を証明している。しかしながら、距離メトリックにおける幾つかのピークが、遅延において対応するピークを持っていなかった。これは、距離メトリックの1次元性質に対する遅延の2次元性質に関係する。

40

#### 【0105】

50

上述したスイッチ・マトリクスの実現は、反復アルゴリズムの出力であった。しかしながら、結果は異なるラン(run)について異なることがあり、また使用される温度パラメータと閾値とコスト関数とに左右される。最適化時間を多くすることにより現在の設計について改善することが可能なことがある。また、これがエラーを最小にするための1つの模範的なアルゴリズムに過ぎないことに留意されたい。また、性能を改善するために他のアルゴリズムを使用するもできる。

#### 【0106】

線形走査を形成するために、モザイク環状アレイのアクティブな開口を下側に位置する2次元アレイにわたって歩進させることが必要である。この歩進(stepping)は、スイッチング回路網を再構成することを必要とする。この歩進を行うことのできる幾つかの方法がある。アレイの分解能及び手近な用途の要件によって決定されるような所要のビーム間隔が、部分素子1個分ずつの歩進を許容できるようなものである場合、アルゴリズムにより導き出した同じスイッチ構成を各ビームについて使用することができる。この場合、スイッチング構成は単純に、各ビームについて1個又は数個の部分素子にわたって歩進させる。再プログラミング、及び再構成するためにシステムによって使用され電力を最小にするために、スイッチ状態を1つの部分素子から隣の部分素子へ直接伝達して、外部でアレイ全体を再プログラミングすることを避けることが可能である。しかしながら、アクセス及びマトリクス・スイッチ・パターンを平行移動させることに加えて、列バス・ラインをシステム・チャンネル・バス・ラインに接続するマルチプレクサはまた変更しなければならない。列バス・ラインの方向にビームを部分素子全部の増分で歩進させると、この変更は単にチャンネルの一回転である。例えば、それぞれA、B、C及びDで表した4つのシステム・チャンネルが特定の構成についての特定の列の4つの列バス・ラインに接続される場合、スイッチング・パターンが次のビーム位置へ走査されるとき、システム・チャンネル/列マルチプレクサの状態は、システム・チャンネルが4つの列バス・ラインの間で回転するよう、例えば、システム・チャンネルB、C、D及びAがこの順序で同じ4つの列バス・ラインにそれぞれ接続されるように、調節しなければならない。この代わりに、システム・チャンネルと列バス・ラインとの間の多重化を変更するよりもむしろ、システムのビームフォーマは幾何学的形状の変更を直接考慮し、従って、4つのチャンネルの遅延を調節して新しい遅延を考慮することができる。

#### 【0107】

前に述べたように、動きが部分素子の整数倍であるように環状リングが歩進させられる場合、各ビームについて最適化し直す必要はない（但し、下側に位置するスイッチ・マトリクスが下側の2次元アレイ全体にわたって一様な電気的特性を持っていると仮定する）。しかしながら、線の間隔を部分素子1個分よりも密にするようなビーム密度が希望される場合がある。この場合、ビームの中心を部分素子1個の分数の増分で歩進させ、例えば、開口のフル・ステップの間にハーフ・ステップだけビームを実効的にステアリングするように開口を変形して、イメージヤの分解能を高くする。このような場合には、最適化は単純に平行移動せず、各々の分数的歩進(fractional step)について最適化を遂行しなければならない。しかしながら、これらの分数的歩進構成は、線形走査を形成するために下側に位置する2次元アレイにわたって環状アレイを歩進させるについて、再び生じことがある。このような場合には、どこで同じ分数的歩進が要求されても、最適化は同じであり且つ再使用することができる。そこで、分数的歩進の場合でも、少数の最適化が必要とされる。このような場合、プログラミング時間及び電力消費を節約するために、特定の構成について全てのビームを発射し、その構成をアレイにわたって粗いビーム間隔で歩進させることが可能であることがある。この場合、1つの部分素子から近隣の部分素子へ直接的に構成を通すことが可能である。粗い走査が完了した後、古い構成からの分数的歩進を表す新しい構成をプログラムして、アレイにわたって歩進させることができる。これは、各分数的歩進について繰り返すことができる。各構成からの結果として生じる粗い間隔のビームは走査変換器によってインターリープして、所望の微細なビーム間隔にすることができる。また、異なる構成からのビームを混合するとき、ビーム形成用利得の相違を保証

10

20

30

40

50

するためにビーム毎に利得を調節し、且つそれらの構成からの線を混合することが必要なことがあることに留意されたい。

【0108】

以上に開示した数値最適化アルゴリズムは再構成可能なアレイのビーム形成性能を改善する。解決すべき問題は、再構成可能なアレイのための簡単化したスイッチング回路網の場合に、遅延、振幅変化及び波形歪みの全てが簡単化したスイッチング回路網に起因して生じることであった。数値最適化の使用は、エラーを最小にし且つ適切なビーム形成性能を維持するのに役立つことができる。このような最適化の特定の一例を探求した。その際に、簡単なメトリックを定義して、様々な構成の性能を特徴付けるために使用した。この例で使用された簡単なメトリックは、所与の部分素子と、列バス・ラインに接続された（すなわち、閉じた状態にあった）最も近いアクセス・スイッチとの間のスイッチ数であった。得られた結果により、簡単なメトリックは、おおざっぱな近似にも拘わらずスイッチング回路網の性能を改善することができる事が判った。簡単なメトリックはまた、多数の構成を検討できるようにし、これは成功の機会を増大する。

10

【0109】

本書に開示した最適化技術は、再構成可能なアレイのための簡単化したスイッチング回路網により撮像性能を改善する。遅延エラー及び歪みの減少は、分解能及びコントラストの改善を含む、ビーム形成の改善に直ちにつながる。

20

【0110】

最適化アルゴリズムは完全な又はまばらなマルチブレクサのいずれかにより使用することができる。このアルゴリズムはそのデータを保存及びその後の使用のために前もって生成することができ、或いはアレイ抵抗の変化に起因して増分的な改善のために撮像中に局部的に生成することができる。アルゴリズムは、理想的な抵抗値を仮定して設計段階の際に、又は測定した実際の抵抗を使用して製造する時に、或いはシステムの経年につれて使用するべき較正段階として又は温度に起因した変動を補償するために現場で周期的に（例えば、超音波撮像装置がターンオンされる度毎に、又は使用中に、較正を行う必要があると決定されたときに常に又はアレイ構成が変更されたときに常に）遂行することができる。例えば、システムは、温度の所定の変化を検出したことに応答して自動的に較正することができる。更に、製造されたcMUTの容量の変動がまた、アレイの性能に影響を及ぼす。このような変動は、製造されたアレイの内の全ての部分素子の各々について正確なcMUTの容量を測定した後に最適化手順を繰り返すことによって、対処できる。

30

【0111】

較正データは各プローブにとって独自のものであり、較正データは各プローブによりROM又はEPROMに記憶させることができ、或いはプローブ自体の中のRAM、EEPROM、FRAM等に局部的に記憶するために、ケーブル内のデータ・リンクを介してプローブにダウンロードされるファイルとして、撮像システム上に記憶させることができる。このデータは走査中に局部的な（プローブ）メモリから読み出され、各々の新しい走査は新しい所要の構成データを読み出す。この代わりに、較正データはシステムの使用中に算出して、プローブにダウンロードすることができる。

40

【0112】

センサ素子をバス・ラインに接続するためにアクセス及びマトリクス・スイッチを取り入れることにより、融通性が大きくなる。本発明の様々な実施形態によれば、下記の特徴の1つ以上を用いることができる。

【0113】

（1）アクセス・スイッチは、所与の数のバス・ラインについて必要とされるアクセス・スイッチの数を減らすために、食違い配置することができる。

【0114】

（2）食違い配置パターン内の1つの部分素子のために单一のアクセス・スイッチを使用することができる。

【0115】

50

(3) バス・ラインに対するアクセス・スイッチのマッピングの順序をランダムにして、繰返しパターンに起因するアーティファクトを低減することができる。

【0116】

(4) 各部分素子内に2つ以上のアクセス・スイッチを使用することができるが、バス・ライン及びシステム・チャンネルの数よりも未だ少ない数とする。

【0117】

(5) バス・ラインは、交点スイッチング・マトリクスを使用してシステム・チャンネルに接続することができる。

【0118】

(6) まばらな交点スイッチを使用して、バス・ラインをシステム・チャンネルに接続することができる。 10

【0119】

(7) スイッチは、マトリクス・スイッチ接続部の長い列の両端にそれぞれの異なるアクセス・スイッチが確実に接続されているように、構成することができる。これらのアクセス・スイッチは、遅延を減らすために同じバス・ラインに接続される。

【0120】

(8) その中に一組のマトリクス・スイッチ及び限られた数のアクセス・スイッチがあるスイッチング構成を用いることができる。マトリクス・スイッチは隣接する部分素子を動的に接続する。アクセス・スイッチは、システム・チャンネルに多重化されるバス・ラインに接続する。 20

【0121】

本発明の様々な実施形態によれば、下記の付加的な特徴の1つ以上がシステムに存在することができる。

【0122】

(1) 1つのバス・ラインあたり1つのアクセス・スイッチが各部分素子に使用される。 30

【0123】

(2) 一列あたり複数のバス・ラインを使用することができる。

【0124】

(3) バス・ラインはアレイ内で垂直及び水平の両方向に配置することができる。一実施形態によれば、一組のバス・ラインが水平方向に配置され、且つ別の一組が垂直方向に配置され、各部分素子又は各群の部分素子がアクセス・スイッチを介して垂直なバス・ラインに接続可能であり、また異なるアクセス・スイッチを介して水平なバス・ラインに接続可能である。しかしながら、バス・ラインが両方向に延在している場合、バス・ラインのために利用可能な電子的地域が乏しく且つより多くのバス・ラインが必要であると共に、1つの部分素子内に唯一つのアクセス・スイッチがあるので、各部分素子のアクセス・スイッチは水平なバス・ライン又は垂直なバス・ラインのいずれかに接続することができ、両方には接続できない。これはまた、所与のバス・ラインについてオンにすることができるスイッチの数が電流の流れ及びラインの大きさによって制限されるときに影響を持つ。 40

【0125】

(4) アクセス・スイッチは、リング(又は他の形状)の両方の縁から等距離に配置して、リング内部の遅延が最小になるように選択することができる。「リングの縁」は、再構成可能性が環状アレイを近似するために使用される場合を表す。この場合、部分素子を接続することによって模倣しようとする或る所望の環状アレイ又はリング構造がある。リングの縁は、近似しようとするリングの境界近くの部分素子を表す。すなわち、それは、部分素子を接続することによって形成されるより大きい素子の縁である。アクセス・スイッチは、全て一方の側ではなく、素子の両側にあるように選択される。形状はリングである必要はなく、他の形状を用いることができ、また部分素子を接続することによって近似される形状の両方の縁にアクセス・スイッチを設けるのが最良であると考えられる。 50

## 【0126】

(5) 1つのバス・ラインあたり2つ以上のアクセス・スイッチを各部分素子に使用することができる。この冗長な接続は装置の歩留まりを改善する。

## 【0127】

(6) 送信と受信との間に及び受信中に複数の間隔でリング・パターンを更新する能力を与えることができる。

## 【0128】

(7) 複数の部分素子よりなる1つの完全なリングに単一のアクセス・スイッチを接続することができ、各部分素子はマトリクス・スイッチによって一緒に接続する。

## 【0129】

(8) 1つの完全なリングに複数のアクセス・スイッチを接続することができ、部分素子の間のマトリクス・スイッチはリングのそれぞれの一部分を形成するようにアクセス・スイッチを持つ。

## 【0130】

(9) 1つの完全なリングに複数のアクセス・スイッチを接続することができ、スイッチは、スイッチ相互の間の部分素子についての信号遅延を低減するためにリングに沿って等距離の間隔をおいて分布させる。

## 【0131】

(10) 複数のリングを形成することができる。その場合、各リングは1つ以上のアクセス・スイッチを使用して1つのシステム・チャンネルに接続され、各アクセス・スイッチは1つのバス・ラインに接続され、該バス・ラインは1つのシステム・チャンネルに接続される。

## 【0132】

(11) 複数の冗長なマトリクス・スイッチ接続を用いて、単一のリングを形成することにより、直列抵抗を減少させて、遅延を小さくすることができる。

## 【0133】

(12) マトリクス・スイッチは所与のアレイについて既知の不良の部分素子を迂回するために使用することができる。

## 【0134】

(13) 遅延を最小にするためにアクセス・スイッチの配置を選択しながら、リング以外のパターンを形成することができる。

## 【0135】

(14) 平行移動における各々の新しい段階で最小遅延アルゴリズムを繰り返し使用することによって、移動するビームを生成するように、完全リング・パターンを平行移動させることができる。

## 【0136】

(15) 素子の中心は、素子の形状を変えることによって部分素子1個よりも小さい増分で歩進させることができる。

## 【0137】

スイッチング電子装置は、CMOS又はBiCMOS、又はSOI、又はMEMS、或いは未だ確認されていないスイッチング技術を使用して、構築することができる。

## 【0138】

本発明を模範的な実施形態に関して説明したが、当業者には、本発明の範囲から逸脱することなく、様々な変更を為すことができ、且つ構成要素を等価物と置換することができることが理解されよう。更に、本発明の範囲から逸脱することなく、特定の状況又は材料を本発明の教示に適合させるように多数の修正をなすことができる。従って、本発明は、発明を実施するための最良の又は唯一の形態として開示した特定の実施形態に制限されず、本発明は特許請求の範囲内に入る全ての実施形態を含むものである。

## 【図面の簡単な説明】

## 【0139】

10

20

30

40

50

【図 1】典型的な c M U T セルの断面図である。

【図 2】スイッチを介在することなく頂部電極同士及び底部電極同士をそれぞれ一緒に接続した 7 つの六角形 M U T セルから形成された、米国特許出願第 10 / 383990 号に記載されているような「ヒナギク」形部分素子を示す斜視図である。

【図 3】米国特許出願第 10 / 383990 号に記載されているように、各素子がモザイク細工の「ヒナギク」形部分素子より成り且つ 1 素子あたりの面積をほぼ等しくするように構成された 4 つの環状素子を有するモザイク・アレイの一部を示す平面図である。

【図 4】共同集積化された c M U T 及び特定用途向け集積回路 ( A S I C ) アレイの断面図である。

【図 5】A S I C スイッチ・マトリクスに接続された c M U T ウェーファの断面図である。

10

【図 6】関連した単位スイッチ・セルの六角形アレイの上に配置した c M U T 部分素子の六角形アレイの平面図である。

【図 7】関連した単位スイッチ・セルの矩形アレイの上に配置した c M U T 部分素子の六角形アレイの平面図である。

【図 8】アレイを横切る環状トランステューサ素子の平行移動の様子を示す略図である。

【図 9】各トランステューサ部分素子が全てのシステム・チャンネルの各々にアクセスできるように全てのシステム・チャンネルをアレイ全体にわたって分布させるアーキテクチャを示す略図である。

【図 10】部分素子の 1 列あたり 1 つのバス・ラインを設けることによって各部分素子内のスイッチの数が制限され、それらのバス・ラインがマルチプレクサを介してシステム・チャンネルに接続されるようにしたアーキテクチャを示す略図である。

【図 11】部分素子の 1 列あたり複数のバス・ラインを設け、同じ列内の異なるシステム・チャンネル上の部分素子をグループ化することができるようしたアーキテクチャを示す略図である。

【図 12】第 1 列内の部分素子のマトリクス・スイッチを介して第 2 列内の隣接する部分素子のアクセス・スイッチに接続することによって、第 1 列内の部分素子を第 2 列の部分素子のためのバス・ラインに接続できるようにした、本発明の一実施形態によるアーキテクチャを示す略図である。

【図 13】c M U T アレイの特定の列内の特定の部分素子を多数のシステム・チャンネル・バス・ラインの内の任意の 1 つに接続できるようにした、本発明の別の実施形態によるアーキテクチャを示す略図である。

20

【図 14】アクセス・スイッチ（黒い点で表す）を介してそれぞれの縦列の部分素子に接続された複数のバス・ラインを持つ部分素子の六角形アレイを示す略図である。

【図 15】幾つかの部分素子がそれぞれのアクセス・スイッチ（黒い点で表す）を介して垂直及び水平のバス・ラインに接続されている、部分素子の六角形アレイを示す略図である。

【図 16】バス・ラインを六角形アレイの自然軸に沿って斜めに配置し、アクセス・スイッチを黒い点で表した、部分素子の六角形アレイを示す略図である。

【図 17】図 13 に示した実施形態に従って特定の音響部分素子に関連した電子回路内の共通接続点への接続を示す略図である。

30

【図 18】米国特許出願第 10 / 248968 号に記載されているような、アクセス・スイッチと該アクセス・スイッチの状態を制御するための回路とを示す概略回路図である。

【図 19】密に詰め込んだ、単一の部分素子の幅を持つ多数のリング（その一部を点線の円弧で表す）と共に使用するためのアクセス・スイッチ（黒い点で表す）及びマトリクス・スイッチ（太く短い線で表す）の配列を示す略図である。

【図 20】分布型 R C 遅延線を表す概略回路図である。

【図 21】20 タップの R C 遅延線についての測定した遅延データのグラフである。

【図 22】列の一端の部分素子がアクセス・スイッチによってバス・ラインに接続されるようにして、マトリクス・スイッチによって直列に接続された一列の部分素子を示す略図

40

50

である。

【図23】列の両端の部分素子がそれぞれのアクセス・スイッチによってバス・ラインに接続されると共に、残りの部分素子がマトリクス・スイッチを介して一方又は他方のアクセス・スイッチに接続されるようにした一列の部分素子を示す略図である。

【図24】列の両端の部分素子と列の中央近くの1つの部分素子とがそれぞれのアクセス・スイッチによってバス・ラインに接続されると共に、残りの部分素子がマトリクス・スイッチを介してそれぞれのアクセス・スイッチに接続されるようにした一列の部分素子を示す略図である。

【図25】単独のアクセス・スイッチからの距離の増加につれて部分素子の環状リングに沿った遅延が増大することを示す略図である。

【図26】各象限に配置されたアクセス・スイッチから距離の増加につれて部分素子の環状リングに沿った遅延が増大することを示す略図である。

【図27】部分素子の環状リングが1つの部分素子の幅よりも大きい幅を持つ場合において、該環状リング内でアクセス・スイッチから距離の増加につれて遅延が増大することを示す略図である。

【図28】黒い点が音響部分素子を表し、白丸がアクセス・スイッチを表し、四角が別の設計によるアクセス・スイッチの配置を表すものとして、環状リングの幅にわたって複数のアクセス・スイッチを使用する場合を示す略図である。

【符号の説明】

【0 1 4 0】

- 2 c M U T トランスデューサ・セル

- 4 基板

- 6 絶縁支持体

- 8 膜

- 1 0 電極

- 1 2 電極

- 1 4 空洞

- 1 6 トランスデューサ部分素子

- 1 8 A、1 8 B、1 8 C、1 8 D 環状の素子

- 3 0 アクセス・スイッチ

- 3 0' アクセス・スイッチ

- 3 2 c M U T 部分素子

- 3 4 バス

- 3 4 a ~ 3 4 d 列バス・ライン

- 3 6 マトリクス・スイッチ

- 3 8 システム・チャンネル

- 4 0 接続点

- 4 2 共通接続点

- 4 6 接続線

- 5 0 C M O S セル

- 5 6 バイア

- 6 0 アレイ

- 6 2 音響裏当て層

- 6 4 ハンダ・バンプ

- 6 5 信号電極

- 6 6 導電パッド

- 7 0 マルチプレクサ

- 7 2 バス・ライン

- 7 4 バス・ライン

- 7 6 バス・ライン

10

20

30

40

50

8 0 バス・ライン

8 2 バス・ライン

8 4 バス・ライン

8 6 駆動装置

【図 1】

FIG.1

【図 2】

FIG.2

【図 3】

FIG.3

【図4】

FIG.4

【図5】

FIG.5

【図6】

FIG.6

【図7】

FIG.7

【図8】

FIG.8

【図9】

FIG.9

【図10】

FIG.10

【図 1 1】

FIG.11

【図 1 2】

FIG.12

【図 1 3】

FIG.13

【図 1 4】

FIG.14

【図 15】

FIG.15

【図 16】

FIG.16

【図 17】

FIG.17

【図 18】

FIG.18

【図19】

FIG. 19

【 図 2 0 】

FIG. 20

### 【図21】

FIG.21

【 図 2 2 】

FIG.22

【 図 2 3 】

FIG.23

【 図 2 4 】

FIG.24

【図 2 5】

FIG.25

【図 2 6】

FIG.26

【図 2 7】

FIG.27

【図 2 8】

FIG.28

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        | International application No<br>PCT/US2005/030237            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. A61B8/14 G06T7/00 B06B1/06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                        |                                                              |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |                                                              |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>A61B G06T B06B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                        |                                                              |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                                                              |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, WPI Data, PAJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                        |                                                              |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                        |                                                              |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Citation of document, with indication, where appropriate, of the relevant passages                     | Relevant to claim No.                                        |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | WO 2004/079654 A2 (WEBER MARTIN [GB]; MARTIN PHILIP JOHN [GB]) 16 September 2004 (2004-09-16) abstract | 1,16,34,<br>38,41                                            |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 6 733 454 B1 (BAKIRCIOLU MUEGE M [US] ET AL) 11 May 2004 (2004-05-11) figures 1,2                   | 1,16,34,<br>38,41                                            |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 2004/174773 A1 (THOMENIUS KAI [US] ET AL) 9 September 2004 (2004-09-09) abstract                    | 1,16,34,<br>38,41                                            |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 5 568 384 A (ROBB RICHARD A [US] ET AL) 22 October 1996 (1996-10-22) figure 8                       | 1,16,34,<br>38,41                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -/-                                                                                                    |                                                              |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        | <input checked="" type="checkbox"/> See patent family annex. |

| <p>* Special categories of cited documents :</p> <p>"A" document defining the general state of the art which is not considered to be of particular relevance</p> <p>"E" earlier document but published on or after the International filing date</p> <p>"L" document which may throw doubt on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)</p> <p>"O" document referring to an oral disclosure, use, exhibition or other means</p> <p>"P" document published prior to the International filing date but later than the priority date claimed</p> <p>"T" later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</p> <p>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</p> <p>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</p> <p>"&amp;" document member of the same patent family</p> |                                                                                                        |                                                              |