(12)实用新型专利

(10)授权公告号 CN 208808516 U

(45)授权公告日 2019.05.03

(21)申请号 201820562088.X

(22)申请日 2018.04.19

(73)专利权人 武汉启佑生物医疗电子有限公司

地址 430074 湖北省武汉市东湖新技术开发区

高新大道818号B区7号楼2层1号

(72)发明人 李腾飞 杜春宁 彭江 胡则肄

(74)专利代理机构 北京汇泽知识产权代理有限公司 11228

代理人 张涛

(51)Int.Cl.

A61B 8/00(2006.01)

权利要求书1页 说明书3页 附图3页

(54)实用新型名称

一种超声LVDS信号接收电路

(57)摘要

本实用新型提供了一种超声LVDS信号接收电路，包括：超声回波接收模数转换(AD)模块和数字信号接收FPGA模块，所述AD模块将超声回波信号转换成LVDS输出信号。所述FPGA模块的相关信号接收引脚配置成单端输入模式；在所述AD输出LVDS正负信号之间接入负载电阻，将负载电阻的一端连接到所述FPGA模块的相关接收引脚，另一端悬空。

1. 一种超声LVDS信号接收电路,包括:超声回波接收模数转换(AD)模块和数字信号接收FPGA模块,所述AD模块将超声回波信号转换成LVDS输出信号,其特征在于:

a. 所述FPGA模块的相关信号接收引脚配置成单端输入模式;

b. 在所述AD输出LVDS正负信号之间接入负载电阻,将负载电阻的一端连接到所述FPGA模块的相关接收引脚,另一端悬空。

2. 根据权利要求1所述的超声LVDS信号接收电路,其特征在于:

所述负载电阻可以是所述AD模块内置的,或者是外接的。

3. 根据权利要求1所述的超声LVDS信号接收电路,其特征在于:

所述负载电阻的阻值可调,使LVDS输出的高低电平达到所述接收引脚所配置的单端模式的电平标准。

4. 根据权利要求1所述的超声LVDS信号接收电路,其特征在于:

所述LVDS信号的中心电平与所述单端电平标准的中心电平不匹配时,可通过添加基本的阻容网络进行电平匹配。

## 一种超声LVDS信号接收电路

### 技术领域

[0001] 本实用新型涉及一种超声LVDS信号接收电路。

### 背景技术

[0002] 低压差分信号 (LowVoltage Differential Signaling,LVDS) 的特点是采用低电压摆幅高速差动传输信号,它具有低功耗、低误码率等优点。常规的超声成像系统采用多通道的方式采集超声回波数据,它的特点是通道多,采样率高,因此, LVDS十分适宜于作为超声回波采集AD模块的数字信号输出标准。虽然LVDS 的高速、低功耗的特点有利于它在超声领域的应用,但是由于它是双端输出,导致AD模块与信号接收FPGA模块之间的LVDS连线数是通道数的2倍,而这对接收模块的引脚数、PCB布线都提出了很高的要求。另外,也不利于超声系统的小型化、集成化设计。

[0003] 因此,有必要设计一种新的超声LVDS信号接收电路,在保留LVDS优点的前提下,减少LVDS连线数。

### 实用新型内容

[0004] 本实用新型的目的在于克服现有技术之缺陷,提供了一种超声LVDS信号接收电路,以达到在保留LVDS优点的前提下减少LVDS连线数的目的。

[0005] 本实用新型是这样实现的:

[0006] 一种超声LVDS信号接收电路,包括:超声回波接收模数转换(AD)模块和数字信号接收FPGA模块,所述AD模块将超声回波信号转换成LVDS输出信号。

[0007] 所述FPGA模块的相关信号接收引脚配置成单端输入模式;在所述AD输出 LVDS正负信号之间接入负载电阻,将负载电阻的一端连接到所述FPGA模块的相关接收引脚,另一端悬空。

[0008] 所述负载电阻可以是所述AD模块内置的,或者是外接的。

[0009] 所述负载电阻的阻值可调,使LVDS输出的高低电平达到所述接收引脚所配置的单端模式的电平标准。

[0010] 所述LVDS信号的中心电平与所述单端电平标准的中心电平不匹配时,可通过添加基本的阻容网络进行电平匹配。

[0011] 本实用新型具有以下有益效果:

[0012] 1、使LVDS连接到FPGA的线数减半,降低了对FPGA引脚数量和PCB布线的要求;

[0013] 2、此电路不影响AD模块的LVDS输出,保持了LVDS信号高速、低功耗的优点。

### 附图说明

[0014] 为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下

下,还可以根据这些附图获得其它的附图。

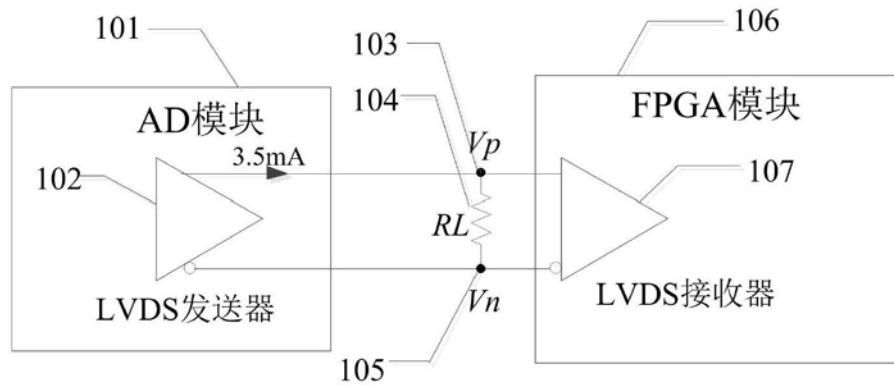

- [0015] 图1a为典型的AD与FPGA之间的LVDS连接示意图;

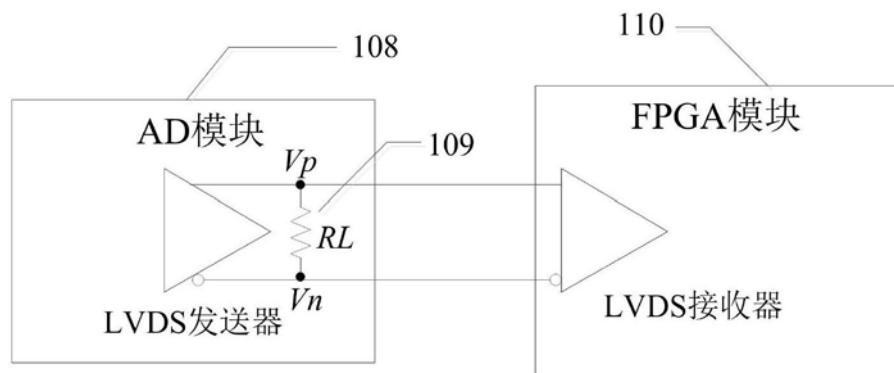

- [0016] 图1b为典型的负载电阻内置的LVDS连接示意图;

- [0017] 图1c为典型的LVDS信号眼图;

- [0018] 图1d为典型的LVDS单端信号波形图;

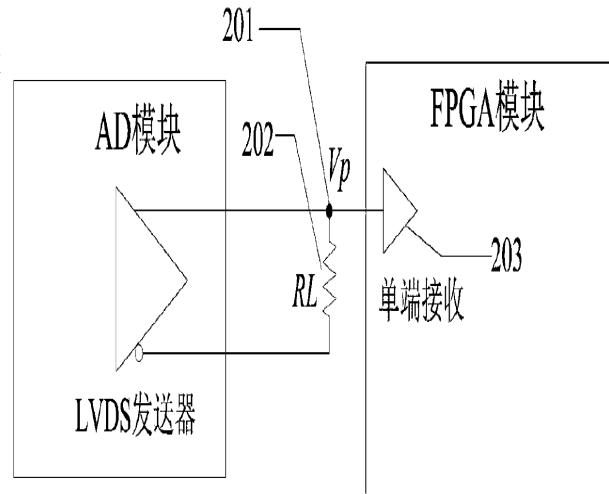

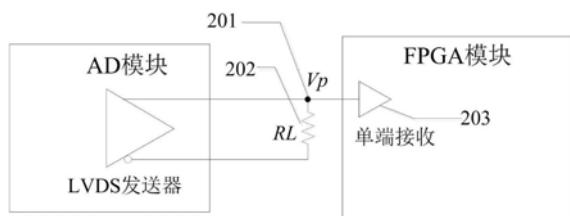

- [0019] 图2a为本实用新型所述的LVDS单端输出与FPGA连接示意图;

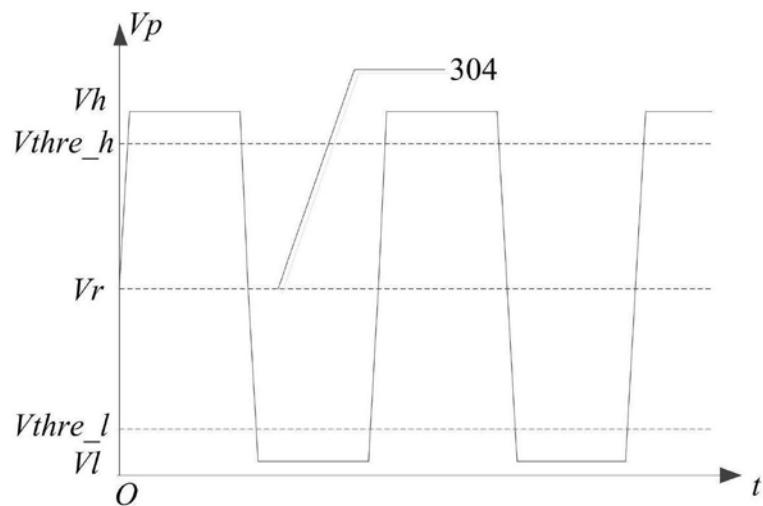

- [0020] 图2b为本实用新型所述的调整负载电阻后的LVDS单端信号波形图;

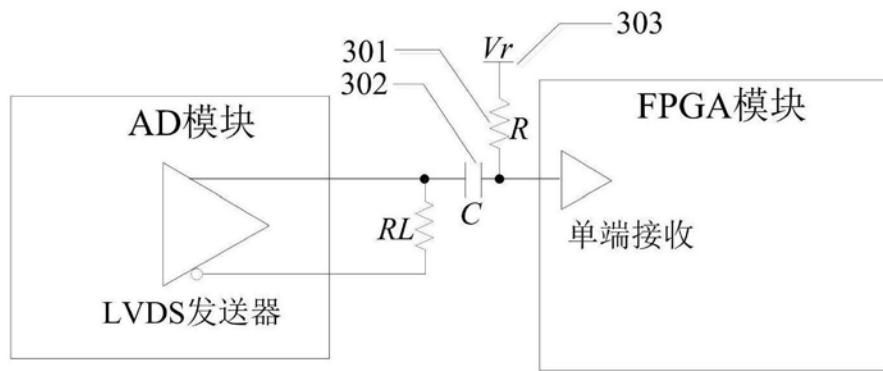

- [0021] 图3a为本实用新型所述的通过阻容网络匹配中心电平的电路示意图;

- [0022] 图3b为本实用新型所述的中心电平匹配后的LVDS单端信号波形图。

## 具体实施方式

[0023] 下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本实用新型保护的范围。

- [0024] 首先,结合附图1a、1b、1c、1d对典型的LVDS连接方式以及输出信号波形进行说明。

- [0025] 超声系统中,AD模块101对超声回波信号进行模数转换并以LVDS的形式输出,LVDS发送器102输出低压差分信号,在正信号(Vp) 103和负信号(Vn) 105之间接入负载电阻(RL) 104,负载电阻104应紧靠FPGA模块106,从负载电阻两端引线接入FPGA中的LVDS接收器107。

- [0026] 由于超声系统中AD模块108和FPGA模块110的PCB布局一般都靠的很近,因此一些主流的超声AD芯片都内置了负载电阻109,以简化LVDS电路的元器件。

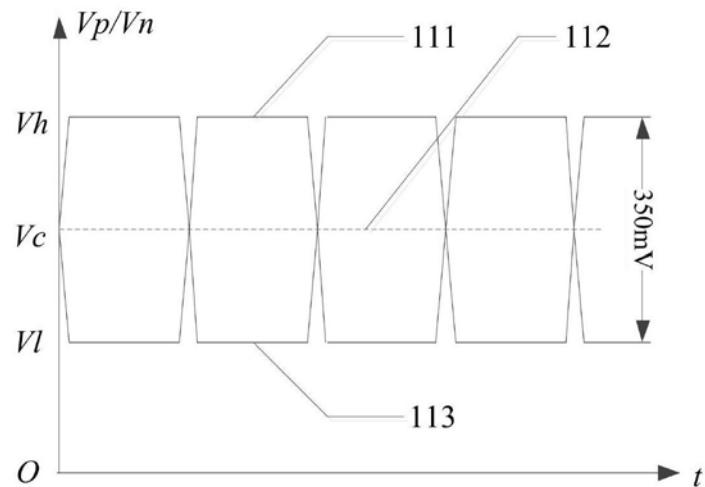

[0027] 图1c为典型的LVDS信号眼图。根据LVDS的电气标准TIA/EIA-644,LVDS 发送器输出大小恒为3.5mA的电流,电流的方向则决定了输出信号的极性,共模电平(Vc) 112约为1.2V,负载电阻104的阻值约为 $100\Omega$ ,因此,眼图中信号的摆幅约为350mV,LVDS输出高电平(Vh) 111约为1.4V,输出低电平(Vl) 113约为1.0V。

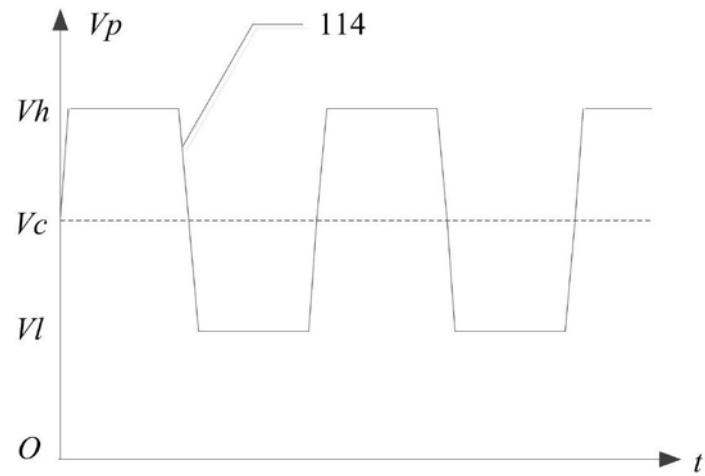

[0028] 图1d为典型的LVDS单端信号波形图。单端信号114携带了LVDS输出信号的全部信息,本实用新型的目的就是让单端信号能够被FPGA正常接收,从而减少LVDS连线数。

[0029] 然后,结合附图2a和2b,对本实用新型所述的LVDS单端接收电路进行说明。

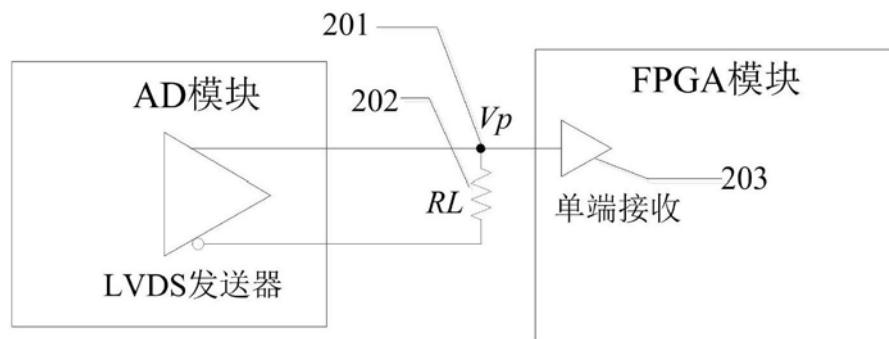

[0030] 图2a为本实用新型所述的LVDS单端输出与FPGA连接示意图,图2b为本实用新型所述的调整负载电阻后的LVDS单端信号波形图。从负载电阻202的一端201引线连接到FPGA单端接收引脚203,并调整负载电阻202的阻值,使单端信号的摆幅209调整到合适的范围。负载电阻202的调整要根据FPGA配置的单端模式的电平标准来确定,主流的FPGA一般都能支持多种单端模式,因此,可以选择一种中心电平接近1.2V的单端模式来配置FPGA相关接收脚203。

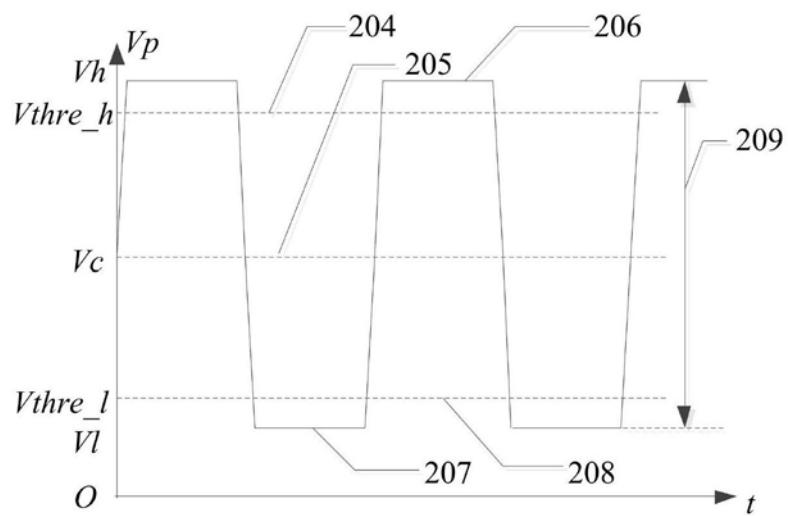

[0031] 下面以SSTL-2单端输入标准为例进行说明。SSTL-2单端输入标准是一种比较型的电平标准,通过比较输入信号和参考电平Vref的大小来判断信号极性。参考电平Vref允许范围 $1.13V \sim 1.38V$ ,可由FPGA的专用引脚进行配置,此实施例中配置为1.2V。SSTL-2对输入电平要求是:负电平小于负门限(Vthre\_l) 208,  $Vthre_l = Vref - 310mV \approx 0.9V$ ;正电平大于正门限(Vthre\_h) 204,  $Vthre_h = Vref + 310mV \approx 1.5V$ 。因此,只需将LVDS单端输出摆幅209

调整到大于620mV 即可。将负载电阻202的阻值增大一倍(从 $100\Omega$  增大到 $200\Omega$ ) ,由于LVDS发送器的输出电流大小恒为3.5mA,则单端信号的摆幅209也将增大一倍(从 350mV增大到700mV) ,且共模电平(Vc) 205保持约1.2V不变,此时,输出高电平(Vh) 206约为1.6V,输出低电平(Vl) 207约为0.8V。负载电阻202 调整后,LVDS单端输出201的高低电平能够满足SSTL-2的电平要求,能够被 FPGA模块正确的接收。

[0032] 上述实施例中,SSTL-2标准配置的1.2V参考电平能够和LVDS的共模电平匹配,只需调整LVDS输出摆幅即可。对于某些特殊场合,比如FPGA支持的所有单端输入标准都不支持1.2V中心电平配置时,则需要通过添加基本的阻容网络来匹配中心电平。

[0033] 图3a为本实用新型所述的通过阻容网络匹配中心电平的电路示意图;图3b 为本实用新型所述的中心电平匹配后的LVDS单端信号波形图。通过添加电阻 (R) 301、电容 (C) 302和上拉电平 (Vr) 303可以将LVDS输出的共模电平调整成上拉电平 (Vr) 303的大小,只需使上拉电平 (Vr) 304和单端标准的中心电平一致,即可实现中心电平的匹配。中心电平匹配后,再调整负载电阻使摆幅达到要求即可。

[0034] 以上所述仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

图1a

图1b

图1c

图1d

图2a

图2b

图3a

图3b

|         |                                                |         |            |

|---------|------------------------------------------------|---------|------------|

| 专利名称(译) | 一种超声LVDS信号接收电路                                 |         |            |

| 公开(公告)号 | <a href="#">CN208808516U</a>                   | 公开(公告)日 | 2019-05-03 |

| 申请号     | CN201820562088.X                               | 申请日     | 2018-04-19 |

| [标]发明人  | 李腾飞<br>杜春宁<br>彭江<br>胡则肄                        |         |            |

| 发明人     | 李腾飞<br>杜春宁<br>彭江<br>胡则肄                        |         |            |

| IPC分类号  | A61B8/00                                       |         |            |

| 代理人(译)  | 张涛                                             |         |            |

| 外部链接    | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

## 摘要(译)

本实用新型提供了一种超声LVDS信号接收电路，包括：超声回波接收模数转换(AD)模块和数字信号接收FPGA模块，所述AD模块将超声回波信号转换成LVDS输出信号。所述FPGA模块的相关信号接收引脚配置成单端输入模式；在所述AD输出LVDS正负信号之间接入负载电阻，将负载电阻的一端连接到所述FPGA模块的相关接收引脚，另一端悬空。