(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0033499

(43) 공개일자 2017년03월27일

(51) 국제특허분류(Int. Cl.)

*G09G 3/32* (2016.01)

(52) CPC특허분류

*G09G 3/3225* (2013.01)

*G09G 2310/08* (2013.01)

(21) 출원번호 10-2015-0131206

(22) 출원일자 2015년09월16일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

김효진

경기도 파주시 탄현면 풍뎅이길 9-34 102

장수혁

경기도 파주시 미래로 562 901동 201호 (와동동,

가람마을9단지남양휴튼아파트)

(뒷면에 계속)

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 15 항

(54) 발명의 명칭 메모리 제어장치 및 그 제어방법과 이를 포함한 유기발광 표시장치

### (57) 요약

본 발명의 메모리 제어장치는 내부 액세스 모드에서는 타이밍 콘트롤러와 메모리 간의 통신을 통해 메모리를 제어하고, 외부 액세스 모드에서는 외부 제어장치와 메모리 간의 통신을 통해 메모리를 제어한다. 본 발명의 메모리 제어장치는 외부 액세스 모드에서 타이밍 콘트롤러를 통하지 않고 외부 제어장치에서 직접 메모리를 제어한다. 이를 통해 본 발명의 메모리 제어장치는 종래 대비 타이밍 콘트롤러의 입출력핀수를 대폭적으로 줄일 수 있다.

대 표 도 - 도3

(52) CPC특허분류

G09G 2320/043 (2013.01)

(72) 발명자

**이정아**

서울특별시 은평구 연서로 208-1 (대조동) 199-5번

지 1층

**이진원**

경기도 과주시 새꽃로 10 609동 1401호 (금촌동, 후

곡마을아파트)

**홍성완**

서울특별시 강남구 선릉로 7 105동 306호 (개포

동, 주공아파트)

## 명세서

### 청구범위

#### 청구항 1

메모리에 억세스하는 메모리 제어장치로서,

전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제1 전송 버퍼(112)와, 상기 제1 전송 버퍼(112)에 내부용 메모리 신호들(Int\_IO 0~3, Int\_CSN, Int\_CLK)을 인가하고 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제1 전송 버퍼(112)의 동작을 제어하는 제1 메모리 제어부(111)를 갖는 타이밍 콘트롤러(11); 및

상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제2 전송 버퍼(312)와, 상기 제2 전송 버퍼(312)에 외부용 메모리 신호들(Ext\_IO 0~3, Ext\_CSN, Ext\_CLK)을 인가하고 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제2 전송 버퍼(312)의 동작을 상기 제1 전송 버퍼(112)와 반대로 제어하는 제2 메모리 제어부(311)를 갖는 외부 제어장치(31)를 포함한 메모리 제어장치.

#### 청구항 2

제 1 항에 있어서,

상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 외부 억세스 모드에서 상기 제1 전송 버퍼(112)는 하이 임피던스 상태가 되고, 상기 제2 전송 버퍼(312)는 입출력 상태가 되며,

상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제2 논리레벨로 입력되는 내부 억세스 모드에서 상기 제1 전송 버퍼(112)는 입출력 상태가 되고, 상기 제2 전송 버퍼(312)는 하이 임피던스 상태가 되는 메모리 제어장치.

#### 청구항 3

제 2 항에 있어서,

상기 내부 억세스 모드 중에 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 경우, 그 입력 시점부터 소정 기간(Td) 경과 후에 상기 내부 억세스 모드에서 상기 외부 억세스 모드로 전환하는 메모리 제어장치.

#### 청구항 4

제 3 항에 있어서,

상기 소정 기간(Td) 동안 상기 타이밍 콘트롤러(11)는 상기 내부 억세스 모드 중에 수행하던 작업을 완료하는 메모리 제어장치.

#### 청구항 5

제 2 항에 있어서,

상기 외부 억세스 모드에서, 제2 전송 버퍼(312)는 상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 직접 접속되며, 상기 외부 제어장치(31)는 상기 메모리(21)를 직접 제어하는 메모리 제어장치.

#### 청구항 6

메모리에 억세스하는 메모리 제어방법으로서,

전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제1 전송 버퍼(112)와, 상기 제1 전송 버퍼(112)에 내부용 메모리 신호들(Int\_IO 0~3, Int\_CSN, Int\_CLK)을 인가하고 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제1 전송 버퍼(112)의 동작을 제어하는 제1 메모리 제어부(111)를 이용하여 타이밍 콘트롤러(11)에서 상기 메모리(21)에 억세스 하는 단계; 및

상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제2 전송 버퍼(312)와, 상기 제2 전송 버퍼(312)에 외부용 메모리 신호들(Ext\_IO 0~3, Ext\_CSN, Ext\_CLK)을 인가하고 상기 외부 억세스 인에이블신호

(Ext\_Access\_EN)에 따라 상기 제2 전송 버퍼(312)의 동작을 상기 제1 전송 버퍼(112)와 반대로 제어하는 제2 메모리 제어부(311)를 이용하여 외부 제어장치(31)에서 상기 메모리(21)에 억세스 하는 단계를 포함한 메모리 제어방법.

#### 청구항 7

제 6 항에 있어서,

상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 외부 억세스 모드에서 상기 제1 전송 버퍼(112)는 하이 임피던스 상태가 되고, 상기 제2 전송 버퍼(312)는 입출력 상태가 되며,

상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제2 논리레벨로 입력되는 내부 억세스 모드에서 상기 제1 전송 버퍼(112)는 입출력 상태가 되고, 상기 제2 전송 버퍼(312)는 하이 임피던스 상태가 되는 메모리 제어방법.

#### 청구항 8

제 7 항에 있어서,

상기 내부 억세스 모드 중에 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 경우, 그 입력 시점부터 소정 기간(Td) 경과 후에 상기 내부 억세스 모드에서 상기 외부 억세스 모드로 전환하는 메모리 제어방법.

#### 청구항 9

제 8 항에 있어서,

상기 소정 기간(Td) 동안 상기 타이밍 콘트롤러(11)는 상기 내부 억세스 모드 중에 수행하던 작업을 완료하는 메모리 제어방법.

#### 청구항 10

제 7 항에 있어서,

상기 외부 억세스 모드에서, 제2 전송 버퍼(312)는 상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 직접 접속되며, 상기 외부 제어장치(31)는 상기 메모리(21)를 직접 제어하는 메모리 제어방법.

#### 청구항 11

표시패널(10); 및

상기 표시패널(10)의 열화에 대한 셈싱값을 메모리(21)에 기입하고, 상기 메모리(21)로부터 상기 표시패널(10)의 열화에 대한 보상값을 리드 아웃하는 메모리 제어장치를 포함하고,

상기 메모리 제어장치는,

전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제1 전송 버퍼(112)와, 상기 제1 전송 버퍼(112)에 내부용 메모리 신호들(Int\_IO 0~3, Int\_CSN, Int\_CLK)을 인가하고 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제1 전송 버퍼(112)의 동작을 제어하는 제1 메모리 제어부(111)를 갖는 타이밍 콘트롤러(11); 및

상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제2 전송 버퍼(312)와, 상기 제2 전송 버퍼(312)에 외부용 메모리 신호들(Ext\_IO 0~3, Ext\_CSN, Ext\_CLK)을 인가하고 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제2 전송 버퍼(312)의 동작을 상기 제1 전송 버퍼(112)와 다르게 제어하는 제2 메모리 제어부(311)를 갖는 외부 제어장치(31)를 포함한 유기발광 표시장치.

#### 청구항 12

제 11 항에 있어서,

상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 외부 억세스 모드에서 상기 제1 전송 버퍼(112)는 하이 임피던스 상태가 되고, 상기 제2 전송 버퍼(312)는 입출력 상태가 되며,

상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제2 논리레벨로 입력되는 내부 억세스 모드에서 상기 제1 전

송 버퍼(112)는 입출력 상태가 되고, 상기 제2 전송 버퍼(312)는 하이 임피던스 상태가 되는 유기발광 표시장치.

### 청구항 13

제 12 항에 있어서,

상기 내부 억세스 모드 중에 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 경우, 그 입력 시점부터 소정 기간(Td) 경과 후에 상기 내부 억세스 모드에서 상기 외부 억세스 모드로 전환하는 유기발광 표시장치.

### 청구항 14

제 13 항에 있어서,

상기 소정 기간(Td) 동안 상기 타이밍 콘트롤러(11)는 상기 내부 억세스 모드 중에 수행하던 작업을 완료하는 유기발광 표시장치.

### 청구항 15

제 12 항에 있어서,

상기 외부 억세스 모드에서, 제2 전송 버퍼(312)는 상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 직접 접속되며, 상기 외부 제어장치(31)는 상기 메모리(21)를 직접 제어하는 유기발광 표시장치.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 메모리 제어장치 및 그 제어방법과 이를 포함한 유기발광 표시장치에 관한 것이다.

### 배경 기술

[0002] 액티브 매트릭스 타입의 유기발광 표시장치는 스스로 발광하는 유기발광다이오드(Organic Light Emitting Diode: 이하, "OLED"라 함)를 포함하며, 응답속도가 빠르고 발광효율, 휙도 및 시야각이 큰 장점이 있다.

[0003] 자발광 소자인 OLED는 애노드전극 및 캐소드전극과, 이들 사이에 형성된 유기 화합물층(HIL, HTL, EML, ETL, EIL)을 포함한다. 유기 화합물층은 정공주입층(Hole Injection layer, HIL), 정공수송층(Hole transport layer, HTL), 발광층(Emission layer, EML), 전자수송층(Electron transport layer, ETL) 및 전자주입층(Electron Injection layer, EIL)으로 이루어진다. 애노드전극과 캐소드전극에 구동전압이 인가되면 정공수송층(HTL)을 통과한 정공과 전자수송층(ETL)을 통과한 전자가 발광층(EML)으로 이동되어 여기자를 형성하고, 그 결과 발광층(EML)이 가시광을 발생하게 된다.

[0004] 유기발광 표시장치는 OLED를 각각 포함한 픽셀들을 매트릭스 형태로 배열하고 비디오 데이터의 계조에 따라 픽셀들의 휙도를 조절한다. 픽셀들 각각은 자신의 게이트전극과 소스전극 사이에 걸리는 전압에 따라 OLED에 흐르는 구동전류를 제어하는 구동 소자 즉, 구동 TFT(Thin Film Transistor)를 포함한다. OLED와 구동 TFT는 온도나 열화에 의해 그 전기적 특성이 변한다. OLED 및/또는 구동 TFT의 전기적 특성이 픽셀들마다 달라지면 동일 비디오 데이터에 대해 픽셀들 간 휙도가 달라지므로 원하는 화상 구현이 어렵다.

[0005] OLED와 구동 TFT에 대한 전기적 특성을 보상하기 위해 외부 보상 기술이 알려져 있다. 외부 보상 기술은 OLED나 구동 TFT의 전기적 특성을 변화를 센싱하여 그 센싱값을 메모리에 저장하고, 이 센싱값에 기초한 보상값으로 디지털 비디오 데이터를 변조한다. 이러한 센싱 및 보상 동작은 유기발광 표시장치가 구동되는 도중에 타이밍 콘트롤러의 제어 하에 빈번히 수행될 수 있다. 타이밍 콘트롤러는 메모리에 대한 라이트(write) 동작을 제어하여 새로운 센싱값을 메모리의 제1 영역에 기입함으로써 센싱값 갱신할 수 있다. 타이밍 콘트롤러는 메모리에 대한 리드(read) 동작을 제어하여 메모리의 제2 영역에 저장된 보상값을 리드 아웃할 수 있다.

[0006] 한편, 메모리에 대한 억세스(Access) 동작은 유기발광 표시장치의 타이밍 콘트롤러에 의해 주로 수행되지만, 경우에 따라서는 유기발광 표시장치에 실장되지 않은 외부 제어장치에 의해 수행될 수도 있다. 외부 제어장치는 제품 출하 전에 메모리 정보(초기 센싱값, 보상값 등)에 대한 초기 셋팅을 위한 경우, 또는 제품 출하 후에

AS(After Service) 용도로 메모리 정보(업데이트 센싱값, 보상값 등)에 대한 데이터 분석이 필요한 경우에 메모리에 억세스할 수 있다.

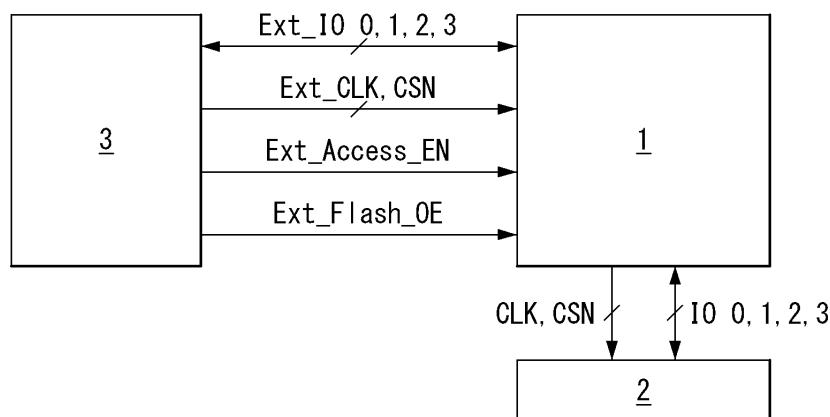

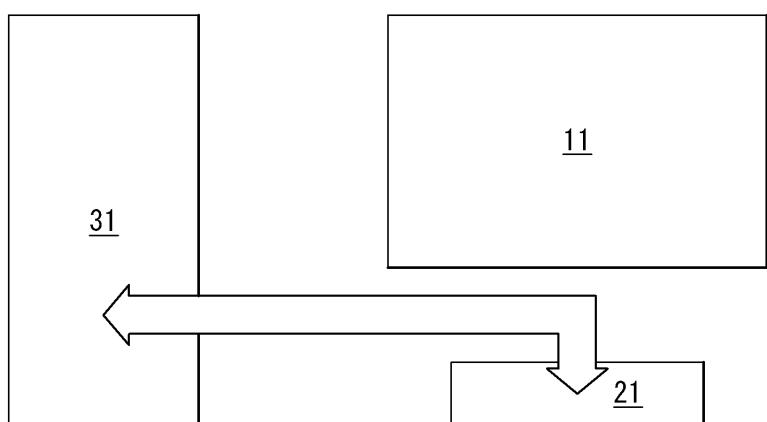

[0007] 도 1에는 외부 제어장치(3)가 타이밍 콘트롤러(1)를 통해 메모리(2)에 억세스하는 종래의 메모리 억세스 방안이 도시되어 있다.

[0008] 타이밍 콘트롤러(1)는 메모리(2)와의 통신을 위해 다수의 제1 입출력핀들을 포함할 수 있다. 예를 들어, 타이밍 콘트롤러(1)는 메모리 동작 신호(CSN)를 전송하기 위한 1개의 전송핀과, 메모리 클럭 신호(CLK)를 전송하기 위한 1개의 전송핀과, 메모리 클럭 신호(CLK)에 동기하여 메모리 데이터(I0 0,1,2,3)를 전송하는 4개의 전송핀들을 포함한 6개의 제1 입출력핀들을 구비할 수 있다. 타이밍 콘트롤러(1)는 도 2a와 같이 제1 입출력핀들을 통해 센싱값을 메모리(2)에 기입함과 아울러, 메모리(2)로부터 보상값을 리드 아웃할 수 있다.

[0009] 외부 제어장치(3)는 타이밍 콘트롤러(1)를 통해 메모리(2)에 억세스한다. 이를 위해, 타이밍 콘트롤러(1)는 외부 제어장치(3)와의 통신을 위해 다수의 제2 입출력핀들을 더 포함한다. 예를 들어, 타이밍 콘트롤러(1)는 외부용 메모리 동작 신호(Ext\_CSN)를 전송하기 위한 1개의 전송핀과, 외부용 메모리 클럭 신호(Ext\_CLK)를 전송하기 위한 1개의 전송핀과, 외부용 메모리 데이터(Ext\_I0 0,1,2,3)를 전송하는 4개의 전송핀들과, 외부용 억세스 인에이블신호(Ext\_Access\_EN)를 전송하는 1개의 전송핀과, 외부용 메모리 출력 인에이블신호(Ext\_Flash\_OE)를 전송하는 1개의 전송핀을 포함한 8개의 제2 입출력핀들을 더 구비할 수 있다.

[0010] 외부 제어장치(3)는 외부용 억세스 인에이블신호(Ext\_Access\_EN)를 타이밍 콘트롤러(1)에 전송하여 외부 억세스 동작을 요청한다. 아울러, 외부 제어장치(3)는 외부용 메모리 동작 신호(Ext\_CSN), 외부용 메모리 클럭 신호(Ext\_CLK), 외부용 메모리 데이터(Ext\_I0 0,1,2,3), 및 외부용 메모리 출력 인에이블신호(Ext\_Flash\_OE)를 타이밍 콘트롤러(1)에 전송한다. 타이밍 콘트롤러(1)는 외부용 메모리 동작 신호(Ext\_CSN), 외부용 메모리 클럭 신호(Ext\_CLK), 및 외부용 메모리 데이터(Ext\_I0 0,1,2,3)를 각각, 메모리 동작 신호(CSN), 메모리 클럭 신호(CLK), 및 메모리 데이터(I0 0,1,2,3)으로서 메모리(2)에 전송한다.

[0011] 타이밍 콘트롤러(1)는 외부용 메모리 출력 인에이블신호(Ext\_Flash\_OE)의 논리 레벨에 따라 메모리(2)의 동작을 서로 다르게 제어한다. 외부용 메모리 출력 인에이블신호(Ext\_Flash\_OE)가 제1 논리 레벨로 입력될 때, 타이밍 콘트롤러(1)는 메모리(2)를 라이팅 모드(Writing Mode)로 제어한다. 그 결과 도 2a와 같이 외부 제어장치(3)로부터 입력되는 외부용 메모리 데이터(Ext\_I0 0,1,2,3)가 타이밍 콘트롤러(1)를 거쳐 메모리(2)에 기입된다. 반면, 외부용 메모리 출력 인에이블신호(Ext\_Flash\_OE)가 제2 논리 레벨로 입력될 때, 타이밍 콘트롤러(1)는 메모리(2)를 리딩 모드(Reading Mode)로 제어한다. 그 결과 도 2b와 같이 메모리(2)에 저장된 메모리 데이터(I0 0,1,2,3)가 타이밍 콘트롤러(1)를 거쳐 외부용 메모리 데이터(Ext\_I0 0,1,2,3)로서 외부 제어장치(3)로 출력된다.

[0012] 이렇게 종래 기술은 타이밍 콘트롤러(1)와 외부 제어장치(3) 간의 메모리 억세스 충돌을 방지하기 위해 메모리(2)에 대한 제어권을 항상 타이밍 콘트롤러(1)에 할당하였고, 외부 제어장치(3)는 타이밍 콘트롤러(1)를 통해만 메모리(2)에 억세스할 수 있었다.

[0013] 이에 따라 종래 기술에서 타이밍 콘트롤러(1)는 메모리(2)와의 통신을 위한 제1 입출력핀들 이외에, 외부 제어장치(3)와의 통신을 위한 제2 입출력핀들을 더 필요로 했기 때문에, 그 내부 로직이 복잡하고 핀수가 증가되는 문제가 있었다.

## 발명의 내용

### 해결하려는 과제

[0014] 따라서, 본 발명의 목적은 메모리에 대한 제어권을 타이밍 콘트롤러와 외부 제어장치가 공유하도록 함으로써 타이밍 콘트롤러의 내부 로직을 간소화하고 핀수를 줄일 수 있도록 한 메모리 제어장치 및 그 제어방법과 이를 포함한 유기발광 표시장치를 제공하는 데 있다.

### 과제의 해결 수단

[0015] 상기 목적을 달성하기 위하여, 본 발명은 메모리에 억세스하는 메모리 제어장치로서, 타이밍 콘트롤러(11)와 외부 제어장치(31)를 포함한다. 타이밍 콘트롤러(11)는 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제1 전송 버퍼(112)와, 상기 제1 전송 버퍼(112)에 내부용 메모리 신호들(Int\_I0 0~3, Int\_CSN, Int\_CLK)을 인

가하고 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제1 전송 버퍼(112)의 동작을 제어하는 제1 메모리 제어부(111)를 갖는다. 외부 제어장치(31)는 상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제2 전송 버퍼(312)와, 상기 제2 전송 버퍼(312)에 외부용 메모리 신호들(Ext\_IO 0~3, Ext\_CS, Ext\_CLK)을 인가하고 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제2 전송 버퍼(312)의 동작을 상기 제1 전송 버퍼(112)와 반대로 제어하는 제2 메모리 제어부(311)를 갖는다.

[0016] 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 외부 억세스 모드에서 상기 제1 전송 버퍼(112)는 하이 임피던스 상태가 되고, 상기 제2 전송 버퍼(312)는 출력력 상태가 되며, 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제2 논리레벨로 입력되는 내부 억세스 모드에서 상기 제1 전송 버퍼(112)는 출력력 상태가 되고, 상기 제2 전송 버퍼(312)는 하이 임피던스 상태가 된다.

[0017] 본 발명은 상기 내부 억세스 모드 중에 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 경우, 그 입력 시점부터 소정 기간(Td) 경과 후에 상기 내부 억세스 모드에서 상기 외부 억세스 모드로 전환한다.

[0018] 상기 소정 기간(Td) 동안 상기 타이밍 콘트롤러(11)는 상기 내부 억세스 모드 중에 수행하던 작업을 완료한다.

[0019] 상기 외부 억세스 모드에서, 제2 전송 버퍼(312)는 상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 직접 접속되며, 상기 외부 제어장치(31)는 상기 메모리(21)를 직접 제어한다.

[0020] 또한, 본 발명은 메모리에 억세스하는 메모리 제어방법으로서, 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제1 전송 버퍼(112)와, 상기 제1 전송 버퍼(112)에 내부용 메모리 신호들(Int\_IO 0~3, Int\_CS, Int\_CLK)을 인가하고 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제1 전송 버퍼(112)의 동작을 제어하는 제1 메모리 제어부(111)를 이용하여 타이밍 콘트롤러(11)에서 상기 메모리(21)에 억세스 하는 단계와, 상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제2 전송 버퍼(312)와, 상기 제2 전송 버퍼(312)에 외부용 메모리 신호들(Ext\_IO 0~3, Ext\_CS, Ext\_CLK)을 인가하고 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제2 전송 버퍼(312)의 동작을 상기 제1 전송 버퍼(112)와 반대로 제어하는 제2 메모리 제어부(311)를 이용하여 외부 제어장치(31)에서 상기 메모리(21)에 억세스 하는 단계를 포함한다.

[0021] 또한, 본 발명에 따른 유기발광 표시장치는 표시패널과, 상기 표시패널의 열화에 대한 센싱값을 메모리에 기입하고, 상기 메모리로부터 상기 표시패널의 열화에 대한 보상값을 리드 아웃하는 메모리 제어장치를 포함한다. 상기 메모리 제어장치는, 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제1 전송 버퍼(112)와, 상기 제1 전송 버퍼(112)에 내부용 메모리 신호들(Int\_IO 0~3, Int\_CS, Int\_CLK)을 인가하고 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제1 전송 버퍼(112)의 동작을 제어하는 제1 메모리 제어부(111)를 갖는 타이밍 콘트롤러(11)와, 상기 전송라인들(TL1~TL6)을 통해 상기 메모리(21)에 접속되는 제2 전송 버퍼(312)와, 상기 제2 전송 버퍼(312)에 외부용 메모리 신호들(Ext\_IO 0~3, Ext\_CS, Ext\_CLK)을 인가하고 상기 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 상기 제2 전송 버퍼(312)의 동작을 상기 제1 전송 버퍼(112)와 반대로 제어하는 제2 메모리 제어부(311)를 갖는 외부 제어장치(31)를 포함한다.

### 발명의 효과

[0022] 본 발명은 타이밍 콘트롤러와 외부 제어장치가 메모리에 대한 제어권을 공유하도록 함으로써 타이밍 콘트롤러의 내부 로직을 간소화하고 편수를 줄일 수 있다.

### 도면의 간단한 설명

[0023] 도 1은 메모리에 대한 제어권이 타이밍 콘트롤러에만 있는 종래의 메모리 제어장치를 보여주는 도면.

도 2a는 종래 기술에서 메모리와 타이밍 콘트롤러 간의 신호 전송 경로를 보여주는 도면.

도 2b는 종래 기술에서 메모리와 외부 제어장치 간의 신호 전송 경로를 보여주는 도면.

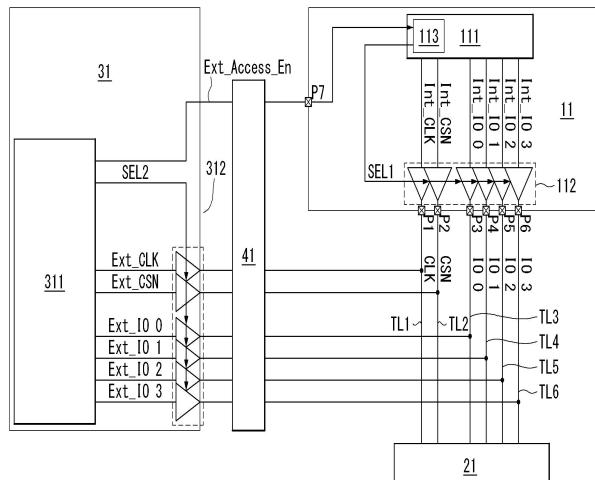

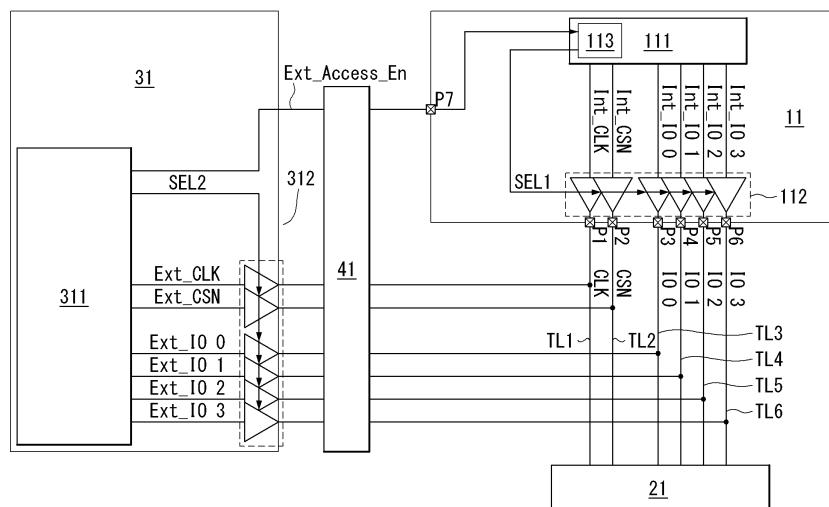

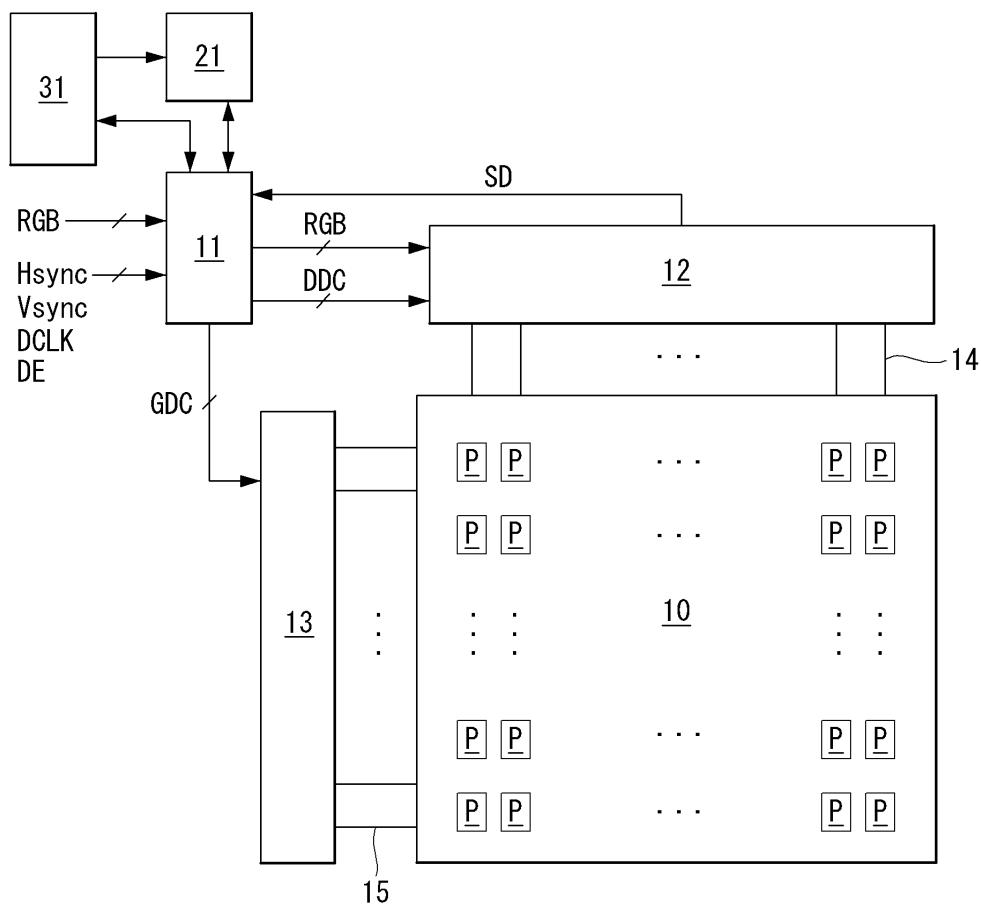

도 3은 본 발명에 따른 메모리 제어장치를 보여주는 도면.

도 4는 본 발명에 따른 메모리 제어 시퀀스로서 메모리에 대한 제어권을 타이밍 콘트롤러와 외부 제어장치가 공유하는 것을 보여주는 도면.

도 5a는 본 발명에서 메모리와 타이밍 콘트롤러 간의 신호 전송 경로를 보여주는 도면.

도 5b는 본 발명에서 메모리와 외부 제어장치 간의 신호 전송 경로를 보여주는 도면.

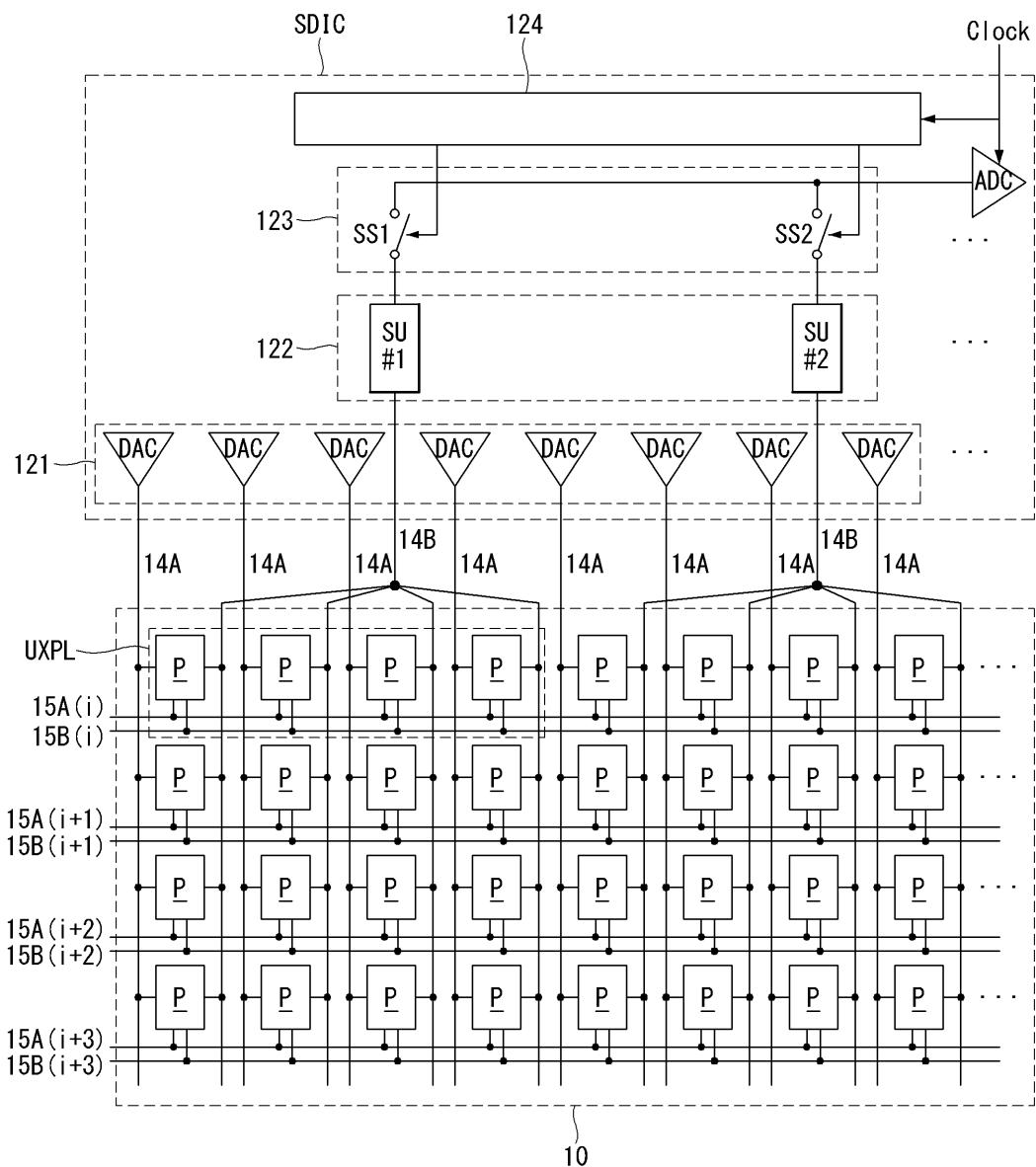

도 6은 본 발명의 메모리 제어장치를 포함한 유기발광 표시장치를 보여주는 도면.

도 7은 화소 어레이와 소스 드라이버 IC의 구성 예를 보여주는 도면.

도 8은 본 발명의 일 화소 구성과 그에 연결되는 센싱 유닛의 구성예를 보여주는 도면.

### 발명을 실시하기 위한 구체적인 내용

[0024] 이하, 도 3 내지 도 8을 참조하여, 본 발명의 바람직한 실시예를 구체적으로 설명한다.

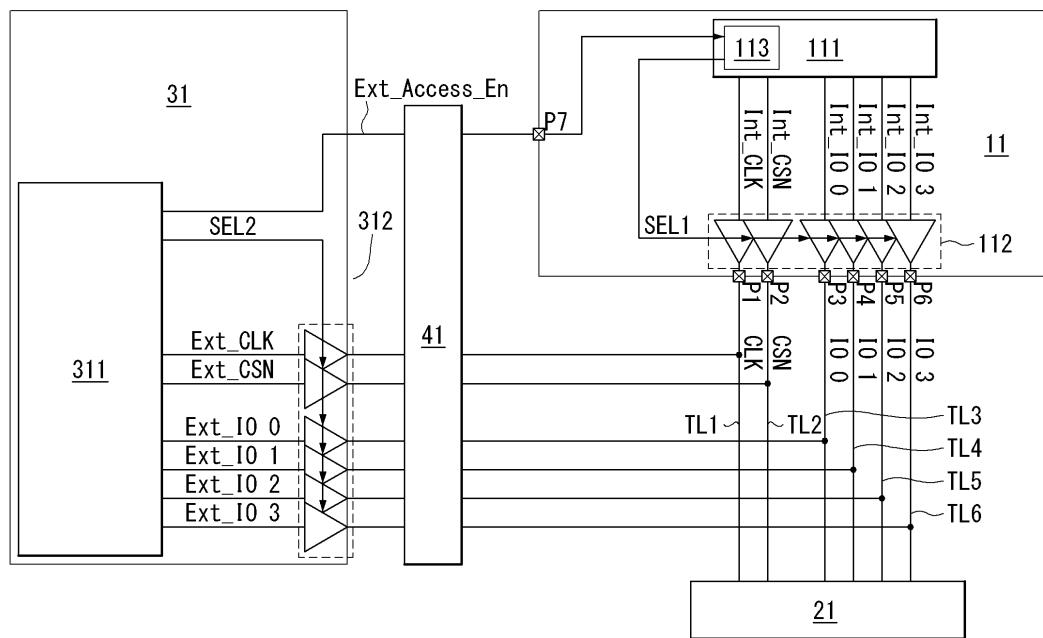

[0025] 도 3은 본 발명에 따른 메모리 제어장치를 보여준다. 도 4는 본 발명에 따른 메모리 제어 시퀀스로서 메모리에 대한 제어권을 타이밍 콘트롤러와 외부 제어장치가 공유하는 것을 보여준다. 도 5a는 본 발명에서 메모리와 타이밍 콘트롤러 간의 신호 전송 경로를 보여준다. 그리고, 도 5b는 본 발명에서 메모리와 외부 제어장치 간의 신호 전송 경로를 보여준다.

[0026] 도 3 및 도 4를 참조하면, 본 발명에 따른 메모리 제어장치는 메모리(21)에 선택적으로 억세스하는 타이밍 콘트롤러(11)와 외부 제어장치(31)를 포함한다.

[0027] 메모리(21)는 플래시 타입(Flash Type)으로 구현될 수 있으며, 표시패널의 열화에 대한 센싱값이 저장되는 제1 영역과, 표시패널의 열화에 대한 보상값이 저장되는 제2 영역을 구비한다. 센싱값은 표시패널의 화소들에 구비된 OLED의 동작점 전압, 구동 TFT의 문턱전압, 및 구동 TFT의 전자이동도 중 적어도 어느 하나를 포함할 수 있다. 보상값은 표시패널의 열화를 보상하기 위해 입력 디지털 비디오 데이터에 반영되는 값으로서, 초기 센싱값과 현재 센싱값 간의 차에 따라 그 크기가 결정될 수 있다.

[0028] 메모리(21)에 대한 억세스(Access) 동작은 내부 억세스 모드에서 타이밍 콘트롤러(11)에 의해 제어되지만, 외부 억세스 모드에서는 외부 제어장치(31)에 의해 제어된다. 외부 제어장치(31)는 제품 출하 전에 메모리 정보(초기 센싱값, 보상값 등)에 대한 초기 설정을 위한 경우, 또는 제품 출하 후에 AS(After Service) 용도로 메모리 정보(업데이트 센싱값, 보상값 등)에 대한 데이터 분석이 필요한 경우에 메모리(21)에 억세스할 수 있다.

[0029] 타이밍 콘트롤러(11)는 외부 억세스 인에이블신호(Ext\_Access\_EN)가 로우 논리레벨(이하, 제2 논리 레벨)로 입력되는 내부 억세스 모드에서 메모리(21)에 억세스하여, 센싱값을 메모리(21)에 기입함과 아울러 보상값을 메모리(21)로부터 리드 아웃한다. 한편, 외부 제어장치(31)는 외부 억세스 인에이블신호(Ext\_Access\_EN)가 하이 논리레벨(이하, 제1 논리 레벨)로 입력되는 외부 억세스 모드에서 메모리(21)에 억세스하여, 초기 센싱값과 보상값을 메모리(21)에 기입함과 아울러 보상값을 메모리(21)로부터 리드 아웃한다.

[0030] 내부 억세스 모드에서 외부 제어장치(31)에 의한 메모리 억세스 동작은 중지되며, 타이밍 콘트롤러(11)만이 메모리(21)에 억세스된다. 반면, 외부 억세스 모드에서 타이밍 콘트롤러(11)에 의한 메모리 억세스 동작은 중지되며, 외부 제어장치(31)만이 메모리(21)에 억세스된다.

[0031] 타이밍 콘트롤러(11)는 제1 메모리 제어부(111)와, 제1 전송 버퍼(112)와, 외부 억세스 모니터링부(113)를 포함한다.

[0032] 제1 전송 버퍼(112)는 3상태 버퍼(3 state buffer)로 구현될 수 있으며, 전송라인들(TL1~TL6)을 통해 메모리(21)에 접속되어, SPI (Serial Peripheral Interface) 방식으로 메모리(21)와 데이터를 주고 받을 수 있다. 제1 전송 버퍼(112)와 전송라인들(TL1~TL6) 사이에는 다수의 제1 전송핀들(P1~P6)이 구비된다. 제1 전송핀들(P1~P6)은 메모리 클럭 신호(CLK)를 전송하기 위한 1개의 전송핀(P1)과, 메모리 동작 신호(CSN)를 전송하기 위한 1개의 전송핀(P2)과, 메모리 클럭 신호(CLK)에 동기하여 메모리 데이터(I0 0,1,2,3)를 전송하는 4개의 전송핀들(P3,P4,P5,P6)을 포함할 수 있다.

[0033] 제1 메모리 제어부(111)는 제1 전송 버퍼(112)에 내부용 메모리 신호들(Int\_I0 0~3, Int\_CSN, Int\_CLK)을 인가하고 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 제1 전송 버퍼(112)의 동작을 제어한다. 외부 억세스 인에이블신호(Ext\_Access\_EN)는 제2 전송핀(P7)을 통해 외부 억세스 모니터링부(113)에 인가된다. 외부 억세스 모니터링부(113)는 제1 메모리 제어부(111)에 내장될 수 있다.

[0034] 외부 억세스 모니터링부(113)는 외부 제어장치(31)로부터 입력되는 외부 억세스 인에이블신호(Ext\_Access\_EN)를 모니터링한다. 외부 억세스 모니터링부(113)는 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 외부 억세스 모드에서 제1 선택신호(SEL1)를 이용하여 제1 전송 버퍼(112)를 하이 임피던스 상태(Hi-

Impedance State)로 제어함으로써, 제1 전송 버퍼(112)와 전송라인들(TL1~TL6) 간의 전기적 연결을 해제시킨다. 외부 억세스 모니터링부(113)는 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제2 논리레벨로 입력되는 내부 억세스 모드에서 제1 선택신호(SEL1)를 이용하여 제1 전송 버퍼(112)를 입출력 상태로 제어한다. 내부 억세스 모드에서 제1 전송 버퍼(112)가 출력 상태로 동작할 때, 제1 메모리 제어부(111)는 제1 전송 버퍼(112)와 전송라인들(TL1~TL6)을 통해 내부용 메모리 신호들(Int\_IO 0~3, Int\_CSN, Int\_CLK)을 메모리(21)에 인가하여 메모리(21)의 셀싱값을 업데이트할 수 있다. 내부 억세스 모드에서 제1 전송 버퍼(112)가 입력 상태로 동작할 때, 제1 메모리 제어부(111)는 전송라인들(TL1~TL6)과 제1 전송 버퍼(112)를 통해 메모리(21)의 보상값을 리드 아웃할 수 있다.

[0035] 외부 제어장치(31)는 제2 전송 버퍼(312)와 제2 메모리 제어부(311)를 포함한다.

[0036] 제2 전송 버퍼(312)는 3상태 버퍼(3 state buffer)로 구현될 수 있으며, 커넥터(41)와 전송라인들(TL1~TL6)을 통해 메모리(21)에 접속되어, SPI (Serial Peripheral Interface) 방식으로 메모리(21)와 데이터를 주고 받을 수 있다.

[0037] 제2 메모리 제어부(311)는 제2 전송 버퍼(312)에 외부용 메모리 신호들(Ext\_IO 0~3, Ext\_CSN, Ext\_CLK)을 인가하고 외부 억세스 인에이블신호(Ext\_Access\_EN)에 따라 제2 전송 버퍼(312)의 동작을 제어한다. 제2 메모리 제어부(311)는 외부 억세스 인에이블신호(Ext\_Access\_EN)를 생성한 후, 커넥터(41)와 제2 전송핀(P7)을 통해 타이밍 콘트롤러(11)의 외부 억세스 모니터링부(113)에 외부 억세스 인에이블신호(Ext\_Access\_EN)를 인가한다.

[0038] 제2 메모리 제어부(311)는 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 외부 억세스 모드에서 제2 선택신호(SEL2)를 이용하여 제2 전송 버퍼(312)를 입출력 상태로 제어한다. 제2 메모리 제어부(311)는 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제2 논리레벨로 입력되는 내부 억세스 모드에서 제2 선택신호(SEL2)를 이용하여 제2 전송 버퍼(312)를 하이 임피던스 상태(Hi-Impedance State)로 제어함으로써, 제2 전송 버퍼(312)와 전송라인들(TL1~TL6) 간의 전기적 연결을 해제시킨다. 외부 억세스 모드에서 제2 전송 버퍼(312)가 출력 상태로 동작할 때, 제2 메모리 제어부(311)는 제2 전송 버퍼(312)와 전송라인들(TL1~TL6)을 통해 외부용 메모리 신호들(Ext\_IO 0~3, Ext\_CSN, Ext\_CLK)을 메모리(21)에 인가하여 메모리(21)의 초기 셀싱값과 보상값을 변경할 수 있다. 외부 억세스 모드에서 제2 전송 버퍼(312)가 입력 상태로 동작할 때, 제2 메모리 제어부(311)는 전송라인들(TL1~TL6)과 제2 전송 버퍼(312)를 통해 메모리(21)의 보상값을 리드 아웃할 수 있다.

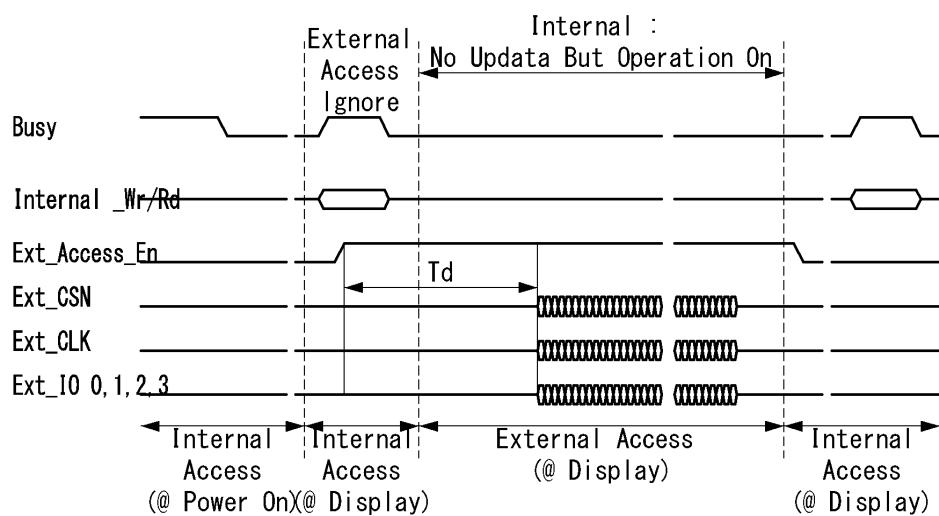

[0039] 도 4를 참조하여 본 발명에 따른 메모리 제어 시퀀스를 설명하면 다음과 같다.

[0040] 구동전원이 온 되면, 메모리(21)에 대한 제어권이 타이밍 콘트롤러(11)에 우선적으로 할당되어 내부 억세스 모드가 시작된다. 내부 억세스 모드에서 타이밍 콘트롤러(11)는 메모리(21)에 억세스하여 구동시간 누적값, 셀싱값 저장 위치 등을 포함한 파라미터 정보와, 보상값 관련 정보 등을 리드 아웃한다. 내부 억세스 모드에서 타이밍 콘트롤러(11)는 셀싱 동작에 따른 셀싱값과 함께 상기 파라미터 정보 등을 메모리(21)에 업데이트한다.

[0041] 내부 억세스 모드 중에 외부 제어장치(31)로부터 메모리 억세스 요청이 있는 경우, 즉 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 경우, 본 발명의 메모리 제어장치는 그 입력 시점(메모리 억세스 요청 타임)부터 소정 기간(Td) 경과 후에 내부 억세스 모드에서 외부 억세스 모드로 전환할 수 있다. 본 발명의 메모리 제어장치는 소정 기간(Td)이 경과할 때까지 타이밍 콘트롤러(11)와 외부 제어장치(31)를 내부 억세스 모드로 제어함으로써 메모리 억세스 요청 타임 이전에 수행하던 작업을 완료할 수 있다. 이를 통해 본 발명의 메모리 제어장치는 메모리 입출력에 대한 동작의 안전성을 확보할 수 있다.

[0042] 본 발명의 메모리 제어장치는 소정 기간(Td)이 경과한 후에 외부 억세스 모드로 전환한다. 외부 억세스 모드하에서, 제2 전송 버퍼(312)는 전송라인들(TL1~TL6)을 통해 메모리(21)에 직접 접속되며, 외부 제어장치(31)는 메모리(21)를 직접 제어한다.

[0043] 한편, 외부 억세스 모드하에서도 타이밍 콘트롤러(11)는 내부 작업(즉, 셀싱 작업 제어 및 셀싱값 임시 저장 작업 등)을 수행할 수 있으며, 내부 억세스 모드로 전환 후에 상기 임시 저장된 셀싱값 등을 메모리(21)에 업데이트 할 수 있다.

[0044] 이와 같이 본 발명의 메모리 제어장치는 도 5a와 같이 내부 억세스 모드에서는 타이밍 콘트롤러(11)와 메모리(21) 간의 통신을 통해 메모리(21)를 제어하고, 도 5b와 같이 외부 억세스 모드에서는 외부 제어장치(31)와 메모리(21) 간의 통신을 통해 메모리(21)를 제어한다. 본 발명의 메모리 제어장치는 외부 억세스 모드에서 타이밍 콘트롤러(11)를 통하지 않고 외부 제어장치(31)에서 직접 메모리(21)를 제어한다. 이를 통해 본 발명의 메모리

제어장치는 종래 대비 타이밍 콘트롤러(11)의 입출력핀수를 대폭적으로 줄일 수 있다.

[0045] 구체적으로 종래 타이밍 콘트롤러는 외부 제어장치와의 통신을 위해 8개의 제2 입출력핀들을 더 필요로 하였으나, 본 발명의 타이밍 콘트롤러(11)는 외부 제어장치(31)로부터 외부 억세스 인에이블신호(Ext\_Access\_EN)만을 입력받는 것만으로 충분하므로 기존 대비 7개의 전송핀들을 제거할 수 있다.

[0046] 도 6은 본 발명의 메모리 제어장치를 포함한 유기발광 표시장치를 보여준다. 도 7은 유기발광 표시장치에 포함된 화소 어레이와 소스 드라이버 IC의 구성 예를 보여준다. 그리고, 도 8은 본 발명의 일 화소 구성과 그에 연결되는 센싱 유닛의 구성예를 보여준다.

[0047] 도 6 내지 도 8을 참조하면, 본 발명의 실시예에 따른 유기발광 표시장치는 표시패널(10), 메모리(21), 메모리 제어장치(11,31), 데이터 구동회로(12), 게이트 구동회로(13)를 포함할 수 있다. 메모리 제어장치는 타이밍 콘트롤러(11)와 외부 제어장치(31)를 포함한다.

[0048] 표시패널(10)에는 다수의 데이터라인들 및 센싱라인들(14A,14B)과, 다수의 게이트라인들(15)이 교차되고, 이 교차영역마다 외부 보상용 화소들(P)이 매트릭스 형태로 배치되어 화소 어레이를 구성한다. 게이트라인들(15)은, 도 7에서와 같이 스캔 제어신호(SCAN)가 공급되는 다수의 제1 게이트라인들(15A)과, 센싱 제어신호(SEN)가 공급되는 다수의 제2 게이트라인들(15B)을 포함할 수 있다. 다만, 도면에 도시되어 있지 않지만 스캔 제어신호(SCAN)와 센싱 제어신호(SEN)가 동위상을 가질 때, 제1 및 제2 게이트라인(15A,15B)은 하나로 단일화될 수 있다.

[0049] 각 화소(P)는 데이터라인들(14A) 중 어느 하나에, 센싱라인들(14B) 중 어느 하나에, 그리고 제1 게이트라인들(15A) 중 어느 하나에, 제2 게이트라인들(15B) 중 어느 하나에 접속될 수 있다. 일 화소 유닛(UPXL)에 포함된 다수의 화소들(P)이 하나의 센싱라인(14B)을 공유할 수 있다. 화소 유닛(UPXL)은 적색 화소, 녹색 화소, 청색 화소, 백색 화소를 포함한 4개의 화소들로 구성될 수 있으나, 그에 한정되지 않는다. 또한, 도시되어 있지 않지만 일 화소 유닛(UPXL)에 포함된 화소들은 하나의 센싱라인을 공유하지 않고 다수의 센싱라인들에 독립적으로 연결될 수도 있다. 화소(P) 각각은 도시하지 않은 전원생성부로부터 고전위 구동전압(EVDD)과 저전위 구동전압(EVSS)을 공급받는다.

[0050] 본 발명의 화소(P)는 OLED, 구동 TFT(DT), 스토리지 커패시터(Cst), 제1 스위치 TFT(ST1), 및 제2 스위치 TFT(ST2)를 구비할 수 있다. TFT들은 P 타입으로 구현되거나 또는, N 타입으로 구현되거나 또는, P 타입과 N 타입이 혼용된 하이브리드 타입으로 구현될 수 있다. 또한, TFT의 반도체층은, 아몰포스 실리콘 또는, 폴리 실리콘 또는, 산화물을 포함할 수 있다.

[0051] OLED는 소스노드(Ns)에 접속된 애노드전극과, 저전위 구동전압(EVSS)의 입력단에 접속된 캐소드전극과, 애노드전극과 캐소드전극 사이에 위치하는 유기화합물층을 포함한다. 유기화합물층은 정공주입층(Hole Injection layer, HIL), 정공수송층(Hole transport layer, HTL), 발광층(Emission layer, EML), 전자수송층(Electron transport layer, ETL) 및 전자주입층(Electron Injection layer, EIL)을 포함할 수 있다.

[0052] 구동 TFT(DT)는 게이트-소스 간 전압(이하, Vgs라 함)에 따라 OLED에 입력되는 구동 TFT(DT)의 소스-드레인 간 전류(이하, Ids라 함)의 크기를 제어한다. 구동 TFT(DT)는 게이트노드에 접속된 게이트전극, 고전위 구동전압(EVDD)의 입력단에 접속된 드레인전극, 및 소스노드(Ns)에 접속된 소스전극을 구비한다. 스토리지 커패시터(Cst)는 게이트노드(Ng)와 소스노드(Ns) 사이에 접속되어 구동 TFT(DT)의 Vgs를 일정 기간 동안 유지시킨다. 제1 스위치 TFT(ST1)는 스캔 제어신호(SCAN)에 따라 데이터라인(14A)과 게이트노드(Ng) 간의 전기적 접속을 스위칭한다. 제1 스위치 TFT(ST1)는 제1 게이트라인(15A)에 접속된 게이트전극, 데이터라인(14A)에 접속된 드레인전극, 및 게이트노드(Ng)에 접속된 소스전극을 구비한다. 제2 스위치 TFT(ST2)는 센싱 제어신호(SEN)에 따라 소스노드(Ns)와 센싱 라인(14B) 간의 전기적 접속을 스위칭한다. 제2 스위치 TFT(ST2)는 제2 게이트라인(15B)에 접속된 게이트전극, 센싱 라인(14B)에 접속된 드레인전극, 및 소스노드(Ns)에 접속된 소스전극을 구비한다.

[0053] 이러한 화소 어레이를 갖는 본 발명의 유기발광 표시장치는 외부 보상 기술을 채용한다. 외부 보상 기술은 화소들에 구비된 유기발광다이오드(Organic Light Emitting Diode: 이하, "OLED"라 함)와 구동 TFT(Thin Film Transistor)의 전기적 특성을 센싱하고 그 센싱값에 따라 입력 비디오 데이터를 보정하는 기술이다. OLED의 전기적 특성은 OLED의 동작점 전압을 의미한다. 구동 TFT의 전기적 특성은 구동 TFT의 문턱전압과 구동 TFT의 전자 이동도를 의미한다.

[0054] 외부 보상용 화소 어레이를 포함한 유기발광 표시장치는 본원 출원인에 의해 기출원된 출원번호 제10-2013-0134256호(2013/11/06), 출원번호 제10-2013-0141334호(2013/11/20), 출원번호 제10-2013-0149395호

(2013/12/03), 출원번호 제10-2014-0086901호(2014/07/10), 출원번호 제10-2014-0079255호(2014/06/26), 출원 번호 제10-2014-0079587호(2014/06/27), 출원번호 제10-2014-0119357호(2014/09/05) 등에 나타나 있다.

[0055] 본 발명의 유기발광 표시장치는 화상 표시 동작과 외부 보상 동작을 수행한다. 외부 보상 동작은 화상 표시 동작 중의 수직 블랭크 기간에서 수행되거나, 또는 화상 표시가 시작되기 전의 파워 온 시퀀스 기간에서 수행되거나, 또는 화상 표시가 끝난 후의 파워 오프 시퀀스 기간에서 수행될 수 있다. 수직 블랭크 기간은 화상 데이터가 기입되지 않는 기간으로서, 1 프레임분의 화상 데이터가 기입되는 수직 액티브 구간들 사이마다 배치된다. 파워 온 시퀀스 기간은 구동 전원이 온 된 후부터 화상이 표시될 때까지의 기간을 의미한다. 파워 오프 시퀀스 기간은 화상 표시가 끝난 후부터 구동 전원이 오프 될 때까지의 기간을 의미한다.

[0056] 타이밍 콘트롤러(11)는 수직 동기신호(Vsync), 수평 동기신호(Hsync), 도트클럭신호(DCLK) 및 데이터 인에이블 신호(DE) 등의 타이밍 신호들에 기초하여 데이터 구동회로(12)의 동작 타이밍을 제어하기 위한 데이터 제어신호(DDC)와, 게이트 구동회로(13)의 동작 타이밍을 제어하기 위한 게이트 제어신호(GDC)를 생성한다. 타이밍 콘트롤러(11)는 화상 표시가 수행되는 기간과 외부 보상이 수행되는 기간을 시간적으로 분리하고, 화상 표시를 위한 제어신호들(DDC,GDC)과 외부 보상을 위한 제어신호들(DDC,GDC)을 서로 다르게 생성할 수 있다.

[0057] 게이트 제어신호(GDC)는 게이트 스타트 펄스(Gate Start Pulse, GSP), 게이트 쉬프트 클럭(Gate Shift Clock, GSC), 게이트 출력 인에이블신호(Gate Output Enable, GOE) 등을 포함한다. 게이트 스타트 펄스(GSP)는 첫 번째 스캔 신호를 발생하는 게이트 스테이지에 인가되어 첫 번째 스캔 신호가 발생되도록 그 게이트 스테이지를 제어한다. 게이트 쉬프트 클럭(GSC)은 게이트 스테이지들에 공통으로 입력되는 클럭신호로써 게이트 스타트 펄스(GSP)를 쉬프트시키기 위한 클럭신호이다. 게이트 출력 인에이블신호(GOE)는 게이트 스테이지들의 출력을 제어하는 마스킹 신호이다.

[0058] 데이터 제어신호(DDC)는 소스 스타트 펄스(Source Start Pulse, SSP), 소스 샘플링 클럭(Source Sampling Clock, SSC), 및 소스 출력 인에이블신호(Source Output Enable, SOE) 등을 포함한다. 소스 스타트 펄스(SSP)는 데이터 구동회로(12)의 데이터 샘플링 시작 타이밍을 제어한다. 소스 샘플링 클럭(SSC)은 라이징 또는 폴링 에지에 기준하여 소스 드라이브 IC들 각각에서 데이터의 샘플링 타이밍을 제어하는 클럭신호이다. 소스 출력 인에이블신호(SOE)는 데이터 구동회로(12)의 출력 타이밍을 제어한다. 데이터 제어신호(DDC)는 데이터 구동회로(12)에 포함된 센싱 유닛(122)의 동작을 제어하기 위한 기준전압 제어신호(PRE)와 샘플링 제어신호(SAM)을 포함한다. 기준전압 제어신호(PRE)는 센싱 라인(14B)에 기준전압을 인가하기 위한 타이밍을 제어한다. 샘플링 제어신호(SAM)는 외부 보상 동작에 따른 아날로그 센싱값을 샘플링하기 위한 타이밍을 제어한다.

[0059] 메모리 제어장치(11,31)는 도 3 및 도 4를 통해 설명한 것과 실질적으로 동일하다. 타이밍 콘트롤러(11)는 외부 보상 동작에 따른 디지털 센싱값(SD)을 데이터 구동회로(12)의 ADC로부터 입력 받는다. 타이밍 콘트롤러(11)는 전술했듯이 내부 억세스 모드에서 동작이 활성화된다. 타이밍 콘트롤러(11)는 내부 억세스 모드에서 제1 전송 버퍼(112)와 전송라인들(TL1~TL6)을 통해 디지털 센싱값(SD)을 메모리(21)의 제1 영역에 기입하고, 현재 센싱값(SD)과 초기 센싱값 간의 차를 리드 어드레스로 하여 메모리(21)의 제2 영역에 저장된 보상값을 리드 아웃한 후에, 이 보상값을 입력 디지털 비디오 데이터(RGB)에 반영하여 화소들 간 구동 TFT의 전기적 특성 편차를 보상하거나, 또는 화소들 간 OLED의 열화 편차를 보상할 수 있다. 타이밍 콘트롤러(11)는 화상 표시를 위한 동작 기간에서 보상값이 반영된 디지털 비디오 데이터(RGB)를 데이터 구동회로(12)에 전송한다.

[0060] 외부 제어장치(31)는 외부 억세스 모드에서 동작이 활성화된다. 외부 제어장치(31)는 제2 전송 버퍼(312)와 전송라인들(TL1~TL6)을 통해 외부용 메모리 신호들(Ext\_IO 0~3, Ext\_CSN, Ext\_CLK)을 메모리(21)에 인가하여 메모리(21)의 초기 센싱값과 보상값을 변경할 수 있다. 외부 제어장치(31)는 전송라인들(TL1~TL6)과 제2 전송 버퍼(312)를 통해 메모리(21)의 보상값을 리드 아웃할 수 있다.

[0061] 구체적으로 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 외부 억세스 모드에서 타이밍 콘트롤러(11)의 제1 전송 버퍼(112)는 하이 임피던스 상태가 되고, 외부 제어장치(31)의 제2 전송 버퍼(312)는 입출력 상태가 될 수 있다. 반면, 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제2 논리레벨로 입력되는 내부 억세스 모드에서 타이밍 콘트롤러(11)의 제1 전송 버퍼(112)는 입출력 상태가 되고, 외부 제어장치(31)의 제2 전송 버퍼(312)는 하이 임피던스 상태가 될 수 있다.

[0062] 한편, 내부 억세스 모드 중에 외부 억세스 인에이블신호(Ext\_Access\_EN)가 제1 논리레벨로 입력되는 경우, 그 입력 시점부터 소정 기간(Td) 경과 후에 내부 억세스 모드에서 상기 외부 억세스 모드로 전환될 수 있다. 이때, 이 소정 기간(Td) 동안 타이밍 콘트롤러(11)는 내부 억세스 모드 중에 수행하던 작업을 완료함으로써, 메모리

입출력에 대한 동작의 안전성을 확보할 수 있다.

[0063] 이렇게 본 발명에 따른 외부 제어장치(31)는 외부 억세스 모드에서, 타이밍 콘트롤러(11)를 거치지 않고 메모리(21)를 직접 제어할 수 있다.

[0064] 데이터 구동회로(12)는 적어도 하나 이상의 소스 드라이버 IC(Integrated Circuit)(SDIC)를 포함한다. 이 소스 드라이버 IC(SDIC)에는 래치 어레이(미도시), 각 데이터라인(14A)에 연결된 다수의 디지털-아날로그 컨버터(이하, DAC)들(121)과, 각 센싱라인(14B)에 연결된 다수의 센싱 유닛들(122), 센싱 유닛들(122)을 선택적으로 아날로그-디지털 컨버터(이하, ADC)에 연결하는 멀티플렉터(123), 선택 제어신호를 생성하여 멀티플렉터(123)의 스위치들(SS1, SS2)을 순차적으로 턴 온 시키는 소프트 레지스터(124)가 구비될 수 있다.

[0065] 래치 어레이는 데이터 제어신호(DDC)를 기반으로 타이밍 콘트롤러(11)로부터 입력되는 각종 디지털 데이터를 래치하여 DAC에 공급한다. DAC는 화상 표시 동작시 타이밍 콘트롤러(11)로부터 입력되는 디지털 비디오 데이터(RGB)를 화상 표시용 데이터전압으로 변환하여 데이터라인들(14A)에 공급할 수 있다. DAC는 외부 보상 동작시 일정 레벨의 외부 보상용 데이터전압을 생성하여 데이터라인들(14A)에 공급할 수 있다.

[0066] 센싱 유닛(122)은 데이터 제어신호(DDC)를 기반으로 센싱 라인(14B)에 초기화전압(Vref)을 공급하거나, 또는 센싱 라인(14B)을 통해 입력되는 아날로그 센싱값(OLED나 구동 TFT에 대한 전기적 특성값)을 샘플링하여 ADC에 공급할 수 있다. 센싱 유닛(122)은 도 6과 같은 전압 센싱형으로 구현될 수도 있다.

[0067] 전압 센싱형 센싱 유닛(122)은 구동 TFT(DT)의  $Ids$ 에 대응하여 센싱 라인(14B)의 라인 커패시터(LCa)에 저장된 전압을 센싱하는 것으로, 초기화 스위치(SW1), 샘플링 스위치(SW2), 및 샘플 앤 홀드부(S/H)를 구비할 수 있다. 초기화 스위치(SW1)는 초기화 제어신호(PRE)에 따라 초기화전압(Vref)의 입력단과 센싱 라인(14B) 간의 전기적 접속을 스위칭한다. 샘플링 스위치(SW2)는 샘플링 제어신호(SAM)에 따라 센싱 라인(14B)과 샘플 앤 홀드부(S/H) 간의 전기적 접속을 스위칭한다. 구동 TFT(DT)의  $Ids$ 에 따라 구동 TFT의 소스 노드 전압이 변할 때, 샘플 앤 홀드부(S/H)는 샘플링 스위치(SW2)가 턴 온 되는 특정 시점에서 센싱 라인(14B)의 라인 커패시터(LCa)에 저장된 구동 TFT(DT)의 소스노드 전압을 아날로그 센싱값으로서 샘플링 및 홀딩한 후 ADC에 전달한다.

[0068] 게이트 구동회로(13)는 게이트 제어신호(GDC)를 기반으로 화상 표시 동작, 외부 보상 동작에 맞게 스캔 제어신호(SCAN)를 생성한 후, 제1 게이트라인들(15A)에 공급한다. 게이트 구동회로(13)는 게이트 제어신호(GDC)를 기반으로 화상 표시 동작, 외부 보상 동작에 맞게 센싱 제어신호(SEN)를 생성한 후, 제2 게이트라인들(15B)에 공급한다.

[0069] 이와 같이, 본 발명은 타이밍 콘트롤러와 외부 제어장치가 메모리에 대한 제어권을 공유하도록 함으로써 타이밍 콘트롤러의 내부 로직을 간소화하고 핀수를 줄일 수 있다.

[0070] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

### 부호의 설명

[0071] 11 : 타이밍 콘트롤러 21 : 메모리

31 : 외부 제어장치 41 : 커넥터

111 : 제1 메모리 제어부 112 : 제1 전송 버퍼

113 : 외부 억세스 모니터링부 311 : 제2 메모리 제어부

312 : 제2 전송 버퍼

## 도면

## 도면1

## 도면2a

## 도면2b

## 도면3

## 도면4

도면5a

도면5b

도면6

도면7

|                |                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 存储器控制装置及其控制方法和使用该装置的OLED显示装置                                                                                            |         |            |

| 公开(公告)号        | <a href="#">KR1020170033499A</a>                                                                                             | 公开(公告)日 | 2017-03-27 |

| 申请号            | KR1020150131206                                                                                                              | 申请日     | 2015-09-16 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                     |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                                                    |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                                                    |         |            |

| [标]发明人         | <p>KIM HYO JIN<br/>김효진<br/>JANG SU HYUK<br/>장수혁<br/>LEE JEONGA<br/>이정아<br/>LEE JIN WON<br/>이진원<br/>HONG SUNG WAN<br/>홍성완</p> |         |            |

| 发明人            | <p>김효진<br/>장수혁<br/>이정아<br/>이진원<br/>홍성완</p>                                                                                   |         |            |

| IPC分类号         | G09G3/32                                                                                                                     |         |            |

| CPC分类号         | G09G3/3225 G09G2310/08 G09G2320/043                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                    |         |            |

## 摘要(译)

本发明的存储器控制单元通过存储器之间的通信来控制外部访问模式中的定时控制器，并且通过外部访问模式存储器中的存储器之间的通信来控制存储器。在本发明的存储器控制单元中是外部访问模式，它不通过时序控制器而是在外部控制装置中控制直接存储器。由此，本发明的存储器控制单元可以大大减少传统比较时序控制器的I/O引脚数。