(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0127177

(43) 공개일자 2017년11월21일

(51) 국제특허분류(Int. Cl.)

*H01L 27/32* (2006.01) *H01L 27/12* (2006.01)

(52) CPC특허분류

*H01L 27/3262* (2013.01)

*H01L 27/1288* (2013.01)

(21) 출원번호 10-2016-0057459

(22) 출원일자 2016년05월11일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

이석현

인천광역시 연수구 옥련로 33, 101동 212호 (옥련

동, 현대1차아파트)

강임국

경기도 파주시 교하로 70, 307동 1302호 (목동동,

산내마을3단지아파트)

박상무

경기도 고양시 일산동구 위시티4로 46, 211동 80

2호 (식사동, 위시티일산자이2단지아파트)

(74) 대리인

특허법인네이트

전체 청구항 수 : 총 7 항

(54) 발명의 명칭 유기발광표시장치 및 그 제조방법

### (57) 요 약

본 발명은, 드레인 전극의 일 부분에 대응하는 돌출 패턴을 형성하고 리던던시 리페어 패턴의 끝이 돌출 패턴 상에 위치하는 유기발광표시장치 및 그 제조 방법을 제공한다.

따라서, 보호층과 평탄화층에 대한 마스크 공정에 의해 발생되는 리던던시 리페어 패턴과 드레인 전극의 전기적 쇼트 문제를 방지할 수 있다.

### 대 표 도

(52) CPC특허분류

*H01L 27/322* (2013.01)

*H01L 27/3223* (2013.01)

*H01L 27/3258* (2013.01)

*H01L 27/3276* (2013.01)

*H01L 2227/323* (2013.01)

*H01L 2251/568* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

제 1 화소영역에 위치하고 반도체층과, 게이트 전극과, 소스 전극과 드레인 전극을 포함하는 박막트랜지스터와;

상기 박막트랜지스터를 덮는 보호층과;

상기 보호층 상에 위치하며 상기 드레인 전극의 제 1 부분에 대응하는 돌출 패턴과;

상기 드레인 전극에 연결되고 상기 제 1 화소영역과 상기 제 1 화소영역에 인접한 제 2 화소영역에 위치하는 제 1 전극과;

상기 제 2 화소영역의 상기 제 1 전극으로부터 상기 제 1 화소영역으로 연장되어 상기 드레인 전극의 제 2 부분과 중첩하고 그 끝이 상기 돌출 패턴 상에 위치하는 리던더시 리페어 패턴과;

상기 제 1 및 제 2 화소영역 각각의 상기 제 1 전극 상에 위치하는 유기 발광층과;

상기 유기 발광층 상의 제 2 전극

을 포함하는 유기발광표시장치.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 및 제 2 화소영역 각각에 대응하며 상기 보호층 상에 위치하는 컬러필터층과;

상기 컬러필터층을 덮는 평탄화층을 포함하는 유기발광표시장치.

#### 청구항 3

제 2 항에 있어서,

상기 돌출 패턴은 상기 평탄화층과 동일물질로 이루어지고 동일층에 위치하는 유기발광표시장치.

#### 청구항 4

제 1 항에 있어서,

상기 돌출 패턴은 상기 드레인 전극의 단차부에 대응하여 위치하는 유기발광표시장치.

#### 청구항 5

제 1 화소영역에 반도체층과, 게이트 전극과, 소스 전극과 드레인 전극을 포함하는 박막트랜지스터를 형성하는 단계와;

상기 박막트랜지스터를 덮는 보호층을 형성하는 단계와;

상기 보호층 상에 컬러필터층을 형성하는 단계와;

상기 컬러필터층을 덮는 평탄화층과, 상기 보호층 상에 위치하며 상기 드레인 전극의 제 1 부분에 대응하는 돌출 패턴을 형성하는 단계와;

상기 제 1 화소영역에 상기 드레인 전극에 연결되는 제 1 전극과, 상기 제 1 화소영역에 인접한 제 2 화소영역

의 제 1 전극으로부터 연장되어 상기 드레인 전극의 제 2 부분과 중첩하고 그 끝이 상기 돌출 패턴 상에 위치하는 리던던시 리페어 패턴을 형성하는 단계와;

상기 제 1 및 제 2 화소영역 각각의 상기 제 1 전극 상에 유기 발광층을 형성하는 단계와;

상기 유기 발광층 상에 제 2 전극을 형성하는 단계

를 포함하는 유기발광표시장치의 제조 방법.

## 청구항 6

제 5 항에 있어서,

상기 평탄화층과 상기 돌출 패턴을 형성하는 단계는,

상기 컬러필터층 상에 제 1 두께를 갖는 유기절연물질층을 형성하는 단계와;

상기 유기절연물질층에 대하여 마스크 공정을 진행하여 상기 제 1 부분에 대응하여 상기 제 1 두께를 갖고 상기 드레인 전극의 제 2 부분에 대응하여 상기 제 1 두께보다 작은 제 2 두께를 갖고 상기 드레인 전극의 제 3 부분에 대응하여 상기 유기절연물질층에 제거하는 단계와;

상기 마스크 공정 이후에, 상기 유기절연물질층에 대하여 제 1 애싱 공정을 진행하여 상기 제 3 부분에 잔류하는 유기절연물질을 완전히 제거하여 상기 보호층을 노출하는 단계와;

상기 노출된 보호층을 식각하여 상기 드레인 전극의 상기 제 3 부분을 노출하는 단계와;

제 2 애싱 공정을 진행하여 상기 제 2 부분의 상기 유기절연물질층을 제거함으로써 상기 평탄화층과 상기 돌출 패턴을 형성하는 단계를 포함하는 유기발광표시장치의 제조 방법.

## 청구항 7

제 5 항에 있어서,

상기 돌출 패턴은 상기 드레인 전극의 단차부에 대응하여 위치하는 유기발광표시장치의 제조 방법.

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 유기발광표시장치에 관한 것으로, 특히 전기적 쇼트 없이 화소 불량을 리페어할 수 있는 유기발광표시장치 및 제조공정이 단순한 유기발광표시장치의 제조방법에 관한 것이다.

#### 배경 기술

[0002] 정보화 사회가 발전함에 따라 화상을 표시하기 위한 표시장치에 대한 요구가 다양한 형태로 증가하고 있다. 종래의 음극선관 표시장치(CRT)를 대신하여 액정표시장치(liquid crystal display (LCD) device), 플라즈마 표시장치(plasma display panel (PDP)) 또는 유기발광표시장치(organic light emitting display(OLED) device) 표시장치를 포함하는 평판표시장치가 활발하게 연구되고 있다.

[0003] 유기발광표시장치는 높은 휘도와 낮은 동작 전압 특성을 갖는다. 또한, 스스로 빛을 내는 자체 발광형이기 때문에 대조비(contrast ratio)가 크고, 초박형 디스플레이의 구현이 가능하며, 응답시간이 짧고 시야각이 넓은 장점을 갖는다.

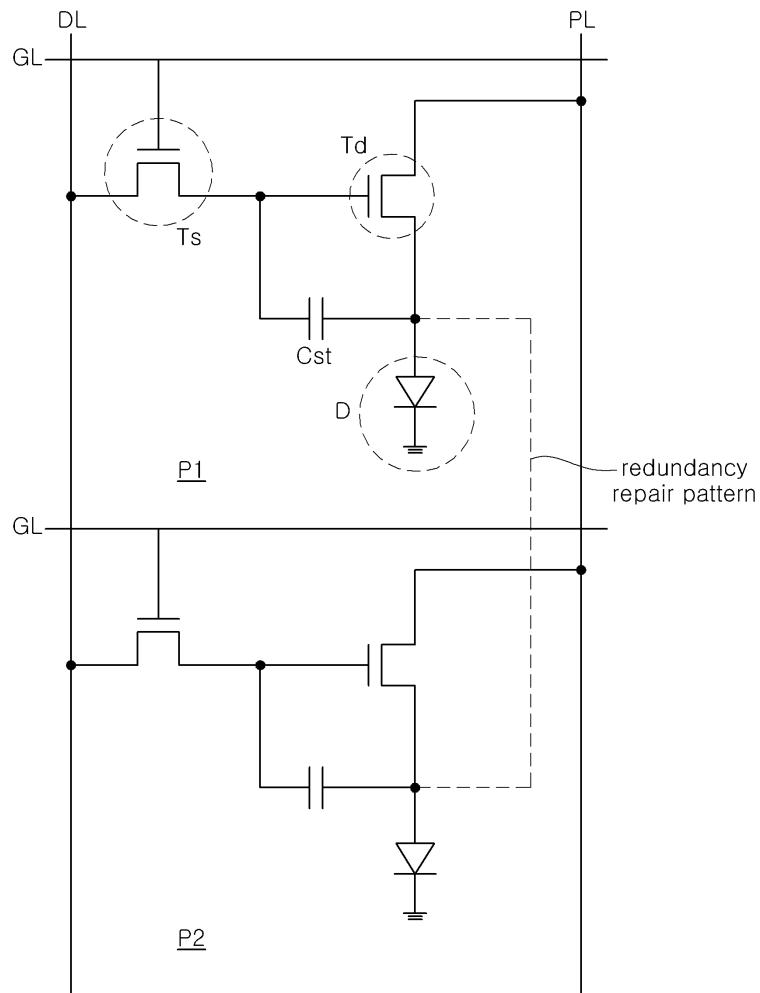

[0004] 도 1은 종래 유기발광표시장치의 개략적인 회로도이다.

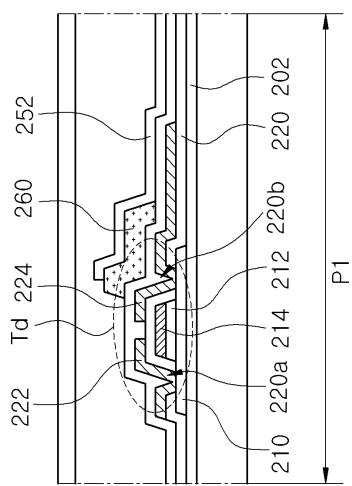

[0005] 도 1에 도시한 바와 같이, 유기발광표시장치에는, 서로 교차하여 제 1 및 제 2 화소영역(P1, P2)을 정의하는 게이트배선(GL), 데이터배선(DL) 및 파워배선(PL)이 형성되고, 화소영역(P)에는, 스위칭 박막트랜지스터(Ts), 구동 박막트랜지스터(Td), 스토리지 커패시터(Cst), 유기발광다이오드(D)가 형성된다.

[0006] 스위칭 박막트랜지스터(Ts)는 게이트배선(GL) 및 데이터배선(DL)에 연결되고, 구동 박막트랜지스터(Td) 및 스토

리지 커페시터(Cst)는 스위칭 박막트랜지스터(Ts)와 파워배선(PL) 사이에 연결되고, 유기발광다이오드(D)는 구동 박막트랜지스터(Td)에 연결된다.

[0007] 이러한 유기발광표시장치의 영상표시 동작을 살펴보면, 게이트배선(GL)에 인가된 게이트신호에 따라 스위칭 박막트랜지스터(Ts)가 턴-온(turn-on) 되면, 데이터배선(DL)에 인가된 데이터신호가 스위칭 박막트랜지스터(Ts)를 통해 구동 박막트랜지스터(Td)의 게이트전극과 스토리지 커페시터(Cst)의 일 전극에 인가된다.

[0008] 구동 박막트랜지스터(Td)는 게이트전극에 인가된 데이터신호에 따라 턴-온 되며, 그 결과 데이터신호에 비례하는 전류가 파워배선(PL)으로부터 구동 박막트랜지스터(Td)를 통하여 유기발광다이오드(D)로 흐르게 되고, 유기발광다이오드(D)는 구동 박막트랜지스터(Td)를 통하여 흐르는 전류에 비례하는 휘도로 발광한다.

[0009] 이때, 스토리지 커페시터(Cst)에는 데이터신호에 비례하는 전압으로 충전되어, 일 프레임(frame) 동안 구동 박막트랜지스터(Td)의 게이트전극의 전압이 일정하게 유지되도록 한다.

[0010] 따라서, 유기발광표시장치는 게이트신호 및 데이터신호에 의하여 원하는 영상을 표시할 수 있다.

[0011] 한편, 화소영역의 불량을 리페어하기 위해 제 1 및 제 2 화소영역(P1, P2)을 가로지르는 리던던시 리페어 패턴(redundancy repair pattern)이 형성된다. 예를 들어, 제 1 화소영역(P1)에 불량이 발생한 경우, 스위칭 박막트랜지스터(Ts)의 연결을 끊고 리던던시 리페어 패턴을 통해 제 1 화소영역(P1)의 유기발광다이오드(D)를 제 2 화소영역(P2)의 구동 박막트랜지스터(Td)에 전기적으로 연결시킴으로써 제 1 화소영역(P1)의 불량을 리페어한다.

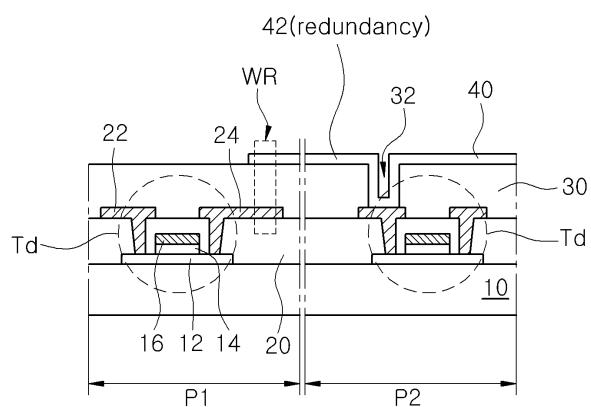

[0012] 종래 유기발광표시장치의 개략적인 단면도인 도 2를 참조하면, 제 1 및 제 2 화소영역(P1, P2) 각각에 대응하여 구동 박막트랜지스터(Td)가 기판(10) 상에 형성된다.

[0013] 예를 들어, 구동 박막트랜지스터(Td)는, 반도체층(12)과, 게이트 전극(16)과, 소스 전극(22) 및 드레인 전극(24)을 포함할 수 있다.

[0014] 상기 반도체층(12)은 상기 기판(10) 상에 위치하며 산화물 반도체 물질 또는 폴리실리콘으로 이루어질 수 있다. 상기 반도체층(12)의 중앙에 대응하여 상기 게이트 전극(16)이 게이트 절연막(14)을 개재하여 위치한다.

[0015] 상기 반도체층(12)의 양단을 노출하는 제 1 및 제 2 콘택홀을 갖는 충간 절연막(20)이 상기 게이트 전극(16)을 덮으며 형성되고, 상기 소스 전극(22)과 상기 드레인 전극(24)은 상기 충간 절연막(20) 상에 형성된다. 상기 소스 전극(22)과 상기 드레인 전극(24)은 상기 제 1 및 제 2 콘택홀을 통해 상기 반도체층(12)에 연결된다.

[0016] 상기 구동 박막트랜지스터(Td) 상에는 상기 드레인 전극(24)을 노출하는 드레인 콘택홀(32)을 갖는 보호층(30)이 형성되고, 상기 보호층(30) 상에는 상기 드레인 콘택홀(32)을 통해 상기 드레인 전극(24)에 연결되는 제 1 전극(40)이 형성된다.

[0017] 이때, 상기 제 2 화소영역(P2)의 상기 제 1 전극(40)은 상기 제 1 화소영역(P1)으로 연장되어 상기 리던던시 리페어 패턴(42)을 이룬다. 상기 리던던시 리페어 패턴(42)은 상기 제 1 화소영역(P1)의 상기 드레인 전극(24)과 중첩한다.

[0018] 도시하지 않았으나, 상기 제 1 전극(40) 상에는 유기발광층과 제 2 전극이 적층되어 유기발광다이오드(도 1의 D)를 구성한다.

[0019] 예를 들어, 상기 제 1 화소영역(P1)에 불량이 발생한 경우, 웨딩 영역(WR)에 대응하여 웨딩(welding) 공정을 진행하여 상기 리던던시 리페어 패턴(42)과 상기 제 1 화소영역(P1)의 드레인 전극(24)을 전기적으로 연결시킴으로써, 리페어 공정이 진행된다.

[0020] 한편, 고색 재현을 위해, 유기발광다이오드는 백색을 발광하고 유기발광다이오드 하부에 컬러필터층을 형성하는 유기발광표시장치가 제안되었는데, 이 경우 컬러필터층에 의한 단차를 평탄화하기 위한 평탄화층이 요구된다. 이에 따라, 유기발광표시장치의 제조 공정이 복잡해지고 제조 원가가 증가하는 문제가 발생한다.

## 발명의 내용

### 해결하려는 과제

[0021] 본 발명에서는, 화소 불량을 방지하기 위한 리페어 패턴을 구비하고 컬러필터층을 구비하여 고색 재현이 가능하면서 제조 원가 상승 및 제조 공정이 복잡해지는 문제를 해결하고자 한다.

## 과제의 해결 수단

[0022]

위와 같은 과제의 해결을 위해, 본 발명은, 드레인 전극의 일 부분에 대응하는 돌출 패턴을 형성하고 리던던시 리페어 패턴의 끝이 돌출 패턴 상에 위치하는 유기발광표시장치 및 그 제조 방법을 제공한다.

## 발명의 효과

[0023]

본 발명에 따른 유기발광표시장치에서는 보호층과, 컬러필터층에 의한 단차를 평탄화하기 위한 평탄화층을 하나의 마스크 공정에 의해 패터닝함으로써, 제조 공정이 단순해지고 제조 원가가 절감된다.

[0024]

또한, 화소 불량을 리페어하기 위한 리던던시 리페어 패턴의 끝단에 돌출 패턴을 형성함으로써, 보호층과 평탄화층에 대한 마스크 공정에 의해 발생되는 리던던시 리페어 패턴과 드레인 전극의 전기적 쇼트 문제를 방지한다.

[0025]

따라서, 전기적 쇼트 없이, 제조 공정이 단순하고 화소 불량을 리페어할 수 있는 유기발광표시장치를 제공할 수 있다.

## 도면의 간단한 설명

[0026]

도 1은 종래 유기발광표시장치의 개략적인 회로도이다.

도 2는 종래 유기발광표시장치의 개략적인 단면도이다.

도 3a 내지 도 3h는 본 발명의 제 1 실시예에 따른 유기발광표시장치에서 리던던시 리페어 패턴 형성 영역에 대한 제조 공정을 보여주는 개략적인 단면도이다.

도 4a 내지 도 4h는 본 발명의 제 1 실시예에 따른 유기발광표시장치의 표시영역에 대한 제조 공정을 보여주는 개략적인 단면도이다.

도 5는 본 발명의 제 2 실시예에 따른 유기발광표시장치의 개략적인 단면도이다.

도 6a 내지 도 6h는 본 발명의 제 2 실시예에 따른 유기발광표시장치에서 리던던시 리페어 패턴 형성 영역에 대한 제조 공정을 보여주는 개략적인 단면도이다.

## 발명을 실시하기 위한 구체적인 내용

[0027]

본 발명은, 제 1 화소영역에 위치하고 반도체층과, 게이트 전극과, 소스 전극과 드레인 전극을 포함하는 박막트랜지스터와, 상기 박막트랜지스터를 덮는 보호층과, 상기 보호층 상에 위치하며 상기 드레인 전극의 제 1 부분에 대응하는 돌출 패턴과, 상기 드레인 전극에 연결되고 상기 제 1 화소영역과 상기 제 1 화소영역에 인접한 제 2 화소영역에 위치하는 제 1 전극과, 상기 제 2 화소영역의 상기 제 1 전극으로부터 상기 제 1 화소영역으로 연장되어 상기 드레인 전극의 제 2 부분과 중첩하고 그 끝이 상기 돌출 패턴 상에 위치하는 리던던시 리페어 패턴과, 상기 제 1 및 제 2 화소영역 각각의 상기 제 1 전극 상에 위치하는 유기 발광층과, 상기 유기발광층 상의 제 2 전극을 포함하는 유기발광표시장치를 제공한다.

[0028]

본 발명의 유기발광표시장치는, 상기 제 1 및 제 2 화소영역 각각에 대응하여 상기 보호층 상에 위치하는 컬러필터층과, 상기 컬러필터층을 덮는 평탄화층을 포함할 수 있다.

[0029]

본 발명의 유기발광표시장치에 있어서, 상기 돌출 패턴은 상기 평탄화층과 동일물질로 이루어지고 동일층에 위치할 수 있다.

[0030]

본 발명의 유기발광표시장치에 있어서, 상기 돌출 패턴은 상기 드레인 전극의 단차부에 대응하여 위치할 수 있다.

[0031]

다른 관점에서, 본 발명은, 제 1 화소영역에 반도체층과, 게이트 전극과, 소스 전극과 드레인 전극을 포함하는 박막트랜지스터를 형성하는 단계와, 상기 박막트랜지스터를 덮는 보호층을 형성하는 단계와, 상기 보호층 상에 컬러필터층을 형성하는 단계와, 상기 컬러필터층을 덮는 평탄화층과, 상기 보호층 상에 위치하며 상기 드레인 전극의 제 1 부분에 대응하는 돌출 패턴을 형성하는 단계와, 상기 제 1 화소영역에 상기 드레인 전극에 연결되는 제 1 전극과, 상기 제 1 화소영역에 인접한 제 2 화소영역의 제 1 전극으로부터 연장되어 상기 드레인 전극의 제 2 부분과 중첩하고 그 끝이 상기 돌출 패턴 상에 위치하는 리던던시 리페어 패턴을 형성하는 단계와, 상기 제 1 및 제 2 화소영역 각각의 상기 제 1 전극 상에 유기 발광층을 형성하는 단계와, 상기 유기발광층 상에

제 2 전극을 형성하는 단계를 포함하는 유기발광표시장치의 제조 방법을 제공한다.

[0032] 본 발명의 유기발광표시장치 제조 방법에 있어서, 상기 평탄화층과 상기 돌출 패턴을 형성하는 단계는, 상기 걸러필터층 상에 제 1 두께를 갖는 유기절연물질층을 형성하는 단계와, 상기 유기절연물질층에 대하여 마스크 공정을 진행하여 상기 제 1 부분에 대응하여 상기 제 1 두께를 갖고 상기 드레인 전극의 제 2 부분에 대하여 상기 제 1 두께보다 작은 제 2 두께를 갖고 상기 드레인 전극의 제 3 부분에 대하여 상기 유기절연물질층에 제거하는 단계와, 상기 마스크 공정 이후에, 상기 유기절연물질층에 대하여 제 1 애싱 공정을 진행하여 상기 제 3 부분에 잔류하는 유기절연물질을 완전히 제거하여 상기 보호층을 노출하는 단계와, 상기 노출된 보호층을 각각하여 상기 드레인 전극의 상기 제 3 부분을 노출하는 단계와, 제 2 애싱 공정을 진행하여 상기 제 2 부분의 상기 유기절연물질층을 제거함으로써 상기 평탄화층과 상기 돌출 패턴을 형성하는 단계를 포함할 수 있다.

[0033] 본 발명의 유기발광표시장치 제조 방법에 있어서, 상기 돌출 패턴은 상기 드레인 전극의 단차부에 대응하여 위치할 수 있다.

[0034] 이하, 본 발명에 따른 바람직한 실시예를 도면을 참조하여 설명한다.

-제 1 실시예-

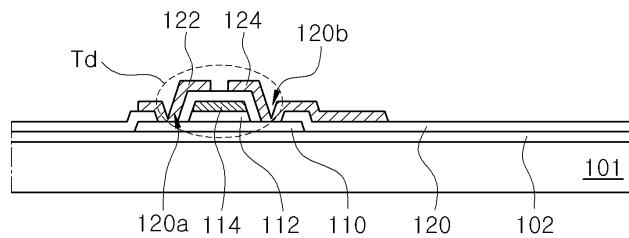

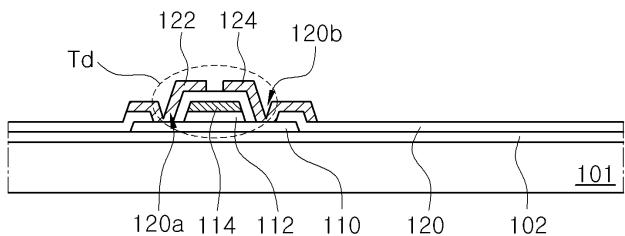

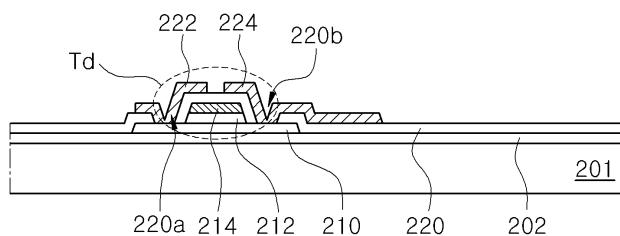

[0036] 도 3a 내지 도 3h는 본 발명의 제 1 실시예에 따른 유기발광표시장치에서 리던던시 리페어 패턴 형성 영역에 대한 제조 공정을 보여주는 개략적인 단면도이고, 도 4a 내지 도 4h는 본 발명의 제 1 실시예에 따른 유기발광표시장치의 표시영역에 대한 제조 공정을 보여주는 개략적인 단면도이다.

[0037] 도 3a 및 도 4a에 도시된 바와 같이, 기판(101) 상에 베퍼층(102)을 형성하고, 상기 베퍼층(102) 상에 구동 박막트랜지스터(Td)를 형성한다.

[0038] 상기 베퍼층(102)은 산화실리콘 또는 질화실리콘과 같은 무기절연물질로 이루어질 수 있고 생략 가능하다.

[0039] 상기 구동 박막트랜지스터(Td)는 반도체층(110), 게이트 전극(112), 소스 전극(122) 및 드레인 전극(124)을 포함한다.

[0040] 상기 반도체층(110)은 상기 베퍼층(102) 상에 형성된다. 예를 들어, 상기 반도체층(110)은 산화물 반도체 물질로 이루어지거나 다결정 실리콘으로 이루어질 수 있다.

[0041] 상기 반도체층(110)이 산화물 반도체 물질로 이루어질 경우 상기 반도체층(110) 하부에는 차광패턴(도시하지 않음)이 형성될 수 있으며, 차광패턴은 상기 반도체층(110)으로 빛이 입사되는 것을 방지하여 상기 반도체층(110)이 빛에 의해 열화되는 것을 방지한다. 이와 달리, 상기 반도체층(110)은 다결정 실리콘으로 이루어질 수도 있으며, 이 경우 상기 반도체층(110)의 양 가장자리에 불순물이 도핑되어 있을 수 있다.

[0042] 상기 반도체층(110) 상부에는 절연물질로 이루어진 게이트 절연막(112)이 형성된다. 상기 게이트 절연막(112)은 산화 실리콘 또는 질화 실리콘과 같은 무기절연물질로 이루어질 수 있다.

[0043] 상기 게이트 절연막(112) 상에는 금속과 같은 도전성 물질로 이루어진 게이트 전극(114)이 상기 반도체층(110)의 중앙에 대응하여 형성된다. 상기 게이트 전극(114)은 스위칭 박막트랜지스터(미도시)에 연결된다.

[0044] 상기 게이트 절연막(112)이 상기 게이트 전극(114)과 동일한 형상인 것이 보여지고 있다. 이와 달리, 상기 게이트 절연막(112)은 상기 기판(101)의 전면에 형성될 수도 있다.

[0045] 상기 게이트 전극(114) 상부에는 절연물질로 이루어진 층간 절연막(120)이 상기 기판(101) 전면에 형성된다. 상기 층간 절연막(120)은 산화 실리콘이나 질화 실리콘과 같은 무기 절연물질로 형성되거나, 벤조사이클로부텐(benzocyclobutene)이나 포토 아크릴(photo-acryl)과 같은 유기 절연물질로 형성될 수 있다.

[0046] 상기 층간 절연막(120)은 상기 반도체층(110)의 양측을 노출하는 제 1 및 제 2 콘택홀(120a, 120b)을 갖는다. 상기 제 1 및 제 2 콘택홀(120a, 120b)은 상기 게이트 전극(114)의 양측에 상기 게이트 전극(114)과 이격되어 위치한다.

[0047] 상기 층간 절연막(120) 상에는 금속과 같은 도전성 물질로 이루어지는 소스 전극(122)과 드레인 전극(124)이 형성된다.

[0048] 상기 소스 전극(122)과 상기 드레인 전극(124)은 상기 게이트 전극(114)을 중심으로 이격되어 위치하며, 각각 상기 제 1 및 제 2 콘택홀(120a, 120b)을 통해 상기 반도체층(110)의 양측과 접촉한다. 상기 소스 전극(122)은

상기 파워 배선(미도시)에 연결된다.

[0049] 상기 반도체층(110)과, 상기 게이트 전극(114), 상기 소스 전극(122), 상기 드레인 전극(124)은 상기 구동 박막 트랜지스터(Td)를 이루며, 상기 구동 박막트랜지스터(Td)는 상기 반도체층(110)의 상부에 상기 게이트 전극(114), 상기 소스 전극(122) 및 상기 드레인 전극(124)이 위치하는 코플라나(coplanar) 구조를 가진다.

[0050] 이와 달리, 구동 박막트랜지스터(Td)는 반도체층의 하부에 게이트 전극이 위치하고 반도체층의 상부에 소스 전극과 드레인 전극이 위치하는 역 스탠더드(inverted staggered) 구조를 가질 수 있다. 이 경우, 반도체층은 비정질 실리콘으로 이루어질 수 있다.

[0051] 한편, 상기 스위칭 박막트랜지스터(미도시)는 상기 구동 박막트랜지스터(Td)와 실질적으로 동일한 구조를 가질 수 있다. 또한, 상기 스위칭 박막트랜지스터에 연결되어 화소영역을 정의하는 게이트 배선 및 데이터 배선이 형성된다.

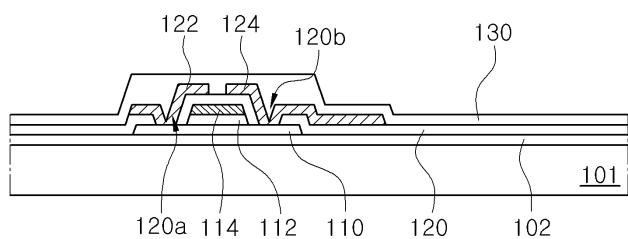

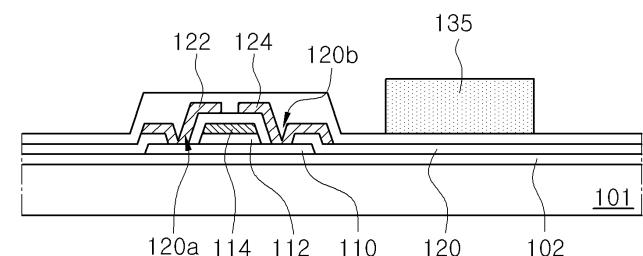

[0052] 다음, 도 3b 및 도 4b에 도시된 바와 같이, 상기 구동 박막트랜지스터(Td)를 덮으며 보호층(130)이 형성된다. 상기 보호층(130)은 산화실리콘 또는 질화실리콘과 같은 무기질연물질로 이루어질 수 있다.

[0053] 상기 보호층(130) 상에는 화소영역의 표시영역에 대응하여 컬러필터층(135)이 형성된다. 상기 컬러필터층(135)은 적색, 녹색 및 청색 컬러필터 패턴을 포함할 수 있다.

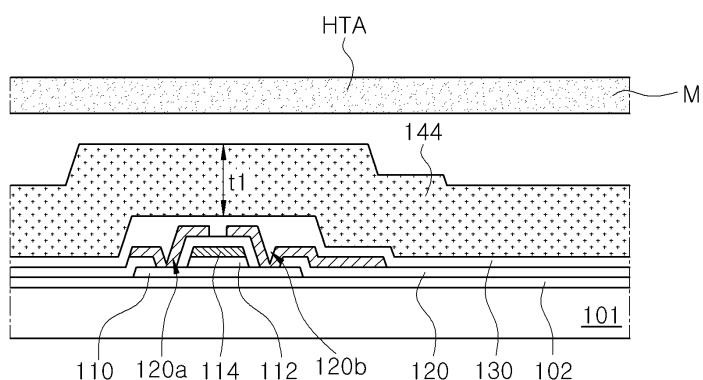

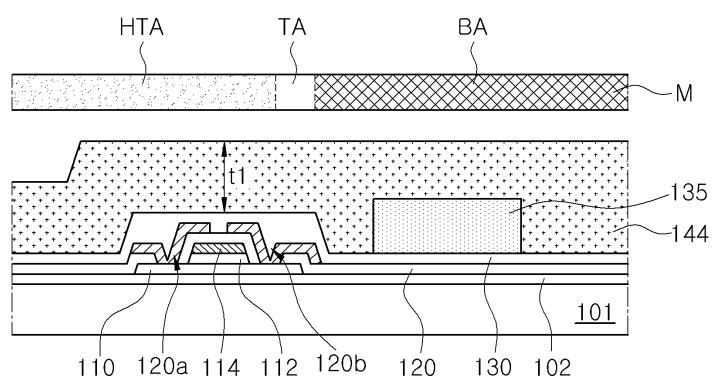

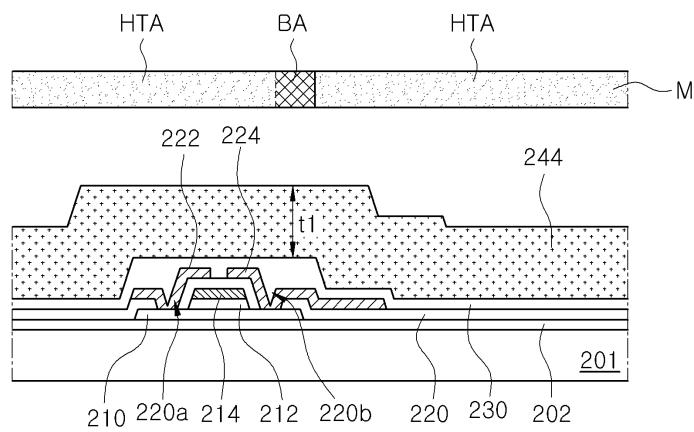

[0054] 다음, 도 3c 및 도 4c에 도시된 바와 같이, 상기 보호층(130) 및 상기 컬러필터층(135)을 덮고 제 1 두께(t1)를 갖는 유기질연물질층(144)이 기판(101)의 전면에 형성된다.

[0055] 상기 유기질연물질층(144)은 감광 특성(photo-sensitive property)을 갖는 물질, 예를 들어 포토-아크릴(photo-acryl) 또는 폴리아미드(polyimide)와 같은 유기질연물질로 이루어질 수 있다.

[0056] 이후, 상기 유기질연물질층(144) 상부에 투과영역(TA), 반투과영역(HTA) 및 차단영역(BA)을 갖는 노광 마스크(M)가 배치된다.

[0057] 상기 투과영역(TA)은 상기 드레인 전극(124)의 일부(드레인 콘택홀(도 4f의 142) 형성 영역)에 대응되며, 상기 차단영역(BA)은 상기 컬러필터층(135)이 형성된 표시영역에 대응되고, 상기 반투과영역(HTA)은 상기 구동 박막 트랜지스터(Td)이 형성된 영역 및 리던던시 리페어 패턴(도 3h의 152)이 형성될 영역에 대응된다.

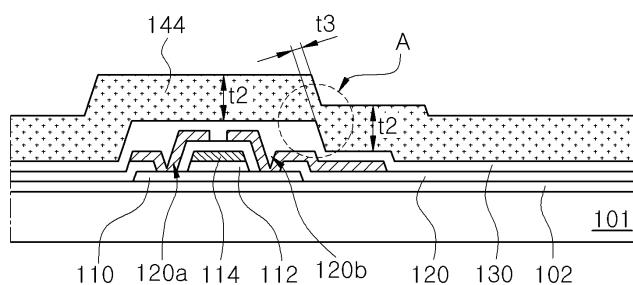

[0058] 상기 노광 마스크(M)를 통한 노광 공정 및 상기 유기질연물질층(144)에 대한 식각 공정을 진행함으로써, 도 3d 및 도 4d에 도시된 바와 같이, 드레인 콘택홀(도 4f의 142)에 대응하여 상기 유기질연물질층(144)은 모두 제거되고 상기 구동 박막트랜지스터(Td)이 형성된 영역 및 리던던시 리페어 패턴(152)이 형성될 영역에서 상기 유기 질연물질층(144)은 상기 제 1 두께(t1)보다 작은 제 2 두께(t2)를 갖게 된다.

[0059] 이때, 상기 반도체층(110)의 끝에서 하부 구성(층간 절연막(120) 및 드레인 전극(124))의 단차에 의해, 상기 보호층(130)은 상기 드레인 전극(124)의 연장 부분에서 경사진 측면(A)을 갖게 된다. 이에 따라, 상기 유기질연물질층(144)은 경사진 측면(A)에서 상기 제 2 두께(t2)보다 작은 제 3 두께(t3)를 갖는다.

[0060] 한편, 상기 컬러필터층(135)을 덮는 상기 유기질연물질층(144)은 제 1 두께(t1)를 유지한다.

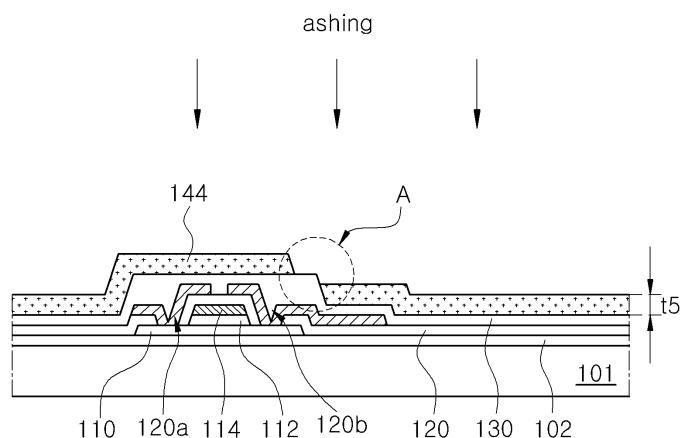

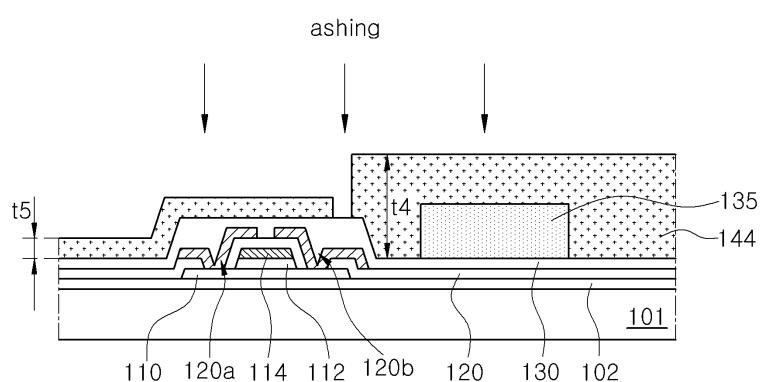

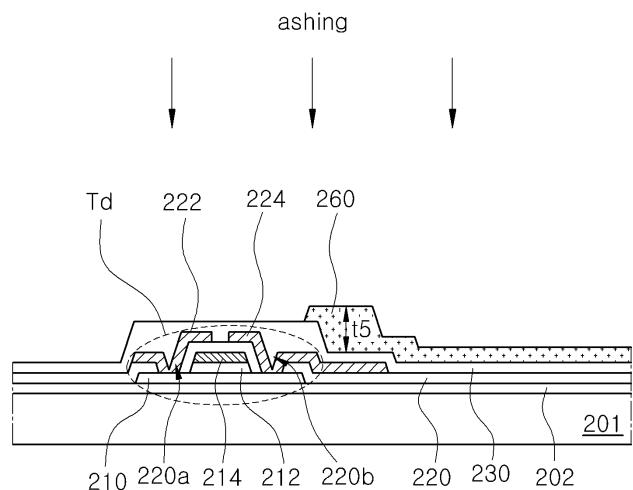

[0061] 다음, 도 3e 및 도 4e에 도시된 바와 같이, 상기 유기질연물질층(144)에 대하여 제 1 애싱(ashing) 공정이 진행되며, 상기 유기질연물질층(144)의 두께가 전체적으로 감소한다. (t1->t4, t2->t5) 드레인 콘택홀(도 4f의 142)이 형성될 영역에 유기질연물질이 남게 되면 보호층(130)의 식각 공정이 불충분하게 진행되기 때문에, 제 1 애싱 공정을 진행하여 드레인 콘택홀(142) 형성 영역의 잔류 유기질연물질을 완전히 제거하여 보호층(130)을 노출시킨다.

[0062] 이때, 제 2 두께(t2)보다 작은 제 3 두께(t3)를 갖는 "A" 영역의 유기질연물질층(144)이 모두 제거되어 "A" 영역에서 보호층(130)이 노출된다.

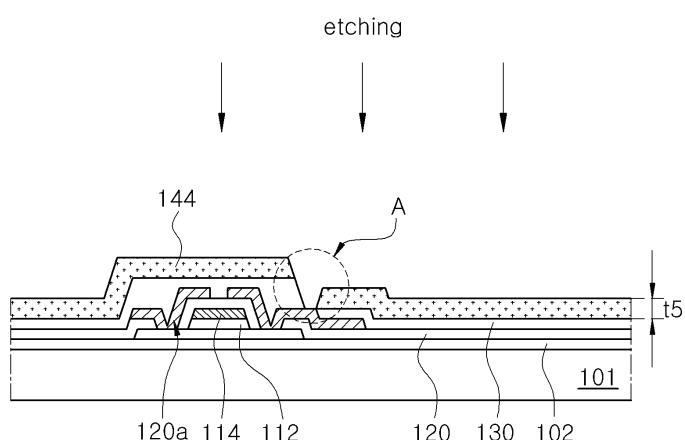

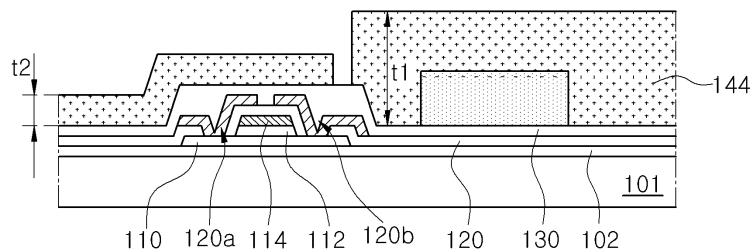

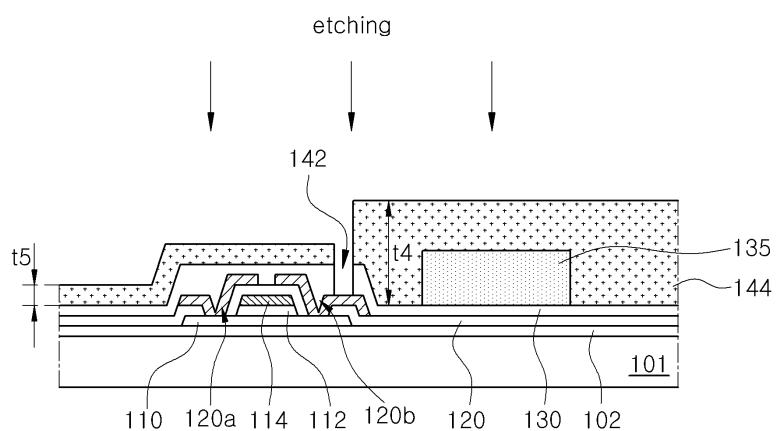

[0063] 다음, 도 3f 및 도 4f에 도시된 바와 같이, 상기 유기질연물질층(144)을 식각 마스크로 하여 상기 보호층(130)에 대한 식각 공정을 진행함으로써, 상기 드레인 전극(124)을 노출하는 드레인 콘택홀(142)을 형성한다. 예를 들어, BOE(buffered oxide etch) 방식의 습식 식각일 수 있다.

[0064] 이때, 상기 "A" 영역에서도 노출된 보호층(130)이 제거되어 드레인 전극(124)의 연장 부분이 노출된다.

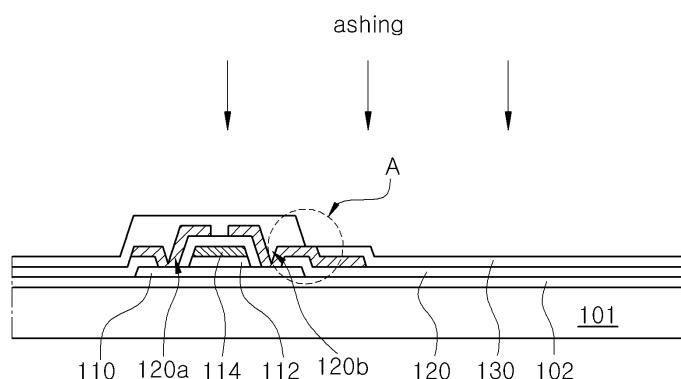

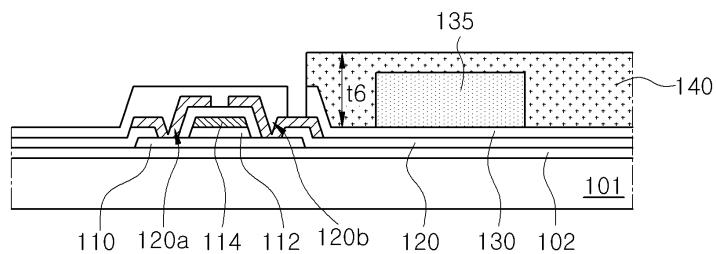

[0065] 다음, 도 3g 및 도 4g에 도시된 바와 같이, 제 2 애싱 공정을 진행함으로써, 제 5 두께(도 3f 및 도 4f의 t5)를 갖는 유기질연물질층(도 3f 및 도 4f의 144)이 제거되고 제 4 두께(도 4f의 t4)를 갖는 유기질연물질층(도 4f의

144)은 그 두께가 감소하여 상기 제 4 두께(t4)보다 작은 제 6 두께(t6)를 갖는 평탄화층(140)을 이룬다.

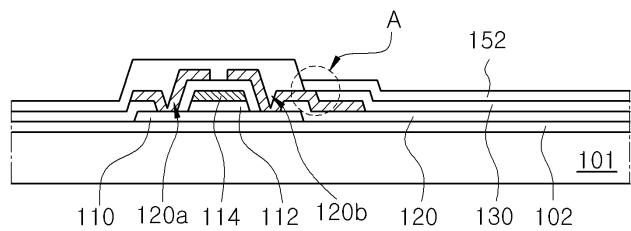

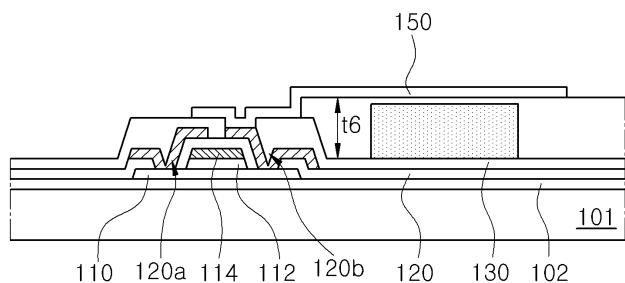

[0066] 다음, 도 3h 및 도 4h에 도시된 바와 같이, 투명 도전 물질층(미도시)을 형성하고 마스크 공정을 진행함으로써, 상기 드레인 콘택홀(142)을 통해 상기 드레인 전극(124)에 연결되는 제 1 전극(150)을 상기 보호층(130) 상에 형성한다. 동시에, 인접한 화소영역의 상기 제 1 전극(150)으로부터 연장되어 상기 드레인 전극(124)과 중첩하는 리던던시 리페어 패턴(152)을 형성한다.

[0067] 다음, 상기 제 1 전극(150)의 가장자리를 덮는 뱅크층(미도시)과, 상기 제 1 전극(150)의 중앙부에 적층되는 유기발광층(미도시) 및 제 2 전극(미도시)이 형성된다. 상기 제 1 전극(150), 상기 유기발광층 및 상기 제 2 전극은 유기발광다이오드(미도시)를 구성한다.

[0068] 상기 유기발광다이오드는 백색을 발광하고 상기 컬러필터층(135)에 의해 풀컬러 영상이 구현되며, 상기 유기발광다이오드로부터의 빛은 상기 기판(101)을 통하여 영상이 표시된다.

[0069] 또한, 컬러필터층(135)을 덮는 평탄화층(140)이 형성되더라도, 상기 평탄화층(140)과 보호층(130)을 하나의 마스크 공정에 의해 패터닝하기 때문에 제조 공정이 증가하지 않는다.

[0070] 또한, 화소영역에 불량이 발생한 경우, 웨딩(welding) 공정을 진행하여 상기 리던던시 리페어 패턴(152)과 상기 드레인 전극(124)을 연결시킴으로써 표시 불량을 해결할 수 있다.

[0071] 그런데, 전술한 바와 같이, "A" 영역에서 보호층(130)이 식각되어 드레인 전극(124)의 일부가 노출되기 때문에, 상기 리던던시 리페어 패턴(152)은 상기 드레인 전극(124)과 접촉하게 된다. 즉, 상기 리더던시 리페어 패턴(152)과 상기 드레인 전극(124) 사이에 전기적 쇼트의 문제가 발생한다.

[0072] -제 2 실시예-

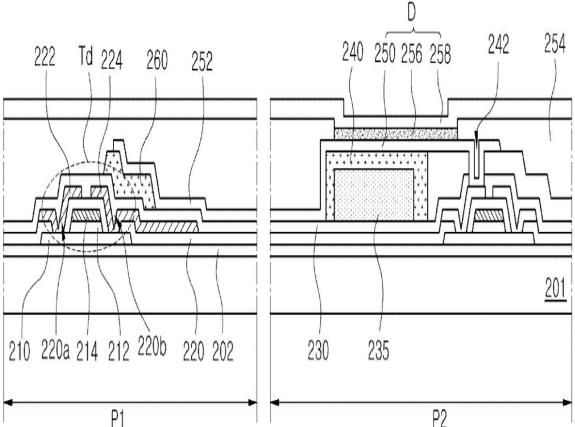

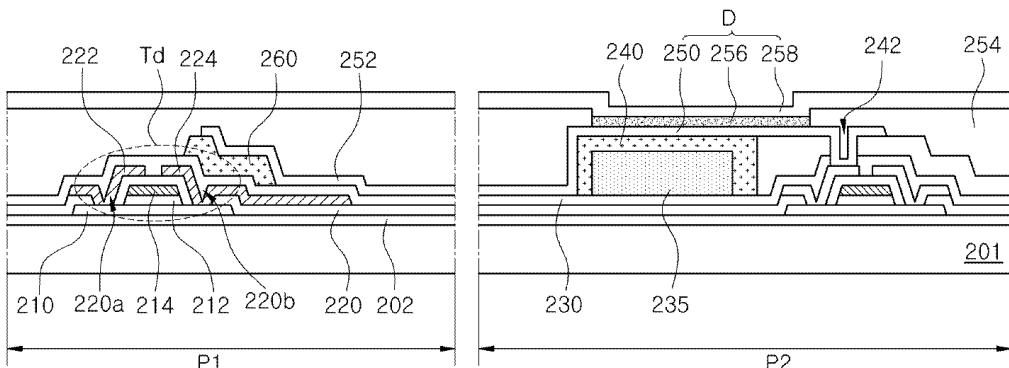

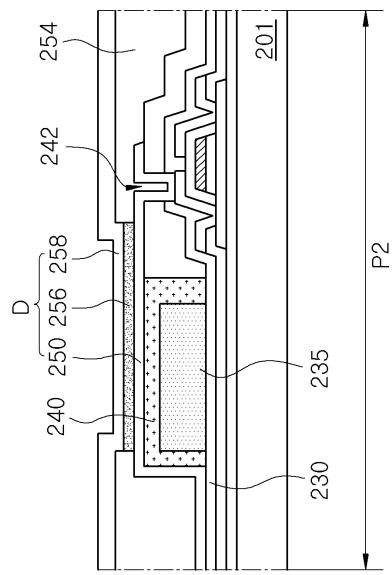

[0073] 도 5는 본 발명의 제 2 실시예에 따른 유기발광표시장치의 개략적인 단면도이다.

[0074] 도 5에 도시된 바와 같이, 본 발명의 제 2 실시예에 따른 유기발광표시장치는 인접한 제 1 및 제 2 화소영역(P1, P2)에 대응하여 기판(201) 상에 형성된 구동 박막트랜지스터(Td)와, 상기 구동 박막트랜지스터(Td)를 덮는 보호층(230)과, 상기 구동 박막트랜지스터(Td)의 일부에 대응하여 상기 보호층(230) 상에 형성된 돌출 패턴(260)과, 상기 구동 박막트랜지스터(Td)에 연결되는 제 1 전극(250)과, 제 2 화소영역(P2)의 제 1 전극(250)으로부터 연장되어 제 1 화소영역(P1)의 드레인 전극(224)과 중첩하고 그 끝이 상기 돌출 패턴(260) 상에 위치하는 리던던시 리페어 패턴(252)과, 상기 제 1 전극(250) 상에 적층되는 유기발광층(256) 및 제 2 전극(258)을 포함한다.

[0075] 또한, 상기 제 1 및 제 2 화소영역(P1, P2) 내의 표시영역에 대응하여 상기 보호층(230) 상에는 컬러필터층(235)이 형성되고, 상기 컬러필터층(235)을 덮는 평탄화층(240)이 형성될 수 있다.

[0076] 상기 기판(201) 상에는 베퍼층(202)이 형성되고, 상기 베퍼층(202) 상에 구동 박막트랜지스터(Td)가 형성된다.

[0077] 상기 베퍼층(202)은 산화실리콘 또는 질화실리콘과 같은 무기절연물질로 이루어질 수 있고 생략 가능하다.

[0078] 상기 구동 박막트랜지스터(Td)는 반도체층(210), 게이트 전극(212), 소스 전극(222) 및 드레인 전극(224)을 포함한다.

[0079] 상기 반도체층(210)은 상기 베퍼층(202) 상에 형성된다. 예를 들어, 상기 반도체층(210)은 산화물 반도체 물질로 이루어지거나 다결정 실리콘으로 이루어질 수 있다.

[0080] 상기 반도체층(210) 상부에는 절연물질로 이루어진 게이트 절연막(212)이 형성된다. 상기 게이트 절연막(212)은 산화 실리콘 또는 질화 실리콘과 같은 무기절연물질로 이루어질 수 있다.

[0081] 상기 게이트 절연막(212) 상에는 금속과 같은 도전성 물질로 이루어진 게이트 전극(214)이 상기 반도체층(210)의 중앙에 대응하여 형성된다. 상기 게이트 전극(214)은 스위칭 박막트랜지스터(미도시)에 연결된다.

[0082] 상기 게이트 절연막(212)이 상기 게이트 전극(214)과 동일한 형상인 것이 보여지고 있다. 이와 달리, 상기 게이트 절연막(212)은 상기 기판(201)의 전면에 형성될 수도 있다.

[0083] 상기 게이트 전극(214) 상부에는 절연물질로 이루어진 층간 절연막(220)이 상기 기판(201) 전면에 형성된다. 상기 층간 절연막(220)은 산화 실리콘이나 질화 실리콘과 같은 무기 절연물질로 형성되거나, 벤조사이클로부텐(benzocyclobutene)이나 포토 아크릴(photo-acryl)과 같은 유기 절연물질로 형성될 수 있다.

- [0084] 상기 충간 절연막(220)은 상기 반도체층(210)의 양측을 노출하는 제 1 및 제 2 콘택홀(220a, 220b)을 갖는다. 상기 제 1 및 제 2 콘택홀(220a, 220b)은 상기 게이트 전극(214)의 양측에 상기 게이트 전극(214)과 이격되어 위치한다.

- [0085] 상기 충간 절연막(220) 상에는 금속과 같은 도전성 물질로 이루어지는 소스 전극(222)과 드레인 전극(224)이 형성된다.

- [0086] 상기 소스 전극(222)과 상기 드레인 전극(224)은 상기 게이트 전극(214)을 중심으로 이격되어 위치하며, 각각 상기 제 1 및 제 2 콘택홀(220a, 220b)을 통해 상기 반도체층(210)의 양측과 접촉한다. 상기 소스 전극(222)은 상기 파워 배선(미도시)에 연결된다.

- [0087] 한편, 상기 스위칭 박막트랜지스터(미도시)는 상기 구동 박막트랜지스터(Td)와 실질적으로 동일한 구조를 가질 수 있다. 또한, 상기 스위칭 박막트랜지스터에 연결되어 화소영역을 정의하는 게이트 배선 및 데이터 배선이 형성된다.

- [0088] 상기 구동 박막트랜지스터(Td)를 덮으며 보호층(130)이 형성된다. 상기 보호층(230)은 산화실리콘 또는 질화실리콘과 같은 무기절연물질로 이루어질 수 있다.

- [0089] 상기 보호층(230) 상에는 화소영역의 표시영역에 대응하여 컬러필터층(235)이 형성된다. 상기 컬러필터층(235)은 적색, 녹색 및 청색 컬러필터 패턴을 포함할 수 있다.

- [0090] 또한, 상기 컬러필터층(235)에 대응하여 평탄화층(240)이 형성되고, 상기 제 1 화소영역(P1)의 상기 드레인 전극(224) 일부에 대응하여 돌출 패턴(260)이 형성된다. 상기 돌출 패턴(260)은 상기 드레인 전극(224)과 상기 보호층(230)의 단차부에 대응하여 위치한다. 상기 돌출 패턴(260)의 평면 형상은 다양하게 변경될 수 있다. 예를 들어, 사각형, 오각형 또는 마름모 형상일 수 있다.

- [0091] 상기 평탄화층(240)과 상기 돌출 패턴(260) 각각은 포토 아크릴 또는 폴리아이미드와 같은 유기절연물질로 이루어질 수 있다.

- [0092] 본 발명의 제 2 실시예에 따른 유기발광표시장치에서는, 상기 드레인 전극(224)의 단차부 상부로 상기 보호층(230) 상에 돌출 패턴(260)이 형성됨으로써, 상기 평탄화층(240)에 대한 애싱 공정과 드레인 콘택홀 형성을 위한 상기 보호층(230)에 대한 식각 공정에서, 상기 드레인 전극(224)의 원하지 않는 부분이 노출되는 것이 방지된다.

- [0093] 상기 평탄화층(240) 상에는 제 1 전극(250)이 형성된다. 상기 제 1 전극(250)은 상기 보호층(230)에 형성되는 드레인 콘택홀(242)을 통해 상기 드레인 전극(224)에 연결된다.

- [0094] 상기 제 1 전극(250)은 일함수 값이 비교적 높은 물질로 이루어져 양극(anode) 역할을 한다. 예를 들어, 상기 제 1 전극(250)은 인듐-틴-옥사이드(indium-tin-oxide, ITO) 또는 인듐-징크-옥사이드(indium-zinc-oxide, IZO)와 같은 투명 도전성 물질로 이루어질 수 있다.

- [0095] 또한, 상기 제 2 화소영역(P2)의 제 1 화소전극(250)은 상기 제 1 화소영역(P1)으로 연장되어 리던던시 리페어 패턴(252)을 이룬다. 즉, 상기 리던던시 리페어 패턴(252)은 상기 제 1 전극(250)과 동일물질로 이루어지고 동일층에 위치한다.

- [0096] 상기 리던던시 리페어 패턴(252)은 상기 제 1 화소영역(P1)의 드레인 전극(224)의 연장부와 중첩하며 그 끝이 상기 돌출 패턴(260) 상에 위치한다.

- [0097] 또한, 상기 제 1 전극(250)의 가장자리와 상기 구동 박막트랜지스터(Td)를 덮는 뱅크층(254)이 형성되고, 상기 제 1 전극(250)의 중앙부에는 유기발광층(256)이 형성된다. 상기 유기발광층(256)은 백색을 발광한다.

- [0098] 상기 유기발광층(256) 및 상기 뱅크층(254)을 덮으며 상기 기판(201)의 전면에 제 2 전극(258)이 형성된다. 상기 제 2 전극(258)은 비교적 일함수 값이 작은 물질로 이루어져 음극(cathode) 역할을 한다. 예를 들어, 상기 제 2 전극(258)은 알루미늄 또는 알루미늄 합금(Al:Mg)으로 이루어질 수 있다.

- [0099] 서로 마주하는 제 1 전극(250) 및 제 2 전극(258)과 이들 사이에 개재된 유기발광층(256)은 유기발광다이오드(D)를 구성하며, 상기 유기발광다이오드(D)는 백색 발광 타입니다.

- [0100] 따라서, 상기 유기발광다이오드(D)로부터의 빛은 상기 컬러필터층(235)을 통하여 상기 기판(201) 방향으로 컬러 영상이 구현된다.

- [0101] 본 발명의 제 2 실시예에 따른 유기발광표시장치에서는, 상기 리던던시 리페어 패턴(252)과 상기 제 1 화소영역(P1)의 드레인 전극(224) 간 웰딩(welding) 리페어 공정을 위해, 상기 제 1 화소영역(P1)의 드레인 전극(224) 연장부 일부에 대하여는 상기 돌출 패턴(260)이 형성되고 드레인 전극(224) 연장부의 나머지 부분에 대하여는 평탄화층(240) 및 돌출 패턴(260) 없이 리던던시 리페어 패턴(252)이 보호층(230)과 접촉하며 형성되어야 한다.

- [0102] 즉, 상기 리던던시 리페어 패턴(252)의 끝 부분은 평탄화층(240)과 동일층에 위치하는 돌출 패턴(260) 상에 위치하고 나머지 부분은 상기 돌출 패턴(260) 하부에 위치하는 보호층(230) 상에 위치한다.

- [0103] 전술한 바와 같이, 본 발명의 제 2 실시예에 따른 유기발광표시장치에서는, 상기 돌출 패턴(260)에 의해 상기 평탄화층(240)에 대한 애싱 공정과 드레인 콘택홀 형성을 위한 상기 보호층(230)에 대한 식각 공정에서 상기 드레인 전극(224)의 원하지 않는 부분이 노출되는 것이 방지되므로, 상기 리던던시 리페어 패턴(252)과 상기 제 1 화소영역(P1)의 드레인 전극(224) 간 전기적 쇼트를 방지할 수 있다.

- [0104] 도 6a 내지 도 6h는 본 발명의 제 2 실시예에 따른 유기발광표시장치에서 리던던시 리페어 패턴 형성 영역에 대한 제조 공정을 보여주는 개략적인 단면도이다.

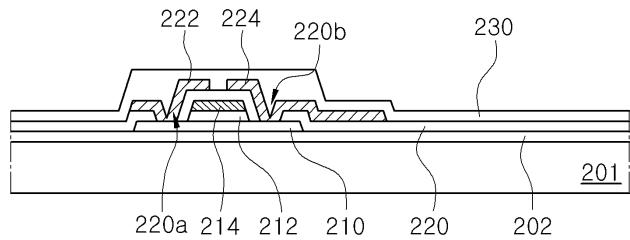

- [0105] 도 6a에 도시된 바와 같이, 기판(201) 상에 베퍼층(202)을 형성하고, 상기 베퍼층(202) 상에 구동 박막트랜지스터(Td)를 형성한다. 상기 베퍼층(202)이 생략된 경우, 상기 구동 박막트랜지스터(Td)는 상기 기판(201) 상에 형성된다.

- [0106] 상기 구동 박막트랜지스터(Td)는 반도체층(210), 게이트 전극(214), 소스 전극(222) 및 드레인 전극(224)을 포함한다. 그 구체적 제조 공정은 도 3a 및 도 4a를 통해 설명되었으므로, 생략한다.

- [0107] 다음, 도 6b에 도시된 바와 같이, 상기 구동 박막트랜지스터(Td)를 덮으며 보호층(230)이 형성된다. 상기 보호층(230)은 산화실리콘 또는 질화실리콘과 같은 무기절연물질로 이루어질 수 있다.

- [0108] 상기 보호층(230) 상에는 화소영역의 표시영역에 대응하여 컬러필터층(도 5의 235)이 형성된다. 상기 컬러필터층(235)은 적색, 녹색 및 청색 컬러필터 패턴을 포함할 수 있다.

- [0109] 다음, 도 6c에 도시된 바와 같이, 상기 보호층(230) 및 상기 컬러필터층(235)을 덮고 제 1 두께(t1)를 갖는 유기절연물질층(244)이 기판(201)의 전면에 형성된다.

- [0110] 상기 유기절연물질층(244)은 감광 특성(photo-sensitive property)을 갖는 물질, 예를 들어 포토-아크릴(photo-acryl) 또는 폴리이미드(polyimide)와 같은 유기절연물질로 이루어질 수 있다.

- [0111] 이후, 상기 유기절연물질층(244) 상부에 투과영역(도 4c의 TA), 반투과영역(HTA) 및 차단영역(BA)을 갖는 노광마스크(M)가 배치된다.

- [0112] 상기 투과영역(TA)은 상기 드레인 전극(224)의 일부(드레인 콘택홀(도 4f의 142) 형성 영역)에 대응되며, 상기 차단영역(BA)은 상기 컬러필터층(235)이 형성된 표시영역 및 돌출 패턴(도 5의 260)이 형성될 영역에 대응되고, 상기 반투과영역(HTA)은 상기 구동 박막트랜지스터(Td)이 형성된 영역 및 리던던시 리페어 패턴(도 5의 252)이 형성될 영역에 대응된다.

- [0113] 즉,

- [0114] 상기 차단영역(BA)은 상기 드레인 전극(224)의 제 1 부분(돌출 패턴 형성 영역)에 대응되고, 상기 반투과영역(HTA)은 상기 드레인 전극(224)의 제 2 부분(리던던시 리페어 패턴 형성 영역)에 대응되며, 상기 투과영역(TA)은 상기 드레인 전극(224)의 제 3 부분(드레인 콘택홀 형성 영역)에 대응된다.

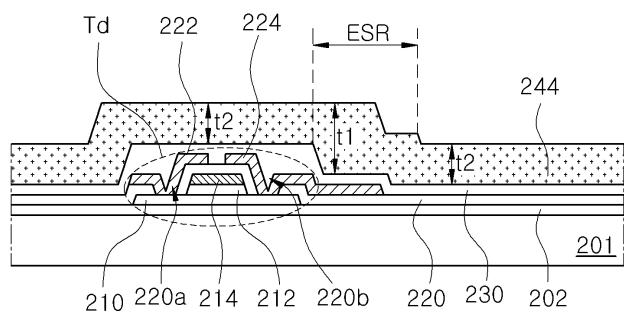

- [0115] 상기 노광 마스크(M)를 통한 노광 공정 및 상기 유기절연물질층(244)에 대한 식각 공정을 진행함으로써, 도 6d에 도시된 바와 같이, 드레인 콘택홀(도 4f의 142)에 대응하여 상기 유기절연물질층(244)은 모두 제거되고 상기 구동 박막트랜지스터(Td)이 형성된 영역 및 리던던시 리페어 패턴(252)이 형성될 영역에서 상기 유기절연물질층(244)은 상기 제 1 두께(t1)보다 작은 제 2 두께(t2)를 갖게 된다. 한편, 상기 돌출 패턴(260)이 형성될 영역과 상기 컬러필터층(235)에 대응하는 유기절연물질층(244)은 제 1 두께(t1)를 유지한다.

- [0116] 다시 말해, 상기 드레인 전극(224)의 일부에 대응하여 상기 보호층(230)의 식각 방지 영역(etch-stopper region, ESR)이 정의되고, 상기 식각 방지 영역(ESR)에서 상기 유기절연물질층(244)은 그 두께가 유지된다.

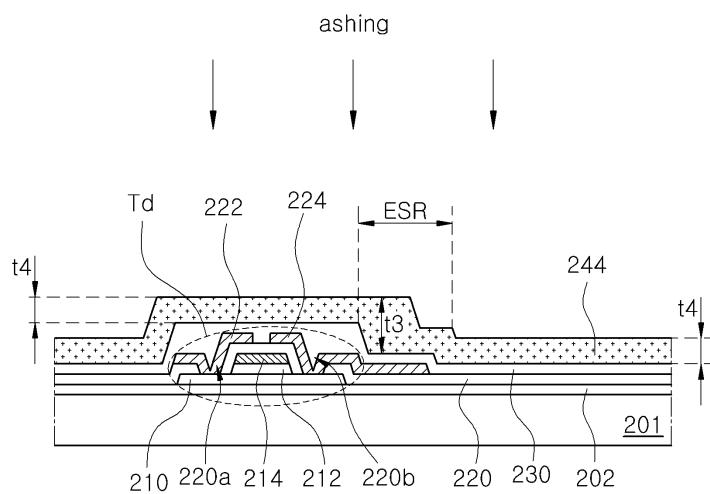

- [0117] 다음, 도 6e에 도시된 바와 같이, 상기 유기절연물질층(244)에 대하여 제 1 애싱(ashing) 공정이 진행되며, 상기 유기절연물질층(244)의 두께가 전체적으로 감소한다. ( $t1 \rightarrow t3$ ,  $t2 \rightarrow t4$ ) 드레인 콘택홀(도 4f의 142)이 형성

될 영역에 유기절연물질이 남게 되면 보호층(230)의 식각 공정이 불충분하게 진행되기 때문에, 제 1 애싱 공정을 진행하여 드레인 콘택홀(142) 형성 영역의 잔류 유기절연물질을 완전히 제거하여 보호층(230)을 노출시킨다.

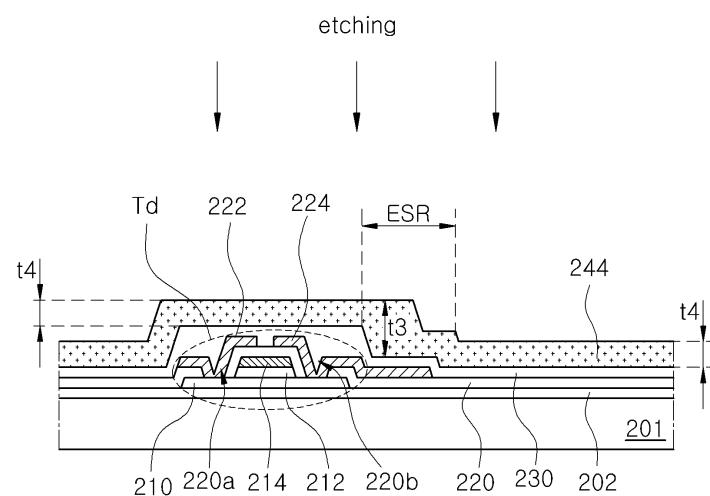

[0118] 다음, 도 6f에 도시된 바와 같이, 상기 유기절연물질층(244)을 식각 마스크로 하여 상기 보호층(230)에 대한 식각 공정을 진행함으로써, 상기 드레인 전극(224)을 노출하는 드레인 콘택홀(도 4f의 142)을 형성한다.

[0119] 본 발명의 제 1 실시예에서는, 상기 식각 공정에서 드레인 전극(124)의 연장부 일부가 노출되었으나 (도 3f), 본 발명의 제 2 실시예에서는 제 3 두께를 갖는 유기절연물질층(244)에 의해 보호층(230)의 식각이 방지되어 원하지 않는 영역에서 드레인 전극(224)의 노출이 방지된다.

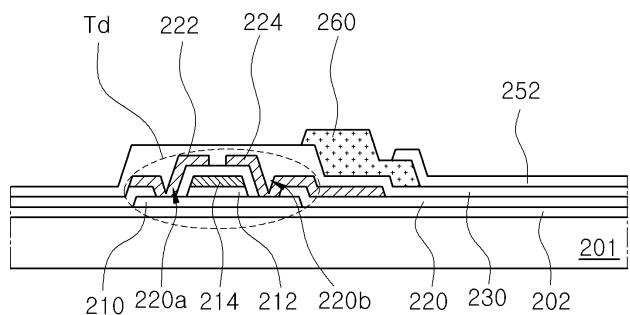

[0120] 다음, 도 6g에 도시된 바와 같이, 제 2 애싱 공정을 진행함으로써, 제 4 두께(도 6f의 t4)를 갖는 유기절연물질층(도 6f의 244)이 제거되고 제 3 두께(도 6f의 t3)를 갖는 유기절연물질층(도 6f의 244)은 그 두께가 감소하여 상기 제 3 두께(t3)보다 작은 제 5 두께(t5)를 갖는 평탄화층(도 5의 240)과 돌출 패턴(260)을 이룬다.

[0121] 다음, 도 6h에 도시된 바와 같이, 투명 도전 물질층(미도시)을 형성하고 마스크 공정을 진행함으로써, 상기 드레인 콘택홀(도 5의 242)을 통해 상기 드레인 전극(224)에 연결되는 제 1 전극(250)을 상기 보호층(230) 및/또는 상기 평탄화층(240) 상에 형성한다. 동시에, 상기 제 2 화소영역(P2)의 제 1 전극(250)으로부터 연장되어 상기 제 1 화소영역(P1)의 드레인 전극(224)과 중첩하는 리던던시 리페어 패턴(252)을 형성한다.

[0122] 상기 리던던시 리페어 패턴(252)의 끝 부분은 평탄화층(240)과 동일층에 위치하는 돌출 패턴(260) 상에 위치하고 나머지 부분은 상기 돌출 패턴(260) 하부에 위치하는 보호층(230) 상에 위치한다.

[0123] 다음, 상기 제 1 전극(250)의 가장자리와 구동 박막트랜지스터(Td)를 덮는 뱅크층(도 5의 254)과, 상기 제 1 전극(250) 상에 적층되는 유기발광층(도 5의 256) 및 제 2 전극(도 5의 258)이 형성된다.

[0124] 본 발명에서는 컬러필터층(235)에 의한 단차를 보상하기 위한 평탄화층(240)과 구동 박막트랜지스터(Td)를 덮는 보호층(230)이 하나의 마스크 공정에 의해 패터닝되므로, 제조 공정 증가가 방지된다.

[0125] 또한, 드레인 전극(224)의 일부에 대응하여 돌출 패턴(260)을 형성함으로써, 하나의 마스크 공정에 의해 리던던시 리페어 패턴(252)과 드레인 전극(224) 사이에 발생될 수 있는 전기적 쇼트 문제가 방지된다.

[0126] 상기에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술분야의 통상의 기술자는 하기의 특허청구범위에 기재된 본 발명의 기술적 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

### 부호의 설명

[0127] 101, 201: 기판 110, 210: 반도체층

112, 212: 게이트 절연막 114, 214: 게이트 전극

120, 220: 충간 절연막 122, 222: 소스 전극

124, 224: 드레인 전극 130, 230: 보호층

135, 235: 컬러필터층 140, 240: 평탄화층

150: 제 1 전극 152, 252: 리던던시 리페어 패턴

254: 뱅크층 256: 유기발광층

258: 제 2 전극 260: 돌출 패턴

Td: 구동 박막트랜지스터 D: 유기발광다이오드

## 도면

## 도면1

## 도면2

도면3a

도면3b

도면3c

도면3d

## 도면3e

## 도면3f

## 도면3g

## 도면3h

## 도면4a

## 도면4b

## 도면4c

## 도면4d

## 도면4e

## 도면4f

도면4g

도면4h

도면5

도면6a

도면6b

도면6c

도면6d

## 도면6e

## 도면6f

## 도면6g

## 도면6h

|                |                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : OLED显示器及其制造方法                                                                                  |         |            |

| 公开(公告)号        | <a href="#">KR1020170127177A</a>                                                                    | 公开(公告)日 | 2017-11-21 |

| 申请号            | KR1020160057459                                                                                     | 申请日     | 2016-05-11 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                            |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                           |         |            |

| [标]发明人         | LEE SEOK HYUN<br>이석현<br>KANG IM KUK<br>강임국<br>PARK SANG MOO<br>박상무                                  |         |            |

| 发明人            | 이석현<br>강임국<br>박상무                                                                                   |         |            |

| IPC分类号         | H01L27/32 H01L27/12                                                                                 |         |            |

| CPC分类号         | H01L27/3262 H01L27/3276 H01L27/3258 H01L27/322 H01L27/3223 H01L27/1288 H01L2251/568<br>H01L2227/323 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                           |         |            |

## 摘要(译)

他的摘要目前正在准备中。更新的KPA将于2017年12月10日之后提供。

\*本标题 ( 54 ) 和代表图显示为申请人提交的。