(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0140291

(43) 공개일자 2014년12월09일

(51) 국제특허분류(Int. Cl.)

*G09G 3/30* (2006.01)

(21) 출원번호 10-2013-0060933

(22) 출원일자 2013년05월29일

심사청구일자 없음

(71) 출원인

네오뷰코오롱 주식회사

충남 홍성군 은하면 천광로 856-14,

(72) 발명자

전성곤

대구광역시 동구 송라로28길 28 (신암동, 71신암

아파트) 2-1

(74) 대리인

황이남

전체 청구항 수 : 총 6 항

(54) 발명의 명칭 표시장치 및 표시방법

### (57) 요 약

본 발명은 발광소자로 유기전계 발광소자를 이용하는 표시장치에 관한 것으로, 표시소자는 n행 m열( $m, n$ 은 각각 자연수)의 복수의 화소회로( $Px(i, j)$ )를 구비하며, 상기 복수의 화소회로는 행 방향으로 서로 인접하는 홀수 행 화소회로( $Pxodd(i, j)$ )와 짝수 행 화소회로( $Pxeven(i, j)$ )로 이루어지는 한 쌍의 화소회로를 단위로 하여, 상기 한 쌍의 화소회로 각각에 행 선택신호를 인가하는 게이트 라인( $Lgi$ )을 공유하고, 상기 홀수 행 화소회로에는 홀수 데이터 라인( $Ldjodd$ )을 통해서 각 열 단위로 제조신호( $Vdata$ )가 인가되고, 상기 짝수 행 화소회로에는 짝수 데이터 라인( $Ldjeven$ )을 통해서 각 열 단위로 제조신호가 인가된다.

대 표 도 - 도4

## 특허청구의 범위

### 청구항 1

$n$ 행  $m$ 열( $m, n$ 은 각각 자연수)의 복수의 화소회로를 구비하는 표시장치로,

상기 복수의 화소회로는 행 방향으로 서로 인접하는 홀수 행 화소회로와 짝수 행 화소회로로 이루어지는 한 쌍의 화소회로를 단위로 하여, 상기 한 쌍의 화소회로 각각에 행 선택신호를 인가하는 게이트 라인을 공유하고,

상기 홀수 행 화소회로에는 홀수 데이터 라인을 통해서 각 열 단위로 계조신호가 인가되고, 상기 짝수 행 화소회로에는 짝수 데이터 라인을 통해서 각 열 단위로 계조신호가 인가되는 표시장치.

### 청구항 2

$n$ 행  $m$ 열( $m, n$ 은 각각 자연수)의 복수의 화소회로를 구비하는 표시장치로,

행 방향으로 서로 인접하는 홀수 행 화소회로와 짝수 행 화소회로로 이루어지는 한 쌍의 화소회로를 단위로 한 복수 쌍의 화소회로와,

상기 한 쌍의 화소회로 단위로 행 선택신호를 인가하는 게이트 라인과,

각 열 단위로 상기 홀수 행 화소회로에 계조신호를 인가하는 홀수 데이터 라인과,

각 열 단위로 상기 짝수 행 화소회로에 계조신호를 인가하는 짝수 데이터 라인을 구비하는 표시장치.

### 청구항 3

청구항 1 또는 2에 있어서,

상기 복수의 화소회로는 각각,

상기 게이트 라인에 인가되는 행 선택신호에 의해 구동하여 화상 데이터의 계조를 나타내는 계조신호를 커패시터의 일단에 인가하는 스위칭 트랜지스터와,

상기 스위칭 트랜지스터에 의해 구동하여 상기 홀수 데이터 라인 또는 상기 짝수 데이터 라인에 인가되는 계조신호에 의거한 전류를 유기EL소자에 공급하는 구동 트랜지스터와,

상기 화상 데이터의 계조를 나타내는 계조신호를 충전하는 커패시터와,

상기 전류의 전류량에 대응하는 휘도로 발광하는 유기EL소자를 포함하는 표시장치.

### 청구항 4

청구항 3에 있어서,

상기 스위칭 트랜지스터는 게이트가 상기 게이트 라인에 접속되고, 소스와 드레인은 상기 홀수 데이터 라인 및 상기 짝수 데이터 라인 중 어느 하나와 상기 구동 트랜지스터의 게이트 및 상기 커패시터의 일단 사이에서 제 1 전류통로를 형성하며,

상기 구동 트랜지스터는 게이트가 상기 제 1 전류통로의 일단 및 상기 커패시터의 일단에 접속되고, 소스와 드레인은 상기 커패시터의 타단 및 애노드 전원 단자와 유기EL소자 사이에서 제 2 전류통로를 형성하는 표시장치.

### 청구항 5

$n$ 행  $m$ 열( $m, n$ 은 각각 자연수)의 복수의 화소회로를 구비하는 표시장치의 표시방법으로,

행 방향으로 서로 인접하는 홀수 행 화소회로와 짝수 행 화소회로로 이루어지는 한 쌍의 화소회로를 단위로 하는 복수 쌍의 화소회로에 순차 행 선택신호를 인가하는 행 선택신호 인가단계와,

선택된 상기 홀수 행 화소회로에 각 열 단위로 계조신호를 인가하는 제 1 계조신호 인가단계와,

선택된 상기 짝수 행 화소회로에 각 열 단위로 계조신호를 인가하는 제 2 계조신호 인가단계를 포함하고,

상기 행 선택신호 인가단계에서 상기 한 쌍의 화소회로는 하나의 게이트 라인을 통해서 상기 행 선택신호가 인가되는 표시방법.

## 청구항 6

청구항 5에 있어서,

상기 제 1 계조신호 인가단계는 상기 행 선택신호의 전체 펄스기간의 전반 1/2 펄스기간이고,

상기 제 2 계조신호 인가단계는 상기 행 선택신호의 전체 펄스기간의 후반 1/2 펄스기간인 표시방법.

## 명세서

### 기술 분야

[0001] 본 발명은 표시장치 및 표시방법에 관한 것으로, 특히 발광소자로 유기전계 발광소자를 사용하는 유기전계발광 표시장치 및 표시방법에 관한 것이다.

### 배경기술

[0002] 유기전계발광소자(이하 「유기EL소자」라 한다)는 유리 등의 투명한 기판상에 형성된 양극과 음극으로 이루어지는 한 쌍의 전극 사이에 유기화합물을 포함하는 유기발광 층을 삽입 형성한 구조를 가지며, 상기 한 쌍의 전극으로부터 유기발광 층에 정공(hole) 및 전자(electron)를 주입하여 재결합시킴으로써 여기자(exciton)를 생성시켜서, 이 여기자의 활성이 상실될 때의 광의 방출을 이용하여 표시 등을 하는 발광소자이다.

[0003] 이 유기EL 발광소자를 발광소자로서 이용하는 유기전계발광 표시장치(이하 간단하게 「유기발광 표시장치」라고 표기하는 경우도 있다)는 경량, 박형이면서 다른 표시장치에 비해 휘도 특성 및 시야각 특성이 우수하여 차세대 평판 표시장치로서 주목받고 있다.

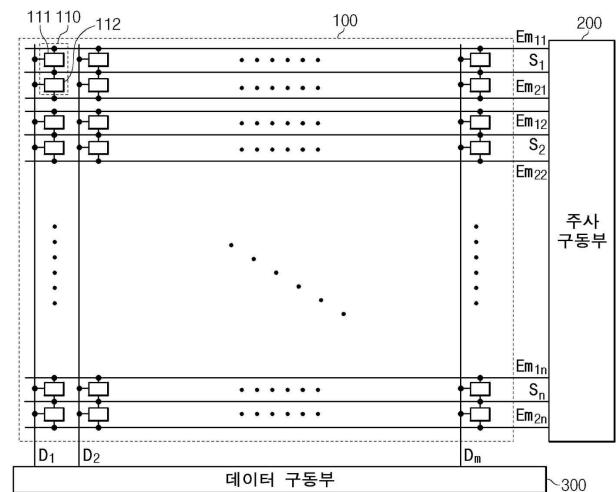

[0004] 도 1은 종래의 일반적인 유기발광 표시장치의 구동부의 구성을 나타내는 도면이다.

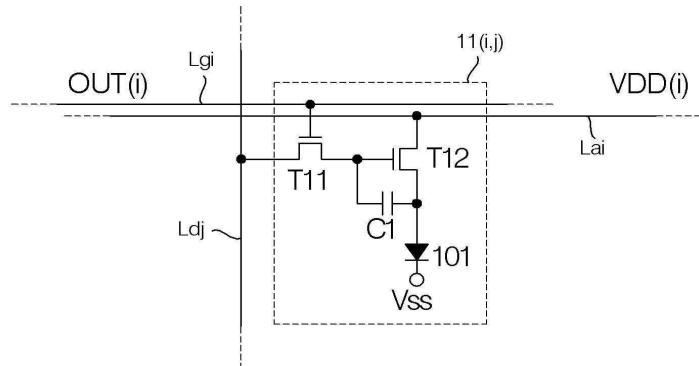

[0005] 도 1 (a)에 도시하는 것과 같이, 종래의 유기발광 표시장치(1)는  $n$ 행,  $m$ 열의 복수의 화소회로( $11(i, j)$ ) ( $i=1 \sim n, j=1 \sim m$ ,  $n$ 은 각각 자연수)와 게이트 드라이버(행 선택 드라이버)(12)와 데이터 드라이버(14)와 컨트롤러(15) 및 미 도시의 애노드 드라이버를 구비한다.

[0006] 또, 화소회로( $11(i, j)$ )는 화상의 각 화소에 대응하는 것으로, 도 1 (b)에 나타내는 것과 같이 각 화소회로( $11(i, j)$ )는 유기EL소자(101)와 2개의 트랜지스터(T11, T12) 및 커패시터(C1)를 구비한다.

[0007] 컨트롤러(15)의 제어 하에 게이트 드라이버(12)가 High 레벨의 출력신호(OUT[k])를 순차 게이트 라인(Lg1, Lg2, ..., Lgn)에 출력하면 화소회로( $11(1, 1) \sim 11(1, m)$ ,  $11(2, 1) \sim 11(2, m)$ , ...,  $11(n, 1) \sim 11(n, m)$ )가 순차 선택되고, 데이터 드라이버(14)는 공급된 화소 데이터에 의한 계조 신호를 각각 데이터 라인(Ld1-Ldm)에 인가하여, 선택된 화소회로( $11(1, 1) \sim 11(1, m)$ ,  $11(2, 1) \sim 11(2, m)$ , ...,  $11(n, 1) \sim 11(n, m)$ )의 각각의 커패시터(C1)에 계조 신호를 기입한다.

[0008] 이상과 같은 방법으로 기입이 완료하면 컨트롤러(15)는 미 도시의 애노드 드라이버를 제어하여, 애노드 드라이버가 High 레벨의 애노드 전압신호(VDD(1)~VDD(n))를 애노드 라인(La(1)~La(n))에 출력하고, 이에 의해 화소회로( $11(i, j)$ )의 트랜지스터(T12)는 각 커패시터(C1)가 보유한 전압을 게이트 전압으로 하여, 이 게이트 전압(Vgs)에 대응하는 전류를 유기EL소자(101)에 공급함으로써 발광한다.

[0009] 그러나 도 1의 유기발광 표시장치(1)에서는 각 행 단위당 1개의 게이트 라인과 각 열 단위당 1개의 데이터 라인을 구비하며, 각 화소회로는 게이트 라인과 데이터 라인이 교차하는 위치에 형성된다.

[0010] 따라서 예를 들어 유기발광 표시장치가 VGA급( $640 \times 480$ )의 해상도를 갖는 표시장치인 경우에는 640개의 게이트 라인이 필요하고, HD급( $1280 \times 720$ )의 해상도를 갖는 표시장치인 경우에는 1280개의 게이트 라인이 필요하다.

[0011] 한편, 도 1에서는 설명의 편의를 위해 컨트롤러를 비롯한 각 드라이버가 복수의 화소회로로 이루어지는 표시부의 좌우 및 상단에 각각 배치되어 있는 것으로 도시되어 있지 않으나, 실제 표시장치에서는 통상 직사각형 형상의 외측 프레임(이 부분을 베젤(bezel)이라 한다)의 중앙부에 표시부가 배치되고, 컨트롤러를 비롯한 각종 드라이버는 각각 IC 등의 형태로 사각형상의 베젤의 하부에 배치되며, 게이트 라인 및 각 애노드 라인 등은 상기 IC로부터 인출되어 좌우 측 베젤을 통해서 각각 행 방향으로 연장 배열되고, 데이터 라인은 상기 IC로부터 표시부

의 수직방향으로 연장 배열된다.

[0012] 따라서 게이트 라인을 비롯한 각종 라인의 개수가 많아질수록 표시장치 베젤의 폭은 넓어질 수밖에 없고, 또, 게이트 라인과 데이터 라인이 교차하는 교차점에서 발생하는 기생 정전용량에 의해 이른바 RC 지연 및 전압강하의 발생도 커지므로 게이트 라인을 비롯한 각종 라인을 구성하는 배선의 수는 가능한 한 적은 것이 좋으며, IC 와 각 화소회로 사이를 연결하는 각 라인의 개수를 줄이기 위해서는 1개의 게이트 라인으로 2개 행 이상의 화소를 구동하는 방법, 즉, 2개 행의 화소가 1개의 게이트 라인을 공유하는 방법, 또는, 2개 열의 화소가 1개의 데이터 라인을 공유하는 방법 등을 생각할 수 있다.

[0013] 상기 방법 중 2개 열의 화소가 1개의 데이터 라인을 공유하는 방법으로 특허문헌 1에 기재된 표시장치가 공지되어 있다.

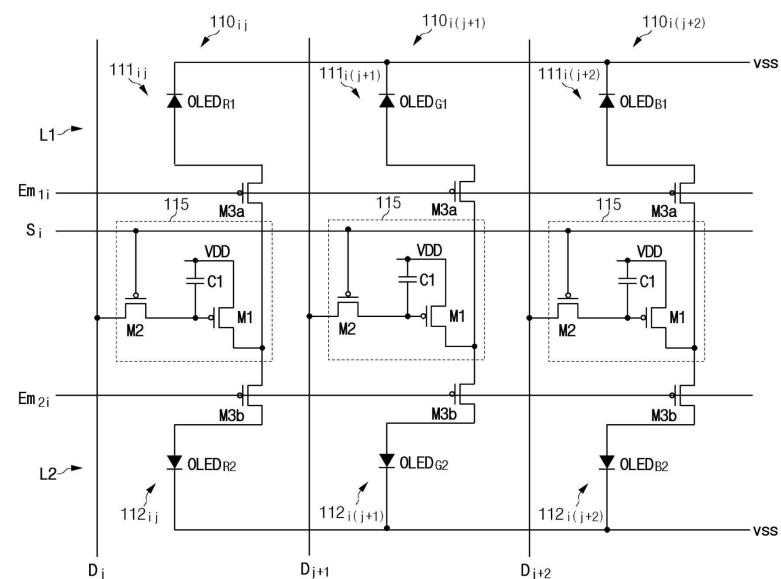

[0014] 도 2는 특허문헌 1에 기재된 종래의 유기발광 표시장치의 개략적인 구성을 나타내는 회로도이다.

[0015] 도 2 (a)에 나타내는 것과 같이, 특허문헌 1의 유기발광 표시장치는 복수의 선택 게이트 라인(S1-Sn)과 복수의 발광 게이트 라인(Em11-Em1n, Em21-Em2n)과 복수의 데이터 라인(D1-Dm) 및 복수의 단위 화소(110)를 포함하고, 각 단위 화소(110)는 열 방향으로 배열된 2개의 서브 픽셀(111, 112)로 이루어진다.

[0016] 또, 도 2 (b)에 나타내는 것과 같이, 하나의 단위 화소에 형성된 2개의 서브 픽셀(111, 112)은 하나의 선택 게이트 라인과 화소 구동부(115)를 공유하며, 화소 구동부(115)는 구동 트랜지스터(M1)와 스위칭 트랜지스터(M2) 및 커패시터(C1)를 포함한다.

[0017] 또, 스캔 드라이버(200)는 하나의 필드를 2개의 서브필드로 분할하여, 각 서브필드에서 복수의 선택 게이트 라인(S1-Sn)에 선택신호를 순차적으로 인가하는 동시에, 하나의 서브필드에서 복수의 발광 게이트 라인(Em11-Em1n)에 발광신호를 순차적으로 인가하고, 다음 서브필드에서 복수의 발광 게이트 라인(Em21-Em2n)에 발광신호를 순차적으로 인가한다.

[0018] 그리고 데이터 드라이버(300)는 데이터 라인(D1-Dn)에 데이터신호를 인가하며, 하나의 서브필드에서는 서브 픽셀(111)에 대응하는 데이터신호를 인가하고 다음 서브필드에서는 서브 픽셀(112)에 대응하는 데이터신호를 인가한다.

[0019] 또, 특허문헌 2 내지 5에도 특허문헌 1과 마찬가지로 복수의 선택 게이트 라인(S1-Sn)과 복수의 발광 게이트 라인(Em11-Em1n, Em21-Em2n)과 복수의 데이터 라인(D1-Dm) 및 복수의 단위 화소(110)를 포함하고, 각 단위 화소(110)는 열 방향으로 배열된 2개의 서브 픽셀(111, 112)로 이루어지며, 각 단위 화소에 형성된 2개의 서브 픽셀은 하나의 선택 게이트 라인과 화소 구동부(115)를 공유하는 표시장치가 기재되어 있다.

## 선행기술문헌

### 특허문헌

[0020] (특허문헌 0001) 특허문헌 1 : 공개특허 2005-0000759호 공보

(특허문헌 0002) 특허문헌 2 : 공개특허 2004-0037266호 공보

(특허문헌 0003) 특허문헌 3 : 공개특허 2004-0037288호 공보

(특허문헌 0004) 특허문헌 4 : 공개특허 2004-0038260호 공보

(특허문헌 0005) 특허문헌 5 : 공개특허 2004-0038261호 공보

## 발명의 내용

### 해결하려는 과제

[0021] 상기 특허문헌 1 내지 5의 기술은 각 단위 화소에 형성된 2개의 서브 픽셀이 하나의 선택 게이트 라인과 화소 구동부를 공유하므로, 1개의 데이터 라인(Dj)과 1개의 선택 게이트 라인(Si) 및 2개의 트랜지스터와 1개의 커패시터(C1)로 이루어지는 화소 구동부(115)가 2개의 서브 픽셀(111, 112)을 공유하게 되며, 이에 의해 데이터 라인(Dj)과 선택 게이트 라인(Si) 및 화소 구동부(115)를 구성하는 트랜지스터 및 커패시터의 개수를 감소시킬 수

있는 것으로도 보인다.

[0022] 그러나 상기 특허문헌 1 내지 5의 표시장치는 각 단위 화소(110)를 열 방향으로 배열된 2개의 서브 픽셀(111, 112)로 구분하여 구동하고 있으므로, 선택 게이트 라인(S1-Sn) 이외에도 별도로 2개의 발광 게이트 라인(Em11-Em1n) 및 발광 게이트 라인(Em21-Em2n)을 복수 필요로 하고, 또, 2개의 발광 게이트 라인(Em11-Em1n) 및 발광 게이트 라인(Em21-Em2n)에 연결된 2개의 트랜지스터(M3a 및 M3b)를 더 필요로 하므로, 결과적으로 단위 화소당 트랜지스터의 개수는 종래와 동일하고, 게이트 라인(게이트 라인)의 수는 오히려 증가하게 되므로, 오히려 각 화소에 신호를 공급하는 신호라인의 개수는 증가한다.

[0023] 본 발명은 상기 과제를 감안하여 이루어진 것으로, 표시장치의 게이트 라인의 개수를 감소시킴으로써 게이트 라인의 연장 배열에 필요한 베젤의 폭을 감소시키는 동시에, 게이트 라인에서 발생하는 RC 지연 및 전압강하를 감소시키며, 나아가서는 게이트 라인의 감소에 따른 개구율의 향상과 아울러 패널의 해상도도 증가시키는 목적으로 한다.

### 과제의 해결 수단

[0024] 상기 과제를 해결하기 위한 본 발명의 표시장치는,  $n$ 행  $m$ 열( $m, n$ 은 각각 자연수)의 복수의 화소회로를 구비하는 표시장치로, 상기 복수의 화소회로는 행 방향으로 서로 인접하는 홀수 행 화소회로와 짝수 행 화소회로로 이루어지는 한 쌍의 화소회로를 단위로 하여, 상기 한 쌍의 화소회로 각각에 행 선택신호를 인가하는 게이트 라인을 공유하고, 상기 홀수 행 화소회로에는 홀수 데이터 라인을 통해서 각 열 단위로 계조신호가 인가되고, 상기 짝수 행 화소회로에는 짝수 데이터 라인을 통해서 각 열 단위로 계조신호가 인가되는 표시장치이다.

[0025] 또, 본 발명의 표시장치는,  $n$ 행  $m$ 열( $m, n$ 은 각각 자연수)의 복수의 화소회로를 구비하는 표시장치로, 행 방향으로 서로 인접하는 홀수 행 화소회로와 짝수 행 화소회로로 이루어지는 한 쌍의 화소회로를 단위로 한 복수 쌍의 화소회로와, 상기 한 쌍의 화소회로 단위로 행 선택신호를 인가하는 게이트 라인과, 각 열 단위로 상기 홀수 행 화소회로에 계조신호를 인가하는 홀수 데이터 라인과, 각 열 단위로 상기 짝수 행 화소회로에 계조신호를 인가하는 짝수 데이터 라인을 구비하는 표시장치이다.

[0026] 상기 복수의 화소회로는 각각, 상기 게이트 라인에 인가되는 행 선택신호에 의해 구동하여 화상 데이터의 계조를 나타내는 계조신호를 커패시터의 일단에 인가하는 스위칭 트랜지스터와, 상기 스위칭 트랜지스터에 의해 구동하여 상기 홀수 데이터 라인 또는 상기 짝수 데이터 라인에 인가되는 계조신호에 의거한 전류를 유기EL소자에 공급하는 구동 트랜지스터와, 상기 화상 데이터의 계조를 나타내는 계조신호를 충전하는 커패시터와, 상기 전류의 전류량에 대응하는 휘도로 발광하는 유기EL소자를 포함하도록 해도 좋다.

[0027] 상기 스위칭 트랜지스터는 게이트가 상기 게이트 라인에 접속되고, 소스와 드레인은 상기 홀수 데이터 라인 및 상기 짝수 데이터 라인 중 어느 하나와 상기 구동 트랜지스터의 게이트단자 및 상기 커패시터의 일단 사이에서 제 1 전류통로를 형성하며, 상기 구동 트랜지스터는 게이트가 상기 제 1 전류통로의 일단 및 상기 커패시터의 일단에 접속되고, 소스와 드레인은 상기 커패시터의 타단 및 애노드 전원단자와 유기EL소자 사이에서 제 2 전류통로를 형성하는 것으로 해도 좋다.

[0028] 본 발명의 표시방법은,  $n$ 행  $m$ 열( $m, n$ 은 각각 자연수)의 복수의 화소회로를 구비하는 표시장치의 표시방법으로, 행 방향으로 서로 인접하는 홀수 행 화소회로와 짝수 행 화소회로로 이루어지는 한 쌍의 화소회로를 단위로 하는 복수 쌍의 화소회로에 순차 행 선택신호를 인가하는 행 선택신호 인가단계와, 선택된 상기 홀수 행 화소회로에 각 열 단위로 계조신호를 인가하는 제 1 계조신호 인가단계와, 선택된 상기 짝수 행 화소회로에 각 열 단위로 계조신호를 인가하는 제 2 계조신호 인가단계를 포함하고, 상기 행 선택신호 인가단계에서 상기 한 쌍의 화소회로는 하나의 게이트 라인을 통해서 상기 행 선택신호가 인가되는 표시방법이다.

[0029] 상기 제 1 계조신호 인가단계는 상기 행 선택신호의 전체 펄스기간의 전반 1/2 펄스기간이고, 상기 제 2 계조신호 인가단계는 상기 행 선택신호의 전체 펄스기간의 후반 1/2 펄스기간으로 해도 좋다.

### 발명의 효과

[0030] 본 발명에 의하면 표시장치를 구성하는 복수의 화소회로를 서로 인접하는 한 쌍의 홀수 행 화소회로와 짝수 행 화소회로 단위로 구분하여, 서로 인접하는 한 쌍의 홀수 행 화소회로와 짝수 행 화소회로가 게이트 드라이버로부터 순차 인가되는 행 선택신호를 공급하는 1개의 게이트 라인을 공유하고 있으므로 종래에 비해 게이트 라인의 수를 절반(1/2)으로 감소시킬 수 있다. 따라서 게이트 라인의 수의 감소에 의해 표시장치의 베젤의 폭을 대

폭 축소시킬 수 있다.

[0031] 또, 게이트 라인의 수의 감소에 의해 게이트 라인이 표시장치 내에서 다른 신호를 공급하는 라인과 교차하는 교차점의 수가 감소되므로, 상기 교차점에서 발생하는 기생정전용량도 감소하며, 이에 의해 데이터 신호의 RC 지연(RC Delay) 및 전압강하(IR Drop)도 대폭 감소시킬 수 있다.

[0032] 또, 게이트 라인의 감소에 따라 표시장치의 개구율이 증가하며, 이에 의해 표시장치의 해상도를 증가시킬 수 있다.

### 도면의 간단한 설명

[0033] 도 1은 종래의 일반적인 유기발광 표시장치의 구동부의 구성을 나타내는 도면이다.

도 2는 종래의 유기발광 표시장치의 개략적인 구성을 나타내는 도면이다.

도 3은 본 발명의 바람직한 실시형태의 표시장치의 구동부의 구성을 나타내는 도면이다.

도 4는 도 3의 표시장치의 화소회로의 개략적인 구성을 나타내는 회로도이다.

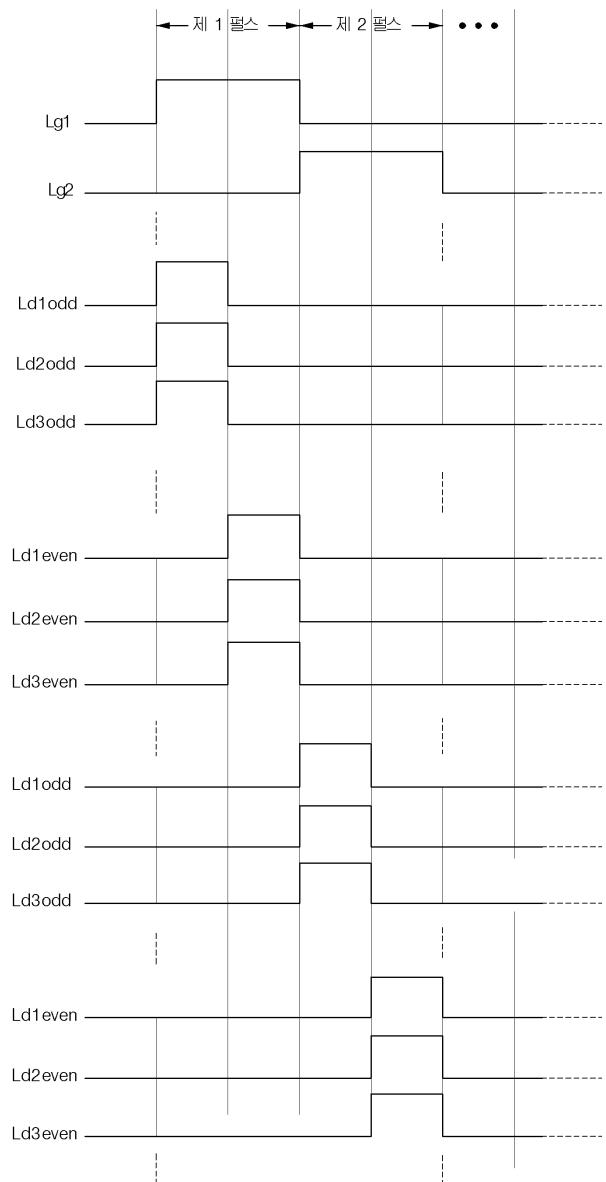

도 5는 본 발명의 바람직한 실시형태의 표시장치의 구동 타이밍을 나타내는 타이밍도이다.

### 발명을 실시하기 위한 구체적인 내용

[0034] 이하, 본 발명의 바람직한 실시형태에 대해서 도면을 참조하면서 상세하게 설명한다.

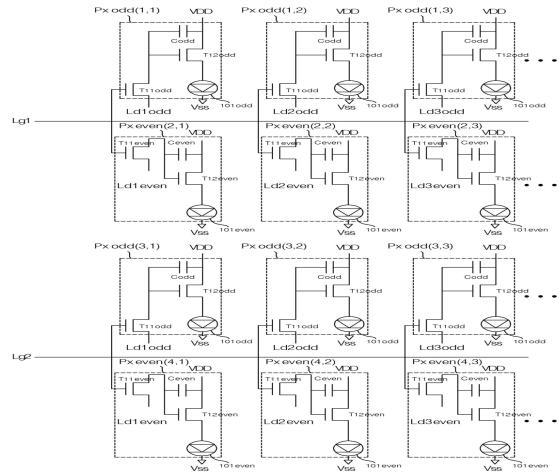

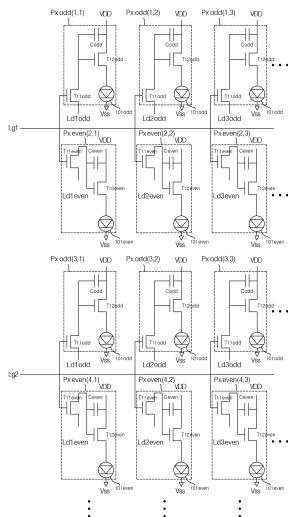

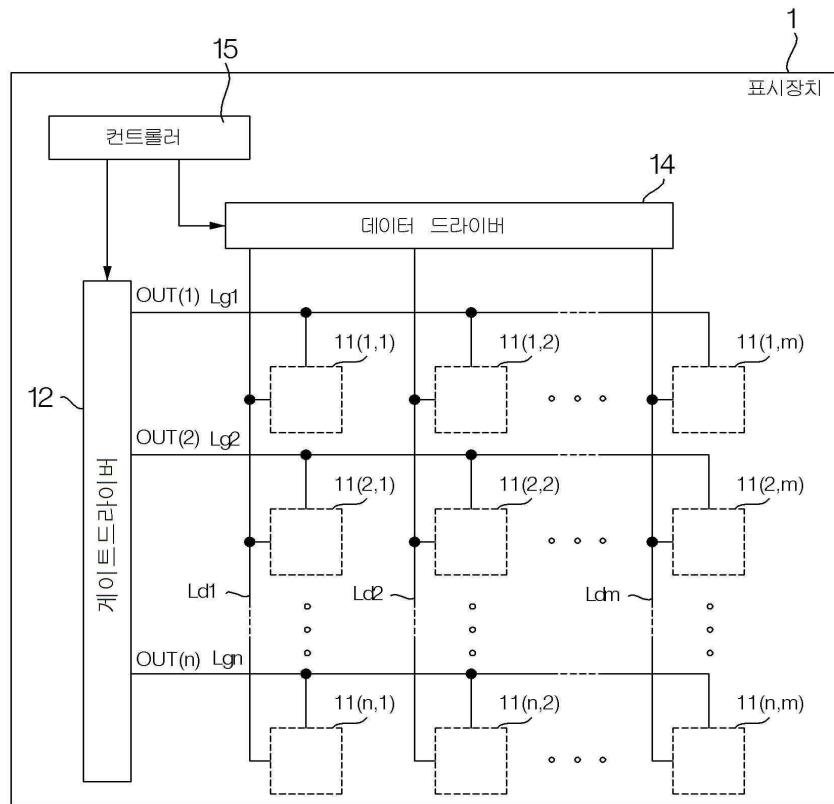

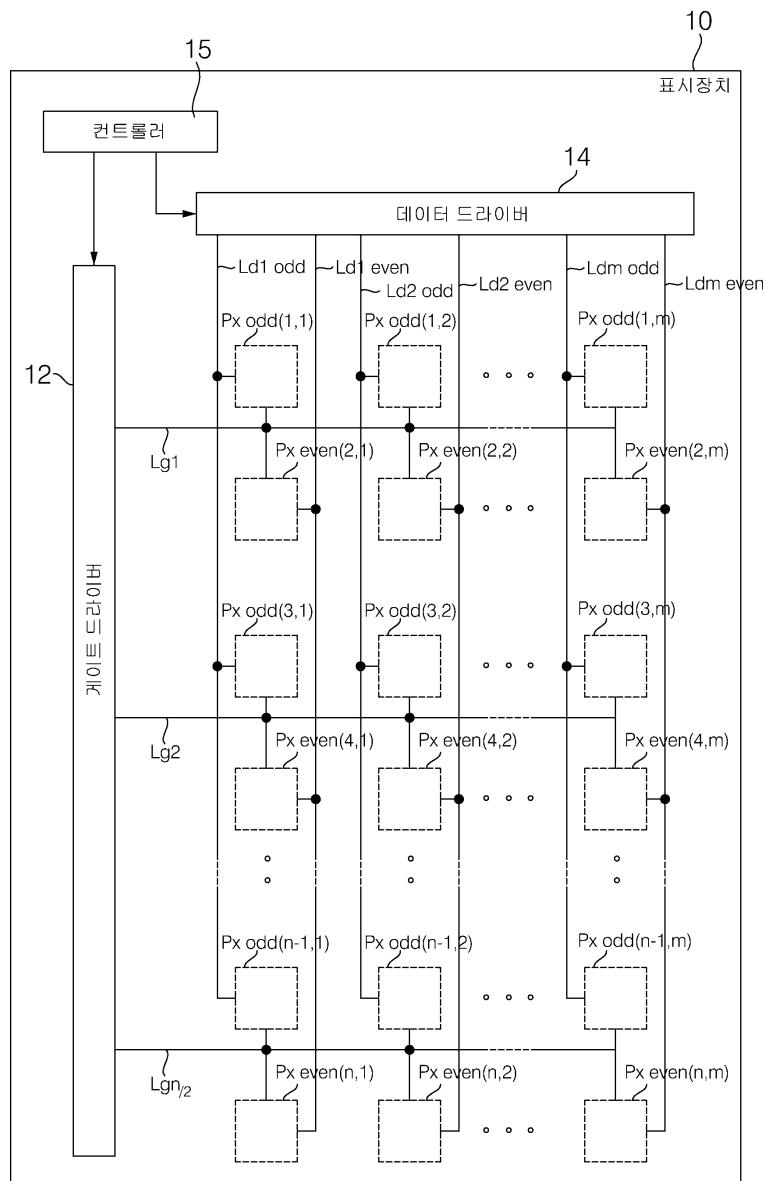

[0035] 도 3은 본 발명의 바람직한 실시형태의 표시장치의 구동부의 구성을 나타내는 도면이고, 도 4는 도 3의 표시장치의 일부 화소회로의 개략적인 구성을 나타내는 회로도이다.

[0036] 도 3에 도시하는 것과 같이, 본 실시형태의 표시장치(10)는  $n$ 행  $m$ 열( $m$ ,  $n$ 은 각각 자연수)의 복수의 화소회로( $Px(i, j)$ )( $i=1 \sim n$ ,  $j=1 \sim m$ ,  $m$ 은 각각 자연수)로 이루어지는 표시부와 게이트 드라이버(행 선택 드라이버)(12)와 데이터 드라이버(14)와 컨트롤러(15) 및 애노드 드라이버(미 도시)를 구비한다.

[0037] 본 실시형태의 표시장치(10)는 표시부를 구성하는  $n$ 행  $m$ 열의 복수의 화소회로가 서로 인접하는 홀수 행과 짝수 행의 2개 행의 화소회로로 이루어지는 한 쌍의 화소회로를 단위로 하는 복수 쌍의 화소회로로 이루어지고, 상기 한 쌍의 화소회로, 즉, 예를 들어 홀수 행 화소회로( $Pxodd(1, 1 \sim 1, m)$ )와 짝수 행 화소회로( $Pxeven(2, 1 \sim 2, m)$ )로 이루어지는 한 쌍의 화소회로가 게이트 드라이버(12)로부터 공급되는 행 선택신호를 각 화소회로에 인가하는 게이트 라인( $Lg1$ )을 공유하고 있다.

[0038] 또, 다음 쌍의 홀수 행 화소회로( $Pxodd(3, 1 \sim 3, m)$ )와 짝수 행 화소회로( $Pxeven(4, 1 \sim 4, m)$ )로 이루어지는 한 쌍의 화소회로도 게이트 드라이버(12)로부터 공급되는 행 선택신호를 각 화소회로에 인가하는 게이트 라인( $Lg2$ )을 공유하고 있다.

[0039] 동일한 방법으로, 마지막 쌍의 홀수 행 화소회로( $Pxodd(n-1, 1 \sim n-1, m)$ )와 짝수 행 화소회로( $Pxeven(n, 1 \sim n, m)$ )로 이루어지는 한 쌍의 화소회로도 게이트 드라이버(12)로부터 공급되는 행 선택신호를 각 화소회로에 인가하는 게이트 라인( $Lgn/2$ , 단  $n$ 은 짝수)을 공유하고 있다.

[0040] 또, 데이터 드라이버(14)로부터 각 화소회로( $Px(i, j)$ )에 데이터신호를 공급하는 데이터 라인을 1개 열의 화소회로( $Px(i, j)$ ) 중 홀수 행 화소회로( $Pxodd(i, j)$ )에 데이터신호를 공급하는 홀수 행 데이터 라인( $Ldjodd$ )과 짝수 행 화소회로( $Pxeven(i+1, j)$ )에 데이터신호를 공급하는 짝수 행 데이터 라인( $Ldjeven$ )으로 구분하고 있다.

[0041] 이와 같이 본 실시형태의 표시장치(10)는 1개의 게이트 라인이 2개 행의 화소회로에 공유되어 있고, 데이터 라인은 1개 열의 화소회로당 2개의 데이터 라인을 가지므로, 결과적으로 종래의 표시장치(1)에 비해 게이트 라인의 수는 절반( $1/2$ )으로 감소한 대신에 데이터 라인의 수는 2배로 증가하고 있다.

[0042] 이와 같이 한 이유는, 앞에서 설명한 것과 같이, 게이트 라인은 표시장치(10)의 하단 및 양 측면의 베젤을 통해서 화소회로의 행 방향으로 연장 배열되고, 데이터 라인은 표시장치(10)의 좌우 측면의 베젤을 통과하지 않고 하단부의 베젤로부터 직접 화소회로의 열 방향으로 연장 배열되는 표시장치에서, 본 발명의 과제인 표시장치(10)의 베젤 폭의 축소를 위해 게이트 라인의 수를 종래의 표시장치에 비해 절반으로 감소시키기 위해서이다.

[0043] 여기서, 화소회로( $Px(i, j)$ )는 화상의 각 화소에 대응하는 것이다.

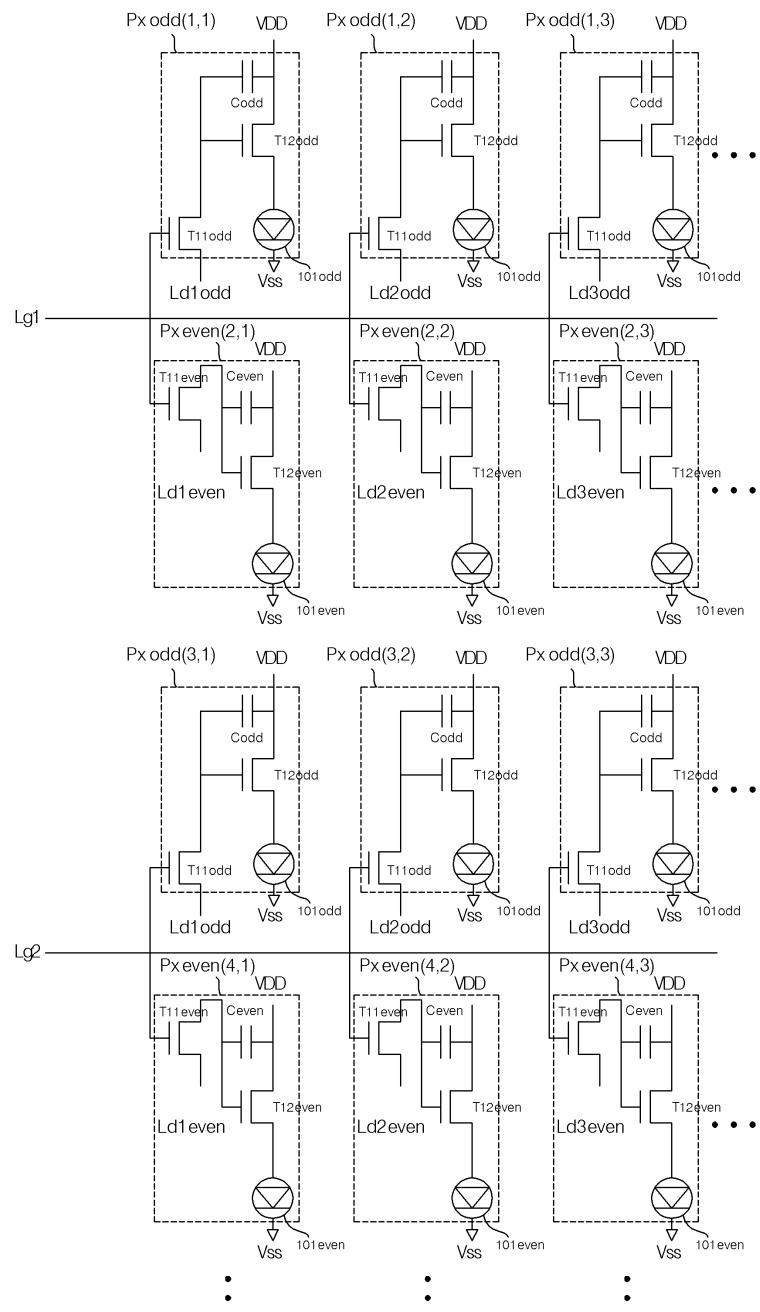

[0044] 도 4는 도 3의 표시장치의 전체 화소 중 일부 화소의 화소회로의 개략적인 구성을 나타내는 회로도이며, 도 4에

서는 설명의 편의상 도 3의  $n$ 행  $m$ 열의 복수의 화소회로 중 표시장치(10)의 좌측 상단으로부터 4행 3열의 화소회로인 화소회로  $Pxodd(1,1)$  내지  $Pxodd(1,3)$ 과  $Pxeven(2,1)$  내지  $Pxeven(2,3)$ ,  $Pxodd(3,1)$  내지  $Pxodd(3,3)$  및  $Pxeven(4,1)$  내지  $Pxeven(4,3)$ 만을 나타내고 있다. 그러나 그 외의 나머지 화소회로의 배열형태도 이와 동일한 형태이다.

또, 이하의 설명에서는 도 4의 4행 3열의 화소회로  $Pxodd(1,1)$  내지  $Pxodd(1,3)$ 과  $Pxeven(2,1)$  내지  $Pxeven(2,3)$ ,  $Pxodd(3,1)$  내지  $Pxodd(3,3)$  및  $Pxeven(4,1)$  내지  $Pxeven(4,3)$ 을 중심으로 설명하나, 그 이외의 화소회로도 상기 4행 3열의 화소회로  $Pxodd(1,1)$  내지  $Pxodd(1,3)$ 과  $Pxeven(2,1)$  내지  $Pxeven(2,3)$ ,  $Pxodd(3,1)$  내지  $Pxodd(3,3)$  및  $Pxeven(4,1)$  내지  $Pxeven(4,3)$ 과 동일한 구성을 갖는다.

도 4에 나타내는 것과 같이, 복수의 화소회로( $Px(i, j)$ )는 서로 인접하는 홀수 행과 짝수 행의 2개 행의 화소회로, 즉 홀수 행 화소회로( $Pxodd(1, 1\sim1, 3)$ )와 짝수 행 화소회로( $Pxeven(2, 1\sim2, 3)$ )로 이루어지는 한 쌍의 화소회로는 게이트 드라이버(12)로부터 인가되는 행 선택신호를 공급하는 게이트 라인( $Lg1$ )을 공유하고 있고, 또, 홀수 행 화소회로( $Pxodd(3, 1\sim3, 3)$ )와 짝수 행 화소회로( $Pxeven(4, 1\sim4, 3)$ )로 이루어지는 한 쌍의 화소회로도 게이트 드라이버(12)로부터 인가되는 행 선택신호를 공급하는 게이트 라인( $Lg2$ )을 공유하고 있다.

도 4에는 도시하고 있지 않으나, 3열째 이후의 화소회로도 홀수 행 화소회로( $Pxodd(1, 4\sim 1, m)$ )와 짝수 행 화소회로( $Pxeven(2, 4\sim 2, m)$ )로 이루어지는 한 쌍의 화소회로 단위로 각각 게이트 라인( $Lg1$ )을 공유하며, 그 다음의 한 쌍의 화소회로인 홀수 행 화소회로( $Pxodd(3, 4\sim 3, m)$ )와 짝수 행 화소회로( $Pxeven(4, 4\sim 4, m)$ )도 게이트 라인( $Lg2$ )을 공유하는 특성을 담연하다.

한편, 종래의 표시장치에서는 데이터 드라이버(14)로부터의 데이터신호를 각 화소회로에 공급하는 데이터 라인을 1열의 화소회로당 1개로 하고 있었으나, 본 실시형태의 표시장치(10)는 종래의 1열당 1개의 데이터 라인을 홀수 데이터 라인과 짝수 데이터 라인의 2개의 데이터 라인으로 분리하여, 홀수 행 화소회로( $Pxodd(i, j)$ )에는 홀수 데이터 라인( $Ldjodd$ )으로부터, 짝수 행 화소회로( $Pxeven(i, j)$ )에는 짝수 데이터 라인( $Ldjeven$ )으로부터 각각 데이터신호를 공급한다.

도 4를 이용하여 구체적으로 설명하면, 홀수 행 화소회로( $Pxodd(1,1)$  및  $Pxodd(3,1)$ )에는 홀수 데이터 라인 ( $Ld1odd$ )으로부터, 홀수 행 화소회로( $Pxodd(1,2)$  및  $Pxodd(3,2)$ )에는 홀수 데이터 라인 ( $Ld2odd$ )으로부터, 홀수 행 화소회로( $Pxodd(1,3)$  및  $Pxodd(3,3)$ )에는 홀수 데이터 라인 ( $Ld3odd$ )으로부터 각각 데이터 신호가 공급된다.

반면에, 짹수 행 화소회로( $Pxeven(2,1)$  및  $Pxeven(4,1)$ )에는 짹수 데이터 라인( $Ld1even$ )으로부터, 짹수 행 화소회로( $Pxeven(2,2)$  및  $Pxeven(4,2)$ )에는 짹수 데이터 라인( $Ld2even$ )으로부터, 짹수 행 화소회로( $Pxeven(2,3)$  및  $Pxeven(4,3)$ )에는 짹수 데이터 라인( $Ld3even$ )으로부터 각각 데이터신호가 공급된다.

도 4에는 도시하고 있지 않으나, 4행째 이후의 홀수 행 화소회로( $Pxodd((3, 5, \dots, n-1), 1)$ )도 마찬가지로 홀수 데이터 라인( $Ld1odd$ )으로부터 각각 데이터신호가 공급되고, 짝수 행 화소회로( $Pxeven((4, 6, \dots, n), 1)$ )도 마찬가지로 짝수 데이터 라인( $Ld1even$ )으로부터 각각 데이터신호가 공급된다.

이상 설명한 본 실시형태의 화소회로의 구성을 일반화하면, 복수의 화소회로 중 서로 인접하는 홀수 행 화소회로( $Pxodd((1, 1\sim 1, m), (3, 1\sim 3, m), \dots, (n-1, 1\sim n-1, m))$ )와 짝수 행 화소회로( $Pxeven((2, 1\sim 2, m), (4, 1\sim 4, m), \dots, (n, 1\sim n, m))$ )로 이루어지는 한 쌍의 화소회로는 각각 게이트 라인( $Lg1, Lg2, \dots, n/2$ )을 공유하고, 복수의 홀수 행 화소회로( $Pxodd((1, 1\sim 1, m), (3, 1\sim 3, m), \dots, (n-1, 1\sim n-1, m))$ ) 중 서로 동일한 열에 속하는 화소회로는 각각 홀수 데이터 라인( $Ld1odd, Ld2odd, \dots, Ldmodd$ )을 공유하며, 복수의 짝수 행 화소회로( $Pxeven((2, 1\sim 2, m), (4, 1\sim 4, m), \dots, (n, 1\sim n, m))$ ) 중 서로 동일한 열에 속하는 화소회로는 각각 짝수 데이터 라인( $Ld1even, Ld2even, \dots, Ldmeven$ )을 공유한다.

홀수 행 화소회로( $Px_{odd}(1, 1\sim 1, m)$ )는 각각 유기EL소자(101odd)와 2개의 트랜지스터(T11odd 및 T12odd) 및 커페시터(Codd)를 구비하고 있고, 또, 짝수 행 화소회로( $Px_{even}(2, 1\sim 2, m)$ )는 유기EL소자(101even)와 2개의 트랜지스터(T11even, T12even) 및 커페시터(Ceven)를 구비하고 있다.

여기서, 유기EL소자(101odd)와 유기EL소자(101even), 트랜지스터(T11odd, T12odd)와 트랜지스터(T11even, T12even) 및 커패시터(Codd, Ceven)는 각각 서로 동일한 구성을 갖는 유기EL소자, 트랜지스터 및 커패시터이며, 커패시터(Codd, Ceven)는 각각 트랜지스터(T12odd, T12even)의 게이트와 드레이 사이에 접속된 커패시터이다.

유기EL소자(101odd, 101even)는 화소 전극(애노드 전극)과 단수 혹은 복수의 캐리어 수송 층으로 이루어지는 유기EL 층 및 대향 전극이 수차 접촉되어 구조를 갖는 표시소자이며, 대향 전극(캐소드 전극)에는 응극 전위( $V_{ss}$ )가

인가되고 있다.

[0056] 트랜지스터(T11odd, T11even, T12odd, T12even)는 n채널형 FET(Field Effect Transistor)로 구성된 TFT이고, 각각 드레인, 소스 및 게이트를 가지며, 드레인과 소스 간에는 반도체 층이 설치되어, 드레인과 소스 간에 소정의 바이어스 전압이 인가되는 동시에 게이트에 문턱 전압보다 큰 전압이 인가된 때 반도체 층 내에 채널이 형성되며, 이 채널이 드레인-소스 간의 전류통로가 된다.

[0057] 그러나 상기 트랜지스터(T11odd, T11even, T12odd, T12even)는 n채널형 FET로 한정되는 것은 아니며, p채널형 FET로 해도 좋다. 트랜지스터(T11odd, T11even, T12odd, T12even)를 p채널형 FET로 하는 경우에는 후술하는 각 드라이버로부터 인가되는 각 신호의 레벨을 n형 FET와 반대로 하면 되며, 이는 본 발명이 속하는 분야의 기술자에게는 자명한 사항이므로 상세한 설명은 생략한다.

[0058] 홀수 행 화소회로(Pxodd(i,j))의 트랜지스터(T11odd)는 커패시터(Codd)의 일단에 화상 데이터(Data)의 계조를 나타내는 계조 신호(Vdata)를 인가하기 위한 스위칭 트랜지스터이며, 소스는 트랜지스터(T12odd)의 게이트 및 커패시터(Codd)의 일단과 접속되고, 드레인은 j번째의 홀수 데이터 라인(Ldjodd)에 접속되고, 홀수 행 화소회로(Pxodd(i,j))의 각 트랜지스터(T11odd)의 게이트는 제 i행째의 게이트 라인(Lgi)에 접속된다.

[0059] 또, 짹수 행 화소회로(Pxeven(i,j))의 트랜지스터(T11even)도 커패시터(Ceven)의 일단에 화상 데이터(Data)의 계조를 나타내는 계조 신호(Vdata)를 인가하기 위한 스위칭 트랜지스터이며, 소스는 트랜지스터(T12even)의 게이트 및 커패시터(Ceven)의 일단과 접속되고, 드레인은 j번째의 짹수 데이터 라인(Ldjeven)에 접속되며, 게이트는 홀수 행 화소회로(Pxodd(i,j))의 트랜지스터(T11even)의 게이트와 마찬가지로 제 i행째의 게이트 라인(Lgi)에 접속된다.

[0060] 즉, 서로 인접하는 홀수 행 화소회로(Pxodd(i,j))와 짹수 행 화소회로(Pxeven(i,j))는 제 i행째의 게이트 라인(Lgi)를 공유하고 있고, 데이터 라인은 서로 다른 데이터 라인인 홀수 데이터 라인(Ldjodd) 및 짹수 데이터 라인(Ldjeven)과 각각 접속된다.

[0061] 그리고 각각의 게이트 라인(Lg1, …, Lgn/2)에 High 레벨의 신호가 순차 출력되면 홀수 행 화소회로(Pxodd(i,j))와 짹수 행 화소회로(Pxeven(i,j))의 각 트랜지스터(T11odd 및 T11even)는 온 하여 홀수 데이터 라인(Ldjodd) 및 짹수 데이터 라인(Ldjeven)에 각각 입력된 계조 신호(Vdata)를 트랜지스터(T12odd 및 T12even)의 게이트 및 커패시터(Codd 및 Ceven)의 일단에 출력한다.

[0062] 트랜지스터(T12odd 및 T12even)는 계조 신호(Vdata)에 의거한 전류의 전류량을 제어하면서 홀수 행 화소회로(Pxodd(i,j))의 유기EL소자(101odd) 및 짹수 행 화소회로(Pxeven(i,j))의 유기EL소자(101even)에 각각 공급하는 구동 트랜지스터이고, 그 게이트가 트랜지스터(T11odd 및 T11even)의 소스 및 커패시터(Codd 및 Ceven)의 일단에 접속되고, 드레인은 전원단자(Vdd) 및 커패시터(Codd 및 Ceven)의 타단에 접속되며, 소스가 유기EL소자(101odd 및 101even)의 애노드에 각각 접속되어 있다.

[0063] 그러나 커패시터(Codd, Ceven)의 위치는 상기 위치에 한정되지는 않으며, 커패시터(Codd, Ceven)는 각각 트랜지스터(T12odd, T12even)의 게이트와 소스 사이에 접속되어도 좋다.

[0064] 게이트 드라이버(12)는 행 단위로 화소회로를 선택하기 위한 드라이버이며, 도 3에 도시하는 것과 같이, 본 실시형태의 게이트 드라이버(12)에는 컨트롤러(15)로부터의 제어에 따라서 출력신호(OUT(1)~(n/2))를 각 게이트 라인(Lg1~Lgn/2)에 순차 출력한다.

[0065] 본 실시형태의 게이트 드라이버(12)의 특징은 서로 인접하는 홀수 행과 짹수 행의 2행의 화소회로, 즉 인접하는 한 쌍의 홀수 행 화소회로(Pxodd(i,j))와 짹수 행 화소회로(Pxeven(i,j))가 1개의 게이트 라인(Lgi)을 공유하며, 1개의 게이트 라인(Lgi)이 홀수 행과 짹수 행의 2행의 화소회로를 동시에 선택한다는 점이다.

[0066] 데이터 드라이버(14)는 각 화소회로(Px(i,j))의 각 커패시터(Codd 및 Ceven)에 공급된 화상데이터(Data)에 의거한 표시신호의 계조신호(Vdata)를 기입하는 드라이버이며, 컨트롤러(15)로부터 공급되는 화상데이터(Data)에 따라서 행 단위로 계조신호(Vdata)를 생성하고, 생성한 계조신호(Vdata)를 각각 홀수 데이터 라인(Ld1odd~Ldmodd) 및 짹수 데이터 라인(Ld1even~Ldmeven)을 통해서 게이트 드라이버(12)가 선택한 화소회로에 공급한다.

[0067] 컨트롤러(15)는 게이트 드라이버(12) 및 데이터 드라이버(14)를 제어하며, CPU(Central Processing Unit), ROM(Read Only Memory) 및 RAM(Random Access Memory) 등을 구비하고, 게이트 드라이버(12)에 클록 신호를 출력한 상태에서 스타트신호를 게이트 드라이버(12)에 공급함으로써 게이트 드라이버(12)가 동작을 개시하도록 하

고, 게이트 드라이버(12)에 리셋 신호로서의 end신호를 공급함으로써 게이트 드라이버(12)의 동작을 정지한다.

[0068] 또, 컨트롤러(15)는 데이터 드라이버(14)에 스타트신호 및 화상 데이터(Data), 클록 신호 등을 공급한다.

[0069] 또, 도 3, 4에는 도시하고 있지 않으나, 표시장치(10)는 애노드 드라이버를 구비하며, 애노드 드라이버는 미 도시의 애노드 라인을 통해서 각각 화소회로( $Px(i, j)$ )의 구동 트랜지스터(T12odd 및 T12even)와 접속되어서, High 레벨 또는 Low 레벨의 전압(VDD)을 화소회로( $Px(i, j)$ )의 구동 트랜지스터(T12odd 및 T12even)에 인가하며, 컨트롤러(15)로부터의 스타트신호에 의해 동작을 개시하여 컨트롤러(15)로부터 공급된 클록 신호에 따라서 동작한다.

[0070] 본 실시형태에서는 유기EL소자(101odd, 101even)의 캐소드 전압(Vss)은 0V로 설정되고, 또, 미 도시의 애노드 드라이버로부터 공급되는 High 레벨의 전압(VDD)은 기입 처리시에 있어서 각 화소회로( $Px(i, j)$ )의 유기EL소자(101odd, 101even)를 발광상태로 하기 위한 전압이며, 예를 들어 +15V로 설정되고, Low 레벨의 전압은 0V 또는 그 이하로 설정된다. 그러나 유기EL소자(101odd, 101even)의 캐소드 전압(Vss) 및 애노드 전압(VDD)은 상기 값으로 한정되는 것은 아니며, 유기EL소자(101odd, 101even)의 특성에 따라서 캐소드 전압(Vss) 및 애노드 전압(VDD)은 적절하게 설정할 수 있다.

[0071] 다음에 본 실시형태의 표시장치(10)의 동작을 설명한다. 도 5는 본 발명의 바람직한 실시형태의 표시장치(10)의 구동 타이밍을 나타내는 타이밍차트이다.

[0072] 먼저, 본 실시형태의 구성상의 특징인 복수의 화소회로 중 서로 인접하는 홀수 행 화소회로( $Pxodd((1, 1\sim 1, m), (3, 1\sim 3, m), \dots (n-1, 1\sim n-1, m))$ )와 짹수 행 화소회로( $Pxeven((2, 1\sim 2, m), (4, 1\sim 4, m), \dots (n, 1\sim n, m))$ )로 이루어지는 한 쌍의 화소회로는 게이트 라인( $Lg(1, 3, \dots, n/2)$ )을 공유하고, 각 홀수 행 화소회로( $Pxodd((1, 1\sim 1, m), (3, 1\sim 3, m), \dots (n-1, 1\sim n-1, m))$ ) 중 서로 동일한 열의 화소회로는 각각 홀수 데이터 라인( $Ld1odd, Ld2odd, \dots, Ldmodd$ )을 공유하며, 각 짹수 행 화소회로( $Pxeven((2, 1\sim 2, m), (4, 1\sim 4, m), \dots (n, 1\sim n, m))$ ) 중 서로 동일한 열의 화소회로는 각각 짹수 데이터 라인( $Ld1even, Ld2even, \dots, Ldmeven$ )을 공유하고 있으므로, 게이트 드라이버(12)로부터 게이트 라인( $Lgi$ )을 통해서 출력하는 행 선택신호의 1 펄스기간에서 데이터 드라이버(14)로부터 데이터 라인( $Ldj$ )을 통해서 출력하는 데이터신호, 즉, 게이트 드라이버(12)가 선택한 행의 화소회로에 공급하는 계조신호( $Vdata$ )는 상기 행 선택신호의 1/2 펄스 주기로 반전된 신호가 된다.

[0073] 도 4, 5를 참조하면서 구체적으로 설명하면, 컨트롤러(15)의 제어에 따라서 게이트 드라이버(12)가 게이트 라인( $Lg1$ )에 High 레벨의 행 선택신호(도 5의 '제 1 펄스')를 출력하면 게이트 라인( $Lg1$ )을 공유하는 한 쌍의 홀수 행 화소회로( $Pxodd(1, 1\sim 1, m)$ )와 짹수 행 화소회로( $Pxeven(2, 1\sim 2, m)$ )의 각 트랜지스터(T11odd 및 T11even)는 상기 High 레벨의 행 선택신호에 의해 온 상태가 된다.

[0074] 이 기간에, 데이터 드라이버(14)는 먼저 상기 제 1 펄스기간의 처음 1/2 펄스기간에 홀수 데이터 라인( $Ld1odd, Ld2odd, \dots, Ldmodd$ )을 통해서 홀수 행 화소회로( $Pxodd(1, 1\sim 1, m)$ )에 계조신호( $Vdata$ )를 인가하며, 이에 의해 홀수 행 화소회로( $Pxodd(1, 1\sim 1, m)$ )의 각 커패시터( $Codd$ )에는 각 트랜지스터(T11odd)를 통해서 이 계조신호( $Vdata$ )가 기입된다.

[0075] 이어서, 상기 제 1 펄스기간의 다음 1/2 펄스기간에 데이터 드라이버(14)는 짹수 데이터 라인( $Ld1even, Ld2even, \dots, Ldmeven$ )을 통해서 짹수 행 화소회로( $Pxeven(2, 1\sim 2, m)$ )에 계조신호( $Vdata$ )를 인가하며, 이에 의해 짹수 행 화소회로( $Pxeven(2, 1\sim 2, m)$ )의 각 커패시터( $Ceven$ )에는 각 트랜지스터(T11even)를 통해서 이 계조신호( $Vdata$ )가 기입된다.

[0076] 동일한 방법으로 게이트 드라이버(12)가 순차 High 레벨의 행 선택신호를 게이트 라인( $Lg2, Lg3, \dots, Lgn/2$ )에 출력하면 그 다음의 한 쌍의 홀수 행 화소회로( $Pxodd(3, 1\sim 3, m)$ )와 짹수 행 화소회로( $Pxeven(4, 1\sim 4, m)$ ), 한 쌍의 홀수 행 화소회로( $Pxodd(5, 1\sim 5, m)$ )와 짹수 행 화소회로( $Pxeven(6, 1\sim 6, m)$ ), ..., 한 쌍의 홀수 행 화소회로( $Pxodd(n-1, 1\sim n-1, m)$ )와 짹수 행 화소회로( $Pxeven(n, 1\sim n, m)$ )가 순차 선택된다.

[0077] 이 기간에 데이터 드라이버(14)는 상기 행 선택신호의 펄스기간 중 처음 1/2 펄스기간에 공급된 화상 데이터에 의거한 계조신호( $Vdata$ )를 각각 홀수 데이터 라인( $Ld1odd, Ld2odd, \dots, Ldmodd$ )에 인가하여 선택된 한 쌍의 화소회로 중 홀수 행 화소회로( $Pxodd(3, 1\sim 3, m)$ ), 홀수 행 화소회로( $Pxodd(5, 1\sim 5, m)$ ), ..., 홀수 행 화소회로( $Pxodd(n-1, 1\sim n-1, m)$ )의 각 커패시터( $Codd$ )에 계조신호( $Vdata$ )를 기입하고, 이어서, 상기 행 선택신호의 펄스기간 중 다음의 1/2 펄스기간에 한 쌍의 화소회로 중 짹수 행 화소회로( $Pxeven(4, 1\sim 4, m)$ ), 짹수 행 화소회로( $Pxeven(6, 1\sim 6, m)$ ), ..., 짹수 행 화소회로( $Pxeven(n, 1\sim n, m)$ )의 각 커패시터( $Ceven$ )에 계조신호( $Vdata$ )를 기입한

다.

[0078] 이와 같은 방법으로 순차 기입동작이 완료하면, 컨트롤러(15)는 미 도시의 애노드 드라이버를 제어하여 High 레벨의 전압(VDD)을 미 도시의 애노드 라인을 통해서 각 화소회로( $Px(i, j)$ )에 출력하고, 이에 의해 각 화소회로( $Px(i, j)$ )의 트랜지스터(T12odd, T12even)는 각 커패시터(Codd, Ceven)가 보유한 전압을 게이트전압( $Vgs$ )으로 하여 이 게이트전압( $Vgs$ )에 대응하는 전류를 유기EL소자(101odd, 101even)에 공급함으로써 유기EL소자(101odd, 101even)는 이 전류의 전류 값에 대응하는 휘도로 발광한다.

[0079] 이상 설명한 것과 같이, 본 실시형태에 의하면  $n$ 행  $m$ 열의 복수의 화소회로로 이루어지는 표시장치에 있어서, 상기 복수의 화소회로를 서로 인접하는 한 쌍의 홀수 행 화소회로와 짝수 행 화소회로 단위로 구분하고, 상기 서로 인접하는 한 쌍의 홀수 행 화소회로와 짝수 행 화소회로는 게이트 드라이버로부터 순차 인가되는 행 선택신호를 공급하는 1개의 게이트 라인을 공유하고 있으므로, 종래에 비해 게이트 라인의 수를 절반(1/2)으로 감소시킬 수 있다.

[0080] 따라서 게이트 라인의 수의 감소에 의해 표시장치의 베젤의 폭을 대폭 축소시킬 수 있다.

[0081] 또, 게이트 라인의 수의 감소에 의해 게이트 라인이 표시장치 내의 다른 신호를 공급하는 라인과 교차하는 교차점의 수가 감소하므로 상기 교차점에서 발생하는 기생전용량도 감소하며, 이에 따라 데이터신호의 RC 지연(RC Delay) 및 전압강하(IR Drop)도 대폭 감소시킬 수 있다.

[0082] 또, 게이트 라인의 감소에 따라 표시장치의 개구율이 증가하며, 이에 의해 표시장치의 해상도를 증가시킬 수 있다.

[0083] 이상 본 발명의 바람직한 실시형태에 대해서 설명하였으나, 본 발명은 상기 실시형태로 한정되는 것은 아니다. 본 발명의 범위 내에서의 다양한 변경 및 변형이 가능하다.

### 부호의 설명

|        |                                    |           |

|--------|------------------------------------|-----------|

| [0084] | 10                                 | 표시장치      |

|        | 12                                 | 게이트 드라이버  |

|        | 14                                 | 데이터 드라이버  |

|        | 15                                 | 컨트롤러      |

|        | $Px(i, j)$                         | 화소회로      |

|        | $Pxodd(i, j)$                      | 홀수 행 화소회로 |

|        | $Pxeven(i, j)$                     | 짝수 행 화소회로 |

|        | $Lg1, Lg2, \dots, Lgn/2$           | 게이트 라인    |

|        | $Ld1odd, Ld2odd, \dots, Ldmodd$    | 홀수 데이터 라인 |

|        | $Ld1even, Ld2even, \dots, Ldmeven$ | 짝수 데이터 라인 |

|        | T11                                | 스위칭 트랜지스터 |

|        | T12                                | 구동 트랜지스터  |

|        | C                                  | 커패시터      |

|        | 101                                | 유기EL소자    |

## 도면

## 도면1

(a)

(b)

## 도면2a

## 도면2b

## 도면3

## 도면4

## 도면5

|                |                                  |         |            |

|----------------|----------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和显示方法                        |         |            |

| 公开(公告)号        | <a href="#">KR1020140140291A</a> | 公开(公告)日 | 2014-12-09 |

| 申请号            | KR1020130060933                  | 申请日     | 2013-05-29 |

| [标]申请(专利权)人(译) | 娜我比可隆株式会社                        |         |            |

| 申请(专利权)人(译)    | Neoview的隆有限公司                    |         |            |

| 当前申请(专利权)人(译)  | Neoview的隆有限公司                    |         |            |

| [标]发明人         | JEON SUNG GON                    |         |            |

| 发明人            | JEON SUNG GON                    |         |            |

| IPC分类号         | G09G3/30                         |         |            |

| 代理人(译)         | HWANG , E NAM                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>        |         |            |

### 摘要(译)

显示装置包括n行m列的多个像素电路Px ( i , j ) ( m和n分别为自然数 )

多个像素电路各自由一对像素电路构成 , 每个像素电路由奇数行像素电路 ( Pxodd ( i , j ) ) 和偶数行像素电路 ( Pxeven ) 组成。奇数行像素电路通过奇数数据线 ( Ldjodd ) 以列为单位提供灰度信号 ( Vdata ) , 偶数 - 通过偶数数据线 ( Ldjeven ) 以列为单位将灰度信号施加到像素电路。