(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2018-0024909

(43) 공개일자 2018년03월08일

(51) 국제특허분류(Int. Cl.)

*H01L 27/32* (2006.01) *H01L 27/12* (2006.01)

*H01L 29/06* (2006.01) *H01L 29/10* (2006.01)

*H01L 51/56* (2006.01)

(52) CPC특허분류

*H01L 27/3262* (2013.01)

*H01L 27/124* (2013.01)

(21) 출원번호 10-2016-0111945

(22) 출원일자 2016년08월31일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

이경언

경기도 수원시 장안구 경수대로976번길 22, 113동

1703호(조원동, 수원 한일타운)

윤민성

경기도 남양주시 경춘로1256번길 24, 1413동 100

2호(평내동, 평내마을금호어울림아파트)

(74) 대리인

박영복

전체 청구항 수 : 총 9 항

(54) 발명의 명칭 구동 트랜지스터와 이를 구비한 유기 발광 다이오드 표시 장치 및 그들의 제조 방법

### (57) 요 약

본 발명은 픽셀 사이즈가 작아지더라도 계조를 넓은 범위의 입력 전압 값으로 조절이 가능하여 더 세분화된 계조를 표현할 수 있는 구동 트랜지스터와 이를 구비한 유기 발광 표시 장치 및 그들의 제조 방법에 관한 것으로, 본 발명에 따른 구동 트랜지스터는, 게이트 전극, 활성층, 백 바이어스 게이트 전극, 상기 게이트 전극과 상기 활성층 사이에 제 1 게이트 절연막 및 상기 백 바이어스 게이트 전극과 상기 활성층 사이에 제 2 게이트 절연막을 구비하고, 상기 제 1 게이트 절연막의 두께는 상기 제 2 게이트 절연막의 두께보다 더 두껍거나 같음에 그 특징이 있다.

대 표 도 - 도2

(52) CPC특허분류

*H01L 27/1251* (2013.01)

*H01L 27/3265* (2013.01)

*H01L 27/3276* (2013.01)

*H01L 29/0661* (2013.01)

*H01L 29/1025* (2013.01)

*H01L 51/56* (2013.01)

*H01L 2251/558* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

게이트 전극, 활성층, 백 바이어스 게이트 전극, 상기 게이트 전극과 상기 활성층 사이에 제 1 게이트 절연막 및 상기 백 바이어스 게이트 전극과 상기 활성층 사이에 제 2 게이트 절연막을 구비하고, 상기 제 1 게이트 절연막의 두께는 상기 제 2 게이트 절연막의 두께보다 두껍거나 같은 구동 트랜지스터.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 게이트 절연막의 두께는 1000Å 내지 4500Å이고, 상기 활성층의 두께는 300Å 내지 800Å이며, 상기 제 2 게이트 절연막의 두께는 500Å 내지 1500Å인 구동 트랜지스터.

#### 청구항 3

서브 픽셀에 구동 트랜지스터 및 OLED를 구비한 유기 발광 다이오드 표시 장치에 있어서,

상기 구동 트랜지스터는 게이트 전극, 활성층, 백 바이어스 게이트 전극, 상기 게이트 전극과 상기 활성층 사이에 제 1 게이트 절연막 및 상기 백 바이어스 게이트 전극과 상기 활성층 사이에 제 2 게이트 절연막을 구비하고, 상기 제 1 게이트 절연막의 두께는 상기 제 2 게이트 절연막의 두께보다 더 두껍거나 같은 특징으로 하는 유기 발광 다이오드 표시 장치.

#### 청구항 4

제 3 항에 있어서,

상기 제 1 게이트 절연막의 두께는 1000Å 내지 4500Å이고, 상기 활성층의 두께는 300Å 내지 800Å이며, 상기 제 2 게이트 절연막의 두께는 500Å 내지 1500Å인 유기 발광 다이오드 표시 장치.

#### 청구항 5

기판상에 게이트 전극을 형성하는 단계;

상기 게이트 전극을 포함한 기판 전면에 제 1 게이트 절연막을 형성하는 단계;

상기 제 1 게이트 절연막상에 활성층을 형성하는 단계;

상기 활성층을 포함한 기판 전면에 상기 제 1 게이트 절연막보다 더 얇거나 같은 두께로 제 2 게이트 절연막을 형성하는 단계;

상기 제 2 게이트 절연막상에 백 바이어스 게이트 전극을 형상하는 단계를 포함하여 이루어지는 구동 트랜지스터의 제조 방법.

#### 청구항 6

제 5 항에 있어서,

상기 제 1 게이트 절연막은 1000Å 내지 4500Å의 두께로 형성하고, 상기 활성층은 300Å 내지 800Å의 두께로 형성하며, 상기 제 2 게이트 절연막은 500Å 내지 1500Å의 두께로 형성하는 구동 트랜지스터의 제조 방법.

#### 청구항 7

기판상에 스토리지 커패시터의 제 1 전극을 형성하는 단계;

상기 제 1 전극이 형성된 기판 전면에 유전체막을 형성하는 단계;

상기 유전체막위에 상기 제 1 전극에 중첩되도록 구동 트랜지스터의 게이트 전극을 형성하는 단계;

상기 게이트 전극을 포함한 기판 전면에 제 1 게이트 절연막을 형성하는 단계;

상기 제 1 게이트 절연막위에 스위칭 트랜지스터, 센싱 트랜지스터용 및 상기 구동 트랜지스터용 활성층들을 형성하는 단계;

상기 활성층을 포함한 기판 전면에 제 2 게이트 절연막을 형성하는 단계;

상기 각 활성층에 대응하여 상기 제 2 게이트 절연막위에 스캔 라인 및 백 바이어스 게이트 전극을 포함한 백 바이어스 라인을 형성하는 단계; 그리고

상기 활성층에 선택적으로 불순물 이온 주입하여 상기 스위칭 트랜지스터, 센싱 트랜지스터 및 상기 구동 트랜지스터용 소오스/드레인 영역을 형성하는 단계를 구비하여 이루어지는 유기 발광 다이오드 표시 장치의 제조 방법.

## 청구항 8

제 7 항에 있어서,

상기 스캔 라인 및 백 바이어스 라인을 포함한 기판 전면에 층간 절연막을 형성하고, 상기 스위칭 트랜지스터의 소오스/드레인 영역, 상기 센싱 트랜지스터의 소오스/드레인 영역 및 상기 구동 트랜지스터의 소오스/드레인 영역에 각각 제 1 내지 제 3 콘택홀을 형성하는 단계;

상기 제 1 콘택홀을 상기 스위칭 트랜지스터의 소오스/드레인 영역과 상기 구동 트랜지스터의 게이트 전극을 연결하는 제 1 금속 플러그, 상기 제 2 콘택홀을 통해 상기 센싱 트랜지스터 및 구동 트랜지스터의 소오스/드레인 영역과 상기 스토리지 커패시터의 제 1 전극이 연결하는 상기 제 2 금속 플러그, 및 상기 제 3 콘택홀을 통해 상기 구동 트랜지스터의 소오스/드레인 영역에 연결되는 고전위 구동 전압 공급 라인을 형성하는 단계;

상기 기판 전면에 제 1 보호막을 형성하고, 상기 스위칭 트랜지스터의 소오스/드레인 영역, 상기 센싱 트랜지스터의 소오스/드레인 영역 및 상기 제 2 금속 플러그상에 각각 제 4 내지 제 6 콘택홀을 형성하는 단계;

상기 제 4 콘택홀을 통해 상기 스위칭 트랜지스터의 소오스/드레인 영역에 연결되는 데이터 라인, 상기 제 5 콘택홀을 통해 상기 센싱 트랜지스터의 소오스/드레인 영역에 연결되는 기준 전압 라인, 및 상기 제 2 금속 플러그에 연결되는 제 4 금속 플러그를 형성하는 단계;

상기 기판 전면에 제 2 보호막 및 평탄화막을 형성하고, 상기 제 4 금속 플러그상에 제 7 콘택홀을 형성하는 단계; 그리고

상기 콘택홀(27)을 통해 상기 제 4 금속 플러그와 연결되도록 상기 평탄화막위에 OLED의 애노드 전극을 형성하고, 발광층 및 상기 OLED의 캐소드 전극을 차례로 형성하는 단계를 더 포함하여 이루어지는 유기 발광 다이오드 표시 장치의 제조 방법.

## 청구항 9

제 7 항에 있어서,

상기 제 1 게이트 절연막은  $1000\text{ \AA}$  내지  $4500\text{ \AA}$ 의 두께로 형성하고, 상기 활성층은  $300\text{ \AA}$  내지  $800\text{ \AA}$ 의 두께로 형성하며, 상기 제 2 게이트 절연막은  $500\text{ \AA}$  내지  $1500\text{ \AA}$ 의 두께로 형성하는 유기 발광 다이오드 표시 장치의 제조 방법.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 구동 트랜지스터와 이를 구비한 유기 발광 다이오드 표시 장치 및 그들의 제조 방법에 관한 것으로, 특히 데이터 입력 전압의 폭을 넓게하여 더 세분화된 계조를 표현할 수 있는 구동 트랜지스터와 이를 구비한 유기 발광 다이오드 표시 장치 및 그들의 제조 방법에 관한 것이다.

### 배경 기술

[0002] 최근, 멀티미디어의 발달과 함께 평판 표시 장치의 중요성이 증대되고 있다. 이에 부응하여 액정 표시 장치, 플

라즈마 표시 장치, 유기 발광 표시 장치 등의 평판 표시 장치가 상용화되고 있다.

[0003] 이러한, 평판 표시 장치 중에서 유기 발광 다이오드(OLED) 표시 장치는 전자와 정공의 재결합으로 유기 발광층을 발광시키는 자발광 소자로 회도가 높고 구동 전압이 낮으며 고속의 응답속도를 가지며, 초박막화가 가능하고 시야각에 문제가 없어 차세대 평판 표시 장치로 주목 받고 있다.

[0004] 유기 발광 다이오드 표시 장치는 적색(R), 녹색(G), 및 청색(B)의 서브 픽셀(Sub-Pixel)를 하나의 단위 픽셀(Unit Pixel)로 구성하고, 3개의 서브 픽셀들을 통해 다양한 색상으로 구성된 하나의 영상을 표시한다.

[0005] OLED 표시 장치를 구성하는 다수의 서브 픽셀 각각은 애노드 및 캐소드와 이들 사이의 유기 발광층으로 구성된 OLED 소자와, 상기 OLED 소자를 독립적으로 구동하는 픽셀 회로를 구비한다.

[0006] 상기 픽셀 회로는 데이터 전압을 공급하여 스토리지 커패시터에 데이터 전압에 상응하는 전압이 충전되게 하는 스위칭 박막 트랜지스터(Thin Film Transistor; TFT)와, 상기 스토리지 커패시터에 충전된 전압에 따라 전류를 제어하여 상기 OLED 소자로 공급하는 구동 박막 트랜지스터(TFT) 등을 포함하고, 상기 OLED 소자는 전류에 비례하는 광을 발생한다.

[0007] 최근에는, 해상도가 증가함에 따라 서브 화소의 사이즈가 작아지게 되었다. 즉, 서브 화소가  $63\mu\text{m} \times 31.5\mu\text{m}$  ( $403\text{ppi}$ ) 사이즈에서  $16.9\mu\text{m} \times 8.45\mu\text{m}$  ( $1500\text{ppi}$ ) 사이즈로 작아지게 되었다. 이와 같이 서브 화소의 사이즈가 감소함에 따라 OLED 소자에 흐르는 전류도 사이즈의 감소 비만큼 작게 된다. 더구나 VR에 이용할 경우 외부 반사를 막기 위해 사용하는 pol이 필요 없기 때문에 같은 전류가 흐른다면 TV나 스마트폰에 적용할 경우보다 밝기가 2배 이상 밝다. VR 제품의 경우 밝기의 화면이면 OLED 소자에 흐르는 전류는 다른 제품보다 절반으로 줄어들 것이다.

[0008] WOLED를 사용할 경우,  $1500\text{ppi}$  사이즈의 경우 하나의 서브 픽셀에 흐르는 전류의 최대치는  $5 \times 10^{-9}$  이하로 예상된다. 이럴 경우 LTPS(Low Temperature Polycrystalline Silicon) TFT(Thin Film Transistor)의 특성을 고려하면 OLED 계조를 표현하기 위하여 사용할 수 있는 데이터 전압의 폭이 넓지 않게 된다. 따라서, 계조 표현에 어려움이 있다.

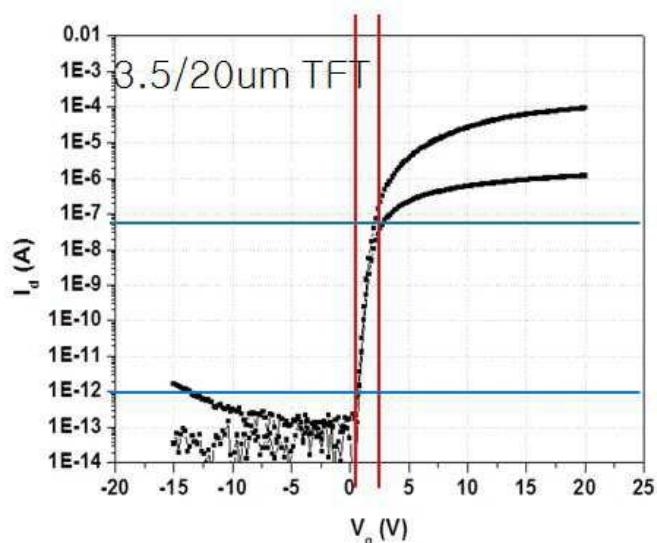

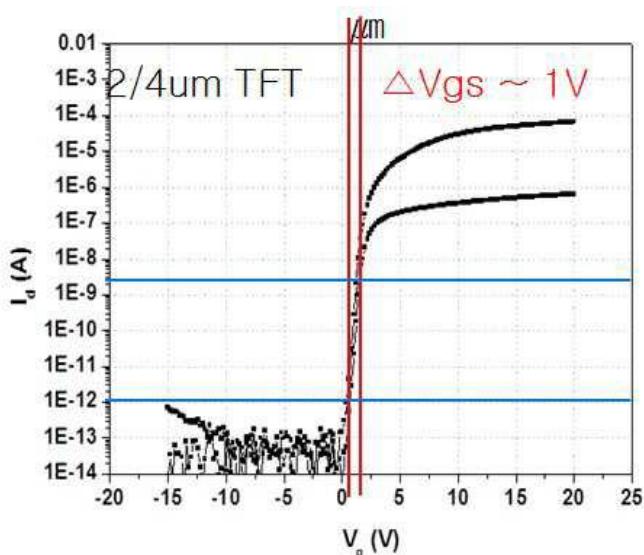

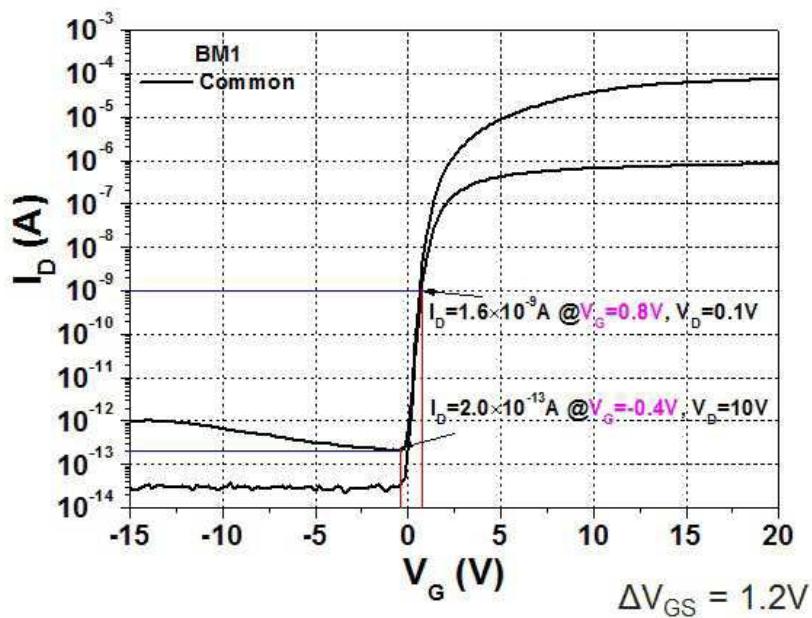

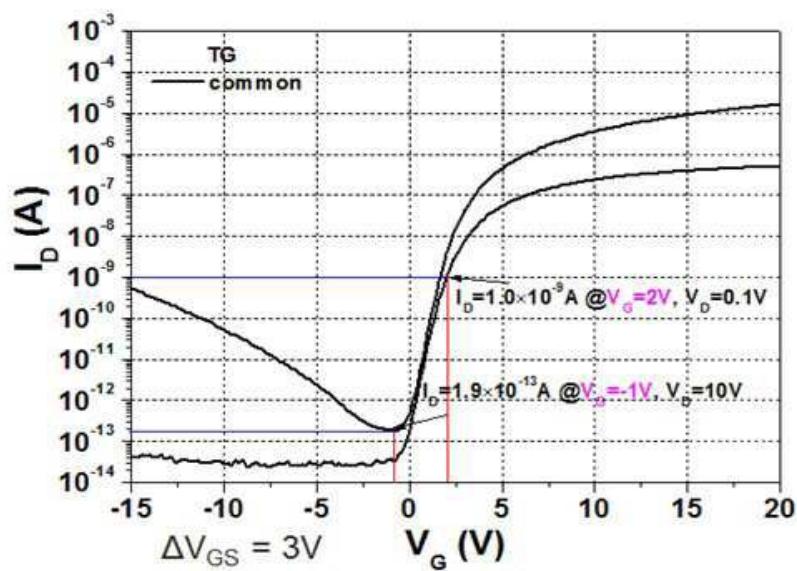

[0009] 도 1a는 서브 픽셀 사이즈가  $403\text{ppi}$ 일 때의 구동 박막트랜지스터의 게이트 전압( $V_g$ )의 범위를 나타낸 그래프이고, 도 1b는 서브 픽셀 사이즈가  $1500\text{ppi}$ 일 때의 구동 박막트랜지스터의 게이트 전압( $V_g$ )의 범위를 나타낸 그래프이다.

[0010] 도 1a 및 도 1b에서 알 수 있는 바와 같이, 고해상도로 발전하면서 서브 픽셀의 사이즈가  $403\text{ppi}$ 에서  $1500\text{ppi}$ 로 작아지게 되면, 구동 박막트랜지스터의 게이트 전압 범위가 좁아지게 되고, 더불어 데이터 전압의 폭이 좁아지므로 계조를 표현하는데 어려움이 있다.

## 발명의 내용

### 해결하려는 과제

[0011] 본 발명은 이와 같은 문제점을 해결하기 위한 것으로, 픽셀 사이즈가 작아지더라도 계조를 넓은 범위의 입력 전압 값으로 조절이 가능하여 더 세분화된 계조를 표현할 수 있는 구동 트랜지스터와 이를 구비한 유기 발광 표시 장치 및 그들의 제조 방법을 제공하는데 그 목적이 있다.

### 과제의 해결 수단

[0012] 상기와 같은 목적을 달성하기 위한 본 발명에 따른 구동 트랜지스터는, 게이트 전극, 활성층, 백 바이어스 게이트 전극, 상기 게이트 전극과 상기 활성층 사이에 제 1 게이트 절연막 및 상기 백 바이어스 게이트 전극과 상기 활성층 사이에 제 2 게이트 절연막을 구비하고, 상기 제 1 게이트 절연막의 두께는 상기 제 2 게이트 절연막의 두께보다 더 두껍거나 같음에 그 특징이 있다.

[0013] 또한, 상기와 같은 목적을 달성하기 위한 본 발명에 따른 유기 발광 다이오드 표시 장치는, 서브 픽셀에 구동 트랜지스터 및 OLED를 구비한 유기 발광 다이오드 표시 장치에 있어서, 상기 구동 트랜지스터는 게이트 전극, 활성층, 백 바이어스 게이트 전극, 상기 게이트 전극과 상기 활성층 사이에 제 1 게이트 절연막 및 상기 백 바이어스 게이트 전극과 상기 활성층 사이에 제 2 게이트 절연막을 구비하고, 상기 제 1 게이트 절연막의 두께는 상기 제 2 게이트 절연막의 두께보다 더 두껍거나 같음에 그 특징이 있다.

[0014] 한편, 상기와 같은 목적을 달성하기 위한 본 발명에 따른 구동 트랜지스터의 제조 방법은, 기판상에 게이트 전극을 형성하는 단계; 상기 게이트 전극을 포함한 기판 전면에 제 1 게이트 절연막을 형성하는 단계; 상기 제 1 게이트 절연막상에 활성층을 형성하는 단계; 상기 활성층을 포함한 기판 전면에 상기 제 1 게이트 절연막보다 더 얇거나 같은 두께로 제 2 게이트 절연막을 형성하는 단계; 상기 제 2 게이트 절연막상에 백 바이어스 게이트 전극을 형성하는 단계를 포함하여 이루어짐에 그 특징이 있다.

[0015] 또한, 상기와 같은 목적을 달성하기 위한 본 발명에 따른 유기 발광 다이오드 표시 장치의 제조 방법은, 기판상에 스토리지 커패시터의 제 1 전극을 형성하는 단계; 상기 제 1 전극이 형성된 기판 전면에 유전체막을 형성하는 단계; 상기 유전체막위에 상기 제 1 전극에 중첩되도록 구동 트랜지스터의 게이트 전극을 형성하는 단계; 상기 게이트 전극을 포함한 기판 전면에 제 1 게이트 절연막을 형성하는 단계; 상기 제 1 게이트 절연막위에 스위칭 트랜지스터, 센싱 트랜지스터용 및 상기 구동 트랜지스터용 활성층들을 형성하는 단계; 상기 활성층을 포함한 기판 전면에 제 2 게이트 절연막을 형성하는 단계; 상기 각 활성층에 대응하여 상기 제 2 게이트 절연막위에 스캔 라인 및 백 바이어스 게이트 전극을 포함한 백 바이어스 라인을 형성하는 단계; 그리고 상기 활성층에 선택적으로 불순물 이온 주입하여 상기 스위칭 트랜지스터, 센싱 트랜지스터 및 상기 구동 트랜지스터용 소오스/드레인 영역을 형성하는 단계를 구비하여 이루어짐에 그 특징이 있다.

[0016] 여기서, 상기 유기 발광 다이오드 표시 장치의 제조 방법은, 상기 스캔 라인 및 백 바이어스 라인을 포함한 기판 전면에 충간 절연막을 형성하고, 상기 스위칭 트랜지스터의 소오스/드레인 영역, 상기 센싱 트랜지스터의 소오스/드레인 영역 및 상기 구동 트랜지스터의 소오스/드레인 영역에 각각 제 1 내지 제 3 콘택홀을 형성하는 단계; 상기 제 1 콘택홀을 상기 스위칭 트랜지스터의 소오스/드레인 영역과 상기 구동 트랜지스터의 게이트 전극을 연결하는 제 1 금속 플러그, 상기 제 2 콘택홀을 통해 상기 센싱 트랜지스터 및 구동 트랜지스터의 소오스/드레인 영역과 상기 스토리지 커패시터의 제 1 전극이 연결하는 상기 제 2 금속 플러그, 및 상기 제 3 콘택홀을 통해 상기 구동 트랜지스터의 소오스/드레인 영역에 연결되는 고전위 구동 전압 공급 라인을 형성하는 단계; 상기 기판 전면에 제 1 보호막을 형성하고, 상기 스위칭 트랜지스터의 소오스/드레인 영역, 상기 센싱 트랜지스터의 소오스/드레인 영역 및 상기 제 2 금속 플러그상에 각각 제 4 내지 제 6 콘택홀을 형성하는 단계; 상기 제 4 콘택홀을 통해 상기 스위칭 트랜지스터의 소오스/드레인 영역에 연결되는 데이터 라인, 상기 제 5 콘택홀을 통해 상기 센싱 트랜지스터의 소오스/드레인 영역에 연결되는 기준 전압 라인, 및 상기 제 2 금속 플러그에 연결되는 제 4 금속 플러그를 형성하는 단계; 상기 기판 전면에 제 2 보호막 및 평탄화막을 형성하고, 상기 제 4 금속 플러그상에 제 7 콘택홀을 형성하는 단계; 그리고 상기 콘택홀(27)을 통해 상기 제 4 금속 플러그와 연결되도록 상기 평탄화막위에 OLED의 애노드 전극을 형성하고, 발광층 및 상기 OLED의 캐소드 전극을 차례로 형성하는 단계를 더 포함함을 특징으로 한다.

[0017] 상기 제 1 게이트 절연막은  $1000\text{\AA}$  내지  $4500\text{\AA}$ 의 두께로 형성되고, 상기 활성층은  $300\text{\AA}$  내지  $800\text{\AA}$ 의 두께로 형성되며, 상기 제 2 게이트 절연막은  $500\text{\AA}$  내지  $1500\text{\AA}$ 의 두께로 형성됨을 특징으로 한다.

### 발명의 효과

[0018] 상기와 같은 특징을 갖는 본 발명에 따른 구동 트랜지스터와 이를 구비한 유기 발광 다이오드 표시 장치 및 그들의 제조 방법에 있어서는 다음과 같은 효과가 있다.

[0019] 첫째, 구동 박막트랜지스터에 백 바이어스 게이트 전극을 형성하고 상기 백 바이어스 게이트 전극에 일정한 전위의 백 바이어스를 인가하므로, 핵셀 사이즈가 작아지더라도 계조를 넓은 범위의 입력 전압 값으로 조절이 가능하여 더 세분화된 계조를 표현할 수 있다.

[0020] 둘째, 상기 백 바이어스 게이트 전극에 일정한 전위의 백 바이어스를 인가하기 위한 백 바이어스 라인이 데이터 라인과 넓은 영역에서 중첩 되도록 하여 백 바이어스 라인이 데이터 라인의 전위를 차폐하므로 데이터 라인이 구동 트랜지스터에 미치는 영향을 줄일 수 있다.

[0021] 셋째, 구동 트랜지스터의 게이트 절연막과 백 바이어스용 게이트 절연막의 두께를 조절하므로 계조를 표현할 수 있는 범위를 증가시킬 수 있다.

### 도면의 간단한 설명

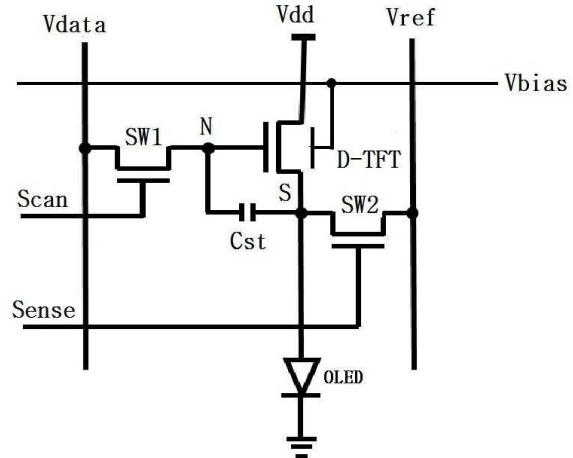

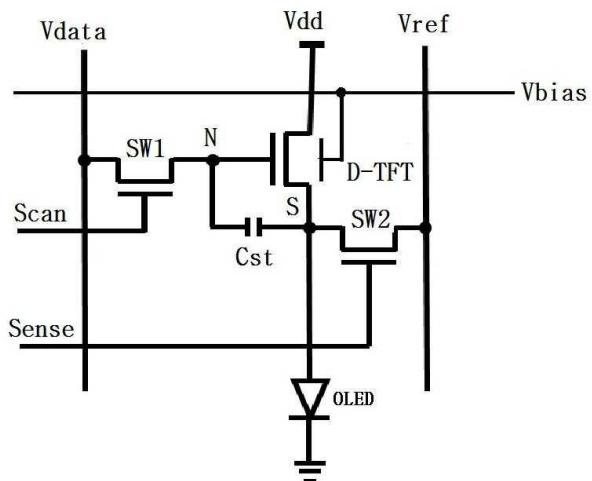

[0022] 도 1a는 서브 핵셀 사이즈가 403ppi일 때의 구동 박막트랜지스터의 게이트 전압( $V_g$ )의 범위를 나타낸 그래프

도 1b는 서브 핵셀 사이즈가 1500ppi일 때의 구동 박막트랜지스터의 게이트 전압( $V_g$ )의 범위를 나타낸 그래프

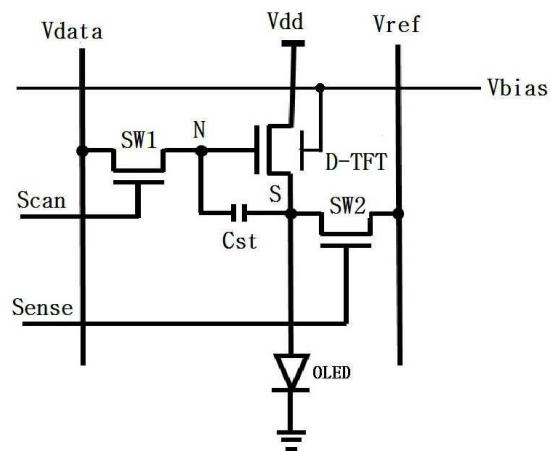

도 2는 본 발명에 따른 유기 발광 다이오드 표시 장치의 단위 서브 픽셀의 회로적 구성도

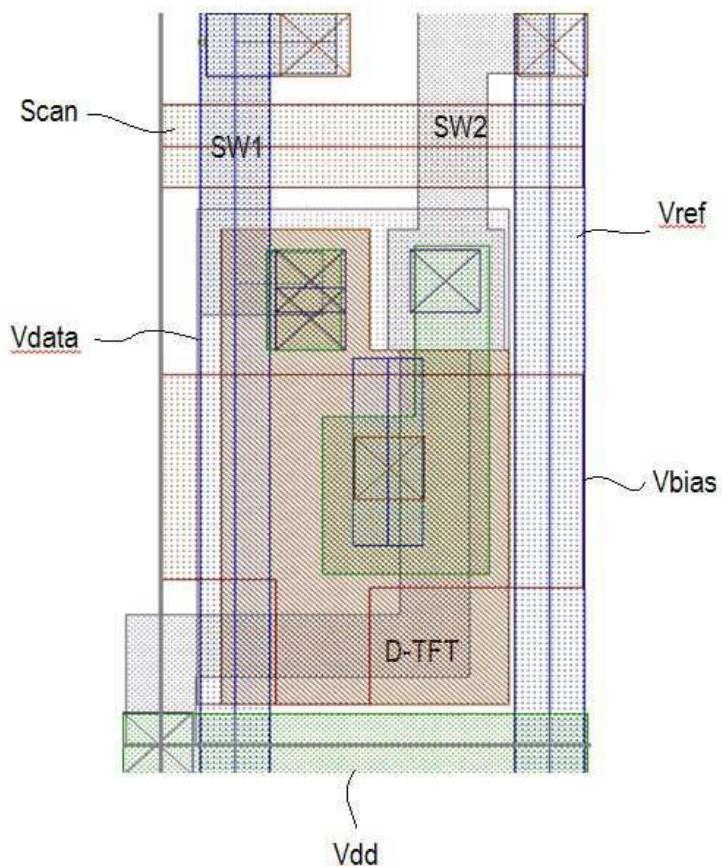

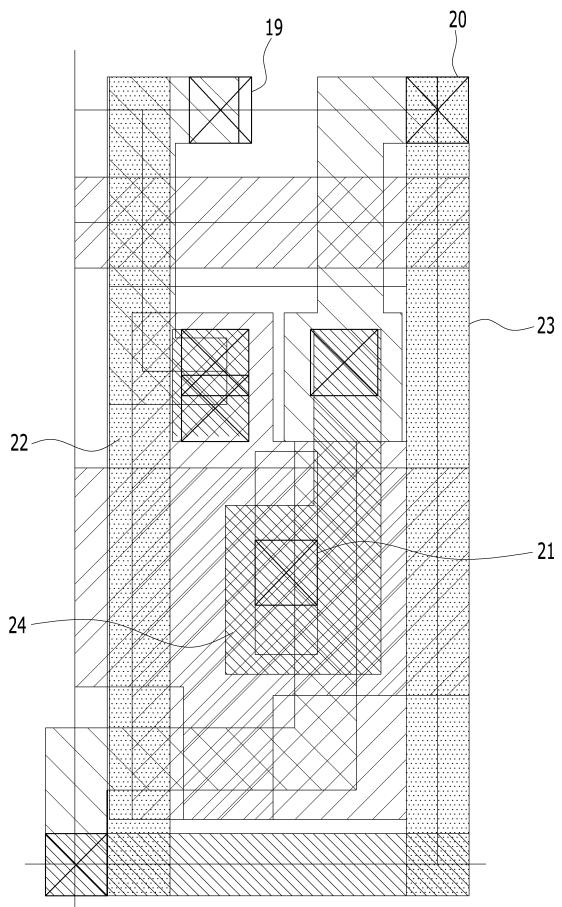

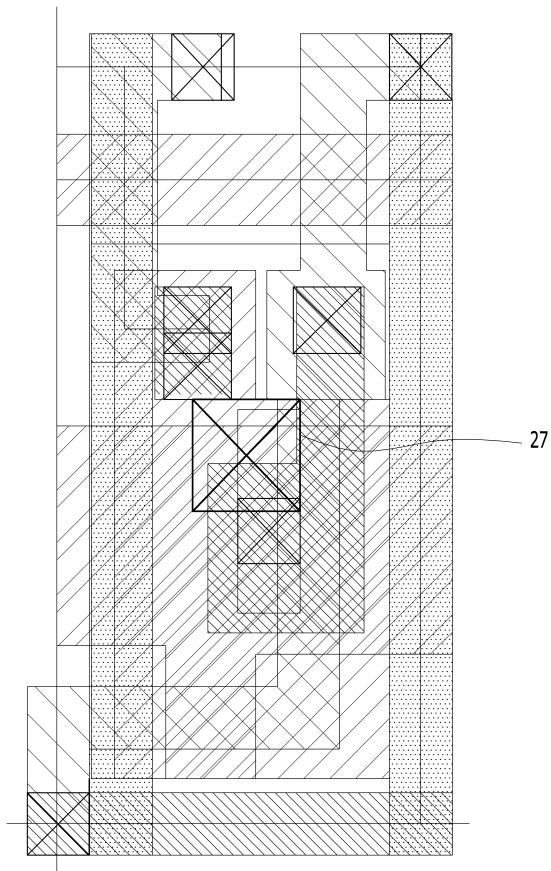

도 3은 본 발명에 따른 유기 발광 다이오드 표시 장치의 단위 서브 픽셀의 레이아웃 구성도

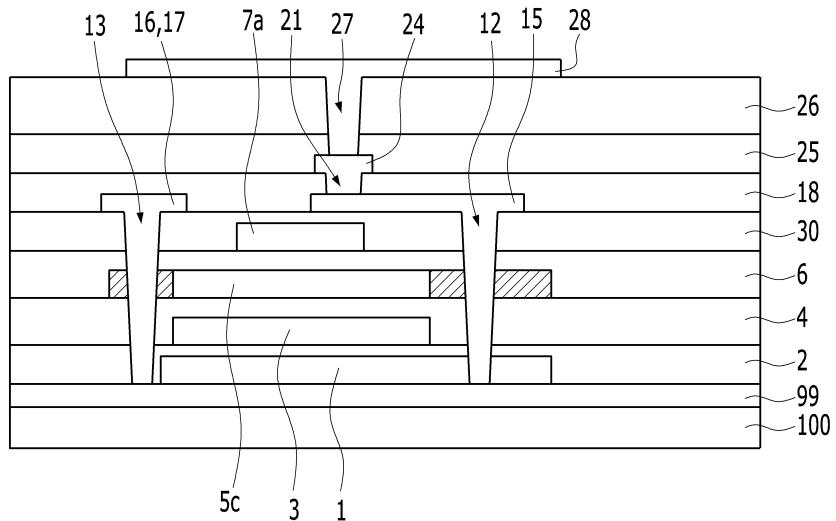

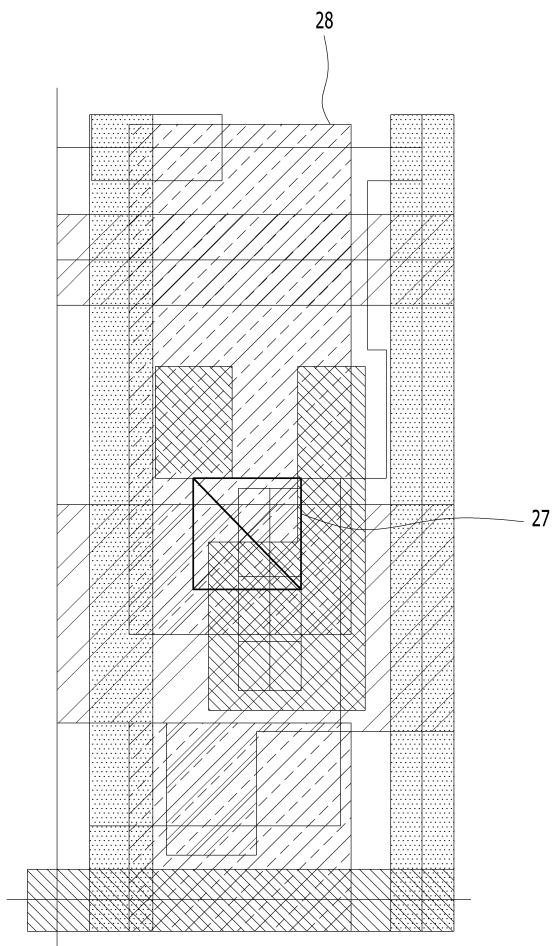

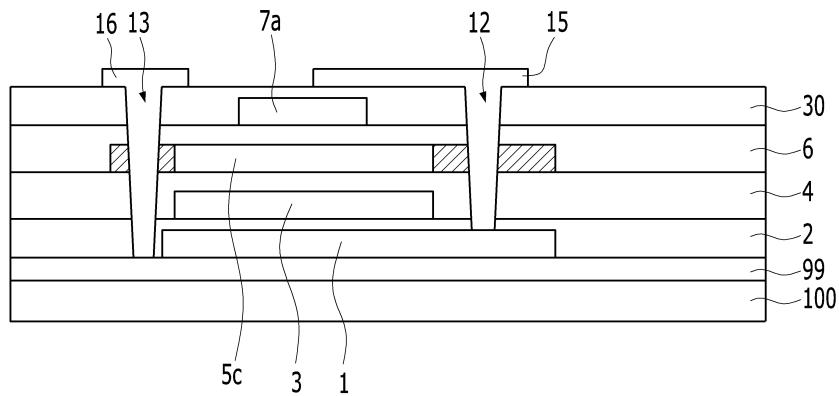

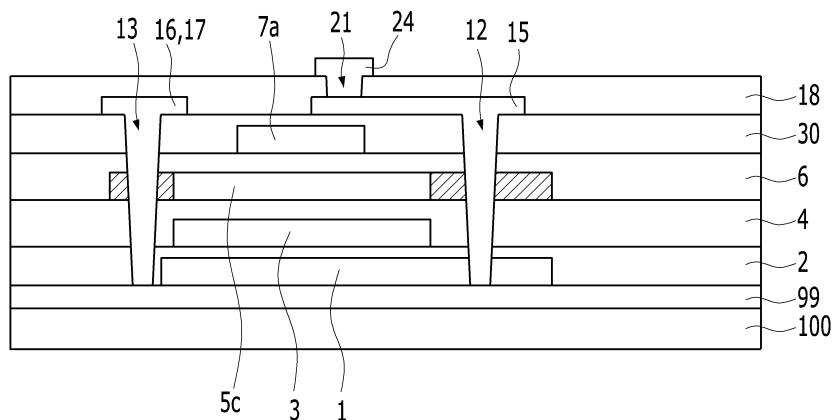

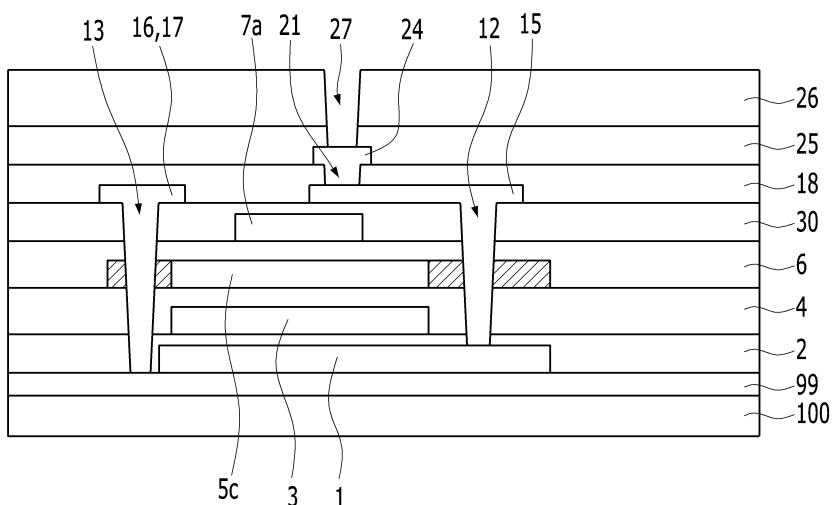

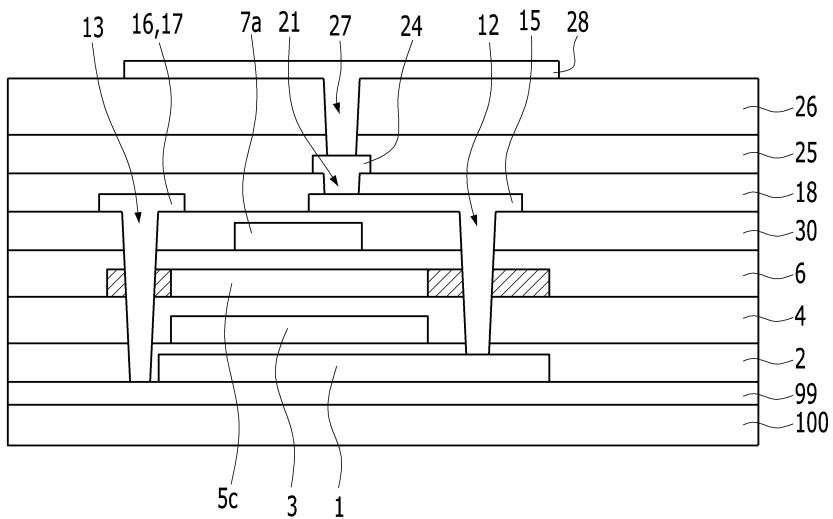

도 4는 본 발명에 따른 유기 발광 다이오드 표시 장치의 단위 서브 픽셀의 단면 구성도

도 5a 내지 5i는 본 발명에 따른 유기 발광 다이오드 표시 장치의 제조 방법을 설명하기 위한 공정 레이 아웃도

도 6a 내지 6i는 본 발명에 따른 유기 발광 다이오드 표시 장치의 제조 방법을 설명하기 위한 공정 단면도

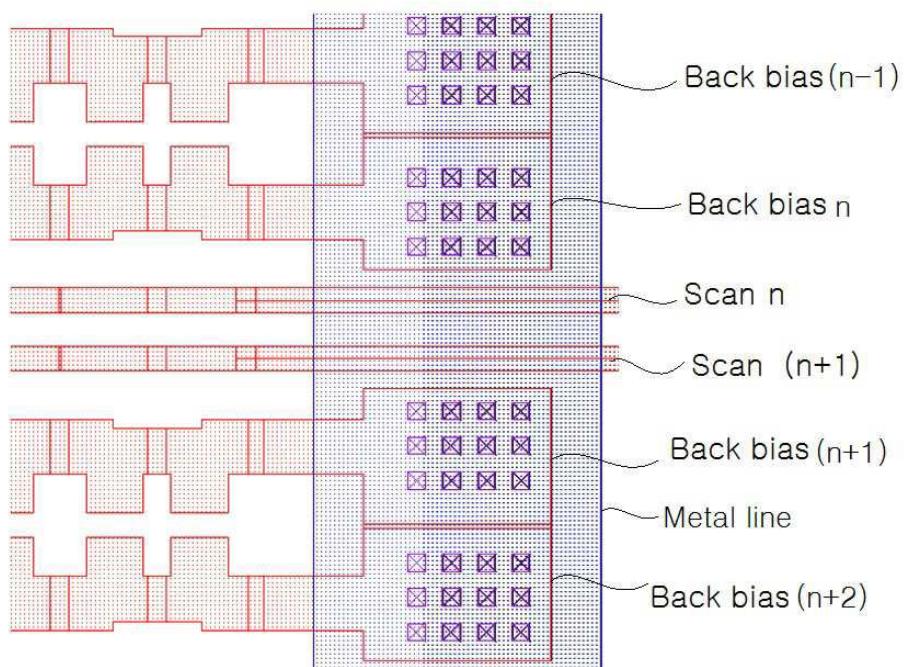

도 7은 본 발명에 따른 유기 발광 다이오드 표시장치의 스캔 라인과 백 바이어스 라인을 도시한 레이 아웃도

도 8a는 종래 구조의 구동 박막트랜지스터의 게이트 전압의 범위를 나타낸 그래프

도 8b는 본 발명에 따른 구동 박막트랜지스터의 게이트 전압의 범위를 나타낸 그래프

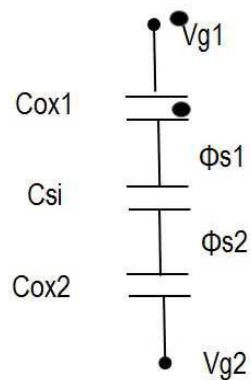

도 9는 본 발명에 따른 입력 데이터 범위가 증가하는 이유를 설명하기 위한 커패시터 모델을 도시한 도면

### 발명을 실시하기 위한 구체적인 내용

- [0023] 상기와 같은 특징을 갖는 본 발명에 따른 구동 트랜지스터 및 이를 구비한 유기 발광 다이오드 표시 장치 및 그들의 제조 방법을 첨부된 도면을 참조하여 보다 상세하게 설명하면 다음과 같다.

- [0024] 도 2는 본 발명에 따른 유기 발광 다이오드(OLED) 표시 장치의 단위 서브 픽셀의 회로적 구성도이고, 도 3은 본 발명에 따른 유기 발광 다이오드 표시 장치의 단위 서브 픽셀의 레이아웃 구성도이며, 도 4는 본 발명에 따른 유기 발광 다이오드 표시 장치의 단위 서브 픽셀의 단면 구성도이다.

- [0025] 본 발명에 따른 OLED 표시 장치의 단위 서브 픽셀은, 도 2 내지 도 4에 도시한 바와 같이, 발광 소자(OLED)와, 이를 구동하는 다수의 트랜지스터를 포함하는 화소 구동 회로를 구비한다. 화소 구동 회로는 구동 트랜지스터(D-TFT), 스위칭 트랜지스터(SW1), 센싱 트랜지스터(SW2) 및 스토리지 커패시터(Cst)를 포함한다.

- [0026] 본 발명의 실시예에서는 3T1C 구조를 가지는 화소 구동 회로를 예를 들어 설명하고 있으나, 반드시 그에 한정되는 것은 아니며, 통상의 기술자가 필요에 따라 그 구조를 변경할 수 있다.

- [0027] 상기 스위칭 트랜지스터(SW1)는 각 서브 픽셀의 스캔 라인(Scan)에 게이트 전극이 접속되고, 데이터 라인(Vdata)에 소오스 전극이 접속되고, 스토리지 커패시터(Cst)의 제 1 단자인 제 1 노드(N)에 드레인 전극이 접속된다.

- [0028] 이에 따라, 상기 스위칭 트랜지스터(SW1)는 각 서브 픽셀의 스캔 라인(Scan)으로부터의 제 1 스캔 신호에 응답하여 데이터 라인(Vdata)의 데이터 전압(Vdata)을 제 1 노드(N)에 공급한다.

- [0029] 상기 구동 트랜지스터(D-TFT)는 상기 제 1 노드(N)에 게이트 전극(3)이 접속되고, 고전위 구동 전압원(Vdd)에 드레인 전극이 접속되고, 발광 소자(OLED)의 애노드 전극(28)에 소오스 전극(15, 24)이 접속된다.

- [0030] 이에 따라, 구동 트랜지스터(D-TFT)는 자신의 소오스-게이트간 전압(Vgs) 즉, 고전위 전압원(Vdd)과 제 1 노드(N)사이에 걸리는 전압에 따라 발광 소자(OLED)에 흐르는 전류량을 조절한다.

- [0031] 상기 센싱 트랜지스터(SW2)는 각 서브 픽셀의 센싱 제어 라인(Sense)에 게이트 전극이 접속되고, 제 2 노드(S)에 소오스 전극이 접속되고, 기준 전압 라인(Vref)에 드레인 전극이 접속된다. 여기서, 상기 센싱 트랜지스터(SW2)는 상기 센싱 제어 라인(Sense) 대신에 상기 스캔 라인(Scan)에 의해 제어되어도 무방하다.

- [0032] 이에 따라, 상기 센싱 트랜지스터(SW2)는 상기 센싱 제어 라인(Sense) 또는 스캔 라인으로부터의 제 2 스캔 신호에 응답하여 기준 전압 라인(Vref)으로부터의 프리차징 전압을 제 2 노드(S)에 공급하거나, 센싱 기간 동안 발광 소자(OLED)의 애노드 전극(28)의 전압을 기준 전압 라인(Vref)에 공급한다.

- [0033] 상기 스토리지 커패시터(Cst)는 제 1 노드(N)에 제 1 단자가 접속되고, 제 2 노드(S)에 제 2 단자가 접속된다. 상기 스토리지 커패시터(Cst)는 제 1 및 제 2 노드(N, S) 각각에 공급되는 전압들 간의 차 전압을 충전하여 상기 구동 트랜지스터(D-TFT)의 구동 전압(Vgs)으로 공급한다. 예를 들어, 상기 스토리지 커패시터(Cst)는 제 1 및 제 2 노드(N, S) 각각에 공급되는 데이터 전압(Vdata)과 프리차징(Vpre) 간의 차 전압을 충전한다.

- [0034] 여기서, 상기 구동 트랜지스터(D-TFT)에는 백 바이어스 게이트 전극이 형성되어 백 바이어스 라인(Vbias)에 연결된다.

- [0035] 상기 바이어스 라인(Vbias)을 통해 일정한 전위를 제공하므로, 픽셀 사이즈가 작아지더라도 계조를 넓은 범위의 입력 전압 값으로 조절이 가능하여 더 세분화된 계조를 표현할 수 있다.

- [0036] 상기 도 3에 도시한 바와 같이, 상기 백 바이어스 게이트 전극에 일정한 전위의 백 바이어스를 인가하기 위한 바이어스 라인(Vbias)이 데이터 라인(Vdata)과 넓은 영역에서 중첩 되도록 하여 바이어스 라인(Vbias)이 데이터 라인(Vdata)의 전위를 차폐하므로 데이터 라인(Vdata)이 구동 트랜지스터(D-TFT)에 미치는 영향을 줄일 수 있다.

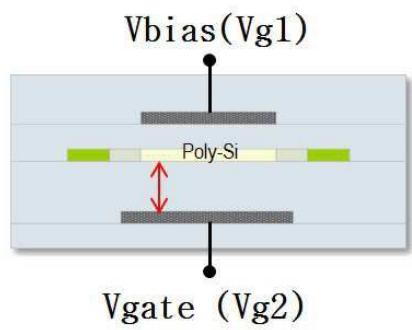

- [0037] 또한, 도 4에 도시한 바와 같이, 구동 트랜지스터는 게이트 전극(3), 활성층(5c) 및 백 바이어스 게이트 전극(7a)로 구성된다. 이와 같은 구조에서, 상기 게이트 전극(3)과 활성층(5c) 사이의 게이트 절연막(4)은 약 3000 Å 정도의 두께로 형성하고, 상기 백 바이어스 게이트 전극(7a)과 상기 활성층(5c) 사이의 게이트 절연막(6)을 약 1000Å 정도의 두께로 형성하면, 계조를 표현할 수 있는 범위를 증가시킬 수 있다. 도 4의 나머지 구성은 6a 내지 6i에서 설명된다.

- [0038] 물론, 상기와 같이, 상기 게이트 절연막(4)의 두께를 상기 게이트 절연막(6)의 두께보다 더 크게 형성하는 것이 계조 표현의 범위를 더 증가시킬 수 있지만, 상기 게이트 절연막(4)과 상기 게이트 절연막(6)의 두께를 동일하게 하여도 계조 표현의 범위를 증가시킬 수 있다. 즉, 상기 게이트 절연막(4)의 두께가 상기 게이트 절연막(6)의 두께보다 더 크거나 같을 수 있다.

- [0039] 이와 같은 구성을 갖는 단위 서브 픽셀의 제조 방법을 설명하면 다음과 같다.

- [0040] 도 5a 내지 5i는 본 발명에 따른 유기 발광 다이오드 표시 장치의 제조 방법을 설명하기 위한 공정 레이아웃도이고, 도 6a 내지 6i는 본 발명에 따른 유기 발광 다이오드 표시 장치의 제조 방법을 설명하기 위한 공정 단면도이다.

- [0041] 즉, 상기 도 5a 내지 5i는 본 발명에 따른 단위 서브 픽셀의 제조 방법을 설명하기 위한 공정 레이아웃도이고, 도 6a 내지 6i는 본 발명에 따른 단위 서브 픽셀 중 구동 트랜지스터의 제조 방법을 설명하기 위한 공정 단면도이다.

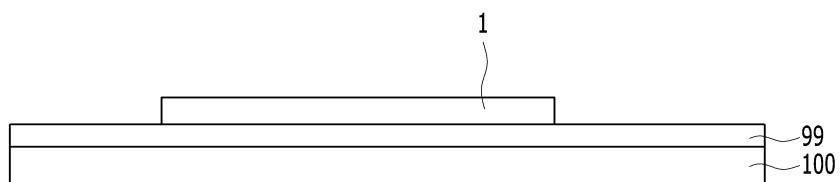

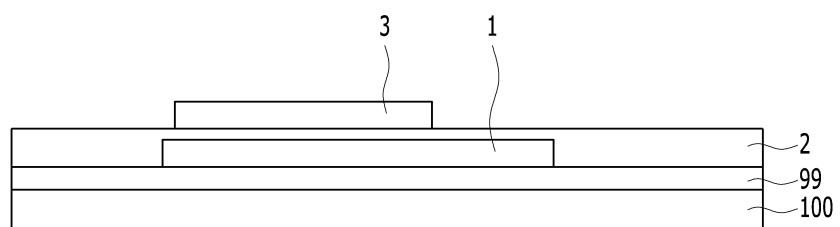

- [0042] 도 5a 및 도 6a에 도시한 바와 같이, 기판(100)상에 약 3000Å 정도의 베퍼층(99)을 형성하고, 상기 베퍼층(99)상에 금속층(Mo)을 약 500Å 정도의 두께로 증착하고 선택적으로 제거하여 스토리지 커페시터(Cst)의 제 1 전극(1)을 형성한다.

- [0043] 도 5b 및 도 6b에 도시한 바와 같이, 상기 제 1 전극(1)이 형성된 기판(100) 전면에 스토리지 커페시터(Cst)용 유전체막(2, SiNx)을 약 1000Å 정도의 두께로 형성한다. 그리고, 상기 유전체막(2)위에 금속층(Mo)을 약 500Å 정도의 두께로 증착하고 선택적으로 제거하여 상기 제 1 전극(1)에 중첩되도록 상기 유전체막(2)위에 구동 트랜지스터(D-TFT)의 게이트 전극(3)을 형성한다. 이 때, 상기 게이트 전극(3)은 상기 스토리지 커페시터(Cst)의 제 2 전극 역할도 한다.

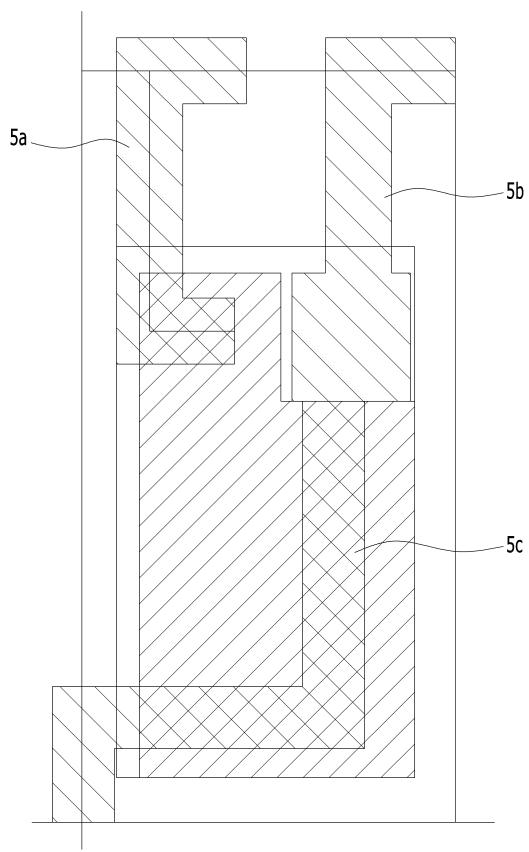

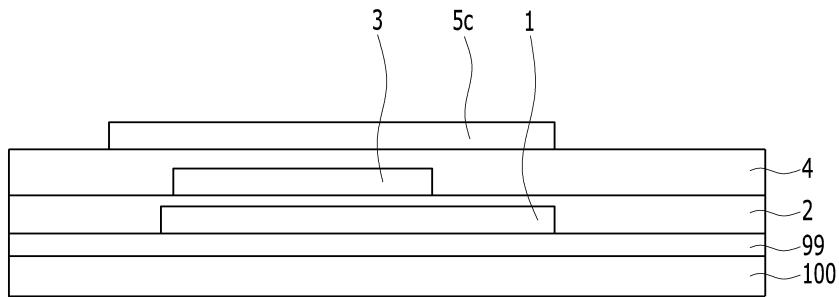

- [0044] 도 5c 및 도 6c에 도시한 바와 같이, 상기 게이트 전극(3)을 포함한 기판 전면에 게이트 절연막(SiO<sub>2</sub>)(4) 및 반도체층(a-Si)을 순차적으로 적층한다. 상기 반도체층을 선택적으로 제거하여 상기 스위칭 트랜지스터(SW1)의 활성층(5a), 상기 센싱 트랜지스터(SW2)의 활성층(5b) 및 상기 구동 트랜지스터(D-TFT)의 활성층(5c)을 형성한다. 여기서, 상기 게이트 절연막(4)은 약 1000Å 내지 4500Å (예를들면 3000Å)의 두께로 형성하고, 상기 활성층(5a, 5b, 5c)은 300Å 내지 800Å (예를들면 500Å)의 두께로 형성한다.

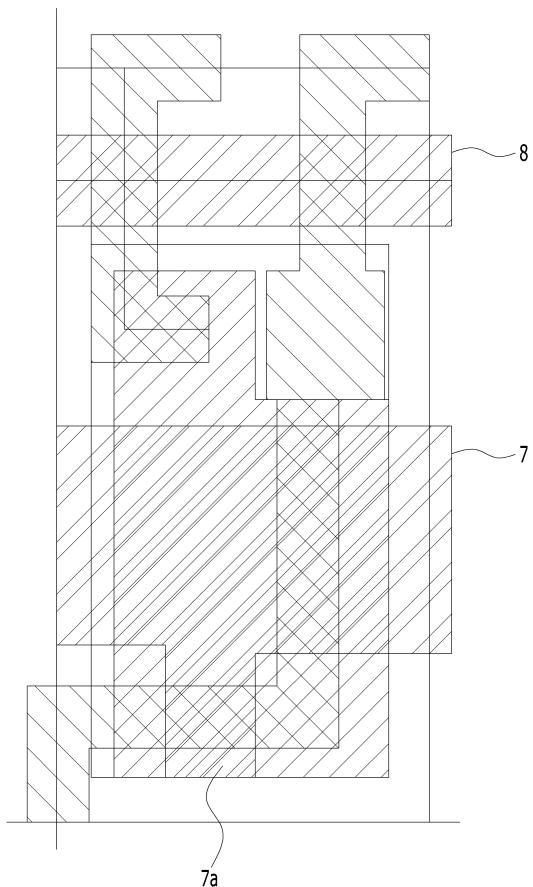

- [0045] 도 5d 및 도 6d에 도시한 바와 같이, 상기 활성층(5a, 5b, 5c)을 포함한 기판 전면에 백 바이어스용, 상기 스위칭 트랜지스터(SW1) 및 센싱 트랜지스터(SW2)용 게이트 절연막(6)을 500Å 내지 1500Å (예를들면 1000Å)의 두께로 형성한다. 그리고, 금속층(Mo)을 증착하고 선택적으로 제거하여, 상기 활성층(5a, 5b, 5c)을 가로지르도록 스캔 라인(8) 그리고 백 바이어스 라인(7) 및 백 바이어스 게이트 전극(7a)를 형성한다.

- [0046] 즉, 상기 스캔 라인(8)은 상기 활성층(5a, 5b)를 가로지르도록 형성되어 상기 스위칭 트랜지스터(SW1) 및 상기 센싱 트랜지스터(SW2)를 형성하고, 상기 백 바이어스 라인(7) 및 백 바이어스 게이트 전극(7a)은 상기 활성층(5c)을 가로지르도록 형성하여 구동 트랜지스터(D-TFT)의 백 바이어스 게이트 전극(7a) 및 백 바이어스 라인(7, Vbias)을 형성한다.

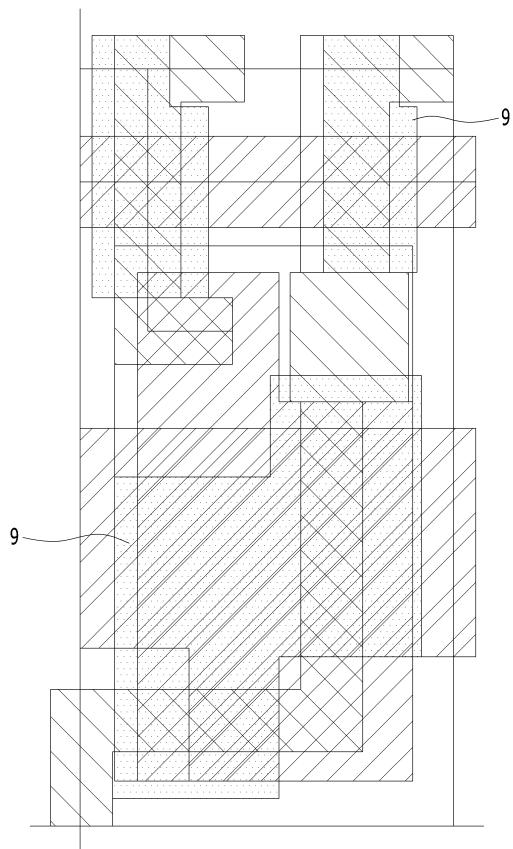

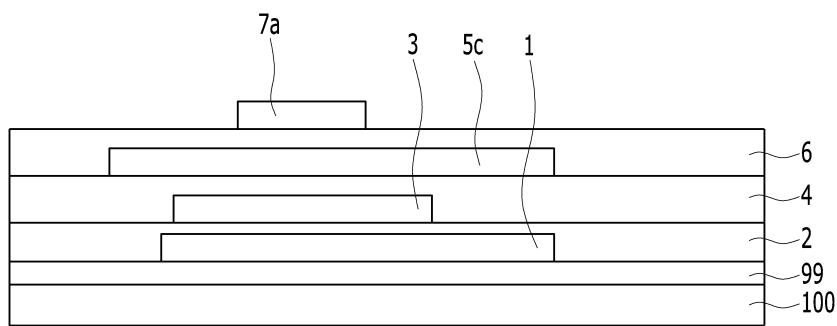

- [0047] 도 5e 및 도 6e에 도시한 바와 같이, 상기 스캔 라인(8) 그리고 백 바이어스 라인(7) 및 백 바이어스 게이트 전극(7a)이 형성된 기판상의 상기 활성층(5a, 5b, 5c)의 채널 부분이 커버되도록 감광막 패턴(9)을 형성하고, 상

기 감광막 패턴(9)을 마스크로 이용하여 상기 활성층(5a, 5b, 5c)에 N형 불순물을 고농도로 주입한다. 그리고, 상기 감광막 패턴(9)을 제거하고, 상기 스캔 라인(8) 그리고 백 바이어스 라인(7) 및 백 바이어스 게이트 전극(7a)를 마스크로 이용하여 상기 활성층(5a, 5b, 5c)에 N형 불순물을 저농도로 주입하여 각 트랜지스터(SW1, SW2, D-TFT)의 LDD 구조의 소오스/드레인 영역(N+)(10a, 10b)을 형성한다.

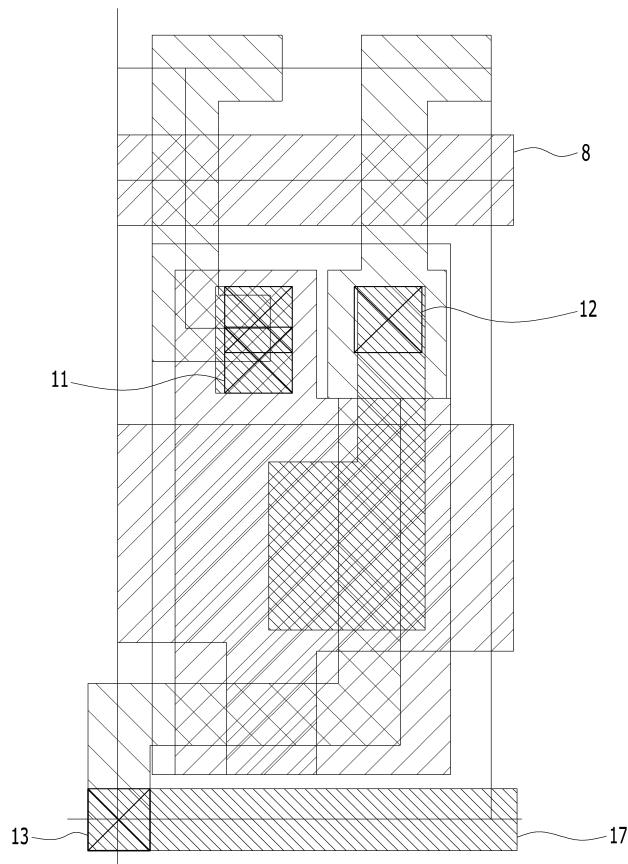

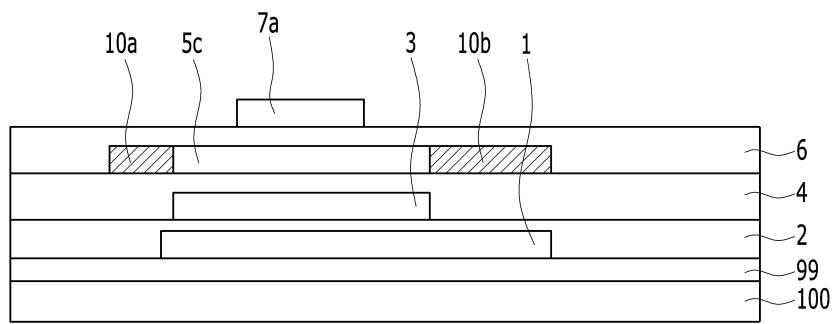

[0048] 도 5f 및 도 6f에 도시한 바와 같이, 상기 스캔 라인(8) 그리고 백 바이어스 라인(7) 및 백 바이어스 게이트 전극(7a)이 형성된 기판 전면에 층간 절연막(11, SiNx)을 약 2000 Å 정도의 두께로 형성한다. 그리고, 상기 스위칭 트랜지스터(SW1)의 소오스/드레인 영역, 상기 센싱 트랜지스터(SW2)의 소오스/드레인 영역 및 상기 구동 트랜지스터(D-TFT)의 소오스/드레인 영역에 각각 콘택홀(11, 12, 13)을 형성한다.

[0049] 그리고, 상기 각각 콘택홀(11, 12, 13)이 채워지도록 상기 층간 절연막(11)상에 금속층을 증착하고 패터닝하여 제 1 내지 제 3 금속 플러그(제 1 금속 플러그는 도시되지 않음, 15, 16) 및 고전위 구동 전압 공급 라인(17, 도 2의 Vdd 참조)을 형성한다.

[0050] 상기 제 1 금속 플러그(도면에는 도시되지 않음)는 상기 스위칭 트랜지스터(SW1)의 소오스/드레인 영역과 상기 구동 트랜지스터(D-TFT)의 게이트 전극(3)을 연결하고, 상기 제 2 금속 플러그(15)는 상기 센싱 트랜지스터(SW2) 및 구동 트랜지스터(D-TFT)의 소오스/드레인 영역(10b)과 상기 스토리지 커페시터(Cst)의 제 1 전극(1)을 연결하며, 상기 제 3 금속 플러그(16)는 상기 구동 트랜지스터(D-TFT)의 소오스/드레인 영역(10a)과 상기 고전위 구동 전압 공급 라인(17)을 연결한다.

[0051] 여기서, 상기 제 1 금속 플러그(14)가 도 2의 제 1 노드(N)에 해당되고, 상기 제 2 금속 플러그(15)가 도 2의 제 2 노드(S)에 해당된다.

[0052] 또한, 상기 제 2 금속 플러그(15)는 상기 백 바이어스 게이트 전극(7a)쪽으로 연장되어 형성된다.

[0053] 도 5g 및 도 6g에 도시한 바와 같이, 상기 제 1 내지 제 3 금속 플러그(14, 15, 16) 및 고전위 구동 전압 공급 라인(17)이 형성된 기판 전면에 제 1 보호막(18)을 형성하고, 상기 스위칭 트랜지스터(SW1)의 소오스/드레인 영역, 상기 센싱 트랜지스터(SW2)의 소오스/드레인 영역 및 상기 제 2 금속 플러그(15)상에 각각 콘택홀(19, 20, 21)을 형성한다.

[0054] 그리고, 전면에 금속층을 증착하고 선택적으로 제거하여, 상기 스위칭 트랜지스터(SW1)의 소오스/드레인 영역에 연결되도록 데이터 라인(22, 도 2의 Vdata 참조)을 형성하고, 상기 센싱 트랜지스터(SW2)의 소오스/드레인 영역에 연결되도록 기준 전압 라인(23, 도 2의 Vref 참조)을 형성하며, 상기 제 2 금속 플러그(15)에 연결되도록 제 4 금속 플러그(24)를 형성한다.

[0055] 도 5h 및 도 6h에 도시한 바와 같이, 상기와 같이 형성된 기판 전면에 제 2 보호막(25) 및 평탄화막(26)을 형성하고, 상기 제 4 금속 플러그(24)상에 콘택홀(27)을 형성한다.

[0056] 도 5i 및 도 6i에 도시한 바와 같이, 상기 평탄화막(26)위에 금속층을 증착하고 선택적으로 제거하여 상기 콘택홀(27)을 통해 상기 제 4 금속 플러그(24)와 전기적으로 연결되도록 OLED의 애노드 전극(28)을 형성하고, 도면에도는 도시되지 않았지만, 상기 애노드 전극(28)상에 발광층 및 상기 OLED의 캐소드 전극을 차례로 형성한다.

[0057] 이상에서 설명한 바와 같이, 본 발명에 따른 유기 발광 다이오드 표시장치를 제조한다.

[0058] 도 7은 본 발명에 따른 유기 발광 다이오드 표시장치의 스캔 라인과 백 바이어스 라인을 도시한 레이 아웃도이다.

[0059] 도 7에 도시한 바와 같이, 단위 서브 픽셀이 상하좌우 대칭되도록 어레이가 배치되는 경우, 복수개의 스캔 라인(Scan n, Scan (n+1)과 복수개의 백 바이어스 라인(Back Bias)은 서로 평행하게 배치되고, 상기 복수개의 백 바이어스 라인은 외곽 영역에서 콘택홀을 통해 별도의 금속 라인(Metal line)에 연결되어 백 바이어스 전류를 공급할 수 있다.

[0060] 도 8a는 종래 구조의 구동 박막트랜지스터의 게이트 전압(Vgs)의 범위를 나타낸 그래프이고, 도 8b는 본 발명에 따른 구동 박막트랜지스터의 게이트 전압(Vgs)의 범위를 나타낸 그래프이다.

[0061] 도 8a 및 8b에서 알 수 있는 바와 같이, 본 발명은 구동 트랜지스터에 백 바이어스 게이트 전극을 형성하고 상기 백 바이어스 게이트 전극에 일정한 바이어스 전류를 인가한다. 따라서, 종래에는 픽셀 사이즈가 1500ppi 정도로 작아짐에 따라 계조를 표현할 수 있는 입력 데이터 범위가 1.2V에 불과하였으나, 본 발명에서는 픽셀 사이즈가 1500ppi 정도로 작아지더라도 계조를 표현할 수 있는 입력 데이터 범위가 3V 정도로 크게 증가 하였다.

- [0062] 이와 같이, 본 발명에서는 계조를 표현할 수 있는 입력 데이터 범위가 3V 정도로 크게 증가하는 이유를 설명하면 다음과 같다.

- [0063] 도 9는 본 발명에 따른 입력 데이터 범위가 증가하는 이유를 설명하기 위한 커패시터 모델을 도시한 것이다.

- [0064] 박막트랜지스터의 게이트 전압의 기울기의 역수를 S-팩터(factor)로 표현한다.

- [0065] 상기 S-팩터는 다음의 [수학식 1]과 같이 근사될 수 있다.

### 수학식 1

$$S = \frac{dVg}{d \log(Id)} = kT/q * \ln(10) * 1 / (d\Phi_s/dVg)$$

- [0066]

- [0067] 본 발명의 구동 트랜지스터(D-TFT)는 활성층(5c) 양쪽에 각각 게이트 절연막(4) 및 게이트 절연막(6)을 사이에 두고 게이트 전극(3) 및 백 바이어스 게이트 전극(7a)이 형성된다.

- [0068] 이와 같은 구조에서, 상기 게이트 전극(3)과 활성층(5c) 사이의 게이트 절연막(4)과 상기 백 바이어스 게이트 전극(7a)과 상기 활성층(5c) 사이의 게이트 절연막(6)의 두께를 조정하여 상기 S-팩터를 바꿀 수 있는 특징을 가지고 있다.

- [0069] 상기 활성층(5c)이 완전 결핍(Fully depletion) 조건을 만족하도록 상기 백 바이어스 전압을 인가하여 상기 구동 트랜지스터를 작동시킬 경우, 본 발명에 따른 구동 트랜지스터에 따른 커패시터 모델은 도 9와 같다.

- [0070] 도 9에서, Vg1은 백 바이어스 게이트 전극(7a)에 인가되는 게이트 전압이고, Vg2은 게이트 전극(3)에 인가되는 게이트 전압이며, ?s1은 상기 활성층(5c)의 탑(Top) 부분의 채널 전위이고, ?s2는 상기 활성층(5c)의 바텀(Bottom) 부분의 채널 전위이다.

- [0071] 상기 백 바이어스 게이트 전극(7a)에 인가되는 게이트 전압(Vg1)을 가변 시켰을 때 상기 활성층(5c)의 탑(Top) 부분의 채널 전위( ?s1)은 다음의 [수학식 2]와 같다.

### 수학식 2

$$\frac{d\Phi_s1}{dVg1} = \frac{1/C_{si} + 1/C_{ox2}}{(1/C_{ox1} + 1/C_{si} + 1/C_{ox2})}$$

- [0072]

- [0073] 또한, 상기 게이트 전극(3)에 인가되는 게이트 전압(Vg2)을 가변 시켰을 때 상기 활성층(5c)의 바텀 부분의 채널 전위( ?s2)은 다음의 [수학식 3]와 같다.

### 수학식 3

$$\frac{d\Phi_s2}{dVg2} = \frac{1/C_{si} + 1/C_{ox1}}{(1/C_{ox1} + 1/C_{si} + 1/C_{ox2})}$$

- [0074]

- [0075] 상기 [수학식 2] 및 [수학식 3]에서 게이트 전압(Vg1, Vg2)에 따라 채널의 전위가 변하는 것을 살펴보면, 상대적으로 백 바이어스가 걸리는 게이트 절연막(6)의 영향을 크게 받는 것으로 나타난다. 즉, 백 바이어스 게이트 전극(7a)로 구동했을 때 S-팩터(St)와, 게이트 전극(3)으로 구동했을 때 S-팩터(Sb)의 비율을 구하면 다음과 같다.

## 수학식 4

$$St = kT/q * \ln(10) * 1 / (d\Phi s_1/dVg_1), Sb = kT/q * \ln(10) * 1 / (d\Phi s_2/dVg_2)$$

$$Sb/St = [d\Phi s_1/dVg_1] / [d\Phi s_2/dVg_2] = (1/C_{Si} + 1/C_{ox2}) / (1/C_{Si} + 1/C_{ox1})$$

[0076]

[0077] 여기서, 상술한 바와 같이, 상기 게이트 절연막(6)의 두께를 1000Å로 형성하고, 상기 게이트 절연막(4)의 두께를 3000Å로 형성한 경우에, 상기 S-팩터의 비율을 유추해 보면 다음과 같다.

[0078]

편의상 상기 게이트 절연막(6)의 두께가 1000Å이었을 때의 상기 게이트 절연막(6)의 커파시턴스 값을 Cox라고 가정하면,

## 수학식 5

$$C_{ox1} = Cox, C_{ox2} = 1/3 * Cox, C_{Si} = 6 Cox \text{ (활성층의 두께가 } 500\text{Å, } \epsilon_{Si} = 11.7, \epsilon_{ox} =$$

3.9 적용)이고,

$$Sb/St = (1/C_{Si} + 1/C_{ox2}) / (1/C_{Si} + 1/C_{ox1}) = [1/(6Cox) + 3/Cox] / [1/(6Cox) + 1/Cox]$$

$$= (1/6 + 3) / (1/6 + 1) = 2.70 \text{이다.}$$

[0079]

[0080] 상기 게이트 절연막(4)의 두께가 상기 게이트 절연막(6)의 두께보다 약 3배 두꺼울 경우, S-팩터가 약 2.7배 커짐을 알 수 있다.

[0081]

상기 [수학식 5]은, 상기 활성층(5c)이 완전 결핍(Fully depletion) 조건을 만족하도록 상기 백 바이어스 전압을 인가할 경우의 수학식이기 때문에,

[0082]

게이트 절연막이 두꺼운 쪽을 게이트 전극으로 하고 게이트 절연막이 얇은 쪽을 백 바이어스 게이트 전극으로 하여 상기 백 바이어스 게이트 전극에 백 바이어스 전압을 가하면 S-팩터가 큰 박막트랜지스터를 형성할 수 있다.

[0083]

일 예로, 상기 게이트 절연막(6)과 게이트 절연막(4)의 두께 비가 1000Å/1500Å였을 때는 S-팩터 비(Sb/St)는  $Sb/St = (1/6 + 1.5) / (1/6 + 1) = 1.4$ 이고, 상기 게이트 절연막(6)과 게이트 절연막(4)의 두께 비가 1000Å/2000Å였을 때 S-팩터 비(Sb/St)는  $Sb/St = (1/6 + 2) / (1/6 + 1) = 1.9$  정도이다.

[0084]

[0084] 지금까지의 설명에서는 구동 트랜지스터가 바텀 게이트형 구조임을 설명하였으나, 이에 한정되지 않고, 상기 구동 트랜지스터가 텁 게이트형 구조를 갖고, 백 바이어스 게이트 전극이 구동 트랜지스터의 바텀에 형성되어도 무방하다.

[0085]

이와 같은 구조에서도, 활성층과 게이트 전극 간의 게이트 절연막의 두께가 상기 활성층과 상기 백 바이어스 게이트 전극 간의 게이트 절연막의 두께보다 크거나 같으면 된다.

[0086]

이상에서 설명한 본 발명은 상술한 실시예 및 첨부된 도면에 한정되는 것이 아니고, 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 여러 가지 치환, 변형 및 변경이 가능하다는 것이 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 있어 명백할 것이다.

## 부호의 설명

1: 제 1 전극 2: 유전체막

3: 게이트 전극 4: 게이트 절연막

5a, 5b, 5c: 활성층 6: 게이트 절연막

7: 바이어스 라인 7a: 백 바이어스 게이트 전극

8: 스캔 라인 9: 감광막 패턴

10a, 10b: 소오스/드레인 영역 11, 12, 13, 19, 20, 21, 27: 콘택홀

15, 16, 24: 금속 플리그 17: 고전위 구동 전압 공급 라인

18, 25: 보호막 22: 데이터 라인

23: 기준 전압 라인 26: 평탄화막

28: 애노드 전극 30: 충간 절연막

## 도면

### 도면1a

### 도면1b

## 도면2

## 도면3

도면4

도면5a

도면5b

도면5c

도면5d

도면5e

도면5f

도면5g

도면5h

도면5*i*

도면6*a*

도면6*b*

도면6c

도면6d

도면6e

도면6f

도면6g

도면6h

도면6i

도면7

도면8a

도면8b

도면9

|                |                                                                                                              |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 驱动晶体管，具有该晶体管的有机发光二极管显示装置及其制造方法                                                                               |         |            |

| 公开(公告)号        | <a href="#">KR1020180024909A</a>                                                                             | 公开(公告)日 | 2018-03-08 |

| 申请号            | KR1020160111945                                                                                              | 申请日     | 2016-08-31 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                     |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                                    |         |            |

| [标]发明人         | LEE KYUNG EON<br>이경언<br>YUN MIN SEONG<br>윤민성                                                                 |         |            |

| 发明人            | 이경언<br>윤민성                                                                                                   |         |            |

| IPC分类号         | H01L27/32 H01L27/12 H01L29/06 H01L29/10 H01L51/56                                                            |         |            |

| CPC分类号         | H01L27/3262 H01L27/3265 H01L27/1251 H01L27/3276 H01L27/124 H01L51/56 H01L2251/558<br>H01L29/0661 H01L29/1025 |         |            |

| 代理人(译)         | Bakyoungbok                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                    |         |            |

### 摘要(译)

[0001]本发明涉及一种即使在像素尺寸小时也能够将灰度调节到宽范围的输入电压值的驱动晶体管，从而表现出更精细的灰度，具有该驱动晶体管的有机发光显示器及其制造方法。栅电极和有源层之间的第一栅极绝缘膜，以及背偏置栅电极和有源层之间的第二栅极绝缘膜，其中第一栅极绝缘膜，第二栅极绝缘膜，栅极绝缘膜的厚度大于或等于第二栅极绝缘膜的厚度。