공개특허 10-2020-0082662

(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2020-0082662

(43) 공개일자 2020년07월08일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/3233* (2016.01) *G06K 9/00* (2006.01)

(52) CPC특허분류

*G09G 3/3233* (2013.01)

*G06K 9/0004* (2013.01)

(21) 출원번호 10-2018-0173480

(22) 출원일자 2018년12월31일

심사청구일자 없음

- (71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

한양대학교 산학협력단

서울특별시 성동구 왕십리로 222(행당동, 한양대

학교내)

(72) 발명자

최병덕

서울특별시 강동구 천호대로 1089, 1102동 501호

(천호동, 강동역 신동아 파밀리에)

유용상

서울특별시 강남구 선릉로 221, 402동 703호(도곡

동, 도곡렉슬아파트)

(뒷면에 계속)

(74) 대리인

특허법인 정안

전체 청구항 수 : 총 8 항

(54) 발명의 명칭 광학 지문 센싱 회로를 포함한 화소 회로, 화소 회로의 구동 방법, 및 유기 발광 표시 장치

**(57) 요약**

본 발명은 광학 지문 센싱 회로를 포함한 화소 회로, 광학 지문 센싱 회로를 포함한 화소 회로의 구동 방법 및 광학 지문 센싱 회로를 포함한 화소 회로를 포함하는 표시 장치에 관한 것이다. 광학 지문 센싱 회로를 포함한 화소회로는 빛을 수신하여 제 1 신호를 생성하는 제 1 수광 소자, 빛을 수신하여 제 2 신호를 생성하는 제 2 수광 소자 및 상기 제 1 신호와 상기 제 2 신호의 차분 신호를 수신하여 출력 신호를 출력하고, 적어도 하나의 트랜지스터 성분과 적어도 하나의 캐패시터 성분을 포함하고, 데이터 신호에 기초하여 빛을 출력하는 자발광 소자를 포함하는 화소 제어회로를 포함한다.

**대 표 도** - 도3

(52) CPC특허분류

G09G 2300/046 (2013.01)

G09G 2354/00 (2013.01)

(72) 발명자

김용덕

서울특별시 노원구 동일로227길 25, 1102동 906호

(상계동, 상계주공11단지아파트)

문정민

경기도 파주시 월롱면 엘지로 245

정순신

경기도 파주시 월롱면 엘지로 245

**송문봉**

경기도 파주시 월롱면 엘지로 245

**정지환**

경기도 파주시 월롱면 엘지로 245

**장기석**

경기도 파주시 월롱면 엘지로 245

## 명세서

### 청구범위

#### 청구항 1

광학 지문 센싱 회로를 포함한 화소회로로서,

상기 화소회로는,

화상을 표시하는 자발광 소자; 상기 자발광 소자에서 출사되어 사용자의 지문을 통해 반사된 광을 수광하여 광 전류로 변환하는 수광소자; 및 화소 제어회로; 를 포함하고,

상기 수광소자는, 제 1 신호를 생성하는 제 1 수광 소자; 및 제 2 신호를 생성하는 제 2 수광 소자를 포함하고,

상기 화소 제어회로는 상기 제 1 신호와 상기 제 2 신호를 연산하여 출력 신호를 생성하고, 적어도 하나의 트랜지스터 성분과 적어도 하나의 캐패시터 성분을 포함하는 화소회로.

#### 청구항 2

제 1항에 있어서,

상기 화소 제어회로는,

상기 제 1 신호와 상기 제 2 신호를 차분하여 노이즈 신호가 제거된 출력신호를 생성하는 것을 특징으로 하는 화소회로.

#### 청구항 3

제 1 항에 있어서,

상기 화소 제어회로는 제 1 트랜지스터, 제 2 트랜지스터, 제 3 트랜지스터, 제 4 트랜지스터, 제 5 트랜지스터, 제 6 트랜지스터, 제 7 트랜지스터, 제 1 캐패시터 및 제 2 캐패시터를 더 포함하고,

상기 제 1 트랜지스터의 제 1 단자는 데이터라인에 연결되고, 상기 제 1 트랜지스터의 제 2 단자는 제 1 노드에 연결되고, 상기 제 1 트랜지스터의 게이트 단자는 n 번째 스캔라인에 연결되고,

상기 제 2 트랜지스터의 제 1 단자는 제 2 노드에 연결되고, 상기 제 2 트랜지스터의 제 2 단자는 제 3 노드에 연결되고, 상기 제 2 트랜지스터의 게이트 단자는 제 4 노드에 연결되고,

상기 제 3 트랜지스터의 제 1 단자는 상기 제 4 노드에 연결되고, 상기 제 3 트랜지스터의 제 2 단자는 상기 제 3 노드에 연결되고, 상기 제 3 트랜지스터의 게이트 단자는 n-1 번째 스캔라인에 연결되고,

상기 제 4 트랜지스터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 4 트랜지스터의 제 2 단자는 상기 제 2 수광 소자의 캐소드(Cathode) 단자에 연결되고, 상기 제 4 트랜지스터의 게이트 단자는 제 1 센싱(sensing) 라인에 연결되고,

상기 제 5 트랜지스터의 제 1 단자는 상기 제 1 수광 소자의 아노드 단자에 연결되고, 상기 제 5 트랜지스터의 제 2 단자는 상기 제 1 노드에 연결되고, 상기 제 5 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고,

상기 제 6 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 6 트랜지스터의 제 2 단자는 접지되고, 상기 제 6 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고,

상기 제 7 트랜지스터의 제 1 단자는 상기 제 2 노드에 연결되고, 상기 제 7 트랜지스터의 제 2 단자는 출력 라인에 연결되고, 상기 제 7 트랜지스터의 게이트 단자는 제 2 센싱 라인에 연결되고,

상기 제 1 캐패시터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 1 캐패시터의 제 2 단자는 상기 제 4 노드에 연결되고,

상기 제 2 캐패시터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 2 캐패시터의 제 2 단자는 접지되고,

상기 제 1 수광 소자의 캐소드 단자는 전원(VDD)에 연결되고, 상기 제 2 수광 소자는 접지되는 것을 특징으로 하는 화소회로.

#### 청구항 4

제 3 항에 있어서,

상기 화소 제어회로는 제 8 트랜지스터, 제 9 트랜지스터, 및 제 10 트랜지스터를 더 포함하고,

상기 제 8 트랜지스터의 제 1 단자는 전원(VDD)에 연결되고, 상기 제 8 트랜지스터의 제 2 단자는 상기 제 1 노드에 연결되고, 상기 제 8 트랜지스터의 게이트 단자는 상기 n-1 번째 스캔라인에 연결되고,

상기 제 9 트랜지스터의 제 1 단자는 상기 전원에 연결되고, 상기 제 9 트랜지스터의 제 2 단자는 상기 제 2 노드에 연결되고, 상기 제 9 트랜지스터의 게이트 단자는 제 1 에미션(emission)라인에 연결되고,

상기 제 10 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 10 트랜지스터의 제 2 단자는 상기 자발광 소자의 아노드 단자에 연결되고, 상기 제 10 트랜지스터의 게이트 단자는 제 2 에미션 라인에 연결되고,

상기 자발광 소자의 캐소드 단자는 접지되는 것을 특징으로 하는 화소회로.

#### 청구항 5

제 1 항에 있어서,

상기 화소 제어회로는 제 1 트랜지스터, 제 2 트랜지스터, 제 3 트랜지스터, 제 4 트랜지스터, 제 5 트랜지스터, 제 6 트랜지스터 및 제 7 트랜지스터를 더 포함하고,

상기 제 1 트랜지스터의 제 1 단자는 데이터라인에 연결되고, 상기 제 1 트랜지스터의 제 2 단자는 제 1 노드에 연결되고, 상기 제 1 트랜지스터의 게이트 단자는 n 번째 스캔라인에 연결되고,

상기 제 2 트랜지스터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 2 트랜지스터의 제 2 단자는 제 2 노드에 연결되고, 상기 제 2 트랜지스터의 게이트 단자는 제 3 노드에 연결되고,

상기 제 3 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 3 트랜지스터의 제 2 단자는 상기 제 2 노드에 연결되고, 상기 제 3 트랜지스터의 게이트 단자는 상기 n 번째 스캔라인에 연결되고,

상기 제 4 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 4 트랜지스터의 제 2 단자는 상기 제 2 수광 소자의 캐소드(Cathode) 단자에 연결되고, 상기 제 4 트랜지스터의 게이트 단자는 제 1 센싱(sensing) 라인에 연결되고,

상기 제 5 트랜지스터의 제 1 단자는 상기 제 1 수광 소자의 아노드(Anode) 단자에 연결되고, 상기 제 5 트랜지스터의 제 2 단자는 상기 제 3 노드에 연결되고, 상기 제 5 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고,

상기 제 6 트랜지스터의 제 1 단자는 상기 제 2 노드에 연결되고, 상기 제 6 트랜지스터의 제 2 단자는 접지되고, 상기 제 6 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고,

상기 제 7 트랜지스터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 7 트랜지스터의 제 2 단자는 출력 라인에 연결되고, 상기 제 7 트랜지스터의 게이트 단자는 제 2 센싱 라인에 연결되고,

상기 제 1 수광 소자의 캐소드 단자는 전원(VDD)에 연결되고, 상기 제 2 수광 소자의 아노드 단자는 접지되는 것을 특징으로 하는 화소회로.

#### 청구항 6

제 5 항에 있어서,

상기 화소 제어회로는 제 8 트랜지스터, 제 9 트랜지스터, 제 10 트랜지스터, 및 제 11 트랜지스터를 더 포함하고,

상기 제 8 트랜지스터의 제 1 단자는 초기화라인에 연결되고, 상기 제 8 트랜지스터의 제 2 단자는 상기 제 3 노드에 연결되고, 상기 제 8 트랜지스터의 게이트 단자는 n-1 번째 스캔라인에 연결되고,

상기 제 9 트랜지스터의 제 1 단자는 초기화라인에 연결되고, 상기 제 9 트랜지스터의 제 2 단자는 상기 자발광 소자의 아노드(anode) 단자에 연결되고, 상기 제 9 트랜지스터의 게이트 단자는 상기 n-1 번째 스캔라인에 연결되고,

상기 제 10 트랜지스터의 제 1 단자는 상기 전원에 연결되고, 상기 제 10 트랜지스터의 제 2 단자는 상기 제 1 노드에 연결되고, 상기 제 10 트랜지스터의 게이트 단자는 에미션(emission)라인에 연결되고,

상기 제 11 트랜지스터의 제 1 단자는 상기 제 2 노드에 연결되고, 상기 제 11 트랜지스터의 제 2 단자는 상기 자발광 소자의 아노드 단자에 연결되고, 상기 제 11 트랜지스터의 게이트 단자는 상기 에미션 라인에 연결되고,

상기 캐패시터의 제 1 단자는 상기 전원에 연결되고, 상기 캐패시터의 제 2 단자는 상기 제 3 노드에 연결되고,

상기 자발광 소자의 캐소드 단자는 접지되는 것을 특징으로 하는 화소회로.

## 청구항 7

제 1 항에 있어서,

상기 화소 제어회로는 제 1 트랜지스터, 제 2 트랜지스터, 제 3 트랜지스터, 제 4 트랜지스터, 제 5 트랜지스터 및 제 6 트랜지스터를 더 포함하고,

상기 제 1 트랜지스터의 제 1 단자는 데이터라인에 연결되고, 상기 제 1 트랜지스터의 제 2 단자는 제 1 노드에 연결되고, 상기 제 1 트랜지스터의 게이트 단자는 n번째 스캔라인에 연결되고,

상기 제 2 트랜지스터의 제 1 단자는 제 2 노드에 연결되고, 상기 제 2 트랜지스터의 제 2 단자는 제 3 노드에 연결되고, 상기 제 2 트랜지스터의 게이트 단자는 상기 제 1 노드에 연결되고,

상기 제 3 트랜지스터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 3 트랜지스터의 제 2 단자는 상기 제 2 수광 소자의 캐소드(Cathode) 단자에 연결되고, 상기 제 3 트랜지스터의 게이트 단자는 제 1 센싱(sensing) 라인에 연결되고,

상기 제 4 트랜지스터의 제 1 단자는 상기 제 1 수광 소자의 아노드 단자에 연결되고, 상기 제 4 트랜지스터의 제 2 단자는 상기 제 1 노드에 연결되고, 상기 제 4 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고,

상기 제 5 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 5 트랜지스터의 제 2 단자는 접지되고, 상기 제 5 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고,

상기 제 6 트랜지스터의 제 1 단자는 상기 제 2 노드에 연결되고, 상기 제 6 트랜지스터의 제 2 단자는 출력 라인에 연결되고, 상기 제 6 트랜지스터의 게이트 단자는 제 2 센싱 라인에 연결되고,

상기 제 1 수광 소자의 캐소드 단자는 전원(VDD)에 연결되고, 상기 제 2 수광 소자의 아노드 단자는 접지되는 것을 특징으로 하는 화소회로.

## 청구항 8

제 7 항에 있어서,

상기 화소 제어회로는 제 7 트랜지스터를 더 포함하고,

상기 제 7 트랜지스터의 제 1 단자는 상기 전원에 연결되고, 상기 제 7 트랜지스터의 제 2 단자는 상기 제 2 노드에 연결되고, 상기 제 7 트랜지스터의 게이트 단자는 에미션(emission)라인에 연결되고,

상기 캐패시터의 제 1 단자는 상기 전원에 연결되고, 상기 캐패시터의 제 2 단자는 상기 제 1 노드에 연결되고,

상기 자발광 소자의 아노드 단자는 상기 제 3 노드에 연결되고, 상기 자발광 소자의 캐소드 단자는 접지되는 것을 특징으로 하는 화소회로.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 광학 지문 센싱 회로를 포함한 화소 회로, 광학 지문 센싱 회로를 포함한 화소 회로의 구동 방법 및

광학 지문 센싱 회로를 포함한 화소 회로를 포함하는 표시 장치에 관한 것이다.

## 배경 기술

- [0002] 화상 표시 장치는 노트북 컴퓨터, 태블릿 파시(tablet PC), 스마트폰(smart phone), 개인 휴대용 정보 단말기(Personal Digital Assistant), 현금 자동 입출금기(Automated Teller Machine), 검색 안내 시스템 등과 같은 컴퓨터 기반 시스템(computer based system)에서 사용되고 있다. 이들 시스템에는 통상적으로 개인 사생활과 관련된 개인정보는 물론 영업정보나 영업기밀과 같이 비밀을 요하는 많은 데이터가 저장되어 있기 때문에, 이들 데이터를 보호하기 위해서는 보안을 강화해야 할 필요성이 있다.

- [0003] 이를 위해 손가락의 지문을 이용하여 시스템의 등록이나 인증을 수행함으로써 보안성을 강화할 수 있는 지문 인식 소자를 포함한 화상 표시 장치에 대한 연구가 활발히 진행되고 있다.

- [0004] 일반적으로 지문 센싱 회로를 갖는 화상 표시 장치는 광학 센싱 방식 또는 정전 용량 방식으로 지문을 인식한다.

- [0005] 광학 센싱 방식으로 지문을 인식하는 화상 표시 장치는 표시 패널에 지문 센서로써 수광 소자를 포함한 지문 인식회로가 구비된다. 상기 수광 소자는 표시 패널로부터 출사되어 지문에 의해 반사된 광을 센싱하여 광전류를 생성한다. 이때, 수광 소자로부터 발생되는 광전류의 양은 광을 반사시킨 물체가 지문의 융선(Ridge)인지 또는 골(Valley)인지에 따라 가변되고, 지문 인식회로는 광전류의 변화량을 통하여 지문의 형태를 인식한다.

- [0006] 광학 센싱 방식으로 지문을 인식하기 위해서는 500PPI 이상의 해상도를 가지는 지문인식회로가 필요하다. 따라서, 지문인식회로와 화소회로의 중복된 소자를 제거하여, 지문인식회로와 화소회로가 통합될 수 있다.

- [0007] 화소회로와 지문인식회로가 통합되는 경우, 화소회로와 지문인식회로의 거리가 가까우므로, 자발광 소자에서 출사된 빛의 상당량이 지문에 도달하지 못하고 유리 또는 전극(electrode)에 반사되어 화소회로의 수광 소자로 돌아올 수 있다. 또한 수광 소자는 표시 장치 외부로부터 입사된 빛, 예를 들면 태양광이나 실내 조명기기의 빛을 수신할 수도 있다. 이렇게 표시 패널 구조로 인하여 지문에 반사되지 않은 두가지의 직광이 지문인식회로에 입사되는 경우, 이러한 직광은 지문에 의한 반사광 보다 광량이 클 수 있기 때문에 수광 소자는 지문에 반사된 빛을 제대로 인식하지 못할 수 있고 최종적으로는 지문인식률을 떨어뜨리는 문제가 발생한다.

## 발명의 내용

### 해결하려는 과제

- [0008] 본 발명은 전술한 문제점을 해결하기 위하여 안출된 것으로, 지문에 반사되지 않은 직광에 영향을 받지 않고, 지문을 인식하는 통합된 화소회로를 제공하는 것을 기술적 과제로 한다.

### 과제의 해결 수단

- [0009] 본 발명은, 광학 지문 센싱 회로를 포함한 화소회로로서, 상기 화소회로는, 화상을 표시하는 자발광 소자; 상기 자발광 소자에서 출사되어 사용자의 지문을 통해 반사된 광을 수광하여 광전류로 변환하는 수광소자; 및 화소 제어회로;를 포함하고, 상기 수광소자는, 제 1 신호를 생성하는 제 1 수광 소자; 및 제 2 신호를 생성하는 제 2 수광 소자를 포함하고, 상기 화소 제어회로는 상기 제 1 신호와 상기 제 2 신호를 연산하여 출력 신호를 생성하고, 적어도 하나의 트랜지스터 성분과 적어도 하나의 캐패시터 성분을 포함하는 것을 특징으로 한다.

- [0010] 상기 화소 제어회로는, 상기 제 1 신호와 상기 제 2 신호를 차분하여 노이즈 신호가 제거된 출력신호를 생성하는 것을 특징으로 한다.

- [0011] 상기 화소 제어회로는 제 1 트랜지스터, 제 2 트랜지스터, 제 3 트랜지스터, 제 4 트랜지스터, 제 5 트랜지스터, 제 6 트랜지스터, 제 7 트랜지스터, 제 1 캐패시터 및 제 2 캐패시터를 더 포함하고, 상기 제 1 트랜지스터의 제 1 단자는 데이터라인에 연결되고, 상기 제 1 트랜지스터의 제 2 단자는 제 1 노드에 연결되고, 상기 제 1 트랜지스터의 게이트 단자는 n 번째 스캔라인에 연결되고, 상기 제 2 트랜지스터의 제 1 단자는 제 2 노드에 연결되고, 상기 제 2 트랜지스터의 제 2 단자는 제 3 노드에 연결되고, 상기 제 2 트랜지스터의 게이트 단자는 제 4 노드에 연결되고, 상기 제 3 트랜지스터의 제 1 단자는 상기 제 4 노드에 연결되고, 상기 제 3 트랜지스터의 제 2 단자는 상기 제 3 노드에 연결되고, 상기 제 3 트랜지스터의 게이트 단자는 n-1 번째 스캔라인에 연결되고, 상기 제 4 트랜지스터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 4 트랜지스터의 제 2

단자는 상기 제 2 수광 소자의 캐소드(Cathode) 단자에 연결되고, 상기 제 4 트랜지스터의 게이트 단자는 제 1 센싱(sensing) 라인에 연결되고, 상기 제 5 트랜지스터의 제 1 단자는 상기 제 1 수광 소자의 아노드 단자에 연결되고, 상기 제 5 트랜지스터의 제 2 단자는 상기 제 1 노드에 연결되고, 상기 제 5 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고, 상기 제 6 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 6 트랜지스터의 제 2 단자는 접지되고, 상기 제 6 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고, 상기 제 7 트랜지스터의 제 1 단자는 상기 제 2 노드에 연결되고, 상기 제 7 트랜지스터의 제 2 단자는 출력 라인에 연결되고, 상기 제 7 트랜지스터의 게이트 단자는 제 2 센싱 라인에 연결되고, 상기 제 1 캐패시터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 1 캐패시터의 제 2 단자는 상기 제 4 노드에 연결되고, 상기 제 2 캐패시터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 2 캐패시터의 제 2 단자는 접지되고, 상기 제 1 수광 소자의 캐소드 단자는 전원(VDD)에 연결되고, 상기 제 2 수광 소자는 접지되는 것을 특징으로 한다.

[0012] 또한, 상기 화소 제어회로는 제 8 트랜지스터, 제 9 트랜지스터, 및 제 10 트랜지스터를 더 포함하고, 상기 제 8 트랜지스터의 제 1 단자는 전원(VDD)에 연결되고, 상기 제 8 트랜지스터의 제 2 단자는 상기 제 1 노드에 연결되고, 상기 제 8 트랜지스터의 게이트 단자는 상기 n-1 번째 스캔라인에 연결되고, 상기 제 9 트랜지스터의 제 1 단자는 상기 전원에 연결되고, 상기 제 9 트랜지스터의 제 2 단자는 상기 제 2 노드에 연결되고, 상기 제 9 트랜지스터의 게이트 단자는 제 1 에미션(emission)라인에 연결되고, 상기 제 10 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 10 트랜지스터의 제 2 단자는 상기 자발광 소자의 아노드 단자에 연결되고, 상기 제 10 트랜지스터의 게이트 단자는 제 2 에미션 라인에 연결되고, 상기 자발광 소자의 캐소드 단자는 접지되는 것을 특징으로 한다.

[0013] 또한, 상기 화소 제어회로는 제 1 트랜지스터, 제 2 트랜지스터, 제 3 트랜지스터, 제 4 트랜지스터, 제 5 트랜지스터, 제 6 트랜지스터 및 제 7 트랜지스터를 더 포함하고, 상기 제 1 트랜지스터의 제 1 단자는 데이터라인에 연결되고, 상기 제 1 트랜지스터의 제 2 단자는 제 1 노드에 연결되고, 상기 제 1 트랜지스터의 게이트 단자는 n 번째 스캔라인에 연결되고, 상기 제 2 트랜지스터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 2 트랜지스터의 게이트 단자는 제 3 노드에 연결되고, 상기 제 3 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 3 트랜지스터의 게이트 단자는 상기 n 번째 스캔라인에 연결되고, 상기 제 4 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 4 트랜지스터의 제 2 단자는 상기 제 2 수광 소자의 캐소드(Cathode) 단자에 연결되고, 상기 제 4 트랜지스터의 게이트 단자는 제 1 센싱(sensing) 라인에 연결되고, 상기 제 5 트랜지스터의 제 1 단자는 상기 제 1 수광 소자의 아노드(Anode) 단자에 연결되고, 상기 제 5 트랜지스터의 제 2 단자는 상기 제 3 노드에 연결되고, 상기 제 5 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고, 상기 제 6 트랜지스터의 제 1 단자는 상기 제 2 노드에 연결되고, 상기 제 6 트랜지스터의 게이트 단자는 접지되고, 상기 제 6 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고, 상기 제 7 트랜지스터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 7 트랜지스터의 제 2 단자는 출력 라인에 연결되고, 상기 제 7 트랜지스터의 게이트 단자는 제 2 센싱 라인에 연결되고, 상기 제 1 수광 소자의 캐소드 단자는 전원(VDD)에 연결되고, 상기 제 2 수광 소자의 아노드 단자는 접지되는 것을 특징으로 한다.

[0014] 또한, 상기 화소 제어회로는 제 8 트랜지스터, 제 9 트랜지스터, 제 10 트랜지스터, 및 제 11 트랜지스터를 더 포함하고, 상기 제 8 트랜지스터의 제 1 단자는 초기화라인에 연결되고, 상기 제 8 트랜지스터의 제 2 단자는 상기 제 3 노드에 연결되고, 상기 제 8 트랜지스터의 게이트 단자는 n-1 번째 스캔라인에 연결되고, 상기 제 9 트랜지스터의 제 1 단자는 초기화라인에 연결되고, 상기 제 9 트랜지스터의 제 2 단자는 상기 자발광 소자의 아노드(anode) 단자에 연결되고, 상기 제 9 트랜지스터의 게이트 단자는 상기 n-1 번째 스캔라인에 연결되고, 상기 제 10 트랜지스터의 제 1 단자는 상기 전원에 연결되고, 상기 제 10 트랜지스터의 제 2 단자는 상기 제 1 노드에 연결되고, 상기 제 10 트랜지스터의 게이트 단자는 에미션(emission)라인에 연결되고, 상기 제 11 트랜지스터의 제 1 단자는 상기 제 2 노드에 연결되고, 상기 제 11 트랜지스터의 게이트 단자는 상기 자발광 소자의 아노드 단자에 연결되고, 상기 제 11 트랜지스터의 게이트 단자는 상기 에미션 라인에 연결되고, 상기 캐패시터의 제 1 단자는 상기 전원에 연결되고, 상기 캐패시터의 제 2 단자는 상기 제 3 노드에 연결되고, 상기 자발광 소자의 캐소드 단자는 접지되는 것을 특징으로 한다.

[0015] 또한, 상기 화소 제어회로는 제 1 트랜지스터, 제 2 트랜지스터, 제 3 트랜지스터, 제 4 트랜지스터, 제 5 트랜지스터 및 제 6 트랜지스터를 더 포함하고, 상기 제 1 트랜지스터의 제 1 단자는 데이터라인에 연결되고, 상기 제 1 트랜지스터의 제 2 단자는 제 1 노드에 연결되고, 상기 제 1 트랜지스터의 게이트 단자는 n 번째 스캔라인

에 연결되고, 상기 제 2 트랜지스터의 제 1 단자는 제 2 노드에 연결되고, 상기 제 2 트랜지스터의 제 2 단자는 제 3 노드에 연결되고, 상기 제 2 트랜지스터의 게이트 단자는 상기 제 1 노드에 연결되고, 상기 제 3 트랜지스터의 제 1 단자는 상기 제 1 노드에 연결되고, 상기 제 3 트랜지스터의 제 2 단자는 상기 제 2 수광 소자의 캐소드(Cathode) 단자에 연결되고, 상기 제 3 트랜지스터의 게이트 단자는 제 1 센싱(sensing) 라인에 연결되고, 상기 제 4 트랜지스터의 제 1 단자는 상기 제 1 수광 소자의 아노드 단자에 연결되고, 상기 제 4 트랜지스터의 제 2 단자는 상기 제 1 노드에 연결되고, 상기 제 4 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고, 상기 제 5 트랜지스터의 제 1 단자는 상기 제 3 노드에 연결되고, 상기 제 5 트랜지스터의 제 2 단자는 접지되고, 상기 제 5 트랜지스터의 게이트 단자는 상기 제 1 센싱 라인에 연결되고, 상기 제 6 트랜지스터의 제 1 단자는 상기 제 2 노드에 연결되고, 상기 제 6 트랜지스터의 제 2 단자는 출력 라인에 연결되고, 상기 제 6 트랜지스터의 게이트 단자는 제 2 센싱 라인에 연결되고, 상기 제 1 수광 소자의 캐소드 단자는 전원(VDD)에 연결되고, 상기 제 2 수광 소자의 아노드 단자는 접지되는 것을 특징으로 한다.

[0016] 또한, 상기 화소 제어회로는 제 7 트랜지스터를 더 포함하고, 상기 제 7 트랜지스터의 제 1 단자는 상기 전원에 연결되고, 상기 제 7 트랜지스터의 제 2 단자는 상기 제 2 노드에 연결되고, 상기 제 7 트랜지스터의 게이트 단자는 에미션(emission)라인에 연결되고, 상기 캐패시터의 제 1 단자는 상기 전원에 연결되고, 상기 캐패시터의 제 2 단자는 상기 제 1 노드에 연결되고, 상기 자발광 소자의 아노드 단자는 상기 제 3 노드에 연결되고, 상기 자발광 소자의 캐소드 단자는 접지되는 것을 특징으로 한다.

### 발명의 효과

[0017] 본 발명은, 충전용 제 1 수광 소자 또는 방전용 제 2 수광 소자에 기초하여 출력 전압이 VREF/2 근처로 유지될 수 있으므로, 화소회로의 출력 전압이 클리핑되는 것을 방지하는 효과를 가진다.

[0018] 또한, 본 발명은, 제 1 수광 소자 및 제 2 수광 소자에 공통으로 흐르는 전류의 차인 차분 신호를 이용하여 지문을 센싱함으로써, 자발광 소자에 의한 빛 또는 외부로부터의 빛으로부터 발생한 신호, 즉 노이즈의 영향을 줄일 수 있고, 클리핑 현상을 방지할 수 있는 효과를 가진다.

### 도면의 간단한 설명

[0019] 도 1은 자발광 소자 및 수광 소자를 포함하는 회로의 단면을 나타낸 도면이다.

도 2는 종래 기술에 따른 화소 회로를 나타낸 도면이다.

도 3은 본 발명의 일 실시예에 따른 화소회로를 나타낸 도면이다.

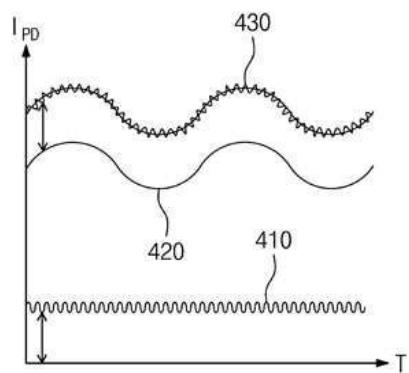

도 4는 종래 기술에 따른 화소회로의 수광 소자에 흐르는 전류를 나타낸 그래프이다.

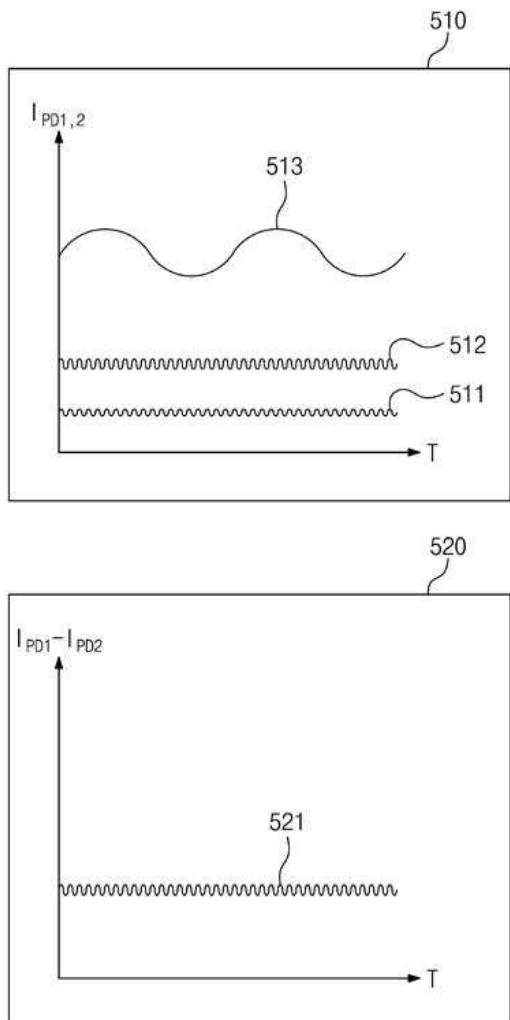

도 5는 본 발명의 일 실시예에 따른 수광 소자에 흐르는 전류를 나타낸 그래프이다.

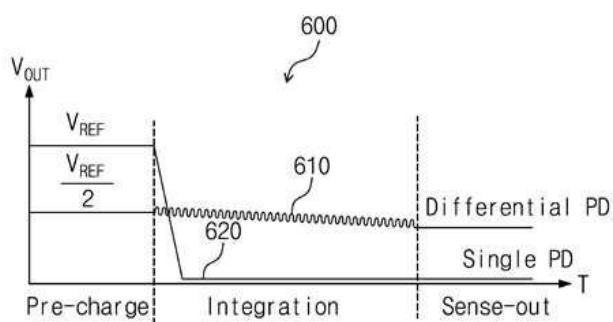

도 6은 본 발명의 일 실시예에 따른 출력 전압을 나타낸 그래프이다.

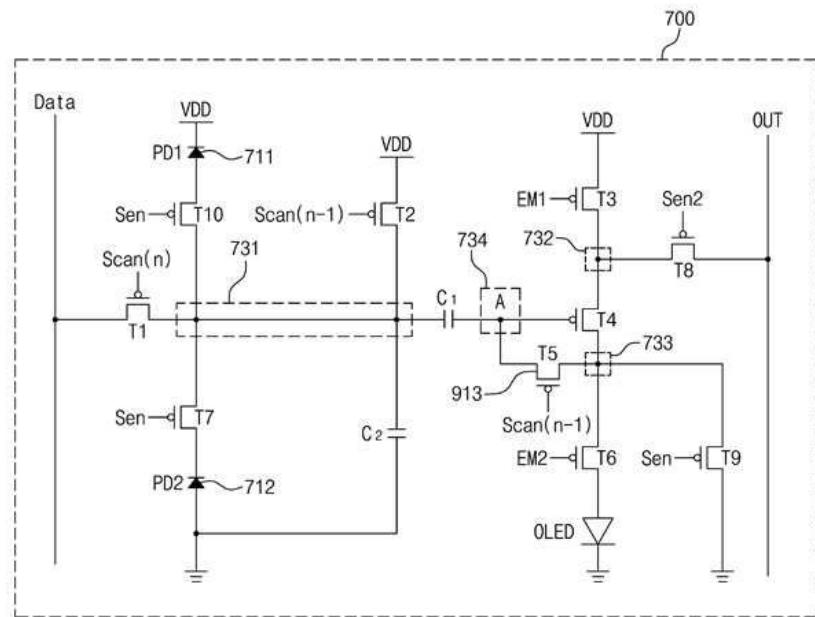

도 7은 본 발명의 일 실시예에 따른 화소회로를 나타낸 도면이다.

도 8은 본 발명의 일 실시예에 따른 화소회로를 나타낸 도면이다.

도 9는 본 발명의 일 실시예에 따른 화소회로를 나타낸 도면이다.

도 10은 본 발명의 일 실시예에 따른 제 1 노드의 전압을 나타낸 그래프이다.

도 11은 본 발명의 일 실시예에 따른 제 1 노드의 전압을 나타낸 그래프이다.

### 발명을 실시하기 위한 구체적인 내용

[0020] 개시된 실시예의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 후술되어 있는 실시예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 수 있으며, 단지 본 실시예들은 본 발명이 완전하도록 하고, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것일 뿐이다.

[0021] 본 명세서에서 사용되는 용어에 대해 간략히 설명하고, 개시된 실시예에 대해 구체적으로 설명하기로 한다.

[0022] 본 명세서에서 사용되는 용어는 본 발명에서의 기능을 고려하면서 가능한 현재 널리 사용되는 일반적인 용어들

을 선택하였으나, 이는 관련 분야에 종사하는 기술자의 의도 또는 판례, 새로운 기술의 출현 등에 따라 달라질 수 있다. 또한, 특정한 경우는 출원인이 임의로 선정한 용어도 있으며, 이 경우 해당되는 발명의 설명 부분에서 상세히 그 의미를 기재할 것이다. 따라서 본 발명에서 사용되는 용어는 단순한 용어의 명칭이 아닌, 그 용어가 가지는 의미와 본 발명의 전반에 걸친 내용을 토대로 정의되어야 한다.

[0023] 본 명세서에서의 단수의 표현은 문맥상 명백하게 단수인 것으로 특정하지 않는 한, 복수의 표현을 포함한다. 또한 복수의 표현은 문맥상 명백하게 복수인 것으로 특정하지 않는 한, 단수의 표현을 포함한다.

[0024] 명세서 전체에서 어떤 부분이 어떤 구성요소를 "포함"한다고 할 때, 이는 특별히 반대되는 기재가 없는 한 다른 구성요소를 제외하는 것이 아니라 다른 구성요소를 더 포함할 수 있음을 의미한다.

[0025] 또한, 명세서에서 사용되는 "부"라는 용어는 소프트웨어 또는 하드웨어 구성요소를 의미하며, "부"는 어떤 역할들을 수행한다. 그렇지만 "부"는 소프트웨어 또는 하드웨어에 한정되는 의미는 아니다. "부"는 어드레싱할 수 있는 저장 매체에 있도록 구성될 수도 있고 하나 또는 그 이상의 프로세서들을 재생시키도록 구성될 수도 있다. 따라서, 일 예로서 "부"는 소프트웨어 구성요소들, 객체지향 소프트웨어 구성요소들, 클래스 구성요소들 및 태스크 구성요소들과 같은 구성요소들과, 프로세스들, 함수들, 속성들, 프로시저들, 서브루틴들, 프로그램 코드의 세그먼트들, 드라이버들, 펌웨어, 마이크로 코드, 회로, 데이터, 데이터베이스, 데이터 구조들, 테이블들, 어레이들 및 변수들을 포함한다. 구성요소들과 "부"들 안에서 제공되는 기능은 더 작은 수의 구성요소들 및 "부"들로 결합되거나 추가적인 구성요소들과 "부"들로 더 분리될 수 있다.

[0026] 본 발명의 일 실시예에 따르면 "부"는 프로세서 및 메모리로 구현될 수 있다. 용어 "프로세서"는 범용 프로세서, 중앙 처리 장치 (CPU), 마이크로프로세서, 디지털 신호 프로세서 (DSP), 제어기, 마이크로제어기, 상태 머신 등을 포함하도록 넓게 해석되어야 한다. 몇몇 환경에서는, "프로세서"는 주문형 반도체 (ASIC), 프로그램 가능 로직 디바이스 (PLD), 필드 프로그램가능 게이트 어레이 (FPGA) 등을 지칭할 수도 있다. 용어 "프로세서"는, 예를 들어, DSP 와 마이크로프로세서의 조합, 복수의 마이크로프로세서들의 조합, DSP 코어와 결합한 하나 이상의 마이크로프로세서들의 조합, 또는 임의의 다른 그러한 구성들의 조합과 같은 처리 디바이스들의 조합을 지칭할 수도 있다.

[0027] 용어 "메모리"는 전자 정보를 저장 가능한 임의의 전자 컴포넌트를 포함하도록 넓게 해석되어야 한다. 용어 메모리는 임의 액세스 메모리 (RAM), 판독-전용 메모리 (ROM), 비-휘발성 임의 액세스 메모리 (NVRAM), 프로그램 가능 판독-전용 메모리 (PROM), 소거-프로그램가능 판독 전용 메모리 (EPROM), 전기적으로 소거가능 PROM (EEPROM), 플래쉬 메모리, 자기 또는 광학 데이터 저장장치, 레지스터들 등과 같은 프로세서-판독가능 매체의 다양한 유형들을 지칭할 수도 있다. 프로세서가 메모리로부터 정보를 판독하고/하거나 메모리에 정보를 기록할 수 있다면 메모리는 프로세서와 전자 통신 상태에 있다고 불린다. 프로세서에 접속된 메모리는 프로세서와 전자 통신 상태에 있다.

[0028] 용어 "신호"는 전압 또는 전류의 전기신호를 의미한다.

[0030] 아래에서는 첨부한 도면을 참고하여 실시예에 대하여 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 상세히 설명한다. 그리고 도면에서 본 발명을 명확하게 설명하기 위해서 설명과 관계없는 부분은 생략한다.

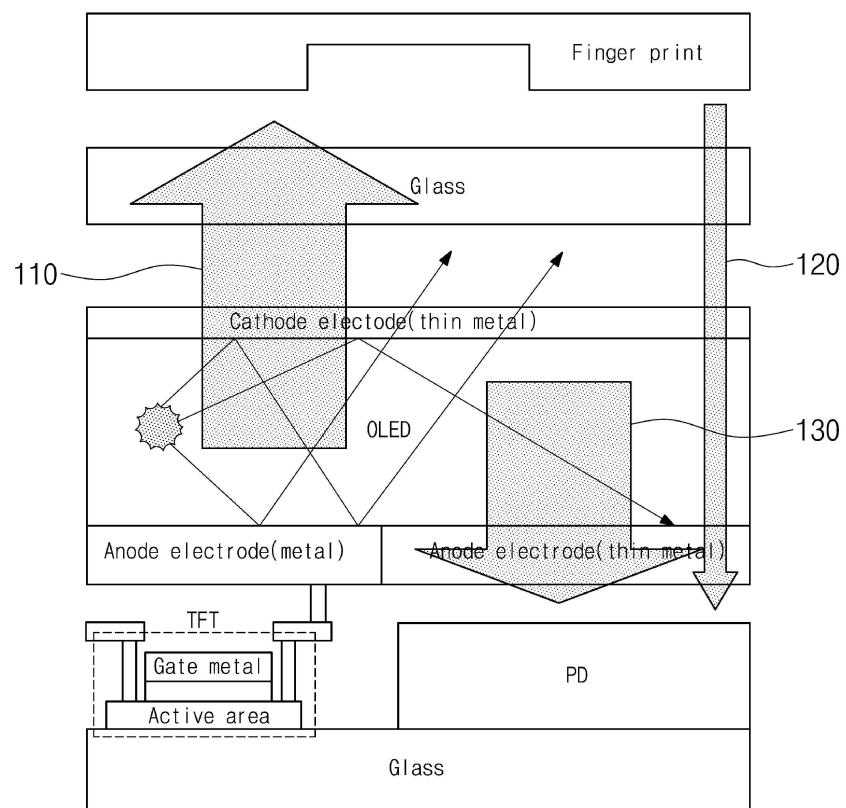

[0031] 도 1은 자발광 소자 및 수광 소자를 포함하는 회로의 단면을 나타낸 도면이다.

[0032] 상기 자발광 소자에는 OLED, QD-LED(quantum dot-LED), Micro-LED 등이 포함될 수 있다. 상기 수광 소자(PD)는 예를 들어 포토다이오드 일 수 있다.

[0033] 도 1에 도시된 바와 같이, 화소회로와 지문인식회로가 통합되는 경우, 화소회로와 지문인식회로의 거리가 가까울 수 있다. 이러한 표시 패널의 구조로 인하여 수광 소자(PD)는 지문(Finger print)에 반사된 빛(120)뿐만 아니라, 자발광 소자에서 출사된 빛(110)이 지문에 도달하지 못하고 유리 또는 전극(electrode)에 반사된 빛을 수광할 수 있다. 또한 표시 장치 외부에서 들어오는 빛(도면 미도시)을 수광할 수 있다. 이렇게 표시 패널 구조로 인하여 지문에 반사되지 않은 두가지의 직광이 지문인식회로에 입사되는 경우, 이러한 직광(130)은 지문에 의한 반사광(120) 보다 광량이 클 수 있기 때문에 수광 소자는 지문에 반사된 빛(120)을 제대로 인식하지 못할 수 있고 최종적으로는 지문인식률을 떨어뜨리는 문제가 발생한다.

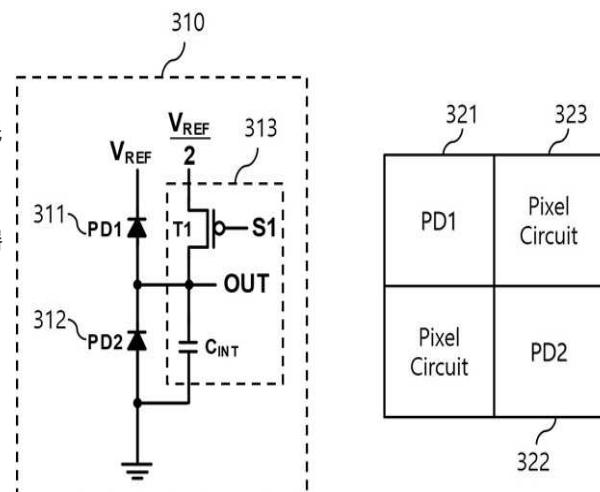

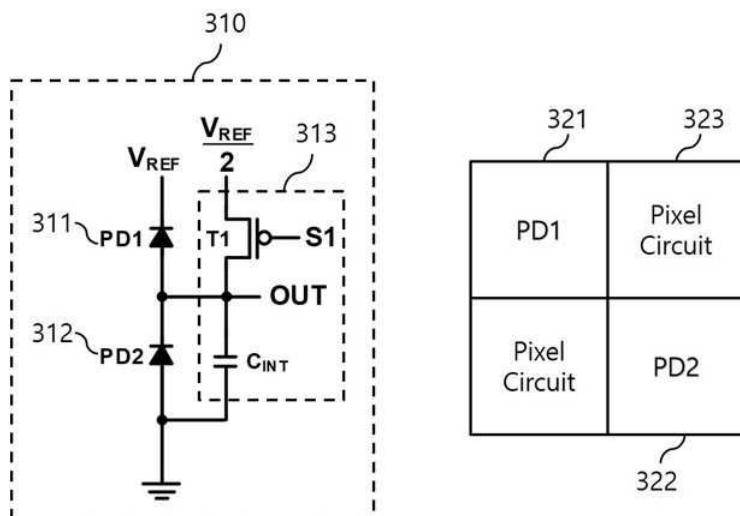

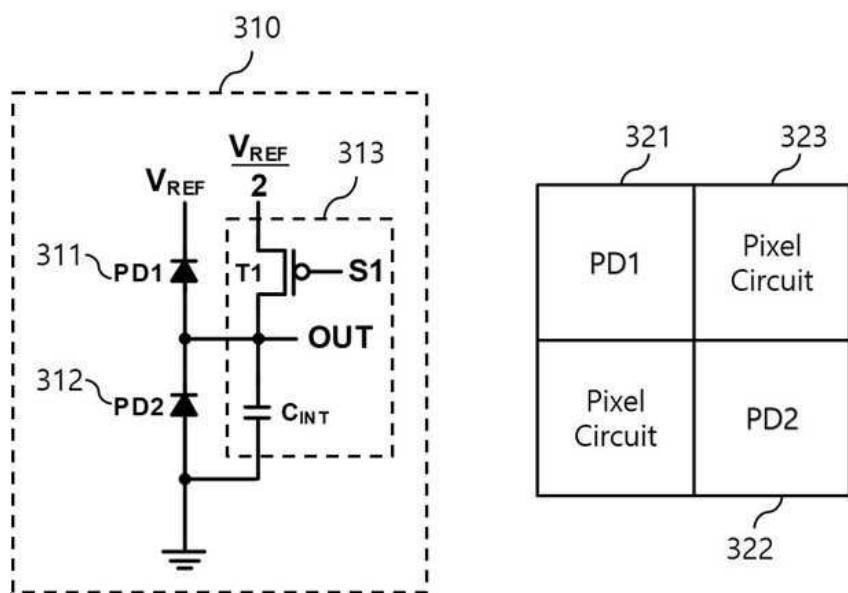

- [0034] 도 2는 종래 기술에 따른 화소 회로를 나타낸 도면이다.

- [0035] 화소회로(210)는 하나의 수광 소자, 적어도 하나의 트랜지스터 성분(T1) 및 적어도 하나의 캐패시터 성분(CINT)을 포함할 수 있다. 화소회로(210)는 표시 패널에 배치될 수 있다. 예를 들어 화소회로(210)의 수광 소자는 제 1 위치(221)에 배치될 수 있다. 또한, 화소회로(210)의 나머지 부분은 제 2 위치(222)에 배치될 수 있다. 하나의 화소회로(210)는 하나의 수광 소자를 포함하며, 수광 소자는 자발광 소자에 의한 빛, 외부로부터의 빛, 및 지문으로부터 반사된 빛을 수신한다.

- [0036] 외부로부터의 빛은 햇볕 또는 형광등과 같은 표시 장치 외부로부터 발생한 빛을 나타낼 수 있다. 또한 자발광 소자에 의한 빛은 자발광 소자에서 발생한 빛 또는 자발광 소자에 의한 빛이 지문이 아닌 표시 패널의 유리 또는 전극 등에 반사된 빛을 나타낼 수 있다. 지문으로부터 반사된 빛은 자발광 소자의 빛 또는 외부의 빛이 지문에 반사되어 지문으로부터 나온 빛을 나타낼 수 있다.

- [0037] 자발광 소자의 빛 및 외부로부터의 빛은 지문으로부터 반사된 빛보다 셀 수 있다. 따라서 화소회로(210)는 지문으로부터 반사된 빛을 이용하여 지문 인식을 하는데 어려움을 겪을 수 있다. 특히 화소회로(210)가 동일 면적 안에 많이 집적될수록 자발광 소자의 빛에 의한 영향이 커질 것이므로 화소회로(210)의 지문 인식률이 떨어질 수 있다.

- [0039] 도 3은 본 발명의 일 실시예에 따른 화소회로를 나타낸 도면이다.

- [0040] 광학 지문 센싱 회로를 포함한 화소회로(310)는 제 1 수광 소자(311) 및 제 2 수광 소자(312) 및 화소 제어회로(313)를 포함할 수 있다.

- [0041] 수광 소자는 자발광 소자로부터 출사되어 사용자의 지문을 통해 반사된 광을 역 방향의 광전류로 변환한다. 이 때, 수광 소자로부터 발생되는 광전류의 양은 광을 반사시킨 물체가 지문의 융선(Ridge)인지 또는 골(Valley)인지에 따라 가변된다. 여기서, 골로부터 반사된 광에 의한 광전류는 융선으로부터 반사된 광에 의한 광전류보다 클 수 있다. 하지만 이에 한정되는 것은 아니며 골로부터 반사된 광에 의한 광전류는 융선으로부터 반사된 광에 의한 광전류보다 작거나 같을 수 있다.

- [0042] 제 1 수광 소자는 빛을 수신하여 제 1 신호를 생성할 수 있다. 제 2 수광 소자는 빛을 수신하여 제 2 신호를 생성할 수 있다. 제 1 수광 소자(311)는 화소 제어회로(313)의 캐패시터 성분(CINT)을 충전할 수 있다. 제 2 수광 소자(312)는 화소 제어회로(313)의 캐패시터 성분(CINT)을 방전할 수 있다. 캐패시터 성분(CINT)은 제 1 신호에 의하여 충전될 수 있으며, 제 2 신호에 의하여 방전될 수 있다. 제 1 신호가 제 2 신호보다 큰 경우 차분 신호는 화소 제어회로(313)으로 흐를 수 있다. 제 1 신호가 제 2 신호보다 작은 경우 차분 신호는 화소 제어회로(313)에서 포토 다이오드들 쪽으로 흐를 수 있다. 제 1 신호가 제 2 신호보다 큰 경우 캐패시터 성분(CINT)은 충전될 수 있다. 제 1 신호가 제 2 신호보다 작은 경우 캐패시터 성분(CINT)은 방전될 수 있다.

- [0043] 화소 제어회로(313)는 제 1 신호와 제 2 신호의 차분 신호를 수신할 수 있다. 또한 화소 제어회로(313)는 차분 신호에 기초하여 출력 라인(OUT)으로 출력 신호를 출력할 수 있다.

- [0045] 설명의 편의를 위하여 도 3의 화소 제어회로(313)는 간략하게 도시되어 있다. 화소 제어회로(313)는 적어도 하나의 트랜지스터 성분(T1)과 적어도 하나의 캐패시터 성분(CINT)을 포함할 수 있다. 트랜지스터 성분(T1)은 소정의 신호(S1)에 따라 온(ON)/오프(OFF)되는 성분을 나타낸다. 상기 트랜지스터 성분(T1)의 스위칭 동작을 통하여 상기 화소회로(310)의 출력(OUT) 전압을 리셋(reset)할 수 있으며, 상기 트랜지스터 성분(T1)이 온(ON)시에는 출력(OUT) 전압은 VREF/2로 리셋 된다. 캐패시터 성분(CINT)은 전압이 변하는 경우 전류를 생성하는 성분을 나타낸다. 화소 제어회로(313)의 트랜지스터 성분(T1) 및 캐패시터 성분(CINT)은 트랜지스터 또는 캐패시터 중 적어도 하나를 이용하여 구현될 수 있다.

- [0046] 화소 제어회로(313)는 자발광 소자(미도시)를 포함할 수 있다. 자발광 소자는 데이터 신호에 기초하여 빛을 출력할 수 있다. 자발광 소자는 데이터 신호에 기초하여 유입되는 전류에 따라 발광한다. 유기발광다이오드(OLE D)를 예로 들어 설명하면, 상기 자발광 소자는 애노드 전극과 캐소드 전극 사이에 형성된 유기 발광셀을 포함한다. 여기서, 유기 발광셀은 정공 수송층/유기 발광층/전자 수송층의 구조, 또는 정공 주입층/정공 수송층/유기 발광층/전자 수송층/전자 주입층의 구조를 가지도록 형성될 수 있다. 또한, 유기 발광셀에는 유기발광층의 발광

효율 및/또는 수명 등을 향상시키기 위한 기능층이 추가로 형성될 수 있다.

[0047] 화소회로(310)는 표시 패널에 배치될 수 있다. 표시 패널은 복수의 화소회로들을 포함할 수 있다. 예를 들어 화소회로(310)의 제 1 수광 소자(311)는 제 1 영역(321)에 포함될 수 있다. 화소회로(310)의 제 2 수광 소자(312)는 제 2 영역(322)에 포함될 수 있다. 화소회로(310)의 화소 제어회로(313) 또는 화소 제어회로(313) 중 일부는 제 3 영역(323)에 포함될 수 있다. 예를 들어 자발광 소자는 제 3 영역(323)에 포함될 수 있다.

[0048] 제 1 수광 소자(311)를 포함한 제 1 영역(321) 및 제 2 수광 소자(312)를 포함한 제 2 영역(322)은 가까울 수 있다. 따라서, 자발광 소자에 의한 빛 또는 외부의 빛은 제 1 수광 소자(311) 및 제 2 수광 소자(312)에 동일한 영향을 미칠 수 있다. 따라서 제 1 수광 소자(311) 및 제 2 수광 소자(312)는 자발광 소자에 의한 빛 또는 외부의 빛에 기초하여 동일한 전류를 생성할 수 있다.

[0049] 지문 인식은 미세한 지문의 골 및 마루에서 반사된 빛을 수광 소자들이 감지하여 수행될 수 있다. 따라서 제 1 수광 소자(311)가 수신한 지문으로부터 반사된 빛은 제 2 수광 소자(312)가 수신한 지문으로부터 반사된 빛과 다를 수 있다. 또한 제 1 수광 소자(311)와 제 2 수광 소자(312)는 지문으로부터 반사된 빛에 기초하여 서로 다른 크기의 전류를 생성할 수 있다.

[0050] 상술한 바와 같이, 자발광 소자의 빛 또는 외부의 빛이 제 1 수광 소자(311) 및 제 2 수광 소자(312)에 동일한 영향을 미치는 반면, 지문으로부터 반사된 빛은 제 1 수광 소자(311)와 제 2 수광 소자(312)에 서로 다른 영향을 미친다. 따라서, 광학 지문 센싱 회로를 포함하는 화소회로(310)는 제 1 수광 소자(311)의 전류와 제 2 수광 소자(312)의 전류의 차분을 이용하여, 정확하게 지문을 인식할 수 있다.

[0051] 예를 들어, 제 1 수광 소자(311)의 전류와 제 2 수광 소자(312)의 전류의 차전류는 화소 제어회로(313)으로 출력될 수 있다. 화소 제어회로(313)는 차전류에 기초한 전류 또는 전압을 출력 라인(OUT)으로 출력할 수 있다. 화소회로(310)를 포함하는 시스템은 출력 라인(OUT)으로 출력된 출력 신호에 기초하여 지문을 정확하게 인식할 수 있다.

[0052] 도 2의 종래의 화소회로(210)에 따르면 출력 전압이 VREF 또는 VSS로 클리핑될 수 있다. 전술한 바와 같이 지문에 반사되지 않은 직광은 그 광량이 매우 커서 수광소자(PD)에 과한 광전류를 발생시키고, 이 과한 광전류는 캐패시터 성분(CINT)을 단시간 내에 높은 전압으로 충전시킬 수 있으므로 출력 전압이 VREF로 클리핑 될 수 있다.

[0053] 하지만 도 3의 본 발명의 일 실시예에 따른 화소회로(310)는, 충전용 제 1 수광 소자(311)와 방전용 제 2 수광 소자(312) 두개의 수광 소자를 포함하여 구성되므로 출력 전압이  $VREF/2$  근처로 유지될 수 있다. 즉, 화소회로(310)의 출력 전압이 클리핑 되는 현상을 방지할 수 있는 효과를 가진다.

[0054] 제 1 수광 소자(311) 및 제 2 수광 소자(312)에 흐르는 전류와 클리핑 현상 방지 원리에 대해서는 도 5에서 자세히 설명한다.

[0056] 먼저 이해를 돋기 위하여 도 5를 설명하기 전에 종래 기술에 따른 수광 소자에 흐르는 전류를 나타낸 도 4를 설명한다.

[0058] 도 4는 종래 기술에 따른 화소회로의 수광 소자에 흐르는 전류를 나타낸 그래프이다.

[0059] 도 4의 가로축은 시간을 나타내며, 세로축은 수광 소자에 흐르는 전류를 나타낸다. 지문광 전류(410)는 지문으로부터 반사된 빛에 기초하여 수광 소자로부터 생성된 전류를 나타낸다. 직광 전류(420)는 자발광 소자에 의한 빛 또는 외부로부터의 빛에 의해 수광 소자로부터 생성된 전류를 나타낸다. 자발광 소자에 의한 빛 또는 외부로부터 빛은 지문으로부터 반사된 빛보다 강하기 때문에, 직광 전류(420)는 반사광 전류(410)보다 클 수 있다. 직광 전류(420)는 노이즈에 의하여 멸림이 있을 수 있다. 합성전류(430)는 반사광 전류(410)와 직광 전류(420)의 합을 나타낸다.

[0060] 직광 전류(420)가 반사광 전류(410)보다 크므로, 직광 전류(420)가 반사광 전류(410)보다 합성전류(430)에 미치는 영향이 클 수 있다. 또한 직광 전류(420)의 노이즈에 의한 영향이 클 수 있다. 또한, 직광 전류(420)의 크기가 크므로 클리핑(clipping)이 일어날 수 있다.

[0062] 도 5는 본 발명의 일 실시예에 따른 수광 소자에 흐르는 전류를 나타낸 그레프이다.

[0063] 그레프(510)의 가로축은 시간을 나타낸다. 그레프(510)의 세로축은 제 1 수광 소자(311) 및 제 2 수광 소자(312)에 흐르는 전류를 나타낸다. 제 2 반사광 전류(511)는 지문으로부터 반사된 빛에 기초하여 제 2 수광 소자(312)로부터 생성된 전류를 나타낸다. 제 1 반사광 전류(512)는 지문으로부터 반사된 빛에 기초하여 제 1 수광 소자(311)로부터 생성된 전류를 나타낸다. 제 1 수광 소자(311) 및 제 2 수광 소자(312)의 거리는 가깝지만, 지문의 골 및 마루 역시 미세하므로, 제 1 수광 소자(311)에서 생성된 제 1 반사광 전류(512)는 제 2 수광 소자(312)에서 생성된 제 2 반사광 전류(511)와 다를 수 있다.

[0064] 직광 전류(513)는 자발광 소자에 의한 빛 또는 외부로부터의 빛에 의해 제 1 수광 소자(311) 및 제 2 수광 소자(312)로부터 생성된 전류를 나타낸다. 자발광 소자에 의한 빛 또는 외부로부터의 빛에 의해 제 1 수광 소자(311) 및 제 2 수광 소자(312)로부터 생성된 전류는 동일할 수 있다. 자발광 소자에 의한 빛 또는 외부로부터 빛은 지문으로부터 반사된 빛보다 강하기 때문에, 직광 전류(513)는 제 2 반사광 전류(511) 또는 제 1 반사광 전류(512)보다 클 수 있다. 직광 전류(513)는 노이즈에 의하여 떨림이 있을 수 있다.

[0065] 제 1 수광 소자(311)에 흐르는 총 전류는 제 1 반사광 전류(512)와 직광 전류(513)의 합일 수 있다. 제 2 수광 소자(312)에 흐르는 총 전류는 제 2 반사광 전류(511)와 직광 전류(513)의 합일 수 있다.

[0066] 그레프(520) 가로축은 시간을 나타낸다. 그레프(520)의 세로축은 제 1 수광 소자(311)에 흐르는 전류와 제 2 수광 소자(312)에 흐르는 전류의 차를 나타낸다. 직광 전류(513)는 제 1 수광 소자(311) 및 제 2 수광 소자(312)에 공통으로 흐르므로, 서로 상쇄될 수 있다. 따라서, 차분 신호(521)는 직광 전류(513)에 의하여 영향을 받지 않을 수 있다. 또한 차분 신호(521)는 합성전류(430)보다 크기가 작을 수 있다. 차분 신호(521)는 도 3의 캐패시터 성분(CINT)을 충전하거나 방전할 수 있다.

[0067] 도 5에서 설명한 바와 같이 화소회로(310)는 자발광 소자에 의한 빛 또는 외부로부터의 빛으로부터 발생한 신호, 즉 노이즈의 영향을 줄일 수 있다. 또한 화소회로(310)는 지문으로부터 반사된 빛에 의한 신호에 기초하여 지문을 인식할 수 있다. 또한 화소회로(310)는 자발광 소자에 의한 빛 또는 외부로부터의 빛에 의한 노이즈를 줄일 수 있으며 클리핑을 예방할 수 있다. 따라서 화소회로(310)는 지문 인식의 정확도를 높일 수 있다.

[0069] 도 6은 본 발명의 일 실시예에 따른 출력 전압을 나타낸 그레프이다.

[0070] 그레프(600)의 가로축은 시간을 나타낸다. 그레프(600)의 세로축은 출력 전압을 나타낸다.

[0071] 먼저 도 2와 함께 종래 기술의 출력 전압(620)을 설명한다. 출력 전압(620)은 종래 기술의 출력 라인(OUT)에서의 전압을 나타낸다. 프리차지(Pre-charge) 단계에서 트랜지스터 성분(T1)은 베이스 단자의 신호에 기초하여 턴온 상태이며, 수광 소자는 빛을 수신하지 않은 상태이다. 캐패시터 성분(CINT)은 VREF에 기초하여 충전된다. 프리차지(Pre-charge) 단계에서 출력 라인(OUT)의 출력 전압(620)은 VREF로 유지된다.

[0072] 인테그레이션(Integration) 단계는 수광 소자가 빛을 수신하는 단계이다. 수광 소자는 빛을 수신하여 전류를 생성하며, 캐패시터 성분(CINT)에 충전된 전하들을 방전시킨다. 또한 트랜지스터 성분(T1)은 턴오프되어 있을 수 있다. 인테그레이션 단계에서 출력 전압(620)은 급격히 줄어들 수 있다. 왜냐하면, 도 4에서 설명한 바와 같이 자발광 소자에 의한 빛 또는 외부로부터의 빛에 의해 수광 소자로부터 생성된 직광 전류(420)가 크기 때문에 캐패시터 성분(CINT)이 완전 방전될 수 있기 때문이다. 자발광 소자에 의한 빛 또는 외부로부터의 빛이 상대적으로 강하므로 지문으로부터 반사된 빛은 출력 전압(620)에 거의 영향을 줄 수 없다.

[0073] 센스아웃(Sense-out) 단계는 화소회로(210)를 포함하는 시스템이 화소회로(210)의 출력 라인(OUT)의 신호를 읽는 단계이다. 출력 전압(620)이 낮게 유지된 상태에서 화소회로(210)를 포함하는 시스템은 신호를 수신한다. 지문으로부터 반사된 빛이 출력 전압(620)에 거의 영향을 미칠 수 없으므로, 시스템은 출력 라인(OUT)으로부터 지문에 의한 빛에 기초하여 생성된 신호를 센싱하기 어려울 수 있다.

[0074] 도 3과 함께 본 발명의 일 실시예에 따른 출력 전압(610)을 설명한다. 출력 전압(610)은 출력 라인(OUT)에서의 전압을 나타낸다. 프리차지 단계에서 트랜지스터 성분(T1)은 베이스 단자의 신호에 기초하여 턴온 상태이며, 수광 소자는 빛을 수신하지 않는 상태이다. 캐패시터 성분(CINT)은 VREF/2에 기초하여 충전된다. 프리차지 단계에서 출력 라인(OUT)의 출력 전압(610)은 VREF/2로 유지된다.

- [0075] 인테그레이션 단계는 수광 소자가 빛을 수신하는 단계이다. 제 1 수광 소자(311) 및 제 2 수광 소자(312)는 빛을 수신하여 전류를 생성한다. 또한 트랜지스터 성분(T1)은 턴오프되어 있을 수 있다.

- [0076] 상술한 바와 같이, 제 1 수광 소자(311) 및 제 2 수광 소자(312)는 지문의 미세한 골 또는 마루에서 반사된 빛에 의하여 서로 다른 전류를 생성할 수 있다. 제 1 수광 소자(311)는 캐패시터(CINT)를 충전시킬 수 있다. 또한 제 2 수광 소자(312)는 캐패시터(CINT)를 방전시킬 수 있다.

- [0077] 캐패시터 성분(CINT)에 흐르는 전류는 제 1 수광 소자(311)가 생성한 제 1 신호와 제 2 수광 소자(312)가 생성한 제 2 신호의 차분 신호일 수 있다. 도 5에서 상술한 바와 같이 제 1 신호 및 제 2 신호는 자발광 소자에 의한 빛 및 외부로부터의 빛으로부터 공통된 영향을 받는다. 따라서 제 1 신호 및 제 2 신호에 기초한 차분 신호는 자발광 소자에 의한 빛 및 외부로부터의 빛에 영향을 받지 않을 수 있다. 차분 신호의 크기는 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 수광 소자에서 생성된 전류의 크기보다 작을 수 있다. 따라서 캐패시터 성분(CINT)에 기초한 출력 전압(610)은 차분 신호에 의하여 서서히 높아지거나 낮아질 수 있다.

- [0078] 제 1 수광 소자(311)가 생성한 제 1 신호가 제 2 수광 소자(312)가 생성한 제 2 신호보다 큰 경우, 캐패시터(CINT)로 전류가 흐를 것이므로 캐패시터(CINT)는 충전될 수 있다. 따라서 출력 전압(610)은 서서히 높아질 수 있다. 반대로 제 1 수광 소자(311)가 생성한 제 1 신호가 제 2 수광 소자(312)가 생성한 제 2 신호보다 작은 경우, 캐패시터 성분(CINT)으로부터 전류가 공급될 것이므로 캐패시터(CINT)는 방전될 수 있다. 따라서 출력 전압(610)은 서서히 낮아질 수 있다.

- [0079] 센스아웃 단계는 화소회로(310)를 포함하는 시스템이 화소회로(310)의 출력 라인(OUT)의 신호를 읽는 단계이다. 시스템은 출력 전압(610)이 VREF/2보다 높은 경우, 제 1 수광 소자(311)가 제 2 수광 소자(312)보다 많은 빛을 수신한 것으로 판단할 수 있다. 또한 시스템은 출력 전압(610)이 VREF/2 보다 낮은 경우, 제 1 수광 소자(311)가 제 2 수광 소자(312)보다 적은 빛을 수신한 것으로 판단할 수 있다. 시스템은 출력 전압(610)에 기초하여 정확하게 지문은 인식할 수 있다.

- [0081] **실시예 1**

- [0082] 도 7은 본 발명의 일 실시예에 따른 화소회로를 나타낸 도면이다.

- [0083] 화소회로(700)는 제 1 수광 소자(711) 및 제 2 수광 소자(712)를 포함할 수 있다. 또한 화소회로(700)는 화소제어회로를 포함할 수 있다. 화소제어회로는 제 1 트랜지스터(T1), 제 2 트랜지스터(T4), 제 3 트랜지스터(T5), 제 4 트랜지스터(T7), 제 5 트랜지스터(T10), 제 6 트랜지스터(T9), 제 7 트랜지스터(T8), 제 1 캐패시터(C1) 및 제 2 캐패시터(C2)를 더 포함할 수 있다.

- [0084] 트랜지스터들의 제 1 단자 또는 제 2 단자는 소스 단자 또는 드레인 단자일 수 있다. 트랜지스터들은 게이트 단자의 신호에 따라 턴온되거나 턴오프될 수 있다.

- [0085] 제 1 트랜지스터(T1)의 제 1 단자는 데이터라인에 연결되고, 제 1 트랜지스터의 제 2 단자는 제 1 노드(731)에 연결되고, 제 1 트랜지스터(T1)의 게이트 단자는 n 번째 스캔라인(Scan(n))에 연결될 수 있다.

- [0086] 제 2 트랜지스터(T4)의 제 1 단자는 제 2 노드(732)에 연결되고, 제 2 트랜지스터(T4)의 제 2 단자는 제 3 노드(733)에 연결되고, 제 2 트랜지스터(T4)의 게이트 단자는 제 4 노드(734)에 연결될 수 있다.

- [0087] 제 3 트랜지스터(T5)의 제 1 단자는 제 4 노드(734)에 연결되고, 제 3 트랜지스터(T5)의 제 2 단자는 제 3 노드(733)에 연결되고, 제 3 트랜지스터(T5)의 게이트 단자는 n-1 번째 스캔라인(Scan(n-1))에 연결될 수 있다.

- [0088] 제 4 트랜지스터(T7)의 제 1 단자는 제 1 노드(731)에 연결되고, 제 4 트랜지스터(T7)의 제 2 단자는 제 2 수광 소자(712)의 캐소드(Cathode) 단자에 연결되고, 제 4 트랜지스터(T7)의 게이트 단자는 제 1 센싱(sensing) 라인(Sen)에 연결될 수 있다.

- [0089] 제 5 트랜지스터(T10)의 제 1 단자는 제 1 수광 소자(711)의 아노드 단자에 연결되고, 제 5 트랜지스터(T10)의 제 2 단자는 제 1 노드(731)에 연결되고, 제 5 트랜지스터(T10)의 게이트 단자는 제 1 센싱 라인(Sen)에 연결될 수 있다.

- [0090] 제 6 트랜지스터(T9)의 제 1 단자는 제 3 노드(733)에 연결되고, 제 6 트랜지스터(T9)의 제 2 단자는 접지되고, 제 6 트랜지스터(T9)의 게이트 단자는 제 1 센싱 라인(Sen)에 연결될 수 있다.

- [0091] 제 7 트랜지스터(T8)의 제 1 단자는 제 2 노드(732)에 연결되고, 제 7 트랜지스터(T8)의 제 2 단자는 출력 라인(OUT)에 연결되고, 제 7 트랜지스터(T8)의 게이트 단자는 제 2 센싱 라인(Sen2)에 연결될 수 있다.

- [0092] 제 1 캐패시터(C1)의 제 1 단자는 제 1 노드(731)에 연결되고, 제 1 캐패시터(C1)의 제 2 단자는 제 4 노드(734)에 연결될 수 있다.

- [0093] 제 2 캐패시터(C2)의 제 1 단자는 제 1 노드(731)에 연결되고, 제 2 캐패시터(C2)의 제 2 단자는 접지될 수 있다.

- [0094] 제 1 수광 소자(711)의 캐소드 단자는 전원(VDD)에 연결되고, 제 2 수광 소자(712)는 접지될 수 있다.

- [0095] 화소 제어회로는 제 8 트랜지스터(T2), 제 9 트랜지스터(T3), 제 10 트랜지스터(T6) 및 자발광 소자(OLED)를 더 포함할 수 있다.

- [0096] 제 8 트랜지스터(T2)의 제 1 단자는 전원(VDD)에 연결되고, 제 8 트랜지스터(T2)의 제 2 단자는 제 1 노드(731)에 연결되고, 제 8 트랜지스터(T2)의 게이트 단자는 n-1 번째 스캔라인(Scan(n-1))에 연결될 수 있다.

- [0097] 제 9 트랜지스터(T3)의 제 1 단자는 전원에 연결되고, 제 9 트랜지스터(T3)의 제 2 단자는 제 2 노드(732)에 연결되고, 제 9 트랜지스터(T3)의 게이트 단자는 제 1 에미션(emission) 라인(EM1)에 연결될 수 있다.

- [0098] 제 10 트랜지스터(T6)의 제 1 단자는 제 3 노드(733)에 연결되고, 제 10 트랜지스터(T6)의 제 2 단자는 자발광 소자(OLED)의 아노드 단자에 연결되고, 제 10 트랜지스터(T6)의 게이트 단자는 제 2 에미션 라인(EM2)에 연결될 수 있다.

- [0099] 자발광 소자(OLED)의 캐소드 단자는 접지될 수 있다.

## 실시예 2

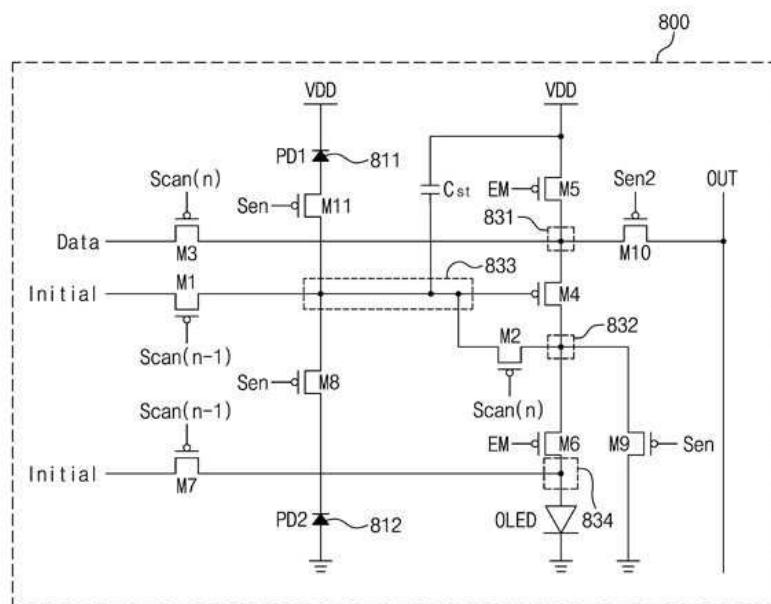

- [0102] 도 8은 본 발명의 일 실시예에 따른 화소회로를 나타낸 도면이다.

- [0103] 화소회로(800)는 내부보상을 이용한 광학 방식 지문 센싱 화소 회로에 트랜지스터와 광학센서를 추가하여 차동 광학 방식 지문 센싱이 가능한 구조를 구현한 것이다.

- [0104] 화소회로(800)는 제 1 수광 소자(811) 및 제 2 수광 소자(812)를 포함할 수 있다. 또한 화소회로(800)는 화소 제어회로를 포함할 수 있다. 화소 제어회로는 제 1 트랜지스터(M1), 제 2 트랜지스터(M4), 제 3 트랜지스터(M2), 제 4 트랜지스터(M8), 제 5 트랜지스터(M11), 제 6 트랜지스터(M9), 제 7 트랜지스터(M10)를 더 포함할 수 있다.

- [0105] 제 1 트랜지스터(M3)의 제 1 단자는 데이터라인(Data)에 연결되고, 제 1 트랜지스터(M3)의 제 2 단자는 제 1 노드(831)에 연결되고, 제 1 트랜지스터(M3)의 게이트 단자는 n 번째 스캔라인(Scan(n))에 연결될 수 있다.

- [0106] 제 2 트랜지스터(M4)의 제 1 단자는 제 1 노드(831)에 연결되고, 제 2 트랜지스터(M4)의 제 2 단자는 제 2 노드(832)에 연결되고, 제 2 트랜지스터(M4)의 게이트 단자는 제 3 노드(833)에 연결될 수 있다.

- [0107] 제 3 트랜지스터(M2)의 제 1 단자는 제 3 노드(833)에 연결되고, 제 3 트랜지스터(M2)의 제 2 단자는 제 2 노드(832)에 연결되고, 제 3 트랜지스터(M2)의 게이트 단자는 n 번째 스캔라인(Scan(n))에 연결될 수 있다.

- [0108] 제 4 트랜지스터(M8)의 제 1 단자는 제 3 노드(833)에 연결되고, 제 4 트랜지스터(M8)의 제 2 단자는 제 2 수광 소자(812)의 캐소드(Cathode) 단자에 연결되고, 제 4 트랜지스터(M8)의 게이트 단자는 제 1 센싱(sensing) 라인(Sen)에 연결될 수 있다.

- [0109] 제 5 트랜지스터(M11)의 제 1 단자는 제 1 수광 소자(811)의 아노드(Anode) 단자에 연결되고, 제 5 트랜지스터(M11)의 제 2 단자는 제 3 노드(833)에 연결되고, 제 5 트랜지스터(M11)의 게이트 단자는 제 1 센싱 라인(Sen)에 연결될 수 있다.

- [0110] 제 6 트랜지스터(M9)의 제 1 단자는 제 2 노드(832)에 연결되고, 제 6 트랜지스터(M9)의 제 2 단자는 접지되고, 제 6 트랜지스터(M9)의 게이트 단자는 제 1 센싱 라인(Sen)에 연결될 수 있다.

- [0111] 제 7 트랜지스터(M10)의 제 1 단자는 제 1 노드(831)에 연결되고, 제 7 트랜지스터(M10)의 제 2 단자는 출력 라인(OUT)에 연결되고, 제 7 트랜지스터(M10)의 게이트 단자는 제 2 센싱 라인(Sen2)에 연결될 수 있다.

- [0112] 제 1 수광 소자(811)의 캐소드 단자는 전원(VDD)에 연결되고, 제 2 수광 소자(812)의 아노드 단자는 접지될 수 있다.

- [0113] 화소 제어회로는 제 8 트랜지스터(M1), 제 9 트랜지스터(M7), 제 10 트랜지스터(M5), 제 11 트랜지스터(M6), 캐패시터(CST), 및 자발광 소자(OLED)를 더 포함할 수 있다.

- [0114] 제 8 트랜지스터(M1)의 제 1 단자는 초기화라인(Initial)에 연결되고, 제 8 트랜지스터(M1)의 제 2 단자는 제 3 노드(833)에 연결되고, 제 8 트랜지스터(M1)의 게이트 단자는 n-1 번째 스캔라인(Scan(n-1))에 연결될 수 있다.

- [0115] 제 9 트랜지스터(M7)의 제 1 단자는 초기화라인(Initial)에 연결되고, 제 9 트랜지스터(M7)의 제 2 단자는 자발광 소자(OLED)의 아노드(anode) 단자에 연결되고, 제 9 트랜지스터(M7)의 게이트 단자는 n-1 번째 스캔라인(Scan(n-1))에 연결될 수 있다.

- [0116] 제 10 트랜지스터(M5)의 제 1 단자는 전원에 연결되고, 제 10 트랜지스터(M5)의 제 2 단자는 제 1 노드(831)에 연결되고, 제 10 트랜지스터(M5)의 게이트 단자는 에미션(emission) 라인(EM)에 연결될 수 있다.

- [0117] 제 11 트랜지스터(M6)의 제 1 단자는 제 2 노드(832)에 연결되고, 제 11 트랜지스터(M6)의 제 2 단자는 자발광 소자(OLED)의 아노드 단자에 연결되고, 제 11 트랜지스터(M6)의 게이트 단자는 에미션 라인(EM)에 연결될 수 있다.

- [0118] 캐패시터(CST)의 제 1 단자는 전원에 연결되고, 캐패시터(CST)의 제 2 단자는 제 3 노드(833)에 연결될 수 있다.

- [0119] 자발광 소자(OLED)의 캐소드 단자는 접지될 수 있다.

- [0120] 화소회로(800)는 초기화라인(Initial)으로부터 초기화 신호를 수신할 수 있다. 화소회로는 데이터 라인(Data)으로부터 데이터 신호를 획득할 수 있다. 화소회로(800)는 에미션 라인(EM)으로부터 에미션 신호를 수신할 수 있다. 화소회로(800)는 n 번째 스캔 라인(Scan(n))으로부터 n번째 스캔 신호를 수신할 수 있다. 화소회로는 n-1 번째 스캔 라인(Scan(n-1))으로부터 n-1 번째 스캔 신호를 수신할 수 있다. n은 양의 정수 일 수 있다. n은 화소회로에서 표시될 영상의 프레임을 나타낼 수 있다. 예를 들어 n번째 스캔 신호는 n번째 프레임에 대한 스캔 신호일 수 있다.

- [0121] 화소회로(800)를 포함하는 시스템은 n 번째 스캔 신호, n-1 번째 스캔 신호, 초기화 신호, 데이터 신호 및 에미션 신호 중 적어도 하나를 조작하여, 자발광 소자(OLED)를 발광시킬 수 있다. 시스템은 프로세서 또는 메모리를 포함할 수 있으며, 프로세서는 메모리에 포함된 명령어 또는 데이터에 따라 n 번째 스캔 신호, n-1 번째 스캔 신호, 초기화 신호, 데이터 신호 및 에미션 신호 중 적어도 하나를 조작할 수 있다.

- [0122] 화소회로(800)를 포함하는 시스템은 초기화 신호에 기초하여 이전 프레임 데이터를 리셋하는 단계를 수행할 수 있다. 화소회로(800)를 포함하는 시스템은 데이터 신호 및 n 번째 스캔 신호 중 적어도 하나에 기초하여 제 2 트랜지스터(M4)의 임계 전압(Vth)을 보상하고, 데이터 신호를 인가하는 단계를 수행할 수 있다. 화소회로(800)를 포함하는 시스템은 제 1 수광 소자(811) 및 제 2 수광 소자(812)에 의한 전류에 기초하여 제 3 노드(833)의 전압 변화시키는 단계를 수행할 수 있다. 화소회로(800)를 포함하는 시스템은 소스 팔로워 동작을 통해서 제 2 트랜지스터(M4)의 게이트 단자 전압인 제 3 노드(833)의 전압을 제 2 트랜지스터(M4)의 제 1 단자인 제 1 노드(831)에 전달하는 단계를 수행할 수 있다. 화소회로(800)를 포함하는 시스템은 제 1 노드(831)의 전압을 출력라인(OUT)으로 출력하는 단계를 수행할 수 있다.

- [0123] 화소회로(800)를 포함하는 시스템은 이전 프레임 데이터를 리셋하는 단계를 수행할 수 있다. 제 8 트랜지스터(M1) 및 제 9 트랜지스터(M7)가 동작할 수 있다. 시스템은 화소회로(800)에 n-1 번째 스캔신호 및 초기화 신호 중 적어도 하나를 전송할 수 있다. 화소회로(800)는 n-1 번째 스캔라인(Scan(n-1))으로부터 n-1 번째 스캔신호를 수신할 수 있다. 화소회로(800)는 초기화라인(Initial)으로부터 초기화 신호를 수신할 수 있다. n-1 번째 스캔신호 및 초기화 신호에 기초하여, 제 8 트랜지스터(M1) 및 상기 제 9 트랜지스터(M7)는 이전 프레임의 데이터를 리셋할 수 있다.

- [0124] 화소회로(800)를 포함하는 시스템은 제 2 트랜지스터(M4)의 임계 전압(Vth)을 보상하고, 데이터 신호를 인가하는 단계를 수행할 수 있다. 단계에서 제 1 트랜지스터(M3) 및 제 3 트랜지스터(M2)가 동작할 수 있다. 시스템은 화소회로(800)에 n 번째 스캔신호 및 데이터 신호 중 적어도 하나를 전송할 수 있다. 화소회로(800)는 n 번째 스캔라인(Scan(n))으로부터 n 번째 스캔신호를 수신할 수 있다. 화소회로(800)는 데이터라인(Data)으로부터 데이터 신호를 수신할 수 있다. n 번째 스캔신호에 기초하여, 제 1 트랜지스터(M1)는 제 1 노드에 데이터 신호를

인가할 수 있다. n 번째 스캔신호에 기초하여, 제 3 트랜지스터(M2)는 제 2 트랜지스터(M4)의 임계 전압( $V_{th}$ )을 보상할 수 있다.

[0125] 화소회로(800)를 포함하는 시스템은 인테그레이션 페이즈(integration phase)를 수행할 수 있다. 인테그레이션 페이즈는 제 1 수광 소자(811) 및 제 2 수광 소자(812)에 의한 전류에 기초하여 제 2 트랜지스터(M4)의 게이트 단자인 제 3 노드(833)의 전압을 변화시키는 단계를 포함할 수 있다. 인테그레이션 페이즈는 소스 팔로워 동작을 통해서 제 2 트랜지스터(M4)의 게이트 단자 전압을 제 2 트랜지스터(M4)의 제 1 단자인 제 1 노드(831)에 전달하는 단계를 포함할 수 있다.

[0126] 화소회로(800)를 포함하는 시스템은 화소회로(800)에 제 1 센싱 신호를 전송할 수 있다. 화소회로(800)는 제 1 센싱 라인(Sen)으로부터 제 1 센싱 신호를 수신할 수 있다. 제 1 수광 소자(811) 및 제 2 수광 소자(812)는 수신한 광량에 따라 전류를 생성할 수 있다. 제 1 센싱 신호, 제 1 수광 소자(811)에 의한 전류 및 제 2 수광 소자(812)에 의한 전류에 기초하여, 제 4 트랜지스터(M8) 및 제 5 트랜지스터(M11)는 제 3 노드(833)에 전압을 인가할 수 있다.

[0127] 제 2 트랜지스터(M4)의 소스 팔로워(Source Follower) 동작에 의하여 제 3 노드(833)에 인가된 전압은 상기 제 1 노드(831)에 전달될 수 있다.

[0128] 화소회로(800)를 포함하는 시스템은 제 1 노드(831)의 전압을 출력 라인(OUT)으로 출력하는 단계를 수행할 수 있다. 시스템은 화소회로(800)에 제 2 센싱 신호를 전송할 수 있다. 화소회로(800)는 제 2 센싱 라인(Sen2)으로부터 제 2 센싱 신호를 수신할 수 있다. 제 2 센싱 신호에 기초하여, 제 7 트랜지스터(M10)는 제 1 노드(831)의 전압을 출력 라인(OUT)으로 출력할 수 있다. 시스템은 화소회로(800)의 출력을 데이터로서 수신할 수 있다. 또한, 시스템은 복수의 화소회로들로부터 수신한 데이터에 기초하여 지문 인식을 할 수 있다.

### 실시예 3

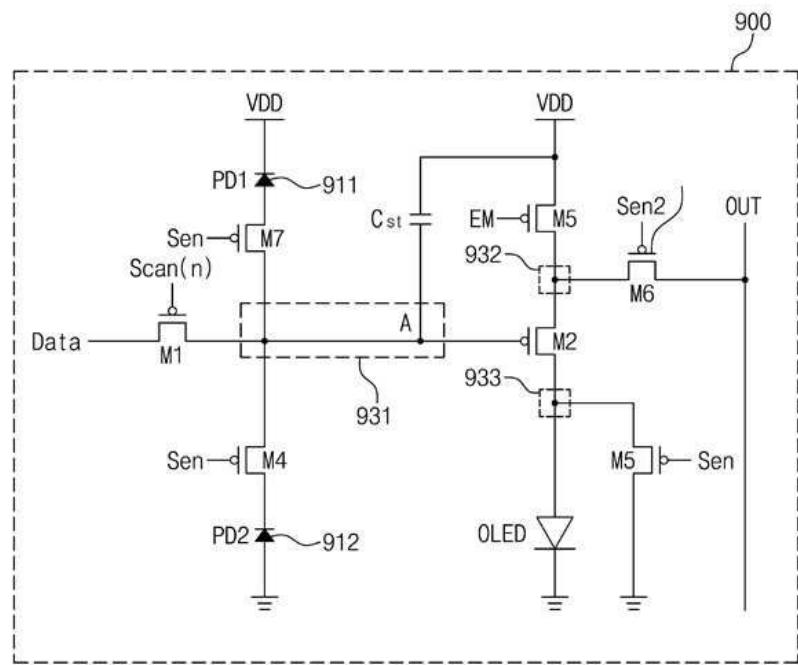

[0131] 도 9는 본 발명의 일 실시예에 따른 화소회로를 나타낸 도면이다.

[0132] 화소회로(900)는 외부보상을 이용한 광학 방식 지문 센싱 화소 회로에 트랜지스터와 광학센서를 추가하여 차동 광학 방식 지문 센싱이 가능한 구조를 구현한 것이다.

[0133] 화소회로(900)는 제 1 수광 소자(911) 및 제 2 수광 소자(912)를 포함할 수 있다. 또한 화소회로(900)는 화소 제어회로를 포함할 수 있다. 화소 제어회로는 제 1 트랜지스터(M1), 제 2 트랜지스터(M2), 제 3 트랜지스터(M4), 제 4 트랜지스터(M7), 제 5 트랜지스터(M5) 및 제 6 트랜지스터(M6)를 포함할 수 있다.

[0134] 제 1 트랜지스터(M1)의 제 1 단자는 데이터라인(Data)에 연결되고, 제 1 트랜지스터(M1)의 제 2 단자는 제 1 노드(931)에 연결되고, 제 1 트랜지스터(M1)의 게이트 단자는 n번째 스캔라인(Scan(n))에 연결될 수 있다.

[0135] 제 2 트랜지스터(M2)의 제 1 단자는 제 2 노드(932)에 연결되고, 제 2 트랜지스터(M2)의 제 2 단자는 제 3 노드(933)에 연결되고, 제 2 트랜지스터(M2)의 게이트 단자는 제 1 노드(931)에 연결될 수 있다.

[0136] 제 3 트랜지스터(M4)의 제 1 단자는 제 1 노드(931)에 연결되고, 제 3 트랜지스터(M4)의 제 2 단자는 제 2 수광 소자(912)의 캐소드(Cathode) 단자에 연결되고, 제 3 트랜지스터(M4)의 게이트 단자는 제 1 센싱(sensing) 라인(Sen)에 연결될 수 있다.

[0137] 제 4 트랜지스터(M7)의 제 1 단자는 제 1 수광 소자(911)의 아노드 단자에 연결되고, 제 4 트랜지스터(M7)의 제 2 단자는 제 1 노드(931)에 연결되고, 제 4 트랜지스터(M7)의 게이트 단자는 제 1 센싱 라인(Sen)에 연결될 수 있다.

[0138] 제 5 트랜지스터(M5)의 제 1 단자는 제 3 노드(933)에 연결되고, 제 5 트랜지스터(M5)의 제 2 단자는 접지되고, 제 5 트랜지스터(M5)의 게이트 단자는 제 1 센싱 라인(Sen)에 연결될 수 있다.

[0139] 제 6 트랜지스터(M6)의 제 1 단자는 제 2 노드(932)에 연결되고, 제 6 트랜지스터(M6)의 제 2 단자는 출력 라인(OUT)에 연결되고, 제 6 트랜지스터(M6)의 게이트 단자는 제 2 센싱 라인(Sen2)에 연결될 수 있다.

[0140] 제 1 수광 소자(911)의 캐소드 단자는 전원(VDD)에 연결되고, 제 2 수광 소자(912)의 아노드 단자는 접지될 수 있다.

- [0141] 화소 제어회로는 제 7 트랜지스터(M3), 캐패시터(CST) 및 자발광 소자(OLED)를 더 포함할 수 있다.

- [0142] 제 7 트랜지스터(M3)의 제 1 단자는 전원(VDD)에 연결되고, 제 7 트랜지스터(M3)의 제 2 단자는 제 2 노드(932)에 연결되고, 제 7 트랜지스터(M3)의 게이트 단자는 에미션(emission)라인(EM)에 연결될 수 있다.

- [0143] 캐패시터(CST)의 제 1 단자는 전원(VDD)에 연결되고, 캐패시터(CST)의 제 2 단자는 제 1 노드(931)에 연결될 수 있다.

- [0144] 자발광 소자(OLED)의 아노드 단자는 제 3 노드(933)에 연결되고, 자발광 소자(OLED)의 캐소드 단자는 접지될 수 있다.

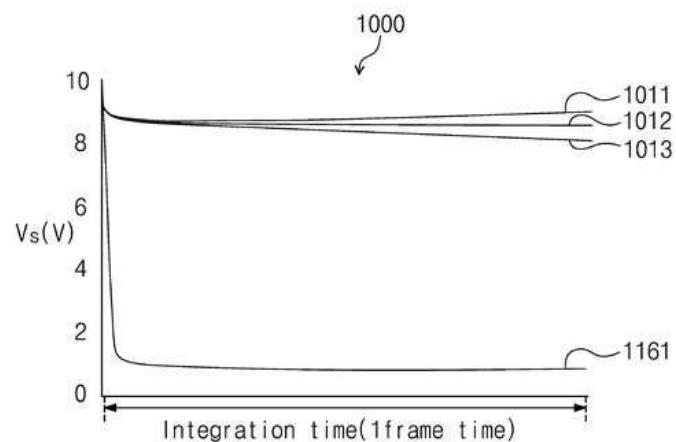

- [0145] 도 10은 본 발명의 일 실시예에 따른 출력 전압을 나타낸 그래프이다.

- [0146] 이하에서는 도 8을 참조하여 도 10을 설명한다. 그래프(1000)의 가로축은 시간을 나타낸다. 또한 그래프의 가로축은 인테그레이션 페이즈의 1 프레임 시간을 나타낼 수 있다. 그래프(1000)의 세로축은 제 1 노드(831)의 전압을 나타낸다. 그래프(1000)는 Low Temperature Poly Silicon(LTPS) Thin Film Transistor(TFT) 리퀴지(leakage), 직광 및 지문으로부터 반사된 빛의 비율이 1:100:0.1 경우를 나타낼 수 있다. 직광은 오프셋과 노이즈를 포함할 수 있다.

- [0147] 수광 소자를 하나만 사용하는 종래 기술에 따르면 자발광 소자에 의한 빛 및 외부로부터의 빛이 너무 강하여 지문으로부터의 빛이 있는지 여부에 상관 없이 전압은 라인(1061)과 같을 수 있다. 따라서 화소회로를 포함하는 시스템은 지문 센싱의 정확도가 낮을 수 있다. 하지만 본 발명의 일 실시예에 따른 화소회로(800)는 아래에서 설명하는 바와 같이 지문 센싱의 정확도를 높일 수 있다.

- [0148] 라인(1011)은 인테그레이션 페이즈에서 제 1 수광 소자(811)에만 지문으로부터의 빛이 수신된 경우를 나타낼 수 있다. 제 2 수광 소자(812)는 지문으로부터의 빛이 너무 적어서 빛의 양이 거의 0에 수렴할 수 있다. 예를 들어 지문의 마루가 밝아서 지문은 빛을 반사하여 제 1 수광 소자(811)는 지문으로부터 빛을 수신할 수 있다. 또한, 지문의 골이 너무 어두워서 지문은 빛을 반사하지 않을 수 있고, 제 2 수광 소자(812)는 지문으로부터 빛을 수신하지 못할 수 있다.

- [0149] 제 1 수광 소자(811)는 지문으로부터의 빛, 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 1 신호를 생성할 수 있다. 제 2 수광 소자(812)는 지문으로부터의 빛을 수신하지 못했으므로, 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 2 신호를 생성할 수 있다. 지문으로부터의 빛에 의하여 제 1 신호가 제 2 신호 보다 큰 값을 가질 수 있다. 제 1 신호와 제 2 신호의 차분 신호는 캐패시터(CST)를 충전 시킬 수 있다. 제 3 노드(833)의 전압은 점점 높아질 수 있다. 제 2 트랜지스터(M4)의 소스 팔로워 동작에 의하여 제 1 노드(831)의 전압 역시 점점 높아 질 수 있다. 따라서 제 1 노드(831)의 전압은 라인(1011)과 같을 수 있다.

- [0150] 라인(1012)은 인테그레이션 페이즈에서 제 1 수광 소자(811) 및 제 2 수광 소자(812)가 수신한 지문으로부터의 빛이 너무 적어서 빛의 양이 거의 0에 수렴하는 경우를 나타낼 수 있다. 예를 들어 지문의 골이 너무 어두워서 지문은 빛을 반사하지 않을 수 있고, 제 1 수광 소자(811) 및 제 2 수광 소자(812)는 지문으로부터 빛을 수신하지 못할 수 있다.

- [0151] 지문으로부터의 빛이 없으므로, 제 1 수광 소자(811)는 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 1 신호를 생성할 수 있다. 제 2 수광 소자(812)는 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 2 신호를 생성할 수 있다. 제 1 신호와 제 2 신호의 차분 신호는 거의 0과 같을 수 있다. 따라서 제 3 노드(833)의 전압은 거의 변하지 않을 수 있다. 제 2 트랜지스터(M4)의 소스 팔로워 동작에 의하여 제 1 노드(831)의 전압 역시 변하지 않을 수 있다. 따라서 제 1 노드(831)의 전압은 라인(1012)과 같을 수 있다.

- [0152] 라인(1013)은 인테그레이션 페이즈에서 제 2 수광 소자(812)에만 지문으로부터의 빛이 수신된 경우를 나타낼 수 있다. 제 1 수광 소자(811)는 지문으로부터의 빛이 너무 적어서 빛의 양이 거의 0에 수렴할 수 있다. 예를 들어 지문의 마루가 밝아서 지문은 빛을 반사하여 제 2 수광 소자(812)는 지문으로부터 빛을 수신할 수 있다. 또한, 지문의 골이 너무 어두워서 지문은 빛을 반사하지 않을 수 있고, 제 2 수광 소자(812)는 지문으로부터 빛을 수신하지 못할 수 있다.

- [0153] 제 2 수광 소자(812)는 지문으로부터의 빛, 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 2 신호를 생성할 수 있다. 제 1 수광 소자(811)는 지문으로부터의 빛을 수신하지 못했으므로, 자발광 소자에 의한 빛 및

외부로부터의 빛에 기초하여 제 1 신호를 생성할 수 있다. 지문으로부터의 빛에 의하여 제 2 신호가 제 1 신호보다 큰 값을 가질 수 있다. 제 1 신호와 제 2 신호의 차분 신호는 캐페시터(CST)를 방전 시킬 수 있다. 제 3 노드(833)의 전압은 점점 낮아질 수 있다. 제 2 트랜지스터(M4)의 소스 팔로워 동작에 의하여 제 1 노드(831)의 전압 역시 점점 낮아 질 수 있다. 따라서 제 1 노드(831)의 전압은 라인(1013)과 같을 수 있다.

[0155] 제 1 노드(831)의 전압은 제 7 트랜지스터(M10)의 동작에 의하여 출력 라인(OUT)에 전달될 수 있다. 시스템은 출력 라인(OUT)으로부터 전달된 출력 신호에 기초하여 지문 인식을 수행할 수 있다. 제 1 수광 소자(811) 및 제 2 수광 소자(812)가 지문으로부터 빛을 수신했는지 여부에 따라 제 1 노드(831)의 전압이 변하므로, 화소회로(800)를 포함하는 시스템은 정확하게 지문인식을 정확하게 수행할 수 있다.

[0156] 또한, 화소회로(800)는 자발광 소자에 의한 빛, 외부로부터의 빛 및 노이즈에 의한 영향을 줄일 수 있다. 또한 화소회로(800)는 자발광 소자에 의한 빛 및 외부로부터의 빛에 의한 클리핑(clipping) 현상을 예방할 수 있다. 또한 화소회로(800)는 지문에 의해 반사된 빛만을 이용하여 지문인식을 수행할 수 있으므로 signal noise ratio(SNR)를 높일 수 있다.

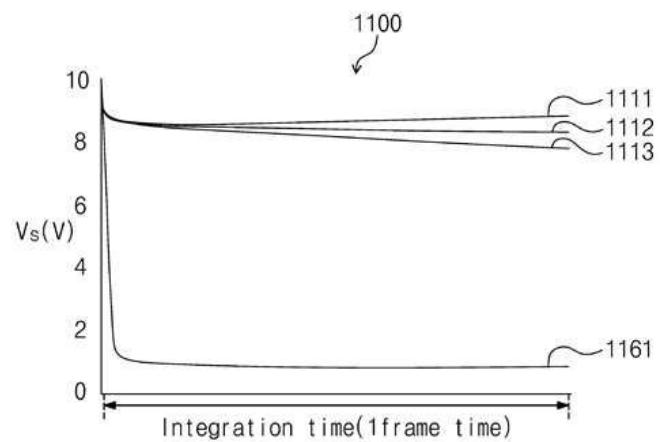

[0158] 도 11 은 본 발명의 일 실시예에 따른 출력 전압을 나타낸 그래프이다.

[0159] 이하에서는 도 8을 참조하여 도 11을 설명한다. 그래프(1100)의 가로축은 시간을 나타낸다. 또한 그래프의 가로축은 인테그레이션 페이즈의 1 프레임 시간을 나타낼 수 있다. 그래프(1100)의 세로축은 제 1 노드(831)의 전압을 나타낸다. 그래프(1100)는 Low Temperature Poly Silicon(LTPS) Thin Film Transistor(TFT) 리퀴지(leakage), 직광 및 지문으로부터 반사된 빛의 비율이 10:100:0.1인 경우를 나타낼 수 있다. 직광은 오프셋과 노이즈를 포함할 수 있다.

[0160] 수광 소자를 하나만 사용하는 종래 기술에 따르면 자발광 소자에 의한 빛 및 외부로부터의 빛이 너무 강하여 지문으로부터의 빛이 있는지 여부에 상관 없이 전압은 라인(1161)과 같을 수 있다. 따라서 화소회로를 포함하는 시스템은 지문 센싱의 정확도가 낮을 수 있다. 하지만 본 발명의 일 실시예에 따른 화소회로(800)는 아래에서 설명하는 바와 같이 지문 센싱의 정확도를 높일 수 있다.

[0161] 라인(1111)은 인테그레이션 페이즈에서 제 1 수광 소자(811)가 제 2 수광 소자(812)보다 지문으로부터 반사된 빛을 많이 수신하는 경우를 나타낸다. 예를 들어 라인(1111)은 제 1 수광 소자(811)가 지문의 밝은 부분에서 반사된 빛을 수신하고 제 2 수광 소자(812)는 지문의 어두운 부분에서 반사된 빛을 수신하는 경우를 나타낼 수 있다.

[0162] 제 1 수광 소자(811)는 지문으로부터의 빛, 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 1 신호를 생성할 수 있다. 제 2 수광 소자(812)는 지문으로부터의 빛, 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 2 신호를 생성할 수 있다. 제 1 수광 소자(811)가 제 2 수광 소자(812)보다 지문으로부터 반사된 빛을 많이 수신했으므로, 제 1 신호가 제 2 신호보다 큰 값을 가질 수 있다. 제 1 신호와 제 2 신호의 차분 신호는 캐페시터(CST)를 충전 시킬 수 있다. 제 3 노드(833)의 전압은 점점 높아질 수 있다. 제 2 트랜지스터(M4)의 소스 팔로워 동작에 의하여 제 1 노드(831)의 전압 역시 변하지 않을 수 있다. 따라서 제 1 노드(831)의 전압은 라인(1111)과 같을 수 있다.

[0163] 라인(1112)은 인테그레이션 페이즈에서 제 1 수광 소자(811) 및 제 2 수광 소자(812)가 수신한 지문으로부터의 빛의 크기가 동일한 경우를 나타낼 수 있다.

[0164] 제 1 수광 소자(811)는 지문으로부터의 빛, 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 1 신호를 생성할 수 있다. 제 2 수광 소자(812)는 지문으로부터의 빛, 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 2 신호를 생성할 수 있다. 제 1 신호와 제 2 신호의 차분 신호는 거의 0과 같을 수 있다. 따라서 제 3 노드(833)의 전압은 거의 변하지 않을 수 있다. 제 2 트랜지스터(M4)의 소스 팔로워 동작에 의하여 제 1 노드(831)의 전압 역시 변하지 않을 수 있다. 따라서 제 1 노드(831)의 전압은 라인(1112)과 같을 수 있다.

[0165] 라인(1113)은 인테그레이션 페이즈에서 제 1 수광 소자(811)가 제 2 수광 소자(812)보다 지문으로부터 반사된 빛을 적게 수신하는 경우를 나타낸다. 예를 들어 라인(1113)은 제 1 수광 소자(811)가 지문의 어두운 부분에서 반사된 빛을 수신하고 제 2 수광 소자(812)는 지문의 밝은 부분에서 반사된 빛을 수신하는 경우를 나타낼 수 있다.

[0166] 제 1 수광 소자(811)는 지문으로부터의 빛, 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 1 신호를

생성할 수 있다. 제 2 수광 소자(812)는 지문으로부터의 빛, 자발광 소자에 의한 빛 및 외부로부터의 빛에 기초하여 제 2 신호를 생성할 수 있다. 제 1 수광 소자(811)가 제 2 수광 소자(812)보다 지문으로부터 반사된 빛을 적게 수신했으므로, 제 1 신호가 제 2 신호보다 작은 값을 가질 수 있다. 제 1 신호와 제 2 신호의 차분 신호는 캐패시터(CST)를 방전 시킬 수 있다. 제 3 노드(833)의 전압은 점점 낮아질 수 있다. 제 2 트랜지스터(M4)의 소스 팔로워 동작에 의하여 제 1 노드(831)의 전압 역시 점점 낮아 질 수 있다. 따라서 제 1 노드(831)의 전압은 라인(1113)과 같을 수 있다.

[0167] 제 1 노드(831)의 전압은 제 7 트랜지스터(M10)의 동작에 의하여 출력 라인(OUT)에 전달될 수 있다. 시스템은 출력 라인(OUT)으로부터 전달된 출력 신호에 기초하여 지문 인식을 수행할 수 있다. 제 1 수광 소자(811) 및 제 2 수광 소자(812)가 지문으로부터 빛을 수신했는지 여부에 따라 제 1 노드(831)의 전압이 변하므로, 화소회로(800)를 포함하는 시스템은 정확하게 지문인식을 정확하게 수행할 수 있다.

[0168] 또한, 화소회로(800)는 자발광 소자에 의한 빛, 외부로부터의 빛 및 노이즈에 의한 영향을 줄일 수 있다. 또한 화소회로(800)는 자발광 소자에 의한 빛 및 외부로부터의 빛에 의한 클리핑(clipping) 현상을 예방할 수 있다. 또한 화소회로(800)는 지문에 의해 반사된 빛만을 이용하여 지문인식을 수행할 수 있으므로 signal noise ratio(SNR)를 높일 수 있다.

[0170] 이제까지 다양한 실시예들을 중심으로 살펴보았다. 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자는 본 발명이 본 발명의 본질적인 특성에서 벗어나지 않는 범위에서 변형된 형태로 구현될 수 있음을 이해할 수 있을 것이다. 그러므로 개시된 실시예들은 한정적인 관점이 아니라 설명적인 관점에서 고려되어야 한다. 본 발명의 범위는 전술한 설명이 아니라 특허청구범위에 나타나 있으며, 그와 동등한 범위 내에 있는 모든 차이점은 본 발명에 포함된 것으로 해석되어야 할 것이다.

[0171] 한편, 상술한 본 발명의 실시예들은 컴퓨터에서 실행될 수 있는 프로그램으로 작성가능하고, 컴퓨터로 읽을 수 있는 기록매체를 이용하여 상기 프로그램을 동작시키는 범용 디지털 컴퓨터에서 구현될 수 있다. 상기 컴퓨터로 읽을 수 있는 기록매체는 마그네틱 저장매체(예를 들면, 톰, 플로피 디스크, 하드디스크 등), 광학적 판독 매체(예를 들면, 시디롬, 디브이디 등)와 같은 저장매체를 포함한다.

### 부호의 설명

[0173] 110: 자발광 소자에서 출사된 빛

120: 지문에 반사된 빛

130: 직광

210: 화소회로

221: 제 1 위치

222: 제 2 위치

310: 화소회로

311: 제 1 수광 소자

312: 제 2 수광 소자

313: 화소 제어회로

321: 제 1 영역

322: 제 2 영역

410: 반사광 전류

420: 직광 전류

430: 합성 전류

511: 제 2 반사광 전류

512: 제 1 반사광 전류

513: 직광 전류

700: 화소회로

711: 제 1 수광 소자

712: 제 2 수광 소자

800: 화소회로

811: 제 1 수광 소자

812: 제 2 수광 소자

900: 화소회로

911: 제 1 수광 소자

912: 제 2 수광 소자

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

도면7

도면8

도면9

도면10

도면11

|                |                                                      |         |            |

|----------------|------------------------------------------------------|---------|------------|

| 专利名称(译)        | 包括光学指纹感测电路的像素电路,像素电路的驱动方法和有机发光显示装置                   |         |            |

| 公开(公告)号        | <a href="#">KR1020200082662A</a>                     | 公开(公告)日 | 2020-07-08 |

| 申请号            | KR1020180173480                                      | 申请日     | 2018-12-31 |

| [标]申请(专利权)人(译) | 乐金显示有限公司<br>汉阳大学校产学协力团                               |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司<br>汉阳大学产学合作基金会                             |         |            |

| [标]发明人         | 최병덕<br>유용상<br>김용덕<br>문정민<br>정순신<br>송문봉<br>정지환<br>장기석 |         |            |

| 发明人            | 최병덕<br>유용상<br>김용덕<br>문정민<br>정순신<br>송문봉<br>정지환<br>장기석 |         |            |

| IPC分类号         | G09G3/3233 G06K9/00                                  |         |            |

| CPC分类号         | G09G3/3233 G06K9/0004 G09G2300/046 G09G2354/00       |         |            |

**摘要(译)**

像素电路技术领域本发明涉及包括光学指纹感测电路的像素电路,包括光学指纹感测电路的像素电路的驱动方法,以及包括具有光学指纹感测电路的像素电路的显示装置。包括光学指纹感测电路的像素电路包括:第一光接收元件,其接收光并产生第一信号;第二光接收元件,其接收光并产生第二信号;以及第一信号和第二信号之间的差。以及一种像素控制电路,其包括接收信号,输出输出信号,包括至少一个晶体管组件和至少一个电容器组件并基于数据信号输出光的自发光元件。