(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0003949

(43) 공개일자 2016년01월12일

(51) 국제특허분류(Int. Cl.)

*H01L 27/32* (2006.01) *H01L 51/52* (2006.01)

*H01L 51/56* (2006.01)

(21) 출원번호 10-2014-0081790

(22) 출원일자 2014년07월01일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

임종혁

부산광역시 연제구 연산9동 135~150 경남아파트

1동 711호

김세준

경기 파주시 미래로 345, 701동 1102호 (동파동,

한울마을7단지삼부르네상스아파트)

(뒷면에 계속)

(74) 대리인

김기문

전체 청구항 수 : 총 29 항

(54) 발명의 명칭 유기전계발광 표시장치 및 그 제조 방법

### (57) 요약

표시영역과 비표시영역으로 정의되는 기판; 상기 표시영역 상에 배치되고 반도체층, 게이트전극, 소스전극 및 드레인전극을 포함하는 박막 트랜지스터; 상기 박막 트랜지스터 상에 배치되는 제 1 전극, 유기발광층 및 제 2 전극을 포함하는 유기발광 소자; 상기 비표시영역 상에 배치되고 금속 또는 금속 합금층으로 형성되는 패드전극; 및 상기 패드전극의 상에 배치되고 비정질 또는 결정질 투명 도전물질로 형성되는 보호전극층;을 포함하고, 상기 보호전극층은 상기 패드전극이 외부로 노출된 영역에 접하여 형성되는 것을 특징으로 한다.

따라서, 본 발명에 따른 유기전계발광 표시장치 및 그 제조방법은, 외부로 노출되는 패드전극에 보호전극층을 형성함으로써, 패드전극에 산소 및 수분이 침투하는 것과 패드전극의 마이그레이션이 발생하는 것을 방지한다. 또한, 보호전극층을 형성하는데 필요한 공정을 단순화 하고, 제조 비용을 감소할 수 있다.

### 대표 도

(72) 발명자

이준석

서울 관악구 난곡로 55, 214동 601호 (신림동, 관

악산휴먼시아2단지아파트)

이소경

경기도 파주시 월롱면 덕은리 파주LCD산업단지

1007번지 정다운마을 A동 1220호

---

이재성

서울 송파구 양재대로 1218, 239동 202호 (방이동,

올림픽선수기자촌아파트)

## 명세서

### 청구범위

#### 청구항 1

표시영역과 비표시영역으로 정의되는 기판;

상기 표시영역 상에 배치되고 반도체층, 게이트전극, 소스전극 및 드레인전극을 포함하는 박막 트랜지스터;

상기 박막 트랜지스터 상에 배치되는 제 1 전극, 유기발광층 및 제 2 전극을 포함하는 유기발광 소자;

상기 비표시영역 상에 배치되고 금속 또는 금속 합금층으로 형성되는 패드전극; 및

상기 패드전극의 상에 배치되고 비정질 또는 결정질 투명 도전물질로 형성되는 보호전극층;을 포함하고,

상기 보호전극층은 상기 패드전극이 외부로 노출된 영역에 접하여 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 2

제 1항에 있어서,

상기 패드전극은 제 1 패드전극 및 상기 제 1 패드전극 상에 형성되는 제 2 패드전극을 포함하는 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 3

제 2 항에 있어서,

상기 제 2 패드전극은 제 1 전극층 및 상기 제 1 전극층 상에 형성되는 제 2 전극층을 포함하는 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 4

제 3 항에 있어서,

상기 제 1 전극층은 MoTi 또는 Ti으로 형성되고, 상기 제 2 전극층은 Cu로 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 5

제 2항에 있어서,

상기 제 1 패드전극이 단층인 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 6

제 2항에 있어서,

상기 제 1 패드전극은 제 1 금속층 및 상기 제 1 금속층 상에 형성되는 제 2 금속층을 포함하고,

상기 제 1 금속층은 MoTi 또는 Ti으로 형성되고, 상기 제 2 금속층은 Cu로 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 7

제 2항에 있어서,

상기 제 1 패드전극은 박막 트랜지스터의 게이트전극과 동일층에서 동일물질로 형성되고,

상기 제 2 패드전극은 박막 트랜지스터의 소스전극 및 드레인전극과 함께 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 8

제 2항에 있어서,

상기 제 2 패드전극의 상면 및 측면에 접하여 보호전극층이 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 9

제 3항에 있어서,

상기 제 2 패드전극 및 보호전극층은 박막 트랜지스터의 소스전극 및 드레인전극과 동일층에서 동일물질로 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 10

제 9항에 있어서,

상기 박막 트랜지스터의 소스전극 및 드레인전극은 제 1 전극층, 상기 제 1 전극층 상에 형성되는 제 2 전극층 및 상기 제 2 전극층 상에 형성되는 제 3 전극층을 포함하고,

상기 제 2 패드전극의 제 1 전극층은 상기 소스전극 및 드레인전극의 제 1 전극층과 동일층에서 동일물질로 형성되고,

상기 제 2 패드전극의 제 2 전극층은 상기 소스전극 및 드레인전극의 제 2 전극층과 동일층에서 동일물질로 형성되고,

상기 제 2 패드전극 상면에 형성되는 보호전극층은 상기 소스전극 및 드레인전극의 제 3 전극층과 동일층에서 동일물질로 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 11

제 10항에 있어서,

상기 보호전극층은 상기 제 2 패드전극의 상면에만 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 12

제 11항에 있어서,

상기 보호전극층을 포함한 기판 상에 상기 보호전극층의 상면을 노출하는 보호막을 더 형성하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 13

제 1항에 있어서,

상기 패드전극은 제 1 패드전극, 상기 제 1 패드전극 상에 형성되는 제 2 패드전극과 상기 제 2 패드전극 및 보호막 상에 형성되는 제 3 패드전극을 포함하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 14

제 13항에 있어서,

상기 제 3 패드전극의 상면 및 측면에 접하여 보호전극층이 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 15

제 13항에 있어서,

상기 제 3 패드전극은 제 1 층 및 상기 제 1 층 상에 형성되는 제 2 층을 포함하고,

상기 제 1 층은 투명 도전물질로 형성되고, 상기 제 2 층은 Ag 또는 Ag 합금으로 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 16

제 1항에 있어서,

상기 유기전계발광 소자의 제 1 전극은 제 1 층, 상기 제 1 층 상에 형성되는 제 2 층 및 상기 제 2 층 상에 형성되는 제 3 층을 포함하고,

상기 제 1 층 및 제 3 층은 투명 도전물질로 형성되고, 상기 제 2 층은 Ag 또는 Ag 합금으로 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 17

제 16항에 있어서,

상기 제 1 전극의 제 1 층은 제 3 패드전극의 제 1 층과 동일층에서 동일물질로 형성되고,

상기 제 1 전극의 제 2 층은 제 3 패드전극의 제 2 층과 동일층에서 동일물질로 형성되고,

상기 제 1 전극의 제 3 층은 제 3 패드전극 상면 및 측면에 접하여 형성되는 보호전극층과 동일층에서 동일물질로 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 18

제 13항에 있어서,

상기 제 3 패드전극은 제 1 층, 상기 제 1 층 상에 형성되는 제 2 층 및 상기 제 2 층 상에 형성되는 제 3 층을 포함하고,

상기 제 1 층 및 제 3 층은 투명 도전물질로 형성되고, 상기 제 2 층은 Ag 또는 Ag 합금으로 형성되는 것을 더 포함하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 19

제 1항에 있어서,

상기 유기전계발광 소자의 제 1 전극은 제 1 층, 상기 제 1 층 상에 형성되는 제 2 층, 상기 제 2 층 상에 형성되는 제 3 층 및 상기 제 3 층 상에 형성되는 제 4 층을 포함하고,

상기 제 1 층, 제 3 층 및 3 층은 투명 도전물질로 형성되고, 상기 제 2 층은 Ag 또는 Ag 합금으로 형성되는 것을 더 포함하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 20

제 19항에 있어서,

상기 제 1 전극의 제 1 층은 제 3 패드전극의 제 1 층과 동일층에서 동일물질로 형성되고,

상기 제 1 전극의 제 2 층은 제 3 패드전극의 제 2 층과 동일층에서 동일물질로 형성되고,

상기 제 1 전극의 제 3 층은 제 3 패드전극의 제 3 층과 동일층에서 동일 물질로 형성되고,

상기 제 1 전극의 제 4층은 제 3 패드전극의 상면 및 측면에 형성되는 보호전극층과 동일층에서 동일물질로 형성되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 21

표시영역과 비표시영역으로 정의되는 기판의 상기 비표시영역 상에 패드전극을 형성하는 단계; 및

상기 패드전극이 외부로 노출된 영역과 접하여 보호전극층을 형성하는 단계;를 포함하고,

상기 패드전극은 금속 또는 금속 합금층으로 형성되고,

상기 보호전극층은 비정질 또는 결정질 투명 도전물질로 형성되는 것을 특징으로 하는 유기전계발광 표시장치 제조방법.

### 청구항 22

제 21항에 있어서,

상기 패드전극을 형성하는 단계는,

상기 비표시영역의 기판 상에 제 1 패드전극을 형성하는 단계;

상기 제 1 패드전극 상에 층간절연막을 형성하는 단계;

상기 층간절연막 상에 제 1 패드전극의 상면을 노출하는 컨택홀을 형성하는 단계; 및

상기 컨택홀을 통해 상기 제 1 패드전극과 접하는 제 2 패드전극을 형성하는 단계를 포함하는 것을 특징으로 하는 유기전계발광 표시장치 제조방법.

### 청구항 23

제 22항에 있어서,

상기 보호전극층을 형성하는 단계는,

상기 제 2 패드전극을 포함하는 기판 전면에 투명 도전물질을 형성하는 단계 이후에,

상기 투명 도전물질을 식각하여, 상기 보호전극층이 상기 제 2 패드전극의 상면 및 측면에 형성되는 단계를 더

포함하는 것을 특징으로 하는 유기전계발광 표시장치 제조방법.

#### 청구항 24

제 22항에 있어서,

제 2 패드전극 및 상기 보호전극층을 형성하는 단계는,

제 1 패드전극을 포함하는 기판 전면에 MoTi 또는 Ti로 이루어진 상기 제 2 패드전극의 제 1 전극 물질층을 형성하는 단계;

상기 제 1 전극 물질층 상에 형성되는 Cu로 이루어진 상기 제 2 패드전극의 제 2 전극 물질층을 형성하는 단계; 및

상기 제 2 전극 물질층 상에 형성되는 투명 도전물질층으로 이루어진 보호전극물질층을 형성하는 단계를 포함하고,

상기 제 2 패드전극의 상기 제 1 전극 물질층, 제 2 전극 물질층 및 투명 도전물질층을 동시에 식각하여, 상기 제 2 패드전극 및 보호전극층을 형성하는 단계를 포함하는 것을 특징으로 하는 유기전계발광 표시장치 제조방법.

#### 청구항 25

제 21항에 있어서,

상기 패드전극을 형성하는 단계는.

제 1 패드전극을 형성하는 단계;

상기 제 1 패드전극 상에 제 2 패드전극을 형성하는 단계;

상기 제 2 패드전극 상에 보호막을 형성하는 단계;

상기 보호막 상에 상기 제 2 패드전극 상면을 노출하는 컨택홀을 형성하는 단계; 및

상기 컨택홀을 통해 상기 제 2 패드전극과 접하는 제 3 패드전극을 형성하는 단계를 더 포함하는 것을 특징으로 하는 유기전계발광 표시장치 제조방법.

#### 청구항 26

제 25항에 있어서,

상기 제 3 패드전극을 형성하는 단계는,

상기 보호막 상에 형성된 컨택홀을 포함하는 기판 전면에 ITO를 포함하는 상기 제 3 패드전극의 제 1 층 물질을 형성하는 단계;

상기 제 1 층 물질 상에 Ag 또는 Ag 합금으로 이루어진 상기 제 3 패드전극의 제 2 층 물질을 형성하는 단계; 및

상기 제 2 층 물질 상에 ITO를 포함하는 상기 제 3 패드전극의 제 3 층 물질을 형성하는 단계;를 포함하고,

상기 제 3 패드전극의 상기 제 1 층 물질, 제 2 층 물질 및 제 3 층 물질을 동시에 식각하여, 상기 제 3 패드전극의 제 1 층, 제 2 층 및 제 3 층을 형성하는 것을 특징으로 하는 유기전계발광 표시장치 제조방법.

#### 청구항 27

제 25항에 있어서,

상기 제 3 패드전극을 포함하는 기판 전면에 투명 도전물질을 형성하는 단계 이후에,

상기 투명 도전물질을 식각하여 보호전극층을 형성하고,

상기 보호전극층이 상기 제 3 패드전극의 상면 및 측면에 형성되는 단계를 더 포함하는 것을 특징으로 하는 유기전계발광 표시장치 제조방법.

### 청구항 28

제 25항에 있어서,

제 3 패드전극 및 상기 보호전극층을 형성하는 단계는,

제 2 패드전극을 포함하는 기판 전면에 비결정질 투명 도전물질로 이루어진 상기 제 3 패드전극의 제 1 층 물질을 형성하는 단계;

상기 제 1 층 물질 상에 Ag 또는 Ag 합금으로 이루어진 제 2 층 물질을 형성하는 단계;

상기 제 2 층 물질 상에 비결정질 투명 도전물질을 기판 전면에 형성하는 단계;

상기 비결정질 투명도전물질 상에 포토레지스트를 형성하는 단계;

상기 포토레지스트를 마스크로 상기 제 3 패드전극의 제 1 층 물질, 제 2 층 물질 및 상기 비결정질 투명 도전물질을 동시에 식각하여, 비결정질의 제 1 층, 제 2 층 및 비결정질의 투명 도전물질층을 형성하는 단계;

상기 비결정질의 제 1 층 및 비결정질의 투명 도전물질층을 결정화하여, 결정질의 상기 제 1 층 및 상기 제 3 패드전극 상에 형성되는 결정질의 투명 도전물질층을 형성하는 단계;

상기 포토레지스트 상면 및 상기 제 3 패드전극과 결정질의 투명 도전물질 측면에 비결정질의 투명 도전물질을 형성하는 단계;

상기 제 3 패드전극과 결정질의 투명 도전물질의 측면에 접촉하는 비결정질의 투명도전물질은 상기 제 3 패드전극 상면 및 측면에 배치되고, 결정질의 투명 도전물질로 이루어진 보호전극층을 형성하는 단계;

상기 포토레지스트 상면에 형성된 비결정질의 투명 도전물질을 식각하는 단계; 및

상기 포토레지스트를 스트립(strip)하는 단계를 포함하는 것을 특징으로 하는 유기전계발광 표시장치 제조방법.

### 청구항 29

제 28항에 있어서,

상기 제 3 패드전극의 제 1 층 및 상기 제 3 패드전극의 상면에 형성된 보호전극층은 160도 내지 180도의 온도에서 이루어지는 열처리를 통해 결정화 되는 것을 특징으로 하는 유기전계발광 표시장치 제조방법.

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 유기전계발광 표시장치 및 그 제조 방법에 관한 것으로, 보다 구체적으로는 유기전계발광 표시장치의 비표시영역에 형성되는 패드전극의 부식을 방지할 수 있는 유기전계발광 표시장치 및 그 제조 방법에 관한 것이다.

### 배경 기술

[0002] 최근, 음극선관(Cathode Ray Tube)의 단점인 무게와 부피를 줄일 수 있는 각종 평판 표시장치들이 개발되고 있다. 이러한 평판 표시장치는 액정 표시장치(Liquid Crystal Display : 이하 "LCD"라 한다), 전계 방출 표시장치

(Field Emission Display : FED), 플라즈마 디스플레이 패널(Plasma Display Panel : 이하 "PDP"라 한다) 및 전계발광소자(Electroluminescence Device) 등이 있다.

[0003] 전계발광소자는 발광층의 재료에 따라 무기발광다이오드 표시장치와 유기발광다이오드 표시장치로 대별되며 스스로 발광하는 자발광소자로서 응답속도가 빠르고 발광효율, 휙도 및 시야각이 큰 장점이 있다.

[0004] 액티브 매트릭스 타입의 유기발광다이오드 표시장치(Active Matrix type Organic Light Emitting Diode display, AMOLED)는 박막트랜지스터(Thin Film Transistor : 이하, "TFT")를 이용하여 유기발광다이오드소자(이하, "OLED"라 함)에 흐르는 전류를 제어하여 화상을 표시한다. 이러한 유기발광다이오드 표시장치는 애노드 전극, 캐소드전극 및 유기발광층을 포함하는 OLED의 구조에 따라 상부 발광(Top emission) 방식 또는 하부 발광(bottom emission) 방식 등의 형태로 화상을 표시한다. 하부 발광 방식이 유기발광층에서 발생된 가시광을 TFT가 형성된 기판 하부쪽으로 표시하는 데 반해, 상부 발광 방식은 유기발광층에서 발생된 가시광을 TFT가 형성된 기판 상부쪽으로 표시한다.

[0005] 또한, 유기발광 표시장치는 표시영역 및 표시영역 외곽의 비표시영역으로 구분된다. 표시영역에는 박막 트랜지스터 및 유기전계발광 소자가 형성된다. 또한, 비표시영역에는 외부전원으로부터 박막 트랜지스터 및 유기전계발광 소자에 신호전압을 인가하기 위한 패드전극이 형성된 패드부가 구비된다. 여기서, 박막 트랜지스터 및 유기전계발광 소자는 패드부와 다수의 배선을 통해 서로 전기적으로 연결된다.

[0006] 여기서, 비표시영역에 형성되는 패드부의 패드전극은 구동부와 박막 트랜지스터 및 유기전계발광 소자와 연결되기 위해 외부로 노출될 수 있다. 이 때, 패드전극이 금속 또는 금속 합금으로 형성될 경우, 외부 습기와 산소로 인해 패드전극의 부식이 발생할 수 있다.

[0007] 또한, 금속 또는 금속 합금으로 형성된 패드전극은 마이그레이션(migration)이 발생할 수 있다. 이로 인해, 패드전극은 인접한 배선과 단락(short)되어 박막 트랜지스터 및 유기전계발광 소자에 신호전압을 인가하는 데 문제가 발생하게 된다.

## 발명의 내용

### 해결하려는 과제

[0008] 본 발명은 외부로 노출되는 패드전극에 보호전극층을 형성함으로써, 패드전극에 산소 및 수분이 침투하는 것과 패드전극의 마이그레이션이 발생하는 것을 방지하는 유기전계발광 표시장치 및 그 제조 방법을 제공하는데 그 목적이 있다.

[0009] 또한, 본 발명은 보호전극층을 형성하는데 필요한 공정을 단순화 하고, 제조 비용을 감소하는 유기전계발광 표시장치 및 그 제조 방법을 제공하는데 그 목적이 있다.

### 과제의 해결 수단

[0010] 상기와 같은 종래 기술의 과제를 해결하기 위한 본 발명의 유기전계발광 표시장치는, 표시영역과 비표시영역으로 정의되는 기판; 상기 표시영역 상에 배치되고 반도체층, 게이트전극, 소스전극 및 드레인전극을 포함하는 박막 트랜지스터; 상기 박막 트랜지스터 상에 배치되는 제 1 전극, 유기발광층 및 제 2 전극을 포함하는 유기발광 소자; 상기 비표시영역 상에 배치되고 금속 또는 금속 합금층으로 형성되는 패드전극; 및 상기 패드전극의 상에 배치되고 비정질 또는 결정질 투명 도전물질로 형성되는 보호전극층;을 포함하고, 상기 보호전극층은 상기 패드전극이 외부로 노출된 영역에 접하여 형성되는 것을 특징으로 한다.

[0011] 또한, 본 발명의 유기전계발광 표시장치 제조방법은, 표시영역과 비표시영역으로 정의되는 기판의 상기 비표시영역 상에 패드전극을 형성하는 단계; 및 상기 패드전극이 외부로 노출된 영역과 접하여 보호전극층을 형성하는 단계;를 포함하고, 상기 패드전극은 금속 또는 금속 합금층으로 형성되고, 상기 보호전극층은 비정질 또는 결정질 투명 도전물질로 형성되는 것을 특징으로 한다.

### 발명의 효과

[0012] 본 발명에 따른 유기전계발광 표시장치 및 그 제조 방법은 외부로 노출되는 패드전극에 보호전극층을 형성함으로써, 패드전극에 산소 및 수분이 침투하는 것과 패드전극의 마이그레이션이 발생하는 것을 방지하는 제 1 효과가 있다.

[0013] 또한, 본 발명에 따른 유기전계발광 표시장치 및 그 제조 방법은 보호전극층을 형성하는데 필요한 공정을 단순화 하고, 제조 비용을 감소하는 제 2 효과가 있다.

### 도면의 간단한 설명

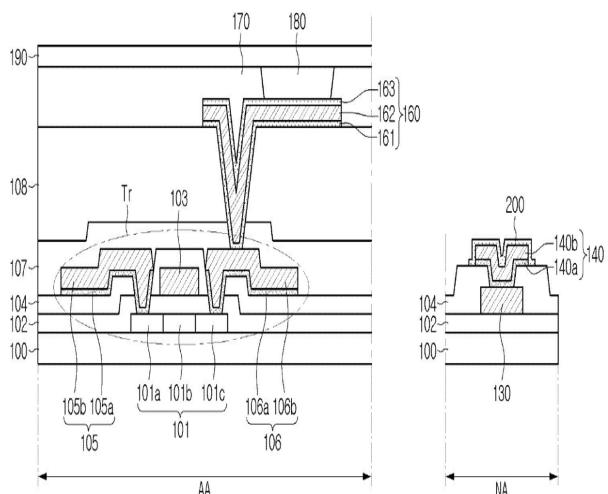

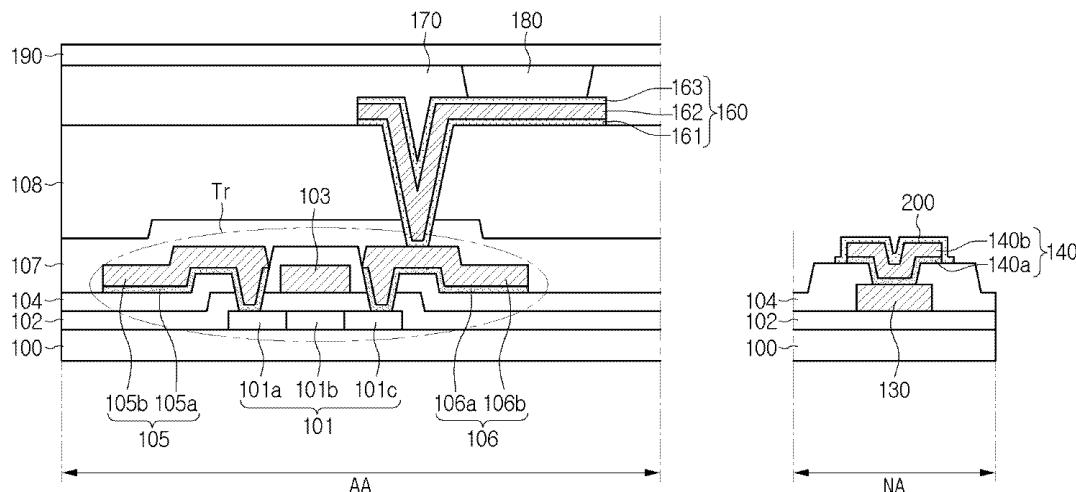

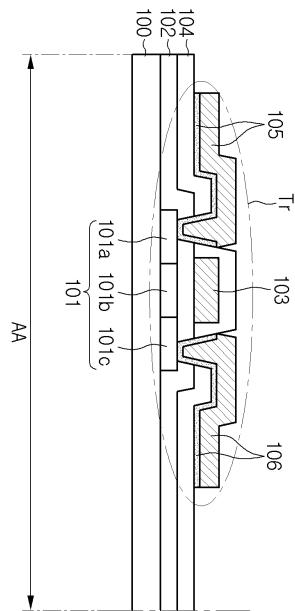

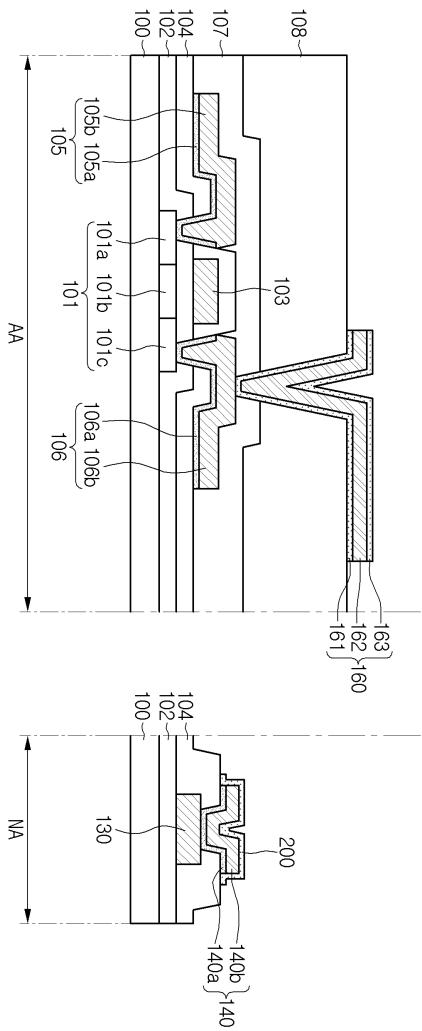

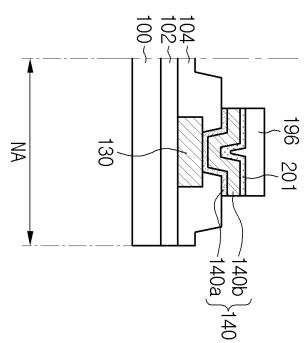

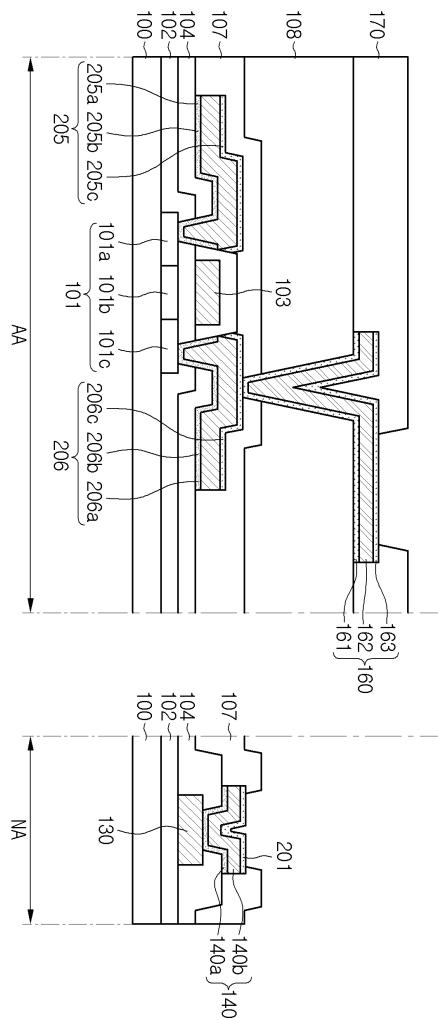

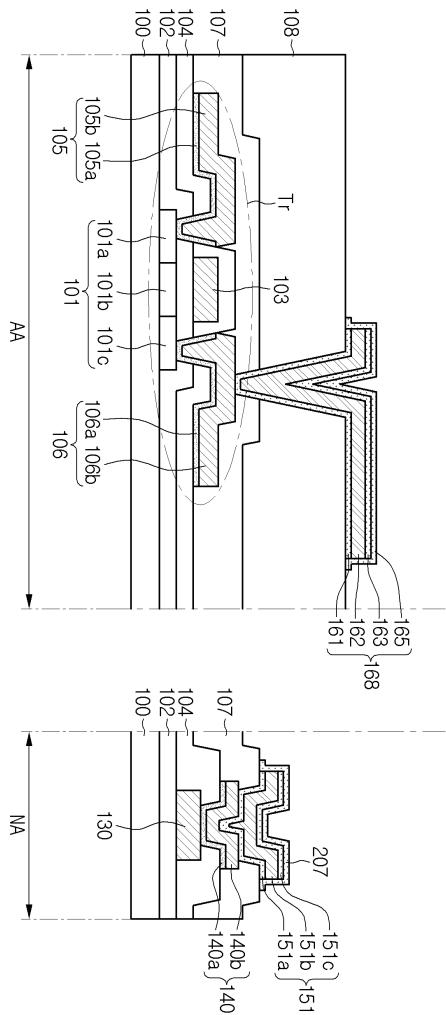

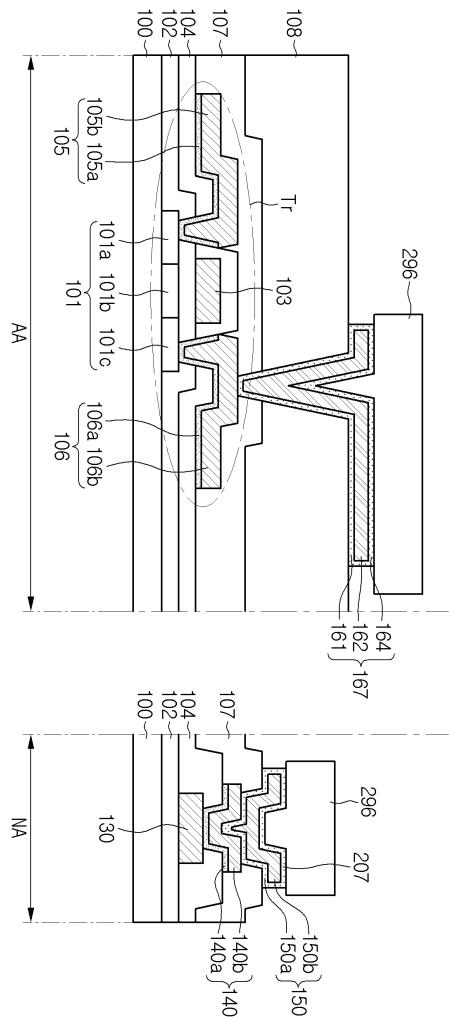

[0014] 도 1은 본 발명의 제 1 실시예에 따른 유기전계발광 표시장치를 도시한 단면도이다.

도 2a 내지 2e는 본 발명의 제 1 실시예에 따른 유기전계발광 표시장치의 제조방법을 도시한 도면이다.

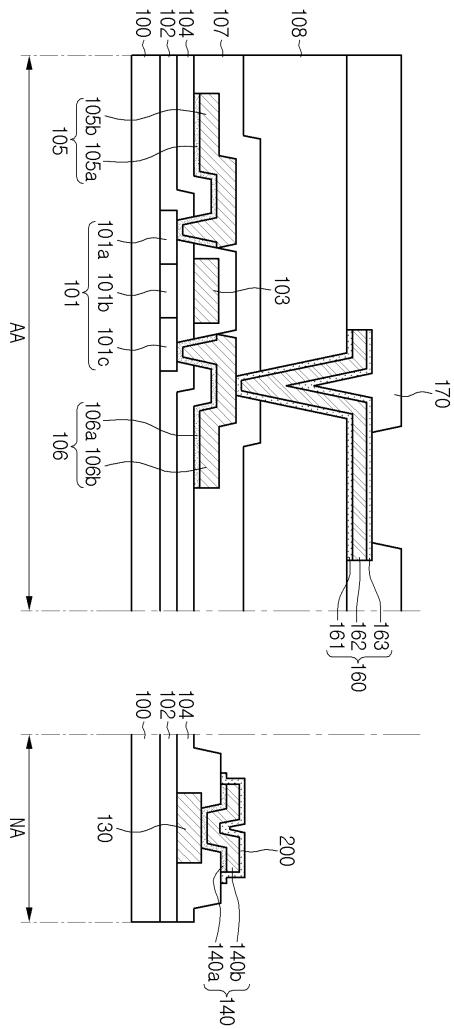

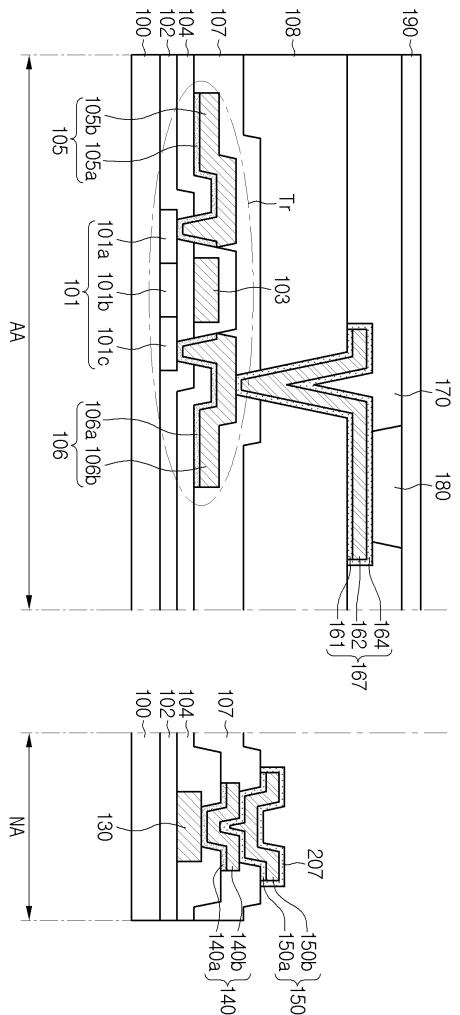

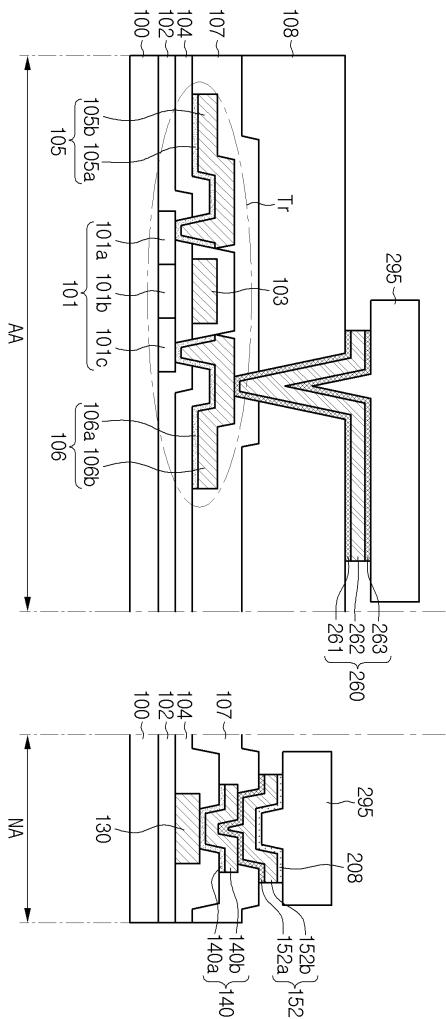

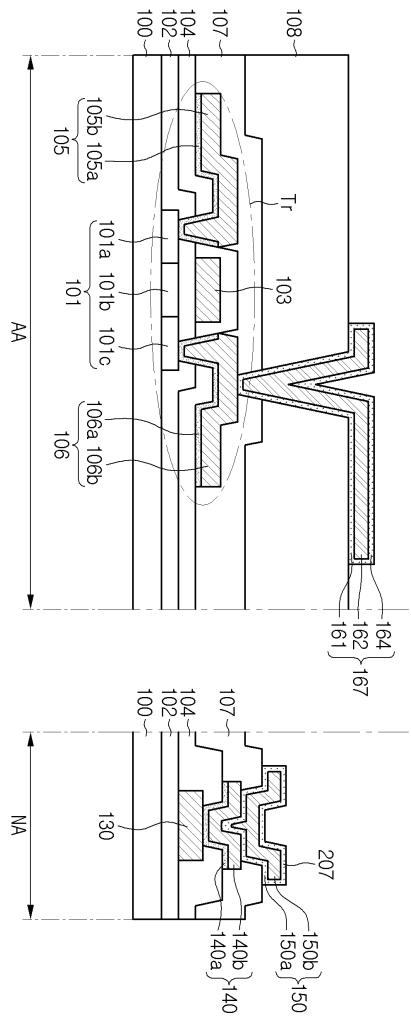

도 3은 본 발명의 제 2 실시예에 따른 유기전계발광 표시장치를 도시한 단면도이다.

도 4a 내지 4e는 본 발명의 제 2 실시예에 따른 유기전계발광 표시장치의 제조방법을 도시한 도면이다.

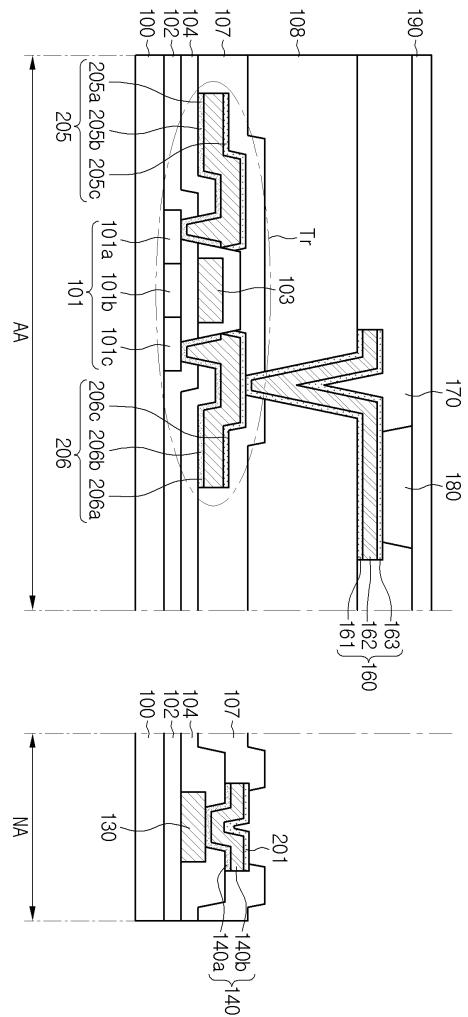

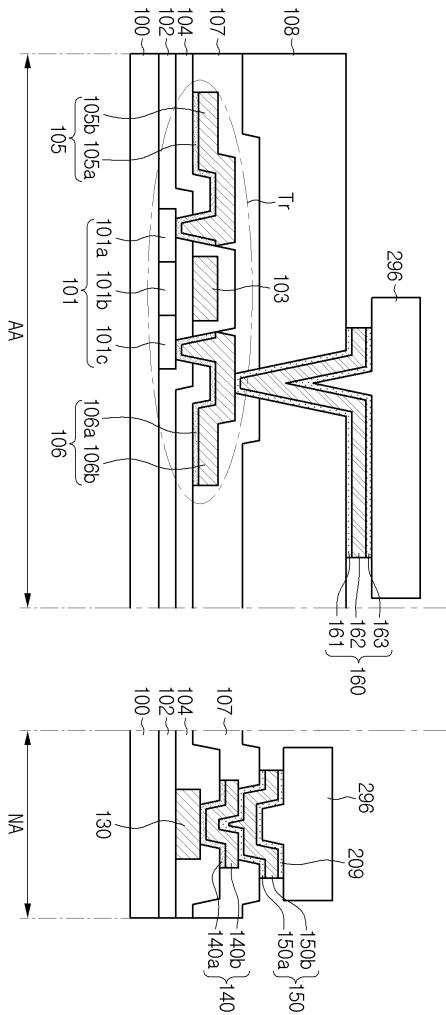

도 5는 본 발명의 제 3 실시예에 따른 유기전계발광 표시장치를 도시한 단면도이다.

도 6은 본 발명의 제 3 실시예에 따른 유기전계발광 표시장치의 제조방법을 도시한 단면도이다.

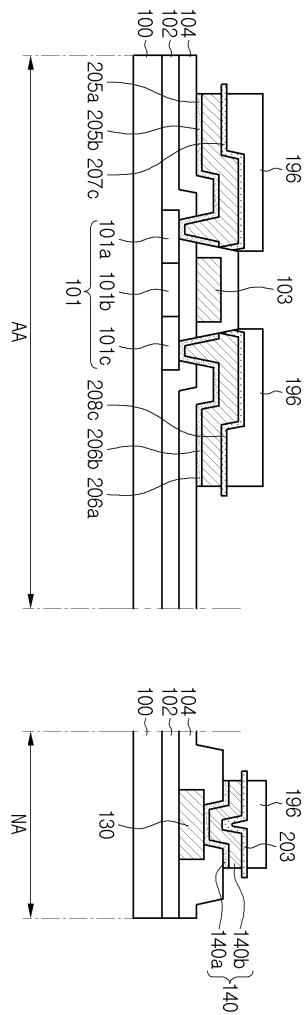

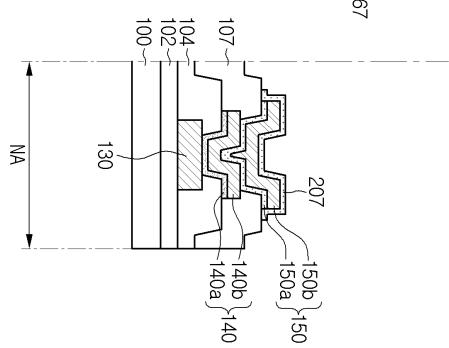

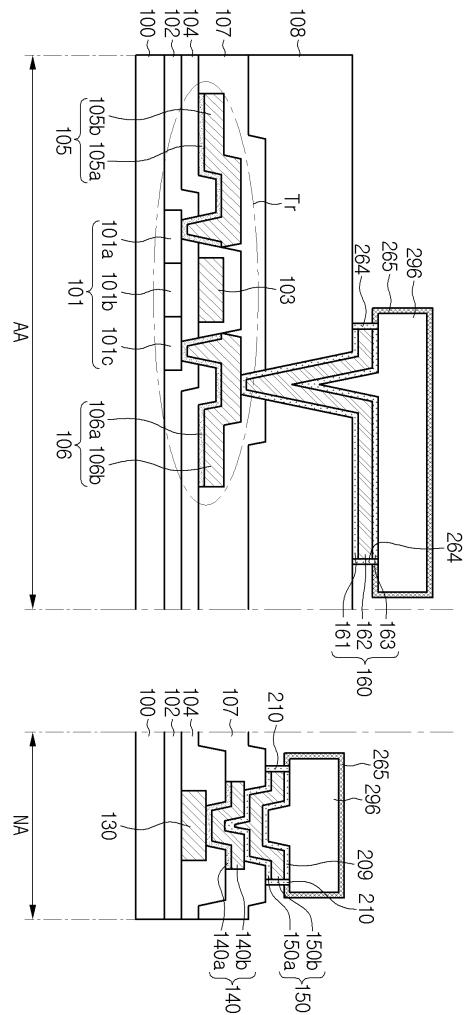

도 7은 본 발명에 따른 유기전계발광 표시장치의 제조방법의 다른 실시예를 도시한 단면도이다.

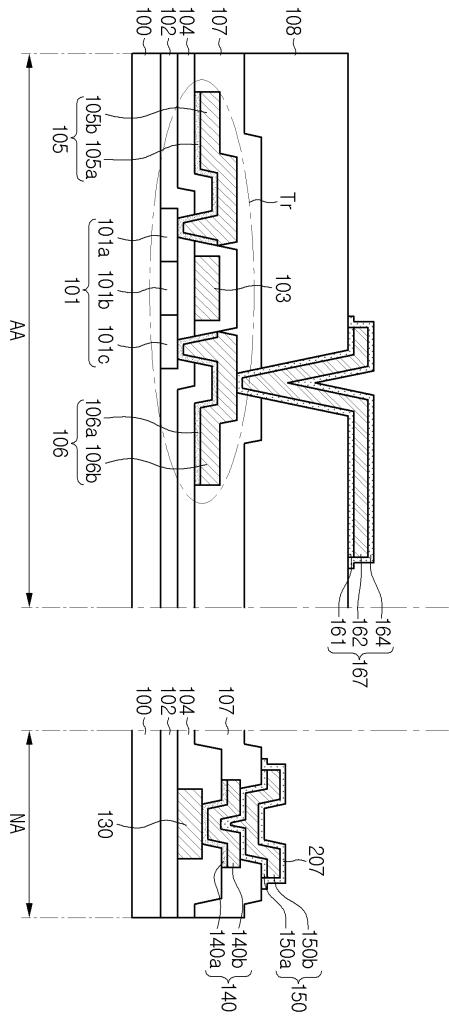

도 8a 내지 8e는 본 발명에 따른 유기전계발광 표시장치의 제조방법의 또 다른 실시예를 도시한 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0015] 이하, 본 발명의 실시예들은 도면을 참고하여 상세하게 설명한다. 다음에 소개되는 실시예들은 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위해 예로서 제공되는 것이다. 따라서, 본 발명은 이하 설명되는 실시예들에 한정되지 않고 다른 형태로 구체화될 수도 있다. 그리고 도면들에 있어서, 장치의 크기 및 두께 등은 편의를 위하여 과장되어 표현될 수도 있다. 명세서 전체에 걸쳐서 동일한 참조번호들은 동일한 구성요소들을 나타낸다.

[0016] 도 1은 본 발명의 제 1 실시예에 따른 유기전계발광 표시장치를 도시한 단면도이다. 도 1을 참조하면, 본 발명에 따른 유기전계발광 표시장치는 표시영역(AA)과 비표시영역(NA)으로 정의된 기판(100)을 포함한다. 상기 기판(100)의 표시영역(AA)에는 박막 트랜지스터(Tr) 및 유기발광소자(160, 180, 190)가 형성된다. 또한, 상기 기판(100)의 비표시영역(NA)에는 패드전극(130, 140)이 형성된다.

[0017] 상기 박막 트랜지스터(Tr)는 반도체층(101), 게이트 절연막(102), 게이트전극(103), 소스전극(105), 드레인전극(106)을 포함한다. 상기 박막트랜지스터(Tr)와 접촉하는 유기발광소자(160, 180, 190)는 제 1 전극(160), 상기 제 1 전극(160)과 대향하여 형성되는 제 2 전극(190) 및 상기 제 1 전극(160)과 제 2 전극(190) 사이에 형성되는 유기발광층(180)을 포함한다. 또한, 상기 패드전극(130, 140)은 제 1 패드전극(130)과 상기 제 1 패드전극 상에 형성되는 제 2 패드전극(140)을 포함한다.

[0018] 상기 표시영역(AA)에는 기판(100) 상에 반도체층(101)이 형성된다. 상기 반도체층(101)은 소스영역(101a), 채널영역(101b) 및 드레인영역(101c)을 포함한다. 여기서, 상기 반도체층(101)을 형성하기 전에, 상기 표시영역(AA) 및 비표시영역(NA)의 기판(100)상에 베퍼층을 형성할 수도 있다. 상기 반도체층(101) 상에 게이트 절연막(102)이 형성되고, 상기 게이트 절연막(102)은 비표시영역(NA)까지 연장되어 형성된다.

[0019] 상기 표시영역(AA)의 반도체층(101) 및 게이트 절연막(102) 상에는 게이트전극(103)이 형성된다. 이와 동시에, 상기 비표시영역(NA)에는 제 1 패드전극(130)이 형성된다.

[0020] 이 때, 상기 게이트전극(103) 및 제 1 패드전극(130)은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 게이트전극(103) 및 제 1 패드전극(130)은 단층 또는 다중층으로 형성될 수 있다. 예를 들면, 2중층으로 형성될 수 있다. 자세하게는, 상기 게이트전극(103) 및 제 1 패드전극(130)은 제 1 금속

층 및 상기 제 1 금속층 상에 형성되는 제 2 금속층으로 형성될 수 있다.

[0021] 상기 제 1 금속층은 상기 제 2 금속층의 접착력을 높이기 위해 형성될 수 있다. 여기서, 상기 제 1 금속층은 MoTi 또는 Ti일 수 있다. 또한, 상기 제 2 금속층은 Cu, Ag, Al, Cr, Ti, Ta 또는 이들의 조합으로부터 형성되는 합금 일 수 있다. 바람직하게는 상기 제 2 금속층은 Cu로 형성될 수 있다.

[0022] 상기 표시영역(AA)에 형성된 상기 게이트전극(103)과 상기 비표시영역(NA)에 형성된 상기 제 1 패드전극(130) 상에 층간절연막(104)이 형성될 수 있다. 상기 층간절연막(104)과 상기 게이트 절연막(102)에는 상기 소스영역(101a) 및 드레인영역(101c)을 노출하는 위한 제 1 컨택홀이 형성된다. 이와 동시에, 상기 비표시영역(NA)에 형성된 상기 층간절연막(104)에는 제 1 패드전극(130)을 노출하는 제 2 컨택홀이 형성된다.

[0023] 이 후, 상기 제 1 컨택홀과 층간절연막(104) 상에는 소스전극(105)과 드레인전극(106)이 형성된다. 이와 동시에, 상기 제 2 컨택홀과 상기 층간절연막(104) 상에는 제 2 패드전극(140)이 형성된다. 상기 소스전극(105) 및 드레인전극(106)은 상기 제 1 컨택홀에 의해 상기 반도체층(101)의 소스영역(101a) 및 드레인영역(101c)과 연결된다. 또한, 상기 제 2 패드전극(140)은 상기 제 2 컨택홀에 의해 상기 제 1 패드전극(130)과 연결된다.

[0024] 여기서, 상기 소스전극(105), 드레인전극(106) 및 상기 제 2 패드전극(140)은 동일한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)은 2중층일 수 있다.

[0025] 이 때, 제 1 전극층(105a, 106a, 140a) 상에 제 2 전극층(105b, 106b, 140b)이 형성될 수 있다. 상기 제 1 전극층(105a, 106a, 140a)은 상기 제 2 전극층(105b, 106b, 140b)의 접착력을 높이기 위해 형성될 수 있다. 여기서, 상기 제 1 전극층(105a, 106a, 140a)은 MoTi 또는 Ti일 수 있다. 그리고 상기 제 2 전극층(105b, 106b, 140b)은 Cu, Ag, Al, Cr, Ti, Ta 또는 이들의 조합으로부터 형성되는 합금 일 수 있다. 바람직하게는 상기 제 2 전극층(105b, 106b, 140b)은 Cu로 형성될 수 있다.

[0026] 또한, 상기 게이트전극(103), 제 1 패드전극(130), 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)은 모두 제 1 전극층 상에 제 2 전극층이 형성되는 구조일 수 있다. 그리고, 상기 게이트전극(103), 제 1 패드전극(130), 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)은 모두 동일한 물질로 형성될 수 있다.

[0027] 이와 같이, 상기 표시영역(AA) 상에는 박막 트랜지스터(Tr)가 형성된다. 또한, 상기 비표시영역(NA)상에는 패드전극(130, 140)이 형성된다.

[0028] 한편, 상기 제 2 패드전극(140)의 상기 제 2 전극층(140b)은 외부로 노출될 경우, 산소 및 수분과 접촉하여 부식이 발생할 수 있다. 때문에 상기 유기전계발광 표시장치의 신뢰성이 떨어질 수 있다.

[0029] 따라서, 상기 비표시영역(NA)에 형성된 상기 패드전극(130, 140)을 둘러싸는 형태로 보호전극층(200)이 형성될 수 있다. 자세하게는, 상기 제 2 패드전극(140)을 둘러싸는 형태로 상기 보호전극층(200)이 형성될 수 있다. 더 자세하게는, 상기 보호전극층(200)은 상기 제 2 패드전극(140)의 상면 및 측면에 형성될 수 있다.

[0030] 이를 통해, 상기 제 2 패드전극(140)이 외부에 노출되어도 상기 보호전극층(200)이 상기 제 2 패드전극(140)의 상면 및 측면으로 침투하는 산소 및 수분을 막아줌으로써, 상기 제 2 패드전극(140)의 부식을 막을 수 있다. 이 때, 상기 보호전극층(200)은 투명 도전물질 일 수 있다. 예를 들면, ITO 일 수 있다.

[0031] 이 후, 상기 박막 트랜지스터(Tr) 상에 보호막(107) 및 평탄화막(108)이 형성된다. 이 때, 상기 보호막(107) 및 평탄화막(108)은 상기 보호전극층(200)이 노출되도록 형성된다. 즉, 상기 보호전극층(200)상에 상기 보호막(107) 및 평탄화막(108)이 형성되지 않을 수 있다.

[0032] 또한, 상기 표시영역(AA)에 형성된 상기 평탄화막(108) 및 보호막(107)에 형성된 컨택홀에 의해 상기 드레인전극(106)과 접속되는 상기 유기발광소자의 제 1 전극(160)이 형성된다. 여기서, 상기 제 1 전극(160)은 애노드(anode) 전극 일 수 있다.

[0033] 상기 제 1 전극(160)은 제 1 층(161) 상에 제 2 층(162)이 형성되고 상기 제 2 층(162)상에 제 3 층(163)이 형성된 3중층 구조로 형성될 수 있다. 여기서, 상기 제 1 층(161) 및 제 3 층(163)은 투명 도전물질일 수 있다. 예를 들면, ITO일 수 있다. 상기 제 2 층(162)은 반사층일 수 있다. 이 때, 상기 제 2 층(162) 금속 합금층일 수 있다. 예를 들면, Ag를 포함하는 금속 합금층일 수 있다.

[0034] 이 때, 상기 제 1 층은 상기 제 2 층의 접착력을 높이기 위해 형성될 수 있다. 또한, 상기 제 3 층은 큰 일함수

를 가짐으로써, 상기 제 1 전극(160)이 애노드 역할을 할 수 있도록 한다. 이를 통해, 상기 유기발광소자는 상기 제 2 전극으로부터 상기 제 1 전극으로 발광하는 빛을 반사하여, 상부로 빛을 발광시키는 상부 발광방식 유기전계발광 표시장치를 구현할 수 있다.

[0035] 상기 제 1 전극(160)이 형성된 평탄화막(108) 상에 맹크 패턴(170)이 형성될 수 있다. 상기 맹크 패턴(170)은 발광 영역과 비발광 영역을 정의할 수 있다. 그리고 상기 맹크 패턴은(170)은 상기 제 1 전극(160)의 측면을 둘러싸는 형태로 형성될 수 있다. 이를 통해, 상기 제 1 전극(160)의 측면이 부식되는 것을 방지할 수 있다.

[0036] 또한, 상기 제 1 전극(160) 상에는 유기발광층(180)이 형성될 수 있다. 상기 유기발광층(180)은 발광물질로 이루어진 단일층으로 구성될 수도 있으며, 발광 효율을 높이기 위해 정공주입층(hole injection layer), 정공수송층(hole transporting layer), 발광층(emitting material layer), 전자수송층(electron transporting layer) 및 전자주입층(electron injection layer)의 다중층으로 구성할 수도 있다.

[0037] 상기 유기발광층(180) 상에는 상기 제 1 전극(160)과 대향하여 제 2 전극(190)이 형성될 수 있다. 이 때, 상기 제 2 전극은 캐소드(cathode)전극 일 수 있다. 상기 제 2 전극은 금속으로 형성될 수 있다. 또한 그리고 도면에는 도시하지 않았으나, 상기 제 2 전극의 전압 강하를 낮추기 위해 상기 표시영역(AA)에 보조전극이 더 형성될 수 있다.

[0038] 본 발명에 따른 유기전계발광 표시장치는 외부에 노출되는 제 2 패드전극(140)의 상면 및 측면에 보호전극층(200)을 형성함으로써, 제 2 패드전극(140)이 산소 및 수분과 접촉하는 것을 방지할 수 있다. 이를 통해, 제 2 패드전극(140)의 부식을 방지하는 효과가 있다.

[0039] 이어서, 도 2a 내지 2e를 참조하여 본 발명의 제 1 실시예에 따른 유기전계발광 표시장치의 제조방법을 설명한다. 도 2a 내지 2e는 본 발명의 제 1 실시예에 따른 유기전계발광 표시장치의 제조방법을 도시한 도면이다. 제 1 실시예에 따른 디스플레이 표시장치는 앞서 설명한 실시예와 동일한 구성요소를 포함할 수 있다. 앞서 설명한 실시예와 중복되는 설명은 생략할 수 있다. 또한, 동일한 구성은 동일한 도면부호를 갖는다.

[0040] 도 2a를 참조하면, 표시영역(AA) 및 비표시영역(NA)으로 정의되는 기판(100)상에 비정질 실리콘 막과 같은 반도체층을 형성한다. 상기 반도체층 상에 포토레지스트를 형성하고, 투과부와 차단부로 이루어진 마스크를 이용하여, 노광 및 현상 공정을 진행하여 포토레지스트 패턴을 형성한다. 상기 포토레지스트 패턴을 이용하여 상기 반도체층을 식각하여 박막 트랜지스터(Tr)의 반도체층(101)을 형성한다. 이 때, 일 부 반도체층(101)은 박막 트랜지스터(Tr)가 형성되는 영역에 형성된다.

[0041] 상기 표시영역(AA)에 형성된 상기 반도체층(101)과 상기 비표시영역(NA) 전면에 게이트 절연막(102)을 형성한다. 상기 게이트 절연막(102) 상에는 상기 게이트 전극(103) 및 제 1 패드전극(130)을 형성하기 위해, 금속층 물질을 형성한다. 이 때, 상기 금속층 물질은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 금속층은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 상기 게이트 금속층은 2중층으로 형성될 수 있다. 이 때, 상기 게이트 금속층은 제 1 금속층 및 상기 제 1 금속층 상에 형성되는 제 2 금속층으로 형성될 수 있다.

[0042] 상기 제 1 금속층은 상기 제 2 금속층의 접착력을 높이기 위해 형성될 수 있다. 여기서, 상기 제 1 금속층 물질은 MoTi 또는 Ti일 수 있다. 또한, 상기 제 2 금속층 물질은 Cu, Ag, Al, Cr, Ti, Ta 또는 이들의 조합으로부터 형성되는 합금 일 수 있다. 바람직하게는 상기 제 2 금속층 물질은 Cu로 형성될 수 있다.

[0043] 이 후, 상기 게이트 금속층 상에 포토레지스트를 형성한다. 그리고 투과부과 차단부로 이루어진 마스크를 이용하여 노광 및 현상 공정을 진행하여 포토레지스트 패턴을 형성하고, 이를 마스크로 하여 금속층 물질을 식각함으로써 게이트전극(103) 및 제 1 패드전극(130)이 형성된다. 즉, 상기 표시영역(AA) 상에 상기 게이트 전극(103)이 형성되고, 상기 비표시영역(NA) 상에 상기 제 1 패드전극(130)이 상기 게이트전극(103)과 동일층에서 동일물질로 형성된다.

[0044] 상기 게이트전극(103)을 마스크로 하여, 고농도의 불순물 이온을 도핑하여 소스영역(101a) 및 드레인영역(101c)이 형성된다. 도면에는 나타나지 않았지만, 저항으로 인해 접합부위에 걸리는 전기장을 감소시켜 오프 전류를 줄이고 온 전류의 감소를 최소화할 수 있도록 소스영역(101a) 및 드레인영역(101c) 형성 이전에, 저농도의 불순물 이온을 도핑하여, 상기 반도체층(101)의 소스영역(101a) 및 드레인영역(101c)에 LDD(Light Doped Drain) 도핑층을 형성할 수 있다. 이 때, 도면에 도시하였지만, 설명하지 않는 101b는 채널영역이다.

- [0045] 이 후, 상기 게이트전극(103) 및 제 1 패드전극(130)이 형성된 기판 전면에 충간절연막(104)이 형성된다. 포토레지스트 공정으로 상기 충간절연막(104)과 게이트 절연막(102)을 식각하여, 상기 표시영역(AA)의 반도체층(101)의 소스영역(101a)과 드레인영역(101c)을 노출시키는 제 1 컨택홀을 형성한다. 이와 동시에 상기 비표시영역(NA)에 형성된 상기 충간절연막(104)에는 상기 제 1 패드전극(130)을 노출하는 제 2 컨택홀이 형성된다.

- [0046] 이 후, 상기 제 1 컨택홀 및 제 2 컨택홀이 형성된 충간절연막(104)을 포함하는 기판(100) 전면에 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)을 형성하기 위해, 전극층 물질을 형성한다. 이 때, 상기 전극층 물질은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 전극층 물질은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 2 중층으로 형성될 수 있다. 자세하게는, 상기 제 1 전극층 및 상기 제 1 전극층 상에 형성되는 제 2 전극층으로 형성될 수 있다.

- [0047] 상기 충간절연막(104)과 접하여 형성되는 상기 제 1 전극층은 상기 제 2 전극층의 접착력을 높이기 위해 형성될 수 있다. 여기서, 상기 제 1 전극층 물질은 MoTi 또는 Ti로 형성될 수 있다. 또한, 상기 제 2 전극층 물질은 Cu, Ag, Al, Cr, Ti, Ta 또는 이들의 조합으로부터 형성되는 합금 일 수 있다. 바람직하게는 상기 제 2 전극층 물질은 Cu로 형성될 수 있다.

- [0048] 이 후, 포토레지스트 공정으로 상기 제 1 전극층 물질 및 제 2 전극층 물질이 식각되어 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)이 형성된다. 즉, 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)은 동일층에서 동일물질로 형성될 수 있다.

- [0049] 상기 소스전극(105)은 상기 컨택홀을 통해 상기 반도체층(101)의 소스영역(101a) 상에 형성되고, 상기 드레인전극(106)은 상기 반도체층(101)의 드레인영역(101c) 상에 형성된다. 또한, 상기 제 2 패드전극(140)은 상기 제 1 패드전극(130) 상에 접하여 형성된다.

- [0050] 이와 같이, 상기 표시영역(AA) 상에는 박막 트랜지스터(Tr)가 형성된다. 또한, 상기 비표시영역(NA) 상에는 패드전극(130, 140)이 형성된다.

- [0051] 도 2b를 참조하면, 상기 비표시영역(NA)에 형성된 상기 제 2 패드전극(140) 상에 보호전극층(200)을 형성하기 위해 상기 기판(100) 전면에 보호전극층(200)을 형성한다. 이 후, 포토레지스트 공정을 이용하여, 상기 보호전극층(200)을 식각하여 상기 2 패드전극(140) 상에 보호전극층(200)을 형성한다. 자세하게는, 상기 보호전극층(200)은 상기 제 2 패드전극의 상면과 측면에 형성된다. 여기서, 상기 보호전극층(200)은 투명 도전물질일 수 있다. 예를 들면, 상기 투명 도전물질은 ITO일 수 있다.

- [0052] 도 2c를 참조하면, 상기 박막 트랜지스터(Tr), 패드전극(130, 140) 및 보호전극층(200)이 형성된 기판(100) 전면에 보호막 물질을 형성한다. 이 후, 상기 표시영역(AA)에 형성된 보호막 물질 상에 평탄화막 물질을 형성한다.

- [0053] 상기 표시영역(AA)에 형성된 평탄화막 물질은 상기 드레인전극(106)을 노출하는 컨택홀을 형성하기 위해 포토레지스트 공정으로 식각된다. 또한, 상기 비표시영역(NA)에 형성된 평탄화막(108)을 모두 식각할 수 있다. 이 후, 상기 평탄화막(108)을 마스크로 하여 상기 보호막(107)이 식각된다. 이를 통해, 상기 평탄화막(108) 및 보호막(107) 상에 드레인전극(106)을 노출하는 컨택홀이 형성된다.

- [0054] 이 후, 상기 노출된 드레인전극(106)과 연결되도록 포토레지스트 공정으로 상기 유기발광소자(160, 180, 190)의 제 1 전극(160)을 형성한다. 이 때, 상기 제 1 전극(160)은 다중층으로 형성될 수 있다. 예를 들면, 3중층으로 형성될 수 있다. 자세하게는, 제 1층(161), 상기 제 1 층(161) 상에 형성되는 제 2 층(162) 및 상기 제 2 층(162) 상에 형성되는 제 3 층(163)으로 형성될 수 있다.

- [0055] 여기서, 상기 제 1 층(161) 및 제 3 층(163)은 투명 도전물질로 형성될 수 있다. 예를 들면, 상기 투명 도전물질은 ITO일 수 있다. 또한, 상기 제 2 층(162)은 반사층일 수 있다. 그리고 상기 제 2 층(162)은 반사층일 수 있다. 이 때, 상기 제 2 층(162) 금속 합금층일 수 있다. 예를 들면, Ag를 포함하는 금속 합금층일 수 있다.

- [0056] 도 2d를 참조하면, 상기 표시영역(AA)에 형성된 상기 유기발광소자(160, 180, 190)의 제 1 전극(160)과 상기 비표시영역(NA)에 형성된 보호막(107)을 포함한 기판(100) 상에 상기 보호전극층(200)이 형성된 상기 패드전극(130, 140) 영역을 제외하고 포토레지스트가 형성된다. 즉, 상기 포토레지스트는 상기 보호전극층(200)이 형성된 상기 제 2 패드전극(140)의 상면 및 측면을 노출하는 영역을 제외한 영역에 형성되면 충분하다.

- [0057] 이를 통해, 상기 비표시영역(NA)에 형성된 보호막(107)이 식각되면서, 상기 보호전극층(200)은 상기 보호막(107)과 이격되어 형성된다. 즉, 상기 보호전극층(200)이 형성된 제 2 패드전극(140)의 상면 및 측면은 외부로

노출된다.

[0058] 도 2e를 참조하면, 상기 유기발광소자(160, 180, 190)의 제 1 전극(160)이 형성된 상기 평탄화막(108) 상에 뱅크 패턴(170)이 형성된다. 이 후, 포토레지스트 공정으로 상기 제 1 전극(160)에 형성된 상기 뱅크 패턴(170)을 식각한다. 이를 통해, 상기 뱅크 패턴(170)은 상기 제 1 전극(160)을 노출하는 형태로 형성된다. 또한, 도면에는 도시하지 않았으나, 상기 뱅크 패턴(170)에 의해 노출된 영역 상에는 유기발광층(180) 및 제 2 전극(190)이 형성된다.

[0059] 본 발명에 따른 유기전계발광 표시장치는 외부에 노출되는 상기 제 2 패드전극(140)의 상면 및 측면에 보호전극 층(200)을 형성함으로써, 상기 제 2 패드전극(140)에 산소 및 수분이 침투하는 것을 방지할 수 있다. 이를 통해, 상기 제 2 패드전극(140)의 부식을 방지하는 효과가 있다.

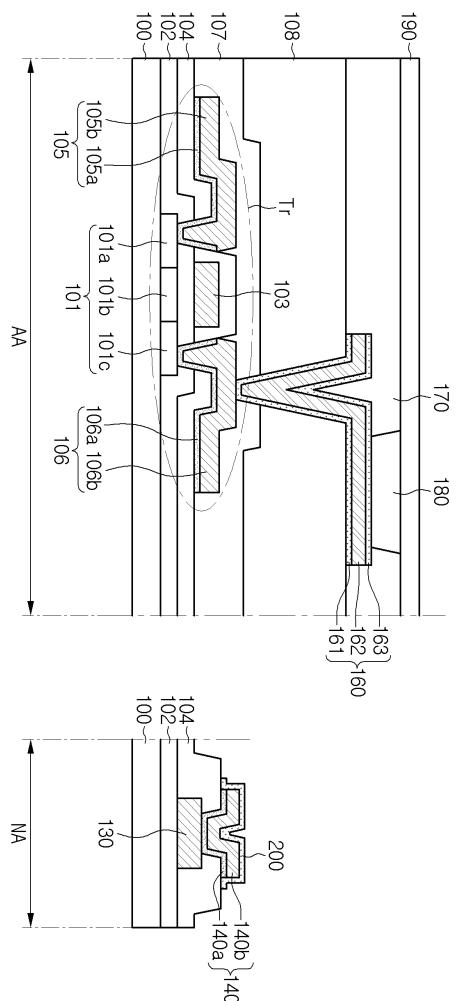

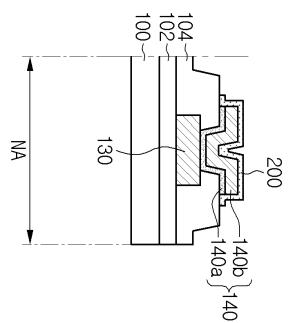

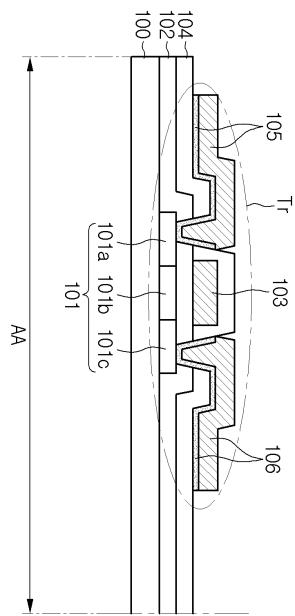

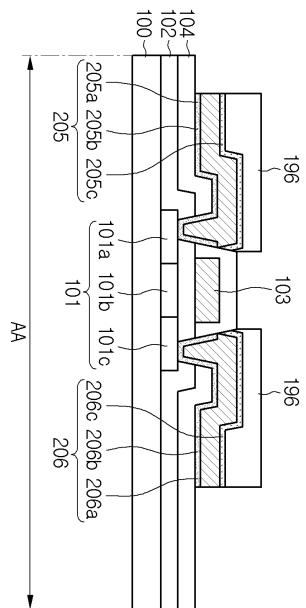

[0060] 이어서, 도 3을 참조하여 본 발명의 제 2 실시예에 따른 유기전계발광 표시장치를 설명한다. 도 3은 본 발명의 제 2 실시예에 따른 유기전계발광 표시장치를 도시한 단면도이다. 제 2 실시예에 따른 디스플레이 표시장치는 앞서 설명한 실시예와 동일한 구성요소를 포함할 수 있다. 앞서 설명한 실시예와 중복되는 설명은 생략할 수 있다. 또한, 동일한 구성은 동일한 도면부호를 갖는다.

[0061] 도 3을 참조하면, 상기 박막 트랜지스터(Tr)는 반도체층(101), 게이트 절연막(102), 게이트전극(103), 소스전극(105), 드레인전극(106)을 포함한다. 상기 박막트랜지스터(Tr)와 접촉하는 유기발광소자(160, 180, 190)는 제 1 전극(160), 상기 제 1 전극(160)과 대향하여 형성되는 제 2 전극(190) 및 상기 제 1 전극(160)과 제 2 전극(190) 사이에 형성되는 유기발광층(180)을 포함한다. 또한, 상기 패드전극(130, 140)은 제 1 패드전극(130)과 상기 제 1 패드전극 상에 형성되는 제 2 패드전극(140)을 포함한다.

[0062] 상기 표시영역(AA)에는 기판(100) 상에 반도체층(101)이 형성된다. 상기 반도체층(101)은 소스(101a), 채널(101b) 및 드레인(101c)을 포함한다. 상기 반도체층(101) 상에 게이트 절연막(102)이 형성되고, 상기 게이트 절연막(102)은 비표시영역(NA)까지 연장되어 형성된다.

[0063] 상기 표시영역(AA)의 반도체층(101) 및 게이트 절연막(102) 상에는 게이트전극(103)이 형성된다. 이와 동시에 상기 비표시영역(NA)에는 제 1 패드전극(130)이 형성된다.

[0064] 이 때, 상기 게이트전극(103)과 제 1 패드전극(130)은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 게이트전극(103) 및 제 1 패드전극(130)은 단층 또는 다중층으로 형성될 수 있다. 예를 들면, 2중층으로 형성될 수 있다. 자세하게는, 상기 게이트전극(103) 및 제 1 패드전극(130)은 제 1 금속층 및 상기 제 1 금속층 상에 형성되는 제 2 금속층으로 형성될 수 있다.

[0065] 상기 표시영역(AA)에 형성된 상기 게이트전극(103)과 상기 비표시영역(NA)에 형성된 상기 제 1 패드전극(130) 상에 충간절연막(104)이 형성될 수 있다. 상기 충간절연막(104)과 상기 게이트 절연막(102)에는 상기 소스영역(101a) 및 드레인영역(101c)을 노출하는 위한 제 1 컨택홀이 형성된다. 이와 동시에, 상기 비표시영역(NA)에 형성된 상기 충간절연막(104)에는 제 1 패드전극(130)을 노출하는 제 2 컨택홀이 형성된다.

[0066] 이 후, 상기 제 1 컨택홀과 충간절연막(104) 상에는 소스전극(205)과 드레인전극(206)이 형성된다. 이와 동시에 상기 제 2 컨택홀과 상기 충간절연막(104) 상에는 제 2 패드전극(140)이 형성된다. 상기 소스전극(205) 및 드레인전극(206)은 상기 제 1 컨택홀에 의해 상기 반도체층(101)의 소스영역(101a) 및 드레인영역(101c)과 연결된다. 또한, 상기 제 2 패드전극(140)은 상기 제 2 컨택홀에 의해 상기 제 1 패드전극(130)과 연결된다.

[0067] 상기 제 2 패드전극(140)은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 제 2 패드전극(140)은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 상기 제 2 패드전극(140)은 2중층일 수 있다. 여기서, 상기 제 2 패드전극(140)은 제 1 전극층(140a) 및 상기 제 1 전극층(140a) 상에 형성되는 제 2 전극층(140b)으로 형성될 수 있다.

[0068] 또한, 상기 소스전극(205) 및 드레인전극(206)은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 소스전극(205) 및 드레인전극(206)은 도면에 한정되지 않으며, 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 상기 소스전극(205) 및 드레인전극(206)은 3중층일 수 있다. 이 때, 상기 소스전극(205) 및 드레인전극(206)은 제 1 전극층(205a, 206a), 상기 제 1 전극층(205a, 206a) 상에 형성되는 제 2 전극층(205b, 206b) 및 상기 제 2 전극층(205b, 206b) 상에 형성되는 제 3 전극층(205c, 206c)으로 형성될 수 있다.

- [0069] 여기서, 상기 제 1 컨택홀 및 제 2 컨택홀이 형성된 기판 전면에 상기 소스전극(205)의 제 1 전극층(205a), 드레인전극(206)의 제 1 전극층(206a) 및 제 2 패드전극(140)의 제 1 전극층(140a)이 동시에 형성될 수 있다. 이 때, 상기 제 1 전극층(205a, 206a, 140a) 물질은 MoTi 또는 Ti일 수 있다.

- [0070] 이 후, 상기 제 1 전극층(205a, 206a, 140a) 상에 상기 소스전극(205)의 제 2 전극층(205b), 드레인전극(206)의 제 2 전극층(206b) 및 제 2 패드전극(140)의 제 2 전극층(140b)이 동시에 형성될 수 있다. 이 때, 상기 제 2 전극층(205b, 206b, 140b)의 물질은 Cu, Ag, Al, Cr, Ti, Ta 또는 이들의 조합으로부터 형성되는 합금층으로 형성될 수 있다. 바람직하게는 상기 제 2 전극층(205b, 206b, 140b) 물질은 Cu로 형성될 수 있다.

- [0071] 한편, 상기 제 2 패드전극(140)의 상기 제 2 전극층(140b)이 외부로 노출될 경우, 산소 및 수분과 접촉하여 부식이 발생하거나 마이그레이션(migration)이 발생할 수 있다. 이를 해결하기 위해, 상기 제 2 패드전극(140)의 제 2 전극층(140b) 상에 보호전극층을 형성할 수 있다. 여기서 상기 보호전극층은 투명 도전물질일 수 있다. 예를 들면, ITO일 수 있다.

- [0072] 이와 동시에, 상기 소스전극(205)의 제 2 전극층(105b) 및 드레인전극(206)의 제 2 전극층(106b) 상면에 상기 보호전극층 물질로 제 3 전극층(205c, 206c)이 형성되면서, 상기 소스전극(205) 및 드레인전극(206)은 3중층으로 형성될 수 있다.

- [0073] 이 때, 상기 제 2 패드전극(140) 상에 형성된 상기 보호전극층(201)의 양 끝단은 상기 제 2 패드전극(140)의 양 끝단과 같거나 작게 형성될 수 있다. 또한, 상기 소스전극(205)의 제 3 전극층(205c) 및 드레인전극(206)의 전극의 제 3 전극층(206c)의 양 끝단은 상기 소스전극(205)의 제 1 및 제 2 전극층(205a, 205b) 및 드레인전극(106)의 제 1 및 제 2 전극층(206a, 206b)의 양 끝단과 같거나 작게 형성될 수 있다.

- [0074] 이와 같이, 상기 소스전극(205) 및 드레인전극(206)은 금속층으로 이루어진 2중층 상에 형성된 투명 도전물질층을 포함하여 3중으로 형성될 수 있다. 또한, 상기 제 2 패드전극(140)은 금속층으로 이루어진 2중층으로 형성되며, 상기 제 2 패드전극 상면에 보호전극층(201)이 형성될 수 있다. 이를 통해, 상기 제 2 패드전극(140)의 상면이 외부에 노출되어도 상기 보호전극층(201)이 상기 제 2 패드전극(140)의 상면으로 침투하는 산소 및 수분을 막아줌으로써, 상기 제 2 패드전극(140)의 부식을 막을 수 있다.

- [0075] 이 후, 상기 박막 트랜지스터(Tr) 상에 보호막(107) 및 평탄화막(108)이 형성된다. 이 때, 상기 보호막(107) 및 평탄화막(108)은 상기 제 1 보호전극층(201)이 노출되도록 형성된다. 즉, 상기 보호전극층(201)상에 상기 보호막(107) 및 평탄화막(108)이 형성되지 않을 수 있다.

- [0076] 이를 통해, 상기 제 2 패드전극(140)의 상면은 보호전극층(201)에 의해 산소 및 수분으로부터 보호될 수 있다. 또한, 상기 제 2 패드전극(140)의 측면은 상기 보호막(107)과 접하여 형성되어 있으므로, 수분으로부터 보호될 수 있다.

- [0077] 또한, 상기 표시영역(AA)에 형성된 상기 평탄화막(108) 및 보호막(107)에 형성된 컨택홀에 의해 상기 드레인전극(106)과 접속되는 상기 유기발광소자의 제 1 전극(160)이 형성된다. 여기서, 상기 제 1 전극(160)은 애노드(anode) 전극 일 수 있다.

- [0078] 상기 제 1 전극(160)은 제 1 층(161) 상에 제 2 층(162)이 형성되고 상기 제 2 층(162)상에 제 3 층(163)이 형성된 3중층 구조로 형성될 수 있다. 여기서, 상기 제 1 층(161) 및 제 3 층(163)은 투명 도전물질일 수 있다. 예를 들면, 상기 투명도전물질은 ITO일 수 있다. 상기 제 2 층(162)은 반사층일 수 있다. 이 때, 상기 제 2 층(162) 금속 합금층일 수 있다. 예를 들면, Ag를 포함하는 금속 합금층일 수 있다.

- [0079] 또한, 상기 제 1 전극(160)이 형성된 평탄화막(108) 상에 뱅크 패턴(170)이 형성된다. 여기서 상기 뱅크 패턴은 (170)은 상기 제 1 전극(160)의 측면을 둘러싸는 형태로 형성될 수 있다. 이를 통해, 상기 제 1 전극(160)의 측면이 부식되는 것을 방지할 수 있다.

- [0080] 상기 제 1 전극(160) 상에는 유기발광층(180)이 형성될 수 있으며, 상기 유기발광층(180) 상에는 상기 제 1 전극(160)과 대향하여 제 2 전극(190)이 형성될 수 있다. 그리고 도면에는 도시하지 않았으나, 상기 뱅크 패턴(170) 사이에 보조전극이 더 형성될 수 있다. 여기서, 상기 제 2 전극(190)은 캐소드(cathode)전극 일 수 있다.

- [0081] 본 발명에 따른 유기전계발광 표시장치는 외부에 노출되는 제 2 패드전극(140)의 상면에 보호전극층(201)을 형성함으로써, 제 2 드레인전극(140)의 상면을 수분으로부터 보호할 수 있다. 또한, 제 2 패드전극(140)의 측면이 보호막(107)과 접하여 형성됨으로써, 제 2 패트전극(140)의 측면이 수분과 접촉하는 것을 방지할 수 있다. 이를

통해, 제 2 패드전극(140)의 상면 및 측면의 부식을 방지할 수 있다.

[0082] 이어서, 도 4a 내지 4f를 참조하여 본 발명의 제 2 실시예에 따른 유기전계발광 표시장치의 제조방법 설명한다. 도 4a 내지 4f는 본 발명의 제 2 실시예에 따른 유기전계발광 표시장치의 제조방법을 도시한 도면이다. 제 2 실시예에 따른 디스플레이 표시장치는 앞서 설명한 실시예와 동일한 구성요소를 포함할 수 있다. 앞서 설명한 실시예와 중복되는 설명은 생략할 수 있다. 또한, 동일한 구성은 동일한 도면부호를 갖는다.

[0083] 도 4a를 참조하면, 표시영역(AA) 및 비표시영역으로 정의되는 기판(100)상에 반도체층을 형성한다. 포토레지스트 공정으로 상기 반도체층을 식각하여 반도체층(101)을 형성한다. 이 후, 상기 기판(100) 전면에 게이트 절연막(102)을 형성한다.

[0084] 상기 게이트 절연막(102) 상에는 상기 게이트 전극(103) 및 제 1 패드전극(130)을 형성하기 위해, 금속층 물질을 형성한다. 이 때, 상기 게이트 금속층은 다양한 물질로 형성될 수 있다. 또한, 상기 금속층은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 상기 금속층은 2중층으로 형성될 수 있다. 이 때, 상기 금속층은 제 1 금속층 및 상기 제 1 금속층 상에 형성되는 제 2 금속층으로 형성될 수 있다.

[0085] 여기서, 상기 제 1 금속층 물질은 MoTi 또는 Ti일 수 있다. 또한, 상기 제 2 금속층 물질은 Cu, Ag, Al, Cr, Ti, Ta 또는 이들의 조합으로부터 형성되는 합금 일 수 있다. 바람직하게는 상기 제 2 금속층 물질은 Cu로 형성될 수 있다.

[0086] 이 후, 포토레지스트 공정으로 금속층 물질을 식각함으로써 게이트전극(103) 및 제 1 패드전극(130)이 동일층에 동일물질로 형성된다. 이 후, 게이트전극(103)을 마스크로하여 소스영역(101a) 및 드레인영역(101c)에 고농도의 불순물을 도핑하여 소스영역(101a)과 드레인영역(101c)을 형성한다. 이 때, 도면에 도시하였지만, 설명하지 않은 101b는 채널영역이다.

[0087] 이 후, 상기 게이트전극(103) 및 제 1 패드전극(130)이 형성된 기판 전면에 충간절연막(104)이 형성된다. 포토레지스트 공정으로 상기 충간절연막(104)과 게이트 절연막(102)을 식각하여, 상기 표시영역(AA)의 반도체층(101)의 소스영역(101a)과 드레인영역(101c)을 노출시키는 제 1 컨택홀을 형성한다. 이와 동시에 상기 비표시영역(NA)에 형성된 상기 충간절연막(104)에는 상기 제 1 패드전극(130)을 노출하는 제 2 컨택홀이 형성된다.

[0088] 이 후, 상기 제 1 컨택홀과 충간절연막(104) 상에는 소스전극(205)의 제 1 전극층(105a)과 제 2 전극층(105b) 및 드레인전극(206)의 제 1 전극층(106a)과 제 2 전극층(106b)이 형성된다. 이와 동시에 상기 제 2 컨택홀과 상기 충간절연막(104) 상에는 제 2 패드전극(140)의 제 1 전극층(140a)과 제 2 전극층(140b)이 형성된다.

[0089] 여기서, 상기 소스전극(205)의 제 1 전극층(105a)과 제 2 전극층(105b), 상기 드레인전극(206)의 제 1 전극층(106a)과 제 2 전극층(106b) 및 상기 제 2 패드전극(140)의 제 1 전극층(140a)과 제 2 전극층(140b)은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 이들은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 상기 제 2 패드전극(140)은 2중층 일 수 있다. 또한, 상기 소스전극(105) 및 드레인전극(106)은 3 중층일 수 있다.

[0090] 상기 제 2 패드전극(140)의 제 1 전극층(140a), 소스전극(205)의 제 1 전극층(205a) 및 드레인전극(206)의 제 1 전극층(206a)을 형성하기 위해, 상기 제 1 컨택홀 및 제 2 컨택홀이 형성된 기판 전면에 제 1 전극층 물질을 형성한다. 이 때, 상기 제 1 전극층 물질은 MoTi 또는 Ti일 수 있다.

[0091] 이 후, 상기 제 1 전극층 상에 상기 제 2 패드전극(140)의 제 2 전극층(140b), 소스전극(205)의 제 2 전극층(205b) 및 드레인전극(206)의 제 2 전극층(206b) 물질인 Cu, Ag, Al, Cr, Ti, Ta 또는 이들의 조합으로부터 형성되는 합금층을 형성한다. 바람직하게는 상기 제 2 전극층(205b, 206b, 140b) 물질은 Cu로 형성될 수 있다.

[0092] 이 후, 상기 제 2 전극층 물질이 형성된 기판 전면에 투명 도전물질을 형성할 수 있다. 예를 들면, 상기 투명 도전물질은 ITO일 수 있다.

[0093] 이 후, 포토리소그래피 공정으로 상기 제 1 전극층 물질, 제 2 전극층 물질 및 투명 도전물질이 동시에 식각 될 수 있다. 이를 통해, 상기 표시영역(AA)에는 상기 제 1 전극층(205a, 206a)과 상기 제 1 전극층(205a, 206a) 상에 형성된 제 2 전극층(205b, 206b) 및 상기 제 2 전극층(205b, 206b) 상에 형성된 제 3 전극층(207c, 208c)으로 이루어진 3중층의 소스전극(205) 및 드레인전극(206)이 형성될 수 있다.

[0094] 또한, 상기 비표시영역(NA)에는 상기 제 1 전극층(140a) 및 상기 제 1 전극층(140a) 상에 형성된 제 2 전극층

(140b)으로 이루어진 제 2 패드전극(140)과 상기 제 2 패드전극(14) 상면에만 형성된 보호전극층(203)이 형성된다. 즉, 상기 제 2 패드전극(140) 및 보호전극층(201)은 상기 소스전극(105) 및 드레인전극(106)과 동일층에서 동일물질로 형성될 수 있다.

[0095] 그러나, 상기 소스전극(205)의 제 3 전극층(207c), 드레인전극(206)의 제 3 전극층(208c) 및 보호전극층(203)은 상기 금속층에 비해 식각되는 속도가 느리다. 때문에, 상기 소스전극(205)의 제 3 전극층(207c), 드레인전극(206)의 제 3 전극층(208c) 및 보호전극층(203)의 양 끝단은 이들 하부에 생성되는 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)의 제 1 전극층(205a, 206a, 140a) 및 제 2 전극층(205b, 206b, 140b)의 양 끝단 보다 크게 형성될 수 있다. 즉, 상기 보호전극층(203)의 양 끝단에 돌출부가 발생하게 된다.

[0096] 이 때, 상기 보호전극층(203) 상에 보호막(107)이 형성될 경우, 상기 보호막(107) 상에 결함이 발생하여 상기 유기전계발광 표시장치의 불량을 일으킬 수 있다. 때문에, 상기 보호전극층(203)의 돌출부는 제거될 필요가 있다.

[0097] 도 4b를 참조하면, 상기 기판(100) 상에 포토레지스트(196)를 형성한다. 이 후, 상기 포토레지스트(196)를 에칭(ashing)하여 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140) 상의 포토레지스트(196)만 남긴다. 여기서, 상기 포토레지스트(196)의 끝단을 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)의 끝단과 동일하거나 작게 형성한다.

[0098] 상기 포토레지스트(196)를 마스크로하여 상기 보호전극층(201)의 돌출된 양 끝단을 식각한 후, 상기 포토레지스트(196)를 스트립(strip)한다. 이를 통해, 상기 보호전극층(201)은 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)의 끝단과 동일하거나 작게 형성될 수 있다.

[0099] 도 4c를 참조하면, 상기 박막 트랜지스터(Tr), 패드전극(130, 140) 및 보호전극층(201, 202)이 형성된 기판(100) 전면에 보호막(107)을 형성한다. 이 후, 상기 표시영역(AA)에 형성된 보호막(107) 상에 평탄화막(108)을 형성한다.

[0100] 상기 표시영역(AA)에 형성된 보호막(107) 및 평탄화막(108) 상에 포토레지스트 공정으로 상기 드레인전극(106)을 노출하는 컨택홀을 형성한다. 이 때, 상기 비표시영역(NA)에 형성된 평탄화막(108)은 모두 식각된다.

[0101] 이 후, 상기 노출된 드레인전극(106)과 연결되도록 포토레지스트 공정으로 제 1 전극(160)을 형성한다. 이 때, 상기 제 1 전극(160)은 다중층으로 형성될 수 있다. 예를 들면, 3중층으로 형성될 수 있다. 자세하게는, 제 1층(161), 상기 제 1 층(161) 상에 형성되는 제 2 층(162) 및 상기 제 2 층(162) 상에 형성되는 제 3 층(163)으로 형성될 수 있다.

[0102] 여기서, 상기 제 1 층(161) 및 제 3 층(163)은 투명 도전물질로 형성될 수 있다. 예를 들면, 상기 투명 도전물질은 ITO일 수 있다. 또한, 상기 제 2 층(162)은 반사층일 수 있다. 그리고 상기 제 2 층(162)은 반사층일 수 있다. 이 때, 상기 제 2 층(162) 금속 합금층일 수 있다. 예를 들면, Ag를 포함하는 금속 합금층일 수 있다.

[0103] 도 4d를 참조하면, 상기 표시영역(AA)에 형성된 상기 유기발광소자(160, 180, 190)의 제 1 전극(160)과 상기 비표시영역(NA)에 형성된 보호막(107)을 포함한 기판(100) 상에 상기 보호전극층(201)이 형성된 상기 패드전극(130, 140) 영역을 제외하고 포토레지스트가 형성된다. 즉, 상기 포토레지스트는 상기 보호전극층(201)이 형성된 상기 제 2 패드전극(140)의 상면을 노출하는 영역을 제외한 영역에 형성되면 충분하다.

[0104] 상기 비표시영역(NA)에 형성된 보호막(107)이 식각되면서, 상기 보호전극층(201)이 형성된 패드전극(130, 140)의 상면은 노출된다. 또한, 상기 보호전극층(201)이 형성된 제 2 패드전극(140)의 측면은 상기 보호막(107)과 접하여 형성된다.

[0105] 도 4e를 참조하면, 상기 유기발광소자(160, 180, 190)의 제 1 전극(160)이 형성된 상기 평탄화막(108) 상에 뱅크 패턴(170)이 형성된다. 이 때, 상기 뱅크 패턴(17)은 상기 제 1 전극(160)을 노출하는 형태로 형성된다. 도면에는 도시하지 않았으나, 상기 뱅크 패턴(170)에 의해 노출된 영역 상에는 유기발광층(180) 및 제 2 전극(190)이 형성된다.

[0106] 본 발명에 따른 유기전계발광 표시장치는 외부에 노출되는 제 2 패드전극(140)의 상면에만 보호전극층(201)을 형성함으로써, 제 2 패드전극(140)의 상면으로부터 산소 및 수분이 침투하는 것을 방지할 수 있다. 또한, 제 2 패드전극(140)의 측면이 보호막(107)과 접하여 형성되므로 보호막(107)을 통해, 제 2 패드전극(140)의 측면으로부터 침투하는 산소 및 수분을 방지할 수 있다. 이를 통해, 제 2 패드전극(140)의 부식을 방지하는 효과가

있다.

[0107] 또한, 보호전극층(201)을 형성하는 공정에서 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)을 형성하는 데 사용되는 마스크를 이용하여 형성하므로, 마스크 추가 없이 보호전극층(201)을 형성할 수 있다. 때문에 공정을 단순화하고, 제조비용을 감소시킬 수 있는 효과가 있다.

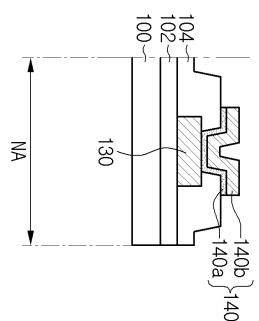

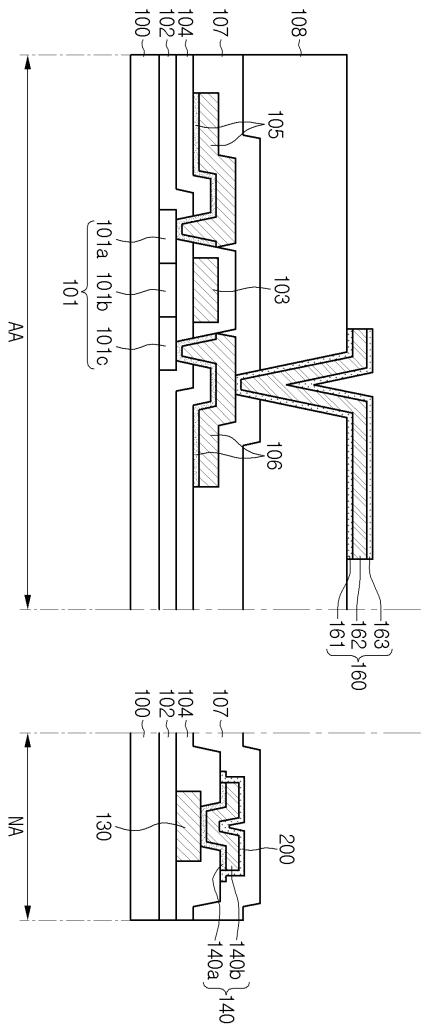

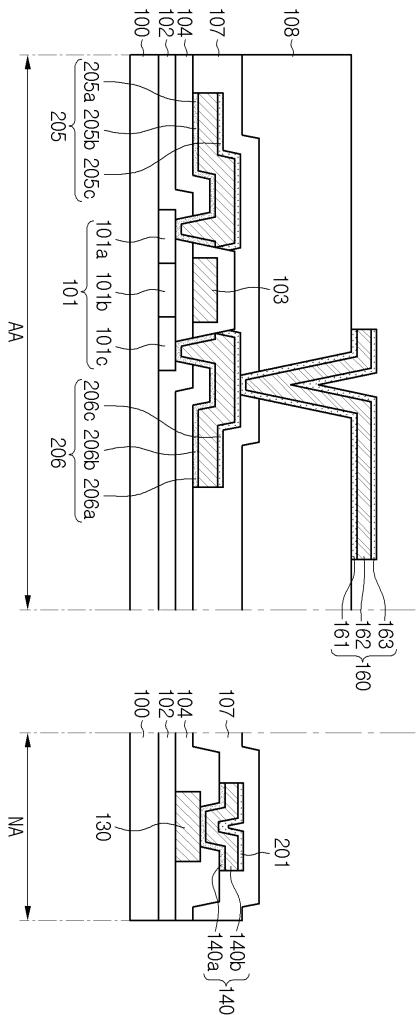

[0108] 이어서, 도 5를 참조하여 본 발명의 제 3 실시예에 따른 유기전계발광 표시장치를 설명한다. 도 5는 본 발명의 제 3 실시예에 따른 유기전계발광 표시장치를 도시한 단면도이다. 제 3 실시예에 따른 디스플레이 표시장치는 앞서 설명한 실시예와 동일한 구성요소를 포함할 수 있다. 앞서 설명한 실시예와 중복되는 설명은 생략할 수 있다. 또한, 동일한 구성은 동일한 도면부호를 갖는다.

[0109] 도 5을 참조하면, 본 발명에 따른 유기전계발광 표시장치는 본 발명에 따른 유기전계발광 표시장치는 표시영역(AA)과 비표시영역(NA)으로 정의된 기판(100)을 포함한다. 상기 표시영역(AA) 상에는 반도체층(101), 게이트 절연막(102), 게이트 전극(103), 충간절연막(104), 소스전극(105) 및 드레인전극(106)으로 이루어진 박막 트랜지스터(Tr)를 포함한다. 여기서, 상기 박막 트랜지스터(Tr)의 게이트 전극(103)이 형성됨과 동시에, 상기 비표시영역(NA) 상에는 제 1 패드전극(130)이 형성된다. 또한, 상기 박막 트랜지스터(Tr)의 소스전극(105) 및 드레인전극(106)이 형성됨과 동시에, 상기 비표시영역(NA) 상에는 제 2 패드전극(140)이 형성된다.

[0110] 여기서, 상기 게이트전극(103), 소스전극(105), 드레인전극(106), 제 1 패드전극(130) 및 제 2 패드전극(140)은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 게이트전극(103), 소스전극(105), 드레인전극(106), 제 1 패드전극(130) 및 제 2 패드전극(140)은 단층 또는 다중층으로 형성될 수 있다. 예를 들면, 2중층으로 형성될 수 있다. 자세하게는, 제 1 금속층 및 상기 제 1 금속층 상에 형성되는 제 2 금속층으로 형성될 수 있다.

[0111] 이 후, 상기 박막 트랜지스터(Tr) 및 패드전극(130, 140)이 형성된 기판(100) 전면에 보호막(107)이 형성된다. 이 후, 상기 보호막(107)이 형성된 기판(100) 상에 상기 패드전극(130, 140) 영역을 제외한 전면에 평탄화막(108)이 형성된다. 즉, 상기 패드전극(130, 140)상에 상기 평탄화막(108)이 형성되지 않을 수 있다.

[0112] 또한, 상기 표시영역(AA)에 형성된 상기 평탄화막(108) 및 보호막(107)에 형성된 컨택홀에 의해 상기 드레인전극(106)이 노출된다. 이와 동시에 상기 비표시영역(NA)에 형성된 상기 보호막(107)에 형성된 컨택홀에 의해 상기 제 2 패드전극(140)이 노출될 수 있다.

[0113] 상기 표시영역(AA) 상에 형성된 컨택홀에 의해 상기 드레인전극(106)에 접속되는 상기 유기발광소자의 제 1 전극(167)이 형성된다. 여기서, 상기 제 1 전극(167)은 애노드(anode) 전극 일 수 있다. 또한, 상기 비표시영역(NA) 상에 형성된 컨택홀에 의해 상기 제 2 패드전극(140)에 접하여 형성되는 제 3 패드전극(150)이 형성될 수 있다.

[0114] 여기서, 상기 제 1 전극(167)은 제 1 층(161) 상에 제 2 층(162)이 형성되고 상기 제 2 층(162)상에 제 3 층(164)이 형성된 3중층 구조로 형성될 수 있다. 여기서, 상기 제 1 층(161) 및 제 3 층(164)은 투명 도전물질일 수 있다. 예를 들면, 상기 투명 도전물질은 ITO일 수 있다. 상기 제 2 층(162)은 반사층일 수 있다. 이 때, 상기 제 2 층(162)은 금속 또는 금속 합금층일 수 있다. 예를 들면, Ag 또는 Ag를 포함하는 금속 합금층일 수 있다.

[0115] 또한, 상기 제 3 패드전극(150)은 제 1 층(150a) 및 상기 제 1 층(150a) 상에 제 2 층(150b)이 형성된 2중층 구조로 형성될 수 있다. 여기서 상기 제 1 층(150b)은 투명 도전물질일 수 있다. 예를 들면, 상기 투명 도전물질은 ITO일 수 있다. 상기 제 2 층(150b)은 반사층일 수 있다. 이 때, 상기 제 2 층(150b)은 금속 또는 금속 합금층일 수 있다. 예를 들면, Ag 또는 Ag를 포함하는 금속 합금층일 수 있다.

[0116] 상기 제 3 패드전극의 형태는 도면에 한정되지 않으며, 제 1 층, 상기 제 1 층 상에 형성된 제 2 층 및 상기 제 2 층 상에 제 3 층이 형성된 3중층 구조로 형성될 수도 있다. 이 때, 상기 제 1 층 및 제 3 층은 투명 도전물질일 수 있다. 예를 들면, 상기 투명 도전물질은 ITO일 수 있다. 상기 제 2 층은 반사층이며, 금속 또는 금속 합금층일 수 있다. 예를 들면, Ag 또는 Ag를 포함하는 금속 합금층일 수 있다.

[0117] 이 때, 상기 제 3 패드전극(150)는 외부로 노출되어 형성될 수 있다. 이 때, 산소 및 수분과 접촉하여 부식 또는 마이그레이션(migration)이 발생할 수 있다. 때문에 유기전계발광 표시장치의 신뢰성이 떨어질 수 있다.

- [0118] 이를 해결하기 위해, 상기 제 3 패드전극(150)을 둘러싸는 형태로 보호전극층(207)이 형성될 수 있다. 자세하게는, 상기 보호전극층(207)은 상기 제 3 패드전극(150)의 상면 및 측면에 접하여 형성될 수 있다.

- [0119] 이를 통해, 상기 제 3 패드전극(150)이 외부에 노출되어도 상기 보호전극층(207)이 상기 제 3 패드전극(150)의 상면 및 측면으로 침투하는 산소 및 수분을 막아줌으로써, 상기 제 3 패드전극(150)의 부식을 막을 수 있다. 이 때, 상기 보호전극층(207)은 투명 도전물질 일 수 있다. 예를 들면, 상기 투명 도전물질은 ITO 일 수 있다.

- [0120] 이 후, 상기 제 1 전극(167)이 형성된 표시영역(AA)의 평탄화막(108) 상에 뱅크 패턴(170)이 형성된다. 이 때, 상기 뱅크 패턴(170)은 상기 제 1 전극(167)을 노출하는 형태로 형성될 수 있다.

- [0121] 또한, 상기 제 1 전극(167) 상에 유기발광층(180)이 형성될 수 있다. 상기 유기발광층(180) 상에는 상기 제 1 전극(167)과 대향하여 제 2 전극(190)이 형성될 수 있다. 상기 제 2 전극은 캐소드(cathode)전극일 수 있다.

- [0122] 본 발명에 따른 유기전계발광 표시장치는 외부에 노출되는 상기 제 3 패드전극(150)의 상면 및 측면에 접하도록 보호전극층(207)을 형성함으로써, 상기 제 3 패드전극(150)이 산소 및 수분과 접촉하는 것을 방지할 수 있다. 이를 통해, 상기 제 3 패드전극(150)의 부식을 방지하는 효과가 있다.

- [0123] 이어서, 도 6을 참조하여 본 발명의 유기전계발광 표시장치 제조방법의 다른 실시예를 설명한다. 도 6은 본 발명의 유기전계발광 표시장치의 제조방법의 실시예를 도시한 단면도이다. 본 발명에 따른 디스플레이 표시장치의 제조방법은 앞서 설명한 실시예들과 동일한 구성요소를 포함할 수 있다. 앞서 설명한 실시예들과 중복되는 설명은 생략할 수 있다. 또한, 동일한 구성은 동일한 도면부호를 갖는다.

- [0124] 표시영역(AA) 및 비표시영역으로 정의되는 기판(100)상에 반도체층을 형성한다. 포토레지스트 공정으로 상기 반도체층을 식각하여 박막 트랜지스터(Tr)의 반도체층(101)을 형성한다. 이 후, 상기 기판(100) 전면에 게이트 절연막(102)을 형성한다.

- [0125] 상기 게이트 절연막(102) 상에는 게이트금속(103) 및 제 1 패드전극(140)을 형성하기 위해, 금속층 물질을 형성한다. 이 때, 상기 금속층 물질은 다양한 물질로 형성될 수 있다. 또한, 상기 금속층은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 상기 금속층은 2중층으로 형성될 수 있다. 이 때, 상기 게이트 금속층은 제 1 금속층 및 상기 제 1 금속층 상에 형성되는 제 2 금속층으로 형성될 수 있다.

- [0126] 이 후, 포토레지스트 공정으로 금속층 물질을 식각함으로써 게이트전극(103) 및 제 1 패드전극(130)이 형성된다. 이 후, 게이트전극(103)을 마스크로하여 소스영역(101a) 및 드레인영역(101c)에 고농도의 불순물을 도핑하여 소스영역(101a)과 드레인영역(101c)을 형성한다. 이 때, 도면에 도시하였지만, 설명하지 않는 101b는 채널영역이다.

- [0127] 이 후, 상기 게이트전극(103) 및 제 1 패드전극(130)이 형성된 기판 전면에 충간절연막(104)이 형성된다. 포토레지스트 공정으로 상기 충간절연막(104)과 게이트 절연막(102)을 식각하여, 상기 표시영역(AA)의 반도체층(101)의 소스영역(101a)과 드레인영역(101c)을 노출시키는 제 1 컨택홀을 형성한다. 이와 동시에 상기 비표시영역(NA)에 형성된 상기 충간절연막(104)에는 상기 제 1 패드전극(130)을 노출하는 제 2 컨택홀이 형성된다.

- [0128] 이 후, 상기 제 1 컨택홀 및 제 2 컨택홀이 형성된 충간절연막(104)을 포함하는 기판(100) 전면에 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)을 형성하기 위해, 전극층 물질을 형성한다. 이 때, 상기 전극층 물질은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 전극층은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 2중층으로 형성될 수 있다. 자세하게는, 제 1 전극층 및 제 1 전극층 상에 형성되는 제 2 전극층으로 형성될 수 있다.

- [0129] 상기 충간절연막(104)과 접하여 형성되는 상기 제 1 전극층은 상기 제 2 전극층의 접착력을 높이기 위해 형성될 수 있다. 여기서, 상기 제 1 전극층 물질은 MoTi 또는 Ti로 형성될 수 있다. 또한, 상기 제 2 전극층 물질은 Cu, Ag, Al, Cr, Ti, Ta 또는 이들의 조합으로부터 형성되는 합금 일 수 있다. 바람직하게는 상기 제 2 전극층 물질은 Cu로 형성될 수 있다.

- [0130] 이 후, 포토레지스트 공정으로 상기 제 1 전극층 물질 및 제 2 전극층 물질이 식각되어 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)이 형성된다. 즉, 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)은 동일층에서 동일물질로 형성될 수 있다.

- [0131] 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)이 형성된 기판(100) 전면에 보호막(107)이 형성된다.

다. 이 후, 상기 표시영역(AA)에 형성된 보호막(107) 상에 평탄화막(108)을 형성한다.

[0132] 상기 표시영역(AA)에 형성된 평탄화막(108) 상에 포토레지스트 공정으로 상기 드레인전극(106)을 노출하는 컨택홀이 형성된다. 이 때, 상기 비표시영역(NA)에 형성된 평탄화막(108)은 모두 제거될 수 있다.

[0133] 이 후, 상기 표시영역(AA)에 형성된 평탄화막(108)을 마스크로 하여, 상기 보호막(107)에 상기 드레인전극(106)을 노출하는 컨택홀을 형성한다. 이와 동시에, 상기 비표시영역(NA)에 형성된 상기 제 2 패드전극(140)을 노출하는 컨택홀을 형성한다.

[0134] 이 후, 상기 컨택홀을 포함하는 상기 기판(100) 상에 제 1 전극 물질이 형성되고, 포토레지스트 공정으로 제 1 전극(160)이 형성된다. 이와 동시에, 비표시영역(NA) 상에서 외부로 노출되는 제 3 패드전극(150)이 형성된다.

[0135] 이 때, 상기 제 1 전극(167)은 다중층으로 형성될 수 있다. 예를 들면, 3중층으로 형성될 수 있다. 자세하게는, 제 1층(161), 상기 제 1 층(161) 상에 형성되는 제 2 층(162) 및 상기 제 2 층(162) 상에 형성되는 제 3 층(164)으로 형성될 수 있다.

[0136] 상기 제 3 패드전극(150)은 제 1 층(150a) 및 상기 제 1 층(150a) 상에 제 2 층(150b)이 형성된 2중층 구조로 형성될 수 있다. 그리고, 제 3 패드전극(150)의 상면 및 측면에 접하여 보호전극층(207)이 형성될 수 있다.

[0137] 이를 위해, 상기 제 1 전극(167)의 제 1 층 물질 및 상기 제 3 패드전극(150)의 제 1 층 물질인 투명 도전물질을 상기 보호막(207)에 형성된 컨택홀을 포함하는 기판(100) 전면에 형성한다. 여기서, 제 1 층 물질은 투명 도전물질일 수 있다. 예를 들면, 상기 투명도전물질은 ITO일 수 있다.

[0138] 이 후, 상기 제 1 층 물질 상에 상기 제 1 전극(167)의 제 2 층 물질 및 상기 제 3 패드전극(150)의 제 2 층 물질인 Ag 또는 Ag 합금층을 형성한다. 이 후, 상기 제 1 층 물질 및 2 층 물질을 동시에 식각한다.

[0139] 그리고, 상기 제 1 전극(167)의 제 2 층 물질 상에 제 1 전극(167)의 제 3 층 물질 및 상기 제 3 패드전극(150)의 2 층 물질 상에 형성되는 투명 도전물질을 형성한다. 이 후, 상기 제 3 층 물질 및 투명 도전물질은 상기 제 1 전극(167) 및 제 3 패드전극(150)의 상면 및 측면에 접하도록 형성되도록 식각된다. 여기서 제 1 전극(167)의 제 3 층 물질은 투명 도전물질일 수 있다. 이를 통해, 제 1 층(161), 제 2 층(162) 및 제 3 층(164)을 포함하는 상기 제 1 전극(167)과 제 1 층(150a) 및 제 2 층(150b)을 포함하는 제 3 패드전극(150) 및 상기 제 3 패드전극(150) 상면 및 측면에 접하여 형성되는 보호전극층(207)이 형성된다.

[0140] 즉, 상기 제 1 전극(167)의 제 1 층(161)과 상기 제 3 패드전극(150)의 제 1 층(150a)은 동일층에서 동일물질로 형성될 수 있다. 또한, 상기 제 1 전극(167)의 제 2 층(162)과 상기 제 3 패드전극(150)의 제 2 층(150b)은 동일층에서 동일물질로 형성될 수 있다. 그리고, 상기 제 1 전극(167)의 제 3 층(164)는 상기 제 3 패드전극(150)의 상면 및 측면에 접하여 형성된 보호전극층(207)과 동일 물질로 형성될 수 있다.

[0141] 본 발명에 따른 유기전계발광 표시장치는 외부에 노출되는 상기 제 3 패드전극(150)의 상면 및 측면에 접하도록 보호전극층(207)을 형성함으로써, 제 3 패드전극(150)의 상면 및 측면으로부터 산소 및 수분이 침투하는 것을 방지할 수 있다. 또한, 보호전극층(207)을 형성하는 공정에서 유기발광소자의 제 1 전극(167)을 형성하는 데 사용되는 마스크를 이용하여 형성하므로, 마스크 추가 없이 보호전극층(207)을 형성할 수 있다. 때문에 공정을 단순화하고, 제조비용을 감소시킬 수 있는 효과가 있다.

[0142] 이어서, 도 7을 참조하여 본 발명에 따른 유기전계발광 표시장치 제조방법의 다른 실시예를 설명한다. 도 7은 본 발명에 따른 유기전계발광 표시장치의 제조방법의 다른 실시예를 도시한 단면도이다. 다른 실시예에 따른 디스플레이 표시장치의 제조방법은 앞서 설명한 실시예들과 동일한 구성요소를 포함할 수 있다. 앞서 설명한 실시예들과 중복되는 설명은 생략할 수 있다. 또한, 동일한 구성은 동일한 도면부호를 갖는다.

[0143] 표시영역(AA) 및 비표시영역으로 정의되는 기판(100) 상에 반도체층을 형성한다. 포토레지스트 공정으로 상기 반도체층을 식각하여 박막 트랜지스터(Tr)의 반도체층(101)을 형성한다. 이 후, 상기 기판(100) 전면에 게이트 절연막(102)을 형성한다.

[0144] 상기 게이트 절연막(102) 상에는 상기 게이트금속(103) 및 제 1 패드전극(130)을 형성하기 위해, 금속층 물질을 형성한다. 이 때, 상기 금속층 물질은 다양한 물질로 형성될 수 있다. 또한, 상기 금속층은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 상기 금속층은 2중층으로 형성될 수 있다. 이 때, 상기 금속층은 제 1 금속층 및 상기 제 1 금속층 상에 형성되는 제 2 금속층으로 형성될 수 있다.

- [0145] 이 후, 포토레지스트 공정으로 금속층을 식각함으로써 게이트전극(103) 및 제 1 패드전극(130)이 형성된다. 이 후, 게이트전극(103)을 마스크로하여 소스영역(101a) 및 드레인영역(101c)에 고농도의 불순물을 도핑하여 소스 영역(101a)과 드레인영역(101c)을 형성한다. 이 때, 도면에 도시하였지만, 설명하지 않는 101b는 채널영역이다.

- [0146] 이 후, 상기 게이트전극(103) 및 제 1 패드전극(130)이 형성된 기판 전면에 충간절연막(104)이 형성된다. 포토레지스트 공정으로 상기 충간절연막(104)과 게이트 절연막(102)을 식각하여, 상기 표시영역(AA)의 반도체층(101)의 소스영역(101a)과 드레인영역(101c)을 노출시키는 제 1 컨택홀을 형성한다. 이와 동시에 상기 비표시영역(NA)에 형성된 상기 충간절연막(104)에는 상기 제 1 패드전극(130)을 노출하는 제 2 컨택홀이 형성된다.

- [0147] 이 후, 상기 제 1 컨택홀 및 제 2 컨택홀이 형성된 충간절연막(104)을 포함하는 기판(100) 전면에 전극층 물질을 형성한다. 이 때, 상기 전극층 물질은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 전극층은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 2중층으로 형성될 수 있다. 자세하게는, 제 1 전극층 및 제 1 전극층 상에 형성되는 제 2 전극층으로 형성될 수 있다.

- [0148] 여기서, 상기 제 1 전극층 물질은 MoTi 또는 Ti로 형성될 수 있다. 또한, 상기 제 2 전극층 물질은 Cu, Ag, Al, Cr, Ti, Ta 또는 이들의 조합으로부터 형성되는 합금 일 수 있다. 바람직하게는 상기 제 2 전극층 물질은 Cu로 형성될 수 있다.

- [0149] 이 후, 포토레지스트 공정으로 상기 제 1 전극층 물질 및 제 2 전극층 물질이 식각되어 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)이 형성된다. 즉, 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)은 동일층에서 동일물질로 형성될 수 있다.

- [0150] 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)이 형성된 기판(100) 전면에 보호막(107)이 형성한다. 이 후, 상기 표시영역(AA)에 형성된 보호막(107) 상에 평탄화막(108)을 형성한다.

- [0151] 상기 표시영역(AA)에 형성된 평탄화막(108) 상에 포토레지스트 공정으로 상기 드레인전극(106)을 노출하는 컨택홀이 형성된다. 이 때, 상기 비표시영역(NA)에 형성된 평탄화막(108)은 모두 제거된다. 이 후, 상기 표시영역(AA)에 형성된 평탄화막(108)을 마스크로 하여, 상기 보호막(107)에 상기 드레인전극(106)을 노출하는 컨택홀을 식각한다. 이와 동시에, 상기 비표시영역(NA)에 형성된 상기 제 2 패드전극(140)을 노출하는 컨택홀을 형성한다.

- [0152] 이 후, 상기 노출된 드레인전극(106)과 연결되도록 포토레지스트 공정으로 제 1 전극(168)이 형성된다. 이와 동시에, 상기 비표시영역(NA)에서 외부로 노출되는 제 3 패드전극(151)이 형성된다.

- [0153] 이 때, 상기 제 1 전극(168)은 다중층으로 형성될 수 있다. 예를 들면, 4중층으로 형성될 수 있다. 자세하게는, 제 1 층(161), 상기 제 1 층(161) 상에 형성되는 제 2 층(162), 상기 제 2 층(162) 상에 형성되는 제 3 층(163) 및 상기 제 3 층(163) 상에 제 4 층(165)이 형성된 4중층 구조로 형성될 수 있다. 상기 제 4층(165)은 상기 제 1 전극(168)의 제 3 층(163)의 상면에 형성되고, 상기 제 1 전극(168)의 제 1 층(161), 제 2 층(162) 및 제 3 층(163)의 양 측면에 형성될 수 있다.

- [0154] 상기 제 3 패드전극(151)은 제 1 층(151a), 상기 제 1 층(151a) 상에 형성된 제 2 층(151b) 및 상기 제 2 층(151b) 상에 제 3 층(151b)이 형성된 3중층 구조로 형성될 수 있다. 그리고, 제 3 패드전극(151)의 상면 및 측면에 접하여 보호전극층(207)이 형성될 수 있다.

- [0155] 이를 위해, 상기 제 1 전극(168)의 제 1 층 물질 및 상기 제 3 패드전극(151)의 제 1 층 물질인 투명 도전물질을 상기 보호막(107)에 형성된 컨택홀을 포함하는 기판(100) 전면에 형성한다. 여기서, 제 1 층 물질은 투명 도전물질일 수 있다. 예를 들면, 상기 투명 도전물질은 ITO일 수 있다.

- [0156] 이 후, 상기 제 1 층 물질 상에 상기 제 1 전극(168)의 제 2 층 물질 및 상기 제 3 패드전극(151)의 제 2 층 물질인 Ag 또는 Ag 합금층을 형성한다. 그리고, 상기 제 2 층 물질 상에 제 1 전극(168)의 제 3 층 물질 및 상기 제 3 패드전극(151)의 제 3 층 물질을 형성한다. 여기서, 상기 제 3 층 물질은 투명 도전물질일 수 있다. 예를 들면, 상기 투명 도전물질은 ITO 일 수 있다. 이 후, 상기 제 1 층 물질, 2 층 물질 및 3 층 물질을 동시에 식각한다.

- [0157] 그리고, 상기 제 1 전극(168)의 제 3 층 물질 상에 상기 제 1 전극(168)의 제 4 층 물질 및 상기 제 3 패드전극(161) 상에 투명 도전물질을 형성한다. 이 후, 상기 제 4 층 물질 및 투명 도전물질은 상기 제 1 전극(168) 및 제 3 패드전극(151)의 상면 및 측면에 접하여 형성되도록 식각된다. 여기서 제 1 전극(168)의 제 4 층 물질은 투명 도전물질일 수 있다. 이를 통해, 제 1 층(161), 제 2 층(162), 제 3 층(163) 및 제 4 층(165)을 포함하는

상기 제 1 전극(168)과 제 1 층(151a), 제 2 층(151b) 및 제 3 층(151c)을 포함하는 제 3 패드전극(151) 및 상기 제 3 패드전극(151) 상면 및 측면에 접하여 형성되는 보호전극층(207)이 형성된다.

[0158] 즉, 상기 제 1 전극(168)의 제 1 층(161)과 상기 제 3 패드전극(151)의 제 1 층(151a)은 동일물질로 형성될 수 있다. 또한, 상기 제 1 전극(168)의 제 2 층(162)과 상기 제 3 패드전극(151)의 제 2 층(151b)은 동일물질로 형성될 수 있다. 그리고, 상기 제 1 전극(168)의 제 3 층(163)은 상기 제 3 패드전극(151)의 제 3 층(151c)과 동일물질로 형성될 수 있다. 또한, 상기 제 1 전극(168)의 제 4 층(165)과 상기 제 3 패드전극(151)의 상면 및 측면에 접하여 형성된 보호전극층(207)은 동일 물질로 형성될 수 있다.

[0159] 본 발명에 따른 유기전계발광 표시장치는 외부에 노출되는 제 3 패드전극(151)의 상면 및 측면에 접하도록 보호전극층(207)을 형성함으로써, 제 3 패드전극(151)의 상면 및 측면으로부터 산소 및 수분이 침투하는 것을 방지할 수 있다. 또한, 보호전극층(207)을 형성하는 공정에서 유기발광소자의 제 1 전극(168)을 형성하는 데 사용되는 마스크를 이용하여 형성하므로, 마스크 추가 없이 보호전극층(207)을 형성할 수 있다. 때문에 공정을 단순화하고, 제조비용을 감소시킬 수 있는 효과가 있다.

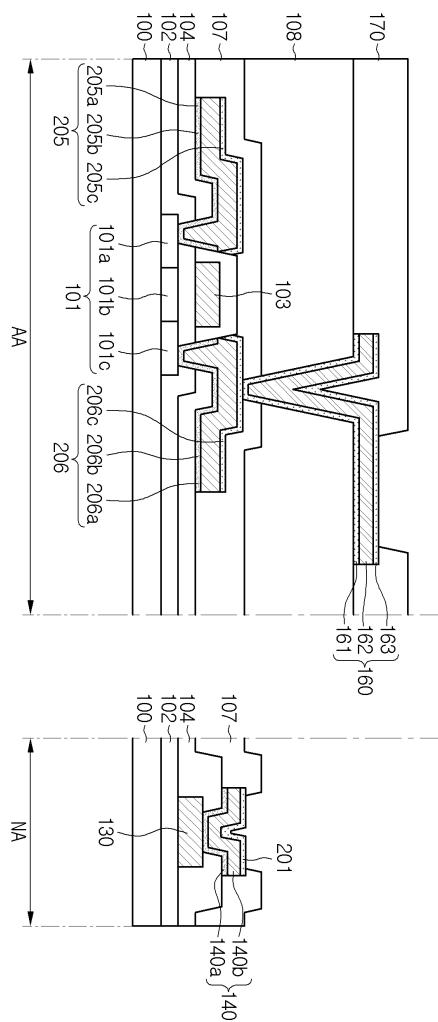

[0160] 이어서, 도 8a 내지 8e를 참조하여 본 발명에 따른 유기전계발광 표시장치 제조방법의 또 다른 실시예를 설명한다. 도 8a 내지 8e는 본 발명에 따른 유기전계발광 표시장치의 제조방법의 또 다른 실시예를 도시한 단면도이다. 또 다른 실시예에 따른 디스플레이 표시장치의 제조방법은 앞서 설명한 실시예들과 동일한 구성요소를 포함할 수 있다. 앞서 설명한 실시예들과 중복되는 설명은 생략할 수 있다. 또한, 동일한 구성은 동일한 도면부호를 갖는다.

[0161] 도 8a를 참조하면, 표시영역(AA) 및 비표시영역으로 정의되는 기판(100)상에 반도체층을 형성한다. 포토레지스트 공정으로 상기 반도체층을 식각하여 박막 트랜지스터(Tr)의 반도체층(101)을 형성한다. 이 후, 상기 기판(100) 전면에 게이트 절연막(102)을 형성한다.

[0162] 상기 게이트 절연막(102) 상에는 상기 게이트 금속 및 제 1 패드전극을 형성하기 위해, 금속층 물질을 형성한다. 이 후, 포토레지스트 공정으로 금속층을 식각함으로써 게이트전극(103) 및 제 1 패드전극(130)이 형성된다. 이 후, 게이트전극(103)을 마스크로하여 소스영역(101a) 및 드레인영역(101c)에 고농도의 불순물을 도핑하여 소스영역(101a)과 드레인영역(101c)을 형성한다. 이 때, 도면에 도시하였지만, 설명하지 않는 101b는 채널영역이다.

[0163] 이 후, 상기 게이트전극(103) 및 제 1 패드전극(130)이 형성된 기판 전면에 충간절연막(104)이 형성된다. 포토레지스트 공정으로 상기 충간절연막(104)과 게이트 절연막(102)을 식각하여, 상기 표시영역(AA)의 반도체층(101)의 소스영역(101a)과 드레인영역(101c)을 노출시키는 컨택홀을 형성한다. 이와 동시에 상기 비표시영역(NA)에 형성된 상기 충간절연막(104)에는 상기 제 1 패드전극(130)을 노출하는 컨택홀이 형성된다.

[0164] 이 후, 상기 컨택홀이 형성된 충간절연막(104)을 포함하는 기판(100) 전면에 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)을 형성하기 위해, 전극층 물질을 형성한다. 이 때, 상기 전극층 물질은 다양한 물질로 형성될 수 있다. 예를 들면, 금속층으로 형성될 수 있다. 또한, 상기 전극층은 단일층 또는 다중층으로 형성될 수 있다. 예를 들면, 2 중층으로 형성될 수 있다. 자세하게는, 상기 제 1 전극층 및 상기 제 1 전극층 상에 형성되는 제 2 전극층으로 형성될 수 있다.

[0165] 이 후, 포토레지스트 공정으로 상기 제 1 전극층 물질 및 제 2 전극층 물질 식각되어 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)이 형성된다. 상기 소스전극(105), 드레인전극(106) 및 제 2 패드전극(140)이 형성된 기판(100) 전면에 보호막(107)이 형성한다. 이 후, 상기 표시영역(AA)에 형성된 보호막(107) 상에 평탄화막(108)을 형성한다.

[0166] 상기 표시영역(AA)에 형성된 평탄화막(108) 상에 포토레지스트 공정으로 상기 드레인전극(106)을 노출하는 컨택홀이 형성된다. 이 때, 상기 비표시영역(NA)에 형성된 평탄화막(108)은 모두 제거될 수 있다. 이 후, 상기 표시영역(AA)에 형성된 평탄화막(108)을 마스크로 하여, 상기 보호막(107)에 상기 드레인전극(106)을 노출하는 컨택홀을 식각한다. 이와 동시에, 상기 비표시영역(NA)에 형성된 상기 제 2 패드전극(140)을 노출하는 컨택홀을 형성한다.

[0167] 이 후, 포토레지스트 공정으로 상기 노출된 드레인전극(106)과 연결되는 유기전계발광 소자의 제 1 전극 물질층

이 상기 기판(100)의 표시영역(AA) 전면에 형성된다. 여기서, 상기 제 1 전극 물질층은 다중층으로 형성될 수 있다. 예를 들면, 3중층으로 형성될 수 있다. 자세하게는, 제 1 층(261), 상기 제 1 층(261) 상에 형성되는 제 2 층(262) 및 상기 제 2 층(262) 상에 형성되는 제 3 층(263)으로 형성될 수 있다.

[0168] 상기 제 3 패드전극(152)은 제 1 층(152a) 및 상기 제 1 층(152a) 상에 제 2 층(152b)이 형성된 2중층 구조로 형성될 수 있다. 그리고, 제 3 패드전극(152)의 상면 및 측면에 접하여 보호전극층(208)이 형성될 수 있다.

[0169] 이를 위해, 상기 제 1 전극(260)의 제 1 층 물질 및 상기 제 3 패드전극(152)의 제 1 층 물질인 투명 도전물질을 상기 보호막(208)에 형성된 컨택홀을 포함하는 기판(100) 전면에 형성한다. 여기서, 제 1 층 물질은 비결정질의 투명 도전물질일 수 있다. 예를 들면, 상기 비결정질의 투명도전물질은 비결정질의 ITO일 수 있다.

[0170] 이 후, 상기 제 1 층 물질 상에 상기 제 1 전극(260)의 제 2 층 물질 및 상기 제 3 패드전극(152)의 제 2 층 물질인 Ag 또는 Ag 합금층을 형성한다. 이 후, 상기 제 1 전극(260)의 제 2 층 물질 상에 제 1 전극(260)의 제 3 층 물질 및 상기 제 3 패드전극(152)의 2 층 물질 상에 형성되는 비결정질의 투명 도전물질을 형성한다. 여기서 제 1 전극(260)의 제 3 층 물질은 비결정질의 투명 도전물질일 수 있다. 예를 들면, 상기 비결정질의 투명도전물질은 비결정질의 ITO일 수 있다.

[0171] 이 후, 상기 제 1 전극(260)의 제 3 층 물질 및 상기 제 3 패드전극(152)의 제 2 층 물질 상에 형성되는 비결정질의 투명 도전물질층 상에 포토레지스트(295)를 형성한다. 그리고, 상기 제 1 전극(260)의 제 1 층 물질, 제 2 층 물질 및 제 3 층 물질과 상기 제 3 패드전극(152)의 제 1 층 물질, 제 2 층 물질 및 상에 형성되는 투명 도전물질을 상기 포토레지스트(295)를 마스크로 하여 동시에 식각한다.

[0172] 이를 통해, 상기 제 1 전극(260)의 비결정질의 제 1 층, 제 2 층 및 비결정질의 제 3 층을 형성할 수 있다. 이와 동시에 상기 제 3 패드전극(152)의 비결정질의 제 1 층, 제 2 층 및 상기 제 2 층 상에 형성되는 비결정질의 투명 도전물질층을 형성할 수 있다.

[0173] 즉, 상기 제 1 전극(260)의 제 1 층(261)과 제 3 층(163), 제 3 패드전극(152)의 제 1 층(152a) 및 보호전극층(208)은 비정질화된 투명 도전물질로 형성될 수 있다. 여기서, 상기 비정질 투명 도전물질은 높은 결합 밀도를 가지고 있기 때문에, 면적항과 비저항이 크다는 단점이 있다.

[0174] 이를 해결하기 위해, 상기 제 1 전극(260)의 제 1 층(261)과 제 3 층(263), 제 3 패드전극(152)의 제 1 층(152a) 및 투명 도전물질(208)을 결정화할 수 있다. 도 8b를 참조하면, 비결정질인 제 1 전극(160), 제 3 패드전극(150) 및 투명 도전물질(209)은 열처리를 통해 결정질 투명도전물질이 될 수 있다. 이 때, 열처리 온도는 160도 내지 180도이며, 열처리 시간은 10 분 이내일 수 있다. 여기서, 상기 제 1 전극(160) 및 보호전극층(209) 상에 형성된 상기 포토레지스트(296)도 동시에 열처리 될 수 있다.

[0175] 여기서, 상기 제 1 전극(160) 및 제 3 패드전극(150)의 측면은 노출되어 있는 구조일 수 있다. 때문에, 상기 제 1 전극(160)의 제 2 층(162) 및 상기 제 3 패드전극(150)의 제 2 층(150b)은 산소 및 수분에 의해 부식이 발생할 수 있다.

[0176] 이를 해결하기 위해, 상기 제 1 전극(160) 및 제 3 패드전극(150)의 측면에 투명 도전물질을 형성하여 부식을 방지할 수 있다. 도 8c를 참조하면, 상기 포토레지스트(296) 상에 비결정질의 투명 도전물질(265)이 형성된다. 이와 동시에, 상기 결정질의 제 1 층(161) 및 제 3 층(163)을 포함하는 제 1 전극(160)의 양 측면에 비결정질의 투명 도전물질(164)이 형성될 수 있다. 또한, 결정질의 제 1 층(150a)을 포함하는 3 패드전극(152)과 결정질의 투명 도전물질의 양 측면에도 비결정질의 투명도전물질(210)이 형성될 수 있다.

[0177] 이 때, 상기 제 1 전극(160)의 양 측면에 형성된 투명 도전물질은(264)은 상기 제 1 전극(160)의 결정화된 제 1 층(261) 및 제 3 층(263)과 맞닿음으로써, 결정화될 수 있다. 또한, 상기 제 3 패드전극(150)의 양 측면에 형성된 투명 도전물질(210)은 상기 제 3 패드전극(150)의 결정화된 제 1 층(150a) 및 상기 제 3 패드전극(150) 상면에 형성된 결정화된 투명 도전물질(209)과 맞닿음으로써 결정화될 수 있다.

[0178] 결국, 상기 제 3 패드전극(150)과 결정질의 투명 도전물질(209) 측면에 접촉하는 비결정질의 투명 도전물질은 상기 제 3 패드전극(150)의 상면 및 측면에 배치되고, 결정질의 투명 도전물질로 이루어진 보호전극층을 형성한다. 여기서, 상기 포토레지스트(296) 상에 형성된 투명 도전물질층은 비정질로 남아있게 된다.

[0179] 도 8d를 참조하면, 상기 비결정질의 투명 도전물질과 결정질의 투명도전물질 사이의 식각선택비를 이용하여 상기 포토레지스트(296) 상에 남아있는 비정질의 투명 도전물질을 습식 식각한다. 자세하게는, 식각선택비를 이용하여 상기 제 1 전극(167) 상의 포토레지스트(296) 상에 형성된 비정질화된 투명 도전물질과 상기 제 3 패드전

극(150) 상의 포토레지스트(296) 상에 형성된 비정질화된 투명 도전물질을 모두 식각한다.

[0180] 여기서, 상기 제 1 전극(167)의 상기 제 1 층(161) 및 측면에 형성된 투명 도전물질을 포함하는 제 3 층(164)은 식각되지 않는다. 또한, 상기 제 3 패드전극(153)의 제 1 층(150a) 및 측면에 형성된 결정화된 투명 도전물질을 포함하는 상기 보호전극층(207) 역시 식각되지 않고 남게 있게 된다. 이를 통해, 상기 제 3 패드전극(150)은 상면과 측면이 상기 결정화된 보호전극층(207)으로 둘러싸이게 된다.

[0181] 도 8e를 참조하면, 상기 제 1 전극(167) 및 상기 제 1 보호전극층(207) 상에 형성된 포토레지스트는 스트립(strip)된다. 이로써, 상기 제 1 전극(167)의 제 1 층(161) 및 측면에 형성된 투명 도전물질을 포함하는 제 3 층(164)은 결정질화된 투명 도전물질로 형성된다. 또한, 상기 제 3 패드전극(150)의 제 1 층(150a) 및 측면에 형성된 보호전극층을 포함하는 상기 보호전극층(207)은 결정질 투명 도전물질로 형성된다.

[0182] 본 발명에 따른 유기전계발광 표시장치는 외부에 노출되는 제 3 패드전극(150)의 상면 및 측면에 접하도록 결정질 보호전극층(207)을 형성함으로써, 상기 제 3 패드전극(150)에 산소 및 수분이 침투하는 것을 방지할 수 있다. 또한, 유기전계발광 소자의 제 1 전극(167)의 측면을 결정질 투명 도전물질로 보호할 수 있다. 여기서, 보호전극층(207) 및 제 1 전극(167)의 측면에 형성된 투명 도전물질이 결정질화 됨으로써, 낮은 면저항과 비저항을 가질 수 있다.

[0183] 또한, 보호전극층(207) 및 제 1 전극(167)의 측면에 형성된 투명 도전물질은 결정화하는 공정에서 마스크의 추가가 없으므로, 공정을 단순화 하고, 제조비용이 감소하는 효과가 있다.

[0184] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특히 청구의 범위에 의해 정하여져야만 할 것이다.

### **부호의 설명**

100: 기판 101: 반도체층

102: 게이트 절연막 103: 게이트전극

104: 층간절연막 105: 소스전극

106: 드레인 전극 107: 보호막

108: 평탄화막 130: 제 1 패드전극

140: 제 2 패드전극 160: 제 1 전극

170: 뱅크패턴 180: 유기발광층

190: 제 2 전극 200: 보호전극층

도면

도면1

도면2a

도면2b

## 도면2c

도면2d

도면2e

## 도면3

도면4a

도면4b

도면4c

도면4d

도면4e

## 도면5

도면6

## 도면7

도면8a

도면8b

## 도면8c

도면8d

## 도면8e

|                |                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光显示装置及其制造方法                                                                                               |         |            |

| 公开(公告)号        | <a href="#">KR1020160003949A</a>                                                                               | 公开(公告)日 | 2016-01-12 |

| 申请号            | KR1020140081790                                                                                                | 申请日     | 2014-07-01 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                       |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                                      |         |            |

| [标]发明人         | IM JONG HYEOK<br>임종혁<br>KIM SE JUNE<br>김세준<br>LEE JOON SUK<br>이준석<br>LEE SO JUNG<br>이소정<br>LEE JAE SUNG<br>이재성 |         |            |

| 发明人            | 임종혁<br>김세준<br>이준석<br>이소정<br>이재성                                                                                |         |            |

| IPC分类号         | H01L27/32 H01L51/52 H01L51/56                                                                                  |         |            |

| CPC分类号         | H01L27/3276 H01L27/3248                                                                                        |         |            |

| 代理人(译)         | KIM KI MOON<br>김기문Ki月亮                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                      |         |            |

**摘要(译)**

由显示区域和非显示区域限定的基板;薄膜晶体管，设置在显示区域上，包括半导体层，栅电极，源电极和漏电极;一种有机发光元件，包括第一电极，有机发光层和设置在薄膜晶体管上的第二电极;并且，保护电极层设置在焊盘电极上并由非晶或结晶透明导电材料形成，其中保护电极层形成在焊盘电极上，并且电极形成与暴露于外部的区域接触。因此，有机发光显示器及其保护电极层以暴露到外部的焊盘电极的制造根据本发明是相同的，通过hyeongseom的方法，以防止焊盘电极的氧和水分的渗透迁移到焊盘电极发生。此外，可以简化形成保护电极层所需的工艺，并且可以降低制造成本。