(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

G09G 3/30 (2006.01)

(45) 공고일자

2007년03월29일

(11) 등록번호

10-0700300

(24) 등록일자

2007년03월21일

(21) 출원번호 10-2000-0060965

(22) 출원일자 2000년10월17일

심사청구일자 2002년04월04일

(65) 공개번호 10-2001-0051068

(43) 공개일자 2001년06월25일

(30) 우선권주장 99-299210 1999년10월21일 일본(JP)

99-336995 1999년11월29일 일본(JP)

(73) 특허권자 가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

(72) 발명자 고야마 준

일본국 243-0036 가나가와Ken 아쓰기시 하세 398 가부시키가 이샤 한도

오따이 에네루기 켄큐쇼 (내)

이누카이 카주타카

일본국 243-0036 가나가와Ken 아쓰기시 하세 398 가부시키가 이샤 한도

오따이 에네루기 켄큐쇼 (내)

야마자키 순페이

일본국 243-0036 가나가와Ken 아쓰기시 하세 398 가부시키가 이샤 한도

오따이 에네루기 켄큐쇼 (내)

오사다 마이

일본국 243-0036 가나가와Ken 아쓰기시 하세 398 가부시키가 이샤 한도

오따이 에네루기 켄큐쇼 (내)

(74) 대리인 이병호

정상구

신현문

이범래

심사관 : 천대식

전체 청구항 수 : 총 18 항

(54) EL 디스플레이 디바이스, 디지털 카메라, 자동차 네비게이션 시스템, 개인용 컴퓨터 및 이동 전화

(57) 요약

본 발명은 복수의 EL 소자들을 포함하는 복수의 픽셀들(pixel)을 갖는 전기 광학 디바이스를 제공하고, 상기 전기 광학 디바이스는 1 프레임(frame) 기간에서 복수의 EL 소자들이 발광하는 시간 기간을 제어함으로써 그레이스케일 디스플레이

(gray scale display)를 제공하고, 복수의 EL 소자들은 제 1 전극 및 제 2 전극을 갖고, 제 1 전극은 일정한 전위로 유지되고; 또한 제 2 전극의 전위는 제 1 및 제 2 전극들에 인가되는 전위들간의 차이인 EL 구동 전압의 극성(polarity)이 1 프레임 기간마다 반전되는 방식으로 변화된다.

## 대표도

도 1

### 특허청구의 범위

#### 청구항 1.

삭제

#### 청구항 2.

복수의 주입형 EL 소자를 구비하는 복수의 픽셀을 포함하는 EL 디스플레이 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 상기 복수의 주입형 EL 소자가 1 프레임 기간에 포함되는 복수의 서브-프레임(sub-frame) 기간들 중에서 발광하는 상기 서브-프레임 기간 길이들의 합을 제어함으로써 그레이 스케일 디스플레이를 제공하고;

상기 복수의 주입형 EL 소자들은 제 1 전극 및 제 2 전극을 포함하고;

상기 제 1 또는 상기 제 2 전극의 전위는 EL 구동 전압의 극성이 1 프레임 기간마다 반전되는 방식으로 변화하고;

상기 EL 구동 전압은 상기 제 1 및 상기 제 2 전극들에 인가되는 상기 전위들간의 차인, EL 디스플레이 디바이스.

#### 청구항 3.

삭제

#### 청구항 4.

복수의 주입형 EL 소자들, 상기 복수의 주입형 EL 소자들의 발광을 제어하는 복수의 EL 구동 TFT들, 및 상기 복수의 EL 구동 TFT들의 구동을 제어하는 복수의 스위칭 TFT들을 구비하는, 복수의 픽셀들을 포함하는 EL 디스플레이 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 상기 복수의 주입형 EL 소자가 1 프레임 기간에 포함되는 복수의 서브-프레임 기간들 중에서 발광하는 상기 서브-프레임 기간들 길이들의 합을 제어함으로써 그레이 스케일 디스플레이를 제공하고;

상기 복수의 주입형 EL 소자들은 제 1 전극 및 제 2 전극을 포함하고;

상기 제 1 또는 상기 제 2 전극의 전위는 EL 구동 전압의 극성이 1 프레임 기간마다 반전되는 방식으로 변화하고;

상기 EL 구동 전압은 상기 제 1 및 상기 제 2 전극들에 인가되는 상기 전위들간의 차인, EL 디스플레이 디바이스.

#### 청구항 5.

삭제

#### 청구항 6.

삭제

청구항 7.

삭제

청구항 8.

삭제

청구항 9.

삭제

청구항 10.

삭제

청구항 11.

삭제

청구항 12.

삭제

청구항 13.

삭제

청구항 14.

삭제

청구항 15.

삭제

청구항 16.

삭제

청구항 17.

디지털 카메라에 있어서,

기판 상에 복수의 주입형 EL 소자들을 구비하는 복수의 픽셀들로서, 각각의 상기 복수의 주입형 EL 소자들은 제 1 전극, 제 2 전극 및 그것들 사이에 개재된 유기 EL 물질을 포함하는, 상기 복수의 픽셀들을 포함하고,

그레이스케일 디스플레이는 상기 복수의 주입형 EL 소자들이 1 프레임 기간에 포함되는 복수의 서브-프레임 기간들 중에서 발광하는 상기 서브-프레임 기간들 길이들의 합을 제어함으로써 제공되고,

상기 제 1 또는 상기 제 2 전극의 전위는 EL 구동 전압의 극성이 1 서브-프레임 기간마다 반전되는 방식으로 변화하고;

상기 EL 구동 전압은 상기 제 1 및 상기 제 2 전극들에 인가되는 상기 전위간의 차인, 디지털 카메라.

청구항 18.

제 17 항에 있어서,

상기 1 프레임 기간은 1/120초 이하인, 디지털 카메라.

### 청구항 19.

제 17 항에 있어서,

상기 유기 EL 물질은 Alq<sub>3</sub>(tris-8-quinolylite-aluminum) 및 TPD(triphenylamine derivative)로 구성된 그룹으로부터 선택된 저분자 유기 물질을 포함하는, 디지털 카메라.

### 청구항 20.

제 17 항에 있어서,

상기 유기 EL 물질은 PPV(polyphenylenevinylene), PVK(polyvinyl-caracole), 및 폴리카보네이트(polycarbonate)로 구성된 그룹으로부터 선택된 폴리머(polymer) 유기 물질을 포함하는, 디지털 카메라.

### 청구항 21.

자동차 네비게이션 시스템에 있어서,

기판상에 복수의 주입형 EL 소자들을 구비하는 복수의 광셀들로서, 각각의 상기 복수의 주입형 EL 소자들은 제 1 전극, 제 2 전극 및 그것들 사이에 개재된 유기 EL 물질을 포함하는, 상기 복수의 광셀들을 포함하고,

그래이 스케일 디스플레이는 상기 복수의 주입형 EL 소자들이 1 프레임 기간에 포함되는 복수의 서브-프레임 기간들 중에서 발광하는 상기 서브-프레임 기간들의 길이들의 합을 제어함으로써 제공되고,

상기 제1 또는 제 2 전극의 전위는 EL 구동 전압의 극성이 1 서브-프레임 기간마다 반전되는 방식으로 변화하고,

상기 EL 구동 전압은 상기 제 1 및 상기 제 2 전극들에 인가되는 상기 전위간의 차인, 자동차 네비게이션 시스템.

### 청구항 22.

제 21항에 있어서,

상기 1 프레임 기간은 1/120초 이하인, 자동차 네비게이션 시스템.

### 청구항 23.

제 21항에 있어서,

상기 유기 EL 물질은 Alq<sub>3</sub>(tris-8-quinolylite-aluminum) 및 TPD(triphenylamine derivative)로 구성된 그룹으로부터 선택된 저분자 유기 물질을 포함하는, 자동차 네비게이션 시스템.

### 청구항 24.

제 21항에 있어서,

상기 유기 EL 물질은 PPV(polyphenylenevinylene), PVK(polyvinyl-caracole), 및 폴리카보네이트(polycarbonate)로 구성된 그룹으로부터 선택된 폴리머(polymer) 유기 물질을 포함하는, 자동차 네비게이션 시스템.

### 청구항 25.

개인용 컴퓨터에 있어서,

기판 상에 복수의 주입형 EL 소자들을 구비하는 복수의 광셀들로서, 각각의 상기 복수의 주입형 EL 소자들은 제 1 전극, 제 2 전극 및 그것들 사이에 개재된 유기 EL 물질을 포함하는, 상기 복수의 광셀들을 포함하고,

그래이 스케일 디스플레이는 상기 복수의 주입형 EL 소자들이 1 프레임 기간에 포함되는 복수의 서브-프레임 기간들 중에서 발광하는 상기 서브-프레임 기간들 길이들의 합을 제어함으로써 제공되고,

상기 제 1 또는 상기 제 2 전극의 전위는 EL 구동 전압의 극성이 1 서브-프레임 기간마다 반전되는 방식으로 변화하고;

상기 EL 구동 전압은 상기 제 1 및 상기 제 2 전극들에 인가되는 상기 전위간의 차인, 개인용 컴퓨터.

### 청구항 26.

제 25 항에 있어서,

상기 1 프레임 기간은 1/120초 이하인, 개인용 컴퓨터.

### 청구항 27.

제 25 항에 있어서,

상기 유기 EL 물질은 Alq<sub>3</sub>(tris-8-quinolylite-aluminum) 및 TPD(triphenylamine derivative)로 구성된 그룹으로부터 선택된 저분자 유기 물질을 포함하는, 개인용 컴퓨터.

### 청구항 28.

제 25 항에 있어서,

상기 유기 EL 물질은 PPV(polyphenylenevinylene), PVK(polyvinyl-caracole), 및 폴리카보네이트(polycarbonate)로 구성된 그룹으로부터 선택된 폴리머 유기 물질을 포함하는, 개인용 컴퓨터.

### 청구항 29.

이동 전화에 있어서,

기판 상에 복수의 주입형 EL 소자들을 구비하는 복수의 광셀들로서, 각각의 상기 복수의 주입형 EL 소자들은 제 1 전극, 제 2 전극 및 그것들 사이에 개재된 유기 EL 물질을 포함하는, 상기 복수의 광셀들을 포함하고,

그래이 스케일 디스플레이는 상기 복수의 주입형 EL 소자들이 1 프레임 기간에 포함되는 복수의 서브-프레임 기간들 중에서 발광하는 상기 서브-프레임 기간들의 길이들 합을 제어함으로써 제공되고,

상기 제 1 또는 상기 제 2 전극의 전위는 EL 구동 전압의 극성이 1 서브-프레임 기간마다 반전되는 방식으로 변화하고;

상기 EL 구동 전압은 상기 제 1 및 상기 제 2 전극들에 인가되는 상기 전위간의 차인, 이동 전화.

### 청구항 30.

제 29 항에 있어서,

상기 1 프레임 기간은 1/120초인, 이동 전화.

### 청구항 31.

제 29 항에 있어서,

상기 유기 EL 물질은 Alq<sub>3</sub>(tris-8-quinolylite-aluminum) 및 TPD(triphenylamine derivative)로 구성된 그룹으로부터 선택된 저분자 유기 물질을 포함하는, 이동 전화.

### 청구항 32.

제 29 항에 있어서,

상기 유기 EL 물질은 PPV(polyphenylenevinylene), PVK(polyvinyl-caracole), 및 폴리카보네이트(polycarbonate)로 구성된 그룹으로부터 선택된 폴리머 유기 물질을 포함하는, 이동 전화.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 기판 상에 EL 소자를 마련함으로써 형성된 EL(electro-luminescence) 디스플레이(전기 광학 디바이스)에 관한 것이다. 특히, 본 발명은 반도체 소자(반도체 박막을 사용한 소자)를 사용하는 EL 디스플레이에 관한 것이다. 더욱이, 본 발명은 디스플레이 부분에 EL 디스플레이가 사용되는 전자 디바이스에 관한 것이다.

최근에는 기판 상에 TFT를 형성하는 기술이 크게 개선되었고, 능동 매트릭스형(active matrix-type) 디스플레이 디바이스에 대한 TFT의 적용 개발이 이루어졌다. 특히, 폴리실리콘막을 사용하는 TFT는 종래의 비결정질 실리콘막을 사용하는 TFT 보다 더 높은 전계 효과 이동성을 갖고, 따라서 TFT는 고속으로 동작할 수 있다. 그러므로, 기판 외부의 구동기 회로에서 실행되었던 픽셀(pixel) 제어는 픽셀과 동일한 기판 상에 형성된 구동기 회로에서 실행될 수 있다.

이러한 능동 매트릭스형 디스플레이 디바이스는 동일한 기판 상에 다양한 회로들 및 소자들을 마련함으로써, 제작 비용에서의 감소, 디스플레이 디바이스 크기의 감소, 수율의 증가, 및 작업량(throughput)의 감소와 같은 다양한 이점을 얻을 수 있다.

또한, 자체 발광 디바이스인 EL 소자를 갖춘 능동 매트릭스형 EL 디스플레이에 대한 연구가 보다 활성화되고 있다. EL 디스플레이는 유기 EL 디스플레이(organic EL display, OELD) 또는 유기 발광 다이오드(organic light-emitting diode, OLED)라 칭하여진다.

액정 디스플레이 디바이스와 달리, EL 디스플레이는 자체 발광형 다이오드이다. EL 소자는 EL층이 한 쌍의 전극들 사이에 샌드위치형으로 위치하는 방식으로 구성된다. 그러나, EL 층은 일반적으로 적층 구조(lamination structure)를 갖는다. 전형적으로, 이스트먼 코닥(Eastman Kodak)사의 탱(Tang) 등에 의해 제안된 "양의 홀(positive hole) 운송층/발광층/전자 운송층"의 적층 구조가 언급될 수 있다. 이 구조는 매우 높은 발광 효율성을 갖고, 이 구조는 현재 연구 및 개발되고 있는 거의 모든 EL 디스플레이에 채용된다.

부가하여, 픽셀 전극상에 양의 홀 주입층/양의 홀 운송층/발광층/전자 운송층, 또는 양의 홀 주입층/양의 홀 운송층/발광층/전자 운송층/전자 주입층이 순서대로 적층되는 구조가 있다. 발광층에는 인광성 색소(phosphorescent dye) 등이 도핑(doping)될 수도 있다.

본 명세서에서, 전극쌍 사이에 제공되는 모든 층들은 일반적으로 EL 층들이라 칭하여진다. 결과적으로, 양의 홀 주입층, 양의 홀 운송층, 발광층, 전자 운송층, 전자 주입층 등은 모두 EL층들에 포함된다.

이로써, 전극쌍으로부터 소정의 전압이 상기 구조를 갖는 EL층에 인가되므로, 발광층에서는 캐리어들(carriers)의 재조합이 이루어져 빛이 방사된다. 부수적으로, 본 명세서에서, EL 소자가 조사된다는 사실은 EL 소자가 구동된다는 사실로 설명된다. 더욱이, 본 명세서에서는 양극, EL층으로 형성된 발광 소자, 및 음극이 EL 소자라 칭하여진다.

EL 디스플레이를 실제로 적용하는데 있어서의 문제점은 EL층의 품질 저하로 인한 EL 소자의 짧은 수명이다. EL층의 수명에 영향을 주는 요소로는 EL 디스플레이를 구동하는 디바이스의 구조, EL층을 구성하는 유기 EL 물질의 특성, 전극의 물질, 및 제작 공정의 조건 등이 언급될 수 있다.

또, 상술된 요소들에 부가하여, EL 층의 수명 길이에 영향을 주는 요소로 최근에 주목된 것은 EL 디스플레이를 구동하는 방법이다.

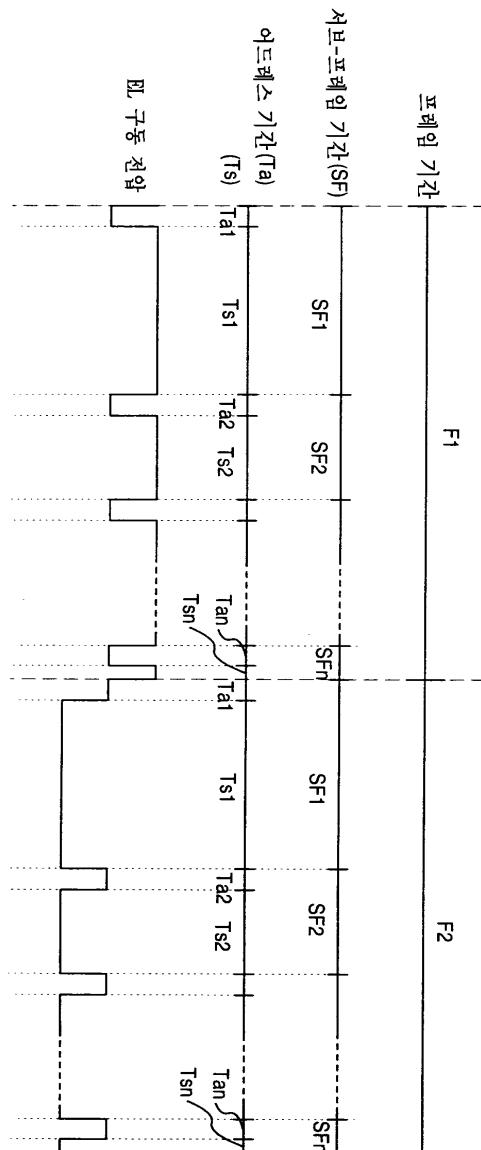

종래에는, EL 소자로부터 발광하기 위해, 두 전극들, 즉 EL 소자를 샌드위칭하는 양극 및 음극에 직류를 인가하는 방법이 일반적으로 사용되었다. 종래의 디지털 스타일 시분할 그레이 스케일 디스플레이에는 도 16을 참고로 설명된다. 여기서는 n-비트 디지털 구동 시스템에  $2^n$  그레이 스케일 전칼라(full color) 디스플레이를 제공하는 경우가 설명된다.

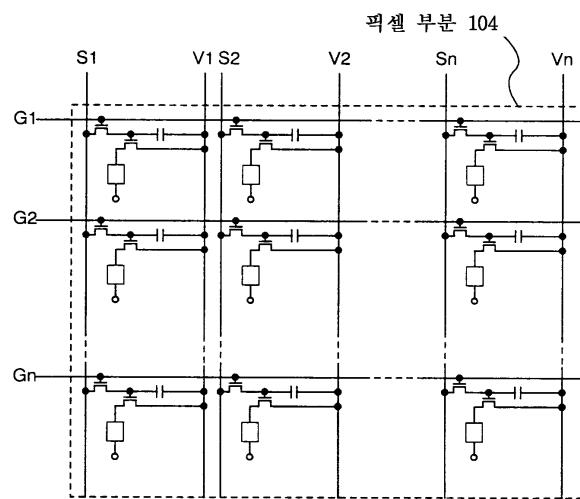

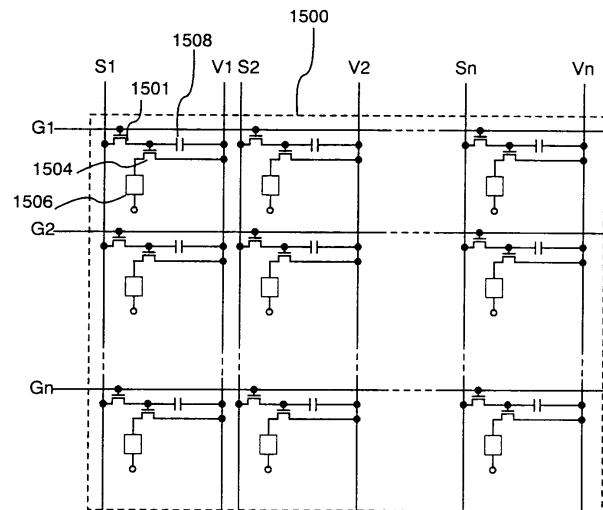

도 15는 EL 디스플레이 픽셀 부분의 구조를 도시한다. 게이트 신호가 입력되는 게이트 신호선들(G1 내지 Gn)은 각 픽셀들에 포함되는 스위칭 TFT(1501)의 게이트 전극에 접속된다. 더욱이, 각 픽셀들에 포함되는 스위칭 TFT(1501)의 소스 영역 또는 드레인 영역 중 하나는 소스 신호선들(또한 데이터 신호선들이라 칭하여지는)(S1 내지 Sn)에 접속되고, 다른 하나는 각각의 픽셀들에 포함되는 EL 구동 TFT(1504)의 게이트 전극 및 각각의 픽셀들에 포함되는 캐패시터(1508)에 각각 접속된다.

각각의 픽셀들에 포함되는 EL 구동 TFT(1504)의 소스 영역 및 드레인 영역 중 하나는 전원 공급선들(V1 내지 Vn)에 접속되고, 다른 하나는 EL 소자(1506)에 접속된다. 전원 공급선들(V1 내지 Vn)의 전위는 전원 전위라 칭하여진다. 전원 공급선들(V1 내지 Vn)의 전위는 각각의 픽셀들에 포함되는 캐패시터(1508)에 접속됨을 주목한다. 디지털 데이터 신호는 디지털 비디오 신호라 칭하여짐을 주목한다.

EL 소자(1506)는 양극 및 음극과, 그 사이에 제공된 EL층을 포함한다. 양극이 EL 구동 TFT(1504)의 소스 영역 및 드레인 영역에 접속된 경우, 즉 양극이 픽셀 전극인 경우, 반대 전극인 음극은 일정한 전위로 유지된다. 반대로, 음극이 EL 구동 TFT(1504)의 소스 영역 또는 드레인 영역에 접속된 경우, 즉 음극이 픽셀 전극인 경우, 반대 전극인 양극은 일정한 전위로 유지된다.

더욱이, 본 명세서에서, 반대 전극의 전위는 정상 전위(stationary potential)라 칭하여진다. 반대 전극에 정상 전위를 제공하는 전원은 정상 전원라 칭하여짐을 주목한다. 양극의 전위는 음극에 인가되는 전위 보다 더 높은 것이 바람직하다. 그러므로, 정상 전위는 반대 전극이 양극 또는 음극이라는 사실에 따라 변한다. 예를 들어, 반대 전극이 양극인 경우, 정상 전위는 전원 전위 보다 더 높게 설정되는 것이 바람직하다. 반대로, 반대 전극이 음극인 경우, 정상 전위는 전원 전위 보다 더 높게 설정되는 것이 바람직하다.

반대 전극의 정상 전위와 픽셀 전극의 전원 전위 사이의 전위차는 EL 구동 전압이고, 이 EL 구동 전압이 EL 층에 인가된다.

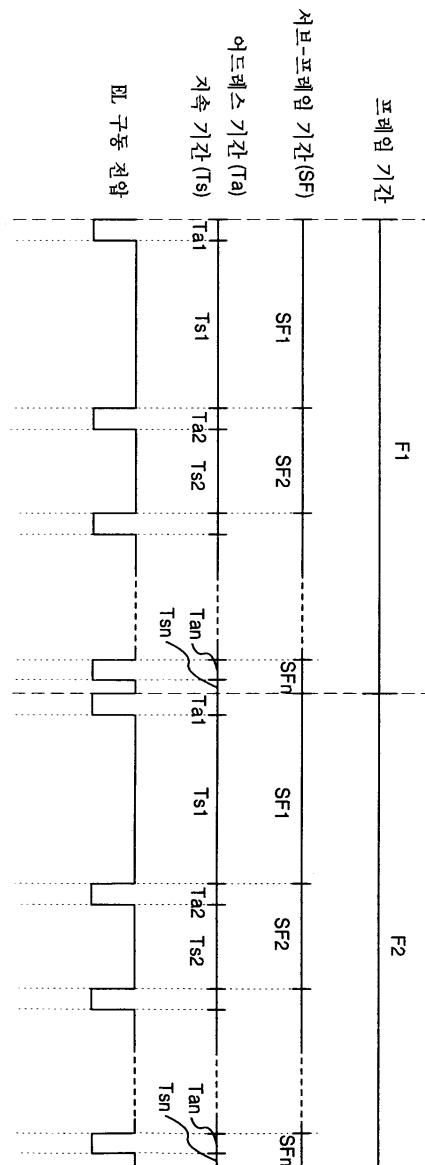

도 16은 종래의 EL 디스플레이에서 직류로 구동하는 디지털 스타일의 타이밍도를 도시한다. 맨 처음에, 1 프레임(frame) 기간은 n 개의 서브-프레임(sub-frame) 기간들(SF1 내지 SFn)로 나뉜다. 픽셀 부분의 모든 픽셀이 한 영상을 디스플레이하는 기간이 1 프레임 기간(F)이라 칭하여짐을 주목한다. 정상적인 EL 디스플레이에서는 발진 주파수가 60 Hz 이상인 프레임 기간이 제공되므로, 즉 1초당 60개 이상의 프레임 기간이 제공되므로, 1초에 60개 이상의 영상이 디스플레이된다. 1초에 디스플레이되는 영상의 수가 60개 이하이면, 플리커(flicker) 등과 같은 영상의 깜빡거림이 시각적으로 뚜렷해진다. 1 프레임 기간이 복수의 기간들로 더 나누어지는 기간은 서브-프레임 기간(sub-frame period)라 칭하여짐을 주목한다. 그레이 스케일 레벨들의 수가 증가하면, 1 프레임 기간의 분할수도 증가하고, 구동기 회로가 고주파수로 구동되어야 한다.

하나의 서브-프레임 기간은 어드레스 기간(Ta) 및 지속 기간(Ts)로 나뉜다. 어드레스 기간은 한 서브-프레임 기간 동안 모든 픽셀들에 데이터를 입력하는데 요구되는 시간이고, 지속 기간(또한 조명(lighting) 기간이라 칭하여지는)은 EL 소자가 밝혀지는 기간이다.

n개의 서브-프레임 기간들(SF1 내지 SFn) 각각에 포함되는 어드레스 기간들의 길이는 동일하다. 서브-프레임 기간들 (SF1 내지 SFn)에 포함되는 지속 기간들(Ts)은 각각 Ts1 내지 Ts<sub>n</sub>으로 설정된다.

지속 기간들의 길이는  $Ts1:Ts2:Ts3:\dots:Ts(n-1):Ts_n = 2^0:2^{-1}:2^{-2}:\dots:2^{-(n-2)}:2^{-(n-1)}$ 로 설정된다. 그러나, 지속 기간들 (SF1 내지 SFn)이 나타나도록 허용되는 순서는 임의의 것이다. 이러한 지속 기간들의 조합으로, 원하는 그레이 스케일 디스플레이가  $2^n$  그레이 스케일 레벨들 중에서 제공될 수 있다.

맨 처음에, 어드레스 기간에서, 전원 공급선들(V1 내지 V<sub>n</sub>)은 정상 전위와 같은 전위로 유지될 수 있다. 본 명세서에서, 디지털 구동 어드레스 기간의 전원 전위는 off 전원 전위라 칭하여진다. off 전원 전위의 높이는 EL 소자(1506)가 발광하지 않는 범위내에서 정상 전위와 동일한 레벨이어야 함을 주목한다. 이때, EL 구동 전압은 off EL 구동 전압이라 칭하여짐을 주목한다. OFF시 EL 구동 전압은 0 V인 것이 바람직하지만, 그 전압은 EL 소자(1506)가 발광하도록 허용하지 않는 범위이다.

이어서, 게이트 신호가 게이트 신호선(G1)에 입력되고, 게이트 신호선(G1)에 접속된 게이트 전극을 갖는 스위칭 TFT들 (1501)은 모두 on 상태가 된다.

그 후에, 게이트 신호선(G1)에 접속된 게이트 전극을 갖는 스위칭 TFT(1501)가 on인 상태에서, 디지털 데이터 신호는 순서대로 소스 신호선들(S1 내지 S<sub>n</sub>)에 입력된다. 디지털 데이터 신호는 "0" 또는 "1"의 정보를 갖고, "0" 및 "1"의 디지털 데이터 신호는 Hi 전압이나 Lo 전압을 갖는 신호를 칭한다. 이로써, 소스 신호선들(S1 내지 S<sub>n</sub>)에 입력된 디지털 데이터 신호는 ON 상태로 스위칭 TFT들(1501)을 통해 EL 구동 TFT들(1504)의 게이트 전극에 입력된다. 더욱이, 디지털 데이터 신호는 캐패시터(1508)에 입력되어 유지된다.

다음에는, 게이트 신호가 게이트 신호선(G2)에 입력되어, 게이트 신호선(G2)에 접속된 게이트 전극을 갖는 모든 스위칭 TFT들(1501)이 on 상태가 된다. 게이트 신호선(G2)에 접속된 게이트 전극을 갖는 스위칭 TFT(1501)가 on인 상태에서, 디지털 데이터 신호는 순서대로 소스 신호선들(S1 내지 S<sub>n</sub>)에 입력된다. 소스 신호선들(S1 내지 S<sub>n</sub>)에 입력된 디지털 신호는 스위칭 TFT(1501)를 통해 EL 구동 TFT들(1504)의 게이트 전극에 입력된다. 더욱이, 디지털 데이터 신호는 또한 캐패시터(1508)에 입력되어 유지된다.

상기 동작이 반복되어, 디지털 데이터 신호는 모든 픽셀들에 입력된다. 디지털 데이터 신호가 모든 픽셀들에 입력되는 기간은 어드레스 기간이다.

어드레스 기간이 완료됨과 동시에 지속 기간이 시작된다. 지속 기간이 시작되면, 전원 공급선들(V1 내지 V<sub>n</sub>)의 전위는 OFF 전원 전위에서 ON 전원 전위로 변한다. 본 명세서에서, 디지털 구동의 경우, 지속 기간의 전원 전위는 전원 전위라 칭하여진다. on 전원 전위와 정상 전위 사이의 전위차는 EL 소자가 발광하는 전위차이어야 한다. 이 전위차는 EL 구동 전위라 칭하여짐을 주목한다. off 전원 전위와 on 전원 전위는 일반적으로 전원 전위라 칭하여진다. 더욱이, on EL 구동 전압 및 off EL 구동 전압은 일반적으로 EL 구동 전압이라 칭하여진다.

지속 기간에서, 스위칭 TFT들(1501)은 off 상태로 된다. 이때, 캐패시터(1508)에 유지되는 디지털 데이터 신호는 EL 구동 TFT들(1504)의 게이트 전극에 입력된다.

디지털 데이터가 "0"의 정보를 갖는 경우, EL 구동 TFT(1504)는 off 상태가 되므로, EL 소자(1506)의 픽셀 전극은 off 전력 전위로 유지된다. 결과적으로, "0"의 정보를 갖는 디지털 데이터 신호가 인가되는 픽셀에 포함되는 EL 소자는 발광하지 않는다.

한편, 디지털 데이터가 "1"의 정보를 갖는 경우, EL 구동 TFT(1504)는 on 상태로 되므로, EL 소자(1506)의 픽셀 전극은 on 전원 전위가 된다. 결과적으로, "1"의 정보를 갖는 디지털 데이터 신호가 인가되는 픽셀에 포함되는 EL 소자(1506)는 발광한다.

모든 스위칭 TFT(1501)가 off 상태인 기간은 지속 기간이다.

EL 소자는 기간들(Ts1 내지 Ts<sub>n</sub>) 중 임의의 기간에서 발광한다. Ts<sub>n</sub>의 기간에서는, 소정의 EL 소자가 발광하도록 허용된다(소정의 픽셀은 밝혀진다).

다음에는, 어드레스 기간이 다시 나타난다. 디지털 데이터 신호가 모든 픽셀들에 입력된 이후에는, 지속 기간이 나타난다. 이때, 지속 기간들(Ts1 내지 Ts<sub>(n-1)</sub>) 중 임의의 것이 나타난다. 여기서는 Ts<sub>(n-1)</sub>이 나타나므로, Ts<sub>(n-1)</sub> 기간에서 소정의 픽셀이 밝혀지도록 허용된다.

이어서, 나머지 n-2개의 서브-프레임들에서 유사한 동작이 반복되고, 지속 기간들(Ts<sub>(n-2)</sub>, Ts<sub>(n-3)</sub>, ..., Ts1)이 차례로 나타나서, 서브-프레임에서 소정의 픽셀이 밝혀지도록 허용된다.

n개 서브-프레임 기간들이 나타날 때, 1 프레임 기간이 완료된다. 이때, 픽셀의 그레이 스케일 레벨은 1 프레임 기간에서 픽셀이 밝혀진 지속 기간, 즉 "1"의 정보를 갖는 디지털 데이터 신호가 픽셀에 적용된 어드레스 기간 직후의 지속 기간의 길이를 합산함으로써 결정될 수 있다.

예를 들어, n=8인 경우, 모든 지속 기간들에서 발광하는 픽셀의 휘도(luminance)가 100%로 설정될 때, 픽셀이 Ts1 및 Ts2에서 발광하는 경우에는 75%의 휘도가 나타내질 수 있다. Ts3, Ts5, 및 Ts8이 선택되는 경우에는, 16%의 휘도가 나타내질 수 있다.

이 방식으로, 종래의 EL 디스플레이는 직류로 구동되고, EL층에 인가되는 EL 구동 전압은 항상 똑같은 극성(polarity)을 갖는다.

그러나, "TSUTSUI.T, Jpn.J.Appl.Phys.Part2 VOL.37, NO. 11B, p. L1406-L1408, 1998"에서 제시된 바와 같이, EL 소자의 전류-전압 특성의 저하는 각각의 기간 동안 EL 소자에 반대 극성을 갖는 EL 구동 전압을 인가함으로써 개선되는 사실을 사용하는 EL 디스플레이 구동 방법에 대해, 또한 그 구동 방법을 사용하는 EL 디스플레이에 대해, 구체적인 제안이 이루어지지 않았다.

### 발명이 이루고자 하는 기술적 과제

따라서, EL 소자의 수명을 연장시키기 위해, 각각의 한정된 기간 동안 EL 소자에 반대 극성을 갖는 EL 구동 전압을 인가함으로써 디스플레이를 제공하도록 EL 디스플레이를 구동하는 방법, 및 그 구동 방법을 사용하는 EL 디스플레이의 제작에 대한 제안이 기대된다. 특별히, 교류 구동으로 디스플레이를 제공하는 능동 매트릭스형 EL 디스플레이의 제작이 기대된다.

### 발명의 구성

본 발명은, EL 디스플레이의 구동시, EL 소자에 포함되는 제 1 전극을 일정한 전위(정상 전위)로 유지하고 전원 공급선의 전위(전원 전위)에는 제 2 극성(polarity)을 유지한다. 그 후에, 각각의 한정된 기간들 동안, 정상 전압은 고정되고 전원 전

위의 높이는 정상 전위와 전원 전위간의 차인 EL 구동 전압의 극성이 반대가 되도록 변화된다. 예를 들면, 정상 전위는  $V_T$ 로 설정되고, 전원 전위는  $V_D$ 로 설정되고, 또한 EL 구동 전압이 특정 기간에서  $V_T - V_D = \Delta V$ 로 설정될 때, 정상 전위는  $V_T$ 로 설정되고, 전원 전위는  $V_D'$ 로 설정되고, 또한 EL 구동 전압은  $V_T - V_D' = -\Delta V$ 로 설정된다.

디지털 스타일 구동기 회로에 의한 시분할 그레이 스케일 디스플레이의 경우, EL 구동 전압의 극성은 각각의 프레임 기간 동안 반대로 변화되는데 반해, EL 구동 전압의 극성은 각각의 서브-프레임(sub-frame) 기간 동안 반대로 변화될 수 있다.

아날로그 스타일 구동기 회로의 경우, EL 구동 전압은 각각의 프레임 기간 동안 반대 극성으로 변화된다.

EL 소자가 특정한 극성을 갖는 EL 구동 전압의 적용에 의해 발광하는 경우에 EL 소자는 다이오드이기 때문에, EL 소자는 반대 극성을 갖는 EL 구동 전압의 적용에 의해서 발광하지 않음을 주목한다.

이러한 구조로, 반대 극성을 갖는 EL 구동 전압은 각각의 한정된 기간 동안 EL 소자에 적용된다. 결과적으로, EL 소자의 전류-전압 특성의 저하가 개선되므로, EL 소자의 수명은 종래 구동 방법과 비교해 연장될 수 있다.

더욱이, 상술된 바와 같이, 영상이 각각의 1 프레임 기간 동안 디스플레이되는 경우에는 관찰자들의 눈에 깜빡거림(flicker)을 생기게 한다.

결과적으로, 본 발명에서 EL 디스플레이는 직류 구동시 관찰자의 눈에 깜빡거림을 발생하지 않는 주파수 보다 2배 더 큰 주파수에서 교류로 구동되는 것이 바람직하다. 다시 말하면, 1초에 120개 이상의 프레임 기간들이 제공되어 60개 이상의 영상들이 디스플레이되는 것이 바람직하다. 상기 구조에서, 교류에 의한 깜빡거림이 방지된다.

더욱이, 본 발명의 교류 구동은 능동 매트릭스형 EL 디스플레이 디바이스 뿐만 아니라 수동형(passive-type) EL 디스플레이 디바이스에도 적용될 수 있다.

본 발명의 구조는 이후 도시된다.

본 발명에 따라, 복수의 EL 소자들을 포함하는 복수의 픽셀들(pixel)을 포함하는 EL 디스플레이 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 1 프레임(frame) 기간에서 상기 복수의 EL 소자들이 발광하는 시간 기간을 제어함으로써 그레이 스케일(gray scale) 디스플레이를 제공하고,

복수의 EL 소자들은 제 1 전극 및 제 2 EL 소자를 갖고,

제 1 전극은 일정한 전위로 유지되고,

제 2 전극의 전위가, 상기 제 1 및 제 2 전극들에 인가되는 전위들간의 차이인 EL 구동 전압의 극성이 각각 1 프레임 기간 동안 반전되는 방식으로 변화하는 것을 특징으로 한다.

본 발명에 따라, 복수의 EL 소자들을 포함하는 복수의 픽셀들을 갖는 전기 광학 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 1 프레임 기간에서 상기 복수의 EL 소자들이 상기 복수의 포함되는 서브-프레임(sub-frame) 기간들 중에서 발광하는 상기 서브-프레임 기간들의 길이를 합을 제어함으로써 그레이 스케일 디스플레이를 제공하고,

복수의 EL 소자들은 제 1 전극 및 제 2 전극을 갖고,

제 1 전극은 일정한 전위로 유지되고,

제 1 및 제 2 전극들에 인가되는 전위들간의 차이인 EL 구동 전압의 극성이 각각 하나의 서브-프레임 기간 동안 반전되는 방식으로 제 2 전극의 전위가 변하는 것을 특징으로 하는 전기 광학 디바이스가 제공된다.

본 발명에 따라, 복수의 EL 소자들, 복수의 EL 소자들의 발광을 제어하는 복수의 EL 구동 TFT들, 및 복수의 EL 구동 TFT들의 구동을 제어하는 복수의 스위칭 TFT들을 포함하는, 복수의 픽셀들을 포함하는 EL 디스플레이 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 1 프레임 기간에서 상기 복수의 EL 소자들이 발광하는 시간 기간을 제어함으로써 그레이 스키일을 제공하고,

복수의 EL 소자들은 제 1 전극 및 제 2 EL 소자를 갖고,

제 1 전극이 일정한 전위로 유지되고,

제 2 전극의 전위는 제 1 및 제 2 전극들에 인가되는 전위들간의 차이인 EL 구동 전압의 극성이 각각 1 프레임 기간 동안 반전되는 방식으로 변하는 것을 특징으로 하는 EL 디스플레이 디바이스가 제공된다.

본 발명에 따라, 복수의 EL 소자들, 복수의 EL 소자들의 발광을 제어하는 복수의 EL 구동 TFT들, 및 복수의 EL 구동 TFT들의 구동을 제어하는 복수의 스위칭 TFT들을 포함하는, 복수의 픽셀들을 포함하는 EL 디스플레이 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 1 프레임 기간에서 상기 복수의 EL 소자들이 상기 복수의 포함되는 서브-프레임 기간들 중에서 발광하는 상기 서브-프레임 기간들의 길이들 합을 제어함으로써 그레이 스키일 디스플레이를 제공하고,

복수의 EL 소자들이 제 1 전극 및 제 2 전극을 갖고,

제 1 전극이 일정한 전위로 유지되고,

제 2 전극의 전위는 제 1 및 제 2 전극들에 인가되는 전위들간의 차이인 EL 구동 전압의 극성이 각각 1 프레임 기간 동안 반전되는 방식으로 변하는 것을 특징으로 하는 EL 디스플레이 디바이스가 제공된다.

본 발명에 따라, 복수의 EL 소자들을 포함하는 복수의 픽셀들을 갖는 EL 디스플레이 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 1 프레임 기간에서 상기 복수의 EL 소자들이 발광하는 시간 기간을 제어함으로써 그레이 스키일 디스플레이를 제공하고,

복수의 EL 소자들은 제 1 전극 및 제 2 EL 소자를 갖고,

제 1 전극이 일정한 전위로 유지되고,

제 2 전극의 전위는 제 1 및 제 2 전극들에 인가되는 전위들간의 차이인 EL 구동 전압의 극성이 각각 1 프레임 기간 동안 반전되는 방식으로 변화하고,

상기 복수의 픽셀들 중 인접하는 픽셀들은 제 2 전극에 인가되는 전압을 공급하는 전원 공급선을 공유하는 것을 특징으로 하는 EL 디스플레이 디바이스가 제공된다.

본 발명에 따라, 복수의 EL 소자들을 포함하는 복수의 픽셀들을 갖는 EL 디스플레이 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 1 프레임 기간에서 상기 복수의 EL 소자들이 상기 복수의 포함되는 서브-프레임 기간들 중에서 발광하는 상기 서브-프레임 기간들의 길이들 합을 제어함으로써 그레이 스키일 디스플레이를 제공하고,

복수의 EL 소자들은 제 1 전극 및 제 2 전극을 갖고,

제 1 전극은 일정한 전위로 유지되고,

제 2 전극의 전위는 제 1 및 제 2 전극들에 인가되는 전위들간의 차이인 EL 구동 전압의 극성이 각각 1 프레임 기간 동안 반전되는 방식으로 변화하고,

상기 복수의 픽셀들 중 인접하는 픽셀들은 제 2 전극에 인가되는 전압을 공급하는 전원 공급선을 공유하는 것을 특징으로 하는, EL 디스플레이 디바이스가 제공된다.

본 발명에 따라, 복수의 EL 소자들, 복수의 EL 소자들의 발광을 제어하는 복수의 EL 구동 TFT들, 및 복수의 EL 구동 TFT들의 구동을 제어하는 복수의 스위칭 TFT들을 포함하는, 복수의 픽셀들을 포함하는 EL 디스플레이 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 1 프레임 기간에서 상기 복수의 EL 소자들이 발광하는 시간 기간을 제어함으로써 그레이스케일을 제공하고,

복수의 EL 소자들은 제 1 전극 및 제 2 EL 소자를 갖고,

제 1 전극은 일정한 전위로 유지되고,

제 2 전극의 전위는 제 1 및 제 2 전극들에 인가되는 전위들간의 차이인 EL 구동 전압의 극성이 각각 1 프레임 기간 동안 반전되는 방식으로 변화하고,

제 2 전극에 인가되는 전압을 공급하는 전원 공급선은 복수의 픽셀들 중 인접한 픽셀들 사이에서 공유되는 것을 특징으로 하는 EL 디스플레이 디바이스가 제공된다.

본 발명에 따라, 복수의 EL 소자들, 복수의 EL 소자들의 발광을 제어하는 복수의 EL 구동 TFT들, 및 복수의 EL 구동 TFT들의 구동을 제어하는 복수의 스위칭 TFT들을 포함하는, 복수의 픽셀들을 포함하는 EL 디스플레이 디바이스에 있어서,

상기 EL 디스플레이 디바이스는 1 프레임 기간에서 상기 복수의 EL 소자들이 상기 복수의 포함되는 서브-프레임 기간들 중에서 발광하는 상기 서브-프레임 기간들의 길이들 합을 제어함으로써 그레이스케일 디스플레이를 제공하고,

복수의 EL 소자들은 제 1 전극 및 제 2 전극을 갖고,

제 1 전극은 일정한 전위로 유지되고,

제 2 전극의 전위는 제 1 및 제 2 전극들에 인가되는 전위들간의 차이인 EL 구동 전압의 극성이 각각 1 프레임 기간 동안 반전되는 방식으로 변화하고,

상기 복수의 픽셀들 중 인접하는 픽셀들은 제 2 전극에 인가되는 전압을 공급하는 전원 공급선을 공유하는 것을 특징으로 하는, EL 디스플레이 디바이스가 제공된다.

EL 구동 TFT들 및 스위칭 TFT들은 n-형 채널 TFT 또는 p형 채널 TFT를 포함한다.

복수의 EL 소자들의 발광은 스위칭 TFT들에 입력되는 디지털 데이터 신호로 제어될 수 있다.

1 프레임 기간은 1/120 sec 이하가다.

본 발명에 따라, 복수의 픽셀들을 갖는 EL 디스플레이 디바이스에 있어서,

복수의 EL 소자들,

복수의 EL 소자들의 발광을 제어하는 복수의 EL 구동 TFT들, 및

복수의 EL 구동 TFT의 구동을 제어하는 복수의 스위칭 TFT들을 포함하고,

상기 EL 디스플레이 디바이스는 아날로그 비디오 신호를 스위칭 TFT의 소스 영역에 입력함으로써 그레이 스케일 디스플레이를 제공하고,

복수의 EL 소자들은 제 1 전극 및 제 2 전극을 갖고,

제 1 전극은 일정한 전위로 유지되고,

제 2 전극은 각각 1 프레임 기간 동안 제 1 전극에 인가되는 전압을 참고하여 반대 극성을 갖는 전압으로 유지되는 것을 특징으로 한다.

본 발명에 따라, 복수의 픽셀들을 갖는 EL 디스플레이 디바이스에 있어서,

복수의 EL 소자들,

복수의 EL 소자들의 발광을 제어하는 복수의 EL 구동 TFT들, 및

복수의 EL 구동 TFT들의 구동을 제어하는 복수의 스위칭 TFT들을 포함하고,

EL 디스플레이 디바이스는 아날로그 비디오 신호를 스위칭 TFT의 소스 영역에 입력함으로써 그레이 스케일 디스플레이를 제공하고,

복수의 EL 소자들은 제 1 전극 및 제 2 전극을 갖고,

제 1 전극은 일정한 전위로 유지되고,

제 2 전극은 각각 1 프레임 기간 동안 제 1 전극에 인가되는 전압을 참고하여 반대 극성을 갖는 전압으로 유지되고,

복수의 픽셀들 중 인접한 픽셀들은 제 2 전극에 인가되는 전압을 공급하는 전원 공급선을 공유하는 것을 특징으로 하는 EL 디스플레이 디바이스가 제공된다.

EL 구동 TFT 및 스위칭 TFT는 n형 채널 TFT 또는 p형 채널 TFT를 포함한다.

1 프레임 기간은 1/120 sec 및 미만이다.

복수의 EL 소자들이 갖는 EL층은 저분자 유기 물질 또는 폴리머(polymer) 유기 물질을 포함한다.

저분자 유기 물질은 Alq3(tris-8-quinonolite-aluminum) 또는 TPD(triphenylamine derivative)를 포함한다.

폴리머 유기 물질은 PPV(polyphenyleine vynyleine), PVK(polyvinyl-caracole) 또는 폴리카보네이트(polycarbonate)를 포함한다.

EL 디스플레이 디바이스가 사용되는 것을 특징으로 하는 컴퓨터가 제공된다.

EL 디스플레이 디바이스가 사용되는 것을 특징으로 하는 비디오 카메라가 제공된다.

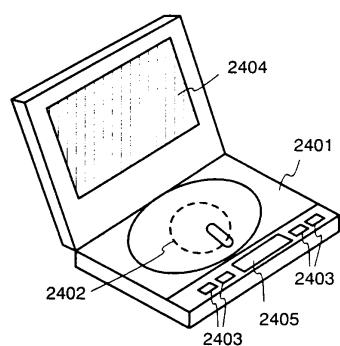

EL 디스플레이 디바이스가 사용되는 것을 특징으로 하는 DVD 플레이어가 제공된다.

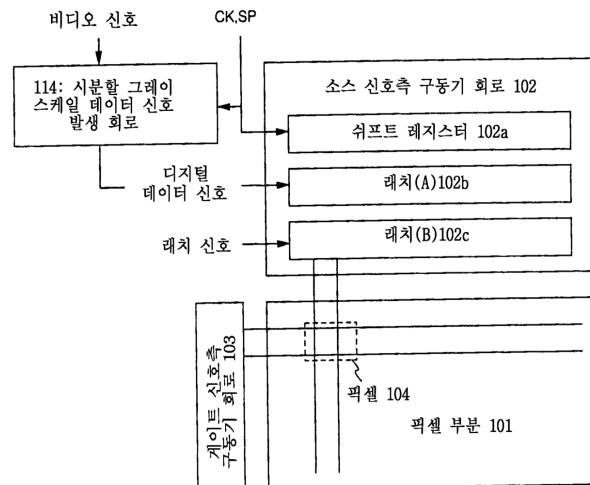

본 발명의 구조는 본 발명에 따른 회로구조의 예를 도시하는 디지털 구동 스타일 시분할 그레이 스케일 디스플레이를 제공하는 EL 디스플레이의 예를 사용해 설명된다. 도 1은 본 발명에 따른 회로 구조의 예를 도시한다.

도 1의 EL 디스플레이에는 기판 상에 TFT로 형성된 픽셀 부분(101), 픽셀 부분(101) 주위에 배열된 소스 신호측 구동기 회로(102), 및 게이트 신호측 구동기 회로(103)를 갖는다. 본 실시예에서는 EL 디스플레이가 각각 소스 신호측 구동기 회로 및 게이트 신호측 구동기 회로를 가짐을 주목한다. 그러나, 본 발명에서는 소스 신호측 구동기 회로가 2개일 수 있다. 더욱이, 게이트 신호측 구동기 회로가 또한 2개일 수 있다.

소스 신호측 구동기 회로(102)는 기본적으로 쉬프트 레지스터(102a), 래치(latch)(A)(102b), 및 래치(B)(102c)를 포함한다. 더욱이, 클럭 신호(CK) 및 시작 펄스(SP)는 쉬프트 레지스터(102a)에 입력된다. 디지털 데이터 신호는 래치(A)(102b)로 입력된다. 래치 신호는 래치(B)(102c)로 입력된다.

또, 도시되지 않았지만, 게이트 신호측 구동기 회로(103)는 쉬프트 레지스터 및 버퍼를 갖는다. 멀티플렉서가 버퍼의 출력 측에 제공될 수 있다.

픽셀 부분(101)에 입력된 디지털 데이터 신호는 시분할 그레이 스케일 데이터 신호 발생 회로(114)에서 형성된다. 이 회로에서는, 아날로그 신호 및 디지털 데이터 신호를 포함하는 비디오 신호(영상 정보를 포함하는 신호)가 시분할 그레이 스케일 디스플레이를 제공하기 위한 디지털 데이터 신호로 변환되고, 동시에 이는 시분할 그레이 스케일 디스플레이를 제공하는데 요구되는 타이밍 펄스 등을 발생하는 회로이다.

전형적으로, 시분할 그레이 스케일 데이터 신호 발생 회로(114)는 1 프레임 기간을  $n$ ( $n$ 은 2 이상의 정수) 비트의 그레이 스케일에 대응하는 복수의 서브-프레임(sub-frame) 기간으로 나누는 수단, 복수의 서브-프레임 기간에서 어드레스 기간 및 지속 기간을 선택하는 수단, 및 지속 기간의 길이를  $Ts1:Ts2:Ts3:\dots:Ts(n-1):Ts(n) = 2^0:2^{-1}:2^{-2}:\dots:2^{-(n-2)}:2^{-(n-1)}$ 로 설정하는 수단을 포함한다.

이때, 시분할 그레이 스케일 데이터 신호 발생 회로(114)는 본 발명에 따른 EL 디스플레이의 외부측 부분에 제공될 수 있다. 이러한 경우, 회로는 거기에 형성된 디지털 데이터 신호가 본 발명에 따른 EL 디스플레이에 입력되는 방식으로 구성된다. 이 경우, 디스플레이로 본 발명에 따른 EL 디스플레이를 갖는 전자 디바이스(EL 디스플레이 디바이스)는 본 발명의 EL 디스플레이와 시분할 그레이 스케일 데이터 신호 발생 회로를 분리된(separate) 구성성분으로 포함한다.

더욱이, 시분할 그레이 스케일 데이터 신호 발생 회로(114)는 IC 칩 등의 형태로 본 발명에 따른 EL 디스플레이에 패키지(package)화될 수 있다. 이러한 경우, 회로는 IC 칩상에 형성된 디지털 데이터 신호가 본 발명에 따른 EL 디스플레이에 입력되는 방식으로 구성된다. 이 경우, 본 발명에서 디스플레이로 EL 디스플레이를 갖는 전자 디바이스는 시분할 그레이 스케일 데이터 신호 발생 회로를 포함하는 IC 칩을 하나의 구성성분으로 패키지화하는 EL 디스플레이를 포함한다.

더욱이, 마지막으로, 시분할 그레이 스케일 데이터 신호 발생 회로(114)는 픽셀 부분(101), 소스 신호측 구동기 회로(102), 및 게이트 신호측 구동기 회로(103)와 똑같은 기판 상에 TFT로 형성될 수 있다. 이 경우, 영상 정보를 포함하는 비디오 신호가 EL 디스플레이에 입력될 때, 비디오 신호는 모두 기판 상에서 처리될 수 있다. 이 경우, 시분할 그레이 스케일 데이터 신호 발생 회로는 폴리실리콘막이 활성층으로 동작하는 TFT로 형성될 수 있다. 더욱이, 이 경우, 디스플레이로 EL 디스플레이를 갖는 전자 디바이스는 시분할 그레이 스케일 데이터 신호 발생 회로가 EL 디스플레이 자체에 포함되어, 전자 디바이스의 소형화를 시도할 수 있게 만든다.

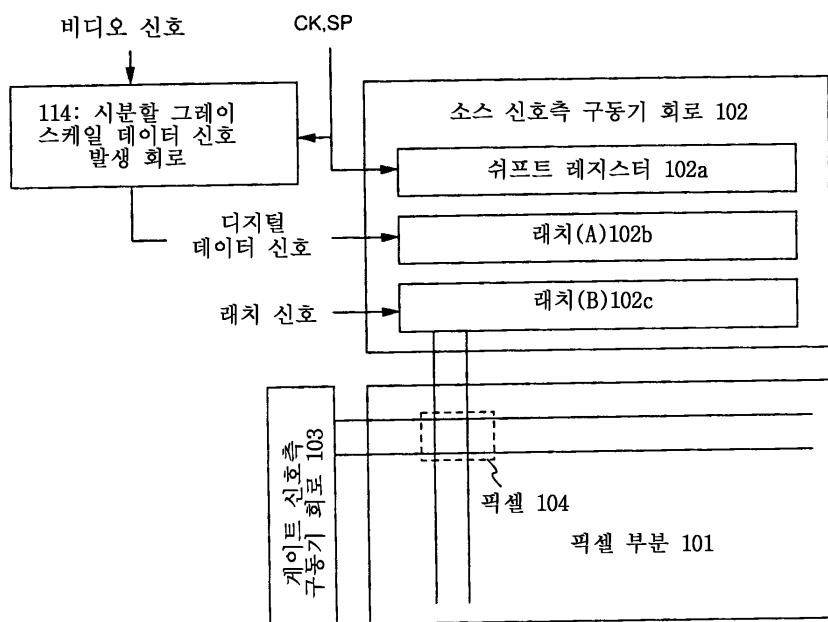

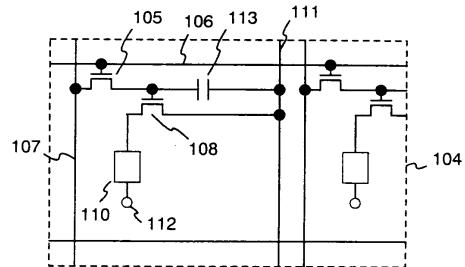

픽셀 부분(101)에는 복수의 픽셀(104)이 매트릭스형의 구성으로 배열된다. 도 2a는 픽셀(104)의 확대도를 도시한다. 도 2a에서, 참고번호(105)는 스위칭 TFT를 나타낸다. 스위칭 TFT(105)의 게이트 전극은 게이트 신호를 입력하는 게이트 신호선(106)에 연결된다. 스위칭 TFT(105)의 소스 영역 및 드레인 영역은 소스 영역 또는 드레인 영역 중 하나가 디지털 데이터 신호를 입력하는 소스 신호선(107)에 연결되고, 다른 하나는 EL 구동 TFT(108)의 게이트 전극 및 각 픽셀이 각각 갖는 캐패시터(113)에 연결되는 방식으로 구성된다.

부가하여, EL 구동 TFT(108)의 소스 영역 및 드레인 영역 중 하나는 전원 공급선(111)에 연결되고, 다른 하나는 EL 소자(110)에 연결된다. 전원 공급선(111)은 캐패시터(113)에 연결된다. 스위칭 TFT(105)가 비선택 모드(off 상태)일 때, 캐패시터(113)는 EL 구동 TFT(108)의 게이트 전압을 유지하도록 제공된다.

EL 소자(110)는 양극 및 음극과, 양극 및 음극 사이에 제공된 EL층을 구비한다. 양극이 EL 구동 TFT(110)의 소스 영역 또는 드레인 영역에 연결되는 경우, 즉 양극이 픽셀 전극인 경우, 음극은 반대 전극이다. 반대로, 음극이 EL 구동 TFT(110)의 소스 영역 또는 드레인 영역에 연결되는 경우, 즉 음극이 픽셀 전극인 경우, 양극은 반대 전극이다.

전원 공급선(111)은 전원 전위에 연결된다. 본 실시예에서, 전원 전위는 항상 일정한 전위로 유지된다.

레지스터는 EL 구동 TFT(108)의 소스 영역 또는 드레인 영역과 EL 소자(110) 사이에 제공될 수 있음을 주목한다. 레지스터를 제공함으로써, EL 구동 TFT에서 EL 소자로 공급되는 전류량이 제어되고, 그에 의해 EL 구동 TFT(108) 특성에 대한 불균형(disparity)의 영향을 방지하게 된다. 레지스터가 EL 구동 TFT의 on 저항에 대한 저항값 보다 충분히 더 큰 저항값을 나타내는 소자이므로, 그 구조는 어떠한 방법으로도 제한되지 않는다. on 레지스터의 저항은 TFT의 드레인 전압을 TFT가 on 상태일 때 흐르는 드레인 전류로 나눔으로써 얻어지는 값임을 주목한다. 레지스터의 저항값은  $1\text{ k}\Omega$  내지  $50\text{ M}\Omega$ 의 범위에서 선택된다(바람직하게  $10\text{ k}\Omega$  내지  $10\text{ M}\Omega$  이상, 보다 바람직하게  $50\text{ k}\Omega$  내지  $1\text{ M}\Omega$ ). 레지스터로 높은 저항값을 갖는 반도체층을 사용하는 것은 레지스터의 형성을 용이하게 하여, 이러한 반도체층의 사용이 바람직해진다.

다음에는 도 2b 및 도 3을 참고로 본 발명에 따른 교류의 구동이 설명된다. 여기서는  $2^n$  그레이 스케일 전칼라(full color) 시분할 그레이 스케일 디스플레이가 n-비트 디지털 구동 스타일에 의해 제공되는 경우가 설명된다.

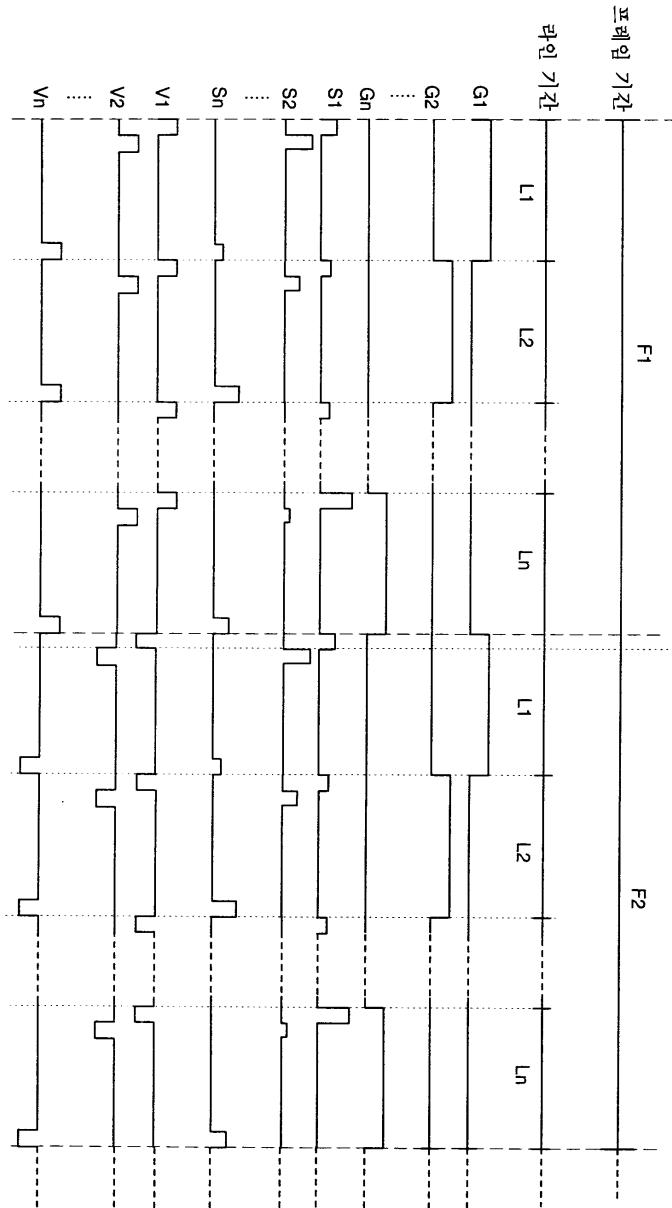

도 2b는 본 발명에 따른 EL 디스플레이에서 픽셀 부분의 구조를 도시한다. 게이트 신호선(G1 내지 Gn)은 각 픽셀에 포함되는 스위칭 TFT의 게이트 전극에 연결된다. 각 픽셀에 포함되는 스위칭 TFT의 소스 영역 또는 드레인 영역 중 하나는 소스 신호선(S1 내지 Sn)에 연결되고, 다른 하나는 EL 구동 TFT의 게이트 전극과 캐패시터에 연결된다. 더욱이, EL 구동 TFT의 소스 영역 및 드레인 영역 중 하나는 전원 공급선(V1 내지 Vn)에 연결되고, 다른 하나는 각 픽셀에 포함되는 EL 소자에 연결된다. 전원 공급선(V1 내지 Vn)은 또한 각 픽셀에 포함되는 캐패시터에 연결된다.

도 3은 도 2a에 도시된 EL 디스플레이의 타이밍도를 도시한다. 맨 처음에, 1 프레임 기간(F)은 n개의 서브-프레임 기간(SF1 내지 SFn)으로 나뉜다. 픽셀 부분 내의 모든 픽셀이 한 영상을 디스플레이하는 포화이 1 프레임 포화이라 칭하여짐을 주목한다. 본 발명에 따른 EL 디스플레이에서는 1초에 120개 이상의 프레임 포화이 제공되어, 1초에 60개 이상의 영상이 디스플레이되는 것이 바람직하다.

1초에 디스플레이되는 영상의 수가 120개 이하일 때는 플리커(flicker) 등과 같은 영상의 깜빡거림이 시각적으로 뚜렷해진다.

1 프레임 포화이 더 나뉘는 복수의 포화은 서브-프레임 포화이라 칭하여짐을 주목한다. 그레이 스케일 레벨의 수가 증가됨에 따라, 1 프레임 포화의 분할수가 증가되고, 구동기 회로가 고주파수에서 구동되어야 한다.

한 서브-프레임 포화은 어드레스 포화(Ta) 및 지속(sustain) 포화(Ts)로 나뉜다. 어드레스 포화은 모든 픽셀에 데이터를 입력하는데 요구되는 시간을 칭하고, 지속 기간(또는 조명(lighting) 기간이라 칭하여지는)은 디스플레이가 제공되는 기간을 칭한다.

n개의 서브-프레임 기간들(SF1 내지 SFn)에 포함되는 어드레스 기간들(Ta1 내지 Tan)의 길이는 각각 모두 동일하다. 서브-프레임들(SF1 내지 SFn)에 포함되는 지속 기간(Ts)은 각각 Ts1 내지 Tsn으로 설정된다.

지속 기간의 길이는  $Ts1:Ts2:Ts3:\dots:Ts(n-1):Tsn = 2^0:2^{-1}:2^{-2}:\dots:2^{-(n-2)}:2^{-(n-1)}$ 로 설정된다. 그러나, SF1 내지 SFn이 나타나도록 허용되는 순서는 임의적이다. 이러한 지속 기간의 조합으로, 원하는 그레이 스케일 디스플레이가  $2^n$  그레이 스케일 레벨 중에서 제공될 수 있다.

맨 처음에, 어드레스 기간에서 반대 전극은 전원 전위와 같은 전위의 정상 전위로 유지된다. 본 명세서에서, 디지털 구동의 어드레스 기간에서 정상 전위는 off 정상 전위라 칭하여진다. off 정상 전위의 높이는 EL 소자가 발광하지 않는 범위내에서 전원 전위의 높이와 똑같음을 주목한다. 이때, EL 구동 전압은 off EL 구동 전압이라 칭하여짐을 주목한다. 이상적으로, off EL 구동 전압은 0 V인 것이 바람직하지만, 전압은 EL 소자가 발광하지 않는 레벨에 있다.

게이트 신호는 게이트 신호선(G1)에 입력되고, 게이트 신호선(G1)에 연결된 게이트 전극을 갖는 모든 스위칭 TFT는 on 상태로 된다.

게이트 신호선(G1)에 연결된 게이트 전극을 갖는 스위칭 TFT가 on으로 된 상태에서, 디지털 데이터 신호는 동시에 모든 소스 신호선(S1 내지 Sn)에 입력된다. 디지털 데이터 신호는 "0" 또는 "1"의 정보를 갖는다. "0" 또는 "1"의 디지털 데이터

신호는 Hi 또는 Lo의 전압을 갖는 신호를 칭한다. 이어서, 소스 신호선(S1 내지 Sn)에 입력된 디지털 데이터 신호는 on 상태에서 스위칭 TFT를 통해 EL 구동 TFT의 게이트 전극에 입력된다. 더욱이, 디지털 데이터 신호는 또한 캐패시터에 연결되어 유지된다.

다음에는 게이트 신호가 게이트 신호선(G2)에 연결되어, 게이트 신호선(G2)에 연결된 게이트 전극을 갖는 모든 스위칭 TFT가 on으로 되는 상태가 발생된다. 이때, 게이트 신호선(G2)에 연결된 게이트 전극을 갖는 스위칭 TFT가 on으로 되는 상태에서, 디지털 데이터 신호는 동시에 모든 소스 신호선(S1 내지 Sn)에 입력된다. 소스 신호선(S1 내지 Sn)에 입력된 디지털 데이터 신호는 스위칭 TFT를 통해 EL 구동 TFT의 게이트 전극에 입력된다. 그외에, 디지털 데이터 신호는 또한 캐패시터에 입력되어 유지된다.

상기 동작이 반복되어 디지털 데이터 신호가 모든 픽셀에 입력된다. 디지털 데이터 신호가 모든 픽셀에 입력되는 기간이 어드레스 기간이다.

어드레스 기간이 완료됨과 동시에, 지속 기간이 시작된다. 지속 기간이 시작될 때, 반대 전극의 전위는 off 정상 전위에서 on 정상 전위로 변한다. 본 명세서에서, 디지털 구동 지속 기간의 정상 전위는 on 정상 전위라 칭하여진다. on 정상 전위는 EL 소자가 발광하는 정도까지 전원 전위와 전위차를 갖는다. 이 전위차는 on EL 구동 전압이라 칭하여짐을 주목한다.

이어서, 스위칭 TFT는 off 상태로 되고, 캐패시터에 유지되는 디지털 데이터 신호는 EL 구동 TFT의 게이트 전극에 입력된다.

실시예의 형태에서, 디지털 데이터 신호가 "0"의 정보를 갖는 경우에, EL 구동 TFT는 off 상태로 되고, EL 소자의 픽셀 전극은 off 정상 전위로 유지된다. 결과적으로, "0"의 정보를 갖는 디지털 데이터 신호가 인가되는 픽셀에 포함되는 EL 소자는 발광하지 않는다.

반대로, 디지털 데이터 신호가 "1"의 정보를 갖는 경우에, EL 구동 TFT는 on 상태로 되므로, 전원 전위가 EL 소자의 픽셀 전극에 주어진다. 결과적으로, "1"의 정보를 갖는 디지털 데이터 신호가 인가되는 픽셀에 포함되는 EL 소자는 발광한다.

모든 스위칭 TFT들이 off 상태인 기간은 지속 기간이다.

EL 소자가 발광하도록(픽셀이 밝혀지도록) 허용되는 기간은 Ts1 내지 Ts<sub>n</sub> 중 임의의 기간이다. 여기서는 소정의 픽셀이 Ts<sub>n</sub>의 기간에 밝혀진다고 가정한다.

다음에는 어드레스 기간이 다시 나타나고, 데이터 신호가 모든 픽셀에 입력되면 지속 기간이 나타난다. 이때, 지속 기간 Ts1 내지 Ts<sub>(n-1)</sub> 중 임의의 것이 나타난다. 여기서, 소정의 픽셀은 Ts<sub>(n-1)</sub>의 기간에 밝혀지도록 허용된다고 가정한다.

이후에는 나머지 n-2개의 서브-프레임에 대해 유사한 동작이 반복되므로, 지속 기간 Ts<sub>(n-2)</sub>, Ts<sub>(n-3)</sub>, ..., Ts1가 설정되고 소정의 픽셀이 각 서브-프레임에 밝혀진다고 가정한다.

n개의 서브-프레임 기간이 나타나면, 1 프레임 기간이 완료된다. 이때, 픽셀이 1 프레임 기간에 밝혀지는 지속 기간, 즉 "1"의 정보를 갖는 디지털 데이터 신호가 픽셀에 인가되는 어드레스 기간 직후의 지속 기간의 길이는 합산되므로, 픽셀의 그레이스케일 레벨이 결정된다. 예를 들면, 픽셀이 n=8의 경우에서 모든 지속 기간에 발광하는 경우 휘도가 100%로 설정되고, 픽셀이 Ts1 및 Ts2에 발광하는 경우 75%의 휘도가 나타내질 수 있다고 가정한다. Ts3, Ts5, 및 Ts8이 선택되는 경우에는 16%의 휘도가 나타내질 수 있다.

1 프레임 기간이 완료될 때, on 정상 전위의 높이는 전원 전압과 on 정상 전압에서의 차이인 on EL 구동 전압의 극성이 다음 프레임 기간에서 서로 반대로 되도록 변한다. 이어서, 이전 프레임 기간과 똑같은 방식으로, 동작이 실행된다. 그러나, 그 프레임 기간에서 on EL 구동 전압은 이전 프레임 기간에서 on EL 구동 전압과 반대되는 극성을 가지므로, 모든 EL 소자는 발광하지 않는다. 본 명세서에서, EL 소자가 영상을 디스플레이하는 프레임 기간은 디스플레이 프레임 기간이라 칭하여진다. 그외에, 반대로, 모든 EL 소자가 발광하지 않고 영상이 디스플레이되지 않는 프레임 기간은 넌-디스플레이(non-display) 프레임 기간이라 칭하여진다.

넌-디스플레이 프레임 기간이 완료되면, 또 다른 디스플레이 프레임 기간이 다음에 시작된다. 이어서, on EL 구동 전압은 넌-디스플레이 프레임 기간에서의 on EL 구동 전압과 반대되는 극성을 갖는 전압으로 변한다.

이 방식으로, 영상은 디스플레이 프레임 기간 및 넌-디스플레이 프레임 기간을 번갈아 반복함으로써 디스플레이된다. 본 발명은 상기의 구조를 가지므로, 반대 극성을 갖는 EL 구동 전압은 각각의 한정된 한 기간 동안 EL 소자에 포함되는 EL총으로 인가된다. 그래서, EL 소자의 전류-전압 특성의 저하는 EL 소자의 수명이 종래 구동 방법과 비교해 연장될 수 있는 결과로 개선된다.

또, 상술된 바와 같이, 영상이 교류 구동으로 각각의 1 프레임 기간 동안 디스플레이되는 경우, 플리커와 같이 관찰자의 눈에 깜빡거림을 일으킨다.

그러므로, 본 발명에 따라, EL 디스플레이는 직류 구동에서 관찰자의 눈에 깜빡거림이 발생되지 않는 주파수의 2배인 주파수에서 교류로 구동된다. 다른 말로 하면, 1초에 120개 이상의 프레임 기간이 제공된다. 결과적으로, 1초에 60개 이상의 영상이 디스플레이된다. 이러한 구조로, 교류 구동으로 인한 깜빡거림이 방지된다.

본 실시예에서 도시된 EL 디스플레이를 구동하는 방법에서, 전원 전위는 일정 레벨로 유지되고, 반대 전위는 EL 구동 전압의 크기가 변함에 따라 어드레스 기간 및 지속 기간에서 변하여, EL 소자의 발광이 제어됨을 주목한다. 그러나, 본 발명은 이 구조에 제한되지 않는다. 본 발명의 EL 디스플레이는 반대 전위가 항상 일정 레벨로 유지되고, 픽셀 전극의 전위가 변할 수 있다. 다른 말로 하면, 실시예의 경우와 반대로, 반대 전극의 전위가 항상 똑같은 레벨로 유지되고, 전원 전위가 어드레스 기간 및 지속 기간에서 변하여, 그에 의해 EL 구동 전압의 크기를 변화시키므로, EL 소자의 발광이 제어될 수 있다.

더욱이, 본 실시예에서는 반대 전극의 전위 및 전원 전위가 어드레스 기간에서 똑같은 전위로 유지되므로, EL 소자는 발광하지 않는다. 그러나, 본 발명은 이 구조에 제한되지 않는다. 디스플레이의 EL 소자가 발광하는 정도로 반대 전극과 전원 전위 사이의 전위차를 항상 제공함으로써 디스플레이 기간과 똑같은 방식으로 어드레스 기간에서 제공될 수 있다. 그러나, 이 경우, 전체적인 서브-프레임 기간은 EI 소자가 발광하는 기간이 되므로, 서브-프레임 기간의 길이는

$SF1:SF2:SF3:\dots:SF(n-1):SFn = 2^0:2^{-1}:2^{-2}:\dots:2^{-(n-2)}:2^{-(n-1)}$ 로 설정된다. 상기 구조로, 어드레스 기간에서 발광을 허용하지 않는 구동 방법과 비교해, 높은 휘도를 갖는 영상이 얻어질 수 있다.

다음에는 도 1 내지 도 2b에 도시된 EL 디스플레이를 아날로그 스타일에서 교류로 구동하는 방법이 설명된다. 도 4는 타이밍도에 대해 참고됨을 주목한다.

아날로그 스타일에서 교류로 구동되는 EL 디스플레이의 픽셀 부분의 구조는 디지털 스타일에서 교류로 구동되는 EL 디스플레이와 똑같고, 게이트 신호선(G1 내지 Gn)은 각 픽셀에 포함되는 스위칭 TFT의 게이트 전극에 연결된다. 각 픽셀에 포함되는 스위칭 TFT의 소스 영역 및 드레인 영역 중 하나는 소스 신호선(S1 내지 Sn)에 연결되고, 다른 하나는 EL 구동 TFT의 게이트 전극 및 캐패시터에 연결된다. EL 구동 TFT의 소스 영역 및 드레인 영역 중 하나는 전원 공급선(V1 내지 Vn)에 연결되고, 다른 하나는 각 픽셀에 포함되는 EL 소자에 연결된다. 전원 공급선(V1 내지 Vn)은 또한 각 픽셀에 포함되는 캐패시터에 연결된다.

도 4는 EL 디스플레이가 아날로그 스타일에서 교류로 구동되는 경우의 타이밍도를 도시한다. 한 게이트 신호선이 선택되는 기간은 한 라인(line) 기간이라 칭하여진다. 더욱이, 모든 게이트 신호선의 선택이 완료될 때까지의 기간은 1 프레임 기간에 대응한다. 본 실시예의 경우에는 n개의 게이트 신호선이 주어지기 때문에 1 프레임 기간에 n개의 라인 기간이 제공된다.

본 발명의 EL 디스플레이로, 1초에 120개 이상의 프레임 기간을 제공하는 것이 바람직하고, 1초에 60개 이상의 영상이 디스플레이되는 것이 바람직함을 주목한다. 1초에 디스플레이되는 영상의 수가 60개 이하일 때, 플리커와 같은 영상의 깜빡거림이 시각적으로 뚜렷해진다.

그래이 스케일 레벨의 수가 증가됨에 따라, 1 프레임 기간에서 라인 기간의 수가 또한 증가되고, 구동 회로는 고주파수에서 구동되어야 한다.

맨 처음에, 전원 전압선(V1 내지 Vn)은 off 전원 전위로 유지된다. 교류로 구동하는 아날로그 스타일의 경우, off 전원 전위의 높이는 EL 소자가 발광하지 않는 범위내에서 정상 전위의 높이와 똑같음을 주목한다. 이때, EL 구동 전압은 off EL 구동 전압이라 칭하여짐을 주목한다. 이상적으로, off EL 구동 전압은 0 V인 것이 바람직하지만, 전압은 EL 소자(1506)가 발광하지 않는 정도가 될 수 있다.

제 1 라인 기간(L1)에서, 아날로그 비디오 신호는 소스 신호선(S1 내지 Sn)에 순서대로 입력된다. 게이트 신호는 제 1 라인 기간(L1)에서 게이트 신호선(G1)에 입력된다. 결과적으로, 소스 신호선(S1)에 입력된 아날로그 비디오 신호는 스위칭 TFT가 on 상태에 있기 때문에 스위칭 TFT(1,1)를 통해 EL 구동 TFT(1,1)의 게이트 전극에 입력된다.

이때, 전원 공급선(V1)의 전위는 off 전원 전위에서 포화 전원 전위로 변한다. 본 명세서에서, 포화 전원 전위는 아날로그 구동에서 EL 소자가 발광하는 정도로 정상 전위와 전위차를 갖는 전위를 칭함을 주목한다.

EL 구동 TFT 채널 형성 영역을 흐르는 전류량은 게이트 전극에 입력되는 아날로그 비디오 신호 전압의 크기에 의존해 제어된다. 아날로그 구동의 경우, 아날로그 비디오 신호는 EL 구동 TFT의 게이트 전극에 입력된다. 소스 영역 또는 드레인 영역 중 하나가 포화 전원 전위로 유지될 때, 다른 전위는 on 전원 전위로 설정된다. 이때, EL 구동 전압은 on EL 구동 전압이라 칭하여진다.

EL 구동 TFT(1,1)의 게이트 전극에 인가되는 아날로그 비디오 신호에 의존해, 크기가 제어되는 on EL 구동 전압은 EL 소자에 인가된다.

다음에, 아날로그 비디오 신호는 똑같은 방식으로 소스 신호선(S2)에 입력되고, 스위칭 TFT는 on 상태가 된다. 결과적으로, 소스 신호선(S2)에 입력된 아날로그 비디오 신호는 스위칭 TFT(2,1)를 통해 EL 구동 TFT(2,1)의 게이트 전극에 입력된다.

그래서, EL 구동 TFT(2,1)는 on 상태로 된다. 이어서, 전원 공급선(V2)의 전위는 off 전원 전위에서 포화 전원 전위로 변한다. 결과적으로, 그 크기가 EL 구동 TFT(2,1)의 게이트 전극에 인가되는 아날로그 비디오 신호로 제어되는 on EL 구동 전압은 EL 소자에 인가된다.

상기 동작이 반복되고, 소스 신호선(S1 내지 Sn)으로의 아날로그 비디오 신호의 입력이 완료되면, 제 1 라인 기간(L1)이 완료된다. 이어서, 다음 제 2 라인 기간(L2)이 시작되므로, 게이트 신호는 게이트 신호선(G2)에 입력된다. 제 1 라인 기간(L1)과 똑같은 방식으로, 아날로그 비디오 신호는 순서대로 소스 신호선(S1 내지 Sn)에 입력된다.

아날로그 비디오 신호는 소스 신호선(S1)에 입력된다. 스위칭 TFT들(1,2)이 on 상태로 되므로, 소스 신호선(S1)에 입력된 아날로그 비디오 신호는 스위칭 TFT들(1,2)을 통해 EL 구동 TFT들(1,2)의 게이트 전극에 입력된다.

결과적으로, EL 구동 TFT(1,2)는 on 상태로 된다. 이어서, 전원 공급선(V1)의 전위는 off 전원 전위에서 포화 전원 전위로 변한다. 그래서, 그 크기가 EL 구동 TFT(1,2)의 게이트 전극에 인가되는 아날로그 비디오 신호로 제어되는 EL 구동 전압은 EL 소자에 인가된다.

상기 동작이 반복되고, 소스 신호선들(S1 내지 Sn)로의 아날로그 비디오 신호의 입력이 완료되면, 제 2 라인 기간(L2)이 완료된다. 이어서, 다음 제3 라인 기간(L3)이 시작되어, 게이트 신호는 게이트 신호선(G3)에 입력된다. 게이트 신호는 1 프레임 기간이 완료된 결과, 순서대로 게이트 신호선들(G1 내지 Gn)에 입력된다.

이 프레임 기간이 완료될 때, 포화 전원 전압은 on 전원 전위가 변한 결과로 다음 프레임 기간으로 변화한다. 이때, on EL 구동 전압은 반대 극성을 갖는 전압으로 변한다. 이어서, 이전 프레임 기간과 똑같은 방식으로, 상기 동작이 실행된다. 그러나, 이 프레임 기간에서 on EL 구동 전압은 이전 프레임 기간에서 on EL 구동 전압의 극성과 반대되는 극성을 갖는다. 따라서, 이전 프레임 기간에서 EL 구동 전압의 극성과 반대되는 극성을 갖는 on EL 구동 전압은 EL 소자가 발광하지 않는 결과 모든 EL 소자에 인가된다. 본 명세서에서, EL 소자가 영상을 디스플레이하는 프레임 기간은 디스플레이 프레임 기간이라 칭하여지고, 반대로 모든 EL 소자가 발광하지 않고 영상이 디스플레이되지 않는 프레임 기간은 년-디스플레이 프레임 기간이라 칭하여진다.

년-디스플레이 프레임 기간이 완료될 때, 또 다른 디스플레이 프레임 기간이 다음 단계에서 시작된다. EL 구동 전압은 년-디스플레이 프레임 기간에서 EL 구동 전압의 극성과 반대되는 극성을 갖는 전압으로 변한다.

이 방식으로, 영상은 디스플레이 프레임 기간 및 년-디스플레이 프레임 기간을 번갈아 반복함으로써 디스플레이된다. 본 발명은 반대 극성을 갖는 on EL 구동 전압이 각각의 한정된 기간에서 EL 소자에 인가되도록, 전술된 구조를 갖는다. 따라서, EL 소자의 전류-전압 특성의 저하가 개선되어, EL 소자의 수명이 종래의 구동 방법과 비교해 연장될 수 있다.

더욱이, 본 실시예에서는 디스플레이 디바이스가 비비월 주사(non-interlace scanning)로 구동되는 경우가 설명되지만, 본 발명의 디바이스는 또한 비월 주사로 구동될 수 있다.

#### (실시예들)

이후에는 본 발명의 실시예가 설명된다.

#### (실시예 1)

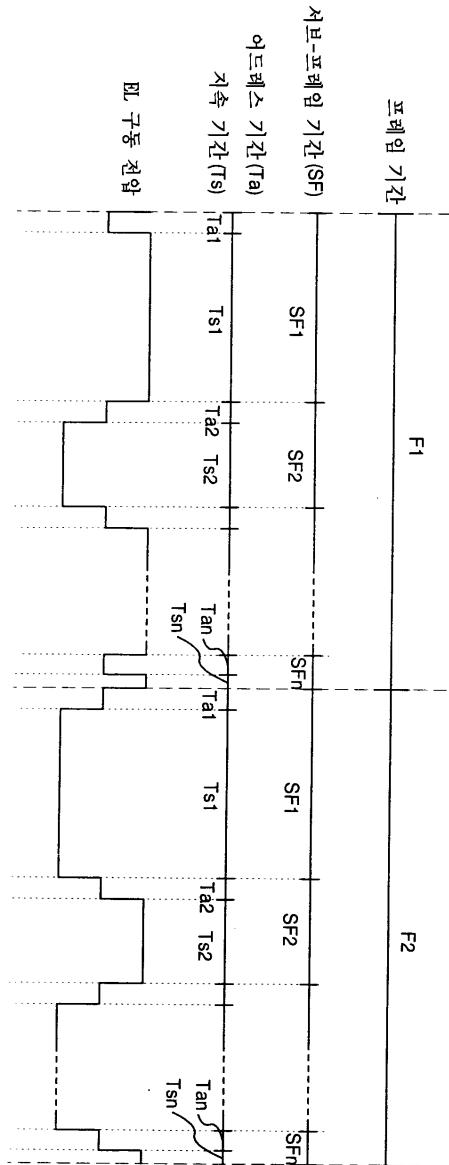

실시예 1에서는 시분할 그레이 스크일 디스플레이가 교류의 디지털 스타일 구동으로 제공되는 경우에, on EL 구동 전압이 서브-프레임 기간마다 반대 극성으로 변하는 경우가 설명된다. 여기서는  $2^n$  그레이 스크일 전칼라 시분할 그레이 스크일 디스플레이가 n-비트 디지털 디바이스 방법에 의해 제공되는 경우가 설명된다.

실시예 1에서 EL 디스플레이 중 픽셀 부분의 구조는 도 2b에 도시된 구조와 똑같다. 게이트 신호선(G1 내지 Gn)은 각 픽셀에 포함되는 스위칭 TFT의 게이트 전극에 연결된다. 각 픽셀에 포함되는 스위칭 TFT의 소스 영역 및 드레인 영역 중 하나는 소스 신호선(S1 내지 Sn)에 연결되고, 다른 하나는 EL 구동 TFT의 게이트 전극 및 캐패시터에 연결된다. 더욱이, EL 구동 TFT의 소스 영역 및 드레인 영역 중 하나는 전원 공급선(V1 내지 Vn)에 연결되고, 다른 하나는 각 픽셀에 포함되는 EL 소자에 연결된다. 전원 공급선(V1 내지 Vn)은 또한 각 픽셀에 포함되는 캐패시터에 연결된다.

도 5는 실시예 1에서 구동 방법의 타이밍도를 도시한다. 맨 처음에, 1 프레임 기간은 n개의 서브-프레임 기간(SF1 내지 SFn)으로 분할된다. 픽셀 부분내의 모든 픽셀이 한 영상을 디스플레이하는 기간은 1 프레임 기간이라 칭하여짐을 주목한다.

1 프레임 기간이 분할되는 복수의 기간은 서브-프레임 기간이라 칭하여짐을 주목한다. 그레이 스크일 레벨의 수가 증가됨에 따라, 1 프레임 기간의 분할수는 증가되므로, 구동 회로는 고주파수에서 구동되어야 한다.

한 서브-프레임 기간은 어드레스 기간(Ta) 및 지속(sustain) 기간(Ts)으로 나뉜다. 어드레스 기간은 한 서브-프레임 기간에서 모든 픽셀에 데이터를 입력하는데 요구되는 시간을 칭하고, 서브-프레임 기간(또는 조명 기간이라 칭하여지는)은 EL 소자가 발광하도록 허용되는 기간을 칭한다.

n개 서브-프레임에 포함되는 어드레스 기간(Ta1 내지 Tan)의 길이는 각각 모두 똑같다. 서브-프레임(SF1 내지 SFn)에 포함되는 지속 기간(Ts)는 각각 Ts1 내지 Tsn으로 설정된다.

지속 기간의 길이는  $Ts1:Ts2:Ts3:\dots:Ts(n-1):Tsn = 2^0:2^{-1}:2^{-2}:\dots:2^{-(n-2)}:2^{-(n-1)}$ 로 설정된다. 그러나, 서브-프레임 기간(SF1 내지 SFn)이 나타나도록 허용되는 순서는 임의적이다. 이러한 지속 기간의 조합으로, 원하는 그레이 스크일 디스플레이가  $2^n$  그레이 스크일 레벨 중에서 제공될 수 있다.

맨 처음에, 반대 전극은 정상 전위로 유지된다. 이어서, 게이트 신호는 게이트 신호선(G1)에 입력된다. 게이트 신호선(G1)에 연결된 게이트 전극을 갖는 모든 스위칭 TFT는 on 상태로 된다.

게이트 신호선(G1)에 연결된 게이트 전극을 갖는 스위칭 TFT가 on으로 된 상태에서, 디지털 데이터 신호는 동시에 모든 소스 신호선(S1 내지 Sn)에 입력된다. 이어서, 소스 신호선(S1 내지 Sn)에 입력된 디지털 데이터 신호는 on 상태에서 스위칭 TFT를 통해 EL 구동 TFT의 게이트 전극에 입력된다. 또한, 디지털 데이터 신호는 또한 캐패시터에 연결되어 유지된다.

상기 동작이 반복되어 디지털 데이터 신호가 모든 픽셀에 입력된다. 디지털 데이터 신호가 모든 픽셀에 입력되는 기간이 어드레스 기간이다.

어드레스 기간이 완료됨과 동시에, 지속 기간이 시작된다. 지속 기간이 시작될 때, 반대 전극의 전위는 off 정상 전위에서 on 정상 전위로 변한다. 이어서, 스위칭 TFT들은 off 상태로 되고, 캐패시터에 유지되는 디지털 데이터 신호는 EL 구동 TFT들의 게이트 전극에 입력된다.

실시예 1에서, on 정상 전위와 전원 전위 사이의 차이인 on EL 구동 전압의 극성은 on 정상 전위의 높이를 변화시킴으로써 서브-프레임 기간마다 서로 반대가 된다. 결과적으로, EL 디스플레이는 서브-프레임 기간마다 on EL 구동 전압의 극성을 반대로 설정함으로써 디스플레이 및 년-디스플레이를 반복한다. 디스플레이가 제공되는 서브-프레임 기간은 디스플레이 서브-프레임 기간이라 칭하여지고, 디스플레이가 제공되지 않는 서브-프레임 기간은 년-디스플레이 서브-프레임 기간이라 칭하여진다.

예를 들어, 제 1 프레임 기간에서, 제 1 서브-프레임 기간이 디스플레이 기간이라 가정하면, 제 2 서브-프레임 기간은 년-디스플레이 기간이고, 제3 프레임 기간은 다시 디스플레이 기간이 된다. 이어서, 모든 서브-프레임 기간이 나타나고, 제 1 프레임 기간이 완료될 때, 제 2 프레임 기간이 시작된다. 제 2 프레임 기간의 제 1 서브-프레임 기간에서는 제 1 프레임 기간의 제 1 서브-프레임 기간에서 EL 소자에 인가되는 EL 구동 전압과 반대되는 극성을 갖는 EL 구동 전압이 EL 소자의 EL층에 인가되므로, 년-디스플레이 기간이 시작된다. 이어서, 다음 제 2 서브-프레임 기간은 디스플레이 기간이 되고, 디스플레이 기간 및 년-디스플레이 기간이 서브-프레임 기간마다 번갈아 제공된다.

본 명세서에서, EL 구동 전압의 극성을 반대로 설정함으로써 디스플레이 및 년-디스플레이가 전환될 때, 디스플레이가 제공되는 기간은 디스플레이 기간이라 칭하여짐을 주목한다. 부가하여, 반대로 디스플레이가 제공되지 않는 기간은 년-디스플레이 기간이라 칭하여진다. 결과적으로, 본 명세서에서는 디스플레이 프레임 기간 및 디스플레이 서브-프레임 기간이 일반적으로 디스플레이 기간이라 칭하여진다. 더욱이, 반대로 년-디스플레이 프레임 기간 및 년-디스플레이 서브-프레임 기간이 일반적으로 년-디스플레이 기간이라 칭하여진다.

실시예 1에서 디지털 데이터 신호가 "0"의 정보를 갖는 경우, EL 구동 TFT는 off 상태로 되고, EL 소자의 픽셀 전극은 off 정상 전위로 유지된다. 결과적으로, "0"의 정보를 갖는 디지털 데이터 신호가 인가되는 픽셀에 포함되는 EL 소자는 발광하지 않는다.

반대로, 디지털 데이터 신호가 "1"의 정보를 갖는 경우, EL 구동 TFT는 on 상태로 되므로, 전원 전위가 EL 소자의 픽셀 전극에 주어진다. 결과적으로, "1"의 정보를 갖는 디지털 신호가 입력되는 픽셀에 포함되는 EL 소자는 발광한다.

모든 스위칭 TFT가 off 상태인 기간은 지속 기간이다.

EL 소자가 발광하도록 허용되는(픽셀이 밝혀지도록 허용되는) 기간은 기간  $T_{s1}$  내지  $T_{sn}$  중 임의의 기간이다. 여기서는 소정의 픽셀이  $T_{sn}$ 의 기간 동안 밝혀지도록 허용된다고 가정한다.

다음에는 어드레스 기간이 다시 나타나고, 데이터 신호가 모든 픽셀에 입력되면, 지속 기간이 시작된다. 이때, 지속 기간  $T_{s1}$  내지  $T_{s(n-1)}$  중 임의의 것이 지속 기간이 된다. 여기서, 소정의 픽셀은  $T_{s(n-1)}$ 의 기간에 밝혀지도록 허용된다고 가정한다.

이후에는 나머지  $n-2$ 개의 서브-프레임에 대해 유사한 동작이 반복되므로,  $T_{s(n-2)}$ ,  $T_{s(n-3)}$ , ...,  $T_{s1}$  및 지속 기간이 순서대로 설정되고 소정의 픽셀이 각 서브-프레임에 밝혀지도록 허용된다.

이 방식으로, 각 서브-프레임에 대해 반대 극성을 갖는 EL 구동 전압이 교류 구동시 시분할 그레이 스케일 디스플레이에서 EL 소자에 인가되는 경우, 한 그레이 스케일 디스플레이에는 2개의 프레임 기간에 제공된다. 픽셀의 그레이 스케일 레벨은 2개의 인접 1 프레임 기간에서 픽셀이 밝혀지는 지속 기간의 길이, 즉 "1"의 정보를 갖는 디지털 데이터 신호가 픽셀에 입력된 어드레스 기간 직후에 지속 기간의 길이를 합산함으로써 결정될 수 있다. 예를 들면, 픽셀이  $n=8$ 의 경우에서 모든 지속 기간에 픽셀이 발광하는 경우 휘도가 100%로 설정될 때, 픽셀이  $T_{s1}$  및  $T_{s2}$ 에 발광하는 경우 75%의 휘도가 나타내질 수 있다.  $T_{s3}$ ,  $T_{s5}$ , 및  $T_{s8}$ 이 선택되는 경우에는 약 16%의 휘도가 나타내질 수 있다.

본 발명은 상기 구조를 가지므로, 반대 전압을 갖는 EL 구동 전압은 각 서브-프레임 기간에서 EL 소자에 포함되는 EL층에 인가된다. 결과적으로, EL 소자의 전류-전압 특성의 저하가 개선될 수 있고, 종래의 구동 방법과 비교해 EL 소자의 수명이 연장될 수 있다.

실시예 1에서는 본 실시예에 도시된 각 프레임 기간 동안 교류로 구동되는 디지털 스타일 EL 디스플레이와 비교해 깜빡거림이 덜 일어나는 효과를 얻게된다.

(실시예 2)

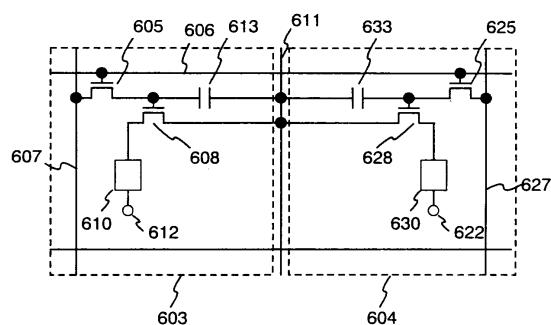

실시예 2에서는 도 2a에 도시된 본 발명에 따른 EL 디스플레이의 픽셀 부분과 다른 예가 도시된다.

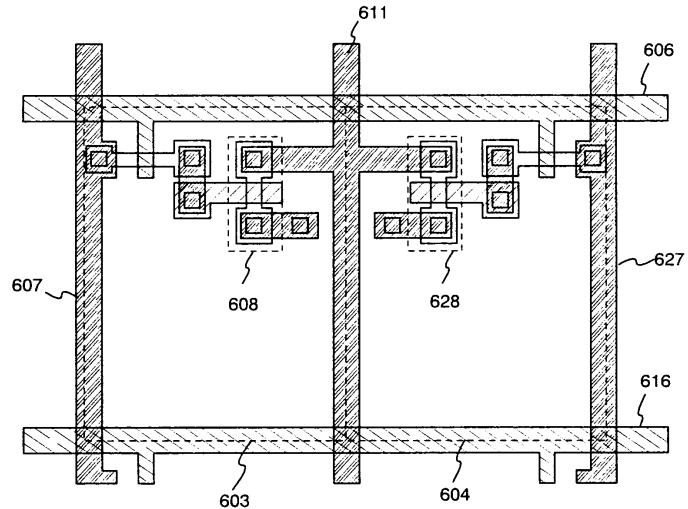

도 6a는 실시예 2에 따른 EL 디스플레이의 픽셀 부분의 확대도 예를 도시하는 회로도이다. 픽셀 부분에는 복수의 픽셀이 매트릭스 구성으로 배열된다. 픽셀(603)과 픽셀(604)은 서로 인접하여 제공된다. 도 6a에서, 참고번호(605, 625)는 스위칭 TFT를 나타낸다. 스위칭 TFT(605, 625)의 게이트 전극은 게이트 신호가 입력된 게이트 신호선(606)에 연결된다. 스위칭 TFT(605, 625)의 소스 영역 및 드레인 영역 중 하나는 디지털 데이터 신호가 입력되는 데이터 신호선(또한 소스 신호선이라 칭하여지는)(607, 627)에 연결되고, 다른 하나는 EL 구동 TFT의 게이트 전극 및 캐패시터(613, 633)에 각각 연결된다.

이어서, EL 구동 TFT들(608, 628)의 소스 영역은 공통된 전원 공급선(611)에 연결되고, 드레인 영역은 EL 소자들(610, 630)에 각각 포함되는 픽셀 전극에 연결된다. 이 방식으로, 실시예 2에서는 2개의 인접한 픽셀이 전원 공급선을 공유한다.

EL 소자들(610, 630)은 양극(실시예 2에서 픽셀 전극), 음극(실시예 2에서 반대 전극), 및 양극과 음극 사이에 각각 제공되는 EL층을 구비한다. 실시예 2에서, EL 구동 TFT들(608, 628)의 드레인 영역은 양극에 연결되고, 음극은 정상 전원들(612, 622)에 연결되어 정상 전위로 유지된다. 본 발명은 이 구조로 제한되지 않는다. EL 구동 TFT들(608, 628)의 드레인 영역은 음극에 연결된다.

레지스터는 각각 EL 구동 TFT들(608, 628)의 드레인 영역과 EL 소자(610, 630)에 각각 포함되는 양극(픽셀 전극) 사이에 제공될 수 있음을 주목한다. 레지스터를 제공함으로써, EL 구동 TFT들에서 EL 소자로 공급되는 전류량이 제어되므로, EL 구동 TFT들에 대한 불균형의 영향이 방지될 수 있다. 레지스터가 EL 구동 TFT들의 on 저항에 대한 저항값 보다 충분히 더 큰 저항값을 나타내는 소자이므로, 그 구조는 어떠한 방법으로도 제한되지 않는다. on 레지스터의 저항은 TFT들의 드레인 전압을 그때 흐르는 드레인 전류로 나눔으로써 얻어지는 값임을 주목한다. 레지스터의 저항값은  $1\text{ k}\Omega$  내지  $50\text{ M}\Omega$ 의 범위에서 선택된다(바람직하게  $10\text{ k}\Omega$  내지  $10\text{ M}\Omega$  이상, 보다 바람직하게  $50\text{ k}\Omega$  내지  $1\text{ M}\Omega$ ). 레지스터로 높은 저항값을 갖는 반도체층이 사용될 때, 레지스터의 형성은 용이하고 바람직해진다.

더욱이, 스위칭 TFT들(605, 625)이 비선택 상태(off 상태)로 설정될 때, 캐패시터들(613, 633)은 EL 구동 TFT들(608, 628)의 게이트 전압을 유지하도록 제공된다. 이들 캐패시터들(613, 633)에 포함되는 두 전극 중 하나는 스위칭 TFT들(605, 625)의 드레인 영역에 접속되고, 다른 전극은 전원 공급선(611)에 연결된다. 캐패시터들(613, 633)이 반드시 제공될 필요가 없음을 주목한다.

도 6b는 도 6a에 도시된 회로도의 구조도이다. 소스 신호선들(607, 627)로 둘러싸인 영역에서는 게이트 신호선들(606, 616), 전원 공급선들(611), 픽셀들(603, 604)이 제공된다. 픽셀들(603, 604)에 각각 포함되는 EL 구동 TFT들(608, 628)의 소스 영역은 모두 전원 공급선(611)에 연결된다. 본 실시예에서는 2개의 인접한 픽셀이 전원 공급선을 공유한다. 결과적으로, 도 2a에 도시된 구조와 비교해, 전체적인 픽셀 부분에서 배선(wiring) 비율이 작아질 수 있다. 전체적인 픽셀 부분에 대한 배선의 비율이 작아질 때, EL층이 발광하는 방향으로 배선이 제공되어, 배선에 의한 빛의 차폐가 억제될 수 있다.

실시예 2에 도시된 구조는 실시예 1과 자유롭게 조합될 수 있다.

(실시예 3)

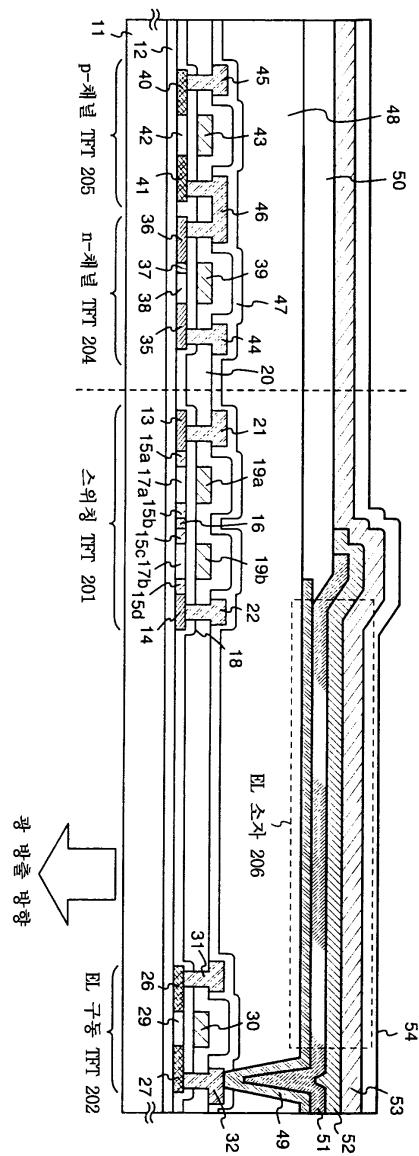

다음에는 본 발명의 EL 디스플레이 디바이스의 단면 구조를 도시하는 도 7이 참고된다.

도 7에서, 참고번호(11)는 기판이고, (12)는 기저(base)인 절연막이다(이후에 이 막은 기저막(base film)이라 나타내진다). 기판(11)으로는 광투과성 기판, 대표적으로 유리 기판, 수정 기판, 유리 세라믹 기판, 또는 결정화된 유리 기판이 사용될 수 있다. 그러나, 제조 과정 중의 최고 처리 온도에 견딜 수 있어야 한다. 기저막(12)은 특히 도전성을 갖는 기판이나 이동가능한 이온을 갖는 기판을 사용할 때 효과적이지만, 반드시 수정 기판에 배치될 필요는 없다. 실리콘을 포함하는 절연막이 기저막(12)으로 사용될 수 있다. 본 명세서에서, "실리콘을 포함하는 절연막"은 실리콘산화물막, 실리콘질화물막, 또는 실리콘질화산화물과 같이, 소정의 비율( $\text{SiO}_x\text{Ny}$ : x 및 y는 임의의 정수)로 실리콘에 산소 또는 질소가 부가된 절연막을 의미함을 주목하여야 한다.

삭제

참고번호(201)는 스위칭 TFT이고,(202)는 EL 구동 TFT이다. 스위칭 TFT는 n-채널형 TFT로 형성되고, EL 구동 TFT는 p-채널형 TFT로 형성된다. EL 발광 방향이 기판의 하단 표면 쪽일 때(하단 표면에는 TFT 또는 EL층이 제공되지 않는다), 상술된 구조는 바람직하다. 그러나, 본 발명에서는 이 구조로 제한될 필요가 없다. 스위칭 TFT 및 EL 구동 TFT에서는 이들 모두에, 또는 그중 하나에 p-채널형 TFT 또는 n-채널형 TFT를 사용하는 것이 가능하다.

스위칭 TFT(201)는 소스 영역(13), 드레인 영역(14), LDD(Lightly-Doped Drain) 영역(15a-15d), 고립 영역(16), 및 채널 형성 영역(17a, 17b)을 포함하는 활성층, 게이트 절연막(18), 게이트 전극(19a, 19b), 제 1 층간 절연막(20), 소스 신호선(21), 및 드레인 배선(wiring line)(22)으로 구성된다. 게이트 절연막(18) 또는 제 1 층간 절연막(20)은 기판상의 모든 TFT에 공통되거나, 회로 또는 소자에 따라 변할 수 있다.

도 7에 도시된 스위칭 TFT(201)에서, 게이트 전극(19a, 19b)은 전기적으로 연결된다. 다른 말로 하면, 이중-게이트 구조가 성립된다. 이중-게이트 구조 뿐만 아니라 삼중-게이트 구조와 같은 다중-게이트 구조도 물론 성립될 수 있다. 다중-게이트 구조는 직렬로 연결된 2개 이상의 채널 형성 영역을 갖는 활성층을 포함하는 구조를 의미한다.

다중-게이트 구조는 off 전류를 감소시키는데 매우 효과적이고, 스위칭 TFT의 off 전류가 충분히 감소되면, 구동기 TFT(202)의 게이트 전극에 접속된 캐패시터에 필요한 최소 용량이 감소될 수 있다. 즉, 캐패시터의 소유 면적이 감소될 수 있으므로, 다중-게이트 구조는 EL 소자의 유효 발광 면적을 넓히는데 효과적이다.

스위칭 TFT(201)에서, LDD 영역(15a-15d)은 게이트 전극(19a, 19b)과 중첩되지 않도록 배치되고, 그들 사이에는 게이트 절연막(18)이 주어진다. 이와 같이 만들어진 구조는 off 전류를 감소시키는데 매우 효과적이다. LDD 영역(15a-15d)의 길이(폭)는 0.5-3.5  $\mu\text{m}$ , 대표적으로 2.0-2.5  $\mu\text{m}$ 이다.

off 전류를 감소시키기 위해서는 채널 형성 영역 및 LDD 영역 사이에 오프셋(offset) 영역(즉, 합성이 채널 형성 영역과 똑같고 게이트 전압이 인가되지 않는 반도체층으로 형성된 영역)을 형성하는 것이 보다 바람직하다. 2개 이상의 게이트 전극을 갖는 다중-게이트 구조에서는 채널 형성 영역 사이에 형성된 고립 영역(16)(즉, 소스 영역 또는 드레인 영역과 농도가 같고, 같은 불순물 원소가 부가되는 영역)이 off 전류를 감소시키는데 효과적이다.

EL 구동 TFT(202)는 소스 영역(26), 드레인 영역(27), 및 채널 형성 영역(29)을 포함하는 활성층, 게이트 절연막(18), 게이트 전극(30), 제 1 층간 절연막(20), 소스 신호선(31), 및 드레인 배선(32)으로 구성된다. 본 실시예에서, EL 구동 TFT(202)는 p-채널형 TFT이다.

스위칭 TFT(201)의 드레인 영역(14)은 EL 구동 TFT(202)의 게이트 전극(30)에 연결된다. 보다 상세하게, EL 구동 TFT(202)의 게이트 전극(30)은 도시되지 않은 드레인선(22)(또한 연결 배선이라 칭하여지는)을 통해 스위칭 TFT(201)의 드레인 영역(14)에 전기적으로 연결된다. 게이트 전극(30)은 본 실시예에서 단일 게이트 구조이지만, 다중-게이트 구조도 적용 가능하다. EL 구동 TFT의 소스 신호선(31)은 전력 공급선에 연결된다.

EL 구동 TFT(202)는 EL 소자에 공급되는 전류량을 제어하는 소자이다. 비교적 많은 양의 전류가 이 소자를 통해 흐를 수 있다. 그러므로, 바람직하게, 채널폭(W)은 스위칭 TFT의 채널폭 보다 더 크게 설계된다. 부가하여, 바람직하게, 채널 길이(L)는 EL 구동 TFT(202)를 통해 과도한 전류가 흐르지 않도록 길게 설계된다. 바람직한 값은 광셀 당 0.5 - 2 mA(바람직하게 1 - 1.5 mA)이다.

TFT의 저하를 방지하는 관점에서, EL 구동 TFT(202)의 활성층(특별히 채널 형성 영역)의 막두께를 두껍게 하는 것이 효과적이다(바람직하게 50 - 100 nm, 보다 바람직하게 60 - 80 nm). 한편, 스위칭 TFT(201)에서 off 전류를 감소하는 관점에서, 활성층(특별히 채널 형성 영역)의 막두께를 얇게 하는 것이 효과적이다(바람직하게 20 - 50 nm, 보다 바람직하게 25 - 40 nm).

위에서는 광셀에 형성된 TFT의 구조가 설명되었다. 이 구조에서는 구동기 회로가 또한 동시에 형성된다. 도 7에서는 구동기 회로를 형성하는 기본 유닛이 되는 CMOS 회로가 도시된다.

도 7에서, 동작 속도를 최대로 줄이지 않고 핫 캐리어(hot carrier) 주입을 감소시키는 구조를 갖는 TFT는 CMOS 회로의 n-채널형 TFT(204)로 사용된다. 여기서 설명되는 구동기 회로는 소스 신호측 구동기 회로 및 게이트 신호측 구동기 회로이다. 또한, 다른 논리 회로(레벨 쉬프터, A/D 변환기, 신호 분할 회로 등)를 형성하는 것이 물론 가능하다.

CMOS 회로의 n-채널형 TFT(204)의 활성층은 소스 영역(35), 드레인 영역(36), LDD 영역(37), 및 채널 형성 영역(38)을 포함한다. LDD 영역(37)은 게이트 전극(39)과 중첩되고, 게이트 절연막(18)은 그 사이에 있다.

드레인 영역(36)측에만 LDD 영역(37)을 형성하는 이유는 동작 속도를 줄이지 않기 때문이다. n-채널형 TFT(204)에서는 off 전류값에 대해 염려할 필요가 없다. 대신에, 동작 속도가 그 이상의 비율로 되어야 한다. 그러므로, 바람직하게, LDD 영역(37)은 게이트 전극상에 완전히 놓여서 가능한한 많이 저항 성분을 줄인다. 즉, 오프셋이 생략되어야 한다.

CMOS 회로의 p-채널형 TFT(205)에서는 핫 캐리어에 의해 발생되는 저하가 매우 무시할 만하기 때문에 특별히 LDD 영역을 제공할 필요가 없다. 그러므로, 활성층은 소스 영역(40), 드레인 영역(41), 및 채널 형성 영역(42)을 포함한다. 그 위에는 게이트 절연막(18) 및 게이트 전극(43)이 배치된다. 또한, 핫 캐리어에 대한 대응책을 취하기 위해 LDD 영역 뿐만 아니라 n-채널형 TFT(204)도 배치하는 것이 물론 가능하다.

n-채널형 TFT(204) 및 p-채널형 TFT(205)는 제 1 층간 절연막(20)으로 덮히고, 소스 배선(44, 45)이 형성된다. 이 둘은 드레인 배선(46)에 의해 전기적으로 연결된다.

참고번호(47)는 제 1 패시베이션막이다. 막두께는 10 nm – 1  $\mu$ m(바람직하게 200 – 500 nm)이다. 그 물질로는 실리콘을 포함하는 절연막(특별히, 실리콘 질화산화물막이나 실리콘질화물막이 바람직하다)이 사용될 수 있다. 패시베이션막(47)은 알칼리 금속 및 습기로부터 형성된 TFT를 보호하도록 동작한다. TFT 위에 마지막으로 배치된 EL층은 나트륨과 같은 알칼리 금속을 포함한다. 다른 말로 하면, 제 1 패시베이션막(47)은 또한 알칼리 금속(이동가능한 이온)이 TFT측에 들어가도록 허용하지 않는 보호층으로 동작한다.

참고번호(48)는 제 2 층간 절연막으로, TFT에 의해 형성된 레벨 차이를 평평하게 하는 평탄화막으로 동작한다. 바람직하게, 제 2 층간 절연막(48)으로는 폴리이미드(polyimide), 폴리아미드(polyamide), 아크릴 수지(acrylic resin), 또는 BCB (benzocyclobutene)와 같은 유기 수지막이 사용된다. 유기 수지막은 양질의 매끄러운 평면이 쉽게 형성될 수 있고 유전 상수가 낮다는 이점을 갖는다. EL층이 거칠기에 매우 민감하기 때문에, 제 2 층간 절연막(48)을 통해 TFT에 의해 발생되는 레벨 차이를 완전히 흡수하는 것이 바람직하다. 부가하여, 게이트 신호선이나 데이터 신호선 및 EL 소자의 음극 사이에 형성된 기생 캐패시턴스를 감소하기 위해, 낮은 유전 상수의 물질을 두껍게 형성하는 것이 바람직하다. 그러므로, 바람직하게, 막의 두께는 0.5 – 5  $\mu$ m(바람직하게 1.5 – 2.5  $\mu$ m)이다.

참고번호(49)는 투명한 도전성막으로 구성된 픽셀 전극(EL 소자의 양극)이다. 접촉 홀(hole)(개구(opening))이 제 2 층간 절연막(48) 및 제 1 패시베이션막(47)에 이루어진 이후에, 전극은 개구를 통해 EL 구동 TFT(202)의 드레인 배선(32)에 연결된다. 도 2a 및 도 2b에서와 같이, 픽셀 전극(49) 및 드레인 영역(27)이 직접 연결되지 않게 배열될 때, EL층의 알칼리 금속은 픽셀 전극을 통해 활성층으로 들어가지 않도록 방지된다.

두께가 0.3 – 1  $\mu$ m인 제3 층간 절연막(50)은 픽셀 전극(49)에 배치된다. 막(50)은 실리콘산화물막, 실리콘 질화산화물막, 또는 유기 수지막으로 이루어진다. 제3 층간 절연막(50)에는 에칭(etching)으로 픽셀 전극(49)에 개구가 제공되고, 개구의 엣지는 테이퍼(taper) 형상을 갖도록 에칭된다. 바람직하게, 테이퍼의 각도는 10 – 60 °이다(바람직하게 30 – 50 °).

EL층(51)은 제3 층간 절연막(50)에 형성된다. EL층(51)은 단일층 구조 또는 적층 구조의 형태로 사용된다. 적층 구조는 발광 효율성이 뛰어나다. 일반적으로, 양의 홀 주입층/양의 홀 운송층/발광층/전자 운송층이 이 순서대로 픽셀 전극상에 형성된다. 대신에, 양의 홀 운송층/발광층/전자 운송층의 순서 또는 양의 홀 주입층/양의 홀 운송층/발광층/전자 운송층/전자 주입층의 순서를 갖는 구조가 사용될 수 있다. 본 발명에서는 공지된 구조 중 하나가 사용될 수 있고, 형광 칼라팅(fluorescent coloring) 물질 등이 EL층에 도핑될 수 있다.

예를 들면, 다음의 미국 특허 또는 공보들에 나타나는 물질이 유기 EL 물질로 사용될 수 있다. 미국 특허 No. 4,356,429: 4,539,507: 4,720,432: 4,769,292: 4,885,211: 4,950,950: 5,059,861: 5,047,687: 5,073,446: 5,059,862: 5,061,617: 5,151,629: 5,294,869: 5,294,870, 및 일본 공개 특허 공보 No. 10-189525: 8-241048: 8-78159가 그것이다.

EL 디스플레이 디바이스는 주로 4개의 칼라 디스플레이 방법을 갖는다. 상기 디스플레이 방법은 R(적색), G(녹색), 및 B(청색)에 각각 대응하는 3종류의 EL 소자를 형성하는 방법, 칼라 필터(칼라링층) 및 백색 휘도의 EL 소자를 조합하는 방법, 형광 본체(형광 칼라 변환층(fluorescent color conversion layer)CCM) 및 청색 또는 청녹색 휘도의 EL 소자를 조합하는 방법, 및 음극(반대 전극)으로 투명 전극을 사용하면서 RGB에 대응하는 EL 소자를 적층시키는 방법을 포함한다.

도 2a 및 도 2b의 구조는 RGB에 대응하는 3종류의 EL 소자를 형성하는 방법이 사용된 예이다. 도 7에서는 단 하나의 픽셀만이 도시된다. 사실상, 각각이 똑같은 구조를 갖는 픽셀은 적색, 녹색, 및 청색의 각 칼라에 대응하도록 형성되므로, 그에 의해 칼라 디스플레이가 실행될 수 있다.

본 발명은 휘도 방법에 관계없이 실행될 수 있어, 4가지 방법 모두를 사용할 수 있다. 그러나, 형광 본체의 응답 속도는 EL보다 더 느려 잔광의 문제점이 있으므로, 형광 본체가 사용되지 않는 방법이 바람직하다. 부가하여, 휘도 밝기를 떨어뜨리는 칼라 필터는 가능하면 사용되지 말아야 한다고 할 수 있다.

EL 소자의 음극(52)은 EL층(51)에 배치된다. 작은 일 함수(work function)을 갖는 마그네슘(Mg), 리튬(Li), 또는 칼슘(Ca)을 포함하는 물질이 음극(52)으로 사용된다. 바람직하게, MgAg(Mg 및 Ag가 Mg:Ag = 10:1의 비율로 혼합된 물질)로 구성된 전극이 사용된다. 대신에, MgAgAl 전극, LiAl 전극, 또는 LiFAI 전극이 사용될 수 있다.

EL 소자(206)는 픽셀 전극(양극)(49), EL층(51), 및 음극(52)으로 형성된다.

각 픽셀에 의해 각기 EL층(51) 및 음극(52)으로 구성된 층 본체를 형성할 필요가 있다. 그러나, EL층(51)은 매우 습기에 약하므로, 통상의 포토리소그라피(photolithography) 기술이 사용될 수 없다. 그러므로, 금속 마스크와 같은 물리적 마스크 물질을 사용하여, 진공 증착법, 스퍼터링(sputtering) 방법, 또는 플라즈마(plasma) CVD 방법과 같은 기상(vapor phase) 방법에 따라 이를 선택적으로 형성하는 것이 바람직하다.

또한, EL층을 선택적으로 형성하는 방법으로 잉크젯(ink jet) 방법, 스크린 프린팅 방법, 스판 코팅(spin coating) 방법 등을 사용하는 것이 가능하다. 그러나, 이들 방법은 기술의 현상태에서는 음극을 연속적으로 형성할 수 없기 때문에, 잉크젯 방법을 제외한 상기 방법이 바람직하다고 말할 수 있다.

참고번호(53)는 보호 전극이다. 이는 외부 습기 등으로부터 음극(52)을 보호하고, 동시에 각 픽셀의 음극(52)을 연결시키기 위한 것이다. 보호 전극(53)으로는 알루미늄(Al), 구리(Cu), 또는 은(Ag)을 포함하는 저저항 물질을 사용하는 것이 바람직하다. EL층의 열을 낮추는 냉각 효과는 보호 전극(53)으로부터 기대될 수 있다.

참고번호(54)는 제 2 패시베이션막이고, 바람직하게 그 막 두께는 10 nm – 1  $\mu$ m(바람직하게 200 – 500 nm)이다. 제 2 패시베이션막(54)을 배치하는 주요 목적은 습기로부터 EL층(51)을 보호하기 위한 것이다. 또한, 이에 냉각 효과를 제공하는 것이 효과적이다. 그러나, EL층은 상술된 바와 같이 열에 약하므로, 막 형성은 저온(바람직하게 실온에서 120도 범위)에서 실행되어야 한다. 그러므로, 바람직한 막 형성 방법은 플라즈마 CVD 방법, 스퍼터링 방법, 진공 증착법, 이온 플레이팅 방법, 또는 용액 적용 방법(스핀 코팅 방법)이라 말할 수 있다.

말할 필요도 없이, 도 7에 도시된 모든 TFT는 활성층으로 본 발명에서 사용되는 폴리실리콘막을 갖는다.

본 발명은 도 7의 EL 디스플레이 디바이스의 구조에 제한되지 않는다. 도 7의 구조는 본 발명을 동작시키는 바람직한 형태 중 하나일 뿐이다.

본 실시예에서 도시된 구조는 실시예 1 또는 실시예 2와 자유롭게 조합하여 동작될 수 있다.

(실시예 4)

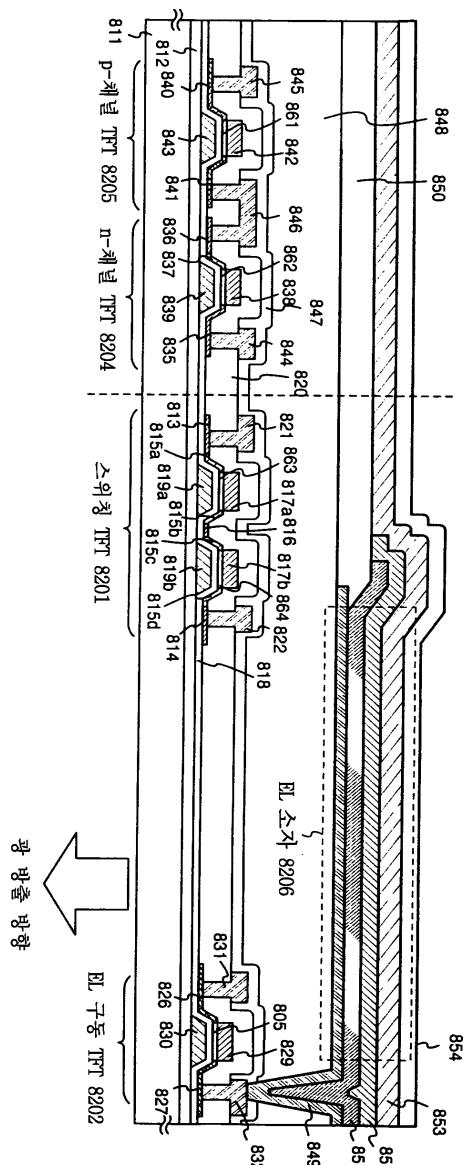

본 실시예에서는 도 7과 다른 예를 사용하여 본 발명의 EL 디스플레이 디바이스의 단면 구조를 도시하는 도 21을 참고한다. TFT의 예는 본 실시예에서 설명되는 바닥(bottom) 게이트형 TFT의 박막 트랜지스터로 사용될 수 있다.

도 21에서, 참고번호(811)는 기판이고, (812)는 기저인 절연막이다(이후에 이 막은 기저막이라 나타내진다). 기판(811)으로는 광투과성 기판, 대표적으로 유리 기판, 수정 기판, 유리 세라믹 기판, 또는 결정화된 유리 기판이 사용될 수 있다. 그러나, 제조 과정 중의 최고 처리 온도에 견딜 수 있어야 한다.

기저막(812)은 특히 도전성을 갖는 기판이나 이동가능한 이온을 갖는 기판을 사용할 때 효과적이지만, 반드시 수정 기판에 배치될 필요는 없다. 실리콘을 포함하는 절연막이 기저막(812)으로 사용될 수 있다. 본 명세서에서, "실리콘을 포함한 절연막"은 실리콘산화물막, 실리콘질화물막, 또는 실리콘 질화산화막과 같이, 소정의 비율(SiO<sub>x</sub>N<sub>y</sub>: x 및 y는 임의의 정수)로 실리콘에 산소 또는 질소가 부가된 절연막을 의미함을 주목하여야 한다.

참고번호(8201)는 스위칭 TFT이고, (8202)는 EL 구동 TFT이다. 스위칭 TFT는 n-채널형 TFT로 형성되고, EL 구동 TFT는 p-채널형 TFT로 형성된다. EL 발광 방향이 기판의 하단 표면 쪽일 때(하단 표면에는 TFT 또는 EL층이 제공되지 않는다), 상술된 구조는 바람직하다. 그러나, 본 발명에서는 이 구조로 제한될 필요가 없다. 스위칭 TFT 및 EL 구동 TFT에서는 이들 모두에, 또는 그중 하나에 p-채널형 TFT 또는 n-채널형 TFT를 사용하는 것이 가능하다.

스위칭 TFT(8201)는 소스 영역(813), 드레인 영역(814), LDD 영역(815a-815d), 고립 영역(816), 및 채널 형성 영역(863, 864)을 포함하는 활성층, 게이트 절연막(818), 게이트 전극(819a, 819b), 제 1 층간 절연막(820), 소스 신호선(821), 및 드레인 배선(822)으로 구성된다. 게이트 절연막(818) 또는 제 1 층간 절연막(820)은 기판상의 모든 TFT에 공통되거나, 회로 또는 소자에 따라 변할 수 있다.

도 21에 도시된 스위칭 TFT(8201)에서, 게이트 전극(819a, 819b)은 전기적으로 연결된다. 다른 말로 하면, 이중-게이트 구조가 성립된다. 이중-게이트 구조 뿐만 아니라 삼중-게이트 구조와 같은 다중-게이트 구조도 물론 성립될 수 있다. 다중-게이트 구조는 직렬로 연결된 2개 이상의 채널 형성 영역을 갖는 활성층을 포함하는 구조를 의미한다.

다중-게이트 구조는 off 전류를 감소시키는데 매우 효과적이고, 스위칭 TFT의 off 전류가 충분히 감소되면, 구동기 TFT(8202)의 게이트 전극에 접속된 캐패시터에 필요한 최소 용량이 감소될 수 있다. 즉, 캐패시터가 차지하는 면적이 감소될 수 있으므로, 다중-게이트 구조는 EL 소자의 유효 발광 면적을 넓히는데 효과적이다.

스위칭 TFT(8201)에서, LDD 영역(815a-815d)은 게이트 전극(819a, 819b)과 중첩되지 않도록 배치되고, 그들 사이에는 게이트 절연막(818)이 주어진다. 이와 같이 만들어진 구조는 off 전류를 감소시키는데 매우 효과적이다. LDD 영역(815a-815d)의 길이(폭)는 0.5-3.5  $\mu\text{m}$ , 대표적으로 2.0-2.5  $\mu\text{m}$ 이다.

off 전류를 감소시키기 위해서는 채널 형성 영역 및 LDD 영역 사이에 오프셋 영역(즉, 합성이 채널 형성 영역과 똑같고 게이트 전압이 인가되지 않는 반도체층으로 형성된 영역)을 형성하는 것이 보다 바람직하다. 2개 이상의 게이트 전극을 갖는 다중-게이트 구조에서는 채널 형성 영역 사이에 형성된 고립 영역(816)(즉, 소스 영역 또는 드레인 영역과 농도가 똑같고 똑같은 불순물 원소가 부가되는 영역)이 off 전류를 감소시키는데 효과적이다.

전류 제어 TFT(8202)는 소스 영역(826), 드레인 영역(827), 및 채널 형성 영역(805)을 포함하는 활성층, 게이트 절연막(818), 게이트 전극(830), 제 1 층간 절연막(820), 소스 신호선(831), 및 드레인 배선(832)으로 구성된다. 본 실시예에서, EL 구동 TFT(8202)는 p-채널형 TFT이다.

스위칭 TFT(8201)의 드레인 영역(814)은 EL 구동 TFT(8202)의 게이트 전극(830)에 연결된다. 보다 상세하게, EL 구동 TFT(8202)의 게이트 전극(830)은 드레인선(822)(또한 연결 배선이라 칭하여지는)을 통해 스위칭 TFT(8201)의 드레인 영역(814)에 전기적으로 연결된다. 게이트 전극(830)이 단일 게이트 구조이지만, 다중-게이트 구조도 적용가능한다. EL 구동 TFT(8202)의 소스 신호선(831)은 전류 공급선에 연결된다.

EL 구동 TFT(8202)는 EL 소자에 공급되는 전류량을 제어하는 소자로, 비교적 많은 양의 전류가 그 소자를 통해 흐를 수 있다. 그러므로, 바람직하게, 채널폭(W)은 스위칭 TFT의 채널폭 보다 더 크게 설계된다. 부가하여, 바람직하게, 채널 길이(L)는 EL 구동 TFT(8202)를 통해 과도한 전류가 흐르지 않도록 길게 설계된다. 바람직한 값은 픽셀 당 0.5 - 2 mA(바람직하게 1 - 1.5 mA)이다.

TFT의 저하를 저지하는 관점에서, EL 구동 TFT(8202)의 활성층(특별히 채널 형성 영역)의 막두께를 두껍게 하는 것이 효과적이다(바람직하게 50 - 100 nm, 보다 바람직하게 60 - 80 nm). 한편, 스위칭 TFT(8201)에서 off 전류를 감소하는 관점에서, 활성층(특별히 채널 형성 영역)의 막두께를 얇게 하는 것이 효과적이다(바람직하게 20 - 50 nm, 보다 바람직하게 25 - 40 nm).

상기에서는 픽셀에 형성된 TFT의 구조가 설명되었다. 이 구조에서는 구동기 회로가 또한 동시에 형성된다. 도 21에서는 구동기 회로를 형성하는 기본 유닛이 되는 CMOS 회로가 도시된다.

도 21에서, 동작 속도를 최대로 줄이지 않고 핫 캐리어 주입을 감소시키는 구조를 갖는 TFT는 CMOS 회로의 n-채널형 TFT(8204)로 사용된다. 여기서 설명되는 구동기 회로는 소스 신호측 구동기 회로 및 게이트 신호측 구동기 회로이다. 또한, 다른 논리 회로(레벨 쉬프터, A/D 변환기, 신호 분할 회로 등)를 형성하는 것이 물론 가능하다.

n-채널형 TFT(8204)의 활성층은 소스 영역(835), 드레인 영역(836), LDD 영역(837), 및 채널 형성 영역(862)을 포함한다. LDD 영역(837)은 게이트 전극(839)과 중첩되고, 게이트 절연막(818)은 그 사이에 있다.

드레인 영역(836)측에만 LDD 영역(837)을 형성하는 이유는 동작 속도를 줄이지 않기 위해서이다. n-채널형 TFT(8204)에서는 off 전류값에 대해 염려할 필요가 없다. 대신에, 동작 속도가 그 이상의 비율로 되어야 한다. 그러므로, 바람직하게, LDD 영역(837)은 게이트 전극상에 완전히 놓여서 가능한한 많이 저항 성분을 줄인다. 즉, 오프셋이 생략되어야 한다.

CMOS 회로의 p-채널형 TFT(8205)에서는 핫 캐리어에 의해 발생되는 저하가 매우 무시할 만하기 때문에 특별히 LDD 영역을 제공할 필요가 없다. 그러므로, 활성층은 소스 영역(840), 드레인 영역(841), 및 채널 형성 영역(861)을 포함한다. 그 위에는 게이트 절연막(818) 및 게이트 전극(843)이 배치된다. 또한, 핫 캐리어에 대한 대응책을 취하기 위해 LDD 영역 뿐만 아니라 n-채널형 TFT(8204)도 배치하는 것이 물론 가능하다.

참고번호(817a, 817b, 829, 838, 842)는 채널 형성 영역(861, 862, 863, 864, 805)을 형성하는 마스크임을 주목하여야 한다.

n-채널형 TFT(8204) 및 p-채널형 TFT(8205)는 각각 그들 사이에 제 1 층간 절연막(820)을 갖춘 소스 신호선(844, 845)를 갖는다. n-채널형 TFT(8204) 및 p-채널형 TFT(8205)의 각 드레인 영역은 그레인 배선(846)에 의해 전기적으로 연결된다.

참고번호(847)는 제 1 패시베이션막이다. 막두께는 10 nm – 1  $\mu$ m(바람직하게 200 – 500 nm)이다. 그 물질로는 실리콘을 포함하는 절연막(특히, 실리콘 질화산화막이나 실리콘질화물막이 바람직하다)이 사용될 수 있다. 패시베이션막(847)은 알칼리 금속 및 습기로부터 형성된 TFT를 보호하도록 동작한다. TFT 위에 마지막으로 배치된 EL층은 나트륨과 같은 알칼리 금속을 포함한다. 다른 말로 하면, 제 1 패시베이션막(847)은 또한 알칼리 금속(이동가능한 이온)이 TFT측에 들어가도록 허용하지 않는 보호층으로 동작한다.

참고번호(848)는 제 2 층간 절연막으로, TFT에 의해 형성된 레벨 차이를 평평하게 하는 평탄화막으로 동작한다. 바람직하게, 제 2 층간 절연막(848)으로는 폴리아미드, 폴리아미드, 아크릴 수지, 또는 BCB(benzocyclobutene)와 같은 유기 수지막이 사용된다. 유기 수지막은 양질의 매끄러운 평면이 쉽게 형성될 수 있고 유전 상수가 낮다는 이점을 갖는다. EL층이 거칠기에 매우 민감하기 때문에, 제 2 층간 절연막(848)을 통해 TFT에 의해 발생되는 레벨 차이를 완전히 흡수하는 것이 바람직하다. 부가하여, 게이트 신호선이나 데이터 신호선 및 EL 소자의 음극 사이에 형성된 기생 캐페시턴스를 감소하기 위해, 낮은 유전 상수의 물질을 두껍게 형성하는 것이 바람직하다. 그러므로, 바람직하게, 막의 두께는 0.5 – 5 (바람직하게 1.5 – 2.5  $\mu$ m)이다.

참고번호(849)는 투명한 도전성막으로 구성된 픽셀 전극(EL 소자의 양극)이다. 접촉 홀(개구)이 제 2 층간 절연막(848) 및 제 1 패시베이션막(847)에 이루어진 이후에, 전극은 개구를 통해 EL 구동 TFT(8202)의 드레인 배선(832)에 연결된다. 도 21에서와 같이, 픽셀 전극(849) 및 드레인 영역(827)이 직접 연결되지 않게 배열될 때, EL층의 알칼리 금속은 픽셀 전극을 통해 활성층으로 들어가지 않도록 방지된다.

두께가 0.3 – 1  $\mu$ m인 제3 층간 절연막(850)은 픽셀 전극(849)에 배치된다. 막(850)은 실리콘산화물막, 실리콘 질화산화막, 또는 유기 수지막으로 이루어진다. 제3 층간 절연막(850)에는 에칭으로 픽셀 전극(849)에 개구가 제공되고, 개구의 옛지는 테이퍼 형상을 갖도록 에칭된다. 바람직하게, 테이퍼의 각도는 10 – 60 °이다(바람직하게 30 – 50 °).

EL층(851)은 제3 층간 절연막(850)에 형성된다. EL층(851)은 단일층 구조 또는 적층 구조의 형태로 사용된다. 적층 구조는 발광 효율성이 뛰어나다. 일반적으로, 양의 홀 주입층/양의 홀 운송층/발광층/전자 운송층이 이 순서대로 픽셀 전극상에 형성된다. 대신에, 양의 홀 운송층/발광층/전자 운송층의 순서 또는 양의 홀 주입층/양의 홀 운송층/발광층/전자 운송층/전자 주입층의 순서를 갖는 구조가 사용될 수 있다. 본 발명에서는 공지된 구조 중 하나가 사용될 수 있고, 형광 칼라링 물질 등이 EL층에 도핑될 수 있다.

도 21의 구조는 RGB에 대응하는 3종류의 EL 소자를 형성하는 방법이 사용된 예이다. 도 21에서는 단 하나의 픽셀만이 도시된다. 사실상, 각각이 똑같은 구조를 갖는 픽셀은 적색, 녹색, 및 청색의 각 칼라에 대응하도록 형성되므로, 그에 의해 칼라 디스플레이가 실행될 수 있다. 본 발명은 휘도 방법에 관계없이 실행될 수 있다.

EL 소자의 음극(852)은 EL층(851)에 배치된다. 작은 일함수를 갖는 마그네슘(Mg), 리튬(Li), 또는 칼슘(Ca)을 포함하는 물질이 음극(852)으로 사용된다. 바람직하게, MgAg(Mg 및 Ag가 Mg:Ag = 10:1의 비율로 혼합된 물질)로 구성된 전극이 사용된다. 대신에, MgAgAl 전극, LiAl 전극, 또는 LiFAI 전극이 사용될 수 있다.

EL 소자(8206)는 픽셀 전극(양극)(849), EL층(851), 및 음극(852)으로 형성된다.

각 픽셀에 의해 각기 EL층(851) 및 음극(852)으로 구성된 층 본체를 형성할 필요가 있다. 그러나, EL층(851)은 매우 습기에 약하므로, 통상의 포토리소그라픽 기술이 사용될 수 없다. 그러므로, 금속 마스크와 같은 물리적 마스크 물질을 사용하여, 진공 증착법, 스퍼터링 방법, 또는 플라즈마 CVD 방법과 같은 기상 방법에 따라 이를 선택적으로 형성하는 것이 바람직하다.

또한, EL층을 선택적으로 형성하는 방법으로 잉크젯 방법, 스크린 프린팅 방법, 스플 코팅 방법 등을 사용하는 것이 가능하다. 그러나, 이들 방법은 기술의 현상태에서는 음극을 연속적으로 형성할 수 없기 때문에, 잉크젯 방법을 제외한 상기 방법이 바람직하다고 말할 수 있다.

참고번호(853)는 보호 전극이다. 이는 외부 습기 등으로부터 음극(852)을 보호하고, 동시에 각 픽셀의 음극(852)을 연결시키기 위한 것이다. 보호 전극(853)으로는 알루미늄(Al), 구리(Cu), 또는 은(Ag)을 포함하는 저저항 물질을 사용하는 것이 바람직하다. EL층의 열을 낮추는 냉각 효과는 보호 전극(853)으로부터 기대될 수 있다.

참고번호(854)는 제 2 패시베이션막이고, 바람직하게 그 막 두께는 10 nm – 1  $\mu$ m(바람직하게 200 – 500 nm)이다. 제 2 패시베이션막(854)을 배치하는 주요 목적은 습기로부터 EL층(851)을 보호하기 위한 것이다. 또한, 이에 냉각 효과를 제공하는 것이 효과적이다. 그러나, EL층은 상술된 바와 같이 열에 약하므로, 막 형성은 저온(바람직하게 실온에서 120도 범위)에서 실행되어야 한다. 그러므로, 바람직한 막 형성 방법은 플라즈마 CVD 방법, 스퍼터링 방법, 진공 증착법, 이온 플레이팅 방법, 또는 용액 적용 방법(스핀 코팅 방법)이라 말할 수 있다.

말할 필요도 없이, 도 21에 도시된 모든 TFT는 활성층으로 본 발명에서 사용되는 폴리실리콘막을 갖는다.

본 발명은 도 21의 EL 디스플레이 디바이스의 구조에 제한되지 않는다. 도 21의 구조는 본 발명을 동작시키는 바람직한 형태 중 하나일 뿐이다.

본 실시예에서 도시된 구조는 실시예 1 또는 실시예 2와 자유롭게 조합될 수 있다.

(실시예 5)

본 발명의 실시예는 픽셀 부분 및 그 픽셀 부분 주위의 구동기 회로 부분에서 TFT를 동시에 제작하는 방법을 설명한다. 구동기 회로에 대해, 도면에서는 간략한 설명을 위한 기본 유닛인 CMOS 회로가 도시된다.

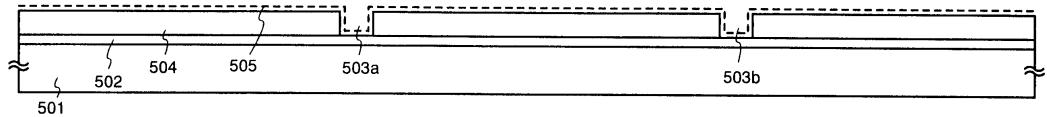

먼저, 표면상에 기저막(도시되지 않은)이 배치된 기판(501)이 도 8a에 도시된 바와 같이 준비된다. 본 실시예에서는 두께가 200 nm인 실리콘질화산화막과 두께가 100 nm인 또 다른 실리콘 질화산화막이 적층되어 결정화된 유리상에 기저막으로 사용된다. 이때, 바람직하게, 결정화된 유리 기판과 접촉하는 막의 질소 농도는 10 – 25 wt%로 유지된다. 물론, 기저막 없이 수정 기판 상에 직접 소자를 형성하는 것이 가능하다.

이어서, 두께가 45 nm인 비결정질 실리콘막(502)이 공지된 막 형성 방법에 의해 기판(501)상에 형성된다. 이를 비결정질 실리콘막으로 제한할 필요는 없다. 대신에, 본 실시예에서는 비결정질 구조를 갖는 반도체막(미세 결정 반도체막을 포함하는)이 사용될 수 있다. 비결정질 실리콘 게르마늄막과 같이, 비결정질 구조를 갖는 합성 반도체막이 여기에 사용될 수도 있다.

여기서부터 도 8c까지의 단계들에 대해, 본 출원인에 의해 출원된 일본 공개 특허 공보 제10-247735호를 완전히 인용하는 것이 가능하다. 이 공보는 Ni와 같은 원소를 촉매로 사용하여 반도체막을 결정화하는 방법에 대한 기술을 설명한다.

먼저, 개구(503a, 503b)을 갖는 보호막(504)이 형성된다. 본 실시예에서는 150 nm 두께의 실리콘산화물막이 사용된다. 니켈(Ni)을 포함하는 층(505)은 스플 코팅 방법에 의해 보호막(504)상에 형성된다. Ni을 포함하는 층의 형성에 대해, 상기 공보의 내용을 참고할 수 있다.

이어서, 도 8b에 도시된 바와 같이, 불활성 분위기에서 14 시간 동안 570 °C로 열처리가 실행되어, 비결정질 실리콘막(502)이 결정화된다. 이때, 결정화는 기관과 나란하게 Ni이 접촉된 영역(506a, 506b)(이후에 Ni 부가 영역이라 나타내지는)으로부터 시작되어 진행된다. 그 결과로, 막대형 결정이 얻어져 선을 형성하는 결정 구조를 갖는 폴리실리콘막(507)이 형성된다.

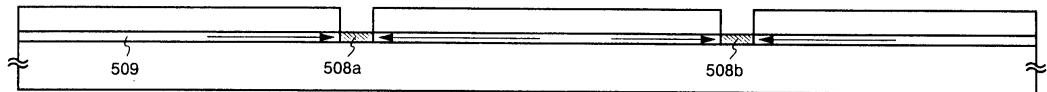

이후에, 도 8c에 도시된 바와 같이, 보호막(504)을 마스크로 남겨두면서, 15족에 속하는 원소(바람직하게 인)가 Ni 부가 영역(506a, 506b)에 부가된다. 그래서, 인이 고농도로 부가된 영역(508a, 508b)(이후 인 부가 영역이라 칭하여지는)이 형성된다.

이후에, 도 8c에 도시된 바와 같이 불활성 분위기에서 12 시간 동안 600 °C로 열처리가 실행된다. 폴리실리콘막(507)에 존재하는 Ni은 이 열 처리에 의해 이동되어, 화살표로 도시된 바와 같이, 거의 모두가 최종적으로 인 부가 영역(508a, 508b)에 의해 포착된다. 이는 인에 의한 금속 원소(본 실시예에서는 Ni)의 게터링 효과(gettering effect)로 발생된 현상이라 생각된다.

이 처리에 의해, 폴리실리콘막(509)에 남아있는 Ni의 농도는 SIMS(secondary ion-mass spectrography)에 의한 측정값에 따라 적어도  $2 \times 10^{17}$  atoms/cm<sup>3</sup>으로 감소된다. 비록 Ni가 반도체의 수명을 줄이지만, 이 범위로 감소될 때는 TFT 특성에 아무런 악영향도 주지 않는다. 부가하여, 이 농도는 기술의 현상태에서 SIMS 분석의 측정 한계이므로, 이는 더 낮은 농도( $2 \times 10^{17}$  atoms/cm<sup>3</sup> 이하)도 나타내게 된다.

그래서, 촉매에 의해 결정화되고 촉매가 TFT의 동작을 방해하지 않는 레벨로 감소된 폴리실리콘막(509)이 얻어질 수 있다. 이어서, 폴리실리콘막(509)만을 사용하는 활성층(510-513)이 패터닝(patterning) 처리에 의해 형성된다. 이때, 이어지는 패터닝에서 마스크 정렬을 실행하는 마커(marker)는 상기 폴리실리콘막을 사용해 형성되어야 한다(도 8d).

이어서, 도 8e에 도시된 바와 같이, 50 nm 두께의 실리콘 질화산화막이 플라즈마 CVD 방법에 의해 형성되고, 불활성 분위기에서 1 시간 동안 950 °C로 열처리를 실행하여, 열적 산화 처리가 실행된다. 산화 분위기는 산소 분위기이거나 할로겐이 부가된 또 다른 산소 분위기가 될 수 있다.

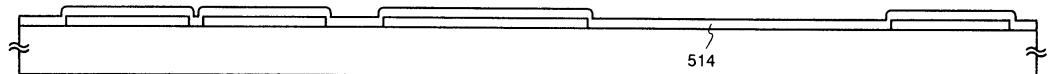

이 열적 산화 처리에서, 산화는 활성층과 실리콘질화산화막 사이의 인터페이스에서 진행되고, 두께가 약 15 nm인 폴리실리콘막이 산화되므로, 두께가 약 30 nm인 실리콘산화물막이 형성된다. 즉, 30 nm 두께의 실리콘산화물막(30)과 50 nm 두께의 실리콘 질화산화막(50)이 적층된 80 nm 두께의 게이트 절연막(514)이 형성된다. 활성층(510-513)의 막 두께는 열적 산화 처리에 의해 30 nm가 된다.

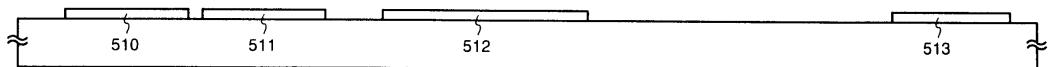

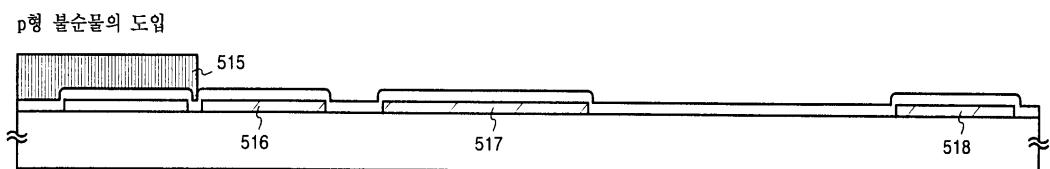

이어서, 도 9a에 도시된 바와 같이, 레지스트 마스크(resist mask)(515)가 형성되고, 게이트 절연막(514)의 매체를 통해 p형을 제공하는 불순물 원소(이후 p형 불순물 원소라 나타내지는)가 활성층(511 내지 513)에 부가된다. p형 불순물 원소로는 13-그룹에 속하는 원소, 대표적으로 봉소나 갈륨이 전형적으로 사용될 수 있다. 이는(채널 도핑 처리라 칭하여지는) TFT의 한계값 전압을 제어하는 처리이다.

본 실시예에서는 B<sub>2</sub>H<sub>6</sub>(diborane)의 질량 분리 없이 플라즈마 여기가 실행되는 이온 도핑 방법에 의해 봉소가 부가된다. 물론, 질량 분리를 실행하는 이온 주입 방법이 사용될 수 있다. 이 처리에 따라,  $1 \times 10^{15}$  내지  $1 \times 10^{18}$  atoms/cm<sup>3</sup>(대표적으로  $5 \times 10^{16}$  내지  $5 \times 10^{17}$  atoms/cm<sup>3</sup>)의 농도로 봉소를 포함하는 불순물 영역(516 내지 518)이 형성된다.

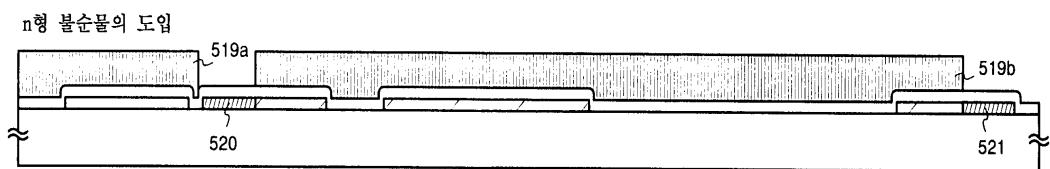

이어서, 도 9b에 도시된 바와 같이, 레지스트 마스크(519a, 519b)가 형성되고, 게이트 절연막(514)의 매체를 통해 n형을 제공하는 불순물 원소(이후 n형 불순물 원소라 나타내지는)가 부가된다. n형 불순물 원소로는 15-그룹에 속하는 원소, 대표적으로 인 또는 비소가 전형적으로 사용될 수 있다. 본 실시예에서는 PH<sub>3</sub>(phosphine)의 질량 분리 없이 플라즈마 여기가 실행되는 플라즈마 도핑 방법이 사용된다. 인은  $1 \times 10^{18}$  atoms/cm<sup>3</sup>의 농도로 부가된다. 물론, 질량 분리를 실행하는 이온 주입 방법이 사용될 수 있다.

선량(dose)은 n형 불순물 원소가  $2 \times 10^{16}$  –  $5 \times 10^{19}$  atoms/cm<sup>3</sup>(대표적으로  $5 \times 10^{17}$  –  $5 \times 10^{18}$  atoms/cm<sup>3</sup>)의 농도로 이 처리에 의해 형성된 n형 불순물 영역(520, 521)에 포함되도록 조정된다.

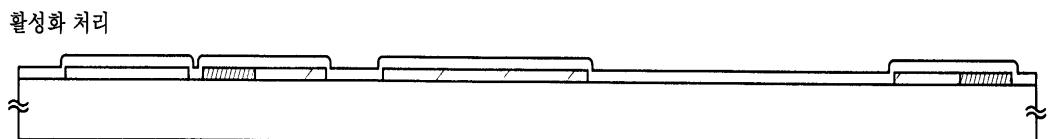

이어서, 도 9c에 도시된 바와 같이, 부가된 n형 불순물 원소 및 부가된 p형 불순물 원소를 활성화하기 위한 처리가 실행된다. 활성화 수단을 제한할 필요는 없지만, 게이트 절연막(514)이 배치되므로, 전자 열적로(electro-thermal furnace)를 사용하는 노 애닐링(furnace annealing) 처리가 바람직하다. 부가하여, 도 9a의 처리에서 채널 형성 영역인 일부의 게이트 절연막과 활성층 사이의 인터페이스를 손상했을 확률이 있기 때문에 가능한한 높은 온도로 열처리를 실행하는 것이 바람직하다.

본 실시예에서는 높은 열저항을 갖는 결정화된 유리가 사용되므로, 활성화 처리는 1시간 동안 800 °C로 노 애닐링에 의해 실행된다. 열적 산화가 산화 분위기로 처리 분위기를 유지하면서 실행되거나, 열처리가 비활성 분위기에서 실행될 수 있다.

이 처리는 n형 불순물 영역(520, 521)의 옛지, 즉 n형 불순물 영역(520, 521)과, n형 불순물 원소가 부가되지 않은 n형 불순물 영역(520, 521) 주위의 영역(도 9a의 처리에 의해 형성된 p형 불순물 영역) 사이의 경계(접합)을 뚜렷하게 한다. 이는 추후 TFT가 완성될 때, LDD 영역 및 채널 형성 영역이 뛰어난 접합을 형성할 수 있음을 의미한다.

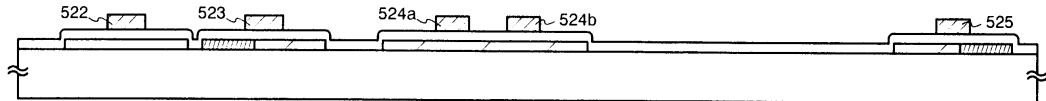

이어서, 200 – 400 nm 두께의 도전성막이 형성되고 패터닝이 실행되므로, 게이트 전극(522-525)이 형성된다. 게이트 전극(522 내지 525)의 폭에 따라, 각 TFT의 채널 길이가 결정된다.

게이트 전극은 단일층의 도전성막으로 구성될 수 있고, 바람직하게 필요한 경우 2층 또는 3층 막과 같은 적층막이 사용된다. 특별히, 알루미늄(Al), 탄탈(Ta), 티타늄(Ti), 몰리브덴(Mo), 텅스텐(W), 크롬(Cr), 및 실리콘(Si)으로 구성된 그룹에서 선택되는 원소의 막, 상술된 원소의 질화물 막(대표적으로 질화탄탈막, 질화텅스텐막, 또는 질화티타늄막), 상술된 원소가 조합된 합금막(대표적으로 Mo-W 합금 또는 Mo-Ta 합금), 또는 상술된 원소의 규화물막(대표적으로 규화텅스텐막 또는 규화티타늄막)이 사용될 수 있다. 이들은 물론 단일층 구조나 적층 구조를 가질 수 있다.

본 실시예에서는 50 nm 두께의 질화텅스텐(WN)막과 350 nm 두께의 텅스텐(W)막으로 구성된 적층막이 사용된다. 이는 스팍터링 방법에 의해 형성될 수 있다. 스팍터링 기체로 Xe 또는 Ne와 같은 불활성 기체를 부가함으로써, 스트레스(stress)에 의해 막이 벗겨지는 것을 방지할 수 있다.

이때, 게이트 전극(523, 525)은 그들 사이에 게이트 절연막(514)을 갖춘 n형 불순물(520, 521)의 쌍과 각각 중첩되도록 형성된다. 중첩된 부분은 추후 게이트 전극과 중첩되는 LDD 영역을 이룬다. 도면의 단면도에 따라, 게이트 전극(524a, 524b)은 분리된 것처럼 보이지만, 사실상으로는 서로 전기적으로 연결된다.

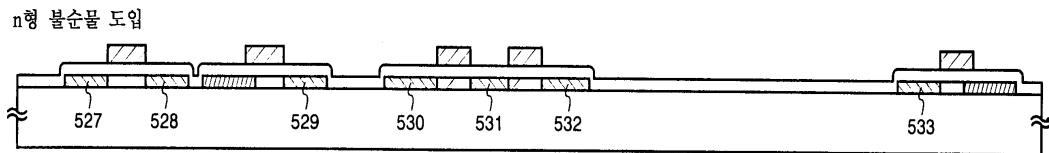

이어서, 게이트 전극(522-525)을 마스크로, n형 불순물 원소(본 실시예에서는 인)가 도 10a에 도시된 바와 자체적으로 조정 가능하게 부가된다. 이때, 조정은 이와 같이 형성된 불순물 영역에 인이 n형 불순물 영역(520, 521)의 농도의 1/2 – 1/10(대표적으로 1/3 – 1/4)인 농도로 부가되도록 실행된다. 바람직하게, 농도는  $1 \times 10^{16} – 5 \times 10^{18}$  atoms/cm<sup>3</sup>(전형적으로  $3 \times 10^{17} – 3 \times 10^{18}$  atoms/cm<sup>3</sup>)이다.

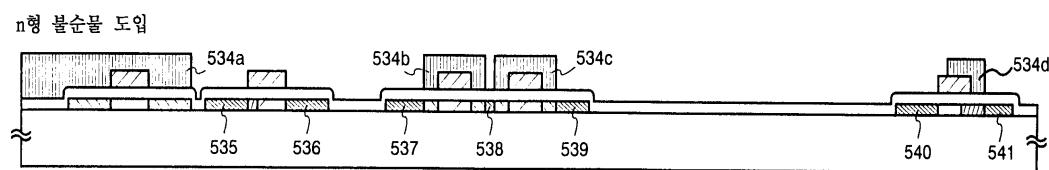

이어서, 도 10b에 도시된 바와 같이, 레지스터 마스크(534a-534d)가 게이트 전극을 덮도록 형성되고, n형 불순물 원소(본 실시예에서는 인)가 부가되고, 또한 높은 농도의 인을 포함하는 불순물 영역(535-541)이 형성된다. 여기서는 PH<sub>3</sub>를 사용하는 이온 도핑 방법이 적용되고, 조정은 이들 영역에서 인의 농도가  $1 \times 10^{20} – 1 \times 10^{21}$  atoms/cm<sup>3</sup>(대표적으로  $2 \times 10^{20} – 5 \times 10^{20}$  atoms/cm<sup>3</sup>)인 정도로 실행된다.

n-채널형 TFT의 소스 영역 또는 드레인 영역은 이 처리를 통해 형성되고, 스위칭 TFT는 도 10a의 처리에서 형성된 n형 불순물 영역(530-532) 중 일부를 남겨둔다. 남겨진 영역은 스위칭 TFT의 LDD 영역에 대응한다.

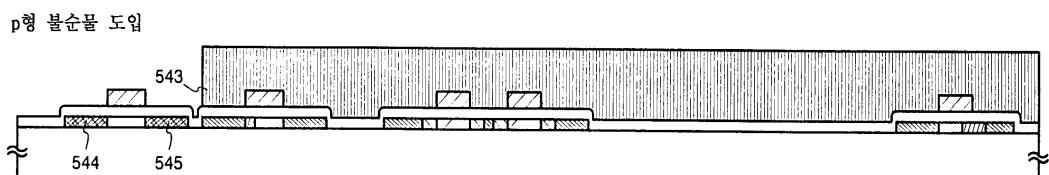

이어서, 도 10c에 도시된 바와 같이, 레지스트 마스크(534a-534d)가 제거되고, 레지스트 마스크(543)가 새롭게 형성된다. 이어서, p형 불순물 원소(본 실시예에서는 붕소)가 부가되어, 높은 농도의 붕소를 포함하는 불순물 영역(544, 545)이 형성된다. 여기서는 B<sub>2</sub>H<sub>6</sub>를 사용한 이온 도핑 방법에 따라, 붕소가 부가되어  $3 \times 10^{20} – 3 \times 10^{21}$  atoms/cm<sup>3</sup>(대표적으로  $5 \times 10^{20} – 1 \times 10^{21}$  atoms/cm<sup>3</sup>)의 농도를 얻는다.

인은  $1 \times 10^{20} - 1 \times 10^{21}$  atoms/cm<sup>3</sup>의 농도로 불순물 영역(544, 545)에 이미 부가되었다. 여기서 부가된 봉소는 적어도 부가된 인 농도의 3배이다. 그러므로, 미리 형성된 n형의 불순물 영역은 p형으로 완전히 변하여, p형 불순물 영역으로 동작한다.

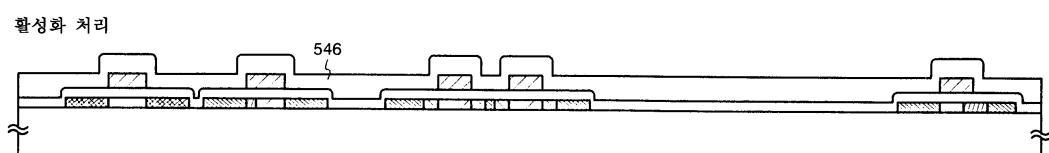

이어서, 도 10d에 도시된 바와 같이, 레지스트 마스크(543)가 제거되고, 제 1 층간 절연막(546)이 형성된다. 제 1 층간 절연막(546)으로는 실리콘을 포함하는 절연막이 단일층 구조 또는 그의 조합인 적층 구조의 형태로 사용된다. 막의 두께는 400 nm – 1.5  $\mu\text{m}$ 이다. 본 실시예에서는 200 nm 두께의 실리콘 질화산화막에 800 nm 두께의 실리콘산화물막이 적층된 구조가 생성된다.

이어서, 각 농도로 부가된 n형 또는 p형 불순물 원소가 활성화된다. 활성화 수단으로는 노 애닐링방법이 바람직하다. 본 실시예에서는 열 처리가 550 °C로 4 시간 동안 질소 분위기에서 전자 열적 노내에 실행된다.

열 처리는 또한 수소화를 위해 3 – 100%의 수소를 포함하는 분위기에서 1 – 12 시간 동안 300 – 450 °C로 실행된다. 이는 열적으로 여기된 수소에 의해 반도체막의 쌍을 이루지 않은 연결자를 수소로 종료시키는 처리이다. 또 다른 수소화 수단으로는 플라즈마 수소화(플라즈마에 의해 여기되는 수소가 사용되는)가 실행될 수 있다.

수소화는 제 1 층간 절연막(546)의 형성 동안 실행될 수 있다. 보다 상세하게, 200 nm 두께의 실리콘 질화산화막이 형성되고, 상술된 바와 같이 수소화가 실행되어, 나머지 800 nm 두께의 실리콘산화물막이 형성될 수 있다.

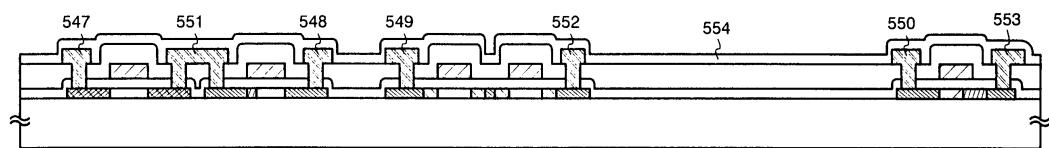

이어서, 도 11a에 도시된 바와 같이, 제 1 층간 절연막(546)에 접촉 홀이 만들어지고, 소스 배선(547-550) 및 드레인 배선(551-553)이 형성된다. 본 실시예에서, 이 전극은 100 nm 두께의 Ti 막, Ti를 포함하는 300 nm 두께의 알루미늄막, 및 150 nm 두께의 Ti 막이 스퍼터링 방법에 따라 연속적으로 형성된 3층 구조의 적층막으로 형성된다.

이어서, 제 1 패시베이션막(554)이 50 – 500 nm 두께로(대표적으로 200 – 300 nm 두께로) 형성된다. 본 실시예에서는 제 1 패시베이션막(554)으로 300 nm 두께의 실리콘 질화산화막이 사용된다. 이는 실리콘질화물막으로 대치될 있다.

이때, 실리콘 질화산화막을 형성하기 이전에 H<sub>2</sub> 또는 NH<sub>3</sub>와 같이 수소를 포함하는 기체를 사용해 플라즈마 처리를 실행하는 것이 효과적이다. 이 예비 처리에 의해 여기된 수소는 제 1 층간 절연막(546)에 공급되고, 열 처리를 통해, 제 1 패시베이션막(554)의 질이 개선된다. 동시에, 제 1 층간 절연막(546)에 부가된 수소가 하단층으로 확산되므로, 활성층이 효과적으로 수소화될 수 있다.

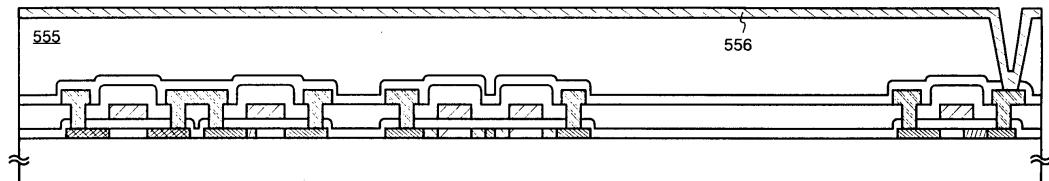

이어서, 도 11b에 도시된 바와 같이, 유기 수지로 구성된 제 2 층간 절연막(555)이 형성된다. 유기 수지로는 폴리이미드, 아크릴 섬유, 또는 BCB(benzocyclobutene)이 사용될 수 있다. 특별히, 제 2 층간 절연막(555)이 TFT에 의해 형성된 레벨 차이를 평평하게 하도록 요구되므로, 매끄러움이 뛰어난 아크릴 섬유가 바람직하다. 본 실시예에서, 아크릴 섬유는 2.5  $\mu\text{m}$ 의 두께로 형성된다.

이어서, 드레인 배선(553)에 이르는 접촉 홀이 제 2 층간 절연막(555) 및 제 2 패시베이션막(553)에 만들어지고, 보호 전극(556)이 형성된다. 거의 알루미늄으로 이루어진 도전성막은 보호 전극(556)으로 사용될 수 있다. 보호 전극(556)은 진공 증착법에 의해 이루어질 수 있다.

이어서, 실리콘을 포함하는 절연막(본 실시예에서는 실리콘산화물막)이 500 nm 두께로 형성되고, 픽셀 전극에 대응하는 위치에 개구가 형성되고, 또한 제3 층간 절연막(557)이 형성된다. 개구가 형성될 때 습식 에칭 방법을 사용하여 기울어진 측벽을 쉽게 형성하는 것이 가능하다. 개구의 측벽이 충분하게 완만한 기울기를 갖지 않으면, 레벨 차이에 의해 발생되는 EL층의 저하가 중요한 문제를 일으킬 것이다.

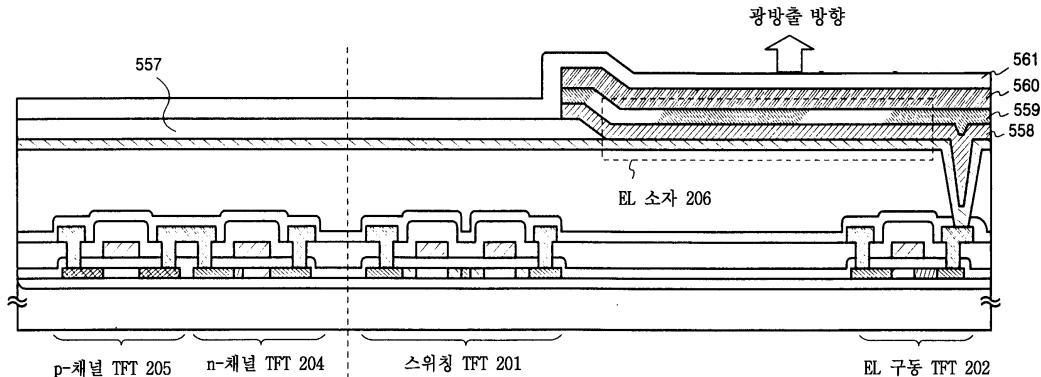

이어서, 음극(MgAg 전극)(558)은 진공 증착법에 의해 연속적으로 형성된다. 바람직하게, 음극(558)의 두께는 180 – 300 nm(전형적으로 200 – 250 nm)이다.

다음에는 진공 증착법에 의해 공기 노출 없이 EL층(559)이 만들어진다. EL층(559)의 막 두께는 800 – 200 nm(전형적으로 100 – 120 nm)이고, 픽셀 전극(양극)(560)의 두께는 100 nm가 될 수 있다.

이 처리에서, EL층 및 픽셀 전극(양극)은 적색에 대응하는 픽셀, 녹색에 대응하는 픽셀, 및 청색에 대응하는 픽셀에 대해 순차적으로 형성된다. 그러나, EL층은 그 용해(solution) 공차가 작으므로, 포토리쏘그래피 기술을 사용하지 않고 각 칼라에 대해 독립적으로 형성되어야 한다. 그래서, 금속 마스크를 사용하여 원하는 것을 제외한 픽셀을 가리고 원하는 픽셀에 대해 EL층 및 픽셀 전극(양극)을 선택적으로 형성하는 것이 바람직하다.

상세하게, 먼저 적색에 대응하는 픽셀을 제외한 모든 픽셀을 가리도록 마스크가 설정되고, 적색 휘도의 EL층 및 픽셀 전극(양극)이 그 마스크에 의해 선택적으로 형성된다. 이어서, 녹색에 대응하는 픽셀을 제외한 모든 픽셀을 가리도록 마스크가 설정되고, 녹색 휘도의 EL층 및 픽셀 전극(양극)이 그 마스크에 의해 선택적으로 형성된다. 이어서, 상기와 같이, 청색에 대응하는 픽셀을 제외한 모든 픽셀을 가리도록 마스크가 설정되고, 청색 휘도의 EL층 및 픽셀 전극(양극)이 그 마스크에 의해 선택적으로 형성된다. 이 경우, 다른 마스크는 각 칼라에 대해 사용된다. 대신에, 그들에 대해 똑같은 마스크가 사용될 수 있다. 바람직하게, EL층 및 픽셀 전극(양극)이 모든 픽셀에 대해 형성될 때까지 진공 상태를 깨지 않고 처리가 실행된다. 바람직하게, 이는 EL층 및 픽셀 전극(양극)이 형성된 이후에 공기 노출 없이 연속적으로 형성된다.

EL층(559)으로는 공지된 물질이 사용될 수 있다. 바람직하게, 공지된 물질로는 구동 전압을 고려한 유기 물질이 있다. 예를 들면, EL층은 양의 홀 주입층, 양의 홀 운송층, 발광층, 및 전자 주입층으로 구성된 4개 층의 구조로 형성될 수 있다. 또한, 픽셀 전극(음극)(560)의 EL 소자로, 산화인듐 및 산화주석(ITO) 막이 형성된다. 2 - 20%의 산화아연(ZnO)과 혼합된 투명 도전층이 산화인듐 대신 사용될 수 있다. 다른 공지된 물질이 사용될 수 있다.

마지막으로, 실리콘질화물막으로 형성된 제 2 패시베이션막(561)이 300 nm 두께로 형성된다.

도 11c에 도시된 바와 같이 구성된 EL 디스플레이 디바이스가 완성된다. 실제로, 바람직하게, 디바이스는 도 11c에 도시된 바와 같이 완성될 때 공기에 노출되지 않게 하기 위해 고기밀 보호막(적층막, 자외선 경합 수지막 등) 또는 세라믹 밀봉캔과 같은 하우징 물질에 의해 패키징(밀봉)된다. 그 상황에서, 하우징 물질의 내부를 불활성 분위기로 만들거나 그 안에 흡습성 물질(예를 들면, 산화바륨)을 배치함으로써 EL층의 신뢰성(수명)이 개선된다.

예를 들어, 패키징에 의해 기밀성을 개선한 이후에, 기판 상에 형성된 회로나 소자로부터 주어지는 단자를 외부 신호 단자에 연결하기 위한 연결기(FPC: flexible print circuit)가 부착되어, 제품이 완성된다. 본 명세서에서, 이와 같이 판매 준비가 된 EL 디스플레이 디바이스는 EL 모듈(module)이라 칭하여진다.

본 실시예에서 도시된 구조는 실시예 1 또는 실시예 2와 자유롭게 조합될 수 있다.

(실시예 6)

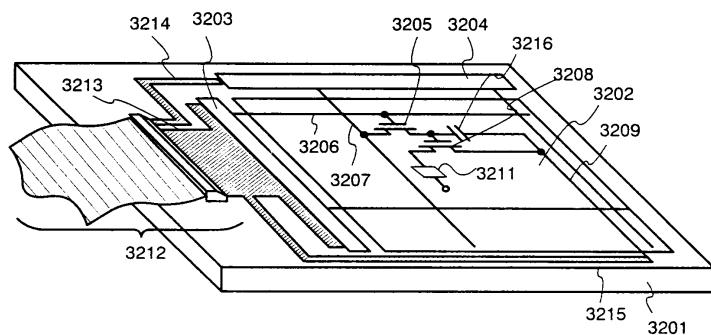

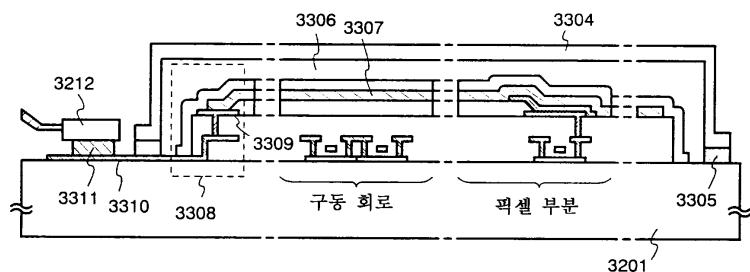

실시예 6에서는 도 12의 투시도를 사용하여 EL 디스플레이의 구조가 설명된다.

유리 기판(3201)에 형성되는 실시예 6에 따른 EL 디스플레이에는 픽셀 부분(3202), 게이트 신호측 구동기 회로(3203), 및 소스 신호측 구동기 회로(3204)를 구비한다. 픽셀 부분(3202)의 스위칭 TFT(3205)는 n-채널형 TFT이고, 게이트 신호측 구동기 회로(3203)에 연결된 게이트 신호선(3206) 및 소스 신호측 구동기 회로(3204)에 연결된 소스 신호선(3207)의 교차 지점에 배열된다. 더욱이, 스위칭 TFT(3205)의 드레인 영역은 EL 구동 TFT(3208)의 게이트에 연결된다.

더욱이, EL 구동 TFT(3208)의 소스 영역은 전원 공급선(3209)에 연결된다. 또한, 전원 공급선(3209) 및 EL 구동 TFT(3208)의 게이트 영역에 연결된 캐패시터(3216)가 제공된다. 실시예 6에서, 전원 전위는 전원 공급선(3209)에 인가된다. 부가하여, EL 소자(3211)의 반대 전극(실시예 6에서는 음극)은 이 정상 전위(실시예 6에서는 0 V)로 유지된다.

이후, 외부 입력 및 출력 단자로서 작용하는 FPC(3212) 상에는 구동기 회로에 신호를 전송하는 입력 및 출력 배선(연결 배선)(3213, 3214)과 전원 공급선(3209)에 연결된 입력 및 출력 배선(3215)이 제공된다.

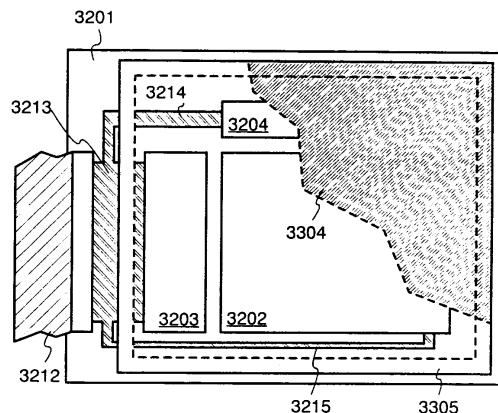

더욱이, 하우징 물질을 포함하는 실시예 6에 따른 EL 모듈은 도 13a 및 도 13b를 사용해 설명된다. 필요에 따라, 도 12에서 사용된 참고번호가 언급됨을 주목한다.

유리 기판(3201)상에는 픽셀 부분(3202), 게이트 신호측 구동기 회로(3203), 및 소스 신호측 구동기 회로(3204)가 형성된다. 각 구동기 회로로부터의 각 배선 종류는 입력 및 출력 배선(3213 내지 3215)을 통해 FPC(3212)로 연장되어 외부 디바이스에 연결된다.

이 때, 하우징 물질(3304)은 적어도 픽셀 부분(3202), 바람직하게 구동기 회로(3203, 3204) 및 픽셀 부분(3302)이 하우징 물질(3304)로 둘러싸이는 방식으로 제공된다. 하우징 물질(3304)은 EL 소자의 외부 지름 보다 더 큰 내부 지름을 갖는 오목 부분을 갖는 구성이거나 시트(sheet) 구성을 가지므로, 하우징 물질은 유리 기판(3201)과 함께 폐쇄 공간을 형성하는 방식으로 접착제(3305)에 의해 유리 기판(3201)에 고정됨을 주목한다. 이 때, EL 소자는 폐쇄된 공간에서 밀폐되므로 외부 분위기로부터 완전히 차폐된다. 하우징 물질(3304)은 복수로 제공될 수 있음을 주목한다.

더욱이, 하우징 물질(3304)의 재료 품질은 바람직하게 유리, 폴리머 등과 같은 절연 물질이다. 예를 들면, 비결정질 유리(붕규산 유리(borosilicate glass), 수정 등), 결정질 유리, 세라믹 유리, 유기 수지(아크릴 수지, 스티렌(styrene) 수지, 폴리카보네이트(polycarbonate) 수지, 에폭시(epoxy) 수지 등), 및 실리콘 수지가 주어질 수 있다. 더욱이, 접착제(3305)가 절연 물질일 때, 스테인레스 합금 등과 같은 금속 물질이 또한 사용될 수 있다.

더욱이, 접착제 에폭시 수지, 아크릴 수지 등이 접착제(3305)의 물질로 사용될 수 있다. 또한, 접착제로 열경화(thermosetting) 수지 및 광경화(light-setting) 수지를 사용하는 것이 가능하다. 그러나, 가능한한 많이 산소나 습기가 스며들지 않는 물질일 것이 요구된다.

더욱이, 하우징 물질(3304)과 유리 기판(3201) 사이의 갭(gap)(3306)은 불활성 기체(아르곤, 헬륨, 질소 등)로 채워지는 것이 바람직하다. 그 외에, 기체에 부가하여 불활성 액체(페플루오로알칸(perfluoroalkane)으로 나타내지는 액상 불화탄소 등)를 사용하는 것이 가능하다. 불활성 액체에 대해, 일본 특허 출원 공개 제 8-78519호에서 사용된 물질이 사용될 수 있다.

더욱이, 갭(3306)에 건조제를 제공하는 것이 효과적이다. 건조제로는 일본 특허 출원 공개 제9-148006호에서 설명된 물질이 사용될 수 있다. 일반적으로 산화바륨이 사용된다.

도 13b에 도시된 바와 같이, 픽셀 부분에는 각각 EL 소자를 고립시킨 복수의 픽셀이 제공됨을 주목한다. 이들 픽셀은 모두 공통 전극으로 보호 전극(3307)을 갖는다. 실시예 6에서는 바람직하게 EL층, 음극(MgAg 전극), 및 보호 전극이 공기 배출 없이 연속적으로 형성되는 것으로 설명된다. 비록 EL층 및 음극은 똑같은 마스크 물질로 형성되지만, 보호 전극만은 다른 마스크 물질로 형성될 수 있다.

이 때, EL층 및 음극은 픽셀 부분에서만 제공될 필요가 있다. EL층 및 음극이 구동기 회로에 제공되도록 요구되지 않는다. 말할 필요도 없이, EL층 및 음극이 구동기 회로에 제공될 때에도 아무런 문제가 발생되지 않는다. EL층이 알칼리 금속을 포함한다고 생각될 때는 바람직하게, EL층 및 음극이 구동기 회로에 제공되지 않는다.

보호 전극(3307)은 참고번호(3308)로 도시된 영역에서 픽셀 전극과 똑같은 물질로 형성된 연결 배선(3309)을 통해 입력 및 출력 배선(3310)에 연결됨을 주목한다. 입력 및 출력 배선(3310)은 전원 전위를 보호 전극(3307)에 인가하기 위한 전원 공급선으로, 도전성 페이스트(paste) 물질(3311)을 통해 FPC(3212)에 연결된다.

실시예 6에 도시된 구조는 실시예 1과 자유롭게 조합되어 실행될 수 있다.

(실시예 7)

실시예 7에서는 본 발명에 따른 EL 디스플레이의 픽셀 구조가 설명된다.

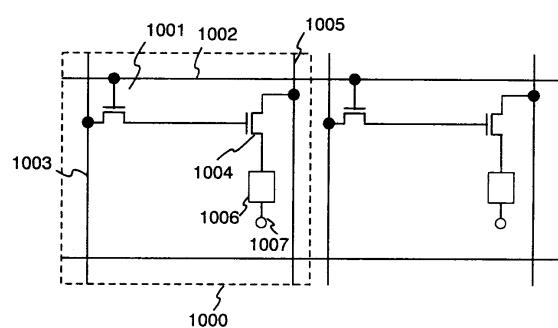

본 발명에 따른 EL 디스플레이의 픽셀 부분에서는 복수의 픽셀이 매트릭스형의 구조로 배열된다. 도 17a는 픽셀의 회로도에 대한 예를 도시한다. 픽셀(1000)에서는 도 17a에서 스위칭 TFT(1001)가 제공된다. 본 발명에서는 스위칭 TFT(1001)로 n-채널형 TFT 또는 p-채널형 TFT가 사용될 수 있음을 주목한다. 도 17a에서는 스위칭 TFT(1001)로 n-채널형 TFT가 사용된다. 스위칭 TFT(1001)의 게이트 전극은 게이트 신호를 입력하는 게이트 신호선(1002)에 연결된다. 스위칭 TFT(1001)의 소스 영역 및 드레인 영역 중 하나는 아날로그 또는 디지털 비디오 신호를 입력하기 위한 데이터 신호선(또한 소스 신호선이라 칭하여지는)에 연결되고, 다른 하나는 EL 구동 TFT(1004)의 게이트 전극에 연결된다.

EL 구동 TFT(1004)의 소스 영역 및 드레인 영역 중 하나는 전원 공급선(1005)에 연결되고, 다른 하나는 EL 소자(1006)에 연결된다.

EL 소자(1006)는 양극, 음극, 및 양극과 음극 사이에 제공된 EL층을 구비한다. 본 발명에 따라, 양극이 픽셀 전극이고 음극이 반대 전극인 경우, EL 구동 TFT(1004)의 소스 영역 또는 드레인 영역은 EL 소자(1006)의 양극에 연결됨을 주목한다. 반대로, 양극이 반대 전극이고 음극이 픽셀 전극인 경우에는 EL 구동 TFT의 소스 영역 또는 드레인 영역이 EL 소자(1006)의 음극에 연결된다. EL 구동 TFT(1004)로는 n-채널형 TFT 또는 p-채널형 TFT가 사용될 수 있음을 주목한다. 그러나, EL 소자(1006)의 양극이 픽셀 전극이고 음극이 반대 전극인 경우에는 EL 구동 TFT(1004)가 p-채널형 TFT인 것이 바람직하다. 더욱이, 반대로, EL 소자(1006)의 양극이 반대 전극이고 음극이 픽셀 전극인 경우에는 EL 구동 TFT(1004)가 n-채널형 TFT인 것이 바람직하다. 도 17a에서는 EL 구동 TFT(1004)로 p-채널형 TFT가 사용된다. EL 소자(1006)의 음극은 정상 전원(1007)에 연결된다.

더욱이, LDD 영역은 EL 구동 TFT(1004)의 활성층에 제공되고, LDD 영역과 게이트 전극이 게이트 절연막을 통해 중첩되는 영역(Lov 영역)이 형성될 수 있다. EL 구동 TFT(1004)가 특별히 n-채널형 TFT인 경우, Lov 영역은 활성층의 드레인 영역측에 형성되므로, on 전류가 증가될 수 있고, EL 구동 TFT(1004)의 게이트 전극과 Lov 영역 사이에 용량이 더 형성될 수 있다.

더욱이, 스위칭 TFT(1001)가 비선택 상태(off 상태)로 설정되는 경우, EL 구동 TFT(1004)의 게이트 전압을 유지하도록 캐패시터가 제공된다. 캐패시터가 제공되는 경우, 캐패시터는 소스 신호선에 연결되지 않은 스위칭 TFT(1001)의 소스 영역 또는 드레인 영역측과 전력 공급선(1005) 사이에 연결된다. 도 17a에 도시된 회로도에서, 전원 공급선(1005)은 소스 신호선(1003)과 평행하게 배열된다.

EL 구동 TFT(1004)의 게이트 전압을 유지하기 위한 캐패시터로 EL 구동 TFT의 Lov 영역을 사용하기 위해서는 픽셀 크기가  $22 \mu\text{m} \times 22 \mu\text{m}$ 이고, 게이트 절연막의 두께가  $800 \text{ \AA}$ 이고, 또한 게이트 절연막의 상대적인 유전 상수가 4.1인 경우, 약  $19.8 \text{ fF}$ 의 용량값이 요구된다. 결과적으로, Lov 영역의 면적(LDD 영역 및 게이트 전극이 게이트 절연막을 통해 중첩되는 면적)으로, 약  $66 \mu\text{m}^2$ 의 면적이 요구된다.

도 17a에 도시된 회로도에서, 스위칭 TFT(1001) 또는 EL 구동 TFT(1004)가 다중-게이트 구조(직렬로 연결된 2개 이상의 채널 형성 영역을 갖는 활성층을 포함하는 구조)로 형성될 수 있음을 주목한다. 도 18a는 도 17a에 도시된 픽셀의 스위칭 TFT(1001)가 다중-게이트 구조로 형성되는 픽셀의 회로도를 도시한다.

스위칭 TFT(1001a) 및 스위칭 TFT(1001b)는 직렬로 연결되어 도 18a에 제공된다. 스위칭 TFT(101a) 및 스위칭 TFT(1001b)을 제외하고, 그 구조는 도 17a에 도시된 회로도와 똑같다. 스위칭 TFT를 다중-게이트 구조(직렬로 연결된 2개 이상의 채널 형성 영역을 갖는 활성층을 포함하는 구조)로 형성함으로써, off 전류가 감소될 수 있다. 도 18a에서는 이중-게이트 구조가 채택됨을 주목한다. 그러나, 실시예 7은 이중-게이트에 제한되지 않는다. 다중-게이트 구조가 사용될 수 있다.

그외에, 도시되지는 않았지만, EL 구동 TFT가 다중-게이트 구조로 형성되는 경우, 열에 의한 EL 구동 TFT의 저하가 억제될 수 있다.

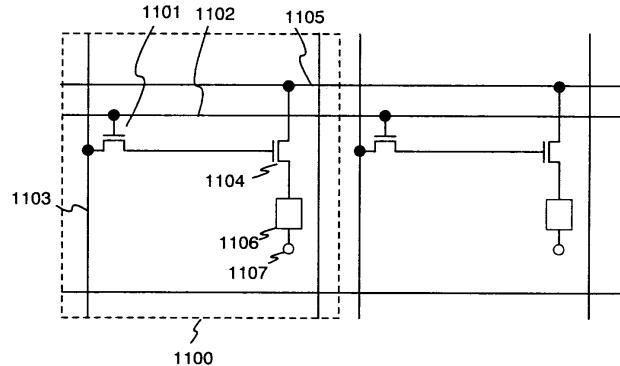

다음에, 도 17b는 본 발명에 따른 픽셀의 회로도에 대한 또 다른 예를 도시한다. 도 17b에서, 스위칭 TFT(1101)는 픽셀(1100)에 제공된다. 본 실시예에서는 n-채널형 TFT 또는 p-채널형 TFT가 스위칭 TFT(1101)로 사용될 수 있음을 주목한다. 도 17b에서는 n-채널형 TFT가 스위칭 TFT(1101)로 사용된다. 스위칭 TFT(1101)의 게이트 전극은 게이트 신호를 입력하기 위한 게이트 신호선(1102)에 연결된다. 스위칭 TFT(1101)의 소스 영역 및 드레인 영역 중 하나는 아날로그 또는 디지털 비디오 신호를 입력하기 위한 디지털 데이터 신호선(또한 소스 신호선이라 칭하여지는)(1103)에 연결되고, 다른 하나는 EL 구동 TFT(1104)의 게이트 전극에 연결된다.

이어서, EL 구동 TFT(1104)의 소스 영역 및 드레인 영역 중 하나는 전원 공급선(1105)에 연결되고, 다른 하나는 EL 소자(106)에 연결된다.

EL 소자(1106)는 양극, 음극, 및 양의 층과 음의 층 사이에 제공된 EL층을 구비한다. 본 발명에서, 양극이 픽셀 전극이고 음극이 반대 전극인 경우, EL 구동 TFT(1104)의 소스 영역 또는 드레인 영역은 EL 소자(1106)의 양극에 연결됨을 주목한다. 반대로, 양극이 반대 전극이고 음극이 픽셀 전극인 경우에는 EL 구동 TFT(1104)의 소스 영역 또는 드레인 영역이 EL 소자(1106)의 음극에 연결된다. EL 구동 TFT(1104)로는 n-채널형 TFT 또는 p-채널형 TFT가 사용될 수 있음을 주목한다. 그러나, EL 소자(1106)의 양극이 픽셀 전극이고 음극이 반대 전극인 경우에는 EL 구동 TFT(1104)가 p-채널형

TFT인 것이 바람직하다. 더욱이, 반대로, EL 소자(1106)의 양극이 반대 전극이고 음극이 픽셀 전극인 경우에는 EL 구동 TFT(1104)가 n-채널형 TFT인 것이 바람직하다. 도 17b에서는 EL 구동 TFT(1104)로 p-채널형 TFT가 사용된다. EL 소자(1106)의 음극은 정상 전원(1107)에 연결된다.

그외에, LDD 영역은 EL 구동 TFT(1104)의 활성층에 제공되므로, LDD 영역과 게이트 전극이 게이트 절연막을 통해 중첩되는 영역(Lov 영역)이 형성될 수 있다. EL 구동 TFT(1104)가 특별히 n-채널형 TFT인 경우, Lov 영역을 활성층의 드레인 영역측에 형성함으로써, on 전류가 증가될 수 있다. 더욱이, EL 구동 TFT(1104)의 게이트 전극과 Lov 영역 사이에 용량이 더 형성될 수 있다.

더욱이, 스위칭 TFT(1101)가 비선택 상태(off 상태)로 설정되는 경우, EL 구동 TFT(1104)의 게이트 전압을 유지하도록 캐패시터가 제공된다. 캐패시터가 제공되는 경우, 캐패시터는 소스 신호선에 연결되지 않은 스위칭 TFT(1101)의 소스 영역 또는 드레인 영역측과 전력 공급선(1105) 사이에 연결된다. 도 17b에 도시된 회로도에서, 전원 공급선(1105)은 게이트 신호선(1102)과 평행하게 배열된다.

도 17b에 도시된 회로도에서, 스위칭 TFT(1101)나 EL 구동 TFT(1104)는 다중-게이트 구조로 형성될 수 있음을 주목한다. 도 18b는 도 17b에 도시된 픽셀의 스위칭 TFT(1101)가 다중-게이트 구조로 형성된 픽셀의 회로도를 도시한다.

스위칭 TFT(1101a) 및 스위칭 TFT(1101b)는 직렬로 연결되어 제공된다. 스위칭 TFT(1101a, 1001b)을 제외하고, 그 구조는 도 17a에 도시된 회로도와 똑같다. 스위칭 TFT를 다중-게이트 구조로 형성함으로써, off 전류가 낮추어질 수 있다. 도 18a 및 도 18b에서는 이중-게이트 구조가 채택됨을 주목한다. 그러나, 실시예는 이중-게이트에 제한되지 않는다. 다중-게이트 구조가 사용될 수 있다.

그외에, 도시되지는 않았지만, EL 구동 TFT가 다중-게이트 구조로 형성되는 경우, 열에 의한 EL 구동 TFT의 저하가 억제될 수 있다.

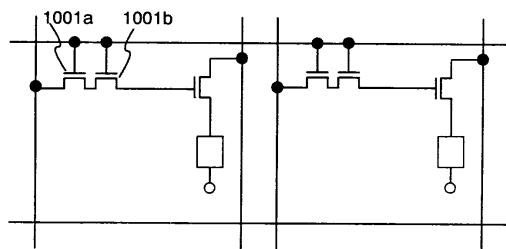

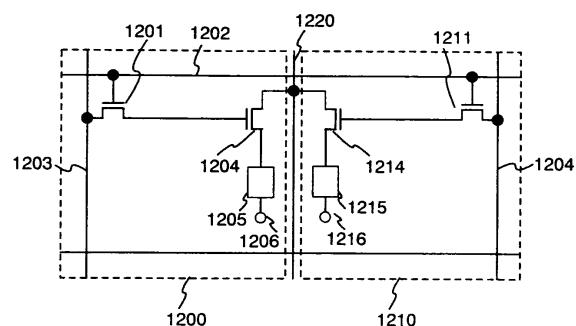

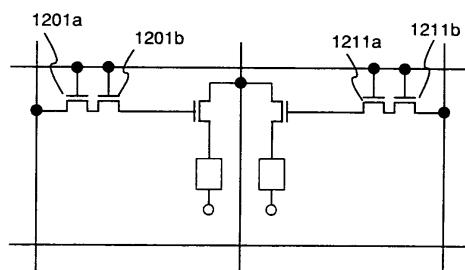

다음에, 도 19a는 본 발명에 따른 픽셀의 회로도에 대한 또 다른 예를 도시한다. 도 19a에서, 픽셀(1200) 및 픽셀(1210)은 서로 인접하게 제공된다. 도 19a에서, 참고번호(1201, 1211)은 스위칭 TFT를 나타낸다. 본 실시예에서는 스위칭 TFT(1201, 1211)로 n-채널형 TFT 또는 p-채널형 TFT가 사용될 수 있음을 주목한다. 도 19a에서는 n-채널형 TFT가 스위칭 TFT(1201) 및 스위칭 TFT(1211)로 사용된다. 스위칭 TFT(1201, 1211)의 게이트 전극은 게이트 신호를 입력하기 위한 게이트 신호선(1202)에 연결된다. 스위칭 TFT의 소스 영역 및 드레인 영역 중 하나는 아날로그(1203) 또는 디지털 비디오 신호(1204)를 입력하기 위한 데이터 신호선(또한 소스 신호선이라 칭하여지는)에 연결되고, 다른 하나는 EL 구동 TFT(1204, 1214)의 게이트 전극에 각각 연결된다.

이어서, EL 구동 TFT(1204, 1214)의 소스 영역 및 드레인 영역 중 하나는 전원 공급선(1220)에 연결되고, 다른 하나는 EL 소자(1205, 1215)에 각각 연결된다. 이러한 방식으로, 실시예 7에서는 2개의 인접한 픽셀이 하나의 전원 공급선(1220)을 공유한다. 결과적으로, 도 17a 내지 도 18b에 도시된 구조와 비교해, 전원 공급선의 수가 감소될 수 있다. 전체 픽셀 부분에 대한 배선의 비율이 작을 때, 배선이 EL층의 발광 방향으로 제공되는 경우 배선에 의한 광차폐가 억제될 수 있다.

EL 소자(1205, 1215)는 양극, 음극, 및 양극과 음극 사이에 제공된 EL층을 각각 구비한다. 본 발명에 따라, 양극이 픽셀 전극이고 음극이 반대 전극인 경우, EL 구동 TFT(1204, 1214)의 소스 영역 또는 드레인 영역은 EL 소자(1205, 1215)의 양극에 연결됨을 주목한다. 반대로, 양극이 반대 전극이고 음극이 픽셀 전극인 경우에는 EL 구동 TFT(1204, 1214)의 소스 영역 또는 드레인 영역이 EL 소자(1205, 1215)의 음극에 연결된다. EL 구동 TFT(1204, 1214)로는 n-채널형 TFT 또는 p-채널형 TFT가 사용될 수 있음을 주목한다. 그러나, EL 소자(1205, 1215)의 양극이 픽셀 전극이고 음극이 반대 전극인 경우에는 EL 구동 TFT(1204, 1214)가 p-채널형 TFT인 것이 바람직하다. 그외에, 반대로, EL 소자(1205, 1215)의 양극이 반대 전극이고 음극이 픽셀 전극인 경우에는 EL 구동 TFT(1204, 1214)가 n-채널형 TFT인 것이 바람직하다. 도 19a에서는 EL 구동 TFT(1204, 1214)로 p-채널형 TFT가 사용된다. EL 소자(1205, 1215)의 음극은 정상 전원(1206, 1216)에 연결된다.

그외에, LDD 영역은 EL 구동 TFT(1204, 1214)의 활성층에 제공되므로, LDD 영역과 게이트 전극이 게이트 절연막을 통해 중첩되는 영역(Lov 영역)이 형성될 수 있다. EL 구동 TFT(1204)가 특별히 n-채널형 TFT인 경우, Lov 영역을 활성층의 드레인 영역측에 형성함으로써, on 전류가 증가될 수 있고, 그 결과로, EL 구동 TFT(1204)의 게이트 전극과 Lov 영역 사이에 용량이 형성될 수 있다.

더욱이, 스위칭 TFT(1201, 1211)가 비선택 상태(off 상태)로 설정될 때, EL 구동 TFT(1204, 1214)의 게이트 전압을 유지하도록 캐패시터가 제공된다. 캐패시터가 제공되는 경우, 캐패시터는 소스 신호선에 연결되지 않은 소스 영역 또는 드레인 영역측과 전력 공급선(1220) 사이에 연결된다.

도 19a에 도시된 회로도에서, 스위칭 TFT(1201, 1211)나 EL 구동 TFT(1204, 1214)는 다중-게이트 구조로 형성될 수 있음을 주목한다. 도 20a는 스위칭 TFT(1201, 1211)가 도 19a에 도시된 픽셀의 다중-게이트 구조로 형성된 픽셀의 회로도를 도시한다.

스위칭 TFT(1201a) 및 스위칭 TFT(1201b)는 직렬로 연결되어 제공된다. 더욱이, 스위칭 TFT(1211a) 및 스위칭 TFT(1211b)는 직렬로 연결되어 제공된다. 스위칭 TFT(1201a, 1201b) 및 스위칭 TFT(1211a, 1211b)을 제외하고, 그 구조는 도 19a에 도시된 회로도와 똑같다. 스위칭 TFT를 다중-게이트 구조로 형성함으로써, off 전류가 낮추어질 수 있다. 도 20a에서는 이중-게이트 구조가 채택되지만, 실시예 7은 이중-게이트에 제한되지 않음을 주목한다. 다중-게이트 구조가 사용될 수 있다.

그외에, 도시되지는 않았지만, EL 구동 TFT가 다중-게이트 구조로 형성되는 경우, 열에 의한 EL 구동 TFT의 저하가 억제될 수 있다.

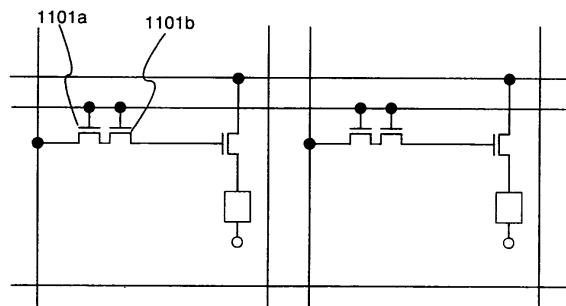

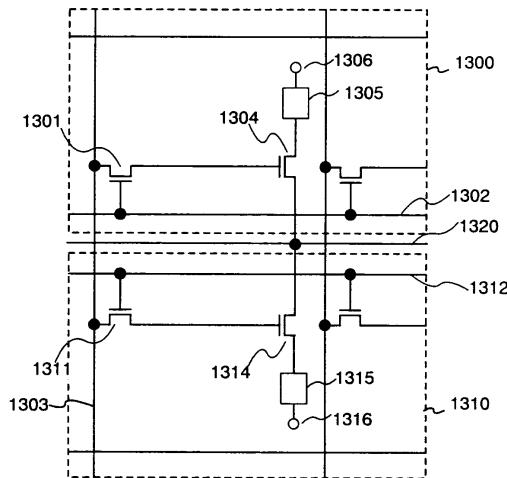

다음에, 도 19b는 본 발명에 따른 픽셀의 회로도에 대한 또 다른 예를 도시한다. 도 19b에서, 픽셀(1300) 및 픽셀(1310)은 서로 인접하게 제공된다. 도 19b에서, 참고번호(1301, 1311)은 스위칭 TFT를 나타낸다. 본 실시예에서는 스위칭 TFT(1301, 1311)로 n-채널형 TFT 또는 p-채널형 TFT가 사용될 수 있음을 주목한다. 도 19b에서는 n-채널형 TFT가 스위칭 TFT(1301) 및 스위칭 TFT(1311)로 사용된다. 스위칭 TFT(1301, 1311)의 게이트 전극은 게이트 신호를 입력하기 위한 게이트 신호선(1302, 1312)에 연결된다. 스위칭 TFT(1301, 1311)의 소스 영역 및 드레인 영역 중 하나는 아날로그 또는 디지털 비디오 신호를 입력하기 위한 데이터 신호선(또한 소스 신호선이라 칭하여지는)(1303)에 연결되고, 다른 하나는 EL 구동 TFT(1304, 1314)의 게이트 전극에 각각 연결된다.

이어서, EL 구동 TFT(1304, 1314)의 소스 영역 및 드레인 영역 중 하나는 전원 공급선(1320)에 연결되고, 다른 하나는 EL 소자(1305, 1315)에 각각 연결된다. 이러한 방식으로, 실시예 7에서는 2개의 인접한 픽셀이 하나의 전원 공급선(1320)을 공유한다. 결과적으로, 도 17a 내지 도 18b에 도시된 구조와 비교해, 전원 공급선의 수가 감소될 수 있다. 전체 픽셀 부분에 대한 배선의 비율이 작을 때, 배선이 EL층의 발광 방향으로 제공되는 경우 배선에 의한 광차폐가 억제될 수 있다. 도 20b에 도시된 회로도에서, 전력 공급선(1320)은 게이트 신호선(1302, 1312)과 평행하게 제공된다.

EL 소자(1305, 1315)는 양극, 음극, 및 양극과 음극 사이에 제공된 EL층을 구비한다. 본 발명에 따라, 양극이 픽셀 전극이고 음극이 반대 전극인 경우, EL 구동 TFT(1304, 1314)의 소스 영역 또는 드레인 영역은 EL 소자(1305, 1315)의 양극에 연결됨을 주목한다. 반대로, 양극이 반대 전극이고 음극이 픽셀 전극인 경우에는 EL 구동 TFT(1304, 1314)의 소스 영역 또는 드레인 영역이 EL 소자(1305, 1315)의 음극에 연결된다. EL 구동 TFT(1304, 1314)로는 n-채널형 TFT 또는 p-채널형 TFT가 사용될 수 있음을 주목한다. 그러나, EL 소자(1305, 1315)의 양극이 픽셀 전극이고 음극이 반대 전극인 경우에는 EL 구동 TFT(1304, 1314)가 p-채널형 TFT인 것이 바람직하다. 그외에, 반대로, EL 소자(1305, 1315)의 양극이 반대 전극이고 음극이 픽셀 전극인 경우에는 EL 구동 TFT(1304, 1314)가 n-채널형 TFT인 것이 바람직하다. 도 19b에서는 EL 구동 TFT(1304, 1314)로 p-채널형 TFT가 사용되므로, EL 소자(1305, 1315)의 음극은 정상 전원(1306, 1316)에 연결된다.

더욱이, LDD 영역은 EL 구동 TFT(1304, 1314)의 활성층에 제공되므로, LDD 영역과 게이트 전극이 게이트 절연막을 통해 중첩되는 영역(Lov 영역)이 형성될 수 있다. EL 구동 TFT(1304, 1314)가 특별히 n-채널형 TFT인 경우, Lov 영역을 활성층의 드레인 영역측에 형성함으로써, on 전류가 증가될 수 있다. 그 외에, EL 구동 TFT(1304, 1314)의 게이트 전극과 Lov 영역 사이에 용량이 형성될 수 있다.

더욱이, 스위칭 TFT(1301, 1311)가 비선택 상태(off 상태)로 설정될 때, EL 구동 TFT(1304, 1314)의 게이트 전압을 유지하도록 캐패시터가 제공된다. 캐패시터가 제공되는 경우, 캐패시터는 소스 신호선에 연결된 소스 영역 및 드레인 영역측과 전력 공급선(1320) 사이에 연결된다.

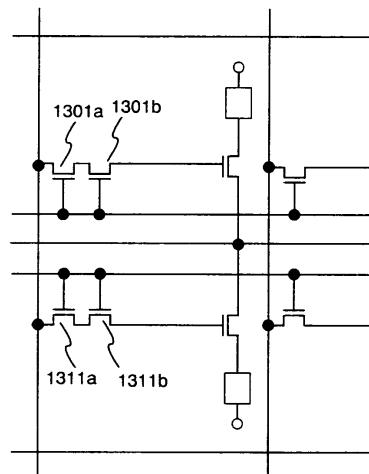

도 19b에 도시된 회로도에서, 스위칭 TFT(1301, 1311)나 EL 구동 TFT(1304, 1314)는 다중-게이트 구조로 형성될 수 있음을 주목한다. 도 20b는 도 19b에 도시된 픽셀의 스위칭 TFT(1301, 1311)가 다중-게이트 구조로 형성된 픽셀의 회로도를 도시한다.

스위칭 TFT(1301a) 및 스위칭 TFT(1301b)는 직렬로 연결되어 제공된다. 더욱이, 스위칭 TFT(1311a, 1311b)는 직렬로 연결되어 제공된다. 스위칭 TFT(1301a, 1301b) 및 스위칭 TFT(1311a, 1311b)을 제외하고, 그 구조는 도 19b에 도시된 회로도와 똑같다. 스위칭 TFT를 다중-게이트 구조로 형성함으로써, off 전류가 낮추어질 수 있다. 도 20b에서는 이중-게이트 구조가 채택됨을 주목한다. 그러나, 실시예 7은 이중-게이트에 제한되지 않는다. 다중-게이트 구조가 사용될 수 있다.

그외에, 도시되지는 않았지만, EL 구동 TFT가 다중-게이트 구조로 형성되는 경우, 열에 의한 EL 구동 TFT의 저하가 억제될 수 있다.

실시예 7에서, 레지스터는 EL 구동 TFT의 드레인 영역과 EL 소자 사이에 제공될 수 있음을 주목한다. 레지스터를 제공함으로써, EL 구동 TFT에서 EL 소자로 공급되는 전류량이 제어되므로, 불균형에 대한 EL 구동 TFT 특성의 영향이 방지될 수 있다. 레지스터는 EL 구동 TFT의 on 저항 보다 충분히 더 큰 저항값을 나타내는 소자이다. 그러므로, 그 구조는 어떠한 방법으로도 제한되지 않는다. on 저항은 TFT가 on 상태일 때 흐르는 드레인 전류로 TFT의 드레인 전압을 나눔으로써 얻어지는 값임을 주목한다. 레지스터의 저항값은  $1\text{ k}\Omega$  내지  $50\text{ M}\Omega$ (바람직하게  $10\text{ k}\Omega$  내지  $10\text{ M}\Omega$  이상, 보다 바람직하게  $50\text{ k}\Omega$  내지  $1\text{ M}\Omega$ )의 범위에서 선택된다. 레지스터로 높은 저항값을 갖는 반도체층이 사용될 때, 형성은 용이해지고 바람직하다..

실시예 7에 도시된 구조는 실시예 1, 3, 4, 5, 또는 6과 자유롭게 조합되어 실시될 수 있다.

(실시예 8)

본 발명은 유기 EL 물질에 제한되지 않고, 무기 EL 물질을 사용해 동작될 수 있다. 이때의 무기 EL 물질은 매우 높은 구동 전압이므로, 사용되는 TFT는 이러한 구동 전압에 저항할 수 있는 저항 압력 특성을 가져야 한다.

더 낮은 구동 전압의 무기 EL 물질이 미래에 개발되면, 본 발명에 적용될 수 있다.

본 발명의 구조는 실시예 1 내지 실시예 7의 구조 중 임의의 것과 자유롭게 조합될 수 있다.

(실시예 9)

본 발명에서, EL층으로 사용되는 유기 물질은 저분자 유기 물질이거나 폴리머(고분자) 유기 물질이다. 저분자 유기 물질로는  $\text{Alq}_3$ (tris-8-quinolylite-aluminum), TPD(triphenylamine derivative) 등에 중심을 둔 물질이 공지되어 있다. 폴리머 유기 물질로는  $\delta$ -결합 폴리머 물질이 주어질 수 있다. 전형적으로, PPV(polyphenylenevinylene), PVK (polyvinylcarbazole), 폴리카보네이트 등이 주어질 수 있다.

폴리머(고분자) 유기 물질은 스판 코팅 방법(또한 용액 적용 방법이라 칭하여지는), 조제 방법, 프린팅 방법, 잉크젯 방법 등과 같은 간단한 박막 형성 방법으로 형성될 수 있다. 폴리머 유기 물질은 저분자 유기 물질과 비교해 높은 열내구성을 갖는다.

더욱이, 본 발명에 따른 EL 디스플레이에 포함되는 EL 소자의 EL층이 전자 운송층 및 양의 홀 운송층을 갖는 경우, 전자 운송층과 양의 홀 운송층은 예를 들면, 비결정(non-crystal) Si 또는 비결정  $\text{Si}_{1-x}\text{C}_x$  등으로 형성된 비결정 반도체와 같은 무기 물질로 형성될 수 있다.

비결정 반도체에서는 많은 양의 트랩(trap) 레벨이 주어지고, 동시에 비결정 반도체는 비결정 반도체가 다른 층과 접촉하는 인터페이스에서 많은 양의 인터페이스 레벨을 형성한다. 결과적으로, EL소자는 저전압에서 발광할 수 있고, 동시에 높은 휘도를 제공하려는 시도가 이루어질 수 있다.

그 외에, 유기 EL층에는 도펀트(dopant)(불순물)가 제공되어, 유기 EL층의 발광 칼라가 변할 수 있다. 이러한 도펀트는 DCM1, 초록빛을 띤 적색(nile red), 루브렌(lubren), 쿠마린(coumarin) 6, TPB, 및 퀸아퀼리돈(quinaquelandon)을 포함한다.

그외에, 실시예 9의 구조는 실시예 1 내지 실시예 7의 구조 중 임의의 것과 자유롭게 조합될 수 있다.

(실시예 10)

다음에는 도 1 내지 도 2b에 도시된 본 발명에 따른 EL 디스플레이를 구동하는 또 다른 방법이 설명된다. 여기서는  $2^n$  그레이 스케일 전칼라 디스플레이가 n-비트 디지털 구동 방법으로 제공되는 경우가 설명된다. 타이밍도는 실시예에 도시된 경우와 똑같음을 주목한다. 도 3이 참고된다.

픽셀 부분(101)에는 복수의 픽셀(104)이 매트릭스형의 구성으로 배열된다. 도 2a는 픽셀(104)의 확대도를 도시한다. 도 2a에서, 참고번호(105)는 스위칭 TFT를 나타낸다. 스위칭 TFT(105)의 게이트 전극은 게이트 신호를 입력하는 게이트 신호선(106)에 연결된다. 스위칭 TFT(105)의 소스 영역 또는 드레인 영역 중 하나는 디지털 데이터 신호를 입력하는 소스 신호선(107)에 연결되고, 다른 하나는 각 픽셀에 각각 포함되는 EL 구동 TFT(108)의 게이트 전극 및 캐패시터(113)에 연결된다.

그외에, EL 구동 TFT(108)의 소스 영역 및 드레인 영역 중 하나는 전원 공급선(111)에 연결되고, 다른 하나는 EL 소자(110)에 연결된다. 전원 공급선(111)은 캐패시터(113)에 연결된다. 스위칭 TFT(105)가 비선택 모드(off 상태)일 때, 캐패시터(113)는 EL 구동 TFT(108)의 게이트 전압을 유지하도록 제공된다.