# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) Int. Cl.

#### **H05B 33/10** (2006.01)

(21) 출원번호 10-2007-0066707(분할)

(22) 출원일자<br/>심사청구일자2007년07월03일(65) 공개번호10-2007-0077493(43) 공개일자2007년07월26일

(62) 원출원 **특허 10-2002-0038176**

원출원일자 **2002년07월03일** 심사청구일자 **2007년07월03일**

(30) 우선권주장

JP-P-2001-00201580 2001년07월03일 일본(JP)

(56) 선행기술조사문헌 KR1020000076950 A KR1020000062593 A KR1020010006343 A

전체 청구항 수 : 총 23

(45) 공고일자 2009년02월17일 (11) 등록번호 10-0884229

(24) 등록일자 2009년02월11일

(73) 특허권자

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와켄 아쓰기시 하세 398

(72) 발명자

순페이 야마자키

일본국 가나가와켄 아쓰기시 하세 398 가부시키가 이샤 한도오따이에네루기 켄큐쇼 내

(74) 대리인 **이범래**, **장훈**

심사관 : 김창균

### (54) 디스플레이 장치

### (57) 요 약

본 발명은 진공에서 플라스틱 막을 이용하여 OLED를 봉지한다. 산소 또는 수분이 내부로 침투되는 것을 방지할수 있는 무기 절연막들과, 무기 절연막들의 내부 응력보다 작은 내부 응력을 가지는 유기 절연막이 플라스틱 막의 내부상에 적충된다. 무기 절연막들 사이에 유기 절연막을 끼움으로써, 응력이 이완될 수 있다. 또한, 복수의무기 절연막들을 적충시킴으로써, 무기 절연막들 중 하나가 균열이 생기는 경우에도, 다른 무기 절연막들이 유기발광 충내로 산소나 수분이 침투하는 것을 효과적으로 방지할 수 있다. 부가적으로, 전체 봉지막의 응력이 이완될 수 있고, 응력으로 인한 균열이 잘 발생하지 않는다.

## 대표도

### 특허청구의 범위

#### 청구항 1

디스플레이 장치에 있어서:

제 1 기판;

제 1 기판상에 형성된 배선;

상기 배선상에 적어도 하나의 접촉 구멍을 갖는 제 2 기판;

상기 접촉 구멍에 제공된 도전성 수지; 및

상기 제 2 기판상에 제공되고 상기 도전성 수지를 통해 상기 배선에 전기적으로 접속된 FPC를 포함하는, 디스플 레이 장치.

#### 청구항 2

디스플레이 장치에 있어서:

제 1 기판;

제 1 기판상에 형성된 배선;

상기 배선상에 적어도 하나의 접촉 구멍을 갖는 제 2 기판;

상기 제 2 기판상에 제공되고 상기 배선에 전기적으로 접속된 FPC;

상기 제 1 기판, 상기 제 2 기판 및 상기 FPC의 일부를 덮는 복수의 절연막들; 및

상기 복수의 절연막들을 덮는 플라스틱 막을 포함하며,

상기 복수의 절연막들 중 적어도 하나의 내부 응력은 다른 절연막들의 내부 응력보다 작은, 디스플레이 장치.

#### 청구항 3

디스플레이 장치에 있어서:

제 1 기판;

제 1 기판상에 형성된 배선;

상기 배선상에 적어도 하나의 접촉 구멍을 갖는 제 2 기판;

상기 접촉 구멍에 제공된 도전성 수지;

상기 제 2 기판상에 제공되고 상기 도전성 수지를 통해 상기 배선에 전기적으로 접속된 FPC;

상기 제 1 기판, 상기 제 2 기판 및 상기 FPC의 일부를 덮는 복수의 절연막들; 및

상기 복수의 절연막들을 덮는 플라스틱 막을 포함하며,

상기 복수의 절연막들 중 적어도 하나의 내부 응력은 다른 절연막들의 내부 응력보다 작은, 디스플레이 장치.

### 청구항 4

디스플레이 장치에 있어서:

제 1 기판;

제 1 기판상에 형성된 디스플레이 소자;

상기 디스플레이 소자상에 적어도 하나의 접촉 구멍을 갖는 제 2 기판;

상기 접촉 구멍에 제공된 도전성 수지; 및

상기 제 2 기판상에 제공되고 상기 도전성 수지를 통해 상기 디스플레이 소자에 전기적으로 접속된 FPC를 포함하는, 디스플레이 장치.

#### 청구항 5

디스플레이 장치에 있어서:

제 1 기판;

제 1 기판상에 형성된 디스플레이 소자;

상기 디스플레이 소자상에 적어도 하나의 접촉 구멍을 갖는 제 2 기판;

상기 제 2 기판상에 제공되고 상기 디스플레이 소자에 전기적으로 접속된 FPC;

상기 제 1 기판, 상기 제 2 기판 및 상기 FPC의 일부를 덮는 복수의 절연막들; 및

상기 복수의 절연막들을 덮는 플라스틱 막을 포함하며,

상기 복수의 절연막들 중 적어도 하나의 내부 응력은 다른 절연막들의 내부 응력보다 작은, 디스플레이 장치.

#### 청구항 6

디스플레이 장치에 있어서:

제 1 기판;

제 1 기판상에 형성된 디스플레이 소자;

상기 디스플레이 소자상에 적어도 하나의 접촉 구멍을 갖는 제 2 기판;

상기 접촉 구멍에 제공된 도전성 수지;

상기 제 2 기판상에 제공되고 상기 도전성 수지를 통해 상기 디스플레이 소자에 전기적으로 접속된 FPC;

상기 제 1 기판, 상기 제 2 기판 및 상기 FPC의 일부를 덮는 복수의 절연막들; 및

상기 복수의 절연막들을 덮는 플라스틱 막을 포함하며,

상기 복수의 절연막들 중 적어도 하나의 내부 응력은 다른 절연막들의 내부 응력보다 작은, 디스플레이 장치.

### 청구항 7

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 제 1 기판은 제 1 플라스틱 기판을 포함하는, 디스플레이 장치.

#### 청구항 8

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 제 1 기판은 폴리에테르 설폰, 폴리카보네이트, 폴리에틸렌 테레프탈레이트 및 폴리에틸렌 나프탈레이트로 구성된 그룹으로부터 선택된 하나를 포함하는, 디스플레이 장치.

#### 청구항 9

제2항, 제3항, 제5항 또는 제6항 중 어느 한 항에 있어서,

상기 다른 절연막들은 실리콘 질화물, 실리콘 산질화물, 알루미늄 산화물, 알루미늄 질화물, 알루미늄 산질화물 및 알루미늄 실리콘 산질화물로 구성된 그룹으로부터 선택된 하나를 포함하는, 디스플레이 장치.

### 청구항 10

제2항, 제3항, 제5항 또는 제6항 중 어느 한 항에 있어서,

상기 복수의 절연막들 중 적어도 하나는 폴리이미드, 아크릴, 폴리아미드, 폴리이미드아미드, 벤조사이클로부텐, 에폭시 수지, 폴리에틸렌, 폴리테트라플루오로에틸렌, 폴리스티렌, 폴리(p-페닐렌 비닐렌),

폴리염화비닐 및 폴리파라크실릴렌계 수지로 구성된 그룹으로부터 선택된 하나를 포함하는, 디스플레이 장치.

#### 청구항 11

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 제 2 기판은 제 2 플라스틱 기판을 포함하는, 디스플레이 장치.

#### 청구항 12

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 제 2 기판은 폴리에테르 설폰, 폴리카보네이트, 폴리에틸렌 테레프탈레이트 및 폴리에틸렌 나프탈레이트로 구성된 그룹으로부터 선택된 하나를 포함하는, 디스플레이 장치.

#### 청구항 13

제2항, 제3항, 제5항 또는 제6항 중 어느 한 항에 있어서,

상기 플라스틱 막은 가요성인, 디스플레이 장치.

#### 청구항 14

제2항, 제3항, 제5항 또는 제6항 중 어느 한 항에 있어서,

상기 플라스틱 막은 폴리에스터, 폴리프로필렌, 폴리염화비닐, 폴리비닐 플로라이드, 폴리스티렌, 폴리아크릴로 니트릴, 폴리에틸렌 테레프탈레이트 및 나일론으로 구성된 그룹으로부터 선택된 하나를 포함하는, 디스플레이 장치.

### 청구항 15

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 디스플레이 장치는 능동 매트릭스형 발광 장치인, 디스플레이 장치.

### 청구항 16

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 디스플레이 장치는 패시브형 발광 장치인, 디스플레이 장치.

#### 청구항 17

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 디스플레이 장치는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 퍼스널 컴퓨터 및 휴대 전화로 구성된 그룹으로부터 선택된 적어도 하나에 합체되는, 디스플레이 장치.

#### 청구항 18

제2항, 제3항, 제5항 또는 제6항 중 어느 한 항에 있어서,

상기 복수의 절연막들은 제 1 절연막, 상기 제 1 절연막을 덮는 제 2 절연막, 상기 제 2 절연막을 덮는 제 3 절연막을 포함하는, 디스플레이 장치.

#### 청구항 19

제18항에 있어서,

상기 제 1 절연막 및 상기 제 3 절연막 중 적어도 하나는 실리콘 질화물, 실리콘 산질화물, 알루미늄 산화물, 알루미늄 질화물, 알루미늄 산질화물 및 알루미늄 실리콘 산질화물로 구성된 그룹으로부터 선택된 하나를 포함하는, 디스플레이 장치.

#### 청구항 20

제18항에 있어서,

상기 제 2 절연막은 폴리이미드, 아크릴, 폴리아미드, 폴리이미드아미드, 벤조사이클로부텐, 에폭시 수지, 폴리에틸렌, 폴리테트라플루오로에틸렌, 폴리스티렌, 폴리(p-페닐렌 비닐렌), 폴리염화비닐 및 폴리파라크실릴렌계수지로 구성된 그룹으로부터 선택된 하나를 포함하는, 디스플레이 장치.

#### 청구항 21

제4항 내지 제6항 중 어느 한 항에 있어서,

상기 디스플레이 소자는 발광 소자인, 디스플레이 장치.

#### 청구항 22

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 FPC는 상기 제 2 기판상에 제공되고, 건조 물질(drying material)이 사이에 끼워지는, 디스플레이 장치.

#### 청구항 23

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 접촉 구멍은 테이퍼 형상을 갖는, 디스플레이 장치.

### 명 세 서

#### 발명의 상세한 설명

### 기술분야

- <1> 1. 발명의 배경

- 본 발명은 반도체 디바이스 제조 방법에 관한 것이며, 특히, 플라스틱 기판상에 형성된 OLED(유기 발광 장치) 패널을 포함하는 발광 장치에 관한 것이다. 또한, 본 발명은 OLED 패널에 대한 제어기를 포함하는 IC를 장착함 으로써 얻어지는 OLED 모듈에 관한 것이다. 본 명세서에서, 발광 장치는 OLED 패널 및 OLED 모듈을 위한 개괄적 인 용어로서 이용된다. 또한, 본 발명에는 발광 장치를 이용하는 전자 기기가 포함되어 있다.

### 배경기술

- <3> 2. 관련 기술의 설명

- <4> 근년에, 기판상에 TFT(박막 트랜지스터)를 형성하는 기술이 크게 발전하여 능동 매트릭스 디스플레이 디바이스들에 대한 TFT들의 적용을 촉진하고 있다. 특히, 폴리실리콘을 이용하는 TFT들은 비정질 실리콘을 이용하는 종래의 TFT들 보다 높은 전계 효과 이동성(이동성이라고도 지칭됨)을 가지며, 따라서, 고속으로 동작한다. 이는 종래에는 기판에 대해 외부에 있는 구동 회로에 의해 제어되어왔던 화소들을 화소들이 형성되어 있는 동일 기판상에 형성된 구동 회로에 의해 제어하는 것을 가능하게 하였다.

- <5> 동일 기판상에 형성된 다양한 회로들 및 소자들과 함께, 능동 매트릭스 디스플레이 디바이스들은 제조 비용의 저하, 디스플레이 디바이스 크기의 감소, 생산량의 증가 및 처리량의 향상을 포함하는 다수의 장점들을 가실 수 있다.

- <6> 자기-발광 소자로서 OLED를 가지는 능동 매트릭스 발광 장치(이하, 단순히 발광 장치라 지칭함)는 활발히 연구되고 있다. 또한, 발광 장치는 유기 EL 디스플레이(OELD) 또는 유기 발광 다이오드(OLED)라고도 지칭된다.

- <7> 자기-발광하기 때문에, OLED는 액정 디스플레이 디바이스들(LCD들)에서는 필수적인 배후광을 필요로 하지 않으며, 따라서, 보다 얇은 디바이스를 제조하기가 용이하다. 부가적으로, 자기-발광 OLED는 높은 가시성을 가지며, 조망 각도에 관한 어떠한 제한도 가지지 않는다. 이들은 OLED들을 이용하는 발광 장치들이 CRT들 및 LCD들을 대체하기 위한 디스플레이 디바이스들로서 주목을 받고 있는 이유들이다.

- <8> OLED는 아노드 층 및 캐소드층에 부가하여, 전계가 적용되었을 때, 발광(전자발광)을 제공하는 유기 콤파운드 (유기 발광 재료)를 함유하는 층을 가진다(이 층은 이하, 유기 발광층이라 지칭됨). 유기 콤파운드로부터 얻어

진 발광(전자발광)은 싱글릿 여기로부터 기저 상태로 복원시의 광 방사(형광)과, 트리플릿 여기로부터 기저 상태로 복원시의 광 방사(인광)으로 분류된다. 본 발명에 따른 발광 장치는 하나 또는 양자 모두의 유형들의 광 방사를 이용할 수 있다.

- 본 명세서에서, OLED의 아노드와 캐소드 사이에 제공된 모든 충들은 함께 유기 발광충을 형성한다. 특히, 유기 발광충은 발광충, 정공 주입충, 전자 주입충, 정공 운반충, 전자 운반충 등을 포함한다. OLED의 기본 구조는 아 노드와, 발광충과, 캐소드가 이 순서대로 적충되어 있는 적충체이다. 기본 구조는 아노드, 정공 주입층, 발광충 및 캐소드가 이 순서대로 적충되어 있는 적충체, 아노드, 정공 주입층, 발광충, 전자 운반층 및 캐소드가 이 순 서대로 적충되어 있는 적충체 등으로 변형될 수 있다.

- <10> 이런 발광 장치의 다양한 응용들이 기대된다. 특히, 발광 장치가 얇고, 따라서, 중량을 감소시키는데 유용하기 때문에, 휴대용 기기에 대한 적용들이 관심을 끌고 있다. 이는 가요성 플라스틱 막상에 OLED를 형성하기 위한 시도들을 촉진하고 있다.

- <11> OLED가 플라스틱 막 같은 가요성 기판상에 형성되어 있는 발광 장치는 얇고 경량이며, 또한, 곡선형 디스플레이 또는 쇼 윈도우 등에 적용될 수 있다. 따라서, 그 용도는 휴대용 기기에 한정되지 않으며, 그 응용 범위는 매우 광범위하다.

- <12> 그러나, 일반적으로, 플라스틱 기판들은 습기나 산소가 잘 통과하며, 이는 유기 발광충들의 열화를 가속시킨다. 따라서, 플라스틱 기판들은 종종 발광 장치들의 수명을 단축시킨다. 이는 종래 기술에서, 습기 및 산소가 유기 발광충으로 도입하는 것을 방지하기 위해, 실리콘 질화물 막 또는 실리콘 산질화물 막 같은 절연막을 플라스틱 기판과 OLED 사이에 배치시킴으로써 해결되어왔다.

- <13> 또한, 일반적으로, 플라스틱 막 기판들은 열에 약하고, 실리콘 질화물 막 또는 실리콘 산질화물 막이 너무 높은 온도에서 형성되는 경우에 쉽게 변형된다. 한편, 절연막이 형성되는 온도가 너무 낮은 경우에, 막의 품질이 감 소되고, 막이 습기 및 산소의 투과를 만족스럽게 방지하지 못하게 된다.

- <14> 습기 및 산소의 투과를 방지하기 위하여, 실리콘 질화물 막 또는 실리콘 산질화물 막 같은 절연막의 두께가 증가할 때, 내부 응력이 증가되어 균열(틈)을 유발하기 쉽다. 두꺼운 절연막은 기판이 굴곡될 때, 균열에 대해 기판이 약해지게 만든다.

## 발명의 내용

#### 해결 하고자하는 과제

<15> 본 발명은 상술한 관점에서 이루어진 것으로, 따라서, 본 발명의 목적은 습기 및 산소의 투과로 인한 열화를 회 피할 수 있는 플라스틱 기판상에 형성된 OLED를 구비한 발광 장치를 제공하는 것이다.

### 과제 해결수단

- 본 발명은 절연면을 갖는 기판상에 형성된 OLED를 봉지하는 기술에 관한 것이다. 본 발명에 따라서, OLED는 내부상에 절연막들의 충들이 입혀져 있는 플라스틱 막을 이용하여 진공 봉지에 의해 봉지된다. 절연막들의 충들은 무기 재료로 이루어지고, 산소 및 습기의 투과를 방지할 수 있는 적어도 하나의 절연막(이하, 무기 절연막이라 지칭함)과, 유기 재료로 이루어지고, 무기 절연막 보다 내부 응력이 작은 절연막을 포함한다.

- <17> 특히, 무기 절연막들의 둘 이상의 충들이 형성되고, 수지를 함유하는 유기 절연막이 무기 절연막들 사이에 배치된다. 내부상에 셋 이상의 절연막들이 입혀진 자루형 플라스틱 막(ba-like plastic film)이 봉지를 위해, OLED가 그 위에 형성되어 있는 기판을 수납하고, 발광 장치를 완성하도록 이용된다.

#### 直 과

- <18> 무기 절연막들을 가지는 플라스틱의 연성을 강화시키기 위해서, 무기 절연막들을 형성하기 위한 반응 가스에 귀족 가스 원소를 첨가함으로써 무기 절연막들의 내부 응력이 완화될 수 있다.

- 본 발명은 무기 절연막들의 복수의 충들을 이용한다. 따라서, 하나의 무기 절연막이 균열되면, 나머지 무기 절연막들이 습기 및 산소가 유기 발광충에 도입하는 것을 효과적으로 방지할 수 있다. 복수의 무기 절연막들의 충들과 함께, 본 발명은 무기 절연막들의 형성 동안 낮은 온도에 의해, 무기 절연막들의 품질이 열화되는 경우에도, 습기 및 산소가 무기 발광충에 도입하는 것을 효과적으로 방지할 수 있다.

- <20> 무기 절연막들 보다 내부 응력이 작은 유기 절연막이 무기 절연막들 사이에 끼워질 때, 절연막들의 내부 응력이 완화될 수 있다. 사이에 유기 절연막을 끼우는 무기 절연막들의 총 두께와 동일한 두께를 가지는 단층 무기 절연막과 비교하면, 사이에 유기 절연막을 끼우고 있는 무기 절연막들에서 내적 응력으로 인한 균열이 덜 빈번히유발된다.

- <21> 무기 절연막들과 유기 절연막을 적충함으로써, 유연성이 향상되고, 굴곡시 균열을 피할 수 있다.

- <22> 무기 적층 막들과 유기 절연막의 적층체(이하, 봉지막으로 지칭함)는 이것이 OLED가 그 위에 형성되어 있는 기판에 긴밀하게 결합되도록 부압식 결합에 의해 형성된다. 따라서, 봉지막은 가시광에 대한 소정 수준의 연성과, 가시광에 대한 투명성 또는 반투명성을 가지는 막이다.

- <23> 본 명세서에서, 가시광에 대해 투명하다는 것은 80 내지 100%의 가시광 투과성을 가지는 것을 의미하며, 가시광 에 대해 반투명이라는 것은 50 내지 80%의 가시광 투과성을 가지는 것을 의미한다.

- <24> 상술한 구조에서, OLED의 열화를 방지하기 위해서, OLED가 그 위에 형성되어 있는 기판과 진공 봉지 플라스틱 막 사이에 건조제를 배치하는 것이 적합하다. 적합한 건조제는 바륨 산화물, 실리카 겔 등이다. 건조제는 가요성 인쇄 기판이 접착되기 전 또는 그 이후에 적소에 투입될 수 있다. 대안적으로, 건조제는 가요성 인쇄 기판을 접착하기 이전에 가요성 인쇄 기판의 가요성 막내에 배치될 수 있다. 건조제의 위치는 플라스틱 막의 부압식 결합 지점의 근방인 것이 적합하다.

- <25> 본 명세서에서, OLED 패널은 그 OLED가 플라스틱 막으로 봉지될 때까지 마감되지 않는다. 그러나, OLED 패널이라는 용어는 플라스틱 막 봉지 이전의 것을 지칭할 수도 있다.

### 발명의 실시를 위한 구체적인 내용

### <26> 실시 형태

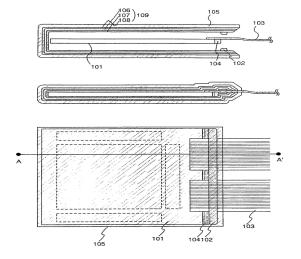

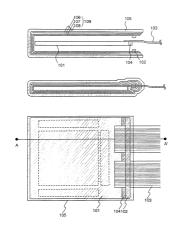

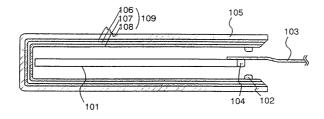

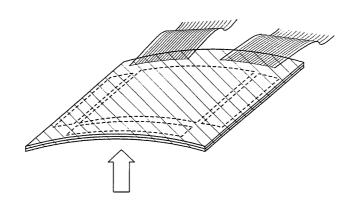

- <27> 먼저, 전원의 전압과 다양한 종류의 신호들을 공급하기 위한 FPC(103)가 플라스틱 기판을 가지는 OLED 패널 (101)에 장착된다. OLED가 산소, 습기 등에 의해 열화되는 것을 방지하기 위해 건조제(104)가 제공된다. 건조제 (104)는 흡습성 물질(바람직하게는 바륨 산화물) 또는 산소를 흡수할 수 있는 물질이다. 여기서, 건조제(104)는 건조제가 FPC(103) 및 기판(101)의 단부면과 접촉하는 위치에 배치된다. 이는 봉지막과 플라스틱 막이 국부적으로 연장되고, 이후의 진공 압착 단계(later vacuum press-fit step)에서 파괴되는 것을 방지한다.

- <28> 다음에, OLED 패널(101)과 건조제(104)가 함께 자루형 플라스틱 막(105)내에 함께 투입된다. 자루형 플라스틱 막의 내부는 봉지막(109)으로 입혀져 있고, 봉지막(109)은 가스 장벽으로서 작용한다. 이 시점에서, OLED 패널 (101)이 FPC(103)에 접속되는 부분은 자루형 플라스틱 막(105)내에 배치된다(도 1a).

- <29> 봉지막(109)은 둘 이상의 무기 절연막들의 충들과, 무기 절연막들 사이에 끼워진 유기 절연막으로 구성된다. 무기 절연막들은 습기 및 산소의 투과를 방지할 수 있는 무기 재료의 절연막이다. 유기 절연막은 무기 절연막들의 재료 보다 내부 응력이 작은 유기 재료의 절연막이다.

- <30> 예로서, 본 실시 형태에서, 봉지막(109)은 플라스틱 막(105)과 접촉하는 무기 절연막(106)과, 무기 절연막(10 6)과 접촉하는 유기 절연막(107) 및 유기 절연막(107)과 접촉하는 무기 절연막(108)이다.

- 동 이상의 무기 절연막들의 충들이 제공되는 것으로 충분하다. 이용이능한 무기 절연막들의 예들은 실리콘 질화물 막, 실리콘 산질화물 막, 알루미늄 산화물 막, 알루미늄 질화물 막, 알루미늄 산질화물 막 및 알루미늄 실리콘 산질화물 막(AlSiON)을 포함한다. 알루미늄 실리콘 산질화물 막은 비교적 높은 열 전도성을 가지며, 따라서, 무기 절연막들을 위해 이용될 때, 소자내에서 발생되는 열을 효과적으로 방사할 수 있다.

- <32> 무기 절연막들은 두께가 50nm 내지 3/m인 것이 적합하다. 무기 절연막들의 형성 방법은 플라즈마 CVD에만 한정되는 것이 아니며, 개별적 경우들에 적합하도록 선택될 수 있다. 예로서, LPCVD, 스퍼터링 등이 무기 절연막들을 형성하도록 이용될 수 있다.

- <33> 유기 절연막을 위해 이용되는 재료는 광 투과성인 것이어야만 하며, 무기 절연막의 내부 응력보다 유기 절연막의 내부 응력이 작도록 할 수 있는 것이어야 하고, 추후 단계에서의 열 처리를 견디기에 충분히 높은 내열성을 유기 절연막에 제공할 수 있는 것이어야만 한다. 유기 절연막 재료의 일반적인 예들은 폴리 이미드, 아크릴, 폴리아미드, 폴리이미드아미드, 벤조사이클로부텐 및 에폭시 수지를 포함한다. 이들 이외의 상술한 특성을 제공하는 다른 수지들이 이용될 수 있다.

- <34> 유기 절연막은 200nm 내지 2μm의 두께인 것이 적합하다.

- <35> 자루형 플라스틱 막(105)은 진공에 도달할 때까지 배기되며, 그후, 플라스틱 막의 입구가 접착제(102)에 의해 봉지된다. 따라서, OLED 패널(101)이 자루형 플라스틱 막(105)내에 봉지되고, 봉지막(109)에 의해 둘러싸여진다. FPC(103)는 전원의 전압 및 다양한 종류의 신호들을 공급하기 위해 자루형 플라스틱 막(105)의 외부으로 부분적으로 돌출한다.

- <36> 도 1b는 부압식 결합 이후의 발광 장치의 단면도를 도시하고 있으며, 도 1c는 그 상면도를 도시한다. 도 1b는 도 1c의 A-A'선을 따라 취한 단면도에 대응한다. 플라스틱 막(105)과 봉지막(109)은 가시광에 대해 투명 또는 반투명하여야 한다. 플라스틱 막(105)은 부압식 결합에 적합한 한, 소정의 재료를 이용할 수 있다.

- <37> 본 실시 형태는 플라스틱 막을 봉지하기 위해 접착제를 이용한다. 대안적으로, 플라스틱 막의 내부가 봉지막으로 입혀지지 않은 영역을 부분적으로 가지고, 그래서, 플라스틱 막이 이 영역에서 열간 가압식 결합에 의해 봉지될 수 있다. 열간 가압식 결합 이후에, 봉지를 강화시키기 위해 가압식 결합부에 접착제가 이용될 수 있다. 막 재료는 열간 가압식 결합 동안 역시, FPC의 가요성 테이프에 접착되는 것인 것이 적합하다.

- <38> 플라스틱 막의 재료는 열가소성 수지 재료(폴리에스터, 폴리프로필렌, 폴리 염화비닐, 폴리스티렌, 폴리아크릴로니트릴, 폴리에틸렌 테레프탈레이트, 나일론 등)이다. 일반적으로, PVF(폴리비닐 플로라이드)막, 마일라 막, 또는 아크릴 수지막이 이용된다.

- <39> 여기에 이용되는 플라스틱은 가방 또는 박스 처럼 성형된다. 대안적으로, 플라스틱 막은 서로 중첩되어 있고 네 측면들이 접착제 또는 열간 가압식 결합에 의해 봉지되어 있는 두 개의 시트들일 수 있다.

- <40> 상술한 단계들은 OLED가 기판상에 형성된 이후에, OLED의 외부 공기에 대한 노출을 가능한 회피하면서 수행되는 것이 적합하다.

- <41> 이 방식으로, 본 발명은 습기, 산소 등에 의한 열화가 감소되어 신뢰성이 향상된, 기판상에 형성된 OLED를 가지는 발광 장치를 제공한다.

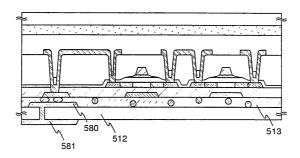

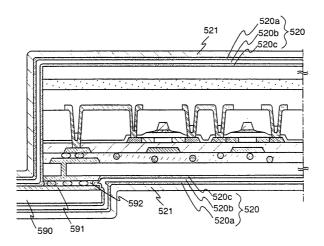

- <42> 본 발명의 실시예들을 하기에 설명한다.

- <43> [제 1 실시예]

- <44> 자루형 플라스틱 막내에 봉지막을 형성하는 방법이 본 실시예에서 설명된다.

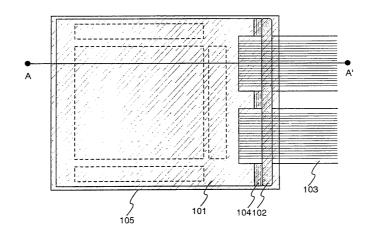

- <45> 도 2는 플라즈마 CVD에 의해 봉지막을 형성하기 위한 장치의 구조를 도시한다. RF 전원(202)과 접지된 전극 (204)에 접속된 전극(203)이 챔버(201)내에 제공된다.

- <46> 전극(203)은 자루형 플라스틱 막(205)을 덮도록 배치된다. 전극(204)은 자루형 플라스틱 막(205) 내부에 배치된다. 전극(203)과 플라스틱 막(205) 사이의 거리와, 전극(204)과 플라스틱 막(205) 사이의 거리는 봉지막이 외부가 아닌, 전적으로, 플라스틱 막(205)의 내부상에 형성되도록 설정된다. 특히, 전극(203)과 플라스틱 막(205)사이의 거리는 전극(204)과 플라스틱 막(205)사이의 거리는 전극(204)과 플라스틱 막(205)사이의 거리는 3mm 이상인 것이 적합하며, 10mm 이상인 것이 더욱 적합하다.

- <47> 플라스틱 막(205)은 홀더(206)에 의해 고정된 위치에 유지된다. 홀더(206)는 자루형 플라스틱 막(205)이 폐쇄되는 것을 방지하도록 구성된다.

- <48> 플라스틱 막(205)의 내부가 봉지막의 형성시 부분적으로 홀더(206)와 긴만하게 접촉하는 경우에, 봉지막이 형성되지 않고 플라스틱 막이 노출되는 영역이 플라스틱 막(205)의 내부상에 형성될 수 있다. OLED 패널이 열간 가압식 결합에 의해 봉지될 때, 플라스틱 막이 노출되는 영역에서, 플라스틱 막은 열적으로 가압식 결합된다.

- <49> 본 실시예는 무기 절연막들의 둘 이상의 충들과 이 무기 절연막들 사이에 끼워진 유기 절연막으로 구성된 봉지막(208)을 플라스틱 막(205)의 내부면상에 형성하는 경우를 설명한다.

- <50> 이용되는 무기 절연막들은 무기 재료를 포함하며, 산소 및 습기의 통과를 방지할 수 있는 절연막들이다. 이용되는 유기 절연막은 무기 절연막의 것 보다 작은 내부 응력을 가지는 유기 재료를 포함하는 절연막이다. 특히, 본실시예는 무기 절연막(209)을 위해 실리콘 산질화물 막을 이용하고, 유기 절연막(210)을 위해 폴리에틸렌 막을 이용하며, 무기 절연막(211)을 위해 실리콘 산질화물막을 이용한다. 무기 절연막(209)은 PET로 형성된 플라스틱막(205)과 접촉한다. 유기 절연막(210)은 무기 절연막(209)과 접촉한다. 무기 절연막(211)은 유기 절연막(210)과 접촉한다.

- <51> 플라스틱 막과 무기 절연막들의 재료들은 위에 주어진 것들에 한정되지 않는다. 플라스틱 막과 무기 절연막들의 재료들은 실시 형태에 나열된 재료들로부터 자유롭게 선택될 수 있다. 그러나, 본 실시예는 봉지막을 형성하기 위해 플라즈마 CVD를 채용하고, 따라서, 플라즈마 CVD에 의해 막들로 형성될 수 있는 재료들이 무기 절연막들을 위해 이용되어야만 한다.

- <52> 유기 절연막의 재료는 폴리에틸렌에 한정되지 않는다. 유기 절연막을 위해 이용될 수 있는 재료는 광의 투과성이고, 무기 절연막들 보다 내부 응력이 작으며, 추후 단계들의 열 처리를 견딜 수 있는 유기 절연막을 형성할수 있어야만 한다. 그러나, 본 실시예는 봉지막을 형성하기 위해 플라즈마 CVD를 채용하고, 따라서, 유기 절연막의 재료가 플라즈마 CVD에 의해 막으로 형성될 수 있는 것이어야만 한다. 이용이능한 유기 절연막 재료의 예들은 폴리에틸렌, 폴리테트라플루오로에틸렌, 폴리스티렌, 벤조사이클로부텐, 폴리(p-페닐렌 비닐렌), 폴리염화비닐 및 폴리파라크릴렌계 수지를 포함한다.

- <53> 먼저, 챔버(201)가 진공에 도달할 때까지 배기된다. 그후, SiH<sub>4</sub>, NH<sub>3</sub>, 및 N<sub>2</sub>0가 반응 가스로서 챔버(201)내로 도 입되고, 실리콘 산질화물 막이 플라즈마 CVD에 의해 무기 절연막(209)으로서 형성된다.

- <54> 다음에, 챔버(201)가 진공에 도달할 때까지 다시 배기되고, 에틸렌이 반응 가스로서 챔버(201)내로 도입되어 플라즈마 CVD에 의해 유기 절연막(210)으로서 폴리에틸렌막을 형성한다.

- <55> 그후, 챔버(201)가 진공에 도달할 때까지 다시 한번 배기되고, SiH<sub>4</sub>, NH<sub>3</sub>, 및 N<sub>2</sub>O가 반응 가스로서 챔버(201)내로 도입되고, 플라즈마 CVD에 의해 실리콘 산질화물 막이 무기 절연막(211)으로서 형성된다.

- <56> 보호성 절연막(207)이 미리 챔버(201)의 내벽상에 형성되는 경우에, 내벽상의 봉지막 재료들의 증착이 회피될 수 있고, 대부분의 재료들이 플라스틱 막(205)상에서 봉지막(208)으로 형성될 수 있다.

- <57> 본 실시예는 봉지막(208)을 형성하기 위해 플라즈마 CVD를 이용하지만, 봉지막을 형성하는 방법은 그에 한정되지 않는다. 예로서, 열간 CVD, 증발, 스퍼터링 또는 저압 열간 CVD가 봉지막을 형성하기 위해 이용될 수 있다.

- <58> [제 2 실시예]

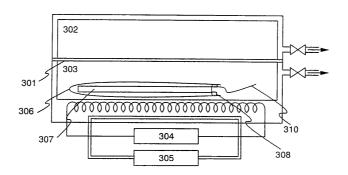

- <59> 플라스틱 막을 이용하여 OLED 패널을 봉지하는 방법이 본 실시예에서 설명된다.

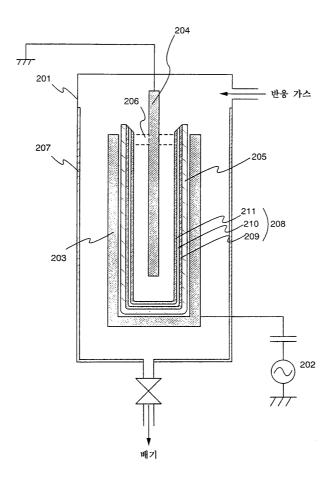

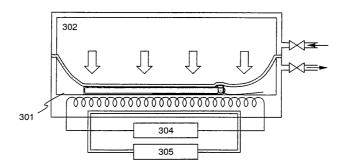

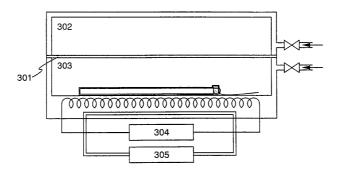

- <60> 도 3a 내지 도 3c는 자루형 플라스틱 막내에 OLED 패널을 봉지하기 위한 장치(봉지 장치)의 구조를 도시한다. 봉지 장치는 두 개의 챔버들, 즉, 챔버 A(302) 및 챔버 B(303)를 가지며, 이들은 경계막(patition film; 30 1)에 의해 서로 분리되어 있다. 경계막(301)은 탄성을 가지며, 외력에 의해 변형되었을 때에도, 변형을 보정하기 위한 힘을 생성하는 특성을 포함한다.

- <61> 챔버 A(302)와, 챔버 B(303)는 각각 배기 시스템을 가진다. 챔버 B(303)는 가열기(304)와 냉각기(305)를 가진다.

- <62> 먼저, 도 3a에 도시된 바와 같이, OLED 패널(307)이 자루형 플라스틱 막(306)내에 배치되고, 이 플라스틱 막이 챔버 B(303)내에 배치된다. 이 시점에서, OLED 패널(307)은 그에 장착된 FPC(310)를 가지고, 접착제(308)가 자루형 플라스틱 막(306)의 입구 근방에 배치된다.

- <63> 다음에, 챔버 A(302)와 챔버 B(303)는 이들이 진공에 도달할 때 까지 배기되고, 그후, 불활성 가스(본 실시예에서는, Ar)가 챔버 B(303)에 도입된다. 이 챔버는 다시 진공에 도달할 때까지 배기되어 챔버 B(303)내의 산소와습기를 제거한다.

- <64> 가열기(304)가 이용되어 접착제(308)를 용융시킨다. 본 실시예에서 이용되는 접착제(308)는 가열 및 용융시 접 착이 이루어지는 고온 용융 접착제이다. 일반적으로, 에틸렌-비닐 아세테이트 공중합체나 폴리아미드 또는 폴리 에스터를 염기로서 이용하는 고온 용융 접착제가 이용된다.

- <65> 접착제(308)가 열에 의해 용용될 때, 공기에 노출시키거나, 다른 조치들에 의해 챔버 A(302)내의 압력이 증가되게 된다. 이는 챔버 A(302)가 도 3b에 도시된 바와 같이, 챔버 B(303)를 누르게 한다. 결과적으로, 탄성 경계막(301)이 플라스틱 막(306)을 가압한다. 용용된 접착제(308)도 자루형 플라스틱 막(306)내에서, OLED 패널(307)을 진공으로 봉지하도록 가압된다.

- <66> 이 상태에서, 접착제(308)가 냉각기(305)에 의해 냉각된다. 따라서, OLED 패널(307)이 자루형 플라스틱 막(306)내에서 진공으로 봉지된 상태로, 접착제(308)가 응고되게 된다.

- <67> 다음에, 도 3c에 도시된 바와 같이, 경계막(301)과 봉지된 OLED 패널(307) 사이에 거리를 부여하도록 챔버 B(303)내의 압력이 증가된다.

- <68> OLED 패널(307)은 상술한 방법에 의해 자루형 플라스틱 막내에서 진공으로 봉지될 수 있다.

- <69> OLED 패널을 봉지하는 방법은 본 실시예에 도시된 것에 한정되지 않는다. 본 실시예는 제 1 실시예와 자유롭게 조합될 수 있다.

- <70> [제 3 실시예]

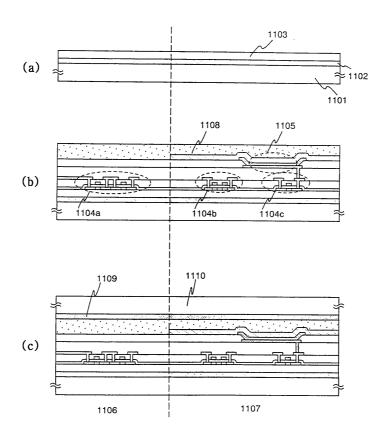

- <71> 본 실시예에서, 플라스틱 기판상에 형성된 OLED를 포함하는 OLED 패널의 제조 방법이 설명된다. 도 4 및 도 5는 화소부 및 구동 회로의 제조 단계들의 단면도이다.

- <72> 도 4의 (a)에서, 비정질 실리콘 막으로 이루어진 제 1 접착층(1102)이 제 1 기판(1101)상에 100 내지 500nm(본 실시예에서는 300nm)의 두께를 갖도록 형성된다. 비록, 본 실시예에서, 제 1 기판(1101)으로서 유리 기판이 이 용되었지만, 석영 기판, 실리콘 기판, 금속 기판 또는 세라믹 기판이 대안적으로 이용될 수 있다. 추후 제조 단 계들에서의 처리 온도에 대한 내성이 있는 한, 소정의 재료가 제 1 기판(1101)을 위해 이용될 수 있다.

- <73> 제 1 접착층(1102)을 형성하는 방법으로서, 저압 열간 CVD법, 플라스마 CVD법, 스퍼터링법 또는 증발법이 이용될 수 있다. 제 1 접착층(1102)상에는 실리콘 산화물 막으로 이루어진 절연막(1103)이 200nm의 두께를 갖도록 형성된다. 절연막(1103)을 형성하는 방법으로서, 저압 열간 CVD법, 플라즈마 CVD법, 스퍼터링법 또는 증발법이 이용될 수 있다. 절연막(1103)은 제 1 접착층(1102)이 제 1 기판(1101)의 탈피(peel off)를 위해 제거될 때, 제 1 기판(1101)상에 형성된 소자를 보호하도록 기능한다.

- <74> 다음에, 절연막(1103)상에 소자가 형성된다(도 4의 (b)). 여기서, 소자는 능동 매트릭스 발광 장치의 경우에, 화소, OLED 등을 위한 스위칭 소자로서 이용되는, MIM 소자 또는 반도체 소자(통상적으로, TFT)를 나타낸다. 수동 발광 장치의 경우에, 소자는 OLED를 나타낸다. 도 4의 (b)에서, 구동 회로(1106)내의 TFT(1104a)와, 화소부 (1107)내의 TFT들(1104b 및 1104c)이 대표적 소자들로서 도시되어 있다.

- <75> 그후, 절연막(1108)이 상술한 소자들을 덮도록 형성된다. 절연막(1108)은 그 형성 이후에 보다 평탄한 표면을 갖는 것이 적합하다. 절연막(1108)을 필수적으로 제공할 필요는 없다.

- <76> 다음에, 도 4의 (c)에 도시된 바와 같이, 제 2 기판(1110)이 제 2 접착충(1109)을 통해 접착된다. 본 실시예에서, 플라스틱 기판이 제 2 기판(1110)으로서 이용된다. 보다 명확하게, 10μm 이상의 두께를 가지는 수지 기판, 예로서, PES(폴리에테르 설폰), PC(폴리카보네이트), PET(폴리에틸렌 테레프탈레이트) 또는 PEN(폴리에틸렌 나프탈레이트)로 제조된 기판이 이용될 수 있다.

- <77> 제 2 접착층(1109)의 재료로서, 제 1 접착층(1102)이 추후 단계에서 제거될 때, 높은 선택비를 제공할 수 있는 재료를 이용하는 것이 필수적이다. 통상적으로, 수지로 제조된 절연막은 제 2 접착층(1109)으로서 이용될 수 있다. 비록, 본 실시예에서 폴리이미드가 제 2 접착층(1109)의 재료로서 이용되지만, 아크릴, 폴리아미드 또는 에 폭시 수지가 선택적으로 이용될 수 있다. 제 2 접착층(1109)이 OLED로부터 볼 때, 관측자의 측면(발광 장치 이용자의 측면)상에 배치되는 경우에, 재료는 광투과성을 가져야할 필요가 있다.

- <78> 다음에, 도 5의 (a)에 도시된 바와 같이, 제 1 기판(1101)과, 제 2 기판(1110)과 모든 원소들 및 그 사이에 형성된 전체 막들이 제 1 접착충(1102)을 제거하도록 할로겐 플로라이드를 함유하는 가스에 노출된다. 본 실시예에서, 클로린 트리플로라이드(C1F₃)가 할로겐 플로라이드로서 이용되며, 질소가 희석 가스로서 이용된다. 대안적으로, 아르곤, 헬륨 또는 네온이 희석 가스로서 이용될 수 있다. 유량은 양자 모두의 가스들에 대해서 500sccm(8.35x10 m²/s)으로 설정될 수 있으며, 반응 압력은 1 내지 10 Torr(1.3x10² 내지 1.3x10³Pa)로 설정될수 있다. 처리 온도는 실온(통상적으로, 20 내지 27℃)일 수 있다.

- <79> 이 경우에, 실리콘 막은 에칭되고, 플라스틱 막, 유리 기판, 폴리이미드 막 및 실리콘 산화물 막은 에칭되지 않는다. 보다 명확하게, 클로린 트리플로라이드에 대한 노출을 통해, 제 1 접착층(1102)이 선택적으로 에칭되어 그 완전한 제거를 초래한다. 유사하게 실리콘 층으로 제조된, TFT의 활성층은 외부로 노출되지 않기 때문에, 이활성층은 클로린 트리플로라이드에 노출되지 않고, 따라서, 에칭되지 않는다.

- <80> 본 실시예에서, 제 1 접착층(1102)은 그 노출된 에지부들로부터 점진적으로 에칭된다. 제 1 기판(1101) 및 절연 막(1103)은 제 1 접착층(1102)이 완전히 제거될 때, 서로 분리된다. 각각 박막들의 적층체를 포함하는 TFT들과

OLED는 제 2 기판(1110)상에 남아있는다.

- <81> 에칭이 제 1 접착층(1102)의 에지들로부터 점진적으로 진행되고, 따라서, 제 1 접착층(1102)의 완전한 제거를 위해 필요한 시간이 크기의 증가와 함께 길어지기 때문에, 대형 기판은 제 1 기판(1101)으로서 부적합하다. 따라서, 본 실시예는 3인치 이하(바람직하게는, 1 인치 이하)의 대각선을 가지는 제 1 기판(1101)을 위해 수행되는 것이 적합하다.

- <82> 이 방식의 제 1 기판(1101)의 탈피 이후에, 제 3 접착층(1113)이 도 5의 (b)에 도시된 바와 같이 형성된다. 그후, 제 3 기판(1112)이 제 3 접착층(1113)을 통해 접착된다. 본 실시예에서, 플라스틱 기판이 제 3 기판(1110)으로서 이용된다. 보다 명확하게, 10µm이상의 두께를 가지는 수지 기판, 예로서, PES(폴리에테르 설폰), PC(폴리카보네이트), PET(폴리에틸렌 테레프탈레이트) 또는 PEN(폴리에틸렌 나프탈레이트)이 제 3 기판으로서 이용될수 있다.

- <83> 제 3 접착층(1113)으로서, 수지(통상적으로, 폴리이미드, 아크릴, 폴리아미드 또는 에폭시 수지)로 이루어진 절 연막이 이용될 수 있다. 제 3 접착층(1113)이 OLED로부터 볼 때, 관측자 측면(발광 장치 이용자의 측면)에 배치 되는 경우에, 재료는 광 투과성을 가질 필요가 있다.

- <84> 이 방식으로, 가요성을 가지는 두 개의 가요성 기판들(1110 및 1112) 사이에 끼워진 가요성 OLED 패널(발광 장치)이 얻어질 수 있다. 제 2 기판(1110)과 제 3 기판(1112)을 위해 동일한 재료를 이용하면, 기판들(1110 및 1112)이 동일한 열 팽창 계수를 가지게 된다. 결과적으로, 기판들(1110 및 1112)은 온도 변화로 인한 응력 변형에 의한 영향을 잘 받지 않게 된다.

- <85> 다음에, 도 5의 (c)에 도시된 바와 같이, OLED 패널이 봉지막(1119)이 그 위에 형성되어 있는 플라스틱 막 (1118)으로 봉지된다. 이때, 봉지막(1119)은 플라스틱 막(1118)과 OLED(1105) 사이에 배치된다.

- <86> 본 실시예에서, 봉지막(1119)으로서, 무기 절연막(1119a)과, 유기 절연막(1119b) 및 무기 절연막(1119c)이 플라 스틱 막(1118)에 근접한 순서로 형성된다.

- <87> 본 실시예에 따라 제조된 발광 장치는 플라스틱 기판의 내열성에 의해 제한받지 않고, 반도체를 이용하는 소자 (예로서, TFT)의 제조를 가능하게 한다. 따라서, 극도로 높은 성능을 가진 발광 장치가 얻어질 수 있다.

- <88> 비록, 본 실시예에서, 제 1 접착층(1102)이 비정질 실리콘으로 이루어지고, 할로겐 플로라이드를 함유하는 가스로 제거되지만, 본 발명은 이 구조에 한정되지 않는다. 제 1 접착층(1102)의 재료 및 제거 방법은 본 발명의 실시자에 의해 적절히 결정될 수 있다. 제 1 접착층(1102) 이외의, 제거되는 것이 바람직하지 못한 기판들, 소자들 및 막들이 제 1 접착층(1102)의 제거와 함께 제거되지 않고, 그래서, 발광 장치의 동작에 영향을 미치지 않도록 제 1 접착층(1102)의 재료 및 제거 방법을 결정하는 것이 중요하다. 또한, 제 1 접착층(1102)의 재료가 제 1 접착층(1102)의 제거 단계 이외의 프로세스에서 그 제거를 허용하지 않는 것이 중요하다.

- <89> 예로서, 레이저 빔의 방사에 의해 전체적으로 또는 부분적으로 기화되는 유기 재료가 제 1 접착층(1102)으로서 이용될 수 있다. 부가적으로, YAG 레이저로부터의 제 2 고조파가 이용되는 경우에 단지 제 1 접착층(1102)에 의 해서만 효과적으로 레이저 빔이 흡수되도록, 레이저 빔 흡수성을 가지는 재료, 예로서, 착색된 또는 검정색 재 료(예로서, 검정색 착색제를 함유하는 수지 재료)가 이용되는 것이 적합하다. 소자 형성 단계들에서의 열 처리 에 의해 기화되지 않는 재료가 제 1 접착층(1102)을 위해 이용된다.

- <90> 제 1, 제 2 및 제 3 접착충들 각각은 단일충 또는 다충일 수 있다. 비정질 실리콘 막 또는 DLC 막이 접착충과 기판 사이에 제공될 수 있다.

- <91> 제 1 접착충(1102)은 비정질 실리콘 막으로 형성될 수 있고, 제 1 기판은 레이저 단계에서, 제 1 접착충(1102) 상으로의 레이저 빔의 방사에 의해 탈피될 수 있다. 이 경우에, 제 1 기판의 탈피를 촉진하기 위해서, 대량의 수소를 포함하는 비정질 실리콘 막을 이용하는 것이 적합하다. 비정질 실리콘 막 내에 함유된 수소는 레이저 빔 의 방사에 의해 기화되고, 그래서, 제 1 기판이 쉽게 탈피될 수 있다.

- <92> 레이저 빔으로서, 펄스 발진 또는 연속파 엑시머 레이저, YAG 레이저 또는 YVO4 레이저가 이용될 수 있다. 레이저 빔은 제 1 기판을 통해 제 1 접착충상으로 방사되며, 그래서, 제 1 기판을 탈피시키기 위해 제 1 접착충만이 기화된다. 따라서, 제 1 기판으로서, 적어도 방사된 레이저 빔이 그를 통해 통과하는 기판, 즉, 일반적으로, 광투과성을 가진 기판, 예로서, 제 2 및 제 3 기판들의 두께 보다 큰 두께를 가지는 유리 기판, 석영 기판 등을 이용하는 것이 적합하다.

- <93> 본 발명에서, 레이저 빔이 제 1 기판을 통과하는 것을 허용하기 위해서, 레이저 빔 및 기판의 유형을 적절히 선택하는 것이 필수적이다. 예로서, 석영 기판이 제 1 기판으로서 이용될 때, YAG 레이저(기본파(1064nm), 제 2 고조파(532nm), 제 3 고조파(355nm) 및 제 4 고조파(266nm))나, 엑시머 레이저(파장: 308nm)가 순차적으로 석영 기판을 통과하는 것을 허용하는 선형 빔을 형성하도록 이용된다. 엑시머 레이저 빔은 유리 기판을 통과하지 못한다는 것을 인지하여야 한다. 따라서, 제 1 기판으로서 유리 기판이 이용될 때, YAG 레이저의 기본파, 제 2 고조파 또는 제 3 고조파, 바람직하게는, 제 2 고조파(파장: 532nm)가, 순차적으로 유리기판을 통과하는 것이 허용되는 선형 빔을 형성하기 위해 이용된다.

- <94> 대안적으로, 예로서, 제 1 접착층상에 유체(압력-적용 유체 또는 가스)를 분사함으로써(통상적으로 워터 제트법) 제 1 기판을 분리시키는 방법이 이용될 수 있다.

- <95> 제 1 접착층이 비정질 실리콘 막으로 이루어지는 경우에, 제 1 접착층은 히드라진(hydrazine)에 의해 제거될 수 있다.

- <96> 대안적으로, 미국 특허 제 5,821,138호에 기술되어 있는 에칭에 의해 제 1 기판을 분리시키는 방법이 이용될 수 있다. 특히, 적용된 실리콘 산화물 막(SOG)은 그후 불화 수소에 의해 제거될 제 1 접착층으로서 이용될 수 있다. 이 경우에, 제거되는 것이 바람직하지 못한 실리콘 산화물 막이 스퍼터링 또는 CVD법을 통해 미세 구조를 갖도록 형성되고, 그래서, 실리콘 산화물 막이 제 1 접착층이 불화 수소에 의해 제거될 때, 높은 선택비를 제공하는 것이 중요하다.

- <97> 이런 구조에서, 극도로 작은 두께, 특히, 50 내지 300μm, 바람직하게는 150 내지 200μm의 두께를 가지는 기판들이 제 2 및 제 3 기판들로서 이용되는 경우에도, 높은 신뢰성을 가진 발광 장치가 얻어질 수 있다. 종래의 공지된 제조 장치들을 이용하여 이런 얇은 기판상에 소자를 형성하는 것은 어렵다. 그러나, 소자가 제 1 기판상에 접착되어 형성되기 때문에, 얇은 기판을 이용하는 제조 장치들은 장치들을 개조하지 않고도 이용될 수 있다.

- <98> 다층 절연막을 포함하는 봉지막을 이용함으로써, 습기 또는 산소의 침투로 인한 열화를 효과적으로 억제하는 것이 가능하다. 또한, 기판의 굴곡시 균열이 발생하는 것이 방지된다. 결과적으로, 개선된 유연성을 가진 발광 장치가 실현될 수 있다.

- <99> 제 1 및 제 2 실시예와 조합하여 제 3 실시예를 구현하는 것이 가능하다는 것을 인지하여야 한다.

- <100> [제 4 실시예]

- <101> 본 실시예에서, 플라스틱 기판상에 형성된 OLED를 포함하는 OLED 패널을 제조하는, 제 3 실시예와는 상이한 방식이 설명된다. 도 6 및 도 7은 화소부 및 구동 회로의 제조 단계들의 단면도이다.

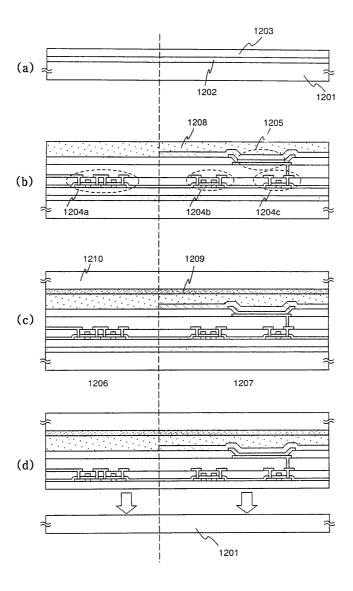

- <102> 도 6의 (a)에서, 비정질 실리콘 막으로 이루어진 제 1 접착층(1202)이 제 1 기판(1201)상에 100 내지 500nm 두 께로 형성된다(본 실시예에서는 300nm). 비록, 본 실시예에서, 유리 기판이 제 1 기판(1201)으로서 이용되었지만, 석영 기판, 실리콘 기판, 금속 기판 또는 세라믹 기판이 대안적으로 이용될 수 있다. 추후의 제조 단계들에서의 처리 온도에 견딜 수 있는 한, 소정의 재료가 제 1 기판(1201)을 위해 이용될 수 있다.

- <103> 제 1 접착층(1202)을 형성하는 방법으로서, 저압 열간 CVD법, 플라즈마 CVD법, 스퍼터링법 또는 증발법이 이용될 수 있다. 제 1 접착층(1202)상에서, 실리콘 산화물 막으로 이루어진 절연막(1203)이 200nm의 두께를 갖도록형성된다. 절연막(1203)을 형성하는 방법으로서, 저압 열간 CVD법, 플라즈마 CVD법, 스퍼터링 법 또는 증발법이이용될 수 있다. 절연막(1203)은 제 1 기판(1201)을 탈피시키도록 제 1 접착층(1202)이 제거될 때, 제 1 기판(1201)상에 형성된 소자를 보호하도록 기능한다.

- <104> 다음에, 절연막(1203)상에 소자가 형성된다(도 6의 (b)). 여기에서, 소자는 능동 매트릭스 발광 장치의 경우에, 화소, OLED 등을 위한 스위칭 소자로서 이용되는 반도체 소자(통상적으로, TFT) 또는 MIM 소자를 나타낸다. 수동 발광 장치의 경우에, 소자는 OLED를 나타낸다. 도 6의 (b)에서, 구동 회로(1206)내의 TFT(1204a)와, 화소부 내의 TFT들(1204b, 1204c)과, OLED(1205)가 대표 소자들로서 도시되어 있다.

- <105> 그후, 상술한 소자들을 덮도록 절연막(1208)이 형성된다. 절연막(1208)은 그 형성 이후에 보다 평탄한 표면을 가지는 것이 적합하다. 절연막(1208)을 제공하는 것은 필수적인 것은 아니다.

- <106> 다음에, 도 6의 (c)에 도시된 바와 같이, 제 2 기판(1210)이 제 2 접착층(1209)을 통해 제 1 기판(1201)에 접착된다. 비록, 본 실시예에서, 유리 기판이 제 2 기판(1210)으로서 이용되었지만, 석영 기판, 실리콘 기판, 금속기판 또는 세라믹 기판도 이용될 수 있다. 재료가 추후 제조 단계에서의 처리 온도에 대한 내성이 있는 한 소정

의 재료가 제 2 기판을 위해 이용될 수 있다.

- <107> 제 2 접착층(1209)의 재료로서, 제 1 접착층(1202)이 추후 단계에서 제거될 때, 높은 선택비를 제공할 수 있는 재료를 이용하는 것이 필수적이다. 또한, 제 2 접착층(1209)을 위해서, 제 3 기판을 접착하도록 기능하는 제 3 접착층이 제 2 접착층의 제거와 함께 제거되지 않고, 제 3 기판의 탈피를 유발하지 않는 재료를 이용하는 것이 필요하다. 본 실시예에서, 일본 특개평 5-315630호에 개시된 폴리이미드 수지의 전구체인 폴리아믹 산 용액이 이용된다. 보다 명확하게, 제 2 접착층(1209)이 미경화 수지인, 폴리아믹 산 용액을 이용하여 10 내지 15/㎞의 두께를 갖도록 형성된 이후에, 제 2 기판(1210) 및 층간 절연막(1208)이 열압착 접착을 통해 서로 접착된다. 그후, 일시적으로 수지를 경화시키도록 가열이 수행된다.

- <108> 본 실시예에서, 제 2 접착층(1209)의 재료는 폴리아믹 산 용액에 제한되지 않는다. 제 1 접착층(1202)이 추후 단계에서 제거될 때, 높은 선택비를 제공하는 한, 그리고, 제 3 기판을 접착하기 위한 제 3 접착층이 제 2 접착 층(1209)의 제거와 함께 제거되지 않고 제 3 기판의 탈피를 유발하지 않는 한, 소정의 재료가 이용될 수 있다. 제 2 접착층(1209)이 제 2 접착층(1209)을 제거하는 단계 이외의 단계들에서 제거되지 않는 재료로 제조되는 것 이 중요하다.

- <109> 다음에, 도 6의 (d)에 도시된 바와 같이, 제 1 기판(1201), 제 2 기판(1210) 및 모든 소자들과 그들 사이에 형성된 전체 막들이 불화 수소를 함유하는 가스에 노출되고, 그래서, 제 1 접착층(1202)을 제거한다. 본 실시예에서, 클로린 트리플로라이드(C1F₃)가 불화 수소로서 이용되고, 질소가 희석 가스로서 이용된다. 대안적으로, 아르곤, 헬륨 또는 네온이 희석 가스로서 이용될 수 있다. 양자 모두의 가스들을 위한 유량은 500ccm(8.35x10-6³3/s)으로 설정될 수 있으며, 반응 압력은 1 내지 10 Torr(1.3x10² 내지 1.3x10³Pa)로 설정될 수 있다. 처리 온도는 실온(통상적으로, 20 내지 27℃)일 수 있다.

- <110> 이 경우에, 실리콘 막은 에칭되고, 플라스틱 막, 유리 기판, 폴리이미드 막 및 실리콘 산화물 막은 에칭되지 않는다. 보다 명확하게, 클로린 트리플로라이드에 대한 노출을 통해, 제 1 접착층(1202)이 선택적으로 에칭되어 그 완전한 제거를 초래한다. 유사하게 실리콘 층으로 제조된, TFT의 활성층은 외부로 노출되지 않기 때문에, 이활성층은 클로린 트리플로라이드에 노출되지 않고, 따라서, 에칭되지 않는다.

- <111> 본 실시예에서, 제 1 접착층(1202)은 그 노출된 에지부들로부터 점진적으로 에칭된다. 제 1 기판(1201) 및 절연 막(1203)은 제 1 접착층(1202)이 완전히 제거될 때, 서로 분리된다. 각각 박막들의 적층체를 포함하는 TFT들과 OLED는 제 2 기판(1210)상에 남아있는다.

- <112> 에칭이 제 1 접착충(1202)의 에지들로부터 점진적으로 진행되고, 따라서, 제 1 접착충(1202)의 완전한 제거를 위해 필요한 시간이 크기의 증가와 함께 길어지기 때문에, 대형 기판은 제 1 기판(1201)으로서 부적합하다. 따라서, 본 실시예는 3인치 이하(바람직하게는, 1 인치 이하)의 대각선을 가지는 제 1 기판(1201)을 위해 수행되는 것이 적합하다.

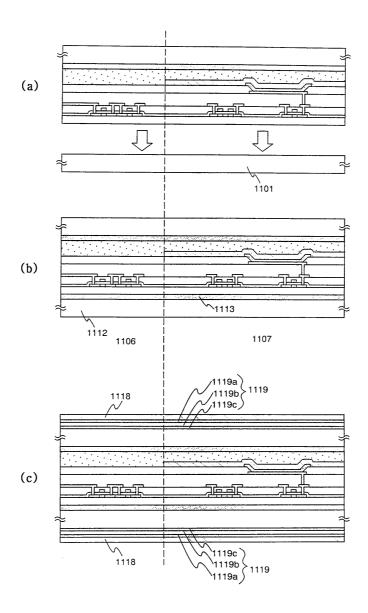

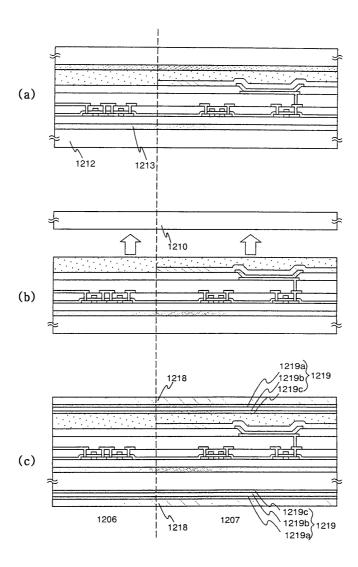

- <113> 이 방식의 제 1 기판(1201)의 제거 이후에, 제 3 접착층(1213)이 도 7의 (a)에 도시된 바와 같이 형성된다. 그후, 제 3 기판(1212)이 제 3 접착층(1213)을 통해 제 2 기판(1210)에 접착된다. 본 실시예에서, 플라스틱 기판이 제 3 기판(1210)으로서 이용된다. 보다 명확하게, 10μm이상의 두께를 가지는 수지 기판, 예로서, PES(폴리에 테르 설폰), PC(폴리카보네이트), PET(폴리에틸렌 테레프탈레이트) 또는 PEN(폴리에틸렌 나프탈레이트)이 제 3 기판으로서 이용될 수 있다.

- <114> 수지(통상적으로, 폴리이미드, 아크릴, 폴리아미드 또는 에폭시 수지)로 이루어진 절연막이 제 3 접착층(1213) 으로서 이용될 수 있다. 제 3 접착층(1213)이 OLED로부터 볼 때, 관측자 측면(발광 장치 이용자의 측면)에 배치되는 경우에, 재료는 광 투과성을 가질 필요가 있다.

- <115> 다음에, 도 7의 (b)에 도시된 바와 같이, 제 2 접착충(1209)이 제 2 기판(1210)을 탈피시키기 위해 제거된다. 보다 명확하게, 제 2 접착충(1209)은 약 1시간 동안 물속에 침지됨으로써 제거되며, 그에 의해, 제 2 기판 (1210)의 탈피를 허용한다.

- <116> 제 2 접착층의 재료, 소자 또는 막들의 재료, 기판의 재료 등에 따라서, 제 2 접착층(1209)을 탈피시키는 방법을 선택하는 것이 중요하다.

- <117> 이 방식으로, 단일 플라스틱 기판(1212)을 이용하는 가요성 OLED 패널(발광 장치)이 얻어질 수 있다.

- <118> 다음에, 도 7의 (c)에 도시된 바와 같이, OLED 패널이 봉지막(1219)이 그 위에 형성되어 있는 플라스틱 막

(1218)으로 봉지된다. 이때, 봉지막(1219)은 플라스틱 막(1218)과 OLED(1205) 사이에 배치된다.

- <119> 본 실시예에서, 봉지막(1219)으로서, 무기 절연막(1219a)과, 유기 절연막(1219b) 및 무기 절연막(1219c)이 플라 스틱 막(1218)에 근접한 순서로 형성된다.

- <120> 플라스틱 기판의 내열성에 의해 제한되지 않고 반도체를 이용하는 소자(예로서, TFT)가 형성될 수 있기 때문에, 극도로 높은 성능을 가지는 발광 장치가 본 실시예에 따라 제조될 수 있다.

- <121> 비록, 본 실시예에서, 제 1 접착층(1202)이 비정질 실리콘으로 제조되고, 할로겐 플로라이드를 함유하는 가스로 제거되지만, 본 발명은 이 구조에 제한되지 않는다. 제 1 접착층(1202)의 재료 및 제거 방법은 본 발명의 실시 자에 의해 적절히 결정될 수 있다. 제 1 접착층(1202) 이외의, 제거되는 것이 바람직하지 못한 기판들, 다른 접 착충들, 소자들 및 막들이 제 1 접착층(1202)의 제거와 함께 제거되지 않고, 그래서, 발광 장치의 동작에 영향을 미치지 않도록 제 1 접착층(1202)의 재료 및 제거 방법을 결정하는 것이 중요하다. 또한, 제 1 접착층(1202)의 재료 및 제거 방법을 결정하는 것이 중요하다. 또한, 제 1 접착층(1202)의 재거 단계 이외의 프로세스에서 그 제거를 허용하지 않는 것이 중요하다.

- <122> 비록, 폴리이미드 수지의 전구체인 폴리아믹 산 용액이, 추후 물로 제거되게 되는 제 2 접착층(1209)을 위해 이용되었지만, 본 발명의 구조는 이에 제한되지 않는다. 제 2 접착층의 재료 및 제거 방법은 본 발명의 실시자에 의해 적절히 결정될 수 있다. 제 2 접착층 이외의, 제거되는 것이 바람직하지 못한 기판들, 다른 접착층들, 소자들 및 막들이 제 2 접착층의 제거와 함께 제거되지 않고, 그래서, 발광 장치의 동작에 영향을 미치지 않도록 제 2 접착층의 재료 및 제거 방법을 결정하는 것이 중요하다. 또한, 제 2 접착층의 재료가 제 2 접착층의 제거 단계 이외의 프로세스에서 그 제거를 허용하지 않는 것이 중요하다.

- <123> 예로서, 레이저 빔의 방사에 의해 전체적으로 또는 부분적으로 기화되는 유기 재료가 제 1 및 제 2 접착충들을 위해 이용될 수 있다. 부가적으로, YAG 레이저로부터의 제 2 고조파가 이용되는 경우에 상기 제 1 및 제 2 접착충들에 의해서만 효과적으로 레이저 빔이 흡수되도록, 레이저 빔 흡수성을 가지는 재료, 예로서, 착색된 또는 검정색 재료(예로서, 검정색 착색제를 함유하는 수지 재료)가 이용되는 것이 적합하다. 소자 형성 단계들에서의 열 처리에 의해 기화되지 않는 재료가 제 1 및 제 2 접착충들이 이용된다.

- <124> 제 1, 제 2 및 제 3 접착충들 각각은 단일충 또는 다충일 수 있다. 비정질 실리콘 막 또는 DLC 막이 접착충과 기판 사이에 제공될 수 있다.

- <125> 제 1 접착층 또는 제 2 접착층은 비정질 실리콘 막으로 형성될 수 있고, 제 1 기판은 추후 단계에서, 제 1 접착 층 또는 제 2 접착층상으로의 레이저 빔의 방사에 의해 탈피될 수 있다. 이 경우에, 제 1 기판의 탈피를 촉진하기 위해서, 대량의 수소를 포함하는 비정질 실리콘 막을 이용하는 것이 적합하다. 비정질 실리콘 막 내에 함유된 수소는 레이저 빔의 방사에 의해 기화되고, 그래서, 기판이 쉽게 탈피될 수 있다.

- <126> 레이저 빔으로서, 펄스 발진 또는 연속파 엑시머 레이저, YAG 레이저 또는 YVO4 레이저가 이용될 수 있다. 레이저 빔은 제 1 기판을 통해 제 1 접착층상으로 방사되며, 그래서, 제 1 기판의 탈피를 위해 제 1 접착층만이 기화된다. 제 2 기판이 탈피되는 경우에, 레이저빔은 제 2 기판을 통해 제 2 접착층상으로 방사되며, 그래서, 제 2 기판의 탈피를 위해 제 2 접착층만이 기화된다. 따라서, 제 1 또는 제 2 기판으로서, 적어도 방사된 레이저 빔이 그를 통해 통과하는 기판, 즉, 일반적으로, 광 투과성을 가진 기판, 예로서, 유리 기판, 석영 기판 등을 이용하는 것이 적합하다.

- <127> 본 발명에서, 레이저 빔이 제 1 또는 제 2 기판을 통과하는 것을 허용하기 위해서, 레이저 빔 및 기판의 유형을 적절히 선택하는 것이 필수적이다. 예로서, 석영 기판이 제 1 기판으로서 이용될 때, YAG 레이저(기본파(1064nm), 제 2 고조파(532nm), 제 3 고조파(355nm) 및 제 4 고조파(266nm))나, 엑시머 레이저(파장: 308nm)가 순차적으로 석영 기판을 통과하는 것을 허용하는 선형 빔을 형성하도록 이용된다. 엑시머 레이저 빔은 유리기판을 통과하지 못한다는 것을 인지하여야 한다. 따라서, 유리 기판이 이용될 때, YAG 레이저의 기본파, 제 2 고조파 또는 제 3 고조파, 바람직하게는, 제 2 고조파(파장: 532nm)가, 순차적으로 유리기판을 통과하는 것이 허용되는 선형 빔을 형성하기 위해 이용된다.

- <128> 대안적으로, 예로서, 제 1 접착층상에 유체(압력-적용 유체 또는 가스)를 분사함으로써(통상적으로 워터 제트법) 제 1 기판을 분리시키는 방법이 이용될 수 있다.

- <129> 제 1 접착층이 비정질 실리콘 막으로 이루어지는 경우에, 제 1 접착층은 히드라진에 의해 제거될 수 있다.

- <130> 대안적으로, 미국 특허 제 5,821,138호에 기술되어 있는 에칭에 의해 제 1 기판을 분리시키는 방법이 이용될 수

있다. 특히, 적용된 실리콘 산화물 막(SOG)은 그후 불화 수소에 의해 제거될 제 1 또는 제 2 접착층으로서 이용될 수 있다. 이 경우에, 제거되는 것이 바람직하지 못한 실리콘 산화물 막이 스퍼터링 또는 CVD법을 통해 미세구조를 갖도록 형성되고, 그래서, 실리콘 산화물 막이 제 1 또는 제 2 접착층이 불화 수소에 의해 제거될 때, 높은 선택비를 제공하는 것이 중요하다.

- <131> 이런 구조에서, 극도로 작은 두께, 특히, 50 내지 300㎞, 바람직하게는 150 내지 200㎞의 두께를 가지는 기판들이 제 2 및 제 3 기판들로서 이용되는 경우에도, 높은 신뢰성을 가진 발광 장치가 얻어질 수 있다. 종래의 공지된 제조 장치들을 이용하여 이런 얇은 기판상에 소자를 형성하는 것은 어렵다. 그러나, 소자가 제 1 및 제 2 기판상에 접착되어 형성되기 때문에, 얇은 기판을 이용하는 제조 장치들은 장치들을 개조하지 않고도 이용될 수있다.

- <132> 다층 절연막을 포함하는 봉지막을 이용함으로써, 습기 또는 산소의 침투로 인한 열화를 효과적으로 억제하는 것이 가능하다. 또한, 기판의 굴곡시 균열이 발생하는 것이 방지된다. 결과적으로, 개선된 유연성을 가진 발광 장치가 실현될 수 있다.

- <133> 제 1 및 제 2 실시예들에서, OLED의 아노드 또는 캐소드 중 어느 하나가 화소 전극으로서 이용될 수 있다.

- <134> 제 1 및 제 2 실시예와 조합하여 제 4 실시예를 구현하는 것이 가능하다는 것을 인지하여야 한다.

- <135> [제 5 실시예]

- <136> 제 5 실시예에서, 본 발명에 따른 발광 장치의 외관과, 그 FPC에 대한 접속이 설명된다.

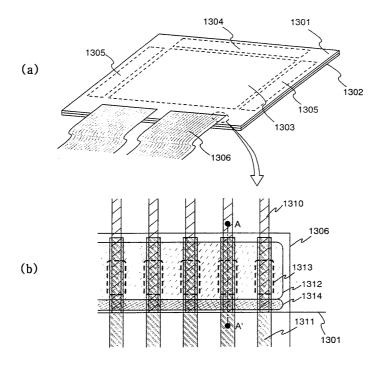

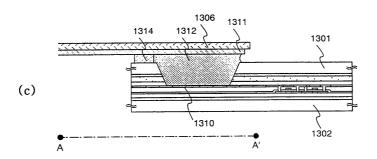

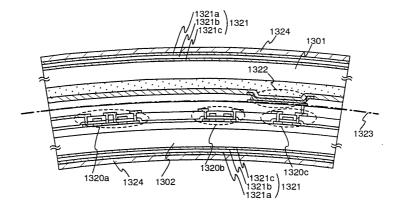

- <137> 도 8의 (a)는 제 3 실시에에 설명된 본 발명에 따른 발광 장치의 상면도의 예를 도시한다. 제 2 기판(1301)과 제 3 기판(1302)은 양자 모두 가요성을 가지는 플라스틱 기판이다. 화소부(1303)와 구동 회로(소스측 구동 회로 (1304) 및 게이트측 구동회로(1305))가 제 2 기판(1301)과 제 3 기판(1302) 사이에 제공된다.

- <138> 도 8의 (a)에서, 화소부(1303)도 그 위에 형성되어 있는 기판상에 소스측 구동회로(1304)와 게이트측 구동회로 (1305)가 형성되는 예를 도시하고 있다. 그러나, 소스측 구동회로(1304)와 게이트측 구동회로(1305)에 의해 대표되는 구동회로들은 화소부(1303)가 그 위에 형성되는 기판과는 상이한 기판상에 형성될 수 있다. 이 경우에, 구동 회로들은 FPC 등을 경유하여 화소부(1303)에 접속될 수 있다.

- <139> 소스측 구동 회로(1304) 및 게이트측 구동 회로(1305)의 수 및 배열은 도 8의 (a)에 도시된 구조에 한정되지 않는다.

- <140> 참조 부호 1306은 FPC를 나타내며, 이를 경유하여 콘트롤러를 포함하는 IC로부터의 신호나 소스 전압이 화소부 (1303), 소스측 구동회로(1304) 및 게이트측 구동 회로(1305)에 공급된다.

- <141> 도 8의 (b)는 FPC(1306)와 제 2 기판(1301)이 서로 접속되는, 도 8의 (a)에 점선으로 둘러싸여진 부분의 확대도 이다. 도 8의 (c)는 도 8의 (b)의 A-A'선을 따라 취한 단면도이다.

- <142> 신호 또는 소스 전압을 화소부(1303), 소스측 구동회로(1304) 및 게이트측 구동회로(1305)에 공급하도록 연장되는 배선들(1310)이 제 2 기판(1301)과 제 3 기판(1302) 사이에 제공된다. 단자들(1311)이 FPC(1306)를 위해 제공된다.

- <143> 1314는 건조 재료를 나타내며, 열화를 조장하는 산소나 수소 같은 물질이 OLED(미도시)에 도입하는 것을 방지하는 효과를 갖는다.

- <144> 제 2 기판(1301)과, 제 2 기판(1301)과 연장된 배선들(1310) 사이에 제공된 절연막 같은 다양한 막들은 접촉 구멍들(1313)을 제공하기 위해 레이저 빔 등에 의해 부분적으로 제거된다. 따라서, 복수의 연장된 배선들(1310)이 접촉 구멍들(1313)을 통해 노출되고, 이방성을 가지는 도전성 수지(1312)를 통해 단자들(1311)에 각각접속된다.

- <145> 비록 연장된 배선들이 제 2 기판의 측면으로부터 부분적으로 노출되는 예가 도 8의 (a) 내지 도 8의 (c)에 도시되어 있지만, 본 발명은 이에 제한되지 않는다. 대안적으로, 연장된 배선들은 제 3 기판(1302)의 측면으로부터 부분적으로 노출될 수 있다.

- <146> 도 9a는 굴곡 상태로 도 8의 (a)에 도시된 발광 장치를 도시한다. 제 3 실시예에 설명된 발광 장치의 제 2 기판 및 제 3 기판 양자 모두가 가요성을 가지기 때문에, 발광 장치는 도 9a에 도시된 바와 같이 소정 정도 굴곡될 수 있다. 따라서, 이런 발광 장치는 곡면을 가진 디스플레이, 쇼 윈도우 등을 위해 이용될 수 있기 때문에 광범

위한 응용 분야들을 가진다. 더욱이, 제 3 실시예에 설명된 발광 장치 뿐만 아니라, 제 4 실시예에 기술된 발 광 장치도 유사하게 굴곡될 수 있다.

- <147> 도 9b는 도 9a에 도시된 발광 장치의 단면도이다. 복수의 소자들이 제 2 기판(1301)과 제 3 기판(1302) 사이에 형성되어 있다. 여기에서, TFT들(1320a, 1320b 및 1320c)과 OLED(1322)가 각각 대표적으로 도시되어 있다. 파 선(1323)은 제 2 기판(1301)과 제 3 기판(1302) 사이의 중앙선을 나타낸다.

- <148> 제 2 기판(1301)은 봉지막(1321)을 통해 플라스틱 막(1324)으로 덮혀져 있다. 또한, 제 3 기판(1302)은 봉지막 (1321)을 통해 플라스틱 막(1324)으로 덮혀져 있다.

- <149> 봉지막(1321)은 플라스틱 막(1324)과 접촉하는 무기 절연막(1321a)과, 무기 절연막(1321a)과 접촉하는 유기 절연막(1321b) 및 유기 절연막(1321b)에 접촉하는 무기 절연막(1321c)을 포함한다.

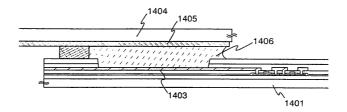

- <150> 다음에, 제 4 실시예에 설명된 발광 장치의 FPC에 대한 접속이 설명된다. 도 10은 제 4 실시예에 설명된 발광 장치와 FPC가 서로 접속되는 부분을 도시하는 단면도이다.

- <151> 연장을 위한 배선(1403)이 제 3 기판(1401)상에 제공된다.

- <152> 제 3 기판(1401)과 연장된 배선(1403) 사이에 제공된 절연막 같은 다양한 막들은 접촉 구멍을 제공하도록 레이저 빔 등에 의해 부분적으로 제거된다. 따라서, 연장된 배선(1403)은 접촉 구멍을 통해 노출되고, 이방성을 가진 도전성 수지(1406)를 통해 FPC(1404)내에 포함된 단자(1405)에 전기적으로 접속된다.

- <153> 비록, 연장된 배선(1403)이 연장된 배선(1403)상에 제공된 절연막의 일부를 제거함으로써 부분적으로 노출되는 예가 도 10에 도시되어 있지만, 본 발명은 이에 한정되지 않는다. 대안적으로, 연장된 배선(1403)은 제 3 기판 (1401)의 측면으로부터 부분적으로 노출될 수 있다.

- <154> 제 5 실시예는 제 1 및 제 2 실시예와 조합하여 구현될 수 있다는 것을 인지하여야 한다.

- <155> [제 6 실시예]

- <156> 제 6 실시예에서, 본 발명의 발광 장치의 제조 방법의 예가 설명된다.

- <157> 도 11a에서, 적용된 실리콘 산화물 막(SOG)으로 이루어진 제 1 접착층(502)이 제 1 기판(501)상에 100 내지 500nm(본 실시예에서는 300nm)의 두께를 갖도록 형성된다. 비록, 본 실시예에서 제 1 기판(501)으로서 유리 기판이 이용되었지만, 석영 기판, 실리콘 기판, 금속 기판 또는 세라믹 기판이 대안적으로 이용될 수 있다. 추후 제조 단계들에서의 열 처리에 대하여 내성이 있는 한, 제 1 기판(501)을 위해 소정의 재료가 이용될 수 있다.

- <158> SOG 막을 형성하는 방법으로서, 요오드 용액이 SOG 용액에 스핀 코팅에 의해 추가되고, 그후, 이는 그로부터 요오드를 제거하기 위해 건조된다. 그후, 400℃에서의 열처리가 SOG 막을 형성하기 위해 수행된다. 제 1 접착층 (502)으로서 SOG 막을 형성하기 위한 방법은 상술한 방법에 제한되지 않는다. 유기 SOG와 무기 SOG 양자 모두가 SOG로서 이용될 수 있으며, SOG는 이것이 추후 단계에서 불화 수소와 함께 제거될 수 있는 한, 소정의 SOG가 이용될 수 있다. 제거되는 것이 바람직하지 못한 실리콘 산화물 막이 제 1 접착층이 불화 수소로 제거될 때, 높은 선택비를 제공하도록 스퍼터링법 또는 CVD법에 의한 미세 구조를 갖도록 형성되는 것이 중요하다.

- <159> 다음에, Al로 이루어진 보호막이 저압 열간 CVD법, 플라스마 CVD법, 스퍼터링법 또는 증발법에 의해 제 1 접착 층(502)상에 형성된다. 본 실시예에서, Al로 이루어진 보호막(503)은 스퍼터링에 의해 제 1 접착층(502)상에 200nm의 두께를 갖도록 형성된다.

- <160> 비록, 본 실시예에서 보호막(503)의 재료로서 Al이 이용되었지만, 본 발명은 이에 제한되지 않는다. 제 1 접착 층(502)의 제거와 함께 제거되지 않고, 보호막(503)의 제거 단계 이외의 프로세스에서 제거되지 않는 재료를 선택하는 것이 중요하다. 또한, 이런 재료가 보호막(503)의 제거 단계에서 다른 막들 및 기판들의 제거를 허용하지 않는 것이 중요하다. 보호막(503)은 제 1 접착층(502)이 제 1 기판(501)의 탈피(peel off)를 위해 제거될때, 제 1 기판(501)상에 형성된 소자를 보호하도록 기능한다.

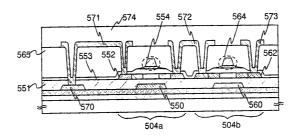

- <161> 다음에, 소자가 보호막(503)상에 형성된다(도 11b). 도 11b에서, 구동 회로의 TFT들(504a 및 504b)이 대표 소자 들로서 도시되어 있다.

- <162> 본 실시예에서, TFT 504a는 n-채널 TFT이며, TFT 504b는 p-채널 TFT이다. TFT들(504a 및 504b)은 CMOS를 형성한다.

- <163> TFT 504a는 보호막(503)상에 형성된 제 1 전극(550)과, 제 1 전극(550)을 덮도록 형성된 절연막(551)과, 절연막

(551)과 접촉하도록 형성된 반도체막(552)과, 반도체막(552)과 접촉하도록 형성된 절연막(553) 및 절연막(553)과 접촉하는 제 2 전극(554)을 포함한다.

- <164> TFT 504b는 제 1 전극(560)과, 제 1 전극(560)을 덮도록 형성된 절연막(551)과, 절연막(551)과 접촉하도록 형성된 반도체막(562)과, 반도체막(562)과 접촉하도록 형성된 절연막(553) 및 절연막(553)과 접촉하는 제 2 전극 (564)을 포함한다.

- <165> 제 1 전극들(550 및 560)과 동시에 형성되는 단자(570)가 보호막(503)상에 제공된다.

- <166> 그후, 절연막(565)은 TFT들(504a 및 504b)을 덮도록 형성된다. 반도체막(552)과 단자(570)와 접촉하는 배선 (571)과, 반도체막들(552, 562)과 접촉하는 배선(572) 및 반도체막(562)과 접촉하는 배선(573)이 절연막들(565, 551, 553)을 통해 형성된 접촉 구멍들을 경유하여 형성된다.

- <167> 비록, 도시되지는 않았지만, OLED가 절연막(565)상에 형성된다. 절연막(574)이 배선들(571, 572 및 573), 절연막(565) 및 OLED를 덮도록 형성된다. 절연막(574)은 그 형성 이후에 보다 평탄한 표면을 가지는 것이 적합하다. 절연막(574)은 필수적으로 형성되어야하는 것은 아니다.

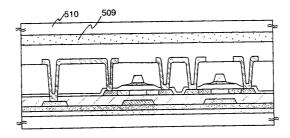

- <168> 다음에, 도 11c에 도시된 바와 같이, 제 2 기판(510)이 제 2 접착층(509)을 통해 제 1 기판에 접착된다. 플라스틱 기판이 본 실시예에서 제 2 기판(510)으로서 이용된다. 보다 명확하게, 10μm이상의 두께를 가지는 수지기판, 예로서, PES(폴리에테르 설폰), PC(폴리카보네이트), PET(폴리에틸렌 테트라프탈레이트) 또는 PEN(폴리에틸렌 나프탈레이트)으로 제조된 기판이 제 2 기판(510)으로서 이용될 수 있다.

- <169> 제 2 접착층(509)의 재료로서, 제 1 접착층(502)이 추후 단계에서 제조될 때, 높은 선택비를 제공할 수 있는 재료를 이용하는 것이 필요하다. 통상적으로, 수지로 제조된 절연막이 이용될 수 있다. OLED로부터 볼 때, 관측자측면(발광 장치 이용자의 측면)상에 제 2 접착충(509)이 배치되는 경우에, 재료는 광 투과성을 가질 필요가 있다.

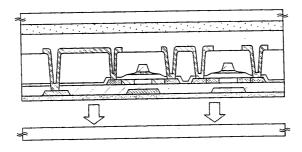

- <170> 다음에, 도 11d에 도시된 바와 같이, 제 1 접착층(502)이 불화 수소로 제거된다. 본 실시예에서, 제 1 및 제 2 기판(501 및 510)과, 그들 사이에 형성된 전체 막들 및 모든 소자들이 제 1 접착층(502)을 제거하도록 버퍼링된 불화수소산(HF/NH4F=0.01 내지 0.2, 예로서, 0.1)내로 침지된다.

- <171> 제거되는 것이 바람직하지 못한 실리콘 산화물막이 스퍼터링 또는 CVD법에 의해 형성된 미세 막으로 이루어지기 때문에, 단지 제 1 접착층만이 불화 수소산으로 제거되게 된다.

- <172> 본 실시예의 경우에, 제 1 접착층(502)은 그 노출된 가장자리부들로부터 점진적으로 에칭된다. 제 1 접착층 (502)이 완전히 제거될 때, 제 1 기판(501)과 보호막(503)이 분리된다. 제 1 접착층(502)의 제거 이후에, 각각 박막들의 적층체를 포함하는 TFT들과 OLED가 제 2 기판(510)상에 잔류한다.

- <173> 그 가장자리들로부터 제 1 접착층(5020을 완전히 제거하기 위해 소요되는 시간이 제 1 기판의 크기 증가와 함께 길어지게 되기 때문에, 대형 기판은 제 1 기판(501)으로서 부적합하다. 따라서, 본 실시예는 3인치 이하(바람직하게는, 1인치 이하)의 대각선을 가지는 제 1 기판(501)을 위해 실시되는 것이 적합하다.

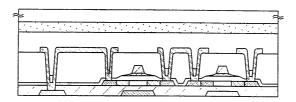

- <174> 다음에, 도 12a에 도시된 바와 같이, 보호막(503)이 제거된다. 본 실시예에서, Al로 이루어진 보호막(503)이 인산형 에칭제를 이용한 습식 에칭에 의해 제거되고, 그래서, 단자(570)와 제 1 전극들(550 및 560)이 노출되게된다.

- <175> 그후, 도 12b에 도시된 바와 같이, 이방성을 가진 도전성 수지로 이루어진 제 3 접착층(513)이 형성된다. 제 3 접착층(513)을 통해, 단자(570)와 제 1 전극들(550 및 560)이 노출되는 측면에 제 3 기판(512)이 부착된다.

- <176> 본 실시예에서, 플라스틱 기판이 제 3 기판(512)으로서 이용된다. 보다 명확하게, 10μm의 두께를 가지는 수지 기판, 예로서, PES(폴리에테르 설폰), PC(폴리카보네이트), PET(폴리에틸렌 테레프탈레이트) 또는 PEN(폴리에틸 렌 나프탈레이트)으로 이루어진 기판이 제 3 기판(512)으로서 이용될 수 있다.

- <177> 제 3 접착층(513)으로서, 수지(통상적으로, 폴리이미드, 아크릴, 폴리아미드 또는 에폭시 수지)로 이루어진 절 연막이 이용될 수 있다. 제 3 접착층(513)이 OLED로부터 볼 때 관측자의 측면상에 배치되는 경우에, 재료가 광 투과성을 가질 필요가 있다.

- <178> 그후, 접촉 구멍이 레이저 빔 등에 의해 제 3 기판(512)을 통해 형성된다. Al은 접촉 구멍이 형성되는 제 3 기판(512)의 부분과 그 외주상에 증발되며, 그에 의해, 서로 전기적으로 접속되어 있는 제 3 기판(512)의 각 표면

들상에 단자들(580 및 581)을 형성한다. 단자들(580 및 581)을 형성하는 방법은 상술한 구조에 한정되지 않는다.

- <179> 제 3 기판(512)상에 형성된 단자(580)는 제 1 전극들(550 및 560)과 동시에 형성된 단자(570)에 제 3 접착층 (513)을 통해 전기적으로 접속된다.

- <180> 이 방식에서, 플라스틱 기판들(510 및 512)사이에 끼워진 가요성 발광 장치가 얻어질 수 있다. 제 2 기판(510) 과 제 3 기판(512)을 위해 동일한 재료를 이용하면, 기판(510 및 512)은 동일한 열 팽창 계수를 가진다. 결과적으로, 기판들(510 및 512)은 온도의 변화로 인한 응력 변형에 잘 영향을 받지 않게 된다.

- <181> 도 12c에 도시된 바와 같이, 제 3 접착층(513)과 접촉하지 않지만, 제 3 기판(512) 및 FPC(590)내에 포함된 단자(591)와는 접촉하도록 형성된 단자(581)가 이방성을 가진 전기 도전성 수지로 이루어진 제 4 접착층(592)을 통해 서로 접속된다.

- <182> 다음에, 도 12c에 도시된, OLED 패널이, 봉지막(520)이 증착되어 있는 플라스틱 막(521)에 의해 봉지된다. 봉지 가 실행될 때, 봉지막(520)이 플라스틱 막(521)과 OLED(도면에는 미도시) 사이에 배열된다.

- <183> 본 실시예에서, 봉지막(520)으로서, 무기 절연막(520a)과 유기 절연막(520b) 및 무기 절연막(520c)이 플라스틱 막(521)의 측면으로부터 형성된다.

- <184> 본 실시예에 따라 제조된 발광 장치는 플라스틱 기판의 내열성에 의해 제한되지 않고, 반도체를 이용하는 소자 (예로서, TFT)를 제조할 수 있게 한다. 따라서, 극도로 높은 성능을 가진 발광 장치가 획득될 수 있다.

- <185> 비록, 본 실시예에서, 제 1 접착층(502)이 SOG로 이루어지고, 불화 수소로 제거되지만, 본 발명은 이 구조에 제한되지 않는다. 제 1 접착층(5020의 재료 및 제거 방법은 본 발명의 실시자에 의해 적절히 결정될 수 있다. 제거되는 것이 바람직하지 못한, 제 1 접착층(502) 이외의 기판들, 소자 및 막들이 제 1 접착층(502)의 제거와 함께 제거되지 않고, 발광 장치의 동작에 영향을 미치지 않도록 제 1 접착층(502)의 재료 및 제거 방법을 결정하는 것이 중요하다. 또한, 제 1 접착층(502)의 재료가 제 1 접착층(502)의 제거 단계가 아닌 프로세스에서 그 제거를 허용하지 않는 것도 중요하다.

- <186> 예로서, 레이저 빔 방사전에 의해 전체적으로, 또는, 부분적으로 기화되는 유기 재료가 제 1 접착층(5020으로서 이용될 수 있다. 부가적으로, 레이저 빔 흡수성을 가진 재료, 예로서, YAG 레이저로부터의 제 2 고조파가 이용되는 경우에 레이저 빔이 제 1 접착층(502)에 의해서만 효과적으로 흡수되도록, 예로서, 착색된 또는 검정색 재료(예로서, 검정색 착색제를 포함하는 수지 재료)가 이용되는 것이 적합하다. 소자 형성 단계들에서 열처리에 의해 기화되지 않는 제 1 접착층(502)이 이용된다.

- <187> 제 1, 제 2 및 제 3 접착층들 각각은 단일층 또는 다층일 수 있다. 비정질 실리콘 막 또는 DLC 막이 접착층과 기판 사이에 제공될 수 있다.

- <188> 제 1 접착충(502)은 비정질 실리콘 막으로 형성될 수 있고, 제 1 기판은 레이저 단계에서, 제 1 접착충(502)상으로의 레이저 범의 방사에 의해 탈피될 수 있다. 이 경우에, 제 1 기판의 탈피를 촉진하기 위해서, 대량의 수소를 포함하는 비정질 실리콘 막을 이용하는 것이 적합하다. 비정질 실리콘 막 내에 함유된 수소는 레이저 범의 방사에 의해 기화되고, 그래서, 제 1 기판이 쉽게 탈피될 수 있다.

- <189> 레이저 빔으로서, 펄스 발진 또는 연속파 엑시머 레이저, YAG 레이저 또는 YVO4 레이저가 이용될 수 있다. 레이저 빔은 제 1 기판을 통해 제 1 접착충상으로 방사되며, 그래서, 제 1 기판을 탈피시키기 위해 제 1 접착충만이 기화된다. 따라서, 제 1 기판으로서, 적어도 방사된 레이저 빔이 그를 통해 통과하는 기판, 즉, 일반적으로, 광투과성을 가진 기판, 예로서, 제 2 및 제 3 기판들의 두께 보다 큰 두께를 가지는 유리 기판, 석영 기판 등을 이용하는 것이 적합하다.

- 본 발명에서, 레이저 범이 제 1 기판을 통과하는 것을 허용하기 위해서, 레이저 범 및 기판의 유형을 적절히 선택하는 것이 필수적이다. 예로서, 석영 기판이 제 1 기판으로서 이용될 때, YAG 레이저(기본파(1064nm), 제 2 고조파(532nm), 제 3 고조파(355nm) 및 제 4 고조파(266nm))나, 엑시머 레이저(과장 : 308nm)가 순차적으로 석영 기판을 통과하는 것을 허용하는 선형 범을 형성하도록 이용된다. 엑시머 레이저 범은 유리 기판을 통과하지 못한다는 것을 인지하여야 한다. 따라서, 제 1 기판으로서 유리 기판이 이용될 때, YAG 레이저의 기본파, 제 2 고조파 또는 제 3 고조파, 바람직하게는, 제 2 고조파(파장 : 532nm)가, 순차적으로 유리기판을 통과하는 것이 허용되는 선형 범을 형성하기 위해 이용된다.

- <191> 대안적으로, 예로서, 제 1 접착충상에 유체(압력-적용 유체 또는 가스)를 분사함으로써(통상적으로 워터 제트법) 제 1 기판을 분리시키는 방법이나, 이 방법과의 조합이 이용될 수 있다.

- <192> 제 1 접착층이 비정질 실리콘 막으로 이루어지는 경우에, 제 1 접착층은 히드라진에 의해 제거될 수 있다.

- <193> 대안적으로, 미국 특허 제 5,821,138호에 기술되어 있는 에칭에 의해 제 1 기판을 분리시키는 방법이 이용될 수 있다. 특히, 적용된 실리콘 산화물 막(SOG)은 그후 불화 수소에 의해 제거될 제 1 접착층으로서 이용될 수 있다. 이 경우에, 제거되는 것이 바람직하지 못한 실리콘 산화물 막이 스퍼터링 또는 CVD법을 통해 미세 구조를 갖도록 형성되고, 그래서, 실리콘 산화물 막이 제 1 접착층이 불화 수소에 의해 제거될 때, 높은 선택비를 제공하는 것이 중요하다.

- <194> 이런 구조에서, 극도로 작은 두께, 특히, 50 내지 300㎞, 바람직하게는 150 내지 200㎞의 두께를 가지는 기판들이 제 2 및 제 3 기판들로서 이용되는 경우에도, 높은 신뢰성을 가진 발광 장치가 얻어질 수 있다. 종래의 공지된 제조 장치들을 이용하여 이런 얇은 기판상에 소자를 형성하는 것은 어렵다. 그러나, 소자가 제 1 기판상에 접착되어 형성되기 때문에, 얇은 기판을 이용하는 제조 장치들은 장치들을 개조하지 않고도 이용될 수 있다.

- <195> 다층 절연막을 포함하는 봉지막을 이용함으로써, 습기 또는 산소의 침투로 인한 열화를 효과적으로 억제하는 것이 가능하다. 또한, 기판의 굴곡시 균열이 발생하는 것이 방지된다. 결과적으로, 개선된 유연성을 가진 발광 장치가 실현될 수 있다.

- <196> 본 실시예는 제 1 또는 제 2 실시예와 자유롭게 조합하여 구현될 수 있다.

- <197> [제 7 실시예]

- 본 실시예에서, 화소부와, 화소부의 주변에 배열된 구동회로(소스 신호 라인 구동 회로 및 게이트 신호 라인 구동 회로)의 TFT를 형성하는 방법이 상세히 설명된다. 본 실시예에서, 구동 회로와 관련하여, CMOS 회로는 단지 단순한 설명을 위해 기본 유니트로서 도시되어 있다.

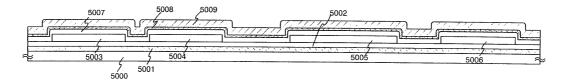

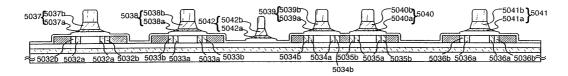

- <199> 먼저, 도 13a에 도시된 바와 같이, 비정질 실리콘막으로 형성된 제 1 접착막(5001)이, CORNING 코포레이션 등의 #7059 유리 및 #1737 유리에 의해 대표되는 알루미노 보로실리케이트 유리나 바륨 보로실리케이트 유리 같은 유리로 형성된 제 1 기판(5000)상에 100 내지 500nm(바람직하게는, 300nm)의 두께로 형성된다. 제 1 접착막(500 1)은 본 실시예에서, 스퍼터링법을 이용하여 형성된다.

- <200> 다음에, 실리콘 산화물 막, 실리콘 산질화물 막 또는 실리콘 질화물 산화물 막 같은 절연막으로 형성된 기저막 (5002)이 제 1 접착막(5001)상에 형성된다. 기저막(5002)은 기판(5000)을 탈피하기 위해 제 1 접착층(5001)이 제거될 때, 기판(5000)상에 형성된 소자를 보호하는 효과를 가진다. 예로서, 플라즈마 CVD법에 의해 SiH₄, NH₃ 및 N₂O로 형성된, 10 내지 200nm(바람직하게는 50 내지 100nm)의 두께를 가지는 실리콘 질화물 산화물 막이 형성된다. 유사하게, SiH₄와 N₂O로 형성된, 50 내지 200nm(바람직하게는 100 내지 150nm)의 두께를 가지는 수화 (hydrogenation)된 실리콘 질화물 산화물 막이 그 위에 적충된다. 본 실시예에서, 기저막(5002)은 2층 구조를 가지지만, 상술한 절연막들 중 하나로 이루어진 단층막으로서 형성되거나, 상술한 절연막들로 이루어진 둘 이상의 층들을 가지는 적층체막으로서 형성될 수도 있다.

- <201> 아일랜드형 반도체충들(5003 내지 5006)이 비정질 구조를 가지는 반도체막상에 레이저 결정화 또는 공지된 열적 결정화를 수행함으로써 얻어진 결정 반도체막으로부터 형성된다. 이들 아일랜드형 반도체 충들(5003 내지 5006) 각각은 25 내지 80nm(바람직하게는 30 내지 60nm)의 두께를 가진다. 결정 반도체막의 재료에는 어떠한 제한도 부여되지 않지만, 결정 반도체막은 실리콘, 실리콘 게르마늄(SiGe) 합금등으로 형성되는 것이 적합하다.

- <202> 결정 반도체 막이 레이저 결정화 방법에 의해 제조될 때, 펄스 발진형 또는 연속 발광형의 액시머 레이저, YAG 레이저 및 YVO4 레이저가 이용된다. 이들 레이저들이 이용될 때, 레이저 방사 디바이스로부터 방사된 레이저 빔이 광학 시스템에 의해 선형 형상으로 수렴되고 그후, 반도체막으로 조사되는 방법을 이용하는 것이 적합하다. 결정화 조건은 작업자에 의해 적절히 선택된다. 액시머 레이저가 이용될 때, 펄스 발진 주파수는 300Hz로 설정되고, 레이저 에너지 밀도는 100 내지 400mJ/cm²(통상적으로 200 내지 300 mJ/cm²)으로 설정된다. YAG 레이저가 이용될 때, 펄스 발진 주파수는 그 제 2 하모닉을 이용함으로써, 30 내지 300kHz로 설정되며, 레이저 밀도는 300 내지 600mJ/cm²(통상적으로, 350 내지 500mJ/cm²)으로 설정되는 것이 적합하다. 선형 형상으로 수렴되고, 100 내지 1000µm, 예로서, 400µm의 폭을 가지는 레이저 빔이 전체 기판면에 조사된다. 이때, 선형 레이저 빔의

중첩비는 50 내지 90%로 설정된다.

- <203> 다음에, 아일랜드형 반도체 충들(5003 내지 5006)을 덮는 게이트 절연막(5007)이 형성된다. 게이트 절연막(5007)은 플라즈마 CVD법 또는 스퍼터링법에 의해 40 내지 150nm의 두께를 가지는 실리콘을 함유하는 절연막으로부터 형성된다. 본 실시예에서, 게이트 절연막(5007)은 120nm 두께의 실리콘 질화물 산화물 막으로 형성된다. 그러나, 게이트 절연막은 이런 실리콘 질화물 산화물 막에 제한되는 것은 아니며, 단충 또는 적충된 충 구조를 가지는, 다른 것을 함유하는 절연막일 수 있다. 예로서, 실리콘 산화물 막이 이용될 때, TEOS(테트라에틸 오르 쏘실리케이트) 및 0₂가 플라즈마 CVD법에 의해 혼합되고, 반응 압력은 40Pa로 설정되며, 기판 온도는 300 내지 400℃로 설정되고, 고주파수(13.56MHZ) 출력 밀도는 전기 방전을 위해 0.5 내지 0.8W/cm²으로 설정된다. 따라서, 실리콘 산화물 막은 방전에 의해 형성될 수 있다. 이방식으로 제조된 실리콘 산화물 막은 그후, 400 내

- <204> 게이트 전극을 형성하기 위한 제 1 도전막(5008)과 제 2 도전막(5009)이 게이트 절연막(5007)상에 형성된다. 본 실시예에서, 50 내지 100nm의 두께를 가지는 제 1 도전막(5008)이 Ta로 형성되고, 100 내지 300nm의 두께를 가 지는 제 2 도전막(5009)이 W로 형성된다.

지 500℃에서의 열적 어닐링에 의해 게이트 절연막으로서 적합한 특성을 획득할 수 있다.

- <205> Ta막은 스퍼터링법에 의해 형성되고, Ta의 타겟은 Ar에의해 스퍼터링된다. 이 경우에, 적절한 양의 Xe 및 Kr이 Ar에 추가될 때, Ta막의 내부 응력이 해제되고, 이 막의 탈피가 방지될 수 있다. α상의 Ta막의 고유저항은 약 20 μΩcm이고, 이 Ta 막은 게이트 전극을 위해 이용될 수 있다. 그러나, β상의 Ta막의 고유저항은 약 180 μΩ cm이며, 게이트 전극을 위해 적합하지 않다. Ta의 α상의 결정 구조에 근접한 결정 구조를 가지며, 약 10 내지 50mm의 두께를 가지는 탄탈륨 질화물이 α상의 Ta막을 형성하기 위해 Ta막을 위한 베이스로서 미리 형성될 때, α상의 Ta막이 쉽게 얻어질 수 있다.

- <206> \[

\text{W막은 타겟으로서 \(\text{W\overline}\) 이용하여 스퍼터링법에 의해 형성된다. 부가적으로, \(\text{W막은 또한 텅스텐 헥사플로라이드 \((\text{WF}\_6)\) \(\text{\overline}\) 이용하여 열적 CVD법에 의해서 형성될 수도 있다. 어떠한 경우라도, 이막을 게이트 전국으로서 이용하기 위해 저항을 감소시키는 것이 필수적이다. \(\text{\overline}\) 막의 고유저항을 20 \(\mu\) \(\Overline\) 요cm 이하로 설정하는 것이 적합하다. \(\text{\overline}\) 막의 결정 입자들이 크기가 증가할 때, \(\text{\overline}\) 막의 고유저항은 감소될 수 있다. 그러나, 산소 등의 많은 불순물 원소들이 \(\text{\overline}\) \(\text{\overline}\) \(\text{\overline}\) 바이 존재할 때, 결정화가 방지되고, 고유저항이 증가된다. \(\text{\overline}\) 나이 청성될 때, \(\text{\overline}\) 막내로 가스 상으로부터 불순물들이 혼입되지 않도록 충분한 주의를 기울임으로써 \(\text{\overline}\) 학성된다. \(\text{\overline}\) 라지 20 \(\mu\) \(\Overline\) \(\text{\overline}\) 고유저항이 실현될 수 있다.

- <207> 본 실시예에서, 제 1 도전막(5008)은 Ta로부터 형성되고, 제 2 도전막(5009)은 W로 형성된다. 그러나, 본 발명은 이 경우에 제한되지 않는다. 이들 도전막들 각각은 Ta, W, Ti, Mo, Al 및 Cu나, 이들 원소들을 주 성분들로가지는 합금 재료 또는 합성 재료로부터 선택된 원소로 형성될 수도 있다. 또한, 인 같은 불순물 원소로 도핑된다결정 실리콘막으로 대표되는 반도체막도 이용될 수 있다. 본 실시예에 도시된 것들 이외의 조합들의 예는 제 1 도전막(5008)이 탄탈륨 질화물(TaN)로 형성되고, 제 2 도전막(5009)이 W로 형성되는 조합, 제 1 도전막(5008)이 탄탈륨 질화물(TaN)로 형성되고, 제 2 도전막(5009)이 Al로 형성되는 조합 및, 제 1 도전막(5008)이 탄탈륨 질화물(TaN)로 형성되고, 제 2 도전막(5009)이 Cu로 형성되는 조합을 포함한다.

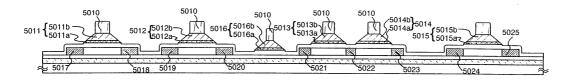

- <208> 다음에, 마스크(5010)가 레지스트로부터 형성되고, 전극 및 배선을 형성하기 위한 제 1 에칭 처리가 수행된다. 본 실시예에서, ICP(유도 결합 플라즈마) 에칭법이 이용되고, CF<sub>4</sub> 및 Cl<sub>2</sub>가 에칭을 위한 가스와 혼합된다. 500W 의 RF(13.56MHZ) 전력이 1Pa의 압력에서 코일형의 전극에 적용되고, 그래서, 플라즈마가 생성된다. 100W 전력의 RF(13.56)도 기판측(샘플 스테이지)에 적용되고, 실질적으로 음의 자기 바이어스 전압이 적용된다. CF<sub>4</sub> 및 Cl<sub>2</sub>가 혼합될 때, W막과 Ta막은 동일한 범위로 에칭된다.

- <209> 상술한 에칭 조건하에서, 제 1 도전층과 제 2 도전층의 단부 부분들은 레지스트로부터 형성된 마스크의 형상을 적절한 형상으로 함으로써, 기판측에 적용된 바이어스 전압의 효과에 의해 테이퍼 형상으로 형성된다. 테이퍼부의 각도는 15° 내지 45°로 설정된다. 케이트 절연막상에 잔류물을 남기지 않는 에칭을 수행하도록, 약 10 내지 20%의 비율만큼 에칭 시간을 증가시키는 것이 적합하다. E막에 대한 실리콘 질화물 산화물 막의 선택비가 2 내지 4(통상적으로는 3)의 범위이기 때문에, 실리콘 질화물 산화물 막의 노출된 표면은 과에칭 처리에 의해 약 20 내지 50nm만큼 에칭된다. 따라서, 제 1 및 제 2 도전층들로 이루어진 제 1 형상의 도전층들(5011 내지 5016)(제 1 도전층들(5011a 내지 5016a)과 제 2 도전층들(5011b 내지 5016b))이 제 1 에칭 처리에 의해 형성된다. 제 1 형상의 도전층들(5011 내지 5016)로 피복되지 않은 영역은 게이트 절연막(5007)에서 약 20 내지 50nm만큼 에칭

되며, 그래서 얇아진 영역이 형성된다(도 13a 참조).

- <210> 그후, n-형 도전성을 제공하기 위한 불순물 원소가 제 1 도핑 처리를 수행함으로써 추가된다. 도핑 방법은 이온 도핑법 또는 이온 주입법 중 어느 한쪽일 수 있다. 이온 도핑법은 투입량이 1x10<sup>13</sup> 내지 5x10<sup>14</sup> atoms/cm<sup>2</sup>으로 설정되고, 가속 전압이 60 내지 100keV로 설정되는 조건하에서 수행된다. 그룹 15에 속하는 원소, 통상적으로, 인(P) 또는 비소(As)가 n-형 도전성을 제공하기 위한 불순물 원소로서 이용된다. 그러나, 여기서는 인(P)이 이용된다. 이 경우에, 도전충들(5011 내지 5015)은 n-형 도전성을 제공하기 위한 불순물 원소에 대한 마스크로서 기능하고, 제 1 불순물 영역들(5017 내지 5025)은 자기 정렬 방식으로 형성된다. n-형 도전성을 제공하기 위한 불순물 원소가 제 1 불순물 영역들(5017 내지 5025)에 1x10<sup>20</sup> 내지 1x10<sup>21</sup> atoms/cm<sup>3</sup>의 농도 범위에서 추가되게 된다(도 13b 참조).

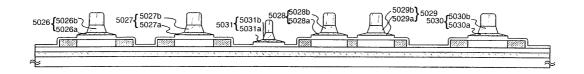

- <211> 도 13c에 도시된 바와 같이, 레지스트 마스크를 제거하지 않고 다음에 제 2 에칭 처리가 수행된다. \( \text{W막이 CF}\_4\), \( \text{Cl}\_2\) 및 02를 이용하여 선택적으로 에칭된다. 제 2 형상의 도전층들(5026 내지 5031)(제 1 도전층들(5026a 내지 5031a)과 제 2 도전층들(5026b 내지 5031b))이 제 2 에칭 처리에 의해 형성된다. 제 2 형상의 도전층들(5026 내지 5031)로 덮혀져 있지 않은 게이트 절연막(5007)의 영역은 약 20 내지 50nm만큼 추가로 에칭되고, 그래서, 얇아진 영역이 형성된다.

- <212> CF<sub>4</sub>와 Cl<sub>2</sub>의 혼합 가스와 Ta막을 이용하는 W막의 에칭에서의 에칭 반응은 생성된 라디칼 또는 이온 종들과 반응부산물들의 증기압으로부터 추정될 수 있다. W와 Ta의 불화물과 염화물의 증기압들이 비교될 때, W의 불화물로서의 WF<sub>6</sub>의 증기압은 극도로 높고, 다른 WCl<sub>5</sub>, TaF<sub>5</sub>, TaCl<sub>5</sub>의증기압들은 거의 서로 동일하다. 따라서, W막과 Ta막 양자 모두가 CF<sub>4</sub>와 Cl<sub>2</sub>의 혼합 가스를 이용하여 에칭된다. 그러나, 적절한 양의 O<sub>2</sub>가 이 혼합 가스에 추가될때, CF<sub>4</sub>와 O<sub>2</sub>는 반응하고, Co와 F가 되며, 그래서, 대량의 F-라디칼들이나 F-이온들이 생성된다. 결과적으로, 그불화물이 높은 증기압을 가지는 W막의 에칭 속도가 증가된다. 이에 대조적으로, F가 증가될 때의 Ta막에 대해서는 에칭 속도의 증가가 상대적으로 작다. Ta가 W에 비해 쉽게 산화되기 때문에, Ta막의 표면은 O<sub>2</sub>를 추가하는 것에 의해 산화된다. 어떠한 Ta의 산화물도 불화물 또는 염화물과 반응하지 못하기 때문에, Ta 막의 에칭 속도 는 추가로 감소된다. 따라서, W 막과 Ta 막 사이의 에칭 속도에 편차를 만드는 것이 가능하고, 그래서, W 막의 에칭 속도가 Ta 막의 에칭 속도보다 높게 설정될 수 있다.

- <213> 도 14a에 도시된 바와 같이, 그후, 제 2 도핑 처리가 수행된다. 이 경우에, 제 1 도핑 처리에서의 투입량보다 낮게 투입량을 감소시킴으로써, 제 1 도핑 처리에서 보다 작은 투입량과 높은 가속 전압에서 n-형 도전성을 제 공하기 위한 불순물 원소가 투입된다. 예로서, 가속 전압은 70 내지 120keV로 설정되고, 투입량은 1x10 atoms/cm²으로 설정된다. 따라서, 새로운 불순물 영역이 도 13b에서 아일랜드형 반도체 층내에 형성된 제 1 불순물 영역 내부에 형성된다. 도핑시, 제 2 형상의 도전층들(5026 내지 5030)이 불순물 원소에 대한 마스크들로서 이용되고, 불순물 원소가 제 1 도전층들(5026a 내지 5030a) 아래측의 영역들에도 추가되도록 도핑이 수행된다. 따라서, 제 3 불순물 영역들(5032 내지 5041)이 형성된다. 제 3 불순물 영역들(5032 내지 5036)은 제 1 도전층들(5026a 내지 5030a)의 테이퍼부들내의 두께 구배와 부합되는 완만한 농도 구배로 인(P)을 함유한다. 제 1 도전층들(5026a 내지 5030a)의 테이퍼부들과 중첩하는 반도체 충들에서, 불순물 농도는 제 1 도전층들(5026a 내지 5030a)의 테이퍼부들과 중첩하는 반도체 충들에서, 불순물 농도는 제 1 도전층들(5026a 내지 5030a)의 테이퍼 부분들의 에지들에서 보다 중앙 둘레에서 다소 낮다. 그러나, 편차는 매우 미소하고, 거의 동일한 불순물 농도가 반도체 충들 전체에 걸쳐 유지된다.

- <214> 그후, 제 3 에칭 처리가 도 14b에 도시된 바와 같이 수행된다. CHF<sub>6</sub>가 에칭 가스로서 이용되고, 반응성 이온 에 칭(RIE)이 이용된다. 제 3 에칭 처리를 통해, 제 1도전층들(5026a 내지 5031a)의 테이퍼 부분들이 부분적으로 에칭되어 제 1 도전층들이 반도체 층들에 중첩되는 영역들을 감소시킨다. 따라서, 제 3 형상 도전층들(5037 내지 5042)(제 1 도전층들(5037a 내지 5042a)와 제 2 도전층들(5037b 내지 5042b)이 형성된다. 이 시점에서, 제 3 형상 도전층들(5037 내지 5042)로 덮여지지 않은 게이트 절연막(5007)의 영역들이 추가로 에칭되고, 약 20 내지 50nm 만큼 얇아진다.

- <215> 제 3 불순물 영역들(5032 내지 5036)이 제 3 에칭 처리를 통해 형성된다. 제 1 도전충들(5037a 내지 5041a)과 각각 중첩하는 제 3 불순물 영역들(5032a 내지 5036a)과 제 2 불순물 영역들(5032b 내지 5036b)이 각각 제 1 불순물 영역과 제 3 불순물 영역 사이에 형성된다.

- <216> 도 14c에 도시된 바와 같이, 제 1 도전형에 대해 반대 도전형을 가진 제 4 불순물 영역들(5043 내지 5054)이 p-

채널 TFT들을 형성하기 위해 아일랜드형 반도체층들(5004 및 5006)내에 형성된다. 제 3 형상 도전층들(5038b 및 5041b)은 불순물 원소에 대한 마스크로서 이용되고, 불순물 영역들은 자기 정렬 방식으로 형성된다. 이 시점에 서, n-채널 TFT들을 형성하기 위한 아일랜드형 반도체 충들(5003 및 5005)과 배선부(5042)는 전체적으로 레지스트 마스크(5200)로 덮여지게 된다. 불순물 영역들(5043 내지 5054)은 상이한 농도들의 인으로 이미 도핑되어 있다. 불순물 영역들(5043 내지 5054)은 디보란이 각 영역내의 인보다 우세해지고, 각 영역이  $2x10^{20}$  내지  $2x10^{21}$  atoms/cm 3 농도의 불순물 원소들을 함유하도록 이온 도핑을 통해 디보란(B<sub>2</sub>H<sub>6</sub>)으로 도핑된다.

- <217> 상술한 단계들을 통해, 불순물 영역들이 각 아일랜드형 반도체 충들내에 형성된다. 아일랜드형 반도체 충들과 중첩하는 제 3 형상 도전충들(5037 내지 5041)은 게이트 전극들로서 기능한다. 참조 부호 5042는 아일랜드형 소 스 신호 라인으로서 기능한다.

- <218> 레지스트 마스크(5200)가 제거된 이후에, 아일랜드형 반도체 층들에 추가된 불순물 원소들을 활성화하는 단계가 수행되어 도전형을 제어한다. 이 프로세스는 노 어닐링을 위해 노를 이용하여 열적 어닐링법에 의해 수행된다. 부가적으로, 레이저 어닐링법 또는 급속 열적 어닐링법(RTA법)이 적용될 수 있다. 열적 어닐링법에서, 이 프로세스는 산소 농도가 1ppm 이하, 바람직하게는 0.1ppnm 이하인 질소 분위기에서, 400 내지 700℃, 통상적으로 500 내지 600℃의 온도로 수행된다. 본 실시예에서, 열처리는 500℃에서 4시간 동안 수행되었다. 제 3 도전층들 (5037 내지 5042)에 이용된 배선 재료가 열에 대해 약할 때, 배선등을 보호하기 위해서, 층간 절연막(주 성분으로서 실리콘을 가지는)이 형성된 이후, 활성화를 수행하는 것이 적합하다.

- <219> 또한, 아일랜드형 반도체층이 수화되도록 3 내지 100%의 수소를 포함하는 분위기내에서 300 내지 450℃의 온도에서 1 내지 12 시간 동안 열처리가 수행된다. 이 단계는 열적으로 여기된 수소에 의해 반도체층의 미결합 화학 손(dangling bond)을 단절하기위한 것이다. 플라즈마 수화(플라즈마에 의해 여기된 수소를 이용하는)도 수화를 위한 다른 조치로서 수행될 수 있다.

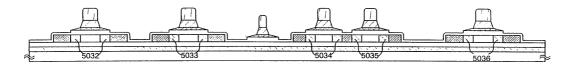

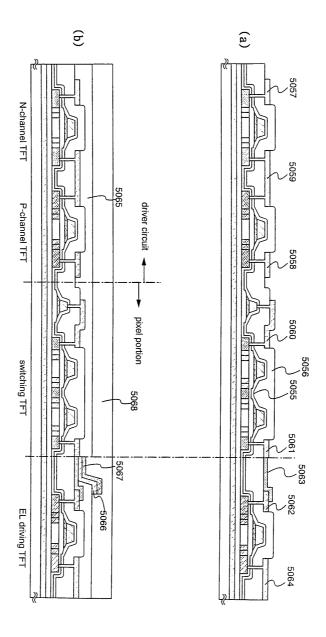

- <220> 다음에, 도 15의 (a)에 도시된 바와 같이, 제 1 층간 절연막(5055)이 실리콘 질화물 산화물 막으로부터 100 내지 200nm 두께로 형성된다. 유기 절연 재료로부터의 제 2 층간 절연막(5056)이 제 1 층간 절연막상에 형성된다. 그후, 접촉 구멍들이 제 1 층간 절연막(5055), 제 2 층간 절연막(5056) 및 게이트 절연막(5007)을 통해 형성된다. 각 배선(접속 배선 및 신호 라인을 포함하는)(5057 내지 5062 및 5064)이 패턴화 및 형성된다. 그후, 접속 배선(5062)과 접촉하는 화소 전극(5063)이 패턴화 및 형성된다.

- <221> 재료로서 유기 수지를 가지는 막이 제 2 층간 절연막(5056)으로서 이용된다. 폴리이미드, 폴리아미드, 아크릴, BCB(벤조사이클로부텐) 등이 이 유기 수지로서 이용될 수 있다. 특히, 제 2 층간 절연막(5056)이 주로 평탄화를 위해 제공되기 때문에, 막의 높이조절에 양호한 아크릴이 적합하다. 본 실시예에서, TFT에 의해 유발된 높이차를 충분히 높이 조절할 수 있는 두께를 가지는 아크릴막이 형성된다. 그 막두께는 1 내지 5㎞으로 설정되는 것이 적합하다(2-4㎞으로 설정되는 것이 보다 바람직하다).

- <222> 접촉 구멍들의 형성에서, n-형 불순물 영역들(5017, 5018, 5021 및 5023) 또는 p-형 불순물 영역들(5043 내지 5054)에 도달한 접촉 구멍들, 배선(5042)에 도달하는 접촉 구멍, 전류 공급 라인(미도시)에 도달하는 접촉 구멍 및 게이트 전극(미도시)들에 도달하는 접촉 구멍들이 형성된다.

- <223> 또한, 3층 구조의 적층체막이 양호한 형상으로 패턴화되고, 배선(접속 배선 및 신호 라인 포함)(5057 내지 5062, 5064)으로서 이용된다. 이 3층 구조에서, 100nm 두께의 Ti막과, 300nm 두께의 Ti 함유 알루미늄막 및, 150nm 두께의 Ti막이 스퍼터링법에 의해 연속적으로 형성된다. 그러나, 다른 도전막들이 이용될 수도 있다.

- <224> 본 실시예에서, 110nm 두께의 ITO막이 화소 전극(5063)으로서 형성되고, 패턴화된다. 접점은 화소 전극(5063)이 접속 전극(5062)과 접촉하고, 이 접속 배선(5062)과 중첩하도록 화소 전극(5063)을 배열함으로써 이루어진다. 또한, 2 내지 20%의 아연 산화물(ZnO)을 인듐 산화물과 혼합함으로써 제공된 투명 도전막도 이용될 수 있다. 이화소 전극(5063)은 OLED의 아노드가 된다(도 15의 (a) 참조).

- <225> 도 15의 (b)에 도시된 바와 같이, 실리콘을 함유하고, 500nm의 두께를 가지는 절연막(본 실시예에서 실리콘 산화물 막)이 다음에 형성된다. 제 3 충간 절연막(5065)이 형성되고, 화소 전극(5063)에 대응하는 위치에 개구가형성된다. 개구가 형성될 때, 개구의 측벽은 습식 에칭법을 이용함으로써, 쉽게 테이퍼 형성될 수 있다. 개구의 측벽이 충분히 완만하지 못할 때, 높이차에 의해 유발된 유기 발광층의 열화가 현저한 문제가 된다.

- <226> 다음에, 유기 발광층(5066)과 캐소드(MgAg 전극; 5067)가 진공 증발법을 이용하여 대기에 노출되지 않고 연속적으로 형성된다. 유기 발광층(5066)은 80 내지 200nm(통상적으로 100 내지 120nm)의 두께를 가지며, 캐소드

(5067)는 180 내지 300nm(통상적으로 200 내지 250nm)의 두께를 가진다.

- <227> 이 프로세스에서, 유기 발광층이 적색에 대응하는 화소와, 녹색에 대응하는 화소 및 청색에 대응하는 화소에 대하여 연속적으로 형성된다. 이 경우에, 유기 발광층이 용액에 대한 불충분한 저항을 가지기 때문에, 유기 발광층은 포토리소그래피 기술을 이용하는 대신 각 색상에 대하여 독립적으로 형성되어야만 한다. 따라서, 유기 발광층이 단지 필요한 부분에만 선택적으로 형성되도록 금속 마스크를 이용하여 원하는 화소를 제외한 부분을 덮는 것이 적합하다.

- <228> 즉, 적색에 대응하는 화소를 제외한 모든 부분들을 덮는 마스크가 가장 먼저 설정되고, 적색광을 방사하기 위한 유기 발광층이 이 마스크를 이용하여 선택적으로 형성된다. 다음에, 녹색에 대응하는 화소를 제외한 모든 부분을 덮는 마스크가 설정되고, 녹색광을 방사하기 위한 유기 발광층이 이 마스크를 이용하여 선택적으로 형성된다. 다음에, 청색에 대응하는 화소를 제외한 모든 부분들을 덮는 마스크가 설정되고, 청색광을 방사하기 위한 유기 발광층이 이 마스크를 이용하여 선택적으로 형성된다. 여기서, 상이한 마스크들이 이용되지만, 동일한 단일 마스크를 반복적으로 이용할 수 있다.

- <229> 여기서, RGB에 대응하는 3종류의 OLED를 형성하기 위한 시스템이 이용되었다. 그러나, 백색광을 발광하기 위한 OLED와 컬러 필터가 조합되는 시스템과, 청색광 또는 청녹색광을 방사하기 위한 OLED가 형광 물질(형광 색상 변환층: CCM)과 조합된 시스템, R, G, B에 각각 대응하는 OLED를 투명 전극을 활용함으로써 캐소드들(상대 전극들)과 중첩시키는 시스템 등이 이용될 수 있다.

- <230> 공지된 재료가 유기 발광충(5066)으로서 이용될 수 있다. 유기 재료가 구동 전압을 고려하여 공지된 재료로서 적합하게 이용된다. 예로서, 정공 주입층, 정공 운반층, 발광층 및 전자 주입층으로 구성되는 4층 구조가 유기 발광층을 위해 적합하게 이용된다.

- <231> 캐소드(5067)는 금속 마스크를 이용하여 게이트 전극이 동일 게이트 신호 라인에 접속되어 있는 스위칭 TFT에 포함된 화소(동일 라인상의 화소) 바로 위에 형성된다. 본 실시예는 캐소드(5067)를 위해 MgAg를 이용하지만, 이에 제한되지는 않는다. 다른 공지된 재료들이 캐소드(5067)를 위해 이용될 수 있다.

- <232> 마지막으로, 실리콘 질화물막으로 형성되어 300nm의 두께를 가지는 평탄화 막(5068)이 형성된다. 실제로, 평탄화 막(5068)은 습기등으로부터 유기 발광층(5066)을 보호하는 역할을 한다. 그러나, OLED의 신뢰성은 평탄화 막(5068)을 형성함으로써 추가로 향상될 수 있다.

- <233> 따라서, 도 15의 (b)에 도시된 바와 같은 상태가 완성된다. 도면에 도시되어 있지는 않지만, 제 1 실시 형태의 제조 방법에 따라서, 봉지막을 제공하는 제 2 기판이 제 2 접착층을 이용하여 평탄화막(5068)에 접착된다. 부가적으로, 추후 단계들이 제 1 실시 형태에 도시된 방법들에 따라 실행될 수 있다. 제 2 실시 형태의 제조 방법에 따라서, 봉지막을 제공하는 제 2 기판이 제 2 접착층을 이용하여 평탄화 막(5068)에 접착된다. 부가적으로, 추후 단계들이 제 2 실시 형태에 도시된 방법에 따라서 실행될 수 있다.

- <234> 본 실시예의 발광 장치 제조 프로세스에서, 본 프로세스의 회로 구조 및 절차들의 편리함을 위해, 소스 신호 라인은 게이트 전극들의 재료인 Ta와 W로 형성되고, 게이트 신호 라인은 소스 및 드레인 전극들의 배선 재료인 Al이다. 그러나 상이한 재료들이 이용될 수도 있다.

- <235> 본 실시예의 발광 장치는 화소부에 부가하여 구동 회로부에 최적의 구조들의 TFT들을 배열함으로써, 매우 높은 신뢰성과 개선된 동작 특성들을 가진다. 또한, 결정화 프로세스에서, Ni 같은 금속 촉매를 추가함으로써 결정성 이 향상될 수 있다. 따라서, 회로를 구동하는 소스 신호 라인의 구동 주파수가 10MHz 이상으로 설정될 수 있다.

- <236> 먼저, 가능한 동작 속도를 감소시키도록 핫 캐리어 주입을 감소시키기 위한 구조를 가지는 TFT가 구동 회로부를 형성하는 CMOS 회로의 n-채널형 TFT로서 이용된다. 여기서, 구동 회로는 시프트 레지스터와, 버퍼와, 레벨 시프 터와, 라인 순차 구동의 래치와, 도트 순차 구동의 트랜스미션 게이트 등을 포함한다.

- <237> 본 실시예의 경우에, n-채널형 TFT의 활성층은 소스 영역과, 드레인 영역과, 게이트 절연막을 통해 게이트 전극과 중첩되어 있는 중첩 LDD 영역(Lov 영역)과, 게이트 절연막을 통해 게이트 전극과 중첩되어 있지 않은 오프셋 LDD 영역(Loff 영역) 및 채널 형성 영역을 포함한다.

- <238> CMOS 회로의 p-채널형의 핫 캐리어 주입에 의한 열화는 거의 무시할 수 있다. 따라서, n-채널형 TFT내에 특별히 LDD 영역을 형성하는 것은 불필요하다. 그러나, n-채널형 TFT와 유사하게, LDD 영역이 고온 캐리어 상쇄조치로서 형성될 수 있다.

- <239> 또한, 채널 형성 영역을 통해 전류를 양방향으로 흘리기 위한 CMOS 회로, 즉, 소스와 드레인 영역들의 역할이 교체된 CMOS 회로가 구동 회로에 이용될 때, 채널 형성 영역이 LDD 영역들 사이에 끼워지도록 LDD 영역들을 형성하기 위해 CMOS 회로를 구성하는 것이 n-채널형 TFT에 적합하다. 이 예로서, 도트 순차 구동에 이용되는 트랜스미션 게이트가 제공된다. OFF 상태 전류값을 가능한 낮추기 위하여 필요한 CMOS 회로가 구동 회로에 이용될 때, CMOS 회로를 형성하는 n-채널형 TFT는 Lov 영역을 갖는 것이 적합하다. 도트 순차 구동에 이용되는 트랜스미션 게이트도 이런 예로서 주어질 수 있다.

- <240> 또한, 본 실시예에 도시된 프로세스들에 따라서, 발광 장치의 제조를 위해 필요한 포토마스트들의 수가 감소될 수 있다. 결과적으로, 프로세스들이 감소될 수 있고, 이는 제조 비용의 감소 및 처리량의 향상에 기여한다.

- <241> 제 7 실시예는 제 1 내지 제 5 실시예와 조합하여 구현될 수 있다는 것을 인지하여야 한다.

- <242> [제 8 실시예]

- <243> 제 8 실시예에서, 본 발명에 따른 인버스-스테거(inverse-stagger)형 TFT들을 이용하는 발광 장치의 구조가 설명된다.

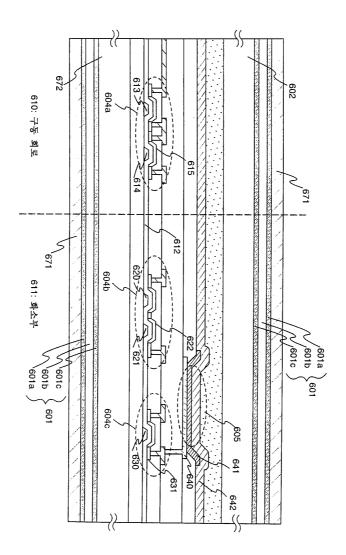

- <244> 도 16은 본 발명에 따른 발광 장치를 도시하는 단면도이다. 봉지막(601)이 가요성 제 2 기판(602)상에 형성된다. 봉지막(601)은 무기 절연막(601a), 유기 절연막(601b) 및 무기 절연막(601c)을 포함한다.

- <245> 가요성 제 2 기판(602)과 제 3 기판(672) 사이에, TFT들, OLED 및 다른 소자들이 형성된다. 본 실시예에서, 구동 회로(610)에 포함된 TFT(604a)와 화소부(611)에 포함된 TFT들(604b 및 604c)이 대표적인 예들로서 도시되어 있다.

- <246> OLED(605)는 화소 전극(640)과, 유기 발광층(641)과 캐소드(642)를 포함한다.

- <247> TFT(604a)는 게이트 전극들(613 및 614)과, 게이트 전극들(613 및 614)과 접촉하도록 형성된 절연막(612)과, 절연막(612)과 접촉하도록 형성된 반도체 막(615)을 포함한다. TFT(604b)는 게이트 전극들(620 및 621)과, 게이트 전극들(620 및 621)과 접촉하도록 형성된 절연막(612)과, 절연막(612)과 접촉하도록 형성된 반도체막(622)을 포함한다. TFT(604c)는 게이트 전극(630)과, 게이트 전극(630)과 접촉하도록 형성된 절연막(612)과, 절연막(612)과 접촉하도록 형성된 반도체 막(631)을 포함한다.

- <248> 비록, 인버스-스테거형 TFT들이 제 3 실시예에 따라 제조된 발광 장치에 이용되는 예가 도시되어 있지만, 본 발명의 구조는 이에 제한되지 않는다. 인버스-스테거형 TFT들은 제 4 실시예에 따라 제조된 발광 장치에 이용될수 있다.

- <249> 제 8 실시예는 제 1 내지 제 5 실시예와 자유롭게 조합하여 수행될 수 있다.

- <250> [제 9 실시예]

- <251> 제 9 실시예에서, 접착층이 그위에 유체를 분사함으로써 제거되는 예가 설명된다.

- <252> 유체를 분사할 때, 물체상에 노즐로부터 고압 수류를 분사하는 방법(워터 제트법이라 지칭됨) 또는 물체상에 고압 가스류를 분사하는 방법이 이용될 수 있다. 워터 제트법의 경우에, 유기 용매, 산 용액 또는 알칼리 용액이물 대신 이용될 수 있다. 가스 흐름으로서, 공기, 질소 가스, 이산화탄소 가스 또는 희유 가스가 이용될 수 있다. 부가적으로, 이들 가스로부터 얻어진 플라즈마도 이용될 수 있다. 접착층의 재료 및 제거되는 것이 바람직하지 못한, 막들 및 기판들의 재료들에 따라서, 이런 막들 및 기판들이 접착층의 제거와 함께 제거되지 않도록적절한 유체를 선택하는 것이 중요하다.

- <253> 접착층으로서, 수소, 산소, 질소 또는 희유 가스가 추가된 실리콘층 또는 다공성 실리콘 층이 이용된다. 다공성 실리콘층이 이용되는 경우에, 비정질 실리콘 막 또는 다결정 실리콘 막은 이용을 위해 그에 다공성을 제공하기 위해 양극처리를 받게 될 수 있다.

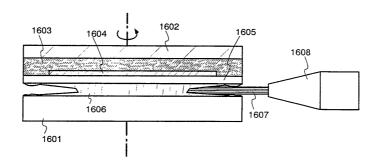

- <254> 도 17은 워터 제트법에 의한 접착층의 제거를 도시하고 있다. OLED(1604)가 기판들(1601 및 1602) 사이에 제공된다. OLED(1604)는 절연막(1603)으로 덮혀 있다.

- <255> 절연막(1605)과 접착충(1606)은 기판(1601)과 OLED(1604) 사이에 제공된다. 접착충(1606)은 기판(1601)과 접촉한다. 비록, OLED만이 도 17에 대표적으로 도시되어 있지만, TFT들 및 다른 소자들이 통상적으로 절연막들(1605 및 1603) 사이에 제공된다.

- <256> 접착층(1606)은 0.1 내지 900ﷺ(바람직하게는, 0.5 내지 10㎜)의 두께를 가질 수 있다. 제 9 실시예에서, 1㎜의 두께를 가진 SOG 막이 접착층(1606)으로서 이용된다.

- <257> 유체(1607)가 노즐(1608)로부터 접착충(1606)상으로 분사된다. 유체(1607)를 접착충(1606)의 전체 노출부상으로 효과적으로 분사하기 위해서, 도 17에 화살표로 표시된 바와 같이, 기판(1601)에 수직인 중앙선 둘레에서 접착 충(1606)을 회전시키면서, 유체를 분사하는 것이 권장된다.

- <258> 1x10<sup>7</sup> 내지 1x10<sup>9</sup>Pa(바람직하게는, 3x10<sup>7</sup> 내지 5x10<sup>8</sup>Pa)의 압력이 적용된 유체(1607)가 노즐(1608)로부터 접착층 (1606)의 노출부상으로 분사된다. 샘플이 회전하기 때문에, 유체(1607)는 접착층(1606)의 노출면을 따라 분사된다.

- <259> 노즐(1608)로부터 방사된 유체가 접착층(1606)상으로 분사될 때, 접착층은 그 약함 때문에, 충격으로 인해 파열된 이후에 제거 되거나, 화학적으로 제거된다. 결과적으로, 접착층(1606)은 파괴 및 제거되어 기판(1601)과 절연막(1605)이 서로 분리된다. 접착층(1606)을 파괴시킴으로써, 분리가 달성되는 경우에, 잔여 접착층은 에칭에의해 제거될 수 있다.

- <260> 유체(1607)로서, 물, 유기 용매, 산 용액 또는 알칼리 용액 같은 액체가 이용될 수 있다. 대안적으로, 공기, 질소 가스, 이산화 탄소 가스 또는 희유 가스가 이용될 수도 있다. 또한, 이들 가스들로부터 얻어진 플라즈마가 이용될 수 있다.

- <261> 제 9 실시예는 제 1 내지 제 8 실시예와 조합하여 수행될 수 있다.

- <262> [제 10 실시예]

- <263> 본 실시예에서, 유기 발광 재료를 이용하여, 트리플릿 엑시톤으로부터의 인광이 광 방사를 위해 이용됨으로써, 외부 발광 퀀텀 효율이 현저히 개선된다. 결과적으로, OLED의 전력 소모가 감소될 수 있으며, OLED의 수명이 연 장될 수 있고, OLED의 중량이 경량화될 수 있다.

- <264> 다음은 외부 발광 퀀텀 효율이 트리플릿 엑시톤을 이용함으로써 향상되는 경우에 대한 보고서이다. K. 혼다 편 저의 T. 츠츠이, C. 아아치, S. 사이토의 조직화된 분자 시스템의 광화학적 프로세스(T. Tsutsui, C. Adachi, S. Saito, Photochemical Processes in Organized Molecular Systems, ed. K. Honda(Elsevier Sci. Pub., Tokyo, 1991) p.437).

- <265> 상기 문헌에 의해 보고된 유기 발광 재료(코마린 염료)의 분자식은 하기와 같이 표현된다.

### 화학식 1

<266>

- <267> M.A. 발도, D.F. 오브라이언, Y. 유, A. 샤우스키코프, S. 시비블레이, M.E. 톰슨, S.R. 포레스트의 1998년 내 츄어 395(M.A. Baldo, D.F.O'Brien, Y. You, A. Shoustikov, S. Sibibley, M.E. Thompson, S.R. Forrest, Nature 395(1998) p.151)

- <268> 상기 문헌에 의해 보고된 유기 발광 재료(Pt 합성물)의 분자식은 하기와 같이 표현된다.

### 화학식 2

<269> <270>

- M.A. 발도, S. 라만스키, P.E. 부로우스, M.E. 톰슨, S.R. 포레스트의 1999년 응용 물리학지 75(M.A. Baldo, S. Lamansky, P.E. Burrows, M.E. Thompson, S.R. Forrest, Appl. Phys. Lett., 75(1999) p.4)

- <271> T. 츠츠이, M.-J. 양, M. 야히로, K. 나카무라, T. 와타나베, T. cm지, Y. 후쿠다, T. 와키모토, S. 마야구치의 1999년 일본 응용 물리학 38(T.Tsutsui, M.-J. Yang, M. Yahiro, K. Nakamura, T. Watanabe, T.Tsuji, Y.Fukuda, T.Wakimoto, S. Mayaguchi, Jpn, Appl. Phys., 38(12B)(1999) L1502)

- <272> 상기 문헌에 의해 보고된 EL 재료(Ir 합성물)의 분자식은 하기와 같이 표현된다.

## 화학식 3

<273>

- <274> 상술한 바와 같이, 트리플릿 엑시톤으로부터의 인광을 실용적으로 이용할 수 있는 경우에, 원론적으로, 싱글릿 엑시톤으로부터의 형광을 이용하는 경우 보다 3 내지 4배 높은 외부 발광 퀀텀 효율을 실현할 수 있다.

- <275> 본 실시예에 따른 구조는 제 1 내지 제 9 실시예 중 소정의 구조들과 자유롭게 조합하여 구현될 수 있다.

- <276> [제 11 실시예]

- <277> 유기 발광 재료로 이루어진 막은 일반적으로 잉크 제트법, 스핀 코팅법 또는 증발법에 의해 형성된다. 제 11 실시예에서, 상술한 방법들 이외의 유기 발광층을 형성하기 위한 방법이 설명된다.

- <278> 본 실시예에서, 유기 발광 재료의 분자 어셈블리들을 함유하는 막이 유기 발광 재료를 구성하는 분자 어셈블리들이 확산되어 있는 콜로이드 용액(또한, 졸이라고도 지칭됨)을 이용하여, 불활성 가스 분위기하의 기판상에 분사에 의해 형성된다. 유기 발광 재료는 액체 내에서 각각 몇 개의 분자들이 결합되어 있는 미립자들로서 존재한다.

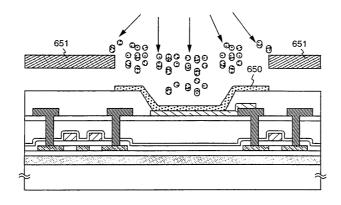

- <279> 도 18은 노즐(미도시)로부터 불활성 가스(본 실시예에서는 질소 가스)내로 합성물을 분사함으로써 유기 발광 충 (650)을 형성하는 것을 도시하고 있다. 합성물은 유기 발광 재료로서 기능하는 이리듐 합성물인 트리(2-페닐피리딘) 이리듐(Ir(ppy)₃)과, 호스트로서 기능하는 유기 발광 재료인 바소쿠푸로인(BCP)(이하, 호스트 물질이라지칭함)을 톨루엔내에 분산시킴으로써 얻어진다.

- <280> 도 18에서, 마스크(651)를 이용하여, 유기 발광층(650)이 25 내지 40nm의 두께를 갖도록 선택적으로 형성된다. 이리듐 합성물과 BCP 양자 모두는 톨루엔에 대해 불용성이다.

- <281> 실제로, 유기 발광층이 단일층 형태로 이용되는 몇몇 경우들과, 다층 형태로 이용되는 다른 경우들이 존재한다. 유기 발광층이 다층 구조로 이용되는 경우에, 다른(나머지) 유기 발광 층(들)은 유기 발광층(650)의 형성 이후

에, 유사한 방식으로 형성된다. 이 경우에, 모든 증착된 유기 발광 층들은 총체적으로 유기 발광층이라 지칭된다.

- <282> 본 실시예의 성막 방법은 액체내의 유기 발광 재료가 어떠한 상태로 존재하는 경우에도 막의 형성을 가능하게 한다. 특히, 본 방법은 잘 용해되지 않는 유기 발광 재료를 이용함으로써, 양호한 품질을 가진 유기 발광충을 형성하는 것을 가능하게 한다. 또한, 캐리어 가스의 이용과 함께 유기 발광 재료를 함유하는 액체를 분사함으로써 막이 형성되기 때문에, 성막은 짧은 시간 기간내에 달성될 수 있다. 유기 발광 재료를 함유하는 분사 대상액체를 제조하는 방법은 극히 단순할 수 있다. 또한, 본 실시예에서, 소정 패턴을 가진 막을 형성하기 위해 마스크가 이용되고, 그래서, 성막은 마스크의 개구를 통해 이루어진다. 부가적으로, 고가의 유기 발광 재료를 효과적으로 이용하기 위해서, 재이용을 위해 마스크에 부착된 유기 발광 재료를 수집하는 것이 가능하다.

- <283> 잉크 제트법과 스핀 코팅법은 용매에 대한 높은 용해성을 가진 유기 발광 재료를 이용할 수 없다는 제약을 갖는다. 증발법은 증발법이 이용되기 이전에 분해하는 유기 발광 재료가 이용될 수 없다는 제약을 갖는다. 그러나, 본 실시예의 성막 방법은 상술한 제약들에 의해 영향을 받지 않는다. 본 실시예의 성막 방법에 적합한 유기 발광 재료의 예들은 퀴나크리돈, 트리스(2-페닐피리딘)이리듐, 바소쿠프로인, 폴리(1,4-페닐엔비닐렌), 폴리(1,4- 나프탈렌비닐렌), 폴리(2-페닐-1,4-페닐렌비닐렌), 폴리티오펜, 폴리(3-페닐티오펜), 폴리(1,4-페닐렌), 폴리(2,7-플로렌) 등이 주어질 수 있다.

- <284> 제 11 실시예의 구조는 제 1 내지 제 10 실시예들 중 소정의 것과 자유롭게 조합하여 실시될 수 있다.

- <285> [제 12 실시예]

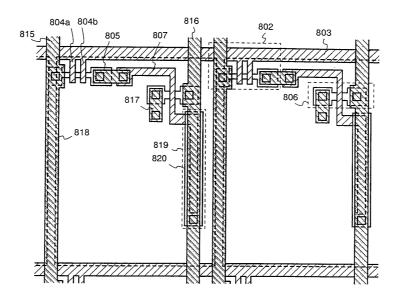

- <286> 본 실시예는 제 12 실시예에서 본 발명에 의해 얻어진 발광 장치의 화소부의 보다 상세한 설명을 제공한다. 화소부의 상부 구조가 도 19a에 도시되어 있으며, 그 회로도가 도 19b에 도시되어 있다. 교차 참조되는 도 19a 및도 19b에는 공통 참조 부호들이 이용되어 있다.

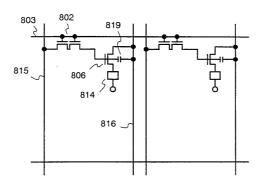

- <287> 스위칭 TFT(802)는 소스 배선(815)에 접속된 소스를 가지며, 드레인 배선(805)에 접속된 드레인을 가지고, 게이트 배선(803)으로부터 파생된 게이트 전극들(804a 및 804b)을 갖는다. 드레인 배선(805)은 전류 제어 TFT(806)의 게이트 전극(807)에 전기적으로 접속되어 있다. 전류 제어 TFT(806)는 전류 공급 라인(816)에 전기적으로 접속된 소스를 가지며, 드레인 배선(817)에 전기적으로 접속된 드레인을 가진다. 드레인 배선(817)은 점선으로 표시된 화소 전극(818)에 전기적으로 접속되어 있다. 참조 부호 814는 EL 소자를 나타낸다.

- <288> 저장 커패시터가 여기에 819로 도시된 영역에 형성되어 있다. 저장 커패시터(819)는 전류 공급 라인(816)에 전 기적으로 접속되어 있는 반도체 막(820)과, 게이트 절연막과 동일층상의 절연막(미도시) 및 게이트 전극(807)으로 구성되어 있다. 게이트 전극(807)과, 제 1 층간 절연막과 동일층(미도시) 및 전류 공급 라인(816)으로 구성된 커패시터도 저장 커패시터로서 이용될 수 있다.

- <289> 제 12 실시예는 제 1 내지 제 11 실시예들과 조합될 수 있다.

- <290> [제 13 실시예]

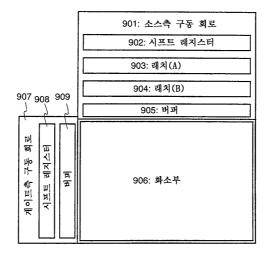

- <291> 본 실시예는 도 20을 참조로 발광 장치의 회로 구조의 예를 도시한다. 본 실시예에 도시된 회로 구조는 디지털 구동을 위한 것이다. 본 실시예에 따른 구조는 소스측 구동 회로(901)와, 화소부(906) 및 게이트측 구동 회로 (907)를 갖는다.

- <292> 소스측 구동 회로(901)는 시프트 레지스터(902)와, 래치(A)(903)와, 래치(B)(904)와, 버퍼(905)를 구비한다. 아 날로그 구동의 경우에, 샘플링 회로(트랜스퍼 게이트)가 래치들(A) 및 (B) 대신 제공된다. 게이트측 구동 회로 (907)는 시프트 레지스터(908)와 버퍼(909)를 구비한다. 그러나, 버퍼(909)는 항상 필수적으로 제공될 필요는 없다.

- <293> 본 실시예에서, 화소부(906)는 각각 OLED를 구비하는 복수의 화소들를 포함한다. OLED의 캐소드는 전류 제어 TFT의 드레인에 전기적으로 접속되는 것이 적합하다.

- <294> 소스측 구동 회로(901)와 게이트측 구동 회로(907)는 제 2 내지 제 4 실시예들에 따라 얻어진 n-채널 TFT들이나 p-채널 TFT들로 구성된다.

- <295> 비록, 도시되지는 않았지만, 다른 게이트측 구동 회로가 화소부(906)를 가로질러 게이트측 구동 회로(907)의 반 대편에 추가될 수 있다. 이 경우에, 게이트측 구동 회로들 중 두 개는 동일 구조를 가지며, 게이트 배선을 공유하고, 그래서, 나머지가 파괴된 것 대신 게이트 신호를 보낼 수 있어서 화소부가 정상적으로 동작하게 한다.

- <296> 본 실시예는 제 1 내지 제 12 실시예와 조합하여 이용될 수 있다.

- <297> [제 14 실시예]

- <298> 자기-발광형인, 발광 소자를 이용하는 발광 장치는 액정 디스플레이 디바이스들 보다 넓은 조망 각도와, 밝은 장소들에서 보다 양호한 가시성을 가진다. 따라서, 발광 장치는 다양한 전기 기기들의 디스플레이 디바이스에 이용될 수 있다.

- <299> 본 발명에 따라 제조된 발광 장치를 이용하는 전기 기기의 예로서는 비디오 카메라들, 디지털 카메라들, 고글형 디스플레이들(헤드 장착 디스플레이들), 항법 시스템들, 오디오 재생 디바이스들(카 오디오 및 오디오 콤포넌트들 같은), 노트북 컴퓨터들, 게임기들, 휴대용 정보 단말기들(이동식 컴퓨터들, 휴대 전화들, 휴대용 게임기들 및 전자 도서들 같은), 및, 기록 매체들을 구비한 이미지 재생 디바이스들(특히, 디지털 비디오 디스크(DVD) 같은 기록 매체내의 데이터를 재생하여 데이터의 이미지를 디스플레이하는 디스플레이 디바이스를 구비한 디바이스들)이 주어진다. 넓은 조망 각도는 휴대용 정보 단말기들에서 특히 중요하며, 그 이유는 그들이 보여지게 될때, 그 스크린이 경사지게 되는 일이 빈번하기 때문이다. 따라서, 휴대용 정보 단말기들에 발광 소자를 이용하는 발광 디스플레이를 이용하는 것이 적합하다. 이들 전기 기기들의 특정 예들이 도 21a 내지 21d에 도시되어 있다.

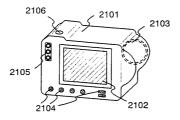

- <300> 도 21a는 디지털 스틸 카메라를 도시하고 있으며, 이는 본체(2101)와, 디스플레이 유니트(2102)와, 이미지 수신 유니트(2103)와, 조작 키들(2104)과, 외부 접속 포트(2105)와, 셔터(2106) 등으로 구성된다. 본 발명에 따라 제 조된 발광 장치는 디스플레이 유니트(2102)에 적용될 수 있다.

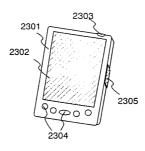

- <301> 도 21b는 이동 컴퓨터를 도시하고 있으며, 이는 본체(2301)와, 디스플레이 유니트(2302)와, 스위치(2303)와, 조 작 키들(2304)과, 적외선 포트(2305) 등으로 구성되어 있다. 본 발명에 따라 제조된 발광 장치는 디스플레이 유 니트(2302)에 적용될 수 있다.

- <302> 도 21c는 고글형 디스플레이(헤드 장착 디스프레이)를 도시하고 있으며, 이는 본체(2501)와, 디스플레이 유니트 (2502)와, 아암 유니트(2503)로 구성되어 있다. 본 발명에 따라 제조된 발광 장치는 디스플레이 유니트(2502)에 적용될 수 있다.

- <303> 도 21d는 휴대 전화를 도시하고 있으며, 이는 본체(2701)와, 케이스(2702)와, 디스플레이 유니트(2703)와, 오디오 입력 유니트(2704)와, 오디오 출력 유니트(2705)와, 조작 키들(2706)과, 외부 접속 포트(2707)와, 안테나(2708) 등으로 구성되어 있다. 본 발명에 따라 제조된 발광 장치는 디스플레이 유니트(2703)에 적용될 수 있다. 디스플레이 유니트(2703)가 검정색 배경상에 흰색 문자들을 디스플레이 하는 경우에, 셀룰러 전화는 보다 적은 전력을 소모하게 된다.

- <304> 유기 재료들로부터 방사된 광의 휘도가 미래에 향상되게 되면, 발광 장치는 렌즈 등을 통해 이미지 정보를 포함 하는 출력된 광을 확대시키고 이 광을 투사하는 전방 또는 후방 투사기들에 이용될 수 있다.

- <305> 이들 전기 기기들은 이제, 인터넷 같은 전자 통신 라인들과, CATV(케이블 텔레비젼)을 통해 보내지는 증가된 주파수 정보, 특히, 애니메이션 정보를 디스플레이 할 수 있다. 유기 재료들이 매우 신속한 응답 속도를 가지기때문에, 발광 장치는 애니메이션 디스플레이에 적합하다.

- <306> 발광 장치에서, 발광부들은 전력을 소모하고, 따라서, 보다 적은 발광부들을 필요로하는 방식으로 정보를 디스플레이하는 것이 적합하다. 휴대용 정보 단말기들, 특히, 주로 문자 정보를 디스플레이하는 셀룰러 전화들 및 오디오 재생 디바이스들의 디스플레이 유니트들에 발광 장치를 이용할 때, 비발광 부분들이 배경을 형성하고, 발광 부분들이 문자 정보를 형성하도록 디바이스를 구동하는 것이 적합하다.

- <307> 상술한 바와 같이, 본 발명의 발광 장치들의 응용 범위는 어떠한 분야의 전기 기기들에도 적용할 수 있을 만큼 넓다. 본 실시예의 전기 기기들은 제 1 내지 제 13 실시예들에 도시된 소정의 발광 장치를 이용할 수 있다.

- <308> [제 15 실시예]

- <309> OLED에 이용되는 유기 발광 재료들은 대략적으로 저분자량 재료들과, 고분자량 재료들로 나누어진다. 본 발명의 발광 장치는 저분자량 유기 발광 재료와 고분자량 유기 발광 재료 양자 모두를 이용할 수 있다.

- <310> 저분자량 유기 발광 재료는 증발법에 의해 막으로 형성된다. 이는 적층체구조를 형성하는 것을 용이하게 하며, 정공 운반층 및 전자 운반층 같은 상이한 기능들의 막들을 적층함으로써 효율이 향상된다.

- <311> 저 분자량 유기 발광 재료의 예들은 트리페닐라민 유도체(TPD)와, 리간드(Alq<sub>3</sub>) 같은 퀴놀리놀을 가지는 알루미 뉴 복합체를 포함하다.

- <312> 한편, 고분자량 유기 발광 재료는 저분자량 재료 보다 물리적으로 강하며, 소자의 내구성을 향상시킨다. 또한, 고분자량 재료는 도포에 의해 막으로 형성될 수 있으며, 따라서, 소자의 제조가 비교적 용이하다.

- <313> 고분자량 유기 발광 재료를 이용하는 발광 소자의 구조는 기본적으로 저분자량 유기 발광 재료를 이용하는 발광 소자의 구조와 동일하며, 캐소드와, 유기 발광층과 아노드를 갖는다. 유기 발광층이 고분자량 유기 발광 재료로 부터 형성될 때, 알려져 있는 것들 중에서 2-층 구조가 대중적이다. 이는 저분자량 유기 발광 재료를 이용하는 경우와는 달리, 고분자량 재료를 이용하여 적층체 구조를 형성하는 것이 곤란하기 때문이다. 보다 명확히, 고분 자량 유기 발광 재료를 이용하는 소자는 캐소드(Al 합금), 발광층, 정공 운반층 및 아노드(ITO)를 갖는다. Ca가 고분자량 유기 발광 재료를 이용하는 발광 소자내의 캐소드 재료로서 이용될 수 있다.

- <314> 소자로부터 발광된 광의 색상은 그 발광층의 재료에 의해 결정된다. 따라서, 적절한 재료를 선택함으로써, 원하는 색상의 광을 방사하는 발광 소자가 형성될 수 있다. 발광층을 형성하도록 이용될 수 있는 고분자량 유기 발광 재료는 폴리파라페닐렌 비닐렌계 재료, 폴리파라페닐렌계 재료, 폴리티오펜계 재료 또는 폴리플루오렌계 재료이다.

- <315> 폴리파라페닐렌 비닐렌계 재료는 폴리(파라페닐렌 비닐렌)(PPV로 표시)의 유도체, 예로서, 폴리(2,5-디알콕시-1,4-페닐렌비닐렌)(RO-PPV로 표시), 폴리(2-(2'-에틸렌-헥속시)-5-메톡시-1,4-페닐렌 비닐렌)(MEH-PPV로 표시), 및 폴리(2-(디알콕시페닐)-1,4-페닐렌 비닐렌)(ROPh-PPV로 표시)이다.

- <316> 폴리파라페닐렌계 재료는 폴리파라페닐렌(PPP로 표시)의 유도체, 예로서, 폴리(2,5-디알콕시-1,4-페닐렌)(RO-PPP로 표시) 및 폴리(2,5-디헥속시-1,4-페닐렌)이다.

- <317> 폴리티오펜계 재료는 폴리티오펜(PT로 표시)의 유도체, 예로서, 폴리(3-알킬티오펜)(PAT로 표시), 폴리(3-핵실 티오펜)(PHT로 표시), 폴리(3-사이클로헥실티오펜)(PCHT로 표시), 폴리(3-사이클로헥실-4-메틸티오펜)(PCHMT로 표시), 폴리(3,4-디사이클로헥실티오펜)(PDCHT로 표시), 폴리[3-(4-옥틸페닐)-티오펜](POPT로 표시) 및 폴리[3-(4-옥틸페닐)-2,2 바이티오펜](PTOPT로 표시)이다.

- <318> 폴리플루오렌계 재료는 폴리플루오렌(PF로 표시)의 유도체, 예로서, 폴리(9,9-디알킬플루오렌)(PDAF로 표시) 및 폴리(9,9-디옥틸플루오렌)(PDOF로 표시)이다.

- <319> 정공들을 운반할 수 있는 고분자량 유기 발광 재료로 형성된 층이, 아노드와, 광을 방사하는 고분자량 유기 발광 재료층 사이에 끼워져 있는 경우에, 아노드로부터의 정공들의 주입이 향상된다. 이 정공 운반 재료는 일반적으로 수용체 재료와 함께 물내로 용해되며, 용액이 스핀 코팅 등에 의해 적용된다. 정공운반 재료가 유기 용매에 불용성이기 때문에, 그 막은 광을 방사하는 상술한 유기 발광 재료층을 가진 적층체를 형성할 수 있다.

- <320> 정공들을 운반할 수 있는 고분자량 유기 발광 재료는 PEDOT를 수용체 물질로서 기능하는 캠퍼 설포닉 산(CSA로 표시)과 혼합시킴으로써 얻어진다. 폴리아닐린(PANI로 표시)과, 수용체 재료로서 기능하는 폴리스티렌 설포닉산(PSS로 표시)의 혼합물도 이용될 수 있다.

- <321> 본 실시예의 구조는 제 1 내지 제 14 실시예의 구조들 중 소정의 것과 자유롭게 조합될 수 있다.

- <322> 본 발명에 따라서, OLED가 그 위에 형성되어 있는 전체 기판이 봉지막을 구비한 플라스틱 막을 이용하여 진공에서 봉지되어 습기 및 산소로 인한 OLED의 열화를 방지하는 효과를 향상시키고, OLED의 안정성을 강화시킨다. 따라서, 본 발명은 매우 신뢰성 있는 발광 장치를 제공할 수 있다.

- <323> 본 발명은 복수의 무기 절연막들을 포함하는 적층체 구조를 가지며, 무기 절연막들중 하나가 균열되는 경우에 조차도 나머지 무기 절연막들이 효과적으로 산소 및 습기가 유기 발광층에 도입되는 것을 방지할 수 있다. 복수의 무기 절연막들의 적충체 구조와 함께, 본 발명은 무기 절연막의 형성 동안 저온에 의해 무기 절연막들의 품질이 열화될 때에도, 유기발광층에 습기 및 산소가 도입하는 것을 효과적으로 방지할 수 있다.

- <324> 무기 절연막들 보다 내부 응력이 작은 유기 절연막이 무기 절연막들 사이에 끼워지는 경우에, 전체 절연막들의 내부 응력이 이완될 수 있다. 사이에 유기 절연막을 끼우고 있는 무기 절연막들의 총 두께와 동일한 두께를 가지는 무기 절연막의 단일층과 비교하여, 내부 응력으로 인한 균열이 유기 절연막이 사이에 끼워져 있는 무기 절연막들에서 덜 빈번하게 발생되게 된다.

<325> 따라서, 사이에 유기 절연막을 끼우고 있는 무기 절연막들은, 사이에 유기 절연막을 끼우고 있는 무기 절연막들 의 총 두께가 단일층 무기 절연막의 두께와 동일한 경우에도, 무기 절연막의 단일층 보다 습기 및 산소가 유기 발광층으로 도입하는 것을 방지하는데 효율적이다. 또한, 사이에 유기 절연막을 끼우고 있는 무기 절연막들은 내부 응력으로 인한 균열에 대하여 강하다.

### 도면의 간단한 설명

- <311> 도 1a 내지 도 1c는 본 발명의 발광 장치의 도면들로서, 도 1a 및 도 1b는 그 단면도, 도 1c는 그 상면도.

- <312> 도 2는 봉지막을 형성하기 위한 장치를 도시하는 도면.

- <313> 도 3a 내지 도 3c는 본 발명의 발광 장치의 봉지 방법을 예시하는 도면.

- <314> 도 4의 (a) 내지 도 4의 (c)는 본 발명에 따른 발광 장치를 제조하는 방법을 도시하는 도면.

- <315> 도 5의 (a) 내지 도 5의 (c)는 본 발명에 따른 발광 장치를 제조하는 방법을 도시하는 도면.

- <316> 도 6의 (a) 내지 도 6의 (d)는 본 발명에 따른 발광 장치를 제조하는 방법을 도시하는 도면.

- <317> 도 7의 (a) 내지 도 7의 (c)는 본 발명에 따른 발광 장치를 제조하는 방법을 도시하는 도면.

- <318> 도 8의 (a) 내지 도 8의 (c)는 봉지 이전의 본 발명에 따른 발광 장치를 도시하는 도면들로서, 도 8의 (a)는 그 외관도, 도 8의 (b) 및 도 8의 (c)는 디바이스가 FPC에 접속되는 그 접속부의 확대도 및 단면도.

- <319> 도 9a 및 도 9b는 굴곡될 때의 본 발명의 발광 장치와 그 단면을 도시하는 도면.

- <320> 도 10은 디바이스가 FPC에 접속되는 그 접속부를 도시하는, 봉지 이전의 본 발명의 발광 장치의 단면도.

- <321> 도 11a 내지 도 11d는 본 발명에 따른 발광 장치의 제조 방법을 도시하는 도면.

- <322> 도 12a 내지 도 12c는 본 발명에 따른 발광 장치의 제조 방법을 도시하는 도면.

- <323> 도 13a 내지 도 13c는 본 발명에 따른 발광 장치의 OLED들과 TFT들을 제조하는 방법들 도시하는 도면.

- <324> 도 14a 내지 도 14c는 본 발명에 따른 발광 장치의 OLED들과 TFT들을 제조하는 방법들 도시하는 도면.

- <325> 도 15의 (a) 내지 도 15의 (b)는 본 발명에 따른 발광 장치의 OLED들과 TFT들을 제조하는 방법들 도시하는 도면.

- <326> 도 16은 본 발명의 발광 장치의 단면도.

- <327> 도 17은 워터 제트법에 의해 접착층이 제거되는 방식을 예시하는 도면.

- <328> 도 18은 분사에 의해 유기 발광층이 형성되는 방식을 예시하는 도면.

- <329> 도 19a 및 도 19b는 화소들의 상면도 및 화소들의 회로도.

- <330> 도 20은 발광 장치의 회로 구조를 도시하는 도면.

- <331> 도 21a 내지 도 21d는 본 발명의 발광 장치를 이용하는 전자 기기를 도시하는 도면.

- <332> \*도면의 주요 부분에 대한 부호의 설명\*

- <333> 101 : OLED 패널 103 : FPC

- <334> 104 : 건조제 105 : 자루형 플라스틱 막

- <335> 106, 108 : 무기 절연막 107 : 유기 절연막

- <336> 109 : 봉지막 202 : RF 전원

- <337> 203, 204 : 전극 206 : 홀더

- <338> 207 : 보호성 절연막 301 : 경계막

- <339> 308 : 접착제 1102 : 제 1 접합층

- <340> 1106 : 구동 회로 1109 : 제 2 접합층

<341> 1213 : 제 3 접합층 1303 : 화소부

<342> 1313 : 접촉 구멍 1312 : 도전성 수지

<343> 5002 : 기저막 5007 : 게이트 절연막

<344> 5008 : 제 1 도전막 5009 : 제 2 도전막

<345> 5055 : 제 1 층간 절연막 5056 : 제 2 층간 절연막

<346> 5066 : 유기 발광층 5067 : 캐소드

<347> 5068 : 평탄화막 907 : 게이트측 구동 회로

908 : 시프트 레지스터 909 : 버퍼

<354> 308 : 접착제 1102 : 제 1 접착층

1106 : 구동 회로 1109 : 제 2 접착층

<356> 1213 : 제 3 접착층 1303 : 화소부

### 도면

<348>

<355>

### 도면1a

## 도면1b

### *도면1c*

# 도면3a

## 도면3b

## 도면3c

## 도면9a

# *도면9b*

# 도면10

# 도면11a

# 도면11b

# 도면11c

# 도면11d

# 도면12a

## *도면12b*

## 도면12c

## 도면13a

# 도면13b

## 도면13c

# 도면14a

## 도면14b

## 도면14c

## 도면19a

# 도면19b

## 도면21a

## 도면21b

# 도면21c

## 도면21d

| 专利名称(译)        | 显示设备                                                                                                                                                                                                                 |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | KR100884229B1                                                                                                                                                                                                        | 公开(公告)日 | 2009-02-17 |

| 申请号            | KR1020070066707                                                                                                                                                                                                      | 申请日     | 2007-07-03 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                                                                                                   |         |            |

| [标]发明人         | YAMAZAKI SHUNPEI                                                                                                                                                                                                     |         |            |

| 发明人            | YAMAZAKI, SHUNPEI                                                                                                                                                                                                    |         |            |

| IPC分类号         | H05B33/10 H01L27/32 H01L33/44 H01L51/52                                                                                                                                                                              |         |            |

| CPC分类号         | H01L51/56 H01L51/0011 H01L2251/5338 H01L27/3288 H05B33/22 H01L27/32 H01L27/3244 H01L2227/326 H01L27/3276 H01L2221/68368 H01L51/5237 H01L51/003 H01L51/0097 H01L51/5246 H01L51/5253 H01L51/5259 Y02E10/549 Y02P70/521 |         |            |

| 代理人(译)         | 李贝尔李昌勋                                                                                                                                                                                                               |         |            |

| 优先权            | 2001201580 2001-07-03 JP                                                                                                                                                                                             |         |            |

| 其他公开文献         | KR1020070077493A                                                                                                                                                                                                     |         |            |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                     |         |            |

### 摘要(译)

本发明在真空中使用塑料膜封装OLED。能够防止氧气或水渗入内部的无机绝缘膜和内部应力小于无机绝缘膜的内应力的有机绝缘膜层叠在塑料膜的内部。通过将有机绝缘膜夹在无机绝缘膜之间,可以放松。此外,即使当通过层叠多个无机绝缘膜中的一个,无机绝缘膜被导致开裂,其它无机绝缘膜,可以有效地防止氧和湿气渗透到有机发光层。另外,可以缓和整个密封膜的应力,并且几乎不会产生由应力引起的裂缝不要。