# (19)대한민국특허청(KR) (12) 공개특허공보(A)

(51) 。Int. Cl.<sup>7</sup> H05B 33/10 (11) 공개번호 (43) 공개일자 10-2005-0076723 2005년07월26일

(21) 출원번호10-2005-0055823(분할)(22) 출원일자2005년06월27일

(22) 물원일자 2005년06월27일 (62) 원출원 특허10-2000-0035607

원출원일자 : 2000년06월27일

심사청구일자

2005년06월27일

(30) 우선권주장 JP-P-1999-00182598 1999년06월28일 일본(JP)

(71) 출원인 가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와켄 아쓰기시 하세 398

(72) 발명자 야마자키 순페이

일본국 243-0036 가나가와켄 아쓰기시 하세 398 가부시키가이샤 한도

오따이 에네루기 켄큐쇼(내)

미즈카미 마유미

일본국 243-0036 가나가와켄 아쓰기시 하세 398 가부시키가이샤 한도

오따이 에네루기 켄큐쇼(내)

고누마 도시미츠

일본국 243-0036 가나가와켄 아쓰기시 하세 398 가부시키가이샤 한도

오따이 에네루기 켄큐쇼(내)

(74) 대리인 정상구

이범래 시청모

신현문

#### 심사청구 : 있음

## (54) 능동 매트릭스 디스플레이 디바이스 제조 방법

#### 요약

본 발명의 목적은 EL 디스플레이 장치 및 그 EL 디스플레이 장치를 포함하는 전자 장치의 제조 비용을 줄이는 것이다.

EL 물질은 액티브 매트릭스 EL 디스플레이 장치에서 프린팅(printing)에 의해 형성된다. 프린팅 방법으로는 릴리프 (relief) 프린팅 또는 스크린(screen) 프린팅이 사용될 수 있다. 그러므로, EL층의 제조 단계가 간략화되고 제조 비용의 감소가 고안된다.

#### 대표도

도 2

#### 색인어

전기광학 장치, 액티브 매트릭스 EL 디스플레이 장치, 박막 트랜지스터, 픽셀 전극, 전자 장치,

#### 명세서

### 도면의 간단한 설명

도 1a 내지 도 1c는 릴리프 프린팅(relief printing) 방법의 원리를 설명하는 도면.

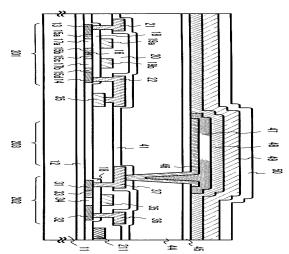

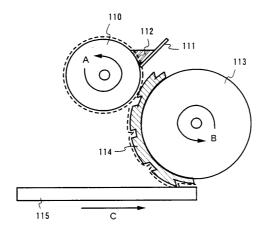

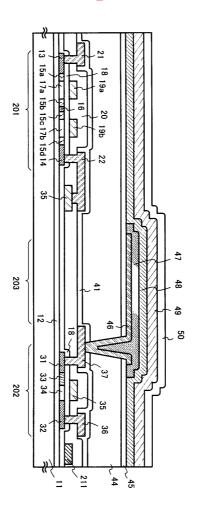

도 2는 EL 디스플레이 장치의 픽셀 부분에서 단면 구조를 도시하는 도면.

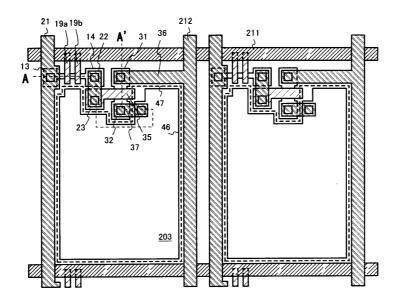

도 3a 및 도 3b는 EL 디스플레이 장치의 픽셀 부분의 상면도 및 그 회로 구조를 도시하는 도면.

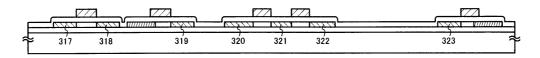

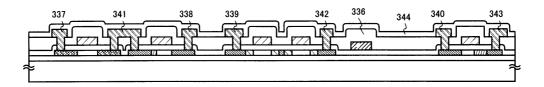

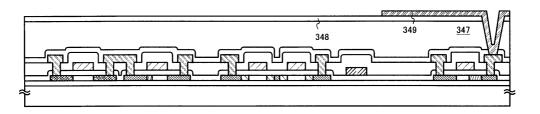

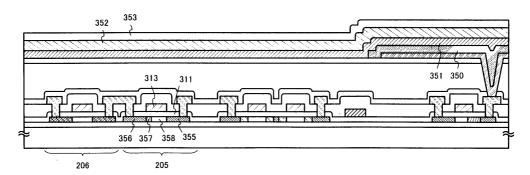

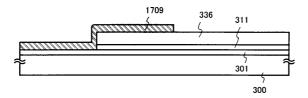

도 4a 내지 도 4e는 액티브 매트릭스형 EL 디스플레이 장치의 제조 단계를 도시하는 도면.

도 5a 내지 도 5d는 액티브 매트릭스형 EL 디스플레이 장치의 제조 단계를 도시하는 도면.

도 6a 내지 도 6c는 액티브 매트릭스형 EL 디스플레이 장치의 제조 단계를 도시하는 도면.

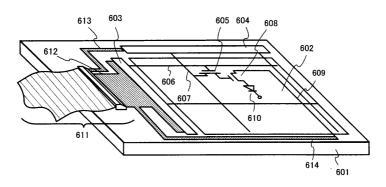

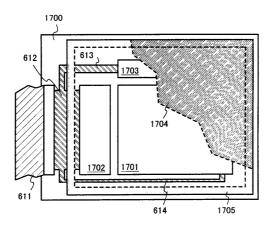

도 7은 EL 모듈의 외형을 도시하는 도면.

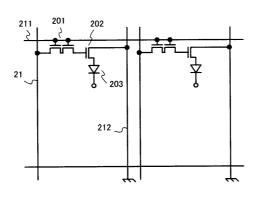

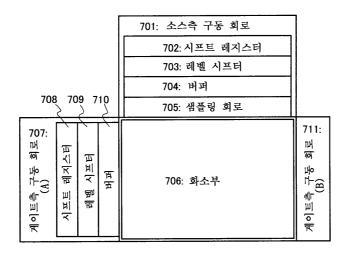

도 8은 EL 디스플레이 장치의 회로 블록 구조를 도시하는 도면.

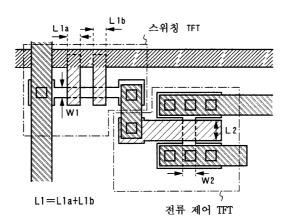

도 9는 EL 디스플레이 장치의 픽셀 부분의 확대도.

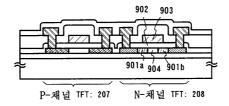

도 10은 EL 디스플레이 장치의 샘플링 회로의 소자 구조를 도시하는 도면.

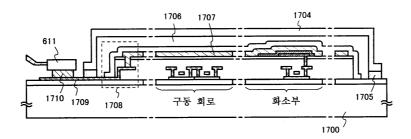

도 11a 및 도 11b는 EL 모듈의 외형 및 단면도를 도시하는 도면.

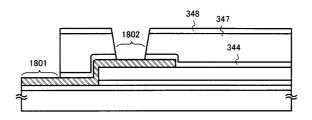

도 12a 내지 도 12c는 접촉 구조의 제조 단계를 도시하는 도면.

도 13은 EL 디스플레이 장치의 픽셀 부분에서 구조를 도시하는 도면.

도 14는 EL 디스플레이 장치의 픽셀 부분의 단면 구조를 도시하는 도면.

도 15는 EL 디스플레이 장치의 픽셀 부분에서 구조를 도시하는 도면.

도 16a 내지 도 16f는 전자 장치의 구체적인 예를 도시하는 도면.

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 기판의 표면상에 반도체 소자들(반도체 박막을 사용한 소자들, 전형적으로 박막 트랜지스터들(thin film transistors))를 제작함(fabricating)으로써 형성된 EL(electroluminescence) 디스플레이 장치로 예시된 전기광학 장치, 및 그 전기광학 장치를 디스플레이로서 포함하는 전자 장치(전자 장비)에 관한 것이다. 특히, 본 발명은 이를 제조하는 방법에 관한 것이다.

최근에는 기판상에 박막 트랜지스터(이후 "TFT"라 언급됨)를 형성하는 기술이 현저하게 진보되었고, 액티브 매트릭스형 디스플레이 장치(active matrix type display device)에 대한 애플리케이션 및 개발이 진행되고 있다. 특히, 폴리실리콘 (polysilicon)막을 사용하는 TFT는 비결정질 실리콘막을 사용하는 종래의 TFT 보다 더 높은 전계 효과 이동성(field effect mobility)을 가지므로, 고속 동작이 이루어질 수 있다. 따라서, 종래에 기판 외부의 구동 회로에 의해 제어되었던 픽 셀(pixel)을 그 픽셀과 똑같은 기판상에 형성된 구동 회로로 제어하는 것이 가능해진다.

똑같은 기판상에 다양한 회로 및 소자를 형성함으로써, 제조 비용 감소, 디스플레이 장치의 소형화, 산출량 증가, 및 처리량 감소와 같은 다양한 이점이 얻어질 수 있으므로, 이러한 액티브 매트릭스형 디스플레이 장치에 관심을 기울이고 있다.

액티브 매트릭스형 EL 디스플레이 장치에서, 각 픽셀에는 TFT로 구성된 스위칭 소자가 제공되고, 전류 제어를 이루는 구동 소자는 스위칭 소자에 의해 동작되어, EL층(발광층)이 발광하게 된다. 예를 들면, 미국 특허 No. 5,684,365호(일본특허 출원 공개 No. Hei-8-234683호을 참고) 또는 일본 특허 출원 공개 공표 No. Hei 10-189252호에서 설명된 EL 디스플레이 장치가 있다.

EL층을 형성하는 방법으로는 다양한 방법이 제안된다. 예를 들면, 진공 증발건조(vacuum evaporation), 스퍼터링 (sputtering), 스핀 코팅(spin coating), 롤 코팅(roll coating), 캐스트 방법(cast method), LB 방법, 이온 플레이팅(ion plating), 침적 방법(dipping method), 잉크젯 방법(inkjet method) 등이 열거될 수 있다.

#### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 EL층의 제조 비용을 줄이고 비싸지 않은 EL 디스플레이 장치를 제공하는 것이다. 본 발명의 또 다른 목적은 EL 디스플레이 장치를 디스플레이로 포함하는 전자 장치(전자 장비)의 제조 비용을 줄이는 것이다.

상기 목적을 이루기 위해, 본 발명은 EL층이 프린팅(printing)에 의해 형성되는 것을 특징으로 한다. 프린팅 방법으로는 릴리프(relief) 프린팅 및 스크린(screen) 프린팅이 사용될 수 있고, 릴리프 프린팅이 특별히 바람직하다. 여기서는 본 발 명에서 릴리프 프린팅을 사용하는 경우가 도 1을 사용해 설명된다.

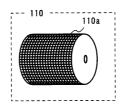

도 1a 내지 도 1c는 본 발명에서 사용되는 릴리프 프린팅 장치의 일부이다. 도 1a 내지 도 1c에서, 참고번호(110)는 아닐록스 롤(anilox roll)을 나타내고;(111)은 닥터 바(doctor bar)(또한 닥터 블레이드(doctor blade)라 언급됨)를 나타내고; EL 소자와 용매(solvent)의 혼합물(112)(이후 EL 형성물이라 언급됨)은 닥터 바(111)에 의해 아닐록스 롤(110)의 표면주위에서 풀링된다. 여기서 언급되는 EL 물질은 형광 유기 화합물(fluorescent organic compound)이고 일반적으로 홀주입층(hole injection layer), 홀 운송층(hole transport layer), 발광층(light emitting layer), 전자 운송층, 또는 전자 주입층이라 언급되는 유기 화합물을 나타냄을 주목한다.

메시 그루브(meshed grooves)(이후 메시(mesh)라 언급됨)(110a)는 도 1b에 도시된 바와 같이 아닐록스 록(110)의 표면에 제공되고, 메시(110a)는 화살표 A의 방향으로 굴림으로서 표면상에 EL 형성물(112)을 유지한다. 도면에 도시된 점선은 EL 형성물이 아닐록스 롤(110)의 표면상에 유지되는 것을 의미함을 주목하여야 한다.

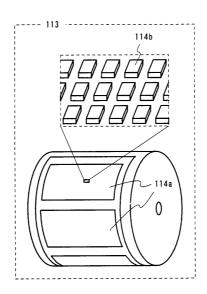

참고번호(113)는 프린팅 롤이고,(114)는 릴리프이고, 릴리프(114)의 표면상에서는 에칭에 의해 비균일(uneveness)이 형성된다. 이러한 상태는 도 1c에 도시된다. 도 1c의 경우, 픽셀 부분(114a)에 대한 패턴은 한 기판 상에 복수의 EL 디스 플레이 장치를 제조하기 위해 릴리프(114)상의 복수 부분에 형성된다. 또한, 돌출부(projection)(114b)는 픽셀 부분 (114a)에 대한 패턴이 확대될 때 복수의 픽셀에 대응하는 위치에 형성된다.

상기 언급된 아닐록스 롤(110)은 롤링(rolling)에 의해 메시(110a) 상에 EL 형상 기판(112)을 유지시킨다. 한편, 프린팅롤(113)은 화살표 B의 방향으로 회전하여, 릴리프(114)의 돌출부(114b)만이 메시(110a)와 접촉한다. 여기서, EL 형성물(112)은 돌출부들(114b)의 표면 상에 코팅된다.

EL 형성물(112)은 프린팅 롤(113)과 같은 속도로 수평 방향에서(화살표 C의 방향) 쉬프트(shift)되는 기판(115)과 돌출부들(114b)이 접촉하는 부분에서 프린팅된다. 그렇게 함으로써, EL 형성물(112)은 매트릭스로의 배열 상태로 기판(115)상에 프린팅된다.

이어서, 진공에서의 열처리를 통해 EL 형성물(112)에 포함된 용매를 증발 건조시킴으로써 EL 물질이 남겨진다. 그러므로, EL 물질의 유리 전이 온도(glass transition temperature)(Tg) 보다 더 낮은 온도에서 증발되는 용매를 사용할 필요가있다. 최종적으로 형성된 EL층은 EL 형성물의 점성률에 의해 결정된다. 이 경우, 속도는 용매의 선택에 의해 제어되고, 10내지 50 cp(바람직하게 20내지 30 cp)의 속도가 바람직하다.

또한, 용매의 증발을 통해 EL 물질을 결정화하는 가능성은 결정질 핵이 될 수 있는 많은 불순물이 EL 형성물(112)에 존재할 때 높아진다. 결정화는 발광 효율성을 감소시키므로, 바람직하지 못하다. EL 형성물(112)에 가능한 적은 불순물이 포함되는 것이 바람직하다.

용매를 정재할 때, EL 물질을 정제할 때, 또는 불순물들을 감소시키도록 EL 물질과 용매를 혼합할 때, 가능한한 청결한 환경을 이루는 것이 중요하고, 또한 도 1의 프린팅 장치에 의해 EL 형성물을 프린팅할 시 대기(atmosphere)에 주위를 기 울이는 것이 바람직하다. 구체적으로, 질소와 같은 불활성 기체로 채워진 청결한 부스에 배치된 프린팅 장치에 의해 상기 에 언급된 EL 형성물의 프린팅 공정을 수행하는 것이 바람직하다.

본 발명은 액티브 매트릭스 EL 디스플레이 장치 및 능동 매트릭스(간단한 매트릭스) EL 디스플레이 장치 모두에 구현될수 있음을 주목한다.

#### 발명의 구성 및 작용

#### [실시예 모드]

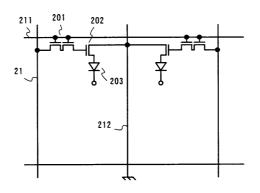

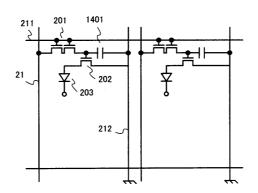

다음에는 본 발명을 실행하는 모드가 도 2와 도 3a 및 도 3b를 참고로 설명될 것이다. 도 2는 본 발명의 EL 디스플레이장치에서 픽셀(pixel) 부분의 단면도이고, 도 3a는 상면도이고, 또한 도 3b는 회로 구조를 도시하는 도면이다. 다수의 픽셀들은 실질적으로 픽셀 부분(영상 디스플레이 부분)이 형성되도록 매트릭스 형태로 배열된다. 도 2는 도 3a의 선 A-A'을따라 취해진 단면도에 대응한다. 그래서, 도 2 및 도 3a에서는 공통된 심볼이 사용되므로, 두 도면은 적절하게 언급될 수있다. 그외에, 비록 도 3의 상면도는 두 픽셀을 도시하지만, 둘 모두가 동일한 구조를 갖는다.

도 2에서, 참고번호(11)는 기판을 나타내고,(12)는 언더코트(undercoat)가 되는 절연막(이후에 기저막(base film)이라 언급됨)을 나타낸다. 기판(11)으로서는 유리 기판(glass substrate), 유리 세라믹 기판, 수정 기판(quartz), 실리콘 기판, 세라믹 기판, 금속 기판, 또는 플라스틱 기판(플라스틱막 포함)이 사용될 수 있다.

비록 기저막(12)이 도전성을 갖는 기판이나 이동가능한 이온을 포함하는 기판을 사용하는 경우 특히 유효하지만, 이는 반드시 수정 기판상에 제공될 필요는 없다. 기저막(12)으로는 실리콘을 포함하는 절연막이 사용된다. 본 명세서를 통해, "실리콘을 포함하는 절연막"은 미리 결정된 비율로 실리콘, 산소, 및 질소를 포함하는 절연막, 예를 들면, 산화실리콘막, 질화실리콘막, 또는 질산화실리콘막(SiO $_{\rm x}$ N $_{\rm y}$ 로 나타내지는)을 나타냄을 주목한다.

EL 소자의 저하(deterioration) 또는 TFT의 저하를 방지하기 위해 기저막(12)이 열 방사 효과를 갖게 함으로써 박막 트랜지스터(이후 TFT라 언급됨)의 열 발생을 방산시키는 것이 효과적이다. 막이 열 방사 효과를 갖게 하기 위해, 알려진 물질이 사용될 수 있다.

여기서, 픽셀에는 2개의 TFT가 형성된다. 참고번호(201)는 스위칭 소자로 동작하는 TFT(이후 스위칭 TFT라 언급됨)를 나타내고,(202)는 EL 소자로 흐르는 전류량을 제어하기 위한 전류 제어 소자로 동작하는 TFT(이후 전류 제어 TFT라 언급됨)를 나타낸다.

n-채널 TFT의 전계 효과 이동성이 p-채널 TFT의 전계 효과 이동성 보다 더 크므로, 그 동작 속도가 높고 큰 전류가 용이하게 흐르게 될 수 있다. 똑같은 양의 전류가 흐르게 될 때, n-채널 TFT의 TFT 크기는 더 작게 만들어질 수 있다. 따라서, 디스플레이 부분의 유효 면적이 넓어지므로, n-채널 TFT를 전류 제어 TFT로 사용하는 것이 바람직하다.

p-채널 TFT는 핫 캐리어(hot carrier) 주입이 거의 문제가 되지 않고 off 전류값이 낮은 이점을 가져, 이것이 스위칭 TFT로서 사용되는 예와 전류 제어 TFT로 사용되는 예가 보고되어 있다. 그러나, 본 발명은 LDD 영역들의 위치들이 상이하게 이루어진 구조를 만듬으로서, 핫 캐리어 주입 및 off 전류값의 문제점들이 n-채널 TFT에서도 해결되어, 픽셀내의 모든 TFT들이 n-채널 TFT들로 이루어지는 것을 특징으로 한다.

그러나, 본 발명에서 스위칭 TFT 및 전류 제어 TFT를 n-채널 TFT로 제한할 필요는 없고, 둘 중 임의의 하나 또는 둘 모두에 p-채널 TFT를 사용하는 것이 가능하다.

스위칭 TFT(201)는 소스 영역(13), 드레인 영역(14), LDD 영역(15a 내지 15d), 고농도 불순물 영역(16) 및 채널 형성 영역(17a, 17b)을 포함하는 활성층, 게이트 절연막(18), 게이트 전극(19a, 19b), 제 1 층간 절연막(20), 소스 와이어선 (21), 및 드레인 와이어선(22)을 포함한다.

그외에, 도 3a에 도시된 바와 같이, 게이트 전극(19a, 19b)은 또 다른 물질(게이트 전극(19a, 19b) 보다 더 낮은 저항을 갖는 물질)로 형성된 게이트 와이어선(211)을 통해 전기적으로 연결된 이중 게이트 구조이다. 물론, 이중 게이트 구조에부가하여, 삼중 게이트 구조 등과 같은, 다중 게이트 구조(직렬로 연결된 둘 이상의 채널 형성 영역들을 갖는 활성층을 포함하는 구조)가 채택될 수 있다. 다중 게이트 구조는 off 전류값을 줄이는데 매우 효과적이고, 본 발명에서는 낮은 off 전류값을 갖는 스위칭 소자를 실현하도록 픽셀의 스위칭 TFT(201)가 다중 게이트 구조로 이루어진다.

활성층은 결정 구조를 포함하는 반도체 막으로 형성된다. 즉, 단일 결정 반도체막이 사용될 수 있거나, 다결정질 반도체막 또는 마이크로결정질 반도체막이 사용될 수 있다. 게이트 절연막(18)은 실리콘을 포함하는 절연막으로 형성된다. 그외에, 도전막은 게이트 전극, 소스 와이어선, 또는 드레인 와이어선으로 사용될 수 있다.

또한, 스위칭 TFT(201)에서, LDD 영역들(15a 내지 15d)은 게이트 전극(19a 및 19b)과 오버랩되지 않도록 제공되고, LDD 영역들과 게이트 전극들 사이에는 게이트 절연막(18)이 놓인다. 이러한 구조는 off 전류값을 줄이는데 매우 효과적이다.

부수적으로, off 전류를 줄이기 위해 채널 형성 영역과 LDD 영역 사이에 오프셋(offset) 영역(게이트 전압이 인가되지 않고, 채널 형성 영역과 똑같은 구성을 갖는 반도체층으로 구성된 영역)을 제공하는 것이 보다 바람직하다. 둘 이상의 게이트 전극을 갖는 다중 게이트 구조의 경우, 채널 형성 영역들 사이에 제공되는 고농도 불순물 영역은 off 전류값을 줄이는데 유효하다.

상술된 바와 같이, 다중 게이트 구조의 TFT를 픽셀의 스위칭 소자(201)로 사용함으로써, 충분히 낮은 off 전류값을 갖는 스위칭 소자를 실현하는 것이 가능하다. 따라서, 일본 특허 출원 공개 No. Hei 10-189252호의 도 2에 도시된 캐패시터가 제공되지 않더라도, 전류 제어 TFT의 게이트 전압은 충분한 시간 동안(선택과 다음 선택 사이의 간격) 유지될 수 있다.

즉, 종래에 유효 발광 영역을 좁히는 팩터인 캐패시터를 제거하는 것이 가능해지고, 유효 발광 영역을 넓히는 것이 가능해진다. 이는 EL 디스플레이 장치의 화상 품질이 밝아질 수 있음을 의미한다.

다음에, 전류 제어 TFT(202)는 소스 영역(31), 드레인 영역(32), LDD 영역(33)과 채널 형성 영역(34)을 포함하는 활성층, 게이트 절연막(18), 게이트 전극(35), 제 1 층간 절연막(20), 소스 와이어선(36), 및 드레인 와이어선(37)을 포함한다. 비록 게이트 전극(35)이 단일 게이트 구조이지만, 다중게이트 구조가 채택될 수 있다.

도 2에 도시된 바와 같이, 스위칭 TFT의 드레인은 전류 제어 TFT의 게이트에 연결된다. 특별히, 전류 제어 TFT(202)의 게이트 전극(35)은 드레인 와이어선(연결 와이어선이라 언급됨)(22)을 통해 스위칭 TFT(201)의 드레인 영역(14)에 전기적으로 연결된다. 소스 와이어선(36)은 전류 공급선(212)에 연결된다.

비록 전류 제어 TFT(202)는 EL 소자의 저하를 고려하여 EL 소자(203)에 주입되는 전류량을 제어하는 소자이지만, 많은 양의 전류를 공급하는 것은 바람직하지 못하다. 따라서, 과도한 전류가 전류 제어 TFT(202)로 흐르는 것을 방지하기 위해, 채널 길이(L)를 다소 길게 설계하는 것이 바람직하다. 양호하게, 전류는 픽셀 당 0.5 내지  $2~\mu A$ (바람직하게  $1~\mu A$ )가 되도록 설계된다.

상기에 대해, 도 9에 도시된 바와 같이, 스위칭 TFT의 채널 길이가 L1(L1 = L1a + L1b), 채널 폭이 W1, 전류 제어 TFT의 채널 길이가 L2, 채널 폭이 W2일 때, W1은 0.1과 5  $\mu m$  사이로(전형적으로 0.5 내지 2  $\mu m$ ) 이루어지고, W2는 0.5와 10  $\mu m$  사이로(전형적으로 2 내지 5  $\mu m$ ) 이루어지는 것이 바람직하다. 그외에, L1은 0.2 내지 18  $\mu m$ (전형적으로 2 내지 15  $\mu m$ )로 이루어지고, L2는 1 내지 50  $\mu m$ (전형적으로 10 내지 30  $\mu m$ )로 이루어지는 것이 바람직하다. 그러나, 본 발명은 상기의 숫자값에 제한되지 않는다.

숫자값의 범위를 선택함으로써, VGA 등급의 픽셀수(640 x 480)를 갖는 El 디스플레이 장치에서 높은 비젼 등급(1920 x 1080 또는 1280 x 1024)까지 모든 표준이 커버될 수 있다.

그외에, 스위칭 TFT(201)에 형성된 LDD 영역의 길이(폭)는 0.5 내지 3.5 μm, 전형적으로 2.0 내지 2.5μm로 이루어지는 것이 적절하다.

그외에, 도 2에 도시된 EL 디스플레이 장치는 또한 LDD 영역(33)이 드레인 영역(32)과 채널 형성 영역(34) 사이에 제공되고, LDD 영역(33)이 게이트 전극(35)과 오버랩되지 않는 영역과 오버랩되는 영역을 포함하여, 게이트 절연막(18)이 전류 제어 TFT(202)에서 그들 사이에 놓이는 것을 특징으로 한다.

전류 제어 TFT(202)는 EL 소자(204)가 발광하게 하는 전류를 공급하고, 그레이 스케일(gray scale)이 디스플레이될 수 있도록 공급량을 제어한다. 그래서, 전류가 공급되더라도 저하가 일어나지 않도록 핫 캐리어 주입으로 인한 저하에 대해 대응책을 취할 필요가 있다. 흑색이 디스플레이될 때, 비록 전류 제어 TFT(202)가 꺼지게 되더라도, 그때, off 전류가 높으면, 명확한 흑색 디스플레이가 불가능해지고, 대조가 낮아진다. 그래서, off 전류값도 억제할 필요가 있다.

핫 캐리어 주입으로 인한 저하에 대해, LDD 영역이 게이트 전극과 오버랩되는 구조는 매우 유효한 것으로 알려져 있다. 그러나, 전체적인 LDD 영역이 게이트 전극과 오버랩되도록 만들어지면, off 전류값은 증가된다. 그래서, 본 출원인은 게이 트 전극과 오버랩되지 않는 LDD 영역이 직렬로 제공되어, 핫 캐리어 대응책 및 off 전류값 대응책의 문제점이 동시에 해결 되도록 새로운 구조를 고안한다.

이때, 게이트 전극과 오버랩되는 LDD 영역의 길이는 0.1 내지 3 μm(전형적으로 0.3 내지 1.5 μm)로 이루어지는 것이 적절하다. 길이가 너무 길면, 기생 캐패시티(parasitic capacity)가 커지고, 너무 짧으면, 핫 캐리어를 방지하는 효과가 약해진다. 그외에, 게이트 전극과 오버랩되지 않는 LDD 영역의 길이는 1.0 내지 3.5 μm(바람직하게 1.5 내지 2.0 μm)로 이루어지는 것이 적절하다. 길이가 너무 길면, 충분한 전류 흐름을 만드는 것이 불가능해지고, 너무 짧으면, off 전류값을 낮추는 효과가 약해진다.

상기 구조에서, 기생 캐패시티는 게이트 전극 및 LDD 영역이 서로 오버랩되는 영역에 형성된다. 그래서, 소스 영역(31)과 채널 형성 영역(34) 사이에 이러한 영역을 제공하지 않는 것이 바람직하다. 전류 제어 TFT에서, 캐리어(여기서는 전자)의 흐름 방향은 항상 똑같으므로, LDD 영역이 드레인 영역의 한 측면에만 제공되는 것으로 충분하다.

그러나, 전류 제어 TFT(202)의 구동 전압(소스 영역과 드레인 영역 사이에 인가되는 전압)이 10 V 이하가 될 때, 핫 캐리어 주입은 거의 문제가 되지 않으므로, LDD 영역(33)을 생략하는 것이 가능해진다. 그 경우, 활성층은 소스 영역(31), 드레인 영역(32), 및 채널 형성 영역(34)으로 구성된다.

흐를 수 있는 전류량을 증가시키는 관점에서, 전류 제어 TFT(202)의 활성층(특히, 채널 형성 영역)의 막 두께(양호하게, 50 내지 100 nm, 보다 양호하게 60 내지 80 nm)를 증가시키는 것이 또한 효과적이다. 반대로, 스위칭 TFT(201)의 경우, off 전류값을 감소시키는 관점에서, 활성층(특히, 채널 형성 영역)의 막 두께(양호하게, 20 내지 50 nm, 보다 양호하게 25 내지 40 nm)를 감소시키는 것이 또한 효과적이다.

다음에, 참고번호(41)는 제 1 패시베이션막(passivation film)을 나타내고, 두께가 10 nm 내지 1 μm(양호하게 200 내지 500 nm)로 이루어지는 것이 적절하다. 물질로는 실리콘을 포함하는 절연막(특히, 질산화실리콘이나 질화실리콘막이 바람직하다)을 사용하는 것이 가능하다. 이 패시베이션막(41)은 형성된 TFT를 알칼리 금속이나 습기로부터 보호하는 기능을 갖는다. 즉, 제 1 패시베이션막(41)은 알칼리 금속(이동가능한 이온)이 TFT 측으로 들어가는 것을 방지하는 기능을 한다.

또한, 제 1 패시베이션막(41)이 열 방사 효과를 갖게 함으로써 EL층의 열적 저하를 방지하는 것이 효과적이다. 그러나, 도 2의 구조의 EL 디스플레이 장치에서는 빛이 기판(11)의 측면으로 방사되므로, 제 1 패시베이션막(41)이 반투명할 필요 가 있다. EL층에 유기체 물질이 사용되는 경우, 산소와 조합되어 저하가 일어나므로, 쉽게 산소를 방출하는 절연막을 사용 하지 않는 것이 바람직하다.

\*알칼리 금속의 투과를 방지하고 열 방출 효과를 갖는 반투명 물질로는 B(붕소), C(탄소), 및 N(질소)로부터 선택된 적어도 하나의 원소나 Al(알루미늄), Si(실리콘), 및 P(인)으로부터 선택된 적어도 하나의 원소를 포함하는 절연막이 언급될 수 있다. 예를 들면, 질화알루미늄(AlxNy)으로 예시화된 알루미늄의 질화물, 탄화실리콘(SixCy)으로 예시화되는 실리콘의 탄화물, 질화붕소(BxNy)로 예시화되는 붕소의 질화물, 또는 인화붕소(BxPy)로 예시화되는 붕소의 인화물을 사용하는 것이 가능하다. 산화알루미늄(AlxOy)으로 예시화된 알루미늄의 산화물은 투명도가 뛰어나고, 열적 도전성은 20 Wm<sup>-1</sup>K이므로, 바람직한 물질 중 하나인 것으로 말할 수 있다. 이들 물질들은 상기의 효과 뿐만 아니라 습기 침투를 방지하는 효과도 갖는다. 부가적으로, 상기 반투명 물질에서, x 및 y는 임의의 정수이다.

또한, 상기 화합물을 다른 원소와 조합하는 것이 가능함을 주목하여야 한다. 예를 들면, 산화알루미늄에 질소를 부가함으로써 AlNxOy로 나타내지는 질산화알루미늄을 사용하는 것이 가능하다. 이 물질은 또한 열 방출 효과에 부가하여 습기나알칼리 금속의 투과를 방지하는 효과를 갖는다. 부수적으로, 상기 질산화알루미늄에서, x 및 y는 임의의 정수이다.

그외에, 일본 특허 출원 공개 No. Sho 62-90260호에서 설명된 물질을 사용하는 것이 가능하다. 즉, Si, Al, N, O, 또는 M(M은 적어도 한 종류의 희토류(rare-earth) 원소이고, 바람직하게 Ce(세륨(cerium)), Yb(이테르븀(ytterbium)), Sm(사마륨(samarium)), Er(에르븀(erbium)), Y(이트륨(yttrium)), La(란턴(lantern)), Gd(가도리늄(gadolinium)), Dy(디스프로슘(dysprosium)), 및 Nd(네오디뮴(neodimium))으로부터 선택된 적어도 하나의 원소)을 포함하는 절연막을 사용하는 것이 또한 가능하다. 이들 물질들은 또한 열 방출 효과에 부가하여 습기나 알칼리 금속의 투과를 방지하는 효과를 갖는다.

그외에, 적어도 다이아몬드 박막 또는 비결정질 탄소막(특히 다이아몬드와 가까운 특성을 갖는 막으로 다이아몬드형 탄소 등으로 언급됨)을 포함하는 탄소막을 사용하는 것이 또한 가능하다. 이들은 매우 높은 열적 도전성을 갖고 열 방출층으로 매우 효과적이다. 그러나, 막이 갈색으로 되고, 막이 두꺼워지면 투과율이 감소되므로, 가능한 최소의 두께(바람직하게 5 내지 100 nm)를 갖는 막을 사용하는 것이 바람직하다.

부가적으로, 제 1 패시베이션막(41)의 주요 목적이 알칼리 금속이나 습기에 대해 TFT를 보호하는 것이므로, 막은 효과를 손상시키지 말아야 한다. 그래서, 비록 상기 열 방출 효과를 갖는 물질로 구성된 박막이 홀로 사용될 수 있더라도, 알칼리 금속이나 습기의 투과를 방지할 수 있는 절연막(전형적으로 질화실리콘막(SixNy) 또는 질산화실리콘막(SiOxNy))과 박막을 적충시키는 것이 효과적이다. 부수적으로, 질화실리콘막이나 질산화실리콘막에서, x 및 y는 임의의 정수이다.

제 2 층간 절연막(평탄화막(planarization film)이라 언급됨)(44)은 각 TFT를 커버하도록 제 1 패시베이션막(41)상에 형성되므로, TFT에 의해 형성된 스텝이 평평해진다. 제 2 층간 절연막(44)으로는 유기체 수지막이 바람직하고, 폴리이미드 (polyimide), 폴리아미드(polyamide), 아크릴(acrylic), BCB(benzocyclobutene) 등이 사용되는 것이 적절하다. 물론, 충분하게 평평해지는 한, 비유기체막이 사용될 수도 있다.

TFT로 인한 스텝을 제 2 층간 절연막(44)에 의해 평평하게 만드는 것은 중요하다. 추후 형성될 EL층이 매우 얇으므로, 스텝의 존재로 인해 열악한 발광이 일어나는 경우가 있다. 그래서, EL층이 가능한한 가장 평평한 표면에 형성될 수 있도록 픽셀 전극이 형성되기 이전에 평평하게 만드는 것이 바람직하다.

참고번호(45)는 제 2 패시베이션막을 나타내고, EL 소자로부터 확산되는 알칼리 금속을 저지하는 매우 중요한 기능을 갖는다. 막의 두께는 5 nm 내지 1  $\mu$ m(전형적으로 20 내지 300 nm)로 만들어지는 것이 적절하다. 알칼리 금속의 투과를 저지할 수 있는 절연막은 제 2 패시베이션막(45)으로 사용된다. 물질로는 제 1 패시베이션막(41)에 사용되는 물질이 사용될수 있다.

제 2 패시베이션막(45)은 또한 EL 소자에 발생된 열을 방산하는 열 방출층으로서 기능한다. 제 2 층간 절연막(44)이 유기체 수지막인 경우, 열에 약하므로, 제 2 패시베이션막은 EL 소자에서 발생된 열이 제 2 층간 절연막(44)에 나쁜 영향을 주는 것을 방지한다.

상술된 바와 같이, 비록 EL 디스플레이 장치가 제조될 때 유기체 수지막으로 TFT를 평탄하게 하는 것이 효과적이지만, EL 소자에서 발생된 열에 의해 발생되는 유기체 수지막의 저하에 관심을 둔 종래의 구조는 없다. 본 발명에서는 제 2 패시 베이션막(45)을 제공함으로써 문제점을 해결하고, 이는 특성 중 하나가 될 수 있다.

제 2 패시베이션막(45)은 열로 인한 저하를 방지하고, EL층의 알칼리 금속이 TFT의 측면으로 확산되는 것을 방지하는 보호막으로 동작하고, 또한 습기나 산소가 TFT의 측면에서 EL층의 측면으로 투과되는 것을 방지하는 보호막으로 동작한다.

상기에 언급된 바와 같이, 높은 열 방출 효과를 갖고 습기 및 알칼리 금속의 투과를 방지할 수 있는 절연막에 의해 TFT측과 EL 소자를 분리하는 것은 본 발명의 가장 중요한 특성 중 하나이고, 이는 종래 EL 디스플레이 장치에서 존재하지 않는 특성인 것으로 말할 수 있다.

참고번호(46)는 투명 도전막으로 구성된 픽셀 전극(EL 소자의 양극)을 나타낸다. 접촉 홀(오프닝)이 제 2 패시베이션막(45), 제 2 층간 절연막(44), 및 제 1 패시베이션막(41)을 통해 형성된 이후에, 픽셀 전극은 형성된 오프닝 부분에서 전류제어 TFT(202)의 드레인 와이어선(37)과 연결되도록 형성된다.

다음에는 EL층(엄격하게, 픽셀 전극과 접촉하는 EL층)(47)이 프린팅에 의해 형성된다. 비록 EL층(47)이 단일층 구조 또는 적층 구조(laminate structure)로 사용되지만, 많은 경우에서는 적층 구조로 사용된다. 그러나, 적층의 경우, 프린팅과기상 성장(특히, 증발건조 방법이 바람직하다)을 조합하는 것이 바람직하다. 프린팅 방법에서, 용매와 EL 물질이 혼합되어 프린팅되므로, 유기체 물질이 아래에 포함되면, 유기체 물질이 다시 용해될 우려가 있다.

그래서, EL층(47)내에서 픽셀 전극과 직접적으로 접촉하는 층이 프린팅에 의해 형성되고 이후에 기상 성장에 의해 층이 형성되는 것이 바람직하다. 말할 필요도 없이, 더 낮은 층의 EL 물질이 용해되지 않는 용매를 사용함으로써 프린팅이 이루 어질 수 있으면, 모든 층은 프린팅에 의해 형성될 수 있다. 홀 주입층, 홀 운송층, 및 발광층은 픽셀 전극과 직접 접촉하는 층으로 주어질 수 있고, 본 발명은 임의의 층을 형성하는 경우에 사용될 수 있다.

본 발명에서, 프린팅이 EL층을 형성하는 방법으로 사용되므로, EL 물질로 폴리머 물질을 사용하는 것이 바람직하다. 전 형적인 폴리머 물질로는 PPV(polyparaphenylene vinylene), PVK(polyvinylcarbazole), 또는 폴리플루오렌 (polyfluorene)과 같은 폴리머가 열거될 수 있다.

프린팅에 의해 폴리머 물질로 구성되는 발광층, 홀 운송층, 또는 홀 주입층을 형성하기 위해, 프린팅은 폴리머 프리커서 (precursor)의 상태로 이루어지고, 진공상태에서 가열되어, 폴리머 물질로 구성된 EL 물질로 변환된다. 필요한 EL 물질은 증발건조 등과 같은 방법으로 그위에 적충되므로, 적충형 EL층이 형성된다.

특별히, 홀 운송층으로, 폴리머 프리커서인 폴리테트라하이드로시오페닐페닐렌(polytetrahydrothiophenylphenylene)이 사용되고 가열함으로써 폴리페닐렌 비닐렌(polyphenylene vinylene)로 변환되는 것이 바람직하다. 막 두께는 30 내지 100 nm(양호하게 40 내지 80 nm)로 이루어지는 것이 적절하다. 발광층으로는 시아노폴리페닐렌 비닐렌(cyanopolyphenylene vinylene)이 적색 발광층으로 사용되고, 폴리페닐렌 비닐렌(polyphenylene vinylene)이 녹색 발광층으로 사용되고, 또한 폴리페닐렌 비닐렌 또는 폴리알킬페닐렌(polyalkylphenylene)이 청색 발광층으로 사용되는 것이 적절하다. 막 두께는 30 내지 150 nm(양호하게 40 내지 100 nm)로 이루어지는 것이 적절하다.

또한, 형성된 EL 물질과 픽셀 전극 사이에 버퍼층으로 구리 프탈로시아닌(copper phthalocyanine)을 제공하는 것이 효과적이다.

그러나, 상기의 예는 단순히 본 발명의 EL 물질로 사용될 수 있는 유기체 EL 물질의 예이고, 본 발명을 이에 제한시킬 필요는 없다. 본 발명에서는 EL 물질과 용매의 혼합이 증발되고 제거되어 EL층이 형성된다. 그래서, 용매의 증발이 EL 층의 유리 전이 온도를 넘지않는 온도에서 실행되도록 조합되는 한, EL 물질은 사용될 수 있다.

전형적으로, 용매로는 클로로포름(chloroform), 디클로메탄(dichloromethane), a-부틸락톤(a-butyllactone), 부틸셀로 솔브(butyl cellosolve), 또는 NMP(N-methyl-2-pyrolidone)와 같은 유기체 용매가 사용되거나 물이 사용될 수 있다. 또 한, EL 형성물의 점성률을 증가시키도록 첨가제를 부가하는 것이 효과적이다.

그외에, EL층(47)이 형성될 때, 처리 대기(treatment atmosphere)는 가능한한 최소의 습기를 갖는 건조 대기로 이루어지고 불활성 기체에서 형성이 실행되는 것이 바람직하다. EL층이 용이하게 습기나 산소의 존재에 의해 저하되므로, 층이형성될 때, 이러한 팩터들을 최대로 제거하는 것이 필요하다. 예를 들면, 건조 질소 대기나 건조 아르곤 대기가 양호하다. 그 목적을 위해, 프린팅 장치는 불활성 기체로 채워진 청결한 부스에 설치되고, 프린팅 공정은 그 대기에서 실행되는 것이바라직하다.

EL층(47)이 상술된 바와 같이 프린팅에 의해 형성될 때, 다음에는 음극(48) 및 보호 전극(49)이 형성된다. 음극(48) 및 보호 전극(49)은 진공 증발건조 방법에 의해 형성된다. 음극(48) 및 보호 전극(49)이 연속적으로 공기에 개방되지 않고 형 성되면, EL층의 저하는 더 억제될 수 있다. 본 명세서에서, 픽셀 전극(양극), EL층, 및 음극으로 형성된 발광 소자는 EL 소 자라 언급된다.

음극(48)으로는 낮은 작업 기능을 갖는 마그네슘(Mg), 리듐(Li), 또는 칼슘(Ca)을 포함하는 물질이 사용된다. 양호하게, MgAg(Mg:Ag = 10:1의 비율로 Mg 및 Ag가 혼합된 물질)로 구성된 전극이 사용된다. 부가하여, MgAgAl 전극, LiAl 전극, 및 LiFAl 전극이 열거될 수 있다. 보호 전극(49)은 외부 습기 등으로부터 음극(48)을 보호하도록 제공된 전극으로, 알루미늄(Al) 또는 은(Ag)을 포함하는 물질이 사용된다. 이 보호 전극(49)은 또한 열 방출 효과를 갖는다.

부수적으로, EL층(47)과 음극(48)은 공기에 개방되지 않고 건조 불활성 기체 대기에서 연속적으로 형성되는 것이 바람직하다. 유기체 물질이 EL층으로 사용되는 경우, 이는 습기에 매우 약하므로, 대기에 개방할 때 습기 흡수를 방지하는 방법이 채택된다. 또한, EL층(47) 및 음극(48) 뿐만 아니라 보호 전극(49)도 연속적으로 형성하는 것이 보다 바람직하다.

도 2의 구조는 RGB 중 하나에 대응하는 한 종류의 EL 소자가 형성되는 단색광 시스템을 사용하는 경우의 예이다. 비록도 2는 한 픽셀만을 도시하지만, 똑같은 구조를 갖는 다수의 픽셀이 픽셀 부분에 매트릭스 형태로 배열된다. 부수적으로, 알려진 물질이 RGB 중 하나에 대응하는 EL층에 채택될 수 있다.

상기 시스템에 부가하여, 백색 발광의 EL 소자와 칼라 필터가 조합된 시스템, 청색 또는 청녹색 발광의 EL 소자와 형광물질(CCM: fluorescent color converting layer)이 조합된 시스템, 투명 전극이 음극(카운터 전극)으로 사용되고 RGB에대응하는 EL 소자가 적충되는 시스템 등을 사용해 칼라 디스플레이가 이루어질 수 있다. 물론, 단일층에 백색 발광의 EL층을 형성함으로써 흑백 디스플레이를 이루는 것이 또한 가능하다.

참고번호(50)는 제 3 패시베이션막을 나타내고, 그 막 두께는 10 nm 내지 1  $\mu$ m(바람직하게 200 내지 500 nm)로 이루어지는 것이 적절하다. 비록 제 3 패시베이션막(50)을 제공하는 주요 목적이 습기로부터 EL층(47)을 보호화는 것이지만, 제 2 패시베이션막(45)과 유사하게, 열 방출 효과도 또한 제공된다. 따라서, 제 1 패시베이션막(41)과 유사한 물질이 형성물로 사용될 수 있다. 그러나, 유기체 물질이 EL층(47)으로 사용되는 경우, 층이 산소와의 결합을 통해 변경될 가능성이 있으므로, 산소를 발하기 쉬운 절연막을 사용하지 않는 것이 바람직하다.

그외에, 상술된 바와 같이, EL층은 열에 약하므로, 가능한한 가장 낮은 온도에서(양호하게 실온에서 120℃까지의 범위에 있는 온도에서) 막을 형성하는 것이 바람직하다. 그래서, 플라스마 CVD, 스퍼터링, 진공 증발건조, 이온 플레이팅, 또는 용 매 적용 방법(스핀 코팅 방법)이 양호한 막 형성 방법이라 말할 수 있다.

이와 같이, 비록 EL 소자의 저하는 단순히 제 2 패시베이션막(45)을 제공함으로써 충분히 억제될 수 있지만, 양호하게, EL 소자는 제 2 패시베이션막(45) 및 제 3 패시베이션막(50)과 같이 EL 소자 양측에 놓이도록 형성된 2-충 절연막에 의해 둘러싸이므로, EL충으로 습기 및 산소의 침입이 방지되고, EL충으로부터 알칼리 금속의 확산이 방지되고, 또한 EL충으로의 열저장이 방지된다. 그 결과로, EL충의 저하가 더 억제되고, 높은 확실성을 갖는 EL 디스플레이 장치가 구해질 수 있다.

본 발명의 EL 디스플레이 장치는 도 2와 같은 구조를 갖는 픽셀로 구성된 픽셀 부분을 갖고, 기능에 따라 다른 구조를 갖는 TFT가 픽셀에 배치된다. 따라서, 현저하게 낮은 off 전류값을 갖는 스위칭 TFT와 핫 캐리어 주입에 강한 전류 제어TFT가 같은 픽셀내에 형성될 수 있어, 높은 확실성을 갖고 뛰어난 화상 디스플레이를 가능하게 하는(높은 동작 성능을 갖는) EL 디스플레이 장치가 구해질 수 있다.

도 2의 픽셀 구조에서는 다중 게이트 구조를 갖는 TFT가 스위칭 TFT로 사용되지만, LDD 영역 등의 배열 구조를 도 2의 구조에 제한시킬 필요는 없다.

또한, 여기서는 기판 표면상에 반도체 장치로 제공되는 TFT에 전기적으로 연결된 EL 소자를 형성할 때 본 발명을 실시하는 예가 도시되지만, 반도체 장치로 실리콘 기판 표면상에 형성된 트랜지스터(이후 MOSFET라 언급됨)를 사용하는 경우에서 본 발명을 실시하는 것도 가능하다.

상기 구성을 통해 제조되는 본 발명은 이후 설명될 실시예를 참고로 보다 상세히 설명된다.

### [실시예 1]

본 발명의 실시예는 도 4a 내지 도 6c를 사용해 설명된다. 여기서는 픽셀 부분과, 그 픽셀 부분의 주변에 형성된 구동 회로 부분의 TFT를 동시에 제조하는 방법이 설명된다. 설명을 간략화하기 위해, CMOS 회로가 구동 회로에 대한 기본 회로로 도시됨을 주목한다.

먼저, 도 4a에 도시된 바와 같이, 기저막(301)은 유리 기판(300)상에 300 nm 두께로 형성된다. 실시예 1에서는 기저막(301)으로 질산화실리콘막이 적충된다. 유리 기판(300)에 접촉하는 막에서 질소 농도는 10 내지 25 wt%로 설정하는 것이좋다.

그외에, 기저막(301)의 일부로, 도 2에 도시된 제 1 패시베이션막(41)과 유사한 물질로 구성된 절연막을 제공하는 것이효과적이다. 전류 제어 TFT는 큰 전류가 흐르므로 열을 발생하기 쉬워서, 가능한한 가까운 위치에 열 방출 효과를 갖는 절연막을 제공하는 것이 효과적이다.

다음에는 비결정질 실리콘막(도면에서 도시되지 않은)이 알려진 피착 방법에 의해 기저막(301)상에 50 nm의 두께로 형성된다. 이를 비결정질 실리콘막에 제한할 필요는 없고, 비결정질 구조를 포함하는 반도체막이라면(마이크로결정질 반도체막을 포함하여) 또 다른 막이 형성될 수 있음을 주목한다. 부가하여, 비결정질 실리콘 게르마늄막과 같이 비결정질 구조를 포함하는 화합물 반도체막이 사용될 수도 있다. 또한, 막 두께는 20 내지 100 nm로 이루어진다.

비결정질 실리콘막은 알려진 방법에 의해 결정화되어, 결정질 실리콘막(또한 폴리결정질 실리콘막 또는 폴리실리콘막이라 언급됨)(302)을 형성한다. 전기 용광로를 사용하는 열적 결정화, 레이저를 사용하는 레이저 어닐링(annealing) 결정화, 및 적외선 램프를 사용하는 램프 어닐링 결정화가 알려진 결정화 방법으로 존재한다. 실시예 1에서는 결정화가 XeCl 기체를 사용하는 엑사이머 레이저(excimer laser)를 형성하는 빛을 사용해 실행된다.

선형으로 형성된 펄스 방사형 엑사이머 레이저광이 실시예 1에서 사용되지만, 직사각형도 사용될 수 있고, 연속 방사 아르곤 레이저광 및 연속 방사 엑사이머 레이저광도 사용될 수 있음을 주목한다.

본 실시예에서는 결정질 실리콘막이 TFT의 활성층으로 사용되지만, 비결정질 실리콘막을 사용하는 것도 가능하다. 그러나, 전류 제어 TFT의 영역을 가능한한 작게 만듬으로서 픽셀의 개구 비율(aperture ratio)을 증가하기 위해, 전류가 쉽게 흐를 수 있는 결정질 실리콘막을 사용하는 것이 유리하다.

비결정질 실리콘막에 의해 off 전류를 줄일 필요가 있는 스위칭 TFT의 활성층을 형성하고, 결정질 실리콘막에 의해 전류 제어 TFT의 활성층을 형성하는 것이 효과적임을 주목한다. 비결정질 실리콘막에서는 캐리어 이동이 낮고 off 전류가 쉽게 흐르지 않으므로 전류가 어렵게 흐른다. 다른 말로 하면, 전류가 쉽게 흐르지 않는 비결정 실리콘막과 전류가 쉽게 흐르는 결정질 실리콘막을 모두 유리하게 만드는 것이 가장 좋다.

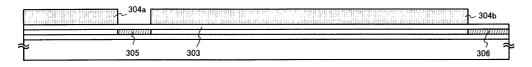

다음에는 도 4b에 도시된 바와 같이, 보호막(303)이 130 nm의 두께를 갖는 산화실리콘막으로 결정질 실리콘막(302)상에 형성된다. 이 두께는 100 내지 200 nm(양호하게 130과 170 nm 사이)의 범위내에서 선택된다. 더욱이, 실리콘을 포함하는 절연막이면, 다른 막도 사용될 수 있다. 보호막(303)은 결정질 실리콘막이 불순물을 부가하는 동안 플라스마에 직접노출되지 않도록, 또한 불순물의 섬세한 농도 제어를 갖는 것을 가능하게 하도록 형성된다.

이어서, 보호막(303)상에는 레지스트 마스크(resist mask)(304a, 304b)가 형성되고, n형 도전성을 나타내는 불순물 원소(이후 n형 불순물 원소)가 보호막(303)을 통해 부가된다. 주기율표 그룹 15에 위치하는 원소가 일반적으로 n형 불순물 원소로 사용되고, 전형적으로 인이나 비소가 사용될 수 있음을 주목한다. 실시예 1에서는 인화수소( $PH_3$ )가 질량 분리 없이 플라스마 활성화되고, 인이  $1 \times 10^{18}$  atoms/cm³의 농도로 부가됨을 주목한다. 질량 분리를 실행하는 이온 주입 방법도 물론 사용될 수 있다.

선량(dose)의 양은 n형 불순물 원소가 2 x 10<sup>16</sup> 내지 5 x 10<sup>19</sup> atoms/cm<sup>3(</sup>전형적으로, 5 x 10<sup>17</sup> 내지 5 x 10<sup>18</sup> atoms/cm<sup>3</sup>)의 농도로 이 공정에 의해 형성된 n형 불순물 영역(305, 306)에 포함되도록 조절된다.

다음에는 도 4c에 도시된 바와 같이, 보호막(303)이 제거되고, 부가된 주기율표 그룹 15 원소의 활성화가 실행된다. 알려진 활성화 기술이 활성화 수단으로 사용되고, 실시예 1에서는 활성화가 엑사이머 레이저광의 조사에 의해 실행된다. 물론, 펼스 방사형 엑사이머 레이저 및 연속 방사형 엑사이머 레이저가 모두 사용될 수 있고, 엑사이머 레이저광의 사용에 제한을 둘 필요는 없다. 목적은 부가된 불순물 원소의 활성화가고, 결정질 실리콘막이 녹지 않는 에너지 레벨로 조사가 실행되는 것이 바람직하다. 레이저 조사는 또한 대신에 보호막(303)으로 실행될 수 있음을 주목한다.

열처리에 의한 활성화도 또한 레이저광에 의한 불순물 원소의 활성화와 함께 실행될 수 있다. 열처리에 의해 활성화가 실행될 때, 기판의 열저항을 고려하여, 450 내지 550 ℃의 정도로 열처리를 실행하는 것이 좋다.

n형 불순물 영역(305, 306)의 엣지를 따라 있는 영역, 즉 n형 불순물 영역(305, 306)에 존재하는 n형 불순물 원소가 부가되지 않은 주변을 따라 있는 영역과의 경계 부분(연결 부분)은 이 공정에 의해 정의된다. 이는 TFT가 추후 완성될 때, LDD 영역과 채널 형성 영역 사이에 매우 양호한 연결이 형성될 수 있음을 의미한다.

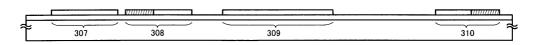

다음에는 도 4d에 도시된 바와 같이, 결정질 실리콘막의 불필요한 부분이 제거되어, 아일랜드형(island type) 반도체막(이후 활성층이라 언급됨)(307 내지 310)이 형성된다.

이어서, 도 4e에 도시된 바와 같이, 게이트 절연막(311)이 형성되어, 활성층(307 내지 310)을 커버한다. 실리콘을 포함하고 10 내지 200 nm, 양호하게 50 내지 150 nm 두께를 갖는 절연막은 게이트 절연막(311)으로 사용된다. 단일층 구조나적층 구조가 사용될 수 있다. 실시예 1에서는 110 nm 두께의 질산화실리콘막이 사용된다.

다음에는 200 내지 400 nm 두께의 도전막이 형성되고 패턴화되어, 게이트 전극(312 내지 316)을 형성한다. 실시예 1에서, 게이트 전극 및 게이트 전극에 전기적으로 연결된 리드 와이어(lead wiring)(이후 게이트 와이어라 언급됨)는 다른 물질로부터 형성됨을 주목한다. 특별히, 게이트 전극 보다 더 낮은 저항을 갖는 물질이 게이트 와이어로 사용된다. 이는 마이크로-프로세스될 수 있는 물질이 게이트 전극으로 사용되기 때문이고, 게이트 와이어가 마이크로-프로세스될 수 없더라도, 와이어로 사용되는 물질은 낮은 저항을 갖는다. 물론, 게이트 전극 및 게이트 와이어는 똑같은 물질로부터 형성될 수 있다.

또한, 게이트 와이어는 단일층 도전막에 의해 형성되고, 필요한 경우 2 또는 3개 층의 적층막을 사용하는 것이 바람직하다. 알려진 모든 도전막은 게이트 전극 물질로 사용될 수 있다. 그러나, 상기에 언급된 바와 같이, 마이크로-프로세스될 수있는 물질, 특별히 2 mm 이하의 선폭으로 패턴화될 수 있는 물질을 사용하는 것이 바람직하다.

전형적으로, 탄탈(Ta), 티타늄(Ti), 몰리브덴(Mo), 텅스텐(W), 크롬(Cr), 및 실리콘(Si)으로부터 선택된 원소를 포함하는 막, 상기 원소의 질화물막(전형적으로, 질화탄탈막, 질화텅스텐막, 또는 질화티타늄막), 상기 원소의 조합의 합금막(전형적으로, Mo-W 합금, Mo-Ta 합금), 또는 상기 원소의 규화물막(전형적으로, 규화텅스덴막, 규화티타늄막)을 사용하는 것이가능하다. 물론, 막은 단일층이나 적층으로 사용될 수 있다.

본 실시예에서는 50 nm 두께를 갖는 질화텅스텐(WN)막과 350 nm 두께를 갖는 텅스텐(W)막의 적층막이 사용된다. 이들은 스퍼터링에 의해 형성될 수 있다. 스퍼터링 기체로 Xe, Ne 등의 불활성 기체가 부가될 때, 스트레스로 인한 막의 벗겨짐이 방지될 수 있다.

게이트 전극(313, 316)은 이때 게이트 절연막(311)을 샌드위치형으로 하여 각각 n형 불순물 영역(305, 306)의 일부와 오버랩되도록 형성된다. 이 오버랩 부분은 추후 게이트 전극과 오버랩되는 LDD 영역이 된다.

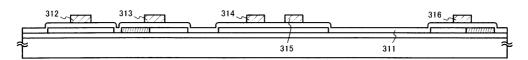

다음에는 도 5a에 도시된 바와 같이 n형 불순물 원소(실시예 1에서는 인이 사용된다)가 마스크(mask)로 게이트 전극 (312 내지 316)과 자체 정렬되는 방식으로 부가된다. 부가되는 것은 인이 불순물 영역(317 내지 323)에 부가되어 n형 불순물 영역(305, 306)의 1/10 내지 1/12(전형적으로 1/4 내지 1/3)의 농도로 형성되도록 조절된다. 특별히,  $1 \times 10^{16}$  내지  $5 \times 10^{18}$  atoms/cm<sup>3</sup>(전형적으로,  $3 \times 10^{17}$  내지  $3 \times 10^{18}$  atoms/cm<sup>3</sup>)의 농도가 바람직하다.

다음에는 도 5b에 도시된 바와 같이 게이트 전극 등을 커버하는 형상으로 레지스트 마스크(324a 내지 324d)가 형성되고, n형 불순물 원소(실시예 1에서는 인이 사용된다)가 부가되어, 높은 인의 농도를 포함하는 불순물 영역(325 내지 331)을 형성한다. 여기서는 인화수소( $PH_3$ )를 사용하는 이온 도핑이 또한 실행되고, 이 영역의 인 농도가  $1 \times 10^{20}$  내지  $1 \times 10^{21}$  atoms/cm<sup>3(</sup>전형적으로,  $2 \times 10^{20}$  내지  $5 \times 10^{20}$  atoms/cm<sup>3</sup>)가 되도록 조절된다.

이 공정에 의해 n-채널 TFT의 소스 영역 또는 드레인 영역이 형성되고, 스위칭 TFT에서는 도 5a의 공정에 의해 형성된 n형 불순물 영역(320 내지 322) 일부가 남아있다. 나머지 영역은 도 2의 스위칭 TFT 중에서 LDD 영역(15a 내지 15d)에 대응한다.

다음에는 도 5c에 도시된 바와 같이, 레지스트 마스크(324a 내지 324d)가 제거되고, 새로운 레지스트 마스크(332)가 형성된다. 이어서, p형 불순물 원소(실시예 1에서는 붕소가 사용된다)가 부가되어, 높은 붕소 농도를 포함하는 불순물 영역 (333, 334)을 형성한다. 여기서, 붕소는  $B_2H_6$ 를 사용한 이온 도핑에 의해  $3 \times 10^{20}$  내지  $3 \times 10^{21}$  atoms/cm<sup>3(</sup>전형적으로,  $5 \times 10^{20}$  내지  $1 \times 10^{21}$  atoms/cm<sup>3)</sup> )의 농도로 불순물 영역(333, 334)을 형성하도록 부가된다.

인은 이미  $1 \times 10^{16}$  내지  $5 \times 10^{18}$  atoms/cm<sup>3</sup>의 농도로 불순물 영역(333, 334)에 부가되었지만, 붕소는 여기서 인의 농도 보다 적어도 3배인 농도로 부가됨을 주목한다. 그러므로, 이미 형성된 n형 불순물 영역은 완전히 p형으로 반전되고, p형 불순물 영역으로 동작한다.

다음에는 레지스트 마스크(332)를 제거한 이후에, 다양한 농도로 부가된 n형 및 p형 불순물 원소가 활성화된다. 활성화수단으로는 용광로 어닐링(furnace annealing), 레이저 어닐링, 또는 램프 어닐링이 실행될 수 있다. 실시예 1에서는 열처리가 전기 용광로에서 550 ℃로 4 시간 동안 질소 대기에서 실행된다.

이때, 대기에서 산소의 양을 가능한한 많이 제거하는 것이 중요하다. 이는 산소가 존재하면, 게이트 전극의 노출 표면이산화되어 저항의 증가를 불러오고, 동시에 저항 접촉을 나중에 만들기 더 어려워지기 때문이다. 그러므로, 상기 활성화 공정의 공정 환경에서 산소의 농도는 1 ppm 이하, 양호하게 0.1 ppm 이하가 되는 것이 바람직하다.

활성화 공정이 완료된 이후에, 다음에는 300 nm 두께의 게이트 와이어(335)가 형성된다. 주요 구성성분으로(구성의 50 내지 100%를 포함하는) 알루미늄(Al) 또는 구리(Cu)를 갖는 금속막이 게이트 와이어(335)의 물질로 사용될 수 있다. 도 3의 게이트 와이어(211)와 같이, 게이트 와이어(335)는 스위칭 TFT의 게이트 전국(314, 315)(도 3의 게이트 전국 19a 및 19b에 대응하는)이 전기적으로 연결되도록 하는 배치로 형성된다(도 5d를 참고).

게이트 와이어의 와이어 저항은 이 종류의 구조를 사용해 매우 작게 만들어질 수 있으므로, 큰 표면적을 갖는 픽셀 디스 플레이 영역(픽셀 부분)이 형성될 수 있다. 즉, 실시예 1의 픽셀 구조는 대각선이 10 인치 이상인(부가하여 대각선이 30인 치 이상인) 스크린 크기를 갖는 EL 디스플레이 장치가 이 구조로 인해 실현되기 때문에 매우 효과적이다.

다음에는 도 6a에 도시된 바와 같이 제 1 층간 절연막(336)이 형성된다. 실리콘을 사용하는 단일층 절연막이 제 1 층간 절연막(336)으로 사용되지만, 적층막이 그 사이에 조합될 수 있다. 또한, 400 nm 내지 1.5 μm의 막 두께가 사용될 수 있다. 실시예 1에서는 200 nm 두께의 질산화실리콘막 위에 800 nm 두께의 산화실리콘막을 갖는 적층 구조가 사용된다.

부가하여, 3 내지 100% 수소를 포함하는 환경에서 300 내지 450 ℃로 12 시간 동안 열처리가 실행되어, 수소화를 실행한다. 이 공정은 열적으로 활성화된 수소에 의해 반도체막에서 댕글링 결합(dangling bond)의 수소를 종결시키는 처리 중하나이다. 수소화의 또 다른 수단으로 플라스마 수소화(플라스마에 의해 활성화된 수소를 사용하는)가 또한 실행될 수 있다.

제 1 층간 절연막(336)을 형성하는 동안 수소화 단계가 또한 삽입될 수 있음을 주목한다. 즉, 상기와 같이 200 nm 두께의 질산화실리콘막을 형성한 이후에 수소 공정이 실행되고, 나머지 800 nm 두께의 산화실리콘막이 형성될 수 있다.

다음에는 제 1 층간 절연막(336)에 접촉홀이 형성되고, 소스 와이어선(337 내지 340) 및 드레인 와이어선(341 내지 343)이 형성된다. 본 실시에에서, 이 전극은 100 nm 두께를 갖는 티타늄막, 티타늄을 포함하고 300 nm 두께를 갖는 알루미늄막, 및 150 nm 두께를 갖는 티타늄막이 스퍼터링에 의해 연속적으로 형성되는 삼층 구조의 적층막으로 구성된다. 물론, 다른 도전막이 사용될 수 있다.

다음에는 제 1 패시베이션막(344)이 50 내지 500 nm(전형적으로 200 내지 300 nm)의 두께로 형성된다. 실시예 1에서는 300 nm 두께의 질산화실리콘막이 제 1 패시베이션막(344)으로 사용된다. 이는 또한 질화실리콘막으로 대치될 수 있다. 물론, 도 2의 제 1 패시베이션막(41)과 똑같은 물질을 사용하는 것이 가능하다.

질산화실리콘막을 형성하기 이전에  $H_2$  또는  $NH_3$ 와 같이 수소를 포함하는 기체를 사용해 플라스마 공정을 실행하는 것이 효과적임을 주목한다. 이 사전 공정에 의해 활성화된 수소는 제 1 층간 절연막(336)에 공급되고, 열처리를 실행함으로 써 제 1 패시베이션막(344)의 질이 개선된다. 동시에, 제 1 층간 절연막(336)에 부가된 수소는 낮은 편으로 확산되어, 활성층이 효과적으로 수소화될 수 있다.

다음에는 도 6b에 도시된 바와 같이, 유기체 수지로 구성된 제 2 층간 절연막(347)이 형성된다. 유기체 수지로는 폴리이 미드, 폴라아미드, 아크릴, BCB(benzocyclobutene) 등을 사용하는 것이 가능하다. 특별히, 제 2 층간 절연막(347)은 주로 평탄화에 사용되므로, 평탄화 특성이 뛰어난 아크릴이 바람직하다. 본 실시예에서, 아크릴막은 TFT에 의해 형성된 스텝 부분을 평탄화하기에 충분한 두께로 형성된다. 두께는 양호하게 1 내지 5  $\mu$ m(보다 양호하게, 2 내지 4  $\mu$ m)로 이루어지는 것이 적절하다.

다음에는 100 nm의 두께를 갖는 제 2 패시베이션막(348)이 제 2 층간 절연막(347)상에 형성된다. 본 실시에에서는 Si, Al, N, O, 및 La를 포함하는 절연막이 사용되므로, 알칼리 금속이 그위에 제공된 EL층으로 확산되는 것을 방지하는 것이 가능하다. 동시에, EL층으로 습기가 칩입하는 것이 저지되고, EL층에서 발생되는 열이 방산되므로, 평평해진 막(제 2 층간 절연막)의 저하 및 열로 인한 EL층의 저하를 억제하는 것이 가능하다.

드레인 와이어선(343)에 이르는 접촉홀은 제 2 패시베이션막(348), 제 2 층간 절연막(347), 및 제 1 패시베이션막(344)을 통해 형성되고, 픽셀 전극(349)이 형성된다. 본 실시에에서는 110 nm 두께를 갖는 ITO(induium-tin oxide)막이 형성되고, 패턴화가 실행되어 픽셀 전극을 형성한다. 이 픽셀 전극(349)은 EL 소자의 양극이 된다. 부수적으로, 또 다른 물질로산화 인듐-티타늄막 또는 산화아연과 혼합된 ITO막을 사용하는 것이 가능하다.

부수적으로, 본 실시예는 픽셀 전극(349)이 드레인 와이어선(342)을 통해 전류 제어 TFT의 드레인 영역(331)에 전기적으로 연결되는 구조를 갖는다. 이 구조는 다음과 같은 이점을 갖는다.

픽셀 전극(349)이 전하 운송층 또는 EL층(발광층)의 유기체 물질과 직접 접촉하므로, EL층 등에 포함된 이동가능한 이온이 픽셀 전극으로 확산될 확률이 있다. 즉, 본 실시예의 구조에서, 픽셀 전극(349)은 활성층의 일부로 드레인 영역(331)에 직접 연결되지 않지만, 드레인 와이어선(343)은 활성층으로 이동가능한 이온의 칩입이 방지될 수 있도록 삽입된다.

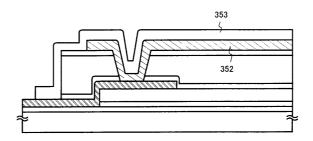

다음에는 도 6C에 도시된 바와 같이, EL층(350)이 도 1을 사용해 설명된 프린팅에 의해 형성되고, 또한 음극(MgAg 전극)(351) 및 보호 전극(352)이 대기에 개방되지 않고 증발 건조에 의해 형성된다. 이때는 EL층(350) 및 음극(351)이 형성되기 이전에 픽셀 전극(349)에 열처리를 실행함으로써 습기를 완전히 제거하는 것이 바람직하다. 본 실시예에서는 비록 MgAg 전극이 EL 소자의 음극으로 사용되지만, 다른 알려진 물질도 수용가능하다.

EL층(350)으로는 본 실시예 모드 섹션에서 설명된 물질이 사용될 수 있다. 본 실시예에서는 홀 운송층과 발광층의 2층 구조가 EL층을 만들지만, 홀 주입층, 전자 주입층, 또는 전자 운송층 중 하나가 제공되는 경우도 있다. 이와 유사하게, 조합 에 대한 다양한 예가 이미 보고되었고, 그에 대한 구조가 사용될 수 있다.

본 실시예에서는 홀 운송층으로, 폴리머 프리커서인 폴리테트라하이드로시오페닐페닐렌 (polytetrahydrothiophenylphenylene)이 프린팅 방법에 의해 형성되고, 열에 의해 폴리페닐렌 비닐(polyphenylene vinylene)로 변환된다. 발광층으로는 30 내지 40%의 1,3,4-옥사디아졸(oxadiazole) 유도체의 PBD를 폴리비닐카바졸 (polyvinylcarbazole)로 분자 분산시켜 구해진 물질이 증발 건조에 의해 형성되고, 녹색 방사의 중심으로 약 1%의 쿠마린 (coumarin) 6이 부가된다.

보호 전극(352)이 습기나 산소로부터 EL층(350)을 보호할 수 있지만, 양호하게 제 3 패시베이션막(353)이 제공될 수 있다. 본 실시예에서, 제 3 패시베이션막(353)으로는 300 nm 두께를 갖는 질화실리콘막이 제공된다. 이 제 3 패시베이션막은 또한 대기에 개방되지 않고 보호 전극(352) 이후에 연속적으로 형성될 수 있다. 물론, 제 3 패시베이션막(353)으로, 도 2의 제 3 패시베이션막(50)과 똑같은 물질이 사용될 수 있다.

그외에, 보호 전극(352)은 MgAg 전극(351)의 붕괴를 방지하도록 제공되고, 주요 성분으로 알루미늄을 포함하는 금속막이 전형적이다. 물론, 또 다른 물질이 사용될 수 있다. EL층(350) 및 MgAg 전극(351)은 습기에 매우 약하므로, EL층이 외부 공기로부터 보호되도록 대기에 개방되지 않고 보호 전극(352)을 연속하여 형성하는 것이 바람직하다.

부수적으로, EL층(350)의 막 두께는 10 내지 400 nm(전형적으로 60 내지 150 nm, 양호하게 100 내지 120 nm)로 이루어지고, MgAg 전극(351)의 두께는 80 내지 200 nm(전형적으로 100 내지 150 nm)로 이루어지는 것이 적절하다.

이 방법으로, 도 6c에 도시된 구조를 갖는 액티브 매트릭스 EL 디스플레이 장치가 완료된다. 본 실시예의 액티브 매트릭스 EL 디스플레이 장치에서, 최적의 구조를 갖는 TFT는 픽셀 부분 뿐만 아니라 구동 회로에도 배치되므로, 매우 높은 확실성이 구해지고 동작 특성이 또한 개선될 수 있다.

먼저, 동작 속도를 가능한한 많이 강하시키지 않도록 핫 캐리어 주입을 감소시키는 구조를 갖는 TFT는 구동 회로를 형성 하는 CMOS 회로의 n-채널 TFT(205)로 사용된다. 부수적으로, 여기서 구동 회로는 쉬프트 레지스터, 버퍼, 레벨 쉬프터 (level shifter), 샘플링 회로(샘플 및 홀드(hold) 회로) 등을 포함한다. 디지털 구동이 실행되는 경우, D/A 변환기와 같은 신호 변환 회로가 또한 포함될 수 있다.

본 실시예의 경우에는 도 6c에 도시된 바와 같이, n-채널 TFT(205)의 활성층이 소스 영역(355), 드레인 영역(356), LDD 영역(357), 및 채널 형성 영역(358)을 포함하고, LDD 영역(357)은 게이트 전극(313)과 오버랩되어, 그들 사이에 게이트 절연막(311)을 놓는다.

동작 속도를 떨어뜨리지 않게 고려하는 것은 LDD 영역이 드레인 영역측에만 형성되는 이유이다. 이 n-채널 TFT(205)에서는 off 전류값을 많이 고려할 필요가 없고, 그 보다는 동작 속도에 중요성을 주는 것이 더 낫다. 그래서, 저항 성분을 최소로 감소시키도록 LDD 영역(357)이 게이트 전극과 완전히 오버랩되게 하는 것이 바람직하다. 즉, 오프셋(offset)을 제거하는 것이 바람직하다.

\*CMOS 회로의 p-채널 TFT(206)에서, 핫 캐리어 주입으로 인한 저하는 거의 무시될 수 있으므로, LDD 영역이 특별히 제공될 필요가 없다. 물론, n-채널 TFT(205)와 유사하게, 핫 캐리어에 대한 대응책을 취하도록 LDD 영역을 제공하는 것도 가능하다.

부수적으로, 구동 회로 중의 샘플링 회로는 다른 회로와 비교해 다소 특별하여, 채널 형성 영역을 통해 큰 전류가 두 방향으로 모두 흐른다. 즉, 소스 영역 및 드레인 영역의 역할이 반대 위치에 놓인다. 또한, off 전류값을 가능한한 최하의 값으로 억제할 필요가 있고, 여기서는 스위칭 TFT와 전류 제어 TFT 사이에 대략 중간 기능을 갖는 TFT를 배치하는 것이 바람직하다.

그래서, n-채널 TFT가 샘플링 회로를 형성할 때, 도 10에 도시된 바와 같은 구조를 갖는 TFT를 배치하는 것이 바람직하다. 도 10에 도시된 바와 같이, LDD 영역(901a, 901b)의 일부는 게이트 절연막(902)을 통해 게이트 전극(903)과 오버랩된다. 이 효과는 전류 제어 TFT(202)의 설명에서 기술된 바와 같고, 다른 점은 샘플링 회로에서, LDD 영역(901a, 901b)이 채널 형성 영역(904)의 양측에 놓이도록 제공된다는 점이다.

도 6c의 상태가 완료될 때, 실제로는 외부 공기에 노출되는 것을 방지하도록 세라믹 봉합 또는 높은 밀폐성과 낮은 기체 제거성을 갖는 보호막(적충막, 자외선 치료 수지막 등)과 같은 수납 멤버에 의해 패키징(봉합)을 하는 것이 바람직하다. 이때, 수납 멤버의 내부가 불활성 기체 대기로 이루어지거나 습기 제거제(예를 들면, 산화바륨)가 내부에 배치될 때, EL층의확실성(수명)이 개선된다.

패키징과 같은 공정에 의해 밀폐성이 상승된 이후에는 제품이 완료되도록 기판상에 형성된 소자나 회로로부터 연장된 단자를 외부 신호 단자에 연결시키는 연결기(FPC: flexible print circuit)가 부착된다. 본 명세서에서는 배송될 수 있는 이러한 상태로 만들어진 EL 디스플레이 장치가 EL 모듈(module)로 언급된다.

여기서, 본 실시예의 액티브 매트릭스 EL 디스플레이 장치의 구조는 도 7의 투시도를 참고로 설명된다. 본 실시예의 액티브 매트릭스 EL 디스플레이 장치는 유리 기판(600)상에 형성된 픽셀 부분(602), 게이트측 구동 회로(603), 및 소스측 구종 회로(604)로 구성된다. 픽셀 부분의 스위칭 TFT(605)는 n-채널 TFT이고, 게이트측 구동 회로(603)에 연결된 게이트 와이어선(606)과 소스측 구동 회로(604)에 연결된 소스 와이어선(607)의 교차점에 배치된다. 스위칭 TFT(605)의 드레인은 전류 제어 TFT(608)의 게이트에 연결된다.

또한, 전류 제어 TFT(608)의 소스는 전류 공급선(609)에 연결되고, EL 소자(610)는 전류 제어 TFT(608)의 드레인에 연결된다.

전류 공급선(609)에 연결된 구동 회로 및 입력-출력 와이어선(614)에 신호를 전송하기 위한 입력-출력 와이어선(연결 와이어선)(612, 613)은 외부 입력-출력 단자로 FPC(611)에 제공된다. 도 7에 도시된 EL 디스플레이 장치의 회로 구조에는 도 8에 도시된다. 본 실시예의 EL 디스플레이 장치는 소스측 구동회로(701), 게이트측 구동 회로(A)(707), 게이트측 구동 회로(B)(711), 및 픽셀 부분(706)을 포함한다. 명세서를 통해, "구동 회로(driving circuit)"란 말은 소스측 구동 회로 및 게이트측 구동 회로를 포함하는 일반적인 용어임을 주목한다.

소스측 구동 회로(701)는 쉬프트 레지스터(702), 레벨 쉬프터(703), 버퍼(704), 및 샘플링 회로(샘플 및 홀드 회로)(705)를 구비한다. 게이트측 구동 회로(A)(707)는 쉬프트 레지스터(708), 레벨 쉬프터(709), 및 버퍼(710)를 포함한다. 게이트측 구동 회로(B)(711)는 또한 유사한 구조를 갖는다.

여기서, 쉬프트 레지스터(702, 708)는 각각 5 내지 16 V(전형적으로 10 V)의 구동 전압을 갖고, 도 6c에서(205)로 나타내진 구조는 회로를 형성하는 CMOS 회로에서 사용되는 n-채널 TFT로 적절하다.

그외에, 레벨 쉬프터(703, 709) 및 버퍼(704, 710)에 대해서는 쉬프트 레지스터와 유사하게, 도 c의 n-채널 TFT(205)를 포함하는 CMOS 회로가 적절하다. 각 회로의 확실성을 개선하도록 게이트 와이어선을 이중 게이트 구조나 삼중 게이트 구조와 같은 다중 게이트 구조로 만드는 것이 효과적임을 주목한다.

또한, 소스 영역 및 드레인 영역이 반전되고, off 전류값을 감소시킬 필요가 있으므로, 도 10의 n-채널 TFT(208)를 포함하는 CMOS 회로가 샘플링 회로(705)에 적절하다.

\*픽셀 부분(706)은 도 2에 도시된 구조를 갖는 픽셀이 배치된다.

상기 구조는 도 4a 내지 도 6c에 도시된 제조 단계에 따라 TFT를 제조함으로써 쉽게 실현될 수 있다. 본 실시에에서는 픽셀 부분 및 구동 회로의 구조만이 도시되지만, 본 실시예의 제조 단계가 사용되면, 신호 구동 회로, D/A 변환기 회로, 연 산 증폭기 회로, a-정정 회로 등과 같이, 구동 회로 이외의 논리 회로를 같은 기판상에 형성하는 것이 가능하고, 또한 메모리 부분, 마이크로프로세서 등이 형성될 수 있을 것으로 가정된다.

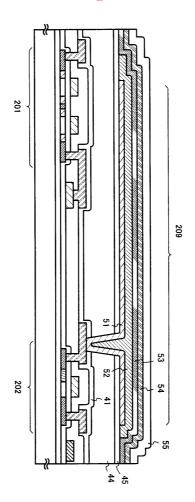

또한, 수납 멤버를 포함하는 본 발명의 EL 모듈은 도 11a 및 도 11b를 참고로 설명된다. 부수적으로, 필요한 경우, 도 7 및 도 8에서 사용되는 참고번호가 인용된다.

픽셀 부분(1701), 소스측 구동 회로(1702), 및 게이트측 구동 회로(1703)는 기판(TFT 이하의 기저막을 포함하여)(1700)상에 형성된다. 각 구동 회로로부터의 각 와이어선은 입력 와이어선(612 내지 614)을 통해 FPC(611)에 이르고, 외부 장비에 연결된다.

이때, 수납 멤버(1704)는 적어도 픽셀 부분, 양호하게 구동 회로 및 픽셀 부분을 둘러싸게 제공된다. 수납 멤버(1704)는 픽셀 부분(1701)의 외부 크기(높이) 보다 더 큰 내부 크기(깊이)를 갖는 리세스 부분을 갖도록 하는 형상이나 시트(sheet) 형상을 갖고, 기관(1700)과 연관되어 밀폐된 공간을 형성하도록 접착제(1705)에 의해 기판(1700)에 고정된다. 이때, EL 소자는 상기 밀폐된 공간에서 완전히 봉합되고 외부 공기와 완전히 차단되는 상태에 놓인다. 부수적으로, 다수의 수납 멤버(1704)가 제공될 수 있다.

수납 멤버(1704)의 물질로는 유리나 폴리머와 같은 절연 물질이 바람직하다. 예를 들면, 비결정질 유리(붕규산 유리, 수정 등), 결정질 유리, 세라믹 유리, 유기체 수지(아크릴 수지, 스티렌(styrene) 수지, 폴라카보네이트(polycarbonate) 수지, 에폭시 수지 등), 및 실리콘 수지가 열거된다. 그외에, 세라믹이 사용될 수 있다. 접착제(1705)가 절연 물질이면, 스테인레스 합금과 같은 금속 물질도 사용될 수 있다.

접착제(1705)의 물질로는 에폭시 수지, 아크릴 수지 등의 접착제가 사용될 수 있다. 또한, 열경화성 수지 또는 광치료 수지(photo-curing resin)도 접착제로 사용될 수 있다. 그러나, 최상으로 산소 및 습기의 투과를 저지하는 물질로 사용할 필요가 있다.

또한, 수납 멤버와 기판(1700) 사이의 공간(1706)이 불활성 기체(아르곤, 헬륨, 질소 등)로 채워지는 것이 바람직하다. 기체 이외에, 불활성 액체(펄플루오르알칸(perfluoroalkane) 등으로 예시되는 액체 불화탄소)도 사용될 수 있다. 불활성 액체에 대해서는 일본 특허 출원 공개 No. Hei 8-78159에서 사용된 물질이 사용된다.

또한, 공간(1706)에는 건조제를 제공하는 것이 효과적이다. 건조제로는 일본 특허 출원 공개 No. Hei 9-148066에서 사용되는 물질이 사용될 수 있다. 전형적으로, 산화바륨이 사용된다.

그외에, 도 11b에 도시된 바와 같이, 각각이 고립된 EL 소자를 포함하는 다수의 픽셀이 픽셀 부분에 제공되고, 이들 모두는 공통 전극으로 보호 전극(1707)을 포함한다. 본 실시예에서는 대기에 개방되지 않고 EL층, 음극(MgAg 전극), 및 보호 전극이 연속적으로 형성되는 것이 바람직하도록 이루어졌지만, EL층과 음극이 똑같은 마스크 멤버를 사용해 형성되고 보호 전극만이 다른 마스크 멤버로 형성되면, 도 11b의 구조가 실현될 수 있다.

이때, EL층과 음극은 픽셀 부분에만 형성되고, 이들을 구동 회로에 제공할 필요는 없다. 물론, 구동 회로에 제공되어도 문제는 일어나지 않지만, 알칼리 금속이 EL층에 포함되는 것을 고려할 때, 제공되지 않는 것이 바람직하다.

부수적으로, 보호 전극(1707)은(1708)에 의해 나타내지는 영역에서 입력 와이어선(1709)에 연결된다. 입력 와이어선 (1709)은 보호 전극(1707)에 미리 결정된 전압(본 실시에에서는 접지 전위, 구체적으로 0V)을 제공하는 와이어선이고, 도전성 패스트(conductive paste) 물질(1710)을 통해 FPC(611)에 연결된다.

여기서는 영역(1708)에 접촉 구조를 실현하는 제조 단계가 도 12를 참고로 설명된다.

먼저, 본 실시예의 단계에 따라, 도 6a의 상태가 구해진다. 이때, 기판의 단말 부분(도 11b에서(1708)로 나타내지는 영역)에서는 제 1 층간 절연막(336) 및 게이트 절연막(311)이 제거되고, 그 위에는 입력 와이어선(1709)이 형성된다. 물론,이는 도 6a의 소스 와이어선 및 드레인 와이어선과 동시에 형성된다(도 12a).

다음에 도 6b에서는 제 2 패시베이션막(348), 제 2 층간 절연막(347), 및 제 1 패시베이션막(344)이 에칭되고,(1801)로 나타내지는 영역이 제거되어, 오프닝 영역(1802)이 형성된다(도 12b).

이 상태로 픽셀 부분에서는 EL 소자의 형성 단계(픽셀 전극, EL층, 및 음극의 형성 단계)가 실행된다. 이때, 도 12에 도시된 영역에서는 EL 소자가 형성되지 않도록 마스크 멤버가 사용된다. 음극(351)이 형성된 이후에, 보호 전극(352)이 또 다른 마스크 멤버를 사용해 형성된다. 이에 의해, 보호 전극(352) 및 입력 와이어선(1709)은 전기적으로 연결된다. 또한, 도 12c의 상태를 구하도록 제 3 패시베이션막(353)이 제공된다.

\*상기 단계를 통해, 도 11b에서(1708)로 나타내지는 영역의 접촉 구조가 실현된다. 입력-출력 와이어선(1709)은 수납 멤버(1704)와 기판(1700) 사이의 갭(gap)을 통해 FPC(611)에 연결된다(그러나, 갭은 접착제(1705)로 채워진다. 즉, 접착제(1705)는 입력-출력 와이어선으로 인한 불균일을 충분히 평탄화할 수 있도록 하는 두께를 갖게 요구된다). 부수적으로, 여기서는 입력-출력 와이어선(1709)에 대해 설명이 주어졌지만, 다른 출력 와이어선(612 내지 614)도 똑같은 방식으로 수납 멤버(1704) 아래 부분을 통해 FPC(611)에 또한 연결된다.

#### [실시예 2]

본 실시예에서는 픽셀의 구조가 도 3b에 도시된 구조와 다르게 이루어진 예가 도 13을 참고로 설명된다.

본 실시예에서, 도 3b에 도시된 두 픽셀은 접지 전압을 공급하는 전류 공급선(212)에 대해 대칭이 되도록 배열된다. 즉,도 13에 도시된 바와 같이, 전류 공급선(212)이 두 인접한 픽셀에 공통되게 만들어져, 필요한 와이어선의 수가 감소될 수있다. 부수적으로, 픽셀에 배열된 TFT 구조 등은 똑같이 유지된다.

이러한 구조가 채택되면, 보다 간결한 픽셀 부분을 제조하는 것이 가능해지고, 영상의 질이 개선된다.

본 실시예의 구조는 실시예 1의 제조 단계에 따라 용이하게 실현될 수 있고, TFT 구조에 대해서는 도 2 또는 실시예 1의 설명이 참고될 수 있다.

#### [실시예 3]

본 실시예에서는 픽셀 부분이 도 2와 다른 구조를 갖는 경우가 도 14를 참고로 설명된다. 제 2 층간 절연막(44)을 형성하는 단계까지의 단계는 실시예 1에 따라 실행될 수 있음을 주목한다. 제 2 층간 절연막(44)으로 커버된 스위칭 TFT(201) 및 전류 제어 TFT(202)가 도 1과 똑같은 구조를 가지므로, 여기서는 설명이 생략된다.

본 실시예의 경우에는 접촉홀이 제 2 패시베이션막(45), 제 2 층간 절연막(44), 및 제 1 패시베이션막(41)을 통해 형성된 이후에, 픽셀 전극(51)이 형성되고, 이어서 음극(52) 및 EL층(53)이 형성된다. 본 실시예에서, 음극(52)이 진공 증발 건조에 의해 형성된 이후에, EL층(53)은 건조 불활성 기체 대기가 유지되는 동안 릴리프(relief) 프린팅 또는 스크린(screen) 프린팅에 의해 형성된다.

본 실시예에서, 150 nm의 두께를 갖는 알루미늄 합금막(1 wt%의 티타늄을 포함하는 알루미늄막)은 픽셀 전극(51)으로 제공된다. 픽셀 전극의 물질로는 금속 물질인 한 임의의 물질이 사용될 수 있지만, 높은 반사력을 갖는 물질이 바람직하다. 음극(52)으로는 120 nm 두께를 갖는 MgAg 전극이 사용되고, EL층(53)의 두께는 120 nm이다.

본 실시예에서, EL 형성물은 30 내지 40%의 1,3,4-옥사디아졸(oxadiazole) 유도체의 PBD를 폴리비닐카바졸 (polyvinylcarbazole)로 분자 분산시켜 구해진 EL 물질에 용매를 혼합시키고, 빛 방사의 중심으로 약 1%의 쿠마린 (coumarin) 6이 부가함으로써 제조된다. EL 형성물은 릴리프 프린팅이나 스크린 프린팅에 의해 적용되고, 가열 처리 (baking treatment)가 실행되어, 50 nm 두께를 갖는 녹색광 발광층이 구해진다. 그 위에는 증발 건조에 의해 70 nm 두께를 갖는 TPD가 형성되어 EL층(53)이 구해진다.

다음에는 투명 도전막(본 실시예에서는 ITO막)으로 구성된 양극(54)이 110 nm의 두께로 형성된다. 이 방법으로, EL층 (209)이 형성되고, 실시예 1에 도시된 물질에 의해 제 3 패시베이션막(55)이 형성될 때, 도 14에 도시된 구조를 갖는 픽셀이 완성된다.

본 실시예의 구조가 채택된 경우에, 각 픽셀에 발생된 녹색광은 TFT가 형성된 기판에 마주 대하는 측면으로 조사된다. 그래서, 픽셀내의 거의 모든 영역, 즉 TFT가 형성된 영역도 또한 유효한 발광 영역으로 사용될 수 있다. 그 결과로, 픽셀의 유효한 발광 영역이 많이 개선되고, 영상의 밝기 및 대비 비율(명암의 비율)이 증가된다.

부수적으로, 본 실시예의 구조는 자유롭게 실시예 1 및 2와 조합될 수 있다.

#### [실시예 4]

비록 실시예 1 내지 4에서 상단 게이트형 TFT의 경우에 대해 설명이 이루어졌지만, 본 발명은 그 TFT 구조에 제한되지 않고, 하단 게이트형 TFT(전형적으로 역 스태거형(reverse stagger type) TFT)에 적용될 수 있다. 그외에, 역 스태거형 TFT는 임의의 수단에 의해 형성될 수 있다.

역 스태거형 TFT는 단계의 수가 상단 게이트형 TFT 보다 용이하게 더 작게 만들어질 수 있는 구조를 가지므로, 본 발명의 목적인 제조 비용 감소에 매우 유리하다. 부수적으로, 본 실시예의 구조는 실시예 2 및 3의 구조와 자유롭게 조합될 수있다.

#### [실시예 5]

도 2 또는 실시예 1의 도 6c의 구조에서 활성층과 기판 사이에 형성되는 기저막으로, 제 2 패시베이션막(45)과 유사하게, 높은 열적 방사 효과를 갖는 물질을 사용하는 것이 효과적이다. 특히, 전류는 전류 제어 TFT에서 오랜 시간 동안 흐르므로, 열이 쉽게 발생되고, 열의 자체 발생으로 인한 저하가 문제점으로 될 수 있다. TFT의 열적 저하는 이러한 종류의 경우에 대해 열적 방사 효과를 갖는 실시예 5의 기저막을 사용함으로써 방지될 수 있다.

기판에서 이동가능한 이온의 확산으로부터 보호하는 효과는 또한 매우 중요하므로, 제 1 패시베이션막(41)과 유사하게, Si, Al, N, O, 및 M을 포함하는 화합물의 적층 구조 및 실리콘을 포함하는 절연막을 사용하는 것이 바람직하다.

실시예 1 내지 4의 임의의 구조와 실시예 5의 구조를 자유롭게 조합하는 것이 가능함을 주목한다.

#### [실시예 6]

실시예 3에 도시된 픽셀 구조가 사용될 때, EL층으로부터 방사되는 빛은 기판에 반대 방향으로 조사되므로, 기판과 픽셀기판 사이에 존재하는 절연막과 같은 물질의 투과율에 관심을 둘 필요가 없다. 다른 말로 하면, 다소 낮은 투과율을 갖는 물질도 사용될 수 있다.

그러므로, 다이아몬드 박막 또는 비결정질 탄소막이라 언급되는 것과 같은 탄소막을 기저막(12), 제 1 패시베이션막(41), 또는 제 2 패시베이션막(45)으로 사용하는 것이 유리하다. 다른 말로 하면, 투과율을 낮추는 것에 대해 염려할 필요가 없기 때문에, 막 두께가 100 내지 500 nm로 설정될 수 있어, 매우 높은 열적 방사 효과를 갖는 것이 가능하다.

제 3 패시베이션막(50)에 상기의 탄소막을 사용하는 것에 대해, 투과율의 감소가 방지되어야 하므로, 막 두께를 5 내지 100 nm로 설정하는 것이 바람직함을 주목한다.

실시예 6에서는 기저막(12), 제 1 패시베이션막(41), 제 2 패시베이션막(45), 및 제 3 패시베이션막(50) 중 임의의 것에서 탄소막이 사용될 때 또 다른 절연막과 적충되는 것이 효과적임을 주목한다.

부가하여, 실시예 6은 실시예 3에 도시된 픽셀 구조가 사용될 때 특히 효과적이지만, 실시예 1, 2, 4, 및 5의 구성과 실시예 6의 구성을 자유롭게 조합하는 것이 가능하다.

#### [실시예 7]

EL 디스플레이 장치의 픽셀에서 스위칭 TFT의 off 전류값의 양은 스위칭 TFT의 다중 게이트 구조를 사용함으로써 감소되고, 본 발명은 저장 캐패시터에 대한 필요성을 제거함으로써 특징지워진다. 이는 방사 영역으로 저장 패키시터에 예정된 표면적을 잘 사용할 수 있게 하는 장치이다.

그러나, 저장 캐패시터가 완전히 제거되지 않더라도, 유효한 방사 표면적을 증가시키는 효과는 배타적인 표면적이 작아진 양 만큼 구해질 수 있다. 다른 말로 하면, 본 발명의 목적은 스위칭 TFT로 다중 게이트 구조를 사용함으로써 off 전류값을 감소시키고, 저장 캐패시터의 배타적인 표면적을 줄임으로서 충분히 이루어질 수 있다.

도 15에 도시된 바와 같은 경우에서는 스위칭 TFT(201)의 드레인에 대해 전류 제어 TFT(202)의 게이트에 평행하게 저장 캐패시터(1401)를 형성하는 것이 수용가능하다.

실시예 7의 구성은 실시예 1 내지 6의 구성과 자유롭게 조합될 수 있다. 즉, 저장 캐패시터는 픽셀내에 단순히 형성되고, TFT 구조, EL층의 물질 등을 제한하지 않는다.

#### [실시예 8]

실시예 1에서는 결정질 실리콘막(302)을 형성하는 수단으로 레이저 결정화가 사용되고, 실시예 8에서는 다른 결정화 수단을 사용하는 경우가 설명된다.

실시예 8에서 비결정질 실리콘막을 형성한 이후에, 결정화는 일본 특허 출원 공개 No. Hei 7-130652에 기록된 기술을 사용해 실행된다. 상기 특허 출원에 기록된 기술은 결정화를 촉진시키는 촉매로 니켈과 같은 원소를 사용해 양호한 결정성 을 갖는 결정질 실리콘막을 구하는 것이다. 또한, 결정화 공정이 완료된 이후에, 결정화에서 사용된 촉매를 제거하는 공정이 실행된다. 이 경우, 촉매는 일본 특허 출원 공개 No. Hei 10-270363 또는 일본 특허 출원 공개 No. Hei 8-330602에 기록된 기술을 사용해 제거된다.

부가하여, TFT는 본 발명의 출원인에 의해 일본 특허 출원 No. Hei 11-076967의 명세서에 기록된 기술을 사용해 형성될 수 있다.

실시예 1에 도시된 제조 공정은 본 발명의 한 실시예이고, 도 2의 구조 또는 실시예 1의 도 6c의 구조가 실현될 수 있다고 가정하면, 다른 제조 공정도 상기와 같이 아무런 문제 없게 사용될 수 있다.

실시예 1 내지 7의 구성와 실시예 8의 구성을 자유롭게 조합하는 것이 가능함을 주목한다.

#### [실시예 9]

본 발명의 EL 디스플레이 장치를 구동할 때는 영상 신호로 아날로그 신호를 사용해 아날로그 구동이 실행될 수 있고, 디지털 구동은 디지털 신호를 사용해 실행될 수 있다.

아날로그 구동이 실행될 때, 아날로그 신호는 스위칭 TFT의 소스 와이어에 전달되고, 그레이 스케일(gray scale) 정보를 포함하는 아날로그 신호는 전류 제어 TFT의 게이트 전압이 된다. 이어서, EL 소자에 흐르는 전류가 전류 제어 TFT에 의 해 제어되고, EL 소자 발광 강도가 제어되어, 그레이 스케일 디스플레이가 실행된다. 전류 제어 TFT는 아날로그 구동을 실행하는 경우 포화 영역에서 동작될 수 있음을 주목한다.

한편, 디지털 구동이 실행될 때, 이는 아날로그형 그레이 스케일 디스플레이와 다르고, 그레이 스케일 디스플레이는 시간 비율의 그레이 스케일 방법에 의해 실행된다. 즉, 발광 시간의 길이를 조절함으로써, 칼라 그레이 스케일이 변화에 따라 가 시적으로 보여질 수 있다. 디지털 구동을 실행하는 경우, 선형 영역에서 전류 제어 TFT를 동작시키는 것이 바람직하다.

EL 소자는 액정 소자와 비교해 매우 빠른 응답 속도를 가지므로, 고속 구동을 갖는 것이 가능하다. 그러므로, EL 소자는 시간 비율의 그레이 스케일 방법에 적절한 것으로, 한 프레임이 다수의 서브프레임으로 분할되어 그레이 스케일 디스플레 이가 실행된다.

본 발명은 소자 구조에 관련된 기술이므로, 임의의 구동 방법이 사용될 수 있다.

#### [실시예 10]

실시예 1에서는 EL층으로 유기체 EL 물질을 사용하는 것이 바람직하지만, 본 발명은 또한 비유기체 EL 물질을 사용해 실시될 수 있다. 그러나, 기존 비유기체 EL 물질은 매우 높은 구동 전압을 가지므로, 아날로그 구동을 실행하는 경우에 구 동 전압을 견딜 수 있는 전압 저항 특성을 갖는 TFT가 사용되어야 한다.

다른 방법으로, 종래 비유기체 EL 물질 보다 더 낮은 구동 전압을 갖는 비유기체 EL 물질이 개발되면, 이들을 본 발명에 적용시키는 것이 가능하다.

또한, 실시예 1 내지 9의 구성과 실시예 10의 구성을 자유롭게 조합하는 것이 가능하다.

#### [실시예 11]

본 발명을 실시함으로써 형성된 액티브 매트릭스 EL 디스플레이 장치(EL 모듈)은 자체 방사형 장치이기 때문에 액정 디스플레이 장치와 비교해 밝은 위치에서 뛰어난 가시력을 갖는다. 그러므로, 직접 시청형 EL 디스플레이(EL 모듈을 포함하는 디스플레이를 나타내는)로서 넓은 범위의 사용도를 갖는다.

EL 디스플레이가 액정 디스플레이에 대해 갖는 한가지 이점으로 넓은 시청 각도가 주어질 수 있음을 주목한다. 그러므로, 본 발명의 EL 디스플레이는 대형 화면으로 TV 방송을 시청하도록 30 인치 이상(전형적으로 40 인치 이상)인 대각선을 갖는 디스플레이(디스플레이 모니터)로 사용될 수 있다.

또한, EL 디스플레이(개인용 컴퓨터 모니터, TV 방송 수신 모니터, 또는 광고 디스플레이 모니터)로 사용될 수 있을 뿐만 아니라, 다양한 전자 장치에 대한 디스플레이로도 사용될 수 있다.

이러한 전자 장치의 예로 다음이 주어질 수 있다: 비디오 카메라; 디지털 카메라; 고글형 디스플레이(머리에 설치되는 디스플레이); 자동차 항해 시스템; 개인용 컴퓨터; 휴대용 정보 단말기(이동 컴퓨터, 이동 전화기, 또는 전자 서적과 같은); 및 기록 매체를 사용하는 영상 재생 장치(특별히, 기록 매체의 재생을 실행하고, 컴팩트 디스크(CD), 레이저 디스크(LD), 또는 디지털 휘발성 디스크(DVD)와 같이, 영상을 디스플레이할 수 있는 디스플레이가 제공되는 장치). 이러한 전자 장치의 예는 도 16a 내지 도 16f에 도시된다.

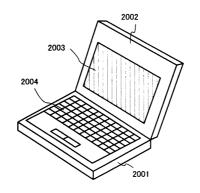

도 16a는 개인용 컴퓨터로서, 메인 본체(2001), 케이스(casing)(2002), 디스플레이 부분(2003), 및 키보드(2004)를 구비한다. 본 발명은 디스플레이 부분(2003)에 사용될 수 있다.

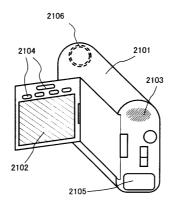

도 16b는 비디오 카메라로서, 메인 본체(2101), 디스플레이 부분(2102), 오디오 입력 부분(2103), 동작 스위치(2104), 배터리(2105), 및 영상 수신 부분(2106)을 구비한다. 본 발명은 디스플레이 부분(2102)에서 사용될 수 있다.

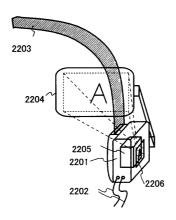

도 16c는 머리에 설치되는 EL 디스플레이(우측편)의 일부로서, 메인 본체(2201), 신호 케이블(2202), 고정 밴드(2203), 디스플레이 모니터(2204), 광학 시스템(2205), 및 디스플레이 장치(2206)를 구비한다. 본 발명은 디스플레이 장치(2206)에 사용될 수 있다.

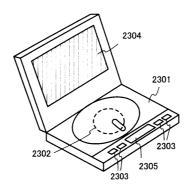

도 16d는 기록 매체가 제공되는 영상 재생 장치(특별히, DVD 재생 장치)로서, 메인 본체(2301), 기록 매체(CD, LD, 또는 DVD와 같은)(2302), 동작 스위치(2303), 디스플레이 부분(a)(2304), 및 디스플레이 부분(b)(2305)을 구비한다. 디스플레이 부분(a)은 주로 영상 정보를 디스플레이하는데 사용되고, 영상 부분(b)은 주로 문자 정보를 디스플레이하는데 사용되며, 본 발명은 영상 부분(a) 및 영상 부분(b)에서 사용될 수 있다. 본 발명은 CD 재생 장치 및 게임 장비와 같은 장치에서 기록 매체가 제공되는 영상 재생 장치로 사용될 수 있음을 주목한다.

도 16e는 이동 컴퓨터로서, 메인 본체(2401), 카메라 부분(2402), 영상 수신 부분(2403), 동작 스위치(2404), 및 디스플레이 부분(2405)을 구비한다. 본 발명은 디스플레이 부분(2405)에 사용될 수 있다.

도 16f는 EL 디스플레이로서, 케이스(2501), 지지대(2502), 및 디스플레이 부분(2503)을 구비한다. 본 발명은 디스플레이 부분(2503)에 사용될 수 있다. EL 디스플레이는 큰 시청 각도를 갖기 때문에, 이는 특히 스크린이 대형인 경우에 유리하고, 10 인치 이상인(특히, 30 인치 이상인) 것에 좋다.

더욱이, EL 물질의 방사 휘도가 미래에 더 높이지면, 렌즈 등에 의해 출력된 영상 정보를 포함하는 빛을 확대하여 투사함으로써 전방형 또는 후방형 프로젝터(projector)에 본 발명을 사용하는 것이 가능해진다.

#### 발명의 효과

이와 같이, 본 발명의 응용 범위는 매우 넓고, 모든 분야에서의 전자 장치에 본 발명을 적용하는 것이 가능하다. 더욱이, 실시예 11의 전자 장치는 실시예 1 내지 10의 구성과 조합하여 사용함으로써 실현될 수 있다.

본 발명을 실시함으로써, EL층의 형성은 매우 낮은 비용으로 이루어질 수 있다. 그래서, EL 장치의 제조 비용이 감소될 수 있다.

그외에, EL층과 TFT 사이에 알칼리 금속의 투과를 방지할 수 있는 절연막을 제공함으로써, 알칼리 금속이 EL층 밖으로 확산되어 TFT 특성에 악영향을 주는 것을 방지하는 것이 가능하다. 그 결과로, EL 디스플레이 장치의 동작 성능 및 확실성이 많이 개선될 수 있다.

그외에, 낮은 비용으로 제조될 수 있는 EL 디스플레이 장치를 디스플레이로 사용함으로써, 전자 장치의 제조 비용이 감소된다. 그외에, 동작 성능 및 확실성이 개선된 EL 디스플레이 장치를 사용함으로써, 뛰어난 화상질 및 내구성(높은 확실성)을 갖는 적용 제품(전자 장치)을 만드는 것이 가능하다.

#### (57) 청구의 범위

#### 청구항 1.

능동 매트릭스 디스플레이 디바이스(active matrix display device)를 제조하는 방법에 있어서,

기판 상에 실리콘을 포함하는 복수의 스위칭 소자들을 형성하는 단계;

상기 복수의 스위칭 소자들 상에 절연막을 형성하는 단계;

상기 절연막 상에 복수의 픽셀 전극들을 형성하는 단계; 및

발광층(light emitting layer)을 형성하기 위하여 롤을 사용함으로써 상기 복수의 픽셀 전극들 상에 전계 발광 형성물을 프린팅하는 단계와;

상기 발광층 상에 대향 전극을 형성하는 단계를 포함하고, 상기 발광층과 상기 대향 전극은 공기 중에 노출되지 않고 계속해서 형성되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 2.

제 1 항에 있어서, 상기 전계 발광 형성물은 전계 발광 물질과 용매의 혼합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 3.

제 1 항에 있어서, 상기 전계 발광 형성물은 유기 화합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 4.

제 1 항에 있어서, 상기 전계 발광 형성물은 불활성 기체로 채워진 청결한 부스(booth)에서 프린팅되는, 능동 매트릭스디스플레이 디바이스 제조 방법.

# 청구항 5.

제 1 항에 있어서, 상기 전계 발광 형성물은 릴리프 프린팅(relief printing)을 사용하는 프린팅 방법에 의해 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 6.

제 1 항에 있어서, 상기 능동 매트릭스 디스플레이 디바이스는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 자동차네비게이션 시스템, 휴대용 정보 단말기, 및 영상 재생 디바이스로 구성된 그룹으로부터 선택된 전자 디바이스 내에 포함되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 7.

제 1 항에 있어서, 상기 전계 발광 형성물은 10 내지 50 cp의 속도를 갖는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 8.

제 1 항에 있어서, 상기 전계 발광 형성물은 각각의 픽셀에 선택적으로 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 9.

능동 매트릭스 디스플레이 디바이스를 제조하는 방법에 있어서,

기판 상에 실리콘을 포함하는 복수의 스위칭 소자들을 형성하는 단계;

상기 복수의 스위칭 소자들 상에 절연막을 형성하는 단계;

상기 절연막 상에 복수의 픽셀 전극들을 형성하는 단계; 및

발광층을 형성하기 위하여 롤을 사용함으로써 상기 복수의 픽셀 전극들 상에 전계 발광 형성물을 프린팅하는 단계와;

상기 발광층 상에 대향 전극을 형성하는 단계를 포함하고, 상기 전계 발광 형성물은 각각의 픽셀에서 선택적으로 프린팅되며.

상기 발광층과 상기 대향 전극은 공기 중에 노출되지 않고 계속해서 형성되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 10.

제 9 항에 있어서, 상기 전계 발광 형성물은 전계 발광 물질과 용매의 혼합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 11.

제 9 항에 있어서, 상기 전계 발광 형성물은 유기 화합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 12.

제 9 항에 있어서, 상기 전계 발광 형성물은 불활성 기체로 채워진 청결한 부스에서 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

# 청구항 13.

제 9 항에 있어서, 상기 전계 발광 형성물은 10 내지 50 cp의 속도를 갖는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 14.

제 9 항에 있어서, 상기 전계 발광 형성물은 릴리프 프린팅을 사용하는 프린팅 방법에 의해 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 15.

제 9 항에 있어서, 상기 능동 매트릭스 디스플레이 디바이스는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 자동차네비게이션 시스템, 휴대용 정보 단말기, 및 영상 재생 디바이스로 구성된 그룹으로부터 선택된 전자 디바이스 내에 포함되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 16.

능동 매트릭스 디스플레이 디바이스를 제조하는 방법에 있어서,

기판 상에 실리콘을 포함하는 복수의 스위칭 소자들을 형성하는 단계;

상기 복수의 스위칭 소자들 상에 절연막을 형성하는 단계;

상기 절연막 상에 복수의 픽셀 전극들을 형성하는 단계; 및

발광층을 형성하기 위하여 롤을 사용함으로써 상기 복수의 픽셀 전극들 상에 전계 발광 형성물을 프린팅하는 단계;

상기 전계 발광 형성물 상에 열처리를 수행하는 단계와;

상기 발광층 상에 대향 전극을 형성하는 단계를 포함하고, 상기 발광층과 상기 대향 전극은 공기 중에 노출되지 않고 계속해서 형성되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 17.

제 16 항에 있어서, 상기 전계 발광 형성물은 전계 발광 물질과 용매의 혼합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 18.

제 16 항에 있어서, 상기 전계 발광 형성물은 유기 화합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 19.

제 16 항에 있어서, 상기 전계 발광 형성물은 불활성 기체로 채워진 청결한 부스에서 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 20.

제 16 항에 있어서, 상기 전계 발광 형성물은 릴리프 프린팅을 사용하는 프린팅 방법에 의해 프린팅되는, 능동 매트릭스디스플레이 디바이스 제조 방법.

### 청구항 21.

제 16 항에 있어서, 상기 능동 매트릭스 디스플레이 디바이스는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 자동차 네비게이션 시스템, 휴대용 정보 단말기, 및 영상 재생 디바이스로 구성된 그룹으로부터 선택된 전자 디바이스 내에 포함되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 22.

제 16 항에 있어서, 상기 전계 발광 형성물은 10 내지 50 cp의 속도를 갖는, 능동 매트릭스 디스플레이 디바이스 제조 방 법.

#### 청구항 23.

제 16 항에 있어서, 상기 전계 발광 형성물은 각각의 픽셀에 선택적으로 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

# 청구항 24.

능동 매트릭스 디스플레이 디바이스를 제조하는 방법에 있어서,

기판 상에 실리콘을 포함하는 복수의 스위칭 소자들을 형성하는 단계;

상기 복수의 스위칭 소자들 상에 절연막을 형성하는 단계;

상기 절연막 상에 복수의 픽셀 전극들을 형성하는 단계; 및

상기 복수의 픽셀 전극들 상에 전계 발광 형성물을 프린팅하는 단계를 포함하고,

상기 프린팅은 롤을 사용함으로써 수행되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 25.

제 24 항에 있어서, 상기 전계 발광 형성물은 전계 발광 물질과 용매의 혼합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

### 청구항 26.

제 24 항에 있어서, 상기 전계 발광 형성물은 유기 화합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 27.

제 24 항에 있어서, 상기 전계 발광 형성물은 불활성 기체로 채워진 청결한 부스에서 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 28.

제 24 항에 있어서, 상기 전계 발광 형성물은 릴리프 프린팅을 사용하는 프린팅 방법에 의해 프린팅되는, 능동 매트릭스디스플레이 디바이스 제조 방법.

## 청구항 29.

제 24 항에 있어서, 상기 능동 매트릭스 디스플레이 디바이스는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 자동차 네비게이션 시스템, 휴대용 정보 단말기, 및 영상 재생 디바이스로 구성된 그룹으로부터 선택된 전자 디바이스 내에 포함되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 30.

제 24 항에 있어서, 상기 전계 발광 형성물은 10 내지 50 cp의 속도를 갖는, 능동 매트릭스 디스플레이 디바이스 제조 방법

#### 청구항 31.

제 24 항에 있어서, 상기 전계 발광 형성물은 각각의 픽셀에 선택적으로 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 32.

제 24 항에 있어서, 상기 프린팅은,

닥터 바(doctor bar)에 의해 아닐록스 롤(anilox roll)의 표면 주위에 상기 전계 발광물을 풀링하는(pooling) 단계;

상기 아닐록스 롤이 회전하는 동안 상기 메시 그루브들(meshed grooves) 상에 상기 전계 발광 형성물을 보존하는 단계;

상기 프린팅 롤이 회전하는 동안 상기 프린팅 롤의 상기 보호물들에 상기 전계 발광물을 제공하는 단계; 및

픽셀 전극 상에 상기 전계 발광물을 프린팅하는 단계를 포함하는 방법에 의해 수행되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 33.

능동 매트릭스 디스플레이 디바이스를 제조하는 방법에 있어서,

기판 상에 실리콘을 포함하는 복수의 스위칭 소자들을 형성하는 단계;

상기 복수의 스위칭 소자들 상에 절연막을 형성하는 단계;

상기 절연막 상에 복수의 픽셀 전극들을 형성하는 단계; 및

상기 복수의 픽셀 전극들 상에 전계 발광 형성물을 프린팅하는 단계와;

상기 프린팅은 아닐록스 롤의 표면 상에 메시 그루브들을 갖는 상기 아닐록스 롤, 상기 아닐록스 롤의 상기 메시 그루브들에 접촉하는 닥터 바, 및 프린팅 롤(printing roll)의 표면 상에 보호물들(protections)을 갖는 상기 프린팅 롤을 사용함으로써 형성되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 34.

제 33 항에 있어서, 상기 전계 발광 형성물은 전계 발광 물질과 용매의 혼합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 35.

제 33 항에 있어서, 상기 전계 발광 형성물은 유기 화합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법,

## 청구항 36.

제 33 항에 있어서, 상기 전계 발광 형성물은 불활성 기체로 채워진 청결한 부스에서 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 37.

제 33 항에 있어서, 상기 능동 매트릭스 디스플레이 디바이스는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 자동차 네비게이션 시스템, 휴대용 정보 단말기, 및 영상 재생 디바이스로 구성된 그룹으로부터 선택된 전자 디바이스 내에 포함되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 38.

제 33 항에 있어서, 상기 전계 발광 형성물은 10 내지 50 cp의 속도를 갖는, 능동 매트릭스 디스플레이 디바이스 제조 방 법

## 청구항 39.

제 33 항에 있어서, 상기 전계 발광 형성물은 각각의 픽셀에 선택적으로 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 40.

제 33 항에 있어서, 상기 프린팅은,

닥터 바에 의해 아닐록스 롤의 표면 주위에 상기 전계 발광물을 풀렁하는 단계;

상기 아닐록스 롤이 회전하는 동안 상기 메시 그루브들 상에 상기 전계 발광 형성물을 보존하는 단계;

상기 프린팅 롤이 회전하는 동안 상기 프린팅 롤의 상기 보호물들에 상기 전계 발광물을 제공하는 단계; 및

픽셀 전극 상에 상기 전계 발광물을 프린팅하는 단계를 포함하는 방법에 의해 수행되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 41.

능동 매트릭스 디스플레이 디바이스를 제조하는 방법에 있어서,

절연 표면 상에 매트릭스 형태로 배열된 복수의 전극들을 형성하는 단계;

발광층을 형성하기 위하여 롤을 사용하여 프린팅함으로써 상기 복수의 전극들 상에 복수의 발광층들을 선택적으로 형성 하는 단계; 및

상기 발광층 상에 대향 전극을 형성하는 단계를 포함하고,

상기 발광층과 상기 대향 전극은 공기 중에 노출되지 않고 계속해서 형성되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 42.

제 41 항에 있어서, 상기 복수의 발광층들은 유기 화합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법,

## 청구항 43.

제 41 항에 있어서, 상기 복수의 발광층들은 불활성 기체로 채워진 청결한 부스에서 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

# 청구항 44.

제 41 항에 있어서, 상기 복수의 발광층들은 릴리프 프린팅을 사용하는 프린팅 방법에 의해 프린팅되는, 능동 매트릭스디스플레이 디바이스 제조 방법.

#### 청구항 45.

제 41 항에 있어서, 상기 능동 매트릭스 디스플레이 디바이스는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 자동차 네비게이션 시스템, 휴대용 정보 단말기, 및 영상 재생 디바이스로 구성된 그룹으로부터 선택된 전자 디바이스 내에 포함되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 46.

제 41 항에 있어서, 상기 복수의 전극들은 투명한 도전막을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법,

## 청구항 47.

능동 매트릭스 디스플레이 디바이스를 제조하는 방법에 있어서,

절연 표면 상에 매트릭스 형태로 배열된 복수의 전극들을 형성하는 단계와;

프린팅함으로써 상기 복수의 전극들 상에 복수의 발광층들을 선택적으로 형성하는 단계를 포함하고,

상기 프린팅은 아닐록스 롤의 표면 상에 메시 그루브들을 갖는 상기 아닐록스 롤, 상기 아닐록스 롤의 상기 메시 그루브들에 접촉하는 닥터 바, 및 프린팅 롤의 표면 상에 보호물들을 갖는 상기 프린팅 롤을 사용함으로써 형성되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

# 청구항 48.

제 47 항에 있어서, 상기 복수의 발광층들은 유기 화합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 49.

제 47 항에 있어서, 상기 복수의 발광층들은 불활성 기체로 채워진 청결한 부스에서 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 50.

제 47 항에 있어서, 상기 복수의 발광층들은 릴리프 프린팅을 사용하는 프린팅 방법에 의해 프린팅되는, 능동 매트릭스디스플레이 디바이스 제조 방법.

#### 청구항 51.

제 47 항에 있어서, 상기 능동 매트릭스 디스플레이 디바이스는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 자동차 네비게이션 시스템, 휴대용 정보 단말기, 및 영상 재생 디바이스로 구성된 그룹으로부터 선택된 전자 디바이스 내에 포함되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

# 청구항 52.

제 47 항에 있어서, 상기 프린팅은,

닥터 바에 의해 아닐록스 롤의 표면 주위에 상기 전계 발광물을 풀렁하는 단계;

상기 아닐록스 롤이 회전하는 동안 상기 메시 그루브들 상에 상기 전계 발광 형성물을 보존하는 단계;

상기 프린팅 롤이 회전하는 동안 상기 프린팅 롤의 상기 보호물들에 상기 전계 발광물을 제공하는 단계; 및

픽셀 전극 상에 상기 전계 발광물을 프린팅하는 단계를 포함하는 방법에 의해 수행되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 53.

제 47 항에 있어서, 상기 복수의 전극들은 투명한 도전막을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 54.

능동 매트릭스 디스플레이 디바이스를 제조하는 방법에 있어서.

절연 표면 상에 매트릭스 형태로 배열된 복수의 전극들을 형성하는 단계와;

릴리프 프린팅을 사용하여 프린팅함으로써 상기 복수의 전극들 상에 복수의 발광층들을 선택적으로 형성하는 단계를 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 55.

제 54 항에 있어서, 상기 복수의 발광층들은 유기 화합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 56.

제 54 항에 있어서, 상기 복수의 발광층들은 불활성 기체로 채워진 청결한 부스에서 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

# 청구항 57.

제 54 항에 있어서, 상기 능동 매트릭스 디스플레이 디바이스는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 자동차 네비게이션 시스템, 휴대용 정보 단말기, 및 영상 재생 디바이스로 구성된 그룹으로부터 선택된 전자 디바이스 내에 포함되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 58.

제 54 항에 있어서, 상기 복수의 전극들은 투명한 도전막을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

### 청구항 59.

능동 매트릭스 디스플레이 디바이스를 제조하는 방법에 있어서,

절연 표면 상에 매트릭스 형태로 배열된 복수의 전극들을 형성하는 단계와;

프린팅함으로써 상기 복수의 전극들 상에 복수의 발광층들을 선택적으로 형성하는 단계를 포함하고,

상기 프린팅은 롤을 사용함으로써 수행되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 60.

제 59 항에 있어서, 상기 복수의 발광층들은 유기 화합물을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 청구항 61.

제 59 항에 있어서, 상기 복수의 발광층들은 불활성 기체로 채워진 청결한 부스에서 프린팅되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 62.

제 59 항에 있어서, 상기 능동 매트릭스 디스플레이 디바이스는 비디오 카메라, 디지털 카메라, 고글형 디스플레이, 자동차 네비게이션 시스템, 휴대용 정보 단말기, 및 영상 재생 디바이스로 구성된 그룹으로부터 선택된 전자 디바이스 내에 포함되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 63.

제 59 항에 있어서, 상기 프린팅은,

닥터 바에 의해 아닐록스 롤의 표면 주위에 상기 전계 발광물을 풀링하는 단계;

상기 아닐록스 롤이 회전하는 동안 상기 메시 그루브들 상에 상기 전계 발광 형성물을 보존하는 단계;

상기 프린팅 롤이 회전하는 동안 상기 프린팅 롤의 상기 보호물들에 상기 전계 발광물을 제공하는 단계; 및

픽셀 전극 상에 상기 전계 발광물을 프린팅하는 단계를 포함하는 방법에 의해 수행되는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

#### 청구항 64.

제 59 항에 있어서, 상기 복수의 전극들은 투명한 도전막을 포함하는, 능동 매트릭스 디스플레이 디바이스 제조 방법.

## 도면

# 도면1a

도면1b

도면1c

# 도면2

# 도면3a

# 도면3b

도면4a

도면4b

도면4c

도면4d

도면4e

도면5a

도면5b

# 도면5c

# 도면5d

# 도면6a

# 도면6b

# 도면6c

# 도면7

# 도면8

# 도면9

# 도면10

도면11a

# 도면11b

# 도면12a

도면12b

도면12c

도면13

# 도면14

도면15

도면16a

# 도면16b

도면16c

도면16d

도면16e

# 도면16f

| 专利名称(译)        | 有源矩阵显示装置的制造方法                                                                                                                                    |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | KR1020050076723A                                                                                                                                 | 公开(公告)日 | 2005-07-26 |

| 申请号            | KR1020050055823                                                                                                                                  | 申请日     | 2005-06-27 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 株式会社绒布器肯kyusyo极限戴哦                                                                                                                               |         |            |

| [标]发明人         | YAMAZAKI SHUNPEI<br>야마자키순페이<br>MIZUKAMI MAYUMI<br>미즈카미마유미<br>KONUMA TOSHIMITSU<br>고누마도시미츠                                                        |         |            |

| 发明人            | 야마자키순페이<br>미즈카미마유미<br>고누마도시미츠                                                                                                                    |         |            |

| IPC分类号         | H01L51/40 H01L27/32 H05B33/10 H01L21/77 H01L51/56 H01L21/20                                                                                      |         |            |

| CPC分类号         | H01L27/3262 H01L51/56 H01L21/2026 H01L27/1214 H01L2251/5315 H01L27/3244 H01L51/0004 H01L27/3258 H01L51/5231 H01L51/0013 H01L21/02686 H01L27/1251 |         |            |

| 代理人(译)         | 李贝尔<br>李昌勋                                                                                                                                       |         |            |

| 优先权            | 1999182598 1999-06-28 JP                                                                                                                         |         |            |

| 外部链接           | Espacenet                                                                                                                                        |         |            |

|                |                                                                                                                                                  |         |            |

# 摘要(译)

包括该电子装置的制造成本本发明的目的是减少EL显示装置和EL显示装置。通过在有源矩阵EL显示装置中的印刷形成EL材料。凸版印刷或丝网印刷可用作印刷方法。因此,简化了电亮度层的制造步骤,并且设计了制造成本的降低。电光器件,有源矩阵EL显示器件,薄膜晶体管,像素电极,电子器件。