### 특허청구의 범위

#### 청구항 1.

각 화소에 EL 소자에 흘리는 전류값을 기억하는 기억 소자와, 구동용 트랜지스터로부터 EL 소자로 흐르는 전류를 온 오프 제어하는 스위칭 수단을 갖는 EL 표시 장치의 구동 방법에 있어서,

표시 장치 상의 화상 데이터의 총합 또는 화상 데이터의 총합에 준하는 데이터를 구하는 단계와,

상기 화상 데이터의 총합 또는 상기 화상 데이터의 총합에 준하는 데이터에 따라서 상기 스위칭 수단과 관련된 뉴티(duty) 비 제어 및 상기 기억 소자와 관련된 기준 전류 제어 중의 적어도 하나의 제어를 실시하는 단계

를 포함하는 EL 표시 장치의 구동 방법.

#### 청구항 2.

EL 소자가 매트릭스 형상으로 형성된 표시 패널과, 상기 표시 패널에 프로그램 전류를 공급하는 소스 드라이버 회로를 구비하고,

상기 소스 드라이버 회로는, 복수의 단위 전류 소자를 갖는 출력단과, 상기 단위 전류 소자가 흘려보내는 전류를 제어하는 가변 회로를 구비하는 EL 표시 장치.

### 청구항 3.

삭제

### 청구항 4.

화면의 비표시 영역과 표시 영역의 비율로, 화면의 회도를 제어하는 EL 표시 장치에 있어서,

EL 소자 및 상기 EL 소자를 구동하는 구동용 트랜지스터가 매트릭스 형상으로 형성된 표시 영역과,

상기 EL 소자를 화소 행마다 온 오프시키는 전압을 전달하는 게이트 신호선과,

상기 게이트 신호선을 구동하는 게이트 드라이버 회로와,

화상 데이터 또는 화상 데이터에 준하는 데이터를 집계하는 집계 회로와,

상기 집계 회로의 집계 결과를, 상기 게이트 드라이버 회로의 스타트 월스 신호로 변환하는 변환 회로를 구비하는 EL 표시 장치.

### 청구항 5.

화면의 비표시 영역과 표시 영역의 비율로, 화면의 회도를 제어하는 EL 표시 장치의 구동 방법에 있어서,

상기 화면의 비표시 영역과 표시 영역의 비율을 제1 비율에서 제2 비율로 변경할 때에, 대기 시간을 발생시키는 EL 표시 장치의 구동 방법.

### 청구항 6.

제5항에 있어서, 표시 영역/(화면의 비표시 영역+ 표시 영역)은 1/16 이상 1/1 이하인 EL 표시 장치의 구동 방법.

### 청구항 7.

각 화소에 컨덴서, EL 소자, 및 상기 EL 소자에 전류를 공급하는 P 채널의 구동용 트랜지스터가 형성되고, 또한 화소가 매트릭스 형상으로 형성된 표시 패널과,

상기 표시 패널에 프로그램 전류를 공급하는 소스 드라이버 회로를 구비하고,

상기 소스 드라이버 회로는, 복수의 단위 전류를 출력하는 N채널의 단위 트랜지스터를 갖는 출력단을 구비하는 EL 표시 장치.

### 청구항 8.

제7항에 있어서, 컨덴서의 용량을  $C_s(\mu F)$ 로 하고, 1 화소가 차지하는 면적을  $S(\text{평방}\mu m)$ 로 하면,  $500/S \leq C_s \leq 20000/S$ 의 조건을 만족하는 EL 표시 장치.

### 청구항 9.

제7항에 있어서, 소스 드라이버 회로로부터의 프로그램 전류  $I(\mu A)$ 는, 화소 사이즈를  $A(\text{평방mm})$ 로 하고, 백 래스터 표시 소정 휘도를  $B(nt)$ 로 하면,  $(A \times B)/20 \leq I \leq (A \times B)$ 의 조건을 만족하는 EL 표시 장치.

### 청구항 10.

제7항에 있어서, 계조 수를  $K$ 로 하고, 단위 트랜지스터의 크기를  $St(\text{평방}\mu m)$ 로 하면,

$40 \leq K/\sqrt{St}$ 이고 또한  $St \leq 300$ 의 조건을 만족하는 EL 표시 장치.

### 청구항 11.

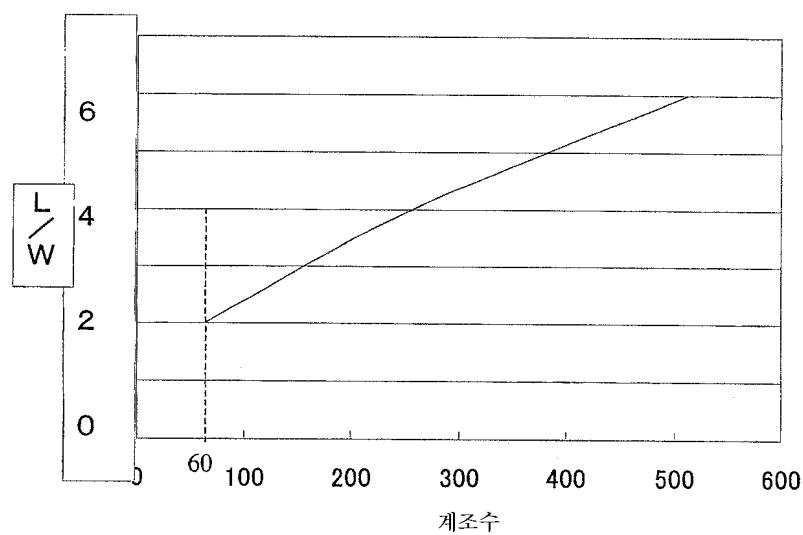

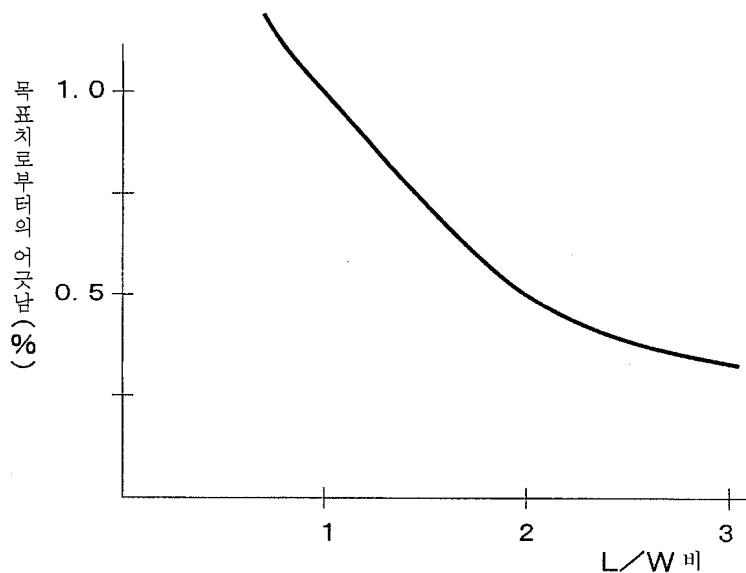

제7항에 있어서, 계조 수를  $K$ 로 하고, 단위 트랜지스터의 채널 길이를  $L(\mu m)$ , 채널 폭을  $W(\mu m)$ 로 했을 때,  $(\sqrt{K}/16) \leq L/W \leq (\sqrt{K}/16) \times 20$ 의 조건을 만족하는 EL 표시 장치.

### 청구항 12.

제1 표시 화면을 갖는 제1 EL 표시 패널과,

제2 표시 화면을 갖는 제2 EL 표시 패널과,

상기 제1 EL 표시 패널의 소스 신호선과 상기 제2 EL 표시 패널의 소스 신호선을 접속하는 플렉시블 기판을 구비하고,

화소를 구동하는 구동 트랜지스터의 채널 폭을  $W(\mu m)$ 로 하고, 채널 길이를  $L(\mu m)$ 로 하면, 상기 제1 표시 화면의 화소를 구동하는 구동 트랜지스터의  $W/L$ 과, 상기 제2 표시 화면의 화소를 구동하는 구동 트랜지스터의  $W/L$ 이 서로 다르게 되어 있는 EL 표시 장치.

## 명세서

### 기술분야

본 발명은 유기 또는 무기 일렉트로 루미네센스(EL) 소자를 이용한 EL 표시 패널 등의 자발광 표시 패널에 관한 것이다. 또한, 이들 표시 패널의 구동 회로(IC)에 관한 것이다. EL 표시 패널의 구동 방법과 구동 회로 및 이들을 이용한 정보 표시 장치 등에 관한 것이다.

### 배경기술

일반적으로, 액티브 매트릭스형 표시 장치에서는, 다수의 화소를 매트릭스 형상으로 배열하고, 공급된 영상 신호에 대응하여 화소마다 광 강도를 제어함으로써 화상을 표시한다. 예를 들면, 전기 광학 물질로서 액정을 이용한 경우에는, 각 화소에 기입되는 전압에 대응하여 화소의 투과율이 변화한다. 전기 광학 변환 물질로서 유기 일렉트로 루미네센스(EL) 재료를 이용한 액티브 매트릭스형의 화상 표시 장치는 화소에 기입되는 전류에 응답하여 발광 휘도가 변화한다.

액정 표시 패널은 각 화소가 셔터로서 동작하고, 백라이트로부터의 빛을 화소인 셔터에 의해 온 오프시킴으로써 화상을 표시한다. 유기 EL 표시 패널은 각 화소에 발광 소자를 갖는 자발광형이다. 그 때문에, 유기 EL 표시 패널은 액정 표시 패널에 비하여 화상의 시인성이 높고, 백라이트가 불필요하며, 응답 속도가 빠르다는 등의 이점을 갖는다.

유기 EL 표시 패널은 각 발광 소자(화소)의 휘도가 전류량에 의해서 제어된다. 즉, 발광 소자가 전류 구동형 혹은 전류 제어형이라는 점에서 액정 표시 패널과는 크게 다르다.

유기 EL 표시 패널도 단순 매트릭스 방식과 액티브 매트릭스 방식의 구성이 가능하다. 전자는 구조는 단순하지만 대형이면서 고정밀의 표시 패널의 실현이 곤란하다. 그러나, 염가이다. 후자는 대형이며, 고정밀 표시 패널을 실현할 수 있다. 그러나, 제어 방법이 기술적으로 어렵고 비교적 고가라고 하는 과제가 있다. 현재는 액티브 매트릭스 방식의 개발이 왕성하게 행해지고 있다. 액티브 매트릭스 방식은 각 화소에 마련한 발광 소자에 흐르는 전류를 화소 내부에 마련한 박막 트랜지스터(트랜지스터)에 의해서 제어한다.

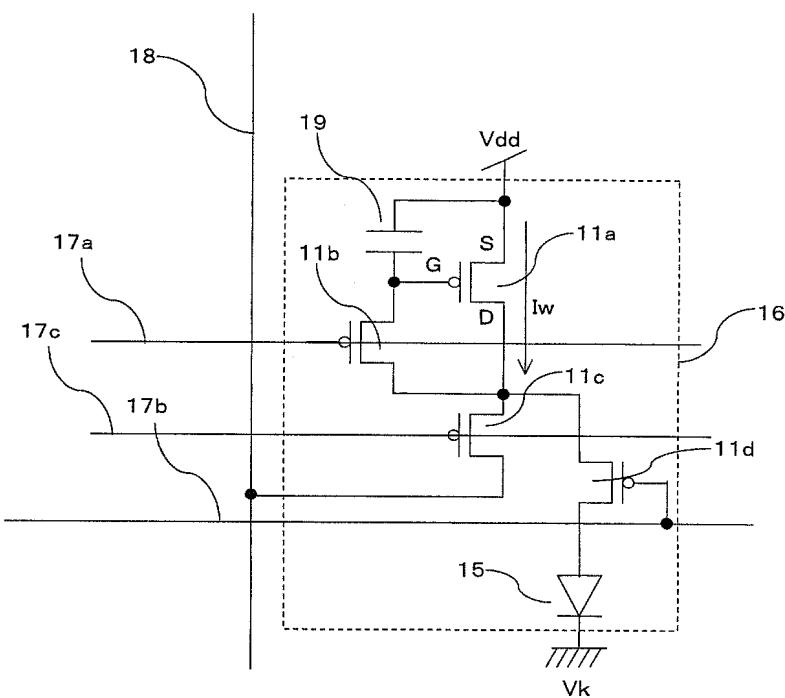

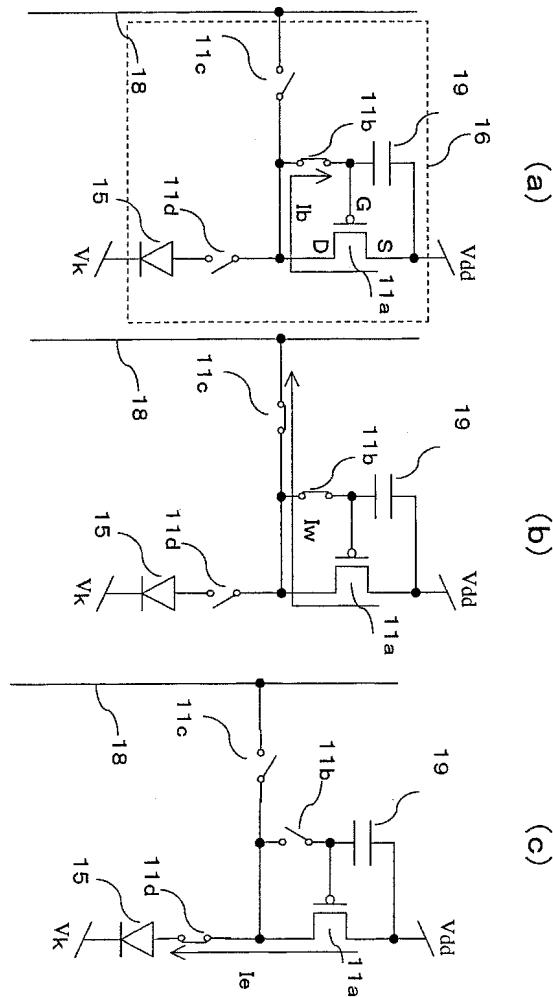

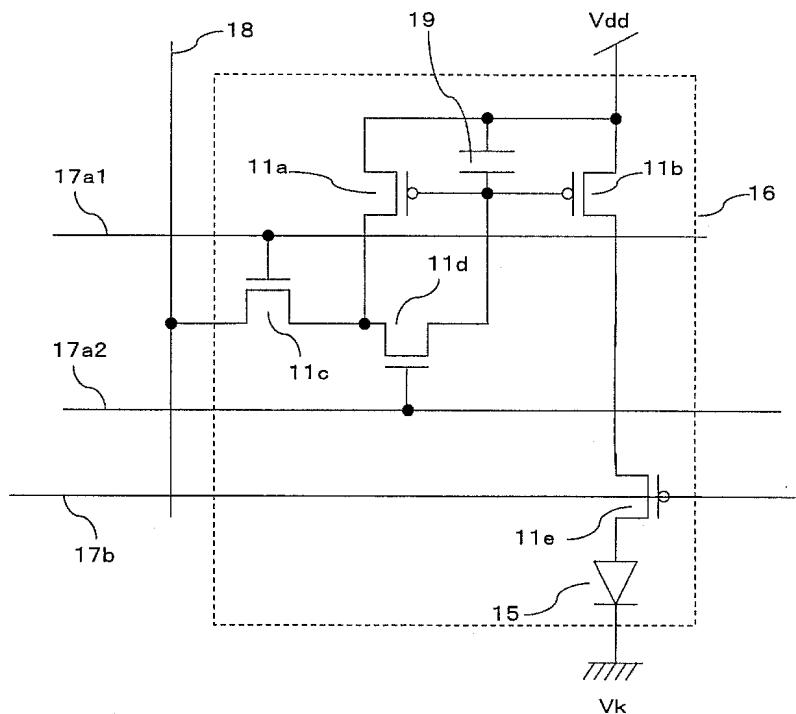

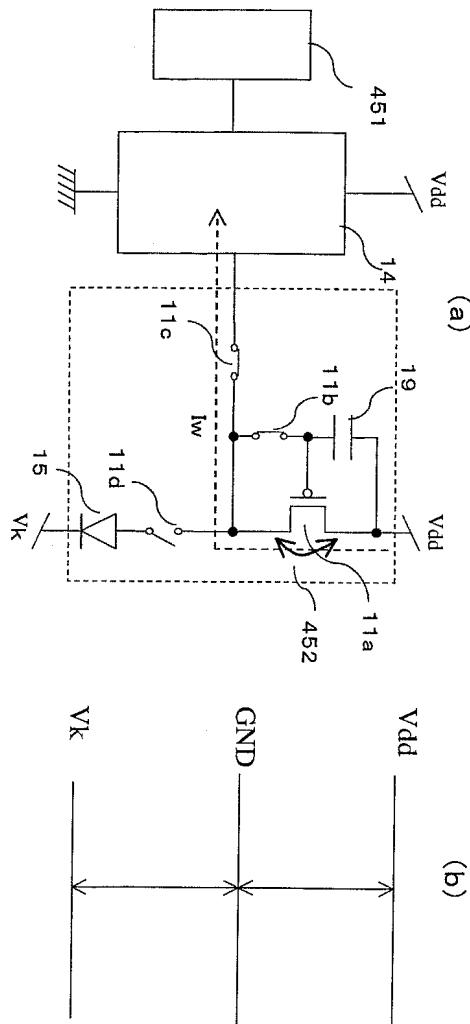

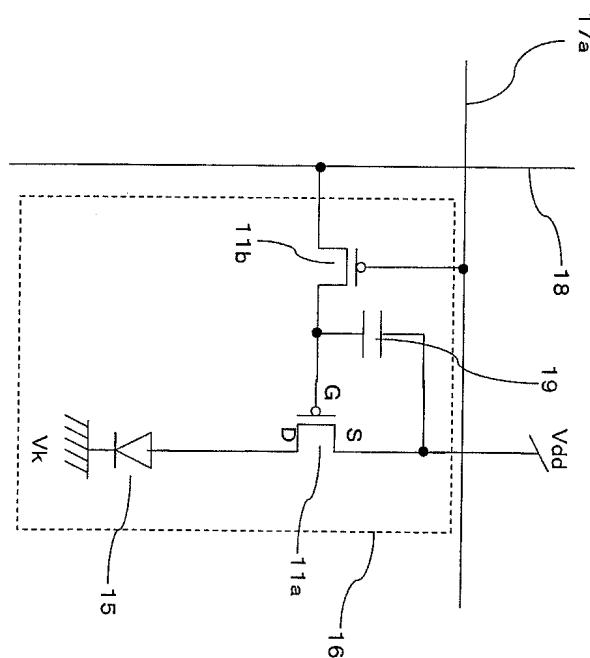

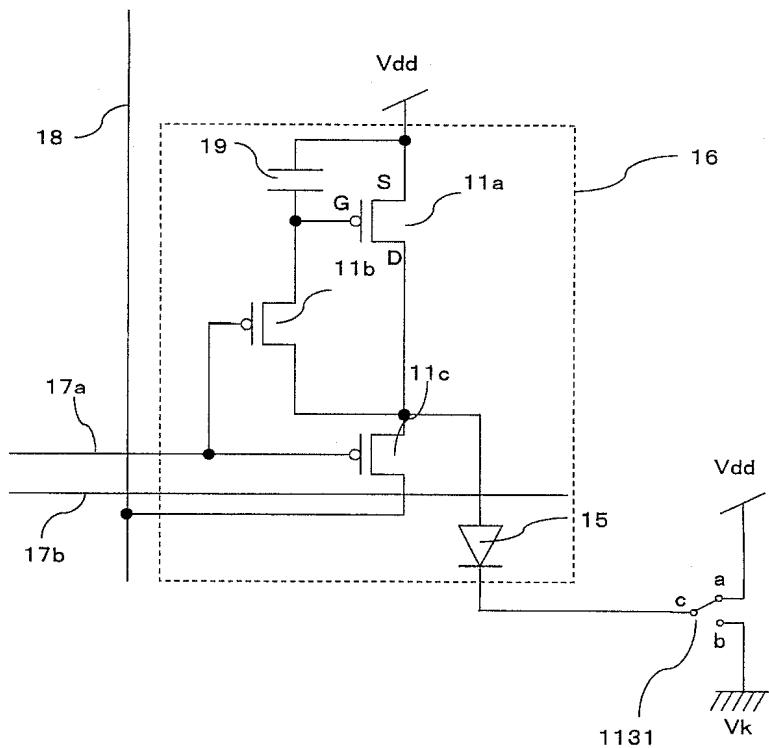

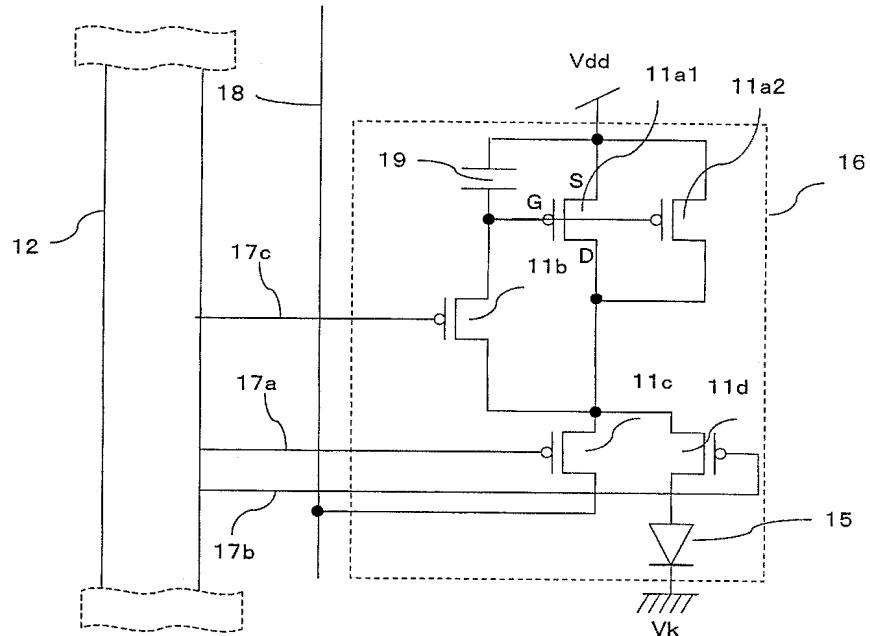

이 액티브 매트릭스 방식의 유기 EL 표시 패널은 일본 특허 공개 평성8-234683호 공보에 개시되어 있다. 이 표시 패널의 1 화소분의 등가 회로를 도 46에 도시한다. 화소(16)는 발광 소자인 EL 소자(15), 제1 트랜지스터(11a), 제2 트랜지스터(11b) 및 축적 용량(19)으로 이루어진다. 발광 소자(15)는 유기 일렉트로 루미네센스(EL) 소자이다. 본 발명에서는 EL 소자(15)에 전류를 공급(제어)하는 트랜지스터(11a)를 구동용 트랜지스터(11)라고 부른다. 또한, 도 46의 트랜지스터(11b)와 같이, 스위치로서 동작하는 트랜지스터를 스위치용 트랜지스터(11)라고 부른다.

유기 EL 소자(15)는 대부분의 경우, 정류성이 있기 때문에, OLED(유기 발광 다이오드)라고 불리는 경우가 있다. 도 46 등에서는 발광 소자(15)로서 다이오드의 기호를 이용하고 있다.

단, 본 발명에서의 발광 소자(15)는 OLED에 한하는 것이 아니고, 소자(15)에 흐르는 전류량에 의해서 휘도가 제어되는 것 이면 된다. 예를 들면, 무기 EL 소자가 예시된다. 그밖에, 반도체로 구성되는 백색 발광 다이오드가 예시된다. 또한, 일반적인 발광 다이오드가 예시된다. 그밖에, 발광 트랜지스터여도 된다. 또한, 발광 소자(15)는 반드시 정류성이 요구되는 것이 아니다. 쌍방향성 다이오드이어도 무방하다. 본 발명의 EL 소자(15)는 이를 어느 것이어도 좋다.

도 46의 예에서는 P 채널형의 트랜지스터(11a)의 소스 단자(S)를 Vdd(전원 전위)로 하고, EL 소자(15)의 캐소드(음극)는 접지 전위(Vk)에 접속된다. 한편, 애노드(양극)는 트랜지스터(11a)의 드레인 단자(D)에 접속되어 있다. 한편, P 채널형의 트랜지스터(11b)의 게이트 단자는 게이트 신호선(17a)에 접속되고, 소스 단자는 소스 신호선(18)에 접속되고, 드레인 단자는 축적 용량(19) 및 트랜지스터(11a)의 게이트 단자(G)에 접속되어 있다.

화소(16)를 동작시키기 위해서, 우선, 게이트 신호선(17a)을 선택 상태로 하고, 소스 신호선(18)에 휘도 정보를 나타내는 영상 신호를 인가한다. 그렇게 하면, 트랜지스터(11b)가 도통하여, 축적 용량(19)이 충전 또는 방전되고, 트랜지스터(11a)의 게이트 전위는 영상 신호의 전위와 일치한다. 게이트 신호선(17a)을 비선택 상태로 하면, 트랜지스터(11b)가 오프로 되고, 트랜지스터(11a)는 전기적으로 소스 신호선(18)으로부터 분리된다. 그러나, 트랜지스터(11a)의 게이트 전위는 축적 용량(컨덴서)(19)에 의해서 안정적으로 유지된다. 트랜지스터(11a)를 통하여 EL 소자(15)에 흐르는 전류는, 트랜지스터(11a)의 게이트/소스 단자 사이 전압 Vgs에 따른 값이 되고, EL 소자(15)는 트랜지스터(11d)를 통하여 공급되는 전류량에 따른 휘도로 계속해서 발광한다.

또, 상기 문헌의 모든 개시는 모조리 그대로 인용함으로써 여기에 일체화한다.

액정 표시 패널은 자발광 디바이스가 아니기 때문에, 백라이트를 이용하지 않으면 화상을 표시할 수 없다고 하는 문제점이 있다. 백라이트를 구성하기 위해서는 소정의 두께가 필요하기 때문에, 표시 패널의 두께가 두꺼워진다고 하는 문제가 있었다. 또, 액정 표시 패널에 컬러 표시를 행하기 위해서는 컬러 필터를 사용할 필요가 있다. 그 때문에, 광 이용 효율이 낮다고 하는 문제점이 있었다. 또, 색 재현 범위가 좁다고 하는 문제점이 있었다.

유기 EL 표시 패널은 저온 폴리실리콘 트랜지스터 어레이를 이용하여 패널을 구성한다. 그러나, 유기 EL 소자는 전류에 의해 발광하기 때문에, 트랜지스터의 특성에 변동이 있으면, 표시 얼룩짐이 발생한다고 하는 과제가 있었다.

표시 열룩짐은 화소를 전류 프로그램 방식의 구성을 채용함으로써 저감하는 것이 가능하다. 전류 프로그램을 실시하기 위해서는 전류 구동 방식의 드라이버 회로가 필요하다. 그러나, 전류 구동 방식의 드라이버 회로에도 전류 출력단을 구성하는 트랜지스터 소자에 변동이 발생한다. 그 때문에, 각 출력 단자로부터의 계조 출력 전류에 변동이 발생하여 양호한 화상 표시를 할 수 없다고 하는 과제가 있었다.

### 발명의 상세한 설명

이 목적을 달성하기 위해서 본 발명의 EL 표시 패널(EL 표시 장치)의 드라이버 회로는, 단위 전류를 출력하는 복수의 트랜지스터를 구비하고, 이 트랜지스터의 개수를 변화시키는 것에 의해 출력 전류를 출력하는 것이다. 또한, 다단의 커런트 미러 회로로 구성된 것을 특징으로 한다. 신호의 교환이 전압 교환이 되는 트랜지스터군은 밀집되게 형성하고, 커런트 미러 회로군과의 신호의 교환은 전류 교환의 구성을 채용한다. 또한, 기준 전류는 복수의 트랜지스터에서 행한다.

제1 본 발명은, 각 화소에 구동용 트랜지스터와 EL 소자 사이의 전류 경로를 온 오프 제어하는 스위치 소자를 갖는 EL 표시 장치의 구동 방법에 있어서,

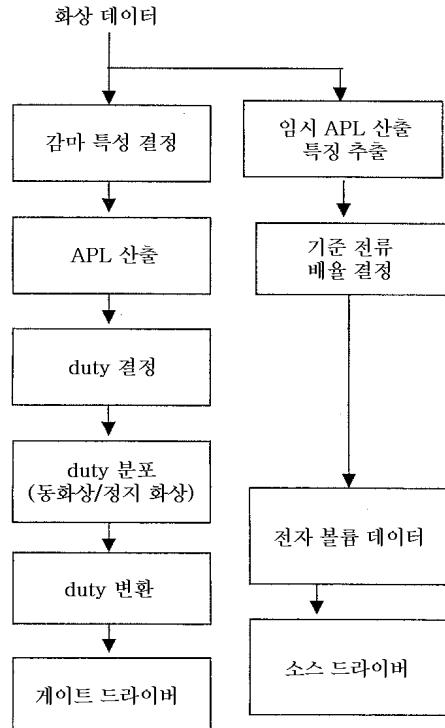

화상 데이터 또는 화상 데이터에 준하는 데이터를 집계하고,

상기 집계한 데이터가 적을 때보다도 클 때 쪽이 상기 스위치 소자를 오프 상태로 하는 기간을 길게 하는 EL 표시 장치의 구동 방법이다.

제2 본 발명은, EL 소자가 매트릭스 형상으로 형성된 표시 패널과,

상기 표시 패널에 프로그램 전류를 공급하는 소스 드라이버 회로를 구비하고,

상기 소스 드라이버 회로는, 복수의 단위 전류 소자를 갖는 출력단과, 상기 단위 전류 소자가 흘려보내는 전류를 제어하는 가변 회로를 구비하는 EL 표시 장치이다.

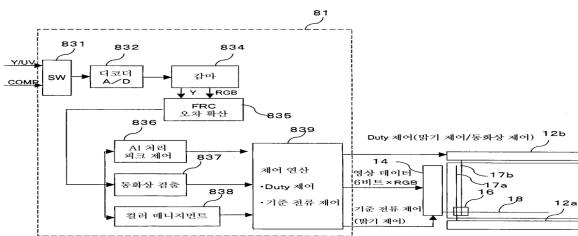

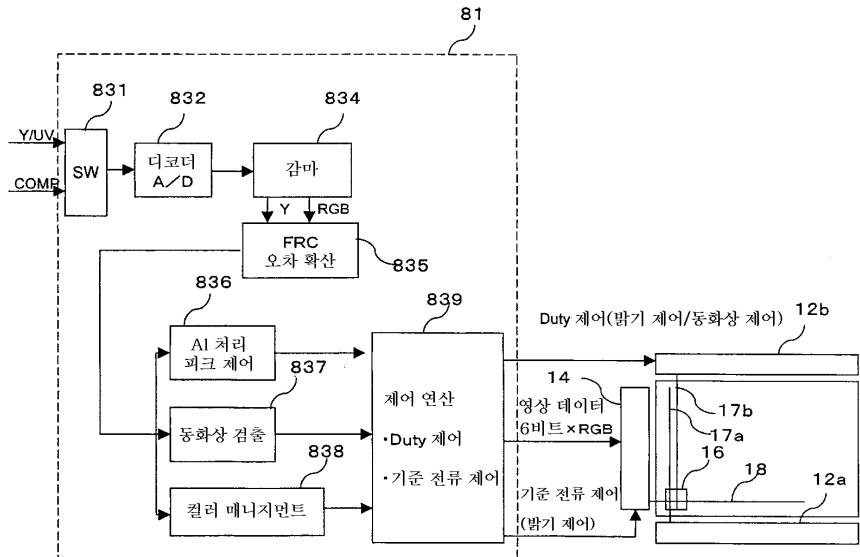

제3 본 발명은, 동화상 검출을 행하는 동화상 검출 회로와, 영상의 특정 추출을 행하는 특정 추출 회로를 갖는 EL 표시 장치를 구동하는 방법에 있어서,

상기 동화상 검출 회로에서의 출력 데이터에 의해 선택하는 화소 행 수를 변경하는 제1 공정과,

상기 특정 추출 회로에서의 출력 데이터에 의해 선택하는 화소 행 수를 변경하는 제2 공정을 구비하는 EL 표시 장치의 구동 방법이다.

제4 본 발명은, 화면의 비표시 영역과 표시 영역의 비율로 화면의 휘도를 제어하는 EL 표시 장치에 있어서,

EL 소자 및 상기 EL 소자를 구동하는 구동용 트랜지스터가 매트릭스 형상으로 형성된 표시 영역과,

상기 EL 소자를 화소 행마다 온 오프시키는 전압을 전달하는 게이트 신호선과,

상기 게이트 신호선을 구동하는 게이트 드라이버 회로와,

화상 데이터 또는 화상 데이터에 준하는 데이터를 집계하는 집계 회로와,

상기 집계 회로의 집계 결과를, 상기 게이트 드라이버 회로의 스타트 펄스 신호로 변환하는 변환 회로를 구비하는 EL 표시 장치이다.

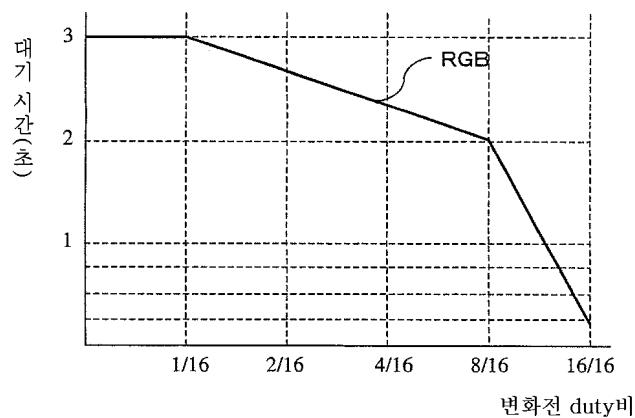

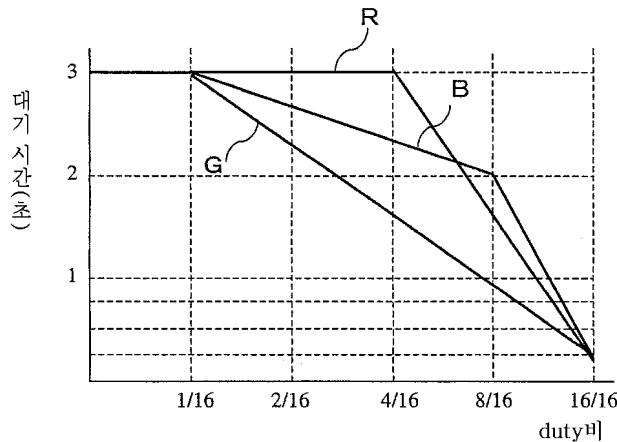

제5 본 발명은, 화면의 비표시 영역과 표시 영역의 비율로 화면의 휘도를 제어하는 EL 표시 장치의 구동 방법에 있어서,

상기 화면의 비표시 영역과 표시 영역의 비율을 제1 비율에서 제2 비율로 변경할 때에, 지연 시간을 발생시키는 EL 표시 장치의 구동 방법이다.

제6 본 발명은, 표시 영역/(화면의 비표시 영역+표시 영역)이 1/16 이상 1/1 이하인 제5 본 발명의 EL 표시 장치의 구동 방법이다.

제7 본 발명은, 각 화소에 컨덴서, EL 소자, 및 상기 EL 소자에 전류를 공급하는 P 채널의 구동용 트랜지스터가 형성되고, 또한 화소가 매트릭스 형상으로 형성된 표시 패널과,

상기 표시 패널에 프로그램 전류를 공급하는 소스 드라이버 회로를 구비하고,

상기 소스 드라이버 회로는, 복수의 단위 전류를 출력하는 N채널의 단위 트랜지스터를 갖는 출력단을 구비하는 EL 표시 장치이다.

제8 본 발명은, 컨덴서의 용량을  $C_s(pF)$ 로 하고, 1 화소가 차지하는 면적을  $S(\text{평방}\mu\text{m})$ 로 하면,  $500/S \leq C_s \leq 20000/S$ 의 조건을 만족하는 제7 본 발명의 EL 표시 장치이다.

제9 본 발명은, 소스 드라이버 회로로부터의 프로그램 전류  $I(\mu A)$ 는, 화소 사이즈를  $A(\text{평방mm})$ 로 하고, 백 래스터 표시 소정 휙도를  $B(nt)$ 로 하면,  $(A \times B)/20 \leq I \leq (A \times B)$ 의 조건을 만족하는 제7 본 발명의 EL 표시 장치이다.

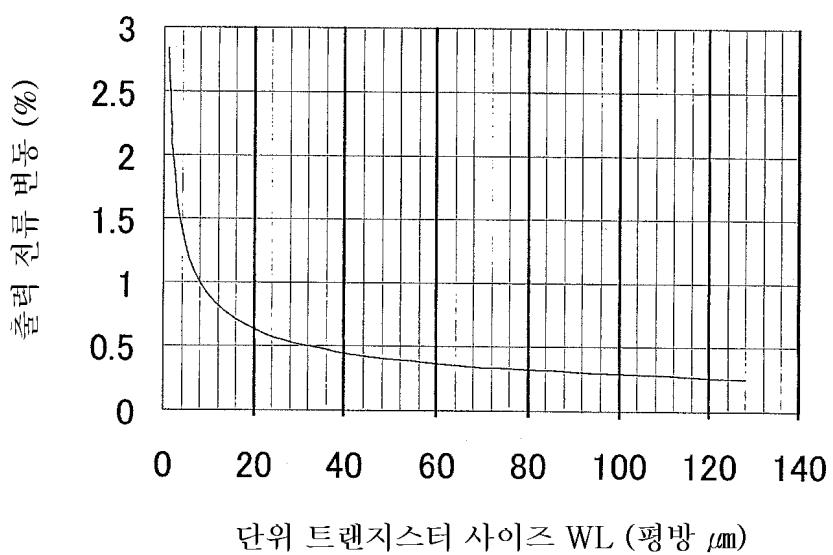

제10의 본 발명은, 계조 수를 K로 하고, 단위 트랜지스터의 크기를  $St(\text{평방}\mu\text{m})$ 로 하면,

$40 \leq K/\sqrt{St}$ 이고 또한  $St \leq 300$ 의 조건을 만족하는, 제7 본 발명의 EL 표시 장치이다.

제11의 본 발명은, 계조 수를 K로 하고, 단위 트랜지스터의 채널 길이를  $L(\mu\text{m})$ , 채널 폭을  $W(\mu\text{m})$ 로 했을 때,  $(\sqrt{K}/16) \leq L/W \leq (\sqrt{K}/16) \times 20$ 의 조건을 만족하는, 제7 본 발명의 EL 표시 장치이다.

제12의 본 발명은, 제1 표시 화면을 갖는 제1 EL 표시 패널과,

제2 표시 화면을 갖는 제2 EL 표시 패널과,

상기 제1 EL 표시 패널의 소스 신호선과 상기 제2 EL 표시 패널의 소스 신호선을 접속하는 플렉시블 기판을 구비하고,

화소를 구동하는 구동 트랜지스터의 채널 폭을  $W(\mu\text{m})$ 로 하고, 채널 길이를  $L(\mu\text{m})$ 로 하면, 상기 제1 표시 화면의 화소를 구동하는 구동 트랜지스터의 W/L과, 상기 제2 표시 화면의 화소를 구동하는 구동 트랜지스터의 W/L이 서로 다르게 되어 있는 EL 표시 장치이다.

### 실시예

본 명세서에 있어서 각 도면은 이해를 용이하게 또는/및 작도를 쉽게 하기 위해서, 생략 또는/및 확대 축소한 개소가 있다. 예를 들면, 도 11에 도시하는 표시 패널의 단면도에서는 박막 밀봉막(111) 등을 충분히 두껍게 도시하고 있다. 한편, 도 10에 있어서, 밀봉 뚜껑(85)은 얇게 도시하고 있다. 또, 생략한 개소도 있다. 예를 들면, 본 발명의 표시 패널 등에서는, 반사 방지를 위해서 원편광판 등의 위상 필름이 필요하다. 그러나, 본 명세서의 각 도면에서는 생략하고 있다. 이상의 것은 이하의 도면에 대하여도 마찬가지이다. 또한, 동일 번호 또는 기호 등을 붙인 개소는 동일 혹은 유사한 형태 혹은 재료 혹은 기능 혹은 동작을 갖는다.

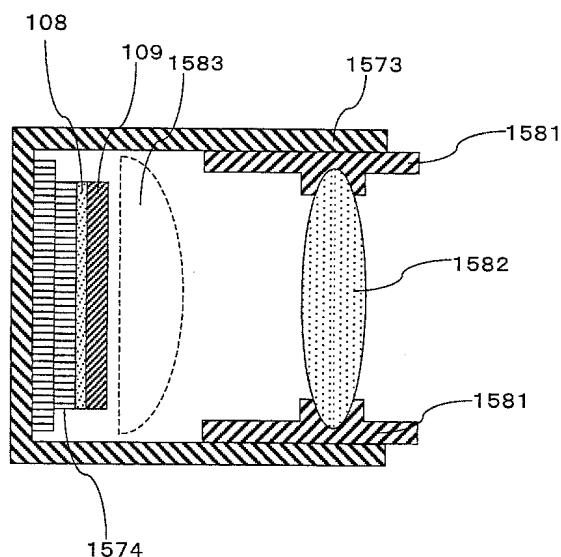

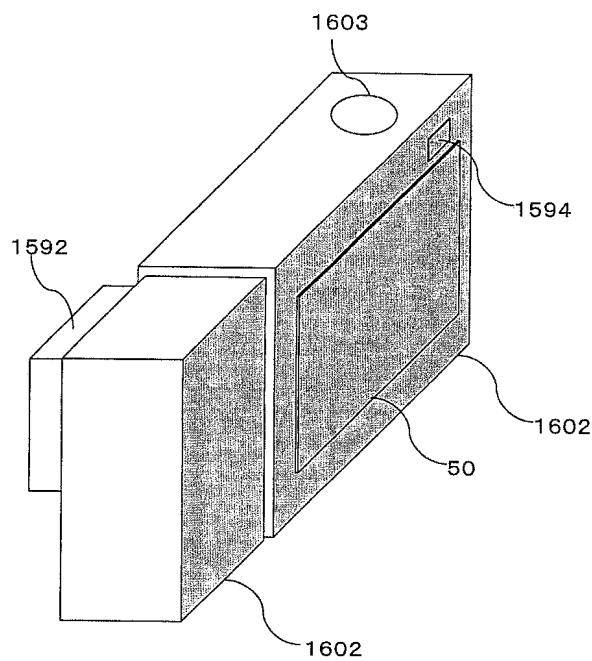

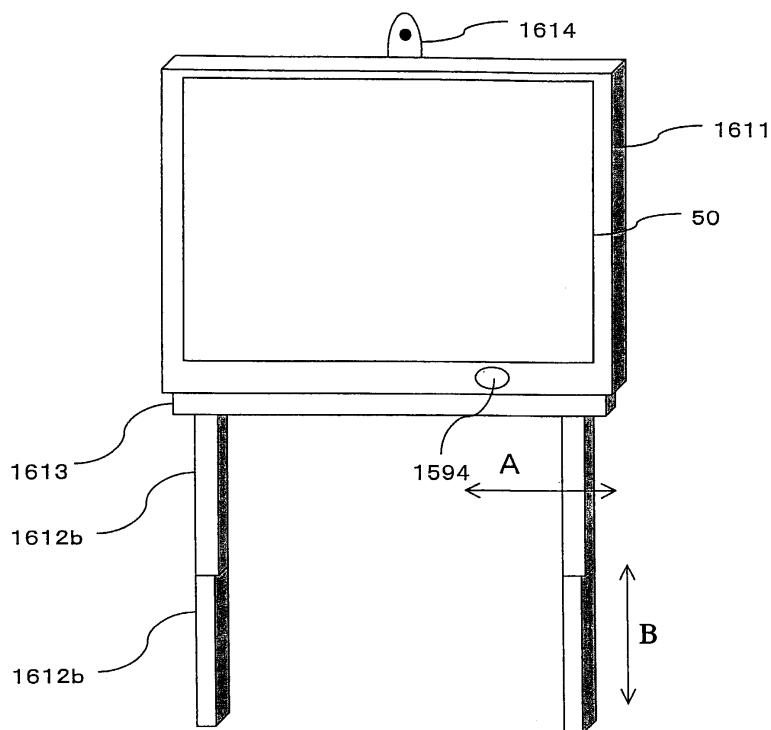

또, 각 도면 등에서 설명한 내용은 특별히 예고가 없더라도 다른 실시예 등과 조합할 수 있다. 예를 들면, 도 8의 표시 패널에 터치 패널 등을 부가하여, 도 157, 도 159 내지 도 161에 도시하는 정보 표시 장치로 할 수 있다. 또한, 확대 렌즈(1582)를 부착하여, 비디오 카메라(도 159 등 참조) 등에 이용하는 뷰 파인더(도 58을 참조)를 구성할 수도 있다. 또한, 도 4, 도 15, 도 18, 도 21, 도 23, 도 29, 도 30, 도 35, 도 36, 도 40, 도 41, 도 44, 도 100 등에서 설명한 본 발명의 구동 방법은, 어느 하나의 본 발명의 표시 장치 또는 표시 패널에 적용할 수 있다.

또, 본 명세서에서는 구동용 트랜지스터(11), 스위칭용 트랜지스터(11)는 박막 트랜지스터로서 설명하지만, 이것에 한정되는 것이 아니다. 박막 다이오드(TFD), 텅 다이오드 등으로도 구성할 수 있다. 또, 박막 소자에 한정되는 것이 아니며, 실리콘 웨이퍼에 형성한 트랜지스터라도 좋다. 어레이 기판(71)을 실리콘 웨이퍼로 형성하면 된다. 물론, FET, MOS-FET,

MOS 트랜지스터, 바이폴라 트랜지스터이더라도 무방하다. 이들도 기본적으로 박막 트랜지스터이다. 그밖에, 바리스터, 사이리스터, 링 다이오드, 포토 다이오드, 포토 트랜지스터, PLZT 소자 등이어도 됨은 물론이다. 즉, 본 발명의 트랜지스터 소자(11), 게이트 드라이버 회로(12), 소스 드라이버 회로(14) 등은 이를 어느 것이라도 사용할 수 있다.

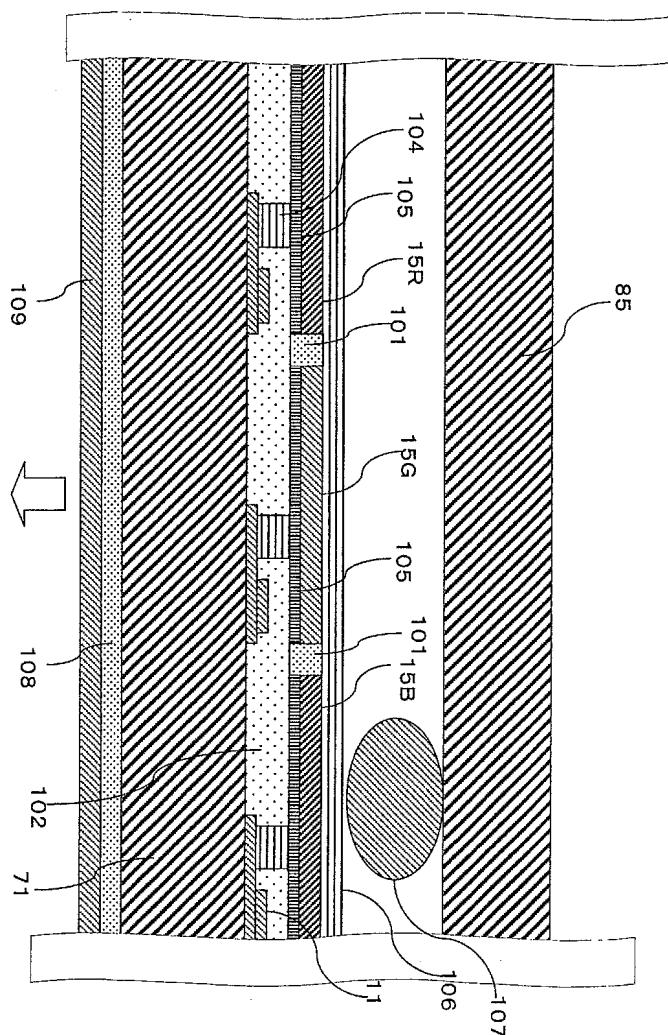

이하, 본 발명의 EL 패널에 대하여 도면을 참조하면서 설명한다. 유기 EL 표시 패널은, 도 10에 도시한 바와 같이, 화소 전극으로서의 투명 전극(105)이 형성된 유리판(71)(어레이 기판)상에, 전자 수송층, 발광층, 정공 수송층 등으로 이루어지는 적어도 1층의 유기 기능층(EL 층)(15), 및 금속 전극(반사막)(캐소드)(106)이 적층된 것이다. 투명 전극(화소 전극)(105)인 양극(애노드)에 플러스, 금속 전극(반사 전극)(106)의 음극(캐소드)에 마이너스의 전압을 가하고, 즉, 투명 전극(105) 및 금속 전극(106) 사이에 직류를 인가하는 것에 의해, 유기 기능층(EL 층)(15)이 발광한다.

금속 전극(106)에는 리튬, 은, 알루미늄, 마그네슘, 인듐, 구리 또는 각각의 합금 등의 일 함수가 작은 것을 이용하는 것이 바람직하다. 특히, 예를 들면 Al-Li 합금을 이용하는 것이 바람직하다. 또한, 투명 전극(105)에는 ITO 등의 일함수가 큰 도전성 재료 또는 금 등을 이용할 수 있다. 또, 금을 전극 재료로서 이용한 경우, 전극은 반투명한 상태가 된다. 또, ITO는 IZO 등의 다른 재료이어도 좋다. 이 사항은 다른 화소 전극(105)에 대하여도 마찬가지이다.

또, 밀봉 뚜껑(85)과 어레이 기판(71)의 공간에는 건조제(107)를 배치한다. 이것은 유기 EL막(15)이 습도에 약하기 때문이다. 건조제(107)에 의해 시일제를 침투하는 수분을 흡수하여 유기 EL막(15)의 열화를 방지한다.

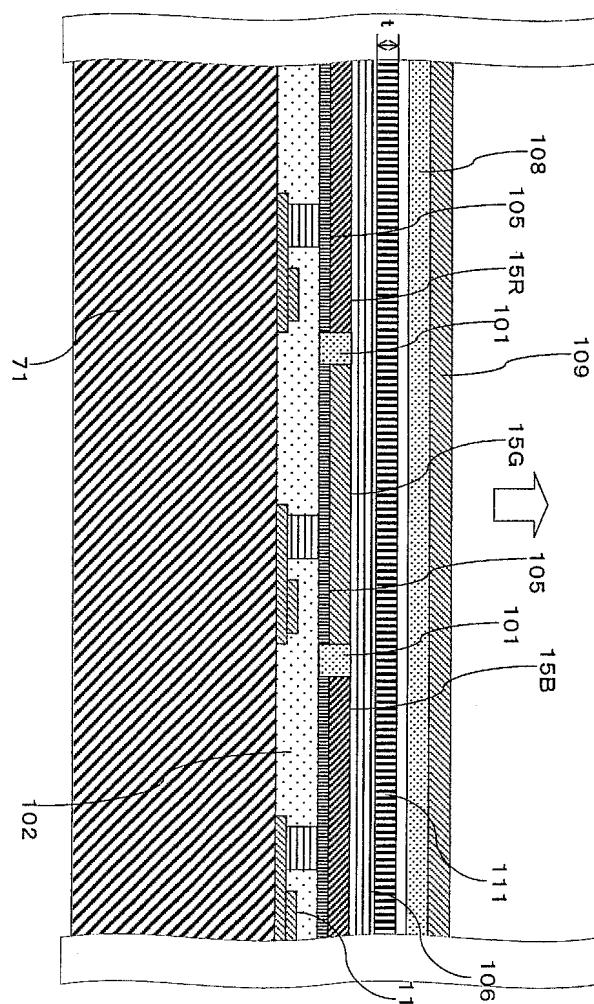

도 10은 유리의 뚜껑(85)을 이용하여 밀봉하는 구성이지만, 도 11과 같이 필름(박막이어도 됨. 즉, 박막 밀봉막임)(111)을 이용한 밀봉이어도 된다. 예를 들면, 밀봉 필름(박막 밀봉막)(111)으로서는 전해 컨덴서의 필름에 DLC(다이아몬드형 카본)을 증착한 것을 이용하는 것이 예시된다. 이 필름은 수분 침투성이 매우 나쁘다(방습 성능이 높음). 이 필름을 박막 밀봉막(111)으로서 이용한다. 또한, DLC(다이아몬드형 카본)막 등을 금속 전극(106)의 표면에 직접 증착하는 구성도 되는 것은 물론이다. 기타, 수지 박막과 금속 박막을 다층으로 적층하여 박막 밀봉막을 구성해도 된다.

박막의 막 두께는  $n \cdot d$ ( $n$ 은 박막의 굴절율이고,  $d$ 는 박막의 막 두께임. 복수의 박막이 적층되어 있는 경우에는 굴절율을 총합(각 박막의  $n \cdot d$ 를 계산)하여 계산함.)가, EL 소자(15)의 발광 주파장  $\lambda$  이하로 되도록 하면 된다. 이 조건을 만족시킴으로써, EL 소자(15)로부터의 광 추출 효율이, 유리 기판으로 밀봉한 경우에 비하여 2배 이상이 된다. 또한, 알루미늄과 은의 합금 혹은 혼합물 혹은 적층물을 형성해도 된다.

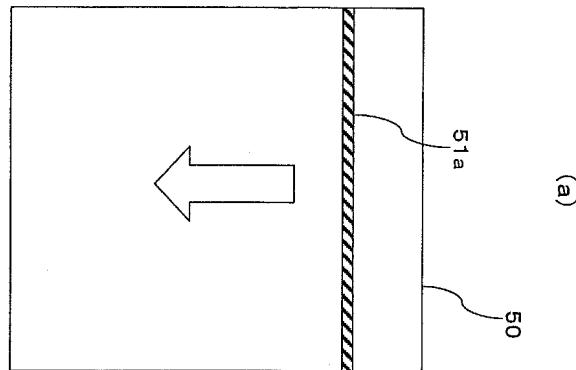

이상과 같이 밀봉 뚜껑(85)을 이용하지 않고, 박막 밀봉막(111)으로 밀봉하는構성을 박막 밀봉이라고 부른다. 어레이 기판(71)측에서 빛을 추출하는 「하부 추출(도 10을 참조, 광 추출 방향은 도 10의 화살표 방향이다)」 인 경우의 박막 밀봉은, EL막을 형성 후, EL막상에 캐소드가 되는 알루미늄 전극을 형성한다. 다음에 이 알루미늄막상에 완충층으로서의 수지층을 형성한다. 완충층으로서는 아크릴, 에폭시 등의 유기 재료가 예시된다. 또한, 막 두께는  $1\mu\text{m}$  이상  $10\mu\text{m}$  이하의 두께가 적합하다. 더욱 바람직하게는, 막 두께는  $2\mu\text{m}$  이상  $6\mu\text{m}$  이하의 두께가 적합하다. 이 완충막(완충층) 상에 밀봉막(111)을 형성한다. 완충막이 없으면, 응력에 의해 EL막의 구조가 무너져, 줄기 형상으로 결함이 발생한다. 박막 밀봉막(111)은 상술한 바와 같이, DLC(다이아몬드형 카본), 혹은 전계 컨덴서의 층 구조(유전체 박막과 알루미늄 박막을 교대로 다층 증착한 구조)가 예시된다.

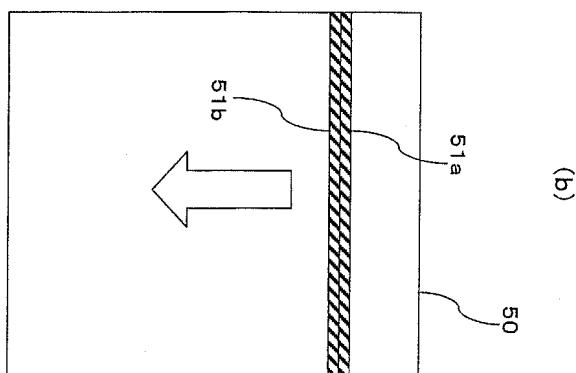

EL층(15)측에서 빛을 추출하는 「상부 추출 도 11을 참조, 광 추출 방향은 도 11의 화살표 방향이다」 인 경우의 박막 밀봉은, EL막(15)을 형성후, EL막(15)상에 캐소드(애노드)가 되는 Ag-Mg막을 20온스트롬 이상 300온스트롬의 막 두께로 형성한다. 그 위에, ITO 등의 투명 전극을 형성하여 저 저항화한다. 다음에 이 전극막상에 완충층으로서의 수지층을 형성한다. 이 완충막상에 박막 밀봉막(111)을 형성한다.

유기 EL층(15)으로부터 발생한 빛의 반은 금속 전극(106)에 의해 반사되어, 어레이 기판(71)을 투과하여 출사된다. 그러나, 금속 전극(106)은 외광을 반사하여 찍혀 들어가는 것이 발생하여 표시 콘트라스트를 저하시킨다. 이 대책을 위해서, 어레이 기판(71)에  $\lambda/4$  위상판(108) 및 편광판(편광 필름)(109)을 배치하고 있다. 이들은 일반적으로 원편광판(원편광 시트)이라고 불린다.

또, 화소가 반사 전극인 경우에는 EL층(15)으로부터 발생한 빛은 위 방향으로 출사된다. 따라서, 위상판(108) 및 편광판(109)을 광 출사측에 배치하는 것은 물론이다. 또, 반사형 화소는 화소 전극(105)을, 알루미늄, 크롬, 은 등으로 구성하여 얻어진다. 또한, 화소 전극(105)의 표면에 볼록부(혹은 요철부)를 마련함으로써 유기 EL층(15)과의 계면이 넓어지고 발광 면적이 커지며, 또한 발광 효율이 향상된다. 또, 캐소드(106)(애노드(105))가 되는 반사막을 투명 전극에 형성하거나, 혹은 반사율을 30% 이하로 저감 가능한 경우에는, 원편광판은 불필요하다. 찍혀 들어가는 것이 대폭 감소하기 때문이다. 또한, 빛의 간섭도 저감되어 바람직하다.

트랜지스터(11)는 LDD(로우 도핑 드레인) 구조를 채용하는 것이 바람직하다. 또한, 본 명세서에서는 EL 소자로서 유기 EL 소자(OEL, PEL, PLED, OLED 등 다종다양한 약칭으로 기술됨)(15)를 예로 들어 설명하지만 이것에 한정되는 것이 아니고, 무기 EL 소자에도 적용되는 것은 물론이다.

우선, 유기 EL 표시 패널에 이용되는 액티브 매트릭스 방식은, 특정 화소를 선택하여 필요한 표시 정보를 공급받는다는 것, 1 프레임 기간을 통하여 EL 소자에 전류를 흘려보낼 수 있다는 것의 2가지 조건을 만족시키지 않으면 안된다.

이 2가지 조건을 만족시키기 위해서, 도 46에 도시하는 종래의 유기 EL의 화소 구성에서는, 제1 트랜지스터(11b)는 화소를 선택하기 위한 스위칭용 트랜지스터, 제2 트랜지스터(11a)는 EL 소자(EL막)(15)에 전류를 공급하기 위한 구동용 트랜지스터로 한다.

이 구성은 이용하여 계조를 표시시키는 경우, 구동용 트랜지스터(11a)의 게이트 전압으로서 계조에 따른 전압을 인가할 필요가 있다. 따라서, 구동용 트랜지스터(11a)의 온 전류의 변동이 그대로 표시에 나타난다.

트랜지스터의 온 전류는 단결정으로 형성된 트랜지스터이면, 매우 균일하지만, 염가의 유리 기판에 형성할 수 있는 형성 온도가 450도 이하의 저온 폴리실리콘 기술로 형성한 저온 다결정 트랜지스터에서는, 그 임계값의 변동이  $\pm 0.2V \sim 0.5V$ 의 범위에서 변동이 있다. 그 때문에, 구동용 트랜지스터(11a)를 흐르는 온 전류가 이에 대응하여 변동하여, 표시에 얼룩짐이 발생한다. 이들 얼룩짐은 임계값 전압의 변동뿐만 아니라, 트랜지스터의 이동도, 게이트 절연막의 두께 등에 의해서도 발생한다. 또한, 트랜지스터(11)의 열화에 의해서도 특성을 변화한다.

이 현상은 저온 폴리실리콘 기술에 한정되는 것이 아니며, 프로세스 온도가 450도(섭씨) 이상의 고온 폴리실리콘 기술에서도, 고상(CGS) 성장시킨 반도체막을 이용하여 트랜지스터 등을 형성한 것에서도 발생한다. 그밖에, 유기 트랜지스터에서도 발생한다. 비정질 실리콘 트랜지스터에서도 발생한다.

이하에 설명하는 본 발명은 이들 기술에 대응하여 대책 할 수 있는 구성 혹은 방식이다. 또, 본 명세서에서는 저온 폴리실리콘 기술로 형성한 트랜지스터를 주제로 설명한다.

따라서, 도 46과 같이, 전압을 기입함으로써 계조를 표시시키는 방법에서는, 균일한 표시를 얻기 위해서, 디바이스의 특성을 염밀하게 제어할 필요가 있다. 그러나, 현상의 저온 다결정 폴리실리콘 트랜지스터 등에서는 이 변동을 소정 범위 이내로 억제한다고 하는 스펙을 만족할 수 없다.

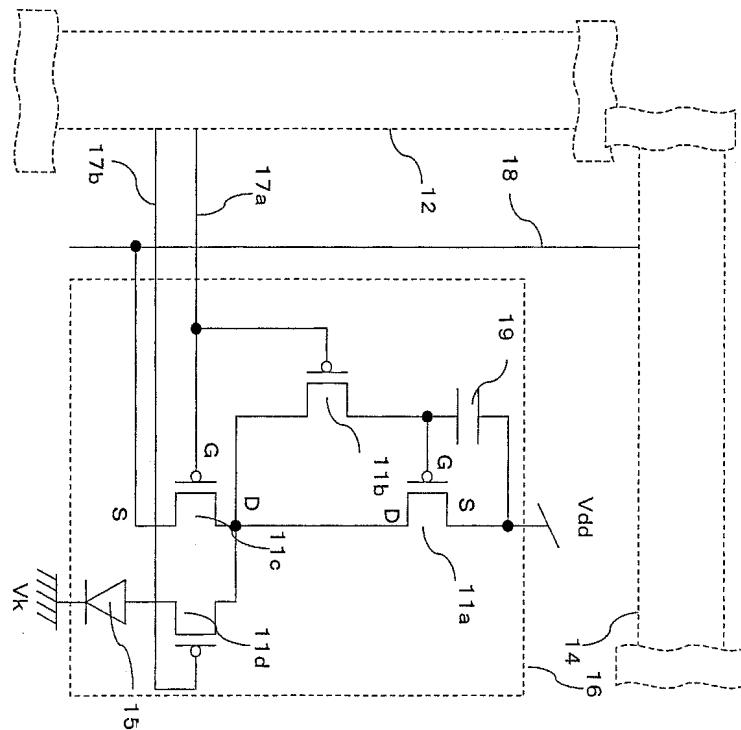

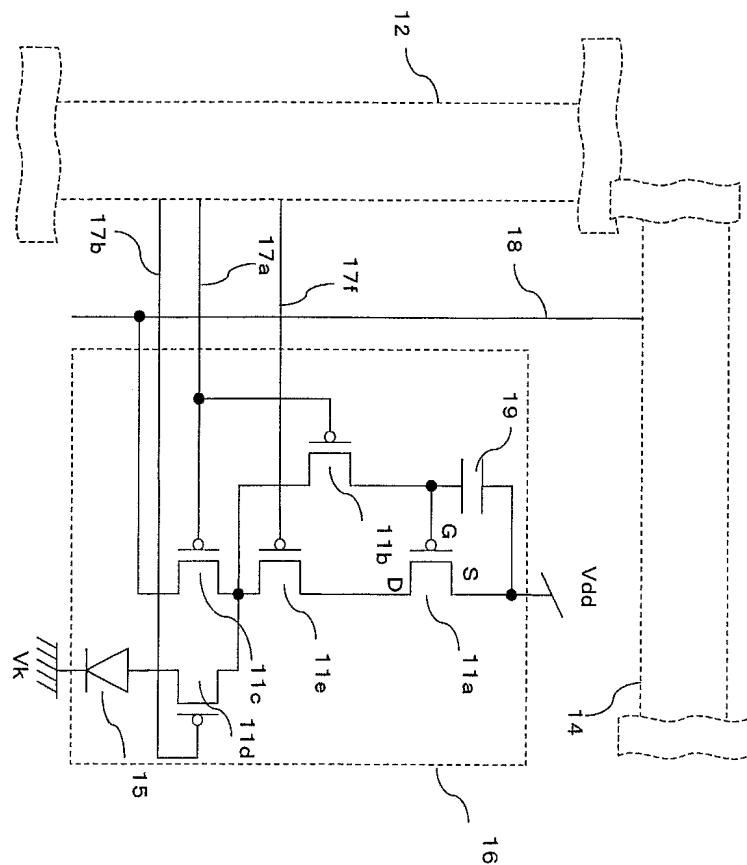

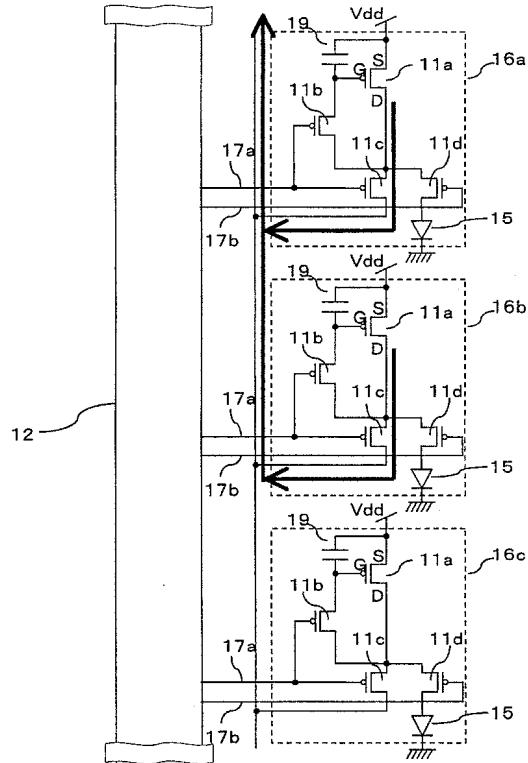

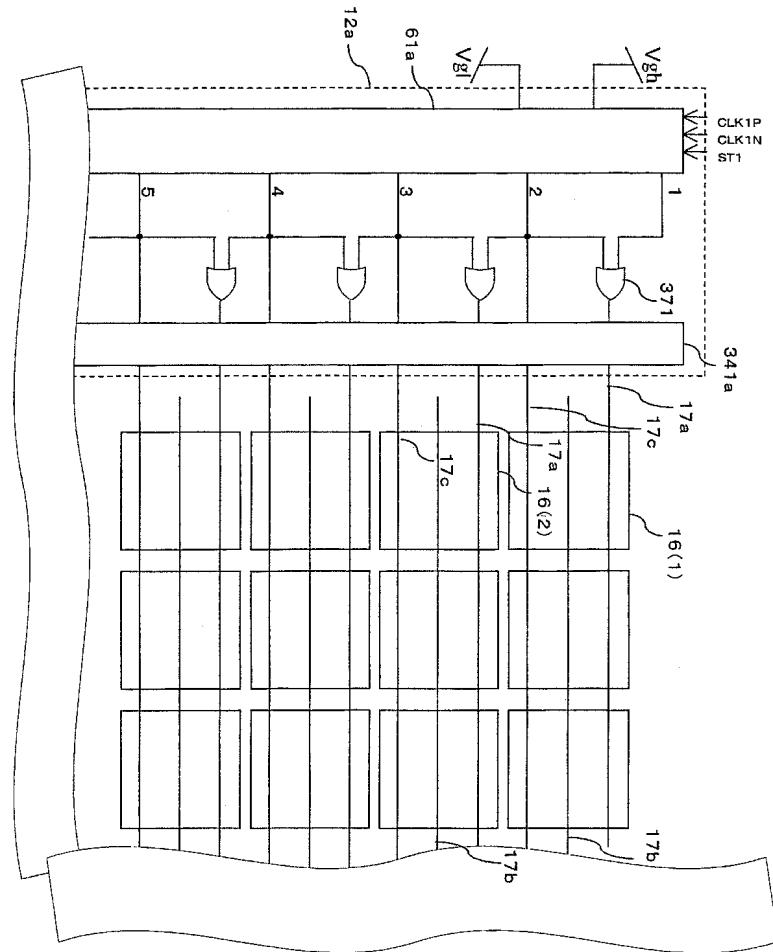

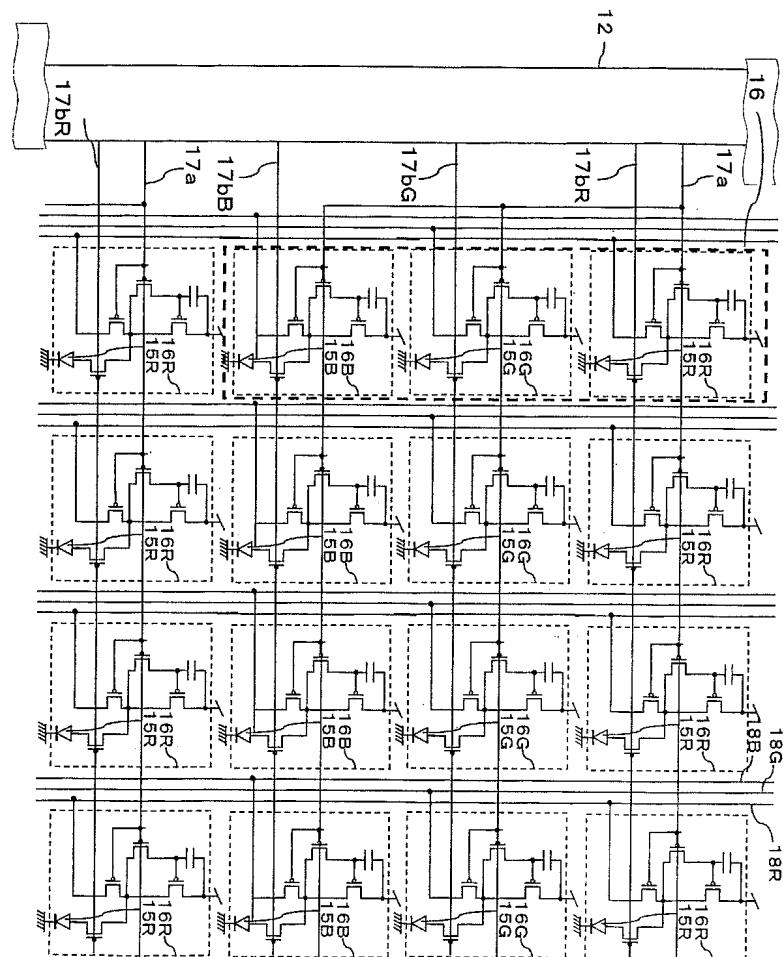

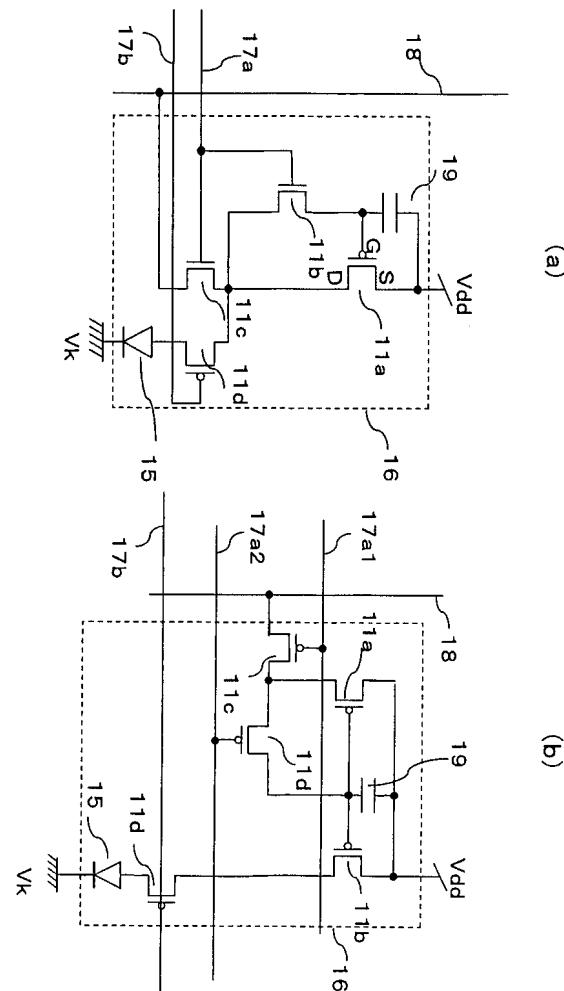

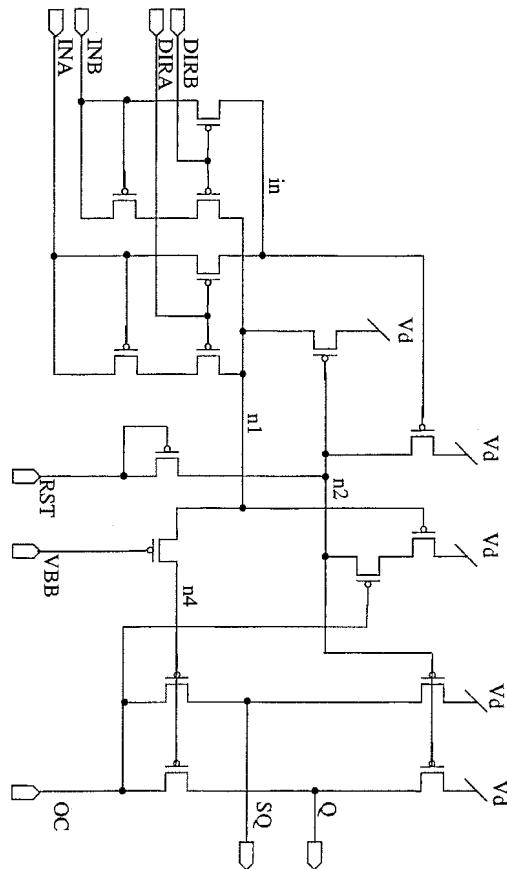

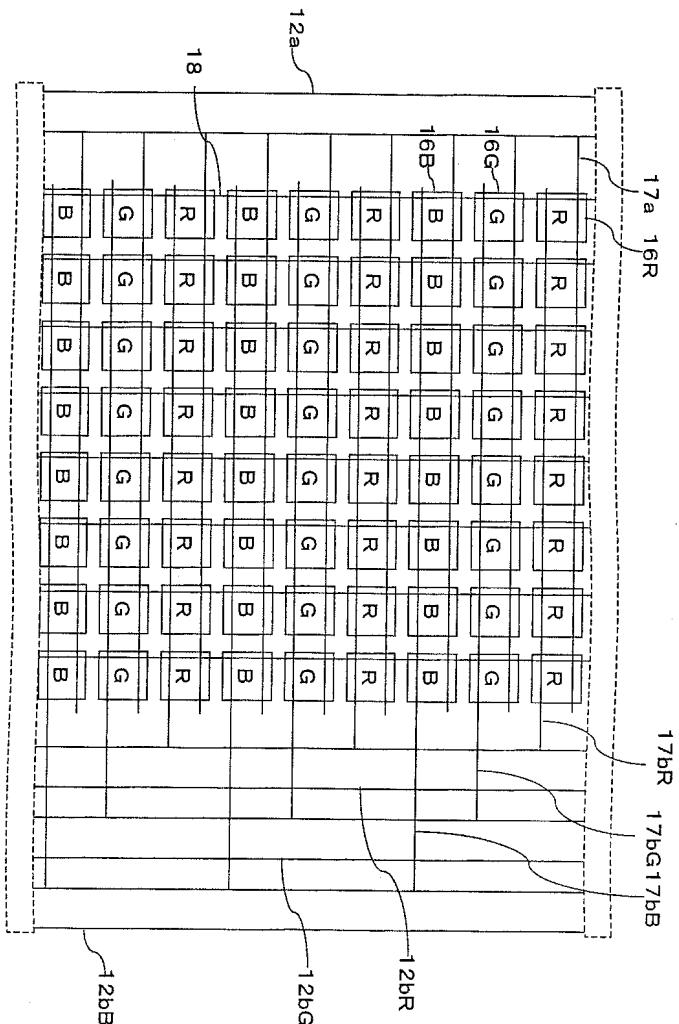

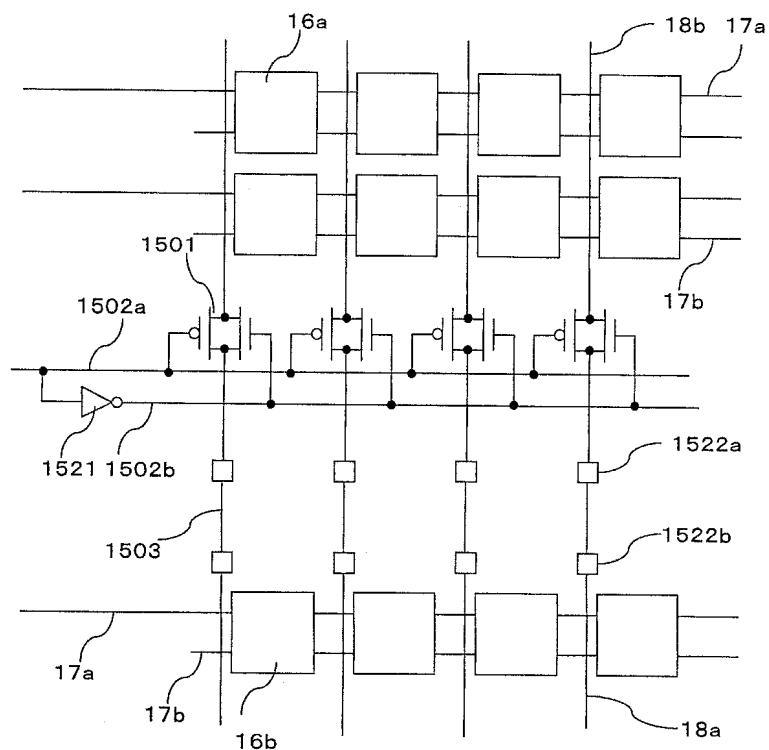

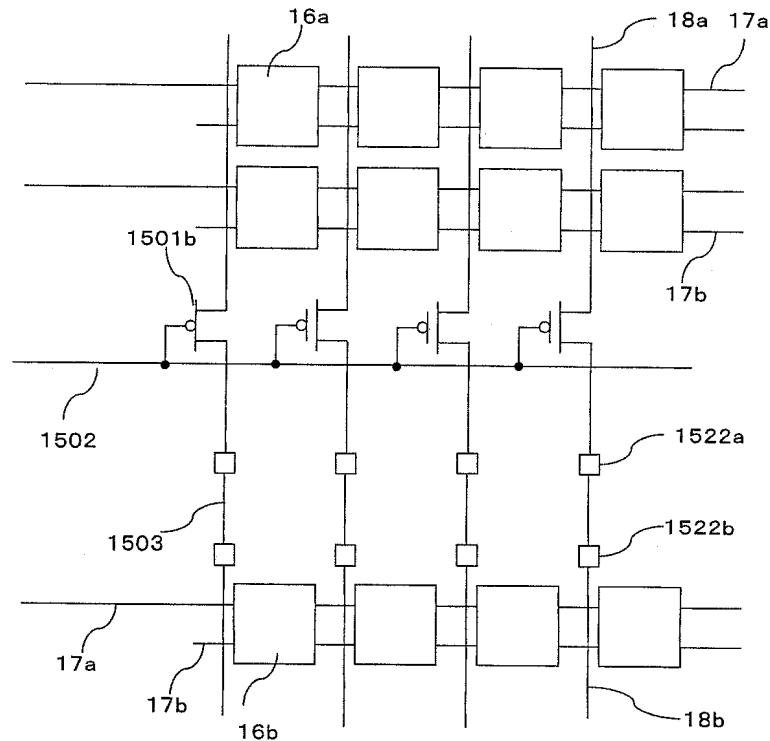

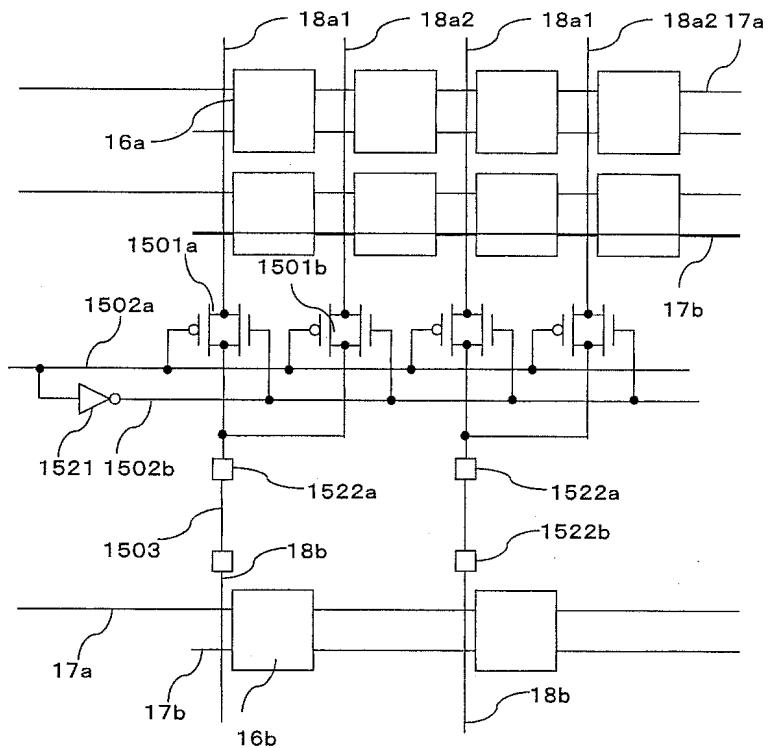

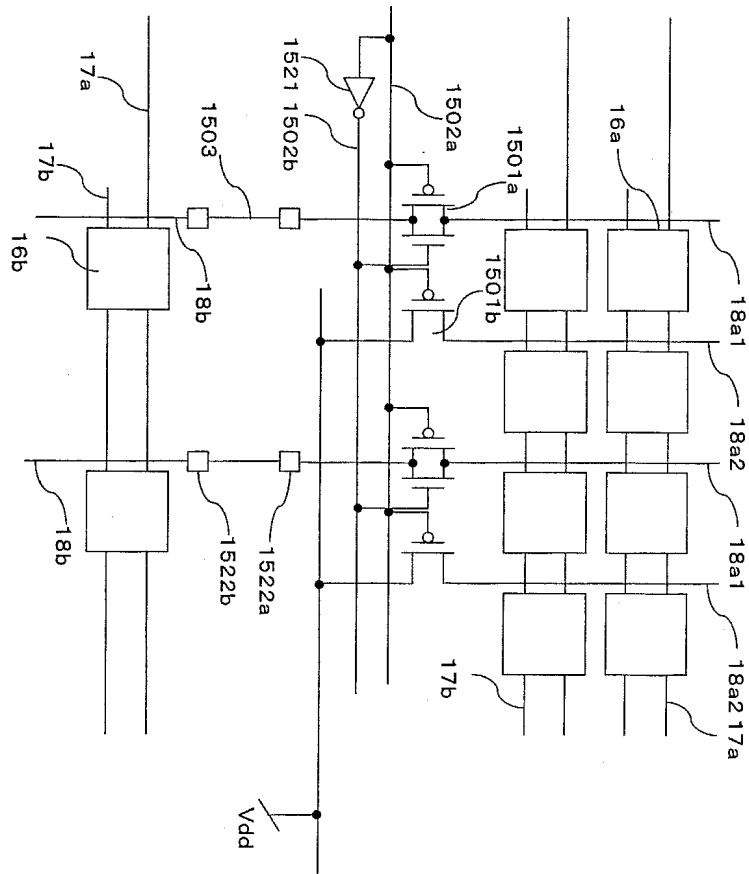

본 발명의 EL 표시 장치의 화소 구조는, 구체적으로는 도 1에 도시한 바와 같이 단위 화소가 최저 4개로 이루어지는 복수의 트랜지스터(11) 및 EL 소자에 의해 형성된다. 화소 전극은 소스 신호선과 중첩되도록 구성한다. 즉, 소스 신호선(18)상에 절연막 혹은 아크릴 재료로 이루어지는 평탄화막을 형성하여 절연하고, 이 절연막 위에 화소 전극(105)을 형성한다. 이와 같이 소스 신호선(18) 상의 적어도 1부에 화소 전극을 중첩하는 구성을 하이 개구(HA) 구조라고 부른다. 불필요한 간섭 광 등이 저감하여 양호한 빛광 상태를 기대할 수 있다.

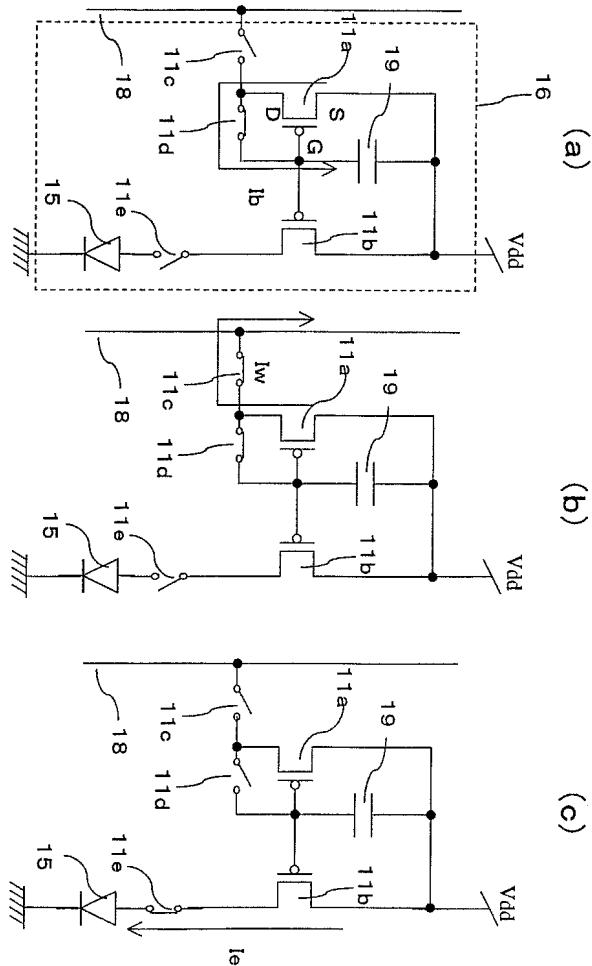

게이트 신호선(제1 주사선)(17a)을 액티브(ON 전압을 인가)로 함으로써 EL 소자(15)의 구동용 트랜지스터(11a) 및 스위치용 트랜지스터(11c)를 통해서, 상기 EL 소자(15)에 흘려야 할 전류값을 소스 드라이버 회로(14)로부터 흘려보낸다. 또한, 트랜지스터(11a)의 게이트와 드레인 사이를 단락하도록 트랜지스터(11b)가 게이트 신호선(17a)을 액티브(ON 전압을 인가)로 하는 것에 의해 개방됨과 함께, 트랜지스터(11a)의 게이트와 소스 사이에 접속된 컨덴서(캐패시터, 축적 용량, 부가 용량)(19)에 트랜지스터(11a)의 게이트 전압(혹은 드레인 전압)을 기억한다(도 3의 (a)를 참조).

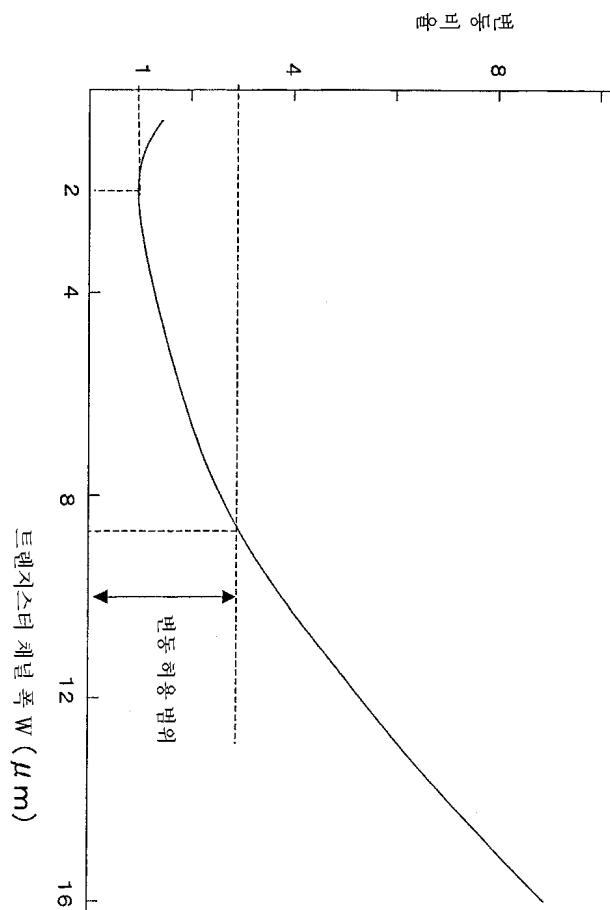

또, 컨덴서(축적 용량)(19)의 크기는  $0.2pF$  이상  $2pF$  이하로 하는 것이 좋고, 그 중에서도 컨덴서(축적 용량)(19)의 크기는  $0.4pF$  이상  $1.2pF$  이하로 하는 것이 좋다. 화소 사이즈를 고려하여 컨덴서(19)의 용량을 결정한다. 1 화소에 필요한 용량을  $C_s(pF)$ 로 하고, 1 화소가 차지하는 면적(개구율이 아님)을  $S_p(\text{평방 } \mu\text{m})$ 로 하면,  $500/S_p \leq C_s \leq 20000/S_p$ 로 되고, 더욱 바람직하게는,  $1000/S_p \leq C_s \leq 10000/S_p$ 로 되도록 한다. 또, 트랜지스터의 게이트 용량은 작기 때문에, 여기서 말하는  $C_s$ 란, 축적 용량(컨덴서)(19) 단독의 용량이다.

게이트 신호선(17a)을 비 액티브(OFF 전압을 인가), 게이트 신호선(17b)을 액티브로 하여, 전류가 흐르는 경로를 상기 제1 트랜지스터(11a) 및 EL 소자(15)에 접속된 트랜지스터(11d) 및 상기 EL 소자(15)를 포함하는 경로로 전환하여, 기억한 전류를 상기 EL 소자(15)에 흘리도록 동작한다(도 3의 (b)를 참조).

이 회로는 1 화소 내에 4개의 트랜지스터(11)를 갖고 있고, 트랜지스터(11a)의 게이트는 트랜지스터(11b)의 소스에 접속되어 있다. 또한, 트랜지스터(11b) 및 트랜지스터(11c)의 게이트는 게이트 신호선(17a)에 접속되어 있다. 트랜지스터(11b)의 드레인은 트랜지스터(11c)의 소스 및 트랜지스터(11d)의 소스에 접속되고, 트랜지스터(11c)의 드레인은 소스 신호선(18)에 접속되어 있다. 트랜지스터(11d)의 게이트는 게이트 신호선(17b)에 접속되고, 트랜지스터(11d)의 드레인은 EL 소자(15)의 애노드 전극에 접속되어 있다.

또, 도 1에서는 모든 트랜지스터는 P 채널로 구성하고 있다. P 채널은 다소 N채널의 트랜지스터에 비하여 모빌리티가 낮지만, 내압이 크고 또 열화도 발생하기 어렵기 때문에 바람직하다. 그러나, 본 발명은 EL 소자 구성을 P 채널로 구성하는 것에만 한정되는 것이 아니다. N채널로만 구성해도 된다. 또, N채널과 P 채널의 양방을 이용하여 구성해도 된다.

최적하게는 화소를 구성하는 트랜지스터(11)를 전부 P 채널로 형성하고, 내장 게이트 드라이버 회로(12)도 P 채널로 형성하는 것이 바람직하다. 이와 같이 어레이를 P 채널만의 트랜지스터로 형성하는 것에 의해, 마스크 매수가 5매로 되어, 저비용화, 고 수율화를 실현할 수 있다.

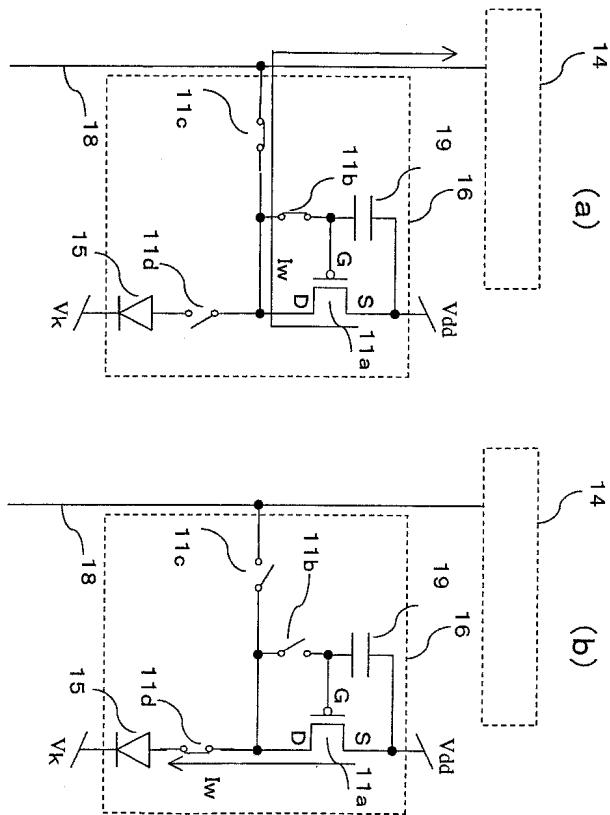

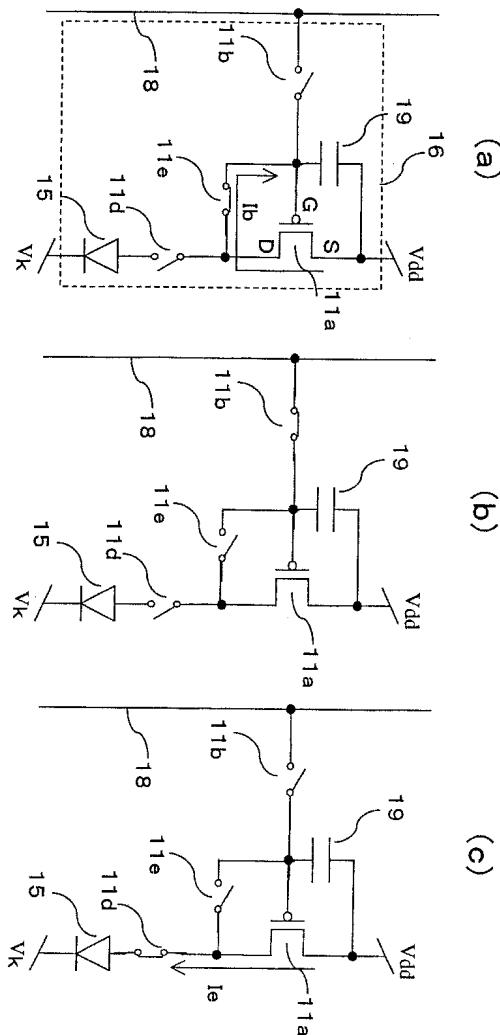

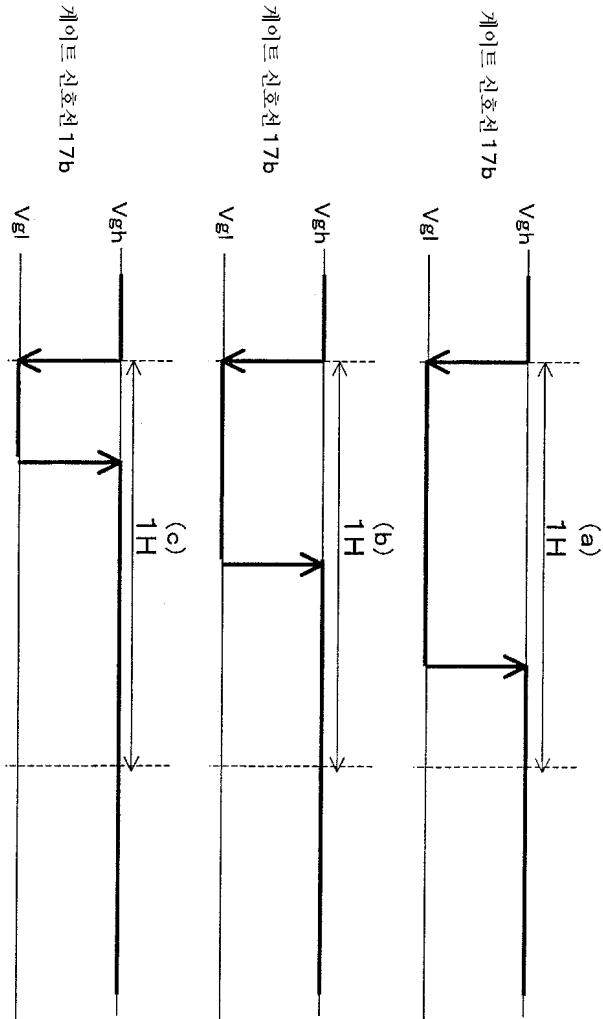

이하, 본 발명의 이해를 더욱 쉽게 하기 위해서, 본 발명의 EL 소자 구성에 대하여 도 3을 이용하여 설명한다. 본 발명의 EL 소자 구성은 2개의 타이밍에 의해 제어된다. 제1 타이밍은 필요한 전류값을 기억시키는 타이밍이다. 이 타이밍에서 트랜지스터(11b) 및 트랜지스터(11c)가 ON함으로써, 등가 회로로서 도 3의 (a)가 된다. 여기서, 신호선으로부터 소정의 전류  $I_w$ 가 기입된다. 이에 의해 트랜지스터(11a)는 게이트와 드레인이 접속된 상태로 되고, 이 트랜지스터(11a)와 트랜지스터(11c)를 통하여 전류  $I_w$ 가 흐른다. 따라서, 트랜지스터(11a)의 게이트-소스의 전압은  $I_1$ 이 흐르는 전압이 된다.

제2 타이밍은 트랜지스터(11b)와 트랜지스터(11c)가 폐쇄되고, 트랜지스터(11d)가 개방되는 타이밍으로, 이 때의 등가 회로는 도 3의 (b)가 된다. 트랜지스터(11a)의 소스-게이트 사이의 전압은 유지된 그대로가 된다. 이 경우, 트랜지스터(11a)는 항상 포화 영역에서 동작하기 때문에,  $I_w$ 의 전류는 일정해진다.

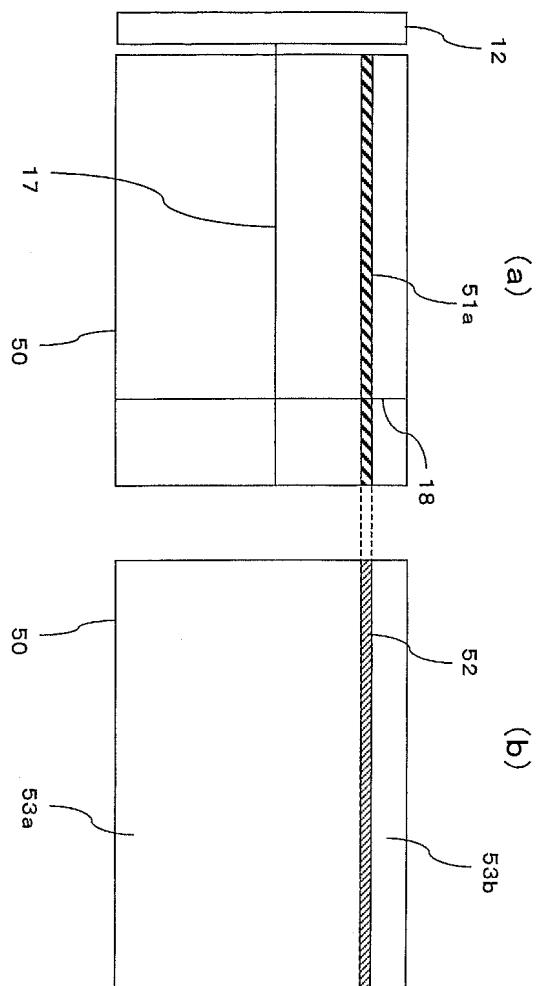

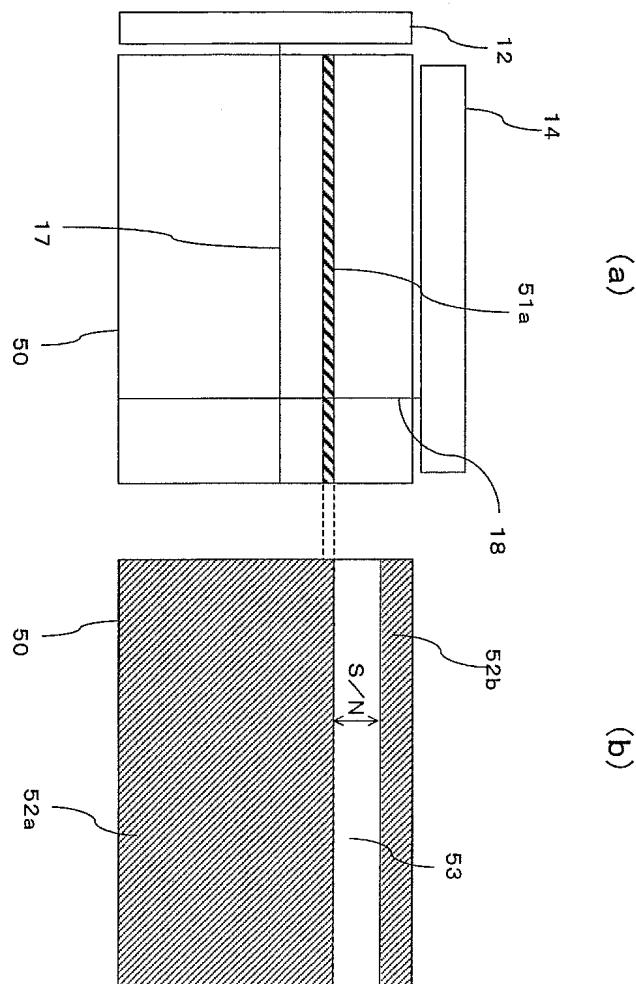

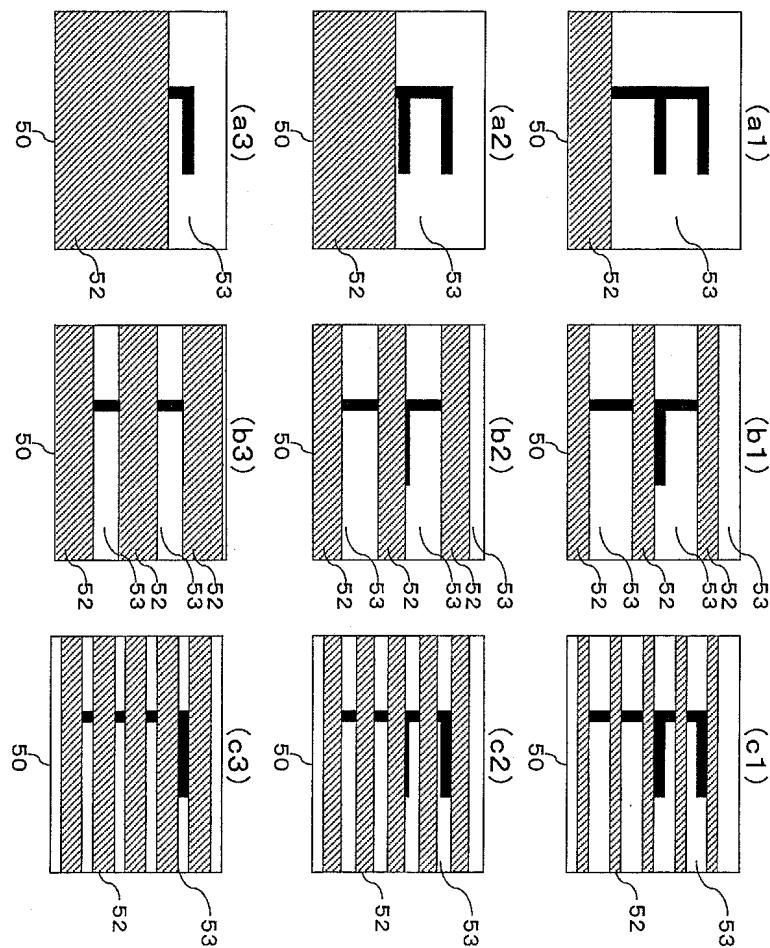

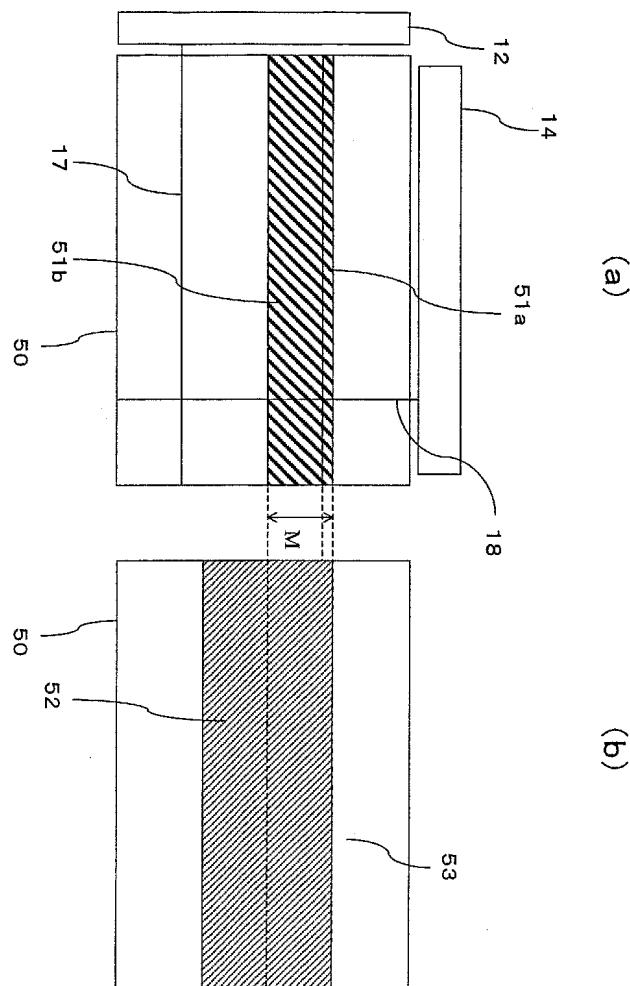

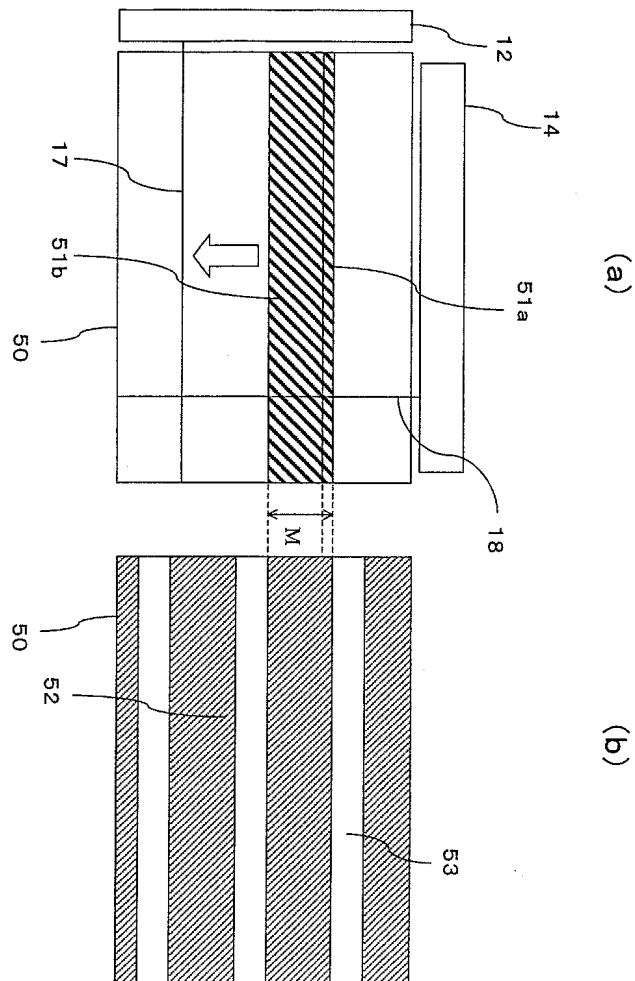

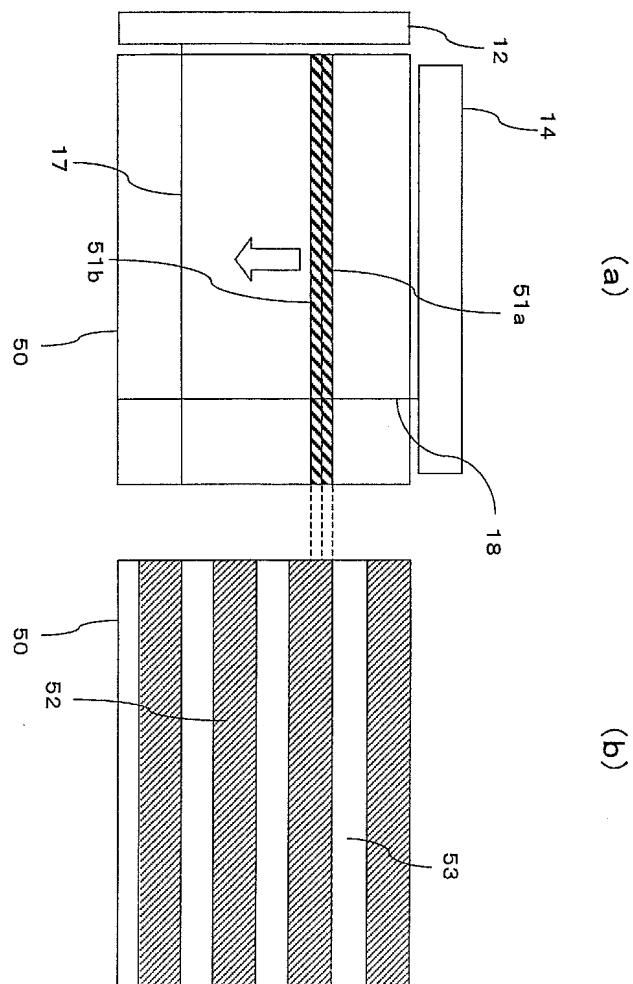

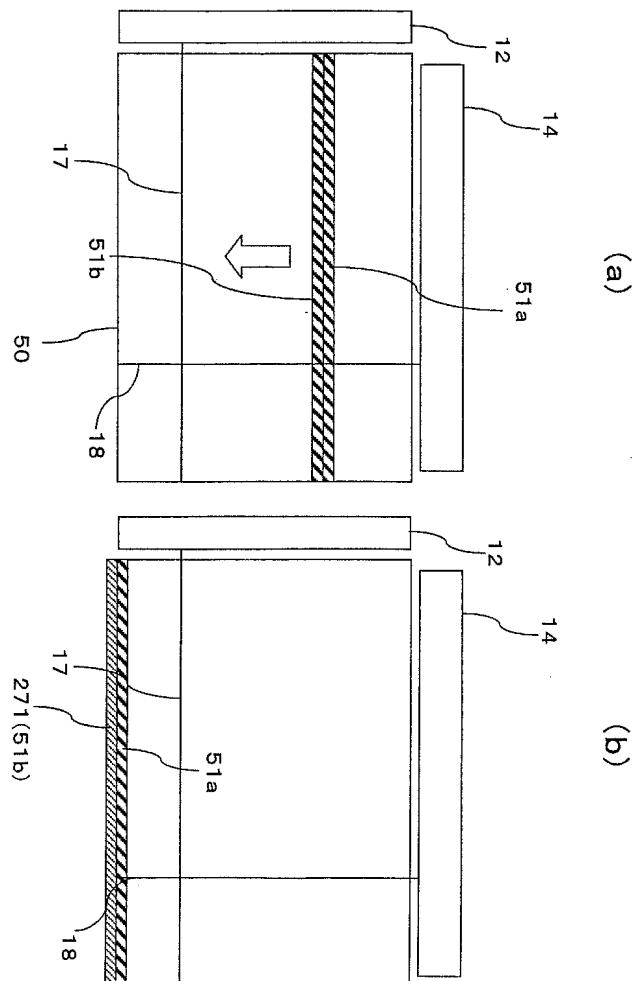

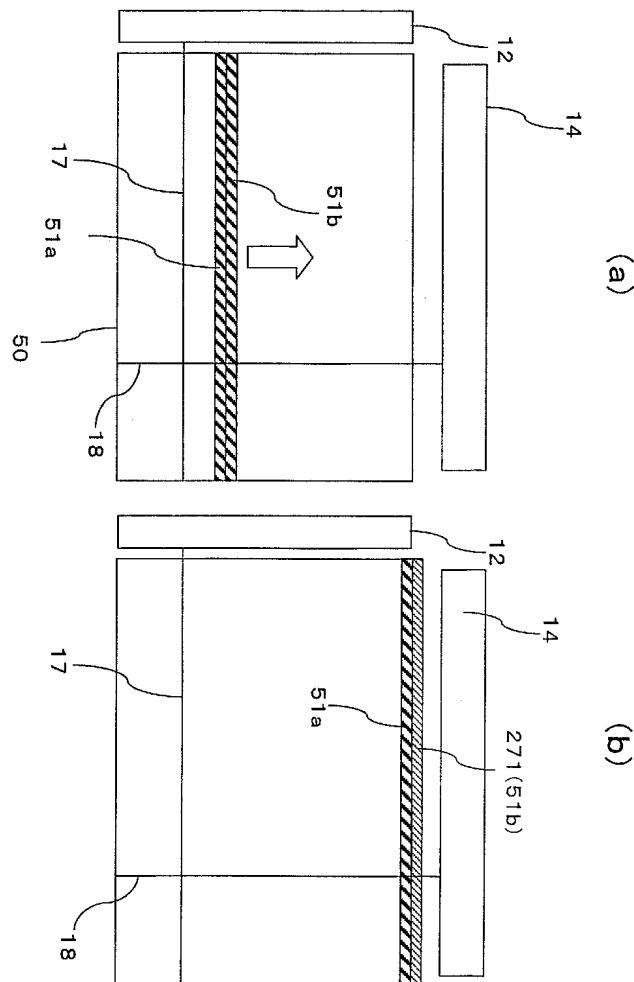

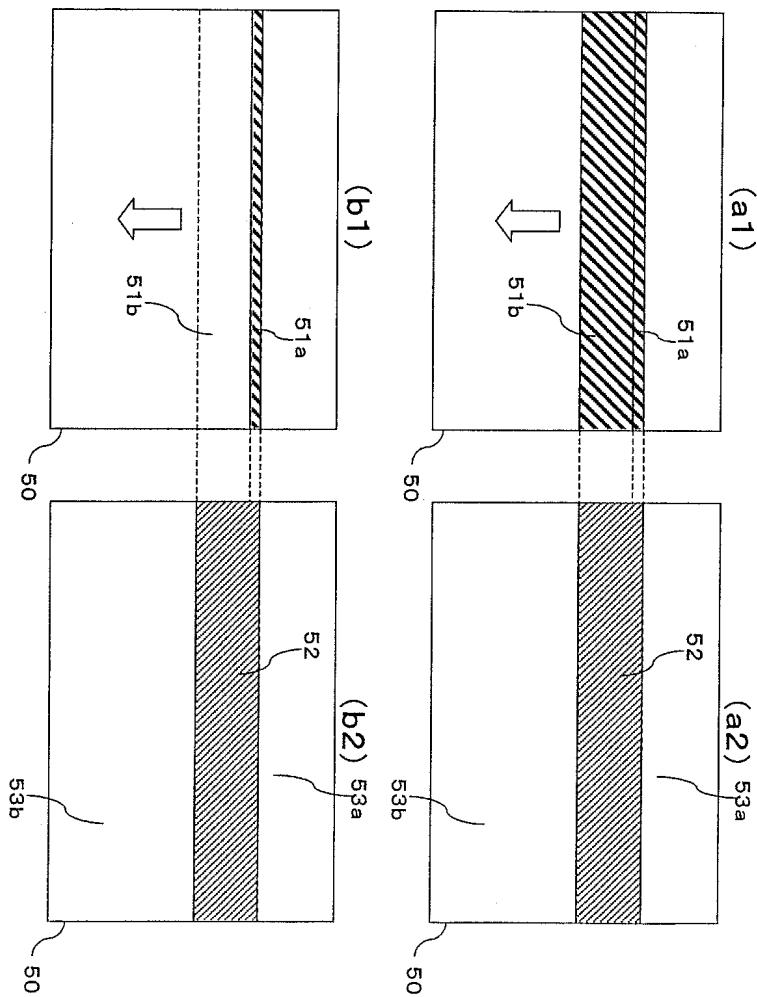

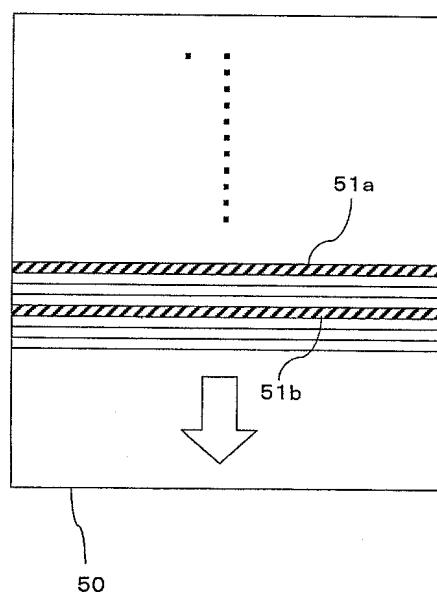

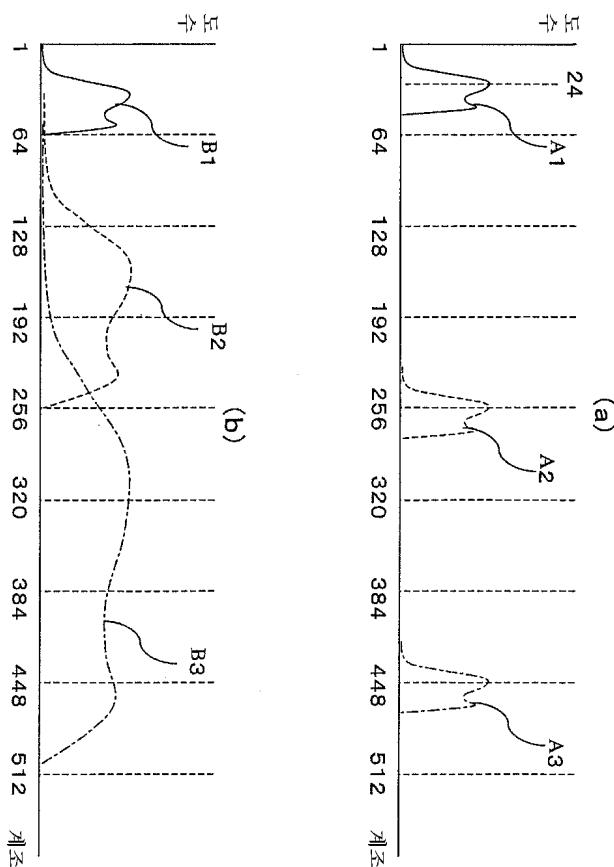

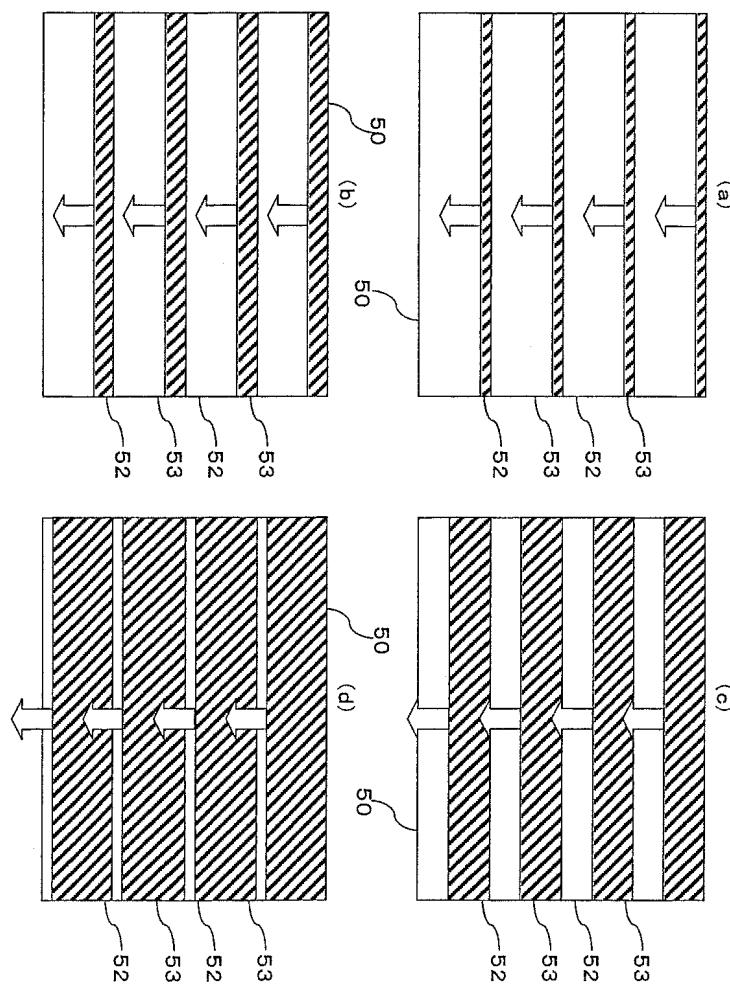

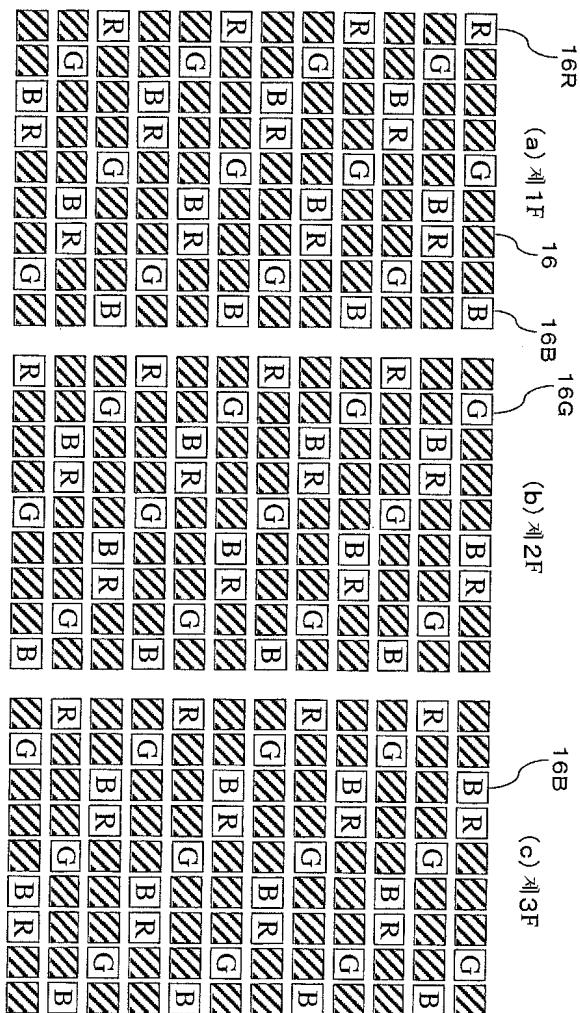

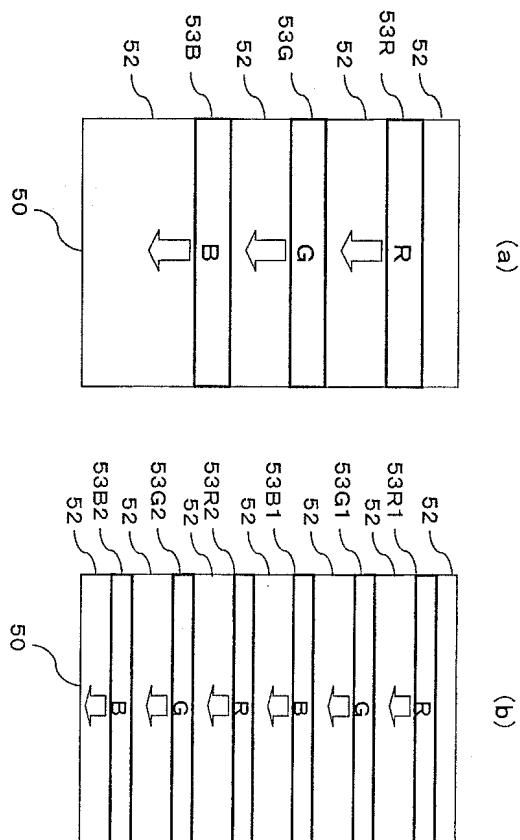

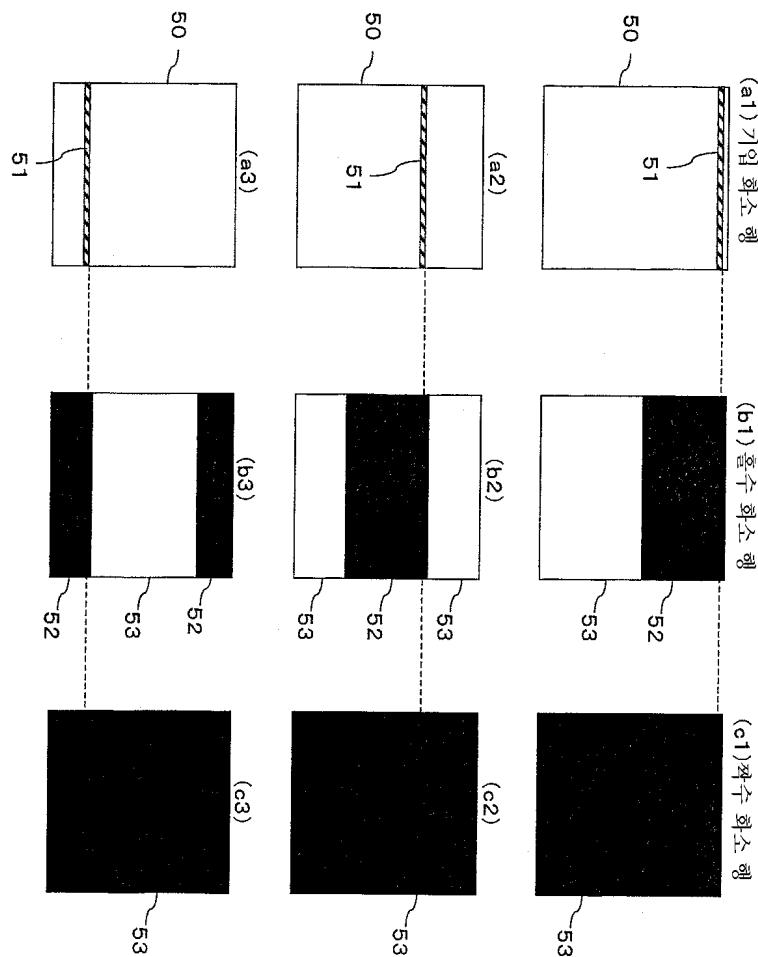

이와 같이 동작시키면, 도 5에 도시하는 바와 같아진다. 즉, 도 5의 (a)의 (51a)는 표시 화면(50)에 있어서의, 어느 시각에서의 전류 프로그램되어 있는 화소(행)(기입 화소 행)를 나타내고 있다. 이 화소(행)(51a)는 도 5의 (b)에 도시하는 바와 같이 비점등(비표시 화소(행))으로 한다. 다른 화소(행)는 표시 화소(행)(53)로 한다(표시 영역(53)의 화소(16)의 EL 소자(15)에는 전류가 흘러, EL 소자(15)가 발광하고 있음).

도 1의 화소 구성인 경우, 도 3의 (a)에 도시한 바와 같이, 전류 프로그램 시에는 프로그램 전류  $I_w$ 가 소스 신호선(18)에 흐른다. 이 전류  $I_w$ 가 트랜지스터(11a)를 흐르고,  $I_w$ 를 흘리는 전류가 유지되도록, 컨덴서(19)에 전압 설정(프로그램)된다. 이 때, 트랜지스터(11d)는 오픈 상태(오프 상태)이다.

다음에, EL 소자(15)에 전류를 흘려보내는 기간에는 도 3의 (b)와 같이, 트랜지스터(11c, 11b)가 오프 상태로 되고, 트랜지스터(11d)가 동작한다. 즉, 게이트 신호선(17a)에 오프 전압( $V_{gh}$ )이 인가되어, 트랜지스터(11b, 11c)가 오프 상태로 된다. 한편, 게이트 신호선(17b)에 온 전압( $V_{gl}$ )이 인가되어, 트랜지스터(11d)가 온 상태로 된다.

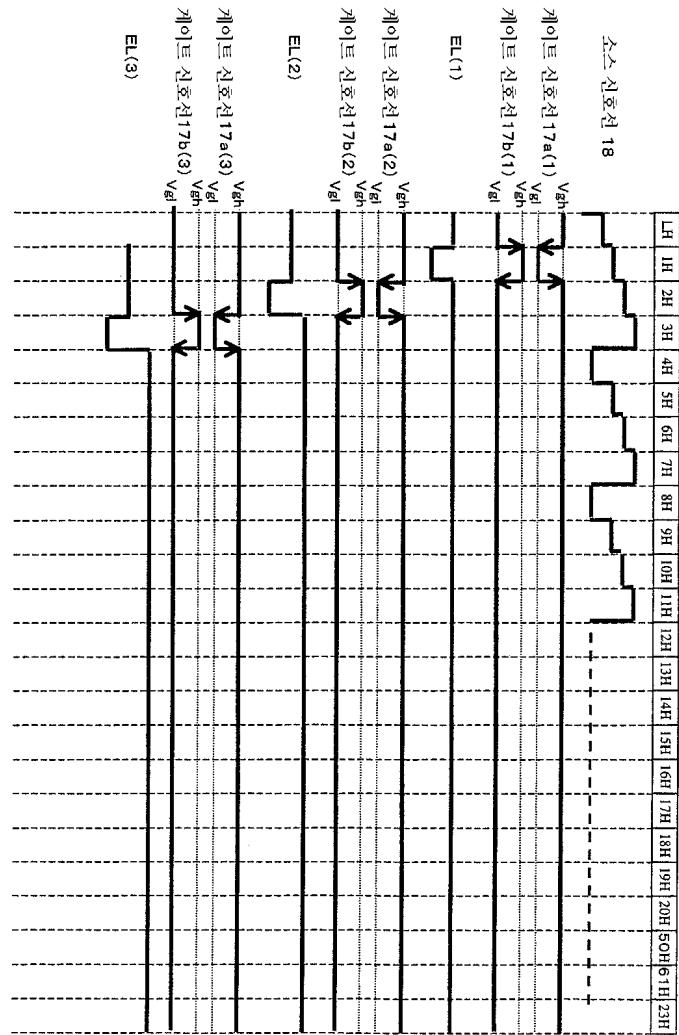

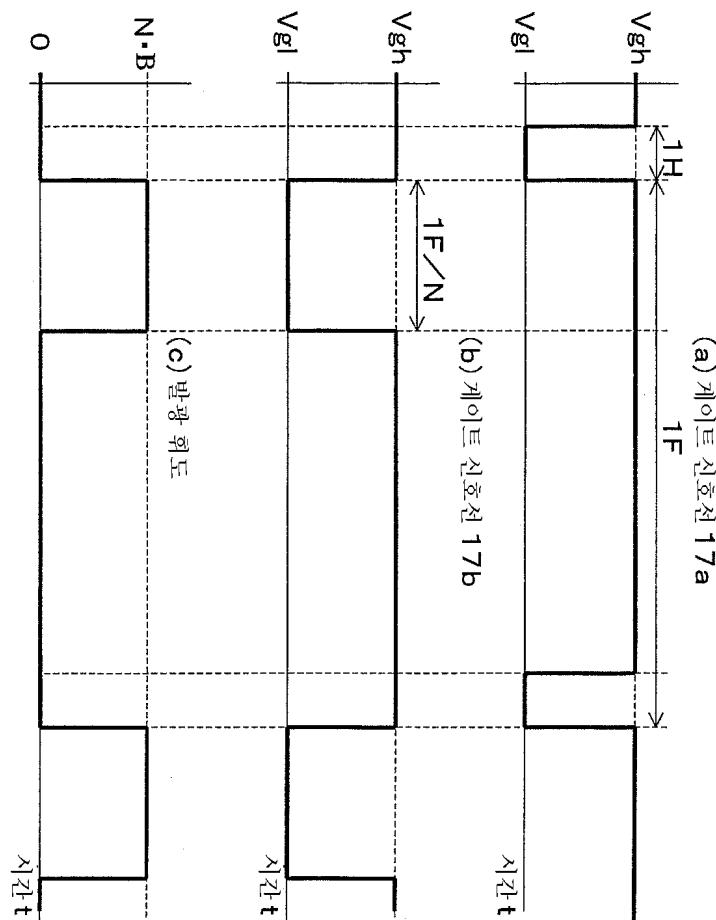

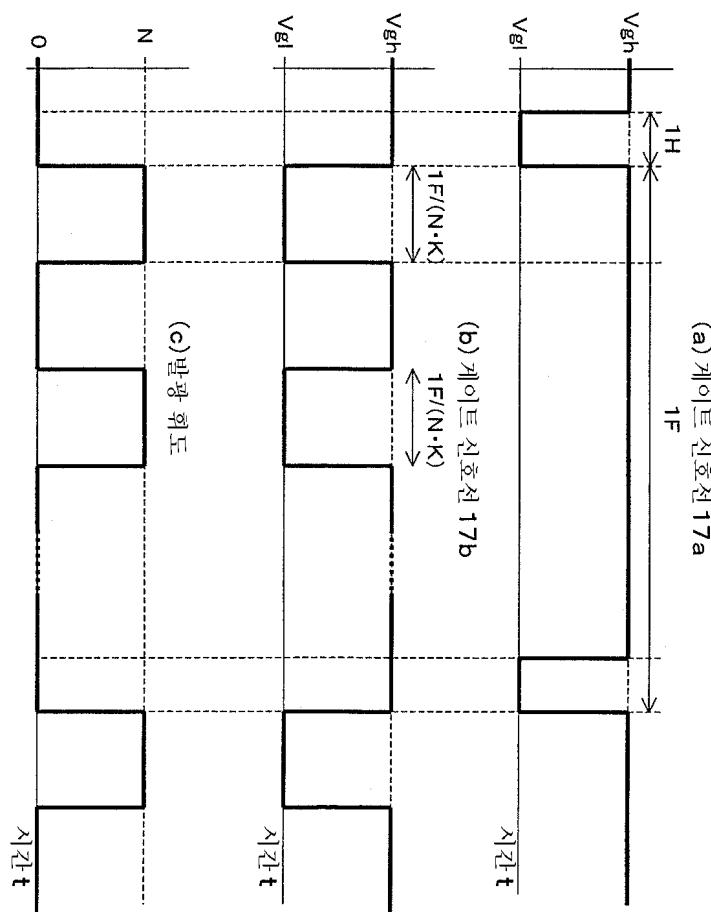

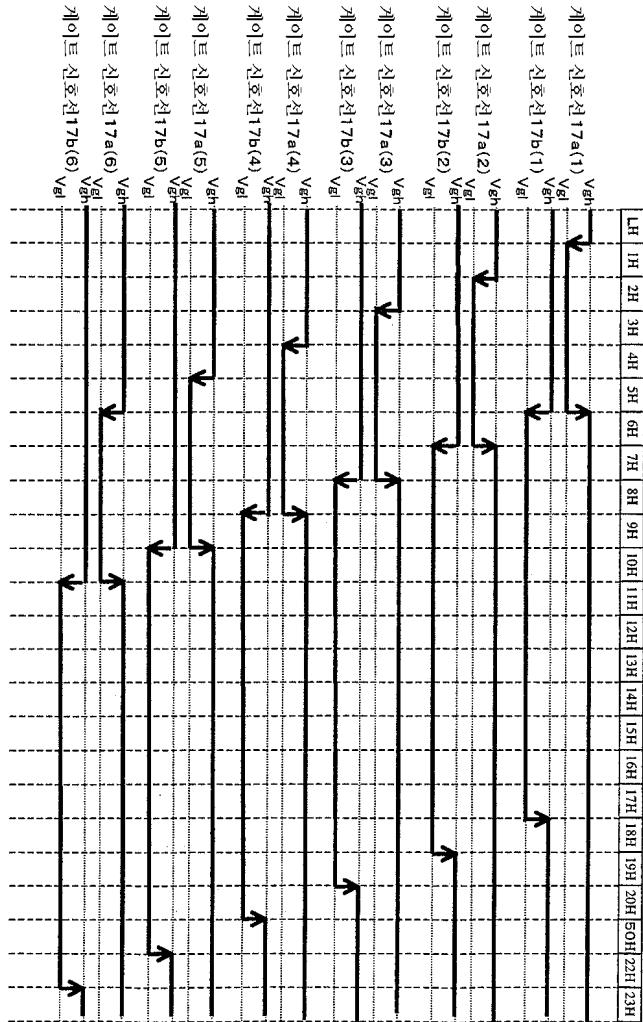

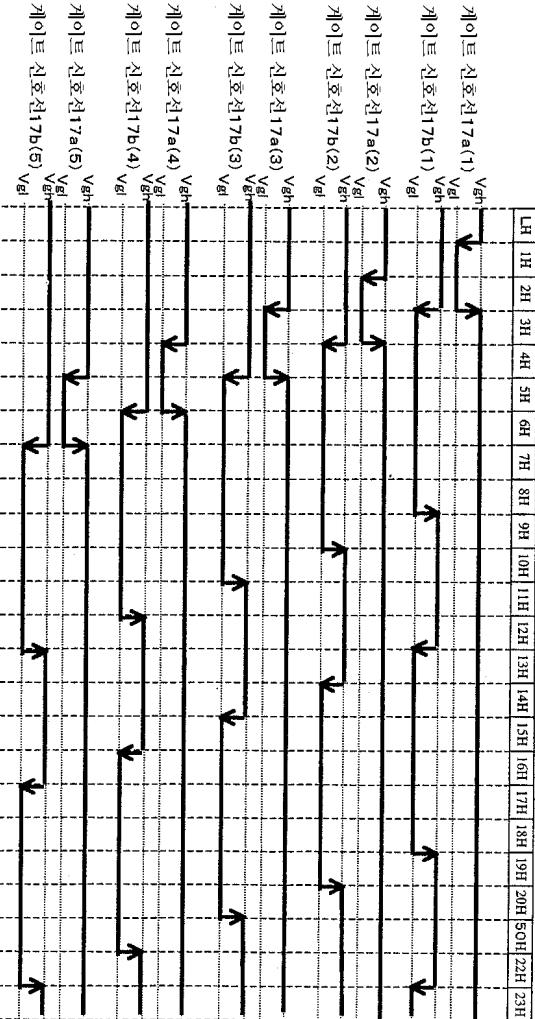

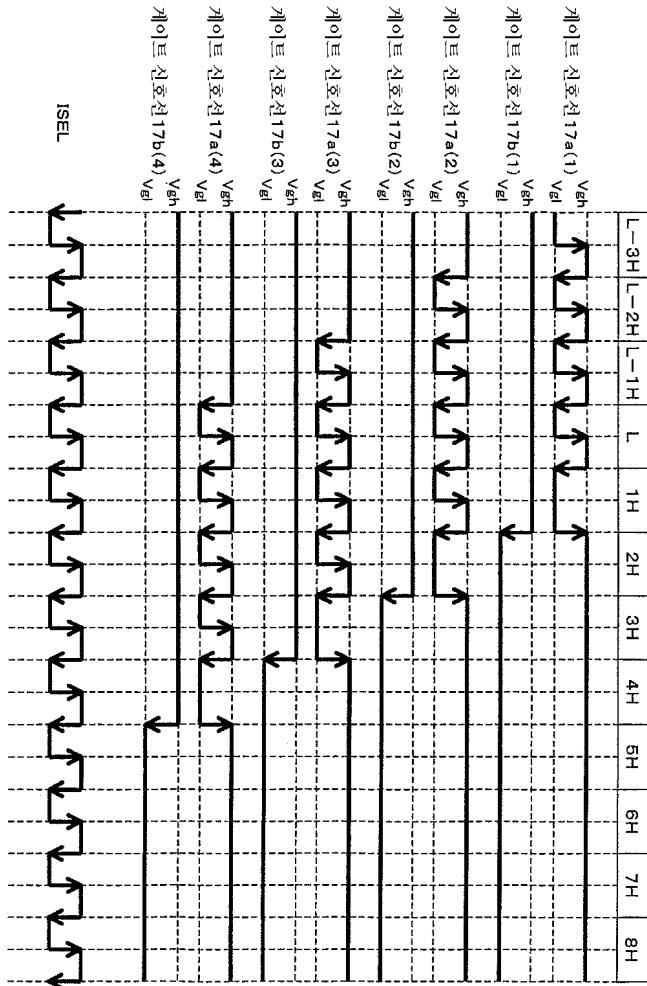

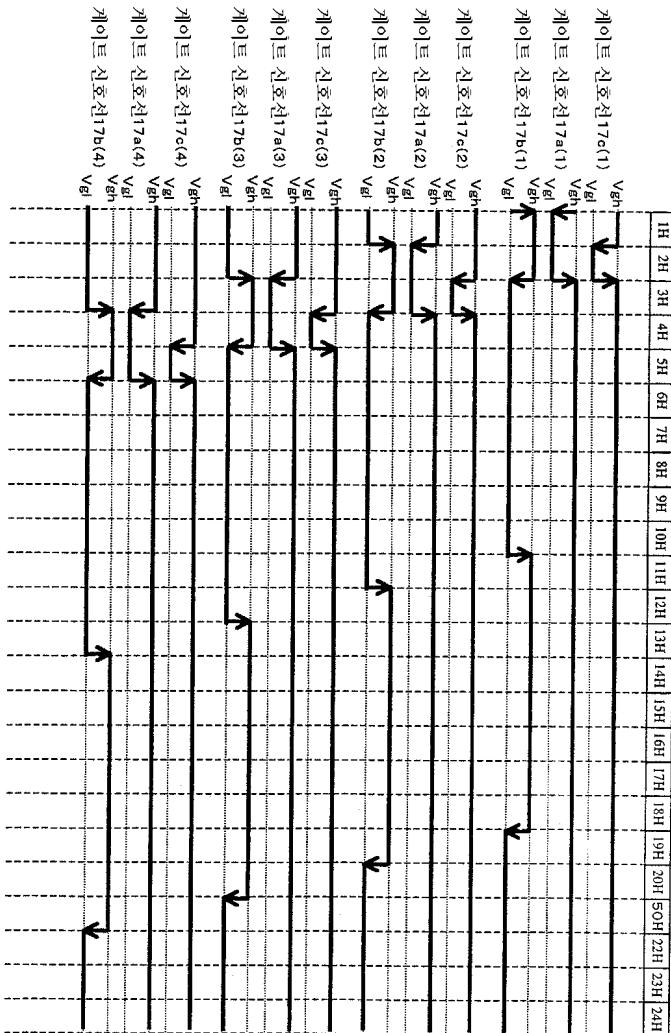

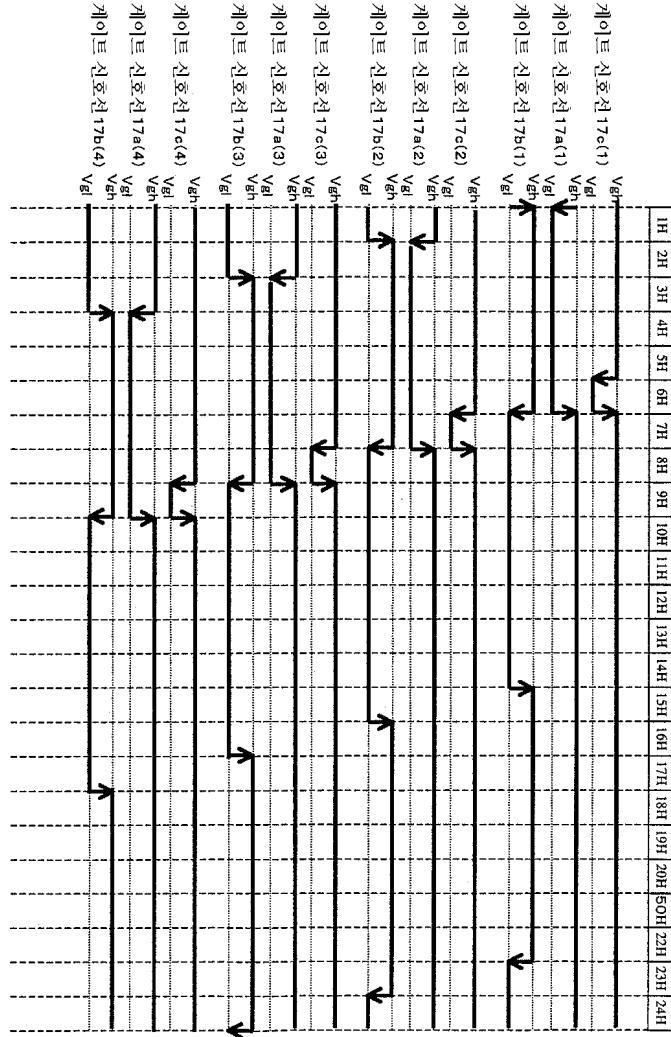

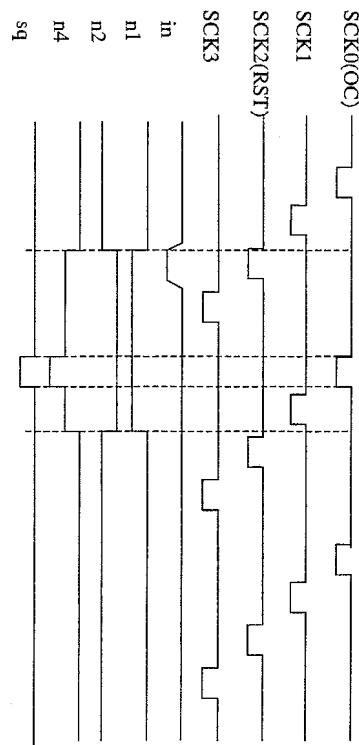

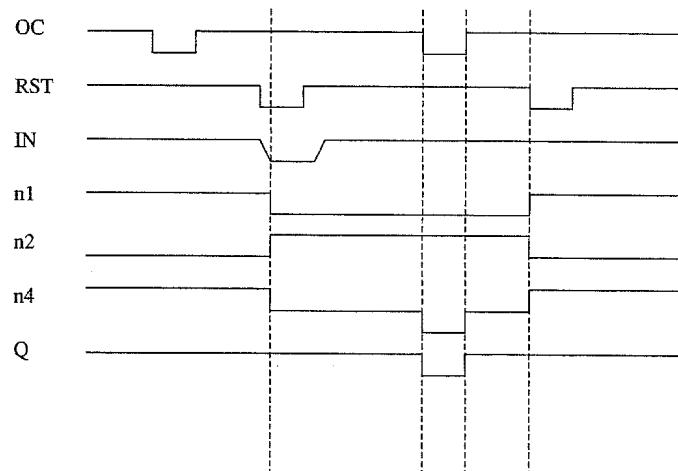

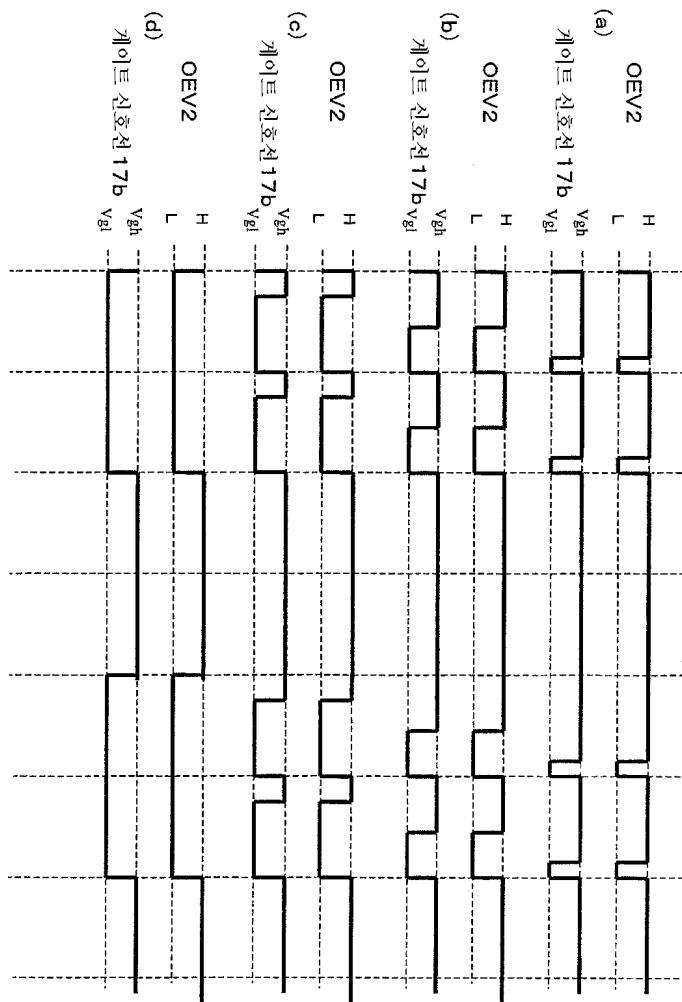

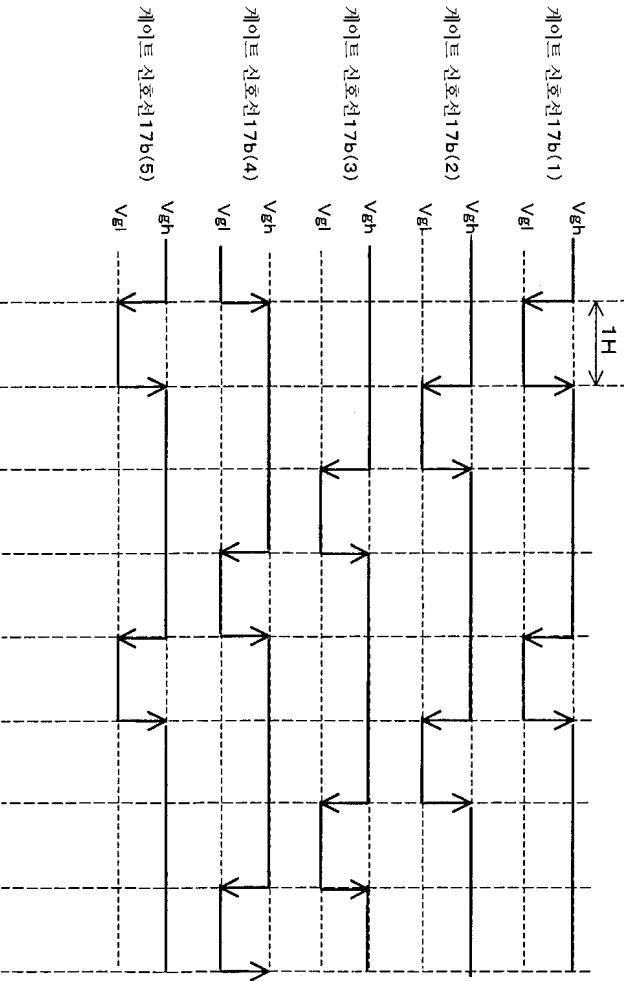

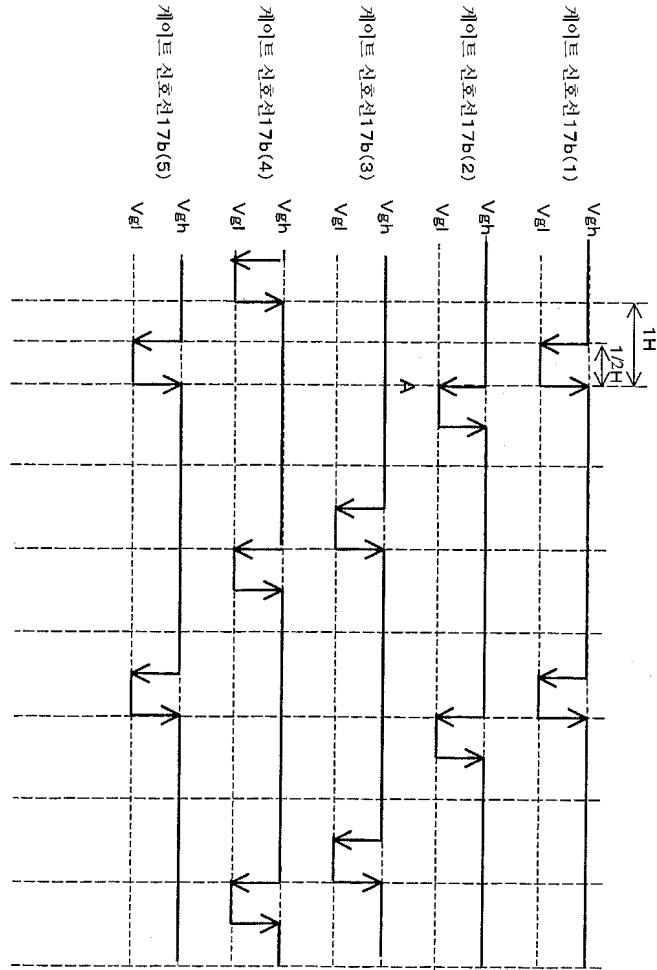

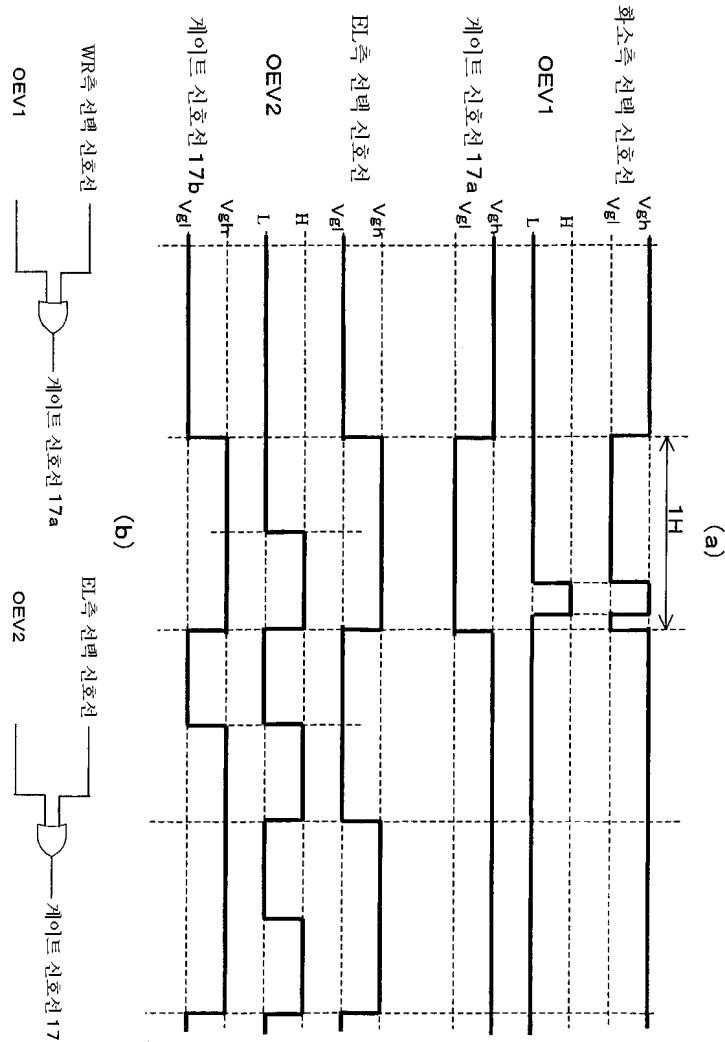

이 타이밍차트를 도 4에 도시한다. 또, 도 4 등에 있어서, 괄호 내의 첨자(예를 들면, (1) 등)는 화소 행의 번호를 나타내고 있다. 즉, 게이트 신호선(17a)(1)이란, 화소 행(1)의 게이트 신호선(17a)을 나타내고 있다. 또한, 도 4의 상단의 \*H(「\*」에는 임의의 기호, 수치가 적합하며, 수평 주사선의 번호를 나타냄)란, 수평 주사 기간을 나타내고 있다. 즉, 1H란 제1번째의 수평 주사 기간이다. 또, 이상의 사항은 설명을 쉽게 하기 위한 것으로, 한정(1H의 번호, 1H 주기, 화소 행 번호의 순서 등)되는 것은 아니다.

도 4에서 알 수 있듯이, 각 선택된 화소 행(선택 기간은 1H로 하고 있음)에 있어서, 게이트 신호선(17a)에 온 전압이 인가되고 있을 때에는, 게이트 신호선(17b)에는 오프 전압이 인가된다. 또한, 이 기간에는 EL 소자(15)에는 전류가 흐르고 있지 않다(비점등 상태). 선택되어 있지 않은 화소 행에 있어서, 게이트 신호선(17a)에는 오프 전압이 인가되고, 게이트 신호선(17b)에는 온 전압이 인가되어 있다. 또한, 이 기간에는 EL 소자(15)에 전류가 흐르고 있다(점등 상태).

또, 트랜지스터(11a)의 게이트와 트랜지스터(11c)의 게이트는 동일한 게이트 신호선(17a)에 접속된다. 그러나, 트랜지스터(11a)의 게이트와 트랜지스터(11c)의 게이트를 서로 다른 게이트 신호선(17)에 접속해도 좋다(도 32를 참조). 1 화소의 게이트 신호선은 3개가 된다(도 1의 구성은 2개임). 트랜지스터(11b)의 게이트의 ON/OFF 타이밍과 트랜지스터(11c)의 게이트의 ON/OFF 타이밍을 개별로 제어함으로써, 트랜지스터(11a)의 변동에 따른 EL 소자(15)의 전류값 변동을 더욱 저감할 수 있다.

게이트 신호선(17a)과 게이트 신호선(17b)을 공통으로 하고, 트랜지스터(11c와 11d)가 서로 다른 도전형(N 채널과 P 채널)으로 하면, 구동 회로의 간략화, 및 화소의 개구율을 향상시킬 수 있다.

이와 같이 구성하면 본 발명의 동작 타이밍으로서는 신호선에서의 기입 경로가 오프로 된다. 즉 소정의 전류가 기억될 때에, 전류가 흐르는 경로에 분기가 있으면 정확한 전류값이 트랜지스터(11a)의 소스(S)-게이트(G)간 용량(컨덴서)에 기억되지 않는다. 트랜지스터(11c)와 트랜지스터(11d)를 서로 다른 도전형으로 하는 것에 의해, 서로의 임계값을 제어함으로써 주사선의 전환 타이밍에서 반드시 트랜지스터(11c)가 오프로 된 후에, 트랜지스터(11d)가 온하는 것이 가능해진다.

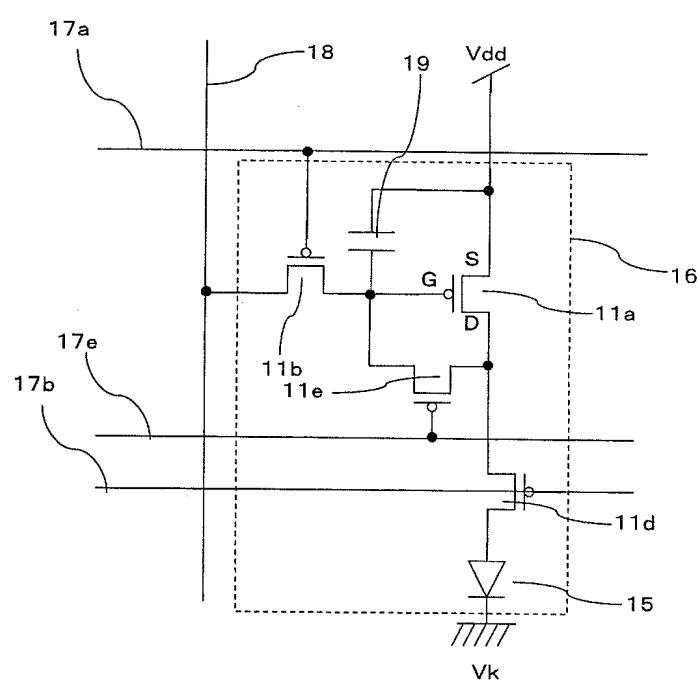

단, 이 경우 서로의 임계값을 정확하게 컨트롤할 필요가 있으므로 프로세스의 주의가 필요하다. 또, 이상 진술한 회로는 최저 4개의 트랜지스터로 실현 가능하지만, 보다 정확한 타이밍의 컨트롤 혹은 후술하는 바와 같이, 미리 효과 저감을 위해 트랜지스터(11e)를 도 2에 도시한 바와 같이, 캐스케이드 접속하여 트랜지스터의 총수가 4 이상으로 되더라도 동작 원리는 동일하다. 이와 같이 트랜지스터(11e)를 가한 구성으로 함으로써, 트랜지스터(11c)를 통하여 프로그램한 전류를 보다 정밀도 좋게 EL 소자(15)에 흘려보낼 수 있게 된다.

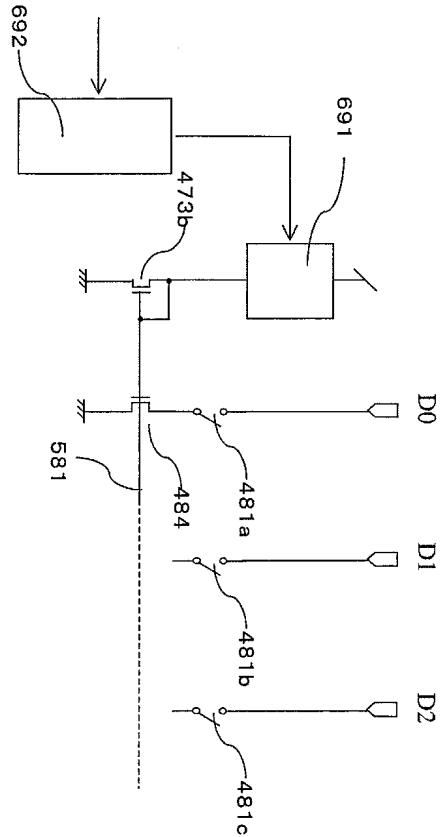

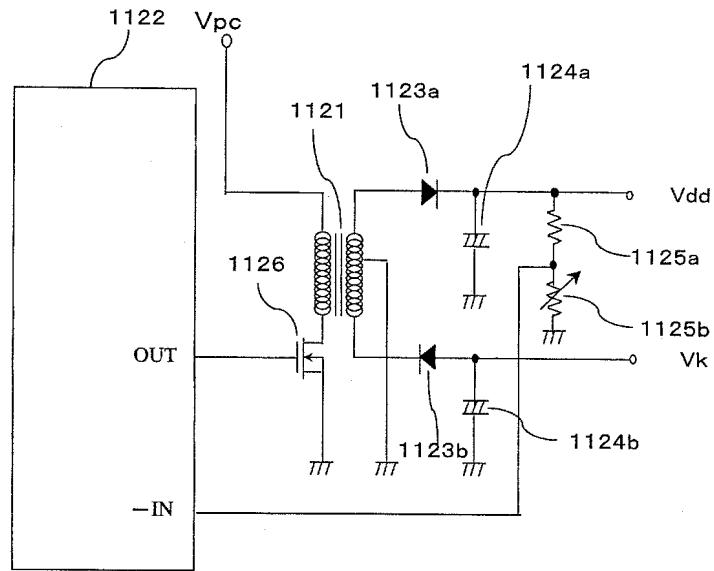

또, 본 발명의 화소 구성은 도 1, 도 2의 구성에 한정되는 것이 아니다. 예를 들면, 도 113과 같이 구성해도 된다. 도 113은, 도 1의 구성에 비하여 트랜지스터(11d)가 없다. 대신에 전환 스위치(1131)가 형성 또는 배치되어 있다. 도 1의 스위치(11d)는 구동용 트랜지스터(11a)로부터 EL 소자(15)에 흐르는 전류를 온 오프(흘린다, 흘리지 않는다) 제어하는 기능을 갖춘다. 이후의 실시예에서도 설명을 하지만, 본 발명은 이 트랜지스터(11d)의 온 오프 제어 기능이 중요한 구성 요소이다. 트랜지스터(11d)를 형성하지 않고 온 오프 기능을 실현하는 것이, 도 113의 구성이다.

도 113에 있어서, 전환 스위치(1131)의 a 단자는 애노드 전압 Vdd에 접속되어 있다. 또, a 단자에 인가하는 전압은 애노드 전압 Vdd에 한정되는 것이 아니며, EL 소자(15)에 흐르는 전류를 오프할 수 있는 전압이면 어느 것이라도 좋다.

전환 스위치(1131)의 b 단자는 캐소드 전압(도 113에서는 접지로 도시함)에 접속되어 있다. 또, b 단자에 인가하는 전압은 캐소드 전압에 한정되는 것이 아니며, EL 소자(15)에 흐르는 전류를 온할 수 있는 전압이면 어느 것이라도 된다.

전환 스위치(1131)의 c 단자에는 EL 소자(15)의 캐소드 단자가 접속되어 있다. 또, 전환 스위치(1131)는 EL 소자(15)에 흐르는 전류를 온 오프시키는 기능을 갖는 것이라도 좋다. 따라서, 도 113의 형성 위치에 한정되는 것이 아니며, EL 소자(15)의 전류가 흐르는 경로이면 어느 것이라도 좋다. 또한, 스위치의 기능이 한정되는 것도 아니고, EL 소자(15)에 흐르는 전류를 온 오프할 수 있으면 어느 것이라도 무방하다. 즉, 본 발명에서는 EL 소자(15)의 전류 경로에 EL 소자(15)에 흘리는 전류를 온 오프할 수 있는 스위칭 수단을 구비하면 어느 화소 구성이라도 좋다.

또한, 오프란 완전히 전류가 흐르지 않는 상태를 의미하는 것이 아니다. EL 소자(15)에 흐르는 전류를 통상보다도 저감 가능한 것이라면 된다. 이상의 사항은 본 발명의 다른 구성에 있어서도 마찬가지이다.

전환 스위치(1131)는 P 채널과 N채널의 트랜지스터를 조합하여 용이하게 실현할 수 있기 때문에 설명이 필요 없을 것이다. 예를 들면, 아날로그 스위치를 2 회로 형성하면 된다. 물론, 스위치(1131)는 EL 소자(15)에 흐르는 전류를 온 오프 상태로 할 뿐이므로, P 채널 트랜지스터 혹은 N채널 트랜지스터로도 형성할 수 있다는 것은 물론이다.

스위치(1131)가 a 단자에 접속되어 있을 때는, EL 소자(15)의 캐소드 단자에 Vdd 전압이 인가된다. 따라서, 구동용 트랜지스터(11a)의 게이트 단자 G가 어떠한 전압 유지 상태이더라도 EL 소자(15)에는 전류가 흐르지 않는다. 따라서, EL 소자(15)는 비점등 상태가 된다.

스위치(1131)가 b 단자에 접속되어 있을 때에는, EL 소자(15)의 캐소드 단자에 GND 전압이 인가된다. 따라서, 구동용 트랜지스터(11a)의 게이트 단자 G에 유지된 전압 상태에 대응하여 EL 소자(15)에 전류가 흐른다. 따라서, EL 소자(15)는 점등 상태가 된다.

이상 내지 도 113의 화소 구성에서는, 구동용 트랜지스터(11a)와 EL 소자(15) 사이에는 스위칭용 트랜지스터(11d)가 형성되어 있지 않다. 그러나, 스위치(1131)를 제어함으로써 EL 소자(15)의 점등 제어를 행할 수 있다.

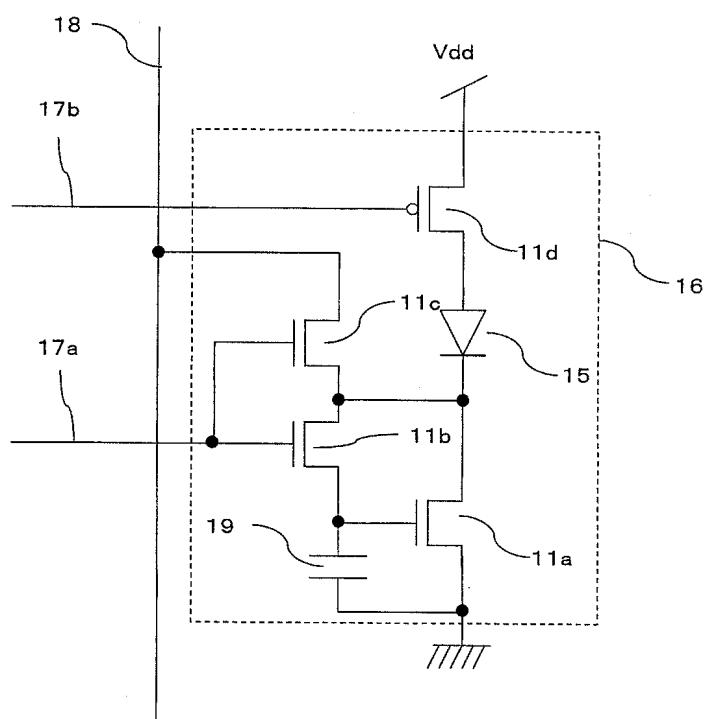

도 1, 도 2 등의 화소 구성에서는, 구동용 트랜지스터(11a)는 1 화소에 대하여 하나이다. 본 발명은 이것에 한정되는 것이 아니고, 구동용 트랜지스터(11a)는 1 화소에 복수 개를 형성 또는 배치해도 된다. 도 116은 그 실시예이다. 도 116에서는

1 화소에 2개의 구동용 트랜지스터(11a1, 11a2)가 형성되고, 2개의 구동용 트랜지스터(11a1, 11a2)의 게이트 단자는 공통의 컨덴서(19)에 접속되어 있다. 구동용 트랜지스터(11a)를 복수개 형성하는 것에 의해, 프로그램되는 전류 변동이 저감한다고 하는 효과가 있다. 다른 구성은 도 1 등과 마찬가지이기 때문에 설명을 생략한다.

도 1, 도 2는 구동용 트랜지스터(11a)가 출력하는 전류를 EL 소자(15)에 흘려보내고, 상기 전류를 구동용 트랜지스터(11a)와 EL 소자(15) 사이에 배치된 트랜지스터(11d)에서 온 오프 제어하는 것이었다. 그러나, 본 발명은 이것에 한정되는 것이 아니다. 예를 들면, 도 117의 구성이 예시된다.

도 117의 실시예에서는 EL 소자(15)에 흘리는 전류가 구동용 트랜지스터(11a)에서 제어된다. EL 소자(15)에 흐르는 전류를 온 오프시키는 것은 Vdd 단자와 EL 소자(15) 사이에 배치된 스위칭 소자(11d)에서 제어된다. 따라서, 본 발명은 스위칭 소자(11d)의 배치는 어디라도 무방하며, EL 소자(15)에 흐르는 전류를 제어할 수 있는 것이면 어느 것이라도 좋다.

트랜지스터(11a)의 특성 변동은 트랜지스터 사이즈와 상관이 있다. 특성 변동을 작게 하기 위해서, 제1 트랜지스터(11a)의 채널 길이가  $5\mu\text{m}$  이상  $100\mu\text{m}$  이하로 하는 것이 바람직하다. 더욱 바람직하게는, 제1 트랜지스터(11a)의 채널 길이가  $10\mu\text{m}$  이상  $50\mu\text{m}$  이하로 하는 것이 바람직하다. 이것은, 채널 길이 L을 길게 한 경우, 채널에 포함되는 임계가 불어나는 것에 의해서 전계가 완화되어 킹크 효과가 낮게 억제되기 때문이라고 생각된다.

이상과 같이, 본 발명은 EL 소자(15)에 전류가 흘러 들어오는 경로, 또는 EL 소자(15)로부터 전류가 흘러 나가는 경로(즉, EL 소자(15)의 전류 경로임)에 EL 소자(15)에 흐르는 전류를 제어하는 회로 수단을 구성 또는 형성 혹은 배치한 것이다.

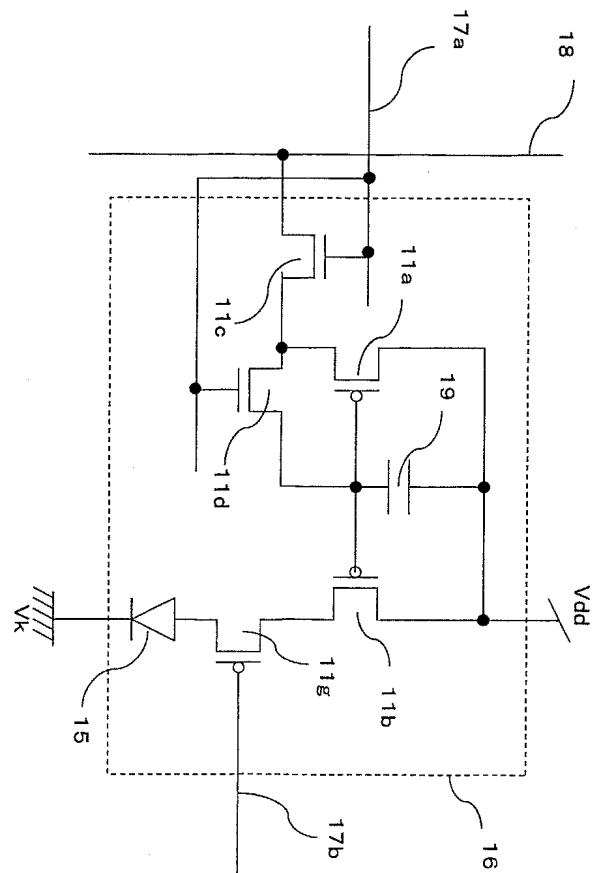

전류 프로그램 방식의 하나인 커런트 미러 방식이더라도, 도 114에 도시하는 바와 같이, 구동용 트랜지스터(11b)와 EL 소자(15) 사이에 스위칭 소자로서의 트랜지스터(11g)를 형성 또는 배치하는 것에 의해 EL 소자(15)에 흐르는 전류를 온 오프할 수 있다(제어할 수 있다). 물론, 트랜지스터(11g)는 도 113의 스위치(1131)로 치환하여도 된다.

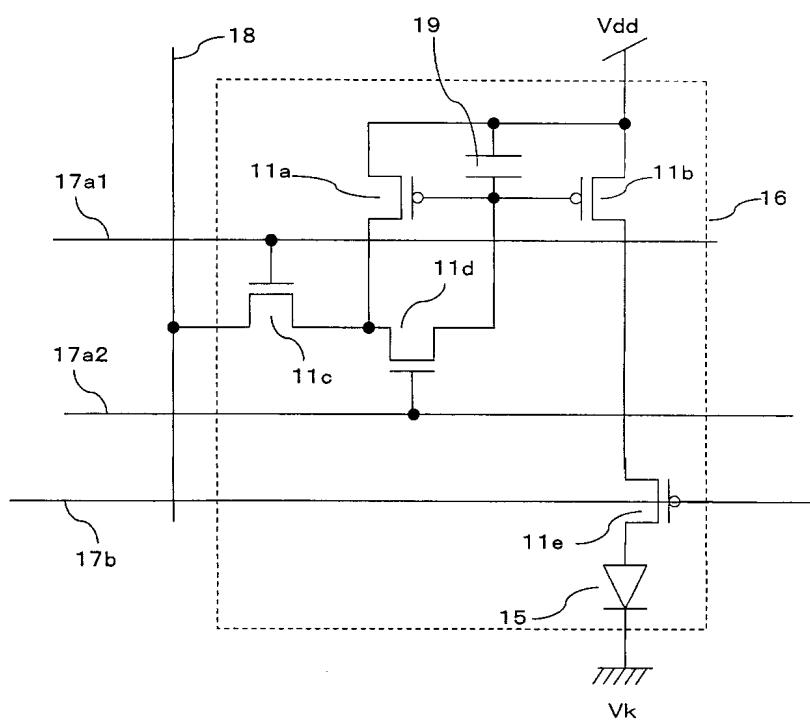

또, 도 114의 스위칭용 트랜지스터(11d, 11c)는 하나의 게이트 신호선(17a)에 접속되어 있지만, 도 115에 도시하는 바와 같이, 트랜지스터(11c)는 게이트 신호선(17a1)에서 제어하고, 트랜지스터(11d)는 게이트 신호선(17a2)에서 제어하도록 구성해도 된다. 도 115의 구성 쪽이 화소(16)의 제어의 범용성이 높아진다.

또한, 도 42의 (a)에 도시하는 바와 같이, 트랜지스터(11b, 11c) 등은 N채널 트랜지스터로 형성해도 된다. 또, 도 42의 (b)에 도시하는 바와 같이 트랜지스터(11c, 11d) 등은 P 채널 트랜지스터로 형성해도 된다.

본 특허의 발명의 목적은, 트랜지스터 특성의 변동이 표시에 영향을 주지 않는 회로 구성을 제안하는 것으로, 이를 위해 4개의 트랜지스터 이상이 필요하다. 이들 트랜지스터의 특성에 의해 회로 상수를 결정하는 경우, 4개의 트랜지스터의 특성이 갖추어지지 않으면, 적절한 회로 상수를 구하는 것이 곤란하다. 레이저 조사의 길이축 방향에 대하여, 채널 방향이 수평인 경우와 수직인 경우에는, 트랜지스터 특성의 임계값과 이동도가 다르게 형성된다. 또, 어느 경우에도 변동의 정도는 동일하다. 수평 방향과 수직 방향에서는 이동도, 임계값의 수치의 평균값이 서로 다르다. 따라서, 화소를 구성하는 모든 트랜지스터의 채널 방향은 동일한 것이 바람직하다.

또한, 축적 용량(19)의 용량값을  $C_s$ , 제2 트랜지스터(11b)의 오프 전류값을  $I_{off}$ 로 한 경우, 다음 식을 만족시키는 것이 바람직하다.

$$3 < C_s / I_{off} < 24$$

더욱 바람직하게는, 다음 식을 만족시키는 것이 바람직하다.

$$6 < C_s / I_{off} < 18$$

트랜지스터(11b)의 오프 전류를  $5\text{pA}$  이하로 함으로써, EL을 흐르는 전류값의 변화를 2% 이하로 억제하는 것이 가능하다. 이것은 리크 전류가 증가하면, 전압 비기입 상태에 있어서 게이트-소스간(컨덴서의 양단)에 축적된 전하를 1 펄드간 유지할 수 없기 때문이다. 따라서, 컨덴서(19)의 축적용 용량이 크면 오프 전류의 허용량도 커진다. 상기 식을 충족함으로써 인접 화소간의 전류값의 변동을 2% 이하로 억제할 수 있다.

또한, 액티브 매트릭스를 구성하는 트랜지스터가 p-채널 폴리실리콘 박막 트랜지스터에 구성되고, 트랜지스터(11b)가 듀얼 게이트 이상인 멀티 게이트 구조로 하는 것이 바람직하다. 트랜지스터(11b)는 트랜지스터(11a)의 소스-드레인간의 스위치로서 작용하기 때문에, 될 수 있는 한 ON/OFF비가 높은 특성이 요구된다. 트랜지스터(11b)의 게이트 구조를 듀얼 게이트 구조 이상의 멀티 게이트 구조로 함으로써 ON/OFF비가 높은 특성을 실현할 수 있다.

화소(16)의 트랜지스터(11)를 구성하는 반도체막은, 저온 폴리실리콘 기술에 있어서, 레이저 어닐링에 의해 형성하는 것이 일반적이다. 이 레이저 어닐링의 조건 변동이 트랜지스터(11) 특성의 변동이 된다. 그러나, 1 화소(16) 내의 트랜지스터(11)의 특성이 일치되어 있으면, 도 1 등의 전류 프로그램을 행하는 방식에서는, 소정의 전류가 EL 소자(15)에 흐르도록 구동할 수 있다. 이 점은 전압 프로그램에 없는 이점이다. 레이저로서는 액시며 레이저를 이용하는 것이 바람직하다.

또, 본 발명에 있어서, 반도체막의 형성은 레이저 어닐링 방법에 한정되는 것이 아니며, 열 어닐링 방법, 고상(CGS) 성장에 의한 방법이어도 좋다. 기타, 저온 폴리실리콘 기술에 한정되는 것이 아니고, 고온 폴리실리콘 기술을 이용하여도 됨은 물론이다. 또한, 비정질 실리콘 기술을 이용하여 형성한 반도체막이어도 된다.

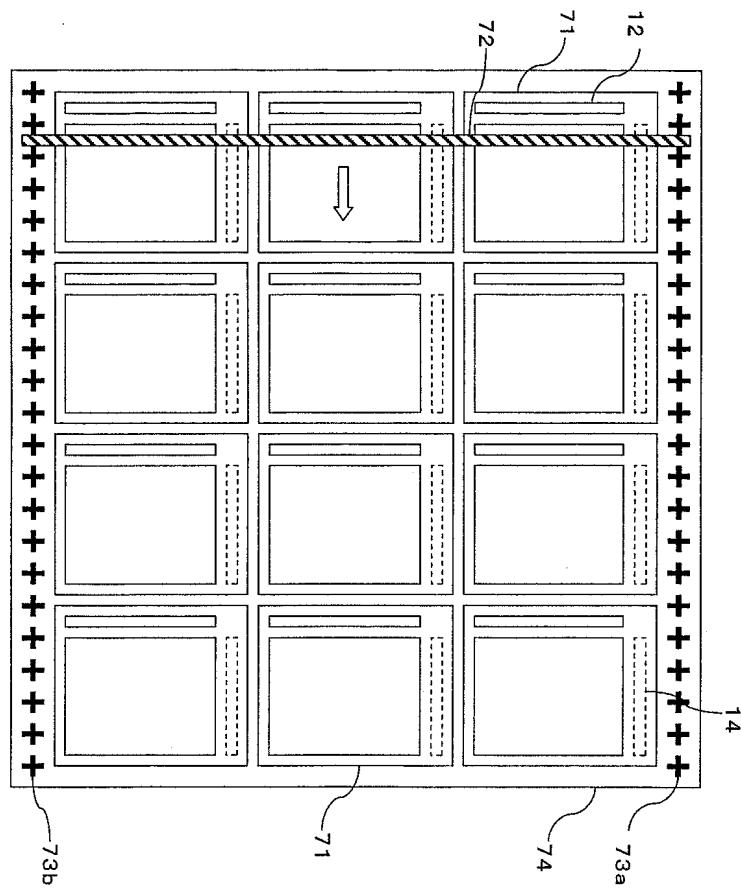

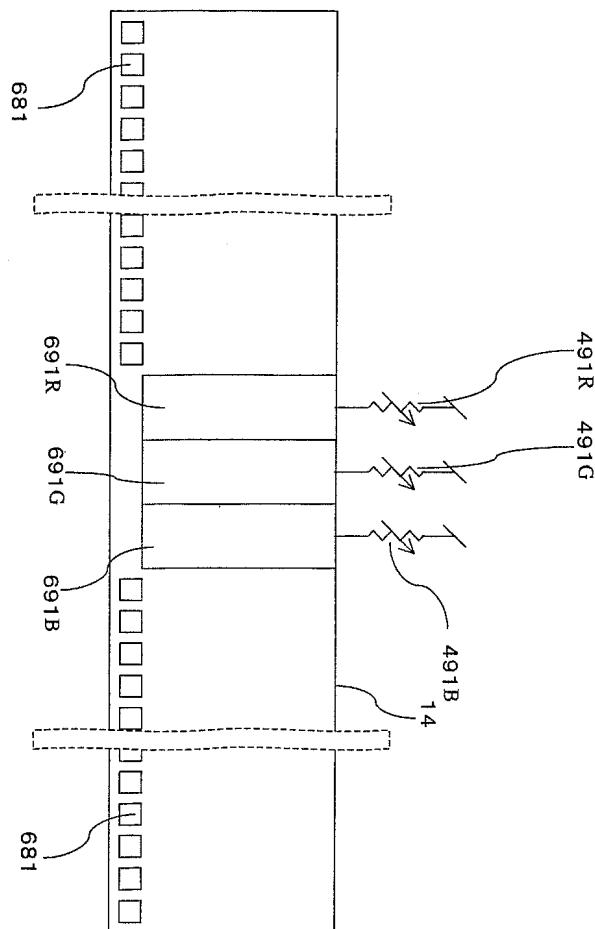

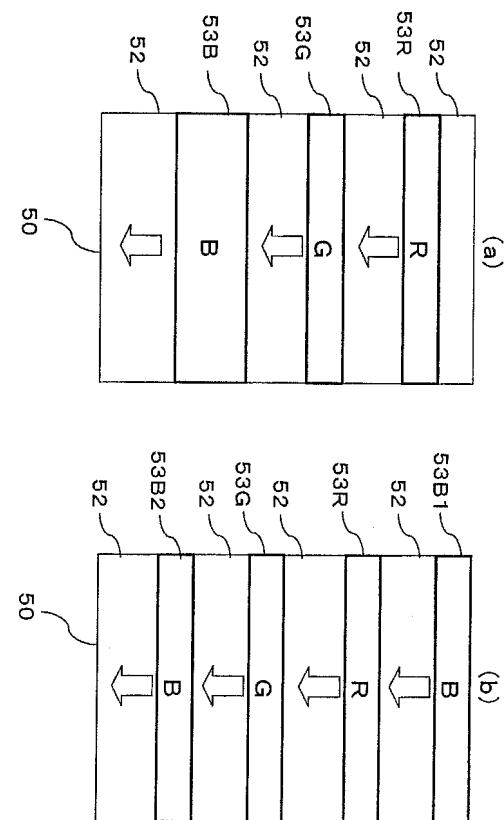

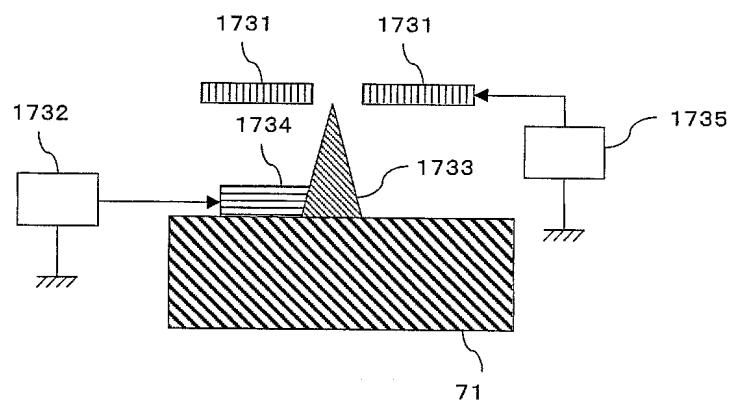

이 과제에 대하여, 본 발명에서는 도 7에 도시한 바와 같이, 어닐링시의 레이저 조사 스폿(레이저 조사 범위)(72)을 소스 신호선(18)에 평행하게 조사한다. 또한, 1 화소 열에 일치하도록 레이저 조사 스폿(72)을 이동시킨다. 물론, 1 화소 열에 한정되는 것이 아니며, 예를 들면, 도 55의 RGB를 1 화소(16)라고 하는 단위로 레이저를 조사해도 된다(이 경우에는, 3 화소 열이 됨). 또한, 복수의 화소에 동시에 조사해도 된다. 또, 레이저의 조사 범위의 이동이 오버랩해도 됨은 말할 필요도 없다(통상, 이동하는 레이저광의 조사 범위는 오버랩하는 것이 보통임).

화소는 RGB의 3 화소로 정방형의 형상이 되도록 제작되어 있다. 따라서, R, G, B의 각 화소는 세로 길이의 화소 형상이 된다. 따라서, 레이저 조사 스폿(72)을 세로 길이로 하여 어닐링하는 것에 의해, 1 화소 내에서는 트랜지스터(11)의 특성 변동이 발생하지 않도록 할 수 있다. 또, 하나의 소스 신호선(18)에 접속된 트랜지스터(11)의 특성(모빌리티,  $V_t$ , S치 등)을 균일하게 할 수 있다(즉, 인접한 소스 신호선(18)의 트랜지스터(11)와는 특성이 다른 경우가 있지만, 하나의 소스 신호선에 접속된 트랜지스터(11)의 특성은 거의 동일하게 할 수 있음).

도 7의 구성에서는, 레이저 조사 스폿(72)의 길이의 범위 내에 3개의 패널이 세로로 배치되도록 형성되어 있다. 레이저 조사 스폿(72)을 조사하는 어닐링 장치는 유리 기판(74)의 위치 결정 마커(73a, 73b)를 인식(패턴 인식에 의한 자동 위치 결정)하여 레이저 조사 스폿(72)을 이동시킨다. 위치 결정 마커(73)의 인식은 패턴 인식 장치에서 행한다. 어닐링 장치(도시하지 않음)는 위치 결정 마커(73)를 인식하여, 화소 열의 위치를 산출해 낸다(레이저 조사 범위(72)가 소스 신호선(18)과 평행하게 되도록 함). 화소 열 위치에 중첩되도록 레이저 조사 스폿(72)을 조사하여 어닐링을 순차 행한다.

도 7에서 설명한 레이저 어닐링 방법(소스 신호선(18)과 평행하게 라인 형상의 레이저 스폿을 조사하는 방식)은, 유기 EL 표시 패널의 전류 프로그램 방식 시에 특히 채용하는 것이 바람직하다. 왜냐하면, 소스 신호선과 평행 방향으로 트랜지스터(11)의 특성이 일치하고 있기 때문이다(세로 방향에 인접한 화소 트랜지스터의 특성이 근사함). 그 때문에, 전류 구동 시에 소스 신호선의 전압 레벨의 변화가 적고, 전류 기입 부족이 발생하기 어렵다.

예를 들면, 백 래스터 표시이면, 인접한 각 화소의 트랜지스터(11a)에 흘리는 전류는 거의 동일하기 때문에, 소스 드라이버 IC(14)로부터 출력하는 전류 진폭의 변화가 적다. 만약, 도 1의 트랜지스터(11a)의 특성이 동일하고, 각 화소에 전류 프로그램하는 전류값이 화소 열에서 동일한 것이면, 전류 프로그램 시의 소스 신호선(18)의 전위는 일정하다.

따라서, 소스 신호선(18)의 전위 변동은 발생하지 않는다. 하나의 소스 신호선(18)에 접속된 트랜지스터(11a)의 특성이 거의 동일하면, 소스 신호선(18)의 전위 변동은 작게 된다. 이것은 도 38 등의 다른 전류 프로그램 방식의 화소 구성에서도 동일하다(즉, 도 7의 제조 방법을 적용하는 것이 바람직함).

또한, 도 27, 도 30 등에서 설명하는 복수의 화소 행을 동시 기입하는 방식에서 균일한 화상 표시(주로 트랜지스터 특성의 변동에 기인하는 표시 얼룩짐이 발생하기 어렵기 때문임)를 실현할 수 있다. 도 27 등은 복수 화소 행 동시에 선택하기 때문에, 인접한 화소 행의 트랜지스터가 균일하면, 세로 방향의 트랜지스터 특성 얼룩짐은 소스 드라이버 회로(14)에서 흡수할 수 있다.

또 도 7에서는, 소스 드라이버 회로(14)가 IC 칩을 적재하도록 도시하고 있지만, 이것에 한정되는 것이 아니고, 소스 드라이버 회로(14)를 화소(16)와 동일 프로세스로 형성해도 되는 것은 물론이다.

본 발명에서는 특히, 구동용 트랜지스터(11b)의 임계 전압 Vth2가 화소 내에서 대응하는 구동용 트랜지스터(11a)의 임계 전압 Vth1보다 낮아지지 않도록 설정하고 있다. 예를 들면, 트랜지스터(11b)의 게이트 길이 L2를 트랜지스터(11a)의 게이트 길이 L1보다도 길게 하고, 이를 박막 트랜지스터의 프로세스 파라미터가 변동해도, Vth2가 Vth1보다도 낮아지지 않도록 한다. 이에 의해, 미소한 전류 누설을 억제하는 것이 가능하다.

또, 이상의 사항은 도 38에 도시하는 커런트 미러의 화소 구성에도 적용할 수 있다. 도 38에서는 신호 전류가 흐르는 구동용 트랜지스터(11a), EL 소자(15) 등으로 이루어지는 발광 소자에 흐르는 구동 전류를 제어하는 구동용 트랜지스터(11b) 외에, 게이트 신호선(17a1)의 제어에 의해서 화소 회로와 데이터선 data를 접속 혹은 차단하는 스위치용 트랜지스터(11c), 게이트 신호선(17a2)의 제어에 의해서 기입 기간 중에 트랜지스터(11a)의 게이트·드레인을 단락하는 스위치용 트랜지스터(11d), 트랜지스터(11a)의 게이트-소스간 전압을 기입 종료 후에도 유지하기 위한 용량 C(19) 및 발광 소자로서의 EL 소자(15) 등으로 구성된다.

도 38에서 트랜지스터(11c, 11d)는 N채널 트랜지스터, 그밖의 트랜지스터는 P 채널 트랜지스터로 구성하고 있지만, 이것은 일례이고, 반드시 이대로 할 필요는 없다. 용량 Cs는 그 한쪽 단자가 트랜지스터(11a)의 게이트에 접속되고, 다른 쪽의 단자는 Vdd(전원 전위)에 접속되어 있지만, Vdd에 한하지 않고 임의의 일정 전위라도 무방하다. EL 소자(15)의 캐소드(음극)는 접지 전위에 접속되어 있다.

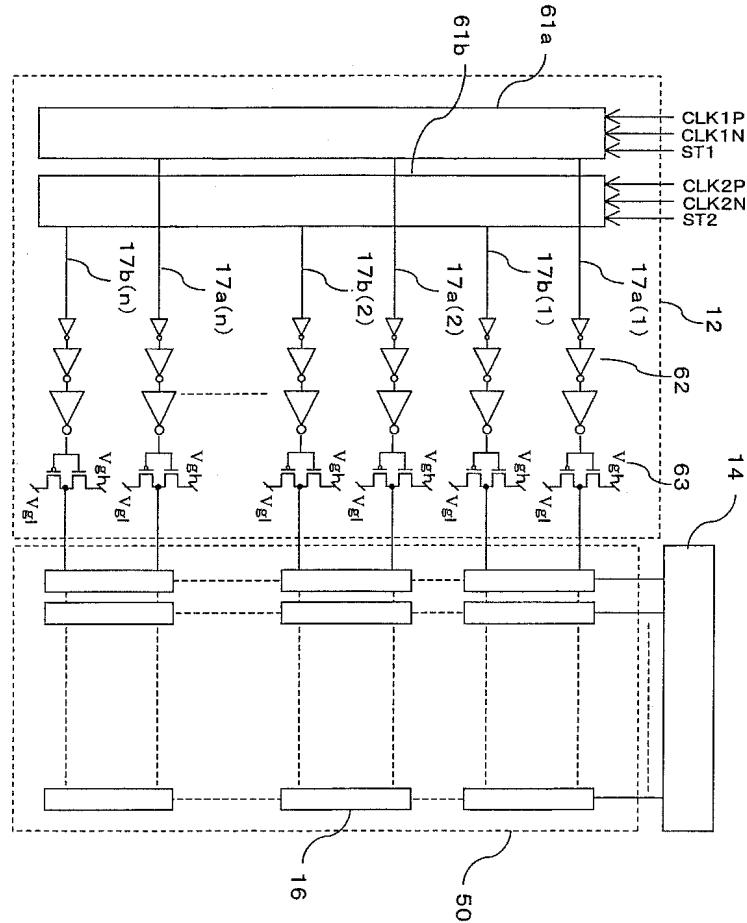

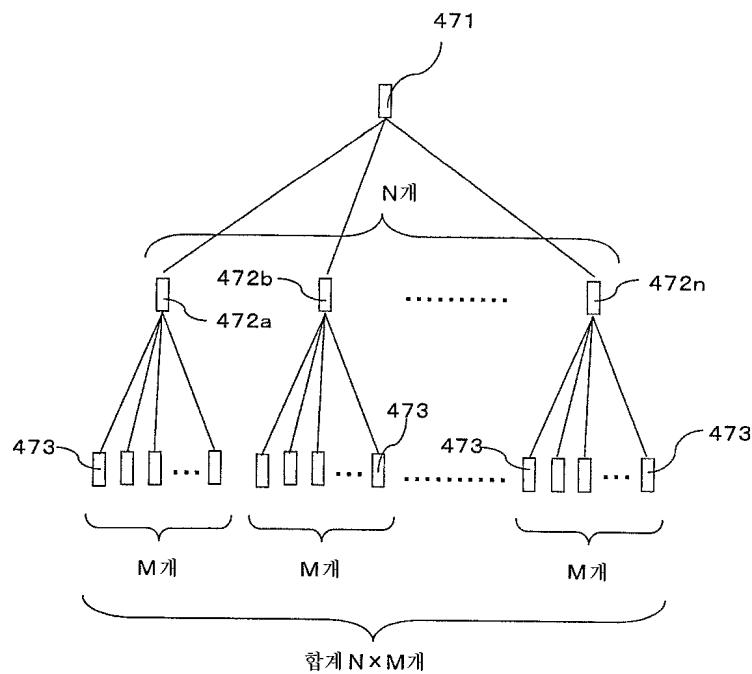

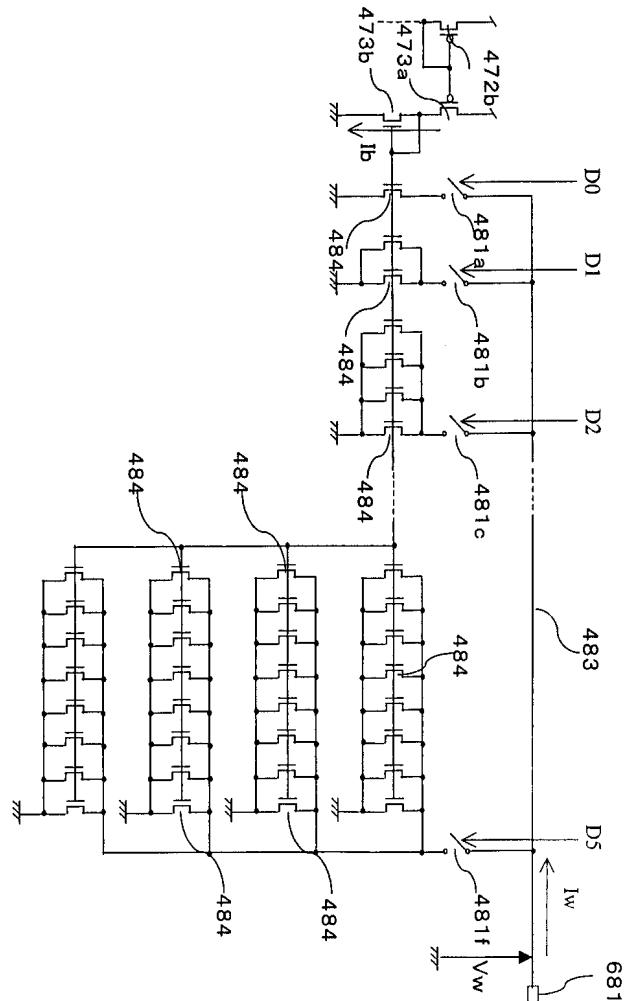

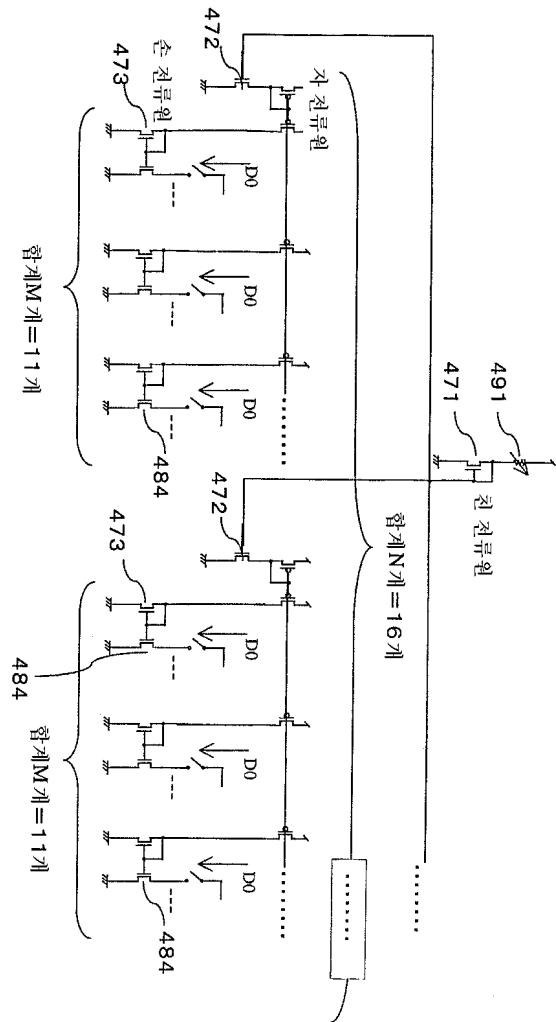

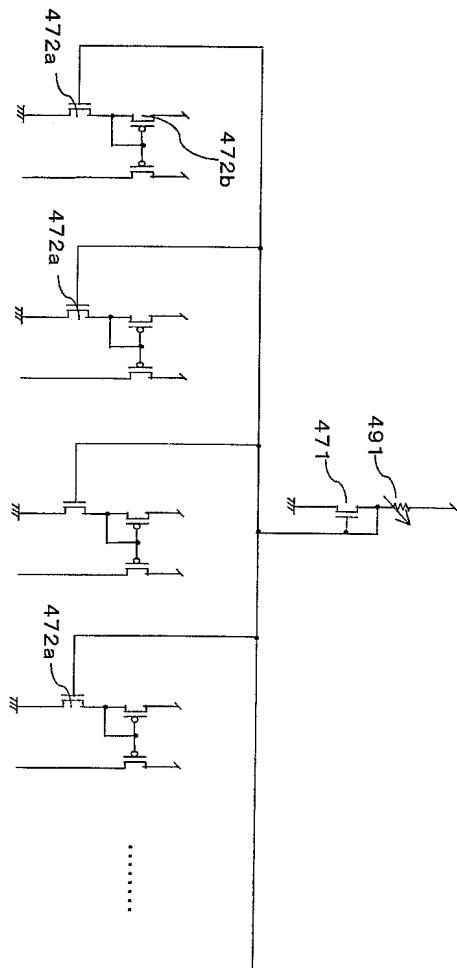

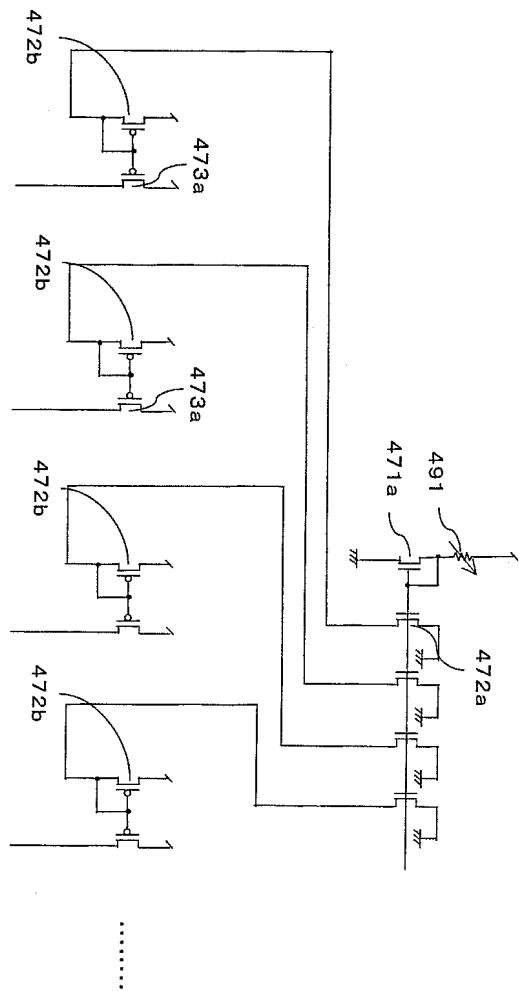

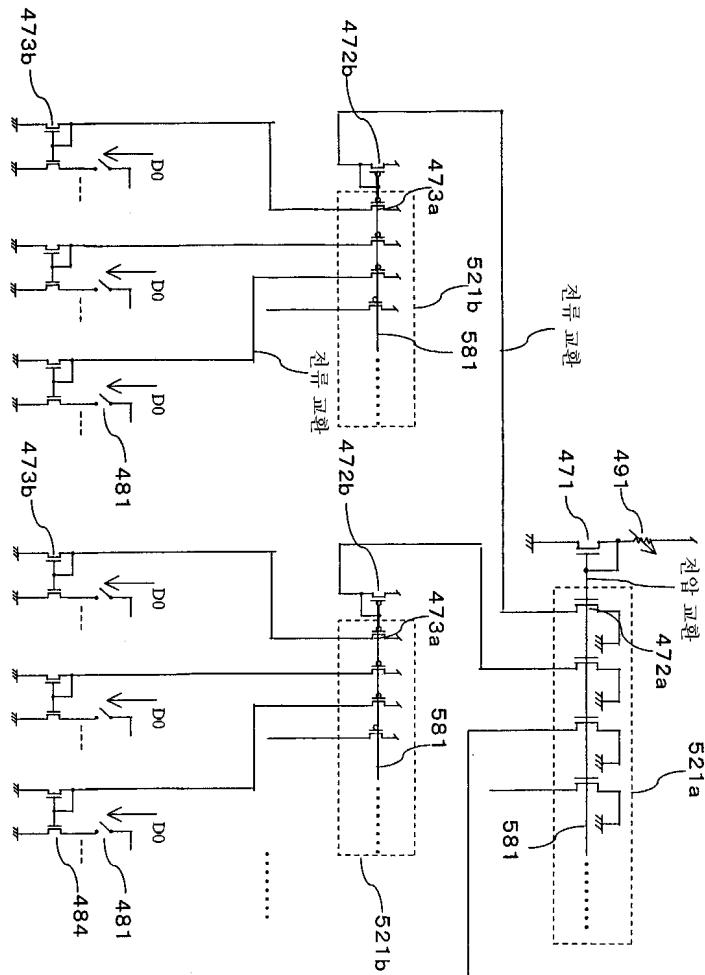

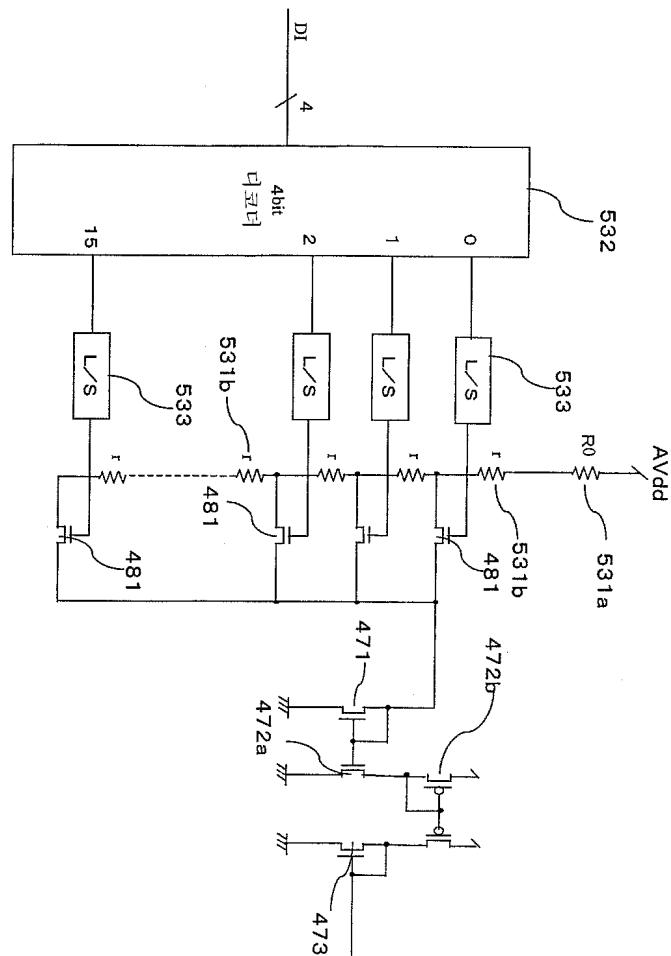

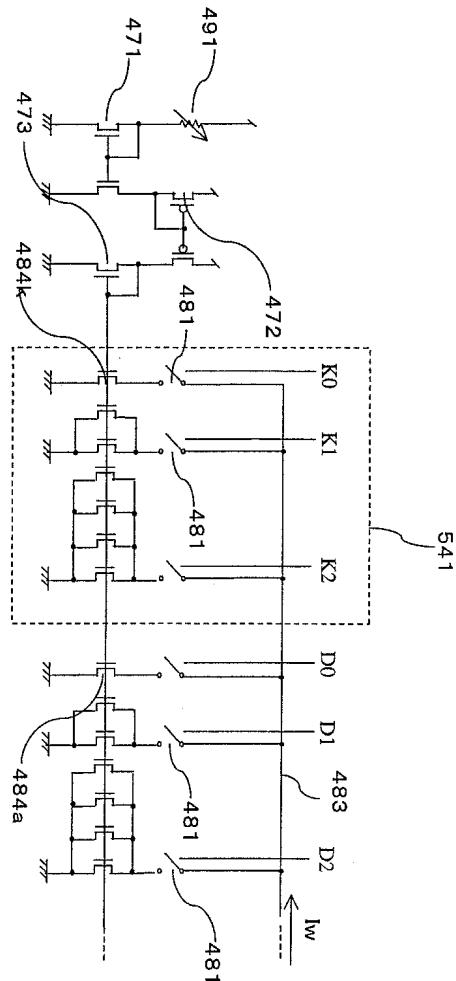

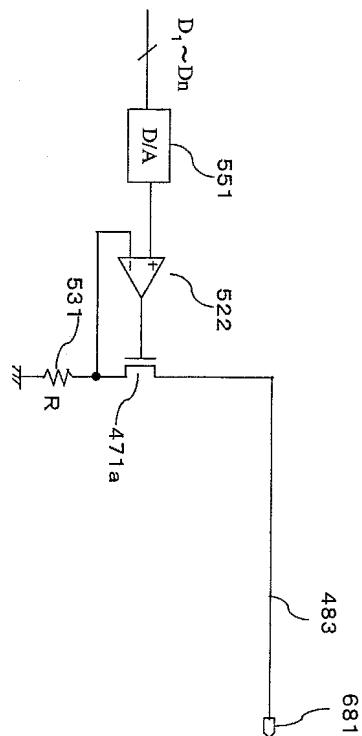

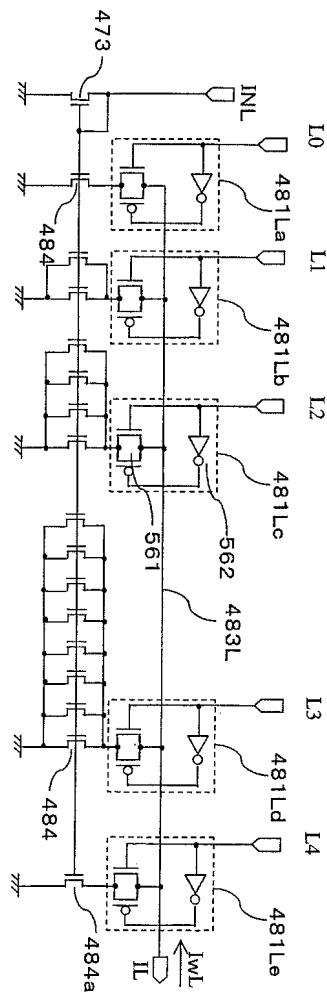

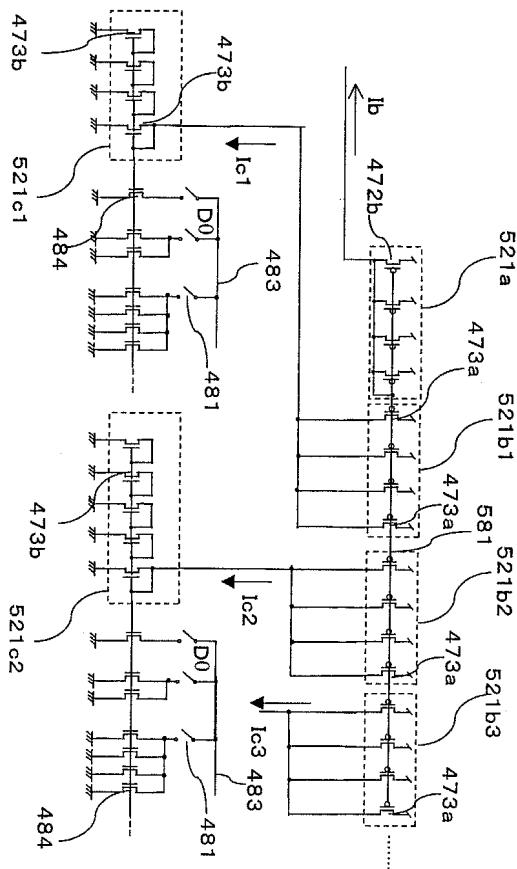

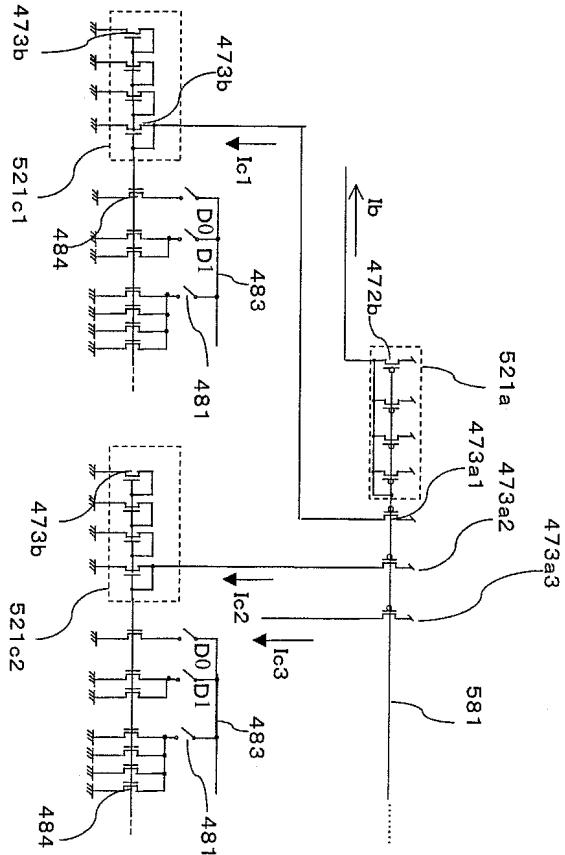

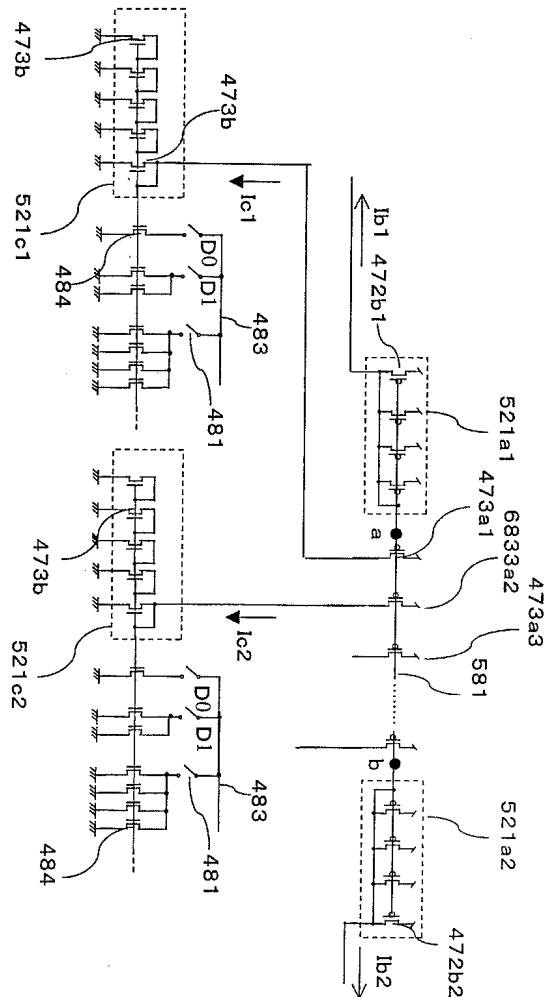

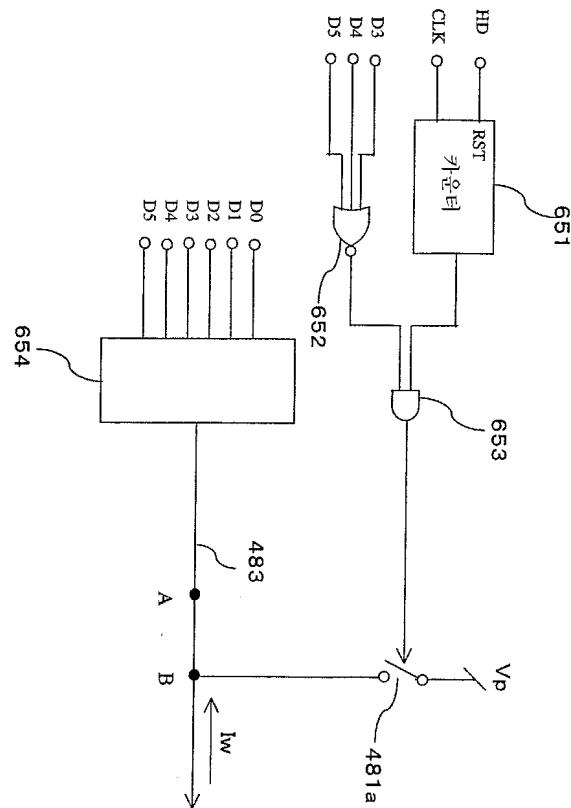

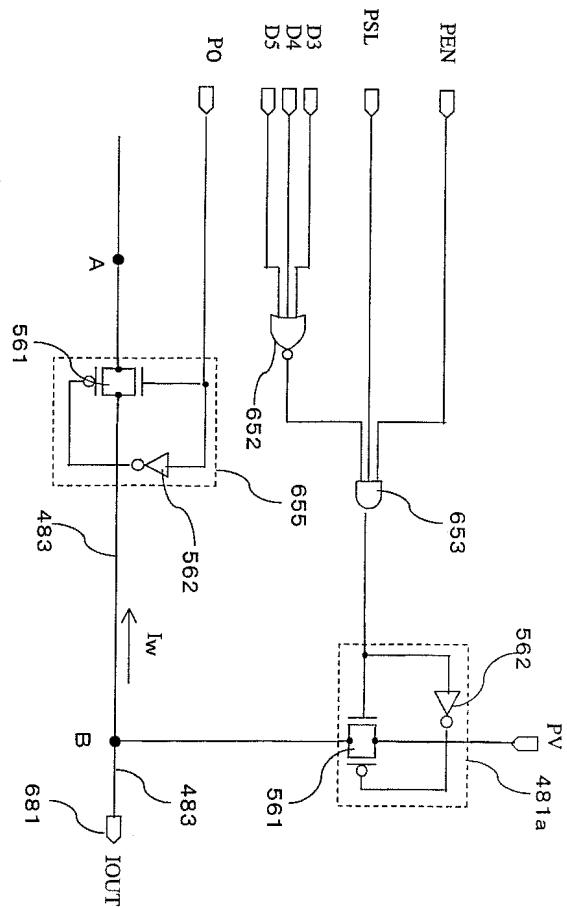

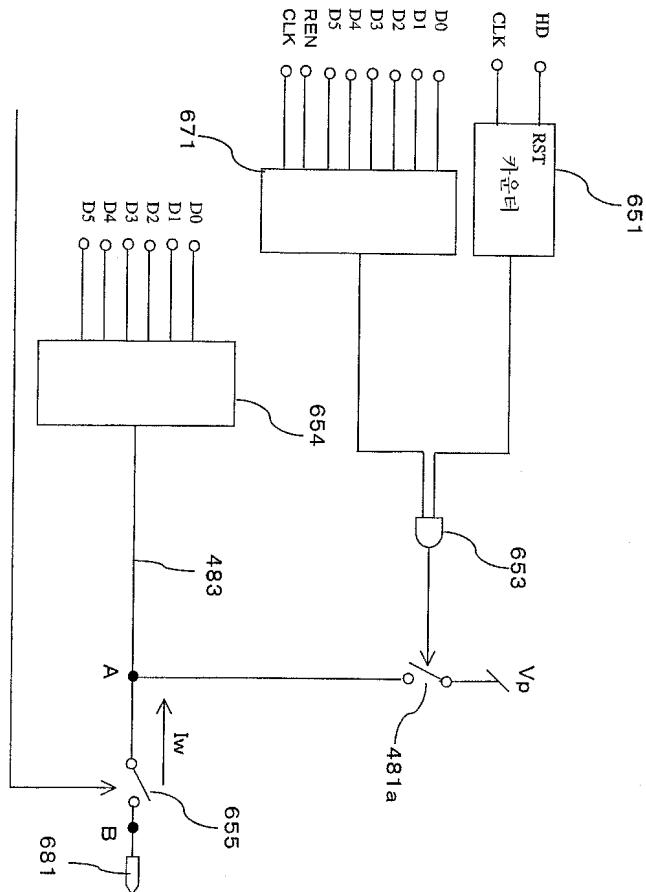

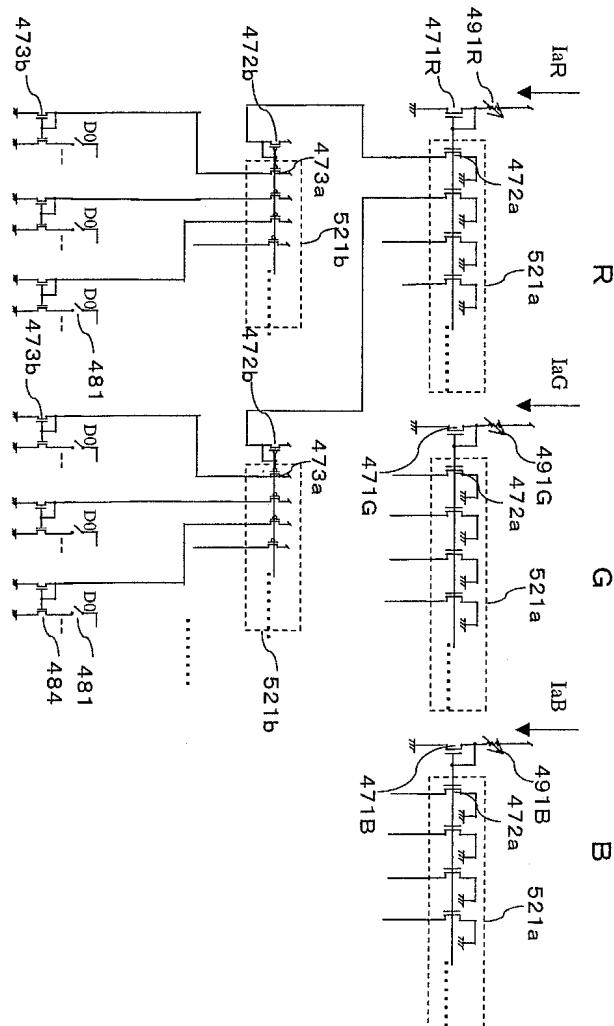

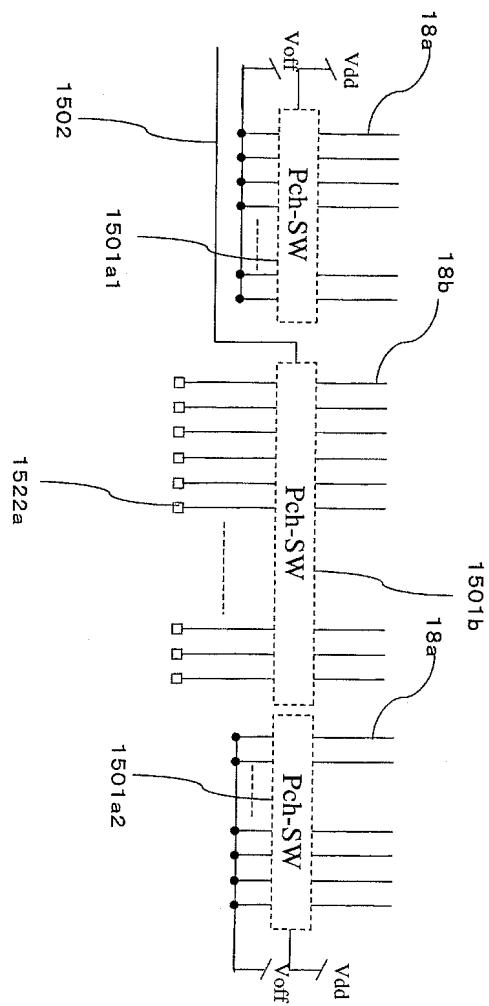

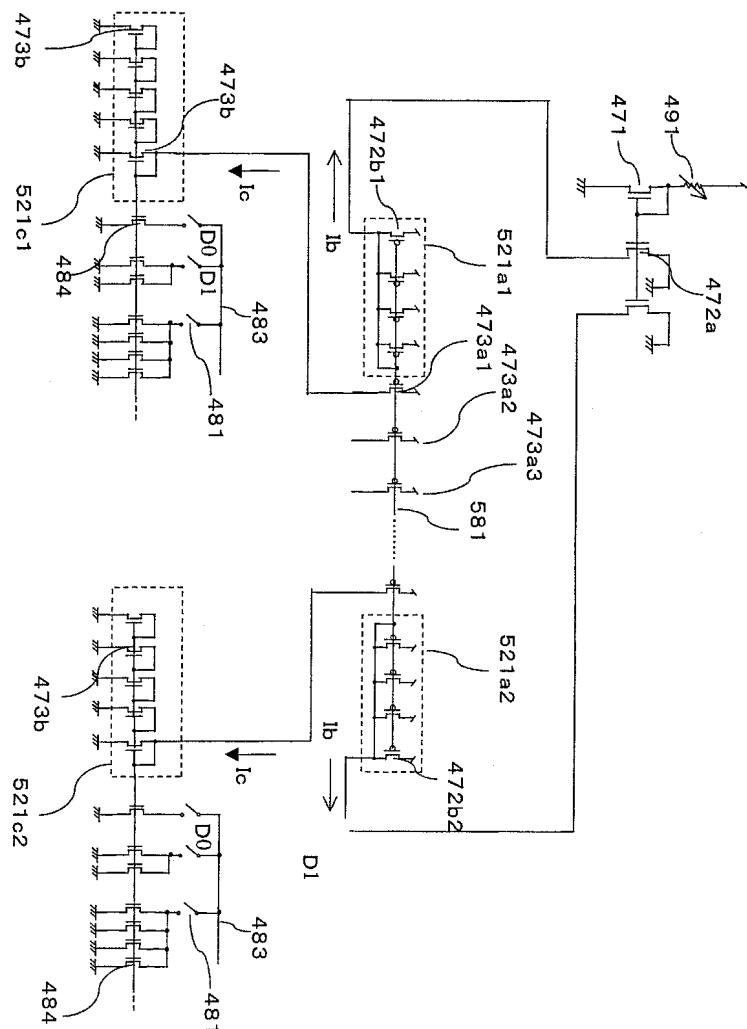

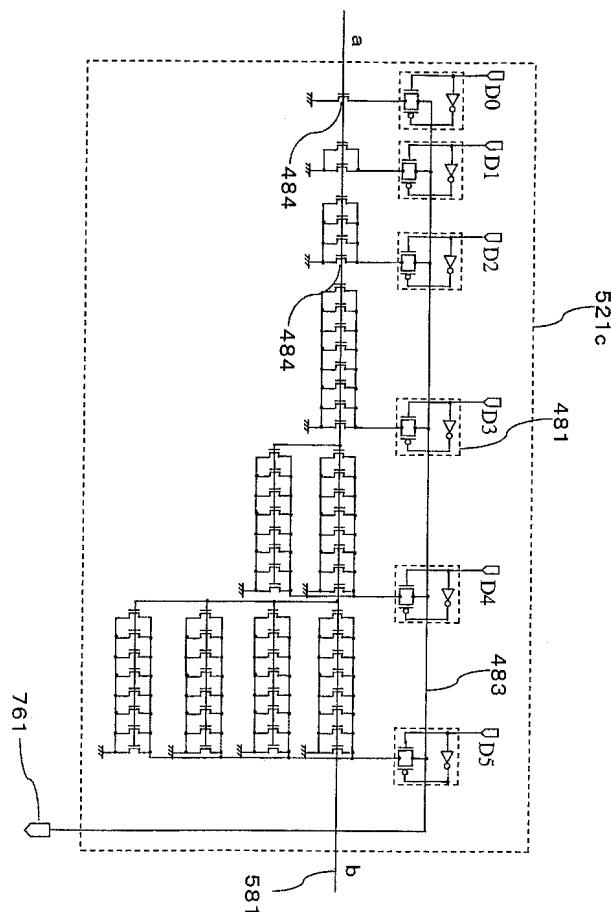

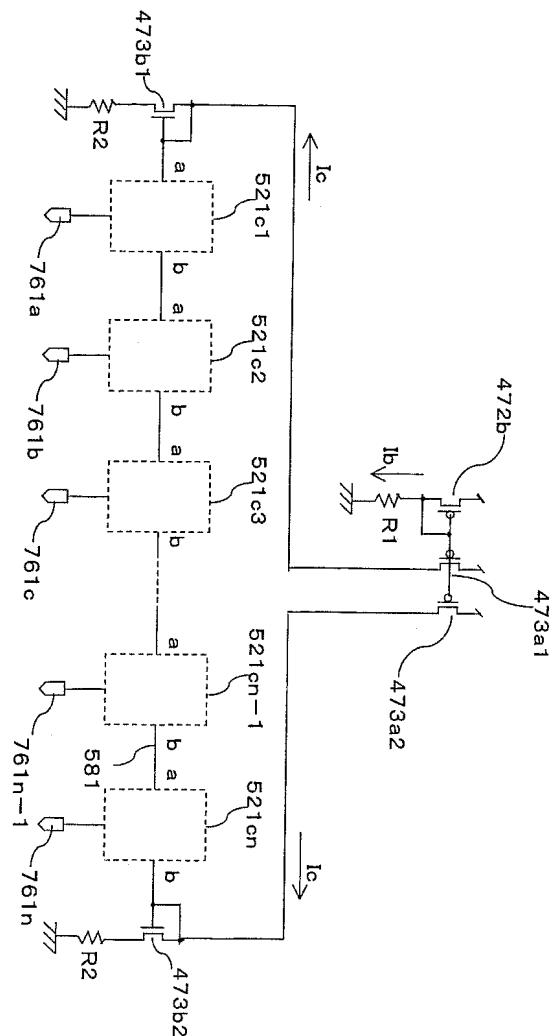

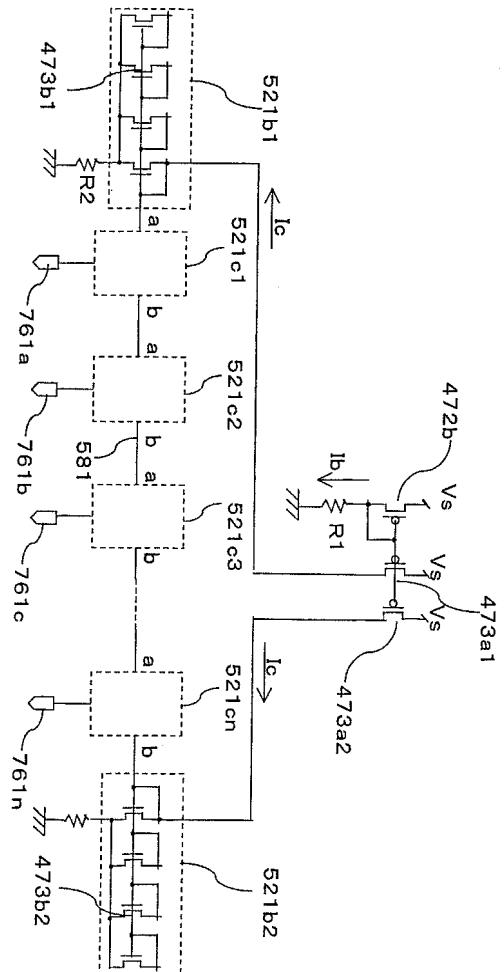

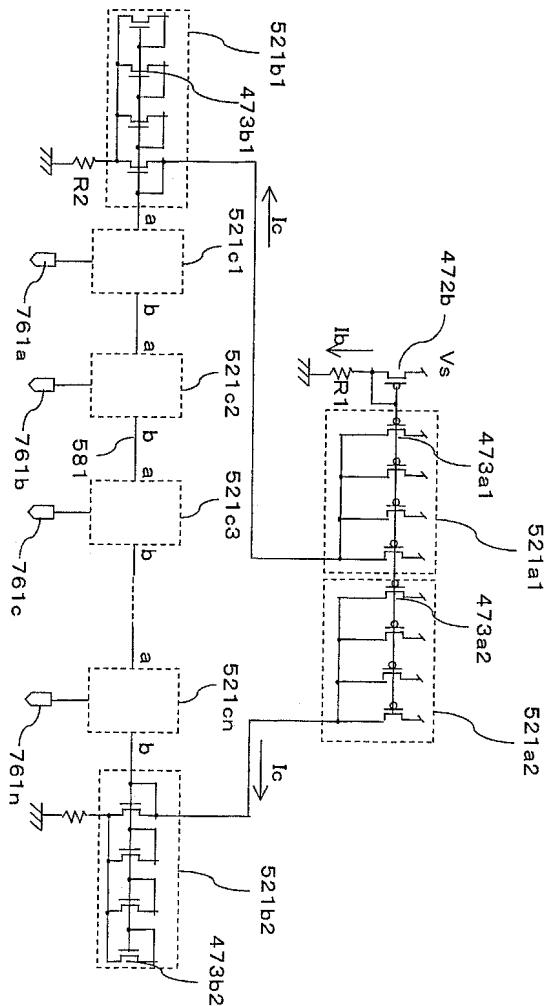

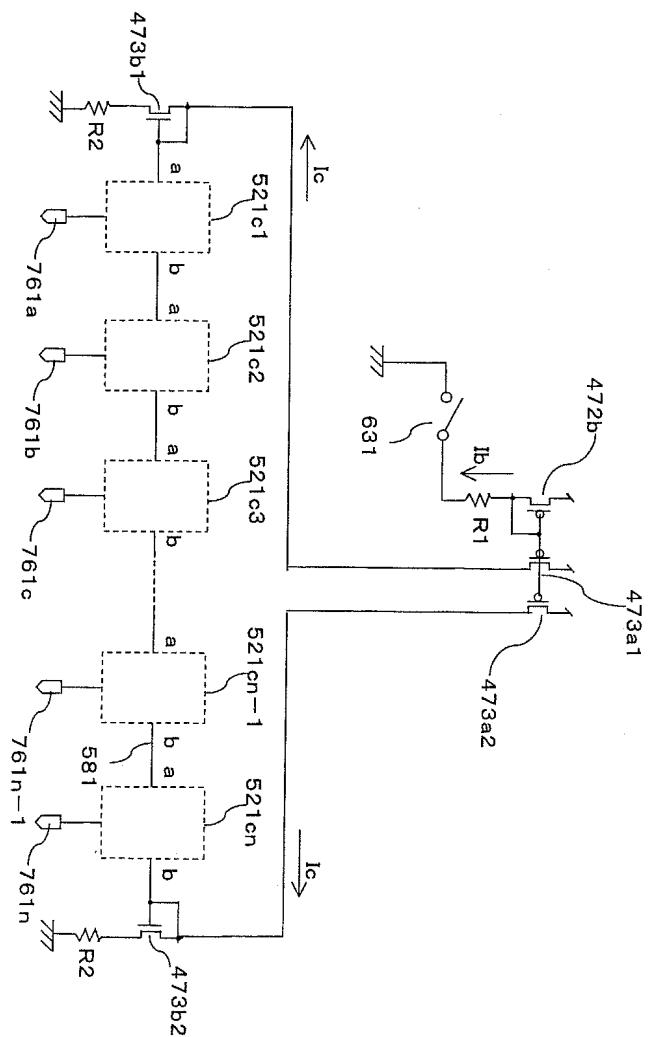

다음에, 본 발명의 EL 표시 패널 혹은 EL 표시 장치에 대하여 설명한다. 도 6은 EL 표시 장치의 회로를 중심으로 한 설명도이다. 화소(16)가 매트릭스 형상으로 배치 또는 형성되어 있다. 각 화소(16)에는 각 화소의 전류 프로그램을 행하는 전류를 출력하는 소스 드라이버 회로(14)가 접속되어 있다. 소스 드라이버 회로(14)의 출력단은 영상 신호의 비트 수에 대응한 커런트 미러 회로가 형성되어 있다(나중에 설명함). 예를 들면, 64 계조이면, 63개의 커런트 미러 회로가 각 소스 신호선에 형성되고, 이들 커런트 미러 회로의 개수를 선택함으로써 원하는 전류를 소스 신호선(18)에 인가할 수 있도록 구성되어 있다(도 48을 참조).

또, 하나의 커런트 미러 회로의 최소 출력 전류는 10nA 이상 50nA로 하고 있다. 특히 커런트 미러 회로의 최소 출력 전류는 15nA 이상 35nA로 하는 것이 좋다. 소스 드라이버 IC(14) 내의 커런트 미러 회로를 구성하는 트랜지스터의 정밀도를 확보하기 위해서이다.

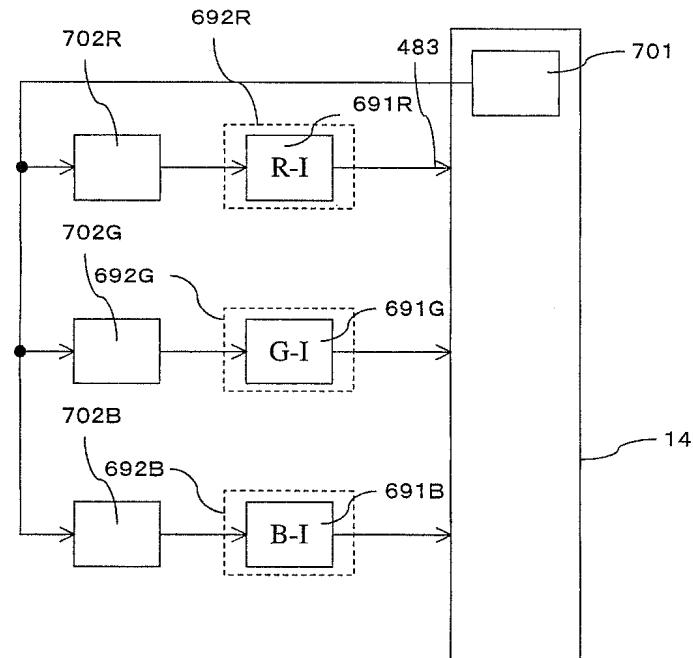

또한, 소스 신호선(18)의 전하를 강제적으로 방출 또는 충전하는 프리차지 혹은 방전 회로를 내장한다. 소스 신호선(18)의 전하를 강제적으로 방출 또는 충전하는 프리차지 혹은 방전 회로의 전압(전류) 출력치는, R, G, B에서 독립적으로 설정할 수 있도록 구성하는 것이 바람직하다. EL 소자(15)의 임계값이 RGB에서 서로 다르기 때문이다(프리차지 회로에 대해서는 도 65, 도 67 및 그 설명을 참조할 것).

유기 EL 소자는 큰 온도 의존성 특성(온특(溫特))이 있다는 것이 알려져 있다. 이 온특에 의한 발광 휘도 변화를 조정하기 위해서, 커런트 미러 회로에 출력 전류를 변화시키는 서미스터 혹은 포지스터 등의 비직선 소자를 부가하고, 온특에 의한 변화를 상기 서미스터 등으로 조정하는 것에 의해 아날로그적으로 기준 전류를 조정한다(변화시킴).

본 발명에 있어서, 소스 드라이버 회로(14)는 반도체 실리콘 칩으로 형성하고, 칩 온 글라스(COG) 기술로 어레이 기판(71)의 소스 신호선(18)의 단자와 접속되어 있다. 소스 드라이버 회로(14)의 실장은 COG 기술에 한정되는 것이 아니며, 칩 온 필름(COF) 기술에 전술의 소스 드라이버 IC(14) 등을 적재하고, 표시 패널의 신호선과 접속한 구성으로 하여도 좋다. 또한, 드라이브 IC는 전원 IC(82)를 별도 제작하여, 3칩 구성으로 하여도 좋다.

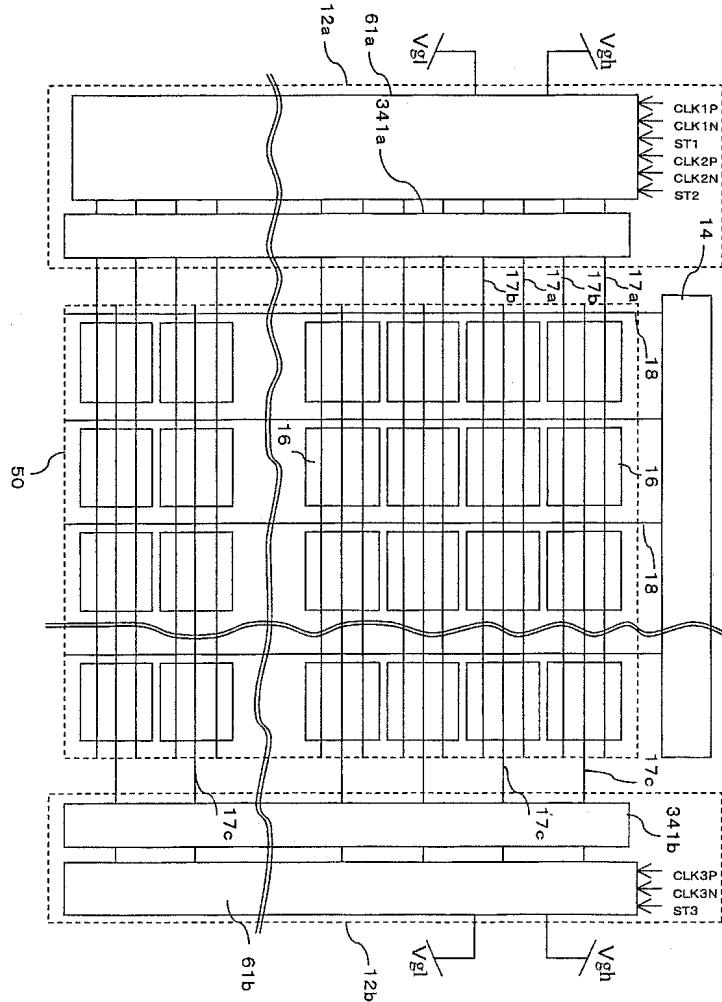

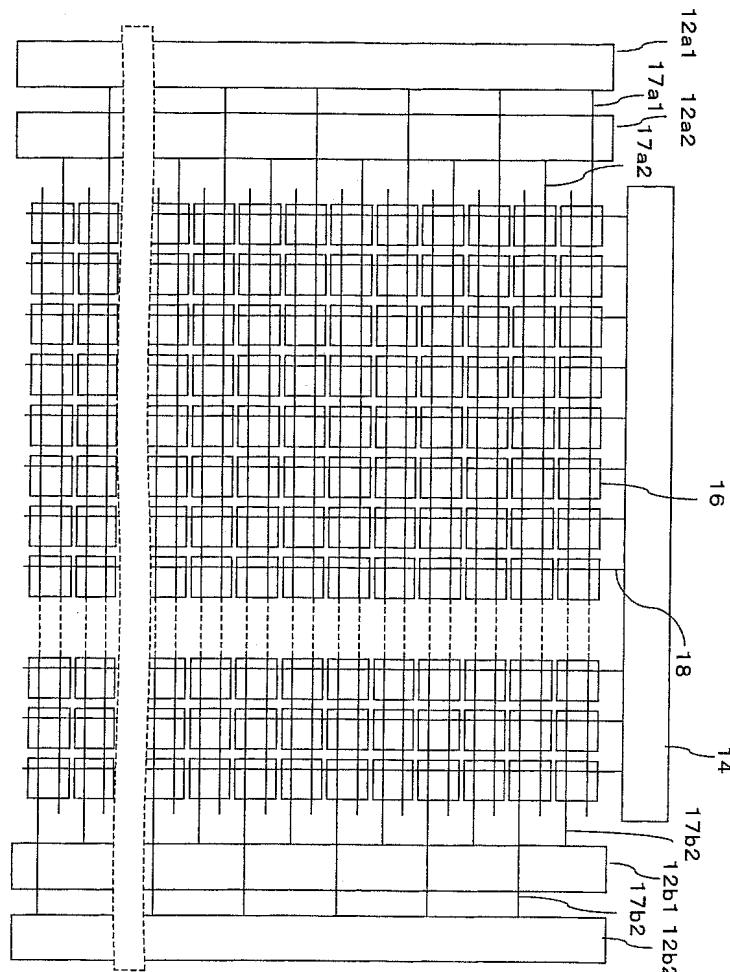

한편, 게이트 드라이버 회로(12)는 저온 폴리실리콘 기술로 형성하고 있다. 즉, 화소의 트랜지스터와 동일한 프로세스로 형성하고 있다. 이것은 소스 드라이버 회로(14)에 비하여 내부의 구조가 용이하고, 동작 주파수도 낮기 때문이다. 따라서, 저온 폴리실리콘기술로 형성해도 용이하게 형성할 수 있고, 또한 협소한 프레임화를 실현할 수 있다. 물론, 게이트 드라이버 회로(12)를 실리콘 칩으로 형성하고, COG 기술 등을 이용하여 어레이 기판(71)상에 실장해도 됨은 물론이다. 또한, 화소 트랜지스터 등의 스위칭 소자, 게이트 드라이버 등은 고온 폴리실리콘 기술로 형성해도 되고, 유기 재료로 형성(유기 트랜지스터)해도 된다.

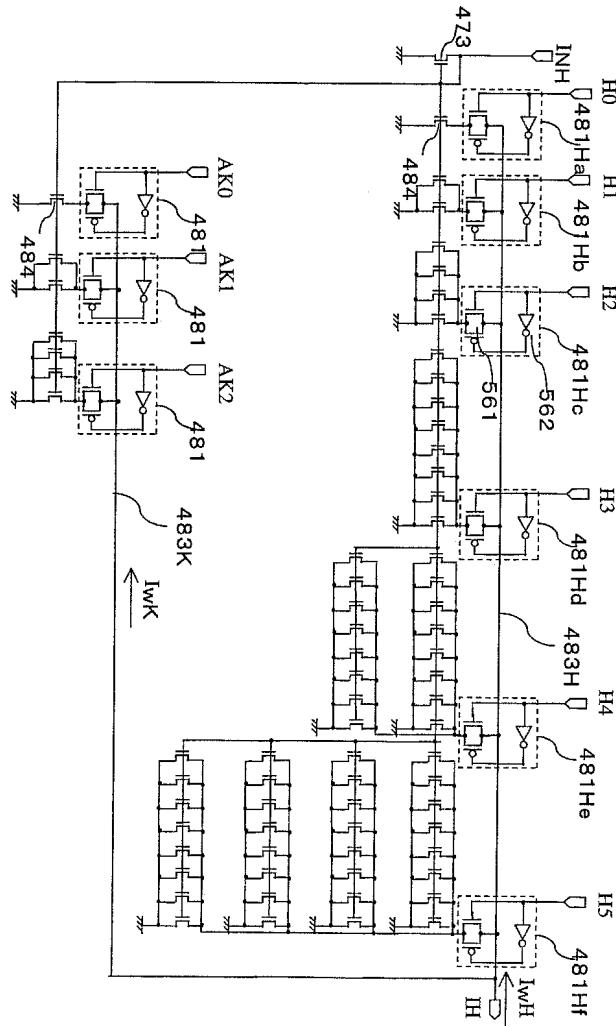

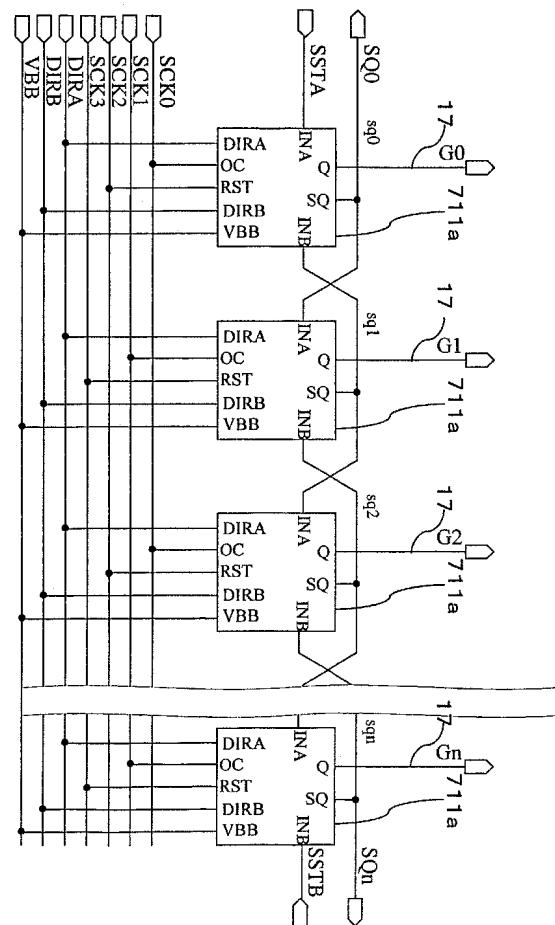

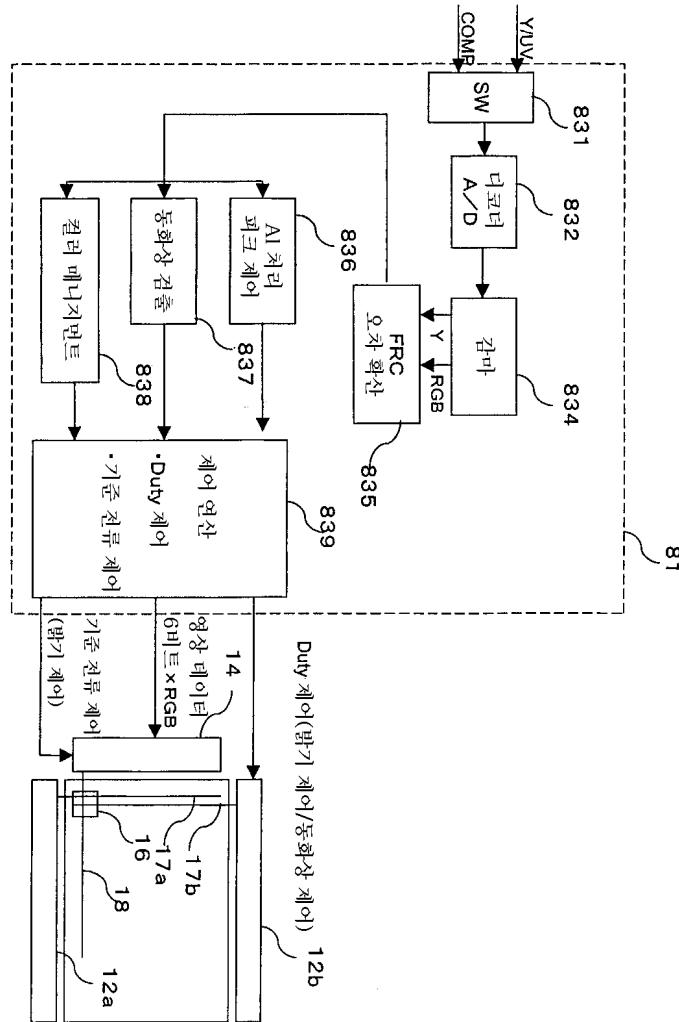

게이트 드라이버 회로(12)는 게이트 신호선(17a)용의 시프트 레지스터 회로(61a)와, 게이트 신호선(17b)용의 시프트 레지스터 회로(61b)를 내장한다. 각 시프트 레지스터 회로(61)는 플러스 상과 마이너스 상의 클럭 신호(CLKxP, CLKxN), 스타트 월스(STx)로 제어된다(도 6을 참조). 그밖에, 게이트 신호선의 출력, 비 출력을 제어하는 인에이블(ENABL) 신호, 시프트 방향을 상하 역전하는 업다운(UPDWM) 신호를 부가하는 것이 바람직하다. 그 외에, 스타트 월스가 시프트 레지스터

에 시프트되고, 그리고 출력되고 있음을 확인하는 출력 단자 등을 마련하는 것이 바람직하다. 또, 시프트 레지스터의 시프트 타이밍은 컨트롤 IC(81)로부터의 제어 신호에 의해 제어된다. 또한, 외부 데이터의 레벨 시프트를 행하는 레벨 시프트 회로를 내장한다.

시프트 레지스터 회로(61)의 버퍼 용량은 작기 때문에, 직접적으로는 게이트 신호선(17)을 구동할 수 없다. 그 때문에, 시프트 레지스터 회로(61)의 출력과 게이트 신호선(17)을 구동하는 출력 게이트(63) 사이에는 적어도 2개 이상의 인버터 회로(62)가 형성되어 있다.

소스 드라이버 회로(14)를 저온 폴리실리콘등의 폴리실리콘기술로 어레이 기판(71)상에 직접 형성하는 경우도 마찬가지로, 소스 신호선(18)을 구동하는 트랜스퍼 게이트 등의 아날로그 스위치의 게이트와 소스 드라이버 회로(14)의 시프트 레지스터 사이에는 복수의 인버터 회로가 형성된다. 이하의 사항(시프트 레지스터의 출력과, 신호선을 구동하는 출력단(출력 게이트 혹은 트랜스퍼 게이트 등의 출력단 사이에 배치되는 인버터 회로에 관한 사항))은, 소스 드라이브 및 게이트 드라이브 회로에 공통된 사항이다.

예를 들면, 도 6에서는 소스 드라이버 회로(14)의 출력이 직접 소스 신호선(18)에 접속되어 있도록 도시했지만, 실제로는 소스 드라이버의 시프트 레지스터의 출력은 다단의 인버터 회로가 접속되고, 인버터의 출력이 트랜스퍼 게이트 등의 아날로그 스위치의 게이트에 접속되어 있다.

인버터 회로(62)는 P 채널의 MOS 트랜지스터와 N채널의 MOS 트랜지스터로 구성된다. 앞에서도 설명한 바와 같이 게이트 드라이버 회로(12)의 시프트 레지스터 회로(61)의 출력단에는 인버터 회로(62)가 다단으로 접속되어 있고, 그 최종 출력이 출력 게이트 회로(63)에 접속되어 있다. 또, 인버터 회로(62)는 P 채널만으로 구성해도 된다. 단, 이 경우에는 인버터가 아니라 단순한 게이트 회로로서 구성해도 된다.

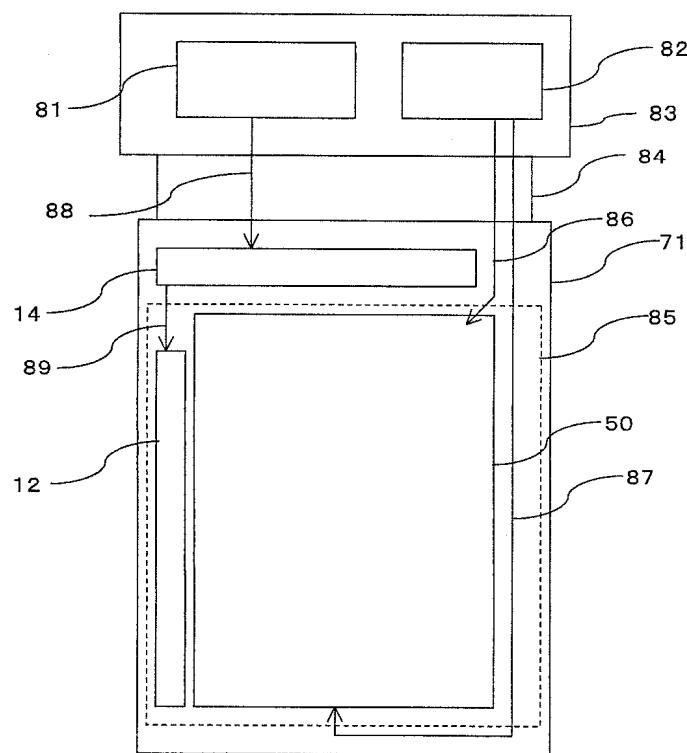

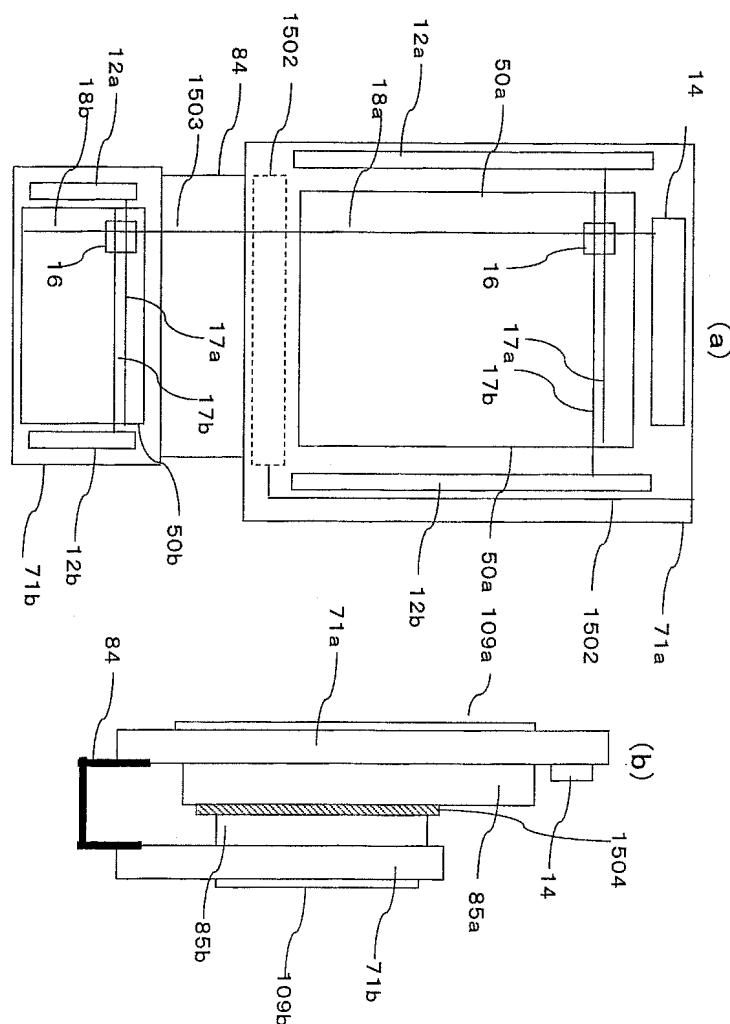

도 8은 본 발명의 표시 장치의 신호, 전압의 공급의 구성도 혹은 표시 장치의 구성도이다. 컨트롤 IC(81)로부터 소스 드라이버 회로(14a)에 공급하는 신호(전원 배선, 데이터 배선 등)는 플렉시블 기판(84)을 통하여 공급한다.

도 8에서 게이트 드라이버 회로(12)의 제어 신호는 컨트롤 IC에서 발생시켜, 소스 드라이버 회로(14)에서, 레벨 시프트를 행한 후, 게이트 드라이버 회로(12)에 인가하고 있다. 소스 드라이버 회로(14)의 구동 전압은 4 내지 8(V)이므로, 컨트롤 IC(81)로부터 출력된 3.3(V) 진폭의 제어 신호를, 게이트 드라이버 회로(12)가 수취할 수 있는 5(V) 진폭으로 변환할 수 있다.

또, 도 8 등에 있어서 (14)를 소스 드라이버라고 기재했지만, 단순한 드라이버 뿐만아니라, 전원 회로, 버퍼 회로(시프트 레지스터 등의 회로를 포함함), 데이터 변환 회로, 래치 회로, 커맨드 디코더, 시프트 회로, 어드레스 변환 회로, 화상 메모리 등을 내장시켜도 좋다. 또, 도 8 등에서 설명하는 구성에 있어서도, 도 9등에서 설명하는 3번 프리 구성 혹은 구성, 구동 방식 등을 적용할 수 있음은 물론이다.

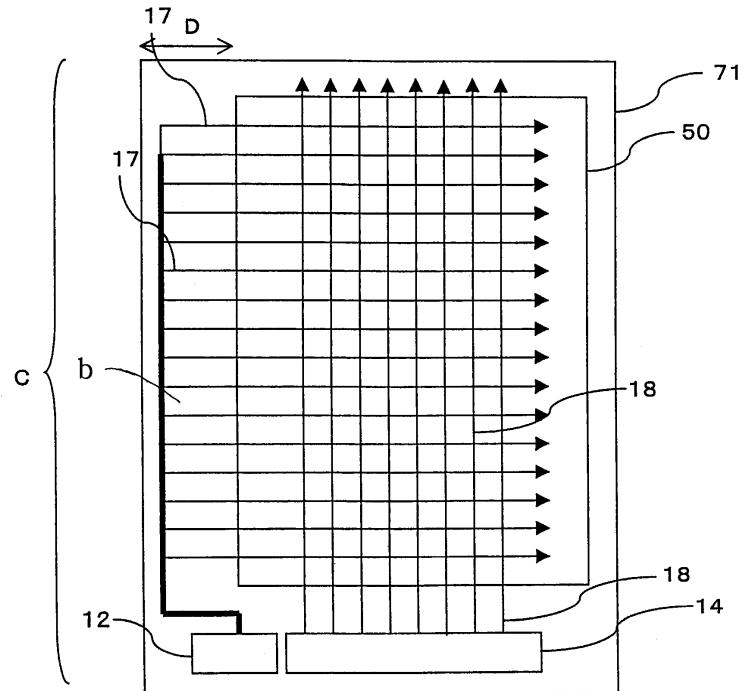

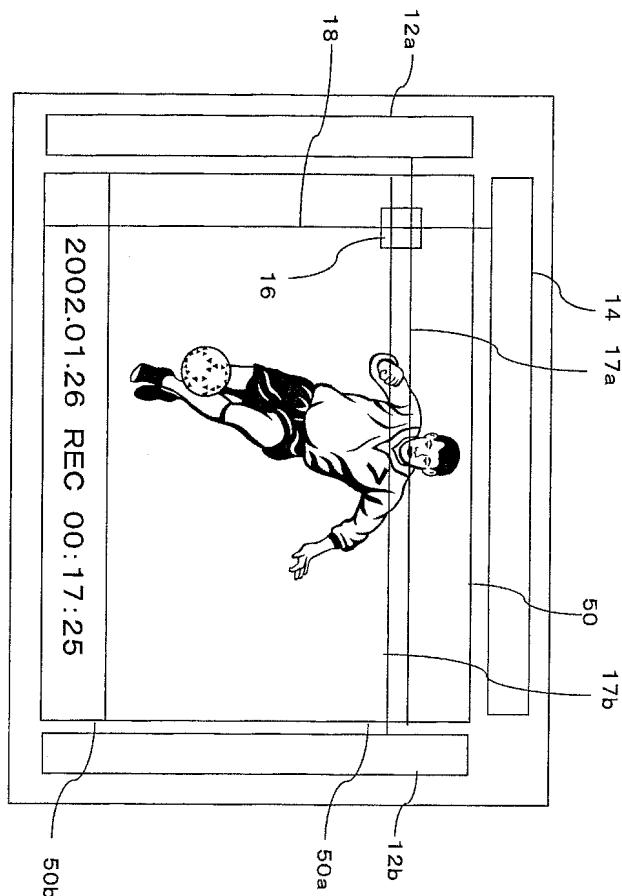

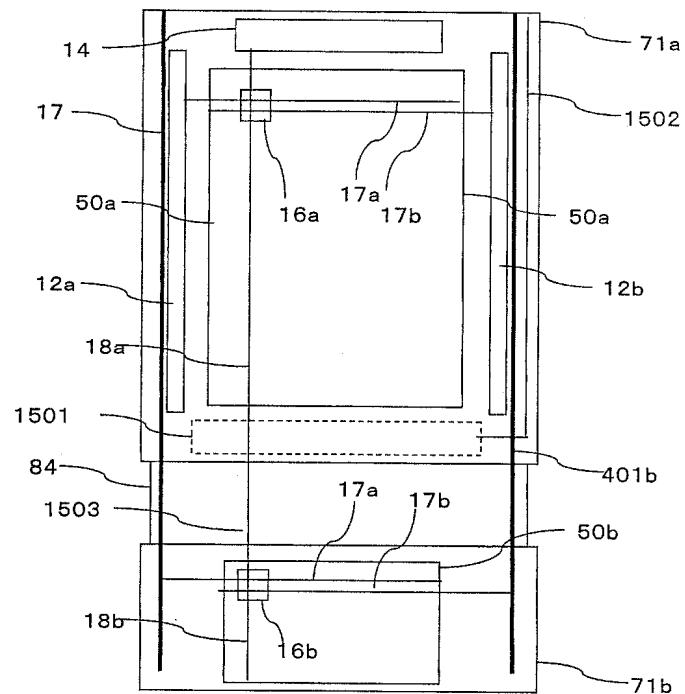

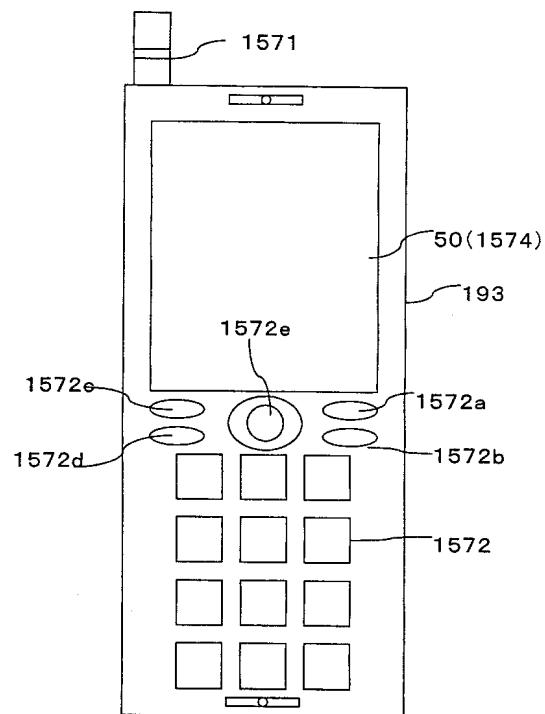

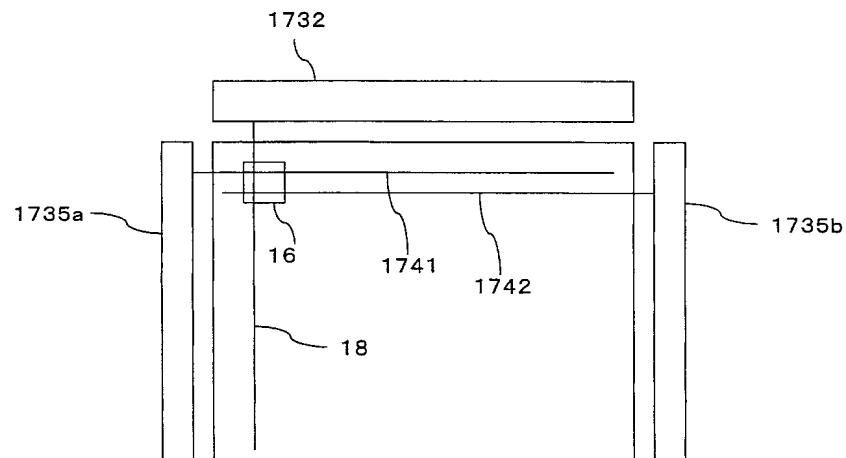

표시 패널을 휴대 전화 등의 정보 표시 장치에 사용하는 경우, 도 9에 도시한 바와 같이, 소스 드라이버 IC(회로)(14), 게이트 드라이버 IC(회로)(12)는, 표시 패널의 1번에 실장(형성)하는 것이 바람직하다(또, 이와 같이 1번에 드라이버 IC(회로)를 실장(형성)하는 형태를 3번 프리 구성(구조)이라고 함. 종래에는, 표시 영역의 X번에 게이트 드라이버 IC(12)가 실장되고, Y번에 소스 드라이버 IC(14)가 실장되어 있었음). 화면(50)의 중심선이 표시 장치의 중심이 되도록 설계하기 쉽고, 또한 드라이버 IC의 실장도 용이해지기 때문이다. 또, 게이트 드라이버 회로를 고온 폴리실리콘 혹은 저온 폴리 실리콘 기술 등으로 3번 프리의 구성으로 제작해도 된다(즉, 도 9의 소스 드라이버 회로(14)와 게이트 드라이버 회로(12) 중, 적어도 한쪽을 폴리실리콘 기술로 어레이 기판(71)에 직접 형성함).

또, 3번 프리 구성이란, 어레이 기판(71)에 직접 IC를 적재 혹은 형성한 구성 뿐만아니라, 소스 드라이버 IC(회로)(14), 게이트 드라이버 IC(회로)(12) 등을 장착한 필름(TCP, TAB 기술 등)을 어레이 기판(71)의 1번(혹은 거의 1번)에 부착한 구성도 포함한다. 즉, 2번에 IC가 실장 혹은 장착되어 있지 않은 구성, 배치 혹은 그것과 유사한 모두를 의미한다.

도 9와 같이 게이트 드라이버 회로(12)를 소스 드라이버 회로(14)의 가로에 배치하면, 게이트 신호선(17)은 변 C를 따라서 형성할 필요가 있다.

또, 도 9 등에서 굵은 실선으로 도시한 개소는 게이트 신호선(17)이 병렬하여 형성된 개소를 도시하고 있다. 따라서, b의 부분(화면 하부)은 주사 신호선의 개수분의 게이트 신호선(17)이 병렬하여 형성되고, a의 부분(화면 상부)은 게이트 신호선(17)이 하나 형성되어 있다.

C면에 형성하는 게이트 신호선(17)의 피치는  $5\mu m$  이상  $12\mu m$  이하로 한다.  $5\mu m$  미만에서는 인접 게이트 신호선에 기생 용량의 영향에 의해 노이즈가 타버린다. 실험에 의하면,  $7\mu m$  이하에서 기생 용량의 영향이 현저히 발생한다. 또한  $5\mu m$  미만에서는 표시 화면에 사탕무 형상 등의 화상 노이즈가 심하게 발생한다. 특히 노이즈의 발생은 화면의 좌우로 다르고, 이 사탕무 형상 등의 화상 노이즈를 저감하는 것은 곤란하다. 또한, 피치가  $12\mu m$ 을 넘으면 표시 패널의 프레임 폭 D가 지나치게 커져 실용적이지 않다.

전술한 화상 노이즈를 저감하기 위해서는, 게이트 신호선(17)을 형성한 부분의 하층 혹은 상층에, 그랜드 패턴(일정 전압에 전압 고정 혹은 전체적으로 안정된 전위로 설정되어 있는 도전 패턴)을 배치하는 것에 의해 저감할 수 있다. 또한, 별도 마련한 실드판(실드박(일정 전압에 전압 고정 혹은 전체적으로 안정된 전위로 설정되어 있는 도전 패턴))을 게이트 신호선(17)상에 배치하면 된다.

도 9의 C면의 게이트 신호선(17)은 ITO 전극으로 형성해도 되지만, 저 저항화하기 위해서, ITO와 금속 박막을 적층하여 형성하는 것이 바람직하다. 또한, 금속막으로 형성하는 것이 바람직하다. ITO와 적층하는 경우에는, ITO 상에 티탄막을 형성하고, 그 위에 알루미늄 혹은 알루미늄과 몰리브덴의 합금 박막을 형성한다. 혹은 ITO 상에 크롬막을 형성한다. 금속 막인 경우에는, 알루미늄 박막, 크롬 박막으로 형성한다. 이상의 사항은 본 발명의 다른 실시예에서도 마찬가지이다.

또, 도 9 등에 있어서, 게이트 신호선(17) 등은 표시 영역의 편측에 배치한다고 했지만 이것에 한정되는 것이 아니고, 양방에 배치해도 된다. 예를 들면, 게이트 신호선(17a)을 표시 화면(50)의 우측에 배치(형성)하고, 게이트 신호선(17b)을 표시 화면(50)의 좌측에 배치(형성)해도 된다. 이상의 사항은 다른 실시예에서도 마찬가지이다.

또한, 소스 드라이버 IC(14)와 게이트 드라이버 IC(12)를 1 칩화 해도 된다. 1 칩화하면, 표시 패널에의 IC 칩의 실장이 하나로 끝난다. 따라서, 실장 비용도 저감할 수 있다. 또한, 1 칩 드라이버 IC 내에서 사용하는 각종 전압도 동시에 발생할 수 있다.

또, 소스 드라이버 IC(14), 게이트 드라이버 IC(12)는 실리콘 등의 반도체 웨이퍼로 제작하여 표시 패널에 실장한다고 했지만, 이것에 한정되는 것이 아니고, 저온 폴리실리콘 기술, 고온 폴리실리콘 기술에 의해 표시 패널(71)에 직접 형성해도 됨은 물론이다.

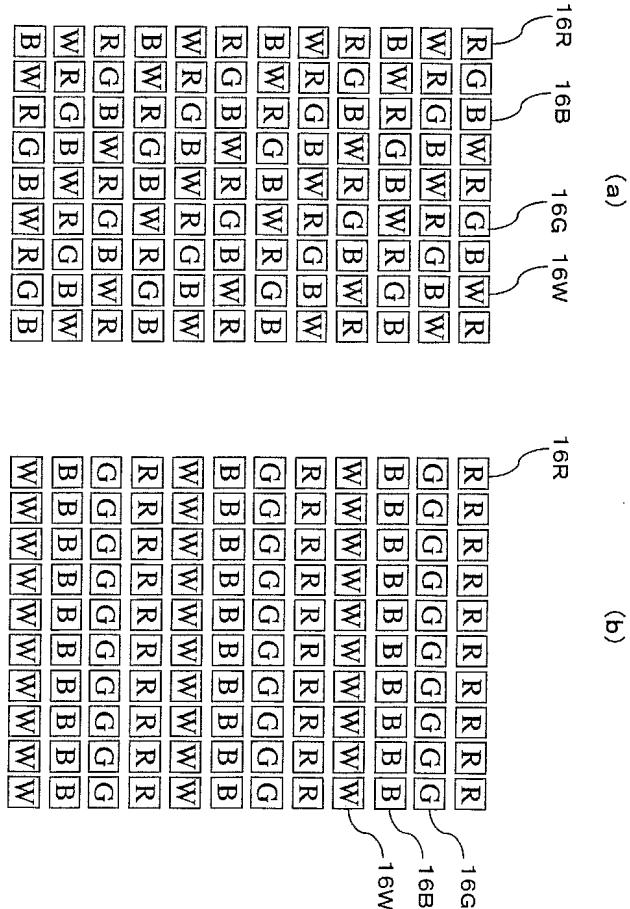

또, 화소는 R, G, B의 3원색으로 했지만 이것에 한정되는 것이 아니고, 시안, 엘로우, 마젠타의 3색이어도 된다. 또한, B와 엘로우의 2색이라도 좋다. 물론, 단색이어도 무방하다. 또한, R, G, B, 시안, 엘로우, 마젠타의 6색이어도 된다. R, G, B, 시안, 마젠타의 5색이어도 좋다. 이들은 내츄럴 컬러로서 색 재현 범위가 확대되어 양호한 표시를 실현할 수 있다. 이상과 같이 본 발명의 EL 표시 장치는 RGB의 3원색으로 컬러 표시를 행하는 것에 한정되는 것이 아니다.

유기 EL 표시 패널의 컬러화에는 주로 3가지 방식이 있는데, 색 변환 방식은 이 중의 하나이다. 발광층으로서 청색만의 단층을 형성하면 되고, 풀컬러화에 필요한 남은 녹색과 적색은 청색 광으로부터 색 변환에 의해서 만들어낸다. 따라서, RGB의 각 층을 분할 도포할 필요가 없고, RGB의 각 색의 유기 EL 재료를 갖출 필요가 없다고 하는 이점이 있다. 색 변환 방식은 분할 도포 방식과 같은 수율 저하가 없다. 본 발명의 EL 표시 패널 등은 이들 어느 방식에서도 적용된다.

또한, 3원색 외에, 백색 발광의 화소를 형성해도 된다. 백색 발광의 화소는 R, G, B발광의 구조를 적층함으로써 제작(형성 또는 구성)하는 것에 의해 실현할 수 있다. 1조의 화소는 RGB의 3원색과, 백색 발광의 화소(16W)로 이루어진다. 백색 발광의 화소를 형성하는 것에 의해, 백색의 피크 휘도가 표현하기 쉬워진다. 따라서, 휘도감이 있는 화상 표시를 실현할 수 있다.

RGB 등의 3원색을 1조의 화소로 하는 경우에서도, 각 색의 화소 전극의 면적은 서로 다르게 한 것이 바람직하다. 물론, 각 색의 발광 효율이 밸런스 좋고, 색 순도도 밸런스가 좋으면, 동일 면적이더라도 상관없다. 그러나, 하나 또는 복수의 색의 밸런스가 나쁘면, 화소 전극(발광 면적)을 조정하는 것이 바람직하다. 각 색의 전극 면적은 전류 밀도를 기준으로 결정하면 된다. 즉, 색 온도가 7000K(켈빈) 이상 12000K 이하의 범위에서 화이트 밸런스를 조정했을 때, 각 색의 전류 밀도의 차가  $\pm 30\%$  이내로 되도록 한다. 더욱 바람직하게는  $\pm 15\%$  이내로 되도록 한다. 예를 들면, 전류 밀도가 100A/평방미터로 하면, 3원색이 어느 것이나 70A/평방미터 이상 130A/평방미터 이하로 되도록 한다. 더욱 바람직하게는, 3원색이 어느 것이나 85A/평방미터 이상 115A/평방미터 이하로 되도록 한다.

유기 EL 소자(15)는 자기 발광 소자이다. 이 발광에 의한 빛이 스위칭 소자로서의 트랜지스터에 입사하면, 포토컨덕터 현상(photoconductor)이 발생한다. 포토컨덕터란, 광 여기에 의해 트랜지스터 등의 스위칭 소자의 오프 시에서의 누설(오프 누설)이 증가하는 현상을 말한다.

이 과제에 대처하기 위해서, 본 발명에서는 게이트 드라이버 회로(12)(경우에 따라서는 소스 드라이버 회로(14))의 하층, 화소 트랜지스터(11)의 하층의 차광막을 형성하고 있다. 차광막은 크롬 등의 금속 박막으로 형성하며, 그 막 두께는 50 nm 이상 150 nm 이하로 한다. 막 두께가 얕으면 차광 효과가 부족하고, 두꺼우면 요철이 발생하여 상층의 트랜지스터(11a1)의 패터닝이 곤란해진다.

드라이버 회로(12) 등은 이면 뿐만아니라, 표면에서의 빛의 진입도 억제해야 된다. 포토컨덕터의 영향에 의해 오동작하기 때문이다. 따라서, 본 발명에서는 캐소드 전극이 금속막인 경우에는, 드라이버(12) 등의 표면에도 캐소드 전극을 형성하여, 이 전극을 차광막으로서 이용하고 있다.

그러나, 드라이버(12) 위에 캐소드 전극을 형성하면, 이 캐소드 전극으로부터의 전계에 의한 드라이버의 오동작 혹은 캐소드 전극과 드라이버 회로의 전기적 접촉이 발생할 가능성이 있다. 이 과제에 대처하기 위해서, 본 발명에서는 드라이버 회로(12) 등의 위에 적어도 1층, 바람직하게는 복수층의 유기 EL막을 화소 전극 상의 유기 EL막 형성과 동시에 형성한다.

화소의 하나 이상의 트랜지스터(11)의 단자간 혹은 트랜지스터(11)와 신호선이 단락하면, EL 소자(15)가 상시 점등하는 휘점이 되는 경우가 있다. 이 휘점은 시각적으로 눈에 띄기 때문에 흑점화(비점등)할 필요가 있다. 휘점에 대해서는, 해당 화소(16)를 검출하고, 컨덴서(19)에 레이저광을 조사하여 컨덴서의 단자 사이를 단락시킨다. 따라서, 컨덴서(19)에는 전하를 유지할 수 없게 되므로, 트랜지스터(11a)는 전류를 흘려보내지 않게 할 수 있다. 레이저광을 조사하는 위치에 대응하는 캐소드막을 제거해 놓는 것이 바람직하다. 레이저 조사에 의해, 컨덴서(19)의 단자 전극과 캐소드막이 쇼트하는 것을 방지하기 위해서이다.

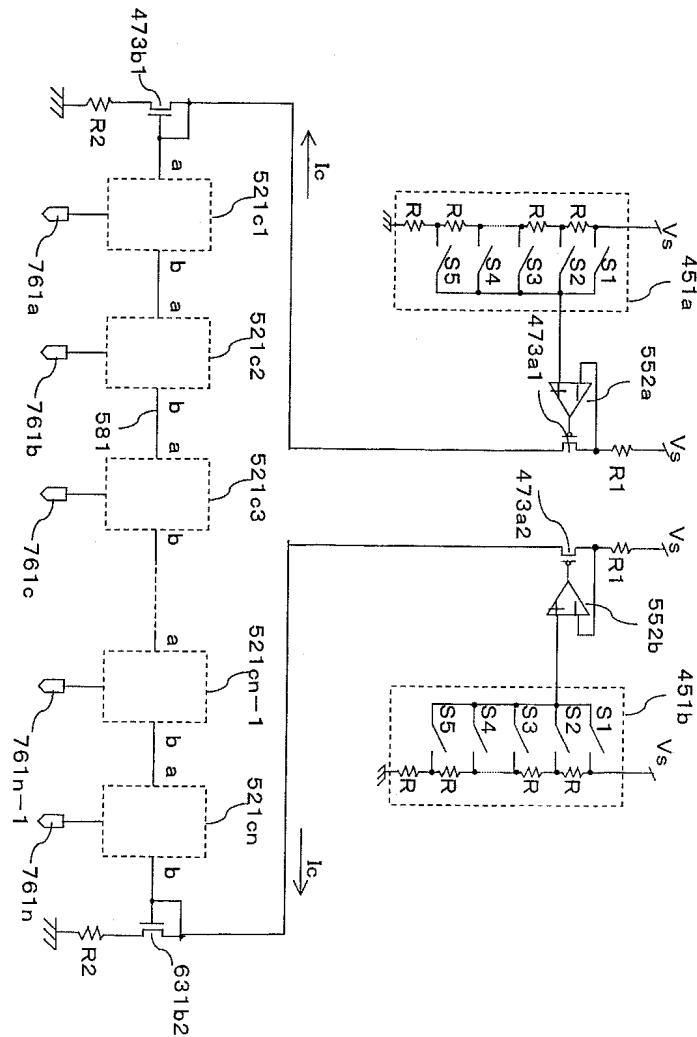

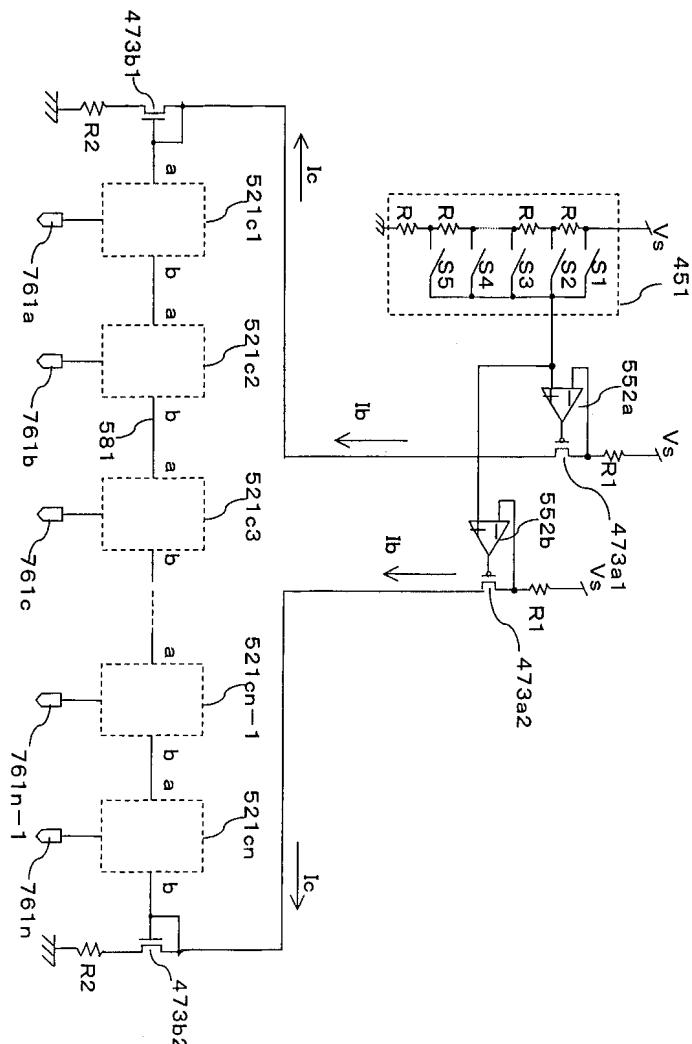

화소(16)의 트랜지스터(11)의 결함은 소스 드라이버 IC(14) 등에도 영향을 준다. 예를 들면, 도 45에서는 구동용 트랜지스터(11a)에 소스-드레인(SD) 쇼트(452)가 발생하고 있으면, 패널의 Vdd 전압이 소스 드라이버 IC(14)에 인가된다. 따라서, 소스 드라이버 IC(14)의 전원 전압은, 패널의 전원 전압 Vdd와 동일 혹은 높게 해 두는 것이 바람직하다. 또, 소스 드라이버 IC에서 사용하는 기준 전류는 전자 볼륨(451)으로 조정할 수 있도록 구성해 놓는 것이 바람직하다.

트랜지스터(11a)에 SD 쇼트(452)가 발생하고 있으면, EL 소자(15)에 과대한 전류가 흐른다. 즉, EL 소자(15)가 상시 점등 상태(휘점)로 된다. 휘점은 결함으로서 눈에 띄기 쉽다. 예를 들면, 도 45에 있어서, 트랜지스터(11a)의 소스-드레인(SD) 쇼트가 발생하고 있으면, 트랜지스터(11a)의 게이트(G) 단자 전위의 대소에 상관없이, Vdd 전압으로부터 EL 소자(15)에 전류가 상시 흐른다(트랜지스터(11d)가 온일 때). 따라서, 휘점이 된다.

한편, 트랜지스터(11a)에 SD 쇼트가 발생하고 있으면, 트랜지스터(11c)가 온 상태일 때, Vdd 전압이 소스 신호선(18)에 인가되고 소스 드라이버 회로(14)에 Vdd 전압이 인가된다. 만약, 소스 드라이버 회로(14)의 전원 전압이 Vdd 이하이면, 내압을 초과하여, 소스 드라이버 회로(14)가 파괴될 우려가 있다. 그 때문에, 소스 드라이버 회로(14)의 전원 전압은 Vdd 전압(패널이 높은 쪽의 전압) 이상으로 하는 것이 바람직하다.

트랜지스터(11a)의 SD 쇼트 등은 점 결함으로 머물지 않고, 패널의 소스 드라이버 회로를 파괴하는 데로 연결될 우려가 있으며, 또한, 휘점은 눈에 띄기 때문에 패널로서는 불량이 된다. 따라서, 트랜지스터(11a)와 EL 소자(15) 사이를 접속하는 배선을 절단하여, 휘점을 흑점 결함으로 할 필요가 있다. 이 절단에는 레이저광 등의 광학 수단을 이용하여 절단하는 것이 좋다.

이하, 본 발명의 구동 방법에 대하여 설명한다. 도 1에 도시한 바와 같이, 게이트 신호선(17a)은 행 선택 기간에 도통 상태(여기서는 도 1의 트랜지스터(11)가 p 채널 트랜지스터이기 때문에 로우 레벨에서 도통이 됨)가 되고, 게이트 신호선(17b)은 비선택 기간일 때에 도통 상태로 된다.

소스 신호선(18)에는 기생 용량(도시하지 않음)이 존재한다. 기생 용량은 소스 신호선(18)과 게이트 신호선(17)의 크로스 부의 용량, 트랜지스터(11b, 11c)의 채널 용량 등에 의해 발생한다.

소스 신호선(18)의 전류값 변화에 요하는 시간  $t$ 는 부유 용량의 크기를  $C$ , 소스 신호선의 전압을  $V$ , 소스 신호선에 흐르는 전류를  $I$ 로 하면  $t=C \cdot V/I$ 이기 때문에 전류값을 10배 크게 할 수 있다는 것은 전류값 변화에 요하는 시간이 10분의 1 가까이 깊게 할 수 있고, 또는 소스 신호선(18)의 기생 용량이 10배로 되어도 소정의 전류값으로 변화할 수 있다는 것을 나타낸다. 따라서, 깊은 수평 주사 기간 내에 소정의 전류값을 기입하기 위해서는 전류값을 증가시키는 것이 유효하다.

입력 전류를 10배로 하면 출력 전류도 10배로 되고, EL의 휘도가 10배로 되기 때문에 소정의 휘도를 얻기 위해서, 도 1의 트랜지스터(11d)의 도통 기간을 종래의 10분의 1로 하고, 발광 기간을 10분의 1로 함으로써, 소정 휘도를 표시하도록 했다. 또, 10배를 예시하여 설명하고 있는 것은 이해를 쉽게 하기 위해서이다. 10배로 한정하는 것이 아님은 물론이다.

즉, 소스 신호선(18)의 기생 용량의 충방전을 충분히 행하고, 소정의 전류값을 화소(16)의 트랜지스터(11a)에 프로그램하기 위해서는, 소스 드라이버 회로(14)로부터 비교적 큰 전류를 출력할 필요가 있다. 그러나, 이와 같이 큰 전류를 소스 신호선(18)에 흘리면 이 전류값이 화소에 프로그램되고, 소정의 전류에 대하여 큰 전류가 EL 소자(15)에 흐른다. 예를 들면, 10배의 전류로 프로그램하면, 당연히 10배의 전류가 EL 소자(15)에 흐르고, EL 소자(15)는 10배의 휘도로 발광한다. 소정의 발광 휘도로 하기 위해서는, EL 소자(15)에 흐르는 시간을 1/10로 하면 된다. 이와 같이 구동함으로써, 소스 신호선(18)의 기생 용량을 충분히 충방전할 수 있어, 소정의 발광 휘도를 얻을 수 있다.

또, 10배의 전류값을 화소의 트랜지스터(11a)(정확하게는 컨텐서(19)의 단자 전압을 설정하고 있음)에 기입하고, EL 소자(15)의 온 시간을 1/10로 한 것으로 했지만 이것은 일례이다. 경우에 따라서는, 10배의 전류값을 화소의 트랜지스터(11a)에 기입하고, EL 소자(15)의 온 시간을 1/5로 하여도 좋다. 반대로 10배의 전류값을 화소의 트랜지스터(11a)에 기입하고, EL 소자(15)의 온 시간을 1/2배로 하는 경우도 있을 것이다.

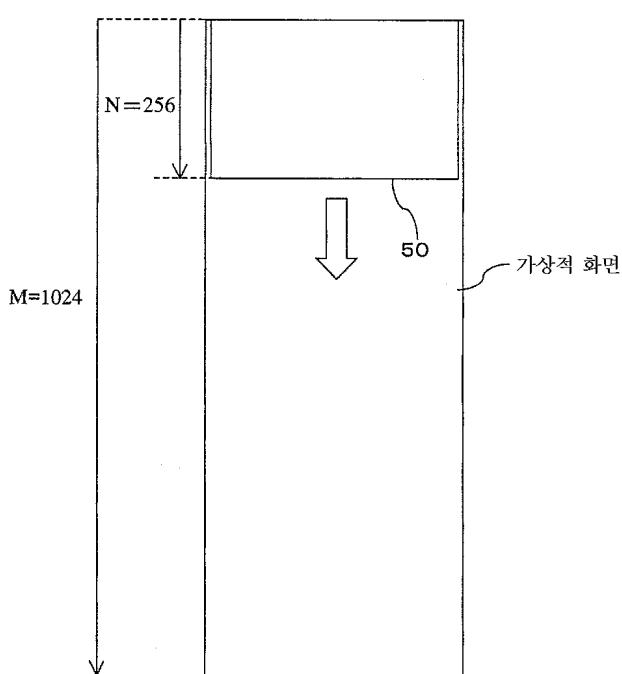

본 발명은 화소에의 기입 전류를 소정값 이외의 값으로 하고, EL 소자(15)에 흐르는 전류를 간헐 상태로 하여 구동하는 것에 특징이 있다. 본 명세서에서는 설명을 쉽게 하기 위해서,  $N$ 배의 전류값을 화소의 트랜지스터(11)에 기입하고, EL 소자(15)의 온 시간을  $1/N$ 배로 하는 것으로 하여 설명한다. 그러나, 이것에 한정되는 것이 아니라,  $N1$ 배의 전류값을 화소의 트랜지스터(11)에 기입하고, EL 소자(15)의 온 시간을  $1/(N2)$ 배( $N1$ 과  $N2$ 는 서로 다름)이어도 됨은 물론이다.

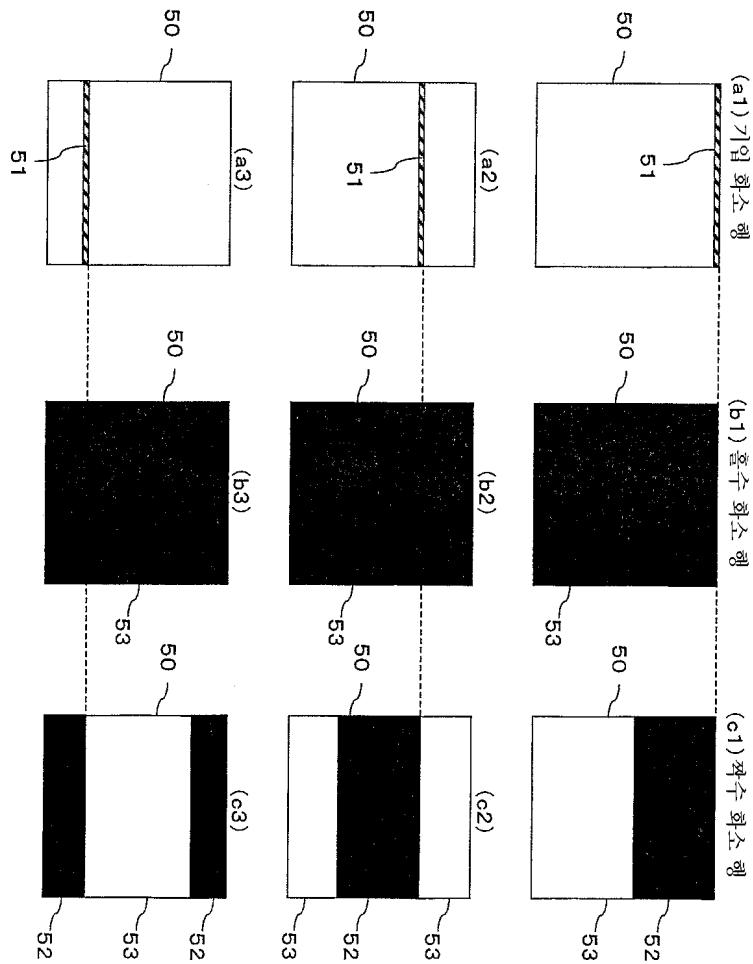

백 래스터 표시에 있어서, 표시 화면(50)의 1 필드(프레임) 기간의 평균 휘도를  $B0$ 으로 가정한다. 이 때, 각 화소(16)의 휘도  $B1$ 이 평균 휘도  $B0$ 보다도 높아지도록 전류(전압) 프로그램을 행하는 구동 방법이다. 또한, 적어도 1필드(프레임) 기간에 있어서, 비표시 영역(52)이 발생하도록 하는 구동 방법이다. 따라서, 본 발명의 구동 방법에서는, 1 필드(프레임) 기간의 평균 휘도는  $B1$ 보다도 낮아진다.

또, 간헐하는 간격(비표시 영역(52)/비표시 영역(53))은 등간격에 한정되는 것이 아니다. 예를 들면, 랜덤하여도 된다(전체적으로, 표시 기간 혹은 비표시 기간이 소정값(일정 비율)이 되면 됨). 또한, RGB에서 서로 다르더라도 무방하다. 즉, 백(화이트) 빌런스가 최적이 되도록, R, G, B 표시 기간 혹은 비표시 기간이 소정값(일정 비율)으로 되도록 조정(설정)하면 된다.

본 발명의 구동 방법의 설명을 쉽게 하기 위해서,  $1/N$ 이란, 1F(1 필드 또는 1 프레임)를 기준으로 하여 이 1F를  $1/N$ 로 하는 것으로 하여 설명한다. 그러나, 1 화소 행이 선택되고, 전류값이 프로그램되는 시간(통상, 1수평 주사 기간(1H))이 있고, 또한, 주사 상태에 따라서는 오차도 발생함은 말할 필요도 없다.

예를 들면,  $N=10$ 배의 전류로 화소(16)에 전류 프로그램하고,  $1/5$ 의 기간 동안, EL 소자(15)를 점등시켜도 좋다. EL 소자(15)는  $10/5=2$ 배의 휘도로 점등한다.  $N=2$ 배의 전류로 화소(16)에 전류 프로그램하고,  $1/4$ 의 기간 동안, EL 소자(15)를 점등시켜도 된다. EL 소자(15)는  $2/4=0.5$ 배의 휘도로 점등한다. 즉, 본 발명은  $N=1$ 배가 아닌 전류로 프로그램하고, 또한 상시 점등( $1/1$ , 즉, 간헐 표시가 아님) 상태 이외의 표시를 실시하는 것이다. 또한, EL 소자(15)에 공급하는 전류를 1 프레임(혹은 1 필드)의 기간에 있어서, 적어도 1회, 오프 상태로 하는 구동 방식이다. 또한, 소정값보다도 큰 전류로 화소(16)에 프로그램하고, 적어도 간헐 표시를 실시하는 구동 방식이다.

유기(무기) EL 표시 장치는 CRT와 같이 전자총으로 선 표시의 집합으로서 화상을 표시하는 디스플레이와는 표시 방법이 기본적으로 다른 점에도 과제가 있다. 즉, EL 표시 장치에서는, 1F(1 필드 혹은 1 프레임)의 기간 동안은 화소에 기입한 전류(전압)를 유지한다. 그 때문에, 동화상 표시를 행하면 표시 화상의 윤곽이 흐려진다고 하는 과제가 발생한다.

본 발명에서는 1F/ $N$ 의 기간 동안만, EL 소자(15)에 전류를 흘려 보내고, 다른 기간( $1F(N-1)/N$ )은 전류를 흘려 보내지 않는다. 이 구동 방식을 실시하여 화면의 일점을 관측한 경우를 생각한다. 이 표시 상태에서는 1F마다 화상 데이터 표시, 즉

표시(비점등)가 반복하여 표시된다. 즉, 화상 데이터 표시 상태가 시간적으로 간헐 표시 상태가 된다. 동화상 데이터 표시를, 간헐 표시 상태에서 보면 화상의 윤곽 흐려짐이 없어져 양호한 표시 상태를 실현할 수 있다. 즉, CRT에 가까운 동화상 표시를 실현할 수 있다.

본 발명의 구동 방법에서는 간헐 표시를 실현한다. 그러나, 간헐 표시는 트랜지스터(11d)를 1H 주기로 온 오프 제어하기 만 하여도 된다. 따라서, 회로의 메인 클럭은 종래와 변하지 않기 때문에, 회로의 소비 전력이 증가하는 일도 없다. 액정 표시 패널에서는 간헐 표시를 실현하기 위해서 화상 메모리가 필요하다. 본 발명은, 화상 데이터는 각 화소(16)에 유지되어 있다. 따라서, 간헐 표시를 실시하기 위한 화상 메모리는 불필요하다.

본 발명은 스위칭의 트랜지스터(11d), 혹은 트랜지스터(11e) 등을 온 오프시키는 것만으로 EL 소자(15)에 흘리는 전류를 제어한다. 즉, EL 소자(15)에 흐르는 전류  $I_w$ 를 오프해도, 화상 데이터는 그대로 컨텐서(19)에 유지되어 있다. 따라서, 다음 타이밍에서 트랜지스터(11d) 등을 온시켜, EL 소자(15)에 전류를 흘리면, 그 흐르는 전류는 전에 흐르고 있던 전류값과 동일하다. 본 발명에서는 흑 삽입(흑 표시 등의 간헐 표시)을 실현할 때에 있어서도, 회로의 메인 클럭을 올릴 필요가 없다. 또한, 시간 축 신장을 실시할 필요도 없기 때문에 화상 메모리도 불필요하다. 또한, 유기 EL 소자(15)는 전류를 인가하고 나서 발광하기까지의 시간이 짧아, 고속으로 응답한다. 그 때문에, 동화상 표시에 적합하고, 또한 간헐 표시를 실시함으로써 종래의 데이터 유지형의 표시 패널(액정 표시 패널, EL 표시 패널 등)의 문제인 동화상 표시의 문제를 해결할 수 있다.

또한, 대형의 표시 장치에서 소스 신호선(18)의 배선 길이가 길어지고, 소스 신호선(18)의 기생 용량이 커지는 경우에는,  $N$ 값을 크게 함으로써 대응할 수 있다. 소스 신호선(18)에 인가하는 프로그램 전류값을  $N$ 배로 한 경우, 게이트 신호선(17b)(트랜지스터(11d))의 도통 기간을 1F/ $N$ 으로 하면 된다. 이에 따라 텔레비전, 모니터 등의 대형 표시 장치 등에도 적용이 가능하다.

이하, 도면을 참조하면서, 본 발명의 구동 방법에 대하여 더욱 자세하게 설명한다. 소스 신호선(18)의 기생 용량은, 인접한 소스 신호선(18) 사이의 결합 용량, 소스 드라이버 IC(회로)(14)의 버퍼 출력 용량, 게이트 신호선(17)과 소스 신호선(18)의 크로스 용량 등에 의해 발생한다. 이 기생 용량은 통상 10pF 이상이 된다. 전압 구동의 경우는, 소스 드라이버 IC(14)로부터는 저 임피던스로 전압이 소스 신호선(18)에 인가되기 때문에, 기생 용량이 다소 크더라도 구동에서는 문제가 되지 않는다.

그러나, 전류 구동에서는 특히 흑 레벨의 화상 표시에서는 20nA 이하의 미소 전류로 화소의 컨텐서(19)를 프로그램할 필요가 있다. 따라서, 기생 용량이 소정값 이상의 크기에서 발생하면, 1 화소 행에 프로그램하는 시간(통상 1H 이내, 단, 2 화소 행을 동시에 기입하는 경우도 있으므로 1H 이내로 한정되는 것은 아님) 내에 기생 용량을 충방전할 수 없다. 1H 기간에 충방전할 수 없으면, 화소에의 기입 부족이 되어, 해상도가 나오지 않는다.

도 1의 화소 구성인 경우, 도 3의 (a)에 도시한 바와 같이, 전류 프로그램 시에는, 프로그램 전류  $I_w$ 가 소스 신호선(18)에 흐른다. 이 전류  $I_w$ 가 트랜지스터(11a)를 흘려,  $I_w$ 를 흘리는 전류가 유지되도록, 컨텐서(19)에 전압 설정(프로그램)된다. 이 때, 트랜지스터(11d)는 오픈 상태(오프 상태)이다.

다음에, EL 소자(15)에 전류를 흘리는 기간은 도 3의 (b)와 같이, 트랜지스터(11c, 11b)가 오프하여, 트랜지스터(11d)가 동작한다. 즉, 게이트 신호선(17a)에 오프 전압( $V_{gh}$ )이 인가되고, 트랜지스터(11b, 11c)가 오프 상태로 된다. 한편, 게이트 신호선(17b)에 온 전압( $V_{gl}$ )이 인가되고, 트랜지스터(11d)가 온 상태로 된다.

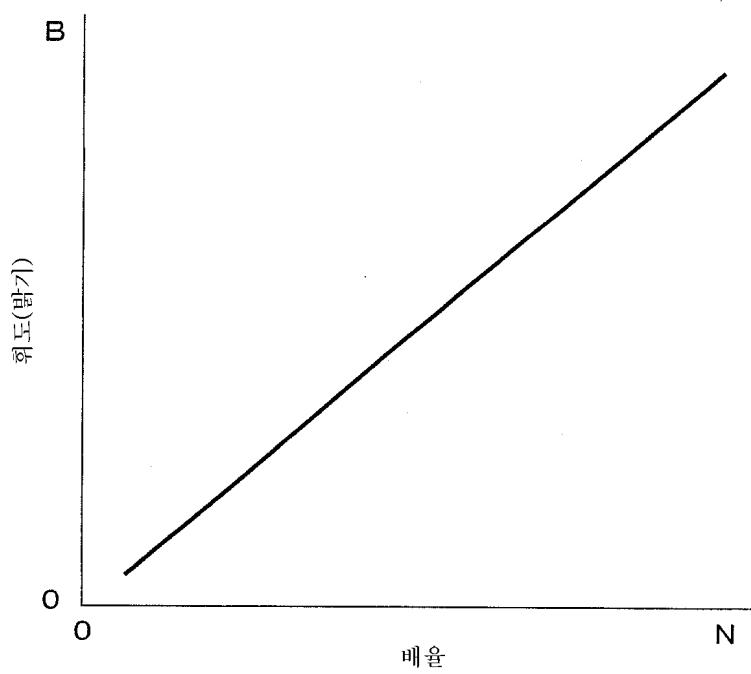

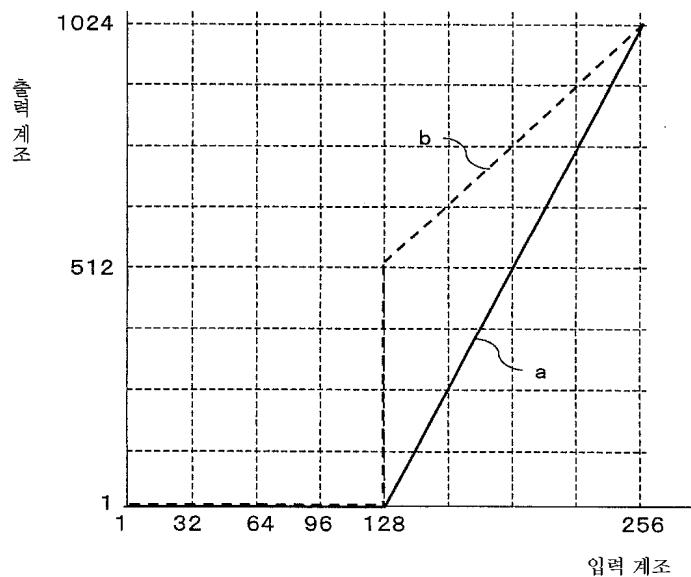

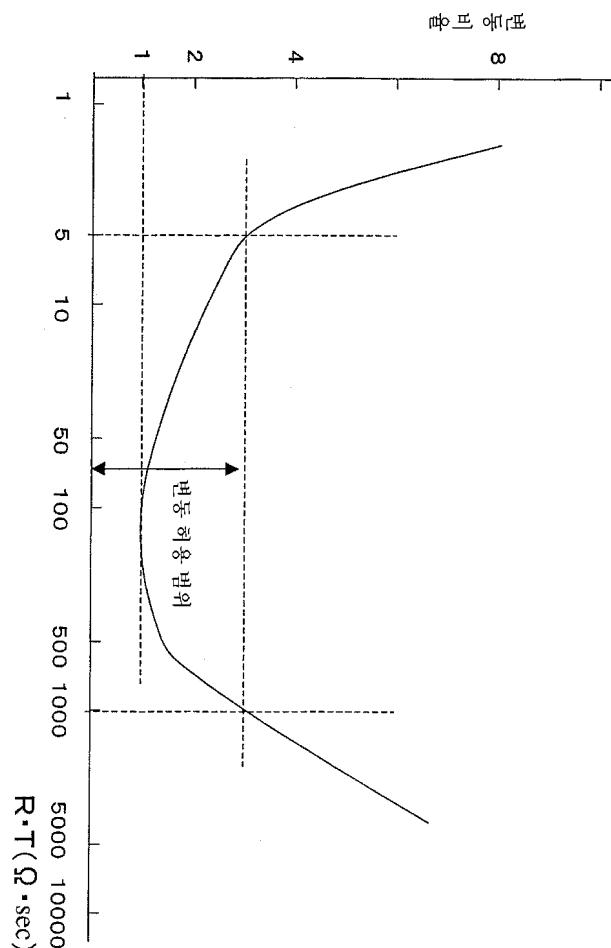

이제, 전류  $I_l$ 이 본래 흘리는 전류(소정값)의  $N$ 배라고 하면, 도 3의 (b)의 EL 소자(15)에 흐르는 전류도  $I_w$ 가 된다. 따라서, 소정값의 10배의 휘도로 EL 소자(15)는 발광한다. 즉, 도 12에 도시하는 바와 같이, 배율  $N$ 을 높게 할수록, 화소(16)의 표시 휘도  $B$ 도 높아진다. 따라서, 배율과 화소(16)의 휘도는 비례 관계가 된다.

그래서, 트랜지스터(11d)를 본래 온하는 시간(약 1F)의  $1/N$ 의 기간만 온시키고, 다른 기간  $(N-1)/N$  기간은 오프시키면, 1F 전체의 평균 휘도는 소정의 휘도가 된다. 이 표시 상태는 CRT이 전자총으로 화면을 주사하고 있는 것과 근사하다. 다른 점은 화면 전체의  $1/N$ (전 화면을 1로 함)이 점등하고 있는 점이다(CRT에서는 점등하고 있는 범위는 1 화소 행임(엄밀하게는 1 화소임)).

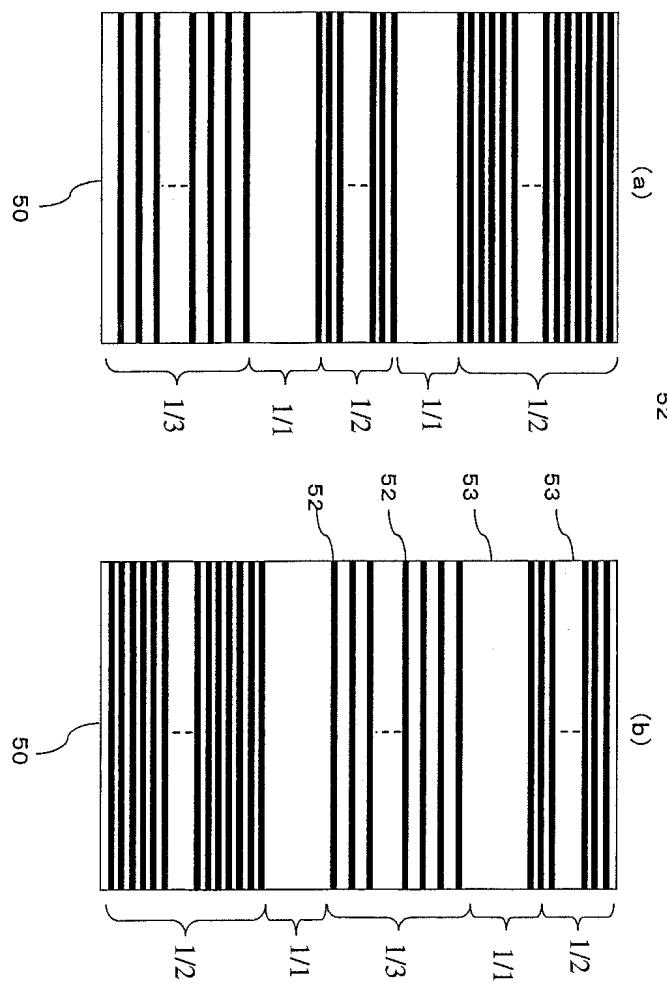

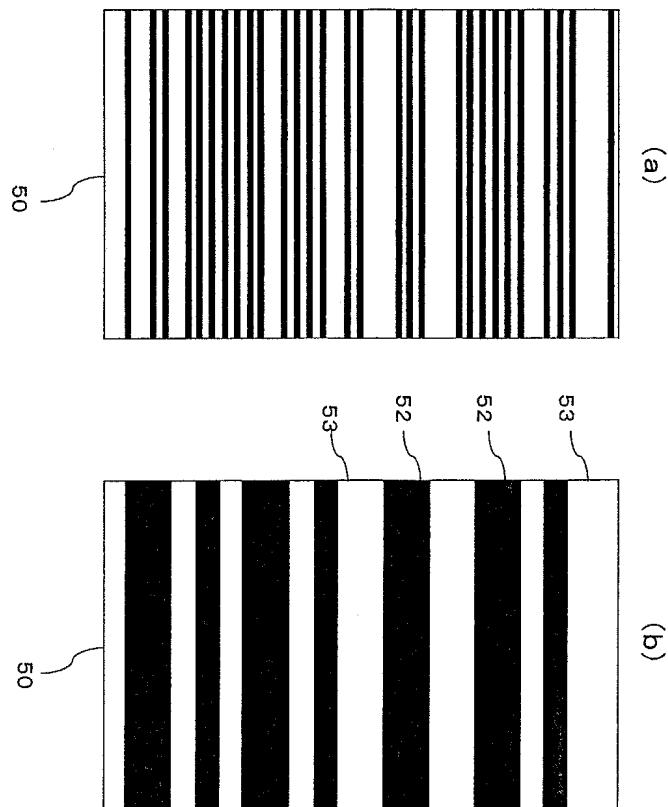

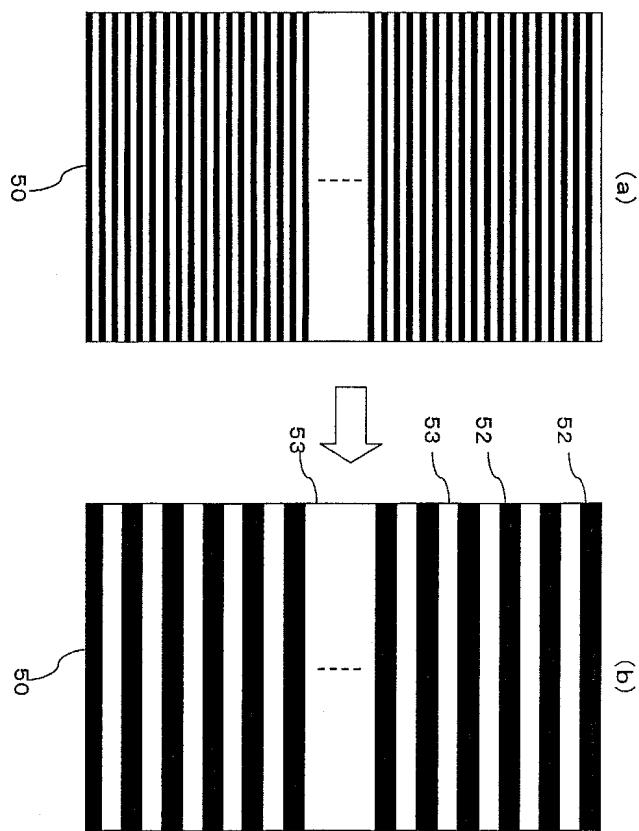

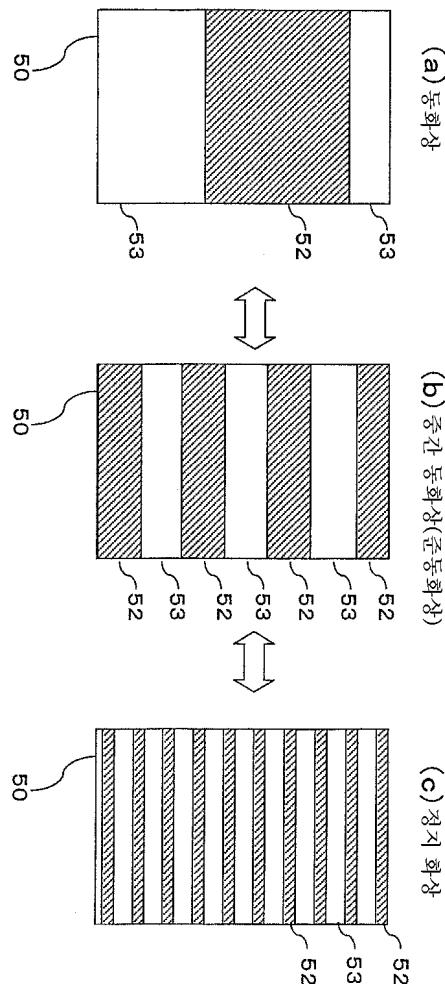

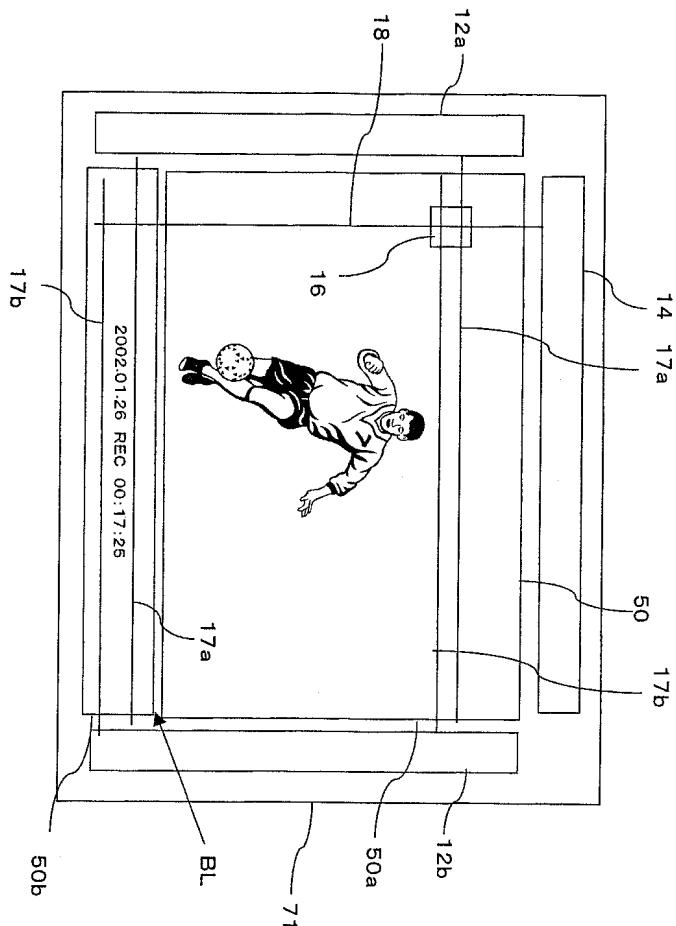

본 발명에서는, 이 1F/ $N$ 의 화상 표시 영역(53)이 도 13의 (b)에 도시한 바와 같이 화면(50)의 위에서 아래로 이동한다. 본 발명에서는 1F/ $N$ 의 기간 동안만, EL 소자(15)에 전류가 흐르고, 다른 기간( $1F \cdot (N-1)/N$ )은 전류가 흐르지 않는다. 따라서, 각 화소(16)는 간헐 표시로 된다. 그러나, 인간의 눈에는 잔상에 의해 화상이 유지된 상태가 되므로, 전 화면이 균일하게 표시되어 있게 보인다.

또, 도 13에 도시하는 바와 같이, 기입 화소 행(51a)은 비점등 표시(52a)로 한다. 그러나, 이것은 도 1, 도 2 등의 화소 구성인 경우이다. 도 38 등에서 도시하는 커런트 미러의 화소 구성에서는, 기입 화소 행(51a)은 점등 상태로 하여도 좋다. 그러나, 본 명세서에서는 설명을 쉽게 하기 위해서, 주로 도 1의 화소 구성을 예시하여 설명한다. 또한, 도 13, 도 16 등의 소정 구동 전류 Iw보다도 큰 전류로 프로그램하고, 간헐 구동하는 구동 방법을 N배 펠스 구동이라고 부른다.

이 표시 상태에서는 1F마다 화상 데이터 표시, 흑 표시(비점등)가 반복하여 표시된다. 즉, 화상 데이터 표시 상태가 시간적으로 띄엄띄엄 표시(간헐 표시) 상태가 된다. 액정 표시 패널(본 발명 이외의 EL 표시 패널)에서는, 1F의 기간, 화소에 데이터가 유지되고 있기 때문에, 동화상 표시의 경우는 화상 데이터가 변화해도 그 변화에 추종할 수 없어, 동화상 불선명으로 되어 있었다(화상의 윤곽 흐려짐). 그러나, 본 발명에서는 화상을 간헐 표시하기 위해서, 화상의 윤곽 흐려짐이 없어져 양호한 표시 상태를 실현할 수 있다. 즉, CRT에 가까운 동화상 표시를 실현할 수 있다.

또, 도 13에 도시하는 바와 같이, 구동하기 위해서는, 화소(16)의 전류 프로그램 기간(도 1의 화소 구성에서는, 게이트 신호선(17a)의 온 전압 Vgl이 인가되어 있는 기간)과, EL 소자(15)를 오프 또는 온 제어하고 있는 기간(도 1의 화소 구성에서는, 게이트 신호선(17b)의 온 전압 Vgl 또는 오프 전압 Vgh가 인가되어 있는 기간)을 독립적으로 제어할 수 있을 필요가 있다. 따라서, 게이트 신호선(17a)과 게이트 신호선(17b)은 분리되어 있을 필요가 있다.

예를 들면, 게이트 드라이버 회로(12)로부터 화소(16)에 배선된 게이트 신호선(17)이 하나인 경우, 게이트 신호선(17)에 인가된 로직(Vgh 또는 Vgl)을 트랜지스터(11b)에 인가하고, 게이트 신호선(17)에 인가된 로직을 인버터로 변환하여 (Vgl 또는 Vgh), 트랜지스터(11d)에 인가한다고 하는 구성에서는, 본 발명의 구동 방법은 실시할 수 없다. 따라서, 본 발명에서는 게이트 신호선(17a)을 조작하는 게이트 드라이버 회로(12a)와, 게이트 신호선(17b)을 조작하는 게이트 드라이버 회로(12b)가 필요해진다.

또한 본 발명의 구동 방법은, 도 1의 화소 구성에서도, 전류 프로그램 기간(1H) 이외의 기간에서도, 비점등 표시로 하는 구동 방법이다.

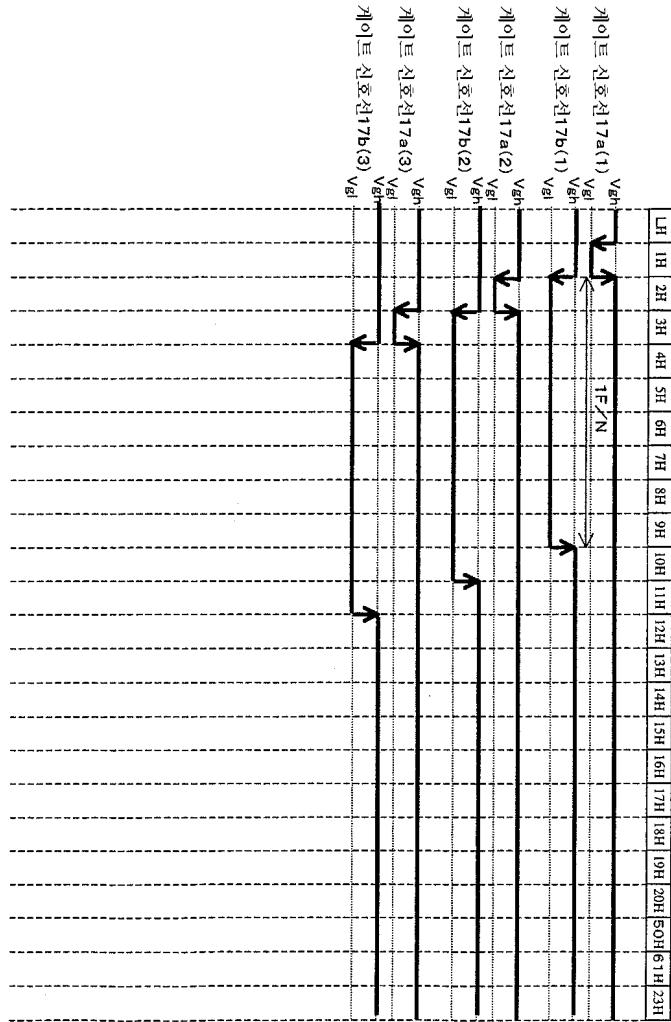

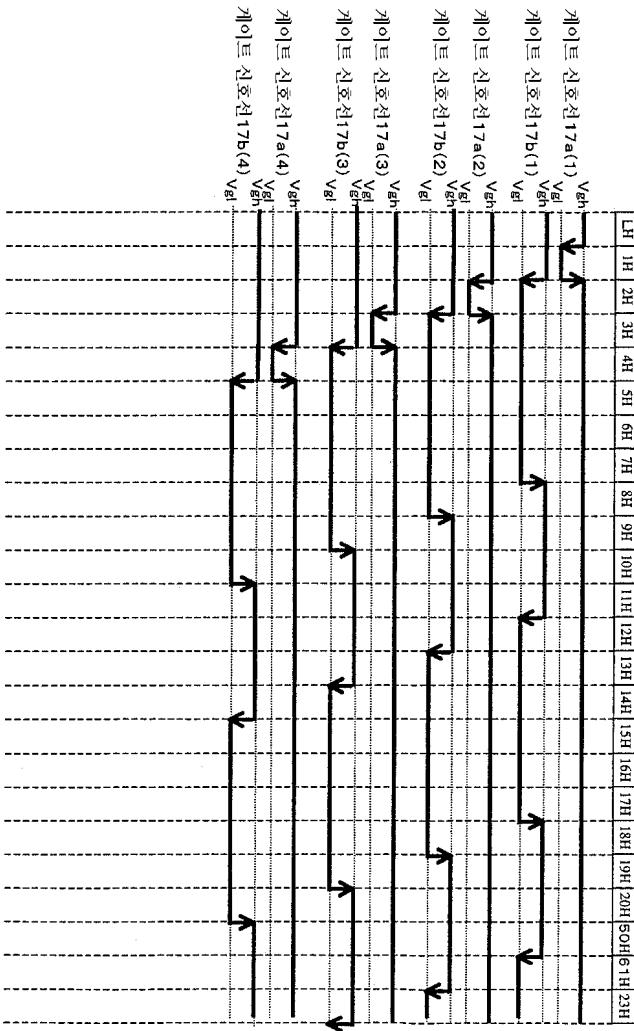

도 13의 구동 방법의 타이밍차트를 도 14에 도시한다. 또, 본 발명 등에 있어서, 특히 거절이 없을 때의 화소 구성은 도 1이라고 한다. 도 14에서 알 수 있듯이, 각 선택된 화소 행(선택 기간은 1H로 하고 있음)에 있어서, 게이트 신호선(17a)에 온 전압(Vgl)이 인가되고 있을 때(도 14의 (a)를 참조)에는, 게이트 신호선(17b)에는 오프 전압(V9h)이 인가되고 있다(도 14의 (b)를 참조). 또한, 이 기간은 EL 소자(15)에는 전류가 흐르고 있지 않다(비점등 상태). 선택되어 있지 않은 화소 행에 있어서, 게이트 신호선(17a)에 오프 전압(Vgh)이 인가되고, 게이트 신호선(17b)에는 온 전압(Vgl)이 인가되고 있다. 또한, 이 기간은 EL 소자(15)에 전류가 흐르고 있다(점등 상태). 또한, 점등 상태에서는, EL 소자(15)는 소정의 N배의 휘도(N·B)로 점등하며, 그 점등 기간은 1F/N이다. 따라서, 1F를 평균한 표시 패널의 표시 휘도는  $(N \cdot B) \times (1/N) = B$ (소정 휘도)가 된다.

도 15는 도 14의 동작을 각 화소 행에 적용한 실시예이다. 게이트 신호선(17)에 인가하는 전압 파형을 나타내고 있다. 전압 파형은 오프 전압을 Vgh(H 레벨)로 하고, 온 전압을 Vgl(L 레벨)로 하고 있다. (1)(2) 등의 침자는 선택하고 있는 화소 행 번호를 나타내고 있다.

도 15에 있어서, 게이트 신호선(17a)(1)이 선택되고(Vgl 전압), 선택된 화소 행의 트랜지스터(11a)에서 소스 드라이버 회로(14)를 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이 프로그램 전류는 소정 값의 N배(설명을 쉽게 하기 위해서, N=10으로 설명함. 물론, 소정 값이란 화상을 표시하는 데이터 전류이므로, 백 레스터 표시 등이 아닌 한 고정치가 아님)이다. 따라서, 컨텐서(19)에는 10배로 전류가 트랜지스터(11a)에 흐르도록 프로그램된다. 화소 행(1)이 선택되었을 때에는, 도 1의 화소 구성에서는 게이트 신호선(17b)(1)은 오프 전압(Vgh)이 인가되어, EL 소자(15)에는 전류가 흐르지 않는다.

1H 후에는, 게이트 신호선(17a)(2)이 선택되고(Vgl 전압), 선택된 화소 행의 트랜지스터(11a)에서 소스 드라이버 회로(14)를 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이 프로그램 전류는 소정 값의 N배(설명을 쉽게 하기 위해서, N=10으로 설명함)이다. 따라서, 컨텐서(19)에는 10배로 전류가 트랜지스터(11a)에 흐르도록 프로그램된다. 화소 행(2)이 선택되었을 때에는, 도 1의 화소 구성에서는 게이트 신호선(17b)(2)은 오프 전압(Vgh)이 인가되어, EL 소자(15)에는 전류가 흐르지 않는다. 그러나, 앞의 화소 행(1)의 게이트 신호선(17a)(1)에는 오프 전압(Vgh)이 인가되고, 게이트 신호선(17b)(1)에는 온 전압(Vgl)이 인가되기 때문에, 점등 상태로 되어 있다.

다음의 1H 후에는 게이트 신호선(17a)(3)이 선택되고, 게이트 신호선(17b)(3)은 오프 전압(Vgh)이 인가되어, 화소 행(3)의 EL 소자(15)에는 전류가 흐르지 않는다. 그러나, 앞의 화소 행(1)(2)의 게이트 신호선(17a)(1)(2)에는 오프 전압(Vgh)이 인가되고, 게이트 신호선(17b)(1)(2)에는 온 전압(Vgl)이 인가되기 때문에, 점등 상태로 되어 있다.

이상의 동작을 1H의 동기 신호에 동기하여 화상을 표시해 간다. 그러나, 도 15의 구동 방식에서는, EL 소자(15)에는 10배의 전류가 흐른다. 따라서, 표시 화면(50)은 약 10배의 휘도로 표시된다. 물론, 이 상태에서 소정의 휘도 표시를 행하기 위해서는, 프로그램 전류를 1/10로 하여 놓으면 되는 것은 물론이다. 그러나, 1/10의 전류이면 기생 용량 등에 의해 기입 부족이 발생하기 때문에, 높은 전류로 프로그램하고, 비점등 영역(52)의 삽입에 의해 소정의 휘도를 얻는 것은 본 발명의 기본적인 주지이다.

또, 본 발명의 구동 방법에 있어서, 소정 전류보다도 높은 전류가 EL 소자(15)에 흐르도록 하여, 소스 신호선(18)의 기생 용량을 충분히 충방전한다고 하는 개념이다. 즉, EL 소자(15)에 N배의 전류를 흘리지 않더라도 무방하다. 예를 들면, EL 소자(15)에 병렬로 전류 경로를 형성하고(더미의 EL 소자를 형성하고, 이 EL 소자는 차광막을 형성하여 발광시키지 않는 등), 더미 EL 소자와 EL 소자(15)로 분류하여 전류를 흘려 보내도 좋다. 예를 들면, 신호 전류가  $0.2\mu A$ 일 때, 프로그램 전류를  $2.2\mu A$ 로 하여, 트랜지스터(11a)에는  $2.2\mu A$ 를 흘린다. 이 전류 중, 신호 전류  $0.2\mu A$ 를 EL 소자(15)에 흘려 보내고,  $2\mu A$ 를 더미의 EL 소자에 흘리는 등의 방식이 예시된다. 즉, 도 27의 더미 화소 행(271)을 항상 선택 상태로 한다. 또, 더미 화소 행은 발광시키지 않는다는지, 혹은 차광막 등을 형성하고, 발광하고 있더라도 시각적으로 보이지 않도록 구성한다.

이상과 같이 구성함으로써, 소스 신호선(18)에 흘리는 전류를 N배로 증가시키는 것에 의해, 구동용 트랜지스터(11a)에 N배의 전류가 흐르도록 프로그램할 수가 있고, 또한, 전류 EL 소자(15)에는, N배보다는 충분히 작은 전류를 흘려 보낼 수 있게 된다. 이상의 방법에서는, 도 5에 도시하는 바와 같이, 비점등 영역(52)을 마련하는 일없이, 전 표시 화면(50)을 화상 표시 영역(53)으로 할 수 있다.

도 13의 (a)는 표시 화면(50)에의 기입 상태를 나타내고 있다. 도 13의 (a)에 있어서, (51a)는 기입 화소 행이다. 소스 드라이버 IC(14)로부터 각 소스 신호선(18)에 프로그램 전류가 공급된다. 또, 도 13 등에서는 1H 기간에 기입하는 화소 행은 1행이다. 그러나, 조금도 1H에 한정되는 것이 아니며, 0.5H 기간이어도, 2H 기간이어도 좋다. 또한, 소스 신호선(18)에 프로그램 전류를 기입한 것으로 했지만, 본 발명은 전류 프로그램 방식에 한정되는 것이 아니며, 소스 신호선(18)에 기입되는 것은 전압인 전압 프로그램 방식(도 46 등)이어도 된다.

도 13의 (a)에 있어서, 게이트 신호선(17a)이 선택되면 소스 신호선(18)에 흐르는 전류가 트랜지스터(11a)에 프로그램된다. 이 때, 게이트 신호선(17b)은 오프 전압이 인가되어 EL 소자(15)에는 전류가 흐르지 않는다. 이것은, EL 소자(15)측에 트랜지스터(11d)가 온 상태이면, 소스 신호선(18)으로부터 EL 소자(15)의 용량 성분이 보여, 이 용량에 영향받아 컨텐서(19)에 충분히 정확한 전류 프로그램을 할 수 없게 되기 때문이다. 따라서, 도 1의 구성을 예로 하면, 도 13의 (b)에서 도시한 바와 같이 전류가 기입되고 있는 화소 행은 비점등 영역(52)이 된다.

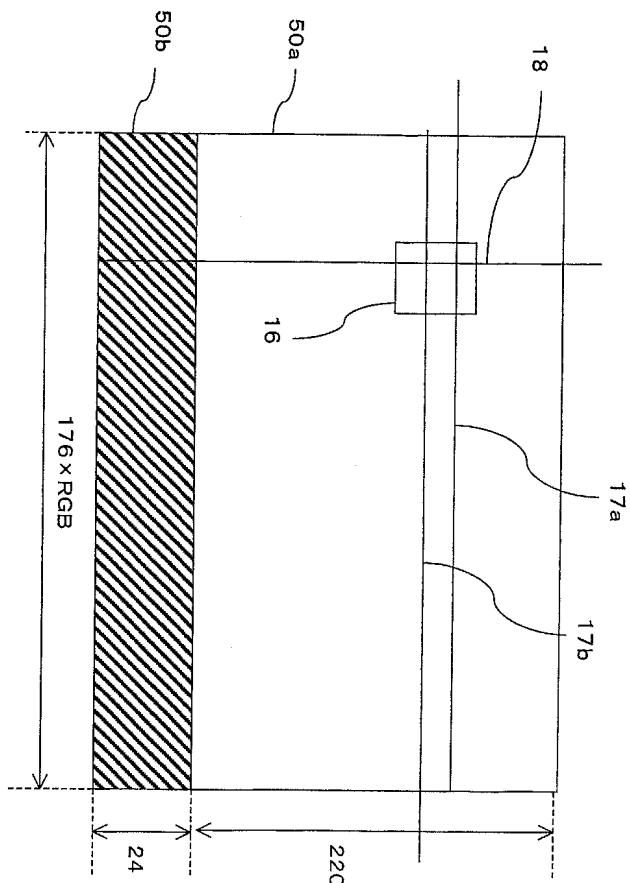

이제, N(여기서는, 앞서 말한 것처럼 N=10으로 함)배의 전류로 프로그램했다고 한다면, 화면의 휘도는 10배가 된다. 따라서, 표시 화면(50)의 90%의 범위를 비점등 영역(52)으로 하면 좋다. 따라서, 화상 표시 영역의 수평 주사선이 QCIF의 220개(S=220)라고 하면, 22개를 표시 영역(53)으로 하고,  $220-22=198$ 개를 비표시 영역(52)으로 하면 된다. 일반적으로 진술하면, 수평 주사선(화소 행 수)을 S라고 하면, S/N의 영역을 표시 영역(53)으로 하고, 이 표시 영역(53)을 N배의 휘도로 발광시킨다. 그리고, 이 표시 영역(53)을 화면의 상하 방향으로 주사한다. 따라서, S(N-1)/N의 영역은 비점등 영역(52)으로 한다. 이 비점등 영역은 혹 표시(비 발광)이다. 또한, 이 비 발광부(52)는 트랜지스터(11d)를 오프시키는 것에 의해 실현한다. 또, N배의 휘도로 점등시킨 것으로 했지만, 당연한 것이지만 밝기 조정, 감마 조정에 의해 N배의 값을 조정하는 것은 물론이다.

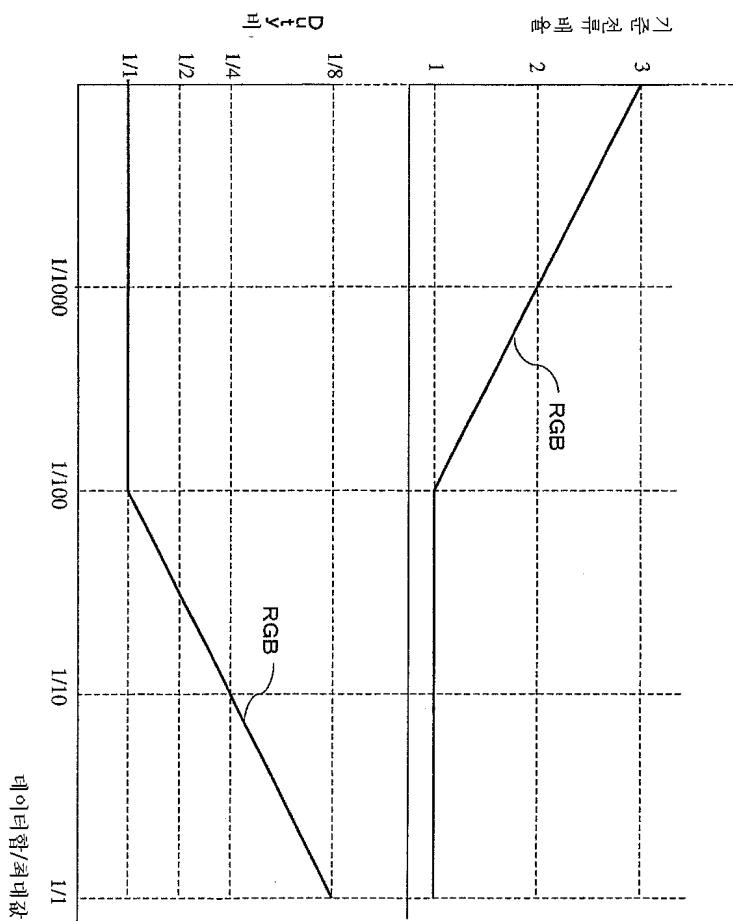

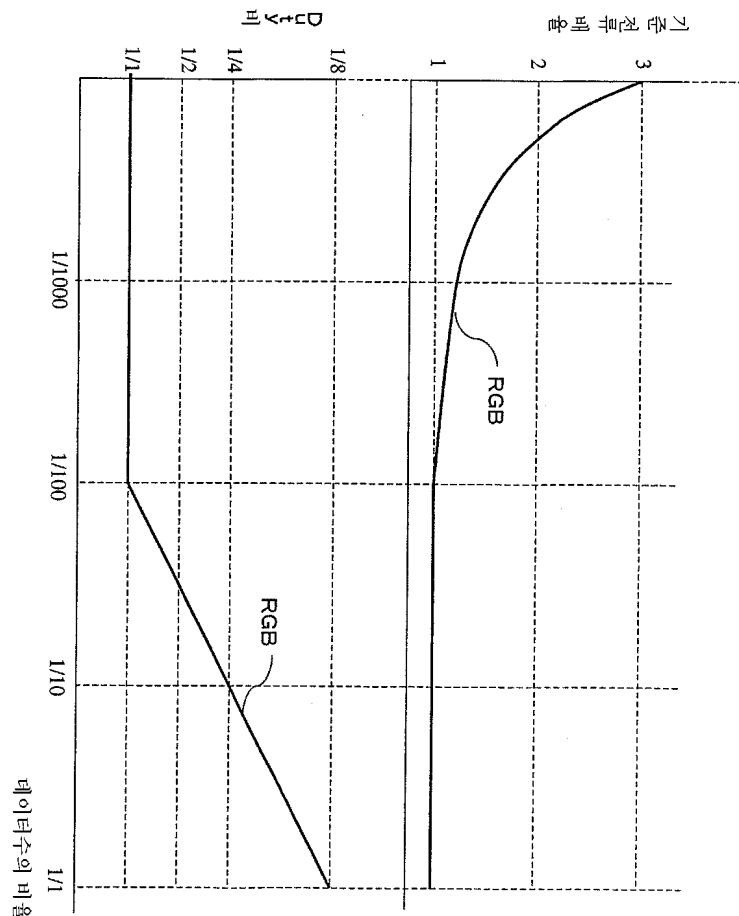

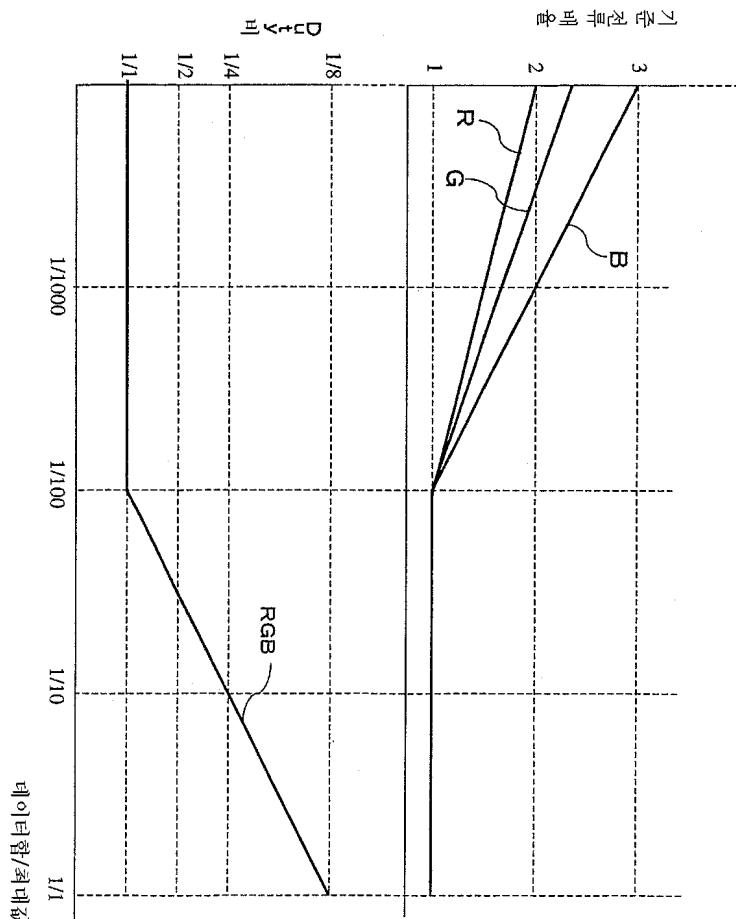

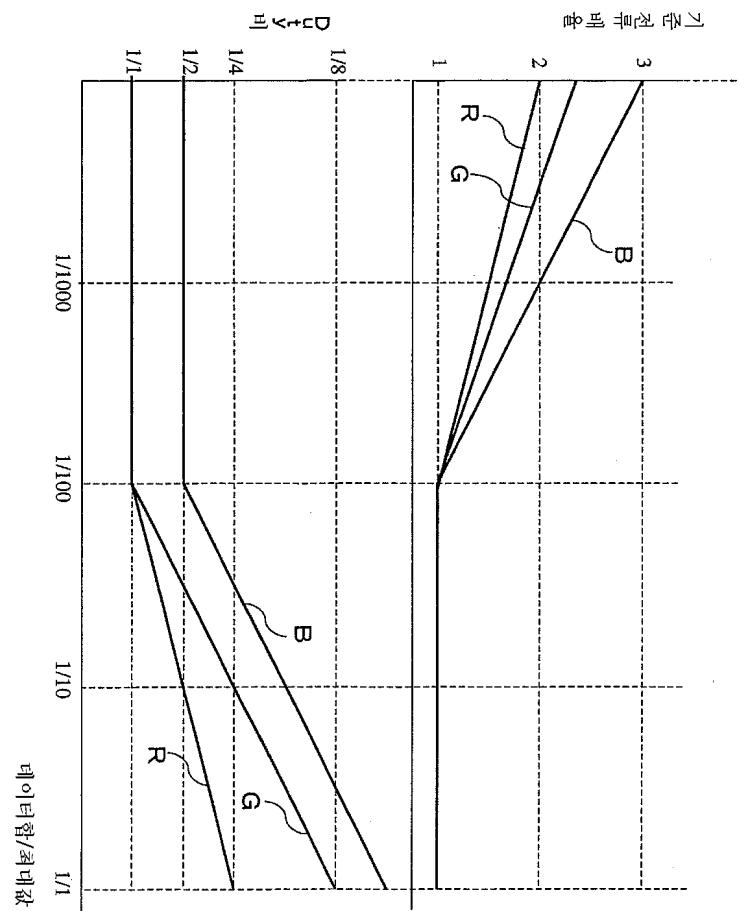

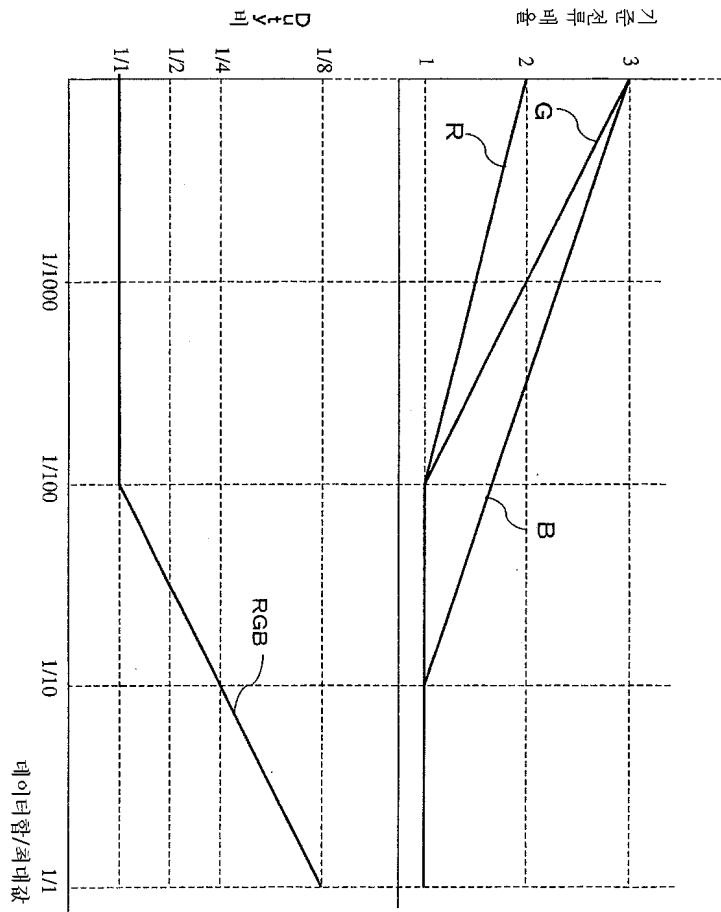

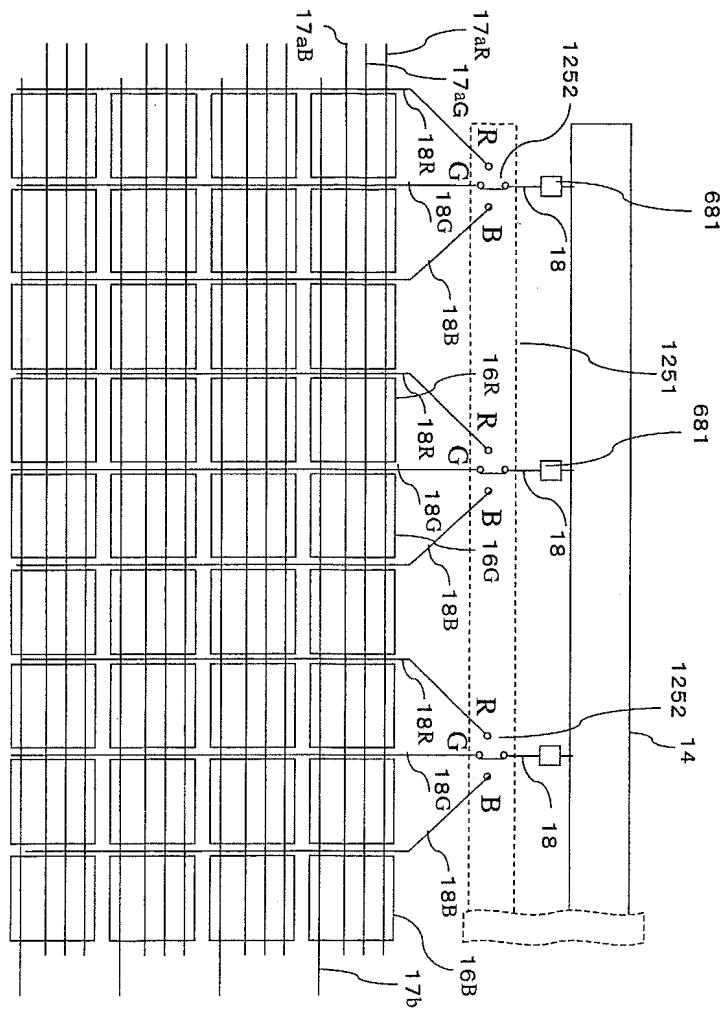

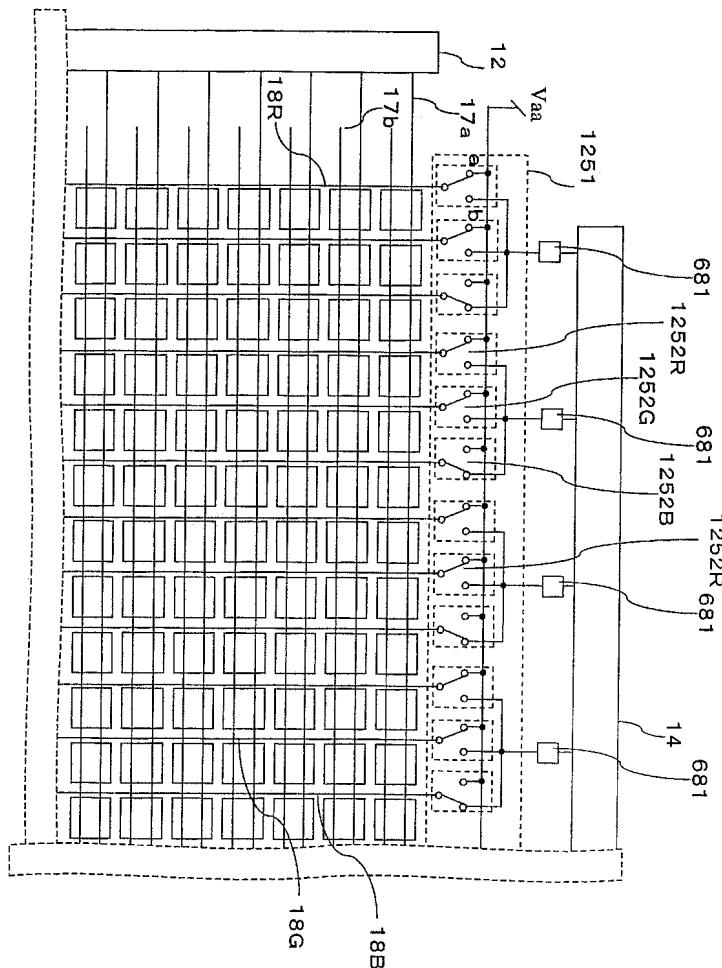

또한, 앞의 실시예에서, 10배의 전류로 프로그램했다고 한다면, 화면의 휘도는 10배가 되고, 표시 화면(50)의 90%의 범위를 비점등 영역(52)으로 하면 된다고 했다. 그러나, 이것은 RGB의 화소를 공통으로 비점등 영역(52)으로 하는 것에 한정되는 것은 아니다. 예를 들면, R의 화소는 1/8을 비점등 영역(52)으로 하고, G의 화소는 1/6을 비점등 영역(52)으로 하고, B의 화소는 1/10을 비점등 영역(52)으로, 각각의 색에 의해 변화시켜도 좋다. 또한, RGB의 색에서 개별로 비점등 영역(52)(혹은 점등 영역(53))을 조정할 수 있도록 하여도 좋다. 이들을 실현하기 위해서는, R, G, B에서 개별적인 게이트 신호선(17b)이 필요하게 된다. 그러나, 이상의 RGB의 개별 조정을 가능하게 함으로써, 화이트 밸런스를 조정하는 것이 가능해져, 각 계조에 있어서 색의 밸런스 조정이 용이해진다(도 41을 참조).

도 13의 (b)에 도시하는 바와 같이, 기입 화소 행(51a)을 포함하는 화소 행을 비점등 영역(52)으로 하고, 기입 화소 행(51a)보다도 위 화면의 S/N(시간적으로는 1F/N)의 범위를 표시 영역(53)으로 한다(기입 주사가 화면의 위에서 아래 방향인 경우, 화면을 아래에서 위로 주사하는 경우에는, 그 역이 됨). 화상 표시 상태는 표시 영역(53)이 띠 형상으로 되고, 화면의 위에서 아래로 이동한다.

도 13의 표시에서는 하나의 표시 영역(53)이 화면의 위에서 아래 방향으로 이동한다. 프레임 레이트가 낮으면, 표시 영역(53)이 이동하는 것이 시각적으로 인식된다. 특히, 눈꺼풀을 감았을 때, 혹은 얼굴을 상하로 이동시켰을 때 등에 인식되기 쉽게 된다.

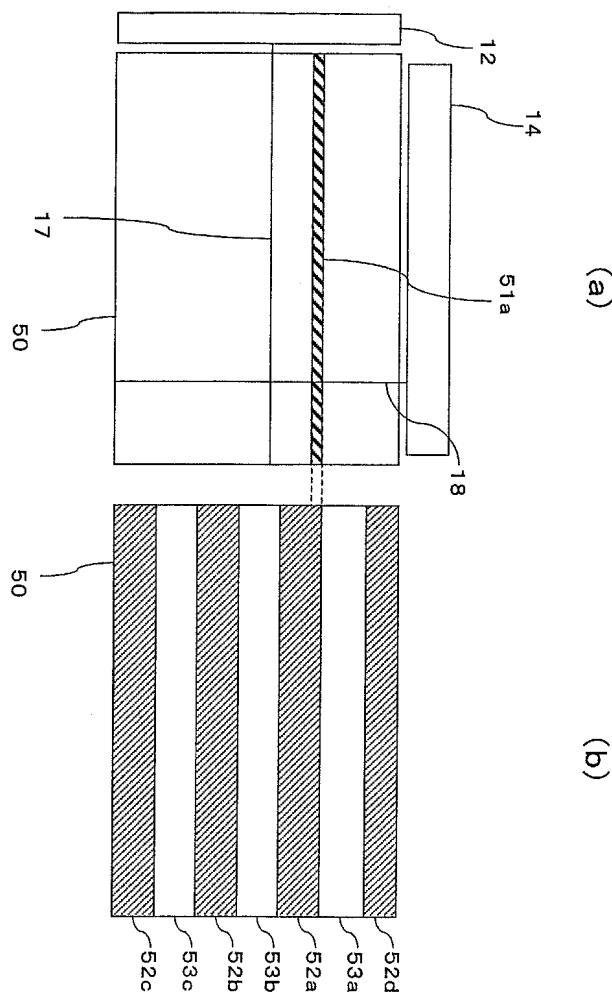

이 과제에 대해서는, 도 16에 도시하는 바와 같이, 표시 영역(53)을 복수로 분할하면 좋다. 이 분할된 총합이 S(N-1)/N의 면적으로 되면, 도 13의 밝기와 동등하게 된다. 또, 분할된 표시 영역(53)은 똑같게 할 필요는 없다. 또한, 분할된 비표시 영역(52)도 똑같게 할 필요는 없다.

이상과 같이, 표시 영역(53)을 복수로 분할하는 것에 의해 화면의 어른거림은 감소한다. 따라서, 깜박임의 발생이 없어, 양호한 화상 표시를 실현할 수 있다. 또, 분할은 더 미세하게 해도 된다. 그러나, 분할할수록 동화상 표시 성능은 저하한다.

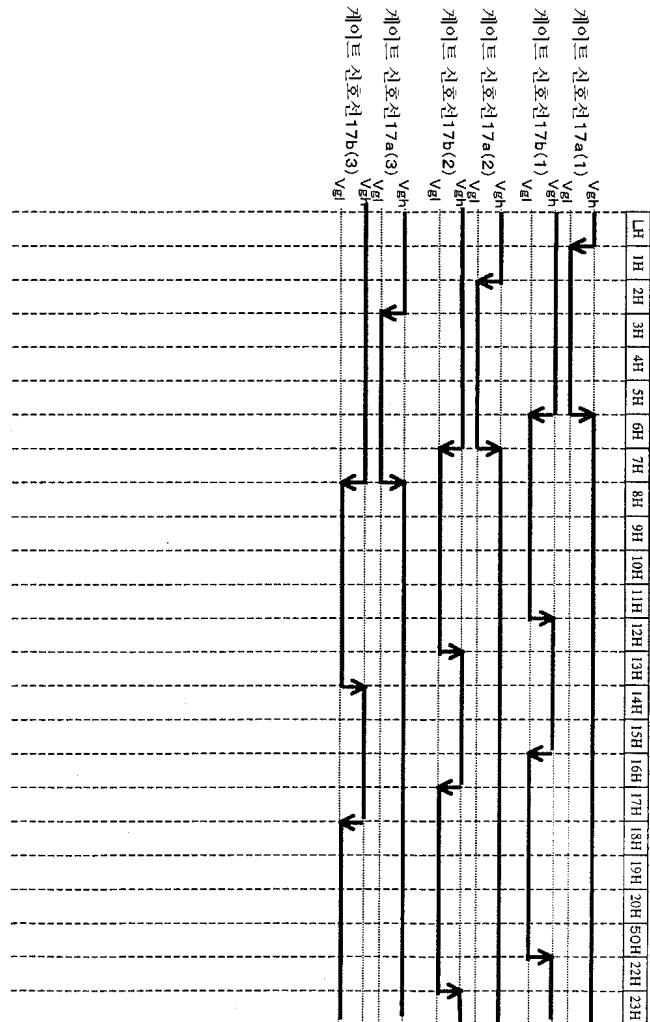

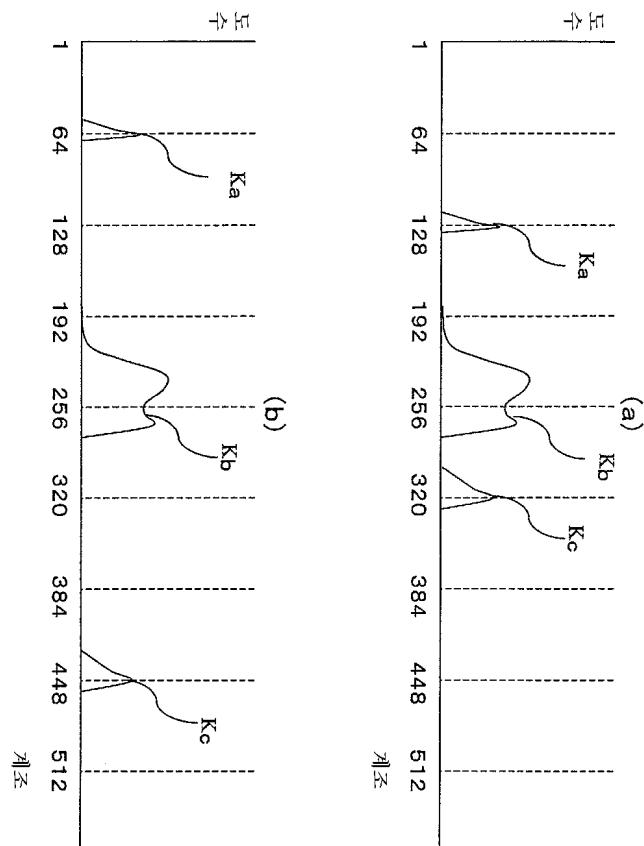

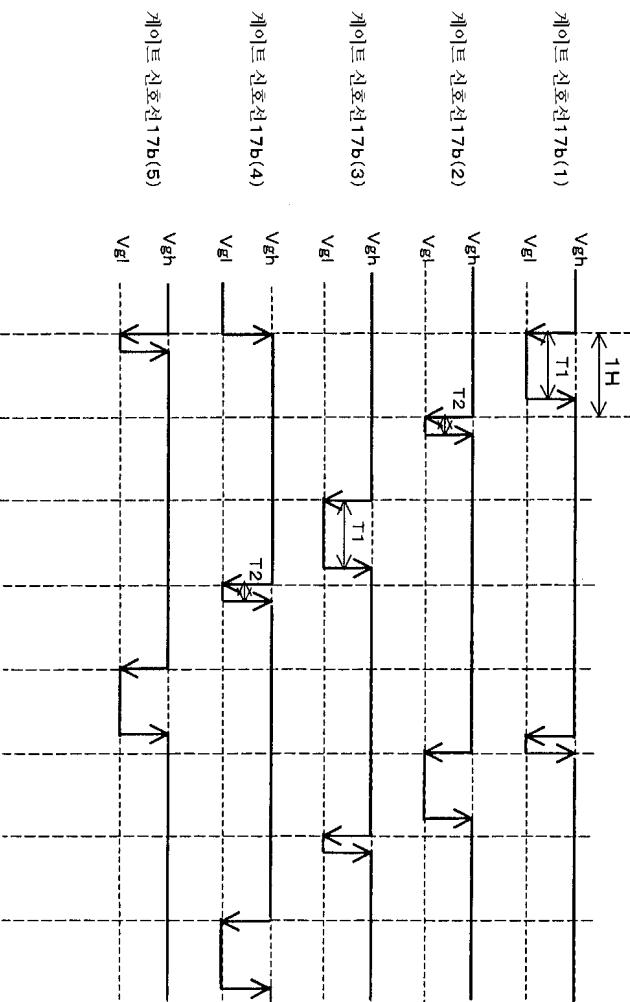

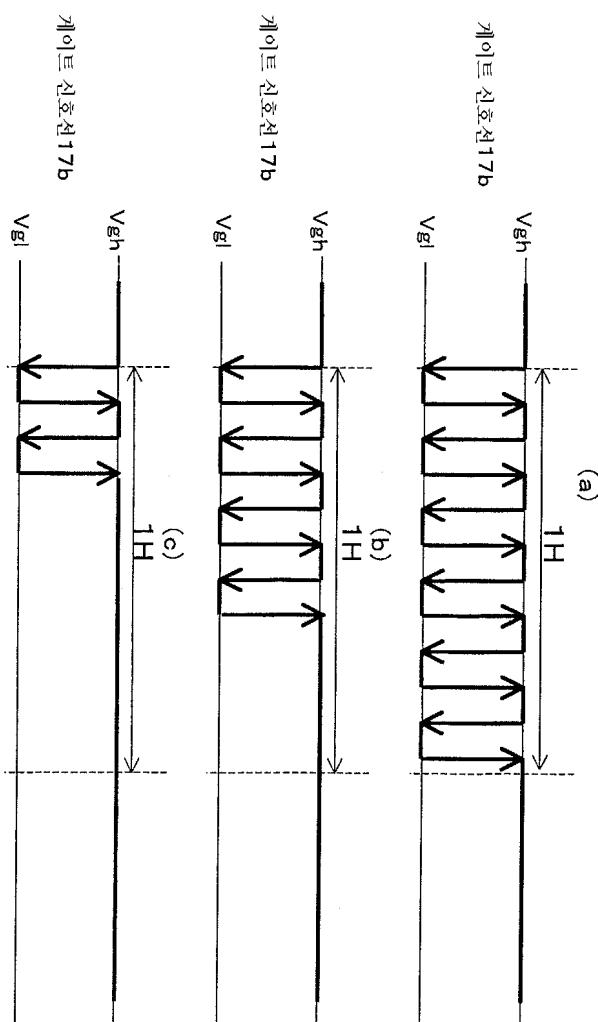

도 17은 게이트 신호선(17)의 전압 파형 및 EL의 발광 휘도를 도시하고 있다. 도 17에서 분명한 바와 같이, 게이트 신호선(17b)을 Vgl로 하는 기간(1F/N)을 복수로 분할(분할 수 K)하고 있다. 즉, Vgl로 하는 기간은 1F/(K·N)의 기간을 K회 실시한다. 이와 같이 제어하면, 깜박임의 발생을 억제할 수 있고, 저 프레임 레이트의 화상 표시를 실현할 수 있다. 또한, 이 화상의 분할 수도 가변할 수 있도록 구성하는 것이 바람직하다. 예를 들면, 사용자가 밝기 조정 스위치를 누르거나, 혹은 밝기 조정볼륨을 돌리는 것에 의해, 이 변화를 검출하여 K의 값을 변경해도 된다. 또, 사용자가 휘도를 조정하도록 구성해도 된다. 표시하는 화상의 내용, 데이터에 의해 수동으로 혹은 자동적으로 변화시키도록 구성해도 된다.

또, 도 17 등에 있어서, 게이트 신호선(17b)을 Vgl로 하는 기간(1F/N)을 복수로 분할(분할 수 K)하고, Vgl로 하는 기간은 1F/(K·N)의 기간을 K회 실시한다고 했지만 이것에 한정되는 것이 아니다. 1F/(K·N)의 기간을 L(L≠K)회 실시해도 된다. 즉, 본 발명은 EL 소자(15)에 흘리는 기간(시간)을 제어함으로써 표시 화면(50)을 표시하는 것이다. 따라서, 1F/(K·N)의 기간을 L(L≠K)회 실시하는 것은 본 발명의 기술적 사상에 포함된다. 또한, L의 값을 변화시키는 것에 의해, 표시 화면(50)의 휘도를 디지털적으로 변경할 수 있다. 예를 들면, L=2와 L=3에서는 50%의 휘도(콘트라스트) 변화가 된다. 또한, 화상의 표시 영역(53)을 분할할 때, 게이트 신호선(17b)을 Vgl로 하는 기간은 동일 기간에 한정하는 것이 아니다.

이상의 실시예는, EL 소자(15)에 흐르는 전류를 차단하고, 또한 EL 소자에 흐르는 전류를 접속하는 것에 의해, 표시 화면(50)을 온 오프(점등, 비점등)하는 것이었다. 즉, 컨텐서(19)에 유지된 전하에 의해 트랜지스터(11a)에 복수회, 대략 동일 전류를 흘려 보내는 것이다. 본 발명은 이것에 한정되는 것이 아니다. 예를 들면, 컨텐서(19)에 유지된 전하를 충방전시킴으로써, 표시 화면(50)을 온 오프(점등, 비점등)하는 방식이어도 좋다.

도 18은 도 16의 화상 표시 상태를 실현하기 위한, 게이트 신호선(17)에 인가하는 전압 파형이다. 도 18과 도 15의 차이는 게이트 신호선(17b)의 동작이다. 게이트 신호선(17b)은 화면을 분할하는 개수에 대응하여, 그 개수만큼 온 오프(Vgl과 Vgh) 동작한다. 다른 점은 도 15와 동일하기 때문에 설명을 생략한다.

EL 표시 장치에서는 후 표시는 완전히 비점등이므로, 액정 표시 패널을 간헐 표시한 경우와 같이 콘트라스트 저하도 없다. 또한, 도 1, 도 2, 도 32, 도 43, 도 117의 구성에서는, 트랜지스터(11d)를 온 오프 조작하는 것만으로 간헐 표시를 실현할 수 있다. 또한, 도 38, 도 51, 도 115의 구성에서는, 트랜지스터 소자(11e)를 온 오프 조작하는 것만으로 간헐 표시를 실현할 수 있다. 또, 도 113에서는 전환 회로(1131)를 제어하는 것에 의해 간헐 표시를 실현할 수 있다. 또한, 도 114에서는, 트랜지스터(11g)를 온 오프 제어함으로써 간헐 표시를 실현할 수 있다. 이것은 컨텐서(19)에 화상 데이터가 메모리(아날로그 값으로 계조 수는 무한대)되어 있기 때문이다. 즉, 각 화소(16)에, 화상 데이터는 1F의 기간중에는 유지되고 있다. 이 유지되고 있는 화상 데이터에 상당하는 전류를 EL 소자(15)에 흘려 보낼지 여부를 트랜지스터(11d, 11e)의 제어에 의해 실현하고 있는 것이다.

따라서, 이상의 구동 방법은 전류 구동 방식에 한정되는 것이 아니고, 전압 구동 방식에도 적용할 수 있는 것이다. 즉, EL 소자(15)에 흘리는 전류가 각 화소 내에서 보존하고 있는 구성에 있어서, 구동용 트랜지스터(11)를 EL 소자(15) 사이의 전류 경로를 온 오프함으로써 간헐 구동을 실현하는 것이다.

컨텐서(19)의 단자 전압을 유지하는 것은 깜박임 저감과 저 소비 전력화에 중요하다. 1 필드(프레임) 기간에 컨텐서(19)의 단자 전압이 변화(충방전)하면, 화면 휘도가 변화한다. 화면 휘도가 변화하면, 프레임 레이트가 저하했을 때에 어른거림(깜박임 등)이 발생하기 때문이다. 트랜지스터(11a)가 1 프레임(1 필드) 기간에 EL 소자(15)에 흘리는 전류는, 적어도 65% 이하로 저하하지 않도록 할 필요가 있다. 이 65%란, 화소(16)에 기입하고, EL 소자(15)에 흘리는 전류의 최초가 100%라고 했을 때, 다음 프레임(필드)에서 상기 화소(16)에 기입하기 직전의 EL 소자(15)에 흘리는 전류를 65% 이상으로 하는 것이다.

도 1의 화소 구성에서는, 간헐 표시를 실현하는 경우로 하지 않는 경우에는, 1 화소를 구성하는 트랜지스터(11)의 개수에 변화가 없다. 즉, 화소 구성은 그대로이고, 소스 신호선(18)의 기생 용량의 영향을 제거하여, 양호한 전류 프로그램을 실현하고 있다. 나아가서는, CRT에 가까운 동화상 표시를 실현하고 있는 것이다.

또한, 게이트 드라이버 회로(12)의 동작 클럭은 소스 드라이버 회로(14)의 동작 클럭에 비하여 충분히 느리기 때문에, 회로의 메인 클럭이 높아진다고 하는 일은 없다. 또한, N의 값의 변경도 용이하다.

또, 화상 표시 방향(화상 기입 방향)은, 1 필드(1 프레임)째에서는 화면의 위에서 아래 방향으로 하고, 다음 제2 필드(프레임)째에서는 화면의 아래에서 위 방향으로 하여도 좋다. 즉, 위에서 아래 방향과, 아래에서 위 방향을 교대로 반복한다.

또한, 1 필드(1 프레임)째에서는 화면의 위에서 아래 방향으로 하여, 일단, 전 화면을 흑 표시(비표시)로 한 후, 다음 제2 필드(프레임)째에서는 화면의 아래에서 위 방향으로 하여도 된다. 또한, 일단, 전 화면을 흑 표시(비표시)로 하여도 좋다.

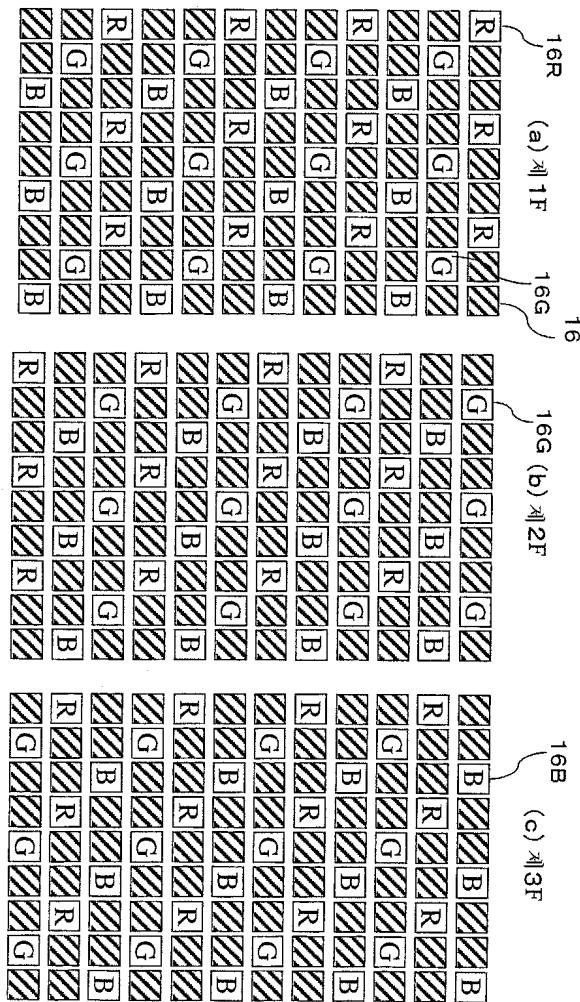

또, 이상의 구동 방법의 설명에서는, 화면의 기입 방법을 화면의 위에서 아래 혹은 아래에서 위로 했지만, 이것에 한정되는 것이 아니다. 화면의 기입 방향은 끊임없이, 화면의 위에서 아래 혹은 아래에서 위로 고정하고, 비표시 영역(52)의 동작 방향을 1 필드째에서는 화면의 위에서 아래 방향으로 하고, 다음 제2 필드째에서는 화면의 아래에서 위 방향으로 하여도 좋다. 또한, 1 프레임을 3 필드로 분할하여, 제1 필드에서는 R, 제2 필드에서는 G, 제3 필드에서는 B로 하여, 3 필드에서 1 프레임을 형성하는 것으로 해도 좋다. 또한, 1수평 주사 기간(1H)마다, R, G, B를 전환하여 표시해도 된다(도 125 내지 도 132와 그 설명 등을 참조). 이상의 사항은 다른 본 발명의 실시예에서도 마찬가지이다.

비표시 영역(52)은 완전히 비점등 상태일 필요는 없다. 미약한 발광 혹은 저휘도의 화상 표시가 있더라도 실용상은 문제없다. 즉, 화상 표시 영역(53)보다도 표시 휘도가 낮은 영역으로 해석해야 된다. 또한, 비표시 영역(52)이란, R, G, B 화상 표시 중 1색 또는 2색만이 비표시 상태라고 하는 경우도 포함된다. 또한, R, G, B 화상 표시 중 1색 또는 2색만이 저휘도의 화상 표시 상태라고 하는 경우도 포함된다.

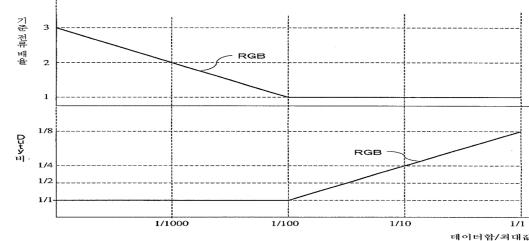

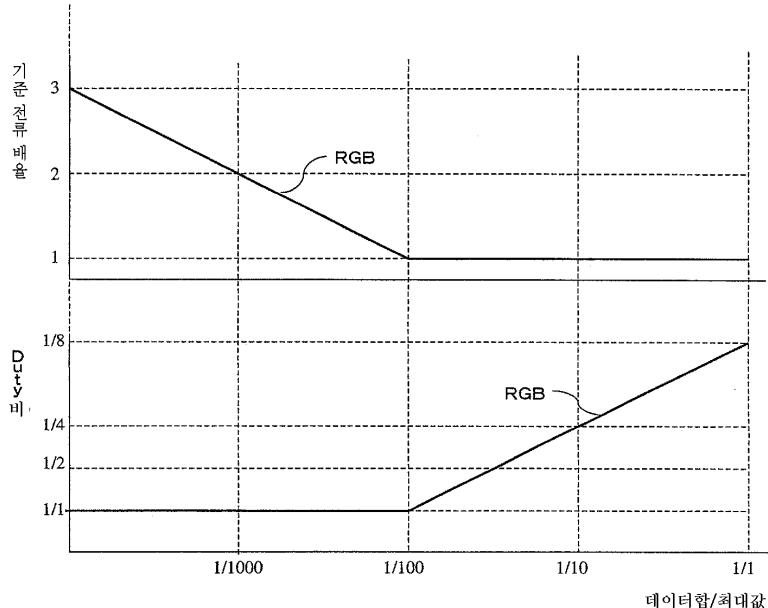

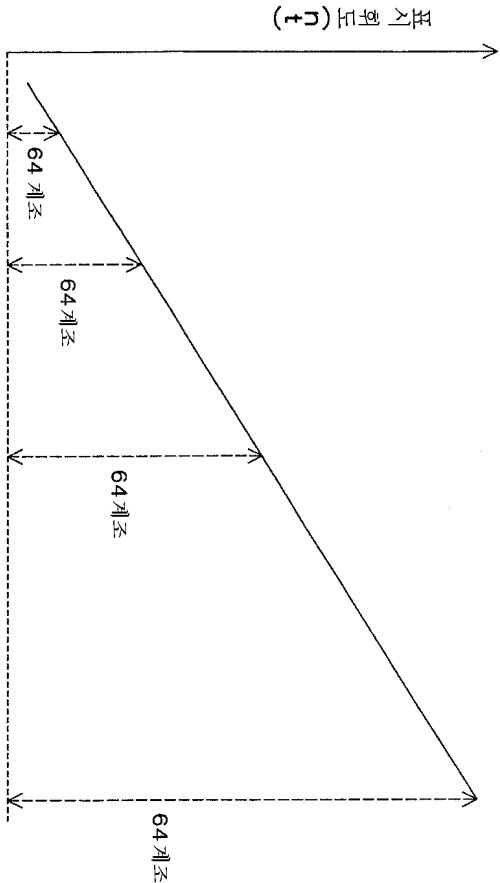

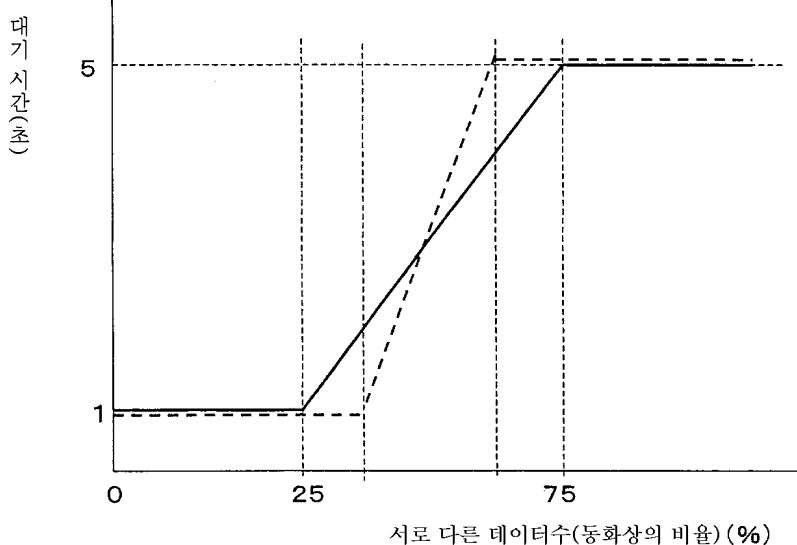

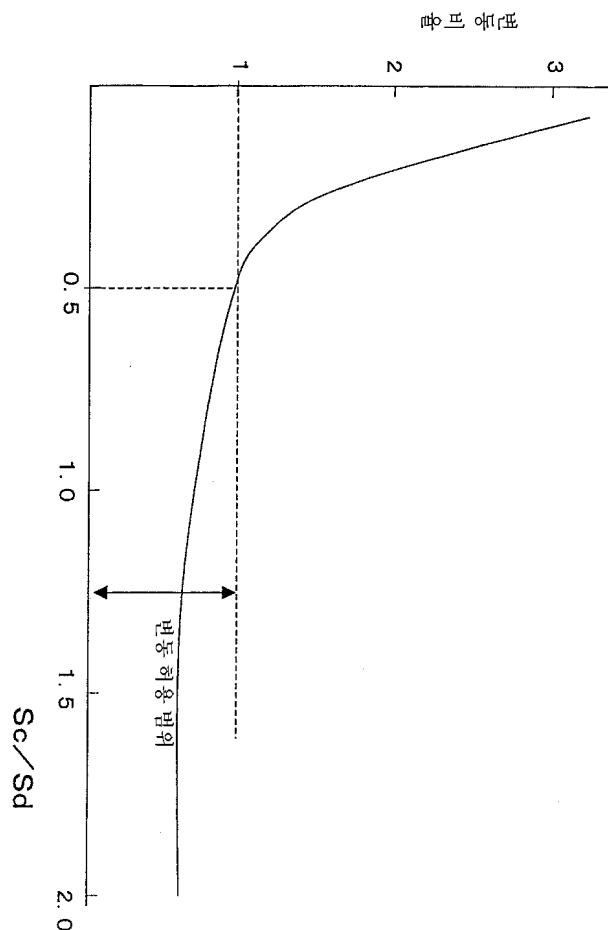

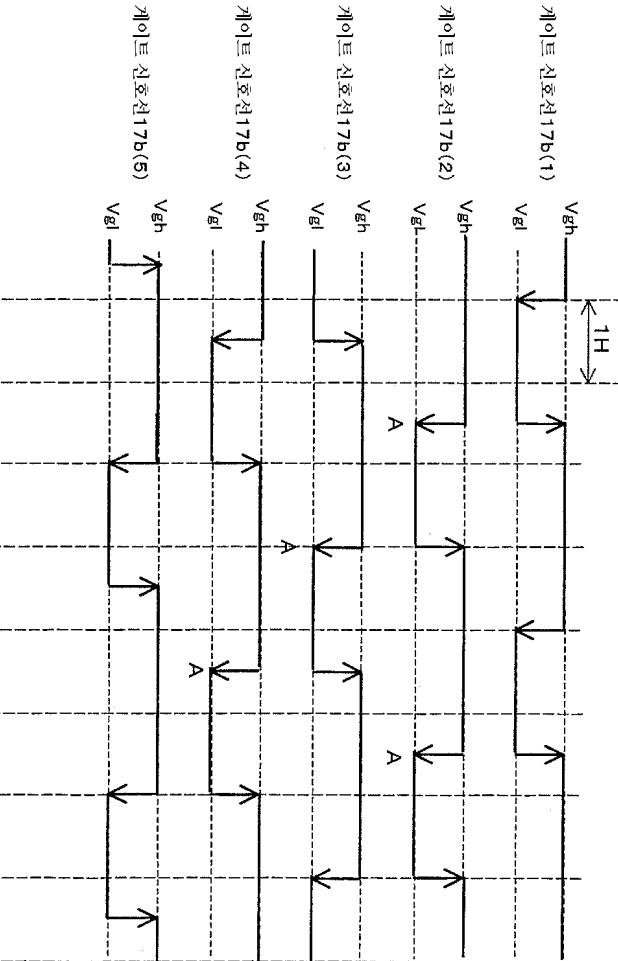

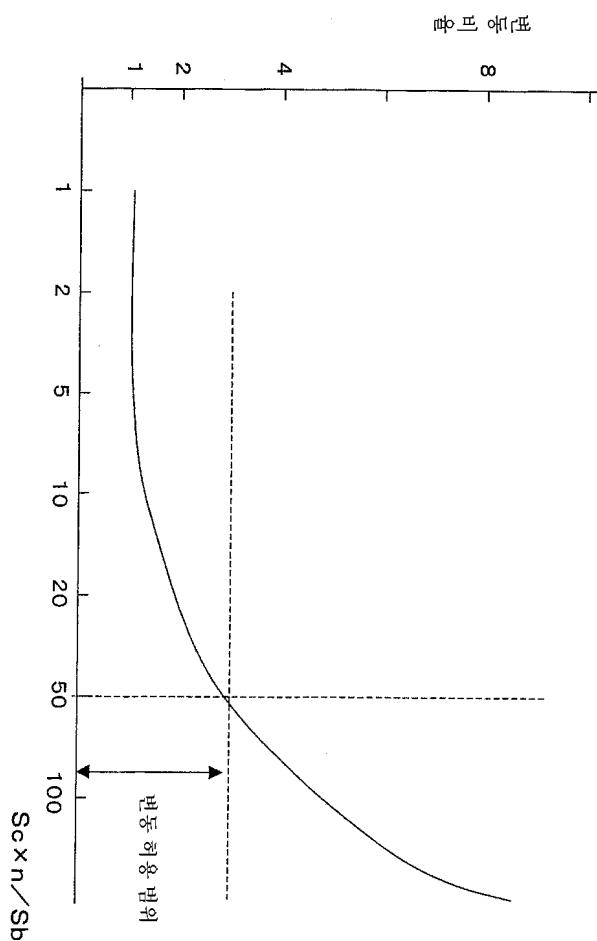

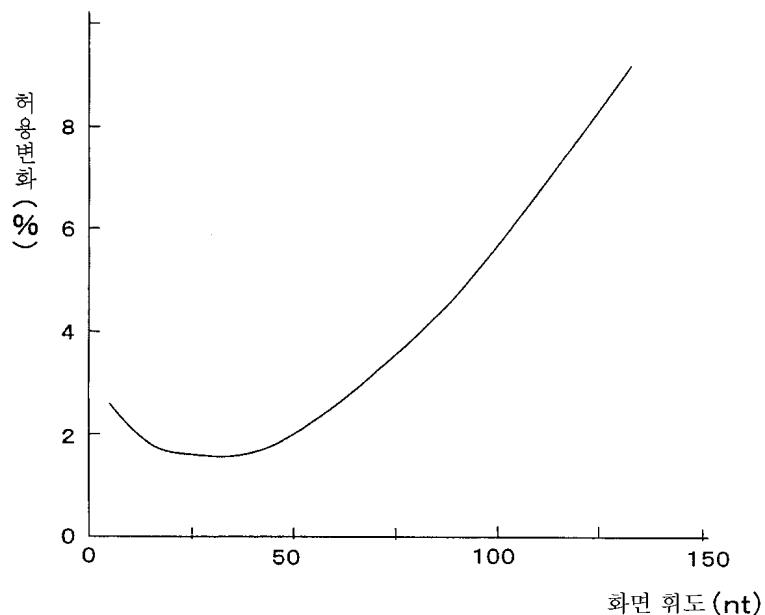

기본적으로는 표시 영역(53)의 휘도(밝기)가 소정 값으로 유지되는 경우, 표시 영역(53)의 면적이 넓어질수록, 화면(50)의 휘도는 높아진다. 예를 들면, 표시 영역(53)의 휘도가 100(nt)인 경우, 표시 영역(53)이 전 화면(50)에 차지하는 비율이 10%에서 20%로 변화하면, 화면의 휘도는 2배가 된다. 따라서, 전 화면(50)에 차지하는 표시 영역(53)의 면적을 변화시키는 것에 의해, 화면의 표시 휘도를 변화시킬 수 있다. 화면(50)의 표시 휘도는 화면(50)에 차지하는 표시 영역(53)의 비율에 비례한다.

표시 영역(53)의 면적은 시프트 레지스터 회로(61)에의 데이터 펄스(ST2)를 제어함으로써 임의로 설정할 수 있다. 또한, 데이터 펄스의 입력 타이밍, 주기를 변화시키는 것에 의해, 도 16의 표시 상태와 도 13의 표시 상태를 전환할 수 있다. 1F 주기에서의 데이터 펄스 수를 많게 하면, 화면(50)은 밝아지고, 적게 하면, 화면(50)은 어둡게 된다. 또한, 연속하여 데이터 펄스를 인가하면 도 13의 표시 상태로 되고, 간헐적으로 데이터 펄스를 입력하면 도 16의 표시 상태가 된다.

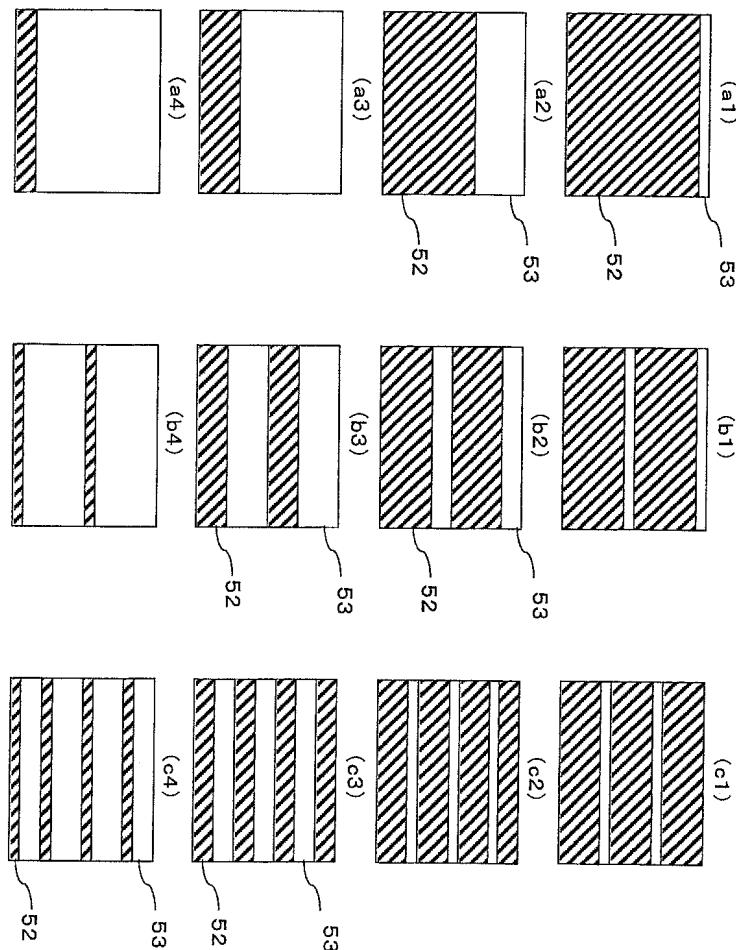

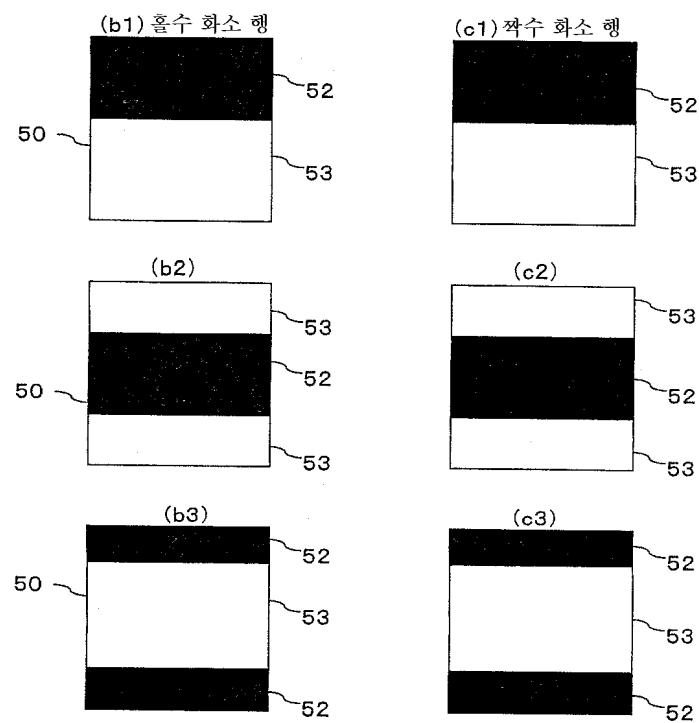

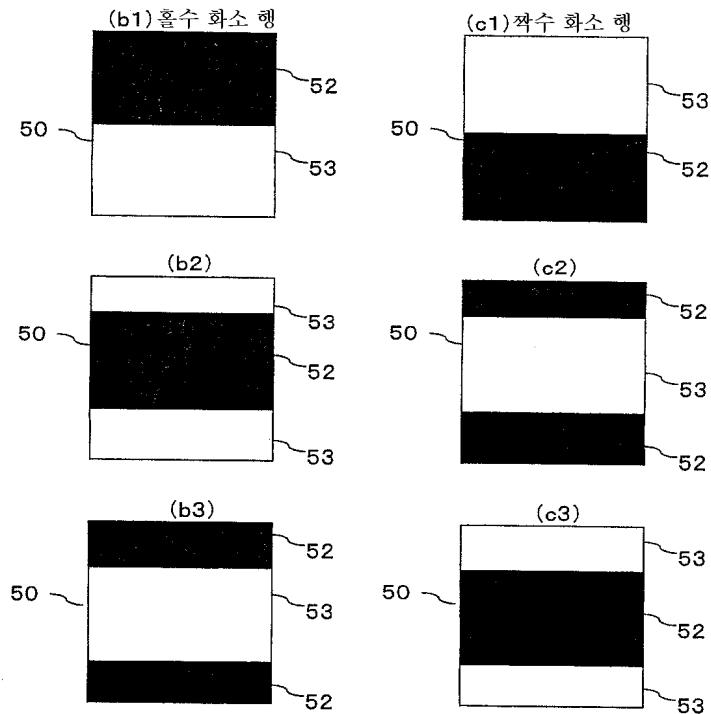

도 19의 (a)는 도 13과 같이 표시 영역(53)이 연속하고 있는 경우의 밝기 조정 방식이다. 도 19(a1)의 화면(50)의 표시 휘도가 가장 밝다. 도 19(a2)의 화면(50)의 표시 휘도가 다음으로 밝고, 도 19(a3)의 화면(50)의 표시 휘도가 가장 어둡다. 도 19의 (a)는 가장 동화상 표시에 적합하다.

도 19(a1)에서 도 19(a3)로의 변화(혹은 그 역)는, 앞에서도 기재한 바와 같이 게이트 드라이버 회로(12)의 시프트 레지스터 회로(61) 등의 제어에 의해 용이하게 실현할 수 있다. 이 때, 도 1의 Vdd 전압은 변화시킬 필요가 없다. 즉, 전원 전압을 변화시키지 않고서 표시 화면(50)의 휘도 변화를 실시할 수 있다. 또한, 도 19(a1)에서 도 19(a3)로의 변화 시에, 화면의 감마 특성은 전혀 변화하지 않는다. 따라서, 화면(50)의 휘도에 상관없이, 표시 화상의 콘트라스트, 계조 특성이 유지된다. 이것은 본 발명의 효과가 있는 특징이다.

종래의 화면의 휘도 조정에서는, 화면(50)의 휘도가 낮을 때에는 계조 성능이 저하한다. 즉, 고휘도 표시 시에는 64 계조 표시를 실현할 수 있더라도, 저휘도 표시 시에는, 반 이하의 계조 수밖에 표시할 수 없는 경우가 대부분이다. 이에 비하여, 본 발명의 구동 방법에서는 화면의 표시 휘도에 의존하지 않고, 최고의 64 계조 표시를 실현할 수 있다.

도 19의 (b)는 도 16과 같이 표시 영역(53)이 분산하고 있는 경우의 밝기 조정 방식이다. 도 19(b1)의 화면(50)의 표시 휘도가 가장 밝다. 도 19(b2)의 화면(50)의 표시 휘도가 다음으로 밝고, 도 19(b3)의 화면(50)의 표시 휘도가 가장 어둡다. 도 19(b1)에서 도 19(b3)로의 변화(혹은 그 역)는, 앞에서도 기재한 바와 같이 게이트 드라이버 회로(12)의 시프트 레지스터 회로(61) 등의 제어에 의해, 용이하게 실현할 수 있다. 도 19의 (b)와 같이 표시 영역(53)을 분산시키면, 저 프레임 레이트에서도 깜박임이 발생하지 않는다.

또한 저 프레임 레이트에서도 깜박임이 발생하지 않도록 하기 위해서는, 도 19의 (c)와 같이 표시 영역(53)을 미세하게 분산시키면 된다. 그러나, 동화상의 표시 성능은 저하한다. 따라서, 동화상을 표시하기 위해서는, 도 19의 (a)의 구동 방법이 적합하다. 정지 화상을 표시하고, 저 소비 전력화를 요망할 때에는, 도 19의 (c)의 구동 방법이 적합하다. 도 19의 (a)에서도 19의 (c)의 구동 방법의 전환도, 시프트 레지스터(61)의 제어에 의해 용이하게 실현 가능하다.

이상의 실시예는 주로, N=2배, 4배 등으로 하는 실시예였다. 그러나, 본 발명은 정수배에 한정되는 것이 아님은 물론이다. 또한, N=2 이상으로 한정되는 것도 아니다. 예를 들면, 어떤 시각에서 표시 화면(50)의 반 이하의 영역을 비점등 영역(52)으로 하는 일도 있다. 소정값의 5/4배의 전류 Iw로 전류 프로그램하고, 1F의 4/5 기간 점등시키면, 소정의 휘도를 실현할 수 있다.

본 발명은 이것에 한정되는 것이 아니다. 일례로서, 10/4배의 전류 Iw로 전류 프로그래밍하여, 1F의 4/5 기간 동안 점등시킨다고 하는 방법도 있다. 이 경우에는 소정 휘도의 2배로 점등한다. 또한, 5/4배의 전류 Iw로 전류 프로그래밍하고, 1F의 2/5 기간 동안 점등시킨다고 하는 방법도 있다. 이 경우에는, 소정 휘도의 1/2배로 점등한다. 또한, 5/4배의 전류 Iw로 전류 프로그래밍하여, 1F의 1/1 기간 동안 점등시킨다고 하는 방법도 있다. 이 경우에는 소정 휘도의 5/4배로 점등한다.

즉, 본 발명은 프로그램 전류의 크기와 1F의 점등 기간을 제어함으로써 표시 화면의 휘도를 제어하는 방식이다. 또한, 1F 기간보다도 짧은 기간 점등시키는 것에 의해, 비점등 영역(52)을 삽입할 수 있고, 동화상 표시 성능을 향상시킬 수 있다. 1F의 기간, 상시 점등시키는 것에 의해 밝은 화면을 표시할 수 있다.

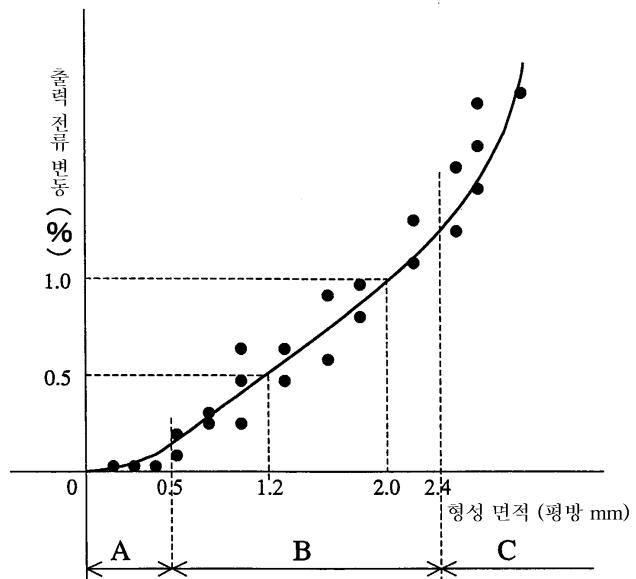

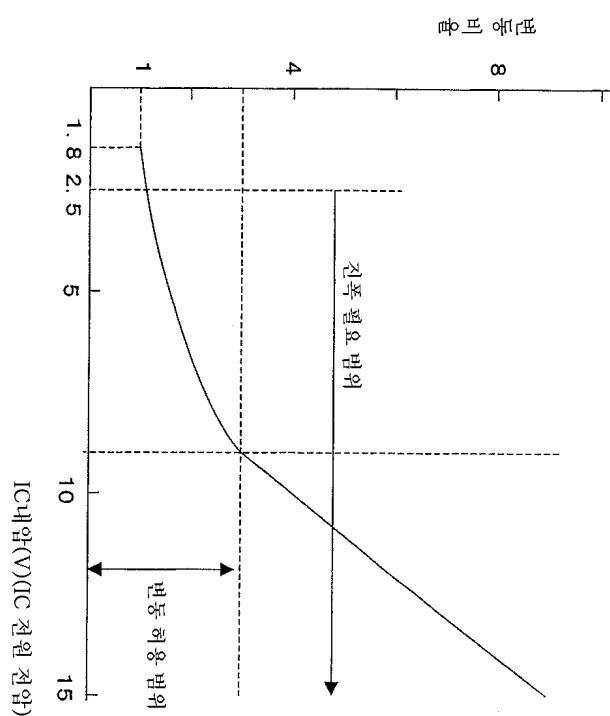

화소에 기입하는 전류(소스 드라이버 회로(14)로부터 출력하는 프로그램 전류)는, 화소 사이즈를 A평방mm로 하고, 백 래스터 표시 소정 휘도를 B(nt)로 했을 때, 프로그램 전류 I( $\mu$ A)는,

$$(A \times B)/20 \leq I \leq (A \times B)$$

의 범위로 하는 것이 바람직하다. 발광 효율이 양호해지고, 또한 전류 기입 부족이 해소된다.

또한 바람직하게는, 프로그램 전류 I( $\mu$ A)는,

$$(A \times B)/10 \leq I \leq (A \times B)$$

의 범위로 하는 것이 바람직하다.

도 20은 소스 신호선(18)에 흐르는 전류를 증대시키는 다른 실시예의 설명도이다. 기본적으로 복수의 화소 행을 동시에 선택하고, 복수의 화소 행을 합한 전류로 소스 신호선(18)의 기생 용량 등을 충방전하여 전류 기입 부족을 대폭 개선하는 방식이다. 단, 복수의 화소 행을 동시에 선택하기 때문에, 1 화소당 구동하는 전류를 감소시킬 수 있다. 따라서, EL 소자(15)에 흐르는 전류를 감소시킬 수 있다. 여기서, 설명을 쉽게 하기 위해서, 일례로서, N=10으로 하여 설명한다(소스 신호선(18)에 흘리는 전류를 10배로 함).

도 20에서 설명하는 본 발명에서, 화소 행은 동시에 M 화소 행을 선택한다. 소스 드라이버 IC(14)로부터는 소정 전류의 N 배 전류를 소스 신호선(18)에 인가한다. 각 화소에는 EL 소자(15)에 흘려보내는 전류의 N/M배의 전류가 프로그램된다. 일례로서, EL 소자(15)를 소정 발광 휘도로 하기 위해서, EL 소자(15)에 흐르는 시간을 1 프레임(1 필드)의 M/N 시간으로

한다(단, M/N에 한정하는 것은 아님. M/N으로 하는 것은 이해를 쉽게 하기 위해서이다. 앞에서도 설명한 바와 같이, 표시하는 화면(50) 휘도에 의해 자유롭게 설정 가능함은 물론임). 이와 같이 구동하는 것에 의해, 소스 신호선(18)의 기생 용량을 충분히 충방전할 수 있어, 양호한 해상도를 소정의 발광 휘도를 얻을 수 있다.

1 프레임(1 펠드)의 M/N의 기간 동안만, EL 소자(15)에 전류를 흘려 보내고, 다른 기간( $1F(N-1)M/N$ )은 전류를 흘려 보내지 않도록 표시한다. 이 표시 상태에서는 1F마다 화상 데이터 표시, 흑 표시(비점등)가 반복하여 표시된다. 즉, 화상 데이터 표시 상태가 시간적으로 띄엄띄엄 표시(간헐 표시) 상태가 된다. 따라서, 화상의 윤곽 흐려짐이 없어져 양호한 동화상 표시를 실현 가능하다. 또한, 소스 신호선(18)에는 N배의 전류로 구동하기 때문에, 기생 용량의 영향을 받지 않고, 고정밀 표시 패널에도 대응할 수 있다.

도 21은 도 20의 구동 방법을 실현하기 위한 구동 파형의 설명도이다. 신호 파형은 오프 전압을  $V_{gh}(H)$  레벨로 하고, 온 전압을  $V_{gl}(L)$  레벨로 하고 있다. 각 신호선의 첨자는 화소 행의 번호((1)(2)(3) 등)를 기재하고 있다. 또, 행 수는 QCIF 표시 패널의 경우에는 220개이고, VGA 패널에서는 480개이다.

도 21에 있어서, 게이트 신호선(17a)(1)이 선택되고( $V_{gl}$  전압), 선택된 화소 행의 트랜지스터(11a)에서 소스 드라이버 회로(14)를 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 여기서는 설명을 쉽게 하기 위해서, 우선 기입 화소 행(51a)이 화소 행(1)번째라고 하여 설명한다.

또한, 소스 신호선(18)에 흐르는 프로그램 전류는 소정값의 N배(설명을 쉽게 하기 위해서,  $N=10$ 으로 하여 설명함. 물론, 소정값이란 화상을 표시하는 데이터 전류이므로, 백 래스터 표시 등이 아닌 한 고정치가 아님)이다. 또한, 5 화소 행이 동시에 선택( $M=5$ )되는 것으로 하여 설명한다. 따라서, 이상적으로는 하나의 화소의 컨덴서(19)에는 2배( $N/M=10/5=2$ )로 전류가 트랜지스터(11a)에 흐르도록 프로그램된다.

기입 화소 행이 (1) 화소 행째일 때, 도 21에서 도시한 바와 같이, 게이트 신호선(17a)은 (1)(2)(3)(4)(5)가 선택되어 있다. 즉, 화소 행(1)(2)(3)(4)(5)의 스위칭용 트랜지스터(11b), 트랜지스터(11c)가 온 상태이다. 또한, 게이트 신호선(17b)은 게이트 신호선(17a)의 역 위상으로 되어 있다. 따라서, 화소 행(1)(2)(3)(4)(5)의 스위칭용 트랜지스터(11d)가 오프 상태이며, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 즉, 비점등 상태(52)이다.

이상적으로는, 5 화소의 트랜지스터(11a)가, 각각  $I_w \times 2$ 의 전류를 소스 신호선(18)에 흘려 보낸다(즉, 소스 신호선(18)에는  $I_w \times 2 \times N = I_w \times 2 \times 5 = I_w \times 10$ . 따라서, 본 발명의 N배 펠스 구동을 실시하지 않는 경우가 소정 전류  $I_w$ 라고 하면,  $I_w$ 의 10배의 전류가 소스 신호선(18)에 흐름).

이상의 동작(구동 방법)에 의해, 각 화소(16)의 컨덴서(19)에는, 2배의 전류가 프로그램된다. 여기서는, 이해를 쉽게 하기 위해서, 각 트랜지스터(11a)는 특성( $V_t$ ,  $S$ 치)이 일치하고 있는 것으로 해서 설명한다.

동시에 선택하는 화소 행이 5 화소 행( $M=5$ )이므로, 5개의 구동용 트랜지스터(11a)가 동작한다. 즉, 1 화소당  $10/5=2$ 배의 전류가 트랜지스터(11a)에 흐른다. 소스 신호선(18)에는 5개의 트랜지스터(11a)의 프로그램 전류를 가한 전류가 흐른다. 예를 들면, 기입 화소 행(51a)에, 본래 기입하는 전류  $I_w$ 로 하고, 소스 신호선(18)에는  $I_w \times 10$ 의 전류를 흘려 보낸다. 기입 화소 행(1)보다 이후에 화상 데이터를 기입하는 기입 화소 행(51b)은 소스 신호선(18)에의 전류량을 증가시키기 위해서, 보조적으로 이용하는 화소 행이다. 그러나, 기입 화소 행(51b)은 후에 정규의 화상 데이터가 기입되기 때문에 문제가 없다.

따라서, 4 화소 행(51b)에 있어서, 1H 기간 동안은 (51a)과 동일 표시이다. 그 때문에, 기입 화소 행(51a)과 전류를 증가시키기 위해서 선택한 화소 행(51b)을 적어도 비표시 상태(52)로 하는 것이다. 단, 도 38과 같은 커런트 미러의 화소 구성, 그밖의 전압 프로그램 방식의 화소 구성에서는 표시 상태로 하여도 좋다.

1H 후에는, 게이트 신호선(17a)(1)은 비선택이 되고, 게이트 신호선(17b)에는 온 전압( $V_{gl}$ )이 인가된다. 또한, 동시에, 게이트 신호선(17a)(6)이 선택되고( $V_{gl}$  전압), 선택된 화소 행(6)의 트랜지스터(11a)에서 소스 드라이버 회로(14)를 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이와 같이 동작하는 것에 의해, 화소 행(1)에는 정규의 화상 데이터가 유지된다.

다음의, 1H 후에는, 게이트 신호선(17a)(2)은 비선택으로 되고, 게이트 신호선(17b)에는 온 전압( $V_{gl}$ )이 인가된다. 또한 동시에, 게이트 신호선(17a)(7)이 선택되고( $V_{gl}$  전압), 선택된 화소 행(7)의 트랜지스터(11a)에서 소스 드라이버 회로(14)를 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이와 같이 동작함으로써, 화소 행(2)에는 정규의 화상 데이터가 유지된다. 이상의 동작과 1 화소 행씩 시프트하면서 주사하는 것에 의해 1 화면이 재기입된다.

도 20의 구동 방법에서는, 각 화소에는 2배의 전류(전압)로 프로그램을 행하기 때문에, 각 화소의 EL 소자(15)의 발광 휘도는 이상적으로는 2배가 된다. 따라서, 표시 화면의 휘도는 소정값보다도 2배로 된다. 이것을 소정의 휘도로 하기 위해서는, 도 16에 도시하는 바와 같이, 기입 화소 행(51)을 포함하고, 또한 표시 화면(50)의 1/2의 범위를 비표시 영역(52)으로 하면 된다.

도 13과 마찬가지로, 도 20과 같이 하나의 표시 영역(53)이 화면의 위에서 아래 방향으로 이동하면, 프레임 레이트가 낮으면, 표시 영역(53)이 이동하는 것이 시각적으로 인식된다. 특히, 눈꺼풀을 감았을 때, 혹은 얼굴을 상하로 이동시켰을 때 등에 인식되기 쉽게 된다.

이 과제에 대해서는, 도 22에 도시하는 바와 같이, 표시 영역(53)을 복수로 분할하면 된다. 분할된 비표시 영역(52)을 가한 부분이  $S(N-1)/N$ 의 면적이 되면, 분할하지 않는 경우와 동일해진다.

도 23은 게이트 신호선(17)에 인가하는 전압 파형이다. 도 21과 도 23의 차이는 기본적으로는 게이트 신호선(17b)의 동작이다. 게이트 신호선(17b)은 화면을 분할하는 개수에 대응하여, 그 개수만큼 온 오프(Vgl와 Vgh) 동작한다. 다른 점은 도 21과 거의 동일 혹은 유추할 수 있기 때문에 설명을 생략한다.

이상과 같이, 표시 영역(53)을 복수로 분할하는 것에 의해 화면의 어른거림은 감소한다. 따라서, 깜박임의 발생이 없어, 양호한 화상 표시를 실현할 수 있다. 또, 분할은 더 미세하게 해도 된다. 그러나, 분할하면 할수록 깜박임은 경감한다. 특히 EL 소자(15)의 응답성이 빠르기 때문에,  $5\mu\text{sec}$ 보다도 작은 시간에 온 오프해도, 표시 휘도의 저하는 없다.

본 발명의 구동 방법에 있어서, EL 소자(15)의 온 오프는 게이트 신호선(17b)에 인가하는 신호의 온 오프로 제어할 수 있다. 그 때문에, 본 발명의 구동 방법에서는 KHz 오더의 저주파 수로 제어가 가능하다. 또한, 혹 화면 삽입(비표시 영역(52) 삽입)을 실현하는 데에는, 화상 메모리 등을 필요로 하지 않는다. 따라서, 저비용으로 본 발명의 구동 회로 혹은 방법을 실현할 수 있다.

도 24는 동시에 선택하는 화소 행이 2 화소 행인 경우이다. 검토한 결과에 따르면, 저온 폴리실리콘 기술로 형성한 표시 패널에서는, 2 화소 행을 동시에 선택하는 방법은 표시 균일성이 실용적이었다. 이것은 인접한 화소의 구동용 트랜지스터(11a)의 특성이 매우 일치하고 있기 때문으로 추정된다. 또한, 레이저 어닐링할 때에, 스트라이프형의 레이저의 조사 방향은 소스 신호선(18)과 평행하게 조사함으로써 양호한 결과가 얻어졌다.

이것은 동일 시간에 어닐링되는 범위의 반도체막은 특성이 균일하기 때문이다. 즉, 스트라이프형의 레이저 조사 범위 내에서는 반도체막이 균일하게 제작되고, 이 반도체막을 이용한 트랜지스터의  $V_t$ , 모빌리티가 거의 같게 되기 때문이다. 따라서, 소스 신호선(18)의 형성 방향에 평행하게 스트라이프형의 레이저 샷을 조사하고, 이 조사 위치를 이동시키는 것에 의해, 소스 신호선(18)에 따른 화소(화소 열, 화면의 상하 방향의 화소)의 특성은 거의 동등하게 제작된다. 따라서, 복수의 화소 행을 동시에 온시켜 전류 프로그램을 행했을 때, 프로그램 전류는 동시에 선택되어 복수의 화소에는 프로그램 전류가 선택된 화소 수로 나눈 전류가, 거의 동일하게 전류 프로그램된다. 따라서, 목표치에 가까운 전류 프로그램을 실시할 수 있어, 균일 표시를 실현할 수 있다. 따라서, 레이저 샷 방향과 도 24 등에서 설명하는 구동 방식은 상승 효과가 있다.

이상과 같이, 레이저 샷의 방향을 소스 신호선(18)의 형성 방향과 대략 일치(도 7을 참조)시키는 것에 의해, 화소의 상하 방향의 트랜지스터(11a)의 특성이 거의 동일하게 되어, 양호한 전류 프로그램을 실시할 수 있다(화소의 좌우 방향의 트랜지스터(11a)의 특성이 일치하지 않더라도). 이상의 동작은 1H(1수평 주사 기간)에 동기하여, 1 화소 행 혹은 복수 화소 행씩 선택 화소 행 위치를 어긋나게 하여 실시한다.

또, 도 8에서 설명한 바와 같이, 레이저 샷의 방향을 소스 신호선(18)과 평행하게 하는 것으로 했지만, 반드시 평행이 아니더라도 무방하다. 소스 신호선(18)에 대하여 경사 방향으로 레이저 샷을 조사해도 하나의 소스 신호선(18)에 따른 화소의 상하 방향의 트랜지스터(11a)의 특성은 거의 일치하여 형성되기 때문이다. 따라서, 소스 신호선에 평행하게 레이저 샷을 조사한다고 함은, 소스 신호선(18)을 따른 임의의 화소의 위 또는 아래에 인접한 화소를, 하나의 레이저 조사 범위로 들어가도록 형성한다는 것이다. 또한, 소스 신호선(18)이란 일반적으로는, 영상 신호가 되는 프로그램 전류 혹은 전압을 전달하는 배선이다.

또, 본 발명의 실시예에서는 1H마다 기입 화소 행 위치를 시프트시키는 것으로 했지만, 이것에 한정되는 것이 아니고, 2H마다 시프트(2 화소 행마다)해도 되며, 또한 그 이상의 화소 행씩 시프트시키더라도 무방하다. 또한, 임의의 시간 단위로 시프트해도 된다. 또, 1 화소 행 건너 띄고 시프트해도 된다.

화면 위치에 대응하여 시프트하는 시간을 변화시켜도 좋다. 예를 들면, 화면의 중앙부에서의 시프트 시간을 짧게 하고, 화면의 상하부에서 시프트 시간을 길게 해도 된다. 예를 들면, 화면(50)의 중앙부는  $200\mu\text{sec}$ 마다 1 화소 행을 시프트하고, 화면(50)의 상하부는  $100\mu\text{sec}$ 마다 1 화소 행을 시프트한다. 이와 같이 시프트하는 것에 의해, 화면(50)의 중앙부의 발광 휘도가 높아져, 주변(화면(50)의 상부와 하부)을 낮게 할 수 있다. 또, 화면(50)의 중앙부와 화면 상부의 시프트 시간, 화면(50)의 중앙부와 화면 하부의 시프트 시간은 순조롭게 시간 변화하도록 하고, 휘도 윤곽이 생기지 않도록 제어하는 것은 물론이다.

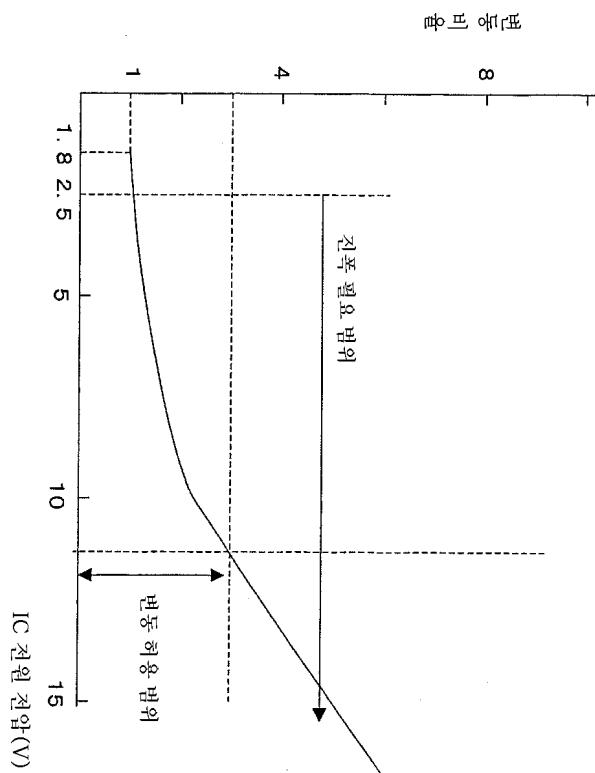

또, 소스 드라이버 회로(14)의 기준 전류를 화면(50)의 주사 위치에 대응하여 변화(도 146 등을 참조)시키더라도 좋다. 예를 들면, 화면(50)의 중앙부의 기준 전류를  $10\mu\text{A}$ 로 하고, 화면(50)의 상하부의 기준 전류는  $5\mu\text{A}$ 로 한다. 이와 같이 화면(50) 위치에 대응하여 기준 전류를 변화시키는 것에 의해, 화면(50)의 중앙부의 발광 휘도가 높아져, 주변(화면(50)의 상부와 하부)을 낮게 할 수 있다. 또, 화면(50)의 중앙부와 화면 상부 사이의 기준 전류, 화면(50)의 중앙부와 화면 하부 사이의 기준 전류의 값은 순조롭게 시간 변화하도록 하고, 휘도 윤곽이 생기지 않도록 기준 전류를 제어하는 것은 물론이다.

또한, 화면 위치에 대응하여, 화소 행을 시프트하는 시간을 제어하는 구동 방법과, 화면(50) 위치에 대응하여 기준 전류를 변화시키는 구동 방법을 조합하여 화상 표시를 행하여도 됨은 물론이다.

프레임마다 시프트 시간을 변화시키더라도 좋다. 또한, 연속한 복수 화소 행을 선택하는 것에 한정되는 것이 아니다. 예를 들면, 1 화소 행 사이에 둔 화소 행을 선택해도 된다.

즉, 제1번째의 수평 주사 기간에 제1번째의 화소 행과 제3번째의 화소 행을 선택하고, 제2번째의 수평 주사 기간에 제2번째의 화소 행과 제4번째의 화소 행을 선택하고, 제3번째의 수평 주사 기간에 제3번째의 화소 행과 제5번째의 화소 행을 선택하고, 제4번째의 수평 주사 기간에 제4번째의 화소 행과 제6번째의 화소 행을 선택하는 구동 방법이다. 물론, 제1번째의 수평 주사 기간에 제1번째의 화소 행과 제3번째의 화소 행과 제5번째의 화소 행을 선택한다고 하는 구동 방법도 기술적 범주이다. 물론, 복수 화소 행 사이에 둔 화소 행 위치를 선택해도 된다.

또, 이상의 레이저 샷 방향과 복수개의 화소 행을 동시에 선택한다고 하는 조합은, 도 1, 도 2, 도 32의 화소 구성에만 한정되는 것이 아니며, 커런트 미러의 화소 구성인 도 38, 도 42, 도 50 등의 다른 전류 구동 방식의 화소 구성에도 적용할 수 있는 것은 물론이다. 또한, 도 43, 도 51, 도 54, 도 46 등의 전압 구동의 화소 구성에도 적용할 수 있다. 즉, 화소 상하의 트랜지스터의 특성이 일치되어 있으면, 동일한 소스 신호선(18)에 인가한 전압값에 의해 양호하게 전압 프로그램을 실시할 수 있기 때문이다.

도 24에 있어서, 기입 화소 행이 (1) 화소 행째일 때, 게이트 신호선(17a)은 (1)(2)가 선택되어 있다(도 25를 참조). 즉, 화소 행(1)(2)의 스위칭용 트랜지스터(11b), 트랜지스터(11c)가 온 상태이다. 따라서, 적어도 화소 행(1)(2)의 스위칭용 트랜지스터(11d)가 오프 상태이고, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 즉, 비점등 상태(52)이다. 또, 도 24에서는 깜박임의 발생을 저감하기 위해서, 표시 영역(53)을 5 분할하고 있다.

이상적으로는, 2 화소(행)의 트랜지스터(11a)가 각각  $I_w \times 5$ ( $N=10$ )인 경우. 즉,  $K=2$ 이므로, 소스 신호선(18)에 흐르는 전류는  $I_w \times K \times 5 = I_w \times 10$ 이 됨)의 전류를 소스 신호선(18)에 흘린다. 그리고, 각 화소(16)의 컨덴서(19)에는 5배의 전류가 프로그램된다.

동시에 선택하는 화소 행이 2 화소 행( $K=2$ )이므로, 2개의 구동용 트랜지스터(11a)가 동작한다. 즉, 1 화소당  $10/2=5$ 배의 전류가 트랜지스터(11a)에 흐른다. 소스 신호선(18)에는 2개의 트랜지스터(11a)의 프로그램 전류를 가한 전류가 흐른다.

예를 들면, 기입 화소 행(51a)에, 본래 기입하는 전류를  $I_w$ 로 하고, 소스 신호선(18)에는  $I_w \times 10$ 의 전류를 흘려 보낸다. 기입 화소 행(51b)은 후에 정규 화상 데이터가 기입되기 때문에 문제가 없다. 화소 행(51b)은 1H 기간 동안은 (51a)와 동일 표시이다. 그 때문에, 기입 화소 행(51a)과 전류를 증가시키기 위해서 선택한 화소 행(51b)을 적어도 비표시 상태(52)로 하는 것이다.

다음의, 1H 후에는, 게이트 신호선(17a)(1)은 비선택으로 되고, 게이트 신호선(17b)에는 온 전압( $V_{gl}$ )이 인가된다. 또한 동시에, 게이트 신호선(17a)(3)이 선택되고( $V_{gl}$  전압), 선택된 화소 행(3)의 트랜지스터(11a)에서 소스 드라이버 회로(14)를 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이와 같이 동작함으로써, 화소 행(1)에는 정규의 화상 데이터가 유지된다.

다음의, 1H 후에는, 게이트 신호선(17a)(2)은 비선택으로 되고, 게이트 신호선(17b)에는 온 전압(Vgl)이 인가된다. 또한 동시에, 게이트 신호선(17a)(4)이 선택되고(Vgl 전압), 선택된 화소 행(4)의 트랜지스터(11a)에서 소스 드라이버 회로(14)를 향하여 소스 신호선(18)에 프로그램 전류가 흐른다. 이와 같이 동작하는 것에 의해, 화소 행(2)에는 정규의 화상 데이터가 유지된다. 이상의 동작과 1 화소 행씩 시프트(물론, 복수 화소 행씩 시프트해도 됨. 예를 들면, 의사 인터레이스 구동이면, 2 행씩 시프트할 것이다. 또한, 화상 표시의 관점에서, 복수의 화소 행에 동일 화상을 기입하는 경우도 있을 것임)하면서 주사하는 것에 의해 1 화면이 재기입된다.

도 16과 마찬가지이지만, 도 24의 구동 방법에서는, 각 화소에는 5배의 전류(전압)로 프로그램을 행하기 때문에, 각 화소의 EL 소자(15)의 발광 휘도는 이상적으로는 5배가 된다. 따라서, 표시 영역(53)의 휘도는 소정값보다도 5배가 된다. 이것을 소정의 휘도로 하기 위해서는, 도 16 등에 도시하는 바와 같이, 기입 화소 행(51)을 포함하고, 또한 표시 화면1의 1/5의 범위를 비표시 영역(52)으로 하면 된다.

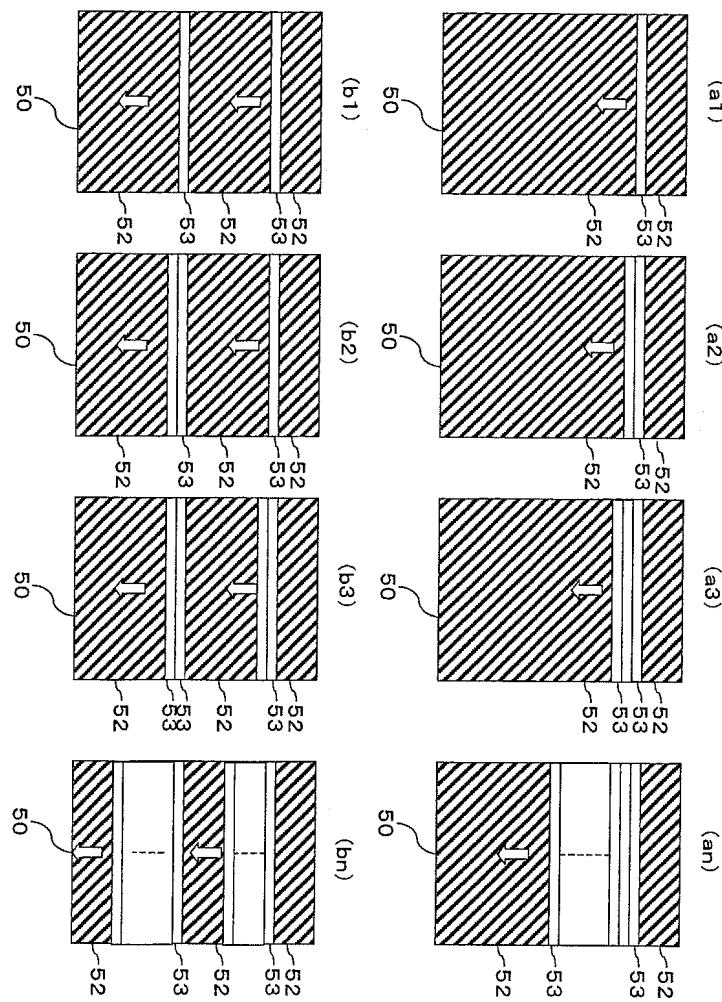

도 27에 도시하는 바와 같이, 2개의 기입 화소 행(51)(51a, 51b)이 선택되고, 화면(50)의 상변에서 하변으로 순차 선택되어 간다(도 26도 참조. 도 26에서는 화소(16a와 16b)가 선택되어 있음). 그러나, 도 27의 (b)와 같이, 화면의 하변까지 오면 기입 화소 행(51a)은 존재하지만, (51b)는 없어진다. 즉, 선택하는 화소 행이 하나밖에 없게 된다. 그 때문에, 소스 신호선(18)에 인가된 전류는 전부 화소 행(51a)에 기입된다. 따라서, 화소 행(51a)에 비하여 2배의 전류가 화소에 프로그램된다.

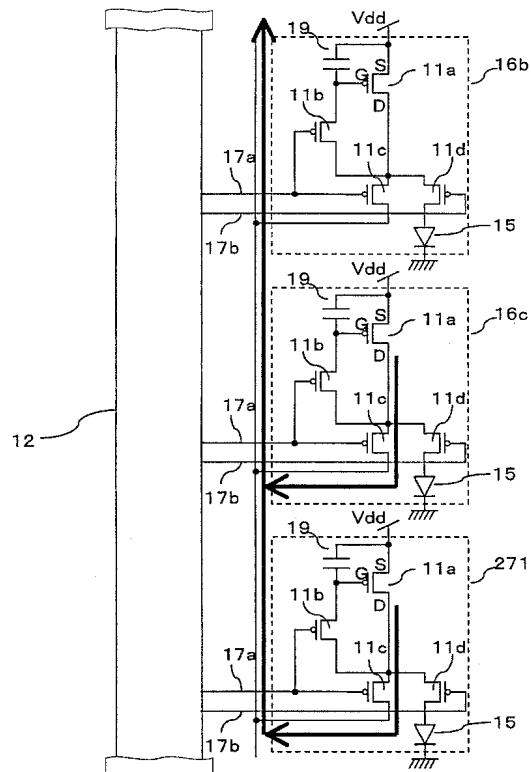

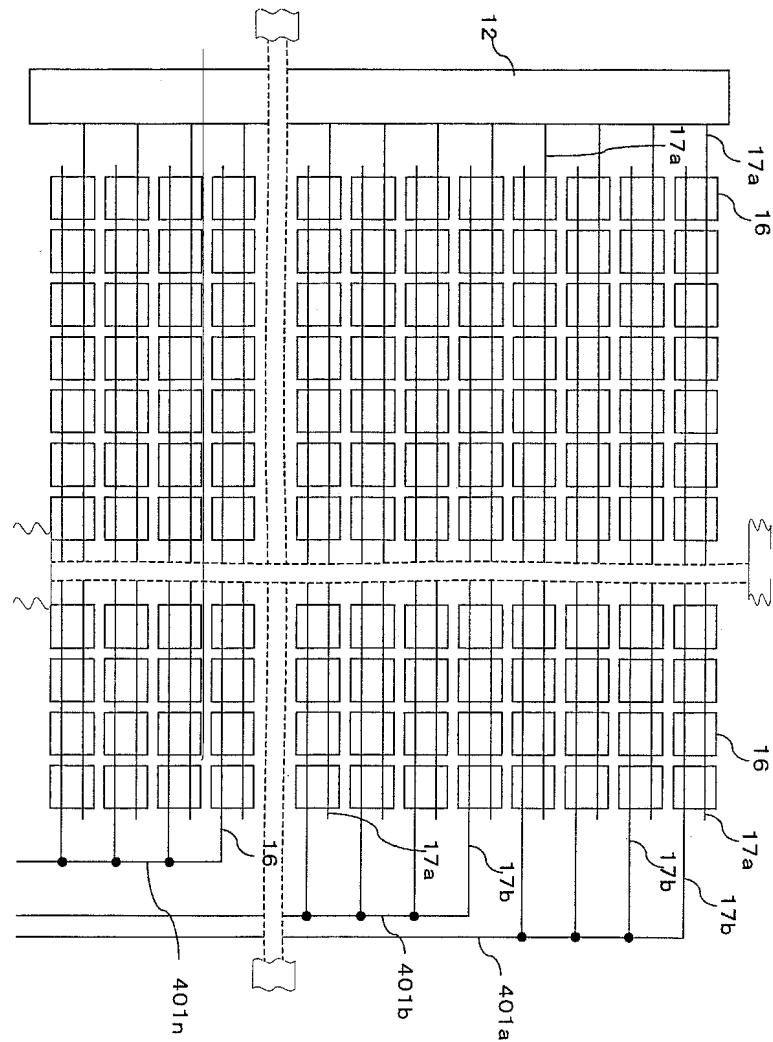

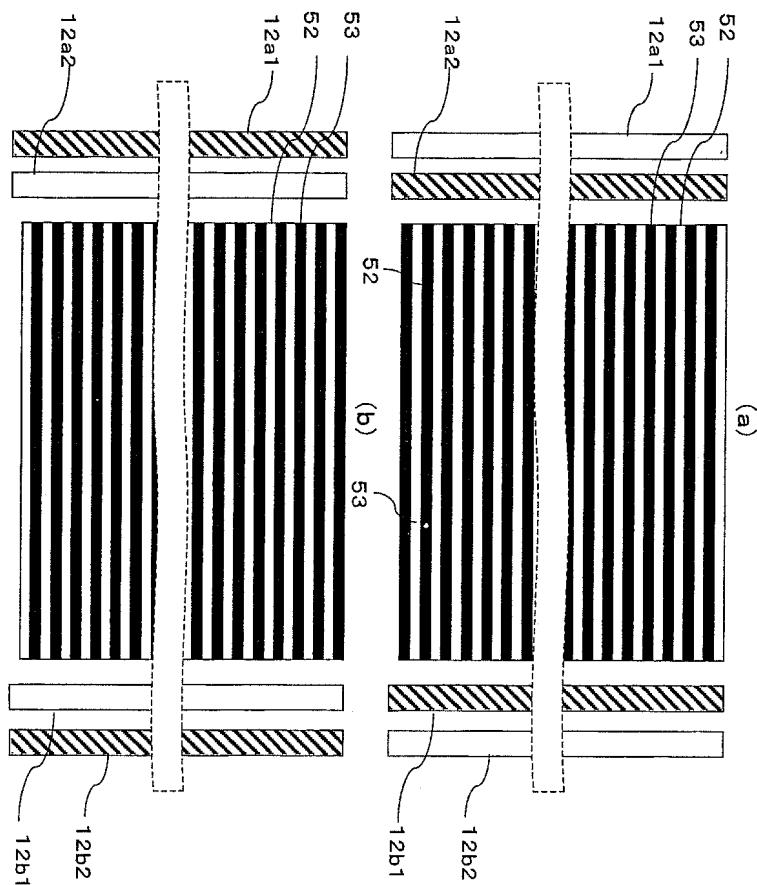

이 과제에 대하여, 본 발명은 도 27의 (b)에 도시하는 바와 같이 화면(50)의 하변에 더미 화소 행(271)을 형성(배치)하고 있다. 따라서, 선택 화소 행이 화면(50)의 하변까지 선택된 경우에는, 화면(50)의 최종 화소 행과 더미 화소 행(271)이 선택된다. 그 때문에, 도 27의 (b)의 기입 화소 행에는 규정대로의 전류가 기입된다.

또, 더미 화소 행(271)은 표시 화면(50)의 상단 혹은 하단에 인접하여 형성한 바와 같이 도시했지만, 이것에 한정되는 것이 아니다. 표시 화면(50)으로부터 떨어진 위치에 형성되어 있어도 좋다. 또한, 더미 화소 행(271)은 도 1의 스위칭용 트랜지스터(11d), EL 소자(15) 등은 형성할 필요는 없다. 형성하지 않음으로써, 더미 화소 행(271)의 사이즈는 작아진다.

도 28은 도 27의 (b)의 상태를 나타내고 있다. 도 28에서 분명한 바와 같이, 선택 화소 행이 화면(50)의 하변의 화소(16c) 행까지 선택된 경우에는, 화면(50)의 최종 화소 행(더미 화소 행)(271)이 선택된다. 더미 화소 행(271)은 표시 화면(50) 밖에 배치한다. 즉, 더미 화소 행(더미 화소)(271)은 점등하지 않거나 혹은 점등시키지 않거나, 혹은 점등해도 표시로서 보이지 않도록 구성한다. 예를 들면, 화소 전극(105)과 트랜지스터(11)의 컨택트홀을 없앤다든지, 더미 화소 행(271)에는 EL 막(15)을 형성하지 않는다든지 하는 것이다. 또한, 더미 화소 행의 화소 전극(105)상에 절연막을 형성하는 구성 등이 예시된다.

도 27에서는 화면(50)의 하변에 더미 화소(행)(271)를 마련(형성, 배치)하는 것으로 했지만, 이것에 한정되는 것이 아니다. 예를 들면, 도 29의 (a)에 도시하는 바와 같이, 화면의 하변에서 상변으로 주사(상하 역전 주사)하는 경우에는, 도 29의 (b)에 도시하는 바와 같이 화면(50)의 상변에도 더미 화소 행(271)을 형성하여야 한다. 즉, 화면(50)의 상변을 하변의 각각에 더미 화소 행(271)을 형성(배치)한다. 이상과 같이 구성함으로써, 화면의 상하 반전 주사에도 대응할 수 있게 된다. 이상의 실시예는 2 화소 행을 동시 선택하는 경우였다.

본 발명은 이것에 한정되는 것이 아니고, 예를 들면, 5 화소 행을 동시 선택하는 방식(도 23을 참조)이라도 좋다. 즉, 5 화소 행 동시 구동인 경우에는, 더미 화소 행(271)은 4 행분 형성하면 된다. 따라서, 더미 화소 행(271)은 동시에 선택하는 화소 행(11)의 화소 수분을 형성하면 된다. 단, 이것은 1 화소 행씩 선택하는 화소 행을 시프트하는 경우이다. 복수 화소 행씩 시프트하는 경우에는, 선택하는 화소 수를 M으로 하고, 시프트하는 화소 행 수를 L로 했을 때,  $(M-1) \times L$  화소 행분을 형성하면 된다.

본 발명의 더미 화소 행 구성 혹은 더미 화소 행 구동은, 적어도 하나 이상의 더미 화소 행을 이용하는 방식이다. 물론, 더미 화소 행 구동 방법과 N배 팰스 구동을 조합하여 이용하는 것이 바람직하다.

복수개의 화소 행을 동시에 선택하는 구동 방법에서는, 동시에 선택하는 화소 행 수가 증가할수록, 트랜지스터(11a)의 특성 변동을 흡수하는 것이 곤란해진다. 그러나, 동시에 선택 화소 행 수 M이 적어지면, 1 화소에 프로그램하는 전류가 커져, EL 소자(15)에 큰 전류를 흘려 보내게 된다. EL 소자(15)에 흘리는 전류가 크면 EL 소자(15)가 열화하기 쉽다.

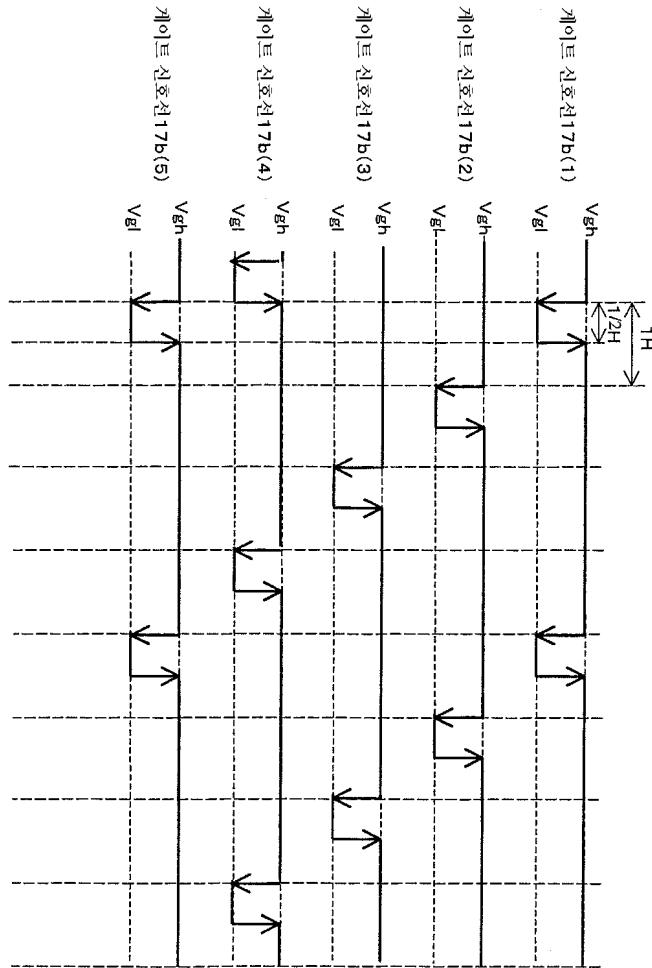

도 30은 이 과제를 해결하는 것이다. 도 30의 기본 개념은, 1/2H(수평 주사 기간의 1/2)는 도 22, 도 29에서 설명한 바와 같이, 복수의 화소 행을 동시에 선택하는 방법이다. 그 후의 (1/2)H(수평 주사 기간의 1/2)는 도 5, 도 13 등에서 설명한 바와 같이, 1 화소 행을 선택하는 방법을 조합한 것이다. 이와 같이 조합하는 것에 의해, 트랜지스터(11a)의 특성 변동을 흡수하여, 보다 고속으로 또한 면내 균일성을 양호하게 할 수 있다. 또, 이해를 쉽게 하기 위해서, (1/2)H로 조작하는 것으로 해서 설명하지만 이것에 한정되는 것이 아니다. 최초의 기간을 (1/4)H로 하고, 후반의 기간을 (3/4)H로 하여도 좋다.

도 30에 있어서, 설명을 쉽게 하기 위해서, 제1 기간에서는 5 화소 행을 동시에 선택하고, 제2 기간에서는 1 화소 행을 선택하는 것으로 하여 설명한다. 우선, 제1 기간(전반의 1/2H)에서는 도 30(a1)에 도시하는 바와 같이, 5 화소 행을 동시에 선택한다. 이 동작은 도 22를 이용하여 설명했기 때문에 생략한다. 일례로서 소스 신호선(18)에 흘리는 전류는 소정값의 25배로 한다. 따라서, 각 화소(16)의 트랜지스터(11a)(도 1의 화소 구성인 경우)에는 5배의 전류(25/5 화소 행=5)가 프로그램된다. 25배의 전류이므로, 소스 신호선(18) 등에 발생하는 기생 용량은 매우 단기간에 충방전된다. 따라서, 소스 신호선(18)의 전위는, 단시간에 목표의 전위로 되어, 각 화소(16)의 컨텐서(19)의 단자 전압도 25배 전류를 흘리도록 프로그램된다. 이 25배 전류의 인가 시간은 전반의 1/2H(1수평 주사 기간의 1/2)로 한다.

당연한 것이지만, 기입 화소 행의 5 화소 행은 동일 화상 데이터가 기입되기 때문에, 표시하지 않도록 5 화소 행의 트랜지스터(11d)는 오프 상태로 된다. 따라서, 표시 상태는 도 30(a2)이 된다.

다음의 후반의 1/2H 기간은 1 화소 행을 선택하여 전류(전압) 프로그램을 행한다. 이 상태를 도 30(b1)에 도시하고 있다. 기입 화소 행(51a)은 앞과 같이 5배의 전류를 흘리도록 전류(전압) 프로그램된다. 도 30(a1)과 도 30(b1)에서 각 화소에 흘리는 전류를 동일하게 하는 것은, 프로그램된 컨텐서(19)의 단자 전압의 변화를 작게 하여, 보다 고속으로 목표의 전류를 흘릴 수 있도록 하기 위해서이다.

즉, 도 30(a1)에서, 복수의 화소에 전류를 흘려 보내, 고속으로 개략의 전류가 흐르는 값까지 근접시킨다. 이 제1 단계에서는, 복수의 트랜지스터(11a)에서 프로그램하고 있기 때문에, 목표치에 대하여 트랜지스터의 변동에 의한 오차가 발생하고 있다. 다음의 제2 단계에서, 데이터를 기입하고 또한 유지하는 화소 행만을 선택하여, 개략의 목표치에서 소정의 목표치까지 완전한 프로그램을 행하는 것이다.

또, 비점등 영역(52)을 화면의 위에서 아래 방향으로 주사하고, 또한 기입 화소 행(51a)도 화면의 위에서 아래 방향으로 주사하는 것은 도 13 등의 실시예와 마찬가지이기 때문에 설명을 생략한다.

도 31은 도 30의 구동 방법을 실현하기 위한 구동 파형이다. 도 31에서 알 수 있듯이, 1H(1수평 주사 기간)는 2개의 페이즈로 구성되어 있다. 이 2개의 페이즈는 ISEL 신호로 전환한다. ISEL 신호는 도 31에 도시하고 있다.

우선, ISEL 신호에 대하여 설명을 해 둔다. 도 30을 실시하는 드라이버 회로(14)는, 전류 출력 회로 A와 전류 출력 회로 B를 구비하고 있다. 각각의 전류 출력 회로는, 8 비트의 계조 데이터를 DA 변환하는 DA 회로와 연산 증폭기 등으로 구성된다. 도 30의 실시예에서는, 전류 출력 회로 A는 25배의 전류를 출력하도록 구성되어 있다. 한편, 전류 출력 회로 B는 5배의 전류를 출력하도록 구성되어 있다. 전류 출력 회로 A와 전류 출력 회로 B의 출력은 ISEL 신호에 의해 전류 출력부에 형성(배치)된 스위치 회로가 제어되어, 소스 신호선(18)에 인가된다.

이 전류 출력 회로는 각 소스 신호선에 배치되어 있다.

ISEL 신호는 L 레벨일 때, 25배 전류를 출력하는 전류 출력 회로 A가 선택되어 소스 신호선(18)으로부터의 전류를 소스 드라이버 IC(14)가 흡수한다(보다 적절하게는, 소스 드라이버 회로(14) 내에 형성된 전류 출력 회로 A가 흡수함). 25배, 5배 등의 전류 출력 회로 전류의 크기 조정은 용이하다. 복수의 저항과 아날로그 스위치로 용이하게 구성할 수 있기 때문이다.

도 30에 도시한 바와 같이 기입 화소 행이 (1) 화소 행째일 때(도 31의 1H의 란을 참조), 게이트 신호선(17a)은 (1)(2)(3)(4)(5)가 선택되어 있다(도 1의 화소 구성인 경우). 즉, 화소 행(1)(2)(3)(4)(5)의 스위칭용 트랜지스터(11b), 트랜지스터(11c)가 온 상태이다. 또한, ISEL이 L 레벨이므로, 25배 전류를 출력하는 전류 출력 회로 A가 선택되고, 소스 신호선(18)과 접속되어 있다. 또한, 게이트 신호선(17b)에는 오프 전압(Vgh)이 인가되어 있다. 따라서, 화소 행(1)(2)(3)(4)(5)의 스위칭용 트랜지스터(11d)가 오프 상태이고, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 즉, 비점등 상태(52)이다.

이상적으로는, 5 화소의 트랜지스터(11a)가 각각  $I_w \times 2$ 의 전류를 소스 신호선(18)에 흘려 보낸다. 그리고, 각 화소(16)의 컨덴서(19)에는 5배의 전류가 프로그램된다. 여기서는, 이해를 쉽게 하기 위해서, 각 트랜지스터(11a)는 특성( $V_t$ ,  $S$ 치)이 일치하고 있는 것으로 설명한다.

동시에 선택하는 화소 행이 5 화소 행( $K=5$ )이므로, 5개의 구동용 트랜지스터(11a)가 동작한다. 즉, 1 화소당  $25/5=5$ 배의 전류가 트랜지스터(11a)에 흐른다. 소스 신호선(18)에는 5개의 트랜지스터(11a)의 프로그램 전류를 가한 전류가 흐른다. 예를 들면, 기입 화소 행(51a)에, 종래의 구동 방법으로 화소에 기입하는 전류  $I_w$ 로 할 때, 소스 신호선(18)에는  $I_w \times 25$ 의 전류를 흘려 보낸다. 기입 화소 행(1)보다 이후에 화상 데이터를 기입하는 기입 화소 행(51b)은, 소스 신호선(18)에의 전류량을 증가시키기 위해서 보조적으로 이용하는 화소 행이다. 그러나, 기입 화소 행(51b)은 후에 정규의 화상 데이터가 기입되기 때문에 문제가 없다.

따라서, 화소 행(51b)은, 1H 기간 동안은 (51a)와 동일 표시이다. 그 때문에, 기입 화소 행(51a)과 전류를 증가시키기 위해서 선택한 화소 행(51b)을 적어도 비표시 상태(52)로 하는 것이다.

다음의 1/2H(수평 주사 기간의 1/2)에서는 기입 화소 행(51a)만을 선택한다. 즉, (1) 화소 행째만을 선택한다. 도 31에서 분명한 바와 같이, 게이트 신호선(17a)(1)만이 온 전압( $V_{gl}$ )이 인가되고, 게이트 신호선(17a)(2)(3)(4)(5)은 오프( $V_{gh}$ )가 인가되어 있다. 따라서, 화소 행(1)의 트랜지스터(11a)는 동작 상태(소스 신호선(18)에 전류를 공급하고 있는 상태)이지만, 화소 행(2)(3)(4)(5)의 스위칭용 트랜지스터(11b), 트랜지스터(11c)가 오프 상태이다. 즉, 비선택 상태이다.

또한, ISEL이 H 레벨이므로, 5배 전류를 출력하는 전류 출력 회로 B가 선택되고, 이 전류 출력 회로 B와 소스 신호선(18)이 접속되어 있다. 또한, 게이트 신호선(17b)의 상태는 앞의 1/2H의 상태와 변화가 없고, 오프 전압( $V_{gh}$ )이 인가되어 있다. 따라서, 화소 행(1)(2)(3)(4)(5)의 스위칭용 트랜지스터(11d)가 오프 상태이고, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 즉, 비점등 상태(52)이다.

이상의 점으로부터, 화소 행(1)의 트랜지스터(11a)가 각각  $I_w \times 5$ 의 전류를 소스 신호선(18)에 흘려 보낸다. 그리고, 화소 행(1)의 컨덴서(19)에는 5배의 전류가 프로그램된다.

다음의 수평 주사 기간에서는 1 화소 행, 기입 화소 행이 시프트한다. 즉, 이번에는 기입 화소 행이 (2)이다. 최초의 1/2H의 기간에는, 도 31에 도시한 바와 같이 기입 화소 행이 (2) 화소 행째일 때, 게이트 신호선(17a)은 (2)(3)(4)(5)(6)이 선택되어 있다. 즉, 화소 행(2)(3)(4)(5)(6)의 스위칭용 트랜지스터(11b), 트랜지스터(11c)가 온 상태이다. 또한, ISEL이 L 레벨이므로, 25배 전류를 출력하는 전류 출력 회로 A가 선택되고, 소스 신호선(18)과 접속되어 있다. 또한, 게이트 신호선(17b)에는 오프 전압( $V_{gh}$ )이 인가되어 있다.

따라서, 화소 행(2)(3)(4)(5)(6)의 스위칭용 트랜지스터(11d)가 오프 상태이고, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 즉, 비점등 상태(52)이다. 한편, 화소 행(1)의 게이트 신호선(17b)(1)은  $V_{gl}$  전압이 인가되고 있기 때문에, 트랜지스터(11d)는 온 상태이고, 화소 행(1)의 EL 소자(15)는 점등한다.

동시에 선택하는 화소 행이 5 화소 행( $K=5$ )이므로, 5개의 구동용 트랜지스터(11a)가 동작한다. 즉, 1 화소당  $25/5=5$ 배의 전류가 트랜지스터(11a)에 흐른다. 소스 신호선(18)에는 5개의 트랜지스터(11a)의 프로그램 전류를 가한 전류가 흐른다.

다음의 1/2H(수평 주사 기간의 1/2)에서는, 기입 화소 행(51a)만을 선택한다. 즉, (2) 화소 행째만을 선택한다. 도 31로 분명한 바와 같이, 게이트 신호선(17a)(2)만이 온 전압( $V_{gl}$ )이 인가되고, 게이트 신호선(17a)(3)(4)(5)(6)은 오프( $V_{gh}$ )가 인가되어 있다.

따라서, 화소 행(1)(2)의 트랜지스터(11a)는 동작 상태(화소 행(1)은 EL 소자(15)에 전류를 흘려 보내고, 화소 행(2)은 소스 신호선(18)에 전류를 공급하고 있는 상태)이지만, 화소 행(3)(4)(5)(6)의 스위칭용 트랜지스터(11b), 트랜지스터(11c)가 오프 상태이다. 즉, 비선택 상태이다.

또한, ISEL이 H 레벨이므로, 5배 전류를 출력하는 전류 출력 회로 B가 선택되고, 이 전류 출력 회로 B와 소스 신호선(18)이 접속되어 있다. 또한, 게이트 신호선(17b)의 상태는 앞의 1/2H의 상태와 변화가 없고, 오프 전압( $V_{gh}$ )이 인가되어 있다. 따라서, 화소 행(2)(3)(4)(5)(6)의 스위칭용 트랜지스터(11d)가 오프 상태이고, 대응하는 화소 행의 EL 소자(15)에는 전류가 흐르고 있지 않다. 즉, 비점등 상태(52)이다.

이상의 점으로부터, 화소 행(2)의 트랜지스터(11a)가 각각  $I_w \times 5$ 의 전류를 소스 신호선(18)에 흘린다. 그리고, 각 화소 행(2)의 컨텐서(19)에는 5배의 전류가 프로그램된다. 이상의 동작을 순차 실시하는 것에 의해 1 화면을 표시할 수 있다.

도 30에서 설명한 구동 방법은, 제1 기간에 G 화소 행(G는 2 이상)을 선택하고, 각 화소 행에는 N배의 전류를 흘리도록 프로그램한다. 제1 기간 후의 제2 기간에서는 B 화소 행(B는 G보다도 작고 1 이상)을 선택하고, 화소에는 N배의 전류를 흘리도록 프로그램하는 방식이다.

그러나, 다른 방책도 있다. 제1 기간에 G 화소 행(G는 2 이상)을 선택하고, 각 화소 행의 총합 전류가 N배의 전류로 되도록 프로그램한다. 제1 기간 후의 제2 기간에서는 B 화소 행(B는 G보다도 작고, 1 이상)을 선택하고, 선택된 화소 행의 총합의 전류(단, 선택 화소 행이 1의 시에는, 1 화소 행의 전류)가 N배로 되도록 프로그램하는 방식이다.

예를 들면, 도 30(a1)에 있어서, 5 화소 행을 동시에 선택하고, 각 화소의 트랜지스터(11a)에는 2배의 전류를 흘려 보낸다. 따라서, 소스 신호선(18)에는  $5 \times 2 = 10$ 배의 전류가 흐른다. 다음의 제2 기간에서는 도 30(b1)에 있어서, 1 화소 행을 선택한다. 이 1 화소의 트랜지스터(11a)에는 10배의 전류를 흘려 보낸다.

또, 도 31에 있어서, 복수의 화소 행을 동시에 선택하는 기간을  $1/2H$ 로 하고, 1 화소 행을 선택하는 기간을  $1/2H$ 로 했는데 이것에 한정되는 것이 아니다. 복수의 화소 행을 동시에 선택하는 기간을  $1/4H$ 로 하고, 1 화소 행을 선택하는 기간을  $3/4H$ 로 하여도 좋다. 또한, 복수의 화소 행을 동시에 선택하는 기간과, 1 화소 행을 선택하는 기간을 가한 기간은  $1H$ 로 했지만 이것에 한정되는 것이 아니다. 예를 들면,  $2H$  기간이라도  $1.5H$  기간이더라도 무방하다.

또한, 도 30에 있어서, 5 화소 행을 동시에 선택하는 기간을  $1/2H$ 로 하고, 다음의 제2 기간에서는 2 화소 행을 동시에 선택하는 것으로 해도 좋다. 이 경우라도 실용상 지장이 없는 화상 표시를 실현할 수 있다.

또한, 도 30에 있어서, 5 화소 행을 동시에 선택하는 제1 기간을  $1/2H$ 로 하고, 1 화소 행을 선택하는 제2 기간을  $1/2H$ 로 하는 2 단계로 했지만 이것에 한정되는 것이 아니다. 예를 들면, 제1 단계는, 5 화소 행을 동시에 선택하고, 제2 기간에는 상기 5 화소 행 중, 2 화소 행을 선택하고, 마지막으로 1 화소 행을 선택하는 3개의 단계로 하여도 된다. 즉, 복수의 단계에서 화소 행에 화상 데이터를 기입하여도 좋다.

이상의 실시 예는, 1 화소 행을 순차 선택하여 화소에 전류 프로그램을 행하는 방식, 혹은 복수의 화소 행을 순차 선택하여 화소에 전류 프로그램을 행하는 방식이다. 그러나, 본 발명은 이것에 한정되는 것이 아니다. 화상 데이터에 대응하여 1 화소 행을 순차 선택하여 화소에 전류 프로그램을 행하는 방식과, 복수의 화소 행을 순차 선택하여 화소에 전류 프로그램을 행하는 방식을 조합하여도 된다.

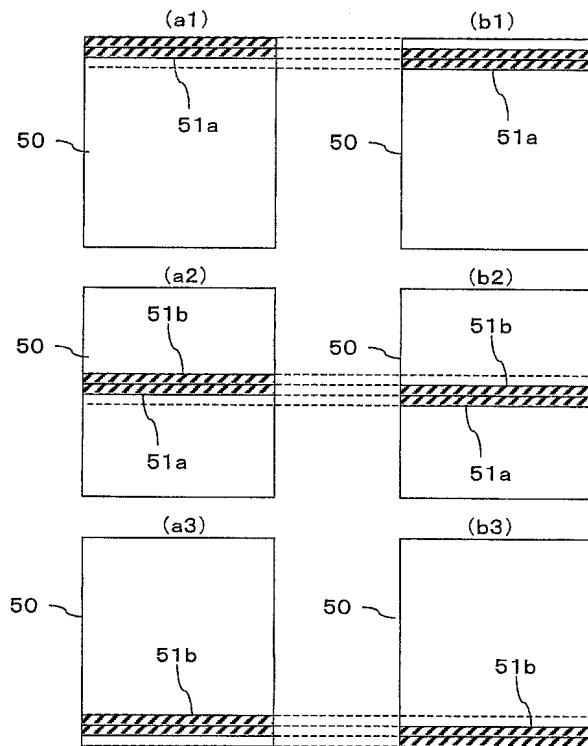

이하, 본 발명의 인터레이스 구동에 대하여 설명한다. 도 133은 인터레이스 구동을 행하는 본 발명의 표시 패널의 구성이다. 도 133에 있어서, 홀수 화소 행의 게이트 신호선(17a)은 게이트 드라이버 회로(12a1)에 접속되어 있다. 짹수 화소 행의 게이트 신호선(17a)은 게이트 드라이버 회로(12a2)에 접속되어 있다. 한편, 홀수 화소 행의 게이트 신호선(17b)은 게이트 드라이버 회로(12b1)에 접속되어 있다. 짹수 화소 행의 게이트 신호선(17b)은 게이트 드라이버 회로(12b2)에 접속되어 있다.

따라서, 게이트 드라이버 회로(12a1)의 동작(제어)에 의해 홀수 화소 행의 화상 데이터가 순차 채기입된다. 홀수 화소 행은 게이트 드라이버 회로(12b1)의 동작(제어)에 의해 EL 소자의 점등, 비점등 제어가 행하여진다. 또한, 게이트 드라이버 회로(12a2)의 동작(제어)에 의해 짹수 화소 행의 화상 데이터가 순차 채기입된다. 또한, 짹수 화소 행은, 게이트 드라이버 회로(12b2)의 동작(제어)에 의해 EL 소자의 점등, 비점등 제어가 행하여진다.

도 134의 (a)는 제1 필드에서의 표시 패널의 동작 상태이다. 도 134의 (b)는 제2 필드에서의 표시 패널의 동작 상태이다. 또, 설명을 쉽게 하기 위해서, 1 프레임은 2 필드로 구성되어 있는 것으로 한다. 도 134에 있어서, 사선을 기입한 게이트 드라이버 회로(12)는 데이터의 주사 동작이 하지 않음을 나타내고 있다. 즉, 도 134의 (a)의 제1 필드에서는, 프로그램 전류의 기입 제어로서 게이트 드라이버 회로(12a1)가 동작하고, EL 소자(15)의 점등 제어로서 게이트 드라이버 회로(12b2)가 동작한다. 도 134의 (b)의 제2 필드에서는, 프로그램 전류의 기입 제어로서 게이트 드라이버 회로(12a2)가 동작하고, EL 소자(15)의 점등 제어로서 게이트 드라이버 회로(12b1)가 동작한다. 이상의 동작이, 프레임 내에서 반복된다.

도 135가 제1 필드에서의 화상 표시 상태이다. 도 135의 (a)가 기입 화소 행(전류(전압) 프로그램을 행하고 있는 홀수 화소 행 위치를 도시하고 있다. 도 135(a1)→(a2)→(a3)로 기입 화소 행 위치가 순차 시프트된다. 제1 필드에서는, 홀수 화소

행이 순차 재기입된다(짝수 화소 행의 화상 데이터는 유지되어 있음). 도 135의 (b)가 홀수 화소 행의 표시 상태를 나타내고 있다. 또, 도 135의 (b)는 홀수 화소 행만을 도시하고 있다. 짝수 화소 행은 도 135의 (c)에 도시하고 있다. 도 135의 (b)에서도 분명한 바와 같이, 홀수 화소 행에 대응하는 화소의 EL 소자(15)는 비점등 상태이다. 한편, 짝수 화소 행은 도 135의 (c)에 도시하고 있는 바와 같이 표시 영역(53)과 비표시 영역(52)을 주사한다(N배 펠스 구동).

도 136은 제2 필드에서의 화상 표시 상태이다. 도 136의 (a)가 기입 화소 행(전류(전압) 프로그램을 행하고 있는 홀수 화소 행 위치)를 도시하고 있다. 도 136(a1)→(a2)→(a3)로 기입 화소 행 위치가 순차 시프트된다. 제2 필드에서는, 짝수 화소 행이 순차 재기입된다(홀수 화소 행의 화상 데이터는 유지되어 있음). 도 136의 (b)가 홀수 화소 행의 표시 상태를 나타내고 있다. 또, 도 136의 (b)는 홀수 화소 행만을 도시하고 있다. 짝수 화소 행은 도 136의 (c)에 도시하고 있다. 도 136의 (b)에서도 분명한 바와 같이, 짝수 화소 행에 대응하는 화소의 EL 소자(15)는 비점등 상태이다. 한편, 홀수 화소 행은, 도 136의 (c)에 도시하고 있는 바와 같이 표시 영역(53)과 비표시 영역(52)을 주사한다(N배 펠스 구동).

이상과 같이 구동함으로써, 인터레이스 구동을 EL 표시 패널로 용이하게 실현할 수 있다. 또, N배 펠스 구동을 실시하는 것에 의해 기입 부족도 발생하지 않고, 동화상 불선명도 발생하지 않는다. 또한, 전류(전압) 프로그램의 제어와, EL 소자(15)의 점등 제어도 용이하고, 회로도 용이하게 실현할 수 있다.

또, 본 발명의 구동 방식은 도 135, 도 136의 구동 방식에 한정되는 것이 아니다. 예를 들면, 도 137의 구동 방식도 예시된다. 도 135, 도 136은 전류(전압) 프로그램을 행하고 있는 홀수 화소 행 또는 짝수 화소 행은 비표시 영역(52)(비점등, 흑표시)으로 하는 것이었다. 도 137의 실시예는, EL 소자(15)의 점등 제어를 행하는 게이트 드라이버 회로(12b1, 12b2)의 양방을 동기시켜 동작시키는 것이다. 단, 전류(전압) 프로그램을 행하고 있는 화소 행(51)은 비표시 영역이 되도록 제어하는 것은 물론이다(도 38의 커런트 미러 화소 구성에서는 그 필요는 없음). 도 137에서는 홀수 화소 행과 짝수 화소 행의 점등 제어가 동일하기 때문에, 게이트 드라이버 회로(12b1과 12b2)의 2개로 설치할 필요는 없다. 게이트 드라이버 회로(12b)를 하나로 점등 제어할 수 있다.

도 137은 홀수 화소 행과 짝수 화소 행의 점등 제어를 동일하게 하는 구동 방법이었다. 그러나, 본 발명은 이것에 한정되는 것이 아니다. 도 138은 홀수 화소 행과 짝수 화소 행의 점등 제어를 다르게 한 실시예이다. 특히, 도 138은 홀수 화소 행의 점등 상태(표시 영역(53), 비표시 영역(52))의 역 패턴을 짝수 화소 행의 점등 상태로 한 예이다. 따라서, 표시 영역(53)의 면적과 비표시 영역(52)의 면적은 동일하게 되도록 하고 있다. 물론, 표시 영역(53)의 면적과 비표시 영역(52)의 면적은 동일하게 되는 것에 한정되는 것이 아니다.

또한, 도 136, 도 135에 있어서, 홀수 화소 행 혹은 짝수 화소 행에서 모든 화소 행이 비점등 상태로 하는 것에 한정되는 것이 아니다.

이상의 실시예는 1 화소 행씩 전류(전압) 프로그램을 실시하는 구동 방법이었다. 그러나, 본 발명의 구동 방법은 이것에 한정되는 것이 아니고, 도 139에 도시하는 바와 같이 2 화소 행(복수 화소 행)을 동시에 전류(전압) 프로그램 행하여도 됨은 말할 필요도 없다(도 27과 그 설명도 참조). 도 139의 (a)는 홀수 필드의 실시예이고, 도 139의 (b)는 짝수 필드의 실시예이다. 홀수 필드에서는, (1, 2) 화소 행, (3, 4) 화소 행, (5, 6) 화소 행, (7, 8) 화소 행, (9, 10) 화소 행, (11, 12) 화소 행, ……(n, n+1) 화소 행(n은 1 이상의 정수)의 조로 2 화소 행을 순차 선택하여, 전류 프로그램을 행하여 간다. 짝수 필드에서는 (2, 3) 화소 행, (4, 5) 화소 행, (6, 7) 화소 행, (8, 9) 화소 행, (10, 11) 화소 행, (12, 13) 화소 행, ……(n+1, n+2) 화소 행(n은 1 이상의 정수)의 조로 2 화소 행을 순차 선택하여, 전류 프로그램을 행하여 간다.

이상과 같이 각 필드에서 복수 화소 행을 선택하여 전류 프로그램을 행함으로써 소스 신호선(18)에 흘리는 전류를 증가할 수 있어, 흑 기입을 양호하게 할 수 있다. 또, 홀수 필드와 짝수 필드에서 선택하는 복수 화소 행의 조를 적어도 1 화소 행 어긋나게 함으로써, 화상의 해상도를 향상시킬 수 있다.

도 139의 실시예는 각 필드에서 선택하는 화소 행을 2 화소 행으로 했지만, 이것에 한정하는 것이 아니고 3 화소 행으로 하여도 좋다. 이 경우에는, 홀수 필드와 짝수 필드에서 선택하는 3 화소 행의 조는 1 화소 행 어긋나게 하는 방법과, 2 화소 행 어긋나게 하는 방법의 2 방식을 선택 가능하다. 또한, 각 필드에서 선택하는 화소 행은 4 화소 행 이상으로 하여도 된다. 또한, 도 125 내지 도 132에 도시하는 바와 같이, 1 프레임을 3 필드 이상으로 구성하도록 하여도 좋다.

또한, 도 139의 실시예에서는 2 화소 행을 동시에 선택하는 것으로 했지만, 이것에 한정되는 것이 아니며, 1H를 전반 1/2H와 후반의 1/2H로 하여, 홀수 필드에서는, 제1H 기간의 전반의 1/2H 기간에 제1 화소 행을 선택하여 전류 프로그램을 행하고, 후반의 1/2H 기간에 제2 화소 행을 선택하여 전류 프로그램을 행한다. 다음의 제2H 기간의 전반의 1/2H 기간에

제3 화소 행을 선택하여 전류 프로그램을 행하고, 후반의 1/2H 기간에 제4 화소 행을 선택하여 전류 프로그램을 행한다. 또한, 다음의 제3H 기간의 제1H 기간의 전반의 1/2H 기간에 제5 화소 행을 선택하여 전류 프로그램을 행하고, 후반의 1/2H 기간에 제6 화소 행을 선택하여 전류 프로그램을 행한다. ……라는 식으로 구동해도 된다.

또한, 짹수 필드에서는, 제1H 기간의 전반의 1/2H 기간에 제2 화소 행을 선택하여 전류 프로그램을 행하고, 후반의 1/2H 기간에 제3 화소 행을 선택하여 전류 프로그램을 행한다. 다음의 제2H 기간의 전반의 1/2H 기간에 제4 화소 행을 선택하여 전류 프로그램을 행하고, 후반의 1/2H 기간에 제5 화소 행을 선택하여 전류 프로그램을 행한다. 또한, 다음의 제3H 기간의 제1H 기간의 전반의 1/2H 기간에 제6 화소 행을 선택하여 전류 프로그램을 행하고, 후반의 1/2H 기간에 제7 화소 행을 선택하여 전류 프로그램을 행한다. ……라는 식으로 구동해도 된다.

이상의 실시예에서도 각 필드에서 선택하는 화소 행을 2 화소 행으로 했지만, 이것에 한정하는 것이 아니며 3 화소 행으로 하여도 좋다. 이 경우에는, 훌수 필드와 짹수 필드에서 선택하는 3 화소 행의 조는 1 화소 행 어긋나게 하는 방법과, 2 화소 행 어긋나게 하는 방법의 2 방식을 선택 가능하다. 또한, 각 필드에서 선택하는 화소 행은 4 화소 행 이상으로 해도 된다.

본 발명의 N배 펄스 구동 방법에서는, 각 화소 행에서 게이트 신호선(17b)의 파형을 동일하게 하여, 1H의 간격으로 시프트시켜 인가해 간다. 이와 같이 주사함으로써, EL 소자(15)가 점등하고 있는 시간을 1F/N으로 규정하면서, 순차, 점등하는 화소 행을 시프트시킬 수 있다. 이와 같이, 각 화소 행에서, 게이트 신호선(17b)의 파형을 동일하게 하여, 시프트시키고 있는 것을 실현하는 것은 용이하다. 도 6의 시프트 레지스터 회로(61a, 61b)에 인가하는 데이터인 ST1, ST2를 제어하면 되기 때문이다. 예를 들면, 입력 ST2가 L 레벨일 때, 게이트 신호선(17b)에 Vgl이 출력되고, 입력 ST2가 H 레벨일 때, 게이트 신호선(17b)에 Vgh가 출력된다고 하면, 시프트 레지스터(61b)에 인가하는 ST2를 1F/N의 기간만큼 L 레벨로 입력하고, 다른 기간은 H 레벨로 한다. 이 입력된 ST2를 1H에 동기한 클럭 CLK2로 시프트해 갈 뿐이다.

또, EL 소자(15)를 온 오프하는 주기는 0.5 msec 이상으로 할 필요가 있다. 이 주기가 짧으면, 인간의 눈의 잔상 특성에 의해 완전한 흑 표시 상태가 되지 않고, 화상이 회미해져, 마치 해상도가 저하된 것처럼 된다. 또한, 데이터 유지형의 표시 패널의 표시 상태가 된다. 그러나, 온 오프 주기가 100 msec 이상으로 되면, 점멸 상태로 보인다. 따라서, EL 소자의 온 오프 주기는 0.5 msec 이상 100 msec 이하로 해야 한다. 더욱 바람직하게는, 온 오프 주기를 2 msec 이상 30 msec 이하로 해야 한다. 더욱 바람직하게는, 온 오프 주기를 3 msec 이상 20 msec 이하로 해야 한다.

앞에서도 기재했지만, 흑 화면(52)의 분할 수는, 하나로 하면 양호한 동화상 표시를 실현할 수 있지만, 화면의 어른거림이 보이기 쉽게 된다. 따라서, 흑 삽입부를 복수로 분할하는 것이 바람직하다. 그러나, 분할 수를 너무나 많게 하면 동화상 불 선명이 발생한다. 분할 수는 1 이상 8 이하로 하여야 한다. 더욱 바람직하게는 1 이상 5 이하로 하는 것이 바람직하다.

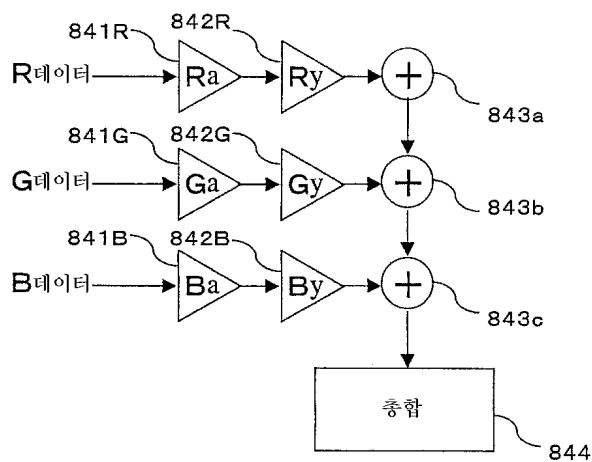

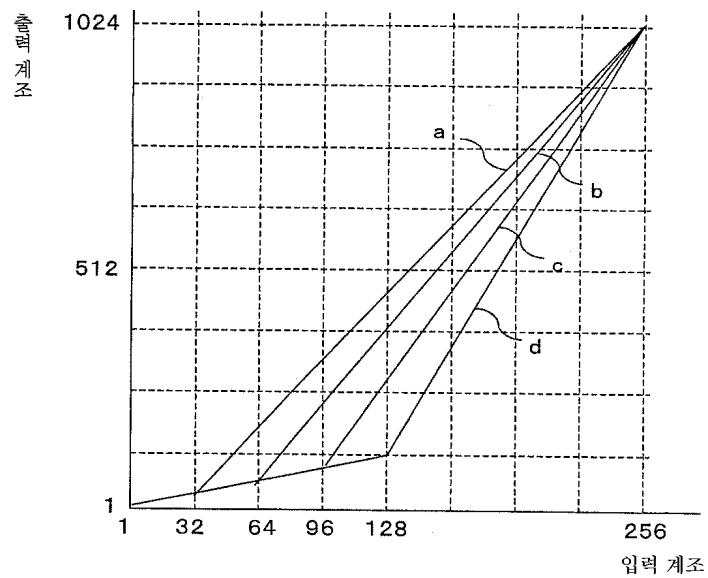

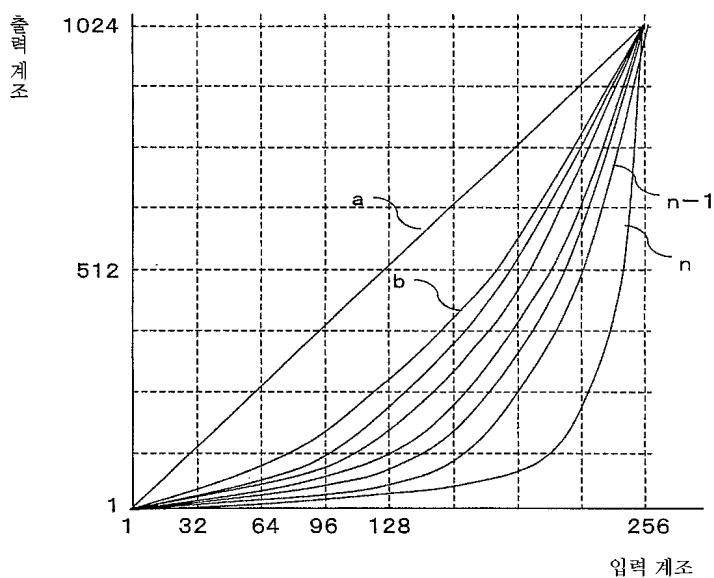

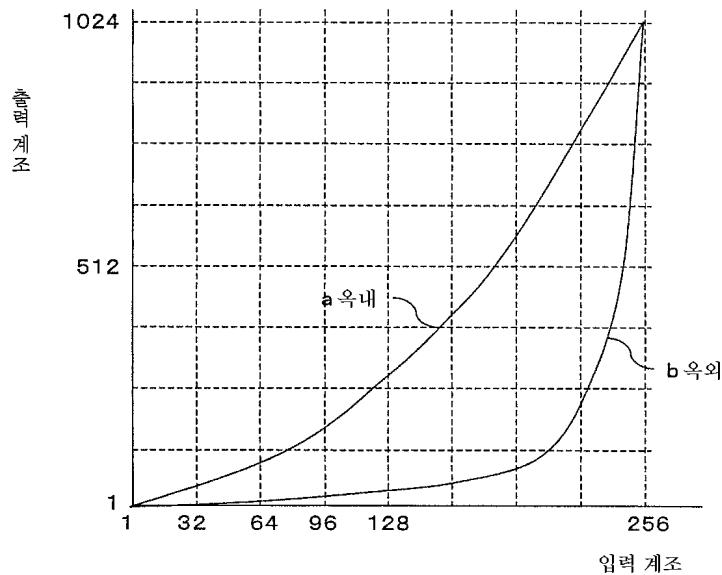

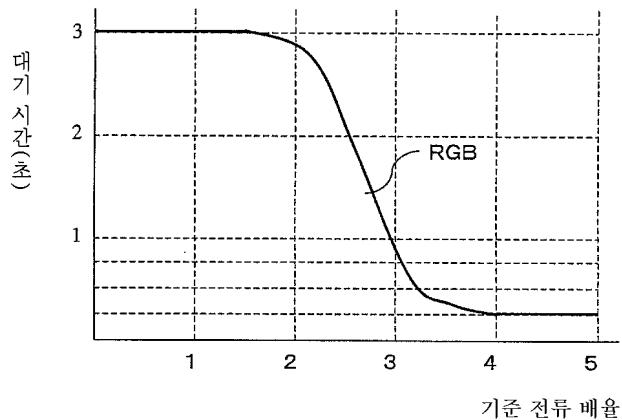

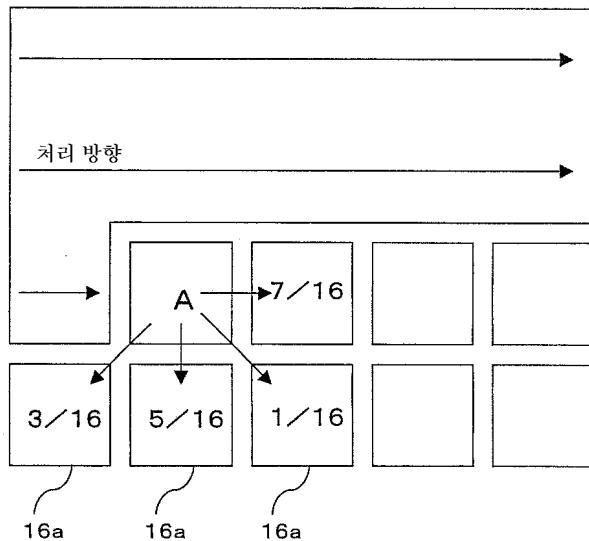

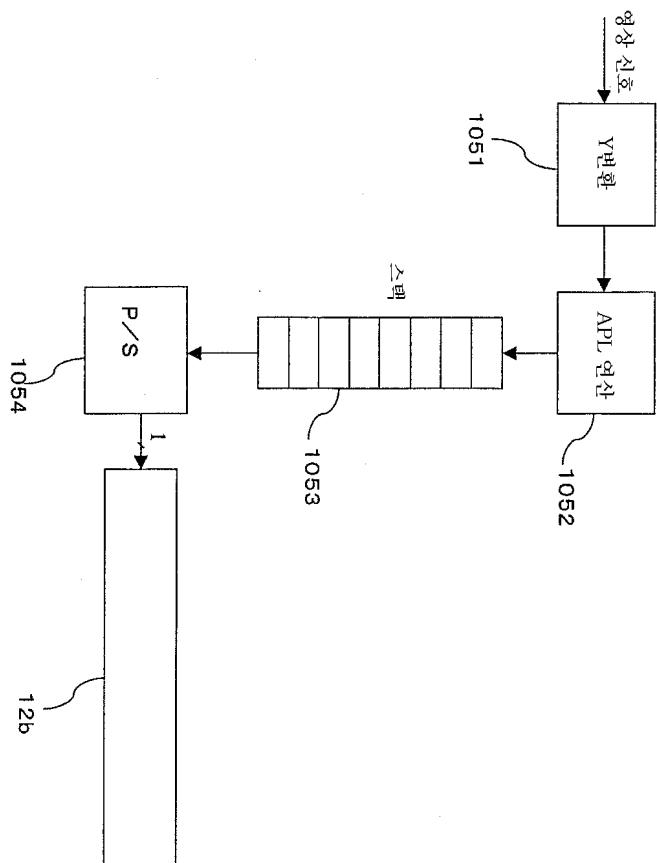

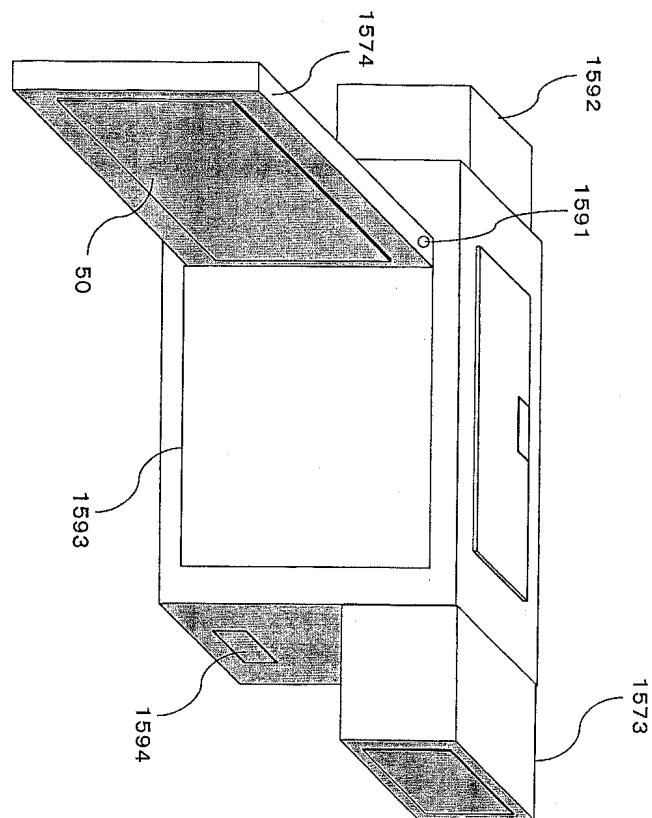

또, 흑 화면의 분할 수는 정지 화상과 동화상으로 변경할 수 있도록 구성하는 것이 바람직하다. 분할 수란, N=4에서는 75%가 흑 화면이고, 25%가 화상 표시이다. 이 때, 75%의 흑 표시부를 75%의 흑 띠 상태에서 화면의 상하 방향으로 주사하는 것이 분할 수 1이다. 25%의 흑 화면과 25/3%의 표시 화면의 3 블록으로 주사하는 것이 분할 수 3이다. 정지 화상은 분할 수를 많게 한다. 동화상은 분할 수를 적게 한다. 전환은 입력 화상에 대응하여 자동적(동화상 검출 등)으로 행하여도 되고, 사용자가 수동으로 행하여도 된다. 또한, 표시 장치의 영상 등의 입력 콘텐츠에 대응하여 전환할 수 있도록 구성하면 된다.