(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) 。 Int. Cl.

G09G 3/30 (2006.01)

(45) 공고일자 2007년05월11일

(11) 등록번호 10-0717200

(24) 등록일자 2007년05월04일

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2002-7002089   | (65) 공개번호   | 10-2002-0025979 |

| (22) 출원일자   | 2002년02월18일       | (43) 공개일자   | 2002년04월04일     |

| 심사청구일자      | 2006년06월02일       |             |                 |

| 번역문 제출일자    | 2002년02월18일       |             |                 |

| (86) 국제출원번호 | PCT/EP2001/006443 | (87) 국제공개번호 | WO 2001/99190   |

| 국제출원일자      | 2001년06월07일       | 국제공개일자      | 2001년12월27일     |

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 리히텐슈타인, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드, 사이프러스,

(30) 우선권주장 0014962.5 2000년06월20일 영국(GB)

(73) 특허권자 코닌클리케 필립스 일렉트로닉스 엔.브이.

네델란드왕국, 아인드호펜, 그로네보드스베그 1

(72) 발명자 영,나이겔,디.

네덜란드엔엘-5656아아아인드호벤,프로프.홀스틀라안6

샤논, 존, 엠.

네덜란드엔엘-5656아아아인드호벤, 프로프. 홀스틀라안6

(74) 대리인 문경진

(56) 선행기술조사문현

EP 0923067 EP 0491436

WO 01/20591 공개특허 제1997-29313호

## 심사관 : 천대식

전체 청구항 수 : 총 11 항

#### (54) 광감지소자를 갖는 매트릭스 어레이 디스플레이 디바이스

(57) 요약

매트릭스 디스플레이 디바이스는 기판(50) 상에 픽셀(10)의 어레이를 구비하는데, 각 픽셀은 예컨대 전기발광 디스플레이 소자인 디스플레이소자(20) 및 연관된 디스플레이소자 제어회로를 구비하며, 상기 제어회로는 저장 캐패시터(36) 및 거기

에 연결된 광감지소자(40)를 포함하여, 예컨대 디스플레이소자의 동작을 조절하기 위하여 상기 디스플레이소자로부터 방출되는 광에 응답하고 저장 캐패시터 상에 저장된 전하를 조절한다. 광감지소자(40)는 기판상에 옆으로 간격을 가지고 배치되어 있는 도핑된 접촉 영역들(53, 54)을 구비하는 반도체 물질의 스트립을 각각 구비하는 박막 반도체 디바이스를 포함하고, 그리고 연관된 저장 캐패시터(36)는 실질적으로 상기 스트립을 그것의 유전 물질이 중간에 끼여져 있는 한 접촉 영역을 덮어 횡단하여 연장하는 전도층(58)에 의해 형성된다. 이 경우 구성요소 층에서 제작 허용공차에 기인한 크기의 변동이 발생하는 경우일지라도 저장 캐패시터 및 광감지 디바이스 특성 사이의 미리 결정된 관계가 보장된다. 바람직하게는, 광감지 디바이스는 그 게이트가 접촉 영역들 중간에 끼어있는 반도체 스트립 영역 위로 연장하는 게이티드 디바이스를 포함한다. 게이트 유전물질 및 저장 캐패시터 유전물질은 공통 층(56)의 부분들을 가질 수 있다. 대안적으로 전도층은 게이트에 대향하는 스트립의 측면에서 제공될 수 있고 또한 주변 광에 대한 차폐부로서도 사용될 수 있다.

## 대표도

도 3

### 특허청구의 범위

#### 청구항 1.

기판 상에 각각 디스플레이소자 및 상기 디스플레이소자의 동작을 제어하기 위한 디스플레이소자 제어회로를 구비하는 어드레싱 가능한 픽셀들의 어레이를 포함하는 매트릭스 디스플레이 디바이스로서,

여기서 상기 디스플레이소자 제어회로는 전하 저장 캐패시터 및 상기 저장 캐패시터에 연결된 연관된 박막 광감지 반도체 디바이스를 포함함으로써 상기 광감지 디바이스상에 입사되는 광에 따라서 상기 저장 캐패시터 상에 저장된 전하를 조절하고,

여기서 상기 광감지 디바이스는 상기 기판상에 옆으로 간격을 가지고 배치되어 있는 도핑된 접촉 영역들 및 중간에 끼인 영역을 구비하는 반도체 물질의 스트립을 포함하고,

또한 여기서 상기 저장 캐패시터는 실질적으로 한 접촉 영역을 덮어 횡단하여 연장하는 상기 반도체 스트립의 전도층을 포함하는데, 상기 전도층과 상기 접촉 영역 사이에는 유전 물질층이 배치되는,

매트릭스 디스플레이 디바이스.

#### 청구항 2.

제 1 항에 있어서, 상기 광감지 디바이스는, 상기 반도체 스트립의 상기 중간에 끼인 영역을 덮어 연장하고 유전 물질에 의해 그것으로부터 분리되는 게이트를 구비하는 게이티드 광감지 디바이스(gated photosensitive device)를 포함하는 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

#### 청구항 3.

제 2 항에 있어서, 상기 광감지 디바이스의 상기 게이트 유전 물질 및 상기 저장 캐패시터의 상기 유전 물질은 하나의 공통층의 일부분을 포함하는 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

#### 청구항 4.

제 2 항 또는 제 3 항에 있어서, 상기 게이티드 광감지 디바이스는 유사하게 도핑된 접촉 영역들 및 상기 접촉 영역들 사이에 연장된 진성 반도체 영역을 구비하는 TFT 구조를 포함하는 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

**청구항 5.**

제 2 항 또는 제 3 항에 있어서, 상기 게이티드 광감지 디바이스는 반대로 도핑된 접촉 영역들 및 그 접촉 영역들 사이에 연장하는 진성 반도체 영역을 구비하는 측면 게이티드 PIN 디바이스(lateral gated pin device)를 포함하는 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

**청구항 6.**

제 2 항 또는 제 3 항에 있어서, 상기 저장 캐패시터의 전도층이 상기 광감지 디바이스의 게이트에 대향하는 상기 광감지 디바이스의 상기 반도체 스트립 측면에 제공되며 그 측면에서 광으로부터 그 부분을 차폐하기 위하여 상기 반도체 스트립의 적어도 일부를 덮는 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

**청구항 7.**

제 2 항 또는 제 3 항에 있어서, 상기 광감지 디바이스의 게이트는 상기 중간에 끈 영역에서의 전류 흐름이 생성된 광전류에 기인하게 하기 위하여 바이어스되도록 구성되는 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

**청구항 8.**

제 1 항 내지 제 3 항 중 어느 한 항에 있어서, 상기 반도체 물질의 스트립 및 상기 한 접촉 영역을 덮는 상기 전도층의 부분은 각각 실질적으로 평행한 측면을 가지며 서로에 대해 대체로 직각으로 연장되는 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

**청구항 9.**

제 1 항 내지 제 3 항 중 어느 한 항에 있어서, 상기 디스플레이소자는 전류-구동 발광소자를 포함하는 것과 그리고 상기 광감지 디바이스는 상기 디스플레이소자에 의해 방출된 광에 응답하도록 구성되는 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

**청구항 10.**

제 9 항에 있어서, 상기 디스플레이소자 제어회로는 상기 픽셀에 인가되고 상기 저장 캐패시터 상에 전하로서 저장된 구동 신호에 기초하여 구동 주기 안에서 상기 디스플레이소자를 통하는 전류를 제어하기 위한 구동 TFT - 상기 캐패시터는 상기 구동 TFT의 게이트에 연결된다 - 를 포함하는 것과, 그리고 상기 광감지 디바이스는 상기 저장 캐패시터 상의 전하를 조절하기 위하여 그리고 그림으로써 상기 구동 TFT의 동작을 조절하기 위하여 동작가능한 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

**청구항 11.**

제 9 항에 있어서, 상기 디스플레이소자는 전기발광 디스플레이소자(electroluminescent display element)를 포함하는 것을 특징으로 하는, 매트릭스 디스플레이 디바이스.

**명세서**

## 기술분야

본 발명은 광감지소자를 갖는 매트릭스 어레이 디스플레이 디바이스에 관한 것이다. 더 상세하게는, 본 발명은 디스플레이 소자를 포함하는 어드레싱 가능한 픽셀 및 광감지소자들을 구비하는 매트릭스 어레이 디스플레이 디바이스에 관한 것이다. 특히 그러나 배타적이지는 않게, 본 발명은 전기발광(electroluminescent) 디스플레이소자, 특히 고분자 전기발광 소자인 PLED를 포함하여, 유기 전기발광 디스플레이소자인 OLED를 사용하는 매트릭스 디스플레이 디바이스에 관한 것이다.

## 배경기술

픽셀이 EL(electroluminescent) 디스플레이소자 및 광감지소자를 포함하는 매트릭스 디스플레이 디바이스의 예가 영국 특허출원 번호 제 0005811.5 호에 개시되어 있다. 상기 개시된 디바이스는 기판 상에 배치된 픽셀 어레이를 구비하는 액티브 매트릭스 디스플레이 디바이스를 포함하는데, 여기서 각각의 픽셀은 두 개의 전극(그 중 하나는 투명하다) 사이에 있는 발광 EL 물질을 포함하는 전류-구동 전기발광 디스플레이소자 및 선행하는 어드레스 주기에 상기 픽셀에 인가된 구동 (데이터) 신호에 기반한 구동 주기에 상기 디스플레이소자를 통하는 상기 전류를 제어하도록, 그리하여 그 광 출력을 제어하도록, 동작가능한 스위칭 디바이스를 포함한다.

다른 액티브 매트릭스 EL 디스플레이소자들에서와 같이, 상기 디스플레이소자는, 광 출력을 생성하기 위하여 연속적으로 전류를 통과시켜야 할 필요가 있는데, 해당 구동 주기 동안의 출력을 결정하는 어드레스 주기 내의 픽셀에 저장된 데이터 신호의 레벨을 통하여 개별 행 어드레스 주기의 픽셀 어드레싱에 후속하는 연장된 주기동안, 한 프레임 시간에 이르기까지, 통전될 수 있다. 상기 구동 디바이스는, 박막트랜지스터(TFT: thin film transistor)의 형태로, 디스플레이소자를 통하여 전류를 제어할 책임이 있으며 인가된 데이터 신호는 이 구동 TFT의 게이트에 연결된 캐패시턴스 상의 전하로서 저장됨으로써 상기 TFT의 동작이 상기 저장된 전하에 의존하게 된다.

영국 특허출원 번호 제 0005811.5 호의 디바이스 내의 픽셀은, 상기 디스플레이소자의 광 출력 레벨에 의존하는 속도로 상기 캐패시터로부터 전하를 누출하도록 구동 주기에 상기 픽셀의 디스플레이소자에 의해 방출된 광에 응답하며 상기 픽셀의 동작시에 역방향 바이어스되도록 구성되는 상기 저장 캐패시턴스에 연결된 (PIN) 광다이오드 또는 광-반응 TFT를 포함하는, 광감지 디바이스를 추가로 포함한다. 이렇게, 광감지 디바이스 덕분에, 상기 캐패시턴스(어드레싱시에 충전된다고 가정하고) 점진적으로 방전함에 의하여 디스플레이소자를 통하여 전류 흐름을 감소시키도록, 그리하여 그 광 출력도 감소시키도록, 구동 주기 동안에 디스플레이소자의 통전(energisation)을 제어하는 상기 구동 TFT의 동작을 점진적으로 조정하는 광-전자적 피드백이 제공된다. 그러므로 디스플레이소자가 통전되는 총 사용가능한 구동 주기의 비율은 상기 소자의 광 출력에 따라 이 피드백 구성에 의하여 조절되며 이 피드백 구성에 의존한다. 이 방식에 있어서, 구동 (프레임) 주기에서 디스플레이소자로부터의 통합적인 광 출력은 특히 상기 디스플레이소자의 전기발광 물질 내에서의 어떠한 노화나 열화 효과를, 특히 동작 시간의 일 주기에 걸쳐 발생할 수 있는, 주어진 구동 전류 레벨을 위한 광 출력 레벨의 감소를 없애도록 제어될 수 있고, 또한 픽셀에 공급하는 전류 운반 라인 내에 발생하는 전압 강하 효과를 보상하도록 제어될 수 있다.

그러한 기술은 픽셀 광 출력이 시간에 따라 일정하고 균일할 수 있다는 것을 보장함으로써 고품질 디스플레이를 달성하는데 가치가 있다. 그러나, 그러한 픽셀 회로의 구현에는 문제점이 있을 수 있다. 만약 대형의 저장 캐패시턴스의 사용이 회피되어야만 한다면, 한 프레임 주기에 걸쳐서 TFT 게이트 전위를 적절하게 제어하기 위하여 상기 광감지 디바이스에 의해 생성된 광전류는 아주 작아야 할 필요가 있다. 상기 캐패시턴스와 상기 광감지 디바이스의 액티브 영역 사이의 관계는 주의깊게 결정되어야 할 필요가 있다. 또한 박막기술을 사용하여 광감지소자를 각 픽셀 회로 내에 제공하는 것은 이상적으로는 제작과정이 과도하게 복잡하지 않아야 한다.

## 발명의 상세한 설명

본 발명에 따라, 기판 상에 각각 디스플레이소자 및 상기 디스플레이소자의 동작을 제어하기 위한 디스플레이소자 제어회로를 구비하는 어드레싱 가능한 픽셀들의 어레이를 포함하는 매트릭스 디스플레이 디바이스가 제공되는데, 여기서 상기 디스플레이소자 제어회로는 전하 저장 캐패시터, 및 상기 저장 캐패시터에 연결된 연관된 박막 광감지 반도체 디바이스를 포함함으로써 상기 광감지 디바이스상에 입사되는 광에 따라서 상기 저장 캐패시터 상에 저장된 전하를 조절하고, 여기서 상기 광감지 디바이스는 상기 기판상에 옆으로 간격을 가지고 배치되어 있는 도평된 접촉 영역들 및 중간에 긴 영역을 구비하는 반도체 물질의 스트립을 포함하고, 또한 여기서 상기 저장 캐패시터는 실질적으로 상기 반도체 스트립을 그것의 한 접촉 영역을 덮어 횡단하여 연장하는 전도층과 함께 상기 전도층 및 해당 접촉 영역 사이에 배치된 유전 물질층을 포함한다.

이렇게 하여, 상기 저장 캐패시터의 한 측면, 또는 판(plate)은 상기 광감지 디바이스의 한 접촉 영역에 의해 구성되며, 그 럼으로써 상기 두 구성요소를 상호연결하기 위하여 별도의 도전체 경로(track)가 제공되어야 할 필요성이 제거되고 결과적으로 콤팩트한 구조로 된다. 더 중요하게는, 상기 광감지 디바이스의 접촉 영역이 상기 캐패시터의 일 측면을 형성하기 때문에, 이때 상기 저장 캐패시터 및 상기 광감지 디바이스 사이, 그리고 특히 상기 저장 캐패시터의 캐패시턴스 값 및 해당 픽셀 안에서 상기 광감지 디바이스의 동작 광-응답 특성 사이의 바람직한 관계가 더욱 안정적으로 보장될 수 있다. 박막 디바이스 기술에서 제조 허용공차에 기인하는 문제들, 그리고 특히 박막 층을 가공(define)하기 위해 공통적으로 채용되는 포토리소그래픽 패턴화 프로세스에서 사용되는 마스킹 및 에칭 단계들로부터 발생하는 문제점, 예컨대 마스크 배치에 있어서 작은 위치적인 오류와 같은 문제점은, 상기 가공된 층들의 크기의 변동을 가져올 수 있다. 상기 캐패시터 및 상기 광감지 디바이스 둘 다 동일한 주요 층, 즉 상기 반도체 스트립을 공유하기 때문에, 이때 상기 프로세스의 사용에 의해 결과로서 일어날 수 있는 이 스트립을 형성하는 상기 가공된 층 안에서의 임의의 라인 폭 크기의 변동은 상기 캐패시터 및 상기 광감지 디바이스 둘 다에 공통으로 될 것이다. 그러므로, 상기 광감지 디바이스의 액티브 영역 및 상기 저장 캐패시터의 캐패시턴스는 함께 크기조정될 것이다. 따라서, 상기 변동의 효과는, 저장 캐패시턴스의 캐패시턴스라는 면에서는, 그것이 그 유전층의 두께가 더욱 정밀하게 제어될 수 있기 때문에 상기 접촉 영역과 상기 전도층 사이의 겹쳐지는 영역에 주로 의존하고, 또한 상기 광감지 디바이스의 액티브 영역이라는 면에서는, 그것이 상기 반도체 스트립의 폭에 대응하는 한 접촉 영역에서의 접합부의 크기에 일반적으로 의존하여, 서로에 대해 상쇄하는 경향이 있다. 그러므로, 상기 캐패시턴스 및 상기 광감지 디바이스의 동작 특성 사이의 원하는, 미리 결정된 관계가 달성될 수 있다.

상기 광감지 디바이스 및 캐패시터 구성요소의 제공은 매트릭스 디스플레이 디바이스, 특히 TFT를 사용하는 액티브 매트릭스 디스플레이 디바이스를 제조하는데 사용되는 표준적인 박막 기술과 완전히 호환되며, 단순한 방식으로 달성될 수 있다. 상기 광감지 디바이스의 기본 구조는 일반적으로 TFT의 구조와 유사하며, 따라서 이들은 공통 박막층을 사용하는 어레이 내에서 TFT로서 동시에 쉽게 제작될 수 있다. 광감지 디바이스는 게이티드 디바이스(gated device)를 포함하는 것이 바람직하며, 유사하게 도핑된 접촉 영역들 및 – 게이트 유전층 및 게이트가 배치된 곳 위에서 – 상기 접촉 영역들 사이의 진성 반도체 영역을 구비하는 TFT 구조를 포함할 수 있다. 대안적으로, 상기 디바이스는 상기 접촉 영역들이 반대로 도핑된 것을 제외하고 유사한 구조를 구비하는 측면 게이티드 PIN 다이오드 디바이스를 포함할 수 있다.

본 발명은 디스플레이소자가 광을 방출하고 광감지 디바이스가 픽셀의 디스플레이소자에 의해 방출된 광에 응답하며 디스플레이소자의 동작을 제어하는 제어회로에서 사용되는 종류의 디스플레이 디바이스, 예컨대 영국 특허출원 번호 제 0005811.5 호에 개시된 바와 같은 디바이스에서 특히 유용하다. 따라서, 본 발명의 일실시예에서, 상기 디스플레이소자는 예컨대 OLED 또는 PLED 소자와 같은 전기발광 디스플레이소자와 같은 발광소자를 포함하며, 상기 제어회로는 게이트에 상기 저장 캐패시터가 연결되며 픽셀에 인가되고 상기 저장 캐패시터 상에 전하로서 저장된 구동 신호에 기초하여 구동 주기 내에서 상기 디스플레이소자를 통하는 전류를 제어하는 구동 TFT를 포함하며 또한 상기 캐패시터 상에 저장된 전하를 조절하기 위하여 상기 디스플레이소자로부터 방출된 광에 응답하는 광감지 디바이스를 포함한다. 상기 픽셀의 동작시, 광 전류를 생성하는 입사광에 응답하여 누설 디바이스로서 동작하도록 하기 위하여 상기 광감지 디바이스는 역방향 바이어스 되도록 구성된다. 이 목적을 위하여, 게이티드 광감지 디바이스의 경우에 상기 게이트는 "오프" 상태에서 해당 디바이스를 유지하도록 적절하게 바이어스된다. 만약, 바람직하게, 상기 저장 캐패시터의 크기가 작게 유지되어야만 한다면, 상기 구동 주기에 걸쳐서 상기 구동 TFT의 게이트 전위를 적절하게 제어하기 위하여는 상기 광감지 디바이스 내에 생성된 광전류가 매우 작아야 할 필요가 있다. 상기 구성으로, 이것은 쉽게 달성될 수 있고 또한 이와 동시에 상기 캐패시터의 캐패시턴스 값과 상기 광감지 디바이스의 액티브 영역 사이의 요구되는 관계(이 관계는 주어진 입력 광 레벨에 응답하여 생성된 광 전류의 레벨을 결정한다)가 유지된다.

본 발명이 특히 위에서 검토한 특정 유형의 픽셀 회로의 구현에 유익하지만, 픽셀이 저장 캐패시터 및 연관된 광감지 디바이스를 포함하기는 해도 다른 방식으로 동작하도록 구성되고 그리고 구동 제어회로 안에서 전기-광학적 피드백 구성의 일부로서 사용되는 경우일 필요가 없는 다른 디스플레이 디바이스 안에서도 유사한 이점을 가지도록 사용될 수 있다는 것이 예견된다. 예컨대, 상기 광감지 디바이스는 입력 광에 응답적일 수 있으며, 상기 디스플레이소자는 광을 방출하기 보다는 조절하는, 예컨대 액정 디스플레이소자일 수 있다.

## 실시예

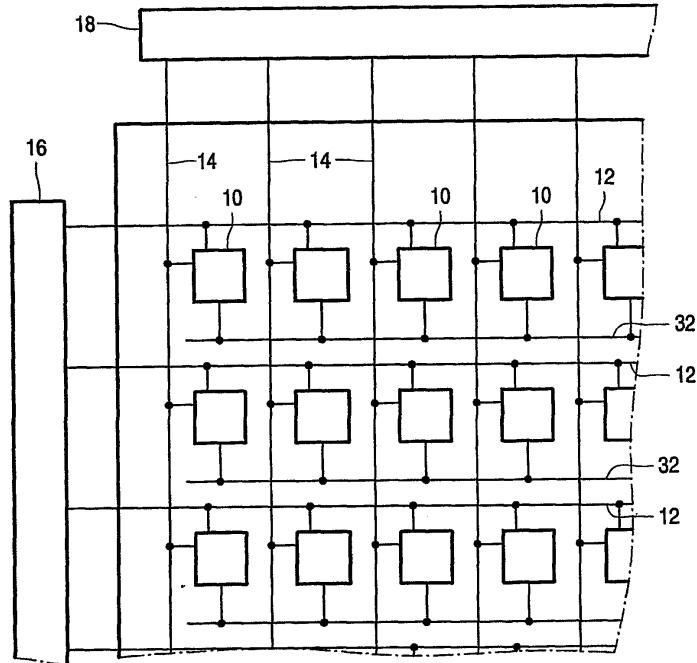

도 1을 참조하면, 액티브 매트릭스 전기발광 디스플레이 디바이스는 규칙적으로 간격을 가지고 배치된 픽셀들의 행 및 열 매트릭스 어레이를 구비하는 패널을 포함하는데, 상기 픽셀들은 블록(10)으로 표시되고, 각 픽셀은 전기발광 디스플레이 소자 및 상기 디스플레이소자를 통하는 전류를 제어하는 연관된 구동 디바이스를 포함하며, 교차하는 행(선택) 및 열(데이터)

터) 어드레스 도전체 즉 라인(12 및 14) 집합 사이의 교차지점에 위치한다. 단순하게 하기 위하여 단지 몇 개의 픽셀만이 본 도면에 도시된다. 픽셀들(10)은 각 도전체 집합의 단부에 연결된 행, 주사, 구동기 회로(16) 및 열, 데이터, 구동기 회로(18)를 포함하는 주변 구동 회로에 의하여 어드레스 도전체 집합을 통해 어드레싱된다.

상기 회로(18)에 의하여 상기 열 도전체로 병렬로 공급된 개별 데이터 신호들에 따라, 상기 어드레스 주기에 후속하는 하나의 프레임 주기 안에서 그들의 개별 디스플레이 출력들을 결정하는 개별 데이터 신호들로 상기 행의 픽셀들을 로딩하도록 하기 위하여, 각 행의 픽셀들은 상기 회로(16)에 의하여 관련 행 도전체(12)로 인가된 하나의 선택 신호를 통하여 하나의 프레임 주기 안에서 차례로 어드레싱된다. 각 행이 어드레싱되는 때, 상기 데이터 신호들은 적절히 동기되어 상기 회로(18)에 의해 공급된다.

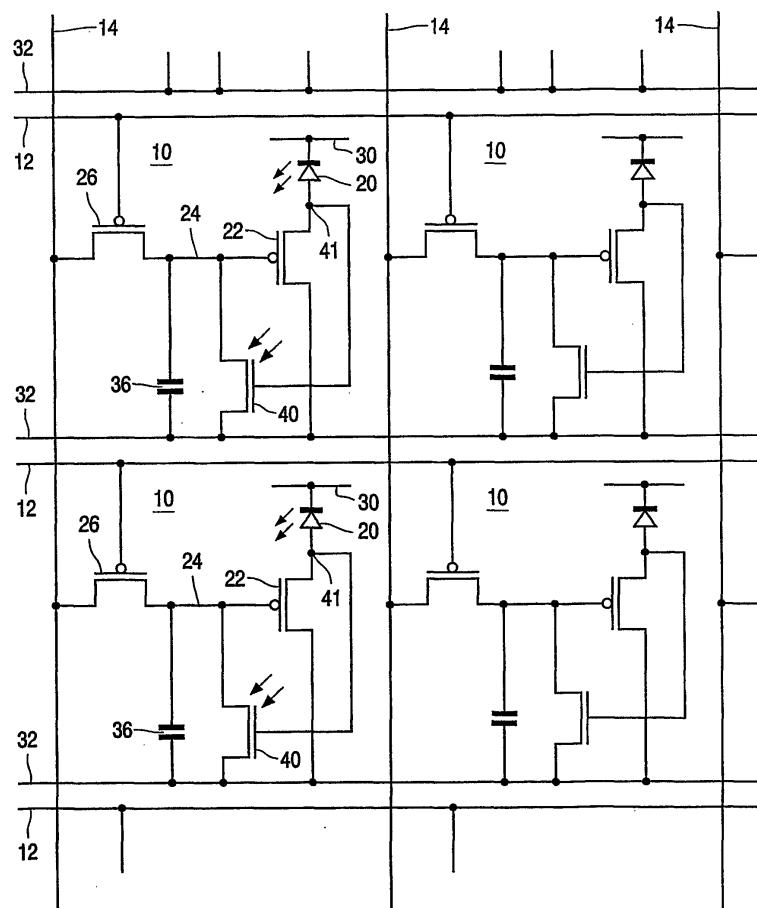

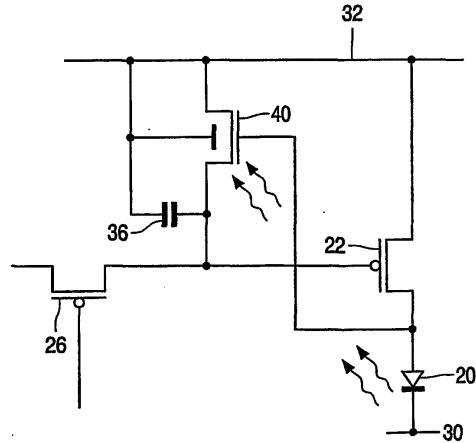

도 2는 몇 개의 전형적인 픽셀들의 회로를 예시한다. 각 픽셀(10)은 본 도면에서 다이오드 소자(LED)로서 표현된 하나의 발광 유기 전기발광 디스플레이 소자(20)를 포함하며, 유기 전기발광 발광 물질의 하나 이상의 액티브층이 사이에 끼워져 있는 한 쌍의 전극을 포함한다. 저분자량 물질과 같은 다른 유기 전기발광 물질이 사용될 수 있기는 하지만, 이 특정 실시 예에서는 상기 물질은 고분자 LED 물질을 포함한다. 상기 어레이의 디스플레이소자는, 연관된 액티브 매트릭스 회로와 함께, 절연 기판의 표면 상에 수용된다. 상기 기판은 투명 물질, 예컨대 유리이며, 상기 기판에 가장 가까운 상기 개별 디스플레이소자(20)의 전극은 상기 기판의 다른쪽면에 있는 보는 사람에게 보여질 수 있도록 하기 위하여 상기 전기발광층에 의해 생성된 광이 이 전극 및 상기 기판을 통하여 전달되도록 ITO와 같은 투명 전도성 물질로 구성된다. 상기 디스플레이소자의 음극(cathode)은 칼슘이나, 마그네슘과 은의 합금, 또는 바륨/알루미늄 이중층과 같은 낮은 일함수를 가지는 금속을 포함한다. 사용될 수 있는 적당한 유기 공액 고분자 물질(organic conjugated polymer material)의 예들이 WO 96/36959에 개시되어 있다. 다른 저분자량 유기 물질의 예들은 EP-A-0717446에 개시되어 있는데, 상기 문헌에는 또한 액티브 매트릭스 전기발광 디바이스의 일반적으로 알려진 형태의 구성 및 동작이 개시되어 있으며, 이러한 면에서 그 개시사항은 본 명세서에 참조로서 병합된다.

각 픽셀(10)은, 상기 픽셀에 인가된 데이터 신호 전압을 기초로 상기 디스플레이소자(20)를 통하는 전류를 제어하고, 그럼으로써 그것의 동작을 제어하는 책임이 있는, 여기서 p-형 전도성인, 저온 폴리실리콘 TFT(22)의 형태인 구동 디바이스를 포함한다. 픽셀을 위해 공급되는 데이터 신호 전압은 픽셀의 각 열들 사이에 공유되는 열(column) 도전체(14)를 통해 공급된다. 열 도전체(14)는 역시 p-형인 어드레스 TFT(26)를 통하여 전류-제어 구동 TFT(22)의 게이트에 연결된다. 한 행의 픽셀들의 어드레스 TFT(26)들을 위한 게이트들은 모두 하나의 공통 행 도전체(12)에 연결된다.

각 행의 픽셀들(10)도 또한 미리 결정된 전위로 유지되고 통상적으로 모든 픽셀들에 공통인 연속 전극으로서 제공되는 하나의 공통 전압 공급 라인(30)과, 하나의 개별 공통 전류 라인(32)을 공유한다. 디스플레이소자(20) 및 구동 TFT(22)는 전압 공급 라인(30)과 디스플레이소자(20)를 통해 흐르는 전류를 위한 전류원으로서 동작하는 공통 전류 라인(32) 사이에서 직렬로 연결된다. 상기 라인(30)은 예컨대 접지 전위일 수 있고, 상기 라인(32)은 상기 공급 라인(30)에 비하여 대략, 예컨대, 12V인 양의 전위일 수 있다. 디스플레이소자(20)를 통하는 전류는 구동 TFT(22)에 의해 조절되며, TFT(22) 상의 게이트 전압의 함수인데, 이는 데이터 신호에 의해 결정된 저장된 제어 값에 의존한다.

상기 픽셀들의 어드레스 TFT(26)를 턴온하여 각 행 어드레스 주기를 한정하는 선택 펄스를 자신의 연관된 행 도전체(12)에 인가하는 상기 행 구동기 회로(16)에 의하여 개별적인 픽셀 행이 선택되고 어드레싱된다. 데이터 신호가, 구동기 회로(18)에 공급되고 상기 구동기 회로(18)에 의하여 열 도전체(14)에 인가된 비디오 정보로부터 유도된 전압 레벨의 형태로, 어드레스 TFT(26)에 의해 구동 TFT(22)의 게이트 노드(24)로 전달된다. 행 어드레스 주기의 끝에서 어드레스 트랜지스터(26)는 턴오프되고, 게이트 노드(24) 상의 전압은 공통 전류 라인(32)과 TFT(22)의 게이트 사이에 연결된 픽셀 저장 캐패시터(36)에 의하여 유지됨으로써, 후속 구동 주기 동안에 디스플레이소자의 동작이 계속되도록 한다.

공통 전류 라인(32)과 TFT(22)의 게이트 사이의 전압은 디스플레이소자(20)를 통과하는 전류를 결정하는데, 디스플레이소자(20)를 통해 흐르는 전류는 구동 TFT(22)의 게이트-소스 전압의 함수이다{p-채널형 TFT(22)의 소스는 공통 전류 라인(32)에 연결되고, TFT(22)의 드레인은 디스플레이소자(20)에 연결됨}. 그 다음에 이 전류는 픽셀의 광 출력 레벨{그레이-스케일(grey-scale)}을 제어한다. TFT(22)는 전류원으로서 바이어스되며 포화상태에서 동작함으로써, 상기 TFT를 통하여 흐르는 전류가 드레인-소스 전압에 둔감하며 게이트-소스 전압에 의존하게 된다. 결과적으로, 드레인 전압의 작은 변동은 디스플레이소자(20)를 통하여 흐르는 전류에 영향을 미치지 않는다. 그러므로 전압 공급 라인(30) 상의 전압은 픽셀의 정확한 동작에는 중요하지 않다.

자신의 개별 구동 신호의 순서로 각 행의 픽셀들을 로딩하기 위하여 그리고 다음에 어드레싱되기 전까지, 대략적으로 한 프레임 주기에 대응하는, 후속 구동 주기 동안에 원하는 디스플레이 출력을 제공하도록 상기 픽셀들을 설정하기 위하여 개별 행 어드레스 패널 내에서 각 픽셀 행이 이런 방식으로 차례로 어드레싱된다.

각 픽셀 내에서 디스플레이소자 열화 효과를 보상하기 위하여 광-전자적 배열이 채용되는데, 그 열화 효과에 의해 주어진 구동 전류에 대해 생성되는 광 출력 레벨의 면에서 그것의 동작의 효율성이 감소된다. 그러한 열화 때문에 더 길고 더 심하게 구동된 디스플레이소자들은 밝기가 감소되고, 디스플레이 비-균일성을 야기한다. 상기 광-전자적 배열은 적절하게 한 구동 주기 내에서 한 소자로부터의 통합된, 전체적인, 광 출력을 제어함에 의하여 어느 정도 이러한 효과들을 막는다. 이런 면에서 픽셀 회로들은 영국 특허 출원번호 제 0005811.5 호에 개시된 것들과 유사한데, 그런 동작에 대한 더 전체적인 설명에 대하여 참조하기를 바라며, 그 개시내용은 이런 면에서 본 명세서에 참조에 의해 병합된다. 요약하면, 구동 주기 동안에 디스플레이소자의 순간 광 방출에 의존하는 속도로 저장 캐패시터를 방전함에 의하여 구동 주기 동안에 저장 캐패시터 상의 전하를 조정하기 위하여 전자-광학적 피드백이 사용된다. 결과적으로, 주어진 데이터 신호 값에 대하여 어드레스 주기에 후속하는 구동 주기 동안에 광을 생성하기 위하여 디스플레이소자가 통전되는 시간의 길이는, 상기 인가된 데이터 신호의 레벨뿐만 아니라, 해당 디스플레이소자의 존재하는 구동 전류/광 방출 레벨 특성에 따라서 조절됨으로써, 열화 효과는, 특히 디스플레이 비-균일성의 면에서, 감소되고, 그후 개별적인 픽셀로부터의 광 출력은 실질적으로 필요한 경우 비-열화된 디스플레이소자를 통해 얻어지는 것과 동일하다.

도 2를 참조하면 이 디바이스 내의 상기 전자-광학적 방전 수단은 게이티드 광-감지 박막 디바이스(gated photo-sensitive thin film device)(40)를 포함하는데, 이것은 여기서는 다른 TFT의 형태인데, 그 다른 TFT의 전류가 통과하는, 소스 및 드레인 전극들이 저장 캐패시터(36)를 통해 구동 트랜지스터(22)의 게이트 노드(24)와 전류 라인(32)에 연결되고, 그 다른 TFT의 게이트는 구동 TFT(22)와 디스플레이소자(20) 사이의 노드(41)에 연결된다. 본 실시예에서는, 구동 TFT(22){및 어드레스 TFT(26)}가 p-형 저온 폴리실리콘 MOS TFT로 이루어져 있고, 상기 디바이스(40)는 그 반대 전도성 유형, 즉 n-형 폴리실리콘 MOS TFT로 되어 있다.

상세히 설명되는 바와 같이, 픽셀은 게이티드 광-감지 디바이스(40)가 픽셀의 동작시 디스플레이소자(20)에 의해 방출된 광에 노출되는 방식으로 구성되고 배열된다. 어드레싱 단계의 끝에서, 인가된 데이터 신호의 레벨에 따라, 구동 TFT(22)의 게이트 노드(24) 상에 전압이 설정되고, 이 전압 레벨로 충전된 캐패시터(36)는 후속 구동 단계에서 적어도 처음에 TFT(22)의 게이트 전압을 유지하도록 한다. 라인(32)에 연결된 광-감지 디바이스(40)의 드레인 접합부는 역방향 바이어스되고 광-응답적이며, 그리고 구동 주기 내에서 디스플레이소자에 의해 방출된 광은 상기 디바이스(40) 내에서 상기 디스플레이소자의 순간 광 출력 레벨에 대략 선형적으로 비례하는 작은 광전류가 생성되도록 한다. 이 광전류의 효과는 저장 캐패시터(36)를 천천히 방전시키는 것인데, 광전류의 양은, 그리고 따라서 방전 속도는, 디스플레이소자의 광 출력 레벨에 의존한다. TFT(40)의 게이트는 양으로 바이어스되며, 그 전압은 노드(41)에서의 전압에 대응하고, 그리고 노드(24)에 대하여 항상 0 또는 음이며 라인(32)에 대해서는 항상 음이고, 이것은 TFT(40)가 그 오프(비 전도적인) 상태에 유지되는 것을 보장한다. 따라서, 트랜지스터(40)는 역방향 바이어스된 광다이오드의 방식으로 단순히 누설 디바이스로서 동작하며, 이 누설 디바이스는 캐패시터(36) 상의 전하의 누설을 야기한다. 구동 주기 내에서 캐패시터(36)의 결과적인 방전에 의하여 구동 TFT(22)의 게이트 상의 전압이 점차적으로 감소하게 되고 이 감소는 차례로 디스플레이소자(20)를 통하여 흐르는 전류를 점진적으로 낮추며 이에 대응하는 방식으로 디스플레이소자(20)의 광출력이 점차적으로 감소하며, 결국 TFT(22)는 자신의 문턱, 턴-오프, 레벨에 도달한다. 디스플레이소자(20)를 통하여 흐르는 전류의 감소에 의하여 노드(41)에서 (양의) 전압 레벨이 점차적으로 증가하게 되지만, 그러나 이것은 단순히 TFT(40)가 계속해서 오프로 유지되는 것을 보장하는 것이다. 결과적으로, 게이트 노드(24) 상의 전압이 TFT의 문턱 전압 아래로 떨어지는 때, 광 출력이 중단된다. 픽셀의 동작시 존재하는 전형적인 전압의 예로서, TFT(22)가 -5 볼트 문턱을 가지는 예를 가정하면, 전압 공급 라인(30)은 약 0 볼트일 수 있고, 공통 전류 라인(32)은 12 볼트일 수 있으며, 그리고 트랜지스터(22)의 게이트 노드에서의 전압이 4 볼트에서 12 볼트까지 변하는 때에 노드(41)에서의 전압은 4 볼트에서 0 볼트까지 변화할 수 있다.

구동 주기 안에서의 디스플레이소자에 의해 방출된 광의 전체적인 통합된 양(이 양은 보는 사람이 밝기(brightness)로서 지각한다)을 조절함에 의해서 디스플레이소자의 열화 효과가 방지될 수 있다. 통합된 광 출력(밝기)은 최초 광 레벨뿐만 아니라 디스플레이소자가 통전되는 구동 주기 내의 시간의 길이에 의존한다. 디스플레이소자가 구동 주기 내에서 통전되는 지속시간을 제어하는 상기 방전 수단의 동작 때문에, 동일한 데이터 신호 값이 공급되는 어레이 내의 서로 다른 픽셀들이 열화에 기인하는 각자의 개별적인 디스플레이소자의 특성에서의 변동에 무관하게 유사하게 지각되는 밝기 레벨을 생성하는 경향을 가질 것이다. 다시 말해서, 동일한 데이터 신호값으로 어드레싱된 개별 디스플레이소자로부터의 광 출력의 통합된 출력은, 구동 주기의 시작에서 그들 각자의 광 출력 레벨들이 열화 효과에 기인하여 다를 수 있음에도 불구하고, 유사할 것이다. 이런 식으로 하여, 디스플레이 출력의 균일성이 개선될 수 있다.

통상적으로, 인가된 데이터 신호의 레벨은 픽셀로부터 서로 다른 그레이-스케일 레벨을 제공하도록 적절하게 조정된다. 만약 데이터 신호가, 그리고 따라서 게이트 노드(24) 상의 전하가 증가되면, TFT(22)가 스위칭 오프되기 전 구동 주기 동안에 디스플레이소자로부터 더 많은 광자(photon)가 요구되어, 그럼으로써 더 높은 그레이-스케일 레벨이 달성되도록 하고, 그 반대로 마찬가지다.

이런 동작 방식은, TFT를 형성하는데 사용되는 박막 제작 프로세스의 본질에서 기인하는 예컨대 문턱 전압, 크기, 및 이동 도에서의 변동으로부터 유래하는 어레이의 여러 픽셀들의 TFT(22)의 동작 특성에서의 변동을 자동적으로 보상하는 데에 효과적이다. 따라서, 어레이 전체에 걸친 디스플레이소자들로부터의 광 출력의 균일성도 또한 개선된다.

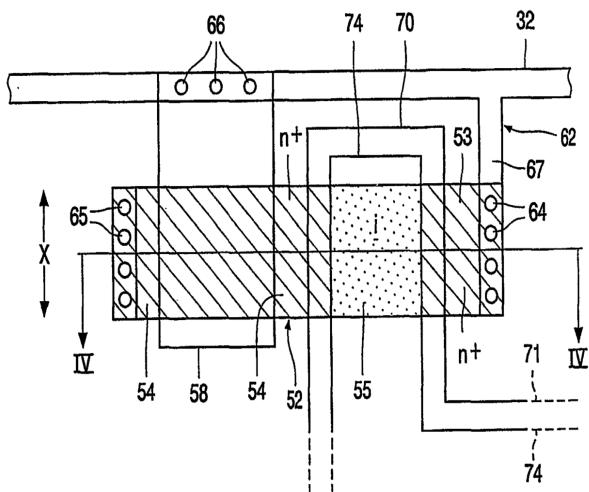

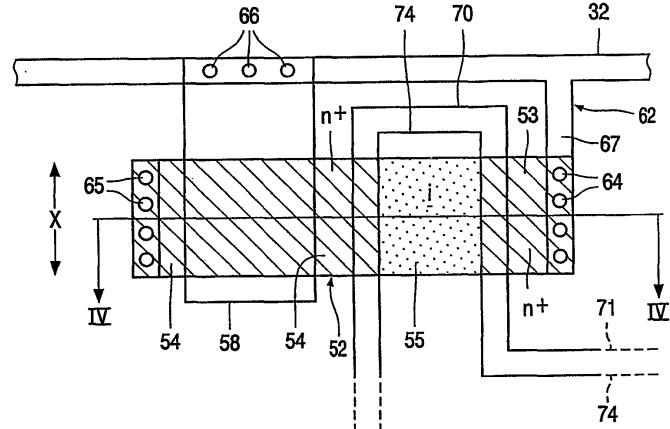

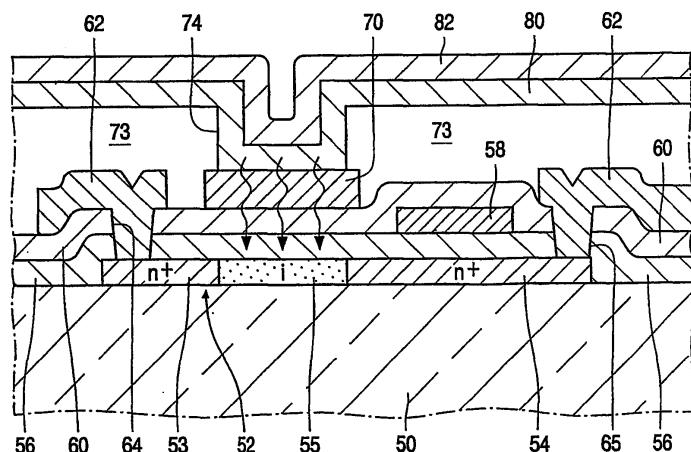

이제 도 3 및 도 4를 참조하면, 광감지 TFT(40)를 포함하는 전형적인 픽셀 하나의 일부분에 대한 그리고 이 영역에서 픽셀 구성의 방식을 예시하는 도식적인 평면도 및 단면도가 도시된다. 도 4는 대략 도 3의 선 IV-IV을 따르는 단면도에 대응 한다. TFT(40)에 추가하여, 도시된 부분은 디스플레이소자(20)와 저장 캐패시터(36) 부분을 포함하지만 어드레싱 및 구동 TFT(26 및 22)를 포함하지는 않는다. 그러나 이들 후자의 구성요소들은 공통 증착층으로부터 그리고 동일한 프로세스를 사용함으로써 도시된 구성요소와 함께 제조된다는 것을 알게 될 것이다.

투명한 절연 기판(50) 상에 길다란 스트립 형태의 그리고 저온 폴리실리콘 물질층으로 이루어진 반도체 섬(island)(52)이 제공된다. 이것은 CVD 증착된 비정질 실리콘 층을 레이저 재결정화하고 이 층을 마스크 및 포토리소그래피 프로세싱을 사용하여 적절하게 패턴화함으로써 얻어진다. 상기 반도체 스트립은 일반적으로 직사각형의 형태이며, 실질적으로 평행한 두개의 주 모서리를 가지며, 따라서 실질적으로 그 길이를 따라 일정한 폭을 가진다. 이 섬의 대향하는 단부 부분은 도핑( $n+$ )되어 옆으로 간격을 가지고 배치된 드레인 및 소드 접촉 전극 영역(53 및 54)을 구성하고, 이 영역들은 각각 TFT(40)의 게이트 제어, 채널, 영역을 형성하는 진성 반도체 물질의 동일-평면 영역(55)에 의해서 분리된다. 대응하는, 유사한 형태의, 폴리실리콘 섬들이 동일한 때에 상기 기판상에 다른 예정된 픽셀 위치들에서 어드레싱 및 구동 TFT(26 및 22)를 위한 반도체 섬과 함께 형성되지만, 이들 후자의 TFT 영역을 구성하는 소스 및 드레인 전극들은 대신 반대로 도핑( $p+$ )된다. 예컨대 이산화실리콘 또는 질화실리콘으로 된 유전층(56)이 상기 기판 위로 이들 섬들을 덮도록 연속적으로 증착되고 게이트 유전층으로서의 역할을 한다.

예컨대 알루미늄 또는 알루미늄 합금으로 된 금속층이 상기 층(56) 위로 증착되고, TFT(26 및 22)의 게이트(미도시됨)를 구성하는 영역과 각 광감지 TFT 위치에서 (드레인) 영역(53)을 겹쳐 덮는 영역(58)을 남기도록 패턴화된다. 동시에, 이 금속층으로부터 필요한 상호연결 라인들이 형성된다. 도 3 및 도 4에서 명백한 바와 같이, 상기 영역(58)은 반도체 섬(52)를 실질적으로 횡단하도록 연장되는 직사각형 평거(finger) 또는 스트립으로서 가공된다. 따라서 이들의 교차되는 영역에서 섬(52)과 평거(58) 둘 다 평행-모서리를 가지며 실질적으로 일정한 폭을 가진다. 겹쳐 덮는 금속층(58) 부분과  $n+$  영역(54) 그리고 유전층(56)인 중간 부분은 함께 픽셀의 저장 캐패시터(36)를 구성하는데, 상기 저장 캐패시터(36)의 캐패시턴스 값은 평거(58)와 섬(52) 사이의 교차 면적 및 상기 층(56)의 두께와 유전 상수에 의하여 결정된다.

예컨대 산화질소실리콘(silicon oxide nitride)과 같은 다른 유전층(60)이 이 구조 위로 형성되어 특히 금속층의 상기 가공된 영역(58)을 덮는다. 그 다음에 다른 금속층이 더 증착되고 전류 라인(32) 및 다른 필요한 상호연결을 형성하는 영역(62)를 남기도록 패턴화된다. 이 층을 증착하기에 앞서, 접촉 개구(64 및 65)가 소스 영역(53) 및 드레인 영역(54) 위로 두 유전층(56 및 60)을 모두 뚫어 에칭함으로써 형성되고, 접촉 개구(66)가 상기 영역(58)의 단부 부분 위로 상기 층(60)을 뚫어서 형성되며, 그리하여 이 금속의 증착 및 패턴화가 후속되며, 통합 연장 암(67)을 통하여 전류 라인(32)과 드레인 전극(53) 사이에, 상기 전류 라인을 형성하는 금속 부분(62)을 통하여 (미도시된 추가의 접촉 개구를 통해) 소스 영역(54)과 게이트 노드(24) 사이에, 그리고 전류 라인(32)과 금속 평거(58) 사이에 상호연결이 제공되도록 한다.

그런 다음 ITO와 같은 투명한 전도성 물질이 증착되고 원하는 디스플레이소자의 형태를 가공하기 위하여 적절하게 형성된 디스플레이소자를 위한 하부(애노드) 전극을 구성하는 영역을 남기도록 패턴화된다. 이 전극 부분은 주 디스플레이소자 영역(71)(작은 부분만이 도시된다)으로부터 멀리 연장되고 그리고 게이트 제어 영역(55) 및 드레인 접합부의 바로 위에서 반도체 섬(52) 위로 횡단하도록 연장되는 통합 레그(70)를 형성한다.

예컨대 질화실리콘(silicon nitride)으로 된 추가의 상대적으로 두껍고 연속적인 유전층(73) 또는 더 두꺼운 ( $1 - 2 \mu\text{m}$ ) 절연 고분자 층이 상기 구조를 완전히 덮도록 증착되고 이 층안에서 상기 레그(70)와 주 디스플레이소자 영역 둘 모두에 있어서 상기 패턴화된 ITO 영역 위로 개구(74)가 형성된다.

그런 다음 밑에 있는 ITO와 직접 접촉하기 위하여, 상기 유전층(73) 위로 그리고 그 안에 형성된 개구(74) 내로 연장하는 연속층(80)으로서 예컨대 스판 코팅에 의하여, 고분자 발광 물질이 증착된다. 이 층(80) 위로 칼슘이나, 마그네슘은 합금 또는 바륨/알루미늄으로 된 연속층(82)이 디스플레이소자 음극(cathode) 전극 및 공급 라인(30)을 이루는 공통 전극층을 형성하도록 증착된다.

각각의 디스플레이소자(20)는 ITO의 개별 영역(71)과 함께 상기 층(80 및 82)들의 겹쳐 덮힌 부분들로 이루어지는데, 상기 층(80 및 82)의 바로 겹쳐 덮혀있는 부분들과 함께 상기 통합 ITO 레그(70)가 상기 아래 및 위 전극 사이에 적절한 전위차가 인가되는 때에 주 디스플레이소자 영역에서 광을 방출하는 디스플레이소자의 통합 연장부를 형성한다는 점을 잘 알게 될 것이다..

게이트 제어 영역(55)을 바로 겹쳐 덮혀 있는 ITO 레그(70) 부분은 게이트 유전물질을 제공하는 아래에 있는 연결된 층들(56 및 60)과 함께 광감지 TFT(40)의 게이트로서 역할을 한다.

픽셀의 동작시, 전극들(71 및 82) 사이에 전류가 통과할 때 상기 층(80)에 의하여 방출된 광은 디스플레이 출력을 생성하기 위하여 ITO 하부 전극 및 기판(50)을 통과하여 전달된다. 디스플레이소자의 레그는 유사하게 광을 생성하며 이것은 광감지 TFT(40)의 게이트 제어 영역(55)으로 입사되기 위하여 ITO 연장부(70)와 아래의 투명한 유전층들(56 및 60)을 통하여 통과한다. 특히 드레인 접합부 상에 떨어지는 광이 광전류의 생성 원인이다. 이렇게 하여, 상기 영역(55) 위로 연장하는 디스플레이소자 레그의 결과로서, 그리고 발광 고분자 물질(80)이 TFT(40)의 게이트 바로 위에 위치하고 또한 상기 TFT 구조 내로 직접 광을 방출하므로, 디스플레이소자와 광감지 TFT(40) 사이의 확실한 광학적 연결이 단순하고 신뢰성 있는 방식으로 보장되고 달성된다.

더 나아가, TFT(40)의 게이트가 디스플레이소자의 음극 부분에 의해 구성되기 때문에, 상기 게이트는 상기 TFT(40)가 오프(즉 그것의 높은 저항, 비-전도성, 상태)로 유지되는 것과 생성된 광전류에 기인되는 누설 전류만이 그 소스 및 드레인 전극 사이에는 흐르는 것을 보장하도록 소스 및 드레인 둘 다에 대하여 항상 요구되는 (음의) 바이어스 상태이다.

전형적인 입력 광 레벨에 응답하여 생성된 광전류 레벨 및 저장 캐패시터(36) 상에 저장된 전하량이라는 점에서의 광감지 TFT(40) 및 저장 캐패시턴스(36) 사이의 관계는, 전자-광학적 피드백 제어가 가장 효과적으로 구현되도록 하기 위하여, 밀접하게 제어될 필요가 있다. 이런 면에서 TFT(40)의 액티브 영역은 측면 ( $n^+ - i$ ) 드레인 접합부의 가장자리를 포함하며, 광전류에 기여하는 것은 드레인 접합부에서 이 비교적 좁은 영역뿐이다. 액티브 영역은 기본적으로 광다이오드와 등가이며, 바람직하게는 구동 (프레임) 주기에 걸쳐 요구되는 방식에서 구동 TFT(22)의 게이트 전위를 제어하기에 충분할 정도로, 그리고 더 큰 저장 캐패시터를 사용해야 하는 필요성을 회피하기에 충분할 정도로, 생성된 광전류의 전형적인 레벨이 낮은 것을 보장할 수 있도록 매우 작아야만 한다. 저장 캐패시터(36)가 캐패시터 유전물질로서 상기 층(56)만을 자신의 구조 안에서 사용하기 때문에, 이때는 주어진 캐패시턴스 값을 제공하기 위하여 캐패시터 구조에 대해 요구되는 영역은, 상기 층들(56 및 60)이 둘 다 사용되는 경우에 요구되어질 영역보다 보다 훨씬 더 작다.

박막 기술을 사용하는 경우 구성요소를 가공하기 위하여 채용되는 프로세스 예컨대 포토리소그래픽 패턴화 프로세스에서 사용되는 마스킹 및 에칭 단계의 속성상 매우 정밀한 크기 값을 가진 구성요소를 형성하는 것은 어려울 수 있다. 상기에 언급된 구조에서 저장 캐패시터(36) 및 광감지 TFT(40)는 둘 다 동일한 주요 층, 즉 반도체 섬(52)을 공유하며 공간적으로 가깝다는 점을 알게 될 것이다. 따라서, 이 부분에서 제조 허용공차에 기인하는 임의의 라인 폭 변동은 둘 다에게 공통일 것이다. 이 주요 지형적 구조, 즉 도 3에서 X로 표시된 바와 같은 스트립-형 섬(52)의 폭이 TFT(40) 및 저장 캐패시터 둘 다에 대해 일정하기 때문에, 이때는 이 공통 부분의 이 물리적 크기에 있어서 의도하는 값으로부터의 임의의 변동은 TFT의 액티브 영역 및 저장 캐패시터의 캐패시턴스 값을 둘 다에 대해 유사하고 대응하는 방식으로 영향을 끼칠 것이다. 더 정확하게 말하면, 상기 TFT의 액티브 영역 및 상기 캐패시턴스 값을 함께 크기조정된다. 상기 섬(52)의 폭에 있어서 그 크기를 증가시키는 경향이 있는 임의의 변동은, 그에 따라 상기 저장 캐패시터의 캐패시턴스를 증가시키는 경향이 있으며, 이는 상기 TFT의 액티브 영역의 크기도 역시 증가시키는 결과를 가져올 것이고, 그 반대도 마찬가지이며, 그럼으로써 이들 두 구성요소의 전기적 특성 사이의 균형이 유지될 것이다. 이렇게 하여, 이들 두 구성요소의 원하는 그리고 미리 결정된 상호-관계가 보장된다.

편리하게는 게이티드 측면 P-I-N 다이오드가 TFT(40) 대신에 사용될 수 있다. 그런 디바이스의 구조는, 반도체 섬(52)의 상기 영역(53)이 상기 영역(54)과는 반대로 즉  $p^+$  형으로 도핑되어질 것을 제외하고는, 도 3에 도시된 바와 일반적으로 유사할 것이다. 역방향 바이어스에 있어서는,  $p^+$  영역(53)이  $n^+$  영역(54)보다 더 큰 양극(positive)이다. 이 경우, 전체 디바이스를 가로지르는 광 입사가 광전류를 생성할 수 있다. 따라서 앞의 TFT 구조에서의 경우보다, 더 큰 거리로 상기 디바이스를 가로질러 상기 광-액티브 접합부가 연장될 것이다.

상기에서 기술된 픽셀 실시예에 있어서, 광감지 TFT(40)는 어드레스 TFT(26) 및 구동 TFT(22) 둘 다와 반대의 전도성 유형이며, TFT(40)의 게이트가 바이어스되는 방식 때문에 TFT(40)가 오프로 유지되는 것과 단순히 구동 주기 동안에 캐패시터(36) 상의 전하를 누출하기 위하여 역방향 바이어스된 광다이오드의 방식으로 동작한다는 점이 보장된다.

그러나, 이 픽셀 회로의 대안적인 형태에 있어서는, TFT(40)는 구동 TFT(22)와 동일한 유형일 수 있고, 오로지 누설 디바이스라기보다는 스위칭 디바이스로서도 동작 가능할 수 있다. 이러한 대안적인 회로의 동작시, 이때 처음에 적어도 구동 주기에서, 디스플레이소자 하부 전극/노드(41) 전위에 대응하는 게이트 전위는, 상기 TFT가 단순한 역방향 바이어스된 누설 디바이스로서 동작하는 것을 보장하도록 하는 전위로 될 것이다. 이 방전이 계속되는 경우, 이때 디스플레이소자를 통하여 흐르는 전류의 결과적인 감소는 노드(41)(도 2)의 (음의) 전압 레벨에 있어서의 점진적인 증가를 야기할 것이다. 전류 레벨이 특정 하부 한계에 도달한 때, 라인(32)에 상대적인 노드(41)의 전압은 TFT(40)의 문턱 전압에 이르를 것이고 그 TFT가 갑자기 턴온(전도하게) 되어 캐패시터(36)를 빠르게 방전하도록 야기함으로써 구동 TFT(22)가 턴오프되도록 하고 디스플레이소자의 통전이 종료되도록 한다. 이런 방식에 있어서 TFT(40)의 스위칭 동작은, 디스플레이소자의 광 출력력이 더욱 정밀한 제어 방식으로 결정된다라는 장점을 가진다. 이러한 스위칭이 없으면, 디스플레이소자의 통전 상태의 끝에 다다르는 경우에 발생되는 바와 같은, 비교적 낮은 광 출력 레벨에 응답하는 광감지 TFT(40)의 동작이 덜 좋게 정의되고 또한 덜 예측 가능하게 된다는 사실에 기인하여, 디스플레이소자의 턴오프 동작은 덜 좋게 제어될 수 있다.

모든 광전류가 오로지 디스플레이소자로부터 방출되는 광에 의해서만 기인되도록 하기 위하여 광감지 TFT(40)는 자체에 비춰지는 주변 광 효과로부터 차폐되어야 하는 것이 필요하다. 이 때문에, 금속 전극층(82)은 패턴의 일측면에서 주변 광으로부터 디바이스를 차폐하는 역할을 한다. 투명 기판(50)를 통하여 다른 측면에서 오는 광에 대한 차폐는 반도체 섬(52)과 상기 기판 표면 사이에 광 차폐층을 증착함에 의하여 달성될 수 있다.

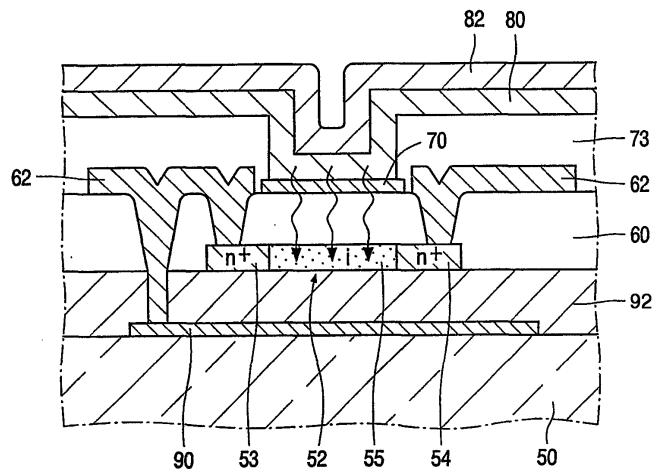

그러나 바람직하게는, 본 발명에 따른 디바이스의 다른 실시예에서, 저장 캐패시터 구조의 일부가 또한 광 차폐부로서 동작하도록 채용되기 위하여 픽셀의 구조가 수정된다. 도 5는 도 4와의 비교를 위하여 상기 수정된 픽셀 구조의 일부를 자른 단면을 도식적으로 예시한다. 이 구조에 있어서, 하나의 금속층이 기판(50)의 표면 위에 증착되고, 그 전체적인 크기가 후속하여 형성되는 TFT(40)(또는 대안적으로 측면 PIN 다이오드)를 위해 사용되는 반도체 섬(52)보다 약간 더 큰 광 차폐부(90)를 각 픽셀에 형성하도록 패턴화된다. 예컨대 질화실리콘으로 된 절연층(92)이 평편한 표면을 형성하도록 기판 표면 전체와 그 금속층들(90) 위를 완전히 덮는 하나의 연속층으로서 증착되는데, 이때 상기 평편한 표면 위로 픽셀 구조가 일반적으로 앞에서 기술한 바와 같이 제작되며, 다만 이 경우에는 앞에서 사용되었던 금속 평거(58)는 생략되고, 또한 반도체 섬(52)의 상기 영역(53)에 접촉하기 위하여 사용되었던 금속층(62) 부분도 상기 섬(52)에서 떨어져서 유전층들(60 및 92)에 형성된 접촉 개구에 의하여 이 층들을 통과하여 상기 광 차폐층(90)의 일 단부에 접촉하도록 배열된다. 유전층(56)은 이 실시예 형태에서는 필요하지 않다.

이 구성에 있어서, 저장 캐패시터(36)는 섬(52)의 접촉 영역(54)을 덮는 광 차폐층(90) 부분과 함께 그 사이에 끼여있는 유전물질을 제공하는 절연층(92) 부분에 의하여 형성된다. 이 픽셀의 등가회로가 도 6에 도시된다. 이 경우에 광감지 TFT(40)는, 하단 게이트를 구성하는 광 차폐부(90)와 함께, 효과적으로 이중 게이트를 구비한다. 이 제2 게이트는 채널(55)에 대하여 양극이 될 것이고 따라서 절연층(92)은 상기 TFT의 문턱 레벨이 도달되지 않는다는 것과 상기 TFT가 턴온되는 것으로부터 방지되는 것을 보장하기 위하여 충분히 두껍게 될 것이 요구된다.

상기 구성에서와 같이 상기 섬(52)을 완전히 덮는 대신, 상기 층(90)은 드레인 접합부 영역과 소스 영역(54)을 완전히 덮도록 연장하여 캐패시터를 형성함으로써 그러나 채널 영역으로서 의미있는 정도로는 전혀 연장하지 않도록 함으로써 TFT(40)의 광-액티브 영역(53)을 광 차폐 목적을 위하여 적당하게 덮도록 구성될 수 있다. 이 목적을 위하여, 상기 층(90)은 상기 두 접촉 영역을 덮는 상기 층(90)의 영역들이 상호 연결되도록 상기 채널 영역의 양 측으로 상기 섬에 평행하게 연장하는 일체형 암(arm)에 의하여 둘러싸인 채널 영역(55)을 덮는 중앙 개구를 가질 수 있다. 이 구성에 있어서, 이때 상기 층이 상기 채널 영역(55)을 직접 덮도록 연장되지 않기 때문에 그것이 제2 게이트로서 동작하게 되는 위험이 회피될 수 있다.

이 다른 실시예에서는, 역시 TFT(40)와 저장 캐패시터(36) 둘 모두 동일한 주요 층, 즉 섬(52)를 공유하며, 따라서 제작 프로세스 허용공차에 기인한 모든 공간적 변동이 두 구성요소에 대해 공통이며 또한 함께 크기조정된다.

본 발명은 또한 상기에서 기술한 실시예들에서와 같은 전압 데이터 신호가 아닌 전류 데이터 신호를 사용하여 구동된 픽셀과 함께, 예컨대 WO 99/65012에 기술된 방식으로 사용될 수 있다.

요약하면, 매트릭스 어레이 디스플레이 디바이스는 기판 상에 픽셀의 어레이를 구비하는데, 각 픽셀은 예컨대 전기발광 디스플레이소자인 디스플레이소자 및 연관된 제어회로를 구비하며, 상기 제어회로는 저장 캐패시터 및 거기에 연결된 광감지소자를 포함하여, 예컨대 디스플레이소자의 동작을 조절하기 위하여 상기 디스플레이소자로부터 방출되는 광에 응답하고 저장 캐패시터 상에 저장된 전하를 조절한다. 광감지소자는 옆으로 간격을 가지고 배치되어 있는 도핑된 접촉 영역들을 구비하는 반도체 물질의 스트립을 각각 구비하는 박막 반도체 디바이스를 포함하고, 그리고 연관된 저장 캐패시터는 실질적으로 상기 스트립을 그것의 유전 물질이 중간에 끼워져 있는 한 접촉 영역을 덮어 횡단하여 연장하는 전도층에 의해 형

성된다. 이 경우 구성요소 층에서 제작 허용공자에 기인한 크기의 변동이 발생하는 경우일지라도 저장 캐不死시터 및 광감지 디바이스 특성 사이의 미리 결정된 관계가 보장된다. 바람직하게는, 광감지 디바이스는 그 게이트가 접촉 영역들 중간에 끼어있는 반도체 스트립 영역 위로 연장하는 게이터드 디바이스를 포함한다. 게이트 유전물질 및 저장 캐不死시터 유전물질은 공통 층의 부분들을 가질 수 있다. 대안적으로 전도층은 게이트에 대향하는 스트립의 측면에서 제공될 수 있고 또한 주변 광에 대한 차폐부로서도 사용될 수 있다.

본 명세서의 개시내용을 읽음으로써, 본 기술분야의 통상의 지식을 가진 자라면 다른 변형예들이 명백할 것이다. 그러한 변형예들은 액티브 매트릭스 전기발광 디스플레이 디바이스 및 그 구성요소 부품들의 분야에서 이미 알려져 있고 여기서 이미 기술되어 있는 특징들에 대신해서 또는 추가해서 사용될 수 있는 다른 특징들을 수반할 수 있다.

## 산업상 이용 가능성

상술한 바와 같이, 본 발명은 광감지소자를 갖는 매트릭스 어레이 디스플레이 디바이스 등에 이용할 수 있다. 더 상세하게는, 본 발명은 디스플레이 소자 및 광감지소자를 포함하는 어드레싱가능한 픽셀들을 구비하는 매트릭스 어레이 디스플레이 디바이스에 이용할 수 있는 것으로서 특히 그러나 배타적이지는 않게, 본 발명은 전기발광(electroluminescent) 디스플레이소자, 특히 고분자 전기발광 소자인 PLED를 포함하여, 유기 전기발광 디스플레이소자인 OLED를 사용하는 매트릭스 디스플레이 디바이스 등에 이용할 수 있다.

## 도면의 간단한 설명

이제 본 발명에 따른 매트릭스 디스플레이 디바이스의 실시예가, 특히 액티브 매트릭스 EL 디스플레이 디바이스로, 첨부된 도면을 참조하여, 예시적으로 기술될 것이다.

도 1은 본 발명에 따른 액티브 매트릭스 EL 디스플레이 디바이스의 일 실시예의 단순화된 개략도.

도 2는 도 1의 디바이스 내의 몇몇 전형적인 픽셀의 등가회로도.

도 3 및 4는 각각 하나의 픽셀의 일부에 대한 개략적인 평면도 및 단면도.

도 5는 다른 실시예에서 픽셀의 대안적인 형태의 일부를 보여주는 개략도.

도 6은 상기 다른 실시예에서 전형적인 하나의 픽셀에 대한 등가회로도.

상기 도면들은 단순히 도식적이다. 동일한 참조 번호가 동일 또는 유사한 부분들을 지칭하기 위하여 상기 도면들 전체에 걸쳐서 사용된다.

## 도면

도면1

도면2

### 도면3

## 도면4

## 도면5

## 도면6

|                |                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种矩阵阵列显示装置，具有光传感元件                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">KR100717200B1</a>                                                                                                                               | 公开(公告)日 | 2007-05-11 |

| 申请号            | KR1020027002089                                                                                                                                             | 申请日     | 2001-06-07 |

| [标]申请(专利权)人(译) | 皇家飞利浦电子股份有限公司                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 科宁欣克利凯恩菲利普斯日元.V.                                                                                                                                            |         |            |

| 当前申请(专利权)人(译)  | 科宁欣克利凯恩菲利普斯日元.V.                                                                                                                                            |         |            |

| [标]发明人         | YOUNG NIGEL D<br>영나이겔디<br>SHANNON JOHN M<br>사논존엠                                                                                                            |         |            |

| 发明人            | 영,나이겔,디.<br>사논,존,엠.                                                                                                                                         |         |            |

| IPC分类号         | G09G3/30 H01L51/50 G09F9/30 G09G3/20 G09G3/32 H01L27/12 H01L27/32 H01L29/49 H01L29/786                                                                      |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0809 G09G2300/0819 G09G2300/0842 G09G2320/043 G09G2320/045<br>G09G2360/148 H01L27/1255 H01L27/3265 H01L27/3269 H01L29/4908 H01L29/78633 |         |            |

| 代理人(译)         | MOON , KYOUNG金                                                                                                                                              |         |            |

| 优先权            | 2000014962 2000-06-20 GB                                                                                                                                    |         |            |

| 其他公开文献         | KR1020020025979A                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                   |         |            |

## 摘要(译)

矩阵显示装置包括基板(50)上的像素(10)的阵列，其中包括显示装置(20)和与其相关的每个像素的显示装置控制电路，例如电致发光显示装置。并且控制电路包括连接到存储电容器(36)的光学检测装置(40)。响应于从显示装置发出的光以控制例如显示装置的操作并存储在存储电容器上的电荷受到控制。光学检测装置(40)由导电层(58)形成，其意味着包括半导体材料条带的相应薄膜半导体器件配备有掺杂接触区域(53,54)，所述接触区域布置在侧面，在所述间隙上具有间隙。基材和它覆盖接触区域，只要其介电材料连接到中心，并且相关的存储电容器(36)实质上穿过带并延伸。在这种情况下，在组件层中，即使出现由制造允许公差人引起的尺寸变化的情况，也能保证光学传感器件特性与存储电容器之间的预定关系。优选地，在光学传感装置中，栅极包括栅极装置，栅极装置向上延伸连接接触区域中心的半导体条带区域。栅极感应电材料和存储电容器介电材料具有共同水平的部分(56)。或者，导电层可以从面向栅极的侧面提供，并且侧面可以用作另外，屏蔽围绕环境光。