## (19)대한민국특허청(KR) (12) 공개특허공보(A)

(51) 。Int. Cl. H01L 27/32 (2006.01) (11) 공개번호

10-2007-0074594

(43) 공개일자

2007년07월12일

(21) 출원번호 10-2007-7009975

(22) 출원일자 2007년05월01일

심사청구일자 없음

번역문 제출일자 2007년05월01일

(86) 국제출원번호 PCT/US2005/037349

국제출원일자 2005년10월17일

(87) 국제공개번호

WO 2006/049859

국제공개일자 2006년05월11일

(30) 우선권주장 10/979,067 2004년11월02일 미국(US)

(71) 출원인 쓰리엠 이노베이티브 프로퍼티즈 컴파니

미국 55133-3427 미네소타주 세인트 폴 피.오.박스 33427 쓰리엠 센터

(72) 발명자 바우드, 폴, 에프.

미국 55133-3427 미네소타주 세인트 폴 포스트 오피스 박스 33427쓰

리엠 센터

테이스, 스티븐, 디.

미국 55133-3427 미네소타주 세인트 폴 포스트 오피스 박스 33427쓰

리엠 센터

하세, 마이클, 에이.

미국 55133-3427 미네소타주 세인트 폴 포스트 오피스 박스 33427쓰

리엠 센터

헴머쉬, 에릭, 더블유.

미국 55133-3427 미네소타주 세인트 폴 포스트 오피스 박스 33427쓰

리엠 센터

(74) 대리인 양영준

백만기

전체 청구항 수 : 총 14 항

# (54) 유기 발광 다이오드들과 함께 집적된 산화 아연 로우 및컬럼 드라이버들을 이용하는 방법 및 디스플레이

#### (57) 요약

방법 및 디스플레이는, ZnO 채널들을 갖는 픽셀 트랜지스터들을 제어하는 ZnO 채널을 갖는 로우 및 컬럼 드라이버들을 이용하고, 디스플레이 화면의 이미지들을 생성하기 위해서 어레이의 OLED를 차례로 어드레스한다. ZnO 로우 및 컬럼 드라이버들 및 OLED를 포함하는 디스플레이 백플레인은 애퍼처 마스킹 또는 포토리소그래피 및 애퍼처 마스킹의 조합을 이용함으로써 구성될 수 있다. 이에 의해 ZnO 픽셀 트랜지스터들과 ZnO 로우 및 컬럼 드라이버들의 모노리식 집적이 달성된다.

#### 대표도

도 1

#### 특허청구의 범위

#### 청구항 1.

디스플레이로서,

백플레인(backplane) 기판;

상기 백플레인 기판 상에 패터닝되고 ZnO 채널들을 포함하는 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트;

상기 백플레인 기판 상의 상기 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트와 모노리식으로 집적되고(monolithically integrated) ZnO 채널들을 포함하는 픽셀 박막 트랜지스터들의 세트; 및

상기 백플레인 기판 상에 패터닝된 충들의 스택(stack)을 포함하는 유기 발광 다이오드들의 세트

를 포함하며,

각각의 상기 유기 발광 다이오드는 상기 픽셀 박막 트랜지스터들의 세트 중 대응하는 하나 이상의 픽셀 박막 트랜지스터들에 의해 광을 생성하도록 활성화되고, 상기 대응하는 하나 이상의 픽셀 박막 트랜지스터들은 상기 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트에 의해 어드레싱되는 디스플레이.

### 청구항 2.

제1항에 있어서,

상기 유기 발광 다이오드들은 상기 백플레인 기판으로부터 멀어지게 방사하는 디스플레이.

#### 청구항 3.

제1항에 있어서,

상기 유기 발광 다이오드들은 상기 백플레인 기판을 통하여 방사하는 디스플레이.

#### 청구항 4.

제1항에 있어서,

상기 픽셀 박막 트랜지스터들의 세트는 셀마다 4개의 박막 트랜지스터들 및 1개의 유기 발광 다이오드를 포함하는 개개의 셀들을 형성하는 디스플레이.

#### 청구항 5.

제1항에 있어서,

상기 박막 트랜지스터 로우 및 컬럼 드라이버들은 4 cm/V-sec를 초과하는 전자 이동도를 갖는 디스플레이.

#### 청구항 6.

디스플레이를 제조하는 방법으로서,

백플레인 기판 상에 ZnO 채널 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트를 패터닝하는 단계;

상기 백프레인 기판 상에 ZnO 채널 픽셀 박막 트랜지스터들의 세트를 패터닝하는 단계 - 상기 픽셀 박막 트랜지스터들은 상기 박막 트랜지스터 로우 및 컬럼 드라이버들과 전기적으로 접속됨 - ; 및

상기 백플레인 기판 상에 상기 픽셀 박막 트랜지스터들과 전기적으로 접속되는 유기 발광 다이오드들의 세트를 패터닝하는 단계

를 포함하며.

각각의 상기 유기 발광 다이오드는 층들의 스택을 포함하는 디스플레이 제조 방법.

#### 청구항 7.

제6항에 있어서,

상기 백플레인 기판 상에 상기 ZnO 채널 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트를 패터닝하는 상기 단계 및 상기 ZnO 채널 픽셀 박막 트랜지스터들의 세트를 패터닝하는 상기 단계는 포토리소그래피에 의해 수행되는 디스플레이 제조 방법.

#### 청구항 8.

제6항에 있어서,

상기 백플레인 기판 상에 상기 ZnO 채널 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트를 패터닝하는 상기 단계 및 상기 ZnO 채널 픽셀 박막 트랜지스터들의 세트를 패터닝하는 상기 단계는 폴리머 애퍼처 마스킹(polymeric aperture masking)에 의해 수행되는 디스플레이 제조 방법.

#### 청구항 9.

제6항에 있어서,

상기 백플레인 기판 상에 상기 유기 발광 다이오드들의 세트를 패터닝하는 상기 단계는 폴리머 애퍼처 마스킹에 의해 상기 유기 발광 다이오드들의 상기 층들의 스택 중 적어도 한 층을 형성하여 수행되는 디스플레이 제조 방법.

#### 청구항 10.

비디오 디스플레이 백플레인을 제조하는 방법으로서,

폴리머 애퍼처 마스킹을 이용하여 백플레인 기판 상에 ZnO 채널 로우 및 컬럼 드라이버들 및 ZnO 채널 픽셀 박막 트랜지스터들을 한정하는 단계; 및

폴리머 애퍼처 마스킹을 이용하여 상기 백플레인 기판 상에 유기 발광 다이오드들을 한정하는 단계

를 포함하는 비디오 디스플레이 백플레인 제조 방법.

#### 청구항 11.

제10항에 있어서.

폴리머 애퍼처 마스킹을 이용하여 ZnO 채널 로우 및 컬럼 드라이버들 및 ZnO 채널 픽셀 박막 트랜지스터들을 한정하는 상기 단계는 상기 로우 및 컬럼 드라이버들과 상기 픽셀 박막 트래지스터들 사이에 전기적 접속을 패터닝하는 단계를 포함하는 비디오 디스플레이 백플레인 제조 방법.

#### 청구항 12.

제10항에 있어서.

폴리머 애퍼처 마스킹을 이용하여 상기 백플레인 기판 상에 유기 발광 다이오드들을 한정하는 상기 단계는 상기 픽셀 박막 트래지스터들과 상기 유기 발광 다이오드들 사이에 전기적 접속을 패터닝하는 단계를 포함하는 비디오 디스플레이 백플레 인 제조 방법.

#### 청구항 13.

제10항에 있어서,

폴리머 애퍼처 마스킹을 이용하여 상기 백플레인 기판 상에 유기 발광 다이오드들을 한정하는 상기 단계는 상기 픽셀 박막 트랜지스터들의 전극층 상에 상기 유기 발광 다이오드들을 형성하는 층들을 패터닝하는 단계를 포함하는 비디오 디스플레 이 백플레인 제조 방법.

#### 청구항 14.

제10항에 있어서.

상기 로우 컬럼 드라이버들 및 상기 픽셀 박막 트랜지스터들 위에 밀봉제층을 패터닝하는 단계를 더 포함하는 비디오 디스 플레이 백플레인 제조 방법.

#### 명세서

#### 기술분야

본 발명은 디스플레이 백플레인(backplane)들 상에 포함된 회로를 포함하는 디스플레이들과 관련된다. 특히, 본 발명은 로우(row) 및 컬럼(column) 드라이버들이 픽셀 트랜지스터들을 제어하기 위해 백플레인의 회로 내에 포함되고, 발광 다이오드들이 픽셀 트랜지스터들에 의해 활성화되는 화소들로서 회로 내에 포함되는 디스플레이들의 백플레인들과 관련된다.

#### 배경기술

디스플레이 백플레인들은, 액정 디스플레이(LCD), 유기 발광 다이오드(organic light emitting diode: OLED) 디스플레이, 또는 다른 디스플레이 기술과 같은 디스플레이 디바이스의 주요한 구성 요소(component)이다. 디스플레이 백플레인들은, 디스플레이 화면(screen)에 이미지들을 표시하기 위해서 회로가 생성되는 플랫폼(platform)을 제공하는 기판을 포함한

다. 통상적으로, 백플레인은, 화소들 또는 픽셀들이 이미지가 보여지게 되는 광을 생성하도록 OLED 셀들과 같은 화소들의 어레이에 전기 신호를 제공하는 픽셀 트랜지스터들의 어레이를 포함한다. 추가 회로는 로우 및 컬럼 드라이버들을 포함하 며, 통상적으로 백플레인으로부터 분리되어 위치된다. 로우 및 컬럼 드라이버들은 픽셀 트랜지스터들을 개별적으로 활성 화시키고 그에 의해 픽셀들을 개별적으로 제어하기 위해 인입(incoming) 비디오 데이터를 디코드 한다.

통상적인 경우에 픽셀 트랜지스터들은 그 백플레인 상에 위치되기 때문에, 픽셀 트랜지스터들은 TFT(thin film transistor)로서 형성되고, 그에 의해 얇은 화면 컴퓨터 및 TV 모니터, 전화기 및 다른 콤팩트 디바이스들과 같은 매우 얇은 디스플레이 화면을 허용한다. 통상적인 경우에 로우 및 컬럼 드라이버들은 백플레인에 위치되지 않기 때문에, 이들은 TFT일 필요는 없다. 그러나, 로우 및 컬럼 드라이버들은 디스플레이 회로 보드 상에 인스톨되는 집적 회로 칩에서와 같이 개별 공간을 차지한다.

로우 및 컬럼 드라이버들과 백플레인 어레이 간의 상호 접속은 복잡할 수 있다. 로우 및 컬럼의 수가 증가함에 따라, 상호 접속 밀도가 증가한다. 로우 및 컬럼 드라이버들이 유리에 접착된 실리콘 칩들이라고 해도, 상호 접속 복잡도(complexity)의 레벨은 엄청날 수 이다.

몇몇 디스플레이 화면 애플리케이션들에서는, 로우 및 컬럼 드라이버 칩에 필요한 공간을 제거하거나 다른 목적을 위해서 제공하고 및/또는 로우 및 컬럼 드라이버들을 픽셀 트랜지스터들과 아주 근접하게 가져오는 것이 바람직하다. 그러므로, 로우 및 컬럼 드라이버들을 픽셀 트랜지스터들과 함께 백플레인 상에 바로 이동시키는 것이 바람직하다. 그러나, 로우 및 컬럼 드라이버들은 매우 빠른 스위칭 능력을 가져야하며, 이에 의해 비결정(amorphous) 실리콘과 같은 낮은 이동성 (mobility) 반도체 채널들을 이용하는 종래의 TFT 구성(construction)은 문제가 발생한다.

특히, OLED 기반 디스플레이에서는, 가능한 한 큰 전자 이동성을 갖는 반도체를 포함하는 TFT들을 구비하는 것이 유리하다. 일반적으로, 전자 이동성은 트랜지스터 속도 및/또는 트랜지스터 사이즈에 직접적으로 영향을 받는다. 비결정 실리콘과 같은 반도체는  $0.5 \, \mathrm{cm}/\mathrm{V}$ -sec 정도의 전계 효과 이동도를 갖는다. 폴리실리콘과 같은 물질은 더 높은 이동도(20  $\, \mathrm{cm}/\mathrm{V}$ -sec 이상)를 갖지만, 더 높은 처리 온도와 더 복잡한 제조 공정을 필요로 한다.

#### 발명의 상세한 설명

본 발명의 실시예들은, 전면 소자로서 OLED를 또한 사용하면서 디스플레이 기판 상에 모놀리식으로(monolithically) 집 적된(즉, 동시에 패터닝되고 실질적으로 동일한 공정에 의함) 로우 및 컬럼 드라이버들과 픽셀 트랜지스터들을 이용하는 디스플레이 및 방법들을 제공함으로써 이들 문제점들 및 다른 문제점들을 제기한다. 로우 및 컬럼 드라이버들은 물론 픽셀 트랜지스터들은, 산화 아연(ZnO) 채널들을 갖는 TFT로서 구성되며, 디스플레이 신호들을 적절히 디코드하고 OLED 픽셀들을 활성화하는데 필요한 스위칭 속도를 달성하는 충분히 높은 이동성을 갖는다. ZnO 로우 및 컬럼 드라이버들은 디스플레이 화면 상에 이미지들을 형성하도록 어레의 OLED를 활성화시키는 ZnO 픽셀 트랜지스터들을 어드레스한다. TFT는 재배치될 수 있는 폴리머 애퍼처 마스크들과 같은 애퍼처 마스크들을 포함하는 프로세스를 통해 패터닝될 수 있다. 대안으로, TFT는 포토리소그래피를 통해 패터닝될 수 있다.

일 실시예는 백플레인 기판을 포함하는 디스플레이이다. ZnO 채널을 포함하는 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트는 상기 백플레인 기판 상에 패터닝된다. 부가적으로, ZnO 채널들을 포함하는 픽셀 박막 트랜지스터들의 세트는 상기 백플레인 기판 상의 상기 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트로 모노리식으로 집적된다. 유기 발광 다이오드들의 세트는 상기 백플레인 기판 상에 패터닝된다. 충들의 스택(stack)을 포함하는 각 유기 발광 다이오드는 상기 픽셀 박막 트랜지스터들의 세트 중 대응하는 하나 이상의 픽셀 박막 트랜지스터들에 의해 광을 생성하도록 활성화되고, 상기 대응하는 하나 이상의 픽셀 박막 트랜지스터들은 상기 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트에 의해 어드레 상된다.

또 다른 실시예에는 디스플레이를 생성하는 방법이다. 이 방법은 백플레인 기판 상의 ZnO 채널 박막 트랜지스터 로우 및 컬럼 드라이버들의 세트를 패터닝하는 단계를 포함한다. 이 방법은, 상기 픽셀 박막 트랜지스터들이 상기 박막 트랜지스터로우 및 컬럼 드라이버들과 전기적 접속을 갖도록 상기 백프레인 기판 상에 ZnO 채널 픽셀 박막 트랜지스터들의 세트를 패터닝하는 단계를 더 포함한다. 이 방법은 또한 상기 픽셀 박막 트랜지스터들과 전기적 접속을 갖는 상기 백플레인 기판 상에 유기 발광 다이오드들의 세트를 패터닝하는 단계를 포함한다. 각각의 상기 유기 발광 다이오드는 충들의 스택들을 포함한다.

또 다른 실시예는 비디오 디스플레이 백플레인을 생성하는 방법이다. 이 방법은 폴리머 애퍼처 마스킹을 이용하여 백플레인 기판 상에 ZnO 채널 로우 및 컬럼 드라이버들 및 ZnO 채널 픽셀 박막 트랜지스터들을 한정하는 단계를 포함한다. 이 방법은 폴리머 애퍼처 마스킹을 이용하여 상기 백플레인 기판 상에 유기 발광 다이오드들을 한정하는 단계를 더 포함한다.

#### 실시예

본 발명의 실시예들은 ZnO의 로우 및 컬럼 드라이버의 조합이 ZnO의 픽셀 트랜지스터 및 OLED와 같은 기판 상에 집적된 디스플레이 백플레인을 제공한다. 이들 실시예는 집적된 로우 및 컬럼 드라이버의 콤팩트성과 함께 OLED의 우수한 뷰잉 특성을 제공한다. 또한, 일부 실시예들은 ZnO의 로우 및 컬럼 드라이버, ZnO의 픽셀 트랜지스터 및 OLED의 패터닝에 폴리머 애퍼처 마스킹을 이용하는 백플레인의 구성을 제공한다. 이들 실시예들 중 일부는 제조 중 OLED의 손상 가능성을 줄이는 OLED의 우수성을 얻으면서 고수율의 백플레인 구성을 달성할 수 있는 폴리머 애퍼처 마스킹 공정의 효율적인 이용을 제공한다.

트랜지스터 패터닝에는 공지의 각종 기술을 이용할 수 있다. 예컨대, 일부 실시예에서는, 포토리소그래피를 이용하여 TFT를 패터닝하고 이어서 애퍼처 마스크를 이용하여 OLED 층을 패터닝할 수 있다. 다른 실시예에서는, 애퍼처 마스크를 이용하여 로우 및 컬럼 드라이버로서의 TFT와 픽셀 TFT뿐만 아니라 OLED 스택을 패터닝할 수도 있기 때문에 전체적으로 습식 화학 처리를 피할 수도 있다.

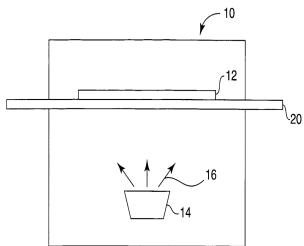

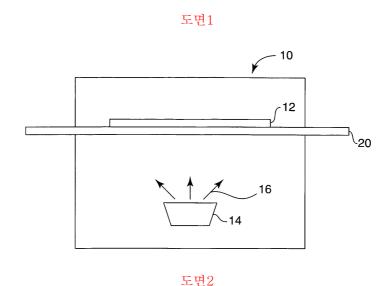

전술한 바와 같이, 본 발명의 일부 실시예들에서는, 섀도우(shadow) 마스크와 같은 애퍼처 마스크를 이용하여 트랜지스터를 마련할 수 있다. 본원에 원용되는 미국 특허 출원 제2003/0152691호 및 제2003/0150384호에는 애퍼처 마스크를 이용한 예시적인 절차가 개시되어 있다. 애퍼처 마스킹 공정을 더 예시하기 위한 것으로, 도 1은 애퍼처 마스크를 이용하여 TFT 로우 및 컬럼 드라이버와 픽셀 TFT뿐만 아니라 OLED 스택을 패터닝할 수 있는 증착소(deposition station)의 개략적 블록도이다. 특히, 증착소(10)는 애퍼처 마스크를 통해 증착 기판 상에 재료를 기화시켜 증착시키는 증착 공정을 행하도록 구성될 수 있다. 그 증착 재료는 각종 소자의 형성에 이용되는 반도체 재료, 유전체 재료 또는 도전성 재료를 포함하는 OLED 층이나 TFT층에 필요한 임의의 재료일 수 있다. 예컨대, 유기 또는 무기 재료가 증착될 수도 있다. 어떤 경우에는, 유기 및 무기 재료가 모두 증착될 수도 있다.

애퍼처 마스크 패턴으로 형성된 애퍼처 마스크(20)는 디스플레이 백플레인 기판(12) 부근에 배치될 수 있도록 증착소(10)를 통과한다. 백플레인 기판(12)은 생성하기 원하는 디스플레이 회로에 따라 각종 재료를 포함할 수 있다. 예컨대, 백플레인 기판(12)은 연성(flexible) 재료나 대안으로 강성(rigid) 재료를 포함할 수 있다. 유리 기판, 실리콘 기판, 강성 플라스틱 기판, 절연층으로 도포된 금속박 등의 백플레인 기판도 이용 가능하다. 어떤 경우에, 백플레인 기판(12)은, 우선 TFT를 포토리소그래피를 이용하여 백플레인 기판(12)에 패터닝하고 이어서 적어도 하나의 OLED 층을 애퍼처 마스크를 이용하여 패터닝하는 경우와 같이 미리 형성한 피처(feature)를 포함할 수도 포함하지 않을 수도 있다. 일부 예에서는, 모든 OLED 층을 애퍼처 마스크를 이용하여 패터닝한다.

증착소(10)는 통상 진공 챔버이다. 애퍼처 마스크(20)의 패턴을 백플레인 기판(12) 부근에 고정한 후, 증착부(14)에서 재료(16)를 기화시킨다. 예컨대, 증착부(14)는 가열하여 재료를 기화시킬 수 있는 재료의 보트(boat)를 포함할 수 있다. 기화된 재료(16)는 백플레인 기판(12)에 적어도 회로층의 일부를 규정하기 위해 애퍼처 마스크(20)의 증착 애퍼처를 통해 백플레인 기판(12)에 증착된다. 증착 시, 재료(16)는 애퍼처 마스크(20)의 패턴에 의해 규정되는 증착 패턴을 형성한다. 애퍼처마스크(20)는 전술한 증착 공정을 이용하여 소회로 소자의 생성을 돕기에 충분히 작은 애퍼처및 갭을 포함할 수 있다. 이와 달리, 애퍼처마스크(20)의 증착 애퍼처의 패턴은 전술한 바와 같이 큰 치수를 가질 수도 있다. 다른 적합한 증착 기술로는 e-빔 증발, 각종 형태의 스퍼터링및 필스형 레이저 증착이 있다. 도 2 및 도 3에 관하여 이하 참조하는 예 1은 애퍼처마스크를 이용하여 TFT와 OLED를 패터닝하는 하나의 예시적인 방법에 대한 상세를 포함한다.

그러므로, 상술된 바와 같이 애퍼처 마스크를 이용하는 것은, 로우 및 컬럼 드라이버들을 구성하는 TFT들 및 디스플레이 백플레인의 픽셀 TFT들을 증착시키기 위한 한가지 방법이다. 더구나, 상술된 바와 같은 애퍼처 마스크는, 또한, 픽셀 TFT에 인접한 기판 상에 존재하는 OLED들의 하나 이상의 충들을 패터닝하기 위한 한가지 방법이다. OLED를 활성화하기 위한 픽셀 TFT에 인접하여 증착된 OLED의 횡단면을 도 2 및 도 3의 예들에 도시한다. 몇몇 디바이스들에서, OLED 스택의 모든 충들은 애퍼처 마스크를 이용하여 패터닝된다.

폴리이미드와 같은 물질들로부터 구성된 폴리머 애퍼처 마스크를 이용하는 것이 유리할 수 있다. OLED 스택을 패터닝하기 위한 폴리머 애퍼처 마스크들을 이용하는 이점은, 애퍼처 마스크에 의해 OLED 물질을 덜 손상시킬 가능성 및 열팽창과 같은 각종 원인들에 기인하여 마스크의 차원적 변화들을 완화시키기 위해, 애퍼처 마스크를 스트레칭하는(stretch) 능력을 포함한다.

애퍼처 마스크 절차들에 대한 대안으로서, ZnO 기반 TFT 회로는 포토리소그래피로 생성될 수 있는 반면, OLED들은 상술된 애퍼처 마스크 절차를 통해 개별적으로 증착된다. 잘 알려져 있는 포토리소그래피 기술을 ZnO 픽셀 회로를 정의하는데 이용할 수 있다. 그러한 포토리소그래피 기술들의 예는, Badih El-Kareh에 의한 Kluwer 아카데미 출판사의 반도체 처리 기술의 기초, 제4장, 590~592페이지, 보스턴(1995)에 개시되어 있다. 부가적으로, 도 2 및 도 3에 대하여 이하에 참조되는 예 2는, OLED 스택을 패터닝하기 위한 섀도우 마스크의 응용에 선행하여, TFT를 먼저 패터닝하기 위한 포토리소그래 피를 적용시키는 설명적 공정에 대한 상세를 포함한다. 따라서, 도 1의 애퍼처 마스크 공정은, 설명을 위해 제공된 것일 뿐, 디스플레이의 TFT들을 패터닝하기 위한 방법을 제한하도록 의도된 것이 아니다.

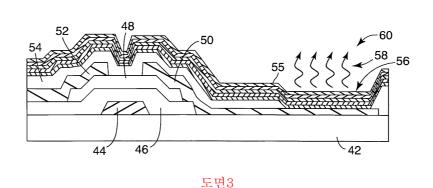

도 2의 예는 공통 기판(42)의 꼭대기에 픽셀 TFT 및 OLED의 증착을 도시한다. 이 예에서, OLED는 상부 방사형이다(즉, 기판을 통해서가 아니라 기판으로부터 덜어지게 방사한다). 도 1을 참조하여 앞서 설명된 바와 같이, 기판(42)은, 유리 및 기타 강성 물질들 등의 각종 재료들로 구성되거나, 금속 호일 및 플라스틱(예를 들어, 폴리이미드, PEN)과 같은 물질들을 이용하여 유연성있게 구성될 수도 있다. 티타늄 및 금과 같은 물질들로 구성된 게이트 전극(44)은, 기판(42) 상에 직접 패터닝된 후,  $SiO_2$  또는  $Al_2O_3$ 와 같은 게이트 유전체(46)가 반도체 채널(48)로부터 게이트 전극(44)을 전체적으로 절연시키기 위해, 게이트 전극(44)의 꼭대기에 패터닝된다. 반도체 채널(48)은 게이트 유전체(46)의 꼭대기 상에 패터닝된 ZnO의 층이다.

알루미늄과 같은 물질들로 구성된 드레인 전극(52)은, 채널(48)의 한면 상에 패터닝되는 반면, 개별 소스 전극(50)은 채널 (48)의 다른 면 상에 패터닝되고, 드레인 전극(52)과 동일한 물질로 구성될 수 있다. 소스 전극(50)은, 기판(42) 상으로 연장하고, 기판(42)과 OLED 스택(56) 사이에 위치된다. 포토 이미지 형성 에폭시와 같은 물질들 또는 SiO<sub>2</sub> 등의 기타 물질로 구성된 캡슐화 층(54)은, 소스/드레인 전극(50, 52) 및 채널(48)을 포함하는 반면, OLED 스택(56)이 패터닝되는 소스전극(50)의 영역 위의 공간을 남겨두는 TFT의 층들 위에 패터닝된다. 선정된 회로 설계에 따라서, OLED 스택(56)에 접촉하는 전극이 소스 또는 드레인 중 하나일 수 있음이 이해될 것이므로, 소스 및 드레인이라는 용어들의 사용은 다소 임의적일 수 있음에 유의해야 한다.

통상적으로, 소스 전극 및 드레인 전극 특징들은, 약 1마이크로미터 내지 약 50마이크로미터(바람직하게는, 약 5마이크로미터 내지 약 20마이크로미터)의 채널 길이가 이들을 분리하도록 패터닝된다. 포토리소그래픽에 의해 패터닝된 TFT에 대하여, 게이트 길이는 1마이크로미터 정도로 짧을 수 있으며, 통상 5마이크로미터이다. 애퍼처 마스크 패터닝된 TFT에 대하여, 게이트 길이는 5 내지 60마이크로미터일 것이며, 통상의 게이트 길이는 20 내지 30마이크로미터이다.

도 2의 픽셀 TFT를 포함하는, TFT의 충들을 패터닝하기 위한 하나의 설명적 공정의 단계들은, TFT들이 애퍼처 마스크의 사용에 의해 패터닝되는 예 1에 상세히 설명된다. 마찬가지로, 도 2의 픽셀 TFT를 포함하는 TFT들의 충들을 패터닝하기 위한 또 다른 설명적 공정의 단계들은 TFT들이 포토리소그래피에 의해 패터닝된 예 2에 상세히 설명된다. 둘 중 하나의 경우에 있어서, TFT들은, TFT 로우 및 컬럼 드라이버들 및 픽셀 TFT들이 디스플레이 기판(42) 상에 모놀리식으로 집적되어 있도록, 실질적으로 동일한 시간에, 그리고 실질적으로 동일한 공정을 통해 패터닝될 수 있다.

OLED 스택(56)은 유기 물질들의 스택으로 구성된다. 이 물질들 및 한가지 설명적 예에 대한 스택(56) 내에서의 그들의 특정 순서가 예 1 및 예 2에 설명된다. OLED 스택(56)을 통한 전류의 경로를 완성하기 위해, 상부 전극(55)이 OLED 스택(56)의 상부 위에 패터닝된다. 이러한 상부 전극(55)은, 빛이 전극(55)을 통해 방사될 수 있도록, 인듐 주석 산화물(ITO)과 같은 투명 물질 또는 얇은 금속층으로 구성된다. 전류를 받으면, OLED 스택(56)의 물질들은 발광하기 시작한다.

도 2의 구성의 동작에 있어서, 드레인 전극(52)에 전압이 인가된다. 그러나, 채널(48)이 비도전성 상태로 남아 있을 때 게이트 전극(44)에도 전압이 인가되지 않는다면 소스 전극(50)에는 극미량의 전류만이 통한다. 게이트 전극(44)에 전압의 인가 시, 채널(48)은 도전 상태가 되고, 채널을 통해 소스 전극(50)으로 그리고 OLED 스택(56)을 통해 전류가 흐름으로써, OLED가 기판(42)으로부터 멀어지게 광(58)을 방출하게 된다. 따라서, 이러한 방식으로 어드레스된 OLED의 어레이는 표시중인 상태의 화상이 된다.

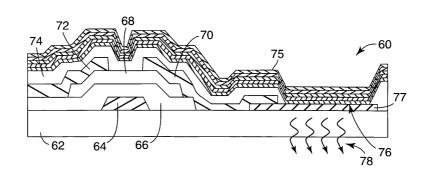

도 3의 예는 OLED가 하부 방출(bottom emitting)(즉, 광이 기판을 통과하여 방출)되고 있는 글래스 또는 투명 플라스틱등의 재료들로 구성된, 공통 투명 기판(62)의 최상측에 있는 OLED 및 픽셀 TFT의 피착을 나타낸다. 기판(62) 상에는 게이트 전극(64)이 직접 패터닝되고, 그 후 게이트 전극(64)의 최상측에 게이트 유 전체(66)가 패터닝되어 반도체 채널(68)로부터 게이트 전극(64)을 전체적으로 아이솔레이션한다. 반도체 채널(68)은 게이트 유전체(66)의 최상측에 패터닝되어 있는 ZnO의 층이다. 채널(68)의 일측 상에는 드레인 전극(72)이 패터닝되어 있고, 채널(68)의 타측 상에는 분리 소스 전극(70)이 패터닝되어 있다. 소스 전극(70)은 ITO 전극 등 투명 OLED 전극(77)과 콘택트되어 있기 때문에, OLED는 전극(77) 및 기판(62)을 통해 광을 방출할 수 있다. 소스/드레인 전극들(70, 72) 및 채널(68)을 포함하는 TFT의 층들 상에는, OLED 스택(76)이 패터닝되어 있는 투명 전극(77)의 영역 위에 보이드(void)를 남기면서, 포토이미지가는 에폭시 (photoimageable epoxy) 등의 재료들 또는 그외 SiO<sub>2</sub> 등의 재료로 다시 구성된 밀봉제층(encapsulant layer)(74)이 패터닝된다. OLED 스택(76)의 최상측에는 상부 전극(75)이 피착되어 있다.

동작에 있어서, 드레인 전극(72)에 전압이 인가된다. 그러나, 채널(68)이 비도전성 상태로 남아 있을 때 게이트 전극(64)에도 전압이 인가되지 않는다면 소스 전극(70)에는 극미량의 전류만이 통한다. 게이트 전극(64)에 전압의 인가 시, 채널(68)은 도전 상태가 되고, 채널을 통해 소스 전극(70)으로 그리고 OLED 스택(76)을 통해 전류가 흐름으로써, OLED가 전극 (77) 및 기판(62)을 통해 광(78)을 방출하게 된다. 이러한 방식으로 어드레스된 OLED의 매트릭스는 표시중인 상태의 화상이 된다.

상기에서는 구체적으로 논의되지 않았지만, OLED는 도 2 및 도 3의 OLED 스택을 둘러싸는 밀봉제를 포함함으로써, 주변 요소들에 노출되는 것으로부터 보호될 수 있다는 것을 이해할 것이다. 도 2 및 도 3의 밀봉제들은 TFT 및 OLED 스택을 더 캡슐화한다.

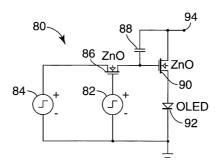

도 4는 2개의 ZnO 픽셀 TFT가 사용되는 단일 광 방출 셀의 회로(80)의 예이다. 제1 전압원(82)이 주기적으로 인에이블 펄스들을 제공하여 ZnO 픽셀 TFT(86)를 게이팅한다. 일단 스위칭 온되면, ZnO 픽셀 TFT(86)는 제2 전압원(84)으로부터의 데이터 펄스에 기초하여, ZnO 픽셀 TFT(90)의 게이트 및 커패시터(88)를 대전시킨다. ZnO 픽셀 TFT(90)의 게이트의 대전은 ZnO 픽셀 TFT(90)를 도전 상태로 전환시킴으로써, 공급 전압(94)으로부터 OLED(92)를 통해 전류를 흐르게하여 화상을 형성하기 위한 광을 생성한다. 인에이블 펄스들을 제공하고 있는 제1 전압원(82)은 도 7 내지 도 9와 관련된 후술할 로우 드라이버 회로로부터의 출력을 나타내며, 데이터 펄스들을 제공하고 있는 제2 전압원(84)은 도 7 내지 도 9와 관련된역시 후술할 컬럼 드라이버 회로로부터의 출력을 나타낸다.

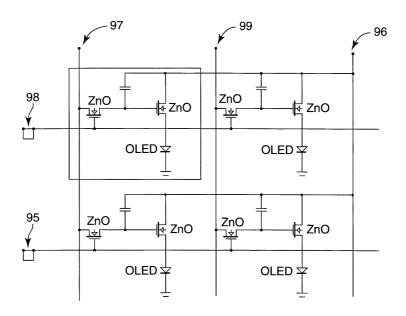

도 5는 도 4에 나타낸 구성에 기초한 광 방출 셀들의 어레이의 예시적인 회로 다이어그램이다. 설명을 위해 4개의 셀이 도시되어 있으며, 본 예에서는 셀 당 2개의 ZnO 픽셀 TFT가 존재한다. 각 셀 중 하나의 ZnO 픽셀 TFT는 로우 드라이버 회로에 기초한 ZnO TFT의 출력(95, 98)으로부터의 인에이블 펼스에 의해 구동되며, 각 셀의 각 OLED는 컬럼 드라이버 회로에 기초한 ZnO TFT의 출력(97, 99)으로부터의 데이터 펄스에 의해 더 구동되어, 전압원(96)으로부터 각 OLED에 전원을 제공한다. 따라서, OLED들의 어레이들은 개개의 OLED를 기동하는 로우 및 컬럼 드라이버 출력들에 의해 디코딩의 결과로서의 화상들을 생성한다.

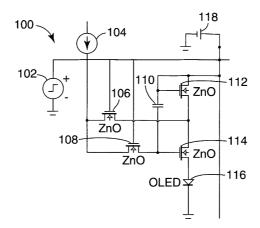

도 6은, ZnO 픽셀 TFT에 기초하고 ZnO TFT 파라미터 변화를 완화시키는(그렇지 않으며 OLED의 성능을 저하시킬 수도 있는) 하나의 대안적 광 방출 셀 디자인을 설명하는 예시적인 회로 다이어그램이다. ZnO 형태의 트랜지스터를 제외하고, 도 4 및 도 6의 일반화된 회로들은 공지되어 있다. 특히, Yi He et al., IEEE Electron Device Letter, Vol.21(12), 590-592(2000)에 의한 도 6의 회로 레이아웃 등이 도시 및 기술되어 있다.

이 도 6의 회로에 있어서, 전압원(102)으로부터 신호에 의해 ZnO 트랜지스터들(106 및 108)이 스위칭 온된다. 전류원 (104)은 이 시간 동안 데이터를 제공하고, ZnO 트랜지스터(114)가 전류원(104)으로부터 전류를 통하게 하면서, ZnO 트랜지스터(114)를 원하는 전류 레벨에 구동하는 데 필요한 전압 레벨까지 저장 커패시터(110)를 대전시킨다. 이 시간 동안, 전원(118)이 ZnO 트랜지스터(114)의 드레인 전극보다 낮은 전압에 있으면, 전류는 ZnO 트랜지스터(112)를 통해 흐르지 않을 것이다. 이 프로세스는 지연 시간을 발생시킬 수도 있는 트랜지스터 문턱 전압 변이들을 축적시킨다. 그 후, ZnO 픽셀트랜지스터(114)를 통해 전류가 OLED(116)를 기동하여 광을 방출한다. 전원(102)으로부터의 선택 신호가 오프되어 있는 경우, ZnO 트랜지스터들(106 및 108)은 오프되지만, 현재 전압원(118)에 의해 소스가 되는 전류는 저장 커패시터(110)가 대전되어 있는 동안 ZnO 트랜지스터(114) 및 OLED(116)를 통해 계속 흐른다. 도 6의 셀은 도 5에 도시된 바와 마찬가지로 셀들의 어레이를 생성하도록 연장될 수도 있다.

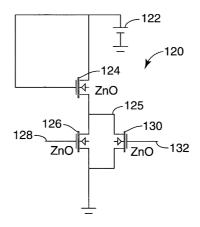

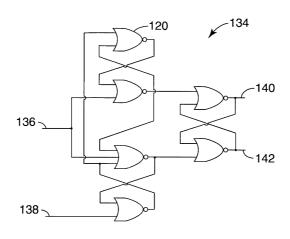

도 7은, 도 4 내지 도 6과 관련하여 상기에서 논의되었던 인에이블 펄스 및 데이터 펄스를 생성하는 로우 및 컬럼 드라이버 회로의 빌딩 블록으로서 사용될 수 있는 ZnO TFT 기반의 디지털 로직 게이트를 도시하는 예시적인 회로도이다. 도 7의 특정 로직 게이트는 "NOT OR"(NOR) 게이트(120)의 일례이다. 그러나, ZnO TFT들로 형성된, OR, AND, "EXCLUSIVE OR"(XOR) 로직 게이트들과 같은, 그외의 로직 게이트 디자인도 로우 및 컬럼 드라이버 회로의 빌딩 블록으로서 사용될 수 있다고 인정될 것이다. 본 예에서, 제1 ZnO TFT(124)는 전압원(122)으로부터 전력을 받는다. TFT(124)는 전도력 있는 상태로 유지되고 TFT(124)의 소스로부터 출력(125)이 취해진다. 그러나, 출력(125)은 ZnO TFT(126)과 ZnO TFT(130)의 드레인에도 접속된다. TFT(126)의 게이트(128) 또는 TFT(130)의 게이트(132) 중 하나에 논리값 하이(high)가 제공되면, 출력은 논리값 로우(low)가 된다.

본 발명의 실시예에서, 이들 로직 게이트들(120)은, ZnO 기반의 픽셀 TFT들 및 OLED들을 따라 도시된 전기적 구성에서, 백플레인 기판 상에 패턴된 ZnO 기반의 TFT들(124, 126, 130)에 의해 형성된다. 로직 게이트들의 ZnO TFT들은, 애퍼처 (aperture) 마스크 기반의 패터닝 또는 포토리소그래피 기반의 패터닝의 전술한 처리들 중의 하나에 의해, 디스플레이의 백플레인 기판 상의 ZnO 기반의 픽셀 TFT들과 함께 모놀리식으로 집적될 수 있다. 로우 및 컬럼 드라이버 회로를 형성하는 ZnO 기반의 로직 게이트들의 전기적 접속들의 패터닝은, 이하에서 논의하는 도 8 및 도 9를 참조하여 분명해질 것이다.

도 8은 표준적인 플립-플롭(134)을 도시하지만, 이 플립-플롭은, 도 7에서 도시된 바와 같이, ZnO 기반의 TFT들로 형성된, 상호 접속된 NOR 게이트들(120)의 집합에 의해 형성된다. 클록 입력(136)이 데이터 입력(138)처럼 제공된다. 플립-플롭(134)은 출력(140) 및 반전된 출력(142)을 제공한다. 로우 및 컬럼 드라이버 회로들을 구성할 때 플립-플롭들 이외에다른 로직 장치들도 사용될 수 있다고 인식될 것이다.

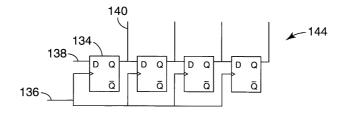

도 9는 표준적인 시프트 레지스터(144)를 도시하지만, 이 시프트 레지스터는 도 8에 도시된 바와 같이, 백플레인 기판 상에 패턴된 ZnO 기반의 TFT들을 포함하는 로직 게이트들로부터 구성된 직렬의 플립-플롭들(134)로 형성된다. 클럭(136)과 데이터 신호들(138)은, 디스플레이 데이터를 생산하는 장치의 비디오 데이터 버스로부터 직렬로 제공된다. 본 예에서, 시프트 레지스터(144)는 픽셀들의 어레이의 컬럼들에 대한 데이터 비트들을 직렬로 수신하지만 그 직렬 데이터를 병렬 데이터로 변환함으로써 직렬 데이터를 역다중화해야 한다. 병렬 데이터는 각 픽셀들이 그 제어 비트 또는 비트들을, 순차적과 대립하는 것으로서, 동시에 수신하게 해준다. 데이터 비트가 디스플레이의 적절한 컬럼에 대응하는 출력(140)으로부터 제공될 때까지, 클럭 신호(136)는 비트들을 직렬의 플립-플롭들로 전파한다. 도시된 간단한 예에서, 들어오는 제1 데이터 비트는 제4 컬럼을 향한 것이고, 따라서 제1 데이터 비트는 4번의 클럭 펄스에 의해 그 목적지 컬럼에 도달했다.

전파 중에, 시프트 레지스터들의 집합과 같은 로직 디바이스일 수도 있는 로우 드라이버 회로는, 데이터 비트들이 로우 시프트 레지스터(144)의 적절한 컬럼 출력(140)에 위치할 때까지 각 로우 라인에 대해 논리값 로우 출력을 유지한다. 이 타이밍은 로우 드라이버 회로의 최후의 논리값 하이 출력 이후부터의 클록 펄스들의 수에 기초한다. 이것은 도 4의 트랜지스터(86)와 같은 게이팅 트랜지스터가, OLED에 직접적으로 접속된 픽셀 트랜지스터의 게이트에 잘못된 비트를 전달하는 것을 방지한다. 비트들이 각 컬럼들에 대하여 적절하게 배열되면, 로우 드라이버 회로는 논리값 하이 출력을 제공하여, 각 출력(140)을 게이팅하는 ZnO 픽셀 TFT들이 도전성이 되도록 한다. 그렇게 하여, 각 컬럼에 대한 비트는 OLED에 직접적으로 접속된 ZnO 픽셀 TFT의 게이트로 보내져서 비트의 값에 따라서 OLED가 광을 방출하거나 또는 방출하지 않도록 만든다.

도 7 내지 도 9는 로우 및 컬럼 회로의 일례를 제공하지만, 디스플레이 기판 상에 패턴된 ZnO 기반의 TFT들로 구성된 로우 및 컬럼 회로의 다양한 변경들이 있을 수 있다는 것이 인식될 것이다. 따라서, 도 7 내지 도 9는 그러한 로우 및 컬럼 회로의 일례를 단지 설명하기 위하여 제공된다.

예 1 및 2는 디스플레이 기판 상에 ZnO TFT들 및 OLED들을 패터닝하는 것의 상세를 즉각적으로 따르고 설명한다. 예 1 및 2의 상세는 ZnO TFT들 및 OLED들을 패터닝하는 것의 개별적인 예들을 단지 설명하기 위하여 제공된다. 애퍼처 마스크 제조 절차 및 대안적인 혼합된 포토리소그래피-애퍼처 마스크 제조 절차 모두에서 다양한 변경들이 있을 수 있다는 것이 인식될 것이다.

#### 실시예

<예 1 -디스플레이를 위한 ZnO TFT 및 OLED 섀도우 마스크 제작 설명(description)>

집적 회로들은 막들을 패터닝하도록 작용하는 플렉서블 마스크들을 통하여 진공 박막 피착에 의해 형성되는 TFT들(thin film transistors) 및 캐패시터들과 같은 회로 요소들로 구성된다. 보통의 박막 물질들은 도체들 또는 전극들을 위해 서는

금속들이고, 캐패시터들을 위해 또는 교차하는 금속 선들 사이의 전기 전도를 막기 위해서는 유전체들이며, 트랜지스터들의 활성층을 위해서는 반도체들이다. 박막 물질들의 예들은 도체들 또는 전극들에 대해서는 금, 티타늄 및 알루미늄; 유전체들에 대해서는  $Al_2O_3$  또는  $SiO_2$ ; 반도체로서는 스퍼터링된 ZnO 또는 열 증착된 펜타센(pentacene)이다.

2"x 2"유리 슬라이드는 알콜로 린스하여 세정되었다. 폴리머 섀도우 마스크(polymeric shadow mask)들은 본원에 참조로서 포함된, 출원인이 발표한 U.S. 특허출원 2003/0152691 및 2003/0150384 호에서 상술된 바와 같이 형성되었다. 레이저 박리(laser ablation)를 이용하여 섀도우 마스크들에 구멍들이 형성되었다.

게이트 레벨 섀도우 마스크 패턴이 유리 기판 상에서 중앙에 오도록 조정되었다. 100Å의 e-beam 된 티타늄이 섀도우 마스크를 통하여 진공실 안에서 유리 기판 상에 피착되고 그 다음 저항성의 가열원으로부터 금이 750Å 증착되었다. 기판 및 섀도우 마스크는 진공 시스템으로부터 제거되었다. 기판은 그 표면을 질소로 불어냄으로써 깨끗하게 되었다.

게이트 유전체는 다음과 같이 피착되었다. 게이트 유전체 패턴 구멍들이 있는 섀도우 마스크는 기판상에 게이트 레벨 피착 패턴들을 이용하여 정렬되고 레지스터(register)되었다. 1600 Å  $SiO_2$ 는 진공실(450W) 안에서 섀도우 마스크에 걸쳐 피착되었다. 기판 및 섀도우 마스크는 진공 시스템으로부터 제거되고 기판은 질소 블로우(blow)로 깨끗해졌다.

ZnO 반도체는 다음과 같이 피착되었다. 반도체 패턴을 위한 구멍들이 있는 섀도우 마스크는 게이트 유전체 및 기판 상의 게이트 레벨 피착 패턴들을 이용하여 정렬되고 및 레지스터 되었다. 500Å ZnO는 진공실 안에서 피착되었다(직경 6인치의 ZnO 타켓으로부터 100W, 0.4 sccm Ar 플로우 내의 10%의  $O_2$ ). 기판 및 섀도우 마스크는 진공 시스템으로부터 제거되고 기판은 질소 블로우를 이용하여 깨끗해졌다.

소스 및 드레인 전극들(AI)은 저항식의 가열원으로부터 진공 증착(vacuum evaporation)에 의해 적절한 섀도우 마스크에 걸쳐 유사하게 피착된다. 이 점에서 집적된 TFT 회로는 완전하다.

OLED 층들을 TET 층들 및 집적된 회로로부터 분리하기 위해 집적된 TFT의 상부에 밀봉제가 피착된다. 밀봉재는 이전에 패터닝된 층들을 이용하여 밀봉재 섀도우 마스크를 정렬시키는 것에 의해 피착된다. 전자 빔으로 증착된  $Al_2O_3$ 가 밀봉제로 쓰이곤 했다. 그것은 3000 Å의 두께로 진공 증착에 의해 피착되었다.

그 후 OLED 스택은 3% 플루오르화된 TCNQ(tetracyanoquinodimethane)로 도핑된 MTDATA(4,4',4"-tris(N-(3-methylphenyl)-N-phenylamine)triphenylamine) 3000Å, NPB(N,N'-Bis(naphthalen-1-yl)-N,N'-bis(phenyl) benzidine) 400Å, C545T(10-(2-benzothiazolyl)-1,1,7,7-tetramethyl-2,3,6,7-tetrahydro-1H,5H,11H benzopyrano (6,7,8-ij) quinolizin-11-one)로 도핑된 Alq<sub>3</sub>(tris-(8-hydroxyquinoline)aluminum) 300Å, Alq<sub>3</sub> 200Å, (0.5Å/sec 의 속도로 피착된) LiF 7Å, Al 50Å 및 마지막으로 Ag 150Å을 진공 증착함으로써 밀봉제층의 상부에 피착될 수 있다.

<예 2 - 디스플레이를 위한 ZnO TFT 포토리소그래피/OLED 섀도우 마스크 제작 설명>

2"x 2"유리 슬라이드는 알콜 린스를 이용하여 세정되었다. 슬라이드는 포토레지스트(PR) 점착력이 향상되도록 60초 동안 120℃에서 프리베이크(prebake)된다. 네거티브 포토레지스트(뉴저지 주 프랭클린의 Futurrex사로부터 입수 가능한 FUTURREX NR7-1000PY)가 스핀 코팅(spin coating)에 의해 슬라이드에 도포되었다(60초 동안 5000RPM으로, 그 후 60초 동안 150℃에서 소프트 베이킹). 포토레지스트는 180mJ/c㎡로 게이트 레벨 마스크에 노광되고 그 후 60초 동안 100℃에서 노광 후 베이킹된다. 노광된 포토레지스트가 있는 슬라이드는 약 10초 동안 FUTURREX RD6 현상액을 사용하여 현상된다. 현상된 슬라이드는 검사되고 그 후 물세정되고 그 후 질소 안에서 건조된다. 이어서, 50Å의 전자 빔 티타늄과 600Å의 금을 전자-빔 및 저항성 열원으로부터 각각 진공 증발시킨다. 아세톤으로 금속을 리프트-오프(lift-off)하고 이어서 메탄올 및 물로 세정함으로써 게이트 금속막의 패터닝이 완성된다.

게이트 유전체인 1600Å의  $SiO_2$ 를 스퍼터링한다(8인치 직경  $SiO_2$  타켓 상에서 450W). 다음, 500Å의 ZnO(6인치 ZnO타켓 상에서 100W, 0.4sccm Ar 플로우에서 10%  $O_2$ )를 스퍼터링한다.

ZnO를 다음과 같이 포토리소그래피 에칭한다. 60초 동안 5000RPM에서 스핀코팅하고 120초 동안 120℃에서 소프트 베이크(soft bake)하여 기판에 포지티브 포토레지스트(FUTURREX PR1-1000A)를 도포한다. 포토리소그래피 마스크를 통

해  $120 \text{mJ/cm}^2$ 에서 레지스트를 노출시킨다. 레지스트를 40초 동안 FUTURREX RD6 현상액에 노출시킴으로써 현상한다. 그 후 샘플을 검사하고 물로 세정하고 질소로 건조한다. 그 후 기판을 6초 동안 0.5% HCI에서 에칭한 후 포토레지스트를 제거한다.

SiO<sub>2</sub>를 다음과 같이 에칭한다. ZnO 에칭된 기판을 60초 동안 120℃에서 프리베이킹(prebake)한다. 프리베이킹된 기판에 포지티브 포토레지스트를 도포한다(60초 동안 5000 RPM에서 FUTURREX PR1-1000A를 스핀 코팅하고 이어서 120초 동안 120℃에서 소프트 베이크한다). 레지스트를 포토리소그래피 마스크를 통해 120mJ/cm²에 노출시키고, FUTURREX RD6 현상액을 사용하여 현상하고, 검사하고, 물로 세정한 후 질소로 건조한다. 그 후 기판을 60초 동안 120℃에서 하드 베이킹한다. 샘플을 90초 동안 PAD ETCH 4(Ashland Specialty Chemicals, Dublin, OH로부터 입수가능함)로 에칭하고 나서 포토레지스트를 제거한다.

소스 및 드레인 전극들을 다음과 같이 포토리소그래피에 의해 패터닝한다. 에칭된 산화물 기판을 60초 동안 120℃에서 프리베이킹한다. 60초 동안 5000 RPM에서 스핀 코팅한 후 60초 동안 150℃에서 소프트 베이크 함으로써 네거티브 포토레지스트층(FUTURREX NR7-1000PY)을 도포한다. 포토레지스트를 소스/드레인 애퍼처 마스크를 통해 180mJ/cm²에서 노광시키고, 60초 동안 100℃에서 포스트 베이킹하고, 10초 동안 FUTURREX RD6을 사용하여 현상하고, 검사하고, 물로세정하고 질소로 건조시킨다. 최종적으로 기판 상부에 Ti/Au/Ag를 순차 피착한다. 피착된 금속들을 아세톤으로 리프트-오프하고 이어서 메탄올과 물로 세정하고, 질소 바람으로 건조시킴으로써, 소스/드레인 금속층의 패터닝을 완성한다.

다음과 같이 밀봉제를 도포한다. 0.45/m 필터를 통해 네거티브, 에폭시형 포토레지스트(MicroChem, Newton, MA로부터 입수가능한 SU-8-2000.5)를 필터링한 후, 60초 동안 5000RPM에서 스핀코팅하고 이어서 2분 동안 100℃에서 소프트베이크 함으로써 일체형 TFT 기판에 도포한다. 포토마스크를 통해 54mJ/cm²의 조명에 샘플을 노출시키고 이어서 2분 동안 100℃에서 포스트 노출 베이크를 행한다. 샘플을 10초 동안 SU-8 DEVELOPER(마이크로켐사)에서 현상하고 이어서 이소프로판올로 세정한다. 샘플을 2분 동안 150℃에서 하드 베이킹한다. 일체형 TFT 회로는 이 시점에서 완성되고 OLED 컴포넌트용으로 준비된다.

3% 플루오르화된 TCNQ(tetracyanoquinodimethane)로 도핑된 3000Å MTDATA(4,4',4"-tris(N-(3-methylphenyl)-N-phenylamine)triphenylamine), 이어서 400Å NPB(N,N'-Bis(naphthalen-1-yl)-N,N'-bis(phenyl)benzidine), C545T(10-(2-benzothiazolyl)-1,1,7,7-tetramethyl-2,3,6,7-tetrahydro-1H,5H,11H benzopyrano (6,7,8-ij) quinolizin-11-one)로 도핑된 300Å Alq<sub>3</sub>(tris-(8-hydroxyquinoline)aluminum), 200Å Alq<sub>3</sub>, 7Å LiF(0.5 Å/초의 속도로 피착됨), 50Å Al, 및 최종적으로 150Å의 Ag를 진공 증발시킴으로써 OLED 스택을 피착한다.

본 발명은 각종 실시예를 참조하여 특별히 도시되고 설명되었지만, 본 기술 분야의 당업자는 본 발명의 정신 및 범위에서 벗어나지 않는다면 각종 다른 형태 및 상세에서의 변경이 이루어질 수 있음을 이해할 것이다.

#### 도면의 간단한 설명

도 1은 ZnO 로우 및 컬럼 드라이버들, ZnO 픽셀 트랜지스터들, 및 공통 기판의 위에 OLED를 구성하는데 이용될 수 있는 애퍼처(aperture) 마스킹 처리를 예시한다.

도 2는 기판으로부터 멀어지게 발광하는 상부(top) 발광 OLED 스택을 구동하는 ZnO TFT 픽셀 트랜지스터를 구비하는 기판의 일례의 단면도를 예시한다.

도 3은 기판을 통해 발광하는 하부(bottom) 발광 OLED 스택을 구동하는 ZnO TFT 픽셀 트랜지스터를 구비하는 기판의 또 다른 예의 단면도를 예시한다.

도 4는 디스플레이의 단일 픽셀을 형성하는 OLED 회로와 ZnO 픽셀 트랜지스터들의 하나의 셀들의 예시적인 일례이다.

도 5는 디스플레이의 픽셀 어레이를 형성하는 OLED 회로와 ZnO 픽셀 트랜지스터들의 셀들의 어레이의 예시적인 일례이다.

도 6은 디스플레이의 단일 픽셀을 형성하는 OLED 회로와 ZnO 픽셀 트랜지스터들의 하나의 셀들의 예시적인 일례이다.

도 7은 도 4 또는 6의 회로에 기초하는 도 5에 도시한 바와 같은 셀들의 어레이와 인터페이스하는 로우 및 컬럼 드라이버 회로를 생성하기 위해 사용되는 디지털 논리 게이트에 기초하는 ZnO TFT의 예시적인 일례이다.

도 8은 로우 및 컬럼 드라이버 회로를 생성하기 위해서 도 7의 디지털 논리 게이트와 같은 디지털 논리 게이트에 기초하는 ZnO TFT에 의해 형성되는 디지털 논리 플립-플롭의 예시적인 일례이다.

도 9는 로우 또는 컬럼 드라이버 회로를 제공하기 위해서 도 8의 디지털 논리 플립-플롭과 같은 디지털 논리 플립-플롭에 기초하는 ZnO TFT에 의해 형성되는 디지털 논리 시프트 레지스터의 예시적인 일례이다.

#### 도면

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

도면9

| 专利名称(译)        | 使用与有机发光二极管集成的氧化锌行和列驱动器的方法和显示                                                                                      |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | KR1020070074594A                                                                                                  | 公开(公告)日 | 2007-07-12 |

| 申请号            | KR1020077009975                                                                                                   | 申请日     | 2005-10-17 |

| [标]申请(专利权)人(译) | 明尼苏达州采矿制造公司                                                                                                       |         |            |

| 申请(专利权)人(译)    | 3M创新湾执行的COM PANY                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 3M创新湾执行的COM PANY                                                                                                  |         |            |

| [标]发明人         | BAUDE PAUL F<br>바우드폴에프<br>THEISS STEVEN D<br>테이스스티븐디<br>HAASE MICHAEL A<br>하세마이클에이<br>HEMMESCH ERIC W<br>헴머쉬에릭더블유 |         |            |

| 发明人            | 바우드,폴,에프.<br>테이스,스티븐,디.<br>하세,마이클,에이.<br>헴머쉬,에릭,더블유.                                                              |         |            |

| IPC分类号         | H01L27/32                                                                                                         |         |            |

| CPC分类号         | H01L27/3262 H01L27/1214 H01L2251/5338 H01L27/3248 H01L29/7869 H01L2251/5315 H01L27/3244 H01L27/1225 H01L27/1218   |         |            |

| 优先权            | 10/979067 2004-11-02 US                                                                                           |         |            |

| 外部链接           | Espacenet                                                                                                         |         |            |

|                |                                                                                                                   |         |            |

#### 摘要(译)

使用具有ZnO沟道控制像素晶体管的低和列驱动器。寻址阵列的OLED以便创建显示屏的图像。通过使用孔掩模或光刻和孔掩模的组合,包括ZnO低的显示器底板,可以包括列驱动器和OLED。由此实现ZnO像素晶体管,ZnO低和单片集成的列驱动器。OLED通道,像素晶体管,显示背板,孔径掩模,低位和列驱动器OLED。