(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년05월09일

(11) 등록번호 10-1033365

(24) 등록일자 2011년04월28일

(51) Int. Cl.

G09G 3/30 (2006.01) H05B 33/08 (2006.01)

H01L 51/50 (2006.01)

(21) 출원번호 10-2009-0011434

(22) 출원일자 2009년02월12일

심사청구일자 2009년02월12일

(65) 공개번호 10-2009-0087831

(43) 공개일자 2009년08월18일

(30) 우선권주장

JP-P-2008-031284 2008년02월13일 일본(JP)

(뒷면에 계속)

(56) 선행기술조사문현

W002075709 A1

KR1020060117196 A

JP2005338591 A

JP09330060 A

전체 청구항 수 : 총 18 항

심사관 : 김홍섭

(54) EL 표시 장치

### (57) 요약

EL 표시 장치는, 영상 신호 전압을 출력하는 소스 드라이버 회로와, 상기 표시 화면 중의 화소를 선택하는 게이트 드라이버 회로와, 상기 영상 신호 전압을 유지하는 제1 컨덴서와, 화소의 상기 EL 소자에 전류를 공급하는 구동 트랜지스터를 갖고, 상기 영상 신호 전압을 상기 구동 트랜지스터에 인가하여 소정 동작을 행함과 함께, 상기 제1 컨덴서에 상기 영상 신호 전압을 기입하고, 상기 제1 컨덴서에 유지된 상기 영상 신호 전압에 의해, 오프셋 캔슬 동작을 행한다.

### 대 표 도 - 도1

(30) 우선권주장

JP-P-2008-033399 2008년02월14일 일본(JP)

JP-P-2008-105475 2008년04월15일 일본(JP)

JP-P-2009-011791 2009년01월22일 일본(JP)

---

## 특허청구의 범위

### 청구항 1

EL 소자를 갖는 화소가 매트릭스 형상으로 복수 배치된 표시 화면을 갖는 EL 표시 장치로서,

영상 신호 전압을 출력하는 소스 드라이버 회로와,

상기 표시 화면 중의 화소를 선택하는 게이트 드라이버 회로와,

상기 영상 신호 전압을 유지하는 제1 컨덴서와,

상기 화소의 상기 EL 소자에 전류를 공급하는 구동 트랜지스터를 갖고,

상기 영상 신호 전압을 상기 구동 트랜지스터에 인가하여 소정 동작을 행함과 함께, 상기 제1 컨덴서에 상기 영상 신호 전압을 기입하고,

상기 제1 컨덴서에 유지된 상기 영상 신호 전압에 의해, 오프셋 캔슬 동작을 행하는 EL 표시 장치.

### 청구항 2

EL 소자를 갖는 화소가 매트릭스 형상으로 복수 배치된 표시 화면을 갖는 EL 표시 장치로서,

영상 신호 전압을 출력하는 소스 드라이버 회로와,

상기 표시 화면 중의 화소를 선택하는 게이트 드라이버 회로와,

동작용 신호 전압을 유지하는 제1 컨덴서와,

상기 화소의 상기 EL 소자에 전류를 공급하는 구동 트랜지스터를 갖고,

상기 동작용 신호 전압을, 상기 구동 트랜지스터를 통하여 상기 화소에 인가하여 소정 동작을 행함과 함께, 상기 제1 컨덴서에 상기 동작용 신호 전압을 기입하고,

상기 동작용 신호 전압의 인가를 정지한 후, 상기 제1 컨덴서에 기입된 상기 동작용 신호 전압에 의해, 상기 소정 동작을 계속하는 EL 표시 장치.

### 청구항 3

제1항 또는 제2항에 있어서,

상기 각 화소에 리세트 전압을 인가하는 제1 스위치 트랜지스터가 형성되고, 상기 제1 스위치 트랜지스터는 멀티 게이트 구조인 EL 표시 장치.

### 청구항 4

제1항 또는 제2항에 있어서,

상기 EL 소자에 흐르는 전류 경로에, 제2 스위치 트랜지스터가 형성되고,

상기 제2 스위치 트랜지스터를 온/오프 제어함으로써, 상기 표시 화면에 디형상의 비표시 영역을 발생시키고,

상기 비표시 영역이 1프레임 주기로 상기 표시 화면을 이동시키는 EL 표시 장치.

### 청구항 5

제1항 또는 제2항에 있어서,

상기 각 화소에 상기 영상 신호 전압을 인가하는 제3 스위치 트랜지스터가 형성되고,

상기 제3 스위치 트랜지스터의 게이트 단자와, 상기 제3 스위치 트랜지스터의 드레인 단자 사이에, 제2 컨덴서가 형성되어 있는 EL 표시 장치.

### 청구항 6

제1항 또는 제2항에 있어서,

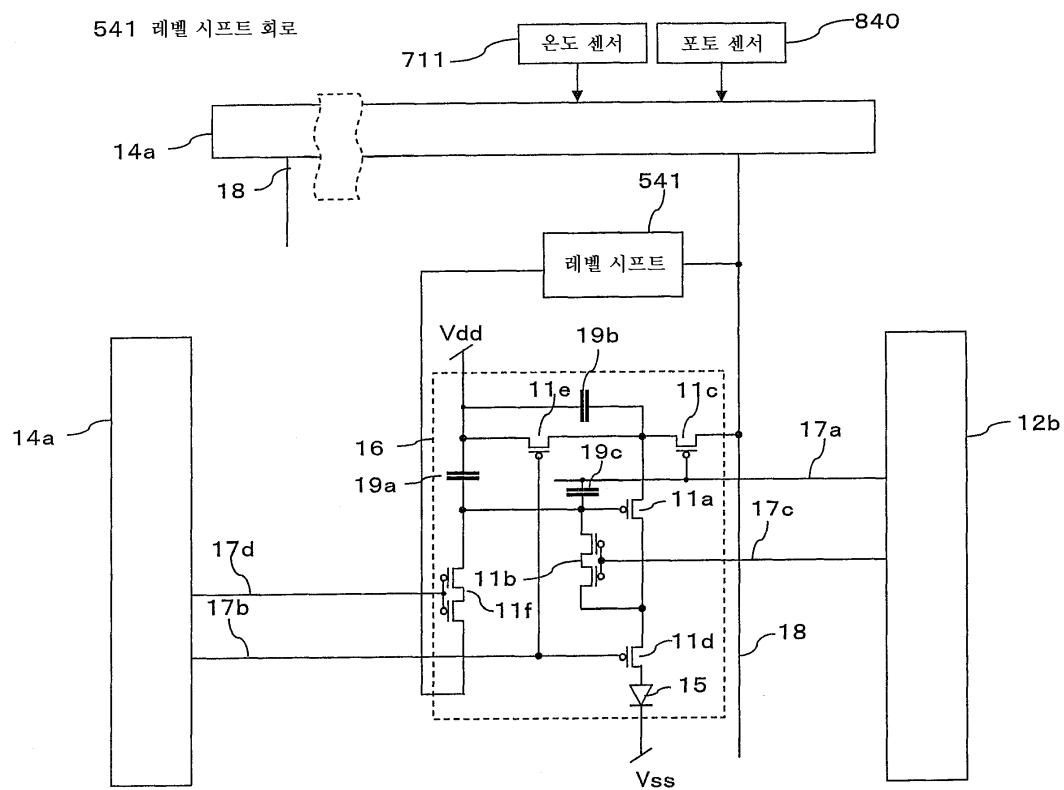

상기 게이트 드라이버 회로, 또는 상기 게이트 드라이버 회로의 입력단에 레벨 시프트 회로가 형성되고,

상기 소스 드라이버 회로로부터 출력된 신호가, 상기 레벨 시프트 회로에서 레벨 시프트하여 상기 게이트 드라

이버 회로에 입력되는 EL 표시 장치.

#### 청구항 7

제1항 또는 제2항에 있어서,

상기 게이트 드라이버 회로는, P채널 트랜지스터 또는 N채널 트랜지스터로 구성되어 있는 EL 표시 장치.

#### 청구항 8

제1항 또는 제2항에 있어서,

상기 소스 드라이버 회로는, 반도체 IC이고,

상기 소스 드라이버 회로는, 상기 표시 화면이 형성된 기판에 실장되고,

상기 소스 드라이버 회로와 상기 기판 사이에 차광막이 형성되어 있는 EL 표시 장치.

#### 청구항 9

제1항 또는 제2항에 있어서,

매트릭스 형상의 동일 열에 배치된 복수의 상기 화소에 대하여, 제1 소스 신호선과 제2 소스 신호선이

형성되고,

상기 제1 소스 신호선에 의해 제1 영상 신호 전압이 인가되는 상기 화소와, 상기 제2 소스 신호선에 의해 제2

영상 신호 전압이 인가되는 상기 화소가 상이한 EL 표시 장치.

#### 청구항 10

제1항 또는 제2항에 있어서,

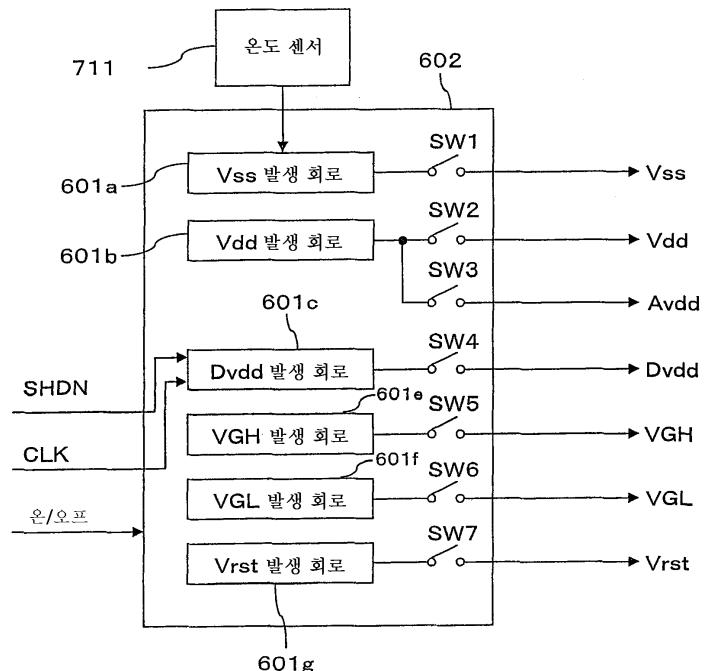

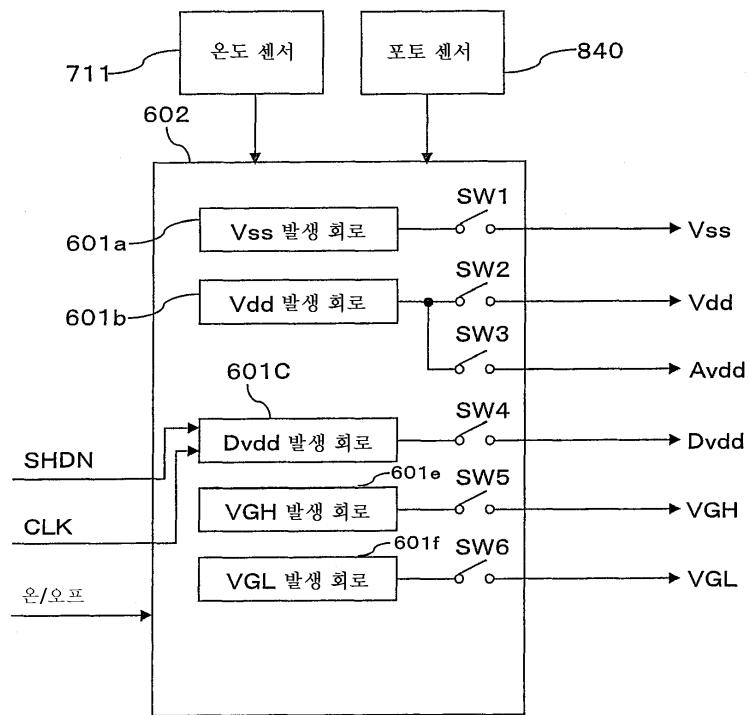

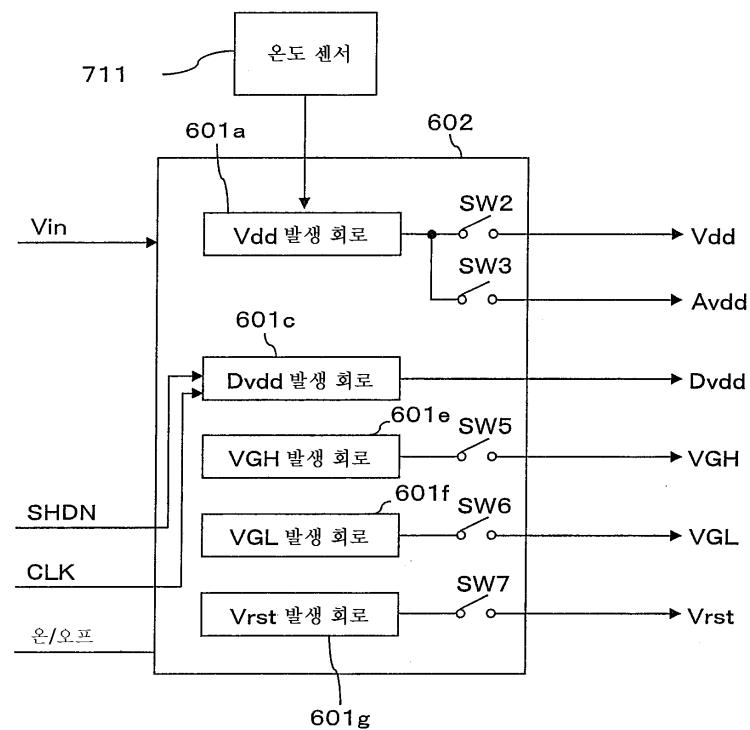

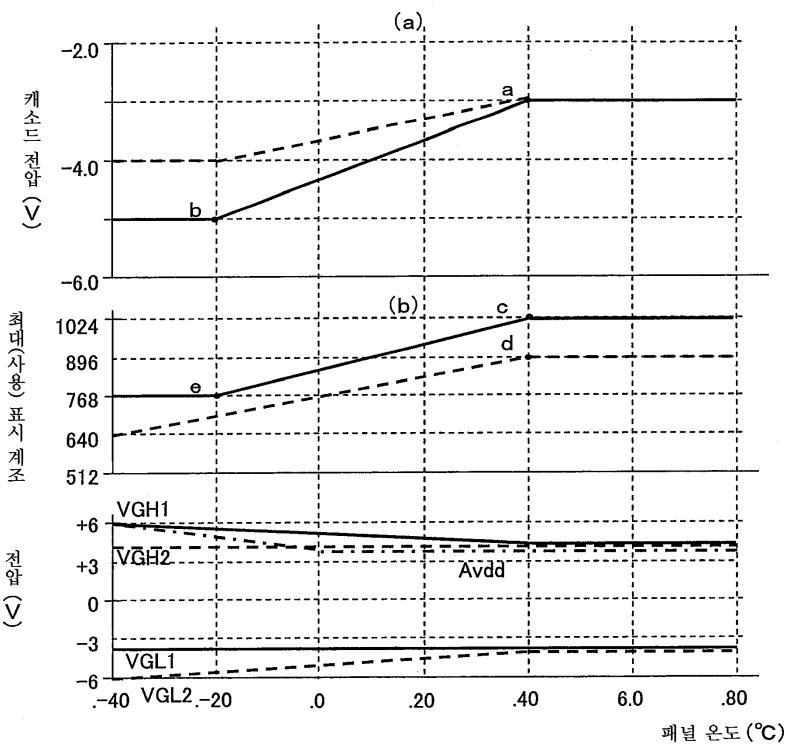

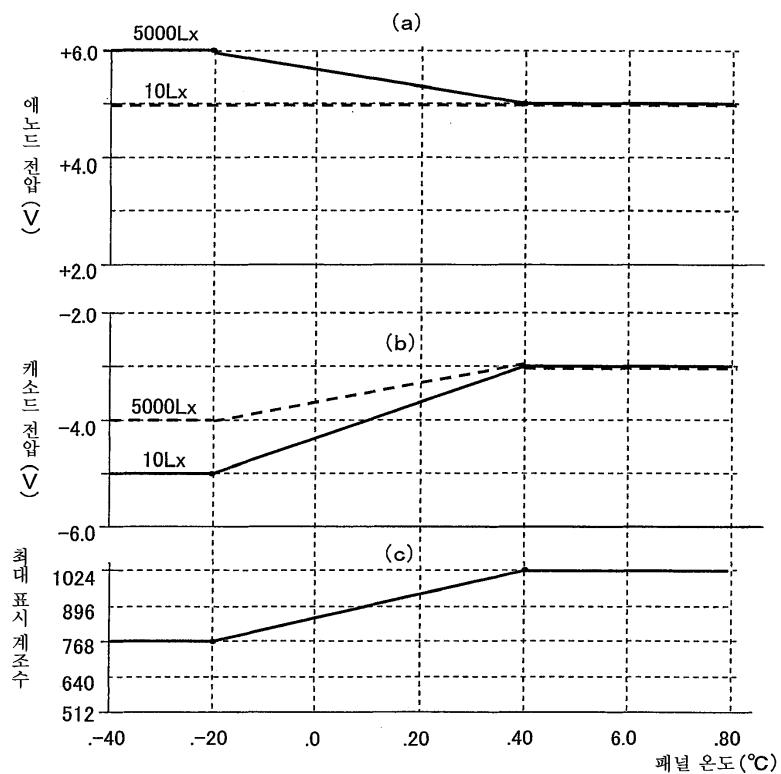

온도 센서와, 상기 EL 소자에 인가하는 전압을 발생하는 전압 발생 회로를 더 갖고,

상기 온도 센서의 출력에 기초하여 상기 전압 발생 회로가 상기 전압을 가변하는 EL 표시 장치.

#### 청구항 11

제1항 또는 제2항에 있어서,

온도 센서를 더 갖고,

상기 온도 센서의 출력에 기초하여, 상기 표시 화면에서 사용하는 최대 표시 계조를 가변하는 EL 표시 장치.

#### 청구항 12

제10항에 있어서,

상기 온도 센서가 상기 소스 드라이버 회로에 내장되어 있는 EL 표시 장치.

#### 청구항 13

제1항 또는 제2항에 있어서,

상기 소스 드라이버 회로는, 소스 신호선을 선택하는 선택 스위치 회로가 복수 내장되어 있는 EL 표시 장치.

#### 청구항 14

제1항 또는 제2항에 있어서,

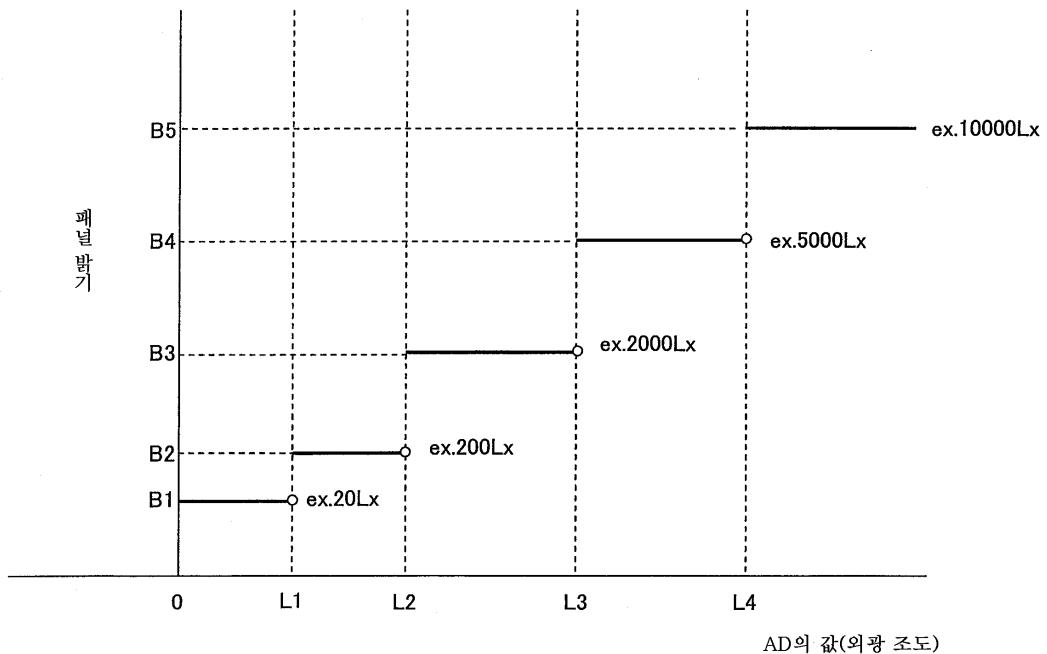

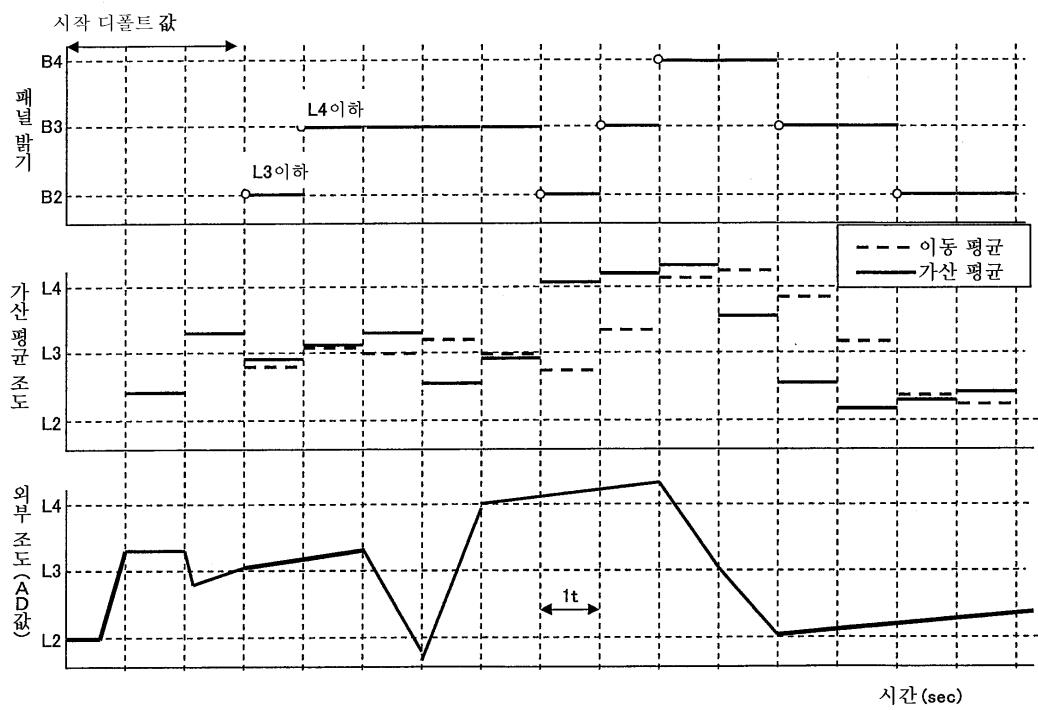

외광의 밝기를 검출하는 포토 센서를 더 갖고,

상기 포토 센서의 출력에 기초하여, 상기 표시 화면의 밝기를 가변하는 EL 표시 장치.

**청구항 15**

제1항 또는 제2항에 있어서,

상기 화소에 인가하는 리세트 전압의 발생 회로를 더 갖고,

상기 리세트 전압은, 상기 영상 신호 전압에 기초하여 가변하는 EL 표시 장치.

**청구항 16**

제1항 또는 제2항에 있어서,

상기 화소가 복수의 색으로 구성되고, 상기 화소의 화소 전극의 면적이 색에 따라서 상이한 EL 표시 장치.

**청구항 17**

제2항에 있어서,

상기 동작용 신호 전압이 상기 영상 신호 전압이고, 상기 소정의 동작이 오프셋 캔슬 동작인 EL 표시 장치.

**청구항 18**

제2항에 있어서,

상기 동작용 신호 전압이 리세트 신호 전압이고, 상기 소정의 동작이 리세트 동작인 EL 표시 장치.

**청구항 19**

삭제

**청구항 20**

삭제

**명세서****발명의 상세한 설명****기술 분야**

[0001]

본 발명은, 유기 또는 무기 일렉트로 루미네센스(EL) 소자 등을 이용하는 EL 표시 패널(표시 장치) 등의 자발광 표시 패널(표시 장치)을 이용한, EL 표시 장치(유기 발광 표시 장치)에 관한 것이다. 또한, 영상 신호 전압(영상 신호 데이터) Vsig를 화소에 소정 기간 유지하는 컨덴서(용량, 부가 컨덴서)를 갖는 표시 패널, 표시 장치에 관한 것이다.

**배경 기술**

[0002]

전기 광학 변환 물질로서 유기 일렉트로 루미네센스(EL) 재료 혹은 무기 EL 재료를 이용한 액티브 매트릭스형의 화상 표시 장치는, 화소에 기입되는 전류에 따라서 발광 휘도가 변화한다. EL 표시 장치는, 각 화소에 발광 소자를 갖는 자발광형이다. EL 표시 장치는, 액정 표시 패널에 비하여 화상의 시인성이 높고, 발광 효율이 높고, 백라이트가 불필요하며, 응답 속도가 빠르다는 등의 이점을 갖는다.

[0003]

유기 EL(PLED, OLED, OEL) 패널은, 액티브 매트릭스 방식의 개발이 활발히 행하여지고 있다. 이 방식은, 각 화소 회로 내부의 발광 소자에 흐르는 전류를, 화소 회로 내부에 형성한 능동 소자(일반적으로는 박막 트랜지스터, TFT, FET, MOS 트랜지스터)에 의해 제어하는 것이다(일본 특허 공개 2003-255856 공보, 일본 특허 공개 2003-271095 공보 참조).

[0004]

유기 EL 표시 패널은, 저온 혹은 고온 폴리실리콘으로 이루어지는 트랜지스터 어레이를 이용하여 패널을 구성한다. 그러나, 유기 EL 소자는, 폴리실리콘 트랜지스터 어레이의 트랜지스터 특성에 변동이 있으면, 표시 불균일이 발생한다.

[0005]

EL 소자(15)에 전류를 공급하는 구동 트랜지스터(11a)에 특성 변동이 있으면, 변환되는 전류 신호에도 변동이

발생한다. 통상적으로, 트랜지스터(11a)는 50% 이상의 특성 변동이 있다. 그 때문에, 구동 트랜지스터의 특성 변동이 표시 불균일으로서 표시되어, 화상 표시 품위를 저하시키고 있었다.

## 발명의 내용

### 해결 하고자하는 과제

[0006] 그래서 본 발명은, 충분한 오프셋 캔슬 기간을 확보하여, 구동 트랜지스터의 특성 변동을 보상하고, 특성 표시 불균일이 없는 화상 표시를 실현할 수 있는 EL 표시 장치를 제공한다.

### 과제 해결수단

[0007] 본 발명은, EL 소자를 갖는 화소가 매트릭스 형상으로 복수 배치된 표시 화면을 갖는 EL 표시 장치로서, 영상 신호 전압을 출력하는 소스 드라이버 회로와, 상기 표시 화면 내의 화소를 선택하는 게이트 드라이버 회로와, 상기 영상 신호 전압을 유지하는 제1 컨텐서와, 상기 화소의 상기 EL 소자에 전류를 공급하는 구동 트랜지스터를 갖고, 상기 영상 신호 전압을 상기 구동 트랜지스터에 인가하여 소정 동작을 행함과 함께, 상기 제1 컨텐서에 상기 영상 신호 전압을 기입하고, 상기 제1 컨텐서에 유지된 상기 영상 신호 전압에 의해, 오프셋 캔슬 동작을 행하는 것을 특징으로 하는 EL 표시 장치이다.

[0008] 또한, 본 발명은, EL 소자를 갖는 화소가 매트릭스 형상으로 복수 배치된 표시 화면을 갖는 EL 표시 장치로서, 영상 신호 전압을 출력하는 소스 드라이버 회로와, 상기 표시 화면 내의 화소를 선택하는 게이트 드라이버 회로와, 신호 전압을 유지하는 제1 컨텐서와, 상기 화소의 상기 EL 소자에 전류를 공급하는 구동 트랜지스터를 갖고, 상기 신호 전압을 상기 구동 트랜지스터를 통하여 상기 화소에 인가하여 소정 동작을 행함과 함께, 상기 제1 컨텐서에 상기 신호 전압을 기입하고, 상기 신호 전압의 인가를 정지한 후, 상기 제1 컨텐서에 기입된 상기 신호 전압에 의해, 상기 소정 동작을 계속하는 것을 특징으로 하는 EL 표시 장치이다.

### 효과

[0009] 본 발명에 따르면, 충분한 오프셋 캔슬 기간을 확보할 수 있으므로, 양호하게 구동 트랜지스터를 오프셋 캔슬할 수 있다. 따라서, 구동 트랜지스터의 특성 변동을 보상하여, 특성 표시 불균일이 없는 화상 표시를 실현할 수 있다.

## 발명의 실시를 위한 구체적인 내용

[0010] 본 발명의 실시예의 EL 표시 장치는, 각 화소에 오프셋 캔슬 동작에 사용하는 소정 전압을 유지하는 컨텐서(오프셋 캔슬 컨텐서)를 구비한다. 오프셋 캔슬 컨텐서는, 화소가 선택되었을 때에, 화소에 인가된 영상 신호 등의 소정 전압을 유지한다. 구동 트랜지스터 화소가 비선택으로 된 후에도, 오프셋 캔슬 컨텐서에 유지된 소정 전압을 이용하여, 구동 트랜지스터에 오프셋 캔슬 동작을 계속시킨다.

[0011] 종래의 화소 구성에서는, 화소가 선택되었을 때에 오프셋 캔슬 동작을 실시하고 있었다. 따라서, 오프셋 캔슬 동작은 화소행의 선택 기간 이내에 한정되기 때문에, 충분한 오프셋 캔슬 동작 시간을 확보할 수 없어, 충분히 오프셋 캔슬을 실현할 수 없었다.

[0012] 본 실시예에 따르면, 오프셋 캔슬 동작을 계속시키는 오프셋 캔슬 컨텐서를 각 화소에 갖고 있기 때문에, 화소가 비선택 상태이어도, 오프셋 캔슬 동작을 계속할 수 있다. 따라서, 구동 트랜지스터는 충분히 오프셋 캔슬 기간을 확보할 수 있으므로, 구동 트랜지스터 구동 트랜지스터(11a)의 특성 변동을 보상하여, 특성 표시 불균일이 없는 화상 표시를 실현할 수 있다.

[0013] <실시예 1>

[0014] 본 발명의 실시예 1에 대하여 설명한다.

[0015] 또한, 각 도면에서 설명에 필요없는 개소, 부분은 생략하고 있다. 따라서, 각 도면에서 도시하고 있지 않아도, 다른 도면에 도시한 사항을 적용 혹은 조합할 수 있다. 또한, 각 도면에는 확대 혹은 축소한 개소, 부분이 있다. 또한, 실시예 1~실시예 7은 상호 조합할 수 있는 것은 물론이다.

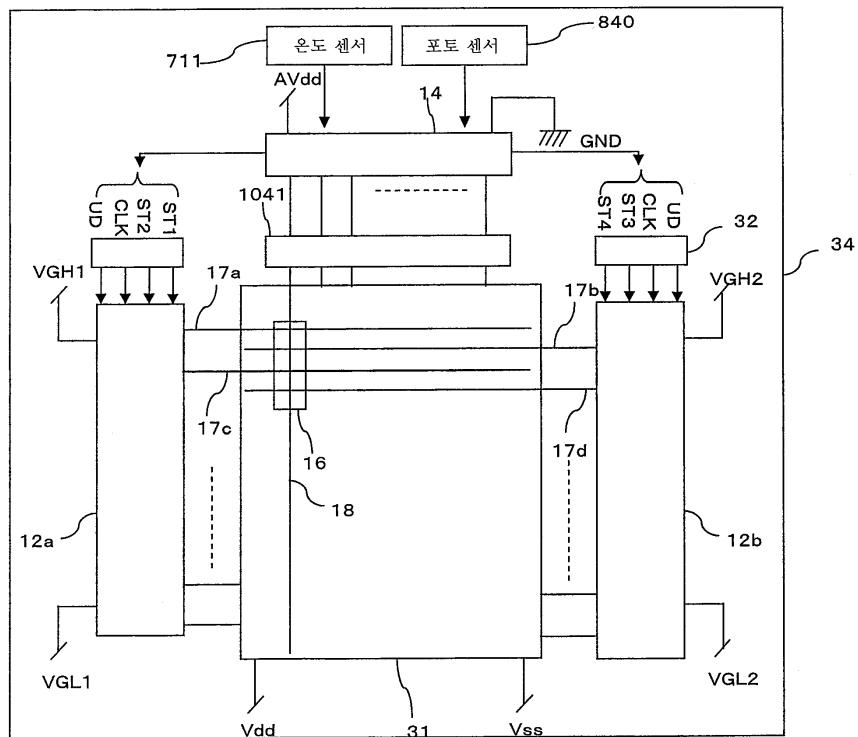

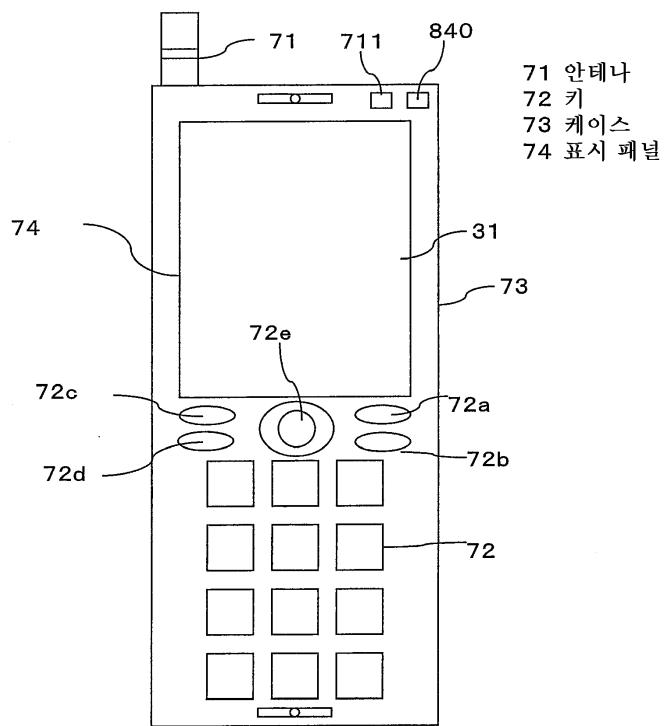

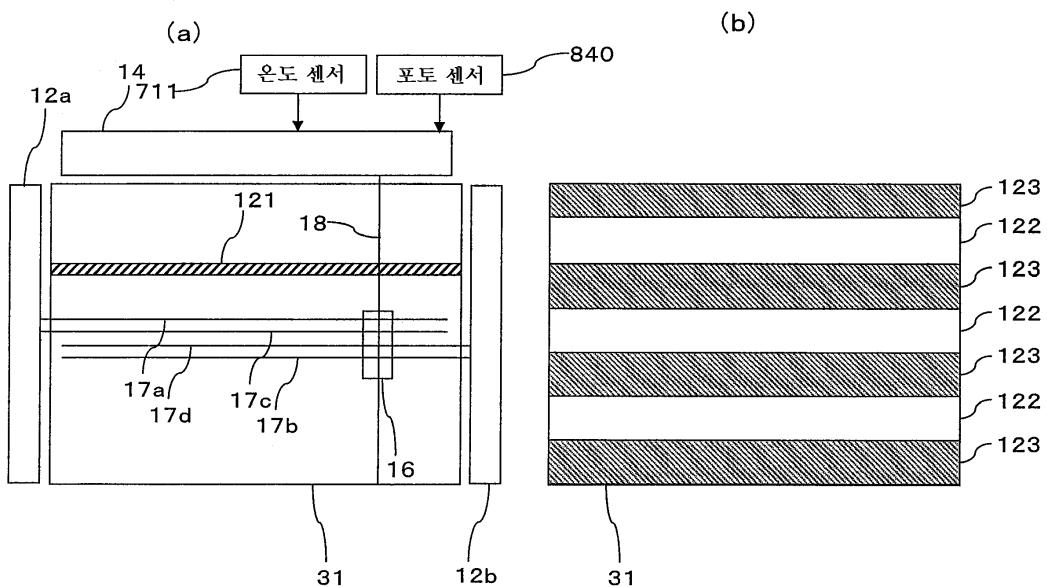

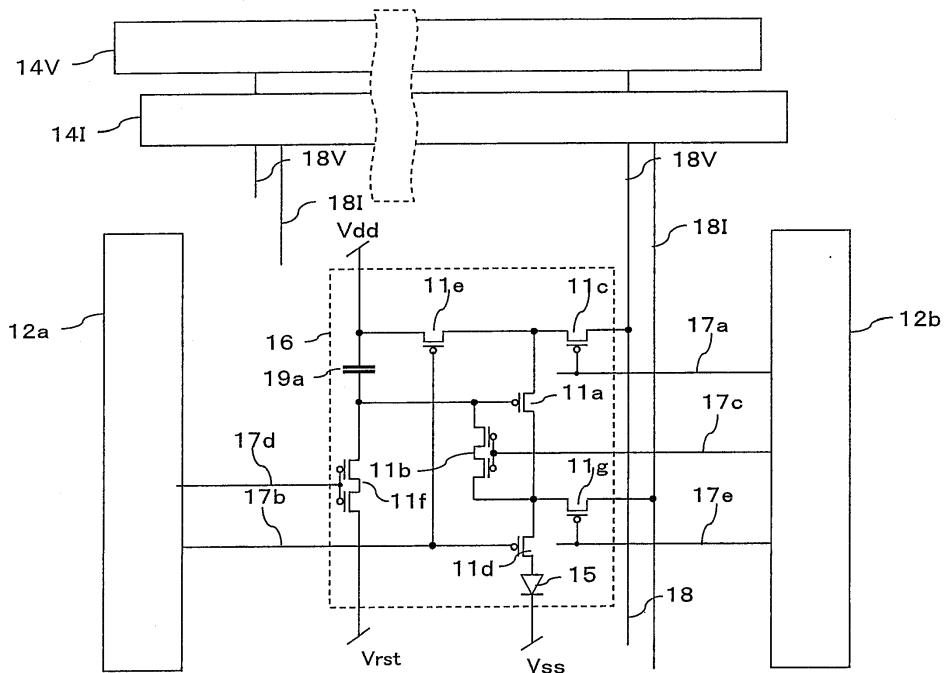

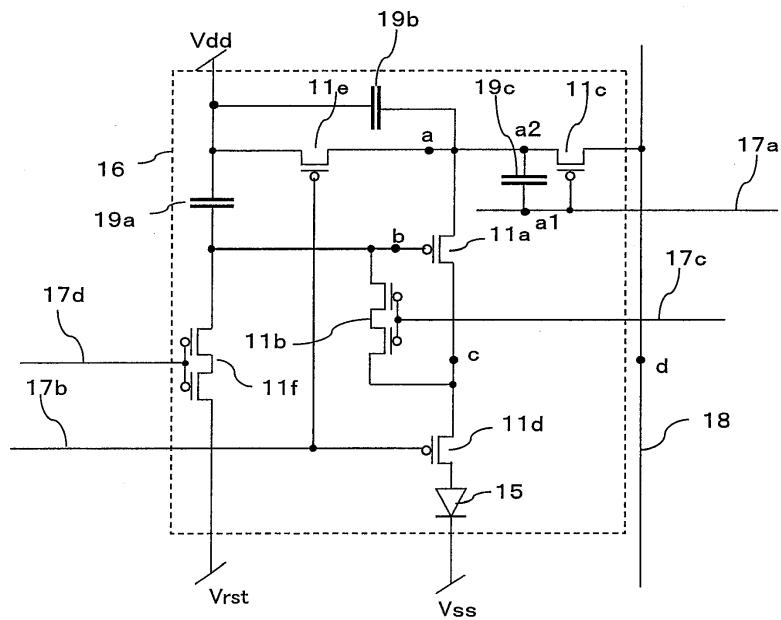

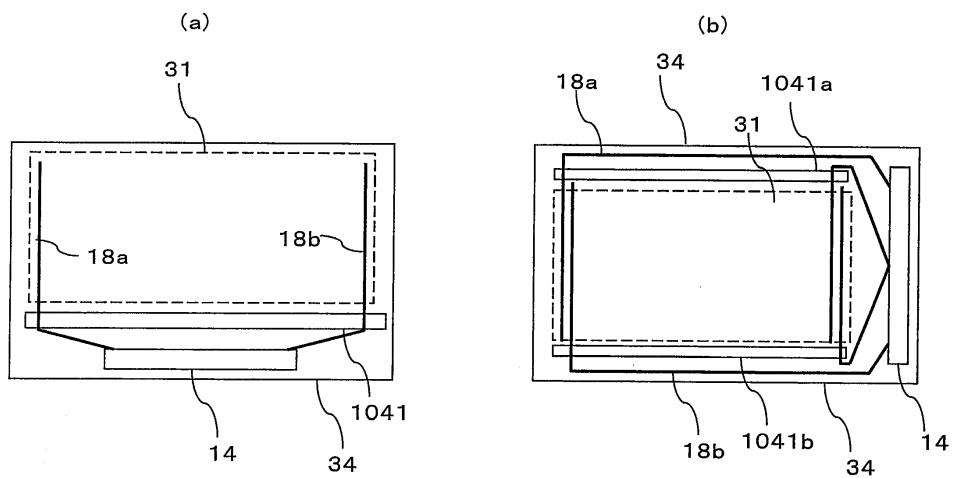

[0016] 도 1은, 실시예 1의 EL 표시 장치의 화소 구성이다. 또한, 도 3은, 화소(16)가 매트릭스 형상으로 배치된 표시

영역(31)에, 게이트 드라이버 회로(12) 및 소스 드라이버 IC(14)가 접속된 구성도이다.

[0017] 도 3에 도시하는 바와 같이, 게이트 드라이버 회로(12)에는, 클럭 신호(CLK), 스타트 신호(ST1, ST2) 등은, 업다운 신호(UD)가 인가된다. 클럭 신호(CLK)는, 수평 동기 신호(HD)에 동기하고 있다. 또한, 필요에 따라서, EL 표시 장치 내에 내장하는 발진 모듈에 의해 클럭 신호(CLK)를 발생시킨다. 스타트 신호(ST2)를 제어함으로써, Duty 구동을 실현할 수 있다.

[0018] 클럭 신호(CLK), 스타트 신호(ST1, ST2), 업다운 신호(UD) 등 게이트 드라이버 회로(12)에 인가하는 신호는, 소스 드라이버 IC(14)에서 발생하고, 어레이 기판에 형성한 레벨 시프터 회로에서 레벨 시프트하여 게이트 드라이버 회로(12)에 인가된다. 게이트 드라이버 회로(12)에서 사용하는 클럭 신호 등은, 소스 드라이버 IC(14)로부터 공급한다.

[0019] 레벨 시프트하는 전압(예를 들면, VGH, VGL)은, 소스 드라이버 IC(14)에서 발생하고, 각 신호(CLK, UD, ST 등) 소스 드라이버 IC(14) 내에 내장된 레벨 시프트 회로에서 레벨 시프트하여 게이트 드라이버 회로(12)에 인가해도 된다.

[0020] 레벨 시프트 회로는, 소스 드라이버 IC(14)로부터 출력되는 로직 레벨 전압(예를 들면, 3V)을 게이트 드라이버 회로(12)에서 사용하는 전압(예를 들면, VGH, VGL 전압)으로 변환하는 것이다. 레벨 시프트 회로는, 게이트 드라이버 회로(12) 내 또는 게이트 드라이버 회로(12)의 입력단 혹은 소스 드라이버 IC(14)의 출력단에 형성 또는 배치된다.

[0021] 클럭 신호(CLK)는, 선택하는 화소행을 순차 이동시키기 위한 신호이다. 스타트 펄스 신호(ST)는, 선택하는 화소행을 지정하기 위한 신호이다. 스타트 펄스 신호(ST)는 클럭 신호(CLK)에 의해, 게이트 드라이버 회로(12)의 시프트 레지스터 회로 내를 이동한다. 업다운 신호(UD)는, 화면의 상하 반전 절환 신호이다. 시프트 레지스터 회로 내의 스타트 펄스 위치에 따라서, 게이트 신호선(17)이 선택된다(게이트 신호선(17)에 온 전압(VGL)이 인가됨).

[0022] 본 발명의 실시예 1은, 화소(16)의 트랜지스터(11)를 P채널 트랜지스터로 형성하고, 게이트 드라이버 회로(12)를 P채널 트랜지스터로 형성한다. 화소(16)의 트랜지스터(11)와 게이트 드라이버 회로(12)의 양방을 P채널 트랜지스터로 형성함으로써, EL 표시 패널의 제조 코스트는 저코스트로 할 수 있다.

[0023] 소스 드라이버 IC(14)로서는, 영상 신호를 전압 신호로서 출력하는 것, 영상 신호를 전류 신호로서 출력하는 것이 예시된다. 본 명세서에서는, 설명을 용이하게 하기 위하여, 소스 드라이버 IC(14)는, 전압 신호를 출력하는 것으로서 설명을 한다. 또한, 도 2, 도 111은 본 실시예의 EL 표시 장치의 구동 방법의 설명도이다.

[0024] 본 실시예의 표시 패널은, R(적), G(녹), B(청)색의 화소가 매트릭스 형상으로 배치되어 있다. 또한, RGB 외에, W(백)색의 화소를 배치해도 된다. 백색 발광의 화소를 형성함으로써, 표시 화상이 높은 휴도를 실현할 수 있다. 따라서, 빛나는 감이 있는 화상 표시를 실현할 수 있다. 특히 W(백) 화소를 갖는 패널 구성은, 도 84, 도 99 등의 duty 구동 방식, 최대 사용 계조 표시 구동 방식과 조합하는 것이 바람직하다.

[0025] 또한, 백색의 화소를 표시 영역의 전체면에 형성하고, 컬러 필터에 의해, RGB 화소를 매트릭스 형상으로 형성해도 된다.

[0026] R, G, B의 화소 개구율(혹은 화소 전극 면적)은, 서로 다르게 해도 된다. 개구율을 서로 다르게 함으로써, 각 RGB의 EL 소자(15)에 흐르는 전류 밀도를 서로 다르게 할 수 있다. 전류 밀도를 서로 다르게 함으로써, RGB의 EL 소자(15)의 열화 속도를 동일하게 할 수 있다. RGB의 열화 속도를 동일하게 하면, 장기간, EL 표시 장치를 사용해도, EL 표시 장치의 표시 화면의 화이트 밸런스 어긋남이 발생하지 않는다.

[0027] 또한, 인접한 화소행에서, 3원색의 배치가 서로 다르도록 배치하는 것이 바람직하다. 예를 들면, 짹수행째가, 좌측으로부터 R, G, B의 배치이면, 홀수행째는 B, G, R의 배치로 한다. 이와 같이 배치함으로써, 적은 화소수라도, 화상의 경사 방향의 해상도가 개선된다. 또한, 화소를 멜타 배치로 해도 된다. 외광 또는 EL 표시 패널 등으로부터 방사되는 광(EL 소자(15)로부터 출사되는 광)이, 소스 드라이버 IC(소스 드라이버 회로)(14)에 조사되면, 포토 컨덕터 현상(포토콘)에 의해 오동작을 야기한다. 이 과정에 대응하기 위하여, 소스 드라이버 IC 칩의 아래 또는, 소스 드라이버 회로(14)의 하층에 차광막을 형성한다. 즉, 소스 드라이버 IC와 어레이 기판 사이에, 차광물을 형성 또는 배치한다. 차광막은, 패널 기판의 표면에 금속 박막, 유기 재료 혹은 무기 재료 등으로 이루어지는 광 흡수막으로서 형성한다. 바람직하게는, 차광막은, EL 소자(15)에 전류를 공급하는 애노드 배선, 캐소드 배선을 사용한다(소스 드라이버 IC 칩 아래에 형성함). 차광막을 애노드 배선, 캐소드 배선으로

형성하면 전류(전압) 공급 배선과 차광막을 겹용할 수 있다. 따라서, 차광막 형성이 용이하고, 저코스트화할 수 있다. 이 구성은, 소스 드라이버 회로(14)가 IC 칩의 경우에 한정되는 것은 아니다. 소스 드라이버 회로(14)가, 저온 폴리실리콘, 고온 폴리실리콘 혹은 고상 성장에 의해 형성된 반도체막(CGS), 아몰퍼스 실리콘 기술을 이용한 경우에도 적용된다. 즉, 이 소스 드라이버 회로(14)의 이면 혹은 하층에 차광막을 형성한다.

[0028] 이상과 같이, 본 실시예의 EL 표시 장치에서, 소스 드라이버 회로(14)는, 반도체 IC(IC chip)이고, 상기 소스 드라이버 회로(14)는, 상기 표시 화면이 형성된 기판에 실장되어 있고, 상기 소스 드라이버 회로의 아래이며, 또한 상기 기판 위에, 차광막이 형성되어 있는 것을 하나의 특징으로 하는 것이다. 소스 드라이버 IC(14)에는, 게이트 드라이버 회로(12)에서 사용하는 전압 VGH, VGL을 발생시키는 차지 펌프 회로를 구성해 두는 것이 바람직하다. 전압 VGH는, 트랜지스터(11)를 오프시키는 전압이고, 전압 VGL은 트랜지스터(11)를 온시키는 전압이다. 단, 이 온/오프 전압은, 트랜지스터(11)가 P채널 트랜지스터인 경우이며, 트랜지스터(11)가 N채널인 경우에는, 전압 VGH는, 트랜지스터(11)를 온시키는 전압이고, 전압 VGL은 트랜지스터(11)를 오프시키는 전압으로 된다. 또한, VGH, VGL은 게이트 드라이버 회로(12)의 전원 전압이다.

[0029] 도 3에서, 게이트 드라이버 회로(12a)는, VGH1, VGL1 전압을 인가하고, 게이트 드라이버 회로(12a)는, VGH2, VGL2 전압을 인가한다. 스위치 트랜지스터(11)가, P채널 트랜지스터인 경우에는, VGL1과 VGL2를 서로 다르게 한다. VGH1과 VGH2는, 공통의 전압으로 한다( $VGH1=VGH2$ ). 스위치 트랜지스터(11)가, N채널 트랜지스터인 경우에는, VGH1과 VGH2를 서로 다르게 한다. VGL1과 VGL2는, 공통의 전압으로 한다( $VGL1=VGL2$ ).

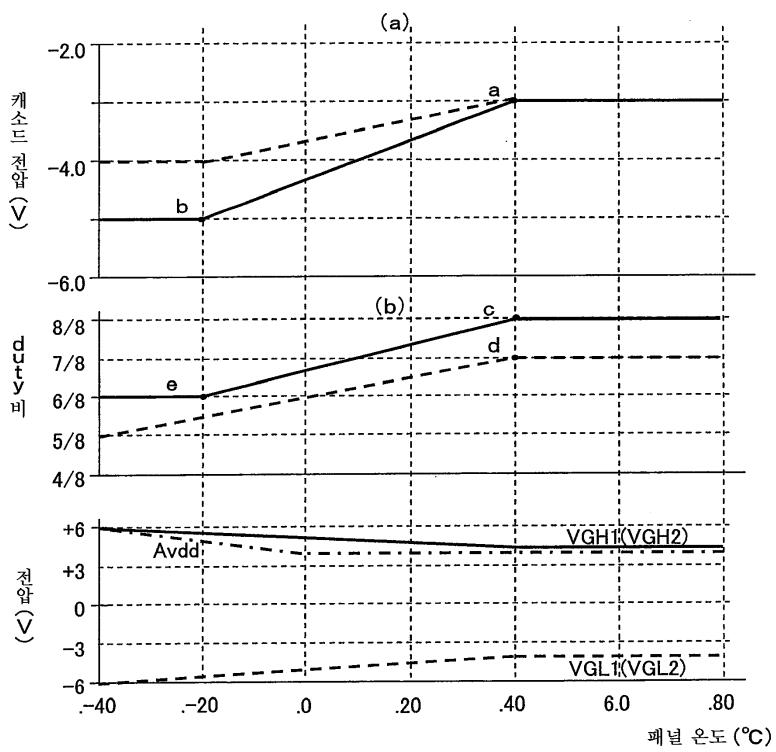

[0030] 도 1의 화소 구성이면, 스위치 트랜지스터(11d)의 온 전압(VGL)은, 스위치 트랜지스터(11c)의 온 전압(VGL)보다도 높게 한다. 혹은, 스위치 트랜지스터(11d)의 오프 전압(VGH)-온 전압(VGL)의 전위차는, 스위치 트랜지스터(11c)의 오프 전압(VGH)-온 전압(VGL)의 전위차보다도 작게 한다. 스위치 트랜지스터(11d)의 온 저항을 비교적 높게 하여, EL 소자(15)의 단자간(애노드-캐소드) 전압의 변화가 구동 트랜지스터(11a)의 채널간 전압에 영향을 주지 않도록 하기 위해서이다. 또한, 스위치 트랜지스터(11b)의 오프 리크 전류의 저감에도 효과가 있다. 스위치 트랜지스터(11c)는, 충분히 온시켜 온 저항을 저하시키는 것이 바람직하다.

[0031] 예를 들면, 오프 전압( $VGH1=VGH2=6.0(V)$ )으로 하면, 스위치 트랜지스터(11c)의 온 전압( $VGL1=-4.0(V)$ ), 스위치 트랜지스터(11d)의 온 전압( $VGL2=-2.0(V)$ )으로 설정한다. 오프 전압 스위치 트랜지스터(11c)의 오프 전압( $VGH1=6.0(V)$ ), 스위치 트랜지스터(11d)의 오프 전압( $VGH2=5.5(V)$ )로 하면, 스위치 트랜지스터(11c)의 오프 전압( $VGH1$ )-온 전압( $VGL1=-10.0(V)$ ), 스위치 트랜지스터(11d)의 오프 전압( $VGH2$ )-온 전압( $VGL2=-8.0(V)$ )으로 설정한다. 또한, 스위치 트랜지스터(11c)의 오프 전압( $VGH1$ )-온 전압( $VGL1$ )은, 스위치 트랜지스터(11d)의 오프 전압( $VGH2$ )-온 전압( $VGL2$ )보다도 1V 이상 4V 이하의 전위차이도록 설정한다. 이상의 사항은 본 발명의 다른 실시예에서도 마찬가지이다.

[0032] 본 실시예는, 트랜지스터(11)를 기본적으로는 P채널로 하여 설명하지만 이것에 한정되는 것은 아니다. 예를 들면, 구동 트랜지스터(11a)를 P채널 트랜지스터로 하고, 다른 스위치 트랜지스터는 N채널 트랜지스터로 해도 된다. 스위치 트랜지스터(11)의 오프 리크 전류가 저감하여, 양호한 콘트라스트를 실현할 수 있다.

[0033] 예를 들면, 도 12에 도시하는 바와 같이, 구동 트랜지스터(11a)를 N채널 트랜지스터로 형성해도 된다. 또한, 스위치 트랜지스터(11c), 스위치 트랜지스터(11b)를 N채널 트랜지스터로 형성해도 된다. 또한, 도 1 등에서, 스위치 트랜지스터(11b, 11f, 11c)는 트랜지스터의 복수의 채널이 직렬로 접속된 구성(멀티 게이트 구조:듀얼 게이트, 트리플 게이트 등)으로 하는 것이 바람직하다. 특히, 영상 신호 전압  $V_{sig}$ 를 화소(16)에 인가하는 스위치 트랜지스터(11c), 리세트 전압  $V_{rst}$ 를 인가하는 스위치 트랜지스터(11f), 구동 트랜지스터(11a)의 게이트 단자와 다른 단자 사이를 단락 상태로 하는 스위치 트랜지스터(11b)는 멀티 게이트 구성으로 하는 것이 바람직하다. 또한, 스위치 트랜지스터(11b, 11f, 11c)는, N채널 트랜지스터로 구성함으로써 오프 리크 전류가 저감하여 바람직하다.

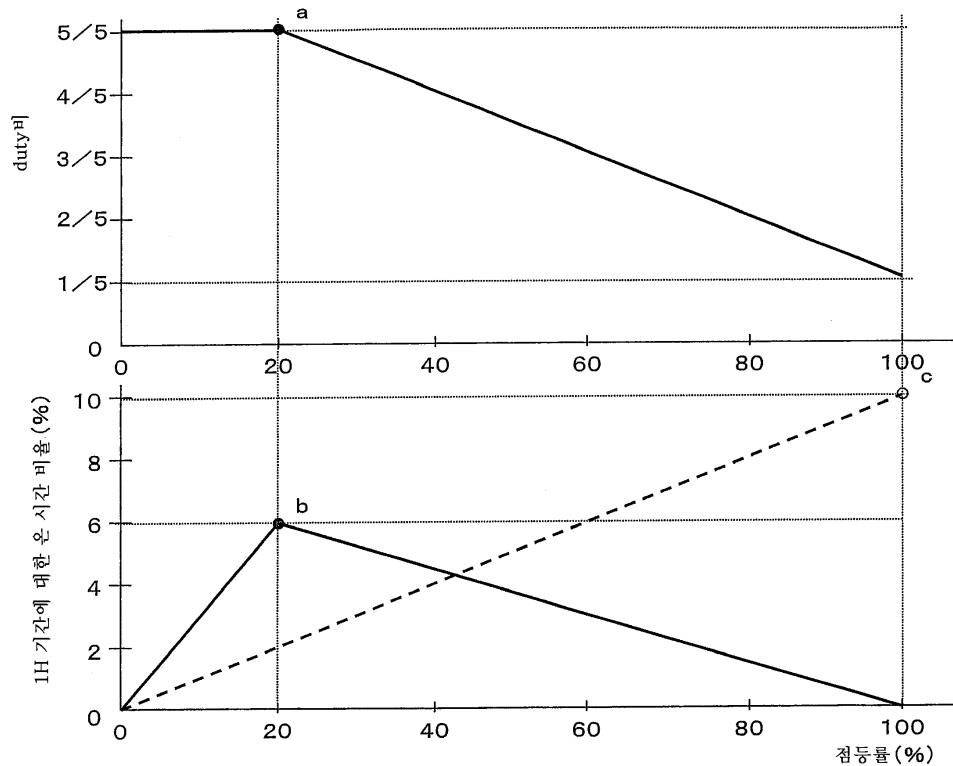

[0034] 여기서 duty 구동(혹 삽입 구동)에 대하여 설명을 행하여 둔다.

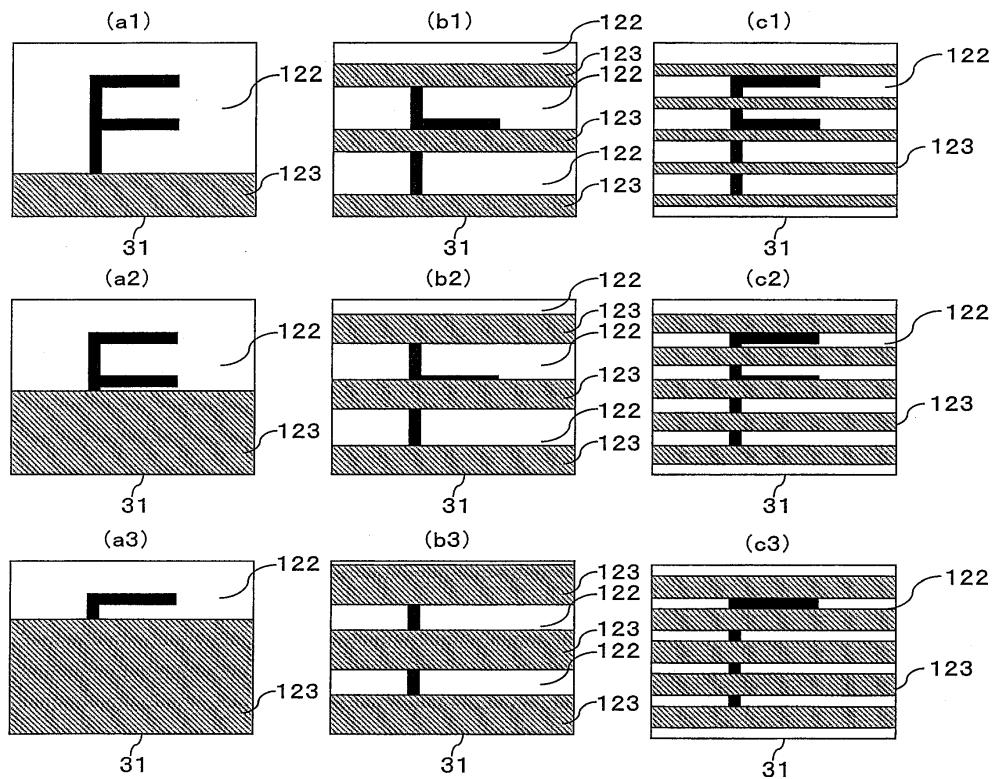

[0035] 도 1 등의 본 발명의 실시예에서, 트랜지스터(11e), 트랜지스터(11d) 중 적어도 한 쪽을 온/오프 제어함으로써, 도 12의 (b)에 도시하는 바와 같은 duty 구동을 실현할 수 있다. 도 12에서, 참조 부호 121은 프로그램 화소행(영상 신호를 기입하고 있는 화소행)이고, 참조 부호 123은 비표시 영역(트랜지스터(11e)와 트랜지스터(11d) 중, 적어도 한 쪽을 오프시킴으로써, 비표시(EL 소자(15)에 전류가 흐르고 있지 않거나, 또는 흘러도 작은 상태)로 한 화소행 또는 화소행의 군)이다. 참조 부호 122는 표시 영역(트랜지스터(11e)와 트랜지스터(11d)의 양방을 온시키고, EL 소자(15)에 전류가 공급되고 있는 화소행 또는 화소행의 군)이다. 비표시 영역(123) 및

표시 영역(122)은 프레임 주기 또는 수평 동기 신호에 동기하여, 표시 화면(31)의 상하 방향에 주사된다.

[0036] 도 13의 (a)의 표시에서는, 1개의 표시 영역(122)이 화면 위로부터 아래 방향으로 이동한다. 프레임 레이트가 낮으면, 표시 영역(122)이 이동하는 것이 시각적으로 인식된다. 특히, 눈꺼풀을 닫았을 때, 혹은 얼굴을 상하로 이동시켰을 때 등에 인식되기 쉬워진다.

[0037] 이 과제에 대해서는, 도 12의 (b)(c)에 도시하는 바와 같이, 표시 영역(122)을 복수로 분할하면 된다. 분할된 표시 영역(122)은 동등하게(등분으로) 할 필요는 없다. 예를 들면, 표시 영역을 4개의 영역으로 분할하여, 분할된 표시 영역(122a)이 면적1이고, 분할된 표시 영역(122b)이 면적2이고, 분할된 표시 영역(122c)이 면적3이고, 분할된 표시 영역(122d)이 면적4이어도 된다.

[0038] 수 프레임(필드)에서의 표시 영역(122)의 면적이 평균하여 목표의 크기로 되도록 제어해도 되는 것은 물론이다. 예를 들면, 표시 화면(31)에서 차지하는 표시 영역(122)의 면적을 1/10로 한다고 하였을 때, 1프레임(필드)째는 표시 영역(122)의 면적을 1/10로 하고, 2프레임(필드)째는 표시 영역(122)의 면적을 1/20로 하고, 3프레임(필드)째는 표시 영역(122)의 면적을 1/20로 하고, 4프레임(필드)째는 표시 영역(122)의 면적을 1/5로 하여, 이상의 4프레임(필드)에서 소정의 표시 면적(표시 휘도)의 1/10을 얻는 구동 방법이 예시된다.

[0039] 또한, R, G, B의 각각이, 수 프레임(필드)에서 L의 기간의 평균이 동등하게 되도록 구동해도 된다. 그러나, 상기 수 프레임(필드)은 4프레임(필드) 이하로 하는 것이 바람직하다. 표시 화상에 따라서는 플리커가 발생하는 경우가 있기 때문이다.

[0040] 또한, 본 실시예에서의 1프레임 혹은 1필드란, 화소(16)의 화상 재기입 주기 또는 표시 화면(31)이 위에서부터 아래까지(아래에서부터 위까지)주사되는 주기와 동의 혹은 유사한 의미라고 생각해도 된다.

[0041] 또한, R, G, B에서, 수 프레임(필드)에서 L의 기간의 평균을 서로 다르게 하여, 적절한 화이트 밸런스가 취해지도록 구동해도 된다. 이 구동 방법은, RGB의 발광 효율이 서로 다를 때에 특히 유효하다. 또한, RGB에서 분할 수 K(표시 영역(122)을 복수로 분할하는 수)를 서로 다르게 해도 된다. 특히 G에서는 시각적으로 눈에 띄기 때문에, G에서는 분할수를 RB에 대하여 많게 하는 것이 유효하다.

[0042] 또한, 이상의 실시예에서는 이해를 용이하게 하기 위하여 표시 영역(122)의 면적을 분할하는 것으로서 설명하고 있다. 그러나, 면적을 분할한다는 것은, 기간(시간)을 분할하는 것이다. 따라서, 도 1에서는 트랜지스터(11d)의 온 기간을 분할하게 되기 때문에, 면적을 분할하는 것은, 기간(시간)을 분할하는 것과 동의 혹은 유사하다.

[0043] 이상과 같이, 표시 영역(122)을 복수로 분할함으로써 화면의 깜박거림은 감소한다. 따라서, 플리커의 발생은 없어, 양호한 화상 표시를 실현할 수 있다. 또한, 분할은 더욱 미세하게 해도 된다. 그러나, 분할할수록 동화상 표시 성능은 저하한다. 또한, 화상 표시의 프레임 레이트를 저감할 수 있어, 저소비 전력화를 실현할 수 있다. 예를 들면, 비점등 영역(123)을 일괄로 한 경우에는, 프레임 레이트 45Hz 이하로 되면 플리커가 발생한다. 그러나, 비점등 영역(123)을 6분할 이상으로 한 경우에는, 20Hz 이하까지 플리커가 발생하지 않는다.

[0044] 도 13의 (a)는 도 13과 같이 표시 영역(122)이 연속하고 있는 경우의 밝기 조정 방식이다. 도 13의 (a1)의 표시 화면(31)의 표시 휘도가 가장 밝다. 도 13의 (a2)의 표시 화면(31)의 표시 휘도가 다음으로 밝고, 도 13의 (a3)의 표시 화면(31)의 표시 휘도가 가장 어둡다. 도 13의 (a1)부터 도 13의 (a3)으로의 변화(혹은 그 반대)는, 앞서도 기재한 바와 같이 게이트 드라이버 회로(12)의 시프트 레지스터 회로(61) 등의 제어에 의해 용이하게 실현할 수 있다. 이 때, 도 1의 Vdd 전압(애노드 전압 등)은 변화시킬 필요가 없다. 또한, 소스 드라이버 회로(14)가 출력하는 프로그램 전류 혹은 프로그램 전압의 크기도 변화시킬 필요가 없다. 즉, 전원 전압을 변화시키지 않고, 또한, 영상 신호를 변화시키지 않고 표시 화면(31)의 휘도 변화를 실시할 수 있다.

[0045] 또한, 도 13의 (a1)로부터 도 13의 (a3)으로의 변화 시, 화면의 감마 특성은 전혀 변화하지 않는다. 따라서, 표시 화면(31)의 휘도에 상관없이, 표시 화상의 콘트라스트, 계조 특성이 유지된다. 이것은 본 실시예의 효과적인 특징이다.

[0046] 종래의 화면의 휘도 조정에서는, 표시 화면(31)의 휘도가 낮을 때에는, 계조 성능이 저하한다. 즉, 고휘도 표시일 때에는 64계조 표시를 실현할 수 있어도, 저휘도 표시일 때에는, 절반 이하의 계조수밖에 표시할 수 없다. 이것과 비교하여, 본 실시예의 구동 방법에서는, 화면의 표시 휘도에 의존하지 않고, 최고의 64계조 표시를 실현할 수 있다.

[0047] 도 13의 (b)는, 도 12에서 설명한 바와 같이 표시 영역(122)이 분산되어 있는 경우의 밝기 조정 방식이다. 도

13의 (b1)의 표시 화면(31)의 표시 휘도가 가장 밝다. 도 13의 (b2)의 표시 화면(31)의 표시 휘도가 다음으로 밝고, 도 13의 (b3)의 표시 화면(31)의 표시 휘도가 가장 어둡다. 도 13의 (b1)로부터 도 13의 (b3)으로의 변화(혹은 그 반대)는, 앞서도 기재한 바와 같이 게이트 드라이버 회로(12)의 시프트 레지스터 회로(61) 등의 제어에 의해, 용이하게 실현할 수 있다. 도 13의 (b)와 같이 표시 영역(122)을 분산시키면, 저프레임 레이트에서도 플리커가 발생하지 않는다.

[0048] 또한, 저프레임 레이트에서도, 플리커가 발생하지 않도록 하기 위해서는, 도 13의 (c)와 같이 표시 영역(122)을 미세하게 분산시키면 된다. 그러나, 동화상의 표시 성능은 저하한다. 따라서, 동화상을 표시하기 위해서는, 도 13의 (a)의 구동 방법이 적합하다. 정지 화상을 표시하고, 저소비 전력화를 요망할 때에는, 도 13의 (c)의 구동 방법이 적합하다. 도 13의 (a)로부터 도 13의 (c)의 구동 방법의 절환도, 시프트 레지스터(61)의 제어에 의해 용이하게 실현할 수 있다.

[0049] 도 13은 비표시 영역(123)이 등간격으로 구성되어 있지만, 이것에 한정되는 것은 아니다. 표시 화면(31)의 1/2의 면적이 연속하여 표시 영역(122)으로 되고, 남은 면적(50)이 도 13의 (c1)과 같이 등간격으로 표시 영역(122)과 비표시 영역(123)이 반복되도록 구동해도 되는 것은 물론이다.

[0050] 또한, 도 83에 도시한 회로 구성을 이용하여, EL 표시 장치에 입력되는 영상 신호를 가산 혹은 가중치 부여 처리를 행하는 것이 바람직하다. 도 83의 회로 구성은 이용함으로써, 표시 화면에 흐르는 전류를 구하거나 또는 예측하고, 상기 구한 전류 등에 의해 화상 화면에 검은 띠형상의 비점등 영역을 발생시키고, 이 검은 띠형상의 비점등 영역의 크기를 변화시킨다. 또는, 검은 띠형상의 비점등 영역의 폭은 일정하게 하고, 영상 신호의 진폭을 변화시킴으로써, 표시 화면에 흐르는 전류의 크기가 일정 이상으로 되지 않도록 제어한다. 또한, 이 제어에 의해, 전원 회로로부터 표시 화면에 흐르는 전류를 일정 이하로 되도록 할 수 있어, EL 표시 장치의 발열을 억제할 수 있다. 또한, 도 98, 도 99에 도시하여 설명을 행하고 있는 바와 같이, 전원 회로(전원 IC)가 출력하는 전압을 가변함으로써, EL 표시 장치의 발열을 억제할 수 있다. 또한, 본 발명의 화소 구성은 이용함으로써, 더욱 양호한 화상 표시를 실현할 수 있는 것은 물론이다.

[0051] 점등률 제어 구동(duty 구동), 퍼크 전류 억제 구동, 최대 표시 계조수 제어 구동(도 12, 도 13, 도 84, 도 98, 도 99, 도 130 등)에 의해, 고화질화, 전류 억제를 실현할 수 있다. 또한, 각 스위치 트랜지스터(1)의 동작에 대응시켜 각 게이트 신호선(17)의 온/오프 전압을 인가하는 제어 타이밍을 제어한다. 게이트 드라이버 회로(12)의 제어는 도 3과 같이, 소스 드라이버 IC(14)로부터의 신호를 레벨 시프트 회로(32)에서 레벨 시프트시켜 인가함으로써 실현한다.

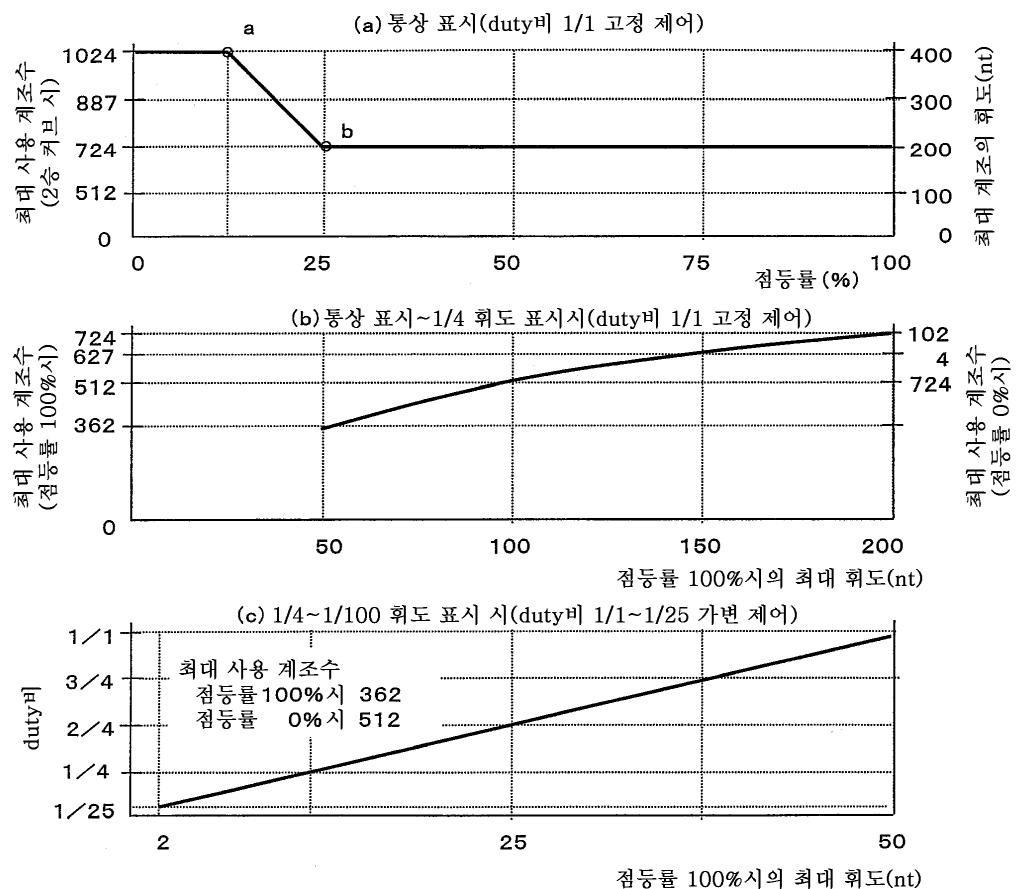

[0052] 본 명세서에서, 점등률에 따라서 duty비 등을 변화시키는 것으로서 설명한다. 그러나, 점등률이란, 일정한 의미는 아니다. 예를 들면, 저점등률이란, 화면(31)에 흐르는 전류가 작은 것을 의미하고 있지만, 화상을 구성하는 저계조 표시의 화소가 많은 것도 의미한다. 즉, 화면(31)을 구성하는 영상은, 어두운 화소(저계조의 화소)가 많다.

[0053] 따라서, 저점등률이란, 화면을 구성하는 영상 데이터의 히스토그램 처리를 하였을 때, 저계조의 영상 데이터가 많은 상태라고 바꿔 말할 수 있다. 고점등률이란, 화면(31)에 흐르는 전류가 큰 것을 의미하고 있지만, 화상을 구성하는 고계조 표시의 화소가 많은 것도 의미한다. 즉, 화면(31)을 구성하는 영상은, 밝은 화소(고계조의 화소)가 많다. 고점등률이란, 화면을 구성하는 영상 데이터의 히스토그램 처리를 하였을 때, 고계조의 영상 데이터가 많은 상태라고 바꿔 말할 수 있다. 즉, 점등률에 대응하여 제어한다는 것은, 화소의 계조 분포 상태 혹은 히스토그램 분포에 대응하여 제어하는 것과 동의 혹은 유사한 상태를 의미하는 경우가 있다.

[0054] 이상의 점으로부터, 점등률에 기초하여 제어한다는 것은, 경우에 따라서 화상의 계조 분포 상태(저점등률=저계조 표시의 화소가 많음. 고점등률=고계조 표시의 화소가 많음)에 기초하여 제어한다고 바꿔 말할 수 있다.

[0055] 또한, 통상 표시 상태에서는, duty비 1/1로 구동하고, 소정의 고점등률 이상에서 단계적으로 혹은 스무스하게 duty비를 저하시킨다는 것은, 저계조 혹은 고계조의 화소수가 일정한 범위 이내일 때에, duty비 1/1로 구동하고, 고계조의 화소수가 일정한 범위 이상의 수로 되었을 때에, 단계적으로 혹은 스무스하게 duty비를 저하시키는 것과 동일 혹은 유사한 동작 혹은 제어이다.

[0056] duty비 제어는, 점등률이 1/10 이상 1/1의 범위에서 실시한다. duty비 1/1에서, 백 래스터 표시이면, 점등률 100%이다(최대의 백 래스터 표시 시). 혹은 래스터이면, 점등률 0%이다(완전 혹은 래스터 표시 시).

[0057] 점등률이란, 패널의 애노드 또는 캐소드에 흐르는 최대 전류에 대한 비율이기도 하다(단, duty비는 1/1로 함). 예를 들면, 캐소드에 흐르는 최대 전류를 100mA로 하면, duty비 1/1에서, 30mA의 전류가 흐르고 있으면 점등률

은  $30/100=30\%(0.3)$ 이다.

[0058] 캐소드에 흐르는 최대 전류를  $100mA$ 로 하고, 이 때, 영상 데이터의 총합의 최대값으로 하면, 점등률 50%란, 캐소드(애노드)에 흐르는 전류는, 최대 전류의 50%이다. 또한, 점등률 20%란, 캐소드에 흐르는 전류는, 최대 전류의 20%이다. 앞으로는, 주로 점등률이란 용어를 이용한다. 점등률은, 패널의 애노드 또는 캐소드에 흐르는 최대 전류에 대한 비율이라고 하였지만, 패널의 전체 EL 소자에 흐르는 최대 전류의 비율이라고도 바꿔 말할 수 있는 것은 물론이다.

[0059] 본 명세서에서는, 점등률이라고 별다른 언급없이 기재할 때에는, duty비 1/1로 하고 있다. 만일 duty비 1/3에서,  $20mA$ 의 전류가 흐르고 있으면, 점등률은  $(20mA \cdot 3)/100mA=60\%(0.6)$ 이다. 즉, 점등률이 100%에서도, duty비가 1/2이면, 애노드(캐소드) 단자에 흐르는 전류는 최대의 전류값의 1/2이다. 점등률 50%, 애노드 전류가  $20mA$ , duty비 1/1이면, duty비 1/2로 되면, 애노드 전류는  $10mA$ 로 된다. 애노드 전류가  $100mA$ , 점등률 40%, duty비 1/1이면, 애노드 전류가  $200mA$ 로 변화하였다고 하면, 점등률은 80%로 변화한 것을 의미한다.

[0060] 이상과 같이, 점등률은, 1회면을 구성하는 영상 데이터의 크기에 대한 비율, EL 표시 패널의 소비 전류(전력) 혹은 그 비율을 나타내고 있다.

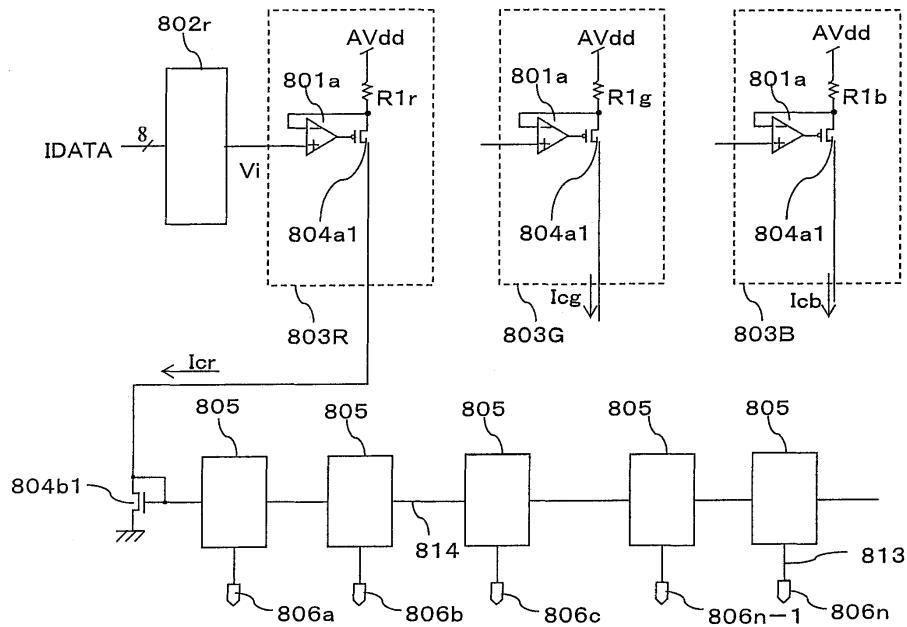

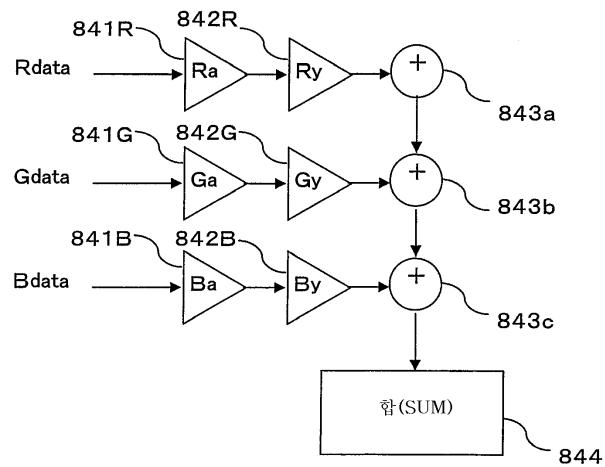

[0061] 일례로서 점등률(점등률)은, 영상 데이터의 합으로부터 구한다(도 83). 즉, 영상 데이터로부터 산출한다. 입력 영상 신호가 Y, U, V인 경우에는, Y(회도) 신호로부터 구해도 된다. 그러나, EL 표시 패널의 경우에는, R, G, B에서 발광 효율이 상이하기 때문에, Y신호로부터 구한 값이 소비 전력으로 되지 않는다. 따라서, Y, U, V 신호의 경우도, 한번 R, G, B신호로 변환하고, R, G, B에 따라서 전류로 환산하는 계수를 곱하여, 소비 전류(소비 전력)를 구하는 것이 바람직하다. 그러나, 간이적으로 Y신호로부터 소비 전류를 구하는 것은 회로 처리가 용이하게 되는 것도 고려해도 된다(도 82, 도 83 등을 참조). 또한, 점등률은, 캐소드(애노드)에 흐르는 전류를 측정하고, 측정한 전류로부터 구해도 된다.

[0062] 점등률은, 패널에 흐르는 전류에 의해 환산한다. 왜냐하면, EL 표시 패널에서는 청(B)의 발광 효율이 나쁘기 때문에, B가 많은, 해(海)의 표시 등이 표시되면, 소비 전력이 한번에 증가하기 때문이다. 또한, 데이터 합이란 단순한 영상 데이터의 가산값이 아니라, 영상 데이터를 소비 전류로 환산한 것으로 하고 있다. 따라서, 점등률도 최대 전류에 대한 각 화상의 사용 전류로부터 구해진 것이다. 또한, 데이터 합은 가산하여 구하는 것만을 의미하는 것은 아니다. 입력되는 영상 데이터를 RGB로 가중치 부여하고, 가산하는 방식이 예시된다. 또한, 화상의 특징을 나타내는 데이터를 추출하고, 추출한 데이터를 처리하여 구해도 된다. 또한, 입력된 영상 데이터를 히스토그램 처리를 행하고, 히스토그램 처리의 특정 범위(예를 들면, 평균값을 중심으로 하여 10의 범위)의 데이터를 추출하여 데이터 합을 구해도 된다. 즉, 데이터 합은 처리를 행한 데이터의 집합 혹은 처리를 행한 결과이다.

[0063] 또한, 입력되는 영상 데이터는, EL 표시 장치에 입력되는 영상 데이터를 의미하지만, EL 표시 장치의 화소에 입력되는 영상 데이터를 의미하는 경우도 있다. 즉, 소스 드라이버 IC(14)로부터 출력된 영상 데이터이다.

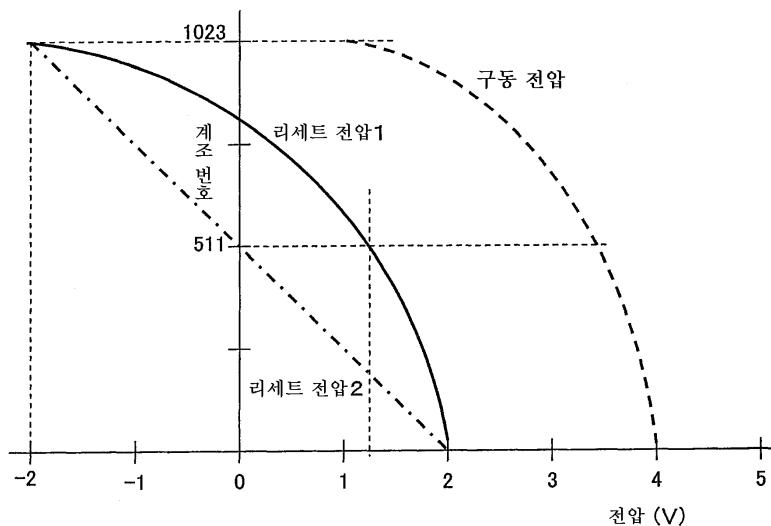

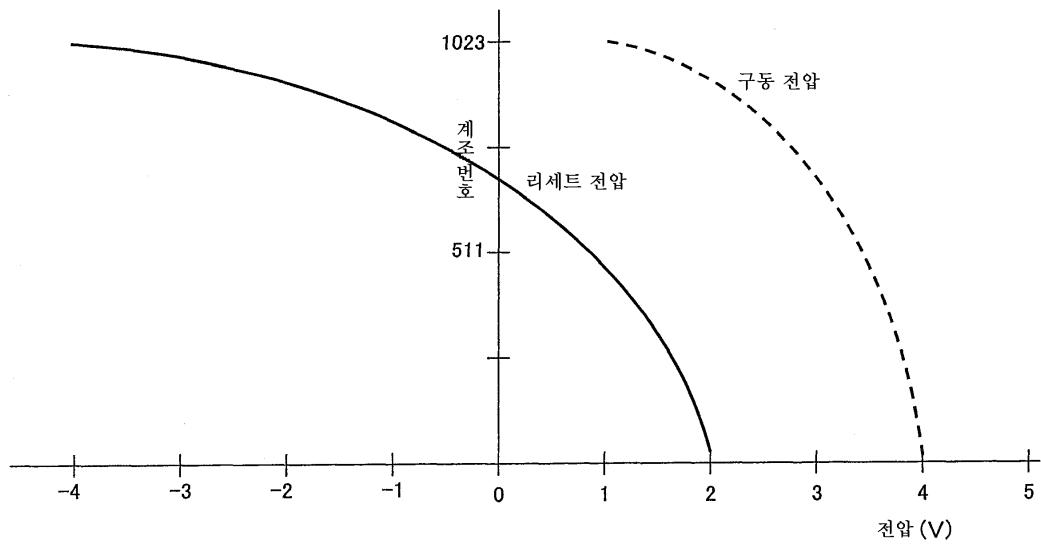

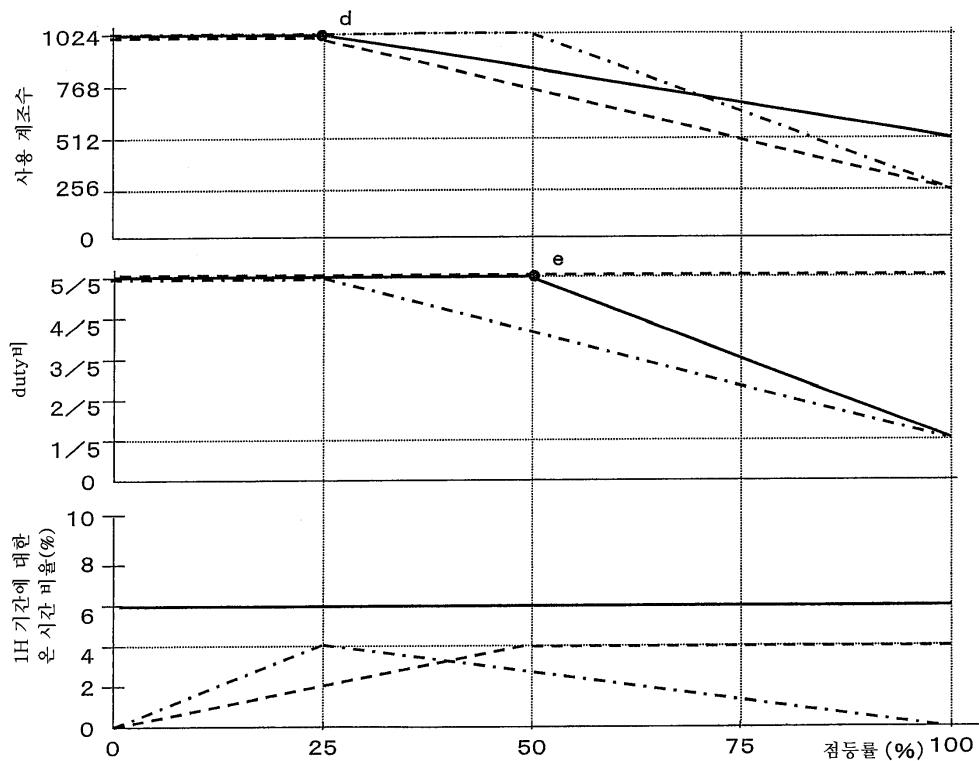

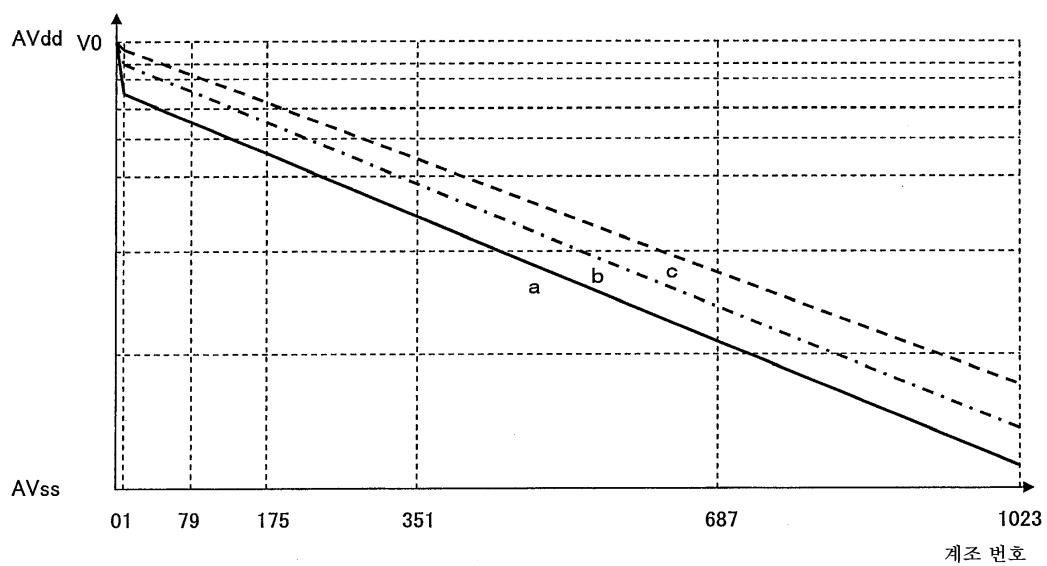

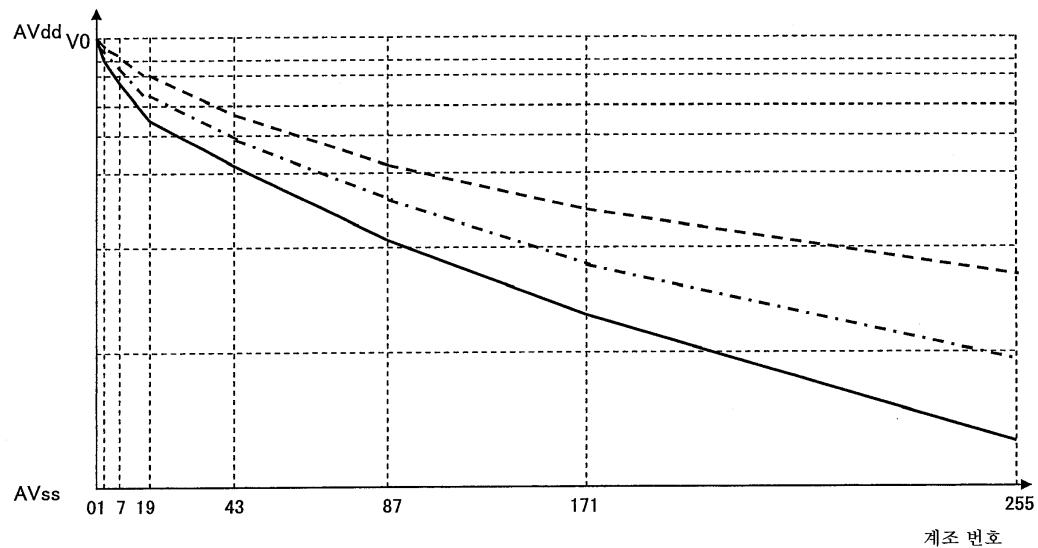

[0064] 점등률에 맞추어 EL 표시 장치에서 표시하는 계조수를 변화시키는 것이 바람직하다. 예를 들면, 점등률이 50% 이상에서는, 풀 계조의 1/2의 범위(1024계조의 경우에는, 512계조)에서 화상을 표시하고, 50% 이하에서는, 풀 계조의 범위에서 화상을 표시한다. 이 실시예는, 도 98, 도 99, 도 130 등을 이용하여 설명을 행하고 있다.

[0065] 또한, 점등률이란, duty 구동 등 피크 전류를 억제하지 않는 노멀의 구동 방식에서, 최대 계조에서의 백 래스터 표시를 100%로 한 비율이다. 따라서, 흑 래스터 표시에서는 점등률은 0%이다.

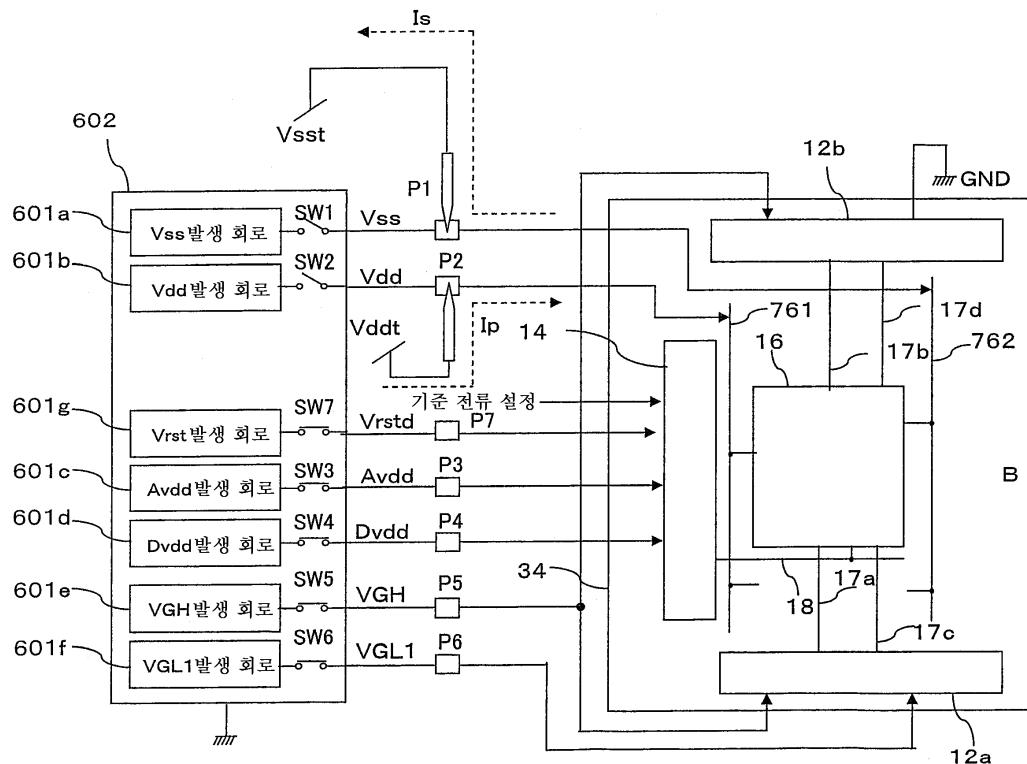

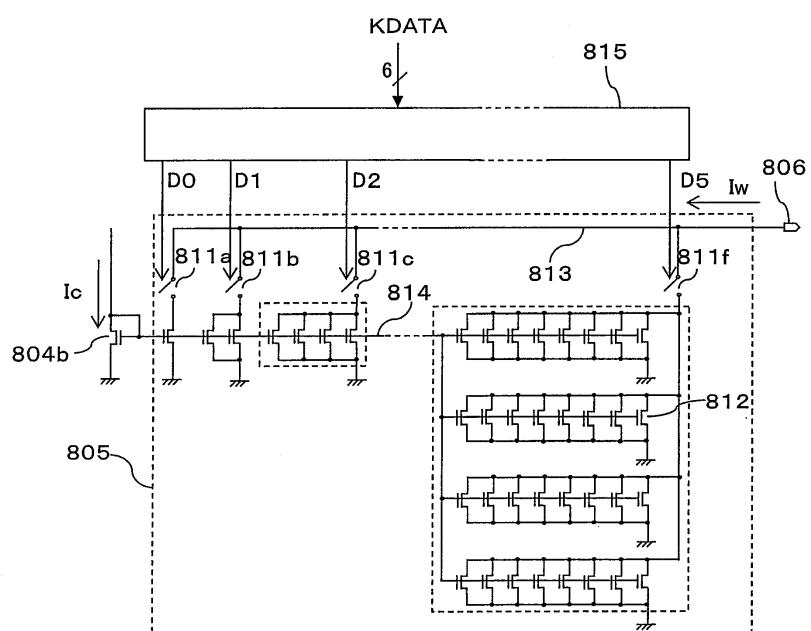

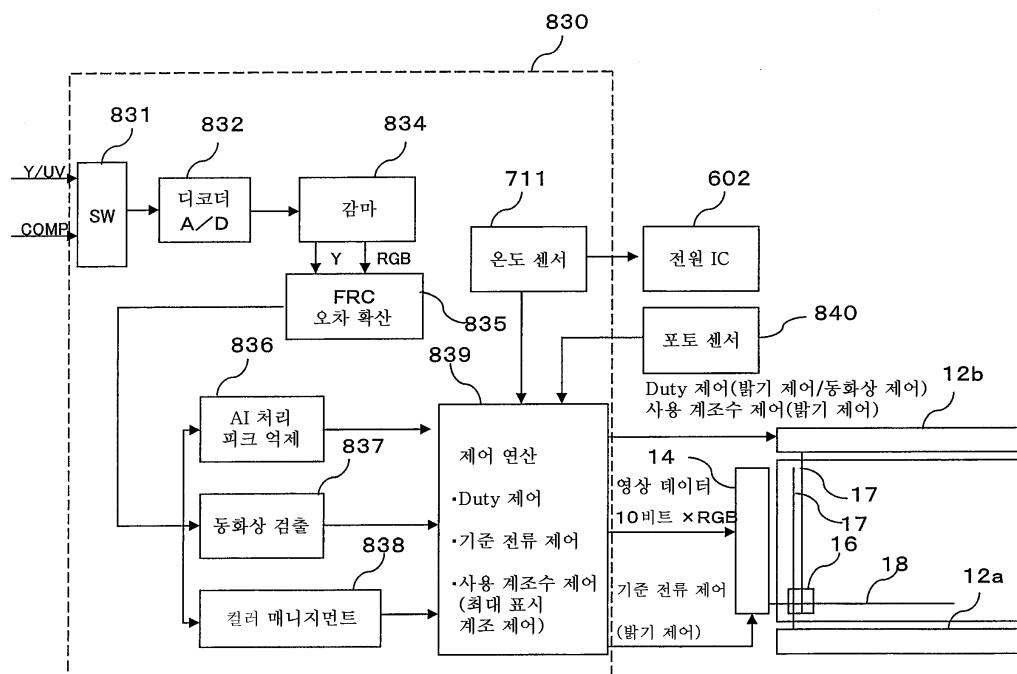

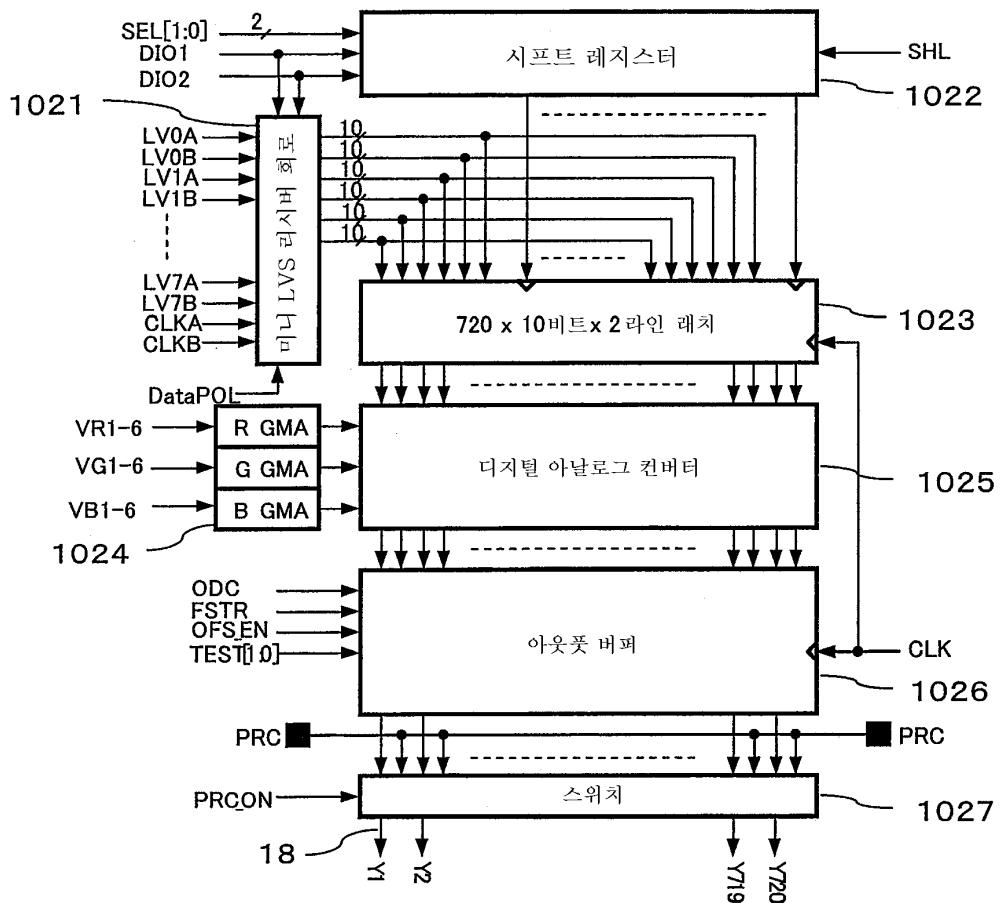

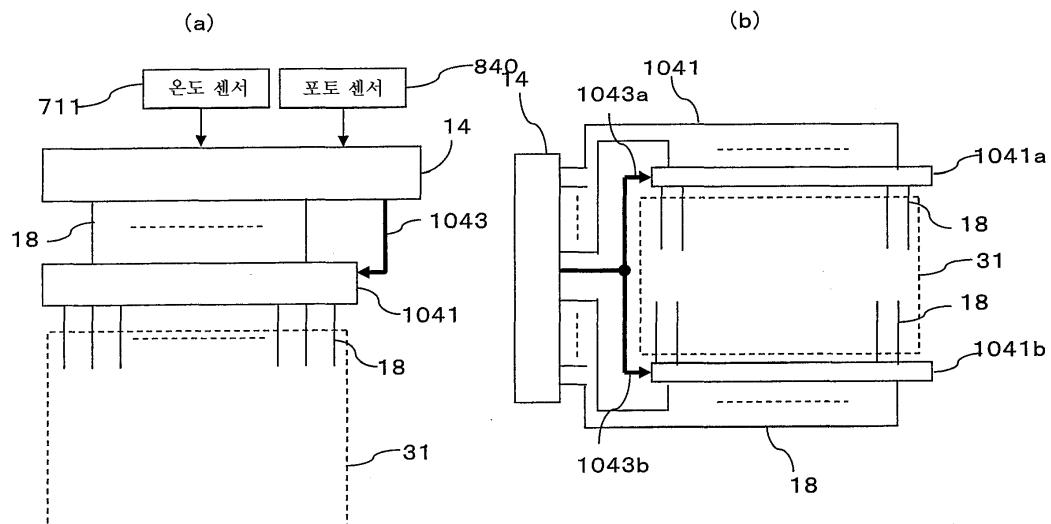

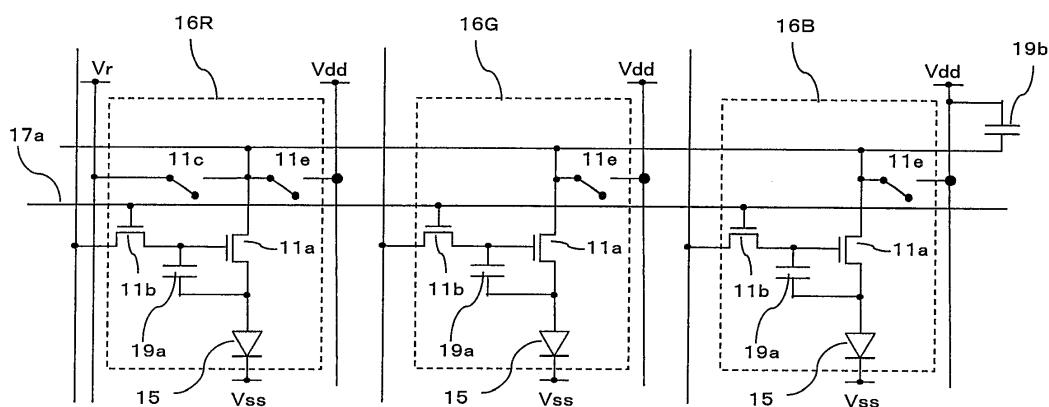

[0066] 도 83은 본 실시예의 구동 회로의 블록도이다. 이하, 본 실시예의 구동 회로에 대하여 설명을 한다. 도 83에서는, 외부로부터 Y/UV 영상 신호와, 콤포지트(COMP) 영상 신호를 입력할 수 있게 구성되어 있다. 어느 쪽에 영상 신호를 입력할지는, 스위치 회로(831)에 의해 선택된다.

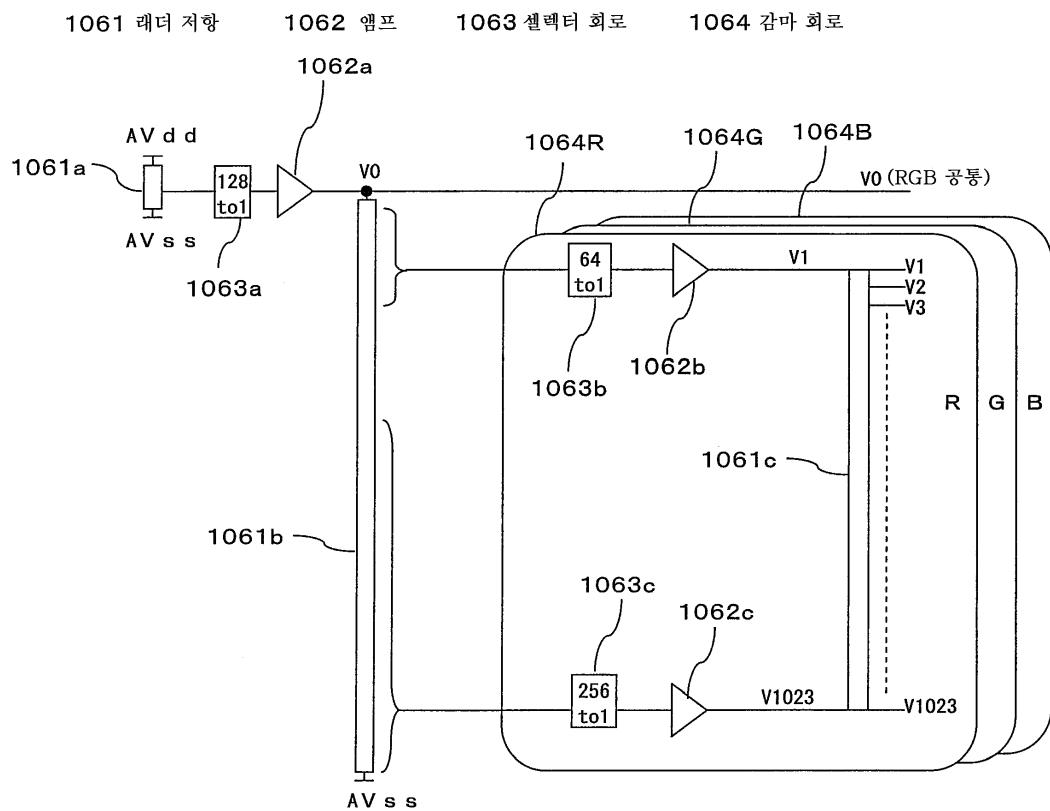

[0067] 스위치 회로(831)에서 선택된 영상 신호는, 디코더 및 A/D 회로에 의해 디코드 및 AD 변환되고, 디지털의 RGB 화상 데이터로 변환된다. RGB 화상 데이터는 각 8비트이다. 또한, RGB 화상 데이터는 감마 회로(834)에서 감마 처리된다. 동시에 회도(Y) 신호가 구해진다. 감마 처리에 의해, RGB 화상 데이터는 각 10비트의 화상 데이터로 변환된다.

[0068] 감마 처리 후, 화상 데이터는 FRC 처리 또는 오차 확산 처리가 처리 회로(835)에서 행하여진다. FRC 처리 또는 오차 확산 처리에 의해 RGB 화상 데이터는 6비트로 변환된다. 이 화상 데이터는 AI 처리 회로(836)에서 AI 처리(최적화 화상 표시 처리) 데이터, duty 구동을 위한 점등률 연산, 최대 표시 계조수 연산 등이 실시된다. 또

한, 동화상 검출 회로(837)에서 동화상 검출이 행하여진다. 동화상 검출 처리의 결과에 기초하여, 도 13 등에서 설명한, 표시 영역(122), 비표시 영역(123)의 분할 구동이 실시된다. 또한, 컬러 매니지먼트 회로(838)에서 컬러 매니지먼트 처리가 행하여진다.

[0069] AI 처리 회로(836), 동화상 검출 회로(837), 컬러 매니지먼트 회로(838)의 처리 결과는 연산 회로(839)에 보내지고, 연산 처리 회로(839)에서 duty비 제어, 기준 전류 제어 데이터로 변환되고, 변환된 결과가, 소스 드라이버 회로(14) 및 게이트 드라이버 회로(12)에 제어 데이터로서 송출된다.

[0070] duty비 제어 데이터는 게이트 드라이버 회로(12b)에 보내지고, duty비 제어가 실시된다. 사용 계조 제어 데이터는 소스 드라이버 IC(14)에 보내지고, 사용 계조수 제어가 실시된다. 한편, 기준 전류 제어 데이터는 소스 드라이버 회로(14)에 보내지고, 기준 전류 제어가 실시된다. 감마 보정되고, 프레임 레이트 컨트롤(FRC) 또는 오차 확산 처리된 화상 데이터도 소스 드라이버 회로(14)에 보내진다.

[0071] EL 표시 패널은, 혹 표시는, EL 소자(15)에 흐르는 전류가 0인 상태이다. 따라서, 본 실시예의 duty비 구동과 같이 화면(31)에 비표시 영역(123)을 발생시켜도, 혹 표시의 휘도는 0이다. 비표시 영역(123)의 면적을 크게 하면 백 표시 휘도는 저하한다. 그러나, 혹 표시의 휘도가 0이기 때문에, 콘트라스트는 무한대이다. 따라서, duty비 구동은, EL 표시 패널에 최적인 구동 방법이다. 이상은, 기준 전류 제어에서도 마찬가지이다. 기준 전류의 크기를 변화시켜도, 혹 표시의 휘도는 0이다. 기준 전류를 크게 하면 백 표시 휘도는 증가한다. 따라서, 기준 전류 제어에서도 양호한 화상 표시를 실현할 수 있다.

[0072] duty비 제어는, 전체 계조 범위에서 계조수가 유지된다. 또한, 전체 계조 범위에서 화이트 밸런스가 유지된다. 또한, duty비 제어에 의해 화면(31)의 휘도 변화는 10배 가까이 변화시킬 수 있다.

[0073] 표시 화면의 휘도는 duty비 혹은 duty비의 역수와 선형의 관계로 되기 때문에, 표시 화면의 밝기 제어도 용이하다.

[0074] 기준 전류 제어는, 화면(31)의 휘도를 높게 할 때에, 기준 전류량을 크게 하는 것이다. 따라서, 화면(31)의 휘도가 높을 때에만, EL 소자(15)에 흐르는 전류가 커진다. 그 때문에, EL 소자(15)가 열화하기 어렵다.

[0075] 본 실시예에서는, 기준 전류 제어와 duty비 제어의 양방을 이용한다. 화면(31)이 백 래스터 표시에 가까울 때에는, 기준 전류는 일정값으로 고정하고, duty비만을 제어하여 표시 휘도 등을 변화시킨다. 화면(31)이 혹 래스터 표시에 가까울 때에는, duty비는 일정값으로 고정하고, 기준 전류만을 제어시켜 표시 휘도 등을 변화시킨다.

[0076] 또한, duty비의 최대는 duty비 1/1로 하고, 최소는 duty비 1/16 이내로 하는 것이 바람직하다. 더욱 바람직하게는, duty비 1/10 이내로 하면 된다. 플리커의 발생을 억제할 수 있기 때문이다. 기준 전류의 변화 범위는, 4배 이내로 하는 것이 바람직하다. 더욱 바람직하게는 2.5배 이내로 한다.

[0077] 또한, 데이터 합은 소비 전류에 의해 산정할지, 휘도에 의해 산정할지는 어느 쪽이라도 된다. 여기서는 설명을 용이하게 하기 위하여, 휘도(화상 데이터)의 가산인 것으로서 설명을 한다. 일반적으로 휘도(화상 데이터)의 가산의 방식이 처리는 용이하고, 컨트롤러 IC의 하드 규모도 작게 할 수 있다. 또한, duty비 제어에 의한 플리커의 발생도 없어, 다이내믹 레인지지를 넓게 취할 수 있기 때문에 바람직하다.

[0078] 이상의 사항은, 도 78, 도 79, 도 84, 도 98, 도 99, 도 101, 도 111, 도 112, 도 130 등의 실시예에도 적용할 수 있는 것은 물론이다. 또한, 상기 실시예와 조합하여 실시할 수 있는 것도 물론이다.

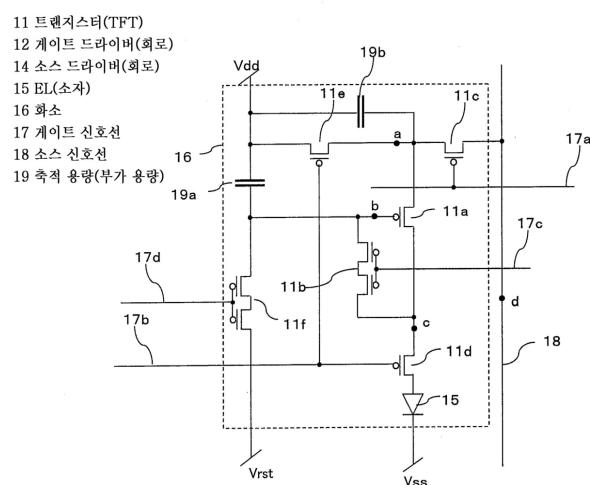

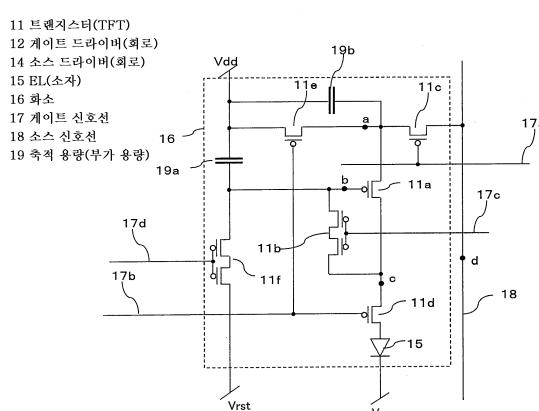

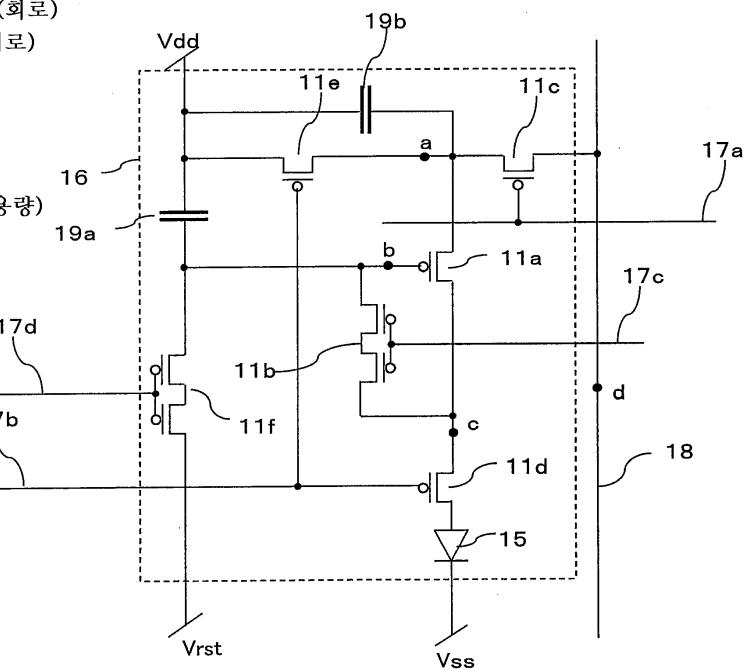

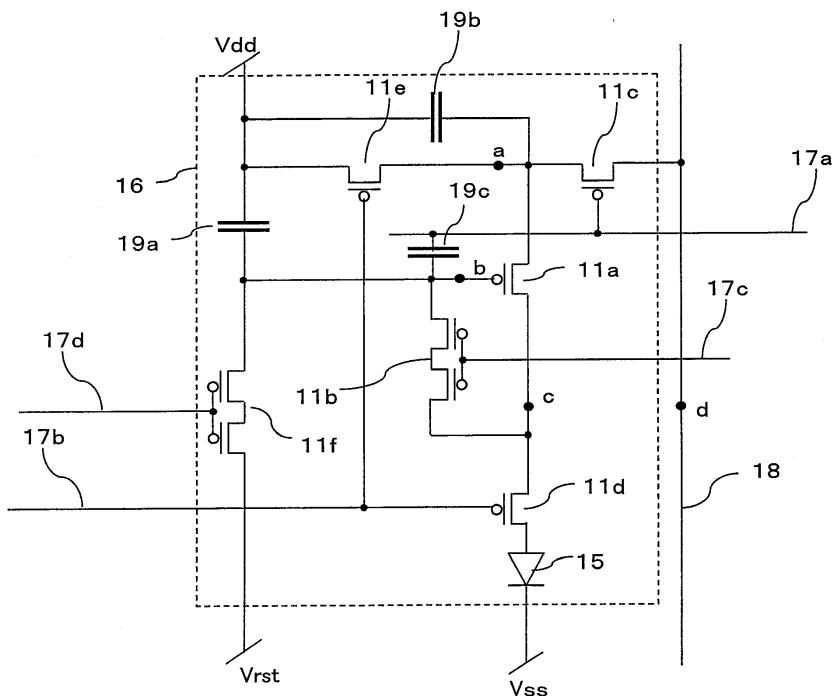

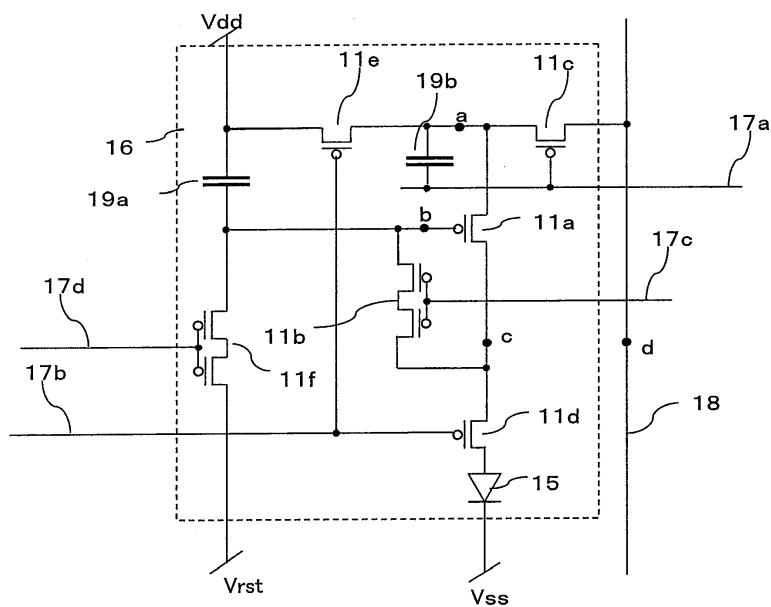

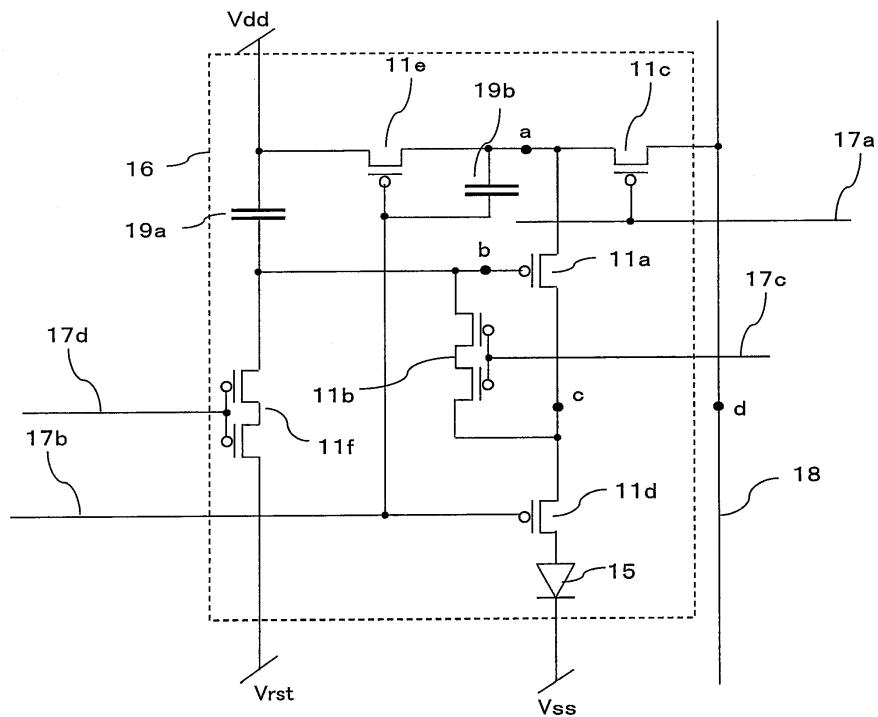

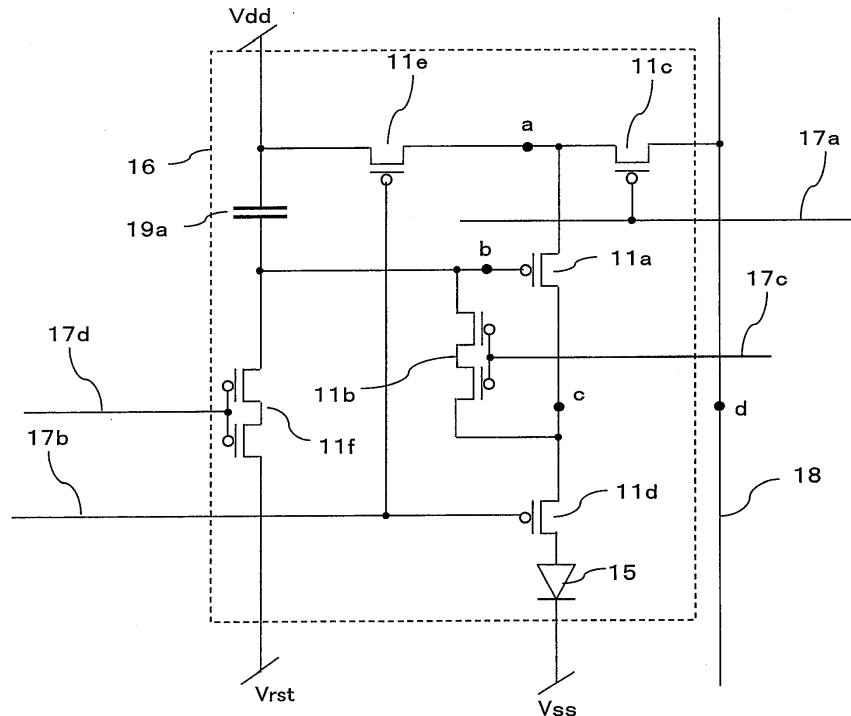

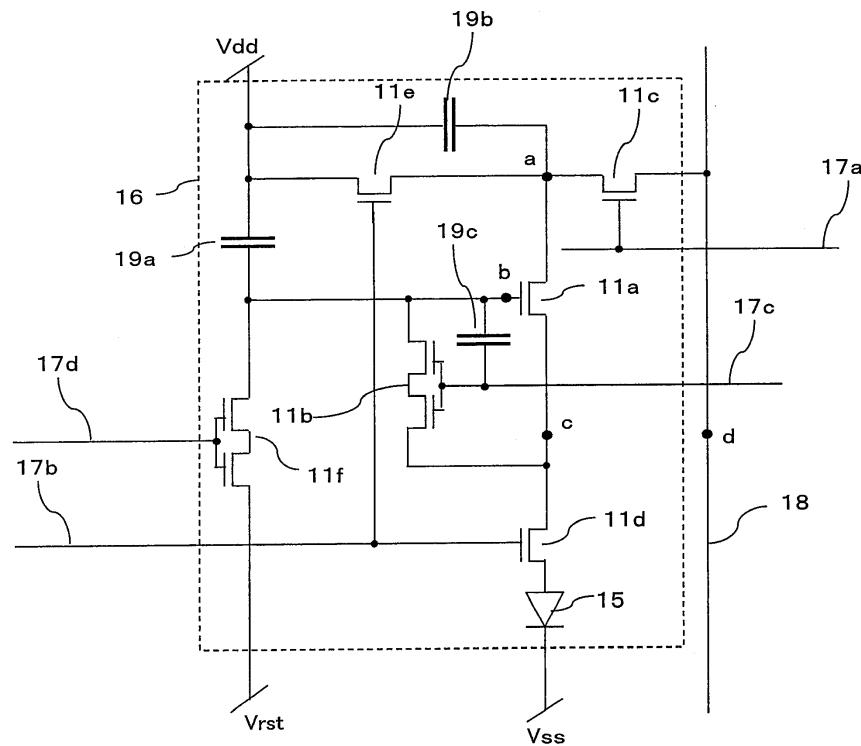

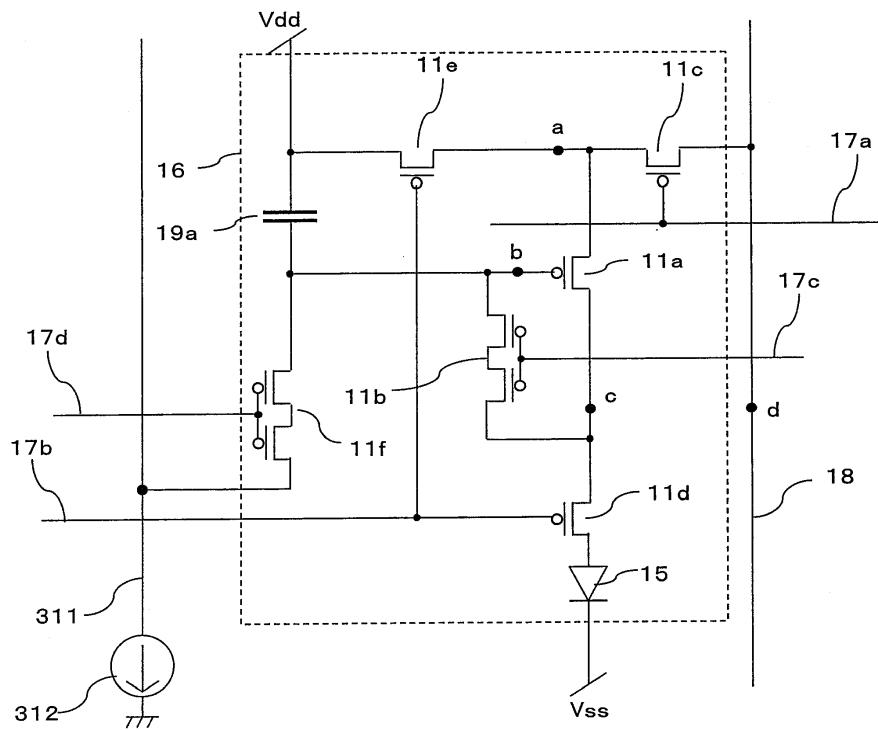

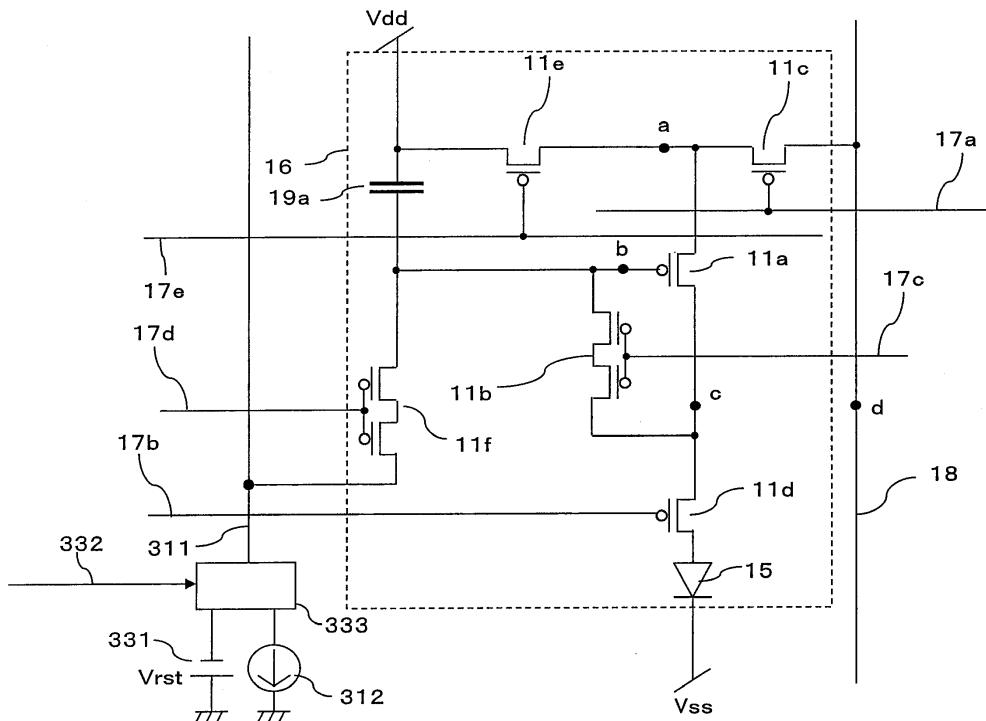

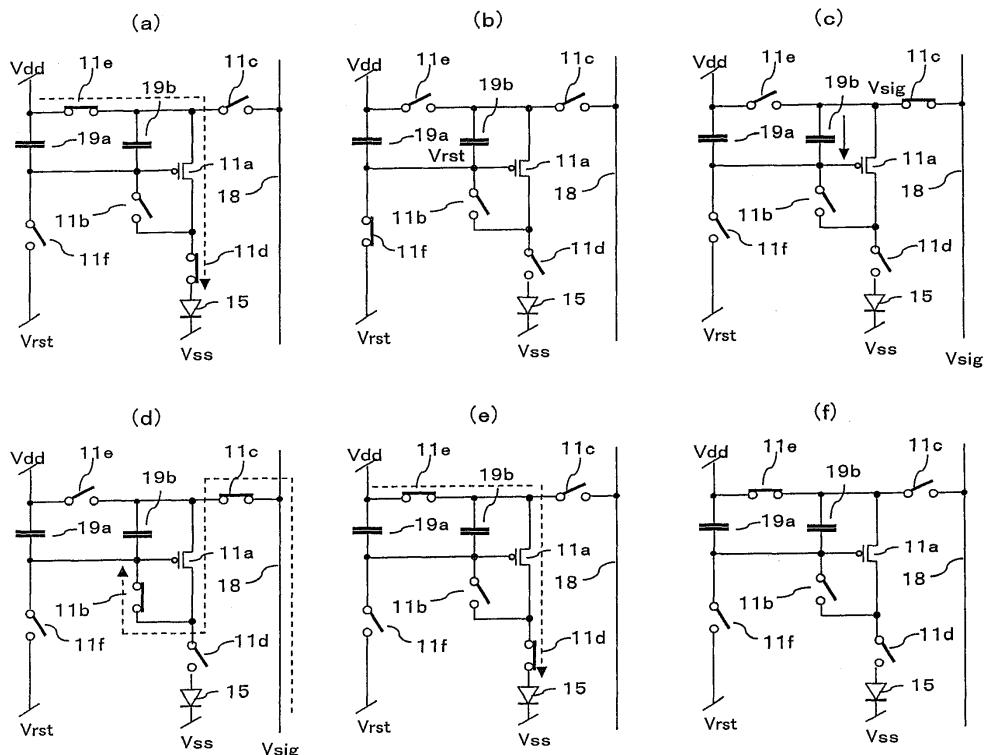

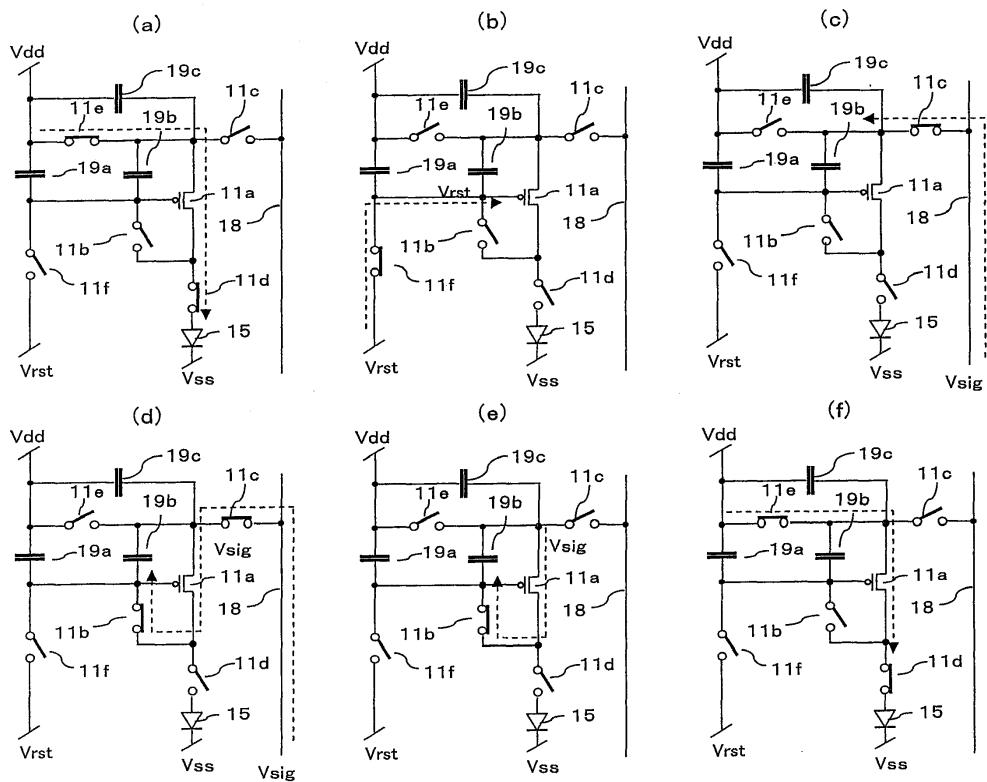

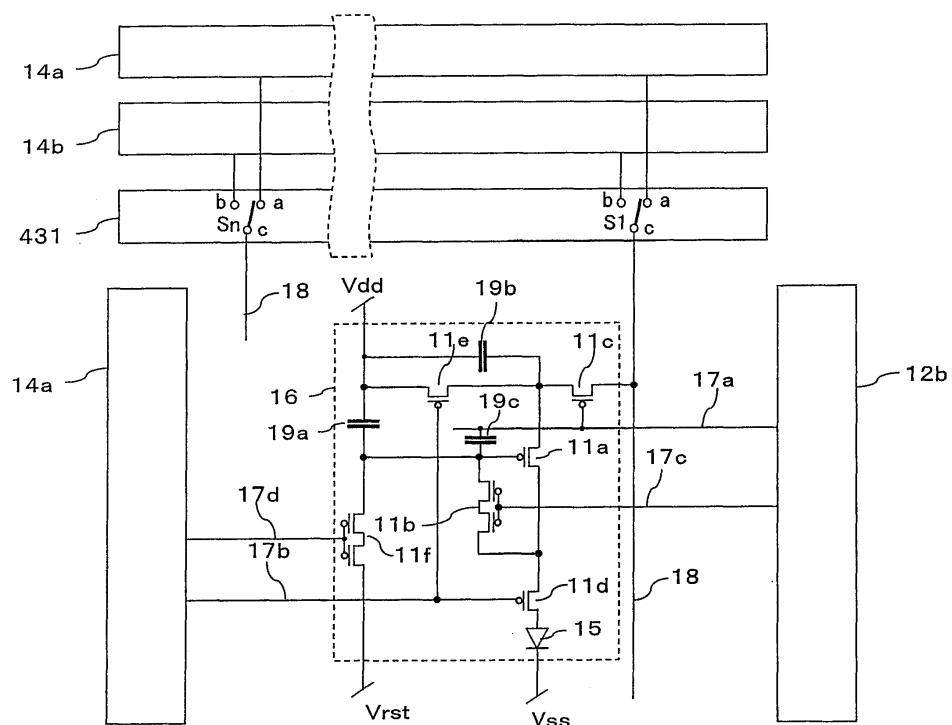

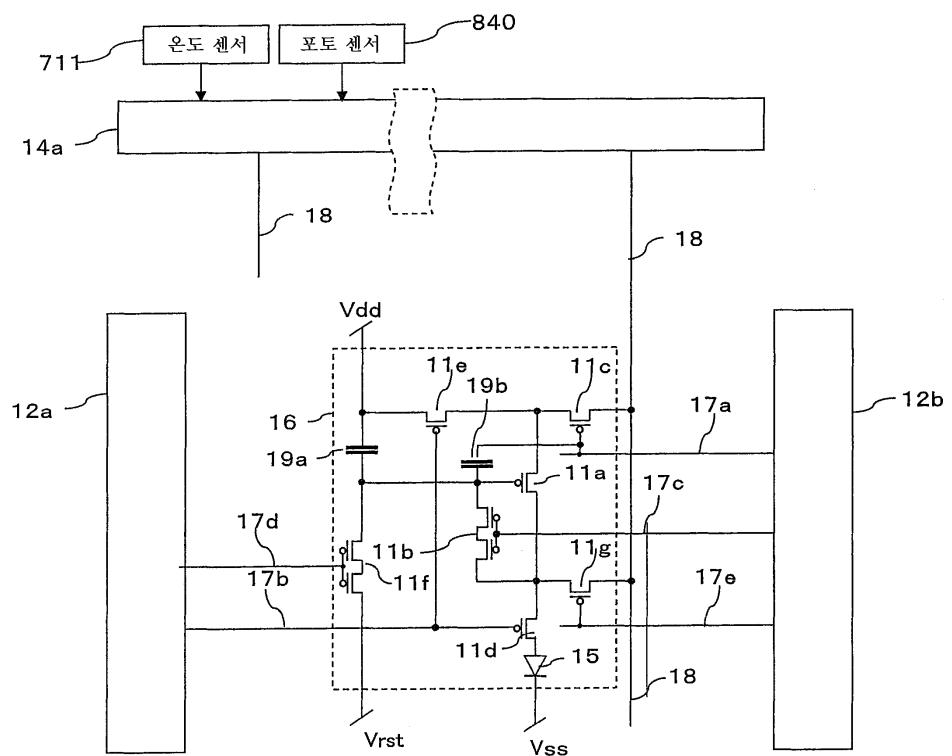

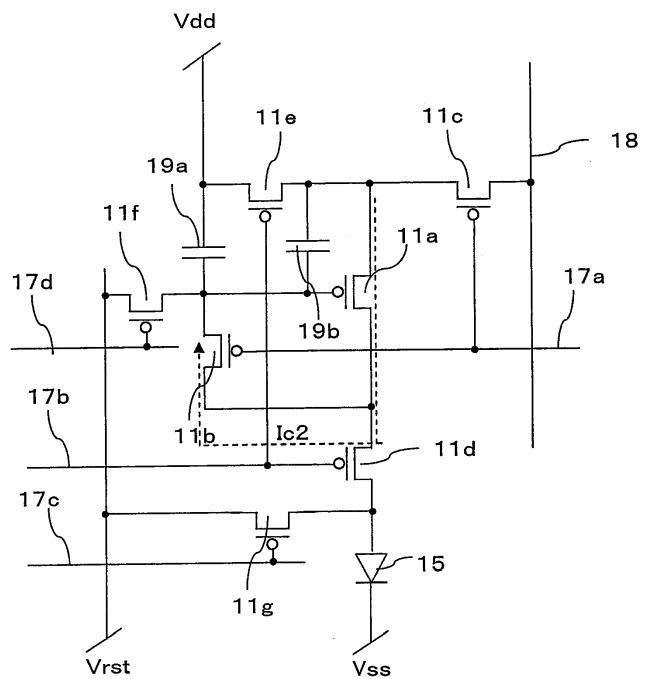

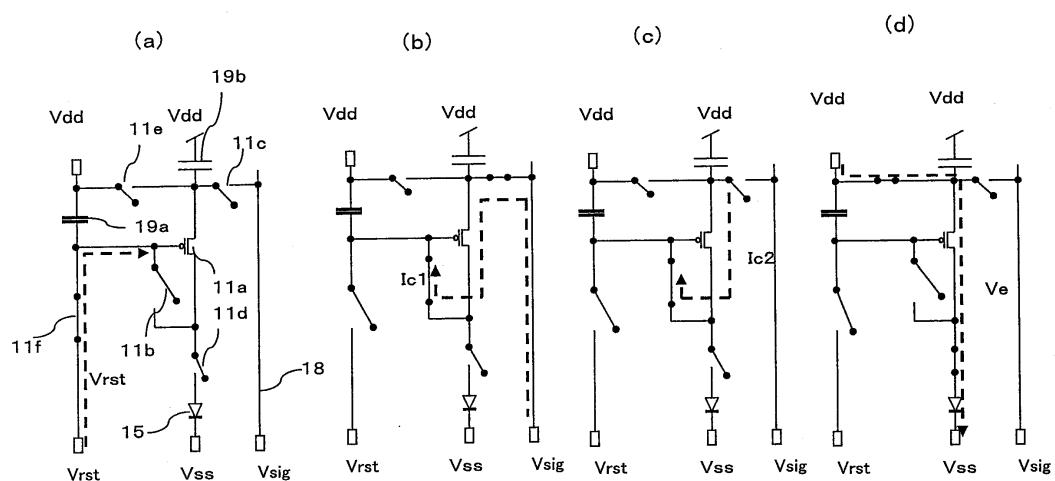

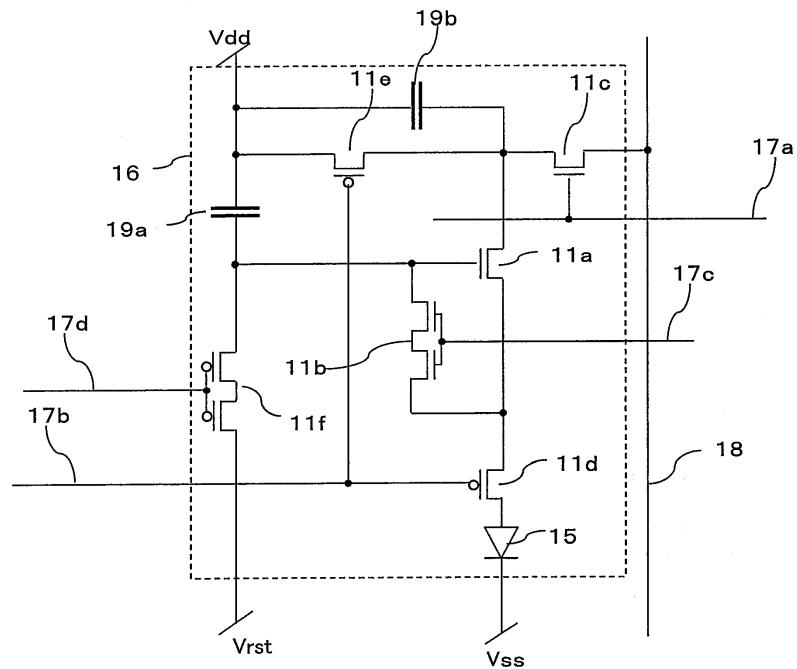

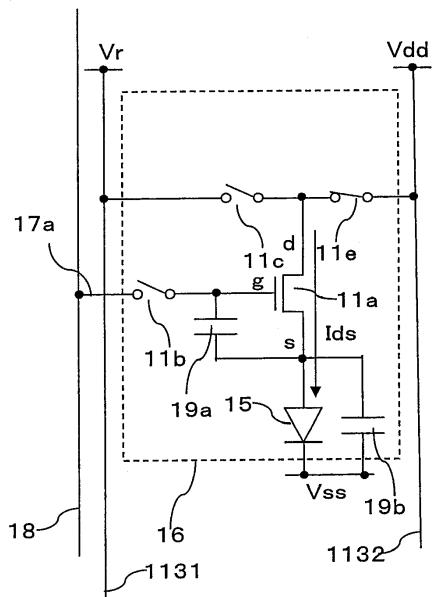

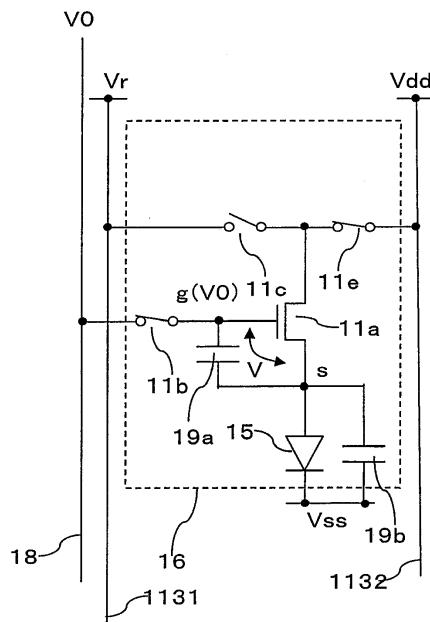

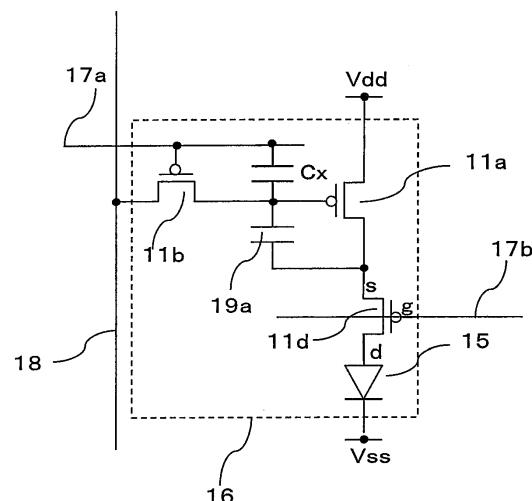

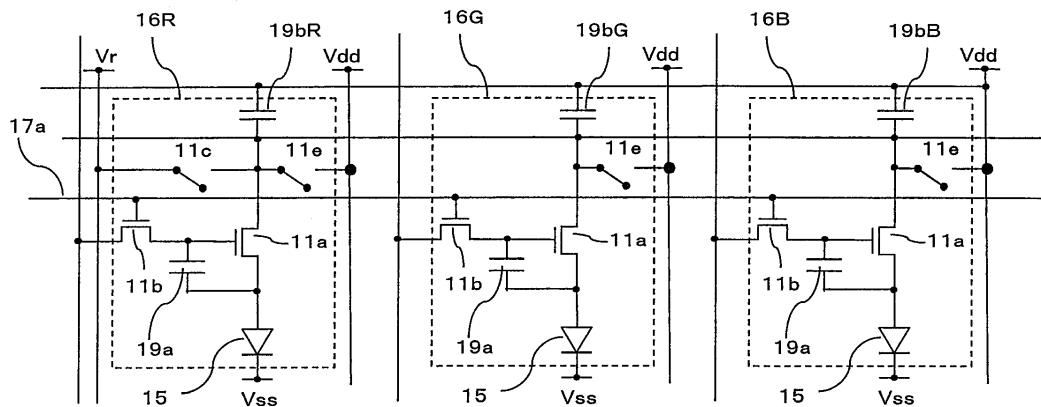

[0079] 도 1에서, 화소(16)는, 2개의 컨덴서(19a, 19b)와 5개의 스위치 트랜지스터(11b, 11c, 11d, 11e, 11f)와 1개의 구동 트랜지스터(11a)로 구성된다. 트랜지스터(11b)는, 트랜지스터(11a)를 다이오드 접속(Diode-connected)시켜, 임계값(역치값) 전압을 보상하기 위한 임계값 전압 보상용의 스위치 트랜지스터이다. 트랜지스터(11f)는, 유지용 컨덴서(19a)를 초기화시키기 위하여, 리세트 전압 Vrst를 인가하기 위한 초기화용의 스위치 트랜지스터이다. 트랜지스터(11d)는, EL 소자(15)의 발광을 제어하기 위한 트랜지스터이다.

[0080] 스위치 트랜지스터(11b, 11f)는 오프 리크로 작게 할 필요가 있기 때문에, 듀얼 게이트 이상의 복수 게이트 구성(멀티 게이트 구조)으로 한다. 단, 스위치 트랜지스터(11b, 11f)의 오프 특성이 충분한 경우에는, 싱글 게이트 구성이어도 된다. 또한, 스위치 트랜지스터(11c)도 멀티 게이트 구조를 채용하는 것이 바람직하다.

[0081] 컨덴서(19a)는, 구동 트랜지스터(11a)의 게이트 단자의 전위를 유지하는 유지용의 컨덴서(이후, 유지용 컨덴서(19a)라고 부름)이다. 기본적으로는, 구동 트랜지스터(11a)의 특성 변동을 오프셋 캔슬한 전압이 유지된다.

- [0082] 스위치 트랜지스터(11c)의 게이트 단자는, 게이트 신호선(17a)에 접속된다. 스위치 트랜지스터(11c)의 소스 단자는, 소스 신호선(18)에 접속된다. 스위치 트랜지스터(11c)는, 게이트 드라이버 회로(12a)로부터의 선택 신호에 의해 온/오프 제어된다.

- [0083] 구동 트랜지스터(11a)의 소스 단자는, 스위치 트랜지스터(11c)의 드레인 단자와 접속된다. 임계값 전압 보상용의 스위치 트랜지스터(11b)의 소스 단자 또는 드레인 단자와, 유지용 컨덴서(19a)의 제1 단자가 접속된다. 구동 트랜지스터 임계값 전압 보상용의 스위치 트랜지스터(11b)가 온(클로즈)함으로써, 구동 트랜지스터(11a)의 게이트 단자에는, 오프셋 캔슬 전압이 유지된다.

- [0084] 임계값 전압 보상용의 스위치 트랜지스터(11b)는, 상기 구동 트랜지스터(11a)의 게이트 단자와 드레인 단자 사이에 접속되고, 게이트 신호선(17c)에 인가되는 스캔 신호에 응답하여 구동 트랜지스터(11a)의 게이트 단자와 드레인 단자 사이를 단락하고, 구동 트랜지스터(11a)를 다이오드 접속 상태로 한다. 따라서, 상기 스캔 신호에 의해 구동 트랜지스터(11a)는, 다이오드와 같은 상태로 되고, 구동 트랜지스터(11a)의 게이트 단자에 전압  $V_{sig-Vth}[V]$ 가 인가되며, 이 전압이, 상기 구동 트랜지스터(11a)의 게이트 전압으로 된다.

- [0085] 또한, 전압  $V_{sig}$ 는, 소스 드라이버 IC(14)가 소스 신호선(18)에 출력한 영상 신호이다. 또한,  $V_{th}$ 는, 구동 트랜지스터(11a)의 임계값 전압이다. 또한,  $V_{th}$ 는 구동 트랜지스터(11a)의 오프셋 캔슬 전압이다.  $V_{th}$ 는, 구동 트랜지스터(11a)의 특성에 의해, 개개에 변동이 있다.

- [0086] 초기화용의 스위치 트랜지스터(11f)는, 리세트 전압 라인  $V_{rst}$ 와 유지용 컨덴서(19a)의 제1 단자 사이에 접속되고, 게이트 신호선(17d)의 스캔 신호에 응답하여, 리세트 전압  $V_{rst}$ 가, 구동 트랜지스터(11a)의 게이트 단자 및 유지용 컨덴서(11a)에 인가된다. 따라서, 유지용 컨덴서(19a)에 충전된 전하는 방전된다. 또한, 구동 트랜지스터(11a)의 게이트 단자에 소정 전압(초기화 전압  $V_{rst}$ )이 인가된다.

- [0087] 또한, 도 1 등의 본 실시예의 화소 구성에서는, 구동 트랜지스터(11a)의 게이트 단자에 직류적으로  $V_{rst}$  전압,  $V_{sig}$  전압을 인가하도록 설명하고 있다. 그러나, 본 실시예는 이것에 한정되는 것이 아니라, 교류적으로  $V_{rst}$  전압,  $V_{sig}$  전압을 인가해도 된다. 구체적으로는, 구동 트랜지스터(11a)의 게이트 단자에 컨덴서를 배치하고, 직류 성분을 차단하여,  $V_{rst}$  전압,  $V_{sig}$  전압을, 구동 트랜지스터(11a)의 게이트 단자에 인가하는 구성을 채용해도 된다.

- [0088] 또한, 도 1 등의 본 발명의 실시예에서, 오프셋 캔슬 컨덴서(11b)의 한 쪽의 단자를 애노드 전압  $V_{dd}$ 에 접속하는 것으로 하였지만, 이것에 한정되는 것이 아니라, 소정의 일정 전압으로 유지되도록 구성하면 되는 것은 물론이다. 일정 전압이란,  $V_{GH}$  전압,  $V_{GL}$  전압 등이 예시된다. 따라서, 스위치 트랜지스터(11e)의 한 쪽의 단자를  $V_{dd}$  전압에 접속(도 1의 접속과 동일)하고, 오프셋 캔슬 컨덴서(11b)의 한 쪽의 단자를  $V_{GH}$  전압 등에 접속해도 된다( $V_{dd}$  전압으로부터  $V_{GH}$  전압으로 변경).

- [0089] 스위치 트랜지스터(11e)는, 애노드 전압  $V_{dd}$  배선 또는  $V_{dd}$  전극과 구동 트랜지스터(11a)의 소스 단자 사이에 접속된다. 스위치 트랜지스터는, 스위치 트랜지스터의 게이트 단자에 접속된 게이트 신호선(17b)에 인가된 온 오프 전압에 의해 제어된다. 스위치 트랜지스터(11e)는, EL 소자(15)를 발광시킬 때에는, 온으로 되고, 애노드 전압  $V_{dd}$ 를 상기 구동 트랜지스터(11a)의 소스 단자에 인가한다.

- [0090] 스위치 트랜지스터(11d)는, 구동 트랜지스터(11a)의 드레인 단자와 EL 소자(15)의 애노드 단자 사이에 접속(배치)되고, 스위치 트랜지스터(11d)의 게이트 단자에 접속된 게이트 신호선(17b)에 인가된 온 오프 신호(발광 제어 신호)에 의해 제어된다. 스위치 트랜지스터(11d)는, 발광 제어 신호에 응답하여 상기 구동 트랜지스터(11a)에서 생성되는 상기 구동 전류를 상기 EL 소자(15)에 전달한다. 즉, 스위치 트랜지스터(11d)는, EL 소자(15)에 흐르는 전류 경로의 전류를 온 오프 제어한다.

- [0091] 유지용 컨덴서(19a)는, 애노드 전압  $V_{dd}$  배선(전극)과 구동 트랜지스터(11a)의 게이트 단자 사이에 접속되고, 애노드 전압  $V_{dd}$ 와 상기 구동 트랜지스터(11a)의 게이트 단자에 인가되는 전압  $V_{sig-Vth}[V]$ 에 해당하는 전하를 1프레임의 동안에는 유지한다.

- [0092] 또한, 게이트 신호선(17)에 인가되는 전압은, 오프 전압( $V_{GH}$ )과 온 전압( $V_{GL}$ )이고,  $V_{GH}$  전압의 인가에 의해, 스위치 트랜지스터(11)(11b, 11c, 11d, 11e, 11f)가 오프하고,  $V_{GL}$  전압의 인가에 의해, 스위치 트랜지스터(11)(11b, 11c, 11d, 11e, 11f)가 온한다. 단, 스위치 트랜지스터가, P채널 트랜지스터인 경우이다.

- [0093] 도 3에 도시하는 바와 같이,  $V_{GL}$  전압은, 게이트 드라이버 회로(12a)에서는,  $V_{GL1}$ 로 하고, 게이트 드라이버 회로(12b)에서는,  $V_{GL2}$ 로 하고 있다. 즉, 게이트 드라이버 회로(12a와 12b)에서는, 온 전압을 서로 다르게 하고

있다.

[0094] 따라서, 게이트 신호선(17a), 게이트 신호선(17c)에 인가되는 온 전압은 VGL1이고, 게이트 신호선(17b), 게이트 신호선(17d)에 인가되는 온 전압은 VGL2이다. 또한, | VGL1 | > | VGL2 | 인 관계로 되도록 설정되어 있다. 또한, 게이트 신호선(17a)에 인가되는 VGH와 게이트 신호선(17d)에 인가되는 VGH는 일치시켜도 된다. 즉, 게이트 드라이버 회로(12a)의 오프 전압 VGH1과 게이트 드라이버 회로(12b)의 VGH2는 동일하게 해도 된다.

[0095] 또한, 본 발명의 실시예에서, 구동 트랜지스터(11a)는 P채널 트랜지스터이지만 이것에 한정되는 것이 아니라, N채널 트랜지스터이어도 된다. 이 경우에는, 온 전압이 VGH로 되고, 오프 전압이 VGL로 된다.

[0096] 또한, 구동 트랜지스터(11a)의 소스 단자는 애노드 전압 Vdd와 접속되어 있는 것으로서 설명하지만, 이것에 한정되는 것은 아니다. 예를 들면, 캐소드 전압 Vss 혹은 그라운드 전압 GND에 접속되어 있어도 된다. 또한, 컨텐서(18)는, 트랜지스터(11)의 게이트 절연막 용량에 의한 컨텐서로 대용해도 된다.

[0097] 게이트 드라이버 회로(12a)에는, 게이트 신호선(17a)을 선택하는 스타트 펄스 ST1, 게이트 신호선(17c)을 선택하는 스타트 펄스 ST2, 스타트 펄스를 순차 시프트하는 클럭 신호(CLK)가 인가된다. UD는, 게이트 드라이버 회로(12a) 내의 스타트 펄스의 상하 시프트 레지스터 방향을 절환하는 신호이다.

[0098] 게이트 드라이버 회로(12b)에는, 게이트 신호선(17b)을 선택하는 스타트 펄스 ST3, 게이트 신호선(17d)을 선택하는 스타트 펄스 ST4, 스타트 펄스를 순차 시프트하는 클럭 신호(CLK)가 인가된다.

[0099] 또한, 필요에 따라서, 게이트 드라이버 회로(12)에는, 인에이블 제어 단자를 부가하는 것이 바람직하다. 게이트 드라이버 회로(12) 내에는, 시프트 레지스터 회로가 형성되어 있고, 스타트 펄스를 클럭 신호(CLK)에 동기하여 순차 시프트시켜, 선택하는 게이트 신호선(17)의 위치를 변화시킨다.

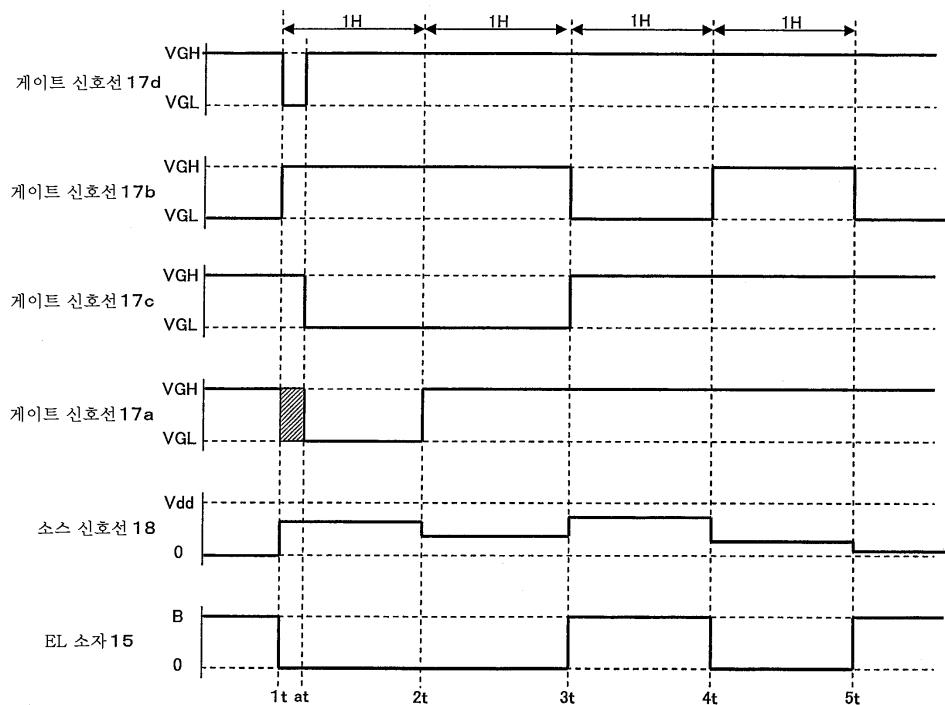

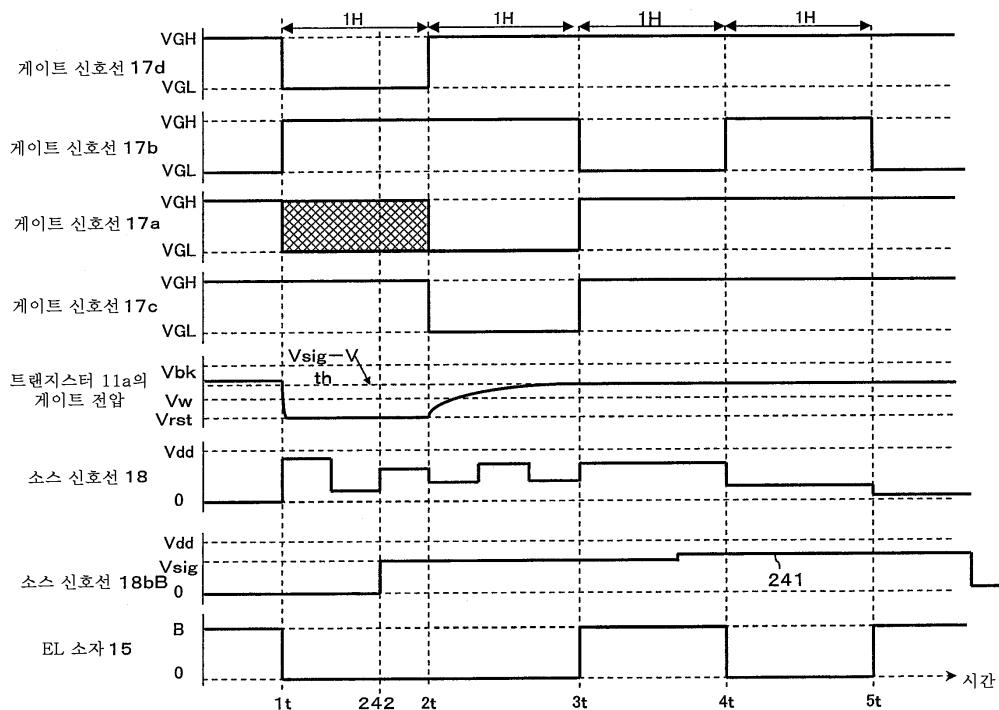

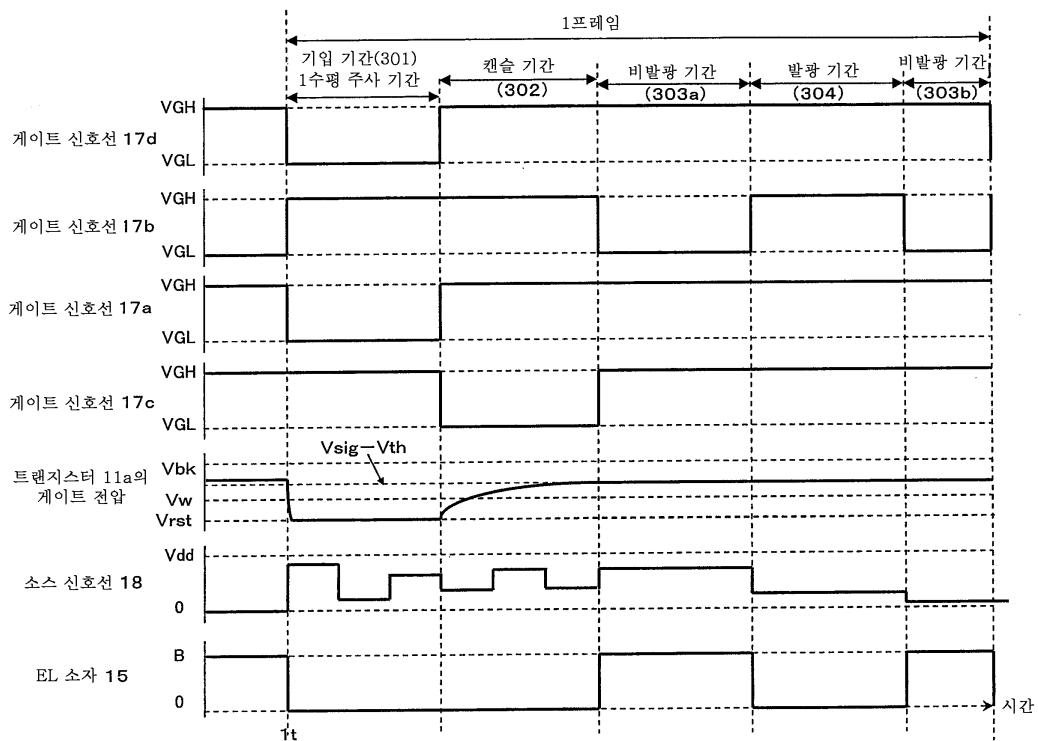

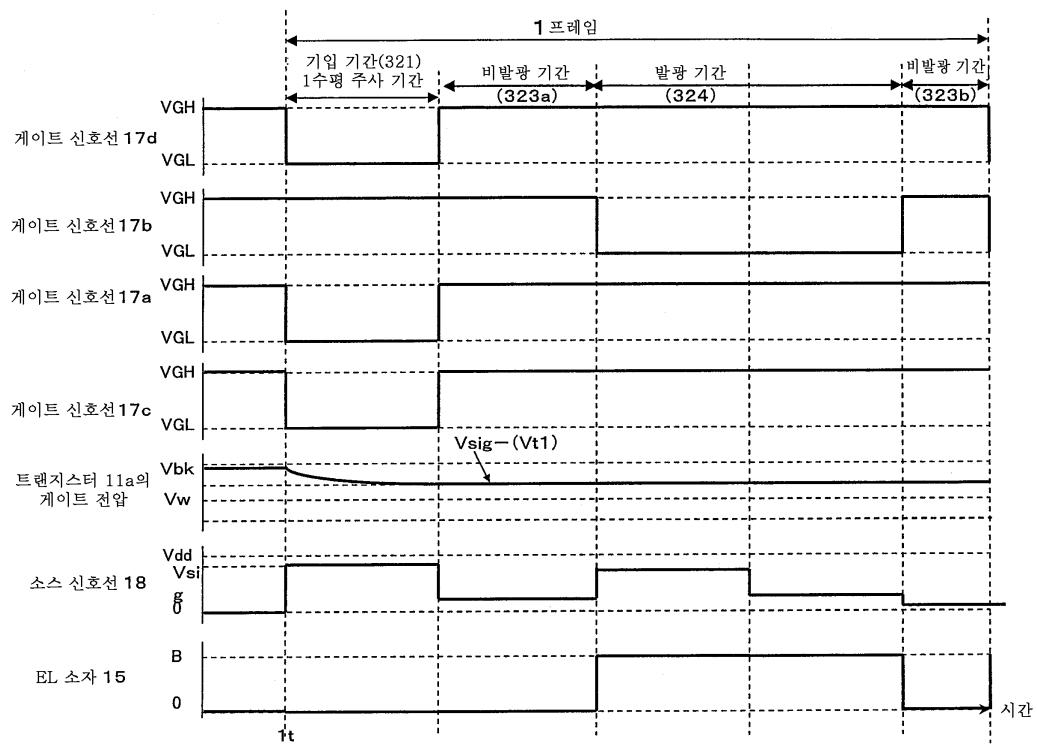

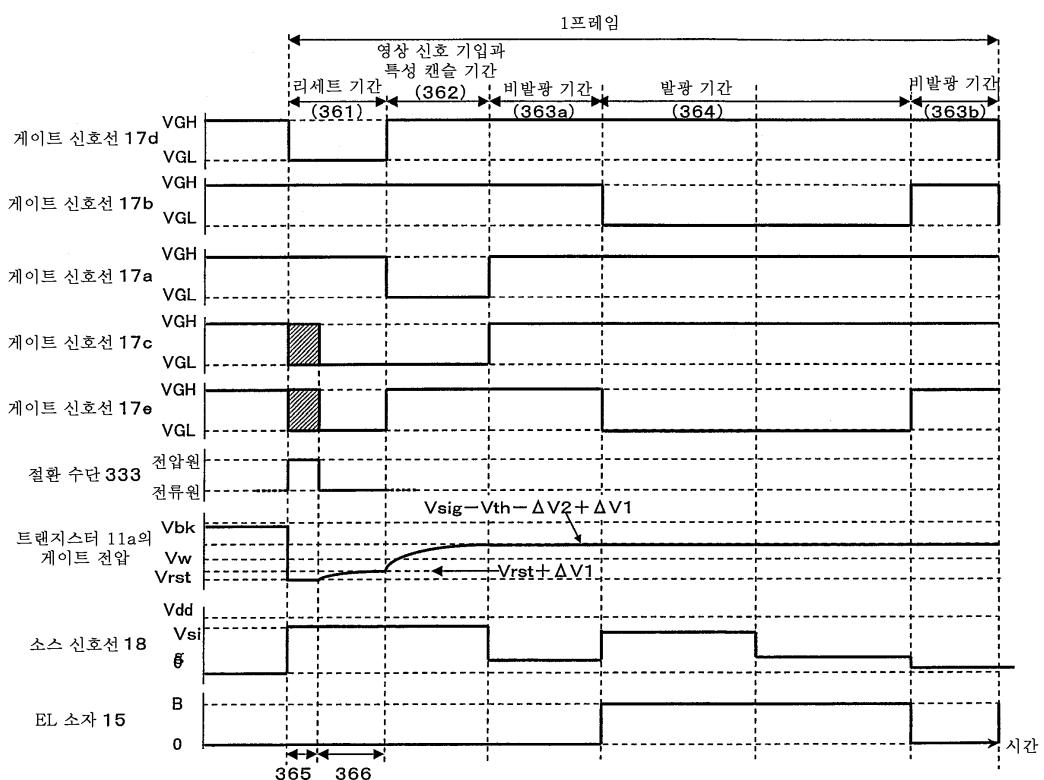

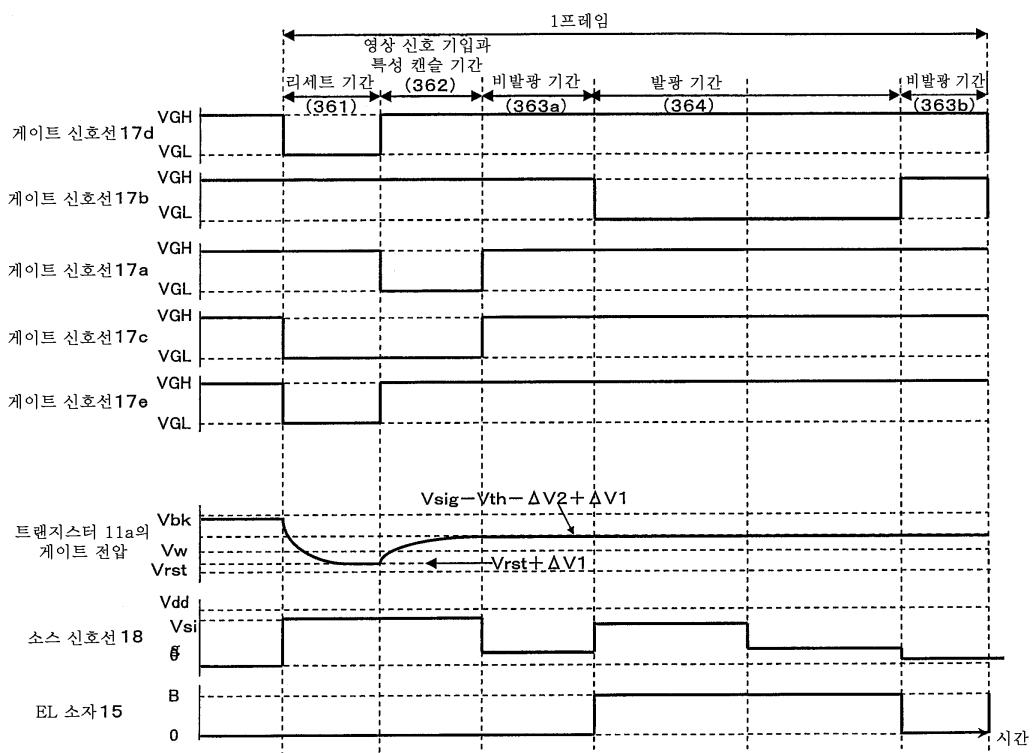

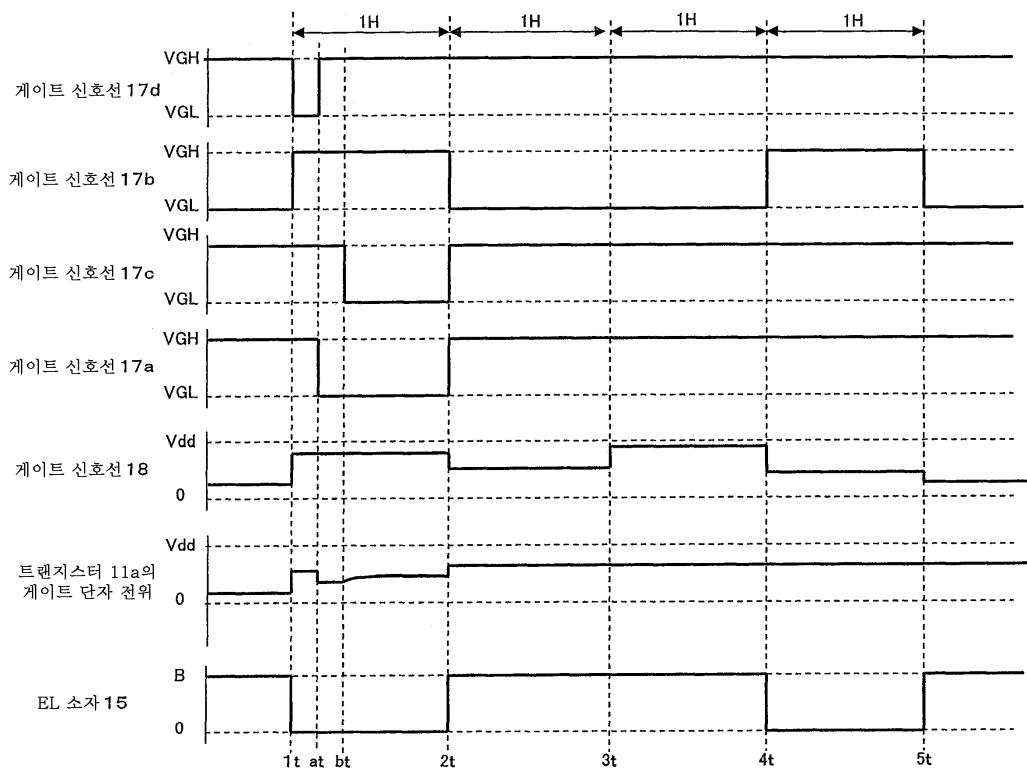

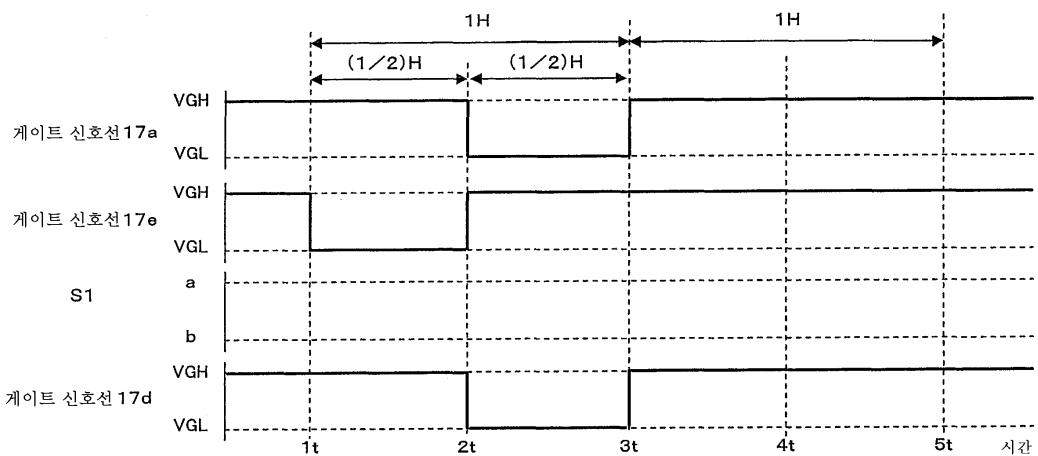

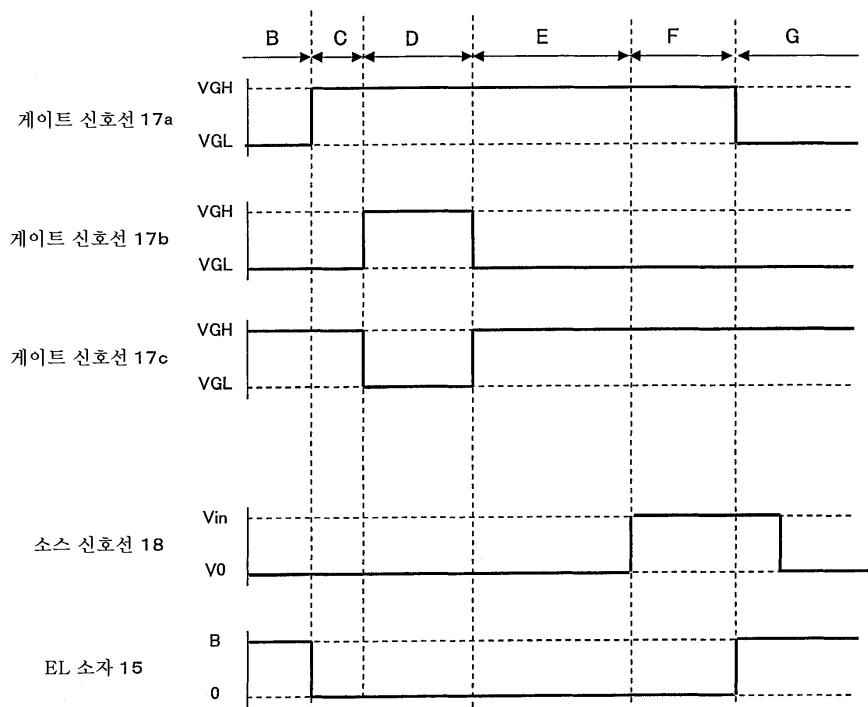

[0100] 도 2는, 게이트 신호선(17a, 17b, 17c, 17d)에 인가되는 구동 전압, 소스 신호선(18)의 영상 신호 전압, EL 소자(15)의 발광 상태를 나타낸다.

[0101] 또한, 도 2는, 각 동작에서의 스위치 트랜지스터의 동작 상태(온/오프 상태), 전류 혹은 전압의 인가 상태를 나타낸다.

[0102] 또한, 도 2에서는, 설명을 용이하게 하기 위하여, 오프 전압을 VGH로 하고, 온 전압을 VGL로 한다. 또한, 소스 신호선(18)에 인가되는 전압 Vsig의 범위는, 그라운드 전압(GND)=0V로 하고, 애노드 전압 Vdd 이하로 하고 있다. 구체적으로는, 영상 신호 전압 Vsig는, 0.2V~5.0V의 범위이다.

[0103] 또한, 1H란 1수평 주사 기간이다. 또한, 도 2는 모식적인 것이며, 1H를 수 H로 치환해도 되고, 1H는 1H보다 짧은 기간으로 치환해도 된다.

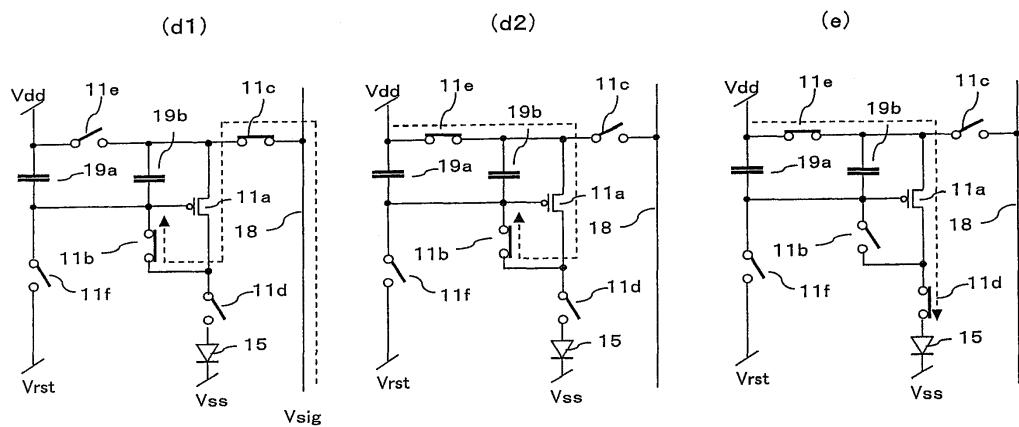

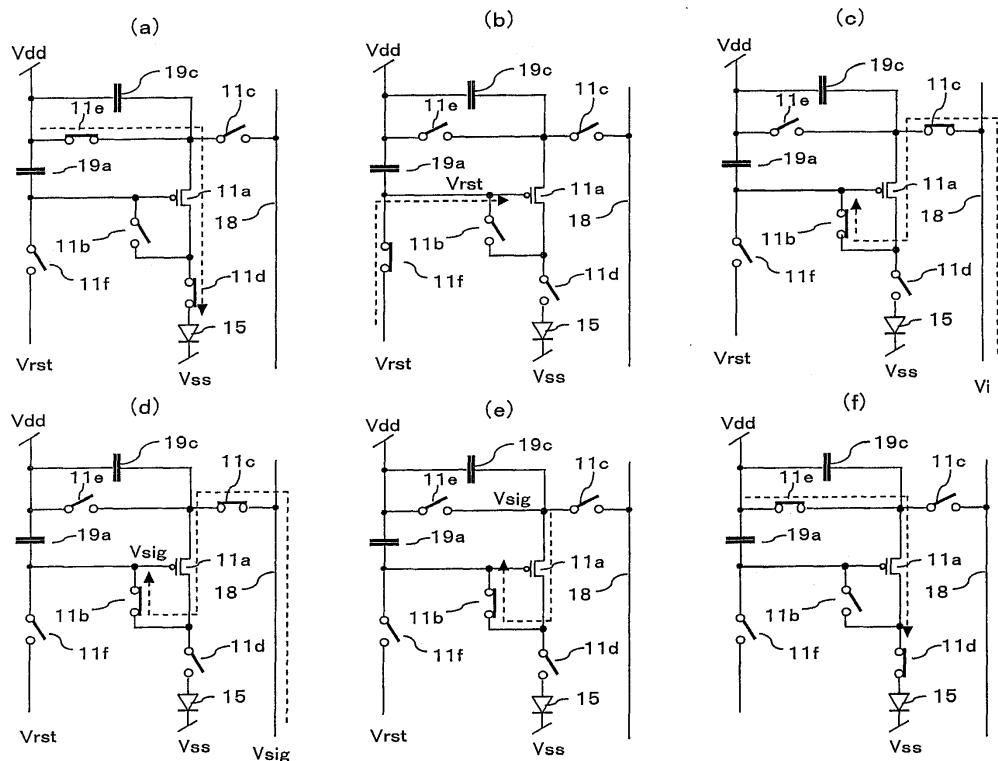

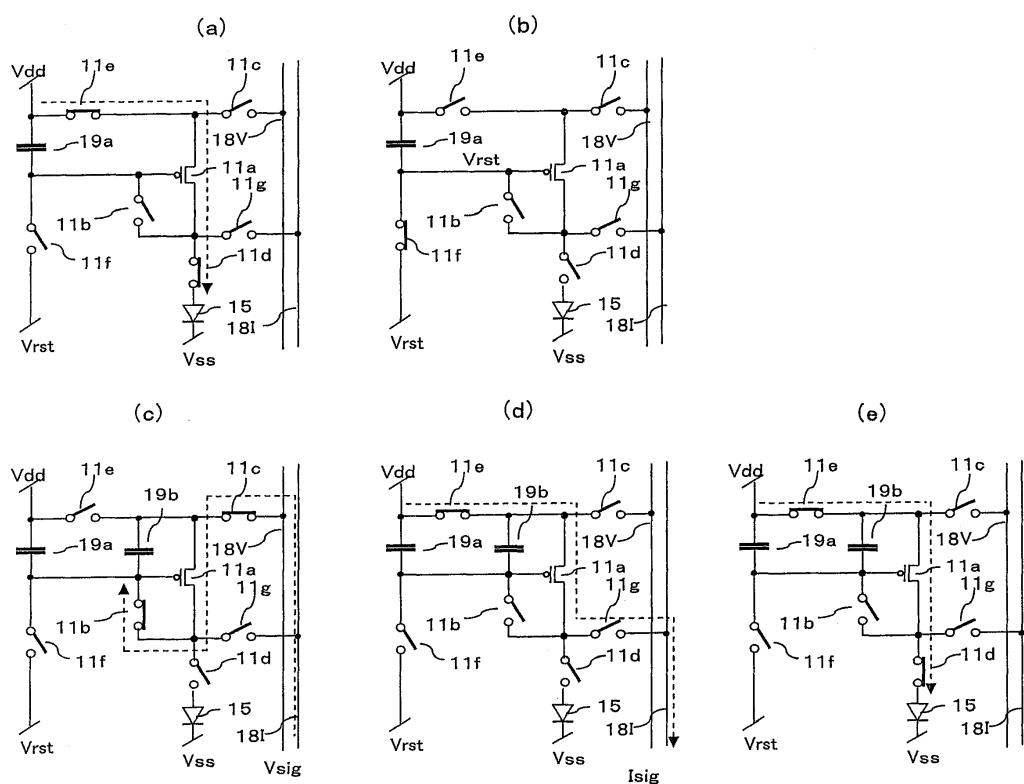

[0104] 도 111은 도 1의 화소의 동작을 설명하기 위한 설명도이다. 도 111에서, 설명을 용이하게 하기 위하여 각 스위치 트랜지스터는 스위치로서 도시하고 있다.

[0105] VGH 전압은, 애노드 전압 Vdd보다도 0.5V 이상 3.0V 이하의 높은 전압으로 설정된다. 예를 들면, 애노드 전압 Vdd가 5V이면, VGH 전압은, 5.5V 이상 8V 이하의 전압으로 설정된다.

[0106] 화소(16)에는, 1t 내지 at의 기간에, 게이트 신호선(17d)에 온 전압이 인가된다. 도 111의 (a)가 대응한다. 온 전압(VGL)의 인가에 의해, 트랜지스터(11f)가 온하고, 리세트 전압 Vrst가 구동 트랜지스터(11a)의 게이트 단자에 리세트 전압 Vrst가 인가된다(a점).

[0107] 리세트 전압 Vrst의 인가에 의해, 구동 트랜지스터(11a)는, 리세트 상태로 된다. 리세트 상태란, 구동 트랜지스터(11a)를 초기화된 상태, 구동 트랜지스터(11a)의 게이트 단자에 소정 전압(초기화 전압)이 인가된 상태, 구동 트랜지스터(11a)가 소정 상태로 된 상태 등이다.

[0108] 또한, 리세트 전압 Vrst는, GND 전압 이하 -5(V) 이상의 전압으로 설정해야 한다. 예를 들면, 리세트 전압 Vrst는, -2.5V로 설정한다. 리세트 전압 Vrst는, VGL1 전압 이상이고, GND 전압 이하의 값으로 설정하는 것이 바람직하다. 더욱 바람직하게는, 영상 신호 전압 Vsig의 최저 전압 -1.0V 이하, 스위치 트랜지스터(11c)의 온 전압(VGL) +1.0 이상의 값으로 설정하는 것이 바람직하다.

[0109] 또한, 리세트 전압 Vrst는, 영상 신호 전압 Vsig에 대응하여 변화시켜도 된다. 예를 들면, 영상 신호의 계조 번호에 대응시켜 리세트 전압 Vrst를 변화시킨다. 또한, 리세트 전압 Vrst는, 적(R), 녹(G), 청(B)의 영상 신호 전압에 의해 변화시켜도 된다. RGB에서 영상 신호의 진폭이 서로 다르기 때문이다. 이 경우에는, 계조 번

호에 대응하지 않고, 각 RGB에서 고정의 리세트 전압 Vrst를 설정해도 된다. 또한, 리세트 전압 Vrst는, 표시화면에서 소비되는 전류에 대응시켜 변화시켜도 된다. 표시하는 화상의 휘도에 대응시켜, 리세트 전압 Vrst를 변화시켜도 된다.

- [0110] 게이트 신호선(17c)은, 리세트 전압 Vrst의 인가 후(at), 온 전압(VGL)을 인가하는 기간은, 1H 이상으로 하고 있지만, 이것에 한정되는 것이 아니라, 1H 이하의 기간이어도 된다. 적어도 게이트 신호선(17c)에 온 전압(VGL)을 인가하는 기간은, 게이트 신호선(17a)에 온 전압(VGL)을 인가하는 기간보다도 길게 한다. 또는, 오버랩시킨다. 또한, 리세트 전압 Vrst의 인가 시간은,  $2\mu\text{sec}$  이상의 시간을 확보하는 것이 바람직하다.

- [0111] 게이트 신호선(17a)에 온 전압(VGL)을 인가함으로써, 스위치 트랜지스터(11c)가 온하고, 소스 신호선(18)에 인가한 Vsig가 오프셋 캔슬용 컨덴서(19a)에 인가된다. a점에 인가된 영상 신호 Vsig는, 스위치 트랜지스터(11b)가 온하고 있는 기간 유지된다.

- [0112] 또한, 도 2에 도시하는 게이트 신호선(17a)의 사선부는, 온 전압(VGL)을 인가해도 오프 전압(VGH)을 인가해도 된다.

- [0113] 스위치 트랜지스터(11c)가 온함으로써, 영상 신호 전압 Vsig가 오프셋 캔슬 컨덴서(11b)에 인가되고, 오프셋 캔슬 컨덴서(11b)에 영상 신호 전압 Vsig가 충전된다.

- [0114] 게이트 신호선(17a)에 온 전압(VGL)이 인가됨으로써, 영상 신호 전압 Vsig를 화소에 인가하는 스위치 트랜지스터(11c)가 온한다(도 2의 1t~2t 혹은 at~2t). 이 상태를 도 111의 (b)에 도시한다. 도 111의 (b)에서는, 스위치 트랜지스터(11d, 11e, 11f)는 오프 상태(오픈 상태)이다. 또한, 스위치 트랜지스터(11c, 11b)는 온 상태(클로즈 상태)이다.

- [0115] 스위치 트랜지스터(11b)가 온함으로써, 소스 신호선(18)으로부터, 구동 트랜지스터(11a) 및 트랜지스터(11b)의 채널 사이에 전류 경로가 발생하고, 오프셋 캔슬 전류 Ic1이 흐른다.

- [0116] 전류 Ic1은 처음에, 비교적 큰 전류가 흐르고, 오프셋 캔슬 동작이 종국에 근접함에 따라서 작아진다. 기본적으로는, 오프셋 캔슬이 완료하면  $Ic1=0$ 으로 된다. 오프셋 캔슬의 동작에 의해, 캔슬 전압이 컨덴서(11a)에 유지된다.

- [0117] 영상 신호 전압 Vsig의 인가에 의해, 구동 트랜지스터(11a)는, 영상 신호 전압 Vsig가 인가된 상태에서, 구동 트랜지스터(11a)의 채널에 전류가 흐르지 않도록, 게이트 단자인 b점의 전위를 변화시킨다(오프셋 캔슬 동작). 변화 후의 전압이, 유지용 컨덴서(19a)에 유지된다. 이 동작에 의해, 구동 트랜지스터(11a)는, 오프셋 캔슬 상태에 가까운 상태까지 오프셋 캔슬된다. 오프셋 캔슬용 컨덴서(19b)에는, 영상 신호 전압 Vsig가 충전된다.

- [0118] 도 2의 1t~2t 기간에서 완전한 오프셋 캔슬을 실시할 수 있는 것이 이상적이다. 그러나, 고정밀의 표시 패널에서는, 1화소행을 선택하는 시간이 짧아, 충분한 오프셋 캔슬 동작을 실현할 수 없다. 오프셋 캔슬이 충분하지 않으면, 구동 트랜지스터(11a)의 특성 변동이 남아, 계조 표시에 의해 화면(31)에 휘도 불균일이 발생한다.

- [0119] 본 실시예는 이 과제를 해결하는 것을 하나의 목적으로 하고 있다.

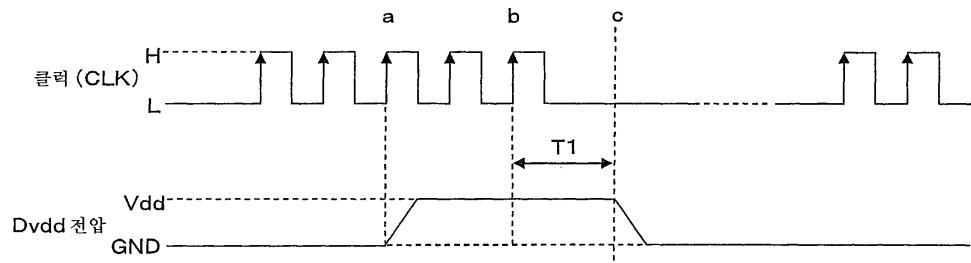

- [0120] 도 2의 2t~3t는, 오프셋 캔슬 동작의 계속 기간이다. 도 2에서는, 2t~3t의 기간이 대응한다. 또한, 도 111의 (c)가 대응한다.

- [0121] 도 111의 (c)에서는, 스위치 트랜지스터(11e, 11d, 11f, 11c)가 오프 상태(오픈 상태)이고, 스위치 트랜지스터(11b)가 온 상태(클로즈 상태)이다. 이 경우에는, 오프셋 캔슬 전류 Ic2가 흐른다. 오프셋 캔슬 전류 Ic2는, 오프셋 캔슬의 종국 상태에서의 전류이기 때문에 매우 작다. 따라서, 오프셋 캔슬 컨덴서(19b)의 용량은 작아도 된다.

- [0122] 또한, 도 2의 실시예에서는, 오프셋 캔슬 동작을 계속하는 기간을 2t~3t 기간으로 하고 있지만, 본 실시예는 이것에 한정되는 것은 아니다. 오프셋 캔슬을 계속하는 기간은, 각각의 패널에 대응시켜 가변 혹은 설정한다. 본 실시예는, 오프셋 캔슬 기간을 적어도 1H(1화소행 선택 기간) 이상의 기간을 행하는 것이다. 오프셋 캔슬 기간은,  $20\mu\text{sec}$  이상 설정하는 것이 바람직하다.

- [0123] 도 2에서, 1t~2t의 기간에 영상 신호 전압 Vsig가 화소(16)에 유지된다. 그 이후의 기간은, 스위치 트랜지스터(11c)가 오프 상태이기 때문에, 소스 신호선(18)에 인가된 영상 신호 전압 Vsig가 변화해도, 상기 화소(16)에 영상 신호 전압 Vsig가 기입되는 일은 없다.

- [0124] 이상의 오프셋 캔슬의 동작 후, 게이트 신호선(17b)에 온 전압이 인가되고, 스위치 트랜지스터(11e)가 온하고, 애노드 전압 Vdd가 구동 트랜지스터(11a)의 소스 단자에 공급된다(도 111의 (d)의 상태). 또한, 스위치 트랜지스터(11d)가 온하고, 구동 트랜지스터(11a)로부터 EL 소자(15)의 구동용 전류가 EL 소자(15)에 공급된다. EL 소자(15)는, 인가된 전류에 의해 발광한다.

- [0125] 도 2에서는, 기간 3t~4t의 기간에 게이트 신호선(17b)에 온 전압(VGL)을 인가하여, 스위치 트랜지스터(11b)를 온시켜 EL 소자(15)에 발광 전류를 공급한다. 또한, 기간 4t~5t에서는, 게이트 신호선(17b)에 오프 전압(VGH)을 인가하고, 스위치 트랜지스터(11d)를 오프하고, EL 소자(15)를 비발광 상태로 한다. 이와 같이 게이트 신호선(17b)에 온/오프 전압을 인가하고, 흐르는 전류를 제어함으로써, 도 78, 도 79, 도 84의 구동 방법을 실현한다.

- [0126] 이상과 같이 게이트 신호선(17b)에는, 온 전압 또는 오프 전압이 인가되고, 온/오프 전압에 동기하여 EL 소자(15)에 전류가 공급된다. 이 온/오프 전압의 인가 상태에 동기하여 EL 소자는 발광 또는 소등한다.

- [0127] EL 소자(15)가 발광 또는 소등하고 있는 동작 시(전압 프로그램 시 이외의 기간, 3t~의 기간)에서는, 트랜지스터(11b)는 오픈 상태이다. 이 때, 트랜지스터(11a)의 소스 단자는, EL 소자(15)가 발광하고 있을 때에는, 애노드 전압 Vdd(트랜지스터(11e)의 채널 전압 강하는 무시함)가 인가되고 있다. EL 소자(15)가 소등 시에는, 트랜지스터(11e) 및 트랜지스터(11d)를 오픈 상태로 한다. 이 EL 소자(15)가 소등 시에는, 구동 트랜지스터(11a)의 소스 단자는, 오프셋 캔슬용 컨덴서(19a)에 의해 애노드 전위 Vdd에 유지되어 있다. 따라서, 트랜지스터(11a)의 전위 안정도가 좋다. 물론, EL 소자(15)의 점등 및 소등은, 트랜지스터(11d)를 duty 제어(트랜지스터(11d) 등을 온/오프시켜, 표시 화면(31)에 따형상의 비표시 영역을 발생하고, 비표시 영역을 표시 화면(31)의 상하 방향으로, 프레임 주기 혹은 필드 주기에 동기하여 화상 표시시킴)해도 된다.

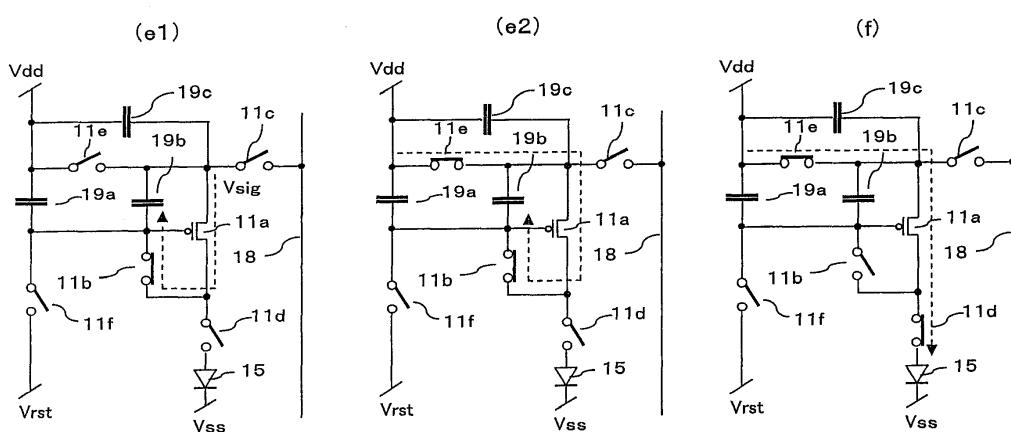

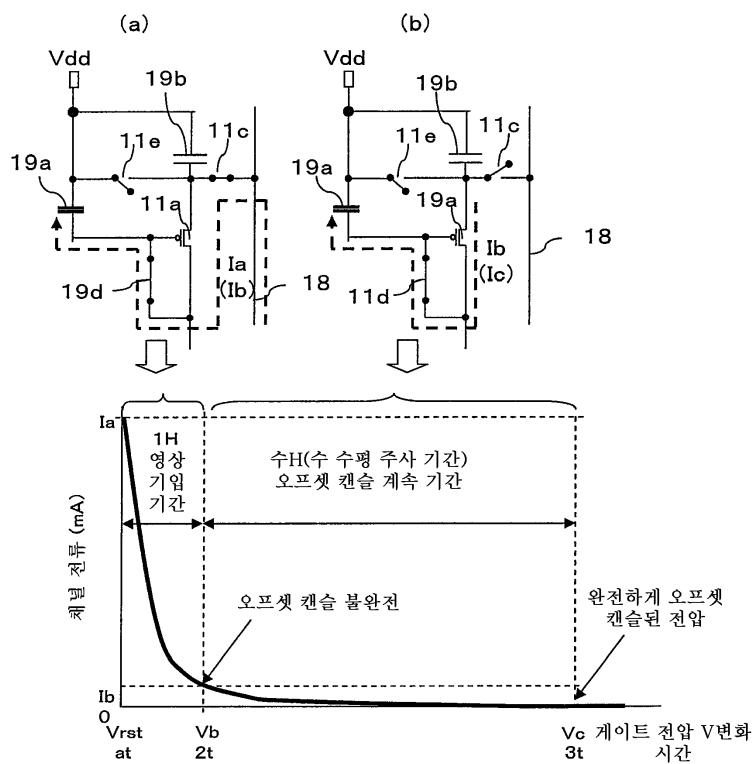

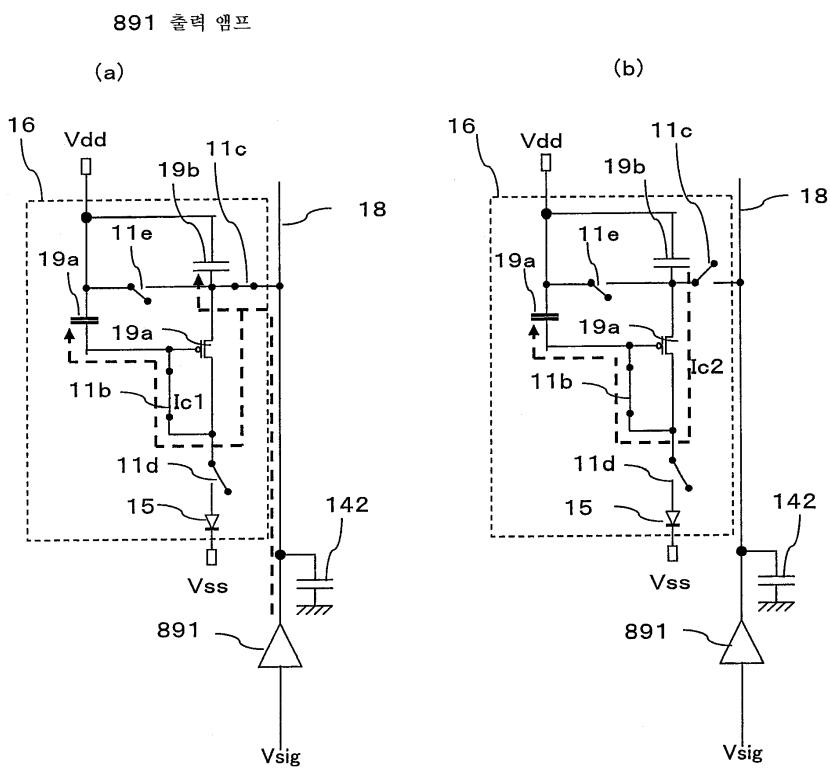

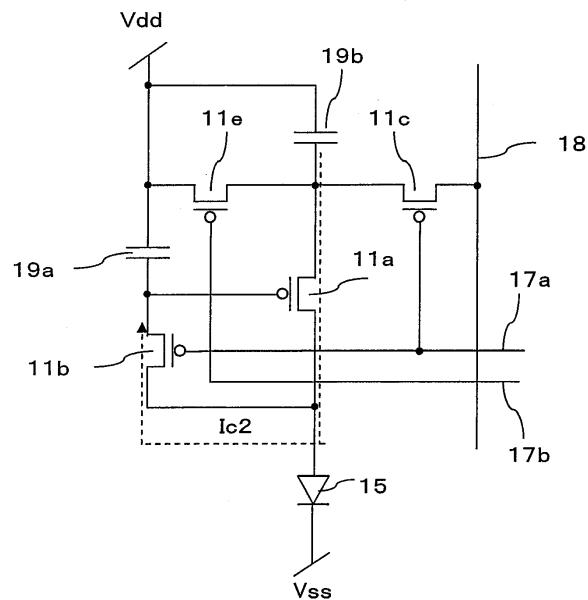

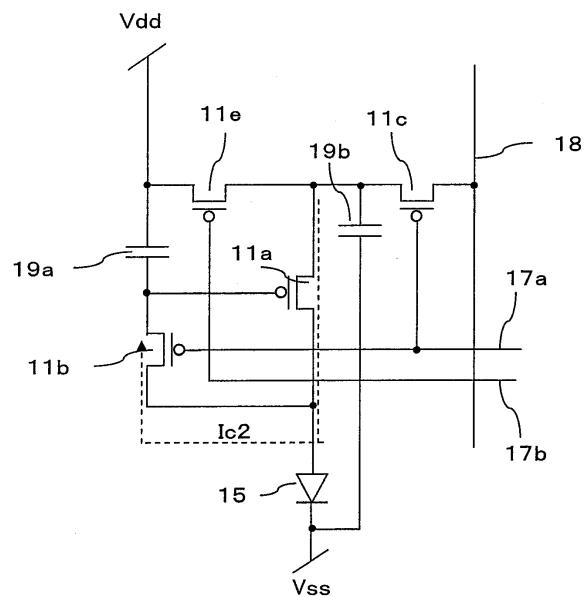

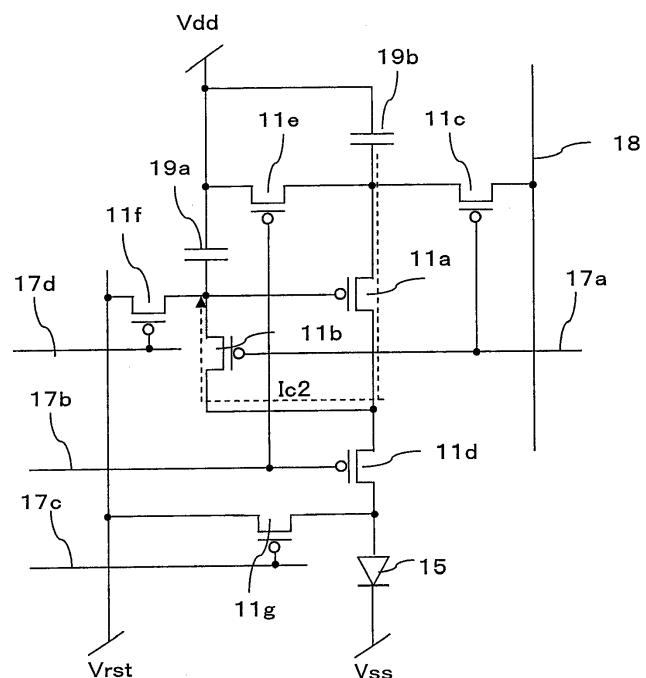

- [0128] 도 89는, 도 111의 (b)(c)의 상태를 더욱 상세하게 기재한 것이다. 도 111의 (b)는, 도 89의 (a)가 대응하고, 도 111의 (c)는, 도 89의 (b)가 대응한다.

- [0129] 도 89의 (a)에서는 출력 앰프(891)로부터 출력된 영상 신호 전압 Vsig가 스위치 트랜지스터(11c)를 통하여 오프셋 캔슬 컨덴서(19b)의 한 쪽의 단자에 인가되며, 동시에, 구동 트랜지스터(11a)의 채널에 오프셋 캔슬 전류 Ic1이 흐른다.

- [0130] 화소(16)의 선택 기간의 경과 후, 도 89의 (b)의 상태로 되고, 스위치 트랜지스터(11c)가 오픈 상태로 된다. 도 89의 (b)의 상태에서는, 오프셋 캔슬 컨덴서(19b)에 유지된 영상 신호 전압 Vsig가 전류의 공급원으로 되고, 계속해서 오프셋 캔슬 전류 Ic2가 흐른다. 도 89의 (b)에서 오프셋 캔슬 전류 Ic2가 거의 0으로 되어, 오프셋 캔슬 동작이 완료한다. 따라서, 이상적인 오프셋 캔슬 동작을 실현할 수 있다.

- [0131] 출력 앰프(891)의 구동 능력(전류 출력 능력)은, 복수의 단계에서 변경할 수 있게 구성한다. 출력 앰프(891)는 소스 드라이버 IC(14)의 출력단에 형성된다. 출력 앰프(891)의 구동 능력은, 커멘드로 변경할 수 있게 구성된다.

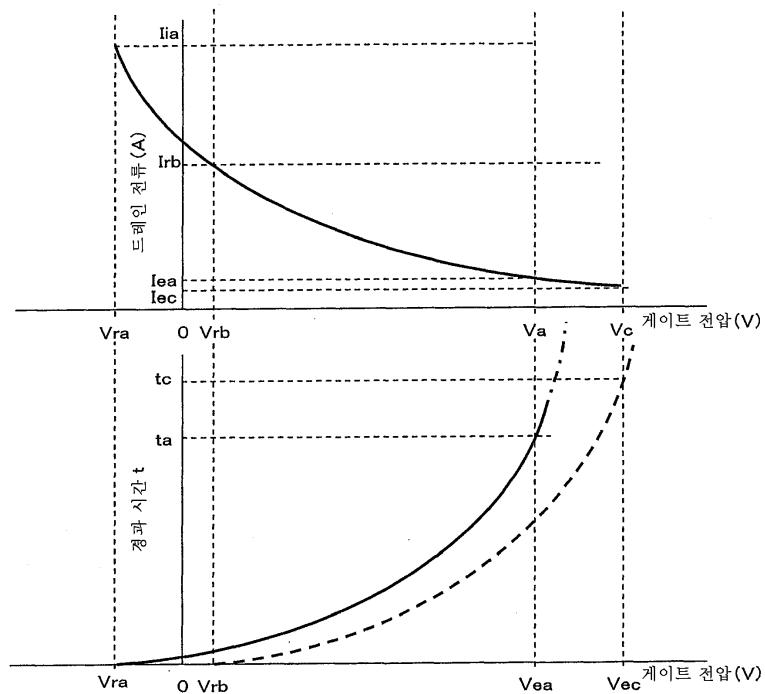

- [0132] 도 88은, 구동 트랜지스터(11a)의 채널에 흐르는 전류(채널 전류 Ic라고 부름)를 도시한 것이다. 도 88에서는, 이상적으로 오프셋 캔슬된 상태에서의 구동 트랜지스터(11a)의 게이트 단자 전압을 Vc로 하고 있다. 불충분한 오프셋 캔슬 전압은 Vb로 하고, 오프셋 캔슬 동작의 개시 전압은, 리세트 전압 Vrst로 하고 있다. 도 88에 도시하는 바와 같이, at~2t의 기간에서, 처음에는 큰 캔슬 전류 Ic1(개시 전류는 Ia로 하고 있음)이 흐르고, 캔슬 전류 Ic1은 급격하게 감소한다. 2t에서는, 캔슬 전류 Ic1=Ib로 하고 있다. 이 Ib일 때에는 아직 전류가 흐르는 상태이기 때문에, 오프셋 캔슬은 불충분한 상태이다.

- [0133] 그 후(2t~3t: 도 89의 (b))에도, 오프셋 캔슬 상태는 계속되고, 오프셋 캔슬 전류 Ic2는 감소하여, t3에서 오프셋 캔슬 전류 Ic2는 0상태로 된다.

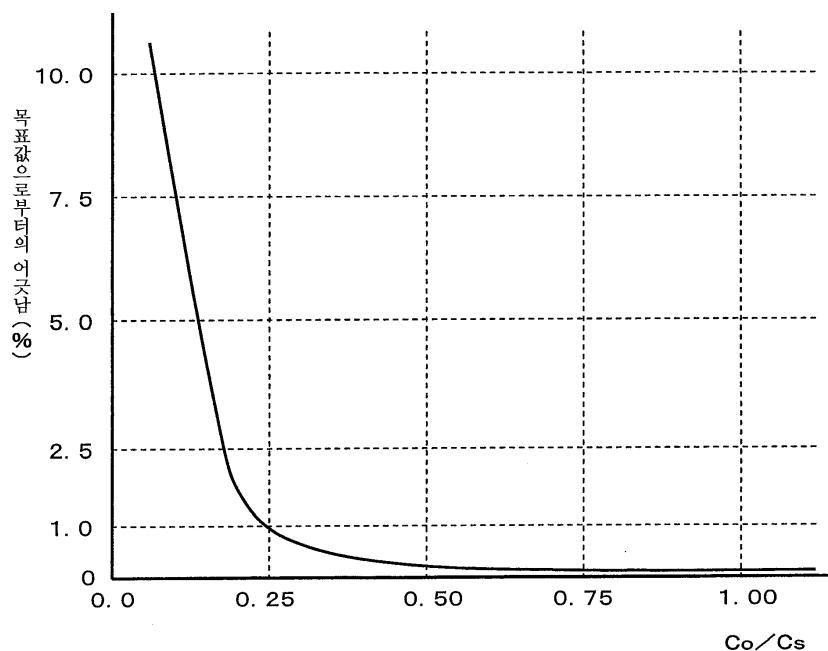

- [0134] 여기서, 유지용 컨덴서(19a)의 용량을 Cs(pF)로 하고, 오프셋 캔슬 컨덴서(19b)의 용량을 Co(pF)로 하면, 도 85의 관계가 있다.

- [0135] 도 85에서, 횡축은, 오프셋 캔슬 컨덴서(19b)의 용량 Co(pF)와 유지용 컨덴서(19a)의 용량 Cs(pF)의 비율 (Co/Cs)을 나타내고 있다. 종축은, 이상적인 오프셋 캔슬 상태로부터의 어긋남을 나타내고 있다. 어긋남이란, 이상적인 구동 트랜지스터(11a)의 게이트 단자 전압에 대한 전압차를 비율로 나타낸 것이다. 예를 들면, 완전하게 오프셋 캔슬 상태에 도달한 구동 트랜지스터(11a)의 게이트 단자 전압을 1.0V로 하였을 때, 오차(과리량) 10%란,  $1.0(V) \cdot (1-0.1)=0.9(V)$ 이다. 오차 2%란,  $1.0(V) \cdot (1-0.02)=0.98(V)$ 이다. Co/Cs가 0.5보다 작은 범위

에서는, 목표값으로부터의 오차가 2% 이상으로 크다. 그 때문에, 오프셋 캔슬 상태는 나쁘다. 또한, Co/Cs의 값이 작아질수록, 급격하게 목표값으로부터의 오차가 커진다.

[0136] Co/Cs가 0.5 이상인 범위에서는, 목표값으로부터의 오차가 2% 이하로 작다. 또한, Co의 값을 크게 해도, 목표값으로부터의 어긋남량의 저감 비율은 작다. Co의 값을 크게 하는 것은 오프셋 캔슬 컨텐서의 용량을 크게 할 필요가 있다. 컨텐서의 용량을 크게 한다는 것은, 화소의 구성상, 곤란한 경우가 많다(고정밀 패널에서는 화소에는 큰 컨텐서는 형성할 수 없음). 한편, 유지용 컨텐서(19a)는 적어도 1프레임 기간(또는 1필드 기간, 또한, 본 명세서에서는 1프레임 기간과 1필드 기간은 동의로서 취급함)의 동안, 전하를 유지해 둘 필요가 있다. 그 때문에, 비교적 큰 용량이며 또한 일정 이상의 용량이 필요하다.

[0137] 이상의 것으로부터, Co/Cs는, 0.25 이상으로 되도록 한다. 즉, Co:Cs=1:4 이상으로 되도록 Co 용량을 형성한다. 또한, Cs의 사이즈 또는 Co에 대한 Cs의 비율의 관점으로부터, Co/Cs=1.0 이하로 하는 것이 바람직하다. 즉, Co:Cs=1:1 이하로 되도록 Co 용량을 형성한다.

[0138] 도 10은, 도 1의 변형예이다. 오프셋 캔슬용 컨텐서(19a)의 1단자는, 게이트 신호선(17a)에 접속되어 있다. 게이트 신호선(17a)에는, 온 전압(VGL) 또는 오프 전압(VGH)이 인가되지만, 영상 신호 전압을 화소(16)에 기입한 후(전압 프로그램 시 이후) 이외의 기간은, 오프 전압(VGH)이 인가되어 있다. 따라서, 오프셋 캔슬용 컨텐서(19a)는 일정한 전하를 유지하여 안정하다. 다른 구성은 도 1에서 설명한 것과 마찬가지이므로 설명을 생략한다.

[0139] 또한, 도 10에서, 오프셋 캔슬용 컨텐서(19a)의 1단자는, 게이트 신호선(17b)과 접속하는 것으로 하였지만, 이 것에 한정되는 것은 아니다. 예를 들면, 도 11에 도시하는 바와 같이, 게이트 신호선(17d)과 접속해도 된다. 도 11의 구성에서는, 게이트 신호선(17d)에는, 리세트 전압 Vrst를 인가할 때에만, 온 전압(VGL)이 인가된다. 그러나, 다른 기간에는, 오프 전압(VGH)이 인가된다. 따라서, 오프셋 캔슬용 컨텐서(19a)는 일정한 전하를 유지하여 안정 상태가 유지된다.

[0140] 도 11은, 도 1의 변형예이다. 오프셋 캔슬용 컨텐서(19a)의 1단자는, 게이트 신호선(17b)에 접속되어 있다. 게이트 신호선(17b)에는, 온 전압(VGL) 또는 오프 전압(VGH)이 인가된다. 그러나, 영상 신호 전압을 화소(16)에 기입 시(전압 프로그램 시)의 기간은, 오프 전압(VGH)이 인가된다. 따라서, 오프셋 캔슬용 컨텐서(19a)는 일정한 전하를 유지하여 안정 상태가 유지되어 있다.

[0141] EL 표시 장치의 게이트 드라이버 회로(12)에 대하여 설명한다.

[0142] 도 3에 도시하는 바와 같이, 표시 화면(31)의 좌단에 게이트 드라이버 회로(12a)를 설치하고, 우단에 게이트 드라이버 회로(12b)를 설치하고 있다. 또한, 게이트 드라이버 회로(12)는, 표시 패널의 빈 영역에 형성하면 된다.

[0143] 게이트 드라이버 회로(12a)는, 게이트 신호선(17a)을 제어하고, 게이트 드라이버 회로(12b)는 게이트 신호선(17b)을 제어한다. 게이트 드라이버 회로(12a, 12b)에는, 게이트 신호선(17)의 온 전압(VGL)과, 게이트 신호선(17)의 오프 전압(VGH)이 공급되어 있다. 오프 전압(VGH)은, 애노드 전압 Vdd 이상 또는 근방의 전압이다. 온 전압(VGL)은, 캐소드 전압 Vss 또는 그라운드 전압(GND) 근방의 전압이다. 또한, 근방의 전압이란, 3V의 범위의 전압이다.

[0144] 본 실시예에서는, 트랜지스터(31)의 오프 전압을 VGH로 하고, 온 전압을 VGL로 하여 설명하지만 이것에 한정되는 것은 아니다. 온 전압(VGL)과 오프 전압(VGH)의 극성은, 구동 트랜지스터(31a)의 채널의 종류(P채널 또는 N채널)에 대응하여 설정한다. 또한, 도 31에 도시하는 바와 같이, 게이트 드라이버 회로(12)의 전압 중 1개 또는 복수를 GND 전압으로 해도 된다. 도 31에서는, 게이트 드라이버 회로(12b)는, VGH 전압과 VGL=GND 전압에서 동작하고 있고, 게이트 드라이버 회로(12a)는, VGH 전압과 VGL1 전압에서 동작하고 있다.

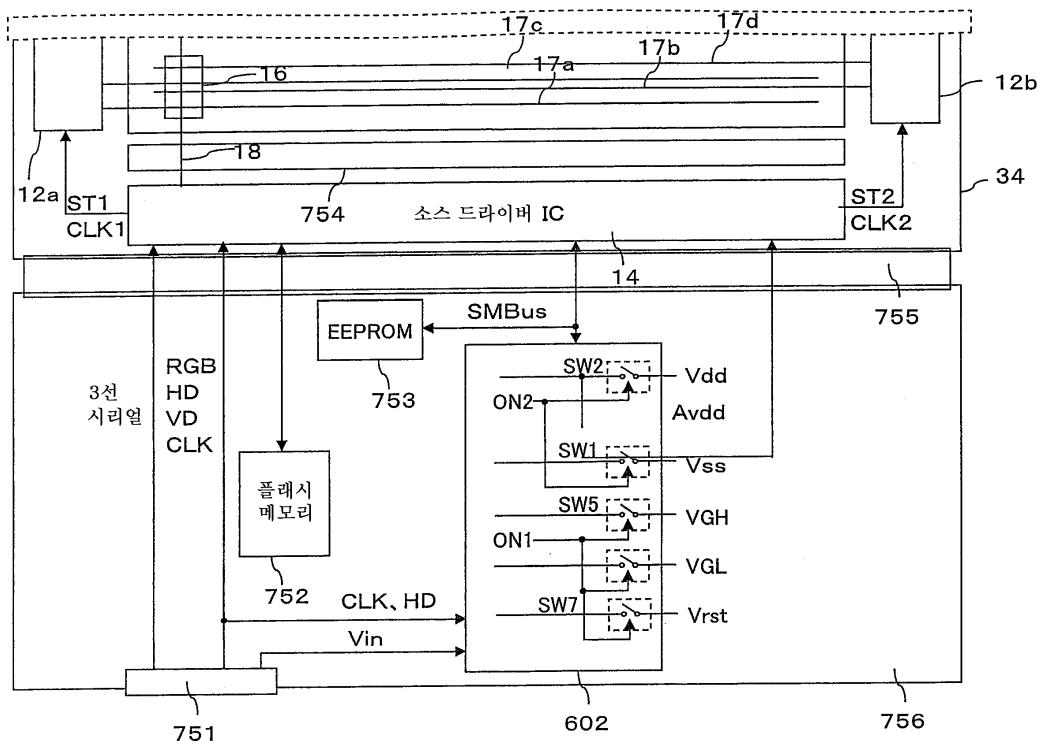

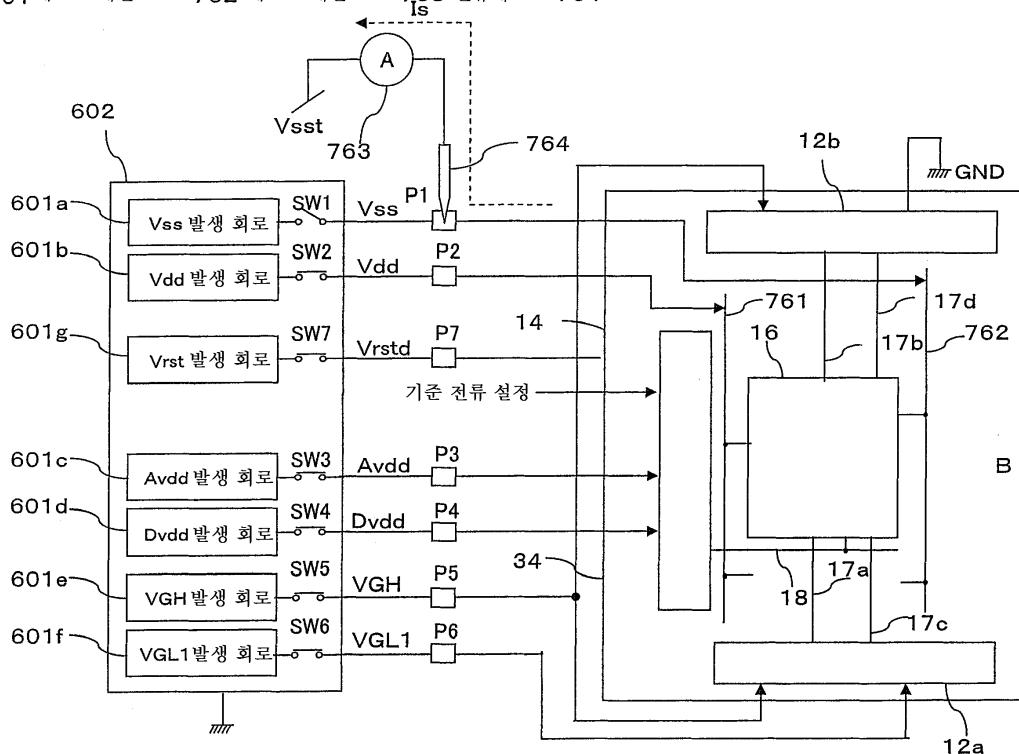

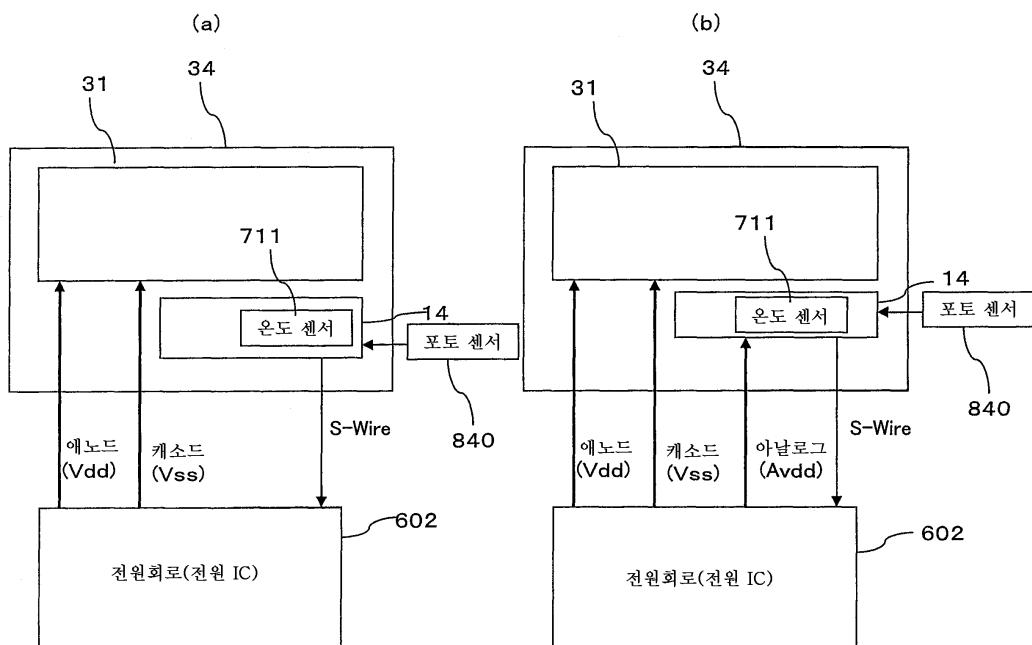

[0145] 본 실시예에서는, 구동 트랜지스터(31a)는 P채널 트랜지스터로 하고 있다. 이 경우에는, 온 전압을 VGL로 하고, 오프 전압을 VGH로 한다. 구동 트랜지스터(31a)가 N채널 트랜지스터인 경우에는, 온 전압을 VGH로 하고, 오프 전압을 VGL로 한다. 또한, 도 2에 적합하도록, VGH1, VGH2, VGL1, VGL2를 내장시켜도 된다. EL 표시 장치를 구동하는 전원(회로) IC로부터의 ON1 커맨드에 의해, 소스 드라이버 회로(14)의 아날로그 전압 AVdd와 게이트 드라이버 회로(12)의 전압 VGH1, VGH2, VGL1, VGL2를 동시에 기동하고, ON2에 의해 애노드 전압 Vdd, 캐소드 전압 Vss를 기동시킨다.

[0146] 도 4는, 도 1의 변형예이다. 도 1과 도 4의 차이는, 컨텐서(11c)가 추가 형성된 점이다. 컨텐서(11c)는, 게이

트 신호선(17a)에 인가된 전압의 변화(VGL→VGH)에 의해, 관통 전압이 발생하여 보다 양호한 흑 표시(고콘트라스트 표시)를 실현하는 것을 하나의 목적으로 한다. VGL→VGH의 동작이란, 화소(16)에 영상 신호를 기입 유지시키는 동작이다. 즉, 스위치 트랜지스터(11c)의 제어 동작이다.

- [0147] 상기 컨덴서(19c)는, 제1 전극이 현재 게이트 신호선(17a) 및 트랜지스터(11c)의 게이트 단자에 접속되고, 제2 전극이 상기 유지용 컨덴서(19a) 및 구동 트랜지스터(11a)의 게이트 단자에 공통 접속되어 있다.

- [0148] 또한, 구동 트랜지스터(11a)가 N채널 트랜지스터인 경우에는, 게이트 신호선(17a)에 인가하는 전압(영상 신호를 화소에 기입하고, 유지시키는 동작 시에 사용하는 전압)을 VGL→VGH로 되도록 화소(16)를 구성한다.

- [0149] 게이트 신호선에 인가하는 오프 전압을 VGH, 온 전압을 VGL로 하면, 게이트 신호선(17a)에 인가하는 전압을, VGL로부터 VGH로 변화시키면, 구동 트랜지스터(11a)의 게이트 전압은, 상기 유지용 컨덴서(19a)와 보조 컨덴서(19c)의 커플링에 의한 보정 전압만큼 상승하게 된다. 따라서, 구동 트랜지스터(11a)의 게이트 단자의 전압이, 애노드 전압 Vdd 전압으로 시프트하여, 양호한 흑 표시를 실현할 수 있다.

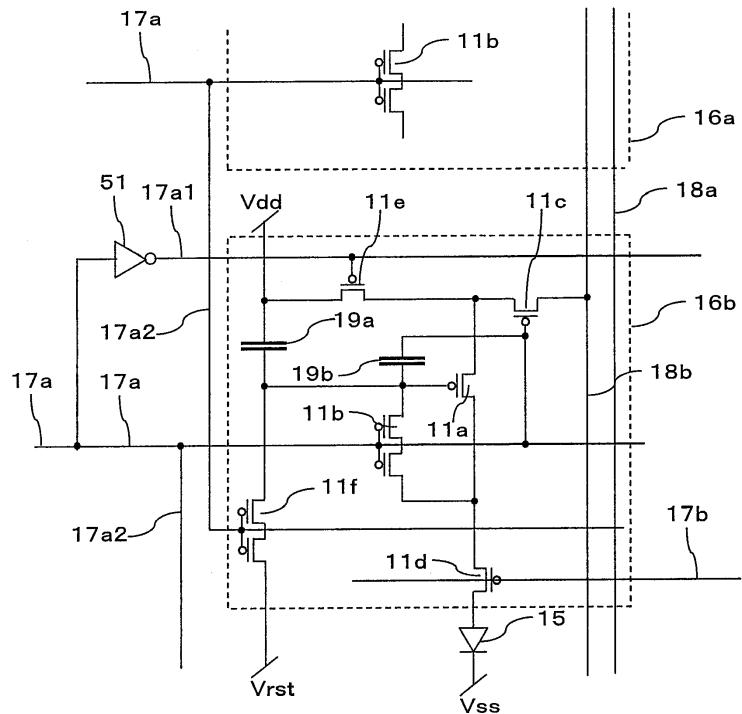

- [0150] 도 5는, 도 1 또는 도 4의 변형예이다. 도 5의 구성도 본 실시예의 EL 표시 장치에 이용할 수 있다. 도 5에서, 화소(16)는, 2개의 컨덴서(19a, 19b)와 5개의 스위치 트랜지스터(11b, 11c, 11d, 11e, 11f)와 1개의 구동 트랜지스터(11a)로 구성된다. 트랜지스터(11b)는, 트랜지스터(11a)를 다이오드 접속(Diode-connected)시켜, 임계값 전압을 보상하기 위한 임계값 전압 보상용의 스위치 트랜지스터이다. 트랜지스터(11f)는, 유지용 컨덴서(19a)를 초기화시키기 위하여 리세트 전압 Vrst를 인가하기 위한 초기화용의 스위치 트랜지스터이다. 그리고, 트랜지스터(11d)는, EL 소자(15)의 발광을 제어하기 위한 트랜지스터이다.

- [0151] 스위치 트랜지스터(11c)는, 게이트 신호선(17a)에 게이트 단자가 접속되고, 소스 신호선(18)에 소스 단자가 접속되며, 게이트 드라이버 회로(12a)로부터의 선택 신호에 의해 온/오프 제어된다.

- [0152] 게이트 신호선(17a)으로부터 게이트 신호선(17a1)과 게이트 신호선(17a2)이 분기되어 있고, 게이트 신호선(17a1)에는, 인버터 회로(51)가 배치되어 있다. 따라서, 게이트 신호선(17a1)과 게이트 신호선(17a2)에는, VGH와 VGL이 반전하여 전압이 인가된다.

- [0153] 또한, 소스 신호선(18a)과 소스 신호선(18b)을 갖고 있고, 상하 방향에 인접한 화소(16)(16a, 16b)는 서로 다른 소스 신호선(18)에 접속되어 있다. 도 5의 실시예에서는, 화소(16b)는 소스 신호선(18b)에 접속되어 있고, 화소(16a)는 소스 신호선(18a)과 접속되어 있다.

- [0154] 도 6은, 도 5의 화소 구성에서, 게이트 신호선(17) 및 소스 신호선(18)과의 접속 상태를 도시하고 있다. 도 5, 도 6과 같이 구성함으로써, 리세트 전압 Vrst를 인가하기 위한 스위치 트랜지스터(11f)를 제어하는 게이트 신호선과, 영상 신호를 인가하기 위한 스위치 트랜지스터(11c)를 제어하는 게이트 신호선을 공통으로 할 수 있다. 그 때문에, 게이트 신호선(17)의 수를 삭감할 수 있고, 화소(16)의 개구율을 향상시킬 수 있다.

- [0155] 또한, 복수 화소행을 동시에 오프셋 캔슬 상태로 할 수 있어, 양호한 오프셋 캔슬을 실현할 수 있다.

- [0156] 도 86은 도 1의 오프셋 캔슬 컨덴서(19b)를 갖는 구성에 컨덴서(11c)를 부가한 구성이다. 도 86에서, 컨덴서(19c)는, 스위치 트랜지스터(11c)의 게이트 단자(게이트 신호선(17a))와 컨덴서(19b)의 1단자(스위치 트랜지스터(11c)의 드레인 단자)에 접속되어 있다.

- [0157] 컨덴서(19c)는 게이트 신호선(17a)의 변동에 의해, 단자 전위가 변화된다. 게이트 신호선(17a)은, 화소(16)가 선택되었을 때에는, 온 전압(VGL)이 인가되고, 선택되지 않을 때에는 오프 전압(VGH)이 인가된다. 즉, 화소(16)가 선택 상태로부터 비선택 상태로 변화되면 컨덴서(19c)의 a1 전압은, VGL→VGH로 변화된다. 따라서, a1 전압의 전압 변화는, a2 전압의 변화에 영향을 미친다. a2 전압은, a1 전압의 변화를 컨덴서(19c)와 컨덴서(19c)에서 분압된 것으로 된다. 한편, a점(a2 전압)은, 화소가 선택되었을 때에는, 영상 신호 전압 Vsig가 인가되어 있다. a2 전압이 VGL→VGH로 변화되면, (VGH-VGL) 전압이 분압되어, 영상 신호 전압 Vsig에 중첩된다. 따라서, a점의 전위는, 영상 신호 전압 Vsig보다도 높아진다.

- [0158] a2점의 전위를 영상 신호 전압 Vsig보다도 높게 하는 것은, 도 111의 (c)의 오프셋 캔슬 동작을 양호한 상태로 할 수 있다. 통상적으로, 오프셋 캔슬 컨덴서(19b)의 용량은 작다. 따라서, 오프셋 캔슬 전류 Ic2가 크면, 오프셋 캔슬 컨덴서(19b)의 단자 전위가 급속하게 저하하게 되어, 오프셋 캔슬 동작의 계속 능력이 저하한다.

- [0159] 도 86의 구성에서는, 영상 신호 전압 Vsig보다도 높은 전압을 a점에 유지할 수 있으므로, 오프셋 캔슬 전압을 약간 높게 설정할 수 있어, 양호한 오프셋 캔슬 동작을 실현할 수 있다.

- [0160] 도 86의 구성에서, 오프셋 캔슬 컨텐서(19b)의 동작, 기능, 효과 등을 도 1에서 설명하였으므로 생략한다.

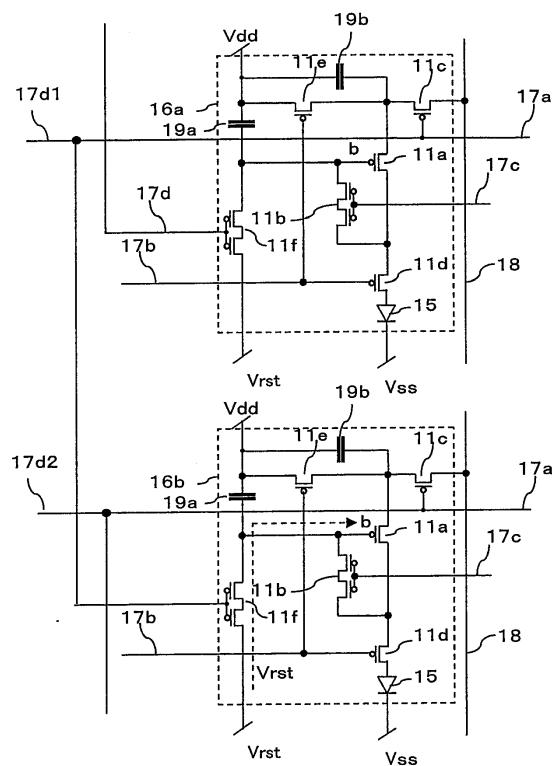

- [0161] 도 87은 도 1의 변경예이다. 도 87에서 화소(16a)의 스위치 트랜지스터(11c)를 온/오프시키는 게이트 신호선(17d1)은, 다음단의 화소(16b)의 스위치 트랜지스터(11f)를 온/오프시키는 게이트 신호선(17d1)과 공통으로 결선되어 있다.

- [0162] 따라서, 게이트 신호선(17d1)에 온 전압을 인가하면, 리세트 전압 Vrst를 인가하는 스위치 트랜지스터(11f)가 온하여, 화소(16b)의 구동 트랜지스터(11a)에 리세트 전압 Vrst를 인가한다. 동시에, 전단의 화소(16a)의 스위치 트랜지스터(11c)가 온하여 영상 신호 전압 Vsig를 화소(16a)에 기입하고, 오프셋 캔슬 동작을 개시한다. 또한, 화소(16a)는 1H 후에는, 도 111의 (c)의 동작으로 된다.

- [0163] 즉, 게이트 신호선(17d)을 순차 선택함으로써, 리세트 전압 Vrst를 인가하는 동작과, 그 밖의 화소행(기본적으로는 전단의 화소행)에 영상 신호 전압 Vsig를 인가하는 동작을 동시에 실현할 수 있다. 따라서, 게이트 드라이버 회로(12)의 구성을 간략화할 수 있어, 좁은 프레임의 EL 표시 장치를 실현할 수 있다.

- [0164] 도 87에서는, 각 화소행의 게이트 신호선(17d)은, 전단의 화소행의 게이트 신호선(17d)과 접속되어 있는 것으로 하였지만, 이것에 한정되는 것은 아니다. 예를 들면, 게이트 신호선(17d)은, 복수 이상의 전 또는 후의 화소행과 접속시켜도 된다.

- [0165] 도 87의 구성에서, 복수의 화소행의 게이트 신호선(17d)이 공통으로 접속되고, 게이트 신호선(17d)이 접속된 화소행이 전단 또는 후단의 화소행과 공통으로 접속되어 있는 점 이외의 구성 혹은 동작은, 도 1 등에서 설명을 행하고 있으므로 설명을 생략한다. 이상의 사항은, 본 명세서의 다른 실시예에도 적용되는 것은 물론이다.

- [0166] 도 90은 본 발명의 다른 실시예이다. 도 1과의 차이는, 스위치 트랜지스터(11d), 스위치 트랜지스터(11f)가 없는 점이다. 다른 구성은 도 1과 마찬가지이다. 이상과 같이 본 실시예의 기술적 사상은 각종 다양한 화소 구성에 대해서도 적용된다.

- [0167] 도 91은, 도 90의 실시예에 대하여, 컨텐서(19b)의 접속 위치를 서로 다르게 하고 있다. 도 91에서는, 컨텐서(19b)의 1단자는, 스위치 트랜지스터(11c)의 드레인 단자와 접속되고, 다른 단자는, 게이트 신호선(17a)과 접속되어 있다. 게이트 신호선(17a)의 전위는, 화소(16)가 선택되어 있을 때 이외에는, 오프 전압(VGH)이 인가되어 있다. 따라서, 화소(16)의 선택 시 이외에는, 안정된 전위로 유지되어 있으므로, 양호하게 영상 신호 전압 Vsig를 유지할 수 있다. 다른 구성 혹은 동작은, 도 1, 도 90과 마찬가지이므로 설명을 생략한다.

- [0168] 도 1 등의 구성에서는, 컨텐서(19b)의 한 쪽의 단자는, 애노드 전압 Vdd에 접속하였다. 그러나, 본 실시예는 이것에 한정되는 것은 아니다. 소정 기간 동안에 안정된 전위로 유지할 수 있는 것이면, 어떤 전위라도 된다. 도 92의 실시예는, 컨텐서(19b)의 한 쪽의 단자를 캐소드 전압 Vss로 되도록 접속을 하고 있다. 다른 구성 혹은 동작은, 도 1, 도 90과 마찬가지이므로 설명을 생략한다.

- [0169] 도 93의 구성은, 도 1의 구성 외에, 스위치 트랜지스터(11g)를 부가한 구성이다. 스위치 트랜지스터(11g)의 게이트 단자는 게이트 신호선(17g)에 접속되어 있다. 따라서, 게이트 신호선(17c)에 온 전압(VGL)을 인가함으로써, EL 소자(15)의 애노드 단자에, 리세트 전압 Vrst를 인가할 수 있다. 다른 구성 혹은 동작은, 도 1, 도 90과 마찬가지이므로 설명을 생략한다.

- [0170] 도 94의 구성은, 도 93에 대하여 컨텐서(19b)의 접속 위치를 변화시킨 것이다. 컨텐서(19b)의 한 쪽의 단자는, 스위치 트랜지스터(11c)의 드레인 단자와 접속되고, 다른 단자는, 구동 트랜지스터(11a)의 게이트 단자와 접속된다. 구동 트랜지스터(11a)의 게이트 단자도 오프셋 전압 혹은 영상 신호 전압 Vsig가 인가되고, 1프레임 기간 동안, 전위가 유지된다. 따라서, 컨텐서(19b)의 유지 전압으로서 이용할 수 있다. 다른 구성 혹은 동작은, 도 1, 도 90과 마찬가지이므로 설명을 생략한다.

- [0171] 또한, 이상의 사항은, 본 명세서의 다른 실시예, 다른 구성에 적용된다. 또한, 다른 실시예, 다른 구성과 조합할 수 있다.

- [0172] <실시예 2>

- [0173] 본 발명의 실시예 2에 대하여 설명한다.

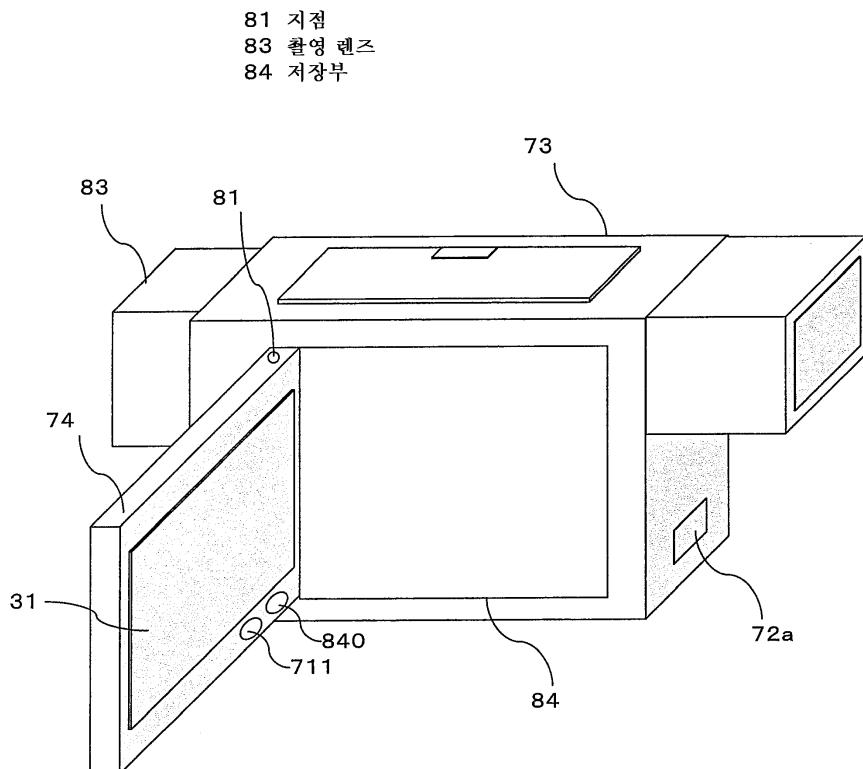

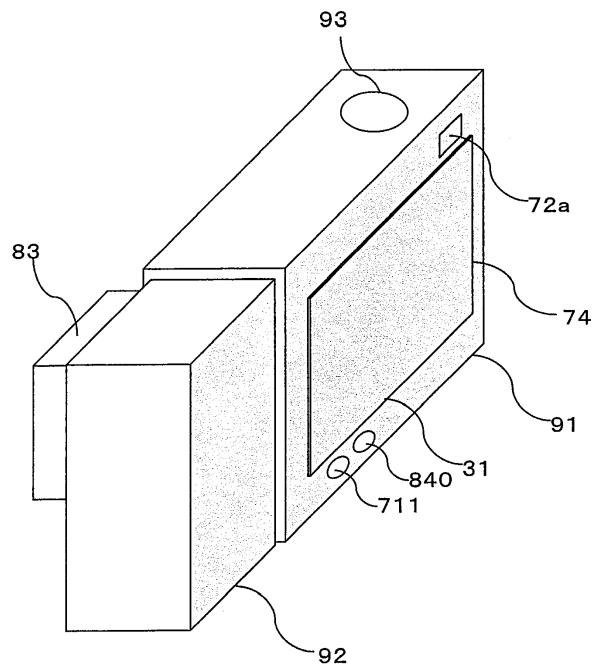

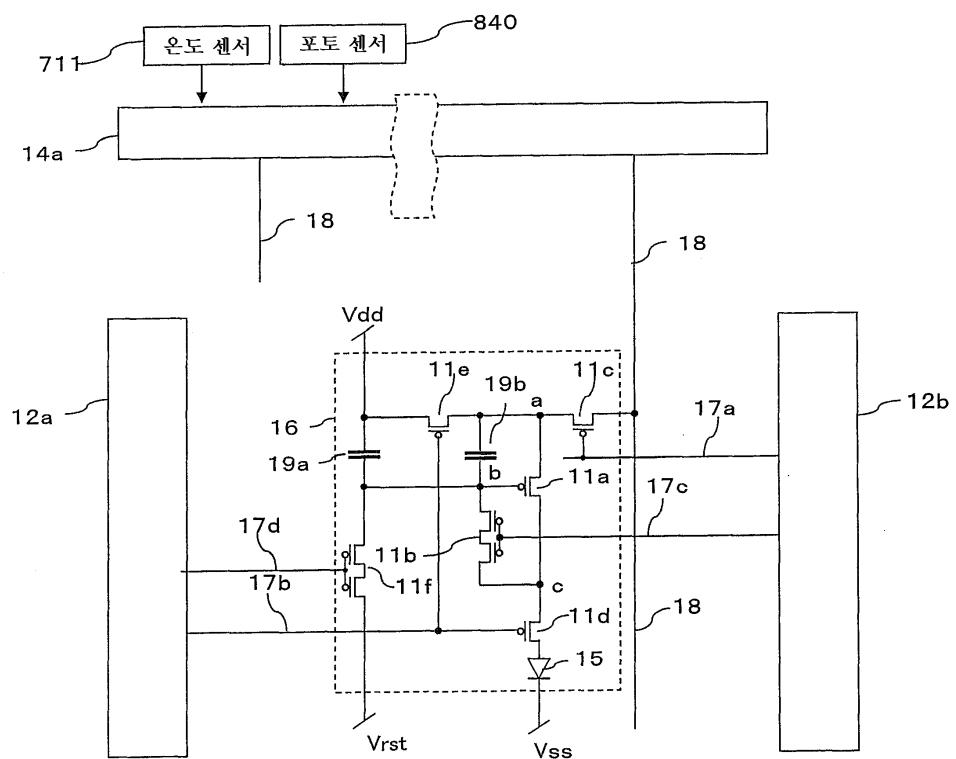

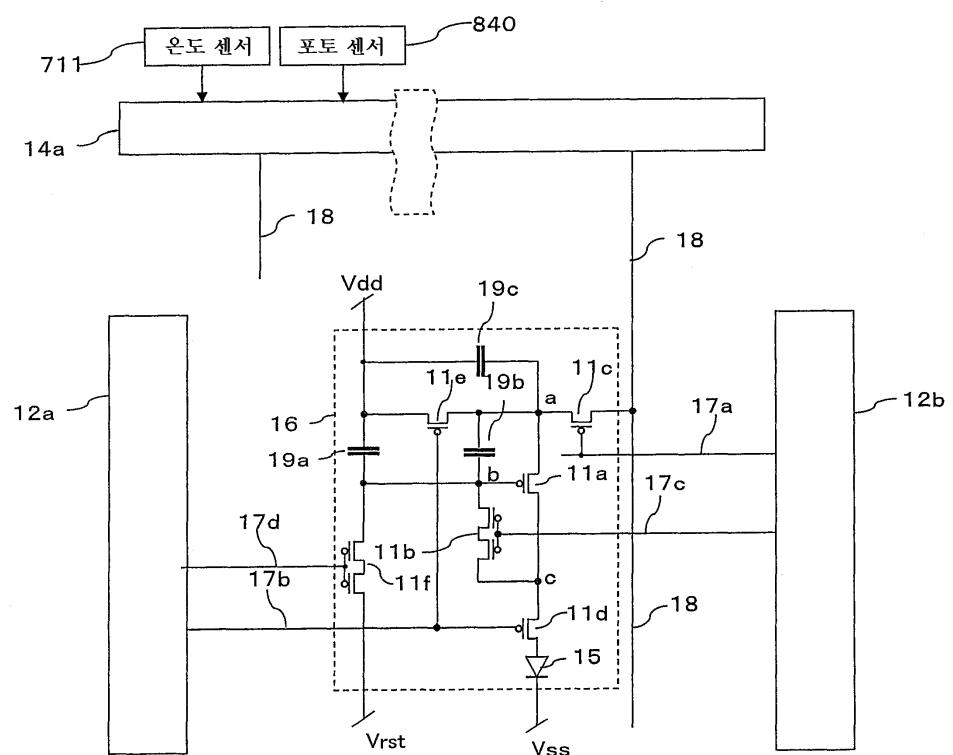

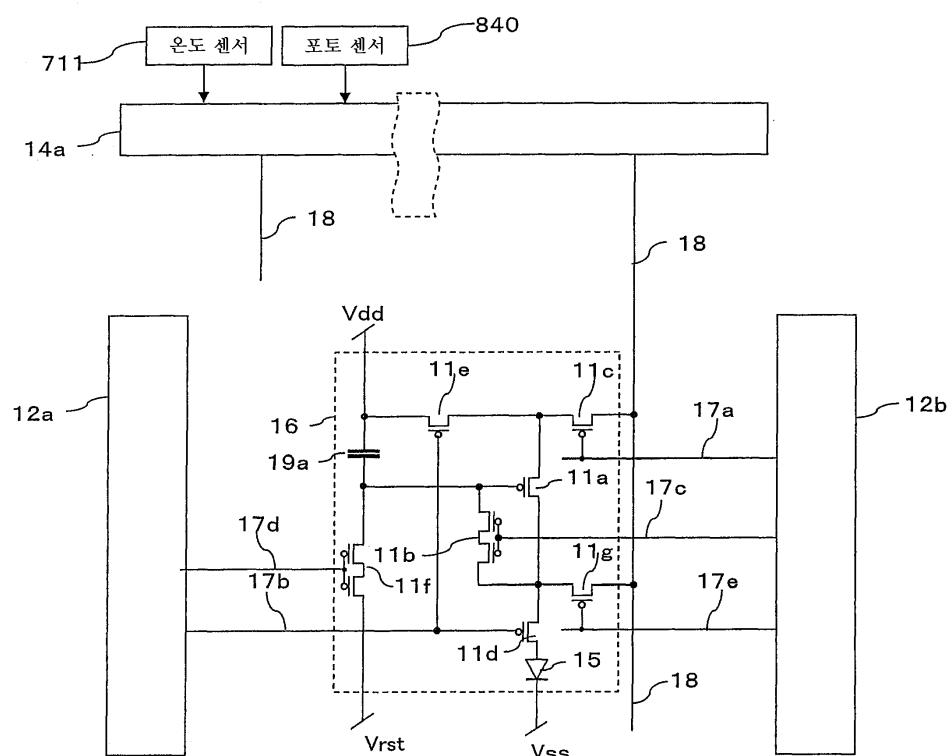

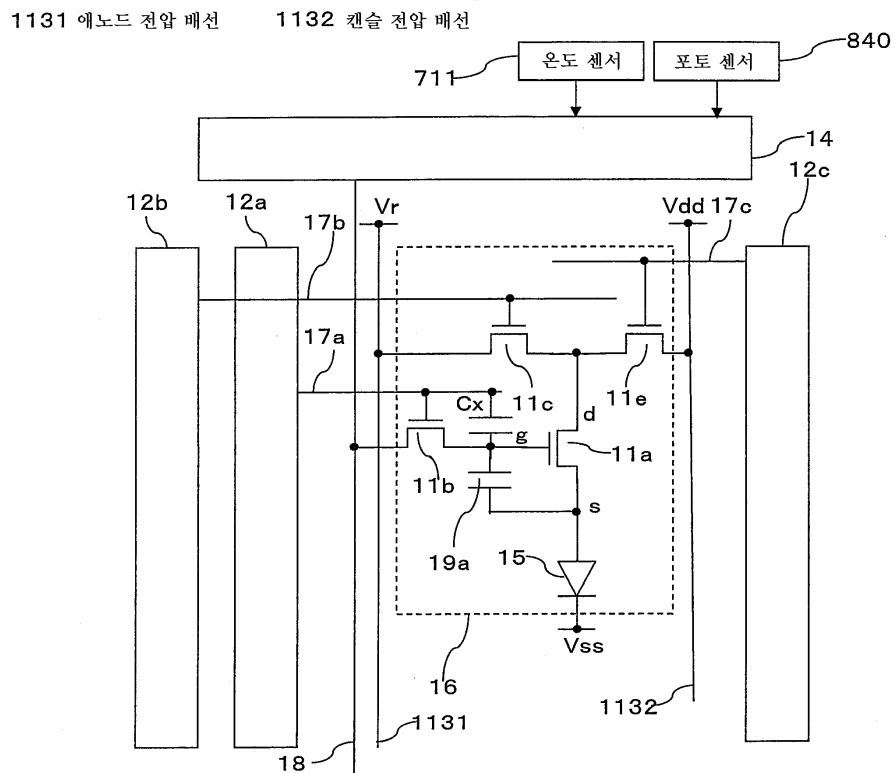

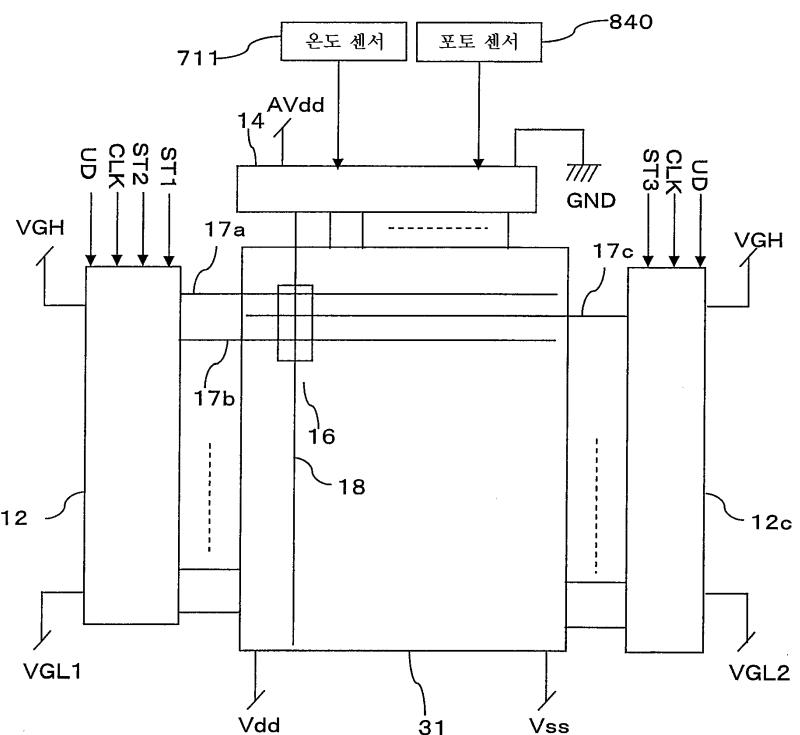

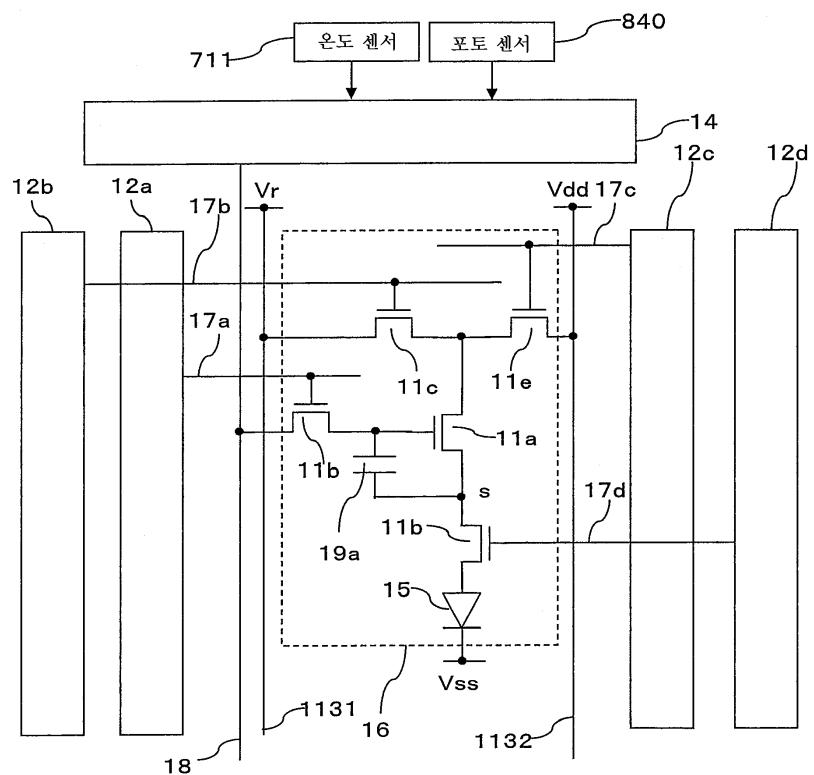

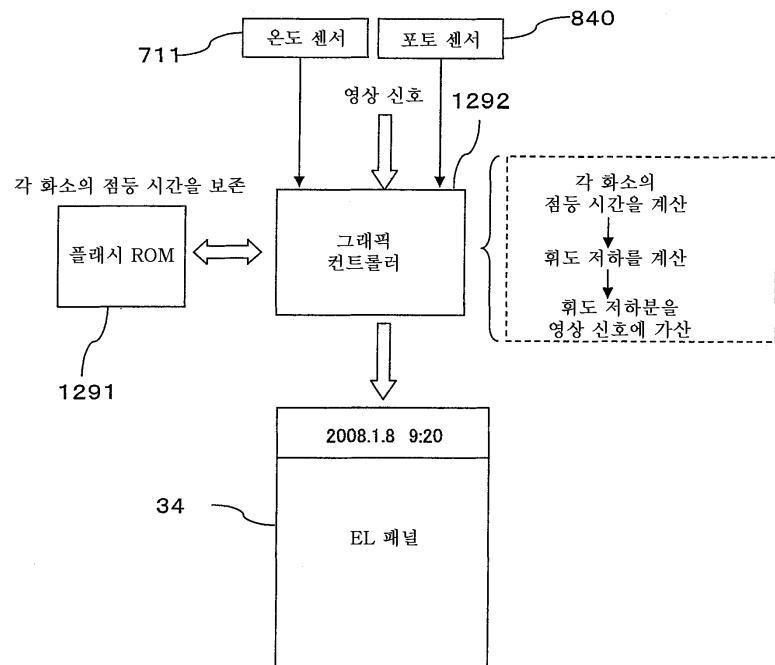

- [0174] 도 114는, 실시예 2에서의 EL 표시 장치의 전체 구성을 도시하는 블록도이다.

- [0175] 본 실시예는, EL 소자(15)가 매트릭스 형상으로 배치된 표시 화면(31)과 이것을 구동하는 구동 회로로 이루어진

다. 즉, 도 114에 도시하는 바와 같이, EL 표시 장치는, 표시 화면(31)과 이것을 구동하는 소스 드라이버 회로 (IC)(18)와, 게이트 단자 게이트 드라이버 회로(12, 12c)로 이루어진다.

[0176] 도 114의 게이트 드라이버 회로(12)는, 도 113의 게이트 드라이버 회로(12a, 12b)가 조합된 것이다.

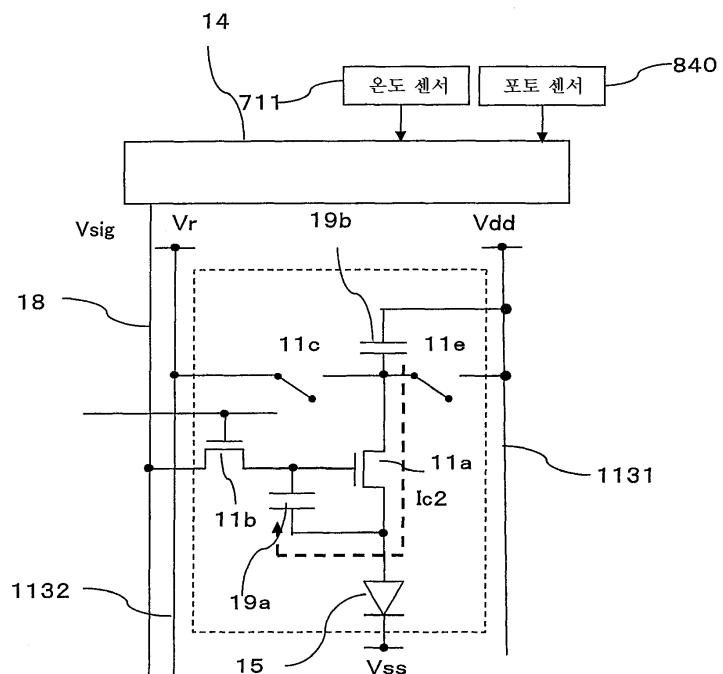

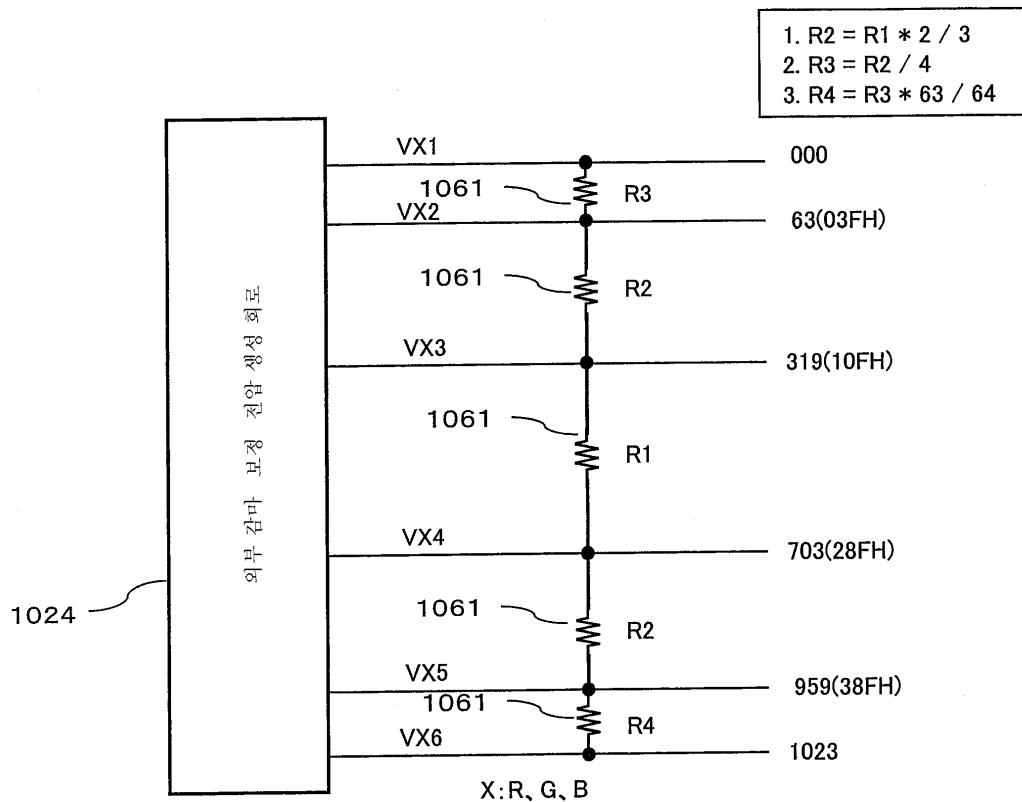

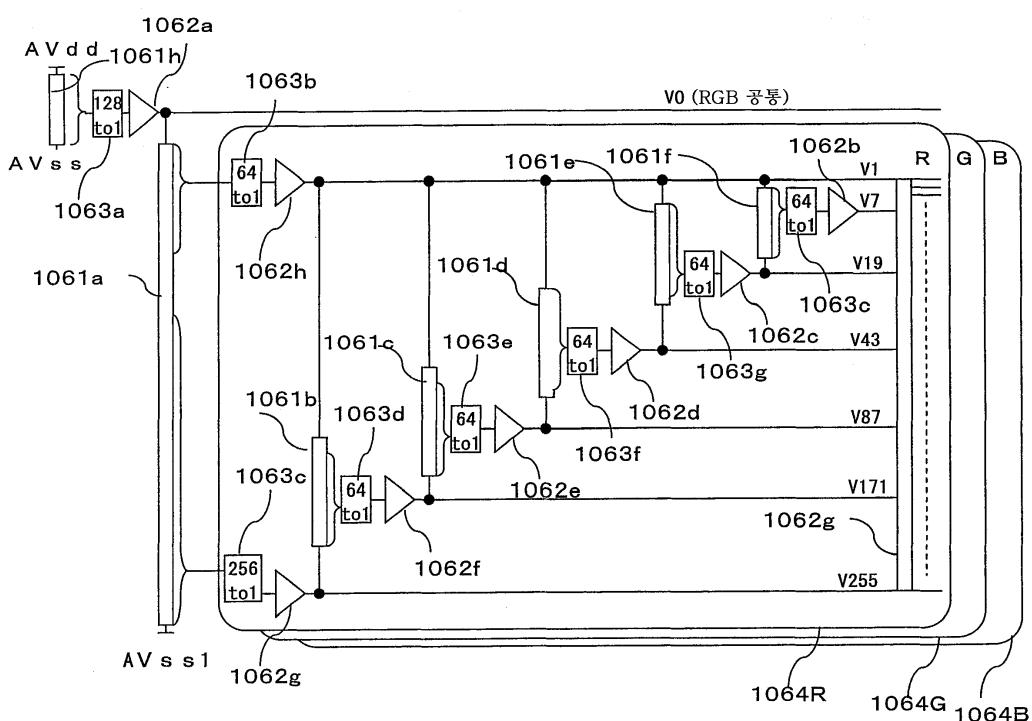

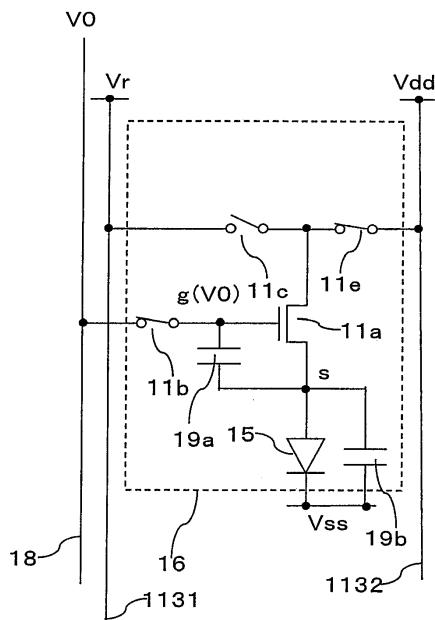

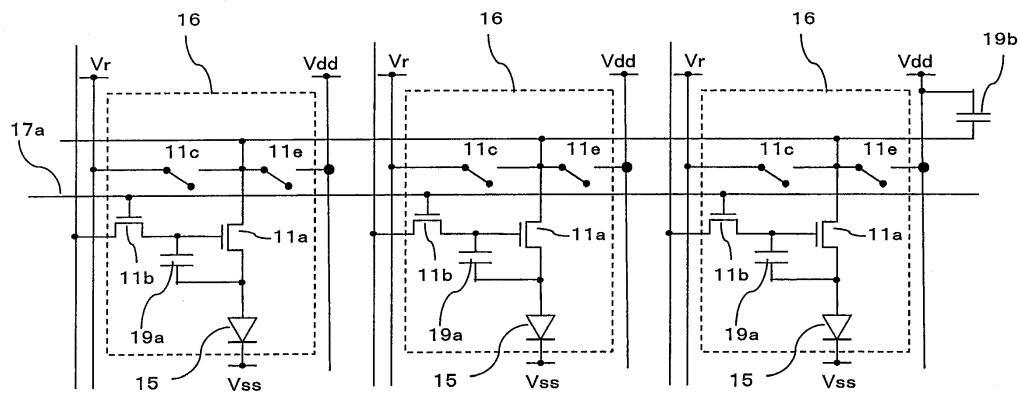

[0177] 표시 화면(31)은, 행 형상의 게이트 신호선(17)과, 열 형상의 소스 신호선(18)과, 양자가 교차하는 부분에 배치된 행렬 형상의 화소(16)와, 각 화소(16)의 각 열에 대응하여 형성된 애노드 전원 배선(1131)을 구비하고 있다. 즉, 애노드 전원 배선(1131)은 화소열과 평행하게 형성되어 있다. 또한, 캔슬 전압 Vr을 공급하는 캔슬 전압 배선(1132)도 화소열과 평행하게 형성되어 있다. 즉, 소스 신호선(18)과 평행하게 형성되어 있다.

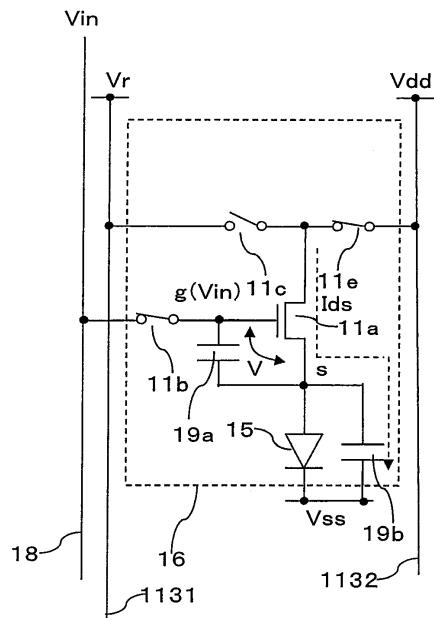

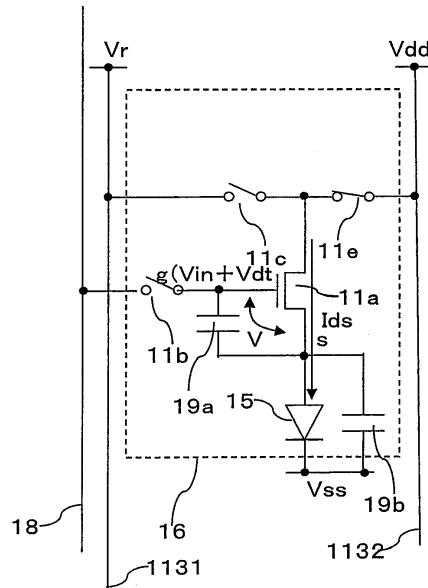

[0178] 도 113은, 도 114에 도시한 EL 표시 장치에 포함되는 화소(16)의 구체적인 구성 및 결선 관계를 나타내는 회로도이다.

[0179] 도 113에 도시하는 바와 같이, 화소(16)는, EL 소자(15) 등으로 대표되는 EL 소자(15)와, 스위치 트랜지스터 (11b, 11c, 11e)와, 구동 트랜지스터(11a)와, 컨덴서(19a)를 포함한다.

[0180] 스위치 트랜지스터(11b)는, 그 게이트 단자 d가 게이트 신호선(17a)에 접속되고, 드레인 단자 d가 소스 신호선 (18)에 접속되며, 소스 단자가 구동 트랜지스터(11a)의 게이트 단자 g에 접속되어 있다.

[0181] 구동 트랜지스터(11a)는, 그 드레인 단자 d가 애노드 전원 배선(1131)에 접속되고, 소스 단자 s가 EL 소자(15)의 애노드 단자에 접속되어 있다.

[0182] EL 소자(15)의 캐소드는, 접지 전극(GND) 또는 캐소드 전극(전압) Vss에 접속되어 있다. 또한, 이 접지 전극 또는 캐소드 전극(전압) Vss는 모든 화소(16)에 대하여 공통으로 배선되어 있다.

[0183] 컨덴서(19a)는, 구동 트랜지스터(11a)의 소스 단자 s와 게이트 단자 g 사이에 접속되어 있다.

[0184] 이러한 구성에서, 스위치 트랜지스터(11b)는, 게이트 신호선(17)으로부터 공급된 제어 신호에 따라서 도통하고, 소스 신호선(18)으로부터 공급된 신호 전위를 샘플링하여 컨덴서(19a)에 유지한다.

[0185] 구동 트랜지스터(11a)는, 스위치 트랜지스터(11e)가 온함으로써, 애노드 전원 배선(1131)으로부터 전류의 공급을 받고, 컨덴서(19a)에 유지된 신호 전위에 따라서 구동 전류를 EL 소자(15)에 흘린다.

[0186] 게이트 드라이버 회로(12)에 대하여 설명한다. 게이트 드라이버 회로(12a)는, 각 게이트 신호선(17a)에 순차적으로 제어 신호(온 전압 또는 오프 전압)를 공급하여 화소(16)를 행 단위로 선순차 주사한다.

[0187] 게이트 드라이버 회로(12b)는, 선순차 조작(화소행을 순서대로 선택하는 동작)에 동기하여, 구동 트랜지스터 (11a)의 드레인 단자 d에 캔슬 전압 Vr을 인가하는 트랜지스터(11c)를 제어한다. 즉, 게이트 드라이버 회로 (12b)는, 게이트 신호선(17b)에 온 전압 또는 오프 전압을 순차 인가한다.

[0188] 게이트 드라이버 회로(12c)는, 이 선순차 주사에 맞추어, 구동 트랜지스터(11a)의 드레인 단자 d에 애노드 전압 Vdd(혹은 캐소드 전압 Vss)를 인가하는 트랜지스터(11e)를 제어한다. 즉, 게이트 드라이버 회로(12c)는, 게이트 신호선(17c)에 온 전압 또는 오프 전압을 순차 인가한다.

[0189] 또한, 게이트 드라이버 회로(12a, 12b, 12c)는 3개의 드라이버로 구성되는 것에 한정되는 것이 아니라, 도 114에 도시하는 바와 같이, 참조 부호 12a, 12c로 1개의 게이트 드라이버 회로(12)를 구성해도 된다.

[0190] 또한, 각 게이트 드라이버 회로(12)가 게이트 신호선(17)에 출력하는 전압(온 전압 또는 오프 전압)은 서로 다른 값으로 하는 것이 바람직하다. 도 114의 실시예에서는, 게이트 드라이버 회로(12)와 게이트 드라이버 회로 (12c)의 온 전압(VGH)은 동일하지만, 오프 전압(VGL)은, 게이트 드라이버 회로(12)는, VGL1로 하고, 게이트 드라이버 회로(12c)는, VGL2로서 서로 다르다. 즉,  $|VGL1| < |VGL2|$ 로 되도록 하고 있다. 또한, VGL1, VGL2는 부전압이기 때문에, 절대값의 기호  $||$ 로 표시하고 있다.  $Vr < Vdd$ 의 관계가 있으며, 구동 트랜지스터(11a)에 충분히 Vr 전압을 인가할 수 있게 구성하고 있다.

[0191] 게이트 드라이버 회로(12)에는, 게이트 신호선(17a)을 선택하는 스타트 펄스 ST1, 게이트 신호선(17b)을 선택하는 스타트 펄스 ST2, 스타트 펄스를 순차 시프트하는 클럭 신호(CLK)가 인가된다. UD는, 게이트 드라이버 회로 (12) 내의 스타트 펄스의 상하 시프트 레지스터 방향을 절환하는 신호이다. 또한, 도 115와 같이 구성해도 된다.

[0192] 게이트 드라이버 회로(12c)에는, 게이트 신호선(17c)을 선택하는 스타트 펄스 ST3, 스타트 펄스를 순차 시프트

하는 클럭 신호(CLK)가 인가된다.

[0193] 또한, 필요에 따라서, 게이트 드라이버 회로(12)에는, 인에이블 제어 단자를 부가하는 것이 바람직하다. 게이트 드라이버 회로(12) 내에는, 시프트 레지스터 회로가 형성되어 있고, 스타트 펄스를 클럭 신호(CLK)에 동기하여 순차 시프트시키고, 선택하는 게이트 신호선(17)의 위치를 변화시킨다.

[0194] 구동 트랜지스터(11a)의 드레인 단자 d에 인가하는, 제1 전위(캔슬 전압)와 애노드 전압 Vdd의 절환은, 스위치 트랜지스터(11c)와 스위치 트랜지스터(11e)에 의해 실현한다. 스위치 트랜지스터(11c)와 스위치 트랜지스터(11e)는, 배타적으로 동작한다.

[0195] 따라서, 스위치 트랜지스터(11c)가 온하고 있을 때에는, 스위치 트랜지스터(11e)는 오프로 제어되고, 스위치 트랜지스터(11c)가 오프하고 있을 때에는, 스위치 트랜지스터(11e)는 온으로 제어된다.

[0196] 스위치 트랜지스터(11c)는, 순차적으로 조작되고, 스위치 트랜지스터(11e)는, EL 소자(15)에 전류를 공급할 때에 주로 온 상태로 된다.

[0197] 또한, 스위치 트랜지스터(11e)를 온/오프 제어함으로써, 도 78, 도 79, 도 84, 도 98에서 설명하는 duty 구동을 실현할 수 있다. 또한, 도 99에서 설명한 구동 방식과도 조합할 수 있다.

[0198] 이상의 사항은, 도 1 등의 실시예와 마찬가지이다. 또한, 도 1 등에서 설명한 실시예 1의 기재 사항은, 실시예 2, 실시예 3에도 적용할 수 있는 것은 물론이다. 본 명세서에 기재한 실시예는 상호 조합할 수 있다.

[0199] EL 소자(15)의 점등 및 소등은, 스위치 트랜지스터(11e)를 duty 구동한다. 이 duty 구동은, 표시 화면(31)에 비표시 영역(123)을 발생(또는, 표시 영역(122)을 발생)시켜, EL 소자(15)에 흐르는 전류를 억제하기 위하여 행한다. 스위치 트랜지스터(11e), 스위치 트랜지스터(11d) 등을 온/오프시켜, 표시 화면(31)에 띠형상의 비표시 영역(123)을 발생하고, 이 비표시 영역(123)을 화면(31)의 상하 방향으로, 프레임 주기(필드 주기)에 동기하여 화상 표시시킨다.

[0200] 소스 신호선(18)에 신호 전압을 공급하는 소스 드라이버 회로(18)는, 스위치 트랜지스터(11b)가 도통한 후에, 소스 신호선(18)에 기준 전위 V0을 공급하고 있는 동안에, 구동 트랜지스터(11a)의 드레인 단자 d에 인가하는 전압을 제1 전위(캔슬 전압)와 제2 전위(애노드 전압 Vdd) 사이에서 절환하고, 구동 트랜지스터(11a)의 임계값 전압 Vth에 상당하는 전압을 컨덴서(19a)에 유지해 둔다.

[0201] 이상에 기재한 임계값 전압 보정 기능에 의해, 각 화소(16)의 구동 트랜지스터(11a)의 특성 변동의 영향을 캔슬 할 수 있다.

[0202] 도 113에 도시한 화소(16)는, 상기한 임계값 전압 보정 기능 외에, 이동도 보정 기능을 구비하고 있다.

[0203] 소스 드라이버 회로(18)는, 스위치 트랜지스터(11b)가 도통한 후, 제1 타이밍에서 소스 신호선(18)을 기준 전위 V0으로부터 신호 전위로 절환한다. 또한, 스위치 트랜지스터(11c 및 11e)를 제어하고, 제1 타이밍 후, 제2 타이밍에서 게이트 신호선(17a)에 대한 온 전압을 해제하여 스위치 트랜지스터(11b)를 비도통 상태로 한다. 제1 및 제2 타이밍 동안의 기간을 적절하게 설정함으로써, 컨덴서(19a)에 신호 전위를 유지할 때, 구동 트랜지스터(11a)의 이동도  $\mu$ 에 대한 보정을 신호 전위에 가한다.

[0204] 이 경우, 게이트 드라이버 회로는, 소스 드라이버 회로(18)가 공급하는 영상 신호와 게이트 드라이버 회로(12b, 12c)가 공급하는 제어 신호의 상대적인 위상차를 조정하여, 제1 및 제2 타이밍 사이의 기간(이동도 보정 기간)을 최적화할 수 있다.

[0205] 또한, 소스 드라이버 회로(18)는, 기준 전위로부터 신호 전위로 절환하는 영상 신호의 상승에 경사를 부여하여, 제1 및 제2 타이밍 동안의 이동도 보정 기간을 신호 전위에 자동적으로 추종시킬 수도 있다.

[0206] 도 113에 도시한 화소(16)는 부트스트랩 기능도 더 구비하고 있다. 게이트 드라이버 회로(12b 및 12c)는, 컨덴서(19a)에 신호 전위가 유지된 단계에서 게이트 신호선(17b)에 오프 전압을 인가하고, 게이트 신호선(17c)에 온 전압을 인가함으로써, 구동 트랜지스터(11a)의 드레인 단자 d의 전위를 Vr로부터 Vdd 전압으로 변화시킨다. 또한, 스위치 트랜지스터(11b)를 비도통 상태로 하여 구동 트랜지스터(11a)의 게이트 단자 g를 소스 신호선(18)으로부터 전기적으로 분리한다. 이 동작에 의해, 구동 트랜지스터(11a)의 소스 전위 Vs의 변동에 게이트 전위 Vg가 연동하여 게이트 단자 g와 소스 단자 s 사이의 전압 Vgs를 일정하게 유지할 수 있다.

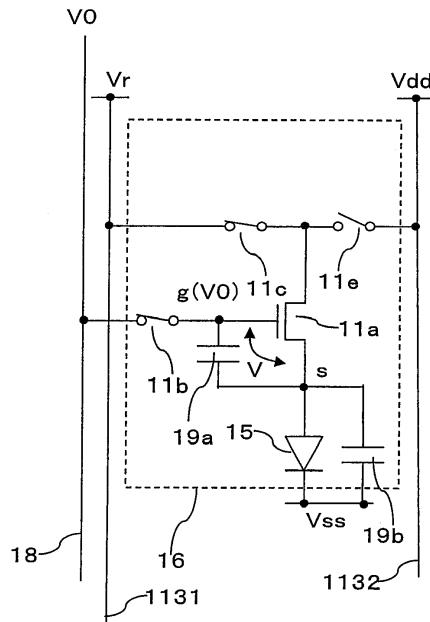

[0207] 도 115는, 도 113에 도시한 화소(16)의 동작 설명에 이용하는 타이밍 차트이다. 시간축을 공통으로 하여, 게이

트 신호선(17a, 17b, 17c)의 전위 변화, 소스 신호선(18)의 전위 변화, EL 소자(15)의 발광 상태를 모식적으로 나타내고 있다.

[0208] 이 타이밍 차트는, 화소(16)의 동작의 변화에 맞추어 기간을 B~G와 같이 편의적으로 구획하고 있다.

[0209] 발광 기간 B에서는 EL 소자(15)가 발광 상태에 있다. 이 후, 선순차 주사의 새로운 필드에 들어가서, 최초의 기간 C에서, 스위치 트랜지스터(11b)가 온하고, 구동 트랜지스터(11a)의 게이트 전위 Vg가 초기화된다.

[0210] 다음으로, 기간 D로 진행하여, 스위치 트랜지스터(11c)가 온하여 구동 트랜지스터(11a)의 드레인 단자 d에 캔슬 전압 Vr이 인가되고, 구동 트랜지스터(11a)의 소스 전위 Vs도 초기화된다. 이와 같이 구동 트랜지스터(11a)의 게이트 전위 Vg 및 소스 전위 Vs를 초기화함으로써, 임계값 전압 보정 동작의 준비가 완료된다. Vr 전압은, EL 소자(15)가 온하지 않고(전류가 흐르지 않음), 구동 트랜지스터(11a)가 오프로 되는 전압이다.

[0211] 다음으로, 임계값 보정 기간 E에서 실제로 임계값 전압 보정 동작이 행하여지고, 구동 트랜지스터(11a)의 게이트 단자 g와 드레인 단자 d 사이에 임계값 전압 Vth에 상당하는 전압이 유지된다. 실제로는, Vth에 상당하는 전압이, 구동 트랜지스터(11a)의 게이트 단자 g와 드레인 단자 d 사이에 접속된 컨덴서(19a)에 기입되게 된다.

[0212] 다음으로, 샘플링 기간/이동도 보정 기간 F로 진행하여, 영상 신호의 신호 전위 Vin이 Vth에 더해지는 형태로 컨덴서(19a)에 기입됨과 함께, 이동도 보정용의 전압  $\Delta V$ 가 컨덴서(19a)에 유지된 전압으로부터 차감된다.

[0213] 다음으로, 발광 기간 G로 진행하여, 신호 전압 Vin에 따른 휘도로 EL 소자(15)가 발광한다. 그 때에 신호 전압 Vin은 임계값 전압 Vth에 상당하는 전압과 이동도 보정용의 전압  $\Delta V$ 에 의해 조정되고 있기 때문에, EL 소자(15)의 발광 휘도는 구동 트랜지스터(11a)의 임계값 전압 Vth나 이동도  $\mu$ 의 변동의 영향을 받는 일이 없다.

[0214] 또한, 발광 기간 G의 처음에서 부트스트랩 동작이 행하여지고, 구동 트랜지스터(11a)의 게이트-소스간 전압  $Vgs=Vin+Vth-\Delta V$ 를 일정하게 유지한 채, 구동 트랜지스터(11a)의 게이트 전위 Vg 및 소스 전위 Vs가 상승한다.

[0215] 도 116~도 121을 참조하여, 도 113에 도시한 화소(16)의 동작을 상세하게 설명한다. 또한, 도 116~도 121의 도면 부호는, 도 115에 도시한 타이밍 차트의 각 기간 B~G에 각각 대응하고 있다. 또한, 이해를 용이하게 하기 위하여, 도 116~도 121은, 설명의 편의상, EL 소자(15)의 용량 성분을 컨덴서(19b)로서 도시하고 있다. 도 116에 도시하는 바와 같이, 발광 기간 B에서는, 스위치 트랜지스터(11b)가 온하고, 스위치 트랜지스터(11c)가 오프로 제어됨으로써, 구동 트랜지스터(11a)의 드레인 단자 d의 전위가 애노드 전압 Vdd에 있고, 구동 트랜지스터(11a)가 구동 전류 Ids를 EL 소자(15)에 공급하고 있다.

[0216] 도시하는 바와 같이, 구동 전류 Ids는 애노드 전압 Vdd로부터 구동 트랜지스터(11a)를 통하여 EL 소자(15)를 통과하고, 공통 접지 전극(GND 등) 또는 캐소드 전극(전압) Vss에 유입되고 있다.

[0217] 다음으로, 기간 C에 들어가면, 도 117에 도시하는 바와 같이, 게이트 신호선(17a)의 전위가 애노드 전압 Vdd측(온 전압이 인가됨)으로 변화됨으로써 스위치 트랜지스터(11b)가 온 상태로 되고, 구동 트랜지스터(11a)의 게이트 전위 Vg는 소스 신호선(18)의 기준 전위 V0으로 초기화(리세트)된다.

[0218] 다음으로, 기간 D로 진행하면, 도 118에 도시하는 바와 같이, 구동 트랜지스터(11a)의 드레인 단자 d의 전위가 애노드 전압 Vdd로부터 소스 신호선(18)의 기준 전위 V0보다 충분히 낮은 캔슬 전압 Vr로 변화된다.

[0219] 이에 의해 구동 트랜지스터(11a)의 소스 전위 Vs가 소스 신호선(18)의 기준 전위 V0보다 충분히 낮은 캔슬 전압 Vr로 초기화(리세트 또는 캔슬)된다.

[0220] 구체적으로는, 구동 트랜지스터(11a)의 게이트-소스간 전압  $Vgs$ (게이트 전위 Vg와 소스 전위 Vs의 차)가 구동 트랜지스터(11a)의 임계값 전압 Vth보다 커지도록, 구동 트랜지스터(11a)의 드레인 단자 d에 저캔슬 전압 Vr을 설정한다.

[0221] 다음으로, 임계값 보정 기간 E로 진행하면, 도 119에 도시하는 바와 같이, 구동 트랜지스터(11a)의 드레인 단자 d의 전위가 저캔슬 전압 Vr로부터 애노드 전압 Vdd로 변화되고, 구동 트랜지스터(11a)의 소스 전위 Vs가 상승을 개시한다.

[0222] 이윽고, 구동 트랜지스터(11a)의 게이트 단자-소스 단자간 전압  $Vgs$ 가 임계값 전압 Vth로 된 시점에서 전류는 컷오프한다(흐르지 않게 된다). 이와 같이 하여 구동 트랜지스터(11a)의 임계값 전압 Vth에 상당하는 전압이 컨덴서(19a)에 기입된다. 이것이 임계값 전압의 보정 동작이다. 이 때 전류가 오로지 컨덴서(19a)측에 흐르고, EL 소자(15)측에는 흐르지 않도록 하기 위하여, EL 소자(15)가 컷오프로 되도록 공통 접지 전극 또는

캐소드 전극(전압)  $V_{ss}$ 의 전위를 설정해 둔다.

[0223] 다음으로, 샘플링 기간/이동도 보정 기간 F로 진행하면, 도 120에 도시하는 바와 같이, 제1 타이밍에서 소스 신호선(18)의 전위가 기준 전위  $V_0$ 으로부터 신호 전위  $V_{in}$ 으로 변화되고, 구동 트랜지스터(11a)의 게이트 전위  $V_g$ 는  $V_{in}$ 으로 된다.

[0224] 이 때 EL 소자(15)는 처음에 컷오프 상태(하이 임피던스 상태)에 있기 때문에 구동 트랜지스터(11a)의 드레인 전류  $I_{ds}$ 는 EL 소자(15)의 컨덴서(19)(기생 용량)(19b)에 유입된다.

[0225] 이에 따라 EL 소자(15)의 컨덴서(19)(기생 용량)(19b)는 충전을 개시한다. 따라서 구동 트랜지스터(11a)의 소스 전위  $V_s$ 는 상승을 개시하고, 제2 타이밍에서 구동 트랜지스터(11a)의 게이트-소스간 전압  $V_{gs}$ 는  $V_{in}+V_{th}-\Delta V$ 로 된다. 이와 같이 하여 신호 전위  $V_{in}$ 의 샘플링과 보정량  $\Delta V$ 의 조정이 행하여진다.  $V_{in}$ 이 높을수록  $I_{ds}$ 는 커지고,  $\Delta V$ 의 절대값도 커진다. 따라서 발광 휘도 레벨에 따른 이동도 보정을 행할 수 있다. 또한  $V_{in}$ 을 일정하게 한 경우, 구동 트랜지스터(11a)의 이동도  $\mu$ 가 클수록  $\Delta V$ 의 절대값도 커진다. 환연하면 이동도  $\mu$ 가 클수록 부귀환량  $\Delta V$ 가 커지므로, 화소(16)마다의 이동도  $\mu$ 의 변동을 제거하는 것이 가능하다.

[0226] 마지막으로, 발광 기간 G로 되면, 도 121에 도시하는 바와 같이, 게이트 신호선(17)이 저전위측으로 변화되고, 스위치 트랜지스터(11b)는 오프 상태로 된다. 이에 의해 구동 트랜지스터(11a)의 게이트 단자 g는 소스 신호선(18)으로부터 분리된다. 동시에 드레인 전류  $I_{ds}$ 가 EL 소자(15)를 흐르기 시작한다. 이에 의해 EL 소자(15)의 애노드 전위는 구동 전류  $I_{ds}$ 에 따라서 상승한다.

[0227] EL 소자(15)의 애노드 전위의 상승은, 즉 구동 트랜지스터(11a)의 소스 전위  $V_s$ 의 상승과 다를 바 없다. 구동 트랜지스터(11a)의 소스 전위  $V_s$ 가 상승하면, 컨덴서(19a)의 부트스트랩 동작에 의해, 구동 트랜지스터(11a)의 게이트 전위  $V_g$ 도 연동하여 상승한다. 게이트 전위  $V_g$ 의 상승량은 소스 전위  $V_s$ 의 상승량과 동등하게 된다. 그러므로, 발광 기간 중 구동 트랜지스터(11a)의 게이트-소스간 전압  $V_{gs}$ 는  $V_{in}+V_{th}-\Delta V$ 로 일정하게 유지된다.

[0228] 도 122는, 도 113의 변경예이다.

[0229] EL 소자(15)의 애노드 단자와 구동 트랜지스터(11a)의 드레인 단자 d 사이에, 제4 스위치 트랜지스터(11d)를 형성하고 있다. 스위치 트랜지스터(11d)는, 게이트 신호선(17d)에 접속되며, 또한, 게이트 신호선(17d)은, 게이트 드라이버 회로(12d)로부터 온/오프 전압이 인가된다.

[0230] 도 120 등에서는, 구동 트랜지스터(11a)의 모빌리티 변동을 보정할 수 있는 것을 설명하였다. 즉, 도 120은, 스위치 트랜지스터(11a)를, 단기간, 스위치 트랜지스터(11e)를 온한 방법이다.

[0231] 단시간이란,  $0.05\ \mu\text{초}$  이상  $5\ \mu\text{초}$  이하의 시간이다. 상기 단시간은, 화소에 인가하는 영상 신호 전압  $V_{sig}$ 에 대응시켜 변화시키는 것이 바람직하다. 또한, 점등률에 대응시켜 변화시키는 것이 바람직하다. 이 변화는, 선형, 비선형에 대응시키는 것을 포함하는 것 외에, 스텝 형상(예를 들면, 점등률 50% 이상에서는, 단시간이란  $0.1\ \mu\text{초}$ , 점등률 50% 미만에서는,  $2\ \mu\text{초}$ )에 대응시켜도 된다.

[0232] 도 115에 도시하는 바와 같이, 점등률에 상관시켜, duty비를 제어 혹은 변화시키는 것이 바람직하다. 피크 전류를 억제하고, 소비 전력을 평균화할 수 있기 때문이다. 점등률이 높을 때에는, duty비를 저하(작게)시킨다. 따라서, 피크 전류를 억제할 수 있다. 또한, 최대 사용 계조수 제어를 실시한다. 이상의 사항은, 도 78, 도 79, 도 83, 도 84, 도 98, 도 99, 도 130 등을 이용하여 설명을 행하고 있다.

[0233] 1수평 주사 기간(1H)에 대한 온 시간 비율%(이하, 온 비율이라고 부름)은, 도 120의 기간이다. 온 시간이란, 스위치 트랜지스터(11b, 11e)의 온 시간(클로즈 시간)을 의미한다. 1H가  $20\ \mu\text{초}$ 인 것으로 하면, 10%란,  $2\ \mu\text{초}$ 로 된다.

[0234] 온 비율이 길수록, 구동 트랜지스터(11a)의 모빌리티의 보정 효과가 높아진다. 그러나, 컨덴서(19)의 전하가 방전되고, 구동 트랜지스터(11a)의 게이트 단자 전위가 높게(애노드 전압측) 변화하여, EL 소자(15)에 흐르는 전류가 변화하게 된다.

[0235] 오프셋 캔슬 구동에서는, 혹의 계조(저계조)는, 오프셋 캔슬되고, 구동 트랜지스터(11a)의 특성 변동은 눈에 띠기 어렵다. 그러나, 백의 계조(고계조)에서는, 오프셋 캔슬점으로부터 떨어져 있기 때문에, 구동 트랜지스터(11a)의 특성 변동이 눈에 띠기 쉽다. 이 구동 트랜지스터(11a)의 특성 변동은 모빌리티에 의한 것이다.

[0236] 점등률이 낮은 경우에는, 저계조 표시의 화소가 많다. 점등률이 높은 경우에는, 고계조 표시의 화소가 많다. 따라서, 온 비율은, 도 115의 아래 도면의 점선으로 도시하는 바와 같이 실시하는 것이 바람직하다. 즉, 저점

등률에서는, 온 비율은 0으로 하고, 고점등률로 됨에 따라서, 온 비율을 크게 한다.

[0237] 그러나, 점등률이 낮을 때에는, 저계조 표시의 화소가 많다고 하는 것은 통계적인 것이며, 실제와 상이한 경우가 있다. 또한, 점등률이 높은 경우에는, 고조 표시의 화소가 많다고 하는 것도 통계적인 것이다. 실제로는 표시 패턴, 영상 신호의 종류에 따라 상이하다. 따라서, 표시 패턴, 입력되는 영상 신호의 종류(PC 영상, AV 영상 등) 등에 따라, 온 비율을 가변할 수 있게 구성해 두는 것이 바람직하다.

[0238] 도 113, 도 123에 도시하는 바와 같이, 기타, 게이트 신호선(17a)과 트랜지스터(11a)의 게이트(G) 단자 사이에 적극적으로 컨덴서 Cx를 형성하고, 관통 전압을 증가시키는 구성도 유효하다. 이 컨덴서 Cx의 용량은 정규의 컨덴서(19a)의 용량의 1/10 이상 1/2 이하로 하는 것이 바람직하다. 나아가서는 1/8 이상 1/3 이하로 하는 것이 바람직하다.

[0239] 관통 전압 발생용의 컨덴서 Cx의 용량(용량을 Cb(pF)로 함)은, 전하 유지용의 컨덴서(19a)의 용량(용량을 Ca(pF)로 함)과, 트랜지스터(11a)의 백 피크 전류 시(화상 표시에서 표시 최대 휘도의 백 래스터 시)의 게이트(G) 단자 전압 Vw(V)를 흑 표시에서의 전류를 훌릴 때(기본적으로는 전류는 0이다. 즉, 화상 표시에서 흑 표시로 하고 있을 때)의 게이트(G) 단자 전압 Vb(V)와 관련된다. 이를 관계는,

$$Ca/(200Cb) \leq |Vw-Vb| \leq Ca/(8Cb)$$

[0241] 의 조건을 만족시키는 것이 바람직하다. 또한,  $|Vw-Vb|$  란, 구동 트랜지스터의 백 표시 시의 단자 전압(V)과 흑 표시 시의 단자 전압(V)의 차의 절대값이다(즉, 변화되는 전압폭).

[0242] 더욱 바람직하게는,  $Ca/(100Cb) \leq |Vw-Vb| \leq Ca/(10Cb)$

[0243] 의 조건을 만족시키는 것이 바람직하다.

[0244] 트랜지스터(11b)는 P채널로 하고, 이 P채널은 적어도 더블 게이트 이상으로 한다. 바람직하게는, 트리플 게이트 이상으로 한다. 더욱 바람직하게는, 4게이트 이상으로 한다. 그리고, 트랜지스터(11b)의 소스-게이트(SD 혹은 게이트-드레인(GD)) 용량(트랜지스터가 온하고 있을 때의 용량)의 1배 이상 10배 이하의 컨덴서를 병렬로 형성 또는 배치하는 것이 바람직하다.

[0245] 또한, 이상의 사항은, 도 113, 도 123의 화소 구성뿐만 아니라, 다른 화소 구성에서도 유효하다. 스위치 트랜지스터(11b)가 오프할 때에, 구동 트랜지스터(11a)에 전류가 흐르지 않도록 시프트하도록, 컨덴서 Cx를 배치한다. 또한, 스위칭 트랜지스터(11b)의 N채널은 더블 게이트 이상으로 한다. 리크 대책을 위해서이다.

[0246] 도 113에서는, 구동 트랜지스터(11a)는, N채널 트랜지스터이고, 영상 신호를 화소에 인가하는 스위치 트랜지스터(11b)도 N채널 트랜지스터이다. 스위치 트랜지스터(11b)를 제어하는 게이트 신호선(17a)은, 화소(16)의 선택 시에는, 높은 전압(VGH)이 인가되고, 비선택으로 되는 경우에는, 낮은 전압(VGL)이 인가된다.

[0247] 화소(16)가 선택 상태로부터 비선택 상태로 될 때에는, 게이트 신호선(17a)에 전기적으로 접속된 컨덴서 Cx의 1단자는 VGH 전압으로부터 VGL 전압으로 변화된다. 컨덴서 Cx는 VGH 전압으로부터 VGL 전압으로의 변화를 관통 전압으로 하여 다른 컨덴서 Cx 단자(구동 트랜지스터(11a)의 게이트 단자에 접속되어 있음)에 전달한다. 따라서, VGH로부터 VGL 전압의 변화에 비례한 전압이, 구동 트랜지스터(11a)의 게이트 단자에 인가되어, 구동 트랜지스터(11a)의 게이트 단자 전압을 저하시킨다. 따라서, 구동 트랜지스터(11a)는 전류를 흘리기 어려운 방향으로 동작한다. 이 동작에 의해, 보다 흑 표시 레벨이 개선되어, 양호한 콘트라스트를 실현할 수 있다.

[0248] 마찬가지로, 도 123에서는, 구동 트랜지스터(11a)는, P채널 트랜지스터이고, 영상 신호를 화소에 인가하는 스위치 트랜지스터(11b)도 P채널 트랜지스터이다. 즉, 구동 트랜지스터(11a)와 스위치 트랜지스터(11b)는 동극성의 채널 트랜지스터로 구성되어 있다. 스위치 트랜지스터(11b)를 제어하는 게이트 신호선(17a)은, 화소(16)의 선택 시에는, 낮은 전압(VGL)이 인가되고, 비선택으로 되는 경우에는, 높은 전압(VGH)이 인가된다.

[0249] 따라서, 화소(16)가 선택 상태로부터 비선택 상태로 될 때에는, 게이트 신호선(17a)에 전기적으로 접속된 컨덴서 Cx의 1단자는 VGL 전압으로부터 VGH 전압으로 변화된다. 컨덴서 Cx는 VGL 전압으로부터 VGH 전압으로의 변화를 관통 전압으로 하여 다른 컨덴서 Cx 단자(구동 트랜지스터(11a)의 게이트 단자에 접속되어 있음)에 전달한다. 그 때문에, VGL로부터 VGH 전압의 변화에 비례한 전압이, 구동 트랜지스터(11a)의 게이트 단자에 인가되어, 구동 트랜지스터(11a)의 게이트 단자 전압을 높은 전압의 방향으로 시프트시킨다. 따라서, 구동 트랜지스터(11a)는 전류를 흘리기 어려운 방향으로 동작한다. 이 동작에 의해, 보다 흑 표시 레벨이 개선되어, 양호한 콘트라스트를 실현할 수 있다.

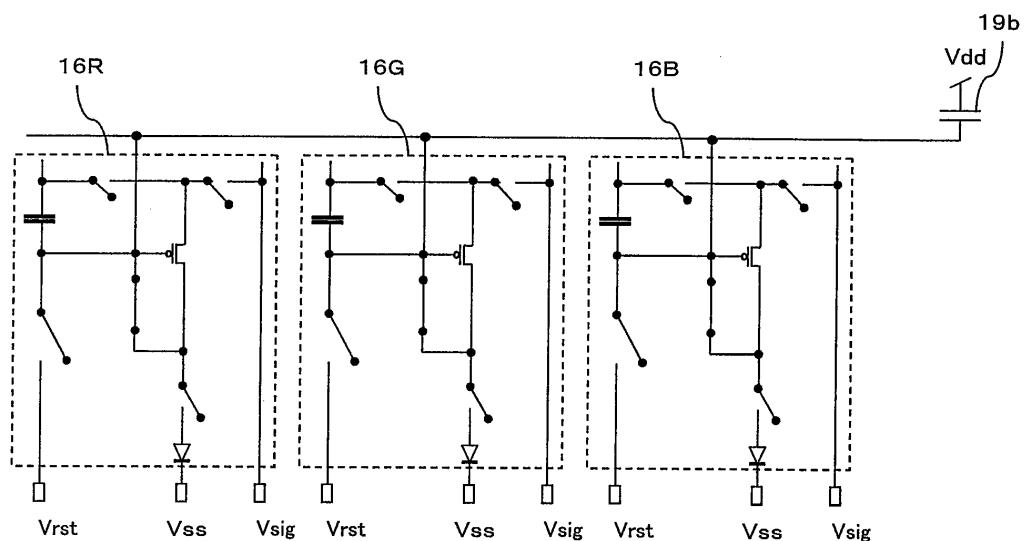

- [0250] 또한, 관통 전압용의 컨덴서 Cx는, 화소가 변조하는 R, G, B에서 크기(용량)를 변화시키는 것이 바람직하다. R, G, B의 각 EL 소자(15)의 구동 전류가 서로 다르기 때문이다. 또한, EL 소자(15)의 컷오프 전압이 서로 다르기 때문이다. 그 때문에, EL 소자(15)의 구동 트랜지스터(11a)의 게이트(G) 단자에 프로그램하는 전압(전류)이 서로 다르기 때문이다. 예를 들면, R의 화소의 컨덴서 CxR을 0.02pF로 한 경우, 다른 색(G, B의 화소)의 컨덴서 CxG, CxB를 0.025pF로 한다. 또한, R의 화소의 컨덴서 CxR을 0.02pF로 한 경우, G의 화소의 컨덴서 CxG를 0.03pF로 하고, B의 화소의 컨덴서 CxB를 0.025pF로 하는 등이다. 이와 같이, R, G, B의 화소마다 컨덴서 Cx의 용량을 변화시킴으로써 오프셋의 구동 전류를 RGB마다 조정할 수 있다. 따라서, 각 RGB의 흑 표시 레벨을 최적값으로 할 수 있다.

- [0251] 이상의 사항은, 도 1 등의 실시예 1, 실시예 3 등의 화소 구성에도 적용된다. 본 명세서에 기재한 실시예는 상호 조합할 수 있다.

- [0252] 이상은, 관통 전압 발생용의 컨덴서 Cx의 용량을 변화시키는 것으로 하였지만, 관통 전압은, 유지용의 컨덴서(19a)와 관통 전압 발생용의 컨덴서 Cx의 용량의 상대적인 것이다. 따라서, 컨덴서 Cx를 R, G, B의 화소에서 변화시키는 것에 한정되는 것은 아니다. 즉, 유지용 컨덴서(19a)의 용량을 변화시켜도 된다.

- [0253] 예를 들면, R의 화소의 컨덴서(11aR)를 1.0pF로 한 경우, G의 화소의 컨덴서(11aG)를 1.2pF로 하고, B의 화소의 컨덴서(11aB)를 0.9pF로 하는 등이다. 이 때, 관통용 컨덴서 Cx의 용량은, R, G, B에서 공통인 값으로 한다. 따라서, 본 실시예는, 유지용의 컨덴서(19a)와 관통 전압 발생용의 컨덴서 Cx의 용량비를, R, G, B의 화소 중, 적어도 1개를 다른 것과 상이하게 한 것이다. 또한, 유지용의 컨덴서(19a)의 용량과 관통 전압 발생용의 컨덴서 Cx의 용량의 양방을 R, G, B 화소에서 변화시켜도 된다.

- [0254] 또한, 화면(31)의 좌우에서 관통 전압용의 컨덴서 Cx의 용량을 변화시켜도 된다.

- [0255] 이상의 사항은, 도 1 등의 실시예 1, 실시예 3~7 등의 화소 구성, 표시 패널(표시 장치) 혹은 구동 방법에도 적용된다. 본 명세서에 기재한 실시예는 상호 조합할 수 있다.

- [0256] 게이트 드라이버 회로(12)에 가까운 위치에 있는 화소(16)는 신호 공급측에 배치되어 있으므로, 게이트 신호의 상승이 빠르기(스루 레이트가 높기) 때문에, 관통 전압이 커진다. 게이트 신호선(17)단에 배치(형성)되어 있는 화소는, 신호 파형이 완만하다(게이트 신호선(17)에는 용량이 있기 때문임). 게이트 신호의 상승이 느리기(스루 레이트가 느리기) 때문에, 관통 전압이 작아지기 때문이다. 따라서, 게이트 드라이버 회로(12)와의 접속측에 가까운 화소(16)의 관통 전압용 컨덴서 Cx를 작게 한다. 또한, 게이트 신호선(17)단은 컨덴서 Cx를 크게 한다. 예를 들면, 화면의 좌우에서 컨덴서의 용량은 10% 정도 변화시킨다.

- [0257] 마찬가지로, 화면(31)의 상하에서 관통 전압용의 컨덴서 Cx의 용량을 변화시켜도 된다. 화면(31)에는, 컨덴서 Ca와 영상 신호의 기입 타이밍의 문제로부터, 휙도 경사가 발생하기 때문이다. 컨덴서 Cx의 값을 또한, 소스 신호선(18)을 따라서 변화시킨다. 예를 들면, 화면의 상하에서 컨덴서 Cx의 용량은 10% 정도 변화시킨다.

- [0258] 발생하는 관통 전압은, 유지용 컨덴서(19a)와 관통 전압 발생용의 컨덴서 Cx의 용량비로 결정된다. 따라서, 화면의 좌우에서 관통 전압 발생용의 컨덴서 Cx의 크기를 변화시키는 것으로 하였지만, 이것에 한정되는 것은 아니다. 관통 전압 발생용의 컨덴서 Cx는 화면의 좌우에서 일정하게 하고, 전하 유지용의 컨덴서(19a)의 용량을 화면의 좌우에서 변화시켜도 된다. 또한, 관통 전압 발생용의 컨덴서 Cx와, 전하 유지용의 컨덴서(19a) 용량의 양방을 화면의 좌우에서 변화시켜도 되는 것은 물론이다. 이상의 사항은, 화면(31)의 상하 방향에 관해서도 마찬가지이다.

- [0259] 도 1의 구성 혹은 방식은, 영상 신호 전압 Vsig를 화소에 형성된 오프셋 캔슬 컨덴서(19b)에 유지하는 것이었다. 오프셋 캔슬 컨덴서(19b)에 영상 신호 전압 Vsig를 유지함으로써, 화소(16)의 선택 후에도 오프셋 캔슬 동작을 계속해서, 양호한 오프셋 캔슬을 실현할 수 있다.

- [0260] 도 95는, 도 113, 도 123 등에서 설명한 본 실시예의 화소 구성 혹은 EL 표시 장치에 컨덴서(19b)를 부가한 구성이다. 컨덴서(19b)는, 영상 신호 전압 Vsig를 유지하는 것이 아니라, 캔슬 전압 Vr을 유지한다.

- [0261] 도 118에 도시하는 바와 같이, 캔슬 전압 Vr을 단시간 동안, 구동 트랜지스터(11a)의 소스 단자(혹은 드레인 단자)에 인가한다. 그러나, 단시간이기 때문에, 충분히 캔슬 동작을 실시할 수 없는 경우가 있다.

- [0262] 도 95와 같이, 캔슬 전압 Vr을 유지하는 컨덴서(19b)를 화소(16)에 형성하면, 스위치 트랜지스터(11c)를 오프한 후에도, 컨덴서(19b)에 유지한 캔슬 전압 Vr을 이용하여, 캔슬 동작을 계속할 수 있다. 따라서, 캔슬 동작을

복수 수평 주사 기간에 걸쳐 실시할 수 있다.

[0263] 이상과 같이, 본 실시예는, 소정의 종류의 전압(영상 신호 전압 Vsig, 캔슬 전압 Vr 등)을 화소(16)에 인가하고, 상기 소정의 종류의 전압의 인가가 완료한 후에도, 소정의 종류의 전압을 컨덴서(19b)에 유지하고, 유지한 전압에 의해 소정 동작(오프셋 캔슬 동작, 캔슬 동작 등)을 계속하는 것이다. 또한, 소정 동작을 계속 할 수 있는 구조 또는 구성이다.

[0264] 또한, 본 발명의 실시예에서, 소정의 종류의 전압(영상 신호 전압 Vsig, 캔슬 전압 Vr 등)을 유지하는 컨덴서(19b)를 화소(16)에 형성하는 것으로 하였지만, 이것에 한정되는 것은 아니다. 예를 들면, 다이오드를 화소에 형성하고, 다이오드의 접합 용량에 상기 소정의 종류의 전압을 유지해도 된다. 또한, 화소에 트랜지스터 소자를 형성하고, 트랜지스터의 기생 용량(게이트 용량 등)에 상기 소정의 종류의 전압을 유지해도 된다.

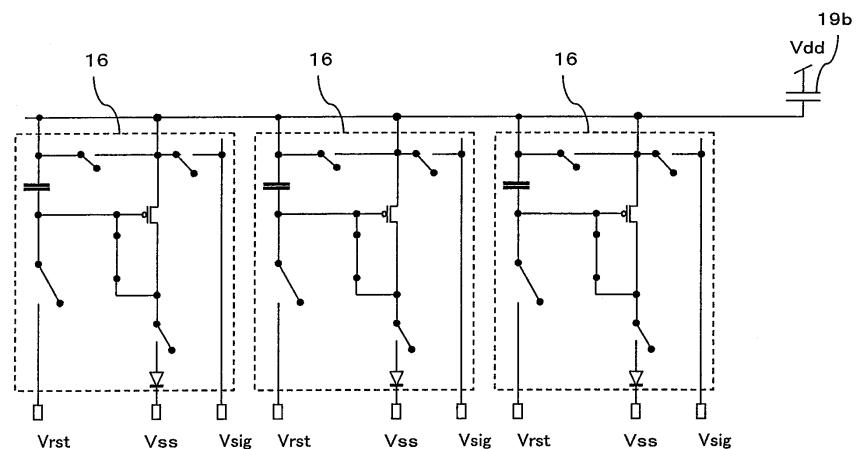

[0265] 또한, 소정의 종류의 전압(영상 신호 전압 Vsig, 캔슬 전압 Vr 등)을 유지하는 컨덴서(19b)를 화소(16)에 형성하는 것으로 하였지만, 이것에 한정되는 것은 아니다. 예를 들면, 도 124~도 126에 도시하는 바와 같이, 복수의 화소(16)를 공통(화소행, 화소열)으로 하여, 1개의 컨덴서(19b)를 배치해도 된다.

[0266] 도 124는, 1화소행에 1개의 컨덴서(19b)를 형성하고, 컨덴서(19b)에 캔슬 전압 Vr을 유지시키는 구성이다. 도 125는, 1화소행에 1개의 컨덴서(19b)를 형성하고, 컨덴서(19b)에 영상 신호 전압 Vsig를 유지시키는 구성이다. 영상 신호 전압 Vsig가 화소행 혹은 화소열에 공통인 신호인 경우에 유효하다. 도 126은, 1화소행에 1개의 컨덴서(19b)를 형성하고, 컨덴서(19b)에 리세트 전압 Vrst를 유지시키는 구성이다.

[0267] 또한, 도 124~도 126의 구성에서, 각 화소에 리세트 전압 Vrst 혹은, 캔슬 전압 Vr을 인가하는 스위치 트랜지스터(11c 혹은 11f)를 배치하고 있지만, 이것에 한정되는 것은 아니다. 예를 들면, RGB의 화소를 1조로 하여, 스위치 트랜지스터(11c 혹은 11f)를 배치해도 된다. 또한, 화소행 혹은 화소열마다, 스위치 트랜지스터(11c 혹은 11f)를 배치해도 된다.

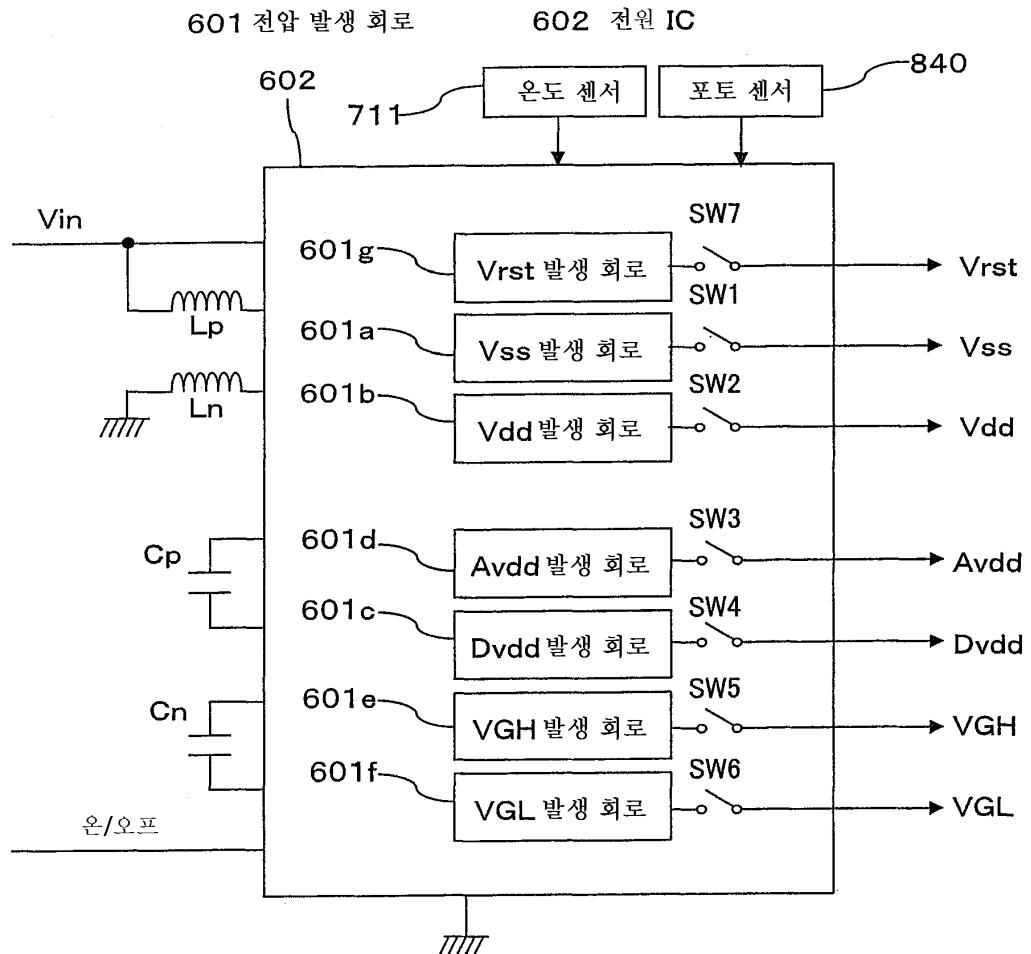

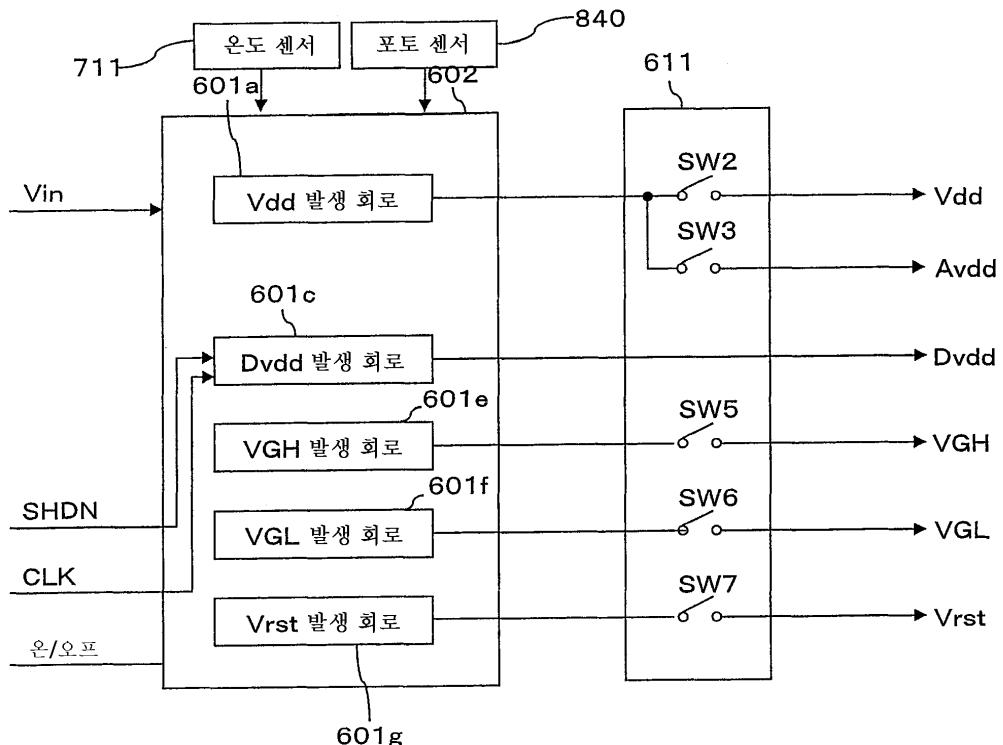

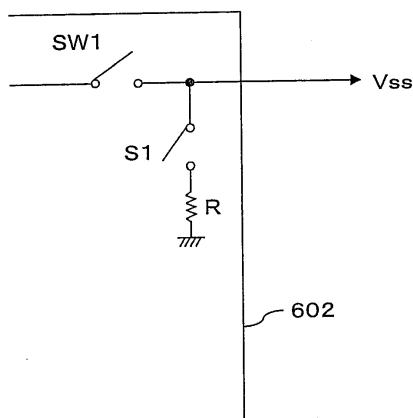

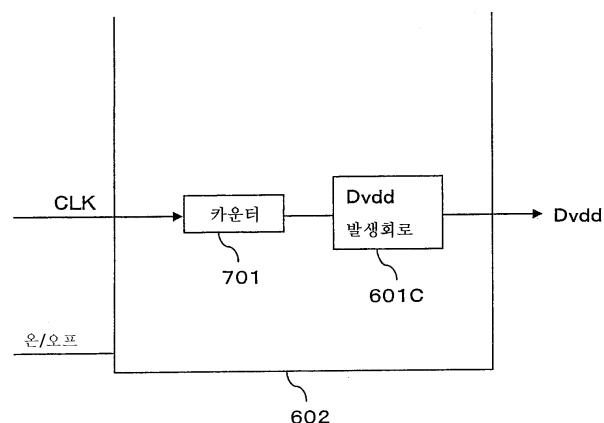

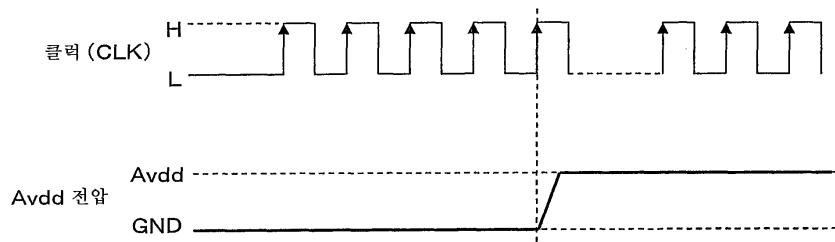

[0268] 애노드 전압 Vdd, 캐소드 전압 Vss 등의 전압을 발생시키는 전원 회로(전원 IC)를 외부에 배치하는 경우에는, 이 전원 회로(전원 IC)를 온/오프 제어시키는 온/오프 신호를 소스 드라이버 IC(14)로부터 발생(지시)시키는 것이 바람직하다. 애노드 전압 Vdd, 캐소드 전압 Vss는, VGH, VGL 전압의 인가(공급) 후에, 패널(34)에 인가(공급)한다.

[0269] 이상의 사항은, 본 명세서의 다른 실시예에도 적용되는 것은 물론이다.

[0270] 도 127에 도시하는 바와 같이, 캔슬 전압 Vr을 인가하는 배선 및 스위치 트랜지스터(11c)를 복수의 화소(예를 들면, RGB의 화소를 1조로 하여)에 1개 형성 또는 설치해도 된다. 또한, 컨덴서(19b)는, RGB에서 서로 다르게 해도 된다. RGB에서 컨덴서(19b)의 용량을 서로 다르게 함으로써, 오프셋 캔슬 동작, 리세트 동작, 캔슬 동작 등을, RGB의 특성에 맞추어 최적으로 설정할 수 있기 때문이다.

[0271] 도 128에 도시하는 바와 같이, 캔슬 전압 Vr을 인가하는 배선 및 스위치 트랜지스터(11c), 컨덴서(19b)를 복수의 화소(예를 들면, RGB의 화소를 1조로 하여)에 1개 형성 또는 설치해도 된다. 화소 구성이 간략화되어, 화소(16)의 개구율을 향상시킬 수 있다. 이상의 사항은, 본 명세서의 다른 실시예에도 적용되는 것은 물론이다.

[0272] 컨덴서(19b)의 용량은, 표시 화면(31)의 부분에서 서로 다르게 해도 된다. 예를 들면, 화면의 좌우와 중앙부에서, 컨덴서(19b)의 용량을 서로 다르게 한다. 화면의 부분에 맞추어, 오프셋 캔슬 동작, 리세트 동작, 캔슬 동작 등을, 최적으로 설정할 수 있기 때문이다. 이상의 사항은, 유지용의 컨덴서(19a)에도 적용할 수 있다. 화면의 부분에 맞추어, 영상 신호 전압 Vsig의 기입, 오프셋 캔슬 동작 등을, 최적으로 설정할 수 있기 때문이다.

[0273] 이상의 사항은, 본 명세서의 다른 실시예에서도 적용되는 것은 물론이다. 또한, 다른 실시예와 조합할 수 있는 것은 물론이다. 따라서, 다른 실시예에서, 도면의 작성, 설명을 용이하게 하기 위하여, 복수의 구성, 실시의 조합은 생략하고 있다. 이상의 사항은, 도 1, 도 4, 도 5, 도 10, 도 11, 도 25, 도 29, 도 31, 도 33, 도 35, 도 37, 도 42, 도 46, 도 52, 도 54, 도 55, 도 58, 도 59, 도 86, 도 90, 도 91, 도 92, 도 93, 도 94, 도 95, 도 113, 도 123, 도 124~도 128 등의 EL 표시 패널 혹은 EL 표시 장치에도 적용할 수 있는 것은 물론이다.

[0274] 이상의 사항은 다른 실시예에서도 마찬가지이다. 예를 들면, 도 12, 도 13, 도 61, 도 75, 도 76, 도 77, 도 78, 도 79, 도 83, 도 84, 도 85, 도 98, 도 99, 도 100, 도 101 등의 방법 혹은 방식, 도 7, 도 8, 도 9, 도 60, 도 83, 도 96, 도 102, 도 103, 도 104, 도 106, 도 107, 도 108, 도 109, 도 110, 도 111, 도 112, 도 129의 구성 혹은 구조 혹은 방법에 관해서도 앞서 예시한 혹은 본 명세서에 기재한 화소 구성과 조합하여 실시

할 수 있는 것은 물론이다.

[0275] <실시예 3>

[0276] 본 발명의 실시예 3에 대하여 설명한다. 또한, 지금까지 설명한 구성, 방식은, 이하에 설명하는 구성 혹은 방식에 적용 혹은 조합할 수 있는 것은 물론이다.

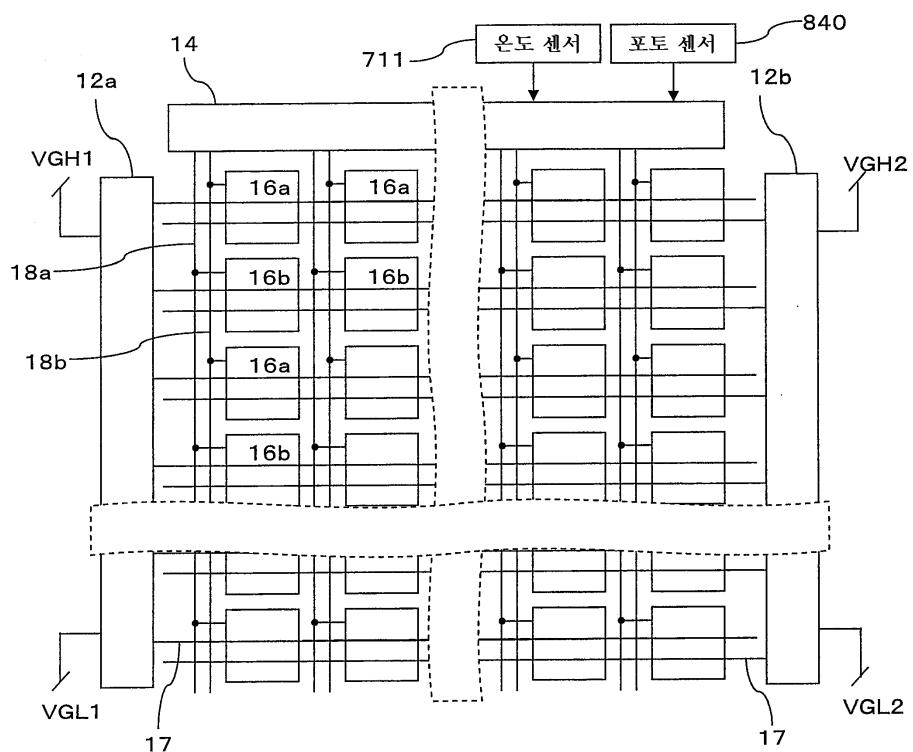

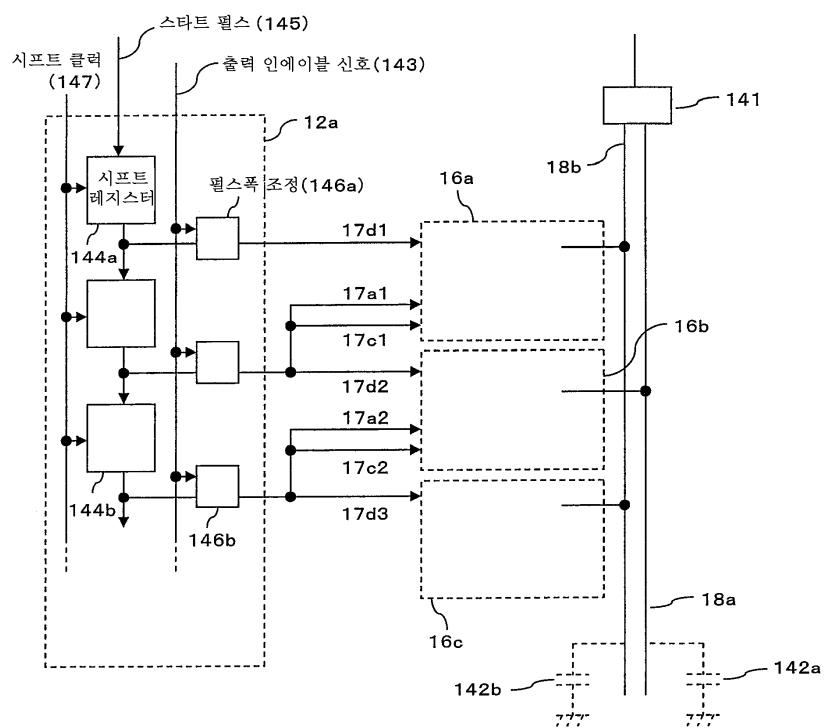

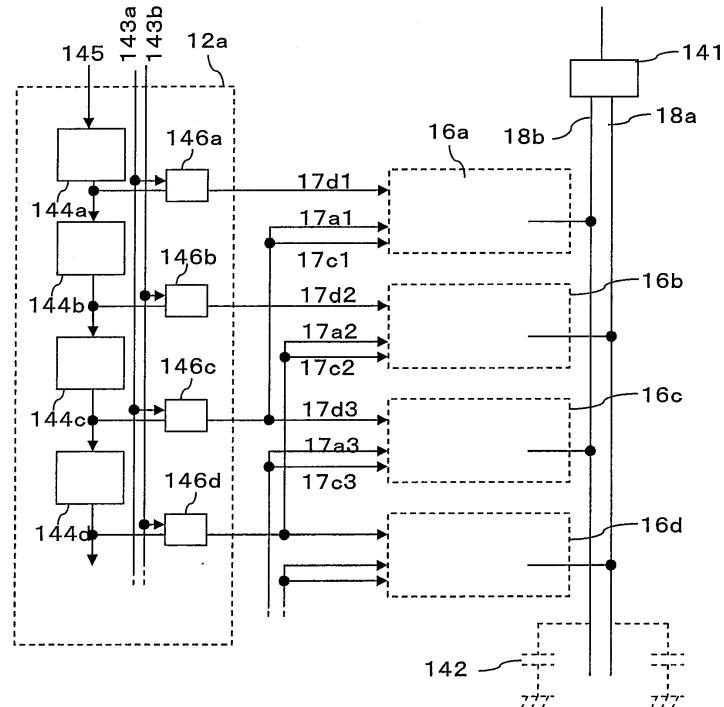

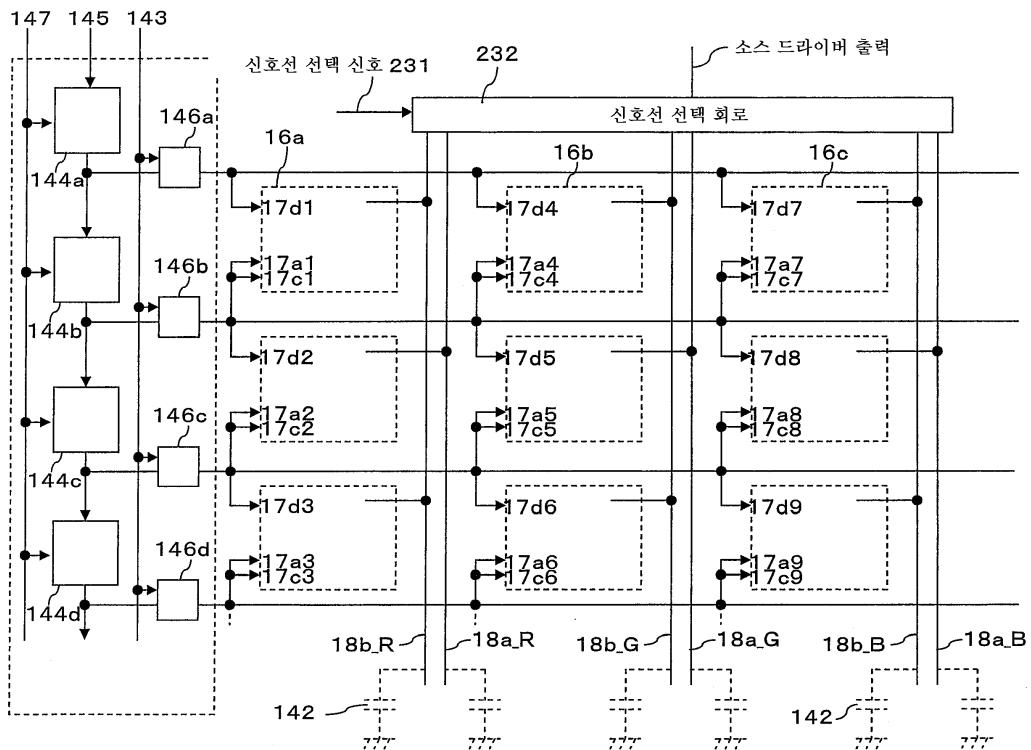

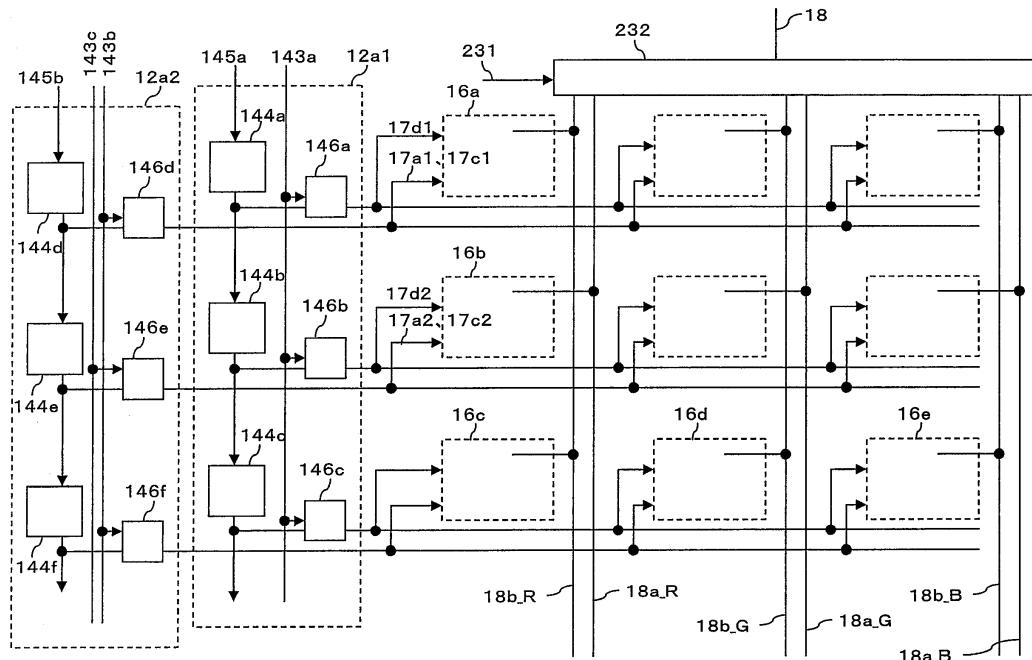

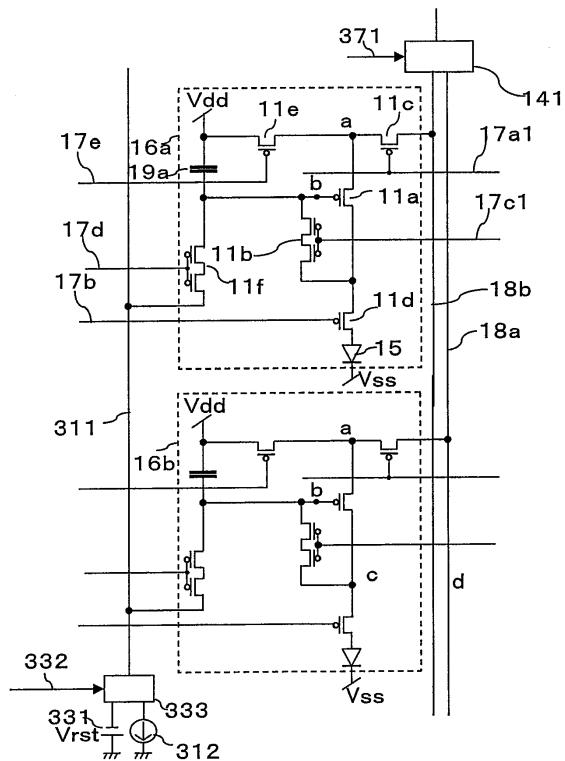

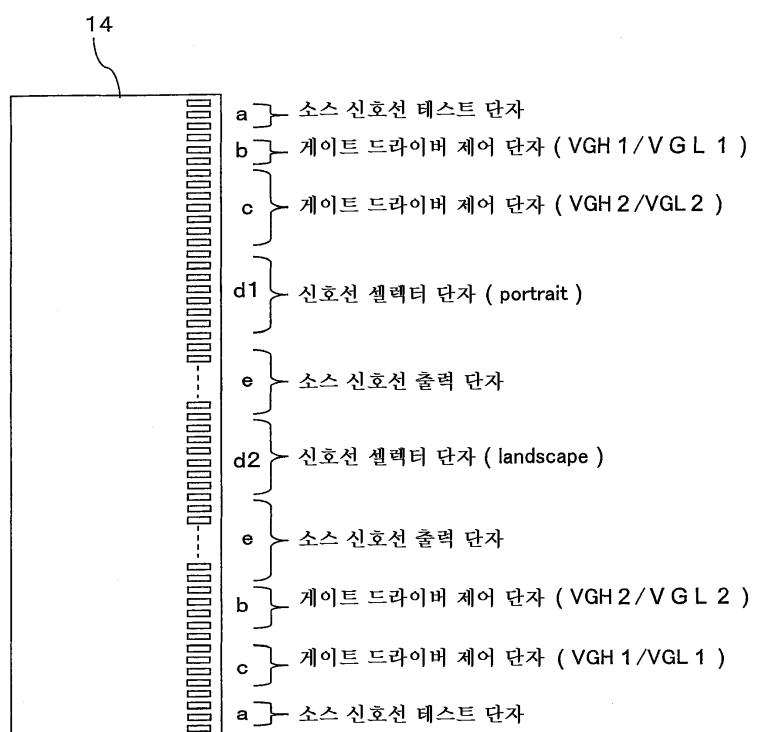

[0277] 도 14는, 본 실시예에서의 EL 표시 패널의 1열분의 회로를 도시한 것이다. 여기서 소스 신호선(18)은 절환 수단(141)을 통하여, 1열에 대하여 2개의 소스 신호선(18a와 18b)이 존재하고, 짹수행과 홀수행의 화소에서 접속되는 소스 신호선이 서로 다른 구성으로 되어 있는 것이 특징이다(도 6 등도 참조).

[0278] 각 화소(16)의 구성은, 예를 들면, 도 1, 도 4, 도 10, 도 25, 도 29, 도 42, 도 46, 도 52, 도 54, 도 55, 도 58, 도 59, 도 86, 도 87, 도 90, 도 91, 도 92, 도 93, 도 94, 도 95, 도 113, 도 122, 도 124~도 128 등의 회로로 구성되어 있다. 즉, 이하의 실시예는, 본 명세서의 다른 실시예에 적용할 수 있다. 또한, 상호 조합할 수 있다.

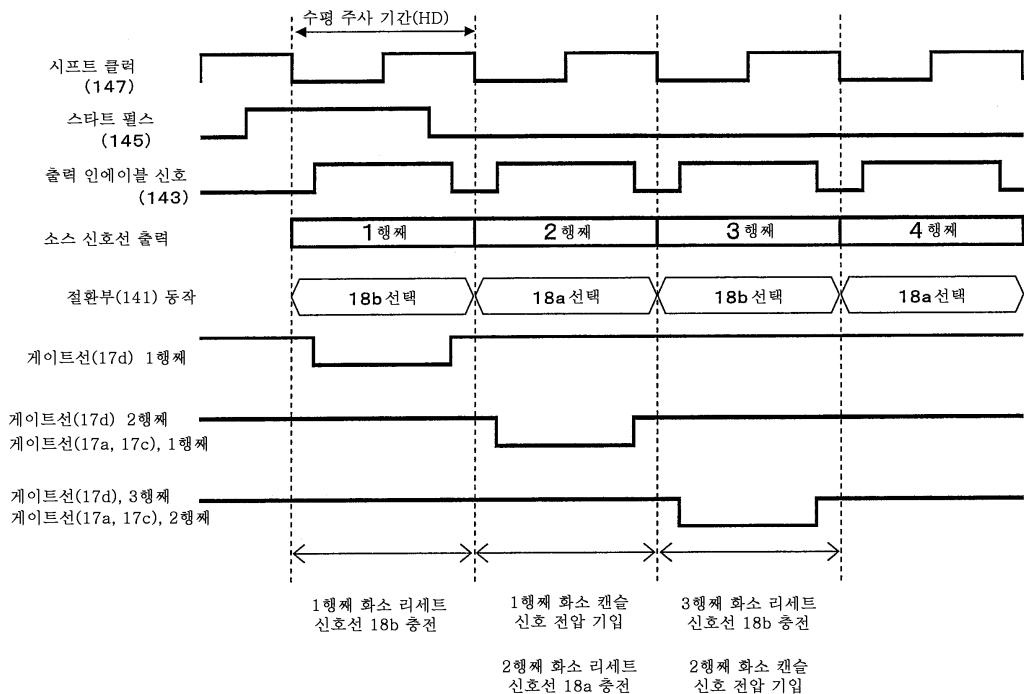

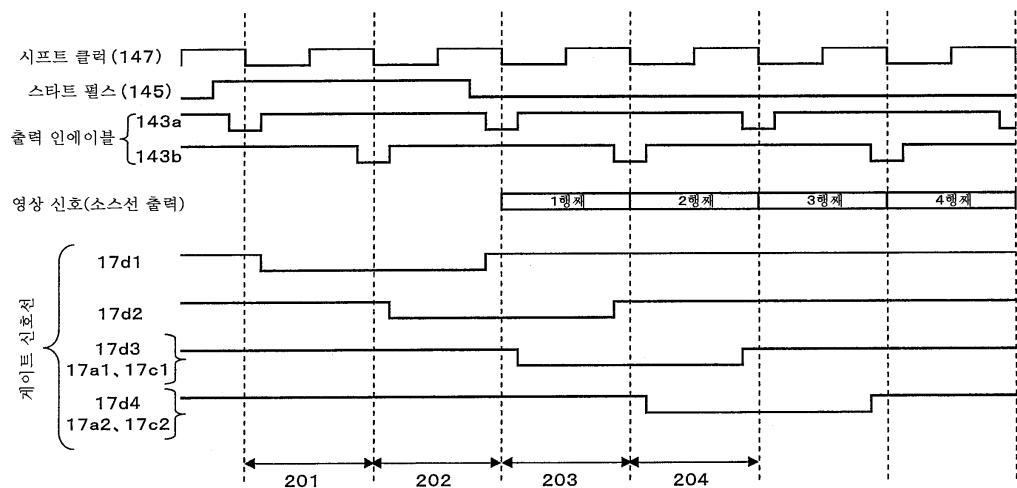

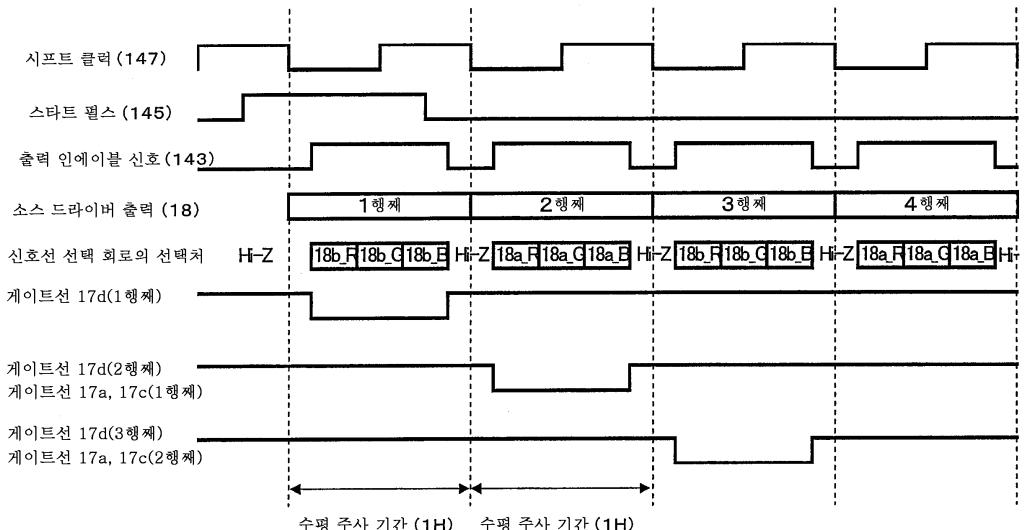

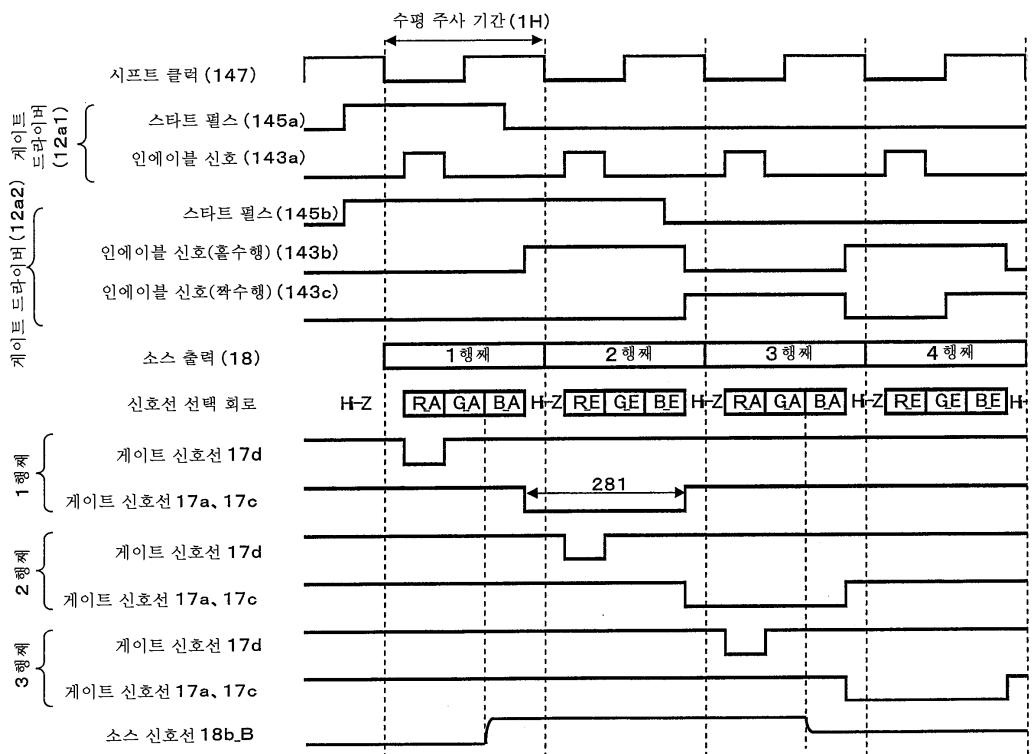

[0279] 게이트 드라이버 회로(12a)는, 시프트 레지스터 구성으로 되어 있고, 클럭마다 펄스가 1단씩 시프트된다. 게이트 신호선(17)에 대한 접속을, 도 14와 같이 행함으로써, 도 15에 도시하는 바와 같은 신호 파형을 실현할 수 있다.

[0280] 시프트 클럭의 주기를 1수평 주사 기간(1H)으로 설정하고, 1수평 주사 기간만 펄스가 출력되는 스타트 펄스가 입력된다. 이로써 각 행 1수평 주사 기간씩 어긋난 타이밍에서 1수평 주사 기간 동안 펄스가 발생하는 회로를 실현할 수 있다.

[0281] 시프트 레지스터의 각 단 출력을 도 14와 같이 게이트 신호선(17)에 공급하고, 절환 수단(141)을 도 15에 도시하는 바와 같이 동작시킴으로써, 처음의 1수평 주사 기간(1H)에서는, 1행째의 화소(16a)의 구동 트랜지스터(11a)의 게이트 전압을 Vrst 전원에 의해 초기화한다. 동시에 소스 신호선으로부터 소정의 계조에 대응하는 1행째의 화소에 대응하는 신호 전압이 절환 수단(141)을 통하여 소스 신호선(18b)에 충전된다. 소스 신호선(18a)에는 충전되지 않는다. 절환 수단(141)에 의해 소스 드라이버 출력으로부터 분리되어 있다.

[0282] 다음의 1수평 주사 기간에서는 절환 수단(141)을 동작시켜, 소스 신호선(18a)을 충전하도록 한다. 이 때 소스 신호선(18b)은, 소스 드라이버 출력으로부터 분리되어 있기 때문에, 소스 신호선의 부유 용량(142b)에 의해 1행째의 화소에 대응하는 신호 전압이 충전된 상태 그대로이다. 따라서, 게이트 신호선(17a) 및 게이트 신호선(17c)을 주사하고, 화소(16a)의 트랜지스터(11c, 11b)를 도통 상태로 하고, 화소의 구동 트랜지스터(11a)에 계조 신호의 기입과, 특성 변동의 캔슬 동작을 실시한다. 동시에 2행째의 화소에 대응하여, 화소(16b)에 대응하는 계조 신호 전압이 소스 신호선(18a)에 충전되고, 구동 트랜지스터(11a)의 게이트 단자가 Vrst 전원에 의해 초기화된다.

[0283] 부유 용량(142)은, 게이트 신호선(17)과 소스 신호선(18)의 교차부에 발생하는 용량, 소스 신호선(18)과 화소 전극의 결합 용량 등으로 구성된다. 도 14 등에서, 컨덴서(142)는 부유 용량으로서 설명하지만 이것에 한정되는 것은 아니다. 소스 신호선(18)을 한 쪽의 전극으로 하여 컨덴서를 형성해도 된다.

[0284] 소스 신호선(18a)과 소스 신호선(18b)을 수평 주사 기간마다 절환하여 이용함으로써, 소스 신호선에 인가시키는 계조 신호가 2수평 주사 기간 유지되기 때문에, 화소 회로(16)에 신호를 기입하는 시간을 길게 할 수 있게 된다.

[0285] 도 1 등의 화소 회로의 구성에서는, 구동 트랜지스터(11a)에 계조 신호를 기입하면서, 특성 변동을 캔슬하는 동작을 행한다. 특성 변동을 캔슬하는 동작은, 트랜지스터(11f, 11d, 11e)가 오프이고 트랜지스터(11b)가 온 상태일 때에 행하여지고, 구동 트랜지스터(11a)의 드레인 전류가 0으로 되도록, 구동 트랜지스터(11a)의 게이트 전위가 변화함으로써, 특성 변동의 캔슬을 행하고 있다.

[0286] 구동 트랜지스터(11a)의 게이트 전위를 변화시키고 있는 것은, 드레인 전류에 의한 전하이며, 최종 상태가 0 혹은 한없이 작은 전류(피코암페어 오더)이기 때문에, 게이트 전위를 지지하고 있는 유지용 컨덴서(19a)의 전하의 충방전에 시간이 걸린다. 그 때문에, 캔슬 동작에는 시간이 걸리는 것을 알 수 있다.

[0287] 1수평 주사 기간(1H)이 긴 경우에는, 1수평 주사 기간 내에 캔슬 동작을 완료시킬 수 있다. 그러나, 수직 라인 수가 많고, 1수평 주사 기간이  $40\mu$ 초보다도 짧은 경우에는, 캔슬 동작이 마지막까지 행하여지지 않아, 특성 보상이 불완전하게 되고, 그 결과, 특성 변동에 따른 불균일이 발생하는 문제가 있다.

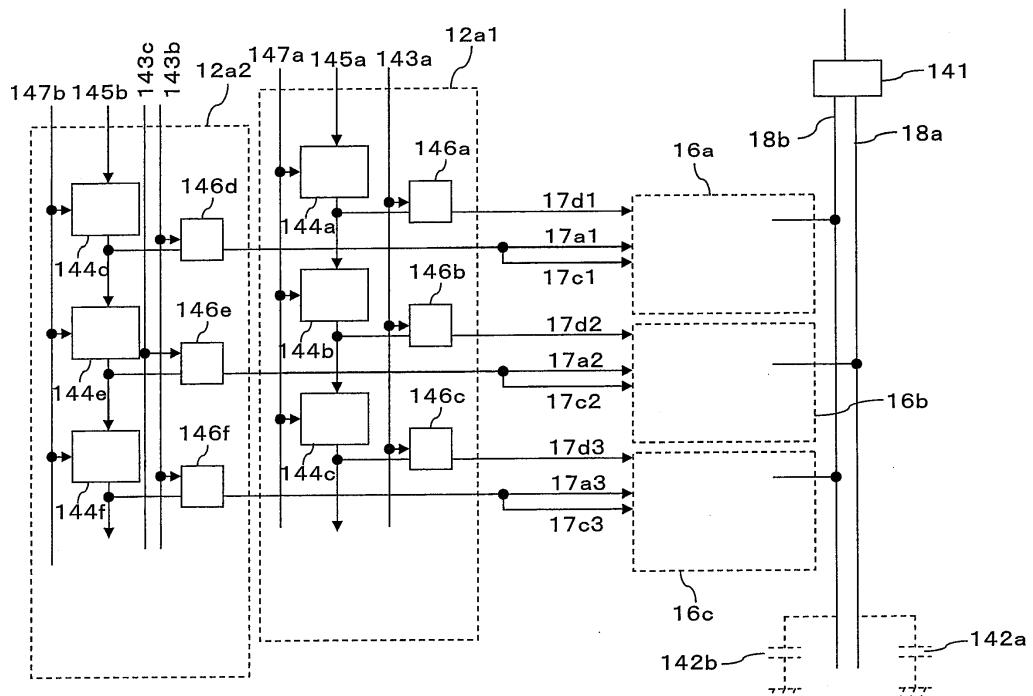

- [0288] 그래서, 캔슬 시간을 1수평 주사 기간 이상으로 확대하는 방법으로서, 도 16에 도시하는 바와 같이 게이트 드라이버 회로(12a)를 다시 2개의 게이트 드라이버 회로(12a1), 게이트 드라이버 회로(12a2)로 구성한다. 구동 트랜지스터(11a)의 초기화를, 대응하는 영상 신호가 입력되는 1수평 주사 기간 전에 미리 실시한다. 또한, 소스 신호선(18a 혹은 18b)에 영상 신호가 입력되는 수평 주사 기간으로부터 구동 트랜지스터(11a)에 계조 전압의 기입 및 특성 캔슬 동작을 행하도록 한다. 절환부(141)의 동작에 의해, 2수평 주사 기간 동안 영상 신호가 유지되기 때문에, 계조 전압의 기입 및 특성 캔슬 동작을 2수평 주사 기간 중 실시하는 것이 가능하게 된다.

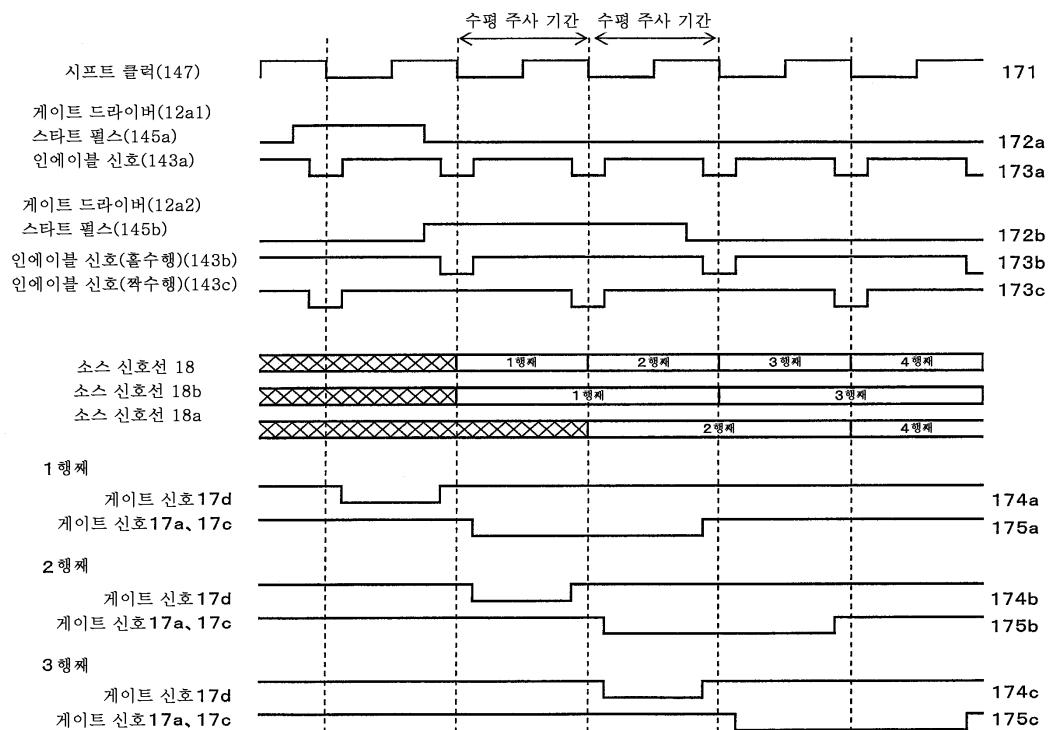

- [0289] 이것을 실현하기 위하여, 도 17에 도시하는 바와 같이, 시프트 레지스터(12a2)의 스타트 펄스(172b)를 입력한다. 각 행의 트랜지스터(17a 및 17c)가 2수평 주사 기간 온된다. 온되는 타이밍은 소스 신호선(18, 18a, 18b)의 영상 신호에 동기하여 실시된다. 영상 신호가 짹수행과 홀수행에서 2개의 소스 신호선(18a 및 18c)으로 분류됨으로써 주파수가 절반으로 되어, 기입 시간을 2배로 할 수 있다.

- [0290] 또한, 인에이블 신호(173)에 대해서는, 펄스 전파 시의 파형 무덤에 의한 복수의 행의 화소에서 동시 선택되는 것을 방지하기 위한 신호로서, 동시 선택이 발생하지 않는 경우나, 동시 선택이라도 문제 없이 동작하는 경우에는, 불필요하다. 인에이블 신호(173)가 없어도 본 실시예를 실시할 수 있다. 예를 들면 도 21과 같이, 특성 캔슬을 행하기 위한 신호를 생성하는 게이트 드라이버 회로(12a2)의 인에이블 신호를 삭제한 경우의 입력 파형 및 동작을 나타낸다.

- [0291] 도 17의 파형에 따르면, 2수평 주사 기간 동안, 구동 트랜지스터(11a)의 특성 보정 동작이 가능하지만, 미리 영상 신호가 입력되는 1수평 주사 기간 전에 구동 트랜지스터(11a)를 초기화하기 위한 동작이 필요하며, 1수평 주사 기간 전에 미리 동작시키는 것이 필요하다. 따라서, 선두행을 검지할 수 없는 경우에는, 미리 초기화를 할 수 없게 될 우려가 있다.

- [0292] 그래서, 도 18에 도시하는 바와 같이, 초기화 동작을, 1행째의 영상 신호 입력 시와 동시에 실시하는 신호 패턴을 발명하였다. 초기화 동작 시에는, 특성 보정 동작을 할 수 없기 때문에, 2수평 주사 기간(2H) 동안에, 초기화 후 특성 보정 동작을 행한다.

- [0293] 도 18의 구성에서는, 2수평 주사 기간 중의 처음의 수평 주사 기간의 전반에 초기화 동작을 행하고, 남은 절반과 다음의 수평 주사 기간에서 화소에의 신호 기입과 특성 보상 동작을 실시한다. 게이트 드라이버가 시프트 레지스터 구성인 경우에는, 수평 주사 기간과 시프트 클럭이 일치하는 경우에는, 인에이블 신호로 펄스 폭을 커트하는 방법에 의해, 수평 주사 기간의 전반과 후반에서 서로 다른 스위치의 동작을 실현한다.

- [0294] 게이트 신호선(17d)이 로우 레벨일 때가, 구동 트랜지스터(11a)의 초기화 기간으로 되고, 게이트 신호선(17a 및 17c)이 로우 레벨일 때에, 구동 트랜지스터(11a)의 특성 캔슬과, 화소에 계조를 기입하는 기간으로 된다.

- [0295] 도 17a 및 도 17c의 로우 레벨 기간을 1수평 주사 기간보다 길게 설정할 수 있기 때문에, 수평 주사 기간이  $30\ \mu\text{초}$ 이어도, 종래비 1.5배의 기간이 취해지기 때문에  $45\ \mu\text{초}$ 의 캔슬 기간이 취해지고, 구동 트랜지스터의 특성 변동을 보정하는 것이 가능하게 된다. 초기화 동작 자체는,  $2\sim10\ \mu\text{초}$  정도에서 완료하기 때문에, 최대 2수평 주사 기간으로부터  $2\sim10\ \mu\text{초}$ 를 뺀 시간까지 캔슬 기간을 확대할 수 있다.

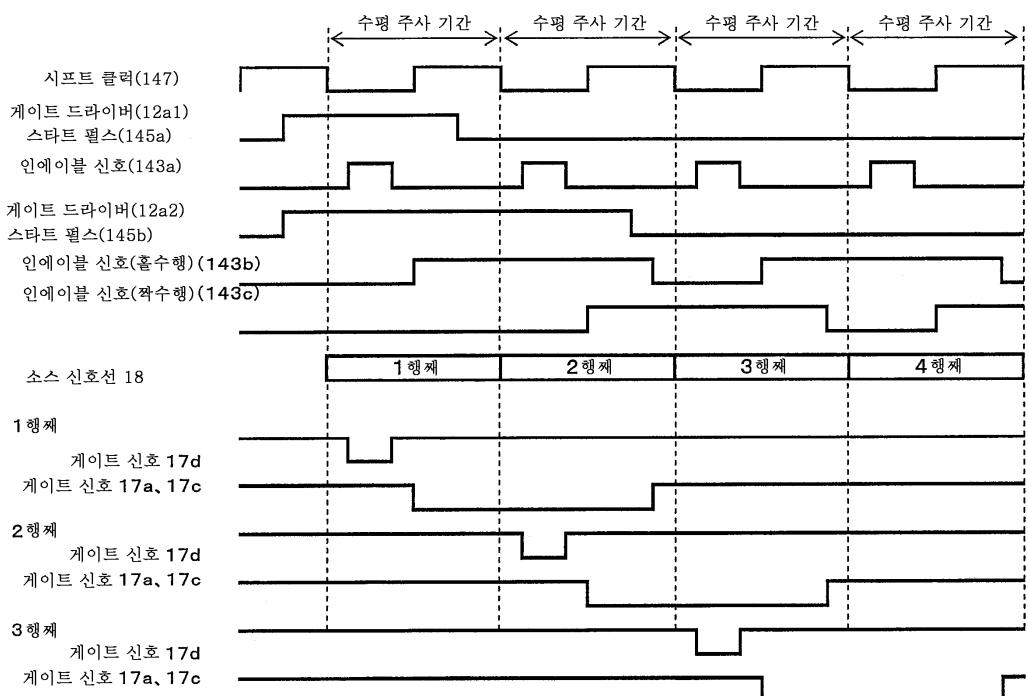

- [0296] 게이트 드라이버 회로(12a)의 시프트 레지스터가 1계통이며 또한 캔슬 기간을 1수평 주사 기간 이상으로 확대하는 방법을 도 19 및 도 20에 도시한다.

- [0297] 예를 들면, 2수평 주사 기간 동안 캔슬하는 경우에는, 2수평 주사 기간 게이트 신호선(17a 및 17c)이 도통 상태에 있을 필요가 있다. 그래서 게이트 드라이버 회로(12a)의 스타트 펄스를 2수평 주사 기간의 길이만큼 입력한다. 이에 의해, 캔슬 및 계조 기입 시간을 2수평 주사 기간으로 설정할 수 있다. 마찬가지로 초기화를 실시하기 위한 게이트 신호선(17d)용의 펄스를 생성할 필요가 있다.

- [0298] 또한, 도 1, 도 25에 도시하는 바와 같은 화소 회로 구성이기 때문에, 게이트 신호선(17d)과 구동 트랜지스터(11a), 스위치 트랜지스터(11c)를 동시에 도통 상태로 하면 안되기 때문에(다른 전압이 쇼트됨), 초기화용의 펄스는, 동일행의 화소에 대한 캔슬 및 계조 기입용의 펄스와 겹치지 않도록 할 필요가 있다.

- [0299] 구체적으로는, 2수평 주사 기간 전의 펄스를 초기화용의 펄스로서 이용하면 된다. 도 19에 도시하는 바와 같이, 시프트 레지스터에 대하여, 게이트 신호선(17d)과 공통인 출력을 캔슬 및 계조 신호 기입용 게이트 신호선에 이용하는 경우에는, 2행분 후단(즉 2수평 주사 기간 후)의 신호를 이용하면, 동일 화소(16a)에 대하여, 도 20에 도시하는 바와 같이, 참조 부호 201, 202의 2수평 주사 기간에서 초기화를 실시한다. 또한, 참조 부호 203, 204의 2수평 주사 기간에서 구동 트랜지스터(11a)의 특성 캔슬 및 계조 신호 기입을 실시하고 있다. 참조

부호 16b, 16c의 화소에서도 마찬가지로 1수평 주사 기간씩 지연된 타이밍에서 실시하고 있다.

[0300] 이 방법은, 2수평 주사 기간의 캔슬뿐만 아니라, 3수평 주사 기간 이상, 필요한 경우라도 실시가 가능하다. 1열분의 화소에 대응하는 소스 신호선의 수를 필요로 하는 수평 주사 기간의 수(정수)분을 준비하고, 게이트 드라이버 회로(12a)의 스타트 펄스의 펄스 폭을 필요한 수평 주사 기간수 입력한다. 초기화에 대응하는 게이트 신호를 취출하는 시프트 레지스터의 단으로부터 필요한 수평 주사 기간 수만큼 후단의 시프트 레지스터로부터 특성 캔슬 및 계조 신호 기입용의 게이트 신호를 취출하여, 동일행의 화소에 입력하면 실현이 가능하다.

[0301] 영상 신호가, 대응하는 행의 화소에 기입되도록 하기 위하여, 스타트 펄스는, 영상 신호에 대하여 미리 입력할 필요가 있다. 적어도 캔슬을 행하는 수평 주사 기간의 길이 분만큼 빨리 입력이 필요하다. 도 20에서도 2수평 주사 기간 빨리 입력하고 있다.

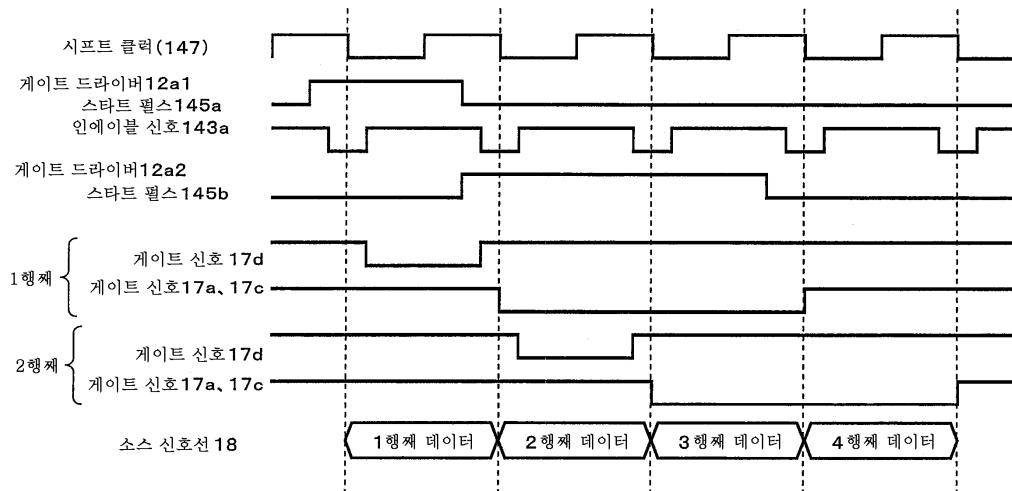

[0302] 소스 드라이버의 코스트 삭감을 위해, 1출력으로부터 시계열로 복수의 화소에 대응하는 전압을 출력하는 선택 구동 방식을 채용하는 경우가 있다. 선택 구동 방식이 없는 경우에 비해, 해당 화소에 대응하는 영상 신호가 입력되는 타이밍이 표시색에 의해 서로 다르게 된다.

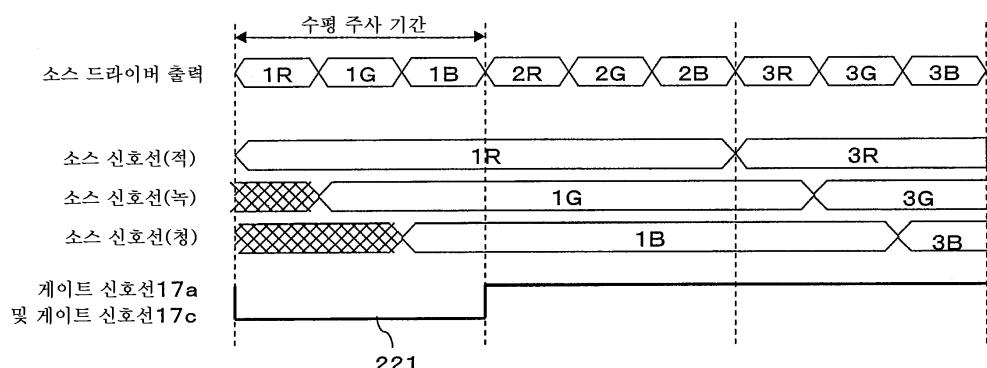

[0303] 예를 들면, 적녹청의 3화소분을 1출력으로 행하는 3선택 구동의 경우에는, 도 22에 도시하는 바와 같이, 적(R)색에 대하여, 녹(G) 및 청(B)은 수평 주사 기간의 처음이 아니라, 도중에서 신호가 변화되고 있는 것을 알 수 있다. 게이트 신호선(17a 및 17c)을 참조 부호 221의 과형에 의해 입력하면 녹 및 청색의 화소에 대해서는, 1행 전의 영상 신호가 화소에 기입되고, 소스 신호선의 변화에 의해 해당 행의 영상 신호가 기입되게 된다.

[0304] 액정 등에서는, 기입 시의 최종 전압(게이트 신호선이 오프로 되는 순간의 전압)이 1프레임간 화소에 유지되고, 소정 휙도로 표시되기 때문에 문제가 없다. 본 실시예에서의 화소 구성을 갖는 유기 EL 표시 패널에서는, 영상 신호를 구동 트랜지스터(11a)에 기입할 때에 구동 트랜지스터(11a)의 특성 변동을 보정하는 동작을 행하고 있다.

[0305] 보정에 필요로 하는 시간을 단축하기 위하여, 기입을 행하기 전에, 초기화 동작을 행하고, 구동 트랜지스터(11a)의 게이트 단자에 낮은 전압(백 표시 시보다도 구동 트랜지스터(11a)가 전류를 더 흘리는 전압)으로 미리 초기화를 행하고 있다.

[0306] 초기화의 전압은 낮을수록 특성 보정이 고속화된다. 선택 구동 시에 1행 전의 전압이 조금이라도 인가되면, 구동 트랜지스터(11a)의 게이트 전압이 1행 전의 전압으로 변화되게 되어, 1행 전의 전압이 인가된 상태에서, 해당 행의 영상 신호에 의한 계조 신호의 기입과 트랜지스터 변동 특성 보정을 행하게 되어, 초기화를 행하는 효과가 없어지게 된다. 이것은 3선택 구동이 아니어도, 2선택 이상의 신호선 선택 구동을 실시할 때에 공통인 과정이다.

[0307] 본 실시예에서는, 선택 구동을 행할 때에, 동일 수평 주사 기간에서 기입을 행하는 신호선의 전압이 전부 확정된 후에 특성 캔슬 동작을 행하도록 하였다.

[0308] 도 23, 도 24 및 도 26에 실시예 중 하나를 도시한다. 여기서 선택 구동은 적녹청의 3개의 신호선을 순서대로 선택하는 3선택 구동 방식으로 하고 있다. 2선택이나, 4선택 이상에서도 마찬가지로 실현할 수 있다.

[0309] 캔슬 시간을 확보하기 위하여, 각 열에 대하여 2개의 신호선을 준비하고, 짹수행과 홀수행에서 서로 다른 소스 신호선을 이용하고 있다. 도 23에서는 게이트 드라이버 회로(12a)를 시프트 레지스터 회로 1계통에서 실시하는 구성을 도시하고 있다. 도 23의 게이트 드라이버 회로(12a)를 이용한 경우의 신호 입력과, 신호선 선택 회로(232)의 동작을 도 26에 도시한다. 1수평 주사 기간 내에서 적(R), 녹(G), 청(B)으로 신호선을 절환하고 있다. 또한 1수평 주사 기간마다 홀수행용의 소스선(18b), 짹수행용의 소스선(18a)을 절환하여 선택을 행하고 있다.

[0310] 이 방식에서는, 초기화의 타이밍과 해당 행의 영상 신호선의 기입이 동일하고, 화소 내부에의 영상 신호의 기입은, 다음의 수평 주사 기간에서 실시되고 있다. 따라서, 구동 트랜지스터(11a)에의 신호선 기입 및 특성 변동 보정의 실시 중에 영상 신호가 변하는 일은 없어, 선택 구동 시에서도 지금까지와 마찬가지의 구동이 실시 가능하다.

[0311] 1화소분에 주목한 타이밍 차트를 도 24에 도시한다. 여기서는 지금까지 기재하고 있지 않았던 게이트 신호선(17b)에 대해서도 기재를 행하고 있다. 게이트 신호선(17b)에 대해서는, 초기화 기간 및 특성 캔슬, 계조 신호를 구동 트랜지스터에 기입을 행하고 있는 기간에서는 반드시, 접속되는 스위치가 비도통 상태일 필요가 있다. 그러나, 그 밖의 기간에서는, 도통, 비도통 상태 어느 쪽이어도 상관없다. 이것은 본 실시예 외의 실시 형태에

서도 마찬가지이다. 도 24에서는, 도통 비도통을 반복하여 실시하고 있는 예를 도시하고 있다.

[0312] 소스 신호선(18)은 3선택 구동 대응용으로 1수평 주사 기간 동안에 3화소분의 신호를 보내고 있다. 신호선 선택 회로에 의해 홀수행째의 청 화소에 대응하는 소스 신호선(18bB)의 전압 변화는 참조 부호 241로 도시하는 파형과 같이 된다.

[0313] 1행째에 대응하는 계조 신호의 변화는 참조 부호 242의 타이밍에서 변화된다. 이 때 게이트 신호선(17b)이 오프 상태로 되어 있고, 구동 트랜지스터(11a)의 게이트 단자에 1행 전의 영상 신호가 기입되는 일이 없게 되어 있다. 게이트 신호선(17a)에 대해서는, 도 23의 게이트 드라이버 회로(12)의 구성에 의하면 오프로 되어 있지만, 온 상태이어도 상관없다. 게이트 드라이버 회로(12)의 구성을 변경하여 온으로 해도 된다. 구동 트랜지스터(11a)의 소스 단자에 1행 전의 전압이 인가되지만, 초기화되어 있는 게이트 단자에는 인가되는 일이 없기 때문이다.

[0314] 시간  $2t$  이후에서 게이트 신호선(17c, 17a)이 도통 상태로 되고, 구동 트랜지스터(11a)에 계조 전압 및 특성 캔슬 동작이 행하여진다. 이 때, 소스 신호선(18bB)은 도 26에서와 같이, 신호선 선택 회로(232)에 의해 각 소스 신호선으로부터 분리된 상태로 된다.

[0315] 소스 신호선의 부유 용량(233)에 의해, 소스 드라이버로부터 기입된 전압이 2수평 주사 기간 동안 유지된다. 유지된 전압값이 화소에 기입되고, 소정 전압이 기입되어 있다. 시간  $2t \sim 3t$  사이에, 구동 트랜지스터(11a)의 게이트 전압은 기입되는 소스 전압(Vsig)으로부터 임계값 전압(Vth)만큼 저하한 전위로 서서히 변화되고, ( $Vsig - Vth$ )로 된다. 시간  $3t$ 에서 소정 전압으로 기입된 후, 게이트 신호(17b)를 도통 상태로 함으로써 소정 전류가 EL 소자(15)에 흐르고, 발광한다.

[0316] 도 27은 게이트 드라이버 회로(12a)를 시프트 레지스터 2계통으로 구성한 경우의 도면이다. 이것에 의하면 스트리트 펄스의 개별 설정에 의해, 게이트 신호선(17d)에 대하여 게이트 신호선(17a 및 17c)의 펄스 폭을 서로 다르게 설정하는 것이 가능하다.

[0317] 도 28에 게이트 드라이버 회로(12a1 및 12a2)의 입력 파형과, 각 게이트 신호선 파형을 도시한다. 초기화용의 신호를 생성하는 게이트 드라이버 회로(12a1)에 대하여, 초기화를 행하기 위한 펄스를 생성한다. 초기화에 필요로 하는 시간은  $Vrst$ 를 발생하는 전원 능력에 의하지만  $10 \mu\text{s}$  정도에서 초기화가 완료된다. 게이트 신호선(17d)이 온 상태로 되는 것은 짧은 시간에서 실시하고 있다.

[0318] 시간이 걸리는 특성 캔슬 기간과 초기화 기간은 동시에 실시할 수 없기 때문에, 2수평 주사 기간 내에서 초기화~특성 캔슬, 계조 신호 기입을 실시하기 위해서는, 초기화를 짧게 하는 것이 중요하기 때문이다.

[0319] 도 27, 도 37의 실시예에서는, 1수평 주사 기간에 2화소행을 선택하는 방식이지만, 본 실시예는 이것에 한정되는 것은 아니다. 3화소행 이상을 동시에 선택해도 된다. 3화소행 이상을 동시에 선택하는 경우에는, 소스 신호선(18)의 개수도 증가시킨다. 기본적으로는, 1수평 주사 기간에 동시에 선택하는 화소행분의 수량의 소스 신호선(18)을 형성한다.

[0320] 또한, 동시에 선택하는 화소행은, 인접하고 있는 것에 한정되지 않는다. 2화소행 단위이어도 된다. 일례로서, 제1 수평 주사 기간에, 제1번째의 화소행과 제3번째의 화소행을 선택하고, 제2 수평 주사 기간에, 제2번째의 화소행과 제4번째의 화소행을 선택하는 구동 방식이 예시된다.

[0321] 또한, 동시에 선택하는 화소행은, 영상 신호 전압  $Vsig$ 의 기입 타이밍을 어긋나게 해도 된다. 예를 들면, 제1 번째의 화소행과 제2번째의 화소행을 선택하는 경우, 제1번째의 화소행을 선택한 후,  $5 \mu\text{s}$  후에 제2번째의 화소행을 선택해도 된다. 선택 타이밍을 서로 다르게 함으로써, 돌입 전류 등을 억제할 수 있다. 또한, 선택 회로(1041)를 형성하고, 선택 회로(1041)와 타이밍 조정을 실시해도 된다.

[0322] 도 28에서는 적색으로 소스 출력이 선택된 기간에서만 실시하고 있지만, 적과 녹색의 선택 기간 혹은 적색의 선택 기간의 일부 등이어도 된다. 해당 행의 영상 신호가 기입되는 것이 가장 느린 청색의 소스 신호선(18aB 혹은 18bB)에서는 청색의 선택 기간으로 될 때까지 해당 화소에 대응하는 전압이 소스 신호선(18aB 혹은 18bB)에 인가되고 있지 않기 때문에, 특성 캔슬 기간으로 이행할 수 없다.

[0323] 특성 캔슬을 할 수 없기 때문에, 적녹 선택 기간은 초기화 기간으로 해도 문제가 없다. 특성 캔슬 및 계조 신호 기입이지만, 게이트 드라이버 회로(12a2)의 시프트 레지스터 회로에 의해 2수평 주사 기간 선택할 수 있는 펄스를 생성하고, 초기화 기간 혹은 영상 신호가 기입되어 있지 않은 기간을 제외하도록, 홀수행 짹수행별로 인

에이블 기간을 설정하는 인에이블 신호를 갖는다.

[0324] 1행째의 특성 캔슬 및 계조 신호 기입 기간은 참조 부호 281로 표시되는 기간으로 된다. 참조 부호 281의 기간의 시작은, 청화소 기입 종료 후로 되어 있지만, 청화소가 신호선 선택 회로에서 선택되고 소정 전압으로 소스 신호선(18aB 혹은 18bB)이 변화한 후이면, 게이트 신호선(17a 및 17c)을 로우 레벨로 해도 된다. 참조 부호 281의 기간의 끝은, 다음에 동일한 소스 신호선에 서로 다른 행의 화소에 대응하는 전압이 인가되기 전으로 설정하면 된다. 신호선 선택 속도가 빠른 경우에는, 기입 종료 후~다음의 수평 주사 기간의 최후까지 특성 캔슬 기간을 설정할 수 있어, 구동 트랜지스터(11a)의 임계값 전압 보정 능력이 높은 표시를 실현 가능하다.

[0325] 또한, 게이트 신호선(17a)에 대해서는, 2수평 주사 기간 전부에서 로우 레벨로 해도 된다. 트랜지스터(11c)가 도통 상태로 되어도, 구동 트랜지스터(11a)의 게이트 전압에는 영향이 없기 때문이다. 이 경우, 게이트 신호선(17c)용에는 인에이블 신호를 통하여 시프트 레지스터 출력이 입력되고, 게이트 신호선(17a)용에는 인에이블 신호를 통하여 시프트 레지스터 출력이 입력되는 구성으로 된다.

[0326] 지금까지는 화소 회로(16)에 이용되는 트랜지스터는 P채널 트랜지스터로 설명을 행해 왔지만, 도 29에 도시하는 N채널 트랜지스터로 구성해도 된다. 이상의 사항은 본 실시예의 다른 화소 구성에서도 마찬가지이다.

[0327] 유기 EL 소자(15)에 대해서는, 애노드와 캐소드의 방향이 반대이며 또한, Vss 전위>Vdd 전위로 하는 구성이여도 된다. 도 29에서는 컨덴서(19b)가 형성되어 있지만, 컨덴서(19b)가 없어도 본 실시예를 마찬가지로 실시하는 것이 가능하다. 이상의 사항은 본 실시예의 다른 화소 구성에서도 마찬가지이다.

[0328] 또한, 도 29와 도 4를 비교하면, 도 4는, 관통 컨덴서(19c)가 게이트 신호선(17a)과 구동 트랜지스터(11a)의 게이트 단자 사이에 배치되어 있는 것에 대하여, 도 29에서는, 관통 컨덴서(19c)가 게이트 신호선(17c)과 구동 트랜지스터(11a)의 게이트 단자 사이에 배치되어 있다.

[0329] 컨덴서(19b)가 형성되어 있으면, 다음에 화소에 영상 신호가 기입될 때까지의 1프레임간 전압이 유지되기 때문에, a점의 전위가 유지된다. 혹은, 다음에 트랜지스터(11c)가 온하고 영상 신호가 화소(16)에 기입될 때까지 a점에 인가된(기입된) 전압이 유지된다.

[0330] 유지된 전위를 바탕으로 트랜지스터(11b)를 도통 상태로 하면 계조 신호에 따른 신호에 의해, 구동 트랜지스터(11a)의 특성 변동을 캔슬하는 것이 가능하다. 이것이 도 30에 도시하는 캔슬 기간(302)으로 된다.

[0331] 이 캔슬 기간(오프셋 캔슬 기간)은 수평 주사 기간의 길이에 상관없이 게이트 드라이버 회로(12)의 구성에 의해 임의로 설정하는 것이 가능하다. 영상 신호의 기입과 구동 트랜지스터(11a)의 초기화는, 캔슬 기간(302)의 전에 실시된다(기간 301). 트랜지스터(11f와 11c)만 도통 상태이다. 이로써 Vrst 전원에 의해 구동 트랜지스터(11a)의 게이트 전위를 초기화하고, 동시에 소스 신호선(18)으로부터 컨덴서(19b)에 소정 전압의 기입을 행하고 있다.

[0332] 컨덴서(19b)에 소정 계조 전압을 유지하기 때문에, 소스 신호선(18)은 1개에서, 1수평 주사 기간만 트랜지스터(11c)를 온시키기만 하면 된다. 소스 신호선(18)을 2개 준비하는 방법으로 소스 신호선(18)의 부유 용량과 컨덴서(19b)의 양방에서 계조 전압을 유지하는 방법을 취해도 된다. 이 경우, 컨덴서(19b)는 작게 할 수 있다.

[0333] 오프셋 캔슬이 완료되면, EL 소자(15)에 전류를 인가하여 소정 회도에 의한 발광을 얻는다. 이 기간이 발광 기간(304)이다. 이 때 트랜지스터(11d와 11e)가 도통 상태로 되어 EL 소자(15)에 전류를 공급한다.

[0334] 전후에 있는 비발광 기간(303)은, 혹 삽입을 행하여 동화상 시인성 향상 등의 효과를 얻을 때에 삽입되는 기간이다. 혹 삽입은 duty 구동이며, 도 12, 도 13, 도 84, 도 98, 도 99 등을 이용하여 설명을 행하고 있다. 이 때에는 적어도 트랜지스터(11d 혹은 11e) 중 어느 한 쪽이 비도통 상태로 되어 있다. 또한, 상시 점등 상태로 하여 혹 삽입을 행하지 않는 경우에는, 기간(303)은 없어도 지장이 없다.

[0335] 또한, 본 실시예에서의 절환부(141) 및 신호선 선택 회로(232)는 반드시 어레이 기판 상에 형성할 필요가 없고, 소스 드라이버 IC에 내장되는 구성이여도 된다.

[0336] 본 실시예에서, 동일 열에 형성된 화소에 접속되는 소스 신호선은 2개인 예로 설명을 행하였지만, 3개 이상인 복수의 소스 신호선이여도 마찬가지로 실시가 가능하다. 일반적으로 N개의 소스 신호선을 준비하고, N화소 걸러 소스 신호선을 접속하면, N수평 주사 기간 동안 소스 신호선은 계조 전압을 유지하는 것이 가능하게 되어, 특성 캔슬 기간을 길게 취할 수 있다. 캔슬 기간을 확보함으로써, 보다 구동 트랜지스터(11a)의 특성에 근접한 게이트 전압을 화소 회로에서 유지할 수 있게 되어, 표시 불균일이 개선된다. 또한, 복수의 화소행을 동시에

선택해도 된다.

- [0337] N개의 소스 신호선에 대하여, 적어도 인접 화소간에서 서로 다른 소스 신호선에 화소 회로를 접속해 두면, 2수 평 주사 기간 동안 소스 신호선에 계조 신호가 유지되기 때문에, 마찬가지로 특성 캔슬 기간을 확대할 수 있어, 표시 불균일이 적은 EL 표시 장치를 얻을 수 있다.

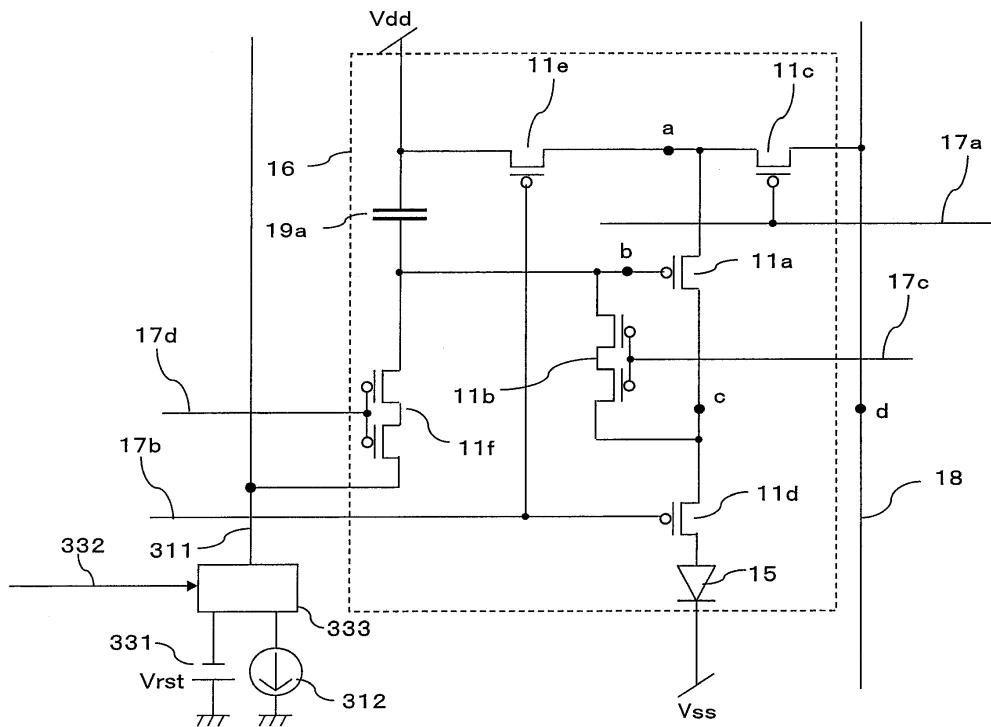

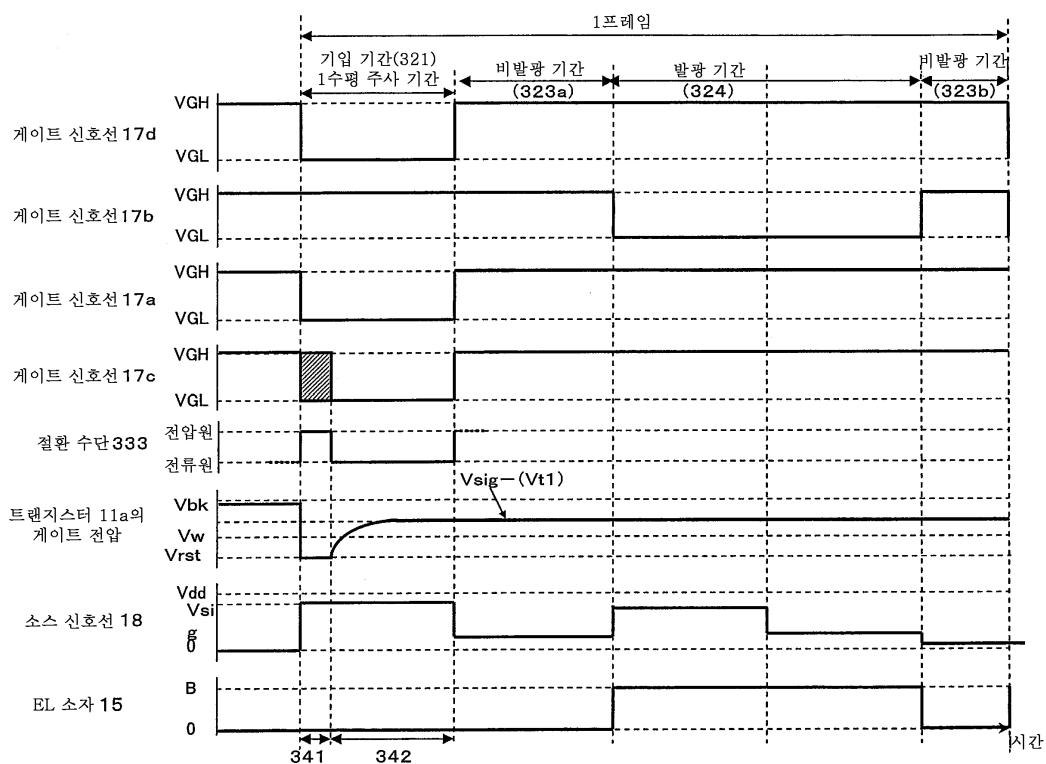

- [0338] 도 31은, 구동 트랜지스터(11a)의 게이트 단자의 전압을 초기화하기 위한 전원(리세트 전압 Vrst)을, 전압원으로부터 전류원으로 변경한 회로이다. 도 32에 도 31의 회로 구성에서의 게이트 신호선의 과정을 도시한다. 도 31의 회로 구성에서, 1화소에서의 동작은, 1프레임 동안에, 기입 기간(321), 발광 기간(324), 비발광 기간(323)으로 나눠진다. 비발광 기간(323)은, 혹 삽입(duty 구동:간헐 표시 구동)을 행하여 동작 시인성을 향상시키는 경우 등에 이용된다. 본 발명의 실시예에서는, 비발광 기간(323)은, 있어도 없어도 된다. 특성 변동의 보상 능력 향상을 마찬가지로 실현할 수 있다.

- [0339] 기입 기간(321)에서, 트랜지스터(11b, 11c, 11f)가 도통 상태로 된다. 이에 의해 소스 신호선(18)의 전압이 구동 트랜지스터(11a)의 소스 단자에 인가된다. 구동 트랜지스터(11a)의 게이트와 드레인 단자는 트랜지스터(11b)에 의해 동전위로 되고, 전류원(312)에 의해 공급되는 전류가 구동 트랜지스터(11a)의 드레인 전류로 되는 게이트, 드레인 전압으로 된다.

- [0340] 따라서, 기입 기간(321)에서, 트랜지스터(11a)의 게이트 전압은, 소스 신호선(18)의 전압이 영상 신호 전압 Vsig이었던 것으로 하면, (Vsigt1)로 된다. 여기서 Vt1은, 구동 트랜지스터(11a)에 전류원(312)의 전류 (Irst)를 흘렸을 때의 소스 드레인간 전압이며, 구동 트랜지스터(11a)의 특성에 따라 상이한 전압값으로 된다.

- [0341] 리세트 전류 Irst가 구동 트랜지스터(11a) 즉 EL 소자(15)에 흐를 때에는, 특성 변동을 보정한 전압이 구동 트랜지스터(11a)의 게이트 단자에 인가되어, 표시 불균일이 없는 EL 표시 장치를 실현할 수 있다.

- [0342] 종래의 구성에서는, Irst=0 즉 혹 표시 시에 완전하게 특성 변동을 보정하고, 전류가 증가함에 따라, 보정을 할 수 없는 이동도 변동에 기인하는 전류 변동이 발생하여, 고계조일수록 표시 불균일이 발생하기 쉬운 상황이었다.

- [0343] 표시 불균일은 회도가 낮을수록 시인하기 어렵고, 중간조~고계조에서는 시인하기 쉬운 성질이 있어, 계조 0에 상당하는 전류로 특성 보정을 행하는 것보다도, 시인하기 쉬운 중간~고계조에서의 보정이 바람직하다. 초기화용의 전류원의 출력 전류 Irst의 전류값을 중간~고계조로 설정하면, 시인되기 쉬운 계조에서의 표시 불균일을 우선하여 없앨 수 있다. 또한, 시인하기 어려운 계조에서는, 이동도 변동이 발생하는 구성이어도 보기 어려운 것을 이용하여, 전체 계조 영역에서의 표시 불균일 레벨의 향상을 실현할 수 있다. 본 실시예는, 구동 트랜지스터의 특성 변동의 캔슬 동작 중에 전류 Irst를 흘리고, 특성 캔슬이 가장 잘 행하여지는 전류 영역을 변경시킬 수 있게 한 것이 특징이다.

- [0344] 도 33의 회로는, 도 31의 구성에 대하여, 초기화용의 전압원(리세트 전압 Vrst를 출력)(331) 및 전압원(331)과 전류원(312)의 절환을 행하는 절환부(333)를 더 갖는 것이 특징이다. 이것은, 전류원(312)에 의해 트랜지스터(11a)의 전압을 변화시키는 경우에, 1프레임 전에 혹 표시를 한 화소이면, 구동 트랜지스터(11a)에 흐르는 전류가 Irst로 변화될 때까지 시간이 걸린다. 그 때문에, 기입 기간(321) 내에 구동 트랜지스터(11a)의 게이트 전압이 Vsigt1로 되기 어려운 문제를 해소하기 위해서이다.

- [0345] 구동 트랜지스터(11a)의 드레인 전류가 많을수록, 기입 기간(321)에서의 구동 트랜지스터(11a)의 게이트 전압을 변화시키기 쉽다. 전류가 많이 흐를수록, 유지용 컨덴서(19a)의 전하의 충방전 속도가 빨라지기 때문에, 게이트 전압이 변화되기 쉬워진다.

- [0346] 그래서, 게이트 전압의 변화 속도 향상을 목적으로 하여, 전압원(331)을 준비하고, 기입 기간(321)의 초기에, 전류원(312) 대신에, 저전압(백 표시일수록 저전압인 도 33의 회로 구성의 경우)의 전압을 구동 트랜지스터(11a)에 공급함으로써, 기입 기간(321)의 초기에 구동 트랜지스터(11a)의 드레인 전류가 많아지도록 하여, 남은 기간에서의, 리세트 전류원(312)에 의한 캔슬 동작을 고속화하도록 하였다.

- [0347] 도 34에 도 33의 회로 구성에서의 게이트 신호 및 절환 수단의 동작을 도시하였다. 기입 기간(321) 중 전압원이 공급되는 기간(341)에서, 구동 트랜지스터(11a)의 게이트 전압은 Vrst로 된다.

- [0348] 리세트 전압 Vrst는 낮은 전압일수록, 절환 수단(333)에 의해 전류원(312)으로 절환하였을 때의 게이트 전압의 변화를 고속화시키지만, 지나치게 저하하면, 소정 계조와의 게이트 전위의 차가 지나치게 커져, 소정값까지 전

암이 더이상 변화하지 못할 가능성이 있다.

[0349] 따라서, 리세트 전압  $V_{rst}$ 는, (백 표시 시의 전압)~(백 표시 시의 전압  $-5(V)$ ) 정도가 바람직하다. 계속되는 참조 부호 342의 기간에서, 전류원(312)과 기입되는 소스 신호선 전압  $V_{sig}$ 에 기초하여 게이트 전압이  $V_{sig}-V_{t1}$ 로 변화된다.

[0350] 이 때, 도 32의 구성에 비해, 트랜지스터(11a)의 드레인 전류가 많고, 축적 컨덴서(19)의 전하의 충방전 속도가 고속화되기 때문에,  $V_{sig}-V_{t1}$ 까지 변화되는 속도는, 전압 인가 기간(341)을 포함시켜도 고속화되어, 보다 단시간에서의 특성 보정이 가능하게 된다.

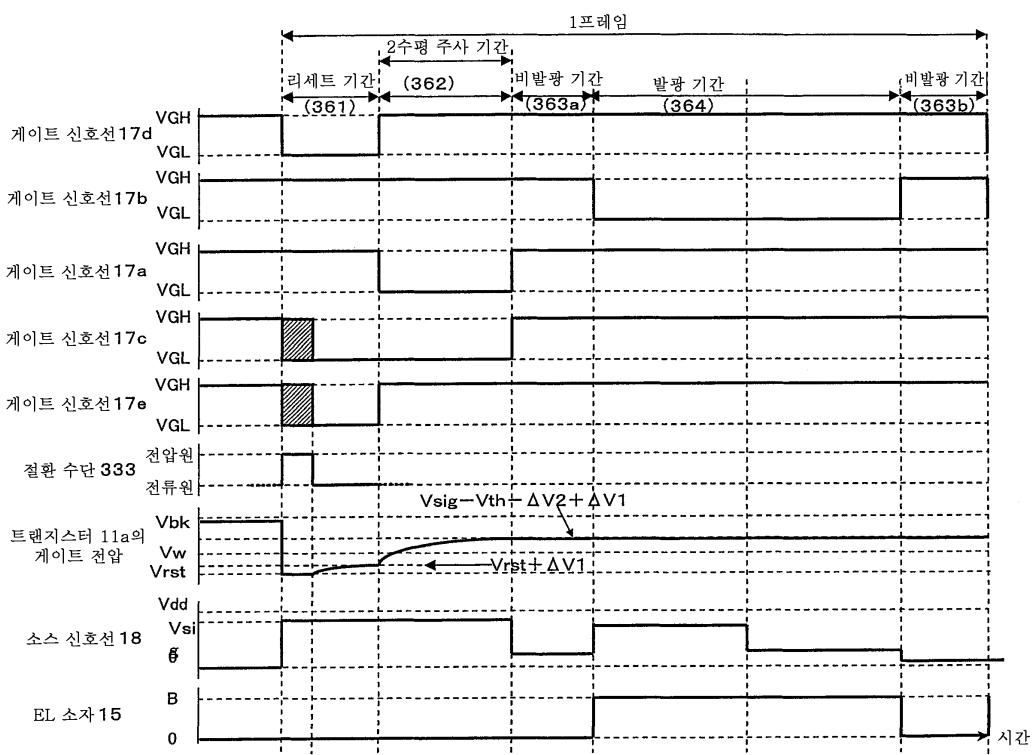

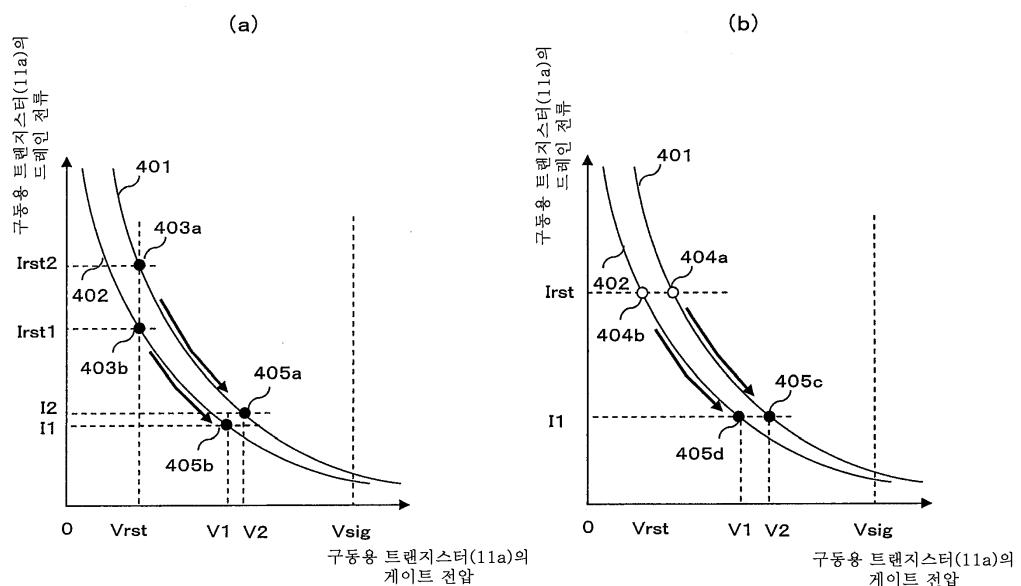

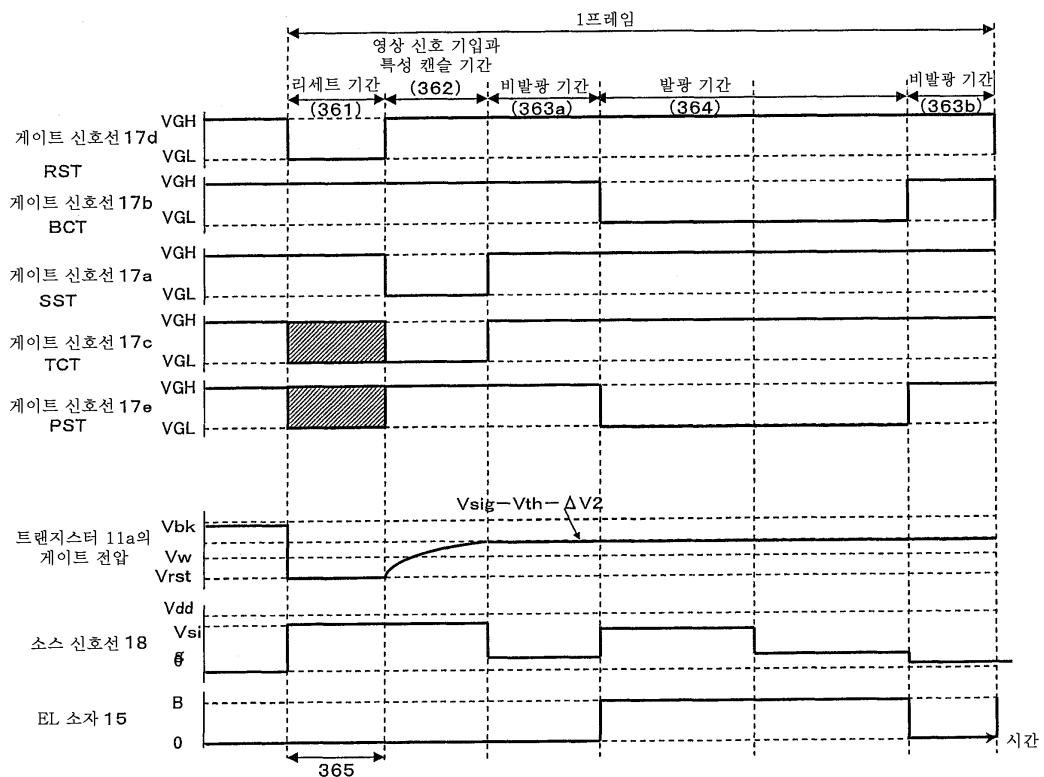

[0351] 도 35는 게이트 신호선을 트랜지스터(11e와 11d)에서 개별 제어로 한 회로 구성을 도시하고 있다. 1화소에서, 1프레임은, 리세트 기간(361), 영상 신호 기입과 특성 캔슬 기간(362), 비발광 기간(363), 발광 기간(364)으로 이루어진다.

[0352] 구동 트랜지스터(11a)의 초기화(리세트)를 행하는 전원이, 전압원(331), 전류원(312)의 2개가 있고, 전압원(331)이 인가되는 리세트 기간을 365, 전류원(312)이 인가되는 리세트 기간을 366으로 한다.

[0353] 또한, 리세트 기간(361)은 전류원(312)으로부터 출력되는 전류를 바탕으로 구동 트랜지스터(11a)를 초기화하고, 또한 동일 열에서 동일한 리세트선(311)을 이용하여 화소에 리세트 전압 및 전류를 기입하기 때문에, 1수평 주사 기간 이내에서 실시할 필요가 있다.