# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl. G09G 3/30 (2006.01) G09G 3/20 (2006.01) (45) 공고일자 2006년11월23일 (11) 등록번호 10-0646988

(24) 등록일자 2006년11월09일

(21) 출원번호10-2005-0080364(22) 출원일자2005년08월30일심사청구일자2005년08월30일

(65) 공개번호 (43) 공개일자

(73) 특허권자 삼성에스디아이 주식회사

경기 수원시 영통구 신동 575

(72) 발명자 엄기명

경기도 수원시 장안구 천천동 325-16번지 303호

(74) 대리인 신영무

(56) 선행기술조사문헌 JP08044302 A

JP62015982 A

JP11339491 A

\* 심사관에 의하여 인용된 문헌

심사관:최정윤

전체 청구항 수 : 총 5 항

#### (54) 구동회로 및 그를 이용한 유기 발광 표시장치

#### (57) 요약

본 발명의 목적은 오동작을 줄여 유기발광 표시장치의 화상의 품위를 더욱 높이도록 하며 배선수를 줄여 배선을 간단히 할수 있도록 하는 구동회로 및 유기 발광 표시장치를 제공하는 것이다.

본 발명은 제 1 신호를 입력받아 클럭신호와 부클럭신호를 생성하여 출력하는 복수의 로컬버퍼를 포함하는 버퍼부; 및 상기 2 개 이상의 로컬버퍼로부터 상기 클럭신호와 상기 부클럭신호를 전달받아 동작하는 복수의 플립플롭을 포함하는 시프트 레지스터을 구비하는 구동회로를 제공하는 것이다.

#### 대표도

도 2

#### 특허청구의 범위

#### 청구항 1.

제 1 신호를 입력받아 클럭신호와 부클럭신호를 생성하여 출력하는 복수의 로컬버퍼를 포함하는 버퍼부; 및

상기 2 개 이상의 로컬버퍼로부터 상기 클럭신호와 상기 부클럭신호를 전달받아 동작하는 복수의 플립플롭을 포함하는 시 프트 레지스터을 구비하는 구동회로.

#### 청구항 2.

제 1 항에 있어서,

상기 로컬버퍼에 적어도 두 개의 플립플롭이 연결되며 상기 두 개의 플립플롭은 클럭신호와 부클럭신호를 전달받는 동일 한 클럭선과 부클럭선이 연결되는 구동회로.

## 청구항 3.

제 1 항에 있어서,

상기 복수의 플립플롭은 동일한 클럭선과 부클럭선을 통해 상기 클럭신호와 상기 부클럭신호를 전달받아 구동하는 구동회로.

# 청구항 4.

주사신호와 데이터 신호를 전달받아 발광하는 화소를 포함하는 화소부;

상기 주사신호를 생성하여 상기 화소부에 전달하는 주사구동부; 및

상기 데이터 신호를 생성하여 상기 화소부에 전달하는 데이터 구동부를 포함하되.

상기 주사구동부는 시프트 레지스터 및 상기 시프트 레지스터에서 출력된 신호를 연산하는 연산부를 포함하며, 상기 시프 트레지스터는 상기 제 1 내지 제 3 항 중 하나의 구동회로인 유기발광표시장치.

# 청구항 5.

주사신호와 데이터 신호를 전달받아 발광하는 화소를 포함하는 화소부;

상기 주사신호를 생성하여 상기 화소부에 전달하는 주사구동부; 및

상기 데이터 신호를 생성하여 상기 화소부에 전달하는 데이터 구동부를 포함하되,

상기 데이터구동부는

순차적으로 시프트 신호를 생성하는 시프트 레지스터;

상기 시프트 신호에 의해 직렬로 입력되는 디지털 신호를 병렬로 출력하는 래치부; 및

상기 디지털 신호를 아날로그 신호로 전환하여 출력하는 D/A 컨버터를 포함하며,

상기 시프트 레지스터는 상기 제 1 내지 제 3 항 중 하나의 구동회로인 유기발광표시장치.

#### 명세서

## 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 구동회로 및 그를 이용한 유기 발광 표시장치에 관한 것으로, 더욱 상세히 설명하면, 크기가 작고 오동작이 방지되는 시프트 레지스터를 이용하는 구동회로 및 그를 이용한 유기 발광 표시장치에 관한 것이다.

퍼스널 컴퓨터, 휴대전화기, PDA 등의 휴대 정보단말기 등의 표시장치나 각종 정보기기의 모니터로서 박형 경량의 평판 표시장치가 이용되고 있다. 이러한 평판 표시장치에는 액정 패널을 이용한 LCD, 유기발광 소자를 이용한 유기발광 표시장 치, 플라즈마 패널을 이용한 PDP 등이 알려져 있다.

이러한 평판 표시장치는 기판 상에 매트릭스 형태로 복수의 화소를 배치하여 표시영역으로 하고, 각 화소에 주사선과 데이터선을 연결하여 화소에 데이터신호를 선택적으로 인가하여 디스플레이를 한다.

현재 평판 표시장치들 중에서 유기 발광 표시장치는 LCD 소자에 비해 약 30,000배 이상의 빠른 응답속도를 가지고 있어 동영상의 구현이 용이하고, 자체적으로 발광하여 휘도가 높고, 시야각이 넓은 장점이 있어 차세대 디스플레이로 주목받고 있다.

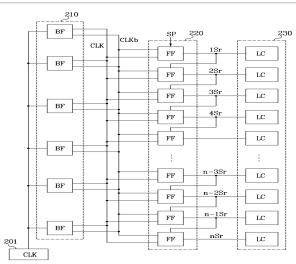

도 1은 종래 기술에 의한 주사구동부를 나타내는 구조도이다. 도 1을 참조하여 설명하면, 주사구동부는 시프트 레지스터 (20)와 시프트레지스터(20)에서 출력된 시프트 신호를 이용하여 주사신호를 생성하는 논리회로부(30)를 포함한다.

시프트레지스터(20)는 복수의 플립플롭(FF)이 위에서 아래로 배열되며 각 플립플롭(FF)은 클럭신호(CLK)와 부클럭신호 (CLKb)를 입력받아 동작한다. 플립플롭(FF)이 스타트 펄스(SP)를 입력받게 되면 클럭신호(CLK)와 부클럭신호(CLKb)에 의해 스타트 펄스(SP)와 동일한 주기를 갖는 제 1 시프트 신호(1sr)를 출력하게 된다. 그리고, 출력된 제 1 시프트 신호 (1sr)는 논리회로부(30)와 하위의 플립플롭(FF)에 전달된다.

하위의 플립플롭(FF)은 상위의 플립플롭(FF)에 입력되는 클럭신호(CLK)와 부클럭신호(CLKb)와 동일한 클럭신호(CLK)와 부클럭신호(CLKb)를 입력받아 동작하며 상위의 플립플롭(FF)에서 출력된 제 1 시프트신호(1sr)를 입력받아 제 2 시프트 신호(2sr)를 출력하게 된다. 따라서, 제 2 시프트 신호(2sr)는 제 1 시프트 신호(1sr)를 입력받은 후에 제 2 시프트 신호(2sr)를 출력하게 되므로, 제 2 시프트 신호(2sr)는 제 1 시프트 신호(1sr) 보다 늦게 출력된다. 이러한 방식으로, 복수의 시프트 신호가 순차적으로 발생하게 된다.

그리고, 시프트레지스터(20)에 입력되는 클럭신호(CLK)와 부클럭신호(CLKb)는 버퍼(10)에서 출력되어 시프트제지스터 (20)의 각 플립플롭(FF)에 입력된다.

논리회로부(30)는 복수의 논리회로(Logic circuit:LC)로 구성되며 시프트레지스터(20)에서 출력되는 복수의 시프트 신호를 연산하여 복수의 주사신호를 생성한다. 복수의 시프트 신호가 순차적으로 발생하게 되므로 복수의 주사신호 역시 순차적으로 발생하게 된다.

상기와 같이 구성된 주사구동부(200)는 클럭신호(CLK)와 부클럭신호(CLKb)를 출력하는 버퍼(10)에 많은 수의 플립플롭 (FF)이 연결되어 클럭신호(CLK)와 부클럭신호(CLKb)가 플리플롭(FF)에 정확한 신호로 입력되도록 하기 위해서는 버퍼 (10)의 크기가 크게 구현되어야 하는 문제점이 있으며, 버퍼(10)가 오동작을 하게 되면 클럭신호(CLK)와 부클럭신호 (CLKb)가 정확히 발생하지 않게 되어 주사구동부(200)가 정확한 동작을 하지 못하게 되는 문제점이 있다.

#### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명은 상기 종래 기술의 문제점을 해결하기 위하여 창출된 것으로, 본 발명의 목적은 오동작을 줄여 유기발광 표시장치의 화상의 품위를 더욱 높이도록 하며 배선수를 줄여 배선을 간단히 할 수 있도록 하는 구동회로 및 유기 발광 표시장치를 제공하는 것이다.

#### 발명의 구성

상기 본 발명의 목적을 달성하기 위하여 본 발명의 제 1 측면은, 제 1 신호를 입력받아 클럭신호와 부클럭신호를 생성하여 출력하는 복수의 로컬버퍼를 포함하는 버퍼부; 및 상기 2 개 이상의 로컬버퍼로부터 상기 클럭신호와 상기 부클럭신호를 전달받아 동작하는 복수의 플립플롭을 포함하는 시프트 레지스터을 구비하는 구동회로를 제공하는 것이다.

상기 본 발명의 목적을 달성하기 위하여 본 발명의 제 2 측면은, 주사신호와 데이터 신호를 전달받아 발광하는 화소를 포함하는 화소부; 상기 주사신호를 생성하여 상기 화소부에 전달하는 주사구동부; 및 상기 데이터 신호를 생성하여 상기 화소부에 전달하는 데이터 구동부를 포함하되, 상기 주사구동부는 시프트 레지스터 및 상기 시프트 레지스터에서 출력된 신호를 연산하는 연산부를 포함하며, 상기 시프트레지스터는 상기 제 1 측면의 구동회로인 유기발광표시장치를 제공하는 것이다.

상기 본 발명의 목적을 달성하기 위하여 본 발명의 제 3 측면은, 주사신호와 데이터 신호를 전달받아 발광하는 화소를 포함하는 화소부; 상기 주사신호를 생성하여 상기 화소부에 전달하는 주사구동부; 및 상기 데이터 신호를 생성하여 상기 화소부에 전달하는 데이터 구동부를 포함하되, 상기 데이터구동부는, 순차적으로 시프트 신호를 생성하는 시프트 레지스터; 상기 시프트 신호에 의해 직렬로 입력되는 디지털 신호를 병렬로 출력하는 래치부; 및 상기 디지털 신호를 아날로그 신호로 전환하여 출력하는 D/A 컨버터를 포함하며, 상기 시프트 레지스터는 상기 제 1 츠면의 구동회로인 유기발광표시장치를 제공하는 것이다.

이하, 본 발명의 실시예를 첨부한 도면을 참조하여 설명하면 다음과 같다.

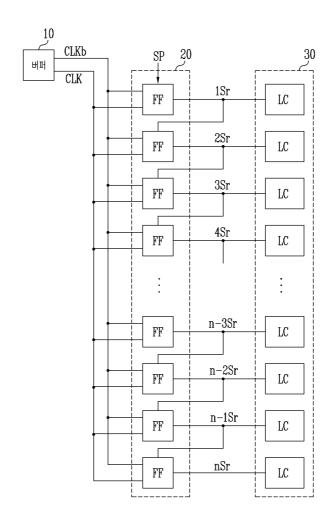

도 2는 본 발명에 따른 주사구동부(200)의 제 1 실시예를 나타내는 구조도이다. 도 2를 참조하여 설명하면, 주사구동부(200)는 버퍼부(210), 시프트레지스터(220) 및 연산부(230)를 포함한다.

버퍼부(210)는 복수의 로컬버퍼(BF)를 포함하며 하나의 로컬버퍼(BF)는 클럭신호 발생부(201)로부터 클럭신호(CLK)를 입력받아 클럭신호(CLK)와 부클럭신호(CLKb)를 생성한다. 즉, 하나의 클럭신호를 이용하여 클럭신호와 부클럭신호를 생성하게 되어 배선이 간단해 질 수 있게 된다. 그리고, 버퍼부(210)의 각 로컬버퍼(BF)에서 출력되는 클럭신호(CLK)들와 부클럭신호(CLKb)들은 각각 하나의 클럭신호선과 하나의 부클럭신호선에 입력된다. 따라서, 복수의 로컬버퍼(BF) 중 일부의 로컬버퍼(BF)에 고장이 발생하여도 다른 로컬버퍼(BF)에 의해 클럭신호선과 부클럭신호선에 클럭신호(CLK)와 부클럭신호(CLKb)가 입력되어 버퍼부(210)에서 출력되는 클럭신호(CLK)와 부클럭신호(CLKb)는 시프트 레지스터(220)정확히 입력될 수 있게 된다. 또한, 시프트 레지스터(220)에 복수의 로컬버퍼(BF)가 연결되어 각 로컬버퍼(BF)의 크기를 작게 구현하는 것이 가능하다.

시프트 레지스터(220)는 복수의 플립플롭(FF)이 위에서 아래로 배열되며 각 플립플롭(FF)은 클럭신호(CLK)와 부클럭신호(CLKb)를 입력받아 동작한다. 플립플롭(FF)이 스타트 펄스(SP)를 입력받게 되면 클럭신호(CLK)와 부클럭신호(CLKb)에 의해 스타트 펄스(SP)와 동일한 주기를 갖는 제 1 시프트 신호(1sr)를 출력하게 된다. 그리고, 출력된 제 1 시프트 신호(1sr)는 연산부(230)의 하나의 논리회로(LC)와 하위의 플립플롭(FF)에 전달된다.

하위의 플립플롭(FF)은 상위의 플립플롭(FF)에 입력되는 클럭신호(CLK)와 부클럭신호(CLKb)와 동일한 클럭신호(CLK)와 부클럭신호(CLKb)를 입력받아 동작하므로 상위의 플립플롭(FF)에서 출력된 제 1 시프트신호(1sr)를 입력받아 제 2 시프트 신호(2sr)를 출력하게 된다. 따라서, 제 2 시프트 신호(2sr)는 제 1 시프트 신호(1sr)를 입력받은 후에 제 2 시프트 신호(2sr)를 출력하게 되므로, 제 2 시프트 신호(2sr)는 제 1 시프트 신호(1sr)보다 늦게 출력된다. 이러한 방식으로, 복수의시프트 신호는 순차적으로 발생하게 된다.

시프트 레지스터(220)의 각 플립플롭(FF)은 복수의 로컬버퍼(BF)로부터 클럭신호(CLK)와 부클럭신호(CLKb)를 전달받게 되어 하나의 로컬버퍼(BF)가 동작을 중지하였어도 다른 로컬버퍼(BF)로 부터 클럭신호(CLK)와 부클럭신호(CLKb)를 전달받을 수 있어 시프트 레지스터(220)의 동작이 멈추지 않게 된다.

연산부(230)는 복수의 논리회로(LC)로 구성되며, 각 논리회로(LC)는 시프트 레지스터(220)에서 출력되는 시프트 신호를 연산하여 주사신호를 생성한다. 시프트 신호가 순차적으로 출력되므로 연산부(230)는 순차적으로 주사신호를 출력하여 일정한 주기로 주사신호가 순차적으로 출력되게 된다.

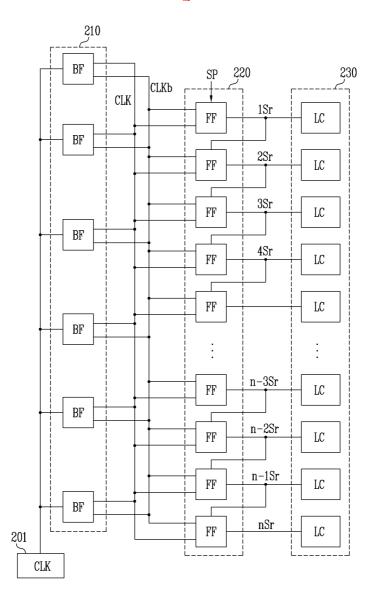

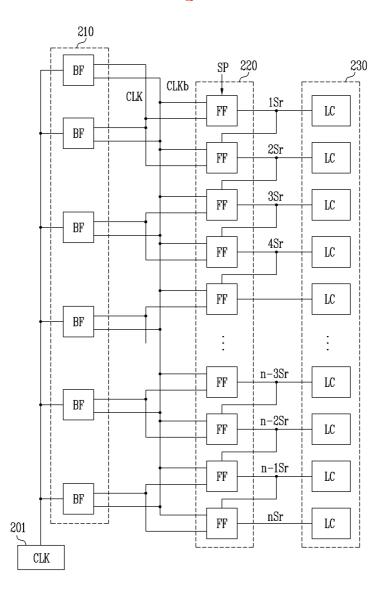

도 3은 본 발명에 따른 주사구동부(200)의 제 2 실시예를 나타내는 구조도이다. 도 3을 참조하여 설명하면, 주사구동부(200)는 버퍼부(210), 시프트 레지스터(220) 및 연산부(230)를 포함한다.

버퍼부(210)는 복수의 로컬버퍼(BF)를 포함하며 하나의 로컬버퍼(BF)는 클럭신호 발생부(201)로부터 클럭신호(CLK)를 입력받아 클럭신호(CLK)와 부클럭신호(CLKb)를 생성한다. 즉, 하나의 클럭신호를 이용하여 클럭신호와 부클럭신호를 생성하게 되어 배선이 간단해 질 수 있게 된다. 그리고, 버퍼부(210)의 각 로컬버퍼(BF)에서 출력되는 클럭신호(CLK)들와 부클럭신호(CLKb)들은 각각 하나의 클럭신호선과 하나의 부클럭신호선에 입력된다. 따라서, 복수의 로컬버퍼(BF) 중 일부의 로컬버퍼(BF)에 고장이 발생하여도 다른 로컬버퍼(BF)에 의해 클럭신호선과 부클럭신호선에 클럭신호(CLK)와 부클럭신호(CLKb)가 입력되어 버퍼부(210)에서 출력되는 클럭신호(CLK)와 부클럭신호(CLKb)는 정확히 입력될 수 있게 된다. 또한, 시프트 레지스터(220)에 복수의 로컬버퍼(BF)가 연결되어 각 로컬버퍼(BF)의 크기를 작게 구현하는 것이 가능하다.

시프트 레지스터(220)는 복수의 플립플롭(FF)이 위에서 아래로 배열되며 각 플립플롭(FF)은 클럭신호(CLK)와 부클럭신호(CLKb)를 입력받아 동작한다. 플립플롭(FF)이 스타트 펄스(SP)를 입력받게 되면 클럭신호(CLK)와 부클럭신호(CLKb)에 의해 스타트 펄스(SP)와 동일한 주기를 갖는 제 1 시프트 신호(1sr)를 출력하게 된다. 그리고, 출력된 제 1 시프트 신호(1sr)는 논리회로(LC)와 하위의 플립플롭(FF)에 전달된다.

하위의 플립플롭(FF)은 상위의 플립플롭(FF)에 입력되는 클럭신호(CLK)와 부클럭신호(CLKb)와 동일한 클럭신호(CLK)와 부클럭신호(CLKb)를 입력받아 동작하며 상위의 플립플롭(FF)에서 출력된 제 1 시프트신호(1sr)를 입력받아 제 2 시프트 신호(2sr)를 출력하게 된다. 따라서, 제 2 시프트 신호(2sr)는 제 1 시프트 신호(1sr)를 입력받은 후에 제 2 시프트 신호(2sr)를 출력하게 되므로, 제 2 시프트 신호(2sr)는 제 1 시프트 신호(1sr)보다 늦게 출력된다. 이러한 방식으로, 복수의 시프트 신호는 순차적으로 발생하게 된다.

시프트 레지스터(220)의 각 플립플롭은 복수의 로컬버퍼(BF)로부터 클럭신호(CLK)와 부클럭신호(CLKb)를 전달받게 되어 하나의 로컬버퍼(BF)가 동작을 중지하였어도 다른 로컬버퍼(BF)로부터 클럭신호(CLKb)와 부클럭신호(CLKb)를 전달받을 수 있어 시프트 레지스터(220)의 동작이 로컬버퍼(BF)멈추지 않게 된다.

연산부(230)는 복수의 논리회로(LC)를 포함하며, 각 논리회로(LC)는 시프트 레지스터(220)에서 출력되는 시프트 신호를 연산하여 주사신호를 생성한다. 시프트 신호가 순차적으로 출력되므로 논리회로(LC)는 시프트 신호를 순차적으로 받아 연산하여 주사신호를 생성하며 일정한 주기로 주사신호가 순차적으로 출력되게 된다.

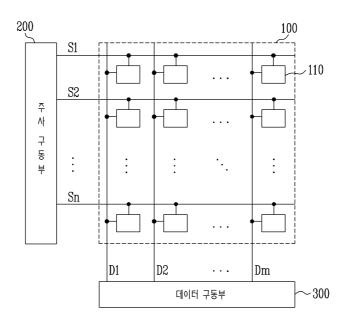

도 4는 도 2 또는 도 3에 도시된 주사구동부가 채용된 유기 발광표시장치의 구조를 나타내는 구조도이다. 도 4를 참조하여 설명하면, 유기 발광표시장치는 화소부(100), 주사구동부(200) 및 데이터 구동부(300)를 포함한다.

화소부(100)는 n×m 화소(110)가 배열되고 각 화소(110)는 화소회로와 유기발광소자(Organic Light Eitting Divice:OLED)가 포함된다. 그리고, 행방향으로 형성되며 주사신호를 전달하는 n 개의 주사선(S1,S2,...Sn)과 열방향으로 형성되며 데이터신호를 전달하는 m 개의 데이터선(D1, D2,....Dm)이 배열된다. 그리고, 화소전원을 전달하는 전원 공급선 (미도시)이 배열된다. 화소부(100)는 주사신호, 데이터신호 및 화소전원에 의해 유기발광소자(OLED)가 발광하여 화상을 표시하다.

주사구동부(200)는 주사신호를 출력하는 수단으로, 주사신호에 의해 화소(110)가 선택되어 데이터 구동부(300)에서 입력되는 데이터 신호가 선택된 화소(110)에 인가되도록 한다. 이때, 주사구동부(200)는 도 2 또는 도 3에 도시된 주사구동부(200)를 채용하여 주사구동부(200)의 오동작을 방지하도록 한다.

데이터 구동부(300)는 화소부(100)에 데이터 신호를 인가하는 수단으로, 데이터 구동부(300)가 화소부(100)의 데이터선 (D1, D2,....Dm-1, Dm)과 연결되어 데이터 신호가 화소(110)에 인가된다.

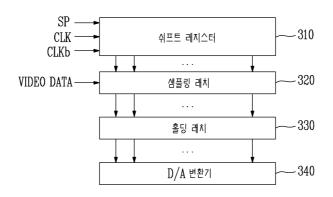

도 5는 도 4에 도시된 유기발광표시장치에서 채용된 데이터 구동부의 구조를 나타내는 구조도이다. 도 5를 참조하여 설명하면, 데이터 구동부(300)는 시프트 레지스터(310), 샘플링 래치(320), 홀딩 래치(330) 및 D/A 컨버터(340)를 포함한다.

시프트 레지스터(310)는 복수의 플리 플롭으로 구성되며, 클럭신호(CLK), 부클럭신호(CLKb)와 동기신호에 대응하여 샘플링 래치(320)를 제어한다. 샘플링 래치(50)는 시프팅 레지스터(40)의 제어 신호에 따라 한 행분의 데이터 신호를 순차적으로 입력받아 병렬적으로 출력하는 방식을 SIPO(Serial In Parallel Out)이라고 한다. 그리고, 홀딩 래치(330)는 신호를 병렬적으로 입력받고 다시 병렬적으로 출력한다. 병렬로 입력받아 병렬로 출력하는 방식을 PIPO(Parallel In Parallel Out)이라고 한다. D/A 컨버터(340)는 디지털 신호로 입력되는 데이터 신호를 아날로그 신호로 출력한다.

상기와 같이 구현된 데이터 구동부(300)에서 도 2 또는 도 3에 도시된 시프트 레지스터를 채용하여 데이터 구동부(300)를 구현하는 것도 가능하다.

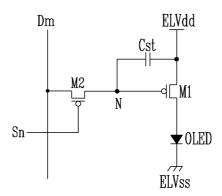

도 6은 도 4에 채용된 화소부의 화소를 나타내는 회로도이다. 도 6을 참조하여 설명하면, 화소(110)는 발광소자(Organic Light Emitting Device: OLED), 제 1 트랜지스터(M1), 제 2 트랜지스트(M2) 및 캐패시터(Cst)를 포함한다. 그리고, 주사선(Sn), 데이타선(Dm) 및 전원배선(ELVdd)이 화소(110)에 연결된다. 주사선(Sn)은 행 방향으로 형성되고, 데이터선 (Dm) 및 전원선(ELVdd)은 열 방향으로 형성된다.

제 1 트랜지스터(M1)는 소스는 전원선(ELVdd)에 연결되고 드레인은 발광소자(OLED)에 연결되며 게이트는 제 1 노드 (N)에 연결되어 게이트의 전압에 따라 소스에서 드레인 방향으로 흐르는 전류량을 조절한다.

제 2 트랜지스터(M2)는 소스는 데이터선(Dm)에 연결되고 드레인은 제 1 노드(N)에 연결되며 게이트는 주사선(Sn)에 연결되어 주사선(Sn)을 통해 전달되는 주사신호에 의해 데이터선(Dm)을 통해 전달되는 데이터신호를 제 1 노드(N)에 전달한다.

캐패시터(Cst)는 제 1 전극은 전원선(ELVdd)에 연결되고 제 2 전극은 제 1 노드(N)에 연결되어 제 1 트랜지스터(M1)의 소스와 게이트의 전압을 일정시간 동안 유지시켜 게이트의 전압이 데이터신호를 유지하도록 한다.

상기와 같은 구성으로 인하여, 제 2 트랜지스터(M2)에 의해 데이터신호가 제 1 트랜지스터(M1) 게이트에 전달되어 제 1 트랜지스터(M1)는 데이터신호에 대응한 전류를 유기발광소자(OLED)에 흐르도록 한다.

본 발명의 바람직한 실시예가 특정 용어들을 사용하여 기술되어 왔지만, 그러한 기술은 단지 설명을 하기 위한 것이며, 다음의 청구범위의 기술적 사상 및 범위로부터 이탈되지 않고 여러 가지 변경 및 변화가 가해질 수 있는 것으로 이해되어져야 한다.

#### 발명의 효과

본 발명에 따른 구동회로 및 그를 이용한 유기 발광 표시장치에 의하면, 시프트 레지스터가 버퍼의 오동작 발생시에 다른 버퍼에 의해 정상적인 신호를 전달받아 신호를 생성할 수 있어 구동회로의 오동작을 방지할 수 있어 유기 발광 표시장치의 오동작을 방지할 수 있다.

#### 도면의 간단한 설명

도 1은 종래 기술에 의한 주사구동부를 나타내는 구조도이다.

도 2는 본 발명에 따른 주사구동부의 제 1 실시예를 나타내는 구조도이다.

도 3은 본 발명에 따른 주사구동부의 제 2 실시예를 나타내는 구조도이다.

도 4는 본 발명에 따른 유기 발광표시장치의 구조를 나타내는 구조도이다.

도 5는 도 4의 유기 발광표시장치에서 채용된 데이터 구동부를 나타내는 구조도이다.

도 6은 도 4의 유기 발광표시장치에서 채용된 화소의 구조를 나타내는 회로도이다.

\*\*\*도면의 주요부분에 대한 부호 설명\*\*\*

100: 화소부 101: 화소

200: 주사구동부 201: 클럭발생부

210: 버퍼부 220: 시프트레지스터

230: 연산부 300: 주사구동부

# 도면

도면4

# 도면5

| 专利名称(译)       | 驱动电路和使用其的有机发光显示器                                 |         |            |  |

|---------------|--------------------------------------------------|---------|------------|--|

| 公开(公告)号       | KR100646988B1                                    | 公开(公告)日 | 2006-11-23 |  |

| 申请号           | KR1020050080364                                  | 申请日     | 2005-08-30 |  |

| 申请(专利权)人(译)   | 三星SD眼有限公司                                        |         |            |  |

| 当前申请(专利权)人(译) | 三星SD眼有限公司                                        |         |            |  |

| [标]发明人        | EOM KI MYEONG                                    |         |            |  |

| 发明人           | EOM,KI MYEONG                                    |         |            |  |

| IPC分类号        | G09G3/30 G09G3/20                                |         |            |  |

| CPC分类号        | G09G3/3266 G09G2310/0286 G09G2310/08 G09G2320/02 |         |            |  |

| 代理人(译)        | SHIN , YOUNG MOO                                 |         |            |  |

| 外部链接          | Espacenet                                        |         |            |  |

|               |                                                  |         |            |  |

#### 摘要(译)

提供一种驱动电路和使用该驱动电路的有机发光显示装置,以通过在错误地操作一个缓冲器时通过从另一缓冲器接收正常信号来产生具有移位寄存器的信号来防止驱动电路的故障。驱动电路包括缓冲单元(210),其具有用于通过接收第一信号来产生和输出时钟信号(CLK)和子时钟信号(CLKb)的本地缓冲器(BF),以及具有翻转的移位寄存器(220)。触发器(FF)通过从至少两个本地缓冲器接收时钟信号和子时钟信号来操作。至少两个触发器连接到本地缓冲器。两个触发器与接收时钟信号和子时钟信号的相同时钟线和子时钟线耦合。