(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) . Int. Cl.

*H05B 33/26* (2006.01)

*H05B 33/10* (2006.01)

(11) 공개번호 10-2007-0057366

(43) 공개일자 2007년06월07일

(21) 출원번호 10-2005-0116745

(22) 출원일자 2005년12월02일

심사청구일자 없음

(71) 출원인 오리온오엘아이 주식회사

경북 구미시 공단동 257번지

(72) 발명자 박성현

경남 창원시 남양동 성원2차아파트 210-1505

(74) 대리인 김영철

전체 청구항 수 : 총 4 항

(54) 유기전계 발광장치용 패널유닛 및 그 분리방법

(57) 요약

본 발명은 유기전계 발광장치용 패널유닛 및 그 분리방법에 관한 것으로, 본 발명에서는 앞 열의 각 기판셀들이 자가 전극 패턴들의 일부를 자체영역이 아니라, 그 뒤 열에 일대일 대응 배치된 다른 기판셀들의 일부로 연장 형성시키고, 이를 통해, 각 기판셀들이 별도의 자체영역 배려 없이, 단지, 뒤 열 기판셀들의 일부영역을 대체 활용하여, 자신에게 필요한 에이징/테스트 처리용 공통전극의 배치공간을 융통성 있게 확보할 수 있도록 유도함으로써, 각 기판셀들이 추가영역 폐기/소모 등의 불필요한 자재낭비 문제점을 유발하지 않고서도, 상호 분리되지 않은 전체시트 상태에서, 일련의 에이징 절차, 테스트 절차를 정상적으로 수행 받을 수 있도록 유도할 수 있다.

또한, 본 발명에서는 각 기판셀들의 전극패턴 일부를 자체영역이 아니라, 그 뒤 열에 일대일 대응 배치된 다른 기판셀들의 일부로 연장 형성시키는 조치를 통해, 각 기판셀들이 별다른 자재낭비 유발 없이, 전체시트 상태에서, 일련의 에이징 절차, 테스트 절차를 수행 받을 수 있도록 유도함으로써, 생산자 측에서, 하나의 모 기판에서 생산할 수 있는 기판셀들의 숫자가 줄어드는 피해를 손쉽게 피하면서도, 전체적인 에이징 효율성, 테스트 효율성, 제품 생산성 등이 일정 수준 이상으로 향상되는 효과를 자연스럽게 향유할 수 있도록 가이드 할 수 있다.

대표도

도 4

특허청구의 범위

청구항 1.

## 모 기판과;

상기 모 기판의 상부에 행렬로 연속 배열되면서, 표시영역의 운용을 위한 전극패턴들을 각기 구비하는 다수의 기판셀들을 포함하며,

상기 기판셀들 중, 앞 열의 각 기판셀들에 구비된 전극패턴들은 그 뒤 열에 각기 일대일 대응 배치된 다른 기판셀들의 일부 까지 연장 형성되는 것을 특징으로 하는 유기전계 발광장치용 패널유닛.

## 청구항 2.

제 1 항에 있어서, 상기 뒤 열 기판셀들의 일부까지 연장 형성된 상기 앞 열 기판셀들의 전극패턴들은 상기 앞 열 기판셀들의 에이징 절차(Aging process) 또는 검사 절차(Inspection process)를 위한 공통전극(Common electrode)으로 작용하는 것을 특징으로 하는 유기전계 발광장치용 패널유닛.

## 청구항 3.

제 2 항에 있어서, 상기 뒤 열 기판셀들의 일부까지 연장된 상기 앞 열 기판셀들의 전극패턴들은 상기 에이징 절차 또는 검사 절차를 위한 치구의 사이즈에 상응하는 규모로, 상기 뒤 열 기판셀들의 일부를 선택적으로 점유하는 것을 특징으로 하는 유기전계 발광장치용 패널유닛.

## 청구항 4.

모 기판의 상부에, 표시영역의 운용을 위한 전극패턴들을 각기 구비한 다수의 기판셀들을 행렬로 연속 배열시킨 상태에서, 상기 모 기판으로부터 상기 기판셀들을 분리하는 유기전계 발광장치용 패널유닛의 분리방법에 있어서,

상기 각 기판셀들 중, 앞 열의 각 기판셀들에 구비된 전극패턴들을 그 뒤 열의 기판셀들 일부까지 연장 형성시킨 상태로, 상기 앞 열 기판셀들의 전극패턴들이 상기 뒤 열 기판셀들의 일부에 최종 잔류하도록 상기 모 기판으로부터 상기 기판셀들을 잘라내는 것을 특징으로 하는 유기전계 발광장치용 패널유닛의 분리방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 유기전계 발광장치에 채용되는 패널유닛에 관한 것으로, 좀더 상세하게는 각 기판셀들의 전극패턴 일부를 자체 영역이 아니라, 그 뒤 열에 일대일 대응 배치된 다른 기판셀들의 일부로 연장 형성시키는 조치를 통해, 각 기판셀들이 별다른 자재낭비 유발 없이, 전체시트 상태에서, 일련의 에이징 절차, 테스트 절차를 수행 받을 수 있도록 유도함으로써, 생산자 측에서, 하나의 모 기판에서 생산할 수 있는 기판셀들의 숫자가 줄어드는 피해를 손쉽게 피하면서도, 전체적인 에이징 효율성, 테스트 효율성, 제품 생산성 등이 일정 수준 이상으로 향상되는 효과를 자연스럽게 향유할 수 있도록 가이드 할 수 있는 유기전계 발광장치용 패널유닛에 관한 것이다. 또한, 본 발명은 이러한 유기전계 발광장치용 패널유닛을 분리하는 유기전계 발광장치용 패널유닛의 분리방법에 관한 것이다.

최근, 전자·전기기기에 대한 수요가 급증하면서, 플라즈마 표시장치, 액정 표시장치, 유기전계 발광장치 등과 같은 각종 평판 표시장치의 기능 또한 급격한 발전을 거듭하고 있다.

이러한 종래의 여러 평판 표시장치들 중, 특히, 유기전계 발광장치는 가시광선 내 모든 영역의 빛을 표시할 수 있다는 장점, 높은 휙도 및 낮은 동작 전압 특성을 가진다는 장점, 명암대비(Contrast ratio)가 크다는 장점, 공정이 간단하여 환경오염이 비교적 적다는 장점, 응답시간이 빠르다는 장점, 시야각의 제한이 없으며, 저온에서도 안정적으로 동작한다는 장점, 구동회로의 제작 및 설계가 용이하다는 장점 등을 두루 갖추고 있기 때문에, 근래에, 차세대를 이끌어갈 대표적인 평판 표시장치로써 큰 주목을 받고 있다.

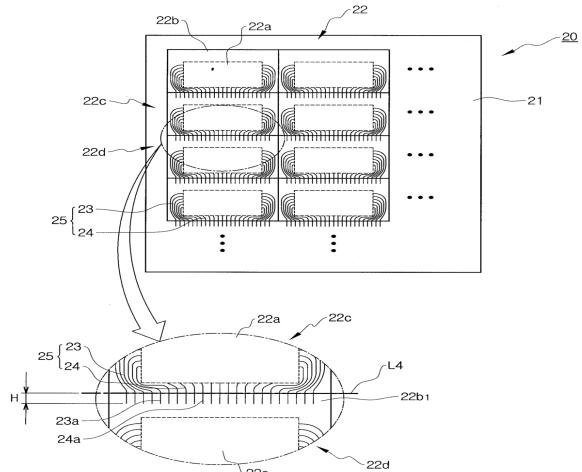

통상, 이러한 종래의 기술에 따른 유기전계 발광장치에 채용되는 패널유닛(10)은 도 1에 도시된 바와 같이, 예컨대, 유리재질의 모 기판(1)과, 이 모 기판(1)의 상부에 행렬을 이루면서, 앞뒤로 연속 배열된 다수의 기판셀들(2)이 조합된 구성을 취하게 된다. 이 경우, 각 기판셀들(2)은 화소 매트릭스를 구비하여, 일련의 화상정보를 표시할 수 있는 표시영역(2a)과, 이 표시영역(2a)을 제외한 비 표시 영역(2b)으로 나뉘게 된다.

이때, 각 기판셀들(2)에는 화소 매트릭스와 전기적으로 연결되는 구조를 취하면서, 화소 매트릭스의 발광상태 조절을 위한 각종 신호, 예컨대, 스캔 신호, 데이터 신호를 화소 매트릭스 측으로 전달하여, 표시영역(2a)의 화상 표시상태를 선택적으로 운용하는 전극패턴들(5)이 추가 배치된다.

이 경우, 전극패턴들(5)은 스캔 신호의 전달을 위한 스캔 전극패턴들(3) 및 데이터 신호의 전달을 위한 데이터 전극패턴들(4)이 상호 유기적으로 조합된 구성을 취하게 된다.

이러한 구조 하에서, 추후, 각 기판셀들(2)은 커팅절차(Cutting process)를 통해, 모 기판(1)으로부터 분리되어, 개별 제품으로 나뉜 후, 일련의 구동 IC 장착과정을 거쳐, 후속공정으로 출하되는 과정을 겪게 된다.

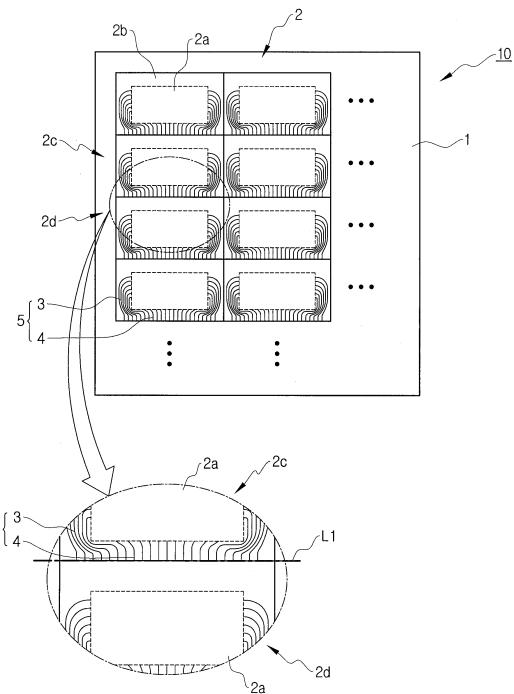

이때, 생산자 측에서는 커팅라인(L1)을 따라, 앞 열 기판셀(2c)을 잘라냄으로써, 도 2에 도시된 바와 같이, 앞 열 기판셀(2c:물론, 이러한 앞 열 기판셀은 자신의 앞에 배치된 기판셀을 상대로 볼 때에는 뒤 열 기판셀에 해당함) 및 뒤 열 기판셀(2d:물론, 이러한 뒤 열 기판셀은 자신의 뒤에 배치된 기판셀을 상대로 볼 때에는 앞 열 기판셀에 해당함)을 서로 분리하는 절차를 진행하게 된다(이 경우, 도 2에 도시된 각 기판셀들의 영역 A는 예컨대, 구동 IC의 장착부위로 작용하게 됨).

한편, 이러한 분리절차 후, 생산자 측에서는 에이징 툴(Aging tool), 테스트 툴(Test tool)의 각 치구(예컨대, 에이징 탐침, 테스트 탐침 등)를 기판셀들(2)의 전극패턴(5) 일부에 접촉시켜, 일련의 에이징 절차(Aging process), 테스트 절차(Test process) 등을 진행시키고, 이를 통해, 최종 출하되는 제품이 일정 수준 이상의 신뢰성을 정상적으로 유지할 수 있도록 유도하게 된다.

그러나, 이처럼, 일련의 에이징 절차, 테스트 절차가 각 기판셀들(2)의 분리절차 다음에, 후속 진행되는 경우, 생산자 측에서는 각 기판셀들(2)을 <모 기판(1)을 포함한 전체시트(Full sheet) 상태>로 다루지 못하고, <낱개의 독립개체>로 일일이 다루어야하기 때문에, 그 핸들링에 있어, 큰 불편함을 고스란히 겪을 수밖에 없게 되며, 결국, 전체적인 에이징 효율성, 테스트 효율성 등이 크게 떨어지는 피해를 피할 수 없게 된다.

더욱이, 상술한 에이징 절차, 테스트 절차 등의 진행 상황에서, 만약, 특정 기판셀(2)이 불량 기판셀로 판정되는 경우, 생산자 측에서는 많은 시간과 노력을 드려, 해당 기판셀(2)을 이미 커팅 완료하거나, 구동 IC를 이미 부착하였음에도 불구하고, 별 수 없이, 이들을 폐기처리 하여야 하는 어려움을 겪을 수밖에 없게 되며, 결국, 전체적인 제품 생산효율이 크게 떨어지거나, 생산비가 대폭 증가하는 등의 막대한 피해를 고스란히 감수할 수밖에 없게 된다.

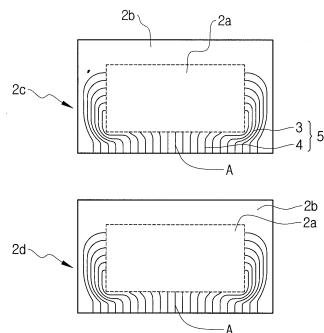

근래에, 이러한 문제점을 해결하기 위한 일 대안으로, 도 3에 도시된 바와 같이, 앞 열 기판셀들(2c)의 자체영역을 D 만큼 더 배려하여, 전극패턴들(5)이 그에 상응하는 길이증가를 이루도록 하고, 이를 통해, 해당 전극패턴들(5)이 예컨대, 에이징 탐침, 테스트 탐침 등과 접촉이 가능할 정도의 규모를 자연스럽게 형성할 수 있도록 유도하는 방안이 유력하게 대두되고 있다.

물론, 이처럼, 앞 열 기판셀들(2c)의 자체영역이 D 만큼 증가하고, 그 결과로, 전극패턴들의 연장부위(3a,4a)가 앞 열 기판셀들(2c)의 에이징 처리, 테스트 처리 등을 위한 공통전극(Common electrode)으로 활용될 수 있게 되는 경우, 앞의 경우와 달리, 각 기판셀들(2)은 상호 분리되지 않은 전체시트 상태에서도, 일련의 에이징 절차, 테스트 절차를 정상적으로 수행 받을 수 있게 된다.

그러나, 이러한 대체방안의 경우, 일련의 에이징 절차, 테스트 절차 등을 전체시트 상태에서 진행시킬 수 있는 이점을 제공하기는 하지만, 기본적으로, 전극패턴들의 연장부위(3a,4a)가 어차피, 앞 열 기판셀들(2c)의 자가영역(2b1)에 위치하고

있다는 편이 못 할 한계를 지니고 있기 때문에, 앞의 대안이 채용된 상황에서, 생산자가 별다른 조치 없이, 커팅라인(L2,L3)을 따라, 앞 열의 기판셀(2c)을 잘라내는 방식을 고수하게 되는 경우, 앞 열 기판셀(2c)은 예컨대, D 만큼의 자가영역(2b1)이 불필요하게 폐기되는 문제점을 항상 겪을 수밖에 없게 되며, 별도의 대처방안 없이, 이러한 메커니즘이 모 기판(1) 전체로 확대되는 경우, 그 여파로, 생산자 측에서는 전체적인 자재낭비가 심해져, 하나의 모 기판(1)에서 생산할 수 있는 기판셀들(2)의 숫자가 크게 줄어드는 문제점을 고스란히 감수할 수밖에 없게 된다.

물론, 커팅라인(L2)만을 따라, 앞 열의 기판셀(2c)을 잘라내어, D 만큼의 자가영역(2b1)을 앞 열의 기판셀들(2c)에 잔류시키는 경우에도, 앞 열 기판셀들(2c)은 D 만큼의 자가영역(2b1)을 불가피하게 소모하는 또 다른 문제점을 유발하게 되며, 결국, 이러한 메커니즘이 모 기판(1) 전체로 확대되는 경우에도, 생산자 측에서는 전체적인 자재낭비가 심해져, 하나의 모 기판(1)에서 생산할 수 있는 기판셀들(2)의 숫자가 크게 줄어드는 문제점을 고스란히 감수할 수밖에 없게 된다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명의 목적은 앞 열의 각 기판셀들이 자가 전극패턴들의 일부를 자체영역이 아니라, 그 뒤 열에 일대일 대응 배치된 다른 기판셀들의 일부로 연장 형성시키고, 이를 통해, 각 기판셀들이 별도의 자체영역 배려 없이, 단지, 뒤 열 기판셀들의 일부영역을 대체 활용하여, 자신에게 필요한 에이징/테스트 처리용 공통전극의 배치공간을 융통성 있게 확보할 수 있도록 유도함으로써, 각 기판셀들이 추가영역 폐기/소모 등의 불필요한 자재낭비 문제점을 유발하지 않고서도, 상호 분리되지 않은 전체시트 상태에서, 일련의 에이징 절차, 테스트 절차를 정상적으로 수행 받을 수 있도록 유도하는데 있다.

본 발명의 다른 목적은 각 기판셀들의 전극패턴 일부를 자체영역이 아니라, 그 뒤 열에 일대일 대응 배치된 다른 기판셀들의 일부로 연장 형성시키는 조치를 통해, 각 기판셀들이 별다른 자재낭비 유발 없이, 전체시트 상태에서, 일련의 에이징 절차, 테스트 절차를 수행 받을 수 있도록 유도함으로써, 생산자 측에서, 하나의 모 기판에서 생산할 수 있는 기판셀들의 숫자가 줄어드는 피해를 손쉽게 피하면서도, 전체적인 에이징 효율성, 테스트 효율성, 제품 생산성 등이 일정 수준 이상으로 향상되는 효과를 자연스럽게 향유할 수 있도록 가이드 하는데 있다.

본 발명의 또 다른 목적들은 다음의 상세한 설명과 첨부된 도면으로부터 보다 명확해질 것이다.

### 발명의 구성

상기와 같은 목적을 달성하기 위하여 본 발명에서는 모 기판과, 상기 모 기판의 상부에 행렬로 연속 배열되면서, 표시영역의 운용을 위한 전극패턴들을 각기 구비하는 다수의 기판셀들을 포함하며, 상기 기판셀들 중, 앞 열의 각 기판셀들에 구비된 전극패턴들은 그 뒤 열에 각기 일대일 대응 배치된 다른 기판셀들의 일부까지 연장 형성되는 것을 특징으로 하는 유기전계 발광장치용 패널유닛을 개시한다.

또한, 본 발명의 다른 측면에서는 모 기판의 상부에, 표시영역의 운용을 위한 전극패턴들을 각기 구비한 다수의 기판셀들을 행렬로 연속 배열시킨 상태에서, 상기 모 기판으로부터 상기 기판셀들을 분리하는 유기전계 발광장치용 패널유닛의 분리방법에 있어서, 상기 각 기판셀들 중, 앞 열의 각 기판셀들에 구비된 전극패턴들을 그 뒤 열의 기판셀들 일부까지 연장 형성시킨 상태로, 상기 앞 열 기판셀들의 전극패턴들이 상기 뒤 열 기판셀들의 일부에 최종 잔류하도록 상기 모 기판으로부터 상기 기판셀들을 잘라내는 것을 특징으로 하는 유기전계 발광장치용 패널유닛의 분리방법을 개시한다.

이하, 첨부된 도면을 참조하여, 본 발명에 따른 유기전계 발광장치용 패널유닛 및 그 분리방법을 좀더 상세히 설명하면 다음과 같다.

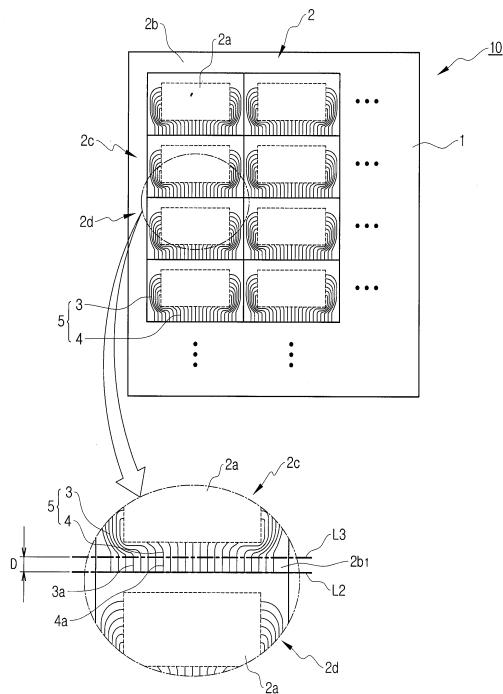

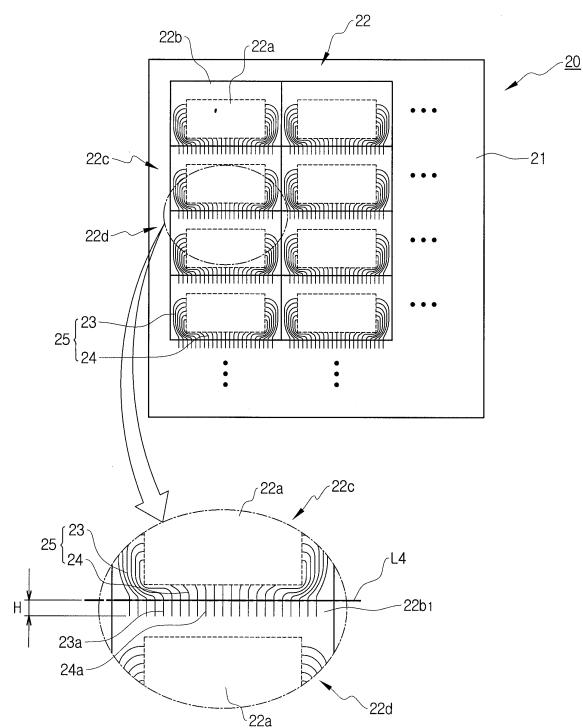

도 4에 도시된 바와 같이, 본 발명에 따른 유기전계 발광장치용 패널유닛(20)은 예컨대, 유리재질의 모 기판(21)과, 이 모 기판(21)의 상부에 행렬을 이루면서, 앞뒤로 연속 배열된 다수의 기판셀들(22)이 조합된 구성을 취하게 된다. 이 경우, 각 기판셀들(22)은 화소 매트릭스를 구비하여, 일련의 화상정보를 표시할 수 있는 표시영역(22a)과, 이 표시영역(22a)을 제외한 비 표시 영역(22b)으로 나뉘게 된다.

이때, 각 기판셀들(22)에는 화소 매트릭스와 전기적으로 연결되는 구조를 취하면서, 화소 매트릭스의 발광상태 조절을 위한 각종 신호, 예컨대, 스캔 신호, 데이터 신호를 화소 매트릭스 측으로 전달하여, 표시영역(22a)의 화상 표시상태를 선택적으로 운용하는 전극패턴들(25)이 추가 배치된다. 이 경우, 전극패턴들(25)은 스캔 신호의 전달을 위한 스캔 전극패턴들(23) 및 데이터 신호의 전달을 위한 데이터 전극패턴들(24)이 상호 유기적으로 조합된 구성을 취하게 된다.

이러한 구조 하에서, 도면에 도시된 바와 같이, 본 발명에서는 앞 열의 각 기판셀들(22c:물론, 이러한 앞 열 기판셀들은 자신의 앞에 배치된 기판셀들을 상대로 볼 때에는 뒤 열 기판셀들에 해당함)의 전극패턴들(25)로부터 연장된 연장패턴(23a,24a)을 자체영역이 아니라, 그 뒤 열에 각기 일대일 대응 배치된 뒤 열 기판셀들(22d:물론, 이러한 뒤 열 기판셀들은 자신의 뒤에 배치된 기판셀들을 상대로 볼 때에는 앞 열 기판셀들에 해당함)의 일부로 연장 형성시키는 조치를 강구한다.

물론, 이러한 조치 하에서, 각 앞열 기판셀들(22c)은 별도의 자체영역 배려 없이도, 단지, 뒤 열 기판셀들(22d)의 일부영역(22b1)을 대체 활용하여, 연장패턴(23a,24a)의 배치공간을 효과적으로 확보할 수 있게 되며, 이 연장패턴(23a,24a)을 자신에게 필요한 에이징/테스트 처리용 공통전극으로 융통성 있게 활용할 수 있게 된다.

이 경우, 뒤 열 기판셀들(22d)의 일부까지 연장된 앞 열 기판셀들(22c)의 연장패턴(23a,24a)은 에이징 절차 또는 검사절차를 위한 치구(예컨대, 에이징 탐침, 테스트 탐침 등)의 사이즈(예컨대, 접촉면적)에 상응하는 규모 H로, 뒤 열 기판셀들(22d)의 일부영역(22b1)을 선택적으로 점유하게 된다.

이 상황에서, 본 발명에서는 에이징 틀, 테스트 틀의 각 치구(예컨대, 에이징 탐침, 테스트 탐침 등)를 각 기판셀들(22)의 연장패턴(23a,24a)에 접촉시켜, 일련의 에이징 절차, 테스트 절차 등을 진행시키고, 이를 통해, 최종 출하되는 제품이 일정 수준 이상의 신뢰성을 정상적으로 유지할 수 있도록 유도하게 된다.

이때, 상술한 바와 같이, 앞 열 기판셀들(22c)의 전극패턴들(25)은 연장패턴(23a,24a)을 추가 포함하여, 그에 상응하는 길이증가를 자연스럽게 이루고 있기 때문에, 예컨대, 에이징 탐침, 테스트 탐침 등과의 접촉이 충분히 가능할 정도의 규모를 자연스럽게 형성할 수 있게 된다.

물론, 이처럼, 뒤 열 기판셀들(22d)의 일부까지 연장된 앞 열 기판셀들(22c)의 연장패턴(23a,24a)이 에이징 절차 또는 검사절차를 위한 치구(예컨대, 에이징 탐침, 테스트 탐침 등)의 사이즈(예컨대, 접촉면적)에 상응하는 규모 H를 유지하고 있고, 그 결과로, 해당 연장패턴(23a,24a)이 앞 열 기판셀들(22c)의 에이징 처리, 테스트 처리 등을 위한 공통전극으로 자연스럽게 활용될 수 있게 되는 경우, 결국, 각 기판셀들(22)은 상호 분리되지 않은 전체시트 상태에서도, 일련의 에이징 절차, 테스트 절차를 정상적으로 수행 받을 수 있게 된다.

당연히, 이러한 본 발명의 구현환경 하에서, 일련의 에이징 절차, 테스트 절차 등이 모 기판(21)을 포함한 전체시트 상태의 기판셀들(22)을 타겟으로 하여, 진행될 수 있게 되는 경우, 생산자 측에서는 각 기판셀들(22)을 <낱개의 독립개체>로 일일이 다루어야하는 불편함을 손쉽게 벗어날 수 있게 되며, 결국, 전체적인 에이징 효율성, 테스트 효율성 등이 일정 수준 이상으로 향상되는 효과를 자연스럽게 향유할 수 있게 된다.

나아가, 이러한 본 발명의 구현환경 하에서, 생산자 측에서는 각 기판셀들(22)을 커팅하거나, 커팅된 개별 기판셀들(22)에 구동 IC를 장착하기 이전 시점에서, 일련의 에이징 절차, 테스트 절차 등을 원활하게 진행시킬 수 있기 때문에, 해당 에이징 절차, 테스트 절차 등의 진행에 의해 만약, 특정 기판셀(22)이 불량 기판셀로 판정되더라도, 전체적인 제품 생산효율이 크게 떨어지거나, 생산비가 대폭 증가하는 등의 막대한 피해를 손쉽게 피할 수 있게 된다.

물론, 본 발명의 구현환경 하에서, 앞 열 기판셀들(22c)은 별도의 자체영역 배려 없이, 단지, 뒤 열 기판셀들(22d)의 일부영역(22b1)을 대체 활용하여, 에이징/테스트 처리용 연장패턴(23a,24a)의 배치공간을 융통성 있게 확보할 수 있기 때문에, 도 5에 도시된 바와 같이, 앞 열 기판셀들(22c)은 이후의 커팅절차에 의해, 모 기판(21)으로부터 독립적으로 잘려나가더라도, 자가영역 일부가 불필요하게 폐기되거나, 자가영역의 일부를 불필요하게 소모하는 등의 문제점을 유발하지 않게 되며, 결국, 생산자 측에서는 하나의 모 기판(21)에서 생산할 수 있는 기판셀들의 숫자가 줄어드는 피해를 손쉽게 피하면서도, 전체적인 에이징 효율성, 테스트 효율성, 제품 생산성 등이 일정 수준 이상으로 향상되는 효과를 자연스럽게 향유할 수 있게 된다.

추후, 각 기판셀들(22)은 일련의 커팅절차를 통해, 모 기판(21)으로부터 분리되어, 개별 제품으로 나뉜 후, 일련의 구동 IC 장착과정을 거쳐, 후속공정으로 출하되는 과정을 겪게 된다.

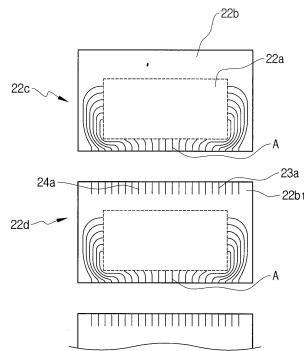

이때, 본 발명에서는 커팅라인(L4)을 따라, 앞 열 기판셀(22c)을 잘라냄으로써, 도 5에 도시된 바와 같이, 앞 열 기판셀들(22c)의 연장패턴(23a,24a)이 뒤 열 기판셀들(22d)의 일부영역(22b1)에 최종 잔류하도록 유도하게 된다(이 경우, 도 5에 도시된 각 기판셀들의 영역 A는 예컨대, 구동 IC의 장착부위로 작용하게 됨).

물론, 이러한 앞 열 기판셀들(22c)의 연장패턴(23a,24a)은 단지 뒤 열 기판셀들(22d)의 비 표시 영역(22b) 일부(22b1)를 소규모 점유할 뿐이기 때문에, 뒤 열 기판셀들(22d)의 기능수행에는 아무런 악영향을 미치지 않게 된다.

이러한 본 발명은 상황에 따라, 다양한 변형을 이룰 수 있다.

예를 들어, 본 발명에서는 상술한 연장패턴(23a,24a) 형성조치를 스캔 전극패턴(23), 데이터 전극패턴(24) 뿐만 아니라, 아이콘 전극패턴(ICON electrode pattern)(참고: 이 아이콘 전극패턴은 핸드폰 등과 같은 전자기기의 표시창에 안테나, 시계 등과 같은 일련의 아이콘을 표시하기 위하여 별도 형성되는 전극패턴임)에 적용하는 변화를 꾀할 수도 있다. 물론, 이 경우, 생산자 측에서는 기판셀(22)의 에이징/테스트 신뢰성이 더욱 향상되는 이점을 융통성 있게 향유할 수 있게 된다.

### 발명의 효과

이상에서 상세히 설명한 바와 같이, 본 발명에서는 앞 열의 각 기판셀들이 자가 전극패턴들의 일부를 자체영역이 아니라, 그 뒤 열에 일대일 대응 배치된 다른 기판셀들의 일부로 연장 형성시키고, 이를 통해, 각 기판셀들이 별도의 자체영역 배려 없이, 단지, 뒤 열 기판셀들의 일부영역을 대체 활용하여, 자신에게 필요한 에이징/테스트 처리용 공통전극의 배치공간을 융통성 있게 확보할 수 있도록 유도함으로써, 각 기판셀들이 추가영역 폐기/소모 등의 불필요한 자재낭비 문제점을 유발하지 않고서도, 상호 분리되지 않은 전체시트 상태에서, 일련의 에이징 절차, 테스트 절차를 정상적으로 수행 받을 수 있도록 유도할 수 있다.

또한, 본 발명에서는 각 기판셀들의 전극패턴 일부를 자체영역이 아니라, 그 뒤 열에 일대일 대응 배치된 다른 기판셀들의 일부로 연장 형성시키는 조치를 통해, 각 기판셀들이 별다른 자재낭비 유발 없이, 전체시트 상태에서, 일련의 에이징 절차, 테스트 절차를 수행 받을 수 있도록 유도함으로써, 생산자 측에서, 하나의 모 기판에서 생산할 수 있는 기판셀들의 숫자가 줄어드는 피해를 손쉽게 피하면서도, 전체적인 에이징 효율성, 테스트 효율성, 제품 생산성 등이 일정 수준 이상으로 향상되는 효과를 자연스럽게 향유할 수 있도록 가이드 할 수 있다.

이러한 본 발명은 단지, 상술한 유기전계 발광장치에 한정되지 않으며, 전극패턴을 채용한 다양한 기종의 전자기기에서 전반적으로 유용한 효과를 발휘한다.

그리고, 앞에서, 본 발명의 특정한 실시예가 설명되고 도시되었지만 본 발명이 당업자에 의해 다양하게 변형되어 실시될 가능성이 있는 것은 자명한 일이다.

이와 같은 변형된 실시예들은 본 발명의 기술적사상이나 관점으로부터 개별적으로 이해되어서는 안되며, 이와 같이 변형된 실시예들은 본 발명의 일부로 본 발명의 범위안에 속한다 해야 할 것이다.

### 도면의 간단한 설명

도 1은 종래의 기술에 따른 유기전계 발광장치용 패널유닛을 도시한 예시도.

도 2는 종래의 기술에 따른 유기전계 발광장치용 패널유닛의 기판셀 분리상태를 도시한 예시도.

도 3은 종래의 기술에 따른 다른 유형의 유기전계 발광장치용 패널유닛을 도시한 예시도.

도 4는 본 발명에 따른 유기전계 발광장치용 패널유닛을 도시한 예시도.

도 5는 본 발명에 따른 유기전계 발광장치용 패널유닛의 기판셀 분리상태를 도시한 예시도.

### 도면

도면1

도면2

도면3

도면4

도면5

|                |                                                 |         |            |

|----------------|-------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于有机电致发光器件的面板单元及其分离方法                           |         |            |

| 公开(公告)号        | <a href="#">KR1020070057366A</a>                | 公开(公告)日 | 2007-06-07 |

| 申请号            | KR1020050116745                                 | 申请日     | 2005-12-02 |

| [标]申请(专利权)人(译) | 四川CCO显示装置                                       |         |            |

| 申请(专利权)人(译)    | 洪시현泗川时期是有限公司                                    |         |            |

| 当前申请(专利权)人(译)  | 洪시현泗川时期是有限公司                                    |         |            |

| [标]发明人         | PARK SEONG HYUN                                 |         |            |

| 发明人            | PARK, SEONG HYUN                                |         |            |

| IPC分类号         | H05B33/26 H05B33/10                             |         |            |

| CPC分类号         | H01L51/56 H01L51/0031 H01L2251/562 H01L2251/566 |         |            |

| 代理人(译)         | KIM , YOUNG CHOL<br>KIM孙杨                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                       |         |            |

### 摘要(译)

本发明涉及用于有机电致发光器件的面板单元和分离方法。并且在本发明中，前热的每个基板单元是电极图案的一部分而不是自身区域。它允许通过点对点映射延伸并形成布置在其中的其他衬底单元的一部分。通过这种方式，每个衬底单元仅利用后热衬底单元的预定部分，而在世界上没有单独的自身区域关注。为了具有柔性，用于自身所需的老化/测试过程的公共电极的布置空间是固定的人所引起的。这样每个基板单元不会造成不必要的材料浪费问题，包括额外的区域丢弃/消耗等。仍然是为了一系列老化程序，和对正常人进行的测试程序可以在不相互分离的整个片状态下进行。此外，在本发明中，每个基板单元的电极图案的一部分不是其自身区域。为了进行一系列的老化程序，并且进行测试程序，它通过配置引起让其延伸并形成其他基板单元的一部分，然后通过点对点映射排列在其中，而不会产生材料浪费。每个基板单元在整个板状态下是特定的。以这种方式，生产者可以容易地避免在一个母板中可以产生的基板单元的数量减少的损坏。它可以引导整个老化效果，测试效率，产品生产率等自然地享受到给定水平的改进效果不规则。