**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl. *H05B 33/00* (2006.01) (45) 공고일자 2006년10월23일

(11) 등록번호 10-0636766

(24) 등록일자 2006년10월13일

---

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2000-0010872 | (65) 공개번호 | 10-2001-0014529 |

| (22) 출원일자 | 2000년03월04일     | (43) 공개일자 | 2001년02월26일     |

---

(30) 우선권주장 1999-058741 1999년03월05일 일본(JP)

(73) 특허권자 산요덴키가부시키가이샤

일본 오사카후 모리구치시 게이한 혼도오리 2쵸메 5반 5고

(72) 발명자 사이또요시노리

일본아이찌肯고난시아까도지조사꾸라미찌182-1

요꼬야마료이찌

일본기후Ken오가끼시아야노5-125-176

(74) 대리인 장수길

구영창

심사관 : 나광표

---

**(54) 일렉트로 루미네센스 표시 장치**

---

**요약**

EL 표시 장치에 있어서, 표시하는 데이터를 일단 기억하기 위한 프레임 버퍼를 사용하지 않고, 확실한 표시를 실현하여, 회로 규모를 작게 한다.

매트릭스형의 수동 EL 표시 장치에 있어서, 각 컬럼 전극을 홀수 라인에 대응하는 제1 컬럼 전극(211)과 짝수 라인에 대응하는 제2 컬럼 전극(212)으로 분할하여 구성하고, 제1 및 제2 컬럼 전극을 각각 독립하여 구동하는 제1 및 제2 컬럼 드라이버(22, 23)와, 로우 전극을 구동하는 로우 드라이버(31)를 설치하고, 인접하는 홀수 라인과 짝수 라인에 대응하는 로우 전극을 동시에 구동하여, 홀수 라인과 짝수 라인의 동시 2라인 표시를 행한다.

**대표도**

도 1

**색인어**

밸광총, 컬럼 전극, 로우 드라이버 회로, 일렉트로 루미네센스 표시 장치, 컬럼 드라이버 회로

**명세서**

## 도면의 간단한 설명

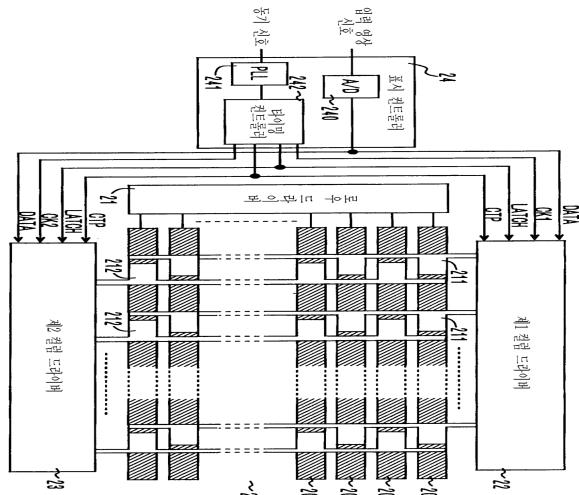

도 1은 본 발명의 실시예를 나타내는 블럭도.

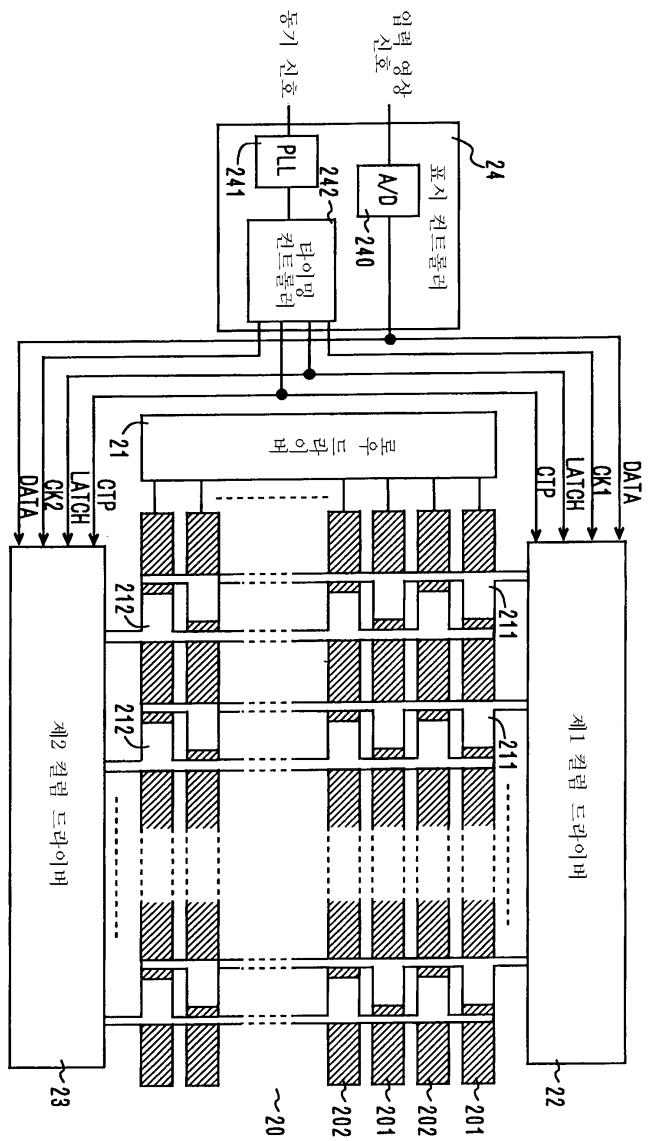

도 2는 본 발명의 다른 실시예를 나타내는 블럭도.

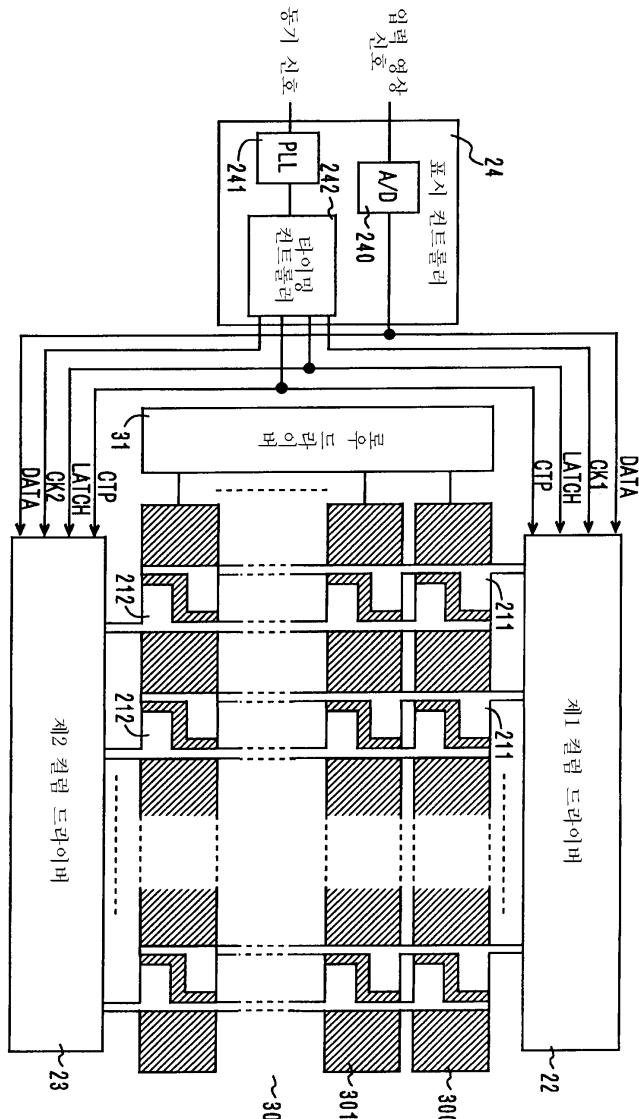

도 3은 본 발명의 실시예의 동작을 설명하기 위한 타이밍차트.

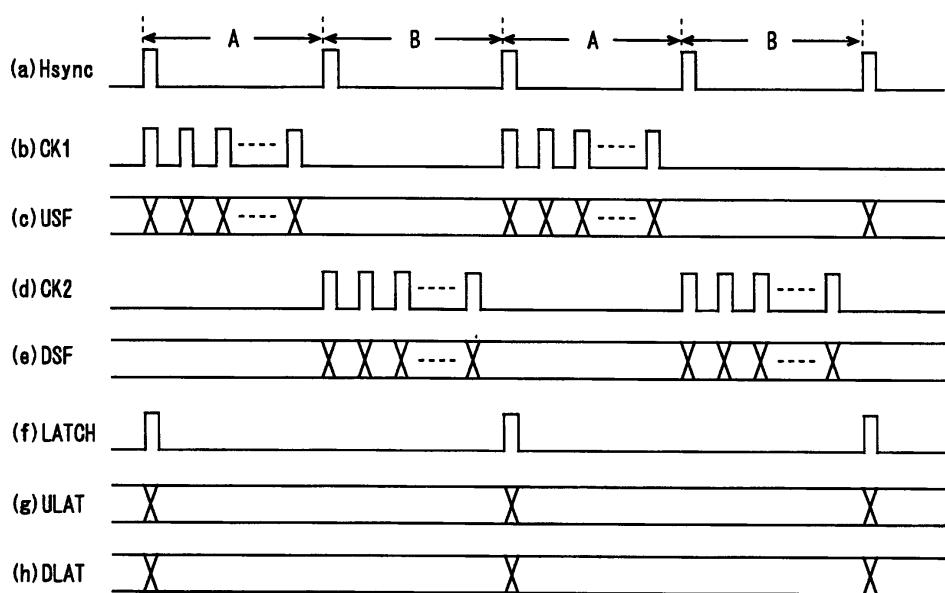

도 4는 실시예에서의 컬럼 드라이버의 구체 구성을 나타내는 회로도.

도 5는 실시예에서의 펄스 폭 변조 회로의 동작을 설명하기 위한 타이밍차트.

도 6은 종래의 EL 표시 장치를 도시하는 블럭도.

도 7은 EL 표시 소자의 개략 구조를 나타내는 단면도.

<도면의 주요 부분에 대한 부호의 설명>

20, 30 : 매트릭스

21, 31 : 로우 드라이버

22 : 제1 컬럼 드라이버

23 : 제2 컬럼 드라이버

201, 202, 300, 301 : 로우 전극

211 : 제1 컬럼 전극

212 : 제2 컬럼 전극

24 : 표시 컨트롤러

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 양극과 음극사이에 발광층을 지니고, 양극 및 음극을 매트릭스형으로 배치한 수동형의 일렉트로 루미네센스 (EL) 표시 장치에 관한 것이다.

유기 EL 소자는 스스로 발광하기 때문에 액정 표시 장치에서 필요한 백라이트가 필요하지 않고 박형화에 최적임과 함께, 시야각에도 제한이 없기 때문에, 차세대의 표시 장치로서 그 실용화가 크게 기대되고 있다.

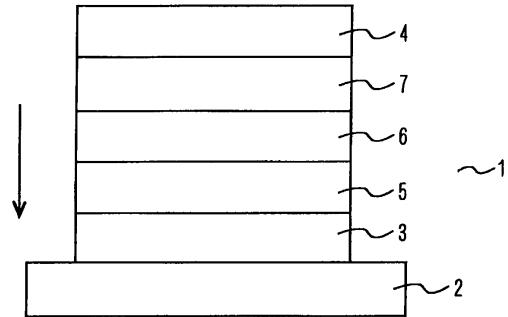

유기 EL 소자(1)는 도 7에 도시된 바와 같이 예를 들면, 투명한 유리 기판(2) 상에 ITO 등의 투명 전극으로 이루어지는 양극(3)을 형성하고, 이 양극(3)과 MgIn 합금으로 이루어지는 음극(4) 사이에, MTDATA로 이루어지는 홀 수송층(5), TPD 와 Rubrene로 이루어지는 발광층(6), Alq3으로 이루어지는 전자 수송층(7)을 순서대로 적층하여 형성되어 있다. 그리고, 양극(3)으로부터 주입된 홀과 음극(4)으로부터 주입된 전자가 발광층(6)의 내부에서 재결합함으로써 빛이 발해지고, 도면 내의 화살표로 나타낸 바와 같이 빛은 투명한 양극층으로부터 외부로 방사된다.

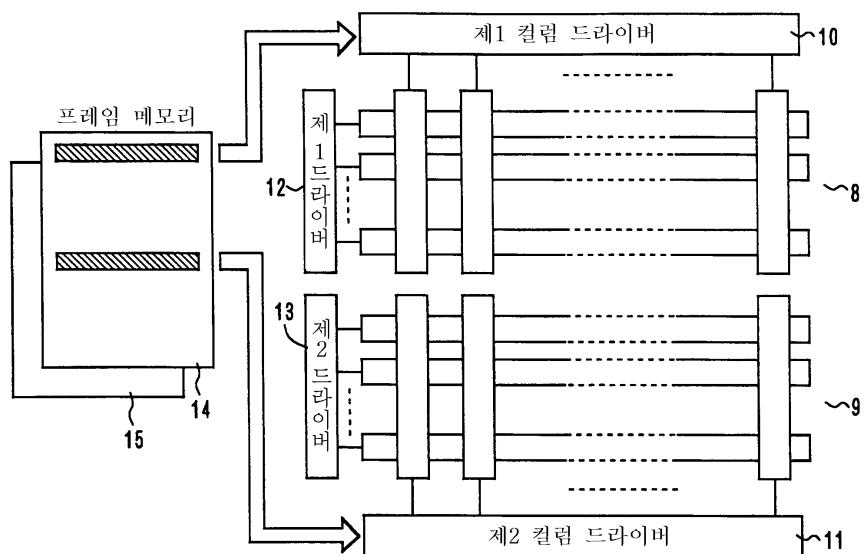

이러한 유기 EL 소자를 구동하는 표시 장치에는 수동형과 TFT를 사용하는 능동형의 2종류가 있고, 수동형의 개략 회로 구성은 도 6에 도시된 바와 같다.

즉, 표시 화면을 상하로 분할하고, 상반분과 하반분의 화면에 대해 각각 독립한 매트릭스(8, 9)를 설치한다. 매트릭스(8, 9)에서는 상술된 EL 소자의 한쌍의 전극 중 양극이 컬럼 전극, 음극이 로우 전극으로 이루어지고, 로우 전극은 각 라인마다 전 컬럼에 걸쳐 형성되었다. 한편, 매트릭스(8)에서의 컬럼 전극은 화면의 상반분에 대응하는 라인에 걸쳐 연속하여 형성되어 있고, 매트릭스(9)에서의 컬럼 전극은 화면의 하반분에 대응하는 라인에 걸쳐 연속하여 형성되어 있다.

또한, 각 매트릭스(8, 9)에는 컬럼 구동 신호를 공급하는 제1 및 제2 컬럼 드리아버(10, 11)와, 스캐닝 신호로서의 로우 구동 신호를 공급하는 제1 및 제2 로우 드라이버(12, 13)가 각각 설치되어 있다.

제1 및 제2 로우 드라이버(12, 13)로부터의 스캐닝 신호는 복수의 행 중 선택된 행만이 2수평 주사(2H) 기간 L 레벨이 되고, 다른 행의 스캐닝 신호는 H 레벨이 된다. 한편, 제1 및 제2 컬럼 드리아버(10, 11)에는 각 화소의 표시 계조를 나타내는 계조 데이터 DATA가 입력되고, 이 계조 데이터에 따른 펄스 폭을 갖는 펄스 신호가 컬럼 구동 신호로서 출력된다. 이 컬럼 구동 신호의 펄스 폭 기간은 H 레벨이고, 따라서 L 레벨의 스캐닝 신호가 입력되어 있는 행의 EL 소자가 발광하게 된다.

통상, 계조 데이터는 각각이 1화면분의 용량을 갖는 프레임 메모리(14, 15)에 일단 기억되고, 1개의 프레임 메모리의 상반분의 데이터가 라인마다 차례로 제1 컬럼 드리아버(10)에 수취되고, 하반분의 데이터가 라인마다 차례로 제2 컬럼 드라이버(11)에 수취된다. 그리고, 제1 로우 드라이버(12)와 제2 로우 드라이버(13)는 동시에 각 라인을 위에서 아래로 차례로 주사하므로, 분할된 상하의 화면에서 동시에 표시가 행해지게 된다.

여기서, 프레임 메모리가 1개밖에 없는 경우에는 하측 화면에서 구프레임의 표시를 행할 때에 상측 화면에서 신프레임의 표시를 행하도록, 상하에서 다른 프레임의 표시를 행할 가능성이 있고, 이러한 결점을 방지하기 위해 2개의 프레임 메모리(14, 15)를 설치하고 있다. 즉, 한쪽 프레임 메모리로부터 데이터의 판독을 행하고 있을 때에는 다른 프레임 메모리에 데이터를 기록하고, 이것을 교대로 반복하면, 정상적인 표시를 행할 수 있다.

### 발명이 이루고자 하는 기술적 과제

종래의 상하 분할 구동을 행하는 수동형의 EL 표시 장치에서는 상술된 바와 같이, 정상적인 표시를 행하기 위해서는 데이터를 일단 기억하기 위한 프레임 메모리가 필수적인 구성 요건이 된다. 이 때문에, 회로 규모가 증대함과 함께 비용고가 될 수밖에 없었다.

본 발명은 양극과 음극사이에 발광층을 지니고, 상기 양극 및 음극의 한쪽을 컬럼 전극으로 하여 다른 로우 전극으로서 매트릭스형으로 배치한 일렉트로 루미네센스 표시 장치에 있어서, 각 컬럼 전극을 홀수 라인에 대응하는 제1 컬럼 전극과 짹수 라인에 대응하는 제2 컬럼 전극으로 분할하여 구성함과 함께, 상기 제1 및 제2 컬럼 전극을 각각 독립하여 구동하는 제1 및 제2 컬럼 드라이버 회로와, 상기 로우 전극을 구동하는 로우 드라이버 회로를 지니고, 홀수 라인과 짹수 라인을 동시에 구동하는 것을 특징으로 한다.

또한, 본 발명에서는 상기 로우 전극은 라인마다 구성되고, 인접하는 홀수 라인과 짹수 라인에 대응하는 2개의 로우 전극을 동시에 구동하는 것을 특징으로 한다.

또한, 본 발명에서는 상기 로우 전극은 인접하는 홀수 라인과 짹수 라인에 걸친 하나의 로우 전극으로 구성된 것을 특징으로 한다.

또한, 본 발명에서는 교대로 도래하는 제1 및 제2 기간 중에, 상기 제1 컬럼 드라이버 회로는 상기 제1 기간에 홀수 라인에 표시하는 데이터를 저장하고, 상기 제2 컬럼 드라이버 회로는 상기 제2 기간에 짹수 라인에 표시하는 데이터를 저장하고, 상기 제1 및 제2 컬럼 드라이버 회로와 로우 드라이버 회로는 상기 제1 및 제2 기간에 걸쳐 구동 신호를 출력하는 것을 특징으로 한다.

### 발명의 구성 및 작용

도 1은 본 발명의 실시예를 나타내는 블력도이고, 유기 EL 소자의 양극을 컬럼 전극(211, 212)으로 하고, 음극을 로우 전극(201, 202)으로서, 매트릭스(20)를 구성하고 있다. 로우 전극(201, 202)은 종래와 마찬가지로, 각 라인마다 설치되고, 홀수 라인의 전극(201)도 짹수 라인의 전극(202)도, 전컬럼에 걸쳐 연속하여 형성되어 있다.

그러나, 컬럼 전극은 종래와 같이 화면의 상하로 분할하는 것은 아니고, 전극이 존재하는 라인이 홀수 라인이나 짹수 라인으로 분할하도록 하고 있다. 즉, 제1 컬럼 전극(211)은 홀수 라인의 로우 전극(201)과 중첩하는 위치에만 존재하는 전극을 연결하여 형성하고, 제2 컬럼 전극(212)은 짹수 라인의 로우 전극(202)과 중첩하는 위치에만 존재하는 전극을 연결하여 형성하고 있다.

그리고, 제1 컬럼 전극(211)과 제2 컬럼 전극(212)의 화소 대응 부분을 컬럼 방향으로 곧바로 번갈아 배치함으로써, 로우 전극과 컬럼 전극이 중첩하여 이루어지는 화소를 컬럼 방향으로 똑바르게 배열하고 있다.

홀수 라인 및 짹수 라인의 각 로우 전극(201, 202)은 로우 구동 신호로서의 스캐닝 신호를 공급하는 유일한 로우 드라이버(21)에 접속되고, 제1 컬럼 전극(211)은 제1 컬럼 구동 신호를 공급하는 제1 컬럼 드라이버(22)에, 그리고 제2 컬럼 전극(212)은 제2 컬럼 구동 신호를 공급하는 제2 컬럼 드라이버(23)에 접속되어 있다. 제1 컬럼 드라이버(22) 및 제2 컬럼 드라이버(23)는 모두 표시 컨트롤러(24)에 접속되고, 이 표시 컨트롤러는 입력 영상 신호를 각 화소의 표시 계조를 나타내는 계조 데이터 DATA로 변환하는 AD 컨버터(240)와, 입력되는 동기 신호에 위상 로크를 거는 PLL 회로(241)와, PLL 회로(241)의 출력 신호에 기초하여 각종 타이밍 신호를 생성하는 타이밍 컨트롤러(242)로 이루어진다.

그리고, 제1 컬럼 드라이버(22) 및 제2 컬럼 드라이버(23)에는 AD 컨버터(240)로부터 출력되는 데이터 DATA와, 타이밍 컨트롤러(242)로부터 출력되는 래치 펠스 LATCH 및 카운터 펠스 CTP가, 공통적으로 입력되고, 또한 타이밍 컨트롤러(242)로부터 출력되는 제1 시프트 클럭 CK1이 제1 컬럼 드라이버(22)에, 제2 시프트 클럭 CK2가 제2 컬럼 드라이버(23)에 입력되어 있다.

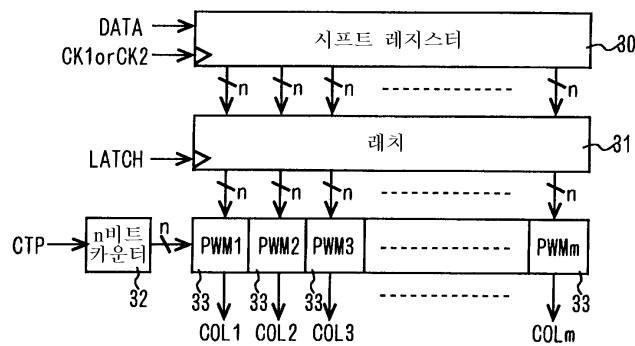

그런데, 제1 컬럼 드라이버(22) 및 제2 컬럼 드라이버(23)는 동일 구성이고, 구체적으로는 도 4에 도시된 구성이다.

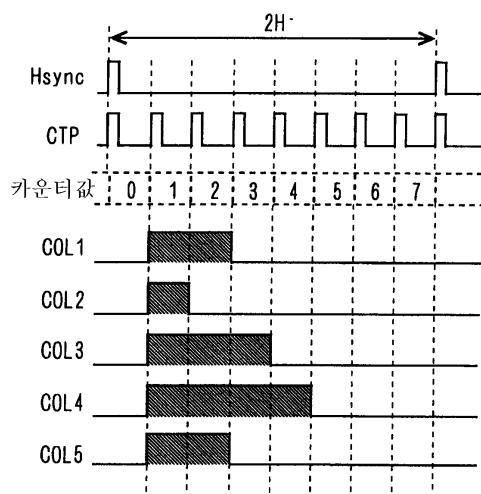

도면에 도시된 바와 같이, 컬럼 드라이버는 각 컬럼마다의 n 비트의 계조 데이터 DATA를 시프트 클럭 CK1 또는 CK2에 따라 입력하는 시프트 레지스터(30)와, 시프트 레지스터(30)에 입력된 데이터를 래치 펠스 LATCH에 따라 래치하는 래치 회로(31)와, 카운터 펠스 CTP를 카운트하여 카운트 값으로 계조 레벨을 나타내는 n비트 카운터(32)와, 각 컬럼마다 설치되어 래치 회로(31)로부터의 n 비트 계조 데이터와 n비트 카운터 값을 비교하여, 계조 데이터에 따른 펠스 폭의 컬럼 구동 신호 COL1, COL2, COL3, …, COLm을 각각 출력하는 m개의 펠스 폭 변조 회로(33)로 구성되어 있다. 그리고, 이들 각 펠스 폭 변조 회로(33)로부터는 도 5에 도시된 바와 같이, 컬럼 구동 신호 COL1, COL2, COL3, …, COLm이 출력된다.

즉, n비트 카운터(32)의 카운터 값을 예를 들면 n=3으로 하면 도 5에 도시된 바와 같이, 2 수평 주사 기간(2H) 내에 그 내용이 「0」, 「1」, …, 「7」로 차례로 변화하고, 컬럼 구동 신호 COL1, COL2, COL3, …, COLm은 카운터 값이 「1」이 되는 타이밍으로 전부 동시에 출력을 개시한다. 그리고, 각 화소의 계조 데이터에 따른 펠스 폭 기간 H레벨을 유지한다. 따라서, 매트릭스(20)에 있어서의 동일 라인의 화소는 도 5에 도시된 펠스 폭 기간 발광하게 되고, 이 발광 기간에 의해 계조가 표현된다.

이어서, 도 1에 도시된 실시예의 동작을 도 3을 참조하여 설명한다.

우선, 제1 시프트 클럭 CK1은 도 3b에 도시된 바와 같이 1H의 A기간만 클럭을 발생시키고, 계속되는 B기간에서는 클럭이 발생하지 않는다. 한편, 제2 시프트 클럭 CK2는 제1 시프트 클럭 CK1과는 반대로 도 3d에 도시된 바와 같이, 1H의 B기간만 클럭을 발생시키고, 계속되는 A기간에서는 클럭이 발생하지 않는다. 그리고, 제1 시프트 클럭 CK1은 제1 컬럼 드라이버(22)에 입력되고, 제2 시프트 클럭 CK2는 제2 컬럼 드라이버(23)에 입력되므로, 입력 데이터 DATA 중 홀수 라인의 데이터가 차례로, A기간에 제1 컬럼 드라이버(22) 내의 시프트 레지스터(30)에 수취되고, 짹수 라인의 데이터가 차례로 B기간에 제2 컬럼 드라이버(23) 내의 시프트 레지스터(30)에 수취되고, 이들 각 시프트 레지스터의 내용 USF, DSF는 도 3c 및 도 3e에 도시된 바와 같이 변화한다. 또한, 래치 펠스 LATCH는 도 3f에 도시된 바와 같이 A기간의 최초에서만 출력되므로, 제1 컬럼 드라이버(22) 및 제2 컬럼 드라이버(23)에서는 각 시프트 레지스터(30)의 내용 USF, DSF가 동시에 래치 회로(31)에 래치된다.

상술된 바와 같이, n 비트 카운터(32)에 입력되는 카운터 펠스 CTP는 도 5에 도시된 바와 같이 2H 기간 내에 소정수(n=3이면 8개)의 펠스를 발생시키므로, 제1 컬럼 드라이버(22) 및 제2 컬럼 드라이버(23) 내의 각 펠스 폭 변조 회로(33)는 A

기간으로부터 B기간에 걸친 2H기간으로, 계조 레벨에 따른 펄스 폭 변조 신호를 컬럼 구동 신호로서 출력한다. 즉, 제1 컬럼 드라이버(22)로부터는 홀수 라인에 대응하는 컬럼 구동 신호가 출력되어, 이것이 매트릭스(20) 내의 제1 컬럼 전극(211)으로 송출되고, 제2 컬럼 드라이버(23)로부터는 짹수 라인에 대응하는 컬럼 구동 신호가 출력되어, 이것이 매트릭스(20) 내의 제2 컬럼 전극(212)으로 송출된다. 또한, 로우 드라이버(21)는 인접하는 홀수 라인과 짹수 라인에 대응하는 2개의 로우 전극(201, 202)을 동시에 주사하고, 이 주사를 상위 라인으로부터 하위 라인을 향해 차례로 반복한다. 따라서, 매트릭스(20)에서는 인접하는 홀수 라인과 짹수 라인의 2개의 라인으로 동시에 EL의 발광이 행해져 표시가 이루어지고, 이 2라인 동시 표시가 상위 라인으로부터 하위 라인을 향해 차례로 실행된다.

이와 같이, 본 실시예에서는 입력 데이터를 기억하는 프레임 메모리를 전혀 사용하지 않고, 확실한 표시를 실현할 수 있다.

이어서, 도 2를 참조하여, 본 발명의 제2 실시예에 대해 설명한다.

이 실시예와 제1 실시예에서 다른 점은 로우 전극(300, 301, ...)과 로우 드라이버(31)의 구성뿐이다.

즉, 도 1에서 각 라인마다 로우 전극을 형성했지만, 본 실시예에서는 인접하는 홀수 라인과 짹수 라인의 2라인분에 대해 1개의 로우 전극을 설치하도록 하고 있다. 제1 실시예에서도 인접하는 홀수 라인과 짹수 라인은 동시에 구동하므로, 로우 전극을 공통화해도 완전히 동일하게 동작한다. 이 경우, 로우 드라이버(31)로서는 구동하는 로우 전극수가 반감하므로 회로 규모를 작게 할 수 있다.

### 발명의 효과

본 발명에 따르면, 표시하는 데이터를 일단 기억하기 위한 프레임 버퍼를 사용하지 않고 확실한 표시를 실현할 수 있고, 회로 규모를 작게 할 수 있다. 또한, 홀수 라인과 짹수 라인에서 공통의 로우 전극을 이용하면, 로우 드라이버의 출력수를 반감할 수 있고, 더욱 회로 규모를 작게 할 수 있다.

## (57) 청구의 범위

### 청구항 1.

양극과 음극사이에 발광층을 포함하고, 상기 양극 및 음극의 한쪽을 컬럼 전극으로 하고 다른 쪽을 로우 전극으로서 매트릭스형으로 배치한 일렉트로 루미네센스 표시 장치에 있어서,

각 컬럼 전극을 홀수 라인에 대응하는 제1 컬럼 전극과 짹수 라인에 대응하는 제2 컬럼 전극으로 분할하여 구성함과 동시에, 상기 제1 및 제2 컬럼 전극을 각각 독립하여 구동하는 제1 및 제2 컬럼 드라이버 회로와, 상기 로우 전극을 구동하는 로우 드라이버 회로를 구비하고, 홀수 라인과 짹수 라인을 동시에 구동하는 것을 특징으로 하는 일렉트로 루미네센스 표시 장치.

### 청구항 2.

제1항에 있어서,

상기 로우 전극은 라인마다 구성되고, 인접하는 홀수 라인과 짹수 라인에 대응하는 2개의 로우 전극을 동시에 구동하는 것을 특징으로 하는 일렉트로 루미네센스 표시 장치.

### 청구항 3.

제1항에 있어서,

상기 로우 전극은 인접하는 홀수 라인과 짝수 라인에 걸친 1개의 로우 전극으로 구성된 것을 특징으로 하는 일렉트로 류미네센스 표시 장치.

#### 청구항 4.

제1항에 있어서,

교대로 도래하는 제1 및 제2 기간 중, 상기 제1 칼럼 드라이버 회로는 상기 제1 기간에 홀수 라인에 표시하는 데이터를 저장하고, 상기 제2 칼럼 드라이버 회로는 상기 제2 기간에 짝수 라인에 표시하는 데이터를 저장하고, 상기 제1 및 제2 칼럼 드라이버 회로와 로우 드라이버 회로는 상기 제1 및 제2 기간에 걸쳐 구동 신호를 출력하는 것을 특징으로 하는 일렉트로 류미네센스 표시 장치.

도면

도면1

## 도면2

도면3

도면4

도면5

도면6

도면7

|                |                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电致发光显示装置                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">KR100636766B1</a>                                                                                                 | 公开(公告)日 | 2006-10-23 |

| 申请号            | KR1020000010872                                                                                                               | 申请日     | 2000-03-04 |

| [标]申请(专利权)人(译) | 三洋电机株式会社<br>山洋电气株式会社                                                                                                          |         |            |

| 申请(专利权)人(译)    | 三洋电机有限公司是分租                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 三洋电机有限公司是分租                                                                                                                   |         |            |

| [标]发明人         | SAITO YOSHINORI<br>사이도요시노리<br>YOKOYAMA RYOICHI<br>요코야마료이찌                                                                     |         |            |

| 发明人            | 사이도요시노리<br>요코야마료이찌                                                                                                            |         |            |

| IPC分类号         | H05B33/00 G09G3/30 G09G3/20 G09G3/32 H01L51/50 H05B33/12 H05B33/14                                                            |         |            |

| CPC分类号         | H01L27/3288 G09G2300/0439 G09G3/2014 G09G2360/18 G09G2310/027 G09G3/3275 G09G2310/0205 G09G3/3216 G09G2310/0224 G09G2310/0218 |         |            |

| 代理人(译)         | CHANG, SOO KIL                                                                                                                |         |            |

| 优先权            | 1999058741 1999-03-05 JP                                                                                                      |         |            |

| 其他公开文献         | KR1020010014529A                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                     |         |            |

## 摘要(译)

对于电致发光显示装置，首先，帧缓冲器用于存储未使用的数据。实现了某种显示。它使电路尺寸变小。同时，对应于奇数线和偶数线的行电极分别与用于驱动第一和第二列电极的原始驱动器(31)相邻，当前驱动的第一和第二列驱动器(22)，对于手动电致发光显示装置，对应于手动电致发光显示装置的每个列电极的奇数线对应的第一列电极(211)驱动的行电极和第二列电极(212)分别对应于连线。同时2携带偶数行和奇数行的行显示。发光层，列电极，原始驱动电路，电致发光显示器，列驱动电路。