**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51). Int. Cl.<sup>7</sup>

H05B 33/26

H05B 33/10

H05B 33/00

(11) 공개번호 10-2005-0020610

(43) 공개일자 2005년03월04일

(21) 출원번호 10-2004-0061751

(22) 출원일자 2004년08월05일

|            |                    |             |        |

|------------|--------------------|-------------|--------|

| (30) 우선권주장 | JP-P-2003-00207936 | 2003년08월19일 | 일본(JP) |

|            | JP-P-2003-00423745 | 2003년12월19일 | 일본(JP) |

|            | JP-P-2004-00162538 | 2004년05월31일 | 일본(JP) |

(71) 출원인 세이코 앱순 가부시키가이샤

일본 도쿄도 신주쿠구 니시신주쿠 2초메 4-1

(72) 발명자 모리야소이치

일본국 나가노켄 스와시 오와 3-3-5 세이코 앱순 가부시키가이샤

내

가와세다케오

일본국 나가노켄 스와시 오와 3-3-5 세이코 앱순 가부시키가이샤

내

하라다미츠아키

일본국 나가노켄 스와시 오와 3-3-5 세이코 앱순 가부시키가이샤

내

(74) 대리인 문두현

문기상

심사청구 : 있음

**(54) 전극, 전극 형성 방법, 박막 트랜지스터, 전자 회로, 유기일렉트로루미네선스 소자, 표시 장치 및 전자 기기**

**요약**

본 발명은 저비용으로 제작 가능하고 또 정공의 주입 효율이 높은 전극, 이러한 전극을 간편하게 제조할 수 있는 전극 형성 방법, 신뢰성이 높은 박막 트랜지스터, 이 박막 트랜지스터를 사용한 전자 회로, 유기 일렉트로루미네선스 소자, 표시 장치, 및 전자 기기를 제공하는 것이다.

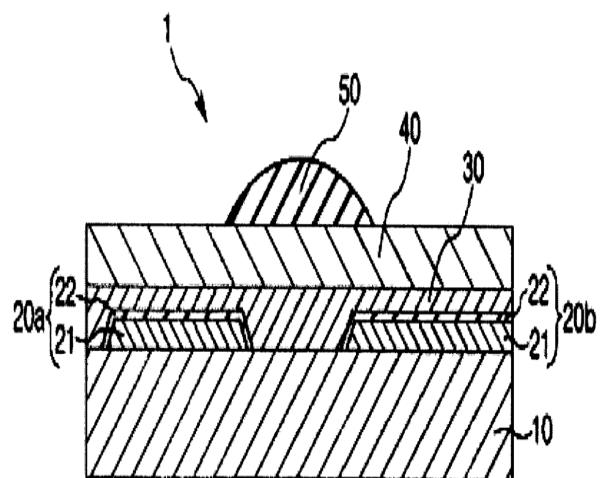

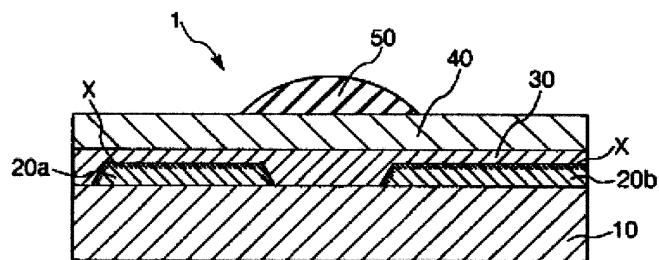

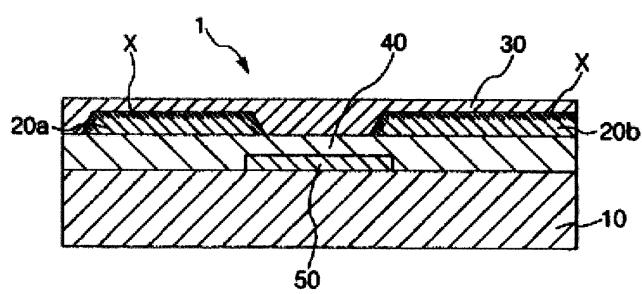

박막 트랜지스터(1)는 톱 게이트형의 박막 트랜지스터로서, 서로 분리하여 설치된 소스 전극(20a) 및 드레인 전극(20b)과, 소스 전극(20a)과 드레인 전극(20b) 사이에 개재하는 유기 반도체층(30)과, 유기 반도체층(30)과 게이트 전극(50) 사이에 위치하는 게이트 질연층(40)을 갖는 구조를 하고 있고, 기판(10)상에 탑재되어 있다. 소스 전극(20a) 및 드레인 전극(20b)은 각각, 하지 전극층(21) 및 표면 전극층(22)의 2층으로 구성되어 있다. 표면 전극층(22)은 Cu, Ni, Co, Ag중 적어도 1종을 포함하는 산화물을 함유하고 있다.

**대표도**

도 1

**색인어**

전극, 전극 형성 방법, 박막 트랜지스터, 전자 회로, 유기 일렉트로루미네선스 소자, 표시 장치, 전자 기기

## 명세서

### 도면의 간단한 설명

도 1은 본 발명의 박막 트랜지스터의 제1 실시 형태를 나타내는 개략 단면도.

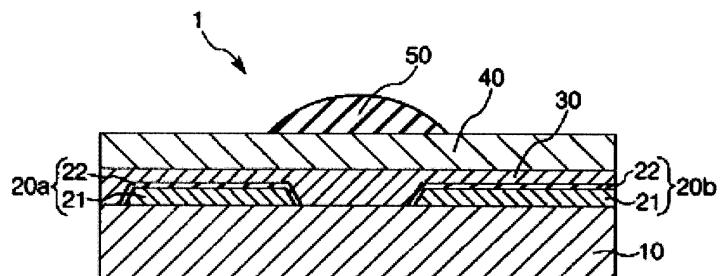

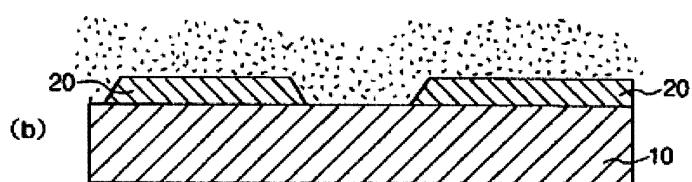

도 2은 도 1에 나타내는 박막 트랜지스터의 제조 방법을 설명하기 위한 도면(종단면도).

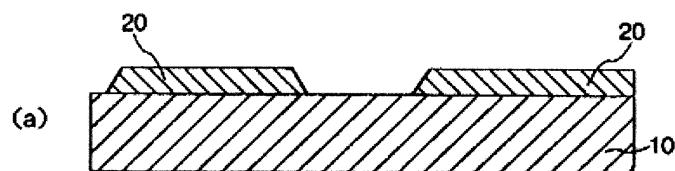

도 3은 도 1에 나타내는 박막 트랜지스터의 제조 방법을 설명하기 위한 도면(종단면도).

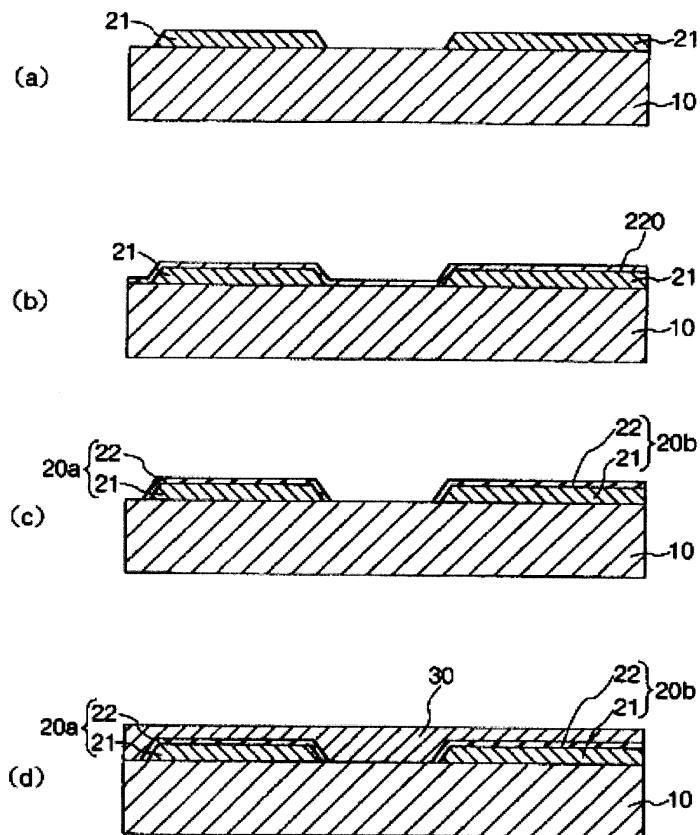

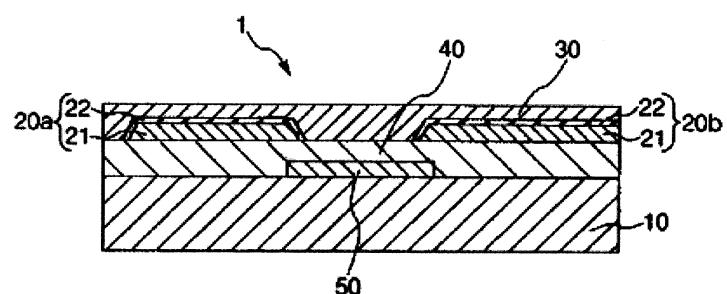

도 4는 본 발명의 박막 트랜지스터의 제2 실시 형태를 나타내는 개략 단면도.

도 5은 도 4에 나타내는 박막 트랜지스터의 제조 방법을 설명하기 위한 도면(종단면도).

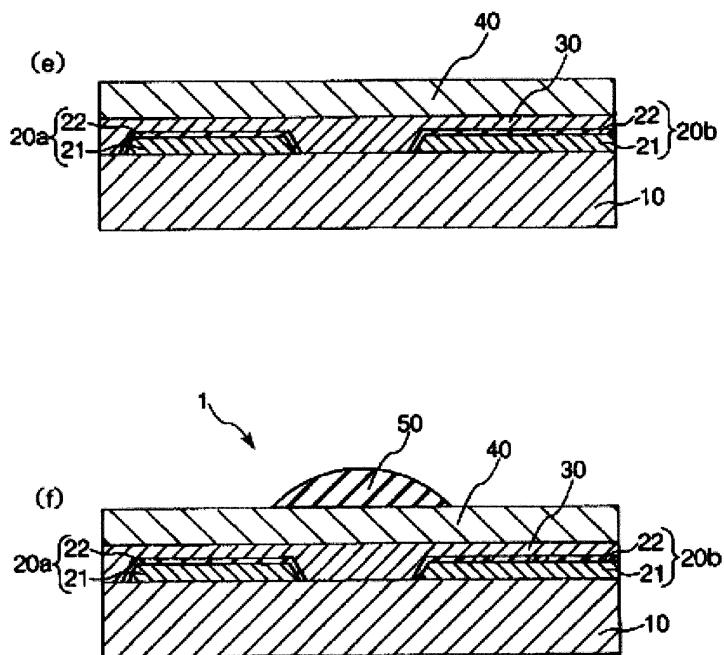

도 6은 본 발명의 박막 트랜지스터의 제3 실시 형태를 나타내는 개략 단면도.

도 7은 본 발명의 박막 트랜지스터의 제4 실시 형태를 나타내는 개략 단면도.

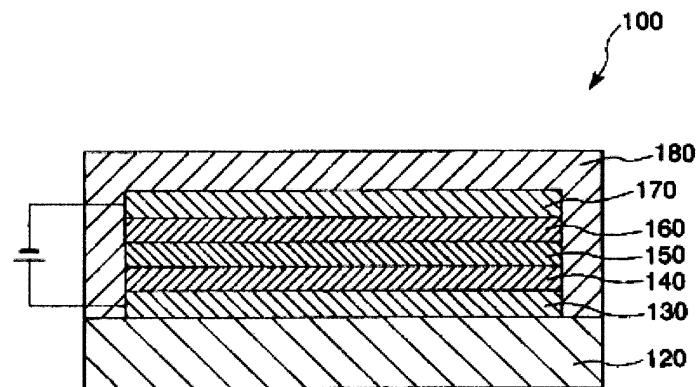

도 8은 본 발명의 유기 EL 소자의 실시 형태를 나타내는 개략 단면도.

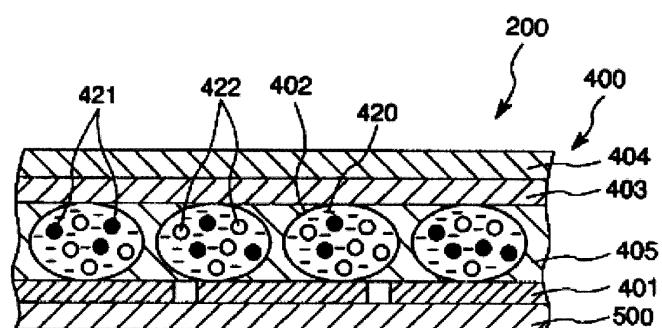

도 9는 본 발명의 표시 장치를 전기영동표시 장치에 적용한 경우의 실시 형태를 나타내는 종단면도.

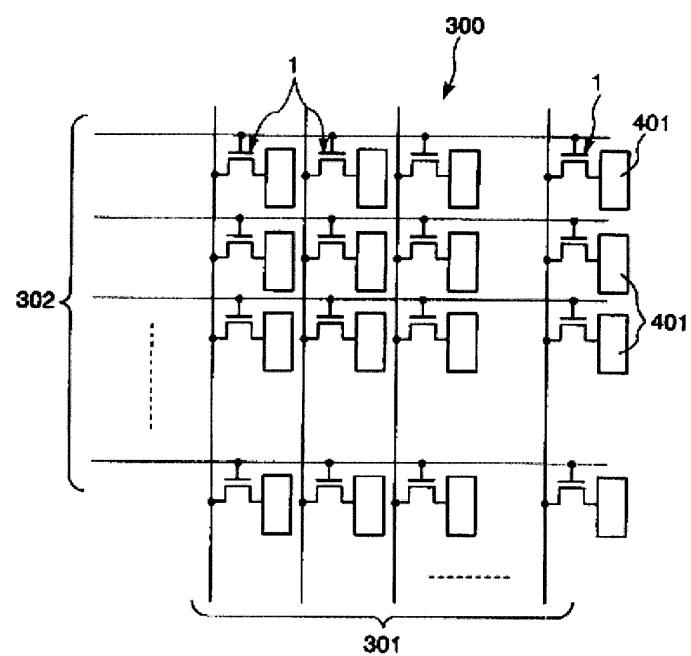

도 10은 도 9에 나타내는 전기영동표시 장치를 구비하는 액티브 매트릭스 장치의 구성을 나타내는 블럭도.

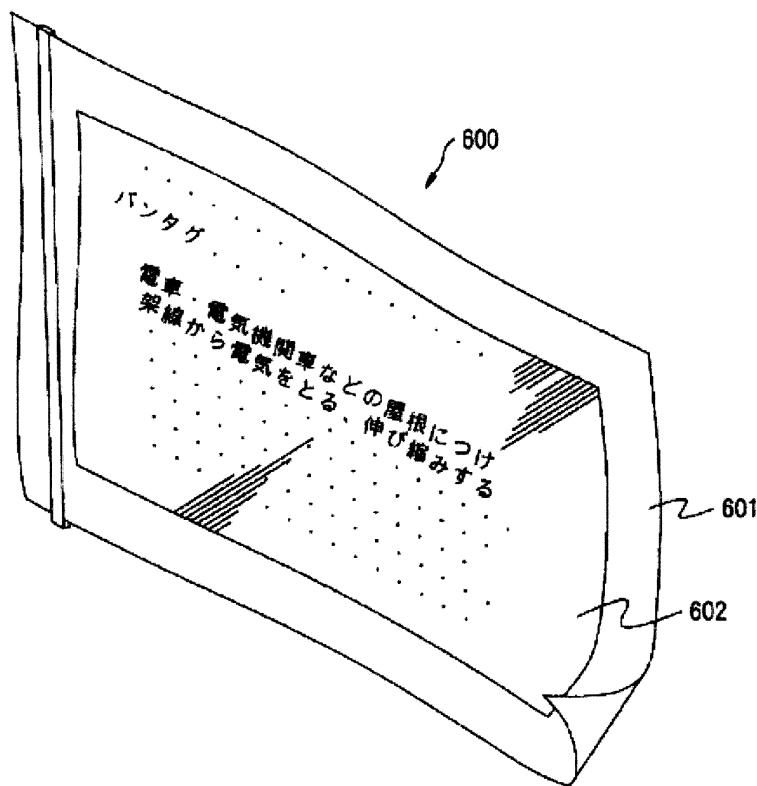

도 11은 본 발명의 전자 기기를 전자 페이퍼에 적용한 경우의 실시 형태를 나타내는 사시도.

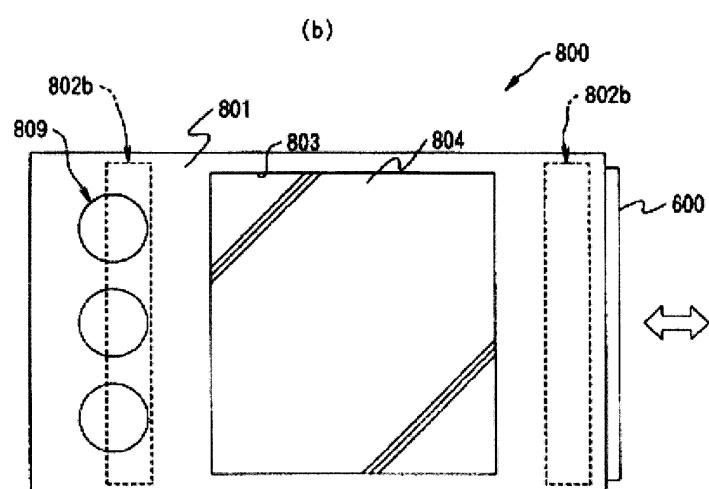

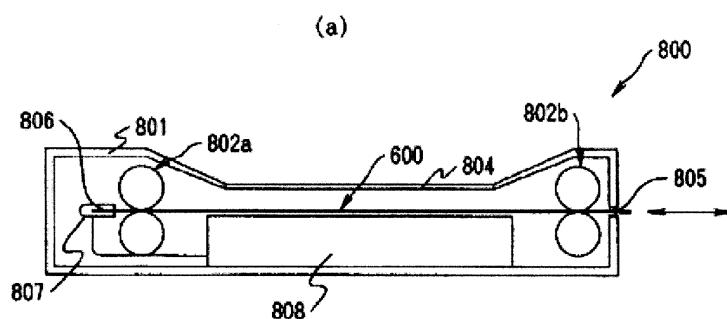

도 12는 본 발명의 전자 기기를 디스플레이에 적용한 경우의 실시 형태를 나타내는 도면.

### 부호의 설명

1… 박막 트랜지스터 10… 기판 20a… 소스 전극 20b… 드레인 전극 20… 금속막 21… 하지 전극층 22… 표면 전극층 220… 괴막 30… 유기 반도체층 40… 게이트 절연층 50… 게이트 전극 100… 유기 EL 소자 120… 기판 130… 양극 140… 정공 수송층 150… 발광층 160… 전자 주입층 170… 음극 180… 밀봉 부재 200… 전기영동표시 장치 300… 액티브 매트릭스 장치 301… 데이터선 302… 주사선 400… 전기영동표시부 401… 화소 전극 402… 마이크로캡슐 420… 전기영동 분산액 421, 422… 전기영동 입자 403… 투명 전극 404… 투명 기판 405… 바인더제 500… 기판 600… 전자 페이퍼 601… 본체 602… 표시 유닛 800… 디스플레이 801… 본체부 802a, 802b… 반송 롤러상 803… 구멍부 804… 투명 유리판 805… 삽입구 806… 단자부 807… 소켓 808… 콘트롤러 809… 조작부

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 전극, 전극 형성 방법, 박막 트랜지스터, 전자 회로, 유기 일렉트로루미네센스 소자, 표시 장치 및 전자 기기에 관한 것이다.

근년, 실리콘으로 대표되는 무기 재료를 사용한 박막 전계 효과형 트랜지스터로부터 치환할 수 있는 디바이스로서, 유기 반도체 재료를 사용한 유기 박막 전계 효과형 트랜지스터가 주목되고 있다.

종래의 전형적인 유기 박막 트랜지스터는 소스, 드레인 전극으로서 금을 사용하는 구조를 갖고 있었다(예를 들어, 비특허 문헌 1 참조).

구체적으로는 비특허 문헌 1 기재의 박막 트랜지스터는 폴리에틸렌테레프탈레이트 기판에 포토리소그래피법 등을 사용하여 ITO(Indium Tin Oxide)을 에칭하여, 게이트 전극을 형성하고, 게이트 절연층으로서 유기 실록산 및 질화 규소를 사용하는 구조를 갖고 있다.

또한, 금의 박막을 증착법으로 형성하고, 마이크로 콘택트 프린팅법을 사용하여, 이것을 패터닝하여, 소스 전극 및 드레인 전극을 형성한다. 마지막으로, 유기 반도체층(p형의 유기 반도체층)을 증착법으로 형성함으로써 제작하고 있다.

그러나, 상기 비특허 문헌 1 기재의 유기 트랜지스터에서는 소스 전극 및 드레인 전극을 고가인 금의 박막을 증착하여 형성하고, 에칭함으로써 형성하고 있기 때문에, 저비용화라고 하는 관점에서 개선의 여지가 있다.

이것에 대해서, 저비용인 Al 등의 금속을 전극으로서 사용하면, 소스 전극과 유기 반도체층의 계면에서 생기는 장벽이 커서 캐리어(정공)의 주입이 효율 좋게 행하여지지 않아, 트랜지스터 특성이 저하하는 문제가 생긴다.

### 비특허 문헌 1

Rogers et al. "Proceedings of the National Academy of Sciences" April 24, 2001. vol. 98. no. 948354840

#### **발명이 이루고자 하는 기술적 과제**

본 발명의 목적은 저비용으로 제작 가능하고 또 정공의 주입 효율이 높은 전극, 이러한 전극을 간편하게 제조할 수 있는 전극 형성 방법, 신뢰성이 높은 박막 트랜지스터, 이 박막 트랜지스터를 사용한 전자 회로, 신뢰성이 높은 유기 일렉트로루미네센스 소자, 표시 장치, 및, 전자 기기를 제공하는 것에 있다.

#### **발명의 구성 및 작용**

이러한 목적은 하기와 같은 본 발명에 의해 달성된다.

본 발명의 전극은 주로 유기 재료로 구성되고 정공을 수송하는 기능을 갖는 유기층에 대해서, 정공을 주입하는 전극으로서,

상기 전극은 그 전극의 적어도 상기 유기층 측의 면에, Cu, Ni, Co 중 적어도 1종을 포함하는 산화물을 함유하는 것을 특징으로 한다. 또한, 면만이 아니고 전극 전체에 산화물을 함유시키는 것도 가능하다.

이것에 의해, 저비용으로 제작 가능하고 또 정공의 주입 효율이 높아진다.

본 발명의 전극에서는 상기 산화물을 함유하는 부분에서, 상기 산화물의 함유량은 50wt% 이상인 것이 바람직하다.

이것에 의해, 정공의 주입 효율을 보다 향상시킬 수 있다.

본 발명의 전극에서는 상기 산화물은 Cu, Ni, Co 이외에, Sr, Al, Ga, Li, Na, K, Rb, Cs 중 적어도 1종을 포함하는 것이 바람직하다.

이것에 의해, 전기 전도도를 높여 정공의 주입을 보다 효율 좋게 행할 수 있다.

본 발명의 전극은 주로 유기 재료로 구성되고 정공을 수송하는 기능을 갖는 유기층에 대해서, 정공을 주입하는 전극으로서,

상기 전극은 복수의 층으로 구성되고,

상기 복수의 층 중, 상기 유기층에 가장 가까운 층이 Cu, Ni, Co 중 적어도 1종을 포함하는 산화물을 함유하는 것을 특징으로 한다.

이것에 의해, 저비용으로 제작 가능하고 또 정공의 주입 효율이 높아진다. 또한, 여기서 복수의 층은 2층 이상이면 좋고, 3층이나 그 이상이라도 좋다. 또한 복수의 층의 모두에 산화물을 함유시키는 것도 가능하다.

본 발명의 전극에서는 상기 유기층에 가장 가까운 층에서, 상기 산화물의 함유량은 50wt% 이상인 것이 바람직하다.

이것에 의해, 정공의 주입 효율을 보다 향상시킬 수 있다.

본 발명의 전극에서는, 상기 산화물은 Cu, Ni, Co 이외에, Sr, Al, Ga, Li, Na, K, Rb, Cs 중 적어도 1종을 포함하는 것이 바람직하다.

이것에 의해, 전기 전도도를 높여 정공의 주입을 보다 효율 좋게 행할 수 있다.

본 발명의 전극에서는 상기 전극을 구성하는 복수의 층 중, 상기 유기층에 가장 가까운 층의 일함수가 가장 큰 것이 바람직하다.

이것에 의해, 유기층으로의 보다 효율이 좋은 정공의 주입이 가능해진다.

본 발명의 전극에서는 상기 전극은 2층으로 구성되며,

상기 2층 중, 상기 유기층과는 반대측의 층은 주로 Cu, Ni, Co 또는 이들을 포함하는 합금으로 구성되어 있는 것이 바람직하다.

이것에 의해, 전극을 염가로 형성할 수 있는 동시에, 2층의 밀착성의 향상을 도모할 수도 있다.

본 발명의 전극은 주로 유기 재료로 구성되고 정공을 수송하는 기능을 갖는 유기층에 대해서, 정공을 주입하는 전극으로서,

상기 전극은 그 전극의 적어도 상기 유기층 층의 면에, 금속 황화물 및 금속 염화물의 적어도 하나를 함유하는 것을 특징으로 한다.

이것에 의해, 저비용으로 제작 가능하고 또 정공의 주입 효율이 높아진다.

본 발명의 전극은 주로 유기 재료로 구성되고 정공을 수송하는 기능을 갖는 유기층에 대해서, 정공을 주입하는 전극으로서,

상기 전극은 복수의 층으로 구성되고,

상기 복수의 층 중, 상기 유기층에 가장 가까운 층이 금속 황화물 및 금속 염화물의 적어도 하나를 함유하는 것을 특징으로 한다.

이것에 의해, 저비용으로 제작 가능하고 또 정공의 주입 효율이 높아진다.

본 발명의 전극에서는 상기 금속 황화물은 Cu를 포함하는 황화물을 주로 하는 것인 것이 바람직하다.

이것에 의해, 정공의 주입 효율이 보다 높아진다.

본 발명의 전극에서는 상기 금속 염화물은 Ag를 포함하는 염화물을 주로 하는 것인 것이 바람직하다.

이것에 의해, 정공의 주입 효율이 보다 높아진다.

본 발명의 전극 형성 방법은, 본 발명의 전극을 형성하는 전극 형성 방법으로서,

주로 Cu, Ni, Co 또는 이들을 포함하는 합금으로 구성되는 금속막을 형성하는 공정과,

그 금속막에 산화 처리를 실시함으로써, 상기 금속막의 표면을 산화시키는 공정을 갖는 것을 특징으로 한다.

이것에 의해, 유기층으로의 정공의 주입 효율이 높은 전극을, 용이하게 또한 확실히 형성할 수 있다.

본 발명의 전극 형성 방법에서는, 상기 산화 처리는 산소를 포함하는 분위기 중에서 행하는 플라즈마 처리인 것이 바람직하다.

이것에 의해, 전극의 표면 부근에 균일하게 산화물을 존재시킬 수 있다.

본 발명의 전극 형성 방법에서는 상기 플라즈마 처리는 대기압하에서 행하여지는 것이 바람직하다.

이것에 의해, 전극의 형성을 보다 용이하게 또한 저비용으로 행할 수 있다.

본 발명의 전극 형성 방법에서는 상기 금속층을, 도금법에 의해 형성하는 것이 바람직하다.

이것에 의해, 전극을 보다 높은 정밀도로 형성할 수 있다.

본 발명의 전극 형성 방법에서는 도금법은 무전계 도금법인 것이 바람직하다. 이것에 의해, 소망한 조성의 전극을 용이하게 또한 확실히 형성할 수 있다.

본 발명의 박막 트랜지스터는 본 발명의 전극으로 구성된 소스 전극과,

상기 유기층으로서, 주로 p형의 유기 반도체 재료로 구성된 유기 반도체층을 갖는 것을 특징으로 한다.

이것에 의해, 신뢰성이 높은 박막 트랜지스터를 얻을 수 있다.

본 발명의 박막 트랜지스터는 본 발명의 전극 형성 방법에 의해 형성된 소스 전극과,

상기 유기층으로서, 주로 p형의 유기 반도체 재료로 구성된 유기 반도체층을 갖는 것을 특징으로 한다.

이것에 의해, 신뢰성이 높은 박막 트랜지스터를 얻을 수 있다.

본 발명의 박막 트랜지스터는 주로 p형의 유기 반도체 재료로 구성된 유기 반도체층과, 그 유기 반도체층에 정공을 주입하는 소스 전극을 구비하는 박막 트랜지스터로서, 상기 소스 전극은 그 소스 전극의 적어도 상기 유기 반도체층 측의 면에, Ag를 포함하는 산화물을 함유하는 것을 특징으로 한다.

이것에 의해, 신뢰성이 높은 박막 트랜지스터를 얻을 수 있다.

본 발명의 박막 트랜지스터는 주로 p형의 유기 반도체 재료로 구성된 유기 반도체층과, 그 유기 반도체층에 정공을 주입하는 소스 전극을 구비하는 박막 트랜지스터로서, 상기 소스 전극은 복수의 층으로 구성되고,

상기 복수의 층 중, 상기 유기 반도체층에 가장 가까운 층이 Ag를 포함하는 산화물을 함유하는 것을 특징으로 한다.

이것에 의해, 신뢰성이 높은 박막 트랜지스터를 얻을 수 있다.

본 발명의 박막 트랜지스터에서는 상기 유기 반도체 재료는 고분자계 유기 반도체 재료를 주성분으로 하는 것인 것에 바람직하다.

이것에 의해, 박막 트랜지스터의 특성(스위칭 특성)을 보다 향상시킬 수 있다.

본 발명의 박막 트랜지스터에서는 상기 소스 전극은 상기 유기 반도체층에 직접 접촉하고 있는 것이 바람직하다.

이것에 의해, 유기 반도체층으로의 정공의 주입을 보다 효율 좋게 행할 수 있다.

본 발명의 전자 회로는 본 발명의 박막 트랜지스터를 구비하는 것을 특징으로 한다.

이것에 의해, 신뢰성이 높은 전자 회로를 얻을 수 있다.

본 발명의 유기 일렉트로루미네선스 소자는 본 발명의 전극으로 구성된 양극과,

상기 유기층을 구비하는 유기 일렉트로루미네선스층을 갖는 것을 특징으로 한다.

이것에 의해, 신뢰성이 높은 유기 일렉트로루미네선스 소자를 얻을 수 있다.

본 발명의 표시 장치는 본 발명의 전자 회로를 구비하는 것을 특징으로 한다.

이것에 의해, 신뢰성이 높은 표시 장치를 얻을 수 있다.

본 발명의 표시 장치는 본 발명의 유기 일렉트로루미네선스 소자를 구비하는 것을 특징으로 한다.

이것에 의해, 신뢰성이 높은 표시 장치가 얻어진다.

본 발명의 전자 기기는 본 발명의 표시 장치를 구비하는 것을 특징으로 한다.

이것에 의해, 신뢰성이 높은 전자 기기가 얻어진다.

#### 발명을 실시하기 위한 최량의 형태

이하, 본 발명의 전극, 전극 형성 방법, 박막 트랜지스터, 전자 회로, 유기 일렉트로루미네선스 소자(이하, "유기 EL 소자"라고 함.), 표시 장치 및 전자 기기에 대해서, 도시한 적합 실시 형태에 의하여 상세하게 설명한다.

#### <박막 트랜지스터>

우선, 본 발명의 전극을 적용한 박막 트랜지스터에 대해서 설명한다.

#### <제1 실시 형태>

우선, 본 발명의 박막 트랜지스터의 제1 실시 형태에 대해서 설명한다.

도 1은 본 발명의 박막 트랜지스터의 제1 실시 형태를 나타내는 개략 단면도, 도 2 및 도 3은 각각, 도 1에 나타내는 박막 트랜지스터의 제조 방법을 설명하기 위한 도면(종단면도)이다.

도 1에 나타내는 박막 트랜지스터(1)는 톱 게이트형의 박막 트랜지스터로서, 서로 분리하여 설치된 소스 전극(20a) 및 드레인 전극(20b)과, 소스 전극(20a)과 드레인 전극(20b) 사이에 개재하는 유기 반도체층(30)과, 유기 반도체층(30)과 게이트 전극(50) 사이에 위치하는 게이트 절연층(40)을 갖는 구조를 하고 있고, 또한 기판(10)상에 탑재되어 있다.

이하, 각부의 구성에 대해서 순차 설명한다.

기판(10)은 박막 트랜지스터(1)를 구성하는 각층(각부)을 지지하는 것이다.

기판(10)으로는, 예를 들어, 유리 기판, 폴리에틸렌 테레프탈레이트(PET), 폴리에틸렌 나프탈레이트(PEN), 폴리에틸술폰(PES), 방향족 폴리에스테르(액정 중합체), 폴리아미드(PI) 등으로 구성되는 플라스틱 기판(수지 기판), 석영 기판, 실리콘 기판, 금속 기판, 갈륨 비소 기판 등을 사용할 수 있다.

박막 트랜지스터(1)에 가요성을 부여하는 경우에는, 기판(10)으로는 플라스틱 기판, 혹은 얇은(비교적 막두께가 작은) 금속 기판이 선택된다.

기판(10)상에는 소스 전극(20a) 및 드레인 전극(20b)이 설치되어 있다.

이 중, 소스 전극(20a)은 후술하는 유기 반도체층(30)에 대해서, 정공을 주입하는 전극(본 발명의 전극)을 구성한다.

소스 전극(20a) 및 드레인 전극(20b)은 각각, 복수의 층(본 실시 형태에서는 하지 전극층(21) 및 표면 전극층(22)의 2층)으로 구성되어 있다.

하지 전극층(기부)(21)은 각종의 금속 재료나, 각종의 도전성 산화물 재료 등으로 구성할 수 있지만, 주로 Cu, Ni, Co 또는 이들을 포함하는 합금, 혹은 Ag 또는 Ag를 포함하는 합금으로 구성하는 것이 바람직하다. 이를 금속 재료는 비교적 염가이기 때문에, 박막 트랜지스터(1)의 제조 비용의 저감을 도모할 수 있다.

또한, 후술하는 바와 같이, 표면 전극층(22)이 Cu, Ni, Co중 적어도 1종을 포함하는 산화물, 또는 Ag를 포함하는 산화물을 함유하여 되는 경우, 하지 전극층(21)을 주로 Cu, Ni, Co 또는 이들을 포함하는 합금, 혹은 주로 Ag 또는 Ag를 포함하는 합금으로 구성함으로써, 하지 전극층(21)과 표면 전극층(22)과의 밀착성을 향상시킬 수 있다.

또한, 표면 전극층(22)이 금속 황화물이나 금속 염화물을 함유하여 되는 경우, 하지 전극층(21)을 주로 상기 금속 황화물이나 금속 염화물을 구성하는 금속 또는 이것을 포함하는 합금으로 구성함으로써, 하지 전극층(21)과 표면 전극층(22)의 밀착성을 향상시킬 수 있다.

표면 전극층(유기 반도체층(30)에 가장 가까운 층)(22)은 하지 전극층(21)을 덮도록 설치되어 있다.

표면 전극층(22)은 Cu, Ni, Co중 적어도 1종을 포함하는 산화물, Ag를 포함하는 산화물, 또는 금속 황화물(이하, 간단히 "황화물"이라고 함.) 및 금속 염화물(이하, 간단히 "염화물"이라고 함.) 중 적어도 하나를 함유하여 되는 것이다.

산화물의 구체적인 예로는  $Cu(II)_{1-x}O$  (단,  $0 \leq x < 1$ 이다.),  $Cu(I)_{2(1-x)}O$ (단,  $0 \leq x < 1$ 이다.)로 표시되는 Cu 산화물,  $Ni_{1-x}O$  (단,  $0 \leq x < 1$ 이다.)로 표시되는 Ni 산화물,  $Co_{1-x}O$  (단,  $0 \leq x < 1$ )로 표시되는 Co 산화물,  $Ag(II)_{1-x}O$ (단,  $0 \leq x < 1$ 이다.),  $Ag(I)_{2(1-x)}O$ (단,  $0 \leq x < 1$ 이다.)로 표시되는 Ag 산화물, 또는 이들에 Cu, Ni, Co 이외의 원소(원자)로서, Sr, Al, Ga, Li, Na, K, Rb, Cs중 적어도 1종을 포함하는 복합 산화물 등 중의 1종 또는 2종 이상을 조합한 것을 들 수 있다.

여기서, 일반적으로, 일함수가 큰 금속 재료는 고가의 것이 많고, 역으로, 염가의 금속 재료는 일함수가 낮은 경향이 있다. 또한, 산화물(금속 화합물)은 일반적으로, 금속 단체에 대해서 일함수가 커지는 것이 많다.

따라서, 표면 전극층(22)을 상기 산화물을 함유하는 구성으로 함으로써, 하지 전극층(21)으로 염가의 금속 재료를 사용하면서, 표면 전극층(산화물 함유층)(22)의 일함수를 하지 전극층(21)의 일함수보다 크게 설정하는 것이 용이해진다. 그 결과, 고비용이 되는 것을 방지하면서, 유기 반도체층(30)으로의 정공의 주입 효율이 높은 소스 전극(20a)을 얻을 수 있다.

또한, 산화물은 금속 단체보다 유기 재료에 대한 활성(유기 재료를 변질, 열화시키는 작용)이 낮다. 이 때문에, 소스 전극(20a) 및 드레인 전극(20b)과 접촉하는 유기층(본 실시 형태에서는 유기 반도체층(30))의 변질, 열화를 적합하게 방지 또는 억제할 수 있고, 결과적으로, 박막 트랜지스터(1)의 내구성의 향상을 도모할 수 있다.

또한 Cu, Ni, Co, Ag 이외에, Sr, Al, Ga, Li, Na, K, Rb, Cs중 적어도 1종을 포함하는 복합 산화물은 캐리어인 홀(정공)의 밀도를 높게, 정밀도 좋게 제어할 수 있다. 이 때문에, 박막 트랜지스터(1)에서는 전기 전도도를 높여 홀(정공)의 주입을 보다 효율 좋게 행하는 것이 가능하다.

또한, 이상에서는 산화물을 대표로 설명했지만, 같은 것이 황화물 및 클로라이드라도 말할 수 있다. 따라서, 표면 전극층(22)을 황화물 및 염화물 중 적어도 하나를 함유하는 구성으로 함으로써도, 상기 산화물을 함유하는 경우와 같은 효과가 얻어진다.

황화물로는 Cu를 포함하는 황화물을 주로 하는 것이 적합하고, 염화물로는 Ag를 포함하는 염화물을 주로 하는 것이 적합하다. 황화물 및 염화물로서, 각각, 이들을 사용함에 의하여, 소스 전극(20a)을 정공의 주입 효율이 보다 높은 것으로 할 수 있다.

Cu를 포함하는 황화물의 구체적인 예로는  $\text{Cu(II)}_{1-x}\text{S}$ (단,  $0 \leq x < 1$ 이다.),  $\text{Cu(I)}_{2(1-x)}\text{S}$ (단,  $0 \leq x < 1$ 이다.), 또는 이들에 Cu이외의 원소(원자)로서, Sr, Al, Ga, Li, Na, K, Rb, Cs중 적어도 1종을 포함하는 복합 황화물 등 중의 1종 또는 2종 이상을 조합한 것을 들 수 있다.

한편, Ag를 포함하는 염화물의 구체적인 예로는  $\text{Ag(II)}_{1-x}\text{Cl}$ (단,  $0 \leq x < 1$ 이다.),  $\text{Ag(I)}_{2(1-x)}\text{Cl}$ (단,  $0 \leq x < 1$ 이다.), 또는 이들에 Ag 이외의 원소(원자)로서, Sr, Al, Ga, Li, Na, K, Rb, Cs중 적어도 1종을 포함하는 복합 황화물 등 중의 1종 또는 2종 이상을 조합한 것을 들 수 있다.

또한, 표면 전극층(22)의 두께(평균)는 특별히 한정되지 않지만, 상술한 바와 같은 산화물, 황화물이나 염화물의 전기 전도도는 금속(금속 단체)과 비교하여 낮기 때문에, 가능한 한 얇고(작고) 또한 균일한 것이 바람직하다.

구체적으로는 표면 전극층(22)의 두께(평균)는 0.1~50nm정도인 것이 바람직하고, 0.5~10nm정도인 것이 보다 바람직하다. 표면 전극층(22)이 너무 얕으면, 산화물, 황화물이나 염화물의 함유율 등에 따라서는 정공의 주입 효율을 향상시키는 효과, 소스 전극(20a) 및 드레인 전극(20b)에 접촉하는 유기층의 변질, 열화를 방지하는 효과가 충분히 발휘되지 않을 우려가 있다. 한편, 표면 전극층(22)이 너무 두꺼우면, 소스 전극(20a) 및 드레인 전극(20b)의 도전성이 매우 저하할 우려가 있다.

표면 전극층(22)에서, 상기 산화물, 황화물이나 염화물의 함유량(함유율)은 가능한 한 많은 편이 바람직하다. 구체적으로는 그 함유량은 50wt% 이상인 것이 바람직하고, 75wt% 이상인 것이 보다 바람직하다. 표면 전극층(22)에서, 산화물, 황화물이나 염화물의 함유량이 상기 하한값 미만의 경우에는 표면 전극층(22)의 두께 등에 따라서는 정공의 주입 효율을 향상시키는 효과, 소스 전극(20a) 및 드레인 전극(20b)에 접촉하는 유기층의 변질, 열화를 방지하는 효과가 충분히 발휘되지 않을 우려가 있다.

또한, 소스 전극(20a) 및 드레인 전극(20b)의 두께(평균)는 특별히 한정되지 않지만, 각각, 10~2000nm정도인 것이 바람직하고, 50~1000nm정도인 것이 보다 바람직하다.

소스 전극(20a) 및 드레인 전극(20b)에 접촉하도록, 유기 반도체층(정공을 수송하는 기능을 갖는 유기층)(30)이 설치되어 있다.

이 유기 반도체층(30)은 주로 p형의 유기 반도체 재료로 구성되어 있다. p형의 유기 반도체 재료로는 중합체 유기 반도체 재료(고분자계 유기 반도체 재료), 저분자계 유기 반도체 재료의 어느 것이나 사용 가능하다.

중합체 유기 반도체 재료로는, 예를 들어, 폴리(3-알킬티오펜), 폴리(3-헥실티오펜)(P3HT), 폴리(3-옥틸티오펜), 폴리(2,5-티에닐렌비닐렌)(PTV), 폴리(파라-페닐렌비닐렌)(PPV), 폴리(9,9-디옥틸플루오렌)(PFO), 폴리(9,9-디옥틸플루오렌-코-비스-N,N'-(4-메톡시페닐)-비스-N,N'-페닐-1,4-페닐렌디아민)(PFMO), 폴리(9,9-디옥틸플루오렌-코-벤조티아디아졸)(BT), 폴루오렌-트리알릴아민 공중합체, 트리알릴아민계 중합체, 폴리(9,9-디옥틸플루오렌-코-디티오펜)(F8T2)과 같은 폴루오렌-비티오펜 공중합체 등을 들 수 있다.

저분자계 유기 반도체의 예로는 C60, 혹은 금속 프탈로시아닌 혹은 그들의 치환 유도체, 혹은 안트라센, 테트라센, 펜타센, 헥사센 등의 아센 분자 재료, 혹은  $\alpha$ -올리고 티오펜류, 구체적으로는 쿼터티오펜(4T), 섹시티오펜(6T), 옥티티오펜(8T), 디헥실쿼터티오펜(DH4T), 디헥실섹시티오펜(DH6T) 등을 들 수 있다.

또한, p형의 유기 반도체 재료로는 중합체 유기 반도체 재료를 주성분으로 하는 것이 적합하다. p형의 유기 반도체 재료로서, 중합체 유기 반도체 재료를 주성분으로 하는 것을 사용함으로써, 유기 반도체층(30)의 형성(성막)을 보다 용이하게 또한 저비용으로 행할 수 있다.

이 유기 반도체층(30)의 두께(평균)는 특별히 한정되지 않지만, 0.1~1000nm정도인 것이 바람직하고, 1~500nm정도인 것이 보다 바람직하고, 1~100nm정도인 것이 더욱 바람직하다.

유기 반도체층(30)상에는 게이트 절연층(40)이 설치되어 있다.

이 게이트 절연층(40)의 구성 재료로는 공자의 게이트 절연체 재료이면, 종류는 특별히 한정되지 않으며, 유기 재료, 무기 재료의 어느 것이나 사용 가능하다.

유기 재료로는 폴리메틸메타크릴레이트, 폴리비닐페놀, 폴리이미드, 폴리스티렌, 폴리비닐알콜, 폴리비닐아세테이트 등을 들 수 있고, 이를 중의 1종 또는 2종 이상을 조합하여 사용할 수 있다.

한편, 무기 재료로는 실리카, 질화규소, 산화알루미늄, 산화탄탈 등의 금속 산화물, 티탄산바륨 스트론튬, 지르코늄 티탄산납 등의 금속 복합 산화물을 들 수 있고, 이를 중의 1종 또는 2종 이상을 조합하여 사용할 수 있다.

게이트 절연층(40)의 두께(평균)는 특별히 한정되지 않지만, 10~5000nm정도인 것이 바람직하고, 50~1000nm정도인 것이 보다 바람직하다. 게이트 절연층(40)의 두께를 상기 범위로 함으로써, 소스 전극(20a) 및 드레인 전극(20b)과 게이트 전극(50)을 확실히 절연하면서, 박막 트랜지스터(1)의 동작 전압을 낮게 할 수 있다.

또한, 게이트 절연층(40)은 단층 구성의 것에 한정되지 않고, 복수층의 적층 구성의 것이라도 좋다.

게이트 절연층(40)상의 소정 위치, 즉, 게이트 전극(20a)과 드레인 전극(20b) 사이의 영역에 대응하는 위치에는 게이트 전극(50)이 설치되어 있다.

이 게이트 전극(50)의 구성 재료로는 공지의 전극 재료이면, 종류는 특별히 한정되는 것이 아니다. 구체적으로는 Cr, Al, Ta, Mo, Nb, Cu, Ag, Au, Pd, In, Ni, Nd, Co 또는 이들을 포함하는 합금과 같은 금속 재료, 및 그들의 산화물을 등을 사용할 수 있다.

또한, 게이트 전극(50)은 도전성 유기 재료로 구성할 수도 있다.

게이트 전극(50)의 두께(평균)는 특별히 한정되지 않지만, 0.1~2000nm정도인 것이 바람직하고, 1~1000nm정도인 것이 보다 바람직하다.

이러한 박막 트랜지스터(1)에서는 소스 전극(20a)과 드레인 전극(20b) 사이에 전압을 인가한 상태에서, 게이트 전극(50)에 게이트 전압을 인가하면, 유기 반도체층(30)의 게이트 절연층(40)과의 계면 부근에 채널이 형성되어, 채널 영역을 캐리어(정공)가 이동함으로써, 소스 전극(20a)과 드레인 전극(20b) 사이에 전류가 흐른다.

즉, 게이트 전극(50)에 전압이 인가되지 않은 OFF 상태에서는, 소스 전극(20a)과 드레인 전극(20b) 사이에 전압을 인가해도, 유기 반도체층(30)중에 거의 캐리어가 존재하지 않기 때문에, 미소한 전류 밖에 흐르지 않는다. 한편, 게이트 전극(50)에 전압이 인가되어 있는 ON 상태에서는, 유기 반도체층(30)의 게이트 절연층(40)에 접한 부분에 전하가 유기(誘起)되어, 채널(캐리어의 유로)이 형성된다. 이 상태에서 소스 전극(20a)과 드레인 전극(20b) 사이에 전압을 인가하면, 채널 영역을 통하여 전류가 흐른다.

이러한 박막 트랜지스터(1)는 예를 들어, 다음과 같이 하여 제조할 수 있다.

도 1에 나타내는 박막 트랜지스터(1)의 제조 방법(제1 제조 방법)은 기판(10)상에 소스 전극(20a) 및 드레인 전극(20b)을 형성하는 공정[A1]과, 소스 전극(20a) 및 드레인 전극(20b)을 덮도록 유기 반도체층(30)을 형성하는 공정[A2]과, 유기 반도체층(30)상에 게이트 절연층(40)을 형성하는 공정[A3]과, 게이트 절연층(40)상에 게이트 전극(50)을 형성하는 공정[A4]을 갖고 있다.

#### [A1] 소스 전극 및 드레인 전극 형성 공정

##### [A1-1] 하지 전극층 형성 공정

기판(10)상에, 하지 전극층(21)을 형성한다(도 2의 (a) 참조.).

이하의 전극층(21)은 예를 들어, 에칭법, 리프트 오프법 등을 사용하여 형성할 수 있다.

에칭법에 의해 하지 전극층(21)을 형성하는 경우에는 I: 우선, 예를 들어, 스퍼터법, 증착법, 도금법 등을 사용하여, 기판(10)의 전체면에 막두께 10nm~10μm 범위로 금속막(금속층)을 성막한다. II: 다음에, 예를 들어 포토레지스트법, 마이크로 콘택트 프린팅법 등을 사용하여, 금속막상(표면)에 레지스트 층을 형성한다. III: 다음에, 이 레지스트 층을 마스크로 사용하여, 금속막에 에칭을 실시하여, 소정의 형상으로 패터닝한다.

또한, 리프트 오프법에 의해 하지 전극층(21)을 형성하는 경우에는 I: 우선, 하지 전극층(21)을 형성하는 이외의 부분을 덮도록, 레지스트 층을 형성한다. II: 다음에, 예를 들어, 증착법, 도금법 등을 사용하여, 기판(10)의 레지스트 층의 전면에, 막두께 10nm~10μm 범위로 금속막(금속층)을 성막한다. III: 다음에, 레지스트 층을 제거한다.

##### [A1-2] 표면 전극층 형성 공정

다음에, 표면 전극층(산화물 함유층)(22)을, 하지 전극층(21)의 표면을 덮도록 형성한다.

표면 전극층(22)은 표면 전극층(22)의 구성 재료를 하지 전극층(21)상에 퇴적시켜, 피막(피복층)(220)을 형성한 후, 이 피막(220)의 불요 부분을 제거함으로써 형성할 수 있다.

우선, 기판(10)의 하지 전극층(21)이 형성된 측의 면에, 피막(220)을 형성한다(도 2의 (b) 참조.).

피막(220)의 형성에는 예를 들어, 레이저 어브레이션법, 스퍼터법(예를 들어, 리액티브 DC 마그네트론 스퍼터법), CVD법, 증착법 등을 사용할 수 있다.

예를 들어, Cu 산화물, Ni 산화물, Co 산화물 또는 Ag 산화물을 함유하는 피막(220)을, 리액티브 DC 마그네트론 스퍼터법을 사용하여 형성하는 경우에는 금속 Cu, 금속 Ni, 금속 Co 또는 금속 Ag를 타겟으로 사용하여, 다음과 같은 조건으로 행할 수 있다.

가스 도입전의 챔버내의 압력(도달 진공도)은  $1\times10^{-2}$ Pa이하인 것이 바람직하고,  $1\times10^{-3}$ Pa이하인 것이 보다 바람직하다.

도입 가스는 산소 가스와 불활성 가스(예를 들어 아르곤, 헬륨 등)의 혼합 가스를 사용하는 것이 바람직하다.

가스 도입후의 챔버내의 압력(성막시의 압력)은 0.1~10Pa 정도인 것이 바람직하고, 0.5~5Pa 정도인 것이 보다 바람직하다.

DC 파워는 10~200W 정도인 것이 바람직하고, 20~100W 정도인 것이 보다 바람직하다.

이상과 같은 조건으로, 산소 가스와 불활성 가스의 혼합비를 적당히 설정함으로써, 피막(220)(표면 전극층(22))에서, 산화물과 금속 단체의 비율을 소망의 것으로 설정할 수 있다.

또한, 산소 가스 대신에, 예를 들어 황화수소 등의 황계 가스를 사용함으로써, 황화물을 포함하는 피막(220)을, 또한, 예를 들어 염화수소, 염소 등의 염소계 가스를 사용함으로써, 염화물을 포함하는 피막(220)을 각각 형성할 수 있다.

또한, 예를 들어,  $\text{SrCu}_2\text{O}_2$ ,  $\text{CuAlO}_2$ ,  $\text{CuGaO}_2$  등의 복합 산화물을 주재료로 하는 피막(220)을 레이저 어브레이션법을 사용하여 형성하는 경우에는 퇴적시키는 복합 산화물에 대응하는 조성의 복합 산화물 소결체를 타겟으로 사용하여, 산소 가스를 공급하면서, 다음과 같은 조건으로 행할 수 있다.

가스 도입전의 챔버내의 압력(도달 진공도)은  $1\times10^{-4}$ Pa 이하인 것이 바람직하고,  $1\times10^{-6}$ Pa 이하인 것이 보다 바람직하다.

조사하는 레이저광은 파장이 150~300nm정도, 펄스 길이가 1~30ns 정도의 펄스광이 바람직하고, 구체적으로는 ArF 엑시머 레이저, KrF 엑시머 레이저가 적합하게 사용된다.

이 레이저광의 에너지 밀도는  $1\text{J/cm}^2$  이상인 것이 바람직하고,  $2\sim6\text{J/cm}^2$  정도인 것이 보다 바람직하다.

산소 가스 도입후의 챔버내의 압력(성막시의 압력)은 0.1~100Pa 정도인 것이 바람직하고, 1~10Pa 정도인 것이 보다 바람직하다.

또한, 염화물을 포함하는 피막(220)은, 예를 들어 염화수소 수용액 등 중에서, 하지 전극층(21)으로 통전하여 전기 분해 처리를 행하여, 하지 전극층(21)의 표면에 염화물을 석출시킴으로써 형성할 수도 있다.

또한, 기판(10)으로서, 플라스틱 기판 등의 가요성 기판을 사용하는 경우에는, 얻어진 피막(220)에 대해서, 광조사법 등을 사용하여, 피막(220)의 결정화를 촉진시키는 처리를 실시하는 것이 바람직하다.

또한, 기판(10)으로서, 석영 기판 등의 경질 기판을 사용하는 경우에는, 예를 들어 200~800°C 정도로 기판(10)을 가열하면서 성막을 행함으로써, 결정성이 높은 피막(220)을 얻을 수 있다.

다음에, 포토리소그래피법, 마이크로 콘택트 프린팅법 등에 의해서 소스 전극(20a) 및 드레인 전극(20b)에 대응하는 형상의 레지스트 층을 형성한다. 이 레지스트 층을 마스크로 사용하여, 피막(220)의 불요 부분을 제거한다(도 2의 (c) 참조.). 이것에 의해, 하지 전극층(21)상에 표면 전극층(22)이 형성되어, 소스 전극(20a) 및 드레인 전극(20b)이 얻어진다.

이 피막(220)의 제거에는, 예를 들어, 플라즈마 에칭, 리액티브 이온 에칭, 범 에칭, 광어시스트 에칭 등의 물리적 에칭법, 웨트 에칭 등의 화학적 에칭법 등 중의 1종 또는 2종 이상을 조합하여 사용할 수 있다.

이와 같이 하여, 소스 전극(20a) 및 드레인 전극(20b)을 형성함으로써, 증착원이나 타겟이 함유하는 산화물의 양이나, 성막 분위기 중에 도입하는 산소 가스 유량 등을 제어하는 간단한 작업으로, 표면 전극층(22)이 함유하는 산화물의 양을 비교적 정밀하게 제어할 수 있다. 또한, 성막 분위기중에 도입하는 황계 가스나 염소계 가스의 유량 등을 제어하는 간단한 작업으로, 표면 전극층(22)이 함유하는 황화물이나 염화물의 양을 비교적 정밀하게 제어할 수 있다. 이것에 의해, 소스 전극(20a) 및 드레인 전극(20b)의 일함수 등의 특성을 용이하게 또한 정확하게 조정할 수 있다.

## [A2] 유기 반도체층 형성 공정

다음에, 소스 전극(20a) 및 드레인 전극(20b)을 덮도록, 유기 반도체층(30)을 형성한다(도 2의 (d) 참조.). 이때, 소스 전극(20a)과 드레인 전극(20b) 사이에는 채널 영역이 형성된다.

유기 반도체층(30)은 중합체 유기 반도체 재료(고분자계 유기 반도체 재료)로 구성하는 경우, 스판 코터 방식이나 딥 방식 등을 사용한 도포법, 잉크젯 방식이나 스크린 인쇄 방식 등을 사용한 인쇄법 등을 사용하여 형성할 수 있다.

또한, 유기 반도체층(30)은 저분자계 유기 반도체 재료로 구성하는 경우, 증착법 혹은 전구체를 사용하여 가용성으로 함으로써, 스펜 코터 방식이나 딥 방식 등을 사용한 도포법, 잉크젯 방식이나 스크린 인쇄 방식 등을 사용한 인쇄법 등을 사용하여 도막을 형성한 후, 이 도막에 대해서 어닐 처리를 행함으로써, 소망한 것으로 형성할 수 있다.

또한, 유기 반도체층(30)의 형성 영역은 도시한 구성에 한정되지 않고, 유기 반도체층(30)은 소스 전극(20a)과 드레인 전극(20b) 사이의 영역(채널 영역)에만 형성해도 좋다. 이것에 의해, 동일 기판상에, 복수의 박막 트랜지스터(소자)(1)을 병렬하는 경우에, 각 소자의 유기 반도체층(30)을 독립하여 형성함으로써, 리크 전류, 각 소자간의 크로스 토크를 억제할 수 있다. 또한, 유기 반도체 재료의 사용량을 삭감할 수 있어, 제조 비용의 삭감을 도모할 수 있다.

#### [A3] 게이트 절연층 형성 공정

다음에, 유기 반도체층(30)상에, 게이트 절연층(40)을 형성한다(도 3의 (e) 참조.).

예를 들어, 게이트 절연층(40)을 유기 고분자 재료로 구성하는 경우, 게이트 절연층(40)은 유기 고분자 재료 또는 그 전구체를 함유하는 용액을, 유기 반도체층(30)상을 덮도록 도포(공급)한 후, 필요에 따라서, 이 도막에 대해서 후처리(예를 들어 가열, 적외선의 조사, 초음파의 부여 등)을 실시함으로써 형성할 수 있다.

유기 고분자 재료 또는 그 전구체를 함유하는 용액을, 유기 반도체층(30)상에 도포(공급)하는 방법으로는 상기 공정 [A2]에서 든 도포법, 인쇄법 등을 사용할 수 있다.

또한, 게이트 절연층(40)을 무기 재료로 구성하는 경우, 게이트 절연층(40)은 예를 들어, 열산화법, CVD법, SOG법에 의해 형성할 수 있다. 또한, 원재료로 폴리실라잔을 사용함으로써, 게이트 절연층(40)으로서, 실리카막, 질화규소막을 습식 공정으로 성막할 수 있다.

#### [A4] 게이트 전극 형성 공정

다음에, 게이트 절연막(40)상에, 게이트 전극(50)을 형성한다(도 3의 (f) 참조.).

우선, 금속막(금속층)을 형성한다.

이것은 예를 들어, 플라즈마 CVD, 열 CVD, 레이저 CVD와 같은 화학 증착법(CVD), 진공 증착, 스퍼터링(저온 스퍼터링), 이온 플레이팅 등의 건식 도금법, 전해 도금, 침지 도금, 무전해 도금 등의 습식 도금법, 용사법, 콜·겔법, MOD법, 금속박의 접합 등에 의해 형성할 수 있다.

이 금속막상에, 레지스트 재료를 도포한 후에 경화시켜, 게이트 전극(50)의 형상에 대응하는 형상의 레지스트 층을 형성한다. 이 레지스트 층을 마스크로 사용하여, 금속막의 불요 부분을 제거한다.

이 금속막의 제거에는 예를 들어, 플라즈마 에칭, 리액티브 이온 에칭, 빔 에칭, 광어시스트 에칭 등의 물리적 에칭법, 웨트 에칭 등의 화학적 에칭법 등 중의 1종 또는 2종 이상을 조합하여 사용할 수 있다.

그 후, 레지스트 층을 제거함으로써, 게이트 전극(50)이 얻어진다.

또한, 게이트 전극(50)은 게이트 절연층(40)상에, 예를 들어, 도전성 입자나, 도전성 유기 재료를 함유하는 도전성 재료를 도포(공급)하여 도막을 형성한 후, 필요에 따라서, 이 도막에 대해서 후처리(예를 들어 가열, 적외선의 조사, 초음파의 부여 등)을 실시함으로써 형성할 수도 있다.

도전성 입자를 함유하는 도전성 재료로는 금속 미립자를 분산시킨 용액, 도전성 입자를 함유하는 중합체 혼합물 등을 들 수 있다.

또한, 도전성 유기 재료를 함유하는 도전성 재료로는 도전성 유기 재료의 용액 또는 분산액을 들 수 있다.

게이트 절연층(40)상에 도전성 재료를 도포(공급)하는 방법의 예로는, 스펜 코트법, 캐스팅법, 마이크로 그라비아 코트법, 그라비아 코트법, 바 코트법, 롤 코트법, 와이어 바 코트법, 딥 코트법, 스프레이 코트법과 같은 도포법, 스크린 인쇄법, 프레소 인쇄법, 오프셋 인쇄법, 잉크젯법, 마이크로 콘택트 프린팅법과 같은 인쇄법 등을 들 수 있고, 이를 중의 1종 또는 2종 이상을 조합하여 사용할 수 있다.

이상과 같은 공정을 거쳐서, 제1 실시 형태의 박막 트랜지스터(1)가 얻어진다.

또한, 본 실시 형태에서는 소스 전극(20a) 및 드레인 전극(20b)은 각각, 하지 전극층(21)과 표면 전극층(22)의 2층 구성이지만, 본 발명에서는 이들의 층(21, 22) 사이나, 하지 전극층(21)의 기판(10)측에는 필요에 따라서, 임의 목적(예를 들어 밀착성의 향상 등)으로, 1층 또는 2층 이상을 추가할 수도 있다.

이 경우, 복수층 중, 유기 반도체층(30)에 가장 가까운 층(최외층)의 일함수를 가장 크게 하면 좋다. 이것에 의해, 유기 반도체층(30)으로의 보다 효율이 좋게 정공의 주입이 가능해진다.

또한, 본 발명에서는 소스 전극(20a)이 상술한 바와 같은 구성이면 좋고, 드레인 전극(20b)은 소스 전극(20a)과 다른 구성이라도 좋다. 또한, 제조 비용을 저감시키는 관점에서는 소스 전극(20a) 및 드레인 전극(20b)은 동일한 구성으로 하는 것이 바람직하다.

또한 본 발명에서는 소스 전극(20a) 및 드레인 전극(20b)과 유기 반도체층(30) 사이, 유기 반도체층(30)과 게이트 절연층(40) 사이, 게이트 절연층(40)과 게이트 전극(50) 사이에는 각각, 임의 목적으로, 1층 또는 2층 이상을 추가 할 수도 있다.

## <제2 실시 형태>

다음에, 본 발명의 박막 트랜지스터의 제2 실시 형태에 대해서 설명한다.

도 4는 본 발명의 박막 트랜지스터의 제2 실시 형태를 나타내는 개략 단면도, 도 5는 도 4에 나타내는 박막 트랜지스터의 제조 방법을 설명하기 위한 도면(종단면도)이다.

이하, 제2 실시 형태의 박막 트랜지스터(1)에 대해서, 상기 제1 실시 형태와의 차이점을 중심으로 설명하고, 같은 사항에 대해서는 그 설명을 생략한다.

제2 실시 형태의 박막 트랜지스터(1)는 소스 전극(20a) 및 드레인 전극(20b)의 구성이 다르고, 그 이외는 상기 제1 실시 형태의 박막 트랜지스터(1)와 같다.

즉, 소스 전극(20a) 및 드레인 전극(20b)은 각각 단층 구성을 이루고, 그의 적어도 유기 반도체층(30)측의 면(도 4에 나타내는 구성에서는 표면을 포함하는 소정 두께의 부분, 이하 "표면 부근"이라고 함.)에, Cu, Ni, Co 중 적어도 1종을 포함하는 산화물, Ag를 포함하는 산화물, 또는 황화물 및 염화물 중 적어도 하나를 함유하여 되는 것이다.

산화물의 구체적인 예로는 상기 제1 실시 형태에서 든 것과 같은 것, 즉,  $Cu(II)_{1-x}O$  (단,  $0 \leq x < 1$ 이다.),  $Cu(I)_{2(1-x)}O$  (단,  $0 \leq x < 1$ 이다.)로 표시되는 Cu 산화물,  $Ni_{1-x}O$  (단,  $0 \leq x < 1$ 이다.)로 표시되는 Ni 산화물,  $Co_{1-x}O$  (단,  $0 \leq x < 1$ )로 표시되는 Co 산화물,  $Ag(II)_{1-x}O$  (단,  $0 \leq x < 1$ 이다.),  $Ag(I)_{2(1-x)}O$  (단,  $0 \leq x < 1$ 이다.)로 표시되는 Ag 산화물, 또는 이들에 Cu, Ni, Co 이외의 원소(원자)로서, Sr, Al, Ga, Li, Na, K, Rb, Cs 중 적어도 1종을 포함하는 복합 산화물 등 중의 1종 또는 2종 이상을 조합한 것을 들 수 있다.

황화물 및 염화물을, 각각, 상기 제1 실시 형태에서 든 것과 같은 것, 즉, Cu를 포함하는 황화물을 주로 하는 것 및 Ag를 포함하는 염화물을 주로 하는 것이 적합하다.

또한, 본 실시 형태의 소스 전극(20a) 및 드레인 전극(20b)에서는 산화물, 황화물이나 염화물을 함유하는 부분(도 4 중, 영역 X)에서, 산화물, 황화물이나 염화물의 함유량은 각각, 50wt% 이상인 것이 바람직하고, 75wt% 정도인 것 이 보다 바람직하다.

이 영역 X의 두께(평균)는 0.1~50nm정도인 것이 바람직하고, 0.5~10nm정도인 것이 보다 바람직하다.

이러한 박막 트랜지스터(1)는 예를 들어, 다음과 같이 하여 제조할 수 있다.

### [B1] 소스 전극 및 드레인 전극 형성 공정

우선, 기판(10)상에, 소스 전극(20a) 및 드레인 전극(20b)으로 되는 금속막(금속층)(20)을 형성한다(도 5의 (a) 참조.).

이 금속막(20)의 형성은 상기 제1 실시 형태의 하지 전극층(21)의 형성에서 설명한 것과 동일하게 하여 행할 수 있지만, 성막 방법으로서, 도금법(습식 도금법)을 사용하는 것이 바람직하다. 도금법에 의하면, 진공 장치 등의 대규모 장치를 사용하지 않고서, 높은 성막 정밀도로, 소망한 막두께의 금속막(20)을 성막할 수 있다.

또한, 도금법 중에서도, 무전해 도금법을 사용하는 것이 보다 바람직하다. 이것에 의해, 보다 높은 성막 정밀도로 금 속막(20)을 성막할 수 있다.

다음에, 금속막(20)에 산화 처리를 실시한다(도 5의 (b) 참조.). 이것에 의해, 금속막(20)의 표면 부근이 산화되어, 금 속막(20)의 구성 재료에 대응한 산화물이 생성된다. 그 결과, 표면 부근에 산화물을 함유하는 소스 전극(20a) 및 드 레인 전극(20b)이 얻어진다.

이 산화물로는 상기한 바와 같은 것이 바람직하므로, 금속막(20)은 주로 Cu, Ni, Co 또는 이들을 포함하는 합금, 혹은 Ag 또는 Ag를 포함하는 합금으로 구성된다.

합금의 예로는 Cu-Ni 합금, Cu-Co 합금, Ni-Co 합금, Cu, Ni, Co 및 Ag 중 적어도 1종과, Sr, Al, Ga, Li, Na, K, Rb 및 Cs 중 적어도 1종의 합금 등을 수 있다.

또한, 금속막(20)의 형성에 무전해 도금법을 사용함으로써, 소망한 조성의 것이 용이하게 또한 확실하게 얻어진다.

또한, 산화 처리 방법으로는, 예를 들어, 산소를 포함하는 분위기 중에서 플라즈마 처리를 행하는 방법(산소 플라즈마 법), 열산화법, 양극 산화법 등을 들 수 있고, 이들 중의 1종 또는 2종 이상을 조합하여 사용할 수 있다.

이들 중에서도, 산화 처리 방법으로는, 산소 플라즈마 법을 사용하는 것이 바람직하다. 이것에 의해, 소스 전극(20a) 및 드레인 전극(20b)은 각각, 그 표면에 균일하게 산화물을 함유하게 된다. 이것에 의해, 유기 반도체층(30)에 불균일이 없이(균일하게) 정공을 주입(공급)할 수 있게 된다.

또한, 산소 플라즈마 법을 사용함으로써, 금속막(20)의 산화뿐만 아니라, 금속막(20)의 표면에 존재하는 유기물도 동시에 제거할 수 있다.

이렇게 하여, 유기 반도체층(30)으로의 정공의 주입 효율이 보다 높은 게이트 전극(20a)을 얻을 수 있다.

또한 이 산소 플라즈마 처리는 감압(진공)하에서 행하는 것이 좋지만, 대기압하에서 행하는 것인 것이 바람직하다. 이것에 의해, 금속막(20)의 산화 처리를 용이하게 또한 저비용으로 행할 수 있다.

또한, 표면 부근에 황화물을 함유하는 소스 전극(20a) 및 드레인 전극(20b)은 각각, 예를 들어 황화수소 등의 황을 함유하는 분위기중에서, 금속막(20)에 대해서 소정의 조건으로 열처리를 행함으로써 얻어진다.

또한, 표면 부근에 염화물을 함유하는 소스 전극(20a) 및 드레인 전극(20b)은 각각, 예를 들어 염화수소, 염소 등의 염소를 함유하는 분위기중에서, 금속막(20)에 대해서 소정의 조건으로 열처리 등을 행함으로써 얻어진다.

#### [B2] 유기 반도체층 형성 공정

상기 공정[A2]과 같은 공정을 행한다.

#### [B3] 게이트 절연층 형성 공정

상기 공정[A3]과 같은 공정을 행한다.

#### [B4] 게이트 전극 형성 공정

상기 공정[A4]과 같은 공정을 행한다.

이상과 같은 공정을 거쳐서, 제2 실시 형태의 박막 트랜지스터(1)가 얻어진다.

이러한 제2 실시 형태의 박막 트랜지스터(1)에 의해서도, 상기 제1 실시 형태의 박막 트랜지스터(1)와 같은 작용·효과가 얻어진다.

#### <제3 실시 형태>

다음에, 본 발명의 박막 트랜지스터의 제3 실시 형태에 대해서 설명한다.

도 6은 본 발명의 박막 트랜지스터의 제3 실시 형태를 나타내는 개략 단면도이다. 이하, 제3 실시 형태의 박막 트랜지스터에 대해서, 상기 제1 실시 형태와의 차이점을 중심으로 설명하고, 같은 사항에 대해서는 그 설명을 생략한다.

제3 실시 형태의 박막 트랜지스터(1)는 전체 구성이 다르고, 그 이외는 상기 제1 실시 형태의 박막 트랜지스터(1)와 같다.

즉, 도 6에 나타내는 박막 트랜지스터(1)는 게이트 전극(50)이 게이트 절연층(40)을 통하여, 소스 전극(20a) 및 드레인 전극(20b)보다 기판(10)측에 위치하는 보텀 게이트형의 박막 트랜지스터이다.

또한, 소스 전극(20a) 및 드레인 전극(20b)이 각각, 상기 제1 실시 형태와 같은 구성으로 되어 있다.

이러한 박막 트랜지스터(1)는 예를 들어, 다음과 같이 하여 제조할 수 있다.

도 6에 나타내는 박막 트랜지스터(1)는 기판(10)상에 게이트 전극(50)을 형성하는 공정[C1]과, 게이트 전극(50)을 덮도록 게이트 절연층(40)을 형성하는 공정[C2]과, 게이트 절연층(40)상에 소스 전극(20a) 및 드레인 전극(20b)을 형성하는 공정[C3]과, 소스 전극(20a), 드레인 전극(20b) 및 게이트 절연층(40)을 덮도록 유기 반도체층(30)을 형성하는 공정[C4]을 갖고 있다.

#### [C1] 게이트 전극 형성 공정

상기 공정[A4]과 같은 공정을 행한다.

특히, 상술한 것과 같은 이유에서, 예를 들어, 예치법, 리프트 오프법 등을 사용하여, 상기 제1 실시 형태에서 설명한 것과 같은 금속막을 형성하는 것이 적합하다.

#### [C2] 게이트 절연층 형성 공정

상기 공정[A3]과 같은 공정을 행한다.

다음 공정[C3]에서, 게이트 절연층(40)상에, 예를 들어, 주로 Cu, Ni, Co 또는 이들을 포함하는 합금, 혹은 Ag 또는 Ag를 포함하는 합금(금속 재료)으로 구성된 하지 전극층(21)을 형성하므로, 게이트 절연층(40)은 상기 제1 실시 형태에서 든 무기 재료를 사용하여 구성하는 것이 바람직하다.

#### [C3] 소스 전극 및 드레인 전극 형성 공정

상기 공정[A1]과 같은 공정을 행한다.

#### [C4] 유기 반도체층 형성 공정

상기 공정[A2]과 같은 공정을 행한다.

이상과 같은 공정을 거쳐서, 제3 실시 형태의 박막 트랜지스터(1)가 얻어진다.

이러한 제3 실시 형태의 박막 트랜지스터(1)에 의해서도, 상기 제1 실시 형태의 박막 트랜지스터(1)와 같은 작용·효과가 얻어진다.

또한 제3 실시 형태의 박막 트랜지스터(1)는 보텀 게이트형이므로, 다음과 같은 이점도 갖는다.

즉, 유기 반도체 재료는 무기 반도체 재료와 비교하여, 열, 및, 산, 알칼리에 대한 내성이 비교적 낮은 것이 많지만, 본 실시 형태와 같은 보텀 게이트형의 구조를 채용함으로써, 게이트 전극(50), 게이트 절연층(40), 소스 전극(20a) 및 드레인 전극(20b)을 형성한 후에, 유기 반도체층(30)을 형성할 수 있다. 이 때문에, 상기 공정[C1]~[C3]에서, 보다 높은 온도에서의 처리 방법이나, 황산 등의 강산을 사용한 처리 방법 등, 보다 최적인 공정 조건을 선택할 수 있다. 그 결과, 얻어지는 박막 트랜지스터(1)의 특성(스위칭 특성)을 보다 향상시킬 수 있다.

### <제4 실시 형태>

다음에, 본 발명의 박막 트랜지스터의 제4 실시 형태에 대해서 설명한다.

도 7은 본 발명의 박막 트랜지스터의 제4 실시 형태를 나타내는 개략 단면도이다.

이하, 제4 실시 형태의 박막 트랜지스터에 대해서, 상기 제1~제3 실시 형태와의 차이점을 중심으로 설명하고, 같은 사항에 대해서는 그 설명을 생략한다.

제4 실시 형태의 박막 트랜지스터(1)는 전체 구성이 다르고, 그 이외는 상기 제2 실시 형태의 박막 트랜지스터(1)와 같다.

즉, 도 7에 나타내는 박막 트랜지스터(1)는 게이트 전극(50)이 게이트 절연층(40)을 통하여, 소스 전극(20a) 및 드레인 전극(20b)보다 기판(10)측에 위치하는 보텀 게이트형의 박막 트랜지스터이다.

또한, 소스 전극(20a) 및 드레인 전극(20b)이 각각, 상기 제2 실시 형태와 같은 구성으로 되어 있다.

이러한 박막 트랜지스터(1)는 예를 들어, 다음과 같이 하여 제조할 수 있다.

#### [D1] 게이트 전극 형성 공정

상기 공정[C1]과 같은 공정을 행한다.

#### [D2] 게이트 절연층 형성 공정

상기 공정[C2]과 같은 공정을 행한다.

#### [D3] 소스 전극 및 드레인 전극 형성 공정

상기 공정[B1]과 같은 공정을 행한다.

#### [D4] 유기 반도체층 형성 공정

상기 공정[C4]과 같은 공정을 행한다.

이상과 같은 공정을 거쳐서, 제4 실시 형태의 박막 트랜지스터(1)가 얻어진다.

이러한 제4 실시 형태의 박막 트랜지스터(1)에 의해서도, 상기 제1~제3 실시 형태의 박막 트랜지스터(1)와 같은 작용·효과가 얻어진다.

<유기 EL 소자>

다음에, 본 발명의 전극을 적용한 유기 EL 소자에 대해서 설명한다.

도 8은 본 발명의 유기 EL 소자의 실시 형태를 나타내는 개략 단면도이다.

도 8에 나타내는 유기 EL 소자(100)는 기판(120)과, 기판(120)상에, 순차 적층된 양극(130), 정공 수송층(140), 발광층(150), 전자 주입층(160) 및 음극(170)과, 각층(130~170)을 덮도록 설치된 밀봉 부재(보호 부재)(180)를 갖고 있다.

이 유기 EL 소자(100)는 발광층(150)으로부터의 광을 음극(170)측으로 취출하여 시인하는 톱 에미션 구조의 소자이다.

또한, 본 실시 형태에서는 정공 수송층(140)과 발광층(150)에 의해, 유기 일렉트로루미네선스층(유기 EL층)이 구성되어 있다.

기판(120)은 유기 EL 소자(100)의 지지체로 되는 것이다.

기판(120)으로는, 예를 들어, 폴리에틸렌 테레프탈레이트(PET), 폴리에틸렌 나프탈레이트(PEN), 폴리에테르솔 폰(PES), 방향족 폴리에스테르(액정 중합체), 폴리이미드(PI), 폴리프로필렌(PP), 폴리아미드(PA), 시클로올레핀 중합체(COP), 폴리메틸메타크릴레이트(PMMA), 폴리카보네이트(PC), 폴리아릴레이트(PAR) 등으로 구성되는 플라스틱 기판(수지 기판), 유리 기판, 석영 기판, 실리콘 기판, 금속 기판, 갈륨 비소 기판 등을 사용할 수 있다.

기판(120)의 두께(평균)는 특별히 한정되지 않지만, 0.1~30mm 정도인 것이 바람직하고, 0.1~10mm 정도인 것이 보다 바람직하다.

또한, 유기 EL 소자(100)에 가요성을 부여하는 경우에는 기판(120)으로는 플라스틱 기판, 혹은 얇은(비교적 막두께가 작은) 금속 기판이 선택된다.

양극(본 발명의 전극)(130)은 정공 수송층(140)에 정공을 주입하는 전극이다.

이 양극(130)에는 상술한 박막 트랜지스터(1)의 제1~제4 실시 형태에서 든 소스 전극(20a)의 구성과 같은 구성이 적용된다.

즉, 단층 구성의 경우, 양극(130)은 그 적어도 표면(정공 수송층(140)측의 면)에, Cu, Ni, Co중 적어도 1종을 포함하는 산화물, 또는 황화물 및 염화물 중 적어도 하나를 함유하고, 적층 구성의 경우, 최외층(가장 정공 수송층(140)측의 층)이 Cu, Ni, Co중 적어도 1종을 포함하는 산화물, 또는 황화물 및 염화물 중 적어도 하나를 함유하고 있다.

이것에 의해, 정공 수송층(140)으로의 정공의 주입 효율이 증대함으로써, 발광 휘도가 높은 유기 EL 소자(100), 즉, 신뢰성이 높은 유기 EL 소자(100)가 얻어진다.

양극(130)의 두께(평균)는 특별히 한정되지 않지만, 10~2000nm정도인 것이 바람직하고, 50~1000nm정도인 것이 보다 바람직하다. 양극(130)의 두께가 너무 얇으면, 양극(130)으로서의 기능이 충분히 발휘되지 않을 우려가 있고, 한편, 양극(130)을 상기 상한치를 넘어 두껍게 하여도 그 이상의 효과의 증대가 기대할 수 없다.

정공 수송층(140)은 양극(130)으로부터 주입된 정공을 발광층(150)까지 수송하는 기능을 갖는 것이다.

이 정공 수송층(140)은 주로 p형의 유기 반도체 재료로 구성되어 있다. p형의 유기 반도체 재료에는 중합체 유기 반도체 재료(고분자계 유기 반도체 재료), 저분자계 유기 반도체 재료 모두 사용 가능하다.

이들 유기 반도체 재료로는 각각, 상기 박막 트랜지스터(1)에서 유기 반도체층(30)의 구성 재료로서 들었던 것 이외, 예를 들어, 다음과 같은 것을 사용할 수도 있다.

중합체 유기 반도체 재료로는, 예를 들어, 폴리(3,4-에틸렌디옥시티오펜/스티렌 설폰산)(PEDOT/PSS), 폴리티오펜, 폴리(티오펜비닐렌), 폴리(2,2'-티에닐페롤), 폴리아닐린 등을 사용할 수도 있다.

저분자계 유기 반도체 재료로는, 예를 들어, 1,1-비스(4-디-파라-트리아미노페닐)시클로헥산, 1,1'-비스(4-디-파라-톨릴아미노페닐)-4-페닐-시클로헥산, 4,4', 4"-트리메틸트리페닐아민, N,N,N',N'-테트라페닐-1,1'-비페닐-4,4'-디아민, N,N'-디페닐-N,N'-비스(3-메틸페닐)-1,1'-비페닐-4,4'-디아민(TPD1), N,N'-디페닐-N,N'-비스

(4-메톡시페닐)-1,1'-비페닐-4,4'-디아민(TPD2), N,N,N',N'-테트라카스(4-메톡시페닐)-1,1'-비페닐-4,4'-디아민(TPD3), N,N'-디(1-나프틸)-N,N'-디페닐-1,1'-비페닐-4,4'-디아민(a-NPD), N,N,N',N'-테트라페닐-파라-페닐렌디아민, N,N,N',N'-테트라(파라-톨릴)-파라-페닐렌디아민, N,N',N'-테트라(메타-톨릴)-메타-페닐렌디아민, 카바졸, N-이소프로필카바졸, N-페닐카바졸, 4-디-파라-톨릴아미노스틸벤, 트리페닐메탄, 1-페닐-3-(파라-디메틸아미노페닐)파라졸린, 1,3,4-옥사디아졸, 2,5-디(4-디메틸아미노페닐)-1,3,4-옥사디아졸, 9-(4-디에틸아미노스티릴)안트라센, 플루오레논, 2,4,7-트리니트로-9-플루오레논, 2,7-비스(2-하이드록시-3-(2-클로로페닐)카바도일)-1-나프틸아조)플루오레논, 1,4-디티오케토-3,6-디페닐-피롤로-(3,4-c)피롤로피롤, 포르피린, 금속 테트라페닐 포르피린, 퀴나크리돈, 동나프탈로시아닌, 바나딜나프탈로시아닌, 모노클로로 갈륨 나프탈로시아닌, N,N'-디(나프탈렌-1-일)-N,N'-디페닐-벤자딘, N,N,N',N'-테트라페닐 벤자딘 등을 사용할 수도 있다.

또한, p형의 유기 반도체 재료로는 중합체 유기 반도체 재료를 주성분으로 하는 것이 바람직하다. p형의 유기 반도체 재료로서, 중합체 유기 반도체 재료를 주성분으로 하는 것을 사용함으로써, 정공 수송층(140)의 형성(성막)을 보다 용이하게 또한 저비용으로 행할 수 있다.

이 정공 수송층(140)의 두께(평균)는 특별히 한정되지 않지만, 0.1~1000nm정도인 것이 바람직하고, 1~500nm정도인 것이 보다 바람직하고, 1~100nm정도인 것이 더욱 바람직하다. 정공 수송층(140)의 두께가 너무 얕으면, 편홀이 생길 우려가 있고, 한편, 정공 수송층(140)이 너무 두께우면, 정공 수송층(140)의 투과율이 나빠지는 원인으로 되어, 유기 EL 소자(100)의 발광색의 색도(색상)가 변화할 우려가 있다.

발광층(150)에는 양극(130)과 후술하는 음극(170) 사이에 통전(전압을 인가)하면, 정공 수송층(140) 및 전자 주입층(160)을 통하여, 각각 정공과 전자가 주입된다. 또한, 발광층(150)중에서 재결합된다. 이 재결합시에 방출된 에너지에 의해 엑시톤(여기자)이 생성하고, 이 엑시톤이 기저 상태로 되돌아올 때에 에너지(형광이나 인광)를 방출(발광)한다. 즉, 발광층(150)이 발광한다.

이 발광광은 음극(170)측 및 양극(140)측으로 발하지만, 상술한 구성의 양극(130)에서는 광반사성이 높아지는 경향이 있기 때문에, 양극(130)측으로 발한 광도 양극(130)에서 반사하여, 음극(170)측으로부터 조사되게 된다. 따라서, 본 실시 형태와 같이, 유기 EL 소자(100)의 구성으로서 틈 에미션 구조를 채용함으로써, 발광 효율이 보다 높은 것으로 할 수 있다.

이 발광층(150)의 구성 재료(발광 재료)로는, 전압 인가시에 양극(130)측으로부터 정공을 또한, 음극(170)측으로부터 전자를 주입할 수 있고, 정공과 전자가 재결합하는 장소를 제공할 수 있는 것임을, 어떠한 것이라도 좋다.

이러한 발광 재료로는 저분자계 발광 재료, 중합체 발광 재료(고분자계발광 재료)의 모두다 사용 가능하다.

또한, 발광 재료로서 저분자계 발광 재료를 주성분으로 하는 것을 사용함으로써, 치밀한 발광층(150)이 얻어지기 때문에, 발광층(150)의 발광 효율을 향상시킬 수 있다. 한편, 중합체 발광 재료를 주성분으로 하는 것을 사용함으로써, 비교적 용이하게 용제에 용해시킬 수 있기 때문에, 잉크젯 인쇄법 등의 각종 도포법에 의해, 발광층(150)을 용이하게 형성(성막)할 수 있다.

저분자계 발광 재료의 예로는 디스티릴 벤젠(DSB), 디아미노디스티릴 벤젠(DADSB), 나프탈렌, 나일 레드, 페난트렌, 크리센, 6-나트로크리센, 페릴렌, N,N'-비스(2,5-디-t-부틸페닐)-3,4,9,10-페릴렌-디-카복시이미드(BPPC), 코로넨, 안트라센, 비스스티릴 안트라센, 퍼렌, 4-(디-시아노메틸렌)-2-메틸-6-(파라-디메틸아미노스티릴)-4H-피란(DCM), 아크리딘, 스틸렌, 2,5-디벤조옥사졸티오펜, 벤조옥사졸, 벤조이미다졸, 2,2'-(파라-페닐렌디비닐렌)-비스벤조티아졸, 비스티릴(1,4-디페닐-1,3-부타디엔), 테트라페닐부타디엔, 나프탈이미드, 쿠마린, 페리논, 옥사디아졸, 1,2,3,4,5-펜타페닐-1,3-시클로펜타디엔(PPCP), 퀴나크리돈, 퀴나크리돈 레드, 피롤로피리딘, 티아디아조로피리딘, 2,2',7,7'-테트라페닐-9,9'-스페로비플루오レン, 트리스(8-하이드록시트퀴노리노레이트)알루미늄(Alq<sub>3</sub>), 트리스(4-메틸-8-퀴노리노레이트)알루미늄(III)(Almq<sub>3</sub>), (8-하이드록시퀴노리노레이트)아연(Znq<sub>2</sub>), (1,10-페난트로린)-트리스-(4,4,4-트리플루오로-1-(2-티에닐)-부탄-1,3-디오네이트)유로퓸(III)(Eu(TTA)<sub>3</sub>(phen)), fac 트리스(2-페닐피리딘)이리듐(Ir(ppy)<sub>3</sub>), (2,3,7,8,12,13, 17,18-옥타에틸-21H, 23H-포르핀)플래티늄 (II) 등을 들 수 있다.

중합체 발광 재료로는, 예를 들어, 폴리(9,9-디옥틸플루오렌)(F8), 폴리(9,9-디옥틸플루오렌-코-디티오펜)(F8T2), 폴리(9,9-디옥틸플루오렌-코-2,1,3-벤조티아디졸)(F8BT), 폴리(9,9-디옥틸플루오렌-코-N-(4-부틸페닐)디페닐아민)(TFB), 트랜스형 폴리아세틸렌, 시스형 폴리아세틸렌, 폴리(디-페닐아세틸렌)(PDPA), 폴리(파라-페닐렌비닐렌)(PPV), 폴리(2,5-디알콕시-파라-페닐렌비닐렌)(RO-PPV), 시아노-치환-폴리(파라-페닐렌비닐렌)(CN-PPV), 폴리(2-디메틸옥틸실릴-파라-페닐렌비닐렌)(DMOS-PPV), 폴리(2-메톡시, 5-(2'-에틸헥실)-파라-페닐렌비닐렌)(MEH-PPV), 폴리(옥시프로필렌)트리올(POPT), a, ω-비스[N,N'-디(메틸페닐)아미노페닐]-폴리[9,9-비스(2-에틸헥실)플루오렌-2, 7-디일](PF2/6am4), 폴리(9,9-디옥틸-2,7-디비닐렌플루오레닐-오르토-코(안트라센-9,10-디일), 폴리(파라-페닐렌)(PPP), 폴리(1,5-디알콕시-파라-페닐렌)(RO-PPP), 폴리(N-비닐카바졸)(PVK), 폴리(메틸페닐실란)(PMPS), 폴리(나프틸페닐실란)(PNPS), 폴리(비페니릴페닐실란)(PBPS) 등을 들 수 있다.

발광층(150)의 두께(평균)는 특별히 한정되지 않지만, 5~1000nm정도인 것이 바람직하고, 10~100nm정도인 것이 보다 바람직하다. 발광층의 두께를 상기 범위로 함으로써, 정공과 전자와의 재결합이 효율적으로 되어, 발광층(150)의 발광 효율을 보다 향상시킬 수 있다.

전자 주입층(160)은 음극(170)으로부터 주입된 전자를 발광층(150)까지 수송하는 기능을 갖는 것이다.

이 전자 주입층(160)의 구성 재료로는 일함수가 작은 금속 재료가 적합하게 사용된다. 이러한 금속 재료의 예로는 Li, Mg, Ca, Sr, La, Ce, Er, Eu, Sc, Y, Yb, Ag, Cu, Al, Cs, Rb 또는 이들을 포함하는 합금, 혹은 이들의 불화물 등을 들 수 있다.

본 실시 형태의 유기 EL 소자(100)는 텁 에미션 구조(음극(170))에서 발광층(150)으로부터의 발광을 시인하는 형태)이기 때문에, 전자 주입층(160)은 가능한 한 얇은 편이 바람직하다. 전자 주입층(160)의 두께(평균)는 특별히 한정되지 않지만, 5~100nm정도인 것이 바람직하고, 20~50nm정도인 것이 보다 바람직하다. 전자 주입층(160)의 두께가 너무 얇으면, 편홀이 생겨 쇼트할 우려가 있고, 한편, 전자 주입층(160)이 너무 두꺼우면, 그 구성 재료의 종류 등에 따라서는 저항값이 높아질 우려가 있다.

음극(170)은 전자 주입층(160)에 전자를 주입하는 전극이다. 또한, 본 실시 형태의 음극(170)은 발광층(150)으로부터의 발광을 시인할 수 있도록, 실질적으로 투명(무색 투명, 유색 투명, 반투명)으로 되어 있다.

이러한 관점에서, 음극(170)의 구성 재료로는 도전성이 우수하고, 또한, 투광성을 갖는 재료를 사용하는 것이 바람직하다.

이러한 음극(170)의 구성 재료의 예로는 ITO(산화 인듐 주석), FTO(불소 함유 ITO), IZO(산화 인듐 아연), ATO(산화 안티몬 주석), AZO(산화 알루미늄 아연) 등의 투명 도전성 산화물 중의 1종 또는 2종 이상을 조합하여 사용하는 것이 적합하다.

투명 도전성 산화물은 도전성 및 투광성의 쌍방의 특성에서 특별히 우수하기 때문에, 음극(170)을 투명 도전성 산화물을 주성분으로서 구성함으로써, 보다 발광 효율이 우수한 유기 EL 소자(100)를 얻을 수 있다.

음극(170)의 두께(평균)는 10nm~1μm정도인 것이 바람직하다. 음극(170)의 두께가 너무 얇으면, 음극(170)으로서의 기능이 충분히 발휘되지 않을 우려가 있고, 한편, 음극(170)이 너무 두꺼우면, 유기 EL 소자(100)의 발광 효율이 저하하거나, 그 구성 재료의 종류 등에 따라서는 광의 투과율이 현저하게 저하하여, 실용에 적합하지 않을 우려가 있다.

밀봉 부재(180)은 유기 EL 소자(100)를 구성하는 각층(130~170)을 기밀적으로 밀봉하여, 산소나 수분을 차단(차폐)하는 기능을 갖는다. 밀봉 부재(180)를 설치함으로써, 유기 EL 소자(100)의 신뢰성을 향상시키는 효과나, 각층(130~170)(특히, 정공 수송층(140) 및 발광층(150))의 변질·열화를 방지하는 효과 등이 발휘된다.

또한, 밀봉 부재(180)의 내부에는 예를 들어, 질소 가스, 각종 희가스 등의 불활성 가스를 충전하여도 좋다. 이것에 의해, 각층(130~170)의 변질·열화 등을 보다 확실히 방지할 수 있다.

밀봉 부재(180)의 구성 재료로는 투광성을 갖는 것이면 좋고, 특별히 한정되지 않지만, 예를 들어, 각종 수지 재료나 각종 유리 재료 등을 사용할 수 있다.

또한, 본 실시 형태에서는 발광층(150)은 정공 수송층(140)과 별개로 설치되어 있지만, 정공 수송층(140)과 발광층(150)의 쌍방의 기능을 결합한 정공 수송성 발광층으로 할 수도 있다. 이 경우, 정공 수송성 발광층의 전자 주입층(160)과의 계면 부근이 발광층(150)으로서 기능한다.

또한, 정공 수송성 발광층을 사용한 경우에는, 양극(130)으로부터 정공 수송성 발광층에 주입된 정공이 전자 주입층(160)에 의해서 갇혀지기 때문에, 정공과 전자의 재결합 효율을 향상시킬 수 있는 이점이 있다.

또한, 양극(130)과 정공 수송층(140) 사이, 정공 수송층(140)과 발광층(150) 사이, 발광층(150)과 전자 주입층(160) 사이 등에는 각각, 임의 목적의 층을 설치해도 좋다.

예를 들어, 양극(130)과 정공 수송층(140) 사이에는 정공 주입층을, 또한, 발광층(150)과 전자 주입층(160) 사이에는 전자 수송층 등을 설치할 수 있다. 기타, 유기 EL 소자(100)에는 정공 블록층이나 전자 블록층 등을 설치해도 좋다.

#### <표시 장치>

다음에, 상술한 바와 같은 박막 트랜지스터(1)를 구비하는 액티브 매트릭스 장치가 조립된 표시 장치에 대해서, 전기영동표시 장치를 일례로 설명한다.

도 9는 본 발명의 표시 장치를 전기영동표시 장치에 적용한 경우의 실시 형태를 나타내는 종단면도, 도 10은 도 9에 나타내는 전기영동표시 장치를 구비하는 액티브 매트릭스 장치의 구성을 나타내는 블럭도이다.

도 9에 나타내는 전기영동표시 장치(200)는 기판(500)상에 설치된 액티브 매트릭스 장치(본 발명의 전자 회로)(300)와, 이 액티브 매트릭스 장치(300)에 전기적으로 접속된 전기영동 표시부(400)로 구성되어 있다.

도 10에 나타내는 바와 같이, 액티브 매트릭스 장치(300)는 서로 직교하는 복수의 데이터선(301)과, 복수의 주사선(302)과, 이를 데이터선(301)과 주사선(302)의 각교점 부근에 설치된 박막 트랜지스터(1)를 갖고 있다.

또한, 박막 트랜지스터(1)가 갖는 게이트 전극(50)은 주사선(302)에, 소스 전극(20a)은 데이터선(301)에, 드레인 전극(20b)은 후술하는 화소 전극(개별 전극)(401)에, 각각 접속되어 있다.

도 9에 나타내는 바와 같이, 전기영동 표시부(400)는 기판(500)상에, 순차 적층된, 화소 전극(401)과, 마이크로캡슐(402)과, 투명 전극(공통 전극)(403) 및 투명 기판(404)을 갖고 있다.

또한, 마이크로캡슐(402)이 바인더재(405)에 의해, 화소 전극(401)과 투명 전극(403) 사이에 고정되어 있다.

화소 전극(401)은 매트릭스 형상으로, 즉, 종횡으로 규칙적으로 배열하도록 분할되어 있다.

각 캡슐(402)내에는 각각, 특성이 다른 복수종의 전기영동 입자, 본 실시 형태에서는 전하 및 색(색상)이 다른 2종의 전기영동 입자(421, 422)를 함유하는 전기영동 분산액(420)이 봉입되어 있다.

이러한 전기영동표시 장치(200)에서는 1개 혹은 복수개의 주사선(302)에 선택 신호(선택 전압)을 공급하면, 이 선택 신호(선택 전압)가 공급된 주사선(302)에 접속되어 있는 박막 트랜지스터(1)가 ON으로 된다.

이것에 의해, 이러한 박막 트랜지스터(1)에 접속되어 있는 데이터선(301)과 화소 전극(401)은 실질적으로 도통한다. 이 때, 데이터선(301)에 소망의 데이터(전압)를 공급한 상태이면, 이 데이터(전압)는 화소 전극(401)에 공급된다.

이것에 의해, 화소 전극(401)과 투명 전극(403) 사이에 전계가 생기고, 이 전계의 방향, 강도, 전기영동 입자(421, 422)의 특성 등에 따라서, 전기영동 입자(421, 422)는 어느 전극의 방향으로 향해 전기영동 한다.

한편, 이 상태로부터, 주사선(302)으로의 선택 신호(선택 전압)의 공급을 정지하면, 박막 트랜지스터(1)는 OFF로 되어, 이러한 박막 트랜지스터(1)에 접속되어 있는 데이터선(301)과 화소 전극(401)은 비도통 상태로 된다.

따라서, 주사선(302)으로의 선택 신호의 공급 및 정지, 혹은 데이터선(301)으로의 데이터의 공급 및 정지를 적당히 조합하여 행함으로써, 전기영동표시 장치(200)의 표시면측(투명 기판(404)측)에, 소망한 화상(정보)을 표시할 수 있다.

특히, 본 실시 형태의 전기영동표시 장치(200)에서는 전기영동 입자(421, 422)의 색을 다르게 함으로써, 다계조의 화상을 표시할 수 있게 되어 있다.

또한, 본 실시 형태의 전기영동표시 장치(200)는 액티브 매트릭스 장치(300)를 가짐으로써, 특정의 주사선(302)에 접속된 박막 트랜지스터(1)를 선택적으로 ON/OFF 할 수 있으므로, 크로스토크의 문제가 생기기 어렵고, 또한, 회로 동작의 고속화가 가능하므로, 높은 품질의 화상(정보)을 얻을 수 있다.

또한, 본 실시 형태의 전기영동표시 장치(200)는 낮은 구동 전압에서 작동하기 때문에, 전력 절약화가 가능하다.

또한, 본 발명의 표시 장치는 이러한 전기영동표시 장치(200)로의 적용에 한정되는 것이 아니고, 전기영동 표시부(400) 대신에, 상술한 바와 같은 유기 EL 소자(100)를 사용한 유기 EL 표시 장치나, 무기 EL 소자를 사용한 무기 EL 표시 장치, 액정 표시 소자를 사용한 액정 표시 장치 등에 적용할 수도 있다.

### <전자 기기>

이러한 전기영동표시 장치(200)(본 발명의 표시 장치)는 각종 전자 기기에 조립할 수 있다. 이하, 전기영동표시 장치(200)를 구비하는 본 발명의 전자 기기에 대해서 설명한다.

### <<전자 페이퍼>>

우선, 본 발명의 전자 기기를 전자 페이퍼에 적용한 경우의 실시 형태에 대해서 설명한다.

도 11은 본 발명의 전자 기기를 전자 페이퍼에 적용한 경우의 실시 형태를 나타내는 사시도이다.

이 도면에 나타내는 전자 페이퍼(600)는 종이와 동일한 질감 및 유연성을 갖는 리라이터블(rewritable) 시트로 구성되는 본체(601)와, 표시 유닛(602)을 구비하고 있다. 이러한 전자 페이퍼(600)에서는 표시 유닛(602)이 상술한 바와 같은 전기영동표시 장치(200)로 구성되어 있다.

### <<디스플레이>>

다음에, 본 발명의 전자 기기를 디스플레이에 적용한 경우의 실시 형태에 대해서 설명한다.

도 12는 본 발명의 전자 기기를 디스플레이에 적용한 경우의 실시 형태를 나타내는 도면으로, (a)는 단면도, (b)는 평면도이다.

이 도면에 나타내는 디스플레이(800)는 본체부(801)와, 이 본체부(801)에 대해서 착탈 자유롭게 설치된 전자 페이퍼(600)를 구비하고 있다. 또한, 이 전자 페이퍼(600)는 상술한 바와 같은 구성, 즉, 도 11에 나타내는 구성과 동일하다.

본체부(801)는 그 측부(도면 중, 우측)에 전자 페이퍼(600)를 삽입 가능한 삽입구(805)가 형성되어, 또한, 내부에 2 조의 반송 룰러쌍(802a, 802b)이 설치되어 있다. 전자 페이퍼(600)를, 삽입구(805)를 통하여 본체부(801)내에 삽입하면, 전자 페이퍼(600)은 반송 룰러쌍(802a, 802b)에 의해 협지된 상태로 본체부(801)에 설치된다.

또한, 본체부(801)의 표시면측(아래 도면 (b)중, 지면 앞측)에는 직사각형 형상의 구멍부(803)가 형성되고, 이 구멍부(803)에는 투명 유리판(804)이 기워 넣어져 있다. 이것에 의해, 본체부(801)의 외부로부터, 본체부(801)에 설치된 상태의 전자 페이퍼(600)를 시인할 수 있다. 즉, 이 디스플레이(800)에서는 본체부(801)에 설치된 상태의 전자 페이퍼(600)를, 투명 유리판(804)에서 시인시킴으로써 표시면을 구성하고 있다.

또한, 전자 페이퍼(600)의 삽입 방향 선단부(도면 중, 좌측)에는 단자부(806)가 설치되어 있고, 본체부(801)의 내부에는 전자 페이퍼(600)를 본체부(801)에 설치한 상태에서 단자부(806)가 접속되는 소켓(807)이 설치되어 있다. 이 소켓(807)에는 콘트롤러(808)와 조작부(809)가 전기적으로 접속되어 있다.

이러한 디스플레이(800)에서는 전자 페이퍼(600)는 본체부(801)에 착탈 자유롭게 설치되어 있어, 본체부(801)로부터 떼어낸 상태로 휴대하여 사용할 수도 있다. 또한, 이러한 디스플레이(800)에서는 전자 페이퍼(600)는 상술한 바와 같은 전기영동표시 장치(200)로 구성되어 있다.

또한, 본 발명의 전자 기기는 이상과 같은 것으로의 적용에 한정되지 않고, 예를 들어, 텔레비전, 뮤파인더형, 모니터, 디지털형의 비디오테이프 레코더, 카내비게이션 장치, 페이퍼, 전자 수첩, 계산기, 전자 신문, 워드 프로세서, 퍼스널 컴퓨터, 워크스테이션, 화상 전화, POS 단말, 터치 패널을 구비한 기기 등을 들 수 있고, 이를 각종 전자 기기의 표시부에, 전기영동표시 장치(200)를 일례로 하는 본 발명의 표시 장치를 적용할 수 있다.

이상, 본 발명의 전극, 전극 형성 방법, 박막 트랜지스터, 전자 회로, 유기 일렉트로루미네센스 소자, 표시 장치 및 전자 기기에 대해서 설명했지만, 본 발명은 이들에 한정되는 것이 아니다.

예를 들어, 본 발명의 전극은 태양 전지(광전 변환 소자)를 구비하는 양극, RF 태그가 구비하는 전극 등에 적용할 수도 있다.

또한, 본 발명의 전극 형성 방법은 상술한 바와 같은 공정에, 필요에 따라서, 1 또는 2이상의 임의 목적의 공정을 추가할 수도 있다.

또한, 본 발명의 박막 트랜지스터, 전자 회로, 유기 일렉트로루미네센스 소자, 표시 장치 및 전자 기기의 각부의 구성은 같은 기능을 발휘할 수 있는 임의 것과 치환할 수 있고, 혹은 임의 구성의 것을 부가할 수도 있다.

### 실시예

다음에, 본 발명의 구체적 실시예에 대해서 설명한다.

#### A1. 박막 트랜지스터의 제조

(실시예 A1)

우선, 유리 기판(NEC Corning 사제, "OA10")을 준비하고, 에탄올을 사용하여 세정함으로써, 표면의 탈지 처리를 행했다.

다음에, 유리 기판을 건조한 후, 농황산 중에 침지함으로써, 유리 기판의 표면을 거칠게 했다. 이것에 의해, 다음 공정에서 형성되는 도금막의 밀착성의 개선을 도모하였다. 그 후, 유리 기판을 순수를 사용하여 세정했다.

다음에, 유리 기판을 감수화액(sensitivity increasing liquid) 중에 15초간 침지한 후, 순수로 세정하는 조작을 1 사이클로하여, 4사이클 반복했다.

또한, 감수화액에는 37wt%의 농염산: 1mL/L에 SnCl<sub>2</sub>: 1g/L를 첨가한 용액(염화주석(II) 용액)을 사용했다.

다음에, 유리 기판을 Ni 도금조(plating bath) 중에 5분간 침지했다. 또한, Ni 도금조의 조건은 이하에 나타내는 바와 같다.

아인산 나트륨 용액: 0.15mol/L

황산암모늄 용액: 0.50mol/L

구연산 나트륨 용액: 0.20mol/L

황산 니켈 용액: 0.10mol/L

이들 4종의 용액을 등량씩 혼합하고, 수산화나트륨 수용액으로 pH 9.0으로 조정

Ni 도금조의 온도: 90°C

이것에 의해, 유리 기판상에, 평균 두께 100nm의 Ni 도금막을 형성했다. 그 후, 순수를 사용하여 유리 기판을 세정한 후, 50°C에서 건조했다.

다음에, 이 Ni 도금막 상에, 레지스트 재료(토오쿄오오카코교 사제, "TSMR 8900")을 공급하고, 노광·현상함(포토리소그래피법)으로써, 소스 전극 및 드레인 전극의 형상에 대응하는 패턴의 레지스트 층을 형성했다.

다음에, 유리 기판을, 5~10wt%의 염화제2철 수용액 중에, 30~40°C×5~10분간 침지했다. 이것에 의해, 레지스트 층으로 덮혀져 있지 않는 부분의 Ni 도금막을 제거하여, 소스 전극 및 드레인 전극에 대응하는 형상으로 패터닝 했다.

다음에, 레지스트 박리액을 사용하여, 레지스트 층을 제거한 후, 유리 기판을 물 및 에탄올을 사용하여, 순차 세정했다.

다음에, Ni 도금막에 대해서, 산소 플라즈마 처리를 실시했다. 또한, 산소 플라즈마 처리의 조건은 이하에 나타내는 바와 같다.

플라즈마 처리 장치: 삼코인터네셔널 켄큐쇼 사제, "PX 1000"

파워: 200W

처리 시간: 5분간

산소 유량: 100sccm

아르곤 유량: 100sccm

이것에 의해, 도 4에 나타내는 구성의 소스 전극 및 드레인 전극을 얻었다.

다음에, 유리 기판상에, F8T2(폴리(9,9-디옥틸풀루오렌-코-디티오펜))의 1%wt/vol 톨루엔 용액을, 스핀 코트법(2400rpm)에 의해 도포한 후, 60°C×10분간 건조했다. 이것에 의해, 평균 두께 50nm의 유기 반도체층을 형성했다.

다음에, 유기 반도체층 상에, 폴리메틸메타아크릴레이트(PMMA)의 5%wt/vol 초산부틸 용액을, 스핀 코트법(2400rpm)에 의해 도포한 후, 60°C×10분간 건조했다. 이것에 의해, 평균 두께 100nm의 게이트 절연층을 형성했다.

다음에, 게이트 절연층 상의, 소스 전극과 드레인 전극 사이의 영역에 대응하는 부분에, PEDOT(폴리에틸렌디옥시티오펜)의 수분산액(점도(상온) 5cps)을 잉크젯법(액적 1방울의 양 20pL)에 의해 도포한 후, 80°C×10분간 건조했다. 이것에 의해, 평균 두께 100nm의 게이트 전극을 형성했다.

이상의 공정에 의해, 박막 트랜지스터를 얻었다.

(실시 예 A2)

화원제로서 디메틸보란을 첨가한 0.1wt% 염화니켈 수용액 중에, 유리 기판을 40°C×5분간 침지하여, Ni 도금막을 형성한 것 이외는 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

또한, 얻어진 Ni 도금막은 평균 두께가 100nm이었다.

(실시 예 A3)

소스 전극 및 드레인 전극을 형성할 때에, Ni 도금막 대신에, Cu 도금막을 형성한 것 이외는 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

또한, 유리 기판의 Cu 도금조로의 침지 시간은 5분간이고, Cu 도금조의 조건은 이하에 나타내는 바와 같다.

포르말린: 0.25mol/리터

에틸렌디아민4초산 나트륨 용액: 0.06mol/리터

황산동 용액: 0.05mol/리터

2,2'-디피리딜 용액: 20mg/리터

헥사시아노철(II) 칼륨 용액: 50mg/리터

이들 5종의 용액을 등량씩 혼합하고, 수산화나트륨 수용액으로 pH 12.5로 조정

Cu 도금조의 온도: 90°C

또한, 얻어진 Cu 도금막은 평균 두께가 100nm이었다.

(실시예 A4)

착화제로서 록셀염(Rochelle salt)을 첨가한 0.5wt% 황산동 수용액 중에, 유리 기판을 20°C×10분간 침지하여, Cu 도금막을 형성한 것 이외는 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

또한, 얻어진 Cu 도금막은 평균 두께가 100nm이었다.

(실시예 A5)

Cu 도금막 대신에, 리프트 오프법을 사용하여 Cu막을 형성한 것 이외는 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

즉, 우선, 유리 기판 상에, 소스 전극 및 드레인 전극에 대응하는 이외의 부분을 덮도록 레지스트 패턴을 설치하여 두고, 전체면에 Cu막을 100nm 증착했다.

다음에, 레지스트 패턴을 제트 스크라이버 장치로 제거함으로써, 소스 전극 및 드레인 전극에 대응하는 형상의 Cu막을 얻었다.

(실시예 A6)

산소 플라즈마 처리시에, 처리 시간을 20분으로 한 것 이외는 상기 실시예 A3와 동일하게 하여 박막 트랜지스터를 얻었다.

또한, 얻어진 Cu 도금막은 평균 두께가 100nm이었다.

(실시예 A7)

0.1wt% 염화코발트 수용액 중에, 유리 기판을 90°C×5분간 침지하여 Co도금막을 형성한 것 이외는 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

또한, 얻어진 Co도금막은 평균 두께가 100nm이었다.

(실시예 A8)

우선, 유리 기판(NEC Corning 사제, "OA10")을 준비하고, 에탄올을 사용하여 세정함으로써, 표면의 탈지 처리를 행했다.

다음에, 유리 기판을 건조한 후, 농황산 중에 침지함으로써, 유리 기판의 표면을 거칠게 했다. 이것에 의해, 다음 공정에서 형성되는 막의 밀착성의 개선을 도모하였다. 그 후, 유리 기판을 순수를 사용하여 세정했다.

다음에, 리액티브 DC 마그네트론 스퍼터법에 의해, 유리 기판상에, 평균 두께 100nm의 NiO를 함유하는 피막을 형성했다.

또한, 리액티브 DC 마그네트론 스퍼터법의 조건은 이하에 나타내는 바와 같다.

타겟: 금속 Ni

챔버내의 도달 진공도:  $5\times10^{-4}$ Pa

DC 파워: 60W

도입 가스: 산소와 아르곤의 혼합 가스(산소:아르곤 =80:20(몰비))

성막시의 챔버내의 압력: 0.65Pa(5mTorr)

다음에, 이 피막상에, 레지스트 재료(토오쿄오오카코교 사제, "TSMR 8900")을 공급하고, 노광·현상함(포토리소그래피법)으로써, 소스 전극 및 드레인 전극의 형상에 대응하는 패턴의 레지스트 층을 형성했다.

다음에, 반응성 이온 에칭에 의해, 레지스트 층으로 덮여져 있지 않는 부분의 피막을 제거하여, 소스 전극 및 드레인 전극에 대응하는 형상으로 패터닝했다.

이것에 의해, 도 4에 나타내는 구성의 소스 전극 및 드레인 전극을 얻었다.

이하, 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A9)

산소와 아르곤의 혼합비를 25:75로 변경한 것 이외는 상기 실시예 A8와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A10)

산소와 아르곤의 혼합비를, 10:90으로 변경한 것 이외는 상기 실시예 A8와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A11~A13)

타겟으로서 금속 Ni 대신에, 금속 Cu를 사용한 것 이외는 각각, 상기 실시예 A8~A10와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A14~A16)

타겟으로서 금속 Ni 대신에, 금속 Co를 사용한 것 이외는 각각, 상기 실시예 A8~A10와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A17)

우선, 유리 기판(NEC Corning 사제, "OA10")을 준비하고, 에탄올을 사용하여 세정함으로써, 표면의 탈지 처리를 행했다.

다음에, 유리 기판을 건조한 후, 농황산 중에 침지함으로써, 유리 기판의 표면을 거칠게 했다.

이것에 의해, 다음 공정에서 형성되는 막의 밀착성의 개선을 도모하였다. 그 후, 유리 기판을 순수를 사용하여 세정했다.

다음에, 레이저 어브레이션법에 의해, 유리 기판상에, 평균 두께 100nm의  $\text{SrCu}_2\text{O}_2$ 로 구성되는 피막을 형성했다.

또한, 레이저 어브레이션법의 조건은 이하에 나타내는 바와 같다.

타겟:  $\text{SrCu}_2\text{O}_2$  소결체

챔버내의 도달 진공도:  $5 \times 10^{-7}\text{Pa}$

레이저

·종류: ArF 엑시머 레이저(파장: 193nm, 펄스 길이: 20ns)

·에너지 밀도:  $5\text{J/cm}^2$

도입 가스: 산소 가스

성막시의 챔버내의 압력: 5Pa

유리 기판의 온도: 250°C

다음에, 이 피막상에, 레지스트 재료(토오쿄오오카코교 사제, "TSMR 8900")을 공급하고, 노광·현상함(포토리소그래피법)으로써, 소스 전극 및 드레인 전극의 형상에 대응하는 패턴의 레지스트 층을 형성했다.

다음에, 반응성 이온 애칭에 의해, 레지스트 층으로 덮여져 있지 않는 부분의 피막을 제거하여, 소스 전극 및 드레인 전극에 대응하는 형상으로 패터닝했다.

이것에 의해, 도 4에 나타내는 구성의 소스 전극 및 드레인 전극을 얻었다.

이하, 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A18)

타겟으로서  $\text{SrCu}_2\text{O}_2$  소결체 대신에,  $\text{CuAlO}_2$  소결체를 사용한 것 이외는 상기 실시예 A17와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A19)

타겟으로서  $\text{SrCu}_2\text{O}_2$  소결체 대신에,  $\text{CuGaO}_2$  소결체를 사용한 것 이외는 상기 실시예 A17와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A20)

우선, 유리 기판(NEC Corning 사제, "OA10")을 준비하고, 에탄올을 사용하여 세정함으로써, 표면의 탈지 처리를 행했다.

다음에, 유리 기판을 건조한 후, 농황산 중에 침지함으로써, 유리 기판의 표면을 거칠게 했다. 이것에 의해, 다음 공정에서 형성되는 막의 밀착성의 개선을 도모하였다. 그 후, 유리 기판을 순수를 사용하여 세정했다.

다음에, 상기 실시예 A3와 동일하게 하여, 평균 두께 80nm의 Cu로 구성된 하지 전극층(일함수 4.7eV)을 형성하고, 그 다음에, 상기 실시예 A11와 동일하게 하여, 평균 두께 20nm의  $\text{Cu}(\text{II})\text{O}$ 로 구성되는 표면 전극층(일함수 5.4eV)을 형성했다.

이것에 의해, 도 1에 나타내는 구성의 소스 전극 및 드레인 전극을 얻었다.

이하, 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A21)

우선, 유리 기판(NEC Corning 사제, "OA10")을 준비하고, 에탄올을 사용하여 세정함으로써, 표면의 탈지 처리를 행했다.

다음에, 유리 기판을 건조한 후, 농황산 중에 침지함으로써, 유리 기판의 표면을 거칠게 했다. 이것에 의해, 다음 공정에서 형성되는 막의 밀착성의 개선을 도모하였다. 그 후, 유리 기판을 순수를 사용하여 세정했다.

다음에, 상기 실시예 A3와 동일하게 하여, 평균 두께 80nm의 Cu로 구성된 하지 전극층(일함수 4.7eV)을 형성하고, 그 다음에, 상기 실시예 A17와 동일하게 하여, 평균 두께 20nm의  $\text{SrCu}_2\text{O}_2$ 로 구성되는 표면 전극층(일함수 5.4eV)을 형성했다.

이것에 의해, 도 1에 나타내는 구성의 소스 전극 및 드레인 전극을 얻었다.

이하, 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A22~A24)

타겟으로서 금속 Ni 대신에, 금속 Ag를 사용한 것 이외는 각각, 상기 실시예 A8~A10와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A25)

$\text{Cu}$  도금막 대신에, 진공 증착법에 의해, 평균 두께 100nm의 Cu 증착막을 형성한 것 이외는 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

(실시예 A26)

산소 플라즈마 처리 대신에, 황화 처리를 실시한 것 이외는 상기 실시예 A25와 동일하게 하여 박막 트랜지스터를 얻었다.

또한, 황화 처리는 Cu 증착막에 대해서, 황화수소 분위기중  $100^{\circ}\text{C} \times 30\text{분}$ 간 열처리를 실시함으로써 행하였다.

#### (실시예 A27)

Cu 도금막 대신에, 진공 증착법에 의해, 평균 두께 100nm의 Ag 증착막을 형성하고, 상기 실시예 A1와 동일하게 하여, 소스 전극 및 드레인 전극에 대응하는 형상으로 패터닝했다.

다음에, Ag 증착막에 대해서, 염소화 처리를 실시했다. 이것에 의해, 도 4에 나타내는 구성의 소스 전극 및 드레인 전극을 얻었다.

또한, 염소화 처리는 Ag 증착막에 대해서, 염화수소 분위기중  $100^{\circ}\text{C} \times 30\text{분}$ 간 열처리를 실시함으로써 행하였다.

이하, 상기 실시예 A1와 동일하게 하여 박막 트랜지스터를 얻었다.

#### (실시예 A28)

염소화 처리 방법을 변경한 것 이외는 상기 실시예 A27와 동일하게 하여 박막 트랜지스터를 얻었다.

즉, 우선, Ag 증착막을, 3M의  $\text{HNO}_3$ 로 전처리한 후, 수세했다.

다음에, 유리 기판을 0.1M의 HCl 수용액에 침지하고, Ag 증착막에 전류 밀도  $0.8\text{mA/cm}^2$ 로 15분간 통전하여, 전기 분해 처리를 행했다.

이것에 의해, 도 1에 나타내는 구성의 소스 전극 및 드레인 전극을 얻었다.

#### (비교예 A1)

산소와 아르곤의 혼합비를 0:100으로 변경한 것 이외는 상기 실시예 A8와 동일하게 하여 박막 트랜지스터를 얻었다.

#### (비교예 A2)

산소와 아르곤의 혼합비를 0:100으로 변경한 것 이외는 상기 실시예 A11와 동일하게 하여 박막 트랜지스터를 얻었다.

#### (비교예 A3)

산소와 아르곤의 혼합비를 0:100으로 변경한 것 이외는 상기 실시예 A14와 동일하게 하여 박막 트랜지스터를 얻었다.

#### (비교예 A4)

산소와 아르곤의 혼합비를 0:100으로 변경한 것 이외는 상기 실시예 A22와 동일하게 하여 박막 트랜지스터를 얻었다.

### A2. 평가

#### A2-1. 산화물의 함유량의 측정

각 실시예 및 각 비교예에서 얻어진 소스 전극 및 드레인 전극에 대해서, 각각, 산화물, 황화물, 염화물(이하, 이들을 총칭하여 "금속 화합물"이라 함.)이 존재하는 부분(영역)의 확인과, 이 부분에서의 금속 화합물의 함유량의 측정을 행했다.

또한, 이 측정은 X선 마이크로 애널라이저(EPMA)법에 의해 행하였다.

#### A2-2. 일함수의 측정

각 실시예 및 각 비교예에서 얻어진 소스 전극 및 드레인 전극에 대해서, 각각, 일함수의 측정을 행했다.

또한, 이 측정에는 간이 UPS 장치(리켄케이키 사제, "AC-1")을 사용했다.

#### A2-3. 트랜지스터 특성의 평가

각 실시예 및 각 비교예에서 얻어진 박막 트랜지스터에 대해서, 각각, 캐리어의 이동도  $\mu$ , 임계 전압  $V_{th}$  및 S치를 측정했다.

또한, 이 측정은 아질렌트(Agilent Technology) 사제, "반도체 파라미터 애널라이저 4156C"를 사용하여 행하였다.

여기서, 임계 전압  $V_{th}$ 이란, 게이트 전압과  $Id^{1/2}$ ( $Id$ : 드레인 전류의 穀)의 관계를 표시하는 근사식(관계식)의 값이 0 이 될 때의 게이트 전압이고, 드레인 전류가 흐르기 시작하는데 필요로 하는 게이트 전압으로 간주할 수 있다.

S치란, 드레인 전류의 값이 1자리수 상승하는데 필요로 하는 게이트 전압의 값이다. 따라서, 캐리어의 이동도  $\mu$ 가 크고, 임계 전압  $V_{th}$ 의 절대치가 작고, S치가 작을수록, 양호한 특성을 갖는 박막 트랜지스터인 것을 의미한다.

그 결과를, 표 1(표 1-1 및 표 1-2)에 나타낸다.

<표 1-1>

| 평균두께 *<br>[nm] | 소스 전극 및 드레인 전극<br>금속 혼합물<br>의 종류 |                |                | 캐리어의<br>이동도 $\mu$<br>[cm <sup>2</sup> /V·s] | 임계 전압<br>$V_{th}$<br>[V] | S치<br>[I] |

|----------------|----------------------------------|----------------|----------------|---------------------------------------------|--------------------------|-----------|

|                | 금속 혼합물<br>의 종류                   | 금속 혼합물<br>의 종류 | 금속 혼합물<br>의 종류 |                                             |                          |           |

| 실시예 A 1 5      | N i O                            | 8 1            | 5. 0           | $3.0 \times 10^{-3}$                        | 0                        | 1. 0      |

| 실시예 A 2 6      | N i O                            | 7 5            | 5. 0           | $3.0 \times 10^{-3}$                        | 0                        | 1. 0      |

| 실시예 A 3 6      | C u (II) O                       | 7 9            | 5. 4           | $4.4 \times 10^{-3}$                        | -1                       | 1. 6      |

| 실시예 A 4 5      | C u (II) O                       | 7 6            | 5. 4           | $4.4 \times 10^{-3}$                        | 0                        | 1. 5      |

| 실시예 A 5 7      | C u (II) O                       | 8 0            | 5. 4           | $4.4 \times 10^{-3}$                        | 0                        | 1. 5      |

| 실시예 A 6 1 0    | C u (II) O                       | 9 5            | 5. 4           | $4.6 \times 10^{-3}$                        | 0                        | 1. 4      |

| 실시예 A 7 5      | C o O                            | 8 5            | 5. 0           | $2.8 \times 10^{-3}$                        | -1                       | 1. 7      |

| 실시예 A 8 1 0 0  | N i O                            | 1 0 0          | 5. 0           | $3.0 \times 10^{-3}$                        | 0                        | 1. 0      |

| 실시예 A 9 1 0 0  | N i O                            | 7 5            | 5. 0           | $3.0 \times 10^{-3}$                        | 0                        | 1. 0      |

| 실시예 A 10 1 0 0 | N i O                            | 5 0            | 5. 0           | $3.0 \times 10^{-3}$                        | -1                       | 1. 2      |

| 실시예 A 11 1 0 0 | C u (II) O                       | 1 0 0          | 5. 4           | $4.4 \times 10^{-3}$                        | 0                        | 1. 5      |

| 실시예 A 12 1 0 0 | C u (II) O                       | 7 5            | 5. 4           | $4.4 \times 10^{-3}$                        | 0                        | 1. 5      |

| 실시예 A 13 1 0 0 | C u (II) O                       | 5 0            | 5. 3           | $4.4 \times 10^{-3}$                        | -1                       | 1. 6      |

| 실시예 A 14 1 0 0 | C o O                            | 1 0 0          | 5. 0           | $2.8 \times 10^{-3}$                        | -1                       | 1. 7      |

| 실시예 A 15 1 0 0 | C o O                            | 7 5            | 5. 0           | $2.8 \times 10^{-3}$                        | -1                       | 1. 8      |

| 실시예 A 16 1 0 0 | C o O                            | 5 0            | 5. 0           | $2.8 \times 10^{-3}$                        | -3                       | 1. 8      |

\* : 소스 전극 및 드레인 전극의 표면으로부터의 금속 혼합물이 존재하는 부분의 평균 두께

<표 1-2>

| 평균 두께<br>[nm] | 소스 전극 및 드레인 전극                  |                                    |             | 캐리어의<br>이동도 $\mu$<br>[cm <sup>2</sup> /Vs] | 임계 전압<br>V <sub>th</sub><br>[V] | S치<br>[V] |

|---------------|---------------------------------|------------------------------------|-------------|--------------------------------------------|---------------------------------|-----------|

|               | 금속<br>화합물<br>의<br>종류            | 금속<br>화합물<br>의<br>함유량<br>[%]       | 일정수<br>[eV] |                                            |                                 |           |

| 실시예 A17       | 1.00                            | SrCu <sub>2</sub> O <sub>2</sub>   | 1.00        | 5. 4                                       | 2.7×10 <sup>-3</sup>            | 0         |

| 실시예 A18       | 1.00                            | CuAlO <sub>2</sub>                 | 1.00        | 5. 4                                       | 2.5×10 <sup>-3</sup>            | 0         |

| 실시예 A19       | 1.00                            | CuGaO <sub>2</sub>                 | 1.00        | 5. 4                                       | 2.4×10 <sup>-3</sup>            | 0         |

| 실시예 A20       | 2.00                            | Cu (II) O                          | 1.00        | 5. 4                                       | 4.4×10 <sup>-3</sup>            | 0         |

| 실시예 A21       | 2.00                            | SrCu <sub>2</sub> O <sub>2</sub>   | 1.00        | 5. 4                                       | 2.7×10 <sup>-3</sup>            | 0         |

| 실시예 A22       | 1.00                            | Ag (I) <sub>2</sub> O              | 1.00        | 5. 3                                       | 3.0×10 <sup>-3</sup>            | -1        |

| 실시예 A23       | 1.00                            | Ag (I) <sub>2</sub> O              | 7.5         | 5. 3                                       | 3.0×10 <sup>-3</sup>            | -1        |

| 실시예 A24       | 1.00                            | Ag (I) <sub>2</sub> O              | 5.0         | 5. 3                                       | 3.0×10 <sup>-3</sup>            | -1        |

| 실시예 A25       | 7                               | Cu (I) <sub>2</sub> O              | 8.0         | 5. 4                                       | 4.4×10 <sup>-3</sup>            | 0         |

| 실시예 A26       | 8                               | Cu (I) <sub>2</sub> S              | 8.6         | 5. 0                                       | 3.0×10 <sup>-3</sup>            | 0         |

| 실시예 A27       | 7                               | Ag (I) <sub>2</sub> C <sub>1</sub> | 9.0         | 5. 2                                       | 2.7×10 <sup>-3</sup>            | -3        |

| 실시예 A28       | 5                               | Ag (I) <sub>2</sub> C <sub>1</sub> | 9.5         | 5. 2                                       | 2.7×10 <sup>-3</sup>            | -3        |

| 비교예 A 1       | 금속<br>화합물을<br>함유하지<br>않고<br>전체가 | Ni                                 | 5. 0        | 3.0×10 <sup>-3</sup>                       | -7                              | 2. 0      |

| 비교예 A 2       | 금속<br>화합물을<br>함유하지<br>않고<br>전체가 | Cu                                 | 4. 7        | 0.5×10 <sup>-3</sup>                       | -8                              | 3. 2      |

| 비교예 A 3       | 금속<br>화합물을<br>함유하지<br>않고<br>전체가 | Co                                 | 5. 0        | 2.8×10 <sup>-4</sup>                       | -7                              | 2. 4      |

| 비교예 A 4       | 금속<br>화합물을<br>함유하지<br>않고<br>전체가 | Ag                                 | 4. 2        | 2.8×10 <sup>-3</sup>                       | -1. 0                           | 3. 0      |

\* : 소스 전극 및 드레인 전극의 표면으로부터의 금속 화합물이 존재하는 부분의 평균 두께

표 1-1 및 표 1-2에 나타내는 바와 같이, 각 실시예의 박막 트랜지스터는 모두, 임계 전압 V<sub>th</sub>의 절대치 및 S치가 작고, 또한, 캐리어의 이동도  $\mu$ 이 커서 특성이 우수하였다.

또한, 소스 전극 및 드레인 전극에서, 산화물(금속 화합물)의 함유량이 증대함에 따라서, 트랜지스터 특성이 향상하는 경향을 나타냈다.

이것에 대해서, 각 비교예의 박막 트랜지스터는 모두, 임계 전압 V<sub>th</sub>의 절대치 및 S치가 크고, 또한, 캐리어의 이동도  $\mu$ 가 작았다.

#### A2-4. 경시 열화의 평가

실시예 A6 및 비교예 A2에서 얻어진 박막 트랜지스터를, 25°C 수분 농도 10ppm 산소 농도 10ppm의 환경하에 방치하고, 방치 3일 후 및 방치 57일 후에, 다시 캐리어의 이동도  $\mu$ , 임계 전압 V<sub>th</sub> 및 S치를 측정했다. 그 결과를, 표 2에 나타낸다.

<표 2>

|         | 경과일수 | 캐리어의<br>이동도 $\mu$<br>[cm <sup>2</sup> /Vs] | 임계<br>전압<br>V <sub>th</sub><br>[V] | S치<br>[V] |

|---------|------|--------------------------------------------|------------------------------------|-----------|

| 실시예 A 6 | 0일   | 4.6×10 <sup>-3</sup>                       | 0                                  | 1. 4      |

|         | 3일후  | 4.6×10 <sup>-3</sup>                       | 0                                  | 1. 4      |

|         | 57일후 | 4.5×10 <sup>-3</sup>                       | 0                                  | 1. 4      |

| 비교예 A 2 | 0일   | 0.5×10 <sup>-3</sup>                       | -6                                 | 2. 6      |

|         | 3일후  | 0.5×10 <sup>-3</sup>                       | -6                                 | 2. 7      |

|         | 57일후 | 0.2×10 <sup>-3</sup>                       | -8                                 | 3. 5      |

표 2에 나타내는 바와 같이, 실시예 A6의 박막 트랜지스터는 방치 57일 후에도 초기의 트랜지스터 특성을 유지하고 있음이 명확하게 되었다.

이것에 대해서, 비교예 A2의 박막 트랜지스터는 트랜지스터 특성의 경시적인 열화가 현저함이 명확하게 되었다.

이 결과는 소스 전극 및 드레인 전극의 표면 부근에 산화물(금속 화합물)을 함유함으로써, 유기층의 변질, 열화를 방지하는 효과를 얻을 수 있음을 시사하는 것이다.

이상과 같은 결과로부터, 소스 전극 및 드레인 전극의 표면 부근에, 소정의 원소를 포함하는 산화물을 함유시킴으로써, 박막 트랜지스터의 특성이 향상하고, 또 그 경시적인 변질, 열화를 방지 또는 억제할 수 있음을 알았다.

### B1. 유기 EL 소자의 제작

#### (실시예 B1)

우선, 유리 기판(NEC Corning 사제, "OA10")을 준비하고, 에탄올을 사용하여 세정함으로써, 표면의 탈지 처리를 행했다.

다음에, 유리 기판을 건조한 후, 농황산 중에 침지함으로써, 유리 기판의 표면을 거칠게 했다. 이것에 의해, 다음 공정에서 형성되는 도금막의 밀착성의 개선을 도모하였다. 그 후, 유리 기판을 순수를 사용하여 세정했다.

다음에, 유리 기판을, 감수화액 중에 15초간 침지한 후, 순수로 세정하는 조작을 1사이클로 하여, 4사이클 반복했다.

또한, 감수화액으로는 37wt%의 농염산: 1mL/L에  $\text{SnCl}_2$ : 1g/L를 첨가한 용액(염화주석(II) 용액)을 사용했다.

다음에, 유리 기판상에, 상기 실시예 A1와 동일하게 하여, 평균 두께 100nm의 양극을 형성했다.

다음에, 양극상에, PEDOT/PSS(폴리(3,4-에틸렌디옥시티오펜/스티렌 셀론산)의 1wt% 수분산액(스타락크위텍(Starck Witek) 사제, "Bitron P")을 스핀 코트법(2400rpm)에 의해 도포한 후, 60°C×10분간 건조했다. 이것에 의해, 평균 두께 50nm의 정공 수송층을 형성했다.

다음에, 정공 수송층 상에, F8T2(폴리(9,9-디옥틸플루오렌-코-디티오펜))의 1%wt/vol 톨루엔 용액을 스핀 코트법(2400rpm)에 의해 도포한 후, 60°C×10분간 건조했다. 이것에 의해, 평균 두께 60nm의 발광층을 형성했다.

다음에, 발광층 상에, 칼슘을 진공 증착법에 의해 성막했다. 이것에 의해, 평균 두께 20nm의 전자 주입층을 형성했다.

다음에, 전자 주입층 상에, 산화인듐아연(IZO)을 스퍼터링법에 의해 성막했다. 이것에 의해, 평균 두께 100nm의 음극을 형성했다.

다음에, 유리 재료로 구성된 밀봉 부재를 유리 기판에 접합하여, 양극, 정공 수송층, 발광층, 전자 주입층 및 음극을 밀봉했다.

이상의 공정에 의해, 도 8에 나타내는 바와 같은 유기 EL 소자를 얻었다.

#### (실시예 B2)

양극을 상기 실시예 A3와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

#### (실시예 B3)

양극을 상기 실시예 A7와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

#### (실시예 B4)

양극을 상기 실시예 A8와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

#### (실시예 B5)

양극을 상기 실시예 A11와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(실시예 B6)

양극을 상기 실시예 A14와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(실시예 B7)

양극을 상기 실시예 A17와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(실시예 B8)

양극을 상기 실시예 A18와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(실시예 B9)

양극을 상기 실시예 A19와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(실시예 B10)

양극을 상기 실시예 A25와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(실시예 B11)

양극을 상기 실시예 A26와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(실시예 B12)

양극을 상기 실시예 A28와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(비교예 B1)

양극을 상기 비교예 A1와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(비교예 B2)

양극을 상기 비교예 A2와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(비교예 B3)

양극을 상기 비교예 A3와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

(참고예)

양극을, 산화인듐주석(ITO)을 스퍼터링법에 의해 성막한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 얻었다.

B2. 평가

B2-1. 산화물의 함유량의 측정

상기 A2-1.와 동일하게 하여 행하였다.

B2-2. 일함수의 측정

A2-2와 와 동일하게 하여 행하였다.

### B2-3. 발광 강도의 측정

각 실시예, 각 비교예 및 참고예에서 얻어진 유기 EL 소자에 대해서, 각각, 양극과 음극 사이에 전압(6V)을 인가했을 때의 발광 강도(휘도)를 측정했다.

그 결과를, 표 3에 나타낸다.

또한, 표 3 중의 각 발광 강도는 비교예 B2에서 측정된 발광 강도를 "1"이라고 했을 때의 상대값으로 나타냈다.

<표 3>

| 양극<br>평균 두께 *<br>[nm] | 금속 화합물<br>의 종류      | 금속 화합물<br>의 함유량<br>[wt%]         | 발광 강도<br>[발상대치]          |             |             |

|-----------------------|---------------------|----------------------------------|--------------------------|-------------|-------------|

|                       |                     |                                  | 금속 화합물<br>의 함유량<br>[wt%] | 일형수<br>[eV] | 일형수<br>[eV] |

| 실시예 B1                | 5                   | NiO                              | 85                       | 5.0         | 2.7         |

| 실시예 B2                | 5                   | Cu (II) O                        | 80                       | 5.4         | 3.2         |

| 실시예 B3                | 5                   | CoO                              | 83                       | 5.0         | 2.4         |

| 실시예 B4                | 100                 | NiO                              | 100                      | 5.0         | 2.5         |

| 실시예 B5                | 100                 | Cu (II) O                        | 100                      | 5.4         | 3.0         |

| 실시예 B6                | 100                 | CoO                              | 100                      | 5.0         | 2.2         |

| 실시예 B7                | 100                 | SrCu <sub>2</sub> O <sub>2</sub> | 100                      | 5.4         | 2.8         |

| 실시예 B8                | 100                 | CuAlO <sub>2</sub>               | 100                      | 5.4         | 2.6         |

| 실시예 B9                | 100                 | CuGaO <sub>2</sub>               | 100                      | 5.4         | 2.7         |

| 실시예 B10               | 6                   | Cu (I) <sub>2</sub> O            | 76                       | 5.4         | 3.0         |

| 실시예 B11               | 8                   | Cu (I) <sub>2</sub> S            | 81                       | 5.0         | 3.0         |

| 실시예 B12               | 5                   | Ag (I) <sub>2</sub> C1           | 90                       | 5.2         | 2.9         |

| 비교예 B1                | 금속 화합물을 함유하지 않고 전체가 | Ni                               | 5.0                      | 0.9         |             |

| 비교예 B2                | 금속 화합물을 함유하지 않고 전체가 | Cu                               | 4.7                      | 1           |             |

| 비교예 B3                | 금속 화합물을 함유하지 않고 전체가 | Co                               | 5.0                      | 0.7         |             |

| 참고예                   | 100                 | ITO                              | 100                      | 4.8         | 2.0         |

\* : 양극의 표면으로부터의 금속 화합물이 존재하는 부분의 평균 두께

표 3에 나타내는 바와 같이, 각 실시예의 유기 EL 소자의 발광 강도는 모두 참고예의 발광 강도와 같거나, 참고예의 발광 강도보다 높은 것 이었다.

이것에 대해, 각 비교예의 유기 EL 소자의 발광 강도는 모두 확실히 낮아, 실용에 적합하지 않았다.

또한, 이 결과는 Ag로 이루어지는 양극을 구비하는 유기 EL 소자라도 마찬가지였다. 즉, 양극을, 상기 비교예 A4와 동일하게 하여 형성한 것 이외는 상기 실시예 B1와 동일하게 하여 유기 EL 소자를 제작했다. 또한, 이 것에 대해서, 상기와 마찬가지로 발광 강도를 측정한 결과, 비교예 B2의 발광 강도에 대해서 0.1~0.5배 정도 이었다.

#### 발명의 효과

본 발명에 의하면, 저비용으로 제작 가능하고 또 정공의 주입 효율이 높은 전극이 얻어진다.

또한, 본 발명에 의하면, 신뢰성이 높은 박막 트랜지스터, 전자 회로, 유기 일렉트로루미네센스 소자, 표시 장치 및 전자 기기를 저비용으로 제조할 수 있다.

#### (57) 청구의 범위

## 청구항 1.

주로 유기 재료로 구성되고 정공을 수송하는 기능을 갖는 유기층에 대해서, 정공을 주입하는 전극으로서, 상기 전극은 그 전극의 적어도 상기 유기층 측의 면에, Cu, Ni, Co중의 적어도 1종을 포함하는 산화물을 함유하는 것을 특징으로 하는 전극.

## 청구항 2.

제1항에 있어서,

상기 산화물을 함유하는 부분에서, 상기 산화물의 함유량은 50wt% 이상인 전극.

## 청구항 3.

제1항 또는 제2항에 있어서,

상기 산화물은 Cu, Ni, Co 이외에, Sr, Al, Ga, Li, Na, K, Rb, Cs중의 적어도 1종을 포함하는 전극.

## 청구항 4.

주로 유기 재료로 구성되고 정공을 수송하는 기능을 갖는 유기층에 대해서, 정공을 주입하는 전극으로서,

상기 전극은 복수의 층으로 구성되고,

상기 복수의 층 중, 상기 유기층에 가장 가까운 층이 Cu, Ni, Co중의 적어도 1종을 포함하는 산화물을 함유하는 것을 특징으로 하는 전극.

## 청구항 5.

제4항에 있어서,

상기 유기층에 가장 가까운 층에서, 상기 산화물의 함유량은 50wt% 이상인 전극.

## 청구항 6.

제4항 또는 제5항에 있어서,

상기 산화물은 Cu, Ni, Co 이외에, Sr, Al, Ga, Li, Na, K, Rb, Cs중의 적어도 1종을 포함하는 전극.

## 청구항 7.

제4항에 있어서,

상기 전극을 구성하는 복수의 층 중, 상기 유기층에 가장 가까운 층의 일함수가 가장 큰 전극.

## 청구항 8.

제7항에 있어서,

상기 전극은 2층으로 구성되고,

상기 2층 중, 상기 유기층과는 반대측의 층은 주로 Cu, Ni, Co 또는 이들을 포함하는 합금으로 구성되어 있는 전극.

## 청구항 9.

주로 유기 재료로 구성되고 정공을 수송하는 기능을 갖는 유기층에 대해서, 정공을 주입하는 전극으로서,

상기 전극은 그 전극의 적어도 상기 유기층 측의 면에, 금속 황화물 및 금속 염화물의 적어도 한쪽을 함유하는 것을 특징으로 하는 전극.

## 청구항 10.

주로 유기 재료로 구성되고 정공을 수송하는 기능을 갖는 유기층에 대해서, 정공을 주입하는 전극으로서,

상기 전극은 복수의 층으로 구성되고,

상기 복수의 층 중, 상기 유기층에 가장 가까운 층이 금속 황화물 및 금속 염화물의 적어도 한쪽을 함유하는 것을 특징으로 하는 전극.

### 청구항 11.

제9항 또는 제10항에 있어서,

상기 금속 황화물은 Cu를 포함하는 황화물을 주로 하는 것인 전극.

### 청구항 12.

제9항 또는 제10항에 있어서,

상기 금속 염화물은 Ag를 포함하는 염화물을 주로 하는 것인 전극.

### 청구항 13.

제1항 기재의 전극을 형성하는 전극 형성 방법으로서,

주로 Cu, Ni, Co 또는 이들을 포함하는 합금으로 구성되는 금속막을 형성하는 공정과,

그 금속막에 산화 처리를 실시함으로써, 상기 금속막의 표면을 산화시키는 공정을 갖는 것을 특징으로 하는 전극 형성 방법.

### 청구항 14.

제1항, 제4항, 제9항 및 제10항 중 어느 한 항 기재의 전극으로 구성된 소스 전극과,

상기 유기층으로서, 주로 p형의 유기 반도체 재료로 구성된 유기 반도체층을 갖는 것을 특징으로 하는 박막 트랜지스터.

### 청구항 15.

주로 p형의 유기 반도체 재료로 구성된 유기 반도체층과,

그 유기 반도체층에 정공을 주입하는 소스 전극을 구비하는 박막 트랜지스터로서,

상기 소스 전극은 그 소스 전극의 적어도 상기 유기 반도체층 측의 면에, Ag를 포함하는 산화물을 함유하는 것을 특징으로 하는 박막 트랜지스터.

### 청구항 16.

주로 p형의 유기 반도체 재료로 구성된 유기 반도체층과,

그 유기 반도체층에 정공을 주입하는 소스 전극을 구비하는 박막 트랜지스터로서,

상기 소스 전극은 복수의 층으로 구성되고,

상기 복수의 층 중, 상기 유기 반도체층에 가장 가까운 층이 Ag를 포함하는 산화물을 함유하는 것을 특징으로 하는 박막 트랜지스터.

### 청구항 17.

제14항 내지 제16항 중 어느 한 항에 있어서,

상기 유기 반도체 재료는 고분자계 유기 반도체 재료를 주성분으로 하는 것인 박막 트랜지스터.

### 청구항 18.

제14항 내지 제16항 중 어느 한 항에 있어서,

상기 소스 전극은 상기 유기 반도체층에 직접 접촉하고 있는 박막 트랜지스터.

### 청구항 19.

제14항 내지 제16항 중 어느 한 항 기재의 박막 트랜지스터를 구비하는 것을 특징으로 하는 전자 회로.

### 청구항 20.

제1항, 제4항, 제9항 및 제10항 중 어느 한 항 기재의 전극으로 구성된 양극과,

상기 유기층을 구비하는 유기 일렉트로루미네선스층을 갖는 것을 특징으로 하는 유기 일렉트로루미네선스 소자.

### 청구항 21.

제19항 기재의 전자 회로를 구비하는 것을 특징으로 하는 표시 장치.

### 청구항 22.

제20항 기재의 유기 일렉트로루미네선스 소자를 구비하는 것을 특징으로 하는 표시 장치.

### 청구항 23.

제21항 또는 제22항 기재의 표시 장치를 구비하는 것을 특징으로 하는 전자 기기.

**도면**

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

|                |                                                                                                                                     |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电极，形成电极的方法，薄膜晶体管，电子电路，有机电致发光元件，显示装置                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">KR1020050020610A</a>                                                                                                    | 公开(公告)日 | 2005-03-04 |

| 申请号            | KR1020040061751                                                                                                                     | 申请日     | 2004-08-05 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 精工爱普生株式会社                                                                                                                           |         |            |

| 当前申请(专利权)人(译)  | 精工爱普生株式会社                                                                                                                           |         |            |

| [标]发明人         | MORIYA SOICHI<br>모리야소이치<br>KAWASE TAKEO<br>가와세다케오<br>HARADA MITSUAKI<br>하라다미쓰아키                                                     |         |            |

| 发明人            | 모리야소이치<br>가와세다케오<br>하라다미쓰아키                                                                                                         |         |            |

| IPC分类号         | H05B33/10 H01L21/02 H01L29/786 H05B33/00 H01L29/417 H01L51/40 H01L29/43 H01L21/28 H01L51/50 H05B33/26 H01L51/10 H01L51/00 H01L51/05 |         |            |

| CPC分类号         | H01L51/0545 H01L51/105 H01L51/0541 H01L51/0021                                                                                      |         |            |

| 代理人(译)         | MOON , KI桑                                                                                                                          |         |            |

| 优先权            | 2003207936 2003-08-19 JP<br>2003423745 2003-12-19 JP<br>2004162538 2004-05-31 JP                                                    |         |            |

| 其他公开文献         | KR100684701B1                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                           |         |            |

## 摘要(译)

用途：提供电极，形成电极的方法，薄膜晶体管，电子电路，有机电致发光元件，显示装置和电子器件，以通过提高导电性来降低制造成本并提高空穴注入效率。