(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0052805

(43) 공개일자 2010년05월20일

(51) Int. Cl.

H05B 33/22 (2006.01) H01L 51/50 (2006.01)

(21) 출원번호 10-2008-0111666

(22) 출원일자 2008년11월11일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

정영효

경북 구미시 인의동 274-17번지 대성빌라 402호

강경민

경남 마산시 회원구 회원1동 61-31

서창기

경북 구미시 구평동 부영아파트 606-1402

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 10 항

(54) 유기전계발광표시장치

### (57) 요 약

본 발명의 실시예는, 제1기판과 제1기판과 대향하는 제2기판; 제1기판 상에 위치하는 트랜ジ스터; 트랜ジ스터 상에 위치하며 트랜ジ스터에 포함된 소오스 또는 드레인에 연결된 콘택전극; 제2기판 상에 위치하는 발광부; 발광부에 포함된 하부전극과 상부전극 사이에 위치하여 발광부 간의 영역을 구분하는 기저부와 상부전극과 콘택전극 간의 전기적인 접촉을 돋는 돌출부를 포함하는 스페이서; 및 기저부 상에 위치하며 중앙영역의 내부가 이격되도록 함몰된 패턴부를 갖는 격벽을 포함하는 유기전계발광표시장치를 제공한다.

**대 표 도** - 도2

## 특허청구의 범위

### 청구항 1

제1기판과 상기 제1기판과 대향하는 제2기판;

상기 제1기판 상에 위치하는 트랜지스터;

상기 트랜지스터 상에 위치하며 상기 트랜지스터에 포함된 소오스 또는 드레인에 연결된 콘택전극;

상기 제2기판 상에 위치하는 발광부;

상기 발광부에 포함된 하부전극과 상부전극 사이에 위치하여 상기 발광부 간의 영역을 구분하는 기저부와 상기 상부전극과 상기 콘택전극 간의 전기적인 접촉을 돋는 돌출부를 포함하는 스페이서; 및

상기 기저부 상에 위치하며 중앙영역의 내부가 이격되도록 함몰된 패턴부를 갖는 격벽을 포함하는 유기전계발광표시장치.

### 청구항 2

제1항에 있어서,

상기 격벽은,

상기 중앙영역의 내부가 이격되도록 함몰된 제1패턴부와, 제2패턴부를 포함하며,

상기 중앙영역의 내부는 상기 제2패턴부에 의해 형성된 폭보다 상기 제1패턴부에 의해 형성된 폭이 더 넓은 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 3

제2항에 있어서,

상기 격벽은,

하부면적보다 상부면적이 넓은 역테이퍼 형상을 갖는 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 4

제2항에 있어서,

상기 제1패턴부 및 상기 제2패턴부 중 적어도 하나는,

하부면이 상부면보다 내측으로 인입되도록 패턴된 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 5

제2항에 있어서,

상기 제2패턴부는,

상기 격벽의 하부에 위치하는 상기 기저부의 일부가 노출되도록 패턴된 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 6

제1항에 있어서,

상기 격벽은,

상기 중앙영역의 내부가 이격되어 상기 기저부의 일부가 노출되도록 패턴되어 제1격벽과 제2격벽으로 구분된 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 7

제1항에 있어서,

상기 스페이서는,

상부면적보다 하부면적이 넓은 부등변사각형인 것을 특징으로 하는 유기전계발광표시장치.

#### 청구항 8

제1항에 있어서,

상기 발광부는,

상기 제2기판 상에 위치하는 하부전극과, 상기 하부전극 상에 위치하는 유기 발광층과, 상기 유기 발광층 상에 위치하는 상기 상부전극을 포함하는 유기전계발광표시장치.

#### 청구항 9

제1항에 있어서,

상기 발광부는,

상기 기저부가 위치하는 영역에 형성되고 상기 제2기판과 상기 하부전극 사이에 위치하는 보조전극을 더 포함하는 유기전계발광표시장치.

#### 청구항 10

제1항에 있어서,

상기 격벽은,

유기물, 무기물 또는 유/무기 복합물 중 어느 하나인 것을 특징으로 하는 유기전계발광표시장치.

### 명세서

#### 발명의 상세한 설명

##### 기술 분야

[0001]

본 발명은 유기전계발광표시장치에 관한 것이다.

##### 배경 기술

[0002]

유기전계발광표시장치에 사용되는 유기전계발광소자는 기판 상에 위치하는 두 개의 전극 사이에 발광층이 형성된 자발광소자였다.

[0003]

유기전계발광표시장치는 빛이 방출되는 방향에 따라 전면발광(Top-Emission) 방식, 배면발광(Bottom-Emission) 방식 또는 양면발광(Dual-Emission) 방식 등이 있다. 그리고, 구동방식에 따라 수동매트릭스형(Passive Matrix)과 능동매트릭스형(Active Matrix) 등으로 나누어져 있다.

[0004]

유기전계발광표시장치는 매트릭스 형태로 배치된 복수의 서브 픽셀에 스캔 신호, 데이터 신호 및 전원 등이 공급되면, 선택된 서브 픽셀이 발광을 하게 됨으로써 영상을 표시할 수 있다.

[0005]

한편, 종래 유기전계발광표시장치 중 일부는 트랜지스터와 유기 발광다이오드를 각각 제1기판과 제2기판에 형성하고 제1기판과 제2기판을 접착부재로 접착 밀봉한 구조가 있다. 이 구조는 제1기판 상에 형성된 트랜지스터와 제2기판 상에 위치하는 유기 발광다이오드 간의 전기적인 연결을 하기 위해 스페이서를 사용하였다. 그리고 스페이서와 인접하는 영역에는 유기 발광층 상에 형성되는 전극이 서브 픽셀별로 분리 형성될 수 있도록 격벽을 사용하였다. 한편, 이와 같은 구조로 형성된 종래 유기전계발광표시장치의 경우 유기 발광층 상에 전극을 형성할 때, 부유성 이물 등과 같은 미소입자들이 격벽에 유착 또는 증착되어 인접하는 서브 픽셀 간의 쇼트나 발광 결함을 유발하는 문제가 있어 이의 개선이 요구된다.

#### 발명의 내용

### 해결 하고자하는 과제

- [0006] 상술한 배경기술의 문제점을 해결하기 위한 본 발명의 실시예는, 부유성 이물 등과 같은 미소입자들이 격벽에 유착 또는 증착되어 서브 팩셀의 암점 발생 또는 인접하는 서브 팩셀 간의 쇼트나 발광 결함을 유발하는 문제를 방지할 수 있는 유기전계발광표시장치를 제공하는 것이다. 또한, 본 발명의 실시예는 소자의 신뢰성과 수명을 향상시킬 수 있는 유기전계발광표시장치를 제공하는 것이다.

### 과제 해결수단

- [0007] 상술한 과제 해결 수단으로 본 발명의 실시예는, 제1기판과 제1기판과 대향하는 제2기판; 제1기판 상에 위치하는 트랜지스터; 트랜지스터 상에 위치하며 트랜지스터에 포함된 소오스 또는 드레인에 연결된 콘택전극; 제2기판 상에 위치하는 발광부; 발광부에 포함된 하부전극과 상부전극 사이에 위치하여 발광부 간의 영역을 구분하는 기저부와 상부전극과 콘택전극 간의 전기적인 접촉을 돋는 돌출부를 포함하는 스페이서; 및 기저부 상에 위치하며 중앙영역의 내부가 이격되도록 함몰된 패턴부를 갖는 격벽을 포함하는 유기전계발광표시장치를 제공한다.

- [0008] 격벽은, 중앙영역의 내부가 이격되도록 함몰된 제1패턴부와, 제2패턴부를 포함하며, 중앙영역의 내부는 제2패턴부에 의해 형성된 폭보다 제1패턴부에 의해 형성된 폭이 더 넓을 수 있다.

- [0009] 격벽은, 하부면적보다 상부면적이 넓은 역테이퍼 형상을 가질 수 있다.

- [0010] 제1패턴부 및 제2패턴부 중 적어도 하나는, 하부면이 상부면보다 내측으로 인입되도록 패턴될 수 있다.

- [0011] 제2패턴부는, 격벽의 하부에 위치하는 기저부의 일부가 노출되도록 패턴될 수 있다.

- [0012] 격벽은, 중앙영역의 내부가 이격되어 기저부의 일부가 노출되도록 패턴되어 제1격벽과 제2격벽으로 구분될 수 있다.

- [0013] 돌출부는, 상부면적보다 하부면적이 넓은 부등변사각형일 수 있다.

- [0014] 발광부는, 제2기판 상에 위치하는 하부전극과, 하부전극 상에 위치하는 유기 발광층과, 유기 발광층 상에 위치하는 상부전극을 포함할 수 있다.

- [0015] 발광부는, 기저부가 위치하는 영역에 형성되고 제2기판과 하부전극 사이에 위치하는 보조전극을 더 포함할 수 있다.

- [0016] 격벽은, 유기물, 무기물 또는 유/무기 복합물 중 어느 하나일 수 있다.

### 효과

- [0017] 본 발명의 실시예는, 부유성 이물 등과 같은 미소입자들이 격벽에 유착 또는 증착되어 서브 팩셀의 암점 발생 또는 인접하는 서브 팩셀 간의 쇼트나 발광 결함을 유발하는 문제를 방지할 수 있는 유기전계발광표시장치를 제공하는 효과가 있다. 또한, 본 발명의 실시예는 소자의 신뢰성과 수명을 향상시킬 수 있는 유기전계발광표시장치를 제공하는 효과가 있다.

### 발명의 실시를 위한 구체적인 내용

- [0018] 이하, 본 발명의 실시를 위한 구체적인 내용을 첨부된 도면을 참조하여 설명한다.

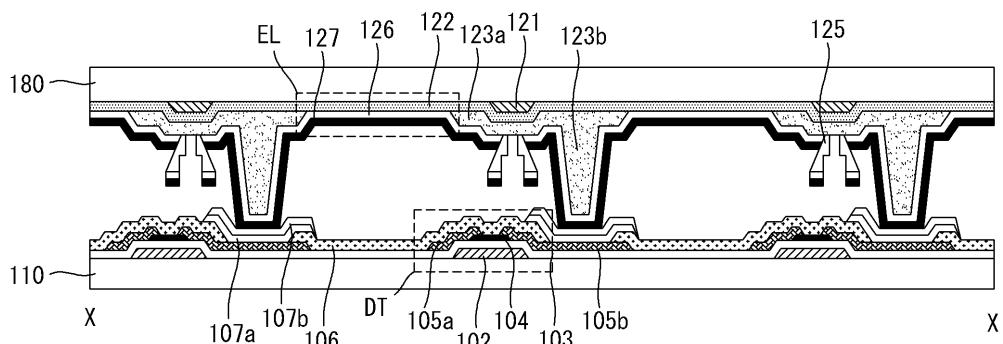

- [0019] 도 1은 본 발명의 실시예에 따른 유기전계발광표시장치의 개략적인 평면도이다.

- [0020] 도 1에 도시된 바와 같이, 본 발명의 실시예에 따른 유기전계발광표시장치는 트랜지스터를 포함하는 제1기판(110)과 발광부를 포함하는 제2기판(180)을 포함할 수 있다. 또한, 제1기판(110) 상에 위치하는 소자들에 구동 신호를 공급하는 구동부(160)를 포함할 수 있다. 또한, 외부로부터 공급되는 각종 신호를 전달하도록 외부회로 기판과 연결되는 패드부(170)를 포함할 수 있다.

- [0021] 제1 및 제2기판(110, 180)은 투광성 또는 비투광성 재료로 형성될 수 있다. 제1 및 제2기판(110, 180)의 재료로

는 유리, 금속, 세라믹 또는 플라스틱(폴리카보네이트 수지, 아크릴 수지, 염화비닐 수지, 폴리에틸렌테레프탈레이트 수지, 폴리아미드 수지, 폴리에스테르 수지, 에폭시 수지, 실리콘 수지, 불소수지 등) 등을 예로 들 수 있다.

[0022] 표시부(AA)는 매트릭스 형태로 배치된 복수의 서브 팩셀(SP)을 포함할 수 있다. 복수의 서브 팩셀(SP) 각각은 제1기판(110) 상에 위치하는 트랜지스터와, 제2기판(180) 상에 위치하는 발광부를 포함할 수 있다. 제1기판(110) 상에 위치하는 트랜지스터와 제2기판(180) 상에 위치하는 발광부는 제1기판(110)과 제2기판(180)이 합착 밀봉되면 상호 전기적으로 연결된다. 한편, 제1기판(110) 상에는 스위칭 트랜지스터, 구동 트랜지스터를 포함하는 트랜지스터는 물론 커패시터가 위치하고, 이들에 전기적으로 연결된 스캔 배선, 데이터 배선, 제1전원 배선 및 제2전원 배선을 포함하는 복수의 배선들이 위치한다. 그리고 제2기판(180) 상에는 하부전극, 유기 발광층 및 상부전극을 포함하는 발광부는 물론 상부전극과 하부전극 간의 전기적인 연결을 돋는 스페이서가 위치한다.

[0023] 구동부(160)는 표시부(AA)에 포함된 복수의 서브 팩셀(SP)에 데이터신호와 스캔신호를 공급하는 데이터구동부와 스캔구동부를 포함할 수 있다. 데이터구동부는 외부로부터 수평 동기 신호 및 영상 데이터신호를 공급받고 수평 동기 신호를 참조하여 데이터신호 등을 생성할 수 있다. 그리고 스캔구동부는 외부로부터 수직 동기 신호를 공급받고 수직 동기 신호를 참조하여 복수의 서브 팩셀(SP)에 공급할 스캔신호 및 제어신호 등을 생성할 수 있다. 여기서, 구동부(160)에 포함된 데이터구동부와 스캔구동부는 제1기판(110) 상에 각각 구분되어 위치할 수도 있다.

[0024] 이하, 단면도를 참조하여 본 발명의 실시예에 따른 유기전계발광표시장치에 대해 더욱 자세히 설명한다.

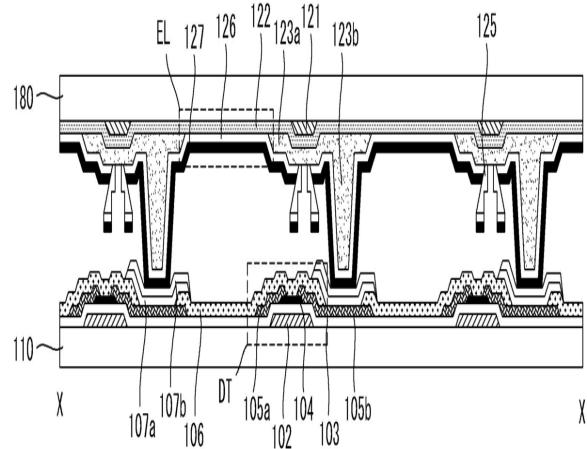

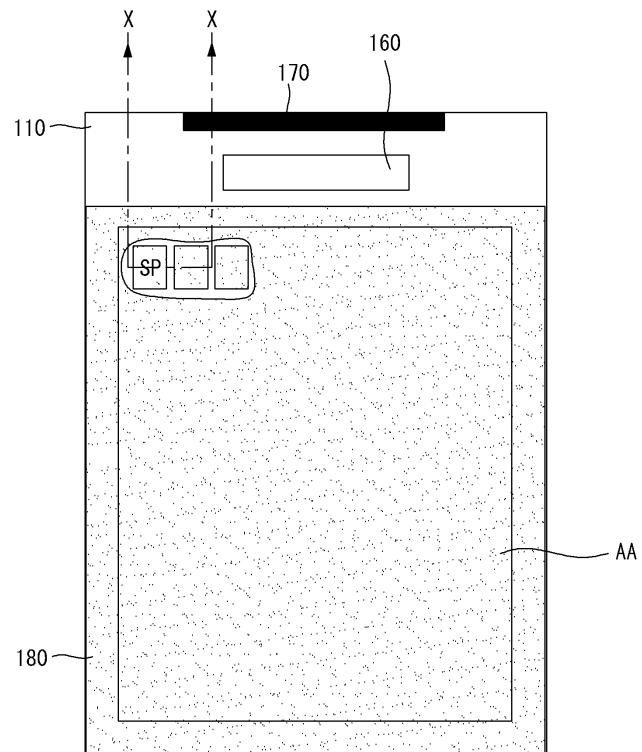

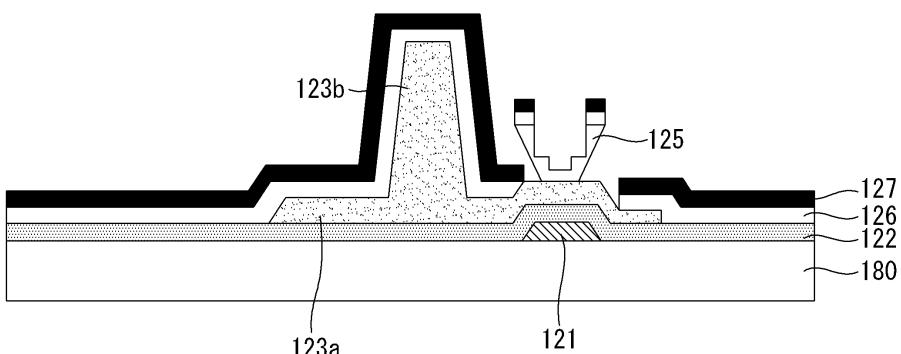

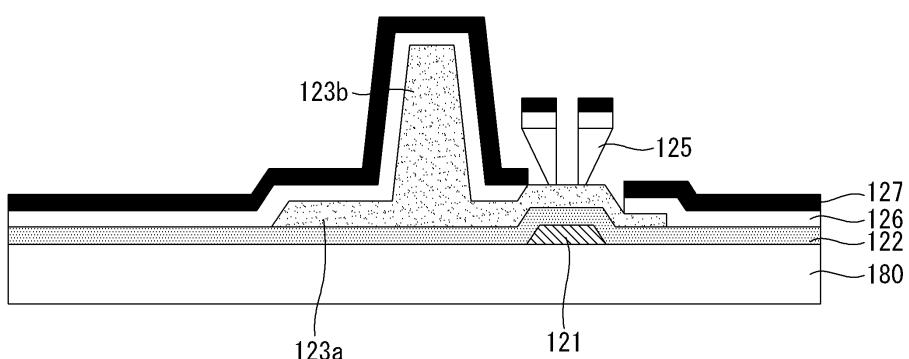

[0025] 도 2는 본 발명의 실시예에 따른 도 1의 X-X 영역의 단면도이다.

[0026] 도 2를 참조하면, 제1기판(110) 상에는 게이트(102)가 위치할 수 있다. 게이트(102)는 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 금(Au), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu)로 이루어진 군에서 선택된 어느 하나 또는 이들의 합금으로 이루어질 수 있다. 또한, 게이트(102)는 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 금(Au), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu)로 이루어진 군에서 선택된 어느 하나 또는 이들의 합금으로 이루어진 다중층일 수 있다. 또한, 게이트(102)는 몰리브덴/알루미늄-네오디뮴 또는 몰리브덴/알루미늄의 2중층일 수 있다.

[0027] 게이트(102) 상에는 제1절연막(103)이 위치할 수 있다. 제1절연막(103)은 실리콘 산화막(SiO<sub>x</sub>), 실리콘 질화막(SiNx) 또는 이들의 다중층일 수 있으나 이에 한정되지 않는다.

[0028] 제1절연막(103) 상에는 액티브층(104)이 위치할 수 있다. 액티브층(104)은 비정질 실리콘 또는 이를 결정화한 다결정 실리콘을 포함할 수 있다. 여기서 도시하지는 않았지만, 액티브층(104)은 채널 영역, 소오스 영역 및 드레인 영역을 포함할 수 있으며, 소오스 영역 및 드레인 영역에는 P형 또는 N형 불순물이 도핑될 수 있다. 또한, 액티브층(104)은 접촉 저항을 낮추기 위한 오믹 콘택층을 포함할 수도 있다.

[0029] 액티브층(104) 상에는 액티브층(104)과 접촉하는 소오스(105a) 및 드레인(105b)이 위치할 수 있다. 소오스(105a) 및 드레인(105b)은 단일층 또는 다중층으로 이루어질 수 있다. 소오스(105a) 및 드레인(105b)이 단일층 일 경우에는 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 금(Au), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu)로 이루어진 군에서 선택된 어느 하나 또는 이들의 합금으로 이루어질 수 있다. 이와 달리, 소오스(105a) 및 드레인(105b)이 다중층일 경우에는 몰리브덴/알루미늄-네오디뮴의 2중층, 몰리브덴/알루미늄/몰리브덴 또는 몰리브덴/알루미늄-네오디뮴/몰리브덴의 3중층으로 이루어질 수 있다.

[0030] 소오스(105a) 및 드레인(105b) 상에는 제2절연막(106)이 위치할 수 있다. 제2절연막(106)은 실리콘 산화막(SiO<sub>x</sub>), 실리콘 질화막(SiNx) 또는 이들의 다중층일 수 있으나 이에 한정되지 않는다. 제2절연막(106)은 패시베이션막 또는 평탄화막일 수 있다.

[0031] 제2절연막(106) 상에는 소오스(105a) 또는 드레인(105b)에 연결된 콘택전극(107a, 107b)이 위치할 수 있다. 콘택전극(107a, 107b)은 도시된 바와 같이 복층 또는 단층으로 형성될 수 있다.

[0032] 이상은 제1기판(110) 상에 위치하는 트랜지스터(DT)가 바탐 게이트형 인 것을 일례로 설명하였다. 그러나, 제1기판(110) 상에 위치하는 트랜지스터(DT)의 구조는 이에 한정되지 않고 탑 게이트형으로도 형성될 수 있다.

[0033] 제2기판(180) 상에는 하부전극(122)이 위치할 수 있다. 하부전극(122)은 애노드 또는 캐소드로 선택될 수 있다.

하부전극(122)이 애노드로 선택된 경우, 애노드의 재료로는 ITO(Indium Tin Oxide), IZO(Indium Zinc Oxide), ITZO(Indium Tin Zinc Oxide), AZO(ZnO doped Al203) 중 어느 하나로 형성될 수 있으나 이에 한정되지 않는다.

[0034] 하부전극(122) 상에는 하부전극(122)의 일부를 노출하는 기저부(123a)와 기저부(123a)보다 돌출된 돌출부(123b)를 포함하는 스페이서(123a, 123b)를 포함할 수 있다. 스페이서(123a, 123b)는 유기물, 무기물 또는 유/무기 복합물 중 어느 하나로 형성될 수 있다.

[0035] 기저부(123a) 상에는 중앙영역의 내부가 이격되도록 합몰된 패턴부를 갖는 격벽(125)이 위치할 수 있다. 격벽(125)은 유기물, 무기물 또는 유/무기 복합물 중 어느 하나로 형성될 수 있다.

[0036] 하부전극(122) 상에는 격벽(125)에 의해 분리 형성된 유기 발광층(126)이 위치할 수 있다. 유기 발광층(126)은 정공주입층, 정공수송층, 발광층, 전자수송층, 전자주입층을 포함할 수 있다.

[0037] 유기 발광층(126) 상에는 격벽(125)에 의해 분리 형성된 상부전극(127)이 위치할 수 있다. 상부전극(127)은 애노드 또는 캐소드로 선택될 수 있다. 하부전극(127)이 캐소드로 선택된 경우, 캐소드의 재료로는 알루미늄(Al), 알루미늄 합금(Al alloy), 알미네리움(AlNd) 중 어느 하나로 형성될 수 있으나 이에 한정되지 않는다. 또한, 하부전극(127)이 캐소드로 선택된 경우, 캐소드의 재료로는 반사도가 높은 재료로 형성하는 것이 유리하다.

[0038] 한편, 제2기판(180) 상에 형성된 발광부(EL)는 기저부가(123a) 위치하는 영역에 형성되고 제2기판(180)과 하부전극(122) 사이에 위치하는 보조전극(121)을 더 포함할 수 있다. 보조전극(121)은 하부전극(122)과 접촉하여 하부전극(122)을 통해 공급되는 전원이 강하하지 않도록 금속재료로 형성될 수 있다. 보조전극(121)은 몰리브덴(Mo), 알루미늄(Al), 크롬(Cr), 금(Au), 티타늄(Ti), 니켈(Ni), 네오디뮴(Nd) 및 구리(Cu) 중 어느 하나로 이루어질 수 있으나 이에 한정되지 않는다.

[0039] 이상 트랜지스터(DT)를 포함하는 제1기판(110)과 발광부(EL)를 포함하는 제2기판(180)은 접착부재 등에 의해 합착 밀봉된다. 여기서, 제1기판(110)과 제2기판(180)이 합착 밀봉되면 제1기판(110) 상에 위치하는 콘택전극(197a, 107b)과 제2기판(180) 상에 위치하는 상부전극(127)은 상부전극(127)의 하부에 위치하는 돌출부(123b)에 의해 전기적으로 연결되는 구조를 갖게 된다. 즉, 돌출부(123b)의 경우 콘택전극(197a, 107b)과 상부전극(127) 간의 전기적인 접촉을 돋는 구조물 역할을 한다. 여기서, 제1기판(110) 상에 도시된 트랜지스터(DT)는 구동 트랜지스터를 나타낸다.

[0040] 제2기판(180) 상에 위치하는 돌출부(123b)의 경우, 제2기판(180) 상에 형성되는 유기 발광층(126)과 상부전극(127)이 하나의 서브 팩셀을 정의하는 영역 내에서 분리되지 않고 중첩될 수 있도록 상부면적보다 하부면적이 넓은 부등변사각형 형태로 형성될 수 있다. 이와 달리, 격벽(125)의 경우, 제2기판(180) 상에 형성되는 유기 발광층(126)과 상부전극(127)이 하나의 서브 팩셀을 정의하는 영역별로 구분되어 형성되도록 합몰된 패턴부를 가질 수 있다. 격벽(125)의 구조에 대한 설명은 이하에서 더욱 자세히 한다.

[0041] 한편, 제1기판(110)과 제2기판(180)이 합착 밀봉될 때, 제1기판(110) 상에 위치하는 제1전원배선과 제2기판(180) 상에 위치하는 하부전극(122)은 전기적으로 연결될 수 있는데, 제1전원배선과 하부전극(122)도 돌출부(123b)와 같은 구조물에 의해 도움을 받아 상호 전기적으로 연결될 수 있다.

[0042] 이하, 도 3을 참조하여 발광부(EL)에 대해 더욱 자세히 설명한다.

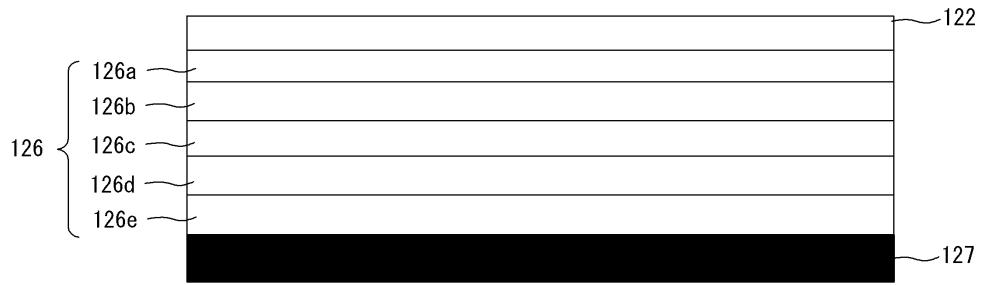

[0043] 도 3은 발광부의 계층 구조 예시도이다.

[0044] 도 3에 도시된 바와 같이, 발광부는 하부전극(122), 정공주입층(126a), 정공수송층(126b), 발광층(126c), 전자수송층(126d), 전자주입층(126e) 및 상부전극(127)을 포함할 수 있다.

[0045] 정공주입층(126a)은 정공의 주입을 원활하게 하는 역할을 할 수 있으며, CuPc(cupper phthalocyanine), PEDOT(poly(3,4)-ethylenedioxothiophene), PANI(polyaniline) 및 NPD(N,N-dinaphthyl-N,N'-diphenyl benzidine)로 이루어진 군에서 선택된 어느 하나 이상으로 이루어질 수 있으나 이에 한정되지 않는다.

[0046] 정공수송층(126b)은 정공의 수송을 원활하게 하는 역할을 하며, NPD(N,N-dinaphthyl-N,N'-diphenyl benzidine), TPD(N,N'-bis-(3-methylphenyl)-N,N'-bis-(phenyl)-benzidine), s-TAD 및 MTDATA(4,4',4"-Tris(N-3-methylphenyl-N-phenyl-amino)-triphenylamine)로 이루어진 군에서 선택된 어느 하나 이상으로 이루어질 수 있으나 이에 한정되지 않는다.

- [0047] 발광층(126c)은 적색, 녹색, 청색 및 백색을 발광하는 물질을 포함할 수 있으며, 인광 또는 형광물질을 이용하여 형성할 수 있다.

- [0048] 발광층(126c)이 적색인 경우, CBP(carbazole biphenyl) 또는 mCP(1,3-bis(carbazol-9-yl)를 포함하는 호스트 물질을 포함하며, PIQIr(acac)(bis(1-phenylisoquinoline)acetylacetone iridium), PQIr(acac)(bis(1-phenylquinoline)acetylacetone iridium), PQIr(tris(1-phenylquinoline)iridium) 및 PtOEP(octaethylporphyrin platinum)로 이루어진 군에서 선택된 어느 하나 이상을 포함하는 도편트를 포함하는 인광물질로 이루어질 수 있고, 이와는 달리 PBD:Eu(DBM)3(Phen) 또는 Perylene을 포함하는 형광물질로 이루어질 수 있으나 이에 한정되지 않는다.

- [0049] 발광층(126c)이 녹색인 경우, CBP 또는 mCP를 포함하는 호스트 물질을 포함하며, Ir(ppy)3(fac tris(2-phenylpyridine)iridium)을 포함하는 도편트 물질을 포함하는 인광물질로 이루어질 수 있고, 이와는 달리, Alq3(tris(8-hydroxyquinolino)aluminum)을 포함하는 형광물질로 이루어질 수 있으나 이에 한정되지 않는다.

- [0050] 발광층(126c)이 청색인 경우, CBP 또는 mCP를 포함하는 호스트 물질을 포함하며, (4,6-F<sub>2</sub>ppy)₂Irpic을 포함하는 도편트 물질을 포함하는 인광물질로 이루어질 수 있다. 이와는 달리, spiro-DPVBi, spiro-6P, 디스틸벤젠(DSB), 디스트릴아릴렌(DSA), PFO계 고분자 및 PPV계 고분자로 이루어진 군에서 선택된 어느 하나를 포함하는 형광물질로 이루어질 수 있으나 이에 한정되지 않는다.

- [0051] 전자수송층(126d)은 전자의 수송을 원활하게 하는 역할을 하며, Alq3(tris(8-hydroxyquinolino)aluminum), PBD, TAZ, spiro-PBD, BA1q 및 SA1q로 이루어진 군에서 선택된 어느 하나 이상으로 이루어질 수 있으나 이에 한정되지 않는다.

- [0052] 전자주입층(126e)은 전자의 주입을 원활하게 하는 역할을 하며, Alq3(tris(8-hydroxyquinolino)aluminum), PBD, TAZ, spiro-PBD, BA1q 또는 SA1q를 사용할 수 있으나 이에 한정되지 않는다.

- [0053] 여기서, 본 발명의 실시예는 도 3에 한정되는 것은 아니며, 정공주입층(126a), 정공수송층(126b), 전자수송층(126d), 전자주입층(126e) 중 적어도 어느 하나가 생략될 수도 있다.

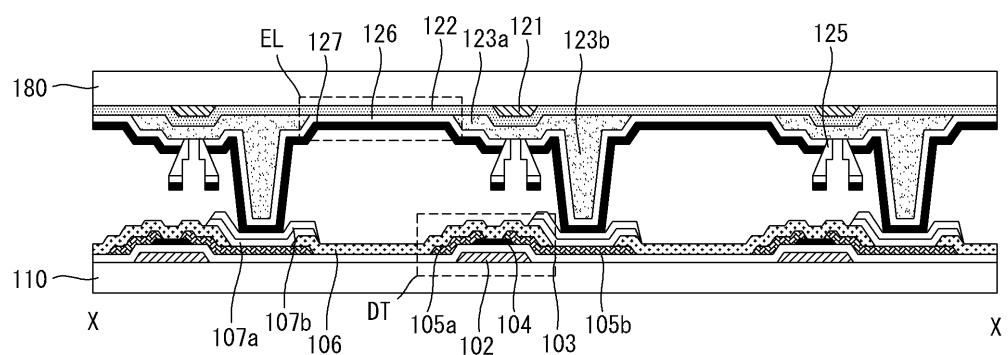

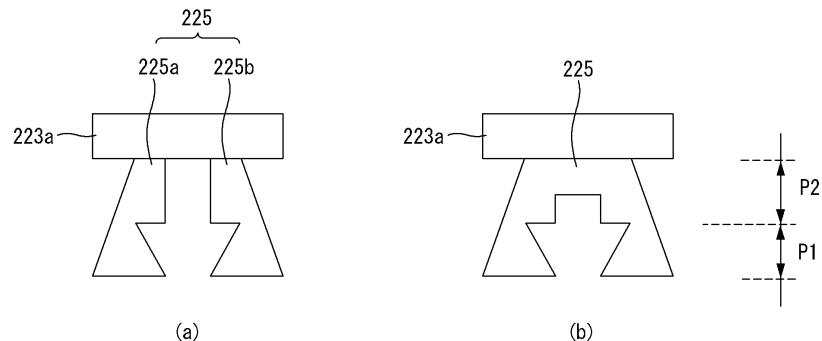

- [0054] 이하, 도 4를 참조하여 격벽(125)에 대해 더욱 자세히 설명한다.

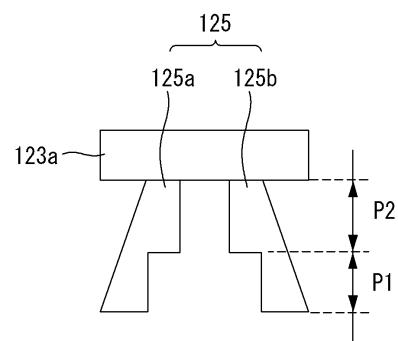

- [0055] 도 4는 실시예에 따른 격벽의 단면 예시도이다.

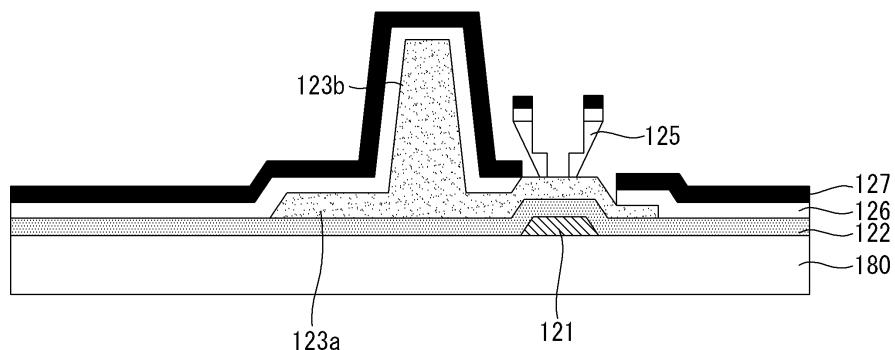

- [0056] 도 4를 참조하면, 격벽(125)은 도시된 바와 같이 하부면적보다 상부면적이 넓은 역테이퍼 형상을 가질 수 있다. 그리고 격벽(125) 중앙영역의 내부가 이격되도록 핵물된 제1패턴부(P1)와, 제2패턴부(P2)를 포함할 수 있다. 제2패턴부(P2)는 격벽(125)의 하부에 위치하는 기저부(123a)의 일부가 노출되도록 패턴될 수 있다. 이 경우, 격벽(125)은 중앙영역의 내부가 이격되어 기저부(123a)의 일부가 노출되도록 패턴되어 제1격벽(125a)과 제2격벽(125b)으로 구분된 형상을 가질 수 있다. 이에 따라, 격벽(125)의 중앙영역의 내부는 제2패턴부(P2)에 의해 형성된 폭보다 제1패턴부(P1)에 의해 형성된 폭이 더 넓은 형태로 형성된다.

- [0057] 이상과 같은 구조를 갖는 격벽(125)을 사용하면, 하부전극(122) 상에 유기 발광층(126) 및 상부전극(127)을 증착할 때 부유성 이물 등과 같은 미소입자들이 격벽(125)에 유착 또는 증착되어 인접하는 서브 픽셀 간의 쇼트나 발광 결함을 유발하는 문제를 방지할 수 있게 된다.

- [0058] 이하, 제2기판(180) 상에 위치하는 스페이서(123a, 123b) 상에 격벽(125)을 형성하는 공정에 대해 더욱 자세히 설명한다.

- [0059] 도 5 내지 도 10은 실시예에 의한 격벽 형성 방법을 설명하기 위한 공정 흐름도이다.

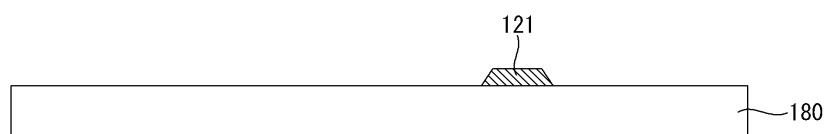

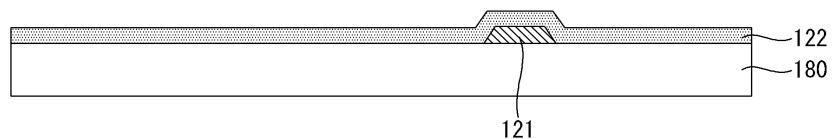

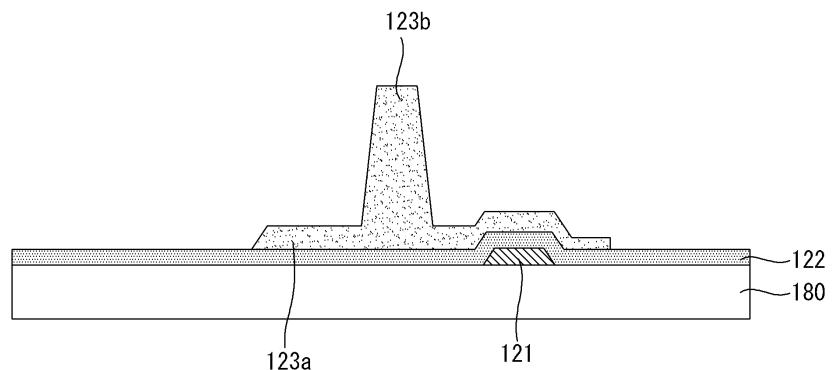

- [0060] 먼저, 도 5 및 도 6에 도시된 바와 같이, 제2기판(180) 상에 보조전극(121)을 형성하고, 보조전극(121) 상에 하부전극(122)을 형성한다.

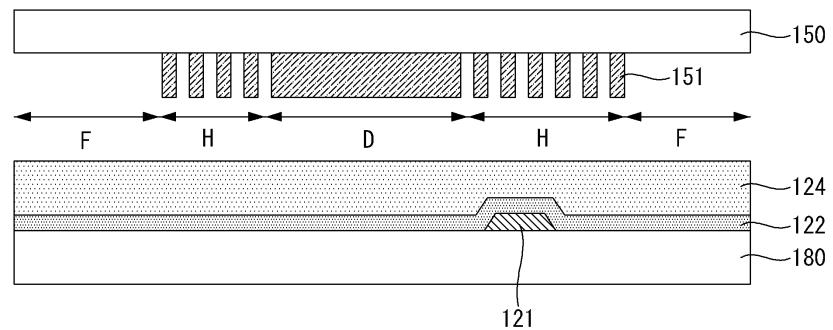

- [0061] 다음, 도 7 및 도 8에 도시된 바와 같이, 제2기판(180) 상에 하부전극(122)을 덮도록 박막(124)을 형성하고, 제2기판(180)과 이격하도록 하프톤마스크(150)를 열라인하고 이를 이용하여 박막(124)을 패터닝한다. 여기서, 하프톤마스크(150)의 경우 패턴할 형상에 적합한 금속막(151)이 하부에 부착된다. 하프톤마스크(150)를 이용하여 패터닝할 때, 도시된 바와 같은 형상의 금속막(151)에 의해 "F"영역은 풀 노광, "H"영역은 하프 노광, "D"영역

은 차단이 되므로, 박막(124)은 기저부(123a)와 돌출부(123b)를 갖는 스페이서(123a, 123b)로 형성된다.

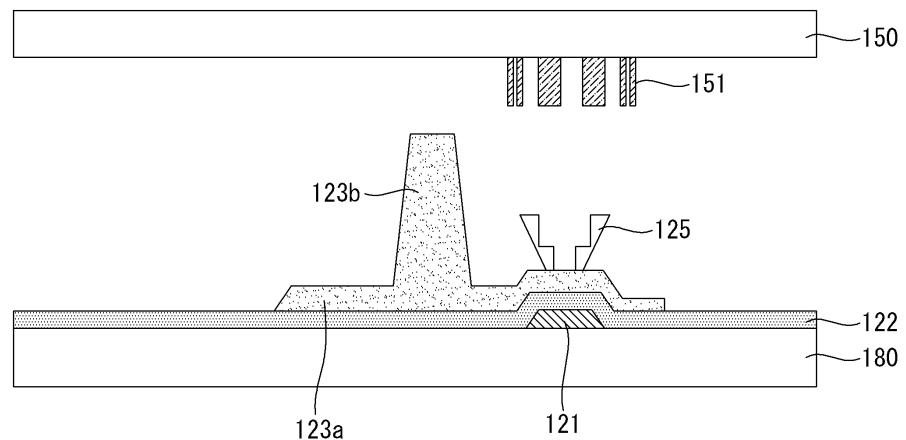

[0062] 다음, 도 9에 도시된 바와 같이, 기저부(123a) 상에 박막을 형성하고, 하프톤마스크(150)를 이용하여 박막을 패터닝하면, 중앙영역의 내부가 이격되도록 함몰된 패턴부를 갖는 격벽(125)이 형성된다. 다만, 격벽(125)을 형성할 때 사용되는 하프톤마스크(150)의 경우, 도 9에 도시된 바와 같은 금속막(151)의 구조 외에 다른 것을 사용하면 다른 형상으로 격벽(125)을 형성할 수 있다.

[0063] 다음, 도 10에 도시된 바와 같이, 앞서 설명한 격벽(125)이 형성된 경우 제2기판(180) 상에 유기 발광층(126)과 상부전극(127)을 차례로 증착하면, 유기 발광층(126)과 상부전극(127)은 기저부(123a)에 의해 노출된 하부전극(122)의 표면과 돌출부(123b)의 표면에 증착되어 격벽(125)이 형성된 부분에서 각각 분리 된다.

[0064] 다른 실시예에 의하면, 격벽(125)은 하프톤마스크(150)에 부착된 금속막(151)의 형태와 노광 정도에 따라 다양한 형상으로 형성될 수 있다.

[0065] 도 11 및 도 12는 다른 실시예에 따른 격벽의 구조를 나타낸 도면이다.

[0066] 먼저, 도 11을 참조하면, 격벽(125)의 형상은 앞서 설명한 도 9의 공정에서 실시되는 노광 정도에 따라 기저부(123a)의 일부를 노출하지 않고 일부만 함몰되도록 패턴될 수도 있다.

[0067] 다음, 도 12를 참조하면, 격벽(125)의 형상은 앞서 설명한 도 9의 공정에서 사용되는 하프톤마스크(150)의 금속막(151)의 형태에 따라 기저부(123a)의 일부를 노출하되 제1격벽과 제2격벽 형태로 구분되도록 패턴될 수도 있다.

[0068] 또 다른 실시예에 의하면, 격벽(125)은 하프톤마스크가 아닌 다른 패턴 방법에 의해서도 다양한 형상으로 형성될 수 있다.

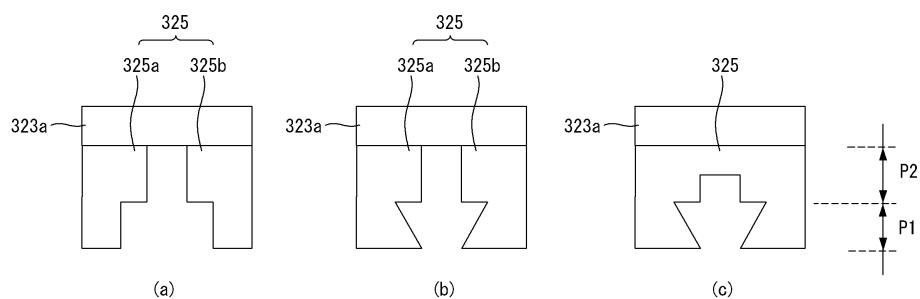

[0069] 도 13 및 도 14는 또 다른 실시예에 따른 격벽의 구조를 나타낸 도면이다.

[0070] 도 13의 (a)를 참조하면, 격벽(225)은 제1패턴부(P1)의 경우 하부면이 상부면보다 내측으로 인입되도록 패턴되고 제2패턴부(P2)의 경우 기저부(223a)의 일부를 노출하도록 패턴되어 제1격벽(225a)과 제2격벽(225b)으로 구분된 형상을 가질 수 있다.

[0071] 이와 달리, 도 13의 (b)를 참조하면, 격벽(225)은 제1패턴부(P1)의 경우 하부면이 상부면보다 내측으로 인입되도록 패턴되고 제2패턴부(P2)의 경우 기저부(223a)의 일부를 노출하지 않고 함몰되도록 패턴된 형상을 가질 수 있다.

[0072] 도 14의 (a)를 참조하면, 격벽(325)은 역테이퍼 형상이 아닌 사각형으로 형성되고 제1패턴부(P1)과 제2패턴부(P2)에 의해 기저부(323a)의 일부를 노출하도록 패턴되어 제1격벽(325a)과 제2격벽(325b)으로 구분된 형상을 가질 수 있다.

[0073] 이와 달리, 도 14의 (b)를 참조하면, 격벽(325)은 사각형으로 형성되어 제1패턴부(P1)의 경우 하부면이 상부면보다 내측으로 인입되도록 패턴되고 제2패턴부(P2)의 경우 기저부(323a)의 일부를 노출하도록 패턴되어 제1격벽(325a)과 제2격벽(325b)으로 구분된 형상을 가질 수 있다.

[0074] 이와 달리, 도 14의 (c)를 참조하면, 격벽(325)은 사각형으로 형성되어 제1패턴부(P1)의 경우 하부면이 상부면보다 내측으로 인입되도록 패턴되고 제2패턴부(P2)의 경우 기저부(323a)의 일부를 노출하지 않고 함몰되도록 패턴된 형상을 가질 수 있다.

[0075] 도 14의 (b) 및 (c)에서는 제1패턴부(P1)가 하부면이 상부면보다 내측으로 인입되도록 패턴된 것을 도시하였지만 제1패턴부(P1) 및 제2패턴부(P2) 중 적어도 하나의 하부면이 상부면보다 내측으로 인입되도록 패턴될 수 있다.

[0076] 이상 본 발명의 실시예는 제1기판 상에 형성된 트랜지스터와 제2기판 상에 형성된 발광부를 포함하는 유기전계 발광표시장치에서 사용하는 격벽의 구조를 변경하여 유기 발광층 상에 전극을 형성할 때, 부유성 이물 등과 같은 미소입자들이 격벽에 유착 또는 증착되어 서브 픽셀의 암점 발생 또는 인접하는 서브 픽셀 간의 쇼트나 발

광 결함을 유발하는 문제를 방지할 수 있는 효과가 있다. 또한, 본 발명의 실시예는 소자의 신뢰성과 수명을 향상시키는 효과가 있다.

[0077] 이상 첨부된 도면을 참조하여 본 발명의 실시예를 설명하였지만, 상술한 본 발명의 기술적 구성은 본 발명이 속하는 기술 분야의 당업자가 본 발명의 그 기술적 사상이나 필수적 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시 예들은 모든 면에서 예시적인 것이며 한정적인 것이 아닌 것으로서 이해되어야 한다. 아울러, 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어진다. 또한, 특허청구범위의 의미 및 범위 그리고 그 등가 개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

### 도면의 간단한 설명

[0078] 도 1은 본 발명의 실시예에 따른 유기전계발광표시장치의 개략적인 평면도.

[0079] 도 2는 본 발명의 실시예에 따른 도 1의 X-X 영역의 단면도.

[0080] 도 3은 발광부의 계층 구조 예시도.

[0081] 도 4는 실시예에 따른 격벽의 단면 예시도.

[0082] 도 5 내지 도 10은 실시예에 의한 격벽 형성 방법을 설명하기 위한 공정 흐름도.

[0083] 도 11 및 도 12는 다른 실시예에 따른 격벽의 구조를 나타낸 도면.

[0084] 도 13 및 도 14는 또 다른 실시예에 따른 격벽의 구조를 나타낸 도면.

[0085] <도면의 주요 부분에 관한 부호의 설명>

[0086] 110: 제1기판 102: 케이트

[0087] 107a, 107b: 콘택전극 122: 하부전극

[0088] 123a, 123b: 스페이서 125: 격벽

[0089] 126: 유기 발광층 127: 상부전극

[0090] 160: 구동부 170: 패드부

[0091] 180: 제2기판

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

## 도면13

## 도면14

|                |                                                                       |         |            |

|----------------|-----------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光显示装置                                                            |         |            |

| 公开(公告)号        | <a href="#">KR1020100052805A</a>                                      | 公开(公告)日 | 2010-05-20 |

| 申请号            | KR1020080111666                                                       | 申请日     | 2008-11-11 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                              |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                             |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                             |         |            |

| [标]发明人         | JUNG YOUNG HYO<br>정영호<br>KANG KYONG MIN<br>강경민<br>SEO CHANG KI<br>서창기 |         |            |

| 发明人            | 정영호<br>강경민<br>서창기                                                     |         |            |

| IPC分类号         | H05B33/22 H01L51/50                                                   |         |            |

| CPC分类号         | H01L51/0533 H01L21/76804 H01L29/41766 H01L29/6656                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                             |         |            |

### 摘要(译)

本发明实施例提供的有机电致发光显示装置包括间隔物，分隔壁包括面对第一基板和第一基板的第二基板，晶体管位于第一基板上，源极，发光单元位于第二基板表面，突出部分帮助基部之间的电接触。源极包含在晶体管中，它位于晶体管的表面或连接到漏极的接触电极上。有助于基部之间的电接触的突出部分位于底部电极和所包括的上电极之间的发光单元中，并且将发光单元与上电极和接触电极之间的区域分类。分隔壁位于基部的表面上并具有凹陷的图案部分，使得中心的内部分离。有机电致发光显示装置，分隔壁和下沉。