## (19) 대한민국특허청(KR)

### (12) 공개특허공보(A)

(51) Int. Cl. (11) 공개번호 10-2006-0041121

*G09G 3/30* (2006.01) (43) 공개일자 2006년05월11일

(21) 출원번호 10-2004-0090603

(22) 출원일자 2004년11월08일

(71) 출원인 삼성에스디아이 주식회사

경기 수원시 영통구 신동 575

(72) 발명자 서미숙

경기 용인시 풍덕천동 삼성5차아파트 526동 1004호

강태옥

경기 성남시 분당구 분당동 샛별마을우방아파트 302동1103호

이을호

경기 용인시 기흥읍 공세리 428-5 삼성SDI중앙연구소

(74) 대리인 박상수

심사청구 : 있음

#### (54) 평판표시장치

##### 요약

흔색성이 우수함과 아울러서 신호지연의 문제가 없는 평판표시장치를 제공한다. 상기 평판표시장치는 기판 및 상기 기판 상에 배열된 신호선들을 구비한다. 상기 신호선들 중 적어도 일부는 스캔라인들과 상기 스캔 라인들을 교차하면서 직선형태로 배열된 데이터 라인들이다. 상기 스캔 라인들과 상기 데이터 라인들의 교차에 의해 적색, 녹색 및 청색 화소구동회로 영역들이 정의된다. 상기 화소구동회로 영역들 중 동일 색에 해당하는 화소구동회로 영역들은 열 방향으로 서로 인접하여 위치한다. 상기 화소구동회로 영역들에 적색, 녹색 및 청색 화소구동회로들이 각각 위치한다. 상기 적색, 녹색 및 청색 화소구동회로들에 적색, 녹색 및 청색 화소전극들이 각각 접속한다. 상기 각 화소전극은 횡방향 및 열방향으로 서로 다른 색 화소전극과 인접한다.

##### 대표도

도 3

##### 색인어

화소 배열, 스트라이프, 멜타, 유기전계발광표시장치

##### 명세서

##### 도면의 간단한 설명

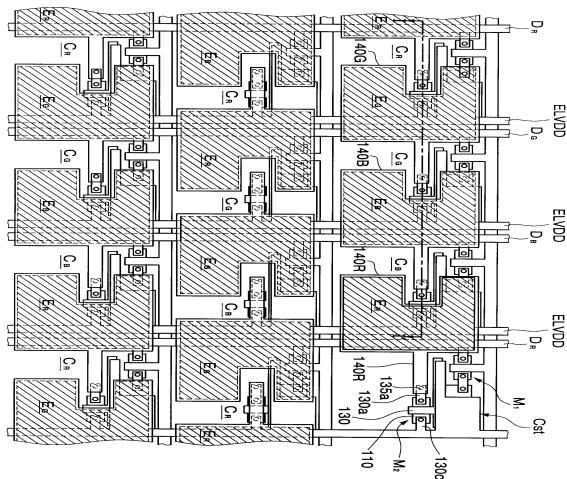

도 1은 종래 기술에 따른 멜타형 화소 배열을 갖는 유기전계발광표시장치를 나타낸 평면도이다.

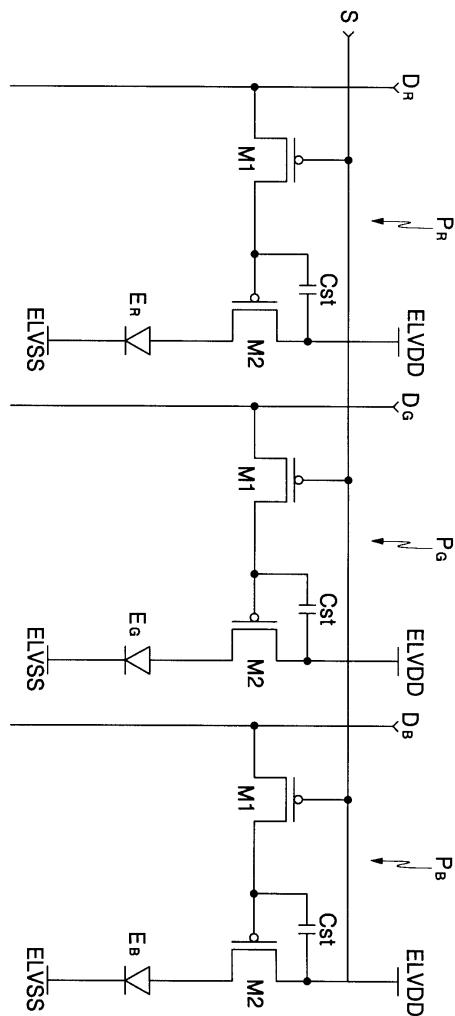

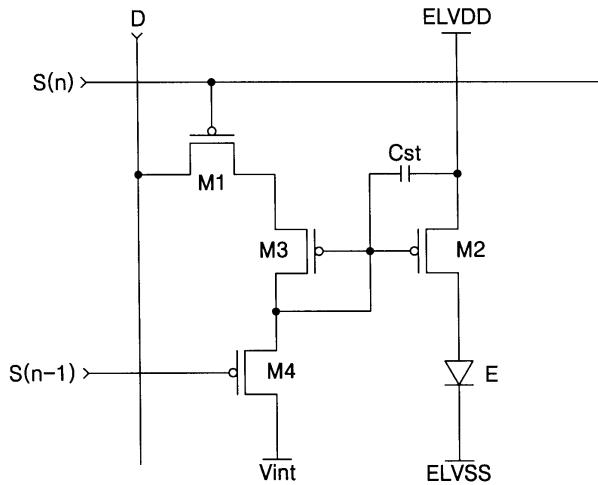

도 2는 본 발명의 일 실시예에 따른 유기전계발광표시장치의 화소 회로를 나타낸 회로도이다.

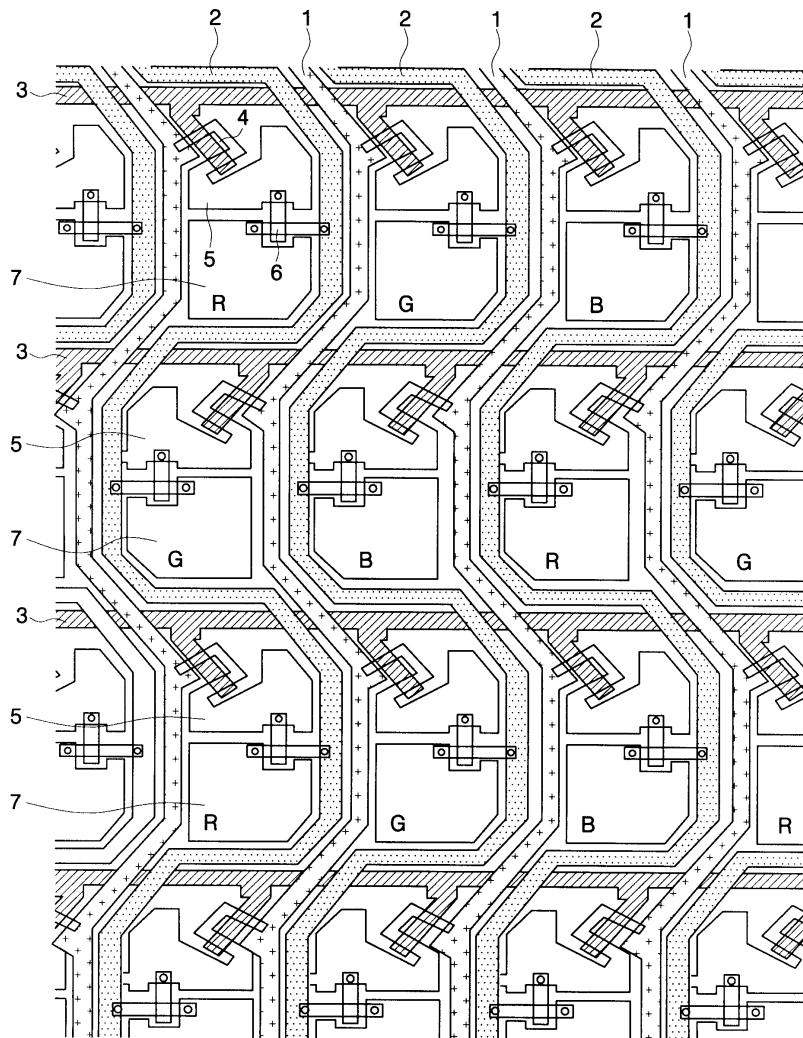

도 3은 본 발명의 일 실시예에 따른 유기전계발광표시장치의 화소 어레이 중 일부분에 한정하여 나타낸 평면도이다.

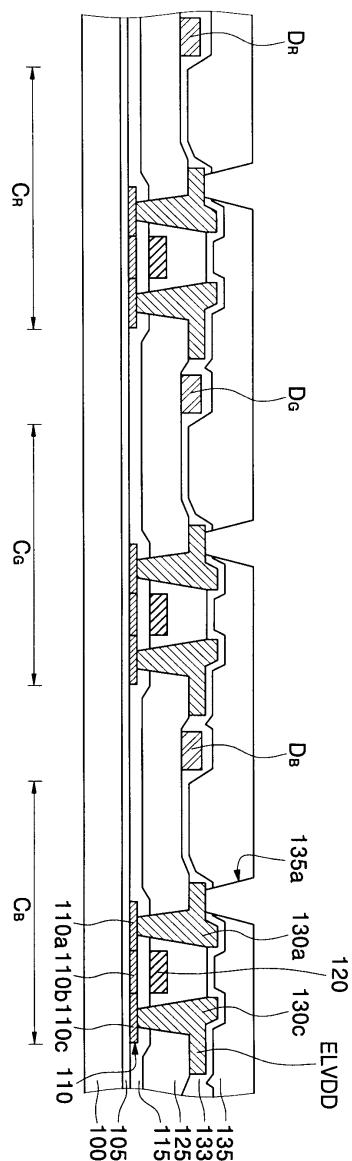

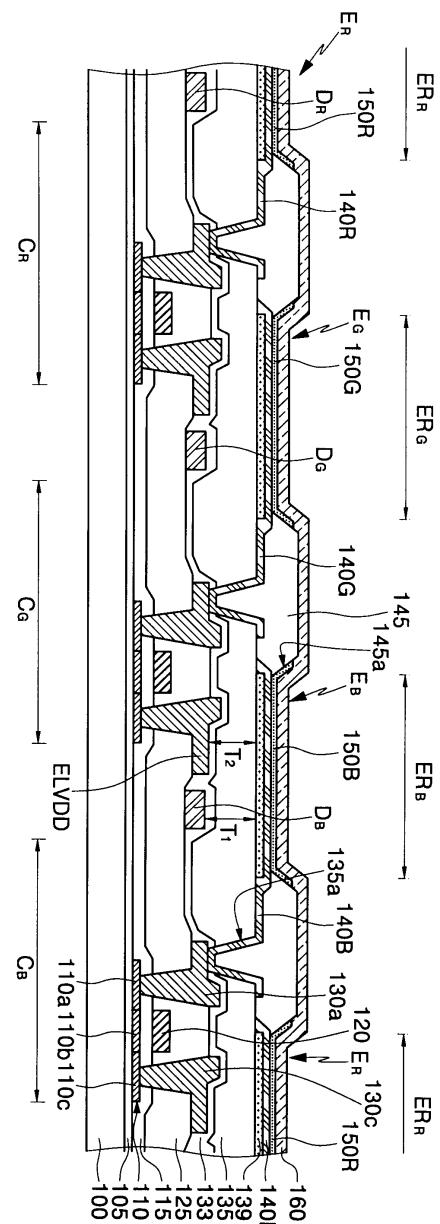

도 4a 및 도 4b는 도 3의 절단선 I-I'를 따라 취해진 본 발명의 일 실시예에 따른 유기전계발광표시장치 및 그의 제조방법을 나타낸 단면도들이다.

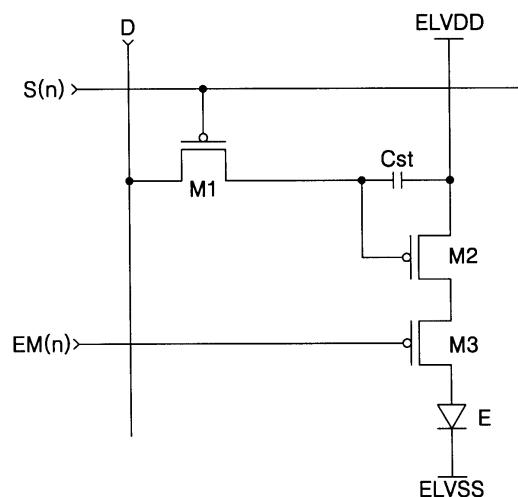

도 5는 본 발명의 다른 실시예에 따른 유기전계발광표시장치의 화소회로를 나타낸 회로도이다.

도 6은 본 발명의 다른 실시예에 따른 유기전계발광표시장치의 화소회로를 나타낸 회로도이다.

(도면의 주요 부위에 대한 부호의 설명)

S : 스캔 라인  $D_R$ ,  $D_G$ ,  $D_B$  : 데이터 라인

ELVDD : 전원 라인  $C_R$ ,  $C_G$ ,  $C_B$  : 화소구동회로영역

140R, 140G, 140B : 화소전극  $E_R$ ,  $E_G$ ,  $E_B$  : 발광 소자

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 평판표시장치에 관한 것으로, 더욱 자세하게는 폴칼라 평판표시장치에 관한 것이다.

평판표시장치는 경량 및 박형 등의 특성으로 인해, 최근 음극선관 표시장치(cathode-ray tube display)를 대체하는 표시장치로서 대두되고 있다. 이러한 평판표시장치의 대표적인 예로서 액정표시장치(Liquid Crystal Display; LCD)와 유기전계발광표시장치(Organic Light Emitting Display; OLED)가 있다. 이 중, 유기전계발광표시장치는 액정표시장치에 비하여 휘도특성 및 시야각 특성이 우수하고 백라이트를 필요로 하지 않아 초박형을 구현할 수 있는 장점이 있다.

이러한 평판표시장치는 적색, 녹색 및 청색 화소들을 구비하여 폴칼라화를 구현할 수 있다. 이 때, 적색, 녹색 및 청색의 화소들은 스트라이프형, 모자이크형 또는 멜타형으로 배열될 수 있다. 상기 멜타형 배열 및 모자이크형 배열은 상기 스트라이프형 배열에 비해 혼색성이 우수하여 동화상 구현에 적합한 특성이 있다.

이러한 멜타형 화소 배열을 갖는 유기전계발광표시장치가 미국특허 제 6,429,599호에 개시된 바 있다.

도 1은 상기 미국특허에 개시된 멜타형 화소 배열을 갖는 유기전계발광표시장치를 나타낸 평면도이다.

도 1을 참조하면, 적색(R), 녹색(G) 및 청색(B)의 화소들이 멜타형으로 배열된다. 즉, 상기 적색(R), 녹색(G) 및 청색(B)의 화소들 중 하나의 화소는 열방향으로 서로 다른 색 화소들에 인접하여 배열된다. 상기 각 화소는 제 1 TFT(4), 캐패시터(5), 제 2 TFT(6) 및 EL 소자의 화소전극(7)을 구비한다. 상기 제 1 TFT(4)에 데이터라인(1) 및 게이트라인(3)이 접속하고, 상기 제 2 TFT(6)에 파워공급라인(2)이 접속한다.

상술한 바와 같이, 상기 적색(R), 녹색(G) 및 청색(B)의 화소들 중 하나의 화소는 열방향으로 서로 다른 색 화소들에 인접하여 배열되고, 상기 데이터라인(1)은 동일 색 화소들의 제 1 TFT(4)에 접속하므로, 상기 데이터라인(1)은 직선으로 배치되지 못하고 좌우로 구부러지면서 배치된다. 이로 인해, 상기 데이터라인(1)의 저항은 증가되고, 이는 데이터신호의 지연을 유발할 수 있다. 또한, 상기 파워공급라인(2) 또한 직선으로 배치되지 못하고 좌우로 구부러지면서 배치된다. 이로 인해, 파워공급라인(2)의 저항은 증가되고, 이는 전압강하를 유발할 수 있다. 상기 데이터 신호의 지연 및 파워공급라인(2)의 전압강하는 화면품질을 저하시킬 수 있다. 이는 표시장치가 대면적화될수록 심각한 문제로 대두될 수 있다. 나아가, 이러한 복잡한 배선 배치는 배선들이 차지하는 면적을 증가시켜 개구율의 감소를 초래할 수 있다.

## 발명이 이루고자 하는 기술적 과제

본 발명이 이루고자 하는 기술적 과제는 상기한 종래기술의 문제점을 해결하기 위한 것으로, 혼색성이 우수함과 아울러서 신호지연 등의 문제가 없는 평판표시장치를 제공함에 있다.

### 발명의 구성 및 작용

상기 기술적 과제를 이루기 위하여 본 발명의 일 실시예는 평판표시장치를 제공한다. 상기 평판표시장치는 기판 및 상기 기판 상에 배열된 신호선들을 구비한다. 상기 신호선들의 교차에 의해 화소구동회로영역들이 정의된다. 상기 화소구동회로영역들에 화소구동회로들이 각각 위치한다. 상기 각 화소구동회로에 화소전극이 접속한다. 상기 화소전극은 상기 신호선들 중 적어도 하나와 중첩한다.

상기 기술적 과제를 이루기 위하여 본 발명의 다른 일 실시예는 다른 평판표시장치를 제공한다. 상기 평판표시장치는 기판 및 상기 기판 상에 배열된 신호선들을 구비한다. 상기 신호선들의 교차에 의해 화소구동회로영역들이 정의된다. 상기 화소구동회로영역들에 화소구동회로들이 각각 위치한다. 상기 화소구동회로들에 화소전극들이 각각 접속한다. 상기 화소전극들은 상기 화소구동회로영역들과 서로 다른 배열을 갖는다.

상기 기술적 과제를 이루기 위하여 본 발명의 다른 일 실시예는 다른 평판표시장치를 제공한다. 상기 평판표시장치는 기판 및 상기 기판 상에 배열된 신호선들을 구비한다. 상기 신호선들 중 적어도 일부는 스캔 라인들과 상기 스캔 라인들을 교차하면서 직선형태로 배열된 데이터 라인들이다. 상기 스캔 라인들과 상기 데이터 라인들의 교차에 의해 화소구동회로영역들이 정의된다. 상기 화소구동회로영역들에 화소구동회로들이 각각 위치한다. 상기 화소구동회로들에 화소전극들이 각각 접속한다. 상기 각 화소전극은 횡방향 및 열방향으로 서로 다른 색에 해당하는 화소전극과 인접한다.

상기 기술적 과제를 이루기 위하여 본 발명의 다른 일 실시예는 다른 평판표시장치를 제공한다. 상기 평판표시장치는 기판 및 상기 기판 상에 배열된 신호선들을 구비한다. 상기 신호선들 중 적어도 일부는 스캔라인들과 상기 스캔 라인들을 교차하면서 직선형태로 배열된 데이터 라인들이다. 상기 스캔 라인들과 상기 데이터 라인들의 교차에 의해 적색, 녹색 및 청색 화소구동회로영역들이 정의된다. 상기 화소구동회로영역들 중 동일 색에 해당하는 화소구동회로영역들은 열 방향으로 서로 인접하여 위치한다. 상기 화소구동회로영역들에 적색, 녹색 및 청색 화소구동회로들이 각각 위치한다. 상기 적색, 녹색 및 청색 화소구동회로들에 적색, 녹색 및 청색 화소전극들이 각각 접속한다. 상기 각 화소전극은 횡방향 및 열방향으로 서로 다른 색에 해당하는 화소전극과 인접한다.

이하, 본 발명을 보다 구체적으로 설명하기 위하여 본 발명에 따른 바람직한 실시예를 첨부된 도면을 참조하여 보다 상세하게 설명한다. 그러나, 본 발명은 여기서 설명되어지는 실시예에 한정되지 않고 다른 형태로 구체화될 수도 있다. 도면들에 있어서, 층이 다른 층 또는 기판 "상"에 있다고 언급되어지는 경우에 그것은 다른 층 또는 기판 상에 직접 형성될 수 있거나 또는 그들 사이에 제 3의 층이 개재될 수도 있다.

도 2는 본 발명의 일 실시예에 따른 유기전계발광표시장치의 화소 회로를 나타낸 회로도이다.

도 2를 참조하면, 스캔 라인(S), 데이터 라인들( $D_R$ ,  $D_G$ ,  $D_B$ ) 및 전원 라인(ELVDD)이 배치된다. 상기 데이터 라인들은 적색 데이터 라인( $D_R$ ), 녹색 데이터 라인( $D_G$ ) 및 청색 데이터 라인( $D_B$ )이다. 상기 적색, 녹색 및 청색 데이터 라인들( $D_R$ ,  $D_G$ ,  $D_B$ )과 상기 스캔라인(S)의 교차에 의해 적색 화소( $P_R$ ), 녹색 화소( $P_G$ ) 및 청색 화소( $P_B$ )가 정의된다. 이 때, 상기 각 데이터 라인( $D_R$ ,  $D_G$  또는  $D_B$ )은 그와 동일 색에 해당하는 화소들에 차례로 접속한다. 이로 인해, 상기 각 데이터 라인( $D_R$ ,  $D_G$  또는  $D_B$ )에는 하나의 색에 해당하는 데이터 신호를 인가할 수 있다. 따라서, 데이터 라인에 서로 다른 색에 해당하는 데이터 신호를 인가하는 경우에 비해 표시장치의 구동이 용이해질 수 있다.

상기 각 화소는 발광소자( $E_R$ ,  $E_G$  또는  $E_B$ ) 및 상기 발광소자를 구동하기 위한 화소구동회로를 구비한다. 상기 화소구동회로는 스위칭 트랜지스터(M1), 캐패시터(Cst) 및 구동 트랜지스터(M2)일 수 있다. 상기 스위칭 트랜지스터(M1)는 게이트가 상기 스캔 라인(S)에 연결되고, 소오스가 상기 데이터 라인( $D_R$ ,  $D_G$  또는  $D_B$ )에 연결되어, 상기 스캔 라인(S)에 인가된 스캔 신호에 의해 상기 데이터 라인에 인가된 데이터 신호를 스위칭한다. 상기 캐패시터(Cst)는 상기 스위칭 박막트랜지스터(M1)의 드레인 및 상기 전원 라인(ELVDD) 사이에 연결되어, 상기 데이터 신호를 일정기간 유지한다. 상기 구동 박막트

랜지스터(M2)는 게이트가 상기 캐패시터(Cst)에 연결되고, 소오스가 상기 전원라인(ELVDD)에 연결되고, 드레인이 상기 발광소자( $E_R$ ,  $E_G$  또는  $E_B$ )에 연결되어, 상기 데이터 신호의 크기에 비례하는 전류를 상기 발광소자에 공급한다. 상기 발광소자는 공급된 전류에 대응하여 발광한다.

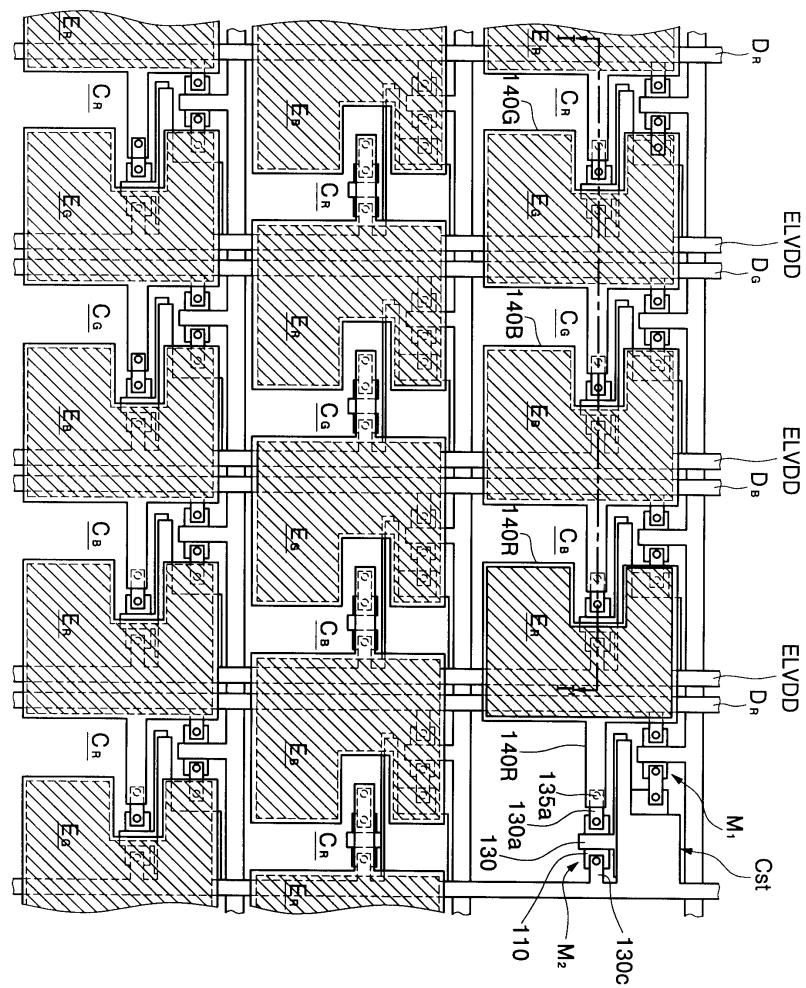

도 3은 본 발명의 일 실시예에 따른 유기전계발광표시장치의 화소 어레이 중 일부분에 한정하여 나타낸 평면도로서, 도 3에 나타난 각 구성요소는 그와 동일 참조부호를 갖는 도 2의 구성요소에 대응한다.

도 3을 참조하면, 기판 상에 신호선들이 배열된다. 상기 신호선들은 복수 개의 스캔 라인(S), 복수 개의 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ ) 및 복수 개의 전원라인(ELVDD)일 수 있다. 상기 각 스캔 라인(S)은 일방향으로 배열된다. 상기 각 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ )은 상기 각 스캔 라인(S)과 서로 절연되면서 교차하고, 다른 일방향으로 배열된다. 또한, 상기 전원라인(ELVDD)은 상기 각 스캔 라인(S)과 서로 절연되면서 교차하고, 상기 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ )과 같은 방향으로 배열된다. 상기 복수 개의 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ )은 적색 데이터 라인( $D_R$ ), 녹색 데이터 라인( $D_G$ ) 및 청색 데이터 라인( $D_B$ )이다.

상기 신호선들, 그 중에서도 상기 스캔 라인(S)과 상기 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ )의 교차에 의해 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ )이 정의된다. 본 명세서에서 화소구동회로영역이라 함은 발광소자에 인가되는 신호를 제어하기 위한 화소구동회로가 위치하는 영역이다. 다시 말해서, 도 1에 도시된 회로도의 화소 회로에서 발광소자를 제외한 나머지 소자들이 기판 상에 실제로 위치하는 영역이다.

상기 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ ) 중 동일 색에 해당하는 화소구동회로영역들 예를 들어, 상기 적색 화소구동회로영역들( $C_R$ )은 열 방향으로 서로 인접하여 위치한다. 즉, 상기 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ )은 스트라이프 형태로 배열된다. 이로 인해, 동일 색에 해당하는 화소들에 차례로 접속하는 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ )을 직선형태로 배치할 수 있다. 따라서, 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ )의 길이는 짧아질 수 있고 이로 인해 선저항이 저감될 수 있어, 상기 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ )에 인가되는 데이터 신호는 지연되지 않을 수 있다. 이와 더불어, 상기 전원 라인(ELVDD) 또한 직선형태로 배치할 수 있다. 따라서, 상기 전원 라인(ELVDD) 또한 선저항이 저감되고, 이로 인해 상기 전원 라인(ELVDD)에 인가되는 전원 전압의 강하를 막을 수 있다. 결과적으로, 화면 표시품질을 향상시킬 수 있다. 나아가, 상기 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ ) 및 상기 전원 라인(ELVDD)이 차지하는 면적을 줄여 개구율의 향상을 기대할 수 있다.

상기 적색, 녹색 및 청색 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ ) 상에 적색, 녹색 및 청색 화소구동회로들이 각각 위치한다. 상기 각 화소구동회로는 스위칭 트랜지스터(M1), 캐패시터(Cst) 및 구동트랜지스터(M2)일 수 있다. 상기 적색, 녹색 및 청색 화소구동회로들은 적색, 녹색 및 청색 화소전극들(140R, 140G, 140B)과 각각 접속한다. 더 자세하게는 상기 구동 트랜지스터(M2)의 드레인 전극(130a)과 상기 화소전극(140R, 140G 또는 140B)이 접속한다. 상기 화소전극(140R, 140G 또는 140B) 내에 발광영역인 개구부가 정의되며, 상기 화소전극(140R, 140G 또는 140B)의 개구부 상에 유기발광층 및 대향전극이 차례로 위치한다. 상기 화소전극(140R, 140G 또는 140B), 상기 유기발광층 및 상기 대향전극은 발광소자( $E_R$ ,  $E_G$  또는  $E_B$ )를 형성한다.

상기 화소전극들(140R, 140G, 140B)은 상기 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ )과 서로 다르게 배열된다. 자세하게는 상기 각 화소전극은 횡방향 및 열방향으로 서로 다른 색에 해당하는 화소전극에 인접하도록 배치된다. 예를 들어, 상기 적색 화소전극(140R)은 횡방향 및 열방향으로 상기 녹색 화소전극들(140G) 및 상기 청색 화소전극들(140B)에 인접하도록 배치된다. 그 결과, 혼색성이 향상되어 표시품질이 양호해질 수 있다. 나아가, 상기 화소전극들(140R, 140G, 140B)은 혼색성이 가장 우수한 델타형태로 배열될 수 있다. 자세하게는 상기 화소전극들(140R, 140G, 140B) 중 홀수열에 위치하는 화소전극들을 그들 각각이 접속하는 상기 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ )에 대해 좌로 이동하여 배치되고, 짹수열에 위치하는 화소전극들을 그들 각각이 접속하는 상기 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ )에 대해 우로 이동하여 배치된다. 상기 홀수열과 짹수열의 이동방향은 서로 바뀔 수 있다. 상기 화소전극들(140R, 140G, 140B)이 상기 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ )에 대해 이동하는 정도는 혼색성을 고려할 때, 0.5 내지 0.15 피치, 바람직하게는 0.75피치일 수 있다. 이 때, 1 피치는 화소구동회로영역의 횡방향 길이이다.

이 때, 상기 화소전극들(140R, 140G, 140B)은 상기 신호선들 중 적어도 일부와 중첩될 수 있다.

상술한 바와 같이, 상기 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ ) 중 동일 색에 해당하는 화소구동회로영역들을 열 방향으로 서로 인접하여 배치하고, 상기 각 화소전극(140R, 140G, 140B)을 횡방향 및 열방향으로 서로 다른 색에 해당하는 화소전극에 인접하도록 배치함으로써, 신호지연이 없고 혼색성이 우수한 양질의 화면을 구현할 수 있다.

도 4a 및 도 4b는 도 3의 절단선 I-I'를 따라 취해진 본 발명의 일 실시예에 따른 유기전계발광표시장치 및 그의 제조방법을 나타낸 단면도들이다.

도 4a를 참조하면, 적색 화소구동회로 영역( $C_R$ ), 녹색 화소구동회로 영역( $C_G$ ) 및 청색 화소구동회로 영역( $C_B$ )을 구비하는 기판(100)을 준비한다. 상기 기판(100)은 투명한 기판 또는 불투명한 기판일 수 있다. 또한, 상기 기판(100)은 유리, 플라스틱, 석영, 실리콘 또는 금속 기판일 수 있다. 상기 기판(100) 상에 베퍼층(105)을 형성할 수 있다. 상기 베퍼층(105)은 실리콘 산화막, 실리콘 질화막, 실리콘 산질화막 또는 이들의 다중층일 수 있다.

상기 베퍼층(105) 상에 반도체층(110)을 형성한다. 상기 반도체층(110)은 비정질 실리콘막 또는 비정질 실리콘막을 결정화한 다결정 실리콘막일 수 있다. 바람직하게는 상기 반도체층(110)은 높은 전하이동도를 갖는 다결정 실리콘막이다. 상기 반도체층(110) 상에 게이트 절연막(115)을 형성한다. 상기 게이트 절연막(115)은 실리콘 산화막, 실리콘 질화막, 실리콘 산질화막 또는 이들의 다중층일 수 있다.

상기 게이트 절연막(115) 상에 상기 반도체층(110)과 중첩하는 게이트 전극(120)을 형성한다. 상기 게이트 전극(120)을 형성함과 동시에 스캔라인(도 3의 S)을 형성할 수 있다. 이어서, 상기 게이트 전극(120)을 마스크로 하여 상기 반도체층(110)에 도전성 불순물을 주입하여 소오스 영역(110c) 및 드레인 영역(110a)을 형성한다. 이 때, 상기 소오스 영역(110c)과 드레인 영역(110a) 사이에 채널 영역(110b)이 정의된다. 상기 게이트 전극(120) 및 상기 반도체층(110) 상에 제 1 층 간절연막(125)을 형성한다. 상기 제 1 층간절연막(125) 내에 상기 소오스/드레인 영역들(110c, 110a)을 각각 노출시키는 콘택홀들을 형성한다. 상기 콘택홀들이 형성된 기판 상에 도전막을 적층한 후, 이를 패터닝하여 소오스 전극(130c), 드레인 전극(130a), 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ ) 및 전원 라인(ELVDD)을 형성한다. 상기 소오스 전극(130c)과 상기 드레인 전극(130a)은 상기 노출된 소오스/드레인 영역들(110c, 110a)에 각각 접한다. 상기 반도체층(110), 상기 게이트 전극(120), 상기 소오스 전극(130c) 및 상기 드레인 전극(130a)은 구동 박막트랜지스터(도 3의 M2)를 형성한다.

상기 소오스/드레인 전극들(130c, 130a)을 포함한 기판 전면 상에 제 2 층간절연막을 형성한다. 상기 제 2 층간절연막은 패시베이션막(133), 평탄화막(135) 또는 상기 패시베이션막(133) 상에 상기 평탄화막(135)이 적층된 이중층일 수 있다. 상기 패시베이션막(133)은 실리콘 산화막, 실리콘 질화막 또는 이들의 다중층으로 형성할 수 있다. 바람직하게는 상기 패시베이션막(133)은 기체 및 수분을 효과적으로 차단하여 하부의 박막트랜지스터를 보호할 수 있고, 수소를 풍부하게 함유하여 상기 다결정 실리콘막의 결정립 경계(grain boundary)에 존재하는 불완전 결합을 패시베이션 할 수 있는 실리콘 질화막인 것이 바람직하다. 상기 평탄화막(135)은 하부 단차를 완화할 수 있는 유기막으로 BCB(benzocyclobutene)막, 폴리아미드막 또는 폴리아크릴막일 수 있다.

상기 제 2 층간절연막 내에 상기 드레인 전극(130a)을 노출시키는 비아홀(135a)을 형성한다.

도 4b를 참조하면, 상기 비아홀(135a)이 형성된 기판 상에 화소전극(140R, 140G, 140B)을 형성한다. 상기 화소전극(140R, 140G, 140B)은 상기 비아홀(135a) 내에 노출된 상기 드레인 전극(130a)에 접속하고, 상기 제 2 층간절연막 상으로 연장된다.

상술한 바와 같이, 상기 화소전극들(140R, 140G, 140B)은 상기 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ )과 서로 다르게 배치된다. 자세하게는 상기 화소전극들(140R, 140G, 140B)은 그들 각각이 접속하는 드레인 전극(130a)이 위치하는 화소구동회로영역들( $C_R$ ,  $C_G$ ,  $C_B$ )에 대해 좌로 이동되어 배치된다. 이 때, 상기 각 화소전극(140R, 140G, 140B)은 상기 신호선들 중 적어도 일부 자세하게는 상기 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ ) 및 상기 전원 라인(ELVDD)과 중첩될 수 있다. 이 경우, 상기 화소전극(140R, 140G, 140B)과 상기 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ ) 사이에 개재된 제 2 층간절연막의 두께(T1) 또는 상기 화소전극(140R, 140G, 140B)과 상기 전원 라인(ELVDD) 사이에 개재된 제 2 절연막의 두께(T2)는 5000Å 이상인 것이 바람직하다. 그 결과, 상기 화소전극(140R, 140G, 140B)과 상기 데이터 라인( $D_R$ ,  $D_G$ ,  $D_B$ ); 및 상기 화소전극(140R, 140G, 140B)과 상기 전원 라인(ELVDD) 사이의 기생용량(parastic capacitance)을 최소화할 수 있다. 나아가, 상기 비아홀(135a)의 종횡비(aspect ratio)를 고려 할 때, 상기 제 2 절연막의 두께는 3μm이하인 것이 바람직하다.

한편, 상기 화소전극(140R, 140G, 140B)은 광반사 도전막을 사용하여 형성할 수 있다. 상기 광반사 도전막은 일함수가 높은 Ag, Al, Ni, Pt, Pd 또는 이들의 합금막이거나, 일함수가 낮은 Mg, Ca, Al, Ag, Ba 또는 이들의 합금막일 수 있다.

이와는 달리, 상기 화소전극(140R, 140G, 140B)을 형성하기 전에 상기 화소전극(140R, 140G, 140B) 하부에 반사막 패턴(139)을 더 형성하고, 상기 화소전극(140R, 140G, 140B)은 광투과 도전막을 사용하여 형성할 수 있다. 상기 광투과 도전막은 ITO(Indium Tin Oxide)막 또는 IZO(Indium Zinc Oxide)막일 수 있다. 상기 반사막 패턴(139)은 60% 이상의 반사율을 갖는 것이 바람직하며, 나아가, 상기 반사막 패턴(139)은 알루미늄(Al), 알루미늄 합금, 은(Ag), 은 합금 또는 이들의 합금막일 수 있다. 이러한 반사막 패턴(139)은 상기 비아홀(135a)로부터 소정 간격 이격되도록 형성할 수 있다.

상기 화소전극(140R, 140G, 140B) 상에 상기 각 화소전극의 적어도 일부영역을 노출시키는 개구부를 갖는 화소정의막(pixel defining layer; 145)을 형성할 수 있다. 상기 화소정의막(145)은 BCB(benzocyclobutene), 아크릴계 포토레지스트, 폐놀계 포토레지스트 또는 이미드계 포토레지스트를 사용하여 형성할 수 있다.

상기 개구부들(145a) 내에 노출된 적색, 녹색 및 청색 화소전극(140R, 140G, 140B) 상에 적색 발광층(150R), 녹색 발광층(150G) 및 청색 발광층(150B)을 각각 형성한다. 상기 각 발광층은 진공증착법, 잉크젯 프린트법 또는 레이저 열전사법을 사용하여 형성할 수 있다. 나아가, 상기 발광층(150R, 150G, 150B)의 상부 또는 하부에 정공주입층, 정공수송층, 정공억제층, 전자수송층 또는 전자주입층을 형성할 수 있다. 이어서, 상기 발광층(150R, 150G, 150B) 상에 대향전극(160)을 형성한다. 상기 대향전극(160)은 상기 기판 전면에 형성될 수 있다. 상기 대향전극(160)은 광투과 도전막으로 형성하는 것이 바람직하다. 상기 광투과 도전막은 ITO막 또는 IZO막이거나, 빛을 투과시킬 수 있을 정도의 얇은 두께를 갖는 Mg, Ca, Al, Ag, Ba 또는 이들의 합금막일 수 있다.

상기 화소전극(140R, 140G, 140B), 상기 발광층(150R, 150G, 150B) 및 상기 대향전극(160)은 발광소자( $E_R$ ,  $E_G$ ,  $E_B$ )를 형성한다. 상기 발광소자( $E_R$ ,  $E_G$ ,  $E_B$ )의 발광영역( $ER_R$ ,  $ER_G$ ,  $ER_B$ )은 상기 개구부들(145a)에 의해 각각 정의된다.

상기 발광소자( $E_R$ ,  $E_G$ ,  $E_B$ )의 구동시에 정공들과 전자들; 또는 전자들과 정공들은 상기 화소전극 및 상기 대향전극으로부터 상기 발광층(150R, 150G, 150B)으로 각각 주입되고, 상기 발광층(150R, 150G, 150B) 내로 주입된 정공과 전자는 발광층(150R, 150G, 150B)에서 결합하여 엑시톤(exciton)을 생성한다. 이러한 엑시톤이 여기상태에서 기저상태로 전이하면서 빛을 방출하게 된다. 상기 발광층(150R, 150G, 150B)으로부터 방출된 빛은 상기 화소전극(광반사 도전막으로 형성된 경우; 140R, 140G, 140B) 또는 상기 화소전극(광투과 도전막으로 형성된 경우; 140R, 140G, 140B) 하부의 반사막 패턴(139)에서 반사되어 상기 광투과 도전막인 대향전극(160)을 투과하여 외부로 방출된다.

도 5는 본 발명의 다른 실시예에 따른 유기전계발광표시장치의 화소회로를 나타낸 회로도이다.

도 5를 참조하면, 신호선들인  $n-1$ 번째 스캔 라인( $S(n-1)$ ),  $n$ 번째 스캔 라인( $S(n)$ ), 데이터 라인( $D$ ), 전원 라인( $ELVDD$ ) 및 프리차지 라인( $Vint$ )이 배열된다. 상기 데이터 라인( $D$ )과 상기 스캔 라인( $S(n)$ )의 교차에 의해 화소가 정의된다. 상기 화소는 발광소자( $E$ ) 및 상기 발광소자( $E$ )를 구동하기 위한 화소구동회로를 구비한다. 상기 화소구동회로는 제 1 내지 제 4 트랜지스터들( $M1$ ,  $M2$ ,  $M3$ ,  $M4$ ) 및 캐패시터( $Cst$ )이다.

상기 제 1 트랜지스터( $M1$ )는 게이트가 상기 스캔 라인( $S$ )에 연결되고, 소오스가 상기 데이터 라인( $D$ )에 연결된다. 상기 제 3 트랜지스터( $M3$ )는 소오스가 상기 제 1 트랜지스터( $M1$ )의 드레인에 연결되고, 게이트 및 드레인은 상호 연결된다. 상기 제 4 트랜지스터( $M4$ )는 게이트가 상기  $n-1$ 번째 스캔 라인( $S(n-1)$ )에, 소오스가 상기 제 3 트랜지스터( $M3$ )의 드레인에, 드레인이 상기 프리차지 라인( $Vint$ )에 연결된다. 상기 제 2 트랜지스터( $M2$ )는 게이트가 상기 제 3 트랜지스터( $M3$ )의 게이트에, 소오스가 상기 전원 라인( $ELVDD$ )에, 드레인이 상기 발광소자( $E$ )에 연결된다. 상기 캐패시터는 상기 제 3 박막트랜지스터( $M3$ )의 게이트와 상기 전원 라인( $ELVDD$ ) 사이에 연결된다. 상기 발광소자( $E$ )는 화소전극, 대향전극 및 상기 화소전극과 상기 대향전극 사이에 개재된 발광층을 구비한다.

이러한 화소 회로를 갖는 유기전계발광표시장치의 화소 레이아웃은 프리차지 라인( $Vint$ )이 횡방향 또는 열방향으로 추가적으로 배열되고, 화소구동회로영역(도 3의  $C_R$ ,  $C_G$ ,  $C_B$ )에 화소구동회로인 상기 제 1 내지 제 4 트랜지스터들( $M1$ ,  $M2$ ,  $M3$ ,  $M4$ ) 및 상기 캐패시터( $Cst$ )가 위치하는 것을 제외하고는 도 3을 참조하여 나타낸 화소 레이아웃과 동일할 수 있다. 이 때, 상기 화소전극은 상기 프리차지 라인( $Vint$ )과도 중첩될 수 있다.

도 6은 본 발명의 다른 실시예에 따른 유기전계발광표시장치의 화소회로를 나타낸 회로도이다.

도 6을 참조하면, 신호선들인 스캔 라인(S(n)), 데이터 라인(D), 전원 라인(ELVDD) 및 발광제어 라인(EM(n))이 배열된다. 상기 데이터 라인(D)과 상기 스캔 라인(S(n))의 교차에 의해 화소가 정의된다. 상기 화소는 발광소자(E) 및 상기 발광소자(E)를 구동하기 위한 화소구동회로를 구비한다. 상기 화소구동회로는 제 1 내지 제 3 트랜지스터들(M1, M2, M3) 및 캐패시터(Cst)이다.

상기 제 1 트랜지스터(M1)는 게이트가 상기 스캔 라인(S)에 연결되고, 소오스가 상기 데이터 라인(D)에 연결된다. 상기 제 2 트랜지스터(M2)는 게이트가 상기 제 1 트랜지스터(M1)의 드레인에, 소오스가 상기 전원 라인(ELVDD)에 연결된다. 상기 캐패시터는 상기 제 2 트랜지스터(M2)의 게이트과 상기 전원 라인(ELVDD) 사이에 연결된다. 상기 제 3 트랜지스터(M3)는 게이트가 상기 발광제어 라인(EM(n))에, 소오스가 상기 제 2 트랜지스터(M2)의 드레인에, 드레인이 상기 발광소자(E)에 연결된다. 상기 발광소자(E)는 화소전극, 대향전극 및 상기 화소전극과 상기 대향전극 사이에 개재된 발광층을 구비한다.

이러한 화소 회로를 갖는 유기전계발광표시장치의 화소 레이아웃은 발광제어 라인(EM(n))이 횡방향 또는 열방향으로 추가적으로 배열되고, 화소구동회로영역에 화소구동회로인 상기 제 1 내지 제 3 트랜지스터들(M1, M2, M3) 및 상기 캐패시터(Cst)가 위치하는 것을 제외하고는 도 3을 참조하여 나타낸 화소 레이아웃과 동일할 수 있다. 이 때, 상기 화소전극은 상기 발광제어 라인(EM(n))과도 중첩될 수 있다.

상술한 실시예들에서는 유기전계발광표시장치들을 예로 들었으나, 본 발명은 이에 한정되지 않고 액정표시장치에도 적용될 수 있을 것이다. 특히, 외부광을 이용하는 반사형 액정표시장치의 경우, 더 용이하게 적용될 수 있을 것이다.

### 발명의 효과

상술한 바와 같이 본 발명에 따르면, 상기 화소구동회로영역들 중 동일 색에 해당하는 화소구동회로영역들을 열 방향으로 서로 인접하도록 배치하고, 각 화소전극을 횡방향 및 열방향으로 서로 다른 색에 해당하는 화소전극에 인접하도록 배치함으로써, 신호 지연이 없고 혼색성이 우수한 양질의 화면을 구현할 수 있다.

상기에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

### (57) 청구의 범위

#### 청구항 1.

기판;

상기 기판 상에 배열된 신호선들;

상기 신호선들의 교차에 의해 정의된 화소구동회로영역들에 각각 위치하는 화소구동회로들; 및

상기 각 화소구동회로에 접속하고, 상기 신호선들 중 적어도 하나와 중첩하는 화소전극을 포함하는 것을 특징으로 하는 평판표시장치.

#### 청구항 2.

제 1 항에 있어서,

상기 화소구동회로영역들 중 동일 색에 해당하는 화소구동회로영역들은 열 방향으로 서로 인접하여 위치하는 것을 특징으로 하는 평판표시장치.

### 청구항 3.

제 1 항 또는 제 2 항에 있어서,

상기 화소전극들은 상기 화소구동회로영역들과 서로 다른 배열을 갖는 것을 특징으로 하는 평판표시장치.

### 청구항 4.

제 3 항에 있어서,

상기 각 화소전극은 횡방향 및 열방향으로 서로 다른 색에 해당하는 화소전극과 인접하는 것을 특징으로 하는 평판표시장치.

### 청구항 5.

제 4 항에 있어서,

상기 화소전극들은 델타형으로 배열된 것을 특징으로 하는 평판표시장치.

### 청구항 6.

제 1 항에 있어서,

상기 신호선들 중 일부는 스캔라인들과 상기 스캔라인들을 교차하면서 직선형태로 배열된 데이터 라인들인 것을 특징으로 하는 평판표시장치.

### 청구항 7.

제 6 항에 있어서,

상기 신호선들 중 다른 일부는 상기 스캔라인들을 교차하면서 직선형태로 배열된 전원 라인들인 것을 특징으로 하는 평판표시장치.

### 청구항 8.

제 1 항에 있어서,

상기 화소전극과 중첩하는 상기 신호선과 상기 화소전극 사이에 개재된 절연막의 두께는  $5000\text{ \AA}$  이상인 것을 특징으로 하는 평판표시장치.

### 청구항 9.

제 8 항에 있어서,

상기 화소전극과 중첩하는 상기 신호선과 상기 화소전극 사이에 개재된 절연막의 두께는  $3\mu\text{m}$  이하인 것을 특징으로 하는 평판표시장치.

### 청구항 10.

제 1 항에 있어서,

상기 평판표시장치는 유기전계발광표시장치인 것을 특징으로 하는 평판표시장치.

### 청구항 11.

제 1 항 또는 제 10 항에 있어서,

상기 화소전극은 광반사 도전막인 것을 특징으로 하는 평판표시장치.

### 청구항 12.

제 1 항 또는 제 10 항에 있어서,

상기 화소전극은 광투과 도전막이고, 상기 화소전극 하부에 위치하는 반사막 패턴을 더 구비하는 것을 특징으로 하는 평판표시장치.

### 청구항 13.

기판;

상기 기판 상에 배열된 신호선들;

상기 신호선들의 교차에 의해 정의되는 화소구동회로영역들;

상기 화소구동회로영역들 각각에 위치하는 화소구동회로들;

상기 화소구동회로들에 화소전극들이 각각 접속하고, 상기 화소전극들은 상기 화소구동회로영역들과 서로 다른 배열을 갖는 것을 특징으로 하는 평판표시장치.

### 청구항 14.

제 13 항에 있어서,

상기 화소구동회로영역들 중 동일 색에 해당하는 화소구동회로영역들은 열 방향으로 서로 인접하여 위치하는 것을 특징으로 하는 평판표시장치.

### 청구항 15.

제 13 항에 있어서,

상기 각 화소전극은 횡방향 및 열방향으로 서로 다른 색에 해당하는 화소전극과 인접하는 것을 특징으로 하는 평판표시장치.

### 청구항 16.

제 15 항에 있어서,

상기 화소전극들은 빌타형으로 배열된 것을 특징으로 하는 평판표시장치.

### 청구항 17.

제 13 항에 있어서,

상기 신호선들 중 일부는 스캔라인들과 상기 스캔라인들을 교차하면서 직선형태로 배열된 데이터 라인들인 것을 특징으로 하는 평판표시장치.

### 청구항 18.

제 17 항에 있어서,

상기 신호선들 중 다른 일부는 상기 스캔라인들을 교차하면서 직선형태로 배열된 전원 라인들인 것을 특징으로 하는 평판표시장치.

### 청구항 19.

제 13 항에 있어서,

상기 평판표시장치는 유기전계발광표시장치인 것을 특징으로 하는 평판표시장치.

### 청구항 20.

제 13 항 또는 제 19 항에 있어서,

상기 화소전극은 광반사 도전막인 것을 특징으로 하는 평판표시장치.

### 청구항 21.

제 13 항 또는 제 19 항에 있어서,

상기 화소전극은 광투과 도전막이고, 상기 화소전극 하부에 위치하는 반사막 패턴을 더 구비하는 것을 특징으로 하는 평판표시장치.

## 청구항 22.

기판;

상기 기판 상에 신호선들이 배열되고, 상기 신호선들 중 적어도 일부는 스캔 라인들과 상기 스캔 라인들을 교차하면서 직선형태로 배열된 데이터 라인들이고;

상기 스캔 라인들과 상기 데이터 라인들의 교차에 의해 정의되는 화소구동회로영역들;

상기 화소구동회로영역들 각각에 위치하는 화소구동회로들;

상기 화소구동회로들에 화소전극들이 각각 접속하고, 상기 각 화소전극은 횡방향 및 열방향으로 서로 다른 색에 해당하는 화소전극과 인접하는 것을 특징으로 하는 평판표시장치.

## 청구항 23.

제 22 항에 있어서,

상기 신호선들 중 다른 일부는 상기 스캔라인들을 교차하면서 직선형태로 배열된 전원 라인들인 것을 특징으로 하는 평판표시장치.

## 청구항 24.

제 22 항에 있어서,

상기 화소구동회로영역들 중 동일 색에 해당하는 화소구동회로영역들은 열 방향으로 서로 인접하여 위치하는 것을 특징으로 하는 평판표시장치.

## 청구항 25.

제 22 항에 있어서,

상기 화소전극들은 텔타형으로 배열된 것을 특징으로 하는 평판표시장치.

## 청구항 26.

제 22 항에 있어서,

상기 평판표시장치는 유기전계발광표시장치인 것을 특징으로 하는 평판표시장치.

## 청구항 27.

제 22 항 또는 제 26 항에 있어서,

상기 화소전극은 광반사 도전막인 것을 특징으로 하는 평판표시장치.

### 청구항 28.

제 22 항 또는 제 26 항에 있어서,

상기 화소전극은 광투과 도전막이고, 상기 화소전극 하부에 위치하는 반사막 패턴을 더 구비하는 것을 특징으로 하는 평판 표시장치.

### 청구항 29.

기판;

상기 기판 상에 신호선들이 배열되고, 상기 신호선들 중 적어도 일부는 스캔라인들과 상기 스캔 라인들을 교차하면서 직선 형태로 배열된 데이터 라인들이고;

상기 스캔 라인들과 상기 데이터 라인들의 교차에 의해 적색, 녹색 및 청색 화소구동회로 영역들이 정의되고, 상기 화소구동회로 영역들 중 동일 색에 해당하는 화소구동회로 영역들은 열 방향으로 서로 인접하여 위치하고;

상기 화소구동회로 영역들 각각에 위치하는 적색, 녹색 및 청색 화소구동회로들;

상기 적색, 녹색 및 청색 화소구동회로들에 적색, 녹색 및 청색 화소전극들이 각각 접속하고, 상기 각 화소전극은 횡방향 및 열방향으로 서로 다른 색 화소전극과 인접하는 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 30.

제 29 항에 있어서,

상기 화소전극들은 델타형으로 배열된 것을 특징으로 하는 평판 표시장치.

### 청구항 31.

제 29 항에 있어서,

상기 평판 표시장치는 유기전계발광표시장치인 것을 특징으로 하는 평판 표시장치.

### 청구항 32.

제 29 항 또는 제 31 항에 있어서,

상기 화소전극은 광반사 도전막인 것을 특징으로 하는 평판 표시장치.

### 청구항 33.

제 29 항 또는 제 31 항에 있어서,

상기 화소전극은 광투과 도전막이고, 상기 화소전극 하부에 위치하는 반사막 패턴을 더 구비하는 것을 특징으로 하는 평판 표시장치.

도면

도면1

## 도면2

## 도면3

도면4a

도면4b

## 도면5

## 도면6

|               |                                                                                                                                      |         |            |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)       | 平板显示器                                                                                                                                |         |            |

| 公开(公告)号       | <a href="#">KR1020060041121A</a>                                                                                                     | 公开(公告)日 | 2006-05-11 |

| 申请号           | KR1020040090603                                                                                                                      | 申请日     | 2004-11-08 |

| 申请(专利权)人(译)   | 三星SD眼有限公司                                                                                                                            |         |            |

| 当前申请(专利权)人(译) | 三星SD眼有限公司                                                                                                                            |         |            |

| [标]发明人        | SUH MI SOOK<br>서미숙<br>KANG TAE WOOK<br>강태욱<br>LEE UL HO<br>이을호                                                                       |         |            |

| 发明人           | 서미숙<br>강태욱<br>이을호                                                                                                                    |         |            |

| IPC分类号        | G09G3/30                                                                                                                             |         |            |

| CPC分类号        | G09G2300/0842 G09G2300/0861 G09G2300/0452 H01L27/3276 H01L27/3211 H01L2251/5315 G09G3/3233 G09G2320/0233 G09G2300/0819 G09G2320/0223 |         |            |

| 代理人(译)        | PARK, 常树                                                                                                                             |         |            |

| 其他公开文献        | <a href="#">KR100741967B1</a>                                                                                                        |         |            |

| 外部链接          | <a href="#">Espacenet</a>                                                                                                            |         |            |

### 摘要(译)

混合色特性也很好，平板显示器没有信号延迟的问题。平板显示器包括基板和布置在基板上的信号线。信号线中的至少一部分是扫描线，并且扫描线可以被称为以其相交的线性类型布置的数据线。红色和绿色和蓝色像素驱动区域由数据线和扫描线的交叉定义。用于驱动与用于驱动像素域帧的电路之间的颜色绑定相对应的像素域帧的电路与列方向相邻并且被定位。红色和绿色和蓝色像素驱动电路位于用于驱动像素域帧的电路中。红色和绿色和蓝色像素电极连接到红色，绿色和蓝色像素驱动电路。每个像素电极与横向和列方向的不同颜色的像素电极相邻。像素阵列，条纹，三角形，有机电致发光显示装置。