# (11) EP 2 084 746 B1

(12)

# **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication and mention of the grant of the patent: **07.06.2017 Bulletin 2017/23**

(21) Application number: 07850227.5

(22) Date of filing: 30.11.2007

(51) Int Cl.: H01L 27/32 (2006.01) H01L 29/786 (2006.01)

(86) International application number: **PCT/JP2007/073619**

(87) International publication number: WO 2008/069286 (12.06.2008 Gazette 2008/24)

# (54) DISPLAY APPARATUS USING OXIDE SEMICONDUCTOR AND PRODUCTION METHOD THEREOF

ANZEIGEVORRICHTUNG MIT EINEM OXIDHALBLEITER UND HERSTELLUNGSVERFAHREN DAFÜR

APPAREIL AFFICHEUR UTILISANT UN SEMI-CONDUCTEUR OXYDE ET PROCÉDÉ DE PRODUCTION DE CET APPAREIL

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC MT NL PL PT RO SE SI SK TR

- (30) Priority: 05.12.2006 JP 2006328307

- (43) Date of publication of application: 05.08.2009 Bulletin 2009/32

- (60) Divisional application: **17000733.0**

- (73) Proprietor: Canon Kabushiki Kaisha Tokyo 146-8501 (JP)

- (72) Inventors:

- SANO, Masafumi Tokyo 146-8501 (JP)

- TAKAHASHI, Kenji Tokyo 146-8501 (JP)

- (74) Representative: WESER & Kollegen Radeckestraße 43 81245 München (DE)

- (56) References cited:

WO-A-2006/051994 US-A1- 2005 191 448

TAKAGI A ET AL: "Carrier transport and electronic structure in amorphous oxide semiconductor, a-InGaZnO4" THIN SOLID FILMS, ELSEVIER-SEQUOIA S.A. LAUSANNE, CH, vol. 486, no. 1-2, 22 August 2005 (2005-08-22), pages 38-41, XP004973608 ISSN: 0040-6090

P 2 084 746 B1

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

25

40

45

#### Description

#### **TECHNICAL FIELD**

**[0001]** The present invention relates to a display apparatus using an oxide semiconductor and a production method thereof, and in particular, relates to a top-emission type, bottom-emission type or two-sided emitting type organic electroluminescent display apparatus or inorganic electroluminescent display apparatus.

#### **BACKGROUND ART**

[0002] ITO (Indium Tin oxide) has been used for a transparent electrode in a transmission type liquid crystal device. However, since  $\ln_2\!O_3$  of a main raw material of ITO contains a rare metal, and it has been feared whether a desired amount of ITO can also be steadily supplied in future. Japanese Patent Application Laid-Open No. 2000-044236 proposes a method of producing a new transparent conductor material which has a reduced content of  $\ln_2\!O_3$ , has a low electrical resistance, has an optical absorption edge in ultraviolet region and has an excellent blue light transmissivity; and an electrode material using the material.

**[0003]** In addition, materials which can be substituted for ITO have been actively researched and developed. For instance, Japanese Patent Application Laid-Open No. H07-235219 proposes a film of zinc oxide (ZnO) and a zinc-indium-based oxide. In addition, Japanese Patent Application Laid-Open No. 2000-044236 proposes an oxide containing zinc-indium-based oxide and a specified amount of an additive such as gallium.

[0004] In addition, there has been an attempt in recent years in which not only an electrode but also a channel layer (hereinafter, also referred to as "active layer") of a transistor is formed of a transparent film. For instance, Japanese Patent Application Laid-Open No. 2002-76356 discloses a TFT (thin film transistor) which employs a polycrystalline thin film of a transparent conductive oxide containing ZnO as a main component, for a channel layer. [0005] In addition, an organic electroluminescent lightemitting device has been actively researched and developed. When the organic electroluminescence is applied to a display unit, it is driven in an active matrix fashion in most cases. For the active matrix drive, a TFT which uses amorphous silicon or polysilicon is generally utilized.

[0006] In addition, Japanese Patent Application Laid-Open No. H09-114398 discloses an organic electroluminescent display unit which prevents degradation of a driving device, can display a television image, and aims at realizing a high-quality/high-luminance display unit. The organic electroluminescent display unit of an active matrix type according to this patent document is intended to prevent degradation of the driving device while keeping the high image quality, by using two MOS (metal oxide semiconductor) field effect transistors which use single-crystal silicon for an active layer.

[0007] In addition, Japanese Patent Application Laid-Open Nos. 2006-165528 and 2006-186319 disclose an example of producing a field effect transistor by using an amorphous oxide which is prepared by adding a specified amount of gallium or the like to a zinc-indium-based oxide to control the electron carrier concentration to less than  $10^{18}$ /cm<sup>3</sup>, and of applying the field effect transistor to an image display apparatus or a light-emitting apparatus.

[0008] In the conventional organic light-emitting/display apparatus, since amorphous silicon or polysilicon is used mainly as an active layer (channel layer) of a driving transistor, the gate insulating layer and the interlayer insulating layer can be used with no distinction. Further, since amorphous silicon or polysilicon used for the active layer originally contains hydrogen atoms, the diffusion of hydrogen in the insulating layers has posed no problem in most cases. Hydrogen in an a-SiN:H film produced by a plasma CVD (chemical vapor deposition) process has been rather considered to have an effect of compensating defects in amorphous silicon.

**[0009]** On the other hand, there has been found such a phenomenon that when an oxide semiconductor is used as an active layer of a driving transistor, there are a case where the transistor performs driving without any particular problem and a case where the off-state current increases during driving for a long period of time for unknown reasons. The phenomenon seems to depend on a method of forming an insulating layer which is in contact with an oxide semiconductor active layer, but the reason has not been clarified. Accordingly, there has been a problem that degradation of the characteristics may sometimes be caused due to the phenomenon. Moreover, the degradation of the characteristics has been intensively occurred during active matrix driving for a long period of time.

[0010] As described above, the conventional oxide semiconductor has the problem that when used in a stacked device, if a large amount of hydrogen is contained in an insulating layer, the degradation of the characteristics is liable to be occurred due to diffusion of the hydrogen. The problem has remarkably appeared in a display apparatus which employs the oxide semiconductor particularly for an active layer of a TFT. In this case, there has been a problem that a display apparatus cannot be realized which is stably driven for a long period of time and displays an image with high definition and less image

**[0011]** WO 2006/051994 A discloses a light-emitting device using a field-effect transistor containing an active layer which is an amorphous oxide.

**[0012]** US 2005/0191448 A discloses a flexible flat panel display where nanoparticles are used for an active layer and the substrate is a flexible plastic.

[0013] And Takagi A. et al., Thin Solid Films, vol. 486, no. 1-2, pp. 38-41 (2005) discloses thin films made of amorphous In-Ga-Zn oxide.

30

40

#### DISCLOSURE OF THE INVENTION

**[0014]** The present invention has been accomplished to dissolve the above described problems, and provides a display apparatus which can be stably driven for a long period of time without degrading the high mobility and high characteristics peculiar to an oxide semiconductor, and can display an image with high definition and less image defect, and a production method of the display apparatus.

[0015] In order to achieve the above-mentioned object, according to one aspect of the present invention, there is provided the display apparatus as claimed in claim 1.

[0016] Further, according to another aspect of the present invention, there is provided the method of producing a display apparatus as claimed in claim 6.

[0017] The other claims relate to further developments. [0018] According to the present invention, a display apparatus is provided which can display an image with high definition and less image defect, because a transistor with an active layer which includes an oxide containing In and Zn and at least a part of which is amorphous can stably perform driving for a long period of time. Thereby, the present invention can provide a bottom-emission type display apparatus or a two-sided emission type high-luminance display apparatus which maintains superior stability for a long period of time.

**[0019]** Further features of the present invention will become apparent from the following description of exemplary embodiments with reference to the attached drawings.

# BRIEF DESCRIPTION OF THE DRAWINGS

# [0020]

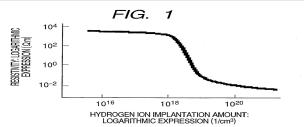

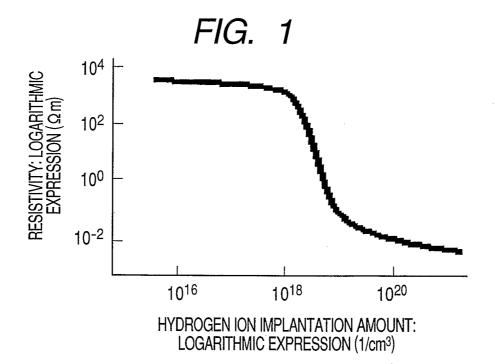

FIG. 1 is a graphical representation illustrating a relationship between the amount of hydrogen ions injected into an In-Ga-Zn-O-based amorphous film and the electrical resistance of the film.

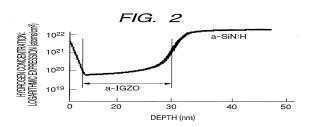

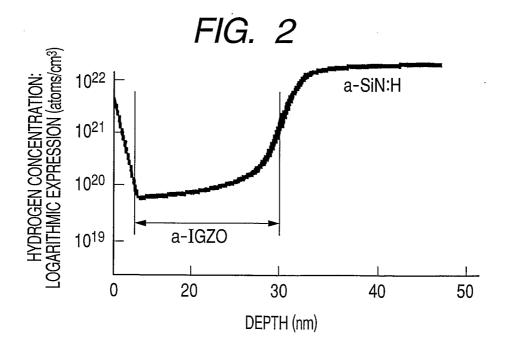

FIG. 2 is a graphical representation illustrating a distributed state of hydrogen atoms contained in an insulating layer, which have diffused into an In-Ga-Zn-O-based amorphous film.

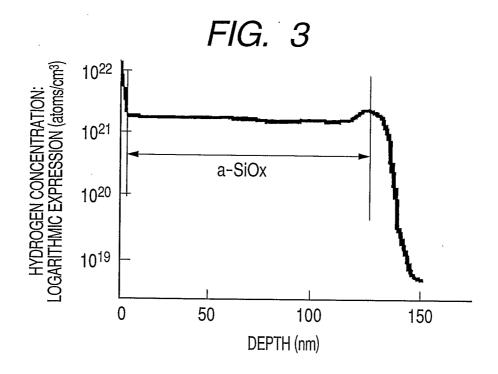

FIG. 3 is a graphical representation illustrating a concentration of hydrogen atoms in an insulating layer according to the present invention.

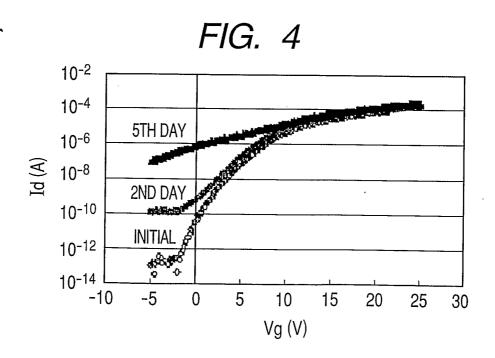

FIG. 4 is a graphical representation illustrating Id-Vg characteristics of a TFT using a gate insulating layer containing a large amount of hydrogen.

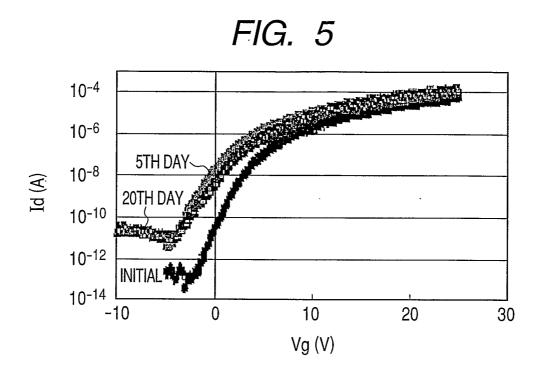

FIG. 5 is a graphical representation illustrating Id-Vg characteristics of a TFT using a gate insulating layer containing a small amount of hydrogen according to the present invention.

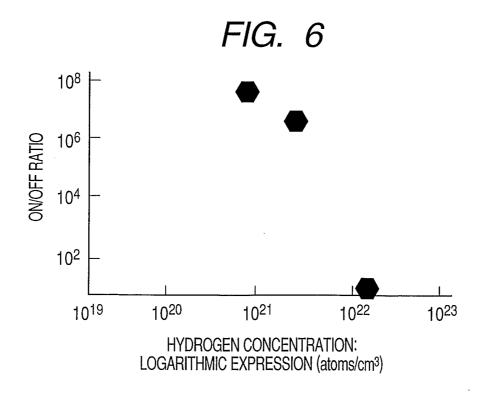

FIG. 6 is a graphical representation illustrating a relationship between a concentration of hydrogen atoms in a gate insulating layer according to the

present invention and an ON/OFF ratio in TFT characteristics.

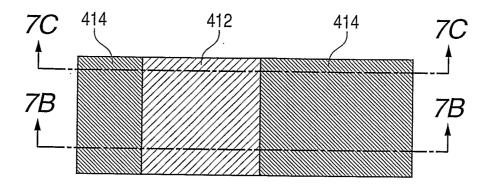

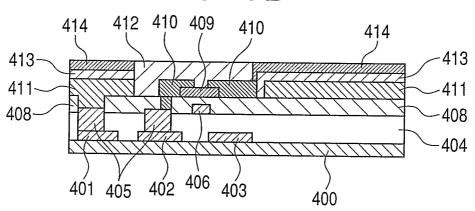

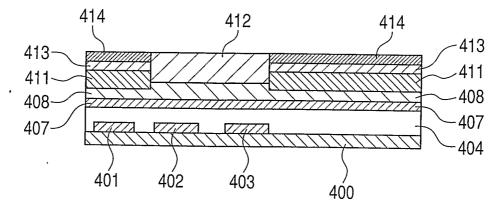

FIG. 7A is a plan view of a representative pixel portion used in a display apparatus according to an embodiment of the present invention; FIG. 7B is a cross-sectional view taken along line 7B-7B in FIG. 7A; and FIG. 7C is a cross-sectional view taken along line 7C-7C in FIG. 7A.

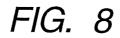

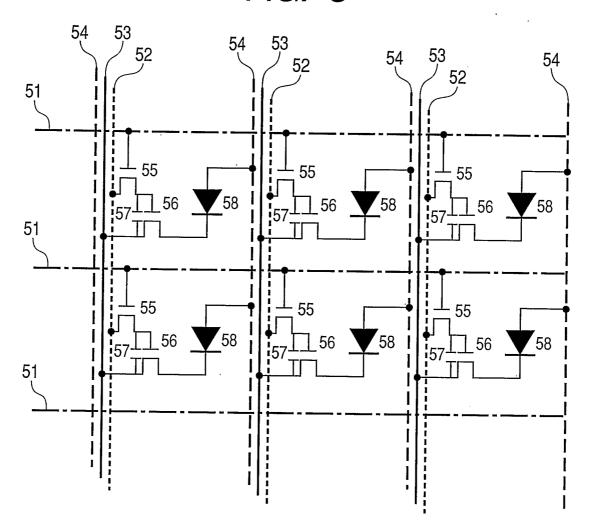

FIG. 8 is a circuit diagram of a display apparatus having a plurality of matrix lines according to an embodiment of the present invention.

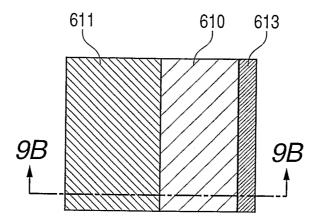

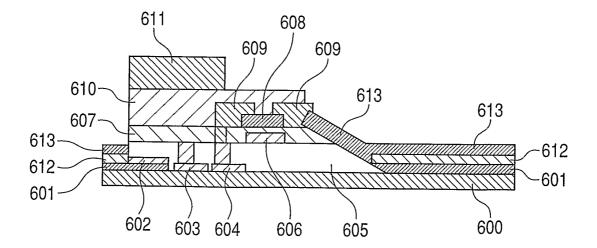

FIG. 9A is a plan view of a representative pixel portion used in a display apparatus according to an embodiment of the present invention; and FIG. 9B is a cross-sectional view taken along line 9B-9B in FIG. 9A.

#### BEST MODE FOR CARRYING OUT THE INVENTION

**[0021]** An embodiment of a display apparatus according to the present invention will now be specifically described below with reference to the drawings.

[0022] At first, a summary of the present invention will now be described.

[0023] The present inventors have energetically carried out a research on an oxide semiconductor active layer, a gate insulating layer, and an interlayer insulating layer of a TFT, and film growth conditions related thereto. As a result, the present inventors have found that a TFT excellent in long-term stability can be obtained by controlling a condition of an oxygen atmosphere during film formation, and controlling the content of hydrogen in the gate insulating layer and the interlayer insulating layer, and then accomplished the present invention.

**[0024]** The present inventors have found that a normally-off type TFT with excellent mobility can be made from an oxide semiconductor active layer having a desired electron carrier concentration and a Y<sub>2</sub>O<sub>3</sub> insulating layer and can be applied to a light-emitting apparatus, an image display apparatus or the like. Thereafter, it has been confirmed that few elements do not normally operate when subjected to a repetitive light emission test of a long period of time and that in particular, a device with a matrix wiring often shows such tendency.

**[0025]** Further thereafter, the present inventors have found that when an interlayer insulating layer in a matrix wiring portion is a-SiNx:H formed by low temperature plasma CVD, the change in stability is remarkable, and have further made extensive study. As a result, the present inventors have found that by forming an insulating layer having a hydrogen content of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup> by using sputtering and then forming an oxide semiconductor active layer of a TFT on the insulating layer, there is obtained an effect of remarkably improving the long-term stability of the TFT. A similar effect can also be obtained by an embodiment in which a portion other than a portion being in a contact with a source electrode and a drain electrode of an oxide semiconductor

25

35

40

45

active layer of a TFT is covered with an insulating layer having the same hydrogen content as described above. **[0026]** Here, the insulating layer in contact with the oxide semiconductor active layer was formed by controlling the hydrogen content to be less than  $3\times 10^{21}$  atoms/cm³. The insulating layer can be formed by using a sputtering process, but the forming method in the present invention is not limited to sputtering. For instance, the hydrogen content can also be controlled to be less than  $3\times 10^{21}$  atoms/cm³ by forming an amorphous silicon nitride (a-SiNx:H) film by using a low-temperature plasma CVD process and heating the film to  $450^{\circ}$ C by using a rapid thermal annealing process. Further, the insulating layer can be made by using a high-temperature plasma CVD process as well.

**[0027]** The present invention has been accomplished based on such findings, and provides a display apparatus using the above described film. Embodiments of the display apparatus according to the present invention will now be described in detail below.

[0028] The display apparatus according to the present embodiment includes (1) TFTs; (2) a light-emitting layer; (3) lower and upper electrodes (a pair of electrodes) which sandwich the light-emitting layer; and (4) a matrix wiring portion having a scanning electrode line, a first insulating layer, and a signal electrode line. In this configuration, an active layer of the TFT includes an oxide which contains In and Zn and at least a part of which is amorphous, and a second insulating layer containing hydrogen in an amount of less than  $3 \times 10^{21}$  atoms/cm³ is disposed between the active layer and the first insulating layer

[0029] In this configuration, the hydrogen content in the second insulating layer is preferably less than that in the first insulating layer. In addition, of the active layer of the TFT, a portion of the active layer other than a portion being in contact with a source electrode and a drain electrode may be covered with the second insulating layer having the above-mentioned hydrogen content of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup>. Furthermore, the first insulating layer may have a hydrogen content of less than 3  $\times$ 10<sup>21</sup> atoms/cm<sup>3</sup>. In addition, the TFTs may be disposed in series on the top of the matrix wiring portion composed of the scanning electrode line, the first insulating layer, and the signal electrode, or disposed in parallel on a part adjacent thereto. Furthermore, the TFTs may be disposed on the top of the matrix wiring portion composed of the scanning electrode line, the first insulating layer, and the signal electrode or on a part adjacent thereto with the second insulating layer formed by a sputtering step being used as a gate insulating layer. The first insulating layer corresponds to the interlayer insulating layer of the matrix wiring portion. The second insulating layer mainly corresponds to a gate insulating layer of the TFT, but is not limited thereto, and may be constituted by an insulating layer wholly covering a portion other than a portion being in contact with a source electrode and a drain electrode of the TFT.

**[0030]** A method of producing a display apparatus according to the present embodiment includes: (1) forming a matrix wiring portion; (2) forming a TFT; (3) forming a second insulating layer; (4) forming a light-emitting layer; and (5) forming a pair of electrodes (lower and upper electrodes) which sandwich the light-emitting layer. The matrix wiring portion has a scanning electrode line, an interlayer insulating layer (a first insulating layer), and a signal electrode line. The TFT has an active layer including an oxide which contains ln and Zn and at least a part of which is amorphous. The second insulating layer has a hydrogen content of  $3 \times 10^{21}$  atoms/cm $^3$ . The pair of the electrodes are the upper and lower electrodes which sandwich the light-emitting layer.

**[0031]** For the display apparatus according to the present embodiment, the following production methods can be adopted.

- 1) First, a matrix wiring portion is formed which is composed of a scanning electrode line, an interlayer insulating layer, and a signal electrode line. Subsequently, a TFT is formed thereon which has an active layer and a second insulating layer formed by a sputtering step. Then, a lower electrode, a light-emitting layer, and an upper electrode are formed.

- 2) First, a matrix wiring portion composed of a scanning electrode line, a first insulating layer, and a signal electrode line, and a lower electrode are formed. Subsequently, a TFT having an active layer and a second insulating layer formed by a sputtering step, a light-emitting layer, and an upper electrode are formed

- 3) First, a matrix wiring portion is formed which is composed of a scanning electrode line, a first insulating layer, and a signal electrode line. Subsequently, a TFT having a portion of an active layer other than a source electrode and a drain electrode covered with a second insulating layer formed by a sputtering step, a light-emitting layer, a lower electrode, and an upper electrode are formed.

- 4) First, a matrix wiring portion composed of a scanning electrode line, a first insulating layer, and a signal electrode line, and a lower electrode are formed. Subsequently, a TFT having a portion of an active layer other than a source electrode and a drain electrode covered with a second insulating layer formed by a sputtering step, a light-emitting layer, and an upper electrode are formed.

- **[0032]** A display apparatus according to the present embodiment will now be described below in detail with particular focus on an oxide semiconductor active layer and the second insulating layer having the hydrogen content of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup>.

(Transparent Amorphous Oxide Film)

[0033] First, as an oxide semiconductor active layer, a

40

45

50

55

transparent amorphous oxide film containing electron carriers in a concentration of less than 10<sup>18</sup>/cm<sup>3</sup> according to the present inventors will be described.

**[0034]** The above-mentioned transparent amorphous oxide film is specifically constituted by including In-Ga-Zn-O and has a composition represented by  $InGaO_3(ZnO)_m$ , wherein m is a natural number of less than 6, in a crystal state, and has an electron carrier concentration of less than  $10^{18}/cm^3$ . It is also preferred to control the electron mobility in this film to be  $1 cm^2/(V \cdot sec)$  or more.

[0035] When the above-mentioned film is used in a channel layer (active layer) of a TFT, a TFT can be produced which is of a normally off type in which the gate current is less than 0.1  $\mu\text{A}$  when the transistor is in an off state, has transistor characteristics of an ON/OFF ratio exceeding 10³, and is transparent to visible light and flexible. In addition, the electron mobility of the above-mentioned transparent amorphous oxide film increases with increase of the number of conduction electrons. As a substrate for formation of the transparent amorphous oxide film, there may be used a metal substrate, a metal thin plate, a glass substrate, a plastic substrate, or a plastic film.

**[0036]** The present inventors have found that such a transparent amorphous oxide film has specific characteristics in which the electron mobility increases as the number of conduction electrons increases. Further, they have also found that a TFT formed by using the film has further improved transistor characteristics such as an ON/OFF ratio, a saturation current in a pinched-off state and a switching speed.

[0037] When using the transparent amorphous oxide film for a channel layer of a thin film transistor, it is preferable to control the electron mobility to be 1 cm²/(V·sec) or more and also to control the electron carrier concentration to be less than  $10^{18}/\text{cm}^3$ . It is further preferable to control the electron mobility to be 5 cm²/(V·sec) or more and to control the electron carrier concentration to be less than  $10^{16}/\text{cm}^3$ . By respectively controlling the electron mobility and the electron carrier concentration within the above-mentioned ranges, the electric current flowing between the drain and source terminals in an off-state (when a gate voltage is not applied) can be made less than  $10~\mu\text{A}$ , preferably less than  $0.1~\mu\text{A}$ .

[0038] By using the thin film, when the electron mobility is 1 cm²/(V·sec) or more and preferably 5 cm²/(V·sec) or more, the saturation current after pinch-off can be made more than 10  $\mu$ A. Further, the ON/OFF ratio can be made 10³ or more. In the TFT in a pinched-off state, a high voltage is applied to the gate terminal, and electrons exist in the channel at a high density.

**[0039]** Thus, according to the present invention, the saturation current value can be increased by an amount corresponding to the increase of the electron mobility. As a result, almost all the transistor characteristics are improved including ON/OFF ratio increase, saturation current increase, and switching speed increase. Inciden-

tally, in a normal compound, when the number of electrons increases, the electron mobility decreases because electrons collide with each other.

**[0040]** As the structure of the above described TFT, a staggered (top gate) structure can be adopted in which a gate insulating film and a gate terminal are sequentially formed on a semiconductor channel layer. Furthermore, an inverted staggered (bottom gate) structure can also be adopted in which a gate insulating film and a semiconductor channel layer are sequentially formed on a gate terminal.

(Film Composition)

[0041] In a transparent amorphous oxide thin film having a composition represented by  $InGaO_3(ZnO)_m$  (wherein m is a natural number of less than 6) in a crystal state, when the value of m is less than 6, the amorphous state is stably kept up to a high temperature of  $800^{\circ}C$  or more. However, as the value of m increases, the ratio of ZnO to  $InGaO_3$  increases, i.e., the composition approaches to a ZnO composition, the film becomes liable to be crystallized. Accordingly, when the film is used for a channel layer of an amorphous TFT, the value of m is preferably less than 6.

(Implantation of Hydrogen Ions into Transparent Amorphous Oxide Film)

[0042] An amorphous oxide of In-Ga-Zn was prepared by using a sputter evaporation process while using a polycrystal sintered body having a composition of  $InGaO_3(ZnO)_m$  (wherein m is a natural number of less than 6) as a target and also using argon gas and oxygen gas as an atmospheric gas. The film formation was performed while controlling the substrate temperature to room temperature, setting the sputtering pressure to 0.48 Pa and setting the oxygen gas ratio to 5%. Hydrogen ions were implanted into the resulting deposited film of the transparent amorphous oxide (a-InGaZn:O), and the change of resistivity ( $\Omega$ m) depending on the implantation amount ( $1/cm^3$ ) of hydrogen ions was observed. The result is shown in FIG. 1.

[0043] It can be seen from the result shown in FIG. 1 that the resistivity of the transparent amorphous oxide film changes by 4 to 5 digits in the vicinity of a hydrogen ion implantation amount of 10<sup>19</sup>/cm³, and the resistance of the film decreases as the hydrogen ion implantation amount increases. This reveals the effect of hydrogen ions implanted into the transparent amorphous oxide (a-InGaZn:O) film. However, the value of hydrogen ion implantation amount of 10<sup>19</sup>/cm³ is not a fixed value, and the hydrogen ion implantation amount at which the resistivity changes will vary depending on the preparation conditions or method.

(Hydrogen Atom Concentration in Insulating Layer)

[0044] The concentrations of hydrogen atoms contained in a-SiN:H, a-SiN<sub>x</sub>, a-SiO<sub>x</sub>:H, and a-SiO<sub>x</sub> prepared by a plasma-CVD process or a sputtering process was measured with an SIMS (Secondary Ion Mass Spectrometry) measurement equipment. The result is shown in FIG. 2. It can be seen from the result shown in FIG. 2 that the concentration of hydrogen atoms in an  $\alpha$ -SiN:H film produced by a plasma-CVD process is 1  $\times$  10 $^{22}$  atoms/cm $^3$ , and that hydrogen atoms diffuse from inside of the a-SiN:H film into an a-InGaZn:O film.

**[0045]** Similarly, the concentration of hydrogen atoms in the insulating layer produced by a sputtering step was measured. The result is shown in FIG. 3. It can be seen from the result that the concentration of hydrogen atoms in the insulating layer (a-SiO $_{\chi}$ ) prepared by the sputtering process is less than  $3 \times 10^{21}$  atoms/cm $^{3}$ .

**[0046]** It has been confirmed from the measurement result that the concentration of hydrogen atoms in an insulating layer can be reduced by the preparation conditions or method.

(Dependency of TFT Characteristics on Amount of Hydrogen Atoms in Gate Insulating Layer)

[0047] The change over time of a TFT including a gate insulating layer containing a large amount of hydrogen atoms (hydrogen atom concentration: 1  $\times$  10²² atoms/cm³) was compared in terms of Id-Vg characteristics. The result is shown in FIG. 4. It can be seen from the result that the off-state current increases with the elapse of time and finally a state in which the TFT cannot turn on/off is reached.

**[0048]** On the other hand, FIG. 5 shows a change over time of a TFT using a gate insulating layer containing a small amount of hydrogen atoms (hydrogen content: less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup>). In this case, little change was observed, and good characteristics were maintained.

[0049] In addition, FIG. 6 shows a relationship between the concentration of hydrogen atoms in the gate insulating layer and an ON/OFF ratio of TFT characteristics at the time of 20 days after the preparation. The results mean that the TFT shows better characteristics when containing the hydrogen atom concentration to at least less than  $3\times 10^{21}$  atoms/cm³. This is considered to be because the resistance of the oxide semiconductor decreased due to the diffusion of hydrogen into the oxide semiconductor layer and a high ON/OFF ratio was not able to be attained, as is seen from the above described results.

**[0050]** As described above,  $SiO_x$  or  $SiN_x$  is preferable for the gate insulating layer to be used in a thin film transistor using a transparent amorphous oxide film. However, it can be seen that in order to maintain the stability for a long period of time, it is indispensable to set the hydrogen content in the insulating layer to be less than  $3 \times 10^{21}$  atoms/cm³, and that in the case of a film having

a large hydrogen content, the characteristics change with the elapse of time and the off-state current increases. Moreover, it is easily assumed that the same also applies to the contents of hydrogen in other insulating layers such as of  $\text{Al}_2\text{O}_3$ ,  $\text{Y}_2\text{O}_3$ , or  $\text{HfO}_2$  film. According to the findings of the present inventors, the effect of the present invention is obtained as long as the hydrogen content in the insulating layer is less than  $3\times 10^{21}$  atoms/cm³, so that there is no lower limit in the hydrogen content in particular. Accordingly, the lower limit of the hydrogen content in the insulating layer is ideally zero.

**[0051]** In addition, when there is a defect in an interface between a gate insulating thin film and a channel layer thin film, the electron mobility decreases and a hysteresis is generated in the transistor characteristics.

**[0052]** In addition, a leak current greatly differs depending on the type of a gate insulating film. Accordingly, a gate insulating film needs to be selected so as to match a channel layer.

**[0053]** In addition, the gate insulating film and the channel layer can be formed at room temperature, so that any TFT structure of a staggered structure and an inverted staggered structure can be formed.

[0054] The TFT is a three-terminal device having a gate terminal, a source terminal, and a drain terminal, and employs a semiconductor thin film formed on an insulation substrate such as of ceramic, glass or plastic as a channel layer through which electrons or holes move. Moreover, the TFT is also an active device which has a function of, in operation, applying a voltage to the gate terminal to control an electric current flowing in the channel layer, thereby switching an electric current between the source terminal and the drain terminal.

**[0055]** In the next place, a display apparatus according to an embodiment of the present invention will be specifically described.

[0056] The present embodiment relates to a display apparatus using the above described transparent amorphous oxide film. Specifically, the embodiment relates to a display apparatus driven by TFTs each using a semiconductor which is the above described transparent amorphous oxide film, and in particular, relates to a light source and a display unit for emitting light by driving an organic EL device. Thereby, the present embodiment can provide a display apparatus using a substrate even made of a plastic or the like which is lightweight and is hardly cracked.

**[0057]** In the next place, a basic configuration of a display apparatus according to the present embodiment will be described with reference to FIGS. 7A, 7B and 7C.

**[0058]** In the figures, reference numeral 400 denotes a substrate, reference numeral 401 denotes a power supply line, reference numeral 402 denotes a GND (grounding) line, reference numeral 403 denotes a signal electrode line, reference numeral 404 denotes a first insulating layer (interlayer insulating layer), and reference numeral 405 denotes a contact electrode embedded in each contact hole. In addition, reference numeral 406 denotes

25

40

45

a gate electrode, reference numeral 407 denotes a scanning electrode line, reference numeral 408 denotes a second insulating layer, reference numeral 409 denotes an amorphous oxide semiconductor, reference numeral 410 denotes a source electrode and a drain electrode, reference numeral 411 denotes a lower electrode, reference numeral 412 denotes a third insulating layer, reference numeral 413 denotes a light-emitting layer, and reference numeral 414 denotes an upper electrode. Among them, the second insulating layer 408 and the third insulating layer 412 together constitute the second insulating layer according to the present invention.

**[0059]** At first, the power supply line 401, the GND line 402, and the signal electrode line 403 are patterned on the substrate 400, and subsequently the first insulating layer 404 is deposited, contact holes are formed at desired positions of the first insulating layer 404, and the contact electrodes 405 are further embedded at the desired positions.

**[0060]** Next, the gate electrode 406 and the scanning electrode line 407 are patterned on the first insulating layer 404. At this time, the gate electrodes 406 are disposed in desired positions according to the necessary number of transistors, and electrodes (not shown) for the necessary number of capacitors are also patterned. Thus, it is one of the key features of the present invention to form a matrix wiring portion before forming a transistor. **[0061]** Subsequently, the second insulating layer 408 having a hydrogen content of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup> is formed by a sputtering step. Furthermore, contact holes are formed at desired positions of the second insulating layer 408, and contact electrodes are embedded in the contact holes.

**[0062]** Next, the lower electrode 411 of the light-emitting portion is formed so as to be connected to the power supply line 401 through the contact electrode 405, and an amorphous oxide semiconductor 409 is patterned on the second insulating layer 408. Subsequently, a source electrode and a drain electrode 410 are formed, and one of the electrodes is connected to a GND line 402 through the contact electrode.

**[0063]** Next, in order to protect the channel portion of the transistor, the third insulating layer 412 having a hydrogen content of less than  $3 \times 10^{21}$  atoms/cm³ is formed by a sputtering step. Subsequently, a light-emitting layer 413 composed of a hole-transporting layer, a light-emitting portion and an electron-transporting layer (not shown) is formed on the lower electrode 411. Subsequently, the upper electrode 414 is deposited on the light-emitting layer 413, and the upper electrode 414 is connected to the other electrode of the source electrode and the drain electrode 410.

**[0064]** The light-emitting layer 413 is not limited to the above described configuration. Further, when the TFT is in an ON state, a voltage is applied to the light-emitting layer 413 to emit light. As the upper electrode 414, a metal electrode is used when the light-emitting device is used as a bottom emission type device, and a transparent

electrode may be used when the light-emitting device is used as a two-sided emission type device. The material can be changed according to the intended use of the light-emitting device.

**[0065]** In the next place, each component of a display apparatus used in the present embodiment will be described in detail.

#### 1. Substrate

[0066] A glass substrate is generally used in a image display apparatus. However, in principle, a substrate to be used in the present invention is not particularly limited as long as it has flatness. Since the TFT used in the present invention can be formed at a low temperature, a plastic substrate, which is generally hard to be used for an active matrix type display apparatus, can be used. Thereby, an image display apparatus is obtained which is lightweight and is hardly broken. The image display apparatus can be bent to a certain extent.

**[0067]** In addition to the glass substrate and the plastic substrate, a semiconductor substrate such as of Si or a ceramic substrate can also be used. In addition, a substrate having an insulating layer provided on a metal substrate can be used as long as it is flat.

#### 2. Transistor

**[0068]** As the active layer, an In-Ga-Zn-O-based semiconductor is used. For this composition, substitution with or addition of an element such as Mg can be performed as long as the semiconductor has desired characteristics, that is, the electron carrier concentration is less than  $10^{18}$ /cm<sup>3</sup> and the electron mobility is more than 1 cm<sup>2</sup>/(V·sec).

**[0069]** As described above, a sputtering process or a pulsed laser evaporation process is suitable for forming the active layer, but various sputtering processes which are advantageous in productivity are more preferable. In addition, it is effective to appropriately insert a buffer layer between the active layer and a substrate.

**[0070]** For the gate insulating film, there are preferably used  $Al_2O_3$ ,  $Y_2O_3$ ,  $HfO_2$ ,  $SiO_x$ , and  $SiN_x$  as described above. However, in order to maintain the long-term stability, it is indispensable that the hydrogen content in the insulating layer is less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup>.

# 3. Lower Electrode

**[0071]** When the light-emitting layer is of a current injection type represented by an organic electroluminescent device, a preferred electrode is adopted according to the configuration thereof. For instance, when the lower electrode is connected as an anode to the light-emitting layer, the lower electrode is preferably a transparent electrode having a large work function. Examples of such material include ITO, electroconductive ZnO or In-Zn-O having an electron carrier concentration of 10<sup>18</sup>/cm<sup>3</sup> or

15

more. Alternatively, In-Ga-Zn-O-based oxide having an electron carrier concentration of 10<sup>18</sup>/cm<sup>3</sup> or more can be used as well. In this case, in contrast to the case of a TFT, a larger carrier concentration, for instance, 10<sup>19</sup>/cm<sup>3</sup> or more is more preferable.

#### 4. Light-Emitting Layer

**[0072]** The light-emitting layer is not particularly limited as long as it can be driven by an In-Ga-Zn-O-based TFT, but is preferably an organic electroluminescent layer in particular.

[0073] The light-emitting layer used in the present invention is generally composed of a plurality of layers such as

- (1) hole-transporting layer/(light-emitting portion + electron-transporting layer)(meaning a light-emitting portion having an electron-transporting function);

- (2) hole-transporting layer/light-emitting portion/electron-transporting layer;

- (3) hole injection layer/hole-transporting layer/lightemitting portion/electron-transporting layer;

- (4) hole injection layer/hole-transporting layer/lightemitting portion/electron-transporting layer/electron injection layer.

[0074] In addition, there are cases where an electron

barrier layer or an adhesion improving layer is additionally provided. Among the above examples, a representative light-emitting layer is composed of hole-transporting layer/light-emitting section/electron-transporting layer. Incidentally, the light-emitting layer according to the present invention is not limited to these configurations. [0075] For the light-emitting layer, fluorescence and phosphorescence are utilized, but it is effective to utilize the phosphorescence from the viewpoint of emission efficiency. As the phosphorescent material, an iridium complex is useful. Further, as the compound used, both a low molecular compound and a high molecular compound are available. In general, the low molecular compound can be formed into a film by vapor deposition, and the high molecular compound can be formed into a film by ink jet or printing. Examples of the low molecular compound include an amine complex, an anthracene, a rare earth complex, and a noble metal complex. Examples of the high molecular compound include n-conjugated or pigment-containing polymers.

**[0076]** As the material of the electron injection layer, there are included an alkali metal, an alkaline earth metal and a compound thereof; and an organic layer doped with an alkali metal.

**[0077]** Further, as the material of the electron-transporting layer, there are included an aluminium complex, oxadiazole, triazole, and phenanthroline.

**[0078]** Moreover, as the material of the hole injection layer includes an arylamine, a phthalocyanine, and an organic layer doped with a Lewis acid.

**[0079]** Furthermore, as the material of the hole-transporting layer, an arylamine is included.

# 5. Upper Electrode

**[0080]** The preferred material of the upper electrode varies depending on whether the light emitting device is used as a two-sided emission type or a bottom emission type, and whether the upper electrode is used an anode or a cathode.

[0081] When used as the two-sided emission type, the upper electrode needs to be transparent. Examples of the material of the transparent electrode includes oxides such as electroconductive ZnO, In-Zn-O, or ITO, which contains at least one element of In and Zn, is formed under deposition conditions including an oxygen flow rate adjusted such that the electron carrier concentration is 10<sup>18</sup>/cm<sup>3</sup> or more, and at least a part of which is amorphous. Alternatively, an In-Ga-Zn-O-based oxide having an electron carrier concentration of 10<sup>18</sup>/cm<sup>3</sup> or more can be used. Moreover, the upper electrode can be prepared by forming an alloy doped with an alkali metal or an alkaline earth metal into a film of several 10 nm or less in thickness and forming a transparent electrode thereon. [0082] In the case of the bottom emission type, the upper electrode does not need to be transparent. Accordingly, when the upper electrode is used as the anode, the usable material includes an Au alloy or a Pt alloy having a large work function, and when used as the cathode, the usable material includes Ag-added Mg, Li-added

Al, a silicide, a boride, and a nitride. [0083] In the present embodiment, a matrix wiring portion is formed beforehand (in which an interlayer insulating film used is normally a-SiOx:H, a-SiNx:H, a-SiNOx:H or the like produced by a PCVD (Plasma Chemical Vapor Deposition) process). Subsequently, an insulating layer is separately formed by using a method which is difficult to incorporate hydrogen into the insulating layer, and then an oxide semiconductor layer is formed and a pixel circuit is produced. As described above, the display apparatus according to the present embodiment uses a TFT formed of or protected by the insulating layer having the small hydrogen content, and therefore can solve the problem that in the case where a conventional oxide semiconductor is used for a stacked device, when an insulating layer contains much hydrogen, the characteristics of the device are liable to be degraded due to the diffusion of the hydrogen. Thereby, the present invention can provide a display apparatus which does not degrade the high mobility and excellent characteristics peculiar to the oxide semiconductor and is stably operated.

(Application Example)

**[0084]** A configuration example in which the above described embodiment is applied to a display apparatus having a plurality of matrix wirings will now be described with reference to FIG. 8.

40

45

[0085] In the figure, reference numeral 55 denotes a selecting transistor which selects a pixel, and reference numeral 56 denotes a driving transistor which drives a light-emitting layer 58. In addition, a capacitor 57 is provided for keeping a selected state, stores an electric charge between a GND line 53 and a source electrode of the selecting transistor 55, and holds a signal of a gate of the driving transistor 56. The pixel is selected by a scanning electrode line 51 and a signal electrode line 52. [0086] Specifically, the operation will now be described. An image signal from a driver circuit (not shown) is applied to a gate electrode in a form of a pulse signal through the scanning electrode line 51. At the same time, another pulse signal from another driver circuit (not shown) is applied to the selecting transistor 55 through the signal electrode line 52, whereby a pixel is selected. At that time, the selecting transistor 55 is turned on, and an electric charge is stored in the capacitor 57 provided between the GND line 53 and the source of the selecting transistor 55. Thereby, a gate voltage of the driving transistor 56 is kept at a desired voltage, and the driving transistor 56 is turned on. This state is maintained until a next signal is received. While the driving transistor 56 is in the ON state, a voltage and an electric current continue to be supplied to the light-emitting layer 58 to continue light emission.

[0087] The example illustrated in FIG. 8 has the configuration in which one pixel has two transistors and one capacitor, but one pixel may have a larger number of transistors integrated therein in order to improve the performance. It is sufficient that an amorphous oxide semiconductor containing at least In and Zn is used in the portion of an active layer of a transistor and an insulating layer having a hydrogen content of less than  $3\times 10^{21}$  atoms/cm³. Further, it is preferred that a matrix wiring portion such as a scanning electrode line, a signal electrode line, and a power supply line is formed prior to the formation of the transistor portion. Thereby, an image display apparatus can be obtained which is excellent in long-term repetition characteristics.

# (Another Embodiment)

**[0088]** In the next place, a basic configuration of a display apparatus according to another embodiment of the present invention will be described with reference to FIGS. 9A and 9B.

[0089] In the figure, reference numeral 600 denotes a substrate, reference numeral 601 denotes a lower electrode, reference numeral 602 denotes a power supply line, reference numeral 603 denotes a signal electrode line, reference numeral 604 denotes a GND line, and reference numeral 605 denotes a first insulating layer (interlayer insulating layer). In addition, reference numeral 606 denotes a gate electrode, reference numeral 607 denotes a second insulating layer, reference numeral 608 denotes an amorphous oxide semiconductor, reference numeral 609 denotes a source electrode and a drain

electrode, reference numeral 610 denotes a third insulating layer, reference numeral 611 denotes a bank, reference numeral 612 denotes a light-emitting layer, and reference numeral 613 denotes an upper electrode. Among the above-mentioned elements, the second insulating layer 607 and the third insulating layer 610 together constitute the second insulating layer according to the present invention.

**[0090]** In the figure, at first, the lower electrode 601 of the light-emitting layer 612 is patterned on the substrate 600. Furthermore, after a metal layer is deposited, the power supply line 602, the signal electrode line 603, and the GND line 604 are also patterned. At this time, the power supply line 602 is patterned so as to be in contact with the lower electrode 601.

[0091] Subsequently, after the first insulating layer 605 is deposited and patterned, contact holes are formed at desired positions of the first insulating layer 605, and then contact electrodes are embedded in the contact holes. Subsequently, the gate electrode 606 and a scanning electrode line (not shown) are patterned at desired positions on the first insulating layer 605. At this time, the gate electrodes 606 are disposed corresponding to the necessary number of transistors, and electrodes (not shown) for the necessary number of capacitors are also patterned. As described above, it is also one of the key features of the present invention that the matrix wiring portion is formed before the formation of the transistor. [0092] Next, the second insulating layer 607 having a hydrogen content of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup> is formed thereon. Furthermore, a contact hole is formed at a desired position of the second insulating layer 607, and a contact electrode is embedded in the contact hole. In addition, an amorphous oxide semiconductor 608 which becomes an active layer of the transistor is patterned on the second insulating layer 607. Subsequently, the source electrode and drain electrode 609 are formed. and one of the electrodes is connected to the GND line 604 through the contact electrode. Next, the third insulating layer 610 having a hydrogen content of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup> is formed thereon with a sputtering step so as to protect the channel portion of the transistor. Subsequently, on the lower electrode 601, the light-emitting layer 612 is formed which is composed of a holetransporting layer, a light-emitting portion, an electrontransporting layer and the like (not shown). Subsequently, the upper electrode 613 is deposited, and the thus formed upper electrode 613 is connected to the other of

[0093] Incidentally, the light-emitting layer 612 is not limited to the above described configuration. Further, when the TFT is in an ON state, a voltage is applied to the light-emitting layer 612 to emit light. As the upper electrode 613, a metal electrode is used when the light-emitting device is used as a bottom emission type device, and a transparent electrode may be used when the light-emitting device is used as a two-sided emission type device. The material can be changed according to the in-

the source electrode and drain electrode 609.

35

40

tended use of the light-emitting device.

**[0094]** A display apparatus according to the present invention and a production method thereof will now be described in detail below.

(Example 1)

**[0095]** In the first place, Example 1 according to the present invention will now be described.

[0096] At first, a  $SiO_2$  glass substrate (1737 manufactured by Corning, Inc.) was prepared as a substrate for film formation. As the pretreatment before film formation, the substrate was ultrasonically degreased and cleaned with acetone, IPA (isopropanol), and ultrapure water sequentially for five minutes each and then dried at  $100^{\circ}$ C in air.

**[0097]** Subsequently, a film with a thickness of 200 nm was deposited by a DC (direct current) sputtering process using Al-Si (5%) as a target material, and then a power supply line, a GND line, and a signal electrode line were patterned at desired positions by using a photolithographic process and a dry process.

[0098] Next, a film of a-SiNx:H was deposited thereon as an interlayer insulating layer in a thickness of 600 nm at a substrate temperature of 300°C using a plasma-CVD process. Subsequently, contact holes were formed in desired positions, and electrodes were embedded so as to contact the power supply line, the GND line, and the signal electrode line. Furthermore, films of Ti/Au/Ti were deposited in thicknesses of 5 nm/40 nm/5 nm respectively with a DC sputtering process using Au and Ti as target materials. Thereafter, a scanning electrode line, two gate electrodes for TFT and an electrode for a capacitor were formed at desired positions with a photolithographic process and a lift-off process.

**[0099]** Thus, a matrix wiring portion was formed on the substrate, and then the gate electrode for the TFT and the electrode for the capacitor were formed thereon.

[0100] Next, a second insulating layer having a hydrogen content of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup> was formed on the substrate having the matrix wiring portion formed thereon. A sintered body (with a size of 98 mm in diameter and 5 mm in thickness) having a composition of SiO<sub>2</sub> was used for the target material. A deposition chamber was controlled to reach a vacuum degree of  $2.0 \times 10^{-4}$ Pa. In the deposition chamber, Ar gas was flown at 133 Pa for 20 minutes before the film formation, and pre-sputtering was performed for five minutes. During the film formation, the total pressure in the chamber was controlled to a constant value of 0.1 Pa, Ar gas was flown at 10 sccm, and the distance between the target and the filmforming substrate was set at 75 mm. The input power was RF 400 W, and the film forming rate was 7 nm/min. The deposited film thickness of the second insulating layer was 200 nm. Furthermore, contact holes were formed in the second insulating layer with a dry etching process. The dry etching was performed under the conditions of CF<sub>4</sub> gas 20 sccm, 5 Pa, and RF 150 W at an etch rate

of 41 nm/min for 5.5 minutes.

[0101] Next, an amorphous oxide semiconductor was formed as the active layer of the TFT. A polycrystal sintered body (with a size of 98 mm in diameter and 5 mm in thickness) having the composition of InGaO<sub>3</sub>(ZnO)<sub>4</sub> was used for the target material. The sintered body was prepared by wet mixing In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub> and ZnO (each 4N reagent) as starting materials (solvent: ethanol), followed by presintering (1,000°C; 2 hours), dry milling, and sintering (1,500°C; 2 hours). The target had an electrical conductivity of 12 S/cm and was in a semi-insulating state. The vacuum reached in the deposition chamber was  $3.0 \times 10^{-4}$  Pa. During the film formation, the total pressure in the deposition chamber was controlled to a constant value of 0.5 Pa, and the oxygen gas ratio was controlled to 5%. In addition, the distance between the target and the film-forming substrate was set at 75 mm. The input power was RF 200 W, and the film-forming rate was set at 7.1 nm/min. The deposited film thickness of the amorphous oxide semiconductor was 40 nm. Furthermore, wet etching was performed by using an aqueous hydrochloric acid solution (HCI:water = 1:10) to pattern the amorphous In-Ga-Zn-O.

[0102] Next, a source electrode and a drain electrode of a TFT and a lower electrode of a light-emitting layer were prepared. A sintered body (with a size of 98 mm in diameter and 5 mm in thickness) having a composition of ITO (Sn: 5%) was used as a target material. The vacuum reached in the deposition chamber was  $3.0 \times 10^{-4}$ Pa. During the film formation, the total pressure in the deposition chamber was controlled to the constant value of 0.3 Pa, Ar gas was flown at 10 sccm, and the distance between the target and the film-forming substrate was set at 75 mm. The input electric power was RF 300 W, and the film-forming rate was set at 60 nm/min. The film thickness was 100 nm. The source electrode, the drain electrode, and the lower electrode of the light-emitting layer were formed by patterning at desired positions with a photolithographic process and a lift-off process.

**[0103]** Next, on the amorphous oxide semiconductor, a film of SiO<sub>x</sub> with a thickness of 200 nm was stacked using a sputtering process by following the same procedure as the formation of the second insulating layer, and a third insulating layer was formed by patterning at desired positions by means of a photolithographic process and a lift-off process.

[0104] Subsequently, a light-emitting layer was formed on the lower electrode for the light-emitting layer. A hole injection layer was formed of 4,4'-bis[N, N-diamino]-4"-phenyl-triphenylamine in a thickness of 45 nm by using a resistive evaporation process. Then, a film of 4,4'-bis[N-(1-naphthyl)-N-phenylamino]biphenyl was formed thereon in a thickness of 25 nm as a hole-transporting layer. Subsequently, a film of 4,4'-bis(2,2'-diphenyl vinyl)-1,1'-biphenyl as a light-emitting layer was formed thereon in a thickness of 30 nm and a film of tris(8-quinolinol) aluminum as an electron-transporting layer was further formed thereon in a thickness of 15 nm, thus com-

pleting an organic EL light-emitting layer as a whole.

**[0105]** Furthermore, an upper electrode of the light-emitting layer was prepared by forming a film of an alloy of Al and Ag in a thickness of 50 nm with a resistive heating evaporation process, and forming an Al film thereon in a thickness of 200 nm. The upper electrode was connected to the drain electrode of the TFT.

**[0106]** Thereafter, the substrate having the films stacked thereon was sealed with a glass cap containing a desiccant (not shown), whereby a display apparatus having basically the same configuration as that shown in FIGS. 7A to 7C was produced.

**[0107]** When a desired voltage and signal was given to each of the power supply line, the GND line, the signal electrode line, and the scanning electrode line of the above described device to thereby drive the TFTs, a blue light was emitted from the lower surface of the substrate, i.e., in a bottom emission type. In addition, when the TFTs were driven 1,000,000 times, there was not observed any special abnormality in light emission.

# (Comparative Example 1)

[0108] As the present comparative example, a display apparatus was made by following the same procedure as Example 1 with the exception that the second insulating layer having a hydrogen content of less than  $3\times 10^{21}$  atoms/cm³ was not used and an interlayer insulating layer was used as a gate insulating layer of the TFT. While the TFTs were operated, the operation was gradually deviated from a normal operation. In the normal operation, an electric charge should be retained and light emission should be observed, while with the display apparatus of the present comparative example, a leak current increased with the lapse of time and the light emission became intermittent.

#### (Example 2)

**[0109]** In the next place, Example 2 according to the present invention will be described.

[0110] At first, as a substrate, a SiO $_2$  glass substrate (1737 manufacture by Corning Inc.) was prepared which had an ITO film with a resistivity of 1.4  $\times$  10<sup>-4</sup>  $\Omega$ ·cm and a thickness of 100 nm formed thereon. As the pretreatment before film formation, the substrate was ultrasonically degreased and cleaned with acetone, IPA, and ultrapure water sequentially for five minutes each and then dried at 100°C in air.

**[0111]** Subsequently, a lower electrode of a light-emitting layer was patterned by a photolithographic process and a wet process.

**[0112]** Subsequently, a film with a thickness of 200 nm was deposited by a DC sputtering process using Al-Si (5%) as a target material, and then a power supply line, a GND line, and a signal electrode line were patterned at desired positions by using a photolithographic process and a dry process. At this time, patterning was performed

such that the lower electrode and the power supply line were in contact with each other.

**[0113]** Next, a film of a-SiNx:H was deposited thereon as an interlayer insulating layer in a thickness of 700 nm at a substrate temperature of 250°C using a plasma-CVD process. Subsequently, contact holes were formed in desired positions, and electrodes were embedded so as to contact the GND line, and the signal electrode line.

**[0114]** Furthermore, films of Ti/Au/Ti were deposited in thicknesses of 5 nm/40 nm/5 nm respectively with a DC sputtering process using Au and Ti as target materials, and a scanning electrode line, two gate electrodes and an electrode for a capacitor were formed at desired positions with a photolithographic process and a lift-off process.

**[0115]** Thus, a matrix wiring portion and a lower electrode for a light-emitting layer were formed on the substrate, and then the gate electrode for the TFT and the electrode for the capacitor were formed thereon.

[0116] Next, a second insulating layer having a hydrogen content of less than  $3 \times 10^{21}$  atoms/cm $^3$  was formed on the substrate having the matrix wiring portion formed thereon. A sintered body (with a size of 98 mm in diameter and 5 mm in thickness) having a composition of SiO<sub>2</sub> was used for the target material. A deposition chamber was controlled to reach a vacuum degree of  $2.0 \times 10^{-4}$ Pa. In the deposition chamber, Ar gas was flown at 133 Pa for 25 minutes before the film formation, and pre-sputtering was performed for five minutes. During the film formation, the total pressure in the chamber was controlled to a constant value of 0.1 Pa, Ar gas was flown at 10 sccm, and the distance between the target and the filmforming substrate was set at 75 mm. The input power was RF 400 W, and the film forming rate was 7 nm/min. The deposited film thickness of the second insulating layer was 220 nm. Furthermore, contact holes were formed in the second insulating layer with a dry etching process. The dry etching was performed under the conditions of CF<sub>4</sub> gas 20 sccm, 5 Pa, and RF 150 W at an etch rate of 41 nm/min for 6.0 minutes.

[0117] Next, an amorphous oxide semiconductor was formed as the active layer of the TFT. A polycrystal sintered body (with a size of 98 mm in diameter and 5 mm in thickness) having the composition of InGaO<sub>3</sub>(ZnO)<sub>4</sub> was used for the target material. The sintered body was prepared by wet mixing In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub> and ZnO (each 4N reagent) as starting materials (solvent: ethanol), followed by presintering (1,000°C; 2 hours), dry milling, and sintering (1,500°C; 2 hours). The target had an electrical conductivity of 12 S/cm and was in a semi-insulating state. The vacuum reached in the deposition chamber was  $3.0 \times 10^{-4}$  Pa. During the film formation, the total pressure in the deposition chamber was controlled to a constant value of 0.5 Pa, and the oxygen gas ratio was controlled to 5.5%. In addition, the distance between the target and the film-forming substrate was set at 75 mm. The input power was RF 200 W, and the film-forming rate was set at 7.1 nm/min. The deposited film thickness of

45

the amorphous oxide semiconductor was 35 nm. Furthermore, wet etching was performed by using an aqueous hydrochloric acid solution (HCI:water = 1:10) to pattern the amorphous In-Ga-Zn-O.

**[0118]** Next, a source electrode and a drain electrode of the TFT were prepared. Au and Ti were used as target materials and films of Ti/Au/Ti were deposited in thicknesses of 5 nm/40 nm/5 nm respectively with a DC sputtering process, and the source electrode and the drain electrode were formed at desired positions with a photolithographic process and a lift-off process.

**[0119]** Next, on the amorphous oxide semiconductor, a film of  $\mathrm{SiO}_{\mathrm{X}}$  with a thickness of 300 nm was stacked using a sputtering process by following the same procedure as the formation of the second insulating layer, and a third insulating layer was formed by patterning at desired positions by means of a photolithographic process and a lift-off process.

[0120] Subsequently, a light-emitting layer was formed on the lower electrode for the light-emitting layer. A hole injection layer was formed of 4,4'-bis[N, N-diamino]-4"-phenyl-triphenylamine in a thickness of 45 nm by using a resistive evaporation process. Then, a film of 4,4'-bis[N-(1-naphthyl)-N-phenylamino]biphenyl was formed thereon in a thickness of 25 nm as a hole-transporting layer. Subsequently, a film of 4,4'-bis(2,2'-diphenyl vinyl)-1,1'-biphenyl as a light-emitting layer was formed thereon in a thickness of 30 nm and a film of tris(8-quinolinol) aluminum as an electron-transporting layer was further formed thereon in a thickness of 15 nm, thus completing an organic EL light-emitting layer as a whole.

**[0121]** Furthermore, an upper electrode of the light-emitting layer was prepared by forming a film of an alloy of Al and Ag in a thickness of 50 nm with a resistive heating evaporation process, and forming an Al film thereon in a thickness of 200 nm. The upper electrode was connected to the drain electrode of the TFT.

**[0122]** Thereafter, the substrate having the films stacked thereon was sealed with a glass cap containing a desiccant (not shown), whereby a display apparatus having basically the same configuration as that shown in FIGS. 9A and 9B was produced.

**[0123]** When a desired voltage and signal was given to each of the power supply line, the GND line, the signal electrode line, and the scanning electrode line of the above described device to thereby drive the TFTs, a blue light was emitted from the lower surface of the substrate, i.e., in a bottom emission type. In addition, when the TFTs were driven 1,000,000 times, there was not observed any special abnormality in light emission.

(Comparative Example 2)

**[0124]** As the present comparative example, a display apparatus was made by following the same procedure as Example 2 with the exception that the second insulating layer having a hydrogen content of less than  $3\times10^{21}$  atoms/cm³ was not used and an interlayer insulating lay-

er was used as a gate insulating layer of the TFT. When the TFTs were operated, an electric charge was held and light emission was observed. However, with the lapse of time, a leak current gradually increased and the light emission became intermittent.

(Example 3)

**[0125]** In the next place, Example 3 according to the present invention will be described.

**[0126]** In the present example, a display apparatus was made by following the same procedure as in Example 1 up to the completion of the matrix wiring portion.

[0127] Next, a second insulating layer having a hydrogen content of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup> was formed on the substrate having the matrix wiring portion formed thereon. A sintered body (with a size of 98 mm in diameter and 5 mm in thickness) having a composition of Si<sub>3</sub>N<sub>4</sub> was used for the target material. A deposition chamber was controlled to reach a vacuum degree of  $2.5 \times 10^{-4}$ Pa. In the deposition chamber, Ar gas was flown at 133 Pa for 20 minutes before the film formation, and pre-sputtering was performed for five minutes. During the film formation, the total pressure in the chamber was controlled to a constant value of 0.1 Pa, Ar gas was flown at 15 sccm, and the distance between the target and the filmforming substrate was set at 75 mm. The input power was RF 400 W, and the film forming rate was 6 nm/min. The deposited film thickness of the second insulating layer was 200 nm. Furthermore, contact holes were formed in the second insulating layer with a dry etching process. The dry etching was performed under the conditions of CF<sub>4</sub> gas 20 sccm, 5 Pa, and RF 160 W at an etch rate of 41 nm/min for 7 minutes.

[0128] Next, an amorphous oxide semiconductor was formed as the active layer of the TFT. A polycrystal sintered body (with a size of 98 mm in diameter and 5 mm in thickness) having the composition of InGaO<sub>3</sub>(ZnO)<sub>4</sub> was used for the target material. The sintered body was prepared by wet mixing In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub> and ZnO (each 4N reagent) as starting materials (solvent: ethanol), followed by presintering (1,000°C; 2 hours), dry milling, and sintering (1,500°C; 2 hours). The target had an electrical conductivity of 12 S/cm and was in a semi-insulating state. The vacuum reached in the deposition chamber was  $3.0 \times 10^{-4}$  Pa. During the film formation, the total pressure in the deposition chamber was controlled to a constant value of 0.5 Pa, and the oxygen gas ratio was controlled to 5%. In addition, the distance between the target and the film-forming substrate was set at 75 mm. The input power was RF 200 W, and the film-forming rate was set at 7.1 nm/min. The deposited film thickness of the amorphous oxide semiconductor was 30 nm. Furthermore, wet etching was performed by using an aqueous hydrochloric acid solution (HCI:water = 1:10) to pattern the amorphous In-Ga-Zn-O.

[0129] Thereafter, the subsequent process was performed by following the same procedure as in Example

35

40

1, a display apparatus having basically the same configuration as that shown in FIGS. 7A to 7C was produced. **[0130]** When a desired voltage and signal was given to each of the power supply line, the GND line, the signal electrode line, and the scanning electrode line of the above described device to thereby drive the TFTs, a blue light was emitted from the lower surface of the substrate, i.e., in a bottom emission type. In addition, when the TFTs were driven 1,000,000 times, there was not observed any special abnormality in light emission.

#### (Example 4)

[0131] In the next place, Example 4 according to the present invention will be described.

**[0132]** In the present example, a display apparatus was made by following the same procedure as in Example 2 up to the completion of the matrix wiring portion.

[0133] Next, a second insulating layer having a hydrogen content of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup> was formed on the substrate having the matrix wiring portion formed thereon. A sintered body (with a size of 98 mm in diameter and 5 mm in thickness) having a composition of Si<sub>3</sub>N<sub>4</sub> was used for the target material. A deposition chamber was controlled to reach a vacuum degree of  $2.5 \times 10^{-4}$ Pa. In the deposition chamber, Ar gas was flown at 133 Pa for 20 minutes before the film formation, and pre-sputtering was performed for five minutes. During the film formation, the total pressure in the chamber was controlled to a constant value of 0.1 Pa, Ar gas was flown at 20 sccm, O2 gas was flown at 3 sccm, and the distance between the target and the film-forming substrate was set at 75 mm. The input power was RF 420 W, and the film forming rate was 6 nm/min. The deposited film thickness of the second insulating layer was 200 nm. Furthermore, contact holes were formed in the second insulating layer with a dry etching process. The dry etching was performed under the conditions of CF<sub>4</sub> gas 20 sccm, 5 Pa, and RF 180 W at an etch rate of 32 nm/min for 7 minutes.

[0134] Next, an amorphous oxide semiconductor was formed as the active layer of the TFT. A polycrystal sintered body (with a size of 98 mm in diameter and 5 mm in thickness) having the composition of InGaO<sub>3</sub>(ZnO)<sub>4</sub> was used for the target material. The sintered body was prepared by wet mixing In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub> and ZnO (each 4N reagent) as starting materials (solvent: ethanol), followed by presintering (1,000°C; 2 hours), dry milling, and sintering (1,500°C; 2 hours). The target had an electrical conductivity of 12 S/cm and was in a semi-insulating state. The vacuum reached in the deposition chamber was 3.0 x 10<sup>-4</sup> Pa. During the film formation, the total pressure in the deposition chamber was controlled to a constant value of 0.5 Pa, and the oxygen gas ratio was controlled to 5.5%. In addition, the distance between the target and the film-forming substrate was set at 75 mm. The input power was RF 220 W, and the film-forming rate was set at 7.1 nm/min. The deposited film thickness of

the amorphous oxide semiconductor was 30 nm. Furthermore, wet etching was performed by using an aqueous hydrochloric acid solution (HCI:water = 1:10) to pattern the amorphous In-Ga-Zn-O.

[0135] Thereafter, the subsequent process was performed by following the same procedure as in Example 2, a display apparatus having basically the same configuration as that shown in FIGS. 9A and 9B was produced. [0136] When a desired voltage and signal was given to each of the power supply line, the GND line, the signal electrode line, and the scanning electrode line of the above described device to thereby drive the TFTs, a blue light was emitted from the lower surface of the substrate, i.e., in a bottom emission type. In addition, when the TFTs were driven 1,000,000 times, there was not observed any special abnormality in light emission.

**[0137]** While the present invention has been described with reference to exemplary embodiments, it is to be understood that the invention is not limited to the disclosed exemplary embodiments and the scope of protection sought is determined by the appended claims.

**[0138]** This application claims the benefit of Japanese Patent Application No. 2006-328307, filed December 5, 2006, which can be used as further reference.

#### **Claims**

30

35

40

45

50

- 1. A display apparatus comprising:

- a light-emitting layer (413, 612);

- a pair of electrodes (411,414;601,613) sandwiching the light-emitting layer;

- a transistor (406,408,409,410;606,607,608,609) with an active layer (409,608) and with a source electrode (410,609) and a drain electrode (410,609) each contacting the active layer, for driving the light-emitting layer through the pair of the electrodes; and

- a matrix wiring portion having a scanning electrode line (407), a signal electrode line (403,603), and a first insulating layer (404,605); wherein the active layer comprises a semiconducting oxide which contains In and Zn and at least a part of which is amorphous;

- characterized in that a second insulating layer (408,607) containing hydrogen in an amount of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup> is disposed between the active layer and the first insulating layer and covers the active layer between the source and drain electrode.

- 2. The apparatus according to claim 1, wherein the hydrogen content in the second insulating layer is less than the hydrogen content in the first insulating layer.

- 3. The apparatus according to claim 1, wherein the first insulating layer contains hydrogen in an amount of

15

less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup>.

- 4. The apparatus according to claim 1, wherein the matrix wiring portion and the transistor are disposed in series or in parallel, and wherein the first insulating layer and the active layer are in contact with each other through the second insulating layer.

- 5. The apparatus according to any one of claims 1 to 4, wherein the active layer is sandwiched between the second insulating layer and a third insulating layer (412,610) containing hydrogen in an amount of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup>, said third insulating layer covering the active layer between the source and drain electrode.

- **6.** A method of producing a display apparatus, comprising the steps of:

forming a matrix wiring portion having a scanning electrode line (407), a first insulating layer (404,605), and a signal electrode line (403,603); forming a transistor (406,408,409,410;606,607,608,609) with an active layer (409,608) comprising a semiconducting oxide which contains In and Zn and at least a part of which is amorphous, and with a source electrode (410,609) and a drain electrode (410,609) each contacting the active layer; and

forming a light-emitting layer (413, 612) and a pair of electrodes (411,414;601,613) sandwiching the light-emitting layer;

**characterized by** further comprising a step of forming a second insulating layer (408,607) containing hydrogen in an amount of less than  $3 \times 10^{21}$  atoms/cm<sup>3</sup> between the first insulating layer and the active layer, so as to cover the active layer between the source and drain electrode.

- **7.** The method according to claim 6, wherein the formation of the transistor is performed after the formation of the matrix wiring portion.

- **8.** The method according to claim 6, wherein the formation of the transistor is performed after the formation of the matrix wiring portion and either one of the pair of the electrodes.

- 9. The method according to any one of claims 6 to 8, further comprising a step of forming a third insulating layer (412,610) containing hydrogen in an amount of less than  $3\times 10^{21}$  atoms/cm³, so as the active layer is sandwiched between the second and the third insulating layer and covered between the source and drain electrode by said third insulating layer.

#### **Patentansprüche**

1. Anzeigevorrichtung, umfassend:

eine Lichtemissionsschicht (413, 612); ein Paar Elektroden (411, 414; 601, 613), welche die Lichtemissionsschicht sandwichartig einfassen;

einen Transistor (406, 408, 409, 410; 606, 607, 608, 609) mit einer aktiven Schicht (409, 608) und mit einer Source-Elektrode (410, 609) und einer Drain-Elektrode (410, 609), die jeweils die aktive Schicht kontaktieren, zum Antreiben der Lichtemissionsschicht über das Paar Elektroden: sowie

einen Matrixverdrahtungsabschnitt, der eine Abtastelektrodenleitung (407), eine Signalelektrodenleitung (403, 603) und eine erste Isolierschicht (404, 605) aufweist;

wobei die aktive Schicht ein halbleitendes Oxid umfasst, das In und Zn enthält und von dem zumindest ein Teil amorph ist;

dadurch gekennzeichnet, dass eine zweite Isolierschicht (408, 607), die Wasserstoff in einer Menge von weniger als  $3\times 10^{21}\,\text{Atome/cm}^3$  enthält, zwischen der aktiven Schicht und der ersten Isolierschicht angeordnet ist und die aktive Schicht zwischen der Source- und der Drain-Elektrode bedeckt.

- Vorrichtung nach Anspruch 1, wobei der Wasserstoffgehalt in der zweiten Isolierschicht geringer als der Wasserstoffgehalt in der ersten Isolierschicht ist.

- 3. Vorrichtung nach Anspruch 1, wobei die erste Isolierschicht Wasserstoff in einer Menge von weniger als  $3 \times 10^{21}$  Atome/cm<sup>3</sup> enthält.

- 4. Vorrichtung nach Anspruch 1, wobei der Matrixverdrahtungsabschnitt und der Transistor in Reihe oder parallel angeordnet sind, und wobei sich die erste Isolierschicht und die aktive Schicht über die zweite Isolierschicht miteinander in Kontakt befinden.

- 45 5. Vorrichtung nach einem der Ansprüche 1 bis 4, wobei die aktive Schicht zwischen der zweiten Isolierschicht und einer dritten Isolierschicht (412, 610), die Wasserstoff in einer Menge von weniger als 3 × 10<sup>21</sup> Atome/cm³ enthält, sandwichartig eingefasst ist und die dritte Isolierschicht die aktive Schicht zwischen der Source- und der Drain-Elektrode bedeckt.

- **6.** Verfahren zum Herstellen einer Anzeigevorrichtung, umfassend die folgenden Schritte:

Erzeugen eines Matrixverdrahtungsabschnitts, der eine Abtastelektrodenleitung (407), eine erste Isolierschicht (404, 605) und eine Signal-

20

25

30

elektrodenleitung (403, 603) aufweist;

Erzeugen eines Transistors (406, 408, 409, 410; 606, 607, 608, 609) mit einer aktiven Schicht (409, 608), die ein halbleitendes Oxid umfasst, das In und Zn enthält und von dem zumindest ein Teil amorph ist, und mit einer Source-Elektrode (410, 609) und einer Drain-Elektrode (410, 609), die jeweils die aktive Schicht kontaktieren; sowie

Erzeugen einer Lichtemissionsschicht (413, 612) und eines Paars Elektroden (411, 414; 601, 613), welche die Lichtemissionsschicht sandwichartig einfassen;