## (11) EP 1 430 467 B1

### (12) EUROPEAN PATENT SPECIFICATION

(45) Date of publication and mention of the grant of the patent: 23.02.2011 Bulletin 2011/08

(21) Application number: 03738528.3

(22) Date of filing: 27.06.2003

(51) Int Cl.: **G09G 3/32** (2006.01)

(86) International application number: **PCT/JP2003/008153**

(87) International publication number: WO 2004/003877 (08.01.2004 Gazette 2004/02)

# (54) CURRENT DRIVE CIRCUIT AND DRIVE METHOD THEREOF, AND ELECTROLUMINESCENT DISPLAY APPARATUS USING THE CIRCUIT

STROMSTEUERSCHALTUNG UND STEURVERFAHREN DAFÜR, UND ELEKTROLUMINESZENTES ANZEIGEGERÄT MIT DIESER SCHALTUNG

DISPOSITIF DE COMMANDE DE COURANT, PROCEDE DE COMMANDE ASSOCIE ET AFFICHEUR UTILISANT CE DISPOSITIF

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IT LI LU MC NL PT RO SE SI SK TR

- (30) Priority: 27.06.2002 JP 2002187803

- (43) Date of publication of application: 23.06.2004 Bulletin 2004/26

- (73) Proprietors:

- CASIO COMPUTER CO., LTD. Shibuya-ku, Tokyo 151-8543 (JP)

- Hattori, Reiji

Fukuoka-shi,

Fukuoka 819-0004 (JP)

- (72) Inventor: HATTORI, Reiji Nishi-ku, Fukuoka-shi, Fukuoka 819-0004 (JP)

(74) Representative: Grünecker, Kinkeldey, Stockmair & Schwanhäusser Anwaltssozietät Leopoldstrasse 4 80802 München (DE)

(56) References cited:

EP-A- 0 478 384 EP-A- 1 182 636 WO-A-02/05254 US-A- 4 447 812 US-A- 5 754 155 US-A- 6 091 203 US-A1- 2002 075 208 US-B1- 6 268 842

• SHIMA T ET AL: "PRINCIPLE AND APPLICATIONS OF AN AUTOCHARGE-COMPENSATED SAMPLE AND HOLD CIRCUIT" IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE INC. NEW YORK, US, vol. 30, no. 8, 1 August 1995 (1995-08-01), pages 906-911, XP000524389 ISSN: 0018-9200

EP 1 430 467 B1

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

#### **Description**

20

30

35

40

45

50

55

**[0001]** The present invention relates to a current drive apparatus, a drive method of the current drive apparatus, and a display apparatus using the current drive apparatus, and more particularly to a current drive apparatus including a structure to operate a plurality of loads by applying a predetermined current thereto, a drive method thereof, and a display apparatus which displays desired image information in a display panel by using the current drive apparatus.

**[0002]** Conventionally, there is known a light emitting element type display including a display panel in which a plurality of organic electroluminescence elements (which will be referred to as "organic EL elements" hereinafter), inorganic electroluminescence elements (which will be referred to as "inorganic EL elements" hereinafter), or self-luminous type light emitting elements (optical elements) such as light emitting diodes are arranged in a matrix form.

**[0003]** As compared with a liquid crystal display (LCD) which has considerably spread in recent years, such a light emitting element type display has a higher display response speed and no field angle dependency, an increase in contrast, realization of high definition of a display image quality and a reduction in power consumption are possible. Further, a reduction in thickness and weight of one layer is possible since it does not require a back light as different from the liquid crystal display. Thus, it has a very excellent characteristic, so that the light emitting element type display has been studied and developed vigorously as a display of the next generation.

**[0004]** Such a display generally includes a display panel in which display pixels including light emitting elements are arranged in the vicinity of respective intersects of scanning lines arranged in a row direction and data lines arranged in a column direction, a data driver which generates a predetermined drive current according to display data and supplies it to each display element through the data lines, and a scanning driver which causes display pixels in a predetermined row to enter a selection state by applying a scanning signal with a predetermined timing. In such an apparatus, by causing each light emitting element to perform the light emitting operation with a predetermined brightness gradation according to the display data by using the drive current supplied to each display pixel, desired image information is displayed in the display panel. A concrete example of the light emitting element type display will be described in detail in conjunction with a later-described embodiment.

**[0005]** Here, in the display drive operation in the display, there are known a current specification type drive mode which sequentially repeats in accordance with each row for one screen the operation which generates drive currents having individual current values according to the display data with respect to a plurality of display pixels, simultaneously supplies the currents to the display pixels in a specific row and causes the light emitting element of each display pixel to emits the light with a predetermined brightness gradation, and a pulse width modulation (PWM) type drive mode which sequentially repeats for one screen the operation which supplies drive currents having a fixed current value with individual time widths (signal widths) according to the display data relative to a plurality of the display pixels to the display pixels in a specific row in the same display period and causes each light emitting element to emit the light with a predetermined brightness gradation.

**[0006]** In these display drive operations, the drive currents having predetermined current values or a fixed current value according to the display data must be supplied to a plurality of the display pixels in each row at the same time or within the same display period. In order to cope with realization of high definition and a large screen of a thin display device in recent years, there is known a display having applied thereto a circuit configuration which includes a plurality of driver chips (semiconductor chips) each having a predetermined number of output terminals as the above-described data drivers, individually generates the drive currents in the respective driver chips and supplies the drive currents to the respective light emitting elements through a data line at the same time.

**[0007]** The display to which the above-described data driver including a plurality of the driver chips is applied has the following problems.

[0008] The conventional data driver having a plurality of the driver chips includes a circuit used to individually generate a drive current in accordance with each driver chip and has a structure to simultaneously supply the drive currents to the respective light emitting elements from the respective driver chips through respective output terminals. Therefore, when irregularities are generated in current values of the drive currents outputted from a plurality of the driver chips, irregularities occur in the light emitting state in each display pixel (brightness gradation of the light emitting element), and the display heterogeneity is produced. Thus, irregularities in the drive currents must be suppressed as much as possible between the respective driver chips and between the respective output terminals.

**[0009]** However, in the field of a semiconductor manufacture technique, there is known the fact that irregularities are necessarily generated in the element characteristic of function elements such as transistor elements, resistance elements or capacitance elements formed on the same semiconductor chip.. Such irregularities in the element characteristic can be suppressed to some degree by, e.g., optimizing manufacturing processes, but they cannot be completely eliminated. Further, there has been reported the fact that irregularities in the number of impurity atoms in channels become relatively actual with a reduction in design minimum dimension applied to the transistor elements and irregularities are thereby generated in a threshold value or the mobility.

[0010] Therefore, there is a problem that it is very difficult to greatly improve the irregularities in the drive currents

between the output terminals of the driver chips caused due to the above-described irregularities in the element characteristic by using only a technique of optimizing the manufacturing processes.

**[0011]** Furthermore, since there is a limit in the number of output terminals which can be set in one semiconductor chip due to a problem of an increase in signal delay owing to an increase in wiring length or to a reduction in production yield with an increase in the number of elements in one chip, the data driver must be necessarily configured by using a plurality of the driver chips. If the semiconductor chips are different from each other, irregularities in the drive currents between the output terminals further become large, and it is very difficult to suppress irregularities in the drive currents in the same driver chip while suppressing the same between the driver chips.

**[0012]** As a technique to correct irregularities in the drive currents in the driver chip, there is known a technique which additionally provides a current setting resistance in accordance with an output terminal of each driver chip and individually adjusts a resistance value of the current setting resistance. In this technique, when the number of the output terminals provided to the same driver chip is increased, adjustment of each current setting resistance becomes complicated, adjustment requires a long time and cost and a resistance setting area in the circuit configuration becomes large. Therefore, it is not suitable as a technique to suppress irregularities in the drive currents between the respective output terminals

**[0013]** Therefore, in order to suppress irregularities in the drive currents between the output terminals in the same driver chip while also suppressing irregularities between the driver chips, a complicated and large-scale circuit configuration must be added between the respective output terminals and between the respective driver chips. Therefore, the data driver including the driver chips and thus the apparatus scale of the display are increased, and there is a problem that a product cost is increased.

**[0014]** US-A-5 754 155 describes a power supply circuit for a display unit comprising a plurality of picture elements. A reference voltage is generated by means of a reference transistor formed on approximately the same structure as the picture element transistors. Thus, a drive voltage of a data signal line and a scanning signal line driver circuit can be set to an optimised voltage value according to the properties of the transistor used for determining reference voltage.

**[0015]** Moreover, as described above, in the display in recent years, although realization of further clearness of gradation display is demanded with realization of high definition in the display image quality, the light emitting element type display which has been currently developed has a problem that it has not reached establishment of a technique to generate an analog output signal which can realize the sufficient gradation display when generating a drive current having an analog signal component from a digital input signal which becomes display data by digital-to-analog conversion.

**[0016]** WO-A-205 254 describes a driving of pixels on the basis of current supplied thereon. A circuit for receiving a current, storing a voltage component corresponding to the received current and outputting a current to light emitting element based on a stored voltage component is connected to each light emitting element.

[0017] The present aims at improving the image quality of the image displayed on a display panel.

[0018] This is achieved by the features of the independent claims.

20

30

35

40

45

50

55

**[0019]** A current drive apparatus according to the present invention has an advantage to suppress irregularities in currents between output terminals of a current drive apparatus which operates by applying currents to a plurality of loads, and also suppress irregularities between chips when the current drive apparatus constructed by a plurality of driver chips. Further, it has an advantage to obtain the excellent display characteristic with display irregularities being suppressed in a display apparatus including the current drive apparatus.

[0020] To achieve this aim, according to a first current drive apparatus of the present invention, there is provided a current drive apparatus which operates a plurality of loads by applying currents thereto, comprising: a plurality of output terminals to which the loads are connected, respectively; a single current generation circuit which outputs an operating current having a predetermined current value; and a plurality of current storage circuits which are provided in accordance with each of the output terminals, sequentially fetch and hold the operating current and simultaneously output drive currents based on the operating current to the respective output terminals. The operating current has a current value according to an input signal, the current storage circuit includes a voltage component holding portion which fetches the operating current outputted from the current generation circuit and holds a voltage component corresponding to a current value of the operating current, and the voltage component holding portion has a capacitance element in which an electric charge corresponding to the operating current is written. Each of the current storage circuits preferably includes a pair of current storage sections which are arranged in parallel and in which an operation to fetch and hold the operating current and an operation to output the drive current based on the held operating current are alternately carried out in parallel, or includes current storage sections on front and rear stages which are arranged in series and in which an operation to fetch and hold the operating current and supply the held current to the current storage section on the rear stage and an operation to fetch and hold the supplied current and output the drive current based on the held current are carried out in parallel.

**[0021]** The current drive apparatus may include a signal input current storage circuit between the current generation circuit and a plurality of the current storage circuits, which fetches and holds the operating current and supplies a current based on the held operating current to a plurality of the current storage circuits so that the drive currents have the same

current value at the respective output terminals, and include a pulse width control circuit which controls a pulse width of each of the drive current in accordance with an input signal.

**[0022]** Preferably, at least a plurality of the current storage circuits and the output terminals in the current drive apparatus are formed on at least one semiconductor chip, and the current generation circuit is formed on a semiconductor chip different from the former semiconductor chip or formed in the former semiconductor chip.

[0023] To achieve the above-described aim, according to a second current drive apparatus of the present invention, there is provided a current drive apparatus which operates a plurality of loads by applying currents thereto, comprising: a plurality of output terminals to which the load are connected, respectively; a single reference current generation circuit which generates and outputs a plurality of reference currents having current values different from each other; at least one reference current storage circuit which fetches and holds each of the plurality of reference currents and outputs a plurality of gradation reference currents based on the respective reference currents; a plurality of current generation circuits which select any of the respective gradation reference currents and generate a gradation current in accordance with an input signal; and a plurality of current storage circuits which sequentially fetch and hold the respective gradation currents and simultaneously output drive currents based on the gradation currents to the respective output terminals. The reference current generation circuit can include a plurality of reference current generation sections which generate and output the respective reference currents and are arranged in parallel, the input signal is a digital signal having a plurality of bits, and a current value of the reference current outputted from each of the reference current generation sections can have a weight corresponding to each bit of the digital signal. The reference current storage circuit preferably includes a plurality of reference current storage sections which individually fetch the respective reference currents outputted from the reference current generation circuit, hold voltage components corresponding to the respective reference currents and output the gradation reference currents based on the respective voltage components, and each of the current generation circuits selects any of the gradation reference currents outputted from the respective reference current storage sections based on a bit value of the input signal, adds the selected gradation reference current and generates the gradation current. The current storage circuit can include a voltage component holding portion which fetches the gradation current outputted from the current generation circuit and holds a voltage component corresponding to a current value of the gradation current, and the voltage component holding portion has a capacitance element in which the an electric charge corresponding to the gradation current is written as the voltage component.

20

30

35

40

45

50

55

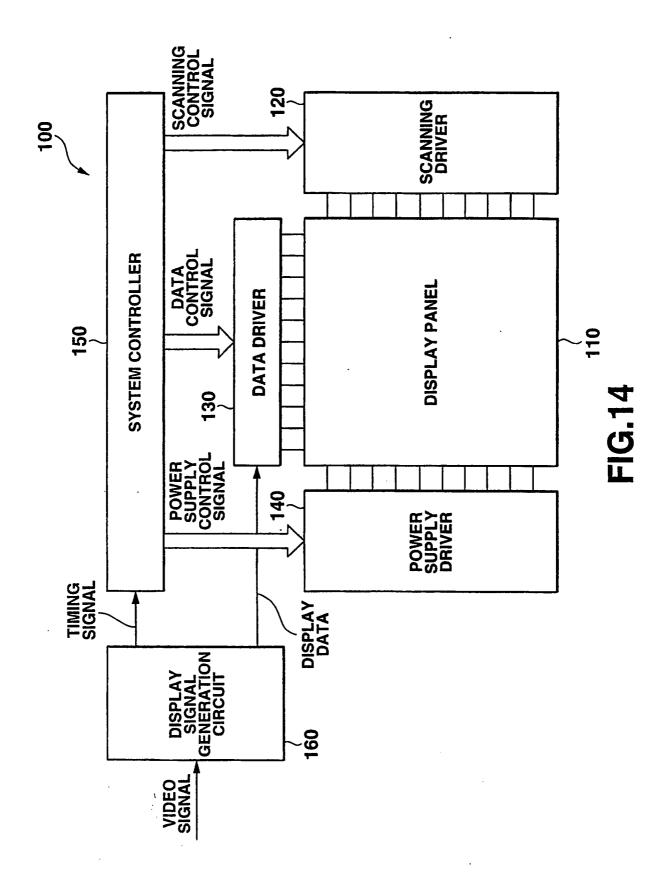

[0024] According to a display apparatus of the present invention, there is provided a display apparatus which supplies a drive current corresponding to a display signal to each display pixel of a display panel including a plurality of display pixels, comprising: a display panel which includes a plurality of display pixels having optical elements which are arranged in the vicinity of intersections of a plurality of scanning lines arranged in a line direction and a plurality of signal lines arranged in a row direction; a signal drive circuit including any of a structure of the first current drive apparatus which includes a single current generation circuit which generates and outputs an operating current having a current value based on the display signal, and a plurality of current storage circuits which are provided in accordance with the respective signal lines, sequentially fetch the operating current outputted from the current generation circuit and simultaneously output a drive current based on the operating current to a plurality of the signal lines, or a structure of the second current drive apparatus which includes a single reference current generation circuit which generates and outputs a plurality of reference currents having current values different from each other, at least one reference current storage circuit which fetches and holds the respective reference currents and outputs a plurality of gradation reference currents based on the respective reference currents, at least one current generation circuit which selects any of the respective reference currents and generates and outputs a gradation current, and a plurality of current storage circuits which are provided in accordance with the respective signal lines, sequentially fetch and hold the gradation current outputted from the current generation circuit, and simultaneously output a drive current based on the gradation current to a plurality of the signal lines; and a scanning drive circuit which outputs a scanning signal used to sequentially select the display pixels connected to the scanning lines, the optical element in the display pixel having a light emitting element, and the optical element having an organic electro luminescent element.

**[0025]** Additional objects and advantages of the invention will be set forth in the description which follows, and in part will be obvious from the description, or may be learned by practice of the invention. The objects and advantages of the invention may be realized and obtained by means of the instrumentalities and combinations particularly pointed out hereinafter.

**[0026]** The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate embodiments of the invention, and together with the general description given above and the detailed description of the embodiments given below, serve to explain the principles of the invention.

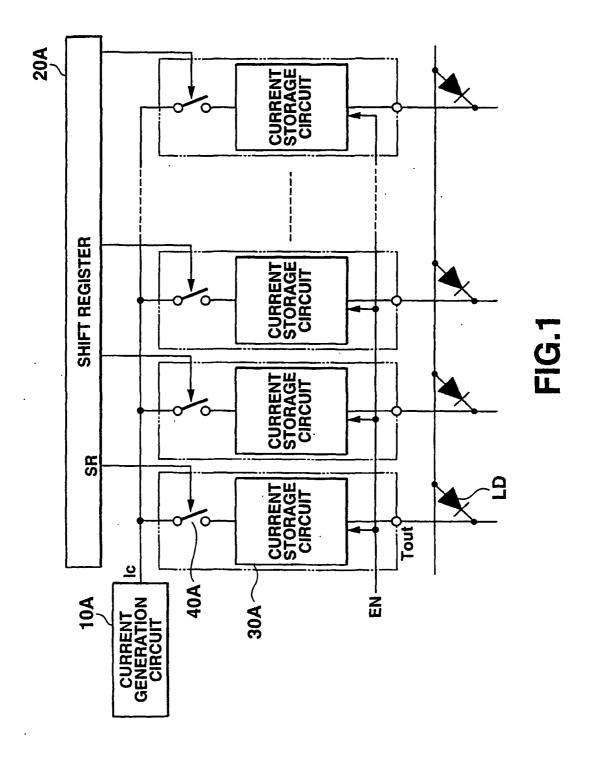

FIG. 1 is a primary structural view showing a first embodiment of a current drive apparatus according to the present invention;

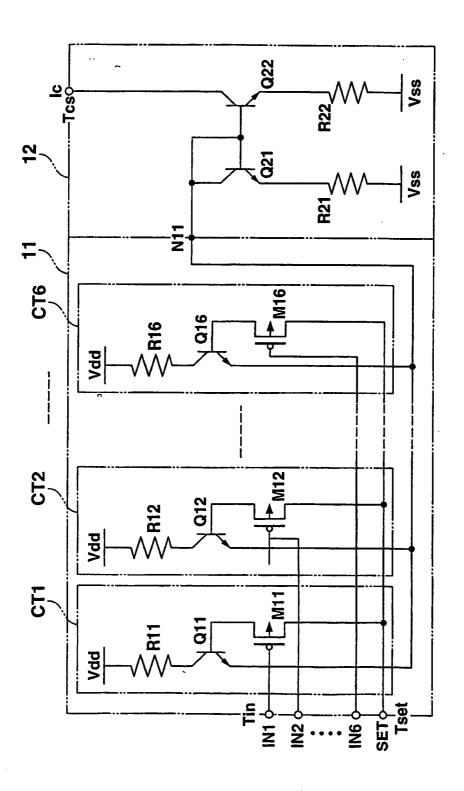

FIG. 2 is a circuit structural view showing a concrete example of a current generation circuit applicable to the embodiment:

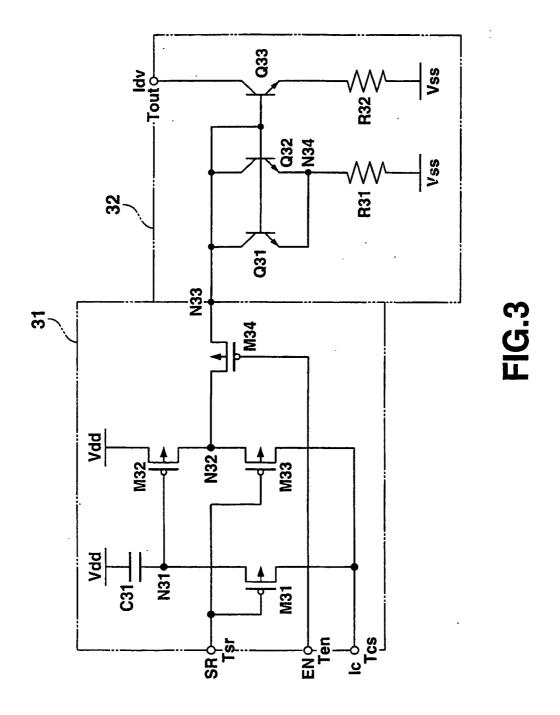

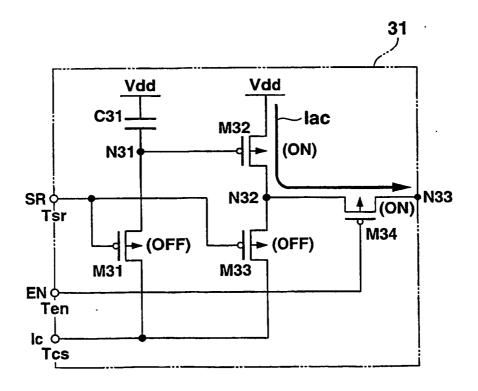

- FIG. 3 is a circuit structural view showing a concrete example of a structure consisting of a current storage circuit and a switch circuit applicable to the embodiment;

- FIGS. 4A and 4B are conceptual views showing a basic operation in the current storage circuit applicable to the embodiment;

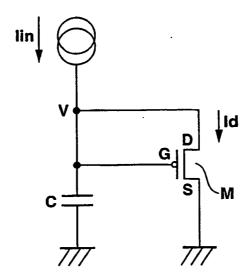

- FIG. 5A is a view of an equivalent circuit showing a structure when an electric charge is accumulated in a capacitance between a gate and a source of a transistor;

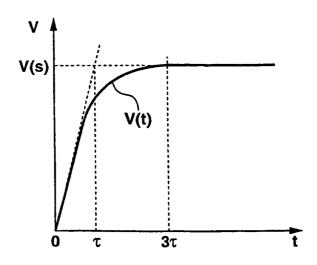

- FIG. 5B is a graph showing an aged change in voltage of the capacitance when the electric charge is accumulated in the capacitance between the gate and the source of the transistor;

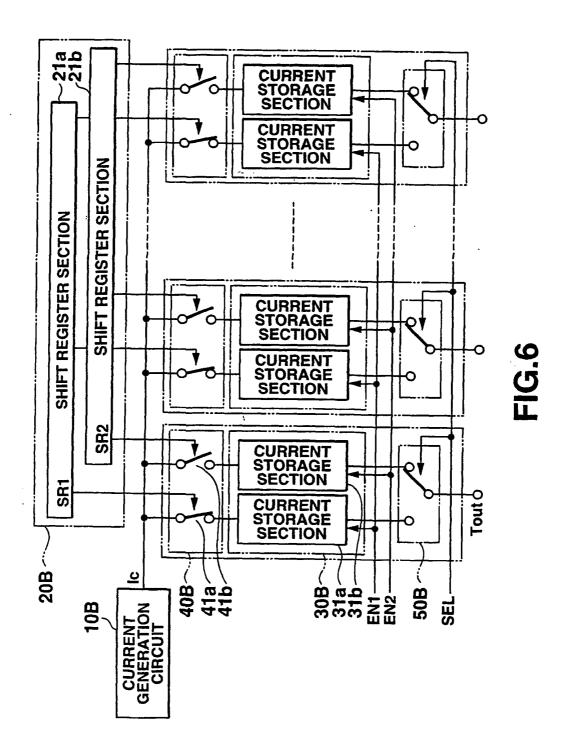

- FIG. 6 is a primary structural view showing a second embodiment of a current drive apparatus according to the present invention;

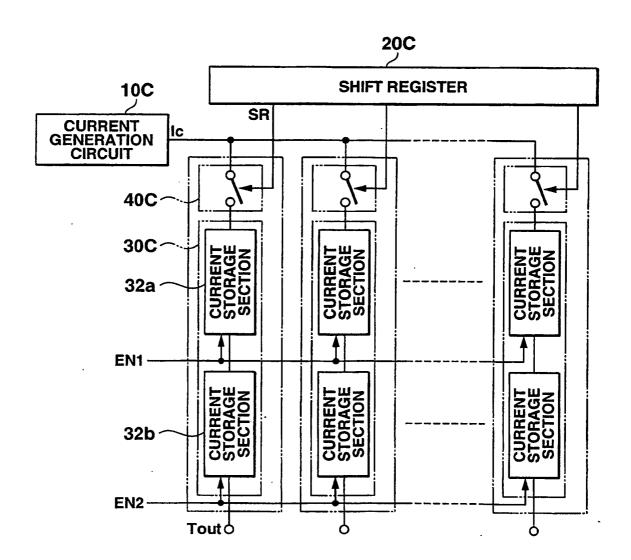

- FIG. 7 is a primary structural view showing a third embodiment of a current drive apparatus according to the present invention;

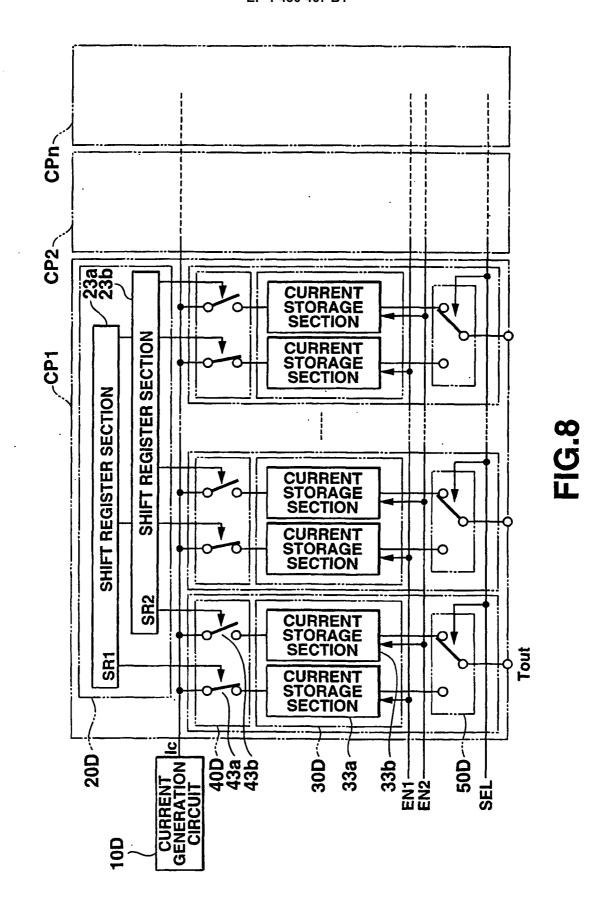

- FIG. 8 is a primary structural view showing a fourth embodiment of a current drive apparatus according to the present invention;

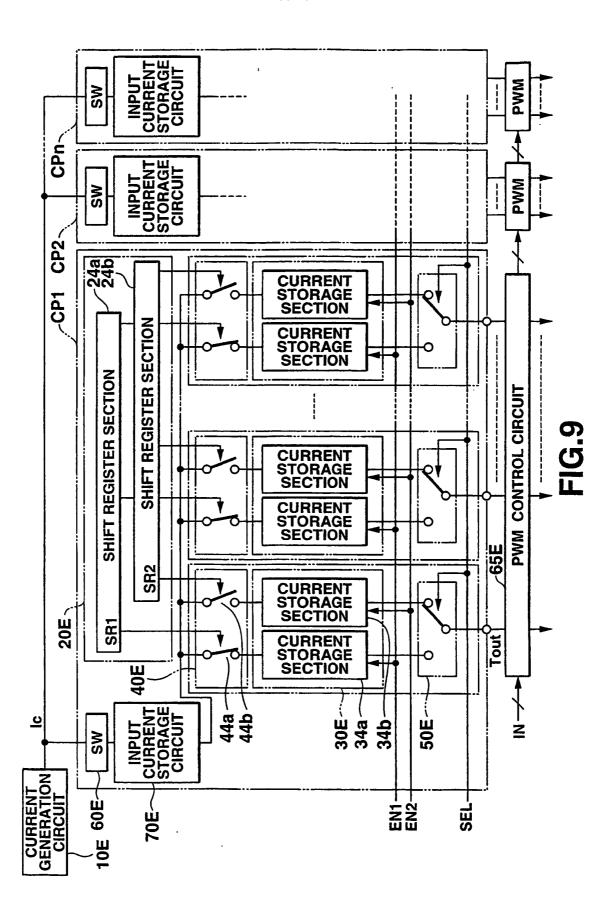

- FIG. 9 is a primary structural view showing a fifth embodiment of a current drive apparatus according to the present invention;

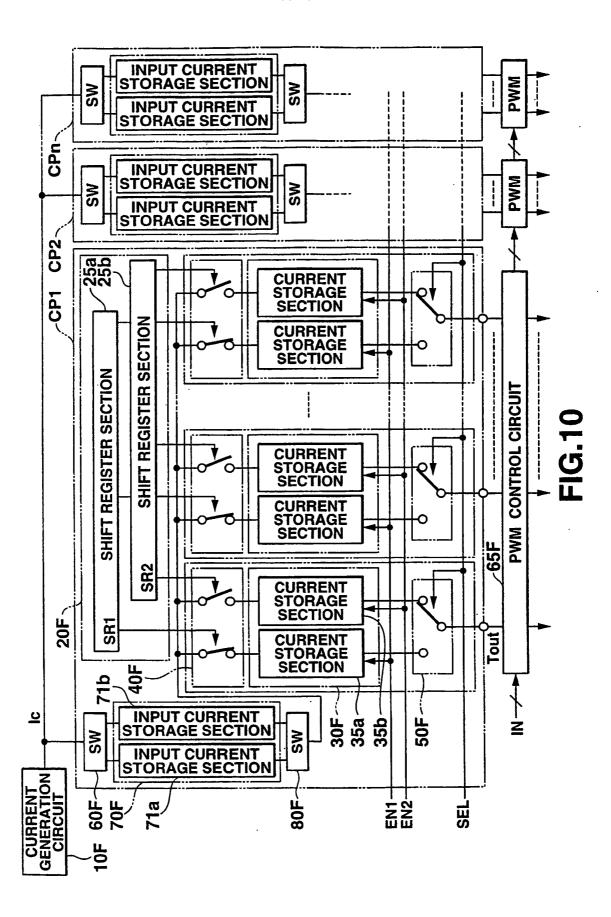

- FIG. 10 is a primary structural view showing a sixth embodiment of a current drive apparatus according to the present invention:

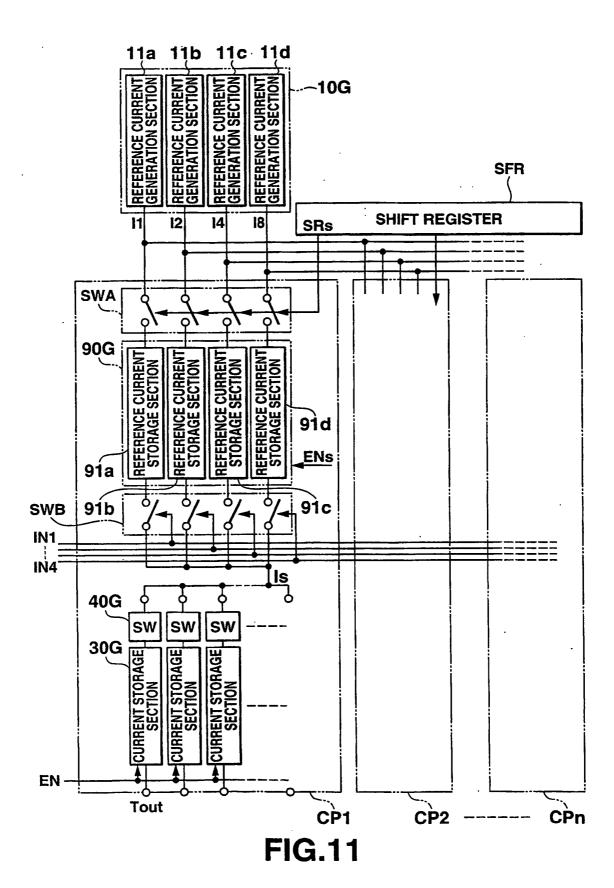

- FIG. 11 is a primary structural view showing a seventh embodiment of a current drive apparatus according to the present invention;

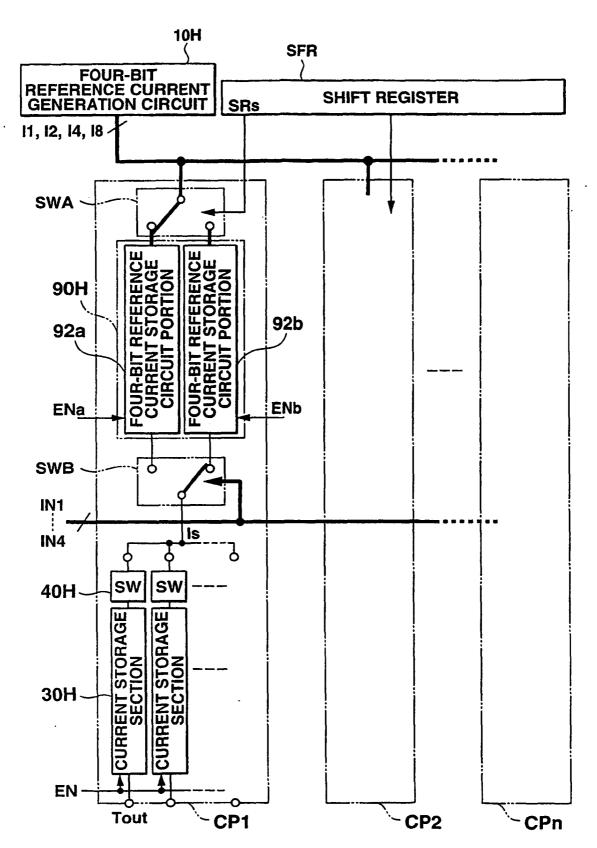

- FIG. 12 is a primary structural view showing an eighth embodiment of a current drive apparatus according to the present invention;

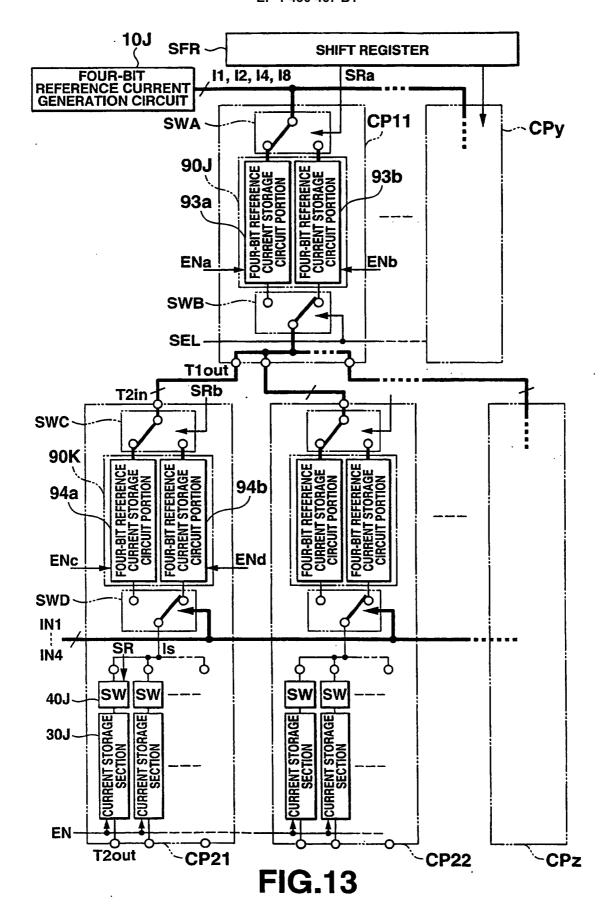

- FIG. 13 is a primary structural view showing a ninth embodiment of a current drive apparatus according to the present invention;

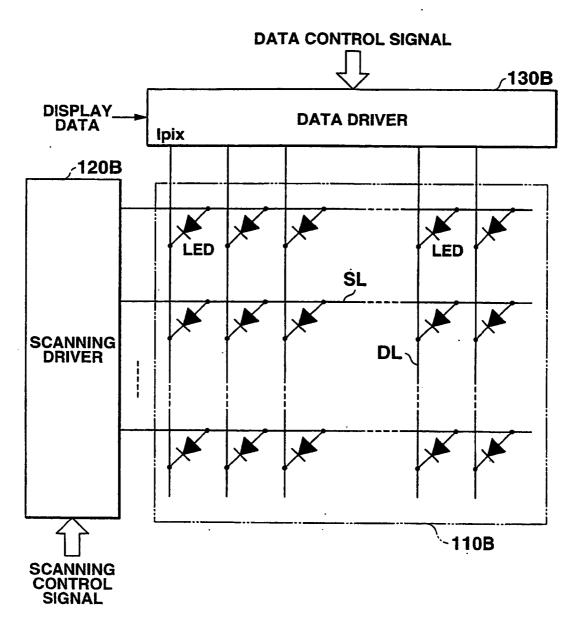

- FIG. 14 is a schematic structural view showing an example of an entire structure of a display apparatus according to the present invention;

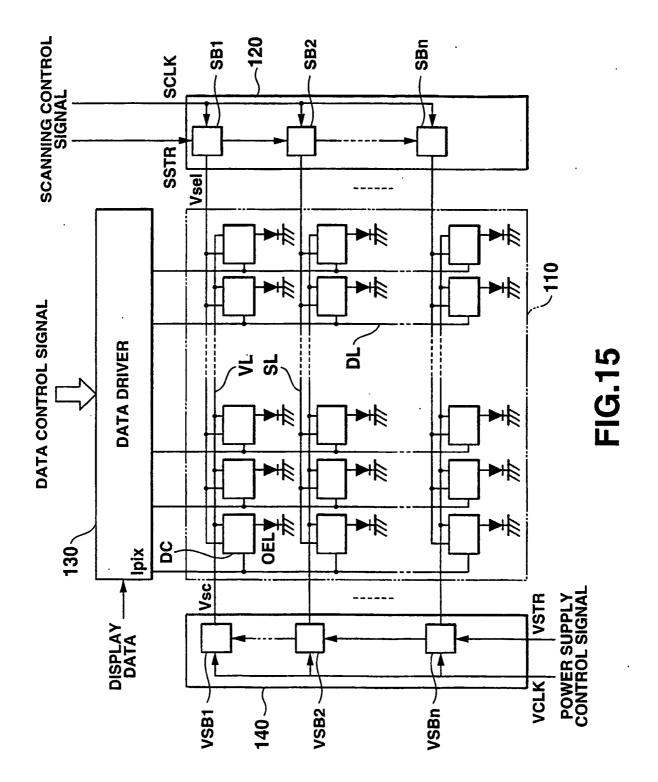

- FIG. 15 is a block diagram showing a primary structure of a data driver, a scanning driver and a display panel applied to the display apparatus according to the embodiment;

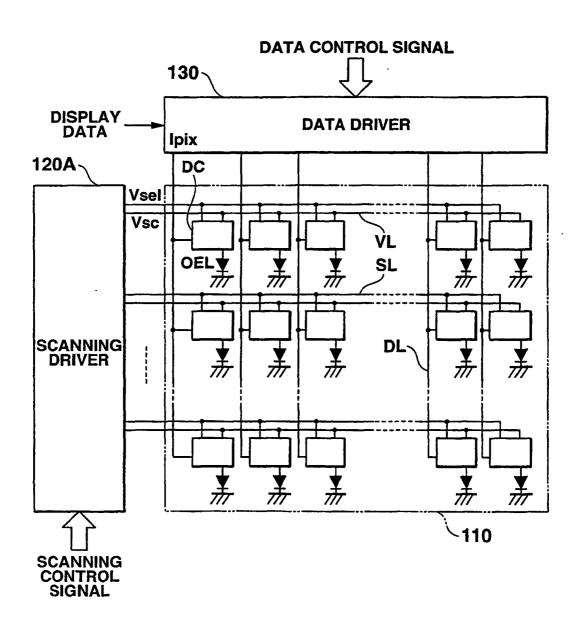

- FIG. 16 is a schematic structural view showing another example of a scanning driver applied to the display apparatus according to the present invention;

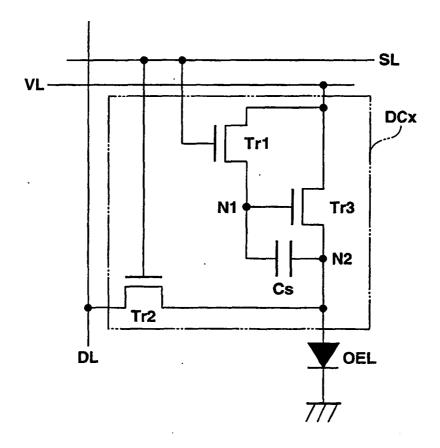

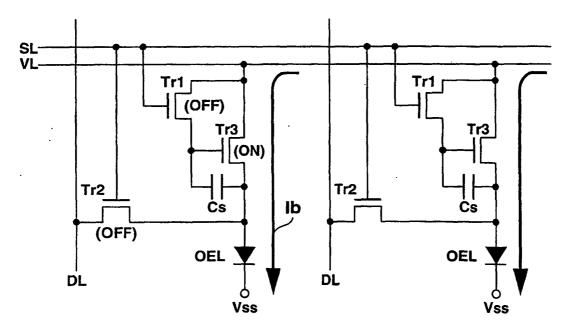

- FIG. 17 is a circuit configuration view showing an example of a basic structure of a pixel drive circuit applicable to the display apparatus according to the present invention;

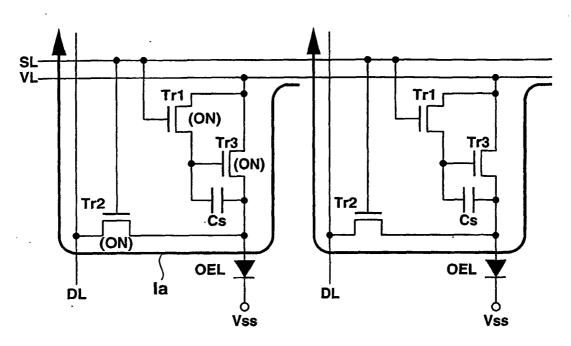

- FIGS. 18A and 18B are conceptual views respectively showing a basic operation in the pixel drive circuit applicable to the embodiment;

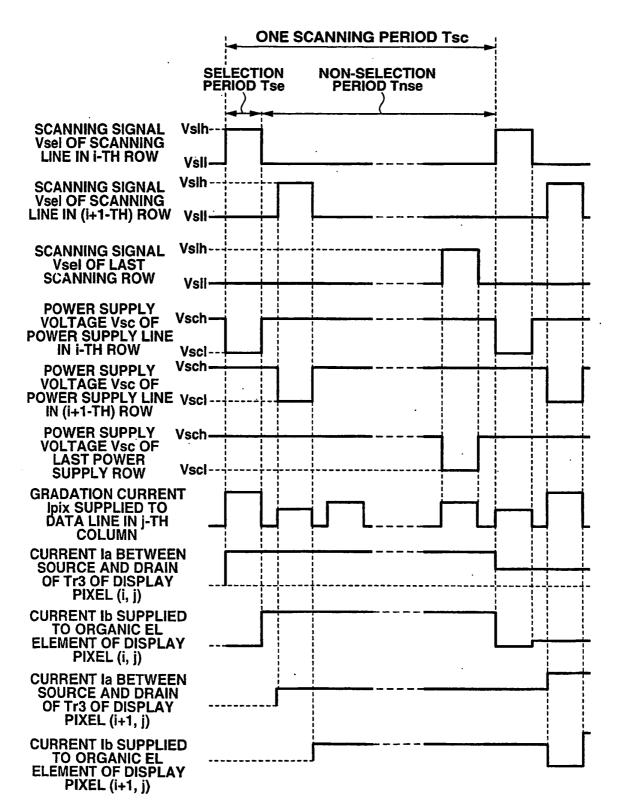

- FIG. 19 is a timing chart showing a display timing of image information in the display apparatus according to the embodiment; and

- FIG. 20 is a schematic block diagram showing a primary structure of still another example of the display apparatus according to the present invention.

- [0027] A current drive apparatus, a drive method thereof, and a display apparatus to which the current drive apparatus is applied according to the present invention will now be described based on illustrated embodiments.

- [0028] First, a current drive apparatus and a drive method thereof will be described with reference to the accompanying drawings.

- 45 <First Embodiment of Current Drive Apparatus>

10

20

30

35

- [0029] FIG. 1 is a primary structural view showing a first embodiment of a current drive apparatus according to the present invention.

- [0030] The current drive apparatus according to the first embodiment has a structure to sequentially hold a current with a predetermined current value supplied from a single current generation circuit in a current storage circuit provided in accordance with each output terminal and thereafter simultaneously output the currents to loads (display elements) through each of the output terminals.

- [0031] As shown in FIG. 1, the current drive apparatus according to this embodiment comprises: a single current generation circuit 10A which generates and outputs an operating current lc having a predetermined current value used to control a drive stage of each load LD (display element) connected to each of a plurality of output terminals Tout; a shift register 20A which sets a timing when supplying the operating current lc supplied from the current generation circuit 10A to each of later-described current storage circuits 30A; a plurality of current storage circuits 30A which are provided in accordance with output terminals Tout, sequentially fetch and hold (store) the operating current lc supplied from the

current generation circuit 10A with a predetermined timing based on the shift register 20A; and a plurality of switch circuits 40A which control a supply state of the operating current Ic from the current generation circuit 10A to each of the current storage circuits 30A based on a timing set by a switch changeover signal (shift output) SR outputted from the shift register 20A with a predetermined timing. In FIG. 1, although the loads LD (display elements) are illustrated in a case that they are applied in a simple matrix type display panel, they are not restricted thereto, and they can be applied to an active matrix type display panel including such a pixel drive circuit as shown in FIG. 17.

[0032] Each of the above structures will now be concretely described hereinafter.

(Current Generation Circuit)

10

20

30

35

40

45

50

55

[0033] FIG. 2 is a circuit structural view showing a concrete example of the current generation circuit applicable to this embodiment.

**[0034]** The current generation circuit 10A substantially generates each operating current Ic having a current value required to drive each of a plurality of the loads in a predetermined drive state, and outputs it to individual current storage circuits 30A provided so as to correspond to each of a plurality of the loads. The current generation circuit 10A is constituted by, e.g., a control current generation circuit 11 on a front stage and an output current generation circuit 12 on a rear stage, as shown in FIG. 2.

**[0035]** The operating currents Ic generated by the current generation circuit 10A may have current values different from each other in accordance with a drive stage of each load, or may have the same current value with respect to all the loads. The detail will be described later.

**[0036]** The current generation circuit illustrated in this embodiment is just an example applicable to the current drive apparatus according to the present invention, and it is not restricted to this circuit configuration. In this embodiment, as the current generation circuit, a structure comprising the control current generation circuit 11 and the current mirror circuit portion 12 is illustrated, but it is not restricted thereto. For example, it may have a circuit configuration consisting of only the control current generation circuit.

[0037] As shown in FIG. 2, in the control current generation circuit 11, as a unit circuit (bit current generation circuit) CT1 having a circuit configuration comprising: a resistance R11 having one end side connected to a high-potential power supply Vdd; a pnp type bipolar transistor (which will be referred to as a "pnp transistor" hereinafter) Q11 having an emitter connected to the other end side of the resistance R11 and a collector connected to an output junction N11 of the control current generation circuit 11 connected to the output current generation circuit 12 on the rear stage; and a P-channel field effect type transistor (which will be referred to as a "PMOS transistor" hereinafter) M11 having a source connected to a base of the pnp transistor Q11, a drain connected to a set terminal Tset to which a set signal SET is inputted and a gate connected to an input terminal Tin to which a digital input signal IN1 is inputted. The unit circuits are connected in parallel for the number of bits of the digital input signals (in this embodiment, description will be given as to a case that unit circuits CT1 to CT6 corresponding to digital input signals IN1 to IN6 of six bits are provided). That is, emitters of the pnp transistors Q11 to Q16 of the respective unit circuits CT1 to CT6 are connected to the output junction N11 in common, and there are provided the PMOS transistors M11 to M16 having sources connected to the bases of the pnp transistors Q11 to Q16, drains connected to the set terminal Tset and gates connected to input terminals Tin to which the digital input signals IN1 to IN6 are inputted.

[0038] Here, the input signals IN1 to IN6 are digital signals (voltage components) consisting of a plurality of bits used to control a drive state of each load, and the set signal SET is a signal voltage which is supplied from a non-illustrated control portion with a timing according to a drive cycle and the like of the loads. Such a control current generation circuit 11 generates control currents having current values corresponding to current values of the input signals IN1 to IN6 by setting the set signal SET to a predetermined voltage level and setting the input signals IN1 to IN6 having the respective bits to a high level or a low level, and outputs the control currents to the output current generation circuit 12 on the rear stage through the output junction N11.

[0039] For example, as shown in FIG. 2, the output current generation circuit 12 is constituted by a current mirror circuit, and comprises: an npn type bipolar transistor (which will be referred to as an "npn transistor" hereinafter) Q21 having a collector and a base connected to the output junction N11 of the control current generation circuit 11; a resistance R21 connected between an emitter of the npn transistor Q21 and a low-potential power supply Vss; an npn transistor Q22 having a collector connected to an output terminal Tcs where an output current (operating current) Ic having a predetermined current component is outputted and a base connected to the output junction N11 of the control current generation circuit 11; and a resistance R22 connected between an emitter of the npn transistor Q22 and the low-potential power supply Vss.

**[0040]** Here, the output current lc is generated by the control current generation circuit 11, and has a current value according to a predetermined current ratio stipulated by the current mirror circuit structure with respect to a current value of the control current inputted through the output junction N11. In this embodiment, by supplying the output current having the negative polarity to the current storage circuit 30A (namely, by setting the current flow direction of the output

current Ic in a direction of the low-potential power supply Vss from the output terminal Tcs side), the current component flows down so as to be pulled in a direction of the current generation circuit 10A from the current storage circuit 30A side. **[0041]** In the current generation circuit 10A illustrated in this embodiment, the current value of the control current generated by the control current generation circuit 11 is set larger than the current value of the output current generated by the current mirror circuit portion 12. The current value of the control value is reduced by the current mirror circuit portion 12 with a predetermined ratio in order to stipulate the current value of the output current (that is, the current value processed in the control signal generation circuit 11 is set larger than the current value of the output current Ic). Therefore, it is possible to improve a processing speed concerning conversion and generation to the output current Ic from the input signals IN1 to IN6 in the control signal generation circuit 11 of the current generation circuit 10A.

**[0042]** Further, in the circuit configuration shown in FIG. 2, it is also possible to employ the circuit configuration which stipulates the current ratio by using only an area ratio of the npn transistors Q21 and Q22 in place of resistances R21 and R22 which are connected to the emitters of the npn transistors Q21 and Q22 constituting the current mirror circuit portion 12, i.e., by eliminating the resistances R21 and R22. As a result, it is possible to suppress occurrence of irregularities in the current component within the circuit caused due to the resistances R21 and R22, thereby greatly restraining the influence to the output current Ic.

(Shift Register)

15

20

25

30

35

40

45

50

55

**[0043]** The shift register 20a shown in FIG. 1 sequentially applies a shift output generated based on control signals (a shift start signal, a shift clock signal and others) supplied from a non-illustrated control portion while sequentially shifting in one direction to each of the switch circuits 40A provided in accordance with the respective loads as a switch changeover signal (switch-on signal) SR.

(Switch Circuit)

[0044] The switch circuits 40A shown in FIG. 1 perform the on operation with different timings based on the switch changeover signals SR sequentially supplied from the shift register 20A, set the output current (operating current) Ic from the current generation circuit 10A in the write state to supply it to the current storage circuits 30A provided in accordance with the respective loads, and control in such a manner that the output current Ic can be fetched and held in each current storage circuit 30A. Here, as the switch circuit 40A, for example, a field effective type transistor can be applied. In this case, the switch circuits 40A can be formed on the same substrate by using the same manufacturing process as that of the circuit element applied to the later-described current storage circuits 30A. The detail will be described with reference to FIG. 3.

(Current Storage Circuit)

**[0045]** FIG. 3 is a circuit configuration view showing a concrete example of a structure of a current storage circuit and a switch circuit applicable to this embodiment, and FIGS. 4A and 4B are conceptual views showing a basic operation in the current storage circuit applicable to this embodiment.

**[0046]** The current storage circuit 30A substantially sequentially fetches the operating current Ic outputted from the current generation circuit 10A with a predetermined timing based on the shift register 20A, holds a voltage component corresponding to this current, and simultaneously outputs a drive current based on the held voltage component to each load through each output terminal Tout. As shown in FIG. 3, this current storage circuit 30A can comprise, e.g., a voltage component holding portion 31 (including the switch circuit 40A) on a front stage and a drive current generation portion 32 constructed by a current mirror circuit on a rear stage.

**[0047]** The current storage circuit illustrated in this embodiment is just an example applicable to the current drive apparatus according to the present invention, and it is not restricted to this circuit configuration. Furthermore, in this embodiment, as the current storage circuit, although a structure including the drive current generation portion having the voltage.component holding and the current mirror circuit is illustrated, the current storage circuit is not restricted thereto, and it may have a circuit configuration having, e.g., only the voltage component holding.

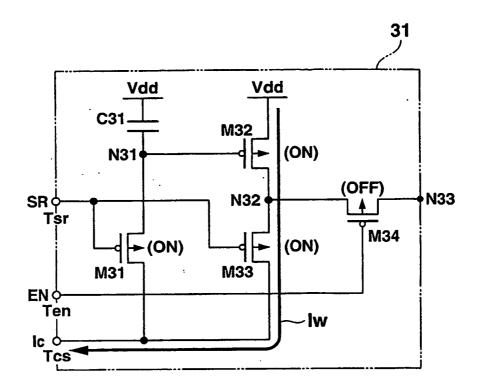

[0048] For example, as shown in FIG. 3, the voltage component holding portion 31 comprises: a PMOS transistor M31 having a source connected to a junction N31, a drain connected to an output terminal Tcs of the current generation circuit 10A and a gate connected to a shift output terminal Tsr of the shift register; a PMOS transistor M32 having a source and a drain respectively connected to a high-potential power supply Vdd and a junction N32 and a gate connected to the junction N31; a PMOS transistor M33 having a source and a drain respectively connected to the junction N32 and the output terminal Tcs of the current generation circuit 10A and a gate connected to the shift output terminal Tsr of the shift register 20A; a storage capacitance C31 connected between the high-potential power supply Vdd and the junction N31; and a PMOS transistor M34 having a source and a drain respectively connected and the junction N32 and an

output junction N33 to the drive current generation portion 32 on the rear stage and a gate connected to an output control terminal Ten to which an output enable signal EN which is supplied from a non-illustrated control portion and controls an output state of the control current to the drive current generation portion 32 on the rear stage is inputted.

**[0049]** Here, the PMOS transistors M31 and M33 which perform on/off operation based on the switch changeover signal SR from the shift register 20A constitute the above-described switch circuit 40A.

**[0050]** The storage capacitance C31 provided between the high-potential power supply Vdd and the junction N31 may be a parasitic capacitance between the gate and the source of the PMOS transistor M32.

[0051] For example, as shown in FIG. 3, the above-described drive current generation portion 32 comprises: npn transistors Q31 and Q32 constituted by the current mirror circuit, each of which has a collector and a base connected to an output junction N33 of the voltage component holding 31 and an emitter connected to a junction N34; a resistance R31 connected between the junction N34 and a low-potential power supply Vss; an npn transistor Q33 having a collector connected to an output terminal Tout from which an output current (drive current ldv) is outputted and a base connected to the output junction N33 of the voltage component holding 31; and a resistance R32 connected between the emitter of the npn transistor Q33 and the low-potential power supply Vss.

[0052] Here, the output current (drive current Idv) has a current value corresponding to a predetermined current ratio stipulated by the current mirror circuit configuration with respect to a current value of the control current outputted from the voltage component holding portion 31 and inputted through the output junction N33. In this embodiment, by supply the output current having the negative polarity to the output terminal Tout (load LD) (that is, by setting the current flow direction of the drive current Idv to a direction of the low-potential power supply Vss from the output terminal Tout side), the current component flows down so as to be pulled in the direction of the current storage circuit 30A from the load LD side. [0053] In the current storage circuit 30A illustrated in this embodiment, a current value of the control current outputted from the voltage component holding portion 31 is set larger than a current value of the output current generated by the current mirror circuit of the drive current generation portion 32. The current value of the control current is reduced by the current mirror circuit with a predetermined ratio in order to stipulate the current value of the output current. That is, by setting the current value processed inside the voltage component holding 31 larger than the current value of the drive current Idv, it is possible to increase a processing speed concerning the fetch holding (storage) and the output operation of the operating current Ic in the voltage component holding 31 of the current storage circuit 30A.

[0054] In the circuit configuration shown in FIG. 3, by applying a circuit configuration which stipulates the current ratio by using only an area ratio of the npn transistors Q31 to Q33 in place of the resistors R31 and R32 which are connected to the emitters of the npn transistors Q31 to Q33 constituting the current mirror circuit of the drive current generation circuit 32 and stipulate the current ratio in the current mirror circuit configuration, i.e., by eliminating the resistances R31 and R32, it is possible to suppress occurrence of irregularities in the current components within the circuit caused to due to the resistances R31 and R32, and irregularities in the output current (drive current Idv) can be greatly restrained. [0055] As to the basic operation in the current storage circuit (including the switch circuit) having such a structure, the current storage operation and the current output operation are executed with respect to the drive cycle of the load with a predetermined timing by which overlap in time is not generated. Each operation will now be described hereinafter.

(Current Storage Operation)

20

30

35

40

45

50

55

[0056] In the current storage operation, as shown in FIG. 4A, the PMOS transistor M34 as the output control circuit performs the off operation by applying a high-level output enable signal EN from the control portion through the output control terminal Ten. In this state, the operating currents Ic having the current component with negative polarity corresponding to the input signals IN1 to IN6 used to control the drive states of the loads are supplied from the current generation circuit 10A through the input terminal Tcs (output terminal Tcs of the current generation circuit 10A), and the low-level switch changeover signal SR is applied with a predetermined timing from the shift register 20A through the shift output terminal Tsr. As a result, the PMOS transistors M31 and M33 as the input control circuits (switch circuits 40A) perform the on operation.

[0057] Consequently, the voltage level as the low level corresponding to the operating currents Ic with the negative polarity is applied to the junction N31 (namely, the gate terminal of the PMOS transistor M32 and one end of the storage capacitance C31), and a potential difference is generated between the high-potential power supply Vdd and the junction N31 (between the gate and the source of the PMOS transistor M32). As a result, the PMOS transistor M32 carries out the on operation, a write current Iw equivalent to the operating current Ic flows down so as to be pulled in a direction of the input terminal Tcs through the PMOS transistors M32 and M33 from the high-potential power supply.

**[0058]** At this moment, the electric charges corresponding to the potential difference generated between the high-potential power supply Vdd and the junction N31, i.e., between the gate and the source of the PMOS transistor M32 are stored in the storage capacitance C31, and the electric charges are held as a voltage component corresponding to the operating current Ic. Here, to the electric charges stored in the storage capacitance C31 are held even after pulling of the write current Iw is stopped by applying the high-level switch changeover signal SR from the shift register 20A through

the shift output terminal Tsr upon completion of the current storage operation to the PMOS transistors M31 and M33 which perform the off operation.

(Current Output Operation)

5

30

35

40

45

50

55

[0059] Subsequently, in the load drive operation after termination of the current storage operation, as shown in FIG. 4B, the PMOS transistor M34 performs the on operation by applying the output enable signal EN on the low level from the control portion through the output control terminal Ten. At this moment, since the potential difference equivalent to that in the current storage operation is generated between the gate and the source of the PMOS transistor M32 by the voltage component held in the storage capacitance C31, a drive control current lac having a current value equivalent to that of the write current lw (= the operating current lc) flows down in a direction of the output junction N33 (current mirror circuit portion 32) from the high-potential power supply through the PMOS transistors M32 and M34.

**[0060]** As a result, the drive control current lac inputted to the current mirror circuit portion 32 is converted into a drive current ldv having a current value corresponding to a predetermined current ratio stipulated by the current mirror circuit configuration, and supplied to each load LD through each output terminal Tout. Here, to the drive current ldv supplied from each current storage circuit 30A to each load LD is applied the high-level output enable signal EN from the control portion through the output control terminal Ten upon completion of the current output operation, and supply is stopped when the PMOS transistor M34 carries out the off operation.

20 (Drive Method of Current Drive Apparatus)

[0061] In the current drive apparatus having the above-described structure, in a current write period, the operating current Ic having a predetermined current value according to the drive state of each load is sequentially generated and outputted by the single current generation circuit 10A, and the switch changeover signal SR sequentially outputted from the shift register 20A is sequentially applied to the switch circuits 40A provided in accordance with the respective output terminals Tout in synchronization with the output timing of the operating current Ic. As a result, the switch circuits 40A sequentially perform the on operation with different timings synchronized with the output timing of the operating current Ic. The write current Iw corresponding to the operating current Ic outputted from the current generation circuit 10A sequentially flows down and is written in the current storage circuits 30A, and held as the voltage component (the above-described current storage operation). Sequentially, in the current output period, output of the switch changeover signal SR from the shift register 20A in the current write period is terminated, all the switch circuits 40A perform the off operation, and the operating current Ic according to the drive states of the loads is held in all the current storage circuits 30A. Thereafter, the output enable signal EN is applied to the respective current storage circuits 30A from the control portion in common with the same timing. As a result, the currents according to the voltage component held in the current storage circuits 30A are simultaneously supplied as the drive currents Idv to the loads through the output terminals Tout (the above-described current output operation).

**[0062]** By repeatedly setting such a current write period and current output period in accordance with a predetermined operating cycle, the loads can be caused to operate with a predetermined drive cycle.

[0063] Therefore, according to the current drive apparatus of this embodiment, the current storage circuits are individually provided to the single current generation circuit so as to correspond to a plurality of the output terminals, the current having a predetermined current value concerning the drive control over the loads is generated by the current generation circuit, and this current is sequentially stored in each current storage circuit with a predetermined timing. Then, the operating current supplied from the single current generation circuits can be held in accordance with respective output terminals by outputting the currents to the respective loads from the respective current storage circuits through the respective output terminals at the same time, and the drive current for each output terminal can be set based on the operating current. Therefore, the drive currents in which irregularities between the respective output terminals are suppressed can be supplied, thereby driving the respective loads with the uniform operating characteristic.

**[0064]** The element structure of the bipolar transistor or the MOS transistor applied to the current drive apparatus illustrated in this embodiment is not restricted, and it may be appropriately subjected to design change in accordance with the element characteristic, a manufacturing technique, a product cost and others.

**[0065]** Specifically, by sequentially repeating in accordance with each row the operation to supply the light emitting drive currents (drive currents) which have the uniform current characteristic and correspond to each display data from the individual current storage circuits to the light emitting elements (loads) each provided in accordance with each of the display pixels constituting the later-described display panel (see FIG. 15), it is possible to write the display data for one screen of the display panel into each display pixel and causes the light emitting operation with a predetermined brightness gradation, thereby enabling excellent display of desired image information while suppressing generation of display irregularities.

[0066] Here, the element structure of the bipolar transistor or the MOS transistor constituting the current storage circuit

according to this embodiment is not particularly restricted, and it may be appropriately subjected to design change in accordance with the element characteristic, the product technique, the product cost and others. In particular, in the MOS transistor constituting the voltage component holding element, in order to obtain necessary operating speed, preferably, as described below, it is possible to excellently apply a transistor having the mobility  $\mu e$  of the MOS transistor being approximately 200 cm<sup>2</sup>/Vs or a larger value.

[0067] FIG. 5A shows an equivalent circuit of a structure when the electric charges are stored in the capacitance between the gate and the source of the transistor, and FIG. 5B is a graph showing an aged change in voltage of the capacitance when the electric charges are stored in the capacitance between the gate and the source of the transistor. [0068] FIG. 5A corresponds to an equivalent circuit when predetermined electric charges are stored in the storage capacitance C31 in the voltage component holding portion 31 of the current storage circuit shown in FIG. 3, and corresponds to a case that the PMOS transistors M32 and M33 are ON and in the conductive state and the PMOS transistor M34 is OFF and in the open state. Here, the transistor M corresponds to the PMOS transistor M32, and the capacitance C corresponds to the storage capacitance C31 which is a sum total of a wiring capacitance, a storage capacitance and a gate capacitance of the transistor M. For the brief explanation, it is determined that the source S of the transistor M and one end of the capacitance C are set to a ground potential. FIG. 5B corresponds to a change of a time t relative to a drain voltage V(t) of the transistor M32, i.e., the voltage of the capacitance C31.

**[0069]** Here, as shown in FIG. 5A, when a current lin is supplied to a drain D of the transistor M from a constant current source, assuming that V(t) is a drain voltage and Id is a drain current of the transistor M, the drain current Id can be represented by the following expression (1).

$$Id = A*V(t)^2 \qquad \dots (1)$$

wherein A = (1/2)\*Cin\* $\mu$ e\*(W/L), Cin is a gate capacitance per unit area of the transistor M,  $\mu$ e is the mobility of the transistor M, W is a channel width of the transistor M, and L is a channel length. Based on this, a differential equation of the following expression (2) can be established.

$$C*dV(t)/dt + AV(t)^2 = Iin ... (2)$$

20

25

35

40

45

50

55

wherein the capacitance C is a sum total of the wiring capacitance, the storage capacitance, and the gate capacitance of the transistor M as described above. A change of the time t relative to the drain voltage V(t) of the transistor M, i.e., the voltage of the capacitance C obtained by solving the above expression is substantially as shown in FIG. 5B. Here,  $\tau$  is a time constant, and it can be represented by the following expression (3) if the gate capacitance in the capacitance C is larger than any other capacitance. Further, with the time  $t=3\tau$ , the voltage V(t) reaches a value which is 99.5% of a saturation voltage V(s).

$$\tau = C/\sqrt{A*Iin} \qquad ... (3)$$

That is, the time constant  $\tau$  is in proportion to a value of the capacitance C and in inverse proportion to the 1/2-th power of the mobility  $\mu e$ .

[0070] Here, assuming that a polysilicon TFT is used as the transistor M, the capacitance C is 6 pF, W/L is 100  $\mu$ m/ 30  $\mu$ m, the mobility  $\mu$ e is 70 m²/Vs, a film thickness of a gate insulating film is 105 nm and an application current lin is 10  $\mu$ A, a time constant  $\tau$  becomes 1.42  $\mu$ sec. Therefore, when the number of the scanning lines in the display panel to be driven is set to as 120, a selection period per scanning line is approximately 139  $\mu$ sec and the number of the data lines in which data can be written within this time is approximately 32.

[0071] In relation to this, when the mobility  $\mu e$  of the transistor M is 245 m²/Vs under the above-described condition, the time constant  $\tau$  is approximately 0.096  $\mu sec$ . As a result, the number of the data lines in which data can be written within the selection period per scanning line in the display panel is approximately 482, and a 1/4 VGA panel having the 120 scanning lines and the 160 ( $\times$  RGB) data lines can be driven.

**[0072]** Alternatively, if the capacitance C is 0.51 pF even though the mobility  $\mu e$  remains as 70 m<sup>2</sup>/Vs, the time constant  $\tau$  likewise becomes approximately 0.096  $\mu sec$ , and the 1/4 VGA panel can be driven like the above.

[0073] That is, in order to drive at least the 1/4 VGA panel, the mobility  $\mu e$  of the transistor M must have a value of approximately 200 cm<sup>2</sup>/Vs or a larger value, or the capacitance C must have a value smaller than approximately 0.5 pF.

[0074] As described above, since the time constant  $\tau$  is in proportion to a value of the capacitance C and in inverse proportion to the 1/2-th power of the mobility  $\mu e$  of the transistor, the time constant  $\tau$  can be further decreased when the capacitance C is further reduced or the mobility  $\mu e$  is further increased, thereby driving the higher-definition display panel. [0075] Although the structure of the transistor realizing the mobility or the capacitance value is not particularly restricted, for example, a polysilicon MOS transistor having a continuous grain boundary formed on an insulating substrate or an MOS transistor formed on a monocrystal silicon substrate can satisfy the above conditions, and it can be preferably used.

<Second Embodiment of Current Drive Apparatus>

20

30

35

40

45

50

55

**[0076]** FIG. 6 is a primary structural view showing a second embodiment of a current drive apparatus according to the present invention. Here, the same or equivalent reference numerals denote structures equivalent to those in the above-described first embodiment, thereby simplifying or eliminating their explanation.

[0077] The current drive apparatus according to the second embodiment includes a pair of current storage sections in accordance with an output terminal to which a load is connected, and is constituted to execute in parallel an operation to sequentially fetch a current having a predetermined current value supplied from a single current generation circuit by the current storage section on one side and hold a corresponding voltage component and operation to simultaneously output the current based on the voltage component which has been already held in the current storage section on the other side through the output terminal.

[0078] As shown in FIG. 6, the current drive apparatus according to this embodiment comprises: a single current generation circuit 10B which sequentially generates and outputs an operating current Ic having a predetermined value according to a drive stage of the load; a plurality of current storage circuits 30B each including a pair of current storage sections 31a and 31b which are provided as a pair in accordance with each output terminal Tout in parallel, alternately (selectively) fetch the operating current Ic supplied from the current generation circuit 10B with individual timings and hold a corresponding voltage component; a shift register 20B (shift register sections 21a and 21b) which is provided as a pair in accordance with the current storage sections 31a and 31b constituting the current storage circuit 30B and sets a timing when supplying the operating current Ic fed from the current generation circuit 10B to each of the current storage sections 31a and 31b; a plurality of input side switch circuits 40B having switches 41a and 41b which are provided as a pair in accordance with the current storage sections 31a and 31b constituting the current storage circuit 30B and control a supply state of the operating current Ic from the current generation circuit 10B to each current storage circuit 30B based on individual timings set by the respective shift register sections 21a and 21b; and a plurality of output side switch circuits 50B each of which is provided in accordance with each output terminal Tout, selects any of the current storage sections 31a and 31b based on a predetermined output selection signal SEL and controls an output stage of the current held in the current storage sections 31a and 31b to each output terminal Tout.

**[0079]** It is determined that the current generation circuit 10B, the shift register 20B (shift register sections 21a and 21b), the current storage circuit 30B (current storage sections 31a and 32b) and the input side switch circuit 40B (switches 41a and 41b) have the structures equivalent to those in the above-described first embodiment, thereby eliminating the detailed explanation.

**[0080]** Here, the first shift register section 21a sequentially outputs a shift output as a switch changeover signal SR1 with a predetermined timing to the first switch 41a provided in accordance with the first current storage section 31a in the current storage circuit 30B provided in accordance with each output terminal Tout. On the other hand, the second shift register section 21b sequentially outputs a shift output as a switch changeover signal SR2 with a timing which does not overlap the timing of the shift output from the shift register section 21a in time to the second switch 41b provided in accordance with the second current storage section 31b in the current storage circuit 30B provided in accordance with each output terminal Tout.

**[0081]** Furthermore, the output side switch circuit 50B is synchronized with the output timings of the switch changeover signals SR1 and SR2 from the shift register sections 21a and 21b based on an output selection signal SEL outputted from a non-illustrated control portion, and operates so as to select the current storage section (non-selected current storage section side) of the switch which is not performing the on operation in the input side switch circuit 40B.

[0082] In the current drive apparatus having such a structure, in a first operation period (a current write period on the first current storage section 31a side/a current output period on the second current storage section 31b side), when the switch changeover signal SR1 from the first shift register section 21a is sequentially outputted to each switch 41a provided in accordance with the current storage section 31a of each current storage circuit 30B, each switch 41a sequentially effects the on operation only in a predetermined period, and electric charges corresponding to an operating current Ic supplied from the current generation circuit 10B are sequentially written in each current storage section 31a as a voltage component. At this moment, the switch changeover signal SR2 is not outputted from the second shift register section 21b, and all the switches 41b are in the off state.

**[0083]** Moreover, at this moment, the output selection signal SEL which changes over and sets the output side switch circuit 50B provided in accordance with each output terminal Tout to the current storage section 31b side is outputted

in common, and an output enable signal EN2 is outputted to all the current storage sections 31b with a predetermined timing in common. As a result, a current based on the electric charges which have been already held in each current storage section 31b is simultaneously outputted as a drive current ldv to each load through each output terminal Tout with the same timing.

[0084] Subsequently, in a second operation period (a current output period on the first current storage section 31a side/a current write period on the second current storage section 31b side) set after termination of the fist operation period, when the switch changeover signal SR2 from the second shift register section 21b is sequentially outputted to each switch 41b provided in accordance with the current storage section 31b of each current storage circuit 30B, each switch 41b sequentially performs the on operation only in a predetermined period, and electric charges corresponding to the operating current Ic supplied from the current generation circuit 10B are sequentially written in each current storage section 31b as a voltage component. At this moment, the switch changeover signal SR1 is not outputted from the shift register section 21a, and all the switches 41a are in the off state.

[0085] Additionally, at this moment, the output selection signal SEL used to change over and set the output side switch circuit 50B to the current storage section 31a side is outputted from the control portion in common, and the output enable signal EN1 is outputted to all the current storage sections 31a with a predetermined timing in common. As a result, a current based on the electric charges held in each current storage section 31a in the first operation period is simultaneously outputted as the drive current Idv to each load through each output terminal Tout with the same timing.

**[0086]** By controlling such a first and second operation period so as to be repeated in accordance with a predetermined operation cycle, the operation to hold the electric charges corresponding to the operating current Ic outputted from the current generation circuit 10B in one of a pair of the current storage sections 31a and 31b, and the operation to output the current based on the electric charges held in the other current storage section as the drive current Idv are alternately executed in parallel.

[0087] Therefore, according to the current drive apparatus of this embodiment, like the above-described first embodiment, the operating current outputted from the single current generation circuit is sequentially fetched and held in each current storage circuit (current storage section), and outputted with a predetermined timing at the same time. As a result, the current with the uniform current characteristic supplied from the single current source can be held in accordance with each output terminal, and irregularities in the drive current between the respective output terminals can be suppressed. Further, a pair of the current storage sections are provided in accordance with each output terminal, and the operation to sequentially write the electric charges corresponding to the current outputted from the current generation circuit on one current storage section side and the operation to simultaneously output the current based on the electric charges held on the other current storage section side are executed in parallel. As a result, the waiting time for the current write operation to the current storage section can be reduced or eliminated, the supply time of the drive current to each load can be extended, and the drive state of each load can be finely controlled. Furthermore, the time to fetch the operating current into each current storage section and hold it can be prolonged, thereby stably carrying out the holding operation in the current storage section.

<Third Embodiment of Current Drive Apparatus>

20

30

35

40

45

50

55

**[0088]** FIG. 7 is a primary structural view showing a third embodiment of a current drive apparatus according to the present invention. Here, the same or equivalent reference numerals denote the structures equivalent to those in the first and second embodiments, thereby simplifying or eliminating their explanation.

**[0089]** The current drive apparatus according to the third embodiment has current storage sections on two stages provided in series in accordance with each output terminal to which a load is connected, and is constituted so as to execute an operation to sequentially hold a current having a predetermined current value supplied from a single current generation circuit by the current storage section on the front stage and an operation to hold the current supplied from the current storage section on the front stage by the current storage section on the rear stage and then collectively outputs it through the output terminal.

[0090] As shown in FIG. 7, the current drive apparatus according to this embodiment comprises: a single current generation circuit 10C which sequentially generates and outputs an operating current Ic having a predetermined current value according to a drive state of the load; a plurality of current storage circuits 30C each including a current storage section 32a on a front stage and a current storage section 32b on a rear stage provided in series in accordance with each output terminal Tout; a shift register 20C which sets a timing when supplying the operating current Ic fed from the current generation circuit 10C to the current storage section 32a on the front stage; and switch circuits 40C each of which controls a supply state of the operating current Ic from the current generation circuit 10C to each current storage circuit 30C. It is to be noted that the current generation circuit 10C, the shift register 20C, the current storage circuit 30C (current storage sections 32a and 32b) and the switch circuit 40C applied to this embodiment have the structures equivalent to, e.g., those in the above-described first embodiment, thereby eliminating their detailed explanation.

[0091] In each current storage circuit 30C, the operating current Ic supplied from the current generation circuit 10B is

fetched into the current storage section 32a with a predetermined timing, a corresponding voltage component is held, and a current based on the held voltage component is supplied to the current storage section 32b on the rear stage with a predetermined timing based on a first output enable signal EN1 fed from a non-illustrated control portion or circuit. At this moment, the current storage section 32b on the rear stage fetches the current fed from the current storage section 32a on the front stage, holds a corresponding voltage component, and outputs a current based on the held voltage component through the output terminal Tout based on a second enable signal EN2 fed from the control portion.

**[0092]** In the current drive apparatus having such a structure, in a first operation period, a switch changeover signal SR from the shift register 20C is sequentially outputted to the switch circuit 40C provided in accordance with each current storage circuit 30C. As a result, the switch circuit 40C sequentially performs the on operation only in a predetermined period, and electric charges (voltage component) corresponding to an operating current Ic supplied from the current generation circuit 10C is sequentially written in the current storage section 32a on the front stage.

**[0093]** Furthermore, at this moment, when the second output enable signal EN2 is outputted from the control portion to all the current storage sections 32b on the rear stages in common with a predetermined timing, a current based on the electric charges which have been already held in each current storage section 32b is simultaneously outputted as a drive current Idv to each load through each output terminal Tout with the same timing.

**[0094]** Then, with a predetermined timing after completion of the first operation period, the first output enable signal EN1 is outputted from the control portion to all the current storage sections 32a on the front stage in common. As a result, the current held in each current storage section 32a in the first operation period is collectively supplied to the current storage section 32b on the rear stage and held (supply operation period).

[0095] Subsequently, in a second operation period set after completion of the supply operation of the current to the rear stage in the current storage circuit 30C, like the above-described first operation period, the switch changeover signal SR from the shift register 20C is again sequentially outputted to each switch circuit 40C. Consequently, the operating current Ic supplied from the current generation circuit 10C is sequentially written in the current storage section 32a on the front stage and, at this moment, the second output enable signal EN2 is outputted to the current storage section 32b on the rear stage in common with a predetermined timing. As a result, the current supplied from and held in each current storage section 32b is simultaneously outputted to each load as the drive current Idv.

**[0096]** By controlling such a series of operation periods so as to be repeated in accordance with a predetermined operation cycle, the operation to hold the electric charges corresponding to the operating current Ic outputted from the current generation circuit 10C in the current storage section 32a on the front stage, and the operation to output the current based on the current fed from the current storage section 32a on the front stage and supplied therefrom, from the current storage section 32b on the rear stage as the drive current Idv are executed in parallel.

[0097] Therefore, according to the current drive apparatus of this embodiment, like the above-described first embodiment, since the drive current of each output terminal is set based on the operating current fed from the single current generation circuit, irregularities in the drive current between the respective output terminals can be suppressed. Moreover, like the above-described second embodiment, the supply time of the drive current to each load can be prolonged, and the drive state of each load can be finely controlled. Additionally, the time to fetch the current into each current storage section and hold it can be extended, thereby stably executing the holding operation in the current storage section.

<Fourth Embodiment of Current Drive Apparatus>

20

30

35

40

45

50

55

**[0098]** FIG. 8 is a primary structural view showing a fourth embodiment of a current drive apparatus according to the present invention. Here, the same or equivalent reference numerals denote structures equivalent to those in the first to third embodiments mentioned above, thereby simplifying or eliminating their explanation.

[0099] In the structure described in conjunction with the first to third embodiments mentioned above, the current drive apparatus according to the fourth embodiment determines as one group a structure including the predetermined number of output terminals, current storage circuits provided in accordance with the output terminals, a shift register and switch circuits, forms each group on an individual semiconductor chip, provides a single current generation circuit with respect to each group (semiconductor chip), and supplies a current having a predetermined current value in common. It is to be noted that, in the following concrete example, although description will be given as to the case where the present invention is applied to the structure explained in conjunction with the second embodiment, but it can be similarly applied to any other embodiment

**[0100]** As shown in FIG. 8, the current drive apparatus according to this embodiment comprises: a predetermined number of output terminals Tout equivalent to, e.g., the structure described in conjunction with the second embodiment (see FIG. 6); a plurality of current storage circuits 30D (current storage sections 33a and 33b) provided in accordance with the output terminals Tout; a shift register 20D (shift register sections 23a and 23b); a plurality of input side switch circuits 40D (switches 43a and 43b); a plurality of semiconductor chips CP1, CP2, ···, CPn on which circuit configurations having a plurality of output side switch circuits 50D are respectively formed; and a single current generation circuit 10D which sequentially generates an operating current Ic having a predetermined current value according to a drive stage

of a load connected to each output terminal Tout with respect to each of the semiconductor chips CP1, CP2, ···, CPn and supplies it in common. Here, the current generation circuit 10D, the shift register 20D (shift register sections 23a and 23b), the current storage circuit 30D (current storage sections 33a and 33b), the current storage circuit 30D (current storage sections 33a and 43b) and the output side switch circuit 40D (switches 43a and 43b) and the output side switch circuit 50D have the structures equivalent to, e.g., those in the second embodiment mentioned above, thereby eliminating their detailed explanation.

**[0101]** Here, the current generation circuit 10D may be formed on a specific semiconductor chip among a plurality of the semiconductor chips CP1, CP2, ··· CPn each having a circuit configuration including the current storage circuit 30D formed thereto. Alternatively, the same circuit may be formed on each of the semiconductor chips CP1, CP2, ··· CPn, and any one of them may be used to cause other semiconductor chips to enter non-operating state or to be bypassed. Further, the current generation circuit 10D may be formed on a semiconductor chip different from a plurality of the semiconductor chips CP1, CP2, ··· CPn.

**[0102]** It is good enough that each of the semiconductor chips CP1, CP2, ··· CPn applied to this embodiment is formed of a semiconductor material such as single crystal silicone, and its material is not restricted in particular.

**[0103]** In the current drive apparatus having such a structure, by executing the operation similar to that of the above-described second embodiment, the operating current Ic outputted from the current generation circuit 10D is supplied to the respective semiconductor chips CP1, CP2, ··· CPn in common, it is sequentially fetched into one of a pair of the current storage sections 33a and 33b in the current storage circuit 30D provided in accordance with each of the semi-conductor chips CP1, CP2, ··· CPn, and a corresponding voltage component is held. Furthermore, a current based on the voltage component held in the other current storage section is simultaneously outputted to the corresponding load through the output terminal Tout of each of the respective semiconductor chips CP1, CP2, ··· CPn. These operations are alternately and continuously executed.

**[0104]** Therefore, according to the current drive apparatus of this embodiment, only the single current generation circuit is provided with respect to semiconductor chips, and individual current circuits are not provided in accordance with the respective semiconductor chips. Accordingly, the circuit configuration formed on each semiconductor chip can be simplified, and the number of terminals can be reduced, thereby achieving minimization of the apparatus scale or decrease in the product cost. Moreover, even if a plurality of semiconductor chips are provided in accordance with the number of the output terminals connected to the loads, since the current having the uniform current characteristic supplied from the single current source can be held in the current storage circuit in each semiconductor chip, irregularities in the drive current between the respective output terminals and between the respective semiconductor chips can be suppressed, thereby driving each load with the uniform operation characteristic.

[0105] Specifically, in the later-described display panel (see FIG. 15), even if the number of display pixels is increased in order to realize the high definition of the display image quality and/or a large screen of the display panel and the data driver is constituted by a plurality of driver chips (semiconductor chips), by sequentially repeating for each row the operation to sequentially supply a predetermined current according to display data outputted from the single current generation circuit to the current storage circuit formed on each driver chip and simultaneously supply the light emitting drive current (drive current) to each light emitting element with a predetermined timing, the display data for one screen of the display panel can be written in each display pixel and the light emitting operation can be performed with a predetermined brightness gradation. Therefore, image information of the high-definition and large-screen size can be excellently display while suppressing occurrence of display irregularities.

<Fifth Embodiment of Current Drive Apparatus>

10

20

30

35

40

45

50

55

**[0106]** FIG. 9 is a primary structural view showing a fifth embodiment of a current drive apparatus according to the present invention. Here, the same or equivalent reference numerals denote structures equivalent to those in the first to fourth embodiments mentioned above, thereby simplifying or eliminating their explanation.