# (12)

# **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

03.10.2012 Bulletin 2012/40

(51) Int Cl.:

G09G 3/32 (2006.01)

(21) Application number: 12174463.5

(22) Date of filing: 12.11.2010

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

**Designated Extension States:**

**BA ME**

(30) Priority: 12.11.2009 CA 2684818

07.12.2009 CA 2687477 17.02.2010 CA 2694086 11.11.2010 US 944477 11.11.2010 US 944488 11.11.2010 US 944491

(62) Document number(s) of the earlier application(s) in accordance with Art. 76 EPC:

10829593.2 / 2 499 633

(71) Applicant: Ignis Innovation Inc.

Waterloo, Ontario N2V 2C5 (CA)

(72) Inventors:

- Chaji, Gholamreza

Waterloo, Ontario N2V 2S3 (CA)

- Nathan, Arokia

Cambridge, Cambridgeshire CB3 0DL (GB)

- Lai, Jackson, Chi Sun Kitchener, Ontario N2G 4Z9 (CA)

- (74) Representative: Grünecker, Kinkeldey, Stockmair & Schwanhäusser Leopoldstrasse 4 80802 München (DE)

### Remarks:

This application was filed on 29-06-2012 as a divisional application to the application mentioned under INID code 62.

# (54) Efficient programming and fast calibration schemes for light-emitting displays and stable current source/sinks for the same

(57) A circuit and driving technique to improve the display resolution of an AMOLED display. Sharing of switch transistors between several sub-pixels in the display leads to improved manufacturing yield by minimizing the number of transistors used. The method also allows for conventional sequential scan driving to be used. A technique to implement a stable and high impedance current sink or source onto a display substrate using a single device is also disclosed. Finally, a technique is disclosed for improving the spatial and/or temporal uniformity of a light-emitting display by providing a faster calibration of reference current sources and reducing the noise effect by improving the dynamic range, despite instability and non-uniformity of the transistor devices.

FIG. 3a

EP 2 506 242 A2

FIG. 3b

40

# Description

### **COPYRIGHT**

[0001] A portion of the disclosure of this patent document contains material which is subject to copyright protection. The copyright owner has no objection to the facsimile reproduction by anyone of the patent disclosure, as it appears in the Patent and Trademark Office patent files or records, but otherwise reserves all copyright rights whatsoever.

## FIELD OF THE PRESENT DISCLOSURE

[0002] The present disclosure generally relates to circuits and methods of driving, calibrating, or programming a display, particularly light emitting displays.

### **BACKGROUND**

[0003] The disclosed technique improves display resolution by reducing the number of transistors in each pixel. The switch transistor is shared between several pixel circuits in several adjacent sub-pixels. A need exists for an improved display resolution and manufacturing yield while at the same time enabling normal sequential scan programming of the display.

[0004] Most backplane technologies offer only one type of thin-film transistor (TFT), either p-type or n-type. Thus, the device-type limitation needs to be overcome to enable integration of more useful circuitry onto the display substrate, which can result in better performance and lower cost. The main circuit blocks for driving amorphous organic light-emitting device (AMOLED) circuits include current sources (or sinks) and voltage-to-current converters.

[0005] For example, p-type devices have been used in conventional current mirror and current sources because the source terminal of at least one TFT is fixed (e.g., connected to VDD). The current output passes through the drain of the TFT, and so any change in the output line will affect the drain voltage only. As a result, the output current will remain constant despite a change in the line voltage, which undesirably leads to high output resistance current sources. On the other hand, if a p-type TFT is used for a current sink, the source of the TFT will be connected to the output line. Thus, any change in the output voltage due to a variation in the output load will affect the gate-source voltage directly. Consequently, the output current will not be constant for different loads. To overcome this problem, a circuit design technique is needed to control the effect of source voltage variability on the output current.

[0006] A need also exists for improving the spatial and/or temporal uniformity of a display, such as an OLED display.

#### **BRIEF SUMMARY**

[0007] EMBODIMENT 1A. A circuit for a display panel having an active area having a plurality of light emitting devices arranged on a substrate, and a peripheral area of the display panel separate from the active area, the circuit comprising: a shared switch transistor connected between a voltage data line and a shared line that is connected to a reference voltage through a reference voltage transistor; a first pixel including a first light emitting device configured to be current driven by a first drive circuit connected to the shared line through a first storage device; a second pixel including a second light emitting device configured to be current driven by a second drive circuit connected to the shared line through a second storage device; and a reference current line configured to apply a bias current to the first and second drive circuits.

[0008] EMBODIMENT 2A. The circuit of EMBODI-MENT 1A, a display driver circuit in the peripheral area and coupled to the first and second drive circuits via respective first and second select lines, to the switch transistor, to the reference voltage transistor, to the voltage data line, and to the reference current line, the display driver circuit being configured to switch the reference voltage transistor from a first state to a second state via a reference voltage control line such that the reference voltage transistor is disconnected from the reference voltage and to switch the shared switch transistor from the second state to the first state via a group select line during a programming cycle of a frame to allow voltage programming of the first pixel and the second pixel, and wherein the bias current is applied during the programming cycle. [0009] EMBODIMENT 3A. The circuit of EMBODI-MENT 2A, wherein the display driver circuit is further configured to toggle the first select line during the programming cycle to program the first pixel with a first programming voltage specified by the voltage data line and stored in the first storage capacitor during the programming cycle and to toggle the second select line during the programming cycle to program the second pixel with a second programming voltage specified by the voltage data line and stored in the second storage capacitor during the programming cycle.

[0010] EMBODIMENT 4A. The circuit of EMBODI-MENT 3A. wherein the display driver circuit is further configured to, following the programming cycle, switch the reference voltage transistor from the second state to the first state via a reference voltage control line and to switch the shared switch transistor via a group select line from the first state to the second state, the display driver circuit including a supply voltage control circuit configured to adjust the supply voltage to turn on the first and second light emitting devices during a driving cycle of the frame that follows the programming cycle, thereby causing the first and second light emitting devices to emit light at a luminance based on the first and second programming voltages, respectively.

**[0011]** EMBODIMENT 5A. The circuit of EMBODI-MENT 2A, wherein the display driver circuit is further coupled to a supply voltage to the first pixel and the second pixel, the display driver circuit being configured to adjust the supply voltage to ensure that the first light emitting device and the second light emitting device remain in a non-emitting state during the programming cycle.

**[0012]** EMBODIMENT 6A. The circuit of EMBODIMENT 1A, wherein the display driver circuit includes a gate driver coupled to the first and second drive circuits via respective first and second select lines in a peripheral area of the display panel.

**[0013]** EMBODIMENT 7A. The circuit of EMBODIMENT 1A, wherein the first drive circuit includes a first drive transistor connected to a supply voltage and to the first light emitting device, a gate of the first drive transistor being connected to the first storage device, and a pair of switch transistors each coupled to the first select line for transferring the bias current from the reference current line to the first storage device during a programming cycle, wherein the first storage device is a capacitor.

**[0014]** EMBODIMENT 8A. The circuit of EMBODIMENT 7A. wherein one of the pair of switch transistors is connected between the reference current line and the first light emitting device and the other of the pair of switch transistors is connected between the first light emitting device and the first storage capacitor.

**[0015]** EMBODIMENT 9A. The circuit of EMBODIMENT 8A, wherein the pair of switch transistors and the drive transistor are p-type MOS transistors.

**[0016]** EMBODIMENT 10A. The circuit of EMBODI-MENT 7A. wherein the second drive circuit includes a second drive transistor connected to the supply voltage and to the second light emitting device, a gate of the second drive transistor being connected to the second storage device, and a pair of switch transistors each coupled to the second select line for transferring the bias current from the reference current line to the second storage device during a programming cycle, wherein the second storage device is a capacitor.

**[0017]** EMBODIMENT 11A.The circuit of EMBODI-MENT 10A, wherein one of the pair of switch transistors is connected between the reference current line and the second light emitting device and the other of the pair of switch transistors is connected between the second light emitting device and the second storage device.

**[0018]** EMBODIMENT 12A.The circuit of EMBODI-MENT 11A, wherein the pair of switch transistors and the drive transistor are p-type MOS transistors.

**[0019]** EMBODIMENT 13A.The circuit of EMBODIMENT 12A, wherein a source of the first drive transistor is connected to the supply voltage, a drain of the first drive transistor is connected to the first light emitting device, a source of one of the pair of switch transistors is connected to a drain of the other of the pair of switch transistors, a drain of the one of the pair of switch transistors is connected to the reference current line, a source of the other of the pair of switch transistors is connected

to the first storage capacitor, a drain of the shared transistor is connected to the first storage capacitor and to the second capacitor, a source of the shared switch transistor is connected to the voltage data line, a source of the reference voltage transistor is connected to the reference voltage, and the first light emitting device is connected between a drain of the gating transistor and a ground potential.

**[0020]** EMBODIMENT 14A. The circuit of EMBODI-MENT 1A, wherein the peripheral area and the pixel area are on the same substrate.

**[0021]** EMBODIMENT 15A.The circuit of EMBODI-MENT 1A, wherein the first drive circuit includes a first drive transistor connected to a supply voltage and a gating transistor connected to the first light emitting device, a gate of the first drive transistor being connected to the first storage device, and a pair of switch transistors each coupled to the select line for transferring the bias current from the reference current line to the first storage device during a programming cycle, wherein the gating transistor is connected to a reference voltage control line that is also connected to the reference voltage transistor.

**[0022]** EMBODIMENT 16A.The circuit of EMBODI-MENT 15A, wherein the reference voltage control line switches both the reference voltage transistor and the gating transistor between a first state to a second state simultaneously, and wherein the reference voltage control line is configured by the display driver circuit to disconnect the reference voltage transistor from the reference voltage and the first light emitting device from the first drive transistor during the programming cycle.

[0023] EMBODIMENT 17A.The circuit of EMBODI-MENT 16A. wherein a source of the first drive transistor is connected to the supply voltage, a drain of the first drive transistor is connected to the first light emitting device, a source of one of the pair of switch transistors is connected to a drain of the other of the pair of switch transistors and to a source of the gating transistor, a drain of the one of the pair of switch transistors is connected to the reference current line, a source of the other of the pair of switch transistors is connected to the first storage capacitor, a drain of the shared transistor is connected to the first storage capacitor and to the second transistor, a source of the shared switch transistor is connected to the voltage data line, a source of the reference voltage transistor is connected to the reference voltage, and the first light emitting device is connected between the drain of the first drive transistor and a ground potential.

**[0024]** EMBODIMENT 18A. The circuit of EMBODI-MENT 1A, wherein the circuit is a current-biased, voltage-programmed circuit.

**[0025]** EMBODIMENT 19A.A method of programming a group of pixels in an active matrix area of a light-emitting display panel, the method comprising: during a programming cycle, activating a group select line to cause a shared switch transistor to turn on; while the group select line is activated, activating a first select line for a first row of pixels in the active matrix area and providing a first

40

45

programming voltage on a voltage data line to program a pixel in the first row by storing the programming voltage in a first storage device; while the group select line is activated, activating a second select line for a second row of pixels in the active matrix area and providing a second programming voltage on the voltage data line to program a pixel in the second row by storing the programming voltage in a second storage device; and while programming the first row and the second row of pixels, applying a bias current to a reference current line connected to a first pixel drive circuit in the first row and to a second pixel drive circuit in the second row.

5

**[0026]** EMBODIMENT 20A. The method of EMBODIMENT 19A, further comprising, during the programming cycle, decreasing the supply voltage to a potential sufficient to cause a first light emitting device in the pixel of the first row and a second light emitting device in the pixel of the second row to remain in a non-luminescent state during the programming cycle.

**[0027]** EMBODIMENT 21A. The method of EMBODI-MENT 20A, further comprising, responsive to the completion of the programming cycle, deactivating the group select line to allow the first storage device to discharge through a first drive transistor of the pixel of the first row and the second storage device to discharge through a second drive transistor of the pixel of the second row.

**[0028]** EMBODIMENT 22A. The method of EMBODI-MENT 20A, further comprising restoring the supply voltage to cause the first light emitting device and the second emitting device to emit light a luminance indicative of the first and second programming voltages, respectively.

**[0029]** EMBODIMENT 23A. The method of EMBODI-MENT 19A, further comprising, during the programming cycle, deactivating a group emission line to turn off a reference voltage transistor connected to a reference voltage during the programming cycle.

**[0030]** EMBODIMENT 24A. The method of EMBODIMENT 23A, wherein the deactivating the group emission line turns off a first gating transistor in the pixel of the first row and a second gating transistor of the pixel in the second row during the programming cycle, the first gating transistor being connected to a first light emitting device in the pixel of the first row and the second gating transistor being connected to a second light emitting device in the pixel of the second row, and wherein a gate of the first gating transistor and a gate of the second gating transistor are connected to the group emission line.

[0031] EMBODIMENT 25A. The method of EMBODI-MENT 24A, further comprising, responsive to the completion of the programming cycle, deactivating the group select line to allow the first storage device to discharge through a first drive transistor of the pixel of the first row and the second storage device to discharge through a second drive transistor of the pixel of the second row thereby causing the first light emitting device and the second emitting device to emit light a luminance indicative of the first and second programming voltages, respectively.

[0032] EMBODIMENT 1B. A high output impedance current source or sink circuit for a light-emitting display, the circuit comprising: an input that receives a fixed reference current and provides the reference current to a node in the current source or sink circuit during a calibration operation of the current source or sink circuit; a first transistor and a second transistor series-connected to the node such that the reference current adjusts the voltage at the node to allow the reference current to pass through the series-connected transistors during the calibration operation; one or more storage devices connected to the node; and an output transistor connected to the node to source or sink an output current from current stored in the one or more storage devices to a drive an active matrix display with a bias current corresponding to the output current.

**[0033]** EMBODIMENT 2B. The circuit of EMBODIMENT 1B, further comprising an output control line connected to a gate of the output transistor for controlling whether the output current is available to drive the active matrix display.

**[0034]** EMBODIMENT 3B. The circuit of EMBODIMENT 1B, wherein the one or more storage devices includes a first storage device connected between the node and the first transistor and a second storage device connected between the node and the second transistor.

**[0035]** EMBODIMENT 4B. The circuit of EMBODI-MENT 1B, wherein the one or more storage devices includes a first storage device connected between the node and the first transistor and a second storage device connected between the first transistor and a gate of the second transistor.

**[0036]** EMBODIMENT 5B. The circuit of EMBODIMENT 1B, further comprising: a first voltage switching transistor controlled by a calibration access control line and connected to the first transistor; a second voltage switching transistor controlled by the calibration access control line and connected to the second transistor; and an input transistor controlled by the calibration access control line and connected between the node and the input.

**[0037]** EMBODIMENT 6B. The circuit of EMBODIMENT 5B, wherein the calibration access control line is activated to initiate the calibration operation of the circuit followed by activating the access control line to initiate the programming of a column of pixels of the active matrix display using the bias current.

**[0038]** EMBODIMENT 7B. The circuit of EMBODIMENT 1B, wherein the one or more storage devices includes a first capacitor and a second capacitor, the circuit further comprising: an input transistor connected between the input and the node; a first voltage switching transistor connected to the first transistor, the second transistor, and the second capacitor; a second voltage switching transistor connected to the node, the first transistor, and the first transistor; and a gate control signal line connected to the gates of the input transistor, the first voltage switching transistor, and the second voltage

switching transistor.

**[0039]** EMBODIMENT 8B. The circuit of EMBODIMENT 1B, further comprising a reference current source external to the active matrix display and supplying the reference current.

[0040] EMBODIMENT 9B. The circuit of EMBODI-MENT 1B, further comprising: an input transistor connected between the input and the node; a gate control signal line connected to the gate of the input transistor; and a voltage switching transistor having a gate connected to the gate control signal line and connected to the second transistor and the one or more storage devices. [0041] EMBODIMENT 10B.The circuit of EMBODI-MENT 1B, wherein the first transistor, the second transistor, and the output transistor are p-type field effect transistors having respective gates, sources, and drains, wherein the one or more storage devices includes a first capacitor and a second capacitor, wherein the drain of the first transistor is connected to the source of the second transistor, and the gate of the first transistor is connected to the first capacitor, and wherein the drain of the output transistor is connected to the node, and the source of the output transistor sinks the output current.

**[0042]** EMBODIMENT 11B.The circuit of EMBODI-MENT 10B, further comprising: a first voltage switching transistor having a gate connected to a calibration control line, a drain connected to a first voltage supply, and a source connected to the first capacitor; a second voltage switching transistor having a gate connected to the calibration control line, a drain connected to a second voltage supply, and a source connected to the second capacitor; and an input transistor having a gate connected to the calibration control line, a drain connected to the node, and a source connected to the input, wherein the gate of the output transistor is connected to an access control line, and the first voltage switching transistor, the second voltage switching transistor, and the input transistor being p-type field effect transistors.

[0043] EMBODIMENT 12B.The circuit of EMBODI-MENT 11B, wherein the second capacitor is connected between the gate of the second transistor and the node. [0044] EMBODIMENT 13B.The circuit of EMBODI-MENT 11B, wherein the second capacitor is connected between the gate of the second transistor and the source of the second transistor.

**[0045]** EMBODIMENT 14B.The circuit of EMBODI-MENT 1B, wherein the first transistor, the second transistor, and the output transistor are n-type field effect transistors having respective gates, sources, and drains, wherein the one or more storage devices includes a first capacitor and a second capacitor, wherein the source of the first transistor is connected to the drain of the second transistor, and the gate of the first transistor is connected to the first capacitor, and wherein the source of the output transistor is connected to the node, and the drain of the output transistor sinks the output current.

**[0046]** EMBODIMENT 15B.The circuit of EMBODI-MENT 14B, further comprising: a first voltage switching

transistor having a gate connected to a gate control signal line, a drain connected to the node, and a source connected to the first capacitor and to the first transistor; a second voltage switching transistor having a gate connected to the gate control signal line, a drain connected to the source of the first transistor, and a source connected to the gate of the second transistor and to the second capacitor; and an input transistor having a gate connected to the gate control signal line, a source connected to the node, and a drain connected to the input, wherein the gate of the output transistor is connected to an access control line, and the first voltage switching transistor, the second voltage switching transistor, and the input transistor are n-type field effect transistors.

[0047] EMBODIMENT 16B. The circuit of EMBODI-MENT 1B, wherein the first transistor, the second transistor, and the output transistor are p-type field effect transistors having respective gates, sources, and drains, wherein the one or more storage devices includes a first capacitor, wherein the drain of the first transistor is connected to the source of the second transistor, and the gate of the first transistor is connected to the first transistor is connected to the node, and the source of the output transistor sinks the output current.

**[0048]** EMBODIMENT 17B. The circuit of EMBODIMENT 16B, further comprising: an input transistor connected between the node and the input, wherein a drain of the input transistor is connected to a reference current source and a source of the input transistor is connected to the node, a gate of the input transistor being connected to a gate control signal line; a voltage switching transistor having a gate connected to the gate control signal line, a source connected to the gate of the second transistor, and a drain connected to a ground potential; wherein the gate of the output transistor is connected to an access control line, and wherein the first capacitor is connected between the gate of the first transistor and the source of the first transistor.

[0049] EMBODIMENT 18B.A method of sourcing or sinking current to provide a bias current for programming pixels of a light-emitting display, comprising: initiating a calibration operation of a current source or sink circuit by activating a calibration control line to cause a reference current to be supplied to the current source or sink circuit; during the calibration operation, storing the current supplied by the reference current in one or more storage devices in the current source or sink circuit; deactivating the calibration control line while activating an access control line to cause sinking or sourcing of an output current corresponding to the current stored in the one or more storage devices; and applying the output current to a column of pixels in an active matrix area of the light-emitting display.

[0050] EMBODIMENT 19B. The method of EMBODI-MENT 18B, further comprising applying a first bias voltage and a second bias voltage to the current source or sink circuit, the first bias voltage differing from the second

15

25

40

45

bias voltage to allow the reference current to be copied into the one or more storage devices.

**[0051]** EMBODIMENT 20B.A voltage-to-current converter circuit providing a current source or sink for a light-emitting display, the circuit comprising: a current sink or source circuit including a controllable bias voltage transistor having a first terminal connected to a controllable bias voltage and a second terminal connected to a first node in the current sink or source circuit; a gate of the controllable bias voltage transistor connected to a second node; a control transistor connected between the first node, the second node, and a third node; a fixed bias voltage connected through a bias voltage transistor to the second node; and an output transistor connected to the third node and sinking an output current as a bias current to drive a column of pixels of an active matrix area of the light-emitting display.

[0052] EMBODIMENT 21B.The voltage-to-current converter circuit of EMBODIMENT 20B, wherein the current sink or source circuit further includes a first transistor series-connected to a second transistor, the first transistor connected to the first node such that current passing through the controllable bias voltage transistor, the first transistor, and the second transistor is adjusted to allow the second node to build up to the fixed bias voltage, and wherein the output current is correlated to the controllable bias voltage and the fixed bias voltage.

[0053] EMBODIMENT 22B.The voltage-to-current converter circuit of EMBODIMENT 20B, wherein a source of the controllable bias voltage transistor is connected to the controllable bias voltage, a gate of the controllable bias voltage transistor is connected to the second node, and a drain of the controllable bias voltage transistor is connected to the first node, wherein a source of the control transistor is connected to the second node, a gate of the control transistor is connected to the first node, and a drain of the control transistor is connected to the third node, wherein a source of the bias voltage transistor is connected to the fixed bias voltage, a drain of the supply voltage transistor is connected to the second node, and a gate of the bias voltage transistor is connected to a calibration control line controlled by a controller of the light-emitting display, and wherein a source of the output transistor is connected to a current bias line carrying the bias current, a drain of the output transistor is connected to the third node, and a gate of the output transistor is coupled to the calibration control line such that when the calibration control line is active low, the gate of the output transistor is active high.

[0054] EMBODIMENT 23B. A method of calibrating a current source or sink circuit for a light-emitting display using a voltage-to-current converter to calibrate an output current, the method comprising: activating a calibration control line to initiate a calibration operation of the current source or sink circuit; responsive to initiating the calibration operation, adjusting a controllable bias voltage supplied to the current source or sink circuit to a first bias voltage to cause current to flow through the current

source or sink circuit to allow a fixed bias voltage to be present at a node in the voltage-to-current converter; deactivating the calibration control line to initiate a programming operation of pixels in an active matrix area of the light-emitting display; and responsive to initiating the programming operation, sourcing or sinking the output current correlated to the controllable bias voltage and the fixed bias voltage to a bias current line that supplies the output current to a column of pixels in the active matrix area.

[0055] EMBODIMENT 24B.The method of EMBODI-MENT 23B, further comprising during the calibration operation, storing the current flowing through the current source or sink circuit as determined by the fixed bias voltage in one or more capacitors of the current source or sink circuit until the calibration control line is deactivated

**[0056]** EMBODIMENT 25B.The method of EMBODI-MENT 23B, further comprising, responsive to deactivating the calibration control line, lowering the controllable bias voltage to a second bias voltage that is lower than the first bias voltage.

[0057] EMBODIMENT 26B.A method of calibrating current source or sink circuits that supply a bias current to columns of pixels in an active matrix area of a lightemitting display, the method comprising: during a calibration operation of the current source or sink circuits in the light-emitting display, activating a first gate control signal line to a first current source or sink circuit for a first column of pixels in the active matrix area to calibrate the first current source or sink circuit with a bias current that is stored in one or more storage devices of the first current source or sink circuit during the calibration operation; responsive to calibrating the first current source or sink circuit, deactivating the first gate control signal line; during the calibration operation, activating a second gate control signal line to a second current source or sink circuit for a second column of pixels in the active matrix area to calibrate the second current source or sink circuit with a bias current that is stored in one or more storage devices of the second current source or sink circuit during the calibration operation; responsive to calibrating the second current source or sink circuit, deactivating the second gate control signal line; and responsive to all of the current source or sink circuits being calibrated during the calibration operation, initiating a programming operation of the pixels of the active matrix area and activating an access control line to cause the bias current stored in the corresponding one or more storage devices in each of the current source or sink circuits to be applied to each of the columns of pixels in the active matrix area.

**[0058]** EMBODIMENT 27B.The method of EMBODI-MENT 26B, wherein the current source or sink circuits include p-type transistors and the gate control signal lines and the access control line are active low or wherein the current source or sink circuits include n-type transistors and the gate control signal lines and the access control line are active high.

[0059] EMBODIMENT 28B. A direct current (DC) voltage-programmed current sink circuit, comprising: a bias voltage input receiving a bias voltage; an input transistor connected to the bias voltage input; a first current mirror, a second current mirror, and a third current mirror each including a corresponding pair of gate-connected transistors, the current mirrors being arranged such that an initial current created by a gate-source bias of the input transistor and copied by the first current mirror is reflected in the second current mirror, current copied by the second current mirror is reflected in the third current mirror, and current copied by the third current mirror is applied to the first current mirror to create a static current flow in the current sink circuit; and an output transistor connected to a node between the first current mirror and the second current mirror and biased by the static current flow to provide an output current on an output line.

**[0060]** EMBODIMENT 29B.The circuit of EMBODI-MENT 28B, wherein the gate-source bias of the input transistor is created by the bias voltage input and a ground potential.

**[0061]** EMBODIMENT 30B.The circuit of EMBODI-MENT 28B, wherein the first current mirror and the third current mirror are connected to a supply voltage.

**[0062]** EMBODIMENT 31B.The circuit of EMBODI-MENT 28B, further comprising a feedback transistor connected to the third current mirror.

**[0063]** EMBODIMENT 32B.The circuit of EMBODI-MENT 31B, wherein a gate of the feedback transistor is connected to a terminal of the input transistor.

**[0064]** EMBODIMENT 33B.The circuit of EMBODI-MENT 31B, wherein a gate of the feedback transistor is connected to the bias voltage input.

**[0065]** EMBODIMENT 34B.The circuit of EMBODI-MENT 31B, wherein the feedback transistor is n-type.

**[0066]** EMBODIMENT 35B.The circuit of EMBODIMENT 28B, wherein the first current mirror includes a pair of p-type transistors, the second mirror includes a pair of n-type transistors, and the third mirror includes a pair of p-type transistors, and wherein the input transistor and the output transistor are n-type.

[0067] EMBODIMENT 36B.The circuit of EMBODI-MENT 35B, further comprising an n-type feedback transistor connected between the third current mirror and the first current mirror, and wherein: a first p-type transistor of the first current mirror is gate-connected to a fourth ptype transistor of the first current mirror; a third n-type transistor of the second current mirror is gate-connected to a fourth n-type transistor of the second current mirror; a second p-type transistor of the third current mirror is gate-connected to a third p-type transistor of the third current mirror; respective sources of the first, second, third, and fourth p-type transistors are connected to a supply voltage and respective sources of the first, second, third, and fourth n-type transistors and the output transistor are connected to a ground potential; the fourth p-type transistor is drain-connected to the fourth n-type transistor; the third p-type transistor is drain-connected

to the third n-type transistor; the second p-type transistor is drain-connected to the second n-type transistor; the first p-type transistor is drain-connected to the first n-type transistor; the drain of the third n-type transistor is connected between the gates of the second and third p-type transistors; the drain of the fourth n-type transistor is connected between the gates of the third and fourth n-type transistors and to the node; and a gate of the output transistor is connected to the node.

[0068] EMBODIMENT 37B.The circuit of EMBODI-MENT 36B, wherein the gate of the second n-type transistor is connected to the gate of the first p-type transistor.

[0069] EMBODIMENT 38B.The circuit of EMBODI-MENT 36B, wherein the gate of the second n-type transistor is connected to the bias voltage input.

**[0070]** EMBODIMENT 39B. The circuit of EMBODIMENT 28B, wherein the circuit lacks any external clocking or current reference signals.

**[0071]** EMBODIMENT 40B.The circuit of EMBODIMENT 28B, wherein the only voltage sources are provided by the bias voltage input, a supply voltage, and a ground potential and no external control lines are connected to the circuit.

**[0072]** EMBODIMENT 41B.The circuit of EMBODI-MENT 28B, wherein the circuit lacks a capacitor.

**[0073]** EMBODIMENT 42B.The circuit of EMBODI-MENT 28B, wherein the number of transistors in the circuit is exactly nine.

[0074] EMBODIMENT 43B.An alternating current (AC) voltage-programmed current sink circuit, comprising: four switching transistors each receiving a clocking signal that is activated in an ordered sequence, one after the other; a first capacitor charged during a calibration operation by the activation of the first clocked signal and discharged by the activation of the second clocked signal following the activation and deactivation of the first clocked signal, the first capacitor being connected to the first and second switching transistors; a second capacitor charged during the calibration operation by the activation of the third clocked signal and discharged by the activation of the fourth clocked signal following the activation and deactivation of the third clocked signal, the second capacitor being connected to the third and fourth switching transistors; and an output transistor connected to the fourth switching transistor to sink, during a programming operation subsequent to the calibration operation, an output current derived from current stored in the first capacitor during the calibration operation.

**[0075]** EMBODIMENT 44B.The circuit of EMBODI-MENT 43B, wherein the four switching transistors are n-type

[0076] EMBODIMENT 45B.The circuit of EMBODI-MENT 43B, further comprising: a first conducting transistor connected to the second switching transistor to provide a conduction path for the first capacitor to discharge through the second switching transistor, wherein a voltage across the first capacitor following the charging of the first capacitor is a function of a threshold voltage and

40

30

35

45

mobility of the first conducting transistor; and a second conducting transistor connected to the fourth switching transistor to provide a conduction path for the second capacitor to discharge through the fourth switching transistor.

[0077] EMBODIMENT 46B.The circuit of EMBODI-MENT 45B, wherein the four switching transistors, the output transistor, the first conducting transistor, and the second conducting transistor are n-type; a gate of the first switching transistor receives the first clocked signal, a drain of the first switching transistor is connected to a first bias voltage; a source of the first switching transistor is connected to a gate of the first conducting transistor, to the first capacitor, and to a source of the second switching transistor; a gate of the second switching transistor receives the second clocked signal, a drain of the second switching transistor is connected to a source of the second conducting transistor and a drain of the first conducting transistor; a gate of the second conducting transistor is connected to the first capacitor; a gate of the second conducting transistor is connected to drain of the third switching transistor, the second capacitor, and a source of the fourth switching transistor; a gate of the third switching transistor receives the third clocked signal, a source of the third switching transistor is connected to a second bias voltage; a gate of the fourth switching transistor receives the fourth clocked signal, a drain of the fourth switching transistor is connected to a source of the output transistor; a gate of the output transistor is connected to an access control line to initiate a programming cycle of the light-emitting display; a drain of the output transistor sinks the output current to a column of pixels of an active matrix area of the light-emitting display; and the first capacitor, a source of the first conducting transistor, and the second capacitor is connected to a ground potential.

**[0078]** EMBODIMENT 47B.The circuit of EMBODI-MENT 43B, wherein the number of transistors in the circuit is exactly seven.

**[0079]** EMBODIMENT 48B.The circuit of EMBODIMENT 43B, wherein the number of capacitors in the circuit is exactly two.

[0080] EMBODIMENT 49B.A method of programming a current sink with an alternating current (AC) voltage, the method comprising: initiating a calibration operation by activating a first clocked signal to cause a first capacitor to charge; deactivating the first clocked signal and activating a second clocked signal to cause the first capacitor to start discharging; deactivating the second clocked signal and activating a third clocked signal to cause a second capacitor to charge; deactivating the third clocked signal and activating a fourth clocked signal to cause the second capacitor to start discharging; and deactivating the fourth clocked signal to terminate the calibration operation and activating an access control line in a programming operation to cause a bias current derived from current stored in the first capacitor to be applied to a column of pixels in an active matrix area of a

light-emitting display during the programming operation. [0081] EMBODIMENT 1C. A calibration circuit for a display panel having an active area having a plurality of light emitting devices arranged on a substrate, and a peripheral area of the display panel separate from the active area, the calibration circuit comprising: a first row of calibration current source or sink circuits; a second row of calibration current source or sink circuits; a first calibration control line configured to cause the first row of calibration current source or sink circuits to calibrate the display panel with a bias current while the second row of calibration current source or sink circuits is being calibrated by a reference current; and a second calibration control line configured to cause the second row of calibration current source or sink circuits to calibrate the display panel with the bias current while the first row of calibration current source or sink circuits is being calibrated by the reference current.

**[0082]** EMBODIMENT 2C. The calibration circuit of EMBODIMENT 1C, wherein the first row and second row of calibration current source or sink circuits are located in the peripheral area of the display panel.

[0083] EMBODIMENT 3C. The calibration circuit of EMBODIMENT 1C, further comprising: a first reference current switch connected between the reference current source and the first row of calibration current source or sink circuits, a gate of the first reference current switch being coupled to the first calibration control line; a second reference current switch connected between the reference current source and the second row of calibration current source or sink circuits, a gate of the second reference current switch being coupled to the second calibration control line; and a first bias current switch connected to the first calibration control line and a second bias current switch connected to the second calibration control line.

[0084] EMBODIMENT 4C. The calibration circuit of EMBODIMENT 1C, wherein the first row of calibration current source or sink circuits includes a plurality of current source or sink circuits, one for each column of pixels in the active area, each of the current source or sink circuits configured to supply a bias current to a bias current line for the corresponding column of pixels, and wherein the second row of calibration current source or sink circuits includes a plurality of current source or sink circuits, one for each column of pixels in the active area, each of the current source or sink circuits configured to supply a bias current to a bias current line for the corresponding column of pixels.

[0085] EMBODIMENT 5C. The calibration current of EMBODIMENT 4C, wherein each of the current source or sink circuits of the first and second rows of calibration current source or sink circuits is configured to supply the same bias current to each of the columns of the pixels in the active area of the display panel.

**[0086]** EMBODIMENT 6C. The calibration circuit of EMBODIMENT 1C, wherein the first calibration control line is configured to cause the first row of calibration cur-

rent source or sink circuits to calibrate the display panel with the bias current during a first frame, and wherein the second calibration control line is configured to cause the second row of calibration current source or sink circuits to calibrate the display panel with the bias current during a second frame that follows the first frame.

**[0087]** EMBODIMENT 7C. The calibration circuit of EMBODIMENT 1C, wherein the reference current is fixed and is supplied to the display panel from a current source external to the display panel.

**[0088]** EMBODIMENT 8C. The calibration circuit of EMBODIMENT 1C, wherein the first calibration control line is active during a first frame while the second calibration control line is inactive during the first frame, and wherein the first calibration control line is inactive during a second frame that follows the first frame while the second calibration control line is active during the second frame.

[0089] EMBODIMENT 9C. The calibration circuit of EMBODIMENT 1C, wherein the calibration current source or sink circuits each calibrate corresponding current-biased, voltage-programmed circuits that are used to program pixels in the active area of the display panel. [0090] EMBODIMENT 10C.A method of calibrating a current-biased, voltage-programmed circuit for a lightemitting display panel having an active area, the method comprising: activating a first calibration control line to cause a first row of calibration current source or sink circuits to calibrate the display panel with a bias current provided by the calibration current source or sink circuits of the first row while calibrating a second row of calibration current source or sink circuits by a reference current; and activating a second calibration control line to cause the second row to calibrate the display panel with the bias current provided by the calibration current or sink circuits of the second row while calibrating the first row by the reference current.

[0091] EMBODIMENT 11C.The method of EMBODI-MENT 10C, wherein the first calibration control line is activated during a first frame to be displayed on the display panel and the second calibration control line is activated during a second frame to be displayed on the display panel, the second frame following the first frame, the method further comprising: responsive to activating the first calibration control line, deactivating the first calibration control line prior to activating the second calibration control line; responsive to calibrating the display panel with the bias current provided by the circuits of the second row, deactivating the second calibration control line to complete the calibration cycle for a second frame. [0092] EMBODIMENT 12C.The method of EMBODI-MENT 10C, further comprising controlling the timing of the activation and deactivation of the first calibration control line and the second calibration control line by a controller of the display panel, the controller being disposed on a peripheral area of the display panel proximate the active area on which a plurality of pixels of the light-emitting display panel are disposed.

**[0093]** EMBODIMENT 13C.The method of EMBODI-MENT 12C, wherein the controller is a current source or sink control circuit.

[0094] EMBODIMENT 14C.The method of EMBODI-MENT 1C, wherein the light-emitting display panel has a resolution of 1920x1080 pixels or less.

**[0095]** EMBODIMENT 15C.The method of EMBODI-MENT 1C, wherein the light-emitting display has a refresh rate of no greater than 120Hz.

O [0096] The foregoing and additional aspects and embodiments of the present disclosure will be apparent to those of ordinary skill in the art in view of the detailed description of various embodiments and/or aspects, which is made with reference to the drawings, a brief description of which is provided next.

## BRIEF DESCRIPTION OF THE DRAWINGS

**[0097]** The foregoing and other advantages of the present disclosure will become apparent upon reading the following detailed description and upon reference to the drawings.

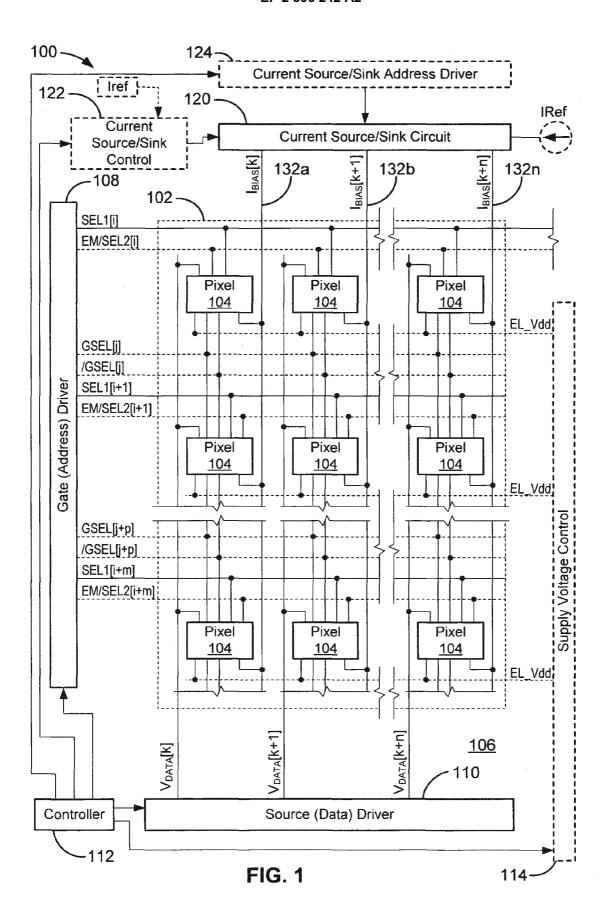

**[0098]** FIG. 1 illustrates an electronic display system or panel having an active matrix area or pixel array in which an array of pixels are arranged in a row and column configuration;

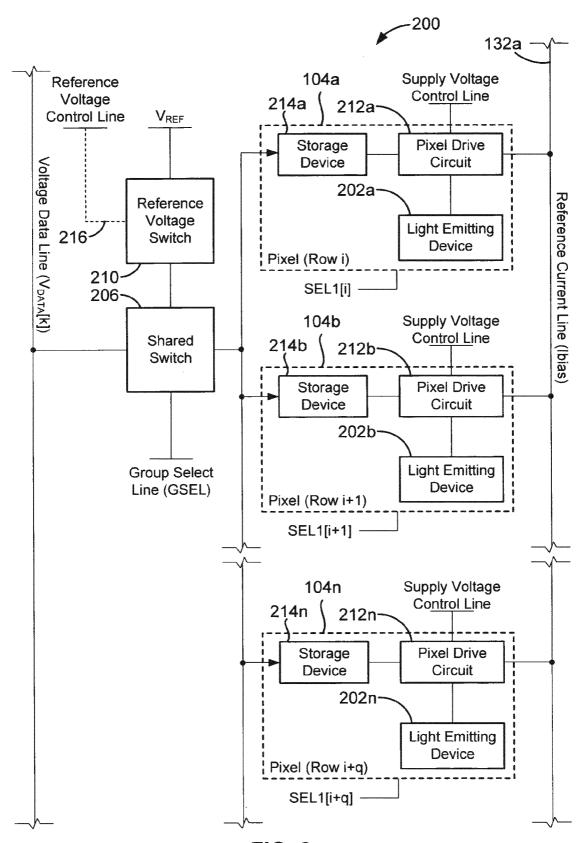

**[0099]** FIG. 2a illustrates a functional block diagram of a current-biased, voltage-programmed circuit for the display panel shown in FIG. 1;

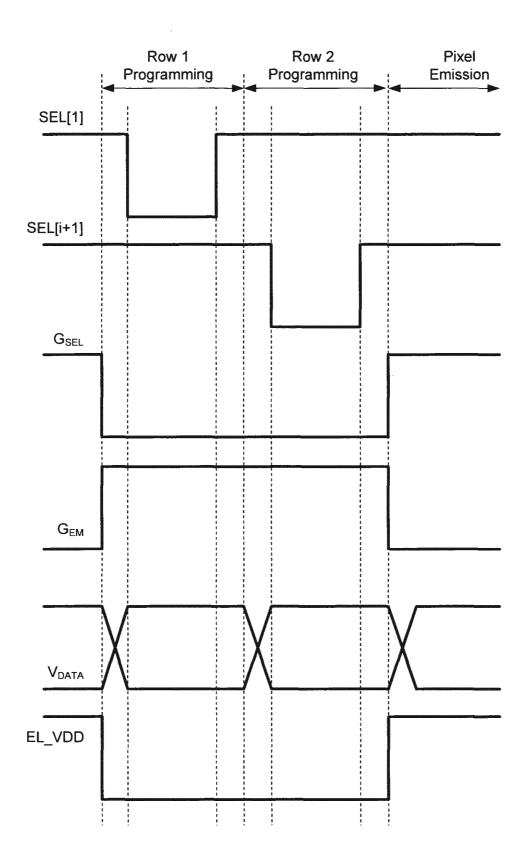

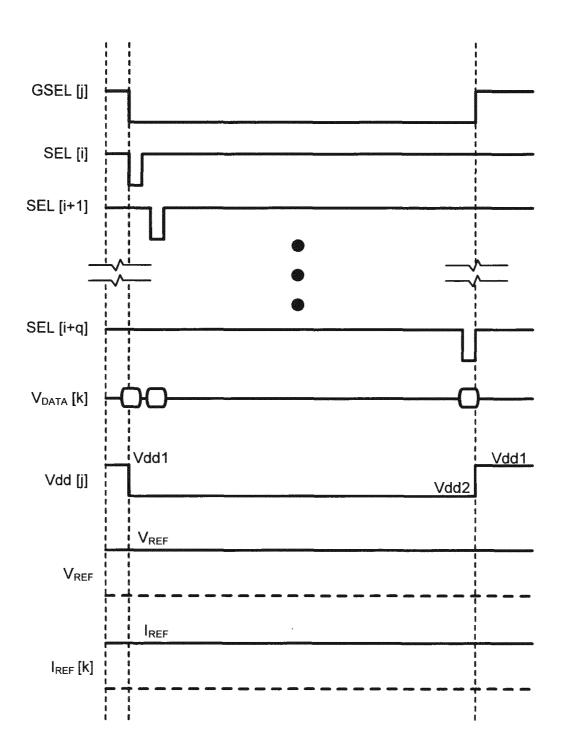

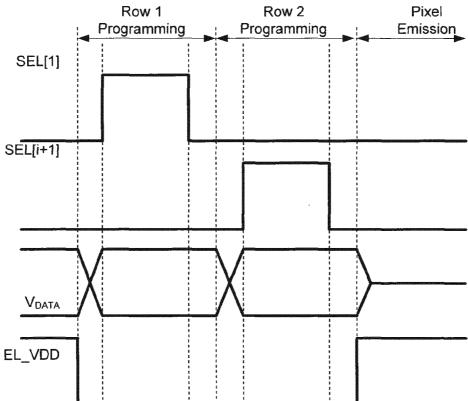

[0100] FIG. 2b is a timing diagram for the CBVP circuit shown in FIG. 2a;

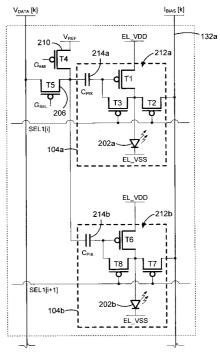

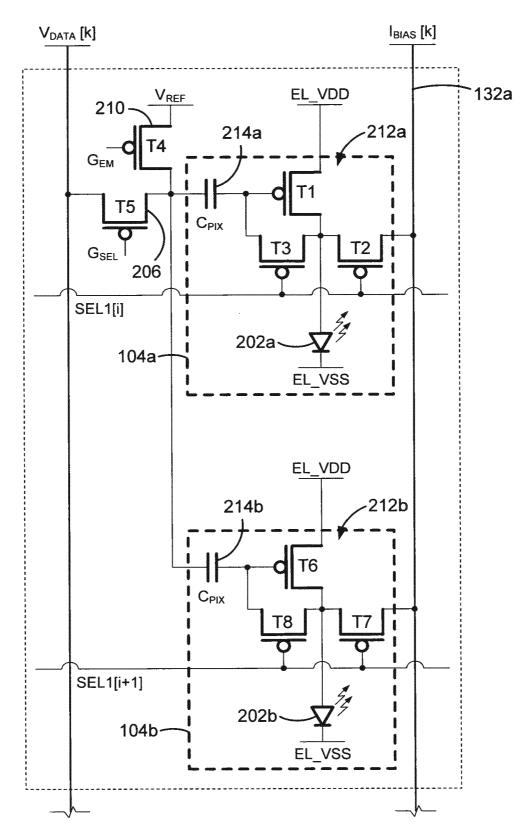

**[0101]** FIG. 3a is a circuit schematic of an exemplary CBVP circuit schematic that can be used in connection with the CBVP circuit shown in FIG. 2a;

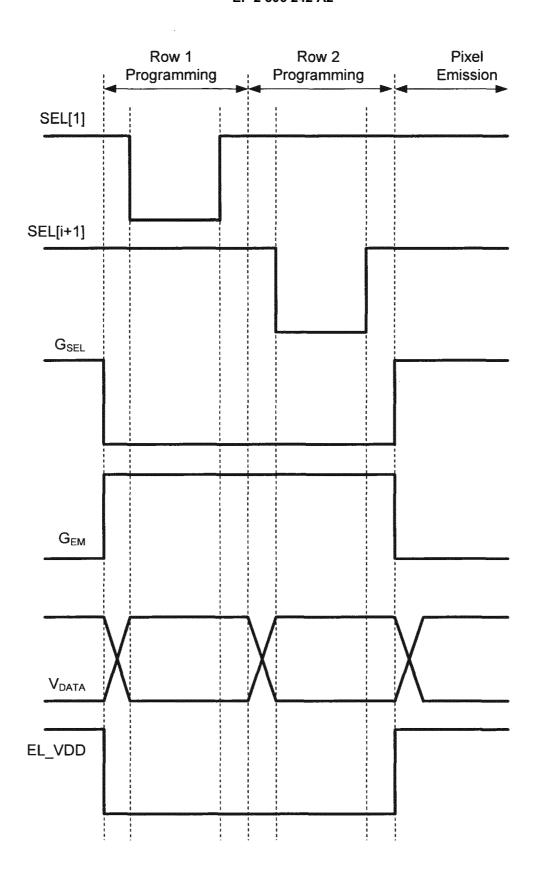

**[0102]** FIG. 3b illustrates an example timing diagram for the CBVP circuit shown in FIG. 3a;

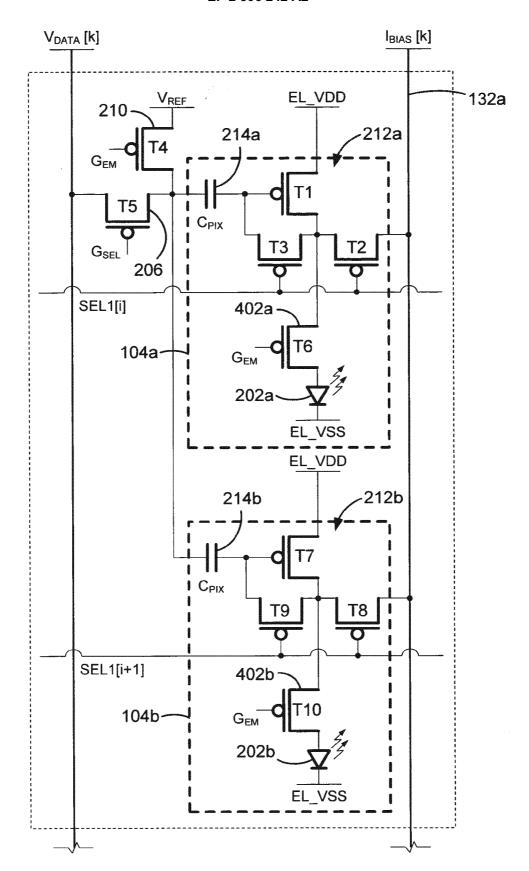

**[0103]** FIG. 4a illustrates a variation of the CBVP circuit shown in FIG. 3a, except that a gating transistor (T6 and T10) is added between the light emitting device and the drive transistor (T1 and T7);

**[0104]** FIG. 4b is a timing diagram for the CBVP circuit shown in FIG. 4a;

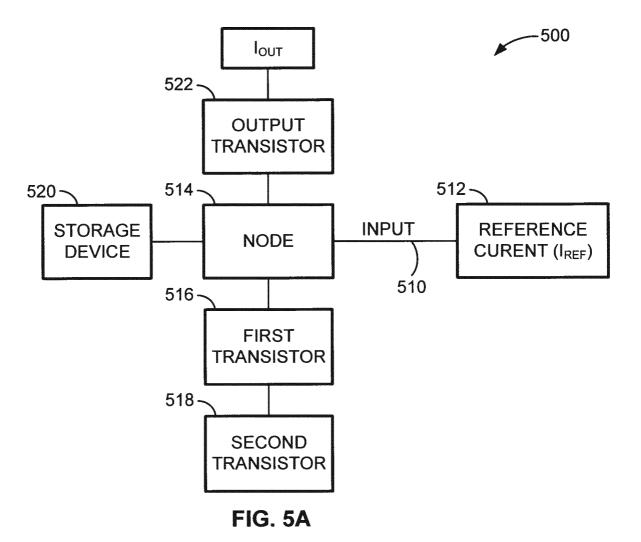

**[0105]** FIG. 5a illustrates a functional block diagram of a current sink or source circuit according to an aspect of the present disclosure;

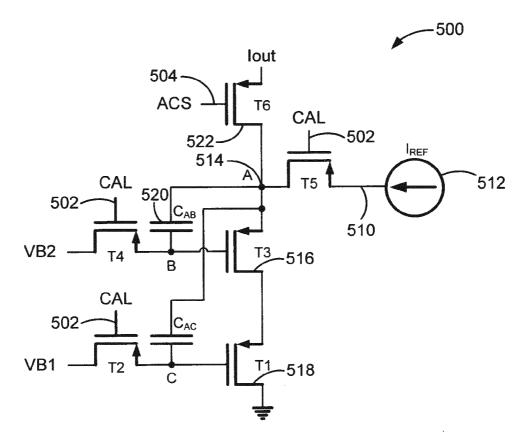

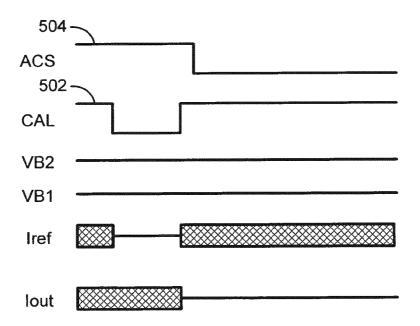

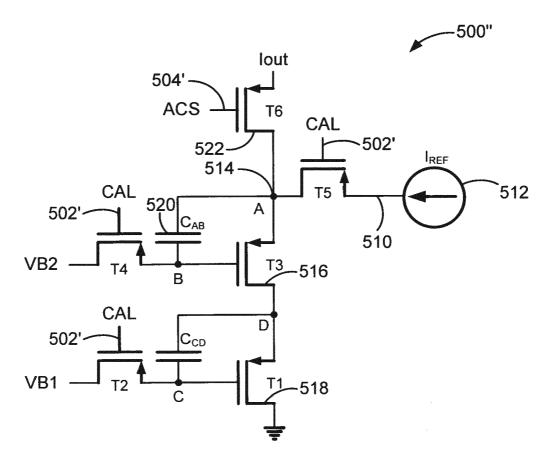

**[0106]** FIG. 5b-1 illustrates a circuit schematic of a current sink circuit using only p-type TFTs;

**[0107]** FIG. 5b-2 is a timing diagram for the current sink circuit shown in FIG. 5b-1;

[0108] FIG. 5c is a variation of FIG. 5b-1 having a different capacitor configuration;

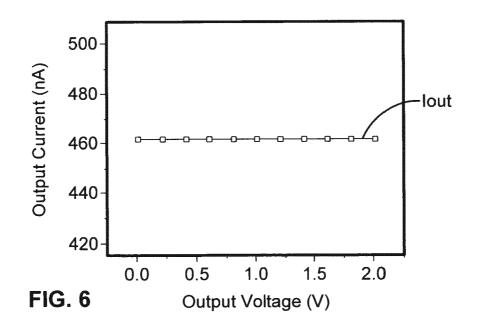

**[0109]** FIG. 6 illustrates a simulation result for the output current, lout, of the current sink circuit shown in FIG. 5b-1 or 5c as a function of output voltage;

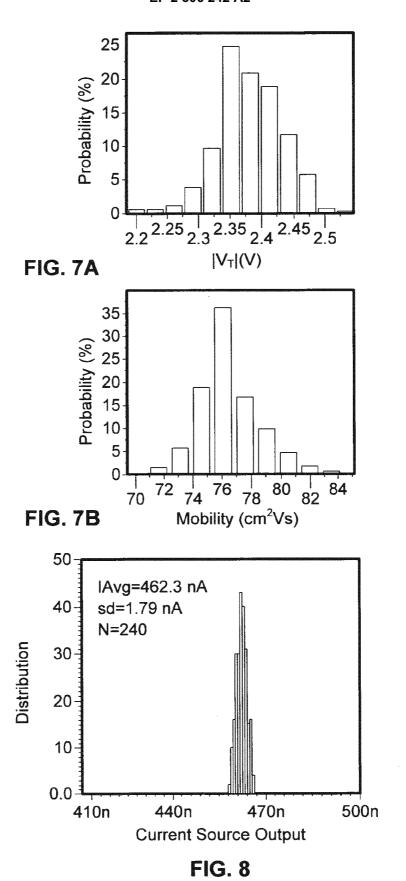

**[0110]** FIGS. 7a and 7b illustrate a parameter (threshold voltage, V<sub>T</sub>, and mobility, respectively) variation in a typical poly-Si process;

[0111] FIG. 8 highlights Monte Carlo simulation results

for the current source output (Ibias);

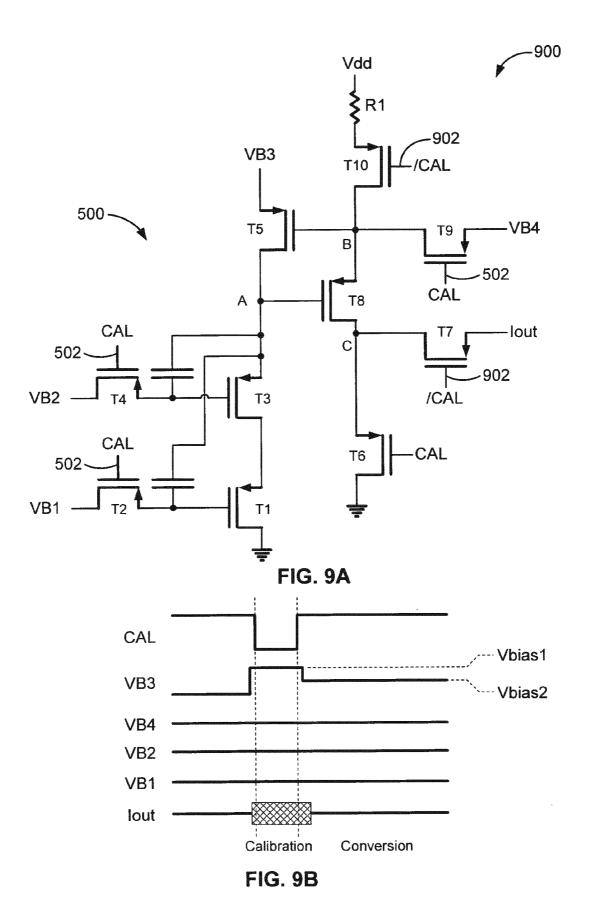

[0112] FIG. 9a illustrates the use of the current sink circuit (such as shown in FIG. 5b-1 or 5c) in a voltageto-current converter circuit;

[0113] FIG. 9b illustrates a timing diagram for the voltage-to-current converter circuit shown in FIG. 9a;

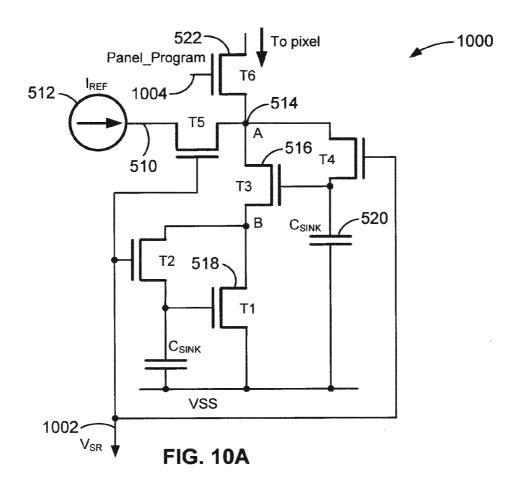

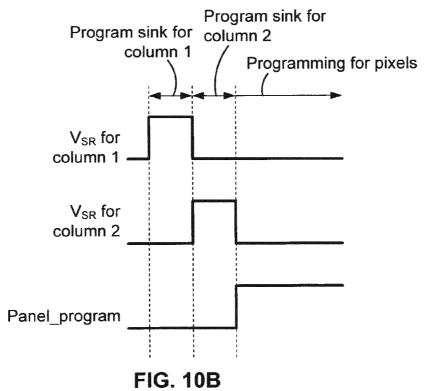

[0114] FIG. 10a illustrates illustrate an N-FET based cascade current sink circuit that is a variation of the current sink circuit shown in FIG. 5b-1;

[0115] FIG. 10b is a timing diagram for two calibration cycles of the circuit shown in FIG. 10a;

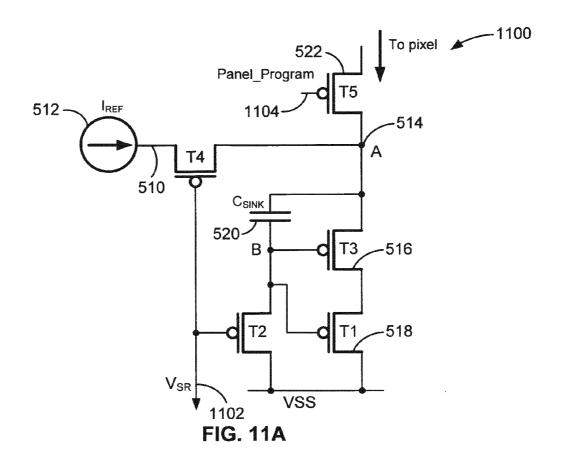

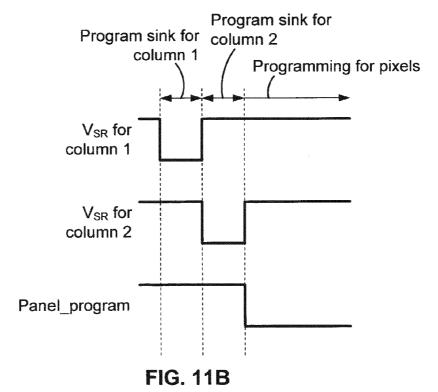

[0116] FIG. 11a illustrates a cascade current source/ sink circuit during activation of the calibration operation; [0117] FIG. 11b illustrates the operation of calibration of two instances (i.e., for two columns of pixels) of the circuit shown in FIG. 11a;

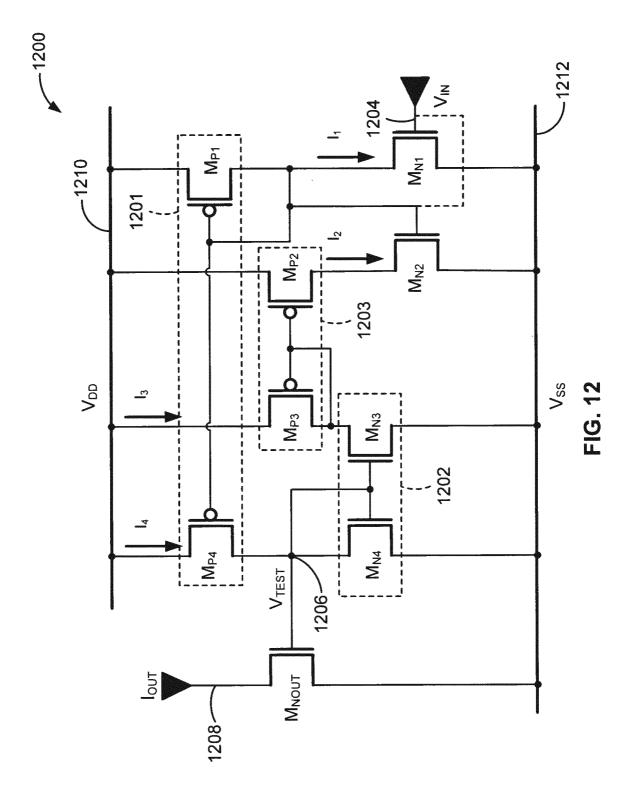

[0118] FIG. 12 illustrates a CMOS current sink/source circuit 1200 that utilizes DC voltage programming;

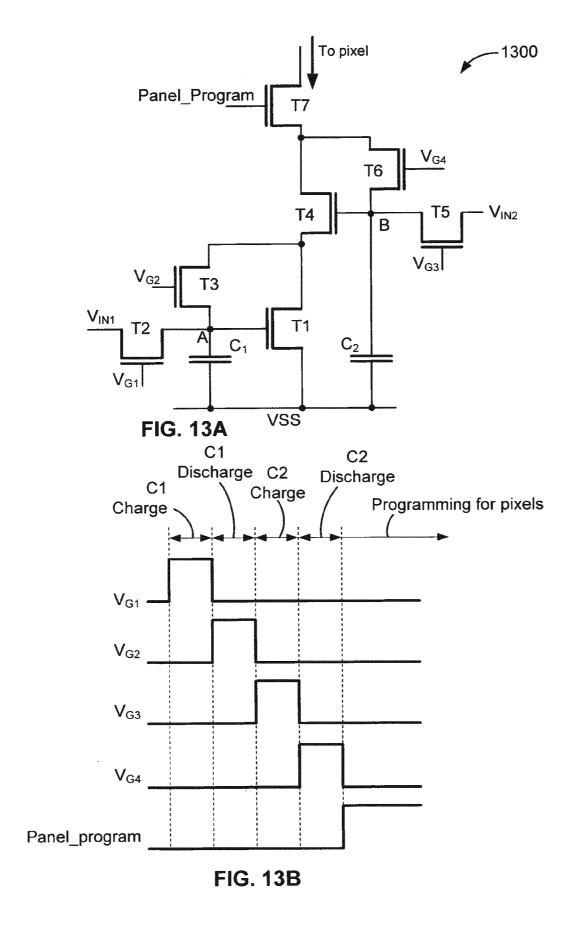

[0119] FIG. 13a illustrates a CMOS current sink circuit with AC voltage programming;

[0120] FIG. 13b is an operation timing diagram for calibrating the circuit shown in FIG. 13a;

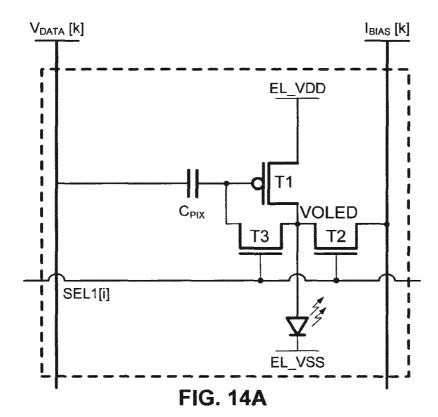

[0121] FIG. 14a illustrates a schematic diagram of a pixel circuit using a p-type drive transistor and n-type switch transistors;

[0122] FIG. 14b is a timing diagram for the pixel circuit shown in FIG. 14a;

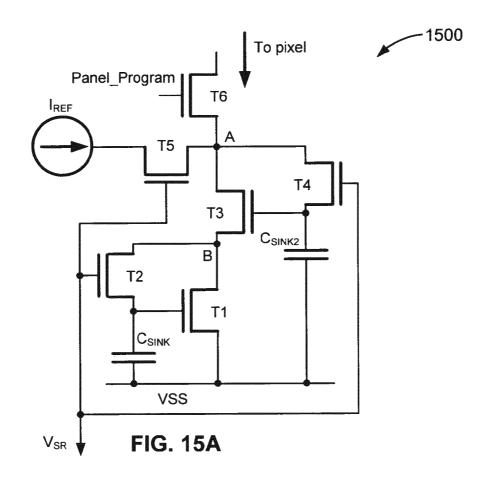

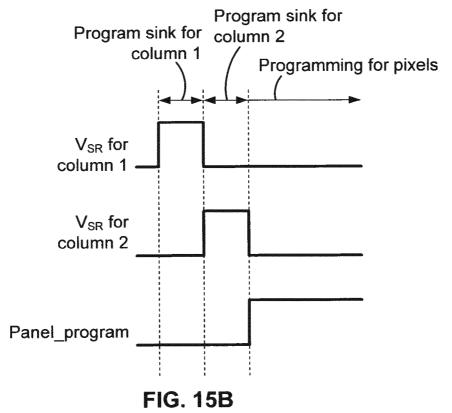

[0123] FIG. 15a illustrates a schematic diagram of a current sink circuit implemented using n-type FETs;

[0124] FIG. 15b illustrates a timing diagram for the circuit shown in FIG. 15a;

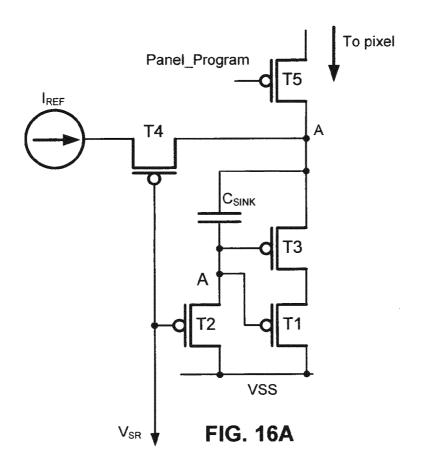

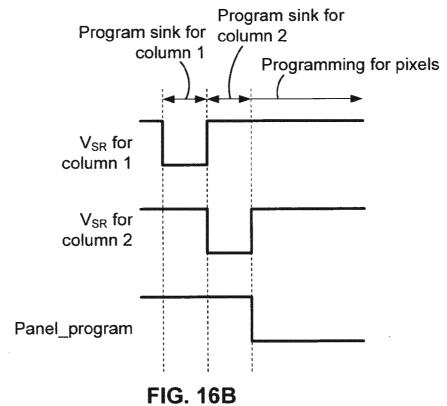

[0125] FIG. 16a illustrates a schematic diagram of a current sink implemented using p-type EFTs;

[0126] FIG. 16b illustrates a timing diagram of the circuit shown in FIG. 16a;

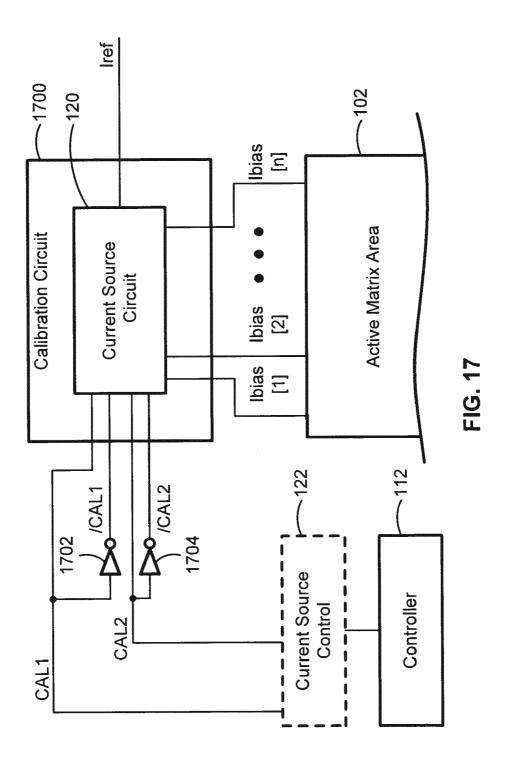

[0127] FIG. 17 illustrates an example block diagram of a calibration circuit:

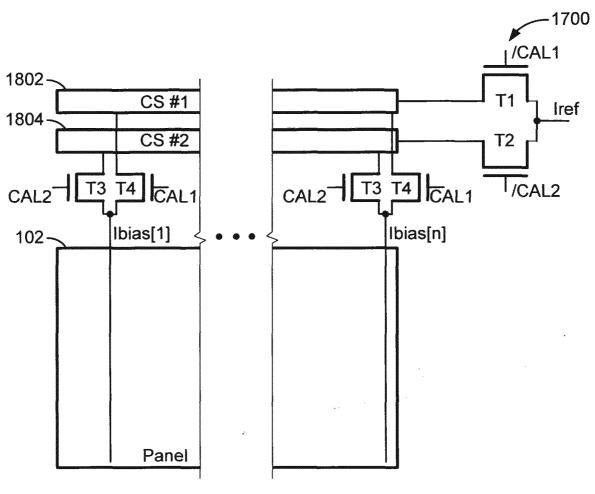

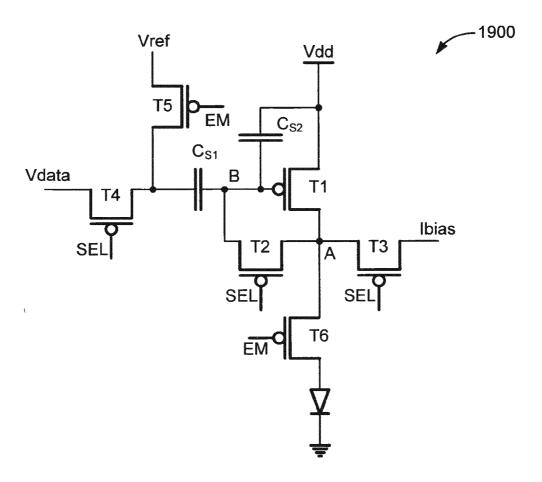

[0128] FIG. 18a illustrates a schematic diagram example of the calibration circuit shown in FIG. 17; and

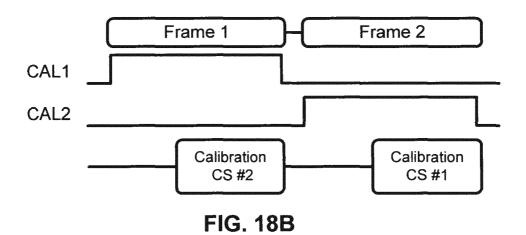

[0129] FIG. 18b illustrates a timing diagram for the calibration circuit shown in FIG. 18a.

[0130] While the present disclosure is susceptible to various modifications and alternative forms, specific embodiments and implementations have been shown by way of example in the drawings and will be described in detail herein. It should be understood, however, that the present disclosure is not intended to be limited to the particular forms disclosed. Rather, the present disclosure is to cover all modifications, equivalents, and alternatives falling within the spirit and scope of the inventions as defined by the appended claims.

# **DETAILED DESCRIPTION**

**[0131]** FIG. 1 is an electronic display system or panel 100 having an active matrix area or pixel array 102 in which an array of pixels 104 are arranged in a row and column configuration. For ease of illustration, only two

rows and columns are shown. External to the active matrix area 102 is a peripheral area 106 where peripheral circuitry for driving and controlling the pixel area 102 are disposed. The peripheral circuitry includes a gate or address driver circuit 108, a source or data driver circuit 110, a controller 112, and an optional supply voltage (e.g., Vdd) control driver or circuit 114. The controller 112 controls the gate, source, and supply voltage drivers 108, 110, 114. The gate driver 108, under control of the controller 112, operates on address or select lines SEL[i], SEL[i+1], and so forth, one for each row of pixels 104 in the pixel array 102. In pixel sharing configurations described below, the gate or address driver circuit 108 can also optionally operate on global select lines GSEL[j] and optionally /GSEL[j], which operate on multiple rows of pixels 104 in the pixel array 102, such as every two rows of pixels 104. The source driver circuit 110, under control of the controller 112, operates on voltage data lines Vdata [k], Vdata[k+1], and so forth, one for each column of pixels 104 in the pixel array 102. The voltage data lines carry voltage programming information to each pixel 104 indicative of a luminance (or brightness as subjectively perceived by an observer) of each light emitting device in the pixel 104. A storage element, such as a capacitor, in each pixel 104 stores the voltage programming information until an emission or driving cycle turns on the light emitting device, such as an organic light emitting device (OLED). The optional supply voltage control circuit 114, under control of the controller 112, controls a supply voltage (EL\_Vdd) line, one for each row of pixels 104 in the pixel array 102, and optionally any of the controllable bias voltages disclosed herein, although the controllable bias voltages can alternately be controlled by the controller 112. During the driving cycle, the stored voltage program-35 ming information is used to illuminate each light emitting device at the programmed luminance.

[0132] The display system or panel 100 further includes a current source (or sink) circuit 120 (for convenience referred to as a current "source" circuit hereafter, but any current source circuit disclosed herein can be alternately a current sink circuit or vice versa), which supplies a fixed bias current (called Ibias herein) on current bias lines 132a, 132b (Ibias[k], Ibias[k+1]), and so forth, one for each column of pixels 104 in the pixel array 102. In an example configuration, the fixed bias current is stable over prolonged usage and can be spatially non-varying. Alternately, the bias current can be pulsed and used only when needed during programming operations. In some configurations, a reference current Iref, from which the fixed bias current (Ibias) is derived, can be supplied to the current source or sink circuit 120. In such configurations, a current source control 122 controls the timing of the application of a bias current on the current bias lines Ibias. In configurations in which the reference current Iref is not supplied to the current source or sink circuit 120 (e.g., FIGS. 9a, 12, 13a), a current source address driver 124 controls the timing of the application of a bias current on the current bias lines Ibias. The current bias

40

50

lines can also be referred to herein as reference current lines.

[0133] As is known, each pixel 104 in the display system 100 needs to be programmed with information indicating the luminance of the light emitting device in the pixel 104. This information can be supplied to each light emitting device in the form of a stored voltage or a current. A frame defines the time period that includes a programming cycle or phase during which each and every pixel in the display system 100 is programmed with a programming voltage indicative of a luminance and a driving or emission cycle or phase during which each light emitting device in each pixel is turned on to emit light at a luminance commensurate with or indicative of the programming voltage stored in a storage element or a programming current. A frame is thus one of many still images that compose a complete moving picture displayed on the display system 100. There are at least schemes for programming and driving the pixels: row-by-row, or frame-by-frame. In row-by-row programming, a row of pixels is programmed and then driven before the next row of pixels is programmed and driven. In frame-byframe programming, all rows of pixels in the display system 100 are programmed first, and all of the pixels are driven row-by-row. Either scheme can employ a brief vertical blanking time at the beginning or end of each frame during which the pixels are neither programmed nor driv-

[0134] The components located outside of the pixel array 102 can be disposed in a peripheral area 130 around the pixel array 102 on the same physical substrate on which the pixel array 102 is disposed. These components include the gate driver 108, the source driver 110, the optional supply voltage control circuit 114, current source control 122, and current source address driver 124, the current source or sink circuit 120, and the reference current source, Iref. Alternately, some of the components in the peripheral area can be disposed on the same substrate as the pixel array 102 while other components are disposed on a different substrate, or all of the components in the peripheral are can be disposed on a substrate different from the substrate on which the pixel array 102 is disposed. Together, the gate driver 108, the source driver 110, and optionally the supply voltage control circuit 114 make up a display driver circuit. The display driver circuit in some configurations can include the gate driver 108 and the source driver 110 but not the supply voltage control circuit 114. In other configurations, the display driver circuit can include the supply voltage control circuit 114 as well.

**[0135]** A programming and driving technique for programming and driving the pixels, including a current-biased, voltage-programmed (CBVP) driving scheme is disclosed herein. The CBVP driving scheme uses a programming voltage to program different gray or color scales to each pixel (voltage programming) and uses a bias current to accelerate the programming and to compensate for time-dependent parameters of a pixel, such

as a shift in the threshold voltage of the driving transistor and a shift in the voltage of the light emitting device, such as an organic light emitting device or OLED.

[0136] A particular type of CBVP scheme is disclosed in which a switch transistor is shared between multiple pixels in the display, resulting in improved manufacturing yield by minimizing the number of transistors used in the pixel array 102. This shared switch scheme also allows a conventional sequential scan driving to be used, in which pixels are programmed and then driven row by row within each frame. An advantage of the shared-transistor configurations disclosed herein is that the total transistor count for each pixel can be reduced. Reducing the transistor count can also improve each pixel's aperture ratio, which is the ratio between the transparent (emissive) area, excluding the pixel's wiring and transistors, and the whole pixel area including the pixel's wiring and transistors.

#### SHARING SWITCH TFTS IN PIXEL CIRCUITS

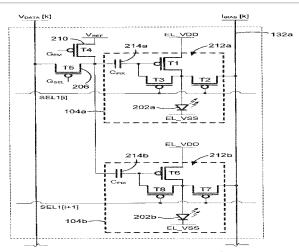

[0137] FIG. 2a illustrates a functional block diagram of a CBVP circuit 200 for the display panel 100 shown in FIG. 1. The CBVP circuit 200 includes the active area 102 shown in FIG. 1 and a peripheral area separate from the active area 102, and the active area 102 includes pixels 104, and each pixel includes a light emitting device 202a arranged on a substrate 204. In FIG. 2a, only two pixels 104a,b are shown for ease of illustration, and a first pixel 104a is in a first row i, and a second pixel 104b is in a second row i+1, adjacent to the first row. The CBVP circuit 200 includes a shared switch transistor 206 connected between a voltage data line Vdata and a shared line 208 that is connected to a reference voltage Vref through a reference voltage transistor 210. The reference voltage can be a direct current (DC) voltage, or a pulsed signal. The first pixel 104a includes a first light emitting device 202a configured to be current-driven by a first drive circuit 212a connected to the shared line 208 through a first storage device 214a, and the second pixel 104b includes a second light emitting device 202b configured to be current-driven by a second drive circuit 212b connected to the shared line 208 through a second storage device 214b.

[0138] The CBVP circuit 200 includes a reference current line 132a configured to apply a bias current lbias to the first and second drive circuits 212a,b. The state (e.g., on or off, conducting or non-conducting in the case of a transistor) of the shared switch transistor 206 can be controlled by a group select line GSEL[j]. The state of the reference voltage switch 210 can be controlled by a reference voltage control line, such as \GSEL[j]. The reference voltage control line 216 can be derived from the group select line GSEL, or it can be its own independent line from the gate driver 108. In configurations where the reference voltage control line 216 is derived from the group select line GSEL, the reference voltage control line 216 can be the inverse of the group select line GSEL

such that when the group select line GSEL is low, the reference voltage control line 216 is high and vice versa. Alternately, the reference voltage control line 216 can be an independently controllable line by the gate driver 108. In a specific configuration, the state of the group select line GSEL is opposite to the state of the reference voltage control line 216.

[0139] Each of the pixels 104a,b is controlled by respective first and second select lines SEL1[i] and SEL1 [i+1], which are connected to and controlled by the gate driver 108. The gate driver 108 is also connected to the shared switch via the group select line GSEL and to the reference voltage transistor via the reference voltage control line 216. The source driver 110 is connected to the shared switch 206 via the voltage data line Vdata, which supplies the programming voltage for each pixel 104 in the display system 100. The gate driver 108 is configured to switch the reference voltage transistor 210 from a first state to a second state (e.g., from on to off) such that the reference voltage transistor 210 is disconnected from the reference voltage Vref during the programming cycle. The gate driver 108 is also configured to switch the shared switch transistor 206 from the second state to the first state (e.g., from off to on) via the group select line GSEL during a programming cycle of a frame to allow voltage programming (via the voltage data line Vdata) of the first and second pixels 104a,b. The reference current line 132k is also configured to apply the bias current Ibias during the programming cycle.

**[0140]** In the example shown, there are a number, i+q, rows of pixels that share the same shared switch 206. Any two or more pixels can share the same shared switch 206, so the number, i+q, can be 2, 3, 4, etc. It is important to emphasize that each of the pixels in the rows i through i+q share the same shared switch 206.

**[0141]** Although, a CBVP technique is used as an example to illustrate the switch sharing technique, it can be applied to different other types of pixel circuits, such as current-programmed pixel circuits or purely voltage-programmed pixel circuits or pixel circuits lacking a current bias to compensate for shifts in threshold voltage and mobility of the LED drive transistors.

[0142] The gate driver 108 is also configured to toggle the first select line SEL1[i] (e.g., from a logic low state to a logic high state or vice versa) during the programming cycle to program the first pixel 104a with a first programming voltage specified by the voltage data line Vdata and stored in the first storage device 214a during the programming cycle. Likewise, the gate driver 108 is configured to toggle the second select line SEL1[i+1] during the programming cycle to program the second pixel 104b with a second programming voltage (which may differ from the first programming voltage) specified by the voltage data line Vdata and stored in the second storage device 214b during the programming cycle.

**[0143]** The gate driver 108 can be configured to, following the programming cycle, such as during an emission cycle, switch the reference voltage transistor 210

via the reference voltage control line 216 from the second state to the first state (e.g., from off to on) and to switch the shared switch transistor 206 via the group select line GSEL from the first state to the second state (e.g., from on to off). The optional supply voltage control circuit 114 shown in FIG. 1 can be configured to adjust a supply voltage, EL\_Vdd, coupled to the first and second light emitting devices 202a,b to turn on the first and second light emitting devices 202a,b during the driving or emission cycle that follows the programming cycle of the frame. In addition, the optional supply voltage control circuit 114 can be further configured to adjust the supply voltage, EL\_Vdd, to a second supply voltage, e.g., Vdd2, to a level that ensures that the first and second light emitting devices 202a,b remain in a non-emitting state (e.g., off) during the programming cycle.

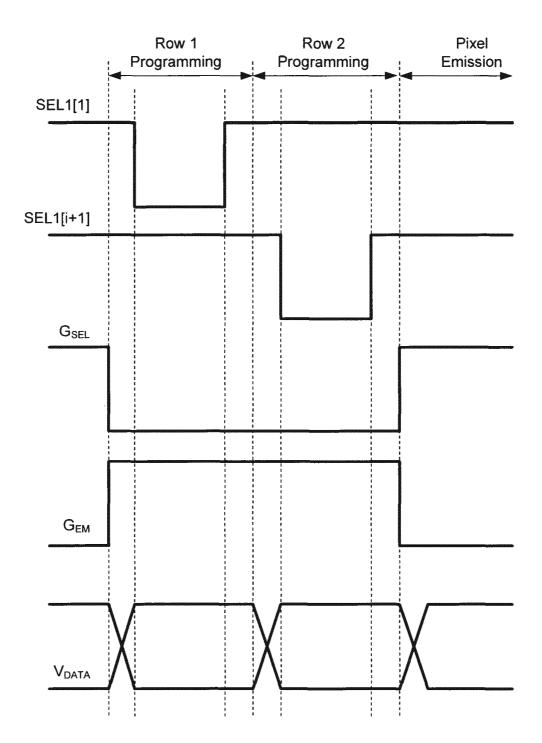

[0144] FIG. 2b is an example timing diagram of the signals used by the CBVP circuit 200 of FIG. 2a or any other shared-transistor circuit disclosed herein during a programming cycle. Starting from the top of the timing diagram, the gate driver 108 toggles the group select line GSEL from a second state to a first state, e.g., from high to low, and holds that line in the first state until all of the pixels in the group of rows shared by the common shared switch 206 are programmed. In this example, there are a number, i+q, rows of pixels that share the same shared switch, where i+q can be 2, 3, 4, etc. The gate driver 108 activates the select line SEL[i] for the ith row in the group to be programmed in the shared pixel circuit, such as the CBVP circuit 200. The pixel in the ith row [i] is programmed by the corresponding programming voltage in Vdata while the SEL[i] line is activated for that ith row [i]. [0145] The gate driver 108 activates the selection line SEL [i+1] for the i+1st row in the group to be programmed in the shared pixel circuit, and the pixel in the i+1st row [i+1] is programmed by the corresponding programming voltage in Vdata while the SEL[i+1] line is activated for the i+1st row [i+1]. This process is carried out for at least two rows and is repeated for every other row in the group of pixels that share the shared switch 206. For example, if there are three rows in the group of pixels, then the gate driver 108 activates the selection line SEL [i+q] for the i+qth row (where q=2) in the group to be programmed in the shared circuit, and the pixel in the i+qth row [i+q] is programmed by the corresponding programming voltage in Vdata while the SEL[i+q] line is activated for the i+qth row [i+q].

**[0146]** While the group select line GSEL is activated, the supply voltage control 114 adjusts the supply voltage, Vdd, to each of the pixels in the group of pixels that share the shared switch 206, from Vdd1 to Vdd2, where Vdd1 is a voltage sufficient to turn on each of the light emitting devices 202a,b,n in the group of pixels being programmed, and Vdd2 is a voltage sufficient to turn off each of the light emitting devices 202a,b,n in the group of pixels being programmed. Controlling the supply voltage in this manner ensures that the light emitting devices 202a,b,n in the group of pixels being programmed cannot be turned

30

35

40

45

on during the programming cycle. Still referring to the timing diagram of FIG. 2b, the reference voltage and the reference current maintain a constant voltage, Vref, and current, Iref, respectively.

# 3Te Pixel Circuit Schematic With Sharing Architecture

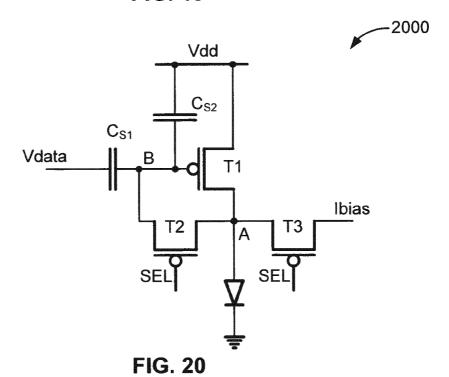

[0147] FIG. 3a is a circuit schematic of an exemplary CBVP circuit schematic that can be used in connection with the CBVP circuit 200 shown in FIG. 2a. This design features eight TFTs in every two row-adjacent pixels (i, i+1) in a column, k, in a pixel-sharing configuration. In this eight-TFT pixel-sharing configuration, there is no gating TFT between the driving TFT (T1 and T7) and the light emitting device 202a,b in both sub-pixels 104a,b. The driving TFTs T1 and T7 are connected directly to their respectively light emitting devices 202a,b at all times. This configuration allows the toggling of the supply voltage, EL\_VDD, to the light emitting devices 202a,b to avoid excessive and unnecessary current drain when the pixel is not in the emission or driving phase.

[0148] In the FIG. 3a circuit schematic example, the first and second storage devices 214a,b are storage capacitors C<sub>PIX</sub>, both having a terminal connected to the shared line 208. Again, only two pixels 104a,b in two rows i and i+1 are shown for ease of illustration. The shared switch 206 (a transistor labeled T5) can be shared among two or more adjacent rows of pixels 104. The transistors shown in this circuit are p-type thin-film transistors (TFTs), but those of ordinary skill in the art will appreciate that the circuit can be converted to an n-type TFT or a combination of n- and p-type TFTs or other types of transistors, including metal-oxide-semiconductor (MOS) transistors. The present disclosure is not limited to any particular type of transistor, fabrication technique, or complementary architecture. The circuit schematics disclosed herein are exemplary.

**[0149]** The first drive circuit 212a of the first pixel 104a includes a first drive transistor, labeled T1, connected to a supply voltage EL\_Vdd and to the first light emitting device 202a. The first drive circuit 212a further includes a pair of switch transistors, labeled T2 and T3, each coupled to the first select line SEL1[i] for transferring the bias current from the reference current line 132a to the first storage device, identified as a capacitor, Cpix, during a programming cycle. The gate of T1 is connected to the capacitor Cpix 214a. T2 is connected between the reference current line 132a and the first light emitting device 202a. T3 is connected between the first light emitting device 202a and the capacitor Cpix 214a.

**[0150]** The second drive circuit 212b of the second pixel 104b includes a second drive transistor, labeled T6, connected to the supply voltage, EL\_VDD, and to the second light emitting device 202b. The gate of T6 is connected to a second storage device 214b, identified as a capacitor, Cpix, and a pair of switch transistors, labeled T7 and T8, each coupled to the second select line, SEL1

[i+1] for transferring the bias current, Ibias, from the reference current line 132a to the capacitor 214b during a programming cycle. T7 is connected between the reference current line 132a and the second light emitting device 202b and T8 is connected between the second light emitting device 202b and the capacitor 214b.

[0151] The details of FIG. 3a will now be described. It should be noted that every transistor described herein includes a gate terminal, a first terminal (which can be a source or a drain in the case of a field-effect transistor), and a second terminal (which can be a drain or a source). Those skilled in the art will appreciate that, depending on the type of the FET (e.g., a n-type or a p-type), the drain and source terminals will be reversed. The specific schematics described herein are not intended to reflect the sole configuration for implementing aspects of the present disclosure. For example, in FIG. 3a, although a p-type CBVP circuit is shown, it can readily be converted to an n-type CBVP circuit.

[0152] The gate of T1 is connected to one plate of the capacitor Cpix 214a. The other plate of the capacitor Cpix 214a is connected to the source of T5. The source of T1 is connected to a supply voltage, EL\_VDD, which in this example is controllable by the supply voltage control 114. The drain of T1 is connected between the drain of T3 and the source of T2. The drain of T2 is connected to the bias current line 132a. The gates of T2 and T3 are connected to the first select line SEL1[i]. The source of T3 is connected to the gate of T1. The gate of T4 receives a group emission line,  $G_{EM}$ . The source of T4 is connected to the reference voltage Vref. The drain of T4 is connected between the source of T5 and the other plate of the first capacitor 214a. The gate of T5 receives the group select line  $G_{\mbox{\scriptsize SEL}},$  and the drain of T5 is connected to the Vdata line. The light emitting device 202a is connected to the drain of T1.

[0153] Turning now to the next sub-pixel in the CBVP circuit of FIG. 3a, the gate of T6 is connected to one plate of the second capacitor 214b and to the drain of T8. The other plate of the second capacitor 214b is connected to the source of T5, the drain of T4, and the other plate of the first capacitor 214a. The source of T6 is connected to the supply voltage EL\_VDD. The drain of T6 is connected to the drain of T8, which is connected to the source of T7. The drain of T7 is connected to the bias current line Ibias 132a. The gates of T7 and T8 are connected to the second select line SEL1[i+1]. The second light emitting device 202b is connected between a ground potential EL\_VSS and the drain of T6.

[0154] FIG. 3b illustrates an example timing diagram for the CBVP circuit shown in FIG. 3a. As mentioned above, this shared-pixel configuration toggles the supply voltage, EL\_VDD, to avoid drawing excess current when the pixel is not in a driving or emission cycle. In general, the supply voltage control 114 lowers the potential of the EL\_VDD line during pixel programming, in order to limit the potential across the light emitting device 202a,b to reduce current consumption and hence brightness dur-

20

ing pixel programming. The toggling of the supply voltage, EL\_VDD, by the supply voltage control 114, combined with the sequential programming operation (in which a group of pixels are programmed and then immediately driven, one group of pixels at a time), implies that the EL\_VDD line 132a is not shared globally among all pixels. The voltage supply line 132a is shared only by the pixels in a common row, and such power distribution is carried out by integrated electronics at the peripheral area 106 of the pixel array 102. The omission of one TFT at the unit pixel level reduces the real-estate consumption of said pixel design, achieving higher pixel resolution than higher-transistor shared-pixel configurations, such as shown in FIG. 4a, at the expense of periphery integrated electronics.