# (11) EP 2 093 748 B1

## (12)

# **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication and mention of the grant of the patent:16.01.2013 Bulletin 2013/03

(21) Application number: 07828924.6

(22) Date of filing: 01.10.2007

(51) Int Cl.: **G09G** 3/32 (2006.01)

(86) International application number: **PCT/JP2007/069184**

(87) International publication number:WO 2008/108024 (12.09.2008 Gazette 2008/37)

## (54) DISPLAY DEVICE AND ITS DRIVING METHOD

ANZEIGEANORDNUNG UND VERFAHREN ZU IHRER ANSTEUERUNG DISPOSITIF D'AFFICHAGE ET SON DISPOSITIF DE COMMANDE

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

HU IE IS IT LI LT LU LV MC MT NL PL PT RO SE

SI SK TR

(30) Priority: **08.03.2007** JP 2007058021

(43) Date of publication of application: **26.08.2009 Bulletin 2009/35**

(60) Divisional application: 11003018.6 / 2 369 571

(73) Proprietor: Sharp Kabushiki Kaisha Osaka-shi Osaka 545-8522 (JP)

(72) Inventor: KISHI, Noritaka Osaka-shi, Osaka 545-8522 (JP) (74) Representative: Müller - Hoffmann & Partner Patentanwälte Innere Wiener Strasse 17 81667 München (DE)

(56) References cited:

WO-A1-2005/013250 JP-A- 2004 252 110 JP-A- 2005 128 521 JP-A- 2005 352 411 JP-A- 2005 352 411 US-A1- 2004 108 518 US-A1- 2004 239 596 US-A1- 2006 139 253

AROKIA NATHAN ET AL: "46.1: Invited Paper: a-Si for AMOLED - Meeting the Performance and Cost Demands of Display Applications (Cell Phone to HDTV)" SID 2006, 2006 SID INTERNATIONAL SYMPOSIUM, SOCIETY FOR INFORMATION DISPLAY, vol. XXXVII, 24 May 2005 (2005-05-24), pages 1543-1545, XP007012784 ISSN: 0006-966X

P 2 093 748 B1

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

#### **Description**

20

30

35

40

45

50

#### **TECHNICAL FIELD**

[0001] The present invention relates to display devices, more particularly, to display devices using an electric current driving element such as an organic EL display or an FED, and a method for driving the same.

#### **BACKGROUND ART**

[0002] Recently, there has been increased demand for thin and lightweight display devices achieving high-speed response. Therefore, there has been actively conducted research and development on organic EL (Electro Luminescence) displays and FEDs (Field Emission Displays).

[0003] An organic EL element included in an organic EL display emits light at higher luminance as a voltage to be applied thereto is high and an electric current flowing therethrough is large in amount. In the organic EL element, however, a relation between the luminance and the voltage varies readily due to influences such as a driving time and an ambient temperature. Consequently, it becomes very difficult to suppress the variations in luminance of the organic EL element if a driving scheme of a voltage control type is adopted for the organic EL display. In contrast to this, the luminance of the organic EL element is almost proportional to the electric current. This proportional relation is less susceptible to an influence of an extraneous factor such as an ambient temperature. Accordingly, it is preferable that a driving scheme of an electric current control type is adopted for the organic EL display.

[0004] Meanwhile, a display device includes a pixel circuit and a drive circuit each of which is configured using a TFT (Thin Film Transistor) made of amorphous silicon, low-temperature polycrystalline silicon, CG (Continuous Grain) silicon or the like. However, such a TFT has characteristics (e.g., threshold voltage, mobility) which vary readily. For this reason, a circuit that compensates the variations in characteristic of the TFT is provided for the pixel circuit of the organic EL display. Thus, the variations in luminance of the organic EL element are suppressed by action of this circuit.

[0005] In the driving scheme of the electric current drive type, a scheme for compensating variations in characteristic of a TFT is broadly divided into an electric current program scheme in which an amount of an electric current flowing through a driving TFT is controlled by an electric current signal and a voltage program scheme in which the amount of this electric current is controlled by a voltage signal. Use of the electric current program scheme allows compensation of variations in threshold voltage and mobility. Use of the voltage program scheme allows compensation of only the variations in threshold voltage.

[0006] However, the electric current program scheme has the following two problems. First, it is difficult to design a pixel circuit and a drive circuit since an electric current to be used herein is considerably small in amount. Second, it is difficult to make a large-area circuit since an influence of a parasitic capacity is exerted readily when an electric current signal is set. In contrast to this, according to the voltage program scheme, an influence of a parasitic capacity or the like is minute and a circuit is designed in a relatively ease manner. Moreover, an influence of variations in mobility to be exerted on an amount of an electric current is smaller than an influence of variations in threshold voltage to be exerted on the amount of the electric current. Further, the variations in mobility can be suppressed to a certain degree in a step of manufacturing a TFT. Accordingly, even a display device that adopts the voltage program scheme can provide satisfactory display quality.

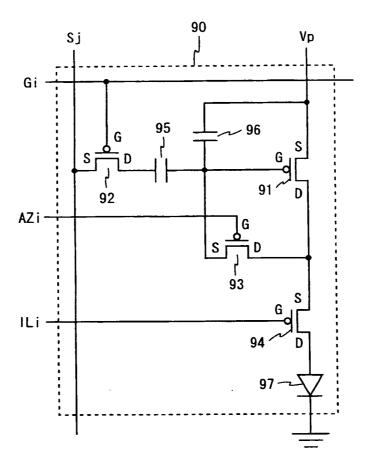

[0007] With regard to an organic EL display that adopts the driving scheme of the electric current drive type, conventionally, there has been known the following pixel circuit. Fig. 11 is a circuit diagram showing a pixel circuit described in Patent Document 1. The pixel circuit 90 shown in Fig. 11 includes a driving TFT 91, switching TFTs 92 to 94, capacitors 95 and 96, and an organic EL element 97 (also referred to as an OLED (Organic Light Emitting Diode)). Each of the TFTs included in the pixel circuit 90 is of a P-channel type.

[0008] In the pixel circuit 90, the driving TFT 91, the switching TFT 94 and the organic EL element 97 are provided in series between a power supply wiring line Vp (potential: VDD) and a common cathode (GND). The capacitor 95 and the switching TFT 92 are provided in series between a gate terminal of the driving TFT 91 and a data line Sj. The switching TFT 93 is provided between the gate terminal and a drain terminal of the driving TFT 91, and the capacitor 96 is provided between the gate terminal of the driving TFT 91 and the power supply wiring line Vp. The switching TFT 92 has a gate terminal connected to a scanning line Gi, the switching TFT 93 has a gate terminal connected to an autozero line AZi and the switching TFT 94 has a gate terminal connected to an illumination line ILi.

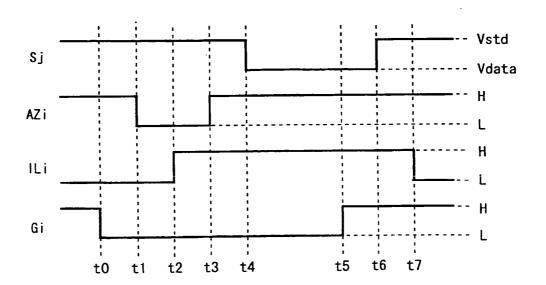

[0009] Fig. 12 is a timing chart showing a timing that data is written to the pixel circuit 90. Prior to a time t0, a potential at the scanning line Gi and a potential at the auto-zero line AZi are controlled to a high level, respectively, a potential at the illumination line ILi is controlled to a low level, and a potential at the data line Sj is controlled to a reference potential Vstd. At the time t0, when the potential at the scanning line Gi is changed to the low level, the switching TFT 92 is changed to a conduction state. At a time t1, next, when the potential at the auto-zero line AZi is changed to the low level, the switching TFT 93 is changed to the conduction state. In the driving TFT 91, thus, the gate terminal and the drain

terminal become equal in potential to each other.

[0010] At a time t2, next, when the potential at the illumination line ILi is changed to the high level, the switching TFT 94 is changed to a non-conduction state. Herein, an electric current flows from the power supply wiring line Vp into the gate terminal of the driving TFT 91 via the driving TFT 91 and the switching TFT 93. The potential at the gate terminal of the driving TFT 91 rises during a period that the driving TFT 91 is in the conduction state. The driving TFT 91 is changed to the non-conduction state when a gate-source voltage becomes a threshold voltage Vth (negative value) (i.e., when the potential at the gate terminal becomes (VDD + Vth)). Accordingly, the potential at the gate terminal of the driving TFT 91 rises to (VDD + Vth).

[0011] At a time t3, next, when the potential at the auto-zero line AZi is changed to the high level, the switching TFT 93 is changed to the non-conduction state. Herein, a difference in potential (VDD + Vth - Vstd) between the gate terminal of the driving TFT 91 and the data line Sj is held at the capacitor 95.

[0012] At a time t4, next, when the potential at the data line Sj is changed from the reference potential Vstd to a data potential Vdata, the potential at the gate terminal of the driving TFT 91 is changed by the same amount (Vdata - Vstd) and then becomes (VDD + Vth + Vdata - Vstd). At a time t5, next, when the potential at the scanning line Gi is changed to the high level, the switching TFT 92 is changed to the non-conduction state. Herein, the gate-source voltage (Vth + Vdata - Vstd) of the driving TFT 91 is held at the capacitor 96. At a time t6, next, the potential at the data line Sj is changed from the data potential Vdata to the reference potential Vstd.

[0013] At a time t7, next, when the potential at the illumination line ILi is changed to the low level, the switching TFT 94 is changed to the conduction state. Thus, an electric current flows from the power supply wiring line Vp into the organic EL element 97 via the driving TFT 91 and the switching TFT 94. An amount of the electric current flowing through the driving TFT 91 increases/decreases in accordance with the potential (VDD + Vth + Vdata - Vstd) at the gate terminal. However, the amount of the electric current is the same as long as the potential difference (Vdata - Vstd) is the same even when the threshold voltage Vth is different. Irrespective of the value of the threshold voltage Vth, accordingly, the electric current flows through the organic EL element 97 in an amount which depends on the potential Vdata, so that the organic EL element 97 emits light at a luminance which depends on the data potential Vdata.

[0014] In addition to this, with regard to the organic EL display, there have been known a method for providing a threshold value correction circuit outside a pixel circuit, and a method for setting a threshold value correction period longer than a period for selecting a pixel circuit. For example, Patent Document 2 describes the following method. That is, an electric current capability of a drive element is measured and is stored in a memory provided outside a pixel circuit, and a voltage to be supplied to a panel is changed in accordance with the stored electric current capability (see Fig. 13). Moreover, Patent Document 3 describes the following method. That is, a switch for applying an initial voltage to one end of a coupling capacitance is provided for setting a threshold value correction period longer than a selection period.

[Patent Document 1] International Publication No. 98/48403 Pamphlet

[Patent Document 2] Japanese Laid-Open Patent Publication No. 2002-278513

[Patent Document 3] Japanese Laid-Open Patent Publication No. 2004-133240

[0015] JP 2005 352411 refers to a driving circuit for current drive type display elements. A driving element controlling a current that flows into an organic electroluminescence element is stopped. A preset voltage is applied to a data line connected to the pixel circuit to initialize voltages at a pixel capacitor and a hold capacitor in a correction circuit associated to a plurality of pixel circuits assigned to the same data line. The pixel capacitor is discharged by closing a circuit comprising the driving element, a transistor connecting a load terminal of the driving element with a data line, the data line and a further transistor connecting the data line with the control terminal of the driving element and the pixel capacitor. The discharge of the pixel capacitor is stopped when the potential at the control terminal of the driving element equals the threshold voltage. The same voltage is reproduced via the data line at the hold capacitor in the correction circuit as a correction voltage. The correction voltage is added/subtracted to/from a data signal voltage applied to the data signal. [0016] US 2004/0108518 A1 refers to a pixel circuit where, in a test mode, a testing device outputs test display data to a control circuit via a data line. A control circuit outputs a corresponding test data line driving signal and, in response to the test data line driving signal, a driver transistor of the pixel circuit drives a current that is output to a current detecting circuit in the testing device via the data line. The testing device compares the detected current values of the pixel circuits with set current values expected for the test data voltages and stores the comparison result. Based on the comparison result a correction voltage is derived. The control circuit uses the correction voltage when display data is converted into the data signal supplied to the pixel circuits.

55

50

10

30

35

40

45

#### DISCLOSURE OF THE INVENTION

10

20

30

35

40

50

55

#### PROBLEMS TO BE SOLVED BY THE INVENTION

**[0017]** As described above, use of the pixel circuit 90 shown in Fig. 11 allows compensation of the variations in threshold voltage of the driving TFT 91 and allows light emission by the organic EL element 97 at a desired luminance. However, this pixel circuit (hereinafter, referred to as the conventional pixel circuit) has the following problems.

[0018] A first problem is that an amplitude of a data voltage can not be utilized efficiently. In the conventional pixel circuit, data is written by capacitance coupling. Consequently, even when a certain data voltage is written from an outside of the pixel circuit, a voltage to be applied actually as an overdrive voltage to the driving TFT becomes Cc/ (Cc + Cs + Cgs) times as large as the written data voltage (where Cc represents a capacitance of the capacitor 95, Cs represents a capacitance of the capacitor 96 and Cgs represents a gate-source capacitance of the driving TFT 91). As described above, since the data voltage can not be utilized efficiently, power consumption in a data driver circuit is increased. When the coupling capacitance Cc is set to be considerably large, the amplitude of the data voltage can be utilized efficiently. However, the pixel circuit is disadvantageously increased in scale. In addition, there arises a problem that the parasitic capacitance Cgs, which can not be controlled with high accuracy, exerts an adverse influence on a drive voltage.

[0019] A second problem is that the threshold value correction is low in accuracy. As described above, since the actual drive voltage becomes Cc/ (Cc + Cs + Cgs) times as large as the voltage applied from the outside, an effect of the threshold value correction also becomes Cc/ (Cc + Cs + Cgs) times. Consequently, it is difficult to completely correct the threshold voltage.

**[0020]** A third problem is that the pixel circuit is increased in scale. As described above, when the coupling capacitance Cc is increased in order to deal with the parasitic capacitance, an area occupied by the capacitor 95 becomes large in the layout of the pixel circuit. Consequently, an aperture ratio is reduced in an organic EL display having a bottom emission configuration in which light is extracted from a bottom side of a substrate. Moreover, since the increase in circuit area results in reduction of a yield in manufacturing, the area of the pixel circuit must be decreased and the number of elements in the pixel circuit must be reduced.

**[0021]** A fourth problem is that an inspection in manufacturing becomes difficult. In the conventional pixel circuit, the gate terminal of the driving TFT is connected to the data line through the capacitor. Consequently, it is difficult to inspect the electric current, which flows through the driving TFT, via the data line. For this reason, it becomes difficult to improve a yield through to the inspection.

[0022] A fifth problem is that the threshold value correction period is restricted to a short time. In the conventional pixel circuit, the threshold value correction and the data write must be performed within the period for selecting the pixel circuit. The threshold value correction requires a time until the gate-source voltage of the diode-connected drive element sufficiently approximates the threshold voltage. In a display device with high definition, however, such a selection period is very short. For example, in a case where a panel having a resolution of VGA is driven at 60 frames/s, a selection period is set at about 30 µs. It is difficult to complete threshold value correction and data write within this short time.

[0023] According to the method described in Patent Document 2, the third problem can be solved. However, since the memory for storing the electric current capability of each drive element is provided, a cost of a peripheral circuit and a layout area are increased. According to the method described in Patent Document 3, moreover, the fifth problem can be solved. However, since the switch for applying the initial voltage is provided, the pixel circuit is further increased in scale.

[0024] Hence, an object of the present invention is to provide a display device that efficiently utilizes an amplitude of a data voltage and performs threshold value correction with high accuracy, without increasing a scale of a pixel circuit.

## 45 MEANS FOR SOLVING THE PROBLEMS

[0025] A first aspect of the present invention is a display device of an electric current driving type, including: a plurality of pixel circuits arranged in correspondence with intersections of a plurality of scanning lines and a plurality of data lines, each pixel circuit including an electro-optical element and a drive element having a control terminal connected to the data line through a switching element; a scanning signal output circuit selecting a write-target pixel circuit through use of the scanning line, and exercising control such that the selected pixel circuit outputs, to the data line, a voltage which depends on a threshold voltage of the drive element; and a display signal output circuit applying, to the data line, a voltage obtained by adding or subtracting a correction voltage corresponding to the threshold voltage to or from a data voltage corresponding to display data, based on the voltage outputted to the data line, wherein the display signal output circuit includes a plurality of analog buffers, and a plurality of correcting capacitances and a plurality of switch circuits provided for each data line, and the switch circuit switches between a state that one electrode of the correcting capacitance is connected to the data line through the analog buffer and the

other electrode thereof is applied with the data voltage.

**[0026]** A second aspect of the present invention is the display device according to the first aspect of the present invention, wherein the electro-optical element and the drive element are provided in series between two power supply wiring lines in the pixel circuit, and the pixel circuit further includes a first switching element connected to a control terminal of the drive element and the data line, a second switching element provided between the control terminal and one conductive terminal of the drive element, a third switching element provided together with the electro-optical element and the drive element in series between the power supply wiring lines, and a capacitance having one end connected to the control terminal of the drive element.

[0027] A third aspect of the present invention is the display device according to the second aspect of the present invention, wherein the scanning signal output circuit controls the write-target pixel circuit such that the first and second switching elements are set at a conduction state, the third switching element is set at a non-conduction state, next, the second switching element is changed to the non-conduction state and the third switching element is changed to the conduction state, and the display signal output circuit applies, to the data line, the voltage obtained by adding or subtracting the correction voltage to or from the data voltage after the second switching element is changed to the non-conduction state, based on a voltage of the data line in the case where the second switching element is in the conduction state.

**[0028]** A fourth aspect of the present invention is the display device according to the second aspect of the present invention, wherein each of the drive element and the first to third switching elements is a thin film transistor, one of the first and third switching elements is of a P-channel type and the other switching element is of an N-channel type, and the first and third switching elements have control terminals connected to a common wiring line.

**[0029]** A fifth aspect of the present invention is the display device according to the second aspect of the present invention, wherein each of the drive element and the first to third switching elements is a thin film transistor, one of the second and third switching elements is of a P-channel type and the other switching element is of an N-channel type, and the second and third switching elements have control terminals connected to a common wiring line.

[0030] A sixth aspect of the present invention is the display device according to the second aspect of the present invention, wherein the drive element is an enhancement P-channel type transistor, and the pixel circuit selected by the scanning signal output circuit outputs, to the data line, a voltage obtained by subtracting an absolute value of the voltage which depends on the threshold voltage of the drive element from a higher one of voltages of the power supply wiring lines.

[0031] A seventh aspect of the present invention is the display device according to the second aspect of the present invention, wherein the drive element is an enhancement N-channel type transistor, and the pixel circuit selected by the scanning signal output circuit outputs, to the data line, a voltage obtained by adding an absolute value of the voltage which depends on the threshold voltage of the drive element to a lower one of voltages of the power supply wiring lines.

[0032] An eighth aspect of the present invention is the display device according to the second aspect of the present invention, wherein the display signal output circuit applies a predetermined constant voltage to the data line at a part of a conduction period of the first switching element.

**[0033]** A ninth aspect of the present invention is the display device according to the first aspect of the present invention, wherein the analog buffer is provided for the plurality of data lines.

[0034] A tenth aspect of the present invention refer to a method for driving a display device according to the first aspect of the invention.

#### **EFFECTS OF THE INVENTION**

20

30

35

40

45

50

55

[0035] According to the first or tenth aspect of the present invention, it is possible to read the voltage which depends on the threshold voltage of the drive element from the selected pixel circuit and to apply, to the control terminal of the drive element, the voltage obtained by adding or subtracting the correction voltage (the voltage corresponding to the threshold voltage) to or from the data voltage. Accordingly, it is possible to detect the threshold voltage of the drive element to compensate variations in threshold voltage, and to allow the electro-optical element to emit light at a desired luminance. Moreover, the threshold value correction circuit is provided outside the pixel circuit and the threshold voltage is detected by use of the data line, leading to reduction in scale and area of the pixel circuit. Further, the threshold voltage is detected as a voltage signal, so that a current-voltage conversion element becomes unnecessary unlike a case where an electric current signal is fed back. Therefore, variations in correction effect can be suppressed. Moreover, a desired voltage is applied to the control terminal of the drive element through no coupling capacitance. Therefore, it is possible to efficiently utilize an amplitude of the data voltage and to reduce power consumption. Moreover, the display signal output circuit can apply, to the data line, the voltage obtained by adding "the difference between the data voltage and the constant voltage" to the voltage of the data line. Accordingly, when the constant voltage is determined appropriately, the voltage obtained by adding or subtracting the correction voltage (the voltage corresponding to the threshold voltage of the drive element) to or from the data voltage can be applied to the data line, based on the voltage outputted from the pixel circuit to the data line. Moreover, this addition or subtraction is performed outside the pixel circuit, leading to

reduction in scale of the pixel circuit. Further, the analog buffer is provided between the correcting capacitance and the data line. Thus, it is possible to suppress attenuation due to coupling of the voltage held at the correcting capacitance and to realize high image quality.

**[0036]** According to the second aspect of the present invention, it is possible to reduce the capacitance to be used for threshold value correction, to improve an aperture ratio and a yield, and to reduce power consumption.

**[0037]** According to the third aspect of the present invention, it is possible to divide the period for selecting the pixel circuit into a period for detecting the threshold voltage and a period for writing the corrected data voltage, and to allow commonality of a feedback line for reading the threshold voltage and a data line for writing the data.

**[0038]** According to the fourth or fifth aspect of the present invention, it is possible to reduce the number of wiring lines in such a manner that the first to third switching elements share the wiring line to be connected to the control terminals thereof. Thus, it is possible to make an aperture ratio of a pixel higher.

**[0039]** According to the sixth aspect of the present invention, the variations in threshold voltage can be compensated in the drive element of the P-channel type when the voltage obtained by subtraction of the absolute value of the threshold voltage is applied to the control terminal. Therefore, it is possible to compensate the variations in threshold voltage of the drive element by use of the voltage outputted from the selected pixel circuit.

**[0040]** According to the seventh aspect of the present invention, the variations in threshold voltage can be compensated in the drive element of the N-channel type when the voltage obtained by addition of the absolute value of the threshold voltage is applied to the control terminal. Therefore, it is possible to compensate the variations in threshold voltage of the drive element by use of the voltage outputted from the selected pixel circuit.

**[0041]** According to the eighth aspect of the present invention, the suitable constant voltage is applied to the control terminal of the drive element. Thus, it is possible to reduce a time which is required until the voltage which depends on the threshold voltage of the drive element is outputted to the data line. Accordingly, it is possible to suppress variations in correction effect and to improve image quality even when the threshold value correction period is short.

**[0042]** According to the ninth aspect of the present invention, it is possible to realize a display panel with high definition in such a manner that the analog buffer having a large circuit scale is not arranged for each data line, but is arranged for the plurality of data lines.

#### BRIEF DESCRIPTION OF THE DRAWINGS

## 30 [0043]

35

40

45

50

55

10

15

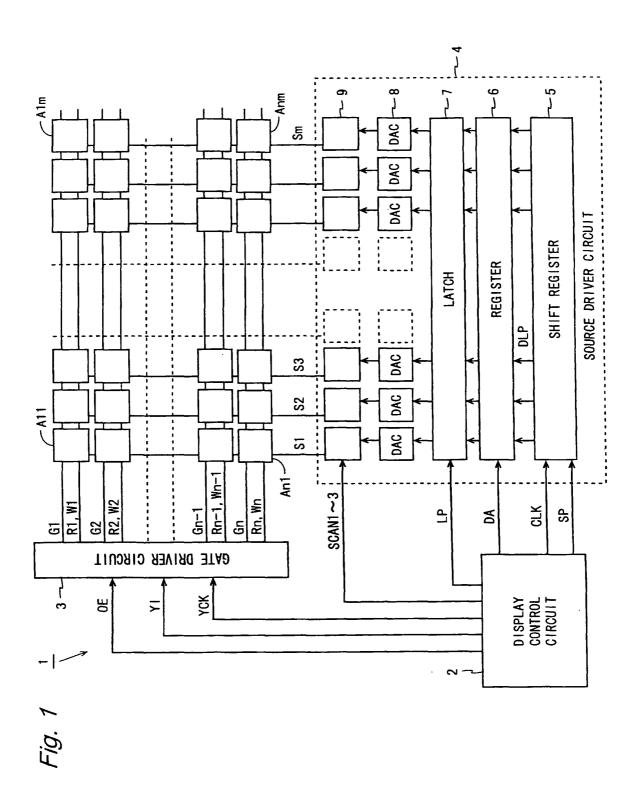

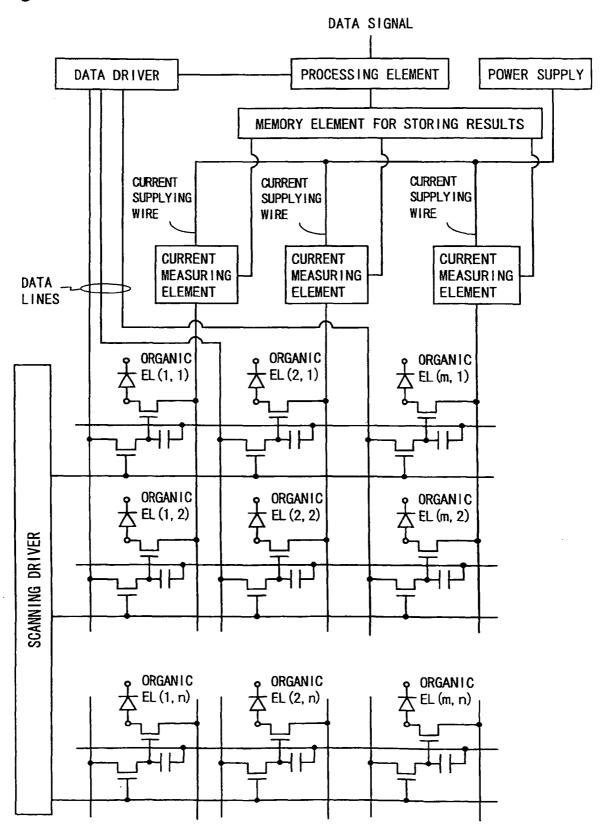

Fig. 1 is a block diagram showing a configuration of display devices according to first to third embodiments of the present invention.

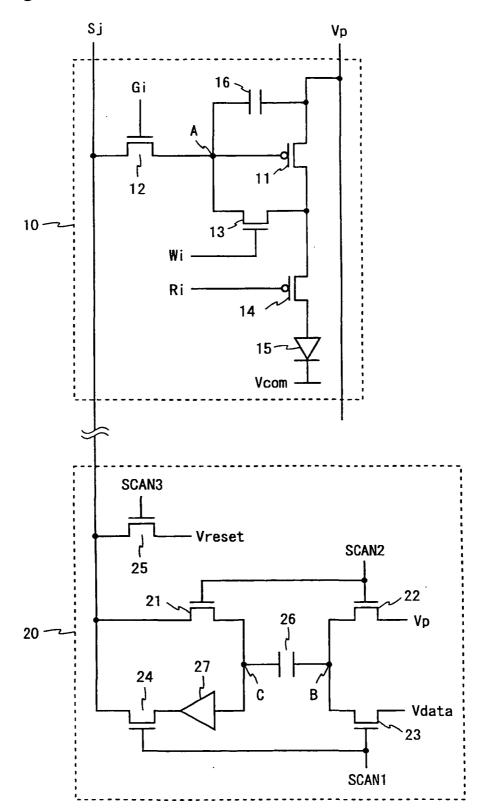

Fig. 2 is a circuit diagram showing a pixel circuit and a threshold value correction circuit each included in the display device according to the first embodiment of the present invention.

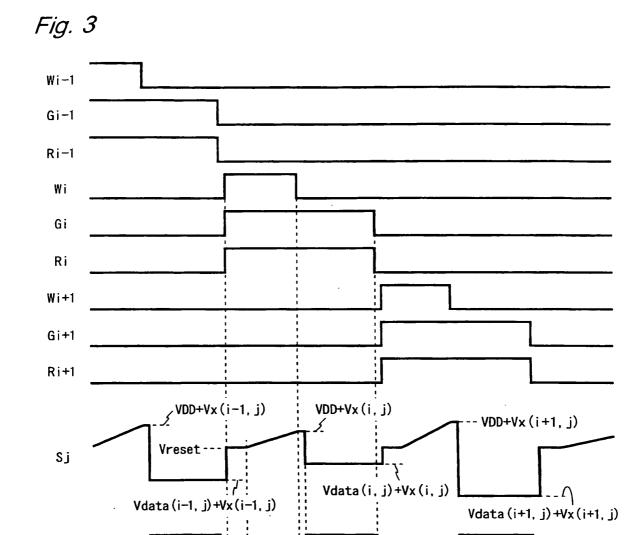

Fig. 3 is a timing chart showing a timing that data is written to the pixel circuit in the display device according to the first embodiment of the present invention.

Fig. 4 shows an example of a temporal change in gate-source voltage of a diode-connected TFT.

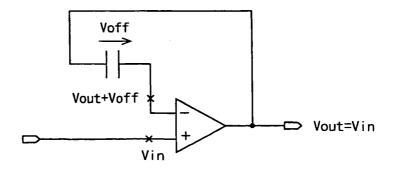

Fig. 5A is a circuit diagram showing a buffer having an offset cancel function.

Fig. 5B is a timing chart for the buffer shown in Fig. 5A.

Fig. 5C shows operations of the buffer shown in Fig. 5A.

Fig. 5D shows operations of the buffer shown in Fig. 5A.

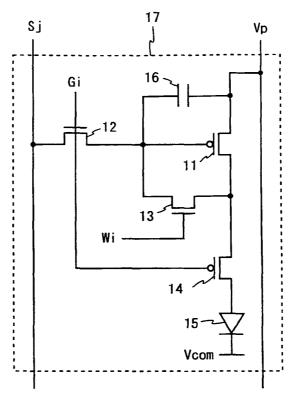

Fig. 6A is a circuit diagram showing a pixel circuit included in a display device according to a first modified example of the first embodiment of the present invention.

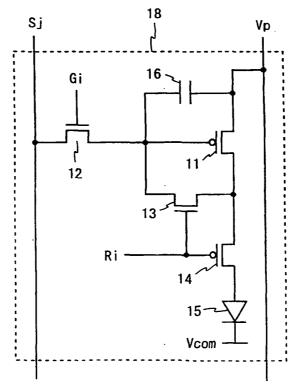

Fig. 6B is a circuit diagram showing a pixel circuit included in a display device according to a second modified example of the first embodiment of the present invention.

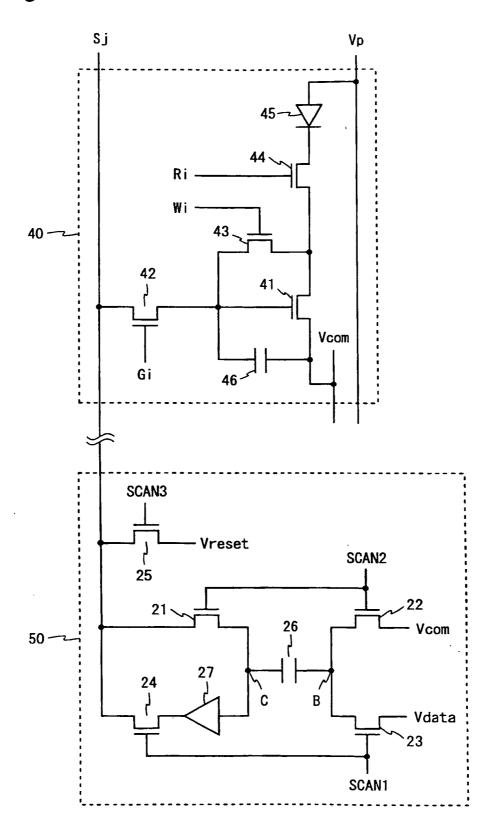

Fig. 7 is a circuit diagram showing a pixel circuit and a threshold value correction circuit each included in the display device according to the second embodiment of the present invention.

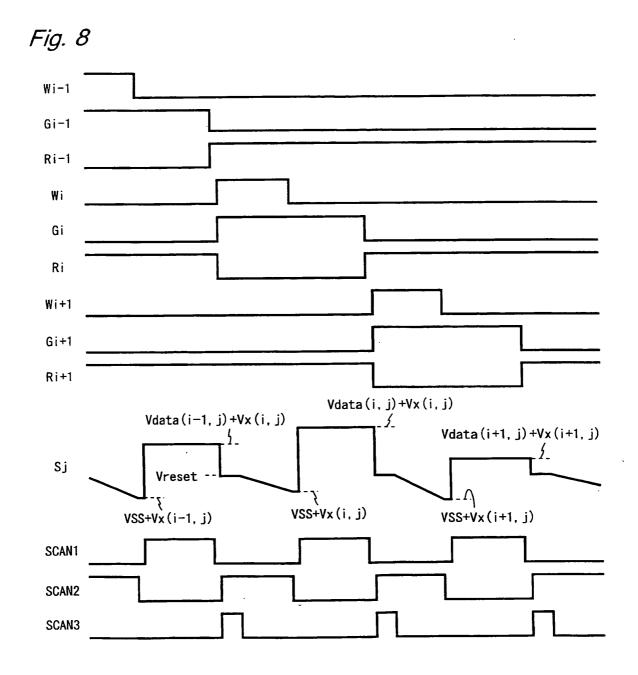

Fig. 8 is a timing chart showing a timing that data is written to the pixel circuit in the display device according to the second embodiment of the present invention.

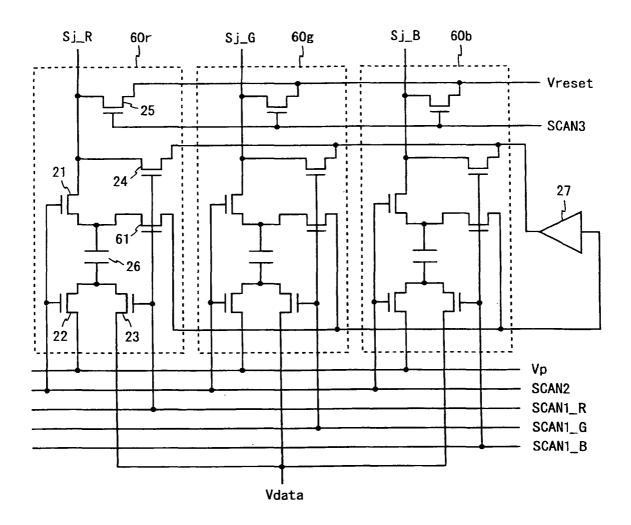

Fig. 9 is a circuit diagram showing a threshold value correction circuit included in the display device according to the third embodiment of the present invention.

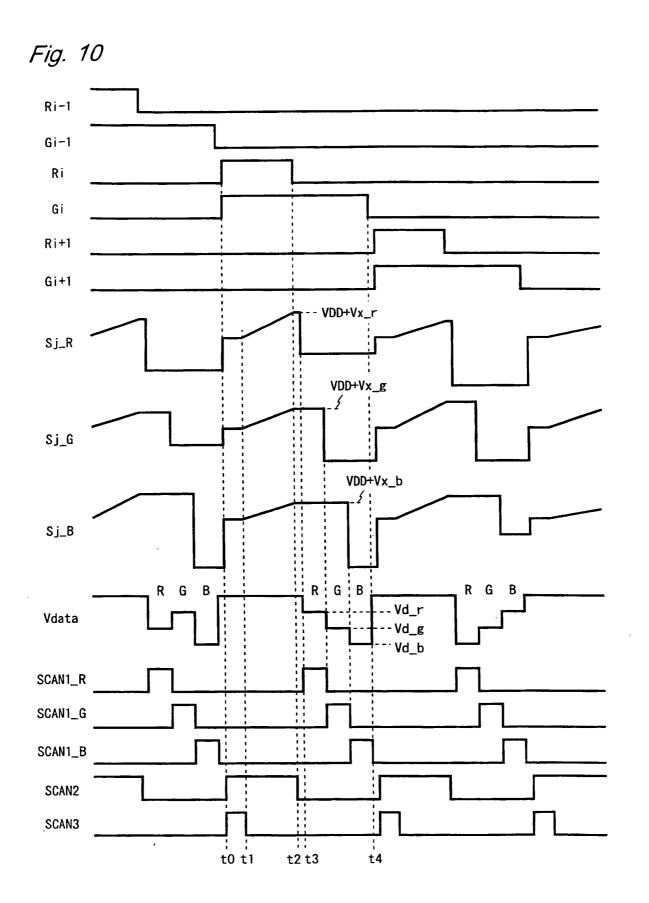

Fig. 10 is a timing chart showing a timing that data is written to a pixel circuit in the display device according to the third embodiment of the present invention.

Fig. 11 is a circuit diagram showing a pixel circuit included in a conventional display device.

Fig. 12 is a timing chart showing a timing that data is written to the pixel circuit shown in Fig. 11.

Fig. 13 is a block diagram showing a configuration of the conventional display device.

#### DESCRIPTION OF REFERENCE SYMBOLS

## [0044]

| 5  | 1                   | Display device                     |  |

|----|---------------------|------------------------------------|--|

|    | 2                   | Display control circuit            |  |

| 10 | 3                   | Gate driver circuit                |  |

|    | 4                   | Source driver circuit              |  |

|    | 5                   | Shift register                     |  |

| 15 | 6                   | Register                           |  |

|    | 7                   | Latch                              |  |

| 20 | 8                   | D/A converter                      |  |

| 20 | 9, 20, 50, 60       | Threshold value correction circuit |  |

|    | Aij, 10, 17, 18, 40 | Pixel circuit                      |  |

| 25 | 11, 41              | Driving TFT                        |  |

|    | 12 to 14, 42 to 44  | Switching TFT                      |  |

| 30 | 15, 45              | Organic EL element                 |  |

|    | 16, 26, 46          | Capacitor                          |  |

|    | 21 to 25, 61        | Switch                             |  |

| 35 | 27                  | Analog buffer                      |  |

## BEST MODE FOR CARRYING OUT THE INVENTION

[0045] With reference to Figs. 1 to 10, description will be given of display devices according to first to third embodiments of the present invention. The display device to be described below includes a pixel circuit including an electro-optical element and a plurality of switching elements. The switching elements included in the pixel circuit may be a low-temperature polysilicon TFT, a CG silicon TFT, an amorphous silicon TFT, and the like. A configuration and a fabrication process of such a TFT are well-known; therefore, description thereof will not be given here. Moreover, it is assumed herein that the electro-optical element included in the pixel circuit is an organic EL element. A configuration of such an organic EL element is also well-known; therefore, description thereof will not be given here. In the following, first, description will be given of a common overall configuration of the display devices according to the first to third embodiments. Thereafter, description will be given of a pixel circuit and a threshold value correction circuit in the display device according to each embodiment.

50 (Overall Configuration of Display Device)

40

**[0046]** Fig. 1 is a block diagram showing the configuration of the display devices according to the first to third embodiments of the present invention. The display device 1 shown in Fig. 1 includes a plurality of pixel circuits Aij (i: an integer in a range between 1 or more and n or less, j: an integer in a range between 1 or more and m or less), a display control circuit 2, a gate driver circuit 3 and a source driver circuit 4. The gate driver circuit 3 functions as a scanning signal output circuit, and the source driver circuit 4 functions as a display signal output circuit.

**[0047]** The display device 1 also includes a plurality of scanning lines Gi which are provided in parallel with one another, and a plurality of data lines Sj which are provided in parallel with one another so as to be orthogonal to the plurality of

scanning lines Gi. The pixel circuits Aij are arranged in a matrix form in correspondence with intersections of the scanning lines Gi and the data lines Sj. Moreover, a plurality of control lines Wi and a plurality of control lines Ri are arranged in parallel with the scanning lines Gi so as to be parallel with one another. The scanning lines Gi and the control lines Wi and Ri are connected to the gate driver circuit 3, and the data lines Sj are connected to the source driver circuit 4. In the arrangement region of the pixel circuits Aij , further, a power supply wiring line Vp and a common cathode Vcom, which are not shown in the figure, are arranged. Herein, cathode wiring lines CAi may be arranged in place of the common cathode Vcom.

[0048] The display control circuit 2 outputs a timing signal OE, a start pulse YI and a clock YCK to the gate driver circuit 3, and outputs a start pulse SP, a clock CLK, display data DA and a latch pulse LP to the source driver circuit 4. Moreover, the display control circuit 2 controls potentials at control lines SCAN1 to SCAN3 of the source driver circuit 4. [0049] The gate driver circuit 3 includes a shift register circuit, a logic operation circuit and a buffer (each of which is not shown in the figure). The shift register circuit sequentially transfers the start pulse YI in synchronization with the clock YCK. The logic operation circuit performs a logic operation between a pulse outputted from each stage of the shift register circuit and the timing signal OE. An output from the logic operation circuit is given to each of the corresponding scanning line Gi and the corresponding control lines Wi and Ri via the buffer. Herein, "m" pixel circuits Aij are connected to one scanning line Gi. The "m" pixel circuits Aij are selected collectively by use of the scanning line Gi.

[0050] The source driver circuit 4 includes an "m"-bit shift register 5, a register 6, a latch 7, "m" D/A converters 8 and "m" threshold value correction circuits 9. The source driver circuit 4 performs a line sequential scan wherein data is transmitted to the pixel circuits Aij in one row at a single timing. More specifically, the shift register 5 has cascade-connected "m" registers. The shift register 5 transfers the start pulse SP supplied to the register on a first stage in synchronization with the clock CLK, and outputs timing pulses DLP from the registers on the respective stages. The display data DA is supplied to the register 6 at an output timing of the timing pulse DLP. The register 6 stores the display data DA corresponding to one row, the display control circuit 2 outputs the latch pulse LP to the latch 7. The latch 7 receives the latch pulse LP and then holds the display data stored in the register 6.

[0051] The D/A converters 8 and the threshold value correction circuits 9 are provided in correspondence with the data lines Sj. The D/A converter 8 converts the display data held by the latch 7 to an analog signal voltage, and outputs the analog signal voltage to the corresponding threshold value correction circuit 9. The threshold value correction circuit 9 receives, via the data line Sj, a voltage outputted from the pixel circuit Aij selected by the gate driver circuit 3 (i.e., a voltage which depends on a threshold voltage of a driving TFT). Based on this voltage, the threshold value correction circuit 9 applies, to the data line Sj, a voltage obtained by adding or subtracting a correction voltage corresponding to the threshold voltage of the driving TFT to or from the output voltage of the D/A converter 8. Thus, variations in threshold voltage of the driving TFT included in the pixel circuit Aij can be compensated by action of the threshold value correction circuit 9 (details thereof will be described later).

[0052] In place of the line sequential scan, herein, the source driver circuit 4 may perform a dot sequential scan wherein data is sequentially transmitted to each pixel circuit. When the dot sequential scan is performed, a voltage of the data line Sj is held by a capacitance of the data line Sj during a period that a certain scanning line Gi is selected. A configuration of the source driver circuit that performs such a dot sequential scan is well-known; therefore, description thereof will not be given here.

(First Embodiment)

30

35

40

45

50

[0053] Fig. 2 is a circuit diagram showing the pixel circuit and the threshold value correction circuit each included in the display device according to the first embodiment of the present invention. The pixel circuit 10 and the threshold value correction circuit 20 in Fig. 2 correspond to the pixel circuit Aij and the threshold value correction circuit 9 in Fig. 1. As shown in Fig. 2, the pixel circuit 10 includes a driving TFT 11, switching TFTs 12 to 14, an organic EL element 15 and a capacitor 16. The driving TFT 11 is of an enhancement P-channel type, each of the switching TFTs 12 and 13 is of an N-channel type, and the switching TFT 14 is of a P-channel type.

**[0054]** The pixel circuit 10 is connected to the power supply wiring line Vp, the common cathode Vcom, the scanning line Gi, the control line Wi, the control line Ri and the data line Sj. Hereinafter, a potential at the power supply wiring line Vp is represented by VDD and a potential at the common cathode Vcom is represented by VSS (herein, VDD > VSS). The common cathode Vcom serves as a common electrode of all the organic EL elements 15 in the display device.

[0055] In the pixel circuit 10, the driving TFT 11, the switching TFT 14 and the organic EL element 15 are provided in series between the power supply wiring line Vp and the common cathode Vcom sequentially from a side of the power supply wiring line Vp. The switching TFT 12 is provided between a gate terminal of the driving TFT 11 and the data line Sj. The switching TFT 13 is provided between the gate terminal and a drain terminal of the driving TFT 11, and the capacitor 16 is provided between the gate terminal of the driving TFT 11 and the power supply wiring line Vp. The switching TFT 12 has a gate terminal connected to the scanning line Gj, the switching TFT 13 has a gate terminal

connected to the control line Wi and the switching TFT 14 has a gate terminal connected to the control line Ri. A potential at each of the scanning line Gi, the control line Wi and the control line Ri is controlled by the gate driver circuit 3, and a potential at the data line Sj is controlled by the source driver circuit 4. Hereinafter, a node to be connected to the gate terminal of the driving TFT 11 is represented by A.

**[0056]** The threshold value correction circuit 20 includes switches 21 to 25, a capacitor 26 and an analog buffer 27, and is connected to the data line Sj. Each of the switches 21 to 25 is an N-channel type transistor, and the analog buffer 27 is a voltage follower circuit (a unity gain amplifier).

[0057] A node to be connected to a first electrode (an electrode illustrated at a right side in Fig. 2) of the capacitor 26 is represented by B, and a node to be connected to a second electrode of the capacitor 26 is represented by C. The switch 21 is provided between the data line Sj and the node C, and the switch 22 is provided between the node B and the power supply wiring line Vp. The switch 23 has a first end connected to the node B. The analog buffer 27 and the switch 24 are provided in series between the node C and the data line Sj sequentially from a side of the node C. The switch 25 has a first end connected to the data line Sj.

[0058] The switch 23 has a second end to which the data voltage Vdata outputted from the D/A converter 8 is applied. The switch 25 has a second end to which an initial voltage Vreset (details thereof will be described later) is applied. The switches 21 and 22 have gate terminals connected to the control line SCAN2, respectively. The switches 23 and 24 have gate terminals connected to the control line SCAN1, respectively. The switch 25 has a gate terminal connected to the control line SCAN3.

[0059] Hereinafter, a threshold voltage of the driving TFT 11 is represented by Vth (negative value). As will be described later, the capacitor 26 functions as a correcting capacitance that holds a correction voltage Vx corresponding to the threshold voltage Vth of the driving TFT 11. Moreover, the switches 21 to 24 function as a switch circuit that switches between a state that the data line Sj is connected with the first electrode of the capacitor 26 and a constant voltage VDD is applied to the second electrode of the capacitor 26 and a state that the data line Sj is connected with the first electrode of the capacitor 26 through the analog buffer 27 and the data voltage Vdata is applied to the second electrode of the capacitor 26.

[0060] Fig. 3 is a timing chart showing a timing that data is written to the pixel circuit 10. With reference to Fig. 3, hereinafter, description will be given of operations to be performed at the time when the data voltage Vdata is written to the pixel circuit 10 connected to the scanning line Gi and the data line Sj. In Fig. 3, a period from a time t0 to a time t4 corresponds to a period for selecting the pixel circuit 10. Prior to a time t2, a process of detecting the threshold voltage of the driving TFT 11 is performed. Subsequent to the time t2, a process of writing the corrected data voltage is performed. [0061] Prior to the time t0, the potential at each of the scanning line Gi, the control line Wi and the control line Ri is controlled to a low level, each of the switching TFTs 12 and 13 is in a non-conduction state, and the switching TFT 14 is in a conduction state. Herein, the driving TFT 11 is in the conduction state, and an electric current flows from the power supply wiring line Vp into the organic EL element 15 via the driving TFT 11 and the switching TFT 14, so that the organic EL element 15 emits light.

30

35

40

50

[0062] At the time t0, when the potential at each of the scanning line Gi, the control line Ri, the control line Wi and the control line SCAN3 is changed to a high level, each of the switching TFT 12, the switching TFT 13 and the switch 25 is changed to the conduction state while the switching TFT 14 is changed to the non-conduction state. Thus, the initial voltage Vreset is applied to the data line Sj, and a potential at each of the data line Sj and the node A becomes Vreset. Subsequent to the time t0, the electric current passing through the driving TFT 11 is fed into the node A via the switching TFT 13.

[0063] At a time t1, next, when the potential at the control line SCAN3 is changed to the low level, the switch 25 is changed to the non-conduction state. Also subsequent to the time t1, the electric current passing through the driving TFT 11 is fed into the node A via the switching TFT 13, and a potential at the node A (a potential at the gate terminal of the driving TFT 11) rises during a period that the driving TFT 11 is in the conduction state. Herein, since the switching TFT 12 is in the conduction state, the potential at the data line Sj is equal to the potential at the node A.

[0064] During a period from the time t0 to the time t2, the potential at the control line SCAN1 is controlled to the low level while the potential at the control line SCAN2 is controlled to the high level. Therefore, each of the switches 21 and 22 is changed to the conduction state while each of the switches 23 and 24 is changed to the non-conduction state. Moreover, the node B is connected to the power supply wiring line Vp and the node C is connected to the data line Sj. Accordingly, the potential at the node B is VDD, and the potential at the node C is equal to the potential at the node A and the potential at the data line Sj.

[0065] At the time t2, next, when the potential at each of the control line Wi and the control line SCAN2 is changed to the low level, each of the switching TFT 13, the switch 21 and the switch 22 is changed to the non-conduction state. At the time t2, the potential at the node A is assumed to be (VDD + Vx) (herein, Vx is a negative value, and Vx has an absolute value which is larger than an absolute value of Vth). At the time t2, the potential at the node C is also (VDD + Vx). Therefore, when each of the switches 21 and 22 is changed to the non-conduction state at the time t2, the voltage Vx is held at the capacitor 26.

[0066] As described above, the potential at the node A rises during the period that the driving TFT 11 is in the conduction state. Accordingly, a satisfactory time allows the potential at the node A to rise until the gate-source voltage of the driving TFT 11 becomes the threshold voltage Vth (negative value) and, finally, reaches (VDD + Vth). At the time t2, the potential (VDD + Vx) at the node A is lower than (VDD + Vth). Moreover, the voltage Vx varies in accordance with the threshold voltage Vth. The absolute value of the voltage Vx becomes larger as the absolute value of the threshold voltage Vth is large.

[0067] At a time t3, next, when the potential at the control line SCAN1 is changed to the high level, each of the switches 23 and 24 is changed to the conduction state. Subsequent to the time t3, the data voltage Vdata outputted from the D/A converter 8 is applied to the node B, and the node C is connected to the data line Sj through the analog buffer 27. When the potential at the node B is changed from VDD to Vdata during the period that the voltage Vx is held at the capacitor 26, the potential at the node C is also changed by the same amount (Vdata - VDD) and becomes (VDD + Vx) + (Vdata - VDD) = (Vdata + Vx).

[0068] Herein, the switch 24 is in the conduction state, and an input voltage and an output voltage are equal to each other in the analog buffer 27. Therefore, the potential at the data line Sj becomes (Vdata + Vx) as in the case of the node C. Moreover, since the switching TFT 12 is also in the conduction state, the potential at the node A also becomes (Vdata + Vx) as in the case of the data line Sj.

10

20

30

40

50

55

[0069] At the time t4, next, when the potential at each of the scanning line Gi, the control line Ri and the control line SCAN1 is changed to the low level, each of the switching TFT 12, the switch 23 and the switch 24 is changed to the non-conduction state while the switching TFT 14 is changed to the conduction state. Herein, the gate-source voltage (VDD - Vdata - Vx) of the driving TFT 11 is held at the capacitor 16. Moreover, an ON potential (low level potential) to be given to the control line Ri is determined such that the switching TFT 14 is operated in a linear region.

[0070] Subsequent to the time t4, the voltage held at the capacitor 16 is not changed; therefore, the potential at the node A is maintained at (Vdata + Vx). Subsequent to the time t4, accordingly, an electric current flows from the power supply wiring line Vp into the organic EL element 15 via the driving TFT 11 and the switching TFT 14 until the potential at the control line Ri becomes the high level again, so that the organic EL element 15 emits light. Herein, an amount of the electric current, which flows through the driving TFT 11, increases/decreases in accordance with the potential (Vdata + Vx) at the node A. As will be described later, however, this electric current amount is the same as long as the potential Vdata is the same even when the threshold voltage Vth is different.

**[0071]** In a case where the driving TFT 11 is operated in a saturated region, a drain-source electric current I<sub>EL</sub> is obtained from the following equation (1) if a channel length modulation effect is neglected.

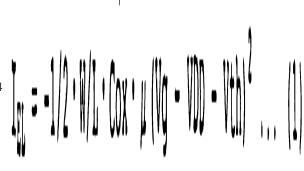

$$I_{EL} = -1/2 \cdot W/L \cdot Cox \cdot \mu (Vg - VDD - Vth)^2 \dots (1)$$

In the equation (1), W/L represents an aspect ratio of the driving TFT 11, Cox represents a gate capacitance, μ represents a mobility, and Vg represents a gate terminal potential (i.e., the potential at the node A).

**[0072]** Typically, the electric current  $I_{EL}$  expressed by the equation (1) varies in accordance with the threshold voltage Vth. In the display device according to this embodiment, the gate terminal potential Vg becomes (Vdata + Vx); therefore, the electric current  $I_{EL}$  is changed as expressed by the following equation (2).

$$I_{EL} = -1/2 \cdot W/L \cdot Cox \cdot \mu \left\{ Vdata - VDD + (Vx - Vth) \right\}^2 \dots (2)$$

In the equation (2), when the voltage Vx matches with the threshold voltage Vth, the electric current I<sub>EL</sub> does not depend on the threshold voltage Vth. Moreover, even when the voltage Vx does not match with the threshold voltage Vth, the electric current I<sub>EL</sub> does not depend on the threshold voltage Vth as long as a difference between the voltage Vx and the threshold voltage Vth is fixed.

[0073] In the display device according to this embodiment, the length of the threshold value correction period (the period from the time t1 to the time t2) and the level of the initial voltage Vreset are determined such that the difference between voltages Vx of two TFTs becomes almost equal to the difference between the threshold voltages Vth of the two TFTs. Thus, the voltage difference (Vx - Vth) in the equation (2) is almost fixed. Accordingly, an electric current flows into the organic EL element 15 in an amount which depends on the data voltage Vdata irrespective of a value of the threshold voltage Vth, so that the organic EL element 15 emits light at a luminance which depends on the data voltage Vdata. In the display device according to this embodiment, the threshold value correction is performed by the threshold value correction circuit 20 provided outside the pixel circuit 10. There is no necessity that the threshold value correction circuit 20 includes a complicated logic circuit and a memory.

[0074] Herein, description will be given of the initial voltage Vreset. When the switching TFT 13 is changed to the

conduction state at the time t0 shown in Fig. 3, the driving TFT 11 is changed to a diode-connected state. In a conventional organic EL display, a period from a timing that a driving TFT is changed to a diode-connected state to a timing that a gate-source voltage Vgs of the driving TFT satisfactorily approximates a threshold voltage Vth corresponds to a threshold value correction period. When the voltage Vgs satisfactorily approximates the threshold voltage Vth, a difference in threshold voltage between the two driving TFTs can be detected.

[0075] In a display device with high definition, however, a period for selecting a pixel circuit is short. Consequently, a voltage Vgs fails to satisfactorily approximate a threshold voltage Vth within the selection period in some instances. In the display device according to this embodiment, particularly, the parasitic capacitance of the capacitor 26 and the parasitic capacitance of the data line Sj must be charged electrically in order to detect the threshold voltage Vth of the driving TFT 11. Therefore, some contrivance must be made in order to perform the process of detecting the threshold voltage and the process of writing the corrected data voltage within the selection period.

[0076] In the display device according to this embodiment, therefore, the constant initial voltage Vreset is applied to the data line Sj by action of the switch 25 in order to detect variations in threshold voltage Vth prior to start of the process of writing the corrected data voltage. Thus, it is possible to reduce a time which is required until the voltage (VDD + Vx) which depends on the threshold voltage Vth of the driving TFT 11 is outputted to the data line Sj. Accordingly, it is possible to suppress variations in correction effect and to improve image quality even when the threshold value correction period is short.

**[0077]** The initial voltage Vreset is determined based on the length of the threshold value correction period, the accuracy to be required for the threshold value correction, and the like. In a case where the switching TFT 13 is in the conduction state and the driving TFT 11 is in the diode-connected state, the following equation (3) is established with regard to an electric current balance in the driving TFT 11.

$$k(Vgs(t)-Vth)^2 = -C \frac{dVgs(t)}{dt} \cdots (3)$$

In the equation (3), k represents a constant, and C represents a sum of a holding capacitance and a signal line capacitance. **[0078]** The following equation (4) is obtained by solving this differential equation.

$$V_{gs}(t) = \frac{1}{\frac{k}{C}t + \frac{1}{V_{gs}0 - Vth}} + Vth \cdots (4)$$

In the equation (4), Vgs0 represents an initial value of the voltage Vgs.

10

20

25

30

35

40

45

50

55

**[0079]** Herein, attention is given to two TFTs which are different in threshold voltage from each other by  $\Delta V$ th. If a difference in voltage Vgs between the two TFTs approximates  $\Delta V$ th after a lapse of a predetermined time, the threshold voltage of each TFT can be detected. This difference in voltage Vgs is obtained from the following equation (5).

$$\Delta V_{gs}(t) = \Delta V_{th} + \frac{1}{\frac{k}{C}t + \frac{1}{V_{gs}0 - V_{th} - \Delta V_{th}}} - \frac{1}{\frac{k}{C}t + \frac{1}{V_{gs}0 - V_{th}}} \cdots (5)$$

Accordingly, it is preferable that the initial value Vgs0 of the voltage Vgs is determined such that  $\Delta$ Vgs(t) in the equation (5) satisfactorily approximates  $\Delta$ Vth within a permissible time, and the initial voltage Vreset is obtained in accordance with the initial value Vgs0.

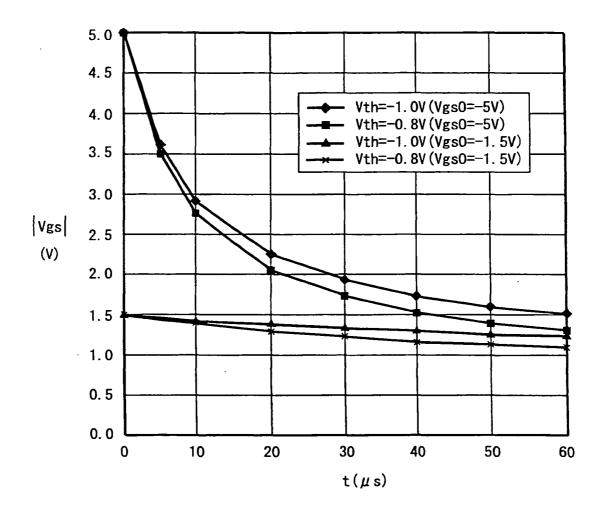

**[0080]** Fig. 4 shows an example of a temporal change in gate-source voltage Vgs of the diode-connected driving TFT. Fig. 4 shows a result obtained when two different initial voltages Vgs0 (Vgs0 = -5 V, Vgs0 = -1.5 V) are applied to two TFTs (Vth = -0.8 V, Vth = -1.0 V) which are different in threshold voltage from each other.

**[0081]** The initial voltage Vgs0 is applied to each of the two TFTs, and the voltages Vgs of the respective TFTs are compared with each other after a lapse of 30  $\mu$ s. In the case of Vgs0 = -5 V, the two voltages are different from final values (-0.8 V and -1.0 V) thereof, respectively, after the lapse of 30  $\mu$ s. However, a difference between the two voltages

is almost equal to a final value (0.2 V) thereof at this time. In the case of Vgs0 = -1.5 V, on the other hand, the two voltages approximate the respective final values after the lapse of 30  $\mu$ s. However, the difference between the two voltages is different from the final value thereof at this time.

[0082] As described above, as an absolute value of the initial voltage Vgs0 is large, the difference between the two voltages Vgs is increased more promptly; therefore, the threshold value correction period can be made short. In order to perform the threshold value correction with high accuracy, accordingly, it is preferable that the absolute value of the initial voltage Vgs0 is made large. On the other hand, when the absolute value of the initial voltage Vgs0 is made large, power consumption is increased due to electric charge/discharge in the data line Sj and the capacitor 26. Accordingly, it is preferable that the initial voltage Vreset is determined in consideration of a degree and a specification of variations in threshold voltage due to a process.

10

20

30

35

40

45

50

55

[0083] Next, description will be given of the analog buffer 27. In a case where the capacitance of the data line Sj is smaller than the capacitance of the capacitor 26 to an ignorable level, there is no necessity that the threshold value correction circuit 20 includes the analog buffer 27. In a display panel having a size of not less than several inches, on the other hand, a capacitance of a data line Sj is not less than several pF in many instances. In such a case, therefore, the analog buffer 27 must be provided. Herein, use of a voltage follower circuit (a unity gain amplifier) as the analog buffer 27 allows enhancement of a driving capability while suppressing an increase of a circuit scale as much as possible. [0084] Moreover, in a case where a typical differential amplifier is used as the analog buffer 27, a transistor that forms a differential pair varies in characteristic, so that the analog buffer 27 varies in characteristic. If there occur such variations, stripe-shaped ghosts appear in a display screen, resulting in degradation of display quality. In order to prevent such a disadvantage, it is preferable that the analog buffer 27 is not formed on the display panel, but is incorporated in a peripheral IC provided outside the display panel. Typically, the circuit incorporated in the peripheral IC is formed with a transistor made of polycrystalline silicon. Accordingly, when the analog buffer 27 is incorporated in the peripheral IC, the variations in characteristic can be made considerably small.

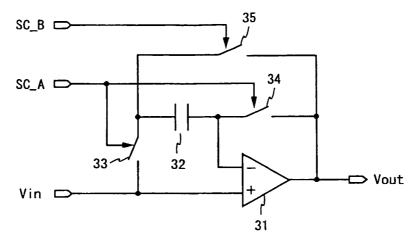

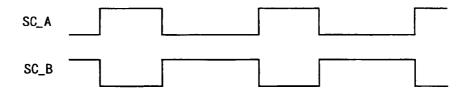

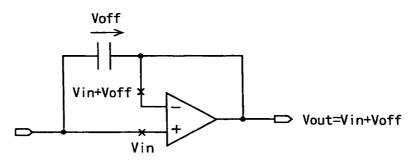

[0085] In order to prevent the disadvantage described above, moreover, a buffer having an offset cancel function (see Figs. 5A to 5D) may be used as the analog buffer 27. In the buffer shown in Fig. 5A, a differential amplifier 31 has a positive-side input terminal connected to an input terminal of the buffer, a negative-side input terminal connected to a first electrode of a capacitor 32, and an output terminal connected to an output terminal of the buffer. A switch 33 is provided between a second electrode of the capacitor 32 and an input terminal of the buffer. A switch 34 is provided between the negative-side input terminal and the output terminal of the differential amplifier 31. A switch 35 is provided between the second electrode of the capacitor 32 and the output terminal of the differential amplifier 31. Each of the switches 33 and 34 is controlled by a control signal SC\_A while the switch 35 is controlled by a control signal SC\_B.

[0086] Each of the control signals SC\_A and SC\_B exclusively becomes a level at which the switch is changed to a conduction state (corresponding to a high level herein), as shown in Fig. 5B. During a period that the control signal SC\_A is at the high level (see Fig. 5C), each of the switches 33 and 34 becomes the conduction state while the switch 35 becomes a non-conduction state. Herein, an offset voltage Voff of the differential amplifier 31. The offset voltage Voff is held by the capacitor 32.

[0087] During a period that the control signal SC\_B is at the high level (see Fig. 5D), each of the switches 33 and 34 becomes the non-conduction state while the switch 35 becomes the conduction state. As a result, a negative-side input voltage of the differential amplifier 31 varies by the offset voltage Voff, and an output voltage of the differential amplifier 31 (i.e., an output voltage of the buffer) also varies by the same amount and becomes equal to an input voltage Vin. As described above, use of the buffer shown in Fig. 5A allows cancellation of the offset voltage of the differential amplifier 31. Herein, the buffer having the offset cancel function may be incorporated in the peripheral IC provided outside the display panel.

[0088] Hereinafter, description will be given of advantageous effects of the display device according to this embodiment. In the display device according to this embodiment, the voltage (VDD + Vx) which depends on the threshold voltage Vth of the driving TFT 11 can be read from the pixel circuit 10 selected by the gate driver circuit 3 and the voltage (Vdata + Vx), which is obtained by adding the correction voltage Vx (the voltage corresponding to the threshold voltage Vth) to the data voltage Vdata, can be applied to the gate terminal of the driving TFT 11. In a driving TFT of a P-channel type, typically, when a voltage, which is obtained by subtraction of an absolute value of a threshold voltage, is applied to a gate terminal, variations in threshold voltage can be compensated. Accordingly, the display device according to this embodiment detects the threshold voltage of the driving TFT 11 to compensate the variations in threshold voltage, and allows the organic EL element 15 to emit light at a desired luminance.

[0089] Moreover, the threshold value correction circuit 20 is provided outside the pixel circuit and the threshold voltage is detected by use of the data line Sj, leading to reduction in scale and area of the pixel circuit 10. Further, the threshold voltage is detected as a voltage signal, so that a current-voltage conversion element becomes unnecessary unlike a case where an electric current signal is fed back. Therefore, variations in correction effect can be suppressed. In addition, the correction voltage Vx corresponding to the threshold voltage is added as it is to the data voltage Vdata, so that the

threshold value correction can be performed with high accuracy. Moreover, a desired voltage is applied to the gate terminal of the driving TFT 11 through no coupling capacitance. Therefore, an amplitude of the data voltage Vdata can be utilized effectively, leading to reduction in power consumption. Further, no capacitance is provided between the data line Sj and the driving TFT 11, so that the driving TFT 11 can be inspected with ease. Upon inspection of the driving TFT 11, preferably, an electric current flows from the power supply wiring line Vp into the data line Sj via the drain terminal and the gate terminal of the driving TFT 11.

**[0090]** The display device according to this embodiment may include a pixel circuit shown in Fig. 6A or 6B in place of the pixel circuit 10. The pixel circuit 17 shown in Fig. 6A is different from the pixel circuit 10 in a point that a switching TFT 14 is connected to a scanning line Gi such that the scanning line Gi and a control line Ri are shared. In the pixel circuit 17, each of switching TFTs 12 and 14 becomes a conduction state exclusively. On the other hand, the pixel circuit 18 shown in Fig. 6B is different from the pixel circuit 10 in a point that a switching TFT 13 is connected to a control line Ri such that the control line Ri and a control line Wi are shared. In the pixel circuit 18, each of switching TFTs 13 and 14 becomes a conduction state exclusively.

**[0091]** Each of the display devices according to these modified examples operates as in the display device including the pixel circuit 10 and has advantageous effects similar to those of the display device including the pixel circuit 10. In addition, the switching TFTs 12 to 14 share a wiring line to be connected to control terminals thereof, so that the number of wiring lines is reduced from three to two. Further, an aperture ratio of a pixel is made higher. Thus, a screen can be made brighter.

## 20 (Second Embodiment)

30

35

40

**[0092]** Fig. 7 is a circuit diagram showing a pixel circuit and a threshold value correction circuit each included in the display device according to the second embodiment of the present invention. The pixel circuit 40 and the threshold value correction circuit 50 in Fig. 7 correspond to the pixel circuit Aij and the threshold value correction circuit 9 in Fig. 1. As shown in Fig. 7, the pixel circuit 40 includes a driving TFT 41, switching TFTs 42 to 44, an organic EL element 45 and a capacitor 46. The driving TFT 41 is of an enhancement N-channel type, and each of the switching TFTs 42 to 44 is of an N-channel type.

[0093] In the pixel circuit 40, the organic EL element 45, the switching TFT 44 and the driving TFT 41 are provided in series between a power supply wiring line Vp and a common cathode Vcom sequentially from a side of the power supply wiring line Vp. The switching TFT 42 is provided between a gate terminal of the driving TFT 41 and a data line Sj. The switching TFT 43 is provided between the gate terminal and a drain terminal of the driving TFT 41, and the capacitor 46 is provided between the gate terminal of the driving TFT 41 and the common cathode Vcom. The switching TFT 42 has a gate terminal connected to a scanning line Gi, the switching TFT 43 has a gate terminal connected to a control line Wi and the switching TFT 44 has a gate terminal connected to a control line Ri.

**[0094]** The threshold value correction circuit 50 has a structure which is equal to that of the threshold value correction circuit 20 according to the first embodiment. In the threshold value correction circuit 50, however, a switch 22 is provided between a node B and the common cathode Vcom. The threshold value correction circuit 50 is equal to the threshold value correction circuit 20 except the point described above.

**[0095]** Fig. 8 is a timing chart showing a timing that data is written to the pixel circuit 40. The display device according to this embodiment operates as in the display device according to the first embodiment, and has advantageous effects similar to those of the display device according to the first embodiment. In a driving TFT of an N-channel type, typically, when a voltage obtained by addition of an absolute value of a threshold voltage is applied to a gate terminal, variations in threshold voltage can be compensated. As in the first embodiment, this embodiment can adopt the modified example that the switching TFTs 42 to 44 share a wiring line to be connected to control terminals thereof.

[0096] As described above, the pixel circuit 40, in which each of the driving TFT 41 and the switching TFT 42, 43 and 44 is of an N-channel type, can be applied to a display panel using amorphous silicon.

## (Third Embodiment)

[0097] In each of the display devices according to the first and second embodiments, the analog buffer 27 is provided for each data line Sj. In a 2-inch QVGA full-color panel (including RGB sub pixels), however, a pitch between the sub pixels is about 42 μm. The capacitor 26 that holds the correction voltage Vx which depends on the threshold voltage of the driving TFT can be arranged at this pitch, but the high-performance analog buffer 27 can not be arranged at this pitch in some instances. In the third embodiment, therefore, description will be given of the display device in which the number of analog buffers 27 is reduced.

[0098] Fig. 9 is a circuit diagram showing a threshold value correction circuit included in the display device according to the third embodiment of the present invention. The threshold value correction circuits 60r, 60g and 60b in Fig. 9 correspond to the threshold value correction circuit 9 in Fig. 1. Moreover, data lines Sj\_R, Sj\_G and Sj\_B in Fig. 9

correspond to the data line Sj in Fig. 1.

30

35

40

50

55

[0099] As shown in Fig. 9, an analog buffer 27 is provided in correspondence with the three data lines Sj\_R, Sj\_G and Sj\_B. The threshold value correction circuit 60r is different from the threshold value correction circuit 20 (Fig. 2) according to the first embodiment in a point that a function of sharing the analog buffer 27 is added thereto. In the threshold value correction circuit 60r, specifically, a switch 61 is provided between a first electrode of a capacitor 26 (an electrode shown at an upper side of Fig. 9) and an input terminal of the analog buffer 27. Moreover, switches 23, 24 and 61 have gate terminals connected to a control line SCAN1\_R. Each of the threshold value correction circuits 60g and 60b is similar in configuration to the threshold value correction circuit 60r.

**[0100]** Fig. 10 is a timing chart showing a timing that data is written to a pixel circuit in the display device according to this embodiment. With reference to Fig. 10, hereinafter, description will be given of operations performed when data is written to each of three pixel circuits connected to a scanning line Gi and the data lines Sj\_R, Sj\_G and Sj\_B. In Fig. 10, a period from a time t0 to a time t4 corresponds to a period for selecting the three pixel circuits. Prior to a time t2, a process of detecting threshold voltages of driving TFTs of the three pixel circuits in parallel is performed. Subsequent to the time t2, a process of writing corrected data voltages to the three pixel circuits in succession is performed. Herein, the display device includes the pixel circuit 18 shown in Fig. 6B; however, a type of the pixel circuit may be arbitrary.

**[0101]** Prior to the time t0, a potential at each of the scanning line Gi and a control line Ri is controlled to a low level. At the time t0, when the potential at each of the scanning line Gi, the control line Ri and a control line SCAN3 is changed to a high level, a potential at each of the data lines Sj\_R, Sj\_G and Sj\_B as well as a potential at each of the gate terminals of the driving TFTs of the three pixel circuits become Vreset.

**[0102]** At a time t1, next, when the potential at the control line SCAN3 is changed to the low level, the potential at each of the data lines Sj\_R, Sj\_G and Sj\_B rises. During a period from the time t0 to the time t2, the potential at each of the control lines SCAN1\_R, SCAN1\_G and SCAN1\_B is controlled to the low level while a potential at a control line SCAN2 is controlled to the high level.

[0103] At the time t2, the potentials at the gate terminals of the driving TFTs of the three pixel circuits are assumed to be (VDD + Vx\_r), (VDD + Vx\_g) and (VDD + Vx\_b), respectively (Vx\_r, Vx\_g, Vx\_r: negative values). At the time t2, when the potential at each of the control line Ri and the control line SCAN2 is changed to the low level, the voltages Vx\_r, Vx\_g and Vx\_b are held at the capacitors 26 of the threshold value correction circuit 60r, 60g and 60b, respectively. [0104] During a period from the time t3 to the time t4, next, the potential at each of the control lines SCAN1\_R, SCAN1\_G and SCAN1\_B becomes the high level by a predetermined time and, in synchronization with this, a data voltage Vdata outputted from a D/A converter 8 is changed to Vd\_r, Vd\_g and Vd\_b. With this configuration, first, the potential at the gate terminal of the driving TFT of the pixel circuit connected to the data line Sj\_R becomes (Vd\_r + Vx\_r). Next, the potential at the gate terminal of the driving TFT of the pixel circuit connected to the data line Sj\_G becomes (Vd\_g + Vx\_g). Finally, the potential at the gate terminal of the driving TFT of the pixel circuit connected to the data line Sj\_B becomes (Vd\_b + Vx\_b).

[0105] At the time t4, next, when the potential at the scanning line Gi is changed to the low level, the voltages (VDD - Vd\_r - Vx\_r), (VDD - Vd\_g - Vx\_g) and (VDD - Vd\_b - Vx\_b) are held at the capacitors of the three pixel circuits, respectively.

**[0106]** Subsequent to the time t4, the potentials at the gate terminals of the driving TFTs of the three pixel circuits are maintained at  $(Vd_r + Vx_r)$ ,  $(Vd_g + Vx_g)$  and  $(Vd_b + Vx_b)$ , respectively. Herein, amounts of electric currents flowing through the respective driving TFTs increase/decrease in accordance with these potentials. The electric current amount is the same as long as the data voltage is the same even when the threshold voltage is different. Accordingly, an electric current flows into an organic EL element of each pixel circuit in an amount which depends on the data voltage Vdata irrespective of a value of the threshold voltage, so that the organic EL element emits light at a luminance which depends on the data voltage Vdata.

[0107] In the foregoing description, the analog buffer is provided in correspondence with the three data lines Sj\_R, Sj\_G and Sj\_B. Alternatively, the analog buffer may be provided in correspondence with "p" (p: an arbitrary integer of two or more) data lines.

**[0108]** As described above, the display device according to this embodiment realizes a display panel with high definition in such a manner that the analog buffer having a large circuit scale is not arranged for each data line, but is arranged for the plurality of data lines.

[0109] In the foregoing embodiments, the pixel circuit includes the organic EL element as an electro-optical element. Alternatively, the pixel circuit may include an electro-optical element of an electric current driving type other than the organic EL element (e.g., a semiconductor LED, a light emitting part of an FED). Moreover, the pixel circuit includes, as a drive element of the electro-optical element, the TFT which is a MOS transistor (including a silicon gate MOS structure) formed on an insulating substrate such as a glass substrate. Alternatively, the pixel circuit may include an arbitrary voltage controlling element having a threshold voltage (i.e., an element that changes an output current in accordance with a control voltage applied to a control terminal thereof and interrupts the output current when the control voltage becomes not less than or not more than a predetermined value). Accordingly, the pixel circuit may include, as

a drive element, a typical insulating gate-type field effect transistor including a MOS transistor formed on a semiconductor substrate

**[0110]** In the first embodiment, the switching TFT 12 is changed to the conduction state and, almost simultaneously, the switching TFT 13 is changed to the conduction state while the switching TFT 14 is changed to the non-conduction state. Alternatively, before the switching TFT 12 is changed to the conduction state, the switching TFT 13 may be changed to the conduction state while the switching TFT 14 may be changed to the non-conduction state. The same thing holds true for the second and third embodiments.

**[0111]** The present invention is not limited to the foregoing embodiments and may be modified variously. Moreover, an embodiment obtained by appropriately combining the technical means disclosed in the different embodiments with one another is also involved in the technical scope of the present invention.

#### INDUSTRIAL APPLICABILITY

**[0112]** The display device according to the present invention has an advantageous effect of efficiently utilizing an amplitude of a data voltage and performing threshold value correction with high accuracy, without increasing a scale of a pixel circuit. Therefore, the display device according to the present invention can be used as a display device for various electronic appliances.

#### 20 Claims

15

25

30

35

40

50

1. A display device of an electric current driving type, comprising:

a plurality of pixel circuits (10, 17, 18, 40) arranged in correspondence with intersections of a plurality of scanning lines (Gi) and a plurality of data lines (Sj), each pixel circuit (10, 17, 18, 40) including an electro-optical element (15, 45) and a drive element (11, 41) having a control terminal connected to the data line (Sj) through a first switching element (12, 42);

a scanning signal output circuit (3) selecting a write-target pixel circuit through use of the scanning line (Gi), and exercising control such that the selected pixel circuit outputs, to the data line (Sj), a voltage which depends on a threshold voltage (Vth) of the drive element (11, 41); and

a display signal output circuit (4) applying, to the data line (Sj), a voltage obtained by adding or subtracting a correction voltage corresponding to the threshold voltage to or from a data voltage corresponding to display data, based on the voltage outputted to the data line (Sj),

#### characterized in that

the display signal output circuit (4) includes a plurality of analog buffers (27), and a plurality of correcting capacitances (26) and a plurality of switch circuits provided for each data line (Sj), and

the switch circuit switches between a state that one electrode of the correcting capacitance (26) is connected to the data line (Sj) and the other electrode thereof is applied with a predetermined constant voltage and a state that one electrode of the correcting capacitance (26) is connected to the data line (Sj) through the analog buffer (27) and the other electrode thereof is applied with the data voltage.

- 2. The display device according to claim 1, wherein

- the electro-optical element (15, 45) and the drive element (11, 41) are provided in series between two power supply wiring lines in the pixel circuit (10, 17, 18, 40), and the pixel circuit (10, 17, 18, 40) further includes the first switching element (12, 42) connected to a control terminal of the drive element (11, 41) and the data line (Sj),

a second switching element (13, 43) provided between the control terminal and one conductive terminal of the drive element (11, 41),