(11) EP 1 646 032 A1

(12)

# **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

12.04.2006 Bulletin 2006/15

(51) Int Cl.: **G09G** 3/32 (2006.01)

(21) Application number: 05109164.3

(22) Date of filing: 04.10.2005

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HU IE IS IT LI LT LU LV MC NL PL PT RO SE SI SK TR

**Designated Extension States:**

AL BA HR MK YU

(30) Priority: 08.10.2004 KR 2004080621

- (71) Applicant: Samsung SDI Co., Ltd. Suwon-si Gyeonggi-do (KR)

- (72) Inventor: Jung, Jin Tae Seoul (KR)

- (74) Representative: Hengelhaupt, Jürgen et al Gulde Hengelhaupt Ziebig & Scheider Wallstrasse 58/59 10179 Berlin (DE)

# (54) Pixel circuit for OLED display with self-compensation of the threshold voltage

(57)A pixel circuit includes a light emitting device (OLED); a driving transistor (M4) to receive first power (Vdd) and supply current corresponding to the voltage applied to its gate electrode to the light emitting device (OLED); a first switching device (M1) to supply a data signal (Dm) in response to a first scan signal (S1.n); a second switching device (M2) to supply second power (Vinit) to the gate electrode of the driving transistor (M4) in response to the first scan signal (S1.n); a capacitor (Cst) to store a voltage corresponding to the data signal (Dm) and the second power (Vdd) according to operations of the first (M1) and second (M2) switching devices; a third switching device (M3) to apply the voltage stored in the capacitor (Cst) to the gate electrode of the driving transistor (M4) in response to a second scan signal (S2.n); and a fourth switching device (M5) to transmit the first power (Vdd) to the driving transistor (M4) in response to a third scan signal (S3.n).

An optional fifth switching device (M6) bypasses the light emitting device (OLED) in response to the third scan signal (S3.n).

The pixel circuit provides a drive current that is independent from voltage drop on the power supply lines and from the threshold voltage of the driving transistors, thus improving luminance uniformity of the display.

FIG. 4

EP 1 646 032 A1

## **Description**

#### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the priority of Korean Patent Application No. 2004-80621, filed on October 8, 2004, in the Korean Intellectual Property Office, the entire disclosure of which is incorporated herein by reference.

#### **BACKGROUND**

10

15

20

30

35

40

45

50

55

#### 1. FIELD OF THE INVENTION

**[0002]** The present invention relates to a pixel circuit and a light emitting display comprising the same, and more particularly, to a pixel circuit and a light emitting display comprising the same, in which a threshold voltage is compensated, thereby improving the uniformity of brightness.

#### 2. Related Art

**[0003]** Recently, various flat panel displays have been developed, to substitute cathode ray tube (CRT) displays because the CRT displays are relatively heavy and bulky. Among the flat panel displays, a light emitting display (LED) is notable because it has high emission efficiency, high brightness, wide view angle, and fast response time.

**[0004]** The light emitting display comprises a plurality of light emitting devices, wherein each light emitting device has a structure in which an emission layer is placed between a cathode electrode and an anode electrode. Here, an electron and a hole are injected into the emission layer and recombined to create an exciton. Light is emitted when the exciton falls to a lower energy level.

[0005] Such a light emitting display is classified into an inorganic light emitting display comprising an inorganic emission layer, and an organic light emitting display comprising an organic emission layer.

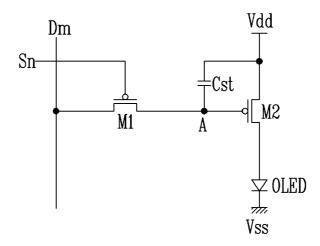

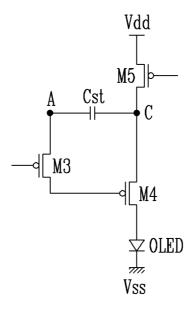

**[0006]** FIG. 1 is a circuit diagram of a pixel provided in a conventional light emitting display. Referring to FIG. 1, the pixel comprises an organic light emitting device OLED, a driving transistor M2, a capacitor Cst, a switching transistor M1. Further, the pixel is connected to a scan line Sn, a data line Dm, a pixel power line Vdd, and a second power supply line Vss. The second power supply line Vss is a voltage lower that the first voltage supply, for example, a ground voltage. Here, the scan line Sn is arranged in a row direction, and the data line Dm and the pixel power line Vdd are arranged in a column direction. For reference, n is an arbitrary integer between 1 and N, and m is an arbitrary integer between 1 and M.

**[0007]** The switching transistor M1 comprises a source electrode connected to the data line Dm, a drain electrode connected to a first node A, and a gate electrode connected to the scan line Sn.

[0008] The driving transistor M2 comprises a source electrode connected to the pixel power line Vdd, a drain electrode connected to the organic light emitting device OLED, and a gate electrode connected to the first node A. Here, the driving transistor M2 supplies current to the organic light emitting device OLED in response to a signal inputted to its gate electrode, thereby allowing the organic light emitting device to emit light. Further, the intensity of the current flowing in the driving transistor M2 is controlled by a data signal transmitted through the data line Dm and switching transistor M1.

[0009] The capacitor Cst comprises a first electrode connected to the source electrode of the driving transistor M2, and a second electrode connected to the first node A. Here, the capacitor Cst maintains voltage applied between the

**[0010]** With this configuration, when the switching transistor M1 is turned on in response to the scan signal transmitted to the gate electrode of the switching transistor M1, the capacitor Cst is charged with a voltage corresponding to the data signal, and then the voltage charged in the capacitor Cst is applied to the gate electrode of the driving transistor M2. Hence, the current flows in the driving transistor M2, thereby allowing the organic light emitting device OLED to emit light.

source and gate electrodes of the driving transistor M2 in response to the data signal, for a predetermined period.

**[0011]** At this time, the current supplied from the driving transistor M2 to the organic light emitting device OLED is calculated by the following equation.

$$I_{OLED} = \frac{\beta}{2} (Vgs - Vth)^2 = \frac{\beta}{2} (Vdd - Vdata - Vth)^2$$

[Equation 1]

where  $I_{OLED}$  is a current flowing in the organic light emitting device OLED; Vgs is a voltage applied between the source and gate electrodes of the driving transistor M2; Vth is a threshold voltage of the driving transistor M2, Vdata is a voltage

corresponding to the data signal; and  $\beta$  is a gain factor of the driving transistor M2.

**[0012]** Referring to the equation 1, the current  $I_{OLED}$  flowing in the organic light emitting device OLED varies depending on the threshold voltage of the driving transistor M2.

**[0013]** However, when the conventional light emitting display is fabricated, deviation arises in the threshold voltage of the driving transistor M2. Thus, the deviation in the threshold voltage of the driving transistor M2 causes in consistencies in the current flowing in the organic light emitting device OLED to be not uniform, thereby deteriorating the uniformity of the brightness of the display device.

**[0014]** Further, the pixel power line Vdd connected to each pixel and supplying pixel power is connected to a first power line (not shown) and supplies the pixel power. In this case, voltage drop arises in the first power supplied from the pixel power line Vdd to the first power line. As the length of the first power line increases, the pixel power line Vdd connected thereto increases in number, thereby causing the voltage drop to get larger.

[0015] Particularly, for a large screen of the flat panel display, the voltage drop in the first power line increases further.

#### SUMMARY OF THE INVENTION

15

20

30

35

40

45

50

55

**[0016]** Accordingly, it is an aspect of the present invention to provide a pixel circuit and a light emitting display comprising the same, in which current flows in a driving transistor regardless of a threshold voltage of the driving transistor and pixel power. This way, the variations of the threshold voltage is compensated, so that the amount of current flowing in the light emitting device does not vary with voltage drop in first voltage used for the pixel power and the decrease in the pixel power, thereby improving the uniformity of brightness.

[0017] In one embodiment, the present invention is a pixel circuit comprising: a light emitting device; a driving transistor to receive a first voltage and supply a current corresponding to the voltage applied to a gate electrode thereof to the light emitting device; a first switching device to supply a data signal in response to a first scan signal; a second switching device to supply a second voltage to the gate electrode of the driving transistor in response to the first scan signal; a capacitor to store a voltage corresponding to the data signal and the second voltage according to operations of the first and second switching devices; a third switching device to apply voltage corresponding to the voltage stored in the capacitor to the gate electrode of the driving transistor in response to a second scan signal; and a fourth switching device to transmit the first voltage to the driving transistor in response to a third scan signal.

In one embodiment, the present invention is a pixel circuit comprising: a light emitting device; a driving transistor to supply a driving current corresponding to a voltage applied to a gate electrode thereof to the light emitting device; a capacitor to store a predetermined voltage corresponding to a data signal and a second voltage applied to the gate electrode of the driving transistor; a first switch to selectively supply the data signal to the capacitor; a second switch to supply either a voltage stored in the capacitor or the second voltage to the gate electrode of the driving transistor; and a third switch to selectively supply a first voltage to the driving transistor. Preferably the voltage stored in the capacitor is equal to a voltage obtained by subtracting a sum of the second voltage and a threshold voltage of the driving transistor from the voltage corresponding to the data signal. Preferably the first, second, and third switches receive first, second, and third scan signals, respectively, and the first, second, and third scan signals are periodic signals, and each period of the first, second, and third scan signals comprises a first period and a second period, and the first scan signal is in an on state for the first and in an off state for the second period; and the second scan signal is in the off state for the first and in the on state for the second period; and the third scan signal is in the off state for the first and in the on state for the second period. Preferably the first switch receives the first scan signal, the second switch selectively receives the first and second scan signals, and the third switch receives the third scan signal. Preferably an absolute value of the difference between the first voltage and the second voltage is larger than or equal to an absolute value of a threshold voltage of the driving transistor.

[0018] In one embodiment, the present invention is a pixel circuit comprising: a light emitting device; a capacitor comprising a first terminal connected to a first node, and a second terminal connected to a third node; a first switching transistor comprising source and drain electrodes connected to a data line and the first node, respetively, and a gate electrode connected to a first scan line; a second switching transistor comprising source and drain electrodes connected to second power and a second node, respetively, and a gate electrode connected to the first scan line; a third switching transistor comprising source and drain electrodes connected to the first node and the second node, respetively, and a gate electrode connected to a second scan line; a driving transistor comprising source and drain electrodes connected to the third node and the light emitting device, respetively, and a gate electrode connected to the second node; and a fourth switching transistor comprising source and drain electrodes connected to first power and the driving transistor, respetively, and selectively supplying the first power to the driving transistor.

**[0019]** In one embodiment, the present invention is a light emitting display comprising: a plurality of scan lines; a plurality of data lines; and a plurality of pixel circuits, wherein each pixel circuit comprising: a light emitting device; a driving transistor to receive a first voltage and supply a current corresponding to voltage applied to a gate electrode thereof to the light emitting device; a first switching device to supply a data signal in response to a first scan signal; a

second switching device to supply a second voltage to the gate electrode of the driving transistor in response to the first scan signal; a capacitor to store voltage corresponding to the data signal and the second power according to operations of the first and second switching devices; a third switching device to apply voltage corresponding to the voltage stored in the capacitor to the gate electrode of the driving transistor in response to a second scan signal; and a fourth switching device to transmit the first voltage to the driving transistor in response to a third scan signal.

## BRIEF DESCRIPTION OF THE DRAWINGS

- **[0020]** These and/or other aspects and advantages of the invention will become apparent and more readily appreciated from the following description of some embodiments of the invention, taken in conjunction with the accompanying drawings of which:

- [0021] FIG. 1 is a circuit diagram of a pixel provided in a conventional light emitting display;

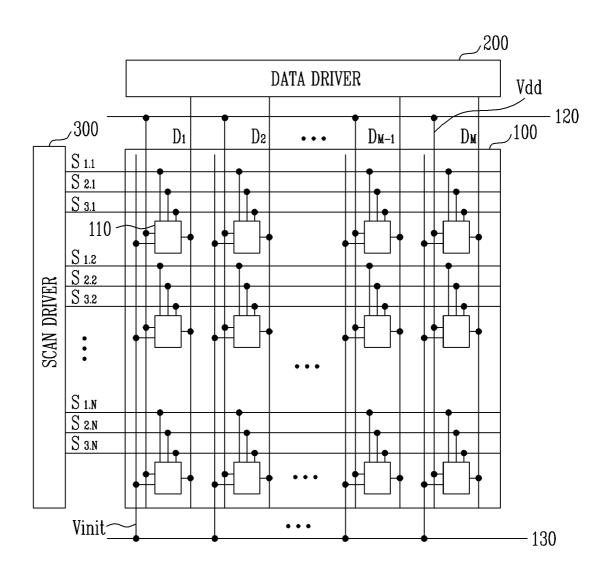

- [0022] FIG. 2 illustrates configuration of a light emitting display according to an embodiment of the present invention;

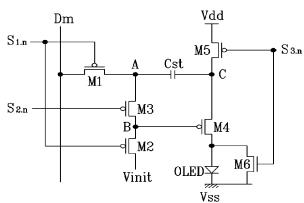

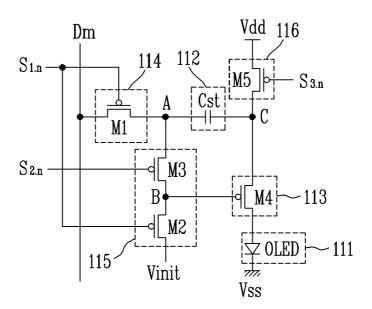

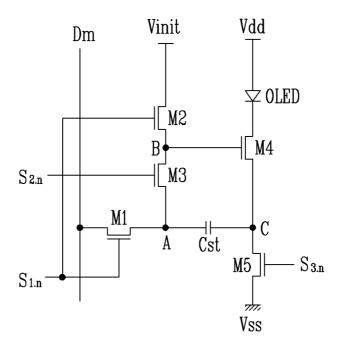

- [0023] FIG. 3 is a circuit diagram of a pixel according to a first embodiment of the present invention;

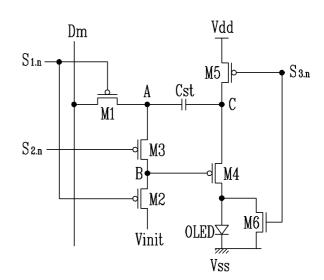

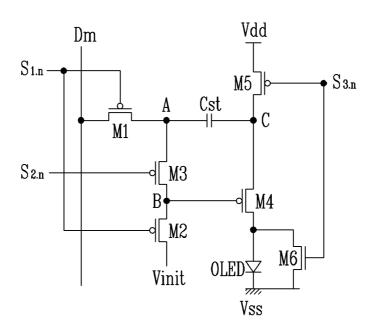

- [0024] FIG. 4 is a circuit diagram of a pixel according to a second embodiment of the present invention;

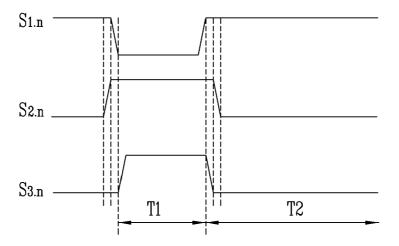

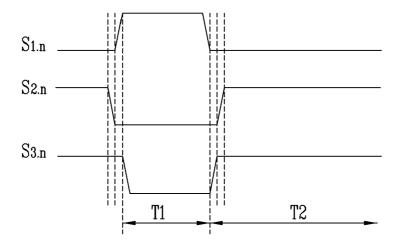

- [0025] FIG. 5 shows timing between signals for driving the pixels shown in FIGs. 3 and 4;

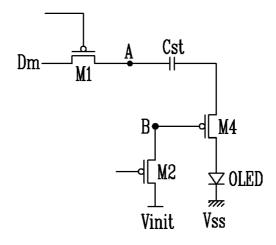

- [0026] FIG. 6 is a circuit diagram for compensating for variations in the threshold voltage of the pixels shown in FIGs. 3 and 4;

- [0027] FIG. 7 is a circuit diagram formed when a driving voltage is applied to the pixels shown in FIGs. 3 and 4;

- [0028] FIG. 8 is a circuit diagram of a pixel comprising NMOS transistors according to an embodiment of the present invention; and

- [0029] FIG. 9 shows timing of signals for driving the pixel shown in FIG. 8.

connected to a first power line 130 and a second power line 120.

## **DETAILED DESCRIPTION**

10

20

25

30

35

55

image.

[0030] FIG. 2 illustrates a configuration of a light emitting display according to an embodiment of the present invention. Referring to FIG. 2, the light emitting display comprises a pixel portion 100, a data driver 200, and a scan driver 300. The pixel portion 100 comprises a plurality of pixels 110 including N×M organic light emitting devices; N first scan lines S1.1, S1.2, ..., S1.N-1, S1.N arranged in a row direction; N second scan lines S2.1, S2.2, ..., S2.N-1, S2.N arranged in the row direction; N third scan lines S3.1, S3.2, ..., S3.N-1, S3.N arranged in the row direction; M data lines D1, D2, ...DM-1, DM arranged in a column direction; M pixel power lines Vdd to supply pixel power; and M compensation power lines Vinit to supply compensation power. Here, each pixel power line Vdd and each compensation power line Vinit are

- [0031] Further, a data signal is transmitted from any of the data lines D1, D2, ...DM-1, DM to a pixel 110 in response to a first scan signal and a second scan signal transmitted through any of the first scan lines S1.1, S1.2, ..., S1.N-1, S1.N, and any of the second scan lines S2.1, S2.2, ..., S2.N-1, S2.N to generate a driving current corresponding to the data signal. Also, the driving current is supplied to a corresponding organic light emitting device OLED in response to a third scan signal transmitted through one of the third scan lines S3.1, S3.2, ..., S3.N-1, S3.N, thereby displaying an

- [0032] The data driver 200 is connected to the data lines D1, D2, ...DM-1, DM and supplies the data signal to the pixels 110. The scan driver 300 is provided on a side of the pixel portion 100, and connected to the first scan lines S1.1, S1.2, ..., S1.N-1, S1.N, the second scan lines S2.1, S2.2, ..., S2.N-1, S2.N, and the third scan lines S3.1, S3.2, ..., S3.N-1, S3.N. The scan driver 300 supplies the first, second and third scan signals to the pixel portion 100, and selects the rows of the pixel portion 100 in sequence. Then, the data driver 200 supplies the data signal to the selected row, thereby allowing a pixel 110 to emit light based on the data signal.

- [0033] FIG. 3 is a circuit diagram of a pixel according to a first embodiment of the present invention. As shown in FIG. 3, the pixel comprises an emission part 111, a storage part 112, a driving device 113, a first switching part 114, a second switching part 115, and a third switching part 116.

- [0034] The driving device 113 comprises source, gate and drain electrodes, and determines the intensity of current inputted to the emission part 111 on the basis of voltage stored in the storage part 112, thereby controlling the brightness of the emission part 111.

- **[0035]** The first switching part 114 receives the data signal and selectively transmits it to the storage part 112. The second switching part 115 selectively transmits either the voltage stored in the storage part 112 or the compensation voltage applied through the compensation power line Vinit to a gate electrode of the driving device 113, based on scan signals S1.n and S2.n.

- **[0036]** The storage part 112 stores a predetermined voltage and supplies the stored voltage to the gate electrode of the driving device 113. Further, the storage part 112 stores voltage obtained by subtracting voltage applied to a source electrode of the driving device 113 from the voltage corresponding to the data signal received through the first switching

part 114. Here, the voltage applied to the source electrode of the driving device 113 is higher than the compensation voltage by the absolute value of the threshold voltage of the driving device 113.

**[0037]** The third switching part 116 prevents the first power Vdd from being applied to the driving device 113 while the pixel power is selectively applied to the pixel through the pixel power line Vdd and stored in the storage part 112. Further, the third switching part 116 supplies the first power Vdd to the driving device 113 when the pixel power is completely stored in the storage part 112.

**[0038]** In other words, the pixel 110 comprises the organic light emitting device OLED and its peripheral circuits including a first switching transistor M1, a second switching transistor M2, a third switching transistor M3, a driving transistor M4, a fourth switching device M5, and a capacitor Cst. Each of the first through third switching transistors M1, M2, M3, the driving transistors M4, and the switching device M5 comprises a gate electrode, a source electrode, and a drain electrode. Further, the capacitor Cst comprises a first electrode and a second electrode.

**[0039]** The gate electrode of the first switching transistor M1 is connected to the first scan line S1.n, the source electrode is connected to the data line Dm, and the drain electrode is connected a first node A. Here, the first switching transistor M1 supplies the data signal to the first node A, in response to the first scan signal inputted through the first scan line S1.n.

**[0040]** The gate electrode of the second switching transistor M2 is connected to the first scan line S1.n, the source electrode is connected to the compensation power line Vinit, and the drain electrode is connected to a second node B. Here, the second switching transistor M2 supplies the compensation power from the compensation power line Vinit to the second node B, in response to the first scan signal inputted through the first scan line S1.n. Further, the compensation power inputted through the compensation power line Vinit is maintained as a high signal.

20

30

35

40

45

50

55

**[0041]** The capacitor Cst is connected between the first node A and a third node C, and charged with the voltage difference between the voltage applied to the first node A and the voltage applied to the third node C, thereby supplying the charged voltage to the gate electrode of the driving transistor M4 for a period corresponding to one frame.

**[0042]** The gate electrode of the third switching transistor M3 is connected to the second scan line S2.n, the source electrode is connected to the first node A, and the drain electrode is connected to the second node B. Here, the third switching transistor M3 supplies the voltage charged in the capacitor Cst to the gate electrode of the driving transistor M4 in response to the second scan signal inputted through the second scan signal S2.n.

**[0043]** The gate electrode of the driving transistor M4 is connected to the second node B, the source electrode is connected to the third node C, and the drain electrode is connected to the anode electrode of the organic light emitting device OLED. Here, the driving transistor M4 controls the current corresponding to the voltage applied to its own gate electrode to flow via its own source and drain electrodes, thereby supplying the current to the organic light emitting device OLED.

**[0044]** The gate electrode of the fourth switching device M5 is connected to the third scan line S3.n, the source electrode is connected to the pixel power line Vdd to supply the pixel power, and the drain electrode is connected to the third node C. Here, the fourth switching device M5 is switched in response to the third scan signal inputted through the third scan line S3.n, and thus selectively supplies the pixel power to the organic light emitting device OLED, thereby controlling the current flowing in the organic light emitting device OLED.

**[0045]** FIG. 4 is a circuit diagram of a pixel according to a second embodiment of the present invention. Referring to FIG. 4, the pixel comprises an additional fifth switching transistor M6 connected in parallel to the organic light emitting device OLED, relative to the pixel circuit of the first embodiment.

**[0046]** The fifth switching transistor M6 comprises a gate electrode connected to a third scan line, a source electrode connected to a cathode electrode of the organic light emitting device OLED, and a drain electrode connected to an anode electrode of the organic light emitting device OLED. Further, the fifth switching transistor M6 has a reverse polarity relative to the fourth switching transistor M5. For example, when the fourth switching device M5 is of a p-type transistor as shown in FIG. 4, the fifth switching transistor M6 is of an n-type transistor. In this case, the fifth switching transistor M6 is turned off while the fourth switching device M5 is turned on. On the other hand, the fifth switching transistor M6 is turned on while the fourth switching device M5 is turned off.

[0047] Therefore, in a case that the organic light emitting device OLED emits light, the fifth switching transistor M6 is turned off, so that the current flows only in the organic light emitting device OLED. On the other hand, in a case that the organic light emitting device OLED does not emit light (particularly, while the threshold voltage is detected), the fifth switching transistor M6 is turned on, so that the current flows in the fifth switching transistor M6 and not in the organic light emitting device OLED, thereby preventing the organic light emitting device OLED from emitting light.

**[0048]** FIG. 5 shows timing of the signals for driving the pixels shown in FIGs. 3 and 4; FIG. 6 is a circuit diagram formed when threshold voltage is compensated in the pixels shown in FIGs. 3 and 4; and FIG. 7 is a circuit diagram formed when the driving voltage is applied to the pixels shown in FIGs. 3 and 4. Referring to FIGs. 5 through 7, operation of the pixel is divided according to a first operation period T1 and a second operation period T2. In the first operation period T1, the first scan signal s1.n is low, and the second scan signal s2.n and the third scan signal s3.n are high. In the second operation period T2, the first scan signal s1.n is high, and the second scan signal s2.n and the third scan

signal s3.n are low.

15

30

35

45

50

55

**[0049]** In the first operation period T1, the first and second switching transistors M1 and M2 are turned on by the first scan signal s1.n, and the third and fourth switching transistors M3 and M4 are turned off by the second scan signal s2.n and the third scan signal s3.n. Hence, the circuit is connected as shown in FIG. 6.

**[0050]** Referring to FIG. 6, the data signal is transmitted to the first node A through the first switching transistor M1, and the compensation power is supplied to the gate electrode of the driving transistor M4 through the second switching transistor M2. At this time, the first scan signal s1.n is changed from a high state to a low state after the second scan signal s2.n is changed from a low state to a high state, so that the first and second switching transistors M1 and M2 are turned on after the third switching transistor M3 is turned off. Therefore, the data signal is not distorted by other voltage and is correctly stored in the capacitor, thereby applying a uniform voltage to the gate of the driving transistor M4.

**[0051]** Because the applied compensation power is a high signal, the driving transistor M4 is maintained in the off state, and thus the voltage applied to the source electrode of the driving transistor M4 is higher than the voltage applied to the gate electrode thereof by the threshold voltage. Therefore, the voltage based on the following equation 2 is applied between the source and gate electrodes of the driving transistor M4 by the capacitor Cst.

Vest = Vdata - (Vinit - Vth) [Equation 2];

where *Vcst* is a voltage charged in the capacitor; *Vdata* is a voltage corresponding to the data signal; *Vinit* is the compensation voltage and *Vth* is the threshold voltage of the driving transistor M4.

**[0052]** In order to correctly operate the driving transistor M4, the pixel power voltage should be larger than or equal to the sum of the compensation voltage and the absolute value of the threshold voltage of the driving transistor M4.

**[0053]** In the second operation period T2, the first scan signal s1.n is maintained in the high state, and the second scan signal s2.n and the third scan signal s3.n are maintained in the low state. The second operation period T2 is maintained for a period corresponding to one frame. During this time, the first and second switching transistors M1 and M2 are turned off by the first scan signal s1.n, and the third and fourth switching transistors M3 and M5 are turned on by the second scan signal s2.n and the third scan signal s3.n. Hence, the circuit is connected as shown in FIG. 7.

[0054] Referring to FIG. 7, the voltage charged in the capacitor Cst is applied to the gate electrode of the driving transistor M4, so that the current corresponding to the voltage charged in the capacitor Cst flows in the organic light emitting device OLED through the driving transistor M4. At this time, the second scan signal s2.n is changed from a high state to a low state after the first scan signal s1.n is changed from a low state to a high state, so that the third switching transistor M3 applies only the voltage charged in the capacitor Cst to the gate electrode of the driving transistor M4, thereby applying a uniform voltage to the gate electrode of the driving transistor M4.

[0055] Therefore, a current based on the following equation 3 flows from the driving transistor M4 to the organic light emitting device OLED.

$I_{OLED} = \frac{\beta}{2} (Vgs - Vth)^2 = \frac{\beta}{2} (Vdata - Vinit)^2$  [Equation 3]

,where  $I_{OLED}$  is a current flowing in the organic light emitting device OLED; Vgs is a voltage applied between the source and gate electrodes of the driving transistor M4; Vdata is a voltage corresponding to the data signal; Vinit is a compensation voltage; and  $\beta$  is a gain factor of the driving transistor M4.

**[0056]** Therefore, as shown in the equation 3, the current flowing in the organic light emitting device OLED corresponds only to the data signal voltage and the compensation voltage, regardless of the threshold voltage of the driving transistor M4 and the pixel power.

**[0057]** At this time, the pixel power allows the current to flow in the light emitting device, so that a voltage drop occurs in the pixel power as the current flows. However, the compensation voltage is connected to the capacitor Cst, so that there is no current flowing to the pixel by the compensation power. Thus, a voltage drop does not occur in the compensation voltage.

**[0058]** Thus, in the pixels shown in FIGs. 3 and 4, the deviation between the threshold voltages of the driving transistors M4 is compensated, and the voltage drop in the pixel power is compensated, so that the pixels are suitable for realizing a large sized light emitting display.

**[0059]** FIG. 8 is a circuit diagram of a pixel comprising NMOS transistors according to an embodiment of the present invention. Referring to FIG. 8, the pixel comprises an organic light emitting device OLED and its peripheral circuits including a first switching transistor M1, a second switching transistor M2, a third switching transistor M3, a driving

transistor M4, a fourth switching device M5, and a capacitor Cst. Each of the first through third switching transistors M1, M2, M3, the driving transistors M4, and the switching device M5 is realized by an NMOS transistor comprising a gate electrode, a source electrode, and a drain electrode. Further, the capacitor Cst comprises a first electrode and a second electrode.

**[0060]** The organic light emitting device OLED is connected to the driving transistor M4, and the fourth switching device M5 is connected between the driving transistor M4 and a cathode electrode.

**[0061]** FIG. 9 shows timing between signals for driving the pixel shown in FIG. 8. Referring to FIG. 9, operation of the pixel is divided according to a first operation period T1 and a second operation period T2. In the first operation period T1, the first scan signal s1.n is high, and the second scan signal s2.n and the third scan signal s3.n are low. In the second operation period T2, the first scan signal s1.n is low, and the second scan signal s2.n and the third scan signal s3.n are high.

**[0062]** In the first operation period T1, the first and second switching transistors M1 and M2 are turned on by the first scan signal s1.n, and the third and fourth switching transistors M3 and M5 are turned off by the second scan signal s2.n and the third scan signal s3.n. Hence, the compensation voltage is supplied from the compensation power line Vinit to the gate electrode of the driving transistor M3, and the capacitor Cst is charged with a voltage based on the equation 2. During this time, the compensation power supplied through the compensation power line Vinit is kept low.

[0063] In the second operation period T2, the first scan signal s1.n is kept low, and the second scan signal s2.n and the third scan signal s3.n are kept high. The second operation period T2 is maintained for a period corresponding to one frame. During this time, the first and second switching transistors M1 and M2 are kept turned off by the first scan signal s1.n, and the third and fourth switching transistors M3 and M5 are kept turned on by the second scan signal s2.n and the third scan signal s3.n. The voltage stored in the capacitor Cst is applied to the organic light emitting device OLED, so that the driving current based on the equation 3 flows therein.

**[0064]** In the foregoing embodiment, the fourth switching device M5 for controlling the current to flow in the organic light emitting device OLED may be an NMOS transistor when other transistors provided in the pixel are PMOS transistors. Alternately, the fourth switching device M5 may be a PMOS transistor when other transistors provided in the pixel are NMOS transistors.

**[0065]** As described above, the present invention provides a pixel circuit and a light emitting display, in which current flows in a driving transistor regardless of threshold voltage of the driving transistor and pixel power. Thus, the difference between the threshold voltages is compensated, so that the intensity of current flowing in the light emitting device does not vary due to voltage drop in first power used for the pixel power and a decrease in the pixel power voltage, thereby improving the uniformity of brightness of the light emitting device.

**[0066]** Although a few embodiments of the present invention have been shown and described, it would be appreciated by those skilled in the art that changes might be made in this embodiment without departing from the principles and spirit of the invention, the scope of which is defined in the claims and their equivalents.

## Claims

20

30

35

40

45

50

1. A pixel circuit comprising:

a light emitting device;

a driving transistor to receive a first voltage and supply a current to the light emitting device, corresponding to voltage applied to a gate electrode thereof;

a first switching device to supply a data signal in response to a first scan signal;

a second switching device to supply a second voltage to the gate electrode of the driving transistor in response to the first scan signal;

a capacitor to store a voltage corresponding to the data signal and the second voltage according to operations of the first and second switching devices;

a third switching device to apply voltage corresponding to the voltage stored in the capacitor to the gate electrode of the driving transistor in response to a second scan signal; and

a fourth switching device to transmit the first voltage to the driving transistor in response to a third scan signal.

- 2. The pixel circuit according to claim 1, further comprising a fifth switching device to interrupt the current from flowing in the light emitting device in response to the third scan signal.

- 3. The pixel circuit according to claim 1 or 2, wherein the voltage stored in the capacitor is equal to voltage obtained by subtracting a sum of the second voltage and a threshold voltage of the driving transistor from the voltage corresponding to the data signal.

55

- **4.** The pixel circuit according to claim 1 or 2, wherein the first, second and third scan signals are of a periodic signal, and each period of the first, second, and third scan signals comprises a first period and a second period, and wherein the first scan signal is in on and off states for the first and second periods, respectively; the second scan signal is in off and on states for the first and second periods, respectively; and the third scan signal is in off and on states for the first and second periods, respectively.

- 5. The pixel circuit according to claim 1 or 2, wherein the second voltage maintains the driving transistor in an off state.

- **6.** The pixel circuit according to claim 1 or 2, wherein an absolute value of the difference between the first voltage and the second voltage is larger than or equal to an absolute value of a threshold voltage of the driving transistor.

- 7. The pixel circuit according to claim 2, wherein the fourth switching device and the fifth switching device are driven by the third scan signal to be in different states.

- 15 **8.** The pixel circuit according to claim 1, wherein

5

10

20

25

35

40

45

50

the capacitor comprises a first terminal connected to a first node, and a second terminal connected to a third node; the first switching device comprises a first switching transistor comprising a source electrode connected to a data line, a drain electrode connected to the first node, and a gate electrode connected to the first scan line;

the second switching device comprises a second switching transistor comprising a source electrode connected to a second power supply, a drain electrode connected to a second node, and a gate electrode connected to the first scan line:

the third switching device comprises a third switching transistor comprising a source electrode connected to the first node, a drain electrode connected to the second node, and a gate electrode connected to a second scan line;

the driving transistor comprises a source electrode connected to the third node, a drain electrode connected to the light emitting device, and a gate electrode connected to the second node; and

the fourth switching device comprises a fourth switching transistor comprising a source electrode connected to a first power supply, a drain electrode connected to the driving transistor, the fourth transistor selectively supplying the first power supply to the driving transistor.

- **9.** The pixel circuit according to claim 8, further comprising a fifth switching device connected to the light emitting device and maintained to have an opposite on/off state to state of the fourth switching transistor.

- **10.** The pixel circuit according to claim 8, wherein the second power supply maintains the driving transistor to be in an off state and/or wherein an absolute value of the difference between the first power supply and the second power supply is larger than or equal to an absolute value of a threshold voltage of the driving transistor.

- 11. A light emitting display comprising:

- a plurality of scan lines;

- a plurality of data lines; and

- a plurality of pixel circuits, wherein

- each pixel circuit comprising:

- a light emitting device;

- a driving transistor to receive a first voltage and supply a current to the light emitting device corresponding to voltage applied to a gate electrode thereof;

- a first switching device to supply a data signal in response to a first scan signal;

- a second switching device to supply a second voltage to the gate electrode of the driving transistor in response to the first scan signal;

- a capacitor to store a voltage corresponding to the data signal and the second voltage according to operations of the first and second switching devices;

- a third switching device to apply voltage corresponding to the voltage stored in the capacitor to the gate electrode of the driving transistor in response to a second scan signal; and

- a fourth switching device to transmit the first voltage to the driving transistor in response to a third scan signal.

- 12. The light emitting display according to claim 11, wherein the voltage stored in the capacitor is equal to voltage obtained by subtracting a sum of the second voltage and a threshold voltage of the driving transistor from the voltage corresponding to the data signal.

- 13. The light emitting display according to claim 11, wherein the first, second, and third scan signals are of a periodic signal, and each period of the first, second, and third scan signals comprises a first period and a second period, and wherein

- the first scan signal is in on and off states for the first and second periods, respectively; the second scan signal is in off and on states for the first and second periods, respectively; and the third scan signal is in off and on states for the first and second periods, respectively.

- **14.** The light emitting display according to claim 11, further comprising a fifth switching device to prevent the supplied current from flowing in the light emitting device in response to the third scan signal and/or further comprising a scan driver to supply the first, second, and third scan signals; and a data driver to supply the data signal.

- **15.** The light emitting display according to claim 14, wherein the second voltage maintains the driving transistor in an off state and/or wherein the fourth switching device and the fifth switching device are driven by the third scan signal to be in different states.

FIG. 1 (PRIOR ART)

FIG. 2

FIG. 3

# FIG. 4

FIG. 5

FIG. 6

# FIG. 7

FIG. 8

# FIG. 9

# **EUROPEAN SEARCH REPORT**

**Application Number**

EP 05 10 9164

|                                          | DOCUMENTS CONSID  Citation of document with ir                                                                                                                       | Relevant                                                                                       | CLASSIFICATION OF THE                                                                               |                                 |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------|

| Category                                 | of relevant passa                                                                                                                                                    |                                                                                                | to claim                                                                                            | APPLICATION (IPC)               |

| Α                                        | US 2004/174354 A1 (<br>9 September 2004 (2<br>* the whole documen                                                                                                    | 004-09-09)                                                                                     | 1-15                                                                                                | G09G3/32                        |

| А                                        | US 2003/227262 A1 (<br>11 December 2003 (2<br>* the whole documen                                                                                                    | 003-12-11)                                                                                     | 1-15                                                                                                |                                 |

| А                                        | US 6 680 580 B1 (SU<br>20 January 2004 (20<br>* column 5, line 10                                                                                                    | <br>NG CHIH-FENG)<br>04-01-20)<br>- line 21; figure 4 '                                        | 2,14                                                                                                |                                 |

|                                          |                                                                                                                                                                      |                                                                                                |                                                                                                     | TECHNICAL FIELDS SEARCHED (IPC) |

|                                          |                                                                                                                                                                      |                                                                                                |                                                                                                     |                                 |

|                                          | The present search report has b                                                                                                                                      | peen drawn up for all claims                                                                   |                                                                                                     |                                 |

|                                          | Place of search                                                                                                                                                      | Date of completion of the search                                                               |                                                                                                     | Examiner                        |

| Munich                                   |                                                                                                                                                                      | 19 January 2006                                                                                | 19 January 2006 Au                                                                                  |                                 |

| X : part<br>Y : part<br>docu<br>A : tech | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone icularly relevant if combined with another of the same category inological background written disclosure | T : theory or princ E : earlier patent after the filing of D : document cite L : document oite | iple underlying the i<br>document, but publi<br>date<br>d in the application<br>d for other reasons | nvention<br>shed on, or         |

## ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 05 10 9164

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

19-01-2006

| F<br>cite | Patent document<br>ed in search report |    | Publication date |          | Patent family member(s) |        | Publication<br>date    |

|-----------|----------------------------------------|----|------------------|----------|-------------------------|--------|------------------------|

| US        | 2004174354                             | A1 | 09-09-2004       | JP       | 2004280059              | Α      | 07-10-200              |

| US        | 2003227262                             | A1 | 11-12-2003       | CN<br>JP | 1490779<br>2004029791   | A<br>A | 21-04-200<br>29-01-200 |

| US        | 6680580                                | B1 | 20-01-2004       | TW       | 564390                  | В      | 01-12-200              |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

|           |                                        |    |                  |          |                         |        |                        |

$\stackrel{\circ}{\mathbb{L}}$  For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

FORM P0459

| 专利名称(译)        | 用于OLED显示器的像素电路具有阈值电压的自补偿                                                        |         |            |  |  |  |  |

|----------------|---------------------------------------------------------------------------------|---------|------------|--|--|--|--|

| 公开(公告)号        | EP1646032A1                                                                     | 公开(公告)日 | 2006-04-12 |  |  |  |  |

| 申请号            | EP2005109164                                                                    | 申请日     | 2005-10-04 |  |  |  |  |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                     |         |            |  |  |  |  |

| 申请(专利权)人(译)    | 三星SDI CO., LTD.                                                                 |         |            |  |  |  |  |

| 当前申请(专利权)人(译)  | 三星SDI CO., LTD.                                                                 |         |            |  |  |  |  |

| [标]发明人         | JUNG JIN TAE                                                                    |         |            |  |  |  |  |

| 发明人            | JUNG, JIN TAE                                                                   |         |            |  |  |  |  |

| IPC分类号         | G09G3/32                                                                        |         |            |  |  |  |  |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0842 G09G2300/0861 G09G2310/0251 G09G2320/043 |         |            |  |  |  |  |

| 代理机构(译)        | hengelhaupt , Jürgen                                                            |         |            |  |  |  |  |

| 优先权            | 1020040080621 2004-10-08 KR                                                     |         |            |  |  |  |  |

| 其他公开文献         | EP1646032B1                                                                     |         |            |  |  |  |  |

| 外部链接           | <u>Espacenet</u>                                                                |         |            |  |  |  |  |

|                |                                                                                 |         |            |  |  |  |  |

## 摘要(译)

像素电路包括发光器件(OLED);驱动晶体管(M4),用于接收第一电源(Vdd),并将与施加到其栅电极的电压对应的电流提供给发光器件(OLED);第一开关装置(M1),用于响应第一扫描信号(S1.n)提供数据信号(Dm);第二开关器件(M2),响应于第一扫描信号(S1. S1.n-n),向驱动晶体管(M4)的栅极提供第二功率(Vinit);电容器(Cst),用于根据第一(M1)和第二(M2)开关器件的操作存储对应于数据信号(Dm)和第二电源(Vdd)的电压;第三开关器件(M3),用于响应于第二扫描信号(S2.n)将存储在电容器(Cst)中的电压施加到驱动晶体管(M4)的栅极;第四开关器件(M5)响应于第三扫描信号(S3.n)将第一电源(Vdd)传输到驱动晶体管(M4)。可选的第五开关装置(M6)响应于第三扫描信号(S3.n)绕过发光器件(OLED)。像素电路提供独立于电源线上的电压降和驱动晶体管的阈值电压的驱动电流,从而改善显示器的亮度均匀性。

FIG. 4