## (19) 日本国特許庁(JP)

# 再 公 表 特 許(A1)

(11) 国際公開番号

W02019/064342

発行日 令和2年7月30日 (2020.7.30)

## (43) 国際公開日 平成31年4月4日(2019.4.4)

| (51) Int.Cl. |       |           | F I  |          |     | テーマコー     | ド (参考) |

|--------------|-------|-----------|------|----------|-----|-----------|--------|

| HO1L 5       | 51/50 | (2006.01) | HO5B | 33/14    | A   | 3 K 1 O 7 |        |

| HO1L 2       | 27/32 | (2006.01) | HO1L | 27/32    |     | 5CO94     |        |

| H05B 3       | 33/04 | (2006.01) | HO5B | 33/04    |     | 5G435     |        |

| HO5B 3       | 33/06 | (2006.01) | HO5B | 33/06    |     |           |        |

| HO5B 3       | 33/22 | (2006.01) | HO5B | 33/22    | Z   |           |        |

|              |       |           | 審查請求 | 有 予備審査請求 | 未請求 | (全 40 頁)  | 最終頁に続く |

|              |       |           |      |          |     |           |        |

特願2019-545420 (P2019-545420) 出願番号 (21) 国際出願番号 PCT/JP2017/034737 (22) 国際出願日 平成29年9月26日 (2017.9.26) AP (BW, GH, GM, KE, LR, LS, MW, MZ, NA, (81) 指定国・地域 RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), EA (AM, AZ, BY, KG, KZ, RU, T J, TM), EP (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB , GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, R 0, RS, SE, S1, SK, SM, TR), 0A (BF, BJ, CF, CG, C1, CM, GA, GN, GQ , GW, KM, ML, MR, NE, SN, TD, TG), AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ , DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, G T, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX

, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, R

S, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM,

(71) 出願人 000005049

シャープ株式会社

大阪府堺市堺区匠町1番地

(74)代理人 100147304

弁理士 井上 知哉

(72) 発明者 三谷 昌弘

大阪府堺市堺区匠町1番地 シャープ株式

会社内

F ターム (参考) 3K107 AA01 BB01 CC21 DD03 DD38

DD89 DD90 EE48 EE49 EE50

EE58 FF15

5C094 AA31 BA03 BA27 DA06 DA07

DA13 DA15 DB02

5G435 AA14 BB05 EE32 KK05

# (54) [発明の名称]表示デバイス、表示デバイスの製造方法、表示デバイスの製造装置

# (57)【要約】

TN, TR, TT

アクティブ側スリット(43)およびFPC側スリット(44)は、各々、第2無機絶縁膜(20)を貫通して第1無機絶縁膜(18)に達している。平面視においては、アクティブ側スリット(43)が、ELデバイス(2)のアクティブ領域とICチップ搭載領域(56)との間に形成されるとともに、ICチップ搭載領域(56)は、アクティブ側スリット(43)およびFPC側スリット(44)によって挟まれている。

#### 【特許請求の範囲】

#### 【請求項1】

複数の無機絶縁膜を含むTFT層と、前記TFT層よりも上層の発光素子層とを備え、前記TFT層には、複数の端子を含む端子領域が、アクティブ領域よりも外側に設けられる表示デバイスであって、

前記複数の無機絶縁膜の少なくとも 1 つを貫通する、第 1 スリットパターンおよび第 2 スリットパターンを含み、

前記第1スリットパターンは、平面視における前記アクティブ領域と前記端子領域との間に形成され、

前記端子領域は、前記第1スリットパターンおよび前記第2スリットパターンによって平面視において挟まれている表示デバイス。

#### 【請求項2】

前記端子領域にICチップが搭載されている請求項1に記載の表示デバイス。

## 【請求項3】

平面視における前記第2スリットパターンと前記表示デバイスのエッジとの間にフレキシブル回路基板が接続されている請求項1または2に記載の表示デバイス。

## 【請求項4】

前記端子の少なくとも一部は、前記複数の無機絶縁膜よりも上層の導電層で形成されている請求項1~3の何れか1項に記載の表示デバイス。

## 【請求項5】

前記第1スリットパターンは、前記端子に繋がる複数の端子配線と交差する方向に伸びる実線状スリットで構成される請求項1~4の何れか1項に記載の表示デバイス。

#### 【請求項6】

前記TFT層よりも下層のバリア層を備える請求項5に記載の表示デバイス。

#### 【請求項7】

前記第1および第2スリットパターンは、前記バリア層に達しない請求項6に記載の表示デバイス。

## 【請求項8】

前記端子配線が前記第1スリットパターンよりも下側を通る請求項7に記載の表示デバイス。

### 【請求項9】

前記端子配線は、前記TFT層のゲート配線と同層に形成されている請求項8に記載の表示デバイス。

# 【請求項10】

前記第1および第2スリットパターンは、前記複数の無機絶縁膜を貫通して前記バリア層内に達するか、あるいは前記複数の無機絶縁膜および前記バリア層を貫通する請求項6に記載の表示デバイス。

## 【請求項11】

前記端子配線が、前記第1スリットパターンの内側面および底面を通る請求項10に記載の表示デバイス。

# 【請求項12】

前記第1スリットパターンが有機絶縁材で埋められ、

前記端子配線が前記有機絶縁材の上を通る請求項10に記載の表示デバイス。

## 【請求項13】

前記端子配線のうちの前記アクティブ領域と前記第1スリットパターンとの間に延設されている本体部は、前記端子と同層に形成されている請求項11または12に記載の表示デバイス。

## 【請求項14】

前記端子配線は、前記アクティブ領域と前記第1スリットパターンとの間に延設されている本体部と、前記第1スリットパターンと交差する交差部とを含み、前記本体部と前記

10

20

30

- -

40

交差部とが異なる導電層で形成されている請求項11または12に記載の表示デバイス。

### 【請求項15】

前記第1スリットパターンは底方向に向けて狭幅となるテーパ形状である請求項11または12に記載の表示デバイス。

## 【請求項16】

前記第1スリットパターンは、前記端子に接続する端子配線と交差する方向に並ぶ複数の島状スリットで構成される列状スリット群を1以上含む請求項1~4の何れか1項に記載の表示デバイス。

#### 【請求項17】

前記端子配線は、前記第1スリットパターンと重ならない請求項16に記載の表示デバイス。

#### 【請求項18】

前記島状スリットは、各列状スリット群について、前記端子配線が該列状スリット群を構成する前記島状スリットの間を 1 対 1 対応に通るように、配置されている請求項 1 7 に記載の表示デバイス。

#### 【請求項19】

前記島状スリットは、各々、前記端子配線のうちの1本のみと交差する請求項16に記載の表示デバイス。

#### 【請求項20】

前記島状スリットは、前記端子配線と1対1対応に交差するように、配置されている請求項19に記載の表示デバイス。

#### 【請求項21】

前記TFT層よりも下層にバリア層が設けられ、

前記第1スリットパターンは、前記複数の無機絶縁膜を貫通して前記バリア層内に達するか、あるいは前記複数の無機絶縁膜および前記バリア層を貫通する請求項17~20の何れか1項に記載の表示デバイス。

### 【請求項22】

前記第1スリットパターンは、複数の列状スリット群を含み、

前記複数の列状スリット群に含まれる複数の島状スリットは、前記端子配線が延伸する方向から見て隙間がないように、平面視において千鳥配置されている請求項16~21のいずれか1項に記載の表示デバイス。

# 【請求項23】

前記複数の島状スリットに含まれる或る島状スリットの端部は、前記複数の島状スリットに含まれる別の島状スリットと、前記端子配線が延伸する方向から見て重畳する請求項22に記載の表示デバイス。

# 【請求項24】

前記端子領域は、前記第1スリットパターンと、実線状スリットで構成された前記第2スリットパターンと、前記端子配線と同方向に伸びる実線状スリットで構成された2つの第4スリットパターンとによって囲まれている請求項5~23の何れか1項に記載の表示デバイス。

# 【請求項25】

前記アクティブ領域と前記第1スリットパターンとの間に折り曲げ領域が形成されており、

前記折り曲げ領域に、前記複数の無機絶縁膜の少なくとも1つを貫通する第3スリット パターンが形成されている請求項5~24の何れか1項に記載の表示デバイス。

# 【請求項26】

前記第1スリットパターンおよび前記第3スリットパターンの深さが同じである請求項 25に記載の表示デバイス。

## 【請求項27】

前記第1スリットパターンおよび前記第3スリットパターンのスリットパターンが同じ

10

20

30

40

である請求項26に記載の表示デバイス。

#### 【請求項28】

前記TFT層よりも下層にバリア層が設けられ、

前記バリア層よりも下層に支持材が設けられ、

前記第1および第3スリットパターンは、前記複数の無機絶縁膜および前記バリア層を 貫通して、前記支持材に達すると共に、有機絶縁材で埋められ、

前記端子配線が前記有機絶縁材の上を通る請求項26または27に記載の表示デバイス

## 【請求項29】

前記発光素子層を覆う封止層を備え、

前記発光素子層からの光が前記封止層を透過する上方発光型であり、

前記第3スリットパターンを折り目として前記端子の表面が下方を向くように折り曲げられている請求項25~28の何れか1項に記載の表示デバイス。

## 【請求項30】

前記端子配線の少なくとも一部は、前記複数の無機絶縁膜よりも上層の導電層で形成されていると共に、前記TFT層よりも上層の有機絶縁膜によって被覆されている請求項5~29の何れか1項に記載の表示デバイス。

#### 【請求項31】

可撓性の支持材を備える請求項1~30の何れか1項に記載の表示デバイス。

#### 【請求項32】

複数の無機絶縁膜を含むTFT層と、前記TFT層よりも上層の発光素子層とを備え、前記TFT層には、複数の端子を含む端子領域が、アクティブ領域よりも外側に設けられた表示デバイスの製造方法であって、

前記複数の無機絶縁膜の少なくとも1つを貫通する第1スリットパターンを、平面視における前記アクティブ領域と前記端子領域との間に形成し、

前記複数の無機絶縁膜の少なくとも1つを貫通する第2スリットパターンを、前記第1 スリットパターンとともに平面視において前記端子領域を挟むように形成する表示デバイスの製造方法。

## 【請求項33】

前記複数の無機絶縁膜の少なくとも 1 つを貫通する第 3 スリットパターンを、前記アクティブ領域と前記第 1 スリットパターンとの間に形成する請求項 3 2 に記載の表示デバイスの製造方法。

#### 【請求項34】

前記第 1 スリットパターンおよび第 3 スリットパターンを同じプロセスで形成する請求項 3 3 記載の表示デバイスの製造方法。

#### 【請求項35】

熱圧着によって前記端子領域に電子回路基板を実装する請求項32~34のいずれか1項に記載の表示デバイスの製造方法。

## 【請求項36】

前記第3スリットパターンを折り目として、前記表示デバイスを折り曲げ、前記端子領域を裏面に配する請求項33または34に記載の表示デバイスの製造方法。

#### 【請求項37】

複数の無機絶縁膜を含むTFT層と、前記TFT層よりも上層の発光素子層とを備え、 前記TFT層には、複数の端子を含む端子領域が、アクティブ領域よりも外側に設けられた表示デバイスの製造装置であって、

前記複数の無機絶縁膜の少なくとも1つを貫通する第1スリットパターンを、平面視における前記アクティブ領域と前記端子領域との間に形成し、

前記複数の無機絶縁膜の少なくとも 1 つを貫通する第 2 スリットパターンを、前記第 1 スリットパターンとともに平面視において前記端子領域を挟むように形成する表示デバイスの製造装置。

10

20

30

40

#### 【発明の詳細な説明】

【技術分野】

[0001]

本発明は、表示デバイスに関する。

【背景技術】

[0002]

特許文献 1 には、有機 E L パネルの表示領域の外側に端子領域を設ける構成が開示されている。

【先行技術文献】

【特許文献】

[0003]

【 特 許 文 献 1 】 特 開 2 0 1 1 - 1 8 6 8 6 号 公 報 ( 平 成 2 3 年 1 月 2 7 日 公 開 )

【発明の概要】

【発明が解決しようとする課題】

[0004]

端子部にICチップ等を搭載する際に端子領域に亀裂が生じ、この亀裂が周囲に伝播するおそれがある。

【課題を解決するための手段】

[0005]

本発明の一態様に係る表示デバイスは、複数の無機絶縁膜を含むTFT層と、前記TFT層よりも上層の発光素子層とを備え、前記TFT層には、複数の端子を含む端子領域が、アクティブ領域よりも外側に設けられる表示デバイスであって、前記複数の無機絶縁膜の少なくとも1つを貫通する、第1スリットパターンおよび第2スリットパターンを含み、平面視においては、前記第1スリットパターンが、平面視における前記アクティブ領域と前記端子領域との間に形成されるとともに、前記端子領域が、前記第1スリットパターンおよび前記第2スリットパターンによって挟まれている構成である。

[0006]

本発明の別の一態様に係る表示デバイスの製造方法は、複数の無機絶縁膜を含むTFT層と、前記TFT層よりも上層の発光素子層とを備え、前記TFT層には、複数の端子を含む端子領域が、アクティブ領域よりも外側に設けられた表示デバイスの製造方法であって、前記複数の無機絶縁膜の少なくとも1つを貫通する第1スリットパターンを、平面視における前記アクティブ領域と前記端子領域との間に形成し、前記複数の無機絶縁膜の少なくとも1つを貫通する第2スリットパターンを、前記第1スリットパターンとともに平面視において前記端子領域を挟むように形成する製造方法である。

[0007]

本発明の別の一態様に係る表示デバイスの製造装置は、複数の無機絶縁膜を含むTFT層と、前記TFT層よりも上層の発光素子層とを備え、前記TFT層には、複数の端子を含む端子領域が、アクティブ領域よりも外側に設けられた表示デバイスの製造装置であって、前記複数の無機絶縁膜の少なくとも1つを貫通する第1スリットパターンを、平面視における前記アクティブ領域と前記端子領域との間に形成し、前記複数の無機絶縁膜の少なくとも1つを貫通する第2スリットパターンを、前記第1スリットパターンとともに平面視において前記端子領域を挟むように形成する製造装置である。

【発明の効果】

[ 0 0 0 8 ]

本発明の一態様によれば、端子領域に亀裂が生じたとしても、第1スリットパターンおよび第2スリットパターンによってこの亀裂が周囲に伝播することを防ぐことができる。

【図面の簡単な説明】

[0009]

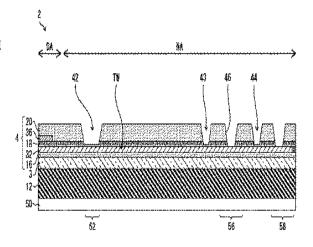

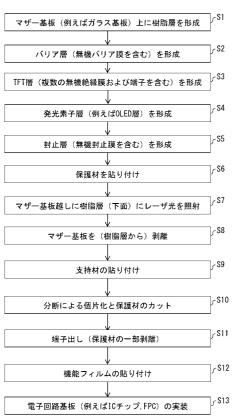

【図1】ELデバイスの製造方法の一例を示すフローチャートである。

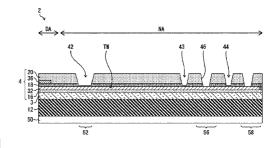

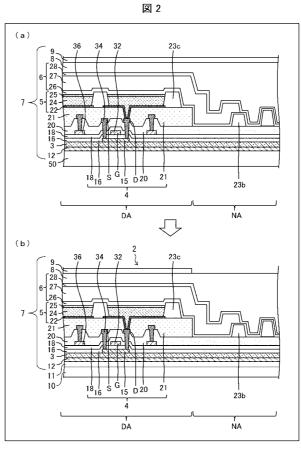

【図2】(a)は、本発明の幾つかの実施形態のELデバイスの形成途中の構成例を示す

10

20

30

40

断面図であり、(b)は、本発明の幾つかの実施形態のELデバイスの構成例を示す断面図である。

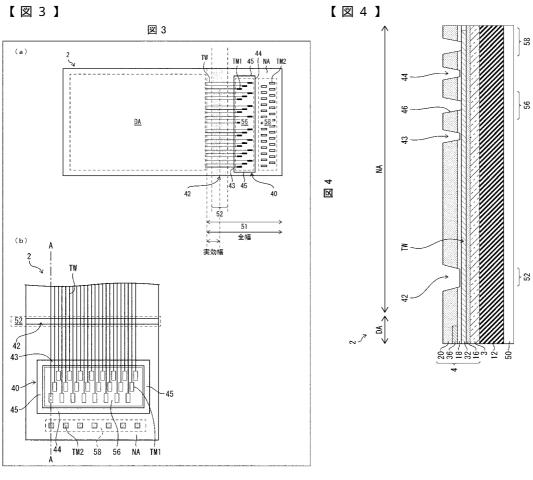

- 【図3】(a)は、本発明の幾つかの実施形態のELデバイスの構成例を示す平面図であり、(b)は、(a)に示された構成例の端子部を強調して示す部分平面図である。

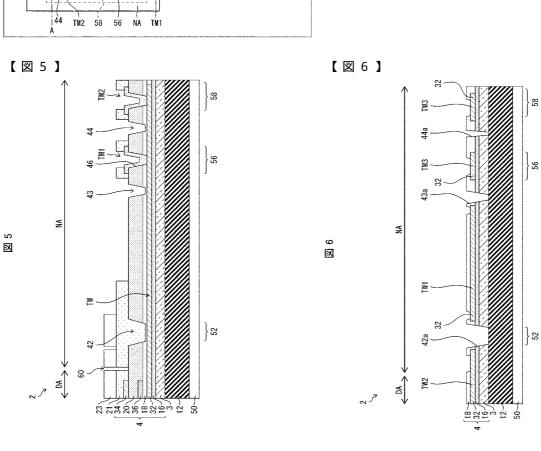

- 【図4】本発明の一実施形態に係るELデバイスの、ソース導電層形成前の断面構成を示す断面図である。

- 【図 5 】本発明の前記一実施形態に係る E L デバイスの、バンク層形成後の断面構成を示す断面図である。

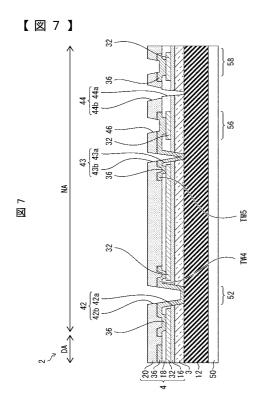

- 【図6】本発明の別の一実施形態に係るELデバイスの、第2無機絶縁膜形成前の断面構成を示す断面図である。

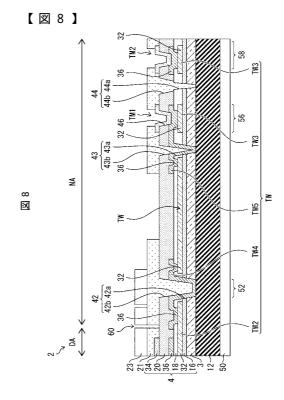

- 【図7】本発明の前記別の一実施形態に係るELデバイスの、ソース導電層形成前の断面構成を示す断面図である。

- 【図8】本発明の前記別の一実施形態に係るELデバイスの、バンク層形成後の断面構成を示す断面図である。

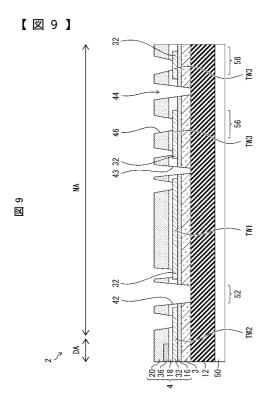

- 【図9】本発明の別の一実施形態に係るELデバイスの、ソース導電層形成前の断面構成を示す断面図である。

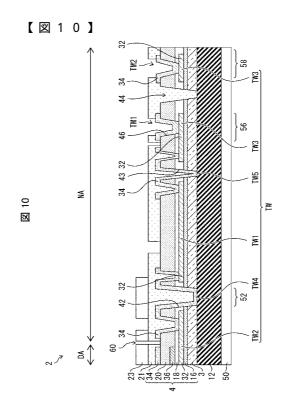

- 【図10】本発明の前記別の一実施形態に係るELデバイスの、バンク層形成後の断面構成を示す断面図である。

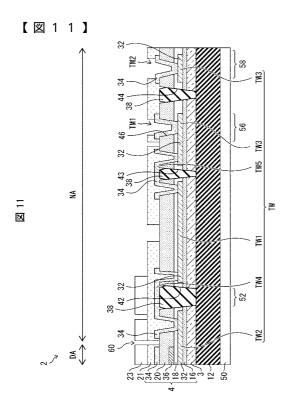

- 【図11】本発明の別の一実施形態に係るELデバイスの断面構成を示す断面図である。

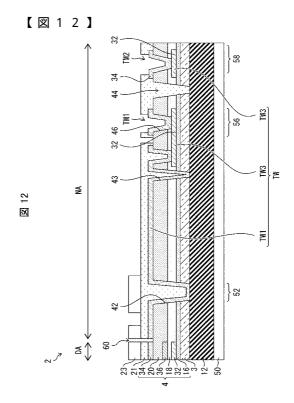

- 【図12】本発明の別の一実施形態に係るELデバイスの断面構成を示す断面図である。

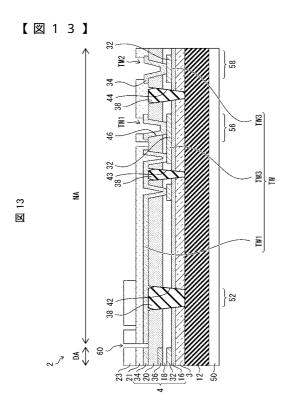

- 【図13】本発明の別の一実施形態に係るELデバイスの断面構成を示す断面図である。

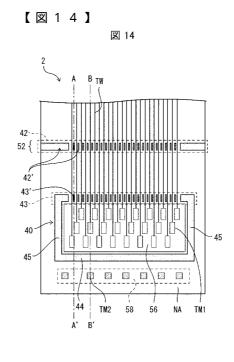

- 【図14】本発明の別の幾つかの実施形態のELデバイスの構成例を示す平面図である。

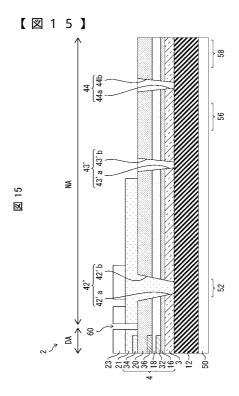

- 【図15】本発明の別の一実施形態に係るELデバイスの断面構成を示す断面図であり、図14のA-A´断面図に相当する。

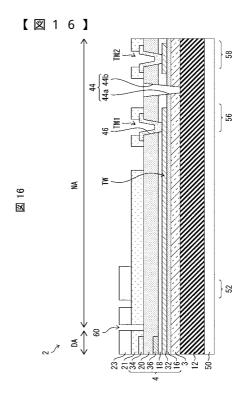

- 【図16】本発明の前記別の一実施形態に係るELデバイスの断面構成を示す別の断面図であり、図14のB-B´断面図に相当する。

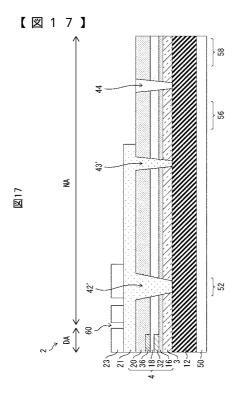

- 【図17】本発明の別の一実施形態に係るELデバイスの断面構成を示す断面図であり、図14のA-A´断面図に相当する。

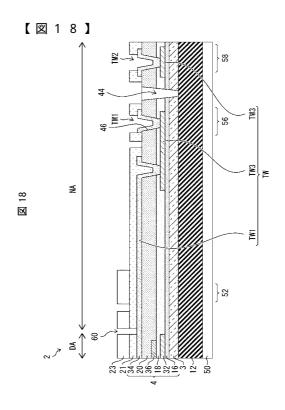

- 【図18】本発明の前記別の一実施形態に係る E L デバイスの断面構成を示す別の断面図であり、図14の B B ´ 断面図に相当する。

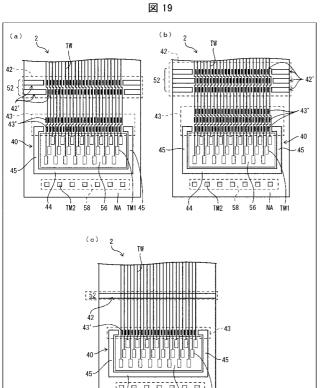

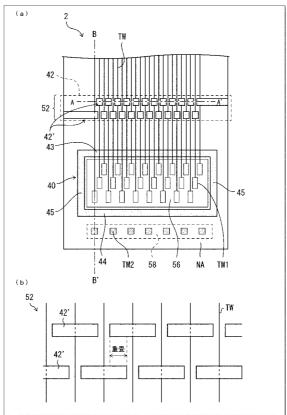

- 【図19】本発明の前記別の幾つかの実施形態のELデバイスのスリットの構成の幾つかの変形例を示す平面図および部分拡大図である。

- 【図20】本発明の別の一実施形態に係るELデバイス2の構成例を示す平面図である。

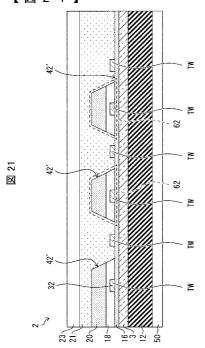

- 【図21】本発明の前記別の一実施形態に係るELデバイスの断面構成を示す断面図であり、図20のA-A´断面図に相当する。

- 【図22】本発明の前記別の一実施形態に係る E L デバイスの断面構成を示す別の断面図であり、図20の B B ´ 断面図に相当する。

- 【図23】本発明の幾つかの実施形態に係るELデバイスの構成を組み合わせて得られる構成例を示す断面図である。

【発明を実施するための形態】

[0010]

図1はELデバイスの製造方法の一例を示すフローチャートである。図2(a)は、本発明の幾つかの実施形態のELデバイスの形成途中の構成例を示す断面図である。図2(b)は、本発明の幾つかの実施形態のELデバイスの構成例を示す断面図である。図3(a)は、本発明の幾つかの実施形態のELデバイスの構成例を示す平面図である。図3(b)は、図3(a)に示された構成例の端子部を強調して示す部分平面図である。

[0011]

フレキシブルな E L デバイスを製造する場合、図 1 ~ 図 2 に示すように、まず、透光性のマザー基板(例えば、ガラス基板) 5 0 上に樹脂層 1 2 を形成する(ステップ S 1)。次いで、無機バリア膜 3 を形成する(ステップ S 2)。次いで、半導体膜 1 5 および複数

10

20

30

40

の無機絶縁膜16・18・20および平坦化膜21および複数の導電層32・34・36を含むTFT層4を形成する(ステップS3)。次いで、バンク層23および発光素子層(例えば、OLED素子層)5を形成する(ステップS4)。次いで、無機封止膜26・28および有機封止膜27を含む封止層6を形成する(ステップS5)。次いで、封止層6上に接着層8を介して保護材9(例えば、PETフィルム)を貼り付ける(ステップS6)。

#### [0012]

次いで、樹脂層12にレーザーを照射する(ステップS7)。ここでは、照射されたレーザーを樹脂層12が吸収することで、樹脂層12の下面(マザー基板50との界面)がアブレーションによって変質し剥離層が形成され、樹脂層12およびマザー基板50間の結合力が低下する。次いで、マザー基板50を樹脂層12から剥離する(ステップS8)。これにより、図2(a)に示す積層体7とマザー基板50とが剥離する。ここで積層体7とは、マザー基板50上に形成されている多層体の全体を指し、図2(a)に示す例では、マザー基板50上に形成されている樹脂層12から、最外層である保護材9までの層を示す。

#### [0013]

次いで、図2(b)に示すように、樹脂層12の下面に、接着層11を介して支持材10(例えば、PETフィルム)を貼り付ける(ステップS9)。次いで、積層体7および支持材10を分断すると共に保護材9をカットし、複数のELデバイスを切り出す(ステップS10)。次いで、TFT層4の端子部51(図3(a)参照)上の保護材9を剥離し、端子出しを行う(ステップS11)。これにより、図2(b)に示すようなELデバイス2を得る。次いで機能フィルムを貼り付け(ステップS12)、ACF等を用いて端子部51に電子回路基板を実装する(ステップS13)。なお、前記各ステップはELデバイスの製造装置が行う。

# [0014]

本発明の一態様に係る E L デバイスの製造方法は、特に前述のステップ S 3 およびステップ S 9 に特徴がある。詳細については後述する。

#### [0015]

樹脂層12の材料としては、例えば、ポリイミド、エポキシ、ポリアミド等が挙げられる。中でもポリイミドが好適に用いられる。

### [0016]

無機バリア膜3は、ELデバイスの使用時に、水分や不純物が、TFT層4や発光素子層5に到達することを防ぐ膜であり、例えば、CVDにより形成される、酸化シリコン膜、窒化シリコン膜、あるいは酸窒化シリコン膜、またはこれらの積層膜で構成することができる。無機バリア膜3の厚さは、例えば、50nm~1500nmである。

#### [0017]

10

20

30

40

10

20

30

40

50

### [0018]

半導体膜15は、例えば低温ポリシリコン(LPTS)あるいは酸化物半導体で構成される。ゲート絶縁膜16は、例えば、CVD法によって形成された、酸化シリコン(SiOx)膜あるいは窒化シリコン(SiNx)膜またはこれらの積層膜によって構成することができる。ゲート電極G、ソース電極S、ドレイン電極D、および端子は、例えば、アルミニウム(A1)、タングステン(W)、モリブデン(Mo)、タンタル(Ta)、クロム(Cr)、チタン(Ti)、銅(Cu)の少なくとも1つを含む金属の単層膜あるいは積層膜によって構成される。なお、図2では、半導体膜15をチャネルとするTFTがトップゲート構造で示されているが、ボトムゲート構造でもよい(例えば、TFTのチャネルが酸化物半導体の場合)。

[0019]

無機絶縁膜18・20は、例えば、CVD法によって形成された、酸化シリコン(SiOx)膜あるいは窒化シリコン(SiNx)膜またはこれらの積層膜によって構成することができる。平坦化膜21は、有機絶縁膜であり、例えば、ポリイミド、アクリル等の塗布可能な感光性有機材料によって構成することができる。

[0020]

発光素子層 5 (例えば、有機発光ダイオード層)は、平坦化膜 2 1 の上側に形成されるアノード電極 2 2 と、アクティブ領域 D A のサブピクセルを規定する隔壁 2 3 c と、非アクティブ領域 N A に形成されるバンク 2 3 b と、アノード電極 2 2 の上側に形成される E L (エレクトロルミネッセンス)層 2 4 と、 E L 層 2 4 の上側に形成されるカソード電極 2 5 とを含み、アノード電極 2 2 、 E L 層 2 4 、およびカソード電極 2 5 によって発光素子 (例えば、有機発光ダイオード)が構成される。

[0021]

隔壁 2 3 c およびバンク 2 3 b は、ポリイミド、エポキシ、アクリル等の塗布可能な感光性有機材料を用いて、例えば同一工程でバンク層 2 3 に形成することができる。非アクティブ領域 N A のバンク 2 3 b は無機絶縁膜 2 0 上に形成される。バンク 2 3 b は有機封止膜 2 7 のエッジを規定する。

[0022]

EL層24は、蒸着法あるいはインクジェット法によって、隔壁23cによって囲まれた領域(サブピクセル領域)に形成される。発光素子層5が有機発光ダイオード(OLED)層である場合、EL層24は、例えば、下層側から順に、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層を積層することで構成される。

[0023]

アノード電極(陽極) 2 2 は、例えばITO(Indium Tin Oxide)とAgを含む合金との積層によって構成され、光反射性を有する。カソード電極 2 5 は、ITO(Indium Tin Oxide)、IZO(Indium Zincum Oxide)等の透明金属で構成することができる。

[0024]

発光素子層 5 が O L E D 層である場合、アノード電極 2 2 およびカソード電極 2 5 間の駆動電流によって正孔と電子が E L 層 2 4 内で再結合し、これによって生じたエキシトンが基底状態に落ちることによって、光が放出される。

[0025]

発光素子層 5 は、OLED素子を構成する場合に限られず、無機発光ダイオードあるいは量子ドット発光ダイオードを構成してもよい。

[0026]

封止層 6 は、隔壁 2 3 c およびカソード電極 2 5 を覆う第 1 無機封止膜 2 6 と、第 1 無機封止膜 2 6 を覆う有機封止膜 2 7 と、有機封止膜 2 7 を覆う第 2 無機封止膜 2 8 とを含む。

[0027]

第1無機封止膜26および第2無機封止膜28はそれぞれ、例えば、CVDにより形成

される、酸化シリコン膜、窒化シリコン膜、あるいは酸窒化シリコン膜、またはこれらの積層膜で構成することができる。有機封止膜27は、第1無機封止膜26および第2無機封止膜28よりも厚い、透光性の有機絶縁膜であり、ポリイミド、アクリル等の塗布可能な感光性有機材料によって構成することができる。例えば、このような有機材料を含むインクを第1無機封止膜26上にインクジェット塗布した後、UV照射により硬化させる。封止層6は、発光素子層5を覆い、水、酸素等の異物の発光素子層5への浸透を防いでいる。

## [0028]

保護材 9 は、接着層 8 を介して封止層 6 上に貼り付けられ、マザー基板 5 0 を剥離した時の支持材として機能する。保護材 9 の材料としては、 P E T (ポリエチレンテレフタレート)等が挙げられる。

[0029]

支持材10は、マザー基板50を剥離した後に樹脂層12の下面に貼り付けることで、柔軟性に優れたELデバイスを製造するためのものであり、その材料としては、例えばポリエチレンテレフタレート(PET)等が挙げられる。支持材10は、ELデバイス2をさらに柔軟にするために、選択的に除去されることができる。例えば、ステップS9において支持材10を貼り付ける前に、除去したい領域に沿って切れ目を支持材10に入れ、ステップS9~S13の何れかにおいて、切れ目に沿って、除去したい領域の支持材10をELデバイス2から剥離することによって、支持材10を、選択的に除去することができる。

[0030]

機能フィルムは、例えば、光学補償機能、タッチセンサ機能、保護機能等を有する。電子回路基板は、例えば、複数の端子TM上に実装されるICチップあるいはフレキシブルプリント基板である。

[0031]

端子部51は、図3に示すように、支持材10が選択的に除去されている屈曲領域52と、ICチップとの接続に用いられる端子TM1が千鳥に配置されたICチップ搭載領域56(端子領域)と、FPCとの接続に用いられる端子TM2が配置されたFPC接続領域58と、を含む。ICチップ搭載領域56は、アクティブ領域DAとFPC接続領域58との間に位置し、屈曲領域52は、アクティブ領域DAとICチップ搭載領域56との間に位置する。ELデバイス2は、アクティブ領域DAが上方を向くと共に、ICチップ搭載領域56およびFPC接続領域58が下方を向くように、屈曲領域52で折り曲げられることができる。このため、端子部51の実効幅が、全幅よりも短くなるので、ELデバイス2を用いた表示装置を狭額縁化することができる。

[0032]

端子配線TWは、アクティブ領域DAから引き出されて、ICチップ搭載領域56内の端子TM1に接続されている。

[0033]

本明細書では、幅と長さとが或る切込み(溝)を、スリットと称する。また、1つのスリットが実線のように途切れることなく延伸している場合、このスリットを、「実線状スリット」と称する。また、複数のスリットが破線のように離間しながら整列している場合、各スリットを「島状スリット」と称し、この複数のスリットを「列状スリット群」と称する。「列状スリット群」の延伸方向は、含まれる「島状スリット」が整列している方向である。例えば、図3の(b)および図19の(c)に示すような屈曲スリット42は、実線状スリットである。例えば、図19の(a)および(b)に示すような屈曲スリット42は、列状スリット群である。また、ELデバイスを屈曲しやすくするためのスリットまたはスリット群を、「屈曲スリット」と称する。

[0034]

(実施形態1)

(ステップS3)

20

10

30

40

以下本発明の一実施形態の特徴である前述のステップS3について説明する。

## [0035]

ステップS3で、図3に示すように、ICチップ搭載領域56(端子領域)を囲むようにICチップ外周スリット40を形成する。また、ICチップ外周スリット40と同一プロセスで、屈曲領域52(折り曲げ領域)に屈曲スリット42(第3スリットパターン)を形成する。

### [0036]

ICチップ外周スリット40は、アクティブ領域DA側にある実線状のアクティブ側スリット43(第1スリットパターン)と、FPC接続領域58側にある実線状のFPC側スリット44(第2スリットパターン)と、ELデバイス2の端側にある2つの実線状のドリット45(2つのスリットパターン)と、から構成されている。アクティブ側スリット43とFPC側スリット44とは、端子配線TWの延伸方向と略平行に延伸し、2つの端側スリット45と屈曲スリット42とは、端子配線TWの延伸方向と略直交するように延伸している。端子配線TWの延伸方向について、アクティブ領域DA、屈曲領域52、アクティブ側スリット43、ICチップ搭載領域56、FPC側スリット44、FPC接続領域58は、この順に並んでいる。なお、ICチップ外周スリット40は、端側スリット45を含まず、アクティブ側スリット43とFPC側スリット44とのみを含んでもよい。

# [0037]

図4は、実施形態1に係るELデバイス2の、ソース導電層34形成前の断面構成を示す断面図である。図5は、実施形態1に係るELデバイス2の、バンク層23形成後の断面構成を示す断面図である。

## [0038]

図4および図5に示すように、屈曲スリット42とアクティブ側スリット43とFPC側スリット44とは、各々同様に第2無機絶縁膜20を貫通し、第1無機絶縁膜18に達している。また、図4および図5に示さないが、端側スリット45も各々同様に、第2無機絶縁膜20を貫通し、第1無機絶縁膜18に達している。

#### [0039]

端子配線TWは、ゲート導電層32のみで形成されている。端子配線TWは、樹脂層1 2よりも上側を通り、屈曲スリット42とアクティブ側スリット43とFPC側スリット 44(以後、纏めて、「スリット42~44」と称する)とよりも下側を通って、屈曲ス リット42およびアクティブ側スリット43と交差している。

#### [0040]

図 5 に示すように、端子TM1・TM2は、各々同様に、(i)コンタクトホール46を通って端子配線TWと接触しており、(ii)端部が平坦化膜21またはバンク層23によって被覆されている。

### [0041]

## (工程順序)

図4および図5のようなスリット42~44と端子配線TWと端子TM1・TM2とは、以下のような工程順序で、ステップ3で形成されることができる。なお、2つの端側スリット45は、記載を省略するが、アクティブ側スリット43およびFPC側スリット44と同一プロセスで形成されている。

## [0042]

まず、半導体膜15とゲート絶縁膜16とを形成する。次いで、ゲート導電層32を形成し、ゲート導電層32でゲート電極Gと共に端子配線TWを形成する。次いで、第1無機絶縁膜18と中間導電層36と第2無機絶縁膜20を形成する。次いで、第1無機絶縁膜18と第2無機絶縁膜20とをエッチングして、端子TM1・TM2のためのコンタクトホール46を形成する。次いで、ソース導電層34を形成し、ソース導電層34でソース電極Sおよびドレイン電極Dと共に端子TM1・TM2を形成する。次いで、第1無機絶縁膜18と第2無機絶縁膜20とを再度エッチングして、スリット42~44を形成す

10

20

30

40

る。次いで、平坦化膜21を形成する。

#### [ 0 0 4 3 ]

なお、スリット42~44を形成するためのエッチングを、第2無機絶縁膜20の形成とコンタクトホール46の形成との間に行っても、コンタクトホール46の形成とソース導電層34の形成との間に行っても、コンタクトホール46の形成するためのエッチングと同時に行ってもよい。ただし、同時に行った場合、スリット42~44は、コンタクトホール46と同じマスクでエッチングされるので、スリット42~44の底面に、ゲート導電層32が露出する。このため、同時に行った場合、平坦化膜21などの絶縁材をスリット42~44に埋設することによって、露出したゲート導電層32を被覆してもよい。

## [0044]

したがって、端子配線TWの短絡を防止する観点から、スリット42~44を形成するためエッチングは、ソース導電層34の形成と平坦化膜21の形成との間に行われることが好ましい。

[0045]

また、ゲート導電層32は、エッチストップ層として機能することが好ましい。

[0046]

(バンク層)

図5に示すように、ステップ4で形成されるバンク層23は、屈曲スリット42の上に形成されて、ELデバイス2の屈曲領域52を補強することが好ましい。なぜならば、屈曲スリット42が設けられている屈曲領域52には、機械的応力が掛かるからである。一方、バンク層23は、ICチップ外周スリット40(スリット43~44を含む)の上に形成されないことが好ましい。なぜならば、ICチップ外周スリット40は、ICチップ搭載領域56の近傍に位置するので、バンク層23がICチップ外周スリット40の上に形成された場合、ICチップを端子TM1に接続することが難しくなるからである。

[0047]

また、ステップ4においてまたはステップ4より後のステップにおいて、アクティブ領域 DAと非アクティブ領域 NAとの境界または境界近傍に、平坦化膜21およびバンク層23を貫通するスリット60を形成することが好ましい。なぜならば、平坦化膜21およびバンク層23は有機絶縁膜なので、スリット60を形成しない場合、平坦化膜21およびバンク層23に浸透した水分が、非アクティブ領域 NAからアクティブ領域 DAへ侵入することがあるからである。

[0048]

(ステップS9)

以下本発明の一実施形態の特徴である前述のステップS9について説明する。

[0049]

ステップS9で、図示を省略するが、屈曲領域52でELデバイス2を柔軟にするために、支持材10を屈曲領域52から選択的に除去する。あるいは、支持材19を、屈曲領域52に選択的に接着しない。

[0050]

(効果)

屈曲領域52には、支持材10が貼り付けられておらず、屈曲スリット42は、図4および図5に示すように、第2無機絶縁膜20を貫通し、第1無機絶縁膜18に達している。このため、ELデバイス2は、屈曲領域52以外の非アクティブNAよりも、屈曲領域52において柔軟であり、屈曲しやすい。

[0051]

図4および図5に示すように、端子配線TWは、屈曲スリット42およびアクティブ側スリット43よりも下側を通り、屈曲スリット42およびアクティブ側スリット43と交差する。このため、屈曲スリット42およびアクティブ側スリット43は、各々、1つの実線状スリットとして形成されることができるので、形成が容易である。

[0052]

10

20

30

図4および図5に示すように、ICチップ搭載領域56を囲むICチップ外周スリット40は、第2無機絶縁膜20を貫通し、第1無機絶縁膜18に達している。このため、ICチップ搭載時などに強い押圧力がかかって、ICチップ搭載領域56の第1無機絶縁膜18と第2無機絶縁膜20との何れか1つ以上に亀裂が入ったとしても、該亀裂の伸展は、ICチップ外周スリット40で止められるので、該亀裂が端子配線TWを断線する可能性は低減され、ELデバイス2の信頼性は維持される。

#### [0053]

# (実施形態2)

以下、本発明の他の実施形態の特徴であるステップS3について、図6~図8を参照しながら説明する。なお、本実施形態の特徴であるステップS9は、前述の実施形態2の特徴であるステップS9と同様であるため、説明を省略する。

#### [0054]

図6は、実施形態2に係るELデバイス2の、第2無機絶縁膜20形成前の断面構成を示す断面図である。図7は、実施形態2に係るELデバイス2の、ソース導電層34形成前の断面構成を示す断面図である。図8は、実施形態2に係るELデバイス2の、バンク層23形成後の断面構成を示す断面図である。

#### [0055]

図6~図8に示すように、屈曲スリット42は、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18とを貫通する実線状の下屈曲スリット42 aと、第2無機絶縁膜20を貫通する実線状の上屈曲スリット42 bと、で構成される。アクティブ側スリット43 も同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18とを貫通する実線状の上アクティブ側スリット43 aと、第2無機絶縁膜20を貫通する実線状の上アクティブ側スリット43 bと、で構成される。FPC側スリット44 も同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18とを貫通する実線状の下FPC側スリット44 bと、で構成される。また、図6~図8に示さないが、2つの端側スリット45 も各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18とを貫通する実線状の下端側スリットと、で構成される。第2無機絶縁膜20を貫通する実線状の上端側スリットと、で構成される。

## [0056]

端子配線TWは、ゲート導電層32で形成された本体部TW1およびアクティブ側部TW2および端子側部TW3と、中間導電層36で形成された屈曲スリットブリッジ部TW4および外周スリットブリッジ部TW5とを含む。端子配線TWのブリッジ部TW4,TW5はそれぞれ、下屈曲スリット42aおよび下アクティブ側スリット43aの内側面および底面を通って、屈曲スリット42およびアクティブ側スリット43と交差している。この端子配線TWのブリッジ部TW4,TW5が露出しないように、端子配線TWのブリッジ部TW4,TW5の上には、平坦化膜21が形成されている。

# [0057]

図 8 に示すように、端子TM1・TM2は、各々同様に、(i)コンタクトホール46を通って端子配線TWの端子側部TW3と接触しており、(ii)端部が平坦化膜21またはバンク層23によって被覆されている。

# [ 0 0 5 8 ]

#### (工程順序)

図6~図8のような端子配線TWとスリット42~44と端子TM1・TM2とは、以下のような工程順序で、ステップ3で形成されることができる。なお、2つの端側スリット45は、記載を省略するが、アクティブ側スリット43およびFPC側スリット44と同一プロセスで形成されている。

#### [0059]

まず、半導体膜15とゲート絶縁膜16とを形成する。次いで、ゲート導電層32を形成し、ゲート導電層32でゲート電極Gと共に端子配線TWの本体部TW1およびアクティブ側部TW2および端子側部TW3を形成する。次いで、第1無機絶縁膜18を形成す

10

20

30

40

10

20

30

40

50

る。次いで、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18とをエッチングして、下屈曲スリット42aと下アクティブ側スリット43aと下FPC側スリット44aと、端子配線TWの本体部TW1およびアクティブ側部TW2および端子側部TW3にブリッジ部TW4,TW5が繋がるためのコンタクトホールと、を形成する。次いで、中間導電層36を形成し、中間導電層36で端子配線TWのブリッジ部TW4,TW5を形成する。次いで、第2無機絶縁膜20をエッチングして、端子TM1・TM2のためのコンタクトホール46を形成する。次いで、ソース導電層34を形成し、ソース導電層34でソース電極Sおよびドレイン電極Dと共に端子TM1・TM2とを形成する。次いで、第2無機絶縁膜20を再度エッチングして、上屈曲スリット42bと上アクティブ側スリット43bと上FPC側スリット44bとを形成する。次いで、平坦化膜21を形成する。

[0060]

なお、上屈曲スリット42 b と上アクティブ側スリット43 b と上FPC側スリット4 4 b とを形成するためのエッチングは、前述の実施形態 1 におけるスリット42~44を形成するためのエッチングと同様に、第2無機絶縁膜20の形成とコンタクトホール46の形成との間に行っても、コンタクトホール46の形成とソース導電層34の形成との間に行っても、コンタクトホール46の形成するためのエッチングと同時に行ってもよい。同時に行った場合、平坦化膜21 などの絶縁材をスリット42~44に埋設することによって、露出したゲート導電層32を被覆してもよい。

[0061]

また、ゲート導電層32および中間導電層36は、エッチストップ層として機能することが好ましい。また、端子配線TWのブリッジ部TW4,TW5が断線しないために、下屈曲スリット42aおよび下アクティブ側スリット43aは、底方向にむけて狭幅となるテーパ形状であることが好ましく、テーパ角度が緩やかであることがより好ましい。また、複数の無機絶縁層をエッチングする1回の工程は、複数回の工程に分けられてもよい。

[0062]

(効果)

屈曲領域52には、支持材10が貼り付けられておらず、屈曲スリット42は、図6~図8に示すように、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。このため、ELデバイス2は、屈曲領域52以外の非アクティブNAよりも、屈曲領域52において柔軟であり、屈曲しやすい。また、図8に示される構成のELデバイス2よりも屈曲しやすい。

[0063]

図 7 および図 8 に示すように、端子配線 T Wのブリッジ部 T W 4 , T W 5 は、下屈曲スリット 4 2 a および下アクティブ側スリット 4 3 a の内側面および底面を通り、屈曲スリット 4 2 およびアクティブ側スリット 4 3 と交差する。このため、屈曲スリット 4 2 およびアクティブ側スリット 4 3 は、各々、1 つの実線状スリットとして形成されることができるので、形成が容易である。

[0064]

図6~図8に示すように、ICチップ搭載領域56を囲むICチップ外周スリット40は、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。このため、ICチップ搭載時などに強い押圧力がかかって、ICチップ搭載領域56の無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20との何れか1つ以上に亀裂が入ったとしても、該亀裂の伸展は、ICチップ外周スリット40で止められるので、該亀裂が端子配線TWを断線する可能性は低減され、ELデバイス2の信頼性は維持される。また、図8に示される構成のELデバイス2は、図5に示される構成のELデバイス2よりも、信頼性が維持される。

[0065]

(実施形態3)

以下、本発明の他の実施形態の特徴であるステップS3について、図9および図10を

(14)

参照しながら説明する。なお、本実施形態の特徴であるステップS9は、前述の実施形態 2の特徴であるステップS9と同様であるため、説明を省略する。

## [0066]

図9は、実施形態3に係るELデバイス2の、ソース導電層34形成前の断面構成を示す断面図である。図10は、実施形態3に係るELデバイス2の、バンク層23形成後の断面構成を示す断面図である。

#### [0067]

図9および図10に示すように、屈曲スリット42とアクティブ側スリット43とFPC側スリット44は、各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。また、図9および図10に示さないが、2つの端側スリット45も各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。

#### [0068]

端子配線TWは、ゲート導電層32で形成された本体部TW1およびアクティブ側部TW2および端子側部TW3と、ソース導電層34で形成された屈曲スリットブリッジ部TW4および外周スリットブリッジ部TW5とを含む。端子配線TWのブリッジ部TW4,TW5はそれぞれ、屈曲スリット42およびアクティブ側スリット43の内側面および底面を通って、屈曲スリット42およびアクティブ側スリット43と交差している。この端子配線TWのブリッジ部TW4,TW5はそれぞれが露出しないように、端子配線TWのブリッジ部TW4,TW5はそれぞれの上には、平坦化膜23が形成されている。

### [0069]

図10に示すように、端子TM1・TM2は、各々同様に、(i)コンタクトホール46を通って端子配線TWの端子側部TW3と接触しており、(ii)端部が平坦化膜21またはバンク層23によって被覆されている。

## [0070]

## (工程順序)

図9および図10のような端子配線TWとスリット42~44と端子TM1・TM2とは、以下のような工程順序で、ステップ3で形成されることができる。なお、2つの端側スリット45は、記載を省略するが、アクティブ側スリット43およびFPC側スリット44と同一プロセスで形成されている。

## [0071]

まず、半導体膜15とゲート絶縁膜16とを形成する。次いで、ゲート導電層32を形成し、ゲート導電層32でゲート電極Gと共に端子配線TWの本体部TW1およびアクティブ側部TW2および端子側部TW3を形成する。次いで、第1無機絶縁膜18と中間導電層36と第2無機絶縁膜20とを形成する。次いで、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とをエッチングし、端子TM1・TM2のためのコンタクトホール46と共に屈曲スリット42とアクティブ側スリット43とFPC側スリット44と、端子配線TWの本体部TW1およびアクティブ側部TW2および端子側部TW3にブリッジ部TW4,TW5が繋がるためのコンタクトホールと、を形成する。次いで、ソース導電層34を形成し、ソース導電層34でソース電極Sおよびドレイン電極Dと共に端子TM1・TM2と端子配線TWのブリッジ部TW4,TW5とを形成する。次いで、平坦化膜21を形成する。

## [0072]

また、ゲート導電層 3 2 および中間導電層 3 6 は、エッチストップ層として機能することが好ましい。また、端子配線 T W のブリッジ部 T W 4 , T W 5 が断線しないために、屈曲スリット 4 2 およびアクティブ側スリット 4 3 は、底方向にむけて狭幅となるテーパ形状であることが好ましく、内側面のテーパ角度が緩やかであることがより好ましい。

## [0073]

## (効果)

図10に示される構成のELデバイス2は、図7に示される構成のELデバイス2と、

20

10

30

40

同様の効果を奏することができる。

### [0074]

さらに、端子TM1・TM2のためのコンタクトホール46と共に、屈曲スリット42とアクティブ側スリット43とFPC側スリット44とを形成することができるので、図10に示される構成のELデバイス2を製造するための製造方法は、図7に示されるELデバイス2を製造するための製造方法よりも、工程数を低減することができる。

#### [0075]

# (実施形態4)

以下、本発明の他の実施形態の特徴であるステップS3について、図11を参照しながら説明する。なお、本実施形態の特徴であるステップS9は、前述の実施形態2の特徴であるステップS9と同様であるため、説明を省略する。

[0076]

図11は、実施形態4に係るELデバイス2の断面構成を示す断面図である。

### [0077]

図11に示すように、屈曲スリット42とアクティブ側スリット43とFPC側スリット44は、各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。また、図11に示さないが、2つの端側スリット45も各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。

# [0078]

端子配線TWは、ゲート導電層32で形成された本体部TW1およびアクティブ側部TW2および端子側部TW3と、ソース導電層34で形成された屈曲スリットブリッジ部TW4および外周スリットブリッジ部TW5とを含む。端子配線TWのブリッジ部TW4,TW5はそれぞれ、屈曲スリット42およびアクティブ側スリット43よりも上側を通って、具体的には、屈曲スリット42およびアクティブ側スリット43に埋設された埋設材38の上面を通って、屈曲スリット42およびアクティブ側スリット43と交差している

## [0079]

埋設材38は、有機絶縁材であり、例えば、ポリイミド、アクリル等の塗布可能な感光性有機材料によって構成することができる。埋設材38は、平坦化膜21と同じ材料から構成されても、異なる材料から構成されてもよい。

# [0080]

端子TM1・TM2は、各々同様に、(i)コンタクトホール46を通って端子配線TWの端子側部TW3と接触しており、(ii)端部が平坦化膜21またはバンク層23によって被覆されている。

## [0081]

# (工程順序)

図11のような端子配線TWとスリット42~44とは、以下のような工程順序で、ステップ3で形成されることができる。なお、2つの端側スリット45は、記載を省略するが、アクティブ側スリット43とFPC側スリット44と同一プロセスで形成されている

## [0082]

まず、半導体膜15とゲート絶縁膜16とを形成する。次いで、ゲート導電層32を形成し、ゲート導電層32でゲート電極Gと共に端子配線TWの本体部分TW1およびアクティブ側部TW2および端子側部TW3を形成する。次いで、第1無機絶縁膜18と中間導電層36と第2無機絶縁膜20とを形成する。次いで、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とをエッチングし、端子TM1・TM2のためのコンタクトホール46とスリット42~44と、端子配線TWの本体部TW1およびアクティブ側部TW2および端子側部TW3にブリッジ部TW4,TW5が繋がるためのコンタクトホールと、を形成する。次いで、屈曲スリット42およびアクティブ側ス

10

20

30

40

リット 4 3 の内部に埋設材 3 8 を埋設する。次いで、ソース導電層 3 4 を形成し、ソース 導電層 3 4 でソース電極 S およびドレイン電極 D と共に端子 T M 1 ・ T M 2 と端子配線 T W のブリッジ部 T W 4 , T W 5 とを形成する。次いで、平坦化膜 2 1 を形成する。

### [0083]

ゲート導電層 3 2 および中間導電層 3 6 は、エッチストップ層として機能することが好ましい。埋設材 3 8 は、FPC側スリット 4 4 および 2 つの端側スリット 4 5 の内部にも埋設されてもよい。

# [0084]

(効果)

図11に示される構成のELデバイス2は、図9に示される構成のELデバイス2と同様の効果を奏することができる。

[0085]

さらに、図11に示される構成によれば、端子配線TWのブリッジ部TW4,TW5は、屈曲スリット42およびアクティブ側スリット43の内側面および底面を通る代わりに、屈曲スリット42およびアクティブ側スリット43に埋設された埋設材38の上を通る。このため、屈曲スリット42およびアクティブ側スリット43の内側面のテーパ角度が急な場合であっても、あるいは、屈曲スリット42およびアクティブ側スリット43の深さが深い場合であっても、端子配線TWのブリッジ部TW4,TW5が断線しにくい。

[0086]

(実施形態5)

以下、本発明の他の実施形態の特徴であるステップS3について、図12を参照しながら説明する。なお、本実施形態の特徴であるステップS9は、前述の実施形態2の特徴であるステップS9と同様であるため、説明を省略する。

[0087]

図12は、実施形態5に係るELデバイス2の断面構成を示す断面図である。

[0088]

図12に示すように、屈曲スリット42とアクティブ側スリット43とFPC側スリット44は、各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。また、図12に示さないが、2つの端側スリット45も各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。

[0089]

端子配線TWは、ゲート導電層32で形成された端子側部TW3と、ソース導電層34のみで形成された本体部TW1とを含む。端子配線TWの端子側部TW3は、アクティブ側外周スリット43とFPC側外周スリット44との間に設けられ、第2無機膜20よりも下層を通る。このため、端子TM1はTFT層4の内部で端子配線TWと接触することができるので、平坦化膜21が形成されていない領域で端子配線TWが露出しない。端子配線TWの本体部TW1は、屈曲スリット42およびアクティブ側スリット43の内側面および底面を通ることによって、屈曲スリット42およびアクティブ側スリット43と交差している。

[0090]

端子TM1・TM2は、各々同様に、(i)コンタクトホール46を通って端子配線TWの端子側部TW3と接触しており、(ii)端部が平坦化膜21またはバンク層23によって被覆されている。

[0091]

(工程順序)

図12のような端子配線TWとスリット42~44とは、以下のような工程順序で、ステップ3で形成されることができる。なお、2つの端側スリット45は、記載を省略するが、アクティブ側スリット43およびFPC側スリット44と同一プロセスで形成されている。

10

20

30

40

### [0092]

まず、半導体膜15とゲート絶縁膜16とを形成する。次いで、ゲート導電層32を形成し、ゲート導電層32で、ゲート電極Gと共に端子配線TWの端子側部TW3を形成する。次いで、第1無機絶縁膜18と中間導電層36と第2無機絶縁膜20とを形成する。次いで、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とをエッチングし、端子TM1・TM2のためのコンタクトホール46と共にスリット42~44と、端子配線TWの端子側部TW3に本体部TW1が繋がるためのコンタクトホールと、を形成する。次いで、ソース導電層34を形成し、ソース導電層34でソース電極Sおよびドレイン電極Dと共に端子TM1・TM2と端子配線TWの本体部TW1とを形成する。次いで、平坦化膜21を形成する。

[0093]

また、ゲート導電層32は、エッチストップ層として機能することが好ましい。また、端子配線TWの本体部TW1が断線しないために、屈曲スリット42およびアクティブ側スリット43は、底方向にむけて狭幅となるテーパ形状であることが好ましく、内側面のテーパ角度が緩やかであることがより好ましい。

[0094]

(効果)

図12に示される構成のELデバイス2は、図10に示される構成のELデバイス2と同様の効果を奏することができる。

[0095]

さらに、図12に示される構成のELデバイス2では、端子配線TWの本体部TW1(特に、そのうちのアクティブ領域DAとアクティブ側外周スリット43との間に延設されている部分)に、ゲート導電層32よりも抵抗の低いソース導電層34が用いられている。このため、図12に示される構成のELデバイス2は、図10に示される構成のELデバイス2よりも、データ信号の遅延を少なくすることができ、設計マージンを広くすることができる。

[0096]

(実施形態6)

以下、本発明の他の実施形態の特徴であるステップS3について、図13を参照しながら説明する。なお、本実施形態の特徴であるステップS9は、前述の実施形態2の特徴であるステップS9と同様であるため、説明を省略する。

[0097]

図13は、実施形態6に係るELデバイス2の断面構成を示す断面図である。

[0098]

図13に示すように、屈曲スリット42とアクティブ側スリット43とFPC側スリット44は、各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。また、図13に示さないが、2つの端側スリット45も各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。

[0099]

端子配線TWは、ゲート導電層32で形成された端子側部TW3と、ソース導電層34のみで形成された本体部TW1とを含む。端子配線TWの端子側部TW3は、第2無機膜20よりも下層を通るので、平坦化膜21が形成されていない領域で端子配線TWが露出しない。端子配線TWの本体部TW1は、屈曲スリット42およびアクティブ側スリット43の内側面および底面を通ることによって、屈曲スリット42およびアクティブ側スリット43と交差している。

[0100]

端子TM1・TM2は、各々同様に、(i)コンタクトホール46を通って端子配線TWの端子側部TW3と接触しており、(ii)端部が平坦化膜21またはバンク層23によって被覆されている。

10

20

30

40

#### [0101]

(工程順序)

図13のような端子配線TWとスリット42~44とは、以下のような工程順序で、ステップ3で形成されることができる。なお、2つの端側スリット45は、記載を省略するが、アクティブ側スリット43とFPC側スリット44と同一プロセスで形成されている

#### [0102]

まず、半導体膜15とゲート絶縁膜16とを形成する。次いで、ゲート導電層32を形成し、ゲート導電層32で、ゲート電極Gと共に端子配線TWの端子側部TW3を形成する。次いで、第1無機絶縁膜18と中間導電層36と第2無機絶縁膜20とを形成する。次いで、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とをエッチングし、端子TMのためのコンタクトホール46と共にスリット42~44と、端子配線TWの端子側部TW3に本体部TW1が繋がるためのコンタクトホールと、を形成する。次いで、屈曲スリット42およびアクティブ側スリット43の内部に埋設材38を埋設する。次いで、ソース導電層34を形成し、ソース導電層34でソース電極Sおよびドレイン電極Dと共に端子TM1・TM2と端子配線TWの本体部TW1とを形成する。次いで、平坦化膜21を形成する。

## [0103]

ゲート導電層 3 2 は、エッチストップ層として機能することが好ましい。埋設材 3 8 は、FPC側スリット 4 4 および 2 つの端側スリット 4 5 の内部にも埋設されてもよい。

### [0104]

(効果)

図 1 3 に示される構成の E L デバイス 2 は、図 1 1 に示される構成の E L デバイス 2 と同様の効果を奏することができる。

# [0105]

さらに、図13に示される構成のELデバイス2では、端子配線TWの本体部TW1(特に、そのうちのアクティブ領域DAとアクティブ側外周スリット43との間に延設されている部分)に、ゲート導電層32よりも抵抗の低いソース導電層34が用いられている。このため、図13に示される構成のELデバイス2は、図11に示される構成のELデバイス2よりも、データ信号の遅延が少なくすることができ、設計マージンを広くすることができる。

# [0106]

(実施形態7)

以下、本発明の他の実施形態の特徴であるステップS3について、図14~図16を参照しながら説明する。なお、本実施形態の特徴であるステップS9は、前述の実施形態2の特徴であるステップS9と同様であるため、説明を省略する。

# [0107]

図14は、実施形態7または後述の実施形態8のELデバイス2の構成例を示す平面図である。

## [0108]

図14に示すように、ICチップ外周スリット40に含まれるアクティブ側スリット43は、1つの実線状スリットである代わりに、複数の島状スリット43~で構成されてもよく、例えば、端子配線TWと交差する方向に整列する複数の島状スリット43~で構成された1つの列状スリット群であってもよい。屈曲スリット42も同様に、1つの実線状スリットである代わりに、複数の島状スリット42~で構成されてもよく、端子配線TWの延伸方向と交差する方向に整列する複数の島状スリット42~で構成された1つの列状スリット群であってもよい。各島状スリット42~,43~は、端子配線TWと交差する方向の長さが、端子配線TWの配線間隔の2倍より短いことが好ましく、さらに、端子配線TWの配線間隔よりも長いことが好ましい。

# [0109]

20

10

30

10

20

30

40

50

端子配線TWは、屈曲スリット42およびアクティブ側スリット43と平面視で重ならない(すなわち交差しない)ように、延設される。このため、端子配線TWは、平面視で、屈曲スリット42に含まれる島状スリット42が間およびアクティブ側スリット43に含まれる島状スリット42が間を通る。屈曲スリット42が間は、互いに異なることが好ましく、(ii)島状スリット42が間の総距離は、小さいことが好ましい。このため、屈曲スリット42に含まれる1つの列状スリット42が間を有成する複数の島状スリット42が間を1対1対応に通るように、配置されることが好ましい。同様に、アクティブ側スリット43に含まれる1つの列状スリット43に含まれる1つの列状スリット43が日ましい。同様に、アクティブ側スリット43に含まれる1つの列状スリット43が目を有成する複数の島状スリット43が日まれることが好ましい。

[0110]

図15は、実施形態7に係るELデバイス2の断面構成を示す断面図であり、図14のA・A ´ 断面図に相当する。図16は、実施形態7に係るELデバイス2の断面構成を示す別の断面図であり、図14のB・B ´ 断面図に相当する。図14のA・A ´ 断面は、端子配線TWを含まず、屈曲スリット42およびアクティブ側外周スリット43を含むように、切断した断面である。また、図14のB・B ´ 断面は、端子配線TWを含み、屈曲スリット42およびアクティブ側外周スリット43を含まないように、切断した断面である

[0111]

図15に示すように、屈曲スリット42とアクティブ側スリット43とFPC側スリット44は、各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。また、図15に示さないが、2つの端側スリット45も各々同様に、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。

[0112]

図16に示すように、端子配線TWは、ゲート導電層32のみで形成されている。端子配線TWは、屈曲スリット42に含まれる島状スリット42 ´ 間およびアクティブ側スリット43に含まれる島状スリット43 ´ 間を通る。

[0113]

端子TM1・TM2は、各々同様に、(i)コンタクトホール46を通って端子配線TWと接触しており、(ii)端部が平坦化膜21またはバンク層23によって被覆されている。

[0114]

(工程順序)

図14~図16のような端子配線TWと島状スリット42 ´ , 43 ´ およびFPC側外周スリット44 (以後、纏めて、「スリット42 ´ , 43 ´ , 44」と称する)とは、以下のような工程順序で、ステップ3で形成されることができる。なお、2つの端側スリット45は、記載を省略するが、アクティブ側スリット43 に含まれる島状スリット43 ´ およびFPC側スリット44と同一プロセスで形成されている。

[0115]

まず、半導体膜15とゲート絶縁膜16とゲート導電層32と第1無機絶縁膜18と中間導電層36と第2無機絶縁膜20とを形成する。次いで、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とをエッチングし、端子TM1・TM2のためのコンタクトホール46と共にスリット42´,43´,44を形成する。次いで、ソース導電層34を形成し、ソース導電層34でソース電極Sおよびドレイン電極Dと共に端子TM1・TM2と端子配線TWとを形成する。次いで、平坦化膜21を形成する。

[0116]

ゲート導電層32は、エッチストップ層として機能することが好ましい。また、スリッ

ト42´,43´,44は、各々、実施例2と同様に、下屈曲スリット42´aと上屈曲スリット42´b、下アクティブ側スリット43´aと上アクティブ側スリット43´b、下FPC側スリット44aと上FPC側スリット44bに分けて、2回のエッチングで形成してもよい。

# [0117]

(効果)

図15および図16に示すように、屈曲領域52には、支持材10が貼り付けられておらず、屈曲スリット42は、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。このため、ELデバイス2は、屈曲領域52以外の非アクティブNAよりも、屈曲領域52において柔軟であり、屈曲しやすい。また、実施形態7に係る構成のELデバイス2は、前述の実施形態1に係る構成のELデバイス2よりも屈曲しやすい。

[0118]

図15に示すように、ICチップ搭載領域56を囲むICチップ外周スリット40は、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。このため、ICチップ搭載領域56の無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20との何れか1つ以上に亀裂が入ったとしても、該亀裂の伸展は、ICチップ外周スリット40で止められるので、該亀裂が端子配線TWを断線する可能性は低減され、ELデバイス2の信頼性は維持される。また、実施形態7に係る構成のELデバイス2は、前述の実施形態1に係る構成のELデバイス2よりも、信頼性が維持される。

[0119]

[0120]

従って、実施形態7に係る構成のELデバイス2は、図9に示される構成のELデバイス2と同様の効果を奏することができる。

[0121]

(変形例)

図 1 9 は、実施形態 7 または後述の実施形態 8 の屈曲スリット 4 2 および I C チップ外周スリット 4 0 の構成の幾つかの変形例を示す平面図である。

[0122]

図19(a)および図19(b)に示すように、屈曲スリット42およびアクティブ側 スリット43は、複数の列状スリット群を含んでもよい。また、該複数の列状スリット群 に含まれる島状スリット42~,43~は、千鳥配置されている。具体的には、同じ列状 スリット群に含まれる島状スリット42 ´,43 ´は、端子配線TWの延伸方向と交差す る方向に整列しており、異なる列状スリット群は、含まれる島状スリット42´,43´ が互い違いに位置するように、端子配線TWの延伸方向に隣接しており、その結果、複数 の列状スリット群に含まれる島状スリット42´,43´は、スタッガード配置されてい る。スタッガード配置は、交互配置の一種である。また、該複数の列状スリット群に含ま れる島状スリット42´,43´は、端子配線TWの延伸方向から見て、複数の列状スリ ット群に含まれる或る列状スリット群の島状スリット42´,43´間の隙間が、該複数 の列状スリット群に含まれる別の列状スリット群の島状スリット42´,43´によって 、塞がれるように、配置されている。好ましくは、該複数の列状スリット群に含まれる島 状スリット42~ \_ , 4 3 ´ は、 複数の列状スリット群に含まれる或る列状スリット群の島 状 ス リ ッ ト 4 2 ´ , 4 3 ´ の 端 部 が 、 端 子 配 線 T W の 延 伸 方 向 か ら 見 て 、 該 複 数 の 列 状 ス リット群に含まれる別のスリット群の島状スリット42 ´ , 43 ´ と重畳するように、配 10

20

30

40

置されている。

## [0123]

端子配線TWは、平面視において、千鳥配置された複数の島状スリット42 ´ , 4 3 ´ を避けるように迂回している。好ましくは、千鳥配置された複数の島状スリット42 ´ , 4 3 ´ は、各列状スリット群について、各端子配線TWが該列状スリット群を構成する島状スリット42 ´ , 4 3 ´ 間を 1 対 1 対応に通るように、配置されることが好ましい。

### [0124]

複数の列状スリット群を含む屈曲スリット42は、1つの列状スリット群である場合よりも、ELデバイス2を柔軟にすることができる。このため、ELデバイス2は屈曲領域5~2においてより屈曲しやすくなる。

#### [ 0 1 2 5 ]

複数の列状スリット群を含むアクティブ側スリット43は、1つの列状スリット群であるの場合よりも、ELデバイス2の信頼性を維持することができる。なぜならば、ICチップ搭載領域56の無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20との何れか1つ以上に亀裂が入り、さらに、該亀裂が、内側の列状スリット群に含まれる島状スリット43<sup>°</sup>間を通って伸展したとしても、該亀裂の伸展は、外側の列状スリット群で止められるからである。

#### [0126]

あるいは、図19(c)に示すように、1つの実線状スリットである屈曲スリット42と、1つ以上の列状スリット群を含むアクティブ側スリット43と、が組み合わされてもよい。このような場合、屈曲スリット42と交差する端子配線TWの構成は、実施形態1(図4および図5参照)、実施形態2(図6~図8参照)、実施形態3(図9および図10参照)、および実施形態4(図11参照)の何れにおける構成と同様であってもよい。

#### [ 0 1 2 7 ]

1 つの実線状スリットである屈曲スリット4 2 は、1 つの列状スリット群である場合よりも、E L デバイス 2 を柔軟にすることができる。このため、E L デバイス 2 は屈曲領域5 2 においてより屈曲しやすくなる。さらに、1 つの実線状スリットである屈曲スリット4 2 は、複数の列状スリット群を含む場合よりも、狭い屈曲領域4 2 に形成されることができる。このため、端子部51の実効幅を小さくすることができる。

## [0128]

### (実施形態8)

以下、本発明の他の実施形態の特徴であるステップS3について、図14と図17と図18とを参照しながら説明する。なお、本実施形態の特徴であるステップS9は、前述の実施形態2の特徴であるステップS9と同様であるため、説明を省略する。

# [0129]

図 1 7 は、実施形態 8 に係る E L デバイス 2 の断面構成を示す断面図であり、図 1 4 の A - A '断面図である。図 1 8 は、実施形態 8 に係る E L デバイス 2 の断面構成を示す別の断面図であり、図 1 4 の B - B '断面図である。

# [0130]

図 1 7 に示すように、スリット 4 2 ´ , 4 3 ´ , 4 4 は、各々同様に、無機バリア膜 3 とゲート絶縁膜 1 6 と第 1 無機絶縁膜 1 8 と第 2 無機絶縁膜 2 0 とを貫通する。また、図 1 7 に示さないが、 2 つの端側スリット 4 5 も各々同様に、無機バリア膜 3 とゲート絶縁膜 1 6 と第 1 無機絶縁膜 1 8 と第 2 無機絶縁膜 2 0 とを貫通する。

# [0131]

図18に示すように、端子配線TWは、ゲート導電層32で形成された端子側部TW3と、ソース導電層34のみで形成された本体部TW1とを含む。端子配線TWの端子側部TW3は、ICチップ搭載領域56およびFPC接続領域58に設けられ、第2無機膜20よりも下層を通る。このため、端子TM1はTFT層4の内部で端子配線TWと接触することができるので、平坦化膜21が形成されていない領域で端子配線TWが露出しない。端子配線TWの本体部TW1は、屈曲スリット42に含まれる島状スリット42、の開

10

20

30

40

口間およびアクティブ側スリット43に含まれる島状スリット43 ´の開口間を通る。このため、屈曲スリット42およびアクティブ側スリット43に含まれる島状スリット42 ´,43 ´の内側面のテーパ角度が急な場合であっても、あるいは、島状スリット42 ´,43 ´の深さが深い場合であっても、端子配線TWが断線しにくい。

## [0132]

端子TM1・TM2は、各々同様に、(i)コンタクトホール46を通って端子配線TWの端子側部TW3と接触しており、(ii)端部が平坦化膜21またはバンク層23によって被覆されている。

# [0133]

# (工程順序)

図14と図17と図18とのような端子配線TWとスリット42 ´,43 ´,44とは、以下のような工程順序で、ステップ3で形成されることができる。なお、2つの端側スリット45は、記載を省略するが、アクティブ側スリット433に含まれる島状スリット43 ´およびFPC側スリット44と同一プロセスで形成されている。

#### [0134]

まず、半導体膜15とゲート絶縁膜16とを形成する。次いで、ゲート導電層32を形成し、ゲート導電層で、ゲート電極と共に端子配線TWの端子側部TW3を形成する。次いで、第1無機絶縁膜18と中間導電層36と第2無機絶縁膜20とを形成する。次いで、無機バリア膜3とゲート絶縁膜16と第1無機絶縁膜18と第2無機絶縁膜20をエッチングして、端子TM1・TM2のためのコンタクトホール46と共にスリット42´,43´,44と、端子配線TWの端子側部TW3に本体部TW1が繋がるためのコンタクトホールと、を形成する。次いで、ソース導電層34を形成し、ソース導電層34でソース電極Sおよびドレイン電極Dと共に端子TM1・TM2と端子配線TWの本体部TW1とを形成する。次いで、平坦化膜21を形成する。

## [ 0 1 3 5 ]

ゲート導電層32は、エッチストップ層として機能することが好ましい。

### [0136]

#### (効果)

従って、実施形態8に係る構成のELデバイス2は、図9に示される構成のELデバイス2と同様の効果を奏することができる。

### [0137]

さらに、実施形態 8 に係る構成の E L デバイス 2 では、端子配線 T W の本体部 T W 1 (特に、そのうちのアクティブ領域 D A とアクティブ側外周スリット 4 3 との間に延設されている部分)に、ゲート導電層 3 2 よりも抵抗の低いソース導電層 3 4 が用いられている。このため、実施形態 8 に係る構成の E L デバイス 2 は、前述の実施形態 7 に係る構成の E L デバイス 2 よりも、データ信号の遅延が少なくすることができ、設計マージンを広くすることができる。

## [0138]

また、実施形態 8 に係る構成の E L デバイス 2 においては、前述の実施形態 7 に係る構成の E L デバイス 2 と同様に、屈曲スリット 4 2 およびアクティブ側スリット 4 3 は、複数の列状スリット群を含んでもよい。複数の列状スリット群を含む屈曲スリット 4 2 は、前述の実施形態 7 の変形例と同様に、 E L デバイス 2 は屈曲領域 5 2 においてより屈曲しやすくすることができる。また、複数の列状スリット群を含むアクティブ側スリット 4 3 は、前述の実施形態 7 の変形例と同様に、 E L デバイス 2 の信頼性をより維持することができる。

# [0139]

あるいは、実施形態 8 に係る構成の E L デバイス 2 においても、 1 つの実線状のスリットである屈曲スリット 4 2 と、 1 つ以上の列状スリット群を含むアクティブ側スリット 4 3 と、が組み合わされてもよい。 1 つの実線状スリットである屈曲スリット 4 2 は、前述の実施形態 7 の変形例と同様に、 E L デバイス 2 は屈曲領域 5 2 においてより屈曲しやす

10

20

30

40

くすることができると共に、端子部51の実効幅を小さくすることができる。

## [0140]

(実施形態9)

以下、本発明の他の実施形態の特徴であるステップS3について、図20~図22を参照しながら説明する。なお、本実施形態の特徴であるステップS9は、前述の実施形態2の特徴であるステップS9と同様であるため、説明を省略する。

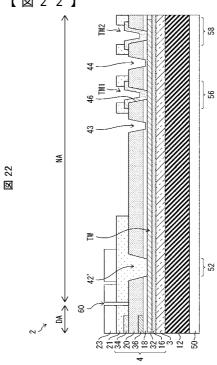

### [0141]

図 2 0 の ( a ) は、実施形態 9 の E L デバイス 2 の構成例を示す平面図であり、図 2 0 の ( b ) は、図 2 0 の ( a ) に示す屈曲領域 5 2 の部分拡大図である。図 2 1 は、図 2 0 の A - A ´断面図である。図 2 2 は、図 2 0 の B - B ´断面図である。

[0142]

図20に示すように、屈曲スリット42は、1つの実線状スリットである代わりに、各 端 子 配 線 T W と 1 対 1 対 応 に 交 差 す る よ う に 配 置 さ れ た 複 数 の 島 状 ス リ ッ ト 4 2 ´ で 構 成 されてもよい。例えば、屈曲スリット42が2つの列状スリット群を含む場合、(i)一 方の列状スリット群に含まれる島状スリット42´は、奇数本目の各端子配線TWと1対 1 対応に交差するように、端子配線TWの延伸方向と交差する方向に整列しており、( i i )他方の列状スリット群に含まれる島状スリット42´は、偶数本目の各端子配線TW と1対1対応に交差するように、端子配線TWの延伸方向と交差する方向に整列しており ( i i i ) 2 つの列状スリット群は、島状スリット 4 2 ´が互い違いに位置するように 、端子配線TWの沿線方向に位置している。このため、図21のように、偶数本目の端子 配線TWと交差する島状スリット42´同士の間には、奇数本目の端子配線TWを覆うバ ン ク 6 2 が 形 成 さ れ る 。 同 様 に 、 奇 数 本 目 の 端 子 配 線 T W と 交 差 す る 島 状 ス リ ッ ト 4 2 ´ 同士の間には、偶数本目の端子配線TWを覆うバンク62が形成される。なお、島状スリ ット42´と端子配線TWとの交差は1対1対応に限らない。各島状スリット42´が交 差 す る 端 子 配 線 T W の 本 数 が 1 本 で あ る と 共 に 、 各 端 子 配 線 T W が 交 差 す る 島 状 ス リ ッ ト 4 2 ´の数が1つ以上であればよい。例えば、1本の端子配線TWが幾つかの島状スリッ ト42′と交差してもよい。

[0143]

好ましくは、屈曲スリット42を構成する複数の島状スリット42´は、端子配線TWの延伸方向に隣接する複数の列状スリット群を構成するように、配置される。この場合、異なる列状スリット群に含まれる島状スリット42´は、互い違いに端子配線TWと交差することができる。好ましくは、屈曲スリット42を構成する複数の島状スリット42´は、端子配線TWの延伸方向から見て、互いに部分的に重畳するように配置される。この場合、端子配線TWの延伸方向から見て、端子配線TW同士の間に、島状スリット42´がない隙間は、存在しない。

[0144]

[0145]

図22に示すように、屈曲スリット42に含まれる各島状スリット42 ´は、第1無機絶縁膜18と第2無機絶縁膜20とを貫通する。各端子配線TWは、ゲート導電層32のみで形成され、各島状スリット42 ´の底面を通って、各島状スリット42 ´と交差している。この端子配線TWが露出しないように、各島状スリット42 ´に平坦化膜21が埋設されている。

#### [0146]

図20および図21に示すように、屈曲スリット42に含まれる各島状スリット42´

10

20

30

40

は、1本のみの端子配線TWと交差する。また、屈曲スリット42に含まれる島状スリット42´は、第1無機絶縁膜18と第2無機絶縁膜20とから構成されるバンク62によって、互いに分離されている。バンク62の上面は、第2無機絶縁膜20の上面であるので、ソース導電層34の残滓が残り難い。このため、屈曲スリット42に含まれる幾つかの島状スリット42´の底面及び内側面にソース導電層34の残滓が残っている場合であっても、該島状スリット42´を囲むバンク62の上面には、ソース導電層34の残滓が残らない。したがって、実施形態9に係るELデバイス2の構成によれば、ソース導電層34の残滓を通じた短絡を防止できるので、島状スリット42´を形成するためのエッチングを、コンタクトホール46の形成するためのエッチングと、同時に行うことは好ましい。

[0147]

屈曲スリット42に含まれる島状スリット42 ´ に関する上述の事項を除いて、実施形態9に係るELデバイス2の構成および工程順序は、前述の実施形態2と同様であるため、説明を省略する。

[0148]

また、ICチップ外周スリット40に含まれるアクティブ側外周スリット43も、同様に、各端子配線TWと1対1対応に交差するように配置された複数の島状スリット43´で構成されてもよい。

[0149]

(効果)

実施形態 9 に係る構成のELデバイス 2 は、実施形態 2 に係る構成のELデバイス 2 と、同様の効果を奏することができる。

[0150]

(まとめ)

本発明の態様1に係る表示デバイスは、複数の無機絶縁膜を含むTFT層と、前記TFT層よりも上層の発光素子層とを備え、前記TFT層には、複数の端子を含む端子領域が、アクティブ領域よりも外側に設けられる表示デバイスであって、前記複数の無機絶縁膜の少なくとも1つを貫通する、第1スリットパターンおよび第2スリットパターンを含み、平面視においては、前記第1スリットパターンが、平面視における前記アクティブ領域と前記端子領域との間に形成されるとともに、前記端子領域が、前記第1スリットパターンおよび前記第2スリットパターンによって挟まれている構成である。

[0151]

本発明の態様 2 に係る表示デバイスは、上記態様 1 において、前記端子領域にICチップが搭載されている構成としてもよい。

[0152]

本発明の態様 3 に係る表示デバイスは、上記態様 1 または 2 において、平面視における前記第 2 スリットパターンと前記表示デバイスのエッジとの間にフレキシブル回路基板が接続されている構成としてもよい。

[0153]

本発明の態様 4 に係る表示デバイスは、上記態様 1 ~ 3 の何れか 1 態様において、前記端子の少なくとも一部は、前記複数の無機絶縁膜よりも上層の導電層で形成されている構成としてもよい。

[0154]

本発明の態様 5 に係る表示デバイスは、上記態様 1 ~ 4 の何れか 1 態様において、前記第 1 スリットパターンは、前記端子に繋がる複数の端子配線と交差する方向に伸びる実線状スリットで構成される構成としてもよい。

[0155]

本発明の態様 6 に係る表示デバイスは、上記態様 5 において、前記TFT層よりも下層のバリア層を備える構成としてもよい。

[0156]

20

10

30

40

10

20

30

40

50

本発明の態様 7 に係る表示デバイスは、上記態様 6 において、前記第 1 および第 2 スリットパターンは、前記バリア層に達しない構成としてもよい。

## [0157]

本発明の態様 8 に係る表示デバイスは、上記態様 7 において、前記端子配線が前記第 1 スリットパターンよりも下側を通る構成としてもよい。

#### [0158]

本発明の態様 9 に係る表示デバイスは、上記態様 8 において、前記端子配線は、前記 T F T 層のゲート配線と同層に形成されている構成としてもよい。

## [0159]

本発明の態様10に係る表示デバイスは、上記態様6において、前記第1および第2スリットパターンは、前記複数の無機絶縁膜を貫通して前記バリア層内に達するか、あるいは前記複数の無機絶縁膜および前記バリア層を貫通する構成としてもよい。

#### [ 0 1 6 0 ]

本発明の態様 1 1 に係る表示デバイスは、上記態様 1 0 において、前記端子配線が、前記第 1 スリットパターンの内側面および底面を通る構成としてもよい。

#### [ 0 1 6 1 ]

本発明の態様12に係る表示デバイスは、上記態様10において、前記第1スリットパターンが有機絶縁材で埋められ、前記端子配線が前記第1スリットパターンよりも上側を通る構成としてもよい。

# [0162]

本発明の態様13に係る表示デバイスは、上記態様11または12において、前記端子配線のうちの前記アクティブ領域と前記第1スリットパターンとの間に延設されている本体部は、前記端子と同層に形成されている構成としてもよい。

#### [ 0 1 6 3 ]

本発明の態様14に係る表示デバイスは、上記態様11または12において、前記端子配線は、前記アクティブ領域と前記第1スリットパターンとの間に延設されている本体部(TW1)と、前記第1スリットパターンと交差する交差部(TW5)とを含み、前記本体部と前記交差部とが異なる導電層で形成されている構成としてもよい。

## [0164]

本発明の態様15に係る表示デバイスは、上記態様11または12において、前記第1 スリットパターンは底方向に向けて狭幅となるテーパ形状である構成としてもよい。

# [0165]

本発明の態様16に係る表示デバイスは、上記態様1~4の何れか1態様において、前記第1スリットパターンは、前記端子に接続する端子配線と交差する方向に並ぶ複数の島状スリットで構成される列状スリット群を1以上含む構成としてもよい。

#### [0166]

本発明の態様 1 7 に係る表示デバイスは、上記態様 1 6 において、前記端子配線は、前記第 1 スリットパターンと重ならない構成としてもよい。

## [0167]

本発明の態様18に係る表示デバイスは、上記態様17において、前記島状スリットは、各列状スリット群について、前記端子配線が該列状スリット群を構成する前記島状スリットの間を1対1対応に通るように、配置されている構成としてもよい。

## [0168]

本発明の態様19に係る表示デバイスは、上記態様16において、前記島状スリットは 、各々、前記端子配線のうちの1本のみと交差する構成としてもよい。

# [0169]

本発明の態様20に係る表示デバイスは、上記態様19において、前記島状スリットは、前記端子配線と1対1対応に交差するように、配置されている構成としてもよい。

## [0170]

本発明の態様21に係る表示デバイスは、上記態様17~20の何れか1態様において

10

20

30

40

50

、前記TFT層よりも下層にバリア層が設けられ、前記第1スリットパターンは、前記複数の無機絶縁膜を貫通して前記バリア層内に達するか、あるいは前記複数の無機絶縁膜および前記バリア層を貫通する構成としてもよい。

# [0171]

本発明の態様 2 2 に係る表示デバイスは、上記態様 1 6 ~ 2 1 の何れか 1 態様において、前記第 1 スリットパターンは、複数の島状スリット群を含み、前記複数の島状スリット群に含まれる複数の島状スリットは、前記端子配線が延伸する方向から見て隙間がないように、平面視において千鳥配置されている構成としてもよい。

## [0172]

本発明の態様23に係る表示デバイスは、上記態様22において、前記複数の島状スリットに含まれる或る島状リットの端部は、前記複数の島状スリットに含まれる別の島状スリットと、前記端子配線が延伸する方向から見て重畳する構成としてもよい。

#### [0173]

本発明の態様 2 4 に係る表示デバイスは、上記態様 5 ~ 2 3 の何れか 1 態様において、前記端子領域は、前記第 1 スリットパターンと、実線状スリットで構成された前記第 2 スリットパターンと、前記端子配線と同方向に伸びる実線状スリットで構成された 2 つの第 4 スリットパターンとによって囲まれている構成としてもよい。

## [0174]

本発明の態様 2 5 に係る表示デバイスは、上記態様 5 ~ 2 4 の何れか 1 態様において、前記アクティブ領域と前記第 1 スリットパターンとの間に折り曲げ領域が形成されており、前記折り曲げ領域に、前記複数の無機絶縁膜の少なくとも 1 つを貫通する第 3 スリットパターンが形成されている構成としてもよい。

## [0175]

本発明の態様 2 6 に係る表示デバイスは、上記態様 2 5 において、前記第 1 スリットパターンおよび前記第 3 スリットパターンの深さが同じである構成としてもよい。

# [0176]

本発明の態様 2 7 に係る表示デバイスは、上記態様 2 6 において、前記第 1 スリットパターンおよび前記第 3 スリットパターンのスリットパターンが同じである構成としてもよい。

# [0177]

本発明の態様 2 8 に係る表示デバイスは、上記態様 2 6 または 2 7 において、前記TFT層よりも下層にバリア層が設けられ、前記バリア層よりも下層に支持材が設けられ、前記第 1 および第 3 スリットパターンは、前記複数の無機絶縁膜および前記バリア層を貫通して、前記支持材に達すると共に、有機絶縁材で埋められ、前記端子配線が前記有機絶縁材の上を通る構成としてもよい。

# [0178]

本発明の態様29に係る表示デバイスは、上記態様25~28の何れか1態様において、前記発光素子層を覆う封止層を備え、前記発光素子層からの光が前記封止層を透過する上方発光型であり、前記第3スリットパターンを折り目として前記端子の表面が下方を向くように折り曲げられている構成としてもよい。

# [0179]

本発明の態様30に係る表示デバイスは、上記態様5~29の何れか1態様において、前記端子配線の少なくとも一部は、前記複数の無機絶縁膜よりも上層の導電層で形成されていると共に、前記TFT層よりも上層の有機絶縁膜によって被覆されている構成としてもよい。

# [0180]

本発明の態様31に係る表示デバイスは、上記態様1~30の何れか1態様において、可撓性の支持材を備える構成としてもよい。

#### [0181]

本発明の態様32に係る表示デバイスの製造方法は、複数の無機絶縁膜を含むTFT層

と、前記TFT層よりも上層の発光素子層とを備え、前記TFT層には、複数の端子を含む端子領域が、アクティブ領域よりも外側に設けられた表示デバイスの製造方法であって、前記複数の無機絶縁膜の少なくとも1つを貫通する第1スリットパターンを、平面視における前記アクティブ領域と前記端子領域との間に形成し、前記複数の無機絶縁膜の少なくとも1つを貫通する第2スリットパターンを、前記第1スリットパターンとともに平面視において前記端子領域を挟むように形成する製造方法である。

[ 0 1 8 2 ]

本発明の態様 3 3 に係る表示デバイスの製造方法は、上記態様 3 2 において、前記複数の無機絶縁膜の少なくとも 1 つを貫通する第 3 スリットパターンを、前記アクティブ領域と前記第 1 スリットパターンとの間に形成する製造方法としてもよい。

[0183]

本発明の態様34に係る表示デバイスの製造方法は、上記態様33において、前記第1 スリットパターンおよび第3スリットパターンを同じプロセスで形成する製造方法として もよい。

[0184]

本発明の態様 3 5 に係る表示デバイスの製造方法は、上記態様 3 2 ~ 3 4 のいずれか 1 態様において、熱圧着によって前記端子領域に電子回路基板を実装する製造方法としても よい。

[0185]

本発明の態様36に係る表示デバイスの製造方法は、上記態様33または34において、前記第3スリットパターンを折り目として、前記表示デバイスを折り曲げ、前記端子領域を裏面に配する製造方法としてもよい。

[0186]

本発明の態様 3 7 に係る表示デバイスの製造装置は、複数の無機絶縁膜を含むTFT層と、前記TFT層よりも上層の発光素子層とを備え、前記TFT層には、複数の端子を含む端子領域が、アクティブ領域よりも外側に設けられた表示デバイスの製造装置であって、前記複数の無機絶縁膜の少なくとも 1 つを貫通する第 1 スリットパターンを、平面視における前記アクティブ領域と前記端子領域との間に形成し、前記複数の無機絶縁膜の少なくとも 1 つを貫通する第 2 スリットパターンを、前記第 1 スリットパターンとともに平面視において前記端子領域を挟むように形成する製造装置である。

[0187]

(付記事項)

本発明は前記した実施形態に限定されるものではなく、異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。さらに、各実施形態にそれぞれ開示された技術的手段を組み合わせることにより、新しい技術的特徴を形成することができる。

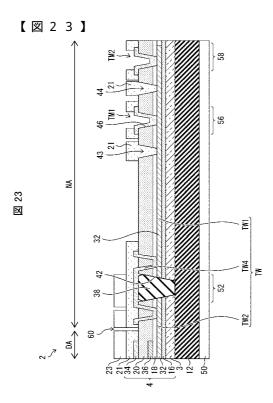

[0188]

例えば、図23のような、実施形態1に係る構成と実施形態4に係る構成とを組み合わせて得られる構成も、本発明の技術的範囲に含まれる。

[0189]

図23は、実施形態1に係るELデバイス2(図5参照)のICチップ外周スリット40の底面にゲート導電層32が露出する場合の構成に、屈曲領域52およびその近傍において、実施形態4に係るELデバイス2(図11参照)の構成を組み合わせて得られる構成例を示す断面図である。図23における屈曲スリット42は、無機バリア層3、ゲート導電層32、および複数の無機絶縁膜16,18,20を貫通する。図23におけるアクティブ側外周スリット43およびFPC側外周スリット44は、第1および第2無機絶縁膜18,20を貫通する。

【符号の説明】

[0190]

2 E L デバイス

10

20

30

40

```

4

TFT層

3

無機バリア膜(バリア層)

5

発光素子層

6

封止層

7

積層体

8、11 接着層

9

保護材

1 0

支持材

1 2

樹脂層(可撓性の支持材)

10

1 3

剥 離 層

半導体膜

1 5

ゲート絶縁膜

1 6

16,18,20

無機絶縁膜

2 1

平坦化膜

アノード電極

2 2

23 バンク層

23b バンク

2 3 c

隔壁

2 4

E L 層

20

2 5

カソード電極

2 6

第 1 無機封止膜

26、28 無機封止膜

2 7

有機封止膜

2 8

第2無機封止膜

ゲート導電層

3 2

3 4

ソース導電層

3 6

中間導電層

3 2 、 3 4 、 3 6 導電層

3 8

埋設材(有機絶縁材)

30

4 0

ICチップ外周スリット

4 2

屈曲スリット(第3スリットパターン)

4 2 ′

島状スリット

アクティブ側外周スリット(第1スリットパターン)

4 3 ′

島状スリット

4 4

FPC側外周スリット(第2スリットパターン)

4 5

端側外周スリット(第4スリットパターン)

4 6

コンタクトホール

5 0

マザー基板

5 1

端子部

40

5 2

屈曲領域(折り曲げ領域)

5 6

ICチップ搭載領域(端子領域)

5 8

FPC接続領域

6 0

スリット

6 2

バンク

アクティブ領域

D A

非アクティブ領域

NΑ

TM、TM1、TM2 端子

T W

端子配線

T W 1

本体部

TW2 アクティブ側部

50

```

- TW3 端子側部

- TW4 屈曲スリットブリッジ部 (交差部)

- TW5 外周スリットブリッジ部(交差部)

# 【図1】

図 1

# 【図2】

【図19】

【図20】

図 20

【図21】

【図22】

# 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2017/034737

## A. CLASSIFICATION OF SUBJECT MATTER

Int. C1. H01L51/50(2006.01)i, G09F9/30(2006.01)i, H01L27/32(2006.01)i, H05B33/10(2006.01)i, H05B33/12(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

Int. Cl. H01L51/50, G09F9/30, H01L27/32, H05B33/10, H05B33/12

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Published examined utility model applications of Japan

Published unexamined utility model applications of Japan

Published registered utility model applications of Japan

Published unexamined utility model applications of Japan

Published unexamined utility model applications of Japan

Published unexamined utility model applications of Japan

Published registered utility model applications of Japan

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                              | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | JP 2017-168308 A (JOLED INC.) 21 September 2017, claims 1-11, fig. 1-10 & US 2017/0271423 A1, claims 1-20, figs. 1-10                                           | 1-37                  |

| A         | JP 2017-123257 A (JAPAN DISPLAY INC.) 13 July 2017, claims 1-15, fig. 1-13 & US 2017/0194599 A1, claims 1-15, fig. 1-13 & KR 10-2017-0082443 A & CN 107017354 A | 1-37                  |

| A         | JP 2017-123217 A (JAPAN DISPLAY INC.) 13 July 2017, claims 1-10, fig. 1-12 & US 2017/0194601 A1, claims 1-10, fig. 1-12B                                        | 1-37                  |

| Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                               | See patent family annex.                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Special categories of cited documents:  "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier application or patent but published on or after the international filing date                                                                                                              | later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention      woment of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone |  |  |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means document published prior to the international filing date but later than the priority date claimed | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art  "&" document member of the same patent family                                                                             |  |  |

| Date of the actual completion of the international search 11.12.2017                                                                                                                                                                                                                                                                                     | Date of mailing of the international search report 26.12.2017                                                                                                                                                                                                                                                                                                               |  |  |

| Name and mailing address of the ISA/ Japan Patent Office 3-4-3, Kasumigaseki, Chiyoda-ku, Tokyo 100-8915, Japan                                                                                                                                                                                                                                          | Authorized officer  Telephone No.                                                                                                                                                                                                                                                                                                                                           |  |  |

| Town DCT(ISA/210 (assent short) (Isausaw 2015)                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                             |  |  |

Form PCT/ISA/210 (second sheet) (January 2015)

# INTERNATIONAL SEARCH REPORT

International application No. PCT/JP2017/034737

|                 | PCT/JP2017,                                                                                                                                                                                            | /034737               |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| C (Continuation | ). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                 |                       |

| Category*       | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                     | Relevant to claim No. |

| A               | JP 2017-91693 A (JAPAN DISPLAY INC.) 25 May 2017, claims 1-8, fig. 1-11F & US 2017/0133594 A1, claims 1-8, fig. 1-11F                                                                                  | 1-37                  |

| A               | JP 2017-22007 A (JAPAN DISPLAY INC.) 26 January 2017, claims 1-11, fig. 1-8 & US 2017/0012243 A1, claims 1-14, fig. 1-8                                                                                | 1-37                  |

| A               | JP 2006-4909 A (SAMSUNG SDI CO., LTD.) 05 January 2006, claims 1-12, fig. 1-17 & US 2005/0285522 Al, claims 1-9, fig. 1A-5C & KR 10-2005-0119892 A & CN 1710999 A                                      | 1-37                  |

| A               | JP 2007-294403 A (CANON INC.) 08 November 2007, claims 1-13, fig. 1-10 & US 2007/0273271 A1, claims 1-13, fig. 1A-10 & US 2009/0267504 A1 & US 2010/0068840 A1 & KR 10-2007-0097365 A & CN 101051675 A | 1-37                  |

| A               | WO 2016/027547 A1 (JOLED INC.) 25 February 2016, claims 1-11, fig. 1-16 & US 2017/0148855 A1, claims 1-11, fig. 1-16                                                                                   | 1-37                  |

|                 |                                                                                                                                                                                                        |                       |

Form PCT/ISA/210 (continuation of second sheet) (January 2015)

#### 国際調査報告

国際出願番号 PCT/JP2017/034737

発明の属する分野の分類(国際特許分類(IPC))

$Int. Cl. \quad H01L51/50 \ (2006, \ 01) \ i, \quad G09F9/30 \ (2006, \ 01) \ i, \quad H01L27/32 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B33/10 \ (2006, \ 01) \ i, \quad H05B33/10 \ (2006, \ 01) \ i, \\ h05B3/10 \ (2006, \ 01) \ i, \quad H05B3/10 \ (2006, \ 01) \ i, \\ h05B3/10 \ (2006, \ 01) \ i, \quad H05B3/10 \ (2006, \ 01) \ i, \\ h05B3/10 \ (2006, \ 01) \ i, \quad H05B3/10 \ (2006, \ 01) \ i, \\ h05B3/10 \ (2006, \ 01) \ i, \quad H05B3/10 \ (2006, \ 01) \ i, \\ h05B3/10 \ (2006, \ 01) \ i, \quad H05B3/10 \ (2006, \ 01) \ i, \\ h05B3/10 \ (2006, \ 01) \ i, \quad H05B3/10 \ (2006, \ 01) \ i, \\ h05B3/10 \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (2006, \ 01) \ (200$ H05B33/12 (2006. 01) i

B. 調査を行った分野

調査を行った最小限資料(国際特許分類(IPC))

Int.Cl. H01L51/50, G09F9/30, H01L27/32, H05B33/10, H05B33/12

最小限資料以外の資料で調査を行った分野に含まれるもの

日本国実用新案公報 1922-1996年 日本国公開実用新案公報 1971-2017年 1996-2017年 日本国実用新案登録公報 日本国登録実用新案公報 1994-2017年

国際調査で使用した電子データベース(データベースの名称、調査に使用した用語)

#### 関連すると認められる文献

| C. 関連すると認められる大脈 |                                                                                                                                                                            |                |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

| 引用文献の<br>カテゴリー* | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                                                          | 関連する<br>請求項の番号 |  |  |  |

| A               | JP 2017-168308 A (株式会社JOLED) 2017.09.21,<br>[請求項 1]-[請求項 11], [図 1]-[図 10]<br>& US 2017/0271423 A1 Claims 120., FIGs. 1-10                                                 | 1-37           |  |  |  |

| A               | JP 2017-123257 A (株式会社ジャパンディスプレイ) 2017.07.13,<br>[請求項 1]-[請求項 15], [図 1]-[図 13]<br>& US 2017/0194599 Al Claims 115., FIGs. 1-13<br>& KR 10-2017-0082443 A & CN 107017354 A | 1–37           |  |  |  |

# ※ C欄の続きにも文献が列挙されている。

パテントファミリーに関する別紙を参照。

- \* 引用文献のカテゴリー

- 「A」特に関連のある文献ではなく、一般的技術水準を示す 「T」国際出願日又は優先日後に公表された文献であって もの

- 「E」国際出願目前の出願または特許であるが、国際出願日 以後に公表されたもの

- 「L」優先権主張に疑義を提起する文献又は他の文献の発行 日若しくは他の特別な理由を確立するために引用す る文献(理由を付す)

- 「O」口頭による開示、使用、展示等に言及する文献

- 「P」国際出願目前で、かつ優先権の主張の基礎となる出願 「&」同一パテントファミリー文献

- の日の後に公表された文献

- 出願と矛盾するものではなく、発明の原理又は理論 の理解のために引用するもの

- 「X」特に関連のある文献であって、当該文献のみで発明 の新規性又は進歩性がないと考えられるもの

- 「Y」特に関連のある文献であって、当該文献と他の1以 上の文献との、当業者にとって自明である組合せに よって進歩性がないと考えられるもの

国際調査を完了した日 国際調査報告の発送日 11. 12. 2017 26.12.2017 9108 2O国際調査機関の名称及びあて先 特許庁審査官(権限のある職員) 日本国特許庁(ISA/JP) 濱野 隆 郵便番号100-8915 東京都千代田区霞が関三丁目4番3号 電話番号 03-3581-1101 内線 3271

様式PCT/ISA/210 (第2ページ) (2015年1月)

国際調査報告

国際出願番号 PCT/JP2017/034737

| C(続き).                  | 関連すると認められる文献                                                                                                                                                                                                   |                |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 引用文献の<br>カテゴリー <b>*</b> | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                                                                                              | 関連する<br>請求項の番号 |

| A                       | JP 2017-123217 A (株式会社ジャパンディスプレイ) 2017.07.13,<br>[請求項1]-[請求項10], [図1]-[図12]<br>& US 2017/0194601 A1 Claims 110., Figs. 1-12B                                                                                   | 1-37           |

| A                       | JP 2017-91693 A (株式会社ジャパンディスプレイ) 2017.05.25,<br>[請求項1]-[請求項8], [図1]-[図11F]<br>& US 2017/0133594 A1 Claims 18., FIGs. 1-11F                                                                                     | 1-37           |

| A                       | JP 2017-22007 A (株式会社ジャパンディスプレイ) 2017.01.26,<br>[請求項 1]-[請求項 11], [図 1]-[図 8]<br>& US 2017/0012243 A1 Claims 114., FIGs. 1-8                                                                                   | 1-37           |

| A                       | JP 2006-4909 A (三星エスディアイ株式会社) 2006.01.05,<br>[請求項1]-[請求項12], [図1]-[図17]<br>& US 2005/0285522 A1 Claims 19., FIGs. 1A-5C<br>& KR 10-2005-0119892 A & CN 1710999 A                                               | 1-37           |

| A                       | JP 2007-294403 A (キヤノン株式会社) 2007.11.08,<br>[請求項1]-[請求項13], [図1]-[図10]<br>& US 2007/0273271 A1 Claims 113., FIGs. 1A-10<br>& US 2009/0267504 A1 & US 2010/0068840 A1<br>& KR 10-2007-0097365 A & CN 101051675 A | 1-37           |

| A                       | WO 2016/027547 A1 (株式会社JOLED) 2016.02.25,<br>[請求項1]-[請求項11], [図1]-[図16]<br>& US 2017/0148855 A1 Claims 111., FIGs. 1-16                                                                                        | 1-37           |

様式PCT/ISA/210 (第2ページの続き) (2015年1月)

# フロントページの続き

| (51) Int.CI. |       |           | FΙ      |       |         | テーマコード(参考) |

|--------------|-------|-----------|---------|-------|---------|------------|

| H 0 5 B      | 33/12 | (2006.01) | H 0 5 B | 33/12 | В       |            |

| H 0 5 B      | 33/10 | (2006.01) | H 0 5 B | 33/10 |         |            |

| G 0 9 F      | 9/30  | (2006.01) | G 0 9 F | 9/30  | 3 3 8   |            |

| G 0 9 F      | 9/00  | (2006.01) | G 0 9 F | 9/30  | 3 6 5   |            |

|              |       |           | G 0 9 F | 9/30  | 3 4 8 A |            |

|              |       |           | G 0 9 F | 9/30  | 3 3 0   |            |

|              |       |           | G 0 9 F | 9/30  | 3 0 9   |            |

|              |       |           | G 0 9 F | 9/30  | 3 0 8 Z |            |

|              |       |           | G 0 9 F | 9/00  | 3 3 8   |            |

|              |       |           | G 0 9 F | 9/00  | 3 4 6 A |            |

(注)この公表は、国際事務局(WIPO)により国際公開された公報を基に作成したものである。なおこの公表に係る日本語特許出願(日本語実用新案登録出願)の国際公開の効果は、特許法第184条の10第1項(実用新案法第48条の13第2項)により生ずるものであり、本掲載とは関係ありません。

| 专利名称(译)        | 显示装置,显示装置的制造方法以及显示装置的制造装置                                                                                                                                                                                                                                                 |                           |                                   |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------|--|--|

| 公开(公告)号        | JPWO2019064342A1                                                                                                                                                                                                                                                          | 公开(公告)日                   | 2020-07-30                        |  |  |

| 申请号            | JP2019545420                                                                                                                                                                                                                                                              | 申请日                       | 2017-09-26                        |  |  |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                    |                           |                                   |  |  |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                      |                           |                                   |  |  |

| [标]发明人         | 三谷昌弘                                                                                                                                                                                                                                                                      |                           |                                   |  |  |

| 发明人            | 三谷 昌弘                                                                                                                                                                                                                                                                     |                           |                                   |  |  |

| IPC分类号         | H01L51/50 H01L27/32 H05B33/04                                                                                                                                                                                                                                             | H05B33/06 H05B33/22 H05B3 | 33/12 H05B33/10 G09F9/30 G09F9/00 |  |  |

| FI分类号          | H05B33/14.A H01L27/32 H05B33/04 H05B33/06 H05B33/22.Z H05B33/12.B H05B33/10 G09F9/30. 338 G09F9/30.365 G09F9/30.348.A G09F9/30.330 G09F9/30.309 G09F9/30.308.Z G09F9/00.338 G09F9/00.346.A                                                                                |                           |                                   |  |  |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC21 3K107/DD03 3K107/DD38 3K107/DD89 3K107/DD90 3K107 /EE48 3K107/EE49 3K107/EE50 3K107/EE58 3K107/FF15 5C094/AA31 5C094/BA03 5C094/BA27 5C094/DA06 5C094/DA07 5C094/DA13 5C094/DA15 5C094/DB02 5G435/AA14 5G435/BB05 5G435 /EE32 5G435/KK05 |                           |                                   |  |  |

| 代理人(译)         | 井上 知哉                                                                                                                                                                                                                                                                     |                           |                                   |  |  |

|                |                                                                                                                                                                                                                                                                           |                           |                                   |  |  |

# 摘要(译)

活性侧缝隙(43)和FPC侧缝隙(44)分别穿透第二无机绝缘膜(20)并到达第一无机绝缘膜(18)。 在平面图中,有源侧缝隙(43)形成在EL器件(2)的有源区域和IC芯片安装区域(56)之间,而IC芯片安装区域(56)为 它被(43)和FPC侧缝(44)夹在中间。