(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-205462

(P2010-205462A)

(43) 公開日 平成22年9月16日(2010.9.16)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H05B 33/22 (2006.01)</b> | H05B 33/22 | Z 3K107     |

| <b>H01L 51/50 (2006.01)</b> | H05B 33/14 | A           |

| <b>H05B 33/12 (2006.01)</b> | H05B 33/22 | C           |

| <b>H05B 33/10 (2006.01)</b> | H05B 33/12 | B           |

|                             | H05B 33/10 |             |

審査請求 未請求 請求項の数 7 O L (全 23 頁)

|           |                            |            |                                                       |

|-----------|----------------------------|------------|-------------------------------------------------------|

| (21) 出願番号 | 特願2009-47503 (P2009-47503) | (71) 出願人   | 000001443<br>カシオ計算機株式会社<br>東京都渋谷区本町1丁目6番2号            |

| (22) 出願日  | 平成21年3月2日 (2009.3.2)       | (74) 代理人   | 100096699<br>弁理士 鹿嶋 英實                                |

|           |                            | (72) 発明者   | 木津 貴志<br>東京都八王子市石川町2951番地の5<br>カシオ計算機株式会社八王子技術センター内   |

|           |                            | (72) 発明者   | 熊谷 稔<br>東京都八王子市石川町2951番地の5<br>カシオ計算機株式会社八王子技術センター内    |

|           |                            | F ターム (参考) | 3K107 AA01 BB01 CC27 CC45 DD71<br>DD84 DD89 DD96 GG13 |

## (54) 【発明の名称】表示装置及びその製造方法

## (57) 【要約】

【課題】有機EL素子を有する表示画素において、非発光領域の発生を抑制することができるパネル構造を有する表示装置及びその製造方法を提供する。

【解決手段】各表示画素PIXの画素形成領域Rpx間に配設する隔壁層17を、非感光性の樹脂材料（例えば、フッ素化合物含有樹脂材料）からなる樹脂層をドライエッチング法を用いてパターニングすることにより形成し、また、該隔壁層17により画定される画素形成領域Rpxに設けられる有機EL層15を構成する正孔注入層15aを、遷移金属の酸化物（例えば、酸化モリブデン）を真空蒸着法やスパッタリング法を用いて成膜することにより形成する。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

一对の電極間に少なくとも担体注入層と有機発光層が積層された素子構造を有する複数の表示素子が、基板上に配列された表示パネルを備えた表示装置において、

前記表示素子における前記有機発光層の形成領域を画定する隔壁層が、非感光性の絶縁材料からなり、かつ、前記担体注入層が、遷移金属の酸化物からなることを特徴とする表示装置。

**【請求項 2】**

前記隔壁層を構成する前記非感光性の絶縁材料は、フッ素化合物系の樹脂材料であることを特徴とする請求項 1 記載の表示装置。

**【請求項 3】**

前記担体注入層は、前記有機発光層の形成領域、及び、該形成領域を画定する前記隔壁層上に設けられていることを特徴とする請求項 1 又は 2 記載の表示装置。

**【請求項 4】**

前記担体注入層を構成する前記遷移金属の酸化物は、酸化モリブデンであることを特徴とする請求項 1 乃至 3 のいずれかに記載の表示装置。

**【請求項 5】**

一对の電極間に少なくとも担体注入層と有機発光層が積層された素子構造を有する複数の表示素子が、基板上に配列された表示パネルを備えた表示装置の製造方法において、

前記基板上に、前記一对の電極のうち、一方の電極を形成する工程と、

前記基板上に、非感光性の絶縁材料からなる絶縁層を成膜し、ドライエッチング法を用いて、前記一方の電極が露出する開口部を有する隔壁層を形成する工程と、

前記開口部内及び前記隔壁層上に、遷移金属の酸化物からなる前記担体注入層を形成する工程と、

を含むことを特徴とする表示装置の製造方法。

**【請求項 6】**

前記隔壁層を形成する前記非感光性の絶縁材料は、フッ素化合物系の樹脂材料であることを特徴とする請求項 5 記載の表示装置の製造方法。

**【請求項 7】**

前記担体注入層を形成する前記遷移金属の酸化物は、酸化モリブデンであることを特徴とする請求項 5 又は 6 記載の表示装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置及びその製造方法に関し、特に、担体輸送性機能材料からなる液状材料を塗布することにより担体輸送層が形成された発光素子を有する複数の表示画素を、2次元配列してなる表示パネルを備えた表示装置及びその製造方法に関する。

**【背景技術】****【0002】**

近年、携帯電話や携帯音楽プレーヤ等の電子機器の表示デバイスとして、有機エレクトロルミネッセンス素子（以下、「有機EL素子」と略記する）を2次元配列した表示パネル（有機EL表示パネル）を備えたものが知られている。

**【0003】**

有機EL素子は、周知のように、例えばガラス基板等の一面側に、アノード（陽極）電極と、有機EL層（発光機能層）と、カソード（陰極）電極と、を順次積層した素子構造を有している。そして、有機EL層に発光しきい値を越えるようにアノード電極に正電圧、カソード電極に負電圧を印加することにより、有機EL層内で注入されたホールと電子が再結合する際に生じるエネルギーに基づいて光（励起光）が放射される。有機EL層は、概略、正孔輸送層や電子輸送層等の担体輸送層、発光層等を積層した構成を有している。

## 【0004】

ここで、有機EL素子は、有機EL層となる担体輸送層を形成する有機材料に応じて、低分子系と高分子系の有機EL素子に大別することができる。高分子系の有機材料や一部の低分子系有機材料を適用した有機EL素子の場合には、一般に、湿式成膜法としてインクジェット法（液滴吐出法）やノズルプリンティング法（液流吐出法）、印刷法等を適用することができる。これによれば、アノード電極上、又は、アノード電極を含む特定の領域にのみ選択的に上記有機材料の溶液を塗布することができるので、低分子系の有機材料を適用した場合に比較して、材料ロスが少なく、効率的な製造プロセスで精度良く有機EL層の薄膜を形成することができるという特徴を有している。それ故、有機EL表示パネルの低コスト化や大画面化に優位な技術として期待されている。

10

## 【0005】

ところで、このような有機EL素子の湿式成膜においては、従来、アノード電極上に形成する正孔注入層として、例えばポリチオフェンとポリスチレンスルホン酸の混合物（P E D O T / P S S）が用いられる。近年、例えば特許文献1に開示されているように、このような高分子系の有機材料に代えて、遷移金属の酸化物を正孔注入層に用いることにより、有機EL素子の素子特性の一層の向上と長寿命化を図る試みがなされている。

## 【0006】

一方、高分子系の有機材料を適用した有機EL素子の製造方法においては、有機EL層を形成するための領域（すなわち、有機材料の塗布領域）を画定するために、基板表面から連続的に突出する隔壁を設けたパネル構造が知られている。

20

## 【先行技術文献】

## 【特許文献】

## 【0007】

## 【特許文献1】特開2005-203340号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0008】

しかしながら、上述した特許文献1に開示された有機EL素子の有機EL層を隔壁にて画定した構造及び製造方法においては、次のような問題を有している。すなわち、本願発明者らの検証によれば、隔壁（画素規制部）の材料として有機樹脂、例えば一般に広く用いられている感光性のポリイミド材料を用い、かつ、正孔注入層として例えば酸化モリブデンを用いたパネル構造において、現像液を用いて感光性のポリイミド材料からなる隔壁をパターニング形成した後、当該隔壁の表面をUVオゾン処理により洗浄し、正孔注入層となる材料を成膜する一連の製造プロセスを適用した場合、表示画素の端部からダークスポットと称される非発光領域が発生し、表示画素部の内部に向かって拡大進行することを見出した。これにより、有機EL表示パネルの製品歩留まりが低下するとともに、表示特性の劣化を招くという問題を有している。なお、表示パネル（特に、隔壁）の製造方法とダークスポットの発生との関係については、後述する実施形態において詳しく説明する。

30

## 【0009】

そこで、本発明は、上述した問題点に鑑み、有機EL素子を有する表示画素において、ダークスポット（非発光領域）の発生を抑制することができるパネル構造を有する表示装置及びその製造方法を提供することを目的とする。

40

## 【課題を解決するための手段】

## 【0010】

請求項1記載の発明は、一対の電極間に少なくとも担体注入層と有機発光層が積層された素子構造を有する複数の表示素子が、基板上に配列された表示パネルを備えた表示装置において、前記表示素子における前記有機発光層の形成領域を画定する隔壁層が、非感光性の絶縁材料からなり、かつ、前記担体注入層が、遷移金属の酸化物からなることを特徴とする。

## 【0011】

50

前記隔壁層を構成する前記非感光性の絶縁材料は、フッ素化合物系の樹脂材料であることが好ましい。

また、前記担体注入層は、前記有機発光層の形成領域、及び、該形成領域を画定する前記隔壁層上に設けられていることが好ましい。

前記担体注入層を構成する前記遷移金属の酸化物は、酸化モリブデンであることが好ましい。

前記一対の電極は、いずれか一方が透明な電極膜からなり、他方が光を反射する電極膜からなることが好ましい。

前記表示素子は、有機エレクトロルミネッセンス素子であり、前記担体注入層は正孔注入層であってもよい。

#### 【0012】

請求項5記載の発明は、一対の電極間に少なくとも担体注入層と有機発光層が積層された素子構造を有する複数の表示素子が、基板上に配列された表示パネルを備えた表示装置の製造方法において、前記基板上に、前記一対の電極のうち、一方の電極を形成する工程と、前記基板上に、非感光性の絶縁材料からなる絶縁層を成膜し、ドライエッチング法を用いて、前記一方の電極が露出する開口部を有する隔壁層を形成する工程と、前記開口部内及び前記隔壁層上に、遷移金属の酸化物からなる前記担体注入層を形成する工程と、を含むことを特徴とする。

#### 【0013】

前記隔壁層を形成する前記非感光性の絶縁材料は、フッ素化合物系の樹脂材料であることが好ましい。

前記担体注入層を形成する前記遷移金属の酸化物は、酸化モリブデンであることが好ましい。

前記一方の電極は、透明な電極材料により形成され、他方の電極が光を反射する電極材料により形成されることが好ましい。

#### 【発明の効果】

#### 【0014】

本発明に係る表示装置及びその製造方法によれば、有機EL素子を有する表示画素において、非発光領域の発生を抑制することができる。

#### 【図面の簡単な説明】

#### 【0015】

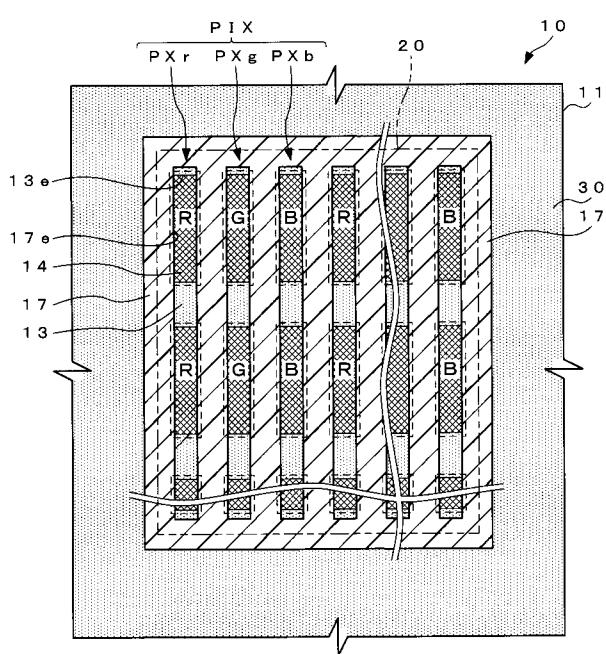

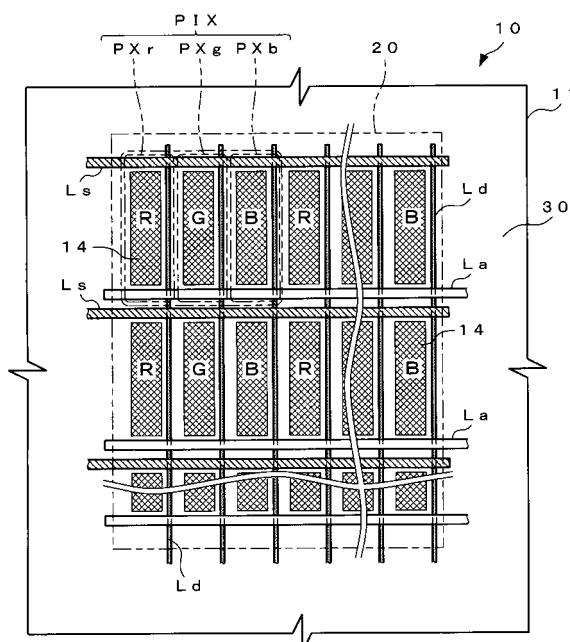

【図1】本発明に係る表示装置に適用される表示パネルの一例を示す概略平面図である。

【図2】図1に示した表示パネルの画素配列状態の一例を示す概略平面図である。

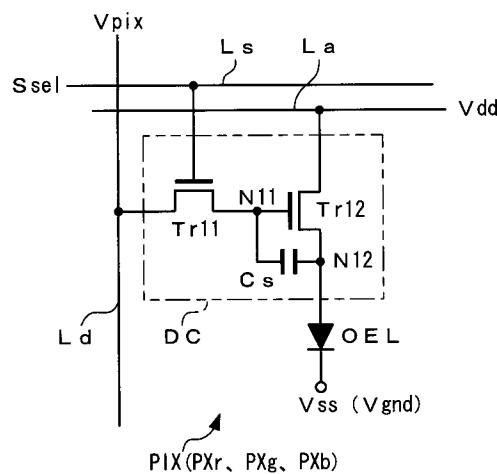

【図3】本実施形態に係る表示パネルに2次元配列される各表示画素の回路構成例を示す等価回路図である。

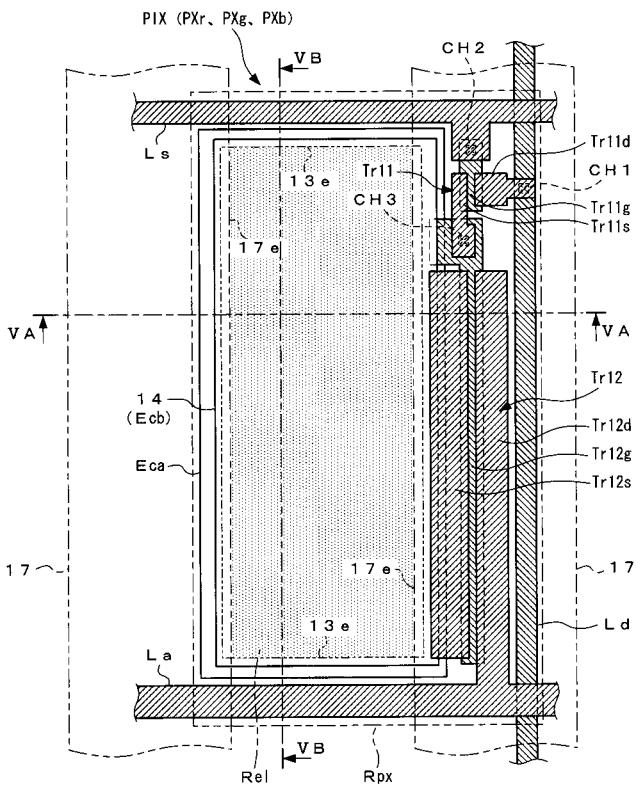

【図4】本実施形態に適用可能な表示画素の一例を示す平面レイアウト図である。

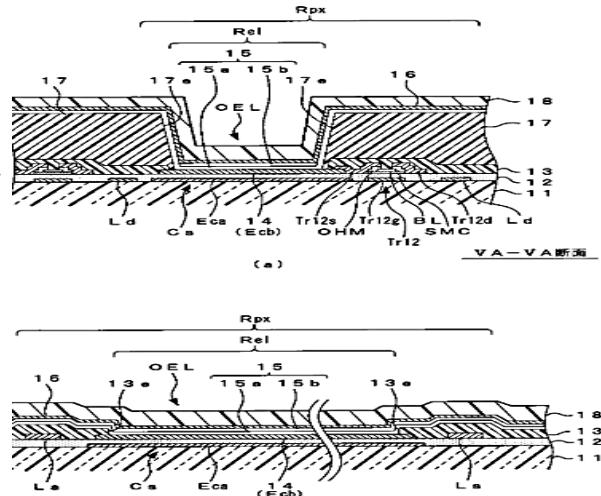

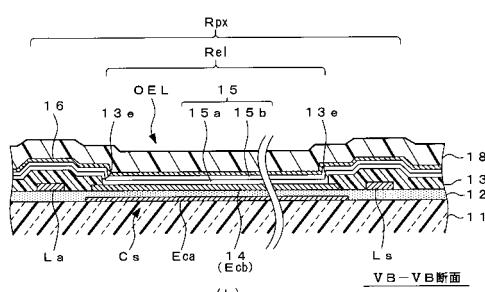

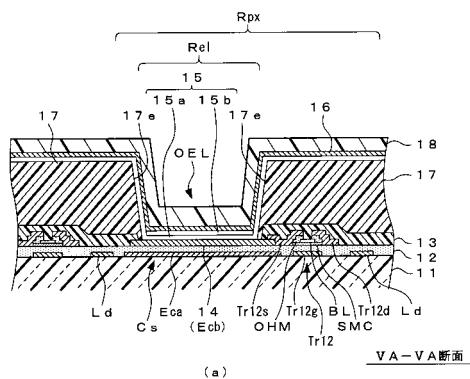

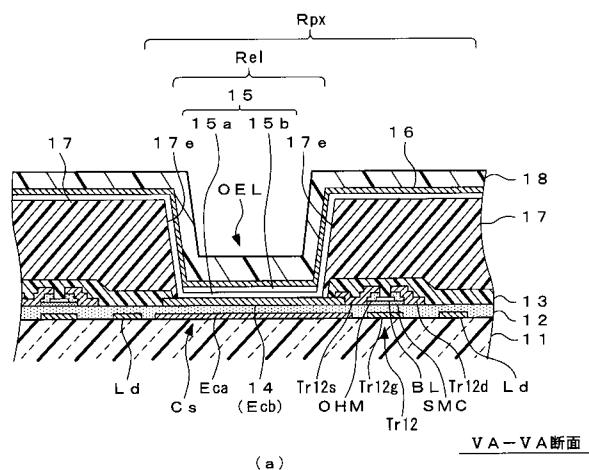

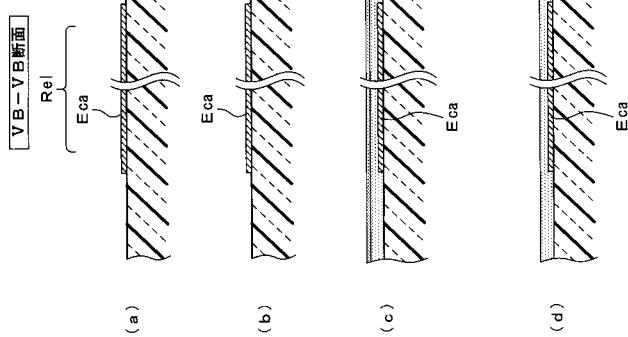

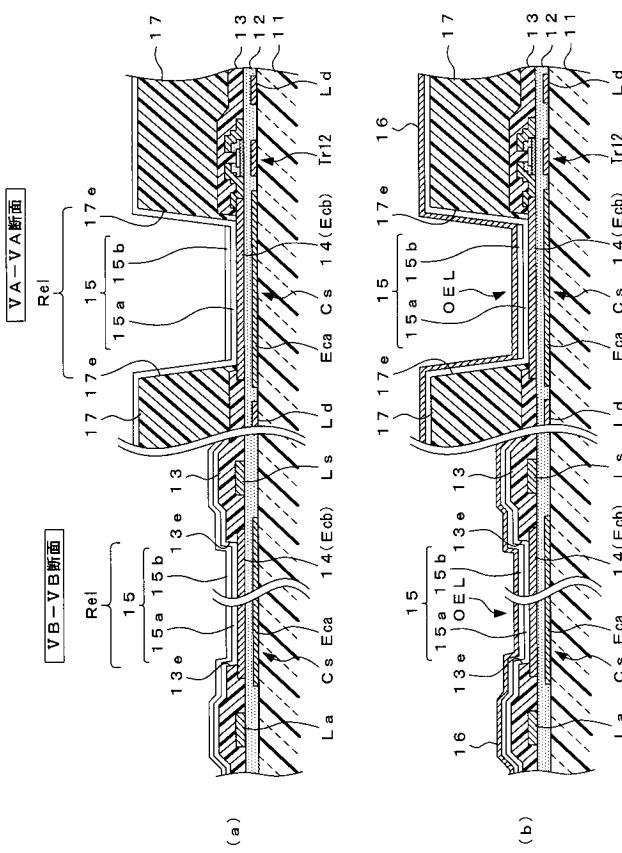

【図5】本実施形態に係る表示パネルの要部断面図である。

【図6】本実施形態に係る表示パネルの製造方法を示す工程断面図（その1）である。

【図7】本実施形態に係る表示パネルの製造方法を示す工程断面図（その2）である。

【図8】本実施形態に係る表示パネルの製造方法を示す工程断面図（その3）である。

【図9】本実施形態に係る表示パネルの製造方法を示す工程断面図（その4）である。

【図10】本実施形態の作用効果を検証するために用いたテスト用の表示パネルを示す概略図である。

【図11】テスト用の表示パネルの各表示画素における発光状態を示す写真画像である。

#### 【発明を実施するための形態】

#### 【0016】

以下、本発明に係る表示装置及びその製造方法について、実施形態を示して詳しく説明する。ここで、以下に示す実施形態においては、表示画素を構成する発光素子（表示素子）として、少なくとも有機材料を塗布して形成される発光層を備えた有機EL素子を適用した場合について説明する。

## 【0017】

(表示パネル)

まず、本発明に係る表示装置に適用される表示パネル(有機EL表示パネル)及び表示画素について説明する。

図1は、本発明に係る表示装置に適用される表示パネルの一例を示す概略平面図であり、図2は、図1に示した表示パネルの画素配列状態(隔壁層や絶縁膜等の下層のパネル構造)の一例を示す概略平面図である。

## 【0018】

ここで、図1に示す平面図においては、説明の都合上、表示パネル(絶縁性基板)の一面側(有機EL素子の形成側)から見た、各表示画素(各色のサブ画素；以下便宜的に「色画素」と記す)に設けられる画素電極の配置と各表示画素(又は発光素子)の形成領域を画定する隔壁層の側壁や絶縁膜等に設けられた開口部との配置関係のみを示す。また、図2に示す平面図においては、画素電極の配置と各配線層の配設構造との関係のみを示し、各表示画素の発光素子(有機EL素子)を発光駆動するために各表示画素に設けられる画素駆動回路(後述する図3参照)内のトランジスタ等の表示を省略した。なお、図1、図2においては、画素電極及び各配線層、隔壁層や絶縁膜等の配置や被覆状態を明瞭にするために、便宜的にハッチングを施して示した。

10

## 【0019】

本発明に係る表示装置に適用可能な表示パネル10は、例えば図1、図2に示すように、ガラス基板等の絶縁性基板11の一面側に、表示領域20と、その周囲の周辺領域30とが設定されている。表示領域20には、複数の表示画素PIXが配列されている。表示画素PIXは、隣接して配列された赤(R)、緑(G)、青(B)の3色からなる一組の各色画素(各色のサブ画素)PXr、PXg、PXbにより形成されている。本実施形態においては、図1、図2に示すように、行方向(図面左右方向)に繰り返し複数配列されたRGB3色の色画素PXr、PXg、PXbを一組として一の表示画素PIXが形成されている。また、列方向(図面上下方向)には同一色の各色画素PXr、PXg、PXbが複数配列されている。

20

## 【0020】

ここで、各色画素PXr、PXg、又は、PXbの画素形成領域の画素電極14(EL素子形成領域)の周囲には、例えば図2に示すように、列方向(図面上下方向)にデータライン(信号ライン)Ldが配設され、また、当該データラインLdに直交する行方向(図面左右方向)に選択ラインLsが配設されている。また、選択ラインLsに並行する行方向には電源電圧ライン(例えばアノードライン)Laが配設されている。そして、詳しくは後述するが、表示パネル10には、絶縁性基板11上に2次元配列された複数の画素電極14に対して共通に対向するように、单一の電極層(べた電極)からなる対向電極(例えばカソード電極)16が形成されている。

30

## 【0021】

また、表示パネル10の表示領域20には、図1に示すように、少なくとも、行方向(図面左右方向)に配列された各色画素PXr、PXg、又は、PXb相互の境界領域を含む領域に、例えば列方向(図面上下方向)に延在する隔壁層17が複数条設けられている。また、列方向(図面上下方向)に配列された各色画素PXr、PXg、又は、PXb相互の境界領域を含む領域には絶縁膜13が露出するように設けられている。これらの絶縁膜13及び隔壁層17により取り囲まれ、画素電極(例えばアノード電極)14が露出する領域が、各色画素PXr、PXg、又は、PXbの発光素子(有機EL素子；表示素子)を形成するためのEL素子形成領域として画定される(後述する図4、図5参照)。そして、このEL素子形成領域、及び、その周囲の境界領域の絶縁膜13及び隔壁層17を含む領域が、各色画素PXr、PXg、又は、PXbの画素形成領域として画定される(後述する図4、図5参照)。

40

## 【0022】

一方、表示パネル10の周辺領域30には、所定の位置に、図示を省略したカソードコ

50

ンタクト電極やカソードコンタクト電極に接続された外部接続端子が配置されている。カソードコンタクト電極は、有機EL素子OELのカソード電極となる対向電極に直接接続されており、図示しない外部回路に接続されたフィルム配線基板の配線と接続された外部接続端子を介して所定の電圧（カソード電圧）をカソード電極に供給する。外部接続端子は、表示パネル外部のフレキシブル基板や駆動用のドライバIC等に電気的に接続される。

#### 【0023】

（表示画素）

図3は、本実施形態に係る表示パネルに2次元配列される各表示画素（発光素子及び画素駆動回路）の回路構成例を示す等価回路図である。10

表示画素PIXの各色画素PXr、PXg、PXbは、図3に示すように、画素駆動回路DCと有機EL素子（発光素子；表示素子）OELとを備えている。画素駆動回路DCは、1乃至複数のトランジスタ（例えばアモルファスシリコン薄膜トランジスタ等；機能素子）を備えた回路構成を有している。また、有機EL素子OELは、画素駆動回路DCにより制御される発光駆動電流が、上記画素電極14に供給されることにより発光動作する。

#### 【0024】

画素駆動回路DCは、具体的には、例えば図3に示すように、トランジスタ（選択トランジスタ）Tr11とトランジスタ（発光駆動トランジスタ）Tr12とキャパシタCsとを備えている。トランジスタTr11は、ゲート端子が選択ラインLsに、ドレイン端子が表示パネル10の列方向に配設されたデータラインLdに、ソース端子が接点N11に各々接続されている。トランジスタTr12は、ゲート端子が接点N11に、ドレイン端子が電源電圧ラインLaに、ソース端子が接点N12に各々接続されている。キャパシタCsは、トランジスタTr12のゲート端子（接点N11）及びソース端子（接点N12）間に接続されている。20

#### 【0025】

ここでは、トランジスタTr11、Tr12は、いずれもnチャネル型の薄膜トランジスタ（電界効果型トランジスタ）が適用されている。トランジスタTr11、Tr12がpチャネル型であれば、ソース端子及びドレイン端子が互いに逆になる。また、キャパシタCsは、トランジスタTr12のゲート-ソース間に形成される寄生容量、又は、該ゲート-ソース間に付加的に設けられた補助容量、もしくは、これらの寄生容量と補助容量からなる容量成分である。30

#### 【0026】

また、有機EL素子OELは、アノード端子（アノード電極となる画素電極14）が上記画素駆動回路DCの接点N12に接続され、カソード端子（カソード電極となる対向電極16）が上述したコンタクト電極及び外部接続端子を介して、例えば所定の低電位電源に直接又は間接的に接続される。したがって、カソード電極となる対向電極16を、絶縁性基板11上に2次元配列された複数の画素電極14に対して、共通に対向する单一の電極層（ベた電極）により構成することにより、全ての表示画素PIX（有機EL素子OEL）に対して、所定の低電圧（基準電圧Vss；例えば接地電位Vgnd）が共通に印加される。40

#### 【0027】

なお、図3に示した表示画素PIX（画素駆動回路DC及び有機EL素子OEL）において、選択ラインLsは、図示を省略した外部接続端子を介して選択ドライバに接続され、所定のタイミングで表示パネル10の行方向に配列された複数の表示画素PIX（色画素PXr、PXg、PXb）を選択状態に設定するための選択電圧Vselが印加される。また、データラインLdは、図示を省略した外部接続端子を介してデータドライバに接続され、上記表示画素PIXの選択状態に同期するタイミングで表示データに応じた階調信号（データ電圧）Vpixが印加される。

#### 【0028】

10

20

30

40

50

また、電源電圧ライン L a は、外部接続端子を介して、例えば所定の高電位電源に直接又は間接的に接続され、各表示画素 P IX (色画素 P X r、P X g、P X b) に設けられる有機 E L 素子 O E L の画素電極 (例えばアノード電極) 1 4 に、表示データに応じた発光駆動電流を流すために、有機 E L 素子 O E L の対向電極 1 6 に印加される基準電圧 V ss より電位の高い、所定の高電圧 (供給電圧 V dd) が印加されている。

#### 【0029】

すなわち、各表示画素 P IX において、直列に接続されたトランジスタ T r 1 2 と有機 E L 素子 O E L の組の両端 (トランジスタ T r 1 2 のドレイン端子と有機 E L 素子 O E L のカソード端子) にそれぞれ供給電圧 V dd と基準電圧 V ss を印加して有機 E L 素子 O E L に順バイアスを付与して有機 E L 素子 O E L が発光できる状態にし、さらに、階調信号 V pix に応じて流れる発光駆動電流の電流値を画素駆動回路 D C により制御している。10

#### 【0030】

##### (表示画素の発光動作)

そして、このような回路構成を有する表示画素 P IX における駆動制御動作は、まず、図示を省略した選択ドライバから選択ライン L s に対して、所定の選択期間に、選択レベル (オンレベル；例えばハイレベル) の選択電圧 S sel を印加することにより、トランジスタ T r 1 1 がオン動作して選択状態に設定される。このタイミングに同期して、図示を省略したデータドライバから表示データに応じた電圧値を有する階調信号 V pix をデータライン L d に印加するように制御する。これにより、トランジスタ T r 1 1 を介して、階調信号 V pix に応じた電位が接点 N 1 1 (すなわち、トランジスタ T r 1 2 のゲート端子) に印加される。20

#### 【0031】

図 3 に示した回路構成を有する画素駆動回路 D C においては、トランジスタ T r 1 2 のドレイン - ソース間電流 (すなわち、有機 E L 素子 O E L に流れる発光駆動電流) の電流値は、ドレイン - ソース間の電位差及びゲート - ソース間の電位差によって決定される。ここで、トランジスタ T r 1 2 のドレイン端子 (ドレイン電極) に印加される供給電圧 V dd と、有機 E L 素子 O E L のカソード端子 (カソード電極) に印加される基準電圧 V ss は固定値であるので、トランジスタ T r 1 2 のドレイン - ソース間の電位差は、供給電圧 V dd と基準電圧 V ss によって予め固定されている。そして、トランジスタ T r 1 2 のゲート - ソース間の電位差は、階調信号 V pix の電位によって一義的に決定されるので、トランジスタ T r 1 2 のドレイン - ソース間に流れる電流の電流値は、階調信号 V pix によって制御することができる。30

#### 【0032】

このように、トランジスタ T r 1 2 が接点 N 1 1 の電位に応じた導通状態 (すなわち、階調信号 V pix に応じた導通状態) でオン動作して、高電位側の供給電圧 V dd からトランジスタ T r 1 2 及び有機 E L 素子 O E L を介して低電位側の基準電圧 V ss (接地電位 V gnd) に、所定の電流値を有する発光駆動電流が流れるので、有機 E L 素子 O E L が階調信号 V pix (すなわち表示データ) に応じた輝度階調で発光動作する。また、このとき、接点 N 1 1 に印加された階調信号 V pix に基づいて、トランジスタ T r 1 2 のゲート - ソース間のキャパシタ C s に電荷が蓄積 (充電) される。40

#### 【0033】

次いで、上記選択期間終了後の非選択期間において、選択ライン L s に非選択レベル (オフレベル；例えばローレベル) の選択電圧 S sel を印加することにより、表示画素 P IX のトランジスタ T r 1 1 がオフ動作して非選択状態に設定され、データライン L d と画素駆動回路 D C とが電気的に遮断される。このとき、上記キャパシタ C s に蓄積された電荷が保持されることにより、トランジスタ T r 1 2 のゲート端子に階調信号 V pix に相当する電圧が保持された (すなわち、ゲート - ソース間の電位差が保持された) 状態となる。

#### 【0034】

したがって、上記選択状態における発光動作と同様に、供給電圧 V dd からトランジスタ

10

20

30

40

50

T r 1 2 を介して、有機 E L 素子 O E L に発光動作状態と同程度の電流値の発光駆動電流が流れ、発光動作状態が継続される。この発光動作状態は、次の階調信号 V pix が印加される（書き込まれる）まで、例えば、1 フレーム期間継続するように制御される。そして、このような駆動制御動作を、表示パネル 1 0 に 2 次元配列された全ての表示画素 P I X ( 各色画素 P X r 、 P X g 、 P X b ) について、例えば各行ごとに順次実行することにより、所望の画像情報を表示する画像表示動作を実行することができる。

#### 【 0 0 3 5 】

なお、図 3においては、表示画素 P I X に設けられる画素駆動回路 D C として、表示データに応じて各表示画素 P I X ( 具体的には、画素駆動回路 D C のトランジスタ T r 1 2 のゲート端子 ; 接点 N 1 1 ) に書き込む階調信号 V pix の電圧値を調整 ( 指定 ) することにより、有機 E L 素子 O E L に流す発光駆動電流の電流値を制御して、所望の輝度階調で発光動作させる電圧指定型の階調制御方式の回路構成を示した。本発明は、これに限定されるものではなく、表示データに応じて各表示画素 P I X に書き込む電流の電流値を調整 ( 指定 ) することにより、有機 E L 素子 O E L に流す発光駆動電流の電流値を制御して、所望の輝度階調で発光動作させる電流指定型の階調制御方式の回路構成を有するものであってもよい。10

#### 【 0 0 3 6 】

##### ( 表示画素のデバイス構造 )

次いで、上述したような回路構成を有する表示画素 ( 画素駆動回路及び有機 E L 素子 ) の具体的なデバイス構造 ( 平面レイアウト及び断面構造 ) について説明する。ここでは、有機 E L 層において発光した光を、絶縁性基板を介して視野側 ( 絶縁性基板の他面側 ) に射出するボトムエミッション型の発光構造を有する有機 E L 表示パネルについて示す。20

#### 【 0 0 3 7 】

図 4 は、本実施形態に適用可能な表示画素の一例を示す平面レイアウト図である。ここでは、図 1 、図 2 に示した表示画素 P I X の赤 ( R ) 、緑 ( G ) 、青 ( B ) の各色画素 P X r 、 P X g 、 P X b のうちの、特定の一の色画素の平面レイアウトを示す。なお、図 4 においては、図 3 に示した画素駆動回路 D C の各トランジスタ及び配線等が形成された層を中心示し、各トランジスタの電極及び各配線層、画素電極の露出領域を明瞭にするために、便宜的にハッチングを施して示した。30

#### 【 0 0 3 8 】

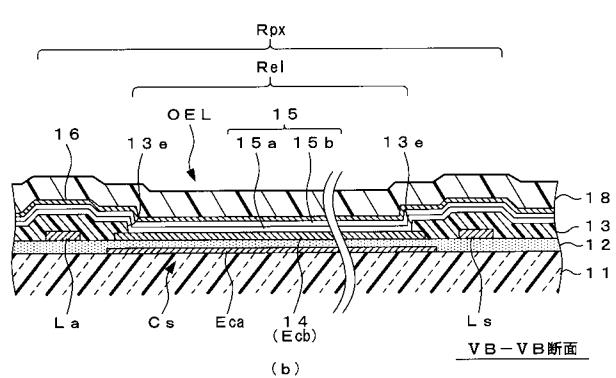

また、図 5 は、本実施形態に係る表示パネルの要部断面図である。ここで、図 5 ( a ) 及び図 5 ( b ) は、各々、図 4 に示した平面レイアウトを有する表示画素における V A - V A 線 ( 本明細書においては図 4 中に示したローマ数字の「 5 」に対応する記号として便宜的に「 V 」を用いる。以下同じ ) 、及び、 V B - V B 線に沿った断面を示す概略断面図である。40

#### 【 0 0 3 9 】

図 3 に示した表示画素 P I X を形成する各色画素 P X r 、 P X g 、 P X b は、具体的には、図 4 に示すように、絶縁性基板 1 1 の一面側に設定された画素形成領域 R px ごとに設けられている。この画素形成領域 R px には、少なくとも、各色画素 P X r 、 P X g 、 P X b の有機 E L 素子 O E L の形成領域 ( E L 素子形成領域 ; 詳しくは後述する ) R e l と、各色画素 P X r 、 P X g 、 P X b 間の境界領域と、が設定されている。40

#### 【 0 0 4 0 】

画素形成領域 R px の図面上方及び下方の縁辺領域には、各々、行方向 ( 図 4 の左右方向 ) に延在するように選択ライン L s 及び電源電圧ライン L a が配設されている。一方、画素形成領域 R px の図面右方の縁辺領域には、上記の選択ライン L s 及び電源電圧ライン L a に直交するように、列方向 ( 図 4 の上下方向 ) に延在するようにデータライン L d が配設されている。

#### 【 0 0 4 1 】

また、上記画素形成領域 R px の左右側の縁辺領域に設定される境界領域には、左右方向に隣接して配列される色画素にまたがって、図 4 、図 5 ( a ) に示すように、列方向に延

在するように隔壁層 17 が配設されている。一方、画素形成領域 Rpx の上下側の縁辺領域に設定される境界領域には、上下方向に隣接して配設される色画素にまたがって、図 4、図 5 ( b ) に示すように、絶縁膜 13 が露出している。そして、隔壁層 17 の側壁 17e と絶縁膜 13 の開口部 13e により囲まれ、画素電極 14 が露出した領域 ( 図 4 中、便宜的にハッチングを施して示す ) が、EL 素子形成領域 Rel として画定されている。

#### 【 0042 】

ここで、データライン Ld は、例えば図 4、図 5 ( a )、( b ) に示すように、選択ライン Ls 及び電源電圧ライン La よりも下層側 ( 絶縁性基板 11 側 ) に設けられている。データライン Ld は、トランジスタ Tr11、Tr12 のゲート電極 Tr11g、Tr12g を形成するためのゲートメタル層をパターニングすることによって、当該ゲート電極と同じ工程で形成される。データライン Ld は、図 4 に示すように、その上に被覆成膜されたゲート絶縁膜 12 に設けられたコンタクトホール CH1 を介して、トランジスタ Tr11 のドレイン電極 Tr11d に接続されている。このように、データライン Ld は、対向電極 16 との間に絶縁膜 13 及び隔壁層 17 に加えてゲート絶縁膜 12 が介在しているため、寄生容量を低減でき、データライン Ld に供給される信号の遅延を抑制できる。

10

#### 【 0043 】

また、選択ライン Ls 及び電源電圧ライン La は、トランジスタ Tr11 及び Tr12 のソース電極 Tr11s、Tr12s、ドレイン電極 Tr11d、Tr12d を形成するためのソース、ドレインメタル層をパターニングすることによって、当該ソース電極、ドレイン電極と同じ工程で形成される。図 4 に示すように、選択ライン Ls は、下層のゲート絶縁膜 12 に設けられたコンタクトホール CH2 を介して、トランジスタ Tr11 のゲート電極 Tr11g に接続されている。また、電源電圧ライン La は、トランジスタ Tr12 のドレイン電極 Tr12d と一体的に形成されている。

20

#### 【 0044 】

ここで、選択ライン Ls 及び電源電圧ライン La は、図示を省略したが、例えば下層配線と上層配線からなる積層配線構造を有するものであってもよい。下層配線は、例えばクロム ( Cr ) やチタン ( Ti ) 等のマイグレーションを低減するための遷移金属層と、当該遷移金属層の上に設けられているアルミニウム単体やアルミニウム合金等の配線抵抗を低減するための低抵抗金属層と、の積層構造を適用することができる。また、上層配線は、アルミニウム単体やアルミニウム合金等の配線抵抗を低減するための低抵抗金属の単層や、クロム ( Cr ) やチタン ( Ti ) 等のマイグレーションを低減するための遷移金属層上に上記低抵抗金属層を設けた積層構造を適用することができる。

30

#### 【 0045 】

また、図 3 に示した画素駆動回路 DC のトランジスタ Tr11 及び Tr12 は、具体的には、図 4 に示すように、データライン Ld に沿って列方向に延在するように配置されている。すなわち、トランジスタ Tr11、Tr12 のチャネルの幅方向が、データライン Ld に並行に設定されている。

#### 【 0046 】

ここで、各トランジスタ Tr11、Tr12 は、周知の電界効果型の薄膜トランジスタ構造を有している。すなわち、トランジスタ Tr11、Tr12 は、図 4、図 5 ( a ) に示すように、各々、ゲート電極 Tr11g、Tr12g と、ゲート絶縁膜 12 を介して各ゲート電極 Tr11g、Tr12g に対応する領域に形成された半導体層 SMC と、該半導体層 SMC の両端部に延在するように形成されたソース電極 Tr11s、Tr12s 及びドレイン電極 Tr11d、Tr12d と、を有している。

40

#### 【 0047 】

なお、図 5 ( a ) に示すように、各トランジスタ Tr11、Tr12 のソース電極 Tr11s、Tr12s とドレイン電極 Tr11d、Tr12d が対向する半導体層 SMC 上には、チャネル保護層 BL が形成されている。チャネル保護層 BL は、酸化シリコン又は窒化シリコン等により形成され、半導体層 SMC へのエッチングダメージを防止する機能を有している。また、ソース電極 Tr11s、Tr12s 及びドレイン電極 Tr11d、

50

T<sub>r</sub>12dと半導体層SMCとの間には、不純物層OHMが形成されている。不純物層OHMは、n型の不純物を含むアモルファスシリコンからなるn<sup>+</sup>シリコン層等により形成され、半導体層SMCとソース電極T<sub>r</sub>11s、T<sub>r</sub>12s及びドレイン電極T<sub>r</sub>11d、T<sub>r</sub>12dとのオーミック接続を実現する機能を有している。

#### 【0048】

そして、図3に示した画素駆動回路DCの回路構成に対応するように、トランジスタT<sub>r</sub>11は、図4に示すように、ゲート電極T<sub>r</sub>11gがゲート絶縁膜12に設けられたコンタクトホールCH2を介して選択ラインLsに接続されている。また、トランジスタT<sub>r</sub>11のドレイン電極T<sub>r</sub>11dは、ゲート絶縁膜12に設けられたコンタクトホールCH1を介してデータラインLdに接続されている。また、トランジスタT<sub>r</sub>11のソース電極T<sub>r</sub>11sは、ゲート絶縁膜12に設けられたコンタクトホールCH3を介してトランジスタT<sub>r</sub>12のゲート電極T<sub>r</sub>12gに接続されている。

#### 【0049】

また、トランジスタT<sub>r</sub>12は、図4に示すように、ゲート電極T<sub>r</sub>12gがゲート絶縁膜12に設けられたコンタクトホールCH3を介して上記トランジスタT<sub>r</sub>11のソース電極T<sub>r</sub>11sに接続されるとともに、キャパシタCsの下部電極Ecaに直接接続されている。また、トランジスタT<sub>r</sub>12のドレイン電極T<sub>r</sub>12dは、図4に示すように、電源電圧ラインLaと一緒に形成されている。また、トランジスタT<sub>r</sub>12のソース電極T<sub>r</sub>12sは、図4、図5(a)に示すように、後述するキャパシタCsの上部電極Ecbを兼用する、有機EL素子OELの画素電極14に直接接続されている。

#### 【0050】

キャパシタCsは、図4、図5(a)、(b)に示すように、下部電極Ecaと、該下部電極Ecaに対向する上部電極Ecbと、下部電極Eca及び上部電極Ecb間に介在するゲート絶縁膜12と、を有している。ここで、ゲート絶縁膜12は、キャパシタCsの誘電体層として兼用されている。また、上部電極Ecbは、後述する有機EL素子OELの画素電極14が兼用されている。すなわち、キャパシタCsは、有機EL素子OELの下層側(絶縁性基板11側)に設けられている。

#### 【0051】

有機EL素子OELは、図4、図5(a)、(b)に示すように、画素電極(例えばアノード電極)14と、有機EL層(発光機能層)15と、対向電極(例えばカソード電極)16と、を順次積層した素子構造を有している。画素電極14は、上記トランジスタT<sub>r</sub>11、T<sub>r</sub>12のゲート絶縁膜12上に設けられ、上述したように、キャパシタCsの上部電極Ecbとして兼用されている。また、画素電極14は、トランジスタT<sub>r</sub>12のソース電極T<sub>r</sub>12sに直接接続されて、画素駆動回路DCから所定の発光駆動電流が供給される。

#### 【0052】

有機EL層15は、少なくとも、絶縁性基板11上に形成された絶縁膜13の開口部13e及び隔壁層17の側壁17eにより画定されたEL素子形成領域Relに露出する画素電極14上に形成される。有機EL層15は、例えば正孔注入層(又は、正孔注入層を含む正孔輸送層；担体輸送層)15a及び電子輸送性発光層15b(担体輸送層)から形成され、これら担体輸送層のうち、発光層として機能する層が有機材料で形成されているものを指す。

#### 【0053】

本実施形態においては、図5(a)、(b)に示すように、有機EL層15のうち、正孔注入層15aが各表示画素PIXのEL素子形成領域Relだけでなく、当該EL素子形成領域Relを画定する絶縁膜13及び隔壁層17上にも設けられている。ここで、正孔注入層15aは、例えば酸化モリブデン等の遷移金属の酸化物を、蒸着法やスパッタリング法を用いて成膜することにより形成される。

#### 【0054】

また、電子輸送性発光層15bは、各表示画素PIXのEL素子形成領域Relだけでな

10

20

30

40

50

く、当該EL素子形成領域ReIを画定する絶縁膜13上にも設けられている。すなわち、図1に示すように、隣り合う隔壁層17により画定される、表示パネル10の列方向に配列された同一色の表示画素PIXのEL素子形成領域ReIを含む領域に対して、電子輸送性発光材料を含有する有機化合物含有液を、インクジェット法等の印刷法を用いて塗布することにより成膜される。なお、有機EL層15の成膜方法については、後述する製造方法において詳しく説明する。

#### 【0055】

対向電極16は、絶縁性基板11上に2次元配列された各表示画素PIXの画素電極14に対して、共通に対向するように設けられている。対向電極16は、例えば絶縁性基板11の表示領域20に対応するように、単一の電極層（べた電極）により形成されている。また、対向電極16は、各表示画素PIXのEL素子形成領域ReIだけでなく、当該EL素子形成領域ReIを画定する絶縁膜13及び隔壁層17上にも延在するように設けられている。さらに、対向電極16は、表示領域20外の周辺領域30にまで延在するように設けられ、周辺領域30に配置された図示を省略したコンタクト電極に電気的に接続されている。これにより、対向電極16には、コンタクト電極及び外部接続端子を通じて、所定の基準電圧Vss（カソード電圧；例えば接地電位Vgnd）が印加される。

10

#### 【0056】

ここで、本実施形態に係る表示パネル10においては、ボトムエミッショントラニジスタ型の発光構造を有しているので、画素電極14は、錫ドープ酸化インジウム（Indium Thin Oxide；ITO）等の光透過特性を有する（透明な）電極材料により形成されている。一方、対向電極16は、アルミニウム（Al）単体やアルミニウム合金等の光反射特性を有する電極材料を含んでいる。

20

#### 【0057】

隔壁層17は、図1に示すように、表示領域20の内部においては、少なくとも、表示パネル10に2次元配列される複数の表示画素PIX（各色画素PXr、PXg、PXb）相互の境界領域のうち、表示パネル10（絶縁性基板11）の列方向に延在するように、縞状に複数条配設されている。また、隔壁層17は、表示領域20の周縁部においては、当該周縁部に沿って、表示パネル10の行方向及び列方向に延在するように配設されている。ここで、隔壁層17は、例えばドライエッチング法を用いてパターニングが可能な絶縁材料、例えば非感光性の絶縁材料であるフッ素化合物系樹脂材料により形成されている。

30

#### 【0058】

一方、絶縁膜13は、図1、図5に示すように、表示領域20においては、表示画素PIX（各色画素PXr、PXg、PXb）相互の境界領域を被覆するように、絶縁性基板11上に設けられている。ここで、上記トランジスタTr11及びTr12は、絶縁膜13及び上記隔壁層17に完全に被覆されて露出しないように表示パネル10の各画素形成領域Rpxの端部に配置されている。

#### 【0059】

また、絶縁膜13には、図1、図4、図5（b）に示すように、各色画素のEL素子形成領域ReI（すなわち、各画素電極14の露出領域）の、列方向の対向する二辺（図1、図4の上下側の二辺であって、図5（b）では左右側の二辺に相当する）を画定するための開口部13eが設けられている。また、図1、図4、図5（a）に示すように、隣り合って配設された隔壁層17の側壁17eにより、各画素電極14の露出領域の、行方向の対向する二辺（図1、図4の左右の二辺であって、図5（a）の左右の二辺に相当する）が画定される。これにより、絶縁膜13及び隔壁層17により画定された領域（画素電極14の露出領域；図4中、便宜的にハッチングを施して示す）が表示画素PIXのEL素子形成領域ReIとして画定される。そして、このEL素子形成領域ReIを含む領域が、有機EL層15のうち、少なくとも電子輸送性発光層15bを形成する際の有機化合物材料の塗布領域として規定される。

40

#### 【0060】

50

そして、上述した画素駆動回路 D C、有機 E L 素子 O E L（画素電極 1 4、有機 E L 層 1 5、対向電極 1 6）、絶縁膜 1 3 及び隔壁層 1 7 が形成された絶縁性基板 1 1 の一面側には封止層 1 8 が形成されて、表示パネル 1 0 が封止されている。ここで、封止層 1 8 に加えて、又は、封止層 1 8 に代えて、図示を省略したメタルキャップ（封止蓋）やガラス等の封止基板を貼り合わせた封止構造を適用することもできる。

#### 【0061】

なお、上述したデバイス構造においては、データライン L d がゲートメタル層をパターニングすることによって形成され、選択ライン L s がソース、ドレインメタル層をパターニングすることによって形成され、これらのデータライン L d 及び選択ライン L s が、各々、コンタクトホール C H 1、C H 2 を介してトランジスタ T r 1 1 のドレイン電極 T r 1 1 d やゲート電極 T r 1 1 g に接続する場合について説明した。本発明はこれに限定されるものではなく、データライン L d がゲートメタル層の代わりにソース、ドレインメタル層をパターニングすることによって形成され、選択ライン L s がドレインメタル層の代わりにゲートメタル層をパターニングすることによって形成されることでコンタクトホール C H 1、C H 2 を介すことなく、トランジスタ T r 1 1 のドレイン電極 T r 1 1 d やゲート電極 T r 1 1 g と一体的に形成されるようにしてもよい。ただし、このとき電源電圧ライン L a をゲートメタル層をパターニングすることによって形成される必要があるので、電源電圧ライン L a とトランジスタ T r 1 2 のドレイン電極 T r 1 2 dとの間のゲート絶縁膜 1 2 にコンタクトホールを形成する必要がある。

#### 【0062】

そして、このようなデバイス構造を有する表示画素 P I Xにおいて、データライン L d を介して供給される表示データに応じた階調信号 V pixに基づいて、所定の電流値の発光駆動電流がトランジスタ T r 1 2 のソース - ドレイン間に流れ、画素電極 1 4 に供給されることにより、有機 E L 素子 O E L が上記表示データに応じた所望の輝度階調で発光動作する。

#### 【0063】

このとき、表示パネル 1 0 の画素電極 1 4 が光透過特性を有し、対向電極 1 6 が光反射特性を有することにより（すなわち、有機 E L 素子 O E L がボトムエミッション型であることにより）、各表示画素 P I X（各色画素 P X r、P X g、P X b）の有機 E L 層 1 5において発光した光は、光透過特性を有する画素電極 1 4 を介して直接、あるいは、光反射特性を有する対向電極 1 6 で反射して、絶縁性基板 1 1 を透過し、視野側である絶縁性基板 1 1 の他面側（図 5（a）、（b）の図面下方）に出射される。

#### 【0064】

なお、本実施形態においては、隔壁層 1 7 を、表示領域 2 0 内の列方向（図 1 の上下方向）に延在するように縞状に配設したパネル構造を示したが、本発明はこれに限定されるものではない。例えば、後述する作用効果の検証（図 10 参照）において模式的に示すように、行、列方向に配列された各表示画素 P I X の画素電極 1 4 のみが露出するように、各表示画素 P I X の上下左右の四方の境界領域に隔壁層 1 7 が格子状に形成されたパネル構造を有するものであってもよい。

#### 【0065】

##### （表示装置の製造方法）

次に、本実施形態に係る表示パネルの製造方法について説明する。

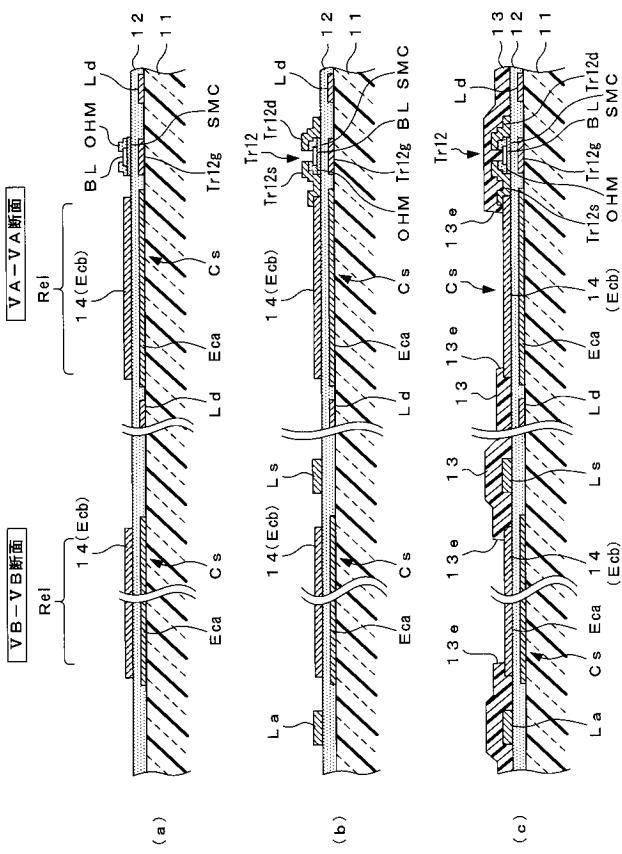

図 6 乃至図 9 は、本実施形態に係る表示パネルの製造方法を示す工程断面図である。ここでは、説明の都合上、便宜的に、図 5（a）に示した図 4 の V A - V A 線に沿った表示画素の断面を、図 6 乃至図 9 の各図の右側に配置し、図 5（b）に示した図 4 の V B - V B 線に沿った表示画素の断面を、図 6 乃至図 9 の各図の左側に配置して示す。

#### 【0066】

上述した表示装置（表示パネル）の製造方法は、まず、図 6（a）～図 7（b）に示すように、ガラス基板等の絶縁性基板 1 1 の一面側に、上述した画素駆動回路 D C（図 3、図 4 参照）を構成するトランジスタ T r 1 1、T r 1 2、キャパシタ C s 等の機能素子や

10

20

30

40

50

、データライン L d 、選択ライン L s 、電源電圧ライン L a 等の配線層を形成する。

#### 【0067】

具体的には、まず、図 6 ( a ) に示すように、透明な絶縁性基板 11 の一面側 ( 図面上側 ) に設定された各表示画素 PIX ( 各色画素 PXr 、 PXg 、 PXb ) の画素形成領域 Rpx ( 図 4 、図 5 参照 ) 内の EL 素子形成領域 Rel に対応する領域ごとに、キャパシタ Cs の下部電極 Eca を形成する。ここで、下部電極 Eca は、 ITO や亜鉛ドープ酸化インジウム ( Indium Zinc Oxide ) 等の透明な ( 光透過特性を有する ) 電極材料膜を堆積後フォトリソグラフィによってパターニングすることによって形成される。このため、有機 EL 素子 OEL が発する光は上部電極 Ecb 、ゲート絶縁膜 12 、下部電極 Eca を順次透過して、絶縁性基板 11 の下面から出射される。

10

#### 【0068】

次いで、図 6 ( b ) に示すように、絶縁性基板 11 の一面側にゲートメタル層を形成し、該ゲートメタル層をフォトリソグラフィ法を用いてパターニングすることにより、上記 EL 素子形成領域 Rel 以外の領域に、ゲート電極 Tr11g 、 Tr12g 及びデータライン Ld を同時に形成する。このとき、図 4 に示すように、ゲート電極 Tr12g の一端が下部電極 Eca 上に延在するようにパターニング形成されて、ゲート電極 Tr12g と下部電極 Eca が電気的に接続される。

#### 【0069】

次いで、絶縁性基板 11 の全域に窒化シリコン等からなるゲート絶縁膜 12 、真性アモルファスシリコン等からなる半導体膜 SMCx 、窒化シリコン等からなる絶縁膜を連続的に被覆形成する。その後、図 6 ( c ) に示すように、上記窒化シリコン等の絶縁膜をフォトリソグラフィ法を用いてパターニングすることにより、半導体膜 SMCx 上のゲート電極 Tr11g 及び Tr12g に対応する領域に、チャネル保護層 BL を形成する。

20

#### 【0070】

次いで、 n 型アモルファスシリコン等からなる不純物層を絶縁性基板 11 の全域に堆積した後、フォトリソグラフィ法を用いて当該不純物層をパターニングし、続いて下層の半導体膜 SMCx をパターニングする。これにより、図 6 ( d ) に示すように、ゲート絶縁膜 12 上に、半導体層 SMC 、及び、当該半導体層 SMC の両端部にオーム接続のための不純物層 OHM を形成する。

#### 【0071】

次いで、 ITO や亜鉛ドープ酸化インジウム等の透明な ( 光透過特性を有する ) 電極材料膜を絶縁性基板 11 の全域に堆積した後、フォトリソグラフィ法を用いて当該電極材料膜をパターニングすることにより、図 7 ( a ) に示すように、各表示画素 PIX の EL 素子形成領域 Rel ごとのゲート絶縁膜 12 上に、図 4 に示すように、例えば矩形状の平面パターンを有する画素電極 14 を形成する ( 画素電極形成工程 ) 。これにより、ゲート絶縁膜 12 を介して、画素電極 14 と下部電極 Eca が対向して配置されたキャパシタ Cs が形成される ( キャパシタ形成工程 ) 。すなわち、画素電極 14 は、有機 EL 素子 OEL のアノード電極であるとともに、下部電極 Eca に対向する上部電極 Ecb として兼用され、また、ゲート絶縁膜 12 は、誘電体層として兼用される。

30

#### 【0072】

このように、キャパシタ Cs の上部電極 Ecb ( 画素電極 14 ) 及び下部電極 Eca が透明な電極材料により形成されていることにより、ボトムエミッション型の発光構造を有する表示パネルであっても、高い開口率を実現することができる。なお、上部電極 Ecb ( 画素電極 14 ) と下部電極 Eca の間に介在するゲート絶縁膜 12 の厚さは、トランジスタ Tr12 に大きな電流 ( 発光駆動電流 ) を流すためには、極力薄い方が良い。しかしながら、ゲート絶縁膜 12 が薄過ぎると、ゲート絶縁膜 12 の下層のデータライン Ld と、後述する上層の選択ライン Ls や電源電圧ライン La との交差部で上下ショートを起こす可能性が高くなり、製品歩留まりを低下させることになる。そのため、ゲート絶縁膜 12 の厚さはシリコン窒化膜換算で概ね数百 nm 程度に設定することが好ましい。

40

#### 【0073】

50

次いで、データライン L d 及びトランジスタ Tr 1 1、Tr 1 2 のゲート電極 Tr 1 1 g、Tr 1 2 g の所定の位置の上面が露出するように、図 4 に示すように、ゲート絶縁膜 1 2 にコンタクトホール CH 1、CH 2、CH 3 をそれぞれ形成する。

#### 【0074】

次いで、図 7 ( b ) に示すように、絶縁性基板 1 1 の一面側にソース、ドレインメタル層を形成し、該ソース、ドレインメタル層をフォトリソグラフィ法を用いてパターニングすることにより、トランジスタ Tr 1 1 及び Tr 1 2 の半導体層 SMC の両端部に、上記不純物層 OHM を介して延在するように、ソース電極 Tr 1 1 s、Tr 1 2 s 及びドレイン電極 Tr 1 1 d、Tr 1 2 d を形成するとともに、選択ライン L s 及び電源電圧ライン L a を同時に形成する。

10

#### 【0075】

このとき、図 4 に示すように、トランジスタ Tr 1 1 のドレイン電極 Tr 1 1 d は、ゲート絶縁膜 1 2 に形成されたコンタクトホール CH 1 を介して、下層のデータライン L d に電気的に接続される。また、トランジスタ Tr 1 1 のソース電極 Tr 1 1 s は、ゲート絶縁膜 1 2 に形成されたコンタクトホール CH 3 を介して、下層のトランジスタ Tr 1 1 のゲート電極 Tr 1 2 g に電気的に接続される。トランジスタ Tr 1 2 のソース電極 Tr 1 2 s は、その一端がゲート絶縁膜 1 2 上に形成された画素電極 1 4 上に延在するように形成されて、ソース電極 Tr 1 2 s と画素電極 1 4 が電気的に接続される。また、選択ライン L s は、ゲート絶縁膜 1 2 に形成されたコンタクトホール CH 2 を介して、下層のゲート電極 Tr 1 1 g に電気的に接続される。電源電圧ライン L a は、ソース電極 Tr 1 2 s と一体的に形成される。

20

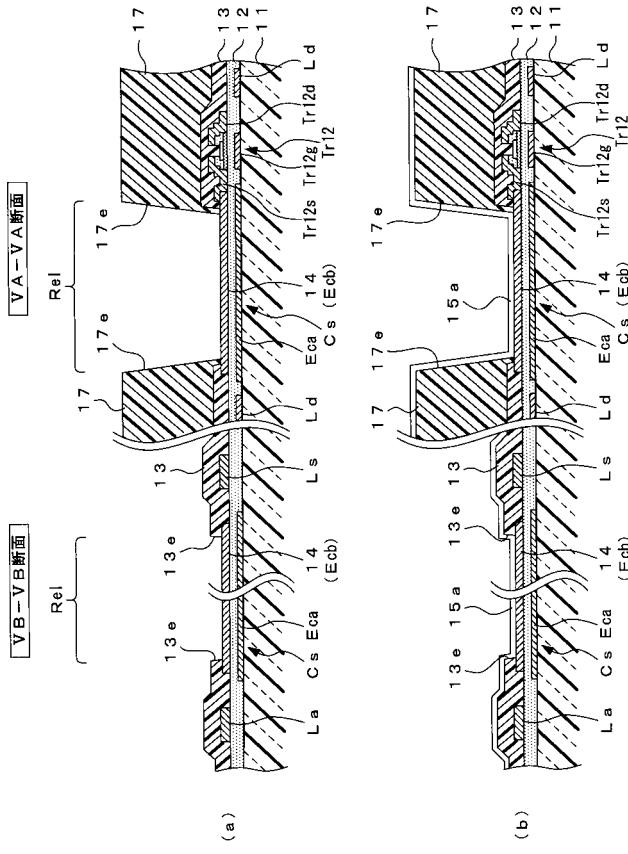

#### 【0076】

次いで、上記画素電極 1 4、トランジスタ Tr 1 1、Tr 1 2、選択ライン L s 及び電源電圧ライン L a を含む絶縁性基板 1 1 の一面側全域を被覆するように、窒化シリコンや酸化シリコン等の無機の絶縁性材料からなり、層間絶縁膜又は保護絶縁膜として機能する絶縁膜 1 3 を形成する。その後、当該絶縁膜 1 3 をパターニングして、図 1、図 7 ( c ) に示すように、各表示画素 PIX の画素電極 1 4 の上面が露出する開口部 1 3 e を形成する。ここで、上記トランジスタ Tr 1 1、Tr 1 2、選択ライン L s 及び電源電圧ライン L a は、絶縁膜 1 3 により完全に被覆される。

30

#### 【0077】

次いで、絶縁膜 1 3 が形成された絶縁性基板 1 1 上に、非感光性の樹脂材料を塗布して、例えば 1 ~ 5 μm の膜厚を有する樹脂層を形成した後、当該樹脂層をドライエッチング法を用いてパターニングすることにより、図 8 ( a ) に示すように、少なくとも、表示領域 2 0 において絶縁性基板 1 1 の一面側に突出するとともに、図 1、図 4 に示すように、列方向 ( 図 1 の上下方向 ) に延在する隔壁層 1 7 を形成する ( 隔壁層形成工程 ) 。ここで、隔壁層 1 7 は、表示領域 2 0 の内部においては、行方向 ( 図 1 の左右方向 ) に配列される隣接する表示画素 PIX 間の境界領域に形成された上記絶縁膜 1 3 を完全に被覆するように、列方向に縞状に形成されている。また、隔壁層 1 7 は、表示領域 2 0 の列方向に配列されて隣接する表示画素 PIX 間の境界領域には形成されておらず、当該領域では上記絶縁膜 1 3 が露出している。

40

#### 【0078】

これにより、各画素形成領域 Rpx において、絶縁膜 1 3 に形成された開口部 1 3 e の列方向 ( 図 4 の上下方向 ) の対向する端部と、隔壁層 1 7 の行方向 ( 図 4 の左右方向 ) の対向する側壁 1 7 e とに囲まれた領域、すなわち画素電極 1 4 の露出領域が E L 素子形成領域 Rel として画定される。

#### 【0079】

ここで、隔壁層 1 7 を形成する非感光性の樹脂材料としては、例えばフッ素系やポリイミド系の非感光性樹脂材料を適用することができる。具体的には、フッ素系の非感光性樹脂材料 ( フッ素化合物含有樹脂材料 ) としては、例えば旭硝子株式会社製のアモルファスフッ素樹脂材料「サイトップ ( 登録商標 ) 」等を良好に適用することができる。また、ポ

50

リイミド系の非感光性樹脂材料としては、例えば東レ株式会社製のポリイミドコーティング剤「セミコファイン（商品名）」等を良好に適用することができる。

#### 【0080】

次いで、絶縁性基板11を純水で洗浄した後、例えば酸素プラズマ処理又はUVオゾン処理等を施すことにより、各EL素子形成領域Relに露出する画素電極14の表面を洗浄する。その後、図8(b)に示すように、各表示画素PIXのEL素子形成領域Relを含む絶縁性基板11の一面側の全域に、真空蒸着法やスパッタリング法等を用いて、遷移金属の酸化物である、例えば酸化モリブデンからなる膜厚30nmの正孔注入層(又は、正孔注入層を含む正孔輸送層)15aを形成する。ここで、正孔注入層15aは、各表示画素PIXのEL素子形成領域Relだけでなく、当該EL素子形成領域Relを画定するための絶縁膜13や隔壁層17上にも形成される。これにより、正孔注入層15aをフォトマスクを用いることなく形成することができる。

10

#### 【0081】

次いで、少なくとも各表示画素PIXのEL素子形成領域Relに、インターレイヤ層材料を有機溶剤に溶解した材料溶液を、連続した液流として吐出するノズルプリンティング(又はノズルコート)法や不連続の液滴として吐出するインクジェット法等の印刷法を用いて塗布、成膜した後、窒素雰囲気中で加熱焼成して、図示を省略したインターレイヤ層を形成する。さらに、各色のEL素子形成領域Relの正孔注入層15a(詳しくは、図示を省略したインターレイヤ層)上に、赤、緑、青色のいずれかの発光色の電子輸送性発光材料を有機溶剤に溶解したELインクを、上記のような印刷法を用いて塗布、成膜した後、加熱乾燥させて、図9(a)に示すように、電子輸送性発光層(担体輸送層)15bを形成する。ここで、ノズルプリンティング(又はノズルコート)法の場合、電子輸送性発光層15bは、各表示画素PIXのEL素子形成領域Relだけでなく、表示パネル10の列方向(図1、図4の上下方向)に配列される同一色の表示画素PIXのEL素子形成領域Rel間の絶縁膜13上にも形成される。インクジェット法の場合、電子輸送性発光層15bは、各表示画素PIXのEL素子形成領域Relに選択的に形成され、EL素子形成領域Rel間の絶縁膜13上に形成されなくてもよい。

20

#### 【0082】

電子輸送性発光層15bは、具体的には、有機高分子系の電子輸送性発光材料(担体輸送性材料)を含む有機化合物含有液(有機溶液)として、例えばポリパラフェニレンビニレン系やポリフルオレン系等の共役二重結合ポリマーを含む赤(R)、緑(G)、青(B)色の発光材料を、適宜水系溶媒或いはテトラリン、テトラメチルベンゼン、メシチレン、キシリレン等の有機溶媒に溶解または分散した0.1wt%~5wt%の溶液を、上記正孔注入層15a(詳しくは、図示を省略したインターレイヤ層)上に塗布する。その後、窒素雰囲気中でホットプレートによる乾燥処理、あるいは、真空中でシーズヒータによる乾燥処理を行って、残留溶媒を除去することにより、正孔注入層15a(詳しくは、インターレイヤ層)上有機高分子系の電子輸送性発光材料を定着させて、担体輸送層であり発光層である電子輸送性発光層15bを形成する。

30

#### 【0083】

ここで、EL素子形成領域Relに形成された上記正孔注入層15aの表面は、インターレイヤ層材料、又は、電子輸送性発光材料を含む有機化合物含有液に対して親液性を有しているので、各EL素子形成領域Relに塗布された有機化合物含有液は、正孔注入層15a上に十分馴染んで広がる。一方、隔壁層17は、塗布される上記有機化合物含有液の量に対して十分高く設定されているので、隣接する表示画素PIXのEL素子形成領域Relへの有機化合物含有液の漏出や乗り越えを抑制することができる。

40

#### 【0084】

これにより、電子輸送性発光層15bの形成工程において、有機化合物含有液をノズルプリンティング法やインクジェット法を用いて塗布し、有機EL層15の発光層(電子輸送性発光層15b)を形成する場合であっても、表示パネル10の行方向(図1、図4の左右方向)に隣接して配置される、異なる色の表示画素PIXのEL素子形成領域Relへ

50

の有機化合物含有液の漏出や乗り越えを抑制することができ、隣接画素相互の混色を抑制して、赤、緑、青色の発光材料の塗り分けを良好に行うことができる。

このように、画素電極 14 上に正孔注入層 15a、インターレイヤ層（図示を省略）及び電子輸送性発光層 15b を順次積層形成することにより、図 9 (a) に示すように、有機 EL 層（発光機能層）15 が形成される（担体輸送層形成工程）。

#### 【0085】

次いで、図 9 (b) に示すように、上記隔壁層 17 及び有機 EL 層 15（正孔注入層 15a 及び電子輸送性発光層 15b）が形成された絶縁性基板 11 上に、光反射特性を有し、各 EL 素子形成領域 Rel の有機 EL 層 15 を介して各画素電極 14 に対向する、共通の対向電極（例えばカソード電極）16 を形成する（対向電極形成工程）。これにより、各表示画素 PIX の EL 素子形成領域 Rel に有機 EL 素子 OEL が形成される。

10

#### 【0086】

対向電極 16 は、具体的には、例えば真空蒸着法やスパッタリング法を用いて、1~10 nm 厚のカルシウム (Ca)、バリウム (Ba)、リチウム (Li)、インジウム (In) 等の仕事関数の低い電子注入層（カソード電極）と、この電子注入層上に 100 nm 以上の厚さのアルミニウム (Al)、クロム (Cr)、銀 (Ag)、パラジウム銀 (AgPd) の単体、又は、これらの合金からなる高仕事関数の薄膜（給電電極）、あるいは、ITO や亜鉛ドープ酸化インジウム等の透明電極膜等からなる給電電極と、を積層した電極構造を適用することができる。

20

#### 【0087】

次いで、上記対向電極 16 が形成された絶縁性基板 11 の一面側であって、カソードコントакт電極や外部接続端子を除く全域にシリコン酸化膜やシリコン窒化膜等からなる封止層 18 を CVD 法等を用いて形成する。これにより、図 5 (a)、(b) に示したような断面構造（ボトムエミッション型の発光構造）を有する表示パネル 10 が完成する。なお、上記封止層 18 に加えて、又は、封止層 18 に代えて、UV 硬化又は熱硬化接着剤を用いて、メタルキャップ（封止蓋）やガラス等の封止基板を、絶縁性基板 11 の一面側に接合して硬化させた保護構造を有するものであってもよい。

30

#### 【0088】

このように、本実施形態に係る表示装置においては、各表示画素 PIX の画素形成領域 Rpx 間に配設する隔壁層 17 として非感光性の樹脂材料（例えば、フッ素化合物含有樹脂材料）を用い、かつ、該隔壁層 17 により画定される画素形成領域 Rpx に設けられる有機 EL 層 15 を構成する正孔注入層 15a として遷移金属の酸化物（例えば、酸化モリブデン）を用いたことを特徴としている。

30

#### 【0089】

また、本実施形態に係る表示装置の製造方法においては、各表示画素 PIX の画素形成領域 Rpx 間に配設する隔壁層 17 を、非感光性の樹脂材料からなる樹脂層をドライエッチング法を用いてパターニングすることにより形成し、また、有機 EL 層 15 を構成する正孔注入層 15a を、遷移金属の酸化物を真空蒸着法やスパッタリング法を用いて成膜することにより形成することを特徴としている。

40

#### 【0090】

仮に、隔壁層 17 として感光性の樹脂材料を用いた場合、TMAH (tetramethyl ammonium hydroxide) 等の現像液によって感光性の樹脂材料をパターニングするが、このような現像液は、隔壁層の表面等に吸着されやすく残留しやすい。特に、アルカリ性を呈する TMAH が、隔壁層 17 や画素電極 14 の表面に残留してしまっている状態で、その隔壁層 17 や画素電極 14 上に酸化モリブデン層などの正孔注入層 15a を成膜した場合、その正孔注入層 15a が TMAH の作用により変質してしまうことがある。つまり、正孔注入層 15a を変質させてしまう TMAH は発光阻害要因となり、変質した正孔注入層 15a の正孔注入性が悪化してしまうことで、非発光領域を発生、成長してしまうことがある。

#### 【0091】

50

本実施形態では、非感光性の樹脂材料からなる隔壁層17を形成したので、隔壁層17や画素電極14の表面は現像液に曝されず、隔壁層17や画素電極14の表面が非発光領域を発生、成長するように変質しない。このため、正孔注入層15aとなる遷移金属の酸化物の正孔注入性が良好に維持され、表示画素にダークスポット（非発光領域）が発生する現象を抑制することができる。

#### 【0092】

##### (作用効果の検証)

次に、上述した特徴を有する表示装置及びその製造方法に特有の作用効果について詳しく説明する。

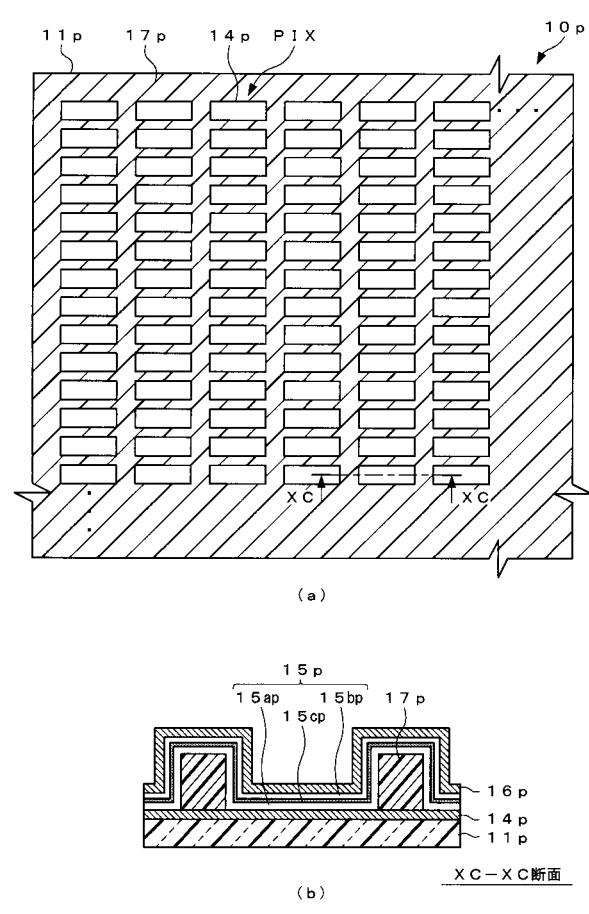

図10は、本実施形態の作用効果を検証するために用いたテスト用の表示パネルを示す概略図である。ここで、図10(a)はテスト用の表示パネルを示す概略平面図であり、図10(b)は、図10(a)に示した表示パネルにおけるXC-XC線（本明細書においては図10(a)中に示したローマ数字の「10」に対応する記号として便宜的に「X」を用いる。）に沿った断面を示す概略断面図である。また、上述した実施形態と同等の構成については、同等の符号を付して示す。

10

#### 【0093】

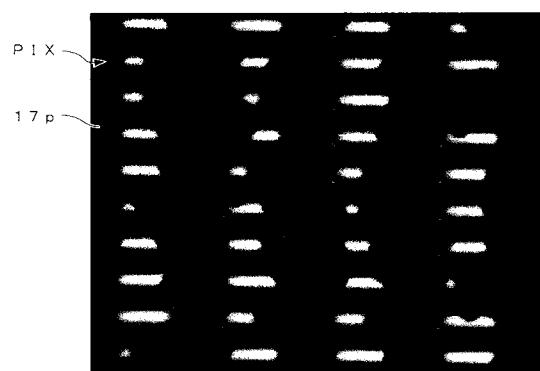

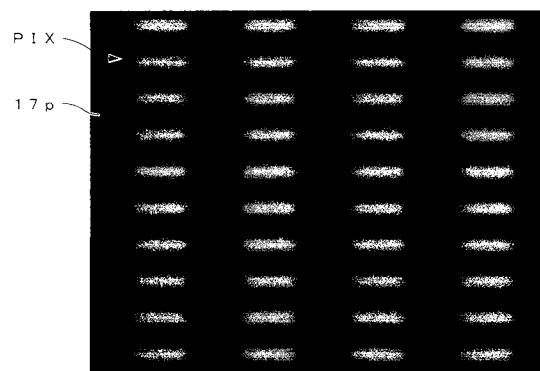

また、図11は、テスト用の表示パネルの各表示画素における発光状態を示す写真画像である。ここで、図11(a)は、比較対象に係る表示パネルにおける各表示画素の発光状態を示す写真画像であり、図11(b)は、本実施形態に基づく表示パネルにおける各表示画素の発光状態を示す写真画像である。図11(a)、(b)のいずれも、評価対象となる表示画素のうち、40画素分の発光状態を示す。

20

#### 【0094】

図10(a)に示すように、検証テスト用の表示パネル10pは、絶縁性基板11pの一面側に行、列方向に計588の表示画素PIXが配列され、各表示画素PIXの画素電極層14pが露出するように、格子状に開口部が形成された隔壁層17pが設けられている。ここで、隔壁層17pは、図10(b)に示すように、絶縁性基板11pの表面から連続的に突出するように形成されている。また、表示パネル10pにおいては、図1、図2に示した表示パネル10とは異なり、便宜的に、絶縁性基板11pの一面側の全域にITO等の透明電極膜からなる画素電極層14pが形成されている。また、上記の隔壁層17pにより画定されたEL素子形成領域（画素電極層14pの露出領域）を含む絶縁性基板11の一面側の全域には、正孔注入層15ap、インターレイヤ層15cp及び発光層15bpを順次積層した有機EL層15pが設けられ、さらに、該有機EL層15p上に対向電極16pが積層形成されている。

30

#### 【0095】

このようなパネル構造を有する検証テスト用の表示パネル10pにおいて、正孔注入層15apとして遷移金属の酸化物である酸化モリブデンを用い、かつ、隔壁層17pとして感光性の樹脂材料を用いた場合（以下、「比較対象に係る表示パネル」と記す）と、非感光性の樹脂材料を用いた場合（以下、「本実施形態に基づく表示パネル」と記す）について、表示画素PIXのダークスポットの発生状況について検証する。

40

#### 【0096】

ここで、比較対象に係る表示パネルにおいては、まず、絶縁性基板11の全域に透明な電極材料膜であるITO膜からなる画素電極層14pを形成した後、ポリイミド系のポジ型の感光性樹脂材料として、例えば東レ株式会社製のフォトニースDL-1000を絶縁性基板11に塗布して、1.5μmの膜厚を有する樹脂層を形成し、その後、当該樹脂層に対して、露光、現像液であるTMASH(tetramethyl ammonium hydroxide)による現像処理を施すことにより、図10(a)に示したように、各表示画素PIXの画素電極層14pが露出する開口部を有する隔壁層17pを形成した。

#### 【0097】

次いで、隔壁層17pが形成された絶縁性基板11pを純水を用いて洗浄した後、画素電極層14pの表面洗浄のため、以下に示すような処理条件でUVオゾン処理を2分間施

50

した。

<UVオゾン処理の処理条件>

- ・使用装置：UV洗浄機（オーク製作所製 HMW-615-N-47）

- ・ランプ出力：100W×7灯（有効照射エリア400mm）

- ・ランプ：低圧水銀灯（VUV-100/A-5.3U）

- ・照射距離：20mm

【0098】

上述したような基板の表面処理（UVオゾン処理）を行なった後、図10(b)に示したように、画素電極層14pが露出する開口部、及び、該開口部が形成された隔壁層17p上に、正孔注入層15apとして酸化モリブデンを真空蒸着法やスパッタリング法等を用いて30nm成膜した。その後、インターレイヤ層材料、及び、緑色の発光材料を有機溶剤に溶かしたELインクを、各々スピンドルコート法により塗布して、インターレイヤ層15cp及び発光層15bpを順次成膜した。さらに、当該絶縁性基板11p上に、真空蒸着法やスパッタリング法を用いてカソード電極及び給電電極からなる対向電極16pを形成した。

10

【0099】

このような比較対象に係る表示パネルを発光動作させた場合、図11(a)に示すように、各表示画素PIXの発光素子（有機EL素子）が形成されたEL素子形成領域内にダークスポット（非発光領域）が発生することが観測された。ここで、ダークスポットの評価は、表示パネルの封止状態の違いによる影響を考慮して、表示パネル10p（絶縁性基板11p）の外周部分に配列された表示画素PIXについては評価を行わず、表示パネル10pの略中央部に配列された100画素を対象にして行った。それによれば、比較対象に係る表示パネルにおいては、100画素中、87画素でダークスポットが発生していることが判明した。

20

【0100】

このようなダークスポットが発生する原因是、感光性樹脂をパターニングして隔壁層を形成する露光、現像処理において、現像液を用いて露光されていない感光性樹脂を除去する際に、画素電極の表面に感光性樹脂材料が残渣として残留することに起因するものと考えられる。発明者らの検証によれば、この残渣は、上述したように隔壁層のパターニング後にUVオゾン処理による基板表面の洗浄処理を行っても十分に除去することができず、画素電極層の表面に残留することが判明した。これらのことから、発明者らは、この感光性樹脂材料の残渣がダークスポットの発生源になっているものと推測した。そこで、本実施形態に適用される表示パネルにおいては、隔壁層として非感光性の樹脂材料を用いることにより、現像処理を行うことなく、隔壁層をパターニング形成することができるパネル構造及び製造方法を適用している。

30

【0101】

すなわち、本実施形態に基づく表示パネルにおいては、上述した実施形態に示したように、感光性樹脂材料に代えて、非感光性の樹脂材料であるフッ素化合物含有樹脂を隔壁層17pに用いたパネル構造及び製造方法を採用している。具体的には、ITO膜からなる画素電極層14pが形成された絶縁性基板11p上に、フッ素系の非感光性樹脂材料（フッ素化合物含有樹脂材料）として、例えば旭硝子株式会社製のサイトップを塗布して、0.9μmの膜厚を有する樹脂層を形成し、その後、当該樹脂層をドライエッティングすることにより、図10(a)に示したように、各表示画素PIXの画素電極層14pが露出する開口部を有する隔壁層17pを形成した。

40

【0102】

その後、上述した比較対象に係る表示パネルの製造方法と同様に、絶縁性基板11pを純水で洗浄した後、画素電極層14pの表面洗浄のため、上述した処理条件でUVオゾン処理を2分間施した。次いで、図10(b)に示したように、画素電極層14pが露出する開口部及び隔壁層17pを含む絶縁性基板11p上に、酸化モリブデンからなる正孔注入層15ap、インターレイヤ層15cp及び緑色の発光材料からなる発光層15bpを順次成

50

膜し、さらに、カソード電極及び給電電極からなる対向電極 16 p を形成した。

【0103】

このような本実施形態に基づく表示パネルを発光動作させた場合、図 11 (b) に示すように、各表示画素 PIX の発光素子（有機 EL 素子 OEL）が形成された EL 素子形成領域内にダークスポット（非発光領域）は観測されなかった。上述した比較対象に係る表示パネルにおける場合と同等の基準で評価を行ったところ、表示パネル 10 p の略中央部に配列された 100 画素中、ダークスポットが発生している画素は皆無（0 画素）であることが判明した。また、発明者らの検証によれば、このような作製から一週間経過後の表示パネル 10 p の経時変化を観測したところ、新たなダークスポットの発生や拡大も観測されないことが判明した。

10

【0104】

このように、本実施形態に適用される表示パネルにおいては、各表示画素の EL 素子形成領域を画定する隔壁層として、フッ素化合物含有樹脂材料等の非感光性樹脂材料を適用し、現像液を用いることなくドライエッティングによりパターニングを行うことにより、画素電極上に樹脂材料が残渣として残留することを抑制している。これにより、正孔注入層 15 a となる遷移金属の酸化物の正孔注入性が良好に維持され、ダークスポットの発生が抑制されるので、表示パネルの製品歩留まりや表示特性を向上させることができる。

20

【0105】

なお、上述した実施形態においては、有機 EL 層 15 の正孔注入層 15 a を形成するための遷移金属の酸化物として、酸化モリブデンを適用した場合について説明したが、本発明はこれに限定されるものではなく、バナジウムやタンゲステン等、他の遷移金属の酸化物を適用するものであってもよい。

20

【0106】

また、上述した実施形態においては、画素電極 14 としてITOや亜鉛ドープ酸化インジウムを適用する場合について説明したが、本発明はこれに限定されるものではなく、他の透明な電極材料を適用するものであってもよい。

30

また、上述した実施形態においては、ボトムエミッション型の発光構造を有する表示パネルについて説明したが、本発明はこれに限定されるものではなく、トップエミッション型の発光構造を有するものであってもよいし、有機 EL 素子以外の他の発光素子を備えた表示パネルに、本発明のパネル構造や製造方法を適用するものであってもよい。

【0107】

さらに、上述した実施形態においては、有機 EL 素子 OEL の有機 EL 層 15 が、正孔注入層 15 a 及び電子輸送性発光層 15 b からなる場合について説明したが、本発明はこれに限定されるものではなく、例えば正孔輸送兼電子輸送性発光層のみでもよく、正孔輸送性発光層及び電子輸送層でもよく、正孔輸送層、電子輸送層及び発光層でもよく、また、各層の間に適宜インターレイヤ層（担体輸送層）が介在してもよく、その他の担体輸送層の組合せであってもよい。

【0108】

また、上述した実施形態においては、画素電極 14 をアノード電極とし、対向電極 16 をカソード電極としたが、これに限らず画素電極 14 をカソード電極とし、対向電極 16 をアノード電極としてもよい。このとき、有機 EL 層 15 は、画素電極 14 に接する担体輸送層が電子輸送性の層であればよい。

40

さらに、上述した実施形態においては、画素駆動回路 DC を備えたアクティブ駆動の表示パネル 10 を示したが、これに限らずパッシブ駆動の表示パネルであってもよい。

【符号の説明】

【0109】

|         |       |

|---------|-------|

| 10、10 p | 表示パネル |

| 11、11 p | 絶縁性基板 |

| 13      | 絶縁膜   |

| 14      | 画素電極  |

50

1 4 p 画素電極層

1 5、1 5 p 有機 E L 層

1 5 a、1 5 ap 正孔注入層

1 5 b 電子輸送性発光層

1 5 bp 発光層

1 5 cp インターレイヤ層

1 6、1 6 p 対向電極

1 7、1 7 p 隔壁層

2 0 表示領域

P I X 表示画素

R px 画素形成領域

R el E L 素子形成領域

O E L 有機 E L 素子

T r 1 1、T r 1 2 トランジスタ

C s キャパシタ

10

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【 四 7 】

【 図 8 】

【 図 9 】

【 図 1 0 】

【図 1 1】

(a)

(b)

|                |                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其制造方法                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2010205462A</a>                                                                      | 公开(公告)日 | 2010-09-16 |

| 申请号            | JP2009047503                                                                                       | 申请日     | 2009-03-02 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                         |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                         |         |            |

| [标]发明人         | 木津貴志<br>熊谷稔                                                                                        |         |            |

| 发明人            | 木津 貴志<br>熊谷 稔                                                                                      |         |            |

| IPC分类号         | H05B33/22 H01L51/50 H05B33/12 H05B33/10                                                            |         |            |

| F1分类号          | H05B33/22.Z H05B33/14.A H05B33/22.C H05B33/12.B H05B33/10 H01L27/32                                |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC27 3K107/CC45 3K107/DD71 3K107/DD84 3K107/DD89 3K107/DD96 3K107/GG13 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                          |         |            |

## 摘要(译)

要解决的问题：提供一种具有面板结构的显示装置及其制造方法，能够在具有有机EL元件的显示像素中抑制光不发光区域的产生。解决方案：通过使用通过使用由非光敏树脂材料（例如，包括氟化合物的树脂材料）构成的树脂层图案化来形成布置在各个显示图像元素PIX的像素形成区域Rpx之间的分隔壁层17。干蚀刻方法和用于构成有机EL层15的空穴注入层15a，其通过形成氧化物膜（例如，氧化钼）形成，所述有机EL层15布置在由分隔壁层17限定的像素形成区域Rpx中。通过使用真空沉积方法或溅射方法制备过渡金属。 ż