(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-114288

(P2007-114288A)

(43) 公開日 平成19年5月10日(2007.5.10)

|                             |                                      |                                      |

|-----------------------------|--------------------------------------|--------------------------------------|

| (51) Int.CI.                | F 1                                  | テーマコード (参考)                          |

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30                            | J 3K107                              |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20                            | 624B 5C080                           |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20<br>G09G 3/20<br>H05B 33/14 | 612F 623B A                          |

|                             | 審査請求 未請求 請求項の数 5 O L (全 15 頁)        | 最終頁に続く                               |

| (21) 出願番号                   | 特願2005-303107 (P2005-303107)         | (71) 出願人 302020207                   |

| (22) 出願日                    | 平成17年10月18日 (2005.10.18)             | 東芝松下ディスプレイテクノロジー株式会社<br>東京都港区港南4-1-8 |

|                             |                                      | (74) 代理人 100058479<br>弁理士 鈴江 武彦      |

|                             |                                      | (74) 代理人 100091351<br>弁理士 河野 哲       |

|                             |                                      | (74) 代理人 100088683<br>弁理士 中村 誠       |

|                             |                                      | (74) 代理人 100108855<br>弁理士 蔵田 昌俊      |

|                             |                                      | (74) 代理人 100075672<br>弁理士 峰 隆司       |

|                             |                                      | 最終頁に続く                               |

(54) 【発明の名称】表示装置及びその駆動方法

## (57) 【要約】

【課題】映像信号として電流信号を書き込む表示装置で、走査方向に依存することなく、有効走査期間において最初に選択する行の画素で、良好な表示ができるようにする。

【解決手段】各々の画素  $P_X$  が駆動回路と表示素子 OLE D とを含んだ表示装置において、各選択期間に映像信号線 D L を介して電流源 CS 1 と駆動回路とを接続して駆動回路に映像信号を書き込む書き動作を行い、各非選択期間に駆動回路と画素電極とを接続して駆動電流を表示素子 OLE D に流す表示動作を行い、ランキング期間に電流源 CS 2 と映像信号線 D L とを接続して映像信号線 D L にプリチャージ信号を書き込むプリチャージ動作を行い、走査信号線 SL 1 の走査方向が映像信号線 D L と電流源 CS 2 との接続位置に近づく方向である場合には、走査方向が接続位置から遠ざかる方向である場合と比較して、プリチャージ信号をより大きくする。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

映像信号線と、

前記映像信号線と交差した複数の走査信号線と、

映像信号を出力する第1電流源と、

プリチャージ信号を出力する第2電流源と、

前記映像信号線と前記複数の走査信号線との交差部に対応して配列し、第1電源端子に接続されると共に入力信号に対応した大きさの駆動電流を出力する駆動回路と、画素電極と第2電源端子に接続された対向電極とそれらの間に介在した活性層とを備えた表示素子とを各々が含んだ複数の画素とを具備し、

各選択期間において、前記映像信号線を介して前記第1電流源と前記駆動回路とを接続して前記駆動回路に前記入力信号として前記映像信号を書き込む書込動作を行い、

各非選択期間において、前記駆動回路と前記画素電極とを接続して前記駆動電流を前記表示素子に流す表示動作を行い、

プランキング期間において、前記第2電流源と前記映像信号線とを接続して前記映像信号線に前記プリチャージ信号を書き込むプリチャージ動作を行い、

前記複数の走査信号線の走査方向が前記映像信号線と前記第2電流源との接続位置に近く方向である場合には、前記走査方向が前記接続位置から遠ざかる方向である場合と比較して、前記プリチャージ信号をより大きくすることを特徴とする表示装置。

**【請求項 2】**

前記第2電流源の出力電流の大きさを変化させることにより前記プリチャージ信号の大きさを変化させることを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記第2電流源と前記映像信号線と接続する時間を変化させることにより前記プリチャージ信号の大きさを変化させることを特徴とする請求項1に記載の表示装置。

**【請求項 4】**

リセット信号を出力する電圧源をさらに具備し、

前記プランキング期間において、前記プリチャージ動作に先立ち、前記電圧源と前記映像信号線とを接続して前記映像信号線に前記リセット信号を書き込むリセット動作を行うことを特徴とする請求項1に記載の表示装置。

**【請求項 5】**

映像信号線と、前記映像信号線と交差した複数の走査信号線と、映像信号を出力する第1電流源と、プリチャージ信号を出力する第2電流源と、前記映像信号線と前記複数の走査信号線との交差部に対応して配列し、第1電源端子に接続されると共に入力信号に対応した大きさの駆動電流を出力する駆動回路と、画素電極と第2電源端子に接続された対向電極とそれらの間に介在した活性層とを備えた表示素子とを各々が含んだ複数の画素とを具備した表示装置の駆動方法であって、

各選択期間において、前記映像信号線を介して前記第1電流源と前記駆動回路とを接続して前記駆動回路に前記入力信号として前記映像信号を書き込む書込動作を行い、

各非選択期間において、前記駆動回路と前記画素電極とを接続して前記駆動電流を前記表示素子に流す表示動作を行い、

プランキング期間において、前記第2電流源と前記映像信号線とを接続して前記映像信号線に前記プリチャージ信号を書き込むプリチャージ動作を行い、

前記複数の走査信号線の走査方向が前記映像信号線と前記第2電流源との接続位置に近く方向である場合には、前記走査方向が前記接続位置から遠ざかる方向である場合と比較して、前記プリチャージ信号をより大きくすることを特徴とする駆動方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置及びその駆動方法に係り、特に画素に映像信号として電流信号

10

20

30

40

50

を供給するアクティブマトリクス型表示装置及びその駆動方法に関する。

【背景技術】

【0002】

特許文献1には、カレントコピー型の回路を画素回路に採用したアクティブマトリクス型有機EL表示装置が記載されている。この表示装置では、各画素に映像信号として電流信号を供給し、有機EL素子を映像信号の大きさに対応した輝度で発光させる。

【0003】

この表示装置を駆動する場合、通常、有効走査期間とプランキング期間（垂直プランキング期間）とを交互に繰り返す。有効走査期間では、例えば、画素を行毎に順次選択し、選択した画素に映像信号を書き込む。各画素の有機EL素子は、有効走査期間のうち選択されていない期間とプランキング期間とにおいて、先の映像信号の大きさに対応した輝度で発光する筈である。ところが、実際には、有効走査期間において最初に選択する行の画素では、階調の再現性が不十分となることがある。10

【0004】

本発明者は、この問題は、以下の理由で生じることを見い出している。

例えば、ラスタ表示を行う場合、最初に選択した行の画素への映像信号の書き込みを終了してから最後に選択する行への映像信号の書き込みを終了するまでの間、映像信号線の電位はほぼ一定である。そのため、これら画素は、ほぼ等しい輝度で発光する。

【0005】

しかしながら、通常、プランキング期間の直後における映像信号線の電位は、先の電位とは大きく異なっている。そのため、最初に選択した行が含む画素では、小さな映像信号を書き込む場合に、映像信号の書き込みが不十分になり易い。その結果、上述した輝度ムラを生ずることとなる。20

【0006】

ところで、有機EL表示装置は、設計が異なる複数の機器に搭載される可能性がある。これら機器における有機EL表示装置の使用形態は多種多様である。例えば、或る機器では走査方向を映像信号線ドライバから遠ざかる方向（以下、順方向という）とし、他の機器では走査方向を映像信号線ドライバに近づく方向（以下、逆方向という）とすることがある。また、同一の機器であっても、或る条件のもとで使用する場合には走査方向を順方向とし、他の条件のもとで使用する場合には走査方向を逆方向とすることがある。30

【特許文献1】米国特許第6373454号明細書

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明の目的は、画素に映像信号として電流信号を書き込む表示装置が、走査方向に依存することなく、有効走査期間において最初に選択する行の画素で、良好な表示ができるようにすることにある。

【課題を解決するための手段】

【0008】

本発明の第1側面によると、映像信号線と、前記映像信号線と交差した複数の走査信号線と、映像信号を出力する第1電流源と、プリチャージ信号を出力する第2電流源と、前記映像信号線と前記複数の走査信号線との交差部に対応して配列し、第1電源端子に接続されると共に入力信号に対応した大きさの駆動電流を出力する駆動回路と、画素電極と第2電源端子に接続された対向電極とそれらの間に介在した活性層とを備えた表示素子とを各々が含んだ複数の画素とを具備し、各選択期間において、前記映像信号線を介して前記第1電流源と前記駆動回路とを接続して前記駆動回路に前記入力信号として前記映像信号を書き込む書込動作を行い、各非選択期間において、前記駆動回路と前記画素電極とを接続して前記駆動電流を前記表示素子に流す表示動作を行い、プランキング期間において、前記第2電流源と前記映像信号線とを接続して前記映像信号線に前記プリチャージ信号を書き込むプリチャージ動作を行い、前記複数の走査信号線の走査方向が前記映像信号線と40

前記第2電流源との接続位置に近づく方向である場合には、前記走査方向が前記接続位置から遠ざかる方向である場合と比較して、前記プリチャージ信号をより大きくすることを特徴とする表示装置が提供される。

#### 【0009】

本発明の第2側面によると、映像信号線と、前記映像信号線と交差した複数の走査信号線と、映像信号を出力する第1電流源と、プリチャージ信号を出力する第2電流源と、前記映像信号線と前記複数の走査信号線との交差部に対応して配列し、第1電源端子に接続されると共に入力信号に対応した大きさの駆動電流を出力する駆動回路と、画素電極と第2電源端子に接続された対向電極とそれらの間に介在した活性層とを備えた表示素子とを各々が含んだ複数の画素とを具備した表示装置の駆動方法であって、各選択期間において、前記映像信号線を介して前記第1電流源と前記駆動回路とを接続して前記駆動回路に前記入力信号として前記映像信号を書き込む書込動作を行い、各非選択期間において、前記駆動回路と前記画素電極とを接続して前記駆動電流を前記表示素子に流す表示動作を行い、ブランкиング期間において、前記第2電流源と前記映像信号線とを接続して前記映像信号線に前記プリチャージ信号を書き込むプリチャージ動作を行い、前記複数の走査信号線の走査方向が前記映像信号線と前記第2電流源との接続位置に近づく方向である場合には、前記走査方向が前記接続位置から遠ざかる方向である場合と比較して、前記プリチャージ信号をより大きくすることを特徴とする駆動方法が提供される。

#### 【発明の効果】

#### 【0010】

本発明によると、画素に映像信号として電流信号を書き込む表示装置が、走査方向に依存することなく、有効走査期間において最初に選択する行の画素で、良好な表示ができるようになる。

#### 【発明を実施するための最良の形態】

#### 【0011】

以下、本発明の態様について、図面を参照しながら詳細に説明する。なお、各図において、同様又は類似した機能を発揮する構成要素には同一の参照符号を付し、重複する説明は省略する。

#### 【0012】

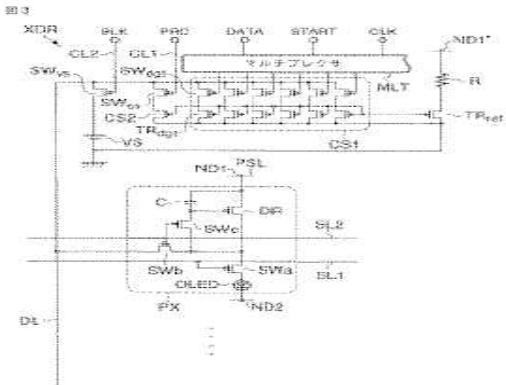

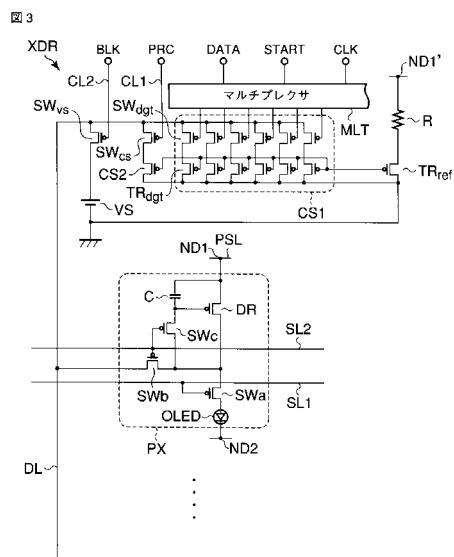

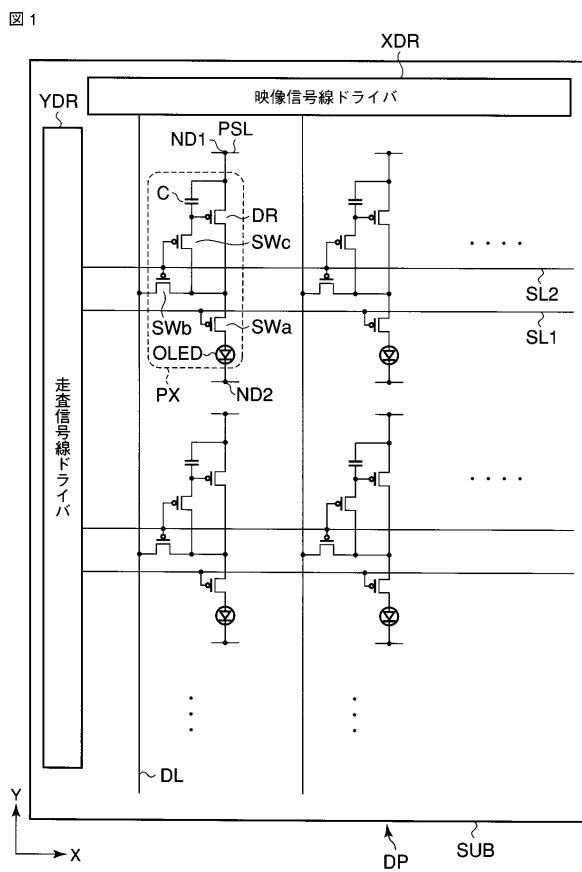

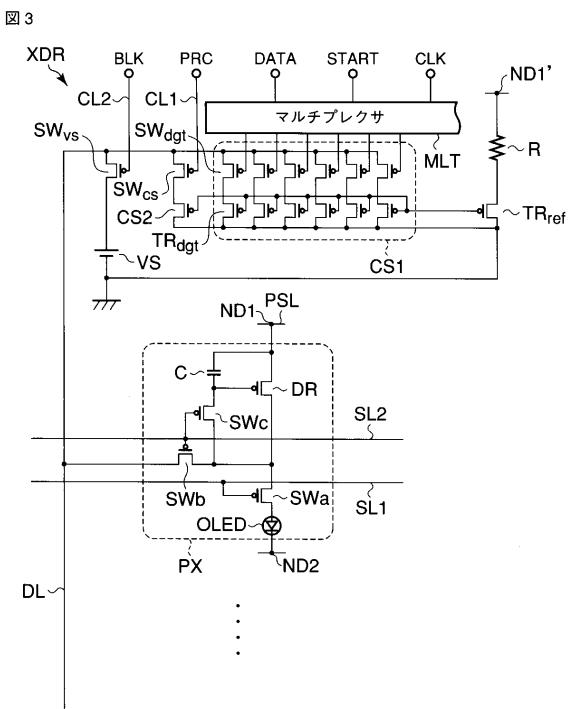

図1は、本発明の第1態様に係る表示装置を概略的に示す平面図である。図2は、図1の表示装置に採用可能な構造の一例を概略的に示す部分断面図である。図3は、図1の表示装置の一部を示す等価回路図である。なお、図2では、表示装置を、その表示面、すなわち前面又は光出射面、が下方を向き、背面が上方を向くように描いている。

#### 【0013】

この表示装置は、アクティブマトリクス型駆動方式を採用した下面発光型の有機EL表示装置である。この表示装置は、走査方向を、順方向と逆方向との間で切り替え可能である。

#### 【0014】

図1の有機EL表示装置は、表示パネルDPと、映像信号線ドライバXDRと、走査信号線ドライバYDRと、図示しないコントローラとを含んでいる。

#### 【0015】

表示パネルDPは、例えば、ガラス基板などの絶縁基板SUBを含んでいる。基板SUB上には、図2に示すように、アンダーコート層UCとして、例えば、SiNx層とSiO<sub>x</sub>層とが順次積層されている。

#### 【0016】

アンダーコート層UC上には、例えばチャネル及びソース・ドレインが形成されたシリコン層である半導体層SC、例えばTEOS(tetraethyl orthosilicate)などを用いて形成され得るゲート絶縁膜GI、及び例えばMoWなどからなるゲートGが順次積層されており、それらはトップゲート型の薄膜トランジスタを構成している。この例では、これら薄膜トランジスタは、pチャネル薄膜トランジスタであり、図1及び図3に示す駆

動制御素子 D R 及びスイッチ S W a 乃至 S W c として利用している。

【 0 0 1 7 】

ゲート絶縁膜 G I 上には、図 1 及び図 3 に示すキャパシタ C の一方の電極と走査信号線 S L 1 及び S L 2 とがさらに配置されている。これらは、ゲート G と同一の工程で形成可能である。

【 0 0 1 8 】

走査信号線 S L 1 及び S L 2 は、図 1 に示すように、各々が画素 P X の行方向 ( X 方向 ) に延びてあり、画素 P X の列方向 ( Y 方向 ) に交互に配列している。これら走査信号線 S L 1 及び S L 2 は、走査信号線 ドライバ Y D R に接続されている。

【 0 0 1 9 】

ゲート絶縁膜 G I 、ゲート G 、走査信号線 S L 1 及び S L 2 、並びにキャパシタ C の一方の電極は、図 2 に示す層間絶縁膜 I I で被覆されている。層間絶縁膜 I I は、例えばプラズマ C V D 法などにより成膜された S i O<sub>x</sub> などからなる。この層間絶縁膜 I I の一部は、キャパシタ C の誘電体層として利用する。

【 0 0 2 0 】

層間絶縁膜 I I 上には、図 1 に示すキャパシタ C の他方の電極、図 2 に示すソース電極 S E 及びドレイン電極 D E 、並びに、図 1 に示す映像信号線 D L 及び電源線 P S L が配置されている。これらは、同一工程で形成可能であり、例えば、M o / A l / M o の三層構造を有している。

【 0 0 2 1 】

ソース電極 S E 及びドレイン電極 D E は、層間絶縁膜 I I に設けられたコンタクトホールを介して薄膜トランジスタのソース及びドレインに電気的に接続されている。

【 0 0 2 2 】

映像信号線 D L は、図 1 に示すように、各々が Y 方向に延びてあり、 X 方向に配列している。これら映像信号線 D L は、映像信号線 ドライバ X D R に接続されている。

電源線 P S L は、この例では、各々が Y 方向に延びてあり、 X 方向に配列している。

【 0 0 2 3 】

ソース電極 S E 、ドレイン電極 D E 、映像信号線 D L 、電源線 P S L 、及びキャパシタ C の他方の電極は、図 2 に示すパッシベーション膜 P S で被覆されている。パッシベーション膜 P S は、例えば S i N<sub>x</sub> などからなる。

【 0 0 2 4 】

パッシベーション膜 P S 上には、図 2 に示すように、前面電極として、光透過性の第 1 電極 P E が互いから離間して並置されている。各第 1 電極 P E は、画素電極であり、パッシベーション膜 P S に設けた貫通孔を介して、スイッチ S W a のドレイン電極 D E に接続されている。

【 0 0 2 5 】

第 1 電極 P E は、この例では陽極である。第 1 電極 P E の材料としては、例えば、I T O ( indium tin oxide ) のような透明導電性酸化物を使用することができる。

【 0 0 2 6 】

パッシベーション膜 P S 上には、さらに、図 2 に示す隔壁絶縁層 P I が配置されている。隔壁絶縁層 P I には、第 1 電極 P E に対応した位置に貫通孔が設けられているか、或いは、第 1 電極 P E が形成する列又は行に対応した位置にスリットが設けられている。ここでは、一例として、隔壁絶縁層 P I には、第 1 電極 P E に対応した位置に貫通孔が設けられることとする。

【 0 0 2 7 】

隔壁絶縁層 P I は、例えば、有機絶縁層である。隔壁絶縁層 P I は、例えば、フォトリソグラフィ技術を用いて形成することができる。

【 0 0 2 8 】

第 1 電極 P E 上には、活性層として、発光層を含んだ有機物層 O R G が配置されている。発光層は、例えば、発光色が赤色、緑色、又は青色のルミネセンス性有機化合物を含ん

10

20

30

40

50

だ薄膜である。この有機物層ORGは、発光層に加え、正孔注入層、正孔注入層、正孔プロッキング層、電子輸送層、電子注入層などもさらに含むことができる。

#### 【0029】

隔壁絶縁層PI及び有機物層ORGは、第1電極に対向して配置された対向電極としての第2電極CEで被覆されている。第2電極CEは、画素PX間で互いに接続された共通電極であり、この例では背面電極として設けられた光反射性の陰極である。第2電極CEは、例えば、パッシベーション膜PSと隔壁絶縁層PIとに設けられたコンタクトホールを介して、映像信号線DLと同一の層上に形成された電極配線（図示せず）に電気的に接続されている。各々の有機EL素子OLEDは、第1電極PE、有機物層ORG及び第2電極CEで構成されている。

10

#### 【0030】

絶縁基板SUB上では、複数の画素PXがマトリクス状に配列している。これら画素PXは、映像信号線DLと走査信号線SL1との交差部近傍に配置されている。

#### 【0031】

各画素PXは、表示素子である有機EL素子OLEDと、駆動回路と、出力制御スイッチSWaとを含んでいる。この例では、駆動回路は、図1及び図3に示すように、駆動制御素子DRと、映像信号供給制御スイッチSWbと、ダイオード接続スイッチSWcと、キャパシタCとを含んでいる。上記の通り、この例では、駆動制御素子DR及びスイッチSWa乃至SWcは、pチャネル薄膜トランジスタである。スイッチSWb及びSWcは、駆動制御素子DRのドレインとゲートと映像信号線DLとの接続を、それらが互いに接続された第1状態と、それらが互いから切断された第2状態との間で切り替えるスイッチ群を構成している。

20

#### 【0032】

駆動制御素子DRと出力制御スイッチSWaと有機EL素子OLEDとは、第1電源端子ND1と第2電源端子ND2との間で、この順に直列に接続されている。この例では、第1電源端子ND1は電源線PSLに接続された高電位電源端子であり、第2電源端子ND2は低電位電源端子である。

20

#### 【0033】

出力制御スイッチSWaのゲートは、走査信号線SL1に接続されている。映像信号供給制御スイッチSWbは映像信号線DLと駆動制御素子DRのドレインとの間に接続されており、そのゲートは走査信号線SL2に接続されている。ダイオード接続スイッチSWcは駆動制御素子DRのドレインとゲートとの間に接続されており、そのゲートは走査信号線SL2に接続されている。

30

#### 【0034】

キャパシタCは、定電位端子と駆動制御素子DRのゲートとの間に接続されている。この例では、キャパシタCは、第1電源端子ND1と駆動制御素子DRのゲートとの間に接続されている。

#### 【0035】

表示パネルDP上には、映像信号線ドライバXDRが配置されている。映像信号線ドライバXDRは、図3に示すように、映像信号線DL毎に、電流源CS1及びCS2とスイッチSWcs及びSWvsとを含んでいる。さらに、映像信号線ドライバXDRは、マルチプレクサMLTと電圧源VSと基準トランジスタTRrefと制御線CL1及びCL2を含んでいる。

40

#### 【0036】

マルチプレクサMLTは、クロック信号CLK、スタート信号DATA、シリアル信号としての映像信号DATAが入力される入力端子を含んでいる。さらに、マルチプレクサMLTは、電流源CS1毎に複数の出力端子を含んでいる。マルチプレクサMLTは、クロック信号CLKとスタート信号DATAとに基づいて、シリアル信号としての映像信号DATAをパラレル信号に変換し、これを各電流源CS1へと出力する。この例では、マルチプレクサMLTは、映像信号を6ビットのデジタル信号として、各電流源CS1に

50

出力する。

【0037】

基準トランジスタ  $T_{R_{ref}}$  は、この例では  $p$  チャネル電界効果トランジスタである。基準トランジスタ  $T_{R_{ref}}$  のソースは抵抗素子  $R$  を介して定電位端子  $N_{D1'}$  に接続されており、そのドレインは接地線に接続されている。この表示装置の駆動時には、基準トランジスタ  $T_{R_{ref}}$  のソース - ドレイン間に基準電流  $I_{ref}$  を流す。

【0038】

電流源  $C_S1$  は、映像信号線ドライバ  $XDR$  の出力端子、すなわち映像信号線  $DL$  に接続された端子、と接地線との間に接続されている。電流源  $C_S1$  は、マルチプレクサ  $MLT$  がパラレル信号として出力するディジタル信号をアナログ信号へと変換する。この例では、電流源  $C_S1$  は、マルチプレクサ  $MLT$  が出力する 6 ビットのディジタル映像信号から、電流信号としてのアナログ映像信号を生成する。

【0039】

電流源  $C_S1$  は、複数の定電流源  $T_{R_{dg_t}}$  と複数のスイッチ  $S_{W_{dg_t}}$  とを含んでいる。定電流源  $T_{R_{dg_t}}$  とスイッチ  $S_{W_{dg_t}}$  とは、それぞれ、映像信号線ドライバ  $XDR$  の出力端子と接地線との間で直列に接続されている。この例では、電流源  $C_S1$  は、6 つの定電流源  $T_{R_{dg_t}}$  と 6 つのスイッチ  $S_{W_{dg_t}}$  とを含んでいる。また、この例では、定電流源  $T_{R_{dg_t}}$  及びスイッチ  $S_{W_{dg_t}}$  は、 $p$  チャネル電界効果トランジスタである。

【0040】

定電流源  $T_{R_{dg_t}}$  のゲートは、それぞれ、基準トランジスタ  $T_{R_{ref}}$  のゲートに接続されている。スイッチ  $S_{W_{dg_t}}$  のゲートは、それぞれ、マルチプレクサ  $MLT$  の出力端子に接続されている。

【0041】

定電流源  $T_{R_{dg_t}}$  は、例えば、それらの 1 つが基準トランジスタ  $T_{R_{ref}}$  と同一の構造を有しており、残りの 5 つがチャネル幅が異なること以外は基準トランジスタ  $T_{R_{ref}}$  と同一の構造を有している。6 つの定電流源  $T_{R_{dg_t}}$  は、それらに接続されているスイッチ  $S_{W_{dg_t}}$  が閉じている間、例えば、基準電流  $I_{ref}$  の 1 倍、2 倍、4 倍、8 倍、16 倍、32 倍の大きさの定電流をそれぞれ出力する。

【0042】

スイッチ  $S_{W_{cs}}$  と電流源  $C_S2$  とは、映像信号線ドライバ  $XDR$  の出力端子と接地線との間で、この順に直列に接続されている。

【0043】

電流源  $C_S2$  は、プリチャージ電流又はプリチャージ信号を電流信号として出力する定電流源である。電流源  $C_S2$  のゲートは、基準トランジスタ  $T_{R_{ref}}$  のゲートに接続されている。

【0044】

スイッチ  $S_{W_{cs}}$  は、この例では、 $p$  チャネル電界効果トランジスタである。スイッチ  $S_{W_{cs}}$  のゲートは、制御線  $CL1$  に接続されている。制御線  $CL1$  には、後述する制御信号  $PRC$  が入力される。

【0045】

スイッチ  $S_{W_{vs}}$  と電圧源  $V_S$  とは、映像信号線ドライバ  $XDR$  の出力端子と接地線との間で、この順に直列に接続されている。

【0046】

電圧源  $V_S$  は、リセット信号として定電圧を出力する。例えば、電圧源  $V_S$  は、映像信号が最低階調である場合に書き動作によって設定されるべき映像信号線  $DL$  の電圧とほぼ等しいか又はそれよりも高い定電圧である。

【0047】

スイッチ  $S_{W_{vs}}$  は、この例では、 $p$  チャネル電界効果トランジスタである。スイッチ  $S_{W_{vs}}$  のゲートは、制御線  $CL2$  に接続されている。制御線  $CL2$  には、例えば、プランギング期間と有効走査期間との切り替わりにほぼ対応して信号レベルが変化する制御信号  $B$

10

20

30

40

50

L K が入力される。

【0048】

表示パネル D P 上には、走査信号線ドライバ Y D R がさらに配置されている。上記の通り、走査信号線ドライバ Y D R には、走査信号線 S L 1 及び S L 2 が接続されている。

【0049】

映像信号線ドライバ X D R 及び走査信号線ドライバ Y D R には、図示しないコントローラが接続されている。

【0050】

コントローラは、映像信号線ドライバ X D R に、クロック信号 C L K 及びスタート信号 D A T A などの制御信号を出力すると共に、シリアル信号としての映像信号 D A T A を出力する。さらに、コントローラは、走査信号線ドライバ Y D R にクロック信号及び制御信号などの制御信号を出力する。走査方向の制御は、例えば、コントローラにより行うことができる。

【0051】

この有機 E L 表示装置は、例えば、以下の方法により駆動する。

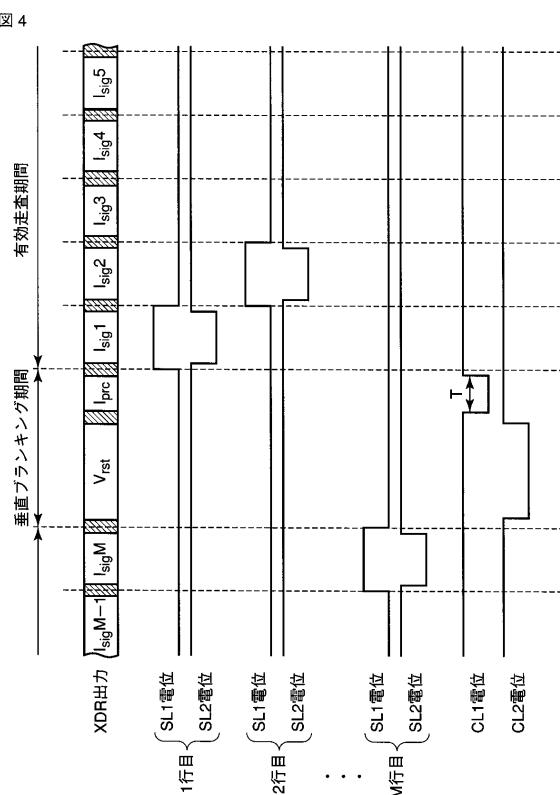

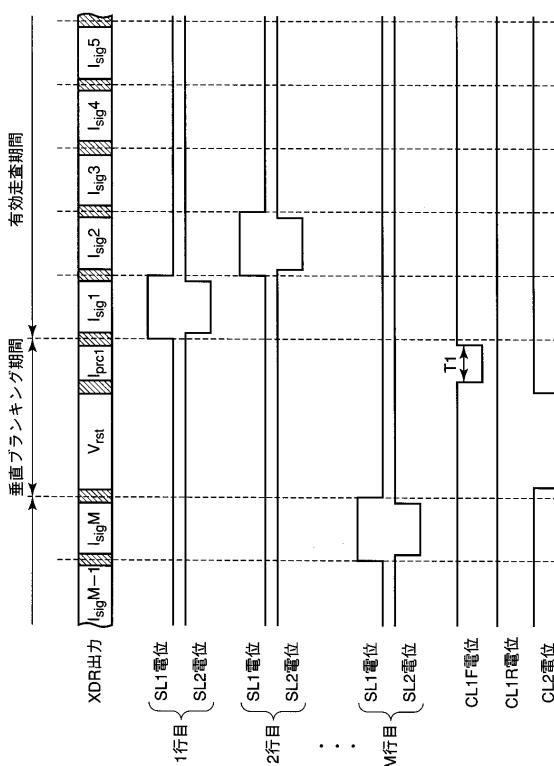

図 4 は、図 1 乃至図 3 に示す表示装置の駆動方法の一例を概略的に示すタイミングチャートである。図 4 には、画素 P X が M 個の行を形成している場合の駆動方法を描いており、横軸は時間を示し、縦軸は電位を示している。

【0052】

図 4において、「X D R 出力」のうち、「 $I_{sigm}$ 」と表記した期間は映像信号線ドライバ X D R が映像信号線 D L に映像信号  $I_{sigm}$  を出力する期間を示し、「 $V_{rst}$ 」と表記した期間は映像信号線ドライバ X D R が映像信号線 D L にリセット信号  $V_{rst}$  を出力する期間を示し、「 $I_{prc}$ 」と表記した期間は映像信号線ドライバ X D R が映像信号線 D L にプリチャージ電流  $I_{prc}$  を出力する期間を示している。また、図 4において、「S L 1 電位」及び「S L 2 電位」で示す波形は走査信号線 S L 1 及び S L 2 の電位をそれぞれ示し、「C L 1 電位」及び「C L 2 電位」で示す波形は制御線 C L 1 及び C L 2 の電位をそれぞれ示している。なお、「m 行目」の「m」は、映像信号線ドライバ X D R に最も近い行から順に付した番号である。

【0053】

この駆動方法では、走査方向を順方向とし、有効走査期間とブランкиング期間とを交互に繰り返す。有効走査期間では、スイッチ  $S W_{vs}$  及び  $S W_{cs}$  は開いたままにしておき、画素 P X を行毎に選択する。各画素 P X の選択期間では書き動作を行い、非選択期間では表示動作を行う。

【0054】

例えば、m 行目の画素を選択している期間（以下、m 行目選択期間という）では、まず、m 行目の画素 P X のスイッチ  $S W_a$  を開く。次いで、マルチプレクサ M L T から各電流源 C S 1 に 6 ビットのデジタル映像信号を出力すると共に、m 行目の画素 P X のスイッチ  $S W_b$  及び  $S W_c$  を閉じる。

【0055】

電流源 C S 1 は、デジタル映像信号をアナログ映像信号としての書き電流  $I_{sigm}$  に変換する。この書き電流  $I_{sigm}$  は、第 1 電源端子 N D 1 から電流源 C S 1 へと流れる。これにより、駆動制御素子 D R のゲート電位を、駆動制御素子 D R のソース - ドレイン間に書き電流  $I_{sigm}$  が流れるとときの値に設定する。

【0056】

その後、スイッチ  $S W_b$  及び  $S W_c$  を開く。さらに、スイッチ  $S W_a$  を閉じることにより、m 行目選択期間を終了する。

【0057】

スイッチ  $S W_a$  を閉じると、有機 E L 素子 O L E D には、書き電流  $I_{sigm}$  に対応した大きさの駆動電流  $I_{drv m}$  が流れる。非選択期間では、スイッチ  $S W_a$  は閉じたままである。したがって、各画素 P X の有機 E L 素子 O L E D は、その画素 P X が次に選択される

10

20

30

40

50

まで、駆動電流  $I_{drv}$  の大きさに対応した輝度で発光し続ける。

【0058】

プランキング期間では、以下のリセット動作とプリチャージ動作とを順次行う。なお、プランキング期間では、全ての画素  $P_X$  で、スイッチ  $S_{Wb}$  及び  $S_{Wc}$  は開いたままとしておく。

【0059】

すなわち、まず、全てのスイッチ  $S_{W_{dg}}$  を開く。次いで、スイッチ  $S_{Wv}$  を閉じて、電圧源  $V_S$  から映像信号線  $D_L$  にリセット信号を出力する。すなわち、映像信号線  $D_L$  の電位をリセット電位  $V_{rst}$  に設定する。その後、スイッチ  $S_{Wv}$  を開く。これにより、リセット動作を完了する。

10

【0060】

次に、映像信号線  $D_L$  にプリチャージ信号を書き込むプリチャージ動作を行う。すなわち、スイッチ  $S_{Wcs}$  を一定時間  $T$  だけ閉じて、映像信号線  $D_L$  から電流源  $C_S 2$  へと定電流であるプリチャージ電流  $I_{prc}$  を流す。このプリチャージ動作により、映像信号線  $D_L$  の電位は、リセット電位  $V_{rst}$  から電流  $I_{prc}$  と時間  $T$  との積  $I_{prc} \times T$  に対応した大きさだけ低くなる。

【0061】

ところで、この表示装置の映像信号線 ドライバ  $XDR$  が電圧源  $V_S$  と電流源  $C_S 2$  とスイッチ  $S_{Wv}$  及び  $S_{Wcs}$  とを含んでいないとすると、プランキング期間において、映像信号線  $D_L$  は浮動状態にあると考えることができる。しかしながら、実際には、映像信号線  $D_L$  に接続した保護回路（図示せず）などに流れるリーク電流に起因して、プランキング期間を開始してから終了するまでの間に、映像信号線  $D_L$  の電位が変動することがある。例えば、プランキング期間を終了した時点における映像信号線  $D_L$  の電位が、書き動作によって設定されるべき映像信号線  $D_L$  の電位の最低値よりもさらに低くなることがある。

20

【0062】

この場合、1行目の画素  $P_X$  で低階調域内の階調を表示するには、1行目選択期間の書き動作により、映像信号線  $D_L$  の電位を大幅に高めなければならない。しかしながら、低階調域内の階調を表示するときの書き電流  $I_{sig}$  1 は小さいため、1行目選択期間内に映像信号線  $D_L$  の電位を十分に変化させることは難しい。そのため、1行目の画素  $P_X$  では、駆動制御素子  $DR$  のゲート電位を書き電流  $I_{sig}$  1 に対応した値に正確に設定できず、低階調域内の各階調を高い再現性で表示することが難しい。

30

【0063】

これに対し、プランキング期間において図 1 乃至図 4 を参照しながら説明したリセット動作を行うと、映像信号線  $D_L$  の電位をリセット電位  $V_{rst}$  とほぼ等しくすることができる。そして、リセット動作に続いてプリチャージ動作を行うことにより、1行目の画素  $P_X$  への書き動作を開始する直前における映像信号線  $D_L$  の電位を、電位  $V_{rst} - (I_{prt} \times t) / C_{DL}$  とほぼ等しくすることができる。なお、 $C_{DL}$  は映像信号線  $D_L$  の配線容量である。

【0064】

したがって、プリチャージ電流  $I_{prc}$  と時間  $T$  とを適宜設定することにより、1行目の画素  $P_X$  で低階調域内の階調を表示するために必要な映像信号線  $D_L$  の電位変動量を著しく小さくすることができる。それゆえ、有効走査期間において最初に選択する行の画素  $P_X$  で、低階調域内の各階調を高い再現性で表示することが可能となる。

40

【0065】

さて、走査方向を順方向とした場合には、上述した方法で駆動することにより、有効走査期間において最初に選択する行の画素  $P_X$  で、低階調域内の各階調を高い再現性で表示することができる。しかしながら、同様の条件のもとで走査方向を逆方向とすると、有効走査期間において最初に選択する行の画素  $P_X$  で、低階調域内の各階調を高い再現性で表示することができない可能性がある。これは、映像信号線  $D_L$  のうち、映像信号線 ドライバ  $XDR$  から遠い部分では、映像信号線 ドライバ  $XDR$  に近い部分と比較して、プリチャ

50

ージ動作を完了した直後における電位がより高いためである。そこで、本態様では、走査方向を逆方向とする場合には、例えば、以下の駆動方法を採用する。

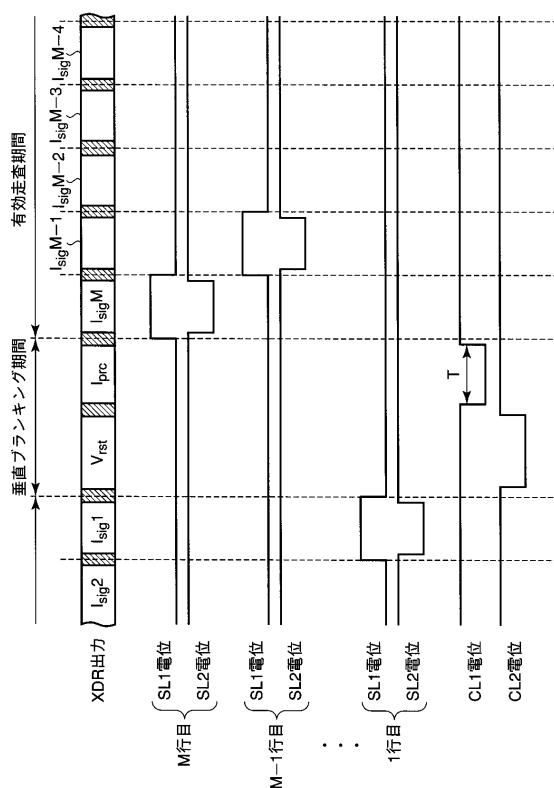

#### 【0066】

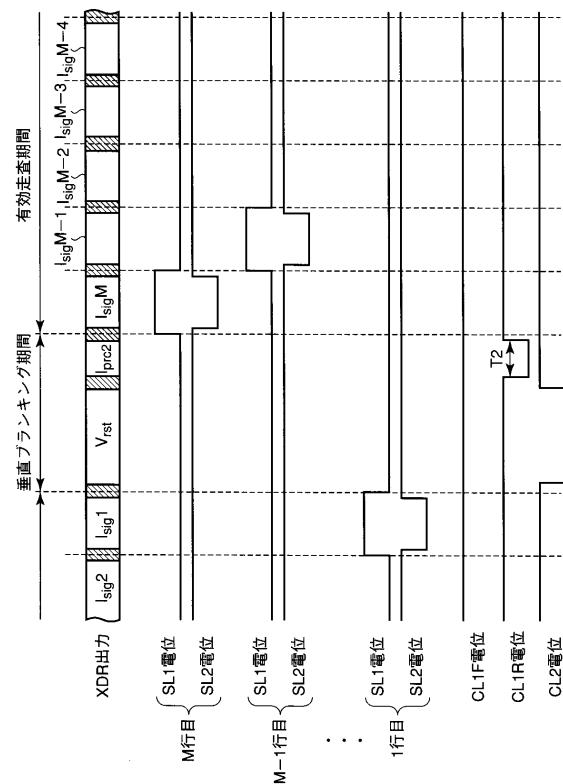

図5は、図1乃至図3に示す表示装置の駆動方法の他の例を概略的に示すタイミングチャートである。図5には、画素P XがM個の行を形成している場合の駆動方法を描いており、横軸は時間を示し、縦軸は電位を示している。

#### 【0067】

図5において、「X D R出力」のうち、「 $I_{sigm}$ 」と表記した期間は映像信号線ドライバX D Rが映像信号線D Lに映像信号 $I_{sigm}$ を出力する期間を示し、「 $V_{rst}$ 」と表記した期間は映像信号線ドライバX D Rが映像信号線D Lにリセット信号 $V_{rst}$ を出力する期間を示し、「 $I_{prc}$ 」と表記した期間は映像信号線ドライバX D Rが映像信号線D Lにプリチャージ電流 $I_{prc}$ を出力する期間を示している。また、図5において、「S L 1電位」と「S L 2電位」で示す波形は走査信号線S L 1及びS L 2の電位をそれぞれ示し、「C L 1電位」と「C L 2電位」で示す波形は制御線C L 1及びC L 2の電位をそれぞれ示している。なお、「m行目」の「m」は、映像信号線ドライバX D Rに最も近い行から順に付した番号である。

#### 【0068】

この駆動方法は、走査方向を逆方向とし且つ時間Tをより長くすること以外は、図4を参照しながら説明した駆動方法と同様である。時間Tをより長くすると、プリチャージ動作を完了した直後における映像信号線D Lの電位が低くなる。したがって、時間Tを適宜設定すれば、有効走査期間において最初に選択する行の画素P Xで、低階調域内の各階調を高い再現性で表示することができる。

#### 【0069】

このように、本態様によると、走査方向を順方向とした場合と逆方向とした場合との双方で、有効走査期間において最初に選択する行の画素P Xで低階調域内の各階調を高い再現性で表示することができる。すなわち、本態様によると、走査方向に依存することなく、有効走査期間において最初に選択する行の画素で良好な表示が可能となる。

#### 【0070】

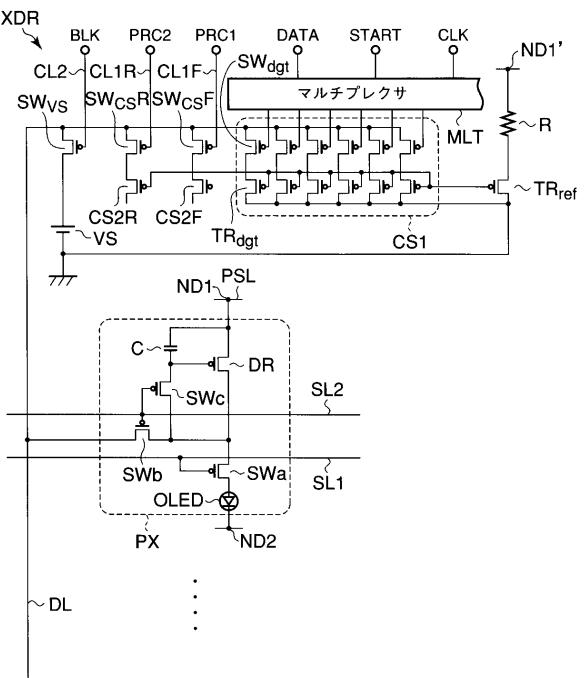

次に、本発明の第2態様について説明する。

図6は、本発明の第2態様に係る表示装置の一部を示す等価回路図である。第2態様は、映像信号線ドライバX D Rに図6の構造を採用すると共に、後述する駆動方法を採用する。これ以外は、第2態様は、第1態様とほぼ同様である。

#### 【0071】

図6の映像信号線ドライバX D Rは、図3の映像信号線ドライバX D Rとは、以下の点で異なっている。すなわち、図6の映像信号線ドライバX D Rは、電流源C S 2及びスイッチ $S W_{cs}$ の代わりに、電流源C S 2 F及びC S 2 R並びにスイッチ $S W_{csF}$ 及び $S W_{csR}$ を含んでいる。電流源C S 2 F及びC S 2 Rは、大きさが互いに異なる第1及び第2プリチャージ電流を出力する電流源を構成している。また、図6の映像信号線ドライバX D Rは、制御線C L 1の代わりに、制御線C L 1 F及びC L 1 Rを含んでいる。

#### 【0072】

スイッチ $S W_{csF}$ と電流源C S 2 Fとは、映像信号線ドライバX D Rの出力端子と接地線との間で、この順に直列に接続されている。

#### 【0073】

電流源C S 2 Fは、第1プリチャージ電流又は第1プリチャージ信号を電流信号として出力する定電流源である。電流源C S 2 Fのゲートは、基準トランジスタ $T R_{ref}$ のゲートに接続されている。

#### 【0074】

スイッチ $S W_{csF}$ は、この例では、pチャンネル電界効果トランジスタである。スイッチ $S W_{csF}$ のゲートは、制御線C L 1 Fに接続されている。制御線C L 1 Fには、後述する制御信号P R C 1が入力される。

10

20

30

40

50

## 【0075】

スイッチ  $S W_{cs} R$  と電流源  $C S 2 R$  とは、映像信号線ドライバ  $X D R$  の出力端子と接地線との間で、この順に直列に接続されている。

## 【0076】

電流源  $C S 2 R$  は、第 2 プリチャージ電流又は第 2 プリチャージ信号を電流信号として出力する定電流源である。この電流源  $C S 2 R$  は、電流源  $C S 2 F$  と比較してより大きな定電流を出力する。電流源  $C S 2 R$  のゲートは、基準トランジスタ  $T R_{ref}$  のゲートに接続されている。

## 【0077】

スイッチ  $S W_{cs} R$  は、この例では、 $p$  チャネル電界効果トランジスタである。スイッチ  $S W_{cs} R$  のゲートは、制御線  $C L 1 R$  に接続されている。制御線  $C L 1 R$  には、後述する制御信号  $P R C 2$  が入力される。

## 【0078】

第 2 様様に係る表示装置は、例えば、以下の方法で駆動する。

図 7 は、本発明の第 2 様様に係る表示装置の駆動方法の一例を概略的に示すタイミングチャートである。図 8 は、本発明の第 2 様様に係る表示装置の駆動方法の他の例を概略的に示すタイミングチャートである。図 7 及び図 8 には、画素  $P X$  が  $M$  個の行を形成している場合の駆動方法を描いており、横軸は時間を示し、縦軸は電位を示している。

## 【0079】

図 7 及び図 8 において、「 $X D R$  出力」のうち、「 $I_{sigm}$ 」と表記した期間は映像信号線ドライバ  $X D R$  が映像信号線  $D L$  に映像信号  $I_{sigm}$  を出力する期間を示し、「 $V_{rst}$ 」と表記した期間は映像信号線ドライバ  $X D R$  が映像信号線  $D L$  にリセット信号  $V_{rst}$  を出力する期間を示し、「 $I_{prc1}$ 」と表記した期間は映像信号線ドライバ  $X D R$  が映像信号線  $D L$  に第 1 プリチャージ電流  $I_{prc1}$  を出力する期間を示し、「 $I_{prc2}$ 」と表記した期間は映像信号線ドライバ  $X D R$  が映像信号線  $D L$  に第 2 プリチャージ電流  $I_{prc2}$  を出力する期間を示している。また、図 7 及び図 8 において、「 $S L 1$  電位」及び「 $S L 2$  電位」で示す波形は走査信号線  $S L 1$  及び  $S L 2$  の電位をそれぞれ示し、「 $C L 1 F$  電位」及び「 $C L 1 R$  電位」で示す波形は制御線  $C L 1 F$  及び  $C L 1 R$  の電位をそれぞれ示し、「 $C L 2$  電位」で示す波形は制御線  $C L 2$  の電位を示している。なお、「 $m$  行目」の「 $m$ 」は、映像信号線ドライバ  $X D R$  に最も近い行から順に付した番号である。

## 【0080】

図 7 の駆動方法では、走査方向を順方向としている。この駆動方法は、以下の点を除き、図 4 を参照しながら説明した駆動方法と同様である。すなわち、図 7 の駆動方法では、スイッチ  $S W_{cs} F$  のスイッチング動作を、図 4 を参照しながら説明したスイッチ  $S W_{cs}$  のスイッチング動作と同様のタイミングで行う。そして、図 7 の駆動方法では、スイッチ  $S W_{cs} R$  は、有効走査期間及びプランギング期間の双方において開いたままとする。

## 【0081】

図 8 の駆動方法では、走査方向を逆方向としている。この駆動方法は、以下の点を除き、図 4 を参照しながら説明した駆動方法と同様である。すなわち、図 8 の駆動方法では、スイッチ  $S W_{cs} R$  のスイッチング動作を、図 4 を参照しながら説明したスイッチ  $S W_{cs}$  のスイッチング動作と同様のタイミングで行う。そして、図 8 の駆動方法では、スイッチ  $S W_{cs} F$  は、有効走査期間及びプランギング期間の双方において開いたままとする。

## 【0082】

本様様では、走査方向を順方向とした場合にスイッチ  $S W_{cs} F$  を閉じている時間  $T 1$  と、走査方向を逆方向とした場合にスイッチ  $S W_{cs} R$  を閉じている時間  $T 2$  とを同一とする。そして、走査方向を逆方向とした場合に映像信号線  $D L$  から電流源  $C S 2$  へと流す第 2 プリチャージ電流  $I_{prc2}$  を、走査方向を順方向とした場合に映像信号線  $D L$  から電流源  $C S 2$  へと流す第 1 プリチャージ電流  $I_{prc1}$  と比較してより大きくする。すなわち、第 1 様様と同様、走査方向が逆方向である場合のプリチャージ信号を、走査方向が順方向である場合のプリチャージ信号と比較してより大きくする。したがって、プリチャージ電流  $I_{pr}$

10

20

30

40

50

$c_1$  及び  $I_{prc_2}$  を適宜設定すれば、有効走査期間において最初に選択する行の画素  $P_X$  で、低階調域内の各階調を高い再現性で表示することができる。

#### 【0083】

このように、本態様によると、走査方向を順方向とした場合と逆方向とした場合との双方で、有効走査期間において最初に選択する行の画素  $P_X$  で低階調域内の各階調を高い再現性で表示することができる。すなわち、本態様によると、走査方向に依存することなく、有効走査期間において最初に選択する行の画素で良好な表示が可能となる。

#### 【0084】

本態様において、時間  $T_1$  は時間  $T_2$  とは異なっていてもよい。例えば、時間  $T_2$  は、時間  $T_1$  と比較してより長くてもよい。すなわち、第2態様に係る技術には、第1態様に係る技術を組み合わせることができる。

#### 【0085】

第1及び第2本態様では、画素  $P_X$  に図1、図3及び図6の構造を採用したが、画素  $P_X$  には他の構造を採用することも可能である。例えば、ダイオード接続スイッチ  $SW_c$  は、駆動制御素子  $DR$  のドレインとゲートとの間に接続する代わりに、駆動制御素子  $DR$  のゲートと映像信号線  $DL$ との間に接続してもよい。或いは、映像信号供給制御スイッチ  $SW_b$  は、駆動制御素子  $DR$  のドレインと映像信号線  $DL$ との間に接続する代わりに、駆動制御素子  $DR$  のゲートと映像信号線  $DL$ との間に接続してもよい。

#### 【図面の簡単な説明】

#### 【0086】

【図1】本発明の第1態様に係る表示装置を概略的に示す平面図。

【図2】図1の表示装置に採用可能な構造の一例を概略的に示す部分断面図。

【図3】図1の表示装置の一部を示す等価回路図。

【図4】図1乃至図3に示す表示装置の駆動方法の一例を概略的に示すタイミングチャート。

【図5】図1乃至図3に示す表示装置の駆動方法の他の例を概略的に示すタイミングチャート。

【図6】本発明の第2態様に係る表示装置の一部を示す等価回路図。

【図7】本発明の第2態様に係る表示装置の駆動方法の一例を概略的に示すタイミングチャート。

【図8】本発明の第2態様に係る表示装置の駆動方法の他の例を概略的に示すタイミングチャート。

#### 【符号の説明】

#### 【0087】

$C \dots$  キャパシタ、 $C_E \dots$  対向電極、 $C_L 1 \dots$  制御線、 $C_L 1 F \dots$  制御線、 $C_L 1 R \dots$  制御線、 $C_L 2 \dots$  制御線、 $C_S 1 \dots$  電流源、 $C_S 2 \dots$  電流源、 $C_S 2 F \dots$  電流源、 $C_S 2 R \dots$  電流源、 $D_E \dots$  ドレイン電極、 $D_L \dots$  映像信号線、 $D_P \dots$  表示パネル、 $D_R \dots$  駆動制御素子、 $G \dots$  ゲート、 $G_I \dots$  ゲート絶縁膜、 $I_I \dots$  層間絶縁膜、 $M_L T \dots$  マルチプレクサ、 $N_D 1 \dots$  電源端子、 $N_D 1' \dots$  定電位端子、 $N_D 2 \dots$  電源端子、 $O_L E D \dots$  有機EL素子、 $O_R G \dots$  有機物層、 $P_E \dots$  画素電極、 $P_I \dots$  隔壁絶縁層、 $P_S \dots$  パッシベーション膜、 $P_S L \dots$  電源線、 $P_X \dots$  画素、 $R \dots$  抵抗素子、 $S_C \dots$  半導体層、 $S_E \dots$  ソース電極、 $S_L 1 \dots$  走査信号線、 $S_L 2 \dots$  走査信号線、 $S_U B \dots$  絶縁基板、 $SW_a \dots$  スイッチ、 $SW_b \dots$  スイッチ、 $SW_c \dots$  スイッチ、 $SW_{cs} \dots$  スイッチ、 $SW_{csF} \dots$  スイッチ、 $SW_{csR} \dots$  スイッチ、 $SW_{dg_t} \dots$  スイッチ、 $SW_{vs} \dots$  スイッチ、 $T_R_{dg_t} \dots$  定電流源、 $T_R_{ref} \dots$  基準トランジスタ、 $U_C \dots$  アンダーコート層、 $V_S \dots$  電圧源、 $X_D R \dots$  映像信号線ドライバ、 $Y_D R \dots$  走査信号線ドライバ。

【図1】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 2 1 F

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 中村 則夫

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 3K107 AA01 BB01 CC33 EE03 HH00 HH04 HH05

5C080 AA06 BB05 DD01 DD09 EE29 FF11 JJ02 JJ03 JJ04 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2007114288A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2007-05-10 |

| 申请号            | JP2005303107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2005-10-18 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 中村則夫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 中村 則夫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.612.F G09G3/20.623.B H05B33/14.A G09G3/20.621.F G09G3/3241 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH00 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD01 5C080/DD09 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/AB12 5C380/AB23 5C380/AB34 5C380/BC02 5C380/BC09 5C380/BC14 5C380/CA04 5C380/CA05 5C380/CA08 5C380/CA13 5C380/CA29 5C380/CA34 5C380/CB01 5C380/CB17 5C380/CB30 5C380/CC12 5C380/CC19 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC63 5C380/CD014 5C380/CF41 5C380/CF48 5C380/CF52 5C380/DA02 5C380/DA06 5C380/DA47 5C380/DA49 |         |            |

| 代理人(译)         | 河野 哲<br>中村诚                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

### 摘要(译)

解决的问题：提供一种显示装置，其中将电流信号写入视频信号，该显示装置可以在有效扫描周期中首先选择的行的像素中良好地显示，而不依赖于扫描方向。在每个像素PX包括驱动电路和显示元件OLED的显示装置中，电流源CS1和驱动电路在每个选择时段中经由视频信号线DL连接，以将视频信号提供给驱动电路。在各非选择期间中，进行使驱动电路与像素电极连接的写入动作，以使驱动电流流入显示元件OLED，在消隐期间中，电流源CS2与视频信号线DL连接。当执行预充电操作时，其中预充电信号被连接并且预充电信号被写入视频信号线DL，并且扫描信号线SL1的扫描方向接近视频信号线DL和电流源CS2之间的连接位置，扫描方向 使预充电信号大于在远离连接位置的方向上的预充电信号。

[选择图]图3