(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-32904

(P2010-32904A)

(43) 公開日 平成22年2月12日(2010.2.12)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | J 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 624B 5C080  |

| <b>G09F 9/30</b> (2006.01)  | G09G 3/20 | 611H 5C094  |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 642A        |

|                             | G09G 3/20 | 670K        |

審査請求 未請求 請求項の数 5 O L (全 20 頁) 最終頁に続く

|           |                              |          |                                        |

|-----------|------------------------------|----------|----------------------------------------|

| (21) 出願番号 | 特願2008-196643 (P2008-196643) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (22) 出願日  | 平成20年7月30日 (2008.7.30)       | (74) 代理人 | 100098785<br>弁理士 藤島 洋一郎                |

|           |                              | (74) 代理人 | 100109656<br>弁理士 三反崎 泰司                |

|           |                              | (74) 代理人 | 100130915<br>弁理士 長谷部 政男                |

|           |                              | (74) 代理人 | 100155376<br>弁理士 田名網 孝昭                |

|           |                              | (72) 発明者 | 杉本 秀樹<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

最終頁に続く

(54) 【発明の名称】表示装置およびその駆動方法ならびに電子機器

## (57) 【要約】

【課題】簡易な構成で、Vth補正に起因する減点化の可能性を低減することの可能な表示装置およびその駆動方法ならびに電子機器を提供する。

【解決手段】Vth補正準備期間のうちの所定の期間において、制御信号21eに応じてゲート線CSLの電圧をVon2からVoff2に下すことにより、トランジスタTcaをオフし、カソード線CTLをフローティングにする。これにより、トランジスタTcaがオフしている期間の分だけ、有機EL素子121R等に大きな逆バイアス電圧が印加される期間が短くなるので、Vth補正準備期間の間ずっと、有機EL素子121R等に大きな逆バイアスがかかり続けることがなくなる。

【選択図】図3

## 【特許請求の範囲】

## 【請求項 1】

発光素子および画素回路を画素ごとに有する表示部と、

映像信号に基づいて前記画素回路を駆動する駆動部と

を備え、

前記画素回路は、第1トランジスタと、第2トランジスタと、第3トランジスタと、保持容量とを有し、

前記駆動部は、第1駆動部と、第2駆動部と、第3駆動部と、第4駆動部と、制御部と

、第1配線と、第2配線と、第3配線と、第4配線と、第5配線を有し、

前記第1トランジスタのゲートが前記第1配線を介して前記第1駆動部に接続され、

前記第1トランジスタのドレインまたはソースが前記第3配線を介して前記第3駆動部

に接続され、

前記第1トランジスタのドレインおよびソースのうち前記第3駆動部に未接続の方が前

記第2トランジスタのゲートおよび前記保持容量の一端に接続され、

前記第2トランジスタのドレインまたはソースが前記第2配線を介して前記第2駆動部

に接続され、

前記第2トランジスタのドレインおよびソースのうち前記第2駆動部に未接続の方が前

記保持容量の他端および前記発光素子のアノードまたはカソードに接続され、

前記第3トランジスタのゲートが前記第4配線を介して前記第4駆動部に接続され、

前記第3トランジスタのドレインまたはソースが前記発光素子のアノードおよびカソ

ードのうち前記第2トランジスタに未接続の方に接続され、

前記第3トランジスタのドレインおよびソースのうち前記発光素子に未接続の方が前記

第5配線に接続され、

前記第1駆動部は、前記第1トランジスタをオンオフ制御する信号を出力可能であり、

前記第2駆動部は、前記発光素子の閾値電圧と前記第5配線の電圧とを足し合せた電圧

よりも低い第1電圧と、前記第1電圧以上の第2電圧とを出力可能であり、

前記第3駆動部は、前記映像信号に応じた大きさの第3電圧を出力可能であり、

前記第4駆動部は、前記第3トランジスタをオンオフ制御する信号を出力可能であり、

前記制御部は、前記第2駆動部が前記第1電圧を出力している期間のうちの所定の期間

、前記第4駆動部に対して、前記第3トランジスタをオフする信号を出力することを指示

する制御信号を出力する表示装置。

10

## 【請求項 2】

前記第2トランジスタがnチャネルトランジスタであり、

前記発光素子のアノードが前記第2トランジスタに接続されている請求項1に記載の表

示装置。

## 【請求項 3】

前記第2トランジスタがpチャネルトランジスタであり、

前記発光素子のアノードが前記第3トランジスタに接続されている請求項1に記載の表

示装置。

## 【請求項 4】

発光素子および画素回路を画素ごとに有する表示部と、

映像信号に基づいて前記画素回路を駆動する駆動部と

を備え、

前記画素回路は、第1トランジスタと、第2トランジスタと、第3トランジスタと、保持

容量とを有し、

前記駆動部は、第1駆動部と、第2駆動部と、第3駆動部と、第4駆動部と、第1配線

と、第2配線と、第3配線と、第4配線と、第5配線とを有し、

前記第1トランジスタのゲートが前記第1配線を介して前記第1駆動部に接続され、

前記第1トランジスタのドレインまたはソースが前記第3配線を介して前記第3駆動部

に接続され、

10

20

30

40

50

前記第1トランジスタのドレインおよびソースのうち前記第3駆動部に未接続の方が前記第2トランジスタのゲートおよび前記保持容量の一端に接続され、

前記第2トランジスタのドレインまたはソースが前記第2配線を介して前記第2駆動部に接続され、

前記第2トランジスタのドレインおよびソースのうち前記第2駆動部に未接続の方が前記保持容量の他端および前記発光素子のアノードまたはカソードに接続され、

前記第3トランジスタのゲートが前記第4配線を介して前記第4駆動部に接続され、

前記第3トランジスタのドレインまたはソースが前記発光素子のアノードおよびカソードのうち前記第2トランジスタに未接続の方に接続され、

前記第3トランジスタのドレインおよびソースのうち前記発光素子に未接続の方が前記第5配線に接続され、

前記第1駆動部は、前記第1トランジスタをオンオフ制御する信号を出力可能であり、

前記第2駆動部は、前記発光素子の閾値電圧と前記第5配線の電圧とを足し合せた電圧よりも低い第1電圧と、前記第1電圧以上の第2電圧とを出力可能であり、

前記第3駆動部は、前記映像信号に応じた大きさの第3電圧を出力可能であり、

前記第4駆動部は、前記第3トランジスタをオンオフ制御する信号を出力可能である表示装置の前記第4駆動部が、前記第2駆動部が前記第1電圧を出力している期間のうちの所定の期間、前記第3トランジスタをオフする信号を出力することを指示する制御信号を出力する表示装置の駆動方法。

#### 【請求項5】

表示装置を備え、

前記表示装置は、

発光素子および画素回路を画素ごとに有する表示部と、

映像信号に基づいて前記画素回路を駆動する駆動部と

を備え、

前記画素回路は、第1トランジスタと、第2トランジスタと、第3トランジスタと、保持容量とを有し、

前記駆動部は、第1駆動部と、第2駆動部と、第3駆動部と、第4駆動部と、制御部と、第1配線と、第2配線と、第3配線と、第4配線と、第5配線を有し、

前記第1トランジスタのゲートが前記第1配線を介して前記第1駆動部に接続され、

前記第1トランジスタのドレインまたはソースが前記第3配線を介して前記第3駆動部に接続され、

前記第1トランジスタのドレインおよびソースのうち前記第3駆動部に未接続の方が前記第2トランジスタのゲートおよび前記保持容量の一端に接続され、

前記第2トランジスタのドレインまたはソースが前記第2配線を介して前記第2駆動部に接続され、

前記第2トランジスタのドレインおよびソースのうち前記第2駆動部に未接続の方が前記保持容量の他端および前記発光素子のアノードまたはカソードに接続され、

前記第3トランジスタのゲートが前記第4配線を介して前記第4駆動部に接続され、

前記第3トランジスタのドレインまたはソースが前記発光素子のアノードおよびカソードのうち前記第2トランジスタに未接続の方に接続され、

前記第3トランジスタのドレインおよびソースのうち前記発光素子に未接続の方が前記第5配線に接続され、

前記第1駆動部は、前記第1トランジスタをオンオフ制御する信号を出力可能であり、

前記第2駆動部は、前記発光素子の閾値電圧と前記第5配線の電圧とを足し合せた電圧よりも低い第1電圧と、前記第1電圧以上の第2電圧とを出力可能であり、

前記第3駆動部は、前記映像信号に応じた大きさの第3電圧を出力可能であり、

前記第4駆動部は、前記第3トランジスタをオンオフ制御する信号を出力可能であり、

前記制御部は、前記第2駆動部が前記第1電圧を出力している期間のうちの所定の期間、前記第4駆動部に対して、前記第3トランジスタをオフする信号を出力することを指示

10

20

30

40

50

する制御信号を出力する電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光素子および画素回路を画素ごとに有する表示部と、画素回路を駆動する駆動部とを備えた表示装置およびその駆動方法に関する。また、本発明は、上記表示装置を備えた電子機器に関する。

【背景技術】

【0002】

近年、画像表示を行う表示装置の分野では、画素の発光素子として、流れる電流値に応じて発光輝度が変化する電流駆動型の光学素子、例えば有機EL(electro luminescence)素子を用いた表示装置が開発され、商品化が進められている。10

【0003】

有機EL素子は、液晶素子などと異なり自発光素子である。そのため、有機EL素子を用いた表示装置(有機EL表示装置)では、光源(バックライト)が必要ないので、光源を必要とする液晶表示装置と比べて画像の視認性が高く、消費電力が低く、かつ素子の応答速度が速い。

【0004】

有機EL表示装置では、液晶表示装置と同様、その駆動方式として単純(パッシブ)マトリクス方式とアクティブマトリクス方式がある。前者は、構造が単純であるものの、大型かつ高精細の表示装置の実現が難しいなどの問題がある。そのため、現在では、アクティブマトリクス方式の開発が盛んに行なわれている。この方式は、画素ごとに配した発光素子に流れる電流を、発光素子ごとに設けた駆動回路内に設けた能動素子(一般にはTFT(Thin Film Transistor;薄膜トランジスタ))によって制御するものである。20

【0005】

ところで、一般的に、有機EL素子の電流-電圧(I-V)特性は、時間の経過に従つて劣化(経時劣化)する。有機EL素子を電流駆動する画素回路では、有機EL素子のI-V特性が経時変化すると、有機EL素子と、有機EL素子に直列に接続された駆動トランジスタとの分圧比が変化するので、駆動トランジスタのゲート-ソース間電圧 $V_{gs}$ も変化する。その結果、駆動トランジスタに流れる電流値が変化するので、有機EL素子に流れる電流値も変化し、その電流値に応じて発光輝度も変化する。30

【0006】

また、駆動トランジスタの閾値電圧 $V_{th}$ や移動度 $\mu$ が経時的に変化したり、製造プロセスのばらつきによって閾値電圧 $V_{th}$ や移動度 $\mu$ が画素回路ごとに異なったりする場合がある。駆動トランジスタの閾値電圧 $V_{th}$ や移動度 $\mu$ が画素回路ごとに異なる場合には、駆動トランジスタに流れる電流値が画素回路ごとにばらつくので、駆動トランジスタのゲートに同じ電圧を印加しても、有機EL素子の発光輝度がばらつき、画面の一様性(ユニフォーミティ)が損なわれる。

【0007】

そこで、有機EL素子のI-V特性が経時変化したり、駆動トランジスタの閾値電圧 $V_{th}$ や移動度 $\mu$ が経時変化したりしても、それらの影響を受けることなく、有機EL素子の発光輝度を一定に保つようにするために、有機EL素子のI-V特性の変動に対する補償機能および駆動トランジスタの閾値電圧 $V_{th}$ や移動度 $\mu$ の変動に対する補正機能を組み込んだ表示装置が開発されている(例えば、特許文献1参照)。40

【0008】

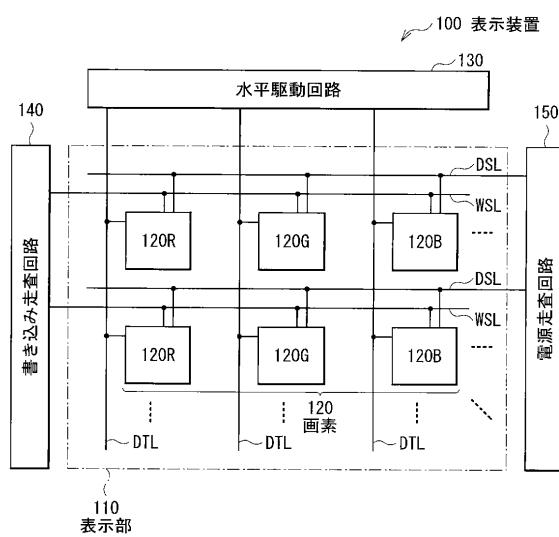

図11は、特許文献1に記載の表示装置の概略構成を表したものである。図11に記載の表示装置100は、複数の画素120がマトリクス状に配置された表示部110と、各画素120を駆動する駆動部(水平駆動回路130、書き込み走査回路140および電源走査回路150)とを備えている。

【0009】

50

各画素 120 は、赤色用の画素 120R、緑色用の画素 120G および青色用の画素 120B からなる。各画素 120R, 120G, 120B は、図 11 に示したように、有機 EL 素子 121（有機 EL 素子 121R, 121G, 121B）およびそれに接続された画素回路 122 により構成されている。画素回路 122 は、サンプリング用のトランジスタ  $T_{WS}$ 、保持容量  $C_s$ 、駆動用のトランジスタ  $T_{Dr}$  によって構成されたものであり、2Tr1C の回路構成となっている。書き込み走査回路 140 から引き出されたゲート線  $W_{SL}$  が行方向に延在して形成されており、トランジスタ  $T_{WS}$  のゲートに接続されている。電源走査回路 150 から引き出された電源線  $P_{SL}$  も行方向に延在して形成されており、トランジスタ  $T_{Dr}$  のドレインに接続されている。また、水平駆動回路 130 から引き出された信号線  $D_{TL}$  は列方向に延在して形成されており、トランジスタ  $T_{WS}$  のドレインに接続されている。トランジスタ  $T_{WS}$  のソースは駆動用のトランジスタ  $T_{Dr}$  のゲートと、保持容量  $C_s$  の一端に接続されており、トランジスタ  $T_{Dr}$  のソースと保持容量  $C_s$  の他端とが有機 EL 素子 121R, 121G, 121B（以下、有機 EL 素子 121R 等と略する。）のアノードに接続されている。有機 EL 素子 121R 等のカソードは、カソード線  $C_{TL}$  に接続されている。

10

## 【0010】

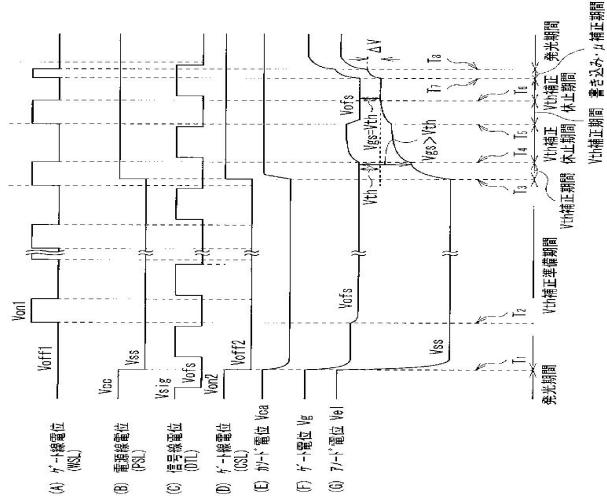

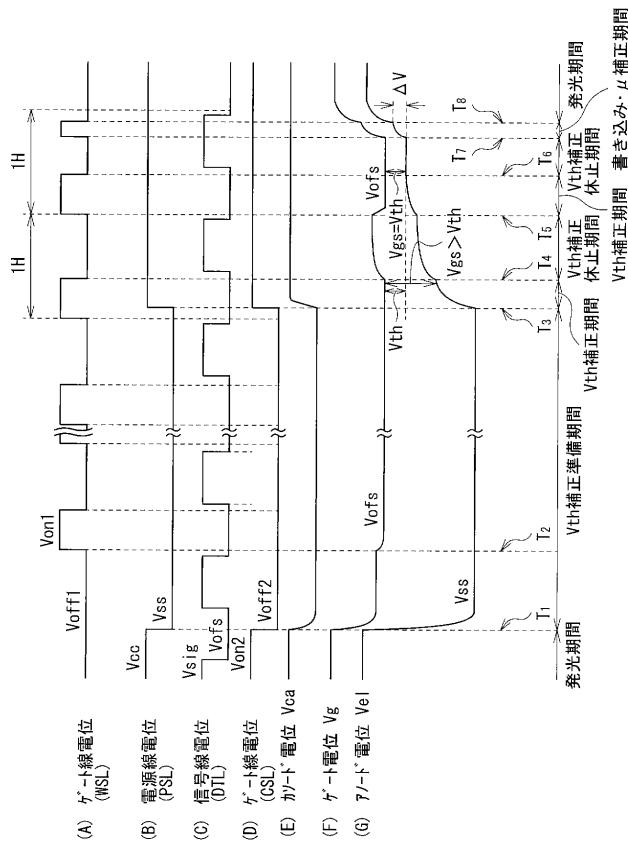

図 12 は、図 11 に記載の表示装置 100 における各種波形の一例を表したものである。図 12 には、ゲート線  $W_{SL}$  に 2 種類の電圧 ( $V_{on}$ 、 $V_{off} (< V_{on})$ ) が、電源線  $P_{SL}$  に 2 種類の電圧 ( $V_{cc}$ 、 $V_{ss} (< V_{threshold} + V_c)$ ) が、信号線  $D_{TL}$  に 2 種類の電圧 ( $V_{sing}$ 、 $V_{ofs}$ ) が印加されている様子が示されている。なお、 $V_{threshold}$  は有機 EL 素子 121R 等の閾値電圧であり、 $V_{ca}$  は有機 EL 素子 121R 等のカソード電圧である。さらに、図 12 には、ゲート線  $W_{SL}$ 、電源線  $P_{SL}$  および信号線  $D_{TL}$  への電圧印加に応じて、トランジスタ  $T_{Dr}$  のゲート電圧  $V_g$  および有機 EL 素子 121R 等のアノード電圧  $V_{e1}$  が時々刻々変化している様子が示されている。

20

## 【0011】

## (Vth 補正準備期間)

まず、 $V_{th}$  補正の準備を行う。具体的には、電源走査回路 150 が電源線  $P_{SL}$  の電圧を  $V_{cc}$  から  $V_{ss}$  に下げる ( $T_1$ )。すると、ソース電圧  $V_s$  が  $V_{ss}$  まで下がり、有機 EL 素子 121 等が消光する。このとき、保持容量  $C_s$  を介したカップリングによりゲート電圧  $V_g$  も下がる。次に、信号線  $D_{TL}$  の電圧が  $V_{ofs}$  となっている間に、書き込み走査回路 140 がゲート線  $W_{SL}$  の電圧を  $V_{off}$  から  $V_{on}$  に上げる ( $T_2$ )。すると、トランジスタ  $T_{WS}$  がオンし、トランジスタ  $T_{Dr}$  のゲート電圧  $V_g$  が  $V_{ofs}$  まで下がる。

30

## 【0012】

## (最初の Vth 補正期間)

次に、 $V_{th}$  の補正を行う。具体的には、信号線  $D_{TL}$  の電圧が  $V_{ofs}$  となっている間に、電源走査回路 150 が電源線  $P_{SL}$  の電圧を  $V_{ss}$  から  $V_{cc}$  に上げる ( $T_3$ )。すると、トランジスタ  $T_{Dr}$  のドレイン - ソース間に電流  $I_{ds}$  が流れるので、保持容量  $C_s$  と有機 EL 素子 121R 等の素子容量（図示せず）とが充電され、ソース電圧  $V_s$  が上昇する。一定時間が経過したのち、書き込み走査回路 140 がゲート線  $W_{SL}$  の電圧を  $V_{on}$  から  $V_{off}$  に下げる ( $T_4$ )。すると、トランジスタ  $T_{WS}$  がオフするので、トランジスタ  $T_{Dr}$  のゲートがフローティングとなり、 $V_{th}$  の補正が一旦停止する。

40

## 【0013】

## (最初の Vth 補正休止期間)

$V_{th}$  補正が休止している期間中は、先の  $V_{th}$  補正を行った行（画素）とは異なる他の行（画素）において、信号線  $D_{TL}$  の電圧のサンプリングが行われる。なお、 $V_{th}$  補正が不十分である場合、すなわち、トランジスタ  $T_{Dr}$  のゲート - ソース間の電位差  $V_g$  がトランジスタ  $T_{Dr}$  の閾値電圧  $V_{th}$  よりも大きい場合には、 $V_{th}$  補正休止期間中にも、先の  $V_{th}$  補正を行った行（画素）において、トランジスタ  $T_{Dr}$  のドレイン - ソース間に電流  $I_{ds}$  が流れ、ソース電圧  $V_s$  が上昇し、保持容量  $C_s$  を介したカップリン

50

グによりゲート電圧  $V_{g_s}$  も上昇する。なお、このとき、有機EL素子121R等には、逆バイアスがかかっているので、有機EL素子121R等が発光することはない。

#### 【0014】

##### (2回目のVth補正期間)

Vth補正休止期間が終了した後、Vthの補正を再び行う。具体的には、信号線DTLの電圧が  $V_{off_s}$  となっており、Vth補正が可能となっている時に、書き込み走査回路140がゲート線WSLの電圧を  $V_{off_f}$  から  $V_n$  に上げ ( $T_5$ )、トランジスタ  $T_{Dr}$  のゲートを信号線DTLに接続する。このとき、ソース電圧  $V_s$  が  $V_{off_s} - V_{th}$  よりも低い場合 (Vth補正がまだ完了していない場合) には、トランジスタ  $T_{Dr}$  がカットオフするまで (電位差  $V_{g_s}$  が  $V_{th}$  になるまで)、トランジスタ  $T_{Dr}$  のドレイン - ソース間に電流  $I_{ds}$  が流れ。その結果、保持容量  $C_s$  が  $V_{th}$  に充電され、電位差  $V_{g_s}$  が  $V_{th}$  となる。その後、水平駆動回路130が信号線DTLの電圧を  $V_{off_s}$  から  $V_{sing}$  に切り替える前に、書き込み走査回路140がゲート線WSLの電圧を  $V_n$  から  $V_{off_f}$  に下げる ( $T_6$ )。すると、トランジスタ  $T_{Dr}$  のゲートがフローティングとなるので、電位差  $V_{g_s}$  を信号線DTLの電圧の大きさに拘わらず  $V_{th}$  のままで維持することができる。このように、電位差  $V_{g_s}$  を  $V_{th}$  に設定することにより、トランジスタ  $T_{Dr}$  の閾値電圧  $V_{th}$  が画素回路122ごとにばらついた場合であっても、有機EL素子121等の発光輝度がばらつくのをなくすことができる。

10

#### 【0015】

##### (2回目のVth補正休止期間)

20

その後、Vth補正の休止期間中に、水平駆動回路130が信号線DTLの電圧を  $V_{off_s}$  から  $V_{sing}$  に切り替える。

#### 【0016】

##### (書き込み・μ補正期間)

Vth補正休止期間が終了した後、書き込みとμ補正を行う。具体的には、信号線DTLの電圧が  $V_{sing}$  となっている間に、書き込み走査回路140がゲート線WSLの電圧を  $V_{off_f}$  から  $V_n$  に上げ ( $T_7$ )、トランジスタ  $T_{Dr}$  のゲートを信号線DTLに接続する。すると、トランジスタ  $T_{Dr}$  のゲート電圧  $V_g$  が  $V_{sing}$  となる。このとき、有機EL素子121R等のアノード電圧  $V_{e1}$  はこの段階ではまだ有機EL素子121R等の閾値電圧  $V_{e1}$  よりも小さく、有機EL素子121R等はカットオフしている。そのため、電流  $I_{ds}$  は有機EL素子121R等の素子容量 (図示せず) に流れ、素子容量が充電されるので、ソース電圧  $V_s$  が  $V$  だけ上昇し、やがて電位差  $V_{g_s}$  が  $V_{sing} + V_{th} - V$  となる。このようにして、書き込みと同時にμ補正が行われる。ここで、トランジスタ  $T_{Dr}$  の移動度  $\mu$  が大きい程、 $V$  も大きくなるので、電位差  $V_{g_s}$  を発光前に  $V$  だけ小さくすることにより、画素ごとの移動度  $\mu$  のばらつきを取り除くことができる。

30

#### 【0017】

##### (発光)

最後に、書き込み走査回路140がゲート線WSLの電圧を  $V_n$  から  $V_{off_f}$  に下げる ( $T_8$ )。すると、トランジスタ  $T_{Dr}$  のゲートがフローティングとなり、トランジスタ  $T_{Dr}$  のドレイン - ソース間に電流  $I_{ds}$  が流れ、ソース電圧  $V_s$  が上昇する。その結果、有機EL素子121R等が所望の輝度で発光する。

40

#### 【0018】

【特許文献1】特開2008-083272号公報

【特許文献2】特開2004-157467号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0019】

ところで、上述したVth補正準備期間では、トランジスタ  $T_{Dr}$  の電位差  $V_{g_s}$  が  $V_{th}$  を超えるようにするために、トランジスタ  $T_{Dr}$  のソース電位 (=アノード電圧  $V_{e1}$ ) をマイナスの電位にしている。そのため、有機EL素子121R等には、この期間の

50

間ずっと逆バイアスがかかり続けている。逆バイアスがかかり続けている期間は、発光期間と消光期間のデューティ比（発光期間 / 消光期間 × 100）によって異なるが、例えば、デューティ比が 25% の場合には、一周期中の 75% もの間に、有機 EL 素子 121R 等に逆バイアスがかかり続けることになる。

#### 【0020】

一般に、有機 EL 素子に逆バイアスをかけたときに絶縁破壊（滅点化）が生じる確率は、逆バイアスの大きさおよび印加時間が大きくなるほど大きくなる。そのため、上記したように、長い時間、有機 EL 素子 121R 等に逆バイアスをかけ続けた場合には、有機 EL 素子 121R 等が滅点化する可能性が高く、歩留りの低下を招きかねない。そこで、例えば、特許文献 2 では、カソード電圧を 2 値の電圧で制御することにより、逆バイアスを低減する方策が提案されている。しかし、そのようにするためにには、新たに外部電源を用意することが必要となるので、回路構成が複雑となるという問題がある。10

#### 【0021】

本発明はかかる問題点に鑑みてなされたもので、その目的は、簡易な構成で、Vth 補正に起因する滅点化の可能性を低減することの可能な表示装置およびその駆動方法ならびに電子機器を提供することにある。

#### 【課題を解決するための手段】

#### 【0022】

本発明の表示装置は、発光素子および画素回路を画素ごとに有する表示部と、画素回路を駆動する駆動部とを備えたものである。画素回路には、第 1 ランジスタと、第 2 ランジスタと、保持容量とが設けられている。駆動部には、第 1 駆動部と、第 2 駆動部と、第 3 駆動部と、第 4 駆動部と、制御部と、第 1 配線と、第 2 配線と、第 3 配線と、第 4 配線と、第 5 配線とが設けられている。第 1 ランジスタのゲートが第 1 配線を介して第 1 駆動部に接続されている。第 1 ランジスタのドレインまたはソースが第 3 配線を介して第 3 駆動部に接続されている。第 1 ランジスタのドレインおよびソースのうち第 3 駆動部に未接続の方が第 2 ランジスタのゲートおよび前記保持容量の一端に接続されている。第 2 ランジスタのドレインまたはソースが第 2 配線を介して第 2 駆動部に接続されている。第 2 ランジスタのドレインおよびソースのうち第 2 駆動部に未接続の方が保持容量の他端および発光素子のアノードまたはカソードに接続されている。第 3 ランジスタのゲートが第 4 配線を介して第 4 駆動部に接続されている。第 3 ランジスタのドレインまたはソースが発光素子のアノードおよびカソードのうち第 2 ランジスタに未接続の方に接続されている。第 3 ランジスタのドレインおよびソースのうち発光素子に未接続の方が第 5 配線に接続されている。第 1 駆動部は、第 1 ランジスタをオンオフ制御する信号を出力可能となっている。第 2 駆動部は、発光素子の閾値電圧と第 5 配線の電圧とを足し合せた電圧よりも低い第 1 電圧と、第 1 電圧以上の第 2 電圧とを出力可能となっている。第 3 駆動部は、映像信号に応じた大きさの第 3 電圧を出力可能となっている。第 4 駆動部は、第 3 ランジスタをオンオフ制御する信号を出力可能となっている。制御部は、第 2 駆動部が第 1 電圧を出力している期間のうちの所定の期間、第 4 駆動部に対して、第 3 ランジスタをオフする信号を出力することを指示する制御信号を出力するようになっている。203040

#### 【0023】

本発明の電子機器は、上記表示装置を備えたものである。

#### 【0024】

本発明の表示装置の駆動方法は、以下の構成を備えた表示装置の第 4 駆動部において、第 2 駆動部が第 1 電圧を出力している期間のうちの所定の期間、第 3 ランジスタをオフする信号を出力するステップを実行するものである。

#### 【0025】

上記駆動方法が用いられる表示装置は、発光素子および画素回路を画素ごとに有する表示部と、画素回路を駆動する駆動部とを備えたものである。画素回路には、第 1 ランジスタと、第 2 ランジスタと、保持容量とが設けられている。駆動部には、第 1 駆動部と

10

20

30

40

50

、第2駆動部と、第3駆動部と、第4駆動部と、第1配線と、第2配線と、第3配線と、第4配線と、第5配線とが設けられている。第1トランジスタのゲートが第1配線を介して第1駆動部に接続されている。第1トランジスタのドレインまたはソースが第3配線を介して第3駆動部に接続されている。第1トランジスタのドレインおよびソースのうち第3駆動部に未接続の方が第2トランジスタのゲートおよび前記保持容量の一端に接続されている。第2トランジスタのドレインまたはソースが第2配線を介して第2駆動部に接続されている。第2トランジスタのドレインおよびソースのうち第2駆動部に未接続の方が保持容量の他端および発光素子のアノードまたはカソードに接続されている。第3トランジスタのゲートが第4配線を介して第4駆動部に接続されている。第3トランジスタのドレインまたはソースが発光素子のアノードおよびカソードのうち第2トランジスタに未接続の方に接続されている。第3トランジスタのドレインおよびソースのうち発光素子に未接続の方が第5配線に接続されている。第1駆動部は、第1トランジスタをオンオフ制御する信号を出力可能となっている。第2駆動部は、発光素子の閾値電圧と第5配線の電圧とを足し合せた電圧よりも低い第1電圧と、第1電圧以上の第2電圧とを出力可能となっている。第3駆動部は、映像信号に応じた大きさの第3電圧を出力可能となっている。第4駆動部は、第3トランジスタをオンオフ制御する信号を出力可能となっている。制御部は、第2駆動部が第1電圧を出力している期間のうちの所定の期間、第4駆動部に対して、第3トランジスタをオフする信号を出力することを指示する制御信号を出力するようになっている。

10

20

30

【0026】

本発明の表示装置およびその駆動方法ならびに電子機器では、第2駆動部が第1電圧を出力している期間のうちの所定の期間、第3トランジスタをオフする信号が出力される。これにより、発光素子のアノードおよびカソードのうち第3トランジスタに接続されている方がフローティングとなるので、第3トランジスタがオフしている期間の分だけ、発光素子に大きな逆バイアス電圧が印加される期間が短くなる。また、第3トランジスタをオンオフする信号電圧を生成する電源回路は他の制御信号を生成する電源回路と共用することが可能であることから、新たな外部電源を設ける必要がない。

40

## 【発明の効果】

## 【0027】

本発明の表示装置およびその駆動方法ならびに電子機器によれば、第2駆動部が第1電圧を出力している期間のうちの所定の期間、第3トランジスタをオフする信号を出力するようにしたので、新たな外部電源を設けることなく、第2駆動部が第1電圧を出力している期間の間ずっと、発光素子に大きな逆バイアス電圧がかかり続けることをなくすることができる。従って、簡易な構成で、滅点化の可能性を低減することができる。

50

## 【発明を実施するための最良の形態】

## 【0028】

以下、本発明の実施の形態について、図面を参照して詳細に説明する。

## 【0029】

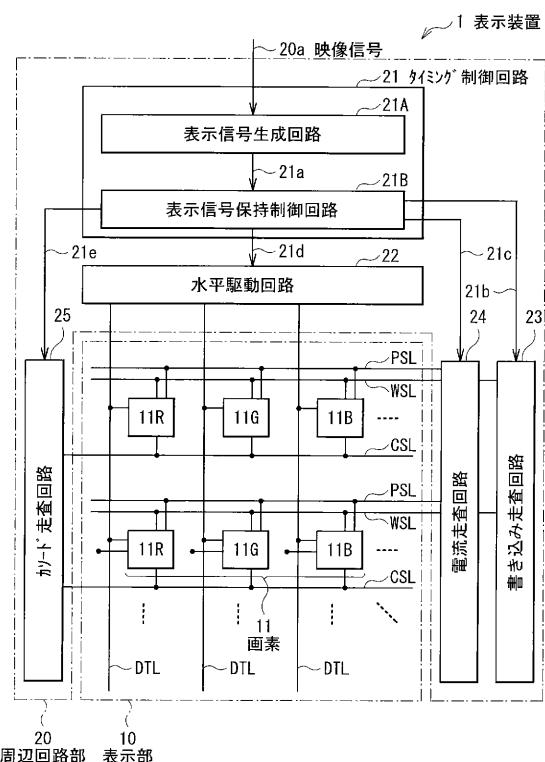

図1は、本発明の一実施の形態に係る表示装置1の全体構成の一例を表したものである。この表示装置1は、例えば、ガラス、シリコン(Si)ウェハあるいは樹脂などによる基板(図示せず)上に、表示部10と、表示部10の周辺に形成された周辺回路部20(駆動部)とを備えている。

## 【0030】

表示部10は、複数の画素11を表示部10の全面に渡ってマトリクス状に配置したものであり、外部から入力された映像信号20aに基づく画像をアクティブマトリクス駆動により表示するものである。各画素11は、赤色用の画素11Rと、緑色用の画素11Gと、青色用の画素11Bとを含んでいる。

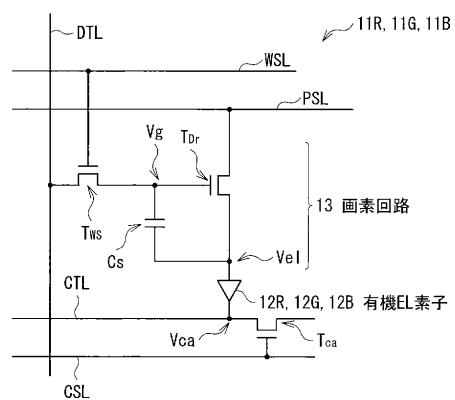

## 【0031】

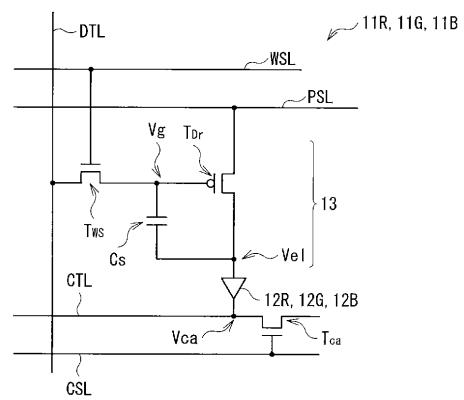

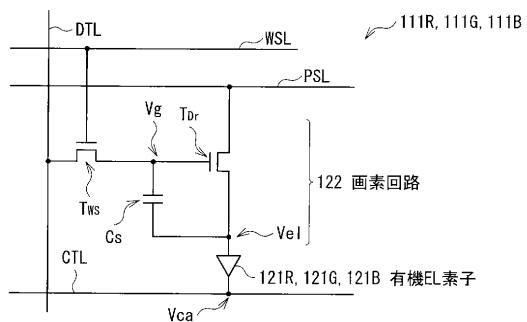

図2は、画素11R, 11G, 11Bの内部構成の一例を表したものである。画素11R, 11G, 11B内には、図2に示したように、有機EL素子12R, 12G, 12B

50

(発光素子)と、画素回路13とが設けられている。

【0032】

有機EL素子12R, 12G, 12B(以下、有機EL素子12R等と称する。)は、例えば、図示しないが、陽極(アノード)、有機層および陰極(カソード)が積層された構成を有している。有機層は、例えば、陽極の側から順に、正孔注入効率を高める正孔注入層と、発光層への正孔輸送効率を高める正孔輸送層と、電子と正孔との再結合による発光を生じさせる発光層と、発光層への電子輸送効率を高める電子輸送層とを積層してなる積層構造を有している。

【0033】

画素回路13は、サンプリング用のトランジスタ $T_{WS}$ (第1トランジスタ)、保持容量 $C_s$ 、駆動用のトランジスタ $T_{Dr}$ (第2トランジスタ)によって構成されたものであり、2Tr1Cの回路構成となっている。トランジスタ $T_{WS}$ ,  $T_{Dr}$ は、nチャネルトランジスタ(例えば、nチャネルMOS型の薄膜トランジスタ(TFT(Thin Film Transistor)))により形成されている。

10

【0034】

周辺回路部20は、タイミング制御回路21(制御部)と、水平駆動回路22(第3駆動部)と、書き込み走査回路23(第1駆動部)と、電源走査回路24(第2駆動部)と、カソード走査回路25(第4駆動部)とを有している。タイミング制御回路21は、表示信号生成回路21Aと、表示信号保持制御回路21Bとを含んでいる。また、周辺回路部20には、ゲート線W<sub>SL</sub>(第1配線)と、電源線P<sub>SL</sub>(第2配線)と、信号線D<sub>TL</sub>(第3配線)と、ゲート線C<sub>SL</sub>(第4配線)と、カソード線C<sub>TL</sub>(第5配線)と、逆バイアス用のトランジスタ $T_{ca}$ (第3トランジスタ)と、電圧源(図示せず)とが設けられている。なお、逆バイアス用のトランジスタ $T_{ca}$ は、例えば、nチャネルMOS型のTFTにより形成されている。

20

【0035】

表示信号生成回路21Aは、外部から入力された映像信号20aに基づいて、例えば1画面ごと(1フィールドの表示ごと)に表示部10に表示するための表示信号21aを生成するものである。

【0036】

表示信号保持制御回路21Bは、表示信号生成回路21Aから出力された表示信号21aを1画面ごと(1フィールドの表示ごと)に、例えばSRAM(Static Random Access Memory)などから構成されたフィールドメモリに格納して保持するものである。この表示信号保持制御回路21Bはまた、各画素11を駆動する水平駆動回路22、書き込み走査回路23、電源走査回路24およびカソード走査回路25が連動して動作するように制御する役割も果たしている。具体的には、表示信号保持制御回路21Bは、書き込み走査回路23に対しては制御信号21bを、電源走査回路24に対しては制御信号21cを、水平駆動回路22に対しては制御信号21dを、カソード走査回路25に対しては制御信号21eをそれぞれ出力するようになっている。

30

【0037】

水平駆動回路22は、表示信号保持制御回路21Bから出力された制御信号21dに応じて、2種類の電圧( $V_{ofs}$ 、 $V_{sing}$ (第3電圧))を出力可能となっている。具体的には、水平駆動回路22は、表示部10の各画素11に接続された信号線D<sub>TL</sub>を介して、書き込み走査回路23により選択された画素11へ2種類の電圧( $V_{ofs}$ 、 $V_{sing}$ )を供給するようになっている。

40

【0038】

ここで、 $V_{sing}$ は、映像信号20aに対応する電圧値となっている。 $V_{sing}$ の最小電圧は $V_{ofs}$ よりも低い電圧値となっており、 $V_{sing}$ の最大電圧は $V_{ofs}$ よりも高い電圧値となっている。

【0039】

書き込み走査回路23は、表示信号保持制御回路21Bから出力された制御信号21b

50

に応じて、2種類の電圧( $V_{o_{n1}}$ 、 $V_{o_{ff1}}$ )を出力可能となっている。具体的には、書き込み走査回路23は、表示部10の各画素11に接続されたゲート線WSLを介して、駆動対象の画素11へ2種類の電圧( $V_{o_{n1}}$ 、 $V_{o_{ff1}}$ )を供給し、サンプリング用のトランジスタ $T_{ws}$ のオンオフ制御を行うようになっている。

#### 【0040】

ここで、 $V_{o_{n1}}$ は、トランジスタ $T_{ws}$ のオン電圧以上の値となっている。 $V_{o_{n1}}$ は、後述の「最初のVth補正期間」や「書き込み・μ補正期間」などに書き込み走査回路23から出力される電圧値である。 $V_{o_{ff1}}$ は、トランジスタ $T_{ws}$ のオン電圧よりも低い値となっており、かつ、 $V_{o_{n1}}$ よりも低い値となっている。 $V_{o_{ff1}}$ は、後述の「Vth補正休止期間」や「発光期間」などに書き込み走査回路23から出力される電圧値である。

10

#### 【0041】

電源走査回路24は、表示信号保持制御回路21Bから出力された制御信号21cに応じて、2種類の電圧( $V_{cc}$ (第2電圧)、 $V_{ss}$ (第1電圧))を出力可能となっている。具体的には、電源走査回路24は、表示部10の各画素11に接続された電源線PSLを介して、駆動対象の画素11へ2種類の電圧( $V_{cc}$ 、 $V_{ss}$ )を供給し、有機EL素子12R等の発光および消光を制御するようになっている。

#### 【0042】

ここで、 $V_{ss}$ は、有機EL素子12R等の閾値電圧 $V_{e1}$ と、有機EL素子12R等のカソード電圧 $V_{ca}$ とを足し合わせた電圧( $V_{e1} + V_{ca}$ )よりも低い電圧値である。また、 $V_{cc}$ は、電圧( $V_{e1} + V_{ca}$ )以上の電圧値である。

20

#### 【0043】

カソード走査回路25は、表示信号保持制御回路21Bから出力された制御信号21eに応じて、2種類の電圧( $V_{o_{n2}}$ 、 $V_{o_{ff2}}$ )を出力可能となっている。具体的には、カソード走査回路25は、表示部10の各画素11に接続されたゲート線CSLを介して、駆動対象の画素11へ2種類の電圧( $V_{o_{n2}}$ 、 $V_{o_{ff2}}$ )を供給し、逆バイアス用のトランジスタ $T_{ca}$ のオンオフ制御を行うようになっている。

#### 【0044】

ここで、 $V_{o_{n2}}$ は、トランジスタ $T_{ca}$ のオン電圧以上の値となっている。 $V_{o_{n2}}$ は、後述の「Vth補正準備期間」などにカソード走査回路25から出力される電圧値である。 $V_{o_{ff2}}$ は、トランジスタ $T_{ca}$ のオン電圧よりも低い値であって、かつ電圧源から電圧の供給を受けずに設定することの可能な値(例えばゼロボルト)となっている。 $V_{o_{ff2}}$ は、後述の「Vth補正準備期間」以外の期間に書き込み走査回路23から出力される電圧値である。

30

#### 【0045】

次に、図2を参照して、各構成要素の接続関係について説明する。書き込み走査回路23から引き出されたゲート線WSLは、行方向に延在して形成されており、トランジスタ $T_{ws}$ のゲートに接続されている。電源走査回路24から引き出された電源線PSLも行方向に延在して形成されており、トランジスタ $T_{Dr}$ のソースまたはドレインに接続されている。また、水平駆動回路22から引き出された信号線DTLは列方向に延在して形成されており、トランジスタ $T_{ws}$ のソースまたはドレインに接続されている。トランジスタ $T_{ws}$ のソースおよびドレインのうち信号線DTLに未接続の方は駆動用のトランジスタ $T_{Dr}$ のゲートと、保持容量 $C_s$ の一端に接続されており、トランジスタ $T_{Dr}$ のソースおよびドレインのうち電源線PSLと未接続の方と保持容量 $C_s$ の他端とが有機EL素子12R等のアノードに接続されている。有機EL素子12R等のカソードは、カソード線CTLに接続されている。

40

#### 【0046】

カソード走査回路25から引き出されたゲート線CSLは、行方向に延在して形成されており、トランジスタ $T_{ca}$ のゲートに接続されている。このトランジスタ $T_{ca}$ はカソード線CTL内に直列挿入されており、行ごとに一つずつ設けられている。このトランジ

50

スタ  $T_{c,a}$  のソースまたはドレインが有機 EL 素子 12R 等のカソードに接続されており、トランジスタ  $T_{c,a}$  のソースおよびドレインのうち有機 EL 素子 12R 等のカソードと未接続の方がカソード線 CTL を介して電圧源（図示せず）に接続されている。

#### 【0047】

この電圧源は、カソード線 CTL に対して所定の電圧（例えばグラウンド電圧）を供給するようになっている。なお、この電圧源は、水平駆動回路 22、書き込み走査回路 23、電源走査回路 24 およびカソード走査回路 25 にも接続されており、水平駆動回路 22 に対して  $V_{o_{f_s}}$ 、 $V_{s_{ing}}$  を供給し、書き込み走査回路 23 に対して  $V_{o_{n_1}}$ 、 $V_{o_{f_{f_1}}}$  を供給し、電源走査回路 24 に対して  $V_{c_c}$ 、 $V_{s_s}$  を供給し、カソード走査回路 25 に対して  $V_{o_{n_2}}$  を供給するようになっている。ここで、カソード走査回路 25 に対して供給する  $V_{o_{n_2}}$  は、書き込み走査回路 23 に対して供給する  $V_{o_{n_1}}$  などと同じ大きさでよいことから、 $V_{o_{n_2}}$  を供給する回路は  $V_{o_{n_1}}$  を供給する回路と共通になっている。つまり、 $V_{o_{n_2}}$  を供給するための回路が電圧源内に別個に設けられていない。なお、 $V_{o_{f_{f_2}}}$  は、電圧源から供給される電圧ではないことから、 $V_{o_{f_{f_2}}}$  を供給する回路についても電圧源内に設けられていない。

10

#### 【0048】

次に、本実施の形態の表示装置 1 の動作（消光から発光までの動作）について説明する。本実施の形態では、有機 EL 素子 12R 等の I - V 特性が経時変化したり、トランジスタ  $T_{D,r}$  の閾値電圧  $V_{t_h}$  や移動度  $\mu$  が経時変化したりしても、それらの影響を受けることなく、有機 EL 素子 12R 等の発光輝度を一定に保つようにするために、有機 EL 素子 12R 等の I - V 特性の変動に対する補償動作およびトランジスタ  $T_{D,r}$  の閾値電圧  $V_{t_h}$  や移動度  $\mu$  の変動に対する補正動作を組み込んでいる。

20

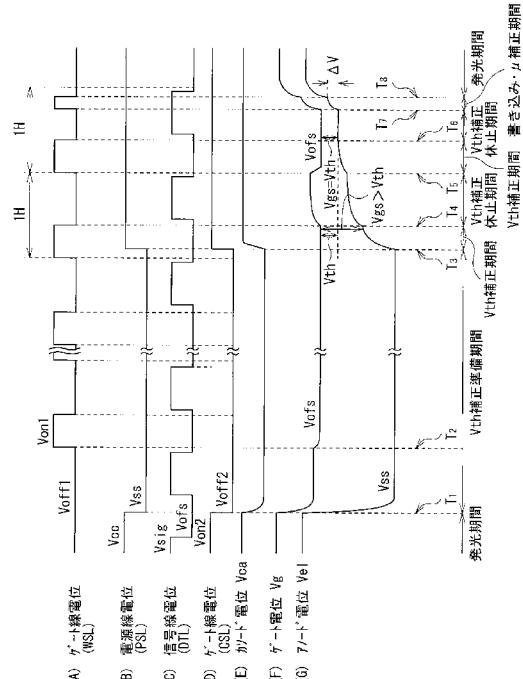

#### 【0049】

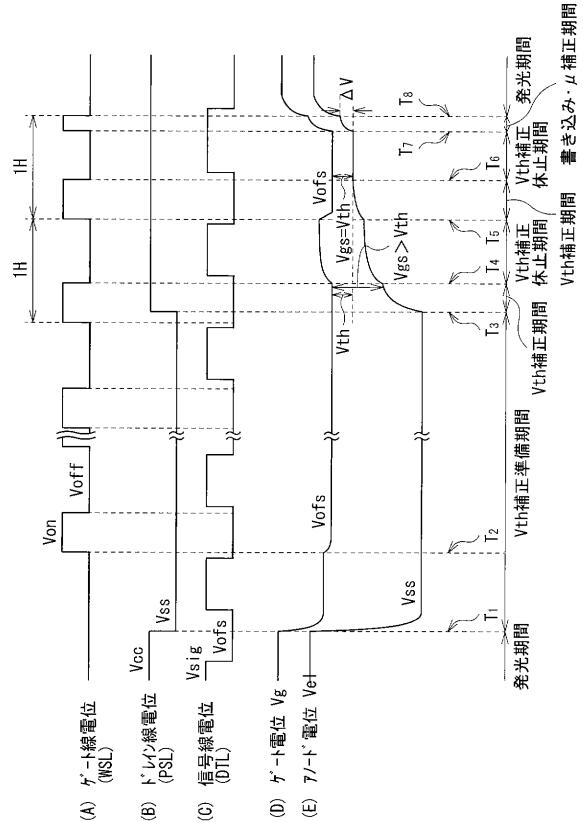

図 3 は、表示装置 1 における各種波形の一例を表したものである。図 3 には、ゲート線 WSL、電源線 PSL、信号線 DTL およびゲート線 CSL において、時々刻々と 2 値の電圧変化が生じている様子が示されている。さらに、図 3 には、ゲート線 WSL、電源線 PSL、信号線 DTL およびゲート線 CSL の電圧変化に応じて、ゲート電圧  $V_g$ 、アノード電圧  $V_{e_1}$  およびカソード電圧  $V_{c_a}$  が時々刻々と変化している様子が示されている。

30

#### 【0050】

##### (Vth 補正準備期間)

まず、 $V_{th}$  補正の準備を行う。具体的には、ゲート線 WSL の電圧が  $V_{o_{f_{f_1}}}$  となっており、信号線 DTL の電圧が  $V_{o_{f_s}}$  となっており、電源線 PSL の電圧が  $V_{c_c}$  となっており、さらにカソード線 CTL の電圧が  $V_{o_{n_2}}$  となっている時（つまり有機 EL 素子 12R 等が発光している時）に、電源走査回路 24 が制御信号 21c に応じて電源線 PSL の電圧を  $V_{c_c}$  から  $V_{s_s}$  に下げる（T<sub>1</sub>）。すると、ソース電圧  $V_s$  が  $V_{s_s}$  まで下がり、有機 EL 素子 12R 等が消光する。このとき、保持容量  $C_s$  を介したカップリングによりゲート電圧  $V_g$  も下がる。次に、電源線 PSL の電圧が  $V_{s_s}$  となっており、かつ信号線 DTL の電圧が  $V_{o_{f_s}}$  となっている間に、書き込み走査回路 23 が制御信号 21b に応じてゲート線 WSL の電圧を  $V_{o_{f_{f_1}}}$  から  $V_{o_{n_1}}$  に上げる（T<sub>2</sub>）。すると、ゲート電圧  $V_g$  が  $V_{o_{f_s}}$  まで下がる。このとき、ゲート電圧  $V_g$  とソース電圧  $V_s$  との電位差  $V_{g_s}$  ( $= V_{o_{f_s}} - V_{i_{n_i}}$ ) がトランジスタ  $T_{D,r}$  の閾値電圧  $V_{t_h}$  よりも小さくなっていてもよいし、それと等しいか、またはそれよりも大きくなっていてよい。

40

#### 【0051】

ところで、カソード走査回路 25 は、上記  $V_{th}$  補正準備期間のうちの所定の期間において、制御信号 21e に応じてゲート線 CSL の電圧を  $V_{o_{n_2}}$  から  $V_{o_{f_{f_2}}}$  に下げるにより、トランジスタ  $T_{c,a}$  をオフし、カソード線 CTL をフローティングにする駆動を行っている。例えば、カソード走査回路 25 は、図 3 に示したように、電源走査回路 24 が制御信号 21c に応じて電源線 PSL の電圧を  $V_{c_c}$  から  $V_{s_s}$  に下げると同時に

50

、制御信号 21e に応じてゲート線 CSL の電圧を  $V_{o_{n_2}}$  から  $V_{o_{ff_2}}$  に下げ、その後、電源走査回路 24 が制御信号 21c に応じて電源線 PSL の電圧を  $V_{ss}$  から  $V_{cc}$  に上げると同時に、制御信号 21e に応じてゲート線 CSL の電圧を  $V_{o_{ff_2}}$  から  $V_{o_{n_2}}$  に上げる。

#### 【0052】

なお、図 3 には、電源線 PSL の電圧変動と、ゲート線 CSL の電圧変動とが同期している場合が例示されているが、これらが同期していなくてもよい。例えば、カソード走査回路 25 は、電源走査回路 24 が制御信号 21c に応じて電源線 PSL の電圧を  $V_{cc}$  から  $V_{ss}$  に下げたのちしばらくしてから、制御信号 21e に応じてゲート線 CSL の電圧を  $V_{o_{n_2}}$  から  $V_{o_{ff_2}}$  に下げ、その後、電源走査回路 24 が制御信号 21c に応じて電源線 PSL の電圧を  $V_{ss}$  から  $V_{cc}$  に上げる少し前に、制御信号 21e に応じてゲート線 CSL の電圧を  $V_{o_{ff_2}}$  から  $V_{o_{n_2}}$  に上げるようにしてもよい。

10

#### 【0053】

##### (最初の Vth 補正期間)

次に、 $V_{th}$  の補正を行う。具体的には、信号線 DTL の電圧が  $V_{of_s}$  となっている間に、電源走査回路 24 が制御信号 21c に応じて電源線 PSL の電圧を  $V_{ss}$  から  $V_{cc}$  に上げる ( $T_3$ )。すると、トランジスタ  $T_{Dr}$  のドレイン - ソース間に電流  $I_{ds}$  が流れ、ソース電圧  $V_s$  が上昇する。その後、水平駆動回路 22 が制御信号 21d に応じて信号線 DTL の電圧を  $V_{of_s}$  から  $V_{sing}$  に切り替える前に、書き込み走査回路 23 が制御信号 21b に応じてゲート線 WSL の電圧を  $V_{on_1}$  から  $V_{off_1}$  に下げる ( $T_4$ )。すると、トランジスタ  $T_{Dr}$  のゲートがフローティングとなり、 $V_{th}$  の補正が一旦停止する。

20

#### 【0054】

##### (最初の Vth 補正休止期間)

$V_{th}$  補正が休止している期間中（すなわち、ゲート線 WSL の電圧が  $V_{off_1}$  となっており、かつ電源線 PSL の電圧が  $V_{cc}$  となっている間）は、先の  $V_{th}$  補正を行った行（画素）とは異なる他の行（画素）において、信号線 DTL の電圧のサンプリングが行われる。具体的には、水平駆動回路 22 が、 $V_{th}$  補正が休止している期間中に、信号線 DTL の電圧を  $V_{of_s}$  から  $V_{sing}$  に切り替えたのち、 $V_{sing}$  から  $V_{of_s}$  に切り替える動作を行い、書き込み走査回路 23 が、信号線 DTL の電圧が  $V_{sing}$  となっている間に、先の  $V_{th}$  補正を行った行（画素）とは異なる他の行（画素）に接続されたゲート線 WSL の電圧を  $V_{off_1}$  から  $V_{on_1}$  に上げたのち、 $V_{on_1}$  から  $V_{off_1}$  に切り替える。従って、水平駆動回路 22 は、ある行（画素）において  $V_{th}$  補正を実行するために 1 周期（図中の 1H で示された期間）の前半に信号線 DTL の電圧を  $V_{of_s}$  とし、他の行（画素）においてサンプリングを行うために 1 周期の後半に信号線 DTL の電圧を  $V_{sing}$  とする動作を実行する。

30

#### 【0055】

なお、 $V_{th}$  補正が不十分である場合、すなわち、トランジスタ  $T_{Dr}$  のゲート - ソース間の電位差  $V_{gs}$  がトランジスタ  $T_{Dr}$  の閾値電圧  $V_{th}$  よりも大きい場合には、 $V_{th}$  補正休止期間中にも、先の  $V_{th}$  補正を行った行（画素）において、トランジスタ  $T_{Dr}$  のドレイン - ソース間に電流  $I_{ds}$  が流れ、ソース電圧  $V_s$  が上昇し、保持容量  $C_s$  を介したカップリングによりゲート電圧  $V_g$  も上昇する。

40

#### 【0056】

##### (2 回目の $V_{th}$ 補正期間)

$V_{th}$  補正休止期間が終了した後、 $V_{th}$  の補正を再び行う。具体的には、電源線 PSL の電圧が  $V_{cc}$  となっており、かつ信号線 DTL の電圧が  $V_{of_s}$  となっており、 $V_{th}$  補正が可能となっている時に、書き込み走査回路 23 が制御信号 21b に応じてゲート線 WSL の電圧を  $V_{off_1}$  から  $V_{on_1}$  に上げ（ $T_5$ ）、トランジスタ  $T_{Dr}$  のゲートを信号線 DTL に接続する。このとき、ソース電圧  $V_s$  が  $V_{of_s} - V_{th}$  よりも低い場合（ $V_{th}$  補正がまだ完了していない場合）には、トランジスタ  $T_{Dr}$  がカットオフする

50

まで（電位差  $V_{g_s}$  が  $V_{t_h}$  になるまで）、トランジスタ  $T_{D_r}$  のドレイン - ソース間に電流  $I_{d_s}$  が流れる。これにより、ゲート電圧  $V_g$  が  $V_{o_f s}$  となり、ソース電圧  $V_s$  が上昇し、その結果、保持容量  $C_s$  が  $V_{t_h}$  に充電され、電位差  $V_{g_s}$  が  $V_{t_h}$  となる。その後、水平駆動回路 22 が信号線 DTL の電圧を  $V_{o_f s}$  から  $V_{s_{ig}}$  に切り替える前に、書き込み走査回路 23 がゲート線 WSL の電圧を  $V_{o_n 1}$  から  $V_{o_f f 1}$  に下げる（ $T_6$ ）。すると、トランジスタ  $T_{D_r}$  のゲートがフローティングとなるので、電位差  $V_{g_s}$  を信号線 DTL の電圧の大きさに拘わらず  $V_{t_h}$  のままで維持することができる。このように、電位差  $V_{g_s}$  を  $V_{t_h}$  に設定することにより、トランジスタ  $T_{D_r}$  の閾値電圧  $V_{t_h}$  が画素回路 13 ごとにばらついた場合であっても、有機 EL 素子 12R 等の発光輝度がばらつくのをなくすることができます。

10

## 【0057】

(2回目の  $V_{t_h}$  補正休止期間)その後、 $V_{t_h}$  補正の休止期間中に、水平駆動回路 22 が信号線 DTL の電圧を  $V_{o_f s}$  から  $V_{s_{ig}}$  に切り替える。

## 【0058】

(書き込み・ $\mu$ 補正期間)

2回目の  $V_{t_h}$  補正休止期間が終了した後、書き込みと  $\mu$  補正を行う。具体的には、信号線 DTL の電圧が  $V_{s_{ig}}$  となっている間に、書き込み走査回路 23 が制御信号 21b に応じてゲート線 WSL の電圧を  $V_{o_f f 1}$  から  $V_{o_n 2}$  に上げ（ $T_7$ ）、トランジスタ  $T_{D_r}$  のゲートを信号線 DTL に接続する。すると、トランジスタ  $T_{D_r}$  のゲートの電圧が信号線 DTL の電圧  $V_{s_{ig}}$  となる。このとき、有機 EL 素子 12R 等のアノードの電圧はこの段階ではまだ有機 EL 素子 12R 等の閾値電圧  $V_{e_1}$  よりも小さく、有機 EL 素子 12R 等はカットオフしている。そのため、電流  $I_{d_s}$  は有機 EL 素子 12R 等の素子容量（図示せず）に流れ、素子容量が充電されるので、ソース電圧  $V_s$  が  $V$  だけ上昇し、やがて電位差  $V_{g_s}$  が  $V_{s_{ig}} + V_{t_h} - V$  となる。このようにして、書き込みと同時に  $\mu$  補正が行われる。ここで、トランジスタ  $T_{D_r}$  の移動度  $\mu$  が大きい程、 $V$  も大きくなるので、電位差  $V_{g_s}$  を発光前に  $V$  だけ小さくすることにより、画素ごとの移動度  $\mu$  のばらつきを取り除くことができる。

20

## 【0059】

(発光)

最後に、書き込み走査回路 23 が制御信号 21b に応じてゲート線 WSL の電圧を  $V_{o_n 1}$  から  $V_{o_f f 1}$  に下げる（ $T_8$ ）。すると、トランジスタ  $T_{D_r}$  のゲートがフローティングとなり、トランジスタ  $T_{D_r}$  のドレイン - ソース間に電流  $I_{d_s}$  が流れ、ソース電圧  $V_s$  が上昇する。その結果、有機 EL 素子 12R 等に閾値電圧  $V_{e_1}$  以上の電圧が印加され、有機 EL 素子 12R 等が所望の輝度で発光する。

30

## 【0060】

本実施の形態の表示装置 1 では、上記のようにして、各画素 11 において画素回路 13 がオンオフ制御され、各画素 11 の有機 EL 素子 12R 等に駆動電流が注入されることにより、正孔と電子とが再結合して発光が起こる。この光は、陽極と陰極との間で多重反射し、陰極等を透過して外部に取り出される。その結果、表示部 10 において画像が表示される。

40

## 【0061】

ところで、従来の表示装置 100 では、図 13 に示したように、 $V_{t_h}$  補正準備期間において、トランジスタ  $T_{D_r}$  の電位差  $V_{g_s}$  が  $V_{t_h}$  を超えるようにするために、アノード電圧  $V_{e_1}$  (=トランジスタ  $T_{D_r}$  のソース電圧) をマイナスの電位にしている。そのため、有機 EL 素子 121R 等には、この期間の間ずっと逆バイアスがかかり続けている。逆バイアスがかかり続けている期間は、発光期間と消光期間のデューティ比（発光期間 / 消光期間 × 100）によって異なるが、例えば、デューティ比が 25% の場合には、一周期中の 75% の間、有機 EL 素子 121R 等に逆バイアスがかかり続けることになる。

50

## 【0062】

一般に、有機EL素子に逆バイアスをかけたときに絶縁破壊（滅点化）が生じる確率は、逆バイアスの大きさおよび印加時間が大きくなるほど大きくなる。そのため、上記したように、長い時間、有機EL素子121R等に逆バイアスをかけ続けた場合には、有機EL素子121R等が滅点化する可能性が高く、歩留りの低下を招きかねない。

## 【0063】

一方、本実施の形態では、アノード電圧 $V_{e_1}$ （=トランジスタ $T_{D_r}$ のソース電圧）をマイナスの電位にしている点では、従来のものと変わらない駆動を行っているが、 $V_{th}$ 補正準備期間のうちの所定の期間において、制御信号 $21e$ に応じてゲート線CSLの電圧を $V_{o_{n_2}}$ から $V_{o_{ff_2}}$ に下げるにより、トランジスタ $T_{c_a}$ をオフし、カソード線CTLをフローティングにしている。これにより、トランジスタ $T_{c_a}$ がオフしている期間の分だけ、有機EL素子121R等に大きな逆バイアス電圧（ $V_{ss}$ から、トランジスタ $T_{c_a}$ をオンしているときのカソード電圧を除算することにより得られる電圧）が印加される期間が短くなるので、 $V_{th}$ 補正準備期間の間ずっと、有機EL素子12R等に大きな逆バイアスがかかり続けることがなくなる。その結果、滅点化の可能性を低減することができる。10

## 【0064】

また、本実施の形態では、トランジスタ $T_{c_a}$ のオンオフ制御に用いる電圧 $V_{o_{n_2}}$ を供給する回路は $V_{o_{n_1}}$ を供給する回路と共にすることが可能であり、 $V_{o_{n_2}}$ を供給するための回路を電圧源内に別個に設ける必要がない。また、トランジスタ $T_{c_a}$ のオンオフ制御に用いる電圧 $V_{o_{ff_2}}$ は、電圧源から電圧の供給を受けずに設定することの可能な値（例えばゼロボルト）となっており、 $V_{o_{ff_2}}$ を供給する回路についても電圧源内に設ける必要がない。従って、有機EL素子12R等にかかる逆バイアスを低減するために、新たな電源を設ける必要がない。従って、本実施の形態では、簡易な構成で、滅点化の可能性を低減することができる。20

## 【0065】

## [変形例]

上記実施の形態では、トランジスタ $T_{ws}$ ,  $T_{D_r}$ がnチャネルトランジスタにより形成されている場合が例示されていたが、pチャネルトランジスタ（例えばpチャネルMOS型のTFT）により形成されていてもよい。ただし、その場合には、図4に示したように、トランジスタ $T_{D_r}$ のソースおよびドレインのうち電源線PSLと未接続の方と保持容量 $C_s$ の他端とを有機EL素子12R等のカソードに接続し、有機EL素子12R等のアノードをカソード線CTLに接続することが好ましい。30

## 【0066】

## (モジュールおよび適用例)

以下、上記実施の形態で説明した表示装置1の適用例について説明する。上記実施の形態の表示装置1は、テレビジョン装置、デジタルカメラ、ノート型パソコンコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなど、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。40

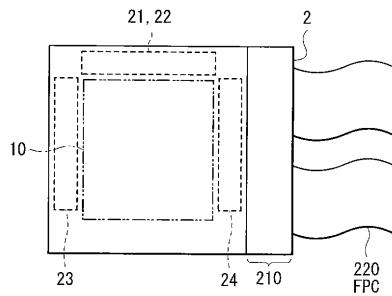

## 【0067】

## (モジュール)

上記実施の形態の表示装置1は、例えば、図5に示したようなモジュールとして、後述する適用例1～5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板2の一辺に、表示部10を封止する部材（図示せず）から露出した領域210を設け、この露出した領域210に、タイミング制御回路21、水平駆動回路22、書き込み走査回路23および電源走査回路24の配線を延長して外部接続端子（図示せず）を形成したものである。外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板（FPC；Flexible Printed Circuit）220が設けられていてよい。

## 【0068】

10

20

30

40

50

(適用例 1)

図 6 は、上記実施の形態の表示装置 1 が適用されるテレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル 310 およびフィルターガラス 320 を含む映像表示画面部 300 を有しており、この映像表示画面部 300 は、上記実施の形態に係る表示装置 1 により構成されている。

【0069】

(適用例 2)

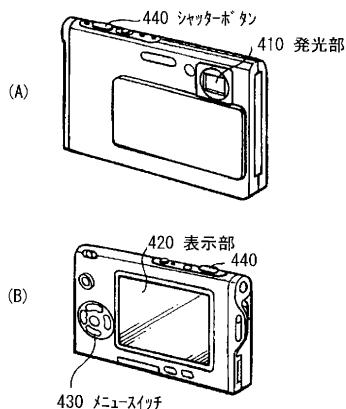

図 7 は、上記実施の形態の表示装置 1 が適用されるデジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部 410、表示部 420、メニュー・スイッチ 430 およびシャッター・ボタン 440 を有しており、その表示部 420 は、上記実施の形態に係る表示装置 1 により構成されている。10

【0070】

(適用例 3)

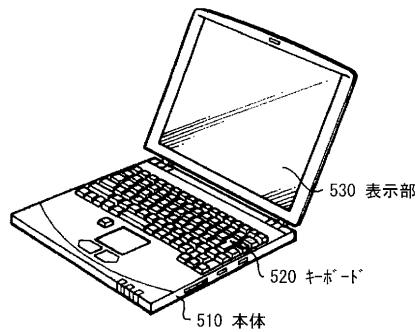

図 8 は、上記実施の形態の表示装置 1 が適用されるノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体 510、文字等の入力操作のためのキーボード 520 および画像を表示する表示部 530 を有しており、その表示部 530 は、上記実施の形態に係る表示装置 1 により構成されている。

【0071】

(適用例 4)

図 9 は、上記実施の形態の表示装置 1 が適用されるビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部 610、この本体部 610 の前方側面に設けられた被写体撮影用のレンズ 620、撮影時のスタート / ストップスイッチ 630 および表示部 640 を有しており、その表示部 640 は、上記実施の形態に係る表示装置 1 により構成されている。20

【0072】

(適用例 5)

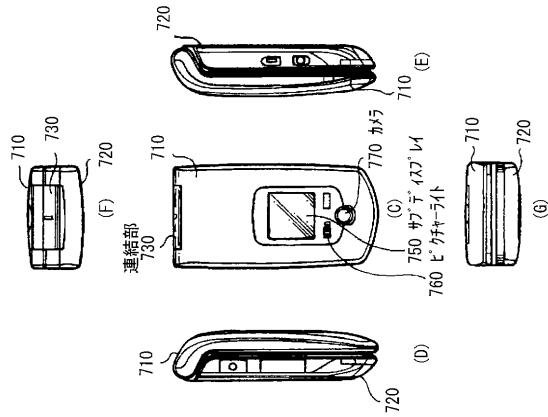

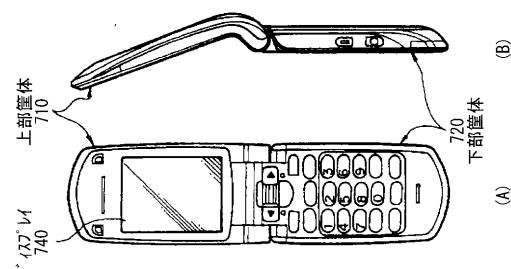

図 10 は、上記実施の形態の表示装置 1 が適用される携帯電話機の外観を表したものである。この携帯電話機は、例えば、上側筐体 710 と下側筐体 720 とを連結部（ヒンジ部）730 で連結したものであり、ディスプレイ 740、サブディスプレイ 750、ピクチャーライト 760 およびカメラ 770 を有している。そのディスプレイ 740 またはサブディスプレイ 750 は、上記実施の形態に係る表示装置 1 により構成されている。30

【0073】

以上、実施の形態および適用例を挙げて本発明を説明したが、本発明は上記実施の形態等に限定されるものではなく、種々変形が可能である。

【0074】

例えば、上記実施の形態等では、表示装置 1 がアクティブマトリクス型である場合について説明したが、アクティブマトリクス駆動のための画素回路 13 の構成は上記実施の形態等で説明したものに限られず、必要に応じて容量素子やトランジスタを画素回路 13 に追加してもよい。その場合、画素回路 13 の変更に応じて、上述した水平駆動回路 22、書き込み走査回路 23、電源走査回路 24 のほかに、必要な駆動回路を追加してもよい。40

【0075】

また、上記実施の形態等では、水平駆動回路 22、書き込み走査回路 23 および電源走査回路 24 の駆動を信号保持制御回路 21B が制御していたが、他の回路がこれらの駆動を制御するようにしてもよい。また、水平駆動回路 22、書き込み走査回路 23 および電源走査回路 24 の制御は、ハードウェア（回路）で行われていてもよいし、ソフトウェア（プログラム）で行われていてもよい。

【図面の簡単な説明】

【0076】

【図 1】本発明の一実施の形態に係る表示装置の一例を表す構成図である。

【図 2】図 1 の画素の内部構成の一例を表す構成図である。50

【図3】図1の表示装置の動作の一例について説明するための波形図である。

【図4】図1の表示装置の一変形例を表す構成図である。

【図5】上記各実施の形態の表示装置を含むモジュールの概略構成を表す平面図である。

【図6】上記実施の形態の表示装置の適用例1の外観を表す斜視図である。

【図7】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図8】適用例3の外観を表す斜視図である。

【図9】適用例4の外観を表す斜視図である。

【図10】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

10

【図11】従来の表示装置の一例を表す構成図である。

【図12】図11の画素の内部構成の一例を表す構成図である。

【図13】図11の表示装置の動作の一例について説明するための波形図である。

【符号の説明】

【0077】

1...表示装置、10...表示部、11, 11R, 11G, 11B...画素、12R, 12G, 12B...有機EL素子、13...画素回路、20...周辺回路部、21...タイミング制御回路、21A...表示信号生成回路、21B...表示信号保持制御回路、21c...水平駆動回路、21d...書き込み走査回路、21e...電源走査回路、22...カソード走査回路、Cs...保持容量、CSL, WSL...ゲート線、CTL...カソード線、DTL...信号線、Id...電流、PSL...ドレイン線、TDr, TwS, Tca...トランジスタ、Vg...ゲート電圧、Vgs...電位差、Vs...ソース電圧、Vth...閾値電圧。

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 10】

【図 9】

【図 11】

【図 12】

【図 13】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 2 G |

| G 0 9 G | 3/20  | 6 2 1 A |

| G 0 9 F | 9/30  | 3 3 8   |

| H 0 5 B | 33/14 | A       |

(72)発明者 内野 勝秀

東京都港区港南1丁目7番1号 ソニー株式会社内

F ターム(参考) 3K107 AA01 BB01 CC21 CC45 EE03 HH02 HH04 HH05

5C080 AA06 BB05 DD05 DD22 DD29 EE29 FF07 FF11 HH09 JJ02

JJ03 JJ04 JJ06 KK01 KK07 KK43 KK47

5C094 AA03 AA04 AA21 AA53 BA03 BA27 CA19 DB04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置，其驱动方法和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2010032904A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2010-02-12 |

| 申请号            | JP2008196643                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2008-07-30 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 杉本秀樹<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 杉本秀樹<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/20 G09F9/30 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| F1分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.611.H G09G3/20.642.A G09G3/20.670.K G09G3/20.622.G<br>G09G3/20.621.A G09F9/30.338 H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC21 3K107/CC45 3K107/EE03 3K107/HH02 3K107/HH04 3K107/<br>/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD22 5C080/DD29 5C080/EE29 5C080/FF07<br>5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C080/KK01 5C080<br>/KK07 5C080/KK43 5C080/KK47 5C094/AA03 5C094/AA04 5C094/AA21 5C094/AA53 5C094/BA03<br>5C094/BA27 5C094/CA19 5C094/DB04 5C380/AA01 5C380/AB06 5C380/AB18 5C380/AB34 5C380<br>/AB46 5C380/AC07 5C380/AC08 5C380/AC09 5C380/AC11 5C380/AC12 5C380/BA14 5C380/BA38<br>5C380/BA39 5C380/BB02 5C380/BD08 5C380/CA12 5C380/CA53 5C380/CA54 5C380<br>/CB17 5C380/CB20 5C380/CB31 5C380/CB32 5C380/CC02 5C380/CC03 5C380/CC04 5C380/CC05<br>5C380/CC06 5C380/CC07 5C380/CC27 5C380/CC33 5C380/CC39 5C380/CC41 5C380/CC62 5C380<br>/CC63 5C380/CD012 5C380/CD013 5C380/CF02 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

### 摘要(译)

要解决的问题：提供一种组成简单且由于Vth校正而减少点数减少的显示装置，并且还提供其驱动方法和电子设备。 ŽSOLUTION：在Vth校正准备时段的规定时段中，根据控制信号21e，栅极线CSL的电压从V on2 下降到V off2。离开晶体管T SB 并使阴极线CTL浮置。通过晶体管T ca 截止的时段缩短了向有机EL元件12R等施加大的反向偏压的时段。然后，在整个Vth校正准备期间，大的反向偏压不会连续地施加到有机EL元件12R。 Ž