(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-17959

(P2005-17959A)

(43) 公開日 平成17年1月20日(2005.1.20)

(51) Int.Cl.<sup>7</sup>**G09G 3/30****G09G 3/20****H05B 33/14**

F 1

G09G 3/30

J

テーマコード(参考)

3K007

G09G 3/20

611D

5C080

G09G 3/20

623C

G09G 3/20

623D

G09G 3/20

641D

審査請求 未請求 請求項の数 3 O L (全 18 頁) 最終頁に続く

(21) 出願番号

特願2003-185968 (P2003-185968)

(22) 出願日

平成15年6月27日 (2003.6.27)

(71) 出願人 000005234

富士電機ホールディングス株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74) 代理人 100108372

弁理士 谷田 拓男

(72) 発明者 川上 春雄

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

(72) 発明者 加藤 久人

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

(72) 発明者 山城 啓輔

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

F ターム(参考) 3K007 BA06 DB03 GA04

最終頁に続く

(54) 【発明の名称】表示装置の駆動方法

## (57) 【要約】

【課題】有機ELディスプレイパネルなどの自発光パネルをスイッチング素子でデューティ駆動する際、off/f状態への切替信号が絶対値の大きな負の値を持つ場合にも、当該信号をスイッチング素子に印加し、かつon/off状態への切替信号の行間の影響を抑制することができる表示装置の駆動方法を提供する。

【解決手段】単一の画素において、印加される消光指示信号が直列接続した表示装置のスイッチング素子65側の端子にパルス状の電界として印加する。予め定めたウインドウ期間C、D中に供給される発光指示信号V<sub>on</sub>もしくは消光指示信号V<sub>off1</sub>、V<sub>off2</sub>に応答して特定の画素60を発光もしくは消光させる際に、デューティ駆動される行については所定電圧を印加すると共に、その他の行についてはウインドウ期間C、D中のみ該所定電圧を既定オフセット値V<sub>c</sub>、V<sub>d</sub>だけオフセットさせた電圧を印加する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

印加される電圧が第1の閾値より小さくなつた後は非導電状態を呈し第1の閾値より大きい第2の閾値より大きくなつた後は導電状態を呈するスイッチング素子と、該スイッチング素子に直列接続された整流特性を有する発光素子とを積層してなる表示装置に、発光制御のための信号を附加することにより該発光素子を電流駆動で発光させる表示装置の駆動方法であつて、

印加される消光指示信号は、該直列接続した表示装置のスイッチング素子側の端子にパルス状の電界を印加することにより得ることを特徴とする表示装置の駆動方法。

**【請求項 2】**

印加される電圧が第1の閾値より小さくなつた後は非導電状態を呈し第1の閾値より大きい第2の閾値より大きくなつた後は導電状態を呈するスイッチング素子と、複数の行および複数の列よりなるマトリックス構成の交点に発光する画素を備え、行方向には一行毎に順次デューティ駆動し且つ同一行内の該当する列には発光制御のための信号を同時に付加することにより、該画素を電流駆動で発光させる発光パネルとを積層してなる表示装置の駆動方法であつて、

所定の期間中に供給される発光指示時信号または消光指示信号に応答して特定の画素を発光または消光させる際に、デューティ駆動される行については所定の電圧を印加すると共に、他の行については前記所定の期間中にのみ該所定の電圧を所定のオフセット値だけオフセットさせた電圧を印加し、

前記所定の期間中に所定の列に印加される消光指示信号の期間内に、該デューティ駆動される行または該所定の列の少なくとも一方に、前記消光指示信号とは別の電圧信号を一定時間印加することを特徴とする表示装置の駆動方法。

**【請求項 3】**

請求項2記載の表示装置の駆動方法において、

前記消光指示信号はパルス状信号であつて前記所定の期間中に該当する行に対して印加されるものであり、前記消光指示信号の期間内に該デューティ駆動される行または該所定の列の少なくとも一方に、前記消光指示信号とは別の電圧信号を一定時間印加し、前記スイッチング素子を非導電状態に遷移させる閾値電圧を超えて前記特定の画素を挟みこむ行と列との電圧差を制御することを特徴とする表示装置の駆動方法。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、有機EL( Electro Luminescence : エレクトロルミネッセンス )ディスプレイパネルの自発光パネルに適用可能な表示装置の駆動方法に関する。

**【0002】****【従来の技術】****【特許文献1】特開平2001-160492号公報****【特許文献2】特願2002-255763**

【非特許文献1】真空蒸着法によるCu : TCNQ錯体薄膜の形成とスイッチング素子、第49回応用物理学関係連合講演会講演予稿集、2002年3月、東海大学湘南校舎、第3分冊27a-M-5

【非特許文献2】L.P.Ma著、Organic Electrical bistable devices and rewritable memory cells, Applied Physics letters, Vol. 80, Number 16, 22 April 2002, 2002 American Institute of Physics

**【0003】**

近年、情報機器用のフラットディスプレイとして液晶ディスプレイの普及が目覚しい。液晶ディスプレイはバックライトの光を液晶が光シャッターとなってon/off制御し、

10

20

30

40

50

カラーフィルターにより色彩をつけるものである。これに対して有機 E L ディスプレイは、R G B のサブピクセルからなる 1 ピクセル（画素）が個々に発光する（すなわち、自発光する）ため、視野角が広くなると共にカラーフィルターが不要になるという利点がある。さらにバックライトが不要であることから薄型化が可能になり、かつフレキシブルな基板上に形成が可能である等、多くの利点を持っている。これらのことから、次世代のディスプレイとして期待されている。

#### 【 0 0 0 4 】

上述の有機 E L ディスプレイパネルの駆動方式は、大別して 2 つの種類に分けることができる。第 1 の駆動方式は所謂パッシブマトリックス型と呼ばれるものであり、その他デューティ駆動方式または単純マトリックス方式とも呼ばれる駆動方式である。このパッシブマトリックス型駆動方式等における発光パネルは、複数の行および列よりなるマトリックスの交点に位置する画素に対し、その発光制御のための信号が行方向には 1 行毎に時系列で走査され同一行の各列には同時に付加されるように構成された発光パネルであり、各画素には制御素子を設けず、行の走査周期のうち各行のデューティ時間にのみ発光制御するようにしたものである。第 2 の駆動方式は所謂アクティブマトリックス型と呼ばれるものであり、各画素に制御素子を持ち、行の走査周期内にわたって発光が可能な駆動方式である。

#### 【 0 0 0 5 】

例えば、100 行 × 150 列のパネルを全面で  $100 \text{ Cd/m}^2$  で発光させる場合、アクティブマトリックス型では、画素の面積率や各種の損失を考慮しないとすると、各画素は  $100 \text{ Cd/m}^2$  で発光すれば良いことになる。これに対して、パッシブマトリックス型では上述のように各行のデューティ時間にのみ発光制御しているため瞬間輝度が非常に高くなる。上記の例では各画素の発光時間のデューティ比が 1 / 100 になるので、その発光時間内での発光強度としては 100 倍の  $10000 \text{ Cd/m}^2$  が必要となる。

#### 【 0 0 0 6 】

一方、有機 E L の発光は電流値により制御されるが、その効率は発光強度が上がると低下していく。その結果、アクティブマトリックス型の駆動方式に比してパッシブマトリックス型では消費電力が大きくなるという不都合が生じ、また発熱等による材料の劣化のため寿命も短くなるという不都合も生じる。さらに加えてパッシブマトリックス型での発光時間のデューティ比は上述のようにパネルの行数の逆数になることから、結果としてパッシブマトリックス型では画素数が制限されることとなり、大面積、高精細度のパネルを実現するにはアクティブマトリックス型の駆動方式を用いる必要があった。

#### 【 0 0 0 7 】

しかし、アクティブマトリックス型の駆動方式では、画素の制御素子としてポリシリコンを用いた薄膜トランジスタ（Thin Film Transistor : TFT）が用いられているため、種々の解決すべき問題点がある。例えば、1 ポリシリコンの TFT を形成するプロセス温度が少なくとも 250 以上の高温のため、フレキシブルなプラスチック基板を用いることが困難である、2 製造コストが高くなり、ディスプレイパネル全体のコストの 50 % 以上を占めてしまうという問題点がある。

#### 【 0 0 0 8 】

上述のような従来の有機 E L ディスプレイパネルが有する種々の問題点を解決するため、特許文献 1 に新しいタイプの有機薄膜 E L 素子が開示されている。特許文献 1 には、「従来の有機薄膜 E L 素子とは異なり、発光・非発光状態が過去の印加電圧の加え方に応じたメモリ性を有し、この結果、ON/OFF 信号を加えることにより発光・非発光状態を制御できるような新しいタイプの有機薄膜 E L 素子とその駆動方法」が記載されている。より具体的に述べると、「有機薄膜と電極の片面又は両面との間に、所定の値以上の電圧を印加することによって絶縁体から導体に転移する物質の薄膜から形成された電流スイッチング層を設ける。電極に所定電圧を印加して、電流スイッチング層を絶縁体から導体に転移させることによって有機薄膜エレクトロルミネッセンス素子の発光状態を出現させ、さらに、電圧を電流スイッチング層が導体から絶縁体に転移するまで減することによって有

10

20

30

40

50

機薄膜エレクトロルミネッセンス素子の非発光状態を出現させるように駆動する。特に好みの様として、該有機薄膜エレクトロルミネッセンス素子に一定電圧を印加した状態に保持し、この一定電圧に正負のパルス電圧を重畠することにより発光状態と非発光状態をスイッチングするよう駆動することができる。」という点が開示されている。

#### 【0009】

上述のスイッチング素子に関する従来技術として、有機LEDの駆動を可能にするための非特許文献1が知られている。さらに、非特許文献2には、アミノイミダゾールジカルボネット(AIDCN)を用いたスイッチング素子を用いて有機EL素子を2値で駆動する方法が開示され、メモリ等への適用可能性を示している。これらの素子は、いずれも、ある電圧に対して2値の抵抗値を持ち、その切替は適切なパルスを印加することにより行われるものである。この抵抗値切替に要する時間は10nsec程度であることから、通常のディスプレイ駆動には充分な応答性が確保できる。しかし、マトリックス構成されたディスプレイ装置を駆動する具体的な方法については、いずれの両文献にも開示されていない。

#### 【0010】

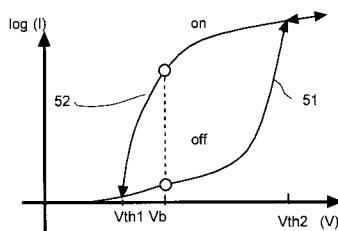

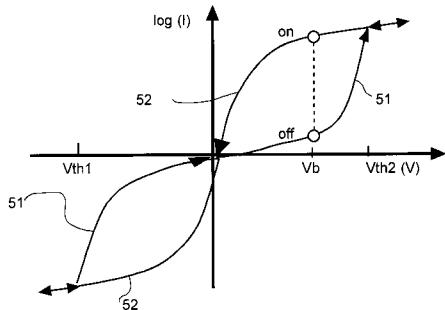

特許文献2にはマトリックス構成の表示装置の駆動方法が開示されている。これによれば、マトリックス構成の表示装置は以下のように駆動される。まず単一の画素の場合について述べる。図16は特許文献2で例示したスイッチング素子の電圧・電流特性を示す。図16において横軸は電圧(V)、縦軸は電流の対数(log(I))である。図16に示されるように、このスイッチング素子は高抵抗特性51(off状態)と低抵抗特性52(on状態)との2つの電圧・電流特性を有している。ここで、バイアスVbをかけた状態で印加電圧を第2の閾値電圧(Vth2)以上にするとoff状態on状態へ遷移し、一方印加電圧を第2の閾値電圧(Vth1)以下にするとon状態off状態へと遷移する特性を有している。従ってoff状態on状態への遷移にはVth2以上のパルスを印加し、on状態off状態への遷移にはVth1以下のパルスを印加することにより、抵抗値の切替が可能である。

#### 【0011】

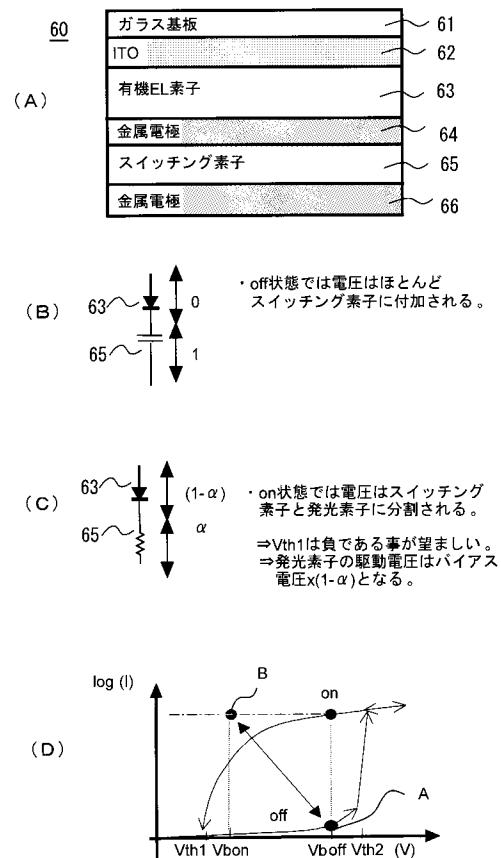

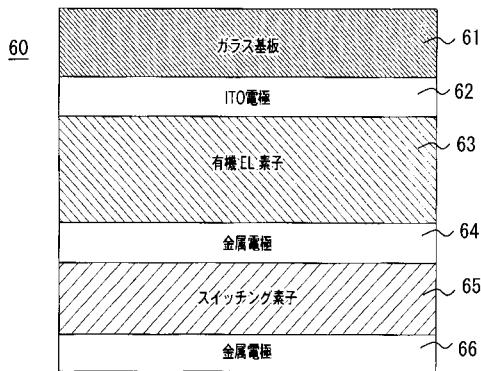

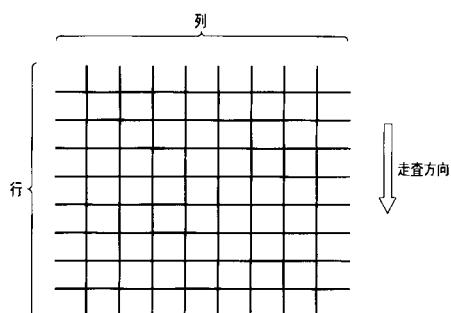

図17はマトリックス構成されたディスプレイ装置について形成される積層構造の表示画素60を示す。図17では通常とは上下が逆に示されているが、ガラス基板61上に陽極としてITO(Indium Tin Oxide)電極61が形成され、ITO電極61上に有機EL素子63が形成され、有機EL素子63上に金属電極64が形成され、金属電極64上にスイッチング素子65が形成され、スイッチング素子65上に陰極として金属電極66が形成されている。図18は表示画素60をマトリックス状に配列した場合を示す。図18に示されるように走査方向は各行毎に順次に行なう方向である。以下、図18のような配列を想定して説明する。

#### 【0012】

図18に示されるようなマトリックス状に配置された多数の表示画素の場合は、ある行の画素につき上述のような抵抗値の切替の制御を行い、次の走査周期までバイアスをVth1からVth2の範囲に維持することにより、デューティ時間に制限されることなくon/off状態のいずれか一方の状態を維持することが可能となる。このような制御を行った場合、以下のような問題点が生じる。まず、従来のパッシブマトリックス型の駆動方式では、ある時点でon状態にあるのは一つの行内の画素だけであり、従って当該行の走査デューティ時間にはその他の行の回路は切られた状態とするため、当該行の状態を切替るための信号が他の行に影響を与えることはない。

#### 【0013】

しかし、図16(および図17)に示されるような特性を有するスイッチング素子65を用いて走査周期中に電圧印加を維持する場合、常にマトリックス全面の画素に電圧が印加されており、当該行以外の行の回路も接続状態に維持されていることから、一つの行の切替信号が他の行すべてに印加されることになる。その結果として、従来のパッシブマトリックス型駆動方式では、図16(および図17)に示されるような特性を有するスイッチ

ング素子 65 を用いてマトリックス全面にある画素の on / off 状態の制御を行うことは困難であるという問題があった。

#### 【 0 0 1 4 】

上述の問題点を解決するために、特許文献 2 にはマトリックス構成の表示装置の駆動方法として、行方向には 1 行毎に順次デューティ駆動し且つ同一行内の該当する列には発光制御のための信号を同時に付加することにより、当該画素を電流駆動で発光させる発光パネルの駆動方法が開示されている。詳しくは、予め定めたウィンドウ期間中に供給される発光指示信号もしくは消光指示信号に応答して特定の画素を発光もしくは消光させる際に、デューティ駆動される行については所定電圧を印加するとともに、その他の行については前記ウィンドウ期間中のみ該所定電圧を既定オフセット値だけオフセットさせた電圧を印加する発光パネルの駆動方法が開示されている。10

#### 【 0 0 1 5 】

##### 【発明が解決しようとする課題】

上述のように特許文献 2 の方法によれば、スイッチング素子 65 の導電状態から非導電状態への第 1 の閾値電圧 ( $V_{th1}$ ) が正、もしくは 0 V 近傍である場合には、所定の動作を実現できる。しかし、図 19 に示されるような電圧・電流特性を有するスイッチング素子を想定されたい。図 19 において横軸は電圧 (V) 、縦軸は電流の対数 (log (I)) であり、図 16 と同じ符号を付した箇所は同じ意味を示すため説明は省略する。図 19 に示されるように、第 1 の閾値電圧 ( $V_{th1}$ ) が負の値であり、その絶対値が第 2 の閾値電圧 ( $V_{th2}$ ) と同程度である場合には、以下のような問題点が生じる。20

#### 【 0 0 1 6 】

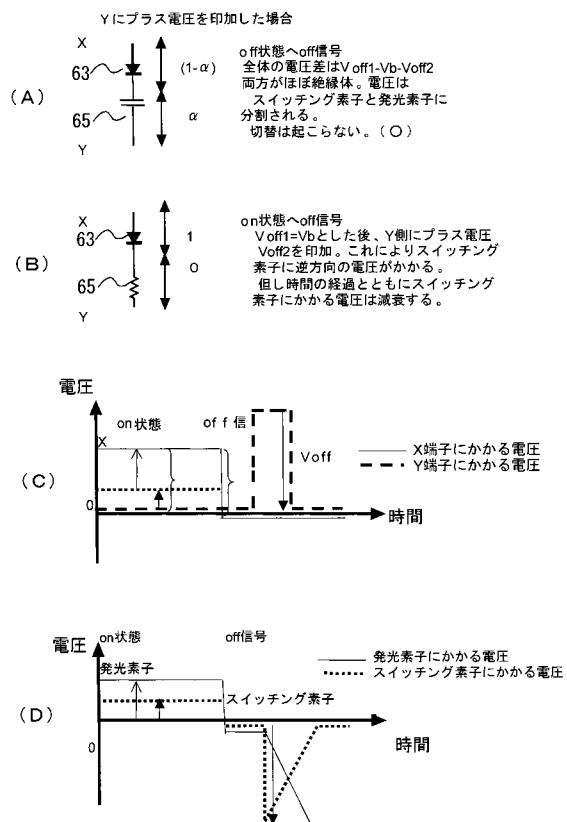

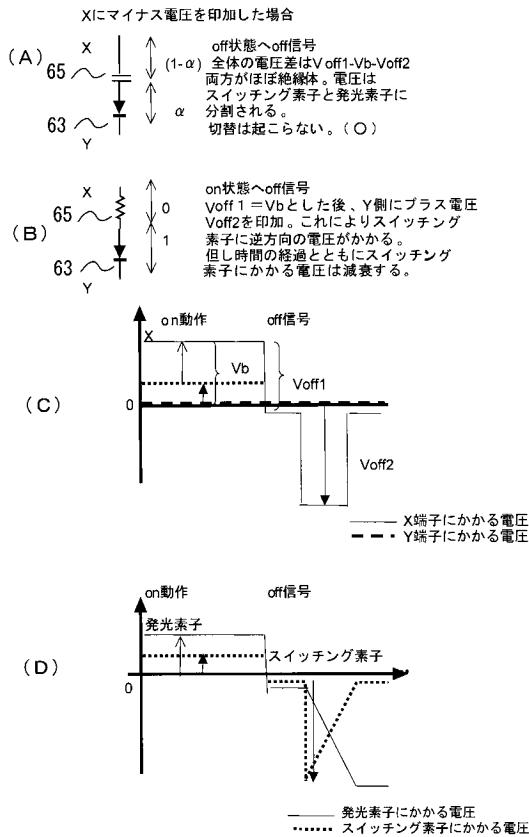

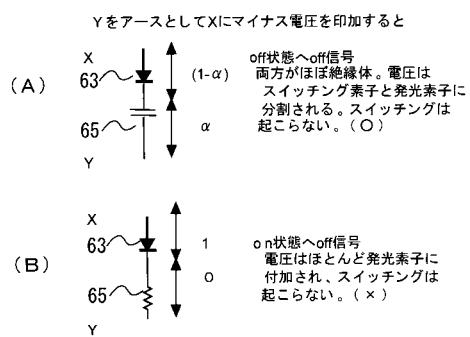

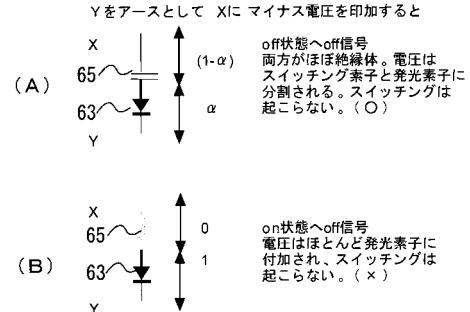

まず単一の画素の場合について説明する。図 20 と図 21 とは、有機 EL 発光素子 63 とスイッチング素子 65 との 2 通りの直列接続を各々示す。

#### 【 0 0 1 7 】

図 20 (A) に示されるように、スイッチング素子 65 が off 状態の時は、等価的にはコンデンサと同等である。例えば、スイッチング素子 65 の特性が図 16 のように非導電状態を呈する第 1 の閾値電圧 ( $V_{th1}$ ) が正、もしくは 0 . 2 V 以下の絶対値の負の値を持つ場合は、図 20 (A) に示されるような直列接続において、スイッチング素子 65 側の端子 Y をアースとし、有機 EL 素子 (発光素子) 63 側の端子 X の電圧を負とすることにより、スイッチング素子 65 にかかる電圧を  $V_{th1}$  以下にすることが可能である。ここで、直列に接続された発光素子 63 およびスイッチング素子 65 に印加された電圧は両方の素子に分圧 (分圧配分) または分割される。スイッチング素子 65 に分圧される割合を  $\alpha$  とおくと、発光素子 63 には  $1 - \alpha$  だけ分圧されるため、図 20 (A) に示されるような電圧が各素子に印加されることになる。この時、発光素子 63 が逆バイアス状態で全く電流が流れなければ、後述するようにスイッチング素子 65 に負の電圧は印加できないが、実際は若干のリーク電流があるため、 $-0.2$  度程度までは印加することが可能である。この結果、off 状態で off 信号を与えても遷移 (スイッチング) は起こらない。30

#### 【 0 0 1 8 】

一方、図 20 (B) に示されるように、スイッチング素子 65 が on 態度の時は、等価的には抵抗と同等である。図 20 (A) と同様の条件の場合、直列に接続された有機 EL 素子 63 およびスイッチング素子 65 に印加された電圧はほとんど発光素子 63 に印加される。この結果、on 状態で off 信号を与えても遷移 (スイッチング) は起こらないという問題があった。40

#### 【 0 0 1 9 】

図 21 (A) は図 20 (A) とは逆の接続を示す。図 21 (A) に示されるように、直列に接続された発光素子 63 およびスイッチング素子 65 に印加された電圧は両方の素子に分圧 (分圧配分) または分割される。発光素子 63 に分圧される割合を  $\alpha$  とおくと、スイッチング素子 65 には  $1 - \alpha$  だけ分圧されるため、図 21 (A) に示されるような電圧が各素子に印加されることになる。図 21 (A) に示される接続においても、発光素子 63 側の端子 Y をアースとし、スイッチング素子 65 側の端子 X の電圧を負とすることにより50

、スイッチング素子 65 にかかる電圧を  $V_{th1}$  以下にすることが可能である。図 20 (A) と同様に、off 状態で off 信号を与えても遷移 (スイッチング) は起こらない。

#### 【0020】

一方、図 21 (B) に示されるように、スイッチング素子 65 が on 態の時は、図 21 (A) と同様の条件の場合、直列に接続された発光素子 63 およびスイッチング素子 65 に印加された電圧はほとんど発光素子 63 に印加される。この結果、on 状態で off 信号を与えても遷移 (スイッチング) は起こらないという問題があった。

#### 【0021】

以上の場合と異なり、スイッチング素子 65 の特性が図 19 に示されるように  $V_{th1}$  が絶対値の大きな負の値の特性を有する場合、図 20、図 21 に示される構成ではスイッチング素子 65 に印加される電圧を  $V_{th1}$  以下にすることは困難である。即ち上記のような構成の表示装置に負の電圧を印加した場合、発光素子 63 がダイオードであるため負の電圧に対しては抵抗が大きくなり、印加された電圧のほとんどが発光素子 63 に分配される。このため、スイッチング素子 65 に大きな負電圧を印加することが困難となり、第 1 の閾値電圧 ( $V_{th1}$ ) が負であり且つその絶対値が第 2 の閾値電圧 ( $V_{th2}$ ) と同程度の大きな値である場合は不都合を生じるという問題があった。

#### 【0022】

そこで、本発明の目的は、上記問題を解決するためになされたものであり、有機ELディスプレイパネルなどの自発光パネルをスイッチング素子でデューティ駆動する際、off 切替信号が絶対値の大きな負の値を持つ場合にも、当該信号をスイッチング素子に印加し、かつ on / off 状態の切替信号の行間の影響を抑制することができる表示装置の駆動方法を提供することにある。

#### 【0023】

##### 【課題を解決するための手段】

本発明の表示装置の駆動方法は、印加される電圧が第 1 の閾値より小さくなつた後は非導電状態を呈し第 1 の閾値より大きい第 2 の閾値より大きくなつた後は導電状態を呈するスイッチング素子と、該スイッチング素子に直列接続された整流特性を有する発光素子とを積層してなる表示装置に、発光制御のための信号を付加することにより該発光素子を電流駆動で発光させる表示装置の駆動方法であつて、印加される消光指示信号は、該直列接続した表示装置のスイッチング素子側の端子にパルス状の電界を印加することにより得ることを特徴とする。

#### 【0024】

本発明の表示装置の駆動方法は、印加される電圧が第 1 の閾値より小さくなつた後は非導電状態を呈し第 1 の閾値より大きい第 2 の閾値より大きくなつた後は導電状態を呈するスイッチング素子と、複数の行および複数の列よりなるマトリックス構成の交点に発光する画素を備え、行方向には一行毎に順次デューティ駆動し且つ同一行内の該当する列には発光制御のための信号を同時に付加することにより、該画素を電流駆動で発光させる発光パネルとを積層してなる表示装置の駆動方法であつて、所定の期間中（好適にはウィンドウ期間中）に供給される発光指示時信号または消光指示信号に応答して特定の画素を発光または消光させる際に、デューティ駆動される行については所定の電圧を印加すると共に、他の行については前記所定の期間中にのみ該所定の電圧を所定のオフセット値だけオフセットさせた電圧を印加し、前記所定の期間中に所定の列に印加される消光指示信号の期間内に、該デューティ駆動される行または該所定の列の少なくとも一方に、前記消光指示信号とは別の電圧信号を一定時間印加することを特徴とする。

#### 【0025】

ここで、本発明の表示装置の駆動方法において、前記消光指示信号はパルス状信号であつて前記所定の期間中に該当する行に対して印加されるものであり、前記消光指示信号の期間内に該デューティ駆動される行または該所定の列の少なくとも一方に、前記消光指示信号とは別の電圧信号を一定時間印加し、前記スイッチング素子を非導電状態に遷移させる閾値電圧を超えて前記特定の画素を挟みこむ行と列との電圧差を制御することができ

10

20

30

40

50

る。

**【0026】**

**【発明の実施の形態】**

**実施の形態1.**

(実施の形態の概要)

本発明の表示装置の駆動方法で用いる表示装置は、1 印加される電圧の大きさに応じて導電状態および非導電状態を呈するスイッチング素子と、2 複数の行および複数の列よりなるマトリックス構成の交点に発光する画素を有する発光パネルとを積層してなる表示装置である。このような表示装置を用いて、マトリックスの行方向には一行毎に順次デューティ (duty) 駆動し且つ同一行内の該当する列には発光制御のための信号を同時に付加することにより、当該画素を電流駆動で発光させることに特徴を有するものである。単一の画素においては、印加される消光指示信号が、直列接続した表示装置のスイッチング素子側の端子にパルス状の電界を印加される。予め定めたウィンドウ期間中に供給される発光指示信号もしくは消光指示信号に応答して特定の画素を発光もしくは消光させる際に、デューティ駆動される行については所定電圧を印加すると共に、その他の行についてはウィンドウ期間中のみ該所定電圧を既定オフセット値だけオフセットさせた電圧を印加する。ウィンドウ期間中に所定の列に印加される消光指示信号の期間内に、デューティ駆動される行には所定電圧を一定時間変化させることを特徴とする。

**【0027】**

以下、本発明の実施の形態につき図面を参照して詳細に説明する。

**【0028】**

まず単一画素に対する駆動方法を説明する。図13は、直列に接続された有機EL素子およびスイッチング素子にプラス電圧(発光素子に関して順方向)を印加した時の電圧配分を説明する図である。図13(A)は本発明の表示装置の駆動方法が適用される積層構造の表示画素60を示す。図13(A)では通常とは上下が逆に示されているが、ガラス基板61上に陽極としてITO電極61が形成され、ITO電極61上有機EL素子63が形成され、有機EL素子63上有金属電極64が形成され、金属電極64上有スイッチング素子65が形成され、スイッチング素子65上有陰極として金属電極66が形成されている。

**【0029】**

図13(B)、(C)は有機EL素子(発光素子)63とスイッチング素子65との2通りの直列接続を各々示す。図13(B)に示されるように、スイッチング素子65がoff状態の時は、等価的にはコンデンサと同等である。したがって、直列に接続された有機EL素子63およびスイッチング素子65に印加された電圧のほとんどは、スイッチング素子65の両端に印加されている。一方、図13(C)に示されるように、スイッチング素子65がon態の時は、直列に接続された有機EL素子63およびスイッチング素子65に印加電圧された電圧は両方の素子に分担(分圧配分)または分割される。ここで、スイッチング素子65に分圧される割合を $\alpha$ とおくと、有機EL素子63に分圧される割合は $1 - \alpha$ となり、図13(C)に示したような電圧が各素子に印加されることになる。有機EL素子63の駆動電圧はバイアス電圧 $V_{bias}$  × ( $1 - \alpha$ )となる。図13(D)は、単体で図16に示すような特性を持つスイッチング素子65を用い且つ有機EL素子63とスイッチング素子65とを直列に接続した場合のスイッチング素子65に付加される電圧と電流との特性を示す。図13(D)において横軸は電圧(V)、縦軸は電流の対数(log(I))である。図13(D)に示されるように、スイッチング素子65は高抵抗特性(off状態)と低抵抗特性(on状態)との2つの電圧・電流特性を有している。 $V_{th1}$ と $V_{th2}$ とは図16と同様に第1、第2の閾値電圧である。図13(B)および(C)で説明したように、off状態でスイッチング素子65に付加される電圧は位置Aの電圧となり、on状態で流れる最大電流は位置Bの電流となる。

**【0030】**

これに対し、単一の画素に対してマイナス電圧を印加する駆動方法のうち、図14は図2

10

20

30

40

50

0の構成に対して、図15は図21の構成に対しての駆動方法を示したものである。なお、プラス電圧を印加する場合は、図20、図21の両構成に対して駆動方法を変える必要は無い。

#### 【0031】

図14(A)に示されるように、スイッチング素子65がoff状態の時は、等価的にはコンデンサと同等である。直列に接続された発光素子63およびスイッチング素子65に印加された電圧は両方の素子に分圧(分圧配分)または分割される。スイッチング素子65に分圧される割合をとおくと、発光素子63には $1 - \alpha$ だけ分圧されるため、図14(A)に示されるような電圧が各素子に印加されることになる。

#### 【0032】

図14(A)においては、消光状態(off状態)への切替信号は、発光素子63側のX端子の電圧を0Vにした後、スイッチング素子65側のY端子に絶対値がVth1より大きなプラス電圧(絶対値Vofff2)を印加する。これによりスイッチング素子65に逆方向の電圧を印加することができる。off状態でoff信号を与えても遷移(スイッチング)は起こらない。

#### 【0033】

一方、図14(B)に示されるように、スイッチング素子65がon状態の時は、等価的には抵抗と同等である。off状態への切替信号(Vofff1)は、X端子の電圧をバイアス電圧(Vb)にした後、Y端子にプラス電圧Vofff2を印加する。これによりスイッチング素子65に逆方向の電圧がかかる。時間の経過とともにX-Y端子間の全電圧は発光素子63に印加されるので、スイッチング素子63に印加される電圧は減衰していくが、遷移状態でスイッチング素子65に逆方向の電圧が印加され逆方向の電流が流れることにより、スイッチング素子65のoff状態への切替えが可能となる。

#### 【0034】

図14(C)はスイッチング素子65がon状態の場合におけるX端子に印加される電圧とY端子に印加される電圧との時間変化を示す。図14(C)において横軸は時間、縦軸は電圧であり、X端子に印加される電圧は線、Y端子に印加される電圧は破線で示す。図14(C)に示されるように、最初Y端子の電圧を0VとしX端子の電圧をバイアス電圧(Vb)とする。これによりスイッチング素子65に順方向の電圧がかかる。次に、X端子の電圧を絶対値の小さい負電圧としY端子にVofff2を印加する。これによりスイッチング素子65に逆方向の電圧がかかる。

#### 【0035】

図14(D)はスイッチング素子65がon状態の場合における発光素子に印加される電圧とスイッチング素子に印加される電圧との時間変化を示す。図14(D)において横軸は時間、縦軸は電圧であり、発光素子に印加される電圧は線、スイッチング素子に印加される電圧は破線で示す。図14(D)に示されるように、スイッチング素子65に印加される電圧はY端子にプラス電圧Vofff2が印加されると逆方向の電圧となるが、時間の経過により減衰していく。

#### 【0036】

次に図15(A)に示される駆動方法について説明する。図15(A)に示されるように、スイッチング素子65がoff状態の時は、等価的にはコンデンサと同等である。直列に接続された発光素子63およびスイッチング素子65に印加された電圧は両方の素子に分圧(分圧配分)または分割される。発光素子63に分圧される割合をとおくと、スイッチング素子65には $1 - \alpha$ だけ分圧されるため、図15(A)に示されるような電圧が各素子に印加されることになる。

#### 【0037】

図15(A)においては、消光状態(off状態)への切替信号は、スイッチング素子65側のX端子に絶対値がVth1より大きなマイナス電圧(絶対値Vofff2)を印加する。これによりスイッチング素子65に逆方向の電圧を印加することができる。off状態でoff信号を与えても遷移(スイッチング)は起こらない。

10

20

30

40

50

## 【0038】

一方、図15(B)に示されるように、スイッチング素子65がon状態の時は、等価的には抵抗と同等である。off状態への切替信号( $V_{off1}$ )は、X端子の電圧をバイアス電圧( $V_b$ )にした後、絶対値が $V_{th1}$ より大きなマイナス電圧(絶対値 $V_{off2}$ )を印加する。Y端子には0Vを印加する。これによりスイッチング素子65に逆方向の電圧がかかる。時間の経過とともにX-Y端子間の全電圧は発光素子63に印加されるので、スイッチング素子63に印加される電圧は減衰して行くが、遷移状態でスイッチング素子65に逆方向の電圧が印加され逆方向の電流が流れることにより、スイッチング素子65のoff状態への切替えが可能となる。

## 【0039】

図15(C)はスイッチング素子65がon状態の場合におけるX端子に印加される電圧とY端子に印加される電圧との時間変化を示す。図15(C)において横軸は時間、縦軸は電圧であり、X端子に印加される電圧は線、Y端子に印加される電圧は破線で示す。図15(C)に示されるように、最初Y端子の電圧を0VとしX端子の電圧をバイアス電圧( $V_b$ )とする。これによりスイッチング素子65に順方向の電圧がかかる。次に、Y端子の電圧を0VにしたままX端子に絶対値の大きい負電圧 $V_{off2}$ を印加する。これによりスイッチング素子65に逆方向の電圧がかかる。

## 【0040】

図15(D)はスイッチング素子65がon状態の場合における発光素子に印加される電圧とスイッチング素子に印加される電圧との時間変化を示す。図15(D)において横軸は時間、縦軸は電圧であり、発光素子に印加される電圧は線、スイッチング素子に印加される電圧は破線で示す。図15(D)に示されるように、スイッチング素子65に印加される電圧はX端子にマイナス電圧 $V_{off2}$ が印加されると逆方向の電圧となるが、時間の経過により減衰していく。

## 【0041】

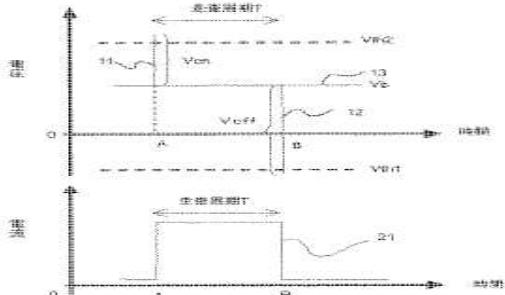

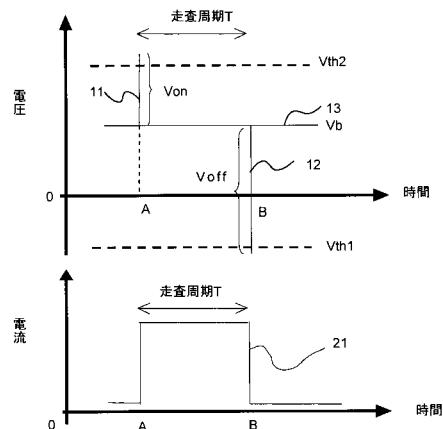

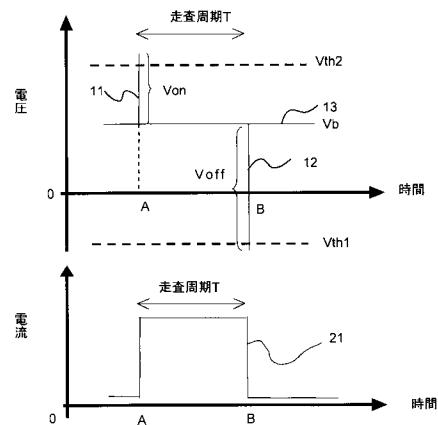

次にマトリックス構成の表示装置の駆動について述べる。図1(A)、(B)は、本発明の実施の形態における、ある画素60のスイッチング素子65に印加される電圧と電流との関係をモデル的に示す図である。図1(A)において横軸は時間、縦軸は電圧を示し、図1(B)において横軸は時間、縦軸は電流を示す。説明を簡単にするため、図1では直列に接続された有機EL素子63に印加される電圧は示していない。このスイッチング素子65にはバイアス電圧 $V_b$ (13)が印加されている。当初スイッチング素子65はoff状態であったが、最初の走査デューティ時間Aの時点でon状態への切替信号 $V_{on}(11)$ が印加されて電流が立ち上がり、走査周期Tの間その電流が維持される。次の走査デューティ時間Bの時点でoff状態への切替信号(符号12で示される- $V_{off}$ )により電流が立ち下がる。図1に示されるように、 $V_{on}$ および $V_{off}$ は、切替の第1の閾値 $V_{th1}$ 、第2の閾値 $V_{th2}$ に対し、 $V_b + V_{on} > V_{th2}$ ,  $V_b - V_{off} < V_{th1}$ となるよう設定されている。

## 【0042】

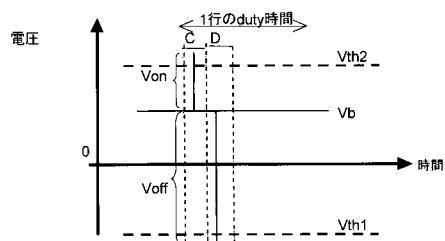

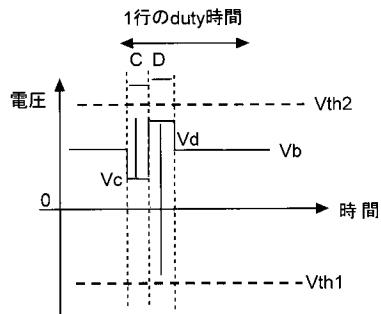

図2は、選択された行における走査デューティ時間を詳細に示す。図2において横軸は時間、縦軸は電圧を示す。図2に示されるように、例えば時間ウィンドウとしてCとDとを設定し、on状態への切替信号 $V_{on}$ はCのウィンドウ内に、off状態への切替信号 $V_{off}$ はDのウィンドウ内に出すこととする。

## 【0043】

図3は、選択された行以外の行における走査デューティ時間を詳細に示す。図3において横軸は時間、縦軸は電圧を示す。図3に示されるように、それぞれのウィンドウC、D内のバイアスを各々- $V_c$ 、 $V_d$ だけオフセットさせることにより、選択された該当行以外の行でスイッチングが起こることを防ぐことができる。

## 【0044】

図3に示した電圧はスイッチング素子65に印加される電圧であるが、実際の発光パネルにおける各行、各列に信号を印加する例を以下に示す。

## 【0045】

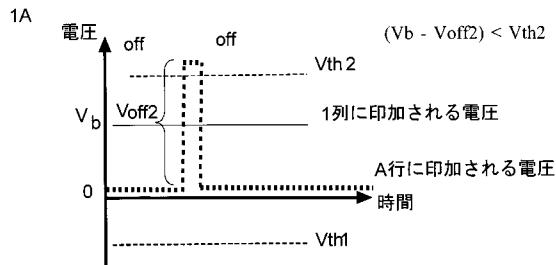

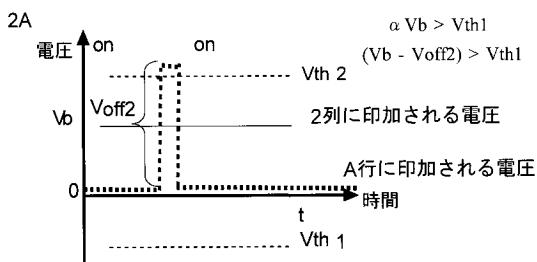

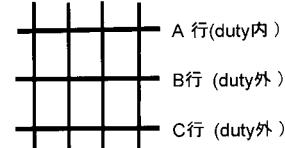

図4は、マトリックス駆動における電気信号印加の一例を示す。ここでは説明を簡単化するためには行はA、B、C行とし、列は1、2、3、4列として駆動を考える。各行の電圧値は通常はアースとするが、本実施の形態におけるウインドウC、D内のバイアス電圧 $V_c$ 、 $V_d$ のオフセット制御は行電極で行われる。デューティ内状態の行における消光指示信号は選択された該当列の信号と行の信号との組合せによって得られる。図4は、A行がデューティ(duty)内状態にあり、B行およびC行はデューティ外状態として、各画素での状態を例示したものである。ここで3列にon状態への切替信号、4列にoff状態への切替信号が与えられたものとする。

## 【0046】

各画素(例えば1列A行の画素は1Aと示す)における電圧条件は図4に示した通りである。図4に示されるように、画素1Aは最初off状態であり、1列には切替信号が与えられないためデューティ内の状態も変化しない。画素2Aは最初on状態であり、2列には切替信号が与えられないためデューティ外の状態も変化しない。画素3Aは最初off状態であり、3列にはon状態への切替信号が与えられるためon状態へ変化する。画素3Bは最初off状態であり、3列には切替信号が与えられるがデューティ外のため状態は変化しない。画素3Cは最初on状態であり、3列にはon状態への切替信号が与えられるがデューティ外のため状態は変化しない。画素4Aは最初on状態であり、4列にはoff状態への切替信号が与えられるためoff状態へ変化する。画素4Bは最初off状態であり、4列にはoff状態への切替信号が与えられるがデューティ外のため状態は変化しない。画素4Cは最初on状態であり、4列にはoff状態への切替信号が与えられるがデューティ外のため状態は変化しない。

10

20

30

## 【0047】

以上における電圧は、上述した記号を用いて以下の(式1)~(式5)に集約される。

## 【0048】

$$V_{on} > V_{th2} - V_b \quad (式1)$$

$$(V_{th1} / ) < (V_b - V_c) < (V_{th2} - V_{on}) \quad (式2)$$

$$(V_{th1} / ) + V_{off1} < (V_b + V_d) < V_{th2} \quad (式3)$$

$$V_{th1} < (V_b - V_{off2}) < V_{th2} \quad (式4)$$

$$V_{off1} - V_{off2} < V_{th1} + V_b \quad (式5)$$

## 【0049】

図5ないし図12は、画素1A、2A、3A~3C、4A~4Cに印加される電圧と閾値との関連を説明する図である。図5ないし図12において、横軸は時間、縦軸は電圧を示し、符号 $V_{th1}$ 等は図1ないし3、14、および15等で用いられた符号と同じ意味を有する。

## 【0050】

図5に示されるように画素1Aについては、A行に印加される電圧はデューティ内のため $V_{off2}$ が印加されるが、1列に印加される電圧は切替信号が与えられないため $V_b$ のままである。このため、off状態は変化しない。

40

## 【0051】

図6に示されるように画素2Aについては、A行に印加される電圧はデューティ内のため $V_{off2}$ が印加されるが、2列に印加される電圧は切替信号が与えられないため $V_b$ のままである。このため、on状態は変化しない。

## 【0052】

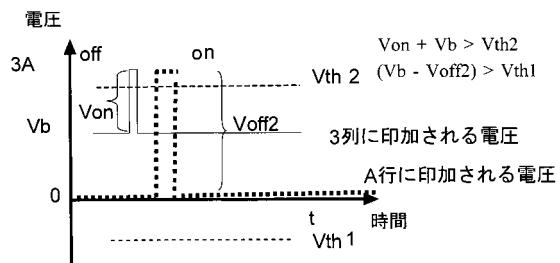

図7に示されるように画素3Aについては、A行に印加される電圧はデューティ内のため $V_{off2}$ が印加され、3列に印加される電圧はon状態への切替信号が与えられるため $V_b + V_{on}$ となる。 $V_b + V_{on} > V_{th2}$ となるためon状態へ変化する。

## 【0053】

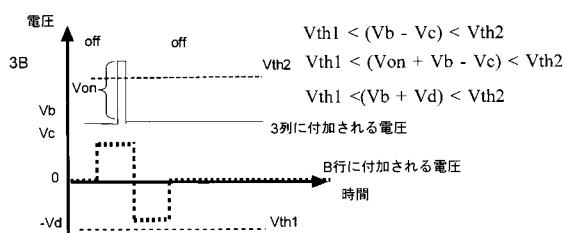

図8に示されるように画素3Bについては、B行に印加される電圧はデューティ外のため、3列にon状態への切替信号が与えられて $V_b + V_{on}$ となった際にオフセット電圧 $V$

50

c が付加される。このため o f f 状態は変化しない。

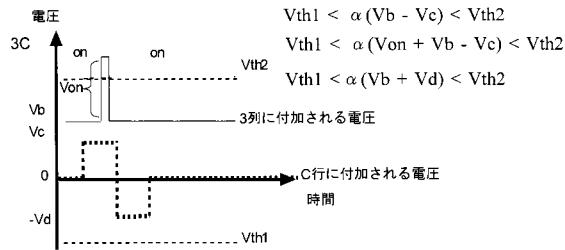

【 0 0 5 4 】

図 9 に示されるように画素 3 C については、C 行に印加される電圧はデューティ外のため、3 列に o n 状態への切替信号が与えられて V b + V o n となった際にオフセット電圧 V c が付加される。このため o n 状態は変化しない。

【 0 0 5 5 】

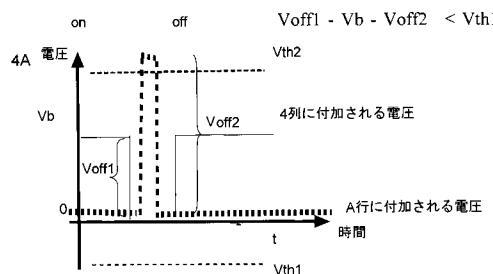

図 10 に示されるように画素 4 A については、A 行に印加される電圧はデューティ内のために V o f f 2 が印加される。4 列には o f f 状態への切替信号が与えられて V b - V o f f 1 となった際にオフセット電圧 V c が減じられる。このため o n 状態は変化しない。4 列に印加される電圧は o f f 状態への切替信号が与えられるため o f f 状態へ変化する。

【 0 0 5 6 】

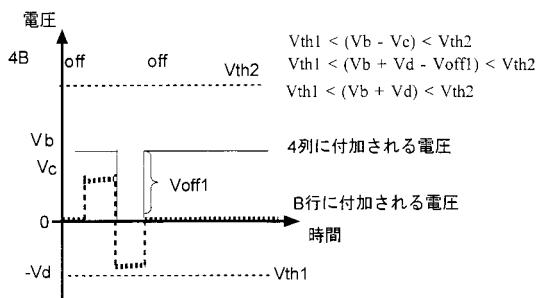

図 11 に示されるように画素 4 B については、B 行に印加される電圧はデューティ外のため、4 列に o f f 状態への切替信号が与えられて V b - V o f f 1 なった際にオフセット電圧 V d が付加される。このため o f f 状態は変化しない。

【 0 0 5 7 】

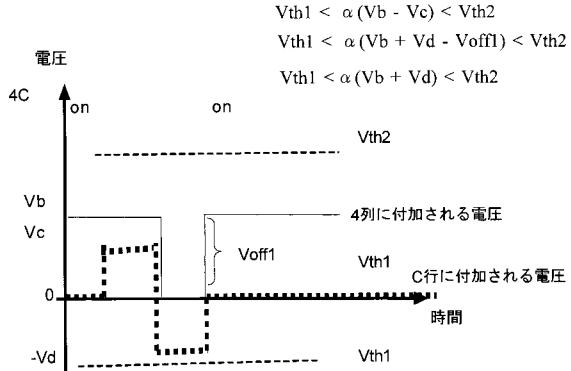

図 12 に示されるように画素 4 C については、C 行に印加される電圧はデューティ外のため、4 列に o f f 状態への切替信号が与えられて V b - V o f f 1 なった際にオフセット電圧 V d が付加される。このため o n 状態は変化しない。

【 0 0 5 8 】

以上より、本発明の実施の形態によれば、2 値で動作するスイッチング素子を用いて有機 E L パネルを制御するにあたり、当該スイッチング素子 6 5 の o f f 切替信号が絶対値の大きな負の値 V o f f 2 を持つ場合にも、当該信号をスイッチング素子 6 5 に印加し、かつ o n / o f f 切替信号の行間の影響を抑制する手段を提供することができる。詳しくは、マトリックスの行方向には一行毎に順次デューティ駆動し且つ同一行内の該当する列には発光制御のための信号を同時に付加することにより、画素 6 0 を電流駆動で発光させることができる。単一の画素においては、印加される消光指示信号が、直列接続した表示装置のスイッチング素子 6 5 側の端子にパルス状の電界として印加される。予め定めたウィンドウ期間 C、D 中に供給される発光指示信号 V o n もしくは消光指示信号 V o f f 1、V o f f 2 に応答して特定の画素 6 0 を発光もしくは消光させる際に、デューティ駆動される行については所定電圧を印加すると共に、その他の行についてはウィンドウ期間 C、D 中のみ該所定電圧を既定オフセット値 V c、V d だけオフセットさせた電圧を印加する。ウィンドウ期間 C、D 中に所定の列に印加される消光指示信号 V o f f 1、V o f f 2 の期間内に、デューティ駆動される行には所定電圧を一定時間変化させる。この結果、o n / o f f 切替信号の行間の影響を抑制することができる。

【 0 0 5 9 】

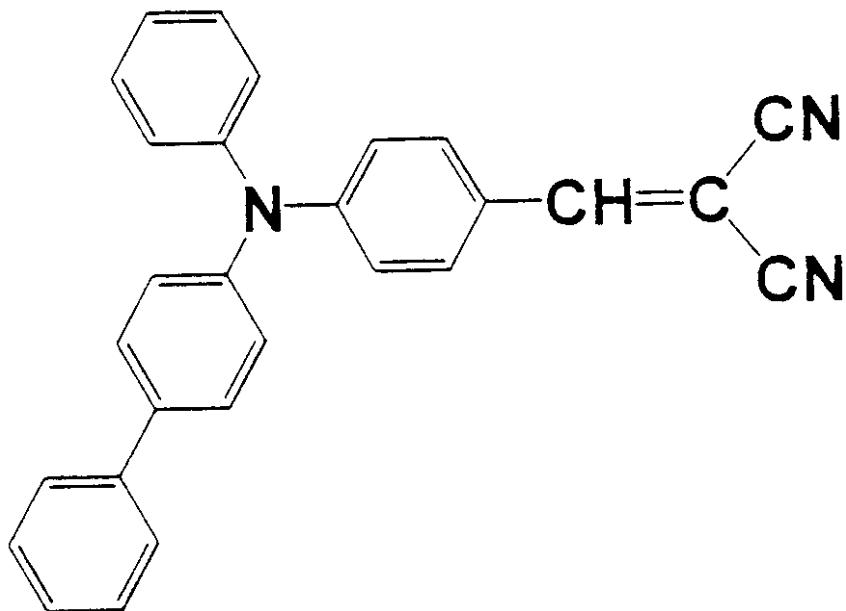

実施例 1 .

I T O 6 2 付ガラス基板 6 1 上にポリエチレンジオキシチオフェン膜とポリフェニレンビニレン膜とをスピンドルコートにより順次形成し、その後、カルシウム膜を真空蒸着により成膜して有機 E L 層 6 3 を形成した。各層の厚さは、それぞれ 1 0 0 n m、1 0 0 n m、1 5 0 n m とした。I T O 6 2 は 1 m m ピッチ、幅 0 . 7 m m で 1 5 列のパターニングが予めなされており、カルシウム蒸着膜は金属マスクを用いて 1 m m ピッチ、幅 0 . 7 m m で 1 0 行のパターニングを行うことにより、1 5 列、1 0 行のマトリックスを形成している。これに連続してアルミニウム、ジシアノ系化合物（化合物 1）、アルミニウムを順次、それぞれ 1 0 0 n m、5 0 n m と 1 0 0 n m 厚さで真空蒸着成膜することにより、有機 E L 層 6 3 部分に直列にスイッチング素子部 6 5 を形成した。スイッチング素子部 6 5 は有機 E L 層 6 3 のカルシウム膜の上に形成され、カルシウム膜と同様の、1 m m ピッチ、幅 0 . 7 m m で 1 0 行のパターニングを行った。

【 0 0 6 0 】

【 化 1 】

10

20

30

40

10

## 【0061】

スイッチング素子65の性能は、V<sub>t h 1</sub>が-5.0V、V<sub>t h 2</sub>が5.0V、バイアスV<sub>b</sub>が4.0Vでのon状態での電流密度が10mA/cm<sup>2</sup>、off状態での電流密度が0.01mA/cm<sup>2</sup>であった。on状態での有機EL素子63の電圧降下は3.5V、発光強度は30Cd/m<sup>2</sup>であり、off状態での電圧降下、発光は観測されなかった。

## 【0062】

パネル全体の走査周波数を60Hz、すなわち走査周期Tを約16.7msecとすると、各行あたりの走査デューティ時間は1.67msecとなる。前述のウインドウCとDとをそれぞれ時間幅0.1msec、切替信号のパルス幅を0.05msecとし、V<sub>b</sub>=4.0V、V<sub>on</sub>=1.5V、V<sub>off1</sub>=4.0V、V<sub>off2</sub>=5.5V、V<sub>c</sub>=1.5V、V<sub>d</sub>=0.8Vと設定することにより、パネルは順調に動作した。ちなみに、ウインドウ時間の間は発光は中断するが、1.67msecのうち少なくともウインドウ時間を除いた1.47msecは発光しており、発光時間比は88%以上となる。これは、従来の単純なパッシブマトリックスの場合の発光時間比10%(=1/10行)と比較すると、十分大きな値である。

## 【0063】

## 実施例2.

実施例1と同様に有機EL素子63を構成した後、これに連続してアルミニウム、化合物1、アルミニウムを順次、それぞれ100nm、70nmと120nm厚さで真空蒸着成膜することにより、有機EL素子部分63に直列にスイッチング素子部65を形成した。スイッチング素子部65は実施例1と同様に有機EL層63のカルシウム膜の上に形成され、カルシウム膜と同様の、1mmピッチ、幅0.7mmで10行のパターニングを行った。

## 【0064】

スイッチング素子63の性能は、V<sub>t h 1</sub>が-5.5V、V<sub>t h 2</sub>が5.5V、バイアスV<sub>b</sub>が4.5Vでのon状態での電流密度が20mA/cm<sup>2</sup>、off状態での電流密度が0.1nA/cm<sup>2</sup>以下であった。on状態での有機EL素子63の電圧降下は4V、発光強度は50Cd/m<sup>2</sup>であり、off状態での電圧降下、発光は観測されなかった。

## 【0065】

パネル全体の走査周期T、各行あたりの走査デューティ時間、ウインドウCとDの時間幅、切替信号のパルス幅は実施例1と同様とし、V<sub>b</sub>=4.5V、V<sub>on</sub>=2.5V、V<sub>o</sub>

20

30

40

50

$V_{ff1} = 4.5V$ 、 $V_{off2} = 6.0V$ 、 $V_c = 2.5V$ 、 $V_d = 0.8V$ と設定することにより、パネルは順調に動作した。

### 【0066】

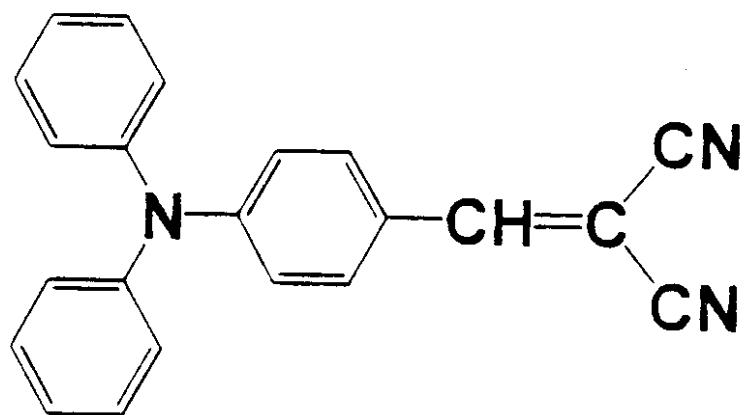

実施例3.

実施例1と同様に有機EL素子63を構成した後、これに連続してアルミニウム、ジシアノ系化合物(化合物2)、アルミニウムを順次、それぞれ100nm、80nm、120nm厚さで合計5層の真空蒸着成膜することにより、有機EL素子部分63に直列にスイッチング素子部65を形成した。スイッチング素子部65は実施例1と同様に有機EL層63のカルシウム膜の上に形成され、カルシウム膜と同様の、1mmピッチ、幅0.7mmで10行のパターニングを行った。

10

### 【0067】

スイッチング素子65の性能は、 $V_{th1} = -4.5V$ 、 $V_{th2} = 4.5V$ 、バイアス $V_b = 3.5V$ でのon状態での電流密度が $10mA/cm^2$ 、off状態での電流密度が $0.01mA/cm^2$ であった。on状態での有機EL素子63の電圧降下は3.0V、発光強度は $20Cd/m^2$ であり、off状態での電圧降下、発光は観測されなかった。

### 【0068】

パネル全体の走査周期T、各行あたりの走査デューティ時間、ウィンドウCとDの時間幅、切替信号のパルス幅は実施例1と同様とし、 $V_b = 3.5V$ 、 $V_{on} = 1.5V$ 、 $V_{ff1} = 3.5V$ 、 $V_{off2} = 5.0V$ 、 $V_c = 1.5V$ 、 $V_d = 0.8V$ と設定することにより、パネルは順調に動作した。

20

### 【0069】

### 【化2】

30

### 【0070】

#### 【発明の効果】

以上説明した通り、本発明の表示装置の駆動方法によれば、単一の画素において、印加される消光指示信号が直列接続した表示装置のスイッチング素子65側の端子にパルス状の電界として印加されることにより、有機ELディスプレイパネルなどの自発光パネルをスイッチング素子でデューティ駆動する際、off切替信号が絶対値の大きな負の値を持つ場合にも、当該信号をスイッチング素子に印加することができる。予め定めたウィンドウ期間C、D中に供給される発光指示信号 $V_{on}$ もしくは消光指示信号 $V_{off1}$ 、 $V_{off2}$ に応答して特定の画素60を発光もしくは消光させる際に、デューティ駆動される行については所定電圧を印加すると共に、その他の行についてはウィンドウ期間C、D中のみ該所定電圧を既定オフセット値 $V_c$ 、 $V_d$ だけオフセットさせた電圧を印加することにより、on/off切替信号の行間の影響を抑制することができる。

40

#### 【図面の簡単な説明】

50

【図1】本発明の実施の形態における、ある画素60のスイッチング素子65に印加される電圧と電流との関係をモデル的に示す図である。

【図2】選択された行における走査デューティ時間を詳細に示す図である。

【図3】選択された行以外の行における走査デューティ時間を詳細に示す図である。

【図4】マトリックス駆動における電気信号印加の一例を示す図である。

【図5】画素1Aに印加される電圧と閾値との関連を説明する図である。

【図6】画素2Aに印加される電圧と閾値との関連を説明する図である。

【図7】画素3Aに印加される電圧と閾値との関連を説明する図である。

【図8】画素3Bに印加される電圧と閾値との関連を説明する図である。

【図9】画素3Cに印加される電圧と閾値との関連を説明する図である。

10

【図10】画素4Aに印加される電圧と閾値との関連を説明する図である。

【図11】画素4Bに印加される電圧と閾値との関連を説明する図である。

【図12】画素4Cに印加される電圧と閾値との関連を説明する図である。

【図13】直列に接続された有機EL素子およびスイッチング素子にプラス電圧(発光素子に関して順方向)を印加した時の電圧配分を説明する図である。

【図14】有機EL発光素子63とスイッチング素子65との一直列接続の場合の駆動方法を示す図である。

【図15】有機EL発光素子63とスイッチング素子65との他の直列接続の場合の駆動方法を示す図である。

【図16】図16は特許文献2で例示したスイッチング素子の電圧・電流特性を示す図である。

【図17】マトリックス構成されたディスプレイ装置について形成される積層構造の表示画素を示す図である。

【図18】表示画素60をマトリックス状に配列した場合を示す図である。

【図19】スイッチング素子の電圧・電流特性を示す図である。

【図20】有機EL発光素子63とスイッチング素子65との一直列接続を示す図である。

【図21】有機EL発光素子63とスイッチング素子65との他の直列接続を示す図である。

#### 【符号の説明】

30

1 1 スイッチング素子をoff状態からon状態へ切替る電圧パルス( $V_{on}$ )

1 2 スイッチング素子をon状態からoff状態へ切替る電圧パルス( $V_{off}$ )

1 3 スイッチング素子へのバイアス電圧( $V_b$ )

2 1 スイッチング素子の電流(I)

C 時間ウインドウC

D 時間ウインドウD

T 走査周期

5 1 スイッチング素子の高抵抗状態(off状態)

5 2 スイッチング素子の低抵抗状態(on状態)

6 1 ガラス基板

6 2 ITO電極

6 3 有機EL素子

6 4 金属電極

6 5 スイッチング素子

6 6 金属電極

40

【図1】

【図2】

【図5】

【図6】

【図3】

【図4】

マトリックス駆動における電気信号

1列 2 3 4

画素 (Pixel)

- |              |                            |

|--------------|----------------------------|

| 1A off → off | 1列には切替信号無し。duty内の状態も変わらない。 |

| 2A on → on   | 2列には切替信号無し。duty外の状態も変わらない。 |

| 3A off → on  | 3列にonへの切替信号が付加される。         |

| 3B off → off | duty外の状態は変わらない。            |

| 3C on → on   | duty外の状態は変わらない。            |

| 4A on → off  | 4列にoffへの切替信号が付加される。        |

| 4B off → off | duty外の状態は変わらない。            |

| 4C on → on   | duty外の状態は変わらない。            |

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

G 0 9 G 3/20 6 8 0 H

H 0 5 B 33/14 A

F ターム(参考) 5C080 AA06 BB05 DD10 FF11 JJ04 JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于驱动显示设备的方法                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2005017959A</a>                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2005-01-20 |

| 申请号            | JP2003185968                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2003-06-27 |

| [标]申请(专利权)人(译) | 富士电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 富士电机控股有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 川上春雄<br>加藤久人<br>山城啓輔                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 川上 春雄<br>加藤 久人<br>山城 啓輔                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F1分类号          | G09G3/30.J G09G3/20.611.D G09G3/20.623.C G09G3/20.623.D G09G3/20.641.D G09G3/20.680.H<br>H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 3K007/BA06 3K007/DB03 3K007/GA04 5C080/AA06 5C080/BB05 5C080/DD10 5C080/FF11 5C080<br>/JJ04 5C080/JJ05 5C080/JJ06 3K107/AA01 3K107/BB01 3K107/CC11 3K107/CC21 3K107/CC31<br>3K107/EE02 3K107/EE65 3K107/HH02 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB07 5C380<br>/BA05 5C380/BA10 5C380/BA28 5C380/CA08 5C380/CA14 5C380/CA53 5C380/CA54 5C380/CB01<br>5C380/CB31 5C380/CC21 5C380/CC31 5C380/CC62 5C380/CD070 5C380/DA33 5C380/HA02 5C380<br>/HA11 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

### 摘要(译)

解决的问题：当诸如有机EL显示面板之类的自发光面板由开关元件进行占空比驱动时，甚至当切换至截止状态的开关信号具有较大的负值时，也要向开关元件施加信号。还提供了一种显示装置的驱动方法，该显示装置的驱动方法能够将开关信号的行之间的影响抑制到导通/截止状态。在单个像素中，所施加的消光指令信号作为脉冲电场被施加至串联连接的显示装置的开关元件65侧的端子。当特定像素60响应于在预定窗口时段C和D期间提供的发光指令信号Von或发光指令信号Voff1和Voff2而发光或关闭时，预定电压被施加到由占空比驱动的行。除了施加之外，仅在窗口时段C和D期间，通过将预定电压偏移预定偏移值Vc和Vd而获得的电压被施加到其他行。[选型图]图1