(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-145445

(P2010-145445A)

(43) 公開日 平成22年7月1日(2010.7.1)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | K 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 624B 5C080  |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 670A        |

|                             | G09G 3/20 | 621A        |

|                             | G09G 3/20 | 641D        |

審査請求 未請求 請求項の数 13 O L (全 34 頁) 最終頁に続く

|           |                              |            |                                                                                                                                  |

|-----------|------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2008-319253 (P2008-319253) | (71) 出願人   | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号                                                                                           |

| (22) 出願日  | 平成20年12月16日 (2008.12.16)     | (74) 代理人   | 100086298<br>弁理士 船橋 國則                                                                                                           |

|           |                              | (72) 発明者   | 山本 哲郎<br>東京都港区港南1丁目7番1号 ソニー株式会社内                                                                                                 |

|           |                              | (72) 発明者   | 内野 勝秀<br>東京都港区港南1丁目7番1号 ソニー株式会社内                                                                                                 |

|           |                              | F ターム (参考) | 3K107 AA01 BB01 CC02 CC45 EE03<br>HH02 HH04<br>5C080 AA06 BB05 CC03 DD04 EE29<br>EE30 FF11 HH09 JJ01 JJ02<br>JJ03 JJ04 JJ05 JJ06 |

(54) 【発明の名称】表示装置、表示装置の駆動方法および電子機器

## (57) 【要約】

【課題】高コスト化を招いたり、動画応答性を損なったりすることなく、高階調の表示輝度を上げる。

【解決手段】花火や宇宙のような画表示、即ち低階調の背景中の一部に高階調が表示されているような画表示のときに、高階調の表示部分で書き込みトランジスタによる信号書き込み時間を他の表示部分よりも短くする。信号書き込み時間が短くなると、信号書き込み期間の終了時ににおける駆動トランジスタのゲート - ソース間電圧  $V_{gs}$  が高くなり ( $V_{gs1} > V_{gs2}$ )、その分だけ有機EL素子に流れる電流値が増加する。結果として、有機EL素子の発光輝度を上げることができる。

【選択図】図 1 6

## 【特許請求の範囲】

## 【請求項 1】

映像信号を書き込む書込みトランジスタと、前記書込みトランジスタによって書き込まれた前記映像信号に応じて電気光学素子の発光駆動を行なう駆動トランジスタと、前記駆動トランジスタのゲート電極とソース電極との間に接続された保持容量とを有し、前記書込みトランジスタによって書き込まれた前記映像信号に応じて前記駆動トランジスタのゲート電圧が変化する画素回路が複数配置された画素アレイ部を備え、

前記書込みトランジスタによって前記映像信号を書き込む信号書込み時間が前記画素アレイ部内で複数存在する

表示装置。

10

## 【請求項 2】

前記信号書込み時間は表示する画像の階調に応じて変化する

請求項 1 記載の表示装置。

## 【請求項 3】

信号書込み時間は、あらかじめ定められた基準階調よりも高い階調の表示部分において当該基準階調よりも低い階調の表示部分よりも短い

請求項 2 記載の表示装置。

20

## 【請求項 4】

前記画素回路は、前記電気光学素子を複数有し、当該複数の電気光学素子に対応して前記駆動トランジスタおよび前記保持容量からなる回路を複数有するとともに、当該複数の回路に対して前記書込みトランジスタが 1 つ以上設けられており、

前記複数の電気光学素子のうちの少なくとも 1 つが欠陥化している画素回路における前記信号書込み時間は、欠陥化している電気光学素子を含まない正常な画素回路における前記信号書込み時間よりも短い

請求項 2 記載の表示装置。

30

## 【請求項 5】

前記書込みトランジスタに与える書込み走査信号のパルス幅によって前記信号書込み時間を変える

請求項 3 または請求項 4 記載の表示装置。

## 【請求項 6】

前記映像信号の基準電位からの遷移タイミングの位相を遅くすることによって前記信号書込み時間を変える

請求項 3 または請求項 4 記載の表示装置。

40

## 【請求項 7】

前記複数の電気光学素子のうちの少なくとも 1 つが欠陥化している画素回路を第 1 画素回路、当該第 1 画素回路の周辺の画素回路を第 2 画素回路、当該第 2 画素回路の周辺の画素回路を第 3 画素回路とするとき、

前記第 2 画素回路における前記信号書込み時間は、前記第 1 画素回路における前記信号書込み時間よりも長く、前記第 3 画素回路における前記信号書込み時間よりも短い

請求項 4 記載の表示装置。

## 【請求項 8】

前記書込みトランジスタは、それぞれパルス幅が異なる書込み走査信号が与えられる互いに並列に接続された複数のトランジスタからなり、

前記複数のトランジスタのうち、前記書込み走査信号のパルス幅が広いトランジスタを前記画素回路から電気的に切り離すことによって前記信号書込み時間を短くする

請求項 4 記載の表示装置。

50

## 【請求項 9】

前記複数のトランジスタの少なくとも 1 つのソース電極またはドレイン電極は、コンタクト部を介してゲート電極の金属配線層と電気的に接続されている

請求項 8 記載の表示装置。

## 【請求項 10】

前記金属配線層上には絶縁膜が存在し、前記電気光学素子のアノード電極が存在しない請求項 9 記載の表示装置。

## 【請求項 11】

前記画素回路は、前記駆動トランジスタに流れる電流に応じた補正量で当該駆動トランジスタのゲート - ソース間の電位差に負帰還をかけることによって前記駆動トランジスタの移動度を補正する移動度補正処理の機能を有する

請求項 1 記載の表示装置。

## 【請求項 12】

映像信号を書き込む書込みトランジスタと、前記書込みトランジスタによって書き込まれた前記映像信号に応じて電気光学素子の発光駆動を行なう駆動トランジスタと、前記駆動トランジスタのゲート電極とソース電極との間に接続された保持容量とを有し、前記書込みトランジスタによって書き込まれた前記映像信号に応じて前記駆動トランジスタのゲート電圧が変化する画素回路が複数配置された表示装置の駆動に当たって、

前記書込みトランジスタによって前記映像信号を書き込む信号書き込み時間を表示する画像の階調に応じて変える

表示装置の駆動方法。

## 【請求項 13】

映像信号を書き込む書込みトランジスタと、前記書込みトランジスタによって書き込まれた前記映像信号に応じて電気光学素子の発光駆動を行なう駆動トランジスタと、前記駆動トランジスタのゲート電極とソース電極との間に接続された保持容量とを有し、前記書込みトランジスタによって書き込まれた前記映像信号に応じて前記駆動トランジスタのゲート電圧が変化する画素回路が複数配置された画素アレイ部を備え、

前記書込みトランジスタによって前記映像信号を書き込む信号書き込み時間が前記画素アレイ部内で複数存在する

表示装置を有する電子機器。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、表示装置、表示装置の駆動方法および電子機器に関し、特に電気光学素子を含む画素が行列状に2次元配置された平面型(フラットパネル型)表示装置、当該表示装置の駆動方法および当該表示装置を有する電子機器に関する。

## 【背景技術】

## 【0002】

近年、画像表示を行う表示装置の分野では、発光素子を含む画素(以下、「画素回路」と記述する場合もある)が行列状に2次元配置されてなる平面型の表示装置が急速に普及している。平面型の表示装置の一つとして、デバイスに流れる電流値に応じて発光輝度が変化するいわゆる電流駆動型の電気光学素子を画素の発光素子として用いた表示装置がある。電流駆動型の電気光学素子としては、有機薄膜に電界をかけると発光する現象を利用した有機EL(Electro Luminescence)素子が知られている。

## 【0003】

この有機EL素子を画素の発光素子として用いた有機EL表示装置は次のような特長を持っている。すなわち、有機EL素子は、10V以下の印加電圧で駆動できるために低消費電力である。有機EL素子は、自発光素子であるために、画素ごとに液晶にて光源からの光強度を制御することによって画像を表示する液晶表示装置に比べて、画像の視認性が高く、しかもバックライト等の光源を必要としないために軽量化および薄型化が容易である。さらに、有機EL素子の応答速度が数μsec程度と非常に高速であるために動画表示時の残像が発生しない。

## 【0004】

有機EL表示装置では、液晶表示装置と同様に、その駆動方式として単純(パッシブ)

10

20

30

40

50

マトリクス方式とアクティブマトリクス方式とを採ることができる。ただし、単純マトリクス方式の表示装置は、構造が簡単であるものの、電気光学素子の発光期間が走査線（即ち、画素数）の増加によって減少するために、大型でかつ高精細な表示装置の実現が難しいなどの問題がある。

【0005】

そのため、近年、電気光学素子に流れる電流を、当該電気光学素子と同じ画素内に設けた能動素子、例えば絶縁ゲート型電界効果トランジスタによって制御するアクティブマトリクス方式の表示装置の開発が盛んに行われている。絶縁ゲート型電界効果トランジスタとしては、一般には、TFT(Thin Film Transistor; 薄膜トランジスタ)が用いられる。アクティブマトリクス方式の表示装置は、電気光学素子が1フレームの期間に亘って発光を継続するために、大型でかつ高精細な表示装置の実現が容易である。

10

【0006】

アクティブマトリクス方式の有機EL表示装置において、画素（画素回路）は、有機EL素子の駆動回路として、少なくとも駆動トランジスタ、書き込みトランジスタおよび保持容量からなる回路構成のものを用いている（例えば、特許文献1参照）。この画素回路において、書き込みトランジスタは、映像信号をサンプリングして画素内に書き込む。保持容量は、書き込みトランジスタによって書き込まれた映像信号を保持する。駆動トランジスタは、保持容量に保持された映像信号に応じた電流を有機EL素子に流すことによって当該有機EL素子を発光駆動する。

20

【0007】

【特許文献1】特開2007-310311号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

ところで、先述したように有機EL素子は自発光素子である。したがって、有機EL素子を画素の発光素子として用いた表示パネルのコントラストは非常に高く、理論的には無限大である。この特性をより活かすために、低階調を背景として当該背景中の一部に高階調が表示されているような画表示、一例として花火や宇宙のような画表示のときに、高階調の表示輝度をより高く設定することでより高画質を得ることができる。

30

【0009】

このように、高画質化を目的として高階調の表示輝度を上げるには、映像信号の信号電圧を上げたり、画素の発光／非発光の割合であるデューティを制御することによって有機EL素子の発光時間を延ばしたりするなどの手法を採ることが必要になる。

【0010】

ここで、映像信号の信号電圧を上げるということは、当該信号電圧を通常の画素における白表示時の信号電圧よりも高く設定することである。したがって、映像信号の信号電圧を上げる手法を採る場合には、当該映像信号の供給源である信号ドライバの耐圧を増加させる必要がある。そして、信号ドライバの耐圧を増加させるには、低耐圧の回路素子に比べて高価な高耐圧の回路素子を用いることになるために信号ドライバの価格が高くなる。その結果、表示装置全体の高コスト化を招く。

40

【0011】

一方、デューティ制御によって有機EL素子の発光時間を延ばして高階調の表示輝度を上げる手法を採る場合は、静止画の場合には問題とならないが、動画の場合には動画表示に対して動画応答性を損なってしまう懸念がある。このような理由から、高コスト化を招いたり、動画応答性を損なったりすることなく、表示輝度を上げることが望まれる。

【0012】

以上では、画素の発光素子（電気光学素子）が有機EL素子の場合を例に挙げて従来の問題点を述べたが、当該問題点については、有機EL素子の場合に限らず、自発光素子の電気光学素子全般に対して言えることである。

【0013】

50

そこで、本発明は、高コスト化を招いたり、動画応答性を損なったりすることなく、表示輝度を上げることが可能な表示装置、当該表示装置の駆動方法および当該表示装置を有する電子機器を提供することを目的とする。

【課題を解決するための手段】

【0014】

上記目的を達成するために、本発明は、

映像信号を書き込む書込みトランジスタと、前記書込みトランジスタによって書き込まれた前記映像信号に応じて電気光学素子の発光駆動を行なう駆動トランジスタと、前記駆動トランジスタのゲート電極とソース電極との間に接続された保持容量とを有し、前記書込みトランジスタによって書き込まれた前記映像信号に応じて前記駆動トランジスタのゲート電圧が変化する画素回路が複数配置された画素アレイ部を備えた表示装置において、

前記書込みトランジスタによって前記映像信号を書き込む信号書き込み時間を前記画素アレイ部内で複数存在させる構成を採っている。

【0015】

上記構成の表示装置において、駆動トランジスタのゲート電圧のトランジェントとソース電圧のトランジェントとを比較した場合、一般的に、保持容量の容量値が電気光学素子の容量値よりも小さいためにゲート電圧のトランジェントの方が早い。このトランジェントの差により、書き込みトランジスタによる映像信号の信号書き込み期間において、駆動トランジスタのゲート - ソース間電圧は一旦増加し、ピークに達した後単調減少するという特性をとる。

【0016】

ここで、信号書き込み時間が画素アレイ部内で複数存在するということは、信号書き込み時間が異なる画素回路が画素アレイ部内に存在するということである。そして、駆動トランジスタのゲート - ソース間電圧が上記特性をとることで、信号書き込み時間が相対的に短い画素回路の方が長い画素回路に比べて、信号書き込み期間の終了時における駆動トランジスタのゲート - ソース間電圧が高くなる。

【0017】

電気光学素子に流れる電流値は、駆動トランジスタのゲート - ソース間電圧によって決まる。したがって、書き込みトランジスタによる映像信号の信号書き込み時間が相対的に短い画素回路では相対的に長い画素回路に比べて、駆動トランジスタのゲート - ソース間電圧が高くなることで、その高くなった分だけ電気光学素子に流れる電流値が増加するために電気光学素子の発光輝度が上昇する。

【発明の効果】

【0018】

本発明によれば、映像信号の信号書き込み時間を相対的に短くすることで、高コスト化を招いたり、動画応答性を損なったりすることなく、電気光学素子の発光輝度を上げることができる。

【発明を実施するための最良の形態】

【0019】

以下、発明を実施するための最良の形態（以下、「実施形態」と記述する）について図面を用いて詳細に説明する。なお、説明は以下の順序で行う。

1. 基本例に係る有機EL表示装置（2Trの画素構成）

2. 実施形態

3. 応用例（半減点対策への応用）

4. 変形例

5. 適用例（電子機器）

【0020】

<1. 基本例に係る有機EL表示装置>

[システム構成]

10

20

30

40

50

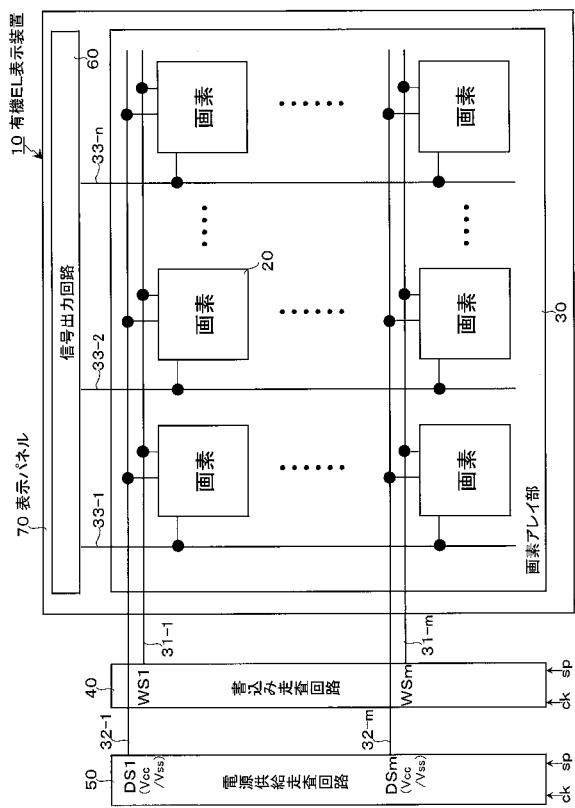

図1は、本発明の基本例に係るアクティブマトリクス型表示装置の構成の概略を示すシステム構成図である。ここでは、一例として、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子、例えば有機EL素子を画素(画素回路)の発光素子として用いたアクティブマトリクス型有機EL表示装置の場合を例に挙げて説明するものとする。

【0021】

図1に示すように、本基本例に係る有機EL表示装置10は、発光素子を含む複数の画素20と、当該画素20が行列状に2次元配置された画素アレイ部30と、当該画素アレイ部30の周辺に配置された駆動部とを有する構成となっている。駆動部は、画素アレイ部30の各画素20を発光駆動する。

10

【0022】

画素20の駆動部は、例えば、書き込み走査回路40および電源供給走査回路50からなる走査駆動系と、信号出力回路60からなる信号供給系とからなる構成となっている。本適用例に係る有機EL表示装置10の場合には、画素アレイ部30が形成された表示パネル70上に信号出力回路60が設けられているのに対して、書き込み走査回路40および電源供給走査回路50はそれぞれ、表示パネル(基板)70の外部に設けられている。

20

【0023】

ここで、有機EL表示装置10が白黒表示対応の場合は、白黒画像を形成する単位となる1つの画素が画素20に相当する。一方、有機EL表示装置10がカラー表示対応の場合は、カラー画像を形成する単位となる1つの画素は複数の副画素(サブピクセル)から構成され、この副画素が画素20に相当する。より具体的には、カラー表示用の表示装置では、1つの画素は、例えば、赤色(R)光を発光する副画素、緑色(G)光を発光する副画素、青色(B)光を発光する副画素の3つの副画素から構成される。

30

【0024】

ただし、1つの画素としては、RGBの3原色の副画素の組み合わせに限られるものではない。すなわち、3原色の副画素にさらに1色あるいは複数色の副画素を加えて1つの画素を構成するようにすることも可能である。より具体的には、例えば、輝度向上のために白色(W)光を発光する副画素を加えて1つの画素を構成したり、色再現範囲を拡大するために補色光を発光する少なくとも1つの副画素を加えて1つの画素を構成したりすることも可能である。

30

【0025】

画素アレイ部30には、m行n列の画素20の配列に対して、行方向(画素行の画素の配列方向/水平方向)に沿って走査線31-1~31-mと電源供給線32-1~32-mとが画素行ごとに配線されている。さらに、列方向(画素列の画素の配列方向/垂直方向)に沿って信号線33-1~33-nが画素列ごとに配線されている。

40

【0026】

走査線31-1~31-mは、書き込み走査回路40の対応する行の出力端にそれぞれ接続されている。電源供給線32-1~32-mは、電源供給走査回路50の対応する行の出力端にそれぞれ接続されている。信号線33-1~33-nは、信号出力回路60の対応する列の出力端にそれぞれ接続されている。

【0027】

画素アレイ部30は、通常、ガラス基板などの透明絶縁基板上に形成されている。これにより、有機EL表示装置10は、平面型(フラット型)のパネル構造となっている。画素アレイ部30の各画素20の駆動回路は、アモルファスシリコン TFT または低温ポリシリコン TFT を用いて形成することができる。低温ポリシリコン TFT を用いる場合には、書き込み走査回路40および電源供給走査回路50についても、表示パネル70上に実装することができる。

【0028】

書き込み走査回路40は、クロックパルスckに同期してスタートパルスspを順にシフト(転送)するシフトレジスタ等によって構成されている。この書き込み走査回路40は、

50

画素アレイ部 30 の各画素 20 への映像信号の書き込みに際して、走査線 31-1 ~ 31-m に順次書き込み走査信号 WS ( WS1 ~ WSm ) を供給することによって画素アレイ部 30 の各画素 20 を行単位で順番に走査する ( 線順次走査 ) 。

【 0029 】

電源供給走査回路 50 は、クロックパルス ck に同期してスタートパルス sp を順にシフトするシフトレジスタ等によって構成されている。この電源供給走査回路 50 は、書き込み走査回路 40 による線順次走査に同期して、第 1 電源電位 Vcc と当該第 1 電源電位 Vcc よりも低い第 2 電源電位 Vss で切り替わる電源電位 DS ( DS1 ~ DSm ) を電源供給線 32-1 ~ 32-m に供給する。この電源電位 DS の Vcc / Vss の切替えにより、画素 20 の発光制御 ( 発光 / 非発光の制御 ) が行なわれる。

10

【 0030 】

信号出力回路 60 は、信号供給源 ( 図示せず ) から供給される輝度情報に応じた映像信号の信号電圧 ( 以下、単に「信号電圧」と記述する場合もある ) Vsig と基準電位 Vofs のいずれか一方を適宜選択して出力する。ここで、信号出力回路 60 から選択的に出力される基準電位 Vofs は、映像信号の信号電圧 Vsig の基準となる電位 ( 例えば、映像信号の黒レベルに相当する電位 ) である。

【 0031 】

信号出力回路 60 は、例えば、周知の時分割駆動方式の回路構成を採る。時分割駆動方式は、セレクタ方式とも呼ばれ、信号供給源であるドライバ ( 図示せず ) の 1 つの出力端に対して複数の信号線を単位 ( 組 ) として割り当てる。そして、この複数の信号線を時分割にて順次選択する一方、その選択した信号線に対してドライバの出力端ごとに時系列で出力される映像信号を時分割で振り分けて供給することによって各信号線を駆動する方式である。

20

【 0032 】

一例として、カラー表示対応の場合を例に挙げると、隣り合う R, G, B の 3 つの画素列を単位とし、ドライバからは 1 水平期間内に R, G, B の各映像信号が時系列で信号出力回路 60 に入力するようとする。信号出力回路 60 は、R, G, B の 3 つの画素列に対応して設けられたセレクタ ( 選択スイッチ ) によって構成され、当該セレクタが時分割にて順次オン動作を行うことで、R, G, B の各映像信号を対応する信号線に対して時分割で書き込む。

30

【 0033 】

ここでは、R, G, B の 3 つの画素列 ( 信号線 ) を単位としたが、これに限られるものではない。そして、この時分割駆動方式 ( セレクタ方式 ) を採用することで、時分割数を x ( x は 2 以上の整数 ) とすると、ドライバの出力数および当該ドライバと信号出力回路 60 、ひいては表示パネル 70 との間の配線数を、信号線の本数の 1 / x に削減できる利点がある。

【 0034 】

信号出力回路 60 から選択的に出力される信号電圧 Vsig / 基準電位 Vofs は、信号線 33-1 ~ 33-n を介して画素アレイ部 30 の各画素 20 に対して行単位で書き込まれる。すなわち、信号出力回路 60 は、信号電圧 Vsig を行 ( ライン ) 単位で書き込む線順次書き込みの駆動形態を採っている。

40

【 0035 】

( 画素回路 )

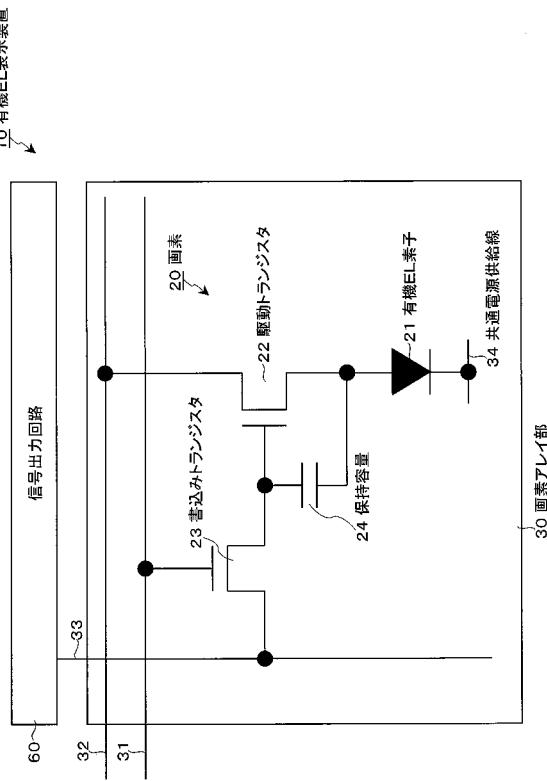

図 2 は、本基本例に係る有機 EL 表示装置 10 に用いられる画素 ( 画素回路 ) 20 の具体的な構成例を示す回路図である。

【 0036 】

図 2 に示すように、画素 20 は、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型の電気光学素子、例えば有機 EL 素子 21 と、当該有機 EL 素子 21 を駆動する駆動回路とによって構成されている。有機 EL 素子 21 は、全ての画素 20 に対して共通に配線 ( いわゆる、ベタ配線 ) された共通電源供給線 34 にカソード電極が接続されて

50

いる。

【0037】

有機EL素子21を駆動する駆動回路は、駆動トランジスタ22、書き込みトランジスタ（サンプリングトランジスタ）23および保持容量24を有する構成となっている。ここでは、駆動トランジスタ22および書き込みトランジスタ23としてNチャネル型のTFTを用いている。ただし、駆動トランジスタ22および書き込みトランジスタ23の導電型の組み合わせは一例に過ぎず、これらの組み合わせに限られるものではない。

【0038】

なお、駆動トランジスタ22および書き込みトランジスタ23としてNチャネル型のTFTを用いると、アモルファスシリコン（a-Si）プロセスを用いることができる。a-Siプロセスを用いることで、TFTを作成する基板の低コスト化、ひいては本有機EL表示装置10の低コスト化を図ることが可能になる。また、駆動トランジスタ22および書き込みトランジスタ23を同じ導電型の組み合わせにすると、両トランジスタ22, 23を同じプロセスで作成することができるため低コスト化に寄与できる。

10

【0039】

駆動トランジスタ22は、一方の電極（ソース／ドレイン電極）が有機EL素子21のアノード電極に接続され、他方の電極（ドレイン／ソース電極）が電源供給線32（32-1～32-m）に接続されている。

【0040】

書き込みトランジスタ23は、ゲート電極が走査線31（31-1～31-m）に接続され、一方の電極（ソース／ドレイン電極）が信号線33（33-1～33-n）に接続され、他方の電極（ドレイン／ソース電極）が駆動トランジスタ22のゲート電極に接続されている。

20

【0041】

駆動トランジスタ22および書き込みトランジスタ23において、一方の電極とは、ソース／ドレイン領域に電気的に接続された金属配線を言い、他方の電極とは、ドレイン／ソース領域に電気的に接続された金属配線を言う。また、一方の電極と他方の電極との電位関係によって一方の電極がソース電極ともなればドレイン電極ともなり、他方の電極がドレイン電極ともなればソース電極ともなる。

30

【0042】

保持容量24は、一方の電極が駆動トランジスタ22のゲート電極に接続され、他方の電極が駆動トランジスタ22の他方の電極および有機EL素子21のアノード電極に接続されている。

【0043】

なお、有機EL素子21の駆動回路としては、駆動トランジスタ22および書き込みトランジスタ23の2つのトランジスタと保持容量24の1つの容量素子とからなる回路構成のものに限られるものではない。例えば、一方の電極が有機EL素子21のアノード電極に、他方の電極が固定電位にそれぞれ接続されることで、有機EL素子21の容量不足分を補う補助容量を必要に応じて設けた回路構成を探ることも可能である。

40

【0044】

上記構成の画素20において、書き込みトランジスタ23は、書き込み走査回路40から走査線31を通してゲート電極に印加されるHighアクティブの書き込み走査信号WSに応答して導通状態となる。これにより、書き込みトランジスタ23は、信号線33を通して信号出力回路60から供給される輝度情報に応じた映像信号の信号電圧Vsigまたは基準電位Vofsをサンプリングして画素20内に書き込む。この書き込まれた信号電圧Vsigまたは基準電位Vofsは、駆動トランジスタ22のゲート電極に印加されるとともに保持容量24に保持される。

【0045】

駆動トランジスタ22は、電源供給線32（32-1～32-m）の電位（以下、「電源電位」と記述する場合もある）DSが第1電源電位Vccにあるときには、一方の電極

50

がドレイン電極、他方の電極がソース電極となって飽和領域で動作する。これにより、駆動トランジスタ22は、電源供給線32から電流の供給を受けて有機EL素子21を電流駆動にて発光駆動する。より具体的には、駆動トランジスタ22は、飽和領域で動作することにより、保持容量24に保持されている信号電圧Vsigの電圧値に応じた電流値の駆動電流を有機EL素子21に供給し、当該有機EL素子21を電流駆動することによって発光させる。

【0046】

駆動トランジスタ22はさらに、電源電位DSが第1電源電位Vccから第2電源電位Vssに切り替わったときは、一方の電極がソース電極、他方の電極がドレイン電極となって線形領域で動作する、即ちスイッチングトランジスタとして動作する。そして、駆動トランジスタ22は、スイッチング動作によって有機EL素子21への駆動電流の供給を停止することで、有機EL素子21を非発光状態にする。すなわち、駆動トランジスタ22は、有機EL素子21の発光/非発光を制御するトランジスタとしての機能をも併せ持っている。

10

【0047】

このようにして、駆動トランジスタ22のスイッチング動作により、有機EL素子21が非発光状態となる期間（非発光期間）を設け、有機EL素子21の発光期間と非発光期間との割合を制御する（いわゆる、デューティ制御）。このデューティ制御により、1フレーム期間に亘って画素20が発光することに伴う残像ボケを低減するために、特に動画の画品位をより優れたものとすることができます。

20

【0048】

電源供給走査回路50から電源供給線32を通して選択的に供給される第1、第2電源電位Vcc、Vssのうち、第1電源電位Vccは有機EL素子21を発光駆動する駆動電流を駆動トランジスタ22に供給するための電源電位である。また、第2電源電位Vssは、有機EL素子21に対して逆バイアスを掛けるための電源電位である。この第2電源電位Vssは、信号電圧Vsigの基準となる基準電位Vofsよりも低い電位、例えば、駆動トランジスタ22の閾値電圧をVthとするときVofs-Vthよりも低い電位、好ましくはVofs-Vthよりも十分に低い電位に設定される。

30

【0049】

（画素構造）

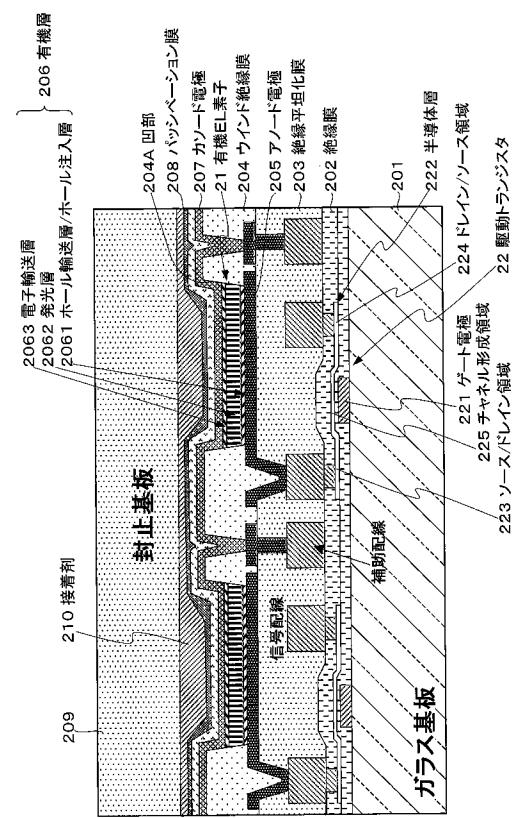

図3は、画素20の断面構造の一例を示す断面図である。図3に示すように、画素20は、駆動トランジスタ22等を含む駆動回路が形成されたガラス基板201上に形成されている。具体的には、ガラス基板201上に絶縁膜202、絶縁平坦化膜203およびウインド絶縁膜204がその順に形成され、当該ウインド絶縁膜204の凹部204Aに有機EL素子21が設けられた構成となっている。ここでは、駆動回路の各構成素子の内、駆動トランジスタ22のみを図示し、他の構成素子については省略している。

【0050】

有機EL素子21は、金属等からなるアノード電極205と、当該アノード電極205上に形成された有機層206と、当該有機層206上に全画素共通に形成された透明導電膜等からなるカソード電極207とから構成されている。アノード電極205は、上記ウインド絶縁膜204の凹部204Aの底部に形成されている。

40

【0051】

この有機EL素子21において、有機層206は、アノード電極205上にホール輸送層/ホール注入層2061、発光層2062、電子輸送層2063および電子注入層（図示せず）が順次堆積されることによって形成される。そして、図2の駆動トランジスタ22による電流駆動の下に、駆動トランジスタ22からアノード電極205を通して有機層206に電流が流れることで、当該有機層206内の発光層2062において電子と正孔が再結合する際に発光するようになっている。

【0052】

駆動トランジスタ22は、ゲート電極221と、半導体層222のゲート電極221と

50

対向する部分のチャネル形成領域 225 と、半導体層 222 のチャネル形成領域 225 の両側のドレイン／ソース領域 223, 224 とから構成されている。ソース／ドレイン領域 223 は、コンタクトホールを介して有機 EL 素子 21 のアノード電極 205 と電気的に接続されている。

【0053】

そして、図 3 に示すように、駆動トランジスタ 22 を含む駆動回路が形成されたガラス基板 201 上に、絶縁膜 202、絶縁平坦化膜 203 およびウインド絶縁膜 204 を介して有機 EL 素子 21 が画素単位で形成される。しかる後、パッシベーション膜 208 を介して封止基板 209 が接着剤 210 によって接合され、当該封止基板 209 によって有機 EL 素子 21 が封止されることによって表示パネル 70 が形成される。

10

【0054】

〔基本例に係る有機 EL 表示装置の回路動作〕

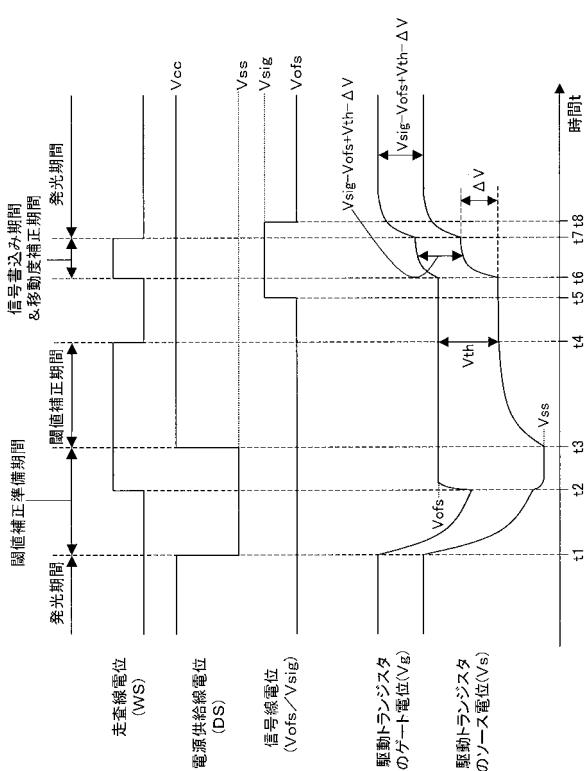

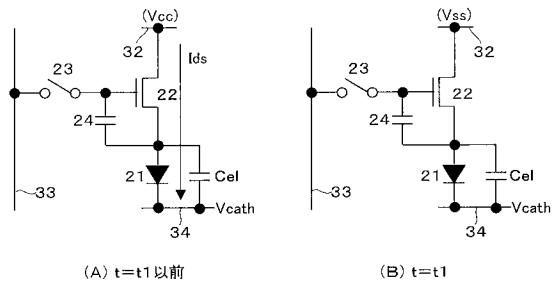

次に、本基本例に係る有機 EL 表示装置 10 の回路動作について、図 4 のタイミング波形図を基に図 5 および図 6 の動作説明図を用いて説明する。

【0055】

なお、図 5 および図 6 の動作説明図では、図面の簡略化のために、書込みトランジスタ 23 をスイッチのシンボルで図示している。また、周知の通り、有機 EL 素子 21 は等価容量（寄生容量） $C_{e1}$  を持っている。したがって、ここでは、等価容量 $C_{e1}$  についても図示している。

20

【0056】

図 4 のタイミング波形図には、走査線 31 の電位（書込み走査信号） $W_S$ 、電源供給線 32 の電位（電源電位） $D_S$ 、信号線 33 の電位（ $V_{of\ s} / V_{sing}$ ）、駆動トランジスタ 22 のゲート電圧 $V_g$  およびソース電圧 $V_s$  の変化を示している。

【0057】

〔前フレームの発光期間〕

図 4 のタイミング波形図において、時刻  $t_1$  以前は、前のフレーム（フィールド）における有機 EL 素子 21 の発光期間となる。この前フレームの発光期間では、電源供給線 32 の電位 $D_S$  が第 1 電源電位（以下、「高電位」と記述する） $V_{cc}$  にあり、また、書込みトランジスタ 23 が非導通状態にある。

30

【0058】

このとき、駆動トランジスタ 22 は飽和領域で動作するように設計されている。これにより、図 5 (A) に示すように、駆動トランジスタ 22 のゲート - ソース間電圧 $V_{gs}$  に応じた駆動電流（ドレイン - ソース間電流） $I_{ds}$  が、電源供給線 32 から駆動トランジスタ 22 を通して有機 EL 素子 21 に供給される。よって、有機 EL 素子 21 が駆動電流 $I_{ds}$  の電流値に応じた輝度で発光する。

【0059】

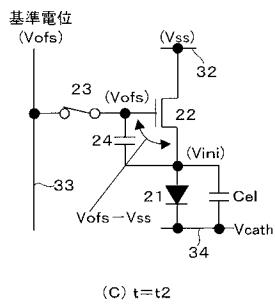

〔閾値補正準備期間〕

時刻  $t_1$  になると、線順次走査の新しいフレーム（現フレーム）に入る。そして、図 5 (B) に示すように、電源供給線 32 の電位 $D_S$  が高電位 $V_{cc}$  から第 2 電源電位（以下、「低電位」と記述する） $V_{ss}$  に切り替わる。低電位 $V_{ss}$  は、信号線 33 の基準電位 $V_{of\ s}$  に対して $V_{of\ s} - V_{th}$  よりも十分に低い電位である。

40

【0060】

ここで、有機 EL 素子 21 の閾値電圧を $V_{th\ e1}$ 、共通電源供給線 34 の電位（カソード電位）を $V_{cat\ h}$  とする。このとき、低電位 $V_{ss}$  を $V_{ss} < V_{th\ e1} + V_{cat\ h}$  とすると、駆動トランジスタ 22 のソース電圧 $V_s$  が低電位 $V_{ss}$  にほぼ等しくなるために、有機 EL 素子 21 は逆バイアス状態となる。したがって、有機 EL 素子 21 は消光する。

【0061】

次に、時刻  $t_2$  で走査線 31 の電位 $W_S$  が低電位側から高電位側に遷移することで、図 5 (C) に示すように、書込みトランジスタ 23 が導通状態となる。このとき、信号出力

50

回路 6 0 から信号線 3 3 に対して基準電位  $V_{of\ s}$  が供給されているために、駆動トランジスタ 2 2 のゲート電圧  $V_g$  が基準電位  $V_{of\ s}$  になる。また、駆動トランジスタ 2 2 のソース電圧  $V_s$  は、基準電位  $V_{of\ s}$  よりも十分に低い電位  $V_{ss}$  にある。

【 0 0 6 2 】

このとき、駆動トランジスタ 2 2 のゲート - ソース間電圧  $V_{gs}$  は  $V_{of\ s} - V_{ss}$  となる。ここで、 $V_{of\ s} - V_{ss}$  が駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  よりも大きくないと、後述する閾値補正処理を行うことができないために、 $V_{of\ s} - V_{ss} > V_{th}$  なる電位関係に設定する必要がある。

【 0 0 6 3 】

このように、駆動トランジスタ 2 2 のゲート電圧  $V_g$  を基準電位  $V_{of\ s}$  に、ソース電圧  $V_s$  を低電位  $V_{ss}$  にそれぞれ固定して（確定させて）初期化する処理が、後述する閾値補正処理を行う前段階の準備（閾値補正準備）の処理である。したがって、基準電位  $V_{of\ s}$  および低電位  $V_{ss}$  は、駆動トランジスタ 2 2 のゲート電圧  $V_g$  およびソース電圧  $V_s$  の各初期化電位となる。

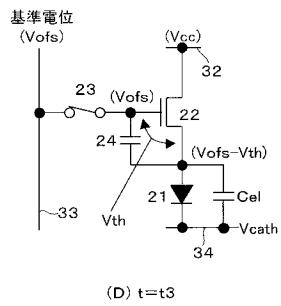

【 0 0 6 4 】

〔 閾値補正期間 〕

次に、時刻  $t_3$  で、図 5 ( D ) に示すように、電源供給線 3 2 の電位  $D\ S$  が低電位  $V_{ss}$  から高電位  $V_{cc}$  に切り替わると、駆動トランジスタ 2 2 のゲート電圧  $V_g$  が保たれた状態で閾値補正処理が開始される。すなわち、ゲート電圧  $V_g$  から駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  を減じた電位に向けて駆動トランジスタ 2 2 のソース電圧  $V_s$  が上昇を開始する。

【 0 0 6 5 】

ここでは、駆動トランジスタ 2 2 のゲート電圧  $V_g$  の初期化電位  $V_{of\ s}$  を基準とし、当該初期化電位  $V_{of\ s}$  から駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  を減じた電位に向けてソース電圧  $V_s$  を変化させる処理を閾値補正処理と呼んでいる。この閾値補正処理が進むと、やがて、駆動トランジスタ 2 2 のゲート - ソース間電圧  $V_{gs}$  が駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  に収束する。この閾値電圧  $V_{th}$  に相当する電圧は保持容量 2 4 に保持される。

【 0 0 6 6 】

なお、閾値補正処理を行う期間（閾値補正期間）において、電流が専ら保持容量 2 4 側に流れ、有機 EL 素子 2 1 側には流れないようにする必要がある。そのために、有機 EL 素子 2 1 がカットオフ状態となるように共通電源供給線 3 4 の電位  $V_{catch}$  を設定しておくこととする。

【 0 0 6 7 】

次に、時刻  $t_4$  で走査線 3 1 の電位  $W\ S$  が低電位側に遷移することで、図 6 ( A ) に示すように、書込みトランジスタ 2 3 が非導通状態となる。このとき、駆動トランジスタ 2 2 のゲート電極が信号線 3 3 から電気的に切り離されることによってフローティング状態になる。しかし、ゲート - ソース間電圧  $V_{gs}$  が駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  に等しいために、当該駆動トランジスタ 2 2 はカットオフ状態にある。したがって、駆動トランジスタ 2 2 にドレイン - ソース間電流  $I_{ds}$  は流れない。

【 0 0 6 8 】

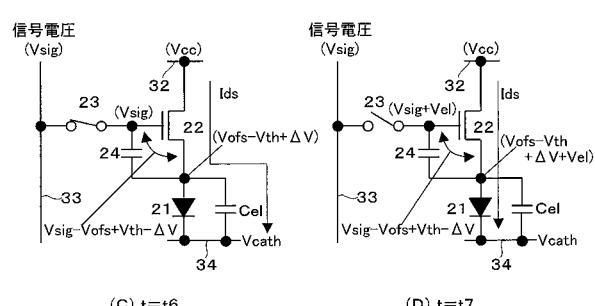

〔 信号書き込み & 移動度補正期間 〕

次に、時刻  $t_5$  で、図 6 ( B ) に示すように、信号線 3 3 の電位が基準電位  $V_{of\ s}$  から映像信号の信号電圧  $V_{sig}$  に切り替わる。続いて、時刻  $t_6$  で、走査線 3 1 の電位  $W\ S$  が高電位側に遷移することで、図 6 ( C ) に示すように、書込みトランジスタ 2 3 が導通状態になって映像信号の信号電圧  $V_{sig}$  をサンプリングし、当該信号電圧  $V_{sig}$  を画素 2 0 内に書き込む。

【 0 0 6 9 】

この書き込みトランジスタ 2 3 による信号電圧  $V_{sig}$  の書き込みにより、駆動トランジスタ 2 2 のゲート電圧  $V_g$  が信号電圧  $V_{sig}$  となる。そして、映像信号の信号電圧  $V_{sig}$

10

20

30

40

50

$g$  による駆動トランジスタ 2 2 の駆動の際に、当該駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  が保持容量 2 4 に保持された閾値電圧  $V_{th}$  に相当する電圧とキャンセルされる。この閾値キャンセルの原理の詳細については後述する。

#### 【0070】

このとき、有機 EL 素子 2 1 はカットオフ状態（ハイインピーダンス状態）にある。したがって、映像信号の信号電圧  $V_{sig}$  に応じて電源供給線 3 2 から駆動トランジスタ 2 2 に流れる電流（ドレイン - ソース間電流  $I_{ds}$ ）は有機 EL 素子 2 1 の等価容量  $C_{el}$  に流れ込む。このドレイン - ソース間電流  $I_{ds}$  により、有機 EL 素子 2 1 の等価容量  $C_{el}$  の充電が開始される。

#### 【0071】

この等価容量  $C_{el}$  の充電により、駆動トランジスタ 2 2 のソース電圧  $V_s$  が時間の経過と共に上昇していく。このとき既に、駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  の画素ごとのばらつきがキャンセルされており、駆動トランジスタ 2 2 のドレイン - ソース間電流  $I_{ds}$  は当該駆動トランジスタ 2 2 の移動度  $\mu$  に依存したものとなる。ここに、移動度  $\mu$  とは、駆動トランジスタ 2 2 のチャネルを構成する半導体薄膜の電子移動度である。

10

#### 【0072】

ここで、映像信号の信号電圧  $V_{sig}$  に対する保持容量 2 4 の保持電圧  $V_{gs}$  の比率が 1（理想値）であると仮定する。この信号電圧  $V_{sig}$  に対する保持電圧  $V_{gs}$  の比率を書き込みゲインと呼ぶ場合もある。すると、駆動トランジスタ 2 2 のソース電圧  $V_s$  が  $V_{of} - V_{th} + V$  の電位まで上昇することで、駆動トランジスタ 2 2 のゲート - ソース間電圧  $V_{gs}$  は  $V_{sig} - V_{of} + V_{th} - V$  となる。

20

#### 【0073】

すなわち、駆動トランジスタ 2 2 のソース電圧  $V_s$  の上昇分  $V$  は、保持容量 2 4 に保持された電圧 ( $V_{sig} - V_{of} + V_{th}$ ) から差し引かれるように作用する。換言すれば、ソース電圧  $V_s$  の上昇分  $V$  は、保持容量 2 4 の充電電荷を放電するように作用し、負帰還がかけられることになる。したがって、駆動トランジスタ 2 2 のソース電圧  $V_s$  の上昇分  $V$  は負帰還の帰還量となる。

#### 【0074】

このように、駆動トランジスタ 2 2 に流れるドレイン - ソース間電流  $I_{ds}$  に応じた帰還量  $V$  でゲート - ソース間電圧  $V_{gs}$  に負帰還をかけることで、駆動トランジスタ 2 2 のドレイン - ソース間電流  $I_{ds}$  の移動度  $\mu$  に対する依存性を打ち消すことができる。この移動度  $\mu$  に対する依存性を打ち消す処理が、駆動トランジスタ 2 2 の移動度  $\mu$  の画素ごとのばらつきを補正する移動度補正処理である。

30

#### 【0075】

より具体的には、駆動トランジスタ 2 2 のゲート電極に書き込まれる映像信号の信号振幅  $V_{in}$  (=  $V_{sig} - V_{of}$ ) が高いほどドレイン - ソース間電流  $I_{ds}$  が大きくなるために、負帰還の帰還量  $V$  の絶対値も大きくなる。したがって、発光輝度レベルに応じた移動度補正処理が行われる。

#### 【0076】

また、映像信号の信号振幅  $V_{in}$  を一定とした場合、駆動トランジスタ 2 2 の移動度  $\mu$  が大きいほど負帰還の帰還量  $V$  の絶対値も大きくなるために、画素ごとの移動度  $\mu$  のばらつきを取り除くことができる。したがって、負帰還の帰還量  $V$  は移動度補正の補正量とも言える。移動度補正の原理の詳細については後述する。

40

#### 【0077】

##### 〔発光期間〕

次に、時刻  $t_7$  で走査線 3 1 の電位  $WS$  が低電位側に遷移することで、図 6 (D) に示すように、書き込みトランジスタ 2 3 が非導通状態となる。これにより、駆動トランジスタ 2 2 のゲート電極は、信号線 3 3 から電気的に切り離されるためにフローティング状態になる。

#### 【0078】

50

ここで、駆動トランジスタ 2 2 のゲート電極がフローティング状態にあるときは、駆動トランジスタ 2 2 のゲート - ソース間に保持容量 2 4 が接続されていることによって、駆動トランジスタ 2 2 のソース電圧  $V_s$  の変動に連動して（追従して）ゲート電圧  $V_g$  も変動する。このように、駆動トランジスタ 2 2 のゲート電圧  $V_g$  がソース電圧  $V_s$  の変動に連動して変動する動作を、本明細書では保持容量 2 4 によるブートストラップ動作と呼ぶこととする。

#### 【0079】

駆動トランジスタ 2 2 のゲート電極がフローティング状態になり、それと同時に、駆動トランジスタ 2 2 のドレイン - ソース間電流  $I_{ds}$  が有機 EL 素子 2 1 に流れ始めることにより、当該ドレイン - ソース間電流  $I_{ds}$  に応じて有機 EL 素子 2 1 のアノード電位が上昇する。

10

#### 【0080】

そして、有機 EL 素子 2 1 のアノード電位が  $V_{thel} + V_{cath}$  を越えると、有機 EL 素子 2 1 に駆動電流が流れ始めると有機 EL 素子 2 1 が発光を開始する。また、有機 EL 素子 2 1 のアノード電位の上昇は、即ち駆動トランジスタ 2 2 のソース電圧  $V_s$  の上昇に他ならない。駆動トランジスタ 2 2 のソース電圧  $V_s$  が上昇すると、保持容量 2 4 のブートストラップ動作により、駆動トランジスタ 2 2 のゲート電圧  $V_g$  も連動して上昇する。

#### 【0081】

このとき、ブートストラップゲインが 1（理想値）であると仮定した場合、ゲート電圧  $V_g$  の上昇量はソース電圧  $V_s$  の上昇量に等しくなる。故に、発光期間中駆動トランジスタ 2 2 のゲート - ソース間電圧  $V_{gs}$  は  $V_{sing} - V_{ofs} + V_{th} - V$  で一定に保持される。そして、時刻  $t_8$  で信号線 3 3 の電位が映像信号の信号電圧  $V_{sing}$  から基準電位  $V_{ofs}$  に切り替わる。

20

#### 【0082】

以上説明した一連の回路動作において、閾値補正準備、閾値補正、信号電圧  $V_{sing}$  の書き込み（信号書き込み）および移動度補正の各処理動作は、1 水平走査期間（1H）において実行される。また、信号書き込みおよび移動度補正の各処理動作は、時刻  $t_6 - t_7$  の期間において並行して実行される。

30

#### 【0083】

なお、ここでは、閾値補正処理を 1 回だけ実行する駆動法を探る場合を例に挙げて説明したが、この駆動法は一例に過ぎず、この駆動法に限られるものではない。例えば、閾値補正処理を移動度補正および信号書き込み処理と共に行う 1H 期間に加えて、当該 1H 期間に先行する複数の水平走査期間に亘って分割して複数回実行する、いわゆる分割閾値補正を行う駆動法を探ることも可能である。

#### 【0084】

この分割閾値補正の駆動法を採用することにより、高精細化に伴う多画素化によって 1 水平走査期間に割り当てられる時間が短くなったとしても、閾値補正期間として複数の水平走査期間に亘って十分な時間を確保することができる。その結果、閾値補正処理を確実に行うことができる。

40

#### 【0085】

##### （閾値キャンセルの原理）

ここで、駆動トランジスタ 2 2 の閾値補正（即ち、閾値キャンセル）の原理について説明する。閾値補正処理は、先述したように、駆動トランジスタ 2 2 のゲート電圧  $V_g$  の初期化電位  $V_{ofs}$  を基準として当該電位  $V_{ofs}$  から駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  を減じた電位に向かって、駆動トランジスタ 2 2 のソース電圧  $V_s$  を変化させる処理である。

#### 【0086】

駆動トランジスタ 2 2 は、飽和領域で動作するように設計されているために定電流源として動作する。定電流源として動作することで、有機 EL 素子 2 1 に対して駆動トランジ

50

スタ 2 2 から、次式(1)で与えられる一定のドレイン - ソース間電流(駆動電流)  $I_{ds}$  が供給される。

$$I_{ds} = (1/2) \cdot \mu (W/L) C_o \times (V_{gs} - V_{th})^2 \quad \dots \dots (1)$$

ここで、Wは駆動トランジスタ 2 2 のチャネル幅、Lはチャネル長、 $C_o$ は単位面積当たりのゲート容量である。

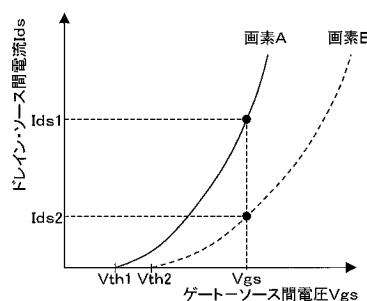

【0087】

図 7 に、駆動トランジスタ 2 2 のドレイン - ソース間電流  $I_{ds}$  対ゲート - ソース間電圧  $V_{gs}$  の特性を示す。

【0088】

この特性図に示すように、駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  の画素ごとのばらつきに対する補正を行わないと、閾値電圧  $V_{th}$  が  $V_{th1}$  のとき、ゲート - ソース間電圧  $V_{gs}$  に対応するドレイン - ソース間電流  $I_{ds}$  が  $I_{ds1}$  になる。

10

【0089】

これに対して、閾値電圧  $V_{th}$  が  $V_{th2}$  ( $V_{th2} > V_{th1}$ ) のとき、同じゲート - ソース間電圧  $V_{gs}$  に対応するドレイン - ソース間電流  $I_{ds}$  が  $I_{ds2}$  ( $I_{ds2} < I_{ds1}$ ) になる。すなわち、駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  が変動すると、当該駆動トランジスタ 2 2 のゲート - ソース間電圧  $V_{gs}$  が一定であってもドレイン - ソース間電流  $I_{ds}$  が変動する。

11

【0090】

一方、上記構成の画素(画素回路) 2 0 では、先述したように、発光時の駆動トランジスタ 2 2 のゲート - ソース間電圧  $V_{gs}$  が  $V_{sig} - V_{ofs} + V_{th} - V$  であるために、これを式(1)に代入すると、ドレイン - ソース間電流  $I_{ds}$  は、次式(2)で表される。

20

$$I_{ds} = (1/2) \cdot \mu (W/L) C_o \times (V_{sig} - V_{ofs} - V)^2 \quad \dots \dots (2)$$

【0091】

すなわち、駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  の項がキャンセルされており、駆動トランジスタ 2 2 から有機EL素子 2 1 に供給されるドレイン - ソース間電流  $I_{ds}$  は、駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  に依存しない。その結果、駆動トランジスタ 2 2 の製造プロセスのばらつきや経時変化により、駆動トランジスタ 2 2 の閾値電圧  $V_{th}$  が画素ごとに変動したとしても、ドレイン - ソース間電流  $I_{ds}$  が変動しないために、有機EL素子 2 1 の発光輝度を一定に保つことができる。

30

【0092】

(移動度補正の原理)

続いて、駆動トランジスタ 2 2 の移動度補正の原理について説明する。移動度補正処理は、先述したように、駆動トランジスタ 2 2 に流れるドレイン - ソース間電流  $I_{ds}$  に応じた補正量  $V$  で駆動トランジスタ 2 2 のゲート - ソース間の電位差に負帰還をかける処理である。この移動度補正処理により、駆動トランジスタ 2 2 のドレイン - ソース間電流  $I_{ds}$  の移動度  $\mu$  に対する依存性を打ち消すことができる。

31

【0093】

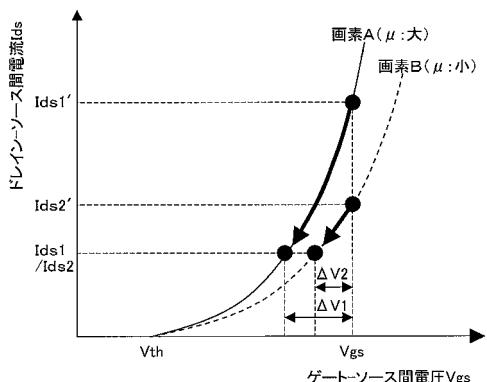

図 8 に、駆動トランジスタ 2 2 の移動度  $\mu$  が相対的に大きい画素 A と、駆動トランジスタ 2 2 の移動度  $\mu$  が相対的に小さい画素 B とを比較した状態で特性カーブを示す。駆動トランジスタ 2 2 をポリシリコン薄膜トランジスタなどで構成した場合、画素 A や画素 B のように、画素間で移動度  $\mu$  がばらつくことは避けられない。

40

【0094】

画素 A と画素 B で移動度  $\mu$  にばらつきがある状態で、駆動トランジスタ 2 2 のゲート電極に例えば両画素 A, B に対して同レベルの信号振幅  $V_{in}$  (=  $V_{sig} - V_{ofs}$ ) を書き込んだ場合を考える。この場合、移動度  $\mu$  の補正を行わないと、移動度  $\mu$  の大きい画素 A に流れるドレイン - ソース間電流  $I_{ds1}$  と移動度  $\mu$  の小さい画素 B に流れるドレイン - ソース間電流  $I_{ds2}$  との間には大きな差が生じてしまう。このように、移

50

動度  $\mu$  の画素ごとのばらつきに起因してドレイン - ソース間電流  $I_{d,s}$  に画素間で大きな差が生じると、画面のユニフォーミティが損なわれる。

【0095】

ここで、先述した式(1)のトランジスタ特性式から明らかなように、移動度  $\mu$  が相対的に大きいとドレイン - ソース間電流  $I_{d,s}$  が大きくなる。したがって、負帰還における帰還量  $V$  は移動度  $\mu$  が大きくなるほど大きくなる。図8に示すように、移動度  $\mu$  が相対的に大きな画素Aの帰還量  $V_1$  は、移動度  $\mu$  が相対的に小さな画素Bの帰還量  $V_2$  に比べて大きい。

【0096】

そこで、移動度補正処理によって駆動トランジスタ22のドレイン - ソース間電流  $I_{d,s}$  に応じた帰還量  $V$  でゲート - ソース間電圧  $V_{g,s}$  に負帰還をかけることにより、移動度  $\mu$  が大きいほど負帰還が大きくかかることになる。その結果、移動度  $\mu$  の画素ごとのばらつきを抑制することができる。

10

【0097】

具体的には、移動度  $\mu$  の大きな画素Aで帰還量  $V_1$  の補正をかけると、ドレイン - ソース間電流  $I_{d,s}$  は  $I_{d,s,1}$  から  $I_{d,s,2}$  まで大きく下降する。一方、移動度  $\mu$  の小さな画素Bの帰還量  $V_2$  は小さいために、ドレイン - ソース間電流  $I_{d,s}$  は  $I_{d,s,2}$  から  $I_{d,s,1}$  までの下降となり、それ程大きく下降しない。結果的に、画素Aのドレイン - ソース間電流  $I_{d,s,1}$  と画素Bのドレイン - ソース間電流  $I_{d,s,2}$  とはほぼ等しくなるために、移動度  $\mu$  の画素ごとのばらつきが補正される。

20

【0098】

以上をまとめると、移動度  $\mu$  の異なる画素Aと画素Bがあった場合、移動度  $\mu$  の大きい画素Aの帰還量  $V_1$  は移動度  $\mu$  の小さい画素Bの帰還量  $V_2$  に比べて大きくなる。つまり、移動度  $\mu$  が大きい画素ほど帰還量  $V$  が大きく、ドレイン - ソース間電流  $I_{d,s}$  の減少量が大きくなる。

【0099】

したがって、駆動トランジスタ22のドレイン - ソース間電流  $I_{d,s}$  に応じた帰還量  $V$  で、ゲート - ソース間電圧  $V_{g,s}$  に負帰還をかけることで、移動度  $\mu$  の異なる画素のドレイン - ソース間電流  $I_{d,s}$  の電流値が均一化される。その結果、移動度  $\mu$  の画素ごとのばらつきを補正することができる。すなわち、駆動トランジスタ22に流れる電流(ドレイン - ソース間電流  $I_{d,s}$ )に応じた帰還量  $V$  で、駆動トランジスタ22のゲート - ソース間電圧  $V_{g,s}$  に負帰還をかける処理が移動度補正処理となる。

30

【0100】

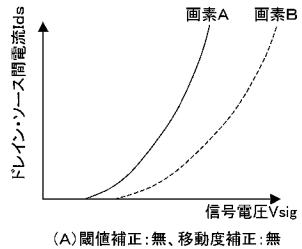

ここで、図2に示した画素(画素回路)20において、閾値補正、移動度補正の有無による映像信号の信号電位(サンプリング電位)  $V_{sig}$  と駆動トランジスタ22のドレイン - ソース間電流  $I_{d,s}$  との関係について図9を用いて説明する。

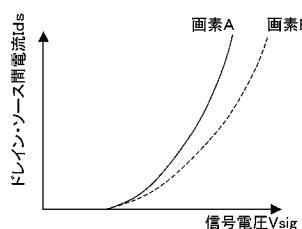

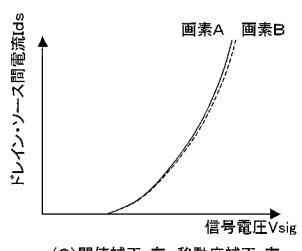

【0101】

図9において、(A)は閾値補正処理および移動度補正処理を共に行わない場合、(B)は移動度補正処理を行わず、閾値補正処理のみを行った場合、(C)は閾値補正処理および移動度補正処理を共に行なった場合をそれぞれ示している。図9(A)に示すように、閾値補正処理および移動度補正処理を共に行わない場合には、閾値電圧  $V_{th}$  および移動度  $\mu$  の画素A, Bごとのばらつきに起因してドレイン - ソース間電流  $I_{d,s}$  に画素A, B間で大きな差が生じることになる。

40

【0102】

これに対して、閾値補正処理のみを行った場合は、図9(B)に示すように、ドレイン - ソース間電流  $I_{d,s}$  のばらつきをある程度低減できるものの、移動度  $\mu$  の画素A, Bごとのばらつきに起因する画素A, B間でのドレイン - ソース間電流  $I_{d,s}$  の差は残る。そして、閾値補正処理および移動度補正処理を共に行なうことで、図9(C)に示すように、閾値電圧  $V_{th}$  および移動度  $\mu$  の画素A, Bごとのばらつきに起因する画素A, B間でのドレイン - ソース間電流  $I_{d,s}$  の差をほぼ無くすことができる。したがって、どの階調に

50

おいても有機EL素子21の輝度ばらつきは発生せず、良好な画質の表示画像を得ることができる。

【0103】

また、図2に示した画素20は、閾値補正および移動度補正の各補正機能に加えて、先述した保持容量24によるブートストラップ動作の機能を備えていることで、次のような作用効果を得ることができる。

【0104】

すなわち、有機EL素子21のI-V特性の経時変化に伴って駆動トランジスタ22のソース電圧Vsが変化したとしても、保持容量24によるブートストラップ動作により、駆動トランジスタ22のゲート-ソース間電位Vgsを一定に維持することができる。したがって、有機EL素子21に流れる電流は変化せず一定となる。その結果、有機EL素子21の発光輝度も一定に保たれるために、有機EL素子21のI-V特性が経時変化したとしても、それに伴う輝度劣化のない画像表示を実現できる。

10

【0105】

<2. 実施形態>

以上説明した有機EL表示装置10において、有機EL素子21が自発光素子であるために、表示パネル70のコントラストは非常に高い。したがって、前にも述べたように、低階調を背景として当該背景中の一部に高階調が表示されているような画表示のときに、高階調の表示輝度をより高く設定することでより高画質を得ることができる。ここで、高階調とは、あらかじめ定められた基準階調よりも高い階調を言う。また、低階調の背景中に一部高階調が表示されているような画表示としては、一例として、花火や宇宙のような画表示が挙げられる。

20

【0106】

本実施形態では、同じレベルの映像信号の信号電圧Vsigの入力に対して、画素の発光輝度（表示輝度）を調整できるようにするために、書き込みトランジスタ23による信号電圧Vsigの書き込み時間を画素アレイ部30内で複数存在させる構成を探っている。ここで、信号書き込み時間が画素アレイ部内で複数存在するということは、信号書き込み時間が異なる画素回路が画素アレイ部30内に存在するということである。

30

【0107】

一例として、低階調を背景中の一部に高階調が表示されているような画表示のときに、高階調の表示部分の画素（画素回路）について、信号書き込み時間を他の表示部分（基準階調よりも低い階調の表示部分）の画素回路よりも短くする場合を考える。

【0108】

ここで、書き込みトランジスタ23による映像信号の信号書き込み期間において、駆動トランジスタ22のゲート-ソース間電圧Vgsは一旦増加し、ピークに達した後単調減少するという特性をとる（その詳細については後述する）。このような特性の下では、信号書き込み時間が短くなることで、信号書き込み期間の終了時における駆動トランジスタのゲート-ソース間電圧Vgsが高くなる。

40

【0109】

そして、駆動トランジスタ22のゲート-ソース間電圧Vgsが高くなった分だけ有機EL素子21に流れる電流値が増加する。その結果、有機EL素子21の発光輝度が上昇する。すなわち、書き込みトランジスタ23による信号電圧Vsigの信号書き込み時間を短くすることで、有機EL素子21の発光輝度を上げることができる。

【0110】

したがって、花火や宇宙のような画表示、即ち低階調の背景中に一部高階調が表示されているような画表示のときに、高階調の表示部分の信号書き込み時間を他の表示部分よりも短くすることで、高階調の表示部分の表示輝度をより高く設定することができる。その結果、表示する画像の高画質化を図ることができる。

【0111】

以下に、書き込みトランジスタ23による信号電圧Vsigの信号書き込み時間を画素アレ

50

イ部30内で複数存在させるために、特定の表示部分の画素回路における信号書き込み時間を相対的に短くする具体的な実施例について説明する。特定の表示部分としては、一例として、低階調の背景中に一部高階調が表示されているような画表示のときの高階調の表示部分が挙げられる。

【0112】

信号書き込み時間を短くする方法としては、先述した回路動作の場合を例に採ると、書き込みトランジスタ23をオン(導通)／オフ(非導通)制御する書き込み走査信号(走査線31の電位)WSのパルス幅を狭くする方法が挙げられる。他に、信号線33上における映像信号の信号電圧Vsigの遷移タイミングの位相、本例では立ち上がり位相を遅くする方法が挙げられる。これらの方法について、以下に具体的に説明する。

10

【0113】

(実施例1)

先ず、実施例1として、書き込み走査信号WSのパルス幅を狭くする方法について説明する。一般的に、書き込み走査信号WSのパルス幅を狭くするには、図1に示す書き込み走査回路40において、書き込み走査信号WSのパルス幅を決めるイネーブル信号enのパルス幅を変化させる方法が採られる。

20

【0114】

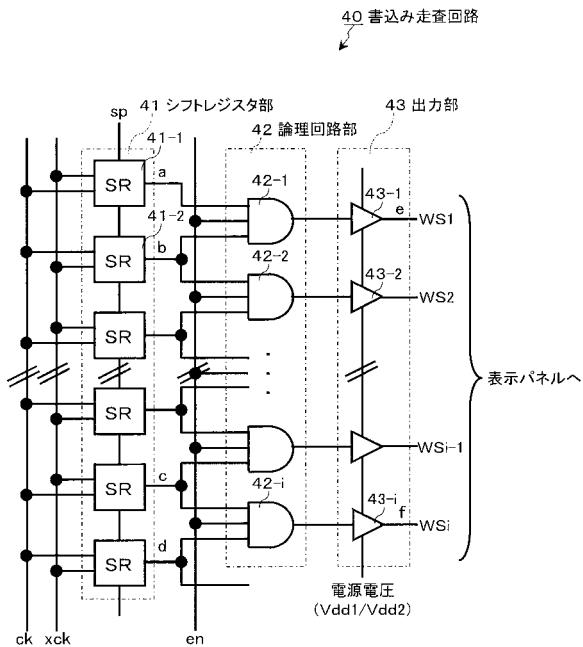

図10は、書き込み走査回路40の回路構成の一例を示すブロック図である。図10に示すように、本例に係る書き込み走査回路40は、シフトレジスタ部41、論理回路部42および出力部43によって構成されている。

20

【0115】

シフトレジスタ部41は、シフトレジスタ(SR)の単位回路であるシフト段(転送段)41-1, 41-2, ...が画素アレイ部30の画素行に対応した数だけ継続接続されている。シフト段41-1, 41-2, ...の各々には互いに逆相のクロックパルスck, xckが与えられる。そして、シフトレジスタ部41は、クロックパルスck, xckに同期してスタートパルスspを順にシフト(転送)することにより、シフト段41-1, 41-2, ...の各々からシフトパルスを出力する。

【0116】

論理回路部42は、画素アレイ部30の画素行に対応した数の3入力AND回路42-1, 42-2, ...によって構成されている。AND回路42-1, 42-2, ...は、シフトレジスタ部41における隣り合う2つのシフト段、即ちシフト段41-1と41-2、41-2と41-3、...の各々から出力されるシフトパルスを2入力とし、イネーブル信号enを残りの1入力としている。イネーブル信号enは、図示せぬタイミング発生部から入力される。

30

【0117】

イネーブル信号enはそのパルス幅によって最終的に得られる書き込み走査信号WSのパルス幅を決める。このイネーブル信号enのパルス幅として複数、例えば2つのパルス幅t1, t2(t1 > t2)を用意する。通常の画表示のときはパルス幅t1のイネーブル信号enを入力する。そして、特定の表示部分、例えば低階調の背景中に一部高階調が表示されているような画表示のときの高階調の表示部分ではパルス幅t2のイネーブル信号enを入力する。

40

【0118】

出力部43は、画素アレイ部30の画素行に対応した数のバッファ43-1, 43-2, ...によって構成されている。バッファ43-1, 43-2, ...の各々は、シフトレジスタ部41の各シフト段から出力され、AND回路42-1, 42-2, ...においてイネーブル信号enによってパルス幅が決められたシフトパルスを書き込み走査信号WS1, WS2, ...として出力する。

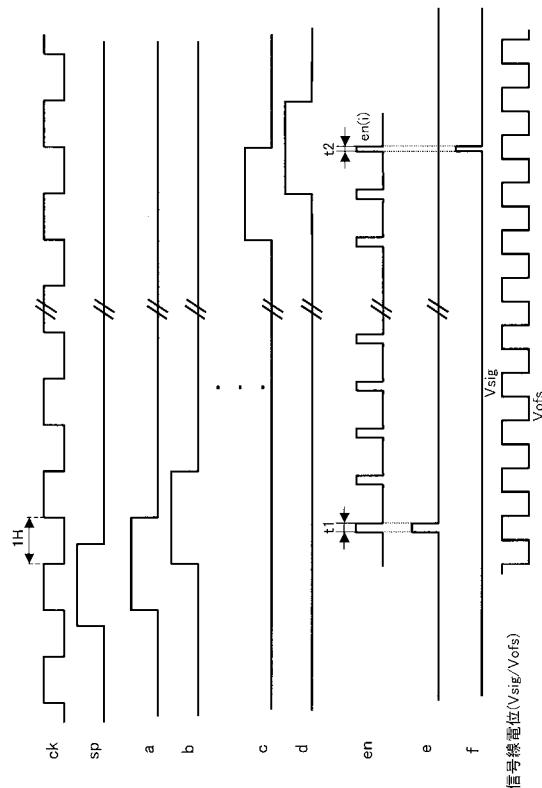

【0119】

図11に、クロックパルスck、スタートパルスsp、シフトパルスa, b, ..., c, d、イネーブル信号en、バッファ43-1, 43-2, ...およびバッファ43-1, 4

50

3 - i の出力 e , f のタイミング関係を示す。図 1 1 には、信号線電位 ( V sig / V of s ) についても示している。

【 0 1 2 0 】

ここでは、i 行目の書込み走査信号 WSi のパルス幅を狭くする場合を例に挙げて示している。i 行目の書込み走査信号 WSi のパルス幅を狭くためには、i 行目の走査タイミングでアクティブ状態になるイネーブル信号 en ( i ) のパルス幅を、他の行のパルス幅 t1 よりも狭いパルス幅 t2 に設定する。すなわち、i 行目の走査タイミングでパルス幅 t2 のイネーブル信号 en ( i ) を、先述したタイミング発生部から本書込み走査回路 40 に入力する。

【 0 1 2 1 】

このイネーブル信号 en ( i ) のパルス幅 t2 によって i 行目の書込み走査信号 WSi のパルス幅が決められる。その結果、i 行目の書込み走査信号 WSi のパルス幅が他の行のパルス幅 t1 よりも狭いパルス幅 t2 になる。この i 行目の書込み走査信号 WSi は、i 行目の画素行の各画素回路における書込みトランジスタ 23 を導通状態にする。したがって、書込み走査信号 WSi のパルス幅がパルス幅 t2 であることで、i 行目の画素行では信号書込み時間が時間 t1 から時間 t2 に短縮される。

10

【 0 1 2 2 】

( 実施例 2 )

続いて、実施例 2 として、信号線 33 上における映像信号の信号電圧 V sig の立ち上がり位相を遅くする方法について説明する。信号線 33 には、図 1 に示す信号出回路 60 から映像信号の信号電圧 V sig と基準電位 V of s とが選択的に出力される。

20

【 0 1 2 3 】

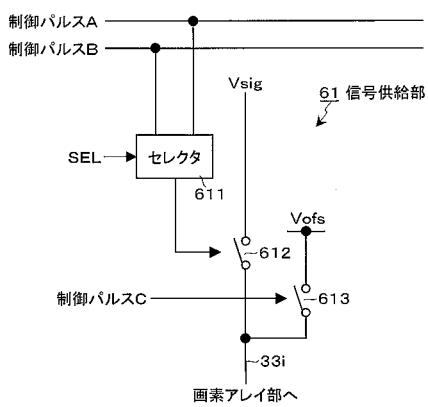

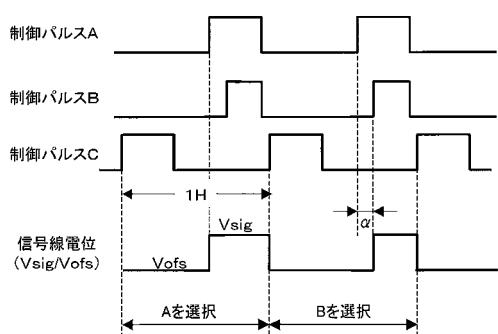

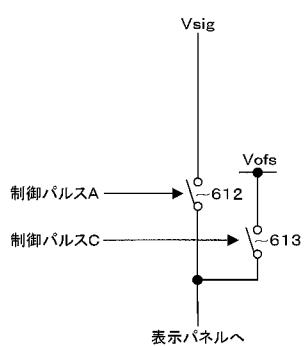

図 1 2 に、信号出回路 60 における j 列目の画素列に対応する回路部分 ( 以下、「信号供給部」と記述する ) の構成の一例を示す。図 1 2 に示すように、信号供給部 61 は、セレクタ 611 および 2 つのスイッチ 612, 613 によって構成されている。

【 0 1 2 4 】

セレクタ 611 は、パルス幅が異なる複数、例えば 2 つの制御パルス A, B を入力しており、後述するパルス選択信号 SEL に基づいていずれか一方を選択する。ここでは、制御パルス B は、制御パルス A よりもパルス幅が狭い。このセレクタ 611 によって選択された制御パルス A / B はスイッチ 612 に与えられる。

30

【 0 1 2 5 】

スイッチ 612 は、制御パルス A / B に応答してオン ( 閉 ) 状態になることで、パネル外部から入力される映像信号の信号電圧 V sig を選択的に j 列目の信号線 33 - j に出力する。スイッチ 613 は、制御パルス C に応答してオン状態になることで、基準電位 V of s を選択的に j 列目の信号線 33 - j に出力する。

【 0 1 2 6 】

図 1 3 に、制御パルス A, B, C および信号線電位 ( V sig / V of s ) のタイミング関係を示す。図 1 3 のタイミング波形図に示すように、制御パルス A, B は、立ち上がりタイミングが同じになっている。制御パルス A, B のパルス幅は A > B の関係にある。したがって、制御パルス A の立ち上がりタイミングに対して制御パルス B の立ち上がりタイミングが遅くなっている。すなわち、制御パルス B の立ち上がり位相が制御パルス A の立ち上がり位相よりも遅い。制御パルス C は、制御パルス A, B のアクティブ期間とオーバーラップしない期間でアクティブ状態になる。

40

【 0 1 2 7 】

セレクタ 611 は、通常の画表示の際には制御パルス A を選択する。これにより、信号線 33 - j には信号供給部 61 から、制御パルス A の立ち上がりタイミングで映像信号の信号電圧 V sig の供給が開始される。また、制御パルス A の非アクティブ期間では、制御パルス C に応答して基準電位 V of s が信号線 33 - j に供給される。

【 0 1 2 8 】

一方、特定の表示部分、例えば低階調の背景中に一部高階調が表示されているような画

50

表示のときの高階調の表示部分でセレクタ 611 にパルス選択信号 SEL が与えられることで、セレクタ 611 は制御パルス A に代えて制御パルス B を選択する。これにより、信号線 33-j には信号供給部 61 から、制御パルス B の立ち上がりタイミングで信号電圧 Vsig の供給が開始される。

【0129】

ここで、制御パルス B の立ち上がり位相が制御パルス A の立ち上がり位相よりも遅い。したがって、信号供給部 61 から信号線 33-j に信号電圧 Vsig の供給が開始されるタイミングが、制御パルス A の選択時よりも制御パルス B の選択時の方が時間だけ遅くなる。これは、信号線 33 上における信号電圧 Vsig の立ち上がり位相が時間だけ遅くなっていることを意味する。そして、信号電圧 Vsig の立ち上がり位相が遅くなることで、その遅くなった時間の分だけ信号書き込み時間が短くなる。

10

【0130】

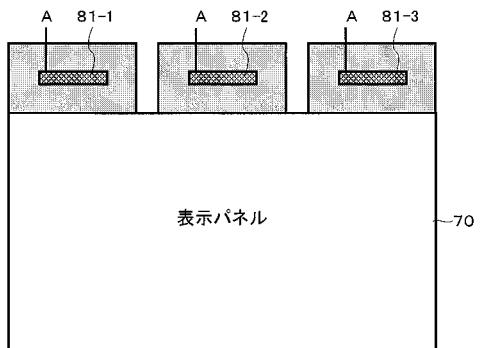

なお、本実施例 2 では、表示パネル 70 上に信号出力回路 60 が搭載されている有機 EL 表示装置を前提としている。これに対して、図 14 に示すように、表示パネル 70 の外部に設けられた複数、例えば 3 個の信号ドライバ 81-1, 81-2, 81-3 から直接信号線 33 に対して、信号電圧 Vsig / 基準電位 Vofs を入力する構成を採る有機 EL 表示装置がある。

【0131】

この種の有機 EL 表示装置に対して実施例 2 に係る方法を適用する場合には、図 15 に示すように、信号電圧 Vsig 用のスイッチ 612 の制御パルス A のパルス幅を制御することで、実施例 2 に係る方法を実現することができる。この場合は、制御パルス A のパルス幅の制御は、信号ドライバ 81-1, 81-2, 81-3 個々、即ちドライバ単位で行われることになる。

20

【0132】

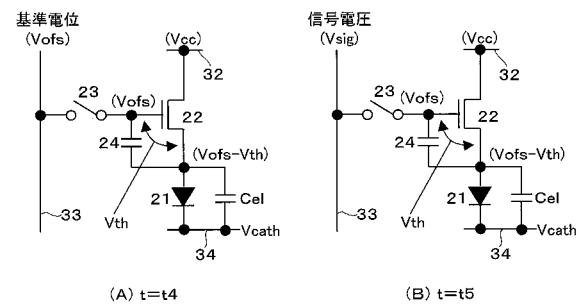

(表示輝度が上昇するメカニズム)

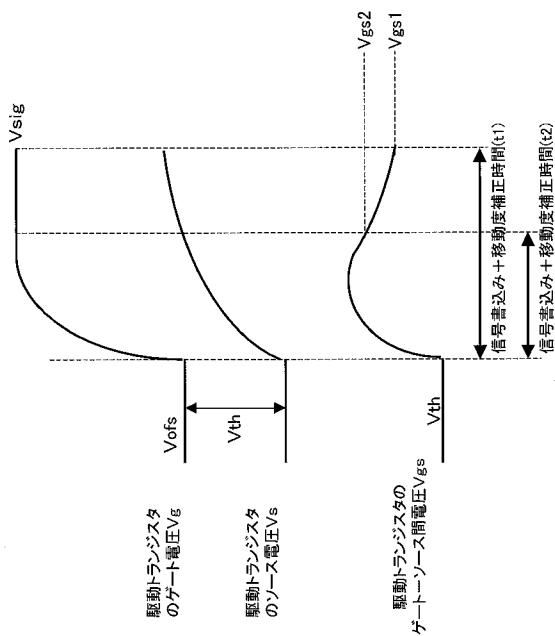

次に、先述した回路動作での信号書き込み + 移動度補正期間（以下、「信号書き込み期間または信号書き込み時間」と記述する）を短くすることで、表示輝度が上昇するメカニズムについて説明する。

【0133】

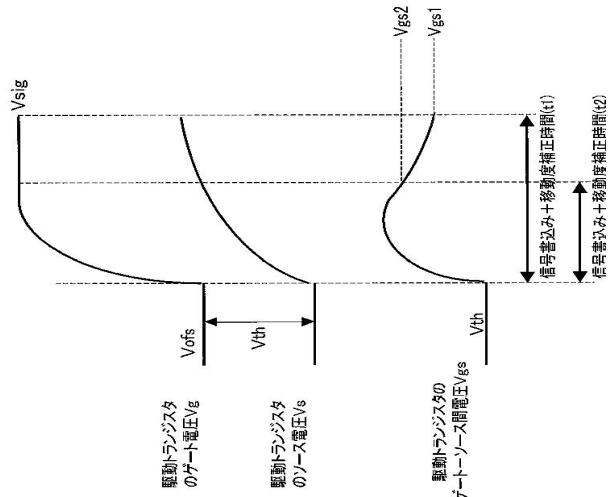

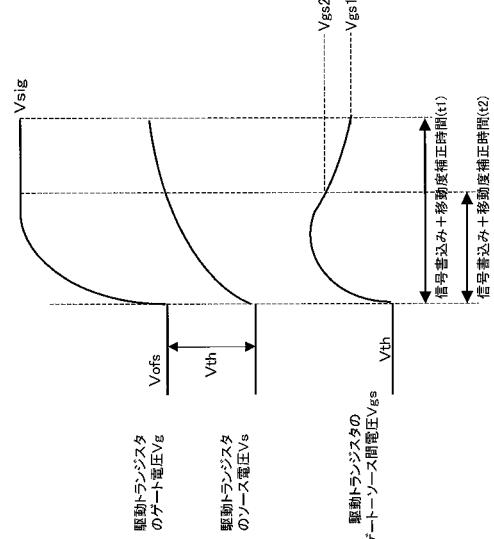

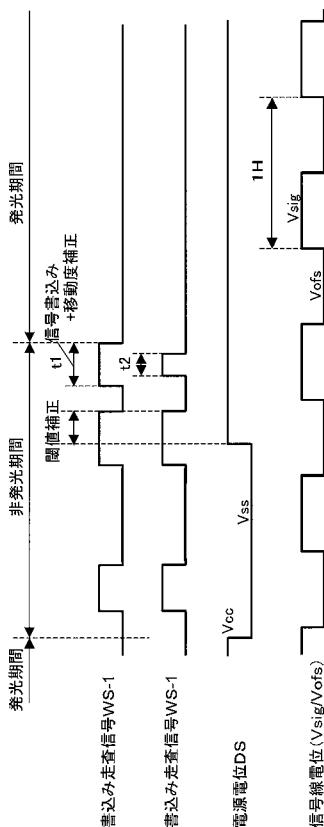

図 16 に、先述した回路動作を前提とした場合における信号書き込み期間での駆動トランジスタ 22 のゲート電圧 Vg、ソース電圧 Vs およびゲート - ソース間電圧 Vgs の変化を示す。

30

【0134】

信号書き込み期間において、映像信号の信号電圧 Vsig は、書き込みトランジスタ 23 によるサンプリング（書き込み）動作によって保持容量 24 に入力される。また、先述したように、信号書き込み処理と同時に（並行して）移動度補正処理が実行される。このとき、電源供給線 32 から駆動トランジスタ 22 を通して電流が流れることで、当該電流によって有機 EL 素子 21 の等価容量（寄生容量）Cel が充電される。

【0135】

ここで、駆動トランジスタ 22 のゲート電圧 Vg のトランジェントとソース電圧 Vs のトランジェントとを比較した場合、ゲート電圧 Vg のトランジェントの方がソース電圧 Vs のトランジェントよりも早い。その理由は次の通りである。

40

【0136】

すなわち、保持容量 24 の容量値 Ccs は、有機 EL 素子 21 の等価容量の容量値 Cel よりも小さい ( $C_{cs} < C_{el}$ )。さらに、前にも述べたように、駆動トランジスタ 22 が飽和領域で動作し、書き込みトランジスタ 23 が線形領域で動作する。したがって、一般的に、書き込みトランジスタ 23 のオン抵抗の方が駆動トランジスタ 22 のオン抵抗よりも小さい。

【0137】

そして、書き込みトランジスタ 23 を通して駆動トランジスタ 22 のゲート電極に電流が

50

流れ込む経路の時定数は、書込みトランジスタ23のオン抵抗と保持容量24の容量値C<sub>cs</sub>とで決まる。また、駆動トランジスタ22を通してそのソース電極に電流が流れ込む経路の時定数は、駆動トランジスタ22のオン抵抗と有機EL素子21の容量値C<sub>el</sub>とで決まる。したがって、駆動トランジスタ22のゲート電圧V<sub>g</sub>のトランジェントの方がソース電圧V<sub>s</sub>のトランジェントよりも早くなる。

【0138】

このように、駆動トランジスタ22のゲート電圧V<sub>g</sub>とソース電圧V<sub>s</sub>とでそのトランジェントに差があることで、図16に特に実線で示すように、駆動トランジスタ22のゲート-ソース間電圧V<sub>gs</sub>は一旦増加し、ピークに達した後単調減少するという特性をとる。因みに、駆動トランジスタ22のゲート-ソース間電圧V<sub>gs</sub>がピークとなるときは駆動トランジスタ22のゲート電圧V<sub>g</sub>の変化量とソース電圧V<sub>s</sub>の変化量とが一致したときである。

【0139】

また、移動度μのばらつきは移動度補正処理によって時間の経過と共に減少してゆき、駆動トランジスタ22のゲート電圧V<sub>g</sub>が信号電圧V<sub>sig</sub>となる。そして、駆動トランジスタ22のゲート-ソース間電圧V<sub>gs</sub>がピークになった後一定期間経過後に移動度μのばらつきの補正が完了する。

【0140】

ここで、信号書込み時間を時間t1から当該時間t1よりも短い時間t2に切り替えたとすると、図16から明らかなように、駆動トランジスタ22のゲート-ソース間電圧V<sub>gs</sub>はV<sub>gs1</sub>からV<sub>gs2</sub>へ増加する。有機EL素子21に流れる電流値は、先述した式(1)から明らかなように、駆動トランジスタ22のゲート-ソース間電圧V<sub>gs</sub>で決まる。したがって、駆動トランジスタ22のゲート-ソース間電圧V<sub>gs</sub>の増加することで、有機EL素子21に流れる電流値が増加する。その結果、信号書込み時間を短くすることで、有機EL素子21の発光輝度が上昇することになる。

【0141】

このように、信号書込み時間を時間t1から時間t2へ短くしたときは、移動度補正時間も短くなってしまう。そのために、白ラスターのような画像に対してはムラやスジといった移動度μのばらつきに起因する画質不良が視認される懸念がある。しかしながら、低階調を背景として当該背景中の一部に高階調が表示されているような画表示のときはラスター発光領域が少なく、図16に示すように、信号書込み時間を短くしてもムラやスジといった移動度μのばらつきに起因する画質不良は視認されない。

【0142】

以上説明したことから明らかなように、一例として、花火や宇宙のような画表示のときに、高階調の表示部分で信号書込み時間を他の表示部分よりも短くすることで、高階調の表示輝度をより高く設定することができる。これにより、信号ドライバの耐圧の増加に伴う当該信号ドライバのコスト上昇を招いたり、動画応答性を損なったりすることなく、書込みトランジスタ23のオン電圧を下げる当該書込みトランジスタ23のオン抵抗を上げるだけの簡単な制御で画質の向上を図ることができる。

【0143】

ここで、低階調を背景として当該背景中の一部に高階調が表示されているような画表示において、高階調の表示部分で信号書込み時間を制御するためには、高階調の表示部分を検出する必要がある。

【0144】

この高階調の表示部分の検出については、例えば、有機EL表示装置全体を制御するシステム制御部(図示せず)において、ライン単位で輝度平均値を演算するなどの手法によって実現できる。そして、輝度平均値の演算結果に基づいて検出した高階調の表示部分の表示タイミングで、書込み走査回路40または信号出力回路60に対して信号書込み時間を切り換えるためのトリガー信号を与えるようにする。

【0145】

10

20

30

40

50

実施例 1 の場合は、高階調の表示部分の表示タイミングで発生されるトリガー信号は、書き込み走査回路 40 内におけるイネーブル信号  $e_n$  を発生するタイミング発生部に与えられる。このタイミング発生部は、トリガー信号が与えられると、当該トリガー信号に応答して図 10 の論理回路部 42 に対してパルス幅  $t_1$  に代えてパルス幅  $t_2$  のイネーブル信号  $e_n$  を供給する。

【0146】

一方、実施例 2 の場合は、高階調の表示部分の表示タイミングで発生されるトリガー信号は、図 12 のセレクタ 611 に対してそのパルス選択信号 SEL として与えられる。セレクタ 611 は、パルス選択信号 SEL が与えられると、当該パルス選択信号 SEL に応答して制御パルス A に代えて当該制御パルス A よりも立ち上がり位相が遅い制御パルス B を選択してスイッチ 612 に供給する。

10

【0147】

これにより、実施例 1 および実施例 2 のいずれの場合にも、図 16 に示すように、高階調の表示部分で信号書き込み時間を時間  $t_1$  から時間  $t_2$  に切り替えることができる。

【0148】

なお、信号書き込み時間を時間  $t_1$  から時間  $t_2$  に切り替えるときの当該時間  $t_2$  の時間として、画素アレイ部 30 内に複数存在しても良い。画素アレイ部 30 内に時間  $t_2$  を複数持つことで、当該時間  $t_2$  を表示する画像に応じて多段階に切り替えことが可能になる。これにより、信号書き込み時間として、表示する画像に対応した最適な時間を設定可能になる。

20

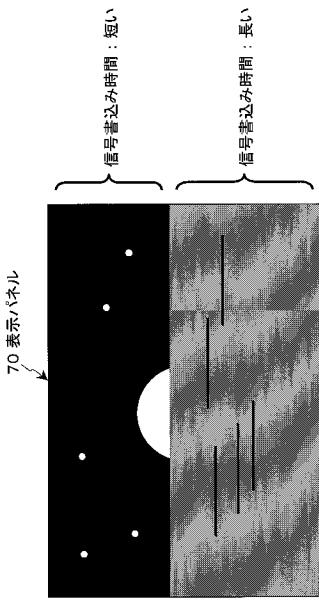

【0149】

一例として、図 17 に示すように、表示パネル 70 の下部で比較的ムラが視認され易い低階調の画像が存在する画表示を考える。このとき、低階調を背景として当該背景中の一部に高階調が表示されている表示パネル 70 の上部では、先述したように、信号書き込み時間を時間  $t_1$  から時間  $t_2$  に切り替える。これにより、表示パネル 70 の上部において、高階調の表示輝度をより高く設定することができる。

【0150】

一方、低階調が存在する表示パネル 70 の下部では、信号書き込み時間として、表示パネル 70 の上部での時間  $t_2$  よりも長い時間を設定する。これにより、比較的ムラが視認され易い低階調が存在する画像においても、画質不良を視認されることがなくなる。その結果、低階調を背景として当該背景中の一部に高階調が表示されている画像や、比較的ムラが視認され易い低階調の画像などが混在する表示画面全体に亘って高画質化を図ることができる。

30

【0151】

<3. 応用例>

ところで、有機 EL 素子 21 は、前にも述べたように、アノード電極とカソード電極との間に、発光層を含む有機膜を挟持した構造となっている。このような構造の有機 EL 素子 21 を画素 20 の発光素子として用いた有機 EL 表示装置において、当該有機 EL 素子 21 を形成する工程で異物が混入すると、画素 20 の輝度欠陥が発生する。

40

【0152】

具体的には、図 2 に示す画素回路において、製造工程で混入する異物が原因となって有機 EL 素子 21 のアノード電極-カソード電極の電極間ショート等が引き起こされる場合がある。この有機 EL 素子 21 の電極間ショートにより、有機 EL 素子 21 が発光しないわゆる滅点と呼称される輝度欠陥が発生する。

【0153】

この異物混入に起因する輝度欠陥に対する対策として、例えば、1 つの副画素（画素 20 に相当）内に有機 EL 素子を含む画素構成素子を複数組設ける技術が用いられている。この技術によれば、いずれかの組の有機 EL 素子がショート等で欠陥化しても、他の組の有機 EL 素子が正常に発光することで、画素 20 の滅点化を防ぐことができる。これにより、有機 EL 表示装置の高歩留化を図ることができる。

50

## 【0154】

## (応用例1)

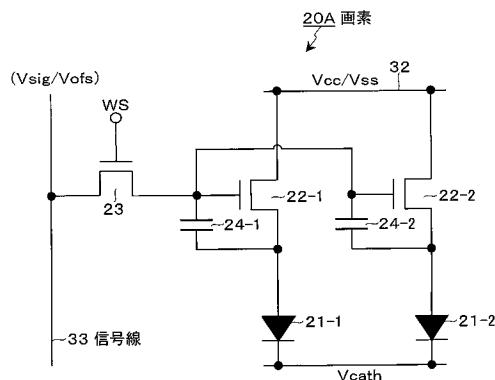

図18は、1つの画素内に有機EL素子を含む画素構成素子を複数組設ける構成を採る場合の応用例1に係る画素の回路構成を示す回路図であり、図中、図2と同等部分には同一符号を付して示している。

## 【0155】

本応用例1に係る画素20Aは、1つの画素内に有機EL素子21を例えれば2個(21-1, 21-2)有する回路構成となっている。駆動回路側については、2個の有機EL素子21-1, 21-2に対して書き込みトランジスタ23が1個共通に設けられ、駆動トランジスタ22および保持容量24については2個ずつ設けられている。

10

## 【0156】

具体的には、駆動トランジスタ22-1のソース電極には有機EL素子21-1が接続され、駆動トランジスタ22-2のソース電極には有機EL素子21-2が接続されている。すなわち、駆動トランジスタ22-1が有機EL素子21-1の駆動を担い、駆動トランジスタ22-2が有機EL素子21-2の駆動を担う。

## 【0157】

上記構成の応用例1に係る画素20Aにおいて、有機EL素子21-1, 21-2のアノード電極は電気的に接続されていないため、一方の有機EL素子21-1が異物による電極間ショート等で欠陥化している場合でも、他方の有機EL素子21-2が正常に発光する。また、他方の有機EL素子21-2が異物による電極間ショート等で欠陥化している場合においても一方の有機EL素子21-1が正常に発光する。

20

## 【0158】

勿論、一方の有機EL素子21-1が異物による電極間ショート等で欠陥化している場合には当該欠陥化した有機EL素子21-1を駆動トランジスタ21-1から切り離してもよい。同様に、他方の有機EL素子21-2が異物による電極間ショート等で欠陥化している場合においても、当該欠陥化した有機EL素子21-2を駆動トランジスタ21-2から切り離してもよい。これらの切り離し処理は、レーザーリペアなどのリペア技術を用いて行うことができる。

## 【0159】

このリペア技術の適用により、有機EL素子21-1, 21-2のいずれか一方が電極間ショート等で欠陥化していても、正常な他方については発光状態を維持できるために、画素20Aが完全に滅点になるのを防ぐことができる。また、2個の有機EL素子21-1, 21-2のいずれか一方が電極間オーブン等で欠陥化している場合にも、画素20Aが完全に滅点(輝度が0)になるのを防ぐことができる。

30

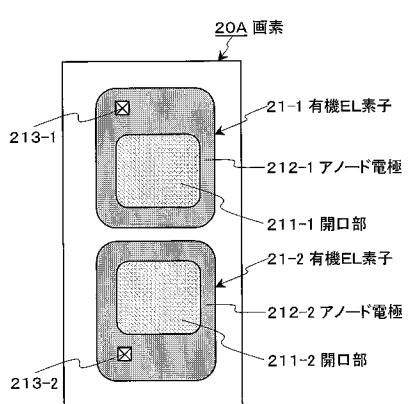

## 【0160】

1つの画素内に2個の有機EL素子21-1, 21-2を設ける場合は、図19に示すように、1つの画素(副画素)の発光領域は、2個の有機EL素子21-1, 21-2によって2分割されることになる。図19において、有機EL素子21-1, 21-2は、発光領域となる開口部211-1, 211-2を有し、アノード電極212-1, 212-2がコンタクト部213-1, 213-2を介して駆動トランジスタ22-1, 22-2の各ソース電極と電気的に接続されている。

40

## 【0161】

ここで、電極間ショートまたは電極間オーブン等で一方の有機EL素子21-1/21-2が欠陥化して発光しないときは、画素20Aが完全に滅点になるのを防ぐことはできるものの、発光輝度は両方が発光しているときの半分に低下する。この場合、欠陥化した有機EL素子21-1/21-2を含む画素20Aは滅点ではないが、いわゆる半滅点という点欠陥として知覚されてしまう。

## 【0162】

このような場合、画素20Aに書き込む映像信号の信号電圧Vsigを上げて正常に発光する有機EL素子21-1/21-2の発光輝度を上げることで、画素全体として半滅

50

点という点欠陥を視認しにくくすることができる。しかしながら、前にも述べたように、信号電圧  $V_{sig}$  を上げる方法を探ると、信号ドライバの耐圧を増加させる必要があるために、信号ドライバの価格が高くなり、表示装置全体の高コスト化を招く。

#### 【0163】

そこで、本応用例1に係る画素20Aでは、半滅点という点欠陥を視認しにくくするために、先述した実施形態に係る表示輝度を上げる技術を適用する。すなわち、電極間ショートまたは電極間オープン等で欠陥化して発光しない有機EL素子（以下、「欠陥化した素子」と記述する）21-1/21-2を含む画素20Aについては、信号書き込み時間を短くなる方向に制御する。

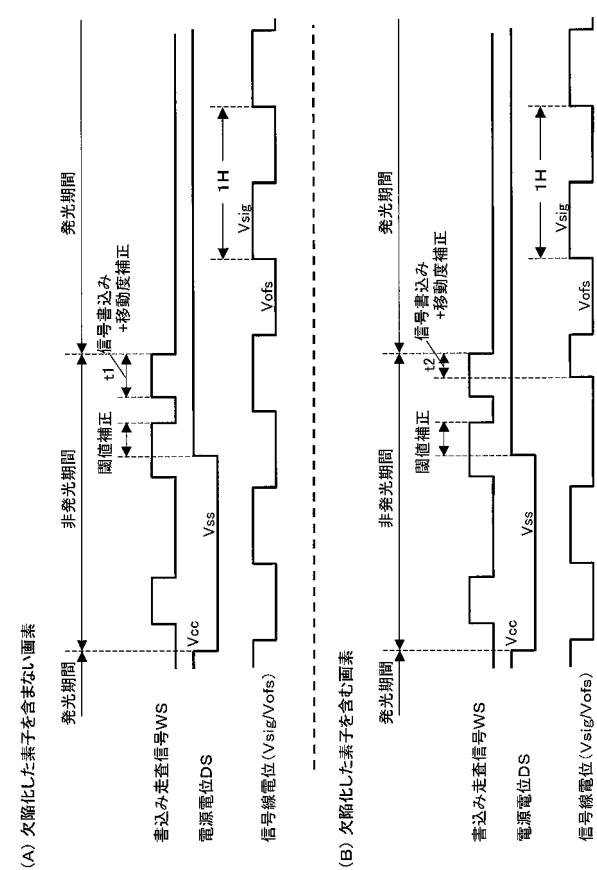

#### 【0164】

具体的には、欠陥化した素子を含む画素の信号書き込み時間を、欠陥化した素子を含まない画素の信号書き込み時間よりも短くする。一例として、先述した実施例2を適用する場合について考えると、図20のタイミング波形図に示すように、欠陥化した素子を含まない画素の場合（A）と比較して、欠陥化した素子を含む画素の場合（B）の信号電圧  $V_{sig}$  の立ち上がり位相を遅くする。信号電圧  $V_{sig}$  の立ち上がり位相が遅くなることで、その遅くなった時間  $t_1 - t_2$  の分だけ信号書き込み時間が短くなる（ $t_1 - t_2$ ）。

#### 【0165】

信号書き込み期間における駆動トランジスタ22のゲート-ソース間電圧  $V_{g_s}$  の先述した特性の下では、信号書き込み時間が短くなると、信号書き込み期間の終了時における駆動トランジスタ22のゲート-ソース間電圧  $V_{g_s}$  が高くなる（図16参照）。そして、駆動トランジスタ22のゲート-ソース間電圧  $V_{g_s}$  が高くなった分だけ有機EL素子21-1/21-2に流れる電流値が増加する。その結果、有機EL素子21-1/21-2の発光輝度が上昇する。これにより、欠陥化した有機EL素子21-1/21-2を含む画素20Aについて、半滅点という点欠陥を視認しにくくすることができる。

#### 【0166】

ここでは、実施例2を適用することにより、欠陥化した素子を含む画素の信号書き込み時間を、欠陥化した素子を含まない画素の信号書き込み時間よりも短くするとしたが、実施例1を適用しても、同様の作用効果を得ることができる。

#### 【0167】

なお、本応用例1では、欠陥化した有機EL素子21-1/21-2を含む画素20Aについて、信号書き込み時間を相対的に短くする方向に制御することで、画素20Aの発光輝度を上げて点欠陥を視認しにくくしている。このとき、欠陥化した素子を含む画素20Aの輝度が上がり過ぎると、周辺の画素に比べて輝度が高いわゆる半輝点の画素として視認される懸念がある。そこで、次のような制御を行うようにするとよい。

#### 【0168】

すなわち、欠陥化した有機EL素子を含む画素20Aだけでなく、当該画素20Aの周辺画素、例えば上下左右に隣接する画素（以下、「隣接画素」と記述する）についても信号書き込み時間  $t_3$  を短くなる方向に制御するようにする。その際に、信号書き込み時間  $t_3$  については、画素20Aの信号書き込み時間  $t_2$  と同じ設定にするのではなく、当該信号書き込み時間  $t_2$  よりも長い時間に設定するようにする。

#### 【0169】

このような大小関係（ $t_1 > t_3 > t_2$ ）に信号書き込み時間を設定することで、欠陥化した素子を含む画素20Aの周辺の輝度を段階的に制御することができる。この周辺の輝度の段階的な制御により、信号書き込み時間を短くすることによって輝度が上昇した画素20Aが、周辺の画素に比べて輝度が高い半輝点の画素と視認されないため、半滅点および半輝点という点欠陥が視認されない高画質の表示画像を得ることができる。

#### 【0170】

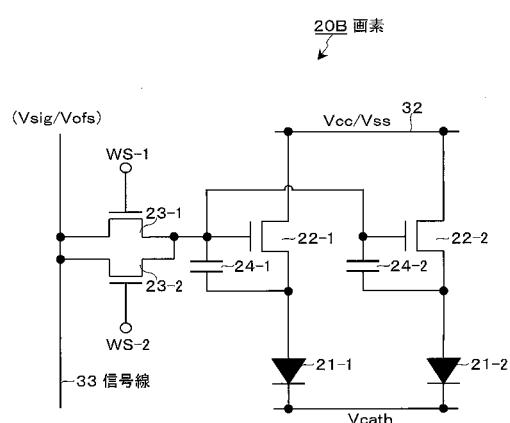

##### （応用例2）

図21は、応用例2に係る画素の回路構成を示す回路図であり、図中、図18と同等部分には同一符号を付して示している。本応用例2に係る画素20Bでは、2個の有機EL

10

20

30

40

50

素子 21-1, 21-2 の駆動回路において、並列接続された複数（本例では、2個）の書き込みトランジスタ 23-1, 23-2 が別々の書き込み走査信号 WS-1, WS-2 によって駆動される構成となっている。

【0171】

図22に、本応用例2に係る画素20Bの駆動タイミングを示す。書き込みトランジスタ 23-1, 23-2 の各ゲート電極には、が別々の書き込み走査信号 WS-1, WS-2 が与えられる。ここで、書き込み走査信号 WS-1 と書き込み走査信号 WS-2 とは、映像信号の信号電圧  $V_{sig}$  を書き込む際にアクティブ状態になる期間（パルス幅）が異なっている。具体的には、書き込み走査信号 WS-1 のパルス幅  $t_1$  は、欠陥化した素子を含まない画素における通常の画表示に対応したパルス幅に設定されている。これに対して、書き込み走査信号 WS-2 のパルス幅  $t_2$  は、書き込み走査信号 WS-1 のパルス幅よりも狭く設定されている。

10

【0172】

このように、信号電圧  $V_{sig}$  を書き込む際のパルス幅が異なる書き込み走査信号 WS-1, WS-2 が与えられる書き込みトランジスタ 23-1, 23-2 が並列接続されている状態では、信号書き込み時間は書き込み走査信号 WS-1 のパルス幅  $t_1$  で決まる時間  $t_1$  となる。一方、パルス幅が長い方の書き込みトランジスタ 23-1 が電気的に画素回路から切り離されると、信号書き込み時間はパルス幅が短い方の書き込み走査信号 WS-2 のパルス幅  $t_2$  で決まる時間  $t_2$  となる。

20

【0173】

そこで、本応用例2に係る画素20Bでは、2個の有機EL素子 21-1, 21-2 の一方が欠陥化したときに半滅点という点欠陥を視認しにくくするために、書き込みトランジスタ 23-1 の配線を、レーザー照射等の技術を用いて切断（溶断）するようとする。このように、パルス幅が長い方の書き込みトランジスタ 23-1 の配線を切断して画素回路から電気的に切り離すことで、信号書き込み時間が時間  $t_1$  から時間  $t_2$  に短くなる。

20

【0174】

先述したように、信号書き込み時間が短くなると、信号書き込み期間の終了時における駆動トランジスタ 22 のゲート-ソース間電圧  $V_{gs}$  が高くなる。そして、駆動トランジスタ 22 のゲート-ソース間電圧  $V_{gs}$  が高くなった分だけ有機EL素子 21-1 / 21-2 に流れる電流値が増加する。その結果、有機EL素子 21-1 / 21-2 の発光輝度が上昇する。これにより、欠陥化した有機EL素子 21-1 / 21-2 を含む画素20Bについて、半滅点という点欠陥を視認しにくくすることができる。

30

【0175】

ここでは、2個の書き込みトランジスタ 23-1, 23-2 を並列に接続し、それそれに与える書き込み走査信号 SW-1, WS-2 のパルス幅を異ならせるとしたが、書き込みトランジスタ 23 の数は2個に限られるものではない。すなわち、書き込みトランジスタ 23 を3個以上並列に接続するとともに、それぞれの異なるパルス幅の書き込み走査信号 WS を与えるようにする。そして、画素回路から電気的に切り離す際には、書き込み走査信号 WS のパルス幅が広い書き込みトランジスタ 23 から切り離すことで、信号書き込み時間を多段階に設定することが可能になる。

40

【0176】

また、書き込みトランジスタ 23-1 を画素回路から電気的に切り離すに当たっては、書き込みトランジスタ 23-1 のノード（ソース電極またはドレイン電極）を、コンタクト部を介してゲート配線の金属配線層と接続されていることが好ましい。一般に、ゲート配線の金属配線層はその膜厚が薄いために、表示パネル70の作成後もEL発光部とは逆側からレーザー照射等によって切断することが可能である。

【0177】

このとき、ゲート配線上には、ゲート絶縁膜、ストッパー絶縁膜、パシベーション絶縁膜、平坦化膜、ウインド絶縁膜等の絶縁膜が存在し、なおかつ有機EL素子 21 のアノード電極が存在しないことが望ましい。このような画素構造を探ることで、表示パネル70

50

の作成後に、有機EL素子21にダメージを与えることなく、書き込みトランジスタ23-1の配線をレーザー照射等によって切断し、当該書き込みトランジスタ23-1を画素回路から切り離すことが可能となる。

【0178】

<4. 变形例>

上記実施形態では、有機EL素子21の駆動回路が、基本的に、駆動トランジスタ22および書き込みトランジスタ23の2つのトランジスタ(Tr)を有する2Tr構成の場合を例に挙げて説明したが、本発明はこの2Tr構成への適用に限られるものではない。

【0179】

2Tr以外には、例えば、有機EL素子21の発光/非発光を制御するトランジスタを有したり、駆動トランジスタ22のゲート電極に基準電位Vofsを選択的に書き込むスイッチングトランジスタを有したりする画素構成など、種々の画素構成のものが考えられる。

【0180】

また、上記実施形態では、画素の電気光学素子として、有機EL素子を用いた有機EL表示装置に適用した場合を例に挙げて説明したが、本発明はこの適用例に限られるものではない。具体的には、本発明は、無機EL素子、LED素子、半導体レーザー素子等、デバイスに流れる電流値に応じて発光輝度が変化する電流駆動型電気光学素子(発光素子)を用いた表示装置全般に対して適用可能である。

【0181】

<5. 適用例>

以上説明した本発明による表示装置は、電子機器に入力された映像信号、若しくは、電子機器内で生成した映像信号を、画像若しくは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。

【0182】

本発明による表示装置によれば、例えば、低階調の背景中の一部に高階調が表示されているような画表示のときに、高階調の表示部分の表示輝度をより高く設定することができるため、画質の向上を図ることができる。したがって、あらゆる分野の電子機器の表示装置として本発明による表示装置を用いることで、当該電子機器の表示装置の表示品質の向上を図ることができる。

【0183】

本発明による表示装置は、封止された構成のモジュール形状のものをも含む。このモジュール形状のものとしては、例えば、画素アレイ部に透明なガラス等の対向部が貼り付けられて形成された表示モジュールが該当する。この透明な対向部には、カラーフィルタ、保護膜等、さらには、上記した遮光膜が設けられてもよい。なお、表示モジュールには、外部から画素アレイ部への信号等を入出力するための回路部やFPC(フレキシブルプリントサーキット)等が設けられていてもよい。

【0184】

以下に、本発明が適用される電子機器の具体例について説明する。一例として、図23～図27に示す様々な電子機器、例えば、デジタルカメラ、ノート型パソコンコンピュータ、携帯電話機等の携帯端末装置、ビデオカメラなどの表示装置に本発明を適用することが可能である。

【0185】

図23は、本発明が適用されるテレビジョンセットの外観を示す斜視図である。本適用例に係るテレビジョンセットは、フロントパネル102やフィルターガラス103等から構成される映像表示画面部101を含んでいる。そして、映像表示画面部101として本発明による表示装置を用いることにより、本適用例に係るテレビジョンセットが作製される。

【0186】

図24は、本発明が適用されるデジタルカメラの外観を示す斜視図であり、(A)は表

10

20

30

40

50

側から見た斜視図、(B)は裏側から見た斜視図である。本適用例に係るデジタルカメラは、フラッシュ用の発光部111、表示部112、メニュー・スイッチ113、シャッターボタン114等を含んでいる。そして、表示部112として本発明による表示装置を用いることにより、本適用例に係るデジタルカメラが作製される。

【0187】

図25は、本発明が適用されるノート型パーソナルコンピュータの外観を示す斜視図である。本適用例に係るノート型パーソナルコンピュータは、本体121に、文字等を入力するときに操作されるキーボード122、画像を表示する表示部123等を含んでいる。そして、表示部123として本発明による表示装置を用いることにより、本適用例に係るノート型パーソナルコンピュータが作製される。

10

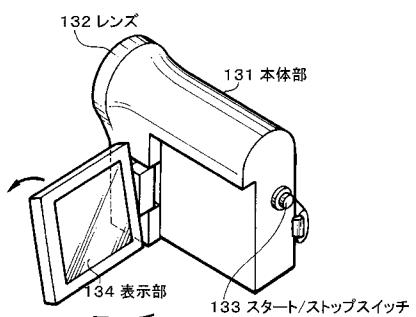

【0188】

図26は、本発明が適用されるビデオカメラの外観を示す斜視図である。本適用例に係るビデオカメラは、本体部131、前方を向いた側面に被写体撮影用のレンズ132、撮影時のスタート/ストップスイッチ133、表示部134等を含んでいる。そして、表示部134として本発明による表示装置を用いることにより、本適用例に係るビデオカメラが作製される。

【0189】

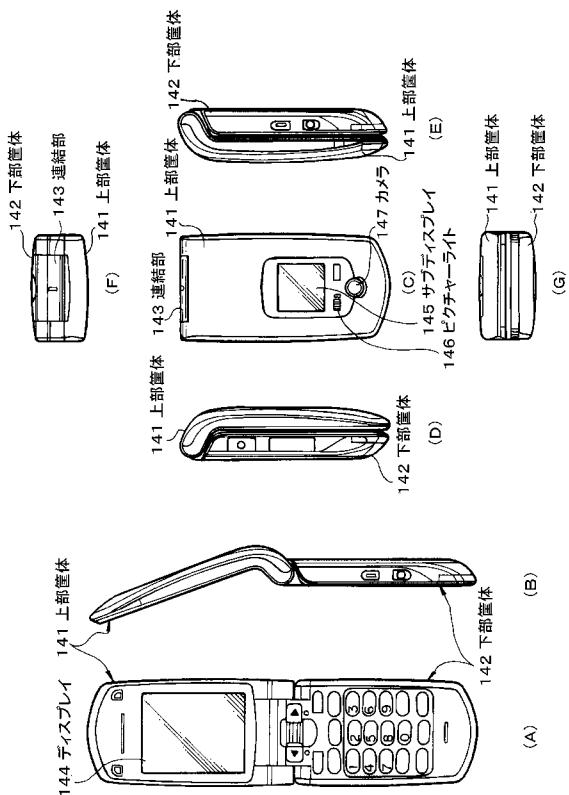

図27は、本発明が適用される携帯端末装置、例えば携帯電話機を示す外観図であり、(A)は開いた状態での正面図、(B)はその側面図、(C)は閉じた状態での正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

20

【0190】

本適用例に係る携帯電話機は、上側筐体141、下側筐体142、連結部(ここではヒンジ部)143、ディスプレイ144、サブディスプレイ145、ピクチャーライト146、カメラ147等を含んでいる。そして、ディスプレイ144やサブディスプレイ145として本発明による表示装置を用いることにより、本適用例に係る携帯電話機が作製される。

【図面の簡単な説明】

【0191】

【図1】本発明の基本例に係る有機EL表示装置の構成の概略を示すシステム構成図である。

30

【図2】画素の基本的な回路構成を示す回路図である。

【図3】画素の断面構造の一例を示す断面図である。

【図4】本基本例に係る有機EL表示装置の回路動作の説明に供するタイミング波形図である。

【図5】本基本例に係る有機EL表示装置の回路動作の説明に供する動作説明図(その1)である。

【図6】本基本例に係る有機EL表示装置の回路動作の説明に供する動作説明図(その2)である。

【図7】駆動トランジスタの閾値電圧V<sub>th</sub>のばらつきに起因する課題の説明に供する特性図である。

40

【図8】駆動トランジスタの移動度μのばらつきに起因する課題の説明に供する特性図である。

【図9】閾値補正、移動度補正の有無による映像信号の信号電圧V<sub>sig</sub>と駆動トランジスタのドレイン・ソース間電流I<sub>ds</sub>との関係の説明に供する特性図である。

【図10】書き込み走査回路の回路構成の一例を示すブロック図である。

【図11】クロックパルスc<sub>k</sub>、スタートパルスs<sub>p</sub>、シフトパルスa<sub>,</sub>b<sub>,</sub>...<sub>,</sub>c<sub>,</sub>d<sub>,</sub>イネーブル信号e<sub>n</sub>、バッファの電源電圧(V<sub>dd1</sub>/V<sub>dd2</sub>)、バッファの出力e<sub>,</sub>fおよび信号線電位(V<sub>sig</sub>/V<sub>ofs</sub>)のタイミング関係を示す図である。

【図12】信号出力回路におけるj列目の画素列に対応する信号供給部の構成の一例を示す回路図である。

50

【図13】制御パルスA, B, Cおよび信号線電位(V<sub>sig</sub> / V<sub>ofs</sub>)のタイミング関係を示すタイミング波形図である。

【図14】表示パネルの外部に設けられた信号ドライバから信号電圧V<sub>sig</sub> / 基準電位V<sub>ofs</sub>を供給する構成の有機EL表示装置の概略構成図である。

【図15】表示パネルの外部に設けられた信号ドライバから信号電圧V<sub>sig</sub> / 基準電位V<sub>ofs</sub>を供給する構成の有機EL表示装置に適用した場合の信号供給部の構成の一例を示す回路図である。

【図16】信号書き込み期間における駆動トランジスタのゲート電圧V<sub>g</sub>、ソース電圧V<sub>s</sub>およびゲート-ソース間電圧V<sub>gs</sub>の変化を示す波形図である。

【図17】パネル下部で比較的ムラが視認され易い低階調の画像が存在する画表示を示す図である。 10

【図18】応用例1に係る画素の回路構成を示す回路図である。

【図19】1つの副画素内に有機EL素子を2個有する場合の有機EL素子のレイアウトを示す平面パターン図である。

【図20】応用例1に係る画素における駆動タイミングを示すタイミング波形図である。

【図21】応用例2に係る画素の回路構成を示す回路図である。

【図22】応用例2に係る画素における駆動タイミングを示すタイミング波形図である。

【図23】本発明が適用されるテレビジョンセットの外観を示す斜視図である。

【図24】本発明が適用されるデジタルカメラの外観を示す斜視図であり、(A)は表側から見た斜視図、(B)は裏側から見た斜視図である。 20

【図25】本発明が適用されるノート型パーソナルコンピュータの外観を示す斜視図である。

【図26】本発明が適用されるビデオカメラの外観を示す斜視図である。

【図27】本発明が適用される携帯電話機を示す外観図であり、(A)は開いた状態での正面図、(B)はその側面図、(C)は閉じた状態での正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

#### 【符号の説明】

##### 【0192】

10 ... 有機EL表示装置、20 (20A, 20B) ... 画素(画素回路)、21 ... 有機EL素子、22 ... 駆動トランジスタ、23 (23-1 ~ 23-4) ... 書込みトランジスタ、24 ... 保持容量、25 ... 補助容量、30 ... 画素アレイ部、31 (31-1 ~ 31-m) ... 走査線、32 (32-1 ~ 32-m) ... 電源供給線、33 (33-1 ~ 33-n) ... 信号線、34 ... 共通電源供給線、40 ... 書込み走査回路、50 ... 電源供給走査回路、60 ... 信号出力回路、70 ... 表示パネル、WS (WS1 ~ WS m) ... 走査線の電位(書き込み走査信号)、DS (DS1 ~ DS m) ... 電源供給線の電位(電源電位) 30

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

(A) 閾値補正:無、移動度補正:無

(B) 閾値補正:有、移動度補正:無

(C) 閾値補正:有、移動度補正:有

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 4】

【図 1 3】

【図 1 5】

【図 16】

【図 17】

【図 18】

【図 19】

【図 20】

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 4】

【図 2 5】

【図 2 6】

【図 27】

## フロントページの続き

| (51)Int.Cl. | F I           | テーマコード(参考) |

|-------------|---------------|------------|

|             | G 0 9 G 3/20  | 6 8 0 H    |

|             | G 0 9 G 3/20  | 6 4 2 D    |

|             | G 0 9 G 3/20  | 6 1 2 U    |

|             | H 0 5 B 33/14 | A          |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置，显示装置的驱动方法和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2010145445A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2010-07-01 |

| 申请号            | JP2008319253                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2008-12-16 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 山本哲郎<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 山本 哲郎<br>内野 勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G09G3/30.K G09G3/20.624.B G09G3/20.670.A G09G3/20.621.A G09G3/20.641.D G09G3/20.680.H<br>G09G3/20.642.D G09G3/20.612.U H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC02 3K107/CC45 3K107/EE03 3K107/HH02 3K107/HH04 5C080<br>/AA06 5C080/BB05 5C080/CC03 5C080/DD04 5C080/EE29 5C080/EE30 5C080/FF11 5C080/HH09<br>5C080/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C380/AA01 5C380/AB06<br>5C380/AB16 5C380/AB22 5C380/AB24 5C380/AB34 5C380/AB35 5C380/AB36 5C380/AC07 5C380<br>/AC08 5C380/AC09 5C380/AC11 5C380/BA12 5C380/BA27 5C380/BA28 5C380/BA29 5C380/BA38<br>5C380/BA39 5C380/BB02 5C380/BB22 5C380/BD02 5C380/BD03 5C380/CA08 5C380/CA12 5C380<br>/CA53 5C380/CB01 5C380/CB12 5C380/CB14 5C380/CB20 5C380/CB31 5C380/CC02 5C380/CC03<br>5C380/CC04 5C380/CC05 5C380/CC07 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC34 5C380<br>/CC41 5C380/CC45 5C380/CC62 5C380/CC63 5C380/CD012 5C380/CD023 5C380/CE19 5C380<br>/CF07 5C380/CF32 5C380/CF51 5C380/CF53 5C380/DA06 5C380/DA32 5C380/DA35 5C380/DA47<br>5C380/FA12 5C380/FA22 |         |            |

| 代理人(译)         | 船桥 国则                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

## 摘要(译)

要解决的问题：增加高灰度级的显示亮度，而不会增加成本并且不会破坏运动图像的响应性。SOLUTION：对于烟花或宇宙的图像显示，即部分在低灰度背景下具有高灰度的图像显示，写入晶体管的信号写入时间在高灰度级的显示部分比其他时间短。显示部件。随着信号写入的时间变短，在信号写入时段结束时驱动晶体管的栅极-源极电压Vgs变高（Vgs1→Vgs2），并且流向有机EL元件的电流相应地增加。因此，可以增加有机EL元件的发光亮度。Z