## 【特許請求の範囲】

## 【請求項 1】

表示素子を駆動する駆動トランジスタを含む画素部が基板上にマトリクス状に配置された表示部と、

列毎に設けられ、各列のそれぞれの画素部と接続する信号線と、

前記信号線を介して前記画素部に映像信号に対応する階調信号を出力する階調信号出力部と、

前記信号線を介して前記画素部に所定の階調電圧を保持させるリセット信号を出力するリセット出力部とを備え、

前記リセット出力部は、前記リセット信号として前記信号線に2段階の電流を流して、前記駆動トランジスタの特性のバラツキを反映した階調電圧を前記画素部に保持させることを特徴とするアクティブマトリクス型表示装置。 10

## 【請求項 2】

前記リセット出力部は、

前記信号線に第1のリセット電流を流す第1の電流源と、

前記信号線に第2のリセット電流を流す第2の電流源と、

前記信号線に前記画素部が最低階調よりも大きい階調の電圧を保持するように前記第1のリセット電流を流し、その後、前記画素部が最低階調の電圧を保持するように前記第2のリセット電流を流すように制御するリセット電流制御部と

を備えたことを特徴とする請求項1に記載のアクティブマトリクス型表示装置。 20

## 【請求項 3】

前記リセット電流制御部は、前記第1、第2のリセット電流を流すそれぞれの時間を制御することを特徴とする請求項2に記載のアクティブマトリクス型表示装置。

## 【請求項 4】

前記リセット出力部を動作させた後に、前記階調電圧出力部を動作させる駆動制御部を更に備えることを特徴とする請求項2に記載のアクティブマトリクス型表示装置。

## 【請求項 5】

表示素子を駆動する駆動トランジスタを含む画素部を基板上にマトリクス状に配置し、列毎に信号線を設けて各列のそれぞれの画素部と接続し、

前記信号線を介して前記画素部に映像信号に対応する階調信号を出力し、 30

前記信号線を介して前記画素部に所定の階調電圧を保持させるリセット信号を出力し、

前記リセット信号の出力では、前記リセット信号として前記信号線に2段階の電流を流して、前記駆動トランジスタの特性のバラツキを反映した階調電圧を前記画素部に保持させることを特徴とするアクティブマトリクス型表示装置の表示方法。

## 【請求項 6】

前記リセット信号の出力では、

第1の電流源を用いて前記信号線に前記画素部が最低階調よりも大きい階調の電圧を保持するように前記第1のリセット電流を流し、その後、第2の電流源を用いて前記画素部が最低階調の電圧を保持するように前記第2のリセット電流を流すように制御することを特徴とする請求項5に記載のアクティブマトリクス型表示装置の表示方法。 40

## 【請求項 7】

前記第1、第2のリセット電流を流すそれぞれの時間を制御することを特徴とする請求項6に記載のアクティブマトリクス型表示装置の表示方法。

## 【請求項 8】

前記リセット信号の出力動作を実行させた後に、前記階調電圧の出力動作を実行させることを特徴とする請求項6に記載のアクティブマトリクス型表示装置の表示方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、アクティブマトリクス型表示装置及びその表示方法に係り、特には、TFT

50

(薄膜トランジスタ)の特性にバラツキがあっても表示品位を保つことのできるアクティブマトリクス型表示装置及びその表示方法に関する。

【背景技術】

【0002】

有機EL素子を用いたアクティブマトリクス型表示装置が開発されている。この装置では、有機EL素子を駆動する薄膜トランジスタ、即ち駆動トランジスタの特性が画素間でほぼ同一であることが要求される。

しかしながら、薄膜トランジスタは、通常ガラス基板などの絶縁体上に形成されるため、画素間で駆動トランジスタの特性にバラツキが生ずることが多い。

【0003】

特許文献1には、カレントコピー型の回路を画素回路に採用したアクティブマトリクス型有機EL表示装置が記載されている。この表示装置では、各画素に映像信号として電流信号を供給し、この電流信号に対応した大きさの駆動電流を有機EL素子に流して有機EL素子を発光させる。この技術によると、駆動トランジスタの特性のバラツキが駆動電流の大きさに与える影響を低減することができる。

【特許文献1】米国特許第6373454号明細書

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところで、このカレントコピー型回路では、映像信号が信号線を介して画素回路に書き込まれる前に、信号線および選択された画素回路の駆動薄膜トランジスタのゲート端子の電位は一旦基準の電位に設定される。

【0005】

通常は、1ライン毎に映像信号に関係なく、最低階調レベルの電位が定電圧源から信号線および選択された画素回路の駆動薄膜トランジスタのゲート端子に書き込まれる。この供給される最低階調レベル電位は、各画素回路で同じ電位である。即ち、供給される最低階調レベル電位は各画素の駆動薄膜トランジスタの閾値のバラツキを補正した電位ではない。このため、駆動薄膜トランジスタの閾値、移動度などの性能にバラツキが存在することによって、低階調ラスタ表示において各画素の明るさが異なり表示ムラが発生していた。

【0006】

本発明はこのような問題点に鑑みてなされたものであり、低階調の映像であっても、駆動薄膜トランジスタの特性バラツキによる表示ムラの少ないアクティブマトリクス型表示装置及びその表示方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記課題を解決するための本発明に係るアクティブマトリクス型表示装置は、表示素子を駆動する駆動トランジスタを含む画素部が基板上にマトリクス状に配置された表示部と、列毎に設けられ、各列のそれぞれの画素部と接続する信号線と、前記信号線を介して前記画素部に映像信号に対応する階調信号を出力する階調信号出力部と、前記信号線を介して前記画素部に所定の階調電圧を保持させるリセット信号を出力するリセット出力部とを備え、前記リセット出力部は、前記リセット信号として前記信号線に2段階の電流を流して、前記駆動トランジスタの特性のバラツキを反映した階調電圧を前記画素部に保持させるアクティブマトリクス型表示装置である。

【0008】

また本発明に係る表示方法は、表示素子を駆動する駆動トランジスタを含む画素部を基板上にマトリクス状に配置し、列毎に信号線を設けて各列のそれぞれの画素部と接続し、前記信号線を介して前記画素部に映像信号に対応する階調信号を出力し、前記信号線を介して前記画素部に所定の階調電圧を保持させるリセット信号を出力し、前記リセット信号の出力では、前記リセット信号として前記信号線に2段階の電流を流して、前記駆動トランジ

10

20

30

40

50

ンジスタの特性のバラツキを反映した階調電圧を前記画素部に保持させるアクティブマトリクス型表示装置の表示方法である。

【発明の効果】

【0009】

本発明によれば、低階調の映像であっても、駆動薄膜トランジスタの特性バラツキの影響があつても表示品位を保つことのできるアクティブマトリクス型表示装置及びその表示方法を提供することができる。

【発明を実施するための最良の形態】

【0010】

以下、本発明の態様について、図面を参照しながら詳細に説明する。なお、各図において、同様又は類似した機能を発揮する構成要素には同一の参照符号を付し、重複する説明は省略する。

なお以下の実施の形態では、アクティブマトリクス型表示装置の内、有機EL表示装置について説明するが、本発明は有機ELに限定されない。

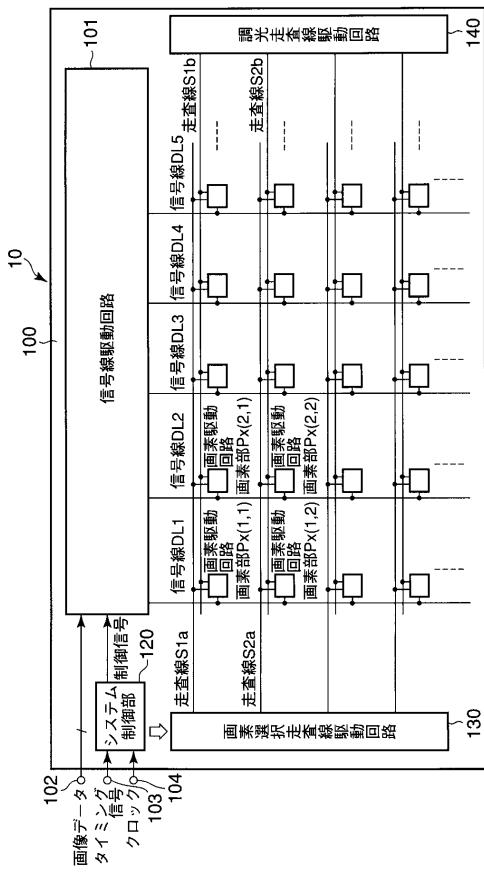

【0011】

図1は、本発明の実施の形態に係るアクティブマトリクス型表示装置を概略的に示すブロック図である。この表示装置10は、アクティブマトリクス型駆動方式を採用した下面発光型の有機EL表示装置である。

【0012】

表示装置10のガラスなどの絶縁支持基板100上には、マトリクス状に配置された画素部PX(1,1)、PX(2,1)・・・、複数の画素選択走査線S1a、S2a、・・・、複数の調光走査線S1b、S2b、・・・、複数の信号線DL1、DL2、・・・が設けられている。

更に絶縁支持基板100上には、信号線駆動回路101、画素選択走査線駆動回路130、調光走査線駆動回路140及びシステム制御部120が駆動回路として備えられている。

【0013】

画素部PXは、有機EL素子と画素駆動回路とを含み、画素選択走査線(調光走査線)と信号線との交差部近傍に配置されている。この画素部PXの構成については後でその詳細を説明する。

【0014】

信号線駆動回路101には、画素の列毎に設けられた信号線DL1、DL2、DL3、...が接続されている。信号線DL1、DL2、・・・は、図1に示すように、各々が画素部PXの列方向(Y方向)に伸びており、画素部PXと行方向(X方向)に交互に配列している。これら信号線DL1、DL2、・・・は、信号線駆動回路101と各列の画素部PXとに接続されている。

【0015】

また、画素選択走査線駆動回路130には、画素の行毎に設けられた走査線が接続されている。1つの画素行に対応する走査線の構成は、画素駆動回路のタイプにより異なるので、ここでは、各行に1本の画素選択走査線S1a、S2a、...を代表して示している。画素選択走査線S1a、S2a、・・・は、図1に示すように、各々が画素部PXの行方向(X方向)に伸びており、画素部PXと列方向(Y方向)に交互に配列している。これら画素選択走査線S1a、S2a、・・・は、画素選択走査線駆動回路130と各行の画素部PXとに接続されている。

【0016】

また、調光走査線駆動回路140には、画素の行毎に設けられた走査線が接続されている。1つの画素行に対応する走査線の構成は、画素駆動回路のタイプにより異なるので、ここでは、各行に1本の画素選択走査線S1b、S2b、...を代表して示している。調光走査線S1b、S2b、・・・は、図1に示すように、各々が画素部PXの行方向(X方向)に伸びており、画素部PXと列方向(Y方向)に交互に配列している。

10

20

30

40

50

## 【0017】

信号線駆動回路101と画素選択走査線駆動回路130と調光走査線駆動回路140は、システム制御部120からのタイミングパルスにより駆動される。システム制御部120には、入力端子103, 104を介して、映像信号に同期したタイミング信号及びクロック信号が供給される。従って、システム制御部120は、信号線駆動回路101と画素選択走査線駆動回路130と調光走査線駆動回路140に対して、映像信号に同期した各種のタイミングパルスを与えることができる。

## 【0018】

画素選択走査線駆動回路130は、映像信号を記憶させるために、行方向(X方向)に配列した複数の画素部PXを選択する。画素選択走査線駆動回路130が、画素選択走査線S1a、S2a、・・・のいずれかを選択してアクティブ状態にすると、アクティブ状態となった画素選択走査線に接続する複数の画素部PXが映像信号(画像データと称しても良い)を記憶可能な状態となる。

10

## 【0019】

信号線駆動回路101は、入力端子102を介して映像信号を取り込む。取込んだ映像信号は、行方向(X方向)の各画素部PX毎の映像信号電流に変換され、対応する信号線DL1、DL2、・・・に出力される。アクティブ状態となっている画素部PXが、対応する信号線DL1、DL2、・・・を介して映像信号電流を取り込み記憶する。

n番目のラインに必要な映像信号が、対応する信号線DL1、DL2、・・・を介してn番目のラインの各画素部PXに供給されると、次のn+1番目のラインに必要な映像信号が、対応する信号線DL1、DL2、・・・を介してn+1番目のラインの各画素部PXに供給される。画素選択走査線S1a、S2a、・・・の選択は、画素選択走査線駆動回路130により行われる。

20

## 【0020】

調光走査線駆動回路140は、各画素部PXに記憶された映像信号に対応した発光電流を有機EL素子に供給するタイミングを指定する。

システム制御部120には、入力端子103、104を介して映像信号に同期したタイミング信号及びクロック信号が供給される。システム制御部120は、このタイミング信号及びクロック信号に基づいて、信号線駆動回路101、画素選択走査線駆動回路130及び調光走査線駆動回路140に対して映像を表示させるための各種のタイミング信号を出力する。

30

## 【0021】

なお、図示していないが、信号線駆動回路101、画素選択走査線駆動回路130、調光走査線駆動回路140及びシステム制御部120には、電源を供給するための電源ラインも導かれている。

また、信号線駆動回路101、画素選択走査線駆動回路130、調光走査線駆動回路140及びシステム制御部120は、基板100上に形成されても良く、基板100の外に外部ICとして設けられても良い。

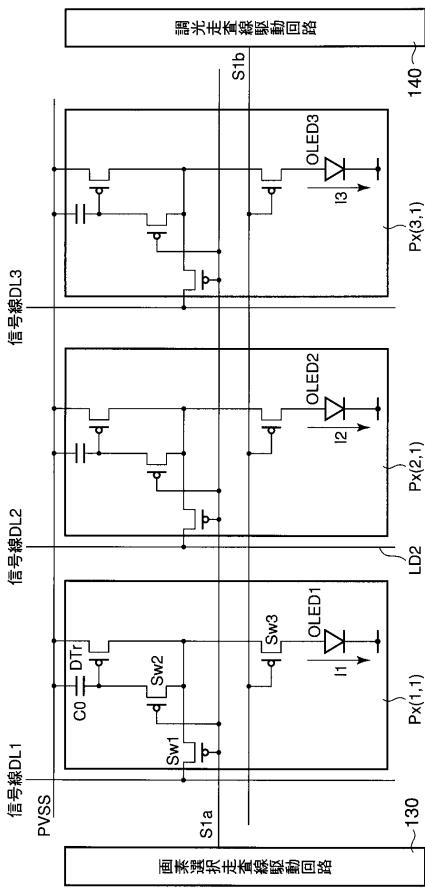

## 【0022】

図2は、信号線DL1, DL2, DL3に接続されている画素部PX(1, 1)、PX(2, 1)、PX(3, 1)の構成例を示している。以下、画素部PX(1, 1)を代表して説明する。

40

## 【0023】

OLED1は、対向した一対の電極間に光活性層を備えた表示素子である。この表示素子OLED1のカソードは電源PVSSに接続され、アノードはこの素子を駆動するための画素回路を介して電源線PVDDに接続されている。表示素子は、ここでは光活性層として少なくとも有機発光層を含んだ有機EL素子であり、例えば、赤、緑、青色に発光する有機EL素子が基板100上で所定の順序で配列している。

## 【0024】

画素回路は、画素選択スイッチSW1、駆動薄膜トランジスタDTr、補正用スイッチ

50

S W 2、出力スイッチ S W 3 を含み、例えばこれらは p チャネル型薄膜トランジスタにより構成される。また、駆動薄膜トランジスタ D T r のゲート - ソース間電圧を保持可能なキャパシタ C O を備える。

【 0 0 2 5 】

有機 E L 素子は出力スイッチ S W 3 を介して駆動薄膜トランジスタ D T r のドレインに接続し、駆動薄膜トランジスタ D T r のソースは電源線 P V D D に接続する。駆動薄膜トランジスタ D T r のゲートは、キャパシタ C O 及び補正用スイッチ S W 2 のドレインに接続する。補正用スイッチ S W 2 は駆動薄膜トランジスタ D T r のゲートおよびドレイン間に接続され、そのゲートは画素選択走査線 S 1 a に接続する。画素選択スイッチ S W 1 は、信号線および駆動薄膜トランジスタ D T r のドレイン間に接続され、そのゲートは画素選択走査線 S 1 a に接続する。出力スイッチ S W 3 は、駆動薄膜トランジスタ D T r のドレイン及び有機 E L 素子間に接続され、そのゲートは調光走査線 S 1 b に接続する。

10

【 0 0 2 6 】

続いて、映像信号書き込み期間及び映像表示期間における画素部 P X の動作について説明する。

信号線駆動回路 1 0 1 は、階調電流を生成して映像信号電流として信号線 D L 1 に供給する。画素 P X ( 1 , 1 ) では、画素選択スイッチ S W 1 及び補正用スイッチ S W 2 をオンとして、信号線 D L 1 より供給される映像信号電流によって駆動薄膜トランジスタ D T r のゲートソース間電圧を保持可能なキャパシタ C O に書き込む。

20

【 0 0 2 7 】

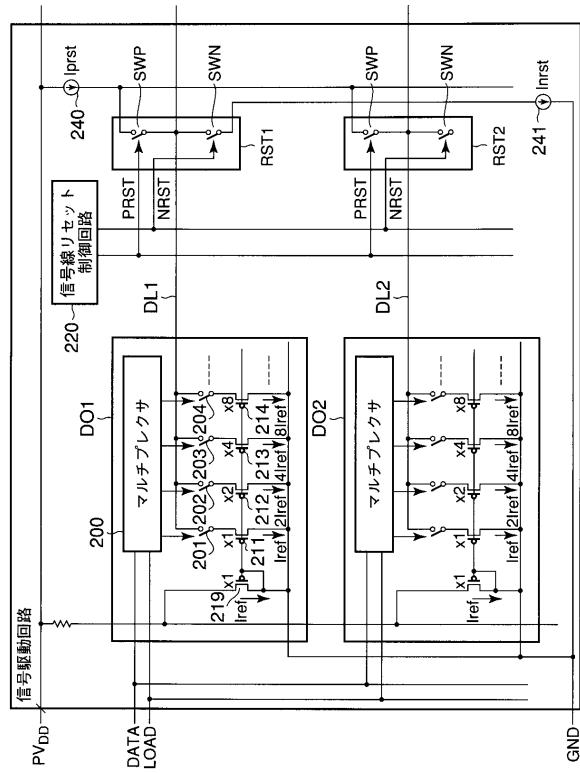

図 3 は、信号線と接続する信号線駆動回路 1 0 1 の各回路を取り出して示す図である。

信号線駆動回路 1 0 1 には、データ出力部 D O 1 、 D O 2 、 . . . 、信号線リセット回路 R S T 1 、 R S T 2 、 . . . 、信号線リセット制御回路 2 2 0 、最低階調リセット電流源 2 4 0 、最高階調リセット電流源 2 4 1 が設けられている。

【 0 0 2 8 】

データ出力部 D O 1 、 D O 2 、 . . . は、入力端子を介して映像信号 D A T A を取り込む。取込んだ映像信号 D A T A はデータ出力部 D O 1 、 D O 2 、 . . . において、行方向 ( X 方向 ) の各画素部 P X 每の映像信号電流に変換され、対応する信号線 D L 1 、 D L 2 、 . . . に出力される。

30

【 0 0 2 9 】

最低階調リセット電流源 2 4 0 は、信号線を最低階調電圧に設定するための電流 ( 以下、最低階調電流 I p r s t という ) をリセット電流としてそれぞれの信号線 D L 1 、 D L 2 、 . . . に流すための電流源である。最高階調リセット電流源 2 4 1 は、信号線を最高階調電圧に設定するための電流 ( 以下、最高階調電流 I n r s t という ) をリセット電流としてそれぞれの信号線 D L 1 、 D L 2 、 . . . に流すための電流源である。

信号線リセット回路 R S T 1 、 R S T 2 、 . . . は、所定のタイミングにおいて、最低階調電流 I p r s t あるいは最高階調電流 I n r s t を信号線 D L 1 、 D L 2 、 . . . に流す。信号線リセット制御回路 2 2 0 は、信号線リセット回路 R S T 1 、 R S T 2 、 . . . の動作を制御する。

40

【 0 0 3 0 】

まず、データ出力部 D O 1 の構成と動作を代表して説明する。

【 0 0 3 1 】

データ出力部 D O 1 には、マルチプレクサ 2 0 0 、スイッチ 2 0 1 、 2 0 2 、 . . . 、 2 0 8 、薄膜トランジスタ 2 1 1 、 2 1 2 、 . . . 、 2 1 9 が設けられている。

マルチプレクサ 2 0 0 は入力端子から供給されるシリアル信号である 1 ラインの画像データ D A T A のうち、所定の 1 画素単位の画素データを取込む。図 3 に示す例では、マルチプレクサ 2 0 0 は、画素データを 8 ビットのデジタル信号に変換してその結果をスイッチ 2 0 1 、 2 0 2 、 . . . のオンオフ状態として出力する。即ち、マルチプレクサ 2 0 0 は、シリアル信号をパラレル信号に変換する。

50

## 【0032】

スイッチ201、202、・・・の一方の端子は共通に信号線DL1に接続され、他方の端子はそれぞれ薄膜トランジスタ211、212、・・・のソースに接続されている。

## 【0033】

薄膜トランジスタ211、212、・・・のドレインはアースライン(GND)に共通に接続され、更にそれぞれの薄膜トランジスタ211、212、・・・のゲートは共通に薄膜トランジスタ219のゲートに接続されている。

一方、薄膜トランジスタ219のドレインはアースライン(GND)に接続され、ゲート・ドレイン間が接続されることにより定電流源を構成している。更に、薄膜トランジスタ219のソースは電源線PVDに接続されている。

10

## 【0034】

従って、この構成により薄膜トランジスタ211、212、・・・、219はカレントミラー回路を形成し、それぞれの薄膜トランジスタ211、212、・・・は、それらに接続されているスイッチ201、202、・・・がオン状態にある間、薄膜トランジスタ219に流れる基準電流 $I_{ref}$ のそれぞれ1倍、2倍、4倍、・・・の大きさの電流を出力する。これにより、信号線DL1には画素データの階調に対応した電流が流れる。

## 【0035】

次に、信号線リセット回路RST1の構成と動作を代表して説明する。

## 【0036】

信号線リセット回路RST1には、最低階調リセット用のリセットスイッチSWPと最高階調リセット用のリセットスイッチSWNが設けられている。これらのリセットスイッチSWP、SWNは、信号線リセット制御回路220からの信号に従ってオンオフするスイッチである。

最低階調信号線PRSTがアクティブになり、リセットスイッチSWPがオンすると、最低階調電流 $I_{prst}$ が信号線DL1に流れる。最高階調信号線Nrstがアクティブになり、リセットスイッチSWNがオンすると、最高階調電流 $I_{nrst}$ が信号線DL1に流れる。

20

## 【0037】

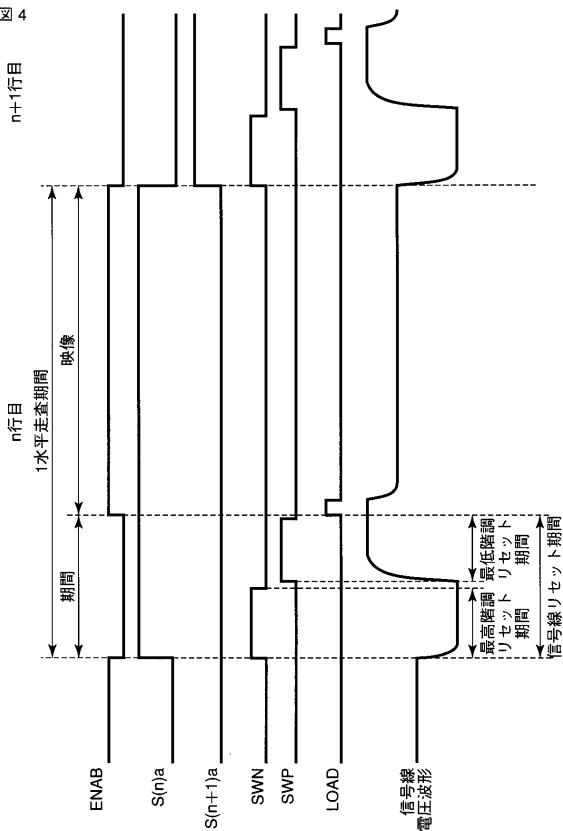

図4は、本発明の実施の形態のアクティブマトリクス型表示装置の電流リセット動作を示すタイムチャートである。

30

図4は、n行目の1水平走査期間における、画素選択走査線( $S(n)a$ ,  $S(n+1)a$ )、リセットスイッチ信号(SWP, SWN)、ロード信号(LOAD)及び信号線電圧波形を示している。

なお、これらの動作は、システム制御部120が統括して制御する。

## 【0038】

画素選択走査線駆動回路130のn番目の画素選択走査線 $Sna$ をアクティブ状態にすると、画素選択走査線 $Sna$ に接続する複数の画素部PXがリセット信号、映像信号を記憶可能な状態となる。

## 【0039】

まず、信号線リセット制御回路220が、最高階調信号線Nrstをアクティブ状態とすると、リセットスイッチSWNがオンして、最高階調電流 $I_{nrst}$ が信号線DL1に流れる。

40

ここで、最高階調電流 $I_{nrst}$ は、画素回路から電流を引き出す方向に流れるため、これによって駆動薄膜トランジスタDTrのゲート電位は時間と共に低下して、所定時間経過後には駆動薄膜トランジスタDTrの特性のバラツキを反映した電圧に保持される。

## 【0040】

次に、信号線リセット制御回路220が、最低階調信号線PRSTをアクティブ状態とすると、リセットスイッチSWPがオンして、最低階調電流 $I_{prst}$ が信号線DL1に流れる。

ここで、最低階調電流 $I_{prst}$ は、画素回路に電流を足しこむ方向に流れるため、こ

50

れによって駆動薄膜トランジスタDTrのゲート電位は時間と共に上昇して、所定時間経過後には駆動薄膜トランジスタDTrの特性のバラツキを反映した黒電圧に保持される。

【0041】

信号リセット期間が経過した後、ロード信号(Load)がマルチプレクサ200に入力される。この結果、上述の動作により信号線は画素データの階調に対応した電位に設定される。

【0042】

本発明の実施の形態では、図4に示すように2段階で電流リセット動作を実行している。以下、2段階で電流リセット動作を行う基本的な考え方について説明する。

【0043】

上述の2段階の電流リセット法は、個々の駆動薄膜トランジスタDTrの特性にバラツキが存在する場合であっても、共通の電流源を用いてリセット動作を行うことを狙って開発したものである。なお、以下の説明はPチャンネルトランジスタの場合である。

【0044】

リセット動作前の各画素は、白から黒の内のいずれかの階調電圧を保持した状態にある。そこで、電流を用いて、黒の階調電圧に保持しようとすれば、外部から電流を足し込むように構成して画素の電位を高める。しかし、この方式で所定時間電流を足し込んだだけでは電圧リセットによるのと同様であり駆動トランジスタの特性のバラツキを解消することはできない。

【0045】

そこで、最初に最高階調リセット動作によって、最高階調電流Inrstを引っ張る。所定時間経過後、信号線の電圧が安定した状態では、駆動薄膜トランジスタDTrの特性のバラツキを反映した電圧が保持されることになる。

次に最低階調リセット動作によって、最低階調電流Iprstを所定時間、足し込む。この最低階調リセット動作により、最高階調リセット動作で保持された電圧に所定の電圧が足し込まれる。この結果、駆動薄膜トランジスタDTrの特性のバラツキを加味した黒電圧を生成することができる。

【0046】

ここで、リセット電流によって電圧を書き換えることについて説明する。

一般に、Q：電荷、C：容量、V：電圧の間には、式(1)で表される関係が成立する。

$$V = Q / C \quad \cdots \text{式(1)}$$

そこで、i：リセット電流、t：電流継続時間、V：変化電圧とすると、式(2)で表される関係が成立する。

$$V = (i \times t) / C \quad \cdots \text{式(2)}$$

なお、Cは画素、信号線の容量の総和を表す。

したがって、リセット電流iと電流継続時間tを制御することによって電圧の変化量を制御することができる。

【0047】

容量Cは、パネルの種類、サイズによって異なるため、パネルによって適宜の書き換え時間を選択することになる。但し、信号線の電圧が安定した状態になれば、それ以上電流を持続する必要はない。また、i × tが同じであったとしても、時間に余裕があれば、電流値を小さくして書き込み時間を長くしたほうがVを精度良く制御できるため表示品位はより優れたものとなる。

【0048】

従って、上述の実施の形態では最高階調電流Inrst、最低階調電流Iprstを流しているが、最高階調電流Inrst、最低階調電流Iprstである必要はなく、1水平走査期間において、十分にリセット動作ができる時間tでリセット電流を定めれば良い。このtは予め最高階調リセット動作、最低階調リセット動作のそれぞれについてパネル毎に設定することができる。

10

20

30

40

50

## 【0049】

また、最高階調リセット動作では、信号線電圧を最高階調の電圧に設定する必要はなく、駆動薄膜トランジスタD<sub>tr</sub>の特性のバラツキを反映した電圧に設定できれば良い。従って、最低階調電圧よりも高い階調の電圧であればよい。但し、最低階調リセット動作では、信号線リセット期間の終了時には黒の状態を保持するため最低階調の電圧にセットする必要がある。

## 【0050】

なお、上述の各回路のトランジスタはNチャンネルで構成しても良い。このときは、回路構成、電位はPチャンネルの場合と逆になるが、その場合であっても、最初に最高階調リセット動作を行い、その後に最低階調リセット動作を行うという本発明の思想は同一である。

10

## 【0051】

なお、この発明は、上記実施形態そのままで限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せててもよい。

## 【図面の簡単な説明】

## 【0052】

【図1】本発明の実施の形態に係るアクティブマトリクス型表示装置を概略的に示すプロック図。

20

【図2】信号線に接続されている画素部の構成を示す図。

【図3】信号線と接続する信号線駆動回路の各回路を取り出して示す図。

【図4】本発明の実施の形態のアクティブマトリクス型表示装置の電流リセット動作を示すタイムチャート。

## 【符号の説明】

## 【0053】

101...表示装置、102...信号線駆動回路、120...システム制御部、130...画素選択走査線駆動回路、140...調光走査線駆動回路、200...マルチブレクサ、201...スイッチ、211...薄膜トランジスタ、220...信号線リセット制御回路、240...最低階調リセット電流源、241...最高階調リセット電流源、C0...キャパシタ、D<sub>L</sub>...信号線、D<sub>tr</sub>...駆動薄膜トランジスタ、OLED...表示素子、OUT01...出力回路、P<sub>X</sub>...画素部、S1a...画素選択走査線、S1b...調光走査線、SW1...画素選択スイッチ、SW2...補正用スイッチ、SW3...出力スイッチ、SWN...リセットスイッチ、SWP...リセットスイッチ。

30

【図 1】

図 1

【図 2】

図 2

【図 3】

図 3

【図 4】

図 4

## フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 A |

| G 0 9 G | 3/20 | 6 2 3 C |

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 中村 則夫

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 5C080 AA06 BB05 DD05 EE28 EE29 FF11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵显示装置及其显示方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2008176060A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2008-07-31 |

| 申请号            | JP2007009420                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2007-01-18 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 中村則夫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 中村 則夫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.K G09G3/30.J G09G3/20.611.H G09G3/20.642.A G09G3/20.641.D G09G3/20.621.A G09G3/20.623.C G09G3/3241 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/AB18 5C380/AB34 5C380/BA38 5C380/BA39 5C380/BB02 5C380/CA04 5C380/CA05 5C380/CA13 5C380/CA35 5C380/CA36 5C380/CA53 5C380/CA54 5C380/CB01 5C380/CB16 5C380/CB18 5C380/CB26 5C380/CC12 5C380/CC26 5C380/CC27 5C380/CC33 5C380/CC39 5C380/CC61 5C380/CC63 5C380/CD014 5C380/CE04 5C380/CE05 5C380/CE20 5C380/CF26 5C380/CF41 5C380/CF48 5C380/CF52 5C380/DA02 5C380/DA06 5C380/DA47 |         |            |

| 代理人(译)         | 河野 哲<br>中村诚                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

## 摘要(译)

甲甚至视频低灰度级，并且其目的是由于在驱动TFT的特性的变化提供一种有源矩阵型显示装置和显示方法更少的显示不均匀。和在其上像素部分PX被布置在包括驱动晶体管DTR用于驱动OLED的基板上以矩阵形式的显示元件显示单元100，设置在每个列中，信号连接到每一列的各像素部和线DL，并且灰度信号输出单元DO，用于输出经由信号线，用于经由所述信号线保持预定灰度电压提供给像素单元的复位信号对应于视频信号到所述像素单元的音调信号输出复位输出单元(220240241，RST)和通过使2级电流给信号线作为复位信号，保持反映在像素部分中的驱动晶体管的特性的变化的灰度级电压设置复位输出部，从而显示图像。点域