## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-3909 (P2007-3909A)

(43) 公開日 平成19年1月11日(2007.1.11)

| (51) Int.C1. | F 1                          | テーマコード (参考)                  |

|--------------|------------------------------|------------------------------|

| GO9G 3/30    | <b>(2006.01)</b> GO9G        | 3 /30 J 3 K O O 7            |

| GO9G 3/20    | <b>(2006.01)</b> G09G        | 3/30 K 5CO8O                 |

| HO1L 51/50   | <b>(2006.01)</b> G09G        | 3/20 6 2 4 B                 |

|              | G09G                         | 3 3/20 6 2 1 A               |

|              | HO5B                         | 33/14 A                      |

|              |                              | 審査請求 未請求 請求項の数 6 OL (全 14 頁) |

| (21) 出願番号    | 特願2005-185150 (P2005-185150) | (71) 出願人 302020207           |

| (22) 出願日     | 平成17年6月24日 (2005.6.24)       | 東芝松下ディスプレイテクノロジー株式会          |

|              |                              | 社                            |

|              |                              | 東京都港区港南4-1-8                 |

|              |                              | (74) 代理人 100058479           |

|              |                              | 弁理士 鈴江 武彦                    |

|              |                              | (74) 代理人 100091351           |

|              |                              | 弁理士 河野 哲                     |

|              |                              | (74) 代理人 100088683           |

|              |                              | 弁理士 中村 誠                     |

|              |                              | (74) 代理人 100108855           |

|              |                              | 弁理士 蔵田 昌俊                    |

|              |                              | (74)代理人 100075672            |

|              |                              | 弁理士 峰 隆司<br>                 |

|              |                              | 最終頁に続く                       |

(54) 【発明の名称】表示装置、アレイ基板、及び表示装置の駆動方法

## (57)【要約】

【課題】各画素で表示する階調を映像信号の大きさで制御する表示装置において、階調再現性が不十分となるのを抑制する。

【解決手段】本発明の表示装置は、ソースが電源端子ND1に接続された駆動トランジスタDRと、画素電極と電源端子ND2に接続された対向電極とそれらの間に介在した活性層とを含んだ表示素子OLEDと、駆動トランジスタのドレインと画素電極との間に接続されたスイッチSWaと、駆動トランジスタDRのドレインとゲートとの間に接続されたスイッチングトランジスタSWcのゲートとの間に接続されたスイッチンジスタSWcのゲートとの間に接続されたスイッチSWeと、スイッチングトランジスタSWcのゲートとスイッチング信号出力端子ND3との間に接続されたスイッチSWdとを各々が備えた複数の画素PXを具備したことを特徴とする。

【選択図】 図1

#### 【特許請求の範囲】

## 【請求項1】

ソースが第1電源端子に接続された駆動トランジスタと、

画素電極と第2電源端子に接続された対向電極とそれらの間に介在した活性層とを含んだ表示素子と、

前記駆動トランジスタのドレインと前記画素電極との間に接続された第1スイッチと、 前記駆動トランジスタのドレインとゲートとの間に接続されたスイッチングトランジス タと、

前記駆動トランジスタのドレインと前記スイッチングトランジスタのゲートとの間に接続された第2スイッチと、

前記スイッチングトランジスタのゲートとスイッチング信号出力端子との間に接続された第3スイッチとを各々が備えた複数の画素を具備したことを特徴とする表示装置。

#### 【請求項2】

前記複数の画素が形成する列に対応して配列した複数の映像信号線をさらに具備し、前記複数の画素のそれぞれは、

定電位端子と前記駆動トランジスタのゲートとの間に接続されたキャパシタと、

前記映像信号線と前記駆動トランジスタのゲートとの間に接続された第4スイッチとをさらに備えたことを特徴とする請求項1に記載の表示装置。

#### 【請求項3】

前記複数の画素が形成する列に対応して配列した複数の映像信号線をさらに具備し、前記複数の画素のそれぞれは、

定電位端子と前記駆動トランジスタのゲートとの間に接続された第1キャパシタと、

一方の電極が前記駆動トランジスタのゲートに接続された第2キャパシタと、

前記第2キャパシタの他方の電極と前記映像信号線との間に接続された第4スイッチとをさらに備えたことを特徴とする請求項1に記載の表示装置。

## 【請求項4】

前記表示素子は有機EL素子であることを特徴とする請求項1に記載の表示装置。

#### 【請求項5】

ソースが第1電源端子に接続された駆動トランジスタと、

画素電極と、

前記駆動トランジスタのドレインと前記画素電極との間に接続された第1スイッチと、 前記駆動トランジスタのドレインとゲートとの間に接続されたスイッチングトランジス タと、

前記駆動トランジスタのドレインと前記スイッチングトランジスタのゲートとの間に接 続された第2スイッチと、

前記スイッチングトランジスタのゲートとスイッチング信号出力端子との間に接続された第3スイッチとを各々が備えた複数の画素回路を具備したことを特徴とするアレイ基板

## 【請求項6】

ソースが第1電源端子に接続された駆動トランジスタと、画素電極と第2電源端子に接続された対向電極とそれらの間に介在した活性層とを含んだ表示素子と、前記駆動トランジスタのドレインとゲートとの間に接続されたスイッチングトランジスタとを各々が備えた複数の画素を具備した表示装置の駆動方法であって、

前記画素電極と前記駆動トランジスタのドレインとの接続を断っている選択期間において、前記スイッチングトランジスタのゲートをスイッチング信号出力端子に接続すると共に前記スイッチング信号出力端子の電位を前記スイッチングトランジスタを閉じるオン電位に設定する第1動作と、前記スイッチングトランジスタのゲートと前記スイッチング信号出力端子との接続を断つ第2動作と、前駆駆動トランジスタのドレインと前記スイッチングトランジスタのゲートとを一時的に接続すると共に前記スイッチング信号出力端子の電位を前記スイッチングトランジスタを開くオフ電位に設定する第3動作と、前記スイッ

10

20

30

40

チングトランジスタのゲートを前記スイッチング信号出力端子に接続する第 4 動作とをこの順に行うことを特徴とする駆動方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、表示装置、アレイ基板、及び表示装置の駆動方法に関する。

【背景技術】

[0002]

アクティブマトリクス型有機エレクトロルミネッセンス(EL)表示装置で画像を表示する場合、例えば、画素を行毎に選択する。画素を選択している選択期間では、その画素に映像信号を書き込む。各画素は、非選択期間において、映像信号に対応した大きさの駆動電流を有機EL素子に流す。有機EL素子は、駆動電流の大きさに対応した輝度で発光する。このように、アクティブマトリクス型有機EL表示装置では、各画素で表示する階調を、映像信号の大きさで制御する。

[00003]

ところで、アクティブマトリクス型有機 EL表示装置では、映像信号として、電流信号及び電圧信号を利用することができる。

[0004]

特許文献1には、映像信号として電流信号を利用するアクティブマトリクス型有機EL表示装置が記載されている。この表示装置の画素は、nチャネル電界効果トランジスタである駆動トランジスタと、有機EL素子と、キャパシタと、第1乃至第3スイッチングトランジスタとを含んでいる。駆動トランジスタと第1スイッチングトランジスタと有機EL素子とは、低電位電源線と高電位電源線との間で、この順に直列に接続されている。キャパシタは、低電位電源線と駆動トランジスタのゲートとの間に接続されている。第2スイッチングトランジスタは、駆動トランジスタのドレインとゲートとの間に接続されている。第3スイッチングトランジスタは、駆動トランジスタのドレインと映像信号線との間に接続されている。

[00005]

特許文献2には、映像信号として電圧信号を利用するアクティブマトリクス型有機EL表示装置が記載されている。この表示装置の画素は、この表示装置の画素は、pチャネル電界効果トランジスタである駆動トランジスタと、有機EL素子と、第1及び第2キャパシタと、第1乃至第3スイッチングトランジスタとを含んでいる。駆動トランジスタと第1スイッチングトランジスタと有機EL素子とは、高電位電源線と低電位電源線との間で、この順に直列に接続されている。第1キャパシタは、高電位電源線と駆動トランジスタのゲートとの間に接続されている。第2キャパシタの一方の電極は、駆動トランジスタのゲートに接続されている。第3スイッチングトランジスタは、映像信号線と第2キャパシタの一方の電極との間に接続されている。

[0006]

特許文献 1 に記載された有機 E L 表示装置では、画素間で駆動トランジスタの閾値電圧及び移動度がばらついていたとしても、それらのばらつきに起因して、有機 E L 素子に流す駆動電流の大きさがばらつくことはない。また、特許文献 2 に記載された有機 E L 表示装置では、画素間で駆動トランジスタの閾値電圧がばらついていたとしても、そのばらつきに起因して、有機 E L 素子に流す駆動電流の大きさがばらつくことはない。したがって、これら有機 E L 表示装置によると、高い階調再現性を実現できる筈である。

[0007]

しかしながら、本発明者は、これら有機 EL表示装置であっても、十分に高い階調再現性を実現できない可能性があることを見い出している。

【 特 許 文 献 1 】 米 国 特 許 第 6 3 7 3 4 5 4 号 明 細 書

【特許文献2】米国特許第6229506号明細書

10

20

30

#### 【発明の開示】

【発明が解決しようとする課題】

#### [00008]

本発明の目的は、各画素で表示する階調を映像信号の大きさで制御する表示装置において、階調再現性が不十分となるのを抑制することにある。

#### 【課題を解決するための手段】

#### [0009]

本発明の第1側面によると、ソースが第1電源端子に接続された駆動トランジスタと、画素電極と第2電源端子に接続された対向電極とそれらの間に介在した活性層とを含んだ表示素子と、前記駆動トランジスタのドレインと前記画素電極との間に接続された第1スイッチと、前記駆動トランジスタのドレインとゲートとの間に接続されたスイッチングトランジスタのゲートとの間に接続された第2スイッチと、前記スイッチングトランジスタのゲートとスイッチング信号出力端子との間に接続された第3スイッチとを各々が備えた複数の画素を具備したことを特徴とする表示装置が提供される。

#### [0010]

本発明の第2側面によると、ソースが第1電源端子に接続された駆動トランジスタと、画素電極と、前記駆動トランジスタのドレインと前記画素電極との間に接続された第1スイッチと、前記駆動トランジスタのドレインとゲートとの間に接続されたスイッチングトランジスタのゲートとの間に接続された第2スイッチと、前記スイッチングトランジスタのゲートとスイッチング信号出力端子との間に接続された第3スイッチとを各々が備えた複数の画素回路を具備したことを特徴とするアレイ基板が提供される。

### [0011]

本発明の第3側面によると、ソースが第1電源端子に接続された駆動トランジスタと、画素電極と第2電源端子に接続された対向電極とそれらの間に介在した活性層とを含んだ表示素子と、前記駆動トランジスタのドレインとゲートとの間に接続されたスイッチ、ガーランジスタのドレインとがートとの間に接続されたスケーである選択期間においてである選択期間においてである選択期間においてである選択期間においてである選択期間においてである選択期間においてである選択期間においてである選択期間においてである選択期間においてである。

### 【発明の効果】

## [0012]

本発明によると、各画素で表示する階調を映像信号の大きさで制御する表示装置において、階調再現性が不十分となるのを抑制することができる。

## 【発明を実施するための最良の形態】

## [0013]

以下、本発明の態様について、図面を参照しながら詳細に説明する。なお、各図において、同様又は類似した機能を発揮する構成要素には同一の参照符号を付し、重複する説明は省略する。

## [0014]

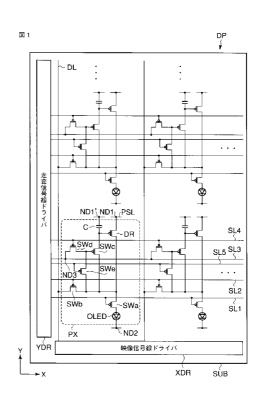

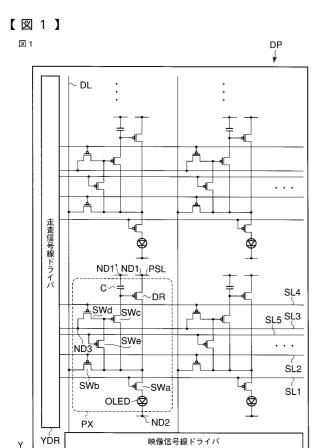

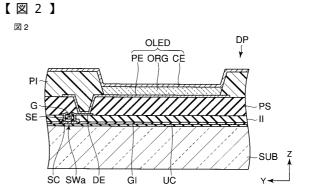

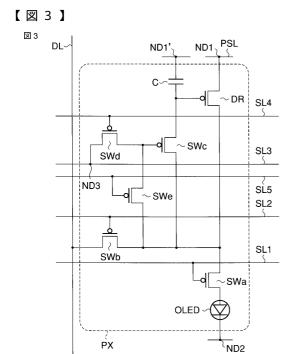

図1は、本発明の第1態様に係る表示装置を概略的に示す平面図である。図2は、図1の表示装置に採用可能な構造の一例を概略的に示す断面図である。図3は、図1の表示装置が含む画素の等価回路図である。なお、図2では、表示装置を、その表示面,すなわち

10

20

30

40

前面又は光出射面、が下方を向き、背面が上方を向くように描いている。

### [0015]

この表示装置は、アクティブマトリクス型駆動方式を採用した下面発光型の有機 E L 表示装置である。この有機 E L 表示装置は、図 1 に示すように、表示パネル D P と、映像信号線ドライバ X D R と、走査信号線ドライバ Y D R とを含んでいる。

#### [0016]

表示パネル D P は、図 1 及び図 2 に示すように、例えば、ガラス基板などの絶縁基板 S U B を含んでいる。

### [0017]

基板 S U B 上には、図 2 に示すように、アンダーコート層 U C が形成されている。アンダーコート層 U C は、例えば、基板 S U B 上に S i N  $_{x}$ 層と S i O  $_{x}$ 層とをこの順に積層してなる。

### [0018]

アンダーコート層UC上では、図2に示す半導体層SCが、後述する画素PXに対応して配列している。各半導体層SCは、例えば、p型領域とn型領域とを含んだポリシリコン層である。この例では、半導体層SCのうち、参照符号Gで示す部材と向き合っている領域はイントリンシック型領域であり、それ以外の領域はp<sup>+</sup>型領域である。

#### [0019]

アンダーコート層UC上では、図示しない下部電極が、画素PXに対応してさらに配列 している。下部電極は、例えば、n<sup>+</sup>型ポリシリコン層である。

#### [0020]

半導体層SC及び下部電極は、図2に示すゲート絶縁膜GIで被覆されている。ゲート 絶縁膜GIは、例えばTEOS(TetraEthyl OrthoSilicate)などを用いて形成すること ができる。

## [0021]

ゲート絶縁膜GI上には、図1及び図3に示す走査信号線SL1乃至SL5が形成されている。走査信号線SL1乃至SL5は、図1に示すように、各々が画素PXの行方向( X方向)に延びており、画素PXの列方向(Y方向)に配列している。走査信号線SL1 乃至SL5は、例えばMoWなどからなる。

## [0022]

ゲート絶縁膜GI上には、図示しない上部電極がさらに配置されている。上部電極は画素PXに対応して配列している。上部電極は、例えばMoWなどからなる。また、上部電極は、走査信号線SL1乃至SL5と同一の工程で形成することができる。

## [0023]

各画素 P X において、走査信号線 S L 1 乃至 S L 5 及び上部電極を含む導体パターンは、半導体層と 6 箇所で交差している。これら交差部は、図 1 及び図 3 に示す駆動トランジスタ D R 及びスイッチ S W a 乃至 S W e を構成している。

### [0024]

また、各画素 P X において、上部電極は下部電極と向き合っている。上部電極及び下部電極とそれらの間に介在した絶縁膜 G I とは図 1 及び図 3 に示すキャパシタ C を構成している。

## [0025]

なお、この例では、駆動トランジスタDR及びスイッチSWa乃至SWeは、トップゲート型のpチャネル薄膜トランジスタである。また、図2に参照符号Gで示す部分は、薄膜トランジスタのゲートである。

## [0026]

## [0027]

50

40

20

20

30

40

50

層間絶縁膜II上には、図1及び図3に示す映像信号線DLと電源線PSLとが形成されている。映像信号線DLは、図1に示すように、各々がY方向に延びており、X方向に配列している。電源線PSLは、この例では、各々がY方向に延びており、X方向に配列している。

## [0028]

層間絶縁膜II上には、図2に示すソース電極SEとドレイン電極DEとがさらに形成されている。ソース電極SE及びドレイン電極DEは、層間絶縁膜II及びゲート絶縁膜GIに設けられたコンタクトホールを介して薄膜トランジスタのソース及びドレインにそれぞれ接続されている。

#### [0029]

映像信号線DLと電源線PSLとソース電極SEとドレイン電極DEとは、例えば、Mo/A1/Moの三層構造を有している。これらは、同一工程で形成可能である。

#### [0030]

映像信号線DLと電源線PSLとソース電極SEとドレイン電極DEとは、図2に示すパッシベーション膜PSで被覆されている。パッシベーション膜PSは、例えばSiN<sub>×</sub>などからなる。

### [0031]

パッシベーション膜PS上では、図2に示す画素電極PEが、画素PXに対応して配列している。各画素電極PEは、パッシベーション膜PSに設けたコンタクトホールを介して、ドレイン電極DEに接続されている。

#### [0032]

画素電極 P E は、この例では光透過性の前面電極である。また、画素電極 P E は、この例では陽極である。画素電極 P E の材料としては、例えば、ITO(Indium Tin Oxide)などの透明導電性酸化物を使用することができる。

## [0033]

パッシベーション膜PS上には、さらに、図2に示す隔壁絶縁層PIが形成されている。隔壁絶縁層PIには、画素電極PEに対応した位置に貫通孔が設けられているか、或いは、画素電極PEが形成する列又は行に対応した位置にスリットが設けられている。ここでは、一例として、隔壁絶縁層PIには、画素電極PEに対応した位置に貫通孔が設けられていることとする。

### [0034]

隔壁絶縁層PIは、例えば、有機絶縁層である。隔壁絶縁層PIは、例えば、フォトリソグラフィ技術を用いて形成することができる。

### [0035]

画素電極PE上には、活性層として、発光層を含んだ有機物層ORGが形成されている。発光層は、例えば、発光色が赤色、緑色、又は青色のルミネセンス性有機化合物を含んだ薄膜である。この有機物層ORGは、発光層に加え、正孔注入層、正孔輸送層、正孔ブロッキング層、電子輸送層、電子注入層などもさらに含むことができる。

## 【0036】

隔壁絶縁層PI及び有機物層ORGは、対向電極CEで被覆されている。この例では、対向電極CEは、画素PX間で互いに接続された電極,すなわち共通電極,である。また、この例では、対向電極CEは、陰極であり且つ光反射性の背面電極である。対向電極CEは、例えば、パッシベーション膜PSと隔壁絶縁層PIとに設けられたコンタクトホールを介して、映像信号線DLと同一の層上に形成された電極配線(図示せず)に電気的に接続されている。各々の有機EL素子OLEDは、画素電極PEと、有機物層ORGと、対向電極CEとを含んでいる。

#### [0037]

各画素PXは、図1及び図3に示すように、駆動トランジスタDRと、スイッチSWa 乃至SWeと、有機EL素子OLEDと、キャパシタCとを含んでいる。上記の通り、この例では、駆動トランジスタDR及びスイッチSWa乃至SWeはpチャネル薄膜トラン ジスタである。

## [0038]

駆動トランジスタDRとスイッチSWaと有機EL素子OLEDとは、第1電源端子ND1と第2電源端子ND2との間で、この順に直列に接続されている。この例では、電源端子ND1は高電位電源端子であり、電源端子ND2は低電位電源端子である。

#### [0039]

スイッチSWaのゲートは、走査信号線SL1に接続されている。スイッチSWbは駆動トランジスタDRのドレインと映像信号線DLとの間に接続されており、そのゲートは走査信号線SL2に接続されている。スイッチSWcは駆動トランジスタDRのドレインとゲートとの間に接続されている。スイッチSWdは走査信号線SL3とスイッチSWcのゲートとの間に接続されており、そのゲートは走査信号線SL4に接続されている。スイッチSWeはスイッチSWcのドレインとゲートとの間に接続されており、そのゲートは走査信号線SL5に接続されている。なお、図1及び図3において、参照符号ND3はスイッチング信号出力端子を示している。

#### [0040]

キャパシタCは、駆動トランジスタDRのゲートと定電位端子ND1′との間に接続されている。この例では、定電位端子ND1′は、電源端子ND1に接続されている。

## [0041]

なお、この表示パネルDPから対向電極CEや有機物層ORGを除いた構造がアレイ基板に相当している。また、画素PXから対向電極CEや有機物層ORGを除いたものが画素回路に相当している。

### [0042]

映像信号線ドライバ X D R 及び走査信号線ドライバ Y D R は、この例では、表示パネル D P に C O G (chip on glass) 実装している。映像信号線ドライバ X D R 及び走査信号線ドライバ Y D R は、 C O G 実装する代わりに、 T C P (tape carrier package) 実装してもよい。

## [ 0 0 4 3 ]

映像信号線ドライバXDRには、映像信号線DLが接続されている。この例では、映像信号線ドライバXDRには、電源線PSLがさらに接続されている。映像信号線ドライバ XDRは、映像信号線DLに映像信号として電流信号を出力すると共に、電源線PSLに 電源電圧を供給する。

## [0044]

走査信号線ドライバYDRには、走査信号線SL1乃至SL5が接続されている。走査信号線ドライバYDRは、走査信号線SL1乃至SL5にそれぞれ第1乃至第5走査信号として電圧信号を出力する。

## [0045]

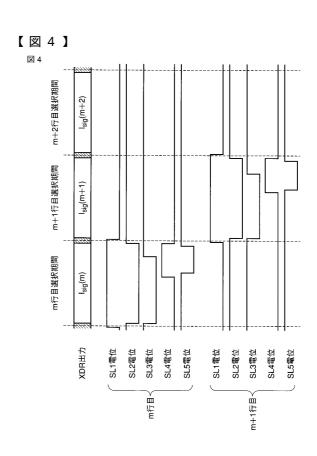

図 4 は、図 1 に示す表示装置の駆動方法の一例を示すタイミングチャートである。図中、横軸は時間を示し、縦軸は電位を示している。

## [0046]

図 4 において、「X D R 出力」のうち、「 $I_{sig}$  (M)」と表記した期間は映像信号線ドライバX D R が映像信号線 D L に映像信号  $I_{sig}$  (M)を出力する期間を示している。また、図 4 において、「S L 1 電位」乃至「S L 5 電位」で示す波形は、走査信号線 S L 1 乃至 S L 5 の電位をそれぞれ示している。

## [0047]

図4の方法では、図1の表示装置が含む画素PXを線順次駆動する。

例えば、m行目の画素 P X で或る階調を表示する場合、m行目の画素 P X を選択する期間,すなわち、m行目選択期間,では、まず、m行目の画素 P X が接続された走査信号線 S L 1 をオフ電位に設定する。これにより、スイッチ S W a を開く(非導通状態)。スイッチ S W a を開いている期間内に、以下の書込動作を行う。

## [0048]

50

40

20

20

30

40

50

まず、m行目の画素 P X が接続された走査信号線 S L 2 をオン電位に設定する。さらに、m行目の画素 P X が接続された走査信号線 S L 3 をオン電位に設定する。このとき、m 行目の画素 P X が接続された走査信号線 S L 4 の電位はオン電位のままとしておき、m行目の画素 P X が接続された走査信号線 S L 5 の電位はオフ電位のままとしておく。すなわち、スイッチ S W d は閉じた(導通状態)ままとしておき、スイッチ S W e は開いたままとしておく。これにより、スイッチ S W b 及び S W c を閉じる。

[0049]

[0050]

次に、m行目の画素 P X が接続された走査信号線 S L 4 をオフ電位に設定して、スイッチ S W d を開く。スイッチ S W d を開いている期間内に、m 行目の画素 P X が接続された走査信号線 S L 3 の電位をオン電位からオフ電位へと変化させる。また、スイッチ S W d を開いている期間内に、m 行目の画素 P X が接続された走査信号線 S L 5 の電位をオフ電位からオン電位に変化させ、さらにオフ電位に戻す。すなわち、スイッチ S W e を一時的に閉じる。これにより、スイッチ S W c のゲート電位を駆動トランジスタ D R のドレイン電位と等しくして、スイッチ S W c を開く。

[0051]

次に、m行目の画素 P X が接続された走査信号線 S L 4 をオン電位に設定して、スイッチ S W d を閉じる。m行目の画素 P X が接続された走査信号線 S L 3 はオフ電位に設定しているので、スイッチ S W c は開いた状態を維持する。

[0052]

さらに、m行目の画素 P X が接続された走査信号線 S L 2 をオフ電位に設定して、スイッチ S W b を開く。その後、m行目の画素 P X が接続された走査信号線 S L 1 をオン電位に設定して、スイッチ S W a を閉じることにより終了する。

[0053]

[0054]

さて、この駆動方法によれば、優れた階調再現性を実現することができる。これについて、以下に説明する。

[0055]

例えば、図1の表示装置からスイッチSWd及びSWe並びに走査信号線SL4及びSL5を省略し、さらに、スイッチSWcのゲートを走査信号線SL3に接続してなる表示装置を図4の方法で駆動する場合を考える。この場合、m行目選択期間において走査信号線SL3の電位をオン電位からオフ電位へと変化させるのに伴い、駆動トランジスタDRのゲート・ソース間電圧が変化する。より詳細には、スイッチSWcのゲート・チャネル間に形成される寄生容量の影響で、走査信号線SL3の電位変化に伴って駆動トランジスタDRのゲート電位が変化する。

[0056]

スイッチSWcのスイッチング動作が速い場合には、スイッチSWcが閉じる過程において、スイッチSWcのソース・ドレイン間で電荷は殆ど移動しない。そのため、スイッ

30

40

50

チSWcのゲートに走査信号を供給することでそのスイッチング動作を制御する場合、走査信号線SL3の電位変化に伴う駆動トランジスタDRの電位変化は大きい。また、この電位変化の大きさは、スイッチSWcの閾値電圧に依存する。

#### [0057]

それゆえ、スイッチSWcの閾値電圧が画素PX間でばらついている場合には、走査信号線SL3の電位変化に伴う駆動トランジスタDRのゲート電位変化の大きさが画素PX間でばらつき、その結果、輝度ムラを生じる可能性がある。すなわち、この場合、優れた階調再現性を実現することは不可能である。

#### [0058]

上記の通り、図1の表示装置では、スイッチSWdを介してスイッチSWcのゲートと走査信号線SL3とを接続すると共に、スイッチSWcのドレインとゲートとの間にスイッチSWeを接続している。また、図4の駆動方法では、スイッチSWdを開いている期間内に、走査信号線SL3の電位をオン電位からオフ電位へと変化させている。さらに、図4の駆動方法では、スイッチSWdを開いている期間内に、スイッチSWeを閉じて駆動トランジスタDRのドレインとスイッチSWcのゲートとを接続することにより、スイッチSWcを開いている。

#### [0059]

スイッチSWeを閉じることによってスイッチSWcを開くとき、スイッチSWeのチャネル抵抗はスイッチSWcのスイッチング動作を遅くする役割を果たす。そのため、スイッチSWeを閉じてからスイッチSWcのゲート・ソース間電圧がその閾値電圧に達するまでの期間においては、スイッチSWcのソース・ドレイン間で電荷が十分に移動することができ、それゆえ、スイッチSWcのソースは駆動トランジスタDRのドレインと等しい電位に維持される。また、スイッチSWcのゲート・ソース間電圧がその閾値電圧に達すると、その寄生容量は消滅するため、スイッチSWcのゲート電位変化に伴う駆動トランジスタDRのゲート電位変化は生じない。

#### [0060]

したがって、図4の方法によると、スイッチSWcの閾値電圧が画素PX間でばらついていたとしても、これに起因した輝度ムラを生じることはない。すなわち、優れた階調再現性を実現することができる。

#### [0061]

次に、本発明の第2態様について説明する。

## [0062]

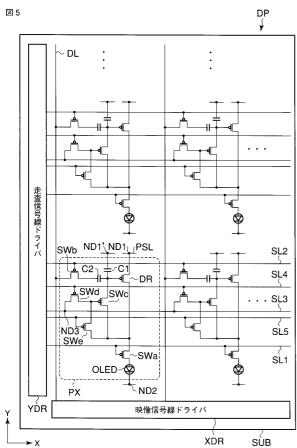

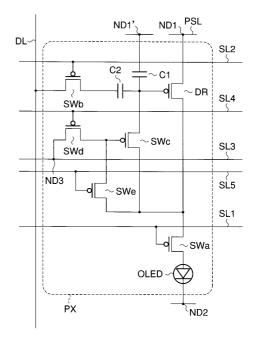

図 5 は、本発明の第 2 態様に係る表示装置を概略的に示す平面図である。図 6 は、図 5 の表示装置が含む画素の等価回路図である。

## [0063]

この表示装置は、アクティブマトリクス型駆動方式を採用した下面発光型の有機 E L 表示装置である。この表示装置は、映像信号として電圧信号を出力する映像信号線ドライバ X D R を使用すると共に、表示パネル D P に以下の構造を採用していること以外は、第 1 態様に係る表示装置とほぼ同様の構造を有している。

#### [0064]

この表示パネルDPでは、画素PX毎に1つのキャパシタCを配置する代わりに、画素PX毎に2つのキャパシタC1及びC2を配置している。各画素PXは、駆動トランジスタDRと、スイッチSWa乃至SWeと、有機EL素子OLEDと、キャパシタC1及びC2とを含んでいる。

#### [0065]

駆動トランジスタDRとスイッチSWaと有機EL素子OLEDとは、第1電源端子ND1と第2電源端子ND2との間で、この順に直列に接続されている。スイッチSWaのゲートは、走査信号線SL1に接続されている。キャパシタC1は、駆動トランジスタDRのゲートと定電位端子ND1,との間に接続されている。この例では、定電位端子ND1,は、電源端子ND1に接続されている。スイッチSWbとキャパシタC2とは、映像

20

30

40

50

信号線DLと駆動トランジスタDRのドレインとの間で、この順に直列に接続されている。スイッチSWbのゲートは、走査信号線SL2に接続されている。スイッチSWcは駆動トランジスタDRのドレインとゲートとの間に接続されている。スイッチSWdは走査信号線SL3とスイッチSWcのゲートとの間に接続されており、そのゲートは走査信号線SL4に接続されている。スイッチSWeは駆動トランジスタDRのドレインとスイッチSWcのゲートとの間に接続されており、そのゲートは走査信号線SL5に接続されている。

[0066]

なお、この表示パネルDPから図2を参照しながら説明した対向電極CEや有機物層ORGを除いた構造がアレイ基板に相当している。また、画素PXから対向電極CEや有機物層ORGを除いたものが画素回路に相当している。

[0067]

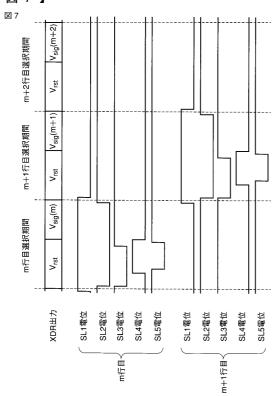

図 7 は、図 5 に示す表示装置の駆動方法の一例を示すタイミングチャートである。図中、横軸は時間を示し、縦軸は電位を示している。

[0068]

図 7 において、「 X D R 出力」のうち、「 V  $_{sig}$  ( M ) 」と表記した期間は映像信号線ドライバ X D R が映像信号線 D L に映像信号 V  $_{sig}$  ( M ) を出力する期間を示し、「 V  $_{rst}$  」と表記した期間は映像信号線ドライバ X D R が映像信号線 D L にリセット信号 V  $_{rst}$  を出力する期間を示している。また、図 7 において、「 S L 1 電位」乃至「 S L 5 電位」で示す波形は、走査信号線 S L 1 乃至 S L 5 の電位をそれぞれ示している。

[0069]

図7の方法では、図5の表示装置が含む画素PXを線順次駆動する。

例えば、m行目の画素 P X で或る階調を表示する場合、m行目の画素 P X を選択する期間,すなわち、m行目選択期間,では、まず、m行目の画素 P X が接続された走査信号線 S L 1 をオフ電位に設定する。これにより、スイッチ S W a を開く(非導通状態)。スイッチ S W a を開いている期間内に、以下のリセット動作と書込動作とを順次行う。

[0070]

まず、m行目の画素 P X が接続された走査信号線 S L 2 をオン電位に設定する。さらに、m行目の画素 P X が接続された走査信号線 S L 3 をオン電位に設定する。このとき、m 行目の画素 P X が接続された走査信号線 S L 4 の電位はオン電位のままとしておき、m行目の画素 P X が接続された走査信号線 S L 5 の電位はオフ電位のままとしておく。すなわち、スイッチ S W d は閉じた(導通状態)ままとしておき、スイッチ S W e は開いたままとしておく。これにより、スイッチ S W b 及び S W c を閉じる。また、このとき、映像信号線 F ライバ X D R から走査信号線 D L にリセット信号を電圧信号として出力する。すなわち、映像信号線 D L の電位はリセット電位 V rst に設定しておく。こうして、駆動トランジスタ D R のゲート・ソース間電圧 V gs を、その閾値電圧 V th に設定する。

[0071]

次に、m行目の画素 P X が接続された走査信号線 S L 4 をオフ電位に設定して、スイッチ S W d を開く。スイッチ S W d を開いている期間内に、m 行目の画素 P X が接続された走査信号線 S L 3 の電位をオン電位からオフ電位へと変化させる。また、スイッチ S W d を開いている期間内に、m 行目の画素 P X が接続された走査信号線 S L 5 の電位をオフ電位からオン電位に変化させ、さらにオフ電位に戻す。すなわち、スイッチ S W e を一時的に閉じる。これにより、スイッチ S W c のゲート電位を駆動トランジスタ D R のドレイン電位と等しくして、スイッチ S W c を開く。なお、この間、映像信号線 D L の電位はリセット電位 V r s t に設定しておく。

[0072]

次に、m行目の画素 P X が接続された走査信号線 S L 4 をオン電位に設定して、スイッチ S W d を閉じる。m行目の画素 P X が接続された走査信号線 S L 3 はオフ電位に設定しているので、スイッチ S W c は開いた状態を維持する。

[0073]

続いて、映像信号線ドライバ X D R から走査信号線 D L に映像信号  $V_{sig}$  ( m ) を電圧信号として出力する。例えば、キャパシタ C 1 とキャパシタ C 2 とでキャパシタンスが等しいとすると、これにより、駆動トランジスタ D R のゲート・ソース間電圧  $V_{gs}$  は電圧  $V_{th}$  + 1 / 2  $\times$  [  $V_{sig}$  ( m ) -  $V_{rst}$  ] に設定される。

### [0074]

さらに、m行目の画素 P X が接続された走査信号線 S L 2 をオフ電位に設定して、スイッチ S W b を開く。その後、m行目の画素 P X が接続された走査信号線 S L 1 をオン電位に設定して、スイッチ S W a を閉じる。m行目選択期間は、スイッチ S W a を閉じることにより終了する。

#### [0075]

この選択期間に続く非選択期間では、m行目の画素 P X は、m行目選択期間において設定した駆動トランジスタ D R のゲート・ソース間電圧  $V_{gs}$ を保持する。なお、m行目の画素 P X の非選択期間において、この画素 P X が接続された走査信号線 S L 1 及び S L 4 の電位はオン電位のままとしておき、走査信号線 S L 2 、 S L 3 及び S L 5 の電位はオフ電位のままとしておく。有機 E L 素子 O L E D には、電圧  $V_{th}$  + 1 / 2 × [ $V_{sig}$ (m) -  $V_{rst}$ ] に対応した大きさの駆動電流  $I_{drv}$ (m) が流れる。有機 E L 素子 O L E D は、駆動電流  $I_{drv}$ (m) の大きさに対応した輝度で発光する。

## [0076]

この駆動方法では、スイッチSWcのスイッチング動作に第1態様で説明したのと同様の方法を採用している。したがって、本態様でも、第1態様で説明したのと同様の効果を得ることができる。

【図面の簡単な説明】

- [0077]

- 【図1】本発明の第1態様に係る表示装置を概略的に示す平面図。

- 【図2】図1の表示装置に採用可能な構造の一例を概略的に示す断面図。

- 【図3】図1の表示装置が含む画素の等価回路図。

- 【図4】図1に示す表示装置の駆動方法の一例を示すタイミングチャート。

- 【 図 5 】 本 発 明 の 第 2 態 様 に 係 る 表 示 装 置 を 概 略 的 に 示 す 平 面 図 。

- 【図6】図5の表示装置が含む画素の等価回路図。

- 【 図 7 】 図 5 に 示 す 表 示 装 置 の 駆 動 方 法 の 一 例 を 示 す タ イ ミ ン グ チャ ー ト 。

【符号の説明】

## [0078]

て…キャパシタ、C1…キャパシタ、C2…キャパシタ、CE…対向電極、DE…ドレイン電極、DL…映像信号線、DP…表示パネル、DR…駆動トランジスタ、G…ゲート、GI…ゲート絶縁膜、II…層間絶縁膜、ND1…電源端子、ND1,…定電位端子、ND2…電源端子、ND3…スイッチング信号出力端子、OLED…有機EL素子、ORG…有機物層、PE…画素電極、PI…隔壁絶縁層、PS…パッシベーション膜、PSL…電源線、PX…画素、SC…半導体層、SE…ソース電極、SL1…走査信号線、SL2…走査信号線、SL3…走査信号線、SL4…走査信号線、SL5…走査信号線、SUB…絶縁基板、SWa…スイッチ、SWb…スイッチ、SWc…スイッチ、SWd…スイッチ、SWd…スイッチ、SWc…スイッチ、SWd…スイッチ、SWc…スイッチ、SWd…スイッチ、SWc…スイッチ、SWd…スイッチ、SWc…表方に号線ドライバ、YDR…走査信号線ドライバ。

10

20

30

SÚB

XDR

【図5】

【図6】

図 6

【図7】

## フロントページの続き

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 澁沢 誠

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 3K007 AB17 BA06 DB03 GA04

5C080 AA06 BB05 DD01 EE29 FF11 JJ03 JJ04 JJ06

| 专利名称(译)        | 显示装置,阵列基板和驱动显示装置的方法                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | JP2007003909A                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2007-01-11 |  |

| 申请号            | JP2005185150                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2005-06-24 |  |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |  |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |

| [标]发明人         | 选沢誠<br>                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |

| 发明人            | 澁沢 誠                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.624.B G09G3/20.621.A H05B33/14.A G09G3/3225 G09G3/3266                                                                                                                                                                                                                                                                                                                                                 |         |            |  |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA04 5C080/AA06 5C080/BB05 5C080/DD01 5C080 /EE29 5C080/FF11 5C080/JJ03 5C080/JJ04 5C080/JJ06 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH02 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB06 5C380/AB12 5C380 /AB23 5C380/AB34 5C380/BA37 5C380/BA39 5C380/BB01 5C380/BB21 5C380/BE05 5C380/CB01 5C380/CB17 5C380/CC04 5C380/CC26 5C380/CC27 5C380/CC33 5C380/CC39 5C380/CC65 5C380 /CD016 |         |            |  |

| 代理人(译)         | 河野 哲中村诚                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |  |

## 摘要(译)

解决的问题:在显示装置中抑制灰度再现性不足,在该显示装置中,每个像素显示的灰度由视频信号的大小控制。 本发明的显示装置包括:驱动晶体管DR,其源极连接至电源端子ND1;对电极,其连接至像素电极和电源端子ND2;以及有源层,介于它们之间。 显示元件OLED,连接在驱动晶体管的漏极和像素电极之间的开关SWa,连接在驱动晶体管DR的漏极和栅极之间的开关晶体管SWc,以及驱动晶体管DR和开关晶体管的漏极。 其特征在于,包括多个像素PX,每个像素具有连接在SWc的栅极之间的开关SWe和连接在开关晶体管SWc的栅极与开关信号输出端子ND3之间的开关SWd。 和 [选型图]图1