(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-106803

(P2018-106803A)

(43) 公開日 平成30年7月5日(2018.7.5)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |       |

|-----------------------------|------------|-------------|-------|

| <b>H05B 33/22</b> (2006.01) | H05B 33/22 | Z           | 3K107 |

| <b>H01L 51/50</b> (2006.01) | H05B 33/14 | A           |       |

| <b>H05B 33/26</b> (2006.01) | H05B 33/22 | D           |       |

| <b>H05B 33/10</b> (2006.01) | H05B 33/26 | Z           |       |

|                             | H05B 33/10 |             |       |

審査請求 未請求 請求項の数 7 O L (全 8 頁)

|           |                              |          |                                                                  |

|-----------|------------------------------|----------|------------------------------------------------------------------|

| (21) 出願番号 | 特願2016-248868 (P2016-248868) | (71) 出願人 | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号                   |

| (22) 出願日  | 平成28年12月22日 (2016.12.22)     | (74) 代理人 | 110000154<br>特許業務法人はるか国際特許事務所                                    |

|           |                              | (72) 発明者 | 前田 典久<br>東京都港区西新橋三丁目7番1号 株式会<br>社ジャパンディスプレイ内                     |

|           |                              |          | F ターム (参考) 3K107 AA01 BB01 CC29 CC45 DD21<br>DD26 DD71 DD89 GG11 |

(54) 【発明の名称】有機EL表示装置および有機EL表示装置の製造方法

## (57) 【要約】

【課題】有機EL表示装置において、隣接する画素間でのリーク電流をより確実に抑制する。

【解決手段】有機EL表示装置であつて、基板と、前記基板上に配置され、複数の画素に対応する下部電極と、前記基板上の隣接する前記下部電極間に配置され、前記複数の画素を区画するバンクと、前記下部電極およびバンク上に配置される有機材料層と、を有し、前記バンク上に、部分的に前記有機材料層の少なくとも一部が存在しない非存在領域が形成されている。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

基板と、

前記基板上に配置され、複数の画素に対応する下部電極と、

前記基板上の隣接する前記下部電極間に配置され、前記複数の画素を区画するバンクと、

前記下部電極およびバンク上に配置される有機材料層と、を有し、

前記バンク上に、部分的に前記有機材料層の少なくとも一部が存在しない非存在領域が形成されている、

有機 E L 表示装置。

10

**【請求項 2】**

前記有機材料層の一部が正孔輸送層を含む、請求項 1 に記載の有機 E L 表示装置。

**【請求項 3】**

前記有機材料層上に配置される上部電極を有し、

前記バンク上の非存在領域において、前記バンクに前記上部電極が接触している、請求項 1 または 2 に記載の有機 E L 表示装置。

**【請求項 4】**

基板上に、複数の画素に対応する下部電極を形成すること、

前記基板上の隣接する前記下部電極間に、前記複数の画素を区画するバンクを形成すること、

20

前記下部電極および前記バンク上に有機材料層を形成すること、

前記バンク上に存在する前記有機材料層を除去すること、

をこの順で含む、有機 E L 表示装置の製造方法。

**【請求項 5】**

前記バンク上に存在する前記有機材料層を粘着シートに転写させることにより除去する、請求項 4 に記載の製造方法。

**【請求項 6】**

前記有機材料層が正孔輸送層を含む、請求項 4 または 5 に記載の製造方法。

**【請求項 7】**

前記除去後、前記有機材料層上に上部電極を形成することをさらに含む、請求項 4 から 6 のいずれかに記載の製造方法。

30

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、有機 E L 表示装置および有機 E L 表示装置の製造方法に関する。

**【背景技術】****【0 0 0 2】**

有機エレクトロルミネッセンス ( E L ) 表示装置は、基板上に薄膜トランジスタ ( TFT ) や有機発光ダイオード ( OLED ) などが形成された表示パネルを有する。OLED は、一対の電極間に有機材料層を備える。有機材料層は、例えば、正孔輸送層、発光層、電子輸送層等が積層されて構成される。このような有機材料層は、代表的には、画素を区画するために予め設けられた凸状のバンクで囲まれた領域に形成される。ここで、例えば、正孔輸送層等の導電性の材料を複数の画素間で共通に設けると、隣接する画素間でリーク電流が流れてしまうという問題がある。具体的には、リーク電流により本来発光すべきでない隣接の画素が発光し、コントラストや色純度の低下を招くという問題がある。このような問題は、高精細化（例えば、隣接する画素間の距離が短くなる）や駆動電圧の低減化（例えば、高移動度材料の採用）が進むほど、顕著に発生し得る。

40

**【0 0 0 3】**

上記のような問題に対し、例えば、下記特許文献 1 では、バンク上の有機材料層にエネルギー線を照射して、有機材料層に含まれる導電性の層を変質させて不導体化する方法が

50

提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2016-18759号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、隣接する画素間でのリーク電流をより確実に抑制することが望まれている。

【0006】

本発明は、上記に鑑み、隣接する画素間でのリーク電流をより確実に抑制し得る有機EL表示装置およびその製造方法の提供を目的とする。

【課題を解決するための手段】

【0007】

本発明の有機EL表示装置は、基板と、前記基板上に配置され、複数の画素に対応する下部電極と、前記基板上の隣接する前記下部電極間に配置され、前記複数の画素を区画するバンクと、前記下部電極およびバンク上に配置される有機材料層と、を有し、前記バンク上に、部分的に前記有機材料層の少なくとも一部が存在しない非存在領域が形成されている。

【0008】

1つの実施形態においては、上記有機材料層の一部は正孔輸送層を含む。

【0009】

1つの実施形態においては、上記有機EL表示装置は、上記有機材料層上に配置される上部電極を有し、上記バンク上の非存在領域において、上記バンクに前記上部電極が接触している。

【0010】

本発明の別の局面によれば、有機EL表示装置の製造方法が提供される。この有機EL表示装置の製造方法は、基板上に、複数の画素に対応する下部電極を形成すること、前記基板上の隣接する前記下部電極間に、前記複数の画素を区画するバンクを形成すること、前記下部電極および前記バンク上に有機材料層を形成すること、前記バンク上に存在する前記有機材料層を除去すること、をこの順で含む。

【0011】

1つの実施形態においては、上記バンク上に存在する上記有機材料層を粘着シートに転写させることにより除去する。

【0012】

1つの実施形態においては、上記製造方法において、上記有機材料層は正孔輸送層を含む。

【0013】

1つの実施形態においては、上記製造方法は、上記除去後、上記有機材料層上に上部電極を形成することをさらに含む。

【図面の簡単な説明】

【0014】

【図1】本発明の実施形態に係る有機EL表示装置の概略の構成を示す模式図である。

【図2】図1に示す有機EL表示装置の表示パネルの一例を示す模式的な平面図である。

【図3】図2のIII-III断面の一例を示す図である。

【図4A】非存在領域の形成方法を説明するための概略断面図である。

【図4B】非存在領域の形成方法を説明するための概略断面図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施形態について、図面を参照しつつ説明する。なお、図面については

10

20

30

40

50

、同一又は同等の要素には同一の符号を付し、重複する説明は省略することがある。

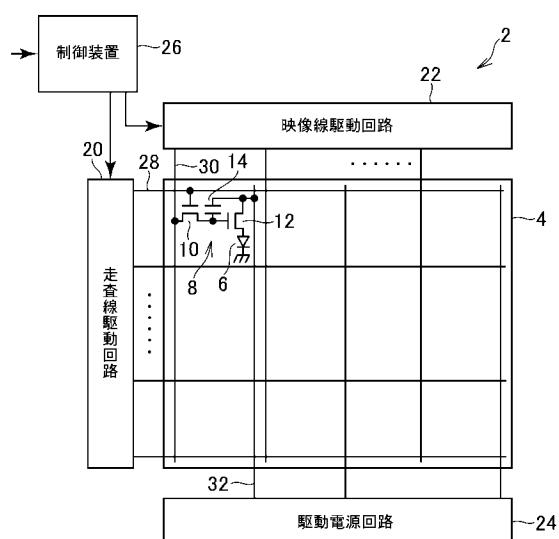

**【0016】**

図1は、本発明の実施形態に係る有機EL表示装置の概略の構成を示す模式図である。有機EL表示装置2は、画像を表示する画素アレイ部4と、画素アレイ部4を駆動する駆動部とを備える。有機EL表示装置2は、基板上にTFTやOLEDなどの積層構造が形成された表示パネルを有する。なお、図1に示した概略図は一例であって、本実施形態はこれに限定されるものではない。

**【0017】**

画素アレイ部4には、画素に対応してOLED6および画素回路8がマトリクス状に配置される。画素回路8は複数のTFT10, 12やキャパシタ14で構成される。

10

**【0018】**

上記駆動部は、走査線駆動回路20、映像線駆動回路22、駆動電源回路24および制御装置26を含み、画素回路8を駆動しOLED6の発光を制御する。

**【0019】**

走査線駆動回路20は、画素の水平方向の並び(画素行)ごとに設けられた走査信号線28に接続されている。走査線駆動回路20は、制御装置26から入力されるタイミング信号に応じて走査信号線28を順番に選択し、選択した走査信号線28に、点灯TFT10をオンする電圧を印加する。

**【0020】**

映像線駆動回路22は、画素の垂直方向の並び(画素列)ごとに設けられた映像信号線30に接続されている。映像線駆動回路22は、制御装置26から映像信号を入力され、走査線駆動回路20による走査信号線28の選択に合わせて、選択された画素行の映像信号に応じた電圧を各映像信号線30に出力する。当該電圧は、選択された画素行にて点灯TFT10を介してキャパシタ14に書き込まれる。駆動TFT12は、書き込まれた電圧に応じた電流をOLED6に供給し、これにより、選択された走査信号線28に対応する画素のOLED6が発光する。

20

**【0021】**

駆動電源回路24は、画素列ごとに設けられた駆動電源線32に接続され、駆動電源線32および選択された画素行の駆動TFT12を介してOLED6に電流を供給する。

30

**【0022】**

ここで、OLED6の下部電極は、駆動TFT12に接続される。一方、各OLED6の上部電極は、全画素のOLED6に共通の電極で構成される。下部電極を陽極(アノード)として構成する場合は、高電位が入力され、上部電極は陰極(カソード)となって低電位が入力される。下部電極を陰極(カソード)として構成する場合は、低電位が入力され、上部電極は陽極(アノード)となって高電位が入力される。

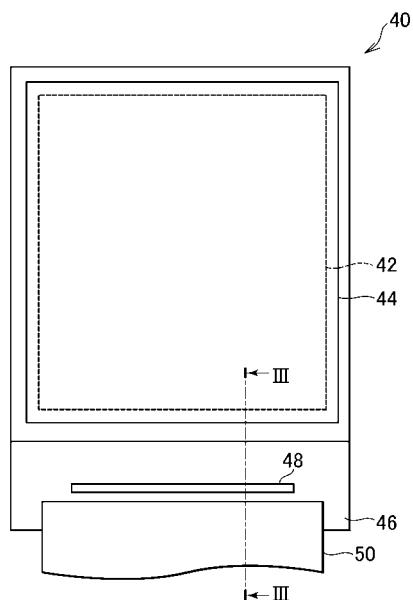

**【0023】**

図2は、図1に示す有機EL表示装置の表示パネルの一例を示す模式的な平面図である。表示パネル40の表示領域42に、図1に示した画素アレイ部4が設けられ、上述したように画素アレイ部4にはOLEDが配列される。上述したようにOLED6を構成する上部電極44は、各画素に共通に形成され、表示領域42全体を覆う。

40

**【0024】**

矩形である表示パネル40の一辺には、部品実装領域46が設けられ、表示領域42につながる配線が配置される。部品実装領域46には、駆動部を構成するドライバ集積回路(IIC)48が搭載されたり、FPC50が接続されたりする。フレキシブルプリント基板(FPC)50は、制御装置26やその他の回路20, 22, 24等に接続されたり、その上にIICを搭載されたりする。

**【0025】**

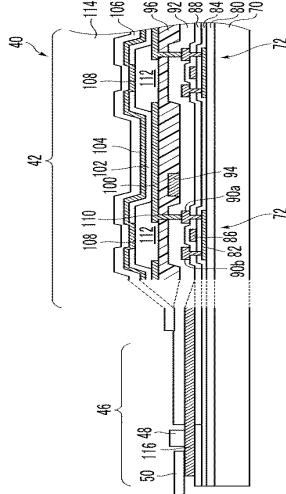

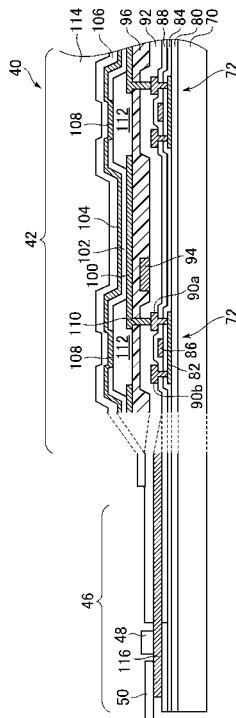

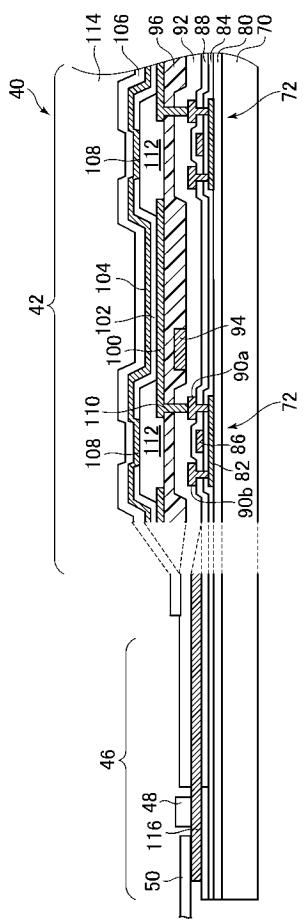

図3は、図2のIII-III断面の一例を示す図である。表示パネル40は、基板70の上にTFT72などからなる回路層、OLED6およびOLED6を封止する封止層106などが積層された構造を有する。基板70は、例えば、ガラス板、樹脂フィルムで構成さ

50

れる。本実施形態においては、画素アレイ部4はトップエミッション型であり、OLED6で生じた光は、基板70側とは反対側(図3において上向き)に出射される。

#### 【0026】

表示領域42の回路層には、上述した画素回路8、走査信号線28、映像信号線30、駆動電源線32などが形成される。駆動部の少なくとも一部分は、基板70上に回路層として表示領域42に隣接する領域に形成することができる。上述したように、駆動部を構成するドライバIC48やFPC50を、部品実装領域46にて、回路層の配線116に接続することができる。

#### 【0027】

図3に示すように、基板70上には、無機絶縁材料で形成された下地層80が配置される。無機絶縁材料としては、例えば、窒化シリコン(SiN<sub>y</sub>)、酸化シリコン(SiO<sub>x</sub>)およびこれらの複合体が用いられる。

#### 【0028】

表示領域42においては、下地層80を介して、基板70上には、トップゲート型のTFT72のチャネル部およびソース・ドレイン部となる半導体領域82が形成される。半導体領域82は、例えば、ポリシリコン(p-Si)で形成される。半導体領域82は、例えば、基板70上に半導体層(p-Si膜)を設け、この半導体層をパターニングし、回路層で用いる箇所を選択的に残すことにより形成される。TFT72のチャネル部の上には、ゲート絶縁膜84を介してゲート電極86が配置される。ゲート絶縁膜84は、代表的には、TEOSで形成される。ゲート電極86は、例えば、スパッタリング等で形成した金属膜をパターニングして形成される。ゲート電極86上には、ゲート電極86を覆うように層間絶縁層88が配置される。層間絶縁層88は、例えば、上記無機絶縁材料で形成される。TFT72のソース・ドレイン部となる半導体領域82(p-Si)には、イオン注入により不純物が導入され、さらにそれらに電気的に接続されたソース電極90aおよびドレイン電極90bが形成され、TFT72が構成される。

#### 【0029】

TFT72上には、層間絶縁膜92が配置される。層間絶縁膜92の表面には、配線94が配置される。配線94は、例えば、スパッタリング等で形成した金属膜をパターニングすることにより形成される。配線94を形成する金属膜と、ゲート電極86、ソース電極90aおよびドレイン電極90bの形成に用いた金属膜とで、例えば、配線116および図1に示した走査信号線28、映像信号線30、駆動電源線32を多層配線構造で形成することができる。この上に、例えば、アクリル系樹脂等の樹脂材料により平坦化膜96が形成され、表示領域42において、平坦化膜96上にOLED6が形成される。

#### 【0030】

OLED6は、下部電極100、有機材料層102および上部電極104を含む。有機材料層102は、例えば、正孔輸送層、発光層、電子輸送層を積層して形成される。OLED6は、代表的には、下部電極100、有機材料層102および上部電極104を基板70側からこの順に積層して形成される。本実施形態では、下部電極100がOLEDの陽極(アノード)であり、上部電極104が陰極(カソード)である。なお、有機材料層は、上記以外の他の層を有し得る。他の層としては、例えば、アノードと発光層との間に配置される正孔注入層や電子プロック層、カソードと発光層との間に配置される電子注入層や正孔プロック層が挙げられる。

#### 【0031】

図3に示すTFT72が、nチャネルを有した駆動TFT12であるとすると、下部電極100は、TFT72のソース電極90aに接続される。具体的には、上述した平坦化膜96の形成後、下部電極100をTFT72に接続するためのコンタクトホール110が形成され、例えば、平坦化膜96表面およびコンタクトホール110内に形成した導電部をパターニングすることにより、TFT72に接続された下部電極100が画素ごとに形成される。

#### 【0032】

10

20

30

40

50

上記構造上には、画素を区画するバンク 112 が配置される。例えば、下部電極 100 の形成後、画素境界にバンク 112 を形成し、バンク 112 で囲まれた画素の有効領域（下部電極 100 の露出する領域）に、有機材料層 102 および上部電極 104 が積層される。バンク 112 は、代表的には、ポリイミド系樹脂、アクリル系樹脂等の樹脂材料で形成される。上部電極 104 は、代表的には、透明電極材料で形成される。バンク 112 の上には、有機材料層 102 が実質的に存在しない非存在領域 108 が形成されている。非存在領域 108 において、バンク 112 に上部電極 104 が接触している。隣接する画素間において、有機材料層 102 が連続して形成されないことで、上述のリーク電流の発生が効果的に抑制される。なお、非存在領域 108 において、図示例とは異なり、有機材料層 102 を構成する層の一部（例えば、膜厚が比較的厚い正孔輸送層）が選択的に存在しない状態であってもよい。また、非存在領域 108 は、全ての画素間において形成されてもよいし、特定の画素の周囲に選択的に（例えば、赤（R）、緑（G）、青（B）の中でもリーク電流による色純度の低下が顕著な G 画素の周囲に選択的に）形成されてもよい。

#### 【0033】

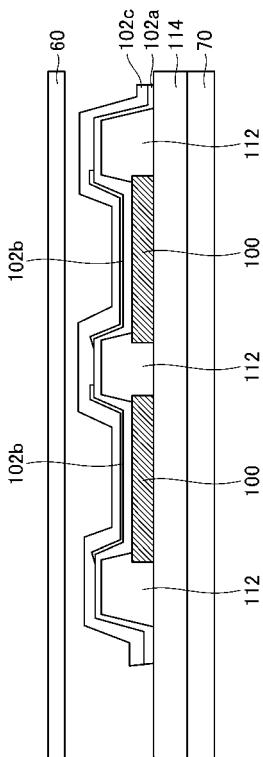

図 4A および図 4B は、非存在領域 108 の形成方法を説明するための概略断面図である。なお、図 4A および図 4B において、図 3 に示す表示パネル 40 の積層構造のうち、基板 70 上の下地層 80 から平坦化膜 96 までの積層構造を上部構造層 114 として簡略化して示している。図 4A に示すように、基板 70 上の隣接する下部電極 100, 100 間に、下部電極 100 の端部を保護するように、画素を区画するバンク 112 を形成し、下部電極 100 およびバンク 112 上に連続して有機材料層 102 を形成する。例えば、トリフェニルアミン構造を有する化合物を含む正孔輸送層 102a を下部電極 100 およびバンク 112 上に連続的に形成し（複数の画素間で共通に設け）、正孔輸送層 102a 上に、各画素の色に対応した発光層 102b を各画素領域に形成し、発光層 102b を覆うように（複数の画素間で共通に）電子輸送層 102c を形成し、有機材料層 102 を形成する。形成された有機材料層 102 上に粘着シート 60 の粘着面を貼り合わせ、図 4B に示すように、バンク 112 上に存在する有機材料層 102d を粘着シート 60 に転写させる。こうして、有機材料層の一部 102d を除去してバンク 112 上に非存在領域 108 を形成した後、有機材料層 102 上に上部電極 104 を形成する。なお、上述のように、正孔輸送層 102a を選択的に除去する場合は、例えば、正孔輸送層 102a 形成直後に粘着シート 60 をバンク 112 上に貼り合わせる。

#### 【0034】

粘着シート 60 は、例えば、基材とこの基材の片側に形成された粘着剤層とを含む積層体である。有機材料層 102 の一部を除去する際、粘着シート 60 は、シート状であってもよいし、ロール状に巻回されていてもよい。

#### 【0035】

上部電極 104 上には、封止層 106 が配置される。封止層 106 は、例えば、OLED 6 を水分等から保護する保護層として機能し得るため、表示領域 42 の全体を覆うように形成される。封止層 106 は、例えば、化学気相成長（CVD）法により  $\text{SiN}_y$  等の無機絶縁材料膜を成膜することにより形成される。また、図示しないが、例えば、表示パネル 40 の表面の機械的な強度を確保するため、表示領域 42 の表面には保護膜が配置され得る。この場合、部品実装領域 46 では、IC や FPC を接続し易くするため、通常、保護膜は設けない。FPC 50 の配線やドライバ IC 48 の端子は、例えば、配線 116 に電気的に接続される。

#### 【0036】

本発明は、上記実施形態に限定されるものではなく、種々の変形が可能である。例えば、上記実施形態で示した構成と実質的に同一の構成、同一の作用効果を奏する構成または同一の目的を達成することができる構成で置き換えることができる。具体的には、上記実施形態では、非存在領域 108 は、粘着シートを用いて有機材料層 102 を部分的に除去することにより形成されているが、例えば、レーザー加工（切断、アブレーション）による除去やカッターを用いた加工（切断、切削）による除去により形成されてもよい。

## 【符号の説明】

## 【0037】

2 有機 E L 表示装置、4 画素アレイ部、6 O L E D 、8 画素回路、10 点灯 T F T 、12 駆動 T F T 、14 キャパシタ、20 走査線駆動回路、22 映像線駆動回路、24 駆動電源回路、26 制御装置、28 走査信号線、30 映像信号線、32 駆動電源線、40 表示パネル、42 表示領域、44 上部電極、46 部品実装領域、48 ドライバ I C 、50 F P C 、60 粘着シート、70 基板、72 T F T 、80 下地層、82 半導体領域、84 ゲート絶縁膜、86 ゲート電極、88 層間絶縁層、90a ソース電極、90b ドレイン電極、92 層間絶縁膜、94 配線、96 平坦化膜、100 下部電極、102 有機材料層、104 上部電極、106 封止層、108 非存在領域、110 コンタクトホール、112 バンク、114 上部構造層、116 配線。 10

【図1】

【図2】

〔 図 3 〕

【図4A】

【 図 4 B 】

|                |                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL显示装置和有机EL显示装置的制造方法                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2018106803A</a>                                                                      | 公开(公告)日 | 2018-07-05 |

| 申请号            | JP2016248868                                                                                       | 申请日     | 2016-12-22 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                          |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                          |         |            |

| [标]发明人         | 前田典久                                                                                               |         |            |

| 发明人            | 前田 典久                                                                                              |         |            |

| IPC分类号         | H05B33/22 H01L51/50 H05B33/26 H05B33/10                                                            |         |            |

| FI分类号          | H05B33/22.Z H05B33/14.A H05B33/22.D H05B33/26.Z H05B33/10                                          |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC29 3K107/CC45 3K107/DD21 3K107/DD26 3K107/DD71 3K107/DD89 3K107/GG11 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                          |         |            |

### 摘要(译)

在有机EL显示装置中，更可靠地抑制相邻像素之间的漏电流。解决方案：将有机EL显示装置，基板，设置在基板上，对于所述多个像素的下电极设置在所述下部电极之间的相邻的衬底上，所述多个像素；堤岸设置在下电极和堤岸上并且在堤上部分地形成其中不存在至少一部分有机材料层的不存在区域。