(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-276744

(P2009-276744A)

(43) 公開日 平成21年11月26日(2009.11.26)

(51) Int.Cl.

**G09G** 3/30 (2006.01)

**G09G** 3/20 (2006.01)

**H01L** 51/50 (2006.01)

**H05B** 33/12 (2006.01)

F 1

|        |      |         |

|--------|------|---------|

| GO 9 G | 3/30 | K       |

| GO 9 G | 3/20 | 6 2 4 B |

| GO 9 G | 3/30 | J       |

| GO 9 G | 3/20 | 6 4 1 P |

| GO 9 G | 3/20 | 6 2 3 D |

### テーマコード（参考）

3K107

5C080

審査請求 未請求 請求項の数 18 O.L. (全 132 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2009-11791 (P2009-11791)   |

| (22) 出願日     | 平成21年1月22日 (2009. 1. 22)     |

| (31) 優先権主張番号 | 特願2008-31284 (P2008-31284)   |

| (32) 優先日     | 平成20年2月13日 (2008. 2. 13)     |

| (33) 優先権主張国  | 日本国 (JP)                     |

| (31) 優先権主張番号 | 特願2008-33399 (P2008-33399)   |

| (32) 優先日     | 平成20年2月14日 (2008. 2. 14)     |

| (33) 優先権主張国  | 日本国 (JP)                     |

| (31) 優先権主張番号 | 特願2008-105475 (P2008-105475) |

| (32) 優先日     | 平成20年4月15日 (2008. 4. 15)     |

| (33) 優先権主張国  | 日本国 (JP)                     |

(71) 出願人 302020207

東芝モバイルディスプレイ株式会社

東京都港区港南4-1-8

(74) 代理人 100059225

弁理士 菊田 環子

(74) 代理人 100076314

弁理士 菊田 正人

(74) 代理人 100112612

弁理士 中村 哲士

(74) 代理人 100112623

弁理士 富田 克幸

(74) 代理人 100124707

弁理士 夫 世進

最終頁に続く

(54) 【発明の名称】 E L 表示装置

(57) 【要約】

【課題】十分なオフセットキャンセル期間を確保して、駆動トランジスタの特性バラツキを補償し、特性表示ムラのない画像表示を実現できる E-L 表示装置を提供する

【解決手段】画素16には、映像信号電圧Vsigを保持するコンデンサ19bが形成されている。スイッチトランジスタ11cがオンすると、映像信号電圧Vsigにより、駆動トランジスタ11aがオフセットキャンセル動作を行うと共に、映像信号電圧Vsigがコンデンサ19bに書き込まれ、画素16の選択期間が終了し、スイッチトランジスタ11cがオフした後、コンデンサ19bに保持された映像信号電圧Vsigにより、オフセットキャンセル動作が継続する。

## 【選択図】 図 1

**【特許請求の範囲】****【請求項 1】**

EL 素子を有する画素がマトリックス状に複数配置された表示画面を有する EL 表示装置であって、

映像信号電圧を出力するソースドライバ回路と、

前記表示画面の中の画素を選択するゲートドライバ回路と、

前記映像信号電圧を保持する第 1 のコンデンサと、

前記画素の前記 EL 素子に電流を供給する駆動トランジスタと、

を有し、

前記映像信号電圧を前記駆動トランジスタに印加して所定動作を行うと共に、前記第 1 のコンデンサに前記映像信号電圧を書き込み、

前記第 1 のコンデンサに保持された前記映像信号電圧により、オフセットキャンセル動作を行う、

ことを特徴とする EL 表示装置。

**【請求項 2】**

EL 素子を有する画素がマトリックス状に複数配置された表示画面を有する EL 表示装置であって、

映像信号電圧を出力するソースドライバ回路と、

前記表示画面の中の画素を選択するゲートドライバ回路と、

動作用信号電圧を保持する第 1 のコンデンサと、

前記画素の前記 EL 素子に電流を供給する駆動トランジスタと、

を有し、

前記動作用信号電圧を、前記駆動トランジスタを介して前記画素に印加して所定動作を行うと共に、前記第 1 のコンデンサに前記動作用信号電圧を書き込み、

前記動作用信号電圧の印加を停止した後、前記第 1 のコンデンサに書き込まれた前記動作用信号電圧により、前記所定動作を継続する、

ことを特徴とする EL 表示装置。

**【請求項 3】**

前記各画素にリセット電圧を印加する第 1 のスイッチトランジスタが形成され、

前記第 1 のスイッチトランジスタはマルチゲート構造である、

ことを特徴とする請求項 1 又は 2 に記載の EL 表示装置。

**【請求項 4】**

前記 EL 素子に流れる電流経路に、第 2 のスイッチトランジスタが形成され、

前記第 2 のスイッチトランジスタをオン / オフ制御することにより、前記表示画面に帯状の非表示領域を発生させ、

前記非表示領域が 1 フレーム周期で前記表示画面を移動させる、

ことを特徴とする請求項 1 又は 2 に記載の EL 表示装置。

**【請求項 5】**

前記各画素に前記映像信号電圧を印加する第 3 のスイッチトランジスタが形成され、

前記第 3 のスイッチトランジスタのゲート端子と、前記第 3 のスイッチトランジスタのドレイン端子間に、第 2 のコンデンサが形成されている、

ことを特徴とする請求項 1 又は 2 に記載の EL 表示装置。

**【請求項 6】**

前記ゲートドライバ回路、又は、前記ゲートドライバ回路の入力段にレベルシフト回路が形成され、

前記ソースドライバ回路から出力された信号が、前記レベルシフト回路でレベルシフトして前記ゲートドライバ回路に入力される、

ことを特徴とする請求項 1 又は 2 に記載の EL 表示装置。

**【請求項 7】**

前記ゲートドライバ回路は、P チャンネルトランジスタ又は N チャンネルトランジスタ

10

20

30

40

50

で構成されている、

ことを特徴とする請求項 1 又は 2 に記載の E L 表示装置。

【請求項 8】

前記ソースドライバ回路は、半導体 I C であり、

前記ソースドライバ回路は、前記表示画面が形成された基板に実装され、

前記ソースドライバ回路と前記基板の間に遮光膜が形成されている、

ことを特徴とする請求項 1 又は 2 に記載の E L 表示装置。

【請求項 9】

マトリックス状の同じ列に配置された複数の前記画素に対して、第 1 のソース信号線と第 2 のソース信号線が形成され、

前記第 1 のソース信号線によって第 1 の映像信号電圧が印加される前記画素と、前記第 2 のソース信号線によって第 2 の映像信号電圧が印加される前記画素とが異なる、

ことを特徴とする請求項 1 又は 2 に記載の E L 表示装置。

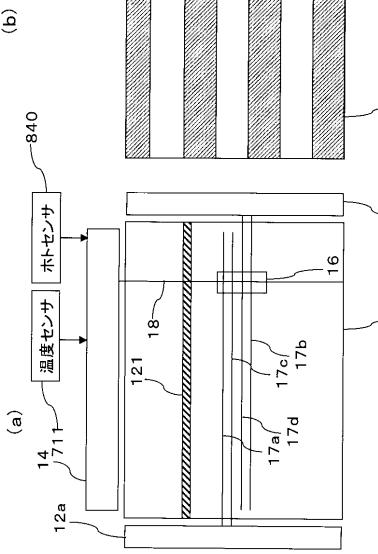

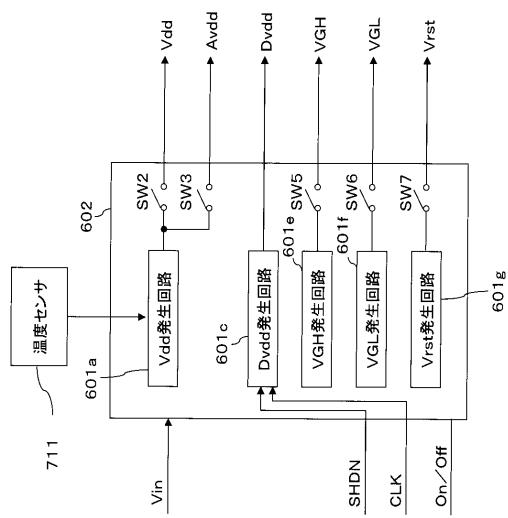

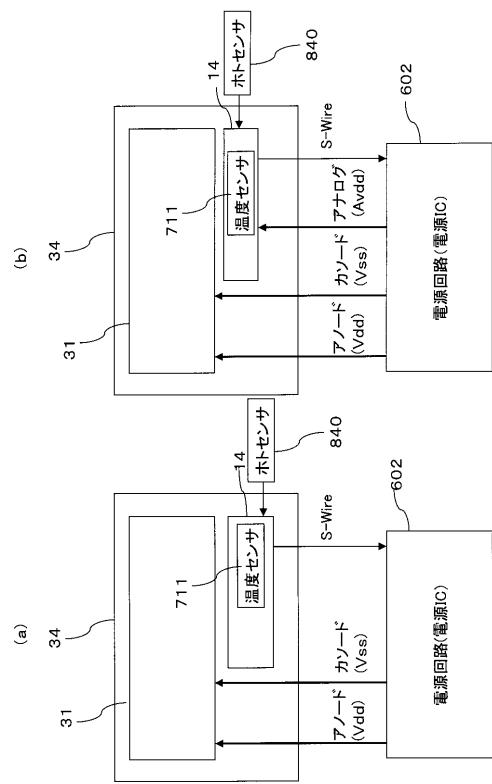

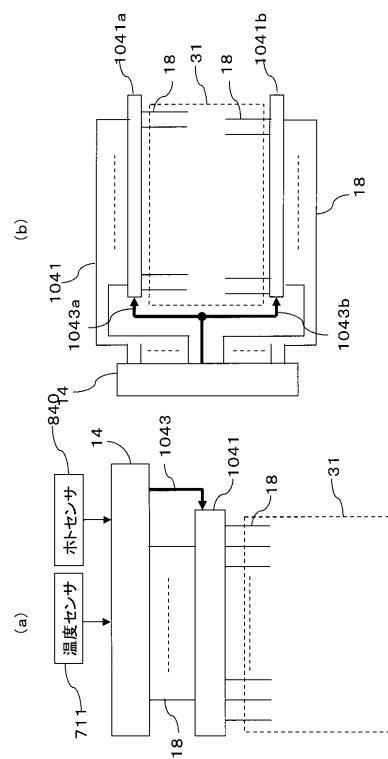

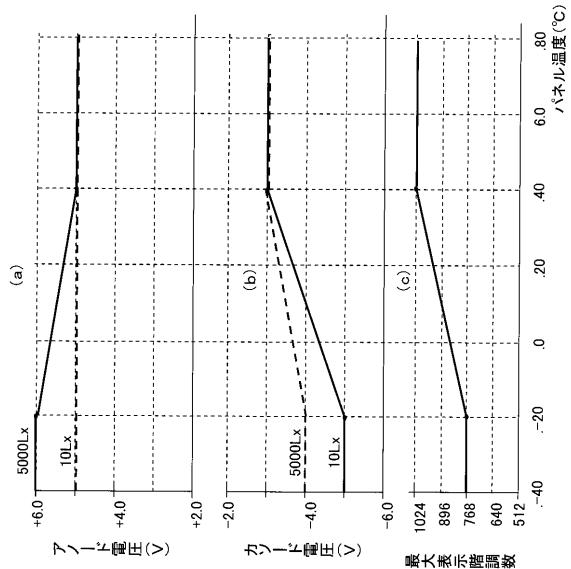

【請求項 10】

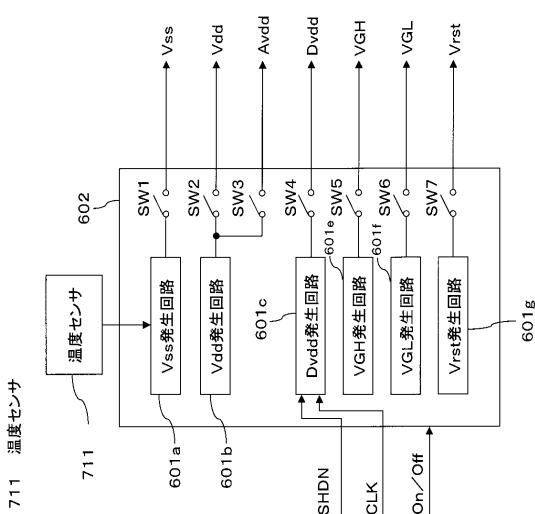

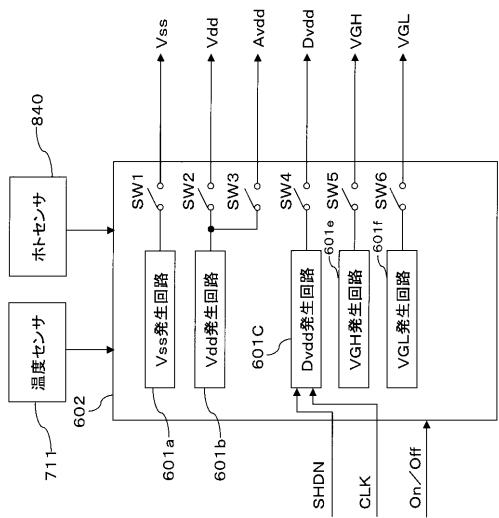

温度センサと、前記 E L 素子に印加する電圧を発生する電圧発生回路とを更に有し、

前記温度センサの出力に基づいて前記電圧発生回路が前記電圧を可変する、

ことを特徴とする請求項 1 又は 2 に記載の E L 表示装置。

【請求項 11】

温度センサを更に有し、

前記温度センサの出力に基づいて、前記表示画面で使用する最大表示階調を可変する、

ことを特徴とする請求項 1 又は 2 に記載の E L 表示装置。

【請求項 12】

前記温度センサが前記ソースドライバ回路に内蔵されている、

ことを特徴とする請求項 10 又は 11 に記載の E L 表示装置。

【請求項 13】

前記ソースドライバ回路は、ソース信号線を選択する選択スイッチ回路が複数内蔵されている、

ことを特徴とする請求項 1 又は 2 に記載の E L 表示装置。

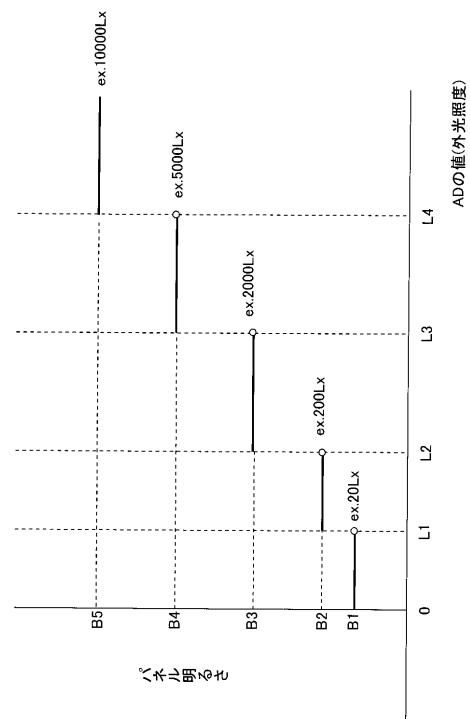

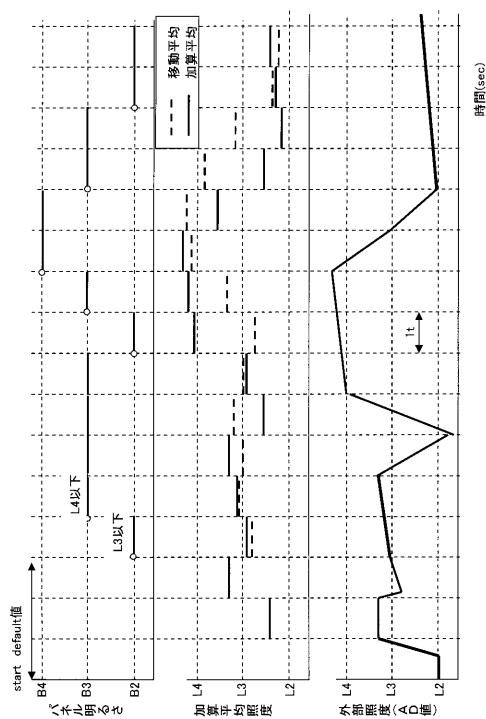

【請求項 14】

外光の明るさを検出するホトセンサを更に有し、

前記ホトセンサの出力に基づいて、前記表示画面の明るさを可変する、

ことを特徴とする請求項 1 又は 2 に記載の E L 表示装置。

【請求項 15】

前記画素に印加するリセット電圧の発生回路を更に有し、

前記リセット電圧は、前記映像信号電圧に基づいて可変する、

ことを特徴とする請求項 1 又は 2 に記載の E L 表示装置。

【請求項 16】

前記画素が複数の色から構成され、前記画素の画素電極の面積が、色によって異なる、

ことを特徴とする請求項 1 又は 2 に記載の E L 表示装置。

【請求項 17】

前記動作用信号電圧が、前記映像信号電圧であり、前記所定の動作がオフセットキャンセル動作である、

ことを特徴とする請求項 2 に記載の E L 表示装置。

【請求項 18】

前記動作用信号電圧が、リセット信号電圧であり、前記所定の動作がリセット動作である、

ことを特徴とする請求項 2 に記載の E L 表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

10

20

30

40

50

本発明は、有機又は無機エレクトロルミネッセンス(EL)素子などを用いるEL表示パネル(表示装置)などの自発光表示パネル(表示装置)を用いた、EL表示装置(有機発光表示装置)に関するものである。また、映像信号電圧(映像信号データ) Vsig を画素に所定期間保持するコンデンサ(容量、付加コンデンサ)を有する表示パネル、表示装置に関するものである。

【背景技術】

【0002】

電気光学変換物質として有機エレクトロルミネッセンス(EL)材料あるいは無機EL材料を用いたアクティブマトリクス型の画像表示装置は、画素に書き込まれる電流に応じて発光輝度が変化する。EL表示装置は、各画素に発光素子を有する自発光型である。EL表示装置は、液晶表示パネルに比べて画像の視認性が高い、発光効率が高い、バックライトが不要、応答速度が速い等の利点を有する。

10

【0003】

有機EL(PLED、OLED、OEL)パネルは、アクティブマトリクス方式の開発が盛んに行なわれている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子(一般には薄膜トランジスタ、TFT、FET、MOSトランジスタ)によって制御するものである(特許文献1, 2参照)。

20

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003-255856公報

【特許文献2】特開2003-271095公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

有機EL表示パネルは、低温あるいは高温ポリシリコンからなるトランジスタアレイを用いてパネルを構成する。しかし、有機EL素子は、ポリシリコントランジスタアレイのトランジスタ特性にバラツキがあると、表示ムラが発生する。

【0006】

EL素子15に電流を供給する駆動トランジスタ11aに特性バラツキがあると、変換される電流信号にもバラツキが発生する。通常、トランジスタ11aは50%以上の特性バラツキがある。そのために、駆動トランジスタの特性バラツキが表示ムラとして表示され、画像表示品位を低下させていた。

30

【0007】

そこで本発明は、十分なオフセットキャンセル期間を確保して、駆動トランジスタの特性バラツキを補償し、特性表示ムラのない画像表示を実現できるEL表示装置を提供する。

【課題を解決するための手段】

【0008】

本発明は、EL素子を有する画素がマトリックス状に複数配置された表示画面を有するEL表示装置であって、映像信号電圧を出力するソースドライバ回路と、前記表示画面の中の画素を選択するゲートドライバ回路と、前記映像信号電圧を保持する第1のコンデンサと、前記画素の前記EL素子に電流を供給する駆動トランジスタと、を有し、前記映像信号電圧を前記駆動トランジスタに印加して所定動作を行うと共に、前記第1のコンデンサに前記映像信号電圧を書き込み、前記第1のコンデンサに保持された前記映像信号電圧により、オフセットキャンセル動作を行う、ことを特徴とするEL表示装置である。

40

【0009】

また、本発明は、EL素子を有する画素がマトリックス状に複数配置された表示画面を有するEL表示装置であって、映像信号電圧を出力するソースドライバ回路と、前記表示画面の中の画素を選択するゲートドライバ回路と、信号電圧を保持する第1のコンデンサ

50

と、前記画素の前記EL素子に電流を供給する駆動トランジスタと、を有し、前記信号電圧を前記駆動トランジスタを介して前記画素に印加して所定動作を行うと共に、前記第1のコンデンサに前記信号電圧を書き込み、前記信号電圧の印加を停止した後、前記第1のコンデンサに書き込まれた前記信号電圧により、前記所定動作を継続する、ことを特徴とするEL表示装置である。

## 【発明の効果】

## 【0010】

本発明によれば、十分なオフセットキャンセル期間を確保できるので、良好に駆動トランジスタをオフセットキャンセルすることができる。したがって、駆動トランジスタの特性バラツキを補償し、特性表示ムラのない画像表示を実現できる。

10

## 【図面の簡単な説明】

## 【0011】

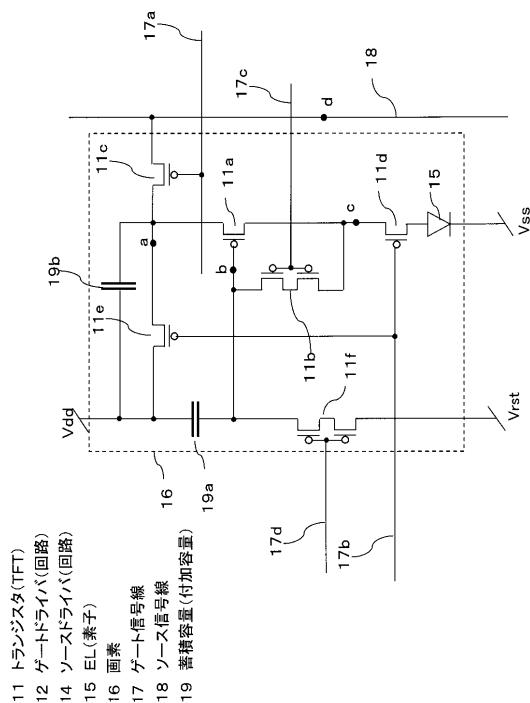

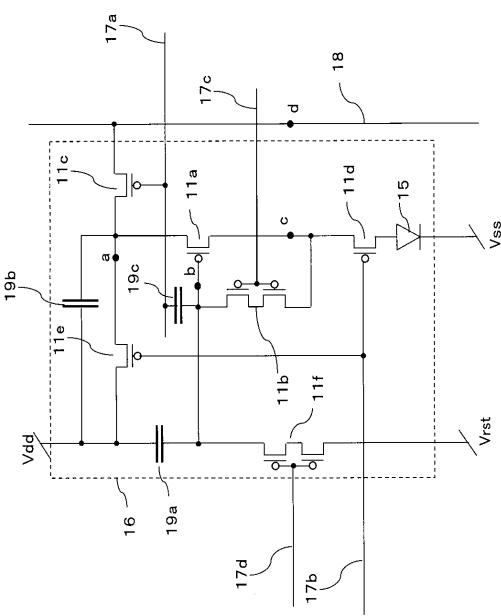

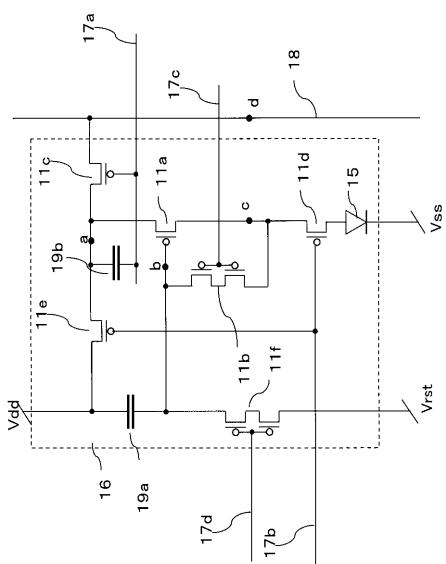

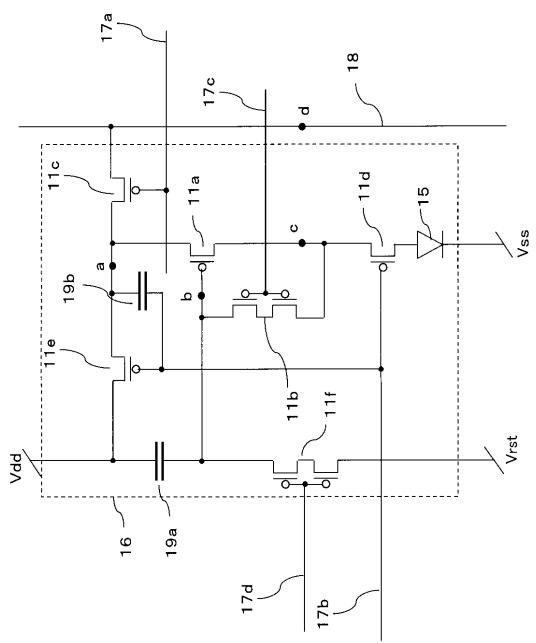

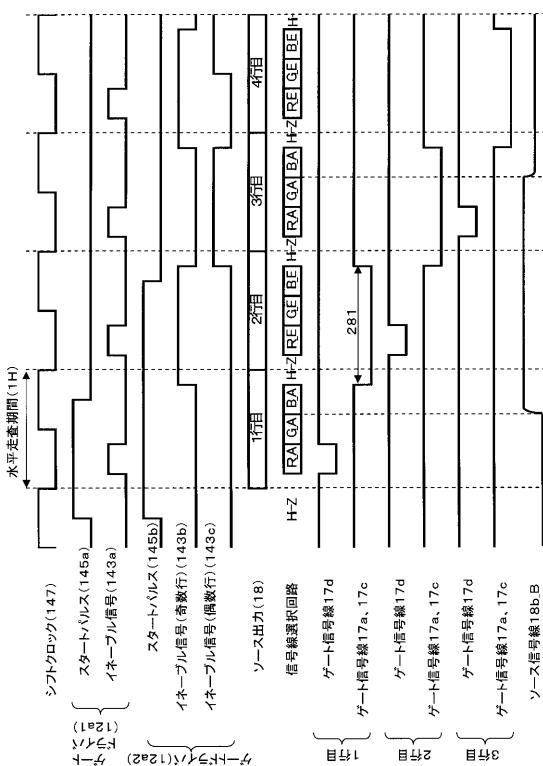

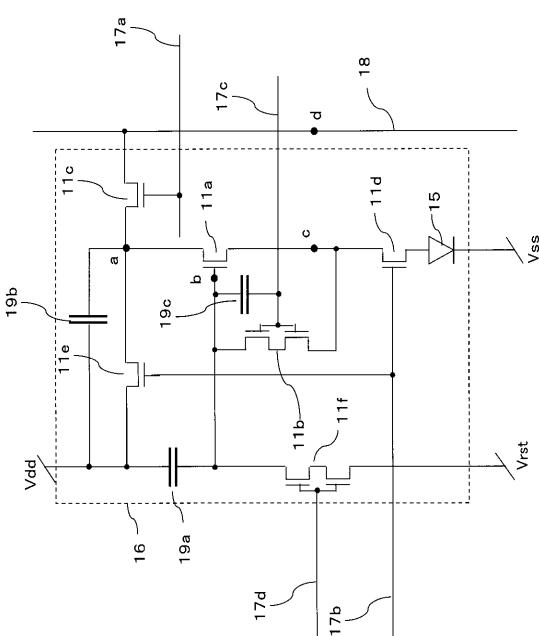

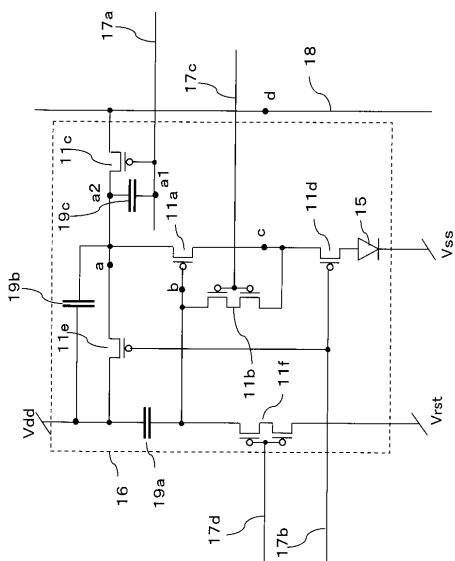

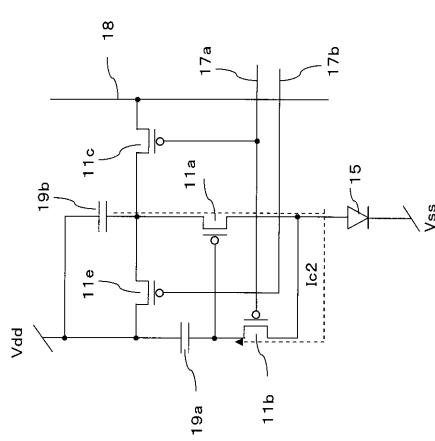

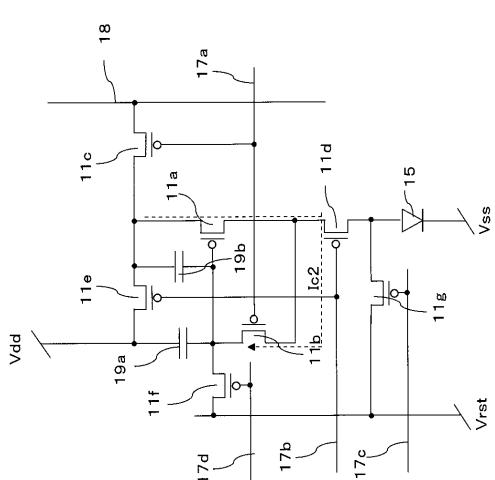

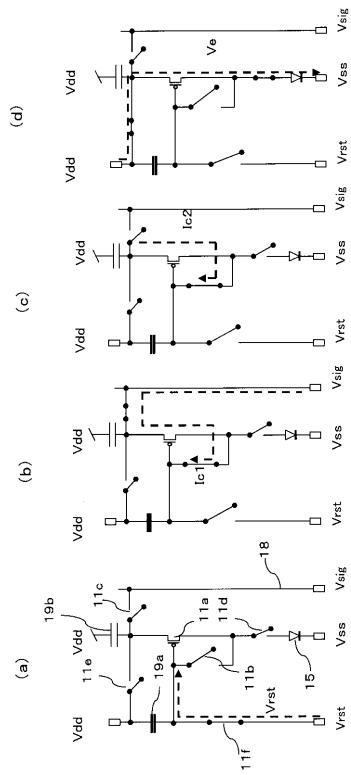

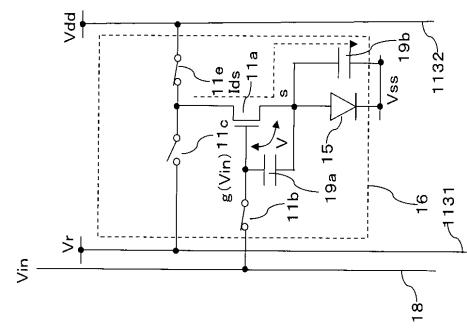

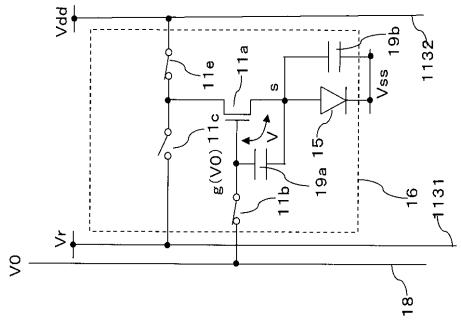

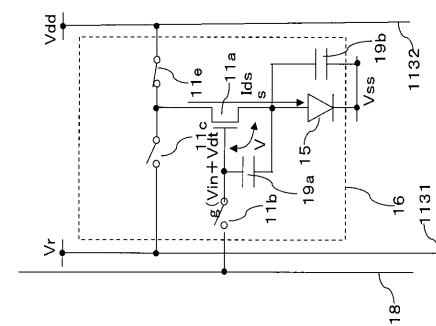

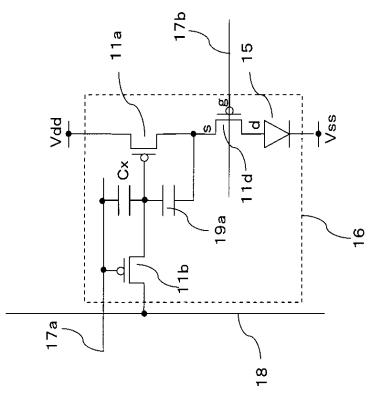

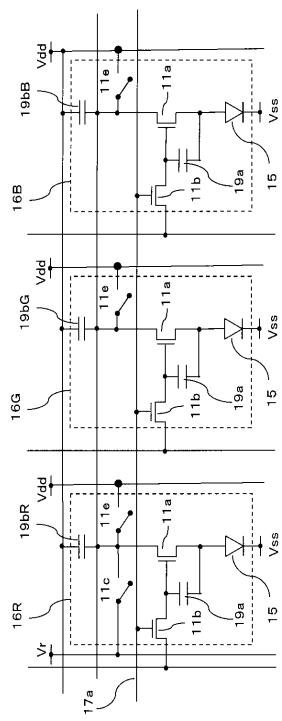

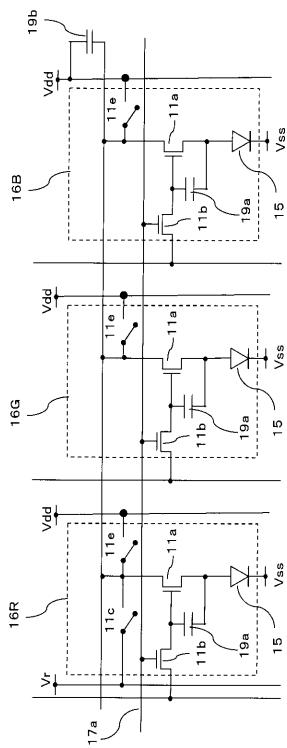

【図1】EL表示装置の画素の構成図である。

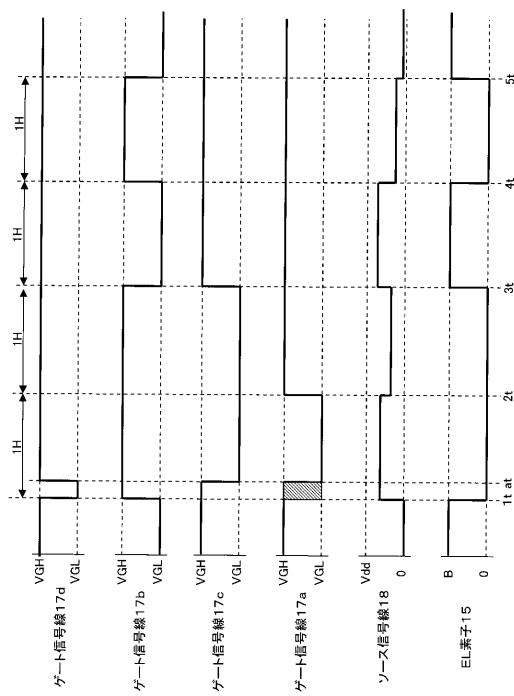

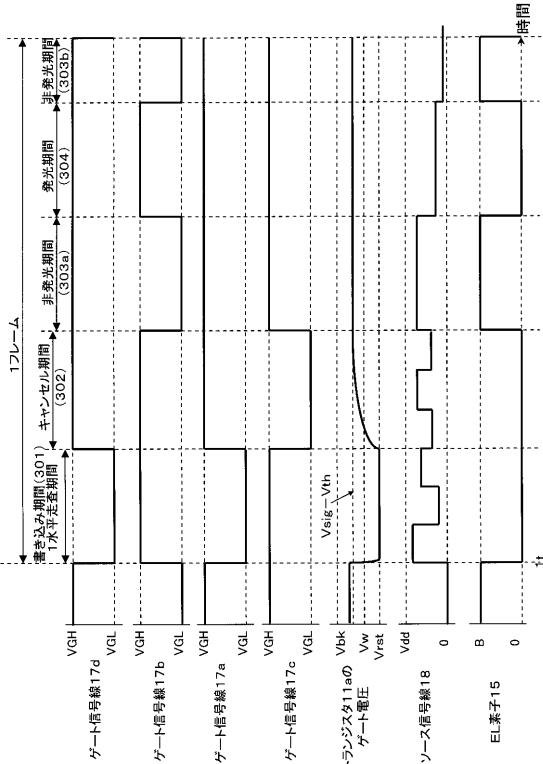

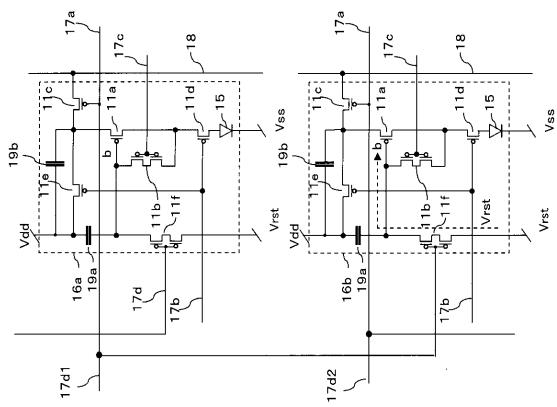

【図2】EL表示装置の駆動方法の説明図である。

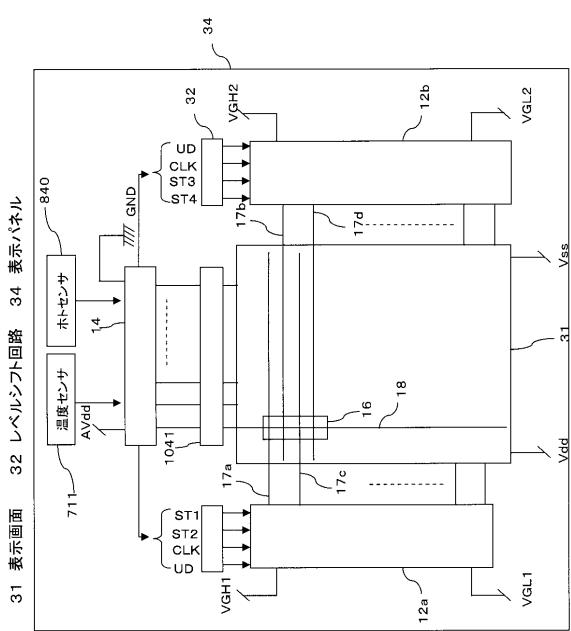

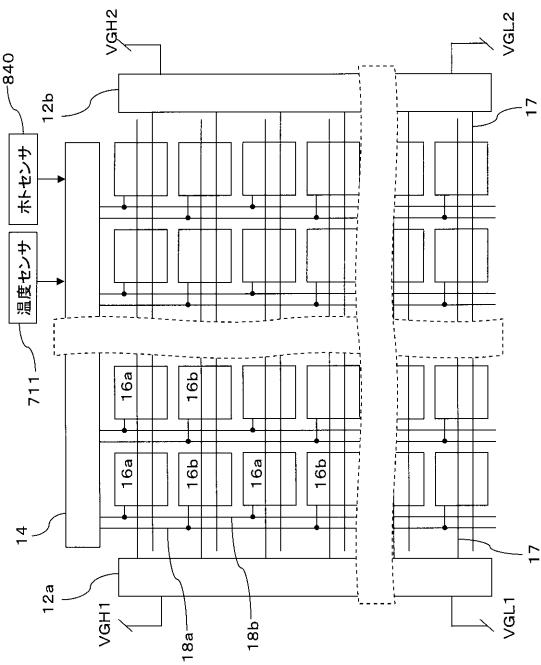

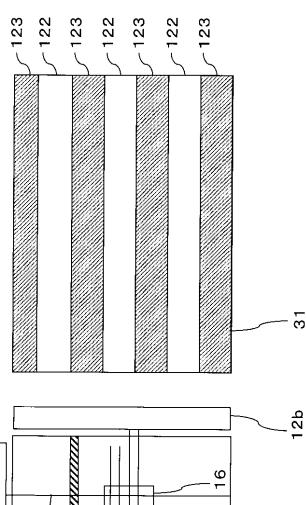

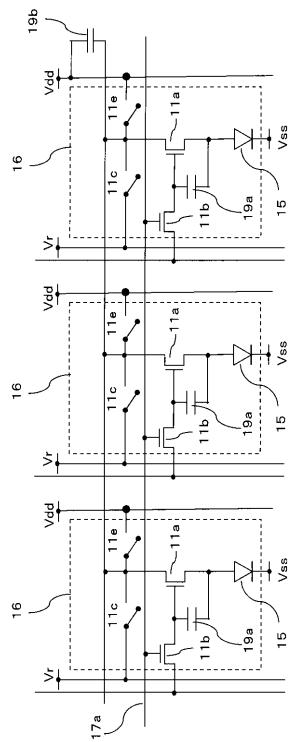

【図3】EL表示装置の説明図である。

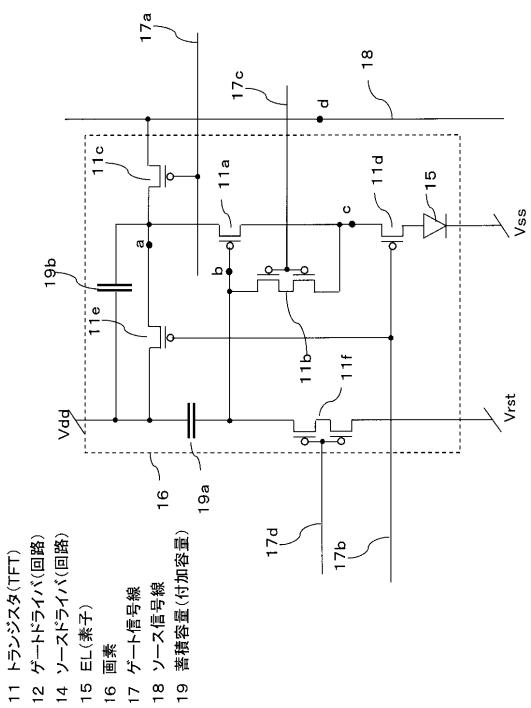

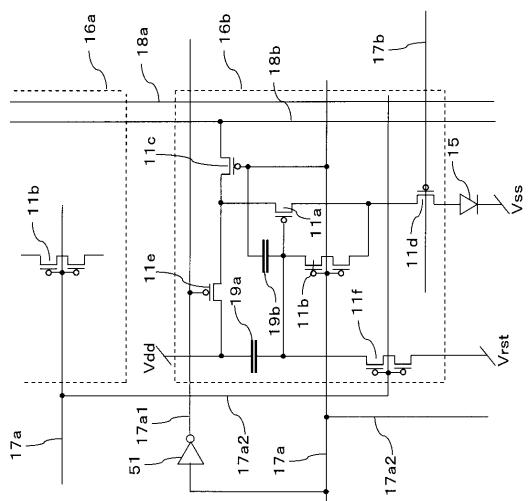

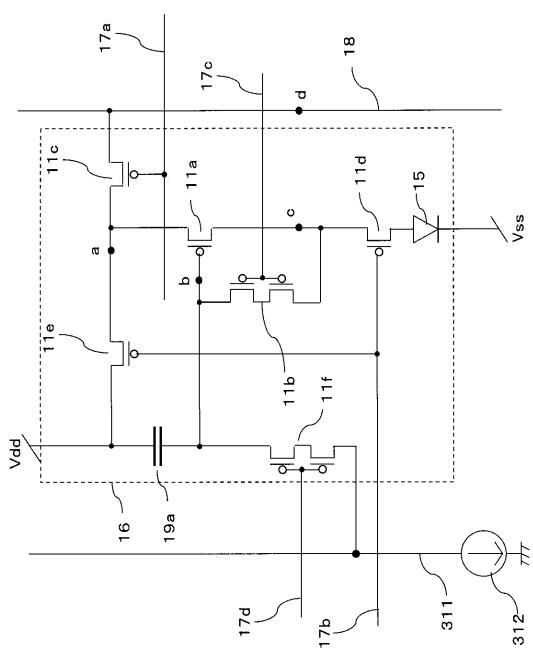

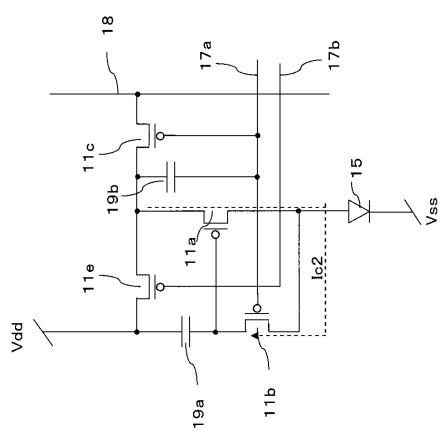

【図4】EL表示装置の画素の構成図である。

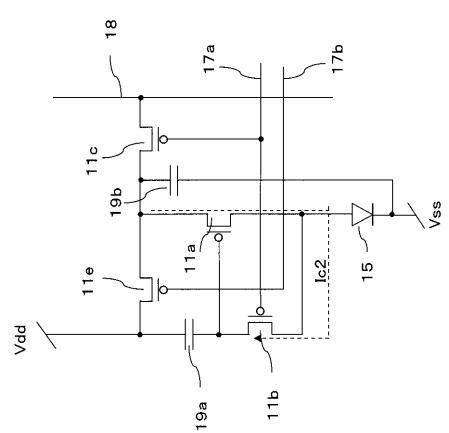

【図5】EL表示装置の画素の構成図である。

【図6】EL表示装置の説明図である。

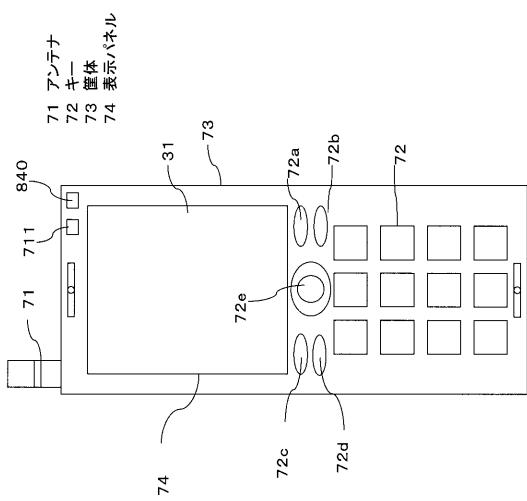

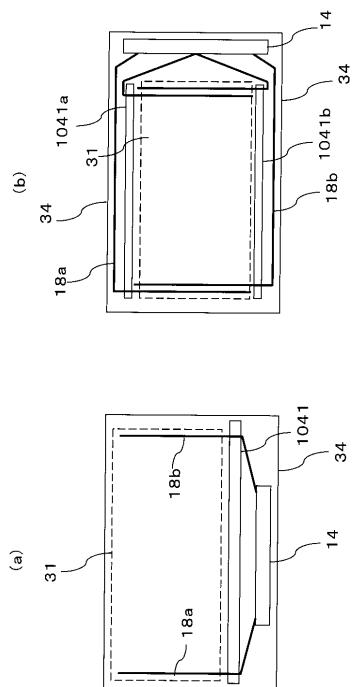

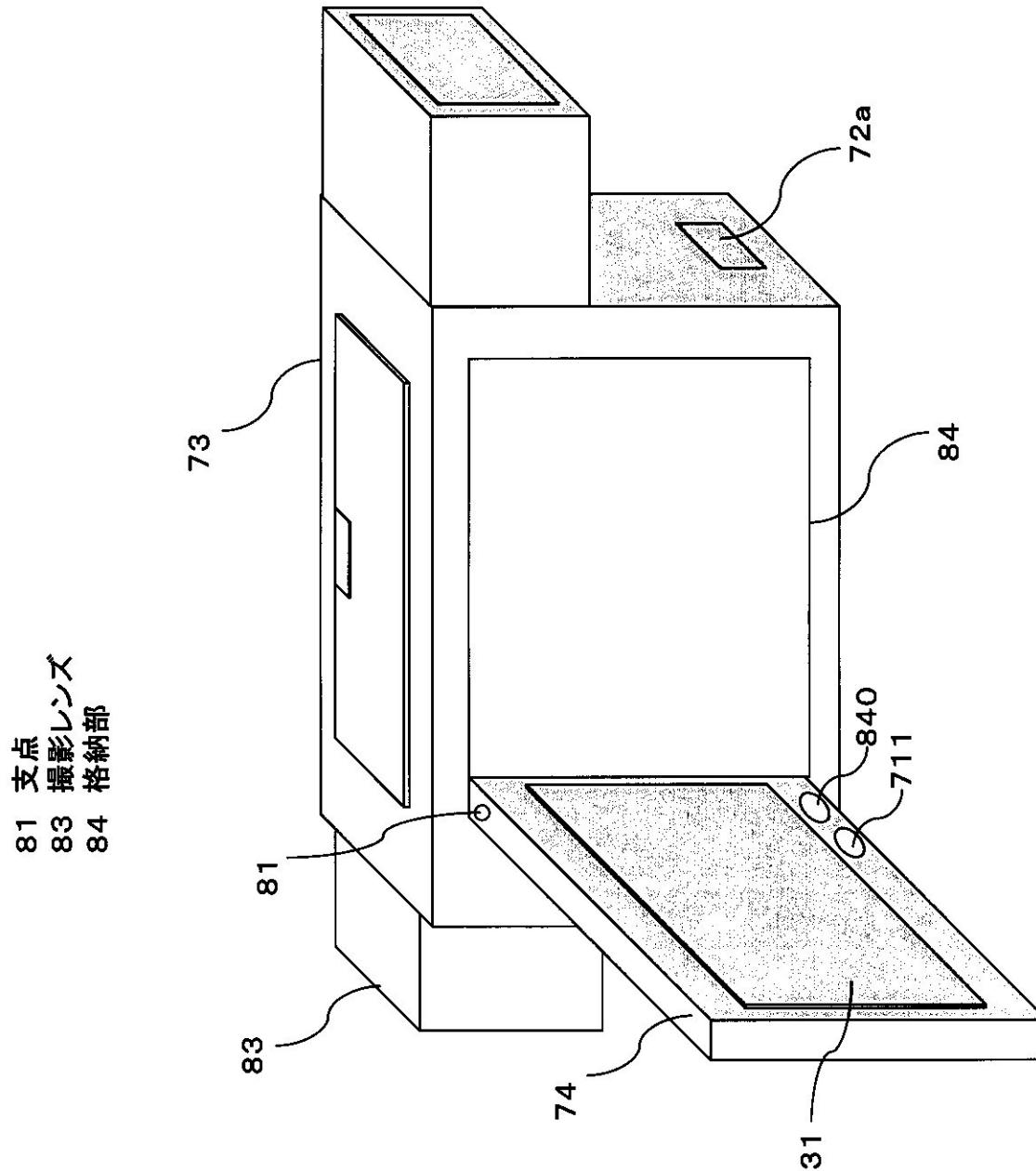

【図7】EL表示装置を用いた機器の説明図である。

20

【図8】EL表示装置を用いた機器の説明図である。

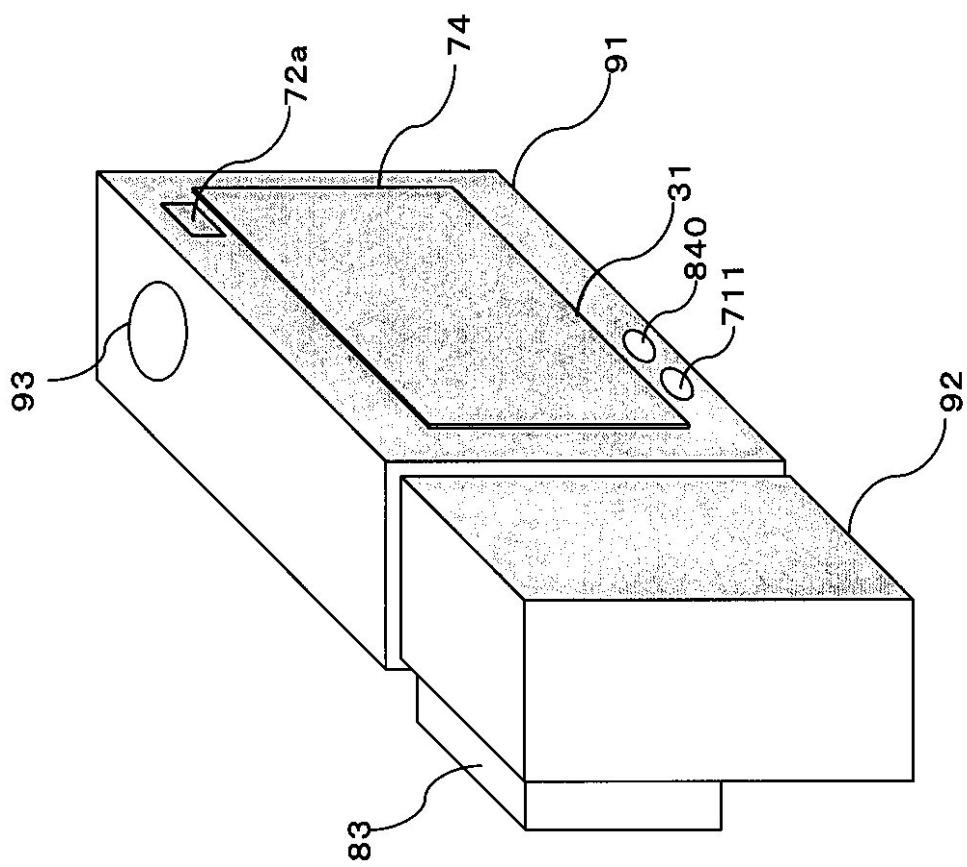

【図9】EL表示装置を用いた機器の説明図である。

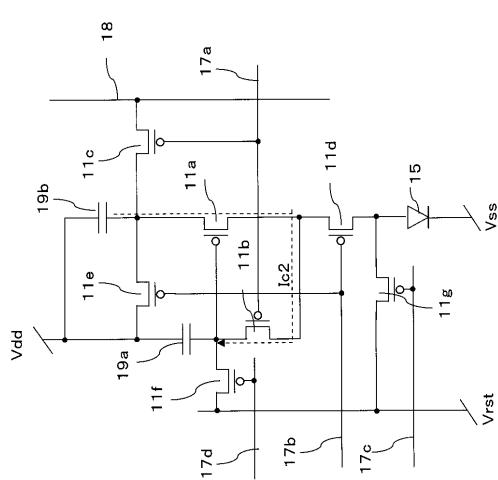

【図10】EL表示装置の画素の構成図である。

【図11】EL表示装置の画素の構成図である。

【図12】EL表示装置の駆動方法の説明図である。

【図13】EL表示装置の駆動方法の説明図である。

【図14】ソース信号線から画素に映像信号を取り込む構成図である。

【図15】図14のゲートドライバ回路12aの動作を示した説明図である。

【図16】本実施例のEL表示装置の説明図である。

30

【図17】図16のゲートドライバ回路12の動作を示した図である。

【図18】図16のゲートドライバ回路12の動作を示した図である。

【図19】本実施例のEL表示装置の駆動方法の説明図である。

【図20】本実施例のEL表示装置の駆動方法の説明図である。

【図21】本実施例のEL表示装置の駆動方法の説明図である。

【図22】本実施例のEL表示装置の駆動方法の説明図である。

【図23】本実施例のEL表示装置の説明図である。

【図24】本実施例のEL表示装置の説明図である。

【図25】本実施例のEL表示装置の説明図である。

【図26】本実施例のEL表示装置の駆動方法の説明図である。

【図27】本実施例のEL表示装置の駆動方法の説明図である。

【図28】本実施例のEL表示装置の駆動方法の説明図である。

40

【図29】本実施例のEL表示装置の説明図である。

【図30】本実施例のEL表示装置の駆動方法の説明図である。

【図31】本実施例のEL表示装置の駆動方法の説明図である。

【図32】本実施例のEL表示装置の駆動方法の説明図である。

【図33】本実施例のEL表示装置の駆動方法の説明図である。

【図34】本実施例のEL表示装置の駆動方法の説明図である。

【図35】本実施例のEL表示装置の駆動方法の説明図である。

【図36】本実施例のEL表示装置の駆動方法の説明図である。

【図37】本実施例のEL表示装置の駆動方法の説明図である。

【図38】本実施例のEL表示装置の駆動方法の説明図である。

50

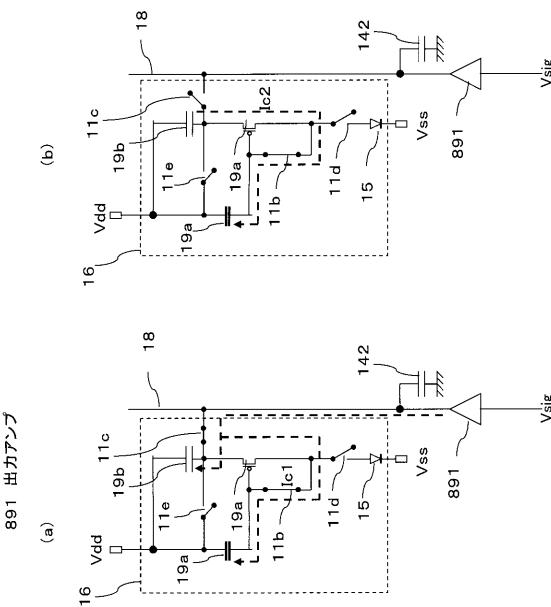

【図 8 9】本実施例の E L 表示装置の駆動方法の説明図である。

【図 9 0】本実施例の E L 表示装置の説明図である。

【図 9 1】本実施例の E L 表示装置の説明図である。

【図 9 2】本実施例の E L 表示装置の説明図である。

【図 9 3】本実施例の E L 表示装置の説明図である。

【図 9 4】本実施例の E L 表示装置の説明図である。

【図 9 5】本実施例の E L 表示装置の説明図である。

【図 9 6】本実施例の E L 表示装置の説明図である。

【図 9 7】本実施例の E L 表示装置の説明図である。

【図 9 8】本実施例の E L 表示装置の駆動方法の説明図である。

【図 9 9】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 0 0】本実施例の E L 表示装置の説明図である。

【図 1 0 1】本実施例の E L 表示装置の駆動方法の説明図である。

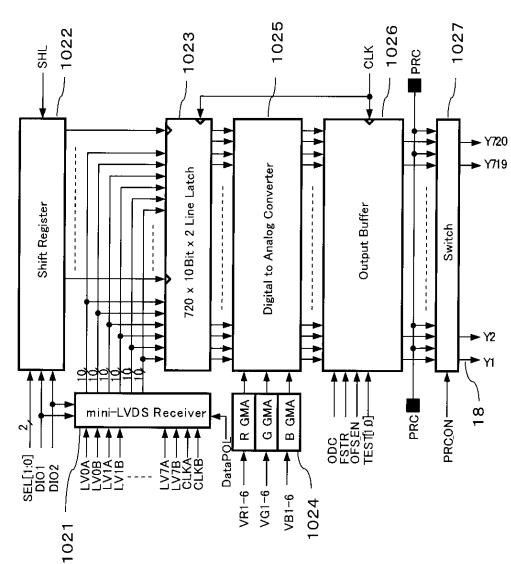

【図 1 0 2】本実施例の E L 表示装置のソースドライバ回路の説明図である。

【図 1 0 3】本実施例の E L 表示装置の説明図である。

【図 1 0 4】本実施例の E L 表示装置の説明図である。

【図 1 0 5】本実施例の E L 表示装置のソースドライバ回路の説明図である。

【図 1 0 6】本実施例の E L 表示装置のソースドライバ回路の説明図である。

【図 1 0 7】本実施例の E L 表示装置のソースドライバ回路の説明図である。

【図 1 0 8】本実施例の E L 表示装置のソースドライバ回路の説明図である。

【図 1 0 9】本実施例の E L 表示装置のソースドライバ回路の説明図である。

【図 1 1 0】本実施例の E L 表示装置のソースドライバ回路の説明図である。

【図 1 1 1】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 1 2】本実施例の E L 表示装置の説明図である。

【図 1 1 3】本実施例の E L 表示装置の説明図である。

【図 1 1 4】本実施例の E L 表示装置の説明図である。

【図 1 1 5】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 1 6】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 1 7】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 1 8】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 1 9】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 2 0】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 2 1】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 2 2】本実施例の E L 表示装置の説明図である。

【図 1 2 3】本実施例の E L 表示装置の説明図である。

【図 1 2 4】本実施例の E L 表示装置の説明図である。

【図 1 2 5】本実施例の E L 表示装置の説明図である。

【図 1 2 6】本実施例の E L 表示装置の説明図である。

【図 1 2 7】本実施例の E L 表示装置の説明図である。

【図 1 2 8】本実施例の E L 表示装置の説明図である。

【図 1 2 9】本実施例の E L 表示装置の駆動方法の説明図である。

【図 1 3 0】本実施例の E L 表示装置の駆動方法の説明図である。

【発明を実施するための形態】

【0 0 1 2】

本発明の実施例の E L 表示装置は、各画素にオフセットキャンセル動作に使用する所定電圧を保持するコンデンサ（オフセットキャンセルコンデンサ）を具備する。オフセットキャンセルコンデンサは、画素が選択された時に、画素に印加された映像信号などの所定電圧を保持する。駆動トランジスタ画素が非選択となった後も、オフセットキャンセルコンデンサに保持された所定電圧を用いて、駆動トランジスタにオフセットキャンセル動作を継続される。駆動トランジスタ

10

20

30

40

50

従来の画素構成では、画素が選択された時にオフセットキャンセル動作を実施していた。したがって、オフセットキャンセル動作は画素行の選択期間以内に限られるため、十分なオフセットキャンセル動作時間を確保できず、十分にオフセットキャンセルを実現することができなかった。

【0013】

本実施例によれば、オフセットキャンセル動作を継続させるオフセットキャンセルコンデンサを各画素に有しているため、画素が非選択状態であっても、オフセットキャンセル動作を継続できる。したがって、駆動トランジスタ十分にオフセットキャンセル期間を確保できるので、駆動トランジスタ駆動トランジスタ11aの特性バラツキを補償し、特性表示ムラのない画像表示を実現できる。

10

【実施例1】

【0014】

本発明の実施例1について説明する。

【0015】

なお、各図面のにおいて説明に必要にない箇所、部分は省略している。したがって、各図面で図示していないとも、他の図面に図示した事項が適用あるいは組み合わせができる。また、各図面には拡大あるいは縮小した箇所、部分がある。また、実施例1～実施例7は相互に組み合わせできることは言うまでもない。

【0016】

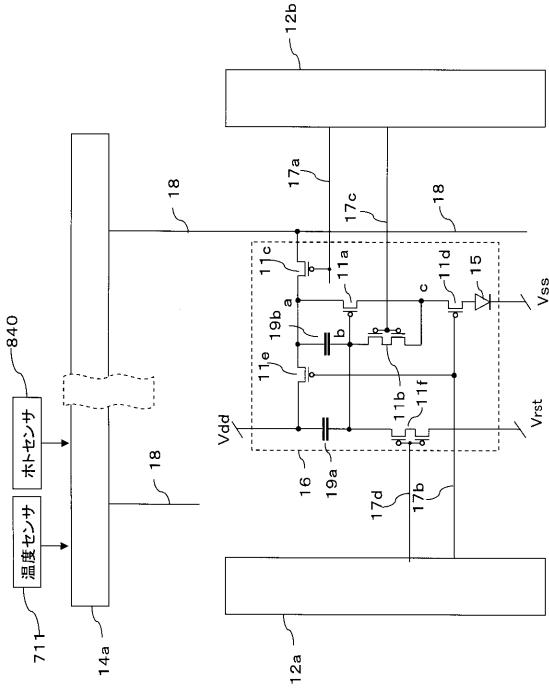

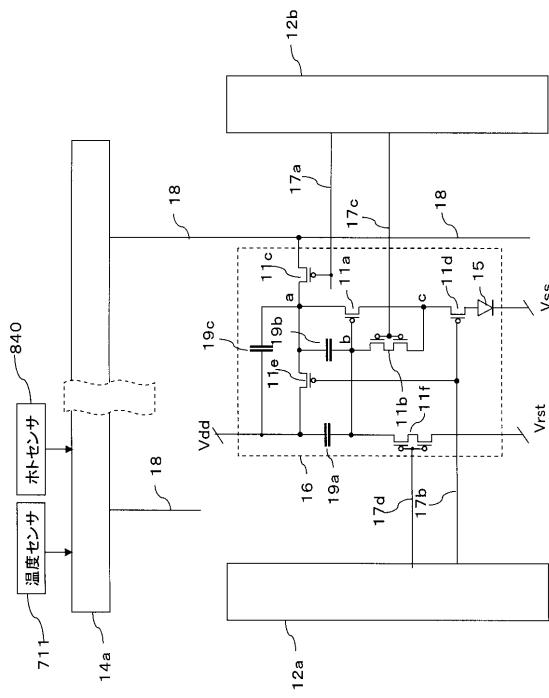

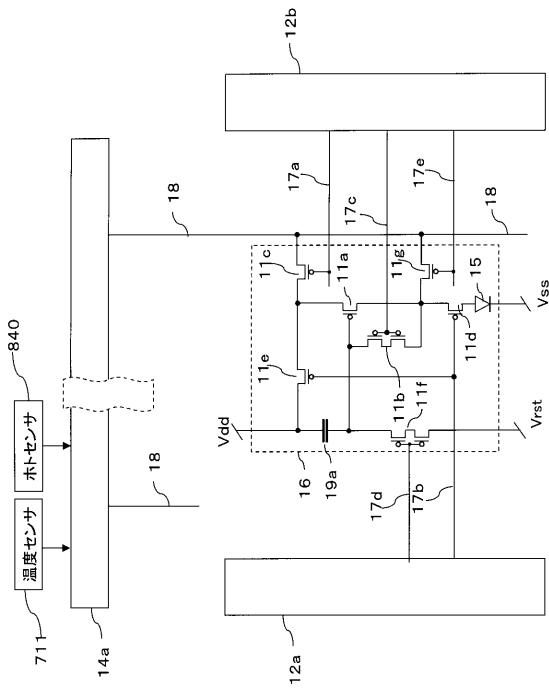

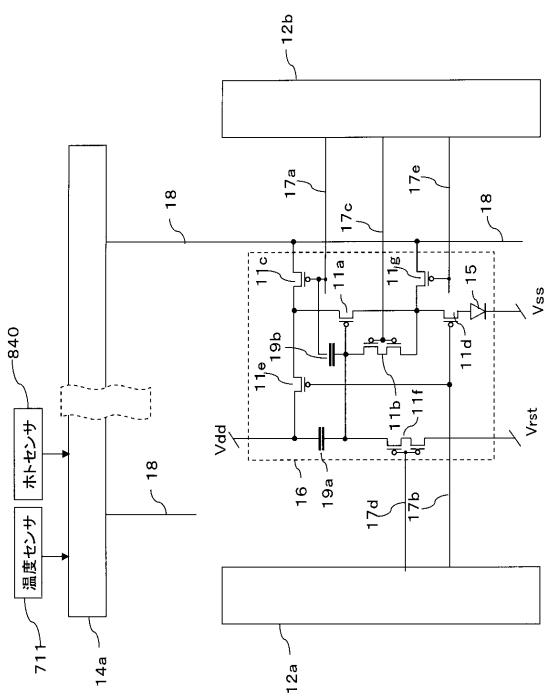

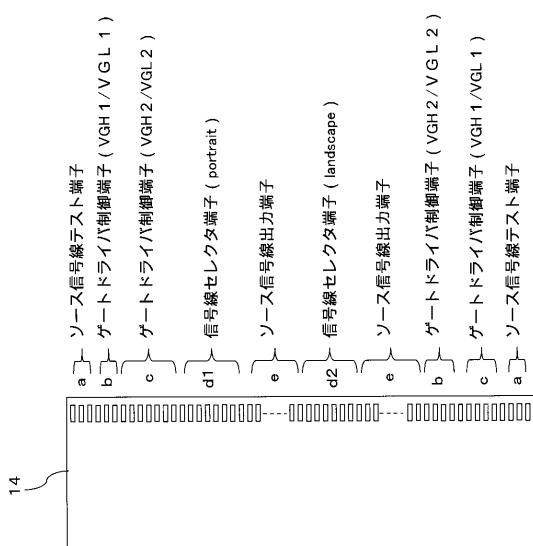

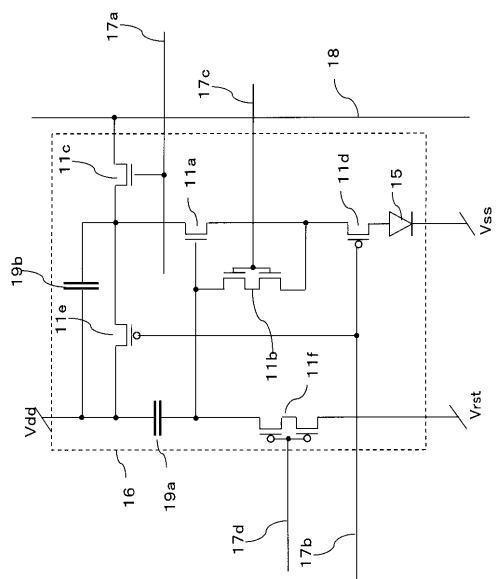

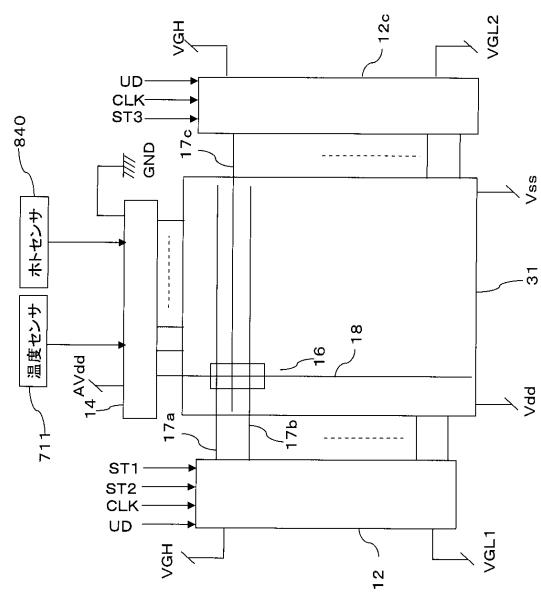

図1は、実施例1のEL表示装置の画素構成である。また、図3は、画素16がマトリックス状に配置された表示領域31に、ゲートドライバ回路12及びソースドライバIC14が接続された構成図である。

20

【0017】

図3に示すように、ゲートドライバ回路12には、クロック信号(CLK)、スタート信号(ST1、ST2)などは、アップダウン信号(UP)が印加される。クロック信号(CLK)は、水平同期信号(HD)に同期している。また、必要に応じて、EL表示装置内に内蔵する発振モジュールでクロック信号(CLK)を発生させる。スタート信号(ST2)を制御することにより、Duty駆動を実現できる。

【0018】

クロック信号(CLK)、スタート信号(ST1、ST2)、アップダウン信号(UP)などゲートドライバ回路12に印加する信号は、ソースドライバIC14で発生し、アレイ基板に形成したレベルシフタ回路でレベルシフトしてゲートドライバ回路12に印加される。ゲートドライバ回路12で使用するクロック信号などは、ソースドライバIC14から供給する。

30

【0019】

レベルシフトする電圧(例えば、VGH、VGL)は、ソースドライバIC14で発生し、各信号(CLK、UD, STなど)ソースドライバIC14内に内蔵されたレベルシフト回路でレベルシフトしてゲートドライバ回路12に印加してもよい。

【0020】

レベルシフト回路は、ソースドライバIC14から出力されるロジックレベル電圧(例えば、3V)をゲートドライバ回路12で使用する電圧(例えば、VGH、VGL電圧)に変換するものである。レベルシフト回路は、ゲートドライバ回路12内又はゲートドライバ回路12の入力段あるいはソースドライバIC14の出力段に形成又は配置される。

40

【0021】

クロック信号(CLK)は、選択する画素行を順次移動させるための信号である。スタートパルス信号(ST)は、選択する画素行を指定するための信号である。スタートパルス信号(ST)はクロック信号(CLK)により、ゲートドライバ回路12のシフトレジスタ回路内を移動する。アップダウン信号(UD)は、画面の上下反転切換信号である。シフトレジスタ回路内のスタートパルス位置にしたがって、ゲート信号線17が選択される(ゲート信号線17にオン電圧(VGL)が印加される)。

50

## 【0022】

本発明の実施例1は、画素16のトランジスタ11をPチャンネルトランジスタで形成し、ゲートドライバ回路12をPチャンネルトランジスタで形成する。画素16のトランジスタ11とゲートドライバ回路12の両方をPチャンネルトランジスタで形成することにより、EL表示パネルの製造コストは低コストにできる。

## 【0023】

ソースドライバIC14としては、映像信号を電圧信号として出力するもの、映像信号を電流信号として出力するものが例示される。本明細書では、説明を容易にするため、ソースドライバIC14は、電圧信号を出力するものをして説明をする。また、図2、図111は本実施例のEL表示装置の駆動方法の説明図である。

10

## 【0024】

本実施例の表示パネルは、R(赤)、G(緑)、B(青)色の画素がマトリックス状に配置されている。また、RGBに加えて、W(白)色の画素を配置してもよい。白色発光の画素を形成することにより、表示画像の高い輝度が実現できる。したがって、輝き感のある画像表示実現できる。特にW(白)画素を有するパネル構成は、図84、図99などのduty駆動方式、最大使用階調表示駆動方式と組み合わせることが好ましい。

## 【0025】

また、白色の画素を表示領域の全面に形成し、カラーフィルターで、RGB画素をマトリックス状に形成してもよい。

## 【0026】

R、G、Bの画素開口率(あるいは画素電極面積)は、異ならせててもよい。開口率を異ならせることにより、各RGBのEL素子15に流れる電流密度を異ならせることができる。電流密度を異ならせることにより、RGBのEL素子15の劣化速度を同一にすることができる。RGBの劣化速度を同一にすれば、長期間、EL表示装置を使用しても、EL表示装置の表示画面のホワイトバランスずれが発生しない。

20

## 【0027】

また、隣接した画素行で、3原色の配置が異なるように配置することが好ましい。例えば、偶数行目が、左からR、G、Bの配置であれば、奇数行目はB、G、Rの配置とする。このように配置することにより、少ない画素数でも、画像の斜め方向の解像度が改善される。また、画素をデルタ配置にしてもよい。外光又は、EL表示パネルなどから放射される光(EL素子15から出射される光)が、ソースドライバIC(ソースドライバ回路)14に照射されると、ホトコンダクタ現象(ホトコン)により誤動作を引き起こす。この課題に対応するため、ソースドライバICチップの下又は、ソースドライバ回路14の下層に遮光膜を形成する。つまり、ソースドライバICとアレイ基板間に、遮光物を形成または配置する。遮光膜は、パネル基板の表面に金属薄膜、有機材料あるいは無機材料などからなる光吸収膜として形成する。好ましくは、遮光膜は、EL素子15に電流を供給するアノード配線、カソード配線を使用する(ソースドライバICチップ下に形成する)。遮光膜をアノード配線、カソード配線で形成すれば電流(電圧)供給配線と遮光膜とを兼用することができる。したがって、遮光膜形成が容易であり、低コスト化できる。この構成は、ソースドライバ回路14がICチップの場合に限定されるものではない。ソースドライバ回路14が、低温ポリシリコン、高温ポリシリコンもしくは固相成長により形成された半導体膜(CGS)、アモルファスシリコン技術を用いた場合にも適用される。つまり、このソースドライバ回路14の裏面あるいは下層に遮光膜を形成する。

30

## 【0028】

以上のように、本実施例のEL表示装置において、ソースドライバ回路14は、半導体IC(IC chip)であり、前記ソースドライバ回路14は、前記表示画面が形成された基板に実装されており、前記ソースドライバ回路の下で、かつ前記基板上に、遮光膜が形成されていることを1つの特徴とするものである。ソースドライバIC14には、ゲートドライバ回路12で使用する電圧VGH、VGLを発生させるチャージポンプ回路を

40

50

構成しておくことが好ましい。電圧  $V_{GH}$  は、トランジスタ 11 をオフさせる電圧であり、電圧  $V_{GL}$  はトランジスタ 11 をオンさせる電圧である。但し、このオン／オフ電圧は、トランジスタ 11 が P チャンネルトランジスタの場合であり、トランジスタ 11 が N チャンネルの場合は、電圧  $V_{GH}$  は、トランジスタ 11 をオンさせる電圧であり、電圧  $V_{GL}$  はトランジスタ 11 をオフさせる電圧となる。また、 $V_{GH}$ 、 $V_{GL}$  はゲートドライバ回路 12 の電源電圧である。

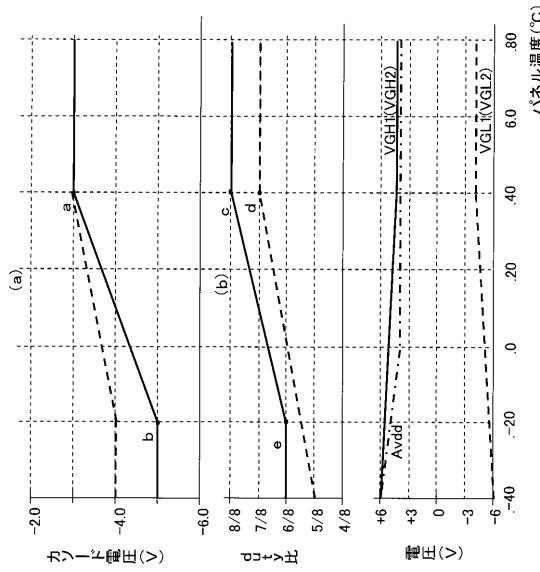

#### 【0029】

図 3において、ゲートドライバ回路 12a は、 $V_{GH1}$ 、 $V_{GL1}$  電圧を印加し、ゲートドライバ回路 12a は、 $V_{GH2}$ 、 $V_{GL2}$  電圧を印加する。スイッチトランジスタ 11 が、P チャンネルトランジスタの場合は、 $V_{GL1}$  と  $V_{GL2}$  を異ならせる。 $V_{GH1}$  と  $V_{GH2}$  とは、共通の電圧にする ( $V_{GH1} = V_{GH2}$ )。スイッチトランジスタ 11 が、N チャンネルトランジスタの場合は、 $V_{GH1}$  と  $V_{GH2}$  を異ならせる。 $V_{GL1}$  と  $V_{GL2}$  とは、共通の電圧にする ( $V_{GL1} = V_{GL2}$ )。

10

#### 【0030】

図 1 の画素構成であれば、スイッチトランジスタ 11d のオン電圧 ( $V_{GL}$ ) は、スイッチトランジスタ 11c のオン電圧 ( $V_{GL}$ ) よりも高くする。もしくは、スイッチトランジスタ 11d のオフ電圧 ( $V_{GH}$ ) - オン電圧 ( $V_{GL}$ ) の電位差は、スイッチトランジスタ 11c のオフ電圧 ( $V_{GH}$ ) - オン電圧 ( $V_{GL}$ ) の電位差よりも小さくする。スイッチトランジスタ 11d のオン抵抗を比較的高くし、EL 素子 15 の端子間 (アノード - カソード) 電圧の変化を駆動トランジスタ 11a にチャンネル間電圧に影響を与えないようにするためである。また、スイッチトランジスタ 11b のオフリーク電流の低減にも効果がある。スイッチトランジスタ 11c は、十分にオンさせてオン抵抗を低下させることが望ましい。

20

#### 【0031】

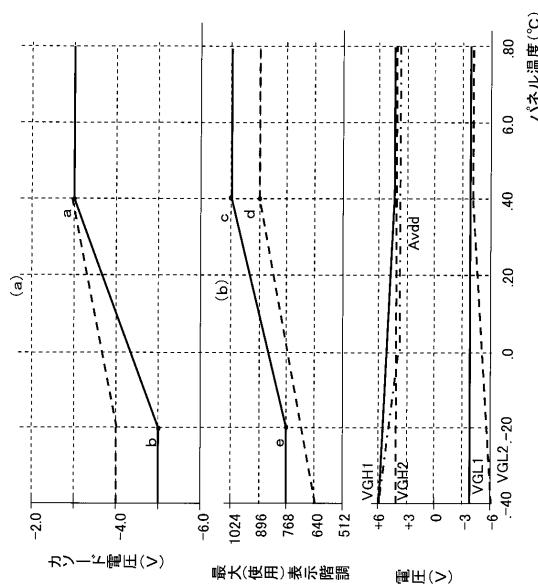

例えば、オフ電圧 ( $V_{GH1} = V_{GH2}$ ) = 6.0 (V) とすれば、スイッチトランジスタ 11c のオン電圧 ( $V_{GL1}$ ) = -4.0 (V)、スイッチトランジスタ 11d のオン電圧 ( $V_{GL2}$ ) = -2.0 (V) に設定する。オフ電圧スイッチトランジスタ 11c のオフ電圧 ( $V_{GH1}$ ) = 6.0 (V)、スイッチトランジスタ 11d のオフ電圧 ( $V_{GH2}$ ) = 5.5 (V) とすれば、スイッチトランジスタ 11c のオフ電圧 ( $V_{GH1}$ ) - オン電圧 ( $V_{GL1}$ ) = -10.0 (V)、スイッチトランジスタ 11d のオフ電圧 ( $V_{GH2}$ ) - オン電圧 ( $V_{GL2}$ ) = -8.0 (V) に設定する。また、スイッチトランジスタ 11c のオフ電圧 ( $V_{GH1}$ ) - オン電圧 ( $V_{GL1}$ ) は、スイッチトランジスタ 11d のオフ電圧 ( $V_{GH2}$ ) - オン電圧 ( $V_{GL2}$ ) よりも 1V 以上 4V 以下の電位差あるように設定する。以上の事項は本発明の他の実施例においても同様である。

30

#### 【0032】

本実施例は、トランジスタ 11 を基本的には P チャンネルとして説明するがこれに限定するものではない。例えば、駆動トランジスタ 11a を P チャンネルトランジスタとし、他のスイッチトランジスタは N チャンネルトランジスタとしてもよい。スイッチトランジスタ 11 のオフリーク電流が低減し、良好なコントラストを実現できる。

40

#### 【0033】

例えば、図 112 に図示するように、駆動トランジスタ 11a を N チャンネルトランジスタで形成してもよい。また、スイッチトランジスタ 11c、スイッチトランジスタ 11b を N チャンネルトランジスタで形成してもよい。また、図 1 などにおいて、スイッチトランジスタ 11b、11f、11c はトランジスタの複数のチャンネルが直列に接続された構成 (マルチゲート構造: ディアルゲート、トリプルゲートなど) にすることが好ましい。特に、映像信号電圧  $V_{sig}$  を画素 16 に印加するスイッチトランジスタ 11c、リセット電圧  $V_{rst}$  を印加するスイッチトランジスタ 11f、駆動トランジスタ 11a のゲート端子と他の端子間を短絡状態にするスイッチトランジスタ 11b はマルチゲート構成にすることが好ましい。また、スイッチトランジスタ 11b、11f、11c は、N チャンネルトランジスタで構成することによりオフリーク電流が低減し、好ましい。

50

## 【0034】

ここで *duty* 駆動（黒挿入駆動）について説明を行っておく。

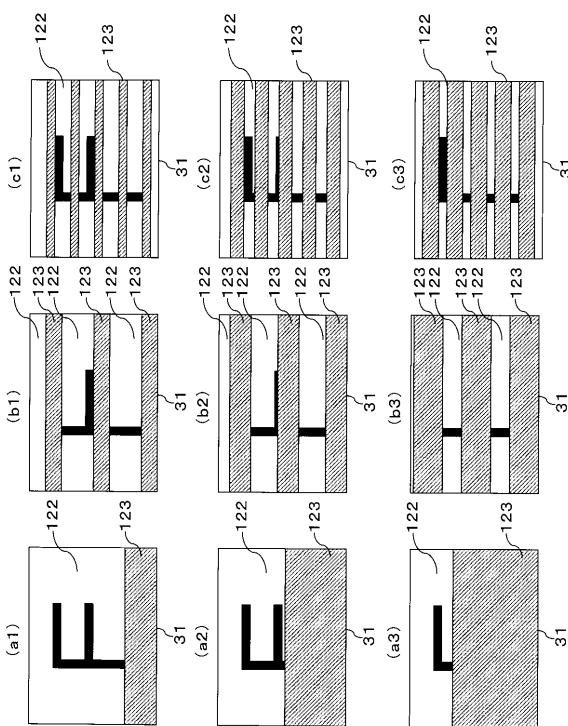

## 【0035】

図1などの本発明の実施例において、トランジスタ11e、トランジスタ11dの少なくとも一方をオン／オフ制御することにより、図12(b)に図示するような *duty* 駆動を実現できる。図12において、121はプログラム画素行（映像信号を書き込んでいる画素行）であり、123は非表示領域（トランジスタ11eとトランジスタ11dのうち、少なくとも一方をオフさせることにより、非表示（EL素子15に電流が流れていない、又は流れても小さい状態）とした画素行又は画素行の群）である。122は表示領域（トランジスタ11eとトランジスタ11dの両方をオンさせ、EL素子15に電流が供給されている画素行又は画素行の群）である。非表示領域123及び表示領域122はフレーム周期又は水平同期信号に同期して、表示画面31の上下方向に走査される。

10

## 【0036】

図13(a)の表示では、1つの表示領域122が画面の上から下方向に移動する。フレームレートが低いと、表示領域122が移動するのが視覚的に認識される。特に、まぶたを閉じた時、あるいは顔を上下に移動させた時などに認識されやすくなる。

## 【0037】

この課題に対しては、図12(b)(c)に図示するように、表示領域122を複数に分割するといい。分割された表示領域122は等しく（等分に）する必要はない。例えば、表示領域を4つの領域に分割し、分割された表示領域122aが面積1で、分割された表示領域122bが面積2で、分割された表示領域122cが面積1で、分割された表示領域122dが面積4でもよい。

20

## 【0038】

数フレーム（フィールド）での表示領域122の面積が平均して目標の大きさになるように制御してもよいことは言うまでもない。例えば、表示画面31に占める表示領域122の面積を1/10にするとした時、1フレーム（フィールド）目は表示領域122の面積を1/10とし、2フレーム（フィールド）目は表示領域122の面積を1/20とし、3フレーム（フィールド）目は表示領域122の面積を1/20とし、4フレーム（フィールド）目は表示領域122の面積を1/5とし、以上の4フレーム（フィールド）で所定の表示面積（表示輝度）の1/10を得る駆動方法が例示される。

30

## 【0039】

また、R、G、Bのそれぞれが、数フレーム（フィールド）でLの期間の平均が等しくなるように駆動してもよい。しかし、前記数フレーム（フィールド）は4フレーム（フィールド）以下にすることが好ましい。表示画像によってはフリッカが発生する場合があるからである。

## 【0040】

なお、本実施例での1フレームあるいは1フィールドとは、画素16の画像書き換え周期又は表示画面31が上から下まで（下から上まで）走査される周期と同義あるいは類似の意味と考えてもよい。

40

## 【0041】

また、R、G、Bで、数フレーム（フィールド）でLの期間の平均を異ならせ、適度なホワイトバランスがとれるように駆動してもよい。この駆動方法は、RGBの発光効率が異なるときに特に有效である。また、RGBで分割数K（表示領域122を複数に分割する数）を異ならせてても良い。特にGでは視覚的にめだつため、Gでは分割数をRBに対して多くすることが有效である。

## 【0042】

なお、以上の実施例では理解を容易にするために表示領域122の面積を分割として説明している。しかし、面積を分割するとは、期間（時間）を分割することである。したがって、図1ではトランジスタ11dのオン期間を分割することになるから、面積を分割することは、期間（時間）を分割することと同義あるいは類似である。

50

## 【0043】

以上のように、表示領域122を複数に分割することにより画面のちらつきは減少する。したがって、フリッカの発生はなく、良好な画像表示を実現できる。なお、分割はもっと細かくしてもよい。しかし、分割するほど動画表示性能は低下する。また、画像表示のフレームレートを低減することができ、低消費電力化を実現できる。例えば、非点灯領域123を一括にした場合は、フレームレート45Hz以下になるとフリッカが発生する。しかし、非点灯領域123を6分割以上とした場合は、20Hz以下までフリッカが発生しない。

## 【0044】

図13(a)は図13のように表示領域122が連続している場合の明るさ調整方式である。図13(a1)の表示画面31の表示輝度が最も明るい。図13(a2)の表示画面31の表示輝度が次に明るく、図13(a3)の表示画面31の表示輝度が最も暗い。図13(a1)から図13(a3)への変化(あるいはその逆)は、先にも記載したようにゲートドライバ回路12のシフトレジスタ回路61などの制御により、容易に実現できる。この際、図1のVdd電圧(アノード電圧など)は変化させる必要がない。また、ソースドライバ回路14が出力するプログラム電流あるいはプログラム電圧の大きさも変化させる必要がない。つまり、電源電圧を変化させず、また、映像信号を変化させずに表示画面31の輝度変化を実施できる。

10

## 【0045】

また、図13(a1)から図13(a3)への変化の際、画面のガンマ特性は全く変化しない。したがって、表示画面31の輝度によらず、表示画像のコントラスト、階調特性が維持される。これは本実施例の効果のある特徴である。

20

## 【0046】

従来の画面の輝度調整では、表示画面31の輝度が低い時は、階調性能が低下する。つまり、高輝度表示の時は64階調表示を実現できても、低輝度表示の時は、半分以下の階調数しか表示できない。これに比較して、本実施例の駆動方法では、画面の表示輝度に依存せず、最高の64階調表示を実現できる。

## 【0047】

図13(b)は、図12で説明したように表示領域122が分散している場合の明るさ調整方式である。図13(b1)の表示画面31の表示輝度が最も明るい。図13(b2)の表示画面31の表示輝度が次に明るく、図13(b3)の表示画面31の表示輝度が最も暗い。図13(b1)から図13(b3)への変化(あるいはその逆)は、先にも記載したようにゲートドライバ回路12のシフトレジスタ回路61などの制御により、容易に実現できる。図13(b)のように表示領域122を分散させれば、低フレームレートでもフリッカが発生しない。

30

## 【0048】

さらに、低フレームレートでも、フリッカが発生しないようにするには、図13(c)のように表示領域122を細かく分散させればよい。しかし、動画の表示性能は低下する。したがって、動画を表示するには、図13(a)の駆動方法が適している。静止画を表示し、低消費電力化を要望する時は、図13(c)の駆動方法が適している。図13(a)から図13(c)の駆動方法の切り替えも、シフトレジスタ61の制御により容易に実現できる。

40

## 【0049】

図13は非表示領域123が等間隔で構成されているが、これに限定するものではない。表示画面31の1/2の面積が連続して表示領域122とし、残りの面積50が図13(c1)のように等間隔に表示領域122と非表示領域123が繰り返すように駆動してもよいことは言うまでもない。

## 【0050】

また、図83に図示した回路構成を用いて、EL表示装置に入力される映像信号を加算あるいは重み付け処理を行うことが好ましい。図83の回路構成を用いることにより、表

50

示画面に流れる電流を求め、又は予測し、前記求めた電流などにより画像画面に黒帯状の非点灯領域を発生させ、この黒帯状の非点灯領域の大きさを変化させる。又は、黒帯状の非点灯領域の幅は一定にし、映像信号の振幅を変化させることにより、表示画面に流れる電流の大きさが一定以上にならないように制御する。また、この制御により、電源回路から表示画面に流れる電流を一定以下となるようにすることができ、E L表示装置の発熱を抑制できる。また、図98、図99に図示して説明を行っているように、電源回路（電源I C）が出力する電圧を可変することにより、E L表示装置の発熱を抑制できる。また、本発明の画素構成を用いることにより、さらに良好な画像表示を実現できることは言うまでもない。

## 【0051】

10

点灯率制御駆動（d u t y駆動）、ピーク電流抑制駆動、最大表示階調数制御駆動（図12、図13、図84、図98、図99、図130など）により、高画質化、電流抑制を実現できる。なお、各スイッチトランジスタ1の動作に対応させて各ゲート信号線17のオン／オフ電圧を印加する制御タイミングを制御する。ゲートドライバ回路12の制御は図3のように、ソースドライバI C14からの信号をレベルシフト回路32でレベルシフトさせて印加することにより実現する。

## 【0052】

本明細書において、点灯率に応じてd u t y比などを変化させるとして説明する。しかし、点灯率とは、一定の意味ではない。例えば、低点灯率とは、画面31に流れる電流が小さいことを意味しているが、画像を構成する低階調表示の画素が多いことも意味する。つまり、画面31を構成する映像は、暗い画素（低階調の画素）が多い。

20

## 【0053】

したがって、低点灯率とは、画面を構成する映像データのヒストグラム処理をした時、低階調の映像データが多い状態といい換えることができる。高点灯率とは、画面31に流れる電流が大きいことを意味しているが、画像を構成する高階調表示の画素が多いことも意味する。つまり、画面31を構成する映像は、明るい画素（高階調の画素）が多い。高点灯率とは、画面を構成する映像データのヒストグラム処理をした時、高階調の映像データが多い状態といい換えることができる。つまり、点灯率に対応して制御するとは、画素の階調分布状態あるいはヒストグラム分布に対応して制御することと同義あるいは類似の状態を意味することができる。

30

## 【0054】

以上のことから、点灯率にもとづいて制御するとは、場合に応じて画像の階調分布状態（低点灯率＝低階調表示の画素が多い。高点灯率＝高階調表示の画素が多い。）にもとづいて制御するといい換えることができる。

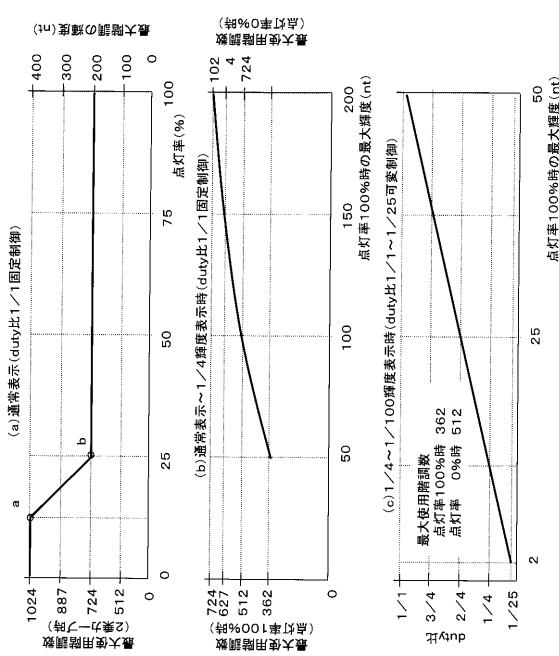

## 【0055】

また、通常表示状態では、d u t y比1/1で駆動し、所定の高点灯率以上で段階的にあるいはスムーズにd u t y比を低下させると、低階調あるいは高階調の画素数が一定の範囲以内の時に、d u t y比1/1で駆動し、高階調の画素数が一定の以上数となった時に、段階的にあるいはスムーズにd u t y比を低下させることと同一あるいは類似の動作もしくは制御である。

40

## 【0056】

d u t y比制御は、点灯率が1/10以上1/1の範囲で実施する。d u t y比1/1で、白ラスター表示であれば、点灯率100%である（最大の白ラスター表示時）。黒ラスターであれば、点灯率0%である（完全黒ラスター表示時）。

## 【0057】

点灯率とは、パネルのアノード又はカソードに流れる最大電流に対する割合である（但し、d u t y比は1/1とする）。例えば、カソードに流れる最大電流を100mAとすれば、d u t y比1/1において、30mAの電流が流れていれば点灯率は30/100=30%（0.3）である。

## 【0058】

50

カソードに流れる最大電流を 100 mA とし、この時、映像データの総和の最大値とすれば、点灯率 50 % とは、カソード（アノード）に流れる電流は、最大電流の 50 % である。また、点灯率 20 % とは、カソードに流れる電流は、最大電流の 20 % である。今後は、主として点灯率の用語を用いる。点灯率は、パネルのアノード又はカソードに流れる最大電流に対する割合であるとしたが、パネルの全 EL 素子に流れる最大電流の割合とも言い換えることができることは言うまでもない。

#### 【0059】

本明細書では、点灯率と断り無く記載する時は、duty 比 1 / 1 としている。もし、duty 比 1 / 3 で、20 mA の電流が流れていれば、点灯率は (20 mA · 3) / 100 mA = 60 % (0.6) である。つまり、点灯率が 100 % でも、duty 比が 1 / 2 であれば、アノード（カソード）端子に流れる電流は最大の電流値の 1 / 2 である。点灯率 50 %、アノード電流が 20 mA、duty 比 1 / 1 であれば、duty 比 1 / 2 になれば、アノード電流は 10 mA となる。アノード電流が 100 mA、点灯率 40 %、duty 比 1 / 1 であれば、アノード電流が 200 mA に変化したとすると、点灯率は 80 % に変化したことを意味する。

10

#### 【0060】

以上のように、点灯率は、1 画面を構成する映像データの大きさに対する割合、EL 表示パネルの消費電流（電力）あるいはその割合を示している。

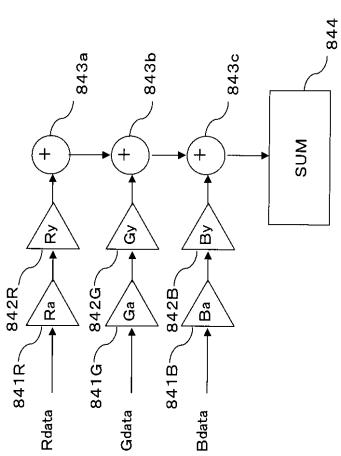

#### 【0061】

一例として点灯率（点灯率）は、映像データの和から求める（図 83）。つまり、映像データから算出する。入力映像信号が Y、U、V の場合は、Y（輝度）信号から求めて良い。しかし、EL 表示パネルの場合は、R、G、B で発光効率が異なるため、Y 信号から求めた値が消費電力にならない。したがって、Y、U、V 信号の場合も、一度 R、G、B 信号に変換し、R、G、B に応じて電流に換算する係数をかけて、消費電流（消費電力）を求めることが好ましい。しかし、簡易的に Y 信号から消費電流を求めるることは回路処理が容易になることも考慮してもよい（図 82、図 83 などを参照のこと）。なお、点灯率は、カソード（アノード）に流れる電流を測定し、測定した電流から求めて良い。

20

#### 【0062】

点灯率は、パネルに流れる電流で換算する。なぜなら、EL 表示パネルでは青（B）の発光効率が悪いため、B が多い、海の表示などが表示されると、消費電力が一気に増加するからである。また、データ和とは単純な映像データの加算値ではなく、映像データを消費電流に換算したものとしている。したがって、点灯率も最大電流に対する各画像の使用電流から求められたものである。また、データ和は加算して求めることだけを意味するものではない。入力される映像データを RGB で重み付けし、加算する方式が例示される。また、画像の特徴を示すデータ抽出して、抽出したデータを処理して求めて良い。また、入力された映像データをヒストグラム処理を行い、ヒストグラム処理の特定範囲（たとえば、平均値を中心として 1 の範囲）のデータを抽出してデータ和を求めて良い。つまり、データ和は処理を行ったデータの集合あるいは処理を行った結果である。

30

#### 【0063】

また、入力される映像データは、EL 表示装置に入力される映像データを意味するが、EL 表示装置の画素に入力される映像データを意味することもある。つまり、ソースドライバ I C 14 から出力された映像データである。

40

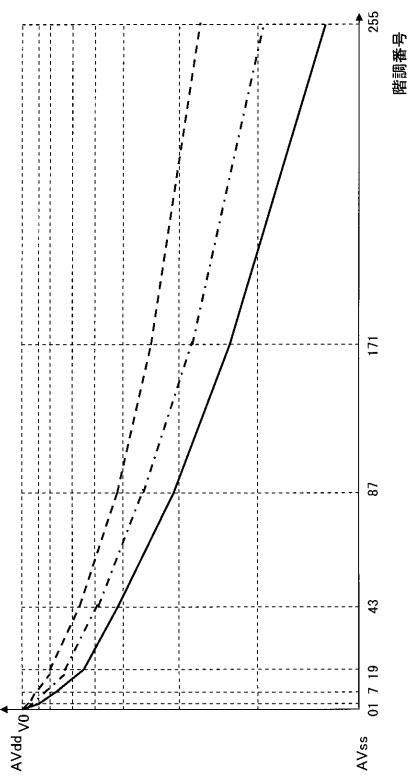

#### 【0064】

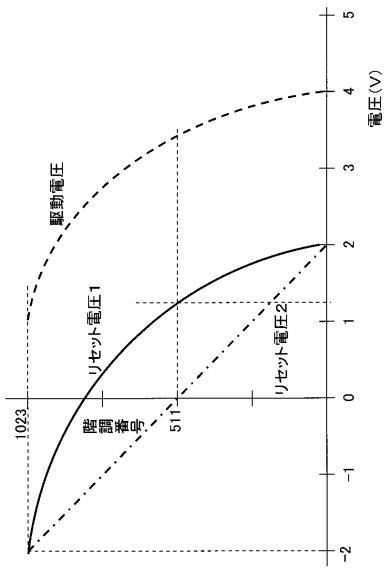

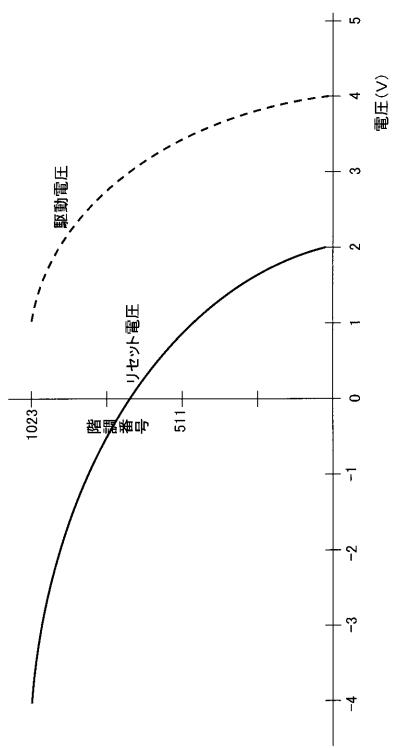

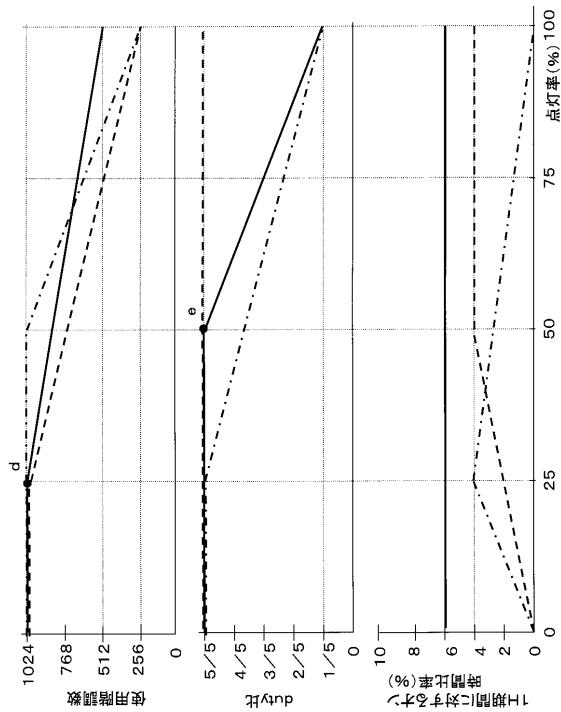

点灯率にあわせて EL 表示装置で表示する階調数を変化させることが好ましい。例えば、点灯率が 50 % 以上では、フル階調の 1 / 2 の範囲（1024 階調の場合は、512 階調）で、画像を表示し、50 % 以下では、フル階調の範囲で画像を表示する。この実施例は、図 98、図 99、図 130 などを用いて説明を行っている。

#### 【0065】

なお、点灯率とは、duty 駆動などピーク電流を抑制しないノーマルの駆動方式において、最大階調での白ラスター表示を 100 % とした割合である。したがって、黒ラスター

50

ー表示では点灯率は 0 % である。

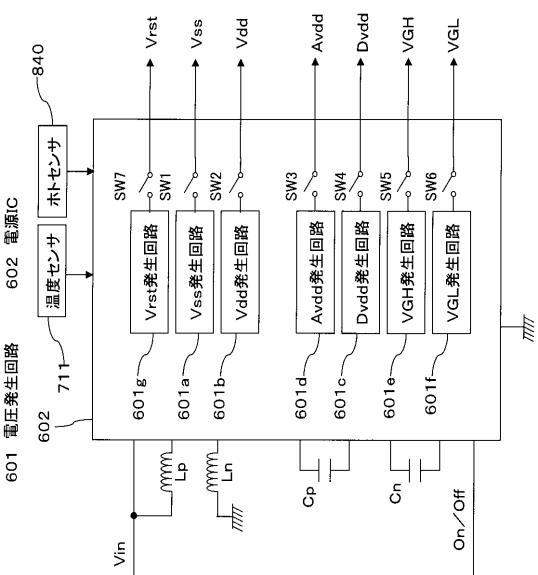

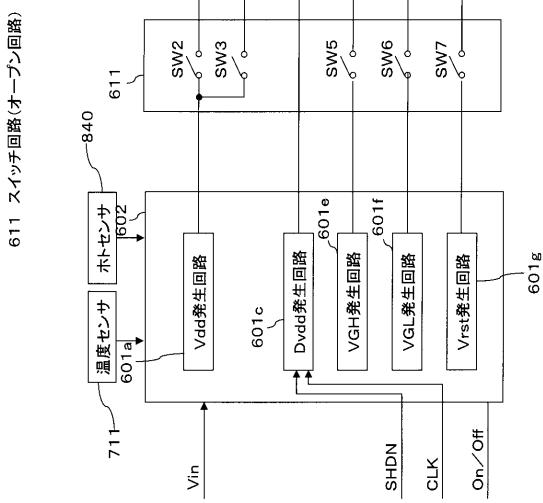

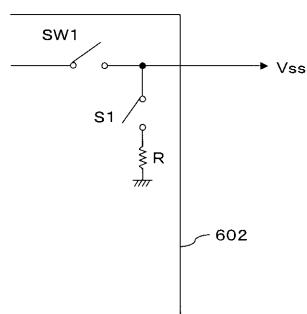

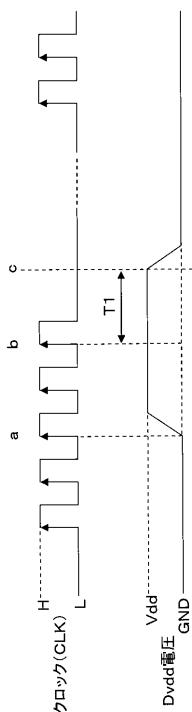

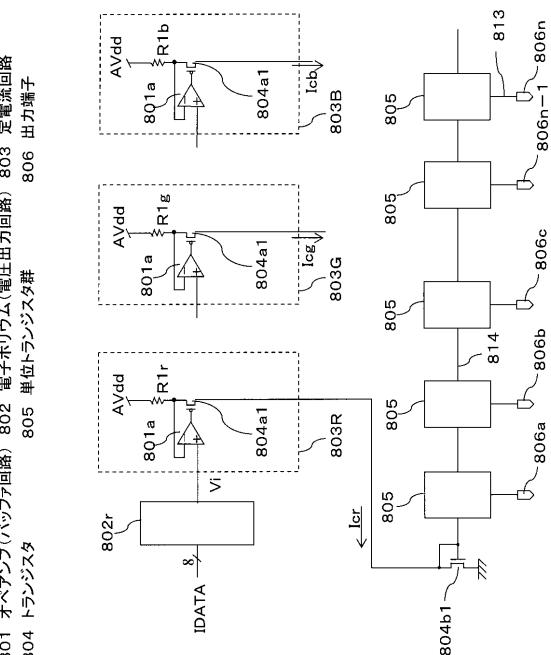

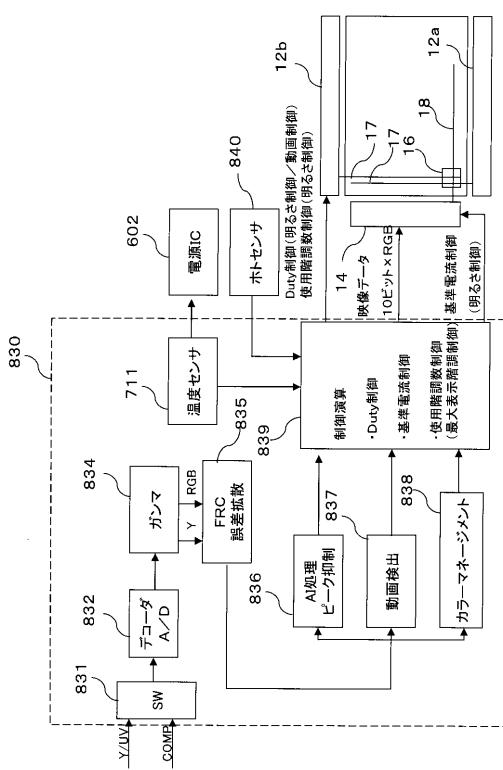

【 0 0 6 6 】

図 8 3 は本実施例の駆動回路のブロック図である。以下、本実施例の駆動回路について説明をする。図 8 3 では、外部から Y / U V 映像信号と、コンポジット ( C O M P ) 映像信号が入力できるように構成されている。どちらに映像信号を入力するかは、スイッチ回路 8 3 1 により選択される。

【 0 0 6 7 】

スイッチ回路 8 3 1 で選択された映像信号は、デコーダ及び A / D 回路によりデコード及び A D 変換され、デジタルの R G B 画像データに変換される。R G B 画像データは各 8 ビットである。また、R G B 画像データはガンマ回路 8 3 4 でガンマ処理される。同時に輝度 ( Y ) 信号が求められる。ガンマ処理により、R G B 画像データは各 1 0 ビットの画像データに変換される。

10

【 0 0 6 8 】

ガンマ処理後、画像データは F R C 処理又は誤差拡散処理が処理回路 8 3 5 で行われる。F R C 処理又は誤差拡散処理により R G B 画像データは 6 ビットに変換される。この画像データは A I 処理回路 8 3 6 で A I 処理 ( 最適化画像表示処理 ) データ、d u t y 駆動のための点灯率演算、最大表示階調数演算などが実施される。また、動画検出回路 8 3 7 で動画検出が行われる。動画検出処理の結果に基づいて、図 1 3 などで説明した、表示領域 1 2 2 、非表示領域 1 2 3 の分割駆動が実施される。また、カラーマネージメント回路 8 3 8 でカラーマネージメント処理が行われる。

20

【 0 0 6 9 】

A I 処理回路 8 3 6 、動画検出回路 8 3 7 、カラーマネージメント回路 8 3 8 の処理結果は演算回路 8 3 9 に送られ、演算処理回路 8 3 9 で d u t y 比制御、基準電流制御データに変換され、変換された結果が、ソースドライバ回路 1 4 及びゲートドライバ回路 1 2 に制御データとして送出される。

20

【 0 0 7 0 】

d u t y 比制御データはゲートドライバ回路 1 2 b に送られ、d u t y 比制御が実施される。使用階調制御データはソースドライバ I C 1 4 に送られ、使用階調数制御が実施される。一方、基準電流制御データはソースドライバ回路 1 4 に送られ、基準電流制御が実施される。ガンマ補正され、フレームレートコントロール ( F R C ) 又は誤差拡散処理された画像データもソースドライバ回路 1 4 に送られる。

30

【 0 0 7 1 】

E L 表示パネルは、黒表示は、E L 素子 1 5 に流れる電流が 0 の状態である。したがって、本実施例の d u t y 比駆動のように画面 3 1 に非表示領域 1 2 3 を発生させても、黒表示の輝度は 0 である。非表示領域 1 2 3 の面積を大きくすると白表示輝度は低下する。しかし、黒表示の輝度が 0 であるから、コントラストは無限大である。したがって、d u t y 比駆動は、E L 表示パネルに最適な駆動方法である。以上のことは、基準電流制御においても同様である。基準電流の大きさを変化させても、黒表示の輝度は 0 である。基準電流を大きくすると白表示輝度は増加する。したがって、基準電流制御においても良好な画像表示を実現できる。

40

【 0 0 7 2 】

d u t y 比制御は、全階調範囲で階調数が保持される。また、全階調範囲でホワイトバランスが維持される。また、d u t y 比制御により画面 3 1 の輝度変化は 1 0 倍近く変化させることができる。

【 0 0 7 3 】

表示画面の輝度は d u t y 比あるいは d u t y 比の逆数と線形の関係になるから、表示画面の明るさ制御も容易である。

【 0 0 7 4 】

基準電流制御は、画面輝度 3 1 を高くするときに、基準電流量を大きくするものである。したがって、画面 3 1 が高いときにしか、E L 素子 1 5 に流れる電流は大きくならない

50

。そのため、E L 素子 1 5 が劣化しにくい。

【0 0 7 5】

本実施例では、基準電流制御と duty 比制御の両方を用いる。画面 3 1 が白ラスター表示に近い時には、基準電流は一定値に固定し、duty 比のみを制御して表示輝度などを変化させる。画面 3 1 に黒ラスター表示に近い時は、duty 比は一定値に固定し、基準電流のみを制御させて表示輝度などを変化させる。

【0 0 7 6】

なお、duty 比の最大は duty 比 1 / 1 とし、最小は duty 比 1 / 1 6 以内にすることが好ましい。さらに好ましくは、duty 比 1 / 1 0 以内にするとよい。フリッカの発生を抑制できるからである。基準電流の変化範囲は、4 倍以内にすることが好ましい。さらに好ましくは 2 . 5 倍以内にする。

10

【0 0 7 7】

なお、データ和は消費電流で算定するか、輝度で算定するかはどちらでもよい。ここでは説明を容易にするため、輝度（画像データ）の加算であるとして説明をする。一般的に輝度（画像データ）の加算の方式が処理は容易であり、コントローラ I C のハード規模も小さくできる。また、duty 比制御によるフリッカの発生もなく、ダイナミックレンジを広く取れることから好ましい。

【0 0 7 8】

以上の事項は、図 7 8 、図 7 9 、図 8 4 、図 9 8 、図 9 9 、図 1 0 1 、図 1 1 1 、図 1 1 2 、図 1 3 0 などの実施例にも適用できることは言うまでもない。また、前記実施例と組み合わせて実施できることも言うまでもない。

20

【0 0 7 9】

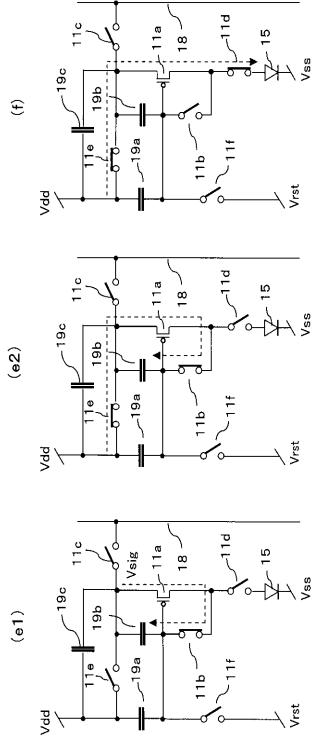

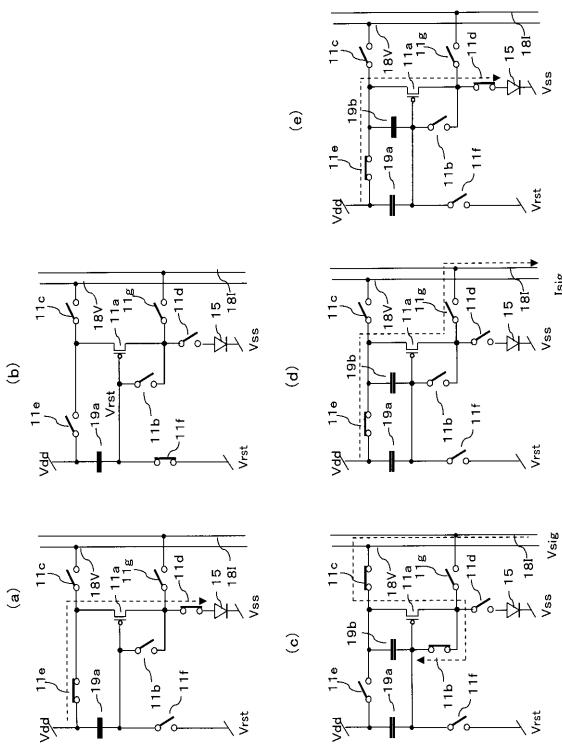

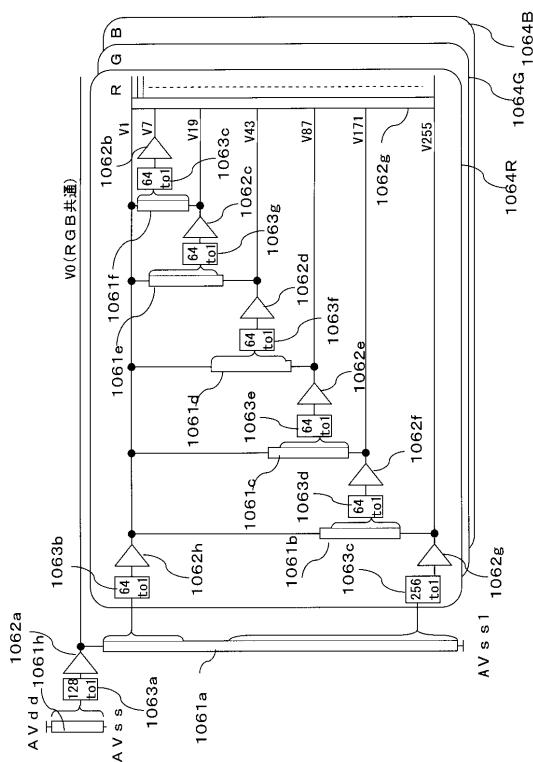

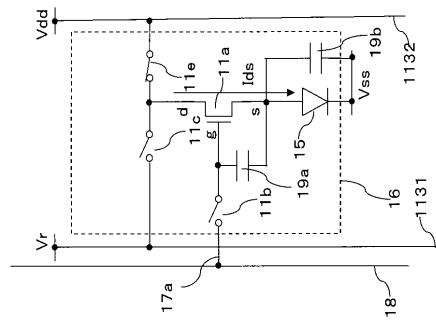

図 1 において、画素 1 6 は、2 つのコンデンサ 1 9 a 、 1 9 b と 5 つのスイッチトランジスタ ( 1 1 b 、 1 1 c 、 1 1 d 、 1 1 e 、 1 1 f ) と 1 つの駆動トランジスタ 1 1 a で構成される。トランジスタ 1 1 b は、トランジスタ 1 1 a をダイオード接続 ( Diode-connected ) させて、しきい値（閾値）電圧を補償するためのしきい値電圧補償用のスイッチトランジスタである。トランジスタ 1 1 f は、保持用コンデンサ 1 9 a を初期化するために、リセット電圧 V r s t を印加するための初期化用のスイッチトランジスタである。トランジスタ 1 1 d は、E L 素子 1 5 の発光を制御するためのトランジスタである。

30

【0 0 8 0】

スイッチトランジスタ 1 1 b 、 1 1 f はオフリードと小さくする必要があるため、ディアルゲート以上の複数ゲート構成（マルチゲート構造）にする。但し、スイッチトランジスタ 1 1 b 、 1 1 f のオフ特性が十分である場合は、シングルゲート構成であってもよい。また、スイッチトランジスタ 1 1 c もマルチゲート構造を採用することが好ましい。

【0 0 8 1】

コンデンサ 1 9 a は、駆動トランジスタ 1 1 a のゲート端子の電位を保持する保持用のコンデンサ（以後、保持用コンデンサ 1 9 a と呼ぶ）である。基本的には、駆動トランジスタ 1 1 a の特性バラツキをオフセットキャンセルした電圧が保持される。

【0 0 8 2】

スイッチトランジスタ 1 1 c のゲート端子は、ゲート信号線 1 7 a に接続される。スイッチトランジスタ 1 1 c のソース端子は、ソース信号線 1 8 に接続される。スイッチトランジスタ 1 1 c は、ゲートドライバ回路 1 2 a からの選択信号によりオン / オフ制御される。

40

【0 0 8 3】

駆動トランジスタ 1 1 a のソース端子は、スイッチトランジスタ 1 1 c のドレイン端子と接続される。しきい値電圧補償用のスイッチトランジスタ 1 1 b のソース端子又はドレイン端子と、保持用コンデンサ 1 9 a の第 1 の端子が接続される。駆動トランジスタ 1 1 b がオン（クローズ）することにより、駆動トランジスタ 1 1 a のゲート端子には、オフセットキャンセル電圧が保持される。

【0 0 8 4】

50

しきい値電圧補償用のスイッチトランジスタ11bは、前記駆動トランジスタ11aのゲート端子とドレイン端子との間に接続され、ゲート信号線17cに印加されるスキャン信号に応答して駆動トランジスタ11aのゲート端子とドレイン端子間を短絡し、駆動トランジスタ11aをダイオード接続状態にする。したがって、前記スキャン信号によって駆動トランジスタ11aは、ダイオードのような状態になり、駆動トランジスタ11aのゲート端子に電圧 $V_{sig} - V_{th}$  [V]が印加され、この電圧が、前記駆動トランジスタ11aのゲート電圧となる。

## 【0085】

なお、電圧 $V_{sig}$ は、ソースドライバIC14がソース信号線18に出力した映像信号である。また、 $V_{th}$ では、駆動トランジスタ11aにしきい値電圧である。また、 $V_{th}$ は駆動トランジスタ11aのオフセットキャンセル電圧である。 $V_{th}$ は、駆動トランジスタ11aの特性によって、個々にバラツキがある。

10

## 【0086】

初期化用のスイッチトランジスタ11fは、リセット電圧ライン $V_{rst}$ と保持用コンデンサ19aの第1の端子との間に接続され、ゲート信号線17dのスキャン信号に応答して、リセット電圧 $V_{rst}$ が、駆動トランジスタ11aのゲート端子および保持用コンデンサ19aに印加される。したがって、保持用コンデンサ19aに充填された電荷は放電される。また、駆動トランジスタ11aのゲート端子に所定電圧（初期化電圧 $V_{rst}$ ）が印加される。

20

## 【0087】

なお、図1などの本実施例の画素構成では、駆動トランジスタ11aのゲート端子に直流的に $V_{rst}$ 電圧、 $V_{sig}$ 電圧を印加するように図示している。しかし、本実施例はこれに限定するものではなく、交流的に $V_{rst}$ 電圧、 $V_{sig}$ 電圧を印加してもよい。具体的には、駆動トランジスタ11aのゲート端子にコンデンサを配置し、直成分を遮断して、 $V_{rst}$ 電圧、 $V_{sig}$ 電圧を、駆動トランジスタ11aのゲート端子に印加する構成を採用してもよい。

20

## 【0088】

また、図1などの本発明の実施例において、オフセットキャンセルコンデンサ11bの一方の端子をアノード電圧 $V_{dd}$ に接続するとしたが、これに限定するものではなく、所定の一定電圧に保持されるように構成すればよいことは言うまでもない。一定電圧とは、 $V_{GH}$ 電圧、 $V_{GL}$ 電圧などが例示される。したがって、スイッチトランジスタ11eの一方の端子を $V_{dd}$ 電圧に接続（図1の接続と同一）し、オフセットキャンセルコンデンサ11bの一方の端子を $V_{GH}$ 電圧などに接続してもよい（ $V_{dd}$ 電圧から $V_{GH}$ 電圧に変更）。

30

## 【0089】

スイッチトランジスタ11eは、アノード電圧 $V_{dd}$ 配線または $V_{dd}$ 電極と駆動トランジスタ11aのソース端子との間に接続される。スイッチトランジスタは、スイッチトランジスタのゲート端子に接続されたゲート信号線17bに印加されたオンオフ電圧により制御される。スイッチトランジスタ11eは、EL素子15を発光させる時は、オンとなり、アノード電圧 $V_{dd}$ を前記駆動トランジスタ11aのソース端子に印加する。

40

## 【0090】

スイッチトランジスタ11dは、駆動トランジスタ11aのドレイン端子とEL素子15のアノード端子間に接続（配置）され、スイッチトランジスタ11dのゲート端子に接続されたゲート信号線17bに印加されたオンオフ信号（発光制御信号）により制御される。スイッチトランジスタ11dは、発光制御信号に応答して前記駆動トランジスタ11aで生成される前記駆動電流を前記EL素子15に伝達する。つまり、スイッチトランジスタ11dは、EL素子15に流れる電流経路の電流をオンオフ制御する。

## 【0091】

保持用コンデンサ19aは、アノード電圧 $V_{dd}$ 配線（電極）と駆動トランジスタ11aのゲート端子との間に接続され、アノード電圧 $V_{dd}$ と前記駆動トランジスタ11aの

50

ゲート端子に印加される電圧  $V_{sig} - V_{th}$  [V] に該当する電荷を 1 フレームの間は保持する。

【0092】

なお、ゲート信号線 17 に印加される電圧は、オフ電圧 (VGH) とオン電圧 (VGL) であり、VGH 電圧の印加により、スイッチトランジスタ 11 (11b, 11c, 11d, 11e, 11f) がオフし、VGL 電圧の印加により、スイッチトランジスタ 11 (11b, 11c, 11d, 11e, 11f) がオンする。但し、スイッチトランジスタが、P チャンネルトランジスタの場合である。

【0093】

図 3 に図示するように、VGL 電圧は、ゲートドライバ回路 12a では、VGL1 とし、ゲートドライバ回路 12b では、VGL2 としている。つまり、ゲートドライバ回路 12a と 12b では、オン電圧を異ならせている。

【0094】

したがって、ゲート信号線 17a、ゲート信号線 17c に印加されるオン電圧は VGL1 であり、ゲート信号線 17b、ゲート信号線 17d に印加されるオン電圧は VGL2 である。また、|VGL1| > |VGL2| なる関係となるように設定されている。なお、ゲート信号線 17a に印加される VGH とゲート信号線 17d に印加される VGH とは一致させてもよい。つまり、ゲートドライバ回路 12a のオフ電圧 VGH1 とゲートドライバ回路 12b の VGH2 は同一にしてもよい。

【0095】

なお、本発明の実施例において、駆動トランジスタ 11a は P チャンネルトランジスタたがこれに限定するものでなく、N チャンネルトランジスタであってもよい。この場合は、オン電圧が VGH となり、オフ電圧が VGL となる。

【0096】

また、駆動トランジスタ 11a のソース端子はアノード電圧 Vdd と接続されているとして説明するが、これに限定するものではない。例えば、カソード電圧 Vss あるいはグランド電圧 GND に接続されていてもよい。また、コンデンサ 18 は、トランジスタ 11 のゲート絶縁膜容量によるコンデンサで代用してもよい。

【0097】

ゲートドライバ回路 12a には、ゲート信号線 17a を選択するスタートパルス ST1、ゲート信号線 17c を選択するスタートパルス ST2、スタートパルスを順次シフトするクロック信号 (CLK) が印加される。UD は、ゲートドライバ回路 12a 内のスタートパルスの上下シフトレジスタ方向を切り替える信号である。

【0098】

ゲートドライバ回路 12b には、ゲート信号線 17b を選択するスタートパルス ST3、ゲート信号線 17d を選択するスタートパルス ST4、スタートパルスを順次シフトするクロック信号 (CLK) が印加される。

【0099】

なお、必要に応じて、ゲートドライバ回路 12 には、イネーブル制御端子を付加することが好ましい。ゲートドライバ回路 12 内には、シフトレジスタ回路が形成されており、スタートパルスをクロック信号 (CLK) に同期して順次シフトさせ、選択するゲート信号線 17 位置を変化させる。

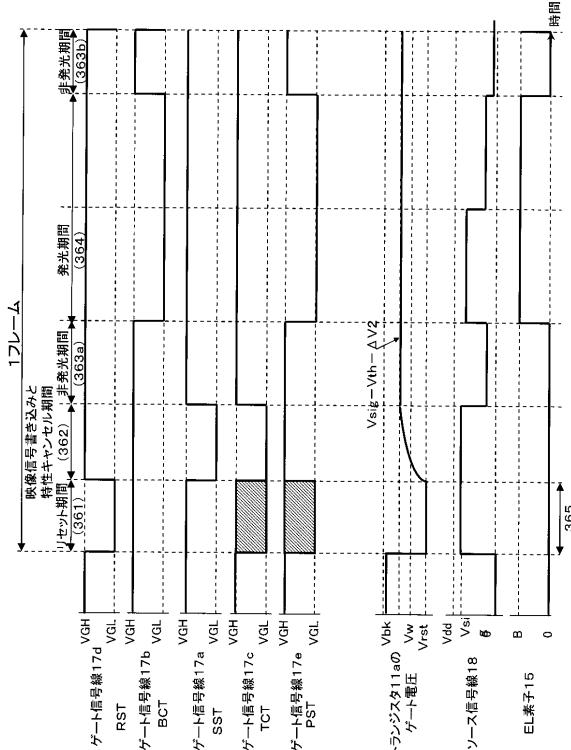

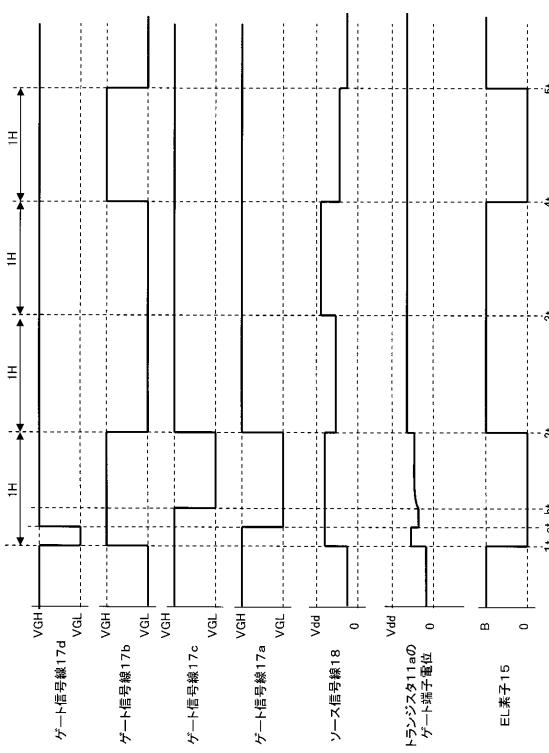

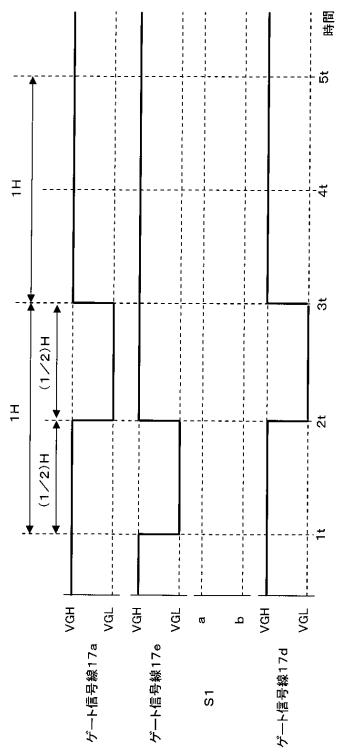

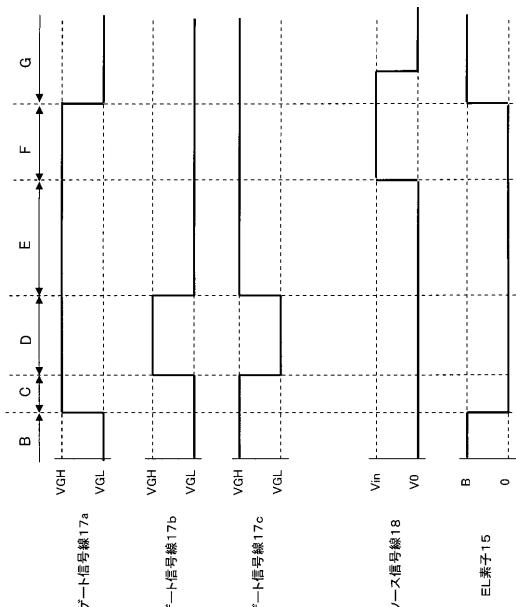

【0100】

図 2 は、ゲート信号線 17a、17b、17c、17d に印加される駆動電圧、ソース信号線 18 の映像信号電圧、EL 素子 15 の発光状態を示す。

【0101】

また、図 2 は、各動作でのスイッチトランジスタの動作状態 (オン / オフ状態)、電流あるいは電圧の印加状態を示す。

【0102】

なお、図 2 では、説明を容易にするため、オフ電圧を VGH とし、オン電圧を VGL と

10

20

30

40

50

する。また、ソース信号線 18 に印加される電圧  $V_{sig}$  の範囲は、グランド電圧 ( GND ) = 0 V とし、アノード電圧  $V_{dd}$  以下としている。具体的には、映像信号電圧  $V_{sig}$  は、0.2 V ~ 5.0 V の範囲である。

#### 【0103】

なお、1 H とは 1 水平走査期間である。また、図 2 は模式的なものであり、1 H を数 H と置き換えるてもよい、1 H は 1 H より短い期間と置き換えるてもよい。

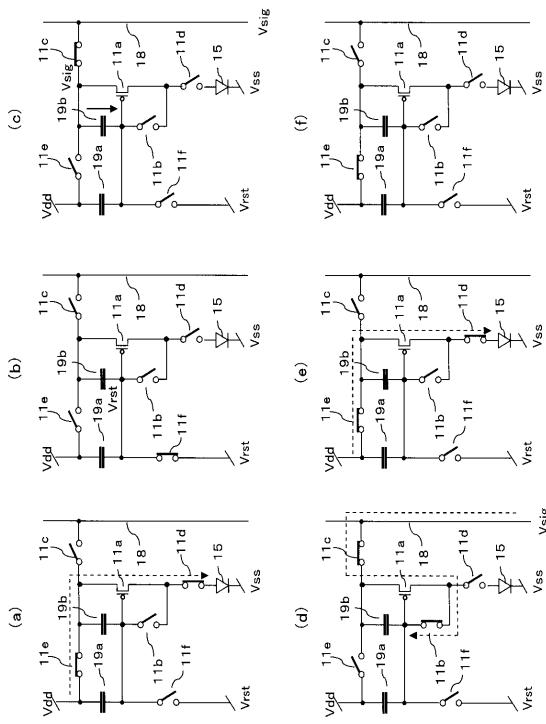

#### 【0104】

図 111 は図 1 の画素の動作を説明するための説明図である。図 111 において、説明を容易にするため各スイッチトランジスタはスイッチとして図示している。

#### 【0105】

$V_{GH}$  電圧は、アノード  $V_{dd}$  電圧よりも 0.5 V 以上 3.0 V 以下の高い電圧に設定される。例えば、アノード電圧  $V_{dd}$  が 5 V であれば、 $V_{GH}$  電圧は、5.5 V 以上 8 V 以下の電圧値に設定される。

#### 【0106】

画素 16 には、1 t から a t の期間に、ゲート信号線 17d にオン電圧が印加される。図 111 ( a ) が対応する。オン電圧 ( $V_{GL}$ ) の印加により、トランジスタ 11f がオンし、リセット電圧  $V_{rst}$  が駆動トランジスタ 11a のゲート端子にリセット電圧  $V_{rst}$  が印加される ( a 点 ) 。

#### 【0107】

リセット電圧  $V_{rst}$  の印加により、駆動トランジスタ 11a は、リセット状態になる。リセット状態とは、駆動トランジスタ 11a を初期化された状態、駆動トランジスタ 11a のゲート端子に所定電圧 ( 初期化電圧 ) が印加された状態、駆動トランジスタ 11a が所定状態にされた状態などである。

#### 【0108】

なお、リセット電圧  $V_{rst}$  は、GND 電圧以下 -5 ( V ) 以上の電圧に設定すべきである。例えば、リセット電圧  $V_{rst}$  は、-2.5 V に設定する。リセット電圧  $V_{rst}$  は、 $V_{GL}$  1 電圧以上で、GND 電圧以下の値に設定することが好ましい。さらに好ましくは、映像信号電圧  $V_{sig}$  の最低電圧 -1.0 V 以下、スイッチトランジスタ 11c のオン電圧 ( $V_{GL}$ ) + 1.0 以上の値に設定することが好ましい。

#### 【0109】

また、リセット電圧  $V_{rst}$  は、映像信号電圧  $V_{sig}$  に対応して変化させてもよい。例えば、映像信号の階調番号に対応させてリセット電圧  $V_{rst}$  を変化させる。また、リセット電圧  $V_{rst}$  は、赤 ( R ) 、緑 ( G ) 、青 ( B ) の映像信号電圧で変化させてもよい。RGB で映像信号の振幅が異なるからである。この場合は、階調番号に対応せず、各 RGB で固定のリセット電圧  $V_{rst}$  を設定してもよい。また、リセット電圧  $V_{rst}$  は、表示画面で消費される電流に対応させて変化させてもよい。表示する画像の輝度に対応させて、リセット電圧  $V_{rst}$  を変化させてもよい。

#### 【0110】

ゲート信号線 17c は、リセット電圧  $V_{rst}$  の印加後 ( a t ) 、オン電圧が印加される。オン電圧 ( $V_{GL}$ ) を印加する期間は、1 H 以上としているが、これに限定するものではなく、1 H 以下の期間であってもよい。少なくともゲート信号線 17c にオン電圧 ( $V_{GL}$ ) を印加する期間は、ゲート信号線 17a にオン電圧 ( $V_{GL}$ ) を印加する期間よりも長くする。または、オーバーラップさせる。なお、リセット電圧  $V_{rst}$  の印加時間は、2  $\mu$  sec 以上の時間を確保することが好ましい。

#### 【0111】

ゲート信号線 17a オン電圧 ( $V_{GL}$ ) を印加することにより、スイッチトランジスタ 11c がオンし、ソース信号線 18 に印加した  $V_{sig}$  がオフセットキャンセル用コンデンサー 19a 印加される。a 点に印加されて映像信号  $V_{sig}$  は、スイッチトランジスタ 11b がオンしている期間保持される。

#### 【0112】

10

20

30

40

50

なお、図2に図示するゲート信号線17aの斜線部は、オン電圧(VGL)を印加してもオフ電圧(VGH)を印加してもよい。

【0113】

スイッチトランジスタ11cがオンすることにより、映像信号電圧Vsigがオフセットキャンセルコンデンサ11bに印加され、オフセットキャンセルコンデンサ11bに映像信号電圧Vsigが充電される。

【0114】

ゲート信号線17aにオン電圧(VGL)が印加されることにより、映像信号電圧Vsigを画素に印加するスイッチトランジスタ11cがオンする(図2の1t~2tあるいは、at~2t)。この状態を図111(b)に図示する。図111(b)では、スイッチトランジスタ11d、11e、11fはオフ状態(オープン状態)である。また、スイッチトランジスタ11c、11bはオン状態(クローズ状態)である。

10

【0115】

スイッチトランジスタ11bがオンすることにより、ソース信号線18から、駆動トランジスタ11a及びトランジスタ11bのチャンネル間に電流経路が発生し、オフセットキャンセル電流Ic1が流れる。

【0116】

電流Ic1は最初、比較的大きな電流が流れ、オフセットキャンセル動作が終局に近づくにしたがって、小さくなる。基本的には、オフセットキャンセルが完了するとIc1=0となる。オフセットキャンセルが動作により、キャンセル電圧がコンデンサ11aに保持される。

20

【0117】

映像信号電圧Vsigの印加により、駆動トランジスタ11aは、映像信号電圧Vsigが印加された状態で、駆動トランジスタ11aのチャンネルに電流が流れないように、ゲート端子であるb点の電位を変化させる(オフセットキャンセル動作)。変化後の電圧が、保持用コンデンサ19aに保持される。この動作により、駆動トランジスタ11aは、オフセットキャンセル状態に近い状態までオフセットキャンセルされる。オフセットキャンセル用コンデンサ19bには、映像信号電圧Vsigが充電される。

20

【0118】

図2の1t~2t期間で完全なオフセットキャンセルが実施できることが理想である。しかし、高精細の表示パネルでは、1画素行を選択する時間が短く、十分なオフセットキャンセル動作を実現できない。オフセットキャンセルが十分でないと、駆動トランジスタ11aの特性バラツキが残り、階調表示により画面31に輝度ムラが発生する。

30

【0119】

本実施例はこの課題を解決することを1つの目的としている。

【0120】

図2の2t~3tは、オフセットキャンセル動作の継続期間である。図2では、2t~3tの期間が対応する。また、図111(c)が対応する。

【0121】

図111(c)では、スイッチトランジスタ11e、11d、11f、11cがオフ状態(オープン状態)であり、スイッチトランジスタ11bがオン状態(クローズ状態)である。この場合は、オフセットキャンセル電流Ic2が流れる。オフセットキャンセル電流Ic2は、オフセットキャンセルの終局状態での電流であるから非常に小さい。したがって、オフセットキャンセルコンデンサ19bの容量は小さくても良い。

40

【0122】

なお、図2の実施例では、オフセットキャンセル動作を継続する期間を2t~3t期間としているが、本実施例はこれに限定するものではない。オフセットキャンセルを継続する期間は、それぞれのパネルに対応させて可変あるいは設定する。本実施例は、オフセットキャンセル期間を少なくとも1H(1画素行選択期間)以上の期間を行うものである。オフセットキャンセル期間は、20μ秒以上設定することが好ましい。

50

## 【0123】

図2において、 $1t \sim 2t$ の期間に映像信号電圧 $V_{sig}$ が画素16に保持される。それ以降の期間は、スイッチトランジスタ11cがオフ状態であるため、ソース信号線18に印加された映像信号電圧 $V_{sig}$ が変化しても、該当画素16に映像信号電圧 $V_{sig}$ が書き込まれることはない。

## 【0124】

以上のオフセットキャンセルの動作後、ゲート信号線17bにオン電圧が印加され、スイッチトランジスタ11eがオンし、アノード $V_{dd}$ 電圧が駆動トランジスタ11aのソース端子に供給される(図111(d)の状態)。また、スイッチトランジスタ11dがオンし、駆動トランジスタ11aからEL素子15の駆動用電流がEL素子15に供給される。EL素子15は、印加された電流により発光する。

10

## 【0125】

図2では、期間 $3t \sim 4t$ の間にゲート信号線17bにオン電圧( $V_{GL}$ )を印加して、スイッチトランジスタ11bをオンさせてEL素子15に発光電流を供給する。また、期間 $4t \sim 5t$ では、ゲート信号線17bにオフ電圧( $V_{GH}$ )を印加し、スイッチトランジスタ11dをオフし、EL素子15を非発光状態にする。このようにゲート信号線17bにオン/オフ電圧を印加し、流れる電流を制御することにより、図78、図79、図84の駆動方法を実現する。

## 【0126】

以上のようにゲート信号線17bには、オン電圧又はオフ電圧が印加され、オン/オフ電圧に同期してEL素子15に電流が供給される。このオン/オフ電圧の印加状態に同期してEL素子は発光又は消灯する。

20

## 【0127】

EL素子15が発光又は消灯している動作時(電圧プログラム時以外の期間、 $3t \sim$ の期間)では、トランジスタ11bはオープン状態である。この時、トランジスタ11aのソース端子は、EL素子15が発光しているときは、アノード電圧 $V_{dd}$ (トランジスタ11eのチャンネル電圧降下は無視する)が印加されている。EL素子15が消灯時は、トランジスタ11e及びトランジスタ11dをオープン状態にされる。このEL素子15が消灯時は、駆動トランジスタ11aのソース端子は、オフセットキャンセル用コンデンサ19aにより、アノード電位 $V_{dd}$ に保持されている。したがって、トランジスタ11aの電位安定度がよい。もちろん、EL素子15の点灯及び消灯は、トランジスタ11dを $-duty$ 制御(トランジスタ11dなどをオン/オフさせて、表示画面31に帯状の非表示領域を発生し、非表示領域を表示画面31の上下方向に、フレーム周期あるいはフィールド周期に同期して画像表示させる)してもよい。

30

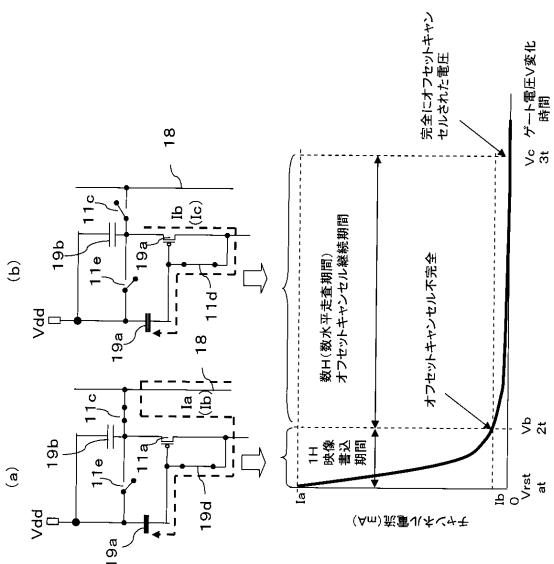

## 【0128】

図89は、図111(b)(c)の状態を更に詳しく記載したものである。図111(b)は、図89(a)が対応し、図111(c)は、図89(b)が対応する。

## 【0129】

図89(a)では出力アンプ891から出力された映像信号電圧 $V_{sig}$ がスイッチトランジスタ11cを介してオフセットキャンセルコンデンサ19bに一方の端子に印加され、同時に、駆動トランジスタ11aのチャンネルにオフセットキャンセル電流 $I_{c1}$ が流れる。

40

## 【0130】

画素16の選択期間の経過後、図89(b)の状態となり、スイッチトランジスタ11cがオープン状態となる。図89(b)の状態では、オフセットキャンセルコンデンサ19bに保持された映像信号電圧 $V_{sig}$ が電流の供給元となり、継続してオフセットキャンセル電流 $I_{c2}$ が流れる。図89(b)でオフセットキャンセル電流 $I_{c2}$ がほぼ0となり、オフセットキャンセル動作が完了する。したがって、理想的なオフセットキャンセル動作を実現できる。

## 【0131】

50

出力アンプ 891 の駆動能力（電流出力能力）は、複数の段階で変更できるように構成する。出力アンプ 891 はソースドライバ IC14 の出力段に形成される。出力アンプ 891 の駆動能力は、コマンドで変更できるように構成される。

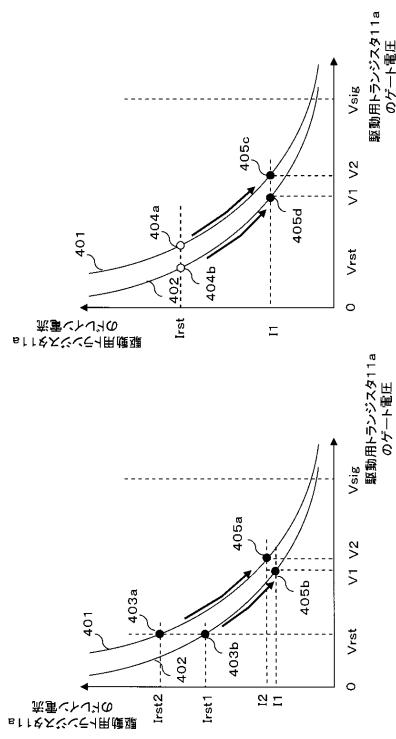

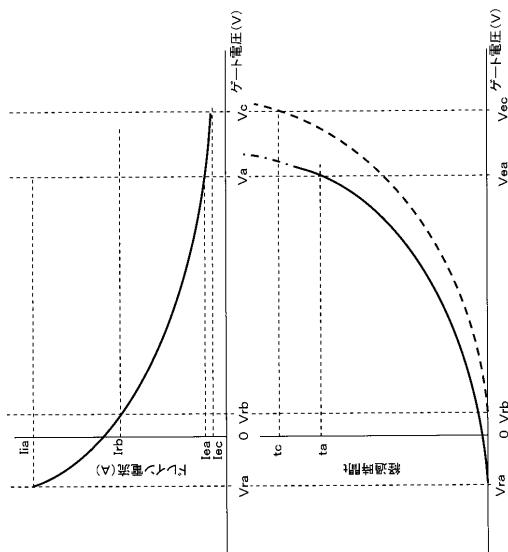

#### 【0132】

図 88 は、駆動トランジスタ 11a のチャンネルに流れる電流（チャンネル電流  $I_c$  と呼ぶ）を図示したものである。図 88 では、理想的にオフセットキャンセルされた状態での駆動トランジスタ 11a のゲート端子電圧を  $V_c$  としている。不十分なオフセットキャンセル電圧は  $V_b$  とし、オフセットキャンセル動作の開始電圧は、リセット電圧  $V_{rst}$  としている。図 88 に図示するように、 $a_t \sim 2t$  の期間において、最初は大きなキャンセル電流  $I_{c1}$ （開始電流は  $I_a$  としている）が流れ、キャンセル電流  $I_{c1}$  は急激に現状する。2t では、キャンセル電流  $I_{c1} = I_b$  としている。この  $I_b$  の時はまだ、電流が流れる状態あるから、オフセットキャンセルは不十分な状態である。

10

#### 【0133】

その後（ $2t \sim 3t$ ：図 89 (b)）も、オフセットキャンセル状態は継続し、オフセットキャンセル電流  $I_{c2}$  は減少し、 $t_3$  でオフセットキャンセル電流  $I_{c2}$  は 0 状態となる。

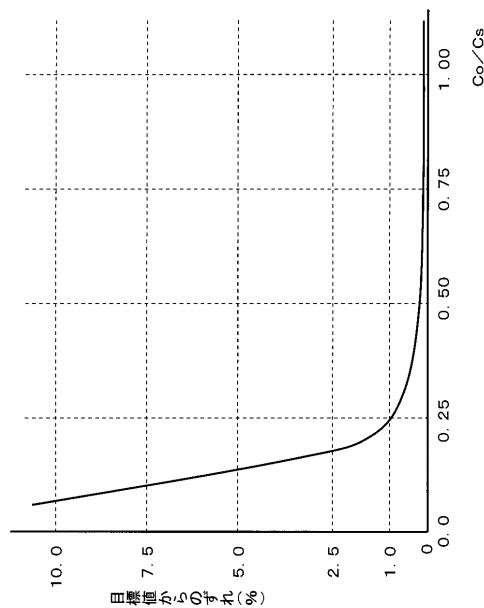

#### 【0134】

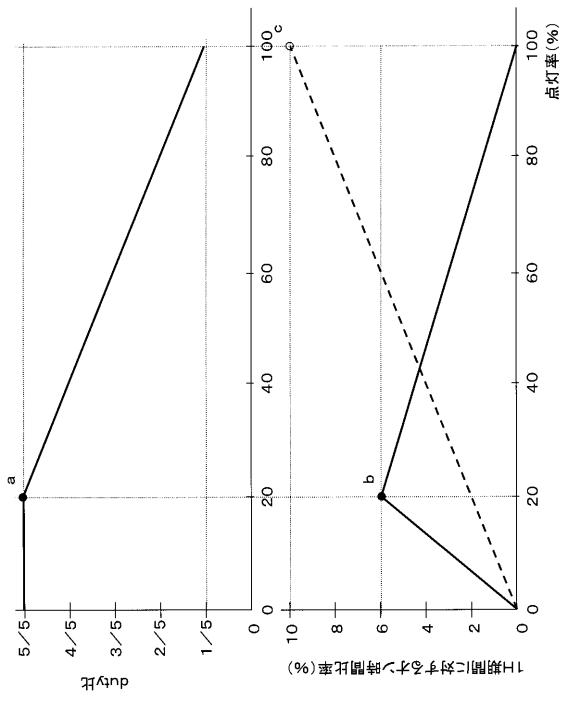

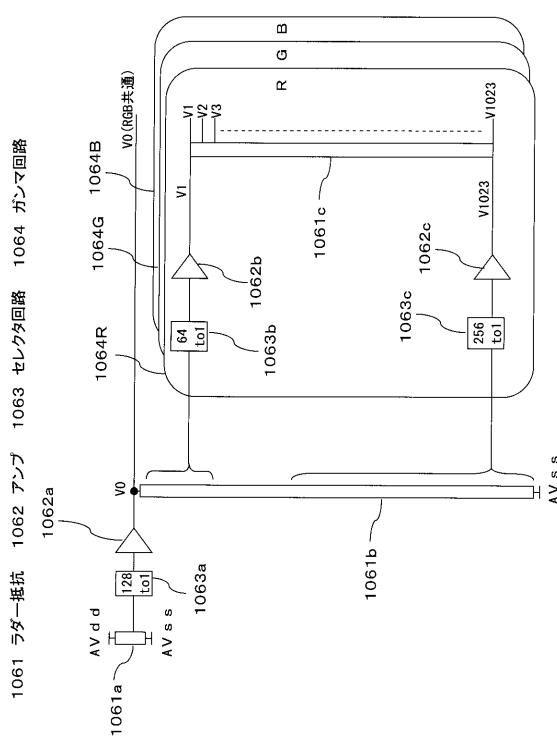

ここで、保持用コンデンサ 19a の容量を  $C_s$  (pF) とし、オフセットキャンセルコンデンサ 19b の容量を  $C_o$  (pF) とすると、図 85 の関係がある。

20

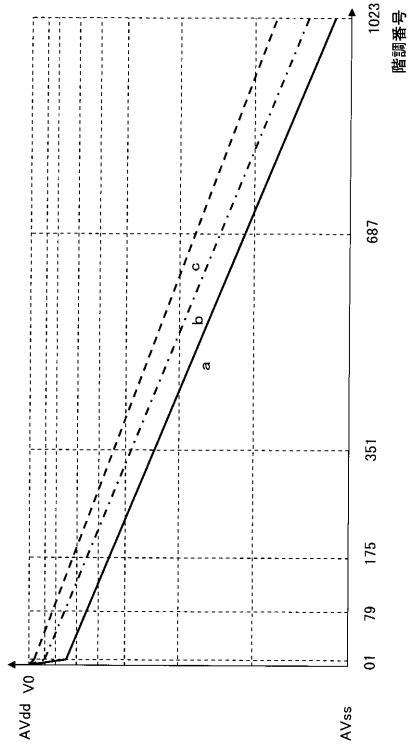

#### 【0135】

図 85において、横軸は、オフセットキャンセルコンデンサ 19b の容量  $C_o$  (pF) と保持用コンデンサ 19a の容量  $C_s$  (pF) との比率 ( $C_o / C_s$ ) を示している。縦軸は、理想的なオフセットキャンセル状態からのずれを示している。ずれとは、理想的な駆動トランジスタ 19a のゲート端子電圧に対する電圧差を比率で示したものである。例えば、完全にオフセットキャンセル状態に到達した駆動トランジスタ 11a のゲート端子電圧を 1.0V としたとき、誤差（乖離量）10% とは、 $1.0(V) \cdot (1 - 0.1) = 0.9(V)$  である。誤差 2% とは、 $1.0(V) \cdot (1 - 0.02) = 0.98(V)$  である。 $C_o / C_s$  が 0.5 より小さい範囲では、目標値からの誤差が 2% 以上と大きい。そのため、オフセットキャンセル状態は悪い。また、 $C_o / C_s$  の値が小さくなるほど、急激に目標値からの誤差が大きくなる。

30

#### 【0136】

$C_o / C_s$  が 0.5 以上の範囲では、目標値からの誤差が 2% 以下と小さい。また、 $C_o$  の値を大きくしても、目標値からのずれ量の低減割合は小さい。 $C_o$  の値を大きくすることはオフセットキャンセルコンデンサの容量を大きくする必要がある。コンデンサの容量を大きくすることは、画素の構成上、困難である場合が多い（高精細パネルでは画素には大きなコンデンサは形成できない）。一方で、保持用コンデンサ 19a は少なくとも 1 フレーム期間（又は 1 フィールド期間、なお、本明細書では 1 フレーム期間と 1 フィールド期間とは同義として取り扱う）の間、電荷を保持しておく必要がある。そのため、比較的大きな容量でかつ一定以上の容量が必要である。

30

#### 【0137】

以上ことから、 $C_o / C_s$  は、0.25 以上となるようにする。つまり、 $C_o : C_s = 1 : 4$  以上となるように、 $C_o$  容量を形成する。また、 $C_s$  のサイズ又は  $C_o$  に対する  $C_s$  の比率の観点から、 $C_o / C_s = 1.0$  以下とすることが好ましい。つまり、 $C_o : C_s = 1 : 1$  以下となるように、 $C_o$  容量を形成する。

40

#### 【0138】

図 10 は、図 1 の変形例である。オフセットキャンセル用コンデンサ 19a の一端子は、ゲート信号線 17a に接続されている。ゲート信号線 17a には、オン電圧 ( $V_{GL}$ ) 又はオフ電圧 ( $V_{GH}$ ) が印加されるが、映像信号電圧を画素 16 に書き込んだ後（電圧プログラム時以降）以外の期間は、オフ電圧 ( $V_{GH}$ ) が印加されている。したがって、オフセットキャンセル用コンデンサ 19a は一定の電荷を保持して安定である。他の構成

50

は図1で説明したのと同様であるので説明を省略する。

【0139】

なお、図10において、オフセットキャンセル用コンデンサ19aの一端子は、ゲート信号線17bと接続するとしたが、これに限定するものではない。例えば、図11に図示するように、ゲート信号線17dと接続してもよい。図11の構成では、ゲート信号線17dには、リセット電圧Vrstを印加するときだけ、オン電圧(VGL)が印加される。しかし、他の期間には、オフ電圧(VGH)が印加される。オフ電圧(VGH)が印加される。したがって、オフセットキャンセル用コンデンサ19aは一定の電荷を保持して安定状態を維持される。

【0140】

図11は、図1の変形例である。オフセットキャンセル用コンデンサ19aの一端子は、ゲート信号線17bに接続されている。ゲート信号線17bには、オン電圧(VGL)又はオフ電圧(VGH)が印加される。しかし、映像信号電圧を画素16に書き込み時(電圧プログラム時)の期間は、オフ電圧(VGH)が印加される。したがって、オフセットキャンセル用コンデンサ19aは一定の電荷を保持して安定状態を維持されている。

10

【0141】

EL表示装置のゲートドライバ回路12について説明する。

【0142】

図3に示すように、表示画面31の左端にゲートドライバ回路12aを設け、右端にゲートドライバ回路12bを設けている。なお、ゲートドライバ回路12は、表示パネルの空き領域に形成すればよい。

20

【0143】

ゲートドライバ回路12aは、ゲート信号線17aを制御し、ゲートドライバ回路12bはゲート信号線17bを制御する。ゲートドライバ回路12a、12bには、ゲート信号線17のオン電圧(VGL)と、ゲート信号線17のオフ電圧(VGH)が供給されている。オフ電圧(VGH)は、アノード電圧Vdd以上又は近傍の電圧である。オン電圧(VGL)は、カソード電圧Vss又はグランド電圧(GND)近傍の電圧である。なお、近傍の電圧とは、3Vの範囲の電圧である。

【0144】

本実施例では、トランジスタ31のオフ電圧をVGHとし、オン電圧をVGLとして説明するがこれに限定するものではない。オン電圧(VGL)とオフ電圧(VGH)の極性は、駆動トランジスタ31aのチャンネルの種類(Pチャンネル又はNチャンネル)に対応して設定する。また、図31に示すように、ゲートドライバ回路12の電圧の1つ又は複数をGND電圧としてもよい。図31では、ゲートドライバ回路12bは、VGH電圧と、VGL=GND電圧で動作しており、ゲートドライバ回路12aは、VGH電圧とVGL1電圧で動作している。

30

【0145】

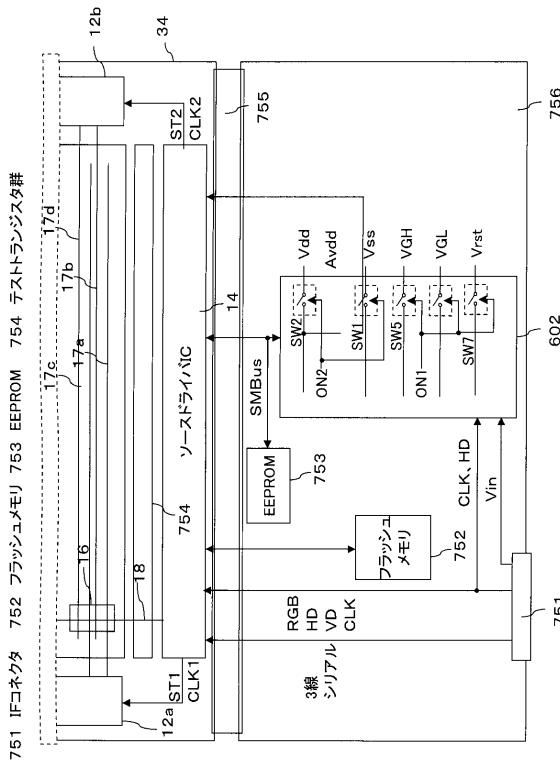

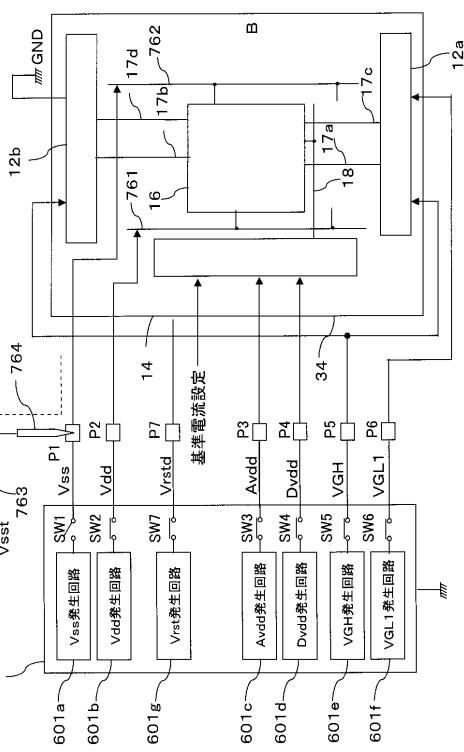

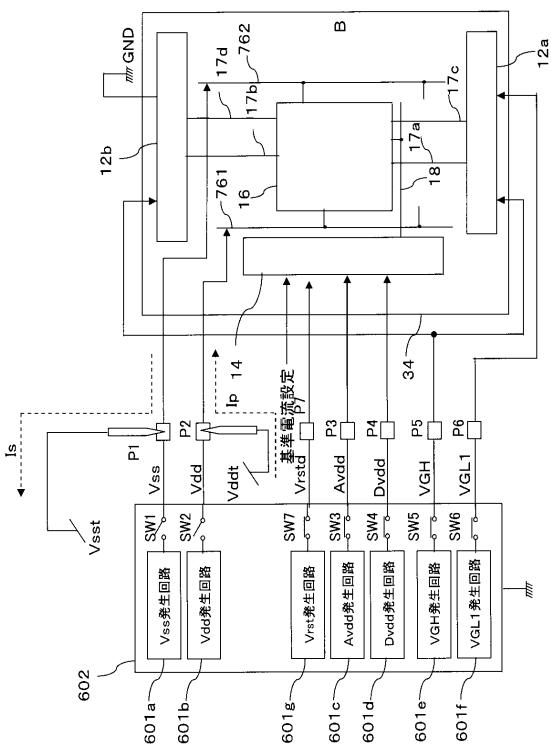

本実施例では、駆動トランジスタ31aはPチャンネルトランジスタとしている。この場合は、オン電圧をVGLとし、オフ電圧をVGHとする。駆動トランジスタ31aがNチャンネルトランジスタの場合は、オン電圧をVGHとし、オフ電圧をVGLとする。なお、図2に適合するように、VGH1、VGH2、VGL1、VGL2を内蔵させてよい。EL表示装置を駆動する電源(回路)ICからのON1コマンドで、ソースドライバ回路14のアナログ電圧AVddとゲートドライバ回路12の電圧VGH1、VGH2、VGL1、VGL2を同時に起動し、ON2でアノード電圧Vdd、カソード電圧Vssを起動させる。

40

【0146】

図4は、図1の変形例である。図1と図4の差異は、コンデンサ11cが追加形成された点である。コンデンサ11cは、ゲート信号線17aに印加された電圧の変化(VGL-VGH)により、突き抜け電圧が発生しより良好な黒表示(高コントラスト表示)を実現することを1つの目的とする。VGL-VGHの動作とは、画素16に映像信号を書き

50

込み保持させる動作である。つまり、スイッチトランジスタ 11c の制御動作である。

【0147】

前記コンデンサ 19c は、第 1 の電極が現在ゲート信号線 17a 及びトランジスタ 11c のゲート端子に接続され、第 2 の電極が前記保持用コンデンサ 19a 及び駆動トランジスタ 11a のゲート端子に共通接続されている。

【0148】

なお、駆動トランジスタ 11a が N チャンネルトランジスタの場合は、ゲート信号線 17a に印加する電圧（映像信号を画素に書き込み、保持させる動作時に使用する電圧）を VGL ～ VGH となるように画素 16 を構成する。

【0149】

ゲート信号線に印加するオフ電圧を VGH 、オン電圧を VGL とすると、ゲート信号線 17a に印加する電圧を、 VGL から VGH に変化させると、駆動トランジスタ 11a のゲート電圧は、前記保持用コンデンサ 19a と補助コンデンサ 19c のカップリングによる補正電圧だけ上昇するようになる。したがって、駆動トランジスタ 11a のゲート端子の電圧が、アノード Vdd 電圧側にシフトし、良好な黒表示を実現できる。

【0150】

図 5 は、図 1 又は図 4 の変形例である。図 5 の構成も本実施例の EL 表示装置に用いることができる。図 5 において、画素 16 は、2 つのコンデンサ 19a 、 19b と 5 つのスイッチトランジスタ（ 11b 、 11c 、 11d 、 11e 、 11f ）と 1 つの駆動トランジスタ 11a で構成される。トランジスタ 11b は、トランジスタ 11a をダイオード接続（ Diode-connected ）させて、しきい値電圧を補償するためのしきい値電圧補償用のスイッチトランジスタである。トランジスタ 11f は、保持用コンデンサ 19a を初期化させるためリセット電圧 Vrst を印加するための初期化用のスイッチトランジスタである。そして、トランジスタ 11d は、 EL 素子 15 の発光を制御するためのトランジスタである。

【0151】

スイッチトランジスタ 11c は、ゲート信号線 17a にゲート端子が接続され、ソース信号線 18 にソース端子が接続され、ゲートドライバ回路 12a からの選択信号によりオン / オフ制御される。

【0152】

ゲート信号線 17a からゲート信号線 17a1 とゲート信号線 17a2 が分岐されており、ゲート信号線 17a1 には、インバータ回路 51 が配置されている。したがって、ゲート信号線 17a1 とゲート信号線 17a2 には、 VGH と VGL が反転して電圧が印加される。

【0153】

また、ソース信号線 18a とソース信号線 18b を有しており、上下方向に隣接した画素 16 ( 16a 、 16b ) は異なるソース信号線 18 に接続されている。図 5 の実施例では、画素 16b はソース信号線 18b に接続されており、画素 16a はソース信号線 18a と接続されている。

【0154】

図 6 は、図 5 の画素構成において、ゲート信号線 17 及びソース信号線 18 との接続状態を示している。図 5 、図 6 のように構成することにより、リセット電圧 Vrst を印加するためのスイッチトランジスタ 11f を制御するゲート信号線と、映像信号を印加するためのスイッチトランジスタ 11c を制御するゲート信号線とを共通にすることができる。そのため、ゲート信号線 17 数を削減でき、画素 16 の開口率を向上できる。

【0155】

また、複数画素行を同時にオフセットキャンセル状態にすることができる、良好なオフセットキャンセルを実現できる。

【0156】

図 8 6 は図 1 のオフセットキャンセルコンデンサ 19b を有する構成にコンデンサ 11

10

20

30

40

50

c を付加した構成である。図 8 6 において、コンデンサ 19 c は、スイッチトランジスタ 11 c のゲート端子（ゲート信号線 17 a）とコンデンサ 19 b の一端子（スイッチトランジスタ 11 c のドレイン端子）に接続されている。

【 0 1 5 7 】

コンデンサ 19 c はゲート信号線 17 a の変動により、端子電位が変化する。ゲート信号線 17 a は、画素 16 が選択されたときには、オン電圧（V G L）が印加され、選択されないときにはオフ電圧（V G H）が印加される。つまり、画素 16 が選択状態から非選択状態に変化するとコンデンサ 19 c の a 1 電圧は、V G L → V G H に変化する。したがって、a 1 電圧の電圧変化は、a 2 電圧の変化に影響する。a 2 電圧は、a 1 電圧の変化をコンデンサ 19 c とコンデンサ 19 c で分圧されたものとなる。一方で、a 点（a 2 電圧）は、画素が選択されたときは、映像信号電圧 V s i g が印加されている。a 2 電圧が V G L → V G H に変化すると、(V G H - V G L) 電圧が分圧されて、映像信号電圧 V s i g に重畠される。したがって、a 点の電位は、映像信号電圧 V s i g よりも高くなる。

【 0 1 5 8 】

a 2 点の電位を映像信号電圧 V s i g よりも高くすることは、図 1 1 1 (c) のオフセットキャンセル動作を良好な状態にすることができる。通常、オフセットキャンセルコンデンサ 19 b の容量は小さい。したがって、オフセットキャンセル電流 I c 2 が大きいと、オフセットキャンセルコンデンサ 19 b の端子電位が急速に低下してしまい、オフセットキャンセル動作の継続能力が低下する。

【 0 1 5 9 】

図 8 6 の構成では、映像信号電圧 V s i g よりも高い電圧を a 点に保持できるので、オフセットキャンセル電圧を高めに設定でき、良好なオフセットキャンセル動作を実現できる。

【 0 1 6 0 】

図 8 6 の構成において、オフセットキャンセルコンデンサ 19 b の動作、機能、効果などは図 1 で説明したので省略する。

【 0 1 6 1 】

図 8 7 は図 1 の変更例である。図 8 7 において画素 16 a のスイッチトランジスタ 11 c をオン / オフさせるゲート信号線 17 d 1 は、次段の画素 16 b のスイッチトランジスタ 11 f をオン / オフさせるゲート信号線 17 d 1 と共に結線されている。

【 0 1 6 2 】

したがって、ゲート信号線 17 d 1 にオン電圧を印加すると、リセット電圧 V r s t を印加するスイッチトランジスタ 11 f がオンして、画素 16 b の駆動トランジスタ 11 a にリセット電圧 V r s t を印加する。同時に、前段の画素 16 a のスイッチトランジスタ 11 c がオンして映像信号電圧 V s i g を画素 16 a に書き込み、オフセットキャンセル動作を開始する。なお、画素 16 a は 1 H 後には、図 1 1 1 (c) 動作となる。

【 0 1 6 3 】

つまり、ゲート信号線 17 d を順次選択することにより、リセット電圧 V r s t を印加する動作と、その他の画素行（基本的には前段の画素行）に映像信号電圧 V s i g を印加する動作とを同時に実現できる。したがって、ゲートドライバ回路 1 2 の構成を簡略化でき、狭額縁の E L 表示装置を実現できる。

【 0 1 6 4 】

図 8 7 では、各画素行のゲート信号線 17 d は、前段の画素行のゲート信号線 17 d と接続されているとしたが、これに限定するものではない。例えば、ゲート信号線 17 d は、複数以上の前又は後の画素行と接続させてもよい。

【 0 1 6 5 】

図 8 7 の構成において、複数の画素行のゲート信号線 17 d が共通に接続され、ゲート信号線 17 d が接続された画素行が前段又は後段の画素行と共に接続されている点以外の構成あるいは動作は、図 1 などで説明を行っているので説明を省略する。以上の事項は、本明細書の他の実施例にも適用されることは言うまでもない。

10

20

30

40

50

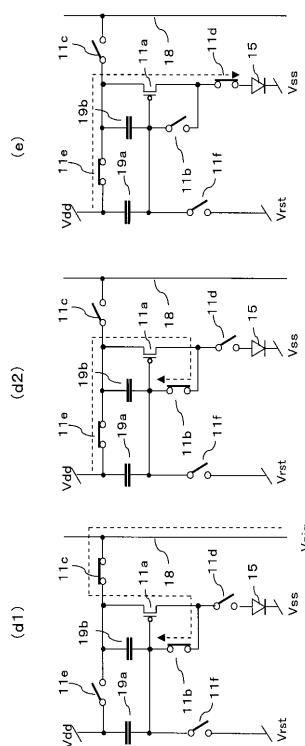

## 【0166】

図90は本発明の他の実施例である。図1との差異は、スイッチトランジスタ11d、スイッチトランジスタ11fがない点である。他の構成は図1と同様である。以上のように本実施例の技術的思想は多種多様な画素構成に対しても適用される。

## 【0167】

図91は、図90の実施例に対して、コンデンサ19bの接続位置を異ならせている。図91では、コンデンサ19bの一端子は、スイッチトランジスタ11cのドレイン端子と接続され、他の端子は、ゲート信号線17aと接続されている。ゲート信号線17aの電位は、画素16が選択されている時以外は、オフ電圧(VGH)が印加されている。したがって、画素16の選択時以外は、安定した電位に保持されているので、良好に映像信号電圧Vsigを保持することができる。他の構成あるいは動作は、図1、図90と同様であるので説明を省略する。

10

## 【0168】

図1などの構成では、コンデンサ19bの一方の端子は、アノード電圧Vddに接続した。しかし、本実施例はこれに限定するものではない。所定期間の間に安定した電位に保持できるものであれば、どんな電位でもよい。図92の実施例は、コンデンサ19bの一方の端子をカソード電圧Vssとなるように接続をしている。他の構成あるいは動作は、図1、図90と同様であるので説明を省略する。

20

## 【0169】

図93の構成は、図1の構成に加えて、スイッチトランジスタ11gを付加した構成である。スイッチトランジスタ11gのゲート端子はゲート信号線17gに接続されている。したがって、ゲート信号線17cにオン電圧(VGL)を印加することにより、EL素子15のアノード端子に、リセット電圧Vrstを印加することができる。他の構成あるいは動作は、図1、図90と同様であるので説明を省略する。

20

## 【0170】

図94の構成は、図93に対してコンデンサ19bの接続位置を変化させたものである。コンデンサ19bの一方の端子は、スイッチトランジスタ11cのドレイン端子と接続され、他の端子は、駆動トランジスタ11aのゲート端子と接続される。駆動トランジスタ11aのゲート端子もオフセット電圧あるいは映像信号電圧Vsigが印加され、1フレーム期間の間、電位が維持される。したがって、コンデンサ19bの保持電圧として用いることができる。他の構成あるいは動作は、図1、図90と同様であるので説明を省略する。

30

## 【0171】

なお、以上の事項は、本明細書の他の実施例、他の構成に適用される。また、他の実施例、他の構成と組み合わせることができる。

## 【実施例2】

## 【0172】

本発明の実施例2について説明する。

## 【0173】

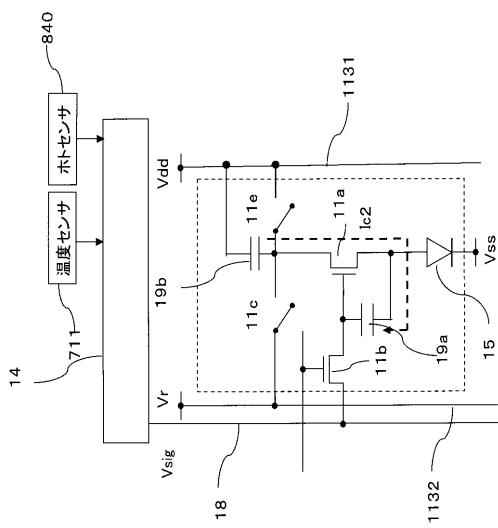

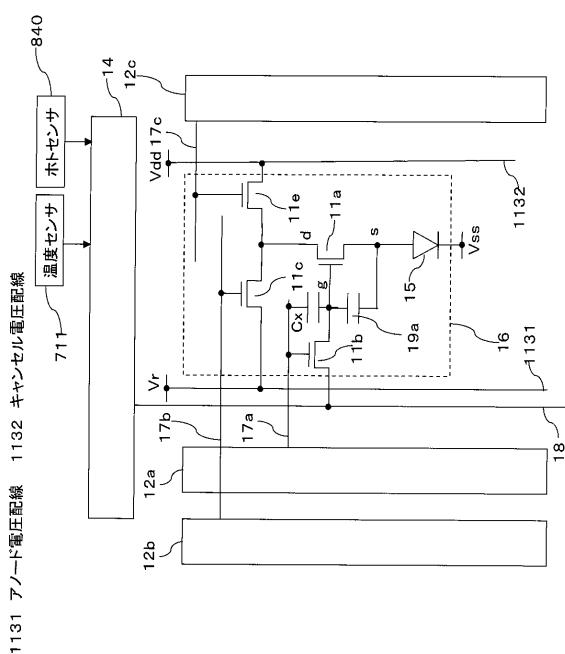

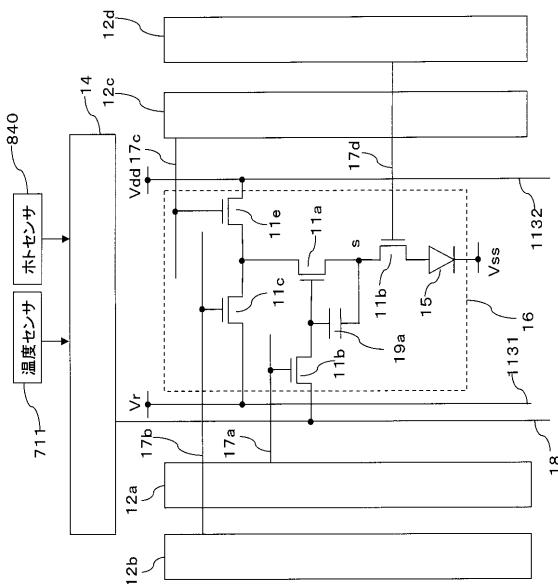

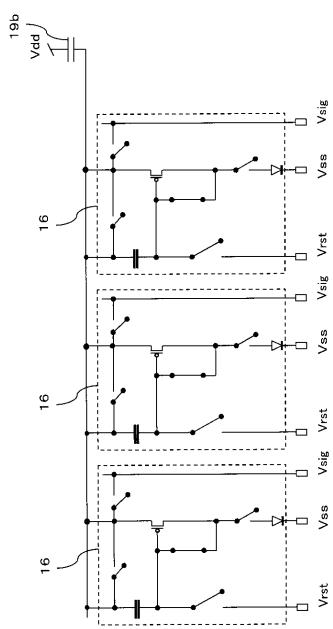

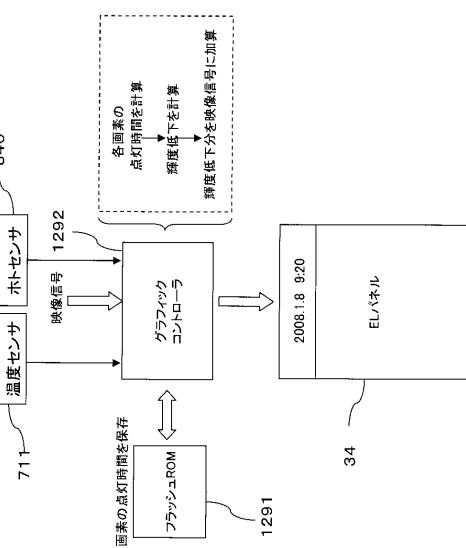

図114は、実施例2におけるEL表示装置の全体構成を示すブロック図である。

40

## 【0174】

本実施例は、EL素子15がマトリックス状に配置された表示画面31とこれを駆動する駆動回路とからなる。すなわち、図114に示すように、EL表示装置は、表示画面31とこれを駆動するソースドライバ回路( I C )18と、ゲート端子ゲートドライバ回路12、12cとからなる。

## 【0175】

図114のゲートドライバ回路12は、図113のゲートドライバ回路12a、12bが組み合せたものである。

## 【0176】

表示画面31は、行状のゲート信号線17と、列状のソース信号線18と、両者が交差

50

する部分に配された行列状の画素 16 と、各画素 16 の各列に対応して形成されたアノード電源配線 1131 を備えている。つまり、アノード電源配線 1131 は画素列に平行に形成されている。また、キャンセル電圧  $V_r$  を供給するキャンセル電圧配線 1132 も画素列に平行に形成されている。すなわち、ソース信号線 18 に平行に形成されている。

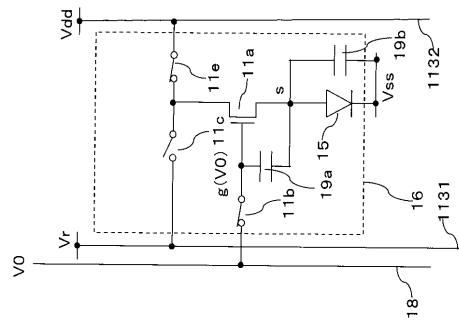

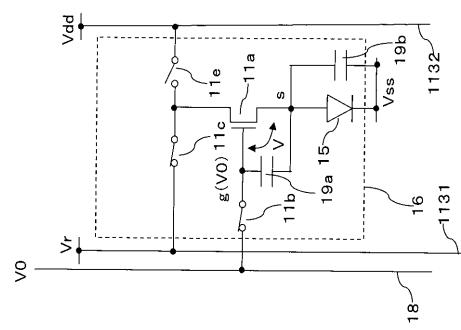

【0177】

図 113 は、図 114 に示した EL 表示装置に含まれる画素 16 の具体的な構成及び結線関係を示す回路図である。

【0178】

図 113 に示すように、画素 16 は、EL 素子 15 などで代表される EL 素子 15 と、スイッチトランジスタ 11b、11c、11e と、駆動トランジスタ 11a と、コンデンサ 19a とを含む。

【0179】

スイッチトランジスタ 11b は、そのゲート端子 d がゲート信号線 17a に接続され、ドレイン端子 d がソース信号線 18 に接続され、ソース端子が駆動トランジスタ 11a のゲート端子 g に接続されている。

【0180】

駆動トランジスタ 11a は、そのドレイン端子 d がアノード電源配線 1131 に接続され、ソース端子 s が EL 素子 15 のアノード端子に接続されている。

【0181】

EL 素子 15 のカソードは、接地電極 (GND) 又はカソード電極 (電圧)  $V_{ss}$  に接続している。なお、この接地電極又はカソード電極 (電圧)  $V_{ss}$  は全ての画素 16 に対して共通に配線されている。

【0182】

コンデンサ 19a は、駆動トランジスタ 11a のソース端子 s とゲート端子 g の間に接続されている。

【0183】

係る構成において、スイッチトランジスタ 11b は、ゲート信号線 17 から供給された制御信号に応じて導通し、ソース信号線 18 から供給された信号電位をサンプリングしてコンデンサ 19a に保持する。

【0184】

駆動トランジスタ 11a は、スイッチトランジスタ 11e がオンすることにより、アノード電源配線 1131 から電流の供給を受け、コンデンサ 19a に保持された信号電位に応じて駆動電流を EL 素子 15 に流す。

【0185】

ゲートドライバ回路 12 について説明する。ゲートドライバ回路 12a は、各ゲート信号線 17a に順次制御信号 (オン電圧又はオフ電圧) を供給して画素 16 を行単位で線順次走査する。

【0186】

ゲートドライバ回路 12b は、線順次操作 (画素行を順番に選択する動作) に同期して、駆動トランジスタ 11a のドレイン端子 d にキャンセル電圧  $V_r$  を印加するトランジスタ 11c を制御する。すなわち、ゲートドライバ回路 12b は、ゲート信号線 17b にオフ電圧又はオフ電圧を順次印加する。

【0187】

ゲートドライバ回路 12c は、この線順次走査に合わせて、駆動トランジスタ 11a のドレイン端子 d にアノード電圧  $V_{dd}$  (もしくはカソード電圧  $V_{ss}$ ) を印加するトランジスタ 11e を制御する。すなわち、ゲートドライバ回路 12c は、ゲート信号線 17c にオフ電圧又はオフ電圧を順次印加する。

【0188】

なお、ゲートドライバ回路 12a、12b、12c は 3 つのドライバから構成されるものに限定されるものではなく、図 114 に示すように、12a、12c で 1 つのゲートド

10

20

30

40

50

ライバ回路 12 に構成してもよい。

【0189】

また、各ゲートドライバ回路 12 がゲート信号線 17 に出力する電圧（オフ電圧又はオフ電圧）は異なる値とすることが好ましい。図 114 の実施例では、ゲートドライバ回路 12 とゲートドライバ回路 12c のオン電圧（VGH）は同一であるが、オフ電圧（VGL）は、ゲートドライバ回路 12 は、VGL1 とし、ゲートドライバ回路 12c は、VGL2 として異なっている。すなわち、|VGL1| < |VGL2| となるようにしている。なお、VGL1、VGL2 は負電圧であるため、絶対値の記号| |で表示している。Vr < Vdd なる関係があり、駆動トランジスタ 11a に十分に Vr 電圧を印加できるように構成している。

10

【0190】

ゲートドライバ回路 12 には、ゲート信号線 17a を選択するスタートパルス ST1、ゲート信号線 17b を選択するスタートパルス ST2、スタートパルスを順次シフトするクロック信号（CLK）が印加される。UD は、ゲートドライバ回路 12 内のスタートパルスの上下シフトレジスタ方向を切り替える信号である。また、図 115 のように構成してもよい。

【0191】

ゲートドライバ回路 12c には、ゲート信号線 17c を選択するスタートパルス ST3、スタートパルスを順次シフトするクロック信号（CLK）が印加される。

20

【0192】

なお、必要に応じて、ゲートドライバ回路 12 には、イネーブル制御端子を付加することが好ましい。ゲートドライバ回路 12 内には、シフトレジスタ回路が形成されており、スタートパルスをクロック信号（CLK）に同期して順次シフトさせ、選択するゲート信号線 17 の位置を変化させる。

【0193】

駆動トランジスタ 11a のドレイン端子 d に印加する、第 1 電位（キャンセル電圧）とアノード電圧 Vdd の切り替えは、スイッチトランジスタ 11c とスイッチトランジスタ 11e で実現する。スイッチトランジスタ 11c とスイッチトランジスタ 11e とは、排他的動作する。

30

【0194】

したがって、スイッチトランジスタ 11c がオンしているときは、スイッチトランジスタ 11e はオフに制御され、スイッチトランジスタ 11c がオフしているときは、スイッチトランジスタ 11e はオンに制御される。

【0195】

スイッチトランジスタ 11c は、順次操作され、スイッチトランジスタ 11e は、EL 素子 15 に電流を供給する時を主にオン状態とされる。

【0196】

また、スイッチトランジスタ 11e をオン / オフ制御することにより、図 78、図 79、図 84、図 98 で説明する duty 駆動を実現することができる。また、図 99 で説明の駆動方式とも組み合わせることができる。

40

【0197】

以上の事項は、図 1 などの実施例と同様である。なお、図 1 などで説明した実施例 1 の記載事項は、実施例 2、実施例 3 にも適用できることは言うまでもない。本明細書に記載した実施例は相互に組み合わせることができる。

【0198】

EL 素子 15 の点灯及び消灯は、スイッチトランジスタ 11e を duty 駆動する。この duty 駆動は、表示画面 31 に非表示領域 123 を発生（又は、表示領域 122 を発生）させて、EL 素子 15 に流れる電流を抑制するために行う。スイッチトランジスタ 11e、スイッチトランジスタ 11d などをオン / オフさせて、表示画面 31 に帯状の非表示領域 123 を発生し、この非表示領域 123 を画面 31 の上下方向に、フレーム周期（

50

フィールド周期)に同期して画像表示させる。

【0199】

ソース信号線18に信号電圧を供給するソースドライバ回路18は、スイッチトランジスタ11bが導通した後で、ソース信号線18に基準電位V0を供給している間に、駆動トランジスタ11aのドレイン端子dに印加する電圧を第1電位(キャンセル電圧)と第2電位(アノード電圧Vdd)との間で切換え、駆動トランジスタ11aのしきい値電圧Vthに相当する電圧をコンデンサ19aに保持しておく。

【0200】

以上に記載してしきい値電圧補正機能により、各画素16の駆動トランジスタ11aの特性バラツキの影響をキャンセルすることができる。

10

【0201】

図113に示した画素16は、上記したしきい値電圧補正機能に加え、移動度補正機能を備えている。

【0202】

ソースドライバ回路18は、スイッチトランジスタ11bが導通した後、第1のタイミングでソース信号線18を基準電位V0から信号電位に切り換える。また、スイッチトランジスタ11c及び11eを制御し、第1のタイミングの後、第2のタイミングでゲート信号線17aに対するオン電圧を解除してスイッチトランジスタ11bを非導通状態とする。第1及び第2のタイミングの間の期間を適切に設定することで、コンデンサ19aに信号電位を保持する際、駆動トランジスタ11aの移動度 $\mu$ に対する補正を信号電位に加える。

20

【0203】

この場合、ゲートドライバ回路は、ソースドライバ回路18が供給する映像信号とゲートドライバ回路12b、12cが供給する制御信号との相対的な位相差を調整して、第1及び第2のタイミングの間の期間(移動度補正期間)を最適化することができる。

【0204】

また、ソースドライバ回路18は、基準電位から信号電位に切り換える映像信号の立ち上がりに傾斜をつけて、第1及び第2のタイミングの間の移動度補正期間を信号電位に自動的に追従させることもできる。

30

【0205】

図113に示した画素16はさらにブートストラップ機能も備えている。ゲートドライバ回路12b及び12cは、コンデンサ19aに信号電位が保持された段階でゲート信号線17bにオフ電圧を印加し、ゲート信号線17cにオン電圧を印加することにより、駆動トランジスタ11aのドレイン端子dの電位をVrからVdd電圧に変化させる。また、スイッチトランジスタ11bを非導通状態にして駆動トランジスタ11aのゲート端子gをソース信号線18から電気的に切り離す。この動作により、駆動トランジスタ11aのソース電位Vsの変動にゲート電位Vgが運動しゲート端子gとソース端子s間の電圧Vgsを一定に維持することができる。

【0206】

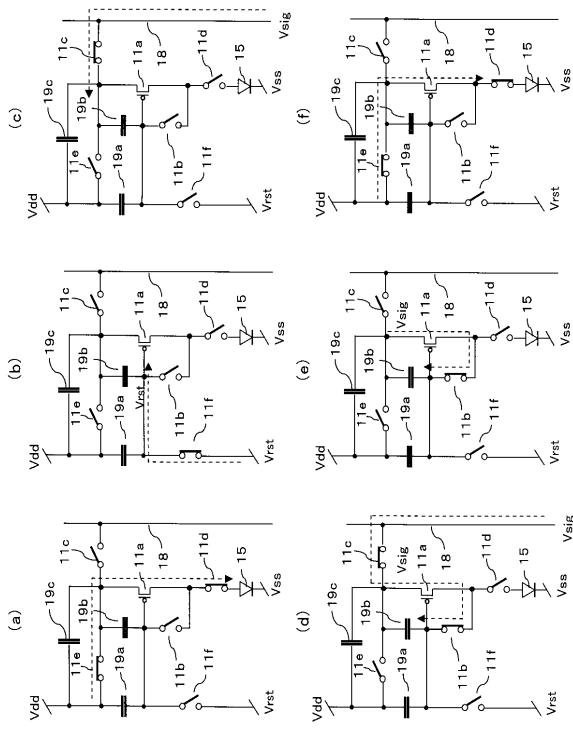

図115は、図113に示した画素16の動作説明に供するタイミングチャートである。時間軸を共通にして、ゲート信号線17a、17b、17cの電位変化、ソース信号線18の電位変化、EL素子15の発光状態と模式的に示している。

40

【0207】

このタイミングチャートは、画素16の動作の変化に合わせて期間をB～Gのように便宜的に区切ってある。

【0208】

発光期間BではEL素子15が発光状態にある。この後、線順次走査の新しいフィールドに入って、最初の期間Cで、スイッチトランジスタ11bがオンし、駆動トランジスタ11aのゲート電位Vgが初期化される。

【0209】

50

次に、期間Dに進み、スイッチトランジスタ11cがオンして駆動トランジスタ11aのドレイン端子dにキャンセル電圧V<sub>r</sub>が印加され、駆動トランジスタ11aのソース電位V<sub>s</sub>も初期化される。このように駆動トランジスタ11aのゲート電位V<sub>g</sub>及びソース電位V<sub>s</sub>を初期化することで、しきい値電圧補正動作の準備が完了する。V<sub>r</sub>電圧は、EL素子15がオンせず（電流が流れない）、駆動トランジスタ11aがオフとなる電圧である。

【0210】

次に、しきい値補正期間Eで実際にしきい値電圧補正動作が行われ、駆動トランジスタ11aのゲート端子gとドレイン端子dとの間にしきい値電圧V<sub>t h</sub>に相当する電圧が保持される。実際には、V<sub>t h</sub>に相当する電圧が、駆動トランジスタ11aのゲート端子gとドレイン端子dとの間に接続されたコンデンサ19aに書き込まれることになる。10

【0211】

次に、サンプリング期間/移動度補正期間Fに進み、映像信号の信号電位V<sub>i n</sub>がV<sub>t h</sub>に足し込まれる形でコンデンサ19aに書き込まれると共に、移動度補正用の電圧Vがコンデンサ19aに保持された電圧から差し引かれる。

【0212】

次に、発光期間Gに進み、信号電位V<sub>i n</sub>に応じた輝度でEL素子15が発光する。そのときに信号電位V<sub>i n</sub>はしきい値電圧V<sub>t h</sub>に相当する電圧と移動度補正用の電圧Vとによって調整されているため、EL素子15の発光輝度は駆動トランジスタ11aのしきい値電圧V<sub>t h</sub>や移動度μのばらつきの影響を受けることがない。20

【0213】

なお、発光期間Gの最初でブートストラップ動作が行われ、駆動トランジスタ11aのゲート-ソース間電圧V<sub>g s</sub>=V<sub>i n</sub>+V<sub>t h</sub>-Vを一定に維持したまま、駆動トランジスタ11aのゲート電位V<sub>g</sub>及びソース電位V<sub>s</sub>が上昇する。

【0214】

図116～図121を参照して、図113に示した画素16の動作を詳細に説明する。なお、図116～図121の図番は、図115に示したタイミングチャートの各期間B～Gにそれぞれ対応している。また、理解を容易にするため、図116～図121は、説明の都合上、EL素子15の容量成分をコンデンサ19bとして図示してある。図116に示すように、発光期間Bでは、スイッチトランジスタ11eがオンし、スイッチトランジスタ11cがオフに制御されることにより、駆動トランジスタ11aのドレイン端子dの電位がアノード電圧V<sub>d d</sub>にあり、駆動トランジスタ11aが駆動電流I<sub>d s</sub>をEL素子15に供給している。30

【0215】

図示する様に、駆動電流I<sub>d s</sub>はアノード電圧V<sub>d d</sub>から駆動トランジスタ11aを介してEL素子15を通り、共通接地電極（GNDなど）又はカソード電極（電圧）V<sub>s s</sub>に流れ込んでいる。

【0216】

次に、期間Cに入ると、図117に示すように、ゲート信号線17aの電位がアノード電圧V<sub>d d</sub>側（オン電圧が印加される）に変化することでスイッチトランジスタ11bがオン状態となり、駆動トランジスタ11aのゲート電位V<sub>g</sub>はソース信号線18の基準電位V<sub>0</sub>に初期化（リセット）される。40

【0217】

次に、期間Dに進むと、図118に示すように、駆動トランジスタ11aのドレイン端子dの電位がアノード電圧V<sub>d d</sub>からソース信号線18の基準電位V<sub>0</sub>より十分低いキャンセル電圧V<sub>r</sub>に変化する。

【0218】

これにより駆動トランジスタ11aのソース電位V<sub>s</sub>がソース信号線18の基準電位V<sub>0</sub>より十分低いキャンセル電圧V<sub>r</sub>に初期化（リセット又はキャンセル）される。

【0219】

10

20

30

40

50

具体的には、駆動トランジスタ 11a のゲート - ソース間電圧  $V_{gs}$  (ゲート電位  $V_g$  とソース電位  $V_s$  の差) が駆動トランジスタ 11a のしきい値電圧  $V_{th}$  より大きくなるように、駆動トランジスタ 11a のドレイン端子 d に低キャンセル電圧  $V_r$  を設定する。

#### 【0220】

次に、しきい値補正期間 E に進むと、図 119 に示すように、駆動トランジスタ 11a のドレイン端子 d の電位が低キャンセル電圧  $V_r$  からアノード電圧  $V_{dd}$  に変化し、駆動トランジスタ 11a のソース電位  $V_s$  が上昇を開始する。

#### 【0221】

やがて、駆動トランジスタ 11a のゲート端子 - ソース端子間電圧  $V_{gs}$  がしきい値電圧  $V_{th}$  となったところで電流はカットオフする (流れなくなる)。このようにして駆動トランジスタ 11a のしきい値電圧  $V_{th}$  に相当する電圧がコンデンサ 19a に書き込まれる。これがしきい値電圧補正動作である。このとき電流が専らコンデンサ 19a 側に流れ、EL 素子 15 側には流れないようにするため、EL 素子 15 がカットオフとなるように共通接地電極又はカソード電極 (電圧)  $V_{ss}$  の電位を設定しておく。

10

#### 【0222】

次に、サンプリング期間 / 移動度補正期間 F に進むと、図 120 に示すように、第 1 のタイミングでソース信号線 18 の電位が基準電位  $V_0$  から信号電位  $V_{in}$  に変化し、駆動トランジスタ 11a のゲート電位  $V_g$  は  $V_{in}$  となる。

#### 【0223】

このとき EL 素子 15 は始めカットオフ状態 (ハイインピーダンス状態) にあるため駆動トランジスタ 11a のドレイン電流  $I_{ds}$  は EL 素子 15 のコンデンサ 19 (寄生容量) 19b に流れ込む。

20

#### 【0224】

これにより EL 素子 15 のコンデンサ 19 (寄生容量) 19b は充電を開始する。よって駆動トランジスタ 11a のソース電位  $V_s$  は上昇を開始し、第 2 のタイミングで駆動トランジスタ 11a のゲート - ソース間電圧  $V_{gs}$  は  $V_{in} + V_{th} - V$  となる。このようにして信号電位  $V_{in}$  のサンプリングと補正量  $V$  の調整が行われる。  $V_{in}$  が高いほど  $I_{ds}$  は大きくなり、  $V$  の絶対値も大きくなる。したがって発光輝度レベルに応じた移動度補正が行える。また  $V_{in}$  を一定とした場合、駆動トランジスタ 11a の移動度  $\mu$  が大きいほど  $V$  の絶対値も大きくなる。換言すると移動度  $\mu$  が大きいほど負帰還量  $V$  が大きくなるので、画素 16 每の移動度  $\mu$  のばらつきを取り除くことが可能である。

30

#### 【0225】

最後に、発光期間 G になると、図 121 に示すように、ゲート信号線 17 が低電位側に変化し、スイッチトランジスタ 11b はオフ状態となる。これにより駆動トランジスタ 11a のゲート端子 g はソース信号線 18 から切り離される。同時にドレイン電流  $I_{ds}$  が EL 素子 15 を流れ始める。これにより EL 素子 15 のアノード電位は駆動電流  $I_{ds}$  に応じて上昇する。

#### 【0226】

EL 素子 15 のアノード電位の上昇は、すなわち駆動トランジスタ 11a のソース電位  $V_s$  の上昇に他ならない。駆動トランジスタ 11a のソース電位  $V_s$  が上昇すると、コンデンサ 19a のブートストラップ動作により、駆動トランジスタ 11a のゲート電位  $V_g$  も連動して上昇する。ゲート電位  $V_g$  の上昇量はソース電位  $V_s$  の上昇量に等しくなる。故に、発光期間中駆動トランジスタ 11a のゲート - ソース間電圧  $V_{gs}$  は  $V_{in} + V_{th} - V$  で一定に保持される。

40

#### 【0227】

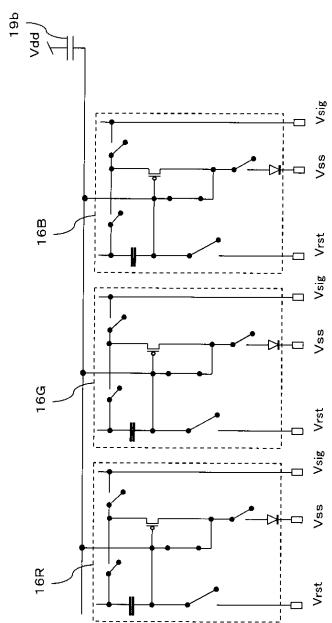

図 122 は、図 113 の変更例である。

#### 【0228】

EL 素子 15 のアノード端子と駆動トランジスタ 11a のドレイン端子 d 間に、第 4 のスイッチトランジスタ 11d を形成している。スイッチトランジスタ 11d は、ゲート信号線 17d に接続され、また、ゲート信号線 17d は、ゲートドライバ回路 12d からオ

50

ン／オフ電圧が印加される。

【0229】

図120などでは、駆動トランジスタ11aのモビリティバラツキを補正できることを説明した。つまり、図120は、スイッチトランジスタ11aを、短期間、スイッチトランジスタ11eをオンした方法である。

【0230】

短時間とは、0.05μ秒以上5μ秒以下の時間である。前記短時間は、画素に印加する映像信号電圧Vsigに対応させて変化させることが好ましい。また、点灯率に対応させて変化させることが好ましい。この変化は、線形、非線形に対応させることを含むほか、ステップ状（例えば、点灯率50%以上では、短時間とは0.1μ秒、点灯率50%未満では、2μ秒）に対応させてもよい。

10

【0231】

図115に図示するように、点灯率に相関させて、duty比を制御あるいは変化させてことが好ましい。ピーク電流を抑制し、消費電力を平均化することができるからである。点灯率が高いときは、duty比を低下（小さく）する。したがって、ピーク電流を抑制できる。また、最大使用階調数制御を実施する。以上の事項は、図78、図79、図83、図84、図98、図99、図130などを用いて説明を行っている。

【0232】

1水平走査期間（1H）に対するオン時間比率（%）（以下、オン比率と呼ぶ）は、図120の期間である。オン時間とは、スイッチトランジスタ11b、11eのオン時間（クローズ時間）を意味する。1Hが、20μ秒とすれば、10%とは、2μ秒となる。

20

【0233】

オン比率が長いほど、駆動トランジスタ11aのモビリティの補正効果が高くなる。しかし、コンデンサ19の電荷が放電され、駆動トランジスタ11aのゲート端子電位が高く（アノード電圧側）の変化し、EL素子15に流れる電流が変化してしまう。

【0234】

オフセットキャンセル駆動では、黒の階調（低階調）は、オフセットキャンセルされ、駆動トランジスタ11aの特性バラツキは目立ちにくい。しかし、白の階調（高階調）では、オフセットキャンセル点から離れているため、駆動トランジスタ11aの特性ばらつきが目立ちやすい。この駆動トランジスタ11aの特性バラツキはモビリティによるものである。

30

【0235】

点灯率が低い場合は、低階調表示の画素が多い。点灯率が高い場合は、高階調表示の画素が多い。したがって、オン比率は、図115の下図の点線で示すように実施することが好ましい。つまり、低点灯率では、オン比率は0とし、高点灯率になるにしたがって、オン比率を大きくする。

【0236】

しかし、点灯率が低い時は、低階調表示の画素が多いというのは、統計的なものであり、実際と異なることがある。また、点灯率が高い場合は、高階調表示の画素が多いというのも統計的なものである。実際には表示パターン、映像信号の種類により異なる。したがって、表示パターン、入力される映像信号の種類（PC映像、AV映像など）などにより、オン比率を可変できるように構成しておくことが好ましい。

40

【0237】

図113、図123に図示するように、その他、ゲート信号線17aとトランジスタ11aのゲート（G）端子間に積極的にコンデンサCxを形成し、突き抜け電圧を増加させる構成も有効である。このコンデンサCxの容量は正規のコンデンサ19aの容量の1/10以上1/2以下にすることが好ましい。さらには1/8以上1/3以下とすることが好ましい。

【0238】

突き抜け電圧発生用のコンデンサCxの容量（容量をCb（pF）とする）は、電荷保

50

持用のコンデンサ 19a の容量 (容量と  $C_a$  (pF) とする) と、トランジスタ 11a の白ピーク電流時 (画像表示で表示最大輝度の白ラスター時) のゲート (G) 端子電圧  $V_w$  (V) を黒表示での電流を流す (基本的には電流は 0 である。つまり、画像表示で黒表示としている時) 時のゲート (G) 端子電圧  $V_b$  (V) が関連する。これらの関係は、

$$C_a / (200Cb) \quad |V_w - V_b| \quad C_a / (8Cb)$$

の条件を満足させることが好ましい。なお、 $|V_w - V_b|$  とは、駆動トランジスタの白表示時の端子電圧 (V) と黒表示時の端子電圧 (V) との差の絶対値である (つまり、変化する電圧幅)。

#### 【0239】

さらに好ましくは、

$$C_a / (100Cb) \quad |V_w - V_b| \quad C_a / (10Cb)$$

の条件を満足させることが好ましい。

10

#### 【0240】

トランジスタ 11b は P チャンネルにし、この P チャンネルは少なくともダブルゲート以上にする。このましくは、トリプルゲート以上にする。さらに好ましくは、4 ゲート以上にする。そして、トランジスタ 11b のソース - ゲート (SD もしくはゲート - ドレイン (GD)) 容量 (トランジスタがオンしているときの容量) の 1 倍以上 10 倍以下のコンデンサを並列に形成又は配置することが好ましい。

#### 【0241】

なお、以上の事項は、図 113、図 123 の画素構成だけでなく、他の画素構成でも有効である。スイッチトランジスタ 11b がオフするときに、駆動トランジスタ 11a に電流が流れないようにシフトするように、コンデンサ  $C_x$  を配置する。なお、スイッチングトランジスタ 11b の N チャンネルはダブルゲート以上とする。リーク対策のためである。

20

#### 【0242】

図 113 では、駆動トランジスタ 11a は、N チャンネルトランジスタであり、映像信号を画素に印加するスイッチトランジスタ 11b も N チャンネルトランジスタである。スイッチトランジスタ 11b を制御するゲート信号線 17a は、画素 16 の選択時は、高い電圧 ( $V_{GH}$ ) が印加され、非選択となる場合は、低い電圧 ( $V_{GL}$ ) が印加される。

30

#### 【0243】

画素 16 が選択状態から非選択状態になる時は、ゲート信号線 17a に電気的に接続されたコンデンサ  $C_x$  の一端子は  $V_{GH}$  電圧から  $V_{GL}$  電圧に変化する。コンデンサ  $C_x$  は  $V_{GH}$  電圧から  $V_{GL}$  電圧への変化をつき抜け電圧として他のコンデンサ  $C_x$  端子 (駆動トランジスタ 11a のゲート端子に接続されている) 伝達する。したがって、 $V_{GH}$  から  $V_{GL}$  電圧の変化に比例した電圧が、駆動トランジスタ 11a のゲート端子に印加され、駆動トランジスタ 11a のゲート端子電圧を低下させる。したがって、駆動トランジスタ 11a は電流を流しにくい方向に動作する。この動作により、より黒表示レベルが改善され、良好なコントラストを実現できる。

#### 【0244】

同様に、図 123 では、駆動トランジスタ 11a は、P チャンネルトランジスタであり、映像信号を画素に印加するスイッチトランジスタ 11b も P チャンネルトランジスタである。つまり、駆動トランジスタ 11a とスイッチトランジスタ 11b とは同極性のチャンネルトランジスタで構成されている。スイッチトランジスタ 11b を制御するゲート信号線 17a は、画素 16 の選択時は、低い電圧 ( $V_{GL}$ ) が印加され、非選択となる場合は、高い電圧 ( $V_{GH}$ ) が印加される。

40

#### 【0245】

したがって、画素 16 が選択状態から非選択状態になる時は、ゲート信号線 17a に電気的に接続されたコンデンサ  $C_x$  の一端子は  $V_{GL}$  電圧から  $V_{GH}$  電圧に変化する。コンデンサ  $C_x$  は  $V_{GL}$  電圧から  $V_{GH}$  電圧への変化をつき抜け電圧として他のコンデンサ  $C_x$  端子 (駆動トランジスタ 11a のゲート端子に接続されている) 伝達する。そのため、

50

V G L から V G H 電圧の変化に比例した電圧が、駆動トランジスタ 11 a のゲート端子に印加され、駆動トランジスタ 11 a のゲート端子電圧を高い電圧の方向にシフトさせる。したがって、駆動トランジスタ 11 a は電流を流しにくい方向に動作する。この動作により、より黒表示レベルが改善され、良好なコントラストを実現できる。

【0246】

また、突き抜け電圧用のコンデンサ C x は、画素が変調する R、G、B で大きさ（容量）を変化させることが好ましい。R、G、B の各 E L 素子 15 の駆動電流が異なるためである。また、E L 素子 15 のカットオフ電圧が異なるためである。そのため、E L 素子 15 の駆動トランジスタ 11 a のゲート（G）端子にプログラムする電圧（電流）が異なるからである。例えば、R の画素のコンデンサ C x R を 0.02 pF とした場合、他の色（G、B の画素）のコンデンサ C x G、C x B を 0.025 pF とする。また、R の画素のコンデンサ C x R を 0.02 pF とした場合、G の画素のコンデンサ C x G と 0.03 pF とし、B の画素のコンデンサ C x B を 0.025 pF とするなどである。このように、R、G、B の画素ごとにコンデンサ C x の容量を変化させることのよりオフセットの駆動電流を R G B ごとに調整することができる。したがって、各 R G B の黒表示レベルを最適値にすることができる。

10

【0247】

以上の事項は、図 1 などの実施例 1、実施例 3 などの画素構成にも適用される。本明細書に記載した実施例は相互に組み合わせることができる。

20

【0248】

以上は、突き抜け電圧発生用のコンデンサ C x の容量を変化させたが、突き抜け電圧は、保持用のコンデンサ 19 a と突き抜け電圧発生用のコンデンサ C x との容量の相対的なものである。したがって、コンデンサ C x を R、G、B の画素で変化することに限定するものではない。つまり、保持用コンデンサ 19 a の容量を変化させてもよい。

30

【0249】

例えば、R の画素のコンデンサ 11 a R を 1.0 pF とした場合、G の画素のコンデンサ 11 a G と 1.2 pF とし、B の画素のコンデンサ 11 a B を 0.9 pF とするなどである。この時、突き抜け用コンデンサ C x の容量は、R、G、B で共通の値とする。したがって、本実施例は、保持用のコンデンサ 19 a と突き抜け電圧発生用のコンデンサ C x との容量比を、R、G、B の画素のうち、少なくとも 1 つを他と異ならせたものである。なお、保持用のコンデンサ 19 a の容量と突き抜け電圧発生用のコンデンサ C x との容量との両方を R、G、B 画素で変化させてもよい。

【0250】

また、画面 31 の左右で突き抜け電圧用のコンデンサ C x の容量を変化させてもよい。

【0251】

以上の事項は、図 1 などの実施例 1、実施例 3 ~ 7 などの画素構成、表示パネル（表示装置）あるいは駆動方法にも適用される。本明細書に記載した実施例は相互に組み合わせることができる。

【0252】

ゲートドライバ回路 12 に近い位置にある画素 16 は信号供給側に配置されているので、ゲート信号の立ち上がりが速い（スルーレートが高いからである）ため、突き抜け電圧が大きくなる。ゲート信号線 17 端に配置（形成）されている画素は、信号波形が鈍っている（ゲート信号線 17 には容量があるためである）。ゲート信号の立ち上がりが遅い（スルーレートが遅い）ため、突き抜け電圧が小さくなるためである。したがって、ゲートドライバ回路 12 との接続側に近い画素 16 の突き抜け電圧用コンデンサ C x を小さくする。また、ゲート信号線 17 端はコンデンサ C x を大きくする。例えば、画面の左右でコンデンサの容量は 10 % 程度変化させる。

40

【0253】

同様に、画面 31 の上下で突き抜け電圧用のコンデンサ C x の容量を変化させてもよい。画面 31 には、コンデンサ C a と映像信号の書き込みタイミングの問題から、輝度傾斜が

50

発生するからである。コンデンサ  $C_x$  の値をまた、ソース信号線 18 に沿って変化させる。例えば、画面の上下でコンデンサ  $C_x$  の容量は 10 % 程度変化させる。

【0254】

発生する突き抜け電圧は、保持用コンデンサ 19a と突き抜け電圧発生用のコンデンサ  $C_x$  の容量比で決定される。したがって、画面の左右で突き抜け電圧発生用のコンデンサ  $C_x$  の大きさを変化させるとしたが、これに限定するものではない。突き抜け電圧発生用のコンデンサ  $C_x$  は画面の左右で一定にし、電荷保持用のコンデンサ 19a の容量を画面の左右で変化させてもよい。また、突き抜け電圧発生用のコンデンサ  $C_x$  と、電荷保持用のコンデンサ 19a 容量の両方を画面の左右で変化させてもよいことは言うまでもない。以上の事項は、画面 31 の上下方向に関しても同様である。

10

【0255】

図 1 の構成あるいは方式は、映像信号電圧  $V_{sig}$  を画素に形成されたオフセットキャンセルコンデンサ 19b に保持するものであった。オフセットキャンセルコンデンサ 19b に映像信号電圧  $V_{sig}$  を保持することにより、画素 16 の選択後もオフセットキャンセル動作を継続し、良好なオフセットキャンセルを実現できる。

【0256】

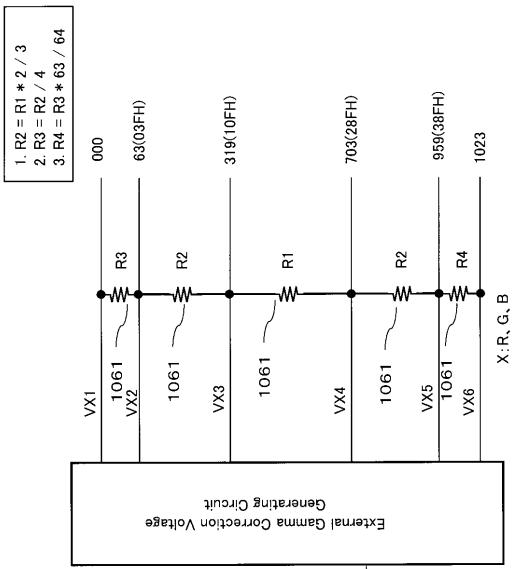

図 95 は、図 113、図 123 などで説明した本実施例の画素構成あるいは E-L 表示装置にコンデンサ 19b を付加した構成である。コンデンサ 19b は、映像信号電圧  $V_{sig}$  を保持するものではなく、キャンセル電圧  $V_r$  を保持する。

20

【0257】

図 118 に図示するように、キャンセル電圧  $V_r$  を短時間の間、駆動トランジスタ 11a のソース端子（もしくはドレイン端子）に印加する。しかし、短時間のため、十分にキャンセル動作を実施できない場合がある。

【0258】

図 95 のように、キャンセル電圧  $V_r$  を保持するコンデンサ 19b を画素 16 に形成すれば、スイッチトランジスタ 11c をオフした後も、コンデンサ 19b に保持したキャンセル電圧  $V_r$  を用いて、キャンセル動作を継続できる。したがって、キャンセル動作を複数水平走査期間に渡り、実施することができる。

【0259】

以上のように、本実施例は、所定の種類の電圧（映像信号電圧  $V_{sig}$ 、キャンセル電圧  $V_r$  など）を画素 16 に印加し、前記所定の種類の電圧の印加が完了後も、所定の種類の電圧をコンデンサ 19b に保持し、保持した電圧により所定動作（オフセットキャンセル動作、キャンセル動作など）を継続するものである。また、所定動作の継続できる構造又は構成である。

30

【0260】

なお、本発明の実施例において、所定の種類の電圧（映像信号電圧  $V_{sig}$ 、キャンセル電圧  $V_r$  など）を保持するコンデンサ 19b を画素 16 に形成するとしたが、これに限定するものではない。例えば、ダイオードを画素に形成し、ダイオードの接合容量に前記所定の種類の電圧を保持してもよい。また、画素にトランジスタ素子を形成し、トランジスタの寄生容量（ゲート容量など）に前記所定の種類の電圧を保持してもよい。

40

【0261】

また、所定の種類の電圧（映像信号電圧  $V_{sig}$ 、キャンセル電圧  $V_r$  など）を保持するコンデンサ 19b を画素 16 に形成するとしたが、これに限定するものではない。例えば、図 124～図 126 に図示するように、複数の画素 16 を共通（画素行、画素列）にして、1 つのコンデンサ 19b を配置してもよい。

【0262】

図 124 は、1 画素行に 1 つのコンデンサ 19b を形成し、コンデンサ 19b にキャンセル電圧  $V_r$  を保持させる構成である。図 125 は、1 画素行に 1 つのコンデンサ 19b を形成し、コンデンサ 19b に映像信号電圧  $V_{sig}$  を保持させる構成である。映像信号電圧  $V_{sig}$  が画素行あるいは画素列に共通の信号である場合に有効である。図 126 は

50

、1画素行に1つのコンデンサ19bを形成し、コンデンサ19bにリセット電圧Vrstを保持させる構成である。

#### 【0263】

また、図124～図126の構成において、各画素にリセット電圧Vrstあるいは、キャセル電圧Vrを印加するスイッチトランジスタ(11cあるいは11f)を配置しているが、これに限定するものではない。例えば、RGBの画素を1組として、スイッチトランジスタ(11cあるいは11f)を配置してもよい。また、画素行あるいは画素列ごとに、スイッチトランジスタ(11cあるいは11f)を配置してもよい。

#### 【0264】

アノード電圧Vdd、カソード電圧Vssなどの電圧を発生させる電源回路(電源IC)を外部に配置する場合は、この電源回路(電源IC)をオン/オフ制御させるオン/オフ信号をソースドライバIC14から発生(指示)させることが好ましい。アノード電圧Vdd、カソード電圧Vssは、VGH、VGL電圧の印加(供給)後に、パネル34に印加(供給)する。

#### 【0265】

以上の事項は、本明細書の他の実施例にも適用されることは言うまでもない。

#### 【0266】

図127に図示するように、キャセル電圧Vrを印加する配線及びスイッチトランジスタ11cを複数の画素(例えば、RGBの画素を1組として)に1つ形成又は設けてよい。また、コンデンサ19bは、RGBで異ならせてても良い。RGBでコンデンサ19bの容量を異ならせることにより、オフセットキャンセル動作、リセット動作、キャンセル動作などが、RGBの特性にあわせて最適に設定できるからである。

#### 【0267】

図128に図示するように、キャセル電圧Vrを印加する配線及びスイッチトランジスタ11c、コンデンサ19bを複数の画素(例えば、RGBの画素を1組として)に1つ形成又は設けてよい。画素構成が簡略化され、画素16の開口率を向上できる。以上の事項は、本明細書の他の実施例にも適用されることは言うまでもない。

#### 【0268】

コンデンサ19bの容量は、表示画面31の部分で異ならせてよい。例えば、画面の左右と中央部で、コンデンサ19bの容量を異ならせる。画面の部分にあわせて、オフセットキャンセル動作、リセット動作、キャンセル動作などが、最適に設定できるからである。以上の事項は、保持用のコンデンサ19aにも適用できる。画面の部分にあわせて、映像信号電圧Vsigの書き込み、オフセットキャンセル動作などが、最適に設定できるからである。

#### 【0269】

以上の事項は、本明細書の他の実施例においても適用されることは言うまでもない。また、他の実施例と組み合わせることができることは言うまでもない。したがって、他の実施例において、図面の作図、説明を容易にするために、複数の構成、実施の組み合わせは省略している。以上の事項は、図1、図4、図5、図10、図11、図25、図29、図31、図33、図35、図37、図42、図46、図52、図54、図55、図58、図59、図86、図90、図91、図92、図93、図94、図95、図113、図123、図124～図128などのEL表示パネルあるいはEL表示装置にも適用できることは言うまでもない。

#### 【0270】

以上の事項は他の実施例においても同様である。例えば、図12、図13、図61、図75、図76、図77、図78、図79、図83、図84、図85、図98、図99、図100、図101などの方法あるいは方式、図7、図8、図9、図60、図83、図96、図102、図103、図104、図106、図107、図108、図109、図110、図111、図112、図129の構成あるいは構造あるいは方法に関しても先に例示したあるいは本明細書に記載した画素構成と組み合わせて実施することは言う

10

20

30

40

50

までもない。

【実施例 3】

【0271】

本発明の実施例 3 について説明する。なお、今までに説明した構成、方式は、以下に説明する構成あるいは方式に、適用あるいは組み合わせることは言うまでもない。

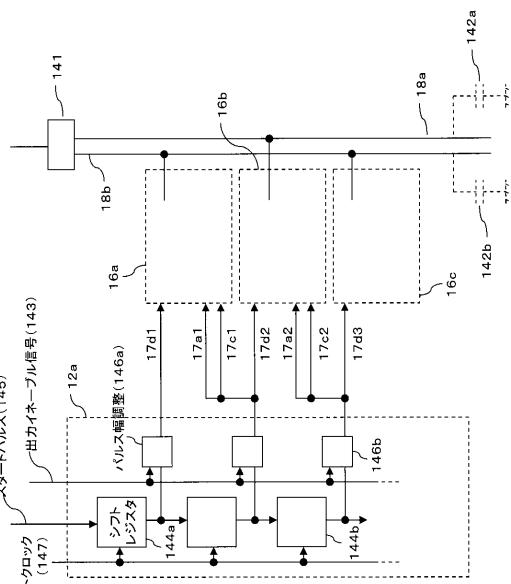

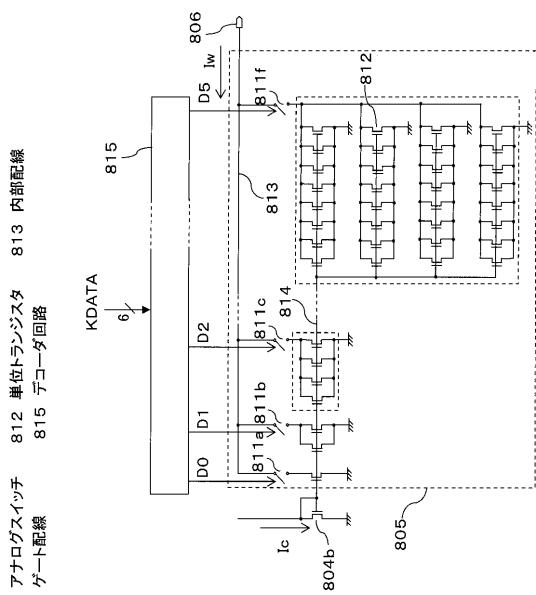

【0272】

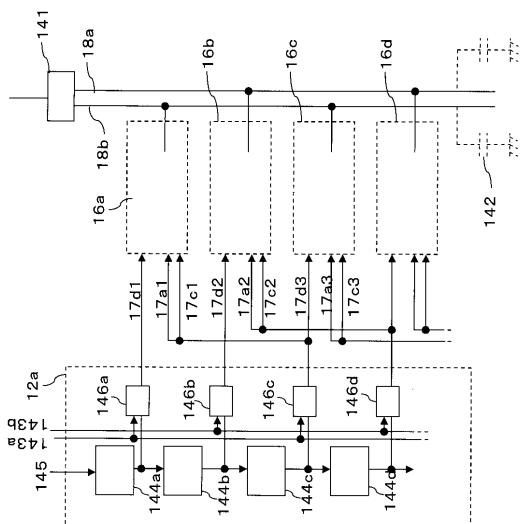

図 14 は、本実施例における E L 表示パネルの 1 列分の回路を示したものである。ここでソース信号線 18 は切り替え手段 141 を介して、1 列に対して 2 本のソース信号線 18a と 18b が存在し、偶数行と奇数行の画素で接続されるソース信号線が異なる構成となっていることが特徴である（図 6 なども参照のこと）。

10

【0273】

各画素 16 の構成は、例えば、図 1、図 4、図 10、図 25、図 29、図 42、図 46、図 52、図 54、図 55、図 58、図 59、図 86、図 87、図 90、図 91、図 92、図 93、図 94、図 95、図 113、図 122、図 124～図 128 などの回路で構成されている。つまり、以下の実施例は、本明細書の他の実施例に適用することができる。また、相互に組み合わせることができる。

【0274】

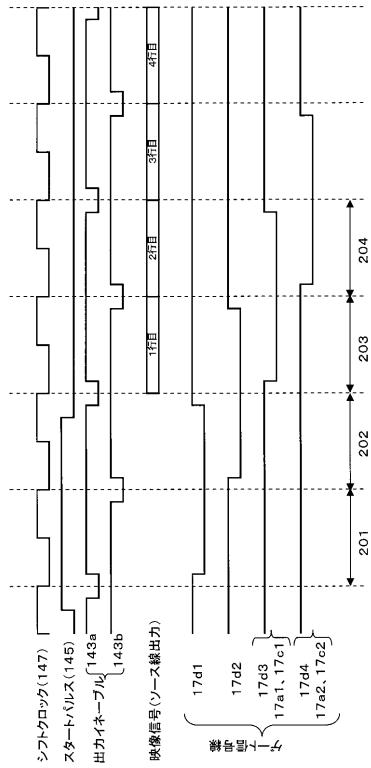

ゲートドライバ回路 12a は、シフトレジスタ構成となっており、クロックごとにパルスが 1 段ずつシフトされる。ゲート信号線 17 に対する接続を、図 14 のように行うことで、図 15 に示すような信号波形を実現することができる。

20

【0275】

シフトクロックの周期を 1 水平走査期間（1H）に設定し、1 水平走査期間のみパルスが出力されるようなスタートパルスが入力される。これで各行 1 水平走査期間ずつずれたタイミングで 1 水平走査期間の間パルスが発生する回路が実現できる。

【0276】

シフトレジスタの各段出力を図 14 のようにゲート信号線 17 に取り込み、切り替え手段 141 を図 15 に示すように動作させることで、始めの 1 水平走査期間（1H）では、1 行目の画素 16a の駆動トランジスタ 11a のゲート電圧を V<sub>rst</sub> 電源により、初期化する。同時にソース信号線から所定の階調に対応する 1 行目の画素に対応する信号電圧が切り替え手段 141 を介してソース信号線 18b に充電される。ソース信号線 18a には充電されない。切り替え手段 141 でソースドライバ出力から切り離されている。

30

【0277】

次の 1 水平走査期間においては切り替え手段 141 を動作させ、ソース信号線 18a を充電するようにする。このときソース信号線 18b は、ソースドライバ出力から切り離されているために、ソース信号線の浮遊容量 142b により 1 行目の画素に対応する信号電圧が充電されたままである。そこで、ゲート信号線 17a 及びゲート信号線 17c を走査し、画素 16a のトランジスタ 11c、11b を導通状態とし、画素の駆動トランジスタ 11a に階調信号の書き込みと、特性バラツキのキャンセル動作を実施する。同時に 2 行目の画素に対応して、画素 16b に対応する階調信号電圧がソース信号線 18a に充電され、駆動トランジスタ 11a のゲート端子が V<sub>rst</sub> 電源により初期化される。

40

【0278】

浮遊容量 142 は、ゲート信号線 17 とソース信号線 18 の交差部に生じる容量、ソース信号線 18 と画素電極との結合容量などで構成される。図 14 などにおいて、コンデンサ 142 は浮遊容量として説明するがこれに限定されるものではない。ソース信号線 18 を一方の電極としてコンデンサを形成してもよい。

【0279】

ソース信号線 18a とソース信号線 18b を水平走査期間ごとに切り替えて利用することで、ソース信号線に印加させる階調信号が 2 水平走査期間保持されるため、画素回路 16 に信号を書き込む時間を長くすることができるようになる。

50

## 【0280】

図1などの画素回路の構成では、駆動トランジスタ11aに階調信号を書き込みながら、特性バラツキをキャンセルする動作を行う。特性バラツキをキャンセルする動作は、トランジスタ11f、11d、11eがオフでトランジスタ11bがオン状態のときに行われ、駆動トランジスタ11aのドレイン電流が0になるように、駆動トランジスタ11aのゲート電位が変化することで、特性バラツキのキャンセルを行っている。

## 【0281】

駆動トランジスタ11aのゲート電位を変化させているのは、ドレイン電流による電荷であり、最終状態が0もしくは限りなく小さい電流（ピコアンペアオーダー）であることから、ゲート電位を支えている保持用コンデンサ19aの電荷の充放電に時間がかかる。そのため、キャンセル動作には時間がかかることがわかる。

10

## 【0282】

1水平走査期間（1H）が長い場合には、1水平走査期間内にキャンセル動作を完了させることができる。しかし、垂直ライン数が多く、1水平走査期間が40μ秒よりも短い場合には、キャンセル動作が最後まで行われず、特性補償が不完全となり、その結果、特性ばらつきに応じたムラが発生する問題がある。

20

## 【0283】

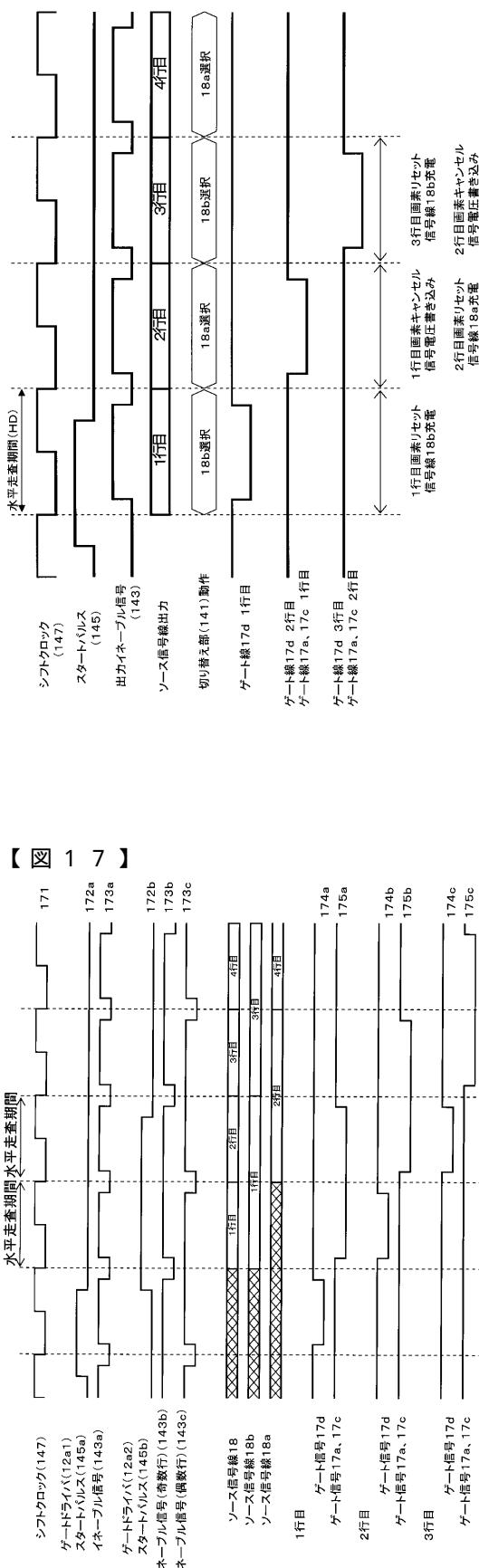

そこで、キャンセル時間を1水平走査期間以上に拡大する方法として、図16に示すようにゲートドライバ回路12aを更に2本のゲートドライバ回路12a1、ゲートドライバ回路12a2で構成する。駆動トランジスタ11aの初期化を、対応する映像信号が入力される1水平走査期間前にあらかじめ実施する。また、ソース信号線18aもしくは18bに映像信号が入力される水平走査期間から駆動トランジスタ11aに階調電圧の書き込み及び特性キャンセル動作を行うようとする。切り替え部141の動作により、2水平走査期間の間映像信号が保持されるため、階調電圧の書き込み及び特性キャンセル動作を2水平走査期間中実施することが可能となる。

20

## 【0284】

これを実現するために、図17に示すように、シフトレジスタ12a2のスタートパルス172bを入力する。各行のトランジスタ17a及び17cが2水平走査期間オンされる。オンされるタイミングはソース信号線18及び18a、18bの映像信号に同期して実施される。映像信号が偶数行と奇数行で2つのソース信号線18a及び18cに振り分けられることで周波数が半分となり、書き込み時間を2倍にことができる。

30

## 【0285】

なお、イネーブル信号173については、パルス伝播の際の波形なまりによる複数の行の画素で同時選択されることを防止するための信号であり、同時選択が起きない場合や、同時選択でも問題なく動作する場合には、不要である。イネーブル信号173がなくても本実施例を実施することができる。例えば図21のように、特性キャンセルを行うための信号を生成するゲートドライバ回路12a2のイネーブル信号を削除した場合の入力波形及び動作を示す。

## 【0286】

図17の波形によれば、2水平走査期間の間、駆動トランジスタ11aの特性補正動作が可能であるが、あらかじめ映像信号が入力される1水平走査期間前に駆動トランジスタ11aを初期化するための動作が必要であり、1水平走査期間前にあらかじめ動作させることが必要である。したがって、先頭行が検知できない場合には、あらかじめ初期化ができなくなる恐れがある。

40

## 【0287】

そこで、図18に示すように、初期化動作を、1行目の映像信号入力時と同時に実施する信号パターンを発明した。初期化動作時には、特性補正動作ができないため、2水平走査期間（2H）の間で、初期化後特性補正動作を行う。

## 【0288】

図18の構成では、2水平走査期間のうちの始めの水平走査期間の前半に初期化動作を

50

行い、残りの半分と次の水平走査期間で画素への信号書き込みと特性補償動作を実施する。ゲートドライバがシフトレジスタ構成である場合には、水平走査期間とシフトクロックが一致する場合には、イネーブル信号でパルス幅をカットする方法により、水平走査期間の前半と後半で異なるスイッチの動作を実現する。

【0289】

ゲート信号線 17d がローレベルの時が、駆動トランジスタ 11a の初期化期間となり、ゲート信号線 17a 及び 17c がローレベルのときに、駆動トランジスタ 11a の特性キャンセルと、画素に階調を書き込む期間となる。

【0290】

17a 及び 17c のローレベル期間が 1 水平走査期間より長く設定できるため、水平走査期間が 30 μ秒であっても、従来比 1.5 倍の期間が取れることから 45 μ秒のキャンセル期間がとれ、駆動トランジスタの特性ばらつきを補正することが可能となる。初期化動作自体は、2 ~ 10 μ秒程度で完了するため、最大 2 水平走査期間から 2 ~ 10 μ秒を引いた時間までキャンセル期間を拡大することができる。

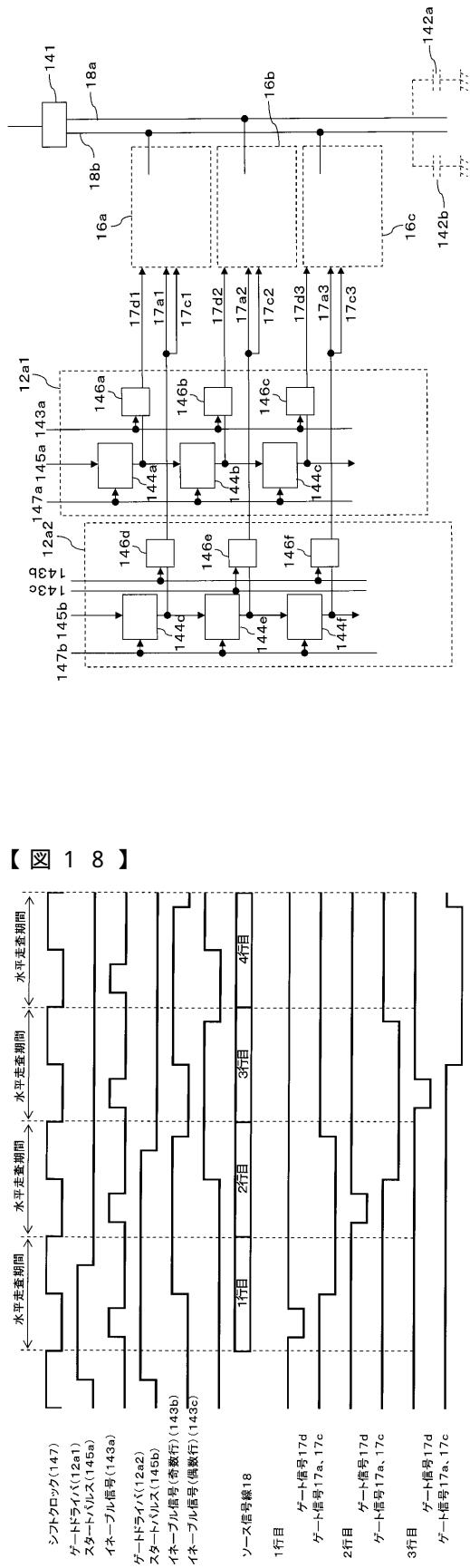

【0291】

ゲートドライバ回路 12a のシフトレジスタが 1 系統でかつキャンセル期間を 1 水平走査期間以上に拡大する方法を図 19 及び図 20 に示す。

【0292】

例えば、2 水平走査期間の間キャンセルする場合には、2 水平走査期間ゲート信号線 17a 及び 17c が導通状態にある必要がある。そこでゲートドライバ回路 12a のスタートパルスを 2 水平走査期間の長さだけ入力する。これにより、キャンセル及び階調書き込み時間を 2 水平走査期間に設定できる。同様に初期化を実施するためのゲート信号線 17d 用のパルスを生成する必要がある。

【0293】

また、図 1、図 25 に示すような画素回路構成であることから、ゲート信号線 17d と駆動トランジスタ 11a、スイッチトランジスタ 11c を同時に導通状態としてはならないため（異なる電圧がショートする）、初期化用のパルスは、同一行の画素に対するキャンセル及び階調書き込み用のパルスと重ならないようにする必要がある。

【0294】

具体的には、2 水平走査期間前のパルスを初期化用のパルスとして利用すればよい。図 19 に示すように、シフトレジスタに対して、ゲート信号線 17d と共通の出力をキャンセル及び階調信号書き込み用ゲート信号線を用いる場合には、2 行分後段（つまり 2 水平走査期間後）の信号を利用すると、同一画素 16a に対して、図 20 に示すように、201、202 の 2 水平走査期間で初期化を実施する。また、203、204 の 2 水平走査期間で駆動トランジスタ 11a の特性キャンセル及び階調信号書き込みを実施している。16b、16c の画素においても同様に 1 水平走査期間ずつ遅れたタイミングで実施している。

【0295】

この方法は、2 水平走査期間のキャンセルばかりでなく、3 水平走査期間以上、必要な場合でも実施が可能である。1 列分の画素に対応するソース信号線の数を必要とする水平走査期間の数（整数）分を用意し、ゲートドライバ回路 12a のスタートパルスのパルス幅を必要な水平走査期間数分入力する。初期化に対応するゲート信号を取り出すシフトレジスタの段から必要な水平走査期間数分後段のシフトレジスタから特性キャンセル及び階調信号書き込み用のゲート信号をとりだして、同一行の画素に入力すれば実現が可能である。

【0296】

映像信号が、対応する行の画素に書き込まれるようにするため、スタートパルスは、映像信号に対してあらかじめ入力する必要がある。少なくともキャンセルを行う水平走査期間の長さ分だけ早く入力が必要である。図 20 においても 2 水平走査期間早く、入力している。

10

20

30

40

50

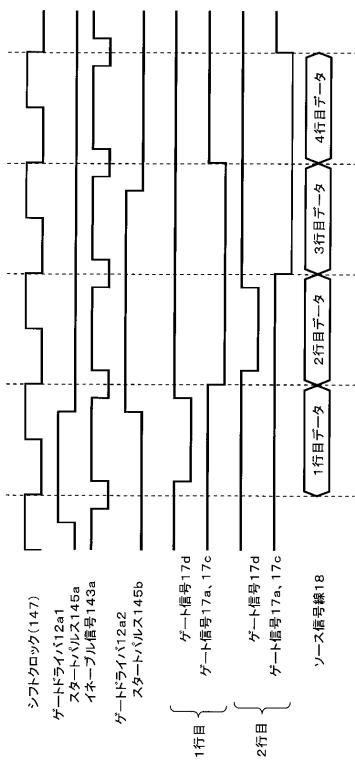

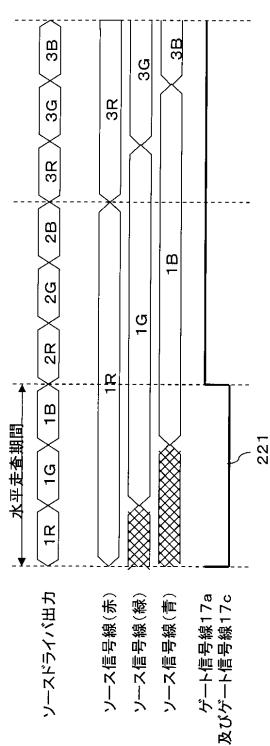

## 【0297】

ソースドライバのコスト削減のために、1出力から時系列に複数の画素に対応する電圧を出力する選択駆動方式を採用することがある。選択駆動方式がない場合に比べて、当該画素に対応する映像信号が入力されるタイミングが表示色によって異なるようになる。

## 【0298】

例えば、赤緑青の3画素分を1出力で行う3選択駆動の場合においては、図22に示すように、赤(R)色に対して、緑(G)及び青(B)は水平走査期間の始めではなく、途中で信号が変化していることがわかる。ゲート信号線17a及び17cを221の波形により入力すると緑及び青色の画素については、1行前の映像信号が画素に書き込まれ、ソース信号線の変化により当該行の映像信号が書き込まれるようになる。

10

## 【0299】

液晶などでは、書き込み時の最終電圧(ゲート信号線がオフになる瞬間の電圧)が1フレーム間画素に保持され、所定輝度で表示されるため問題がない。本実施例における画素構成を持つ有機EL表示パネルにおいては、映像信号を駆動トランジスタ11aに書き込む際に駆動トランジスタ11aの特性バラツキを補正する動作を行っている。

## 【0300】

補正に要する時間を短縮するため、書き込みを行う前に、初期化動作を行い、駆動トランジスタ11aのゲート端子に低い電圧(白表示時よりもさらに駆動トランジスタ11aが電流を流す電圧)にあらかじめ初期化を行っている。

20

## 【0301】

初期化の電圧は低いほど特性補正が高速化される。選択駆動時に1行前の電圧が少しでも印加されると、駆動トランジスタ11aのゲート電圧が1行前の電圧に変化してしまい、1行前の電圧が印加された状態で、当該行の映像信号による階調信号の書き込みとトランジスタばらつき特性補正を行うこととなり、初期化を行う効果がなくなってしまう。これは3選択駆動でなくても、2選択以上の信号線選択駆動を実施する際に共通の課題である。

## 【0302】

本実施例では、選択駆動を行う際に、同一水平走査期間で書き込みを行う信号線の電圧がすべて確定した後に特性キャンセル動作を行うようにした。

30

## 【0303】

図23、図24及び図26に実施例の1つを示す。ここで選択駆動は赤緑青の3つの信号線を順に選択する3選択駆動方式としている。2選択や、4選択以上でも同様に実現できる。

## 【0304】

キャンセル時間を確保するために、各列に対して2本の信号線を用意し、偶数行と奇数行で異なるソース信号線を利用している。図23ではゲートドライバ回路12aをシフトレジスタ回路1系統で実施する構成を示している。図23のゲートドライバ回路12aを用いた場合の信号入力と、信号線選択回路232の動作を図26に示す。1水平走査期間内で赤(R)、緑(G)、青(B)に信号線を切り替えている。また1水平走査期間ごとに奇数行用のソース線18b、偶数行用のソース線18aを切り替えて選択を行っている。

40

## 【0305】

この方式では、初期化のタイミングと当該行の映像信号線の書き込みが同一で、画素内部への映像信号の書き込みは、次の水平走査期間にて実施されている。したがって、駆動トランジスタ11aへの信号線書き込み及び特性ばらつき補正の実施中に映像信号が変わることなく、選択駆動時でもこれまで同様の駆動が実施可能である。

## 【0306】

1画素分に注目したタイミングチャートを図24に示す。ここではこれまで記載していなかった、ゲート信号線17bについても記載を行っている。ゲート信号線17bについては、初期化期間及び特性キャンセル、階調信号を駆動トランジスタに書き込みを行って

50

いる期間では必ず、接続されるスイッチが非導通状態である必要がある。しかし、その他の期間では、導通、非導通状態いずれであってもかまわない。これは本実施例のほかの実施の形態でも同様である。図24では、導通非導通を繰り返し実施している例を示している。

【0307】

ソース信号線18は3選択駆動対応用に1水平走査期間の間に3画素分の信号を送っている。信号線選択回路により奇数行目の青画素に対応するソース信号線18bBの電圧変化は241に示す波形のようになる。

【0308】

1行目に対応する階調信号の変化は242のタイミングで変化する。このときゲート信号線17bがオフ状態となっており、駆動トランジスタ11aのゲート端子に1行前の映像信号が書き込まれることが無いようになっている。ゲート信号線17aについては、図23のゲートドライバ回路12の構成によればオフとなっているが、オン状態であってもかまわない。ゲートドライバ回路12の構成を変更してオンとしてもよい。駆動トランジスタ11aのソース端子に1行前の電圧が印加されるが、初期化されているゲート端子には印加されることが無いためである。

【0309】

時間2t以降でゲート信号線17c、17aが導通状態となり、駆動トランジスタ11aに階調電圧及び特性キャンセル動作が行われる。このとき、ソース信号線18bBは図26でもあったように、信号線選択回路232により各ソース信号線から切り離された状態となる。

【0310】

ソース信号線の浮遊容量233により、ソースドライバから書き込まれた電圧が2水平走査期間の間保持される。保持された電圧値が画素に書き込まれ、所定電圧が書き込まれている。時間2t～3tの間で、駆動トランジスタ11aのゲート電圧は書き込まれるソース電圧( $V_{sig}$ )からしきい値電圧( $V_{th}$ )分低下した電位に徐々に変化し、( $V_{sig} - V_{th}$ )となる。時間3tで所定電圧に書き込まれた後、ゲート信号17bを導通状態にすることで所定電流がEL素子15に流れ、発光する。

【0311】

図27はゲートドライバ回路12aをシフトレジスタ2系統で構成した場合の図である。これによればスタートパルスの個別設定にて、ゲート信号線17dに対してゲート信号線17a及び17cのパルス幅を異ならせて設定することが可能である。

【0312】

図28にゲートドライバ回路12a1及び12a2の入力波形と、各ゲート信号線波形を示す。初期化用の信号を生成するゲートドライバ回路12a1について、初期化を行うためのパルスを生成する。初期化に要する時間は $V_{rst}$ を発生する電源能力によるが10μ秒程度で初期化が完了する。ゲート信号線17dがオン状態となるのは短い時間で実施している。

【0313】

時間がかかる特性キャンセル期間と初期化期間は同時に実施することができないため、2水平走査期間内で初期化～特性キャンセル、階調信号書き込みを実施するためには、初期化を短くすることが重要であるためである。

【0314】

図27、図37の実施例では、1水平走査期間に2画素行を選択する方式であるが、本実施例はこれに限定するものではない。3画素行以上を同時に選択してもよい。3画素行以上を同時に選択する場合は、ソース信号線18の本数も増加させる。基本的には、1水平走査期間に同時に選択する画素行分の数量のソース信号線18を形成する。

【0315】

また、同時に選択する画素行は、隣接していることに限定されない。2画素行単位でもよい。一例として、第1水平走査期間に、第1番目の画素行と第3番目の画素行を選択し

10

20

30

40

50

、第2水平走査期間に、第2番目の画素行と第4番目の画素行を選択する駆動方式が例示される。

【0316】

また、同時に選択する画素行は、映像信号電圧  $V_{sig}$  の書き込みタイミングをずらしてもよい。例えば、第1番目の画素行と第2番目の画素行を選択する場合、第1番目の画素行を選択した後、5  $\mu$ 秒後に第2番目の画素行を選択してもよい。選択タイミングを異なることにより、突入電流などを抑制することができる。また、選択回路 1041 を形成し、選択回路 1041 とタイミング調整を実施してもよい。

【0317】

図28では赤色にソース出力が選択された期間のみで実施しているが、赤と緑の選択期間もしくは赤色の選択期間の一部などであってもよい。最も当該行の映像信号が書き込まれるのが遅い青色のソース信号線 18aB もしくは 18bB においては青色の選択期間になるまで当該画素に対応する電圧がソース信号線 18aB もしくは 18bB に印加されていないため、特性キャンセル期間に移行することができない。

10

【0318】

特性キャンセルができないことから、赤緑選択期間は初期化期間としても問題が無い。特性キャンセル及び階調信号書き込みであるが、ゲートドライバ回路 12a2 のシフトレジスタ回路により2水平走査期間選択できるパルスを生成し、初期化期間もしくは映像信号が書き込まれていない期間を除くように、奇数行偶数行別にイネーブル期間を設けるイネーブル信号を有する。

20

【0319】

1行目の特性キャンセル及び階調信号書き込み期間は 281 で示される期間となる。281 の期間の始めは、青画素書き込み終了後となっているが、青画素が信号線選択回路で選択され所定電圧にソース信号線 18aB もしくは 18bB が変化した後であれば、ゲート信号線 17a 及び 17c をローレベルにしてもよい。281 の期間の終わりは、次に同一のソース信号線に異なる行の画素に対応する電圧が印加される前に設定すればよい。信号線選択速度が速い場合には、書き込み終了後～次の水平走査期間の最後まで特性キャンセル期間を設定することができ、駆動トランジスタ 11a のしきい値電圧補正能力が高い表示が実現可能である。

30

【0320】

なお、ゲート信号線 17a については、2水平走査期間すべてにおいてローレベルとしてもよい。トランジスタ 11c が導通状態となっても、駆動トランジスタ 11a のゲート電圧には影響がないためである。この場合、ゲート信号線 17c 用にはイネーブル信号を介してシフトレジスタ出力が入力され、ゲート信号線 17a 用にはイネーブル信号を介さずもしくは、別途のイネーブル信号を介してシフトレジスタ出力が入力される構成となる。

30

【0321】

これまでに画素回路 16 に用いられるトランジスタは P チャンネルトランジスタで説明を行ってきたが、図29に示す N チャンネルトランジスタで構成してもよい。以上の事項は本実施例の他の画素構成においても同様である。

40

【0322】

有機EL素子 15 については、アノードとカソードの向きが逆でかつ、 $V_{ss}$  電位 >  $V_{dd}$  電位という構成であってもよい。図29ではコンデンサ 19b が形成されているが、コンデンサ 19b がなくても本実施例を同様に実施することが可能である。以上の事項は本実施例の他の画素構成においても同様である。

【0323】

なお、図29と図4とを比較すると、図4は、突き抜けコンデンサ 19c がゲート信号線 17a と駆動トランジスタ 11a のゲート端子間に配置されているのに対して、図29では、突き抜けコンデンサ 19c がゲート信号線 17c と駆動トランジスタ 11a のゲート端子間に配置されている。

50

## 【0324】

コンデンサ19bが形成されると、次に画素に映像信号が書き込まれるまでの1フレーム間電圧が保持されるため、a点の電位が保持される。あるいは、次にトランジスタ11cがオンし映像信号が画素16に書き込まれる時までa点に印加された（書き込まれた）電圧が保持される。

## 【0325】

保持された電位を元にトランジスタ11bを導通状態とすれば階調信号に応じた信号で、駆動トランジスタ11aの特性バラツキをキャンセルすることが可能である。これが図30に示すキャンセル期間302となる。

## 【0326】

このキャンセル期間（オフセットキャンセル期間）は水平走査期間の長さによらずゲートドライバ回路12の構成によって任意に設定することが可能である。映像信号の書き込みと駆動トランジスタ11aの初期化は、キャンセル期間302の前に実施される（期間301）。トランジスタ11fと11cのみ導通状態である。これでVrst電源により駆動トランジスタ11aのゲート電位を初期化し、同時にソース信号線18からコンデンサ19bに所定電圧の書き込みを行っている。

10

## 【0327】

コンデンサ19bに所定階調電圧を保持することから、ソース信号線18は1本で、1水平走査期間のみトランジスタ11cをオンさせるだけでよい。ソース信号線18を2本用意する方法でソース信号線18の浮遊容量とコンデンサ19bの両方で階調電圧を保持する方法をとってもよい。この場合、コンデンサ19bは小さくすることができる。

20

## 【0328】

オフセットキャンセルが完了したら、EL素子15に電流を印加して所定輝度による発光を得る。この期間が発光期間304である。このときトランジスタ11dと11eが導通状態となりEL素子15に電流を供給する。

## 【0329】

前後にある非発光期間303は、黒挿入を行い動画視認性向上等の効果を得る際に挿入される期間である。黒挿入はduty駆動であり、図12、図13、図84、図98、図99などを用いて説明を行っている。このときは少なくともトランジスタ11dもしくは11eのいずれか一方が非導通状態になっている。また、常時点灯状態にして黒挿入を行わない場合には、期間303はなくても差し支えない。

30

## 【0330】

なお、本実施例における切り替え部141及び信号線選択回路232は必ずしもアレイ基板上に形成する必要が無く、ソースドライバICに内蔵される構成であってもよい。

## 【0331】

本実施例において、同一列に形成された画素に接続されるソース信号線は2本である例で説明をおこなったが、3本以上の複数のソース信号線であっても同様に実施が可能である。一般にN本のソース信号線を用意し、N画素おきにソース信号線を接続すれば、N水平走査期間の間ソース信号線は階調電圧を保持することが可能となり、特性キャンセル期間を長く取ることができる。キャンセル期間を確保することにより、より駆動トランジスタ11aの特性に近づいたゲート電圧を画素回路で保持することができるようになり、表示ムラが改善する。また、複数の画素行を同時に選択してもよい。

40

## 【0332】

N本のソース信号線について、少なくとも隣接画素間で異なるソース信号線に画素回路を接続しておけば、2水平走査期間の間ソース信号線に階調信号が保持されることから、同様に特性キャンセル期間を拡大することができ、表示ムラが少ないEL表示装置を得ることができる。

## 【0333】

図31は、駆動トランジスタ11aのゲート端子の電圧を初期化するための電源（リセット電圧Vrst）を、電圧源から電流源に変更した回路である。図32に図31の回路

50

構成におけるゲート信号線の波形を示す。図31の回路構成において、1画素での動作は、1フレームの間に、書き込み期間321、発光期間324、非発光期間323に分けられる。非発光期間323は、黒挿入(duty駆動：間欠表示駆動)を行って動作視認性を向上させる場合などに用いられる。本発明の実施例においては、非発光期間323は、あってもなくてもよい。特性バラツキの補償能力向上を同様に実現できる。

#### 【0334】

書き込み期間321において、トランジスタ11b、11c、11fが導通状態となる。これによりソース信号線18の電圧が駆動トランジスタ11aのソース端子に印加される。駆動トランジスタ11aのゲートとドレイン端子はトランジスタ11bにより同電位となり、電流源312により供給される電流が駆動トランジスタ11aのドレイン電流となるようなゲート、ドレイン電圧となる。

10

#### 【0335】

したがって、書き込み期間321において、トランジスタ11aのゲート電圧は、ソース信号線18の電圧が映像信号電圧Vsigであったとすると、(Vsig - Vt1)となる。ここでVt1は、駆動トランジスタ11aに電流源312の電流(Irst)を流したときのソースドレイン間電圧であり、駆動トランジスタ11aの特性により異なる電圧値となる。

20

#### 【0336】

リセット電流Irstが駆動トランジスタ11aつまりEL素子15に流れるときには、特性バラツキを補正した電圧が駆動トランジスタ11aのゲート端子に印加され、表示ムラのないEL表示装置が実現できる。

20

#### 【0337】

従来の構成においては、Irst = 0つまり黒表示時に完全に特性ばらつきを補正し、電流が増加するにつれ、補正ができない移動度ばらつきに起因する電流ばらつきが発生し、高階調ほど表示ムラが発生しやすい状況であった。

30

#### 【0338】

表示ムラは輝度が低いほど視認しにくく、中間調～高階調では視認しやすい性質があり、階調0に相当する電流で特性補正を行うよりも、視認しやすい中間～高階調での補正が望ましい。初期化用の電流源の出力電流Irstの電流値を中間～高階調に設定すれば、視認されやすい階調での表示ムラを優先してなくせる。また、視認しにくい階調では、移動度ばらつきがおこる構成であっても見えにくいことを利用し、全階調領域における表示ムラレベルの向上を実現できる。本実施例は、駆動トランジスタの特性バラツキのキャンセル動作中に電流Irstを流し、特性キャンセルがもっともよく行われる電流領域を変更させることができるようにしたことが特徴である。

30

#### 【0339】

図33の回路は、図31の構成に対して、さらに初期化用の電圧源(リセット電圧Vrstを出力)331及び電圧源331と電流源312の切り替えを行う切り替え部333を有することが特徴である。これは、電流源312によりトランジスタ11aの電圧を変化させる場合に、1フレーム前に黒表示をした画素であると、駆動トランジスタ11aに流れる電流がIrstに変化するまでに時間がかかる。そのため、書き込み期間321内に駆動トランジスタ11aのゲート電圧がVsig - Vt1になりにくい問題を解消するためである。

40

#### 【0340】

駆動トランジスタ11aのドレイン電流が多いほど、書き込み期間321における駆動トランジスタ11aのゲート電圧を変化させやすい。電流が多く流れるほど、保持用コンデンサ19aの電荷の充放電速度が速くなるため、ゲート電圧が変化しやすくなる。

40

#### 【0341】

そこで、ゲート電圧の変化速度向上を目的として、電圧源331を用意し、書き込み期間321の初期に、電流源312に変わり、低電圧(白表示ほど低電圧の図33の回路構成の場合)の電圧を駆動トランジスタ11aに供給することで、書き込み期間321の初

50

期に駆動トランジスタ 11a のドレイン電流が多くなるようにして、残りの期間での、リセット電圧源 312 によるキャンセル動作を高速化するようにした。

【0342】

図 34 に図 33 の回路構成におけるゲート信号及び切り替え手段の動作を示した。書き込み期間 321 のうち電圧源が供給される期間 341 において、駆動トランジスタ 11a のゲート電圧は  $V_{rst}$  となる。

【0343】

リセット電圧  $V_{rst}$  は低い電圧であるほど、切り替え手段 333 により電流源 312 に切り替えた際のゲート電圧の変化を高速化させるが、低下しすぎると、所定階調とのゲート電位の差が大きくなりすぎ、所定値まで電圧が変化しきれない可能性がある。

10

【0344】

したがって、リセット電圧  $V_{rst}$  は、(白表示時の電圧) ~ (白表示時の電圧 - 5 (V)) 程度が好ましい。続く 342 の期間において、電流源 312 と書き込まれるソース信号線電圧  $V_{sig}$  に基づいてゲート電圧が  $V_{sig} - V_{t1}$  に変化する。

【0345】

この時、図 32 の構成に比べて、トランジスタ 11a のドレイン電流が多く、蓄積コンデンサ 19 の電荷の充放電速度が高速化されることから、 $V_{sig} - V_{t1}$  までに変化する速度は、電圧印加期間 341 を含めても高速化され、より短時間での特性補正が可能となる。

20

【0346】

図 35 はゲート信号線をトランジスタ 11e と 11d で個別制御にした回路構成を示している。1 画素において、1 フレームは、リセット期間 361、映像信号書き込みと特性キャンセル期間 362、非発光期間 363、発光期間 364 からなる。

【0347】