#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-286997 (P2008-286997A)

(43) 公開日 平成20年11月27日(2008.11.27)

| F 1                                                  |                                                                               | テーマコード (参考)                                                                                                                                                                                                       |

|------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>(2006.01)</b> GO9G                                | 3/30 J                                                                        | 3K1O7                                                                                                                                                                                                             |

| <b>(2006.01)</b> GO9G                                | 3/20 6 4 2 A                                                                  | 5C080                                                                                                                                                                                                             |

| <b>(2006.01)</b> GO9G                                | 3/20 6 2 4 B                                                                  |                                                                                                                                                                                                                   |

| GO9G                                                 | 3/20 6 2 3 R                                                                  |                                                                                                                                                                                                                   |

| GO9G                                                 | 3/20 6 2 1 K                                                                  |                                                                                                                                                                                                                   |

| 審査請求 未                                               | 清求 請求項の数 4 OL                                                                 | (全 11 頁) 最終頁に続く                                                                                                                                                                                                   |

| 願2007-131783 (P2007-131783)<br>成19年5月17日 (2007.5.17) |                                                                               |                                                                                                                                                                                                                   |

| Ę                                                    | (2006.01) GO9G<br>(2006.01) GO9G<br>(2006.01) GO9G<br>GO9G<br>GO9G<br>審査請求 未記 | (2006.01) GO9G 3/30 J   (2006.01) GO9G 3/20 642A   (2006.01) GO9G 3/20 624B   GO9G 3/20 623R   GO9G 3/20 621K   審査請求 精球項の数4 OL   類2007-131783 (P2007-131783) (71) 出願人 3020202027   或19年5月17日 (2007.5.17) 東芝松下ディン社 |

(74)代理人 100058479

弁理士 鈴江 武彦

(74)代理人 100091351

弁理士 河野 哲

(74)代理人 100088683

弁理士 中村 誠

(74)代理人 100108855

弁理士 蔵田 昌俊

(74)代理人 100075672

弁理士 峰 隆司

最終頁に続く

## (54) 【発明の名称】アクティブマトリクス型有機EL表示装置

## (57)【要約】

【課題】各画素に映像信号として電圧信号を供給すると 共に表示する階調を映像信号の大きさで制御する表示装 置において、階調再現性のばらつきが発生するのを抑制 する。

【解決手段】基板と、基板上でマトリクス状に配列した 複数の表示画素と、複数の表示画素の列に対応して配列 して複数の表示画素のそれぞれと接続するリセット電流 線と、それぞれのリセット電流線の一端と接続して配さ れて、リセット電流線に表示画素をリセットするリセット電流を流す複数のリセット電流部と、フレーム毎にリ セット電流部に一括して所定の電流を書き込むと共に、 時間順次でリセット電流部を走査駆動してリセット電流 線にリセット電流を流す走査制御部とを備え、走査制御 部が駆動するリセット電流部の走査方向が一方向ではな いアクティブマトリクス型有機EL表示装置である。

## 【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

基板と、

前記基板上でマトリクス状に配列した複数の表示画素と、

前記複数の表示画素の列に対応して配列して前記複数の表示画素のそれぞれと接続するリセット電流線と、

前記それぞれのリセット電流線の一端と接続して配されて、前記リセット電流線に前記表示画素をリセットするリセット電流を流す複数のリセット電流部と、

フレーム毎に前記リセット電流部に一括して所定の電流を書き込むと共に、時間順次で前記リセット電流部を走査駆動して前記リセット電流線に前記リセット電流を流す走査制御部とを備え、

前記走査制御部が駆動する前記リセット電流部の走査方向が一方向ではないことを特徴とするアクティブマトリクス型有機 EL表示装置。

### 【請求項2】

前記リセット電流部は、前記所定の電流を書き込み前記リセット線に前記リセット電流を流すための同一構成の定電流部を2つ有し、

前記走査制御部は、フレーム毎に、一方の定電流部が前記所定の電流を書き込んでいるときは、他方の電流部が前記リセット線に前記リセット電流を流すように交互に制御すること

を特徴とする請求項1記載のアクティブマトリクス型有機EL表示装置。

#### 【請求項3】

前記複数の表示画素のそれぞれは、陰極が低電位電源配線に接続された有機 E L ダイオードと、ドレイン電極が前記有機 E L ダイオードの陽極に接続された第1スイッチトランジスタと、ドレイン電極がリセット電流線に接続されソース電極が前記第1スイッチトランジスタのソース電極に接続された第2スイッチトランジスタと、ドレイン電極が前記第1スイッチトランジスタのソース電極に接続されソース電極が高電位電源配線に接続された駆動トランジスタと、一方の電極が前記駆動トランジスタのゲート電極に接続された保持容量とを少なくとも有すること

を特徴とする請求項1または2に記載のアクティブマトリクス型有機EL表示装置。

### 【請求項4】

前記走査制御部が駆動する前記リセット電流部の走査方向が少なくとも1フレーム毎に逆転することを特徴とする請求項1乃至3のいずれか1項に記載のアクティブマトリクス型有機EL表示装置。

【発明の詳細な説明】

## 【技術分野】

#### [0001]

本発明は、薄膜トランジスタ(以下、TFTと記す)を用いてTFTアレイ基板を構成したアクティブマトリクス型有機EL表示装置に関する。

#### 【背景技術】

## [ 0 0 0 2 ]

アクティブマトリクス型有機エレクトロルミネッセンス(EL)表示装置では、各画素で表示する階調を、映像信号の大きさで制御する。特許文献 1 には、映像信号として電圧信号を利用するアクティブマトリクス型有機EL表示装置が記載されている。

#### [0003]

特許文献1に記載された表示装置の画素は、 p チャネル電界効果トランジスタである駆動トランジスタと、有機 E L 素子と、第1及び第2キャパシタと、第1乃至第3スイッチングトランジスタとを含んでいる。駆動トランジスタと第1スイッチングトランジスタと有機 E L 素子とは、高電位電源線と低電位電源線との間で、この順に直列に接続されている。第1キャパシタは、高電位電源線と駆動トランジスタのゲートとの間に接続されている。第2スイッチングトランジスタは、駆動トランジスタのドレインとゲートとの間に接

10

20

30

40

続されている。第 2 キャパシタの一方の電極は、駆動トランジスタのゲートに接続されている。第 3 スイッチングトランジスタは、映像信号線と第 2 キャパシタの他方の電極との間に接続されている。

#### [0004]

この表示装置では、画素間で駆動トランジスタの閾値電圧または移動度がばらついている場合、それに起因して、駆動電流の大きさがばらつく。そのため、この表示装置では、 階調再現性が画素ごとにばらつく可能性がある。

【特許文献1】米国特許第6229506号明細書

【発明の開示】

【発明が解決しようとする課題】

[00005]

本発明の目的は、各画素に映像信号として電圧信号を供給すると共に表示する階調を映像信号の大きさで制御する表示装置において、階調再現性のばらつきが発生するのを抑制することにある。

【課題を解決するための手段】

[0006]

上記課題を解決するための本発明は、基板と、前記基板上でマトリクス状に配列した複数の表示画素と、前記複数の表示画素の列に対応して配列して前記複数の表示画素のそれぞれと接続するリセット電流線と、前記それぞれのリセット電流線の一端と接続して配されて、前記リセット電流線に前記表示画素をリセットするリセット電流を流す複数のリセット電流部と、フレーム毎に前記リセット電流部に一括して所定の電流を書き込むと共に、時間順次で前記リセット電流部を走査駆動して前記リセット電流線に前記リセット電流を流す走査制御部とを備え、前記走査制御部が駆動する前記リセット電流部の走査方向が一方向ではないアクティブマトリクス型有機EL表示装置である。

【発明の効果】

[0007]

本発明によれば、各画素に映像信号として電圧信号を供給すると共に表示する階調を映像信号の大きさで制御する表示装置において、階調再現性のばらつきが発生するのを抑制するアクティブマトリックス型有機 EL表示装置を提供できる。

【発明を実施するための最良の形態】

[00008]

以下、本発明の態様について、図面を参照しながら詳細に説明する。なお、各図において、同様又は類似した機能を発揮する構成要素には同一の参照符号を付し、重複する説明は省略する。

なお以下の実施の形態では、アクティブマトリックス型表示装置の内、有機EL表示装置について説明するが、本発明は有機ELに限定されない。

[0009]

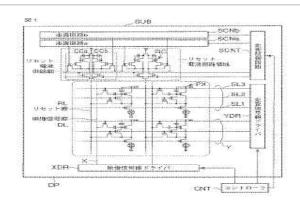

図1は、本発明の一態様に係る有機EL表示装置を概略的に示す平面図である。

図1に示すように、有機 E L 表示装置は、パネル D P 、及びパネル D P を制御するコントローラ C N T を備えている。

[0010]

パネルDPには、ガラス板等の光透過性絶縁基板SUB上にマトリクス状に配列され画素領域を構成したm(列)×n(行)個の表示画素PX、映像信号線ドライバXDR、走査信号線ドライバYDR、各列に対応して設けられリセット電流回路領域を構成したm個のリセット電流回路RC、走査回路a、b及び走査制御回路SCNTが設けられている。

[0011]

映像信号線ドライバ X D R は、表示画素 P X の各列に対応して設けられた複数の信号線 X (1~m)を駆動する。走査信号線ドライバ Y D R は、表示画素 P X の各行に対応して設けられた複数の制御線(1~n)を駆動する。なお、制御線は、各行に3本(S L 1、S L 2、S L 3)設けられている。

10

20

30

40

#### [0012]

リセット電流回路RCは各表示画素PXにリセット電流を流す。走査回路a(SCNa)と走査回路b(SCNb)は、リセット電流回路RCを走査して駆動する。走査制御回路SCNTは、リセット電流回路RC、走査回路a(SCNa)と走査回路b(SCNb)の動作を制御する。

#### [0013]

図1に示すコントローラCNTはパネルDPの外部に配置されたプリント回路基板上に形成され、走査信号線ドライバYDR、映像信号線ドライバXDR及び走査制御回路SCNTを制御する。コントローラCNTは外部から供給されるデジタル映像信号および同期信号を受け取り、垂直走査タイミングを制御する垂直走査制御信号、および水平走査タイミングを制御する水平走査制御信号を同期信号に基づいて発生する。そして、これら垂直走査制御信号および水平走査制御信号をそれぞれ走査信号線ドライバYDRおよび映像信号線ドライバXDRに供給すると共に、水平および垂直走査タイミングに同期してデジタル映像信号を映像信号線ドライバXDRに供給する。

#### [0014]

映像信号線ドライバ X D R は水平走査制御信号の制御により各水平走査期間において順次得られる映像信号 D a t a 1 ~ D a t a mをアナログ形式に変換し電流信号として複数の信号線 X (1~m)に並列的に供給する。走査信号線ドライバ Y D R は、シフトレジスタ、出力バッファ等を含み、外部から供給される水平走査スタートパルスを順次次段に転送し、出力バッファを介して各行の表示画素 P X に制御信号を供給する。

#### [0015]

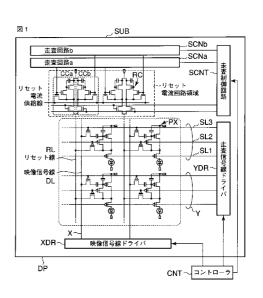

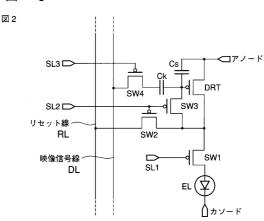

図2は、電圧を映像信号とした有機 EL表示装置の画素回路を示す図である。

有機 E L 表示装置は、 E L ダイオード( E L )、 第 1 スイッチ T F T ( S W 1 )、 駆動 T F T ( D R T )、 保持容量( C s )、 第 2 スイッチ T F T ( S W 2 )、 第 3 スイッチ T F T ( S W 3 )、 第 4 スイッチ T F T ( S W 4 )及び書き込み容量( C k )とで構成されている。

#### [0016]

第1スイッチTFT(SW1)は、ELダイオードに流れる電流のオンオフ制御を行う。 駆動TFT(DRT)は、ELダイオードに流す電流量を映像信号に基づいて制御する。保持容量(Cs)は、駆動TFTに印加されるゲート・ソース間電圧を保持する。第2スイッチTFT(SW2)は、リセット電流を画素回路に送る。第3スイッチTFT(SW3)は、リセット電流書き込み時にDRTのゲート電極とドレイン電極とを短絡させる。第4スイッチTFT(SW4)は、映像信号を画素回路に流す。書き込み容量(Ck)は、映像信号を駆動TFTのゲート電極に与える。

## [0017]

続いて画素回路の動作を説明する。

画素回路に映像信号を書き込む前には、まず駆動TFTのしきい値電圧ばらつきを補償するためのリセット動作を行う。制御線SL1,2,3が駆動されて、第1スイッチTFTは非導通状態にされ、第2、第3および第4スイッチTFTは導通状態にされる。この状態でアノードから駆動TFTを経由してリセット線RLに一定のリセット電流を流すと、駆動TFTのゲート・ソース間電圧はしきい値電圧などのTFT特性に因らずリセット電流を流す状態にセットされ、その電圧は保持容量Csに保持される。

同時に映像信号線DLにリセット電位が与えられる。このリセット電位は第4スイッチ TFTを介して書き込み容量Ckの一方の電極に与えられる。書き込み容量Ckの他方の 電極は駆動TFTのゲート電位になっている。

#### [0018]

引き続いて第2および第3スイッチTFTを非導通状態に変えて、映像信号の書き込み動作を実行する。即ち、映像信号線DLの電位をリセット電位から所定の信号電位に変位させる。すると駆動TFTのゲート電位もその変位量に応じて変化し、その変化した電位は保持容量Csによって保持される。

ここで、映像信号電圧Vsigのリセット電位からの変化量 Vsigと、駆動TFTのゲー

10

20

30

40

ト電位 V g s の変化量 V g s とは、式(1)で表される関係にある。従って、保持容量 C s には、リセット電位を基準として映像信号電圧の変化量に比例した電位が保持される

## [0019]

Vgs = Vsig x Ck / (Ck + Cs) · · ·式(1)

その後第4スイッチTFTを非導通状態にして第1スイッチTFTを導通状態にすると、保持容量Csに保持された駆動TFTのゲート電位Vgsに応じた電流が駆動TFTおよび第1スイッチTFT経由でELダイオードに流れ、ELダイオードは所定の輝度レベルで発光する。

#### [0020]

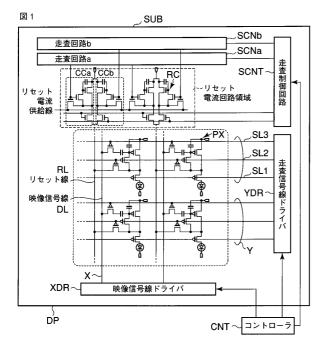

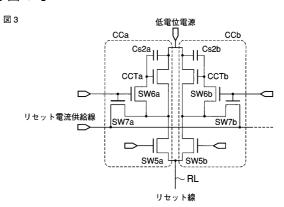

図3は、画素回路から一定のリセット電流を吸い出すリセット電流回路RCの構成を示す図である。

#### [0021]

リセット電流回路 R C は、同一構成の定電流回路(C C a , C C b)を並列に接続した構成である。そして、リセット線 R L に接続されている第 5 a および第 5 b スイッチTFT(S W 5 a , S W 5 b)が、どちらの定電流回路がリセット線 R L から定電流を吸い込むかを選択する。

各々の定電流回路は、定電流 T F T ( C C T a , C C T b )、第 2 保持容量 ( C s 2 a , C s 2 b )、第 6 a および第 6 b スイッチ T F T ( S W 6 a , S W 6 b )、及び第 7 a および第 7 b スイッチ T F T ( S W 7 a , S W 7 b )とで構成されている。

定電流TFT(CCTa,CCTb)は、リセット線RLから吸い出す電流量を制御する。第2保持容量(Cs2a,Cs2b)は、定電流TFTに印加されるゲート・ソース間電圧Vgsを保持する。第6aおよび第6bスイッチTFT(SW6a,SW6b)は、リセット電流の書き込み時に定電流TFTのゲート電極とドレイン電極とを短絡させる。第7aおよび第7bスイッチTFT(SW7a,SW7b)は、リセット電流を定電流回路に送る。

#### [0022]

リセット電流回路RCと画素領域とは、リセット線RLを介して第5aおよび第5bスイッチTFTにより接続される。走査回路aからの制御線は、リセット電流回路RCの第6a、第7aスイッチTFTのゲート電極に接続されている。走査回路bからの制御線は、リセット電流回路RCの第6b、第7bスイッチTFTのゲート電極に接続されている。そして、各列の第6a、第7aスイッチTFTおよび第6b、第7bスイッチTFTのゲート電極は走査回路aと走査回路bの出力により時間順次に導通もしくは非導通の電位が印加される。

また、各列の第5aおよび第5bスイッチTFTのゲート電極は一括して走査制御回路SCNTからの制御線に接続され、総てに同時に導通もしくは非導通の電位が印加できるようになっている。

#### [0023]

続いて、リセット電流回路RCの動作について説明する。

まず一方の定電流回路、例えば定電流回路 C C a にリセット電流を書き込む。走査制御回路 S C N T は制御信号を出力して第 5 a スイッチTFTを非導通状態にし、走査回路 a は制御信号を出力して第 6 a および第 7 a スイッチTFTを導通状態にする。この状態でリセット電流供給源(不図示)が、リセット電流供給線から定電流TFT(C C T a)を経由して低電位電源に一定のリセット電流を流す。そうすると定電流TFTのゲート・ソース間電圧はしきい値電圧などのTFT特性に因らずリセット電流を流す状態にセットされ、その電圧は第 2 保持容量(C s 2 a)に保持される。

#### [0024]

この時もう一方の定電流回路CCbでは、走査回路bが制御信号を出力して第6bおよび第7bスイッチTFTを非導通状態にし、走査制御回路SCNTが制御信号を出力して第5bスイッチTFTを導通状態としている。従って、第5bスイッチTFT、定電流T

10

20

30

40

F T ( C C T b )を介してリセット線 R L から低電位電源にリセット電流が流れている状態である。

## [0025]

引き続いて走査回路 a が制御信号を出力して第 6 a および第 7 a スイッチTFTを非導通状態に変えた後、走査制御回路 S C N T が制御信号を出力して第 5 a スイッチTFTを導通状態にする。そうすると、第 2 保持容量(C s 2 a)に保持された駆動TFTのゲート電位に応じた電流が第 5 a スイッチTFTおよび定電流TFT(C C T a)経由でリセット線 R L から低電位電源に流れる。

#### [0026]

この時もう一方の定電流回路 C C b は、リセット電流を書き込む動作を実行中である。即ち、走査制御回路 S C N T は制御信号を出力して第 5 b スイッチTFTを非導通状態にし、走査回路 b は制御信号を出力して第 6 b および第 7 b スイッチTFTを導通状態にする。この状態でリセット電流供給源(不図示)が、リセット電流供給線から定電流TFT(C C T b)を経由して低電位電源に一定のリセット電流を流す。そうすると定電流TFTのゲート・ソース間電圧はしきい値電圧などのTFT特性に因らずリセット電流を流す状態にセットされ、その電圧は第 2 保持容量(C s 2 b)に保持される。

#### [0027]

このように二つの定電流回路がリセット電流の書き込みとリセット電流の供給とを交互 に行うように駆動される。

## [ 0 0 2 8 ]

続いて、有機EL表示装置のリセット動作について説明する。

図 4 は、有機 E L 表示装置のリセット電流回路 R C の駆動電位を表す概略のタイムチャートである。

#### [0029]

まず奇数フレーム(K, K+2,・・・)においては、走査制御回路SCNTが総ての第5aスイッチTFTを非導通状態にし、総ての第5bスイッチTFTを導通状態にする。そして、上述のように奇数フレームでは定電流回路CCaにリセット電流を書き込み、画素回路から吸い出したリセット電流を定電流回路CCbに流す。

#### [0030]

具体的には、対応するフレーム期間に走査回路aにより第6aおよび第7aスイッチTFTを順次導通状態にしていくことで各列に対応した定電流回路CCaに所定のリセット電流を順次書き込む。そして総ての定電流回路CCaへのリセット電流の書き込みが終了し、さらにこのフレーム期間での画素回路への書き込みが終了して偶数フレーム(K+1,K+3,・・・)に移行した時に、走査制御回路SCNTは第5bスイッチTFTを非導通状態にし、第5aスイッチTFTを導通状態にする。これによって偶数フレームにおいては定電流回路CCaによりリセット電流を画素回路から吸い出すことができ、定電流回路CCbにリセット電流を書き込むことができる。

ところで図3に示すリセット電流回路RCでは第6aあるいは第6bスイッチTFTのリーク電流により、書き込まれたリセット電流に対応して保持された定電流TFTのゲート電位が経時的に変化する。その結果、リセット線RLを介して画素PXから吸い出せる電流が書き込まれたリセット電流とは異なったものになってしまう。

#### [ 0 0 3 1 ]

さらに図4に示したように列に対応して設けられたリセット電流回路RCは時間順次で走査されるため、リセット電流の書き込みが完了してからリセット電流が吸い出されるまでの時間、即ち保持時間が徐々に変化する。従って、リセット線RLから吸い出せる電流量も列方向に徐々に変化することになる。リセット線RLから吸い出す電流量は発光電流の基準となる電流であるため、これが徐々に変化すると列方向での発光電流も変化することになり、画面左右方向の輝度に傾斜を生じさせる。

#### [0032]

〔バリエーション 1〕

10

20

30

40

図 5 は、バリエーションに係るリセット電流回路 R C の駆動電位を表す概略のタイムチャートである。

## [0033]

まず K フレームにおいては、走査制御回路 S C N T が総ての第 5 a スイッチ T F T を非導通状態にし、総ての第 5 b スイッチ T F T を導通状態にする。そして上述のように定電流回路 C C a にリセット電流を書き込み、画素回路から吸い出したリセット電流を定電流回路 C C b に流す。

具体的には、対応するフレーム期間において、走査回路 a はリセット電流回路 R C の第 1 列から第m列まで時間順次で選択電位を印加して、各列に対応した定電流回路 C C a に 所定のリセット電流を第 1 列から第m列まで時間順次で書き込む。

[0034]

続く k + 1 フレームにおいては、走査制御回路 S C N T が総ての第 5 a スイッチ T F T を導通状態にし、総ての第 5 b スイッチ T F T を非導通状態にする。こうすることでリセット電流を画素回路から吸い出して定電流回路 C C b に書き込む。

そしてこのフレームの間に走査回路 b によりリセット電流回路 R C に第m列から第 1 列まで時間順次で選択電位が印加され、所定のリセット電流が各列に対応した定電流回路 C b に第m列から第 1 列まで時間順次で書き込まれる。

以降これら2つのフレームの動作が繰り返される。

[0035]

以上述べたような駆動方法によれば、リセット電流保持時間が列方向に異なることに起因する定電流回路 C C a でのリセット電流量の列方向への傾斜と、定電流回路 C C b でのリセット電流量の列方向への傾斜とがちょうど逆の関係になる。その結果 K フレームで生じる発光輝度の列方向傾斜と K + 1 フレームで生じる発光輝度の列方向傾斜とが逆の関係になり、表示装置としては列方向に輝度傾斜の無い表示を得ることができる。

[0036]

[バリエーション2]

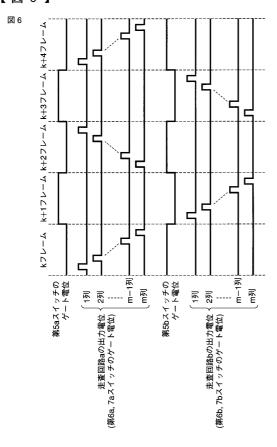

図 6 は、バリエーションに係るリセット電流回路 R C の駆動電位を表す概略のタイムチャートである。

[ 0 0 3 7 ]

まず K フレームにおいては、走査制御回路 S C N T が総ての第 5 a スイッチ T F T を非 導通状態にし、総ての第 5 b スイッチ T F T を導通状態にする。そして上述のように定電 流回路 C C a にリセット電流を書き込み、画素回路から吸い出したリセット電流を定電流 回路 C C b に流す。

具体的には、対応するフレーム期間において、走査回路 a はリセット電流回路 R C の第 1 列から第m列まで時間順次で選択電位を印加して、各列に対応した定電流回路 C C a に所定のリセット電流を第 1 列から第m列まで時間順次で書き込む。

[0038]

続く k + 1 フレームにおいては、走査制御回路 S C N T が総ての第 5 a スイッチ T F T を導通状態にし、総ての第 5 b スイッチ T F T を非導通状態にする。こうすることでリセット電流を画素回路から吸い出して定電流回路 C C b に書き込む。

そしてこのフレームの間に走査回路 b によりリセット電流回路 R C に第 1 列から第m列まで時間順次で選択電位が印加され、所定のリセット電流が各列に対応した定電流回路 C b に第 1 列から第m列まで時間順次で書き込まれる。

[0039]

引き続き K + 2 フレームにおいては、走査制御回路 S C N T が総ての第 5 a スイッチ T F T を非導通状態にし、総ての第 5 b スイッチ T F T を導通状態にする。そして上述のように定電流回路 C C a にリセット電流を書き込み、画素回路から吸い出したリセット電流を定電流回路 C C b に流す。

10

20

30

50

そしてこのフレームの間に走査回路 a によりリセット電流回路 R C に第m列から第 1 列まで時間順次で選択電位が印加され、所定のリセット電流が各列に対応した定電流回路 C C b に第m列から第 1 列まで時間順次で書き込まれる。

#### [0040]

さらに続くK+3フレームにおいては、走査制御回路SCNTが総ての第5aスイッチTFTを導通状態にし、総ての第5bスイッチTFTを非導通状態にする。そして上述のように定電流回路CCbにリセット電流を書き込み、画素回路から吸い出したリセット電流を定電流回路CCaに流す。

そしてこのフレームの間に走査回路 b によりリセット電流回路 R C に第m列から第 1 列まで時間順次で選択電位が印加され、所定のリセット電流が各列に対応した各列に対応した定電流回路 C C b に第m列から第 1 列まで時間順次で書き込まれる。

以降これらの4フレームの動作が繰り返される。

#### [0041]

以上述べたような駆動方法によれば、リセット電流保持時間が列方向に異なることに起因する定電流回路 C C a でのリセット電流量の列方向への傾斜が k フレームと k + 2 フレームとでちょうど逆の関係になる。またリセット電流保持時間が列方向に異なることに起因する定電流回路 C C b でのリセット電流量の列方向傾斜も k + 1 フレームと k + 3 フレームで生じる発光輝度の列方向傾斜と k + 2 フレームで生じる発光輝度の列方向傾斜ともちょうど逆の関係になり、また k + 1 フレームで生じる発光輝度の列方向傾斜と k + 3 フレームで生じる発光輝度の列方向傾斜と b もちょうど逆の関係になり、表示装置としては列方向に輝度傾斜の無い表示を得ることができる。

#### [0042]

〔本実施の形態の効果〕

本実施の形態のアクティブマトリクス型有機EL表示装置では、リセット電流を用いて画素回路の駆動TFTをしきい値電圧などのTFT特性に因らない状態に設定する。従って、階調再現性のばらつきが発生するのを抑制することができる。

#### [ 0 0 4 3 ]

また、本実施の形態のアクティブマトリクス型有機 EL表示装置では、リセット電流の変化に対応して発生する輝度傾斜を抑制することができる。

#### [0044]

リセット電流の変化の大小はリセット電流が書き込まれてからの保持時間に依存する。 そして保持時間は書き込み順に依存するため、書き込みの走査方向が一方向であると列ご とのリセット電流の大小関係間が固定化され、これが輝度傾斜となって現れてしまう。

そこで上述の実施の形態で説明したように、書き込みの走査方向を双方向とする。そして、単独のフレームでは存在する輝度傾斜をフレームごとで逆方向の輝度傾斜にし、複数のフレーム間で平均化することで輝度傾斜を抑制させる。

その結果、リセット電流回路内において、TFTリークによるリセット電流の変化が生じた場合でも、画面左右方向の輝度傾斜が無いアクティブマトリックス型有機EL表示装置を提供することができる。

## [0045]

更に、本実施の形態のアクティブマトリクス型有機 E L 表示装置では、パネル上にリセット電流回路を設けている。従って、外部にこれらの回路を設ける場合に比してコストの増加を抑制することができる。

#### [0046]

なお、この発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せてもよい。

10

20

30

#### 【図面の簡単な説明】

### [0047]

- 【図1】本発明の一態様に係る有機EL表示装置を概略的に示す平面図。

- 【図2】電圧を映像信号とした有機EL表示装置の画素回路を示す図。

- 【図3】画素回路から一定のリセット電流を吸い出すリセット電流回路の構成を示す図。

- 【図4】有機EL表示装置のリセット電流回路の駆動電位を表す概略のタイムチャート。

- 【 図 5 】 バ リ エ ー シ ョ ン に 係 る リ セ ッ ト 電 流 回 路 の 駆 動 電 位 を 表 す 概 略 の タ イ ム チ ャ ー ト

【図6】バリエーションに係るリセット電流回路の駆動電位を表す概略のタイムチャート

## 【符号の説明】

#### [0048]

DP… E L パネル、 C N T … コントローラ、 S U B … 光透過性絶縁基板、 P X … 表示画素、 X D R … 映像信号線ドライバ、 Y D R … 走査信号線ドライバ、 R C … リセット電流回路、 S C N T … 走査制御回路、 R L … リセット線、 D L … 映像信号線、 C s … 保持容量、 C k … 書き込み容量。

## 【図1】

## 【図2】

【図3】

## 【図4】

## 【図5】

第5aスイッチの (第6a, 7aスイッチのケート電位 (第6b, 7bスイッチのケート電位) (第6b, 7bスイッチのケート電位) (第6b, 7bスイッチのケート電位) (第6b, 7bスイッチのケート電位) (第6b, 7bスイッチのケート電位)

# 【図6】

## フロントページの続き

(51) Int.CI. F I テーマコード (参考)

G 0 9 G 3/20 6 1 1 H H 0 5 B 33/14 A

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 渋沢 誠

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 3K107 AA01 BB01 CC33 EE03 HH02 HH04 HH05

5C080 AA06 BB05 DD05 EE29 FF07 FF11 HH09 JJ02 JJ03 JJ04

| 专利名称(译)        | 有源矩阵型有机EL显示器件                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | <u>JP2008286997A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2008-11-27 |

| 申请号            | JP2007131783                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2007-05-17 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 渋沢誠                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09G3/30.J G09G3/20.642.A G09G3/20.624.B G09G3/20.623.R G09G3/20.621.K G09G3/20.611.H H05B33/14.A G09G3/325 G09G3/3266 G09G3/3275 G09G3/3283 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH02 3K107/HH04 3K107/HH05 5C080 /AA06 5C080/BB05 5C080/DD05 5C080/EE29 5C080/FF07 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/BA38 5C380/BA39 5C380/BB01 5C380 /BB02 5C380/CA03 5C380/CA04 5C380/CA12 5C380/CA13 5C380/CA25 5C380/CA32 5C380/CA48 5C380/CA52 5C380/CA53 5C380/CA57 5C380/CB01 5C380/CB14 5C380/CB16 5C380/CB17 5C380 /CC01 5C380/CC13 5C380/CC26 5C380/CC33 5C380/CC38 5C380/CC39 5C380/CC52 5C380/CC64 5C380/CD025 5C380/CE04 5C380/CF07 5C380/CF12 5C380/CF22 5C380/CF43 5C380/CF52 5C380 /DA02 5C380/DA06 5C380/DA35 5C380/DA47 |         |            |

| 代理人(译)         | 河野 哲<br>中村诚                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

甲抑制由视频信号灰度显示的大小来控制供给作为视频信号到每个像素的电压信号的显示装置中,所产生的灰度再现性的变化。 多个显示像素以矩阵形式排列在基板上;复位电流线对应于多个显示像素的列布置并连接到多个显示像素中的每一个;布置成与所述复位电流线的一端连接,多个复位电流部分中流动复位电流在复位电流线复位的显示像素,与共同复位电流部分针对每一帧写入预定的电流一起和扫描控制部,其按时间顺序的复位电流单元扫描驱动器中流动的复位电流的复位电流线,要驱动的复位电流单元的扫描控制单元的有源矩阵的扫描方向不是一个方向的有机EL显示它是。 点域1