(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-94893

(P2015-94893A)

(43) 公開日 平成27年5月18日(2015.5.18)

(51) Int.Cl. F 1 テーマコード (参考)

**G09G** 3/30 (2006.01) G09G 3/30 K 3K107

**G09G** 3/20 (2006.01) G09G 3/20 624B 5C080

**H01L** 51/50 (2006.01) G09G 3/20 641P 5C380

G09G 3/20 642C

G09G 3/20 642D

審査請求 未請求 請求項の数 10 O.L. (全 12 頁) 最終頁に続く

|           |                              |          |                                              |

|-----------|------------------------------|----------|----------------------------------------------|

| (21) 出願番号 | 特願2013-235241 (P2013-235241) | (71) 出願人 | 502356528                                    |

| (22) 出願日  | 平成25年11月13日 (2013.11.13)     |          | 株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号            |

|           |                              | (74) 代理人 | 110001737<br>特許業務法人スズエ国際特許事務所                |

|           |                              | (74) 代理人 | 100091351<br>弁理士 河野 哲                        |

|           |                              | (74) 代理人 | 100084618<br>弁理士 村松 貞男                       |

|           |                              | (74) 代理人 | 100087653<br>弁理士 鈴江 正二                       |

|           |                              | (72) 発明者 | 大山 敦則<br>東京都港区西新橋三丁目7番1号 株式会<br>社ジャパンディスプレイ内 |

(54) 【発明の名称】 表示装置

(57)【要約】

【課題】階調特性を損なうことなく輝度調整を行うことのできる表示装置を提供する。

【解決手段】自発光素子OLEDと、自発光素子に駆動電流を供給する画素回路（BCT、RST、DRT、SSST）と、輝度調整用信号BNCに基づいて、画素回路に対して駆動電流の供給を可又は不可とする信号を供給する輝度制御回路BCとを有する表示装置であって、輝度調整用信号は、駆動電流の供給を可とする状態と、不可とする状態とを所定の周期で繰り返す二値信号である。

### 【選択図】図 4

图 4

**【特許請求の範囲】****【請求項 1】**

自発光素子と、

前記自発光素子に駆動電流を供給する画素回路と、

輝度調整用信号に基づいて、前記画素回路に対して前記駆動電流の供給を可又は不可とする信号を供給する輝度制御回路とを有し、

前記輝度調整用信号は、前記駆動電流の供給を可とする状態と、不可とする状態とを所定の周期で繰り返す二値信号である、表示装置。

**【請求項 2】**

前記画素回路は、前記画素回路に対して前記駆動電流の供給を可又は不可とする信号によって、当該画素回路用の電源を前記自発光素子に電気的に接続する電路を導通状態又は非導通状態に切り替える、請求項 1 に記載の表示装置。

**【請求項 3】**

前記自発光素子と画素回路とを有する画素は、基板上にマトリクス状に配置され、

全自発光素子に対して前記駆動電流の供給の可又は不可が同一タイミングで制御される、請求項 2 に記載の表示装置。

**【請求項 4】**

前記輝度制御回路は、少なくとも 1 行の画素回路群に対して 1 つ設けられ、

前記輝度調整用信号は、全ての輝度制御回路に同一タイミングで入力される、請求項 3 に記載の表示装置。

**【請求項 5】**

前記輝度調整用信号における前記駆動電流の供給を可とする状態の割合は、10%以上で 100%以下の任意の値に設定可能になれる、請求項 1 に記載の表示装置。

**【請求項 6】**

前記画素回路は、

前記自発光素子の一端に接続された第 1 電極と、リセット配線に接続された第 2 電極と、制御電極とを有した駆動トランジスタと、

第 1 電源と前記駆動トランジスタの第 2 電極との間に接続され、前記第 1 電源と前記駆動トランジスタの第 2 電極との間を制御電極に入力される信号によって導通状態又は非導通状態に切替える出力スイッチと、

映像信号線と前記駆動トランジスタの制御電極との間に接続され、映像信号線を通して与えられる信号を前記駆動トランジスタの制御電極側に取り込むかどうかを切替える画素スイッチと、

前記駆動トランジスタの第 1 電極と制御電極との間に接続された保持容量と、を備える請求項 1 に記載の表示装置。

**【請求項 7】**

前記駆動電流の供給を可又は不可とする信号は、前記出力スイッチの制御電極に入力される、請求項 6 に記載の表示装置。

**【請求項 8】**

前記自発光素子と画素回路とを有する画素は、基板上にマトリクス状に配置され、

全自発光素子に対して前記駆動電流の供給の可又は不可が同一タイミングで制御される、請求項 7 に記載の表示装置。

**【請求項 9】**

前記輝度制御回路は、少なくとも 1 行の画素回路群に対して 1 つ設けられ、

前記輝度調整用信号は、全ての輝度制御回路に同一タイミングで入力される、請求項 8 に記載の表示装置。

**【請求項 10】**

前記輝度調整用信号における前記駆動電流の供給を可とする状態の割合は、10%以上で 100%以下の任意の値に設定可能になれる、請求項 6 に記載の表示装置。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明の実施形態は、表示装置に関する。

**【背景技術】****【0002】**

近年、薄型、軽量、低消費電力の特徴を活かして、液晶表示装置に代表される平面表示装置の需要が急速に伸びている。中でも、オン画素とオフ画素とを電気的に分離し、かつオン画素への映像信号を保持する機能を有する画素スイッチを各画素に設けたアクティブマトリクス型表示装置は、携帯情報機器を始め、種々のディスプレイに利用されている。

**【0003】**

このような平面型のアクティブマトリクス型表示装置として、自己発光素子を用いた有機EL表示装置が注目され、盛んに研究開発が行われている。有機EL表示装置は、バックライトを必要とせず、高速な応答性から動画再生に適し、さらに低温で輝度低下しないために寒冷地での使用にも適しているという特徴を有している。

**【0004】**

一般に、有機EL表示装置は、複数行、複数列に並んで設けられた複数の画素を備えている。各画素は、自己発光素子である有機EL素子、及び有機EL素子に駆動電流を供給する画素回路により構成され、有機EL素子の発光輝度を制御することにより表示動作を行う。

**【0005】**

画素回路の駆動方式としては、電圧信号により行なう方式が知られている。また、電圧電源をスイッチングし、ロー、ハイを切り換えるとともに、映像信号配線から映像信号及び初期化信号の両方を出力することにより、画素の構成素子数と配線数とを削減し、画素のレイアウト面積を小さくすることにより高精細化を図った表示装置が提案されている。

**【先行技術文献】****【特許文献】****【0006】**

【特許文献1】米国特許第6,229,506号明細書

【特許文献2】特開2007-310311号公報

【特許文献3】特開2011-145622号公報

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

ところで、液晶表示装置ではバックライトが設けられているため、そのバックライトを明るくしたり、暗くしたりすることで階調特性を損なうことなく、容易に輝度調整を行うことが可能である。

**【0008】**

一方、有機EL表示装置ではバックライトが存在しないため、表示するデータを加工処理することで輝度調整が行われている。しかしながら、デジタル処理によって輝度調整のためのデータ処理が行なわれるため階調潰れが発生して階調特性が損なわれるという問題が指摘されている。

**【0009】**

この発明は以上の点に鑑みなされたもので、階調特性を損なうことなく輝度調整を行うことのできる表示装置を提供することを目的とする。

**【課題を解決するための手段】****【0010】**

一実施形態に係る表示装置は、自発光素子と、前記自発光素子に駆動電流を供給する画素回路と、輝度調整用信号に基づいて、前記画素回路に対して前記駆動電流の供給を可又は不可とする信号を供給する輝度制御回路とを有し、前記輝度調整用信号は、前記駆動電流の供給を可とする状態と、不可とする状態とを所定の周期で繰り返す二値信号である、

10

20

30

40

50

表示装置。

【図面の簡単な説明】

【0011】

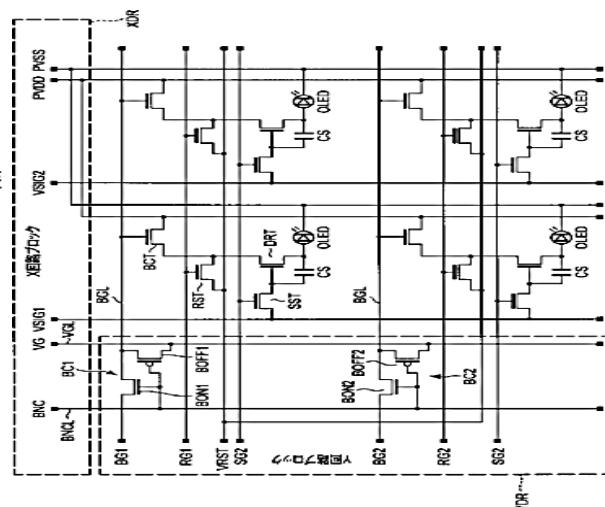

【図1】本実施形態に係る表示装置を概略的に示す平面図である。

【図2】本実施形態に係る表示装置の画素の等価回路を示す図である。

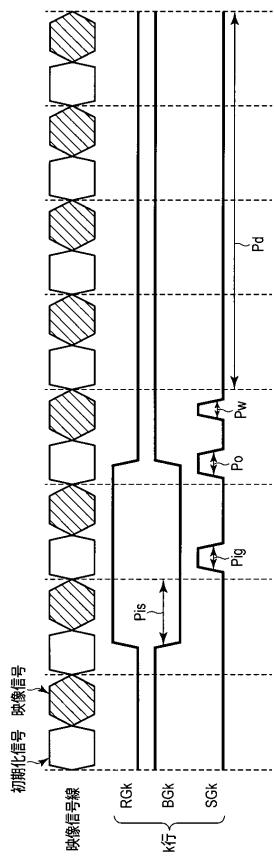

【図3】本実施の形態に係る表示装置のそれぞれの表示動作時のY回路ブロックの制御信号を示すタイミングチャートである。

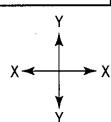

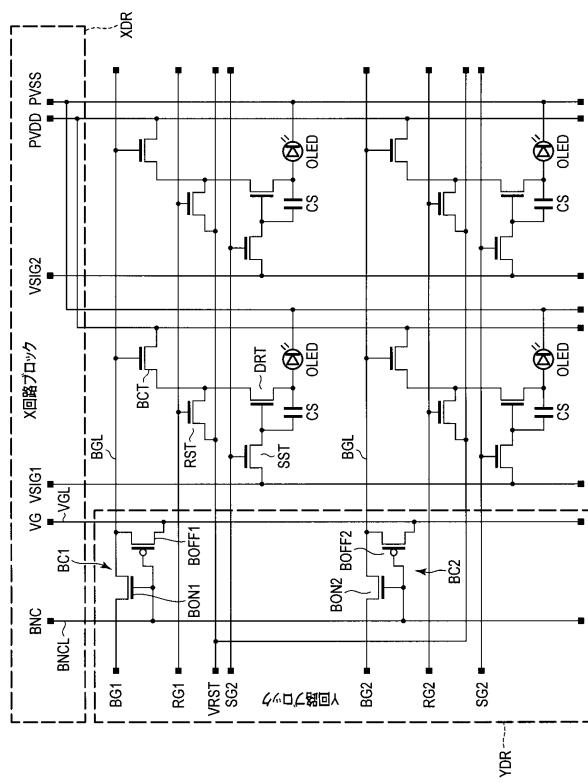

【図4】本実施の形態に係る表示装置の輝度調整に関わる回路構成を示す図である。

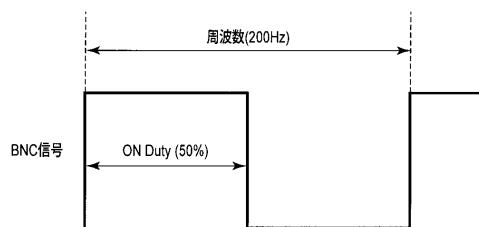

【図5】本実施の形態に係る表示装置の輝度調整用信号を例示するタイムチャートである。

10

【発明を実施するための形態】

【0012】

以下、図面を参照しながら実施形態に係る表示装置について詳細に説明する。この実施形態において、表示装置は、アクティブマトリクス型の表示装置であり、より詳しくはアクティブマトリクス型の有機EL（エレクトロルミネッセンス）表示装置である。

【0013】

図1は、本実施形態に係る表示装置を概略的に示す平面図である。図1に示すように、本実施形態に係る表示装置は、例えば、2型以上のアクティブマトリクス型の表示装置として構成され、表示パネルDPと、表示パネルDPの動作を制御するコントローラ12とを含んでいる。この実施の形態において、表示パネルDPは、有機ELパネルである。

20

【0014】

表示パネルDPは、ガラス板等の光透過性を有する絶縁基板SUB、絶縁基板SUBの矩形状の表示領域上にマトリクス状に配列されたm×n個の画素PX、複数本（m本）の走査信号線SGL（1～m）と、複数本（m本）の制御信号線BGL（1～m）と、複数本（m本）のリセット信号線RGL（1～m）と、複数本（m本）のリセット電源線VRSTL（1～m）と、複数本（n本）の映像信号線VL（1～n）とを備えている。

【0015】

画素PXは、列方向Yにm個、行方向Xにn個並べられている。走査信号線SGL、制御信号線BGL、リセット信号線RGL及びリセット電源線VRSTLは、行方向Xに延出して設けられている。映像信号線VLは、列方向Yに延出して設けられている。

30

【0016】

走査信号線SGL（1～m）、制御信号線BGL（1～m）、リセット信号線RGL（1～m）、リセット電源線VRSTL（1～m）、及び映像信号線VL（1～n）は、それぞれ、走査信号SG（1～m）、制御信号BG（1～m）、リセット信号RG（1～m）、及びリセット電圧VRST（1～m）、及び映像信号SIG（1～n）を画素PXに供給する。

【0017】

表示パネルDPは、走査信号線SGL（1～m）、制御信号線BGL（1～m）、リセット信号線RGL（1～m）及びリセット電源線VRSTL（1～m）を画素PXの行毎に順に駆動するY回路ブロックYDR、映像信号線VL（1～n）を駆動するX回路ブロックXDRを備えている。Y回路ブロックYDR及びX回路ブロックXDRは、絶縁基板SUBの表示領域外側の非表示領域上に一体的に形成され、コントローラ12とともに駆動部を構成している。

40

【0018】

一方、コントローラ12は表示パネルDPの外部に配置されたプリント回路基板（図示せず）上に形成され、Y回路ブロックYDR及びX回路ブロックXDRを制御する。コントローラ12は外部から供給されるデジタル映像信号および同期信号を受け取り、垂直走査タイミングを制御する垂直走査制御信号、および水平走査タイミングを制御する水平走査制御信号を同期信号に基づいて発生する。

【0019】

50

そして、コントローラ 1 2 は、これら垂直走査制御信号および水平走査制御信号をそれぞれ Y 回路ブロック Y D R 及び X 回路ブロック X D R に供給するとともに、水平および垂直走査タイミングに同期してデジタル映像信号及び初期化信号を X 回路ブロック X D R に供給する。

【 0 0 2 0 】

X 回路ブロック X D R は、水平走査制御信号の制御により各水平走査期間において順次得られる映像信号をアナログ形式に変換し階調に応じた映像信号 V S I G を複数の映像信号線 V L ( 1 ~ n ) に並列的に供給する。また、X 回路ブロック X D R は、初期化信号 V i n i ( 後述 ) を映像信号線 V L に供給する。

【 0 0 2 1 】

Y 回路ブロック Y D R は、図示しないシフトレジスタ、出力バッファ等を含み、外部から供給される水平走査スタートパルスを順次次段に転送し、出力バッファを介して各行の画素 P X に 3 種類の制御信号、すなわち、走査信号 S G 、制御信号 B G 、リセット信号 R G を供給する。また、Y 回路ブロック Y D R は、リセット電源線 V R S T L に対して、固定されたリセット電位 V R S T を供給する。

10

【 0 0 2 2 】

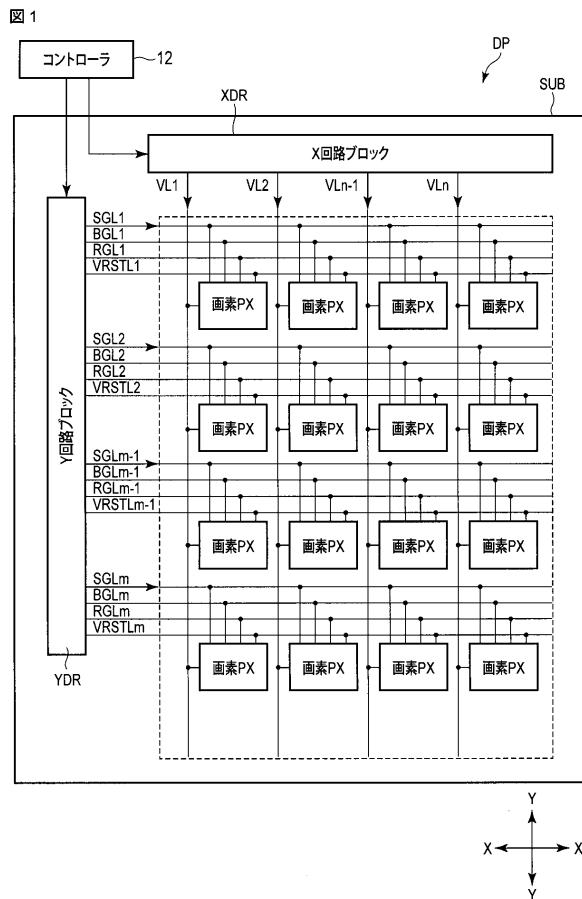

図 2 は、本実施の形態の表示装置における画素 P X の等価回路を示す図である。

【 0 0 2 3 】

各画素 P X は、高電位 P v d d に固定される高電位電源線と、低電位 P v s s に固定される低電位電源線とに接続されている。そして各画素 P X は、表示素子 E L と、表示素子 E L に駆動電流を供給する画素回路と、を含んでいる。表示素子 E L は、例えば自己発光素子であり、本実施形態では、光活性層として少なくとも有機発光層を備えた有機 E L ダイオード O L E D ( 以下、ダイオード O L E D と言う。 ) を用いている。

20

【 0 0 2 4 】

図 2 に示すように、各画素 P X の画素回路は、電圧信号からなる映像信号 V S I G に応じてダイオード O L E D の発光を制御する電圧信号方式の画素回路であり、画素スイッチ S S T 、駆動トランジスタ D R T 、出力スイッチ B C T 、リセットスイッチ R S T 及び保持容量 C s を有している。保持容量 C s は、キャパシタである。

【 0 0 2 5 】

画素スイッチ S S T 、駆動トランジスタ D R T 、出力スイッチ B C T 及びリセットスイッチ R S T は、ここでは同一導電型、例えば N チャネル型の T F T ( 薄膜トランジスタ ) により構成されている。本実施形態に係る表示装置において、各駆動トランジスタ及び各スイッチをそれぞれ構成した T F T は全て同一工程、同一層構造で形成され、半導体層にポリシリコンを用いたトップゲート構造の薄膜トランジスタである。

30

【 0 0 2 6 】

画素 P X の画素回路において、駆動トランジスタ D R T 及び出力スイッチ B C T は、高電位電源線 ( 高電位 P V D D ) と低電位電源線 ( 高電位 P V S S ) との間でダイオード O L E D と直列に接続されている。高電位 P V D D は例えば 10 V の電位に設定され、低電位 P V S S は、例えば 1.5 V の電位に設定されている。

【 0 0 2 7 】

出力スイッチ B C T において、ドレイン電極は高電位電源線 ( 高電位 P V D D ) に接続され、ソース電極は駆動トランジスタ D R T のドレイン電極に接続され、ゲート電極は制御信号線 B G L に接続されている。これにより、出力スイッチ B C T は、制御信号線 B G L からの制御信号 B G によりオン ( 導通状態 ) 、オフ ( 非導通状態 ) 制御される。出力スイッチ B C T は、制御信号 B G に応答して、ダイオード O L E D の発光時間を制御する。

40

【 0 0 2 8 】

駆動トランジスタ D R T において、ドレイン電極は出力スイッチ B C T のソース電極及びリセットトランジスタ R S T のドレイン電極に接続され、ソース電極はダイオード O L E D の一方の電極 ( ここでは陽極 ) に接続されている。ダイオード O L E D の他方の電極 ( ここでは陰極 ) は、低電位電源線 ( 高電位 P V S S ) に接続されている。駆動トランジ

50

スタ D R T のゲート電極は画素スイッチ S S T のドレイン電極に接続され、駆動トランジスタ D R T のゲート電極とソース電極とは保持容量 C s を介して接続されている。駆動トランジスタ D R T は、映像信号 V S I G に応じた電流量の駆動電流をダイオード O L E D に出力する。

【0029】

画素スイッチ S S T において、ソース電極は映像信号線 V L に接続され、ドレイン電極は駆動トランジスタ D R T のゲート電極に接続され、ゲート電極は信号書き込み制御用ゲート配線として機能する走査信号線 S G L に接続されている。画素スイッチ S S T は、走査信号線 S G L から供給される走査信号 S G によりオン、オフ制御される。そして、画素スイッチ S S T は、走査信号 S G に応答して、画素回路と映像信号線 V L との接続、非接続を制御し、対応する映像信号線 V L から映像信号 V S I G を画素回路に取り込む。

10

【0030】

リセットスイッチ R S T において、ソース電極はリセット電源線 V R S T L に接続され、ドレイン電極は駆動トランジスタ D R T のドレイン電極に接続され、ゲート電極はリセット制御用ゲート配線として機能するリセット信号線 R G L に接続されている。リセットスイッチ R S T は、リセット信号線 R G L を通して与えられるリセット信号 R G に応じて、リセット電源線 V R S T L と駆動トランジスタ D R T のドレイン電極との間を導通状態（オン）又は非導通状態（オフ）に切替える。

20

【0031】

次に、上記のように構成された表示装置（有機 E L 表示装置）の動作について説明する。

【0032】

図 3 は、本実施の形態の表示装置における、それぞれの動作時の Y 回路ブロック Y D R の制御信号を示すタイミングチャートである。

30

【0033】

画素回路の動作は、ソース初期化期間 P i s に行われるソース初期化動作と、ゲート初期化期間 P i g に行われるゲート初期化動作と、オフセットキャンセル期間 P o に行われる、オフセットキャンセル（O C）動作と、映像信号書き込み期間 P w に行われる映像信号書き込み動作と、表示期間 P d（発光期間）に行われる表示動作（発光動作）と、に分けられる。

【0034】

[ソース初期化動作]

ソース初期化動作では、Y 回路ブロック Y D R から、走査信号 S G が画素スイッチ S S T をオフ状態とするレベル（オフ電位：ここではローレベル）、制御信号 B G が出力スイッチ B C T をオフ状態とするレベル（オフ電位：ここではローレベル）、リセット信号 R G がリセットスイッチ R S T をオン状態とするレベル（オン電位：ここではハイレベル）に設定される。

40

【0035】

出力スイッチ B C T 、画素スイッチ S S T がそれぞれオフ（非導通状態）、リセットスイッチ R S T がオン（導通状態）となり、ソース初期化動作が開始される。リセットスイッチ R S T がオンすることで、駆動トランジスタ D R T のソース電極及びドレイン電極がリセット電源の電位（リセット電位 V R S T ）と同電位にリセットされ、ソース初期化動作は完了する。ここで、リセット電位 V R S T は、例えば - 2 V に設定されている。

【0036】

[ゲート初期化動作]

ゲート初期化動作では、Y 回路ブロック Y D R から、走査信号 S G が画素スイッチ S S T をオン状態とするレベル（オン電位：ここではハイレベル）、制御信号 B G が出力スイッチ B C T をオフ状態とするレベル、リセット信号 R G がリセットスイッチ R S T をオン状態とするレベルに設定される。出力スイッチ B C T がオフ、画素スイッチ S S T 及びリセットスイッチ R S T がオンとなり、ゲート初期化動作が開始される。

50

## 【0037】

ゲート初期化期間  $P_{ig}$  において、映像信号線  $VL$  から出力された初期化信号  $V_{ini}$  (初期化電圧) は、画素スイッチ  $SS$   $T$  を通して駆動トランジスタ  $DR$   $T$  のゲート電極に印加される。これにより、駆動トランジスタ  $DR$   $T$  のゲート電極の電位は、初期化信号  $V_{ini}$  に対応する電位にリセットされ、前フレームの情報が初期化される。初期化信号  $V_{ini}$  の電圧レベルは、例えば、2Vに設定されている。

## 【0038】

## [オフセットキャンセル動作]

オフセットキャンセル動作では、走査信号  $SG$  がオン電位、制御信号  $BG$  がオン電位 (ハイレベル)、リセット信号  $RG$  がオフ電位 (ローレベル) となる。これによりリセットスイッチ  $RS$   $T$  がオフ、画素スイッチ  $SS$   $T$  及び出力スイッチ  $BCT$  がオンとなり、閾値のオフセットキャンセル動作が開始される。

10

## 【0039】

オフセットキャンセル期間  $P_o$  において、駆動トランジスタ  $DR$   $T$  のゲート電極には映像信号線  $VL$  及び画素スイッチ  $SS$   $T$  を通して初期化信号  $V_{ini}$  が与えられ、駆動トランジスタ  $DR$   $T$  のゲート電極の電位は固定される。

## 【0040】

また、出力スイッチ  $BCT$  はオン状態にあり、高電位電源線  $PSH$  から駆動トランジスタ  $DR$   $T$  に電流が流れ込む。駆動トランジスタ  $DR$   $T$  のソース電極の電位は、ソース初期化期間  $P_{is}$  に書き込まれた電位 (リセット電位  $V_{RST}$ ) を初期値とし、駆動トランジスタ  $DR$   $T$  のドレイン電極 - ソース電極間を通じて流れ込む電流分を徐々に減少させながら、駆動トランジスタ  $DR$   $T$  の  $TF$   $T$  特性ばらつきを吸収・補償しつつ、高電位側にシフトしていく。本実施形態では、オフセットキャンセル期間  $P_o$  は例えば  $1\ \mu\ sec$  程度の時間に設定されている。

20

## 【0041】

オフセットキャンセル期間  $P_o$  終了時点で、駆動トランジスタ  $DR$   $T$  のソース電極の電位は、 $V_{ini} - V_{th}$  となる。なお、 $V_{ini}$  は初期化信号  $V_{ini}$  の電圧値であり、 $V_{th}$  は駆動トランジスタ  $DR$   $T$  の閾値電圧である。これにより、駆動トランジスタ  $DR$   $T$  のゲート電極 - ソース電極間の電圧は、キャンセル点 ( $V_{gs} = V_{th}$ ) に到達し、このキャンセル点に相当する電位差が保持容量  $C_s$  に蓄えられる (保持される)。

30

## 【0042】

## [映像信号書き込み動作]

続いて、映像信号書き込み期間  $P_w$  では、走査信号  $SG$  が画素スイッチ  $SS$   $T$  をオン状態とするレベル、制御信号  $BG$  が出力スイッチ  $BCT$  をオン状態とするレベル、リセット信号  $RG$  がリセットスイッチ  $RS$   $T$  をオフ状態とするレベルに設定される。すると、画素スイッチ  $SS$   $T$  及び出力スイッチ  $BCT$  がオン、リセットスイッチ  $RS$   $T$  がオフとなり、映像信号書き込み動作が開始される。

30

## 【0043】

映像信号書き込み期間  $P_w$  において、映像信号線  $VL$  から画素スイッチ  $SS$   $T$  を通じて駆動トランジスタ  $DR$   $T$  のゲート電極に映像信号  $VSIG$  が書き込まれる。また、高電位電源線から出力スイッチ  $BCT$  及び駆動トランジスタ  $DR$   $T$  を通り、低電位電源線に電流が流れれる。

40

## 【0044】

その後、映像信号書き込み期間  $P_w$  終了時には、駆動トランジスタ  $DR$   $T$  のゲート電極の電位は  $VSIG$  となり、保持容量  $C_s$  の両端の電圧値は、駆動トランジスタ  $DR$   $T$  の閾値電圧によるばらつきの影響が補正された値となる。

## 【0045】

## [表示動作]

最後に、表示期間  $P_d$  では、走査信号  $SG$  が画素スイッチ  $SS$   $T$  をオフ状態とするレベル、制御信号  $BG$  が出力スイッチ  $BCT$  をオン状態とするレベル、リセット信号  $RG$  がリ

50

セットスイッチ R S T をオフ状態とするレベルに設定される。出力スイッチ B C T がオン、画素スイッチ S S T 及びリセットスイッチ R S T がオフとなり、表示動作が開始される。

【0046】

駆動トランジスタ D R T は、保持容量 C s に書込まれたゲート制御電圧に対応した電流量の駆動電流 I e I を出力する。この駆動電流 I e I がダイオード O L E D に供給される。これにより、ダイオード O L E D が駆動電流 I e I に応じた輝度で発光し、表示動作を行う。ダイオード O L E D は、1 フレーム期間後に、再び制御信号 B G がオフ電位となるまで発光状態を維持する。

【0047】

なお、発光期間において、ダイオード O L E D に流れる駆動電流 I e I は、駆動トランジスタ D R T の飽和領域の電流値として、駆動トランジスタ D R T の閾値 V t h に依存しない値となる。そのため、駆動トランジスタ D R T の閾値のバラツキによる影響を排除することができる。

【0048】

上述したソース初期化動作、ゲート初期化動作、オフセットキャンセル動作、映像信号書き込み動作、及び表示動作を順次、各画素 P X で繰り返し行うことにより、所望の画像を表示する。

【0049】

図 4 は、本実施の形態の表示装置の輝度調整に関わる回路構成を示す図である。図 4 に示す構成では、輝度調整に関わる回路である複数 (m 個) の輝度制御回路 B C (1 ~ m) は、Y 回路ブロック Y D R 内に行毎に設けられている。そして、制御信号 B G (1 ~ m) は、輝度制御回路 B C を介して画素 P X に出力される。

【0050】

なお、図 4 では、リセット電源線 V R S T L が 1 行目と 2 行目で同じリセット電源端子から分岐されているが、この形態に限られず、任意の複数本のリセット電源線 V R S T L を同じリセット電源端子から分岐するようにしても良い。

【0051】

次に、輝度制御回路 B C の構成について輝度制御回路 B C 1 を例として説明する。なお、他の輝度制御回路 B C (2 ~ m) についても同様の構成である。

【0052】

輝度制御回路 B C 1 は、輝度オンスイッチ B O N 1 及び輝度オフスイッチ B O F F 1 を備えている。そしてこの輝度制御回路 B C 1 を駆動する輝度調整用信号 B N C が X 回路ブロック X D R から輝度調整用信号線 B N C L を介して供給される。また、X 回路ブロック X D R から切替電圧 V G が切替電圧線 V G L を介して供給される。切替電圧 V G は、出力スイッチ B C T をオフ状態とするレベル (オフ電位: ここではローレベル) の信号である。

【0053】

輝度オンスイッチ B O N 1 は、例えば N チャネル型の T F T (薄膜トランジスタ) により構成されている。輝度オンスイッチ B O N 1 のソース電極は制御信号 B G 1 の供給端子に接続され、ドレイン電極は制御信号線 B G L 及び輝度オフスイッチ B O F F 1 のドレイン電極に接続され、ゲート電極は輝度調整用信号線 B N C L に接続されている。

【0054】

輝度オフスイッチ B O F F 1 は、例えば P チャネル型の T F T (薄膜トランジスタ) により構成されている。輝度オフスイッチ B O F F 1 のソース電極は切替電圧線 V G L に接続され、ドレイン電極は制御信号線 B G L 及び輝度オンスイッチ B O N 1 のドレイン電極に接続され、ゲート電極は輝度調整用信号線 B N C L に接続されている。

【0055】

続いて輝度制御回路 B C 1 の動作について説明する。輝度調整用信号 B N C が輝度オンスイッチ B O N 1 をオン状態とするレベル (オン電位: ここではハイレベル) に設定され

10

20

30

40

50

ると、輝度オフスイッチ B O F F 1 は、オフ状態（オフ電位：ここではハイレベル）となる。そのため、制御信号線 B G L にはハイレベルの制御信号 B G 1 が出力され出力スイッチ B C T をオン状態とする。したがって、この状態ではダイオード O L E D は高電位電源線（高電位 P V D D ）と低電位電源線（高電位 P V S S ）との間で接続され、上述の画素回路の動作に従って駆動される。

【 0 0 5 6 】

輝度調整用信号 B N C が輝度オンスイッチ B O N 1 をオフ状態とするレベル（オフ電位：ここではローレベル）に設定されると、輝度オフスイッチ B O F F 1 は、オン状態（オン電位：ここではローレベル）となる。そのため、制御信号線 B G L にはローレベルの切替電圧 V G が出力され出力スイッチ B C T をオフ状態とする。したがって、この状態ではダイオード O L E D は高電位電源線（高電位 P V D D ）と非接続状態となり、発光は行われない。

10

【 0 0 5 7 】

ここで、輝度調整用信号線 B N C L は行毎に設けられている輝度制御回路 B C ( 1 ~ m ) の全てと接続している。したがって、全画面のダイオード O L E D に対して高電位 P V D D の供給を同時にオン / オフすることができる。

【 0 0 5 8 】

図 5 は、本実施の形態の表示装置における、輝度調整用信号 B N C を例示するタイムチャートである。本実施の形態では、輝度調整用信号 B N C の周波数を 2 0 0 H z ( 周期 : 5 m s e c ) とし、デューティ ( D u t y ) を 1 0 ~ 1 0 0 % 可変として構成している。

20

【 0 0 5 9 】

実機における適用結果では、 D u t y 1 0 0 % での輝度を 1 0 0 % としたとき、 D u t y 5 0 % での輝度は 5 0 % であり、 D u t y 1 0 % での輝度は 1 0 % とリニアに輝度を変更することができた。また、階調特性についても輝度 1 0 0 % と輝度 5 0 % とで階調特性に差は見られなかった。

【 0 0 6 0 】

したがって、本実施の形態の表示装置においては、輝度調整用信号 B N C の D u t y を変更することで、階調特性を損なうことなく、バックライト ( B / L ) と同様にして輝度調整を行うことができる。例えば、ユーザが表示装置に設けられた輝度変更手段を操作したときは、コントローラ 1 2 は、操作入力に対応して輝度調整用信号 B N C の D u t y を指定された値に変更する。これによって、輝度が調整される。

30

【 0 0 6 1 】

なお、輝度調整用信号 B N C については、上述の例で示した周波数、 D u t y に限られない。フリッカなどによる視認性の劣化が認められない限り、周波数、 D u t y は任意の値を用いることができる。

【 0 0 6 2 】

なお、図 2 に示す画素回路ではリセットスイッチ R S T が設けられているが、このリセットスイッチ R S T は、例えば Y 回路ブロック Y D R 行毎に共通して 1 個を設け、各行の画素回路にはリセットスイッチ R S T で切り替えた後のリセット信号を供給するように構成しても良い。

40

【 0 0 6 3 】

また、図 4 に示す構成では、輝度制御回路 B C は 1 行毎に 1 個設けられているが、複数行に対して 1 個設けるように構成しても良い。

【 0 0 6 4 】

なお、上述の画素回路の構成において、高電位電源を第 1 電源、定電位電源を第 2 電源、ソース電極を第 1 電極、ドレイン電極を第 2 電極、ゲート電極を制御電極と読み替えることで構成を一般化することができる。

【 0 0 6 5 】

上述のいくつかの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが

50

可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

### 【0066】

なお、上述の実施の形態で説明した各機能は、ハードウェアを用いて構成しても良く、また、ソフトウェアを用いて各機能を記載したプログラムをコンピュータに読み込ませて実現しても良い。また、各機能は、適宜ソフトウェア、ハードウェアのいずれかを選択して構成するものであっても良い。

### 【0067】

上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せててもよい。

### 【符号の説明】

### 【0068】

D P ... 表示パネル、P X ... 画素、S G L ... 走査信号線、B G L ... 制御信号線、R G L ... リセット信号線、V R S T L ... リセット電源線、V L ... 映像信号線、V R S T ... リセット電圧、Y D R ... Y回路ブロック、X D R ... X回路ブロック、V R S T ... リセット電位、P v d d ... 高電位、P v s s ... 低電位、O L E D ... E L ダイオード、S S T ... 画素スイッチ、D R T ... 駆動トランジスタ、B C T ... 出力スイッチ、R S T ... リセットスイッチ、C s ... 保持容量、R S T ... リセットトランジスタ、B C ... 輝度制御回路、B N C L ... 輝度調整用信号線、V G ... 切替電圧、V G L ... 切替電圧線、1 2 ... コントローラ。

10

20

【図1】

【図2】

【図3】

図3

【図4】

図4

【図5】

図5

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 1 1 H |

| H 0 5 B | 33/14 | A       |

F ターム(参考) 3K107 AA01 BB01 CC31 EE03 HH04 HH05

5C080 AA06 BB05 EE28 FF11 JJ02 JJ03 JJ04

5C380 AA01 AB06 AB23 BA39 BB21 BB22 CA12 CB11 CB18 CC04

CC07 CC27 CC30 CC33 CC39 CC64 CD014 CF07 CF22 CF51

DA02 DA06 DA19 DA32 DA35 DA47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2015094893A</a>                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2015-05-18 |

| 申请号            | JP2013235241                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2013-11-13 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 大山敦則                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 大山 敦則                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09G3/30.K G09G3/20.624.B G09G3/20.641.P G09G3/20.642.C G09G3/20.642.D G09G3/20.611.H H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3291                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC31 3K107/EE03 3K107/HH04 3K107/HH05 5C080/AA06 5C080 /BB05 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/AB23 5C380/BA39 5C380/BB21 5C380/BB22 5C380/CA12 5C380/CB11 5C380/CB18 5C380 /CC04 5C380/CC07 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC39 5C380/CC64 5C380/CD014 5C380/CF07 5C380/CF22 5C380/CF51 5C380/DA02 5C380/DA06 5C380/DA19 5C380/DA32 5C380 /DA35 5C380/DA47 |         |            |

| 代理人(译)         | 河野 哲                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

## 摘要(译)

解决的问题：提供一种能够在不损害灰度特性的情况下调节亮度的显示装置。自发光元件OLED，基于亮度调节信号BNC将驱动电流提供给自发光元件的像素电路 ( BCT , RST , DRT , SST ) 和驱动电流来提供给像素电路。在具有用于提供启用或禁用信号的亮度控制电路BC的显示装置中，亮度调节信号使得以预定周期设置可以提供驱动电流的状态和不能提供驱动电流的状态。它是重复的二进制信号。[选择图]图4