(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-90492

(P2015-90492A)

(43) 公開日 平成27年5月11日(2015.5.11)

| (51) Int.Cl.               | F 1       | テーマコード (参考) |

|----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01) | G09G 3/30 | J 5C080     |

| <b>G09G 3/20</b> (2006.01) | G09G 3/20 | 624B 5C380  |

|                            | G09G 3/20 | 623C        |

|                            | G09G 3/20 | 612E        |

|                            | G09G 3/20 | 621F        |

審査請求 未請求 請求項の数 3 O L (全 27 頁) 最終頁に続く

|           |                              |          |                                                   |

|-----------|------------------------------|----------|---------------------------------------------------|

| (21) 出願番号 | 特願2013-231562 (P2013-231562) | (71) 出願人 | 514188173<br>株式会社 J O L E D<br>東京都千代田区神田錦町三丁目23番地 |

| (22) 出願日  | 平成25年11月7日 (2013.11.7)       | (74) 代理人 | 100189430<br>弁理士 吉川 修一                            |

|           |                              | (74) 代理人 | 100190805<br>弁理士 傍島 正朗                            |

|           |                              | (72) 発明者 | 中川 博文<br>大阪府門真市大字門真1006番地 パナソニック株式会社内             |

|           |                              | (72) 発明者 | 高原 博司<br>大阪府門真市大字門真1006番地 パナソニック株式会社内             |

最終頁に続く

(54) 【発明の名称】 E L 表示装置

## (57) 【要約】

【課題】表示パネルが大型化及び高精細化されてもソースドライバICの発熱問題が発生しないEL表示装置を提供する。

【解決手段】本発明のEL表示装置は、映像信号を伝達するソース信号線18と、電圧発生回路22と、電荷蓄積回路23と、切り替え回路25を具備し、画素16は、EL素子15と、駆動用のトランジスタ11aと、トランジスタ11eと、ソース信号線18とトランジスタ11aとを導通させるトランジスタ11bとを有し、第1の期間に、入出配線19と電荷蓄積回路23とが接続され、トランジスタ11e及び11bが導通することで、ソース信号線18と電荷蓄積回路23とが接続され、第2の期間に、入出配線19と電圧発生回路22とが接続され、トランジスタ11eが導通することで、トランジスタ11aのゲート端子に電圧発生回路22の電圧が印加される。

【選択図】図5

## 【特許請求の範囲】

## 【請求項 1】

複数の画素がマトリックス状に配置された表示画面を有するアクティブマトリックス型 E L 表示装置であって、

前記複数の画素のそれぞれに印加する映像信号を出力するソースドライバ回路と、

前記ソースドライバ回路が出力する前記映像信号を伝達するソース信号線と、

前記画素を選択する選択電圧、または前記画素を非選択にする非選択電圧を出力するゲートドライバ回路と、

前記ゲートドライバ回路が出力する前記選択電圧または前記非選択電圧を伝達する第 1 のゲート信号線と第 2 のゲート信号線と、

第 1 の電圧を供給する電圧回路と、

電荷を蓄積する蓄積回路と、

前記電圧回路及び前記蓄積回路を選択する選択回路を具備し、

前記複数の画素のそれぞれは、

画素電極と、

前記画素電極とカソード電極間に形成された E L 素子と、

前記 E L 素子に電流を供給する駆動用トランジスタと、

前記駆動用トランジスタのゲート端子に第 1 の端子が電気的に接続され、第 1 の配線に第 2 の端子が接続された第 1 のスイッチ用トランジスタと、

前記映像信号を前記駆動用トランジスタのゲート端子に供給する第 2 のスイッチ用トランジスタとを有し、

前記第 1 のスイッチ用トランジスタのゲート端子は、前記第 1 のゲート信号線に接続されており、

前記第 2 のスイッチ用トランジスタのゲート端子は、前記第 2 のゲート信号線に接続されており、

第 1 の期間では、

前記選択回路が前記第 1 の配線に前記蓄積回路を接続し、前記ゲートドライバ回路が前記第 1 のゲート信号線に前記選択電圧を印加して前記第 1 のスイッチ用トランジスタを導通状態とし、かつ、前記第 2 のゲート信号線に前記選択電圧を印加して前記第 2 のスイッチ用トランジスタを導通状態とすることにより、前記ソース信号線と前記蓄積回路とが電気的に接続され、

前記第 1 の期間と異なる第 2 の期間では、

前記選択回路が前記第 1 の配線に前記電圧回路を接続し、前記ゲートドライバ回路が前記第 1 のゲート信号線に前記選択電圧を印加して前記第 1 のスイッチ用トランジスタを導通状態とすることにより、前記駆動用トランジスタのゲート端子に前記電圧回路の電圧に印加される

ことを特徴とする E L 表示装置。

## 【請求項 2】

前記駆動用トランジスタは、N チャンネルトランジスタである

ことを特徴とする請求項 1 記載の E L 表示装置。

## 【請求項 3】

前記電圧回路の前記第 1 の電圧は、前記映像信号の最小電圧値以上、かつ最大電圧値以下の電圧値である

ことを特徴とする請求項 1 記載の E L 表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本開示は、有機エレクトロルミネッセンス (Organic Electro-Luminescence: 以下、E L、または O L E D と呼ぶことがある。) 素子などを有する E L 表示装置に関するものである。

10

20

30

40

50

**【背景技術】****【0002】**

有機EL表示パネル(OLED)を大型化することにより、動画表示性能、色再現性がよく、高画質のモニターテレビ、映像表示テレビを構成することができる。

**【0003】**

しかしながら、表示パネルが大型になるにつれ、ソース信号線の負荷容量及び配線抵抗が大きくなる。そのため、ソースドライバIC(回路)に必要な駆動能力を高くする必要がある。

**【0004】**

特許文献1には、ソースドライバICの駆動能力を補助するため、ソース信号線にプリチャージ用のトランジスタを配置する構成が開示されている。また、特許文献2には、隣接したソース信号線間をスイッチで短絡することにより、チャージ(電荷)シェアを行い、ソースドライバIC(回路)の駆動を補助する構成が開示されている。

**【先行技術文献】****【特許文献】****【0005】**

【特許文献1】特開2008-39893号公報

【特許文献2】特開2010-164666号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

本開示は、表示パネルが大型化及び高精細化されてもソースドライバICの発熱問題が発生せず、良好に画素に映像信号を書き込め、良好な画像表示を実現できるEL表示装置を提供する。

**【課題を解決するための手段】****【0007】**

本開示の一態様に係るEL表示装置は、複数の画素がマトリックス状に配置された表示画面を有するアクティブマトリックス型EL表示装置であって、前記複数の画素のそれぞれに印加する映像信号を出力するソースドライバ回路と、前記ソースドライバ回路が出力する前記映像信号を伝達するソース信号線と、前記画素を選択する選択電圧、または前記画素を非選択にする非選択電圧を出力するゲートドライバ回路と、前記ゲートドライバ回路が出力する前記選択電圧または前記非選択電圧を伝達する第1のゲート信号線と第2のゲート信号線と、第1の電圧を供給する電圧回路と、電荷を蓄積する蓄積回路と、前記電圧回路及び前記蓄積回路を選択する選択回路を具備し、前記複数の画素のそれぞれは、画素電極と、前記画素電極とカソード電極間に形成されたEL素子と、前記EL素子に電流を供給する駆動用トランジスタと、前記駆動用トランジスタのゲート端子に第1の端子が電気的に接続され、第1の配線に第2の端子が接続された第1のスイッチ用トランジスタと、前記映像信号を前記駆動用トランジスタのゲート端子に供給する第2のスイッチ用トランジスタとを有し、前記第1のスイッチ用トランジスタのゲート端子は、前記第1のゲート信号線に接続されており、前記第2のスイッチ用トランジスタのゲート端子は、前記第2のゲート信号線に接続されており、第1の期間では、前記選択回路が前記第1の配線に前記蓄積回路を接続し、前記ゲートドライバ回路が前記第1のゲート信号線に前記選択電圧を印加して前記第1のスイッチ用トランジスタを導通状態とし、かつ、前記第2のゲート信号線に前記選択電圧を印加して前記第2のスイッチ用トランジスタを導通状態とすることにより、前記ソース信号線と前記電荷蓄積回路とが電気的に接続され、前記第1の期間と異なる第2の期間では、前記選択回路が前記第1の配線に前記電圧回路を接続し、前記ゲートドライバ回路が前記第1のゲート信号線に前記選択電圧を印加して前記第1のスイッチ用トランジスタを導通状態とすることにより、前記駆動用トランジスタのゲート端子に前記電圧回路の電圧に印加されることを特徴とする。

**【発明の効果】**

10

20

30

40

50

## 【0008】

本開示に係るEL表示装置によれば、映像信号電圧の画素書き込み前に、ソース信号線と電荷蓄積回路とが電気的に接続されるので、書き込み時のソースドライバI/Cの負荷を低減できる。よって、良好に画素に映像信号を書き込め、良好な画像表示を実現することが可能となる。

## 【画面の簡単な説明】

## 【0009】

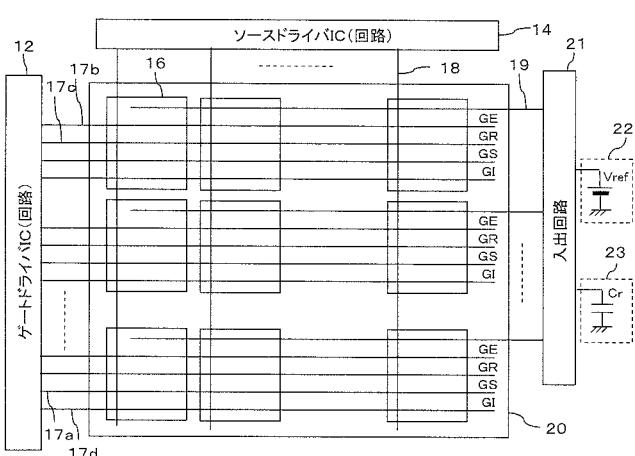

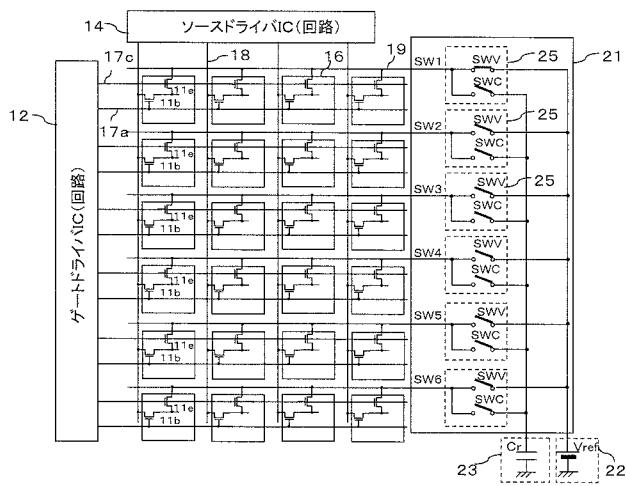

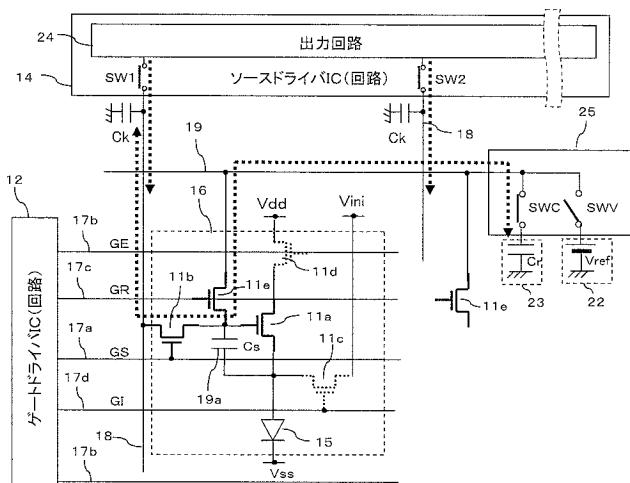

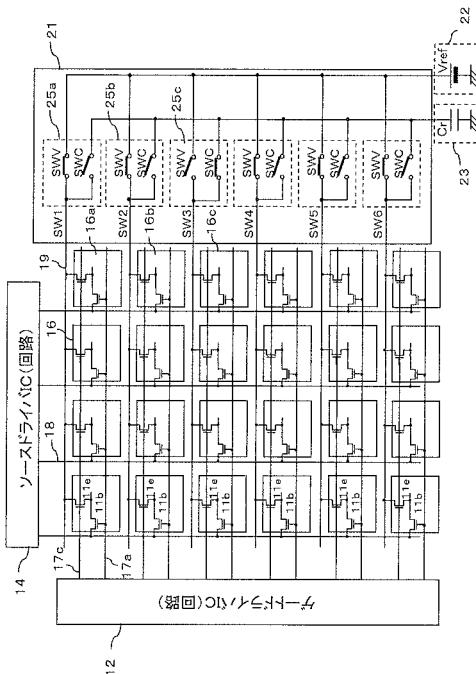

【図1】実施の形態に係るEL表示装置のブロック構成図である。

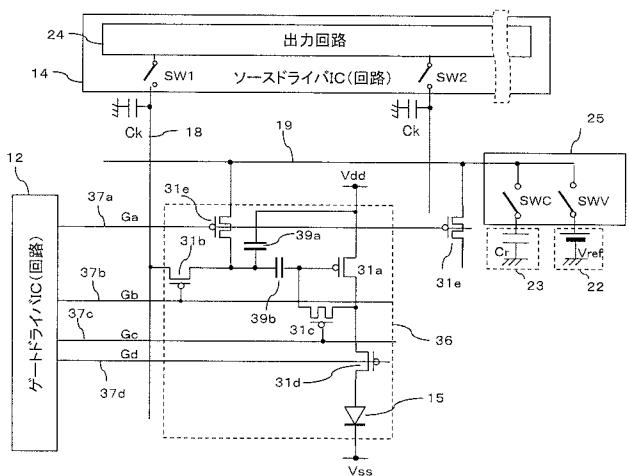

【図2】実施の形態に係るEL表示装置の画素回路の例を示す図である。

【図3】実施の形態に係る入出回路の一例を示す図である。

10

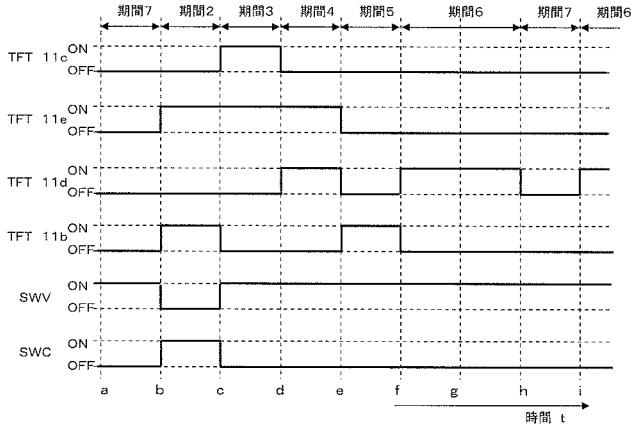

【図4】実施の形態に係るEL表示装置の駆動方法を説明するタイミングチャートである。

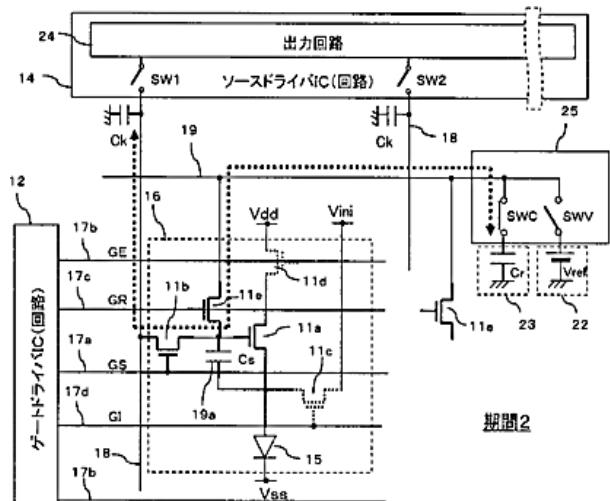

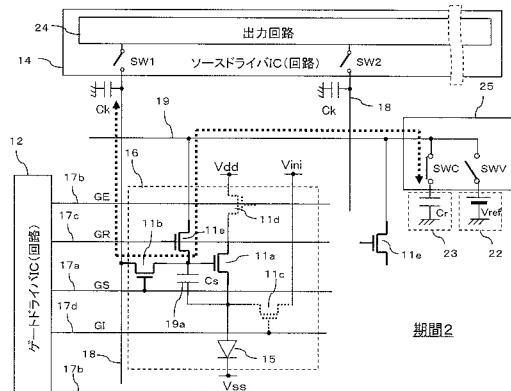

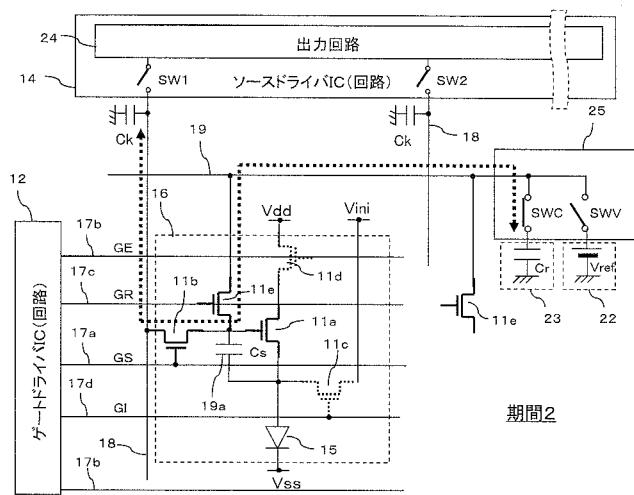

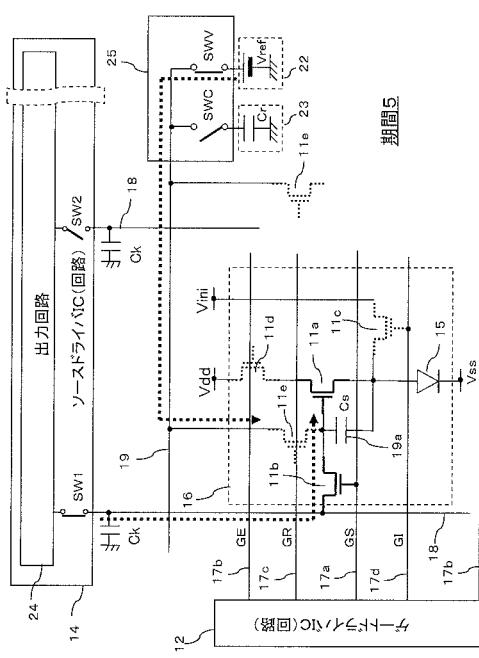

【図5】実施の形態に係る画素回路の期間2における状態遷移図である。

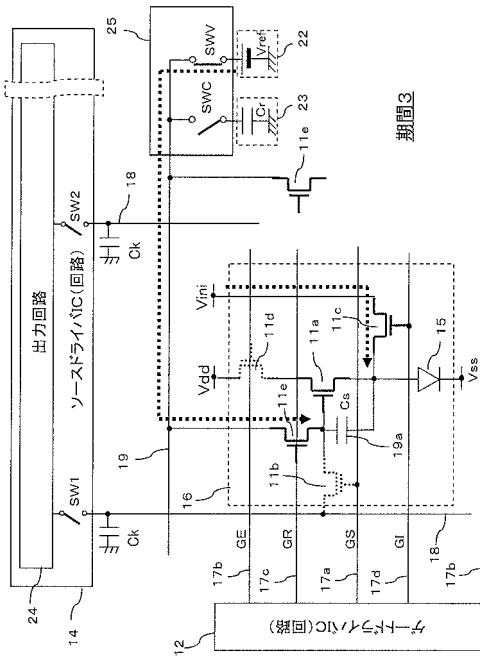

【図6】実施の形態に係る画素回路の期間3における状態遷移図である。

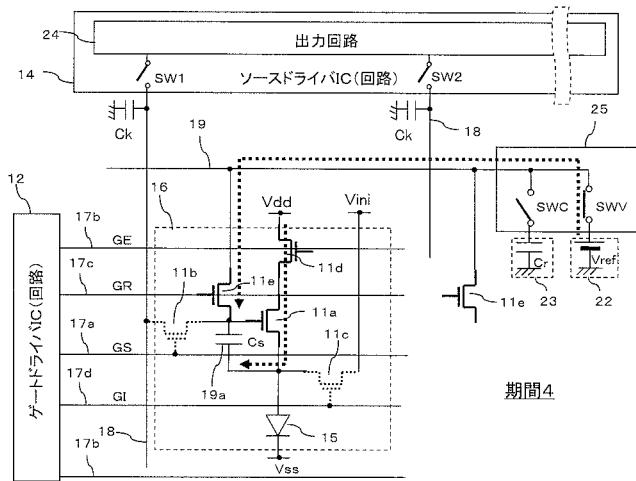

【図7】実施の形態に係る画素回路の期間4における状態遷移図である。

【図8】実施の形態に係る画素回路の期間5における状態遷移図である。

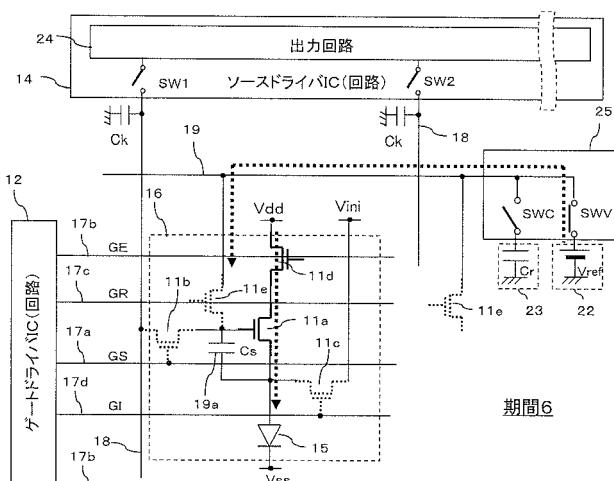

【図9】実施の形態に係る画素回路の期間6における状態遷移図である。

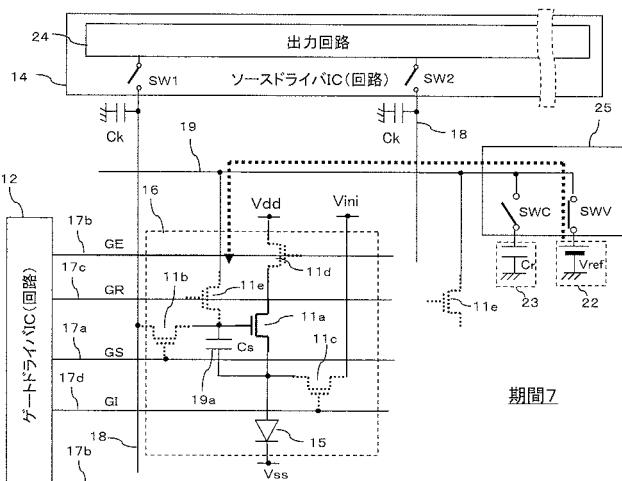

【図10】実施の形態に係る画素回路の期間7における状態遷移図である。

【図11】実施の形態の変形例に係る画素回路の期間2における状態遷移図である。

20

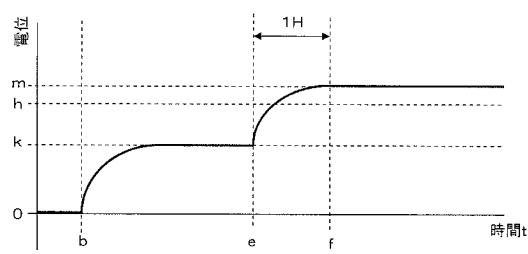

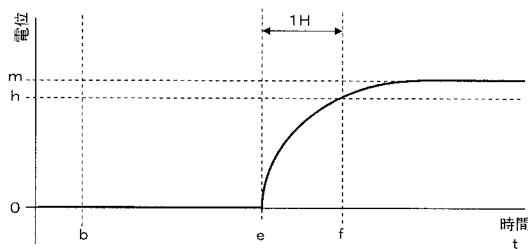

【図12】予備充電がない場合のソース信号線の充電状態を模式的に表すグラフである。

【図13】予備充電がある場合のソース信号線の充電状態を模式的に表すグラフである。

【図14】b行が選択された場合の入出回路の動作を説明する図である。

【図15】c行が選択された場合の入出回路の動作を説明する図である。

【図16】実施の形態の変形例に係るEL表示装置の画素回路の例を示す図である。

【図17】実施の形態に係るEL表示装置を用いたディスプレイの概観図である。

【図18】実施の形態に係るEL表示装置を用いたカメラの概観図である。

【図19】実施の形態に係るEL表示装置を用いたコンピュータの概観図である。

## 【発明を実施するための形態】

## 【0010】

(本開示の基礎となつた知見)

30

以下、本開示を説明する前に、本開示の基礎となつた知見について説明する。

## 【0011】

有機EL表示パネル(OLED)を、大型化することにより、動画表示性能、色再現性がよく、高画質のモニターテレビ、映像表示テレビを構成することができる。

## 【0012】

しかし、EL表示パネルが大型化、高精細化されると、パネルの信号線の負荷容量が大きくなる。また、1画素行を選択する期間(画素行への映像書き込み時間)が短くなる。そのため、ソースドライバI/Cの駆動負荷が大きくなり、ソースドライバI/Cが発熱し、ソースドライバI/Cが焼損したり、ドライバI/C発熱により、表示領域のEL素子が劣化するという課題がある。

40

## 【0013】

そこで、本発明者らは、パネルが大型化及び高精細化されてもソースドライバI/Cの発熱問題が発生せず、良好に画素に映像信号を書き込め、良好な画像表示を実現できるEL表示装置を創作するに至った。

## 【0014】

以下、適宜図面を参照しながら、実施の形態を詳細に説明する。但し、必要以上に詳細な説明は省略する場合がある。例えば、既によく知られた事項の詳細説明や実質的に同一の構成に対する重複説明を省略する場合がある。これは、以下の説明が不必要に冗長になるのを避け、当業者の理解を容易にするためである。

## 【0015】

50

なお、発明者らは、当業者が本開示を十分に理解するために添付図面および以下の説明を提供するのであって、これらによって特許請求の範囲に記載の主題を限定することを意図するものではない。

#### 【0016】

本発明において、各図面は理解を容易にするために、また、作図を容易にするために、省略、拡大あるいは縮小した箇所がある。

#### 【0017】

本発明の実施例に図示あるいは明細書で説明した事項あるいは内容は、他の実施例においても適用される。また、本発明の実施例で説明あるいは図示したEL表示パネルの構成などは、本発明のEL表示装置に採用できる。たとえば、図19のノート型パソコンのEL表示装置として、本発明の実施例で図示した、あるいは説明したEL表示装置(EL表示パネル)を採用できる。また、情報機器を構成することができることは言うまでもない。

10

#### 【0018】

同一番号または、記号等を付した箇所は、同一もしくは類似の形態もしくは材料あるいは機能もしくは動作、あるいは関連する事項、作用などを有する。なお、異なる場合もある。

#### 【0019】

本発明のEL表示装置とは、情報機器などのシステム機器を含む概念である。EL表示パネルの概念は、広義には情報機器などのシステム機器を含む。

20

#### 【0020】

##### (実施の形態)

以下、図面を参照しながら、実施の形態を説明する。

#### 【0021】

##### [1. EL表示装置の構成]

##### [1-1. 全体構成]

図1は、実施の形態に係るEL表示装置のブロック構成図である。同図において、表示画面(表示領域)20には、画素16がマトリックス状に配置されている。各画素16には、4本のゲート信号線17a、17b、17c及び17dが接続されている。

30

#### 【0022】

ゲート信号線17aは、ゲート信号線GSと表現することがあり、ゲート信号線17bはゲート信号線GEと表現することがある。また、ゲート信号線17cはゲート信号線GRと表現することがあり、ゲート信号線17dはゲート信号線GIと表現することがある。

#### 【0023】

また、各画素16には、ソース信号線18が接続されている。ソース信号線18の一端には、ソースドライバIC(回路)14が接続されている。

#### 【0024】

ソースドライバIC(回路)14は、DA(デジタルアナログ)変換回路を内蔵し、外部から差動入力信号により入力された映像信号(階調データ)をデコードし、ソース信号線18に電圧あるいは電流信号を出力する。

40

#### 【0025】

本実施の形態において、ソースドライバIC(回路)14は、各端子あるいはブロックごとに映像信号とゲートドライバIC(回路)12との出力タイミングを設定できるマルチディレイ機能を有する。マルチディレイ駆動(方式)は、各画素行で、ゲート信号線のオフタイミングもしくはオンタイミングを基準として、ソースドライバIC(回路)14が出力する映像信号のタイミング調整を行う。

#### 【0026】

ソースドライバIC(回路)14は、COF(Chip On Film)(図示せず)に実装されている。ソースドライバIC(回路)14は、映像信号を出力し、映像信号

50

は、ソース信号線 18 に供給あるいは印加される。COF に実装されたドライバIC の表面に放熱板が配置または形成され、当該ドライバIC が放熱する。また、COF の裏面に放熱シート、放熱板が配置または形成され、ドライバIC が発生する熱が放熱される。

#### 【0027】

ゲートドライバIC (回路) 12 は、COG (Chip On Glass) 実装、COF 実装などの外付けの半導体 IC に限定されるものではない。たとえば、低温ポリシリコン技術、TAOS (Transparent Amorphous Oxide Semiconductors) 技術などにより、画素内のトランジスタと同一プロセス等で構成あるいは形成したゲートドライバ回路であってもよいことは言うまでもない。

#### 【0028】

##### [1-2. 画素構成]

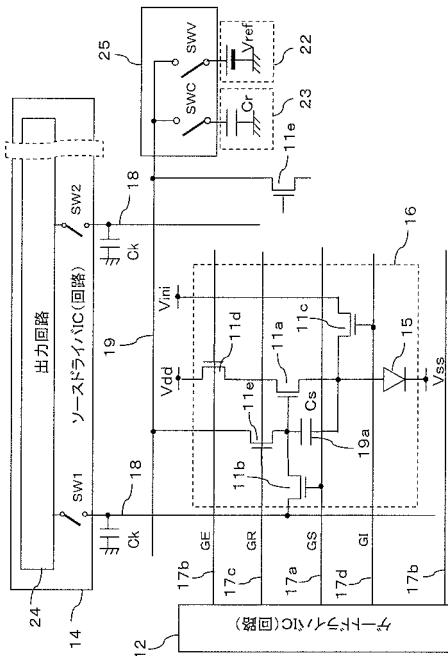

図2は、実施の形態に係るEL表示装置の画素回路の例を示す図である。

#### 【0029】

トランジスタ 11a ~ 11e は、もちろん、FET、MOS-FET、MOSトランジスタ、バイポーラトランジスタ、MIS でもよい。これらも基本的に薄膜トランジスタである。その他、バリスタ、サイリスタ、リングダイオード、ホトダオード、ホトトランジスタ、PLZT 素子などでもよいことは言うまでもない。

#### 【0030】

本実施の形態のトランジスタ 11a ~ 11e は、Nチャンネル及びPチャンネルによらず LDD (Lightly Doped Drain) 構造を採用することが好ましい。

トランジスタ 11a ~ 11e は、高温ポリシリコン (HTPS : High-Temperature Polycrystalline Silicon)、低温ポリシリコン (LTPS : Low-Temperature Polycrystalline Silicon)、連続粒界シリコン (CGS : Continuous Grain Silicon)、透明アモルファス酸化物半導体 (TAOS : Transparent Amorphous Oxide Semiconductors, IZO)、アモルファスシリコン (AS : Amorphous Silicon)、赤外線 RTA (RTA : Rapid Thermal Annealing) 技術を用いて形成したもののうち、いずれでもよい。

#### 【0031】

また、トランジスタ 11a ~ 11e は、薄膜素子に限定するものではなく、シリコンウエハに形成したトランジスタでもよい。たとえば、シリコンウエハでトランジスタを構成し、剥がしてガラス基板に転写したものが例示される。また、シリコンウエハでトランジスタチップ (ドライバ回路など) を形成し、ガラス基板のボンディング実装した表示パネルが例示される。

#### 【0032】

なお、図2などでは、画素を構成するすべてのトランジスタ 11a ~ 11e は Nチャンネルで構成している。しかし、本開示のトランジスタ 11a ~ 11e を、Nチャンネルで構成することに限定するものではない。Pチャンネルのトランジスタのみで構成してもよい。また、NチャンネルとPチャンネルの両方を用いて画素回路を構成あるいは形成してもよい。また、駆動用のトランジスタ 11a を Pチャンネルトランジスタと Nチャンネルトランジスタの両方を用いて構成あるいは形成してもよい。

#### 【0033】

また、トランジスタ 11a ~ 11e のチャンネル間は双方向であるため、ソース端子とドレイン端子の名称は、説明を容易にするためであり、ソース端子とドレイン端子は入れ替てもよい。ソース端子とドレイン端子の名称は、便宜上あるいは説明を容易にするためであり、他のソース端子とドレイン端子は第1の端子、第2の端子などとしてもよい。

#### 【0034】

また、トランジスタ 11a ~ 11e はトップゲート構造にすることが好ましい。トップゲート構造により寄生容量が低減する。また、トップゲートのゲート電極パタ

10

20

30

40

50

ーンが、遮光層となり、EL素子15から出射された光を遮光層で遮断し、トランジスタの誤動作、オフリーケ電流を低減できるからである。また、LDD構造を採用することが好ましい。

#### 【0035】

また、各スイッチ用のトランジスタ11b及び11cなどは、複数のトランジスタで形成してもよい。各スイッチ用のトランジスタ11b及び11cなどをダブルゲート、トリプルゲートなどのマルチゲート構成にする。マルチゲート構成により、オフリーケが低減し、良好なコントラスト表示、オフセットキャンセル動作を実現できる。

#### 【0036】

なお、画素16の画素電極は、ITO、IGZO（インジウム（Indium）、ガリウム（Gallium）、亜鉛（Zinc）、酸素（Oxygen））、IZO、透明アモルファス酸化物半導体（TAOS）などからなる透明電極を用いることができる。10

#### 【0037】

なお、本実施の形態に係るEL表示装置では、画素16の位置に対応して、赤（R）、緑（G）、青（B）からなるカラーフィルタ（図示せず）が形成されている。なお、カラーフィルタは、RGBに限定されるものではなく、シアン（C）、マゼンダ（M）、イエロー（Y）色の画素が形成されてもよい。

#### 【0038】

また、白（W）の画素が形成されてもよい。つまり、表示画面20にR、G、B、W画素をマトリックス状に配置する。白（W）の画素にはカラーフィルタは形成または配置されていない。20

#### 【0039】

画素はRGBの3画素、RGBWの4画素で正方形の形状となるように作製されている。したがって、R、G、B、Wの各画素は縦長の画素形状となる。したがって、レーザー照射スポットを縦長にしてアニールすることにより、1画素内ではトランジスタの特性バラツキが発生しないようにすることができる。

#### 【0040】

なお、R、G、B、Wの画素開口率あるいは画素電極面積は、異ならせてよい。開口率または画素電極面積を異ならせることにより、各RGBのEL素子15に流れる電流密度を異ならせることができる。電流密度を異ならせることにより、R、G、B画素のEL素子15の劣化速度を同一にすることができる。劣化速度を同一にすれば、EL表示装置のホワイトバランスずれが発生しない。30

#### 【0041】

白（W）の画素を形成する場合、画素は、R、G、B、Wから構成される。R、G、B、Wに構成することにより、高輝度化が可能となる。また、R、G、B、Gとする構成も例示される。

#### 【0042】

本発明は、RGBの3原色に加えて、W（白）の画素16（図示せず）を有している。画素16を形成または配置することにより、色ピーケ輝度を良好に実現できる。また、高輝度表示を実現できる。40

#### 【0043】

EL表示装置のカラー化は、マスク蒸着により行うが、本発明はこれに限定するものではない。たとえば、青色発光のEL層を形成し、発光する青色光を、R、G、Bの色変換層（CCM：カラーチェンジミディアムズ）でR、G、B光に変換してもよい。

#### 【0044】

なお、EL表示装置の光出射面には、円偏光板（円偏光フィルム）（図示せず）を配置している。偏光板と位相フィルムを一体したものは円偏光板（円偏光フィルム）と呼ばれる。

#### 【0045】

[1 - 3 . ソースドライバ構成]

10

20

30

40

50

ソースドライバIC(回路)14の内部には、スイッチSWn(nは1以上の整数)が形成または配置されている。スイッチSWnは、一例としてアナログスイッチが例示される。スイッチSWnは、ソースドライバIC14の各出力端子に対応して配置または形成されている。スイッチSWnをオープン状態にすることにより、ソース信号線18とソースドライバIC(回路)14の出力回路24とは、電気的に切り離される。

#### 【0046】

スイッチSWnは、ソースドライバIC(回路)14内に形成されることに限定されるものではなく、ガラス基板に低温ポリシリコンなどの技術を用いて、画素16のトランジスタ11a～11eと同時、あるいは同一プロセス工程で形成してもよいことは言うまでもない。

10

#### 【0047】

なお、他のスイッチは、隣接したソース信号線18間にも形成または配置されている(図示せず)。このスイッチをオンさせることにより、隣接したソース信号線が短絡され、チャージシェアリングが実施される。

#### 【0048】

##### [1-4. ゲートドライバ構成]

図1及び図2などにおいて、作図を容易にするため、1つのゲートドライバIC(回路)12を記載している。実際には、例えば、表示画面20の左側にゲートドライバIC(回路)12aが配置(実装)され、表示画面20の右側にゲートドライバIC(回路)12bが配置されている。

20

#### 【0049】

ソースドライバIC(回路)14が出力する映像信号Vsigを画素16に印加するためのトランジスタ11bに対してゲート信号GSを伝達するゲート信号線17a、及び、トランジスタ11dを制御するためのゲート信号GEを伝達するゲート信号線17bは、ゲートドライバIC12a及びゲートドライバIC12bの双方に接続されている。一例として、ゲートドライバIC12aは、表示画面20の左側に配置され、ゲートドライバIC12bは、表示画面20の右側に配置される。

#### 【0050】

ゲート信号線17a及び17bに、2つのゲートドライバIC12a及び12bが配置されているのは、以下の理由による。

30

#### 【0051】

ゲート信号線17aは、トランジスタ11bに接続され、画素を選択する選択電圧、または画素を非選択にする非選択電圧を伝達する第2のゲート信号線である。トランジスタ11bは、映像信号を画素16に書き込むためのトランジスタであり、トランジスタ11bを高速でオンオフ(高スルーレート動作)させる必要がある。このため、ゲート信号線17aを、2つのゲートドライバIC12a及び12bで駆動することにより、高スルーレートの表示動作を実現できる。

#### 【0052】

ゲート信号線17bは、トランジスタ11dに接続されている。トランジスタ11dは、トランジスタ11aのオフセットキャンセル動作を実施するためのトランジスタであり、トランジスタ11dを高速でオンオフ(高スルーレート動作)させる必要がある。このため、ゲート信号線17bを、2つのゲートドライバIC12a及び12bで駆動することにより、高スルーレートの表示動作を実現できる。

40

#### 【0053】

また、ゲート信号線17a及び17bを、2つのゲートドライバIC12a及び12bで駆動することにより、表示画面20の左右または中央での輝度傾斜などがなくなり、良好な画像表示を実現できる。また、ゲート信号線17a及び17bの負荷容量が大きくても、良好に駆動することができる。

#### 【0054】

ゲート信号線17c及び17dは、1つのゲートドライバIC12aに接続されている

50

。ゲート信号線 17c は、画素を選択する選択電圧、または画素を非選択にする非選択電圧を伝達する第 1 のゲート信号線である。ゲート信号線 17c には、トランジスタ 11e が接続されている。トランジスタ 11e は、リファレンス電圧  $V_{ref}$  をトランジスタ 11a に印加する機能を有する。リファレンス電圧  $V_{ref}$  を印加する動作は、低スルーレートで十分である。また、ゲート信号線 17d には、トランジスタ 11c が接続されている。トランジスタ 11c は、イニシャル電圧  $V_{ini}$  をトランジスタ 11a のソース端子に印加する機能を有する。イニシャル電圧  $V_{ini}$  を印加する動作は、低スルーレートで十分である。

#### 【0055】

ゲートドライバ I C 12 は、ゲート信号線 17a ~ 17d に、オフ電圧 ( $V_{off1}$ 、 $V_{off2}$ ) 及びオン電圧 ( $V_{on}$ ) の 3 つの電圧を出力することができる。この場合、3 つの電圧を出力するので、ゲート電圧 3 値駆動と呼ぶ。または、ゲートオーバードライブ駆動と呼ぶ。

#### 【0056】

また、オフ電圧 ( $V_{off1}$ ) 及びオン電圧 ( $V_{on}$ ) の 2 つの電圧で駆動する駆動方法を、ゲート電圧通常駆動あるいは、ゲート電圧 2 値駆動と呼ぶ。

#### 【0057】

ゲート電圧 2 値駆動とゲート電圧 3 値駆動とは、ゲートドライバ I C (回路) 12 の SEL 端子 (図示せず) に印加するロジック電圧で決定する。

#### 【0058】

オン電圧 ( $V_{on}$ ) は、画素 16 のトランジスタ 11a ~ 11e をオンさせるための電圧である。オフ電圧 ( $V_{off1}$  及び  $V_{off2}$ ) は、画素 16 のトランジスタ 11a ~ 11e をオフさせるための電圧である。具体的には、 $V_{on}$  は、15 (V) 以上 30 (V) 以下である。 $V_{off2}$  は、-15 (V) 以上 -8 (V) 以下である。また、 $V_{off1}$  は、-8 (V) 以上 -3 (V) 以下である。

#### 【0059】

ゲートドライバ I C 12 が  $V_{on}$  を出力する期間は、nH 期間 (n は 1 以上の整数、H は水平走査期間または 1 画素行の選択期間) である。また、 $V_{off2}$  を出力する期間は、1H 期間である。

#### 【0060】

ゲート電圧 3 値駆動は、ゲート信号線 GS に対して実施される。つまり、映像信号を画素 16 に書き込むためのトランジスタ 11b が接続されたゲート信号線 17a に対してゲート電圧 3 値駆動が実施される。

#### 【0061】

$V_{off2}$  が 1H 期間印加されるのは、映像信号を印加するために選択された画素に対して、映像信号が書込まれた後、当該画素を高速に非選択 (オフ) とするためである。また、 $V_{off1}$  で保持するのは、トランジスタ 11b のゲート端子に深い電圧 ( $V_{off2}$ ) が継続して印加されることで  $V_t$  シフトなどトランジスタ特性が変化してしまうことを抑制するためである。

#### 【0062】

ゲート電圧 2 値駆動では、 $V_{on}$  から  $V_{off1}$  に変化する期間  $t_1$  が長期間となる。期間  $t_1$  が長いと、当該期間に画素に書き込まれた映像信号がリークし、また、上下に隣接した画素間でクロストークなどが発生する。

#### 【0063】

これに対して、ゲート電圧 3 値駆動を実施すると、 $V_{on}$  から  $V_{off1}$  に変化する期間  $t_2$  が非常に短期間となる。したがって、画素に書き込まれた映像信号がリークせず、また、上下に隣接した画素間でクロストークなどが発生することがない。

#### 【0064】

なお、ソース信号線 18 及びゲート信号線 17a ~ 17d 上に、アノード電極あるいはカソード電極が配置または形成されることにより、ソース信号線 18 及びゲート信号線 1

10

20

30

40

50

7 a ~ 17 d からの電界が、アノード電極あるいはカソード電極で遮蔽される。当該遮蔽により画像表示へのノイズを低減させることができる。

#### 【0065】

また、ソース信号線 18 及びゲート信号線 17 a ~ 17 d に、絶縁膜あるいはアクリル材料からなる絶縁膜（平坦化膜：図示せず）が形成されて絶縁され、当該絶縁膜上に画素電極（図示せず）が形成される。

#### 【0066】

上記のように、ゲート信号線 17 a ~ 17 d 等の上の少なくとも 1 部に画素電極を重ねる構成を、ハイアパー・チャ（H A）構造と呼ぶ。これにより、不要な干渉光などが低減し、良好な発光状態を実現できる。

10

#### 【0067】

##### [ 1 - 5 . 画素回路の接続関係 ]

本実施の形態に係る E L 表示装置は、マトリックス状に E L 素子を有する表示画面と、当該表示画面の画素行ごとに配置されたゲート信号線 17 a ~ 17 d と、当該表示画面の画素列ごとに配置されたソース信号線 18 と、ゲート信号線 17 a ~ 17 d を駆動するゲートドライバ I C (回路) 12 と、ソース信号線 18 を駆動するソースドライバ I C (回路) 14 と、入出回路 21 とを具備する。

#### 【0068】

図 2 で図示するように、E L 素子 15 のカソード端子には、カソード電圧 V ss が印加されている。トランジスタ 11 a のソース端子と E L 素子のアノード電圧端子とが電気的に接続されている。トランジスタ 11 c のソース端子は、トランジスタ 11 a のソース端子と電気的に接続されている。また、トランジスタ 11 c のドレイン端子には、イニシャル電圧 V ini が印加あるいは供給されている。

20

#### 【0069】

なお、電気的に接続とは、電圧の経路、電流の経路が形成されている状態あるいは形成される状態である。たとえば、第 1 のトランジスタと第 2 のトランジスタ間に、第 3 のトランジスタが配置されていても、第 1 のトランジスタと第 2 のトランジスタは電気的に接続されている。また、本明細書において、接続を、電気的に接続の意味として使用する場合がある。

30

#### 【0070】

トランジスタ 11 b のソース端子はトランジスタ 11 a のゲート端子と接続されており、トランジスタ 11 b のドレイン端子は、ソース信号線 18 と接続されている。トランジスタ 11 b は、映像信号をトランジスタ 11 a のゲート端子に供給する第 2 のスイッチ用トランジスタである。

#### 【0071】

トランジスタ 11 e は、第 1 の端子であるソース端子が、トランジスタ 11 a のゲート端子と接続されており、第 2 の端子であるドレイン端子が入出配線 19 と接続された第 1 のスイッチ用トランジスタであり、当該ドレイン端子にはリファレンス電圧 V ref が印加あるいは供給されている。なお、入出配線 19 は、切り替え回路 25 の接続された第 1 の配線である。

40

#### 【0072】

コンデンサ 19 a は、トランジスタ 11 a のゲート端子とトランジスタ 11 a のソース端子との間に接続されている。

#### 【0073】

ここで、図 2 などの実施例において、アノード電圧 V dd > リファレンス電圧 V ref > カソード電圧 V ss > イニシャル電圧 V ini 、なる関係にすることが好ましい。

#### 【0074】

具体的には、一例として、アノード電圧 V dd = 8 ~ 18 (V) 、リファレンス電圧 V ref = 1.5 ~ 3 (V) 、カソード電圧 V ss = 0.5 ~ 2.5 (V) 、イニシャル電

50

圧  $V_{ini} = 0 \sim -3$  (V) である。

【0075】

映像信号の最小電圧（最小階調での電圧）は、0.5 ~ 1.0 (V) であり、映像信号の最大電圧（最大階調での電圧）は、4 ~ 7 (V) である。

【0076】

したがって、リファレンス電圧  $V_{ref} = 1.5 \sim 3$  (V) は、映像信号の最小電圧（最小階調での電圧）以上であり、かつ、映像信号の最大電圧（最大階調での電圧）以下の電圧である。つまり、リファレンス電圧  $V_{ref} = 1.5 \sim 3$  (V) は、映像信号の中間電圧である。なお、中間電圧とは、狭義には、中央部の電圧近傍であるが、広義には最小電圧より大きく、最大電圧より小さい電圧の範囲である。

10

【0077】

トランジスタ 11d は、トランジスタ 11a のソース端子と EL 素子 15 のアノード端子との間に配置または形成されてもよい。

【0078】

トランジスタ 11d のゲート端子は、ゲート信号線 17b（ゲート信号線 GE）に接続されている。トランジスタ 11e のゲート端子は、ゲート信号線 17c（ゲート信号線 GR）に接続されている。トランジスタ 11b のゲート端子は、ゲート信号線 17a（ゲート信号線 GS）に接続されている。トランジスタ 11c のゲート端子は、ゲート信号線 17d（ゲート信号線 GI）に接続されている。

20

【0079】

ゲート信号線 17a ~ 17d のそれぞれに、オン電圧を印加することにより、各ゲート信号線に接続されたトランジスタがオン状態となる。一方、ゲート信号線 17a ~ 17d のそれぞれに、オフ電圧を印加することにより、各ゲート信号線に接続されたトランジスタがオフ状態となる。

【0080】

ゲート信号線 17b (GE) にオン電圧が印加されると、トランジスタ 11d がオン状態となり、トランジスタ 11a からの発光電流が EL 素子 15 に供給される。EL 素子 15 は、発光電流の大きさに基づき発光する。発光電流の大きさは、ソース信号線 18 に印加された映像信号が、トランジスタ 11b を介して画素 16 に印加されることにより決定される。

30

【0081】

トランジスタ 11a のゲート端子には、コンデンサ 19a の一端子が接続され、コンデンサ 19a の他端子は、トランジスタ 11a のソース端子と接続されている。トランジスタ 11b のドレイン端子は、ソース信号線 18 と接続されている。ソースドライバ IC 14 は、ソース信号線 18 に映像信号を印加する。

【0082】

ゲート信号線 17a 及び 17b は、表示画面 20 の左右に配置されたゲートドライバ IC 12a 及び 12b に接続されている。また、ゲート信号線 17c 及び 17d は、表示画面 20 の左に配置されたゲートドライバ IC 12a に接続されている。

40

【0083】

ゲートドライバ IC 12 は、画素の選択電圧（オン電圧  $V_{on}$ ）をゲート信号線 17a ~ 17d に印加する。ゲート信号線 17b のオン電圧が印加されると、トランジスタ 11b がオン状態となり、ソース信号線 18 に印加された映像信号が画素 16 に印加される。

【0084】

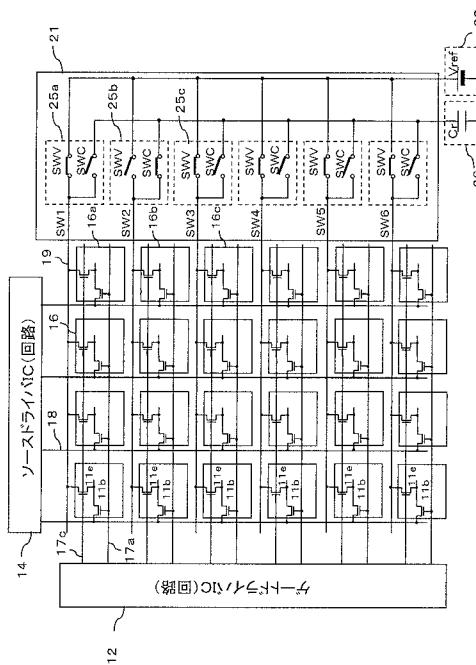

[ 1 - 6 . 画素周辺回路の構成 ]

図 1 に示された出入回路 21 は、出入配線 19 を駆動（制御）する。出入配線 19 は、画素行ごとに配置され、当該画素行に属する画素 16 に接続されている。出入配線 19 は、ゲート信号線 17a ~ 17d またはソース信号線 18 と同一あるいは類似の構成である。また、ゲート信号線 17a ~ 17d などの信号線と同時に形成される。

【0085】

50

入出配線 19 は、トランジスタ 11e の 1 端子に接続されている。トランジスタ 11e をオン状態とすることにより、入出配線 19 に印加されている電圧が画素に印加される。また、入出配線 19 を介して、画素 16 と入出回路 21 との電気経路が形成される。

#### 【0086】

図 3 は、実施の形態に係る入出回路の構成の一例を示す図である。入出回路 21 は、ゲートドライバ I C (回路) 12 と同期をとって、各画素行に対応するスイッチ SWV 及び SWC を制御する。スイッチ SWV 及び SWC は、切り替え回路 25 として各画素行に対応して配置または形成されている。スイッチ SWV 及び SWC は、いずれかがオンするか、もしくは SWV 及び SWC の両方がオフ状態に制御される。

#### 【0087】

入出回路 21 には、電圧発生回路 22 と電荷蓄積回路 23 とが接続されている。電圧発生回路 22 は、第 1 の電圧であるリファレンス電圧 Vref を供給する電圧回路であり、直流電圧スイッチング回路、D C D C コンバータ、または、電圧可変レギュレータなどからなる電圧発生回路が例示される。

#### 【0088】

電圧発生回路 22 が発生する電圧値は、映像信号の最小電圧値以上かつ最大電圧値以下である。

#### 【0089】

なお、電圧発生回路 22 は、自ら電圧を発生することに限定されるものではない。入力あるいは印加された電圧を分圧または昇圧することにより所定あるいは所望の電圧を出力するものであってもよい。

#### 【0090】

電荷蓄積回路 23 は、電荷を蓄積する蓄積回路であり、回路電気 2 層コンデンサ、電解コンデンサ、または、積層セラミックコンデンサなどが例示され、また、乾電池などの一次電池、または、Ni-H、リチウム、及び Ni-Cd 2 次電池などが例示される。

#### 【0091】

電荷蓄積回路 23 及び電圧発生回路 22 は、「外付け」としたが、これに限定されるものではない。たとえば、表示パネルに「内蔵」されていてもよい。電荷蓄積回路 23 を「内蔵」させる方法として、低温ポリシリコン技術で、コンデンサを形成し、当該コンデンサを電荷蓄積回路 23 とする構成が例示される。また、電圧発生回路 22 を「内蔵」させる方法として、低温ポリシリコン技術で、画素 16 と同時に、D C D C 変換回路をガラス基板(図示せず)上に形成し、当該 D C D C 変換回路を電圧発生回路 22 とする構成が例示される。

#### 【0092】

切り替え回路 25 は、スイッチ SWC をオンさせることにより、電荷蓄積回路 23 を入出配線 19 と電気的に接続する。また、スイッチ SWV をオンさせることにより、電圧発生回路 22 を入出配線 19 と電気的に接続する。つまり、切り替え回路 25 は、電圧発生回路 22 及び電荷蓄積回路 23 を選択する選択回路である。

#### 【0093】

切り替え回路 25 は、各画素行あるいは複数の画素行に対応して形成または配置されている。ゲートドライバ I C (回路) 12 が選択する画素行位置に同期して、切り替え回路 25 のスイッチ SWV 及び SWC をオンオフさせる。

#### 【0094】

なお、ゲート信号線 17a ~ 17d、または、ソース信号線 18、もしくは、ゲート信号線 17a ~ 17d 及びソース信号線 18 の両方の配線材料として、銅配線または銅合金配線を採用できるプロセスを実施することが好ましい。信号線の配線抵抗を低減でき、より大型の E L 表示パネルを実現できるからである。

#### 【0095】

また、ゲートドライバ I C (回路) 12 が駆動(制御)するゲート信号線 17a ~ 17d は、低インピーダンス化されていることが好ましい。また、ソース信号線 18 の構成あ

10

20

30

40

50

るいは構造に関しても同様である。

【0096】

また、トランジスタは、低温ポリシリコン（LTPS）を採用することが好ましい。これにより、トランジスタはトップゲート構造であり寄生容量が小さく、NチャンネルおよびPチャンネルトランジスタを作製でき、また、プロセスに銅配線または銅合金配線プロセスを用いることができる。なお、銅配線は、Ti-Cu-Tiの3層構造を採用することが好ましい。

【0097】

また、配線は、透明アモルファス酸化物半導体（TAOS）の場合には、モリブデン（Mo）-Cu-Moの3層構造を採用することが好ましい。

10

【0098】

[1-7.E L表示装置の動作]

図4は、実施の形態に係るEL表示装置の駆動方法を説明するタイミングチャートである。また、図5は、実施の形態に係る画素回路の期間2における状態遷移図である。また、図6は、実施の形態に係る画素回路の期間3における状態遷移図である。また、図7は、実施の形態に係る画素回路の期間4における状態遷移図である。また、図8は、実施の形態に係る画素回路の期間5における状態遷移図である。また、図9は、実施の形態に係る画素回路の期間6における状態遷移図である。また、図10は、実施の形態に係る画素回路の期間7における状態遷移図である。なお、図4において、期間2は時刻b-cに対応し、期間3は時刻c-dに対応し、期間4は時刻d-eに対応し、期間5は時刻e-fに対応し、期間6は時刻f-hに対応し、期間7は時刻a-b及び時刻h-iに対応する。

20

【0099】

図4のタイミングチャートにおいて、各トランジスタ、スイッチSWV及びSWCのオンオフ状態（ON、OFF）を図示している。電位レベルがON（図4でハイレベル）の時、トランジスタ及びスイッチが動作（オン）となる。電位レベルがOFF（図4でローレベル）の時、トランジスタ及びスイッチが非動作（オフ）となる。

30

【0100】

なお、ここでは、電荷蓄積回路23はコンデンサで構成されているものとして説明をする。また、電荷蓄積回路23は、本実施の形態のようにコンデンサに限定されるものではなく、電荷を蓄積及び放電できるものであればいずれのものであってもよい。

【0101】

[1-7-1. 非発光期間（期間7）]

トランジスタ11dがオン状態のとき、EL素子15にアノード電圧Vddから供給され、EL素子15が発光状態にある（発光期間：時刻i以降）。このとき、アノード電圧Vddからトランジスタ11aを通してEL素子15に駆動電流（ドレイン・ソース間電流）Idが供給されるため、EL素子15が駆動電流Idに応じた輝度で発光する。

40

【0102】

一方、トランジスタ11dがオフ状態のとき、EL素子15に供給する電流が遮断されて、EL素子15は非発光状態となる。トランジスタ11dがオフ状態とすることにより、EL素子15に流れる電流が遮断され、EL素子15の発光が停止する（非発光期間：時刻a-b）。

【0103】

[1-7-2. ソース信号線18の充放電期間（期間2）]

次に、図4に示されるように、第1の期間である期間2において、トランジスタ11e及びトランジスタ11bをオン状態とする。また、切り替え回路25のスイッチSWCをオン状態とする。スイッチSWV、トランジスタ11d及び11cはオフ状態に設定されている。これにより、図5に示されるように、トランジスタ11e、11b、及びスイッチSWCがオン状態となり、電荷蓄積回路23とソース信号線18との間に電気的経路が形成される。したがって、電荷蓄積回路23、入出配線19、トランジスタ11e、トランジスタ11b、スイッチSWCが並列接続される。

50

ンジスタ 11 b、及びソース信号線 18 の間で電荷移動が可能な状態となる。

【0104】

ソース信号線 18 と電荷蓄積回路 23 とが電気的に接続されることにより、ソース信号線 18 の電位が高い場合は、電荷蓄積回路 23 からソース信号線 18 に電荷が供給される。

【0105】

電荷蓄積回路 23 あるいはソース信号線 18 の寄生容量  $C_k$  からの電荷の移動により、ソース信号線 18 の電位は、電位が低い場合は高く変化し、電位が高い場合は低く変化する。

【0106】

ソースドライバ I C (回路) 14 は映像信号を各ソース信号線に印加する。映像信号は、当該映像信号の印加前のソース信号線 18 の電位が基準となってソース信号線 18 に印加される。ここで、ソース信号線 18 に印加される映像信号の電圧を A とし、映像信号を書き込む（書き換える前）前のソース信号線 18 の電圧を B とすれば、ソースドライバ I C (回路) 14 がソース信号線 18 に印加する差電圧は、A - B となる。電圧 B が、電圧 A に近いほど、ソースドライバ I C (回路) 14 が出力する映像振幅の変化量は小さくなる。したがって、ソースドライバ I C (回路) 14 の消費電力は小さくなる。

10

【0107】

本充放電期間において、ソース信号線 18 の電位が高い場合は、電荷が電荷蓄積回路 23 に蓄積され、ソース信号線 18 の電位が低い場合は、電荷が電荷蓄積回路 23 からソース信号線 18 に供給される。したがって、電荷蓄積回路 23 には、ソース信号線 18 の電位（ソースドライバ I C (回路) 14 から供給される映像信号線の電位）が平均された電位が保持される。

20

【0108】

本充放電期間では、ゲートドライバ I C (回路) 12 が選択する画素行位置に同期して、切り替え回路 25 のスイッチ SWC がオン状態となり、電荷蓄積回路 23 に電荷が充放電される。電荷蓄積回路 23 には、1 フレーム期間におけるソース信号線 18 の平均的な電位が保持される。ここで、平均的な電位とは、結果的にソースドライバ I C (回路) 14 がソース信号線に印加する映像信号の平均レベルである。したがって、定性的には、ソース信号線 18 の電位は、1 画面に印加される映像信号の平均レベルに保持されている。そのため、ソースドライバ I C (回路) 14 がソース信号線 18 に書き込む映像信号の振幅電圧（差）を小さくすることができる。

30

【0109】

なお、本実施の形態において、映像信号は電圧信号を例示して記載するが、これに限定されるものではない。映像信号は、電流駆動方式のように、電流信号であってもよい。

【0110】

また、電荷蓄積回路 23 のコンデンサは、表示画面 20 に 1 つ配置されるものとしているが、これに限定されるものではない。たとえば、表示画面 20 を複数に分割し、分割した各表示画面 20 に、独立したコンデンサが配置または形成されてもよい。

40

【0111】

また、ソース信号線 18 に印加される映像信号の階調電圧が高階調である場合は、コンデンサ A を選択し、ソース信号線 18 に印加される映像信号の階調電圧が低階調である場合は、コンデンサ B を選択する方式であってもよい。

【0112】

なお、図 5 に図示されるように、入出配線 19、トランジスタ 11 e、トランジスタ 11 b、及びソース信号線を介した電気経路を形成した後、スイッチ SWV をオン状態とし、ソース信号線 18 に電圧発生回路 22 が発生する電圧を印加した後、電荷蓄積回路 23、入出配線 19、トランジスタ 11 e、トランジスタ 11 b、及びソース信号線 18 の間で電荷移動が可能な状態としてもよい。

【0113】

50

## [ 1 - 7 - 3 . オフセットキャンセル補正の準備期間 (期間 3) ]

次に、図 4 に示されるように、第 2 の期間である期間 3 では、トランジスタ 11c 及び 11e、ならびにスイッチ SWV をオン状態とし、トランジスタ 11b 及び 11d、ならびにスイッチ SWC をオフ状態とする。これらにより、図 6 に示されるように、イニシャル電圧  $V_{ini}$  が EL 素子 15 のアノード端子に印加され、リファレンス電圧  $V_{ref}$  がトランジスタ 11a のゲート端子に印加される。そして、トランジスタ 11a のゲート電位  $V_g$  は、リファレンス電圧  $V_{ref}$  となり、トランジスタ 11a のソース電位  $V_s$  は、リファレンス電圧  $V_{ref}$  よりも十分に低いイニシャル電圧  $V_{ini}$  となる。

## 【 0114 】

イニシャル電圧  $V_{ini}$  は、トランジスタ 11a のゲート - ソース間電圧  $V_{gs}$  が、トランジスタ 11a のオフセットキャンセル電圧  $V_{th}$  よりも大きくなるように設定しておくこととする。以上のように、トランジスタ 11a のゲート電位  $V_g$  をリファレンス電圧  $V_{ref}$  に、また、ソース電位  $V_s$  を低電位  $V_{ini}$  にそれぞれ初期化することで、オフセットキャンセル補正動作の準備が完了する。

10

## 【 0115 】

## [ 1 - 7 - 4 . オフセットキャンセル補正期間 (期間 4) ]

図 4 に示されるように、第 2 の期間である期間 4 では、トランジスタ 11d 及び 11e をオン状態とし、トランジスタ 11c 及び 11b をオフ状態とする。これにより、図 7 に示されるように、トランジスタ 11a のドレイン端子にアノード電圧  $V_{dd}$  が印加される。すると、トランジスタ 11a のソース電位  $V_s$  が上昇を開始する。

20

## 【 0116 】

なお、本期間ににおいても、スイッチ SWC をオフ状態とし、スイッチ SWV をオン状態とすることにより、リファレンス電圧  $V_{ref}$  がトランジスタ 11a のゲート端子に印加される。

## 【 0117 】

やがて、トランジスタ 11a のゲート - ソース間電圧  $V_{gs}$  がトランジスタ 11a のオフセットキャンセル電圧  $V_{th}$  になり、当該オフセットキャンセル電圧  $V_{th}$  に相当する電圧が、画素 16 のコンデンサ 19a に書き込まれる。

## 【 0118 】

便宜上、オフセットキャンセル電圧  $V_{th}$  に相当する電圧をコンデンサ 19a に書き込む期間をオフセットキャンセル補正期間と呼んでいる。

30

## 【 0119 】

オフセットキャンセル補正期間において、電流が専らコンデンサ 19a 側に流れ、EL 素子 15 側には流れないようにするために、EL 素子 15 がカットオフ状態となるようにカソード電極のカソード電圧  $V_{ss}$  を設定しておく。したがって、 $V_{ss} > V_{ini}$  としておく。たとえば、 $V_{ss} = +2(V)$  であれば、 $V_{ini} = -2(V)$  が例示される。

## 【 0120 】

図 6 に図示するように、期間 3 でトランジスタ 11d、11c をオフ状態にする。このとき、トランジスタ 11a のゲートがフローティング状態になるが、ゲート - ソース間電圧  $V_{gs}$  がトランジスタ 11a のオフセットキャンセル電圧  $V_{th}$  に等しいため、トランジスタ 11a はカットオフ状態にある。したがって、ドレイン - ソース間電流  $I_d$  は流れない。

40

## 【 0121 】

なお、画素 16 がオフセットキャンセル動作などを行っているときは、基本的には、ソースドライバ I C (回路) 14 内のスイッチ SWn (n は 1 以上の整数、最大数は画素列数) は、オフ状態とする。ソースドライバ I C (回路) 14 が映像信号をソース信号線 18 に出力する際は、スイッチ SWn をオン状態とする。

## 【 0122 】

## [ 1 - 7 - 5 . 書き込み期間 (期間 5) ]

次に、図 4 に示されるように、期間 5 では、トランジスタ 11b をオン状態とし、トランジ

50

ンジスタ 11c、11e 及び 11d をオフ状態とする。また、図 8 に示されるように、スイッチ SW1 をオン状態とし、ソース信号線 18 にソースドライバ IC(回路)14 から映像信号電圧 V sig が、トランジスタ 11a のゲート端子に印加されるとともに、トランジスタ 11a のドレイン端子はフローティングとなっている。このとき、EL 素子 15 はカットオフ状態(ハイインピーダンス状態)にあるために、コンデンサ(Ce1 と呼ぶ)とみなすことができる。

#### 【0123】

なお、図 8 の状態では、スイッチ SWC をオフ状態とし、スイッチ SWV をオン状態とすると図示しているが、トランジスタ 11e がオフ状態であるため、スイッチ SWV 及びスイッチ SWC のオンオフ状態は不問である。

10

#### 【0124】

トランジスタ 11a のゲート端子に印加された映像信号電圧 V sig は、コンデンサ 19a の容量 Cs と EL 容量 Ce1 とで分圧されて、トランジスタ 11a のゲート - ソース端子間に印加される。容量 Cs に比較して EL 容量 Ce1 は小さいため、映像信号電圧 V sig の多くがトランジスタ 11a のゲート - ソース端子間に印加される。

#### 【0125】

なお、EL 素子 15 を EL 容量 Ce1 として利用するとしたが、これに限定されるものではない。EL 素子 15 に並列に、別途コンデンサを形成してもよいことは言うまでもない。

20

#### 【0126】

##### [1-7-6. 発光期間(期間6)]

次に、図 4 に示されるように、期間 6 では、トランジスタ 11d をオン状態とし、トランジスタ 11c、11e 及び 11b をオフ状態とする。これにより、図 9 に示されるように、トランジスタ 11a のドレイン端子にアノード電圧 V dd が印加される。アノード電圧 V dd の印加により、電流 Id が流れ始め、電流 Id に比例して、EL 素子 15 が発光する。

#### 【0127】

なお、トランジスタ 11d をオンオフさせることにより、表示画面 20 に複数の黒帯表示を実施することができる。また、オンまたはオフする時間を変化させることにより、表示画面 20 の輝度(明るさ)を調整あるいは設定することができる。また、duty 駆動を実現できる。

30

#### 【0128】

##### [1-7-7. 非発光期間(期間7)]

次に、図 4 に示されるように、期間 7 では、トランジスタ 11d をオフ状態とする。これにより、EL 素子 15 に供給する電流が遮断される。したがって、画素 16 は非点灯となる。

#### 【0129】

以上のようにして、表示パネルの各画素 16 に対してオフセットキャンセル補正、各画素の点灯及び非点灯が実行される。

40

#### 【0130】

##### [1-8. 予備充電または予備放電]

図 5 などに図示して説明したように、リファレンス電圧 V ref をソース信号線 18 に印加することにより、ソース信号線 18 を予備充電あるいは予備放電することができる。これにより、ソースドライバ IC(回路)14 が、ソース信号線 18 に映像信号を書き込む場合、ソース信号線 18 の電圧から差分した映像信号を書き込めばよい。よって、ソースドライバ IC 14 からソース信号線 18 に書き込む振幅電圧は小さくてすむ。

#### 【0131】

したがって、ソースドライバ IC(回路)14 が過熱することを抑制できる。また、ソースドライバ IC(回路)14 が発熱して EL 素子 15 などが劣化することもない。

#### 【0132】

50

なお、図5において、スイッチSWVをオンさせ、所定の電圧をソース信号線18に印加してもよい。所定の電圧は、ソースドライバIC(回路)14が出力する映像信号電圧に基づいて設定される。

#### 【0133】

また、上記実施の形態において、図5の回路状態では、ソースドライバIC(回路)14内のスイッチSWnをオフ状態(スイッチSWはハイインピーダンスあるいはオープン)にするとした。しかし、本発明はこれに限定されるものではない。

#### 【0134】

図11は、実施の形態の変形例に係る画素回路の期間2における状態遷移図である。図11に図示するように、ソース信号線18に電荷蓄積回路23を接続するとともに、ソースドライバIC(回路)14の出力回路24から映像信号などを出力してもよい。ソース信号線18は、ソースドライバIC(回路)14及び画素16の両方から電流あるいは電荷が流れ込み充電される。

10

#### 【0135】

また、スイッチSWnは、ソースドライバIC(回路)14から出力する映像信号の大きさ(電位)に対応してオンオフ制御を行ってもよい。たとえば、リファレンス電圧Vrefに映像信号電圧が近い場合は、スイッチSWnをオン状態とする。また、先に1H期間にソース信号線18に充電されている電圧に対応して、スイッチSWnをオンオフ制御してもよい。先の1H期間の映像信号レベルと次の映像信号レベルとが近い場合は、スイッチSWnをオフ状態とする。つまり、所定電圧以上、電位が離れている場合は、スイッチSWnをオン状態とする。同様に、トランジスタ11bをオンオフ制御してもよい。

20

#### 【0136】

図12は、予備充電がない場合のソース信号線の充電状態を模式的に表すグラフである。具体的には、図12のグラフは、電荷蓄積回路23によるソース信号線18の予備充電がない場合の、ソース信号線18の充電状態を模式的に表している。時刻e(図4の時刻e)において、ソースドライバIC(回路)14からソース信号線18に映像信号が印加されている。1H期間が経過した時刻fでも、ソース信号線18の電位はhであり、目標電位のmには到達しない。

30

#### 【0137】

図13は、実施の形態に係る予備充電がある場合のソース信号線の充電状態を模式的に表すグラフである。具体的には、図13のグラフは、電荷蓄積回路23によるソース信号線18の予備充放電(プリチャージ、ディスクチャージ)がある場合の、ソース信号線18の充電状態を模式的に表している。電荷蓄積回路23による予備充放電は、時刻b(図4の時刻b)から開始される。電荷蓄積回路23による充放電により、時刻eには、ソース信号線18の電位はkまで上昇する。時刻eにおいて、ソースドライバIC(回路)14からソース信号線18に映像信号が印加される。

30

#### 【0138】

本実施の形態に係る予備充電がある場合、ソース信号線18への充電は、電位kからの充電で良い。つまり、少ない電位変化で目標電位のmまで到達する。したがって、1H期間が経過後、十分に、目標電位のmに到達する。

40

#### 【0139】

図14は、b行が選択された場合の入出回路の動作を説明する図である。図14では、画素16bが属する画素行が選択され、図5(期間2)での状態が図示されている。選択された画素行に対応する切り替え回路25bのスイッチSWCがオン状態に設定されている。したがって、電荷蓄積回路23とソース信号線18との間が電気的に接続されている。他の画素行に接続された切り替え回路のスイッチSWCはオフ状態に設定されている。

#### 【0140】

図15は、c行が選択された場合の入出回路の動作を説明する図である。つまり、図15に示された回路状態は、図14に示された回路状態から1水平走査期間(1H)後の状態が表されている。図15では、画素16cが属する画素行が選択され、図5(期間2)

50

での状態が図示されている。選択された画素行に対応する切り替え回路 25c のスイッチ SWC がオン状態に設定されている。したがって、電荷蓄積回路 23 とソース信号線 18 との間が電気的に接続されている。他の画素行に接続された切り替え回路のスイッチ SWC はオフ状態に設定されている。

#### 【0141】

##### [1-9. 画素回路の変形例]

図 16 は、実施の形態の変形例に係る EL 表示装置の画素回路の例を示す図である。本変形例に係る画素回路は、図 2 に示された画素回路と比較して、回路を構成する複数のトランジスタのうち少なくとも 1 つを P チャネル型としている点、及び、当該 P チャネルのトランジスタを LDD 型及びマルチゲート型としている点が構成として異なる。以下、図 2 に示された画素回路と異なる点を中心に、本変形例の画素回路について説明する。

10

#### 【0142】

ゲート信号線 37a (G<sub>a</sub>) は、スイッチ用のトランジスタ 31e のゲート端子に接続され、トランジスタ 31e をオンオフ制御する。ゲート信号線 37b (G<sub>b</sub>) は、スイッチ用のトランジスタ 31b のゲート端子に接続され、トランジスタ 31b をオンオフ制御する。ゲート信号線 37c (G<sub>c</sub>) は、スイッチ用のトランジスタ 31c のゲート端子に接続され、トランジスタ 31c をオンオフ制御する。ゲート信号線 37d (G<sub>d</sub>) は、スイッチ用のトランジスタ 31d のゲート端子に接続され、トランジスタ 31d をオンオフ制御する。

#### 【0143】

図 16 の画素構成では、ゲート信号線 37a 及び 37b に、ゲートドライバ IC 12a 及び 12b が接続され、両側駆動が実施される。ゲート信号線 37c 及び 37d には、ゲートドライバ IC 12a のみが接続され、片側駆動が実施される。

20

#### 【0144】

図 16において、P チャンネルである駆動用のトランジスタ 31a のドレイン端子に、トランジスタ 31d のソース端子が接続され、トランジスタ 31d のドレイン端子に EL 素子 15 のアノード端子が接続されている。EL 素子 15 のカソード端子には、カソード電圧 V<sub>ss</sub> が印加されている。トランジスタ 31a のソース端子には、アノード電圧 V<sub>dd</sub> が印加されている。

30

#### 【0145】

ゲート信号線 37d にオン電圧が印加されると、トランジスタ 31d がオン状態となり、トランジスタ 31a からの発光電流が EL 素子 15 に供給される。EL 素子 15 は、発光電流の大きさに基づき発光する。

#### 【0146】

トランジスタ 31a のゲート端子とドレイン端子との間には、トランジスタ 31b のソース端子とドレイン端子とが接続され、ゲート信号線 37c にオン電圧が印加されることにより、トランジスタ 31a のゲート端子とドレイン端子間とが短絡（接続）される。

40

#### 【0147】

トランジスタ 31a のゲート端子には、コンデンサ 39b の一端子が接続され、コンデンサ 39b の他端子は、トランジスタ 31b のドレイン端子と接続されている。トランジスタ 31b のソース端子は、ソース信号線 18 と接続されている。

#### 【0148】

ゲート信号線 37b にオン電圧が印加されると、トランジスタ 31b がオン状態となり、ソース信号線 18 に印加された映像信号（電圧、電流）V<sub>s</sub> が、画素 36 に印加される。なお、本発明において映像信号は、映像信号電圧としているが、映像信号電流であってもよい。

#### 【0149】

コンデンサ 39a の一端子は、トランジスタ 31b のドレイン端子と接続され、他端子は、アノード電極と接続され、アノード電圧 V<sub>dd</sub> が印加される。

#### 【0150】

10

20

30

40

50

なお、コンデンサ39aの他端子は、アノード電極と接続されたが、これに限定されるものではない。たとえば、他の任意の直流電圧と接続されてもよい。

#### 【0151】

トランジスタ31aのソース端子は、アノード電極と接続されたが、これに限定されるものではない。たとえば、他の任意の直流電圧と接続されてもよい。つまり、コンデンサ39aの他端子とトランジスタ31aのソース端子とは、異なる電位の端子と接続されてもよい。

#### 【0152】

一例として、トランジスタ31aのソース端子は、アノード電圧 $V_{dd}$ が印加された電極または配線と接続され、コンデンサ39aの他端子は、直流電圧 $V_b = 5$ (V)の電圧が印加された電極または配線と接続される構成が例示される。

10

#### 【0153】

トランジスタ31eのドレイン端子は、トランジスタ31bのドレイン端子と接続され、トランジスタ31eのソース端子は、入出配線19と接続されている。ゲート信号線37aにオン電圧が印加されることにより、トランジスタ31eがオン状態となり、リファレンス電圧 $V_{ref}$ がコンデンサ39aに印加される。または、トランジスタ31bと電荷蓄積回路23とが接続される。

#### 【0154】

トランジスタ31c及びトランジスタ31eは、Pチャンネルであり、LDD構造を採用している。また、このトランジスタ31c及び31eは、少なくともダブルゲート(ディアルゲート)以上とする。好ましくは、トリプルゲート以上とする。つまり、複数のトランジスタのゲートが直列に接続された構造を採用している。

20

#### 【0155】

LDD構造及びマルチゲート(ディアルゲート、トリプルゲート、あるいはそれ以上のゲート数)を採用することにより、トランジスタ31c及び31eのオフ特性を良好にできる。トランジスタ31c及びトランジスタ31eのオフ特性を良好にしないと、コンデンサ39a及び39bの電荷を良好に保持できなくなる。

30

#### 【0156】

トランジスタ31c及び31e以外のトランジスタもPチャンネルとし、LDD構造を採用することが好ましい。また、必要に応じて、トランジスタはマルチゲート構造とすることが好ましい。トランジスタのマルチゲート構造(ディアルゲート以上)を用いることにより、また、LDD構造と組み合わせることにより、オフリーケを抑制でき、良好なコントラスト、オフセットキャンセル動作を実現できる。また、良好な高輝度表示、画像表示を実現できる。たとえば、図16の画素回路では、トランジスタ31e及び31cはディアルゲート構成としている。

30

#### 【0157】

なお、本変形例に係る上記構成は、他の実施形態にも適用されることはあるまでもない。

#### 【0158】

図16の画素構成においても、切り替え回路25のスイッチSWC、トランジスタ31e及び31bをオンさせることにより、電荷蓄積回路23とソース信号線18とを電気的に接続することができる。つまり、図5に示された期間2の状態を構成できる。画素回路の動作については、他の構成、動作、図5～図11などと同様あるいは類似であるので説明を省略する。

40

#### 【0159】

以上、本実施の形態に係るEL表示装置は、画素16に印加する映像信号を出力するソースドライバIC(回路)14と、ソースドライバIC(回路)14が出力する映像信号を伝達するソース信号線18と、ゲートドライバIC(回路)12と、画素16を選択する選択電圧または画素を非選択にする非選択電圧を伝達する第1のゲート信号線であるゲート信号線17c及び第2のゲート信号線であるゲート信号線17aと、第1の電圧であ

50

るリファレンス電圧  $V_{ref}$  を供給する電圧発生回路 22 と、電荷を蓄積する電荷蓄積回路 23 と、電圧発生回路 22 または電荷蓄積回路 23 を選択する切り替え回路 25 とを具備する。

#### 【0160】

各画素 16 は、画素電極であるアノード電極と、アノード電極とカソード電極との間に形成されたEL素子 15 と、EL素子 15 に電流を供給する駆動用のトランジスタ 11a と、トランジスタ 11a のゲート端子に一端子が接続され、第1の配線である出入配線 19 に他端子が接続された第1のスイッチ用トランジスタであるトランジスタ 11e と、映像信号をトランジスタ 11a のゲート端子に供給する第2のスイッチ用トランジスタであるトランジスタ 11b とを有する。

10

#### 【0161】

トランジスタ 11e のゲート端子はゲート信号線 17c に接続されており、トランジスタ 11b のゲート端子はゲート信号線 17a に接続されている。

#### 【0162】

動作期間は、少なくとも第1の期間と第2の期間とがある。第1の期間である期間 2 において、切り替え回路 25 は出入配線 19 に電荷蓄積回路 23 を接続し、ゲートドライバ I C (回路) 12 は、トランジスタ 11e をオン状態とし、かつ、トランジスタ 11b をオン状態とすることにより、ソース信号線 18 と電荷蓄積回路 23 とが電気的に接続される。第2の期間である期間 3 または期間 4 において、切り替え回路 25 は出入配線 19 に電圧発生回路 22 を接続し、ゲートドライバ I C (回路) 12 は、トランジスタ 11e をオン状態とすることにより、トランジスタ 11a のゲート端子にリファレンス電圧  $V_{ref}$  が印加される。

20

#### 【0163】

上記構成によれば、映像信号電圧の画素書き込み前に、ソース信号線と電荷蓄積回路とが電気的に接続されるので、大型パネルでソース信号線の負荷（配線抵抗、負荷容量など）が大きくても、また、高精細パネルで1画素行の選択期間（書き込み時間）が短くとも、各画素に良好に映像信号を書き込むことできる。また、ソース信号線 18 に印加する電圧振幅が小さいため、ソースドライバ I C (回路) 14 の負荷を低減でき、また、使用電力を小さくでき、ソースドライバ I C 14 が過熱することがない。また、ソースドライバ I C (回路) 14 などの発熱が原因で EL 素子 15 などが劣化することもない。よって、良好に画素に映像信号を書き込め、良好な画像表示を実現することが可能となる。

30

#### 【0164】

##### [2. EL表示装置を備えた電子機器の構成]

上記実施の形態の各々の図で述べた内容（一部でもよい）を様々な電子機器に適用することができる。具体的には、電子機器の表示部に適用することができる。

#### 【0165】

そのような電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等）、記録媒体を備えた画像再生装置（具体的には Digital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。

40

#### 【0166】

図 17 は、実施の形態に係る EL 表示装置を用いたディスプレイの概観図である。同図に示されたディスプレイは、筐体 172 と、保持台 173 と、本実施の形態に係る EL 表示装置（EL 表示パネル）171 とを備える。図 17 に示されたディスプレイは、様々な情報（静止画、動画、テキスト画像など）を表示部に表示する機能を有する。なお、図 17 に示すディスプレイが有する機能はこれに限定されず、様々な機能を有することができる。

#### 【0167】

50

図18は、実施の形態に係るEL表示装置を用いたカメラの概観図である。同図に示されたカメラは、シャッター181と、ビューファインダ182と、カーソル183と、本実施の形態に係るEL表示装置(EL表示パネル)171とを備える。図18に示されたカメラは、静止画を撮影する機能を有する。また、動画を撮影する機能を有する。なお、図18に示すカメラが有する機能はこれに限定されず、様々な機能を有することができる。

#### 【0168】

図19は、実施の形態に係るEL表示装置を用いたコンピュータの概観図である。同図に示されたコンピュータは、キーボード191と、タッチパッド192と、本実施の形態に係るEL表示装置(EL表示パネル)171とを含む。図19に示されたコンピュータは、様々な情報(静止画、動画、テキスト画像など)を表示部に表示する機能を有する。なお、図19に示すコンピュータが有する機能はこれに限定されず、様々な機能を有することができる。

10

#### 【0169】

かかる電子機器の表示部に、上記実施の形態で説明したEL表示装置(EL表示パネル)もしくは駆動方式を用いた構成として、上述の図17～図19の情報機器などを、画素劣化が抑制された高画質と/orして、また、低消費電力に基づいた低成本化を実現できる。

20

#### 【0170】

上記実施の形態及びその変形例は、他の実施の形態と適宜組み合わせて実施することが可能である。

20

#### 【0171】

なお、上記実施の形態において、EL表示装置として説明をした。しかし、本明細書に記載した技術的思想は、EL表示装置だけでなく、他の表示装置にも適用できることは言うまでもない。たとえば、図5の予備充電あるいはその方式は、他の表示パネル/EL表示装置にも適用できることは言うまでもない。以上のように、本明細書で記載した事項は、EL素子を用いたEL表示装置のみに限定されるものではない。たとえば、液晶表示デバイス、FED(フィールドエミッションディスプレイ)、SED(キャノンと東芝が開発したディスプレイ)などの他のディスプレイにも適用できることは言うまでもない。

30

#### 【0172】

本実施の形態に係るEL表示装置とは、情報機器などのシステム機器を含む概念である。表示パネルの概念は、広義には情報機器などのシステム機器を含む。

#### 【0173】

以上のように、本開示における技術の例示として、実施の形態を説明した。そのために、添付図面及び詳細な説明を提供した。

40

#### 【0174】

したがって、添付図面及び詳細な説明に記載された構成要素の中には、課題解決のために必須な構成要素だけでなく、上記技術を例示するために、課題解決のために必須でない構成要素も含まれ得る。そのため、それらの必須ではない構成要素が添付図面や詳細な説明に記載されていることをもって、直ちに、それらの必須ではない構成要素が必須であるとの認定をするべきではない。

#### 【0175】

また、上述の実施の形態は、本開示における技術を例示するためのものであるから、特許請求の範囲またはその均等の範囲において種々の変更、置き換え、付加、省略などを行うことができる。

#### 【産業上の利用可能性】

#### 【0176】

本発明は、特に、アクティブ型の有機ELフラットパネルディスプレイに有用である。

#### 【符号の説明】

#### 【0177】

50

- 1 1 a、1 1 b、1 1 c、1 1 d、1 1 e、3 1 a、3 1 b、3 1 c、3 1 d、3 1 e

トランジスタ (TFT)

- 1 2、1 2 a、1 2 b ゲートドライバIC (回路)

- 1 4 ソースドライバIC (回路)

- 1 5 EL 素子

- 1 6、1 6 b、1 6 c、3 6 画素

- 1 7 a、1 7 b、1 7 c、1 7 d、3 7 a、3 7 b、3 7 c、3 7 d ゲート信号線

- 1 8 ソース信号線

- 1 9 入出配線

- 1 9 a、3 9 a、3 9 b コンデンサ 10

- 2 0 表示画面 (表示領域)

- 2 1 入出回路

- 2 2 電圧発生回路

- 2 3 電荷蓄積回路

- 2 4 出力回路

- 2 5、2 5 b、2 5 c 切り替え回路

- 1 7 1 EL 表示装置 (EL 表示パネル)

- 1 7 2 筐体

- 1 7 3 保持台

- 1 8 1 シャッター 20

- 1 8 2 ビューファインダ

- 1 8 3 カーソル

- 1 9 1 キーボード

- 1 9 2 タッチパッド

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 3 】

【 図 1 2 】

【 図 1 4 】

【 図 1 5 】

【図 16】

【図 17】

【図 18】

【図 19】

---

フロントページの続き

|              |         |              |

|--------------|---------|--------------|

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|              | G 0 9 G | 3/20 6 2 1 A |

|              | G 0 9 G | 3/20 6 2 2 D |

|              | G 0 9 G | 3/20 6 2 1 G |

|           |       |      |      |      |      |      |      |      |      |       |      |

|-----------|-------|------|------|------|------|------|------|------|------|-------|------|

| F ターム(参考) | 5C080 | AA06 | BB05 | CC03 | DD05 | DD08 | DD10 | DD20 | DD26 | EE28  | EE29 |

|           | FF11  | JJ02 | JJ03 | JJ04 | KK02 | KK07 | KK20 | KK23 | KK43 | KK47  |      |

| 5C380     | AA01  | AB06 | AB18 | AB21 | AB22 | AB23 | AB24 | AB34 | AB36 | AB37  |      |

|           | AC04  | AC07 | AC08 | AC09 | AC11 | AC12 | AC13 | BA01 | BA05 | BA10  |      |

|           | BA19  | BA38 | BA39 | BA46 | BB02 | BB08 | BC02 | BC12 | BC13 | BD05  |      |

|           | CA04  | CA12 | CA13 | CA32 | CA34 | CA51 | CA54 | CB17 | CB18 | CB26  |      |

|           | CB31  | CC04 | CC07 | CC26 | CC27 | CC33 | CC39 | CC65 | CC71 | CD015 |      |

|           | CD025 | CE04 | CF43 | CF51 | DA02 | DA06 | DA19 | DA47 | HA02 | HA05  |      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | EL表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2015090492A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2015-05-11 |

| 申请号            | JP2013231562                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2013-11-07 |

| [标]申请(专利权)人(译) | 日本有机雷特显示器股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 株式会社JOLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 中川博文<br>高原博司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 中川 博文<br>高原 博司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F1分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.623.C G09G3/20.612.E G09G3/20.621.F G09G3/20.621.A<br>G09G3/20.622.D G09G3/20.621.G G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3283 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD05 5C080/DD08 5C080/DD10 5C080/DD20 5C080/<br>/DD26 5C080/EE28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/KK02<br>5C080/KK07 5C080/KK20 5C080/KK23 5C080/KK43 5C080/KK47 5C380/AA01 5C380/AB06 5C380/<br>/AB18 5C380/AB21 5C380/AB22 5C380/AB23 5C380/AB24 5C380/AB34 5C380/AB36 5C380/AB37<br>5C380/AC04 5C380/AC07 5C380/AC08 5C380/AC09 5C380/AC11 5C380/AC12 5C380/AC13 5C380/<br>/BA01 5C380/BA05 5C380/BA10 5C380/BA19 5C380/BA38 5C380/BA39 5C380/BA46 5C380/BB02<br>5C380/BB08 5C380/BC02 5C380/BC12 5C380/BC13 5C380/BD05 5C380/CA04 5C380/CA12 5C380/<br>/CA13 5C380/CA32 5C380/CA34 5C380/CA51 5C380/CA54 5C380/CB17 5C380/CB18 5C380/CB26<br>5C380/CB31 5C380/CC04 5C380/CC07 5C380/CC26 5C380/CC27 5C380/CC33 5C380/CC39 5C380/<br>/CC65 5C380/CC71 5C380/CD015 5C380/CD025 5C380/CE04 5C380/CF43 5C380/CF51 5C380/<br>/DA02 5C380/DA06 5C380/DA19 5C380/DA47 5C380/HA02 5C380/HA05 |         |            |

| 代理人(译)         | 吉川修<br>Sobashima正雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

## 摘要(译)

解决的问题：提供一种即使将显示面板制成大型且高清晰度也不会发生源极驱动器IC的发热的问题的EL显示装置。本发明的EL显示装置包括用于传输视频信号的源信号线18，电压产生电路22，电荷存储电路23和开关电路25，并且像素16包括EL元件15。在第一时段中，驱动晶体管11a，用于将晶体管11a与输入/输出布线19电连接的晶体管11e，以及用于将源信号线18和晶体管11a与输入/输出布线19电连接的晶体管11b。在第二时段中，连接了电荷存储电路23，并且晶体管11e和11b导通，从而连接了源信号线18和电荷存储电路23，并且连接了输入/输出布线19和电压生成电路11。然后，晶体管11e导通，从而电压产生电路22的电压被施加到晶体管11a的栅极端子。[选择图]图5