## (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2015-201327 (P2015-201327A)

(43) 公開日 平成27年11月12日(2015.11.12)

| (51) Int.Cl. |               |            | F I  |       |   | テーマコード(   | 参考) |

|--------------|---------------|------------|------|-------|---|-----------|-----|

| H05B         | 33/08         | (2006.01)  | HO5B | 33/08 |   | 3 K 1 O 7 |     |

| H05B         | <i>33/2</i> 6 | (2006.01)  | HO5B | 33/26 | Z |           |     |

| HO1L         | 51/50         | (2006, 01) | HO5B | 33/14 | Α |           |     |

## 審査請求 未請求 請求項の数 4 〇L (全 15 頁)

|           |                            |            | Library Mark Strasser 1 1 7 7 72 SAV |

|-----------|----------------------------|------------|--------------------------------------|

| (21) 出願番号 | 特願2014-79209 (P2014-79209) | (71) 出願人 5 | 502356528                            |

| (22) 出願日  | 平成26年4月8日 (2014.4.8)       | <b>*</b>   | 株式会社ジャパンディスプレイ                       |

|           |                            | ]          | 東京都港区西新橋三丁目7番1号                      |

|           |                            | (74)代理人 1  | 10000154                             |

|           |                            | 4          | 時許業務法人はるか国際特許事務所                     |

|           |                            | (72) 発明者 ( | 恵田 尚紀                                |

|           |                            | ]          | 東京都港区西新橋三丁目7番1号 株式会                  |

|           |                            | 7          | 社ジャパンディスプレイ内                         |

|           |                            | (72) 発明者 [ | 田畠 弘志                                |

|           |                            | ]          | 東京都港区西新橋三丁目7番1号 株式会                  |

|           |                            |            | 杜ジャパンディスプレイ内                         |

|           |                            | F ターム (参考  | *) 3K107 AA01 BB01 CC29 CC35 CC43    |

|           |                            |            | DD44Z EE65 FF15 HH05                 |

|           |                            |            |                                      |

|           |                            |            |                                      |

|           |                            | I          |                                      |

## (54) 【発明の名称】有機エレクトロルミネッセンス表示装置

## (57)【要約】

【課題】隣り合う2つの画素に共通の金属層の上に、一方の画素に対応する第1電極の一部と、他方の画素に対応する第1電極の一部と、が形成される場合において、各第1電極形成時のエッチング残渣に起因する画素間ショートを抑制する。

【解決手段】第1の画素に対応するアノード電極32g、及び第1の画素の隣の第2の画素に対応するアノード電極32bは、それぞれ、その一部が、金属層26の上に形成されている。ここで、金属層26は、平面図で見た場合において、金属層26の形成領域とそれ以外の領域との境界線BL上のいずれか2点を、両アノード電極32g、32bの間の区間内で選択したとき、金属層26の一部が、当該2点を結ぶ線分(例えば、点Q1と点Q2とを結ぶ線分Q1Q2)から突出するように形成されている。

【選択図】図7

## 【特許請求の範囲】

## 【請求項1】

第1の画素と前記第1の画素の隣の第2の画素とに共通の金属層と、

その一部が前記金属層の上に形成される、前記第1の画素に対応する第1電極と、

その一部が前記金属層の上に形成される、前記第2の画素に対応する第1電極と、

各第1電極の上に形成される有機発光層と、

前記有機発光層の上に形成される第2電極と、

前記金属層と前記第1の画素に対応する前記第1電極との間、及び前記金属層と前記第 2の画素に対応する前記第1電極との間、に形成される容量層と、

を含み、

前記金属層は、

平面図で見た場合において、前記金属層の形成領域とそれ以外の領域との境界線上のいずれか2点を、前記第1の画素に対応する前記第1電極と前記第2の画素に対応する前記第1電極との間の区間内で選択したとき、前記形成領域の一部が当該2点を結ぶ線分から突出するように形成されている、

有機エレクトロルミネッセンス表示装置。

## 【請求項2】

請求項1に記載の有機エレクトロルミネッセンス表示装置において、

前記金属層は、

平面図で見た場合に、前記形成領域の一部が、前記境界線の両第1電極間の部分、の両端点を結ぶ線分から突出するように、形成されている、

有機エレクトロルミネッセンス表示装置。

## 【請求項3】

請求項2に記載の有機エレクトロルミネッセンス表示装置において、

前記金属層は、

平面図で見た場合に、前記両端点を結ぶ線分から突出する突出部を含み、前記突出部の 先端が鋭角である、

有機エレクトロルミネッセンス表示装置。

## 【請求項4】

請求項2又は3に記載の有機エレクトロルミネッセンス表示装置において、

前記金属層は、

平面図で見た場合に、前記両端点を結ぶ線分から突出する突出部を含み、該線分と前記突出部の先端との距離が、 0 . 5 マイクロメートル以上且つ 1 0 マイクロメートル以下である、

有機エレクトロルミネッセンス表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、有機エレクトロルミネッセンス表示装置に関する。

【背景技術】

## [00002]

下記特許文献1には、表示装置で用いられるTFTアレイ基板が開示されている。このTFTアレイ基板では、ゲート電極の膜厚よりソース / ドレイン電極の膜厚を薄くすることにより、ゲート電極の低抵抗化、ソース電極のキャパシタ容量の低減等を図っている。

## [0003]

TFTアレイ基板を用いる表示装置としては、液晶表示装置や有機エレクトロルミネッセンス表示装置等がある。有機エレクトロルミネッセンス表示装置では、各画素に対応する有機エレクトロルミネッセンス発光素子が、TFTアレイ基板上に形成される。有機発光素子は、少なくとも、第1電極、有機発光層、及び第2電極により構成され、第1電極

10

20

30

40

は、例えばドライバTFTのソース/ドレイン電極に接続される。

【先行技術文献】

【特許文献】

[0004]

【特許文献 1 】特開 2 0 0 5 - 5 7 2 4 0 号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

ところで、有機エレクトロルミネッセンス表示装置において、例えば高細密化のため、画素サイズを小さくした場合、いわゆる保持容量が不足する場合がある。そこで、保持容量を補うために、補助容量を画素ごとに形成することが考えられる。例えば、各画素に共通の金属層を設け、その上層に各有機エレクトロルミネッセンス発光素子の第1電極を設けるとともに、金属層と各第1電極との間に容量層を設けることが考えられる。こうすれば、金属層と第1電極との対により補助容量を形成することができる。

[0006]

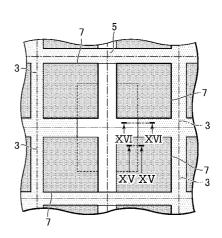

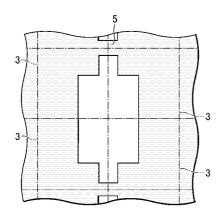

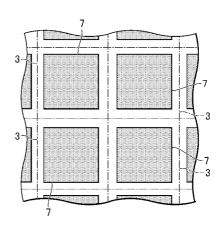

図12万至図15は、補助容量を形成する場合の構成の例を示す。図12は、補助容量を形成する場合における画素の平面図の例であり、図15は、XV-XV線における画素の断面を示す断面図の例である。図12では、4つの画素3が示されている。一点鎖線で囲まれる矩形が一つの画素3を示し、各画素3に共通の金属層5が形成され、その上層に、各第1電極7が形成される。金属層5は、図13に示す形状を有し、第1電極7は、図14に示す形状を有している。図12乃至図14から分かるように、第1電極7は、その一部が金属層5の上に形成される。

[0007]

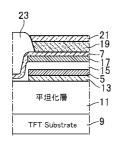

具体的には、図15に示すように、TFTアレイ基板9の上に形成された平坦化層11の上に、透明導電膜13及び金属層5が形成されている。また、平坦化層11及び金属層5の上に容量層15が形成され、容量層15の上に、反射膜17、及び透明導電膜である第1電極7が形成されている。ここで、第1電極7は、透明導電膜の層の形成後、エッチングによるパターニングにより形成される。

[0008]

また、第1電極7の上に、有機発光層19及び第2電極21が形成される。第1電極7 、有機発光層19、及び第2電極21により、有機エレクトロルミネッセンス発光素子が 形成される。なお、符号23は、リブを示している。

[0009]

この構成によれば、金属層 5 、容量層 1 5 、及び第 1 電極 7 により、補助容量を形成することができる。但し、以下に説明するような問題がある。

[0010]

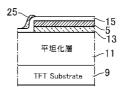

図16及び図17は、補助容量を形成する場合の問題点を説明するための図であり、図16は、XVI・XVI線(図12参照)における断面図であり、2つの第1電極7の間の領域における断面図である。図15に示すように、補助容量を形成する場合、容量層15は平坦ではなく、容量層15には金属層5に起因する段差ができる。この段差の周辺に形成された透明導電膜はエッチングにより除去されにくく、第1電極7の形成時、図16に示すように、段差の周辺にエッチング残渣25が残ってしまう。そのため、場合によっては、図17に示すように、段差の周辺に残ったエッチング残渣25が隣り合う2つの第1電極7を電気的に接続し、画素間ショートが発生する虞がある。

[0011]

本発明は上記課題に鑑みてなされたものであって、隣り合う2つの画素に共通の金属層の上に、一方の画素に対応する第1電極の一部と、他方の画素に対応する第1電極の一部と、が形成される場合において、各第1電極形成時のエッチング残渣に起因する画素間ショートを抑制できる有機エレクトロルミネッセンス表示装置を提供することである。

【課題を解決するための手段】

10

20

30

40

### [0012]

上記課題を解決するための本発明に係る有機エレクトロルミネッセンス表示装置は、第1の画素と前記第1の画素の隣の第2の画素とに共通の金属層と、その一部が前記金属層の上に形成される、前記第1の画素に対応する第1電極と、その一部が前記金属層の上に形成される、前記第2の画素に対応する第1電極と、各第1電極の上に形成される有機発光層と、前記有機発光層の上に形成される第2電極と、前記金属層と前記第1の画素に対応する前記第1電極との間、及び前記金属層と前記第2の画素に対応する前記第1電極との間、に形成される容量層と、を含み、前記金属層は、平面図で見た場合において、前記金属層の形成領域とそれ以外の領域との境界線上のいずれか2点を、前記第1の画素に対応する前記第1電極との間の区間内で選択したとき、前記形成領域の一部が当該2点を結ぶ線分から突出するように形成されていることを特徴としている。

[0013]

本発明の一態様では、前記金属層は、平面図で見た場合に、前記形成領域の一部が、前記境界線の両第1電極間の部分、の両端点を結ぶ線分から突出するように、形成されていてもよい。また、前記金属層は、平面図で見た場合に、前記両端点を結ぶ線分から突出する突出部を含み、前記突出部の先端が鋭角であってもよい。また、前記金属層は、平面図で見た場合に、前記両端点を結ぶ線分から突出する突出部を含み、該線分と前記突出部の先端との距離が、0.5マイクロメートル以上且つ10マイクロメートル以下であってもよい。

【図面の簡単な説明】

[0014]

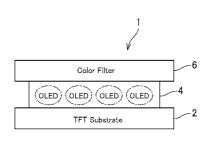

【図1】本発明の実施形態に係る有機エレクトロルミネッセンス表示装置の構成を模式的に示す図である。

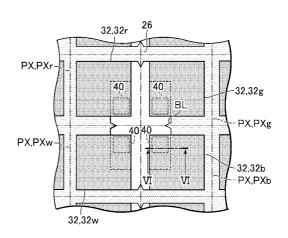

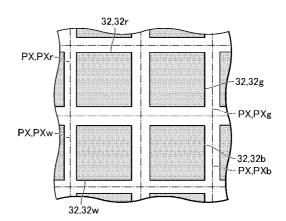

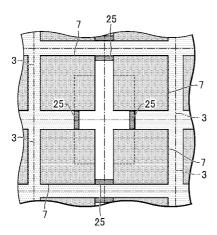

- 【図2】画素の平面図である。

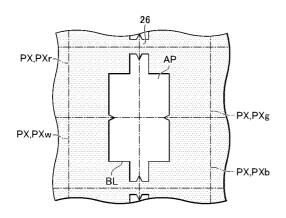

- 【図3】金属層の平面図である。

- 【図4】アノード電極の平面図である。

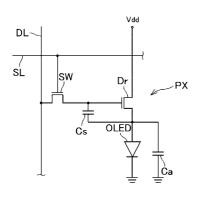

- 【図5】画素にて実現される等価回路を示す図である。

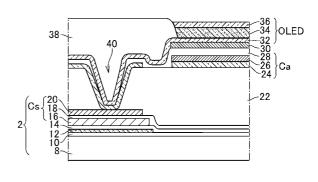

- 【図6】 VI・VI線における画素の断面図である。

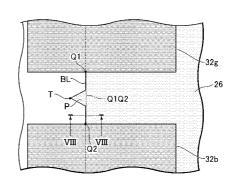

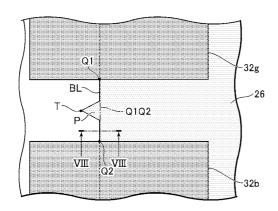

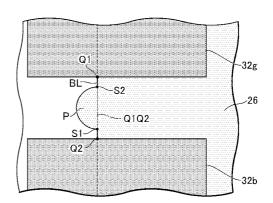

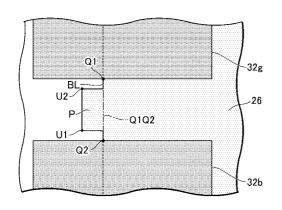

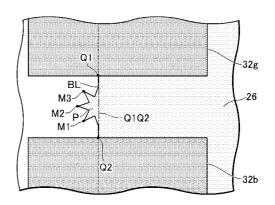

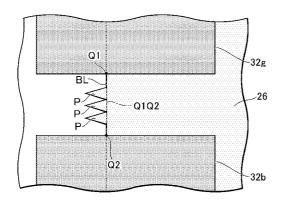

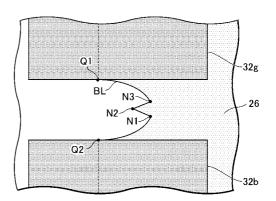

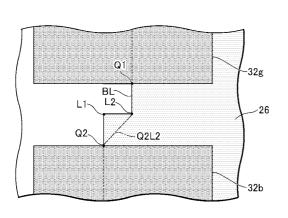

- 【図7】隣り合う2つのアノード電極の間の区間を拡大した拡大図である。

- 【図8】VIII・VIII線での断面図である。

- 【図9】エッチング残渣が形成される様子を示す図である。

- 【図10】X-X線での断面図である。

- 【図11A】金属層の他の形状を示す図である。

- 【図11B】金属層の他の形状を示す図である。

- 【図11C】金属層の他の形状を示す図である。

- 【図11D】金属層の他の形状を示す図である。

- 【図11E】金属層の他の形状を示す図である。

- 【図11F】金属層の他の形状を示す図である。

- 【図11G】金属層の他の形状を示す図である。

- 【図12】補助容量を形成する場合における画素の平面図である。

- 【図13】金属層を示す平面図である。

- 【図14】第1電極を示す平面図である。

- 【図15】XV-XV線における画素の断面図である。

- 【図16】XVI・XVI線における断面図である。

- 【図17】補助容量を形成する場合の問題点を説明するための図である。

【発明を実施するための形態】

[0015]

以下に、本発明の実施の形態について、図面を参照しつつ説明する。なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到

10

20

30

40

-

し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。

## [0016]

図1は、本発明の実施形態に係る有機エレクトロルミネッセンス表示装置1(以下、有機 E L 表示装置1と表記する)の構成を模式的に示す図である。本実施形態では、有機 E L 表示装置1は、カラーフィルタ方式でカラー化を行う有機 E L 表示装置として実現され、同図に示すように、下から、薄膜トランジスタがアレイ状に形成されたTFTアレイ基板 2 と、白色発光する有機エレクトロルミネッセンス発光素子OLEDが画素PXごとに形成される発光部4と、カラーフィルタ基板6と、を備える。また、図示していないドライバIC等も備える。発光部4から出力される白色光がカラーフィルタ基板により、四色にカラー化される。ここではトップエミッション方式が採用されており、カラーフィルタ基板6の上面が画像の表示面にあたる。

## [0017]

以下、図2乃至図6を参照して、有機EL表示装置1の構成を詳細に説明する。図2は、画素PXの平面図であり、図3は、後述する金属層26の平面図である。また、図4は、後述するアノード電極32の平面図である。

### [0018]

図2は、画素PXの外観を示す。一点鎖線で囲まれる矩形が一つの画素PXを示してい る。ここでは、画素PXを、赤を表現する画素PXr、緑を表現する画素PXg、青を表 現する画素PXb、及び白を表現する画素PXwの4種類で区別している。符号40は画 素 P X ごとに形成されるコンタクトホール 4 0 を示す。有機 E L 表示装置 1 では、各画素 PXに共通の金属層26(図3参照)の上層に、画素PXごとに形成される有機エレクト ロルミネッセンス発光素子OLEDのアノード電極32(図4参照)が形成される。ここ で、境界線BL(図2及び図3参照)は、金属層26が形成される領域とそれ以外の領域 との境界線を示す。図2及び図3から分かるように、金属層26には、金属層26がコン タクトホール40を覆わないように画素PXr、画素PXg、画素PXb、及び画素PX w に 共 通 の 開 口 部 A P が 設 け ら れ る 。 図 2 及 び 図 4 か ら 分 か る よ う に 、 ア ノ ー ド 電 極 3 2 は、コンタクトホール40を覆うようになっているため、アノード電極32は、その一部 が金属層26の上に形成され、残り部分が開口部APの上に形成されることになる。この 金属層26の意義については後述する。なお、ここでは、各アノード電極32を、4種類 の符号32r、32g、32b、及び32wで区別している。アノード電極32rは、画 素PXrに対応するアノード電極であり、より詳しくは、画素PXrに形成される有機エ レクトロルミネッセンス発光素子OLEDのアノード電極である。アノード電極32gは 、画素PXgに対応するアノード電極であり、より詳しくは、画素PXgに形成される有 機エレクトロルミネッセンス発光素子OLEDのアノード電極である。また、アノード電 極32bは、画素PXbに対応するアノード電極であり、より詳しくは、画素PXbに形 成される有機エレクトロルミネッセンス発光素子OLEDのアノード電極である。また、 アノード電極32wは、画素PXwに対応するアノード電極であり、より詳しくは、画素 PXwに形成される有機エレクトロルミネッセンス発光素子OLEDのアノード電極であ る。

## [0019]

有機EL表示装置1では、図5に例示する等価回路が画素PXにて実現される。同図に示すように、画素PXでは、ゲートが走査線SLに接続され且つソースがデータ線DLに接続された薄膜トランジスタであるスイッチSWが形成される。また、画素PXでは、ゲートがスイッチSWに接続され且つソースが電圧源Vddに接続された薄膜トランジスタである駆動トランジスタDrが形成される。また、画素PXでは、駆動トランジスタDrのゲートとドレインとに接続されている保持容量Csが形成される。また、画素PXでは、アノード電極32が駆動トランジスタDrのドレインに接続された有機エレクトロルミネッセンス発光素子OLEDが形成される。

10

20

30

### [0020]

さらに、画素 P X では、有機エレクトロルミネッセンス発光素子 O L E D に並列な補助容量 C a も形成される。上述した金属層 2 6 の存在により、この補助容量 C a が形成される

## [0021]

具体的には、VI・VI線(図2参照)における画素PXの断面図たる図6に示すように、画素PXでは、基板8の上に形成されたアンダーコート層10の上に、駆動トランジスタDrを構成する半導体層12の一部が形成されている。また、半導体層12の上の中間層14が形成され、中間層14の上に、駆動トランジスタDrのゲートに接続される容量配線層16、絶縁層18、及び駆動トランジスタDrのドレイン配線を構成する配線層20が順に形成されている。配線層20、絶縁層18、及び容量配線層16により、保持容量Csが形成される。

### [0022]

また、画素 P X では、配線層 2 0 の上に、コンタクトホール 4 0 を備える平坦化層 2 2 が形成されている。

## [0023]

補助容量 C a が不要であれば、平坦化層 2 2 の上面にアノード電極 3 2 を形成すればよい。しかし、この有機 E L 表示装置 1 では、補助容量 C a を形成するために、平坦化層 2 2 の上面の平坦な部分に、透明導電膜 2 4 及び上述した金属層 2 6 が形成されている。また、金属層 2 6 の上に、金属層 2 6 を覆うシリコン窒化膜である容量層 2 8 が形成され、容量層 2 8 の上に、反射膜 3 0 と、透明導電膜であるアノード電極 3 2 が形成されている。アノード電極 3 2 は、透明導電膜の層の形成後、エッチングによるパターニングにより形成されるものであり、コンタクトホール 4 0 にて透明導電膜 2 4 を介し駆動トランジスタ D r のドレインに接続される。このように、アノード電極 3 2 の下に、容量層 2 8 及び金属層 2 6 が形成されるので、アノード電極 3 2、容量層 2 8、及び金属層 2 6 により補助容量 C a が形成されるようになっている。

## [0024]

また、画素 P X では、コンタクトホール 4 0 を覆うリブ 3 8 が形成されている。また、有機エレクトロルミネッセンス発光素子 O L E D を形成するべく、アノード電極 3 2 の上に、白色発光する有機発光層 3 4 及びカソード電極 3 6 が形成されている。有機発光層 3 4 及びカソード電極 3 6 は、各画素 P X ごとに設けられてもよいし、各画素 P X に共通に設けられてもよい。

## [0025]

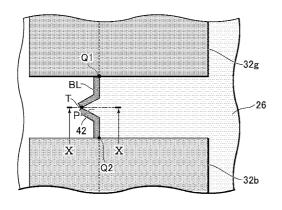

ところで、図2に示すように、境界線BLは、隣り合う2つのアノード電極32の間の区間において直線にはなっていない。図7は、図2において隣り合う2つのアノード電極32g、32bの間の区間を拡大した拡大図である。図7に示すように、この区間において、境界線BLは直線になっておらず、金属層26に突起部Pが設けられている。ここで、突起部Pは、金属層26の一部であり、境界線BLの上記区間における部分の両端点Q1、Q2を結ぶ線分Q1Q2から突出している。図7に示す突起部Pの先端Tは鋭角であり、線分Q1Q2と先端Tとの距離は0.5マイクロメートル以上10マイクロメートル以下の距離(例えば、3マイクロメートル)となっている。

## [0026]

このような突起部 P を設けたのは以下の理由からである。すなわち、図 6 をみると分かるように、有機 E L 表示装置 1 では、金属層 2 6 が形成されるので、容量層 2 8 は平坦にはならず、容量層 2 8 には金属層 2 6 に起因する段差ができる。この段差の周辺に形成された透明導電膜はエッチングにより除去されにくく、アノード電極 3 2 の形成時、VIII・VIII線(図 7 参照)での断面図たる図 8 に示すように、段差の周辺にエッチング残渣 4 2 が残ってしまう。そのため、段差の周辺に残ったエッチング残渣 4 2 が隣り合う2 つのアノード電極 3 2 g、 3 2 b を電気的に接続し、画素間ショートが発生する虞がある。

10

20

30

40

## [0027]

この点、この有機 E L 表示装置 1 では、境界線 B L が外に屈曲するところではエッチング残渣 4 2 が残りにくいことに着目し、金属層 2 6 に突起部 P が設けられている。そのため、例えば図 9 に示すようにエッチング残渣 4 2 が形成され、 X - X 線(図 9 参照)での断面図たる図 1 0 に示すように、境界線 B L が屈曲する先端 T ではエッチング残渣 4 2 が残りにくくなる。従って、エッチング残渣 4 2 が先端 T の付近で途切れやすくなり、画素間ショートの発生が抑制される。

## [0028]

以上のように、この有機 E L 表示装置 1 では、隣り合う 2 つのアノード電極 3 2 の間の区間において、金属層 2 6 に突起部 P が設けられている。すなわち、金属層 2 6 の一部が、線分 Q 1 Q 2 (図 7 参照)から突き出ている。よって、エッチング残渣 4 2 に起因する画素間ショートを抑制することができる。また、先端 T が鋭角となっているので、先端 T が鈍角である場合に比して先端 T でエッチング残渣 4 2 が残りにくくなる。よって、より確実に画素間ショートを抑制することができる。

## [0029]

なお、隣り合う 2 つのアノード電極 3 2 の間の区間における金属層 2 6 の形状は、以上で説明したものに限らず、他の形状であってもよい。

### [0030]

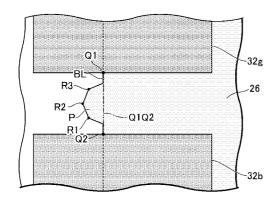

例えば、金属層26の形状は、図11Aに示す形状であってもよい。図11Aは、金属層26の他の形状を示す図であり、アノード電極32gとアノード電極32bとの間の区間の平面図である。図11Aでは、突起部Pが複数の頂点R1、R2、及びR3を有している。図11Aでは、境界線BLが外に屈曲する、点R1、点R2、及び点R3の付近でエッチング残渣42が途切れやすくなる。よって、図11Aに示す形状でも、画素間ショートの発生を抑制できる。

## [0031]

また、例えば、金属層 2 6 の形状は、図 1 1 Bに示す形状であってもよい。図 1 1 Bは、金属層 2 6 の他の形状を示す図であり、アノード電極 3 2 gとアノード電極 3 2 b との間の区間の平面図である。図 1 1 Bでは、突起部 P が半円形状を有している。図 1 1 Bでは、境界線 B L が、点 S 1 から点 S 2 までの区間において曲線となっており、点 S 1 から点 S 2 までのどこにおいても境界線 B L が外に屈曲しているということになる。よって、点 S 1 から点 S 2 までのどこかでエッチング残渣 4 2 が途切れやすくなり、図 1 1 Bに示す形状でも、画素間ショートの発生を抑制できる。

## [0032]

また、例えば、金属層 2 6 の形状は、図 1 1 C に示す形状であってもよい。図 1 1 C は、金属層 2 6 の他の形状を示す図であり、アノード電極 3 2 g とアノード電極 3 2 b との間の区間の平面図である。図 1 1 C では、突起部 P が矩形形状を有している。図 1 1 C では、境界線 B L が外に屈曲する、点 U 1 及び点 U 2 の付近でエッチング残渣 4 2 が途切れやすくなる。よって、図 1 1 C に示す形状でも、画素間ショートの発生を抑制できる。

## [0033]

また、例えば、金属層 2 6 の形状は、図 1 1 Dに示す形状であってもよい。図 1 1 Dは、金属層 2 6 の他の形状を示す図であり、アノード電極 3 2 gとアノード電極 3 2 b との間の区間の平面図である。図 1 1 Dでは、突起部 P が星形形状をしている。図 1 1 Dでは、境界線 B L が外に屈曲する、点 M 1、点 M 2、及び点 M 3 の付近でエッチング残渣 4 2 が途切れやすくなる。よって、図 1 1 Dに示す形状でも、画素間ショートの発生を抑止できる。

## [0034]

また、例えば、金属層 2 6 の形状は、図 1 1 E に示す形状であってもよい。図 1 1 E は、金属層 2 6 の他の形状を示す図であり、アノード電極 3 2 g とアノード電極 3 2 b との間の区間の平面図である。図 1 1 E では、突起部 P が複数形成される。よって、突起部 P が 1 つのみの場合より確実に画素間ショートを抑制できる。

10

20

30

40

## [0035]

また、金属層 2 6 が、上記点 Q 1 及び上記点 Q 2 を結ぶ線分から突出する部分(すなわち、突起部 P )を有していなくても、画素間ショートを抑制することは可能である。例えば、金属層 2 6 の形状は、図 1 1 F に示す形状であってもよい。図 1 1 F は、金属層 2 6 の他の形状を示す図であり、アノード電極 3 2 g とアノード電極 3 2 b との間の区間の平面図である。図 1 1 F では、境界線 B L が外に屈曲する点 N 2 付近でエッチング残渣 4 2 が途切れやすくなる。よって、図 1 1 F に示す形状でも、画素間ショートの発生を抑制できる。また、例えば、金属層 2 6 の形状は、図 1 1 G に示す形状であってもよい。図 1 1 G による属層 2 6 の他の形状を示す図であり、アノード電極 2 g とアノード電極 3 2 b との間の区間の平面図である。図 1 1 G では、上記点 Q 1 から上記点 Q 2 までの区間において、境界線 B L が段差を有している。図 1 1 G では、境界線 B L が外に屈曲する点 L 1 付近でエッチング残渣 4 2 が途切れやすくなる。よって、図 1 1 G に示す形状でも、画素間ショートの発生を抑制できる。

[0036]

つまり、境界線BL上のいずれか2点を上記点Q1から上記点Q2に至るまでの境界線BLの部分のうちで選択したときに、当該選択した2点を結ぶ線分から金属層26の一部が突出するように、金属層26を形成しさえすれば、画素間ショートの発生を抑制できる。なぜなら、当該選択した2点の間のどこかで、境界線BLが必ず外に屈曲することになるからである。その証拠に、例えば図7では、金属層26の一部が境界線BL上の点Q1及び点Q2を結ぶ線分Q1Q2から突出しているが、それがためにこの2点の間にある先端Tで境界線BLが外に屈曲している。また、例えば図11Fでは、金属層26の一部が境界線BL上の点N1及び点N3を結ぶ線分から突出しているが、それがためにこの2点の間にある点N2で境界線BLが外に屈曲している。また、図11Gでは、金属層26の一部が境界線BLからに回り2点の間にある点L1で境界線BLが外に屈曲している。

[0037]

なお、本発明は、上述した実施形態に限定されるものではなく種々の変形が可能である

[0038]

例えば、本発明は、有機 E L 表示装置 1 において、画素 P X w をのぞく 3 種類の画素 P X が形成される場合においても、適用可能である。例えば、画素 P X r に赤色発光する有機エレクトロルミネッセンス発光素子が備えられ、且つ、画素 P X g に緑色発光する有機エレクトロルミネッセンス発光素子が備えられ、画素 P X b に青色発光する有機エレクトロルミネッセンス発光素子が備えられる場合においても適用可能である。

[0039]

また、例えば、本発明は、有機 E L 表示装置 1 において、ボトムエミッション方式が採用される場合においても、適用可能である。

[0040]

また例えば、実施形態で説明した構成は、実質的に同一の構成、同一の作用効果を奏する構成又は同一の目的を達成することができる構成で置き換えることができる。

【符号の説明】

[ 0 0 4 1 ]

1 有機エレクトロルミネッセンス表示装置、 2 TFTアレイ基板、4 発光部、6 カラーフィルタ基板、8 基板、10 アンダーコート層、12 半導体層、14中間層、16 容量配線層、18 絶縁層、20 配線層、22 平坦化層、24 透明導電膜、26 金属層、28 容量層、30 反射膜、32,32r,32g,32b,32w アノード電極、34 有機発光層、36 カソード電極、38 リブ、40 コンタクトホール、42 エッチング残渣、AP 開口部、BL 境界線、Ca 補助容量、Cs 保持容量、DL データ線、Dr 駆動トランジスタ、L1,L2,M1,M2,M3,N1,N2,N3,R1,R2,R3,S1,S2,U1,U2 点、OLED

10

20

30

40

有機エレクトロルミネッセンス発光素子、P 突起部、PX,PXr,PXg,PXb ,PXw 画素、Q1,Q2 端点、Q1Q2,Q2L2 線分、SL 走査線、SW スイッチ、T 先端。

【図1】 【図2】

【図3】 【図4】

【図5】 【図6】

【図7】 【図8】

#### 【図9】 【図10】

【図11A】 【図11B】

【図11C】 【図11D】

【図11E】 【図11F】

【図12】 【図11G】

【図13】 【図14】

【図15】 【図16】

# 【図17】

| 专利名称(译)        | 有机电致发光显示装置                                                                                          |         |            |

|----------------|-----------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | <u>JP2015201327A</u>                                                                                | 公开(公告)日 | 2015-11-12 |

| 申请号            | JP2014079209                                                                                        | 申请日     | 2014-04-08 |

| [标]申请(专利权)人(译) | 株式会社日本显示器                                                                                           |         |            |

| 申请(专利权)人(译)    | 有限公司日本显示器                                                                                           |         |            |

| [标]发明人         | 徳田尚紀<br>田畠弘志                                                                                        |         |            |

| 发明人            | 徳田 尚紀<br>田畠 弘志                                                                                      |         |            |

| IPC分类号         | H05B33/08 H05B33/26 H01L51/5                                                                        | 0       |            |

| CPC分类号         | Y02B20/343                                                                                          |         |            |

| FI分类号          | H05B33/08 H05B33/26.Z H05B33/14.A                                                                   |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC29 3K107/CC35 3K107/CC43 3K107/DD44Z 3K107/EE65 3K107/FF15 3K107/HH05 |         |            |

| 外部链接           | Espacenet                                                                                           |         |            |

|                |                                                                                                     |         |            |

## 摘要(译)

解决的问题:在与两个相邻像素共用的金属层上形成与一个像素相对应的第一电极的一部分和与另一个像素相对应的第一电极的一部分。 在其中,抑制了当形成每个第一电极时由于蚀刻残留物引起的像素之间的短路。 对应于第一像素的阳极电极32g和对应于与第一像素邻近的第二像素的阳极电极32b分别部分地形成在金属层26上。 是 在此,金属层26是在俯视时将金属层26的形成区域与另一区域之间的边界线BL上的任意两点定义为阳极电极32g,32b之间的部分。 当在其中选择时,金属层26的一部分形成为从连接两个点的线段(例如,连接点Q1和Q2的线段Q1Q2)突出。 [选择图]图7

| (21) 出願番号 | 特願2014-79209 (P2014-79209) | (71) 出願人 | 502356528                         |

|-----------|----------------------------|----------|-----------------------------------|

| (22) 出願日  | 平成26年4月8日 (2014.4.8)       |          | 株式会社ジャパンディスプレイ                    |

|           |                            |          | 東京都港区西新橋三丁目7番1号                   |

|           |                            | (74)代理人  | 110000154                         |

|           |                            |          | 特許業務法人はるか国際特許事務所                  |

|           |                            | (72) 発明者 | 徳田 尚紀                             |

|           |                            |          | 東京都港区西新橋三丁目7番1号 株式会               |

|           |                            |          | 社ジャパンディスプレイ内                      |

|           |                            | (72) 発明者 | 田畠 弘志                             |

|           |                            |          | 東京都港区西新橋三丁目7番1号 株式会               |

|           |                            |          | 社ジャパンディスプレイ内                      |

|           |                            | Fターム(参   | 考) 3K107 AA01 BB01 CC29 CC35 CC43 |

|           |                            |          | DD44Z EE65 FF15 HH05              |