(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-108575

(P2007-108575A)

(43) 公開日 平成19年4月26日(2007.4.26)

| (51) Int.CI. |              | F 1                 | テーマコード (参考) |       |

|--------------|--------------|---------------------|-------------|-------|

| <b>G09G</b>  | <b>3/30</b>  | (2006.01) G09G 3/30 | K           | 3K107 |

| <b>G09G</b>  | <b>3/20</b>  | (2006.01) G09G 3/30 | J           | 5C080 |

| <b>H01L</b>  | <b>51/50</b> | (2006.01) G09G 3/20 | 624B        |       |

|              |              |                     | G09G 3/20   | 611H  |

|              |              |                     | G09G 3/20   | 641D  |

審査請求 未請求 請求項の数 11 O L (全 24 頁) 最終頁に続く

|                   |                              |          |                                            |

|-------------------|------------------------------|----------|--------------------------------------------|

| (21) 出願番号         | 特願2005-301625 (P2005-301625) | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日          | 平成17年10月17日 (2005.10.17)     | (74) 代理人 | 100065385<br>弁理士 山下 橿平                     |

| (特許庁注：以下のものは登録商標) |                              |          |                                            |

| 1. セルフオック         |                              | (74) 代理人 | 100122921<br>弁理士 志村 博                      |

|                   |                              | (74) 代理人 | 100130029<br>弁理士 永井 道雄                     |

|                   |                              | (72) 発明者 | 川崎 素明<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

|                   |                              | (72) 発明者 | 郷田 達人<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】電流供給装置及び表示装置

## (57) 【要約】

【課題】有機EL素子を用いたアクティブマトリクス型表示装置の電流プログラミング動作を改善する。

【解決手段】画素回路は、各々のゲートが接続され且つ各々のドレイン、ソースが電気的に接続された第1及び第2の電界効果トランジスタM1、M2を有する。第1の電界効果トランジスタのソースと第2の電界効果トランジスタのドレインとの間にスイッチS3を設け、共通接続されたゲートと共に接続されたソース・ドレインとの間にスイッチS2を設ける。電流プログラム期間にスイッチS2、S3をオンして、第1及び第2の電界効果トランジスタを並列に接続して設定電流を書き込む。そして、電流供給期間にはスイッチS2、S3をオンして、第1及び第2の電界効果トランジスタを直列に接続して設定電流のほぼ1/4の電流を供給する。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

第 1 の電界効果トランジスタと、

制御電極が前記第 1 の電界効果トランジスタの制御電極と共に接続されるとともに、一方の主電極が前記第 1 の電界効果トランジスタの一方の主電極と共に接続される第 2 の電界効果トランジスタと、

前記第 1 及び第 2 の電界効果トランジスタの前記制御電極が共通接続された第 1 共通接続部と前記第 1 及び第 2 の電界効果トランジスタの前記一方の主電極が共通接続された第 2 共通接続部との間に設けられた第 1 のスイッチと、

前記第 1 及び第 2 の電界効果トランジスタの他の主電極間に設けられた第 2 のスイッチと、

を備え、

前記第 1 及び第 2 のスイッチをオンして前記第 1 及び第 2 の電界効果トランジスタを並列接続する第 1 のモードと、前記第 1 及び第 2 のスイッチをオフして前記第 1 及び第 2 の電界効果トランジスタを直列接続する第 2 のモードとを有し、

前記第 1 のモードにおいて、並列接続された第 1 及び第 2 の電界効果トランジスタに流す設定電流を、前記第 1 共通接続部と、前記第 2 のスイッチにより共通接続された前記第 1 及び第 2 の電界効果トランジスタの他の主電極との間の電圧値として書き込み、

前記第 2 のモードにおいて、前記電圧値に基づいて、直列接続された前記第 1 及び第 2 の電界効果トランジスタから電流を供給する電流供給装置。

10

20

30

40

50

## 【請求項 2】

請求項 1 に記載の電流供給装置において、前記第 2 共通接続部と前記設定電流を供給する配線との間に設けられた第 3 のスイッチと、前記第 2 の電界効果トランジスタの他の主電極に接続された第 4 のスイッチとを有し、

前記第 1 のモードにおいて、前記第 3 のスイッチをオン、前記第 4 のスイッチをオフし、

前記第 2 のモードにおいて、前記第 3 のスイッチをオフ、前記第 4 のスイッチをオンすることを特徴とする電流供給装置。

## 【請求項 3】

請求項 1 又は 2 に記載の電流供給装置において、前記第 1 の電界効果トランジスタは、制御電極と他の主電極との間に容量を有する電流供給装置。

## 【請求項 4】

請求項 1 から 3 のいずれか 1 項に記載の電流供給装置において、前記第 1 及び第 2 の電界効果トランジスタは同じ導電型であることを特徴とする電流供給装置。

## 【請求項 5】

請求項 1 から 4 のいずれか 1 項に記載の電流供給装置において、前記第 2 のモードにおいて供給された電流を電流駆動型素子に流すことを特徴とする電流供給装置。

## 【請求項 6】

請求項 5 に記載の電流供給装置において、前記電流駆動型素子は電流駆動型発光素子であることを特徴とする電流供給装置。

## 【請求項 7】

請求項 6 に記載の電流供給装置において、前記電流駆動型発光素子はエレクトロルミネッセンス素子であることを特徴とする電流供給装置。

## 【請求項 8】

請求項 5 に記載の電流供給装置と前記電流駆動型素子とが単位回路を構成し、該単位回路は一次元状又は二次元状に配されていることを特徴とする回路装置。

## 【請求項 9】

請求項 6 又は 7 に記載の電流供給装置と前記電流駆動型発光素子とが単位回路を構成し、該単位回路は一次元状又は二次元状に配されていることを特徴とする発光装置。

## 【請求項 10】

請求項 6 又は 7 に記載の電流供給装置と前記電流駆動型発光素子とが単位回路を構成し、該単位回路は一次元状又は二次元状に配されていることを特徴とする表示装置。

#### 【請求項 11】

請求項 6 又は 7 に記載の電流供給装置と前記電流駆動型発光素子とが単位回路を構成し、

該単位回路が一次元状又は二次元状に配されて構成される発光装置と、入力画像データに対応する設定電流に応じた前記発光装置からの画像光が照射される感光体とを有する画像記録装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、電流供給装置及びこの電流供給装置を用いた回路装置、発光装置、表示装置及び画像記録装置に係わる。特に電流を注入して発光するエレクトロルミネッセンス素子(以後 E L 素子と言う)を画像表示に使用したアクティブマトリクス型表示装置に好適に用いられるものである。

##### 【背景技術】

##### 【0002】

<アクティブマトリクス型表示装置>

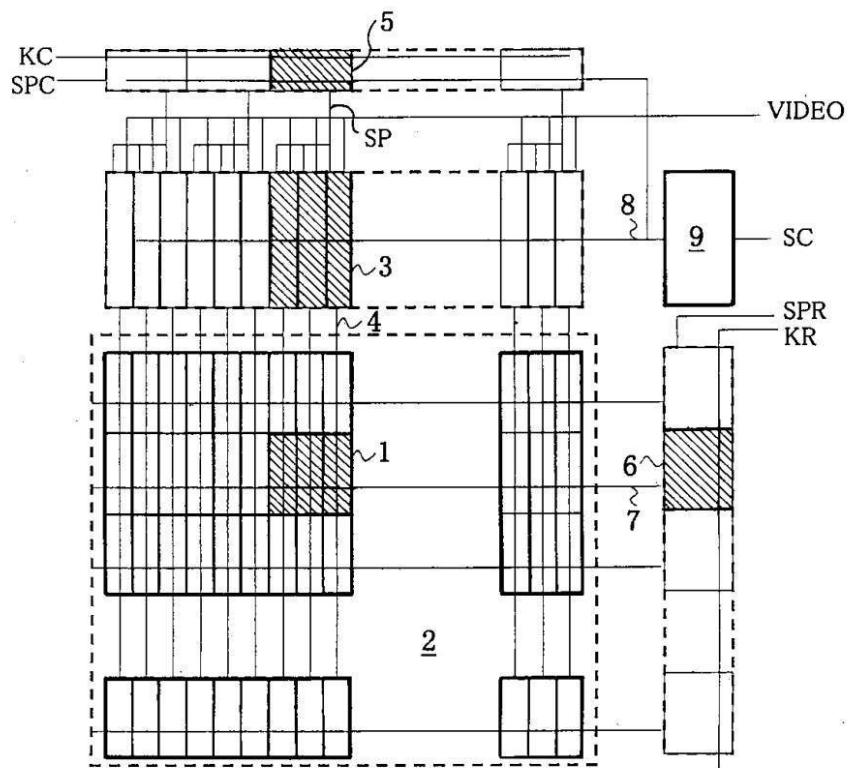

図 12 は、アクティブマトリクス型のカラー表示装置の全体構成例を示すものである。表示領域 2 にはマトリクス状に画素回路(単位回路となる) 1 が配置され、各々の画素回路 1 には対応する対応する列の信号線 4 と走査線 7 が接続される。走査線 7 の制御信号によって、該当する行の画素部は一斉に対応する信号線 4 に供給される表示信号を画素回路 1 に取り込む。走査信号が次行に移行すると、各々の画素回路 1 に含まれる表示素子を取り込まれた表示信号に応じた輝度で点灯させる。カラー表示するため、R G B 三原色の表示素子をもつ 3 つ画素回路 1 の組みから構成される。

##### 【0003】

各走査線 7 の走査信号は、行クロック K R と行走査開始信号 S P R が入力される行数分のレジスタブロックを有する行レジスタ 6 によって生成される。各信号線 4 に供給される各列の表示信号は、列数分の列制御回路 3 によって生成される。3 列ごとに配列される R G B 三原色の表示素子に対応して列制御回路 3 は 3 個の組みから構成される。各列の列制御回路 3 には、映像信号 V I D E O とサンプリング信号 S P 及び水平制御信号 8 によって所望の表示信号を各列の信号線 4 に供給する。

##### 【0004】

制御回路 9 には映像信号 V I D E O に対応した水平同期信号 S C が入力され、制御回路 9 は水平制御信号 8 を生成する。サンプリング信号 S P は列制御回路 3 の 1 / 3 の数のレジスタからなる列レジスタ 5 によって生成される。列レジスタ 5 には列クロック K C と列走査開始開始信号 S P C 及び主に列レジスタのリセット動作を行なう水平制御信号 8 が入力される。

<有機 E L 素子特性>

図 12 に示すアクティブマトリクス型表示装置で使用される代表的な表示素子として有機 E L 素子がある。

##### 【0005】

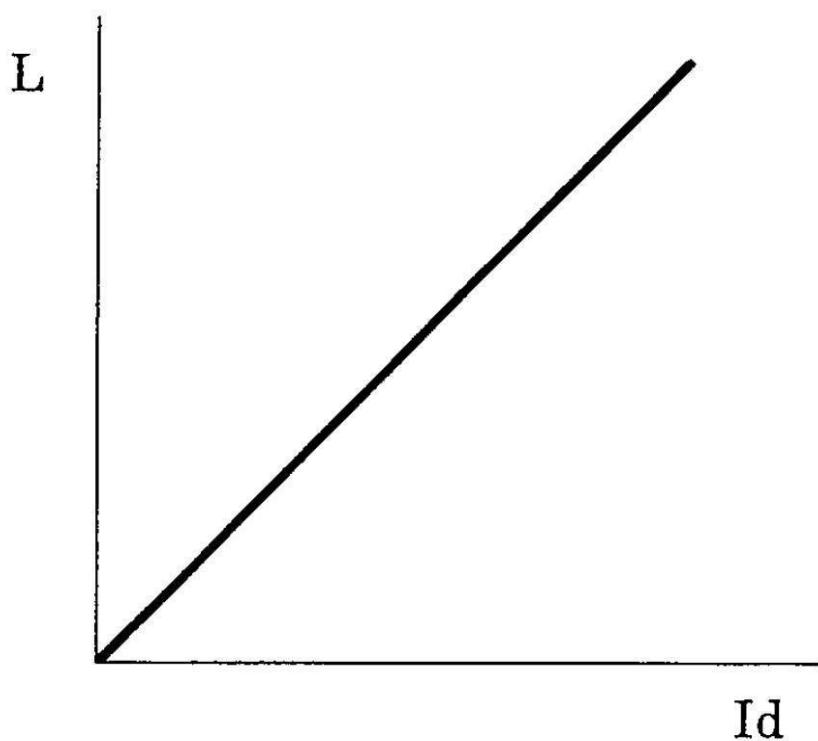

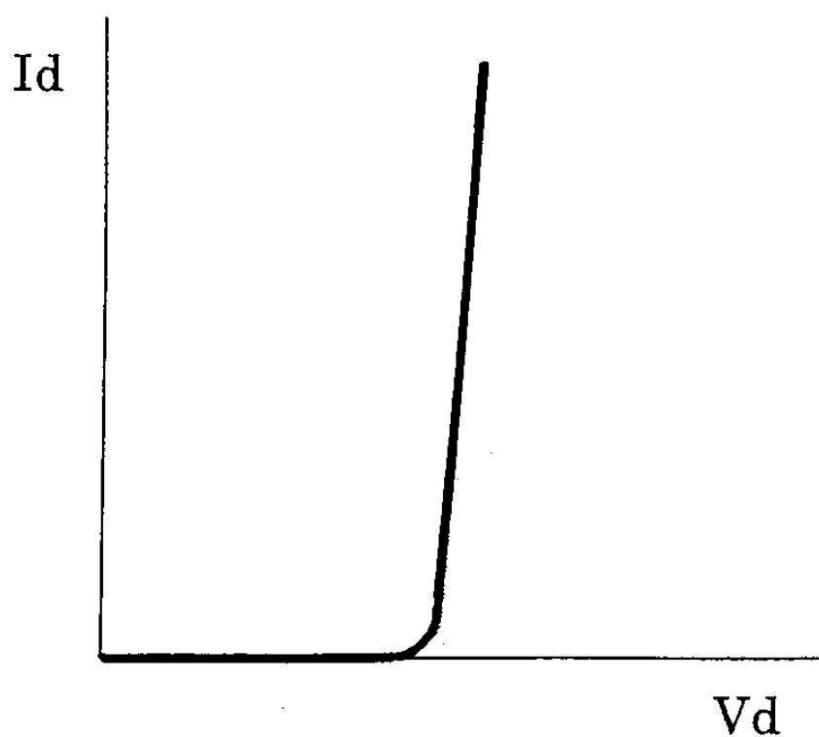

有機 E L 素子の発光輝度 L は図 13 に示される様に注入電流 I d に対して概ね比例した特性を示す。また有機 E L 素子は図 14 に示される様に動作電圧 V d 対してダイオード特性を持ち閾値電圧から急激に電流 I d が流れる。

<有機 E L パネル駆動方式>

前述した有機 E L 素子を使用した T F T 素子で構成されるアクティブマトリクス型表示装置の画素回路 1 は表示期間で電流駆動が望ましい。T F T 素子はトランジスタバラツキが大きいためこれに対処した画素回路 1 の構成が望まれる。

##### 【0006】

10

20

30

40

50

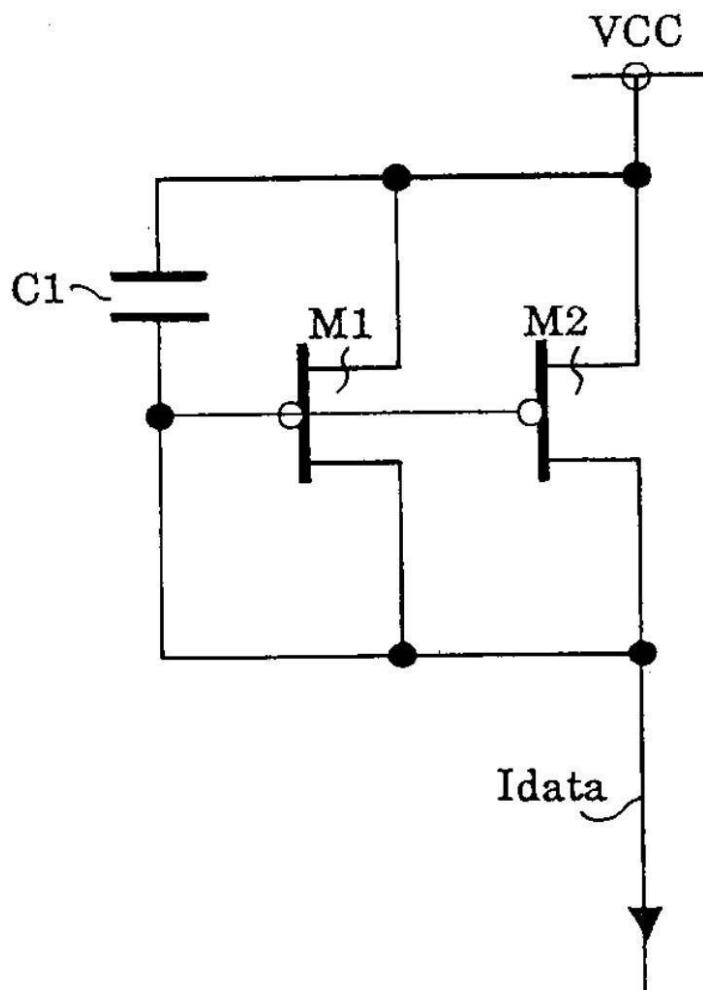

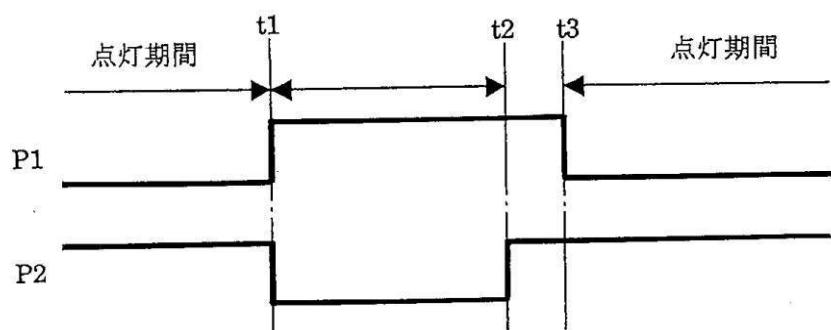

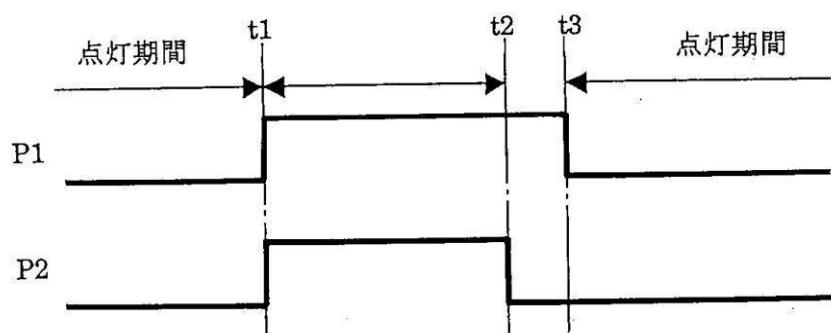

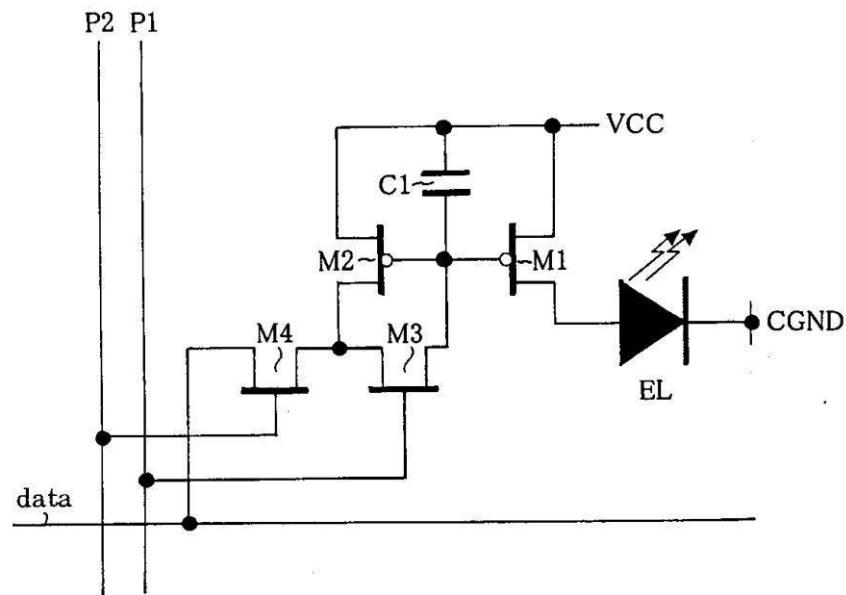

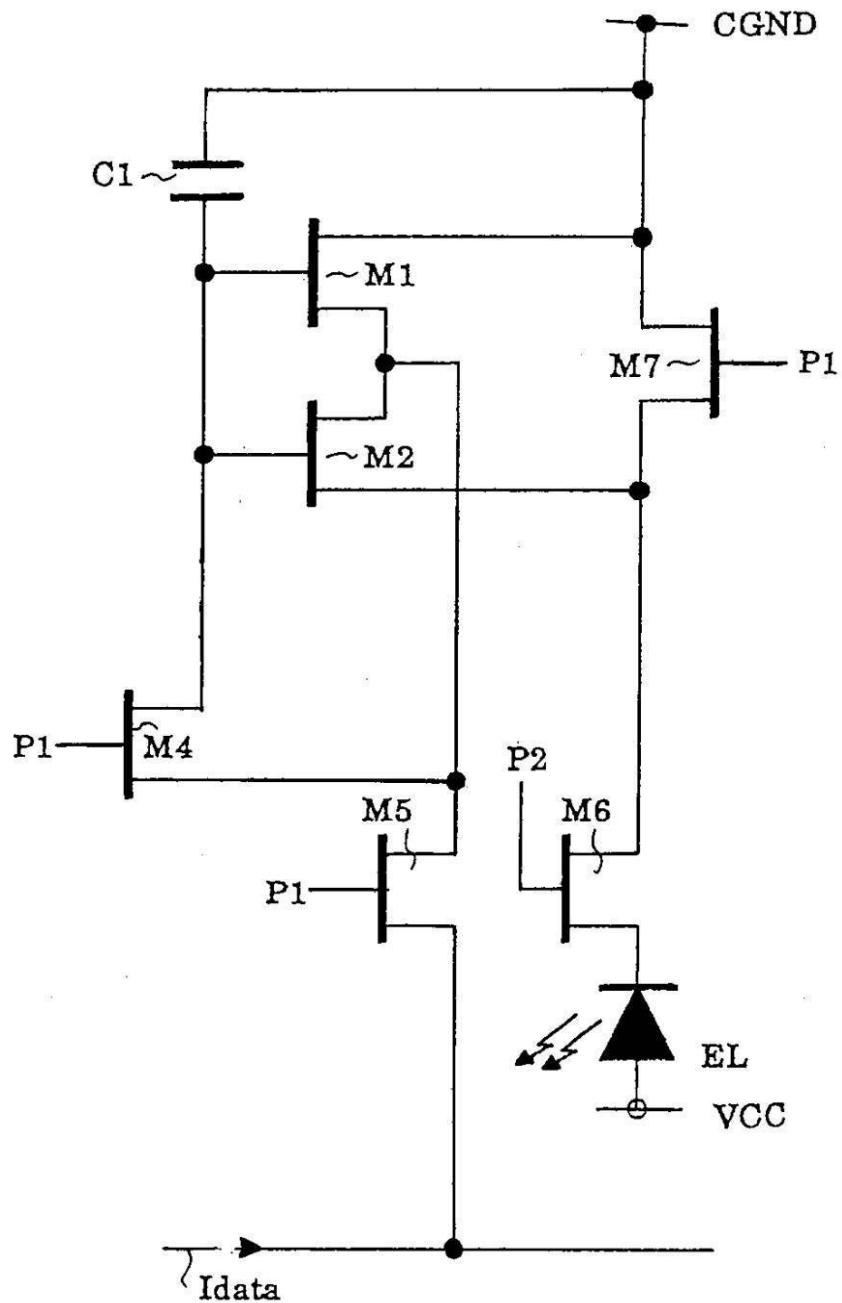

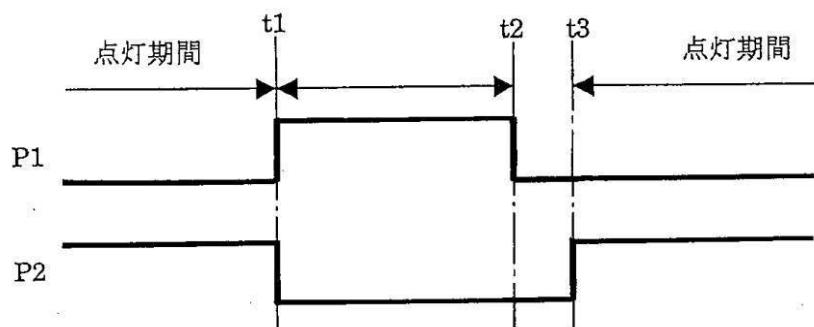

電流プログラミング方式の画素回路が、特許文献1において提案されている。図10はこれを使用した画素回路1の構成である。図10において、信号線には列制御回路3によって生成された電流表示信号dataが入力され、走査線には行レジスタ6から生成された走査信号P1、P2が使用される。図7は走査信号P1、P2のタイムチャートである。時刻t1～t2が画素回路1のプログラミング期間で時刻t2～t3が点灯期間への待機期間である。時刻t1以前も点灯期間である。詳しい動作説明は省くが、図10に示すように、各画素回路1においてトランジスタM2及びM1からなるカレントミラー回路によって表示制御される。トランジスタM2及びM1は近接に配置されているため相対バラツキは比較的小さい。

## 【0007】

10

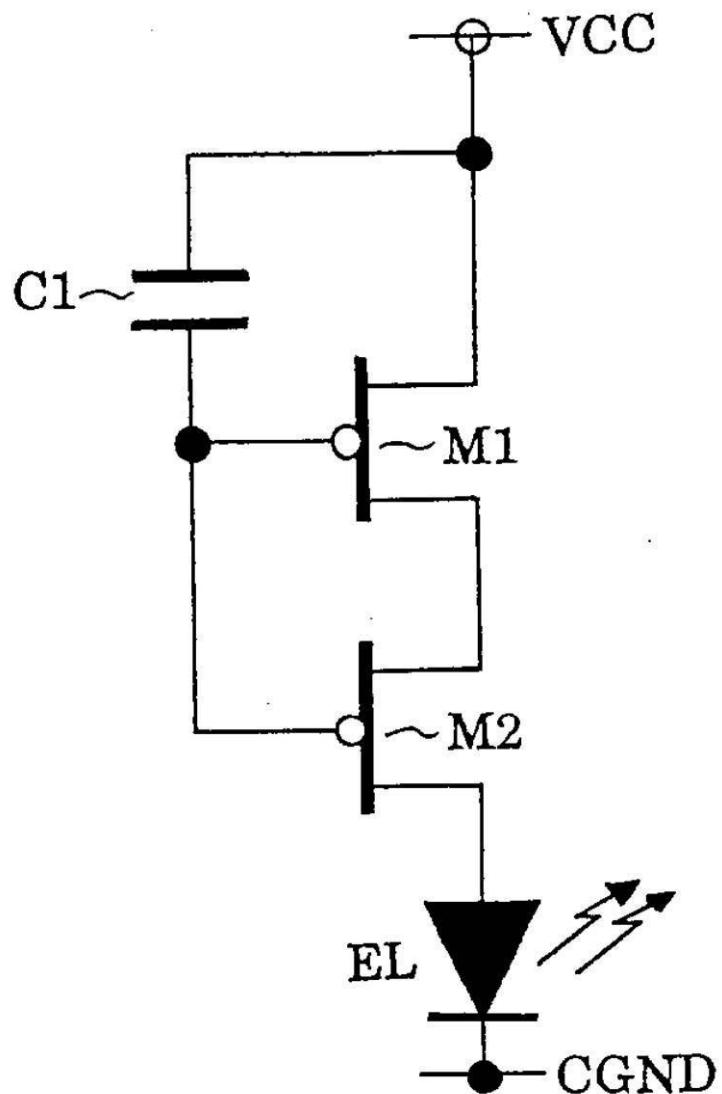

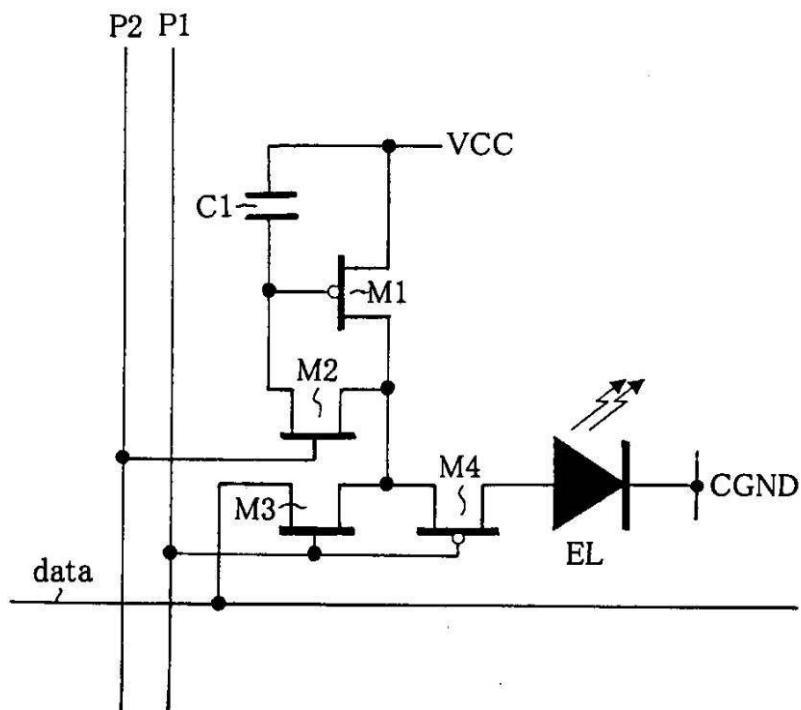

電流プログラミング方式の他の画素回路構成としては、特許文献2が提案されている。図11は、これを使用した画素回路1の構成である。図11において信号線には列制御回路3によって生成された電流表示信号dataが入力され、走査線には行レジスタ6から生成された走査信号P1、P2が使用される。図7は走査信号P1、P2のタイムチャートである。詳しい動作説明は省略する。図11の構成の場合、電流プログラミング時と点灯時に使用されるトランジスタが同一のトランジスタM1であるため、基本的にはTFTの閾値電圧Vth及び駆動係数のバラツキの影響を動作上受けることがない。したがって、有機EL素子を使用したアクティブマトリクス型表示装置の画素回路1において有望な構成である。

## 【特許文献1】米国特許第6501466号

20

## 【特許文献2】米国特許第6373454号

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0008】

本発明は、EL素子の画素回路に好適に用いることができ、小電流領域における電流プログラミング動作をより安定化させ、各画素回路におけるトランジスタバラツキによる駆動電流変動をより抑制しうる電流供給装置を提供するものである。

## 【課題を解決するための手段】

## 【0009】

30

本発明の電流供給装置は、第1の電界効果トランジスタと、

制御電極が前記第1の電界効果トランジスタの制御電極と共に接続されるとともに、一方の主電極が前記第1の電界効果トランジスタの一方の主電極と共に接続される第2の電界効果トランジスタと、

前記第1及び第2の電界効果トランジスタの前記制御電極が共通接続された第1共通接続部と前記第1及び第2の電界効果トランジスタの前記一方の主電極が共通接続された第2共通接続部との間に設けられた第1のスイッチと、

前記第1及び第2の電界効果トランジスタの他の主電極間に設けられた第2のスイッチと、

を備え、

前記第1及び第2のスイッチをオンして前記第1及び第2の電界効果トランジスタを並列接続する第1のモードと、前記第1及び第2のスイッチをオフして前記第1及び第2の電界効果トランジスタを直列接続する第2のモードとを有し、

前記第1のモードにおいて、並列接続された第1及び第2の電界効果トランジスタに流す設定電流を、前記第1共通接続部と、前記第2のスイッチにより共通接続された前記第1及び第2の電界効果トランジスタの他の主電極との間の電圧値として書き込み、

前記第2のモードにおいて、前記電圧値に基づいて、直列接続された前記第1及び第2の電界効果トランジスタから電流を供給する電流供給装置である。

## 【0010】

40

本発明の回路装置、発光装置、表示装置及び画像記録装置は上記電流供給装置を用いたものである。

50

**【発明の効果】****【0011】**

本発明の電流供給装置によれば、電流供給装置により供給される供給電流が小さくても、電流供給装置に書き込む設定電流を供給電流よりも大きくできるので、設定電流の書き込み動作を安定化させることができる。

**【0012】**

また、設定電流書き込み時と供給電流の供給時に用いるトランジスタと同じにすることができる。そして、設定電流書き込み時には二つの電界効果トランジスタは並列接続され、供給電流の供給時には二つの電界効果トランジスタは直列接続される。これらの構成により、二つの電界効果トランジスタの特性バラツキによる供給電流変動を抑制することができる。10

**【0013】**

特に、本発明の電流供給装置は電流駆動型発光素子を使用したアクティブマトリクス型表示装置に好適に用いることができる。そして、小電流領域における電流プログラミング（設定電流の書き込み）動作を安定化できるとともに、各画素回路におけるトランジスタバラツキによる駆動電流（供給電流）変動を大幅に抑制できる。そのため、低輝度領域の画質劣化を大きく改善できる。

**【発明を実施するための最良の形態】****【0014】**

本発明においてトランジスタの「主電極」とは、ソースまたはドレイン電極を意味する。一般に、Pチャネル型のトランジスタでは、電流が流れ込む端子をソース電極、電流が流れ出す端子をドレイン電極といい、Nチャネル型ではその逆である。しかし、本発明においては、接続状態によって電流の流れる方向がある程度異なるので、ソース／ドレインの呼称は使わず、各文脈において適宜に、「一方の主電極」と「他方の主電極」ということとする。電流は、一方の主電極から他方の主電極に流れるときもあれば、その逆に流れることもある。20

**【0015】**

本発明においてトランジスタの「並列接続」とは、2つ（またはそれ以上）のトランジスタのいずれか一方の主電極同士が共通に接続され、他方の主電極同士も共通に接続されたときの、共通に接続された電極をそれぞれ端子とする2端子間の結線状態を言う。共通に接続された主電極の一方から流れ込んだ電流は、2つのトランジスタに分岐して流れ、共通に接続されたもう一方の主電極から流れ出す。30

**【0016】**

本発明においてトランジスタの「直列接続」とは、2つのトランジスタにおいて、いずれかの主電極同士が共通に接続されたときの、他方の主電極をそれぞれ端子としてみたときの2端子間の結線状態をいう。一方の端子から流れ込む電流は、その端子に接続されたトランジスタを流れた後、共通に接続された電極を経て他方のトランジスタを流れ、他方の端子から流れ出る。

**【0017】**

以下、本発明の実施の形態について図面を用いて詳細に説明する。40

**【0018】**

以下本発明の実施形態として、電界発光素子（EL；エレクトロルミネッセンス素子）に駆動電流を供給するアクティブマトリクス表示装置を例に取って説明する。

**【0019】**

本発明の電流供給装置を電流駆動型素子と組み合わせて単位回路を構成し、単位回路を一次元状又は二次元状に配して回路装置を構成することができる。電流駆動型素子としては例えばEL素子、LED等の電流駆動型発光素子があり、この場合、本発明の電流供給装置を電流駆動型発光素子と組み合わせた単位回路を一次元状又は二次元状に配して発光装置や表示装置を構成することができる。

**【0020】**

10

20

30

40

50

かかる発光装置は、部分発光、面発光又は画像情報を示す線状発光源、面状発光源を構成し、表示装置は画像情報を表示する線状表示装置、アクティブマトリクス型表示装置を構成することができる。画像情報を示す線状発光源はスキャナとして感光体と組み合わせて光プリンタ、複写機等の画像記録装置を構成することができる。アクティブマトリクス型表示装置は平面型テレビ、デジタルカメラ、デジタルビデオカメラ等に用いられるビューア、携帯電話機の表示部等に用いることができる。電流駆動型素子としては、他に例えば電流の一部を電子として放出する電子放出素子があり、かかる電子放出素子を用いて画素回路を構成して基板上に二次元状に配置し、真空容器内で蛍光体と対向させて画像表示装置を構成することができる。例えば、特開平2-257551号公報や特開平4-28137号公報等に開示される画像表示装置がある。

10

## 【0021】

また本発明の電流供給装置は、書き込み電流を電界効果トランジスタのソース・ドレン電流として任意に取り出す制御をおこなってアナログメモリとして用いることもできる。

## 【0022】

また本発明の電流供給装置は、トランジスタの近接バラツキによって発生する出力電流バラツキを大きく抑制できる減衰型カレントミラー回路として使用できる。

## [実施形態1]

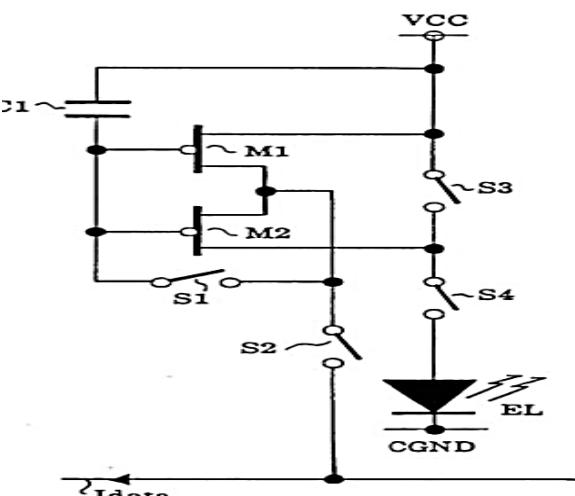

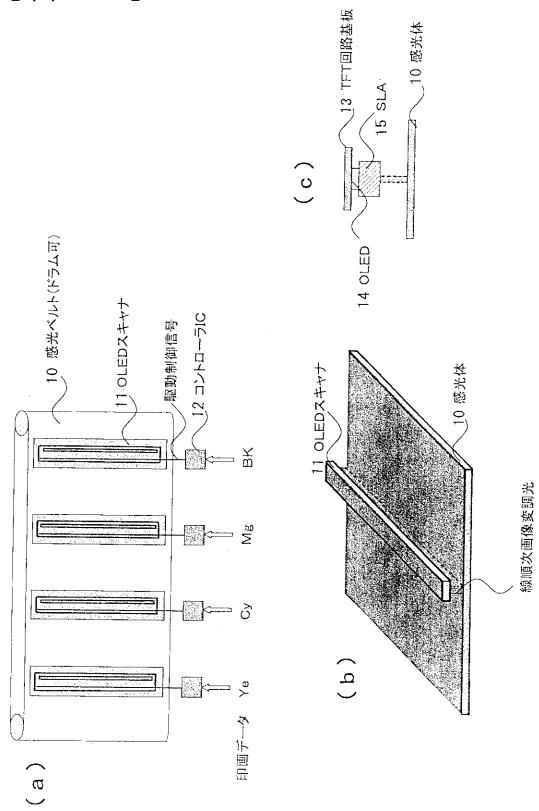

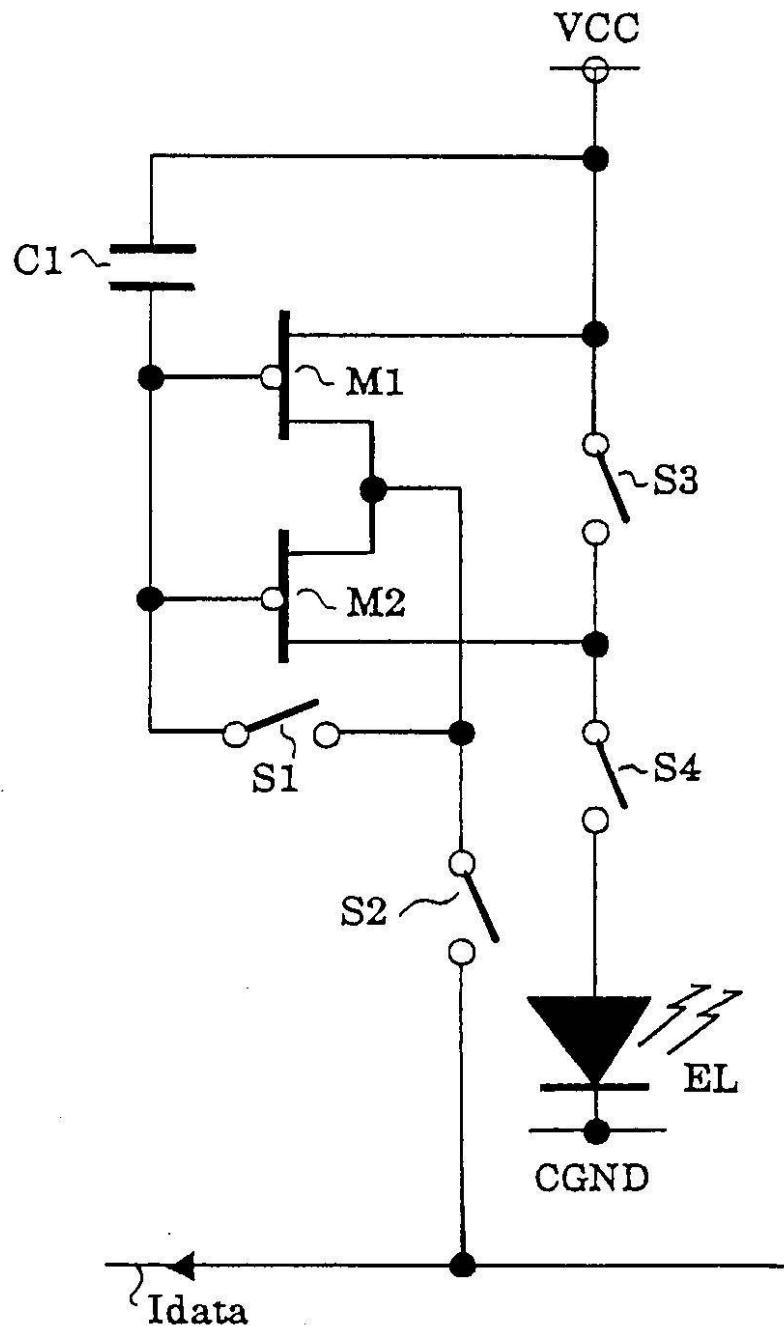

図1は本発明による電流供給装置を使用したアクティブマトリクス型表示装置の画素回路1の第1実施形態を示す回路構成図である。図2はプログラミング期間（第1のモード）における図1の画素回路の回路構成を示す回路図である。図3は駆動時（第2のモード：電流供給時）における図1の画素回路の回路構成を示す回路図である。

20

## 【0023】

電流I<sub>data</sub>が供給される信号線4（図12に図示）はスイッチS2の一端子に接続され、スイッチS2の他端子はトランジスタM1及びM2の一方の主電極（ソース、ドレン）の共通の接続点（第2共通接続部となる）に接続される。さらにスイッチS2の他端子は、スイッチS1を介してトランジスタM1及びM2の制御電極（ゲート）の共通の接続点（第1共通接続部）に接続される。共通接続された制御電極は保持容量C1を介して電源V<sub>CC</sub>に接続される。またトランジスタM1の他方の主電極も電源V<sub>CC</sub>に接続される。トランジスタM2の他方の主電極はスイッチS3を介して電源V<sub>CC</sub>に接続されるとともに、スイッチS4を介して有機EL素子のアノード電極に接続される。またスイッチS3はトランジスタM1及びM2の他方の主電極間に設けられ、トランジスタM1及びM2の並列接続、直列接続を切り換えている。

30

## 【0024】

トランジスタM1及びM2は第1及び第2の電界効果トランジスタを構成し、スイッチS1、S3、S2、S4は第1、2、3、4のスイッチを構成する。

## 【0025】

## &lt;動作説明&gt;

電流プログラミング期間では、スイッチS1、S2、S3は全てON、スイッチS4はOFFになり、図2に示すようにトランジスタM1、M2が並列接続され電流（設定電流）I<sub>data</sub>をプログラミングする。

40

## 【0026】

有機EL素子駆動時では、スイッチS1、S2、S3はOFF、スイッチS4はONになり、図3に示すようにトランジスタM1、M2が直列接続される。このとき、トランジスタM2の主電極（ドレン）は有機EL素子のアノード電極に接続され駆動電流I<sub>d</sub>が注入される。

## 【0027】

トランジスタM1、M2は近接配置されるため閾値電圧V<sub>th</sub>及び駆動係数は比較的揃っている。その為、トランジスタM1、M2の共通の制御電極の電圧（ゲート電圧）がプログラミング時と電流駆動時で等しい場合、駆動電流I<sub>d</sub>はプログラミング電流I<sub>data</sub>

50

の1/4程度になる。このためプログラミング電流I dataを図11の画素回路に比べて4倍程度に増加することができ、小さな駆動電流領域のプログラミング動作を大きく改善できるため、低輝度領域の表示画質を改善できる。

#### 【0028】

また図1の画素回路では、図11の画素回路と同様にプログラミング時と電流駆動時に使用されるトランジスタが同一であるため、近接バラツキによる駆動電流I dの変動は図10の画素回路に比べて低減できる。プログラミング時では、トランジスタM1、M2は並列に接続されているため概ねバラツキは半減される。そして、電流駆動時においてもトランジスタM1、M2は直列接続されているため概ねバラツキは半減される。したがって、全体として近接バラツキは1/4程度に抑制される。

10

#### 【0029】

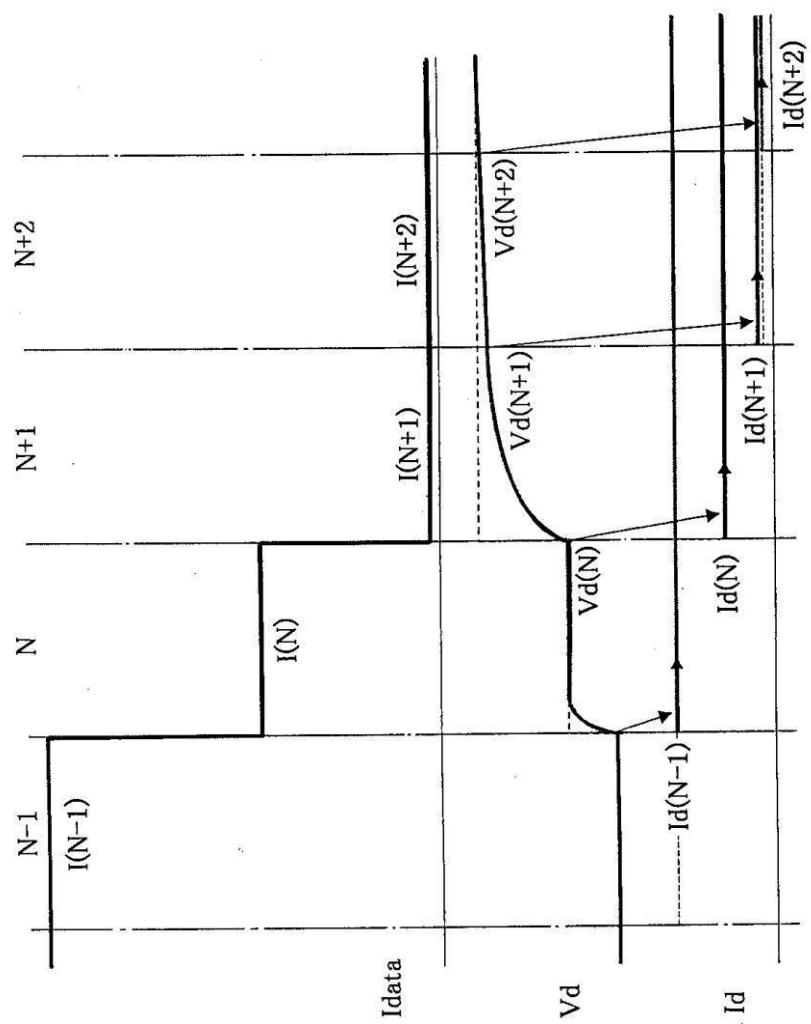

図4は図1の画素回路1の電流プログラミング動作を説明するものである。

#### 【0030】

(N-1)行プログラミング期間では大きな表示信号(I data)として大きな電流I(N-1)が供給され図2に示す回路に電流プログラミングされる。

#### 【0031】

次に、(N)行プログラミング期間において電流プログラミングが行われる。そして、その(N)行プログラミング期間に、(N-1)行プログラミング期間でプログラミングされた電流I(N-1)のほぼ1/4の駆動電流I d(N-1)が図3に示す回路により(N-1)行の対応する有機EL素子に注入される。

20

#### 【0032】

(N)行プログラミング期間では電流I(N-1)より小さいが比較的大きな電流I(N)が供給され、電流プログラミングされるが、電流減少に対応するため信号線4の動作電圧V d(N)は上昇しなければならない。このとき、寄生容量があるため動作電圧V d(N)は図の様に電圧遷移を有する。しかし、電流I(N)が比較的大きいため行プログラミング期間内に寄生容量の充電が完了し、信号線4の動作電圧V d(N)が平衡する。つまり、プログラミング電流I dataが増加するため電圧遷移期間は短く、行プログラミング期間内で動作電圧V dを平衡状態にすることができる。

#### 【0033】

次に、(N+1)行プログラミング期間において電流プログラミングが行われる。そして、その(N+1)行プログラミング期間に、(N)行プログラミング期間でプログラミングされた電流I(N)のほぼ1/4の駆動電流I d(N)が図3に示す回路により(N)行の対応する有機EL素子に注入される。

30

#### 【0034】

(N+1)行プログラミング期間ではI(N)より小さい電流I(N+1)が供給され、電流減少に対応する信号線4の動作電圧V d(N+1)は上昇しなければならない。電流I(N+1)が小さいため寄生容量の充電がプログラミング期間内に完全には終了することができず、点線で示す所望動作電圧より低い動作電圧V d(N+1)でプログラミングが終了する。しかし、プログラミング電流I dataが大きくなっているため、図4の点線で示される所望動作電圧に漸近している。このため(N+2)行プログラミング期間において、点線で示す所望駆動電流よりわずかに大きな駆動電流I d(N+1)が対応する有機EL素子に注入される。しかし、駆動電流I d(N+1)は所望駆動電流(図中、点線で示す)よりわずかに大きいだけであるため画質劣化は少ない。

40

#### 【0035】

次に、(N+2)行プログラミング期間では引き続き小さな電流I(N+2)(=I(N+1))が供給され、信号線4の動作電圧V d(N+1)は点線で示される所望電圧に向かって引き続き上昇しなければならない。(N+1)行プログラミング期間で所望電圧に漸近していることに加えてプログラミング電流が大きいため、寄生容量の充電がプログラミング期間内にほぼ終了する。

#### 【0036】

50

次に、(N+3)行プログラミング期間において電流プログラミングが行われる。そして、その(N+3)行プログラミング期間に、(N+2)行プログラミング期間でプログラミングされた電流I(N+2)のほぼ1/4の駆動電流Id(N+2)が対応する有機EL素子に注入され、ほぼ正常な画像表示が実現される。

#### 【0037】

図1の画素回路1のトランジスタM1及びM2の行間の閾値電圧Vth及び駆動係数のバラツキが有ったとしても、低輝度領域の画質は安定する。なぜなら、プログラミング電流が大きくなっているため、低電流プログラミングにおける動作電圧Vdの行間での追従動作が大幅に改善されるからである。

#### 【0038】

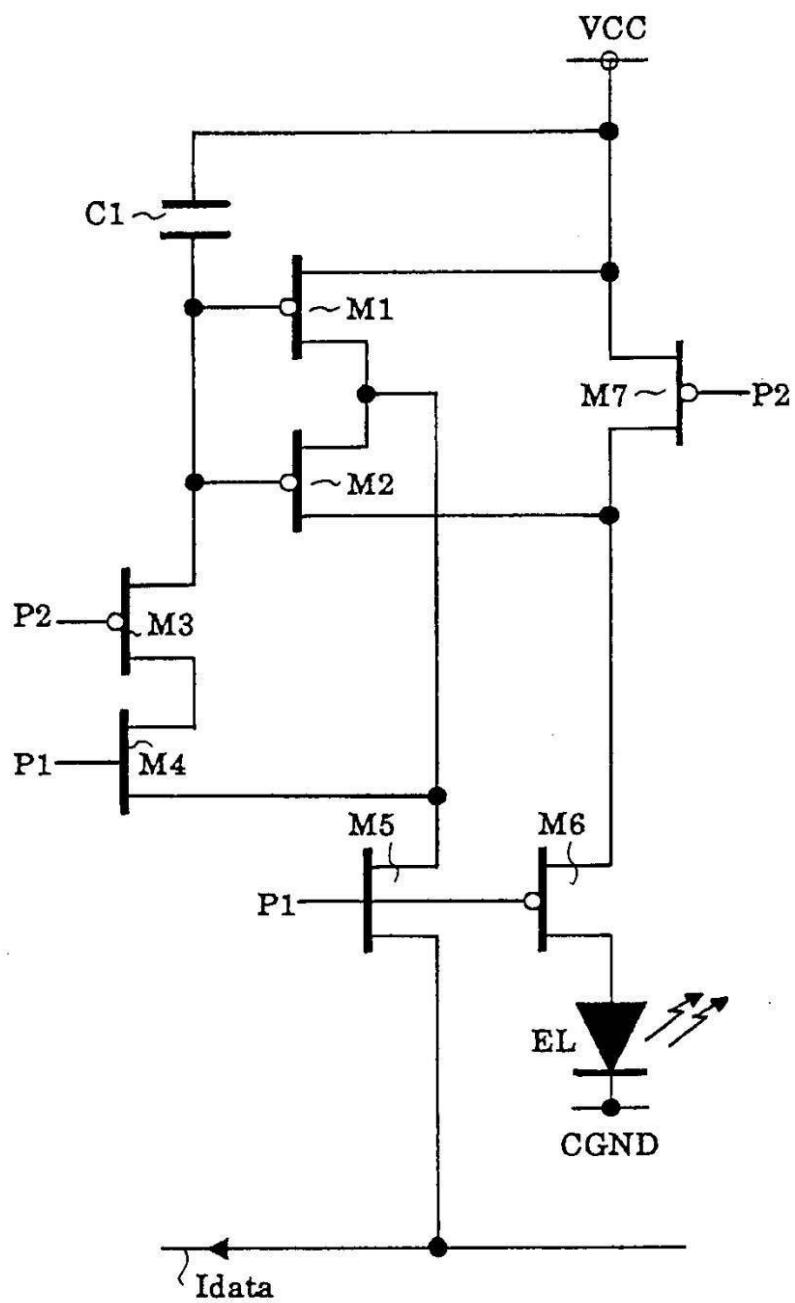

図5は図1の画素回路に使用されるスイッチをトランジスタに置き換えた具体的な回路構成を示す図である。図1に示すスイッチS1～S4は各々、トランジスタM3及びM4、M5、M7、M6が対応する。走査信号はP1、P2である。トランジスタM1、M2、M3、M6、M7はPMOSトランジスタ、トランジスタM4、M5はNMOSトランジスタである。

#### 【0039】

図6は走査信号P1、P2のタイムチャートである。時刻t1～t2が画素回路1のプログラミング期間で、時刻t2～t3が点灯期間への待機期間である。時刻t1以前も点灯期間である。トランジスタM3を設けることで、プログラミング終了時刻t2における、走査信号P2から保持容量C1へのフィードスルー動作によりトランジスタM1、M2の共通の制御電極の電圧(ゲート電圧)が増加する。つまり、トランジスタM3のゲートに印加される走査信号P2がLレベルからHレベルになったときに、トランジスタM3のゲート-ドレイン間容量を介してトランジスタM1、M2の共通の制御電圧(ゲート電圧)が増加する。そして、トランジスタM1、M2の共通の制御電極電圧を増加させ、最小駆動電流Idを減少させることによって表示コントラストを向上させることができる。トランジスタM3を設けず、短絡しても良い。また期間t2～t3の待機期間はプログラミングから電流駆動への遷移動作を確実にするものであるため基本的には無くても良い。

#### 【実施形態2】

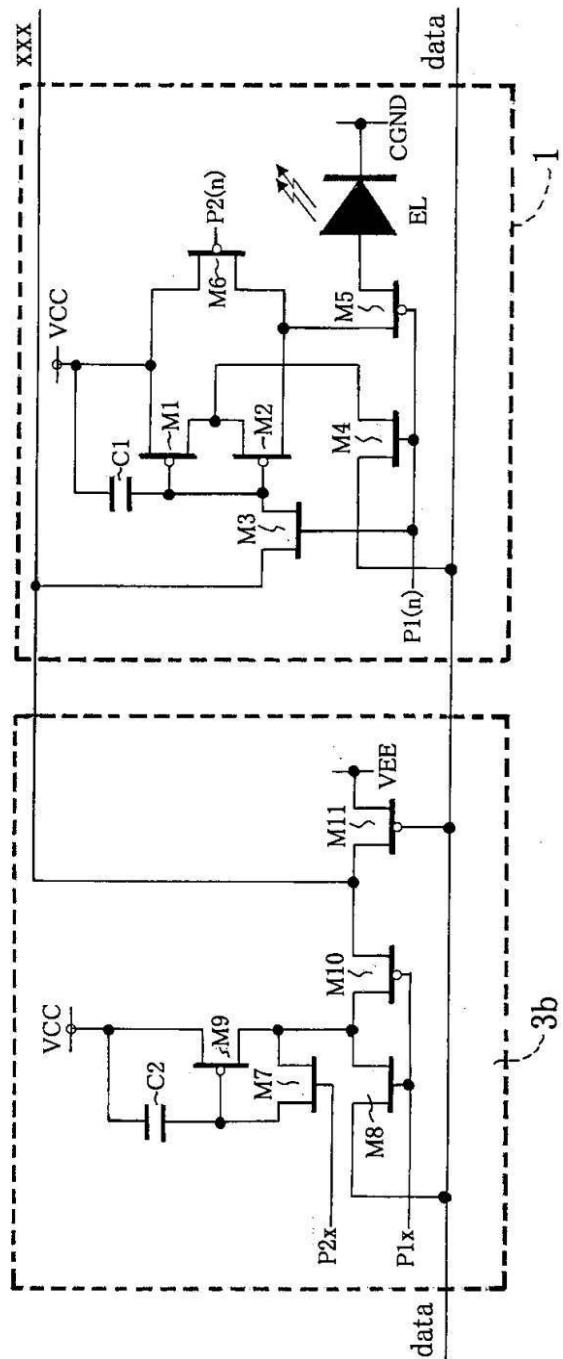

図8は本発明の電流供給装置を使用した画素回路1の他の実施形態である。図1の画素回路1と同一構成部材については同一符号を付する。以下、図1の画素回路1と図8の画素構成との違いについて説明する。

#### 【0040】

画素回路1におけるトランジスタM1、M2の共通の制御電極(ゲート)はトランジスタM3のドレインに接続され、トランジスタM3のソースは補助信号線xxxに接続され、制御電極(ゲート)には走査信号P1(n)が印加される。信号線dataはソースホロワ回路3bの中のトランジスタM11の制御電極(ゲート)に接続される。トランジスタM11のソースは補助信号線xxxに接続される。トランジスタM11のソース電流は信号線dataに接続されたトランジスタM7～M10によって構成される電流プログラミング型電流源によって生成される。この電流プログラミング動作は有効表示期間外で行なう必要がある。またソースホロワ回路3bは列制御回路3の中に含まれ各列において1つ構成すればよい。

#### 【0041】

走査信号P1(n)、P2(n)は図6に示すタイムチャートの信号P1、P2と同様の信号である。また制御信号P1x、P2xは図7に示すタイムチャートの信号P1、P2と同様の信号である。この場合点灯期間は電流保持期間である。図1の画素回路と同じく図4で示す電流プログラミング動作を行なうことができる。ただし補助信号線xxxの動作電圧Vdは、ソースホロワ回路3bの中のトランジスタM11のゲート-ソース間電圧だけ下降する。

#### 【0042】

10

20

30

40

50

本実施形態の画素回路は、プログラミング期間の画素回路の保持容量 C 1 の充放電がデータ線電圧に応じたソースホロワ回路 3 b の出力で行われる。このような構成により、データ電流が小さいときの保持容量 C 1 の充放電動作を向上させることができる。

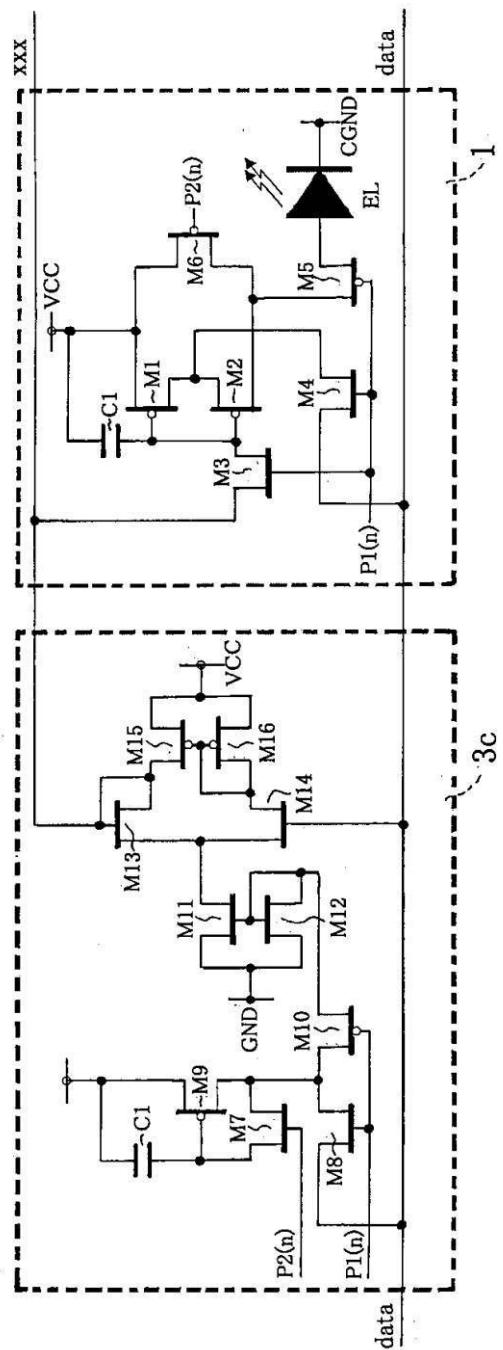

#### [実施形態 3]

図 9 は本発明の電流供給装置を使用した画素回路 1 の更に他の実施形態である。図 8 の画素回路 1 と同一構成部材については同一符号を付する。画素回路 1 は図 8 で示す構成と同じである。信号線 d a t a は電圧バッファ回路 3 c に接続され、データ電流（設定電流）は電圧バッファ回路 3 c に入力される。また、データ電流（設定電流）はトランジスタ M 1 1 ~ M 1 6 によって構成される電圧バッファのトランジスタ M 1 4 のゲートに入力され、トランジスタ M 1 3 のドレインの電圧出力信号が補助信号線 × × × に出力される。電圧バッファのソース電流はトランジスタ M 7 ~ M 1 0 によって構成される電流プログラミング型電流源によって生成される。

#### 【0043】

本実施形態の回路構成は、図 8 のソースホロワ回路 3 b を電圧バッファ回路 3 c に置き換えたものであり、出力インピーダンスを小さくし、より正確な電流プログラミングを実現するものである。

#### 【0044】

走査信号 P 1 ( n )、P 2 ( n )は図 6 に示すタイムチャートの信号 P 1 、P 2 と同様の信号である。また制御信号 P 1 x 、P 2 x は図 7 に示すタイムチャートの信号 P 1 、P 2 と同様の信号である。この場合点灯期間は電流保持期間である。図 1 の画素回路と同じく図 4 で示す電流プログラミング動作を行なうことができる。補助信号線 × × × の動作電圧 V d は、図 1 の画素回路 1 とほぼ等しい。

#### [実施形態 4]

本実施形態は、図 5 に示す画素回路のトランジスタの導電型を反対導電型にした場合の構成例を示すものである。ただし、トランジスタ M 4 , M 5 はリーク電流を抑制するために N M O S トランジスタのままとした。

#### 【0045】

図 1 5 は図 5 に示す画素回路のトランジスタの導電型を反対導電型にした場合の回路構成図、図 1 6 はその動作を示すタイミングチャートである。

#### 【0046】

図 1 5 の構成において、図 5 の画素回路との違いは、トランジスタ M 6 、M 7 を N M O S トランジスタで構成しており、E L 素子の極性を逆に接続し、電流供給回路に E L 素子からの電流が流入する構成になっていることである。

#### 【0047】

本発明は、図 8 と図 9 の構成例の画素回路 1 の構成を限定するものでない。

#### 【0048】

また本発明の電流供給装置はトランジスタの近接バラツキによって発生する出力電流バラツキを大きく抑制できる減衰型カレントミラー回路として使用できるものであり用途は画素回路 1 に留まらない。

#### [実施形態 5]

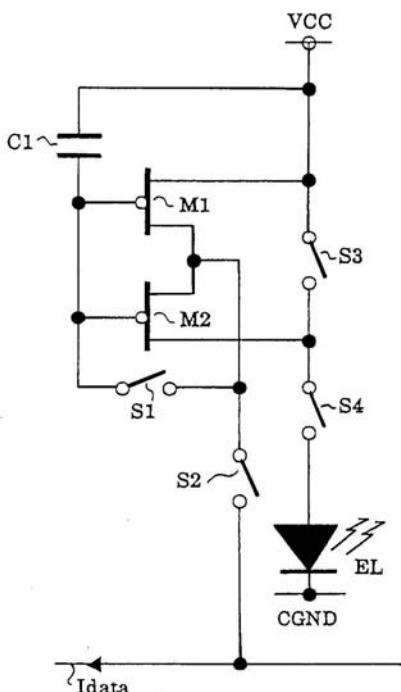

本実施形態は本発明に係わる電流供給装置と電界発光素子とで画素回路を構成し、画素回路を一次元状に配列して一次元の発光装置となるスキャナを構成したものである。

#### 【0049】

実施形態 1 ~ 4 に示したような画素回路を線状に配して感光体を露光する O L E D ( 有機 E L ) スキャナとして用いる。図 1 7 に示すように Y e ( イエロー ) 、C y ( シアン ) 、M g ( マゼンダ ) 、B K ( ブラック ) の各色の印画データをコントローラ I C 1 2 を介して駆動制御信号として 4 つの O L E D ( 有機 E L ) スキャナ 1 2 に入力する。そして、O L E D ( 有機 E L ) スキャナ 1 2 を発光させ、感光ベルト ( 感光ドラムでもよい ) 1 0 を露光する。O L E D ( 有機 E L ) スキャナ 1 2 は T F T 回路基板 1 3 に図 5 、図 8 、図 9 又は図 1 5 に示すような画素回路を列状に配した画素回路列が設けられ、さらに図 1 2

10

20

30

40

50

に示したような列制御回路、列レジスタが設けられて構成される。OLED(有機EL)14が線状に配置され、線順次画像変調光が感光体ベルト10を露光する。必要に応じてセルフォックレンズアレイ(SLA)等の導光体をOLED(有機EL)14と感光体ベルト10との間に設ける。

#### 【0050】

上記構成により各色の印画データを移動する感光体ベルトに露光する。感光ベルトは回転して不図示の各色ごとに設けられた現像装置で各色のトナーが付与されて現像され、Ye, Cy, Mg, Bkの順でトナー像が順次紙に転写され、定着装置で定着させる。かかる構成は光プリンタ、イメージセンサと組み合わせた複写機等に用いることができる。

#### [実施形態6]

本発明に係わる電流供給装置はアナログメモリとして用いることができる。図5、図8、図9又は図15の画素回路において、電界発光素子ELを設けず、トランジスタM6を信号P1やP2とは別の信号でオン・オフ制御するように単位回路を構成する。かかる構成により、データ電流値に対応する電流を並列接続されたトランジスタM1、M2のソースゲート電圧として記憶し、直列接続されたトランジスタM1、M2から書き込まれた電流を取り出すことで、アナログメモリとして機能する。この単位回路を一次元又は二次元状に配することでアナログラインメモリやアナログフィールドメモリとして用いることができる。

#### 【産業上の利用可能性】

#### 【0051】

本発明は電界発光素子(EL素子)やLED等の電流駆動型素子を用いたアクティブマトリクス型表示装置、光プリンタ、複写機のスキャナやアナログメモリに用いられるものである。

#### 【図面の簡単な説明】

#### 【0052】

【図1】本発明を使用した基本画素回路の回路図である。

【図2】図1のプログラミング期間の回路構成を示す回路図である。

【図3】図1の駆動時の回路構成を示す回路図である。

【図4】図1の動作を説明するタイムチャートである。

【図5】本発明を使用した第1の実施形態を示す回路図である。

【図6】図1、図8、図9を説明するタイムチャートである。

【図7】図1、図8、図9、図10、図11を説明するタイムチャートである。

【図8】本発明を使用した第2の実施形態を示す回路図である。

【図9】本発明を使用した第3の実施形態を示す回路図である。

【図10】従来の画素回路例を示す回路図である。

【図11】従来の画素回路例を示す回路図である。

【図12】アクティブマトリクス型表示装置の構成を示す図である。

【図14】有機EL素子の電圧-電流特性を示す特性図である。

【図13】有機EL素子の電流-輝度特性を示す特性図である。

【図15】図4に示す画素回路のトランジスタの導電型を反対導電型にした第4の実施形態の回路構成図である。

【図16】図15の回路の動作を示すタイミングチャートである。

【図17】電流供給装置と電界発光素子とで画素回路を構成し、画素回路を一次元状に配列して一次元の発光装置となるスキャナを示す図である。

#### 【符号の説明】

#### 【0053】

1 画素回路

2 表示領域

3 列制御回路

4 信号線

10

20

30

40

50

- 5 列レジスタ

- 6 行レジスタ

- 7 走査線

- 8 制御信号

- 9 制御回路

【図17】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

H 05 B 33/14

A

(72)発明者 山下 孝教

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

Fターム(参考) 3K107 AA01 BB01 CC33 EE03 HH05

5C080 AA06 BB05 DD05 EE29 FF11 JJ03 JJ04 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 电流供应装置和显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2007108575A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2007-04-26 |

| 申请号            | JP2005301625                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2005-10-17 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 佳能公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 川崎素明<br>郷田達人<br>山下孝教                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 川崎 素明<br>郷田 達人<br>山下 孝教                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| F1分类号          | G09G3/30.K G09G3/30.J G09G3/20.624.B G09G3/20.611.H G09G3/20.641.D H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE29 5C080/FF11 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AB06 5C380/AB29 5C380/AB34 5C380/AC07 5C380/AC10 5C380/AC11 5C380/BA38 5C380/BA39 5C380/BA40 5C380/BB02 5C380/BB23 5C380/CA08 5C380/CA13 5C380/CA17 5C380/CB01 5C380/CB17 5C380/CC13 5C380/CC14 5C380/CC18 5C380/CC19 5C380/CC26 5C380/CC27 5C380/CC28 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC63 5C380/CC64 5C380/CC65 5C380/CD014 5C380/CD016 5C380/CD017 |         |            |

| 代理人(译)         | 永井道雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

### 摘要(译)

要解决的问题：提供适合用于EL器件的像素电路的电流供应装置，进一步稳定小电流区域中的电流编程操作，并防止由于每个像素中的晶体管变化引起的驱动电流的变化电路。解决方案：像素电路具有第一和第二场效应晶体管M1，M2，其中每个栅极连接并且每个漏极/源极电连接。开关S3布置在第一场效应晶体管的源极和第二场效应晶体管的漏极之间，开关S2连接在共同连接的栅极和共同连接的源极/漏极之间。开关S2和S3在当前编程周期期间导通，并且第一和第二场效应晶体管并联连接以写入编程电流。然后，开关S2和S3在电流供应周期期间导通，并且第一和第二场效应晶体管串联连接以提供基本上四分之一的编程电流。