(51) Int.Cl<sup>7</sup>

H 05 B 33/10

33/06

識別記号

F I

H 05 B 33/10

33/06

テマコード(参考)

3 K 0 0 7

審査請求 未請求 請求項の数 30 L (全 10数)

(21)出願番号 特願2001 - 103487(P2001 - 103487)

(22)出願日 平成13年4月2日(2001.4.2)

(71)出願人 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(72)発明者 深谷 顕成

愛知県刈谷市昭和町1丁目1番地 株式会社

デンソー内

(72)発明者 大西 真司

愛知県刈谷市昭和町1丁目1番地 株式会社

デンソー内

(74)代理人 100100022

弁理士 伊藤 洋二 (外2名)

最終頁に続く

(54)【発明の名称】 E L表示素子の製造方法

## (57)【要約】

【課題】 E L表示素子における上部電極の取出部を形成するにあたって、取出部における上部電極の断線防止と素子のクラック発生防止を実現可能とする。

【解決手段】 電極取出領域1aに、上部電極6の形状に対応してパターニングされた電極膜2aを形成し、電極膜2a上および電極膜2aの間に下部絶縁層3形成し、電極膜2aの間に形成された下部絶縁層3の上に発光層4を積層し、次に、その上に上部絶縁層5を積層し、次に、電極膜2aの上の層を機械的に除去して電極膜2aを露出させ、しかる後、露出した電極膜2aの上に上部電極6を積層する。

## 【特許請求の範囲】

【請求項1】 ガラス基板(1)上に、下部電極(2)、下部絶縁層(3)、発光層(4)、上部絶縁層(5)、上部電極(6)を順次積層してなるEL表示素子において、

前記ガラス基板のうち表示領域(1b)以外の電極取出領域(1a)にて前記上部電極を取り出すようにした製造方法であって、

前記電極取出領域に、前記上部電極の形状に対応してパターニングされた電極膜(2a)を形成する工程と、

前記電極取出領域にて前記電極膜上および前記電極膜の間に前記下部絶縁層を形成する工程と、

前記電極取出領域にて前記電極膜の間に形成された前記下部絶縁層の上に前記発光層を積層する工程と、

次に、前記電極取出領域に前記上部絶縁層を積層する工程と、

次に、前記電極取出領域にて前記電極膜の上の層を機械的に除去して前記電極膜を露出させる工程と、

しかる後、露出した前記電極膜の上に前記上部電極を積層する工程と、を備えることを特徴とするEL表示素子の製造方法。

【請求項2】 前記電極取出領域(1a)にて前記電極膜(2a)の間に形成された前記下部絶縁層(3)の上に積層する前記発光層(4)を、前記表示領域の前記発光層とは離した位置に形成することを特徴とする請求項1に記載のEL表示素子の製造方法。

【請求項3】 前記電極取出領域(1a)にて前記電極膜(2a)の間に形成された前記下部絶縁層(3)の上に前記発光層(4)を積層する工程では、前記発光層を、前記電極取出領域の外周端部よりも前記電極取出領域の内側にて前記電極膜上にも積層することを特徴とする請求項1または2に記載のEL表示素子の製造方法。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】 本発明は、ガラス基板上に、下部電極、下部絶縁層、発光層、上部絶縁層、上部電極を順次積層してなるEL表示素子の製造方法に関し、特に、上部電極の取出部の形成方法に関する。

## 【0002】

【従来の技術】 EL表示素子の一般的な製造方法は、次40のようである。まず、ガラス基板上に、スパッタリング法等によりITO(インジウム-チン-オキサイド)等の導電膜を形成し、これを所定形状にエッチングして下部電極とする。その上に、ALE法(原子層成長法)等にて下部絶縁層を積層し、その上に蒸着法等にて発光層を積層し、ALE等にて上部絶縁層を積層した後、下部電極と同様にして、上部電極を積層し、EL表示素子を完成させる。

【0003】 ここにおいて、ガラス基板のうち表示領域以外の部位(通常は、ガラス基板の周辺部)には、下部50

電極、上部電極を外部と電気的接続させるための電極取出領域が設けられ、下部及び上部電極が露出した状態になるようにしている。下部電極の取出部(露出部)については、下部電極から上部絶縁層まで形成した後、下部電極の上層を、研削や研磨等にて機械的に除去することで形成される。

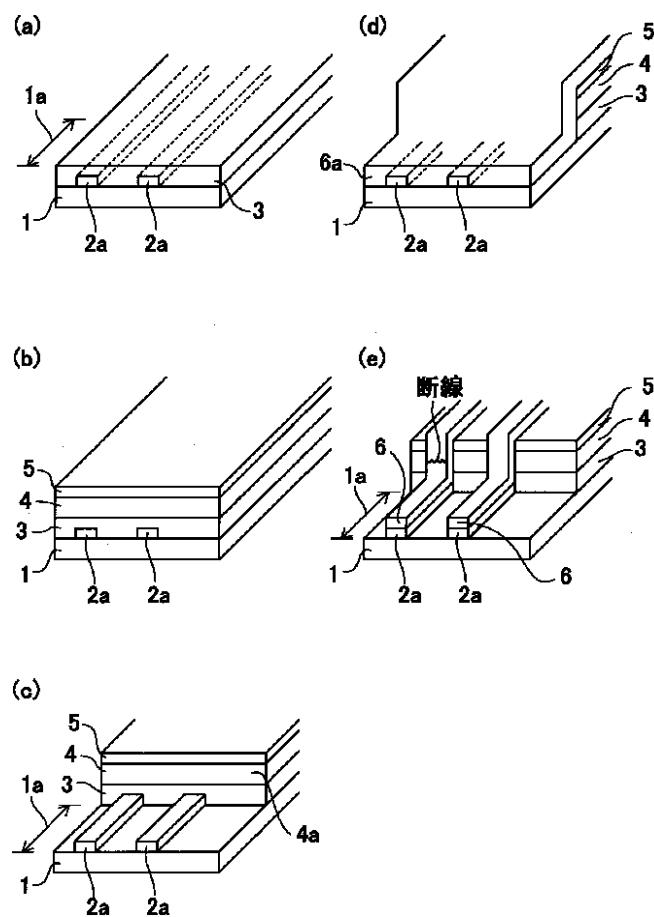

【0004】 一方、上部電極の取出部の形成については、次に示す2つの方法が従来の一般的な方法として用いられている。1つ目の方法を、図7及び図8に示す。

10 図7は模式的な斜視図、図8は上部電極の部分の概略断面図である。

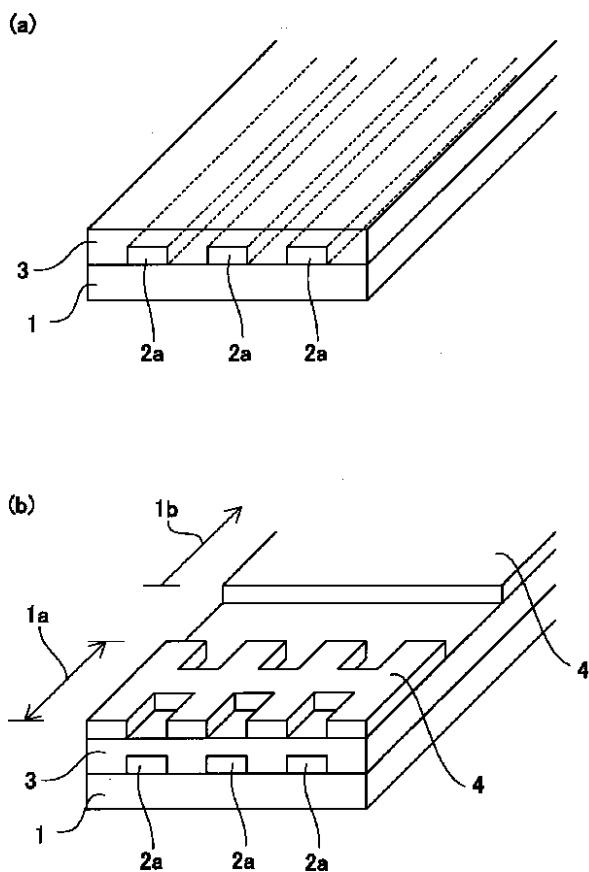

【0005】 まず、図7(a)及び図8(a)に示す様に、ガラス基板1のうち電極取出領域1aに、上部電極の形状に対応してパターニングされた電極膜2aを形成し、電極膜2aの上およびパターニングされた電極膜2aの間に、表示領域と共に下部絶縁層3を積層する。

【0006】 ここで、電極膜2aは、表示領域の下部電極(図示せず)と同時に、当該下部電極と同様にしてパターニング形成するもので、最終的に、ガラス基板上における上部電極の高さを合わせたり、上部電極と下部電極との両取出部の抵抗値を合わせる等のために必要なもの(ダミー下部電極)である。

【0007】 次に、図8(b)に示す様に、ガラス基板1の全域において下部絶縁層3の上に発光層4を積層し、続いて、その上に、図7(b)及び図8(c)に示す様に、上部絶縁層5を積層する。

【0008】 次に、図7(c)及び図8(d)に示す様に、液体ホーニング等の機械的研削方法によって、電極取出領域1aを研削することにより、電極膜2aの上の層3~5を除去し、電極膜2aを露出させる。次に、図7(d)に示す様に、電極取出領域1aを含むガラス基板1上の全域に、上部電極となる導電膜6aを形成する。

【0009】 続いて、ウェットエッチングにより、導電膜6aをパターニングすることにより、図7(e)及び図8(e)に示す様に、上部電極6が形成される。こうして、上部電極6は、電極取出領域1aにおいては、電極膜2aの上に積層された2層構造を有し、この電極取出領域1aに位置する上部電極6の部分が、取出部となる。

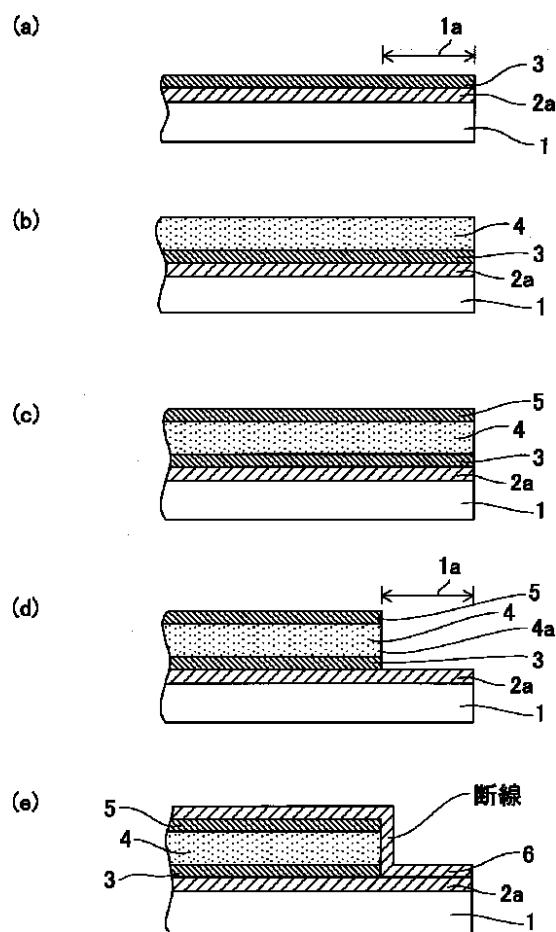

【0010】 2つ目の方法を、図9及び図10に示す。図9は模式的な斜視図、図10は上部電極の間の部分の概略断面図である。まず、図9(a)及び図10(a)に示す様に、上記1つ目の方法と同様にして、電極膜2a、下部絶縁層3を積層する。

【0011】 次に、ガラス基板1の全域において下部絶縁層3の上に発光層4を積層した後、上記1つ目の方法とは異なり、図9(b)及び図10(b)に示す様に、フォトエッチングにより電極取出領域1aにおける発光層4を除去する。続いて、その上に、図9(c)及び図10(c)に示す様に、上部絶縁層5を積層する。

10 ( c ) に示す様に、ガラス基板 1 の全域に上部絶縁層 5 を積層する。

【0012】次に、図9 ( d ) 及び図10 ( d ) に示す様に、液体ホーニング等の機械的研削方法によって、電極取出領域 1 a を研削することにより、電極膜 2 a の上の両絶縁層 3 、 5 を除去し、電極膜 2 a を露出させる。

【0013】次に、図10 ( e ) に示す様に、電極取出領域 1 a を含むガラス基板 1 上の全域に、上部電極となる導電膜 6 a を形成し、ウェットエッチングにより、当該導電膜をパターニングすることにより、図9 ( e ) に示す様に、上部電極 6 が形成される。

【0014】こうして、上部電極 6 は、上記1つ目の方法と同様、電極取出領域 1 a において電極膜 2 a の上に上部電極 6 が積層された2層構造を有する上部電極 6 の取出部が形成される。

【0015】

【発明が解決しようとする課題】しかしながら、上記した2つの上部電極の取出部の形成方法においては、次のような問題が生じる。まず、上記1つ目の方法では、図7 ( c ) に示す様に、電極膜 2 a の上の層 3 ~ 5 を除去し、電極膜 2 a を露出させた際、当該除去領域と非除去領域との境界において電極膜 2 a 上にて発光層 4 の端面 4 a が露出する。

【0016】そして、図7 ( d ) に示す様に、上部電極となる導電膜 6 a を形成するが、このとき、導電膜 6 a は、発光層 4 における露出した端面 4 a にも形成される。

【0017】そのため、続いて、ウェットエッチングにより導電膜 6 a をパターニングして上部電極 6 の形状とする際に、エッチング液が、導電膜 6 a のエッチング領域から非エッチング領域まで回り込み、上部電極 6 の下の発光層 4 をもエッチングしてしまう。

【0018】すると、上部電極 6 の下の発光層 4 が無くなったり、発光層 4 の露出端面 4 a 上の上部電極 6 が必要以上にエッチングされたりするため、上部電極 6 の強度が低下し、断線するという問題が生じる。

【0019】一方、上記2つ目の方法では、図9 ( b ) 及び図10 ( b ) に示す様に、フォトエッチングにより電極取出領域 1 a における発光層 4 を除去するため、電極取出領域 1 a を機械的に除去する前の段階で、パターニングされた電極膜 2 a の間には、ガラス基板 1 の上に両絶縁層 3 、 5 が積層された形となる。

【0020】ここで、EL表示素子に用いられる絶縁層（特に、ALe法にて成膜されたもの）は、膜応力が大きい。しかも、2層の絶縁層 3 、 5 が積層されているため、その膜応力は非常に大きくなり、それによってガラス基板 1 と両絶縁層 3 、 5 との界面には大きな歪みが生じると考えられる。

【0021】そして、この界面が歪んだ状態で、両絶縁層 3 、 5 を機械的に除去すべく研削等を行うと、パター

ニングされた電極膜 2 a の間においては、ガラス基板 1 や両絶縁層 3 、 5 にクラックが発生しやすくなると考えられる。実際に、本発明者等の検討によれば、図9 ( d ) に示す様に、クラック K が発生し、EL表示素子の強度低下や耐圧性低下等の問題が生じた。

【0022】そこで、本発明は上記問題に鑑み、EL表示素子における上部電極の取出部を形成するにあたって、取出部における上部電極の断線防止と素子のクラック発生防止を実現可能とすることを目的とする。

【0023】

【課題を解決するための手段】上記目的を達成するため、請求項1に記載の発明は、ガラス基板 ( 1 ) 上に、下部電極 ( 2 ) 、下部絶縁層 ( 3 ) 、発光層 ( 4 ) 、上部絶縁層 ( 5 ) 、上部電極 ( 6 ) を順次積層してなるEL表示素子において、ガラス基板のうち表示領域 ( 1 b ) 以外の電極取出領域 ( 1 a ) にて上部電極を取り出すようにした製造方法であって、ガラス基板における電極取出領域にて、次のような工程を行っていくことを特徴としたものである。

【0024】まず、電極取出領域に、上部電極の形状に対応してパターニングされた電極膜 ( 2 a ) を形成する工程を行う。次に、電極膜上および電極膜の間に下部絶縁層を形成する工程を行う。次に、電極膜の間に形成された下部絶縁層の上に発光層を積層する工程を行う。次に、その上に上部絶縁層を積層する工程を行う。次に、電極膜の上の層を機械的に除去して電極膜を露出させる工程を行う。かかる後、露出した電極膜の上に上部電極を積層する工程を行う。

【0025】それによれば、電極膜の間に形成された下部絶縁層の上に発光層を積層するため、電極膜の上には発光層を無い状態にできる。そのため、電極膜の上の層を機械的に除去して電極膜を露出させた際に、当該除去領域と非除去領域との境界において、電極膜の上では従来のような発光層の露出端面が存在しないようにできる。

【0026】そのため、電極膜の上にて上部電極となる膜を積層し、この膜を上部電極の形状にパターニングするためのエッチングを行っても、そもそも、発光層がエッチングされることによる上部電極の断線といった上記の問題は発生しない。

【0027】また、電極膜の上の層を機械的に除去して電極膜を露出させる工程において、電極膜の間では、下部絶縁層、発光層及び上部絶縁層が積層された3層膜を機械的に除去することとなる。この3層膜は、両絶縁層間に膜応力の小さい発光層が介在しているため、従来の下部絶縁層と上部絶縁層との2層絶縁膜よりも膜応力が小さい。

【0028】そのため、当該3層膜を機械的に除去した際に、ガラス基板や下部絶縁層及び上部絶縁層に対してクラックが発生しにくくなる。従って、本発明によれ

ば、取出部における上部電極の断線を防止し、素子のクラックの発生を防止することのできるEL表示素子の製造方法を提供することができる。

【0029】また、請求項2に記載の発明では、電極取出領域(1a)にて電極膜(2a)の間に形成された下部絶縁層(3)の上に積層する発光層(4)を、表示領域の発光層とは離した位置に形成することを特徴としている。

【0030】それによれば、表示領域の発光層と電極取出領域の発光層とが離れているから、電極取出領域(1a)に上部絶縁層(5)を積層する工程において同時に表示領域にも上部絶縁層を形成するようにすれば、表示領域の発光層を上部絶縁層にて完全に覆うことができ、好みしい。

【0031】また、請求項3に記載の発明では、電極取出領域(1a)にて電極膜(2a)の間に形成された下部絶縁層(3)の上に発光層(4)を積層する工程では、発光層を、電極取出領域の外周端部よりも電極取出領域の内側にて電極膜上にも積層することを特徴としている。

【0032】それによれば、請求項1の発明の効果を発揮できることに加えて、電極膜の上の層を機械的に除去する際に、当該電極膜の上の層の一部は、下部及び上部絶縁層の間に除去しやすい発光層が介在した積層構造となるため、除去速度が向上するという効果がある。

【0033】なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示す一例である。

【0034】

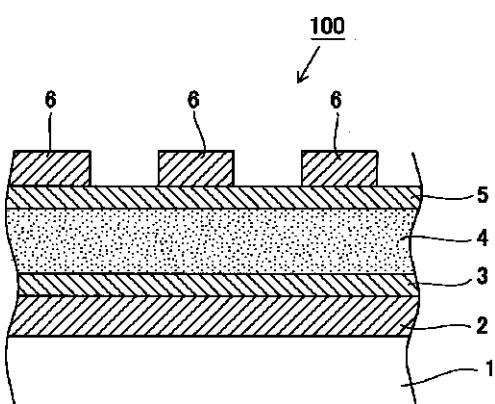

【発明の実施の形態】以下、本発明を図に示す実施形態について説明する。図1は、本発明の実施形態に係るEL表示素子100の表示領域の縦断面構造を模式的に示す図である。EL表示素子100は、ガラス基板1上に、下部電極2、下部絶縁層3、発光層4、上部絶縁層5及び上部電極6を順次積層して形成されている。

【0035】下部電極2は、本例ではITO(酸化インジウム・錫)よりなり、その平面形状は図1中の左右方向に延びるストライプ状に形成されている。下部絶縁層3は、本例ではALe法によって形成された $Al_2O_3/ TiO_2$ 積層構造膜(以下、ATO膜という)によりなり、下部電極2の上及び下部電極2の間のガラス基板1上に形成され、これらの部位を被覆している。

【0036】発光層4は無機EL材料よりなり、下部絶縁層3を被覆している。本例では、発光層4は、硫化スズ(SnS)を母体材料とし、発光中心としてMnを添加したもの(SnS:Mn)を、蒸着法にて形成したものを採用している。また、上部絶縁層5は、発光層4を被覆しており、本例ではALe法により成膜されたATO膜を採用している。

【0037】上部電極6は、上記下部電極2と同様の材

料を用いて形成することができる。本例では、上部電極6はITOよりなり、下部電極2と直交するように平面形状がストライプ状に形成されている。そして、これら両電極2、6が互いに重なり合う部分が発光画素を形成している。

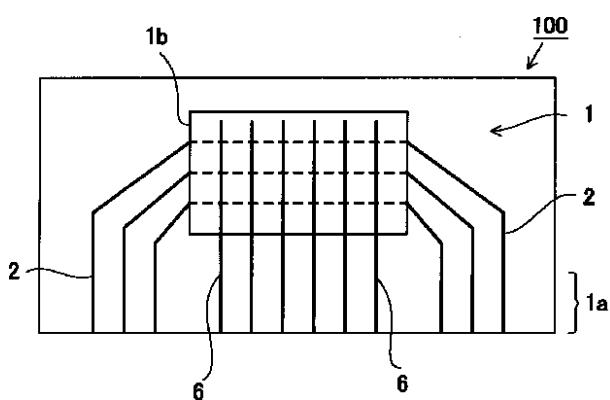

【0038】ここで、図2は、EL表示素子100における表示領域1bと電極取出領域1aとの位置関係の一例を示す模式的な平面図であり、ガラス基板1上の上部電極6と下部電極2のみを模式的に示してある。図2に示す様に、ガラス基板1の一端側の周辺部に設けられた電極取出領域1aまで、下部及び上部の両電極2、6がそれぞれ引き回され、取出部を形成している。

【0039】そして、この電極取出領域1aにて、両電極2、6は、配線部材を介する等により、外部の駆動回路と電気的に接続されようになっている。そして、上記駆動回路から、両電極2、6間に電圧を印加することで、発光層4を発光させ、表示が行われるようになっている。

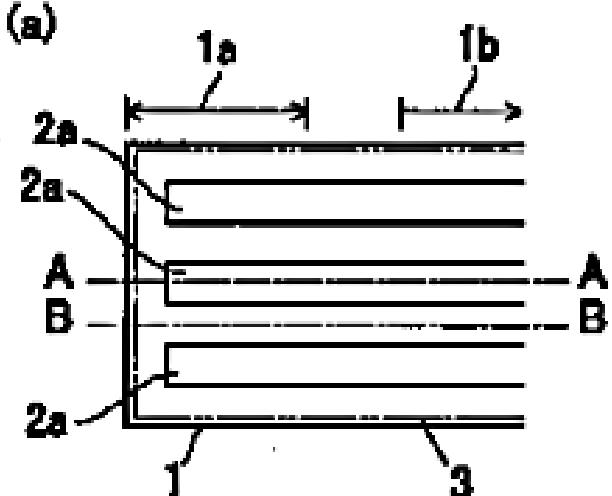

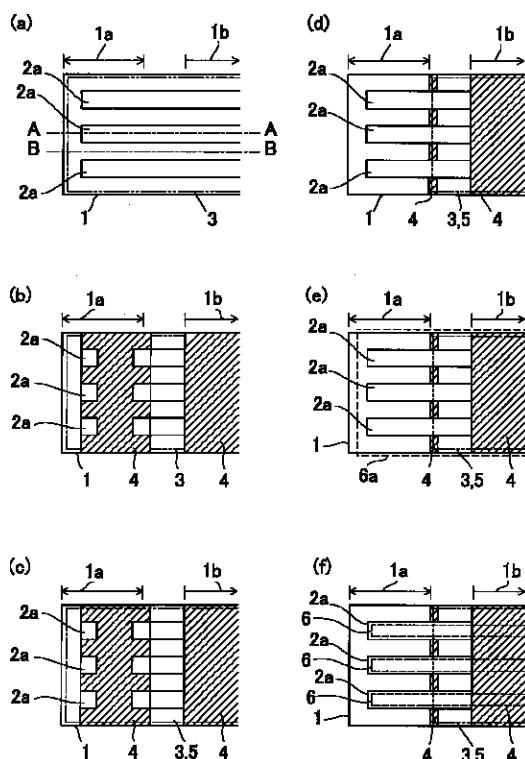

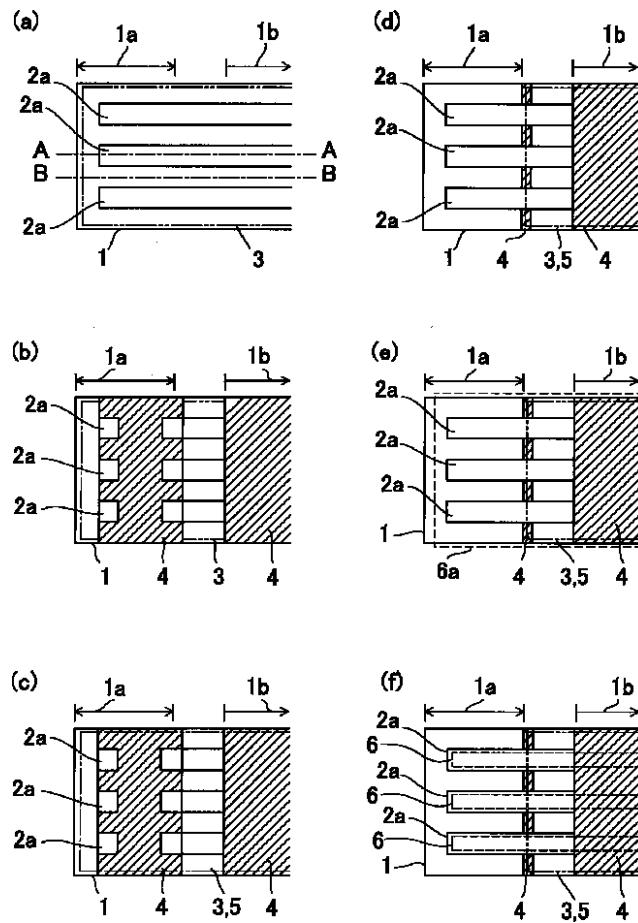

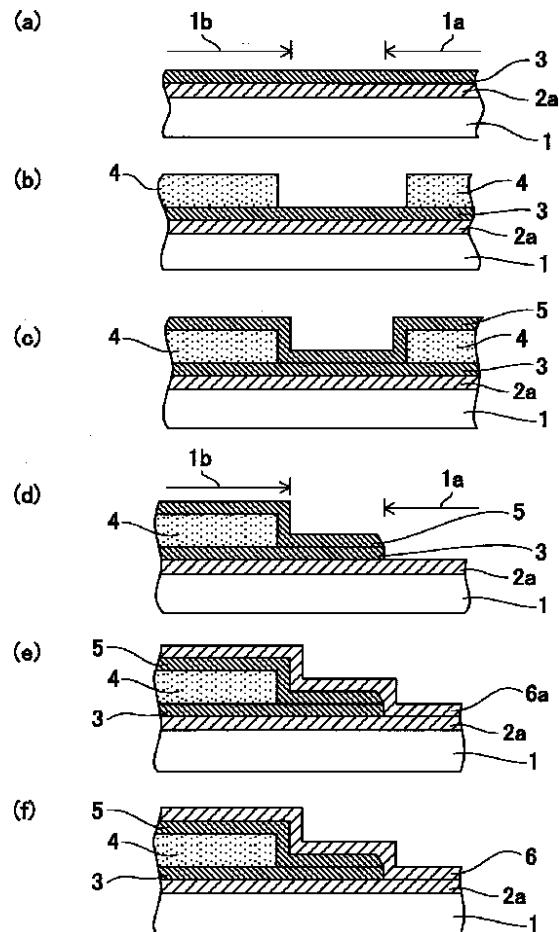

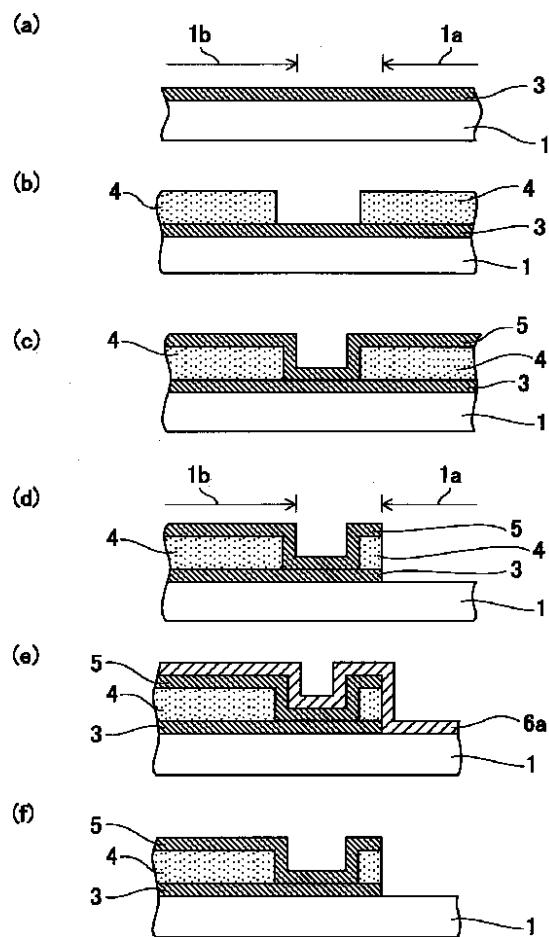

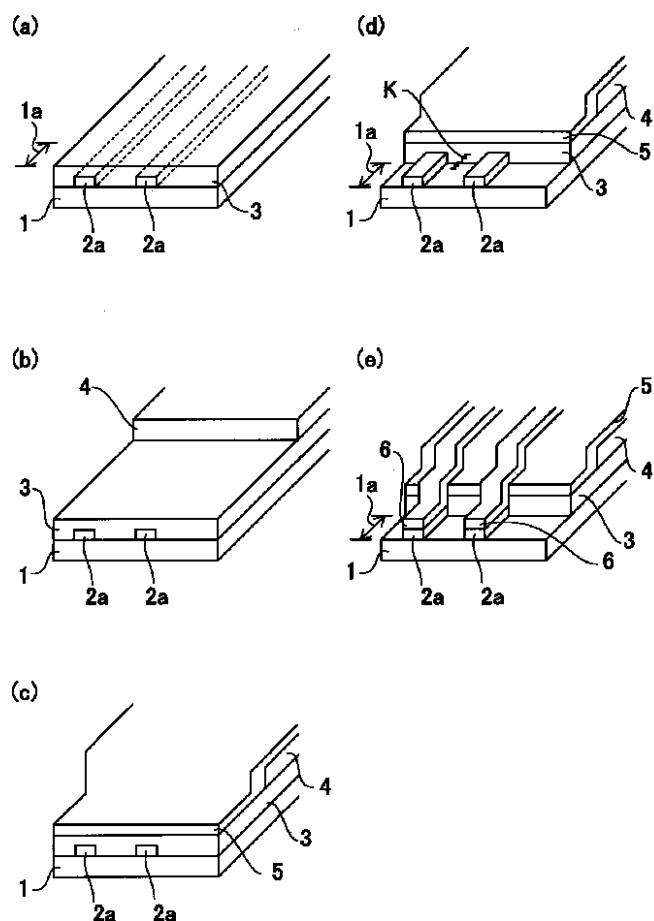

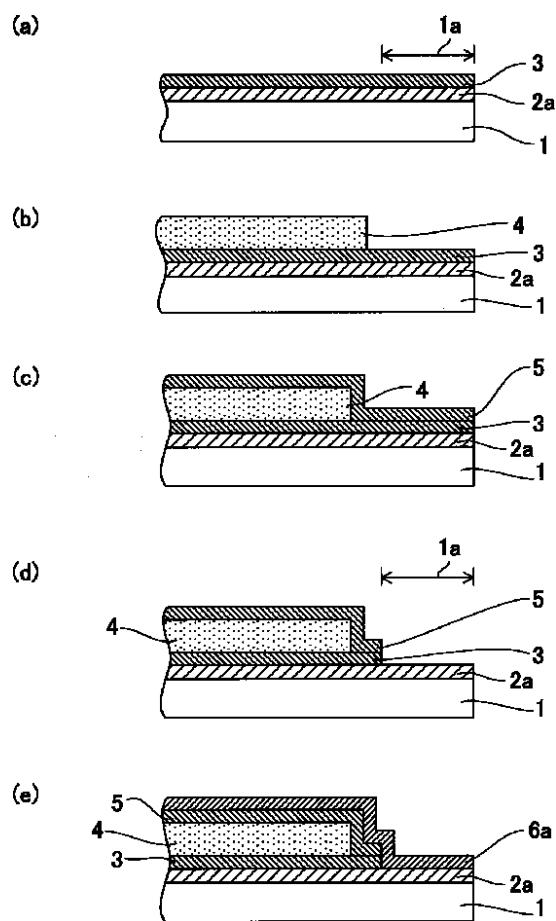

【0040】次に、本実施形態に係るEL表示素子の製造方法について、上記図1、図2及び図3～図6に示す工程説明図を参照して、上部電極6の取出部の形成方法を中心述べる。なお、図3は電極取出領域1a近傍の平面図、図4は上部電極6部分の断面図(図3(a)のA-A断面に相当)、図5は上部電極6の間の部分の断面図(図3(a)のB-B断面に相当)、図6は電極取出領域1a近傍の斜視図である。

【0041】まず、ガラス基板1上に、スパッタリング法にて例えば厚さ1μmのITO膜を成膜した後、塩酸と塩化第二鉄の混合溶液でウェットエッチングする。それにより、上記の下部電極2を形成すると共に、図3(a)、図4(a)、図5(a)、図6(a)に示す様に、上部電極6の形状に対応してパターニングされたストライプ状の電極膜2aを電極取出領域1aに形成する。

【0042】この電極膜2aは、上述したように、最終的に、ガラス基板1上における上部電極6の高さを合わせる等のために必要なもの(ダミー下部電極)であり、下部電極6とは電気的に絶縁するように分離してパターニングされる。

【0043】次に、その上に、ALe法にて例えば厚さ250nmのATO膜よりなる下部絶縁層3を成膜する。これにより、上記図1に示す様に、下部電極2が下部絶縁層3にて被覆されると共に、図3～図6の各(a)に示す様に、電極膜2aの上およびパターニングされた電極膜2aの間が、下部絶縁層3にて被覆される。

【0044】なお、図3(a)においては、下部絶縁層3の外縁は2点鎖線で示し、識別上、この下部絶縁層3の外縁はガラス基板1の外縁とは、ずらしているが、実際は、これら両者の外縁は略一致している。

【0045】次に、下部絶縁層3の上に、電子ビーム蒸着法にて例えば厚さ1μmのSnS: Mnよりなる発光層4を成膜する。これにより、上記図1に示す様に、発光層4が形成される。次に、この発光層4をウェットエッチングして、表示領域1bと電極取出領域1aとに分離する。

【0046】このとき、図3～図6の各(b)に示す様に、電極取出領域1aにおいては、発光層4は、少なくとも電極膜2aの間に形成された下部絶縁層3の上に積層するようとする。本例では、さらに、発光層4を、電極取出領域1aの外周端部よりも電極取出領域1aの内側にて電極膜2a上にも積層している。なお、図3では、識別上、発光層4に斜線ハッキングを施してある。

【0047】次に、その上に、ALD法にて例えば厚さ250nmのATO膜よりなる上部絶縁層5を成膜する。これにより、図3～図5の各(c)に示す様に、表示領域1b及び電極取出領域1aにおいて、発光層4及び発光層4の非形成部の上に上部絶縁層5が積層される。なお、図3(c)においては、下部絶縁層3及び上部絶縁層5の外縁を2点鎖線で示している。

【0048】次に、電極取出領域1aにて電極膜2aの上の層(両絶縁層3、5及び発光層4)を、テープ研磨法により機械的に除去する。それにより、図3～図5の各(d)に示す様に、電極膜2aが露出するとともに、電極膜2aの間では、ガラス基板1が露出する。なお、電極膜2aの間においては、多少、絶縁層3、5が残っていても構わない。また、図示しないが、この工程により、電極取出領域1aにて下部電極2も露出する。

【0049】次に、図3～図5の各(e)に示す様に、表示領域1bおよび電極取出領域1aのうちに、最終的に上部電極6となる導電膜6aを形成する。この導電膜6aは、スパッタリング法にて例えば厚さ1μmのITO膜として成膜する。なお、図3(e)では、導電膜6aの外縁を破線にて示してあり、識別上、ガラス基板1の外縁とは、ずらしてあるが、実際は、これら両者の外縁は略一致している。

【0050】そして、この導電膜6aを塩酸と塩化第二鉄の混合溶液でウェットエッチングすることにより、表示領域1bにて、上部電極6を形成すると共に、図3～図5の各(f)に示す様に、電極取出領域1aにて、露出した電極膜2aの上に上部電極6を積層形成する。

【0051】なお、図3(f)では、上部電極6の外縁を破線にて示してあり、識別上、電極膜2aの外縁とは、ずらしてあるが、実際は、これら両者の外縁は略一致している。また、図示しないが、下部電極2の露出部においても、積層された導電膜6aが下部電極2の形状にパターニングされる。

【0052】こうして、上記図1に示すEL表示素子100が出来上がると共に、下部電極2及び上部電極6の取出部が形成される。そして、下部電極2の取出部は、

下部電極2の上に導電膜6aが積層された2層構造であり、上部電極6の取出部は、電極膜2aの上に上部電極6が積層された2層構造となり、ガラス基板1上における両取出部の高さは略同等のものとなる。

【0053】ところで、本実施形態によれば、電極膜2aの間に形成された下部絶縁層3の上に発光層4を積層するため、電極膜2aの上には発光層を無い状態にできる(図3(b)、図4(b)、図6(b)参照)。

【0054】そのため、上部絶縁層5を成膜した後、電極取出領域1aにて電極膜2aの上の層を機械的に除去して電極膜2aを露出させたときに、従来(上記図8(d)参照)のように、当該除去領域と非除去領域との境界において、電極膜2a上にて発光層4の端面が露出することが無い。

【0055】そして、露出した電極膜2aの上に、上部電極6となる導電膜6aを積層し、この導電膜6aを上部電極6の形状にパターニングするためのエッチングを行っても、そもそも、発光層4がエッチングされることによる上部電極6の断線といった問題は発生しない。

【0056】なお、本実施形態では、電極取出領域1aにて発光層4を積層する工程では、電極膜2aの間に形成された下部絶縁層3の上に積層する以外にも、電極取出領域1aの外周端部よりも電極取出領域1aの内側にて電極膜2a上にも、発光層4を積層している。

【0057】しかし、あくまでも、電極膜2aの上の層を機械的に除去する際の除去領域と非除去領域との境界では、電極膜2a上には発光層4を存在させないようにしてあるため、上記した上部電極の断線防止効果は十分に発揮される。

【0058】しかも、電極膜2aの上の層を機械的に除去する際に、発光層4が積層された部分における電極膜2aの上の層は、下部及び上部絶縁層3、5の間に比較的柔らかい発光層4が介在した積層構造であるため、下部及び上部絶縁層3、5の2層構造よりも除去しやすく、除去速度が向上するという効果がある。なお、電極取出領域1aでは、電極膜2aの間に形成された下部絶縁層3の上にのみ、発光層4を形成しても良いことは勿論である。

【0059】また、本実施形態では、電極膜2aの上の層を機械的に除去して電極膜2aを露出させる工程において、電極膜2aの間では、下部絶縁層3、発光層4及び上部絶縁層5が積層された3層膜を機械的に除去することとなる。この3層膜は、両絶縁層3、5間に膜応力の小さい発光層4が介在しているため、従来の下部絶縁層と上部絶縁層との2層絶縁膜よりも膜応力が小さい。

【0060】そのため、当該3層膜を機械的に除去した際に、ガラス基板1や下部絶縁層3及び上部絶縁層5に對してクラックが発生しにくくなる。従って、本製造方法によれば、取出部における上部電極6の断線を防止し、素子のクラックの発生を防止することのできるEL

表示素子を製造することができる。

【0061】また、本実施形態では、電極取出領域1aにて電極膜2aの間に形成された下部絶縁層3の上に積層する発光層(以下、電極間発光層という)4を、表示領域の発光層4とは離した位置に形成している。

【0062】電極取出領域1aにて、電極間発光層4を表示領域の発光層4と連続して形成しても、上記した取出部における上部電極断線防止及び素子のクラック発生防止は達成できる。しかし、表示領域の発光層4と電極間発光層4とが離れていれば、次に行う、上部絶縁層5を積層する工程において、表示領域の発光層4を上部絶縁層5にて完全に覆うことができ、より好ましい。

【0063】なお、電極取出領域1aにて電極膜2aの上の層を機械的に除去する方法としては、テープ研磨法以外にも、液体ホーニング、乾式プラスト、超音波加工、ラッピング加工、ブラシ加工等を用いることができる。

#### 【図面の簡単な説明】

【図1】本発明の実施形態に係るEL表示素子の表示領域の模式的断面図である。

【図2】上記実施形態に係るEL表示素子における表示領域と電極取出領域との位置関係を示す模式的平面図である。

【図3】上部電極の取出部の形成方法を平面的に示す工程図である。

【図4】上部電極の取出部の形成方法を上部電極部分の断面として示す工程図である。

【図5】上部電極の取出部の形成方法を上部電極間の断面として示す工程図である。

【図6】上部電極の取出部の形成方法を示す斜視図である。

【図7】従来の上部電極の取出部の1つ目の形成方法を示す斜視図である。

【図8】図7に示す従来の上部電極の取出部の1つ目の形成方法を上部電極部分の断面として示す工程図である。

【図9】従来の上部電極の取出部の2つ目の形成方法を示す斜視図である。

【図10】図9に示す従来の上部電極の取出部の2つ目の形成方法を上部電極間の断面として示す工程図である。

#### 【符号の説明】

20 1...ガラス基板、1a...電極取出領域、1b...表示領域、2...下部電極、2a...電極膜、3...下部絶縁層、4...発光層、5...上部絶縁層、6...上部電極。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

フロントページの続き

(72)発明者 津田 浩志

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

F ターム(参考) 3K007 AB11 AB18 CA01 CB01 CC05

DA05 DB02 DC02 EA02 EC00

EC02 FA01

|                |                                                                                                                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | EL显示元件的制造方法                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2002299053A</a>                                                                                                                                                              | 公开(公告)日 | 2002-10-11 |

| 申请号            | JP2001103487                                                                                                                                                                               | 申请日     | 2001-04-02 |

| [标]申请(专利权)人(译) | 日本电装株式会社                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | Denso公司                                                                                                                                                                                    |         |            |

| [标]发明人         | 深谷顕成<br>大西真司<br>津田浩志                                                                                                                                                                       |         |            |

| 发明人            | 深谷顕成<br>大西真司<br>津田浩志                                                                                                                                                                       |         |            |

| IPC分类号         | H05B33/10 H05B33/06                                                                                                                                                                        |         |            |

| FI分类号          | H05B33/10 H05B33/06                                                                                                                                                                        |         |            |

| F-TERM分类号      | 3K007/AB11 3K007/AB18 3K007/CA01 3K007/CB01 3K007/CC05 3K007/DA05 3K007/DB02 3K007/DC02 3K007/EA02 3K007/EC00 3K007/EC02 3K007/FA01 3K107/AA09 3K107/BB01 3K107/DD38 3K107/DD92 3K107/FF15 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                  |         |            |

## 摘要(译)

解决的问题：在EL显示元件中形成上部电极的引出部时，实现防止上部电极的断线和防止引出部中的元件破裂的问题。解决方案：在电极引出区域1a中，形成与上电极6的形状相对应的图案化的电极膜2a，并且在电极膜2a上以及电极膜2a，2a之间形成下部绝缘层3。将发光层4层压在两者之间形成的下部绝缘层3上，然后将上部绝缘层5层压在其上，然后机械去除电极膜2a上的层。为了使电极膜2a露出，之后，在露出的电极膜2a上层叠上部电极6。