## 【特許請求の範囲】

## 【請求項 1】

画素回路をマトリックス状に配置して形成された表示部と、

前記表示部の信号線に信号線用駆動信号を出力する信号線駆動回路と、

前記表示部の電源用走査線及び書込用走査線に電源用駆動信号及び書込信号を出力する走査線駆動回路とを有し、

前記画素回路は、

発光素子と、

ゲートソース間電圧に応じた駆動電流により前記発光素子を駆動する駆動トランジスタと、

前記ゲートソース間電圧を保持する保持容量と、

前記保持容量の一端の電圧を前記信号線用駆動信号の電圧に設定する書込トランジスタとを少なくとも有し、

前記発光素子を発光させる発光期間と、前記発光素子の発光を停止させて前記発光素子の発光輝度を設定する非発光期間とを交互に繰り返し、

前記書込信号による前記書込トランジスタの制御により、前記保持容量の一端の電圧を信号線用駆動信号の電圧に設定して、前記発光期間と前記非発光期間とを開始し、

前記非発光期間において、前記電源用駆動信号による前記駆動トランジスタの制御により、前記駆動トランジスタを介して前記保持容量の他端の電圧を立ち下げた後、

前記電源用駆動信号による前記駆動トランジスタの制御により、前記駆動トランジスタを介して前記保持容量の端子間電圧を放電し、前記保持容量の端子間電圧を前記駆動トランジスタのしきい値電圧に応じた電圧に設定し、

続いて前記書込信号による前記書込トランジスタの制御により、前記保持容量の端子電圧を前記信号線用駆動信号の電圧に設定して、前記発光素子の発光輝度を設定して前記発光期間を開始し、

前記表示部は、

複数ライン単位で連続するラインがグループ化され、

前記走査線駆動回路は、

ライン毎に、順次 1 水平走査期間ずつ遅延させて前記書込信号を出力し、

前記表示部のグループ毎に、前記複数ラインに対応する複数の水平走査期間ずつ遅延させて前記電源用駆動信号を生成し、

対応するグループの前記電源用駆動信号と、前記対応するグループの前記電源用駆動信号に対して前記複数の水平走査期間だけ先行した前記電源用駆動信号とを前記ライン毎に切り換えて前記電源用駆動信号を出力し、前記グループ内において、遅れて発光期間を開始するライン程、前記複数ラインに対応する複数フィールドの期間又は前記複数フィールドの期間の整数倍の期間に占める前記先行した前記電源用駆動信号が順次増大するよう設定する

画像表示装置。

## 【請求項 2】

前記画素回路は、

前記電源用駆動信号による前記駆動トランジスタの制御により、前記駆動トランジスタを介して前記保持容量の他端の電圧を立ち下げると共に、前記書込信号による前記書込トランジスタの制御により、前記信号線を介して前記保持容量の前記一端の電圧を設定することにより、前記保持容量の端子間電圧を前記駆動トランジスタのしきい値電圧以上の電圧に設定した後、

前記保持容量の端子間電圧を前記駆動トランジスタのしきい値電圧に応じた電圧に設定する

請求項 1 に記載の画像表示装置。

## 【請求項 3】

前記発光素子が、有機 E L 素子である

10

20

30

40

50

請求項 2 に記載の画像表示装置。

【請求項 4】

画素回路をマトリックス状に配置して形成された表示部と、

前記表示部の信号線に信号線用駆動信号を出力する信号線駆動回路と、

前記表示部の電源用走査線及び書込用走査線に電源用駆動信号及び書込信号を出力する

走査線駆動回路とを有する画像表示装置の駆動方法において、

前記画素回路は、

発光素子と、

ゲートソース間電圧に応じた駆動電流により前記発光素子を駆動する駆動トランジスタ

と、

前記ゲートソース間電圧を保持する保持容量と、

前記保持容量の一端の電圧を前記信号線用駆動信号の電圧に設定する書込トランジスタ

とを少なくとも有し、

前記発光素子を発光させる発光期間と、前記発光素子の発光を停止させて前記発光素子

の発光輝度を設定する非発光期間とを交互に繰り返し、

前記書込信号による前記書込トランジスタの制御により、前記保持容量の一端の電圧を

信号線用駆動信号の電圧に設定して、前記発光期間と前記非発光期間とを開始し、

前記非発光期間において、前記電源用駆動信号による前記駆動トランジスタの制御により、

前記駆動トランジスタを介して前記保持容量の他端の電圧を立ち下げた後、

前記電源用駆動信号による前記駆動トランジスタの制御により、前記駆動トランジスタ

を介して前記保持容量の端子間電圧を放電し、前記保持容量の端子間電圧を前記駆動トランジスタのしきい値電圧に応じた電圧に設定し、

続いて前記書込信号による前記書込トランジスタの制御により、前記保持容量の端子電

圧を前記信号線用駆動信号の電圧に設定して、前記発光素子の発光輝度を設定して前記發

光期間を開始し、

前記画像表示装置の駆動方法は、

前記表示部の連続するラインを、複数ライン単位でグループ化し、

ライン毎に、順次 1 水平走査期間ずつ遅延させて前記書込信号を出力し、

前記表示部のグループ毎に、前記複数ラインに対応する複数の水平走査期間ずつ遅延さ

せて前記電源用駆動信号を生成し、

対応するグループの前記電源用駆動信号と、前記対応するグループの前記電源用駆動信

号に対して前記複数の水平走査期間だけ先行した前記電源用駆動信号とを前記ライン毎に

切り換えて前記電源用駆動信号を出力し、前記グループ内において、遅れて発光期間を開

始するライン程、前記複数ラインに対応する複数フィールドの期間又は前記複数フィール

ドの期間の整数倍の期間に占める前記先行した前記電源用駆動信号が順次増大するよう

に設定する

画像表示装置の駆動方法。

10

20

30

40

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像表示装置及び画像表示装置の駆動方法に関し、例えば有機 E L (Electro Luminescence) 素子によるアクティブマトリックス型の画像表示装置に適用することができる。本発明は、対応するグループの電源用駆動信号と、先行する電源用駆動信号とを

ライン毎に切り換えて電源用駆動信号を出力し、グループ内において、遅れて発光期間を開

始するライン程、一定期間に占める先行する電源用駆動信号が順次増大するよう

に設定することにより、ユニットドライブ方式において、長期の使用による輝度ムラを防止する

50

。

### 【背景技術】

#### 【0002】

近年、有機EL素子を用いたアクティブマトリックス型の画像表示装置の開発が盛んになっている。ここで有機EL素子を用いた画像表示装置は、電界の印加により発光する有機薄膜の発光現象を利用した画像表示装置である。有機EL素子は、10[V]以下の印加電圧で駆動することができる。従ってこの種の画像表示装置は、消費電力を低減することができる。また有機EL素子は、自発光素子である。従ってこの種の画像表示装置は、バックライト装置を必要とせず、軽量化、薄型化することができる。さらに有機EL素子は、応答速度が数μ秒程度と速い特徴がある。従ってこの種の画像表示装置は、動画像表示時に残像が殆ど発生しない特徴がある。10

#### 【0003】

具体的に、有機EL素子を用いたアクティブマトリックス型の画像表示装置は、有機EL素子と有機EL素子を駆動する駆動回路とによる画素回路をマトリックス状に配置して表示部が形成される。この種の画像表示装置は、表示部に設けられた信号線及び走査線をそれぞれ介して、表示部の周囲に配置した信号線駆動回路及び走査線駆動回路により各画素回路を駆動して所望の画像を表示する。

#### 【0004】

この有機EL素子を用いた画像表示装置に関して、特開2007-310311号公報には、2つのトランジスタを用いて画素回路を構成する方法が開示されている。従ってこの特開2007-310311号公報に開示の方法によれば、構成を簡略化することができる。またこの特開2007-310311号公報には、有機EL素子を駆動する駆動トランジスタのしきい値電圧のばらつき、移動度のばらつきを補正する構成が開示されている。従ってこの特開2007-310311号公報に開示の構成によれば、駆動トランジスタのしきい値電圧のばらつき、移動度のばらつきによる画質劣化を防止することができる。20

#### 【0005】

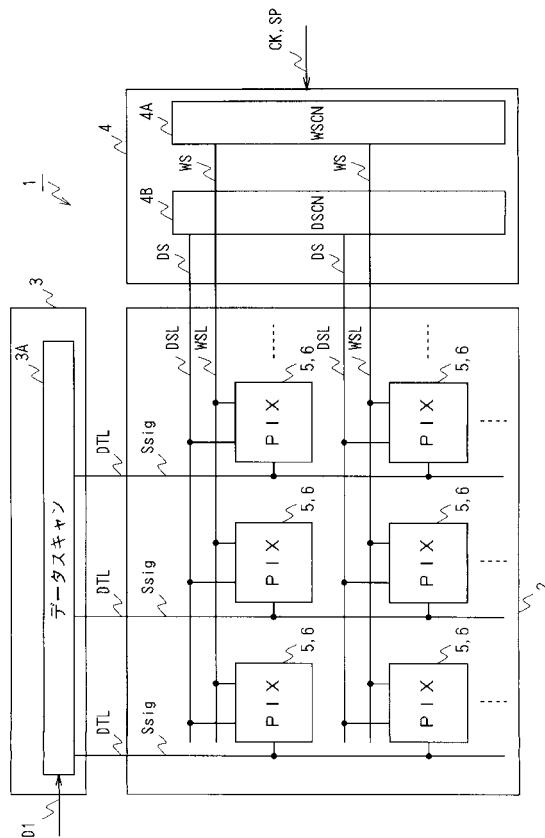

ここで図6は、特開2007-310311号公報に開示の画像表示装置を示すプロック図である。この画像表示装置1は、ガラス等の絶縁基板に表示部2が作成される。画像表示装置1は、この表示部2の周囲に信号線駆動回路3及び走査線駆動回路4が作成される。30

#### 【0006】

ここで表示部2は、画素回路5をマトリックス状に配置して形成され、画素回路5に設けられた有機EL素子により画素(PIX)6が形成される。なおカラー画像の画像表示装置では、赤色、緑色及び青色による複数のサブ画素により1つの画素が構成されることから、カラー画像の画像表示装置の場合、表示部2は、赤色、緑色及び青色のサブ画素をそれぞれ構成する赤色用、緑色用及び青色用の画素回路5を順次配置して構成される。

#### 【0007】

信号線駆動回路3は、表示部2に設けられた信号線DTLに信号線用の駆動信号SSigを出力する。より具体的に、信号線駆動回路3は、データスキャン回路3Aにおいて、ラスタ走査順に入力される画像データD1を順次ラッチして画像データD1を信号線DTLに振り分けた後、それぞれディジタルアナログ変換処理する。信号線駆動回路3は、このディジタルアナログ変換結果を処理して駆動信号SSigを生成する。これにより画像表示装置1は、例えればいわゆる線順次により各画素回路5の階調を設定する。40

#### 【0008】

走査線駆動回路4は、表示部2に設けられた書込信号用の走査線WSL及び電源用の走査線DSLにそれぞれ書込信号WS及び駆動信号DSを出力する。ここで書込信号WSは、各画素回路5に設けられた書込トランジスタをオンオフ制御する信号である。また駆動信号DSは、各画素回路5に設けられた駆動トランジスタのドレイン電圧を制御する信号である。走査線駆動回路4は、それぞれライトスキャン回路(WSCN)4A及びドライ

10

20

30

40

50

プスキャン回路（D S C N）4 Bにおいて、所定のサンプリングパルスS PをクロックC Kで処理して書込信号W S及び駆動信号D Sを生成する。

#### 【0009】

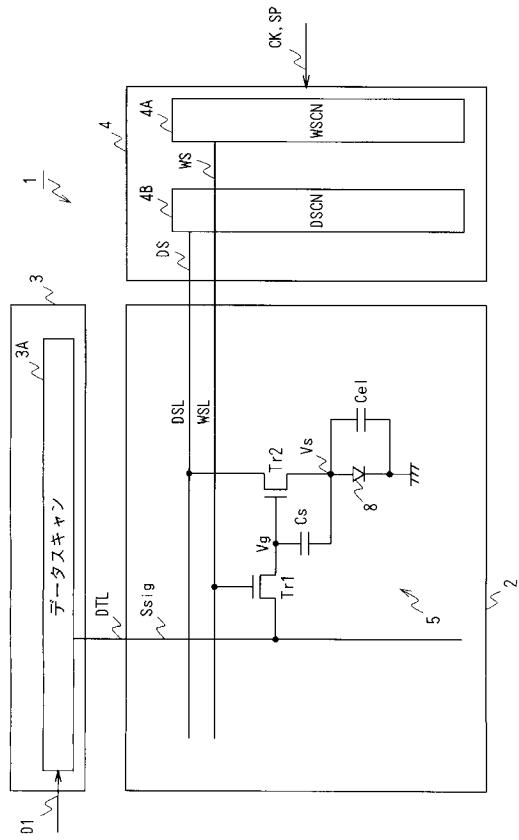

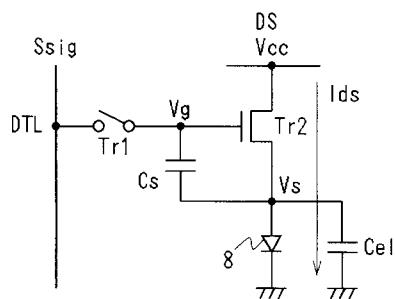

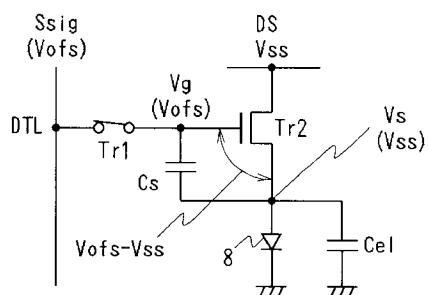

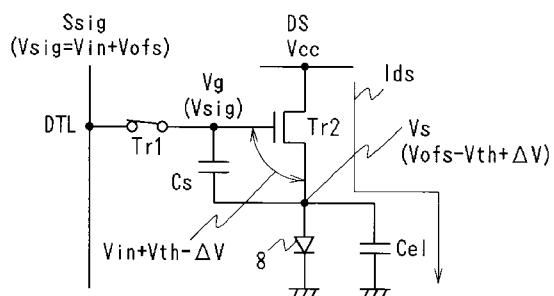

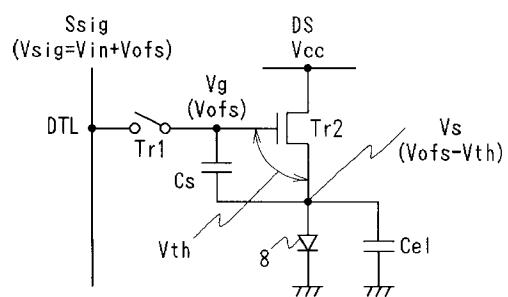

図7は、画素回路5の構成を詳細に示す接続図である。画素回路5は、有機EL素子8のカソードが所定の負側電圧に設定され、この図7の例ではこの負側電圧がアースラインの電圧に設定される。画素回路5は、有機EL素子8のアノードが駆動トランジスタTr2のソースに接続される。なお駆動トランジスタTr2は、例えばTFTによるNチャンネル型トランジスタである。画素回路5は、この駆動トランジスタTr2のドレインが電源用の走査線DSLに接続され、この走査線DSLに走査線駆動回路4から電源用駆動信号D Sが供給される。これらにより画素回路5は、ソースフォロワ回路構成の駆動トランジスタTr2を用いて有機EL素子8を電流駆動する。

10

#### 【0010】

画素回路5は、この駆動トランジスタTr2のゲート及びソース間に保持容量Csが設けられ、書込信号WSによりこの保持容量Csのゲート側端電圧が駆動信号SSigの電圧に設定される。その結果、画素回路5は、駆動信号SSigに応じたゲートソース間電圧Vgsにより駆動トランジスタTr2で有機EL素子8を電流駆動する。なおここでこの図7において、容量Ce1は、有機EL素子8の浮遊容量である。また以下において、容量Ce1は、保持容量Csに比して十分に容量が大きいものとし、駆動トランジスタTr2のゲートノードの寄生容量は、保持容量Csに対して十分に小さいものとする。

20

#### 【0011】

すなわち画素回路5は、書込信号WSによりオンオフ動作する書込トランジスタTr1を介して、駆動トランジスタTr2のゲートが信号線DTLに接続される。なおここで書込トランジスタTr1は、例えばTFTによるNチャンネル型トランジスタである。ここで信号線駆動回路3は、階調設定用電圧Vsig及びしきい値電圧の補正用電圧Vofsを所定のタイミングで切り換えて駆動信号SSigを出力する。しきい値電圧補正用の固定電圧Vofsは、駆動トランジスタTr2のしきい値電圧のばらつき補正に使用する固定電圧である。また階調設定用電圧Vsigは、有機EL素子8の発光輝度を指示する電圧であり、階調電圧Vinにしきい値電圧補正用の固定電圧Vofsを加算した電圧である。また階調電圧Vinは、有機EL素子8の発光輝度に対応する電圧である。階調電圧Vinは、各信号線DTLに振り分けた画像データD1をそれぞれデジタルアナログ変換処理して信号線DTL毎に生成される。

30

#### 【0012】

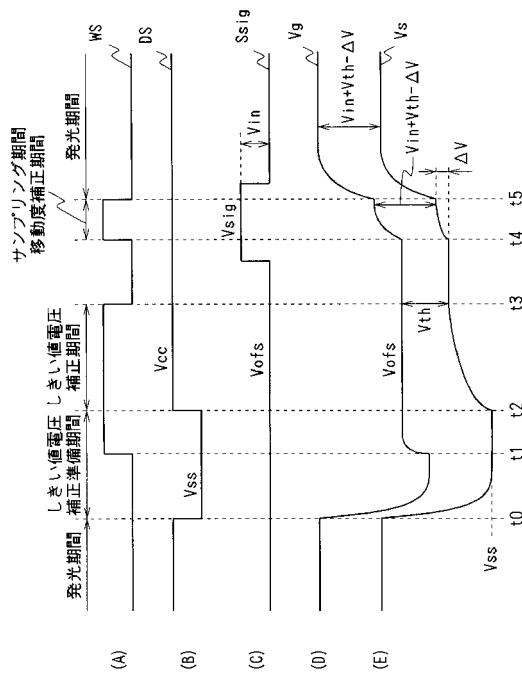

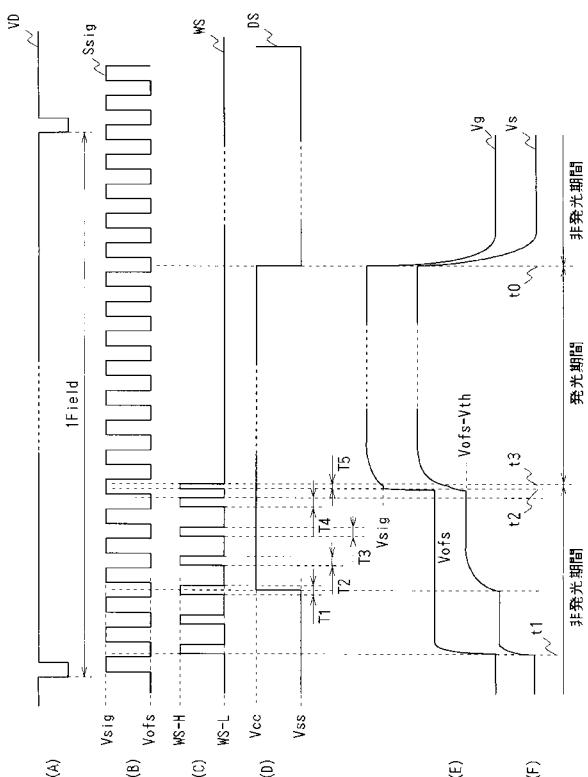

画素回路5は、図8に示すように、有機EL素子8を発光させる発光期間の間、書込信号WSにより書込トランジスタTr1がオフ状態に設定される（図8（A））。また画素回路5は、発光期間の間、電源用駆動信号D Sによって駆動トランジスタTr2に電源電圧Vccが供給される（図8（B））。これにより画素回路5は、図9に示すように、発光期間の間、保持容量Csの端子間電圧である駆動トランジスタTr2のゲートソース間電圧Vgs（図8（D）及び（E））に応じた駆動電流Idsで有機EL素子8を発光させる。

40

#### 【0013】

画素回路5は、発光期間が終了する時点 $t_0$ で、電源用駆動信号D Sが所定の固定電圧Vsに立ち下げる（図8（B））。ここでこの固定電圧Vsは、駆動トランジスタTr2のドレインをソースとして機能させるのに十分に低い電圧であって、かつ有機EL素子8のカソード電圧より低い電圧である。

40

#### 【0014】

これにより画素回路5は、図10に示すように、駆動トランジスタTr2を介して、保持容量Csの有機EL素子8側端の蓄積電荷が走査線に流出する。その結果、画素回路5は、駆動トランジスタTr2のソース電圧Vsがほぼ電圧Vsに立ち下がり（図8（E））、有機EL素子8が発光を停止する。また画素回路5は、このソース電圧Vsの立ち下がりに連動して、駆動トランジスタTr2のゲート電圧Vgが低下する（図8（D））

50

。

### 【0015】

画素回路5は、続く所定の時点 $t_1$ で、書込信号WSにより書込トランジスタTr1がオン状態に切り換えられ(図8(A))、駆動トランジスタTr2のゲート電圧Vgが信号線DTLに設定されたしきい値電圧補正用の固定電圧VofSに設定される(図8(C)及び(D))。これにより画素回路5は、図11に示すように、駆動トランジスタTr2のゲートソース間電圧Vgsがほぼ電圧VofS-Vssに設定される。ここで画素回路5は、電圧VofS、Vssの設定により、この電圧VofS-Vssが駆動トランジスタTr2のしきい値電圧Vthより大きな電圧に設定される。

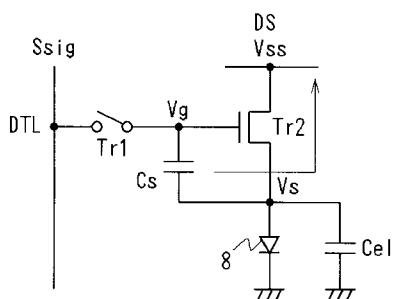

### 【0016】

その後、画素回路5は、時点 $t_2$ で駆動信号DSにより駆動トランジスタTr2のドレイン電圧が電源電圧Vccに立ち上げられる(図8(B))。これにより画素回路5は、図12に示すように、駆動トランジスタTr2を介して保持容量Csの有機EL素子8側端に電源Vccから充電電流Idsが流入する。その結果、画素回路5は、保持容量Csの有機EL素子8側端の電圧Vsが徐々に上昇する。この場合、画素回路5において、駆動トランジスタTr2を介して有機EL素子8に流入する電流Idsは、有機EL素子8の容量Celeと保持容量Csの充電にのみ使用され、その結果、有機EL素子8を発光させることなく、単に駆動トランジスタTr2のソース電圧Vsのみが上昇することになる。

### 【0017】

ここで画素回路5は、保持容量Csの端子間電圧が駆動トランジスタTr2のしきい値電圧Vthとなると、駆動トランジスタTr2を介した充電電流Idsの流入が停止することになる。従ってこの場合、この駆動トランジスタTr2のソース電圧Vsの上昇は、保持容量Csの両端電位差が駆動トランジスタTr2のしきい値電圧Vthとなると、停止することになる。これにより画素回路5は、駆動トランジスタTr2を介して保持容量Csの端子間電圧を放電させ、保持容量Csの端子間電圧を駆動トランジスタTr2のしきい値電圧Vthに設定する。

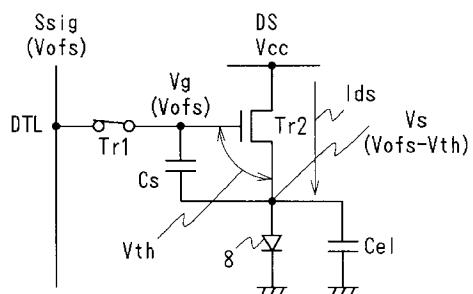

### 【0018】

画素回路5は、保持容量Csの端子間電圧を駆動トランジスタTr2のしきい値電圧Vthに設定するのに十分な時間が経過して時点 $t_3$ になると、図13に示すように、書込信号WSにより書込トランジスタTr1がオフ状態に切り換えられる(図8(A))。続いて図14に示すように、信号線DTLの電圧が階調設定用電圧Vsig(=Vin+VofS)に設定される。

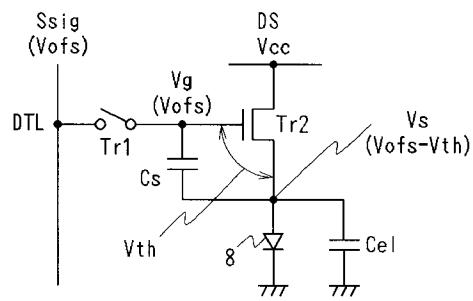

### 【0019】

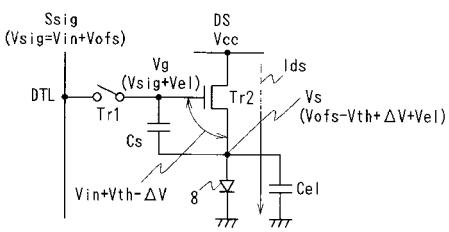

画素回路5は、続く時点 $t_4$ で書込トランジスタTr1がオン状態に設定される(図8(A))。これにより画素回路5は、図15に示すように、駆動トランジスタTr2のゲート電圧Vgが階調設定用電圧Vsigに設定され、駆動トランジスタTr2のゲートソース間電圧Vgsは、階調電圧Vinに駆動トランジスタTr2のしきい値電圧Vthを加算した電圧に設定される。これにより画素回路5は、駆動トランジスタTr2のしきい値電圧Vthのばらつきを有效地に回避して有機EL素子8を駆動することができ、有機EL素子8の発光輝度のばらつきによる画質劣化を防止することができる。

### 【0020】

画素回路5は、この駆動トランジスタTr2のゲート電圧Vgを階調設定用電圧Vsigに設定する際に、駆動トランジスタTr2のドレイン電圧を電源電圧Vccに保持した状態で、一定期間の間、駆動トランジスタTr2のゲートが信号線DTLに接続される。これにより画素回路5は、併せて駆動トランジスタTr2の移動度μのばらつきが補正される。

### 【0021】

すなわち保持容量Csの端子間電圧を駆動トランジスタTr2のしきい値電圧Vthに設定した状態で、書込トランジスタTr1をオン状態に設定して駆動トランジスタTr2

10

20

30

40

50

のゲートを信号線 D T L に接続した場合、駆動トランジスタ Tr 2 のゲート電圧 V g は、固定電圧 V o f s から徐々に上昇して階調設定用電圧 V s i g に設定される。

【 0 0 2 2 】

ここで画素回路 5 は、この駆動トランジスタ Tr 2 のゲート電圧 V g の立ち上がりに要する書込時定数が、駆動トランジスタ Tr 2 によるソース電圧 V s の立ち上がりに要する時定数に比して短くなるように設定される。

【 0 0 2 3 】

この場合、書込トランジスタ Tr 1 がオン動作すると、駆動トランジスタ Tr 2 のゲート電圧 V g は、速やかに階調設定用電圧 V s i g ( $V_{o f s} + V_{i n}$ ) に立ち上がることになる。このゲート電圧 V g の立ち上がり時、有機 EL 素子 8 の容量 C e 1 が保持容量 C s に比して十分に大きければ、駆動トランジスタ Tr 2 のソース電圧 V s は変動しないことになる。

10

【 0 0 2 4 】

しかしながら駆動トランジスタ Tr 2 のゲートソース間電圧 V g s がしきい値電圧 V t h より増大すると、駆動トランジスタ Tr 2 を介して電源 V c c から電流 I d s が流入し、駆動トランジスタ Tr 2 のソース電圧 V s が徐々に上昇することになる。その結果、画素回路 5 は、保持容量 C s の端子間電圧が駆動トランジスタ Tr 2 により放電し、ゲートソース間電圧 V g s の上昇速度が低下することになる。

20

【 0 0 2 5 】

この端子間電圧の放電速度は、駆動トランジスタ Tr 2 の能力に応じて変化する。より具体的には、駆動トランジスタ Tr 2 の移動度  $\mu$  が大きい場合程、放電速度は、早くなる。

20

【 0 0 2 6 】

その結果、画素回路 5 は、移動度  $\mu$  が大きい駆動トランジスタ Tr 2 程、保持容量 C s の端子間電圧が低下するよう設定され、移動度のばらつきによる発光輝度のばらつきが補正される。なおこの移動度  $\mu$  の補正に係る端子間電圧の低下分を図 8、図 15 及び図 16 では V で示す。

30

【 0 0 2 7 】

画素回路 5 は、この移動度の補正期間が経過すると、時点 t 5 で書込信号 W S が立ち下げる。その結果、画素回路 5 は、発光期間が開始し、図 16 に示すように、保持容量 C s の端子間電圧に応じた駆動電流 I d s により有機 EL 素子 8 を発光させる。なお画素回路 5 は、発光期間が開始すると、いわゆるブートストラップ回路により駆動トランジスタ Tr 2 のゲート電圧 V g 及びソース電圧 V s が上昇する。図 16 における V e 1 は、この上昇分の電圧である。

30

【 0 0 2 8 】

これらにより画素回路 5 は、時点 t 0 から時点 t 2 までの駆動トランジスタ Tr 2 のゲート電圧を電圧 V s s に立ち下げている期間で、駆動トランジスタ Tr 2 のしきい値電圧を補正する処理の準備を実行する。また続く時点 t 2 から時点 t 3 までの期間で、保持容量 C s の端子間電圧を駆動トランジスタ Tr 2 のしきい値電圧 V t h に設定して、駆動トランジスタ Tr 2 のしきい値電圧を補正する。また時点 t 4 から時点 t 5 までの期間で、駆動トランジスタ Tr 2 の移動度を補正すると共に、階調設定用電圧 V s i g をサンプリングする。

40

【 0 0 2 9 】

また特開 2007-133284 号公報には、駆動トランジスタ Tr 2 のしきい値電圧のばらつきを補正する処理を複数回に分けて実行する構成が提案されている。この特開 2007-133284 号公報に開示の構成によれば、高精度化して画素回路の階調設定に割り当てる時間が短くなった場合でも、しきい値電圧のばらつき補正に十分な時間を割り当てることができる。従って高精度化した場合でも、しきい値電圧のばらつきによる画質劣化を防止することができる。

50

【 0 0 3 0 】

従って特開2007-310311号公報に開示の手法に、特開2007-133284号公報に開示の手法を適用すると、簡易な構成により、高精度化した場合にあっても高い画質を維持することが可能な画像表示装置を得ることができると考えられる。

### 【0031】

図17は、図8との対比により、特開2007-310311号公報に開示の手法に、特開2007-133284号公報に開示の手法を適用した場合に考えられる画素回路のタイムチャートである。

### 【0032】

この場合、信号線DTLには、しきい値電圧補正用の固定電圧Vofsを間に挟んで、信号線DTLに接続された各画素回路5の階調設定用電圧Vsigが出力される。画素回路5は、この信号線DTLの駆動に対応して書込信号WSが間欠的に立ち上げられ、複数の期間で、保持容量Csの端子間電圧を駆動トランジスタTr2を介して放電させる。具体的に、この図17の例では、駆動トランジスタTr2のしきい値電圧のばらつき補正を、期間T1、T2、T3、T4の4回の期間に分けて実行した後、期間T5で移動度補正処理及び階調設定処理を実行する。なおこの図23において、VDは、垂直同期信号である。

10

【特許文献1】特開2007-310311号公報

【特許文献2】特開2007-133284号公報

### 【発明の開示】

#### 【発明が解決しようとする課題】

20

### 【0033】

ところで図8、図17の構成では、保持容量Csの端子間電圧を駆動トランジスタTr2のしきい値電圧以下の電圧に設定しても、有機EL素子8の発光を停止することができる。従って駆動トランジスタTr2のドレイン電圧の制御に代えて、書込信号WSにより書込トランジスタTr1を制御して保持容量Csの端子間電圧を立ち下げ、非発光期間を開始することができる。

### 【0034】

ここで書込トランジスタTr1の制御により保持容量Csの端子間電圧を立ち下げて非発光期間を開始する場合、電源用駆動信号DSを電圧Vssに立ち下げて保持容量Csのソース側端電圧を設定する処理は、非発光期間において、しきい値電圧補正処理に影響を与えない範囲で、所望する時点で実行することができる。従ってこの場合、電源用駆動信号DSを複数のラインで共通化し、いわゆるユニットドライブ方式により各画素回路を駆動することができる。

30

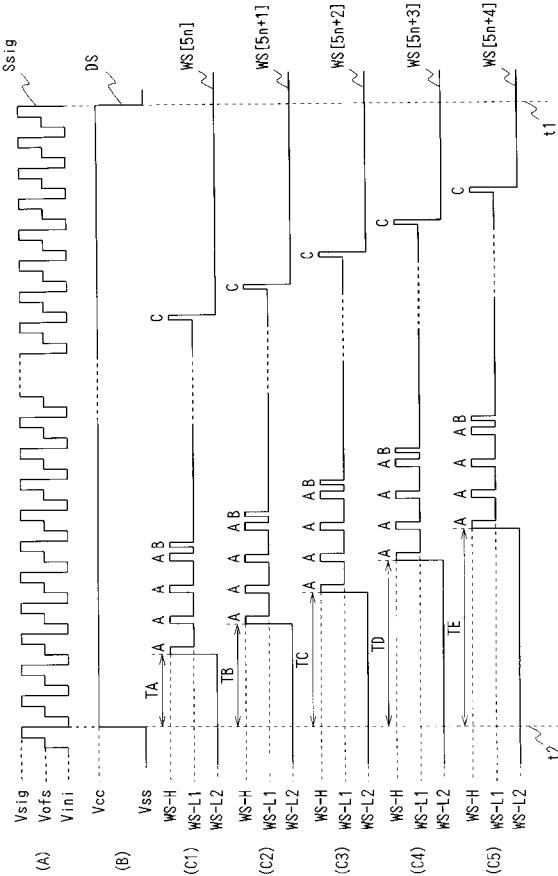

### 【0035】

図18は、このユニットドライブ方式による画像表示装置の動作の説明に供するタイムチャートである。この画像表示装置は、表示部を構成する画素回路5を5ライン単位でグループ化し、各グループで電源用駆動信号DSを共通化する。なおこの図18では、5ライン単位のグループ化に対応して、1つのグループを構成する連続する5つのラインを5n、5n+1、5n+2、5n+3、5n+4(nは整数)により表し、電源用駆動信号DS及び書込信号WSの対応関係を示す。また以下においては、このグループ化によるグループをユニットと呼ぶ。

40

### 【0036】

ここで画像表示装置は、ユニットとは無関係に、連続するラインで順次、1水平走査期間ずつ遅延するように、書込信号WS[5n]、WS[5n+1]、WS[5n+2]、WS[5n+3]、WS[5n+4]を生成する(図18(B)、(C1)、(C2)、(C3)、(C4)及び(C5))。これにより画像表示装置は、ライン順次で各画素回路5の階調を設定する。

### 【0037】

また画像表示装置は、階調設定用電圧Vsig、ばらつき補正用の固定電圧Vofs、消灯用の基準電圧Vinjを順次循環的に信号線DTLに出力する(図18(A))。な

50

お消灯用の基準電圧  $V_{ini}$  は、画素回路 5 の発光を停止させる基準電圧であり、ばらつき補正用の固定電圧  $V_{ofs}$  より十分に低い電圧である。消灯用の基準電圧  $V_{ini}$  は、有機 EL 素子 8 のカソード電圧  $V_{cath}$  に、有機 EL 素子 8 のしきい値電圧  $V_{thel}$  及び駆動トランジスタ Tr 2 のしきい値電圧  $V_{th}$  を加算した電圧  $V_{cath} + V_{thel} + V_{th}$  以下の電圧である。

#### 【0038】

また画像表示装置は、ユニット毎に電源用駆動信号 DS を生成する（図 18（B））。すなわちユニット内においては、最先に書込信号 WS を立ち上げるタイミングより一定時間前に駆動信号 DS を電源電圧 Vcc に立ち上げた後（時点 t2）、最後に消灯用の基準電圧  $V_{ini}$  を設定した後、一定時間経過して駆動信号 DS を電圧 Vss に立ち下げる（時点 t1）。また連続するユニットでは、順次、1つのユニットを構成するライン数に対応する 5 水平走査期間ずつ遅延させて駆動信号 DS を生成する。

10

#### 【0039】

この場合、画素回路 5 は、発光期間の間、書込信号 WS により書込トランジスタ Tr 1 がオフ状態に設定され、電源用駆動信号 DS によって駆動トランジスタ Tr 2 に電源電圧 Vcc が供給される。その結果、画素回路 5 は、発光期間の間、保持容量 Cs の端子間電圧である駆動トランジスタ Tr 2 のゲートソース間電圧  $V_{gs}$  に応じた駆動電流 Ids で有機 EL 素子 8 を発光させる。

20

#### 【0040】

画素回路 5 は、発光期間が終了する時点で、書込信号 WS が立ち上げられて書込トランジスタ Tr 1 がオン状態に設定され、保持容量 Cs の端子電圧が消灯用の基準電圧  $V_{ini}$  に設定される。これにより画素回路 5 は、保持容量 Cs の端子間電圧を駆動トランジスタ Tr 2 のしきい値電圧  $V_{th}$  以下に立ち下げ、駆動トランジスタ Tr 2 による有機 EL 素子 8 の駆動を停止する。

20

#### 【0041】

続いて画素回路 5 は、所定の時点 t1 で、電源用駆動信号 DS が所定の固定電圧 Vss に立ち下げる。これにより画素回路 5 は、駆動トランジスタ Tr 2 を介して、保持容量 Cs の有機 EL 素子 8 側端の蓄積電荷が走査線 Dsl に流出する。その結果、画素回路 5 は、駆動トランジスタ Tr 2 のソース電圧 Vs がほぼ電圧 Vss に立ち下がり、このソース電圧 Vs の立ち下がりに連動して、駆動トランジスタ Tr 2 のゲート電圧  $V_g$  が低下する。これにより画素回路 5 は、駆動トランジスタ Tr 2 のしきい値電圧補正処理の準備処理に関して、保持容量 Cs のソース側端電圧が設定される。

30

#### 【0042】

画素回路 5 は、続く所定の時点 t2 で、電源用駆動信号 DS が電源電圧 Vcc に立ち上げられる。その後、画素回路 5 は、信号線 DTL の駆動信号 Ssing がしきい値電圧補正用の固定電圧  $V_{ofs}$  に設定されている期間の間、書込信号 WS により書込トランジスタ Tr 1 がオン状態に切り換えられる。これにより画素回路 5 は、駆動トランジスタ Tr 2 のしきい値電圧補正処理の準備処理に関して、保持容量 Cs のゲート側端電圧が設定され、保持容量 Cs の端子間電圧が駆動トランジスタ Tr 2 のしきい値電圧  $V_{th}$  以上の電圧に設定される。また保持容量 Cs の端子間電圧が駆動トランジスタ Tr 2 のしきい値電圧  $V_{th}$  以上の電圧に立ち上ると、画素回路 5 は、駆動トランジスタ Tr 2 のしきい値電圧補正処理が実行される。なお以下においては、この駆動トランジスタ Tr 2 のしきい値電圧補正処理を実行する期間を、符号 A により示す。従ってこの図 18 の例では、駆動トランジスタ Tr 2 のしきい値電圧補正処理を実行する期間を、4 回の期間に分けて実行することになる。

40

#### 【0043】

画素回路 5 は、その後、信号線 DTL の駆動信号 Ssing が対応する階調設定用電圧 Vsing に設定されている期間で、一定期間の間、書込トランジスタ Tr 1 がオン状態に設定される。その結果、画素回路 5 は、駆動トランジスタ Tr 2 の移動度  $\mu$  のばらつきを補正して保持容量 Cs の端子間電圧が階調設定用電圧 Vsing に対応する電圧に設定され、

50

発光期間を開始する。なお以下において、この移動度をばらつき補正して階調を設定する期間を、符号Bにより示す。また消灯用の基準電圧 $V_{ini}$ を設定する期間を符号Cにより示す。

#### 【0044】

なおこの図18の例において、画像表示装置は、しきい値電圧補正処理を開始した後、消灯用の基準電圧 $V_{ini}$ を設定するまでの間、書込信号WSのLレベル電圧WS-L1を、この期間以外の期間におけるLレベル電圧WS-L2より高い電圧に保持する。これにより画像表示装置は、発光期間における書込トランジスタTr1のオフリーケを抑え、輝度ばらつきを抑制することができる。

#### 【0045】

なお消灯用の基準電圧 $V_{ini}$ に代えて、ばらつき補正用の固定電圧 $V_{ofs}$ のタイミングで書込トランジスタTr1をオン動作させて非発光期間を開始するようにしてもよい。この場合には、消灯用の基準電圧 $V_{ini}$ を省略し、階調設定用電圧 $V_{sig}$ と固定電圧 $V_{ofs}$ との繰り返しにより信号線DTLの駆動信号 $S_{sig}$ を作成するようにしてもよい。

#### 【0046】

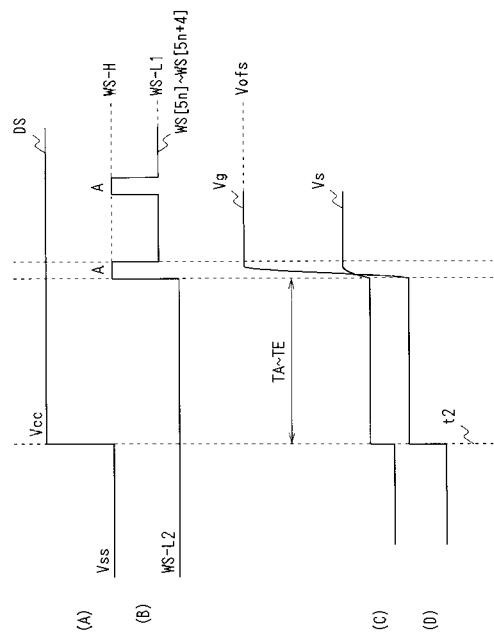

ところで図18との対比により図19に示すように、この図18の構成において、各画素回路5の駆動トランジスタTr2は、時点t2で電源用駆動信号DSを電源電圧 $V_{cc}$ に立ち上げた後、書込トランジスタTr1をオン動作させるまでの期間TA、TB、TC、TD、TEの間、ドレインソース間電圧 $V_{ds}$ がバイアスされた状態で、ゲートソース間電圧 $V_{gs}$ が逆バイアスされた状態に保持される。

#### 【0047】

なおここでこれら期間TA～TEの間、駆動トランジスタTr2のゲート電圧は、次式により表される。ここで $V_{thg d}$ は、駆動トランジスタTr2のドレインをソースとして機能させた場合の、ゲート及びドレイン間のしきい値電圧である。 $C_{gd}$ は、駆動トランジスタTr2のゲートドレイン間容量 $C_{gd}$ である。但し、保持容量 $C_s$ の容量は、駆動トランジスタTr2のゲートソース間容量 $C_{gs}$ に比して十分に大きいものとする。

#### 【0048】

#### 【数1】

10

20

30

$$C_{gd} \times (V_{ss} - V_{cc})$$

$$V_g = V_{ss} + V_{thg d} + \frac{C_{gd} \times (V_{ss} - V_{cc})}{C_{gd} + C_s} \dots\dots (1)$$

#### 【0049】

またこれら期間TA～TEの間、駆動トランジスタTr2のソース電圧は、次式により表される。なおここで $V_{the1}$ は、有機EL素子8のしきい値電圧、 $V_{cath}$ は、有機EL素子8のカソード電圧である。またG1は、駆動信号DSを電圧 $V_{cc}$ に立ち上げた際に、駆動トランジスタTr2がブートストラップ回路として機能することにより、ゲート電圧 $V_g$ の低下に連動してソース電圧が低下する際の利得である。またG2は、ゲート電圧 $V_g$ の電圧上昇にリンクした容量結合による電圧上昇の利得である。

#### 【0050】

40

【数2】

$$V_s = V_{thel} + V_{cath}$$

$$\frac{(V_{ini} - (G_1 + 1) \times (V_{ss} + V_{thdg}))}{G_1}$$

10

$$+ \frac{(V_{ss} - V_{cc}) \times C_{gd} \times G_2}{C_{gd} + C_s} \dots\dots (2)$$

20

【0051】

駆動トランジスタTr2を構成するTFTは、長期間、ドレインソース間電圧Vdsがバイアスされた状態で、ゲートソース間電圧Vgsが逆バイアスされた状態に保持されると、徐々に特性が経時変化する欠点がある。

【0052】

これにより図18の構成では、長期間の使用により、1つのユニットを構成する連続するライン5n、5n+1、5n+2、5n+3、5n+4間で、徐々に輝度差が発生し、横スジによる輝度ムラが発生する問題がある。

【0053】

本発明は以上の点を考慮してなされたもので、ユニットドライブ方式において、長期の使用による輝度ムラを防止することができる画像表示装置及び画像表示装置の駆動方法を提案しようとするものである。

30

【課題を解決するための手段】

【0054】

上記の課題を解決するため請求項1の発明は、画像表示装置に適用して、画素回路をマトリックス状に配置して形成された表示部と、前記表示部の信号線に信号線用駆動信号を出力する信号線駆動回路と、前記表示部の電源用走査線及び書込用走査線に電源用駆動信号及び書込信号を出力する走査線駆動回路とを有する。ここで前記画素回路は、発光素子と、ゲートソース間電圧に応じた駆動電流により前記発光素子を駆動する駆動トランジスタと、前記ゲートソース間電圧を保持する保持容量と、前記保持容量の一端の電圧を前記信号線用駆動信号の電圧に設定する書込トランジスタとを少なくとも有し、前記発光素子を発光させる発光期間と、前記発光素子の発光を停止させて前記発光素子の発光輝度を設定する非発光期間とを交互に繰り返し、前記書込信号による前記書込トランジスタの制御により、前記保持容量の一端の電圧を信号線用駆動信号の電圧に設定して、前記発光期間と前記非発光期間とを開始し、前記非発光期間において、前記電源用駆動信号による前記駆動トランジスタの制御により、前記駆動トランジスタを介して前記保持容量の他端の電圧を立ち下げる後、前記電源用駆動信号による前記駆動トランジスタの制御により、前記駆動トランジスタを介して前記保持容量の端子間電圧を放電し、前記保持容量の端子間電圧を前記駆動トランジスタのしきい値電圧に応じた電圧に設定し、続いて前記書込信号に

40

50

よる前記書込トランジスタの制御により、前記保持容量の端子電圧を前記信号線用駆動信号の電圧に設定して、前記発光素子の発光輝度を設定して前記発光期間を開始する。前記表示部は、複数ライン単位で連続するラインがグループ化される。前記走査線駆動回路は、ライン毎に、順次1水平走査期間ずつ遅延させて前記書込信号を出力し、前記表示部のグループ毎に、前記複数ラインに対応する複数の水平走査期間ずつ遅延させて前記電源用駆動信号を生成し、対応するグループの前記電源用駆動信号と、前記対応するグループの前記電源用駆動信号に対して前記複数の水平走査期間だけ先行した前記電源用駆動信号とを前記ライン毎に切り換えて前記電源用駆動信号を出力し、前記グループ内において、遅れて発光期間を開始するライン程、前記複数ラインに対応する複数フィールドの期間又は前記複数フィールドの期間の整数倍の期間に占める前記先行した前記電源用駆動信号が順次増大するように設定する。

10

20

30

40

50

## 【0055】

また請求項4の発明は、画素回路をマトリックス状に配置して形成された表示部と、前記表示部の信号線に信号線用駆動信号を出力する信号線駆動回路と、前記表示部の電源用走査線及び書込用走査線に電源用駆動信号及び書込信号を出力する走査線駆動回路とをする画像表示装置の駆動方法に適用する。ここで画素回路は、発光素子と、ゲートソース間電圧に応じた駆動電流により前記発光素子を駆動する駆動トランジスタと、前記ゲートソース間電圧を保持する保持容量と、前記保持容量の一端の電圧を前記信号線用駆動信号の電圧に設定する書込トランジスタとを少なくとも有し、前記発光素子を発光させる発光期間と、前記発光素子の発光を停止させて前記発光素子の発光輝度を設定する非発光期間とを交互に繰り返し、前記書込信号による前記書込トランジスタの制御により、前記保持容量の一端の電圧を信号線用駆動信号の電圧に設定して、前記発光期間と前記非発光期間とを開始し、前記非発光期間において、前記電源用駆動信号による前記駆動トランジスタの制御により、前記駆動トランジスタを介して前記保持容量の他端の電圧を立ち下げた後、前記電源用駆動信号による前記駆動トランジスタの制御により、前記駆動トランジスタを介して前記保持容量の端子間電圧を放電し、前記保持容量の端子間電圧を前記駆動トランジスタのしきい値電圧に応じた電圧に設定し、続いて前記書込信号による前記書込トランジスタの制御により、前記保持容量の端子電圧を前記信号線用駆動信号の電圧に設定して、前記発光素子の発光輝度を設定して前記発光期間を開始する。前記画像表示装置の駆動方法は、前記表示部の連続するラインを、複数ライン単位でグループ化し、ライン毎に、順次1水平走査期間ずつ遅延させて前記書込信号を出力し、前記表示部のグループ毎に、前記複数ラインに対応する複数の水平走査期間ずつ遅延させて前記電源用駆動信号を生成し、対応するグループの前記電源用駆動信号と、前記対応するグループの前記電源用駆動信号に対して前記複数の水平走査期間だけ先行した前記電源用駆動信号とを前記ライン毎に切り換えて前記電源用駆動信号を出力し、前記グループ内において、遅れて発光期間を開始するライン程、前記複数ラインに対応する複数フィールドの期間又は前記複数フィールドの期間の整数倍の期間に占める前記先行した前記電源用駆動信号が順次増大するよう設定する。

## 【0056】

請求項1、又は請求項4の構成により、対応するグループの電源用駆動信号、前記対応するグループの前記電源用駆動信号に対して前記複数の水平走査期間だけ先行した前記電源用駆動信号をライン毎に切り換えて電源用駆動信号を出力し、グループ内において、遅れて発光期間を開始するライン程、前記複数の水平走査期間又は前記複数の水平走査期間の整数倍の期間に占める前記先行した前記電源用駆動信号が順次増大するよう設定すれば、この複数の水平走査期間又はこの複数の水平走査期間の整数倍の期間において、駆動トランジスタに電源の供給を開始した後、書込トランジスタにより保持容量の端子電圧を設定するまでの総合の期間を、1つのグループを構成する各ラインで同一に設定することができる。従って駆動トランジスタにおいて、ドレインソース間がバイアスされた状態で、ゲートソース間電圧が逆バイアスされた状態に保持される期間を、1つのグループを構成する各ラインで同一に設定することができ、1つのグループを構成するライン間で、経

時変化の相違を防止することができる。これによりユニットドライブ方式において、長期の使用による輝度ムラを防止することができる。

**【発明の効果】**

**【0057】**

本発明によれば、ユニットドライブ方式において、長期の使用による輝度ムラを防止することができる。

**【発明を実施するための最良の形態】**

**【0058】**

以下、適宜図面を参照しながら本発明の実施の形態を詳述する。

第1の実施の形態

10

[実施の形態の構成]

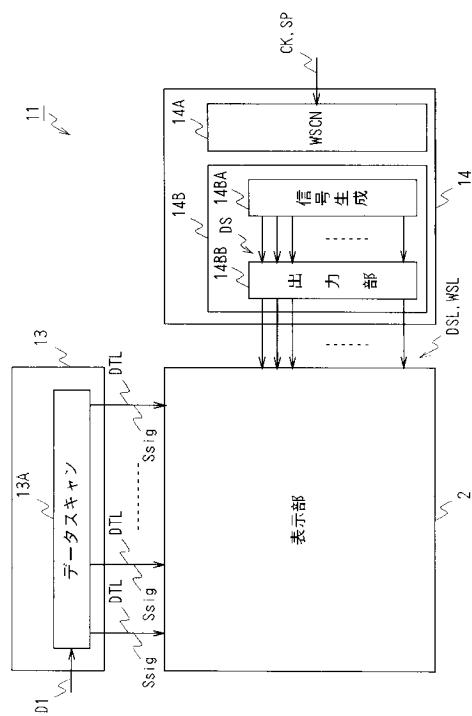

図2は、図7との対比により本発明の第1の実施の形態に係る画像表示装置を示すブロック図である。この画像表示装置11は、信号線駆動回路3、走査線駆動回路4に代えて、信号線駆動回路13、走査線駆動回路14が設けられる点を除いて、図7の画像表示装置1と同一に構成される。

**【0059】**

ここで信号線駆動回路13は、図18について上述したように、データスキャン回路13Aにより、ラスタ走査順に入力される画像データD1を順次ラッチして画像データD1を信号線DTLに振り分けた後、それぞれディジタルアナログ変換処理して階調電圧Vi<sub>n</sub>を生成する。信号線駆動回路13は、この階調電圧Vi<sub>n</sub>に固定電圧Vofsを加算して階調設定用電圧Vsingを生成し、階調設定用電圧Vsing、ばらつき補正用の固定電圧Vofs、消灯用の基準電圧Vin<sub>i</sub>を順次循環的に切り換えて信号線用の駆動信号Ssingを生成する。

20

**【0060】**

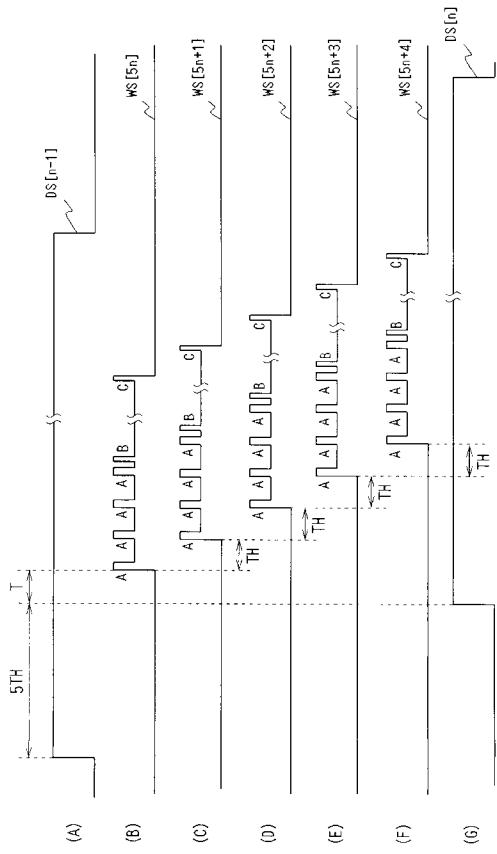

走査線駆動回路14は、所定のサンプリングパルスSPをクロックCKで処理し、表示部2の連続するラインを5ライン単位でグループ化したユニットドライブ方式による書き込み信号WS及び電源用駆動信号DSを出力する。すなわち図18との対比により図3に示すように、ライトスキャン回路(WSCN)14Aは、ライン毎に、順次1水平走査期間THずつ遅延させて書き込み信号WSを生成して出力する(図3(B)~(F))。

30

**【0061】**

ドライブスキャン回路14Bは、ライトスキャン回路14Aと同様にして電源用駆動信号DSを生成する。すなわちドライブスキャン回路14Bにおいて、信号生成部14BAは、表示部2のユニット毎に、1つのユニットを構成するライン数に対応する5水平走査期間ずつ遅延させて電源用の駆動信号DSを生成する。

30

**【0062】**

このとき信号生成部14BAは、1つのユニットに対して、当該ユニット用に生成した駆動信号DS[n](図3(G))に加えて、直前のユニット用の駆動信号DS[n-1](図3(A))を当該ユニットで使用可能に、電圧Vssへの立ち下げのタイミングを設定して駆動信号DSを生成する。すなわち対応するユニットの書き込み信号WS[5n]~WS[5n+4]と、続くユニットの書き込み信号WS[5(n+1)]~WS[5(n+1)+4]とに対して、最先に書き込み信号WSを立ち上げるタイミングより一定時間T前に電源用駆動信号DSを電源電圧Vccに立ち上げる。また最後に消灯用の基準電圧Vin<sub>i</sub>を設定した後、一定時間経過して電源用駆動信号DSを電圧Vssに立ち下げる。

40

**【0063】**

また最もラスタ走査開始端側のユニット用の駆動信号DS[1]に対して、駆動信号DS[n]に対する駆動信号DS[n-1]の時間関係を有する駆動信号DS[0]を生成する。これにより信号生成部14BAは、表示部2に設定された1つのユニットに対して、当該ユニット用の駆動信号DS[n]と、1つのユニットを構成するライン数に対応する5水平走査期間だけ当該ユニット用の駆動信号DS[n]に先行した駆動信号DS[n-1]との双方を使用可能に設定して、表示部2のユニット数Xに対して、X+1種類の

50

駆動信号 D S を生成する。

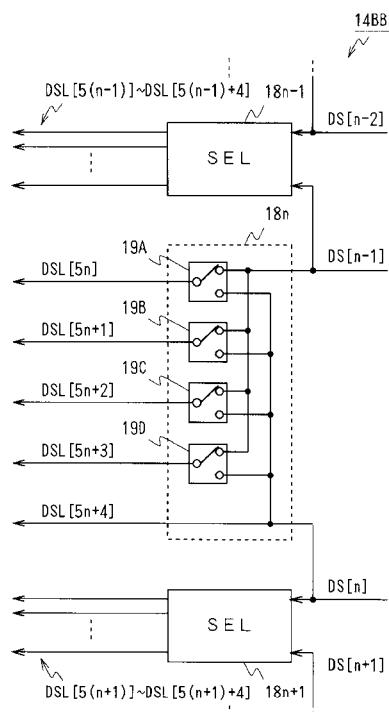

【 0 0 6 4 】

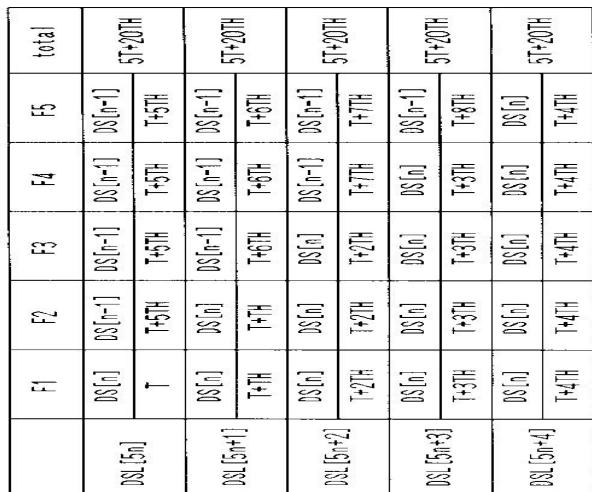

出力部 1 4 B B は、この信号生成部 1 4 B A で生成した駆動信号 D S を対応する走査線 D S L に出力する。このとき出力部 1 4 B B は、各ユニットにおいて、対応するユニットの駆動信号 D S [ n ] と、この対応するユニットの駆動信号 D S [ n ] に対して 1 つのユニットを構成するライン数に対応する複数の水平走査期間だけ先行した電源用駆動信号（直前ユニット用の電源用駆動信号である） D S [ n - 1 ] とをライン毎に切り換えて電源用駆動信号を出力する。またこの駆動信号 D S [ n ] 、 D S [ n - 1 ] の切り換えを、ユニット内において、遅れて発光期間を開始するライン程、1 つのユニットを構成するライン数に対応する複数フィールドの期間、又はこの複数フィールドの期間の整数倍の期間に占める先行したユニット用の電源用駆動信号が順次増大するように設定する。10

【 0 0 6 5 】

すなわち図 4 は、出力部 1 4 B B の一部構成を示すブロック図である。出力部 1 4 B B は、表示部 2 のユニット毎に、セレクタ部（ S E L ） 1 8 ( 1 8 n - 1 、 1 8 n 、 1 8 n + 1 …… ) が設けられる。各セレクタ部 1 8 は、対応するユニット用の駆動信号 D S [ n ] と、このユニットの駆動信号 D S [ n ] に対して先行する電源用駆動信号 D S [ n - 1 ] とを選択出力するスイッチ回路 1 9 A 、 1 9 B 、 1 9 C 、 1 9 D が設けられ、それぞれスイッチ回路 1 9 A 、 1 9 B 、 1 9 C 、 1 9 D を介してラスタ走査開始端側の 4 つの走査線 D S L [ n ] 、 D S L [ n + 1 ] 、 D S L [ n + 2 ] 、 D S L [ n + 3 ] に駆動信号を出力する。20

【 0 0 6 6 】

出力部 1 4 B B は、図 1 に示すように、1 つのユニットを構成するライン数に対応する 5 フィールド周期でこれらスイッチ回路 1 9 A 、 1 9 B 、 1 9 C 、 1 9 D の設定を切り替え、ユニット内において、遅れて発光期間を開始するライン程、5 フィールドの期間で、先行したユニット電源用駆動信号が順次増大するように設定する。

【 0 0 6 7 】

すなわち出力部 1 4 B B は、連続する 5 フィールド F 1 、 F 2 、 F 3 、 F 4 、 F 5 の先頭フィールド F 1 では、対応するユニット用の駆動信号 D S [ n ] を選択出力するように、スイッチ回路 1 9 A 、 1 9 B 、 1 9 C 、 1 9 D を設定する。従って先頭フィールド F 1 において、走査線 D S L [ n ] 、 D S L [ n + 1 ] 、 D S L [ n + 2 ] 、 D S L [ n + 3 ] 、 D S L [ n + 4 ] に接続された画素回路 5 は、駆動トランジスタ T r 2 のドレイン電圧が電源電圧 V c c に立ち上がった後、書き信号 W S が立ち上がるまでの期間が、それぞれ T 、 T + T H 、 T + 2 T H 、 T + 3 T H 、 T + 4 T H に設定される。30

【 0 0 6 8 】

また出力部 1 4 B B は、続くフィールド F 2 では、先頭ラインの走査線 D S L [ 5 n ] に対してのみ、先行する電源用駆動信号 D S [ n - 1 ] を出力し、残りの走査線 D S L [ 5 n + 1 ] 、 D S L [ n + 2 ] 、 D S L [ n + 3 ] に対しては、対応する駆動信号 D S [ n ] を出力する。従ってこの続くフィールド F 2 において、走査線 D S L [ n ] 、 D S L [ n + 1 ] 、 D S L [ n + 2 ] 、 D S L [ n + 3 ] 、 D S L [ n + 4 ] に接続された画素回路 5 は、駆動トランジスタ T r 2 のドレイン電圧が電源電圧 V c c に立ち上がった後、書き信号 W S が立ち上がるまでの期間が、それぞれ T + 5 T H 、 T + T H 、 T + 2 T H 、 T + 3 T H 、 T + 4 T H に設定される。40

【 0 0 6 9 】

また出力部 1 4 B B は、続くフィールド F 3 では、先頭ラインの走査線 D S L [ 5 n ] と続く走査線 D S L [ 5 n + 1 ] に対してのみ、先行する電源用駆動信号 D S [ n - 1 ] を出力し、残りの走査線 D S L [ n + 2 ] 、 D S L [ n + 3 ] に対しては、対応する駆動信号 D S [ n ] を出力する。従ってこの続くフィールド F 3 において、走査線 D S L [ n ] 、 D S L [ n + 1 ] 、 D S L [ n + 2 ] 、 D S L [ n + 3 ] 、 D S L [ n + 4 ] に接続された画素回路 5 は、駆動トランジスタ T r 2 のドレイン電圧が電源電圧 V c c に立ち上がった後、書き信号 W S が立ち上がるまでの期間が、それぞれ T + 5 T H 、 T + 6 T H 、50

$T + 2 \text{ TH}$ 、 $T + 3 \text{ TH}$ 、 $T + 4 \text{ TH}$ に設定される。

【0070】

また出力部14BBは、続くフィールドF4では、走査線DSL[5n]、DSL[5n+1]、DSL[5n+2]に対して、先行する電源用駆動信号DS[n-1]を出力し、残りの走査線DSL[n+3]に対しては、対応する駆動信号DS[n]を出力する。従ってこの続くフィールドF4において、走査線DSL[n]、DSL[n+1]、DSL[n+2]、DSL[n+3]、DSL[n+4]に接続された画素回路5は、駆動トランジスタTr2のドレイン電圧が電源電圧Vccに立ち上がった後、書き込み信号WSが立ち上がるまでの期間が、それぞれ $T + 5 \text{ TH}$ 、 $T + 6 \text{ TH}$ 、 $T + 7 \text{ TH}$ 、 $T + 3 \text{ TH}$ 、 $T + 4 \text{ TH}$ に設定される。

10

【0071】

また出力部14BBは、最後のフィールドF5では、走査線DSL[5n]、DSL[5n+1]、DSL[5n+2]、DSL[5n+3]に対して、先行する電源用駆動信号DS[n-1]を出力する。従ってこの続くフィールドF5において、走査線DSL[n]、DSL[n+1]、DSL[n+2]、DSL[n+3]、DSL[n+4]に接続された画素回路5は、駆動トランジスタTr2のドレイン電圧が電源電圧Vccに立ち上がった後、書き込み信号WSが立ち上がるまでの期間が、それぞれ $T + 5 \text{ TH}$ 、 $T + 6 \text{ TH}$ 、 $T + 7 \text{ TH}$ 、 $T + 8 \text{ TH}$ 、 $T + 4 \text{ TH}$ に設定される。なおこれらにより出力部14BBは、切り換え対象である電源用駆動信号DS[n]、DS[n-1]が共に電圧Vssに設定されている期間で、これら電源用駆動信号DS[n]、DS[n-1]の出力を切り換える。

20

【0072】

これらによりこの5フィールドF1～F5の期間の間、走査線DSL[n]、DSL[n+1]、DSL[n+2]、DSL[n+3]、DSL[n+4]に接続された画素回路5は、駆動トランジスタTr2のドレイン電圧が電源電圧Vccに立ち上がった後、書き込み信号WSが立ち上がるまでの期間が、総合で、 $T + 20 \text{ TH}$ に設定される。従って5フィールドF1～F5の期間で、駆動トランジスタTr2に電源Vccの供給を開始した後、書き込みトランジスタTr1により保持容量Csの端子電圧を設定するまでの総合の期間を、1つのグループを構成する各ラインで同一に設定することができる。従って駆動トランジスタTr2において、ドレインソース間がバイアスされた状態で、ゲートソース間電圧が逆バイアスされた状態に保持される期間を、1つのグループを構成する各ラインで同一に設定することができ、1つのグループを構成するライン間で、経時変化の相違を防止することができる。

30

【0073】

[実施の形態の動作]

以上の構成において、この画像表示装置11では(図2)、信号線駆動回路13において、順次入力される画像データD1が信号線DTLに振り分けられた後、デジタルアナログ変換処理される。これにより画像表示装置11では、信号線DTLに接続された各画素の階調を指示する階調電圧Vinが信号線DTL毎に作成される。画像表示装置1では、この階調電圧Vinに、しきい値電圧のばらつき補正用の固定電圧Vofsが加算されて階調設定用電圧Vsigが生成される。またこの階調設定用電圧Vsig、固定電圧Vofs、消去用の基準電圧Vin\_iが順次切り換えられて各信号線DTLの駆動信号SSigが生成され、この駆動信号SSigが対応する信号線DTLに出力される。

40

【0074】

この信号線DTLの駆動に対応して、画像表示装置11は、走査線駆動回路14により書き込み信号WS、電源用駆動信号DSが作成され、これら書き込み信号WS、電源用駆動信号DSによる画素回路5に設けられた書き込みトランジスタTr1、駆動トランジスタTr2の制御により、線順次で各画素回路5に設けられた発光素子8の階調が設定される。これにより画像表示装置11では、画像データD1による画像を表示部2で表示することができる。

50

## 【0075】

より具体的に、画像表示装置11では、線順次により保持容量Csの端子間電圧が画像データD1に応じた電圧、消去用の基準電圧Vinに交互に設定され、これにより各画素回路5で発光期間及び非発光期間が繰り返される。また発光期間においては、駆動トランジスタTr2により保持容量Csに設定された端子間電圧に応じた駆動電流で発光素子8が電流駆動され、これにより画像データD1に応じた発光輝度により発光素子8を発光させて所望の画像を表示することができる。

## 【0076】

しかしながらこれら画素回路5に適用される駆動トランジスタTr2は、しきい値電圧Vthのばらつきが大きい欠点がある。その結果、画像表示装置11では、単に保持容量Csのゲート側端電圧を階調電圧Vinに応じた電圧Vsigに設定したのでは、駆動トランジスタTr2のしきい値電圧Vthのばらつきにより有機EL素子8の発光輝度がばらつき、画質が劣化する。

10

## 【0077】

そこで画像表示装置11では、非発光期間が開始すると、電源用駆動信号DSの立ち下げにより保持容量Csの有機EL素子8側端電圧を立ち下げた後、書きトランジスタTr1を介して駆動トランジスタTr2のゲート電圧がしきい値電圧補正用の固定電圧Vofsに設定される(図8)。これにより画像表示装置11では、保持容量Csの端子間電圧が駆動トランジスタTr2のしきい値電圧Vth以上に設定される。その後、駆動トランジスタTr2を介して、この保持容量Csの端子間電圧が放電される。これらの一連の処理により、画像表示装置11では、保持容量Csの端子間電圧が、事前に、駆動トランジスタTr2のしきい値電圧Vthに設定される。

20

## 【0078】

その後、画像表示装置11では、階調電圧Vinに固定電圧Vofsを加算した階調設定用電圧Vsigが駆動トランジスタTr2のゲート電圧に設定される。これにより画像表示装置11では、駆動トランジスタTr2のしきい値電圧Vthのばらつきによる画質劣化を防止することができる。

30

## 【0079】

また駆動トランジスタTr2を介した保持容量Csの端子間電圧の放電が複数回の期間で実行される。これにより高解像度化により1回の放電によっては、駆動トランジスタTr2を介した放電により保持容量Csの端子間電圧を駆動トランジスタTr2のしきい値電圧Vthに設定するのに十分な時間を割り当てることが困難な場合でも、この駆動トランジスタTr2を介した放電に十分な時間を割り当て、十分に駆動トランジスタTr2のばらつきを補正することができる。

## 【0080】

また一定時間の間、駆動トランジスタTr2に電源を供給した状態で、駆動トランジスタTr2のゲート電圧を階調設定用電圧Vsigに保持することにより、駆動トランジスタTr2の移動度のばらつきによる画質劣化を防止することができる。

40

## 【0081】

画像表示装置11では、この移動度のばらつき補正処理による保持容量Csの端子間電圧の設定により各画素回路5の発光期間が開始する。また消灯用の基準電圧Vinを用いて同様に保持容量Csの端子間電圧が設定されて非発光期間が開始する(図3、図18)。これにより画像表示装置11は、各画素回路5の発光期間、非接触発光期間が書き信号WSによる書きトランジスタTr1の制御により実行される。その結果、電源用駆動信号DSを複数ラインで共通化したユニットドライブ方式により所望の画像を表示し、駆動信号DSの生成に係る構成を簡略化することができる。

## 【0082】

しかしながらこのように電源用駆動信号DSを複数ラインで共通化した場合(図18及び図19)、電源用駆動信号DSを電源電圧Vccに立ち上げた後、書きトランジスタTr1をオン動作させるまでの期間TA、TB、TC、TD、TEの間、ドレンインソース間

50

電圧  $V_{ds}$  がバイアスされた状態で、ゲートソース間電圧  $V_{gs}$  が逆バイアスされた状態に保持され、この期間 T A、T B、T C、T D、T E が、1つのユニットを構成するライン毎に相違することになる。

#### 【0083】

これに対して駆動トランジスタ Tr 2 を構成する TFT は、長期間、ドレインソース間電圧  $V_{ds}$  がバイアスされた状態で、ゲートソース間電圧  $V_{gs}$  が逆バイアスされた状態に保持されると、徐々に特性が経時変化する。

#### 【0084】

これにより図 18 の構成では、長期間の使用により、1つのユニットを構成する連続するライン 5n、5n+1、5n+2、53+3、5n+4 間で、徐々に輝度差が発生し、横スジによる輝度ムラが徐々に発生することになる。

10

#### 【0085】

そこでこの画像表示装置 11 では、ユニットの数に対して、1つ余分に電源用の駆動信号 DS を生成し、1つのユニットの画素回路 5 を、対応する駆動信号 DS[n] と、直前のユニット用の先行する駆動信号 DS[n-1] とにより駆動可能に、これら駆動信号 DS が作成される（図 3）。

#### 【0086】

また対応するユニットのライン毎に、この2つの駆動信号 DS[n] 及び DS[n-1] を切り換えて出力するようにして、遅れて発光期間を開始するライン程、1つのユニットを構成する複数ラインに対応する複数フィールドの期間で、先行する駆動信号 DS[n-1] が順次増大するように設定される（図 1）。またこの複数フィールドの期間の設定が繰り返される。

20

#### 【0087】

これにより画像表示装置 11 では、この複数フィールドにおいて、駆動トランジスタ Tr 2 に電源 Vcc の供給を開始した後、書きトランジスタ Tr 1 により保持容量 Cs の端子電圧を設定するまでの総合の期間を、1つのグループを構成する各ラインで同一に設定することができる。従って駆動トランジスタ Tr 2 において、ドレインソース間がバイアスされた状態で、ゲートソース間電圧が逆バイアスされた状態に保持される期間を、1つのグループを構成する各ラインで同一に設定することができる。

30

#### 【0088】

これにより画像表示装置 11 では、1つのグループを構成するライン間で、経時変化の相違を防止することができ、この経時変化の相違による横スジの輝度ムラを防止することができる。

#### 【0089】

##### [実施の形態の効果]

以上の構成によれば、対応するグループの電源用駆動信号と、先行する電源用駆動信号とをライン毎に切り換えて電源用駆動信号を出力し、グループ内において、遅れて発光期間を開始するライン程、一定期間に占める先行する電源用駆動信号が順次増大するよう設定することにより、ユニットドライブ方式において、長期の使用による輝度ムラを防止することができる。

40

#### 【0090】

またこの構成において、電源用駆動信号及び書き信号による制御により保持容量の端子間電圧を駆動トランジスタのしきい値電圧以上の電圧に設定した後、保持容量の端子間電圧を駆動トランジスタのしきい値電圧に応じた電圧に設定することにより、簡易な構成により駆動トランジスタのしきい値電圧のばらつきを有効に回避して画質を向上することができる。

##### 変形例

なお上述の実施の形態においては、スイッチ回路 19A ~ 19D を順次切り換えて、遅れて発光期間を開始するライン程、一定期間に占める先行する電源用駆動信号が順次増大するよう設定する場合について述べたが、本発明はこれに限らず、要は、一定期間に占

50

める先行する電源用駆動信号が順次増大するように設定すればよく、例えば図1との対比により図5に示すように、この一定期間で、時間軸方向に不規則に、スイッチ回路19Aを切り換えるようにしてもよい。

#### 【0091】

また上述の実施の形態においては、1フィールド毎にスイッチ回路19A～19Dの設定を切り換えて、5フィールドの期間で、駆動トランジスタに電源電圧の供給を開始した後、書きトランジスタにより保持容量の端子電圧を設定するまでの総合の期間を、1つのグループを構成する各ラインで同一に設定する。しかしながら本発明はこれに限らず、例えば2フィールド毎にスイッチ回路19A～19Dの設定を切り換えて、10フィールドの期間で、駆動トランジスタに電源電圧の供給を開始した後、書きトランジスタにより保持容量の端子電圧を設定するまでの総合の期間を、1つのグループを構成する各ラインで同一に設定する場合等、1つのユニットを構成する複数ラインに対応する複数フィールドの期間の整数倍の期間に占める先行した電源用駆動信号が順次増大するように設定して上述の実施の形態と同様の効果を得ることができる。

10

#### 【0092】

また上述の実施の形態においては、信号線を介して保持容量のゲート側端電圧を電圧 $V_{ofS}$ に設定することにより、保持容量の端子間電圧を駆動トランジスタTr2のしきい値電圧以上の電圧に設定する場合について述べたが、本発明はこれに限らず、別途、トランジスタを設け、このトランジスタを介して保持容量のゲート側端電圧を電圧 $V_{ofS}$ に設定する場合等にも広く適用することができる。

20

#### 【0093】

また上述の実施の形態においては、駆動トランジスタを介した保持容量の端子間電圧の放電を複数回の期間で実行する場合について述べたが、本発明はこれに限らず、この放電の処理を1回の期間で実行する場合にも広く適用することができる。

20

#### 【0094】

また上述の実施の形態においては、Nチャンネル型のトランジスタを駆動トランジスタに適用する場合について述べたが、本発明はこれに限らず、Pチャンネル型のトランジスタを駆動トランジスタに適用する画像表示装置等に広く適用することができる。

30

#### 【0095】

また上述の実施の形態においては、本発明を有機EL素子の画像表示装置に適用する場合について述べたが、本発明はこれに限らず、電流駆動型の各種自発光素子による画像表示装置に広く適用することができる。

#### 【産業上の利用可能性】

#### 【0096】

本発明は、例えば有機EL素子によるアクティブマトリックス型の画像表示装置に適用することができる。

#### 【図面の簡単な説明】

#### 【0097】

【図1】本発明の第1の実施の形態に係る画像表示装置に適用される走査線駆動回路の動作の説明に供する図表である。

40

【図2】本発明の第1の実施の形態に係る画像表示装置を示すブロック図である。

【図3】図2の画像表示装置の動作の説明に供するタイムチャートである。

【図4】図2の画像表示装置の出力部を示すブロック図である。

【図5】本発明の他の実施の形態に係る画像表示装置に適用される走査線駆動回路の動作の説明に供する図表である。

【図6】従来の画像表示装置を示すブロック図である。

【図7】図6の画像表示装置の詳細構成を示す接続図である。

【図8】図6の画像表示装置の動作の説明に供するタイムチャートである。

【図9】図6の画像表示装置の動作の説明に供する接続図である。

【図10】図9の続きの説明に供する接続図である。

50

【図11】図10の続きの説明に供する接続図である。

【図12】図11の続きの説明に供する接続図である。

【図13】図12の続きの説明に供する接続図である。

【図14】図13の続きの説明に供する接続図である。

【図15】図14の続きの説明に供する接続図である。

【図16】図15の続きの説明に供する接続図である。

【図17】しきい値電圧のばらつきを補正する処理を複数回で実行する場合の説明に供する信号波形図である。

【図18】駆動トランジスタの経時変化の説明に供するタイムチャートである。

【図19】図8の信号波形図を部分的に拡大して示す信号波形図である。 10

#### 【符号の説明】

#### 【0098】

1、11……画像表示装置、2……表示部、3、13……信号線駆動回路、3A、13A……データスキャン回路、4、14……走査線駆動回路、4A、14A……ライトスキャン回路、4B、14B……ドライブスキャン回路、5……画素回路、8……有機EL素子、DTL……信号線、DSL、WSL……走査線、Cs……保持容量、Tr1……書込トランジスタ、Tr2……駆動トランジスタ

【図1】

|           | F1       | F2       | F3       | F4       | F5       | total   |

|-----------|----------|----------|----------|----------|----------|---------|

| DSL[5n]   | DSL[n-1] | DSL[n-1] | DSL[n-1] | DSL[n-1] | DSL[n-1] | 5T+20TH |

| T         | T+5TH    | T+5TH    | T+5TH    | T+5TH    | T+5TH    | 5T+20TH |

| DSL[5n+1] | DSL[n]   | DSL[n]   | DSL[n]   | DSL[n]   | DSL[n]   | 5T+20TH |

| T+1H      | T+1H     | T+6TH    | T+6TH    | T+6TH    | T+6TH    | 5T+20TH |

| DSL[5n+2] | DSL[n]   | DSL[n]   | DSL[n]   | DSL[n]   | DSL[n]   | 5T+20TH |

| DSL[5n+3] | DSL[n]   | DSL[n]   | DSL[n]   | DSL[n]   | DSL[n]   | 5T+20TH |

| DSL[5n+4] | DSL[n]   | DSL[n]   | DSL[n]   | DSL[n]   | DSL[n]   | 5T+20TH |

|           | Tr4TH    | Tr4TH    | Tr4TH    | Tr4TH    | Tr4TH    | Tr4TH   |

【図2】

【図3】

【図4】

【図5】

|           | F1      | F2      | F3      | F4      | F5      | total   |

|-----------|---------|---------|---------|---------|---------|---------|

| DSL[5n]   | DS[n-1] | DS[n]   | DS[n-1] | DS[n-1] | DS[n-1] | 5T+20TH |

| DSL[5n+1] | T+5TH   | T+5TH   | T       | T+5TH   | T+5TH   | 5T+20TH |

| DSL[5n+2] | DS[n]   | DS[n-1] | DS[n]   | DS[n-1] | DS[n-1] | 5T+20TH |

| DSL[5n+3] | T+6TH   | T+7TH   | T+6TH   | T+7TH   | T+6TH   | 5T+20TH |

| DSL[5n+4] | DS[n]   | DS[n-1] | DS[n]   | DS[n-1] | DS[n]   | 5T+20TH |

| DSL[5n+5] | T+2TH   | T+7TH   | T+2TH   | T+7TH   | T+2TH   | 5T+20TH |

| DSL[5n+6] | DS[n]   | DS[n-1] | DS[n]   | DS[n]   | DS[n]   | 5T+20TH |

| DSL[5n+7] | T+3TH   | T+5TH   | T+8TH   | T+3TH   | T+3TH   | 5T+20TH |

| DSL[5n+8] | DS[n]   | DS[n]   | DS[n]   | DS[n]   | DS[n]   | 5T+20TH |

| DSL[5n+9] | T+4TH   | T+4TH   | T+4TH   | T+4TH   | T+4TH   | 5T+20TH |

【図6】

【図 7】

【図 8】

【図 9】

【図 11】

【図 10】

【図 12】

【図 1 3】

【図 1 5】

【図 1 4】

【図 1 6】

【図 1 7】

【図 1 8】

【図 19】

---

フロントページの続き

(51)Int.Cl.

| F I          | テマコード(参考) |

|--------------|-----------|

| G 09 G 3/20  | 670 J     |

| G 09 G 3/20  | 641 D     |

| G 09 G 3/20  | 612 D     |

| G 09 G 3/20  | 624 Z     |

| G 09 G 3/20  | 622 Z     |

| H 05 B 33/14 | A         |

| H 05 B 33/08 |           |

(72)発明者 内野 勝秀

東京都港区港南1丁目7番1号 ソニー株式会社内

Fターム(参考) 3K107 AA01 BB01 CC31 EE03 HH04

5C080 AA06 BB05 CC03 DD05 DD29 EE29 EE30 FF03 FF11 HH10

JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------|------------|

| 专利名称(译)        | 图像显示装置和图像显示装置的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |         |            |

| 公开(公告)号        | <a href="#">JP2010054876A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  | 公开(公告)日 | 2010-03-11 |

| 申请号            | JP2008220667                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  | 申请日     | 2008-08-29 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |         |            |

| [标]发明人         | 伴田智壮<br>豊村直史<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |         |            |

| 发明人            | 伴田 智壮<br>豊村 直史<br>内野 勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 H05B33/08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |         |            |

| CPC分类号         | Y02B20/343 Y02B20/346                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |         |            |

| FI分类号          | G09G3/30.K G09G3/20.642.A G09G3/20.611.H G09G3/20.621.A G09G3/20.624.B G09G3/20.670.J<br>G09G3/20.641.D G09G3/20.612.D G09G3/20.624.Z G09G3/20.622.Z H05B33/14.A H05B33/08 G09G3<br>/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC31 3K107/EE03 3K107/HH04 5C080/AA06 5C080/BB05 5C080<br>/CC03 5C080/DD05 5C080/DD29 5C080/EE29 5C080/EE30 5C080/FF03 5C080/FF11 5C080/HH10<br>5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/AB34 5C380/AB46 5C380<br>/BA10 5C380/BA12 5C380/BA20 5C380/BA34 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BC20<br>5C380/BD02 5C380/BD12 5C380/CA04 5C380/CA08 5C380/CA12 5C380/CA26 5C380/CA32 5C380<br>/CA53 5C380/CA54 5C380/CB01 5C380/CB02 5C380/CB20 5C380/CB27 5C380/CB31 5C380/CC02<br>5C380/CC03 5C380/CC04 5C380/CC05 5C380/CC06 5C380/CC07 5C380/CC26 5C380/CC27 5C380<br>/CC33 5C380/CC41 5C380/CC62 5C380/CC72 5C380/CD022 5C380/CE04 5C380/CF09 5C380/CF48<br>5C380/CF51 5C380/DA02 5C380/DA06 5C380/DA32 5C380/DA47 5C380/HA03 5C380/HA05 |  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |         |            |

## 摘要(译)

本发明应用于例如使用有机EL元件的有源矩阵型图像显示装置，并且防止由于在单元驱动系统中长期使用而导致的亮度不均匀。根据本发明，将相应组的电源驱动信号DS [n]和先前的电源驱动信号DS [n-1]提供给线DSL [5n]，DSL [5n + 1]，DSL [5n + 2]，DSL [5n + 3]和DSL [5n + 4]被切换以输出用于电源的驱动信号，并且以组中的延迟开始发光时段的线路在特定时段内具有优先权。电源驱动信号DS [n-1]设置为依次增加。[选型图]图1