(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-130005

(P2009-130005A)

(43) 公開日 平成21年6月11日(2009.6.11)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H01L 51/50</b> (2006.01) | H05B 33/14 | A 3K107     |

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30  | K 5C080     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/30  | Z           |

| <b>H05B 33/22</b> (2006.01) | G09G 3/20  | 641D        |

|                             | G09G 3/20  | 624B        |

審査請求 未請求 請求項の数 11 O L (全 44 頁) 最終頁に続く

|           |                              |          |                                        |

|-----------|------------------------------|----------|----------------------------------------|

| (21) 出願番号 | 特願2007-301118 (P2007-301118) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (22) 出願日  | 平成19年11月21日 (2007.11.21)     | (74) 代理人 | 100086298<br>弁理士 船橋 國則                 |

|           |                              | (72) 発明者 | 山本 哲郎<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

|           |                              | (72) 発明者 | 内野 勝秀<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

|           |                              | (72) 発明者 | 豊村 直史<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

最終頁に続く

## (54) 【発明の名称】表示装置

## (57) 【要約】

【課題】有機EL表示装置において、並走する配線の異物によるショートを防止する。

【解決手段】電源供給線105DSLと映像信号線106HSの画素回路Pの内側を上層配線にする。書込走査線104WSを下層配線にする。映像信号線106HSは、同層の電源供給線105DSLと交差する部分をオーバーラップさせる必要があるので下層配線にする。映像信号線106HSの上層配線を隣接する次行の画素回路Pの境界まで延在させ、次行の同層の電源供給線105DSLと交差する部分でオーバーラップさせる。異なる配線層にレイアウトされている書込走査線104WSと電源供給線105DSLは、導電性を有する異物が何れか一方の層に載っていても、書込走査線104WSと電源供給線105DSLが異物で接続される事態は起きない。

【選択図】図9

## 【特許請求の範囲】

## 【請求項 1】

駆動電流を生成する駆動トランジスタ、映像信号の信号振幅に応じた情報を保持する保持容量、前記駆動トランジスタの出力端側に接続された電気光学素子、および前記保持容量に前記信号振幅に応じた情報を書き込むサンプリングトランジスタを具備し、前記保持容量に保持された情報に基づく駆動電流を前記駆動トランジスタで生成して前記電気光学素子に流すことで当該電気光学素子が発光する画素回路が行列状に配置されている画素アレイ部と、

トランジスタを具備し、当該トランジスタを制御することで前記駆動電流を一定に維持する駆動信号一定化回路と

を備え、

前記画素回路内および隣接する画素回路の境界部分では、前記画素回路や前記駆動信号一定化回路を構成するトランジスタを制御するための隣接する2つの走査線が、異なる配線層に形成されている

ことを特徴とする表示装置。

## 【請求項 2】

前記隣接する2つの走査線のそれぞれの全体が、前記異なる配線層に形成されていることを特徴とする請求項1に記載の表示装置。

## 【請求項 3】

前記隣接する2つの走査線の内の一方の全体と、他方の一部を除く大部分とが、前記異なる配線層に形成されている

ことを特徴とする請求項1に記載の表示装置。

## 【請求項 4】

前記隣接する2つの走査線と交差する交差配線を有し、

前記隣接する2つの走査線の内の前記他方は、前記一部が前記交差配線と同層に形成されている

ことを特徴とする請求項3に記載の表示装置。

## 【請求項 5】

前記画素回路内には、前記画素回路や前記駆動信号一定化回路を構成するトランジスタを制御するための同方向に並走する走査線を偶数本有し、

前記偶数本の走査線が、前記画素回路が配置される画素ピッチ内で、上層配線と下層配線で交互に形成されている

ことを特徴とする請求項1に記載の表示装置。

## 【請求項 6】

前記画素回路内には、前記画素回路や前記駆動信号一定化回路を構成するトランジスタを制御するための同方向に並走する走査線を奇数本有し、

前記奇数本の内の1本の走査線が、前記画素回路が配置される画素ピッチ内の方の最端部において上層配線と下層配線の何れか一方に形成されており、

前記奇数本の内の他の1本の走査線が、前記画素回路が配置される画素ピッチ内の方の最端部において前記上層配線と下層配線の他方に形成されている

ことを特徴とする請求項1に記載の表示装置。

## 【請求項 7】

前記奇数本の内の偶数本の走査線が、前記画素回路が配置される画素ピッチ内で、上層配線と下層配線で交互に形成されている

ことを特徴とする請求項6に記載の表示装置。

## 【請求項 8】

隣接する2つの画素回路において、

一方の画素回路における他方の画素回路と隣接する最端部に形成されている上層配線および下層配線の内の一方の配線と、他方の画素回路における前記一方の画素回路と隣接する最端部に形成されている前記上層配線および下層配線の内の他方の配線とが、絶縁層を

10

20

30

40

50

挟んで積層されている

ことを特徴とする請求項 5, 6 に記載の表示装置。

【請求項 9】

前記駆動信号一定化回路は、基準電位と信号電位で切り替わる映像信号をサンプリングトランジスタに供給するとともに、駆動電流を前記電気光学素子に流すために使用される第1電位に対応する電圧が前記駆動トランジスタの電源供給端に供給されかつ映像信号における基準電位が前記サンプリングトランジスタに供給されている時間帯で前記サンプリングトランジスタを導通させることで前記駆動トランジスタの閾値電圧に対応する電圧を前記保持容量に保持させる閾値補正機能を実現するように構成されたものである

ことを特徴とする請求項 1 に記載の表示装置。

10

【請求項 10】

前記駆動信号一定化回路は、前記駆動トランジスタの閾値電圧に対応する電圧を前記保持容量に保持させる閾値補正機能と、閾値補正動作の後に、前記サンプリングトランジスタを導通させることで前記保持容量に信号電位に応じた情報を書き込む際、前記駆動トランジスタの移動度に対する補正分を前記保持容量に書き込まれる信号に加える移動度補正機能とを実現するように構成されたものである

ことを特徴とする請求項 1 に記載の表示装置。

20

【請求項 11】

前記駆動信号一定化回路は、前記保持容量が前記駆動トランジスタの制御入力端と出力端側の間に接続されることでブートストラップ機能を実現するように構成されたものである

ことを特徴とする請求項 1 に記載の表示装置。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電気光学素子（表示素子や発光素子とも称される）を具備する画素回路（画素とも称される）が行列状に配列された画素アレイ部を有する表示装置に関する。より詳細には、駆動信号の大小によって輝度が変化する電気光学素子を表示素子として有する画素回路が行列状に配置されてなり、画素回路ごとに能動素子を有して当該能動素子によって画素単位で表示駆動が行なわれるアクティブマトリクス型の表示装置に関する。

30

【背景技術】

【0002】

画素の表示素子として、印加される電圧や流れる電流によって輝度が変化する電気光学素子を用いた表示装置がある。たとえば、印加される電圧によって輝度が変化する電気光学素子としては液晶表示素子が代表例であり、流れる電流によって輝度が変化する電気光学素子としては、有機エレクトロルミネッセンス（Organic Electro Luminescence, 有機EL, Organic Light Emitting Diode, OLED；以下、有機ELと記す）素子が代表例である。後者の有機EL素子を用いた有機EL表示装置は、画素の表示素子として、自発光素子である電気光学素子を用いたいわゆる自発光型の表示装置である。

40

【0003】

有機EL素子は下部電極と上部電極との間に有機正孔輸送層や有機発光層を積層させてなる有機薄膜（有機層）を設けてなり、有機薄膜に電界をかけると発光する現象を利用した電気光学素子であり、有機EL素子を流れる電流値を制御することで発色の階調を得ている。

【0004】

有機EL素子は比較的低い印加電圧（たとえば10V以下）で駆動できるため低消費電力である。また有機EL素子は自ら光を発する自発光素子であるため、液晶表示装置では必要とされるバックライトなどの補助照明部材を必要とせず、軽量化および薄型化が容易である。さらに、有機EL素子の応答速度は非常に高速である（たとえば数μs程度）ので、動画表示時の残像が発生しない。これらの利点があることから、電気光学素子として

50

有機EL素子を用いた平面自発光型の表示装置の開発が近年盛んになっている。

【0005】

ところで、液晶表示素子を用いた液晶表示装置や有機EL素子を用いた有機EL表示装置を始めとする電気光学素子を用いた表示装置においては、その駆動方式として、単純(パッシブ)マトリクス方式とアクティブマトリクス方式とを探ることができる。ただし、単純マトリクス方式の表示装置は、構造が単純であるもの、大型でかつ高精細の表示装置の実現が難しいなどの問題がある。

【0006】

このため、近年、画素内部の発光素子に供給する画素信号を、同様に画素内部に設けた能動素子、たとえば絶縁ゲート型電界効果トランジスタ(一般には、薄膜トランジスタ(Tin Film Transistor; TFT)をスイッチングトランジスタとして使用して制御するアクティブマトリクス方式の開発が盛んに行なわれている。

10

【0007】

ここで、画素回路内の電気光学素子を発光させる際には、映像信号線を介して供給される入力画像信号をスイッチングトランジスタ(サンプリングトランジスタと称する)で駆動トランジスタのゲート端(制御入力端子)に設けられた保持容量(画素容量とも称する)に取り込み、取り込んだ入力画像信号に応じた駆動信号を電気光学素子に供給する。

【0008】

電気光学素子として液晶表示素子を用いる液晶表示装置では、液晶表示素子が電圧駆動型の素子であることから、保持容量に取り込んだ入力画像信号に応じた電圧信号そのもので液晶表示素子を駆動する。これに対して、電気光学素子として有機EL素子などの電流駆動型の素子を用いる有機EL表示装置では、保持容量に取り込んだ入力画像信号に応じた駆動信号(電圧信号)を駆動トランジスタで電流信号に変換して、その駆動電流を有機EL素子などに供給する。

20

【0009】

有機EL素子を代表例とする電流駆動型の電気光学素子では、駆動電流値が異なると発光輝度も異なる。よって、安定した輝度で発光させるためには、安定した駆動電流を電気光学素子に供給することが肝要となる。たとえば、有機EL素子に駆動電流を供給する駆動方式としては、定電流駆動方式と定電圧駆動方式とに大別できる(周知の技術であるので、ここでは公知文献の提示はしない)。

30

【0010】

有機EL素子の電圧-電流特性は傾きの大きい特性を有するので、定電圧駆動を行なうと、僅かな電圧のばらつきや素子特性のばらつきが大きな電流のばらつきを生じ大きな輝度ばらつきをもたらす。よって、一般的には、駆動トランジスタを飽和領域で使用する定電流駆動が用いられる。もちろん、定電流駆動でも、電流変動があれば輝度ばらつきを招くが、小さな電流ばらつきであれば小さな輝度ばらつきしか生じない。

【0011】

逆に言えば、定電流駆動方式であっても、電気光学素子の発光輝度が不变であるためには、入力画像信号に応じて保持容量に書き込まれ保持される駆動信号が一定であることが重要となる。たとえば、有機EL素子の発光輝度が不变であるためには、入力画像信号に応じた駆動電流が一定であることが重要となる。

40

【0012】

ところが、プロセス変動により電気光学素子を駆動する能動素子(駆動トランジスタ)の閾値電圧や移動度がばらついてしまう。また、有機EL素子などの電気光学素子の特性が経時に変動する。このような駆動用の能動素子の特性ばらつきや電気光学素子の特性変動があると、定電流駆動方式であっても、発光輝度に影響を与えてしまう。

【0013】

このため、表示装置の画面全体に亘って発光輝度を均一に制御するため、各画素回路内で上述した駆動用の能動素子や電気光学素子の特性変動に起因する輝度変動を補正するための仕組みが種々検討されている。

50

【0014】

【特許文献1】特開2006-215213号公報

【0015】

たとえば、特許文献1に記載の仕組みでは、有機EL素子用の画素回路として、駆動トランジスタの閾値電圧にばらつきや経時変化があった場合でも駆動電流を一定にするための閾値補正機能や、駆動トランジスタの移動度にばらつきや経時変化があった場合でも駆動電流を一定にするための移動度補正機能や、有機EL素子の電流-電圧特性に経時変化があった場合でも駆動電流を一定にするためのブートストラップ機能が提案されている。

【発明の開示】

【発明が解決しようとする課題】

10

【0016】

しかしながら、閾値補正機能や、移動度補正機能や、ブートストラップ機能を働かせるためには、各種のトランジスタをオン/オフ制御する必要があり、そのために各種の走査線を画素アレイ部に縦方向や横方向に形成する必要がある。

【0017】

同方向に延びる走査線を同じ配線層で並走させる場合、その配線間隔が狭いと、つまり、近接して並走させると、製造時に導電性を有する異物によって配線間が電気的に接続されてしまい歩留まりが低下する可能性がある。走査線が長いほどその可能性が高くなる。

【0018】

また、特許文献1に記載の仕組みでは、前述のように、5TR駆動の構成を採っており、画素回路の構成が複雑である。画素回路の構成要素が多いことから、表示装置の高精細化の妨げとなる。その結果、5TR駆動の構成では、携帯機器（モバイル機器）などの小型の電子機器で用いられる表示装置への適用が困難になる。

20

【0019】

このため、画素回路の簡素化を図りつつ、並走する走査線の異物による接続を防止する仕組みの開発要求がある。この際には、並走する走査線の異物による接続を防止するとともに、画素回路の簡素化に伴って、5TR駆動の構成では生じていない問題が新たに発生することがないようにすることも考慮されるべきである。

【0020】

本発明は、上記事情に鑑みてなされたもので、先ず、並走する走査線の異物による接続を防止し、表示特性の向上を図ることのできる仕組みを提供することを目的とする。

30

【0021】

さらに好ましくは、画素回路の簡素化により表示装置の高精細化を可能にする仕組みを提供することを目的とする。

【0022】

また、画素回路の簡素化に当たっては、好ましくは、駆動トランジスタや電気光学素子の特性ばらつきによる輝度変化を抑制することの可能な仕組みを提供することを目的とする。

【課題を解決するための手段】

【0023】

40

本発明に係る表示装置の一実施形態は、映像信号に基づいて画素回路内の電気光学素子を発光させる表示装置であって、先ず、画素アレイ部に行列状に配される画素回路内に、少なくとも、駆動電流を生成する駆動トランジスタ、駆動トランジスタの出力端側に接続された電気光学素子、映像信号線を介して供給される映像信号の内の信号電位に応じた情報を保持する保持容量、および保持容量に映像信号における信号電位に応じた情報を書き込むサンプリングトランジスタを備える。この画素回路においては、保持容量に保持された情報に基づく駆動電流を駆動トランジスタで生成して電気光学素子に流すことで電気光学素子を発光させる。

【0024】

サンプリングトランジスタで保持容量に信号電位に応じた情報を書き込むので、サンプ

50

リングトランジスタは、その入力端（ソース端もしくはドレイン端の一方）に信号電位を取り込み、その出力端（ソース端もしくはドレイン端の他方）に接続された保持容量に信号電位に応じた情報を書き込む。もちろん、サンプリングトランジスタの出力端は、駆動トランジスタの制御入力端にも接続されている。

【0025】

なお、ここで示した画素回路の接続構成は、駆動トランジスタとサンプリングトランジスタと言った2つのトランジスタを含む最も基本的な2TR構成を示したもので、画素回路は、少なくとも前述の各構成要素を含むものであればよく、これらの構成要素以外（つまり他の構成要素）が含まれていてもよい。また、「接続」は、直接に接続されている場合に限らず、他の構成要素を介在して接続されている場合でもよい。

10

【0026】

たとえば、接続間には、必要に応じてさらに、スイッチング用のトランジスタや、ある機能を持った機能部などを介在させるなどの変更が加えられることがある。典型的には、表示期間（換言すれば非発光時間）を動的に制御するためにスイッチング用のトランジスタを、駆動トランジスタの出力端と電気光学素子との間に、もしくは駆動トランジスタの電源供給端（ドレイン端が典型例）と電源供給用の配線である電源線との間に、もしくは駆動トランジスタの出力端と基準電圧線との間に配することがある。

【0027】

このような変形態様の画素回路であっても、本項（課題を解決するための手段）で説明する構成や作用を実現し得るものである限り、それらの変形態様も、本発明に係る表示装置の一実施形態を実現する画素回路である。

20

【0028】

また、画素回路を駆動するための周辺部には、たとえば、サンプリングトランジスタを水平周期で順次制御することで画素回路を線順次走査して、1行分の各保持容量に映像信号の信号電位に応じた情報を書き込む書込走査部と、書込走査部での線順次走査に合わせて映像信号がサンプリングトランジスタに供給されるように制御する水平駆動部を具備する制御部を設ける。

【0029】

また、表示装置は、駆動電流を一定に維持する駆動信号一定化回路を備えたものとする。駆動信号一定化回路は、画素回路を構成する素子の接続態様や画素回路を走査駆動する走査部の組合せで構成される。これに対応して、制御部には、駆動信号一定化回路を制御する走査部を設ける。

30

【0030】

駆動信号一定化回路とは、電気光学素子の電流・電圧特性の経時変化や駆動トランジスタの特性変化があった場合でも、駆動トランジスタの駆動電流を一定に維持しようとする回路を意味する。その具体的な回路構成はどのようなものであってもよい。サンプリングトランジスタ（スイッチングトランジスタの一例）および駆動トランジスタ以外に、駆動電流を一定に維持する制御を行なうための他のスイッチングトランジスタが設けられることがある。

【0031】

たとえば、好ましくは、制御部は、駆動トランジスタの閾値電圧に対応する電圧を保持容量に保持するための閾値補正動作を行なうように制御する。2TR構成の場合、好ましくは、駆動電流を電気光学素子に流すために使用される第1電位に対応する電圧が駆動トランジスタの電源供給端に供給されかつ映像信号における基準電位がサンプリングトランジスタに供給されている時間帯でサンプリングトランジスタを導通させることで閾値電圧に対応する電圧を保持容量に保持させる。

40

【0032】

このため、2TR構成の場合、好ましくは、書込走査部での線順次走査に合わせて1行分の各駆動トランジスタの電源供給端に印加される電源供給を制御するための走査駆動パルスを出力する駆動走査部を制御部に設け、また、水平駆動部は、各水平周期内で基準電

50

位と信号電位で切り替わる映像信号をサンプリングトランジスタに供給する。サンプリングトランジスタは、駆動信号一定化機能に関わるスイッチングトランジスタとして機能し、その機能の実現のために、オン／オフ動作が制御される。

【0033】

閾値補正動作は、必要に応じて、信号電位の保持容量への書き込みに先行する複数の水平周期で繰り返し実行するとよい。ここで「必要に応じて」とは、1水平周期内の閾値補正期間では駆動トランジスタの閾値電圧に相当する電圧を十分に保持容量へ保持させることができない場合を意味する。閾値補正動作の複数回の実行により、確実に駆動トランジスタの閾値電圧に相当する電圧を保持容量に保持させるのである。

【0034】

また、さらに好ましくは、制御部は、閾値補正動作に先立って、駆動トランジスタの制御入力端と出力端の電位や保持容量を、両端の電位差が閾値電圧以上になるように初期化を実行するように制御する。2TR構成の場合、好ましくは、第2電位に対応する電圧が駆動トランジスタの電源供給端に供給されかつサンプリングトランジスタの入力端（ソース端もしくはドレイン端の一方）に基準電位が供給されている時間帯でサンプリングトランジスタを導通させて駆動トランジスタの制御入力端を基準電位に設定しつつ出力端を第2電位に設定する。

【0035】

さらに好ましくは、制御部は、閾値補正動作の後、サンプリングトランジスタを導通させることで保持容量に信号電位に応じた情報を書き込む際、駆動トランジスタの移動度に対する補正分を保持容量に書き込まれる信号に加えるように制御する移動度補正機能を実現するようにする。この際、2TR構成の場合、好ましくは、サンプリングトランジスタに信号電位が供給されている時間帯内の所定位置で、その時間帯より短い期間だけサンプリングトランジスタを導通させるとよい。

【0036】

さらに好ましくは、保持容量は、ブートストラップ機能を実現するべく、駆動トランジスタの制御入力端と出力端側（事実上、電気光学素子の一方の端子側）の間に接続する。制御部は、保持容量に信号電位に対応する情報が書き込まれた時点でサンプリングトランジスタを非導通状態にして駆動トランジスタの制御入力端への映像信号の供給を停止させ、駆動トランジスタの出力端の電位変動に制御入力端の電位が連動するブートストラップ動作を行なうように制御する。

【0037】

通常の画素回路においては、水平走査用の縦配線と垂直走査用の横配線が必要であるから、基本的には、縦配線と横配線とのオーバーラップのために、最低でも2層配線が必要になる。ここで、本発明に係る表示装置の一実施形態における特徴的な事項として、2層配線を利用して、画素回路内もしくは隣接する2つの画素回路の間ににおいて、近くを並走する走査線（隣接配線と称する）の全体もしくは一部を異なる配線層にレイアウトする。異なる配線層にレイアウトされている隣接配線の部分については、導電性を有する異物が何れか一方の層に載っていても、隣接配線が異物で接続される事態は起きない。

【発明の効果】

【0038】

本発明の一実施形態によれば、近くを並走する隣接配線の全体もしくは一部を異なる配線層にレイアウトするようにしたので、少なくとも、異なる配線層にレイアウトされている隣接配線の部分については、導電性を有する異物による隣接配線間の同層ショートが起こり得ないので、高歩留まりが実現可能である。

【0039】

近くを並走する隣接配線の全体を異なる配線層にレイアウトすれば、導電性を有する異物による隣接配線間の同層ショートの可能性を完全に排除できる。

【0040】

一方、近くを並走する隣接配線の一部を異なる配線層にレイアウトすれば、その一部で

10

20

30

40

50

は導電性を有する異物による隣接配線間の同層ショートが起こり得るので、同層ショートの可能性を完全に排除することはできない。しかしながら、その一部（つまり同層になる部分）では、縦配線および横配線の何れか一方と、それに対しての交差配線（縦配線に対しての横配線、横配線に対しての縦配線）を、異なる配線層にレイアウトすることができる。これにより、交差配線を上層配線と下層配線で繋ぐことでオーバーラップさせるという処理が不要になり、ブリッジ（上層配線と下層配線を繋ぐこと）の回数を少なくすることができるため、交差配線の負荷を軽減することができる。

#### 【0041】

ここで、画素回路内において並走する配線が幾つになるかは画素回路の構成次第である。この際、閾値補正機能およびそれに先立つ閾値補正準備機能（初期化機能）や移動度補正機能を実現するに当たって、駆動トランジスタの電源供給端を第1電位と第2電位との間で遷移させる、つまり電源電圧をスイッチングパルスとして使用することが有効に機能する。すなわち、閾値補正機能や移動度補正機能を組み込むため、各画素回路の駆動トランジスタに供給する電源電圧をスイッチングパルスとして使用すると、補正用のスイッチングトランジスタやその制御入力端を制御する走査線が不要になる。

10

#### 【0042】

結果として、2TR駆動の構成をベースとして各トランジスタの駆動タイミングなどの変形を加えるだけでよく、画素回路の構成素子数と配線本数が大幅に削減でき、画素アレイ部を縮小することができ、表示装置の高精細化を達成し易くなる。画素回路の簡素化を図りつつ、導電性を有する異物による隣接配線間の同層ショートを防止することができる。素子数や配線数が少ないため高精細化に適しており、高精細の表示が求められる小型の表示装置を容易に実現できる。

20

#### 【発明を実施するための最良の形態】

#### 【0043】

以下、図面を参照して本発明の実施形態について詳細に説明する。

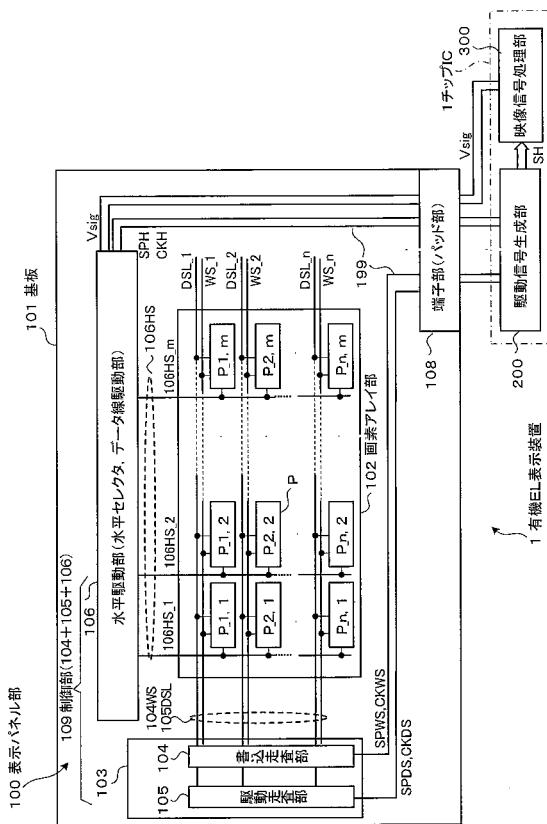

#### 【0044】

##### <表示装置の全体概要>

図1は、本発明に係る表示装置の一実施形態であるアクティブマトリクス型表示装置の構成の概略を示すブロック図である。本実施形態では、たとえば画素の表示素子（電気光学素子、発光素子）として有機EL素子を、能動素子としてポリシリコン薄膜トランジスタ（TFT；Thin Film Transistor）をそれぞれ用い、薄膜トランジスタを形成した半導体基板上に有機EL素子を形成してなるアクティブマトリクス型有機ELディスプレイ（以下「有機EL表示装置」と称する）に適用した場合を例に採って説明する。

30

#### 【0045】

なお、以下においては、画素の表示素子として有機EL素子を例に具体的に説明するが、これは一例であって、対象となる表示素子は有機EL素子に限らない。一般的に電流駆動で発光する表示素子の全てに、後述する全ての実施形態が同様に適用できる。

#### 【0046】

図1に示すように、有機EL表示装置1は、複数の表示素子としての有機EL素子（図示せず）を持った画素回路（画素とも称される）Pが表示アスペクト比である縦横比がX:Y（たとえば9:16）の有効映像領域を構成するように配置された表示パネル部100と、この表示パネル部100を駆動制御する種々のパルス信号を発するパネル制御部の一例である駆動信号生成部200と、映像信号処理部300を備えている。駆動信号生成部200と映像信号処理部300とは、1チップのIC（Integrated Circuit；半導体集積回路）に内蔵されている。

40

#### 【0047】

製品形態としては、図示のように、表示パネル部100、駆動信号生成部200、および映像信号処理部300の全てを備えたモジュール（複合部品）形態の有機EL表示装置1として提供されることに限らず、たとえば、表示パネル部100のみで有機EL表示装置1として提供することも可能である。また、このような有機EL表示装置1は、半導体

50

メモリやミニディスク（MD）やカセットテープなどの記録媒体を利用した携帯型の音楽プレイヤーやその他の電子機器の表示部に利用される。

【0048】

表示パネル部100は、基板101の上に、画素回路Pがn行×m列のマトリクス状に配列された画素アレイ部102と、画素回路Pを垂直方向に走査する垂直駆動部103と、画素回路Pを水平方向に走査する水平駆動部（水平セレクタあるいはデータ線駆動部とも称される）106と、外部接続用の端子部（パッド部）108などが集積形成されている。すなわち、垂直駆動部103や水平駆動部106などの周辺駆動回路が、画素アレイ部102と同一の基板101上に形成された構成となっている。

【0049】

垂直駆動部103としては、たとえば、書込走査部（ライトスキャナWS；Write Scan）104や電源供給能力を有する電源スキャナとして機能する駆動走査部（ドライブスキャナDS；Drive Scan）105を有する。

【0050】

垂直駆動部103と水平駆動部106とで、信号電位の保持容量への書き込みや、閾値補正動作や、移動度補正動作や、ブートストラップ動作を制御する制御部109が構成される。

【0051】

図示した垂直駆動部103および対応する走査線の構成は、画素回路Pが後述する本実施形態の2TR構成の場合に適合させて示したものであるが、画素回路Pの構成によっては、その他の走査部が設けられることもある。

【0052】

画素アレイ部102は、一例として、図示する左右方向の一方側もしくは両側から書き走査部104および駆動走査部105で駆動され、かつ図示する上下方向の一方側もしくは両側から水平駆動部106で駆動されるようになっている。

【0053】

端子部108には、有機EL表示装置1の外部に配された駆動信号生成部200から、種々のパルス信号が供給されるようになっている。また同様に、映像信号処理部300から映像信号Vsigが供給されるようになっている。

【0054】

一例としては、垂直駆動用のパルス信号として、垂直方向の書き込み開始パルスの一例であるシフトスタートパルスSPDS, SPWSや垂直走査クロックCKDS, CKWSなど必要なパルス信号が供給される。また、水平駆動用のパルス信号として、水平方向の書き込み開始パルスの一例である水平スタートパルスSPHや水平走査クロックCKHなど必要なパルス信号が供給される。

【0055】

端子部108の各端子は、配線199を介して、垂直駆動部103や水平駆動部106に接続されるようになっている。たとえば、端子部108に供給された各パルスは、必要に応じて図示を割愛したレベルシフタ部で電圧レベルを内部的に調整した後、バッファを介して垂直駆動部103の各部や水平駆動部106に供給される。

【0056】

画素アレイ部102は、図示を割愛するが（詳細は後述する）、表示素子としての有機EL素子に対して画素トランジスタが設けられた画素回路Pが行列状に2次元配置され、この画素配列に対して行ごとに走査線が配線されるとともに、列ごとに信号線が配線された構成となっている。

【0057】

たとえば、画素アレイ部102には、走査線（ゲート線）104WS、電源供給線105DSL、および映像信号線（データ線）106HSが形成されている。両者の交差部分には図示を割愛した有機EL素子とこれを駆動する薄膜トランジスタ（TFT；Thin Film Transistor）が形成される。有機EL素子と薄膜トランジスタの組み合わせで画素回路Pを構

10

20

30

40

50

成する。

【0058】

具体的には、マトリクス状に配列された各画素回路Pに対しては、書込走査部104によって書込駆動パルスWSで駆動されるn行分の書込走査線104WS\_1～104WS\_nおよび駆動走査部105によって電源駆動パルスDSLで駆動されるn行分の電源供給線105DS\_L\_1～105DSL\_nが画素行ごとに配線される。

【0059】

書込走査部104および駆動走査部105は、駆動信号生成部200から供給される垂直駆動系のパルス信号に基づき、書込走査線104WSおよび電源供給線105DSLを介して各画素回路Pを順次選択する。水平駆動部106は、駆動信号生成部200から供給される水平駆動系のパルス信号に基づき、選択された画素回路Pに対し映像信号線106HSを介して映像信号Vsигの内の所定電位をサンプリングして保持容量に書き込ませる。

10

【0060】

本実施形態の有機EL表示装置1においては、一例として線順次駆動について考えており、垂直駆動部103の書込走査部104および駆動走査部105は線順次で(つまり行単位で)画素アレイ部102を走査するとともに、これに同期して水平駆動部106が、画像信号を、1水平ライン分を同時に、画素アレイ部102に書き込む。

【0061】

たとえば、水平駆動部106は、線順次駆動に対応するため、全列の映像信号線106HS上に設けられた図示を割愛したスイッチを一斉にオンさせるドライバ回路を備えて構成され、映像信号処理部300から入力される画素信号を、垂直駆動部103によって選択された行の1ライン分の全ての画素回路Pに同時に書き込むべく、全列の映像信号線106HS上に設けられた図示を割愛したスイッチを一斉にオンさせる。

20

【0062】

垂直駆動部103の各部は、線順次駆動に対応するため、論理ゲートの組合せ(ラッチも含む)によって構成され、画素アレイ部102の各画素回路Pを行単位で選択する。なお、図1では、画素アレイ部102の一方側にのみ垂直駆動部103を配置する構成を示しているが、画素アレイ部102を挟んで左右両側に垂直駆動部103を配置する構成を探ることも可能である。

30

【0063】

同様に、図1では、画素アレイ部102の一方側にのみ水平駆動部106を配置する構成を示しているが、画素アレイ部102を挟んで上下両側に水平駆動部106を配置する構成を探ることも可能である。

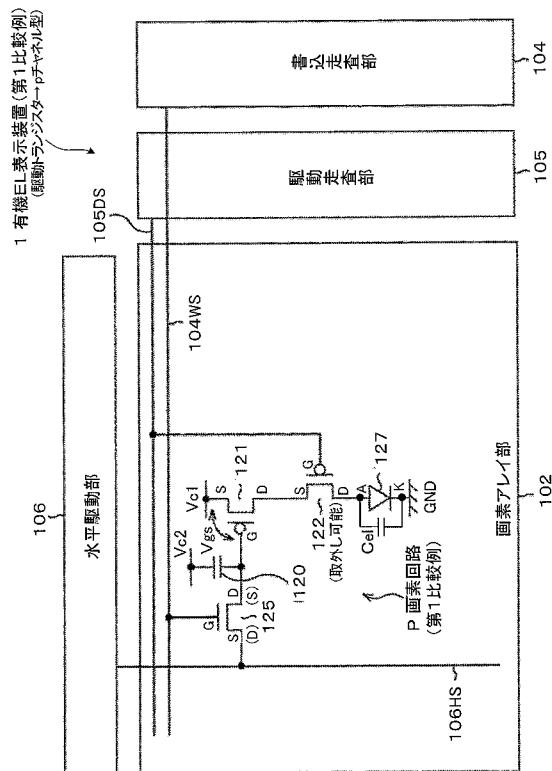

【0064】

<画素回路>

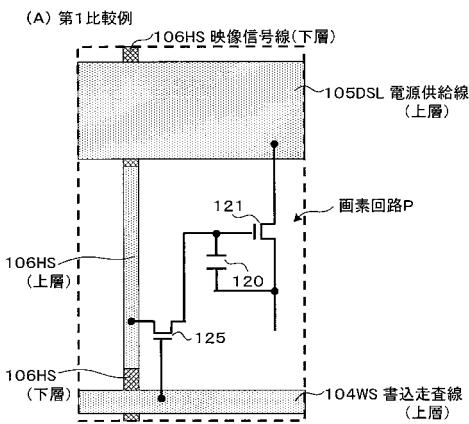

図2は、図1に示した有機EL表示装置1を構成する本実施形態の画素回路Pに対する第1比較例を示す図である。なお、表示パネル部100の基板101上において画素回路Pの周辺部に設けられた垂直駆動部103と水平駆動部106も合わせて示している。

【0065】

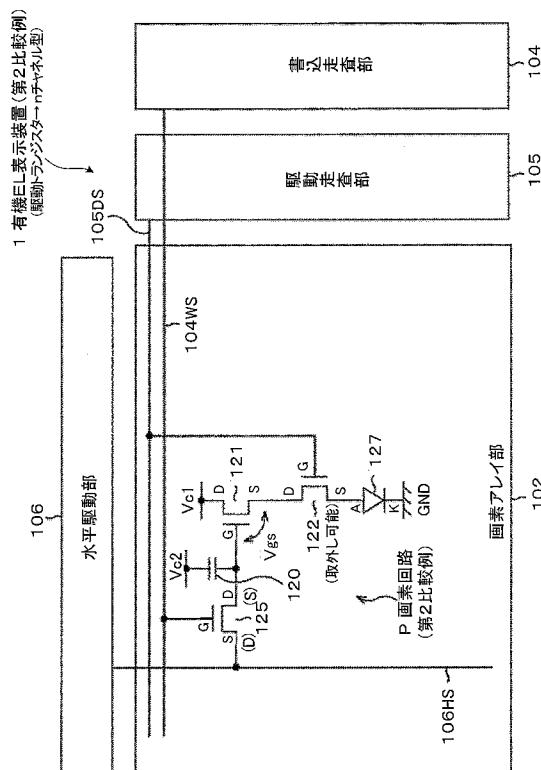

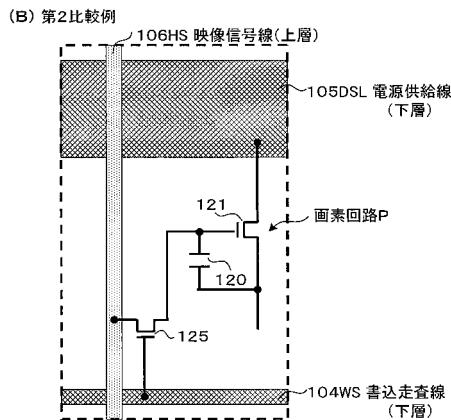

図3は、本実施形態の画素回路Pに対する第2比較例を示す図である。なお、表示パネル部100の基板101上において画素回路Pの周辺部に設けられた垂直駆動部103と水平駆動部106も合わせて示している。

40

【0066】

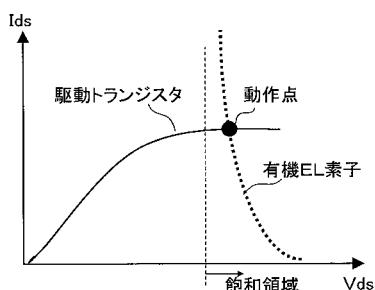

図4は有機EL素子や駆動トランジスタの動作点を説明する図である。図4Aは、有機EL素子や駆動トランジスタの特性ばらつきが駆動電流I<sub>ds</sub>に与える影響を説明する図である。

【0067】

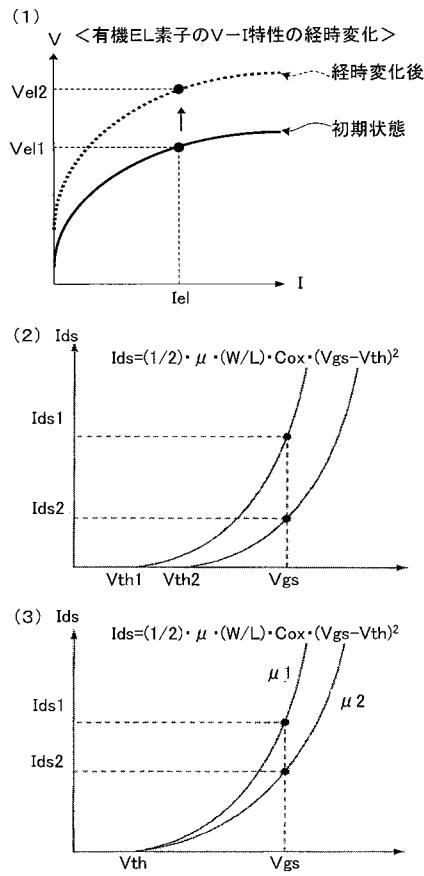

図5は、本実施形態の画素回路Pの構成例を示す図である。なお、表示パネル部100の基板101上において画素回路Pの周辺部に設けられた垂直駆動部103と水平駆動部106も合わせて示している。

50

## 【0068】

<比較例の画素回路：第1例>

図2に示すように、第1比較例の画素回路Pは、基本的にpチャネル型の薄膜電界効果トランジスタ(TFT)でドライブトランジスタが構成されている点に特徴を有する。また、ドライブトランジスタの他に走査用に2つのトランジスタを使用した3Tr駆動の構成を採っている。

## 【0069】

具体的には、第1比較例の画素回路Pは、pチャネル型の駆動トランジスタ121、アクティブLの駆動パルスが供給されるpチャネル型の発光制御トランジスタ122、アクティブHの駆動パルスが供給されるnチャネル型のサンプリングトランジスタ125、電流が流れることで発光する電気光学素子(発光素子)の一例である有機EL素子127、および保持容量(画素容量とも称される)120を有する。駆動トランジスタ121は、制御入力端子であるゲート端Gに供給される電位に応じた駆動電流を有機EL素子127に供給するようになっている。

10

## 【0070】

なお、一般的には、サンプリングトランジスタ125はアクティブLの駆動パルスが供給されるpチャネル型に置き換えることもできる。発光制御トランジスタ122はアクティブHの駆動パルスが供給されるnチャネル型に置き換えることもできる。

## 【0071】

サンプリングトランジスタ125は、駆動トランジスタ121のゲート端G(制御入力端子)側に設けられたスイッチングトランジスタであり、また、発光制御トランジスタ122もスイッチングトランジスタである。

20

## 【0072】

一般に、有機EL素子127は整流性があるためダイオードの記号で表わしている。なお、有機EL素子127には、寄生容量Ceiが存在する。図では、この寄生容量Ceiを有機EL素子127と並列に示す。

30

## 【0073】

画素回路Pは、垂直走査側の各走査線104WS, 105DSと水平走査側の走査線である映像信号線106HSの交差部に配されている。書き走査部104からの書き走査線104WSは、サンプリングトランジスタ125のゲート端Gに接続され、駆動走査部105からの駆動走査線105DSは発光制御トランジスタ122のゲート端Gに接続されている。

## 【0074】

サンプリングトランジスタ125は、ソース端Sを信号入力端として映像信号線106HSに接続され、ドレイン端Dを信号出力端として駆動トランジスタ121のゲート端Gに接続され、その接続点と第2電源電位Vc2(たとえば正電源電圧、第1電源電位Vc1と同じでもよい)との間に保持容量120が設けられている。括弧書きで示すように、サンプリングトランジスタ125は、ソース端Sとドレイン端Dとを逆転させ、ドレイン端Dを信号入力端として映像信号線106HSに接続し、ソース端Sを信号出力端として駆動トランジスタ121のゲート端Gに接続することもできる。

40

## 【0075】

駆動トランジスタ121、発光制御トランジスタ122、および有機EL素子127は、第1電源電位Vc1(たとえば正電源電圧)と基準電位の一例である接地電位GNDの間で、この順に直列に接続されている。具体的には、駆動トランジスタ121は、ソース端Sが第1電源電位Vc1に接続され、ドレイン端Dが発光制御トランジスタ122のソース端Sに接続されている。発光制御トランジスタ122のドレイン端Dが、有機EL素子127のアノード端Aに接続され、有機EL素子127のカソード端Kが接地電位GNDに接続されている。

## 【0076】

なお、より簡易な構成としては、図2に示した画素回路Pの構成においては、最も単純な回路として、発光制御トランジスタ122を取り外した2Tr駆動の構成を採ることも

50

できる。この場合、有機 E L 表示装置 1 としては駆動走査部 105 を取り外した構成を採ることになる。

【0077】

図 2 に示した 3 Tr 駆動や図示を割愛した 2 Tr 駆動の何れにおいても、有機 E L 素子 127 は電流発光素子のため、有機 E L 素子 127 に流れる電流量をコントロールすることで発色の諧調を得る。このため、駆動トランジスタ 121 のゲート端 G への印加電圧を変化させることで、有機 E L 素子 127 に流れる電流値をコントロールする。

【0078】

具体的には、まず書込走査部 104 からアクティブ H の書込駆動パルス WS を供給して書込走査線 104 WS を選択状態とし、水平駆動部 106 から信号線 106 HS に画素信号 Vsig を印加すると、n チャネル型のサンプリングトランジスタ 125 が導通して画素信号 Vsig が保持容量 120 に書き込まれる。

【0079】

保持容量 120 に書き込まれた信号電位が駆動トランジスタ 121 のゲート端 G の電位となる。続いて、書込駆動パルス WS をインアクティブ（本例では L レベル）にして書込走査線 104 WS を非選択状態とすると、信号線 106 HS と駆動トランジスタ 121 とは電気的に切り離されるが、駆動トランジスタ 121 のゲート・ソース間電圧 Vgs は保持容量 120 によって、原理的には、安定に保持される。

【0080】

続いて、駆動走査部 105 からアクティブ L の走査駆動パルス DS を供給して駆動走査線 105 DS を選択状態にすると、p チャネル型の発光制御トランジスタ 122 が導通し、第 1 電源電位 Vc1 から接地電位 GND に向かって駆動電流が駆動トランジスタ 121、発光制御トランジスタ 122、および有機 E L 素子 127 を流れる。

【0081】

次に、走査駆動パルス DS をインアクティブ（本例では H レベル）にして駆動走査線 105 DS を非選択状態とすると、発光制御トランジスタ 122 がオフし、駆動電流は流れなくなる。

【0082】

発光制御トランジスタ 122 は、1 フィールド期間に占める有機 E L 素子 127 の発光時間（デューティ）を制御するために挿入されたものであり、先にも述べたことから推測されるように、画素回路 P としては、当該発光制御トランジスタ 122 を備えていることは必須ではない。

【0083】

駆動トランジスタ 121 および有機 E L 素子 127 に流れる電流は、駆動トランジスタ 121 のゲート・ソース間電圧 Vgs に応じた値となり、有機 E L 素子 127 はその電流値に応じた輝度で発光し続ける。

【0084】

このように、書込走査線 104 WS を選択して信号線 106 HS に与えられた画素信号 Vsig を画素回路 P の内部に伝える動作を、以下「書込み」と呼ぶ。このように、一度信号の書き込みを行なえば、次に書き換えられるまでの間、有機 E L 素子 127 は一定の輝度で発光を続ける。

【0085】

このように、第 1 比較例の画素回路 P では、駆動トランジスタ 121 のゲート端 G に供給する印加電圧を入力信号（画素信号 Vsig）に応じて変化させることで、E L 有機 E L 素子 127 に流れる電流値を制御している。このとき、p チャネル型の駆動トランジスタ 121 のソース端 S は第 1 電源電位 Vc1 に接続されており、この駆動トランジスタ 121 は常に飽和領域で動作している。

【0086】

< 比較例の画素回路 : 第 2 例 >

次に、本実施形態の画素回路 P の特徴を説明するまでの比較例として、図 3 に示す第 2

10

20

30

40

50

比較例の画素回路 P について説明する。画素アレイ部 102 に第 2 比較例の画素回路 P を備える有機 E L 表示装置 1 を第 2 比較例の有機 E L 表示装置 1 と称する。

【0087】

第 2 比較例および本実施形態の画素回路 P は、基本的に n チャネル型の薄膜電界効果トランジスタでドライブトランジスタが構成されている点に特徴を有する。

【0088】

p チャネル型のトランジスタではなく、n チャネル型のトランジスタで駆動トランジスタを構成することができれば、トランジスタ作成において従来のアモルファスシリコン (a - Si) プロセスを用いることが可能になる。これにより、トランジスタ基板の低コスト化が可能となり、このような構成の画素回路 P の開発が期待される。

10

【0089】

第 2 比較例の画素回路 P は、基本的に n チャネル型の薄膜電界効果トランジスタでドライブトランジスタが構成されている点で本実施形態と同じであるが、有機 E L 素子 127 の経時劣化による駆動電流  $I_{ds}$  に与える影響を防ぐための駆動信号一定化回路が設けられていない。

【0090】

具体的には、第 2 比較例の画素回路 P は、それぞれ n チャネル型の駆動トランジスタ 121、発光制御トランジスタ 122、およびサンプリングトランジスタ 125 と、電流が流れることで発光する電気光学素子の一例である有機 E L 素子 127 とを有する。

20

【0091】

駆動トランジスタ 121 は、ドレイン端 D が第 1 電源電位  $V_{c1}$  に接続され、ソース端 S が発光制御トランジスタ 122 のドレイン端 D に接続されている。発光制御トランジスタ 122 のソース端 S が、有機 E L 素子 127 のアノード端 A に接続され、有機 E L 素子 127 のカソード端 K が接地電位 GND に接続されている。このような画素回路 P では、駆動トランジスタ 121 のドレイン端 D 側が第 1 電源電位  $V_{c1}$  に接続され、ソース端 S が有機 E L 素子 127 のアノード端 A 側に接続されることで、全体としてソースフォロワ回路を形成するようになっている。

【0092】

サンプリングトランジスタ 125 は、ソース端 S が映像信号線 HS に接続され、ドレイン端 D は駆動トランジスタ 121 のゲート端 (制御入力端) G に接続され、その接続点と第 2 電源電位  $V_{c2}$  (たとえば正電源電圧、第 1 電源電位  $V_{c1}$  と同じでもよい) を供給する基準線との間に保持容量 120 が設けられている。括弧書きで示すように、サンプリングトランジスタ 125 は、ソース端 S とドレイン端 D とを逆転させた接続様式とすることもできる。

30

【0093】

このような画素回路 P では、発光制御トランジスタを設けるか否かに関わらず、有機 E L 素子 127 を駆動するときには、駆動トランジスタ 121 のドレイン端 D 側が第 1 電源電位  $V_{c1}$  に接続され、ソース端 S が有機 E L 素子 127 のアノード端 A 側に接続されることで、全体としてソースフォロワ回路を形成するようになっている。

40

【0094】

なお、より簡易な構成としては、図 3 に示した画素回路 P の構成においても、最も単純な回路として、発光制御トランジスタ 122 を取り外した 2 Tr 駆動の構成を探ることもできる。この場合、有機 E L 表示装置 1 としては駆動走査部 105 を取り外した構成を探ることになる。

【0095】

次に、図 3 に示す第 2 比較例の画素回路 P の動作を説明する。ここでは、発光制御トランジスタ 122 の動作を割愛して説明する。先ず、信号線 HS から供給される映像信号  $V_{sig}$  の電位 (以下、映像信号線電位とも称する) の内の有効期間の電位 (信号電位と称する) をサンプリングし、発光素子の一例である有機 E L 素子 127 を発光状態にする。

50

【0096】

具体的には、映像信号線 106 HSが映像信号  $V_{sig}$  の有効期間である信号電位にある時間帯に、書込走査線 WSの電位が高レベルに遷移することで、nチャネル型のサンプリングトランジスタ 125 はオン状態となり、信号線 HSから供給される映像信号線電位を保持容量 120 に充電する。これにより駆動トランジスタ 121 のゲート端 Gの電位（ゲート電位  $V_g$ ）は上昇を開始し、ドレイン電流を流し始める。そのため、有機 EL 素子 127 のアノード電位は上昇し発光を開始する。

#### 【0097】

この後、書込駆動パルス WSが低レベルに遷移すると、保持容量 120 にその時点の映像信号線電位、つまり、映像信号  $V_{sig}$  の電位の内の有効期間の電位（信号電位）が保持される。これによって、駆動トランジスタ 121 のゲート電位  $V_g$  が一定となり、発光輝度が次のフレーム（またはフィールド）まで一定に維持される。書込走査線 WSの電位が高レベルにある期間が映像信号  $V_{sig}$  のサンプリング期間となり、書込駆動パルス WSが低レベルに遷移した以降が保持期間となる。

10

#### 【0098】

<発光素子の  $I_{el}$  -  $V_{el}$  特性と駆動トランジスタの  $I$  -  $V$  特性>

一般的に、図 4 に示すように、駆動トランジスタ 121 はドレイン・ソース間電圧に関わらず駆動電流  $I_{ds}$  が一定となる飽和領域で駆動される。よって、飽和領域で動作するトランジスタのドレイン端 - ソース間に流れる電流を  $I_{ds}$ 、移動度を  $\mu$ 、チャネル幅（ゲート幅）を  $W$ 、チャネル長（ゲート長）を  $L$ 、ゲート容量（単位面積当たりのゲート酸化膜容量）を  $C_{ox}$ 、トランジスタの閾値電圧を  $V_{th}$  とすると、駆動トランジスタ 121 は下記の式（1）に示した値を持つ定電流源となっている。なお、“ $\wedge$ ”はべき乗を示す。式（1）から明らかなように、飽和領域ではトランジスタのドレイン電流  $I_{ds}$  はゲート・ソース間電圧  $V_{gs}$  によって制御され定電流源として動作する。

20

#### 【0099】

#### 【数 1】

$$I_{ds} = \frac{1}{2} \mu \frac{W}{L} C_{ox} (V_{gs} - V_{th})^2 \dots (1)$$

30

#### 【0100】

ところが、一般的に有機 EL 素子を始めとする電流駆動型の発光素子の  $I$  -  $V$  特性は、図 4 A (1) に示すように時間が経過すると劣化する。図 4 A (1) に示す有機 EL 素子で代表される電流駆動型の発光素子の電流 - 電圧 ( $I_{el}$  -  $V_{el}$ ) 特性において、実線で示す曲線が初期状態時の特性を示し、破線で示す曲線が経時変化後の特性を示している。

#### 【0101】

たとえば、発光素子の一例である有機 EL 素子 127 に発光電流  $I_{el}$  が流れると、そのアノード・カソード間電圧  $V_{el}$  は一意的に決定される。ところが、図 4 A (1) に示すように、発光期間中では、有機 EL 素子 127 のアノード端 A は駆動トランジスタ 121 のドレイン・ソース間電流  $I_{ds}$  (= 駆動電流  $I_{ds}$ ) で決定される発光電流  $I_{el}$  が流れ、それによって有機 EL 素子 127 のアノード・カソード間電圧  $V_{el}$  が上昇する。

40

#### 【0102】

図 2 に示した第 1 比較例の画素回路 P は、この有機 EL 素子 127 のアノード・カソード間電圧  $V_{el}$  分の上昇の影響は駆動トランジスタ 121 のドレイン端 D 側に現れるが、駆動トランジスタ 121 が飽和領域で動作する定電流駆動であるため、有機 EL 素子 127 には定電流  $I_{ds}$  が流れ続け、有機 EL 素子 127 の  $I_{el}$  -  $V_{el}$  特性が劣化してもその発光輝度が経時劣化することはない。

#### 【0103】

駆動トランジスタ 121 と発光制御トランジスタ 122 と保持容量 120 とサンプリングトランジスタ 125 とを備え、図 2 に示した接続態様とされた画素回路 P の構成にて、

50

電気光学素子の一例である有機EL素子127の電流-電圧特性の変化を補正して駆動電流を一定に維持する駆動信号一定化回路が構成されるようになっているのである。

【0104】

つまり、画素回路Pを映像信号Vsigで駆動するとき、pチャネル型の駆動トランジスタ121のソース端Sは第1電源電位Vc1に接続されており、常に飽和領域で動作するよう設計されているので、式(1)に示した値を持つ定電流源となる。

【0105】

また、第1比較例の画素回路Pにおいては、有機EL素子127のIel-Vel特性の経時変化(図4A(1))とともに、駆動トランジスタ121のドレイン端Dの電圧が変化してゆくが、駆動トランジスタ121は、保持容量120のブートストラップ機能によってゲート・ソース間電圧Vgsが原理的には一定に保持されるため、駆動トランジスタ121は定電流源として動作し、その結果、有機EL素子127には一定量の電流が流れ、有機EL素子127を一定の輝度で発光させることができ、発光輝度は変化しない。

10

【0106】

第2比較例の画素回路Pでも、駆動トランジスタ121のソース端Sの電位(ソース電位Vs)は、駆動トランジスタ121と有機EL素子127との動作点で決まるし、駆動トランジスタ121は飽和領域で駆動されるので、動作点のソース電圧に対応したゲート・ソース間電圧Vgsに関し、前述の式(1)に規定された電流値の駆動電流Idsを流す。

【0107】

ところが、第1比較例の画素回路Pのpチャネル型の駆動トランジスタ121をnチャネル型に変更した単純な回路(第2比較例の画素回路P)では、ソース端Sが有機EL素子127側に接続されてしまう。その結果、前述の図4A(1)に示したように経時劣化する有機EL素子127のIel-Vel特性により、同じ発光電流Ielに対するアノード・カソード間電圧VelがVel1からVel2へと変化することで、駆動トランジスタ121の動作点が変化してしまい、同じゲート電位Vgを印加しても駆動トランジスタ121のソース電位Vsは変化してしまう。これにより、駆動トランジスタ121のゲート・ソース間電圧Vgsは変化してしまう。

20

【0108】

特性式(1)から明らかなように、ゲート・ソース間電圧Vgsが変動すると、たとえゲート電位Vgが一定であっても駆動電流Idsが変動し、同時に有機EL素子127に流れる電流値(発光電流Iel)が変化し、発光輝度は変化してしまうことになる。

30

【0109】

このように第2比較例の画素回路Pでは、発光素子の一例である有機EL素子127のIel-Vel特性の経時変動による有機EL素子127のアノード電位変動が、駆動トランジスタ121のゲート・ソース間電圧Vgsの変動となって現れ、ドレイン電流(駆動電流Ids)の変動を引き起こす。この原因による駆動電流Idsの変動は画素回路Pごとの発光輝度のばらつきや経時変動となって現れ、画質の劣化が起きる。

【0110】

これに対して、詳細は後述するが、nチャネル型の駆動トランジスタ121を使用する場合においても、駆動トランジスタ121のソース端Sの電位Vsの変動にゲート端Gの電位Vgが連動するようにするブートストラップ機能を実現する回路構成および駆動タイミングとすることで、有機EL素子127の特性の経時変動による有機EL素子127のアノード電位変動(つまり駆動トランジスタ121のソース電位変動)があっても、その変動を相殺するようにゲート電位Vgを変動させる。これにより、画面輝度の均一性(ユニフォーミティ)を確保できる。ブートストラップ機能により、有機EL素子を代表とする電流駆動型の発光素子の経時変動補正能力を向上させることができる。

40

【0111】

もちろん、このブートストラップ機能は、発光開始時点で、有機EL素子127に発光電流Ielが流れ始め、それによってアノード・カソード間電圧Velが安定となるまで上昇していく過程で、そのアノード・カソード間電圧Velの変動に伴って駆動トランジスタ1

50

2 1 のソース電位  $V_s$  が変動する際にも機能する。

【 0 1 1 2 】

< 駆動トランジスタの  $V_{gs}$  -  $I_{ds}$  特性 >

また、第 1 および第 2 比較例では、駆動トランジスタ 1 2 1 の特性については特に問題視していなかったが、画素ごとに駆動トランジスタ 1 2 1 の特性が異なると、その影響が駆動トランジスタ 1 2 1 に流れる駆動電流  $I_{ds}$  に影響を及ぼす。一例としては、式(1)から分かるように、移動度  $\mu$  や閾値電圧  $V_{th}$  が画素によってばらついた場合や経時的に変化した場合、ゲート・ソース間電圧  $V_{gs}$  が同じであっても、駆動トランジスタ 1 2 1 に流れる駆動電流  $I_{ds}$  にはばらつきや経時変化が生じ、有機 EL 素子 1 2 7 の発光輝度も画素ごとに変化してしまうことになる。

10

【 0 1 1 3 】

たとえば、駆動トランジスタ 1 2 1 の製造プロセスのばらつきにより、画素回路 P ごとに閾値電圧  $V_{th}$  や移動度  $\mu$  などの特性変動がある。駆動トランジスタ 1 2 1 を飽和領域で駆動する場合においても、この特性変動により、駆動トランジスタ 1 2 1 に同一のゲート電位を与えて、画素回路 P ごとにドレイン電流(駆動電流  $I_{ds}$ )が変動し、発光輝度のばらつきになって現れる。

【 0 1 1 4 】

たとえば、図 4 A (2) は、駆動トランジスタ 1 2 1 の閾値ばらつきに着目した電圧電流 ( $V_{gs}$  -  $I_{ds}$ ) 特性を示す図である。閾値電圧が  $V_{th1}$  と  $V_{th2}$  で異なる 2 個の駆動トランジスタ 1 2 1 について、それぞれ特性カーブを挙げてある。

20

【 0 1 1 5 】

前述のように、駆動トランジスタ 1 2 1 が飽和領域で動作しているときのドレイン電流  $I_{ds}$  は、特性式(1)で表される。特性式(1)から明らかなように、閾値電圧  $V_{th}$  が変動すると、ゲート・ソース間電圧  $V_{gs}$  が一定であってもドレイン電流  $I_{ds}$  が変動する。つまり、閾値電圧  $V_{th}$  のばらつきに対して何ら対策を施さないと、図 4 A (2) に示すように、閾値電圧が  $V_{th1}$  のとき  $V_{gs}$  に対応する駆動電流が  $I_{ds1}$  となるのに対して、閾値電圧が  $V_{th2}$  のときの同じゲート電圧  $V_{gs}$  に対応する駆動電流  $I_{ds2}$  は  $I_{ds1}$  と異なってしまう。

【 0 1 1 6 】

また、図 4 A (3) は、駆動トランジスタ 1 2 1 の移動度ばらつきに着目した電圧電流 ( $V_{gs}$  -  $I_{ds}$ ) 特性を示す図である。移動度が  $\mu_1$  と  $\mu_2$  で異なる 2 個の駆動トランジスタ 1 2 1 について、それぞれ特性カーブを挙げてある。

30

【 0 1 1 7 】

特性式(1)から明らかなように、移動度  $\mu$  が変動すると、ゲート・ソース間電圧  $V_{gs}$  が一定であってもドレイン電流  $I_{ds}$  が変動する。つまり、移動度  $\mu$  のばらつきに対して何ら対策を施さないと、図 4 A (3) に示すように、移動度が  $\mu_1$  のとき  $V_{gs}$  に対応する駆動電流が  $I_{ds1}$  となるのに対して、移動度が  $\mu_2$  のときの同じゲート電圧  $V_{gs}$  に対応する駆動電流が  $I_{ds2}$  となり、 $I_{ds1}$  と異なってしまう。

【 0 1 1 8 】

図 4 A (2) や図 4 A (3) に示すように、閾値電圧  $V_{th}$  や移動度  $\mu$  の違いで  $V_{in}$  -  $I_{ds}$  特性に大きな違いが出てしまうと、同じ信号振幅  $V_{in}$  を与えても、駆動電流  $I_{ds}$  すなはち発光輝度が異なってしまい、画面輝度の均一性(ユニフォーミティ)が得られない。

40

【 0 1 1 9 】

< 閾値補正および移動度補正の概念 >

これに対して、閾値補正機能および移動度補正機能を実現する駆動タイミング(詳細は後述する)とすることで、それらの変動の影響を抑制でき、画面輝度の均一性(ユニフォーミティ)を確保できる。

【 0 1 2 0 】

本実施形態の閾値補正動作および移動度補正動作では、詳細は後述するが、書込みゲインが 1(理想値)であると仮定した場合、発光時のゲート・ソース間電圧  $V_{gs}$  が “ $V_{in} +$

50

$V_{th} - V$ " で表されるようにすることで、ドレイン・ソース間電流  $I_{ds}$  が、閾値電圧  $V_{th}$  のばらつきや変動に依存しないようにするとともに、移動度  $\mu$  のばらつきや変動に依存しないようにする。結果として、閾値電圧  $V_{th}$  や移動度  $\mu$  が製造プロセスや経時により変動しても、駆動電流  $I_{ds}$  は変動せず、有機 EL 素子 127 の発光輝度も変動しない。

## 【0121】

移動度補正時には、大きな移動度  $\mu_1$  に対しては移動度補正パラメータ  $V_1$  が大きくなるようにする一方、小さい移動度  $\mu_2$  に対しては移動度補正パラメータ  $V_2$  も小さくなるように負帰還をかけることになる。こう言った意味で、移動度補正パラメータ  $V$  を負帰還量  $V$  とも称する。

## 【0122】

10

## &lt;本実施形態の画素回路&gt;

図3に示す第2比較例の画素回路Pにおける有機EL素子127の経時劣化による駆動電流変動を防ぐ回路(ブートストラップ回路)を搭載し、また駆動トランジスタ121の特性変動(閾値電圧ばらつきや移動度ばらつき)による駆動電流変動を防ぐ駆動方式を採用したのが図5に示す本実施形態の画素回路Pである。本実施形態の画素回路Pを画素アレイ部102に備える有機EL表示装置1を本実施形態の有機EL表示装置1と称する。

## 【0123】

本実施形態の画素回路Pは、第2比較例の画素回路Pと同様に、nチャネル型の駆動トランジスタ121を使用する。加えて、有機EL素子の経時劣化による当該有機EL素子への駆動電流  $I_{ds}$  の変動を抑制するための回路、すなわち電気光学素子の一例である有機EL素子の電流-電圧特性の変化を補正して駆動電流  $I_{ds}$  を一定に維持する駆動信号一定化回路を備えた点に特徴を有する。さらに、有機EL素子の電流-電圧特性に経時変化があった場合でも駆動電流を一定にする機能を備えた点に特徴を有する。

20

## 【0124】

すなわち、駆動トランジスタ121の他に走査用に1つのスイッチングトランジスタ(サンプリングトランジスタ125)を使用する2TR駆動の構成を採るとともに、各スイッチングトランジスタを制御する電源駆動パルスDSLおよび書込駆動パルスWSのオン/オフタイミングの設定により、有機EL素子127の経時劣化や駆動トランジスタ121の特性変動(たとえば閾値電圧や移動度などのばらつきや変動)による駆動電流  $I_{ds}$  に与える影響を防ぐ点に特徴を有する。

30

## 【0125】

2TR駆動の構成であり、素子数や配線数が少ないため、高精細化が可能であることに加えて、映像信号  $V_{sig}$  の劣化なくサンプリングできるため、良好な画質を得ることができる。

## 【0126】

40

図3に示した第2比較例に対しての構成上の大きな違いは、保持容量120の接続態様を変形して、有機EL素子127の経時劣化による駆動電流変動を防ぐ回路として、駆動信号一定化回路の一例であるブートストラップ回路を構成する点にある。駆動トランジスタ121の特性変動(たとえば閾値電圧や移動度などのばらつきや変動)による駆動電流  $I_{ds}$  に与える影響を抑制する方法としては、各トランジスタ121, 125の駆動タイミングを工夫することで対処する。

## 【0127】

具体的には、本実施形態の画素回路Pは、保持容量120、nチャネル型の駆動トランジスタ121、およびアクティブH(ハイ)の書込駆動パルスWSが供給されるnチャネル型のサンプリングトランジスタ125、電流が流れることで発光する電気光学素子(発光素子)の一例である有機EL素子127を有する。

## 【0128】

駆動トランジスタ121のゲート端G(ノードND122)とソース端Sとの間に保持容量120が接続され、駆動トランジスタ121のソース端Sが直接に有機EL素子127のアノード端Aに接続されている。保持容量120は、ブートストラップ容量としても

50

機能するようになっている。有機EL素子127のカソード端Kは基準電位としてのカソード電位V<sub>cath</sub>とされる。好ましくはこのカソード電位V<sub>cath</sub>は、図3に示した第2比較例と同様に基準電位を供給する全画素共通の配線V<sub>cath</sub>（好ましくはGND）に接続されている。

【0129】

駆動トランジスタ121のドレイン端Dは、電源スキャナとして機能する駆動走査部105からの電源供給線105DSLに接続されている。電源供給線105DSLは、この電源供給線105DSLそのものが、駆動トランジスタ121に対しての電源供給能力を備える点に特徴を有する。

【0130】

具体的には、駆動走査部105は、駆動トランジスタ121のドレイン端Dに対して、それぞれ電源電圧に相当する高電圧側の第1電位V<sub>cc</sub>と低電圧側の第2電位V<sub>ss</sub>とを切り替えて供給する電源電圧切替回路を具備している。

【0131】

第2電位V<sub>ss</sub>としては、映像信号線106HSにおける映像信号V<sub>sig</sub>の基準電位V<sub>o</sub>（オフセット電位V<sub>ofs</sub>とも称する）より十分低い電位とする。具体的には、駆動トランジスタ121のゲート・ソース間電圧V<sub>gs</sub>（ゲート電位V<sub>g</sub>とソース電位V<sub>s</sub>の差）が駆動トランジスタ121の閾値電圧V<sub>th</sub>より大きくなるように、電源供給線105DSLの低電位側の第2電位V<sub>ss</sub>を設定する。なお、オフセット電位V<sub>ofs</sub>は、閾値補正動作に先立つ初期化動作に利用するとともに映像信号線106HSを予めプリチャージにしておくためにも利用する。

【0132】

サンプリングトランジスタ125は、ゲート端Gが書込走査部104からの書込走査線104WSに接続され、ドレイン端Dが映像信号線106HSに接続され、ソース端Sが駆動トランジスタ121のゲート端G（ノードND122）に接続されている。そのゲート端Gには、書込走査部104からアクティブHの書込駆動パルスWSが供給される。

【0133】

サンプリングトランジスタ125は、ソース端Sとドレイン端Dとを逆転させた接続様式とすることもできる。また、サンプリングトランジスタ125としては、ディプレション型およびエンハンスマント型の何れをも使用できる。

【0134】

<本実施形態の画素回路の動作>

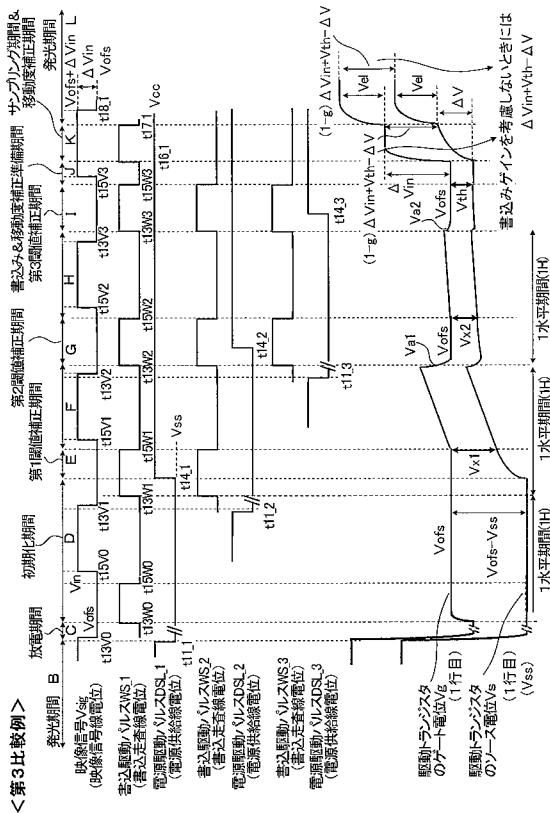

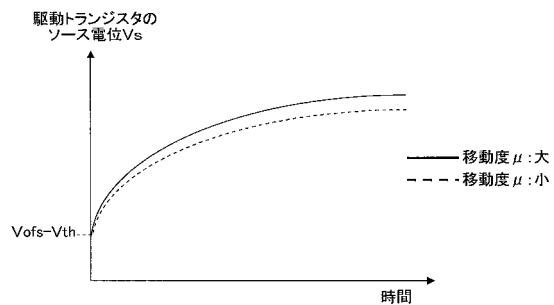

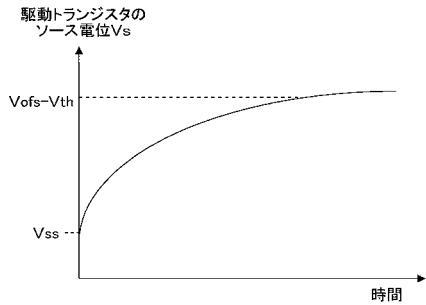

図6は、図5に示した本実施形態の画素回路Pに関する本実施形態の駆動タイミングの基本例を説明するタイミングチャートである。図6B～図6Lは、図6に示したタイミングチャートの各期間における等価回路と動作状態を説明する図である。図7は、閾値補正動作時における駆動トランジスタ121のソース電位V<sub>s</sub>の変化を示す図である。図7Aは、移動度補正動作時における駆動トランジスタ121のソース電位V<sub>s</sub>の変化を示す図である。

【0135】

以下では、説明や理解を容易にするため、特段の断りのない限り、書き込みゲインが1（理想値）であると仮定して、保持容量120に信号振幅V<sub>in</sub>の情報を、書き込む、保持する、あるいはサンプリングするなどと簡潔に記して説明する。書き込みゲインが1未満の場合、保持容量120には信号振幅V<sub>in</sub>の大きさそのものではなく、信号振幅V<sub>in</sub>の大きさに対応するゲイン倍された情報が保持されることになる。

【0136】

因みに、信号振幅V<sub>in</sub>に対応する保持容量120に書き込まれる情報の大きさの割合を、書き込みゲインG<sub>input</sub>と称する。ここで、書き込みゲインG<sub>input</sub>は、具体的には、電気回路的に保持容量120と並列に配置される寄生容量を含めた全容量C1と、電気回路的に保持容量120と直列に配置される全容量C2との容量直列回路において、信号振幅V<sub>in</sub>を容量直列回路に供給したときに容量C1に配分される電荷量に関係する。式で表せば

10

20

30

40

50

、  $g = C_1 / (C_1 + C_2)$  とすると、書込みゲイン  $G_{input} = C_2 / (C_1 + C_2) = 1 - C_1 / (C_1 + C_2) = 1 - g$  となる。以下の説明において、“ $g$ ”が登場する記載は書込みゲインを考慮したものである。

#### 【0137】

また、説明や理解を容易にするため、特段の断りのない限り、ブートストラップゲインが 1 (理想値) であると仮定して簡潔に記して説明する。因みに、駆動トランジスタ 121 のゲート・ソース間に保持容量 120 が設けられている場合に、ソース電位  $V_s$  の上昇に対するゲート電位  $V_g$  の上昇率をブートストラップゲイン (ブートストラップ動作能力)  $G_{bst}$  と称する。ここで、ブートストラップゲイン  $G_{bst}$  は、具体的には、保持容量 120 の容量値  $C_s$ 、駆動トランジスタ 121 のゲート・ソース間に形成される寄生容量  $C_{121gs}$  の容量値  $C_{gs}$ 、ゲート・ドレイン間に形成される寄生容量  $C_{121gd}$  の容量値  $C_{gd}$ 、およびサンプリングトランジスタ 125 のゲート・ソース間に形成される寄生容量  $C_{125gs}$  の容量値  $C_{ws}$  に関係する。式で表せば、ブートストラップゲイン  $G_{bst} = (C_s + C_{gs}) / (C_s + C_{gs} + C_{gd} + C_{ws})$  となる。

10

#### 【0138】

図 6においては、時間軸を共通にして、書込走査線 104WS の電位変化、電源供給線 105DSL の電位変化、および映像信号線 106HS の電位変化を表してある。また、これらの電位変化と並行に、1 行分 (図では 1 行目) について駆動トランジスタ 121 のゲート電位  $V_g$  およびソース電位  $V_s$  の変化も表してある。

20

#### 【0139】

基本的には、書込走査線 104WS や電源供給線 105DSL の 1 行ごとに、1 水平走査期間だけ遅れて同じような駆動を行なう。図 6 における各タイミングや信号は、処理対象行を問わず、第 1 行目のタイミングや信号と同じタイミングや信号で示す。そして、説明中において区別が必要とされるときには、そのタイミングや信号に、処理対象行を “\_” 付きの参照子で示すことで区別する。

30

#### 【0140】

また、本実施形態の駆動タイミングでは、映像信号  $V_{sig}$  が非有効期間であるオフセット電位  $V_{ofs}$  にある期間を 1 水平期間の前半部とし、有効期間である信号電位 ( $V_{ofs} + V_{in}$ ) にある期間を 1 水平期間の後半部とする。また、映像信号  $V_{sig}$  の有効期間と非有効期間を合わせた 1 水平期間ごとに、閾値補正動作を 3 回に亘って繰り返すようとする。その各回の映像信号  $V_{sig}$  の有効期間と非有効期間の切替タイミング ( $t_{13V}, t_{15V}$ )、および書込駆動パルス WS のアクティブとインアクティブの切替タイミング ( $t_{13W}, t_{15W}$ ) については、そのタイミングに、各回を “\_” なしの参照子で示すことで区別する。

#### 【0141】

本実施形態では、1 水平期間を処理サイクルとして、閾値補正動作を 3 回に亘って繰り返すようにしているが、この繰り返し動作は必須ではなく、1 水平期間を処理サイクルとして、1 回のみの閾値補正動作を実行するようにしてもよい。

30

#### 【0142】

1 水平期間が閾値補正動作の処理サイクルとなるのは、行ごとに、サンプリングトランジスタ 125 が信号振幅  $V_{in}$  の情報を保持容量 120 にサンプリングする前に、閾値補正動作に先立って、電源供給線 105DSL の電位を第 2 電位  $V_{ss}$  にセットし、また駆動トランジスタ 121 のゲートをオフセット電位  $V_{ofs}$  にセットし、さらにソース電位を第 2 電位  $V_{ss}$  にセットする初期化動作を経てから、電源供給線 105DSL の電位が第 1 電位  $V_{cc}$  にある状態でかつ映像信号線 106HS がオフセット電位  $V_{ofs}$  にある時間帯でサンプリングトランジスタ 125 を導通させて駆動トランジスタ 121 の閾値電圧  $V_{th}$  に対応する電圧を保持容量 120 に保持させようとする閾値補正動作を行なうからである。

40

#### 【0143】

必然的に、閾値補正期間は、1 水平期間よりも短くなってしまう。したがって、保持容量 120 の容量  $C_s$  や第 2 電位  $V_{ss}$  の大きさ関係やその他の要因で、この短い 1 回分の閾

50

値補正動作期間では、閾値電圧  $V_{th}$  に対応する正確な電圧を保持容量 120 に保持仕切れないケースも起こり得る。本実施形態において、閾値補正動作を複数回実行するのは、この対処のためである。すなわち、信号振幅  $V_{in}$  の情報の保持容量 120 へのサンプリング（信号書き込み）に先行する複数の水平周期で、閾値補正動作を繰り返し実行することで、確実に駆動トランジスタ 121 の閾値電圧  $V_{th}$  に相当する電圧を保持容量 120 に保持させるのである。

#### 【0144】

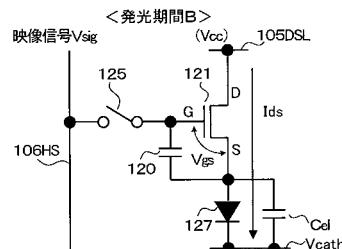

ある行（ここでは第1行目とする）について、タイミング  $t_{11}$  以前の前フィールドの発光期間 B では、書き駆動パルス WS がインアクティブ L でありサンプリングトランジスタ 125 が非導通状態である一方、電源駆動パルス DSL は高電位の電源電圧側である第1電位  $V_{cc}$  にある。10

#### 【0145】

したがって、図 6 B に示すように、映像信号線 106 HS の電位に関わらず、前フィールドの動作によって保持容量 120 に保持されている電圧状態（駆動トランジスタ 121 のゲート・ソース間電圧  $V_{gs}$ ）に応じて有機 EL 素子 127 に駆動トランジスタ 121 から駆動電流  $I_{ds}$  が供給され、全画素共通の配線  $V_{cath}$ （好ましくは GND）に流れ込むことで、有機 EL 素子 127 が発光状態にある。このとき、駆動トランジスタ 121 は飽和領域で動作するように設定されているため、有機 EL 素子 127 に流れる駆動電流  $I_{ds}$  は保持容量 120 に保持されている駆動トランジスタ 121 のゲート・ソース間電圧  $V_{gs}$  に応じて式（1）に示される値をとる。20

#### 【0146】

この後、線順次走査の新しいフィールドに入って、先ず、駆動走査部 105 は、書き駆動パルス WS がインアクティブ L にある状態で、1 行目の電源供給線 105 DSL\_1 に与える電源駆動パルス DSL\_1 を高低電位側の第1電位  $V_{cc}$  から低電位側の第2電位  $V_{ss}$  に切り替える（ $t_{11\_1}$ ：図 6 C を参照）。このタイミング（ $t_{11\_1}$ ）は、図 6 に示すように、映像信号  $V_{sig}$  が有効期間の信号電位（ $V_{ofs} + V_{in}$ ）にある期間内としている。しかし、 $t_{11\_1}$  は、必ずしもこのタイミングで遷移させる必要はない。

#### 【0147】

次に、書き走査部 104 は、電源供給線 105 DSL\_1 が第2電位  $V_{ss}$  にある状態のまま、書き駆動パルス WS をアクティブ H に切り替える（ $t_{13W0}$ ）。このタイミング（ $t_{13W0}$ ）は、直前の水平期間における映像信号  $V_{sig}$  が非有効期間であるオフセット電位  $V_{ofs}$  から有効期間の信号電位（ $V_{ofs} + V_{in}$ ）に切り替わり、その後に、オフセット電位  $V_{ofs}$  に切り替わるタイミング（ $t_{13V0}$ ）と同じかそれよりも少し遅れたタイミングにする。この後に書き駆動パルス WS をインアクティブ L に切り替えるタイミング（ $t_{15W0}$ ）は、オフセット電位  $V_{ofs}$  から信号電位（ $V_{ofs} + V_{in}$ ）に切り替わるタイミング（ $t_{15V0}$ ）と同じかそれよりも少し前のタイミングにする。30

#### 【0148】

つまり、好ましくは、書き駆動パルス WS をアクティブ H にする期間（ $t_{13W} \sim t_{15W}$ ）は、映像信号  $V_{sig}$  が非有効期間であるオフセット電位  $V_{ofs}$  にある時間帯（ $t_{13V} \sim t_{15V}$ ）内とする。これは、電源供給線 105 DSL が第1電位  $V_{cc}$  にある状態のときで映像信号  $V_{sig}$  が信号電位（ $V_{ofs} + V_{in}$ ）にあるときに書き駆動パルス WS をアクティブ H にすると信号振幅  $V_{in}$  の情報の保持容量 120 へのサンプリング動作（信号電位の書き込み動作）がなされてしまい、閾値補正動作としては不都合が生じるからである。40

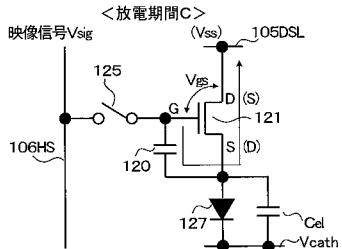

#### 【0149】

タイミング  $t_{11\_1} \sim t_{13W0}$ （放電期間 C と称する）では、電源供給線 105 DSL の電位は第2電位  $V_{ss}$  まで放電され、さらに駆動トランジスタ 121 のソース電位  $V_s$  は第2電位  $V_{ss}$  に近い電位まで遷移する。さらに、駆動トランジスタ 121 のゲート端 G とソース端 S との間には保持容量 120 が接続されており、その保持容量 120 による効果によって、駆動トランジスタ 121 のソース電位  $V_s$  の変動にゲート電位  $V_g$  が連動する。

#### 【0150】

10

20

30

40

50

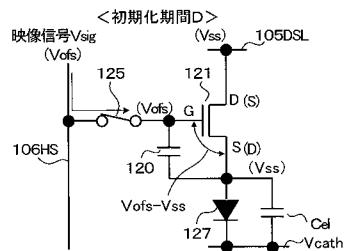

電源駆動パルスDSLを低電位側の第2電位Vssにしたままで、書込駆動パルスWSをアクティブHに切り替えると(t13W0)、図6Dに示すように、サンプリングトランジスタ125が導通状態になる。

【0151】

このとき、映像信号線106HSはオフセット電位Vofsにある。したがって、駆動トランジスタ121のゲート電位Vgは導通したサンプリングトランジスタ125を通じて映像信号線106HSのオフセット電位Vofsとなる。これと同時に、駆動トランジスタ121がオンすることで、駆動トランジスタ121のソース電位Vsは低電位側の第2電位Vssに固定される。

【0152】

つまり、電源供給線105DSLの電位が高電位側の第1電位Vccから映像信号線106HSのオフセット電位Vofsより十分低い第2電位Vssにあることで、駆動トランジスタ121のソース電位Vsが映像信号線106HSのオフセット電位Vofsより十分低い第2電位Vssに初期化(リセット)される。このようにして、駆動トランジスタ121のゲート電位Vgおよびソース電位Vsを初期化することで、閾値補正動作の準備が完了する。次に電源駆動パルスDSLを高電位側の第1電位Vccにするまでの期間(t13W0~t14\_1)が、初期化期間Dとなる。なお、放電期間Cと初期化期間Dとを合わせて、駆動トランジスタ121のゲート電位Vgとソース電位Vsを初期化する閾値補正準備期間とも称する。

【0153】

電源供給線105DSLの配線容量が大きい場合は比較的早いタイミングで電源供給線105DSLを高電位Vccから低電位Vssに切り替えるとよい。この放電期間Cおよび初期化期間D(t11\_1~t14\_1)を十分に確保することで、配線容量やその他の画素寄生容量の影響を受けないようにしておく。このため、本実施形態では、初期化処理を2回行なうようにしている。すなわち、電源供給線105DSL\_1が第2電位Vssにある状態のままで、書込駆動パルスWSをインアクティブLに切り替えた後(t15W0)、映像信号Vsigを信号電位(Vofs+Vin)に切り替える(t15V0)。さらに、映像信号Vsigをオフセット電位Vofsに切り替えた後(t13V1)、書込駆動パルスWSをアクティブHに切り替える(t13W1)。

【0154】

放電期間Cにおいて、第2電位Vssが有機EL素子127の閾値電圧VthELとカソード電位Vcathの和よりも小さいとき、つまり“Vss < VthEL + Vcath”であれば有機EL素子127は消光する。また、駆動トランジスタ121のソース端とドレイン端が事実上逆転して電源供給線105DSLが駆動トランジスタ121のソース側となり、有機EL素子127のアノード端Aは第2電位Vssに充電される(図6Cを参照)。

【0155】

さらに、初期化期間Dにおいては、駆動トランジスタ121のゲート・ソース間電圧Vgsは“Vofs - Vss”という値をとる(図6Dを参照)。この“Vofs - Vss”が駆動トランジスタ121の閾値電圧Vthよりも大きくないと閾値補正動作を行なうことができないために、“Vofs - Vss > Vth”とする。

【0156】

次に、書込駆動パルスWSをアクティブHにしたままで、電源供給線105DSLに与える電源駆動パルスDSLを第1電位Vccに切り替える(t14\_1)。駆動走査部105は、それ以降は、次のフレーム(あるいはフィールド)の処理まで、電源供給線105DSLの電位を第1電位Vccに保持しておく。

【0157】

電源供給線105DSLを第1電位Vccに切り替えると(t14\_1)、駆動トランジスタ121のソース端とドレイン端が再度逆転して電源供給線105DSLが駆動トランジスタ121のドレイン側となる(図6Eを参照)。これにより、駆動電流Idsが保持容量120に流れ込み、駆動トランジスタ121の閾値電圧Vthを補正(キャンセル)する第1回

10

20

30

40

50

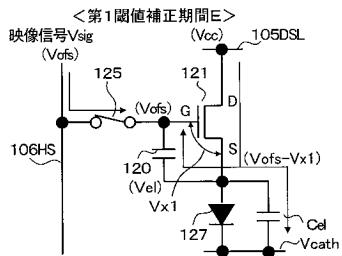

目の閾値補正期間（第1閾値補正期間Eと称する）に入る。この第1閾値補正期間Eは、書き駆動パルスWSがインアクティブLにされるタイミング（t15W1）まで継続する。

【0158】

ここで、本実施形態の駆動走査部105は、電源供給線105DSLの電位を、低電位側である第2電位Vssから高電位側である第1電位Vccに遷移させるタイミング（t14\_1）を、映像信号線106HSが映像信号Vsigの非有効期間であるオフセット電位Vofsにある時間帯（t13V1～t15V1）、さらに好ましくは書き駆動パルスWSがアクティブである時間帯（t13W1～t15W1）とする。

【0159】

ところで、タイミング（t14\_1）以降の第1閾値補正期間Eでは、図6Eに示すように、電源供給線105DSLの電位が低電位側の第2電位Vssから高電位側の第1電位Vccに遷移することで、駆動トランジスタ121のソース電位Vsが上昇を開始する。

【0160】

すなわち、駆動トランジスタ121のゲート端Gは映像信号Vsigのオフセット電位Vofsに保持されており、駆動トランジスタ121のソース端Sの電位Vsが上昇して駆動トランジスタ121がカットオフするまで駆動電流Idsが流れようとする。カットオフすると駆動トランジスタ121のソース電位Vsは“Vofs - Vth”となる。

【0161】

すなわち、有機EL素子127の等価回路はダイオードと寄生容量Celの並列回路で表されるため、“Vel - Vcath + VthEL”である限り、つまり、有機EL素子127のリーキ電流が駆動トランジスタ121に流れる電流よりもかなり小さい限り、駆動トランジスタ121の駆動電流Idsは保持容量120と寄生容量Celを充電するために使われる。

【0162】

この結果、駆動トランジスタ121に駆動電流Idsが流れると、有機EL素子127のアノード端Aの電圧VelつまりノードND121の電位は、図7に示すように、時間とともに上昇してゆく。そして、ノードND121の電位（ソース電位Vs）とノードND122の電圧（ゲート電位Vg）との電位差がちょうど閾値電圧Vthとなったところで閾値補正期間を終了させる。つまり、一定時間経過後、駆動トランジスタ121のゲート・ソース間電圧Vgsは閾値電圧Vthという値をとる。

【0163】

ゲート・ソース間電圧Vgsが閾値電圧Vthとなるまでは、駆動トランジスタ121のゲート・ソース間電圧Vgsは閾値電圧Vthよりも大きいため、図6Eに示すように駆動電流Idsが流れる。このとき、有機EL素子127には逆バイアスがかかっているため有機EL素子127が発光することはない。

【0164】

ここで、実際には、閾値電圧Vthに相当する電圧が、駆動トランジスタ121のゲート端Gとソース端Sとの間に接続された保持容量120に書き込まれることになる。しかしながら、第1閾値補正期間Eは、書き駆動パルスWSをアクティブHにしたタイミング（t13W1）（詳しくはその後に電源駆動パルスDSLを第1電位Vccに戻した時点 t14）からインアクティブLに戻すタイミング（t15W1）までであり、この期間が十分に確保されていないときには、それ以前に終了してしまうこととなる。

【0165】

具体的には、ゲート・ソース間電圧VgsがVx1（>Vth）になったとき、つまり、駆動トランジスタ121のソース電位Vsが低電位側の第2電位Vssから“Vofs - Vx1”になったときに終わってしまう。このため、第1閾値補正期間Eが完了した時点（t15W1）では、Vx1が保持容量120に書き込まれる。

【0166】

次に、駆動走査部105は、1水平期間の後半部で、書き駆動パルスWSをインアクティブLに切り替え（t15W1）、さらに水平駆動部106は、映像信号線106HSをオフセット電位Vofsから信号電位（Vofs + Vin）に切り替える（t15V1）。これにより、

10

20

30

40

50

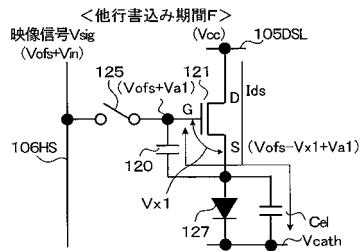

図6 Fに示すように、映像信号線106HSが信号電位( $V_{ofs} + V_{in}$ )に変化する一方、書込走査線104WSの電位(書込駆動パルスWS)はローレベルになる。

#### 【0167】

このときには、サンプリングトランジスタ125は非導通(オフ)状態にあり、それ以前に保持容量120に保持された $V_{x1}$ に応じたドレン電流が有機EL素子127に流れることで、ソース電位 $V_s$ が僅かに上昇する。この上昇分を $V_{a1}$ とすると、ソース電位 $V_s$ は“ $V_{ofs} - V_{x1} + V_{a1}$ ”となる。さらに、駆動トランジスタ121のゲート端Gとソース端Sとの間には保持容量120が接続されており、その保持容量120による効果によって、駆動トランジスタ121のソース電位 $V_s$ の変動にゲート電位 $V_g$ が連動することで、ゲート電位 $V_g$ が“ $V_{ofs} + V_{a1}$ ”となる。

10

#### 【0168】

第1閾値補正期間E後の、水平駆動部106が映像信号線106HSを信号電位( $V_{ofs} + V_{in}$ )からオフセット電位 $V_{ofs}$ に切り替え( $t_{13V2}$ )、駆動走査部105が書込駆動パルスWSをアクティブHに切り替える( $t_{13W2}$ )までの期間(他行書き込み期間と称する)Fは、他の行の画素に対する信号振幅 $V_{in}$ の情報のサンプリング期間となり、この処理対象行のサンプリングトランジスタ125はオフ状態にする必要がある。これで、1回目の1水平期間の処理が完結する。

#### 【0169】

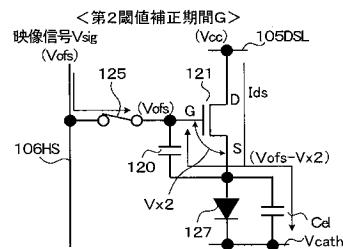

次の1水平周期(1H)の前半になると、水平駆動部106が映像信号線106HSを信号電位( $V_{ofs} + V_{in}$ )からオフセット電位 $V_{ofs}$ に切り替え( $t_{13V2}$ )、駆動走査部105が書込駆動パルスWSをアクティブHに切り替える( $t_{13W2}$ )。これにより、ドレン電流が保持容量120に流れ込み、駆動トランジスタ121の閾値電圧 $V_{th}$ を補正(キャンセル)する第2回目の閾値補正期間(第2閾値補正期間Gと称する)に入る。この第2閾値補正期間Gは、書込駆動パルスWSがインアクティブLにされるタイミング( $t_{15W2}$ )まで継続する。

20

#### 【0170】

第2閾値補正期間Gでは、第1閾値補正期間Eと同様の動作をする。具体的には、図6Gに示すように、駆動トランジスタ121のゲート端Gは映像信号 $V_{sig}$ のオフセット電位 $V_{ofs}$ に保持されることとなり、ゲート電位が直前の“ $V_g = \text{オフセット電位} V_{ofs} + V_{a1}$ ”からオフセット電位 $V_{ofs}$ に切り替わる。このときの駆動トランジスタのゲート端Gの電位変動量 $V_{a1}$ の情報が、保持容量120、駆動トランジスタのゲートソース間の寄生容量 $C_{gs}$ を介して駆動トランジスタのソース端Sに入力される。このときのソース端Sへの入力量は $g V_{a1}$ と表され、ソース電位 $V_s$ は、直前の“ $V_{ofs} - V_{x1} + V_{a1}$ ”から $g V_{a1}$ だけ低下するので、“ $V_{ofs} - V_{x1} + (1 - g) V_{a1}$ ”となる。

30

#### 【0171】

ここで、駆動トランジスタ121のゲート・ソース間電圧 $V_{x1} - (1 - g) V_{a1}$ が駆動トランジスタ121の閾値電圧 $V_{th}$ よりも大きいならば、この後、駆動トランジスタ121のソース端Sの電位 $V_s$ が上昇して駆動トランジスタ121がカットオフするまでドレン電流が流れようとする。カットオフすると駆動トランジスタ121のソース電位 $V_s$ は“ $V_{ofs} - V_{th}$ ”となる。

40

#### 【0172】

しかしながら、第2閾値補正期間Gは、書込駆動パルスWSをアクティブHにしたタイミング( $t_{13W2}$ )からインアクティブLに戻すタイミング( $t_{15W2}$ )までであり、この期間が十分に確保されていないときには、それ以前に終了してしまうこととなる。この点は、第1閾値補正期間Eと同じであり、ゲート・ソース間電圧 $V_{gs}$ が $V_{x2}$ ( $< V_{x1}$ 、かつ $> V_{th}$ )になったとき、つまり、駆動トランジスタ121のソース電位 $V_s$ が“ $V_{ofs} - V_{x1}$ ”から“ $V_{ofs} - V_{x2}$ ”になったときに終わってしまう。このため、第2閾値補正期間Gが完了した時点( $t_{15W2}$ )では $V_{x2}$ が保持容量120に書き込まれる。

#### 【0173】

次に、駆動走査部105は、1水平期間の後半部で、他の行の画素に対する信号電位の

50

サンプリングを行なうため、書込駆動パルスWSをインアクティブLに切り替え( $t_{15W2}$ )、さらに水平駆動部106は、映像信号線106HSをオフセット電位 $V_{ofs}$ から信号電位( $V_{ofs} + V_{in}$ )に切り替える( $t_{15V2}$ )。これにより、図6Hに示すように、映像信号線106HSが信号電位( $V_{ofs} + V_{in}$ )に変化する一方、書込走査線104WSの電位(書込駆動パルスWS)はローレベルになる。

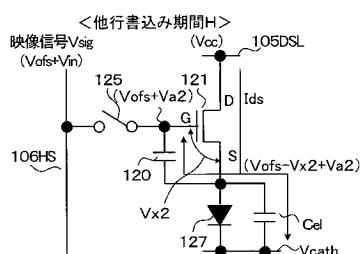

#### 【0174】

このときには、サンプリングトランジスタ125は非導通(オフ)状態にあり、それ以前に保持容量120に保持された $V_{x2}$ に応じたドレイン電流が有機EL素子127に流れることで、ソース電位 $V_s$ が僅かに上昇する。この上昇分を $V_{a2}$ とすると、ソース電位 $V_s$ は“ $V_{ofs} - V_{x2} + V_{a2}$ ”となる。さらに、駆動トランジスタ121のゲート端Gとソース端Sとの間には保持容量120が接続されており、その保持容量120による効果によって、駆動トランジスタ121のソース電位 $V_s$ の変動にゲート電位 $V_g$ が連動することで、ゲート電位 $V_g$ が“ $V_{ofs} + V_{a2}$ ”となる。

10

#### 【0175】

第2閾値補正期間G後の、水平駆動部106が映像信号線106HSを信号電位( $V_{ofs} + V_{in}$ )からオフセット電位 $V_{ofs}$ に切り替え( $t_{13V3}$ )、駆動走査部105が書込駆動パルスWSをアクティブHに切り替える( $t_{13W3}$ )までの期間(他行書き込み期間と称する)Hは、他の行の画素に対する信号振幅 $V_{in}$ の情報のサンプリング期間となり、この処理対象行のサンプリングトランジスタ125はオフ状態にする必要がある。これで、2回目の1水平期間の処理が完結する。

20

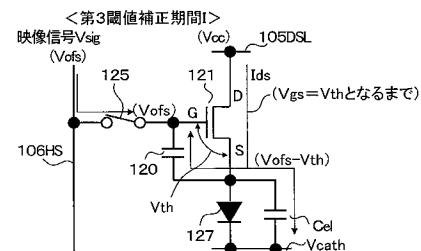

#### 【0176】

さらに、次の1水平周期(1H)の前半になると、水平駆動部106が映像信号線106HSを信号電位( $V_{ofs} + V_{in}$ )からオフセット電位 $V_{ofs}$ に切り替え( $t_{13V3}$ )、駆動走査部105が書込駆動パルスWSをアクティブHに切り替える( $t_{13W3}$ )。これにより、ドレイン電流が保持容量120に流れ込み、駆動トランジスタ121の閾値電圧 $V_{th}$ を補正(キャンセル)する第3回目の閾値補正期間(第3閾値補正期間Iと称する)に入る。この第3閾値補正期間Iは、書込駆動パルスWSがインアクティブLにされるタイミング( $t_{15W3}$ )まで継続する。

#### 【0177】

この第3閾値補正期間Iでは、第1閾値補正期間Eや第2閾値補正期間Gと同様の動作をする。具体的には、図6Iに示すように、駆動トランジスタ121のゲート端Gは映像信号 $V_{sig}$ のオフセット電位 $V_{ofs}$ に保持されることとなり、ゲート電位が直前の“ $V_g = \text{オフセット電位 } V_{ofs} + V_{a2}$ ”からオフセット電位 $V_{ofs}$ に切り替わる。このときの駆動トランジスタのゲート端Gの電位変動量 $V_{a2}$ の情報が、保持容量120、駆動トランジスタのゲートソース間の寄生容量 $C_{gs}$ を介して駆動トランジスタのソース端Sに入力される。このときのソース端Sへの入力量は $gV_{a2}$ と表され、ソース電位 $V_s$ は、直前の“ $V_{ofs} - V_{x2} + V_{a2}$ ”から $gV_{a2}$ だけ低下するので、“ $V_{ofs} - V_{x1} + (1 - g)V_{a2}$ ”となる。

30

#### 【0178】

この後、駆動トランジスタ121のソース端Sの電位 $V_s$ が上昇して駆動トランジスタ121がカットオフするまでドレイン電流が流れようとする。ゲート・ソース間電圧 $V_{gs}$ がちょうど閾値電圧 $V_{th}$ となったところでドレイン電流がカットオフする。カットオフすると駆動トランジスタ121のソース電位 $V_s$ は“ $V_{ofs} - V_{th}$ ”となる。

40

#### 【0179】

つまり、複数回(本例では3回)に亘る閾値補正期間での処理によって、駆動トランジスタ121のゲート・ソース間電圧 $V_{gs}$ は閾値電圧 $V_{th}$ という値をとる。ここで、実際には、閾値電圧 $V_{th}$ に相当する電圧が、駆動トランジスタ121のゲート端Gとソース端Sとの間に接続された保持容量120に書き込まれることになる。

#### 【0180】

なお、3回に亘る閾値補正期間E, G, Iでは、何れもドレイン電流が専ら保持容量1

50

20側や有機EL素子127の寄生容量C<sub>el</sub>側に流れ、カソード電位V<sub>cath</sub>側には流れないようにするために、有機EL素子127がカットオフとなるように共通接地配線cathの電位V<sub>cath</sub>を設定しておく。

#### 【0181】

この後、水平駆動部106により信号線106HSに信号電位(V<sub>ofs</sub> + V<sub>in</sub>)を実際に供給して、書込駆動パルスWSをアクティブHにする期間を、保持容量120への信号振幅V<sub>in</sub>の情報の書き込み期間(サンプリング期間とも称する)とする。この信号振幅V<sub>in</sub>の情報は駆動トランジスタ121の閾値電圧V<sub>th</sub>に足し込む形で保持される。詳しくは、書き込みゲインG<sub>input</sub>を考慮したとき、前述の比率gが関与する。

#### 【0182】

この結果、駆動トランジスタ121の閾値電圧V<sub>th</sub>の変動は常にキャンセルされる形となるので、閾値補正を行なっていることになる。この閾値補正によって、保持容量120に保持されるゲート・ソース間電圧V<sub>gs</sub>は“V<sub>in</sub> + V<sub>th</sub>”となる。書き込みゲインG<sub>input</sub>を考慮したときには、(1 - g)V<sub>in</sub> + V<sub>th</sub> = G<sub>input</sub> · V<sub>in</sub> + V<sub>th</sub>となる。また、同時に、このサンプリング期間で移動度補正を実行する。すなわち、本実施形態の駆動タイミングにおいて、サンプリング期間は移動度補正期間を兼ねることとなる。信号振幅V<sub>in</sub>は階調に応じた電圧である。

#### 【0183】

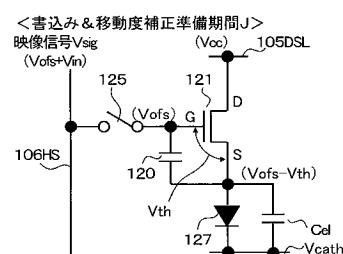

具体的には、先ず、書込駆動パルスWSをインアクティブLに切り替え(t<sub>15W3</sub>)、さらに水平駆動部106は、映像信号線106HSをオフセット電位V<sub>ofs</sub>から信号電位(V<sub>ofs</sub> + V<sub>in</sub>)に切り替える(t<sub>15V3</sub>)ことで、最後(本例では3回目)の閾値補正期間を完了させる。こうすることで、図6Jに示すように、サンプリングトランジスタ125が非導通(オフ)状態とされ、次のサンプリング動作および移動度補正動作の準備が完了する。次に書込駆動パルスWSをアクティブHにするタイミング(t<sub>16\_1</sub>)まで期間を書き込み&移動度補正準備期間Jと称する。

#### 【0184】

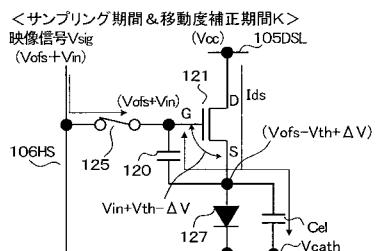

次に、映像信号線106HSを信号電位(V<sub>ofs</sub> + V<sub>in</sub>)に保持したままで、書込走査部104は、書込駆動パルスWSをアクティブHに切り替え(t<sub>16\_1</sub>)、水平駆動部106が映像信号線106HSを信号電位(V<sub>ofs</sub> + V<sub>in</sub>)からオフセット電位V<sub>ofs</sub>に切り替えるタイミング(t<sub>18\_1</sub>)までの間での適当なタイミングで、つまり、映像信号線106HSが信号電位(V<sub>ofs</sub> + V<sub>in</sub>)にある時間帯での適当なとき、インアクティブLに切り替える(t<sub>17\_1</sub>)。この書込駆動パルスWSがアクティブHにある期間(t<sub>16\_1</sub> ~ t<sub>17\_1</sub>)を、サンプリング期間&移動度補正期間Kと称する。

#### 【0185】

これにより、図6Kに示すように、サンプリングトランジスタ125が導通(オン)状態となり、駆動トランジスタ121のゲート電位V<sub>g</sub>は信号電位(V<sub>ofs</sub> + V<sub>in</sub>)となる。したがって、サンプリング期間&移動度補正期間Kでは、駆動トランジスタ121のゲート端Gが信号電位(V<sub>ofs</sub> + V<sub>in</sub>)に固定された状態で、駆動トランジスタ121に駆動電流I<sub>ds</sub>が流れる。

#### 【0186】

駆動トランジスタ121のゲート電位V<sub>g</sub>はサンプリングトランジスタ125をオンしているために信号電位(V<sub>ofs</sub> + V<sub>in</sub>)となるが、電源供給線105DSLから電流が流れるためソース電位V<sub>s</sub>は時間とともに上昇してゆく。

#### 【0187】

後述するが、有機EL素子127の閾値電圧をV<sub>thEL</sub>としたとき、書き込みゲインを考慮したときは“V<sub>ofs</sub> - V<sub>th</sub> + gV<sub>in</sub> + V < V<sub>thEL</sub> + V<sub>cath</sub>”と設定しておくことで、有機EL素子127は、逆バイアス状態にされ、カットオフ状態(ハイインピーダンス状態)にあるため、発光することなく、また、ダイオード特性ではなく単純な容量特性を示すようになる。このときのソース電位V<sub>s</sub>が有機EL素子127の閾値電圧V<sub>thEL</sub>とカソード電位V<sub>cath</sub>の和を越えなければ、駆動トランジスタ121に流れるドレイン電流(

駆動電流  $I_{ds}$  ) は保持容量 120 の容量値  $C_s$  と有機 EL 素子 127 の寄生容量 (等価容量)  $C_{el}$  の容量値  $C_{el}$  の両者を結合した容量 “ $C = C_s + C_{el}$ ” に書き込まれていく。これにより、駆動トランジスタ 121 のソース電位  $V_s$  は上昇していく。このとき、駆動トランジスタ 121 の閾値補正動作は完了しているため、駆動トランジスタ 121 が流す駆動電流  $I_{ds}$  は移動度  $\mu$  を反映したものとなる。

#### 【0188】

図 6 のタイミングチャートでは、この上昇分を  $V$  で表してある。書き込みゲインを考慮したときは、この上昇分、すなわち移動度補正パラメータである負帰還量  $V$  は、閾値補正によって保持容量 120 に保持されるゲート・ソース間電圧 “ $V_{gs} = (1 - g) V_{in} + V_{th}$ ” から差し引かれることになり、“ $V_{gs} = (1 - g) V_{in} + V_{th} - V$ ” となるので、負帰還をかけたことになる。このとき、駆動トランジスタ 121 のソース電位  $V_s$  は、ゲート電位  $V_g$  ( $= V_{ofs} + V_{in}$ ) から保持容量に保持される電圧 “ $V_{gs} = (1 - g) V_{in} + V_{th} - V$ ” を差し引いた値 “ $(1 - g) V_{ofs} + g (V_{ofs} + V_{in}) - V_{th} + V$ ” = “ $V_{ofs} + g V_{in} - V_{th} + V$ ” となる。

10

#### 【0189】

このようにして、本実施形態の駆動タイミングでは、サンプリング期間 & 移動度補正期間  $K$  ( $t_{16} \sim t_{17}$ ) において、映像信号  $V_{sig}$  における信号振幅  $V_{in}$  の情報のサンプリングと移動度  $\mu$  を補正する負帰還量 (移動度補正パラメータ)  $V$  の調整が行なわれる。負帰還量  $V$  は  $V = I_{ds} \cdot (C_{el} + C_{gs} + C_s) / t$  である。

20

#### 【0190】

書き走査部 104 は、サンプリング期間 & 移動度補正期間  $K$  の時間幅を調整可能であり、これにより保持容量 120 に対する駆動電流  $I_{ds}$  の負帰還量を最適化することができる。ここで「負帰還量を最適化する」とは、映像信号電位の黒レベルから白レベルまでの範囲で、どのレベルにおいても適切に移動度補正を行なうことができるようすることを意味する。

20

#### 【0191】

負帰還量  $V$  は  $V = I_{ds} \cdot (C_{el} + C_{gs} + C_s) / t$  であるから、ゲート・ソース間電圧  $V_{gs}$  にかける負帰還量  $V$  は、ドレイン電流  $I_{ds}$  の取り出し時間すなわちサンプリング期間 & 移動度補正期間  $K$  に依存しており、この期間を長くとるほど、負帰還量が大きくなる。その際、移動度補正期間  $t$  は必ずしも一定である必要はなく、逆に駆動電流  $I_{ds}$  に応じて調整することが好ましい場合がある。たとえば、駆動電流  $I_{ds}$  が大きい場合、移動度補正期間  $t$  は短めにし、逆に駆動電流  $I_{ds}$  が小さくなると、移動度補正期間  $t$  は長めに設定することがよい。

30

#### 【0192】

また、負帰還量  $V$  は  $V = I_{ds} \cdot (C_{el} + C_{gs} + C_s) / t$  であるから、駆動トランジスタ 121 のドレイン・ソース間電流である駆動電流  $I_{ds}$  が大きいほど、負帰還量  $V$  は大きくなる。逆に、駆動トランジスタ 121 の駆動電流  $I_{ds}$  が小さいとき、負帰還量  $V$  は小さくなる。このように、負帰還量  $V$  は駆動電流  $I_{ds}$  に応じて決まる。

30

#### 【0193】

また、信号振幅  $V_{in}$  が大きいほど駆動電流  $I_{ds}$  は大きくなり、負帰還量  $V$  の絶対値も大きくなる。したがって、発光輝度レベルに応じた移動度補正を実現できる。その際、サンプリング期間 & 移動度補正期間  $K$  は必ずしも一定である必要はなく、逆に駆動電流  $I_{ds}$  に応じて調整することが好ましい場合がある。たとえば、駆動電流  $I_{ds}$  が大きい場合、移動度補正期間  $t$  は短めにし、逆に駆動電流  $I_{ds}$  が小さくなると、サンプリング期間 & 移動度補正期間  $K$  は長めに設定するのがよい。

40

#### 【0194】

たとえば、映像信号線電位 (信号線 106 HS の電位) の立ち上りもしくは書き走査線 104 WS の書き走査駆動パルス WS の遷移特性に傾斜をつけることで、移動度補正期間を映像線信号電位に自動的に追従させて、その最適化を図る。信号線 106 HS の電位が高いとき (駆動電流  $I_{ds}$  が大きいとき) 補正期間が短くなり、信号線 106 HS の電位が低いとき (駆動電

50

流  $I_{ds}$  が小さいとき) 補正期間は長くなるように、自動的に調整する。こうすることで、映像信号電位(映像信号  $V_{sig}$ )に追従して、適切な補正期間を自動的に設定できるため、画像の輝度や絵柄によらず最適な移動度補正が可能となる。

#### 【0195】

また、負帰還量  $V$  は、 $I_{ds} \cdot (C_{el} + C_{gs} + C_s) / t$  であり、画素回路  $P$  ごとに移動度  $\mu$  のばらつきに起因して駆動電流  $I_{ds}$  がばらつく場合でも、それに応じた負帰還量  $V$  となるので、画素回路  $P$  ごとの移動度  $\mu$  のばらつきを補正することができる。つまり、信号振幅  $V_{in}$  を一定とした場合、図 7 A に示すように、駆動トランジスタ 121 の移動度  $\mu$  が大きいほど駆動電流  $I_{ds}$  が大きく、ソース電位  $V_s$  の上昇が早く、負帰還量  $V$  の絶対値が大きくなる。逆に移動度  $\mu$  が小さいものは駆動電流  $I_{ds}$  が小さく、ソース電位  $V_s$  の上昇は遅く、負帰還量  $V$  の絶対値が小さくなる。換言すると、移動度  $\mu$  が大きいほど負帰還量  $V$  が大きくなるので、駆動トランジスタ 121 のゲート・ソース間電圧  $V_{gs}$  は移動度  $\mu$  を反映して小さくなり、一定時間経過後に完全に移動度  $\mu$  を補正するゲート・ソース間電圧  $V_{gs}$  となるので、画素回路  $P$  ごとの移動度  $\mu$  のばらつきを取り除くことができる。

10

#### 【0196】

このようにして、本実施形態の駆動タイミングでは、サンプリング期間 & 移動度補正期間  $K$  にて、信号振幅  $V_{in}$  の情報のサンプリングと移動度  $\mu$  のばらつきを補正するための負帰還量  $V$  の調整が同時に実行される。もちろん、負帰還量  $V$  はサンプリング期間 & 移動度補正期間  $K$  の時間幅を調整することで最適化可能である。

20

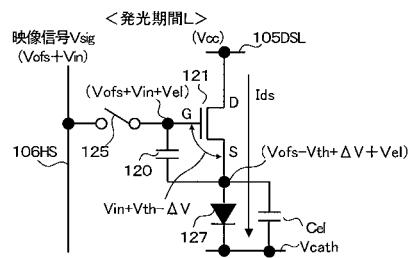

#### 【0197】

次に、書込走査部 104 は、映像信号線 106 HS が信号電位 ( $V_{ofs} + V_{in}$ ) にある状態で、書込駆動パルス  $WS$  をインアクティブ  $L$  に切り替える ( $t_{17\_1}$ )。これにより、図 6 L に示すように、サンプリングトランジスタ 125 が非導通(オフ)状態となり発光期間  $L$  に進む。水平駆動部 106 は、その後の適当な時点で映像信号線 106 HS への信号電位 ( $V_{ofs} + V_{in}$ ) の供給を停止してオフセット電位  $V_{ofs}$  に戻す ( $t_{18\_1}$ )。この後、次のフレーム(もしくはフィールド)に移って、再び、閾値補正準備動作、閾値補正動作、移動度補正動作、および発光動作が繰り返される。

#### 【0198】

この結果、駆動トランジスタ 121 のゲート端  $G$  は映像信号線 106 HS から切り離される。駆動トランジスタ 121 のゲート端  $G$  への信号電位 ( $V_{ofs} + V_{in}$ ) の印加が解除されるので、駆動トランジスタ 121 のゲート電位  $V_g$  は上昇可能となる。

30

#### 【0199】

このとき、駆動トランジスタ 121 に流れる駆動電流  $I_{ds}$  は有機  $EL$  素子 127 に流れ、有機  $EL$  素子 127 のアノード電位は駆動電流  $I_{ds}$  に応じて上昇する。この上昇分を  $V_{el}$  とする。やがて、ソース電位  $V_s$  の上昇に伴い、有機  $EL$  素子 127 の逆バイアス状態は解消されるので、駆動電流  $I_{ds}$  の流入により有機  $EL$  素子 127 は実際に発光を開始する。このときの有機  $EL$  素子 127 のアノード電位の上昇 ( $V_{el}$ ) は、駆動トランジスタ 121 のソース電位  $V_s$  の上昇に他ならず、駆動トランジスタ 121 のソース電位  $V_s$  は、“ $(1 - g) V_{ofs} + g (V_{ofs} + V_{in}) - V_{th+} - V + V_{el}$ ” = “ $V_{ofs} + g V_{in} - V_{th+} - V + V_{el}$ ” となる。

40

#### 【0200】

駆動電流  $I_{ds}$  対ゲート電圧  $V_{gs}$  の関係は、先のトランジスタ特性を表した式(1)の  $V_{gs}$  に “ $V_{in} - V + V_{th}$ ” を代入することで、式(2-1)のように表すことができる。書き込みゲインを考慮したときには、式(1)の  $V_{gs}$  に “ $(1 - g) V_{in} - V + V_{th}$ ” を代入することで、式(2-2)のように表すことができる。式(2-1)や式(2-2) (纏めて式(2)と称する)において、 $k = (1/2) (W/L) C_{ox}$  である。

#### 【0201】

## 【数2】

$$\left. \begin{aligned} I_{ds} &= k\mu(V_{gs} - V_{th})^2 = k\mu(V_{in} - \Delta V)^2 \cdots (2-1) \\ I_{ds} &= k\mu(V_{gs} - V_{th})^2 = k\mu((1-g)V_{in} - \Delta V)^2 \cdots (2-2) \end{aligned} \right\} \cdots (2)$$

## 【0202】

この式(2)から、閾値電圧  $V_{th}$  の項がキャンセルされており、有機EL素子127に供給される駆動電流  $I_{ds}$  は駆動トランジスタ121の閾値電圧  $V_{th}$  に依存しないことが分かる。基本的に駆動電流  $I_{ds}$  は信号振幅  $V_{in}$  によって決まる。換言すると、有機EL素子127は信号振幅  $V_{in}$  に応じた輝度で発光することになる。

10

## 【0203】

その際、保持容量120に保持される情報は帰還量  $V$  で補正されている。この補正量  $V$  はちょうど式(2)の係数部に位置する移動度  $\mu$  の効果を打ち消すように働く。したがって、駆動電流  $I_{ds}$  は実質的に信号振幅  $V_{in}$  のみに依存することになる。駆動電流  $I_{ds}$  は閾値電圧  $V_{th}$  に依存しないので、閾値電圧  $V_{th}$  が製造プロセスにより変動しても、ドレン・ソース間の駆動電流  $I_{ds}$  は変動せず、有機EL素子127の発光輝度も変動しない。

20

## 【0204】

また、駆動トランジスタ121のゲート端  $G$  とソース端  $S$ との間には保持容量120が接続されており、その保持容量120による効果により、発光期間の最初でブートストラップ動作が行なわれ、駆動トランジスタ121のゲート・ソース間電圧  $V_{gs}$  を一定に維持したまま、駆動トランジスタ121のゲート電位  $V_g$  およびソース電位  $V_s$  が上昇する。駆動トランジスタ121のソース電位  $V_s$  が “ $V_{ofs} + gV_{in} - V_{th} + V + V_{el}$ ” となることで、ゲート電位  $V_g$  は “ $V_{ofs} + V_{in} + V_{el}$ ” となる。

## 【0205】

このとき、駆動トランジスタ121のゲート・ソース間電圧  $V_{gs}$  は一定であるので、駆動トランジスタ121は、一定電流(駆動電流  $I_{ds}$ )を有機EL素子127に流す。その結果、有機EL素子127のアノード端  $A$  の電位(=ノードND121の電位)は、有機EL素子127に飽和状態での駆動電流  $I_{ds}$  という電流が流れ得る電圧まで上昇する。

30

## 【0206】

ここで、有機EL素子127は、発光時間が長くなるとそのI-V特性が変化してしまう。そのため、時間の経過とともに、ノードND121の電位も変化する。しかしながら、このような有機EL素子127の経時劣化によりそのアノード電位が変動しても、保持容量120に保持されたゲート・ソース間電圧  $V_{gs}$  は常に一定に維持される。

## 【0207】

駆動トランジスタ121が定電流源として動作することから、有機EL素子127のI-V特性が経時変化し、これに伴って駆動トランジスタ121のソース電位  $V_s$  が変化したとしても、保持容量120によって駆動トランジスタ121のゲート・ソース間電圧  $V_{gs}$  が一定( $V_{in} - V + V_{th}$  もしくは  $(1-g)V_{in} - V + V_{th}$ )に保たれているため、有機EL素子127に流れる電流は変わらず、したがって有機EL素子127の発光輝度も一定に保たれる。

40

## 【0208】

このような、有機EL素子127の特性変動に拘らず、駆動トランジスタ121のゲート・ソース間電圧を一定に維持し輝度を一定に維持する補正のための動作(保持容量120の効果による動作)をブートストラップ動作と呼ぶ。このブートストラップ動作により、有機EL素子127のI-V特性が経時的に変化しても、それに伴う輝度劣化のない画像表示が可能になる。

50

## 【0209】

つまり、本実施形態の画素回路Pとそれを駆動する本実施形態の駆動タイミングでは、電気光学素子の一例である有機EL素子127の電流-電圧特性の変化を補正して駆動電流を一定に維持する駆動信号一定化回路の一例であるブートストラップ回路が構成され、ブートストラップ動作が機能するようになっているのである。よって、有機EL素子127のI-V特性が劣化しても一定電流I<sub>ds</sub>が常に流れ続けるため、有機EL素子127は画素信号V<sub>sig</sub>に応じた輝度で発光を続けることになり輝度が変化することはない。

## 【0210】

また、本実施形態の画素回路Pとそれを駆動する本実施形態の駆動タイミングでは、駆動トランジスタ121の閾値電圧V<sub>th</sub>を補正して駆動電流を一定に維持する駆動信号一定化回路の一例である閾値補正回路が構成され閾値補正動作が機能するようになっている。駆動トランジスタ121の閾値電圧V<sub>th</sub>を反映させたゲート・ソース間電位V<sub>gs</sub>として、当該閾値電圧V<sub>th</sub>のばらつきの影響を受けない一定電流I<sub>ds</sub>を流すことができる。

10

## 【0211】

特に、本実施形態の駆動タイミングでは、1回の閾値補正動作の処理サイクルを1水平期間とし、複数回に亘って閾値補正動作を繰り返すようにしており、確実に閾値電圧V<sub>th</sub>を保持容量120に保持させるようにしている。このため、閾値電圧V<sub>th</sub>の画素間差が確実に除去され、階調に拘らず、閾値電圧V<sub>th</sub>のばらつきに起因する輝度ムラを抑制できる。

20

## 【0212】

これに対して、閾値補正動作を1回にするなど閾値電圧V<sub>th</sub>の補正が不十分な場合は、つまり閾値電圧V<sub>th</sub>が保持容量120に保持されていない場合には、異なる画素回路Pの間で、低階調の領域では輝度(駆動電流I<sub>ds</sub>)に差が出てしまう。よって閾値電圧の補正が不十分な場合は、低階調で輝度のムラが現れ画質を損なうことになる。

## 【0213】

加えて、本実施形態の駆動タイミングでは、サンプリングトランジスタ125による信号振幅V<sub>in</sub>の情報の保持容量120への書き込み動作と連動して駆動トランジスタ121の移動度μを補正して駆動電流を一定に維持する駆動信号一定化回路の一例である移動度補正回路が構成され移動度補正動作が機能するようになっている。駆動トランジスタ121のキャリア移動度μを反映させたゲート・ソース間電位V<sub>gs</sub>として、当該キャリア移動度μのばらつきの影響を受けない一定電流I<sub>ds</sub>を流すことができる。

30

## 【0214】

つまり、本実施形態の画素回路Pは、駆動タイミングを工夫することで、閾値補正回路や移動度補正回路が自動的に構成され、駆動トランジスタ121の特性ばらつき(本例では閾値電圧V<sub>th</sub>およびキャリア移動度μのばらつき)による駆動電流I<sub>ds</sub>に与える影響を防ぐために、閾値電圧V<sub>th</sub>およびキャリア移動度μによる影響を補正して駆動電流を一定に維持する駆動信号一定化回路として機能するようになっているのである。

## 【0215】

ブートストラップ動作だけでなく、閾値補正動作と移動度補正動作とを実行しているため、ブートストラップ動作で維持されるゲート・ソース間電圧V<sub>gs</sub>は、閾値電圧V<sub>th</sub>に相当する電圧と移動度補正用の電圧Vとによって調整されているため、有機EL素子127の発光輝度は駆動トランジスタ121の閾値電圧V<sub>th</sub>や移動度μのばらつきの影響を受けることがないし、有機EL素子127の経時劣化の影響も受けない。入力される信号振幅V<sub>in</sub>に対応する安定した階調で表示でき、高画質の画像を得ることができる。

40

## 【0216】

また、本実施形態の画素回路Pは、nチャネル型の駆動トランジスタ121を用いたソースフォロア回路によって構成することができるため、現状のアノード・カソード電極の有機EL素子をそのまま用いても、有機EL素子127の駆動が可能になる。

## 【0217】

また、駆動トランジスタ121およびその周辺部のサンプリングトランジスタ125を

50

も含めて n チャネル型のみのトランジスタを用いて画素回路 P を構成することができ、 TFT 作成においてもアモルファスシリコン ( a - Si ) プロセスを用いることができるようになるため、 TFT 基板の低コスト化が図れることになる。

【 0 2 1 8 】

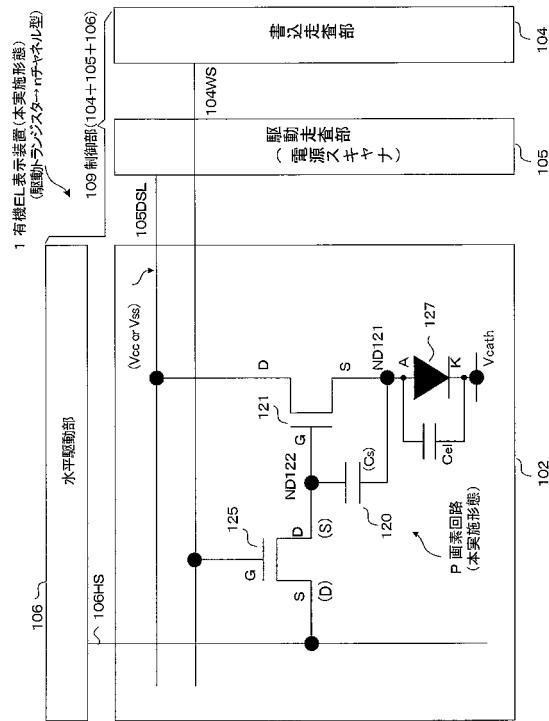

< < 垂直配線と水平配線について > >

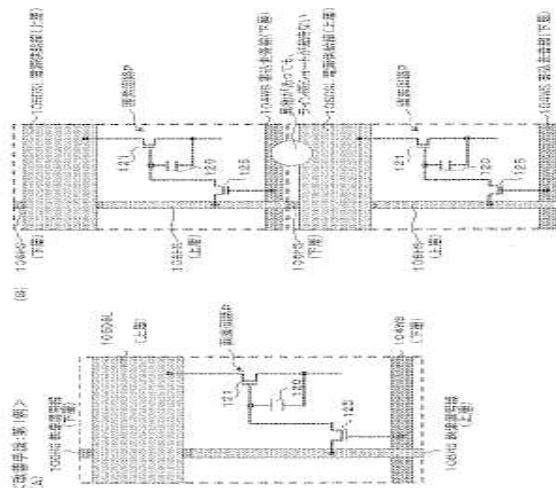

図 8 および図 8 A は、画素アレイ部 102 の垂直配線と水平配線の配線形態 ( レイアウト ) の比較例を説明する図である。図 8 は、1 画素分の走査配線のレイアウトを示しており、図 8 A は、垂直方向に隣接する 2 行分の画素回路 P の走査配線のレイアウトを示している。

【 0 2 1 9 】

図 5 に示した画素回路 P の場合、画素アレイ部 102 においては、少なくとも垂直走査系統に関する書込走査線 104 WS および電源供給線 105 DSL が縦 / 横の一方の配線 ( たとえば横配線とする ) となり、これに対して水平走査系統に関する映像信号線 106 HS が縦 / 横の他方の配線 ( たとえば縦配線とする ) となる。また、有機 EL 素子 127 のカソード電位 V cath をベタ配線ではなく通常の配線とする場合であれば、カソード電位 V cath 用の配線 ( 以下カソード配線 W cath と称する ) が横配線もしくは縦配線となる。

【 0 2 2 0 】

ここで、前述の各配線 ( 書込走査線 104 WS 、電源供給線 105 DSL 、映像信号線 106 HS ) は、横方向または縦方向に延び、画素アレイ部 102 の周辺に設けられた対応する走査部 ( 書込走査部 104 、駆動走査部 105 、水平駆動部 106 ) と接続される。

【 0 2 2 1 】

画面の左右方向について考察した場合、詳細説明図は割愛するが、1 行内の全ての画素回路 P に対して書込駆動パルス WS は書込走査部 104 から共通に供給されるので、書込駆動パルス WS の波形が配線容量や配線抵抗の影響で、書込走査部 104 から遠い画素回路 P ( 遠側画素と称する ) の方が書込走査部 104 から近い画素回路 P ( 近側画素と称する ) よりも、その波形鈍りが大きくなってしまう。そのため、配線容量や配線抵抗の分布特性が、閾値補正や移動度補正の動作に影響を与えることがある。

【 0 2 2 2 】

同様のことは、電源供給線 105 DSL や映像信号線 106 HS ( あるいはカソード配線 W cath ) についても言えることであり、配線容量や配線抵抗の分布特性が、閾値補正や移動度補正の動作に影響を与えることがある。

【 0 2 2 3 】

これらの点を考慮して、各配線は、一般的に、低抵抗にするべく、アルミニウム Al やモリブデン Mo などによる光透過性を有しない金属配線を使用して配線される。前述のように、縦配線と横配線が必要であるから、基本的には、縦配線と横配線の交差部でのオーバーラップのために、最低でも 2 層の金属配線が必要になる。

【 0 2 2 4 】

たとえば、図 8 ( A ) に示す第 1 比較例では、サンプリングトランジスタ 125 のゲート端を駆動するための書込走査線 104 WS と、駆動トランジスタ 121 のドレイン端の電源電圧を第 1 電位 V cc と第 2 電位 V ss とでスイッチングさせるための電源供給線 105 DSL とを上層側および下層側の一方 ( ここでは上層側とする ) の金属配線にしている。

【 0 2 2 5 】

また、サンプリングトランジスタ 125 のソース端に映像信号 V sig を供給するための映像信号線 106 HS に関しては、画素回路 P 部分では上層側および下層側の一方 ( ここでは上層側とする ) の金属配線にしているのに対して、同層の ( 上層側の金属配線である ) 書込走査線 104 WS や電源供給線 105 DSL と交差する部分はオーバーラップさせる必要があるので、上層側および下層側の他方 ( ここでは下層側とする ) の金属配線にしている。

【 0 2 2 6 】

また、図 8 ( B ) に示す第 2 比較例では、サンプリングトランジスタ 125 のゲート端

10

20

30

40

50

を駆動するための書込走査線 104WS と、駆動トランジスタ 121 のドレイン端の電源電圧を第 1 電位 Vcc と第 2 電位 Vss とでスイッチングさせるための電源供給線 105DSL とを上層側および下層側の一方（ここでは下層側とする）の金属配線にしている。

### 【0227】

また、サンプリングトランジスタ 125 のソース端に映像信号 Vsig を供給するための映像信号線 106HS に関しては、全体を上層側および下層側の他方（ここでは上層側とする）の金属配線にしている。こうすることで、図 8 (A) に示す第 1 比較例のような下層側の金属配線とのブリッジ（異なる層の金属配線を繋ぐこと）を避けている。

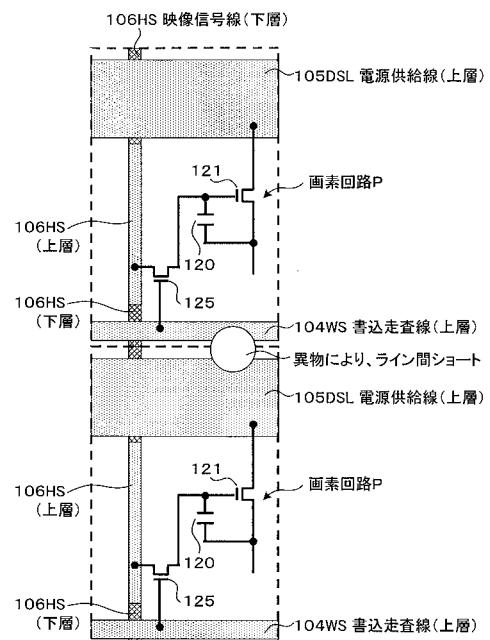

### 【0228】

図 8 (A) に示す第 1 比較例および図 8 (B) に示す第 2 比較例の何れにおいても、書込走査線 104WS と電源供給線 105DSL は同層の金属配線でレイアウトされており、1 画素内では離して（画素回路 P の上端と下端にて）並走させたとしても、図 8 A に示すように、隣接する画素回路 P との関係においては同層（同じレイヤ）でごく近くを並走（隣接）することになる。また、前述のように、書込走査線 104WS および電源供給線 105DSL は、画素アレイ部 102 周辺（パネル端）の対応する書込走査部 104、駆動走査部 105 までレイアウトされるため、非常に長い。したがって、配線間スペースが狭いと、導電性を有するダストなどの異物によって同層の配線間が接続（ショート）する可能性が高くなり、歩留まり低下の原因となる。

### 【0229】

そこで、本実施形態では、同層で並走する金属配線がダストなどによって接続（ショート）する可能性を低減することのできる仕組みを探る。以下、具体的に説明する。

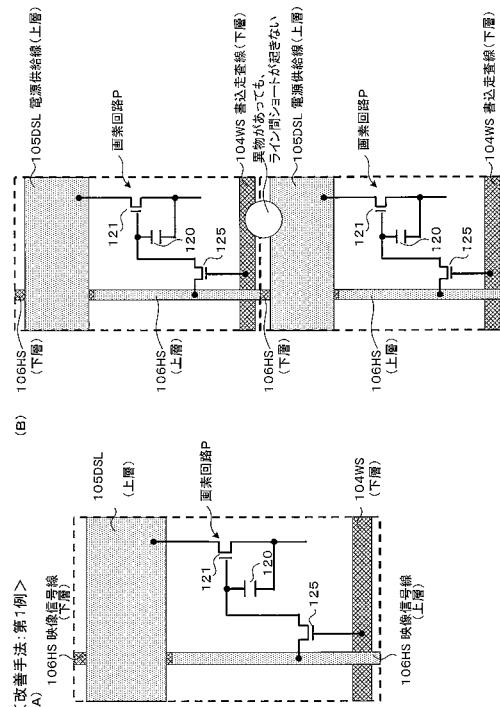

### 【0230】

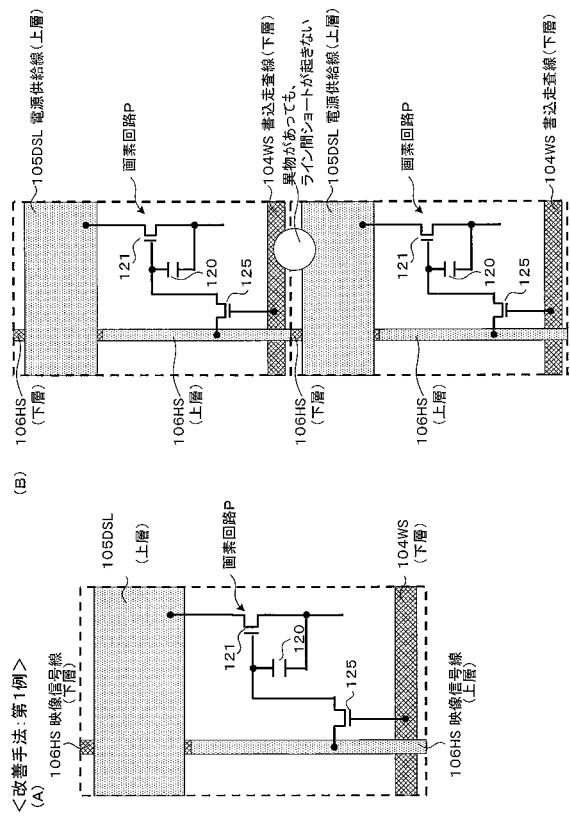

<垂直配線と水平配線の改善手法：第 1 例>

図 9 は、本実施形態で採用する画素アレイ部 102 の垂直配線と水平配線の配線形態（レイアウト）の第 1 例を説明する図である。図 9 (A) は、1 画素分の走査配線のレイアウトを示しており、図 9 (B) は、垂直方向に隣接する 2 行分の画素回路 P の走査配線のレイアウトを示している。

### 【0231】

第 1 例のレイアウトは、1 画素内の並走配線（同方向に並走する各走査線）が偶数の場合に、画素回路 P 内では、各並走配線の全体を上層配線と下層配線で交互にレイアウトすることで、隣接配線を異なる層の金属配線でレイアウトする点に特徴を有する。縦配線と交差する部分は、横配線に対しての交差配線である縦配線を上層配線と下層配線で繋ぐことでオーバーラップさせる。オーバーラップ部分は、上層配線と下層配線とが電気的に接触するがないように、絶縁層を挟んで積層するのは言うまでもない（以下同様である）。こうすることで、画素回路 P 内および画素回路 P 外の何れにおいても、隣接配線の全体を異なる層の金属配線でレイアウトすることができ、ダストなどによる配線間ショート数を軽減することができる。

### 【0232】

具体的には、第 1 例のレイアウトにおいては特に 1 画素内の横配線が 2 本の場合で示している。駆動トランジスタ 121 のドレイン端の電源電圧を第 1 電位 Vcc と第 2 電位 Vss とでスイッチングさせるための電源供給線 105DSL と、サンプリングトランジスタ 125 のソース端に映像信号 Vsig を供給するための映像信号線 106HS の画素回路 P の内側（画素回路 P が配置される画素ピッチ内における縦方向の中央部を意味する：以下同様）を、それぞれ上層側および下層側の一方（ここでは上層側とする）の金属配線にしている。また、サンプリングトランジスタ 125 のゲート端を駆動するための書込走査線 104WS を上層側および下層側の他方（ここでは下層側とする）の金属配線にしている。

### 【0233】

映像信号線 106HS は、同層の（上層側の金属配線である）電源供給線 105DSL と交差する部分をオーバーラップさせる必要があるので下層側の金属配線にしている。加えて、映像信号線 106HS の上層側の金属配線を隣接する次行の画素回路 P の境界まで延在さ

10

20

30

40

50

せ、次行の同層の（上層側の金属配線である）電源供給線 105DSL と交差する部分でオーバーラップさせるようにしている。

【0234】

図9(A)に示すように、1画素内では書込走査線 104WS と電源供給線 105DSL を離して（画素回路 P の上端と下端にて）並走させている。このとき、図9(B)に示すように、隣接する画素回路 P との関係においては、異なる層でごく近くを並走（隣接）することになる。

【0235】

このように、ごく近くを並走（隣接）することになる横方向の金属配線を異なる配線層にレイアウトすれば、上層側で導電性を有するダストなどの異物があっても上層レイヤと下層レイヤは接続（ショート）されることはないため、隣接配線間のショート対策を実現でき、高い歩留まりが実現できる。ダストなどによる隣接配線間の同層ショートが起こり難いレイアウトにでき、高歩留まりが実現可能となる。

【0236】

画素回路 P 内および隣接する 2 つの画素回路 P の間において、隣接配線を異なる層の金属配線でレイアウトすることで、導電性を有する異物による配線間ショート数を軽減することができ、高歩留まりが実現できるのである。

【0237】

また、図8(A)に示す第1比較例との対比においては、縦配線である映像信号線 106HS と横配線との下層側の金属配線とのブリッジ（異なる層の金属配線を繋ぐこと）間の距離を少なくできるので、映像信号線 106HS の負荷を軽減することができる。

【0238】

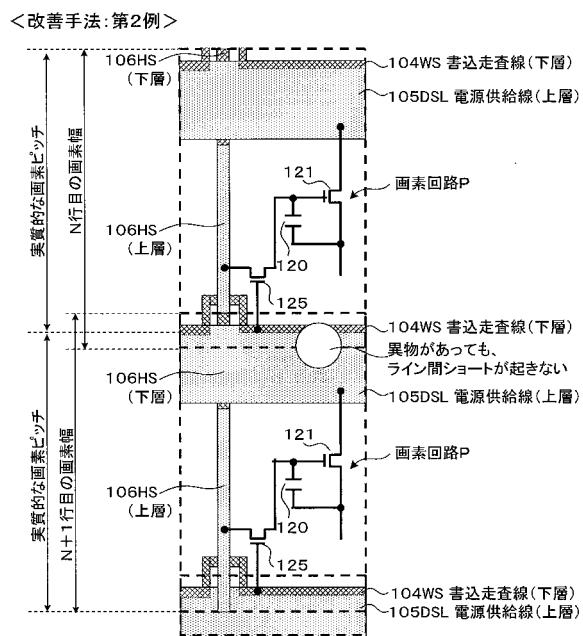

<垂直配線と水平配線の改善手法：第2例>

図9Aは、本実施形態で採用する画素アレイ部 102 の垂直配線と水平配線の配線形態（レイアウト）の第2例を説明する図であり、垂直方向に隣接する 2 行分の画素回路 P の走査配線のレイアウトを示している。

【0239】

第2例のレイアウトは、第1例のレイアウト手法を採用しつつ、ある行の最下端の上層側および下層側の一方の配線と、次行の最上端の上層側および下層側の他方の配線とを積層することで、垂直方向の画素ピッチの狭小化を図るようにした点に特徴を有する。積層部分はオーバーラップ部分と同様に、上層配線と下層配線とが電気的に接觸するがないように、絶縁層を挟んで積層するのは言うまでもない。

【0240】

図示した例では、図9に示したレイアウトをベースとして、ある行の下層側の書込走査線 104WS と、次行の上層側の電源供給線 105DSL とを積層させることで、垂直方向の画素ピッチの狭小化を図る。

【0241】

ここで、書込走査線 104WS と映像信号線 106HS とが交差する部分については、電源供給線 105DSL と映像信号線 106HS とを交差させる下層側の金属配線を避けるように、書込走査線 104WS 用の下層側の金属配線を自列の画素回路 P 側に迂回させて映像信号線 106HS とオーバーラップさせる。

【0242】

第1例のレイアウトでは、各行の画素幅が画素ピッチと一致するのに対して、第2例のレイアウトでは、各行（図では N 行目と N + 1 行目）の画素幅が画素ピットと一致せず、N 行目の下層側の書込走査線 104WS と N + 1 行目の上層側の電源供給線 105DSL とを積層させたことで、垂直方向の画素ピッチを画素の積層分の 1 / 2 だけ狭くすることができる。

【0243】

このような垂直方向の画素ピッチの狭小化を図るようにした第2例のレイアウトであっても、ごく近くを並走（隣接）することになる横方向の金属配線を異なる配線層にレイア

10

20

30

40

50

ウトしているので、横方向の金属配線同士に関しては、上層側で導電性の異物があつても上層レイヤと下層レイヤは接続（ショート）されることはないと実現できる。すなわち、縦配線である映像信号線 106HS と横配線である書込走査線 104WS のオーバーラップする部分以外は、隣接配線は異なる層の金属配線であるので、隣接配線間のショート対策の効果はある。

#### 【0244】

加えて、第1例と同様に、図8(A)に示す第1比較例との対比においては、縦配線である映像信号線 106HS と横配線との下層側の金属配線とのブリッジ間距離を短くできるので、映像信号線 106HS の負荷を軽減することができる。

10

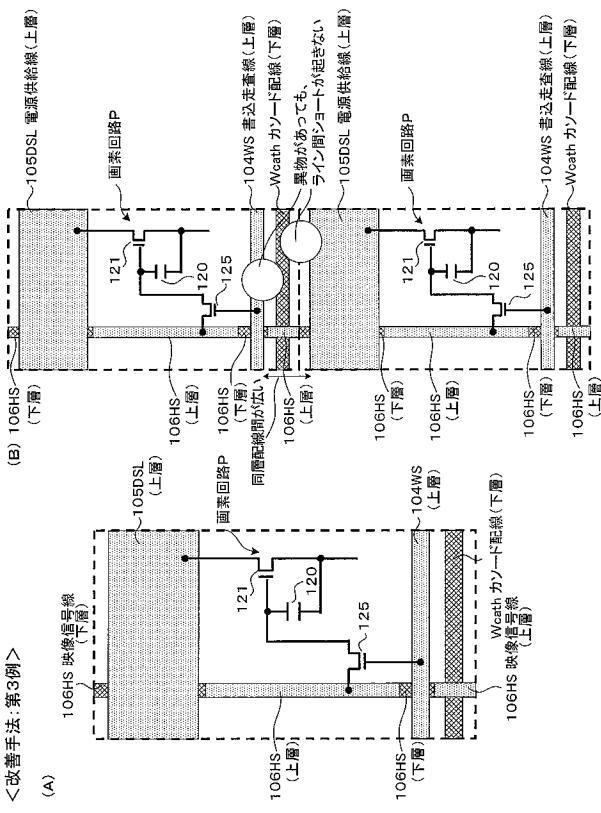

#### 【0245】

<垂直配線と水平配線の改善手法：第3例>

図9Bは、本実施形態で採用する画素アレイ部 102 の垂直配線と水平配線の配線形態（レイアウト）の第3例を説明する図である。図9B(A)は、1画素分の走査配線のレイアウトを示しており、図9B(B)は、垂直方向に隣接する2行分の画素回路 P の走査配線のレイアウトを示している。

20

#### 【0246】

第3例のレイアウトは、1画素内の並走配線（同方向に並走する各走査線）が奇数の場合に、その内の1本の走査線を画素回路 P が配置される画素ピッチ内の方の最端部において上層配線と下層配線の何れか一方に形成し、他の1本の走査線を画素回路 P が配置される画素ピッチ内の方（一方に対しての反対側）の最端部において上層配線と下層配線の他方に形成する点に特徴を有する。残りの内の偶数分は、好ましくは、第1例のレイアウトを適用して上層配線と下層配線を交互にレイアウトする。それでも残る最後の1本を上層側および下層側の何れか一方にレイアウトする。

30

#### 【0247】

つまり、画素回路 P の内側では、上層配線と下層配線の何れかを両側の最端部にレイアウトし、残りの内の偶数分は第1例のレイアウトを適用して上層配線と下層配線を交互にレイアウトし、最後の1本を上層側および下層側の何れか一方にレイアウトすることで、画素間の隣接配線の全体を異なる層の金属配線でレイアウトする。もちろん、縦配線と交差する部分は、横配線に対しての交差配線である縦配線を上層配線と下層配線で繋ぐことでオーバーラップさせる。こうすることで、少なくとも隣接する2つの画素回路 P の間ににおいては、隣接配線の全体を異なる層の金属配線でレイアウトすることができ、ダストなどによる配線間ショート数を軽減することができる。

30

#### 【0248】

具体的には、第3例のレイアウトは、カソード配線 Wcath を横方向の走査線として取り扱い、このカソード配線 Wcath を画素回路 P 内で横方向の走査線である書込走査線 104WS と近接して並走させるようにした例である。図示のように、駆動トランジスタ 121 のドレイン端の電源電圧を第1電位 Vcc と第2電位 Vss とでスイッチングさせるための電源供給線 105DSL と、サンプリングトランジスタ 125 のゲート端を駆動するための書込走査線 104WS と、サンプリングトランジスタ 125 のソース端に映像信号 Vsig を供給するための映像信号線 106HS の画素回路 P 部分およびカソード配線 Wcath と交差する部分を、それぞれ上層側および下層側の一方（ここでは上層側とする）の金属配線にしている。また、有機EL素子 127 のカソード配線 Wcath を上層側および下層側の他方（ここでは下層側とする）の金属配線にしている。

40

#### 【0249】

映像信号線 106HS は、同層の（上層側の金属配線である）電源供給線 105DSL や書込走査線 104WS と交差する部分をオーバーラップさせる必要があるので下層側の金属配線にしている。加えて、カソード配線 Wcath と交差する映像信号線 106HS の上層側の金属配線を隣接する次行の画素回路 P まで延在させ、次行の同層の（上層側の金属配線である）電源供給線 105DSL と交差する部分でオーバーラップさせるようにしている。

50

#### 【0250】

図9B(A)に示すように、1画素内では電源供給線105DSLを上端にレイアウトし書込走査線104WSおよびカソード配線Wcathを下端にレイアウトすることで、電源供給線105DSLと書込走査線104WSおよびカソード配線Wcathを離して並走させている。このとき、カソード配線Wcathと書込走査線104WSは、異なる層でごく近くを並走(隣接)することになる。

#### 【0251】

また、図9B(B)に示すように、隣接する画素回路Pとの関係においては、前行のカソード配線Wcathと次行の電源供給線105DSLとは、異なる層でごく近くを並走(隣接)することになる。

#### 【0252】

このように、ごく近くを並走(隣接)することになる横方向の金属配線を異なる配線層にレイアウトすれば、上層レイヤである上層側でダストなどがあっても上層レイヤと下層レイヤは接続(ショート)されることはないため、隣接配線間のショート対策を実現でき、高い歩留まりが実現できる。

#### 【0253】

画素回路P内でも隣接配線を異なる層の金属配線でできるだけレイアウトし、また隣接する2つの画素回路Pの間においても隣接配線を異なる層の金属配線でレイアウトすることで、ダストなどによる配線間ショート数を軽減することができ、高歩留まりが実現できるのである。

#### 【0254】

加えて、画素の境界では同層配線間を広くできるので、つまり、画素の境界(カソード配線Wcathも)を挟んで同層でレイアウトすることになる前行の書込走査線104WSと次行の電源供給線105DSLの関係においては、その配線間隔を大きくすることができるので、導電性を有する異物の径がその大きな配線間隔以上でなければ接続(ショート)されることはないため、高い歩留まりが実現できる。

#### 【0255】

詳細説明は割愛するが、この第3例のレイアウトを採用しつつ、第2例のレイアウト手法と同様に、ある行の下層側のカソード配線Wcathと、次行の上層側の電源供給線105DSLとを積層させることで、垂直方向の画素ピッチの狭小化を図ることもできる。

#### 【0256】

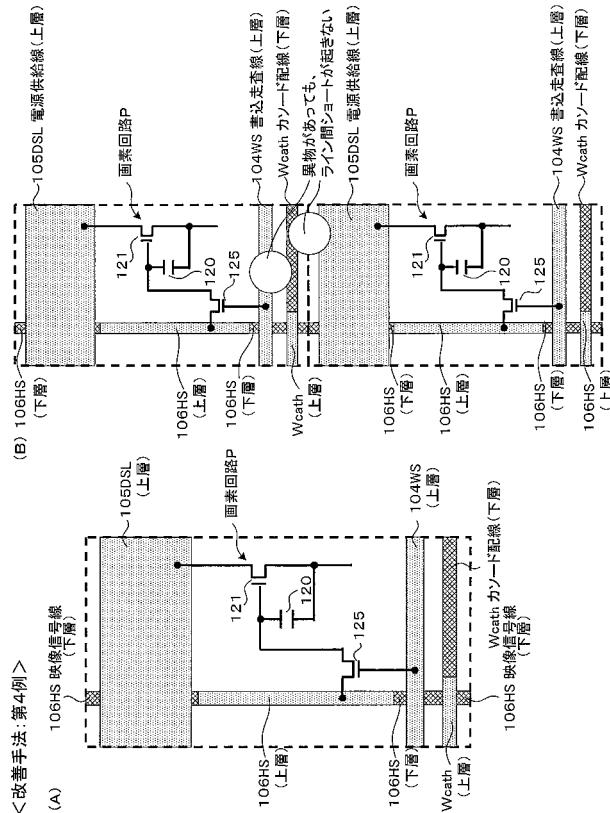

##### <垂直配線と水平配線の改善手法：第4例>

図9Cは、本実施形態で採用する画素アレイ部102の垂直配線と水平配線の配線形態(レイアウト)の第4例を説明する図である。図9C(A)は、1画素分の走査配線のレイアウトを示しており、図9C(B)は、垂直方向に隣接する2行分の画素回路Pの走査配線のレイアウトを示している。

#### 【0257】

第4例のレイアウトは、隣接配線のそれについて全体を異なる配線層にレイアウトするのではなく、何れかの配線については、一部分を隣接配線と同層にレイアウトする点に特徴を有する。縦配線と交差する部分は、縦配線を上層配線と下層配線で繋ぐことでオーバーラップさせる。こうすることで、一部分を隣接配線と同層にした所では、隣接配線間のショートが起こる可能性が生じるもの、縦配線による横配線とのブリッジ(異なる層の金属配線を繋ぐこと)の回数を少なくでき、縦配線の負荷を軽減することができる。もちろん、一部分を隣接配線と同層にした所以外では、隣接配線は異なる配線層にレイアウトされるので隣接配線間のショート対策の効果が得られる。

#### 【0258】

図示する例は、図9Bに示した第3例のレイアウト手法をベースとして、カソード配線Wcathに関して第4例の手法を適用したものである。図示のように、駆動トランジスタ121のドレイン端の電源電圧を第1電位Vccと第2電位Vssとでスイッチングさせるための電源供給線105DSLと、サンプリングトランジスタ125のゲート端を駆動するための書込走査線104WSと、サンプリングトランジスタ125のソース端に映像信号Vsig

10

20

30

40

50

を供給するための映像信号線 106HS の画素回路 P の内側を、それぞれ上層側および下層側の一方（ここでは上層側とする）の金属配線にしている。

【0259】

有機 E L 素子 127 のカソード配線 Wcath は、映像信号線 106HS と交差する部分は上層側および下層側の一方（ここでは上層側とする）の金属配線にし、映像信号線 106HS と交差する部分以外は上層側および下層側の他方（ここでは下層側とする）の金属配線にしている。

【0260】

映像信号線 106HS は、同層の（上層側の金属配線である）電源供給線 105DSL や書込走査線 104WS やカソード配線 Wcath と交差する部分をオーバーラップさせる必要があるので下層側の金属配線にしている。加えて、書込走査線 104WS やカソード配線 Wcath と交差する映像信号線 106HS の下層側の金属配線を隣接する次行の画素回路 P まで延在させ、次行の同層の（上層側の金属配線である）電源供給線 105DSL と同層としている。

【0261】

図 9C (A) に示すように、1 画素内では電源供給線 105DSL を上端にレイアウトし書込走査線 104WS およびカソード配線 Wcath を下端にレイアウトすることで、電源供給線 105DSL と書込走査線 104WS およびカソード配線 Wcath を離して並走させている。このとき、カソード配線 Wcath と書込走査線 104WS は、映像信号線 106HS と交差する部分以外では異なる層でごく近くを並走（隣接）することになる。隣接する書込走査線 104WS とカソード配線 Wcath とは全体が異なる層の配線ではなく、映像信号線 106HS とオーバーラップする部分は同層の配線となっている。

【0262】

また、図 9C (B) に示すように、隣接する画素回路 P との関係においては、前行のカソード配線 Wcath と次行の電源供給線 105DSL とは、映像信号線 106HS と交差する部分以外では異なる層でごく近くを並走（隣接）することになる。隣接する前行のカソード配線 Wcath と次号の電源供給線 105DSL は全体が異なる層の配線ではなく、映像信号線 106HS とオーバーラップする部分は同層の配線となっている。

【0263】

このように、第 4 例のレイアウトでは、カソード配線 Wcath と映像信号線 106HS とが交差する部分以外では、第 3 例のレイアウト手法と同様のレイアウトであるから、第 3 例のレイアウト手法と同様の効果を享受できる。すなわち、映像信号線 106HS とカソード配線 Wcath とがオーバーラップする部分以外については、近接する隣接配線は異なる配線層にレイアウトされるので隣接配線間のショート対策の効果はある。

【0264】

加えて、横配線であるカソード配線 Wcath と、横配線に対しての交差配線である縦配線としての映像信号線 106HS とが交差する部分では、それぞれが異なる配線層にレイアウトされるので、映像信号線 106HS を上層配線と下層配線で繋ぐことでオーバーラップさせるという処理が不要になる。映像信号線 106HS のブリッジの回数を少なくすることができるため、映像信号線 106HS の負荷を軽減することができる。

【0265】

近接する横方向の隣接配線は、映像信号線 106HS（縦配線）とオーバーラップする部分のみ同じ層にレイアウトし、その他の部分は異なる配線層にレイアウトすることで、映像信号線 106HS の負荷を小さくしつつ高歩留まりが実現可能となる。

【0266】

以上、本発明について実施形態を用いて説明したが、本発明の技術的範囲は上記実施形態に記載の範囲には限定されない。発明の要旨を逸脱しない範囲で上記実施形態に多様な変更または改良を加えることができ、そのような変更または改良を加えた形態も本発明の技術的範囲に含まれる。

【0267】

10

20

30

40

50

また、上記の実施形態は、クレーム（請求項）に係る発明を限定するものではなく、また実施形態の中で説明されている特徴の組合せの全てが発明の解決手段に必須であるとは限らない。前述した実施形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜の組合せにより種々の発明を抽出できる。実施形態に示される全構成要件から幾つかの構成要件が削除されても、効果が得られる限りにおいて、この幾つかの構成要件が削除された構成が発明として抽出され得る。

【0268】

<駆動タイミングの変形例>

駆動タイミングの側面では、電源供給線105DSLの電位が第2電位Vssから第1電位Vccに遷移するタイミングを映像信号Vsigの非有効期間であるオフセット電位Vofsの期間としつつ、様々な変形が可能である。

10

【0269】

たとえば、第1の変形例として、図示を割愛するが、図6に示した駆動タイミングに対して、サンプリング期間&移動度補正期間Kの設定方法を変形することができる。具体的には、先ず映像信号Vsigがオフセット電位Vofsから信号電位(Vofs+Vin)に遷移するタイミングt15Vを図6に示した駆動タイミングよりも1水平期間の後半側にシフトさせて、信号電位(Vofs+Vin)の期間を狭くする。

【0270】

また、閾値補正動作の完了時（閾値補正期間Iの完了時）には、先ず、書込駆動パルスWSをアクティブHにしたままで、水平駆動部106により映像信号線106HSに信号電位(Vofs+Vin)を供給して(t15)、書込駆動パルスWSをインアクティブLにするまで(t17)の間を、保持容量120への信号振幅Vinの情報の書き込み期間とする。この信号振幅Vinの情報は駆動トランジスタ121の閾値電圧Vthに足し込む形で保持される。この結果、駆動トランジスタ121の閾値電圧Vthの変動は常にキャンセルされる形となるので、閾値補正を行なっていることになる。この閾値補正動作によって、保持容量120に保持されるゲート・ソース間電圧Vgsは“(1-g)Vin+Vth”となる。また、同時に、信号書込期間t15～t17で移動度補正を実行する。すなわち、タイミングt15～t17は、信号書込期間と移動度補正期間の双方を兼ねることとなる。

20

【0271】

なお、この移動度補正を実行する期間t15～t17では、有機EL素子127は実際には逆バイアス状態にあるので発光することはない。この移動度補正期間t15～t17では、駆動トランジスタ121のゲート端Gが映像信号Vsigのレベルに固定された状態で、駆動トランジスタ121に駆動電流Idsが流れる。以下、図6に示した駆動タイミングと同様である。

30

【0272】

各駆動部(104, 105, 106)は、水平駆動部106が映像信号線106HSに供給する映像信号Vsigと書込走査部104が供給する書込駆動パルスWSとの相対的な位相差を調整して、移動度補正期間を最適化することができる。

【0273】

ただし、書込み&移動度補正準備期間Jが存在せずに、タイミングt15V3～t17がサンプリング期間&移動度補正期間Kとなる。このため、書込走査線104WSや映像信号線106HSの配線抵抗や配線容量の距離依存の影響に起因する波形特性の相違がサンプリング期間&移動度補正期間Kに影響を与えてしまう可能性がある。画面の書込走査部104に近い側と遠い側(すなわち画面の左右)でサンプリング電位や移動度補正時間が異なることになるので、画面の左右で輝度差が生じ、シェーディングとして視認される難点が懸念される。

40

【0274】

また、第2の変形例として、電源供給のオフタイミング(第2電位Vss側への遷移タイミング)に変更を加えることもできる。具体的には、当該行のオフタイミングとオンタイミングの双方を同じ水平期間にすることができる。

50

## 【0275】

この第2の変形例の駆動タイミングでは、ともに映像信号  $V_{sig}$  のオフセット電位  $V_{ofs}$  の期間に電源スイッチング動作をさせており、またこのときにはサンプリングトランジスタ 125 をオンさせて駆動トランジスタ 121 のゲート端 G をオフセット電位  $V_{ofs}$  に固定してローインピーダンス化しており電源パルス（電源駆動パルス  $DSL$  ）に起因するカップリングノイズに対する耐性が向上する。

## 【0276】

<画素回路の変形例>

画素回路の側面では、駆動電流を一定に維持する駆動信号一定化回路の一例であるブーストストラップ回路や閾値 & 移動度補正回路の構成例として、駆動トランジスタ 121 として n チャネル型を用いた 2TR 構成としつつ駆動タイミングを工夫する例を示したが、これは有機 EL 素子 127 を駆動するための駆動信号を一定に維持する駆動信号一定化回路および駆動タイミングの一例に過ぎず、有機 EL 素子 127 の経時劣化や n チャネル型の駆動トランジスタ 121 の特性変動（たとえば閾値電圧や移動度などのばらつきや変動）による駆動電流  $I_{ds}$  に与える影響を防ぐための駆動信号一定化回路としては、その他の様々な回路を適用することができる。

10

## 【0277】

たとえば、回路理論上は「双対の理」が成立するので、画素回路 P に対しては、この観点からの変形を加えることができる。この場合、図示を割愛するが、先ず、図 5 に示した 2TR 構成の画素回路 P が n チャネル型の駆動トランジスタ 121 を用いて構成しているのに対し、p チャネル型の駆動トランジスタ（以下 p 型駆動トランジスタ 121p と称する）を用いて画素回路 P を構成する。これに合わせて、映像信号  $V_{sig}$  の信号振幅  $V_{in}$ （信号電位（ $V_{ofs} + V_{in}$ ））の極性や電源電圧の大小関係を逆転させるなど、双対の理に従った変更を加える。

20

## 【0278】

なお、ここで説明した変形例は、図 5 に示した 2TR 構成に対して「双対の理」に従った変更を加えたものであるが、回路変更の手法はこれに限定されるものではなく、サンプリングトランジスタ（スイッチングトランジスタの一例）および駆動トランジスタ以外に、駆動電流を一定に維持する制御を行なうための他のスイッチングトランジスタが設けられた、2TR 構成以外であってもよい。ただし、高精細の表示が求められる小型の表示装置を実現する点では、2TR 構成にて駆動信号一定化機能を実現するのが最適である。

30

## 【0279】

ここで、各種の変形例においても、近接した隣接配線をできるだけ異なる配線層にレイアウトする本実施形態の仕組みを適用することで、導電性を有する異物による配線間ショートを軽減することができる。

30

## 【0280】

この際、画素回路 P 内にて縦方向もしくは横方向に並走する配線数が、偶数の場合には第 1 例（あるいはその変形例である第 2 例）のレイアウト手法を適用し、奇数の場合には第 3 例（あるいはその変形例である第 2 例）のレイアウト手法を適用すればよい。また、何れについても、第 4 例のレイアウト手法を適用することもできる。

40

## 【図面の簡単な説明】

## 【0281】

【図 1】本発明に係る表示装置の一実施形態であるアクティブマトリクス型表示装置の構成の概略を示すプロック図である。

40

【図 2】本実施形態の画素回路に対する第 1 比較例を示す図である。

【図 3】本実施形態の画素回路に対する第 2 比較例を示す図である。

【図 4】有機 EL 素子や駆動トランジスタの動作点を説明する図である。

【図 4A】有機 EL 素子や駆動トランジスタの特性ばらつきが駆動電流に与える影響を説明する図である。

【図 5】本実施形態の画素回路の構成例を示す図である。

50

【図 6】図 5 に示した本実施形態の画素回路に関する本実施形態の駆動タイミングの基本例を説明するタイミングチャートである。

【図 6 B】図 6 に示した駆動タイミングにおける発光期間 B の等価回路と動作説明の図である。

【図 6 C】図 6 に示した駆動タイミングにおける放電期間 C の等価回路と動作説明の図である。

【図 6 D】図 6 に示した駆動タイミングにおける初期化期間 D の等価回路と動作説明の図である。

【図 6 E】図 6 に示した駆動タイミングにおける第 1 闘値補正期間 E の等価回路と動作説明の図である。

【図 6 F】図 6 に示した駆動タイミングにおける他行書き込み期間 F の等価回路と動作説明の図である。

【図 6 G】図 6 に示した駆動タイミングにおける第 2 闘値補正期間 G の等価回路と動作説明の図である。

【図 6 H】図 6 に示した駆動タイミングにおける他行書き込み期間 H の等価回路と動作説明の図である。

【図 6 I】図 6 に示した駆動タイミングにおける第 3 闘値補正期間 I の等価回路と動作説明の図である。

【図 6 J】図 6 に示した駆動タイミングにおける書き込み & 移動度補正準備期間 J の等価回路と動作説明の図である。

【図 6 K】図 6 に示した駆動タイミングにおけるサンプリング期間 & 移動度補正期間 K の等価回路と動作説明の図である。

【図 6 L】図 6 に示した駆動タイミングにおける発光期間 L の等価回路と動作説明の図である。

【図 7】闘値補正動作時における駆動トランジスタのソース電位の変化を示す図である。

【図 7 A】移動度補正動作時における駆動トランジスタのソース電位 V<sub>S</sub> の変化を示す図である。

【図 8】画素アレイ部の配線形態の比較例を説明する図(1画素分)である。

【図 8 A】画素アレイ部の配線形態の比較例を説明する図(2行分)である。

【図 9】本実施形態で採用する画素アレイ部の配線形態の第 1 例を説明する図である。

【図 9 A】本実施形態で採用する画素アレイ部の配線形態の第 2 例を説明する図である。

【図 9 B】本実施形態で採用する画素アレイ部の配線形態の第 3 例を説明する図である。

【図 9 C】本実施形態で採用する画素アレイ部の配線形態の第 4 例を説明する図である。

【符号の説明】

【0 2 8 2】

1 ... 有機 E L 表示装置、1 0 0 ... 表示パネル部、1 0 1 ... 基板、1 0 2 ... 画素アレイ部、1 0 3 ... 垂直駆動部、1 0 4 ... 書込走査部、1 0 5 ... 駆動走査部、1 0 6 ... 水平駆動部、1 0 9 ... 制御部、1 2 0 ... 保持容量、1 2 1 ... 駆動トランジスタ、1 2 2 ... 発光制御トランジスタ、1 2 5 ... サンプリングトランジスタ、1 2 7 ... 有機 E L 素子(電気光学素子の一例)、2 0 0 ... 駆動信号生成部、3 0 0 ... 映像信号処理部、C e l ... 寄生容量、P ... 画素回路

10

20

30

40

【 図 1 】

【 図 2 】

( 义 3 )

〔 図 4 〕

【 図 4 A 】

【 図 5 】

【 図 6 】

【 図 6 B 】

【 図 6 C 】

【 図 6 D 】

【 図 6 E 】

( 四 6 H )

【図6-I】

【 図 6 F 】

【図6G】

【 义 6 J 】

【 図 6 K 】

【図 6 L】

【図 7 A】

【図 7】

【図 8】

【図 8 A】

【 図 9 】

【 図 9 A 】

【 図 9 B 】

【 図 9 C 】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 8 0 H |

| G 0 9 G | 3/20  | 6 2 1 A |

| G 0 9 G | 3/20  | 6 1 1 H |

| G 0 9 G | 3/20  | 6 4 2 A |

| G 0 9 G | 3/20  | 6 7 0 A |

| H 0 5 B | 33/22 | Z       |

F ターム(参考) 3K107 AA01 BB01 CC29 CC33 CC35 DD39 EE04 HH05

5C080 AA06 BB05 DD05 DD09 DD17 EE28 EE29 FF11 JJ02 JJ03

JJ04 JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2009130005A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2009-06-11 |

| 申请号            | JP2007301118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2007-11-21 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |